Page 1

A

1 1

B

C

D

E

VIQY1

(Y510)

2 2

NM_A032 Rev1.0 Schematic

Intel Haswell Processor with DDRIII + Lynx point PCH

3 3

4 4

A

nVIDIA N14P GT + 2nd VGA N14P GT

2013-03-19 Rev1.0

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

B

2012/07/ 01

2012/07/ 01

2012/07/ 01

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2014/07/ 01

2014/07/ 01

2014/07/ 01

D

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

Y510 NM-A032

Y510 NM-A032

Y510 NM-A032

Y510 NM-A032

Y510 NM-A032

Y510 NM-A032

Y510 NM-A032Y510 NM-A032

Y510 NM-A032Y510 NM-A032

Y510 NM-A032Y510 NM-A032

E

1 69

1 69

1 69

1.0

1.0

1.0

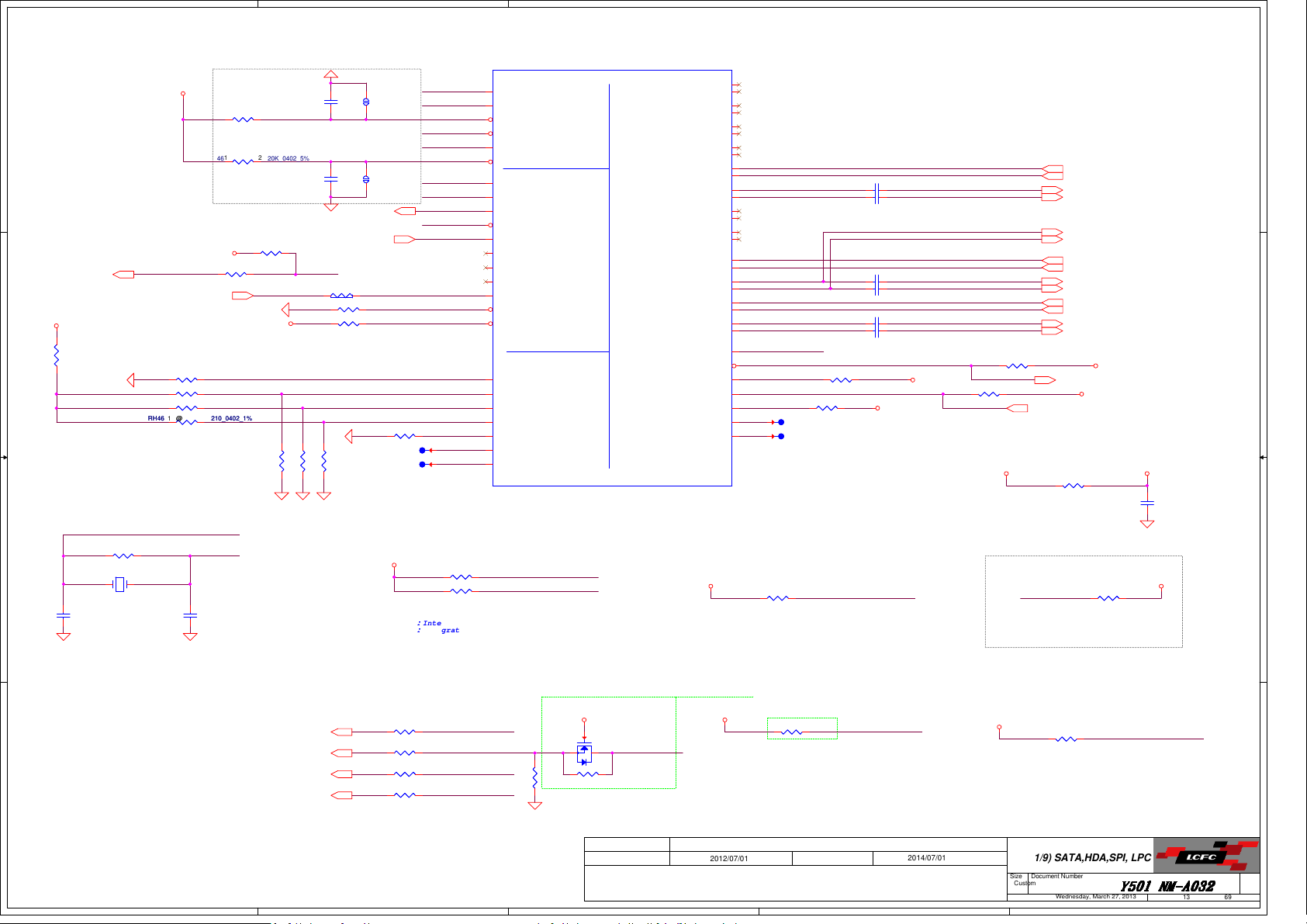

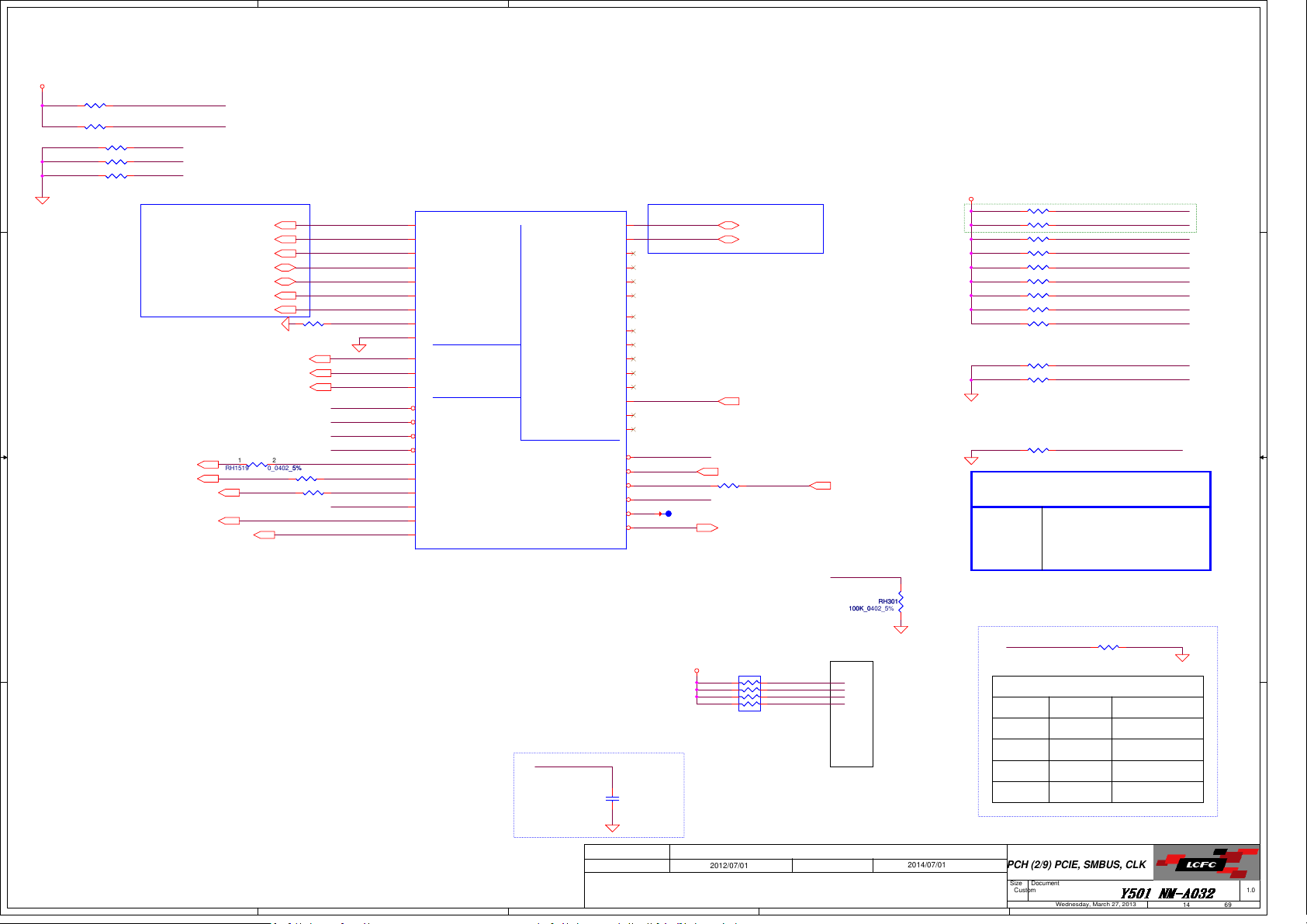

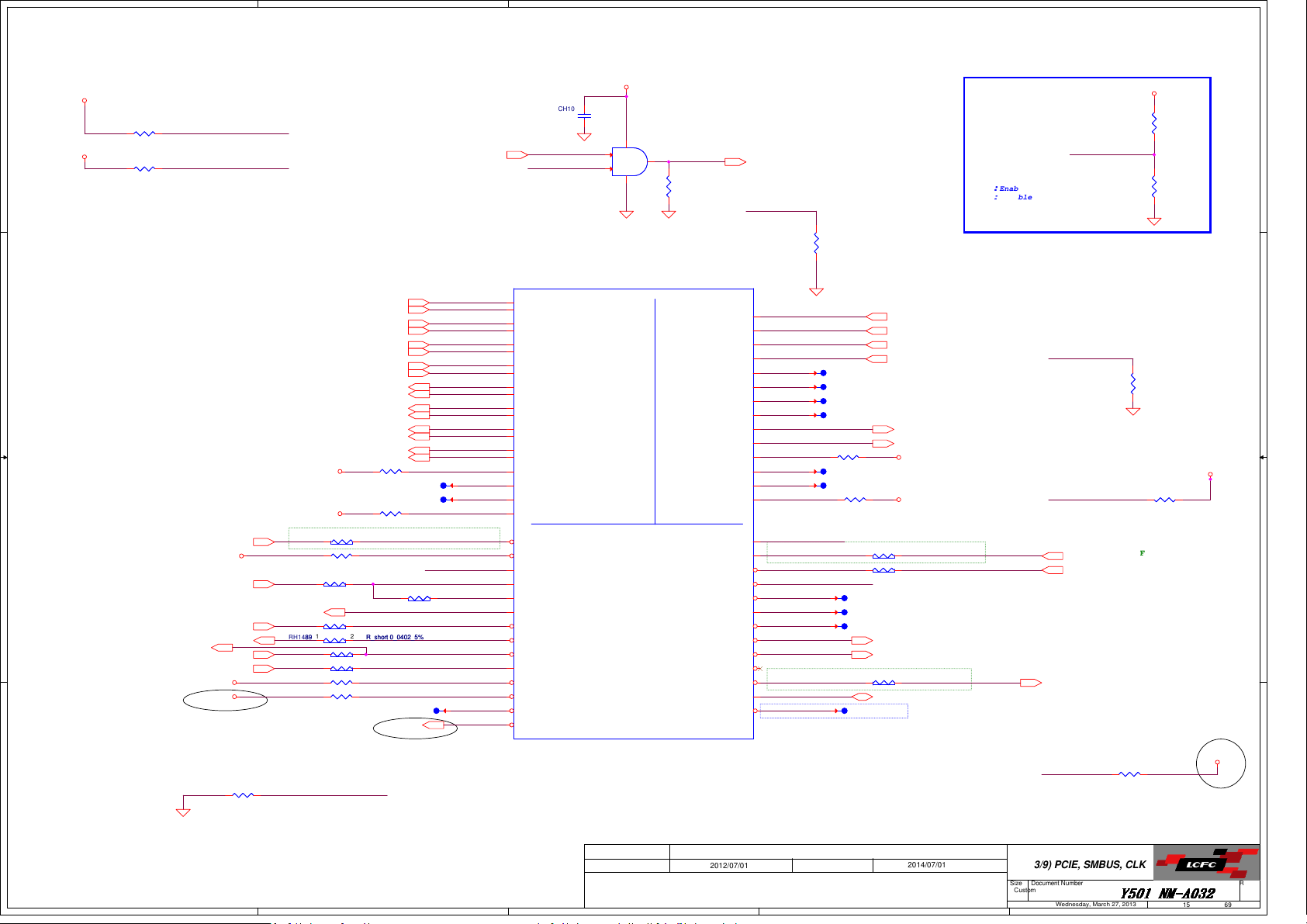

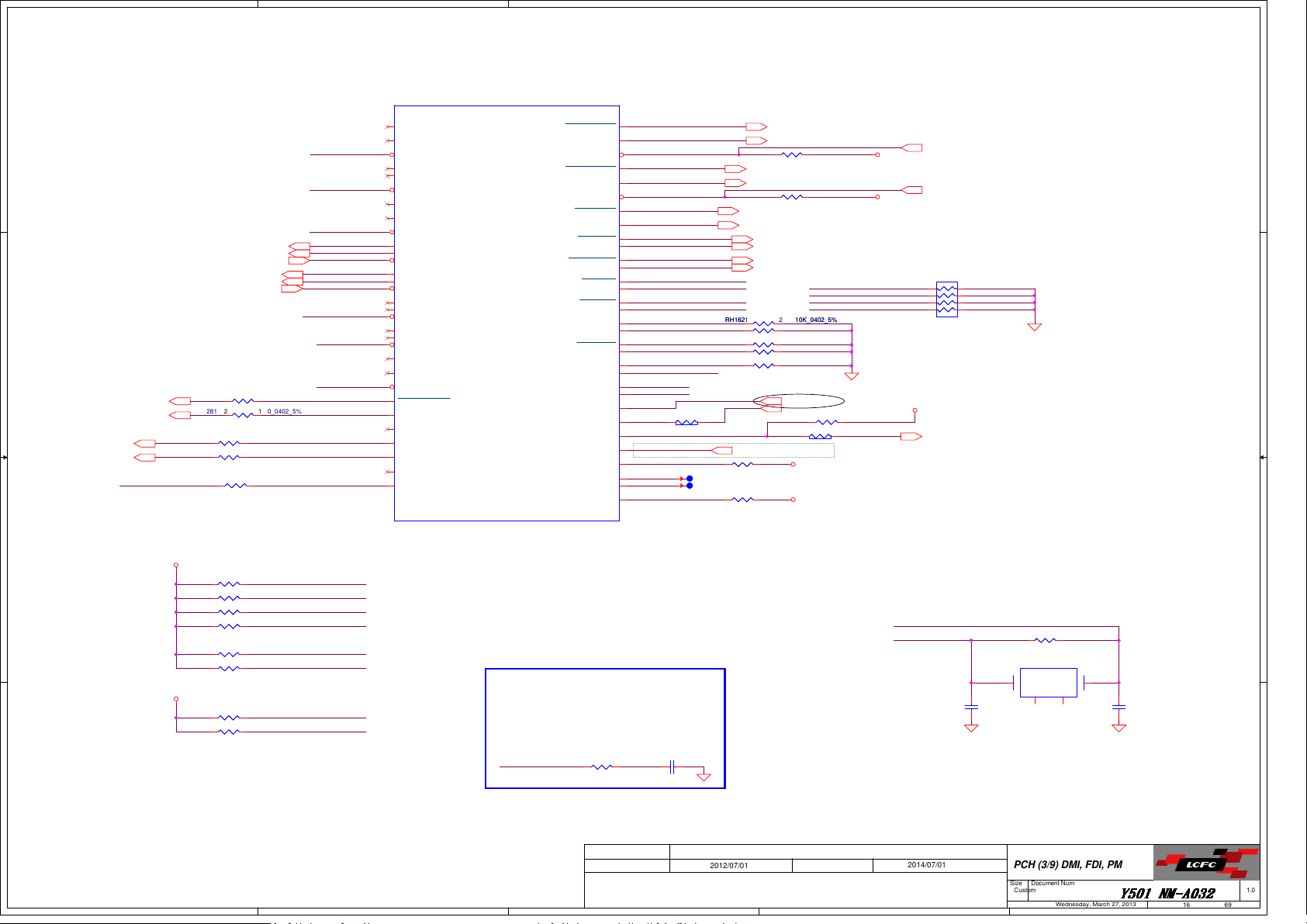

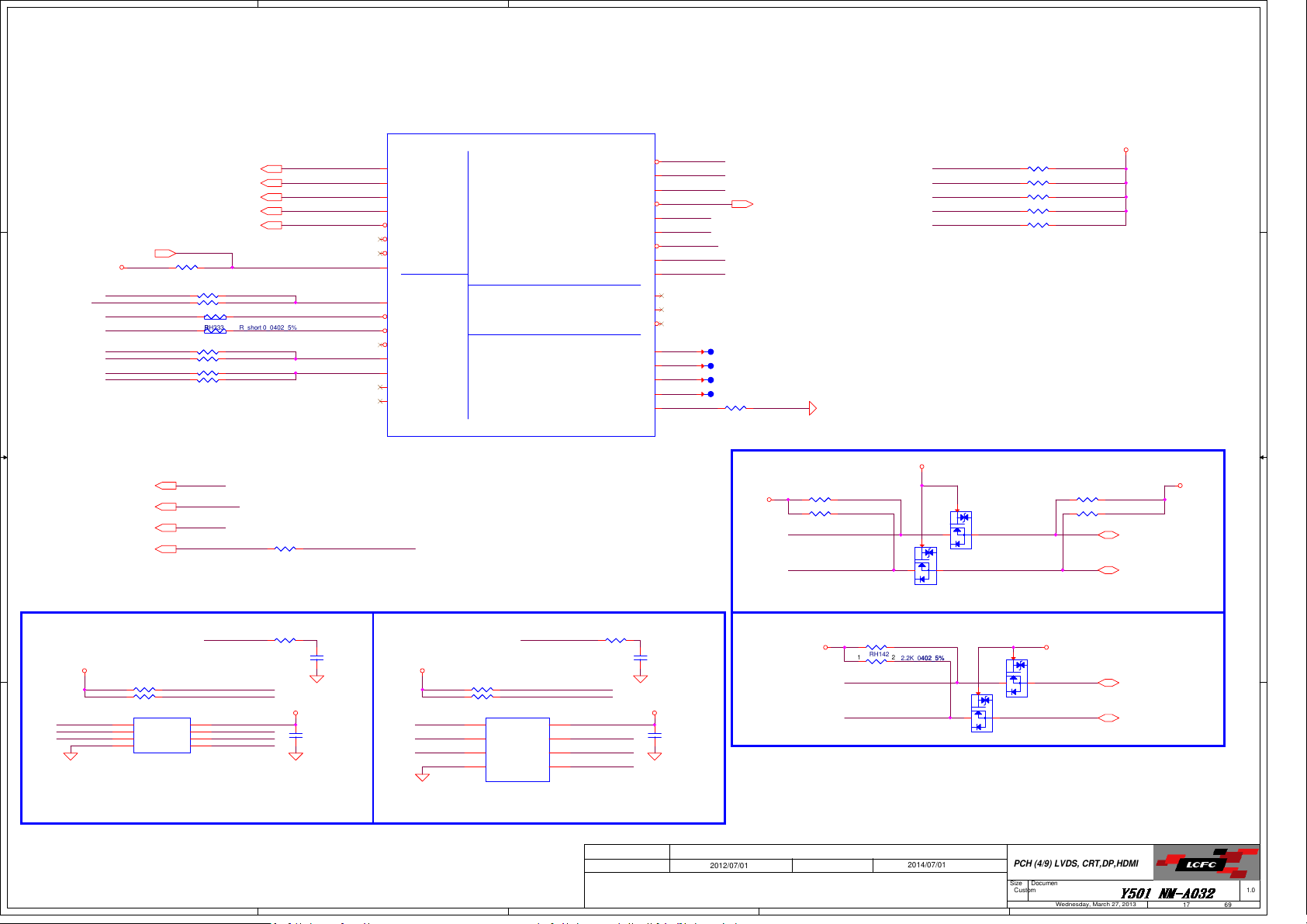

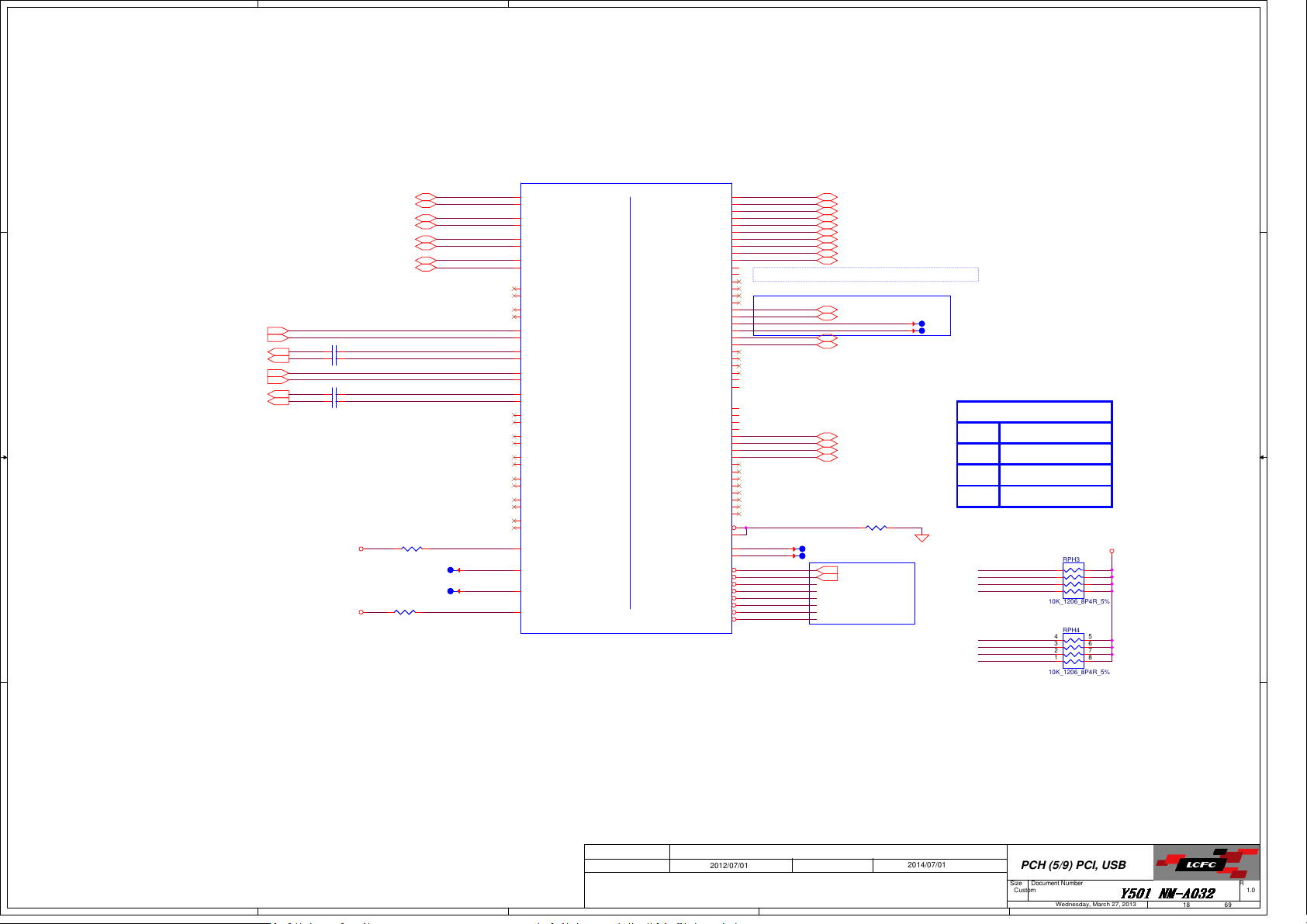

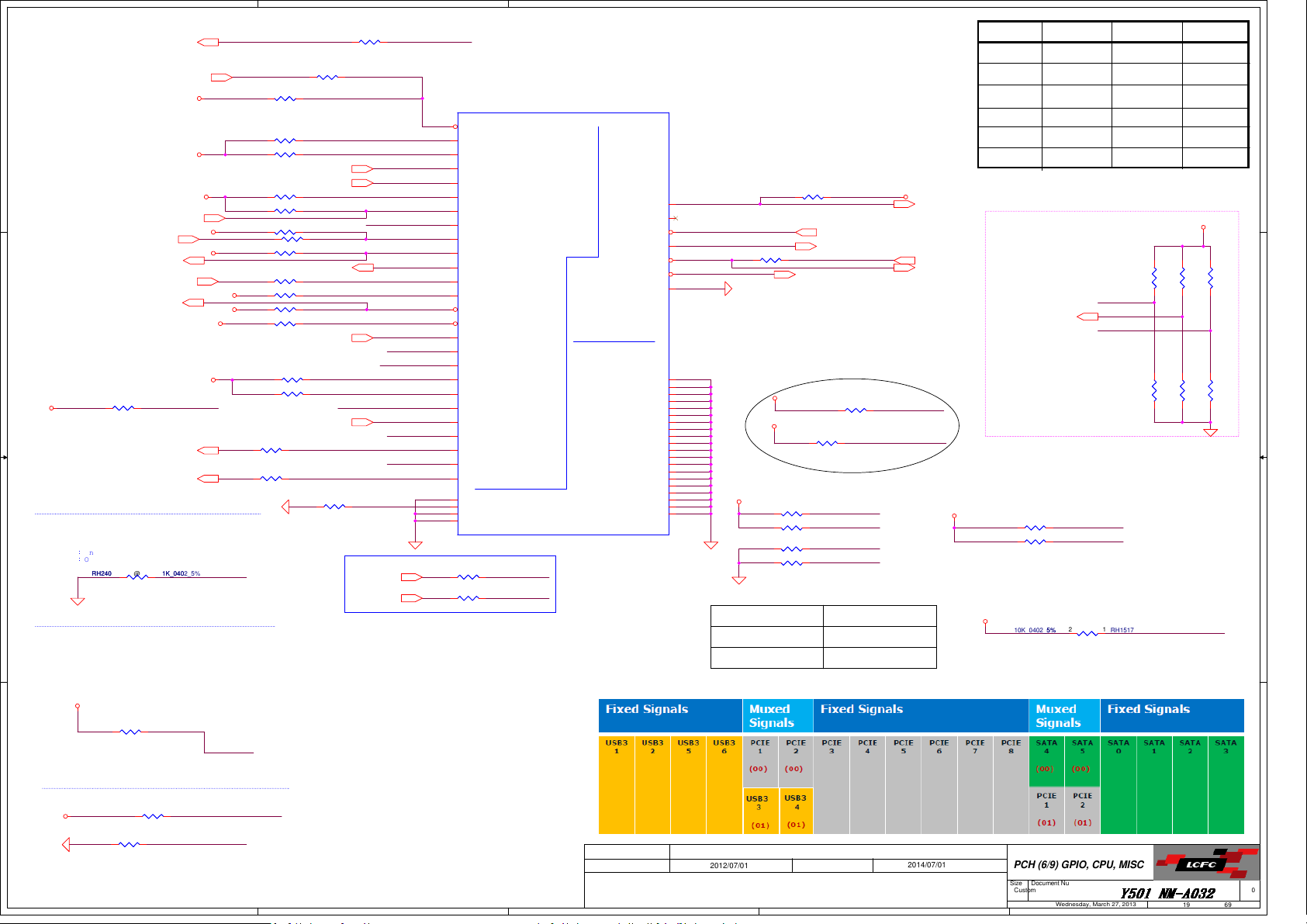

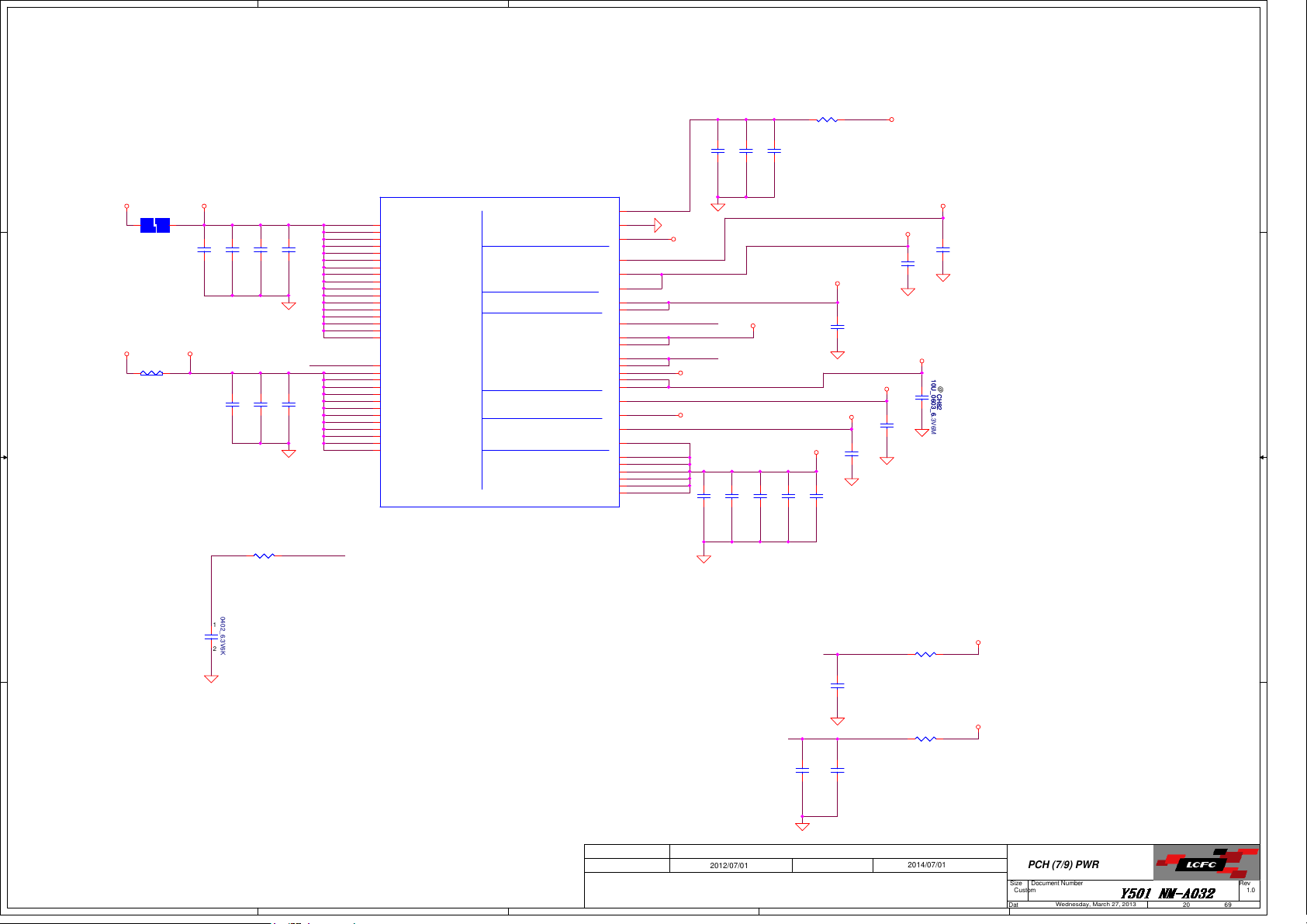

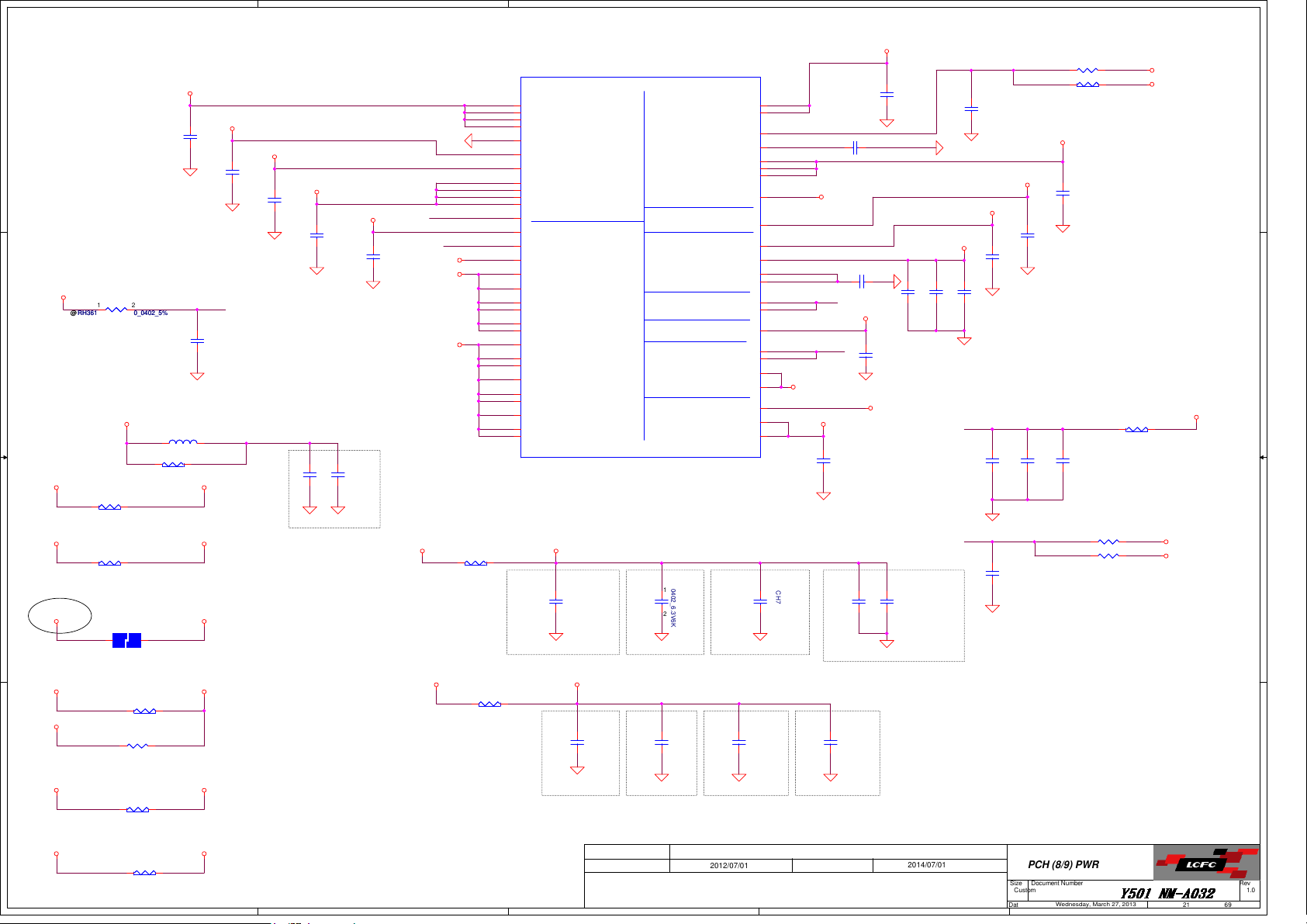

Page 2

A

B

C

D

E

PCI-Express 16X Gen3

Intel CPU

P

G 0~7PEG 8~15

E

2

d VGA, N14P-GT1

1 1

n

V

AM 64*32

R

GDDR5* 8

Sub/B

HDMI Conn. CRT Conn.

HDMI1.4b

2 2

3 3

Page 39 Page 36

Page 32 Page 23,24,25,26,27,28,29,30,31,33

MUX

Page 37

LVDS Conn.

HDMI

Page 35

RJ45 Conn.

Page 42

Card reader

Conn.

Page 48

LVDS

N

4P-GT1

1

VRAM 64*32

GDDR5* 8

MUX

Page 37

eDP to LVDS

PS8625

Page 34

Atheros

QCA8171-BL3A-R

PCIe port 3

SPI ROM

(4MB+2MB)

SATA HDD

SATA ODD

Card reader IC

GL3213

CRT

MUX

Page 38

Page 41

Page 17

SATA Port 5

page 44

SATA Port 2

page 44

Page 48

eDP

eDP

PCIe Gen1

1.5V 5GT/s

SPI BUS

3.3V 33MHz

SATA Gen3 Port 5

3V 6GHz(600MB/s)

SATA Gen1 Port2

3V 3GHz(300MB/s)

USB 3.0 Port6

5V 5GT/s

USB 2.0 Port4

5V 480MHz

FDI *2

2.7GT/s

Haswell

rPGA946

37.5mm*37.5mm

Page 5,6,7,8,9,10

DMI *4

5GT/s

Intel PCH

Lynx point

FCBGA 695Balls

20mm*20mm

Page 13,14,15,16,17,18,19,20,21,22

LPC BUS

3.3V 33MHz

1

35V DDRIIIL 1066/1333/1600 MT/s

.

USB 2.0 Port1

5V 480MHz

USB 2.0

5V 480MHz

USB 3.0

5V 5GT/s

USB 2.0

5V 480MHz

PCIe Gen1

5V 480MHz

SATA Gen3

5V 6GHz(600MB/s)

HD Audio

3.3V 24MHz

M

mory BUS (DDRIII)

e

Dual Channel

USB Charger IC

GL887T

USB Left

USB 2.0 Port 2

USB 3.0 Port 2

Int. Camera

USB 2.0 Port 0

PCIeMini Card

WLAN

PCIeMini Card

WLAN

Page 50

Page 49

Page 35

PCIe Port 4

page 40

USB Port 10

page 40

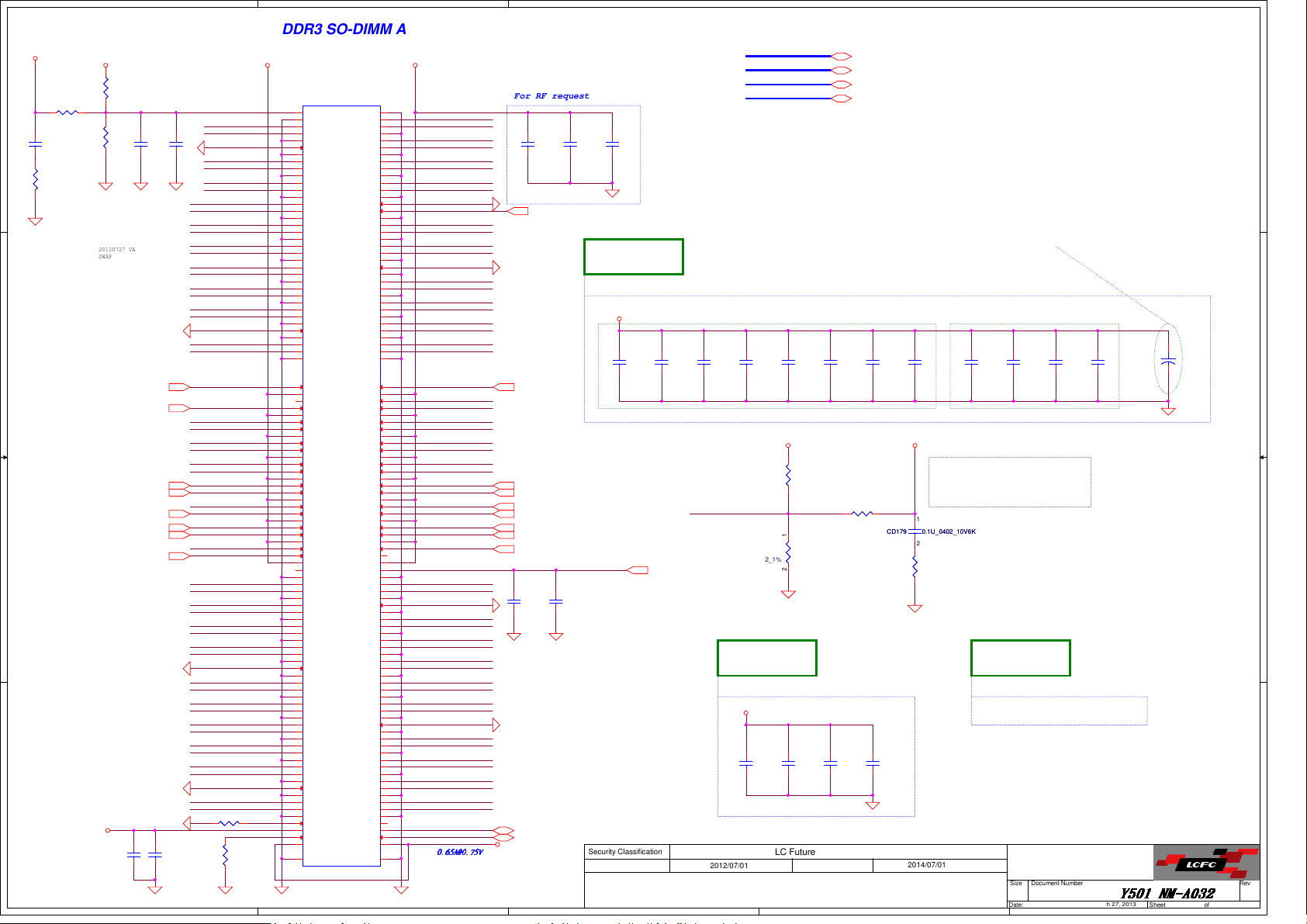

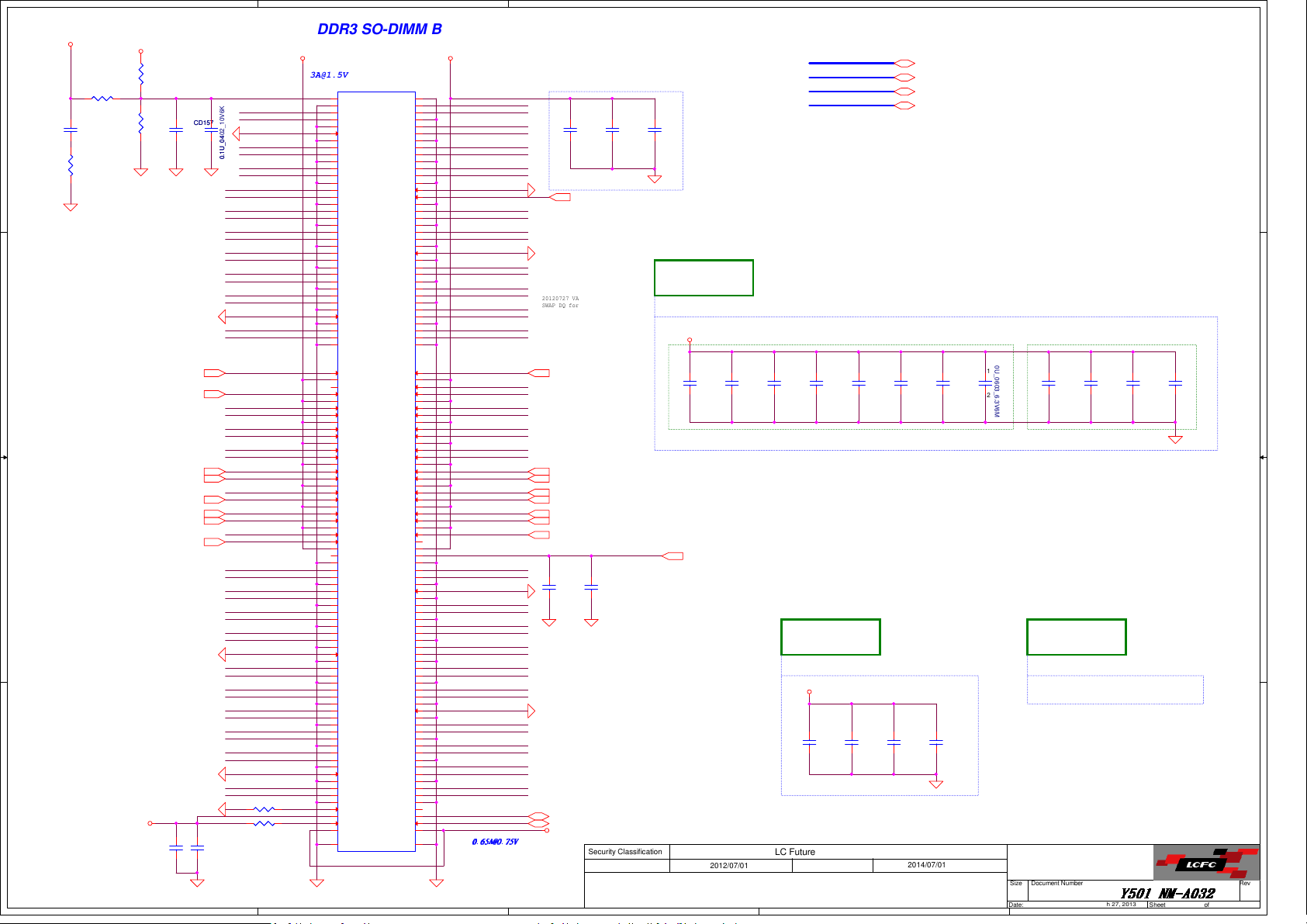

DDR3-SO-DIMM X2

B

ANK 0, 1, 2, 3

P TO 16G

U

Page 11,12

USB Charger

Conn.

Sub/B

USB Left

USB 2.0 Port 3

USB 3.0 Port 5

Touch panel

USB 2.0 Port 8

NGFF SSD

Page 50

Page 49

Page 50

SATA Port 4

page 40

Debug Port

Page 40

Power Circuit DC/DC

Page 56,57 ,58,59,60, 61,

62,63 ,64,65,66

4 4

DC/DC Interface CKT.

POWER/B Conn. AUDIO, USB/B Conn.

ODD/B Conn.

Page 55

Page 52 Page 50

page 44

A

RTC CKT.

NOVO/B Conn.

Page 56

Page 52

Touch Pad

B

EC

ITE IT8586E-FX

Page 46

Int.KBD

Page 47

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

Issued Date

Issued Date

Issued Date

Page 47

C

Thermal Sensor

EMC 1403

2012/07/01

2012/07/01

2012/07/01

Page 43

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Codec

ALC282CG

Int. MIC Conn.

(JCMOS Conn.)

Page 35 Page 50

2014/07/01

2014/07/01

2014/07/01

D

Page 45

SPK Conn.

Page 45

Ext. MIC Conn.

Sub/B

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

HP Conn.

Sub/B

Page 50

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

E

2 69

2 69

2 69

1.0

1.0

1.0

Page 3

A

B

C

D

E

Voltage Rails

( O --> Means ON ,

Power Plane

1 1

B+

S

tate

S0

S3

2 2

S5 S4/AC Only

S5 S4

Battery only

O

O

O

O

S5 S4

AC & Battery

X X

don't exist

SMBUS Control Table

SOURCE

3 3

IT

8580EEC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

C_SMB_DA2

E

SMB_CLK_S3

SMB_DATA_S3

+3VALW

IT8580E

+3VS

PCH

+3VS

Main

V

GA

X

V

+3VS +3VS

X X

X --> Means OFF )

+5VS

+3VS

+1.5VS

+VCCSA

+V1.5S_VCC P

+3VALW

+1.5V

+5VALW

+CPU_CORE

+VGA_CORE

GFX_CORE

+

+1.8VS

+1.05VS

+0.75VS

+3.3VS_VGA

+1.5VS_VGA

+1.05VS_VG A

O O O

OO

O

X

X X

X

2nd

VGA

BATT SODIMM

IT8580E

X X

+3VALW

V

X

X

X X X

X

X

V V

+3VS

WLAN

WiMAX

X

X

V

X

X

X

X

Thermal

Sensor

V

+3VS

PCH

XV

V

+3V_PCH

+3V_PCH+3VS

IGNAL

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

S

USB Port Table

USB 3.0USB 2.0 Port

XHCI

EHCI1

2

5

6

EHCI2

TP

M

odule

XX

X

V

+3VS

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

BOM Structure Table

4 External

USB Port

0

1

USB Port (Right Side)

2

3

USB Port (Left Side)

USB Port (Left Side)

4

5

6

7

8

9

10

Mini Card(WLAN)

11

12

13

PCIE PORT LIST

Port Device

1

2

3

4

5

6

7

8

LAN

WLAN

Camera

Card Reader

Touch panel

GT@

GT1@

CMOS@

SURGE@

X76@

GC6@

NOGC6@

AOAC@

KBL@

ME@

@

DS3@

daul@

887T@

887@

TI@

EDP@

SLI@

47W@

37W@

ON ON

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

BTO ItemBOM Structure

NV GT750M

NV GT755M

CMOS Camera part

QCA8171 LAN surge part

X76 Level part for VRAM

NV CG6 support part

NV no CG6 support part

AOAC support part

K/B Light part

ME part

Unpop

Deep S3 support part

Support daul channel panel function

GENESYS 887T USB charger solution

GENESYS 887 USB charger solution

TI USB charger solution

Support EDP panel function

For SLI function part

For 47W CPU part

For 37W CPU part

A

Address

0001 011X b

EC SM Bus2 address

Device

Thermal Sen sor EMC1403-2

Master VGA

Slave VGA

B

Address

1001_101xb

0x9E

0x9C

PCH SM Bus address

Device Address

DDR DIMM0

DDR DIMM2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

C

1001 000Xb

1001 010Xb

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2014/07/01

2014/07/01

2014/07/01

D

4 4

EC SM Bus1 address

Device

Smart Battery

ZZZ1

ZZZ1

DAZ0SF00100

DAZ0SF00100

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

E

3 69

3 69

3 69

1.0

1.0

1.0

Page 4

5

4

3

2

1

Hot plug detect for IFP link E

VGA and GDDR5 Voltage Rails (N14Px GPIO)

GPIO I/O ACTIVE Function Description

GPIO0

D D

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

C C

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

B B

IN FB_CLAMP_MON-

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

IN

OUT

IN

IN

IN

+3VS_VGA

+VGA_CORE

+1.5VS_VGA

+1.05VS_VGA

-

NAOUT

VGA_BL_PWM

-

-

VGA_ENVDD

- VGA_ENBKL

NA

-

FB_CLAMP_TOGGLE_REQ#

-

NA

-

OVERT#

-

VGA_ALERT#

-

Memory VREF Control

-

NVVDD PWM_VID-OUT

-

AC Power Detect Input

DPRSLPVR_VGA -

NA

-

-

NA

-

NA

-

VGA_EDP_HPD

-

DGPU_HDMI_HPD

NA

-

tNVVDD >0

tFBVDDQ >0

tPEX_VDD >0

1. all power r ail ramp up ti me should be la rger than 40us

(10K pull High)

Performance Mode P0 TDP at Tj = 102 C* (GDDR5)

GPU Mem NVCLK

(4) (1,5) (6)

Products

(W) (W) (MHz)

N14X

128bit

1GB

GDDR5

Physical

Strapping pin

ROM_SCLK

ROM_SI

ROM_SO FB[0]

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

N13P-GT

(28nm)

/MCLK NVVDD

(V) (A) (W) (A) (W)

TBD TBDTBD TBD TBD TBD TBD TBD T BD TBD TBD TBD TBD TBD TBD TBD TBD TBD

Power Rail

+3VS_VGA

+3VS_VGA

+

3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

Device ID

0x0FCD

Logical

Strapping Bit3

PCI_DEVID[4]

FB[1]

PCI_DEVID[3] PCI_DEVID[2] PCI_DEVID[1] PCI_DEVID[0]

SOR3_EXPOSED

RESERVED PCIE_SPEED_

3GIO_PAD_CFG_ADR [2] 3GIO_PAD_CFG_ADR [1]3GIO_PAD_CFG_ADR [3]

setting

SMB_ALT_ADDR

(ROM_SO Bit 1)

0

1

ROM_SO ROM_SCLK

GPU

N14P-GT

28nm

PU 10K PD 25K

FB Memory (GDDR5)

Samsung

3000MHz

Hynix

3000MHz

Samsung

2500MHz

2500MHz

PD 15K

PU 45K

PU 25K PD 35KPU 45KPU 20K PD 10K PD 5K PD 10K

GPU

K4G20325FD-FC03

64Mx32

H5GQ2H24AFR-R0C

64Mx32 PD 25K

K4G20325FD-FC04

64Mx32

H5GQ2H24AFR-T2CHynix

64Mx32

PD 5K

N14P-GT

ROM_SI

PD 30K

PD 25K

FBVDDQ PCI Express I/O and

FBVDD

(GPU+Mem)

(1.35V)(1.35V)

(A) (W) (W)(mA) (W) (W) (W)(mA) (mA) (mA)

Logical

Strapping Bit2

SUB_VENDOR

SER[2] USER[1] USER[0]USER[3]

U

SOR2_EXPOSED SOR1_EXPOSED

CHANGE_GEN3

I2C Slave addrees ID

0x9E

0x9C

STRAP2STRAP1STRAP0

N14P-GT1

ROM_SI

PD 30K

(1.05V)

Logical

Strapping Bit1

SLOT_CLK_CFG

RAM_CFG[1]RAM_CFG[3] RAM_CFG [2]

PCIE_MAX_SPEED DP_PLL _VDD33V

STRAP3

STRAP4

PU 5K PD 45K

PLLVDD

Master

Slave

I/O and

PLLVDD

Logical

Strapping Bit0

PEX_PLL_EN_TERM

R

AM_CFG[0]

VGA_DEVICESMB_ALT_ADDR

3GIO_PAD_CFG_ADR [0]

SOR0_EXPOSED

Other

(3.3V)(1.05V)(1.8V)

Other Power rail

A A

+3VS_VGA

power-off <10m s

T

1.all GPU powe r rails should be turned off within 10ms

. Optimus syst em VDD33 avoid s drop down ear lier than NVDD and FBVDDQ

2

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

VGA Notes List

VGA Notes List

VGA Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

4 69

4 69

4 69

1.0

1.0

1.0

Page 5

5

4

3

2

1

D D

Haswell rPGA EDS

Haswell rPGA EDS

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FDI_CSYNC

FDI_INT

IN

IN

TEL_HASWELL_HAS WELL

TEL_HASWELL_HAS WELL

12

12

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CSYNC_R

FDI_INT_R

DMI_CRX_PTX_N0<15>

DMI_CRX_PTX_N1<15>

DMI_CRX_PTX_N2<15>

DMI_CRX_PTX_N3<15>

DMI_CRX_PTX_P0<15>

DMI_CRX_PTX_P1<15>

DMI_CRX_PTX_P2<15>

DMI_CRX_PTX_P3<15>

DMI_CTX_PRX_N0<15>

C C

FDI_CSYNC<15>

FDI_INT<15>

B B

DMI_CTX_PRX_N1<15>

DMI_CTX_PRX_N2<15>

DMI_CTX_PRX_N3<15>

DMI_CTX_PRX_P0<15>

DMI_CTX_PRX_P1<15>

DMI_CTX_PRX_P2<15>

DMI_CTX_PRX_P3<15>

RC3 0_0402_5%RC3 0_0402_5%

RC87 0_0402_5%RC87 0_0402_5%

JCPUA

JCPUA

PEG_RCOMP

PEG

PEG

DMI FDI

DMI FDI

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

1 OF 9

1 OF 9

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

E23

PEG_COMP

M29

PCIE_CRX_GTX_N0

K28

PCIE_CRX_GTX_N1

M31

PCIE_CRX_GTX_N2

L30

PCIE_CRX_GTX_N3

M33

PCIE_CRX_GTX_N4

L32

PCIE_CRX_GTX_N5

M35

PCIE_CRX_GTX_N6

L34

PCIE_CRX_GTX_N7

E29

PCIE_CRX_GTX_N8

D28

PCIE_CRX_GTX_N9

E31

PCIE_CRX_GTX_N10

D30

PCIE_CRX_GTX_N11

E35

PCIE_CRX_GTX_N12

D34

PCIE_CRX_GTX_N13

E33

PCIE_CRX_GTX_N14

E32

PCIE_CRX_GTX_N15

L29

PCIE_CRX_GTX_P0

L28

PCIE_CRX_GTX_P1

L31

PCIE_CRX_GTX_P2

K30

PCIE_CRX_GTX_P3

L33

PCIE_CRX_GTX_P4

K32

PCIE_CRX_GTX_P5

L35

PCIE_CRX_GTX_P6

K34

PCIE_CRX_GTX_P7

F29

PCIE_CRX_GTX_P8

E28

PCIE_CRX_GTX_P9

F31

PCIE_CRX_GTX_P10

E30

PCIE_CRX_GTX_P11

F35

PCIE_CRX_GTX_P12

E34

PCIE_CRX_GTX_P13

F33

PCIE_CRX_GTX_P14

D32

PCIE_CRX_GTX_P15

H35

PCIE_CTX_GRX_N0

H34

PCIE_CTX_GRX_N1

J33

PCIE_CTX_GRX_N2

H32

PCIE_CTX_GRX_N3

J31

PCIE_CTX_GRX_N4

G30

PCIE_CTX_GRX_N5

C33

PCIE_CTX_GRX_N6

B32

PCIE_CTX_GRX_N7

B31

PCIE_CTX_GRX_N8

A30

PCIE_CTX_GRX_N9

B29

PCIE_CTX_GRX_N10

A28

PCIE_CTX_GRX_N11

B27

PCIE_CTX_GRX_N12

A26

PCIE_CTX_GRX_N13

B25

PCIE_CTX_GRX_N14

A24

PCIE_CTX_GRX_N15

J35

PCIE_CTX_GRX_P0

G34

PCIE_CTX_GRX_P1

H33

PCIE_CTX_GRX_P2

G32

PCIE_CTX_GRX_P3

H31

PCIE_CTX_GRX_P4

H30

PCIE_CTX_GRX_P5

B33

PCIE_CTX_GRX_P6

A32

PCIE_CTX_GRX_P7

C31

PCIE_CTX_GRX_P8

B30

PCIE_CTX_GRX_P9

C29

PCIE_CTX_GRX_P10

B28

PCIE_CTX_GRX_P11

C27

PCIE_CTX_GRX_P12

B26

PCIE_CTX_GRX_P13

C25

PCIE_CTX_GRX_P14

B24

PCIE_CTX_GRX_P15

PEG_COMP

CAD Note:

Trace width=12 mils ,Spacing=15mil

Max length= 400 mils.

PCIE_CRX_GTX_N[0..15] <23,32>

PCIE_CRX_GTX_P[0..15] <23,32>

CC1 0.22U_0402_10V6KCC1 0.22U_0402_10V6K

CC2 0.22U_0402_10V6KCC2 0.22U_0402_10V6K

CC3 0.22U_0402_10V6KCC3 0.22U_0402_10V6K

CC4 0.22U_0402_10V6KCC4 0.22U_0402_10V6K

CC5 0.22U_0402_10V6KCC5 0.22U_0402_10V6K

CC6 0.22U_0402_10V6KCC6 0.22U_0402_10V6K

CC7 0.22U_0402_10V6KCC7 0.22U_0402_10V6K

CC8 0.22U_0402_10V6KCC8 0.22U_0402_10V6K

CC9 0.22U_0402_10V6KCC9 0.22U_0402_10V6K

CC10 0.22U_ 0402_10V6KCC10 0.22U_0402_10V6 K

CC11 0.22U_ 0402_10V6KCC11 0.22U_0402_10V6 K

CC12 0.22U_ 0402_10V6KCC12 0.22U_0402_10V6 K

CC13 0.22U_ 0402_10V6KCC13 0.22U_0402_10V6 K

CC14 0.22U_ 0402_10V6KCC14 0.22U_0402_10V6 K

CC15 0.22U_ 0402_10V6KCC15 0.22U_0402_10V6 K

CC16 0.22U_ 0402_10V6KCC16 0.22U_0402_10V6 K

CC20 0.22U_ 0402_10V6KCC20 0.22U_0402_10V6 K

CC23 0.22U_ 0402_10V6KCC23 0.22U_0402_10V6 K

CC25 0.22U_ 0402_10V6KCC25 0.22U_0402_10V6 K

CC30 0.22U_ 0402_10V6KCC30 0.22U_0402_10V6 K

CC18 0.22U_ 0402_10V6KCC18 0.22U_0402_10V6 K

CC22 0.22U_ 0402_10V6KCC22 0.22U_0402_10V6 K

CC28 0.22U_ 0402_10V6KCC28 0.22U_0402_10V6 K

CC32 0.22U_ 0402_10V6KCC32 0.22U_0402_10V6 K

CC19 0.22U_ 0402_10V6KCC19 0.22U_0402_10V6 K

CC24 0.22U_ 0402_10V6KCC24 0.22U_0402_10V6 K

CC29 0.22U_ 0402_10V6KCC29 0.22U_0402_10V6 K

CC17 0.22U_ 0402_10V6KCC17 0.22U_0402_10V6 K

CC21 0.22U_ 0402_10V6KCC21 0.22U_0402_10V6 K

CC27 0.22U_ 0402_10V6KCC27 0.22U_0402_10V6 K

CC26 0.22U_ 0402_10V6KCC26 0.22U_0402_10V6 K

CC31 0.22U_ 0402_10V6KCC31 0.22U_0402_10V6 K

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+VCCIOA_OUT

12

RC224.9_0402_1% RC224.9_0402_1%

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P15

1: Normal Operation; Lane # definition matches

socket pin map definition

:Lane Reversed

0

*

PCIE_CTX_C_GRX_N[0..15] <23,32>

PCIE_CTX_C_GRX_P[0..15] <23,32>

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

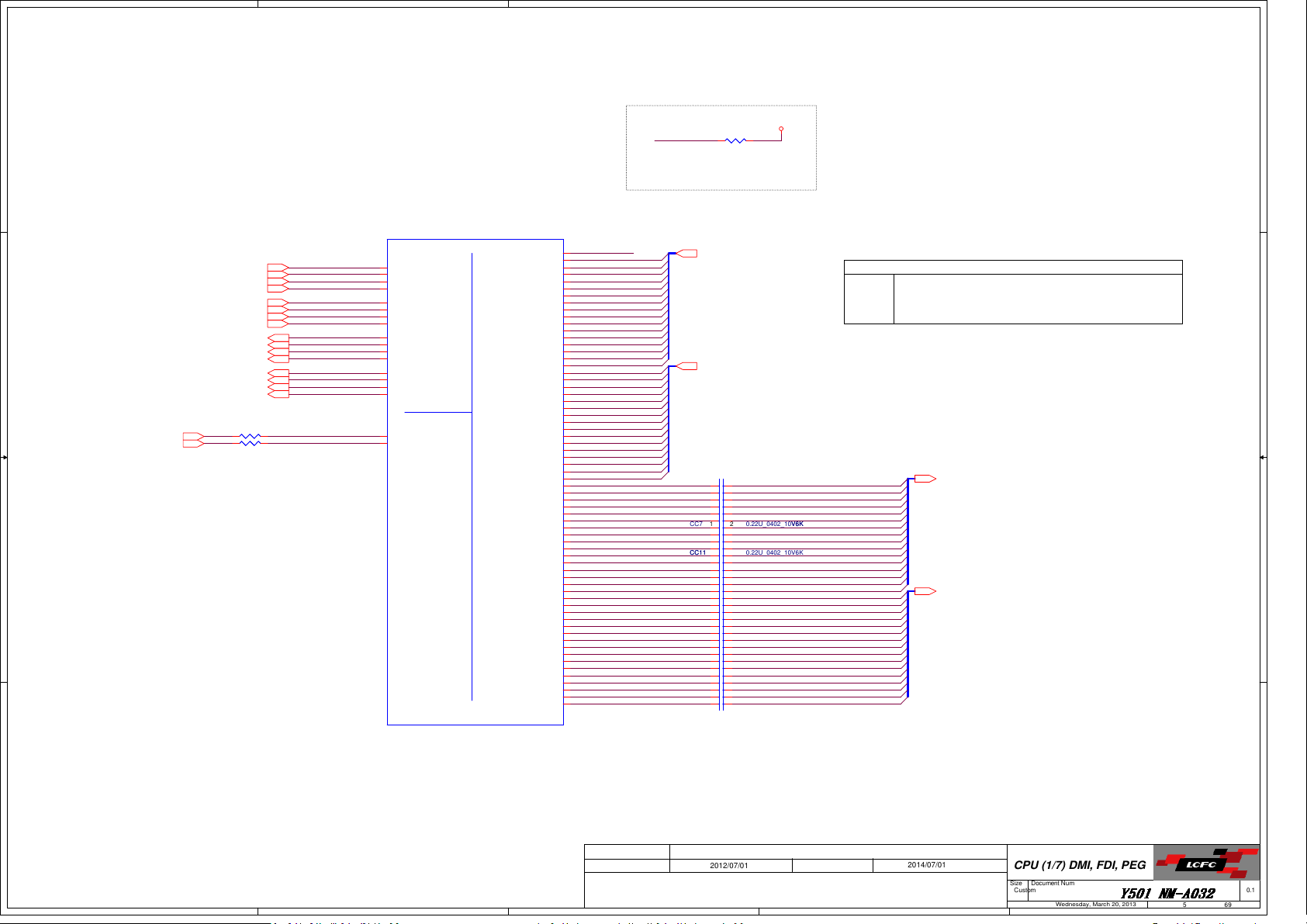

CPU (1/7) DMI, FDI, PEG

CPU (1/7) DMI, FDI, PEG

CPU (1/7) DMI, FDI, PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 20, 2013

Wednesday, March 20, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 20, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

5 69

5 69

5 69

0.1

0.1

0.1

Page 6

5

4

3

2

1

+1.35V

RC60

RC60

1 2

0_0402_5%

0_0402_5%

D

S

D

S

H_DRAMRST#

RC1544

D D

DRAMRST_CNTRL_PC H<17>

DRAMRST_CNTRL<7>

DRAMRST_CNTRL_EC<46>

RC42 0_0402_5%

RC42 0_0402_5%

Reserve for Deep S3

RC1544

4.99K_0402_1% @

4.99K_0402_1% @

1 2

@

@

RC1545

RC1545

1 2

R_short 0_0402_5%

R_short 0_0402_5%

1 2

DRAMRST_CNTRL

@

@

G

G

2

1

2

13

DDR3_DRAMRST#_R

QC3

QC3

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

CC50

CC50

0.047U_0402_16V4Z@

0.047U_0402_16V4Z@

RC62

1K_0402_5%

1K_0402_5%

12

@RC62

@

RC1543

RC1543

1 2

0_0402_5%

0_0402_5%

DDR3_DRAMRST# <11,12>

RC5 need to close to JCPU1

H_CPUPWRGD H_CPUP WRGD_XDP

SIO_PWRBTN#_R<15>

CPU_PWR_DEBU G<9>

+1.05VS

1 2

RC5 1K_0402_1%RC5 1K_0402_1%

1 2

RC6 0_0402_5%@RC6 0_0402_5%@

VGATE<15,64>

CLK_CPU_ITP<16>

CLK_CPU_ITP#<16>

1 2

PU/PD for JTAG signals

C C

XDP_DBRESET#_R

XDP_TMS

XDP_TDI

XDP_PREQ#

XDP_TDO

XDP_TCLK

XDP_TRST#

B B

PM_DRAM_PWR GD<15>

A A

RC19 1K_040 2_1%RC19 1K_0402_1%

RC27 51_0402_1 %@RC 27 51_0402_1%@

RC29 51_0402_1 %@RC 29 51_0402_1%@

RC32 51_0402_1 %@RC 32 51_0402_1%@

RC35 51_0402_1 %@RC 35 51_0402_1%@

RC40 51_0402_1 %RC40 51_0402_1%

RC41 51_0402_1 %RC41 51_0402_1%

SM_DRAMPWROK with DDR Power Gating Topology

SYS_PWROK<15>

12

12

12

12

12

12

12

RC88 0_0402_5%

RC88 0_0402_5%

+3VS

+1.05VS

H_PECI<46>

1 2

H_PROCHOT#<46,57>

H_PM_SYNC<15>

H_CPUPWRGD<19>

CLK_CPU_DPLL#<16>

CLK_CPU_DPLL<16>

CLK_CPU_SSC_DPLL#<16>

CLK_CPU_SSC_DPLL<16>

+3V_PCH

200_0402_5%

200_0402_5%

12

RC89

RC89

RC1547 0_ 0402_5%@RC1547 0_ 0402_5%@

RUN_ON_CPU1.5VS3#<10>

+3V_PCH

12

RC84

RC84

1

2

CC156

CC156

1 2

0.1U_0402_25V6K

0.1U_0402_25V6K

5

P

B

4

O

A

G

UC4

UC4

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

3

12

100K_0402_5%

100K_0402_5%

@

@

12

RC57 56_0402_5%RC57 56_0402_5%

RC25

RC25

R_short 0_0402_5%

R_short 0_0402_5%

RC51 0_0402_5%RC51 0_0402_5%

RC52 0_0402_5%RC52 0_0402_5%

RC43 0_0402_5%RC43 0_0402_5%

RC22 0_0402_5%RC22 0_0402_5%

@

@

2

G

G

H_THRMTRIP#<19>

1 2

12

12

12

12

CLK_CPU_DMI#<16>

CLK_CPU_DMI<16>

497750_497750_SH RKBY_MBL_SCH_CH KLST 0.5

page19 item 3.6 SM_DRAMPWROK

+1.35V_CPU_VDDQ

1.8K_0402_1%

1.8K_0402_1%

12

RC16

RC16

RC28 0_0402_5%RC28 0_0402_5%

3.3K_0402_1%

3.3K_0402_1%

39_0402_5%

39_0402_5%

12

RC14

RC14

@RC64

@

RC64

SSM3K7002FU_SC70-3

SSM3K7002FU_SC70-3

1 2

13

D

D

@

@

QC1

QC1

S

S

H_CATERR#

H_PECI

T55PAD @T55PAD @

H_PROCHOT#_R

H_THRMTRIP#

H_PM_SYNC

VCCPWRGOOD_0_R

PM_DRAM_PWR GD_CPU

BUF_CPU_RST#

CPU_DPLL#

CPU_DPLL

CPU_SSC_DPLL#

CPU_SSC_DPLL

CLK_CPU_DMI#

CLK_CPU_DMI

12

PM_DRAM_PWR GD_CPURUNPWROK_AND

AP32

SKTOCC

AN32

CATERR

AR27

PECI

AK31

RSVD

AM30

PROCHOT

AM35

THERMTRIP

AT28

PM_SYNC

AL34

PWRGOOD

AC10

SM_DRAMPWR OK

AT26

PLTRSTIN

G28

DPLL_REF_CLKN

H28

DPLL_REF_CLKP

F27

SSC_DPLL_REF_CLKN

E27

SSC_DPLL_REF_CLKP

D26

BCLKN

E26

BCLKP

Haswell rPGA EDS

Haswell rPGA EDS

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

JCPUB

JCPUB

MISC

MISC

THERMAL

THERMAL

PWR

PWR

CPU_PLTRST#<19>

AP3

SM_RCOMP0

AR3

SM_RCOMP1

AP2

SM_RCOMP2

AN3

H_DRAMRST#

AR29

XDP_PRDY#

AT29

XDP_PREQ#

AM34

XDP_TCLK

AN33

XDP_TMS

AM33

XDP_TRST#

AM31

XDP_TDI XDP_TDI_R

TDI

AL33

XDP_TDO XDP_TDO_R

AP33

AR30

XDP_OBS0_R

AN31

XDP_OBS1_R

AN29

XDP_OBS2_R

AP31

XDP_OBS3_R

AP30

XDP_OBS4_R

AN28

XDP_OBS5_R

AP29

XDP_OBS6_R

AP28

XDP_OBS7_R

DDR3

DDR3

CLOCK

CLOCK

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST

PRDY

PREQ

JTAG

JTAG

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

2 OF 9

2 OF 9

TCK

TMS

TRST

TDO

DBR

For ESD

Buffered Reset to CPU

+VCCIO_OUT

.05V

1

1 2

0_0402_5%

0_0402_5%

RC46

RC46

XDP Connector

XDP_PREQ#_R

XDP_PRDY#_R

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

CFD_PWRBTN#_X DP

CPU_PWR_DEBU G

VGATE

CLK_CPU_ITP

CLK_CPU_ITP#

XDP_RST#_RBUF_CPU_RST#

XDP_DBRESET#

RC81K_0402_1% RC81K_0402_1%

XDP_TDO_R

XDP_TRST#_R

XDP_TDI_R

XDP_TMS_R

XDP_TCK_R

20120806 VA

change XDP connector to 28 pin

1 2

RC47 0_0402_5%RC 47 0_0402_5%

1 2

RC48 0_0402_5%RC 48 0_0402_5%

1 2

RC50 0_0402_5%RC 50 0_0402_5%

1 2

RC53 0_0402_5%RC 53 0_0402_5%

1 2

RC54 0_0402_5%RC 54 0_0402_5%

1 2

RC23 0_0402_5%RC23 0_0402_5%

1 2

RC24 0_0402_5%RC24 0_0402_5%

RC26 0_0402_5%RC26 0_0402_5%

1 2

RC30 0_0402_5%RC30 0_0402_5%

1 2

RC31 0_0402_5%RC31 0_0402_5%

1 2

RC33 0_0402_5%RC33 0_0402_5%

1 2

RC34 0_0402_5%RC34 0_0402_5%

1 2

RC36 0_0402_5%RC36 0_0402_5%

1 2

RC37 0_0402_5%RC37 0_0402_5%

1 2

RC38 0_0402_5%RC38 0_0402_5%

1 2

RC39 0_0402_5%RC39 0_0402_5%

VCCPWRGOOD_0_RBUF_CPU_RST#

1

@

@

CC61

CC61

220P_0402_25V8J

220P_0402_25V8J

2

+1.05VS

BUF_CPU_RST#

RC126

RC128

RC44

RC44

1 2

@RC126

@

1 2

@RC128

@

1 2

12

@

@

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

MOLEX 52435-2671

MOLEX 52435-2671

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

1

CC60

CC60

220P_0402_25V8J

220P_0402_25V8J

2

H_THRMTRIP#

100_0402_1%

100_0402_1%

H_CATERR#

49.9_0402_1%

49.9_0402_1%

H_PROCHOT#

62_0402_5%

62_0402_5%

JXDP

XDP_DBRESET#XDP_DBRESET#_R

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

@JXDP

@

Place near JXDP1

27

28

+1.05VS

@

@

0.1U_0402_25V6K

0.1U_0402_25V6K

0.1U_0402_25V6K

0.1U_0402_25V6K

1

1

CC65

CC65

CC66

CC66

@

@

2

2

DDR3 COMPENSATION SIGNALS

RC1539

RC1539

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

For ESD concern, please put near CPU

CPU_SSC_DPLL

CPU_SSC_DPLL#

SSC CLOCK TERMINATION, IF NOT USED, stuff RC20,RC21

1 2

1 2

RC55 75_0402_1%RC 55 75_0402_1%

1 2

RC49 100_0402_ 1%RC49 100_0402_1%

VCCPWRGOOD_0_R

CAD Note:

Avoid stub in the PWRGD path

while placing resistors RC25 & RC130

1 2

1 2

10K_0402_5%

10K_0402_5%

12

+VCCIO_OUT

RC2010K_0402_5% @RC2010K_0402_5% @

RC2110K_0402_5% @RC2110K_0402_5% @

100_0402_1%

100_0402_1%

RC130

RC130

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

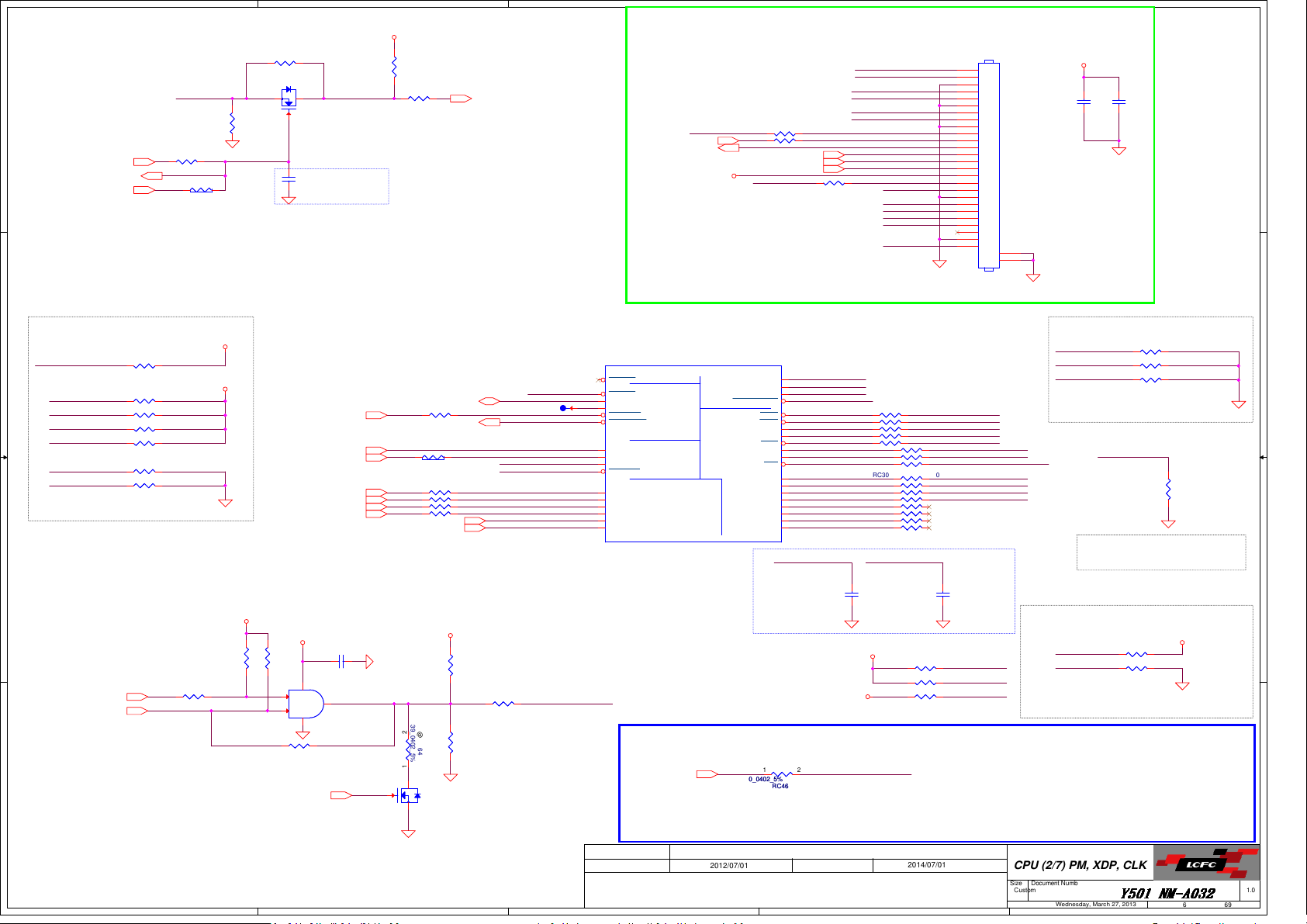

CPU (2/7) PM, XDP, CLK

CPU (2/7) PM, XDP, CLK

CPU (2/7) PM, XDP, CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

6 69

6 69

6 69

1.0

1.0

1.0

Page 7

5

DDRA_DQ[0..63]<11>

D D

C C

+VREF_CA_R

B B

+V_DDR_REFA_R

+V_DDR_REFB_R

DDRA_DQ0

DDRA_DQ1

DDRA_DQ2

DDRA_DQ3

DDRA_DQ4

DDRA_DQ5

DDRA_DQ6

DDRA_DQ7

DDRA_DQ8

DDRA_DQ9

DDRA_DQ10

DDRA_DQ11

DDRA_DQ12

DDRA_DQ13

DDRA_DQ14

DDRA_DQ15

DDRA_DQ16

DDRA_DQ17

DDRA_DQ18

DDRA_DQ19

DDRA_DQ20

DDRA_DQ21

DDRA_DQ22

DDRA_DQ23

DDRA_DQ24

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ28

DDRA_DQ29

DDRA_DQ30

DDRA_DQ31

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ35

DDRA_DQ36

DDRA_DQ37

DDRA_DQ38

DDRA_DQ39

DDRA_DQ40

DDRA_DQ41

DDRA_DQ42

DDRA_DQ43

DDRA_DQ44

DDRA_DQ45

DDRA_DQ46

DDRA_DQ47

DDRA_DQ48

DDRA_DQ49

DDRA_DQ50

DDRA_DQ51

DDRA_DQ52

DDRA_DQ53

DDRA_DQ54

DDRA_DQ55

DDRA_DQ56

DDRA_DQ57

DDRA_DQ58

DDRA_DQ59

DDRA_DQ60

DDRA_DQ61

DDRA_DQ62

DDRA_DQ63

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AM9

AM8

AJ10

AK10

AM3

AN9

AN8

AR9

AT9

AR8

AT8

AK9

AK6

AK7

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

D12

D11

AJ9

AJ6

AJ7

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

B11

A11

E11

B12

A12

F16

F13

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

3 OF 9

3 OF 9

JCPUC

JCPUC

4

Haswell rPGA EDS

Haswell rPGA EDS

RSVD_AC7

SA_CK_N_0

SA_CK_P_0

SA_CKE_0

SA_CK_N_1

SA_CK_P_1

SA_CKE_1

SA_CK_N_2

SA_CK_P_2

SA_CKE_2

SA_CK_N_3

SA_CK_P_3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

RSVD_V10

SA_RAS

SA_WE

SA_CAS

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

TEL_HASWELL_HAS WELL

TEL_HASWELL_HAS WELL

IN

IN

AC7

U4

V4

AD9

U3

V3

AC9

U2

V2

AD8

U1

V1

AC8

M7

L9

M9

M10

M8

L7

L8

L10

V5

U5

AD1

V10

U6

U7

U8

V8

DDRA_MA0

AC6

DDRA_MA1

V9

DDRA_MA2

U9

DDRA_MA3

AC5

DDRA_MA4

AC4

DDRA_MA5

AD6

DDRA_MA6

AC3

DDRA_MA7

AD5

DDRA_MA8

AC2

DDRA_MA9

V6

DDRA_MA10

AC1

DDRA_MA11

AD4

DDRA_MA12

V7

DDRA_MA13

AD3

DDRA_MA14

AD2

DDRA_MA15

AP15

DDRA_DQS#0

AP8

DDRA_DQS#1

AJ8

DDRA_DQS#2

AF3

DDRA_DQS#3

J3

DDRA_DQS#4

E2

DDRA_DQS#5

C5

DDRA_DQS#6

C11

DDRA_DQS#7

AP14

DDRA_DQS0

AP9

DDRA_DQS1

AK8

DDRA_DQS2

AG3

DDRA_DQS3

H3

DDRA_DQS4

E3

DDRA_DQS5

C6

DDRA_DQS6

C12

DDRA_DQS7+VREF_CA_R

T64 PAD@T64 PAD@

DDRA_CLK0# <11>

DDRA_CLK0 <11>

DDRA_CKE0 <11>

DDRA_CLK1# <11>

DDRA_CLK1 <11>

DDRA_CKE1 <11>

DDRA_CS0# <11>

DDRA_CS1# <11>

DDRA_ODT0 <11>

DDRA_ODT1 <11>

DDRA_BS0# <11>

DDRA_BS1# <11>

DDRA_BS2# <11>

DDRA_RAS# <11>

DDRA_WE# <11>

DDRA_CAS# <11>

DDRA_MA[0..15] <11>

DDRA_DQS#[0..7] <11>

DDRA_DQS[0..7] <11>

3

DDRB_DQ[0..63]<12>

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRB_DQ16

DDRB_DQ17

DDRB_DQ18

DDRB_DQ19

DDRB_DQ20

DDRB_DQ21

DDRB_DQ22

DDRB_DQ23

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ28

DDRB_DQ29

DDRB_DQ30

DDRB_DQ31

DDRB_DQ32

DDRB_DQ33

DDRB_DQ34

DDRB_DQ35

DDRB_DQ36

DDRB_DQ37

DDRB_DQ38

DDRB_DQ39

DDRB_DQ40

DDRB_DQ41

DDRB_DQ42

DDRB_DQ43

DDRB_DQ44

DDRB_DQ45

DDRB_DQ46

DDRB_DQ47

DDRB_DQ48

DDRB_DQ49

DDRB_DQ50

DDRB_DQ51

DDRB_DQ52

DDRB_DQ53

DDRB_DQ54

DDRB_DQ55

DDRB_DQ56

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ60

DDRB_DQ61

DDRB_DQ62

DDRB_DQ63

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AT12

AR12

AN12

AM11

AT11

AR11

AM12

AN11

AR5

AR6

AM5

AM6

AT5

AT6

AN5

AN6

AK4

AM1

AN1

AK2

AK1

G10

D15

D14

AJ4

AJ1

AJ2

J10

E15

A15

B15

E14

A14

B14

L2

M2

L4

M4

L1

M1

L5

M5

G7

J8

G8

G9

J7

J9

A8

B8

A9

B9

D8

E8

D9

E9

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

4 OF 9

4 OF 9

2

Haswell rPGA EDS

JCPUD

JCPUD

I

I

N

N

Haswell rPGA EDS

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

TEL_HASWELL_HAS WELL

TEL_HASWELL_HAS WELL

RSVD

SB_CKN0

SB_CK0

SB_CKE_0

SB_CKN1

SB_CK1

SB_CKE_1

SB_CKN2

SB_CK2

SB_CKE_2

SB_CKN3

SB_CK3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

RSVD

SB_RAS

SB_WE

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

AG8

Y4

AA4

AF10

Y3

AA3

AG10

Y2

AA2

AG9

Y1

AA1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

R7

P8

AA9

R10

R6

P6

P7

R8

DDRB_MA0

Y5

DDRB_MA1

Y10

DDRB_MA2

AA5

DDRB_MA3

Y7

DDRB_MA4

AA6

DDRB_MA5

Y6

DDRB_MA6

AA7

DDRB_MA7

Y8

DDRB_MA8

AA10

DDRB_MA9

R9

DDRB_MA10

Y9

DDRB_MA11

AF7

DDRB_MA12

P9

DDRB_MA13

AA8

DDRB_MA14

AG7

DDRB_MA15

AP18

DDRB_DQS#0

AP11

DDRB_DQS#1

AP5

DDRB_DQS#2

AJ3

DDRB_DQS#3

L3

DDRB_DQS#4

H9

DDRB_DQS#5

C8

DDRB_DQS#6

C14

DDRB_DQS#7

AP17

DDRB_DQS0

AP12

DDRB_DQS1

AP6

DDRB_DQS2

AK3

DDRB_DQS3

M3

DDRB_DQS4

H8

DDRB_DQS5

C9

DDRB_DQS6

C15

DDRB_DQS7

T63 PAD@ T63 PAD@

DDRB_CLK0# <12>

DDRB_CLK0 <12>

DDRB_CKE0 <12>

DDRB_CLK1# <12>

DDRB_CLK1 <12>

DDRB_CKE1 <12>

DDRB_CS0# <12>

DDRB_CS1# <12>

DDRB_ODT0 <12>

DDRB_ODT1 <12>

DDRB_BS0# <12>

DDRB_BS1# <12>

DDRB_BS2# <12>

DDRB_RAS# <12>

DDRB_WE# <12>

DDRB_CAS# <12>

DDRB_MA[0..15] <12>

DDRB_DQS#[0..7] <12>

DDRB_DQS[0..7] <12>

1

DRAMRST_CNTRL<6>

+VREF_DQ_DIMMA_R

+VREF_DQ_DIMMB_R

A A

5

6/8: Add M3 Circuit (Processor Generated SO-DIMM VREF_DQ)

4

DRAMRST_CNTRL

DRAMRST_CNTRL

2

G

G

QC11 BSS138_SOT23

QC11 BSS138_SOT23

1 3

D

S

D

S

@

@

1 2

RC1548 0_0402_ 5%RC1548 0_0402_5%

1 2

RC92 0_0402_5%RC92 0_0402_5%

@

@

1 3

D

S

D

S

QC9 BSS138_SOT23

QC9 BSS138_SOT23

G

G

2

+V_DDR_REFA_R

+V_DDR_REFB_R

12

12

RC143

@ RC143

@

RC144

@RC144

@

1K_0402_1%

1K_0402_1%

1K_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

1K_0402_1%

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2012/07/01

2012/07/01

2012/07/01

3

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

Title

Title

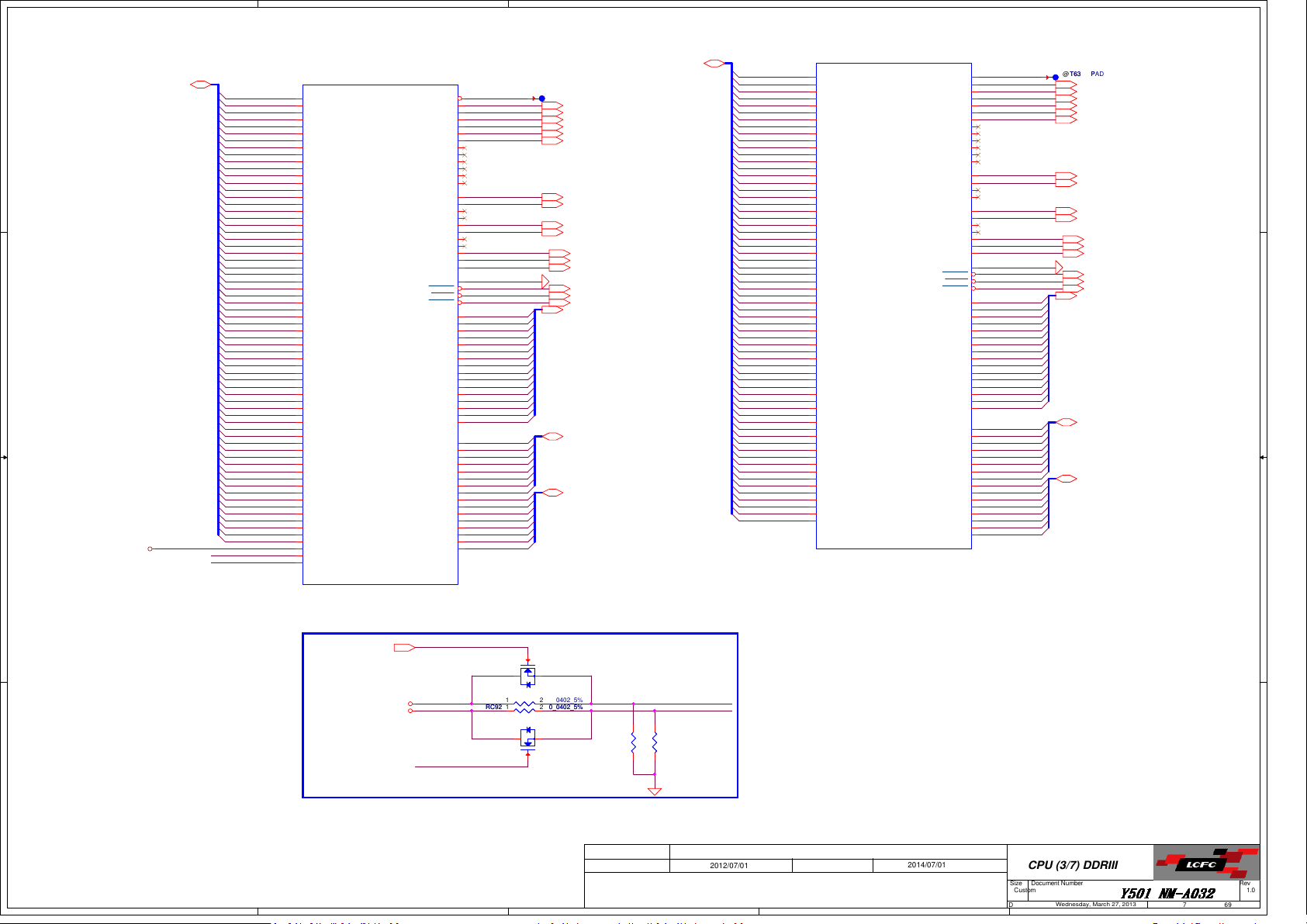

CPU (3/7) DDRIII

CPU (3/7) DDRIII

CPU (3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

7 69

7 69

7 69

1.0

1.0

1.0

Page 8

5

4

3

2

1

CFG STRAPS for CPU

CFG2

D D

PEG Static Lane Reversal - CFG2 is for the 16x

*

20120829 VA1

Add net for add HDMI MUX

CPU_HDMI_TX2-<37>

CPU_HDMI_TX2+<37>

CPU_HDMI_TX1-<37>

CPU_HDMI_TX1+<37>

CPU_HDMI_TX0-<37>

CPU_HDMI_TX0+<37>

CPU_HDMI_CLK-<37>

check CLK item

CPU_HDMI_CLK+<37>

COMPENSATION PU FOR eDP

12

C C

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

+VCCIOA_OUT

12

RC124.9_0402_1% RC12 4.9_0402_1%

+VCCIO_OUT

10K_0402_5%

10K_0402_5%

RC45 49.9_0402_1%RC45 49.9_0402_1%

RC58 49.9_0402_1%RC58 49.9_0402_1%

RC59 49.9_0402_1%RC59 49.9_0402_1%

RC65

RC65

H_CPU_TESTLO

12

CFG_RCOMP

12

H_CPU_RSVD

HPD INVERSION FOR EDP

1 2

EDP_HPD_IN#

BSS138_SOT23

BSS138_SOT23

13

D

D

QC6

QC6

CPU_EDP_HPD<38>

B B

A A

2

G

G

S

100K_0402_5%

100K_0402_5%

12

RC75

RC75

S

T70 PAD@T70 PAD@

T71 PAD@T71 PAD@

T72 PAD@T72 PAD@

T73 PAD@T73 PAD@

T77 PAD@T77 PAD@

T76 PAD@T76 PAD@

T80 PAD@T80 PAD@

T79 PAD@T79 PAD@

T94 PAD@T94 PAD@

+VCC_CORE

T82 PAD@T82 PAD@

T81 PAD@T81 PAD@

T85 PAD@T85 PAD@

T84 PAD@T84 PAD@

T83 PAD@T83 PAD@

T173PAD@ T173PAD@

T116PAD@ T116PAD@

T117PAD@ T117PAD@

T126PAD@ T126PAD@

T129PAD@ T129PAD@

T130PAD@ T130PAD@

T131PAD@ T131PAD@

T132PAD@ T132PAD@

T133PAD@ T133PAD@

T134PAD@ T134PAD@

T135PAD@ T135PAD@

T136PAD@ T136PAD@

T137PAD@ T137PAD@

T138PAD@ T138PAD@

T142PAD@ T142PAD@

T143PAD@ T143PAD@

H_CPU_RSVD

H_CPU_TESTLO

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

Haswell rPGA EDS

Haswell rPGA EDS

T28

DDIB_TXBN_0

U28

DDIB_TXBP_0

T30

DDIB_TXBN_1

U30

DDIB_TXBP_1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

AT1

AT2

AD10

A34

A35

W29

W28

G26

W33

AL30

AL29

F25

C35

B35

AL25

W30

W31

W34

AT20

CFG0

AR20

AP20

AP22

AT22

AN22

AT25

AN23

AR24

AT23

AN20

AP24

AP26

AN25

AN26

AP25

Haswell rPGA EDS

Haswell rPGA EDS

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCC

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

TESTLO

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

INT

INT

EL_HASWELL_HASW ELL

EL_HASWELL_HASW ELL

JCPUH

JCPUH

eDP

eDP

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

RSVD

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

DDI

DDI

8 OF 9

8 OF 9

JCPUI

JCPUI

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

9 OF 9

9 OF 9

CPU_EDP_AUX#

CPU_EDP_AUX

EDP_HPD_IN#

EDP_COMP

CPU_EDP_TX0CPU_EDP_TX0+

CPU_EDP_TX1CPU_EDP_TX1+

FDI_CTX_PRX_N0

FDI_CTX_PRX_P0

FDI_CTX_PRX_N1

FDI_CTX_PRX_P1

C23

B23

D24

D23

AT31

AR21

AR23

AP21

AP23

AR33

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG_RCOMP

CFG16

CFG18

CFG17

CFG19

CPU_EDP_AUX# <38>

CPU_EDP_AUX <38>

T69PAD @T69PAD @

CPU_EDP_TX0- <38>

CPU_EDP_TX0+ <38>

CPU_EDP_TX1- <38>

CPU_EDP_TX1+ <38>

FDI_CTX_PRX_N0 <15>

FDI_CTX_PRX_P0 <15>

FDI_CTX_PRX_N1 <15>

FDI_CTX_PRX_P1 <15>

T86PAD @T86PAD @

T78PAD @T78PAD @

T87PAD @T87PAD @

T88PAD @T88PAD @

T156PAD @T156PAD @

T164PAD @T164PAD @

T165PAD @T165PAD @

T166PAD @T166PAD @

T91PAD @T91PAD @

T90PAD @T90PAD @

T92PAD @T92PAD @

T89PAD @T89PAD @

T93PAD @T93PAD @

T95PAD @T95PAD @

T104PAD @T104PAD @

T96PAD @T96PAD @

T98PAD @T98PAD @

T97PAD @T97PAD @

T100PAD @T100PAD @

T99PAD @T99PAD @

T102PAD @T102PAD @

T101PAD @T101PAD @

CFG[6:5]

CFG2

Display Port Presence Strap

1 : Disabled; No Physical Display Port

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

*

connected to the Embedded Display Port

CFG5

CFG6

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

*

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

*

CFG7

1K_0402_1%

1K_0402_1%

12

@RC76

@

RC76

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG4

1K_0402_1%

1K_0402_1%

1K_0402_1%

1K_0402_1%

12

12

@RC83

@

RC83

RC85

RC85

1K_0402_1%

1K_0402_1%

12

RC77

RC77

PCIE Port Bifurcation Straps

CFG7

1K_0402_1%

1K_0402_1%

12

@RC86

@

RC86

PEG DEFER TRAINING

1: (Default) PEG Train immediately

following xxRESETB de assertion

0: PEG Wait for BIOS for training

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

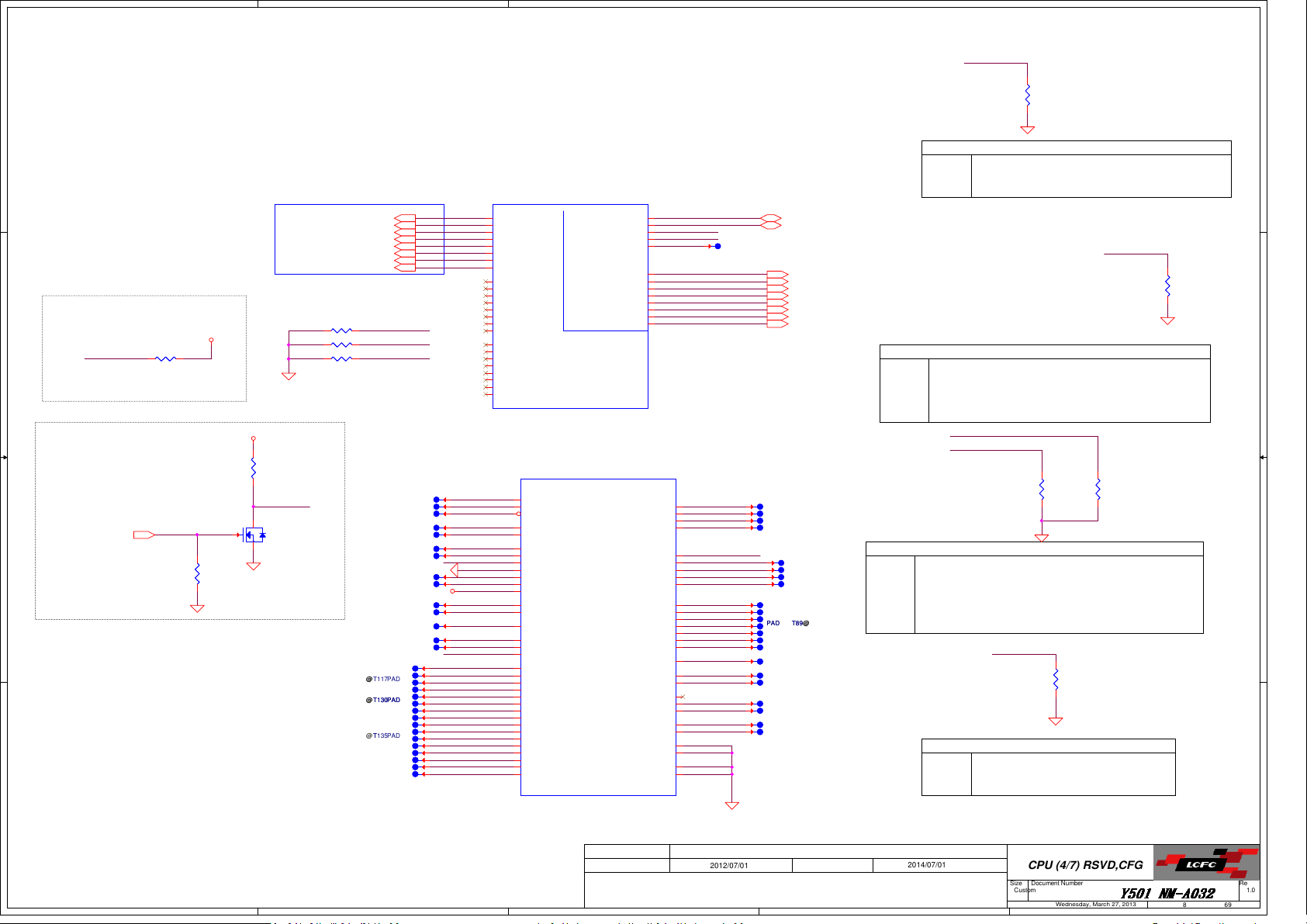

CPU (4/7) RSVD,CFG

CPU (4/7) RSVD,CFG

CPU (4/7) RSVD,CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, March 27, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

8 69

8 69

8 69

1.0

1.0

1.0

Page 9

5

4

3

2

1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

+VCC_CORE

Haswell rPGA EDS

Haswell rPGA EDS

AB11

AB2

AB5

AB8

AE11

AE2

AE5

AE8

AH11

K11

N11

W11

N26

K26

AL27

AK27

AL35

E17

AN35

A23

W32

AL16

AL13

AM28

AM29

AL28

AP35

H27

AP34

AT35

AR35

AR32

AL26

AT34

AL22

AT33

AM21

AM25

AM22

AM20

AM24

AL19

AM23

AT32

K27

L27

T27

V27

N8

T11

T2

T5

T8

W2

W5

W8

F22

J27

Y25

Y26

Y27

Y28

Y29

Y30

Y31

Y32

Y33

Y34

Y35

RSVD

RSVD

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

RSVD

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIO2PCH

VCCIOA_OUT

RSVD

RSVD

VSS

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VSS

PWR_DEBUG

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

TEL_HASWELL_HAS WELL

TEL_HASWELL_HAS WELL

IN

IN

T107 PAD@ T107 PAD@

T106 PAD@ T106 PAD@

D D

+1.35V

CC151 0.1U_04 02_25V6KCC151 0.1U_04 02_25V6K

CC152 0.1U_04 02_25V6KCC152 0.1U_04 02_25V6K

C C

VCC_SENSE

VCCSENSE<64>

need connect to power

VSSSENSE<64>

B B

+1.35V_CPU_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC171

CC171

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC33

A A

CC33

2

+VCC_CORE

100_0402_1%

100_0402_1%

12

RC66

RC66

CAD Note: RC67 SHOULD BE PLACED CLOSE TO CPU

VCCSENSE VCCSENSE_R

RC67

RC67

12

R_short 0_0402_5%

R_short 0_0402_5%

CAD Note: RC68 SHOULD BE PLACED CLOSE TO CPU

VSSSENSE VSSSENSE_R

RC68

RC68

100_0402_1%

100_0402_1%

12

RC70

RC70

12

R_short 0_0402_5%

R_short 0_0402_5%

VDDQ DECOUPLING

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC169

CC169

CC170

CC170

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC35

CC35

CC34

CC34

2

2

@

@

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC168

CC168

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC36

CC36

2

10U_0603_6.3V6M

1

1

CC161

CC161

CC162

CC162

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC37

CC37

CC38

CC38

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC163

CC163

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC39

CC39

2

2

RC4

RC4

+1.05VS +VCCIO_OUT

VSSSENSE_R <10>

Power

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC164

CC164

CC165

CC165

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC41

CC41

CC40

CC40

2

@

@

330U_D2_2VM_R6M

330U_D2_2VM_R6M

330U_D2_2VM_R6M

330U_D2_2VM_R6M

1

1

CC167

CC167

CC172

1

CC166

CC166

@

@

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC42

CC42

2

CC172

+

+

+

+

@

@

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC43

CC43

2

0_0603_5% @

0_0603_5% @

VR_SVID_ALRT#<64>

VR_SVID_CLK<64>

VR_SVID_DAT<64>

+1.05VS

150_0402_1%

150_0402_1%

12

@

@

CPU_PWR_DEBU G

10K_0402_5%

10K_0402_5%

12

12

RC61 43_0402_5%RC61 43_0402_5%

1 2

12

RC63

RC63

@

@

130_0402_1%

130_0402_1%

+VCCIO_OUT

RC69

RC69

CPU_PWR_DEBU G <6>

@

@

RC71

RC71

need connect to power

T112 PAD@ T112 PAD@

T113 PAD@ T113 PAD@

12

12

placement

T115 PAD@ T115 PAD@

+VCC_CORE

T151 PAD@ T151 PAD@

T152 PAD@ T152 PAD@

T153 PAD@ T153 PAD@

+VCCIO_OUT

+1.05VS

+VCCIOA_OUT

T160 PAD@ T160 PAD@

T159 PAD@ T159 PAD@

T154 PAD@ T154 PAD@

VR_SVID_ALRT#_R

VR_SVID_CLK

VR_SVID_DAT

CPU_PWR_DEBU G

T157 PAD@ T157 PAD@

T158 PAD@ T158 PAD@

T162 PAD@ T162 PAD@

T163 PAD@ T163 PAD@

+1.35V_CPU_VDDQ

VCCSENSE_R

+VCC_CORE

JCPUE

JCPUE

5 OF 9

5 OF 9

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

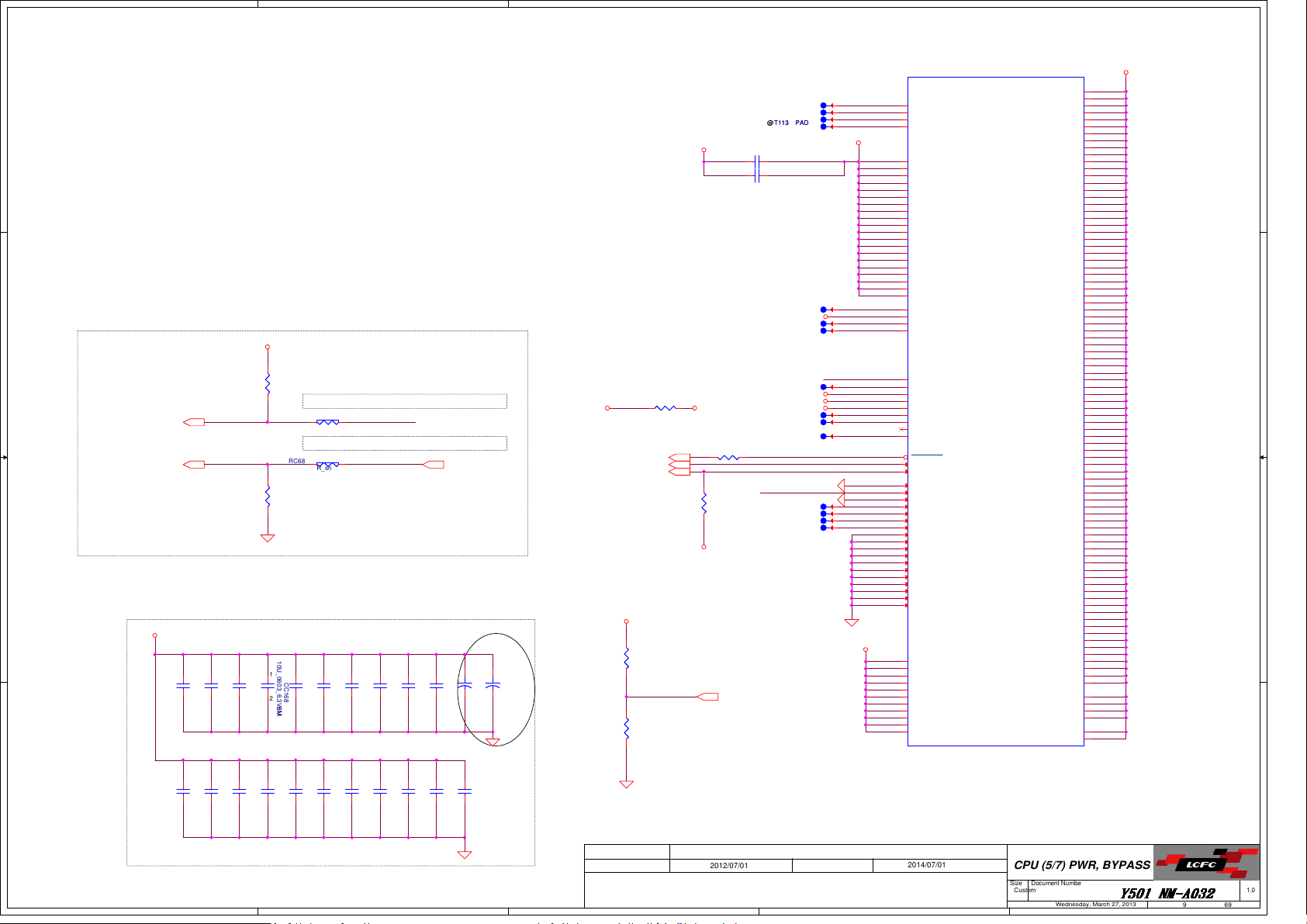

CPU (5/7) PWR, BYPASS

CPU (5/7) PWR, BYPASS

CPU (5/7) PWR, BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, March 27, 2013

Wednesday, March 27, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet

Wednesday, March 27, 2013

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

Y501 NM-A032Y501 NM-A032

1

9 69

9 69

9 69

of

1.0

1.0

1.0

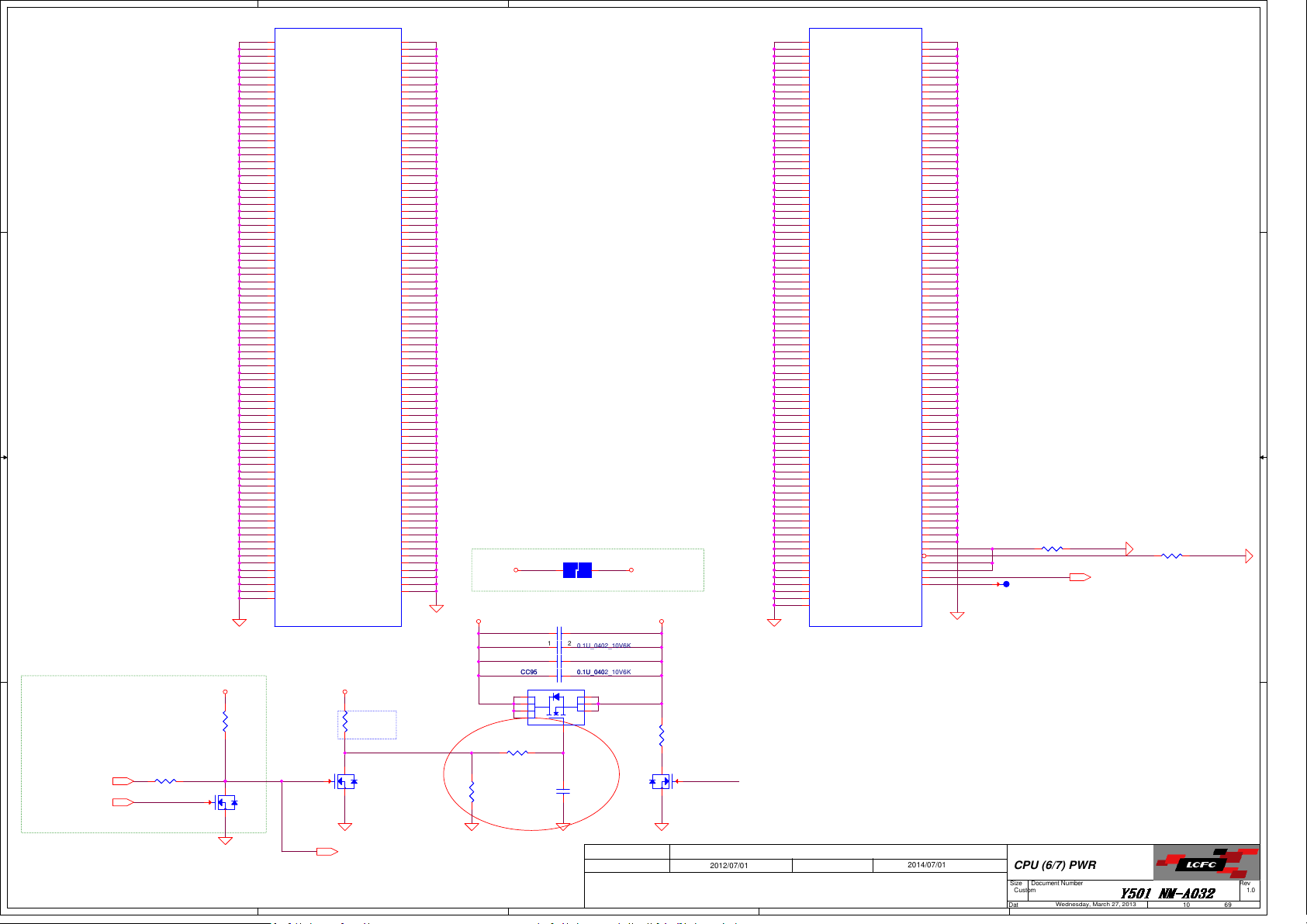

Page 10

5

Haswell rPGA EDS

Haswell rPGA EDS

A10

VSS

A13

VSS

A16

VSS

A19

VSS

A22

VSS

A25

VSS

A27

VSS

A29

VSS

A3

VSS

A31

VSS

A33

VSS

A4

D D

C C

B B

AA11

AA25

AA27

AA31

AA29

AB1

AB10

AA33

AA35

AB3

AC25

AC27

AB4

AB6

AB7

AB9

AC11

AD11

AC29

AC31

AC33

AC35

AD7

AE1

AE10

AE25

AE29

AE3

AE27

AE35

AE4

AE6

AE7

AE9

AF11

AF6

AF8

AG11

AG25

AE31

AG31

AE33

AG6

AH1

AH10

AH2

AG27

AG29

AH3

AG33

AG35

AH4

AH5