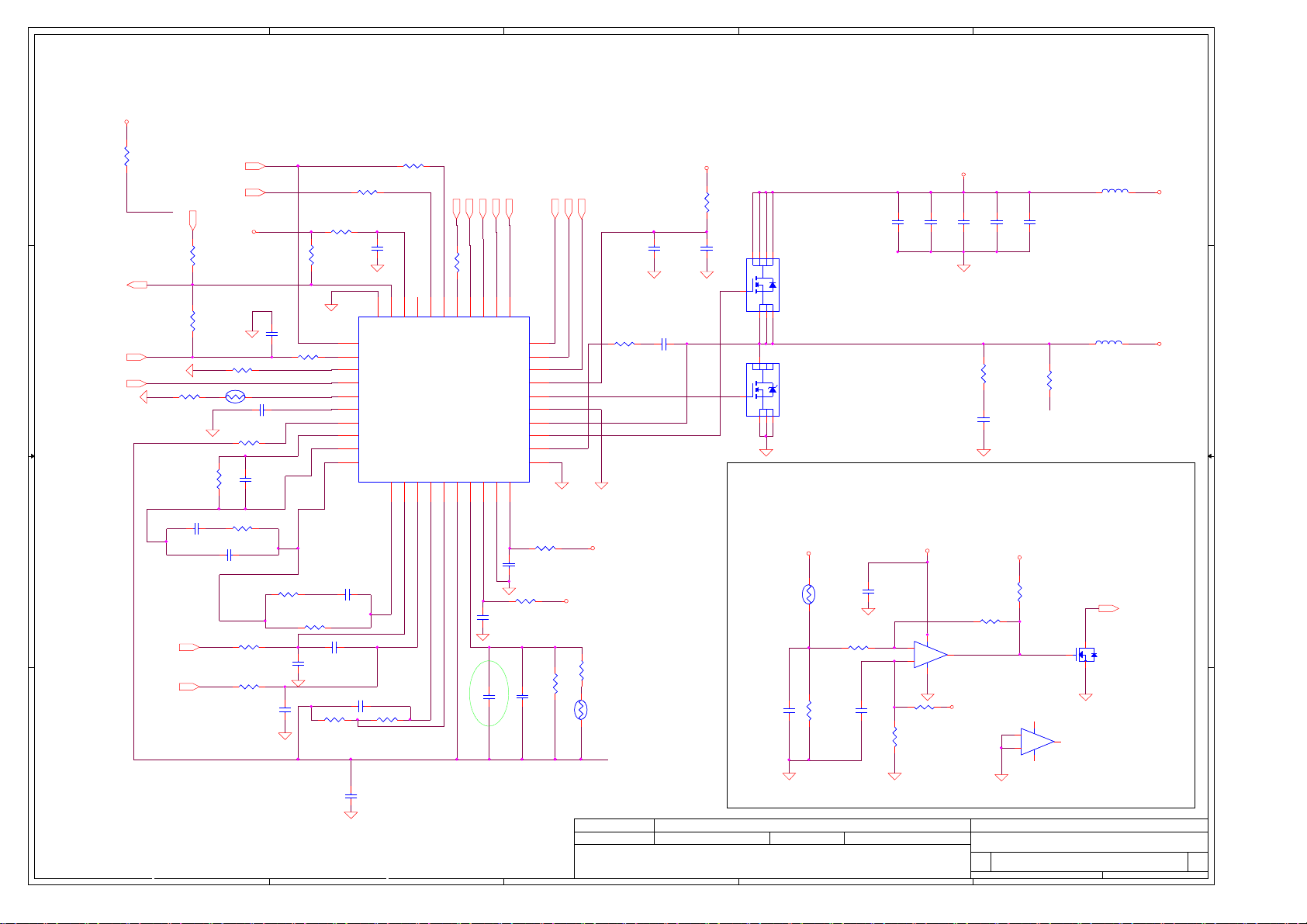

Page 1

A

1 1

B

C

D

E

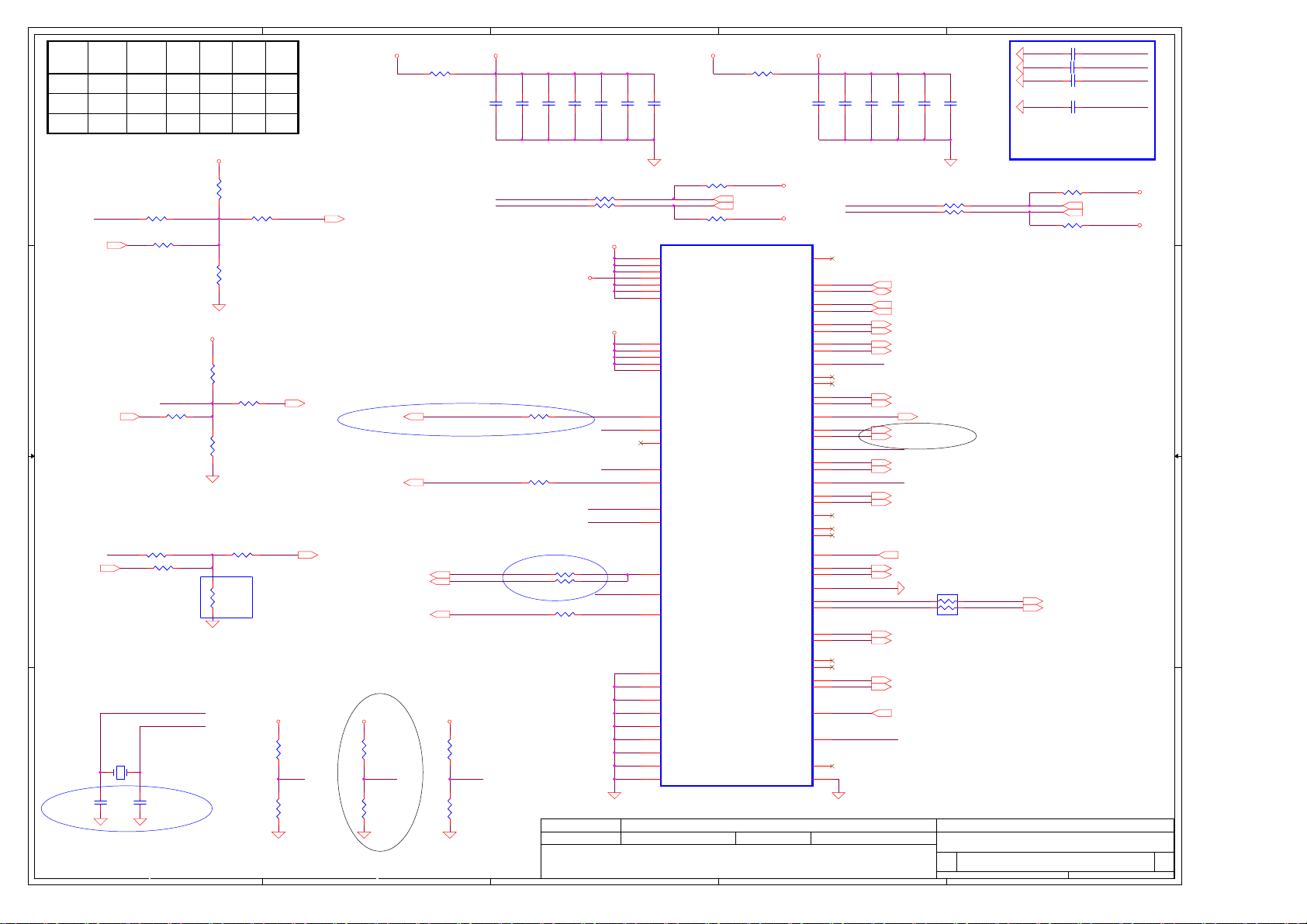

Compal confidential

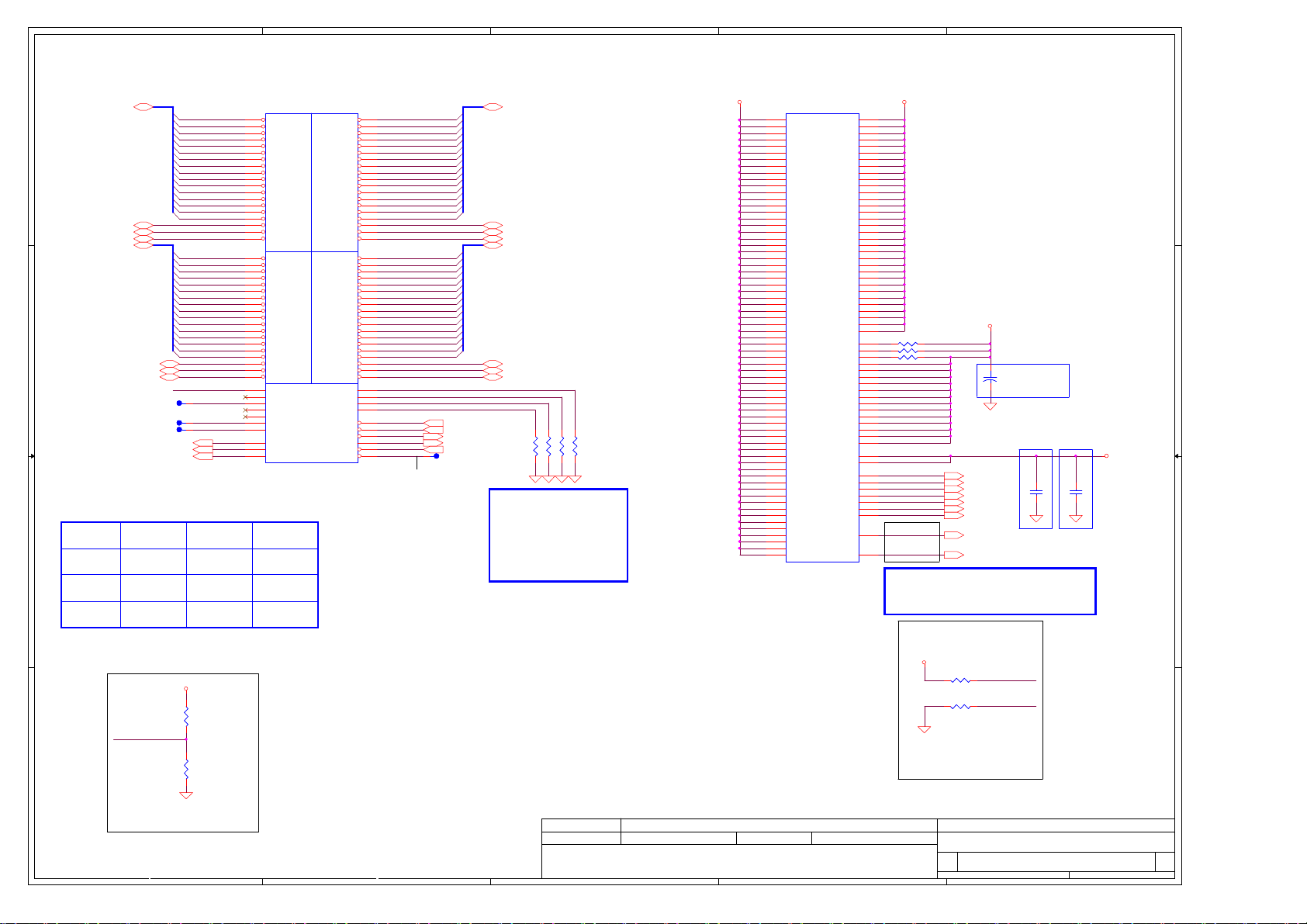

Schematics Document

2 2

Mobile Penryn uFCPGA with Intel

Cantiga_GM+ICH9-M SFF core logic

3 3

ULV core logic HDI board

DISCRETE VGA M92

4 4

Security Classification Compal Secret Data

Security Classification Compal Secret Data

A

Security Classification Compal Secret Data

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009-06-19 V.03

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LS-5588

LS-5588

LS-5588

E

1 35Wednesday, July 01, 2009

1 35Wednesday, July 01, 2009

1 35Wednesday, July 01, 2009

0.3

0.3

0.3

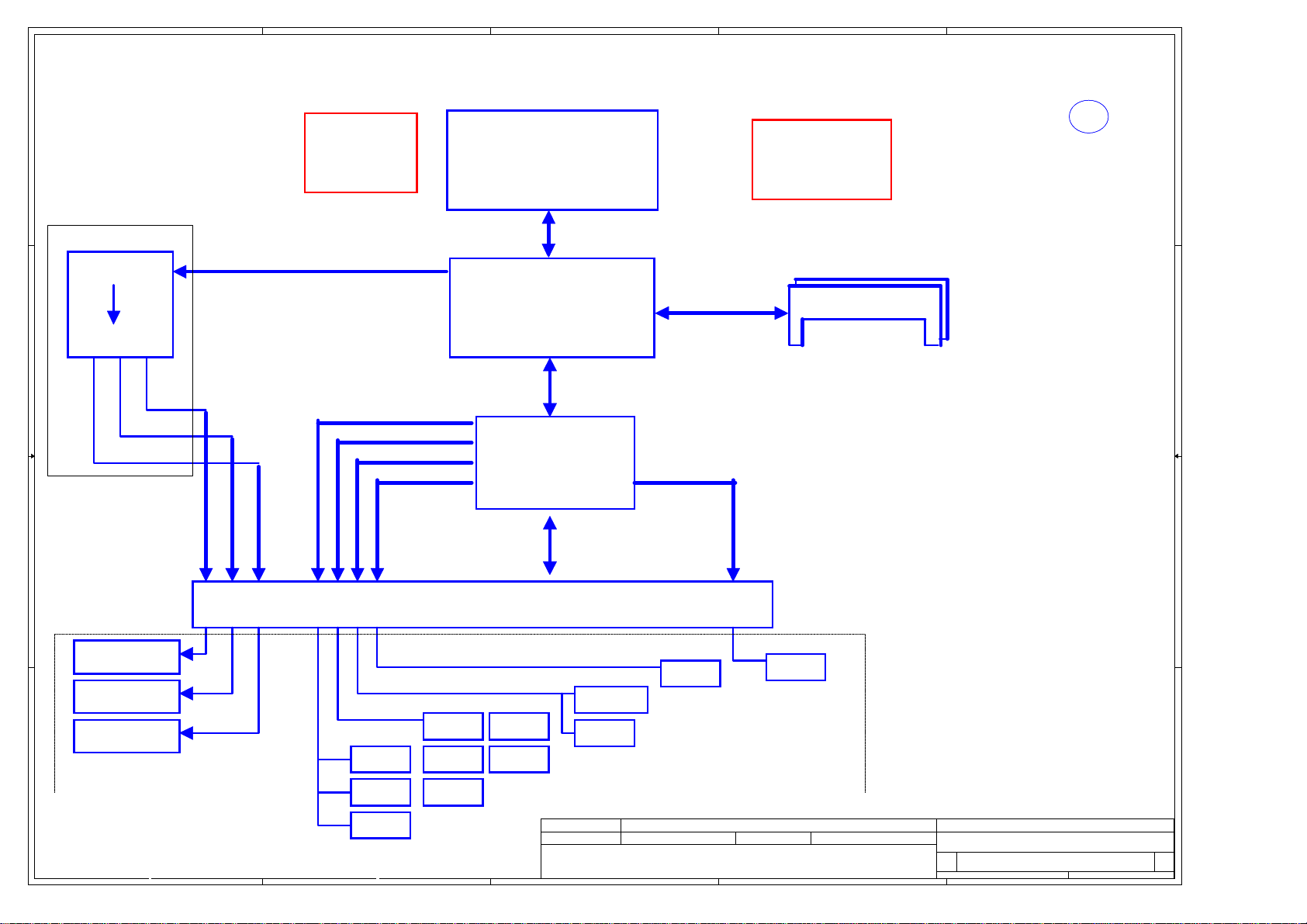

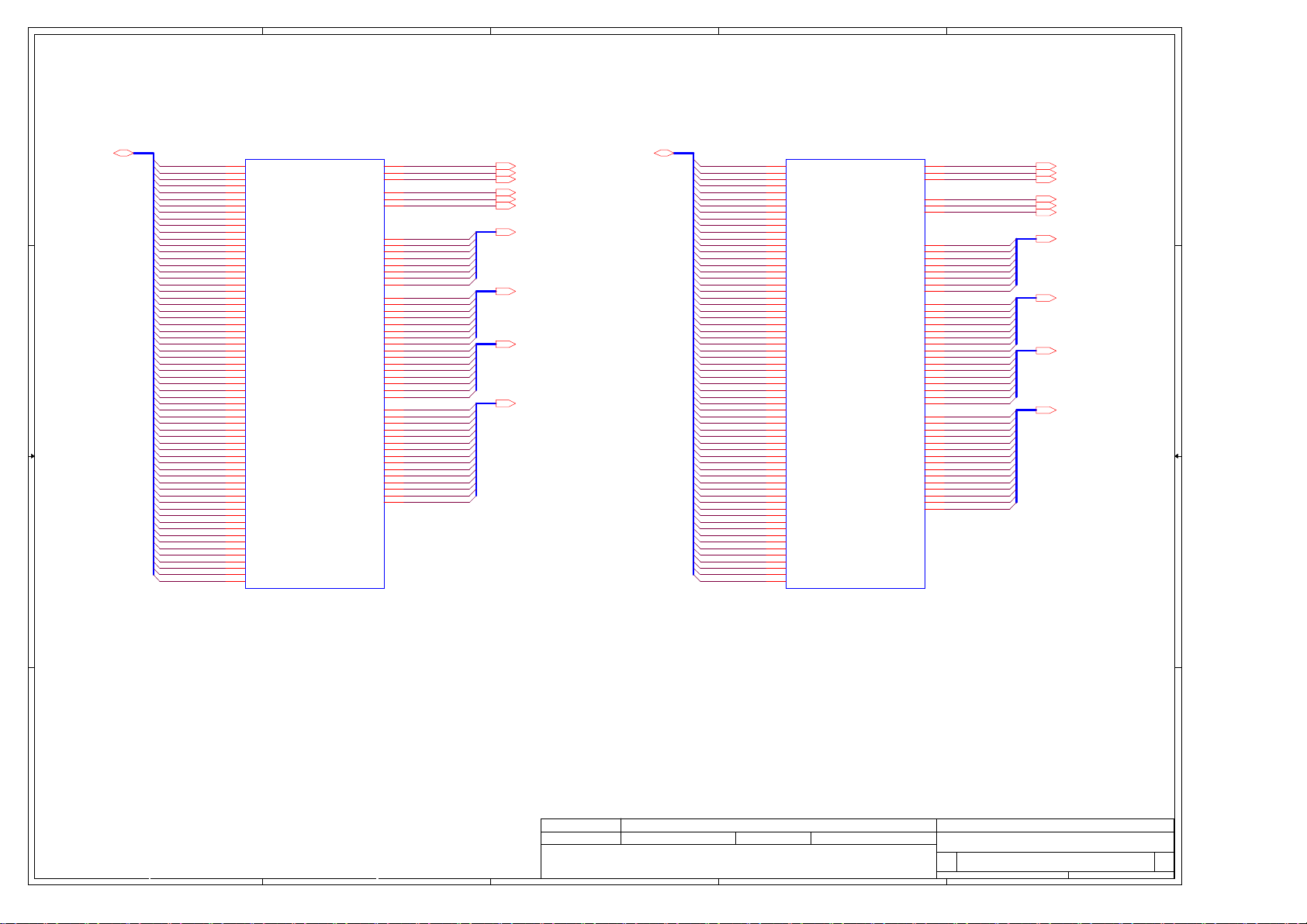

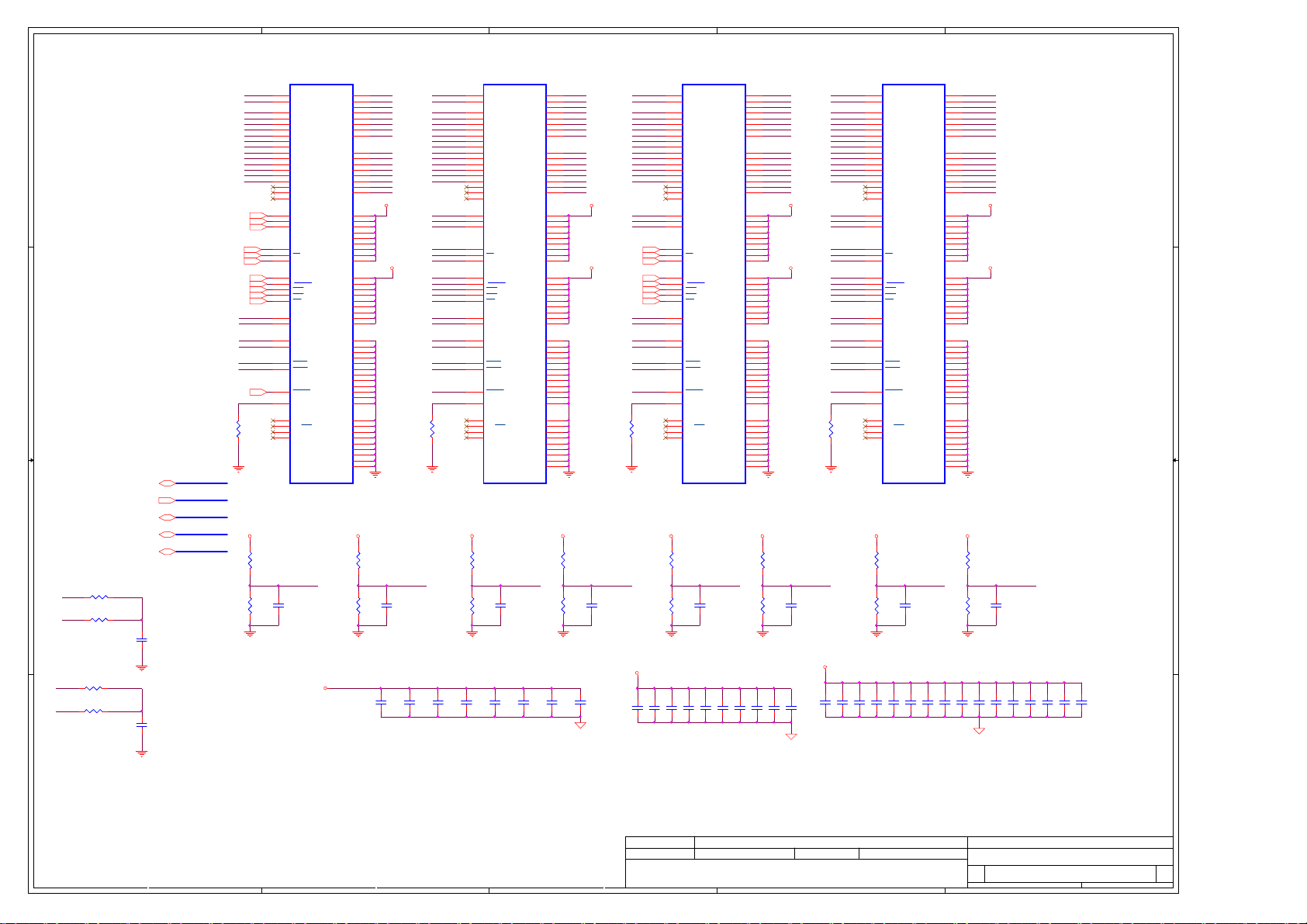

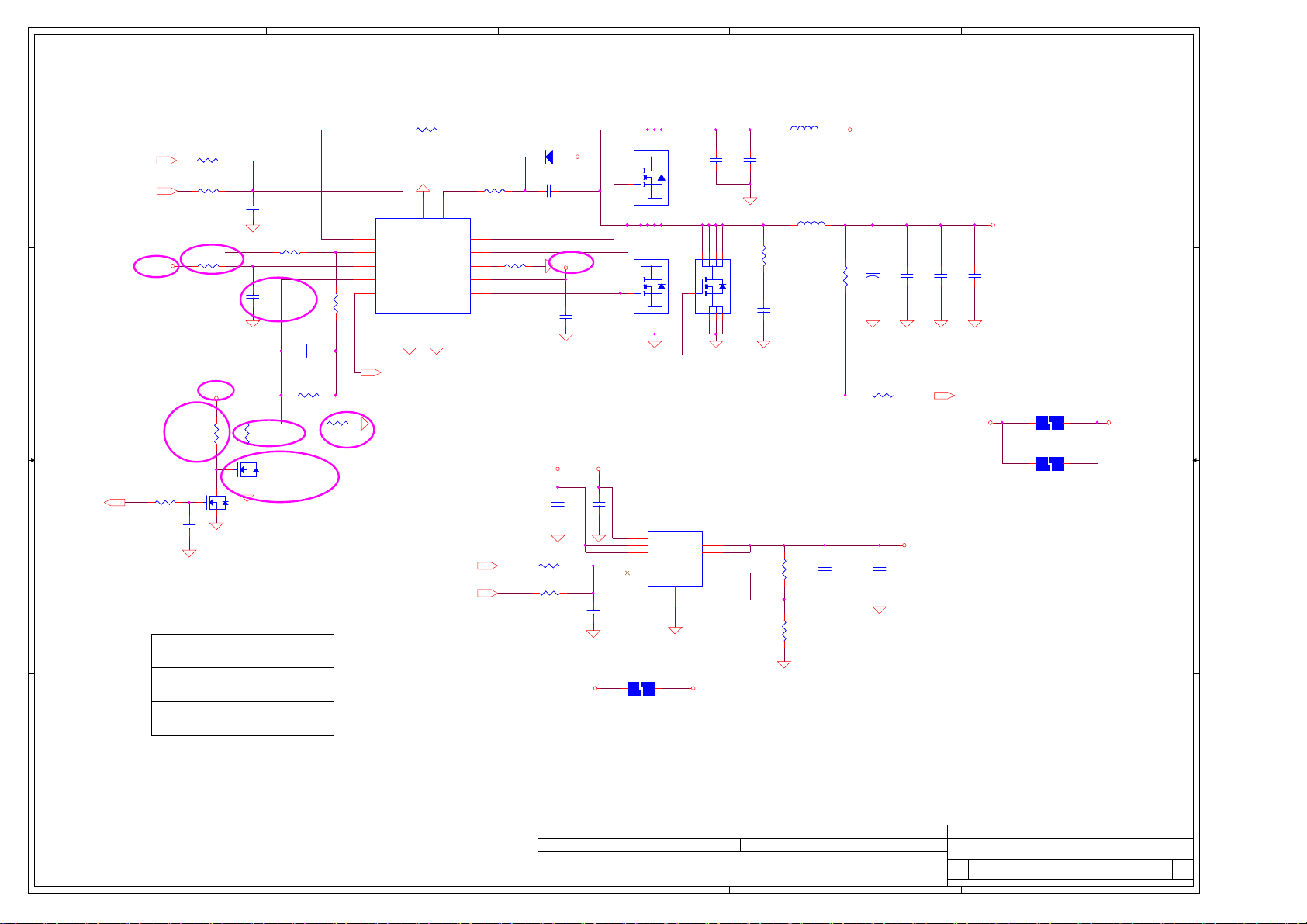

Page 2

A

Compal confidential

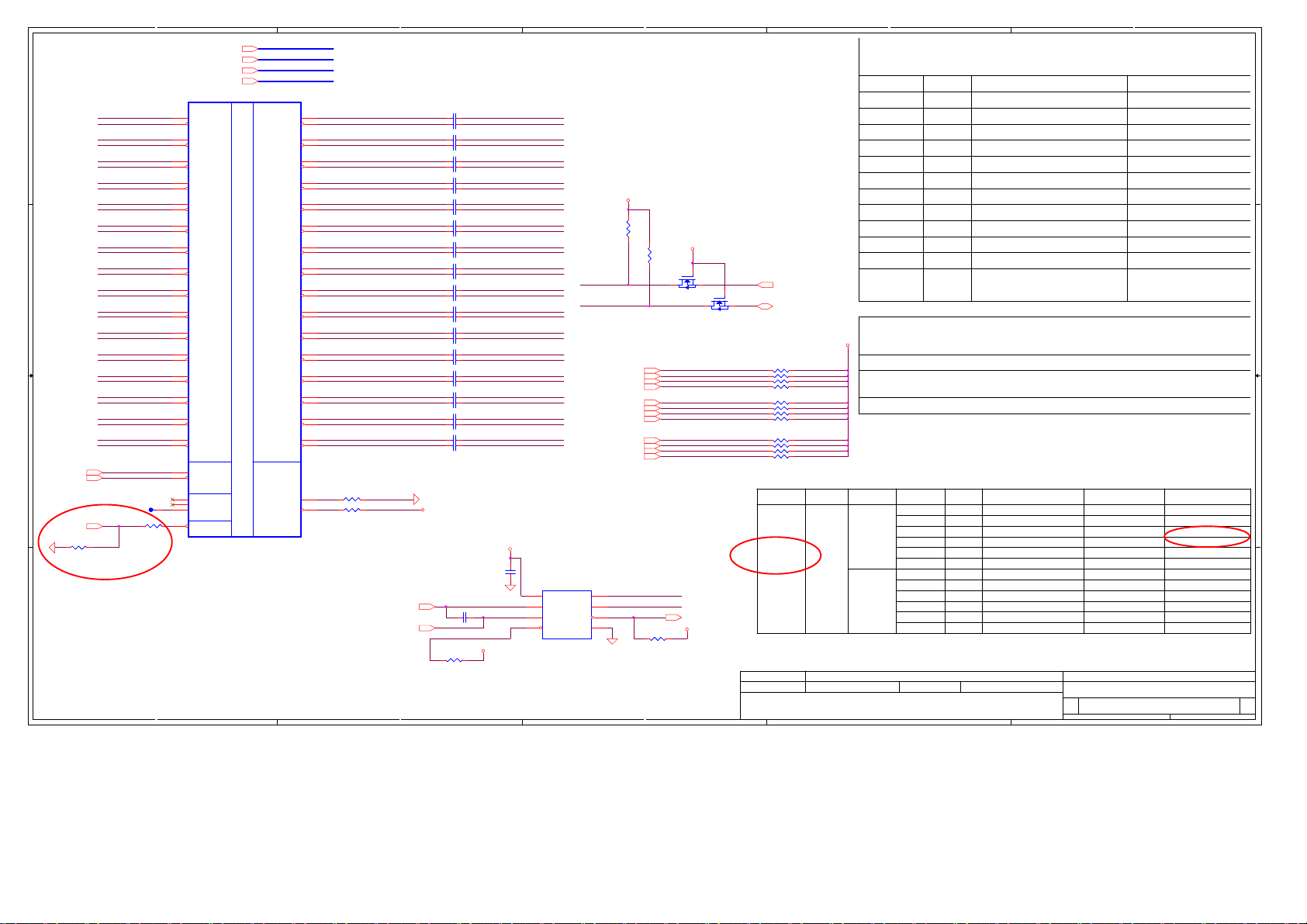

Model Name : NAW20

File Name : LS-5588P

B

ULV

C

D

E

ZZZ

ZZZ

1 1

Thermal Sensor

Mobile Peryn

LV/ULV Dual Core

uFCPGA-956 CPU - SFF

page 4

DISCRETE VGA HDI BRD

page 17,18,19,20,21

ATI M92 S2

Intel Cantiga GS

600MHz

VRAM DDR3

512MB(64Mx16)

2 2

page 4,5,6,7

H_A#(3..35)

H_D#(0..63)

FSB

667/800/1066MHz 1.05V

FCBGA 1363 - SFF

page 8,9,10,11,12,13

DDR3 1066MHz 1.5V

Dual Channel

CK505

Clock Generator

ICS9LPRS387BKLFT

MLF 72P

page 16

DDR3-SO-DIMM X 2

BANK 0, 1, 2, 3

page 14,15

PCB-MB

PCB-MB

DMI X4

RGB

Single Channel

3 3

SATA x3

USB x9

PCIE*3

LPC

Intel ICH9-M

WBMMAP-569 - SFF

page 22,23,24,25

HDA

HDMI

CRT

Golden finger

LPC

PCIE

HDI to I/O board

miniPCIE*1

page 26

EC

HDA

AUDIO

USB

LVDS

SATA

ODD

4 4

HDD

USB*2

CardReader

BT

ESATA

A

B

CMOS

miniPCIE

*2

LAN

I/O BRD PORTION

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LS-5588

LS-5588

LS-5588

E

2 35Wednesday, July 01, 2009

2 35Wednesday, July 01, 2009

2 35Wednesday, July 01, 2009

0.3

0.3

0.3

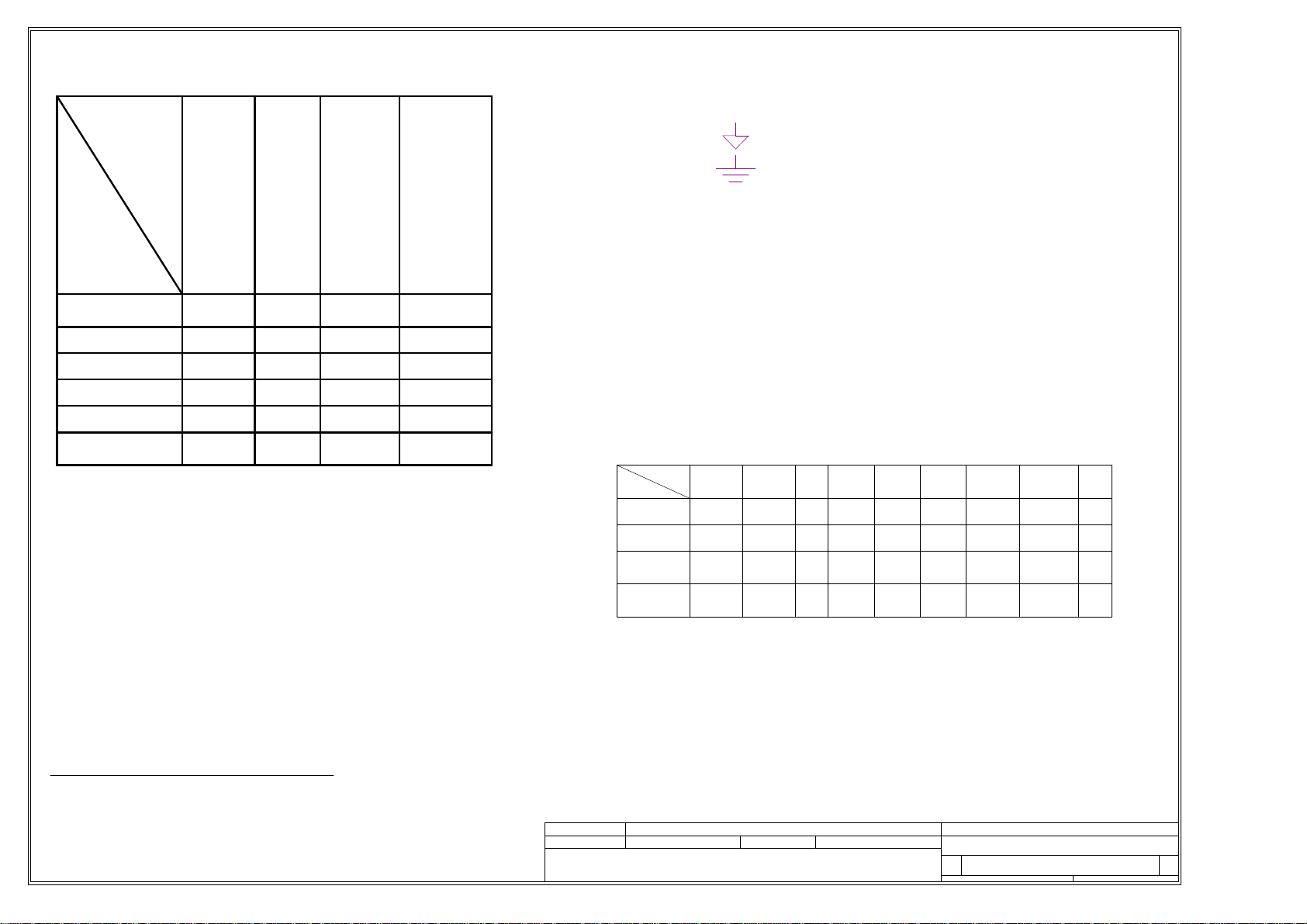

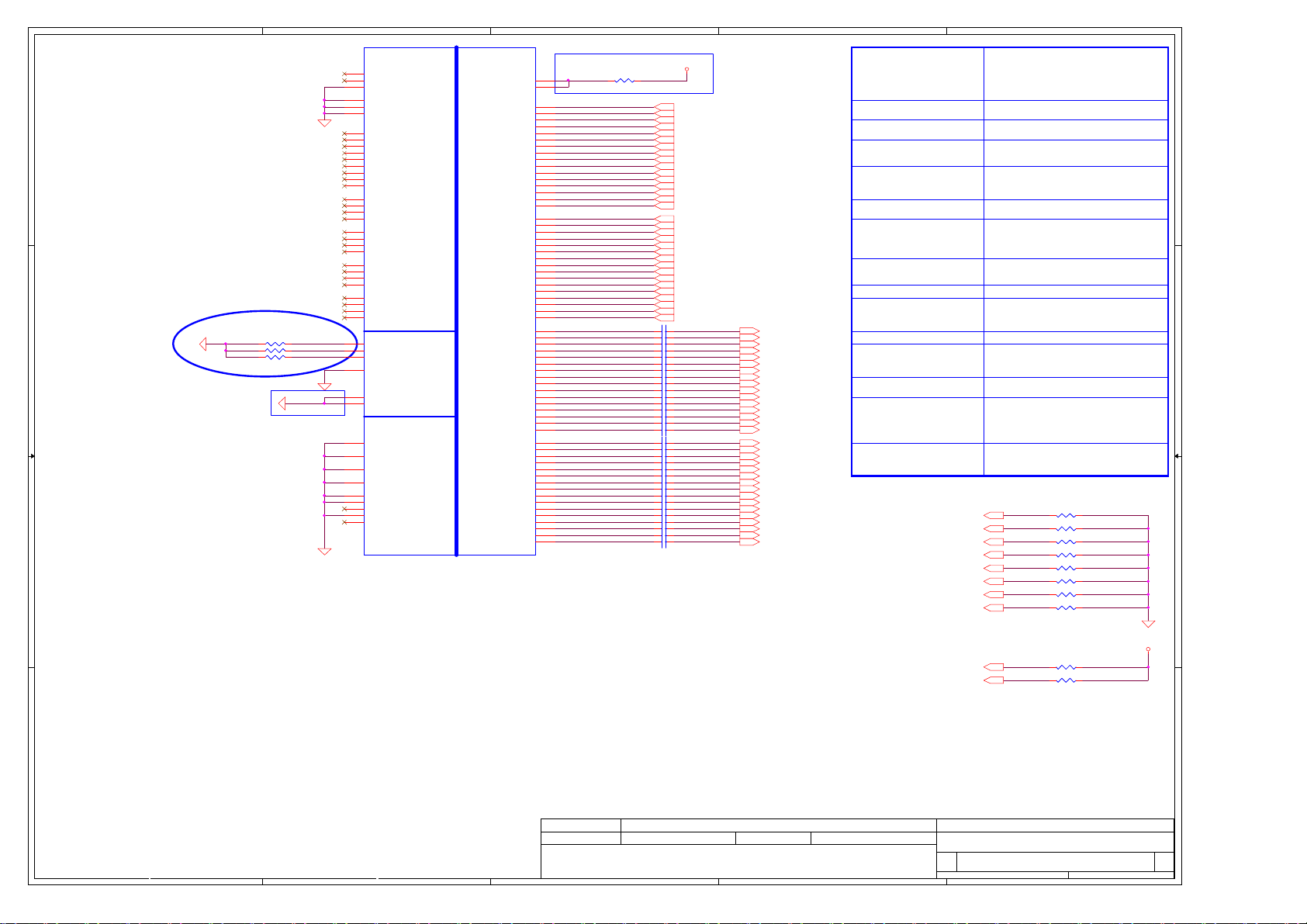

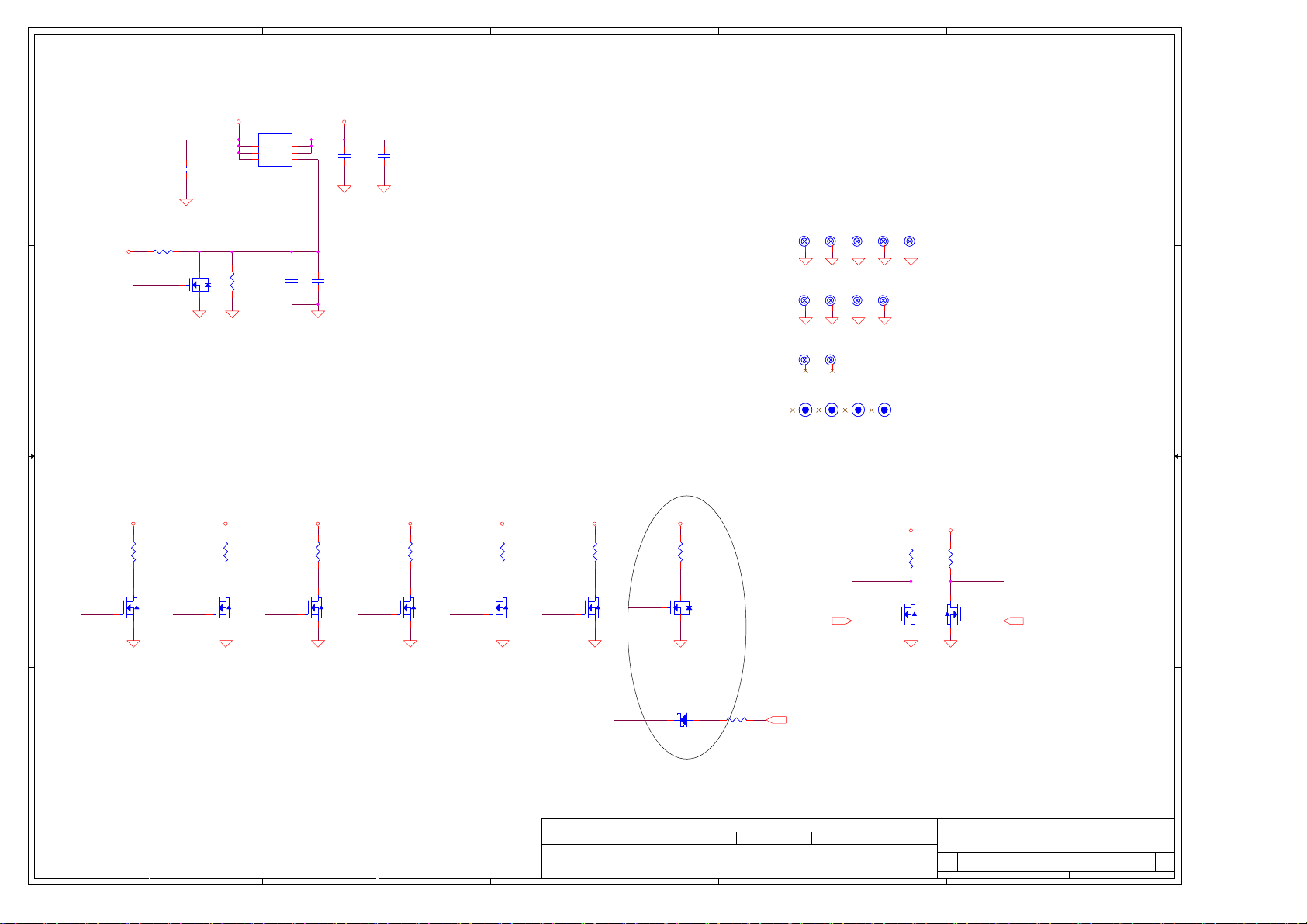

Page 3

A

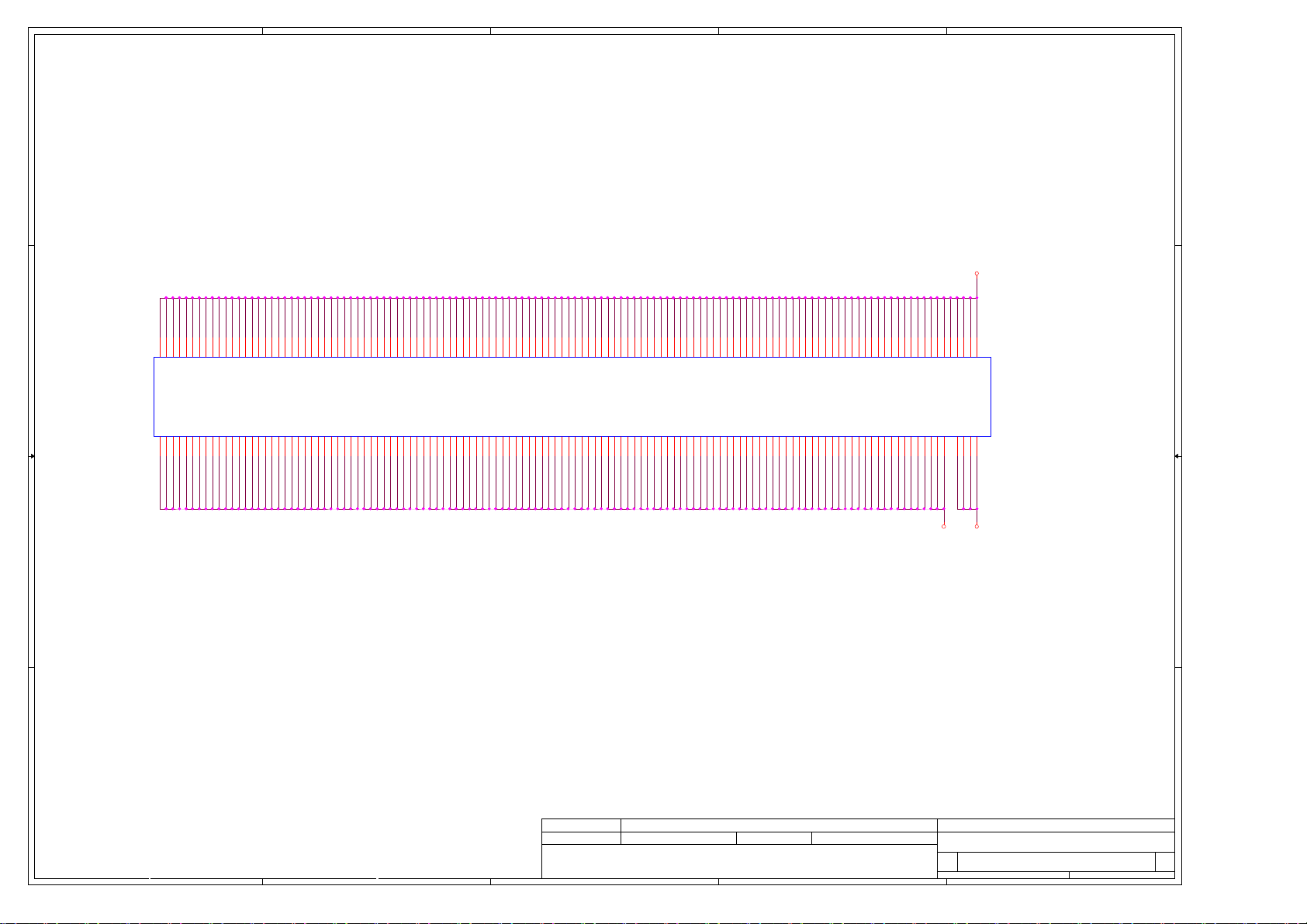

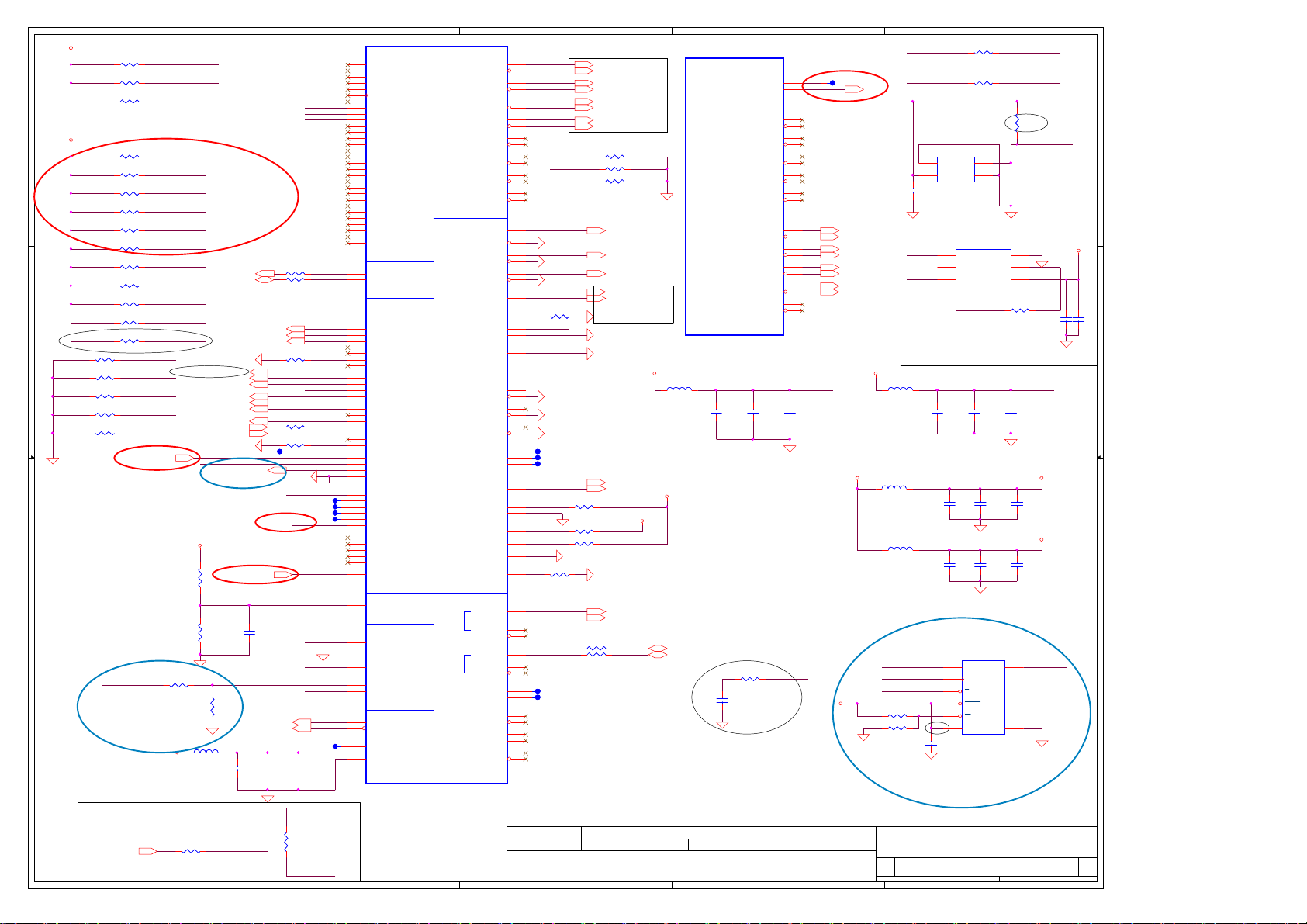

Voltage Rails

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

( O MEANS ON X MEANS OFF )

+B

+3VL

power

plane

O

O

O

O

O

X

+5VALW

+3VALW

+1.5V

O

O

O

O

X

O

X X

X

X X X

+5VS

+3VS

+1.5VS

+0.75VS

+VCCP

+CPU_CORE

+VGA_CORE

+1.1VS

+1.8VS

OO

OO

X

X

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMB_CK_CLK1

SMB_CK_DAT1ICH9

LCD_CLK

LCD_DAT

KB926

KB926

Cantiga

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

ME@ : means ME part.

45@ : means install after SMT.

INVERTERBATTEEPROM

X

X

X

XX

SERIAL

VV

XX

X

X

XX

THERMAL

SENSOR

SODIMMCLK CHIP

(CPU)

XX

X

V

X

V V V

X X

X

X

MINI CARD

LCD

XX

X

X

X

X

V

I2C / SMBUS ADDRESSING

DEVICE

DDR SO-DIMM 0

CLOCK GENERATOR (EXT.)

HEX ADDRESS

A0

D2

1 0 1 0 0 0 0 0

1 1 0 1 0 0 1 0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LS-5588

LS-5588

LS-5588

3 35Wednesday, July 01, 2009

3 35Wednesday, July 01, 2009

3 35Wednesday, July 01, 2009

0.3

0.3

0.3

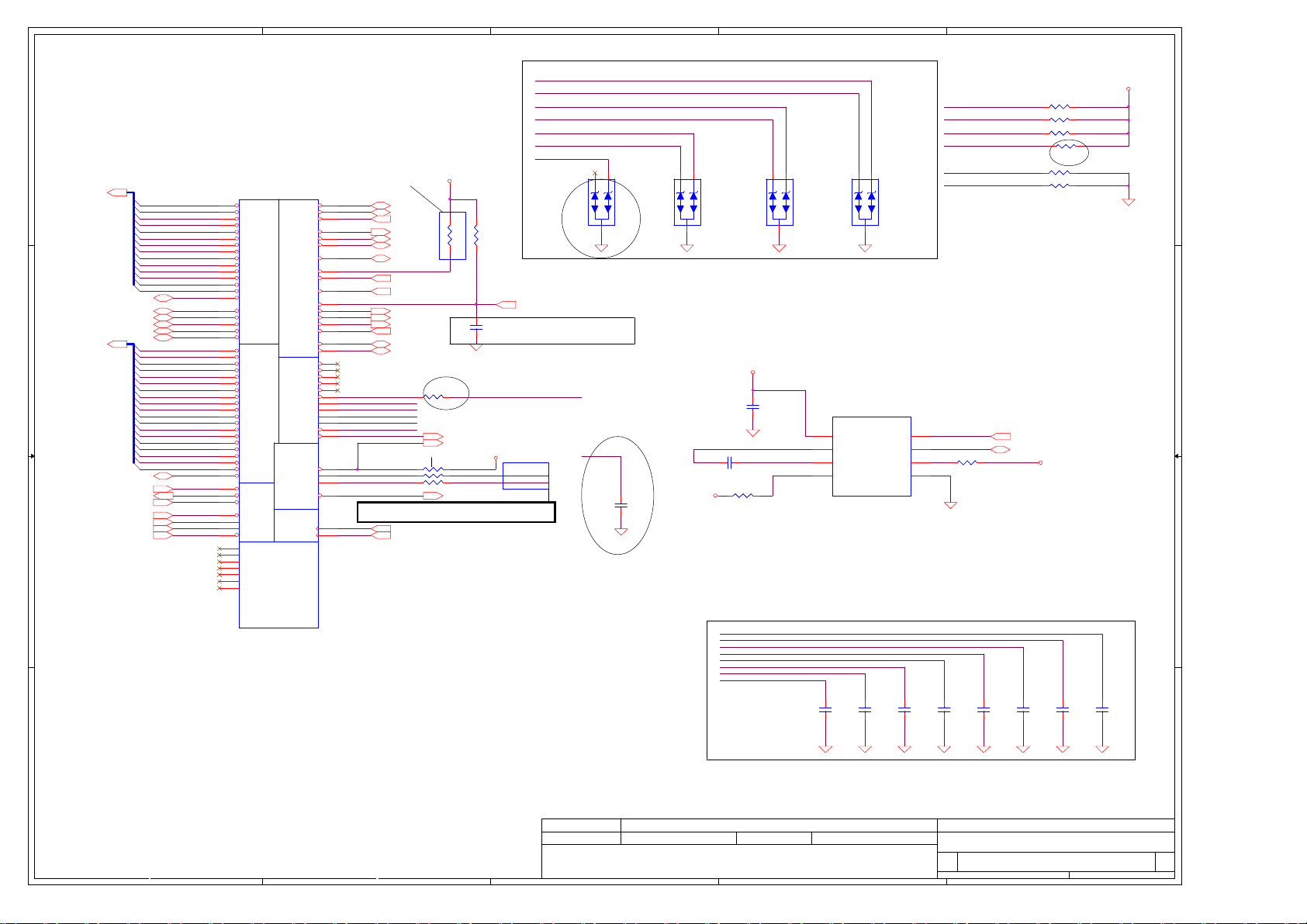

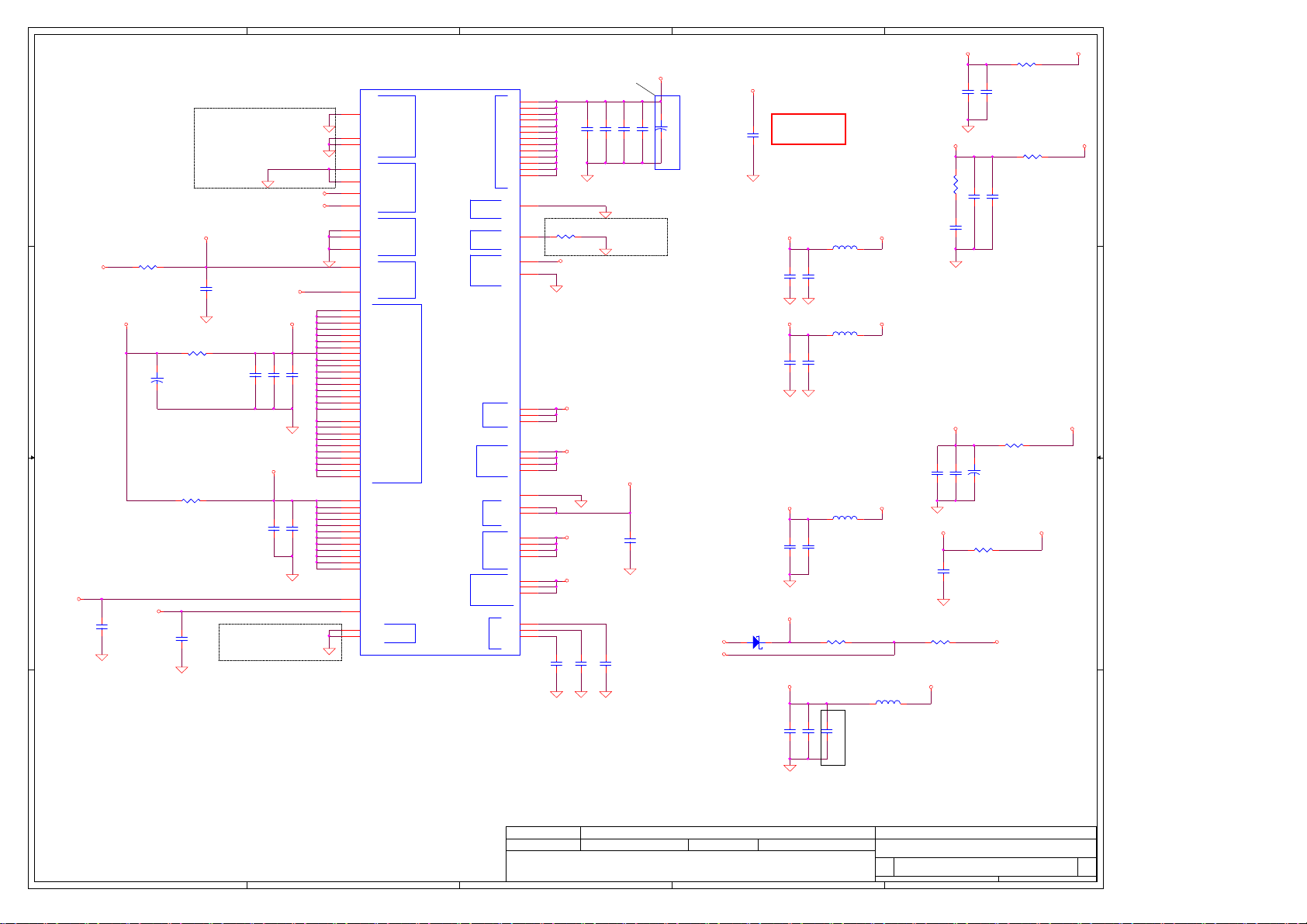

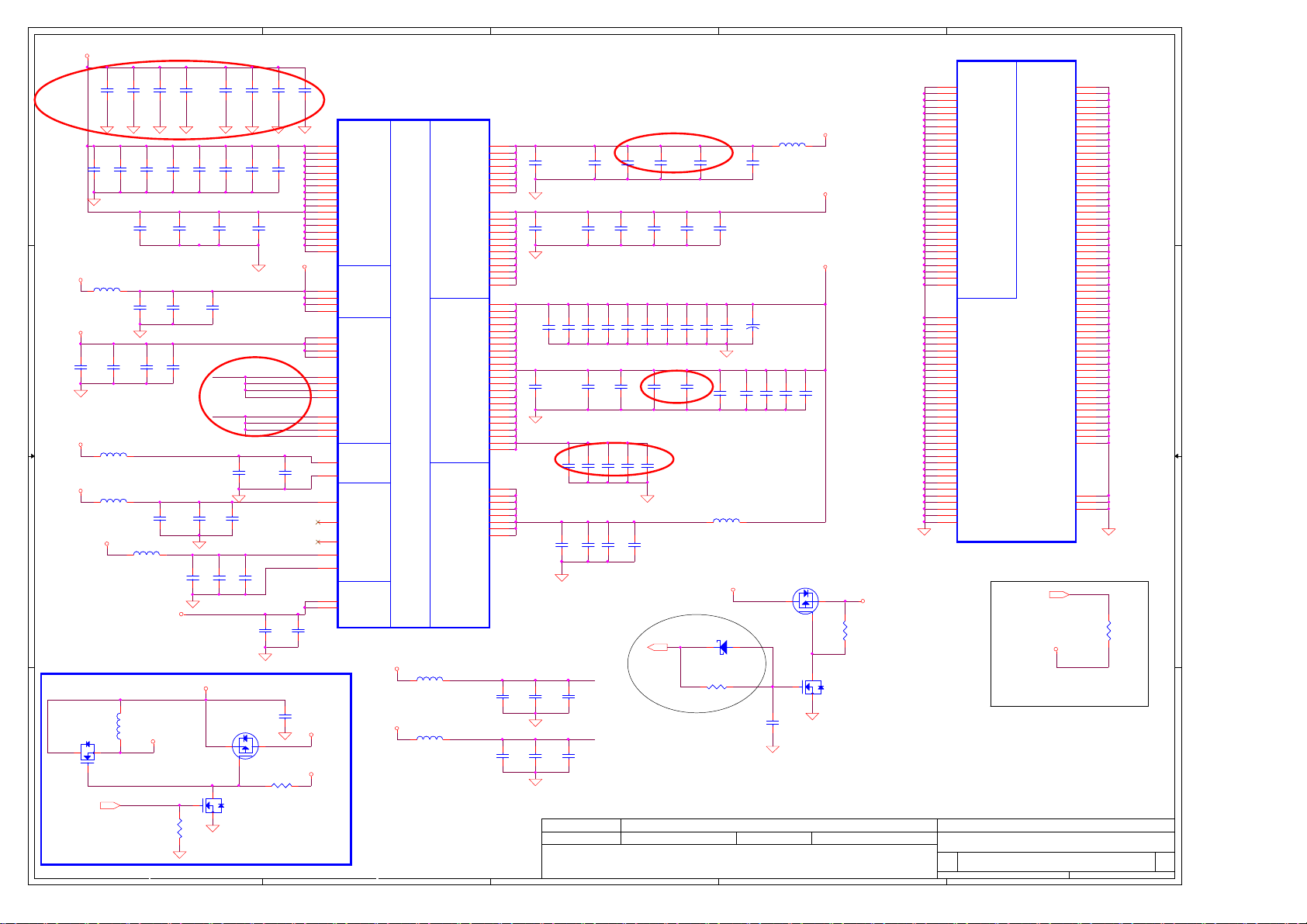

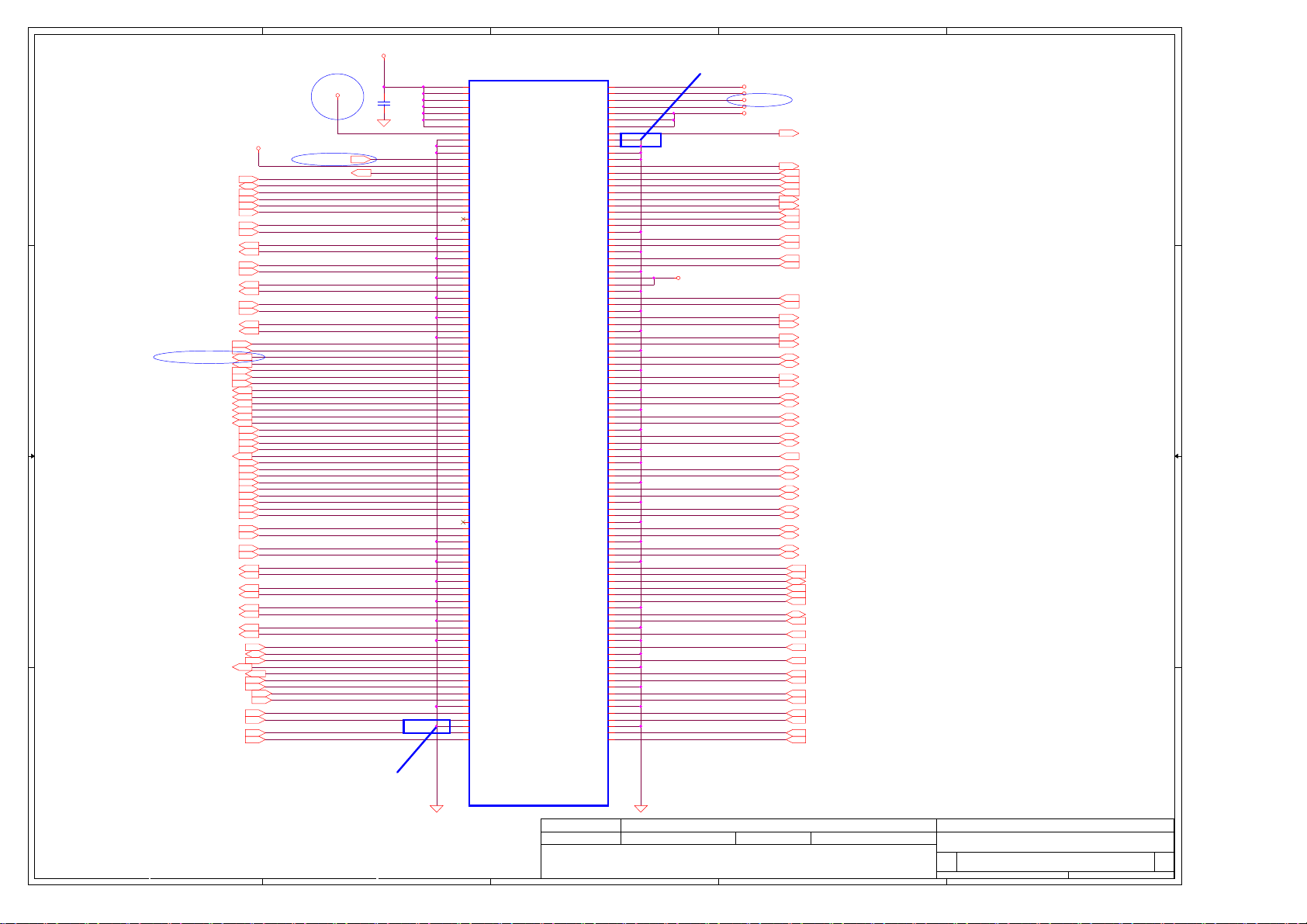

Page 4

5

4

3

2

1

XDP_TDI

XDP_DBRESET#

XDP_TDO

XDP_TMS

0518/'09

H_RESET# [8]

@

@

R03

H_THERMDA

H_THERMDC

XDP_TRST#

XDP_TCK

XDP_BPM#5

For ESD

XDP_BPM#5

R03

For EMI

H_PROCHOT#

R03

2

3

1

@

@

D12

D12

PJDLC05_SOT23-3

PJDLC05_SOT23-3

@

@

1

C1045

C1045

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

3

1

@

@

2

D9

D9

PJDLC05_SOT23-3

PJDLC05_SOT23-3

+3VS

C1035

C1035

1 2

2200P_0402_50V7K

2200P_0402_50V7K

R306

R306

1 2

10K_0402_5%

10K_0402_5%

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C1034

C1034

@

@

2

3

1

H_THERMDA

H_THERMDC

THERM#

D10

D10

PJDLC05_SOT23-3

PJDLC05_SOT23-3

U7

U7

1

2

3

4

EMC1402-1-ACZL-TR_MSOP8

EMC1402-1-ACZL-TR_MSOP8

Address:100_1100

VDD

DP

DN

THERM#

3

1

@

@

2

D11

D11

PJDLC05_SOT23-3

PJDLC05_SOT23-3

SMCLK

SMDATA

ALERT#

GND

8

7

6

5

D D

H_A#[3..16][8]

H_A#[17..35][8]

C C

B B

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0[8]

H_REQ#0[8]

H_REQ#1[8]

H_REQ#2[8]

H_REQ#3[8]

H_REQ#4[8]

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1[8]

H_A20M#[23]

H_FERR#[23]

H_IGNNE#[23]

H_STPCLK#[23]

H_INTR[23]

H_NMI[23]

H_SMI#[23]

U1A

U1A

P2

A[3]#

V4

A[4]#

W1

A[5]#

T4

AA1

AB4

T2

AC5

AD2

AD4

AA5

AE5

AB2

AC1

Y4

R1

R5

U1

P4

W5

AN1

AK4

AG1

AT4

AK2

AT2

AH2

AF4

AJ5

AH4

AM4

AP4

AR5

AJ1

AL1

AM2

AU5

AP2

AR1

AN5

C7

D4

F10

F8

C9

C5

E5

V2

Y2

AG5

AL5

J9

F4

H8

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD01

RSVD02

RSVD03

RSVD04

RSVD05

RSVD06

RSVD07

ADDR GROUP 0 ADDR GROUP 1

ADDR GROUP 0 ADDR GROUP 1

ICH

ICH

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

CONTROL

CONTROL

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

M4

J5

L5

N5

F38

J1

M2

B40

D8

N1

G5

K2

H4

K4

L1

H2

HIT#

F2

AY8

BA7

BA5

AY2

AV10

AV2

AV4

TCK

AW7

TDI

AU1

AW5

AV8

J7

D38

BB34

BD34

B10

A35

C35

RESERVED

RESERVED

H_BPRI# [8]

H_DEFER# [8]

H_INIT# [23]

H_LOCK# [8]

H_RESET#

H_TRDY# [8]

XDP_BPM#5_R

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT#

Place Close to U1.

H_THERMDA_R

H_THERMDC_R

H_THERMTRIP#

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

CLK_CPU_BCLK [16]

CLK_CPU_BCLK# [16]

Place close to U1.

+VCCP

H_ADS# [8]

H_BNR# [8]

H_DRDY# [8]

H_DBSY# [8]

H_BR0# [8]

H_RS#0 [8]

H_RS#1 [8]

H_RS#2 [8]

H_HIT# [8]

H_HITM# [8]

R22 68_0402_5%

R22 68_0402_5%

R23 0_0402_5%R23 0_0402_5%

R24 0_0402_5%R24 0_0402_5%

R25

R25

1 2

1 2

1 2

1 2

1 2

R9

R9

56_0402_5%

56_0402_5%

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0_0402_5%

0_0402_5%

XDP_DBRESET# [24]

H_PROCHOT# [31]

H_THERMTRIP# [8,23]

R10

R10

51_0402_1%

51_0402_1%

9/20

1 2

1

C1251

C1251

2

Add 0 ohm per EMI request.

10/17

+VCCP

XDP_TDI

XDP_TMS

XDP_TDO

XDP_BPM#5

XDP_TRST#

XDP_TCK

This shall place near CPU

SMB_EC_CK2

SMB_EC_DA2

R305 10K_0402_5%

R305 10K_0402_5%

1 2

R1 54.9_0402_1%R1 54.9_0402_1%

1 2

R2 54.9_0402_1%R2 54.9_0402_1%

1 2

R3 54.9_0402_1%R3 54.9_0402_1%

1 2

R4 54.9_0402_1%R4 54.9_0402_1%

1 2

R03

R6 51_0402_1%

R6 51_0402_1%

1 2

R7 54.9_0402_1%R7 54.9_0402_1%

1 2

EC_SMB_CK2 [17,26]

EC_SMB_DA2 [17,26]

+3VS

+VCCP

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

For ESD 4/21

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1

1

1

C1037

C1037

C1036

C1036

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

@

@

2

1

C1038

C1038

C1039

C1039

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

@

@

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LS-5588

LS-5588

LS-5588

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1

C1041

C1041

C1040

C1040

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

@

@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Penryn(1/3)-AGTL+/ITP-XDP

Penryn(1/3)-AGTL+/ITP-XDP

Penryn(1/3)-AGTL+/ITP-XDP

1

1

C1043

C1043

C1042

C1042

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

@

@

0.3

0.3

4 35Wednesday, July 01, 2009

4 35Wednesday, July 01, 2009

4 35Wednesday, July 01, 2009

1

0.3

Page 5

5

4

3

2

1

H_D#[0..15][8]

D D

H_DSTBN#0[8]

H_DSTBP#0[8]

H_DINV#0[8]

H_D#[16..31][8]

C C

layout note: Route TEST3 & TEST5 traces on

ground referenced layer to the TPs

H_DSTBN#1[8]

H_DSTBP#1[8]

H_DINV#1[8]

CPU_BSEL0[16]

CPU_BSEL1[16]

CPU_BSEL2[16]

V_CPU_GTLREF

T8T8

T9T9

T10T10

H_D#0

H_D#1

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

TEST2

TEST5

TEST6

CPU_BSEL CPU_BSEL2 CPU_BSEL1

B B

166

200

0 1

0

1

U1B

U1B

F40

D[0]#

G43

D[1]#

E43

D[2]#

J43

D[3]#

H40

D[4]#

H44

D[5]#

G39

D[6]#

E41

D[7]#

L41

D[8]#

K44

D[9]#

N41

D[10]#

T40

D[11]#

M40

D[12]#

G41

D[13]#

M44

D[14]#

L43

D[15]#

K40

DSTBN[0]#

J41

DSTBP[0]#

P40

DINV[0]#

P44

D[16]#

V40

D[17]#

V44

D[18]#

AB44

D[19]#

R41

D[20]#

W41

D[21]#

N43

D[22]#

U41

D[23]#

AA41

D[24]#

AB40

D[25]#

AD40

D[26]#

AC41

D[27]#

AA43

D[28]#

Y40

D[29]#

Y44

D[30]#

T44

D[31]#

U43

DSTBN[1]#

W43

DSTBP[1]#

R43

DINV[1]#

AW43

GTLREF

E37

TEST1

D40

TEST2

C43

TEST3

AE41

TEST4

AY10

TEST5

AC43

TEST6

A37

BSEL[0]

C37

BSEL[1]

B38

BSEL[2]

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

CPU_BSEL0

1

0

D[32]#

D[33]#

D[34]#

DATA GROUP 0 DATA GROUP 1

DATA GROUP 0 DATA GROUP 1

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

DATA GROUP 2DATA GROUP 3

DATA GROUP 2DATA GROUP 3

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

MISC

MISC

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Cause CPU core power change to

1 phase, and not need support

the pin, leave it as TP. 10/02

AR43

AH40

AF40

AJ43

AG41

AF44

AH44

AM44

AN43

AM40

AK40

AG43

AP40

AN41

AL41

AK44

AL43

AJ41

AV38

AT44

AV40

AU41

AW41

AR41

BA37

BB38

AY36

AT40

BC35

BC39

BA41

BB40

BA35

AU43

AY40

AY38

BC37

AE43

AD44

AE1

AF2

G7

B8

C41

E7

D10

BD10

H_PSI#

H_D#33

H_D#34H_D#2

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

COMP1

COMP2

COMP3

H_D#32

AP44

H_DPRSTP# [8,23,31]

H_DPSLP# [23]

H_DPWR# [8]

H_PWRGOOD [23]

H_CPUSLP# [8]

T11T11

H_D#[32..47] [8]

H_DSTBN#2 [8]

H_DSTBP#2 [8]

H_DINV#2 [8]

H_D#[48..63] [8]

H_DSTBN#3 [8]

H_DSTBP#3 [8]

H_DINV#3 [8]

R32

R32

R33

R33

R31

R31

R30

R30

12

12

12

12

27.4_0402_1%

27.4_0402_1%

54.9_0402_1%

54.9_0402_1%

27.4_0402_1%

27.4_0402_1%

54.9_0402_1%

54.9_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

266 0 0 0

+VCC_CORE +VCC_CORE

U1C

U1C

F32

VCC[001]

G33

VCC[002]

H32

VCC[003]

J33

VCC[004]

K32

VCC[005]

L33

VCC[006]

M32

VCC[007]

N33

VCC[008]

P32

VCC[009]

R33

VCC[010]

T32

VCC[011]

U33

VCC[012]

V32

VCC[013]

W33

VCC[014]

Y32

VCC[015]

AA33

VCC[016]

AB32

VCC[017]

AC33

VCC[018]

AD32

VCC[019]

AE33

VCC[020]

AF32

VCC[021]

AG33

VCC[022]

AH32

VCC[023]

AJ33

VCC[024]

AK32

VCC[025]

AL33

VCC[026]

AM32

VCC[027]

AN33

VCC[028]

AP32

VCC[029]

AR33

VCC[030]

AT34

VCC[031]

AT32

VCC[032]

AU33

VCC[033]

AV32

VCC[034]

AY32

VCC[035]

BB32

VCC[036]

BD32

VCC[037]

B28

VCC[038]

B30

VCC[039]

B26

VCC[040]

D28

VCC[041]

D30

VCC[042]

F30

VCC[043]

F28

VCC[044]

H30

VCC[045]

H28

VCC[046]

D26

VCC[047]

F26

VCC[048]

H26

VCC[049]

K30

VCC[050]

K28

VCC[051]

M30

VCC[052]

M28

VCC[053]

K26

VCC[054]

M26

VCC[055]

P30

VCC[056]

P28

VCC[057]

T30

VCC[058]

T28

VCC[059]

V30

VCC[060]

V28

VCC[061]

P26

VCC[062]

T26

VCC[063]

V26

VCC[064]

Y30

VCC[065]

Y28

VCC[066]

AB30

VCC[067]

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP_001

VCCP_002

VCCP_003

VCCP_004

VCCP_005

VCCP_006

VCCP_007

VCCP_008

VCCP_009

VCCP_010

VCCP_011

VCCP_012

VCCP_013

VCCP_014

VCCP_015

VCCP_016

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB28

AD30

AD28

Y26

AB26

AD26

AF30

AF28

AH30

AH28

AF26

AH26

AK30

AK28

AM30

AM28

AP30

AP28

AK26

AM26

AP26

AT30

AT28

AV30

AV28

AY30

AY28

AT26

AV26

AY26

BB30

BB28

BD30

R27 0_0402_5%R27 0_0402_5%

1 2

J11

R28 0_0402_5% R28 0_0402_5%

1 2

E11

R29 0_0402_5% R29 0_0402_5%

1 2

G11

J37

K38

L37

N37

P38

R37

U37

V38

W37

AA37

AB38

AC37

AE37

B34

D34

BD8

BC7

BB10

BB8

BC5

BB4

AY4

VCCSENSE

BD12

VSSSENSE

BC13

Length match within 25 mils.

The trace width/space/other is

20/7/25.

+VCCP

1

+

+

330U_D2E_2.5VM_R9M

330U_D2E_2.5VM_R9M

2

CPU_VID0 [31]

CPU_VID1 [31]

CPU_VID2 [31]

CPU_VID3 [31]

CPU_VID4 [31]

CPU_VID5 [31]

CPU_VID6 [31]

VCCSENSE [31]

VSSSENSE [31]

C5

C5

0.01U_0402_16V7K

0.01U_0402_16V7K

Near pin B34

Change to 330u_R9,

casue high

limitation. 12/14

1

1

C6

C6

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+1.5VS

C7

C7

Near pin D34

+VCC_CORE

R34

R34

+VCCP

12

R36

Z=55 ohm

V_CPU_GTLREF

A A

Close to CPU pin AW43

within 500mils.

R36

1K_0402_1%

1K_0402_1%

12

R37

R37

2K_0402_1%

2K_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

1 2

100_0402_1%

100_0402_1%

R35

R35

1 2

100_0402_1%

100_0402_1%

Close to CPU pin

within 500mils.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCCSENSE

VSSSENSE

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Penryn(2/3)-AGTL+/ITP-XDP

Penryn(2/3)-AGTL+/ITP-XDP

Penryn(2/3)-AGTL+/ITP-XDP

LS-5588

LS-5588

LS-5588

1

0.3

0.3

5 35Wednesday, July 01, 2009

5 35Wednesday, July 01, 2009

5 35Wednesday, July 01, 2009

0.3

Page 6

5

D D

AL37

AN37

AP38

B32

C33

D32

E35

E33

F34

G35

F36

H36

J35

L35

N35

K36

R35

U35

P36

V36

W35

AA35

AC35

AB36

AE35

C C

VCCP_021

VCCP_022

VCCP_023

VCCP_024

VCCP_025

VCCP_026

VCCP_027

VCCP_028

VCCP_029

VCCP_030

VCCP_031

VCCP_032

VCCP_033

VCCP_034

VCCP_035

VCCP_036

VCCP_037

VCCP_038

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

F24

F22

B22

B24

D22

D24

BD28

BB26

H24

BD26

T24

H22

K24

K22

P24

P22

M24

M22

AG35

VCCP_039

VCCP_040

VCCP_041

VCCP_042

VCCP_043

VCCP_044

VCCP_045

VCCP_046

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

T22

V24

V22

Y24

Y22

AB24

AB22

AD24

4

AJ35

AF36

AL35

AN35

AK36

AP36

B12

B14

C13

D12

D14

E13

F14

F12

G13

H14

H12

J13

K14

K12

L13

L11

M14

N13

N11

K10

P14

P12

R13

R11

T14

U13

U11

V14

V12

VCCP_047

VCCP_048

VCCP_049

VCCP_050

VCCP_051

VCCP_052

VCCP_053

VCCP_054

VCCP_055

VCCP_056

VCCP_057

VCCP_058

VCCP_059

VCCP_060

VCCP_061

VCCP_062

VCCP_063

VCCP_064

VCCP_065

VCCP_066

VCCP_067

VCCP_068

VCCP_069

VCCP_070

VCCP_071

VCCP_072

VCCP_073

VCCP_074

VCCP_075

VCCP_076

VCCP_077

VCCP_078

VCCP_079

VCCP_080

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

F18

F16

B16

B18

AF24

AF22

AD22

AH24

AT24

AH22

AT22

AK24

AK22

AP24

AP22

AV24

AV22

AM24

AY24

AM22

B20

AY22

BB24

BB22

BD24

BD22

F20

D16

D18

H18

H16

D20

H20

K18

K16

VCCP_081

VCC_161

3

W13

W11

P10

V10

Y14

AA13

AA11

AB14

AB12

AC13

AC11

AD14

AB10

AE13

AE11

AF14

AF12

AG13

AG11

AH14

AJ13

AJ11

AF10

AK14

AK12

AL13

AL11

AN13

AN11

AP12

AR13

AR11

AK10

AP10

VCCP_082

VCCP_083

VCCP_084

VCCP_085

VCCP_086

VCCP_087

VCCP_088

VCCP_089

VCCP_090

VCCP_091

VCCP_092

VCCP_093

VCCP_094

VCCP_095

VCCP_096

VCCP_097

VCCP_098

VCCP_099

VCCP_100

VCCP_101

VCCP_102

VCCP_103

VCCP_104

VCCP_105

VCCP_106

VCCP_107

VCCP_108

VCCP_109

VCCP_110

VCCP_111

VCCP_112

VCCP_113

VCCP_114

VCCP_115

VCC_162

VCC_163

VCC_164

VCC_165

VCC_166

VCC_167

VCC_168

VCC_169

VCC_170

VCC_171

VCC_172

VCC_173

VCC_174

VCC_175

VCC_176

VCC_177

VCC_178

VCC_179

VCC_180

VCC_181

VCC_182

VCC_183

VCC_184

VCC_185

VCC_186

VCC_187

VCC_188

VCC_189

VCC_190

VCC_191

VCC_192

VCC_193

VCC_194

VCC_195

T18

T16

K20

M18

M16

M20

T20

P18

P16

V18

V16

P20

V20

Y18

Y16

Y20

AF18

AF16

AB18

AB16

AD18

AD16

AF20

AB20

AD20

AH18

AH16

AH20

AK18

AK16

AP18

AP16

AM18

AM16

2

AU13

AU11

VCCP_116

VCCP_117

VCCP_118L9VCCP_119L7VCCP_120N9VCCP_121N7VCCP_122R9VCCP_123R7VCCP_124U9VCCP_125U7VCCP_126W9VCCP_127W7VCCP_128

VCC_196

VCC_197

VCC_198

VCC_199

VCC_200

VCC_201

VCC_202

VCC_203

AT18

AT16

AK20

AP20

AV18

AV16

AY18

AM20

1

+VCCP

AA9

AA7

AC9

AC7

AE9

AE7

AG9

AG7

AJ9

AJ7

AL9

AL7

AN9

AN7

AR9

AR7

A33

A13

U1F

U1F

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

VCCP_129

VCCP_130

VCCP_131

VCCP_132

VCCP_133

VCCP_134

VCCP_135

VCCP_136

VCCP_137

VCCP_138

VCCP_139

VCCP_140

VCCP_141

VCCP_142

VCCP_143

VCCP_144

VCCP_145

VCC_204

VCC_205

VCC_206

VCC_207

VCC_208

VCC_209

VCC_210

VCC_211

VCC_212

VCC_213

VCC_214

VCC_215

VCC_216

VCC_217

VCC_218

VCC_219

VCC_220

VCCP_020

VCCP_018

VCCP_019

VCCP_017

AT20

AY16

AV20

AY20

BB18

AT14

BB16

BD18

BD16

BB20

BD20

AP14

AM14

AJ37

AF38

AV14

AY14

BB14

BD14

AK38

AG37

+VCC_CORE +VCCP

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Penryn(3/3)-Power

Penryn(3/3)-Power

Penryn(3/3)-Power

LS-5588

LS-5588

LS-5588

1

0.3

0.3

6 35Wednesday, July 01, 2009

6 35Wednesday, July 01, 2009

6 35Wednesday, July 01, 2009

0.3

Page 7

5

U1E

U1D

U1D

B42

VSS[001]

F44

VSS[002]

D44

VSS[003]

D42

VSS[004]

F42

VSS[005]

H42

VSS[006]

K42

VSS[007]

M42

VSS[008]

P42

VSS[009]

T42

VSS[010]

V42

VSS[011]

Y42

D D

C C

B B

A A

VSS[012]

AB42

VSS[013]

AD42

VSS[014]

AF42

VSS[015]

AH42

VSS[016]

AK42

VSS[017]

AM42

VSS[018]

AP42

VSS[019]

AY44

VSS[020]

AV44

VSS[021]

AT42

VSS[022]

AV42

VSS[023]

AY42

VSS[024]

BA43

VSS[025]

BB42

VSS[026]

C39

VSS[027]

E39

VSS[028]

G37

VSS[029]

H38

VSS[030]

J39

VSS[031]

L39

VSS[032]

M38

VSS[033]

N39

VSS[034]

R39

VSS[035]

T38

VSS[036]

U39

VSS[037]

W39

VSS[038]

Y38

VSS[039]

AA39

VSS[040]

AC39

VSS[041]

AD38

VSS[042]

AE39

VSS[043]

AG39

VSS[044]

AH38

VSS[045]

AJ39

VSS[046]

AL39

VSS[047]

AM38

VSS[048]

AN39

VSS[049]

AR39

VSS[050]

AR37

VSS[051]

AT38

VSS[052]

AU39

VSS[053]

AU37

VSS[054]

AW39

VSS[055]

AW37

VSS[056]

BA39

VSS[057]

BC41

VSS[058]

BD40

VSS[059]

BD38

VSS[060]

B36

VSS[061]

H34

VSS[062]

D36

VSS[063]

K34

VSS[064]

M34

VSS[065]

M36

VSS[066]

P34

VSS[067]

T34

VSS[068]

V34

VSS[069]

T36

VSS[070]

Y34

VSS[071]

AB34

VSS[072]

AD34

VSS[073]

Y36

VSS[074]

AD36

VSS[075]

AF34

VSS[076]

AH34

VSS[077]

AH36

VSS[078]

AK34

VSS[079]

AM34

VSS[080]

AP34

VSS[081]

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

5

AM36

AR35

AU35

AV34

AW35

AW33

AY34

AT36

AV36

BA33

BC33

BB36

BD36

C27

C29

C31

E29

E27

G29

G27

E31

G31

J29

J27

L29

L27

N29

N27

J31

L31

N31

R29

R27

U29

U27

R31

U31

W29

W27

W31

AA29

AA27

AC29

AC27

AA31

AC31

AE29

AE27

AG29

AG27

AJ29

AJ27

AE31

AG31

AJ31

AL29

AL27

AN29

AN27

AL31

AN31

AR29

AR27

AR31

AU29

AU27

AW29

AW27

AU31

AW31

BA29

BA27

BC29

BC27

BA31

BC31

C21

C23

C25

E25

E23

E21

U1E

G25

VSS_164

G23

VSS_165

G21

VSS_166

J25

VSS_167

J23

VSS_168

J21

VSS_169

L25

VSS_170

L23

VSS_171

L21

VSS_172

N25

VSS_173

N23

VSS_174

N21

VSS_175

R25

VSS_176

R23

VSS_177

R21

VSS_178

U25

VSS_179

U23

VSS_180

U21

VSS_181

W25

VSS_182

W23

VSS_183

W21

VSS_184

AA25

VSS_185

AA23

VSS_186

AA21

VSS_187

AC25

VSS_188

AC23

VSS_189

AC21

VSS_190

AE25

VSS_191

AE23

VSS_192

AE21

VSS_193

AG25

VSS_194

AG23

VSS_195

AG21

VSS_196

AJ25

VSS_197

AJ23

VSS_198

AJ21

VSS_199

AL25

VSS_200

AL23

VSS_201

AL21

VSS_202

AN25

VSS_203

AN23

VSS_204

AN21

VSS_205

AR25

VSS_206

AR23

VSS_207

AR21

VSS_208

AU25

VSS_209

AU23

VSS_210

AU21

VSS_211

AW25

VSS_212

AW23

VSS_213

AW21

VSS_214

BA25

VSS_215

BA23

VSS_216

BA21

VSS_217

BC25

VSS_218

BC23

VSS_219

BC21

VSS_220

C17

VSS_221

C19

VSS_222

E19

VSS_223

E17

VSS_224

G19

VSS_225

G17

VSS_226

J19

VSS_227

J17

VSS_228

L19

VSS_229

L17

VSS_230

N19

VSS_231

N17

VSS_232

R19

VSS_233

R17

VSS_234

U19

VSS_235

U17

VSS_236

W19

VSS_237

W17

VSS_238

AA19

VSS_239

AA17

VSS_240

AC19

VSS_241

AC17

VSS_242

AE19

VSS_243

AE17

VSS_244

AG19

VSS_245

AG17

VSS_246

AJ19

VSS_247

AJ17

VSS_248

AL19

VSS_249

AL17

VSS_250

AN19

VSS_251

AN17

VSS_252

AR19

VSS_253

AR17

VSS_254

AU19

VSS_255

AU17

VSS_256

AW19

VSS_257

AW17

VSS_258

BA19

VSS_259

BA17

VSS_260

BC19

VSS_261

BC17

VSS_262

C11

VSS_263

C15

VSS_264

E15

VSS_265

G15

VSS_266

H10

VSS_267

M12

VSS_268

J15

VSS_269

L15

VSS_270

N15

VSS_271

M10

VSS_272

T12

VSS_273

R15

VSS_274

U15

VSS_275

W15

VSS_276

T10

VSS_277

Y12

VSS_278

AD12

VSS_279

PENRYN SFF_UFCBGA956

PENRYN SFF_UFCBGA956

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

VSS_361

VSS_362

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

AA15

AC15

Y10

AD10

AH12

AE15

AG15

AJ15

AH10

AM12

AL15

AN15

AR15

AM10

AT12

AV12

AW13

AW11

AY12

AU15

AW15

AT10

BA13

BA11

BB12

BC11

BA15

BC15

B6

D6

E9

F6

G9

H6

K8

K6

M8

M6

P8

P6

T8

T6

V8

V6

U5

Y8

Y6

AB8

AB6

AD8

AD6

AF8

AF6

AH8

AH6

AK8

AK6

AM8

AM6

AP8

AP6

AT8

AT6

AU9

AV6

AU7

AW9

AY6

BA9

BB6

BC9

BD6

B4

C3

E3

G3

J3

L3

N3

R3

U3

W3

AA3

AC3

AE3

AG3

AJ3

AL3

AN3

AR3

AU3

AW3

BA3

BC3

D2

E1

G1

AW1

BA1

BB2

A41

A39

A29

A27

A31

A25

A23

A21

A19

A17

A11

A15

A7

A5

A9

BD4

4

+VCC_CORE

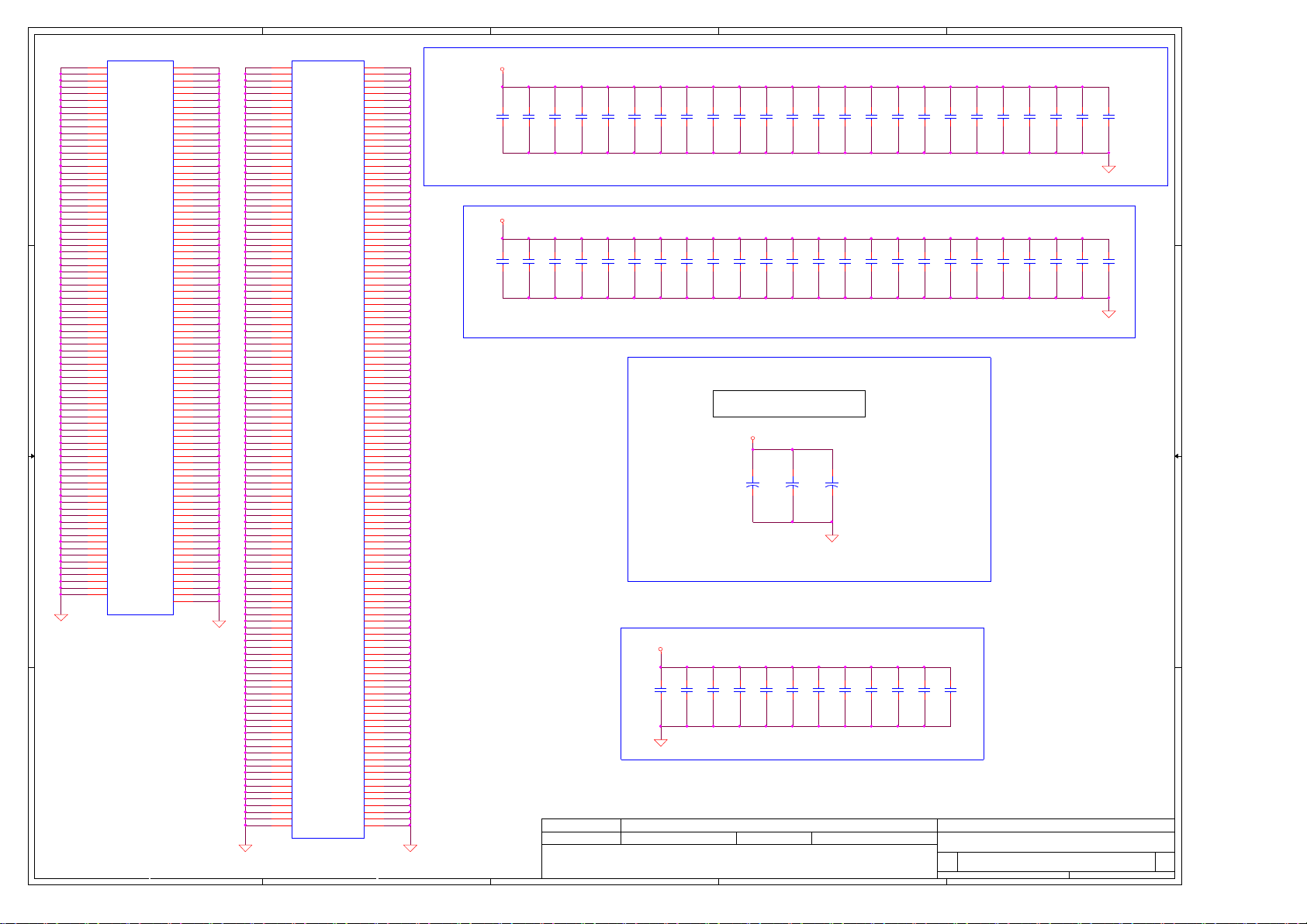

10U_0603_6.3V6M

10U_0603_6.3V6M

C8

C8

+VCC_CORE

1U_0402_6.3V6K

1U_0402_6.3V6K

C32

C32

Mid Frequence Decoupling

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

1

2

1

C9

C9

C10

C10

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C33

C33

C34

C34

2

2

3

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C11

C11

2

High Frequence Decoupling

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C35

C35

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C13

C13

C12

C12

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C37

C37

C36

C36

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C14

C14

2

1

C38

C38

2

1

1

C16

C16

C15

C15

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C39

C39

C40

C40

2

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C17

C17

C18

C18

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C41

C41

C42

C42

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C19

C19

C20

C20

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C44

C44

C43

C43

2

2

10U_0603_6.3V6M

1

1

C21

C21

C22

C22

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C46

C46

C45

C45

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C24

C24

C23

C23

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C48

C48

C47

C47

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C25

C25

2

1

C49

C49

2

1

1

C27

C27

C26

C26

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C51

C51

C50

C50

2

2

1

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C28

C28

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C52

C52

2

10U_0603_6.3V6M

1

1

C29

C29

2

1

C53

C53

2

1

C30

C30

C31

C31

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C54

C54

C55

C55

2

2

6/14 :Replace 12pcs 10uF_0805 to 24 pcs 1uF_0402 for CPU transient fail issue.

ESR <= 1.5m ohm

Near CPU CORE regulator

+VCC_CORE

220U_D2_2VK_R9

220U_D2_2VK_R9

1

+

+

C56

C56

2

Del C37 to improve power plan. 6/14

+VCCP

1U_0402_6.3V6K

1U_0402_6.3V6K

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C60

C60

C59

C59

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C63

C61

C61

2

C63

C62

C62

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

220U_D2_2VK_R9

220U_D2_2VK_R9

220U_D2_2VK_R9

1

C57

C57

2

1

C64

C64

2

220U_D2_2VK_R9

1

+

+

+

+

C58

C58

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C65

C65

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C66

C66

C67

C67

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C68

C68

2

1

1

C70

C70

C69

C69

2

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Penryn(3/3)-GND/Bypass

Penryn(3/3)-GND/Bypass

Penryn(3/3)-GND/Bypass

LS-5588

LS-5588

LS-5588

1

0.3

0.3

7 35Wednesday, July 01, 2009

7 35Wednesday, July 01, 2009

7 35Wednesday, July 01, 2009

0.3

Page 8

5

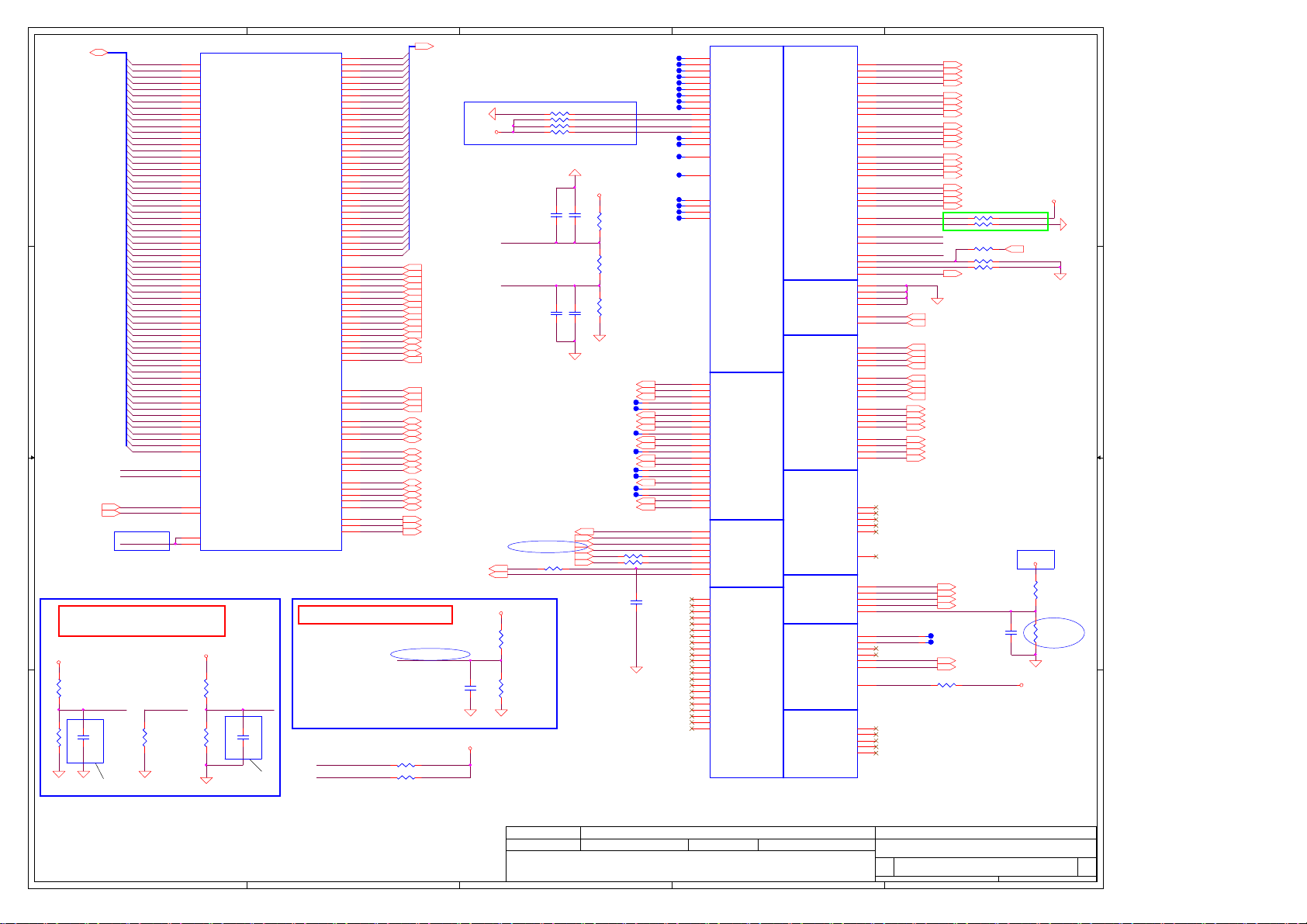

U3A

H_D#[0..63][5]

D D

C C

H_RESET#[4]

H_CPUSLP#[5]

layout note:

B B

Route H_SCOMP and H_SCOMP# with trace width,

spacing and impedance (55 ohm) same as FSB data

traces

Layout Note:

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

+VCCP

12

R55

R55

1K_0402_1%

1K_0402_1%

H_VREF

12

R592K_0402_1%

R592K_0402_1%

1

C78

<BOM Structure>

<BOM Structure>

A A

C78

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

within 100 mils from NB

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWNG

H_RCOMP

H_VREF

Trace < = 500mils

H_RCOMP

12

R60

R60

24.9_0402_1%

24.9_0402_1%

U3A

J7

H_D#_0

H6

H_D#_1

L11

H_D#_2

J3

H_D#_3

H4

H_D#_4

G3

H_D#_5

K10

H_D#_6

K12

H_D#_7

L1

H_D#_8

M10

H_D#_9

M6

H_D#_10

N11

H_D#_11

L7

H_D#_12

K6

H_D#_13

M4

H_D#_14

K4

H_D#_15

P6

H_D#_16

W9

H_D#_17

V6

H_D#_18

V2

H_D#_19

P10

H_D#_20

W7

H_D#_21

N9

H_D#_22

P4

H_D#_23

U9

H_D#_24

V4

H_D#_25

U1

H_D#_26

W3

H_D#_27

V10

H_D#_28

U7

H_D#_29

W11

H_D#_30

U11

H_D#_31

AC11

H_D#_32

AC9

H_D#_33

Y4

H_D#_34

Y10

H_D#_35

AB6

H_D#_36

AA9

H_D#_37

AB10

H_D#_38

AA1

H_D#_39

AC3

H_D#_40

AC7

H_D#_41

AD12

H_D#_42

AB4

H_D#_43

Y6

H_D#_44

AD10

H_D#_45

AA11

H_D#_46

AB2

H_D#_47

AD4

H_D#_48

AE7

H_D#_49

AD2

H_D#_50

AD6

H_D#_51

AE3

H_D#_52

AG9

H_D#_53

AG7

H_D#_54

AE11

H_D#_55

AK6

H_D#_56

AF6

H_D#_57

AJ9

H_D#_58

AH6

H_D#_59

AF12

H_D#_60

AH4

H_D#_61

AJ7

H_D#_62

AE9

H_D#_63

B6

H_SWING

D4

H_RCOMP

J11

H_CPURST#

G9

H_CPUSLP#

L17

H_AVREF

K18

H_DVREF

CANTIGA GMCH SFF_FCBGA1363

CANTIGA GMCH SFF_FCBGA1363

+VCCP

12

221_0603_1%

221_0603_1%

12

100_0402_1%

100_0402_1%

R56

R56

R61

R61

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Near B6 pin

H_SWNG

1

2

H_ADSTB#_0

H_ADSTB#_1

HOST

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

layout note:

Place them close to U4 pin BC51.

Layout Note: V_DDR_MCH_REF trace

width and spacing is 20/20.

C79

C79

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

PM_EXTTS#0

PM_EXTTS#1

4

H_A#3

L15

H_A#4

B14

H_A#5

C15

H_A#6

D12

H_A#7

F14

H_A#8

G17

H_A#9

B12

H_A#10

J15

H_A#11

D16

H_A#12

C17

H_A#13

D14

H_A#14

K16

H_A#15

F16

H_A#16

B16

H_A#17

C21

H_A#18

D18

H_A#19

J19

H_A#20

J21

H_A#21

B18

H_A#22

D22

H_A#23

G19

H_A#24

J17

H_A#25

L21

H_A#26

L19

H_A#27

G21

H_A#28

D20

H_A#29

K22

H_A#30

F18

H_A#31

K20

H_A#32

F20

H_A#33

F22

H_A#34

B20

H_A#35

A19

F10

A15

C19

C9

B8

C11

E5

D6

AH10

AJ11

G11

H2

C7

F8

A11

D8

L9

N7

AA7

AG3

K2

N3

AA3

AF4

L3

M2

Y2

AF2

J13

L13

C13

G13

G15

F4

F2

G7

R62 10K_0402_5%

R62 10K_0402_5%

1 2

R63 10K_0402_5%R63 10K_0402_5%

1 2

Del R48. 9/27

H_A#[3..35] [4]

H_ADS# [4]

H_ADSTB#0 [4]

H_ADSTB#1 [4]

H_BNR# [4]

H_BPRI# [4]

H_BR0# [4]

H_DEFER# [4]

H_DBSY# [4]

CLK_MCH_BCLK [16]

CLK_MCH_BCLK# [16]

H_DPWR# [5]

H_DRDY# [4]

H_HIT# [4]

H_HITM# [4]

H_LOCK# [4]

H_TRDY# [4]

H_DINV#0 [5]

H_DINV#1 [5]

H_DINV#2 [5]

H_DINV#3 [5]

H_DSTBN#0 [5]

H_DSTBN#1 [5]

H_DSTBN#2 [5]

H_DSTBN#3 [5]

H_DSTBP#0 [5]

H_DSTBP#1 [5]

H_DSTBP#2 [5]

H_DSTBP#3 [5]

H_REQ#0 [4]

H_REQ#1 [4]

H_REQ#2 [4]

H_REQ#3 [4]

H_REQ#4 [4]

H_RS#0 [4]

H_RS#1 [4]

H_RS#2 [4]

DDR3_NB_REF

3

Add them for Boundary Scan. 10/23

R38 1K_0402_5%@R38 1K_0402_5%@

1 2

R39 4.7K_0402_5%@R39 4.7K_0402_5%@

1 2

R40 4.7K_0402_5%@R40 4.7K_0402_5%@

1 2

R41 1K_0402_5%@R41 1K_0402_5%@

+3VS

H_THERMTRIP#[4,23]

PM_DPRSLPVR[24,31]

+1.5V

C77

C77

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+3VS

1 2

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

SMRCOMP_VOH

SMRCOMP_VOL

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

PM_BMBUSY#[24]

H_DPRSTP#[5,23,31]

PM_EXTTS#0[14]

PM_EXTTS#1[15]

PM_PWROK[24,26,31]

PLT_RST#[17,22,26]

1 2

R51 0_0402_5%R51 0_0402_5%

Add R428 in 9/26

12

R54

R54

10K_0402_1%

10K_0402_1%

12

R57

R57

10K_0402_1%

10K_0402_1%

1

C71

C71

C72

C72

2

1

C73

C73

C74

C74

2

+1.5V

1

12

R42

R42

0.01U_0402_25V7K

0.01U_0402_25V7K

2

1K_0402_1%

1K_0402_1%

12

R45

R45

3.01K_0402_1%

3.01K_0402_1%

12

R48

R48

1

1K_0402_1%

1K_0402_1%

2

0.01U_0402_25V7K

0.01U_0402_25V7K

MCH_CLKSEL0[16]

MCH_CLKSEL1[16]

MCH_CLKSEL2[16]

T30T30

T31T31

CFG5[10]

CFG6[10]

CFG7[10]

T32T32

CFG9[10]

CFG10[10]

T33T33

CFG12[10]

CFG13[10]

T34T34

T35T35

CFG16[10]

T36T36

T37T37

CFG19[10]

CFG20[10]

PM_EXTTS#0

PM_EXTTS#1

R49 0_0402_5%R49 0_0402_5%

1 2

R50 100_0402_1% R50 100_0402_1%

1 2

T12T12

T13T13

T14T14

T15T15

T16T16

T17T17

T18T18

T19T19

T20T20

TCK

TDI

TDO

TMS

T21T21

T22T22

T23T23

T24T24

T25T25

T26T26

T27T27

T28T28

C750.1U_0402_16V4Z@ C750.1U_0402_16V4Z@

1

2

RSVD1

L43

RSVD2

J41

RSVD3

L41

RSVD4

AN11

RSVD5

AM10

RSVD6

AK10

RSVD7

AL11

RSVD8

F12

RSVD9

AN45

RSVD10

AP44

RSVD11

AT44

RSVD12

AN47

RSVD13

C27

RSVD14

D30

RSVD15

J9

RSVD17

AW42

RSVD20

BB20

RSVD22

BE19

RSVD23

BF20

RSVD24

BF18

RSVD25

K26

CFG_0

G23

CFG_1

G25

CFG_2

J25

CFG_3

L25

CFG_4

L27

CFG_5

F24

CFG_6

D24

CFG_7

D26

CFG_8

J23

CFG_9

B26

CFG_10

A23

CFG_11

C23

CFG_12

B24

CFG_13

B22

CFG_14

K24

CFG_15

C25

CFG_16

L23

CFG_17

L33

CFG_18

K32

CFG_19

K34

CFG_20

J35

PM_SYNC#

F6

PM_DPRSTP#

J39

PM_EXT_TS#_0

L39

PM_EXT_TS#_1

AY39

PWROK

BB18

RSTIN#

K28

THERMTRIP#

K36

DPRSLPVR

A7

NC_1

A49

NC_2

A52

NC_3

A54

NC_4

B54

NC_5

D55

NC_6

G55

NC_7

BE55

NC_8

BH55

NC_9

BK55

NC_10

BK54

NC_11

BL54

NC_12

BL52

NC_13

BL49

NC_14

BL7

NC_15

BL4

NC_16

BL2

NC_17

BK2

NC_18

BK1

NC_19

BH1

NC_20

BE1

NC_21

G1

NC_22

CANTIGA GMCH SFF_FCBGA1363

CANTIGA GMCH SFF_FCBGA1363

U3B

U3B

J43

2

BB32

SA_CK_0

BA25

SA_CK_1

BA33

SB_CK_0

BA23

SB_CK_1

BA31

SA_CK#_0

BC25

SA_CK#_1

BC33

SB_CK#_0

BB24

SB_CK#_1

BC35

SA_CKE_0

BE33

SA_CKE_1

BE37

SB_CKE_0

BC37

SB_CKE_1

BK18

SA_CS#_0

BK16

SA_CS#_1

BE23

SB_CS#_0

BC19

SB_CS#_1

BJ17

SA_ODT_0

BJ19

SA_ODT_1

BC17

SB_ODT_0

BE17

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

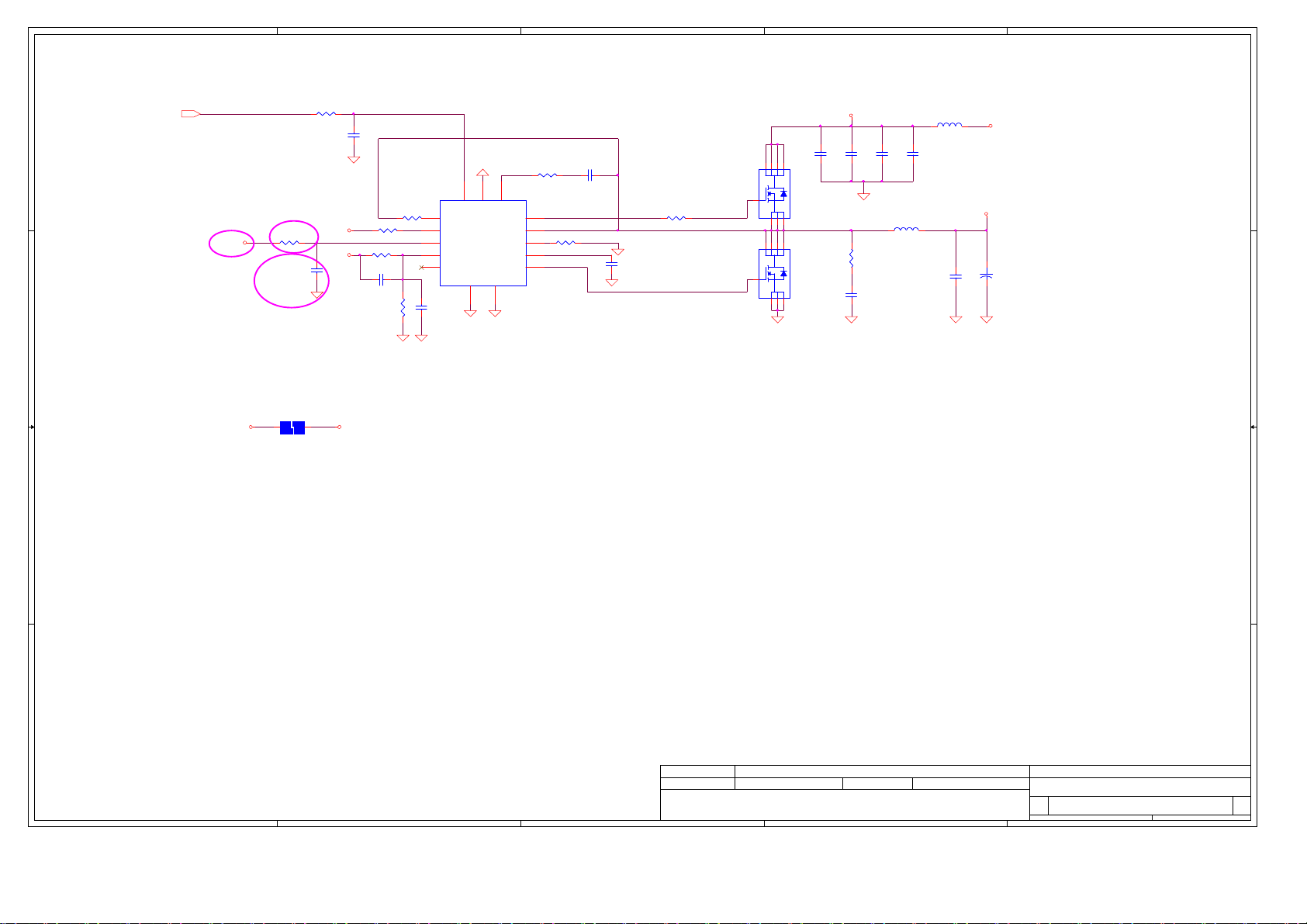

PEG_CLK

PEG_CLK#

CLK

CLK

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

CFGRSVD

CFGRSVD

PM

PM

NC

NC

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI

DMI

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

ME

ME

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

MISC

MISC

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

HDA

HDA

BL25

BK26

BK32

BL31

BC51

AY37

BH20

BA37

B42

D42

B50

D50

R49

P50

AG55

AL49

AH54

AL47

AG53

AK50

AH52

AL45

AG49

AJ49

AJ47

AG47

AF50

AH50

AJ45

AG45

G33

G37

F38

F36

G35

G39

AK52

AK54

AW40

AL53

AL55

F34

F32

B38

A37

C31

K42

D10

C29

B30

D28

A27

B28

SMRCOMP

SMRCOMP#

SMRCOMP_VOH

SMRCOMP_VOL

DDR3_NB_REF

SM_PWROK

SM_REXT

SM_DRAMRST#

CLK_MCH_3GPLL [16]

CLK_MCH_3GPLL# [16]

DMI_TXN0 [24]

DMI_TXN1 [24]

DMI_TXN2 [24]

DMI_TXN3 [24]

DMI_TXP0 [24]

DMI_TXP1 [24]

DMI_TXP2 [24]

DMI_TXP3 [24]

DMI_RXN0 [24]

DMI_RXN1 [24]

DMI_RXN2 [24]

DMI_RXN3 [24]

DMI_RXP0 [24]

DMI_RXP1 [24]

DMI_RXP2 [24]

DMI_RXP3 [24]

CL_VREF

TSATN#

R58 54.9_0402_1%R58 54.9_0402_1%

1 2

T38T38

T39T39

R46 10K_0402_1%@R46 10K_0402_1%@

R47 499_0402_1%R47 499_0402_1%

1

M_CLK_DDR0 [14]

M_CLK_DDR1 [14]

M_CLK_DDR2 [15]

M_CLK_DDR3 [15]

M_CLK_DDR#0 [14]

M_CLK_DDR#1 [14]

M_CLK_DDR#2 [15]

M_CLK_DDR#3 [15]

DDR_CKE0_DIMMA [14]

DDR_CKE1_DIMMA [14]

DDR_CKE2_DIMMB [15]

DDR_CKE3_DIMMB [15]

DDR_CS0_DIMMA# [14]

DDR_CS1_DIMMA# [14]

DDR_CS2_DIMMB# [15]

DDR_CS3_DIMMB# [15]

M_ODT0 [14]

M_ODT1 [14]

M_ODT2 [15]

M_ODT3 [15]

R43 80.6_0402_1%

R43 80.6_0402_1%

1 2

R44 80.6_0402_1%R44 80.6_0402_1%

R429 0_0402_5%R429 0_0402_5%

SM_DRAMRST# [14,15]

1 2

1 2

1 2

1 2

1.5V_PGOOD [28]

Modify in 9/26

+VCCP

CL_CLK0 [24]

CL_DATA0 [24]

M_PWROK [24]

CL_RST# [24]

1

C76

C76

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CLKREQ#_B [16]

MCH_ICH_SYNC# [24]

2

+VCCP

+1.5V

12

R52

R52

1K_0402_1%

1K_0402_1%

12

R53

R53

499_0402_1%

499_0402_1%

5

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/04/20 2010/04/30

2009/04/20 2010/04/30

2009/04/20 2010/04/30

3

Deciphered Date

Deciphered Date

Deciphered Date

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cantiga(1/6)-AGTL/DMI/DDR

Cantiga(1/6)-AGTL/DMI/DDR

Cantiga(1/6)-AGTL/DMI/DDR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LS-5588

LS-5588

LS-5588

8 35Wednesday, July 01, 2009

8 35Wednesday, July 01, 2009

8 35Wednesday, July 01, 2009

1

0.3

0.3

0.3

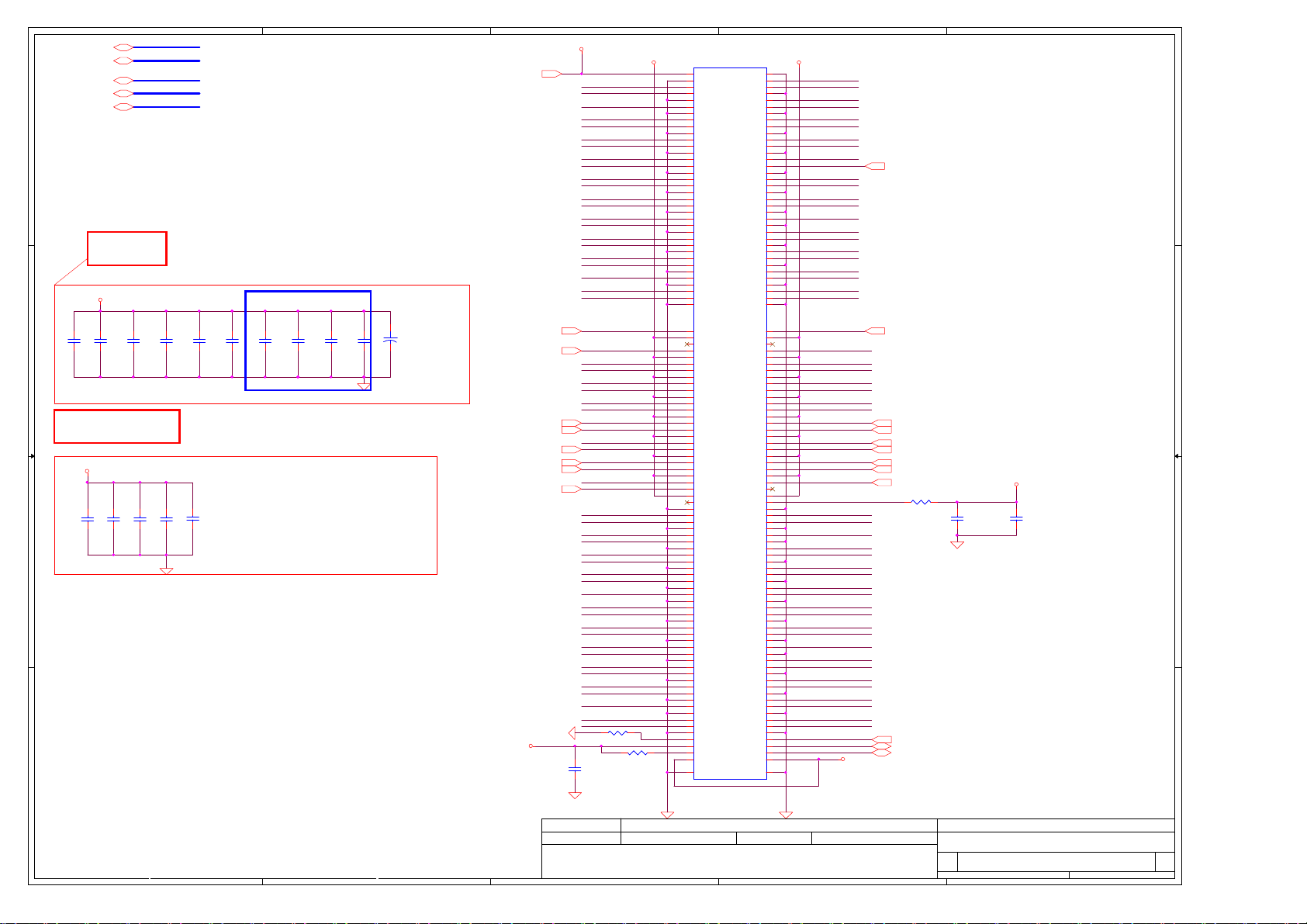

Page 9

5

D D

DDR_A_D[0..63][14]

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

U3D

U3D

AP46

SA_DQ_0

AU47

SA_DQ_1

AT46

SA_DQ_2

AU49

SA_DQ_3

AR45

SA_DQ_4

AN49

SA_DQ_5

AV50

SA_DQ_6

AP50