5

D D

C C

4

3

2

1

Compal confidential

Schematics Document

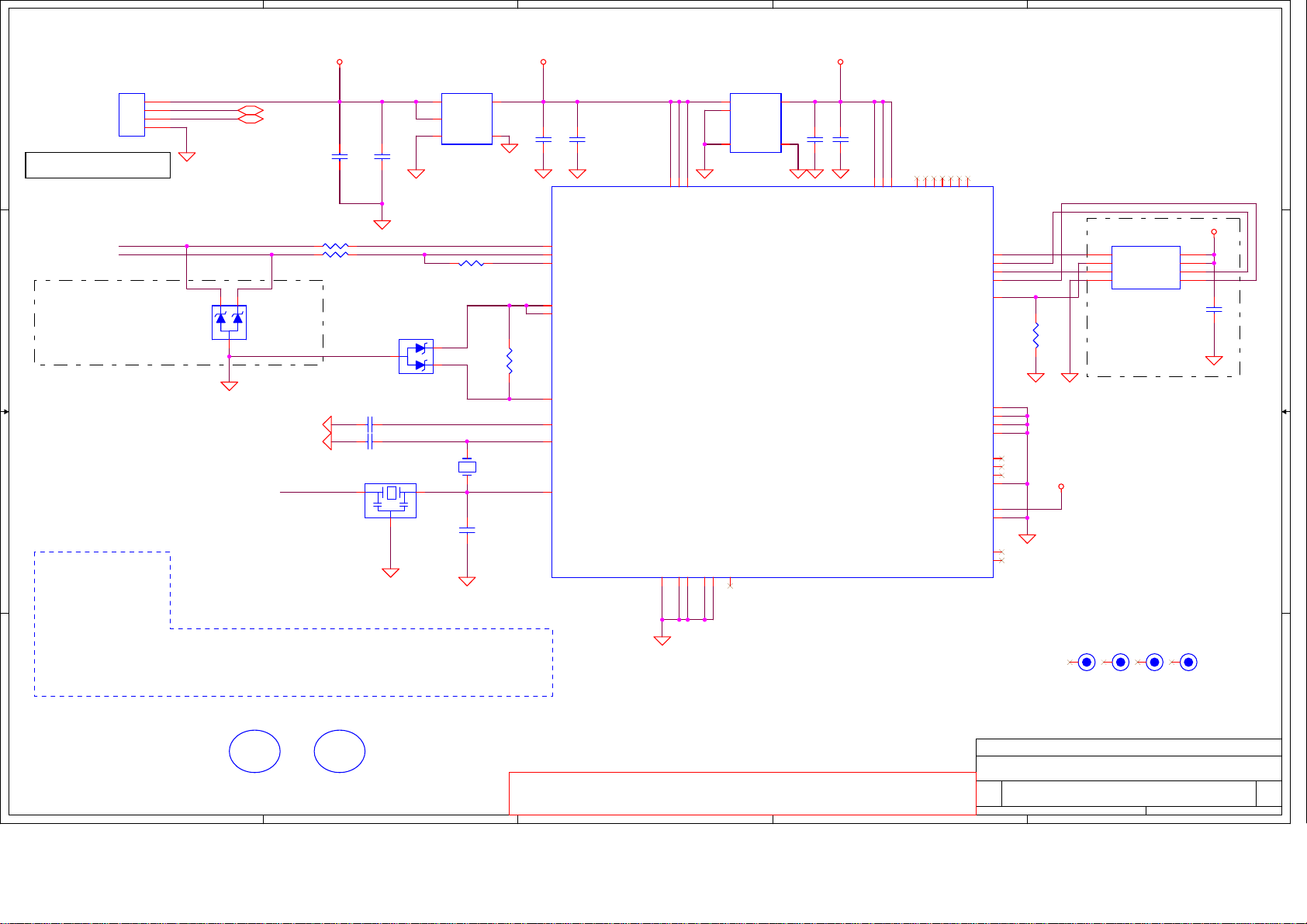

LS-4022P FINGERPRINT BOARD

2007-11-02

B B

A A

5

4

REV:0.1

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LS-4022P

1

0.1

of

13Friday, November 02, 2007

5

+3V_FP +3VDD_L +1.8VDD_L

4

3

2

1

U3

NCP584LSN18T1G_SOT23-5~D

4

D7

A8

B4

VDD1_IO

VDD2_IO

VDD_EXCITE

VSSA2

GND_CORE

B1

VSSA1

GND1_IO

GND2_IO

A6

A7

B8

D2

VIN1VOUT

ECO

CE#3GND

5

2

AES2810

VSSODA

C9

1

C7

2

1

C8

2

0.1U_0402_10V

4.7U_0805_10V4Z

A3

B9

A5

VDD2_CORE1

VDD2_CORE2

SIO3 / SF_CS_N / AUTOBAUD_EN

SIO4 / SF_CLK / BAUD_SEL[2]

SIO5 / SF_WP_N / BAUD_SEL[1]

SIO6 / SF_MOSI / BAUD_SEL[0]

SIO7 / SF_SOMI / SLEEP_N

AES2810-C-IB-TR-BB00_BGA45~D

VDDA1 / 2

B10

C10

D9

B11

D10

SUP_3P3

EN_3P3_N

EN_1P8_N

LOAD_3P3

SIO8 / GPIO[2]

SIO9 / GPIO[1]

SIO10 / GPIO[0]

ANALOG_TST3V

OVC_ATST

ANALOG_TST

TEST_MODE

CLK_SEL0

CLK_SEL1

OVC_SEL0

OVC_SEL1

D11

SUP_1P8

LOAD_1P8D

D12

LOAD_1P8A

IOSEL

D3

A10

D4

A11

A12

C5

D5

D6

C1

B5

C7

A2

C6

C4

C3

C8

C12

R4

1 2

100K_0402_1%

+3VDD_L

U4

1

S#

2

Q

3

W#

4

VSS

W25X40VSSIG_SOIC 8P

VCC

HOLD#

8

7

6

C

5

D

MEMORY OPTION Devices U4 and C9

are only required if

template storage is

utilized.

+3VDD_L

1

C9

2

0.1U_0402_10V

JP1

@

Vin 3.3 +-0.2V, Iin <100mA peak

1

1

USB20_N8

2

D D

FPC_R39x236-P2_4P

2

USB20_P8

3

3

4

4

Wire hot bar 10/29

USB20_N8 DMINUS

USB20_P8

UNPROTECTED HOST

OPTION:

C C

Populate D2 only if

Host has no input

protection.

B B

USB20_N8 22

USB20_P8 22

R1 24_0402_1%

1 2

R2 24_0402_1%

1 2

2

3

D2

VMZ6.8N_VMD3~D

1

0.5 mm trace

SYS_CLK

12MHZ_33PF_CSTCE12M0G15L10-R0

1

C1

2

TVS_RTN

1

C2

2

10U_0805_6.3V6M

VMZ6.8N_VMD3~D

C10

12

0.1U_0402_10V

12

10P_0402_50V8J

C12

Y2

@

1 3

1

2

Layout Note:

5

4

FPF2004_SC70-5~D

0.1U_0402_10V

D1

U2

Vin

ON

GND2FlagB

DPLUS

R3 1.5K_0402_1%

2

3

12MHZ_16P_DSX840GA

12

1

2

C13

Vout

FRNG

FDRV

10P_0402_50V8J

1

3

12

R5

RST

SYS_CLK

Y1

1

1

C3

2

2

10U_0805_6.3V6M

U5

B7

SIO1 / DMINUS / RTR

B12

SIO0 / DPLUS / RXD

A9

SIO2 / VTERM / TXD

A1

FINGERRINGT1

D1

FINGERRINGT2

D8

FDRV

B3

RESET_N

A4

XTAL_IN

B6

XTAL_OUT

C14

0.1U_0402_10V

12

47_0402_5%

1- Place R5 close to U5.

2- D1 close to R5.

FM1

FM2

FM3

3- D1-1 and D2-1 to FP_GND should be short trace, <20 mils long using 3 vias to connect to FP_GND.

1

1

1

FM4

1

4- If crystal op t i o n ( Y1 ) i s u s e d : Y2 i s NI . If resonator option (Y2) is used: Y1, C12, C13 are NI.

A A

ZZZ1

PCB

5

ZZZ

45@

Fingerprint wire

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

B

Date: Sheet

FINGERPRINT BOARD

LS-4022P

1

0.1

of

23Friday, November 02, 2007

5

4

3

2

1

Version Change List ( P. I. R. List )

Item Change Description Cut-In DatePage# Title

D D

C C

B B

A A

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Custom

Date: Sheet

Change List

LS-4022P

1

0.1

of

33Friday, November 02, 2007

Loading...

Loading...