Page 1

A B C D E F G H

P419-A02: MXM-I, G86M, 256/128MB, 64-bit

1

32M16 or 16M16(4 pcs) DDR2

1

LVDS,DVI_A,TV_OUT,VGA, HDMI/HDCP

2

Table of Contents

Page 1: PAGE OVERVIEW

Page 2: PCI EXPRESS INTERFACE

Page 3: GPU MEMORY INTERFACE

Page 4: FRAME BUFFER PARTITION A

Page 5: MEMORY DECOUPLING CAPS

Page 6: DAC A/B/C

Page 7: LVDS(LINK A/B), TMDS(LINK C/D)

Page 8: MXM CONNECTOR

3

4

SKU

B

1

2

3

4

5

6

7

8

9

10

5

11

12

13

14

15

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

Page 9: GPIO. JTAG, TEMP SENSOR, SPDIF

Page 10: MIOB, VBIOS, HDCP ROM

Page 11: SPREAD SPECTURM, MIOA

Page 12: NVVDD POWER SUPPLY

Page 13: FBVDDQ POWER SUPPLY

Page 14: STRAPS

Page 15: FBVDDQ POWER SUPPLY

Page 16: STRAPS

VARIANT ASSEMBLY

BASE

SKU0001

SKU0002

SKU0003

SKU0004

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

NVPN

600-10419-0000-000

600-10419-0001-000

600-10419-0002-000

600-10419-0003-000

600-10419-0004-000

<UNDEFINED?

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED><UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

G86M ?/? 256MB(64bit) DDR2 16Mx16 84FBGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA

G86M ?/? 128MB(64bit) DDR2 16Mx16 84FBGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA

G86M ?/? 256MB(64bit) DDR2 16Mx16 84FBGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA

G86M ?/? 128MB(64bit) DDR2 16Mx16 84FBGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA

<UNDEFINED?

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED><UNDEFINED>

<UNDEFINED>

<UNDEFINED>

C GE

ASSEMBLY

PAGE DETAIL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE OVERVIEW

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

Document number:4059HI

VERSION:C SHEET 1 OF 14

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10419-0000-000

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

2

3

4

5

PAGEID

18-DEC-2006

DATE

HFDBA

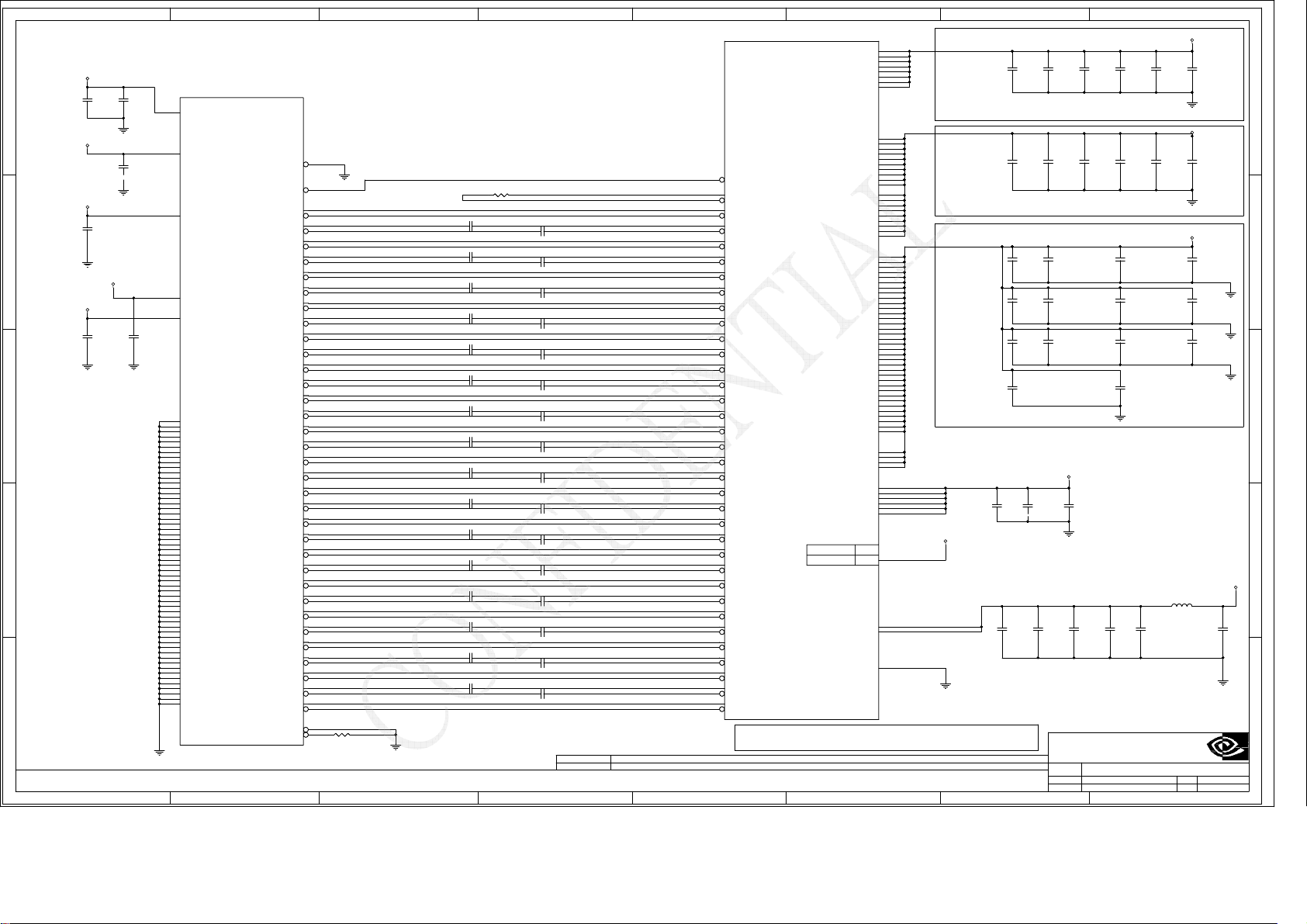

Page 2

A B C D E F G H

CN1A

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C653

C653

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

CN1A

@electro_mechanic.con_mxm(chips):page2_i894

@electro_mechanic.con_mxm(chips):page2_i894

(NPHY,NONPHY)-X16(_SLI)

(NPHY,NONPHY)-X16(_SLI)

NONPHY-X16

NONPHY-X16

COMMON

COMMON

1/2 PCI-Express, Power

1/2 PCI-Express, Power

238

3V3RUN

(1.5A)

2

1V8RUN

(3.5A)

1

PWR_SRC

(4A)

234

2V5RUN

(0.5A)

18

5VRUN

(0.5A)

17

GND

20

GND

41

GND

44

GND

47

GND

50

GND

53

GND

56

GND

59

GND

62

GND

65

GND

68

GND

71

GND

74

GND

77

GND

80

GND

83

GND

86

GND

89

GND

92

GND

95

GND

98

GND

101

GND

104

GND

107

GND

110

GND

113

GND

116

GND

119

GND

122

GND

125

GND

128

GND

131

GND

138

GND

142

GND

146

GND

150

GND

154

GND

158

GND

164

GND

176

GND

182

GND

188

GND

194

GND

199

GND

200

GND

205

GND

206

GND

211

GND

212

GND

218

GND

223

GND

229

GND

235

GND

236

GND

241

GND

@

@

CLK_REQ

PEX_RST

PEX_REFCLK

PEX_REFCLK

PEX_RX0

PEX_RX0

PEX_TX0

PEX_TX0

PEX_RX1

PEX_RX1

PEX_TX1

PEX_TX1

PEX_RX2

PEX_RX2

PEX_TX2

PEX_TX2

PEX_RX3

PEX_RX3

PEX_TX3

PEX_TX3

PEX_RX4

PEX_RX4

PEX_TX4

PEX_TX4

PEX_RX5

PEX_RX5

PEX_TX5

PEX_TX5

PEX_RX6

PEX_RX6

PEX_TX6

PEX_TX6

PEX_RX7

PEX_RX7

PEX_TX7

PEX_TX7

PEX_RX8

PEX_RX8

PEX_TX8

PEX_TX8

PEX_RX9

PEX_RX9

PEX_TX9

PEX_TX9

PEX_RX10

PEX_RX10

PEX_TX10

PEX_TX10

PEX_RX11

PEX_RX11

PEX_TX11

PEX_TX11

PEX_RX12

PEX_RX12

PEX_TX12

PEX_TX12

PEX_RX13

PEX_RX13

PEX_TX13

PEX_TX13

PEX_RX14

PEX_RX14

PEX_TX14

PEX_TX14

PEX_RX15

PEX_RX15

PEX_TX15

PEX_TX15

PRSNT1

PRSNT2

137

139

135

133

129

127

132

130

123

121

126

124

117

115

120

118

111

109

114

112

105

103

108

106

99

97

102

100

93

91

96

94

87

85

90

88

81

79

84

82

75

73

78

76

69

67

72

70

63

61

66

64

57

55

60

58

51

49

54

52

45

43

48

46

39

37

42

40

134

38

PRSNT2_C

PAGE 2) PCI-EXPRESS

GND

NET_NAME

PEX_TX0_C

PEX_TX0_C*

PEX_TX1_C

PEX_TX1_C*

PEX_TX2_C

PEX_TX2_C*

PEX_TX3_C

PEX_TX3_C*

PEX_TX4_C

PEX_TX4_C*

PEX_TX5_C

PEX_TX6_C

PEX_TX7_C

PEX_TX7_C*

PEX_TX8_C

PEX_TX8_C*

PEX_TX9_C

PEX_TX9_C*

PEX_TX10_C

PEX_TX10_C*

PEX_TX11_C

PEX_TX11_C*

PEX_TX12_C

PEX_TX12_C*

PEX_TX13_C

PEX_TX13_C*

PEX_TX14_C

PEX_TX14_C*

PEX_TX15_C

PEX_TX15_C*

R43

R43

1 2

0_0402_5%

0_0402_5%

NV_CRITICAL_NET

DIFF_PAIR

PEX_TX5_C 100DIFF1

NV_IMPEDANCE

100DIFF1PEX_TX0_C

100DIFFPEX_TX0_C 1

100DIFF1PEX_TX1_C

100DIFF PEX_RX11

1PEX_TX2_C 100DIFF

1PEX_TX3_C 100DIFF

1PEX_TX4_C 100DIFF

100DIFF1PEX_TX5_C

100DIFF1PEX_TX6_C

100DIFF1PEX_TX6_C

100DIFF1PEX_TX7_C

100DIFF1PEX_TX8_C

100DIFF1PEX_TX9_C

100DIFF PEX_RX91

100DIFF1PEX_TX10_C

100DIFF1PEX_TX11_C

100DIFF1PEX_TX12_C

100DIFF1PEX_TX13_C

100DIFF1PEX_TX14_C

100DIFF1PEX_TX15_C

100DIFF PEX_RX151

GND

C GE

PEX_RST

R35

200_0402_1%

R35

200_0402_1%

1 2

C592 0.1U_0402_16V7KC592 0.1U_0402_16V7K

12

C584 0.1U_0402_16V7KC584 0.1U_0402_16V7K

12

C577 0.1U_0402_16V7KC577 0.1U_0402_16V7K

12

C571 0.1U_0402_16V7KC571 0.1U_0402_16V7K

12

C566 0.1U_0402_16V7KC566 0.1U_0402_16V7K

12

C561 0.1U_0402_16V7KC561 0.1U_0402_16V7K

12

C559 0.1U_0402_16V7KC559 0.1U_0402_16V7K

12

C557 0.1U_0402_16V7KC557 0.1U_0402_16V7K

12

C553 0.1U_0402_16V7KC553 0.1U_0402_16V7K

12

C551 0.1U_0402_16V7KC551 0.1U_0402_16V7K

12

C548 0.1U_0402_16V7KC548 0.1U_0402_16V7K

12

C546 0.1U_0402_16V7KC546 0.1U_0402_16V7K

12

C544 0.1U_0402_16V7KC544 0.1U_0402_16V7K

12

C542 0.1U_0402_16V7KC542 0.1U_0402_16V7K

12

C538 0.1U_0402_16V7KC538 0.1U_0402_16V7K

12

C536 0.1U_0402_16V7KC536 0.1U_0402_16V7K

12

NV_IMPEDANCE NV_CRITICAL_NET DIFF_PAIR NET_NAME

12

C588 0.1U_0402_16V7KC588 0.1U_0402_16V7K

12

C580 0.1U_0402_16V7KC580 0.1U_0402_16V7K

12

C572 0.1U_0402_16V7KC572 0.1U_0402_16V7K

12

C569 0.1U_0402_16V7KC569 0.1U_0402_16V7K

12

C562 0.1U_0402_16V7KC562 0.1U_0402_16V7K

12

C560 0.1U_0402_16V7KC560 0.1U_0402_16V7K

12

C558 0.1U_0402_16V7KC558 0.1U_0402_16V7K

12

C554 0.1U_0402_16V7KC554 0.1U_0402_16V7K

12

C552 0.1U_0402_16V7KC552 0.1U_0402_16V7K

12

C549 0.1U_0402_16V7KC549 0.1U_0402_16V7K

12

C547 0.1U_0402_16V7KC547 0.1U_0402_16V7K

12

C545 0.1U_0402_16V7KC545 0.1U_0402_16V7K

12

C543 0.1U_0402_16V7KC543 0.1U_0402_16V7K

12

C540 0.1U_0402_16V7KC540 0.1U_0402_16V7K

12

C537 0.1U_0402_16V7KC537 0.1U_0402_16V7K

12

C531 0.1U_0402_16V7KC531 0.1U_0402_16V7K

3V3RUN

12

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

12

C1

C1

0.1U_0402_16V7K

0.1U_0402_16V7K

1V8RUN

PWR_SRC

1

C519

C519

0.1U_0603_25V7K

0.1U_0603_25V7K

2

GND

5VRUN

12

C524

C524

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

2V5RUN

C2

C2

GND

12

C27

C27

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

GND

PEX_TCLK1100DIFF

100DIFF 1 PEX_TX0

ASSEMBLY

PAGE DETAIL

G1A

G1A

@digital.u_gpu_g3_64_8x(chips):page2_i832

@digital.u_gpu_g3_64_8x(chips):page2_i832

BGA533

BGA533

COMMON

COMMON

1/12 PCI_EXPRESS

1/12 PCI_EXPRESS

AC6

PEX_RST

AF13

PEX_TSTCLK*

PEX_TCLK1100DIFF

REFCLK

PEX_RCLK1100DIFF

REFCLK*

PEX_RCLK1100DIFF

PEX_TX0

PEX_TX01100DIFF

PEX_TX0*

PEX_RX0

PEX_RX01100DIFF

PEX_RX0*

PEX_RX01100DIFF

PEX_TX1

PEX_TX11100DIFF

PEX_TX1*

PEX_TX11100DIFF

PEX_RX1

PEX_RX1*

PEX_RX11100DIFF

PEX_TX2

PEX_TX21100DIFF

PEX_TX2*

PEX_TX21100DIFF

PEX_RX2

PEX_RX21100DIFF

PEX_RX2*

PEX_RX21100DIFF

PEX_TX3

PEX_TX31100DIFF

PEX_TX3*

PEX_TX31100DIFF

PEX_RX3

PEX_RX31100DIFF

PEX_RX3*

PEX_RX31100DIFF

PEX_TX4

PEX_TX41100DIFF

PEX_TX4*

PEX_TX41100DIFF

PEX_RX4

PEX_RX41100DIFF

PEX_RX4*

PEX_RX41100DIFF

1100DIFF PEX_TX5

1 PEX_RX6100DIFF

1 PEX_RX6100DIFF

1100DIFF PEX_TX7

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PCI EXPRESS INTERFACE

PEX_TX5

PEX_TX5*

PEX_TX51100DIFF

PEX_RX5

PEX_RX51100DIFF

PEX_RX5*

PEX_RX51100DIFF

PEX_TX6

PEX_TX61100DIFF

PEX_TX6*

PEX_TX61100DIFF

PEX_RX6

PEX_RX6*

PEX_TX7

PEX_TX7*

PEX_TX71100DIFF

PEX_RX7

PEX_RX71100DIFF

PEX_RX7*

PEX_RX71100DIFF

PEX_TX8

PEX_TX81100DIFF

PEX_TX8*

PEX_TX81100DIFF

PEX_RX8

PEX_RX81100DIFF

PEX_RX8*

PEX_RX81100DIFF

PEX_TX9

PEX_TX91100DIFF

PEX_TX9*

PEX_TX91100DIFF

PEX_RX9

PEX_RX9*

PEX_RX91100DIFF

PEX_TX10

PEX_TX101100DIFF

PEX_TX10*

PEX_TX101100DIFF

PEX_RX10

PEX_RX101100DIFF

PEX_RX10*

PEX_RX101100DIFF

PEX_TX11

PEX_TX111100DIFF

PEX_TX11*

PEX_TX111100DIFF

PEX_RX11

PEX_RX111100DIFF

PEX_RX11*

PEX_RX111100DIFF

PEX_TX12

PEX_TX121100DIFF

PEX_TX12*

PEX_TX121100DIFF

PEX_RX12

PEX_RX121100DIFF

PEX_RX12*

PEX_RX121100DIFF

PEX_TX13

PEX_TX131100DIFF

PEX_TX13*

PEX_TX131100DIFF

PEX_RX13

PEX_RX131100DIFF

PEX_RX13*

PEX_RX131100DIFF

PEX_TX14

PEX_TX141100DIFF

PEX_TX14*

PEX_TX141100DIFF

PEX_RX14

PEX_RX141100DIFF

PEX_RX14*

PEX_RX141100DIFF

PEX_TX15

PEX_TX151100DIFF

PEX_TX15*

PEX_TX151100DIFF

PEX_RX15

PEX_RX151100DIFF

PEX_RX15*

PEX_TSTCLK_OUT

AF14

PEX_TSTCLK_OUT

AE3

PEX_REFCLK

AE4

PEX_REFCLK

AD5

PEX_TX0

AD6

PEX_TX0

AF1

PEX_RX0

AG2

PEX_RX0

AE6

PEX_TX1

AE7

PEX_TX1

AG3

PEX_RX1

AG4

PEX_RX1

AD7

PEX_TX2

AC7

PEX_TX2

AF4

PEX_RX2

AF5

PEX_RX2

AE9

PEX_TX3

AE10

PEX_TX3

AG6

PEX_RX3

AG7

PEX_RX3

AD10

PEX_TX4

AC10

PEX_TX4

AF7

PEX_RX4

AF8

PEX_RX4

AE12

PEX_TX5

AE13

PEX_TX5

AG9

PEX_RX5

AG10

PEX_RX5

AD13

PEX_TX6

AC13

PEX_TX6

AF10

PEX_RX6

AF11

PEX_RX6

AC15

PEX_TX7

AD15

PEX_TX7

AG12

PEX_RX7

AG13

PEX_RX7

AE15

PEX_TX8

AE16

PEX_TX8

AG15

PEX_RX8

AG16

PEX_RX8

AC18

PEX_TX9

AD18

PEX_TX9

AF16

PEX_RX9

AF17

PEX_RX9

AE18

PEX_TX10

AE19

PEX_TX10

AG18

PEX_RX10

AG19

PEX_RX10

AC21

PEX_TX11

AD21

PEX_TX11

AF19

PEX_RX11

AF20

PEX_RX11

AE21

PEX_TX12

AE22

PEX_TX12

AG21

PEX_RX12

AG22

PEX_RX12

AD22

PEX_TX13

AD23

PEX_TX13

AF22

PEX_RX13

AF23

PEX_RX13

AF25

PEX_TX14

AE25

PEX_TX14

AG24

PEX_RX14

AG25

PEX_RX14

AE24

PEX_TX15

AD24

PEX_TX15

AG26

PEX_RX15

AF27

PEX_RX15

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

NV_PLLAVDD

NV_PLLAVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

G72 G86

G72 G86

PEX_PLLAVDD

PEX_PLLDVDD

PEX_PLLGND

VDD_LP

VDD_LP

VDD_LP

VDD_LP

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

AB10

AB11

AB14

AB15

W17

W18

AB20

AB21

AA4

AB5

AB6

AB7

AB8

AB9

AC9

AC11

AB12

AC12

AB13

AB16

AC16

AB17

AC17

AB18

AB19

AC19

AC20

J9

VDD

M9

VDD

R9

VDD

T9

VDD

J10

VDD

J11

VDD

M11

VDD

N11

VDD

R11

VDD

T11

VDD

L12

VDD

M12

VDD

T12

VDD

U12

VDD

L13

VDD

M13

VDD

T13

VDD

U13

VDD

W13

VDD

M14

VDD

T14

VDD

L15

VDD

M15

VDD

T15

VDD

U15

VDD

W15

VDD

L16

VDD

M16

VDD

T16

VDD

U16

VDD

W16

VDD

M17

VDD

N17

VDD

R17

VDD

T17

VDD

W9

W10

W11

W12

J12

F13

J13

F14

J15

J16

NVVDD

NVVDD

N9

VDD

Y6

AA5

PEX_PLL_DVDD

PLACE UNDER GPU

12

C586

C586

0.1U_0402_16V7K

0.1U_0402_16V7K

12

12

C607

C607

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C582

C582

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C602

C602

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C567

C567

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C608

C608

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C578

C578

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C587

C587

0.1U_0402_16V7K

0.1U_0402_16V7K

PLACE UNDER GPU

C599

C599

4700P_0402_25V7K

4700P_0402_25V7K

PLACE UNDER GPU

12

C595

C595

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C585

C585

0.1U_0402_16V7K

0.1U_0402_16V7K

PLACE UNDER GPU

PLACE UNDER GPU

12

C600

C600

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C575

C575

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C594

C594

0.1U_0402_16V7K

0.1U_0402_16V7K

3V3RUN

12

C605

C605

0.01U_0402_25V7Z

0.01U_0402_25V7Z

12

C611

C611

1U_0402_6.3V6K

1U_0402_6.3V6K

GND

12

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C604

C604

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C596

C596

1U_0402_6.3V6K

1U_0402_6.3V6K

C635

C635

12

C591

C591

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C573

C573

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C593

C593

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C597

C597

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C570

C570

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C601

C601

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

12

C640

C640

1U_0402_6.3V6K

1U_0402_6.3V6K

12

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

12

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

12

C645

C645

1U_0402_6.3V6K

1U_0402_6.3V6K

PEX1V2

12

C556

C556

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

PEX1V2

1

C565

C565

2

GND

NVVDD

12

1U_0603_10V6K

1U_0603_10V6K

12

1U_0603_10V6K

1U_0603_10V6K

12

1U_0603_10V6K

1U_0603_10V6K

LB506

LB506

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

C633

C633

C37

C37

10U_0805_10V4Z

10U_0805_10V4Z

C576

C576

C568

C568

C603

C603

GND

GND

GND

PEX1V2

12

C643

C643

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

2

3

4

AA6

GND

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

Document number:4059HI

GND

5

VERSION:C SHEET 2 OF 14

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10419-0000-000

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

PAGEID

DATE

18-DEC-2006

HFDBA

Page 3

A B C D E F G H

FBAD[63..0]

1

PAGE 3) FBA INTERFACE

2

3

4

4

BI

FBAD0

0

FBAD1

1

FBAD2

2

FBAD3

3

FBAD4

4

FBAD5

5

FBAD6

6

FBAD7

7

FBAD8

8

FBAD9

9

FBAD10

10

FBAD11

11

FBAD12

12

FBAD13

13

FBAD14

14

FBAD15

15

FBAD16

16

FBAD17

17

FBAD18

18

FBAD19

19

FBAD20

20

FBAD21

21

FBAD22

22

FBAD23

23

FBAD24

24

FBAD25

25

FBAD26

26

FBAD27

27

FBAD28

28

FBAD29

29

FBAD30

30

FBAD31

31

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBAD48

48

FBAD49

49

FBAD50

50

FBAD51

51

FBAD52

52

FBAD53

53

FBAD54

54

FBAD55

55

FBAD56

56

FBAD57

57

FBAD58

58

FBAD59

59

FBAD60

60

FBAD61

61

FBAD62

62

FBAD63

FBADQM[7..0]

4

OUT

63

FBADQM0

0

FBADQM1

1

FBADQM2

2

FBADQM3

3

FBADQM4

4

FBADQM5

5

FBADQM6

6

FBADQM7

7

FBADQS0

4

BI

FBADQS1

4

BI

FBADQS2

4

BI

FBADQS3

4

BI

FBADQS4

4

BI

FBADQS5

4

BI

FBADQS6

4

BI

FBADQS7

4

BI

FBADQS0*

4

BI

FBADQS1*

4

BI

FBADQS2*

4

BI

FBADQS3*

4

BI

FBADQS4*

4

BI

FBADQS5*

4

BI

FBADQS6*

4

BI

FBADQS7*

4

BI

G1B

G1B

@digital.u_gpu_g3_64_8x(chips):page3_i403

@digital.u_gpu_g3_64_8x(chips):page3_i403

BGA533

BGA533

COMMON

COMMON

2/12 FRAME_BUFFER

2/12 FRAME_BUFFER

A26

FB_DQ0

C24

FB_DQ1

B24

FB_DQ2

A24

FB_DQ3

C22

FB_DQ4

A25

FB_DQ5

B25

FB_DQ6

D23

FB_DQ7

G22

FB_DQ8

J23

FB_DQ9

E24

FB_DQ10

F23

FB_DQ11

J24

FB_DQ12

F24

FB_DQ13

G23

FB_DQ14

H24

FB_DQ15

D16

FB_DQ16

E16

FB_DQ17

D17

FB_DQ18

F18

FB_DQ19

E19

FB_DQ20

E18

FB_DQ21

D20

FB_DQ22

D19

FB_DQ23

A18

FB_DQ24

B18

FB_DQ25

A19

FB_DQ26

B19

FB_DQ27

D18

FB_DQ28

C19

FB_DQ29

C16

FB_DQ30

C18

FB_DQ31

N26

FB_DQ32

N25

FB_DQ33

R25

FB_DQ34

R26

FB_DQ35

R27

FB_DQ36

T25

FB_DQ37

T27

FB_DQ38

T26

FB_DQ39

AB23

FB_DQ40

Y24

FB_DQ41

AB24

FB_DQ42

AB22

FB_DQ43

AC24

FB_DQ44

AC22

FB_DQ45

AA23

FB_DQ46

AA22

FB_DQ47

T24

FB_DQ48

T23

FB_DQ49

R24

FB_DQ50

R23

FB_DQ51

R22

FB_DQ52

T22

FB_DQ53

N23

FB_DQ54

P24

FB_DQ55

AA24

FB_DQ56

AA27

FB_DQ57

AA26

FB_DQ58

AB25

FB_DQ59

AB26

FB_DQ60

AB27

FB_DQ61

AA25

FB_DQ62

W25

FB_DQ63

D21

FB_DQM0

F22

FB_DQM1

F20

FB_DQM2

A21

FB_DQM3

V27

FB_DQM4

W22

FB_DQM5

V22

FB_DQM6

V24

FB_DQM7

B22

FB_DQS_WP0

D22

FB_DQS_WP1

E21

FB_DQS_WP2

C21

FB_DQS_WP3

V25

FB_DQS_WP4

W24

FB_DQS_WP5

U24

FB_DQS_WP6

W26

FB_DQS_WP7

A22

FB_DQS_RN0

E22

FB_DQS_RN1

F21

FB_DQS_RN2

B21

FB_DQS_RN3

V26

FB_DQS_RN4

W23

FB_DQS_RN5

V23

FB_DQS_RN6

W27

FB_DQS_RN7

FB_CMD10

FB_CMD11

FB_CMD12

FB_CMD13

FB_CMD14

FB_CMD15

FB_CMD16

FB_CMD17

FB_CMD18

FB_CMD19

FB_CMD20

FB_CMD21

FB_CMD22

FB_CMD23

FB_CMD24

FB_CMD25

FB_CMD26

FB_CMD27

FB_CMD28

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FB_DEBUG

G72

G72

G86

G86

H_PLLVDD

FB_PLLAVDD

FB_PLLGND

SNN_FB_VREF

NC

NC

FB_PLLAVDD

FB_PLLAVDD

FB_PLLGND

FB_PLLGND

A16

FB_VREF

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_CMD0

FB_CMD1

FB_CMD2

FB_CMD3

FB_CMD4

FB_CMD5

FB_CMD6

FB_CMD7

FB_CMD8

FB_CMD9

FB_CLK0

FB_CLK0

FB_CLK1

FB_CLK1

ASSEMBLY

PAGE DETAIL

E15

F15

F16

J17

J18

L19

N19

R19

U19

W19

F17

F19

J19

M19

T19

J22

L22

P22

U22

Y22

G27

D25

F26

F25

G25

J25

J27

M26

C27

C25

D24

N27

G24

J26

M27

C26

M25

D26

D27

K26

K25

K24

F27

K27

G26

B27

N24

M23

M24

L24

K23

M22

N22

D15

E13

H22

K22

D14

D13

C15

FBA_A3

FBA_A0

FBA_A2

FBA_A1

FBB_A3

FBB_A4

FBB_A5

FBA_BA2

FBA_CS0*

FBA_WE*

FBA_BA0

FBA_CKE

FBA_ODT_GPU

FBB_A2

FBA_A12

FBA_RAS*

FBA_A11

FBA_A10

FBA_BA1

FBA_A8

FBA_A9

FBA_A6

FBA_A5

FBA_A7

FBA_A4

FBA_CAS*

SNN_FBA_A13

SNN_FBA_A14

SNN_FBA_A15

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBCAL_PD

FBCAL_PU

FBCAL_TERM

FBA_DEBUG

FB_PLLAVDD

GND

GPU MEMORY INTERFACE

3

4

5

2

R533

R533

R537

R537

R528

R528

FBB_A[5..2]

3

0

2

1

12

11

10

8

9

6

5

7

4

1 2

40.2_0402_1%

40.2_0402_1%

1 2

40.2_0402_1%

40.2_0402_1%

1 2

40.2_0402_1%

40.2_0402_1%

@

@

FBA_A[12..0]

4

OUT

4

OUT

4

OUT

4

OUT

OUT

R47

R47

4

OUT

4

OUT

OUT

4

OUT

4

OUT

4

OUT

4

OUT

1 2

R526

0_0402_5%

R526

0_0402_5%

@

@

PLACE NEAR BALLS

FBVTT=FBVDDQ FOR UNTERMINATED MEMORIES

12

12

12

C530

C530

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C504

C504

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C30

C30

4700P_0402_25V7K

4700P_0402_25V7K

C507

C507

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C41

C41

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C26

C26

4700P_0402_25V7K

4700P_0402_25V7K

C32

C32

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C23

C23

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C535

C535

4700P_0402_25V7K

4700P_0402_25V7K

12

C517

C517

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C509

C509

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C36

C36

4700P_0402_25V7K

4700P_0402_25V7K

12

C42

C42

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C40

C40

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C43

C43

4700P_0402_25V7K

4700P_0402_25V7K

12

C20

C20

1U_0603_10V6K

1U_0603_10V6K

12

C19

C19

1U_0603_10V6K

1U_0603_10V6K

FBVDDQ

GND

4

OUT

4

OUT

FBA_CLK0

4

1 2

0_0402_5%

0_0402_5%

4

FBA_ODT

4

OUT

FBVDDQ

GND

GND

Place the differential termination resistor at the end of the transmission line.

PLACE NEAR GPU

C581

12

C589

C589

0.01U_0402_25V7Z

0.01U_0402_25V7Z

GND

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C581

12

1U_0402_6.3V6K

1U_0402_6.3V6K

GND GND

LB501

LB501

1 2

FBMA-11-100505-301T_0402

FBMA-11-100505-301T_0402

12

C579

C579

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

PEX1V2

GND

R510

R510

R44

R44

1 2

1 2

12

C46

C46

0.1U_0402_16V7K

0.1U_0402_16V7K

121_0402_1%

121_0402_1%

121_0402_1%

121_0402_1%

12

12

C47

C47

C48

C48

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

FBVDDQ

12

R512

R512

0_0402_5%

0_0402_5%

@

@

FBACLK_C0

R508

R508

12

C513

C513

0.01U_0402_25V7Z

0.01U_0402_25V7Z

@

@

GND

FBVDDQ

12

R45

R45

0_0402_5%

0_0402_5%

@

@

1 2

FBACLK_C1

R46

R46

12

C29

C29

0.01U_0402_25V7Z

0.01U_0402_25V7Z

@

@

GND

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

12

C49

C49

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

121_0402_1%

121_0402_1%

FBA_CLK0*

FBA_CLK1*

1 2

121_0402_1%

121_0402_1%

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

Document number:4059HI

VERSION:C SHEET 3 OF 14

600-10419-0000-000

PAGEID

DATE

HFDBA

1

2

3

4

5

18-DEC-2006

Page 4

A B C D E F G H

PAGE 4) MEMORY PARTITION A

M501C

M501C

@memory.u_mem_sd_ddr2_x16(chips):page4_i48

@memory.u_mem_sd_ddr2_x16(chips):page4_i48

BGA84

BGA84

COMMON

3,4

IN

3,4

IN

3,4

1

3,4

2

3,4

IN

3,4

IN

FBA_A[13..0] FBA_A[13..0] FBA_A[13..0]

IN

3,4

3,4

3,4

3,4

3,4

3,4

IN

0

1

2

3

4

5

6

7

8

9

10

11

12

SNN_R8_M1 SNN_R8_M2 SNN_R8_M3

SNN_R3_M1 SNN_R3_M2 SNN_R3_M3

SNN_R7_M1 SNN_R7_M2 SNN_R7_M3

FBA_BA0 FBA_BA0 FBA_BA0

IN

FBA_BA1 FBA_BA1 FBA_BA1

IN

FBA_BA2 FBA_BA2 FBA_BA2

IN

FBA_CKE FBA_CKE FBA_CKE

IN

FBA_CLK0 FBA_CLK0

IN

FBA_CLK0* FBA_CLK0*

IN

FBA_ODT FBA_ODT FBA_ODT

12

R527

R527

SNN_A2_M1 SNN_A2_M2 SNN_A2_M3

10K_0402_5%

10K_0402_5%

SNN_E2_M1 SNN_E2_M2 SNN_E2_M3

GND

COMMON

FBA_RAS* FBA_RAS* FBA_RAS*

FBA_CAS* FBA_CAS* FBA_CAS*

FBA_WE* FBA_WE* FBA_WE*

FBA_CS0* FBA_CS0* FBA_CS0*

FBA_A0 FBA_A0 FBA_A0

FBA_A1 FBA_A1 FBA_A1

FBA_A2 FBA_A2

FBA_A3 FBA_A3

FBA_A4 FBA_A4

FBA_A5 FBA_A5

FBA_A6 FBA_A6 FBA_A6

FBA_A7 FBA_A7 FBA_A7

FBA_A8 FBA_A8 FBA_A8

FBA_A9 FBA_A9 FBA_A9

FBA_A10 FBA_A10 FBA_A10

FBA_A11 FBA_A11 FBA_A11

FBA_A12 FBA_A12 FBA_A12

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

VRAM@

VRAM@

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

P9

VSS

A7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

GND

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

FBAVREF1

R503

R503

1K_0402_1%

1K_0402_1%

R501

R501

665_0402_1%

665_0402_1%

FBVDDQ

12

12

12

0.1U_0402_16V7K

0.1U_0402_16V7K

0

1

2

3

4

5

6

7

8

9

10

11

12

C502

C502

GND

3

FBAD[63..0]

3,4

BI

M501A

M1C

M1C

@memory.u_mem_sd_ddr2_x16(chips):page4_i20

@memory.u_mem_sd_ddr2_x16(chips):page4_i20

BGA84

BGA84

COMMON

COMMON

2/2

F9

DQ<0>

H7

DQ<1>

G8

DQ<2>

F1

DQ<3>

H9

DQ<4>

G2

DQ<5>

H1

DQ<6>

H3

DQ<7>

F3

DQM

F7

DQS

E8

DQS

M2C

M2C

VRAM@

VRAM@

@memory.u_mem_sd_ddr2_x16(chips):page4_i19

@memory.u_mem_sd_ddr2_x16(chips):page4_i19

BGA84

BGA84

COMMON

COMMON

H3

DQ<0>

H1

DQ<1>

H9

DQ<2>

H7

DQ<3>

G2

DQ<4>

G8

DQ<5>

F1

DQ<6>

F9

DQ<7>

F3

DQM

F7

DQS

E8

DQS

VRAM@

VRAM@

2/2

2/2

2/2

FBAD8

8

FBAD9

9

FBAD10

10

FBAD11

11

FBAD12

12

FBAD13

13

FBAD14

14

FBAD15

15

FBADQS1

FBADQS1*

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBADQS5

FBADQS5*

FBAD0

0

FBAD1

1

FBAD2

2

FBAD3

3

FBAD4

4

4

FBADQM[7..0]

3,4

BI

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

5

Document number:4059HI

VERSION:C SHEET 4 OF 14

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

FBAD5

5

FBAD6

6

FBAD7

7

FBADQM0 FBADQM1 FBADQM2 FBADQM3

FBADQS0

FBADQS0*

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBADQM4 FBADQM5 FBADQM6

FBADQS4

FBADQS4*

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

M501A

@memory.u_mem_sd_ddr2_x16(chips):page4_i30

@memory.u_mem_sd_ddr2_x16(chips):page4_i30

BGA84

BGA84

COMMON

COMMON

H1

H3

F9

G2

H7

F1

G8

H9

F3

F7

E8

M502C

M502C

VRAM@

VRAM@

@memory.u_mem_sd_ddr2_x16(chips):page4_i29

@memory.u_mem_sd_ddr2_x16(chips):page4_i29

BGA84

BGA84

COMMON

COMMON

C8

DQ<0>

D1

DQ<1>

D3

DQ<2>

B9

DQ<3>

B1

DQ<4>

D9

DQ<5>

C2

DQ<6>

D7

DQ<7>

B3

DQM

B7

DQS

A8

DQS

VRAM@

VRAM@

C GE

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

M1A

M1A

@memory.u_mem_sd_ddr2_x16(chips):page4_i138

@memory.u_mem_sd_ddr2_x16(chips):page4_i138

BGA84

BGA84

COMMON

COMMON

K7

L7

K3

L8

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

VRAM@

VRAM@

2/2

2/2

2/2

2/2

RAS

CAS

WE

CS

A<0>

A<1>

A<2>

A<3>

A<4>

A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

A<12>

NC/A<13>

NC/A<14>

NC/A<15>

BA<0>

BA<1>

NC/BA<2>

CKE

CLK

CLK

ODT

NC

NC

1/2

1/2

FBAD16

16

FBAD17

17

FBAD18

18

FBAD19

19

FBAD20

20

FBAD21

21

FBAD22

22

FBAD23

23

FBADQS2

FBADQS2*

48

49

50

51

52

53

54

55

FBAD48

FBAD49

FBAD50

FBAD51

FBAD52

FBAD53

FBAD54

FBAD55

FBADQS6

FBADQS6*

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

M1B

M1B

@memory.u_mem_sd_ddr2_x16(chips):page4_i110

@memory.u_mem_sd_ddr2_x16(chips):page4_i110

BGA84

BGA84

COMMON

COMMON

C8

DQ<0>

B9

DQ<1>

D3

DQ<2>

D9

DQ<3>

B1

DQ<4>

D7

DQ<5>

D1

DQ<6>

C2

DQ<7>

B3

DQM

B7

DQS

A8

DQS

M502A

M502A

VRAM@

VRAM@

@memory.u_mem_sd_ddr2_x16(chips):page4_i109

@memory.u_mem_sd_ddr2_x16(chips):page4_i109

BGA84

BGA84

COMMON

COMMON

F9

DQ<0>

G2

DQ<1>

H3

DQ<2>

G8

DQ<3>

H1

DQ<4>

F1

DQ<5>

H7

DQ<6>

H9

DQ<7>

F3

DQM

F7

DQS

E8

DQS

VRAM@

VRAM@

FBVDDQ

FBAVREF3

2/2

2/2

2/2

2/2

ASSEMBLY

PAGE DETAIL

K7

L7

K3

L8

0

FBB_A[5..2]

3,4

GND

2

IN

3

4

5

FBA_CLK1

3,4

IN

FBA_CLK1*

3,4

IN

M8

1

M3

FBB_A2

M7

FBB_A3

N2

FBB_A4

N8

FBB_A5

N3

6

N7

7

P2

8

P8

9

P3

10

M2

11

P7

12

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

R40

R40

665_0402_1%

665_0402_1%

FBVDDQ

12

R41

R41

1K_0402_1%

1K_0402_1%

12

12

C22

C22

0.1U_0402_16V7K

0.1U_0402_16V7K

A2

E2

GND

M501B

M501B

@memory.u_mem_sd_ddr2_x16(chips):page4_i136

@memory.u_mem_sd_ddr2_x16(chips):page4_i136

BGA84

BGA84

COMMON

COMMON

2/2

FBAD24

24

FBAD25

25

FBAD26

26

FBAD27

27

FBAD28

28

FBAD29

29

FBAD30

30

FBAD31

31

FBADQS3

FBADQS3*

VRAM@

VRAM@

FBAD56

56

FBAD57

57

FBAD58

58

FBAD59

59

FBAD60

60

FBAD61

61

FBAD62

62

FBAD63

63

FBADQM7

FBADQS7

FBADQS7*

VRAM@

VRAM@

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

FRAME BUFFER PARTITION A

2/2

D9

DQ<0>

D7

DQ<1>

C2

DQ<2>

C8

DQ<3>

D3

DQ<4>

B9

DQ<5>

D1

DQ<6>

B1

DQ<7>

B3

DQM

B7

DQS

A8

DQS

M2A

M2A

@memory.u_mem_sd_ddr2_x16(chips):page4_i135

@memory.u_mem_sd_ddr2_x16(chips):page4_i135

BGA84

BGA84

COMMON

COMMON

2/2

2/2

D3

DQ<0>

B9

DQ<1>

D9

DQ<2>

D1

DQ<3>

B1

DQ<4>

C2

DQ<5>

C8

DQ<6>

D7

DQ<7>

B3

DQM

B7

DQS

A8

DQS

M2B

M2B

@memory.u_mem_sd_ddr2_x16(chips):page4_i154

@memory.u_mem_sd_ddr2_x16(chips):page4_i154

BGA84

BGA84

COMMON

COMMON

1/2

1/2

RAS

CAS

WE

CS

A<0>

A<1>

A<2>

A<3>

A<4>

A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

A<12>

NC/A<13>

NC/A<14>

NC/A<15>

BA<0>

BA<1>

NC/BA<2>

CKE

CLK

CLK

ODT

NC

NC

VRAM@

VRAM@

VREF = FBVDDQ * R2/(R1 + R2)

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

P9

VSS

A7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

GND

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

FBAVREF2

1K_0402_1%

1K_0402_1%

R49

R49

665_0402_1%

665_0402_1%

3,4

3,4

3,4

3,4

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3,4

3,4

FBVDDQ

12

R48

R48

12

12

C44

C44

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

GND

NET

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

FBAVREF1

FBAVREF2

NET

FBA_CLK0

IN

FBA_CLK0*

IN

FBA_CLK1

IN

FBA_CLK1*

IN

FBADQS0

FBADQS0*

FBADQS1

FBADQS1*

FBADQS2

FBADQS2*

FBADQS3

FBADQS3*

FBADQS4

FBADQS4*

FBADQS5

FBADQS5*

FBADQS6

FBADQS6*

FBADQS7

FBADQS7*

FBA_A[12..0]

FBB_A[5..2]

IN

IN

FBA_BA0

FBA_BA1

IN

FBA_CKE

IN

FBA_BA2

IN

IN

FBA_RAS*

IN

FBA_CAS*

IN

FBA_WE*

IN

FBA_CS0*

IN

FBA_CS1*

IN

FBAD[63..0]

FBADQM[7..0]

BI

BI

FBA_DEBUG

IN

FBA_ODT

IN

FBA_ODT_GPU

IN

FBA_RAS*

FBA_CAS*

FBA_WE*

FBA_CS0*

FBA_A[13..0]

0

FBB_A[5..2]

1

2

3

4

5

6

7

8

9

10

11

12

SNN_R8_M4

SNN_R3_M4

SNN_R7_M4

FBA_BA2

3,4

IN

SNN_A2_M4

SNN_E2_M4

10K_0402_5%

10K_0402_5%

DIFFPAIR

FBA_CLK0 100DIFF1

K7

L7

K3

L8

FBA_A0

M8

FBA_A1

M3

FBB_A2

M7

FBB_A3

N2

FBB_A4

N8

FBB_A5

N3

FBA_A6

N7

FBA_A7

P2

FBA_A8

P8

FBA_A9

P3

FBA_A10

M2

FBA_A11

P7

FBA_A12

R2

R8

R3

R7

FBA_BA0

L2

FBA_BA1

L3

L1

FBA_CKE

K2

FBA_CLK1

J8

FBA_CLK1*

K8

FBA_ODT

K9

A2

E2

VRAM@

VRAM@

12

R502

R502

GND

MIN_LINE_WIDTH

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

M502B

M502B

@memory.u_mem_sd_ddr2_x16(chips):page4_i246

@memory.u_mem_sd_ddr2_x16(chips):page4_i246

BGA84

BGA84

COMMON

COMMON

1/2

1/2

RAS

CAS

WE

CS

A<0>

A<1>

A<2>

A<3>

A<4>

A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

A<12>

NC/A<13>

NC/A<14>

NC/A<15>

BA<0>

BA<1>

NC/BA<2>

CKE

CLK

CLK

ODT

NC

NC

CRITICAL

600-10419-0000-000

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

665_0402_1%

665_0402_1%

VOLTAGE

1 100DIFFFBADQS1

1 100DIFFFBADQS3

1 100DIFFFBADQS6

2 50OHM

2 50OHM

2 50OHM

2 50OHM

HFDBA

FBVDDQ

1K_0402_1%

1K_0402_1%

FBAVREF4

R519

R519

0.9V16.00

0.9V16.00

IMPEDANCE

100DIFF1FBA_CLK0

100DIFF1FBA_CLK1

100DIFF1FBA_CLK1

100DIFF1FBADQS0

100DIFF1FBADQS0

100DIFF1FBADQS1

100DIFF1FBADQS2

100DIFF1FBADQS2

100DIFF1FBADQS3

100DIFF1FBADQS4

100DIFF1FBADQS4

100DIFF1FBADQS5

100DIFF1FBADQS5

100DIFF1FBADQS6

100DIFF1FBADQS7

100DIFF1FBADQS7

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

PAGEID

DATE

GND

12

GND

FBVDDQ

12

R520

R520

12

C539

C539

0.1U_0402_16V7K

0.1U_0402_16V7K

18-DEC-2006

1

2

3

4

5

Page 5

A B C D E F G H

1

1

PAGE 5) Memory Decoupling Caps

FBVDDQ

12

C35

C35

0.022U_0402_16V7K

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

0.022U_0402_16V7K

FBVDDQ

12

0.022U_0402_16V7K

0.022U_0402_16V7K

FBVDDQ

FBVDDQ

12

C515

C515

0.022U_0402_16V7K

0.022U_0402_16V7K

C574

C574

12

C33

C33

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C521

C521

0.022U_0402_16V7K

0.022U_0402_16V7K

ASSEMBLY

PAGE DETAIL

12

12

C533

C533

C39

C39

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

12

12

C512

C512

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C24

C24

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C505

C505

0.1U_0402_16V7K

0.1U_0402_16V7K

12

0.1U_0402_16V7K

0.1U_0402_16V7K

C528

C528

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C508

C508

0.022U_0402_16V7K

0.022U_0402_16V7K

12

C25

C25

0.022U_0402_16V7K

0.022U_0402_16V7K

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

MEMORY DECOUPLING CAPS

12

C522

C522

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C564

C564

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C529

C529

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C28

C28

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C541

C541

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

12

C525

C525

C501

C501

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

12

12

C45

C45

C506

C506

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

12

12

C511

C511

C503

C503

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

Document number:4059HI

VERSION:C SHEET 5 OF 14

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10419-0000-000

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

2

3

4

5

PAGEID

DATE

18-DEC-2006

HFDBA

Page 6

A B C D E F G H

PAGE 6) DAC_A, DAC_B, DAC_C

1

2

3V3RUN

3

LB507

LB507

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

C644

C644

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

3V3RUN

12

GND

LB502

LB502

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

12

4700P_0402_25V7K

4700P_0402_25V7K

C636

C636

12

0.01U_0402_25V7Z

0.01U_0402_25V7Z

C629

C629

DACA_VDD

DACA_VREF

12

DACB_VDD

12mil

12

R549

R549

124_0402_1%

124_0402_1%

12mil

1

12

12

4700P_0402_25V7K

4700P_0402_25V7K

C620

C620

C621

GND

1

C598

C598

470P_0402_50V7K

470P_0402_50V7K

2

C621

12

0.01U_0402_25V7Z

0.01U_0402_25V7Z

C606

C606

470P_0402_50V7K

470P_0402_50V7K

2

124 ohm is good for G86M ?

DACB_VREF

C628

C628

GND

124 ohm is good for G86M ?

R560

R560

124_0402_1%

124_0402_1%

AE2

AB4

AD3

G1D

G1D

@digital.u_gpu_g3_64_8x(chips):page6_i282

@digital.u_gpu_g3_64_8x(chips):page6_i282

BGA533

BGA533

COMMON

COMMON

3/12 DAC_A

3/12 DAC_A

DAC_A_VDD

DAC_A_VREF

DAC_A_RSET

G1C

G1C

@digital.u_gpu_g3_64_8x(chips):page6_i283

@digital.u_gpu_g3_64_8x(chips):page6_i283

BGA533

BGA533

COMMON

COMMON

4/12 DAC_B

4/12 DAC_B

F8

DAC_B_VDD

E7

DAC_B_VREF

D6

DAC_B_RSET

I2CA_SCL

I2CA_SDA

DAC_A_HSYNC

DAC_A_VSYNC

DAC_A_RED

DAC_A_GREEN

DAC_A_BLUE

DAC_A_IDUMP

I2CB_SCL

I2CB_SDA

DAC_B_HSYNC

DAC_B_VSYNC

DAC_B_CSYNC

DAC_B_RED

DAC_B_GREEN

DAC_B_BLUE

DAC_B_IDUMP

R544

33_0402_5%

R544

33_0402_5%

33_0402_5%

1 2

12

R555

R555

150_0402_1%

150_0402_1%

GND

33_0402_5%

12

R27

R27

150_0402_1%

150_0402_1%

GND

1 2

R583

R583

D10

I2CA_SDA

E10

DACA_HSYNC

AD4

DACA_VSYNC

AC4

DACA_RED

AE1

DACA_GREEN

AD1

DACA_BLUE

AD2

1 2

R547

R547

U9

GND

I2CB_SCL I2CB_SCL_R

F9

F10

SNN_DACB_HSYNC

E6

SNN_DACB_VSYNC

F5

SNN_DACB_CSYNC

F7

DACB_RED

F4

DACB_GREEN

E4

DACB_BLUE

D5

50OHM 1

50OHM 1

L9

GND

GND

33_0402_5%

33_0402_5%

12

R551

R551

150_0402_1%

150_0402_1%

GND

12

R26

R26

150_0402_1%

150_0402_1%

150OHM

GND

3V3RUN 3V3RUN

12

R553

R553

4.7K_0402_5%

4.7K_0402_5%

12

R25

R25

150_0402_1%

150_0402_1%

GND

R582

33_0402_5%

R582

33_0402_5%

1 2

12

R558

R558

150_0402_1%

150_0402_1%

12

R546

R546

4.7K_0402_5%

4.7K_0402_5%

I2CA_SCL_R

I2CA_SDA_R

Place close to GPU

3V3RUN 3V3RUN

12

R589

R589

4.7K_0402_5%

4.7K_0402_5%

OUT

OUT

OUT

8

8

8

12

R574

R574

4.7K_0402_5%

4.7K_0402_5%

NV_CRITICAL NV_IMPEDANCE

50OHM1

50OHM1

50OHM1

I2CB_SDA_R

8

OUT

8

BI

8

OUT

8

OUT

8

OUT

8

OUT

8

OUT

8

OUT

8

BI

1

2

3

G1E

G1E

@digital.u_gpu_g3_64_8x(chips):page6_i284

GND

1 50OHM

H4

H5

C1

B1

@digital.u_gpu_g3_64_8x(chips):page6_i284

BGA533

BGA533

COMMON

COMMON

10/12 XTAL_PLL

10/12 XTAL_PLL

PLLVDD

PLLGND

XTAL_SS_IN

XTAL_IN

Y1

Y1

27 MHZ_18P_10PPM

27 MHZ_18P_10PPM

12

PEX1V2

4

C642

C642

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

12

GND

LB503

LB503

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

12

C641

C641

1U_0603_10V6K

1U_0603_10V6K

12

C630

C630

4700P_0402_25V7K

4700P_0402_25V7K

11

IN

PLLVDD

12mil

1

C624

C624

470P_0402_50V7K

470P_0402_50V7K

2

SSFOUT

XTALIN

1

C652

C652

18P_0402_50V8J

18P_0402_50V8J

2

GND

C GE

XTAL_OUT_BUF

XTAL_OUT

NV_CRITICNV_IMPEDANCENV_CRITIC NV_IMPEDANCE

1 50OHM

ASSEMBLY

PAGE DETAIL

C3

C2

DAC A/B

BXTALOUT

XTALOUT

1

2

GND

C654

C654

18P_0402_50V8J

18P_0402_50V8J

R23

22_0402_5%

R23

12

R30

R30

10K_0402_5%@

10K_0402_5%@

INTERNAL SS : STUFF

EXTERNAL SS : NO STUFF

1 2

22_0402_5%

11

OUT

GND

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

Document number:4059HI

VERSION:C SHEET 6 OF 14

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10419-0000-000

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

4

5

PAGEID

DATE

18-DEC-2006

HFDBA

Page 7

A B C D E F G H

PAGE 7)LVDS / TMDS Interface

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

Loading options for IFPAB outputs

Option #1) IFPAB outputs to LVDS only.

Option #2) IFPAB outputs to DVI-C only.

Option #3) Controlled with GPIO9, IFPAB dynamically outputs to LVDS or DVI-C.

13

IN

FB_PWRGOOD

13

IN

3V3RUN

12

R568

R568

10K_0402_5%

10K_0402_5%

GPIO9_LVDS_SYS*

9

IN

TMDSIOVDD_AB_EN*

13

D

D

Q510

2

G

G

RUNPWROK

Q510

SI2305DS-T1-E3_SOT23

SI2305DS-T1-E3_SOT23

S

S

2

G

G

GND

3V3RUN

8,11,12,13

IN

13

2

G

G

GND

13

D

D

RTR040N03_TSMT3

RTR040N03_TSMT3

Q509

Q509

S

S

D

D

Q508

Q508

RTR040N03_TSMT3

RTR040N03_TSMT3

S

S

2

1V8RUN

Load for

option #3.

LVDSIOVDD_ISOL

13

D

D

Q511

Q511

G

G

RTR040N03_TSMT3

RTR040N03_TSMT3

S

S

12

12

C650

C650

0.1U_0402_16V7K

0.1U_0402_16V7K

GND

TMDSIOVDD_C_EN*

2

G

G

R4

R4

10K_0402_5%

10K_0402_5%

10K_0402_5%

10K_0402_5%

TMDS_LVDS_IOVDD

13

D

D

Q2

Q2

SI2305DS-T1-E3_SOT23

SI2305DS-T1-E3_SOT23

S

S

12

R572

R572

12

R6

R6

10K_0402_5%

10K_0402_5%

Load for

option

#1.

@

@

12

R1

R1

0_0402_5%

0_0402_5%

Load for

options

#1 and #3.

RTR040N03_TSMT3

RTR040N03_TSMT3

GND

13

D

D

Q1

Q1

S

S

12

C3

C3

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2

G

G

current on

IFPA_IOVDD.

LVDS

Sequencing

Circuit

LB509

LB509

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

GND

Delay to

control

inrush

12

C9

C9

0.1U_0402_16V7K

0.1U_0402_16V7K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1V8RUN

C646

C646

C649

C649

Load for option #2.

LB1

LB1

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

@

@

1V8RUN

GND

3V3RUN

13

D

D

Q507

Q507

SI2305DS-T1-E3_SOT23

SI2305DS-T1-E3_SOT23

2

G

G

S

S

TMDSIOVDD_C

C GE

12

C656

C656

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

12mil

12

C651

C651

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

LB508

LB508

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

LB505

LB505

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

1 2

MBK1608121YZF_0603

MBK1608121YZF_0603

12

GND

12

GND

C648

C648

12

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

ASSEMBLY

PAGE DETAIL

G1F

G1F

@digital.u_gpu_g3_64_8x(chips):page7_i458

@digital.u_gpu_g3_64_8x(chips):page7_i458

BGA533

BGA533

COMMON

COMMON

5/12 IFP_AB

IFPABVPROBE

TP502TP502

LB504

LB504

12

C639

C639

0.1U_0402_16V7K

0.1U_0402_16V7K

12

C637

C637

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

GND

C631

C631

12

0.1U_0402_16V7K

0.1U_0402_16V7K

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

LVDS(LINK A/B), TMDS(LINK C/D)

12mil

12

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C638

C638

GND

16mil

12

C634

C634

0.022U_0402_16V7K

0.022U_0402_16V7K

TP501TP501

12mil

12

C626

C626

4700P_0402_25V7K

4700P_0402_25V7K

12mil

C625

C625

12

4700P_0402_25V7K

4700P_0402_25V7K

IFPABPLLVDD

12

C623

C623

4700P_0402_25V7K

4700P_0402_25V7K

IFPAIOVDD

12

C632

C632

4700P_0402_25V7K

4700P_0402_25V7K

IFPCVPROBE

IFPCPLLVDD

1

C619

C619

2

470P_0402_50V7K

470P_0402_50V7K

IFPC_IOVDD

C618

C618

1

2

470P_0402_50V7K

470P_0402_50V7K

IFPABRSET

1

470P_0402_50V7K

470P_0402_50V7K

C617

C617

2

1

C627

C627

2

470P_0402_50V7K

470P_0402_50V7K

5/12 IFP_AB

N6

IFP_AB_VPROBE

V5

IFP_AB_PLL_VDD

U6

IFP_AB_RSET

12

R545

R545

1K_0402_1%

1K_0402_1%

V6

IFP_AB_PLL_GND

W4

IFP_A_IO_VDD

Y4

IFP_B_IO_VDD

G1G

G1G

@digital.u_gpu_g3_64_8x(chips):page7_i485

@digital.u_gpu_g3_64_8x(chips):page7_i485

BGA533

BGA533

COMMON

COMMON

12/12 IFPC

12/12 IFPC

M5

IFPC_VPROBE

M4

IFPCBRSET

IFPC_PLL_VDD

J3

IFPC_RSET

12

R29

R29

1K_0402_1%

1K_0402_1%

M6

IFPC_PLL_GND

L4

IFPC_IO_VDD

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

A

DATA

DATA

B

B

A

A

CLOCK

CLOCK

B

B

LVDS

DATA

DATA

CLOCK

CLOCK

TMDS(SINGLE)

IFP_A_TXD0

IFP_A_TXD0

IFP_A_TXD1

IFP_A_TXD1

IFP_A_TXD2

IFP_A_TXD2

IFP_A_TXD3

IFP_A_TXD3

IFP_B_TXD4

IFP_B_TXD4

IFP_B_TXD5

IFP_B_TXD5

IFP_B_TXD6

IFP_B_TXD6

IFP_B_TXD7

IFP_B_TXD7

IFP_A_TXC

IFP_A_TXC

IFP_B_TXC

IFP_B_TXC

IFPC_TXD0

IFPC_TXD0

IFPC_TXD1

IFPC_TXD1

IFPC_TXD2

IFPC_TXD2

IFPC_TXC

IFPC_TXC

IFPATXD0*

N5

IFPATXD0

N4

IFPATXD1*

R4

IFPATXD1

R5

IFPATXD2*

T6

IFPATXD2

T5

IFPATXD3*

P6

IFPATXD3

R6

IFPBTXD4*

W2

IFPBTXD4

W3

IFPBTXD5*

AA3

IFPBTXD5

AA2

IFPBTXD6*

AA1

IFPBTXD6

AB1

IFPBTXD7*

AB2

IFPBTXD7

AB3

IFPATXC*

U4

IFPATXC

T4

IFPBTXC*

W6

IFPBTXC

W5

R1

T1

T2

T3

V3

V2

W1

V1

NET NAME DIFFPAIR

IFPCTXD0*

IFPCTXD0

IFPCTXD1*

IFPCTXD1

IFPCTXD2*

IFPCTXD2

IFPCTXC*

IFPCTXC

100DIFF1IFPATXD0

100DIFF1IFPATXD0

100DIFF1IFPATXD1

100DIFF1IFPATXD1

100DIFF1IFPATXD2

100DIFF1IFPATXD2

100DIFF1IFPATXD3

100DIFF1IFPATXD3

100DIFF1IFPBTXD4

100DIFF1IFPBTXD4

100DIFF1IFPBTXD5

100DIFF1IFPBTXD5

100DIFF1IFPBTXD6

100DIFF1IFPBTXD6

100DIFF1IFPBTXD7

100DIFF1IFPBTXD7

100DIFF1IFPATXC

100DIFF1IFPATXC

100DIFF1IFPBTXC

100DIFF1IFPBTXC

NV_CRITICAL_NET

NV_IMPEDANCE

100DIFF1IFPCTXD0

100DIFF1IFPCTXD0

100DIFF1IFPCTXD1

100DIFF1IFPCTXD1

100DIFF1IFPCTXD2

100DIFF1IFPCTXD2

100DIFF1IFPCTXC

100DIFF1IFPCTXC

Compal Electronics. inc

SCHEMATIC, VGA/B LS-3582P

VERSION:C SHEET 7 OF 14

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10419-0000-000

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Document number:4059HI

PAGEID

DATE

18-DEC-2006

HFDBA

1

8

8

8

8

8

8

2

8

8

8

8

8

8

8

8

8

8

8

8

8

8

3

8

8

8

8

8

8

4

8

8

5

Page 8

A B C D E F G H

PAGE 8) MXM CONNECTOR

1

1

9

OUT

6

IN

6

BI

DVI_A_HPD

I2CB_SCL_R

I2CB_SDA_R

CN1B

CN1B

@electro_mechanic.con_mxm(chips):page8_i123

@electro_mechanic.con_mxm(chips):page8_i123

(N,NON)PHY(-X16,-HE)

(N,NON)PHY(-X16,-HE)

NONPHY-X16

NONPHY-X16

COMMON

COMMON

2/2 IO - LVDS,DVI,VGA,TV

2/2 IO - LVDS,DVI,VGA,TV

217

DVI_A_HPD

232

DDCB_SCLK

230

DDCB_SDATA

2

9

OUT

6