A

1 1

B

C

D

E

Compal Confidential

2 2

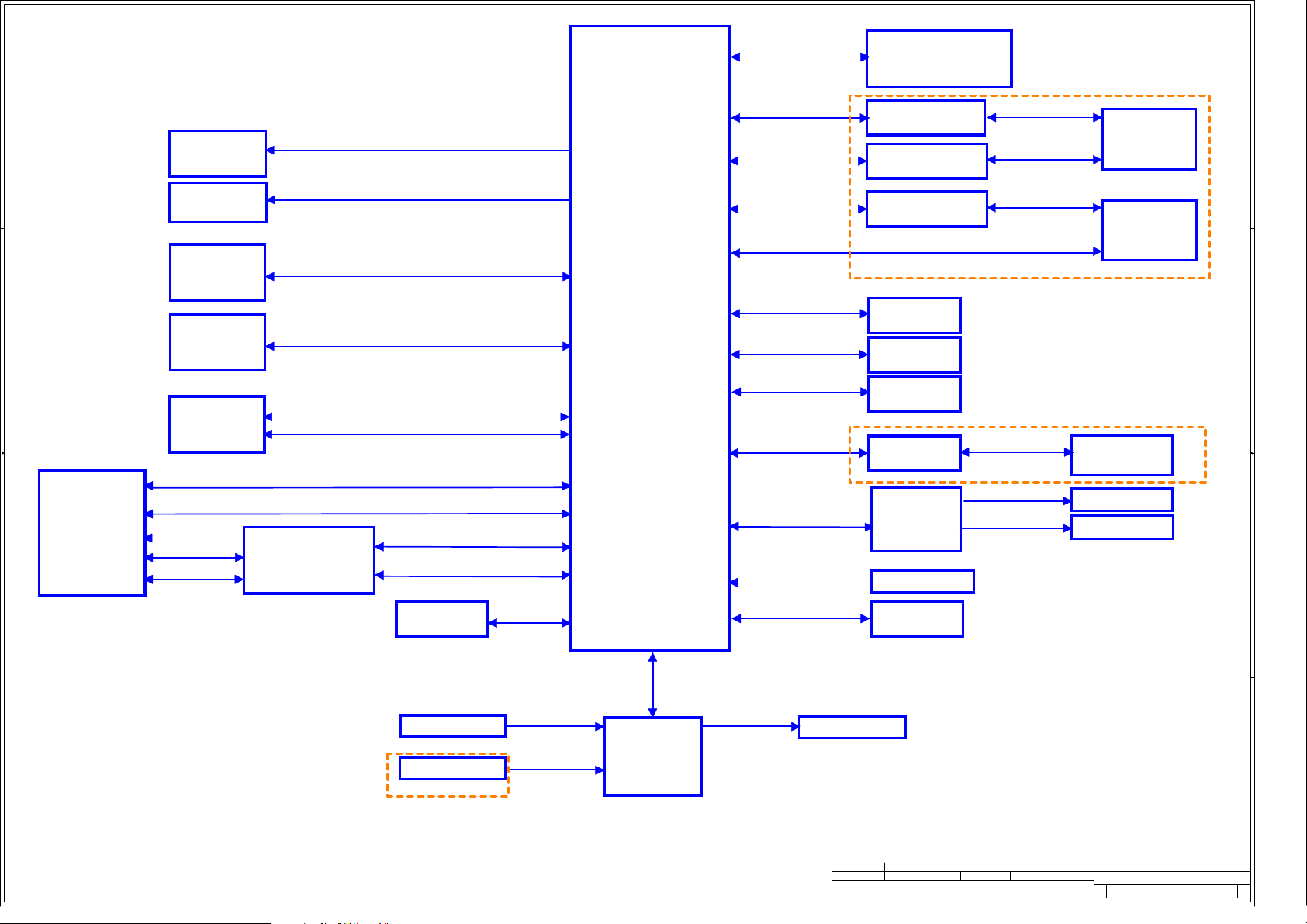

UMA M/B Schematic Document

AMD Renoir Processor with DDR4 Memory Down

S550

3 3

2020-01-10

LA-J701P

R E V

:

:

::

1 . 0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2020/01/ 10 2022/01/ 10

2020/01/ 10 2022/01/ 10

2020/01/ 10 2022/01/ 10

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet of

D

Date : Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-J701P

LA-J701P

LA-J701P

E

1.0

1.0

1.0

o f

1 39Friday, January 10, 2020

1 39Friday, January 10, 2020

1 39Friday, January 10, 2020

A

(opt i on)

B

C

D

E

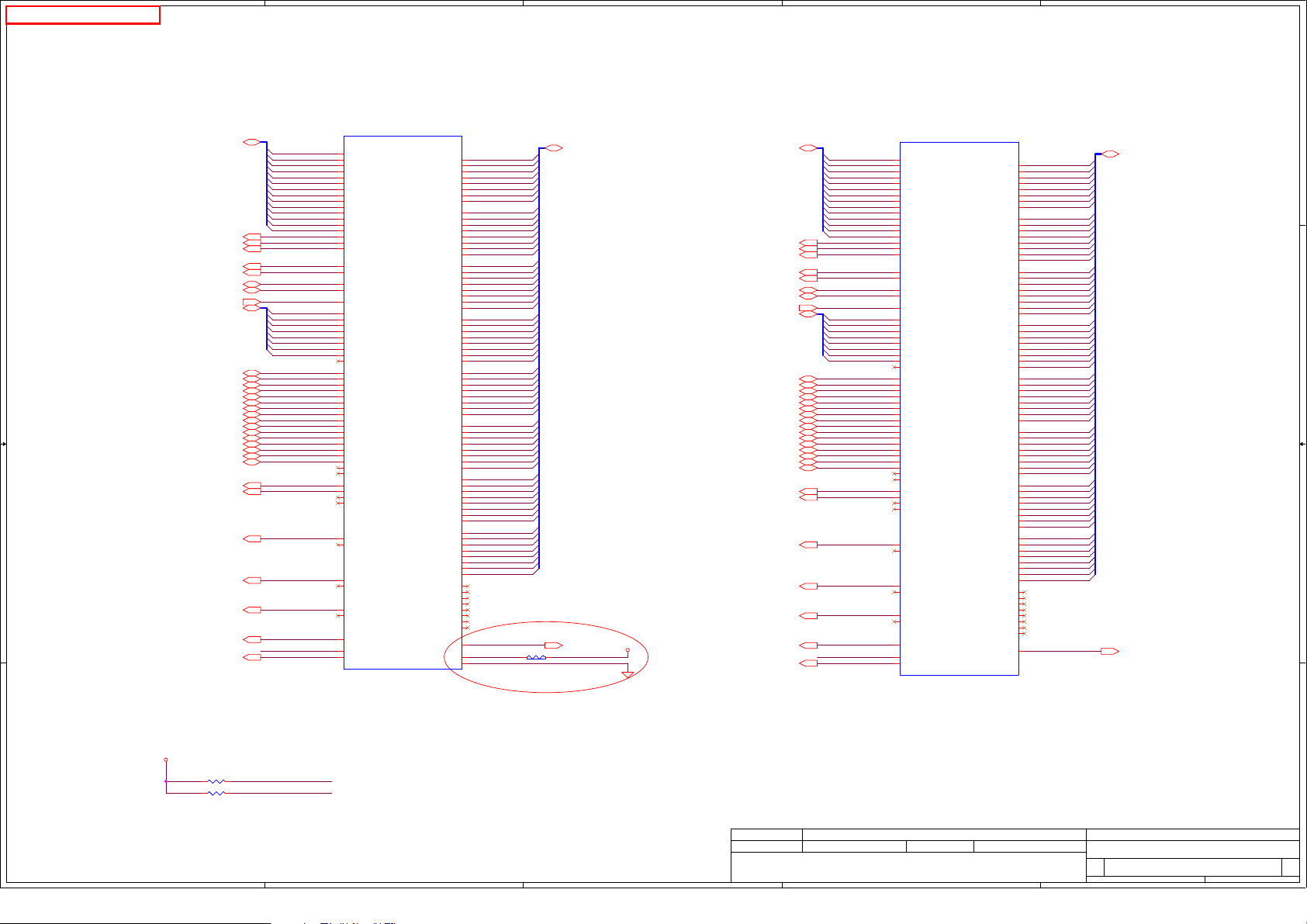

DDR4 3200MHz

CH-A on board RAM x4

CH-B on board RAM x4

1 1

eDP Panel

FHD LCD

HDMI Conn.

eDP x4

DDI x4

USB2.0 x1

USB3.1 x1

USB3.1 x1

USB Charger

TI SN1702001

USB3 redriver

Parade PS8719

USB3 redriver

Parade PS8719

USB2.0 x1

USB3.1 x1

USB3.1 x1

USB Conn.

with AOU

USB Conn.

NGFF (Key M)

PCIE/SATA SSD

2242/2280 conn.

2 2

NGFF (Key M)

PCIE/SATA SSD

2242 conn.

NGFF (Key E)

WLAN/BT

2230 conn.

PCIe x4

SATA

PCIe x4

SATA

PCIe x1

USB2.0 x1

AMD Renoir

25W

1140pin BGA

USB2.0 x1

Type-C Conn.

USB3.1 Gen1

3 3

VBus

SBU

CC/Vconn

CC+PD

Realtek RTS5457V

USBC/DP

I2C

AUX

USB2.0 x1

USB2.0 x1

USB2.0 x1

USB2.0 x1

PCIe x1

HDA

DMIC

FingerPrint

Int. Camera

Touch Panel

Card Reader

Realtek RTS5232S

Audio Codec

Realtek ALC3287

Int. Array Mic *2

HP

SPK

IO Board

SDIO

IO Board

SD Card Conn.

Combo Jack

Int. Speaker

SPI ROM

16MB

SPI

I2C

TouchPad

LPC

Int. KBD

LED

KBC

Hall Sensor

4 4

A

IO Board

B

ENE KB9022

C

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERT Y OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERT Y OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERT Y OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPET ENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPET ENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPET ENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size

Document Number Rev

Size

Document Number Rev

Size

Document Number Rev

Custom

Custom

Custom

LA-J701P

LA-J701P

LA-J701P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

2 3 9Friday, January 10, 2020

2 3 9Friday, January 10, 2020

2 3 9Friday, January 10, 2020

1.0

1.0

1.0

1

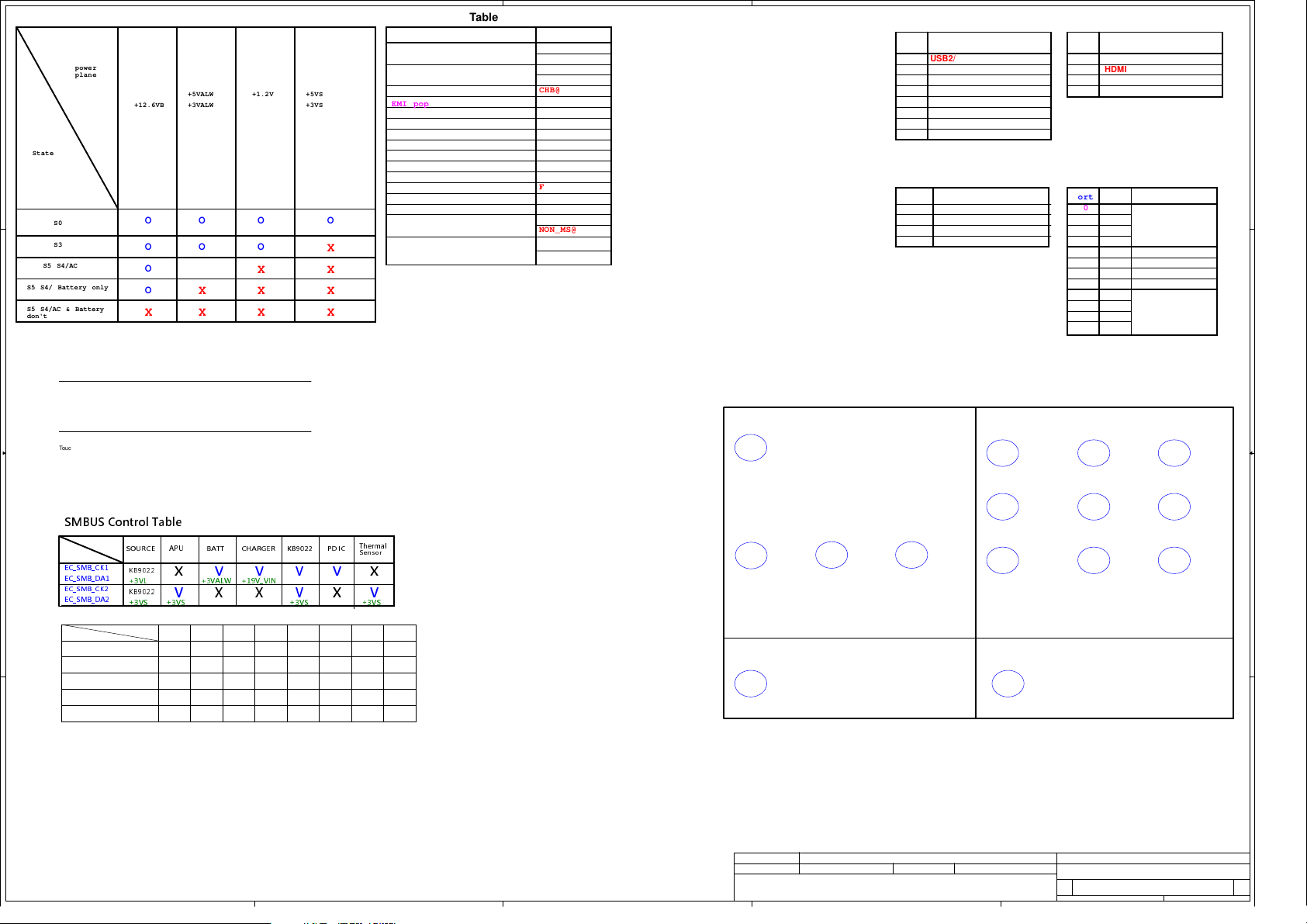

Voltage Rails

power

plane

+5VALW

A A

State

S0

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

B B

+12.6V B

+3VALW

+1.8VAL W

+0.75VAL W +0.75V S

O

O

O

O

O

O

O

X

X

+1.2V

+2.5V

O O

O

X

+5VS

+3VS

+1.8VS

+0.6VS

+APU_COR E

+APU_COR E_SOC

X

XX

X

XXX

2

BOM Structure Table

Item

Memory Down - SDP Package

Memory Down - DDP Package

Channel B Memory Down

EMI pop

EMI un-pop

ESD pop

ESD un-pop

RF po p

RF un-pop

Debug

Normal FP

SLIM_ FP

CAMERA POWE R CIRCUIT

Modern standby

DP Power Switch

BOM Structure

SDP@

SDP_C HB@

DDP@

DDP_C HB@

CHB@

EMI@

@EMI@

ESD@

@ESD@

RF@

@RF@

HDT@

KBL@Keyboard BackLight

FP@

SLIM_ FP@

CAM@

MS@

NON_M S@

DPS11 55@

DPS11 13@

3

4

USB 2.0 Port Table

External USB Por tPort

USB2/3 Port (Type-C)

0

USB2/3 Port (IO - 1)

1

Camera

2

Touch Screen

3

4

USB2/3 Port (IO - 2)

5

Fingrt Print

6

NGFF BT

7

USB 3.0 Port Table

Port

0

USB2/3 Port (Type-C)

1

USB2/3 Port (IO - 1)

4

5

USB2/3 Port (IO - 2)

5

DDI Port Table

Port Lane

0

eDP

1

HDMI

2

TYPE C (PD + CC)

3

GPP Port Table

Port

Lane

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

SSD1

CardReader

NGFF WLAN

SSD2

EC SM Bus1 address

Device

Smart Battery

Charger (ISL88739A)

PCH SM Bus address

Device

Touch pad

Address

0001 011x 16h

0001 001x 12h

Address

SMBUS Control Table

SOURCE

C C

D D

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

KB90 22

+3VL +3VALW

KB90 22

+3VS +3VS

SIGNAL

EC SM Bus2 address

Device

Thermal Sensor (F75305M)

Device

APU

V

X

X

V

+3VS

SLP_S1 #

LOW

HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW

LOWLOW

Address

1001_101xb 9Ah

Address

Thermal

V

ONONON

ON

ON

ON

ON

PD ICKB9022BATT

Sensor

VV

X

+3VS

ON

ON

OFF

OFF

OFF

OFF

OFF

CHARGER

V

+19V_V IN

X

SLP_S4 #SLP_S3 # +V+VALWSLP_S5 # Clock+VS

HIGHHIGHHIGH

HIGH

HIGH

HIGH

HIGH

LOWLOW

Renoir APU ES

UC1

APU_ES@

RYZEN9 100-000000082-21 2G ES BGA 1140 APU

SA0000D1710

Renoir APU IP

UC1

APU_R7@

X

AMD Ryzen 7 4700U 2.0G

SA0000D4980

UC1

APU_R5@

AMD Ryzen 5 4500U 2.375G

SA0000D4A80

UC1

APU_R3@

AMD Ryzen 3 4300U 2.7G

SA0000D3V80

ON BOARD RAM X76

ZZZ10

X76_S4G@ ZZZ11

X76 SAMSUNG 4GB SINGEL

X7684838L55

ZZZ13

X76_S8G@

X76 SAMSUNG 8GB DUAL

X7684838L58

X76_S16G@

ZZZ16

X76 SAMSUNG 16GB DUAL

X7684838L61

X76 HYNIX 4GB SINGEL

X7684838L56

ZZZ15

X76 MICRON 8GB DUAL

X7684838L59

ZZZ17

X76 HYNIX 16GB DUAL

X7684838L62

X76_H4G@

X76_M8G@

X76_H16G@

ZZZ12

X76_M4G@

X76 MICRON 4GB SINGEL

X7684838L57

ZZZ14

X76_H8G@

X76 HYNIX 8GB DUAL

X7684838L60

X76_M16G@

ZZZ18

X76 MICRON 16GB DUAL

X7684838L63

V

ONON

LOW

OFF

OFF

OFF

PCB PN

ZZZ

PCB FLMA0 LA-J701P LS-J701P 02

DAZ2VF00100

X4E

ZZZ1

SMT EMC RENOIR B12 SJ701 FLMA0

X4EAKM38L01

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

1

2

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

LA-J701P

LA-J701P

LA-J701P

Date : Sheet of

Date : Sheet of

Date : Sheet

5

3 39Friday, January 10, 2020

3 39Friday, January 10, 2020

3 39Friday, January 10, 2020

1.0

1.0

1.0

of

5

4

3

2

1

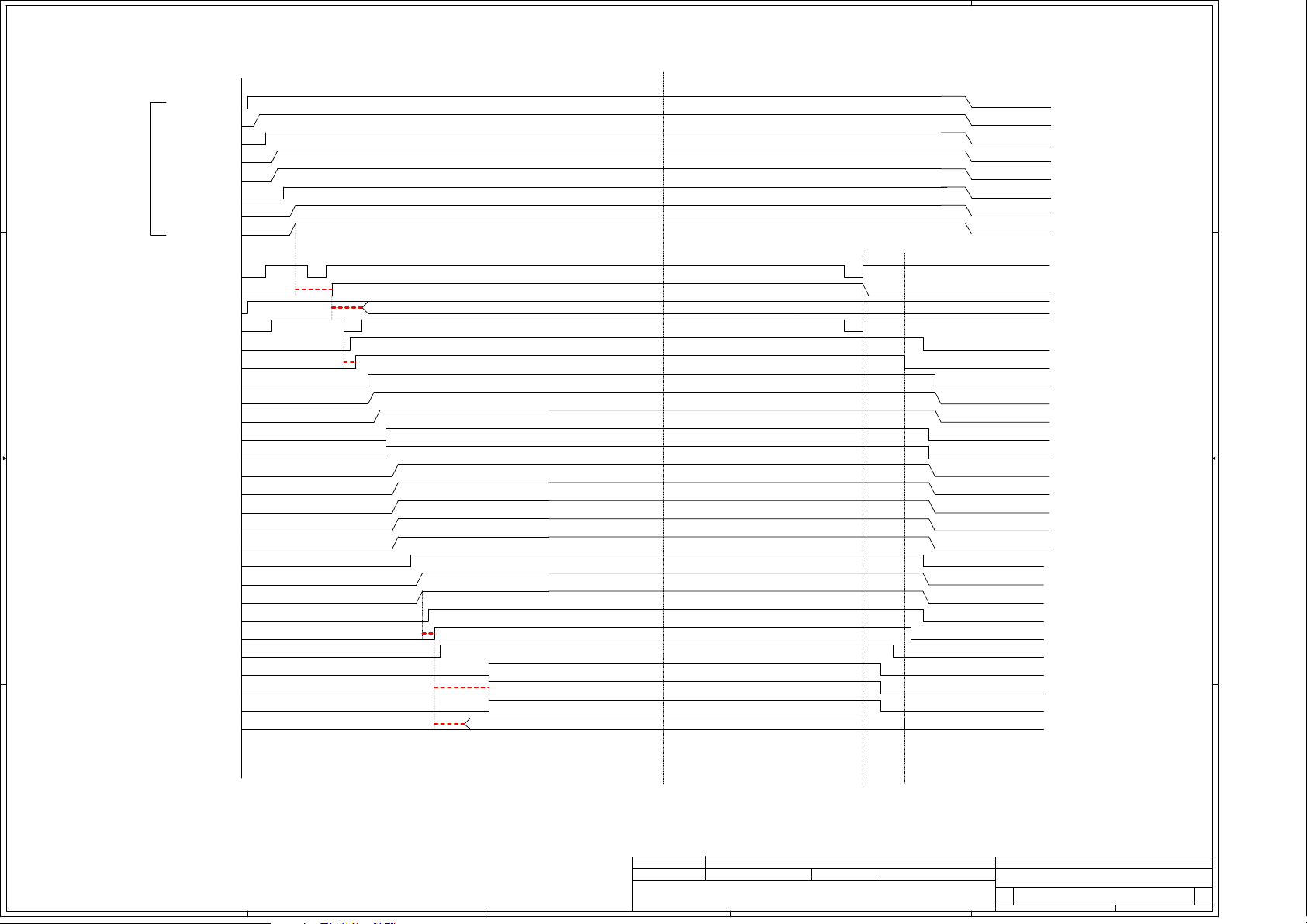

Power Sequence

EC Pin 110 Intput

D D

EC Pin 112 Output

AC Plug

EC Pin 114 Intput

EC Pin 100 Output

EC Pin 122 Output

C C

EC Pin 123 Intput

EC Pin 6 Intput

EC Pin 95 Output

EC Pin 116 Output

EC Pin 99 Output

B B

EC Pin 121 Output

EC Pin 36 Intput

EC Pin 32 Output

EC Pin 13 Intput

VCIN 1_AC _IN

+3V LP

EC_ ON

+5V ALW

+3V ALW

3V/5 VALW _PG

+1.8 VAL W

+0.8 VAL W

ON/O FF#

EC_R SMRS T#

RTC_ CLK RTC_ CLK

PBTN _OU T#

PM_S LP_S 5#

PM_S LP_S 3#

SYS ON

+2.5 V_M EM

+1.2 V_D DR

SUS P#

0.75V S_P WR_ EN

+5V S

+3V S

+1. 8VS

+0.7 5VS

+0. 6VS

VR_ ON

+APU _CO RE

+APU_ COR E_S OC

VGA TE

PCH_ PWR OK

APU_ PWR GD

PLT_ RST #

PCIR ST#

APU_ RST #

CLK_ PCI E

T1_Min : 10ms

Boot

T2 : 15ms~26ms

T3 : 30us~64us

T5_Min : 1ms

T8 : 15ms~17ms

T9 : 12ms~14.6ms

Shut

Down

VCIN 1_AC _IN

+3V LP

EC_ ON

+5V ALW

+3V ALW

3V/5 VALW _PG

+1.8 VAL W

+0.8 VAL W

ON/O FF#

EC_R SMRS T#

PBTN _OU T#

PM_S LP_S 5#

PM_S LP_S 3#

SYS ON

+2.5 V_M EM

+1.2 V_D DR

SUS P#

0.8V S_PW R_E N

+5V S

+3V S

+1. 8VS

+0. 8VS

+0. 6VS

VR_ ON

+APU _CO RE

+APU_ COR E_S OC

VGA TE

PCH_ PWR OK

APU_ PWR GD

PLT_ RST #

PCIR ST#

APU_ RST #

CLK_ PCI E

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Power Sequence

Power Sequence

Document Number Re v

Document Number Re v

Document Number Re v

Power Sequence

LA-J701P

LA-J701P

LA-J701P

1

4 39Friday, January 10, 2020

4 39Friday, January 10, 2020

4 39Friday, January 10, 2020

1.0

1.0

1.0

of

of

of

Main Func = CPU

5

4

3

2

1

D D

DDR_A_MA[ 13..0]<12>

DDR_A_W E#<12>

DDR_A_CAS #<12>

DDR_A_RAS #<12>

DDR_A_BA 0<12>

DDR_A_BA 1<12>

DDR_A_BG 0<1 2>

DDR_A_BG 1<1 2>

DDR_A_ACT#<12>

DDR_A_DM[7 ..0]<12>

C C

DDR_A_DQS 0<12>

DDR_A_DQS 0#<12>

DDR_A_DQS 1<12>

DDR_A_DQS 1#<12>

DDR_A_DQS 2<12>

DDR_A_DQS 2#<12>

DDR_A_DQS 3<12>

DDR_A_DQS 3#<12>

DDR_A_DQS 4<12>

DDR_A_DQS 4#<12>

DDR_A_DQS 5<12>

DDR_A_DQS 5#<12>

DDR_A_DQS 6<12>

DDR_A_DQS 6#<12>

DDR_A_DQS 7<12>

DDR_A_DQS 7#<12>

DDR_A_CLK 0<12>

DDR_A_CLK 0#<12>

DDR_A_CS0 #<12>

B B

DDR_A_CKE 0<12>

DDR_A_ODT0<12>

DDR_A_AL ERT#<12>

DDR_A_RST#<12>

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA1 0

DDR_A_MA1 1

DDR_A_MA1 2

DDR_A_MA1 3

DDR_A_BG 0

DDR_A_BG 1

DDR_A_ACT#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_EV ENT#

AK26

AG24

AG23

AG26

AG27

AF21

AF22

AF25

AF24

AE21

AL21

AF27

AE23

AM23

AM21

AL27

AL24

AL22

AK27

AE27

AE26

AD22

AP27

AW23

AT21

AV18

AA21

AP23

AP24

AW22

AV22

AT20

AR20

AR18

AT18

AL25

AM26

AD24

AD25

AM24

AM27

AE24

AK23

AD27

W24

AJ25

AJ24

AJ22

AJ21

L27

N23

R27

Y24

M25

M24

P22

P21

T24

R24

Y21

Y26

Y27

MA_ADD0/RSVD

MA_ADD1/RSVD

MA_ADD2/MAB_CA0

MA_ADD3/MAA_CA4

MA_ADD4/MAA_CA5

MA_ADD5/MAA_CA3

MA_ADD6/MAA_CA2

MA_ADD7/RSVD

MA_ADD8/RSVD

MA_ADD9/RSVD

MA_ADD10/MAB_CS_L1

MA_ADD11/MAA_CKE1

MA_ADD12/MAA_CKE0

MA_ADD13_BANK2/RSVD

MA_WE_L_ADD14/MAB_CKE1

MA_CAS_L_ADD15/RSVD

MA_RAS_L_ADD16/MAB_CKE0

MA_BANK0/MAB_CS_L0

MA_BANK1/MAB_CA1

MA_BG0/MAA_CS_L1

MA_BG1/MAA_CS_L0

MA_ACT_L/RSVD

MA_DM0/MAA_DM1

MA_DM1/MAA_DM0

MA_DM2/MAA_DM2

MA_DM3/MAA_DM3

MA_DM4/MAB_DM2

MA_DM5/MAB_DM3

MA_DM6/MAB_DM1

MA_DM7/MAB_DM0

RSVD_52

MA_DQS_H0/MAA_DQS_H1

MA_DQS_L0/MAA_DQS_L1

MA_DQS_H1/MAA_DQS_H0

MA_DQS_L1/MAA_DQS_L0

MA_DQS_H2/MAA_DQS_H2

MA_DQS_L2/MAA_DQS_L2

MA_DQS_H3/MAA_DQS_H3

MA_DQS_L3/MAA_DQS_L3

MA_DQS_H4/MAB_DQS_H2

MA_DQS_L4/MAB_DQS_L2

MA_DQS_H5/MAB_DQS_H3

MA_DQS_L5/MAB_DQS_L3

MA_DQS_H6/MAB_DQS_H1

MA_DQS_L6/MAB_DQS_L1

MA_DQS_H7/MAB_DQS_H0

MA_DQS_L7/MAB_DQS_L0

RSVD_58

RSVD_59

MA_CLK_H0/MAA_CKT

MA_CLK_L0/MAA_CKC

MA_CLK_H1/MAB_CKT

MA_CLK_L1/MAB_CKC

MA_CS_L0/MAB_CA2

MA_CS_L1/MAB_CA5

MA_CKE0/MAA_CA1

MA_CKE1/MAA_CA0

MA_ODT0/MAB_CA3

MA_ODT1/MAB_CA4

MA_ALERT_L/TEST31A

MA_EVENT_L

MA_RESET_L

FP6_BGA 1140

UC1A

@

MEMORY A

FP6 REV 0.92

PART 1 OF 13

MA_DATA0/MAA_DATA8

MA_DATA1/MAA_DATA9

MA_DATA2/MAA_DATA13

MA_DATA3/MAA_DATA12

MA_DATA4/MAA_DATA11

MA_DATA5/MAA_DATA10

MA_DATA6/MAA_DATA15

MA_DATA7/MAA_DATA14

MA_DATA8/MAA_DATA0

MA_DATA9/MAA_DATA1

MA_DATA10/MAA_DATA5

MA_DATA11/MAA_DATA4

MA_DATA12/MAA_DATA7

MA_DATA13/MAA_DATA6

MA_DATA14/MAA_DATA2

MA_DATA15/MAA_DATA3

MA_DATA16/MAA_DATA17

MA_DATA17/MAA_DATA16

MA_DATA18/MAA_DATA21

MA_DATA19/MAA_DATA20

MA_DATA20/MAA_DATA19

MA_DATA21/MAA_DATA18

MA_DATA22/MAA_DATA23

MA_DATA23/MAA_DATA22

MA_DATA24/MAA_DATA30

MA_DATA25/MAA_DATA31

MA_DATA26/MAA_DATA26

MA_DATA27/MAA_DATA27

MA_DATA28/MAA_DATA28

MA_DATA29/MAA_DATA29

MA_DATA30/MAA_DATA24

MA_DATA31/MAA_DATA25

MA_DATA32/MAB_DATA17

MA_DATA33/MAB_DATA16

MA_DATA34/MAB_DATA21

MA_DATA35/MAB_DATA20

MA_DATA36/MAB_DATA19

MA_DATA37/MAB_DATA18

MA_DATA38/MAB_DATA23

MA_DATA39/MAB_DATA22

MA_DATA40/MAB_DATA30

MA_DATA41/MAB_DATA31

MA_DATA42/MAB_DATA26

MA_DATA43/MAB_DATA27

MA_DATA44/MAB_DATA28

MA_DATA45/MAB_DATA29

MA_DATA46/MAB_DATA24

MA_DATA47/MAB_DATA25

MA_DATA48/MAB_DATA11

MA_DATA49/MAB_DATA10

MA_DATA50/MAB_DATA14

MA_DATA51/MAB_DATA15

MA_DATA52/MAB_DATA12

MA_DATA53/MAB_DATA13

MA_DATA54/MAB_DATA9

MA_DATA55/MAB_DATA8

MA_DATA56/MAB_DATA6

MA_DATA57/MAB_DATA7

MA_DATA58/MAB_DATA2

MA_DATA59/MAB_DATA3

MA_DATA60/MAB_DATA4

MA_DATA61/MAB_DATA5

MA_DATA62/MAB_DATA1

MA_DATA63/MAB_DATA0

MA_PAROUT/RSVD

M_LPDDR4

@

UC1I

MEMORY B

FP6 REV 0.92

PART 9 OF 13

MB_DATA0/MBA_DATA8

MB_DATA1/MBA_DATA9

MB_DATA2/MBA_DATA13

MB_DATA3/MBA_DATA12

MB_DATA4/MBA_DATA11

MB_DATA5/MBA_DATA10

MB_DATA6/MBA_DATA15

MB_DATA7/MBA_DATA14

MB_DATA8/MBA_DATA0

MB_DATA9/MBA_DATA1

MB_DATA10/MBA_DATA5

MB_DATA11/MBA_DATA4

MB_DATA12/MBA_DATA7

MB_DATA13/MBA_DATA6

MB_DATA14/MBA_DATA2

MB_DATA15/MBA_DATA3

MB_DATA16/MBA_DATA21

MB_DATA17/MBA_DATA22

MB_DATA18/MBA_DATA20

MB_DATA19/MBA_DATA19

MB_DATA20/MBA_DATA17

MB_DATA21/MBA_DATA16

MB_DATA22/MBA_DATA18

MB_DATA23/MBA_DATA23

MB_DATA24/MBA_DATA30

MB_DATA25/MBA_DATA31

MB_DATA26/MBA_DATA26

MB_DATA27/MBA_DATA27

MB_DATA28/MBA_DATA28

MB_DATA29/MBA_DATA29

MB_DATA30/MBA_DATA25

MB_DATA31/MBA_DATA24

MB_DATA32/MBB_DATA16

MB_DATA33/MBB_DATA17

MB_DATA34/MBB_DATA21

MB_DATA35/MBB_DATA20

MB_DATA36/MBB_DATA19

MB_DATA37/MBB_DATA18

MB_DATA38/MBB_DATA23

MB_DATA39/MBB_DATA22

MB_DATA40/MBB_DATA29

MB_DATA41/MBB_DATA28

MB_DATA42/MBB_DATA24

MB_DATA43/MBB_DATA25

MB_DATA44/MBB_DATA27

MB_DATA45/MBB_DATA26

MB_DATA46/MBB_DATA30

MB_DATA47/MBB_DATA31

MB_DATA48/MBB_DATA11

MB_DATA49/MBB_DATA10

MB_DATA50/MBB_DATA14

MB_DATA51/MBB_DATA15

MB_DATA52/MBB_DATA12

MB_DATA53/MBB_DATA13

MB_DATA54/MBB_DATA9

MB_DATA55/MBB_DATA8

MB_DATA56/MBB_DATA4

MB_DATA57/MBB_DATA5

MB_DATA58/MBB_DATA2

MB_DATA59/MBB_DATA3

MB_DATA60/MBB_DATA6

MB_DATA61/MBB_DATA7

MB_DATA62/MBB_DATA1

MB_DATA63/MBB_DATA0

MB_PAROUT/RSVD

DDR_B_DQ0

C27

DDR_B_DQ7

A28

DDR_B_DQ5

F29

DDR_B_DQ3

F31

DDR_B_DQ6

B27

DDR_B_DQ2

D27

DDR_B_DQ1

E32

DDR_B_DQ4

F30

DDR_B_DQ8

H31

DDR_B_DQ1 0

H30

DDR_B_DQ1 3

K31

DDR_B_DQ1 5

L30

DDR_B_DQ1 4

G30

DDR_B_DQ1 2

H29

DDR_B_DQ9

K30

DDR_B_DQ1 1

K29

DDR_B_DQ1 6

N32

DDR_B_DQ1 7

N29

DDR_B_DQ1 9

P30

DDR_B_DQ2 0

L32

DDR_B_DQ2 2

L31

DDR_B_DQ2 3

M30

DDR_B_DQ1 8

L29

DDR_B_DQ2 1

N31

DDR_B_DQ2 8

R30

DDR_B_DQ2 7

R32

DDR_B_DQ2 9

V30

DDR_B_DQ3 1

V32

DDR_B_DQ2 4

P29

DDR_B_DQ2 6

P31

DDR_B_DQ2 5

U31

DDR_B_DQ3 0

U29

DDR_B_DQ3 5

AT29

DDR_B_DQ3 9

AU32

DDR_B_DQ3 7

AW31

DDR_B_DQ3 8

AW30

DDR_B_DQ3 4

AR30

DDR_B_DQ3 2

AT31

DDR_B_DQ3 3

AV30

DDR_B_DQ3 6

AW29

DDR_B_DQ4 4

AY29

DDR_B_DQ4 6

AY32

DDR_B_DQ4 1

BC27

DDR_B_DQ4 3

BB26

DDR_B_DQ4 5

BC25

DDR_B_DQ4 7

BA25

DDR_B_DQ4 2

BB30

DDR_B_DQ4 0

BA28

DDR_B_DQ4 8

BA24

DDR_B_DQ5 4

BC24

DDR_B_DQ5 1

BC22

DDR_B_DQ5 3

BA22

DDR_B_DQ5 2

BB25

DDR_B_DQ5 0

BD25

DDR_B_DQ5 5

BB22

DDR_B_DQ4 9

BD22

DDR_B_DQ6 0

BA21

DDR_B_DQ5 7

BC21

DDR_B_DQ6 1

BC18

DDR_B_DQ6 2

BB18

DDR_B_DQ6 3

BB20

DDR_B_DQ5 6

BB21

DDR_B_DQ5 9

BB19

DDR_B_DQ5 8

BA18

W30

RSVD_56

W29

RSVD_55

AA30

RSVD_65

AB29

RSVD_67

V29

RSVD_50

V31

RSVD_51

AA29

RSVD_64

AA31

RSVD_66

DDR_B_PA R

AM31

DDR_B_DQ[ 63..0] <13>

DDR_B_PA R <13 >

1 2

DDR_A_DQ[ 63..0] <12>

DDR_A_PA R <12 >

+1.2V

DDR_A_DQ0

K27

DDR_A_DQ4

L26

DDR_A_DQ6

N26

DDR_A_DQ3

N27

DDR_A_DQ5

G27

DDR_A_DQ1

H27

DDR_A_DQ2

M27

DDR_A_DQ7

N24

DDR_A_DQ1 5

L23

DDR_A_DQ8

N21

DDR_A_DQ1 0

T21

DDR_A_DQ1 3

T22

DDR_A_DQ1 2

M22

DDR_A_DQ9

L24

DDR_A_DQ1 4

R21

DDR_A_DQ1 1

R23

DDR_A_DQ1 6

P24

DDR_A_DQ2 1

R26

DDR_A_DQ1 9

T27

DDR_A_DQ2 2

V27

DDR_A_DQ2 0

P25

DDR_A_DQ1 7

P27

DDR_A_DQ2 3

V23

DDR_A_DQ1 8

T25

DDR_A_DQ2 4

W22

DDR_A_DQ2 8

Y23

DDR_A_DQ2 9

AC24

DDR_A_DQ2 7

AC23

DDR_A_DQ2 5

V21

DDR_A_DQ3 0

W21

DDR_A_DQ2 6

AA24

DDR_A_DQ3 1

AA22

DDR_A_DQ3 2

AP26

DDR_A_DQ3 6

AN24

DDR_A_DQ3 7

AR25

DDR_A_DQ3 5

AU26

DDR_A_DQ3 8

AN25

DDR_A_DQ3 3

AN27

DDR_A_DQ3 4

AR27

DDR_A_DQ3 9

AU27

DDR_A_DQ4 4

AV25

DDR_A_DQ4 5

AW25

DDR_A_DQ4 2

AV20

DDR_A_DQ4 3

AW20

DDR_A_DQ4 0

AV27

DDR_A_DQ4 1

AW26

DDR_A_DQ4 7

AU21

DDR_A_DQ4 6

AW21

DDR_A_DQ4 9

AT22

DDR_A_DQ5 2

AP21

DDR_A_DQ5 1

AN19

DDR_A_DQ5 0

AN18

DDR_A_DQ5 5

AU23

DDR_A_DQ4 8

AR22

DDR_A_DQ5 3

AN20

DDR_A_DQ5 4

AP19

DDR_A_DQ6 1

AT19

DDR_A_DQ6 0

AW18

DDR_A_DQ5 9

AU16

DDR_A_DQ5 8

AW16

DDR_A_DQ5 7

AW19

DDR_A_DQ5 6

AU19

DDR_A_DQ6 3

AP16

DDR_A_DQ6 2

AT16

W27

RSVD_54

W25

RSVD_53

AC26

RSVD_68

AC27

RSVD_69

V26

RSVD_49

V24

RSVD_48

AA27

RSVD_63

AA25

RSVD_62

DDR_A_PA R

AK24

AN21

AN22

RC627 0_0402_ 5%@

M_DDR4

DDR_B_MA[ 13..0]<13>

DDR_B_W E#<13>

DDR_B_CAS #<13>

DDR_B_RAS #<13>

DDR_B_BA 0<13>

DDR_B_BA 1<13>

DDR_B_BG 0<13>

DDR_B_BG 1<13>

DDR_B_ACT#<13 >

DDR_B_DM[7 ..0]<13>

DDR_B_DQS 0<13>

DDR_B_DQS 0#<13>

DDR_B_DQS 1<13>

DDR_B_DQS 1#<13>

DDR_B_DQS 2<13>

DDR_B_DQS 2#<13>

DDR_B_DQS 3<13>

DDR_B_DQS 3#<13>

DDR_B_DQS 4<13>

DDR_B_DQS 4#<13>

DDR_B_DQS 5<13>

DDR_B_DQS 5#<13>

DDR_B_DQS 6<13>

DDR_B_DQS 6#<13>

DDR_B_DQS 7<13>

DDR_B_DQS 7#<13>

DDR_B_CLK 0<13 >

DDR_B_CLK 0#<13>

DDR_B_CS0 #<13 >

DDR_B_CKE 0<13>

DDR_B_ODT0<13>

DDR_B_AL ERT#<13>

DDR_B_RST#<13 >

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA1 0

DDR_B_MA1 1

DDR_B_MA1 2

DDR_B_MA1 3

DDR_B_BG 0

DDR_B_BG 1

DDR_B_ACT#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_EV ENT#

AM29

AH31

AJ30

AH29

AG32

AG30

AG31

AF30

AG29

AF29

AM30

AF31

AE32

AP30

AP31

AP29

AN29

AN31

AM32

AD29

AD31

AD30

AU30

BD28

BB23

BD20

W31

AU29

AU31

BA27

BB27

BC23

BA23

BC20

BA20

AJ31

AK30

AK32

AL31

AN30

AR31

AC31

AC29

AP32

AR29

AE30

AL30

AC32

C30

H32

M29

T29

E29

D28

J31

J29

N30

M31

T30

T31

Y32

Y30

MB_ADD0/RSVD

MB_ADD1/RSVD

MB_ADD2/MBB_CA0

MB_ADD3/MBA_CA4

MB_ADD4/MBA_CA5

MB_ADD5/MBA_CA3

MB_ADD6/MBA_CA2

MB_ADD7/RSVD

MB_ADD8/RSVD

MB_ADD9/RSVD

MB_ADD10/MBB_CS_L1

MB_ADD11/MBA_CKE1

MB_ADD12/MBA_CKE0

MB_ADD13_BANK2/RSVD

MB_WE_L_ADD14/MBB_CKE1

MB_CAS_L_ADD15/RSVD

MB_RAS_L_ADD16/MBB_CKE0

MB_BANK0/MBB_CS_L0

MB_BANK1/MBB_CA1

MB_BG0/MBA_CS_L1

MB_BG1/MBA_CS_L0

MB_ACT_L/RSVD

MB_DM0/MBA_DM1

MB_DM1/MBA_DM0

MB_DM2/MBA_DM2

MB_DM3/MBA_DM3

MB_DM4/MBB_DM2

MB_DM5/MBB_DM3

MB_DM6/MBB_DM1

MB_DM7/MBB_DM0

RSVD_57

MB_DQS_H0/MBA_DQS_H1

MB_DQS_L0/MBA_DQS_L1

MB_DQS_H1/MBA_DQS_H0

MB_DQS_L1/MBA_DQS_L0

MB_DQS_H2/MBA_DQS_H2

MB_DQS_L2/MBA_DQS_L2

MB_DQS_H3/MBA_DQS_H3

MB_DQS_L3/MBA_DQS_L3

MB_DQS_H4/MBB_DQS_H2

MB_DQS_L4/MBB_DQS_L2

MB_DQS_H5/MBB_DQS_H3

MB_DQS_L5/MBB_DQS_L3

MB_DQS_H6/MBB_DQS_H1

MB_DQS_L6/MBB_DQS_L1

MB_DQS_H7/MBB_DQS_H0

MB_DQS_L7/MBB_DQS_L0

RSVD_61

RSVD_60

MB_CLK_H0/MBA_CKT

MB_CLK_L0/MBA_CKC

MB_CLK_H1/MBB_CKT

MB_CLK_L1/MBB_CKC

MB_CS_L0/MBB_CA2

MB_CS_L1/MBB_CA5

MB_CKE0/MBA_CA1

MB_CKE1/MBA_CA0

MB_ODT0/MBB_CA3

MB_ODT1/MBB_CA4

MB_ALERT_L/TEST31B

MB_EVENT_L

MB_RESET_L

FP6_BGA 1140

EVENT# pull high

+1.2V

A A

5

1 2

RC1 1K_04 02_5%

1 2

RC2 1K_04 02_5%

DDR_B_EV ENT#

DDR_A_EV ENT#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : She et of

Date : She et of

Date : She et of

Compal Electronics, Inc.

FP6 DDR4 MEMORY I/F

FP6 DDR4 MEMORY I/F

FP6 DDR4 MEMORY I/F

LA-J701P

LA-J701P

LA-J701P

1

5 39Friday, January 10, 2020

5 39Friday, January 10, 2020

5 39Friday, January 10, 2020

1.0

1.0

1.0

5

4

3

2

1

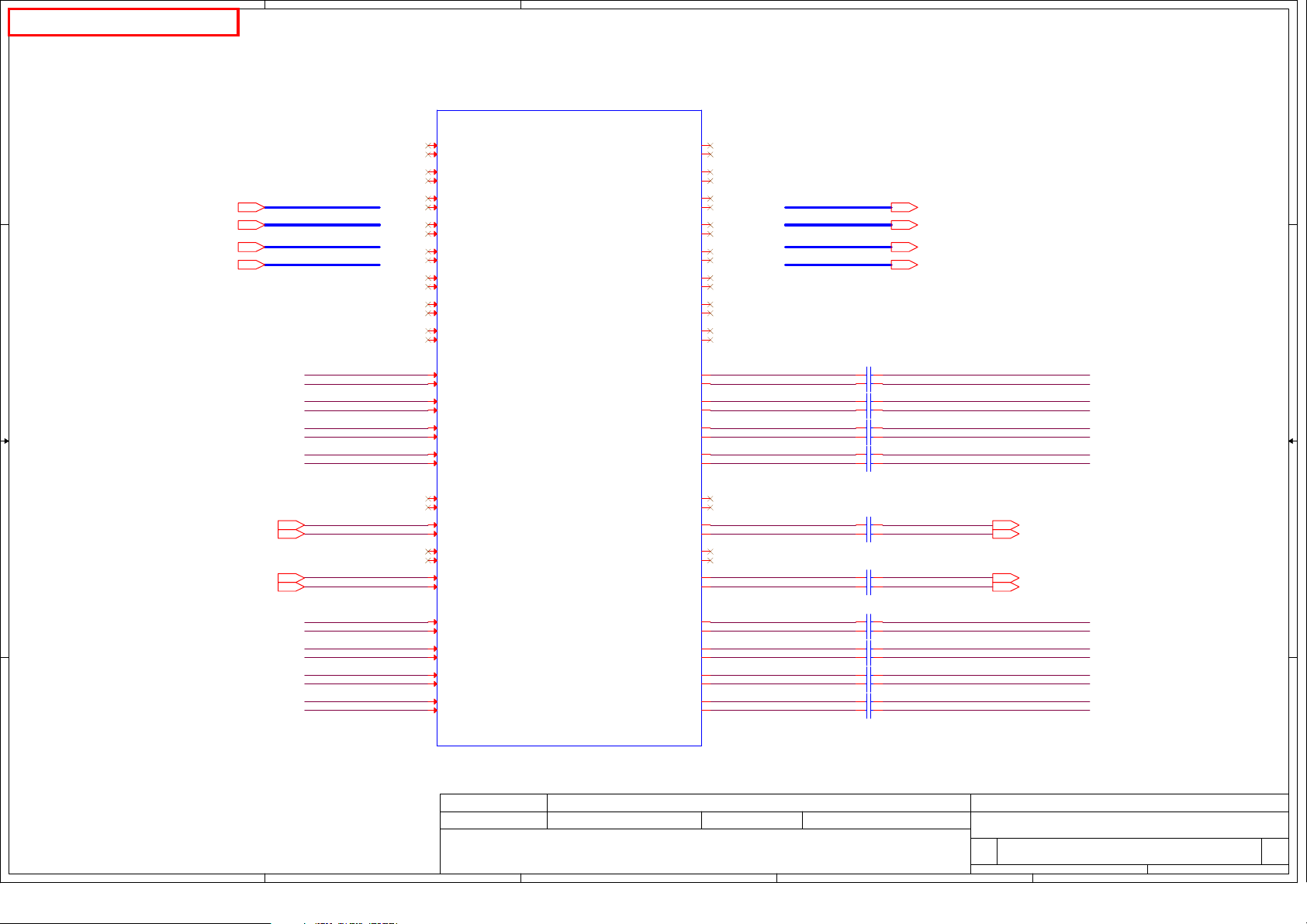

Main Func = CPU

UC1B

@

D D

G13

P_GFX_RXP0

F13

P_GFX_RXN0

J14

P_GFX_RXP1

H14

P_GFX_RXN1

G15

Main _SS D

2nd_SSD

C C

PCIE_ARX_DTX_P[0..3]<16>

PCIE_ARX_DTX_N[0..3]<16>

PCIE_ARX_DTX_P[8..11]<17>

PCIE_ARX_DTX_N[8..11]<17>

PCIE_ARX_DTX_P[0..3]

PCIE_ARX_DTX_N[0..3]

PCIE_ARX_DTX_P[8..11] PCIE_ATX_C_DRX_P[8..11]

PCIE_ARX_DTX_N[8..11]

F15

J15

K15

H16

J16

F18

G18

J18

K18

H19

G19

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

PCIE

F4

P_GFX_TXP0

F2

P_GFX_TXN0

F3

P_GFX_TXP1

E4

P_GFX_TXN1

E1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

C1

D5

E6

C6

D6

B6

C7

D8

B8

C8

A8

PCIE_ATX_C_DRX_P[0..3]

PCIE_ATX_C_DRX_N[0..3]

PCIE_ATX_C_DRX_N[8..11]

PCIE_ATX_C_DRX_P[0..3] <16>

PCIE_ATX_C_DRX_N[0..3] <16>

PCIE_ATX_C_DRX_P[8..11] <17>

PCIE_ATX_C_DRX_N[8..11] <17>

Main _SS D

2nd_SSD

PCIE_ARX_DTX_P0

PCIE_ARX_DTX_N0

PCIE_ARX_DTX_P1

PCIE_ARX_DTX_N1

PCIE_ARX_DTX_P2

PCIE_ARX_DTX_N2

PCIE_ARX_DTX_P3

PCIE_ARX_DTX_N3

Card Rea der

B B

WLAN

A A

5

PCIE_ARX_DTX_P5<26>

PCIE_ARX_DTX_N5<26>

PCIE_ARX_DTX_P7<18>

PCIE_ARX_DTX_N7<18>

PCIE_ARX_DTX_P5

PCIE_ARX_DTX_N5

PCIE_ARX_DTX_P7

PCIE_ARX_DTX_N7 PCIE_ATX_DRX_N7

PCIE_ARX_DTX_P8

PCIE_ARX_DTX_N8

PCIE_ARX_DTX_P9

PCIE_ARX_DTX_N9

PCIE_ARX_DTX_P10

PCIE_ARX_DTX_N10

PCIE_ARX_DTX_P11

PCIE_ARX_DTX_N11 PCIE_ATX_DRX_N11

G11

P_GPP_RXP0

F11

P_GPP_RXN0

J10

P_GPP_RXP1

H10

P_GPP_RXN1

G8

P_GPP_RXP2/SATA0_RXP

F8

P_GPP_RXN2/SATA0_RXN

G6

P_GPP_RXP3/SATA1_RXP

F7

P_GPP_RXN3/SATA1_RXN

M9

P_GPP_RXP4

M8

P_GPP_RXN4

L7

P_GPP_RXP5

L6

P_GPP_RXN5

K7

P_GPP_RXP6

K8

P_GPP_RXN6

H6

P_GPP_RXP7

H7

P_GPP_RXN7

L9

P_GPP_RXP8/SATA2_RXP

L10

P_GPP_RXN8/SATA2_RXN

K11

P_GPP_RXP9/SATA3_RXP

J11

P_GPP_RXN9/SATA3_RXN

J12

P_GPP_RXP10

H12

P_GPP_RXN10

J13

P_GPP_RXP11

K13

P_GPP_RXN11

FP6 REV 0.92

FP6_BGA1140

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRA NSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRA NSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRA NSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

PART 2 OF 13

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2/SATA0_TXP

P_GPP_TXN2/SATA0_TXN

P_GPP_TXP3/SATA1_TXP

P_GPP_TXN3/SATA1_TXN

P_GPP_TXP4

P_GPP_TXN4

P_GPP_TXP5

P_GPP_TXN5

P_GPP_TXP6

P_GPP_TXN6

P_GPP_TXP7

P_GPP_TXN7

P_GPP_TXP8/SATA2_TXP

P_GPP_TXN8/SATA2_TXN

P_GPP_TXP9/SATA3_TXP

P_GPP_TXN9/SATA3_TXN

P_GPP_TXP10

P_GPP_TXN10

P_GPP_TXP11

P_GPP_TXN11

Compal Secret Data

Compal Secret Data

Compal Secret Data

3

PCIE_ATX_DRX_P0

L3

PCIE_ATX_DRX_N0 PCIE_ATX_C_DRX_N0

L1

PCIE_ATX_DRX_P1

L4

PCIE_ATX_DRX_N1 PCIE_ATX_C_DRX_N1

L2

PCIE_ATX_DRX_P2

M4

PCIE_ATX_DRX_N2 PCIE_ATX_C_DRX_N2

M2

PCIE_ATX_DRX_P3

N3

PCIE_ATX_DRX_N3 PCIE_ATX_C_DRX_N3

N1

T2

T4

PCIE_ATX_DRX_P5

R1

PCIE_ATX_DRX_N5

R3

P2

P4

PCIE_ATX_DRX_P7

N2

N4

K2

PCIE_ATX_DRX_N8 PCIE_ATX_C_DRX_N8

K4

PCIE_ATX_DRX_P9

J4

PCIE_ATX_DRX_N9

J2

PCIE_ATX_DRX_P10

H3

PCIE_ATX_DRX_N10

H1

PCIE_ATX_DRX_P11

H4

H2

Deciphered Date

Deciphered Date

Deciphered Date

1 2

CC1 0.22U_0402_6.3V6K

CC2 0.22U_0402_6.3V6K

1 2

1 2

CC3 0.22U_0402_6.3V6K

CC4 0.22U_0402_6.3V6K

1 2

CC5 0.22U_0402_6.3V6K

1 2

1 2

CC6 0.22U_0402_6.3V6K

CC7 0.22U_0402_6.3V6K

1 2

1 2

CC8 0.22U_0402_6.3V6K

1 2

CC11 0.1U_0201_10V6K

1 2

CC12 0.1U_0201_10V6K

1 2

CC9 0.1U_0201_10V6K

CC10 0.1U_0201_10V6K

1 2

1 2

CC109 0.22U_0402_6.3V6K

CC110 0.22U_0402_6.3V6K

1 2

CC106 0.22U_0402_6.3V6K

1 2

1 2

CC107 0.22U_0402_6.3V6K

CC113 0.22U_0402_6.3V6K

1 2

1 2

CC112 0.22U_0402_6.3V6K

1 2

CC108 0.22U_0402_6.3V6K

1 2

CC111 0.22U_0402_6.3V6K

2

PCIE_ATX_C_DRX_P0

PCIE_ATX_C_DRX_P1

PCIE_ATX_C_DRX_P2

PCIE_ATX_C_DRX_P3

PCIE_ATX_C_DRX_P8PCIE_ATX_DRX_P8

PCIE_ATX_C_DRX_P9

PCIE_ATX_C_DRX_N9

PCIE_ATX_C_DRX_P10

PCIE_ATX_C_DRX_N10

PCIE_ATX_C_DRX_P11

PCIE_ATX_C_DRX_N11

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Dat e: Sheet o f

Dat e: Sheet o f

Dat e: Sheet o f

PCIE_ATX_C_DRX_P5 <26>

PCIE_ATX_C_DRX_N5 <2 6>

PCIE_ATX_C_DRX_P7 <18>

PCIE_ATX_C_DRX_N7 <1 8>

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

FP6 PCIE/UMI

FP6 PCIE/UMI

FP6 PCIE/UMI

LA-J701P

LA-J701P

LA-J701P

Card Rea der

WLAN

1

1.0

1.0

1.0

6 39Friday, January 10, 2020

6 39Friday, January 10, 2020

6 39Friday, January 10, 2020

A

B

C

D

E

Main Func = CPU

ENBKL_R

INVTPWM_ R

+1.8VS

QC1

2

Gate

1

Drain

3

Source

LBSS139 WT1G_SC70 -3

SB00001 GC00

+1.8VS

5

1

P

NC

Y

2

A

G

UC6

3

74AUP1G 07GW_SC7 0-5

SA0000C 2700

ENBKL <14,2 0>

INVTPWM

ENBKL

ENBKL_R

ENVDD

4

INVTPWM <1 4>

INVTPWM_ R

EDP_HPD

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST31

DP_STEREOS YNC

Pull High for HDMI audio function / BIOS code notice

SMU_ZVDDP

1 2

RC4 4.7K_0 402_5%

1 2

RC5 2.2K_0 402_5%

1 2

RC6 100K_0 402_5%

1 2

RC8 100K_0 402_5%

1 2

RC9 100K_0 402_5%

1 2

RC10 100K_0402_5 %

1 2

RC11 10K_0402 _5%@

1 2

RC12 10K_0402 _5%@

1 2

RC13 10K_0402 _5%@

1 2

RC14 10K_0402 _5%@

1 2

RC15 1K_0402_5%@

1 2

RC16 1K_0402_5%@

1 2

RC17 1K_0402_5%

1 2

RC18 1K_0402_5%

@

1 2

RC22 196_0402 _1%

+3VS

+1.8VS

+1.8VS

+1.8VS

+0.75VS

DP0: eDP

DP1: HDMI

DP2: Type-C

DP3: N/A

UC1C

@

D9

B9

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

TDI

TDO

TCK

TMS

TRST_L

DBREQ_L

RESET_L

PWROK

SIC

SID

ALERT_L

THERMTRIP_L

PROCHOT_L

SVC0

SVD0

SVT0

DISPLAY/SVI2/JTAG/TES T

FP6 REV 0.92

PART 3 OF 13

FP6_BGA 1140

DP_STEREOSYNC

VDDP_S5_SENSE

VDDCR_SOC_SENSE

VDDIO_MEM_S3_SENSE

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRE Q#

APU_RST#

APU_PW RGD

APU_ALE RT#

THERMTRIP#

H_PROCHOT#

D11

B11

C11

A11

D10

B10

G23

H23

F22

G22

G21

H21

F20

G20

AP3

AU1

AR2

AU3

AR4

AT2

AW3

AW4

B22

D22

C22

AN9

B25

D25

C25

A25

EDP_TXP0<14>

1 1

e

DP

HDMI

2 2

EDP_TXN0<14>

EDP_TXP1<14>

EDP_TXN1<14>

APU_DP1_ P0<15>

APU_DP1_ N0<1 5>

APU_DP1_ P1<15>

APU_DP1_ N1<1 5>

APU_DP1_ P2<15>

APU_DP1_ N2<1 5>

APU_DP1_ P3<15>

APU_DP1_ N3<1 5>

1 2

APU_RST#_ R<24>

APU_PW RGD<35>

EC_SMB_C K2<20,2 2>

EC_SMB_D A2<20,2 2>

EC_THERMTRIP#<20>

H_PROCHOT#<20>

VR_ALERT#<24 >

APU_SVC<35 >

APU_SVD<35 >

APU_SVT_R<35>

RC603 0_ 0402_5%@

1 2

RC21 0_0402_5 %@

RC602 0_0402_ 5%@

12

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP0_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP2_AUXP

DP2_AUXN

DP2_HPD

DP3_AUXP

DP3_AUXN

DP3_HPD

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST31

TEST41

ANALOGIO_0

ANALOGIO_1

SMU_ZVDD

VDDP_SENSE

VDDCR_SENSE

VSS_SENSE_A

VSS_SENSE_B

ENBKL_R

A22

D23

ENVDD

INVTPWM_ R

C23

D12

B12

C12

J20

K20

L21

L19

M19

USBC0_PD _HPD_R

M20

M14

L14

L16

DP_STEREOS YNC

B23

APU_TEST4

BB6

APU_TEST5

BD5

AG12

APU_TEST14

G25

APU_TEST15

K25

APU_TEST16

F25

APU_TEST17

F26

APU_TEST31

H26

APU_TEST41

AK9

APU_TEST470

AK21

APU_TEST471

AG21

SMU_ZVDDP

P3

AK7

AK12

J23

K22

J21

VSS_SEN SE_A

J22

VSS_SEN SE_B

AJ12

T2414

ENVDD <14>

EDP_AUXP <14 >

EDP_AUXN <1 4>

EDP_HPD <14>

APU_DP1_ CTRL_CLK <15>

APU_DP1_ CTRL_DAT <15>

APU_DP1_ HPD <1 5>

USBC0_AU XP < 24>

USBC0_AU XN <24>

T1

T2

T4

T5

T6

T7

T8

T9

T10

T11

1 2

RC594 0_0402_ 5%@

1 2

RC595 0_0402_ 5%@

1 2

RC597 0_0402_ 5%@

+LCDVDD_CONN PWR switch enable pin VIH=1.2V

eDP

HDMI

TYPE-C PD

T12

T13

T14

T15

APU_VDDP _S5_SEN_H <34>

APU_CORE SOC_SEN_H <35>

APU_CORE _SEN_H <35>

VDDIO_MEM_ S3_SENSE_ H <3 2>

T16

T2412

T2413

APU_VSS _SEN_L <35>

VDDIO_MEM_ S3_SENSE_ L <32>

APU_VDDP _S5_SEN_L <34>

3 3

+1.8VALW

1 2

RC25 4.7K_0402_5%

1 2

RC24 4.7K_0402_5%

+3VS

1 2

RC31 1K_0402 _5%

1 2

RC28 1K_0402 _5%

1 2

RC29 1K_0402 _5%

1 2

RC30 220_040 2_5%@

APU_PW RGD

APU_RST#

APU_ALE RT#

H_PROCHOT#

THERMTRIP#

APU_PW RGD

APU_RST#_ EC<20>

Reserve for Sequence Tuning

ESD

4 4

1 2

CC17 100P_0 402_50V8JESD@

1 2

CC18 100P_0 402_50V8JESD@

1 2

CC19 100P_0 402_50V8JESD@

A

H_PROCHOT#

APU_PW RGD

APU_RST#

USBC0_PD _HPD<24>

2

G

+3VS

5

1

NC

2

A

3

RC111 0_040 2_5%@

+3VS

12

RC62

@

100K_04 02_5%

USBC0_PD _HPD_3VEN

61

D

@

QC2A

2N7002K DW_SOT363 -6

S

1 2

RC628 0_0402_ 5%

B

P

4

Y

G

UC22

74AUP1G 07GW_SC7 0-5

SA00007 WE00

@

12

5

G

APU_RST#

12

RC63

@

4.7K_04 02_5%

USBC0_PD _HPD_R

34

D

@

QC2B

2N7002K DW_SOT363 -6

S

USBC0_PD _HPD_RUSBC0_PD _HPD

1 2

RHDT6 33_0402_5%HDT@

1 2

RHDT7 10K_0402_5%HDT@

1 2

RHDT8 10K_0402_5%HDT@

1 2

RHDT9 10K_0402_5%HDT@

HDT+ (debug + HDT@)

+1.8VALW

JHDT1

1

1

3

3

5

5

7

APU_TRST#_RAPU_TRST#

C

7

9

9

11

11

13

13

15

15

17

17

19

19

SAMTE_ASP -136446-07-B

ME@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

MAYBE US ED BY OR DISCLOSED TOANY THIRDPARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE US ED BY OR DISCLOSED TOANY THIRDPARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE US ED BY OR DISCLOSED TOANY THIRDPARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

APU_TCK

2

2

APU_TMS

4

4

APU_TDI

6

6

APU_TDO

8

8

APU_PW RGD_BUF

10

10

APU_RST#_ BUF

12

12

14

14

APU_DBRE Q#

16

16

18

18

20

20

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

APU_TRST#

RHDT1 1K_0402_5 %HDT@

APU_TCK

RHDT2 1K_0402_5 %HDT@

APU_TMS

RHDT3 1K_0402_5 %HDT@

APU_TDI

RHDT4 1K_0402_5 %HDT@

APU_DBRE Q#

RHDT5 1K_0402_5 %HDT@

APU_TDI

APU_DBRE Q#

APU_TRST#

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

CHDT1 0.01U_0402 _16V7K

CHDT2 0.01U_0402 _16V7K

CHDT3 0.01U_0402 _16V7K

1 2

1 2

1 2

1 2

1 2

@

1 2

HDT@

1 2

HDT@

1 2

+1.8VALW

APU_RST#

RHDT10 0_0402_5%@

1

2

APU_PW RGD A PU_PWRGD_ BUF

3

RHDT11 0_0402_5%@

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : She et of

Date : She et of

Date : She et of

12

U20

A1

GND

A2

NC7WV0 7P6X_SC70 -6

HDT@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

FP6 DISP/MISC/HDT

FP6 DISP/MISC/HDT

FP6 DISP/MISC/HDT

Y1

VCC

Y2

12

LA-J701P

LA-J701P

LA-J701P

E

6

5

4

APU_RST#_ BUF

+1.8VALW

7 39Friday, January 10, 2020

7 39Friday, January 10, 2020

7 39Friday, January 10, 2020

1.0

1.0

1.0

Main Func = CPU

A

B

C

D

E

Capacity OBRAM_ID0OBRAM_ID1OBRAM_ID2Description

Total

SS D4 K4A8G165WC-BCWE SDP

HY D4 H5AN8G6NCJR-XNC SDP

4GB

8Gb-3200

1 1

16Gb-3200

MC D4 MT40A512M16TB-062E:J SDP

SS D4 K4A8G165WC-BCWE SDP

8GB

HY D4 H5AN8G6NCJR-XNC SDP

MC D4 MT40A512M16TB-062E:J SDP

SS D4 K4AAG165WA-BCWE SDP

HY D4 H5ANAG6NCMR-XNC DDP

16GB

MC D4 MT40A1G16KD-062E:E SDP

12

RC560

10K_0402_5%

@

12

RC561

10K_0402_5%

@

12

RC124

10K_0402_5%

@

OBRAM_ID2 OBRAM_ID0OBRAM_ID3 OBRAM_ID1

12

RC123

10K_0402_5%

@

12

RC122

10K_0402_5%

@

12

RC119

10K_0402_5%

@

Channel B

V

V

V

V

V

V

+1.8VS+1.8VS+1.8VS+1.8VS

OBRAM_ID3

0 0 0 0

0 0 0 1

0 0 0

0

0

0

0

0

1 0 0

12

RC121

10K_0402_5%

@

12

RC120

10K_0402_5%

@

0

1 0

1 0

1

1 1

1

1

1

0

1

0

1

1

0

Function

S550 0

MODEL_ID0

MODEL_ID1

MODEL_ID1

(AGPIO90)

MODEL_ID0

(AGPIO89)

1 0

+3VS

RC112

10K_0402_5%

@

1 2

RC115

10K_0402_5%

1 2

0

10

1 2

1 2

RC568

10K_0402_5%

@

RC569

10K_0402_5%

@

ON BOARD RAM ID

UC1D

I-IO33S5- S

I-IO33S5- S

B-IO33S5- S

1

2

ACPI/AUDIO/I2 C/GPIO/ MISC

@

CC114

0.1U_0201_10V6K

C

FP6 REV 0.92

PART 4 OF 13

@

S5_3.3V

S5_3.3V

B-I2C-OD

B-I2C-OD

S0_1.8V

S0_1.8V

S0_1.8V

I2C2_SCL/EGPIO113/SMBUS0_I2C_SCL

S0_1.8V

I2C2_SDA/EGPIO114/SMBUS0_I2C_SDA

B-I2C_S5-O D

I2C3_SCL/AGPIO19/SMBUS1_I2C_SCL

B-I2C_S5-O D

I2C3_SDA/AGPIO20/SMBUS1_I2C_SDA

S5_3.3V

B-IO33S5-O D

B-IO33S5-O D

S0_3.3V

S0_3.3V

S0_3.3V

FP6_BGA1140

+3VALW +3VALW

5

UC7

1

P

NC

4

Y

2

A

G

74AUP1G07GW_SC70-5

3

SA00007WE00

@

RC64 0_0402_5%@

1 2

PM_SLP_S3# <20,22>

S5_3.3V

S5_3.3V

SATA_ACT_L/AGPIO130

S5_3.3V

SFH_IPIO271

SFH_IPIO272

SFH_IPIO273

SFH_IPIO274

SFH_IPIO39

SFH_IPIO41

I2C0_SCL/EGPIO145

I2C0_SDA/EGPIO146

I2C1_SCL/EGPIO147

I2C1_SDA/EGPIO148

SFH1_SCL

SFH1_SDA

AGPIO3

AGPIO4/SATAE_IFDET

AGPIO5/DEVSLP0

AGPIO6/DEVSLP1

AGPIO9

AGPIO40

AGPIO69

AGPIO86/SPI_CLK2

INTRUDER_ALERT

SPKR/AGPIO91

BLINK/AGPIO11

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

FANIN0/AGPIO84

FANOUT0/AGPIO85

12

RC55

8.2K_0402_5%

APU_FCH_PWRGD_R

APU_PCIE_RST#_R

12

AM3

AT4

AM1

AJ8

AW7

AU2

AP14

AN14

AP2

AN3

AN12

AP12

AM9

AM10

D24

B24

BB7

BA6

AK10

BC6

AW15

AU4

AP7

AV13

BB12

AU7

AR11

AW11

AV15

AU14

AT10

AU10

RC72

10K_0402_5%

I2C_0_SCL_R

I2C_0_SDA_R

OBRAM_ID0

OBRAM_ID1

OBRAM_ID2

OBRAM_ID3

Not Implemented Need Pull down by SW

Not Implemented Need Pull down by SW

PCIE_DET2

PCIE_DET1

DEVSLP0

DEVSLP1

AUX_RESET#

GPIO_RESERVE

HDA_SPKR

APU_FP_RST_R

MODEL_ID0

MODEL_ID1

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

RC73 0_0402_5%@

Issued Date

Issued Date

Issued Date

RC585 0_0402_5%@

1 2

1 2

RC586 0_0402_5%@

PCIE_DET2 <17>

PCIE_DET1 <16>

DEVSLP0 <17>

DEVSLP1 <16>

TP_INT# <20,21>

AUX_RESET# <16,17>

HDA_SPKR <19>

APU_FP_RST_R <22>

+3VALW

5

2

P

B

4

Y

1

A

G

UC8

MC74VHC1G08DFT2G SC70 5P

3

SA00000OH00

@

1 2

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

1

@

CC26

0.1U_0201_10V6K

2

D

I2C_0_SCL

I2C_0_SDA

APU_PCIE_RST# <16,17,18,26>

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

I2C_0_SCL <21>

I2C_0_SDA <21>

Touch Pad

APU_SPI_CLK_R<9>

STRAPS

STRAPS

SPI_CLK

SYS_RST#

RC620 10K_0402_5%@

DEVSLP0

DEVSLP1

GPIO_RESERVE

1 2

RC621 10K_0402_5%@

1 2

RC614 10K_0402_5%@

RC615 10K_0402_5%@

1 2

1 2

GPIO Reserve

+3VALW+1.8VALW

RC59

10K_0402_5%

1 2

RC65

2K_0402_5%

@

1 2

12

12

SYS_RESET#

DEFINITION

1 : Use 48MHZ Crystal C lock and Gene rate both internal

and external clo cks (Default)

0 : Use 100MHZ PCIE clock as reference clock

and generate internal clocks only

1 : Normal reset mode (Default)

0 : short reset mode

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FP6 GPIO/AZ/MISC/STRAPS

FP6 GPIO/AZ/MISC/STRAPS

FP6 GPIO/AZ/MISC/STRAPS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

LA-J701P

LA-J701P

LA-J701P

E

+3VALW

RC60

10K_0402_5%

RC66

2K_0402_5%

@

+3VS

1.0

1.0

1.0

8 39Friday, January 10, 2020

8 39Friday, January 10, 2020

8 39Friday, January 10, 2020

+1.8VALW

2 2

3 3

4 4

RC36 22K_0402_5%

1 2

1

CC22

0.1U_0201_10V6K

2

@ESD@

1 2

CC23 100P_0402_50V8J

ESD@

CC24 100P_0402_50V8J

1 2

+3VALW

1 2

RC593 10K_0402_5%

RC45 10K_0402_5%

1 2

1 2

RC47 10K_0402_5%

RC48 10K_0402_5%@

1 2

RC611 10K_0402_5%

1 2

1 2

RC610 2.2K_0402_5%

1 2

RC50 1K_0402_5%

RC53 10K_0402_5%@

1 2

1 2

RC54 10K_0402_5%@

RC601 10K_0402_5%

1 2

+3VS

RC56 2.2K_0402_5%@

1 2

1 2

RC57 2.2K_0402_5%@

+3VALW

1 2

RC624 2.2K_0402_5%

RC625 2.2K_0402_5%

1 2

+1.8VALW

1 2

RC606 10K_0402_5%

RC607 10K_0402_5%

1 2

HDA_BIT_CLK_R<19>

HDA_SDOUT_R<19>

HDA_SYNC_R<19>

DMIC_CLK0_APU

DMIC_DAT0_APU

RC67 33_0402_5%EMI@

1 2

1 2

RC68 33_0402_5%

RC69 33_0402_5%

1 2

RC70 1K_0402_5%

1 2

1 2

RC71 1K_0402_5%

A

EC_RSMRST# <20>

EC_RSMRST#

SYS_RESET#

PCIE_DET2

PCIE_DET1

PBTN_OUT#

APU_PCIE_WAKE#

EC_LOW_BATT#

S0A3_GPIO

HDA_RST#

HDA_SDIN0

HDA_BIT_CLK

AUX_RESET#

I2C_0_SCL

I2C_0_SDA

I2C_0_SCL

I2C_0_SDA

ESD

DMIC_CLK0_APU

DMIC_DAT0_APU

HDA_BIT_CLK

HDA_SDOUT

HDA_SYNC

SB00001GC00

EMI

APU_PCIE_RST#_R APU_PCIE1_RST#

150P_0402_50V8J

+1.8VALW

SB00001GC00

S

Q206

R4024 0_0402_5%@

G

S

Q207 LBSS139WT1G_SC70-3

R4025 0_0402_5%@

1 2

1 2

2

13

D

CC20

G

2

SOC_DMIC_CLK0

13

D

LBSS139WT1G_SC70-3

SOC_DMIC_DAT0

B

1 2

RC34 33_0402_5%

RC35 33_0402_5%@

1 2

2

1

PBTN_OUT#<20>

PM_SLP_S5#<20,32>

AC_PRESENT<20>

EC_LOW_BATT#<20>

KBL_ID<21>

HDA_SDIN0<19>

APU_BT_OFF#<18>

APU_WL_OFF#<18>

SOC_DMIC_CLK0 <14>

SOC_DMIC_DAT0 <14>

S0A3_GPIO

PM_SLP_S3#_R

APU_PCIE0_RST#

EC_RSMRST#

PBTN_OUT#

APU_FCH_PWRGD_R

SYS_RESET#

APU_PCIE_WAKE#

PM_SLP_S3#_R

PM_SLP_S5#

S0A3_GPIO

DMIC_CLK0_APU

DMIC_DAT0_APU

HDA_BIT_CLK

HDA_SDIN0

HDA_RST#

HDA_SYNC

HDA_SDOUT

SYS_PWRGD_EC<20>

RC598 0_0402_5%

AP6

PCIE_RST0_L/EGPIO26

AT13

PCIE_RST1_L/EGPIO27

AR8

RSMRST_L

AT12

PWR_BTN_L/AGPIO0

AW2

PWR_GOOD

AL2

SYS_RESET_L/AGPIO1

AW12

WAKE_L/AGPIO2

AT11

SLP_S3_L

AV11

SLP_S5_L

AW13

S0A3_GPIO/AGPIO10

BA8

AC_PRES/AGPIO23

AV6

LLB_L/AGPIO12

AW8

EGPIO42

AG6

ACP_WOV_CLK/ACP_IPIO28

AG7

ACP_WOV_MIC0_MIC1_DATA/ACP_IPIO29

AJ6

ACP_WOV_MIC2_MIC3_DATA/ACP_IPIO30

AN6

AZ_BITCLK/TDM_BCLK_MIC

AL6

AZ_SDIN0/CODEC_GPI

AM7

AZ_SDIN1/SW_DATA1B/TDM_BCLK_PLAYBACK

AJ9

AZ_SDIN2/SW_DATA2/TDM_DATA_PLAYBACK/ACP_WOV_MIC4_MIC5_DATA

AM6

AZ_RST_L/SW_DATA1A/SW_DATA3/TDM_DATA_MIC

AN8

AZ_SYNC/TDM_FRM_MIC

AK6

AZ_SDOUT/TDM_FRM_PLAYBACK

AM4

SW_MCLK/TDM_BCLK_BT

AL3

SW_DATA0/TDM_DOUT_BT

AM2

AGPIO7/FCH_ACP_I2S_SDIN_BT

AL4

AGPIO8/FCH_ACP_I2S_LRCLK_BT

+3VALW

5

2

P

B

4

Y

1

A

G

UC23

MC74VHC1G08DFT2G SC70 5P

3

SA00000OH00

@

12

S5_3.3V

I-IO33S5- S

B-IO33S5- S

SYS_PWRGD_EC

A

B

C

D

E

Main Func = CPU

4

8MHz CRYSTAL

1 1

48M_X1_R 48M_X1

12

RC75 1M_0402_5%

2

2

3

3

1

CC27

2P_0402_50V

2

SE08220AC80

1

1

4

4

1

2

RC74 33_0402_5%EMI@

RC76 33_0402_5%EMI@

YC1

48MHZ_8PF_7V48000010

SJ10000JP00

CC28

2P_0402_50V

SE08220AC80

1 2

1 2

32.768KHz CRYSTAL

12

2 2

+3VS

3 3

+3VALW

1 2

RC98 100K_0402_5%

RC99 100K_0402_5%

1 2

1 2

4 4

RC608 4.7K_0402_5%@

RC609 4.7K_0402_5%@

1 2

+1.8VALW

1 2

RC618 4.7K_0402_5%

RC619 4.7K_0402_5%

1 2

RC86 20M_0402_5%

1 2

1

CC30

8.2P_0402_50V

SE07182AD80

2

12

RC89 10K_0402_5%

RC90 10K_0402_5%

12

12

RC91 10K_0402_5%

RC574 10K_0402_5%

12

USB3.1 Type-C

USB3.1 Type-A Port 1

Camer a

Touch Screen

USB3.1 Type-A Port 2

Finger Print

NGFF_B T

EC_PCIE_WAKE#<18,20>

USB_OC0#

USB_OC1#

USBC_I2C_SCL

USBC_I2C_SDA

USBC_I2C_SCL

USBC_I2C_SDA

A

YC2

32.768KHZ_9PF_X1A000141000200

SJ10000PW00

1

CC31

8.2P_0402_50V

SE07182AD80

2

CLKREQ_SSD1#

CLKREQ_WLAN#

CLKREQ_SD#

CLKREQ_SSD2#

1 2

RC617 0_0402_5%@

32K_X1

32K_X2

EMI

48M_X248M_X2_R

CLKREQ_SD#<26>

CLKREQ_SSD1#<16>

CLKREQ_SSD2#<17>

CLKREQ_WLAN#<18>

2nd_SSD

WLAN

@

FP6 REV 0.92

PART 10 OF 13

UC1J

USB

CLK_PCIE_SD<26>

CLK_PCIE_SD#<26>

CLK_PCIE_SSD1<16>

CLK_PCIE_SSD1#<16>

CLK_PCIE_SSD2<17>

CLK_PCIE_SSD2#<17>

CLK_PCIE_WLAN<18>

CLK_PCIE_WLAN#<18>

RC87 22 +-5% 0402@

USBC0_TX1P/USB0_TXP/DP2_TXP2

USBC0_TX1N/USB0_TXN/DP2_TXN2

USBC0_RX1P/USB0_RXP/DP2_TXP3

USBC0_RX1N/USB0_RXN/DP2_TXN3

USBC4_TX1P/USB4_TXP/DP3_TXP2

USBC4_TX1N/USB4_TXN/DP3_TXN2

USBC4_RX1P/USB4_RXP/DP3_TXP3

USBC4_RX1N/USB4_RXN/DP3_TXN3

12

USBC0_TX2P/DP2_TXP1

USBC0_TX2N/DP2_TXN1

USBC0_RX2P/DP2_TXP0

USBC0_RX2N/DP2_TXN0

USBC4_TX2P/DP3_TXP1

USBC4_TX2N/DP3_TXN1

USBC4_RX2P/DP3_TXP0

USBC4_RX2N/DP3_TXN0

USB1_TXP

USB1_TXN

USB1_RXP

USB1_RXN

USB5_TXP

USB5_TXN

USB5_RXP

USB5_RXN

CardRe ader

Main_ SSD

RTC_CLK_R<18>

USB20_P0

AC6

USB20_P0<24>

USB20_N0<24>

USB20_P1<26>

USB20_N1<26>

USB20_P2<14>

USB20_N2<14>

USB20_P3<14>

USB20_N3<14>

USB20_P5<26>

USB20_N5<26>

USB20_P6<22>

USB20_N6<22>

USB20_P7<18>

USB20_N7<18>

USBC_I2C_SCL<24>

USBC_I2C_SDA<24>

USB_OC0#<26>

USB_OC1#<26>

USB20_N0

USB20_P1

USB20_N1

USB20_P2

USB20_N2

USB20_P3

USB20_N3

USB20_P5

USB20_N5

USB20_P6

USB20_N6

USB20_P7

USB20_N7

USBC_I2C_SCL

USBC_I2C_SDA

USB_OC0#

USB_OC1#

PCIE_WAKE#_SOC

USBC0_DP/USB0_DP

AC7

USBC0_DN/USB0_DN

AA8

USB1_DP

AA9

USB1_DN

Y10

USB2_DP

Y9

USB2_DN

Y7

USB3_DP

Y6

USB3_DN

AC9

USBC4_DP/USB4_DP

AC10

USBC4_DN/USB4_DN

AA11

USB5_DP

AA12

USB5_DN

W8

USB6_DP

W9

USB6_DN

W11

USB7_DP

W12

USB7_DN

AL9

USBC_I2C_SCL

AL8

USBC_I2C_SDA

AE9

USB_OC0_L/AGPIO16

AE10

USB_OC1_L/AGPIO17

S5_3.3V

AE6

USB_OC2_L/AGPIO18

AE7

USB_OC3_L/AGPIO24

CLKREQ_SD#

CLKREQ_SSD1#

CLKREQ_SSD2#

CLKREQ_WLAN#

CLK_PCIE_SD

CLK_PCIE_SD#

CLK_PCIE_SSD1

CLK_PCIE_SSD1#

CLK_PCIE_SSD2

CLK_PCIE_SSD2#

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

48M_X1

48M_X2

RTC_CLK

32K_X1

32K_X2

USBC0_ATX_DRX_P1

AA1

USBC0_ATX_DRX_N1

AA3

USBC0_ARX_DTX_P1

AA2

USBC0_ARX_DTX_N1

AA4

USBC0_ATX_DRX_P2

AC2

USBC0_ATX_DRX_N2

AC4

USBC0_ARX_DTX_P2

AC1

USBC0_ARX_DTX_N2

AC3

USB3_ATX_DRX_P1

AE1

USB3_ATX_DRX_N1

AE3

USB3_ARX_DTX_P1

AD8

USB3_ARX_DTX_N1

AD9

V3

V1

U4

U2

W2

W4

W1

W3

USB3_ATX_DRX_P2

AD2

USB3_ATX_DRX_N2

AD4

USB3_ARX_DTX_P2

AD12

USB3_ARX_DTX_N2

AD11

AR13

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AP10

CLK_REQ1_L/AGPIO115

AR15

CLK_REQ2_L/AGPIO116

AT14

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AN11

CLK_REQ4_L/OSCIN/EGPIO132

AN13

CLK_REQ5_L/EGPIO120

AN15

CLK_REQ6_L/EGPIO121

AF11

GPP_CLK0P

AF12

GPP_CLK0N

AG4

GPP_CLK1P

AG2

GPP_CLK1N

AG3

GPP_CLK2P

AG1

GPP_CLK2N

AF2

GPP_CLK3P

AF4

GPP_CLK3N

AH2

GPP_CLK4P

AH4

GPP_CLK4N

AJ2

GPP_CLK5P

AJ4

GPP_CLK5N

AF8

GPP_CLK6P/WIFIBT_CLKP

AF9

GPP_CLK6N/WIFIBT_CLKN

AK1

X48M_OSC

BB3

X48M_X1

BA5

X48M_X2

AG10

RSVD_71

AG9

RSVD_70

AW10

RTCCLK

AY1

X32K_X1

AY4

X32K_X2

C250 0.22U_0201_6.3V6M

1 2

C251 0.22U_0201_6.3V6M

1 2

CT43 0.33U_0201_6.3V6M

1 2

1 2

CT44 0.33U_0201_6.3V6M

C252 0.22U_0201_6.3V6M

1 2

1 2

C253 0.22U_0201_6.3V6M

1 2

CT45 0.33U_0201_6.3V6M

CT49 0.33U_0201_6.3V6M

1 2

S0_3.3V

FP6_BGA1140

B

@

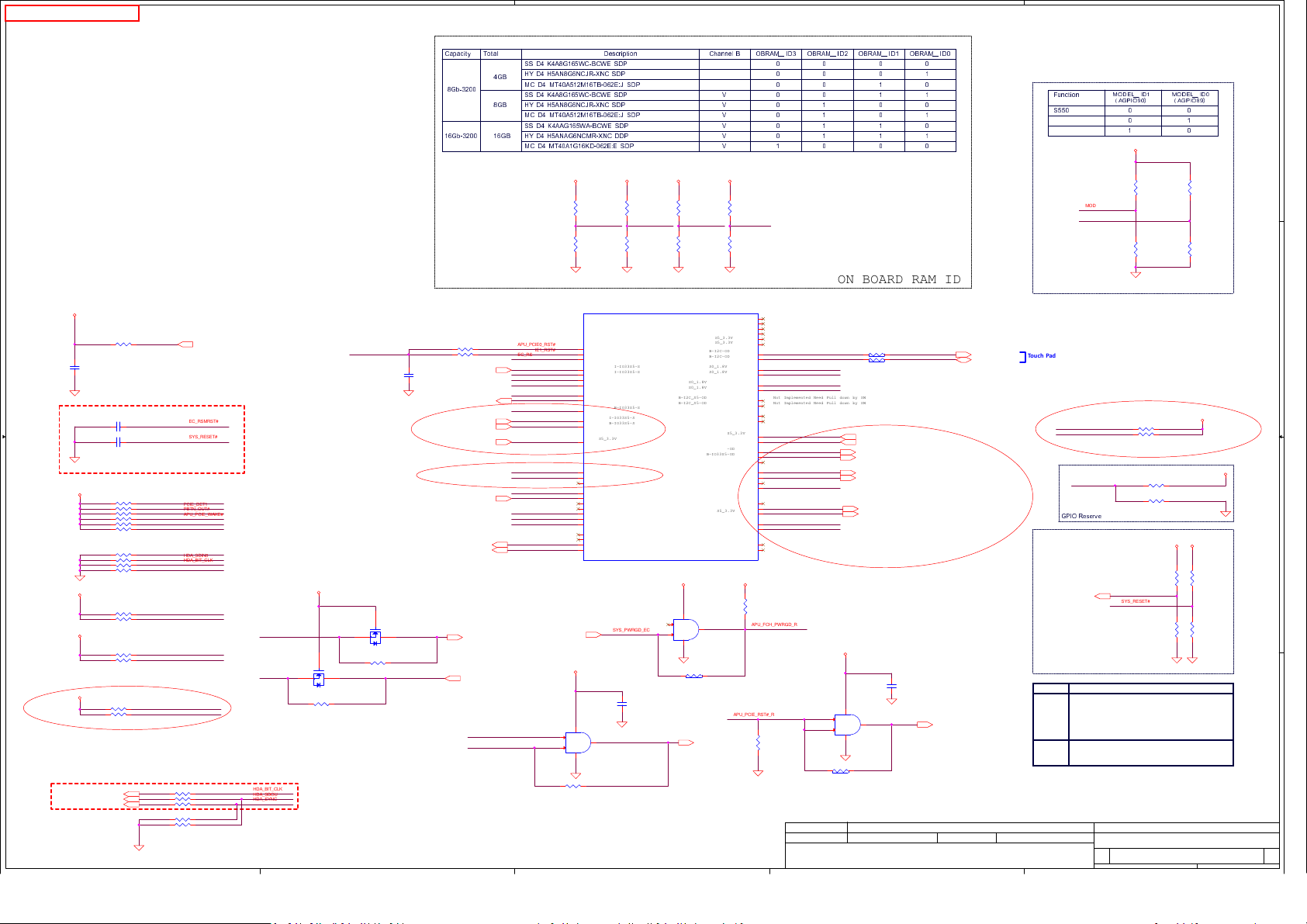

CLK/LPC/EMMC/SD/SPI/eS PI/UART

FP6 REV 0.92

PART 5 OF 13

USB3_ATX_DRX_P1 <26>

USB3_ATX_DRX_N1 <26>

USB3_ARX_DTX_P1 <26>

USB3_ARX_DTX_N1 <26>

USB3_ATX_DRX_P2 <26>

USB3_ATX_DRX_N2 <26>

USB3_ARX_DTX_P2 <26>

USB3_ARX_DTX_N2 <26>

C

UC1E

S0_3.3V

FP6_BGA1140

USBC0_ATX_C_DRX_P1

USBC0_ATX_C_DRX_N1

USBC0_ARX_C_DTX_P1

USBC0_ARX_C_DTX_N1

USBC0_ATX_C_DRX_P2

USBC0_ATX_C_DRX_N2

USBC0_ARX_C_DTX_P2

USBC0_ARX_C_DTX_N2

Type-A left port1

Type-A left port2

LPC_PD_L/AGPIO21

LAD0/ESPI1_DATA0/EGPIO104

LAD1/ESPI1_DATA1/EGPIO105

LAD2/ESPI1_DATA2/EGPIO106

LAD3/ESPI1_DATA3/EGPIO107

LPCCLK0/EGPIO74

LPC_CLKRUN_L/AGPIO88

S0_3.3V

LPCCLK1/EGPIO75

LFRAME_L/EGPIO109

LPC_RST_L/AGPIO32

LPC_PME_L/AGPIO22

SPI_ROM_REQ/EGPIO67

SPI_ROM_GNT/EGPIO76

ESPI_RESET_L/KBRST_L/AGPIO129

ESPI_ALERT_L/LDRQ0_L/EGPIO108

SPI_CLK/ESPI_CLK

SPI_WP_L/ESPI_DAT2

SPI_HOLD_L/ESPI_DAT3

SPI_CS2_L/ESPI_CS_L/AGPIO30

SPI_CS3_L/AGPIO31

SPI_TPM_CS_L/AGPIO29

EGPIO141/UART0_RXD

EGPIO143/UART0_TXD

EGPIO142/UART0_RTS_L/UART1_RXD

EGPIO140/UART0_CTS_L/UART1_TXD

AGPIO144/SHUTDOWN_L/UART0_INTR

AW14

EGPIO70

BB13

LPCPD#

LPC_AD0_R

BA16

LPC_AD1_R

BA15

LPC_AD2_R

BC13

LPC_AD3_R

BB14

LPC_CLK0

BB15

BD13

CLKRUN#

BA12

BC15

SERIRQ/AGPIO87

BA13

LPC_RST#

BC12

AU12

AGPIO68

AP4

BA11

BB11

AT15

ESPI_ALERT#

BC11

APU_SPI_CLK

BC10

APU_SPI_MISO

BA10

SPI_DI/ESPI_DATA

APU_SPI_MOSI

BB8

SPI_DO

APU_SPI_WP#

BA9

APU_SPI_HOLD#

BC8

APU_SPI_CS1#

BD11

SPI_CS1_L

BC9

BB10

BD8

BA17

BC16

BD15

BC17

BB16

USBC0_ATX_C_DRX_P1 <24>

USBC0_ATX_C_DRX_N1 <24>

USBC0_ARX_C_DTX_P1 <24>

USBC0_ARX_C_DTX_N1 <24>

USBC0_ATX_C_DRX_P2 <24>

USBC0_ATX_C_DRX_N2 <24>

USBC0_ARX_C_DTX_P2 <24>

USBC0_ARX_C_DTX_N2 <24>

Not Implemented Need Pull down by SW

T17

12

RC77 10_0402_5%

RC78 10_0402_5%

12

RC79 10_0402_5%

12

12

RC80 10_0402_5%

RC81 22_0402_5%

12

12

RC82 33_0402_5%

LPC_AD0 <20>

LPC_AD1 <20>

LPC_AD2 <20>

LPC_AD3 <20>

LPC_CLK0_EC <20>

CLKRUN# <20>

SERIRQ <20>

LPC_FRAME# <20>

LPC_RST#_R <20>

EC_SCI# <20>

KB_RST# <20>

RC84 10_0402_1%EMI@

UART_0_ARXD_DTXD

UART_0_ATXD_DRXD

12

E

MI

APU_SPI_CLK_R <8>

UART_0_ARXD_DTXD <18>

UART_0_ATXD_DRXD <18>

TYPE- C

+1.8VALW

RC92 10K_0402_5%@

12

RC93 10K_0402_5%

12

12

RC94 10K_0402_5%

RC96 10K_0402_5%

12

12

RC95 10K_0402_5%

RC97 10_0402_5%@EMI@

1

CC33

10P_0402_50V8J

@EMI@

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS, INC.

2020/01/10 2022/01/10

2020/01/10 2022/01/10

2020/01/10 2022/01/10

D

12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

APU_SPI_MOSI

APU_SPI_MISO

APU_SPI_WP#

APU_SPI_HOLD#

APU_SPI_CS1#

APU_SPI_CLK

APU_SPI_CS1#

APU_SPI_MISO

APU_SPI_WP# APU_SPI_CLK_R

EMI

LPC_RST#_R

ESPI_ALERT#

KB_RST#

12

RC83 100K_0402_5%@

CC29 150P_0402_50V8J

12

RC616 10K_0402_5%

12

RC85 10K_0402_5%@

12

SPI ROM (Winbond)

UC2

1

CS

2

DO(IO1)

3

WP(IO2)

4

GND

W25Q128JWSIQ_SO8

8

VCC

7

HOLD/RESET(IO3)

6

CLK

5

DI(IO0)

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FP6 SATA/CLK/USB/SPI

FP6 SATA/CLK/USB/SPI

FP6 SATA/CLK/USB/SPI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-J701P

LA-J701P

LA-J701P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

E

APU_SPI_HOLD#

APU_SPI_MOSI

+3VS

+1.8VALW

1

CC32

0.1U_0201_10V6K

@

2

9 39Wednesday, January 15, 2020

9 39Wednesday, January 15, 2020

9 39Wednesday, January 15, 2020

1.0

1.0

1.0

A

Main Func = CPU

B

C

D

E

+1.2V

1 1

CC118

22U_0603_6.3V6M

CC119

22U_0603_6.3V6M

1

1

2

2

All BU(on bottom side under SOC)

CC38

22U_0603_6.3V6M

CC37

CC117

22U_0603_6.3V6M

1

1

2

2

CC35

22U_0603_6.3V6M

CC116

22U_0603_6.3V6M

1

2

22U_0603_6.3V6M

CC36

22U_0603_6.3V6M

1

@

2

1

1

2

2

CC40

22U_0603_6.3V6M

CC43

CC52

22U_0603_6.3V6M

CC39

22U_0603_6.3V6M

1

1

@

@

2

2

1U_0201_6.3V6M

1

1

@

2

2

CC45

180P_0402_50V8J

CC44

1U_0201_6.3V6M

1

1

2

2

Across VDDIO & VSS split.

CC47

180P_0402_50V8J

CC48

CC46

180P_0402_50V8J

1

1

2

2

.22U 6.3V K X5R 0402

1

2

.22U 6.3V K X5R 0402

1

2

CC51

CC49

1

2

.22U 6.3V K X5R 0402