A

1 1

B

C

D

E

Compal Confidential

2 2

FH50P MB Schematics Document

AMD Picasso Platform

AMD R18M-G1-90

3 3

LA-H901P REV:1A

2019-05-13

4 4

Security Classif ication

Security Classif ication

Security Classif ication

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Shared with Comp al

Shared with Comp al

A

B

Shared with Comp al

2018/ 12 /18 2019/12/ 18

2018/ 12 /18 2019/12/ 18

2018/ 12 /18 2019/12/ 18

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

COVER PAGE

COVER PAGE

COVER PAGE

FH50P M/B LA-H901P

FH50P M/B LA-H901P

FH50P M/B LA-H901P

E

1A

1A

1A

1 99Wednesd ay, May 15, 2019

1 99Wednesd ay, May 15, 2019

1 99Wednesd ay, May 15, 2019

A

Compal Confidential

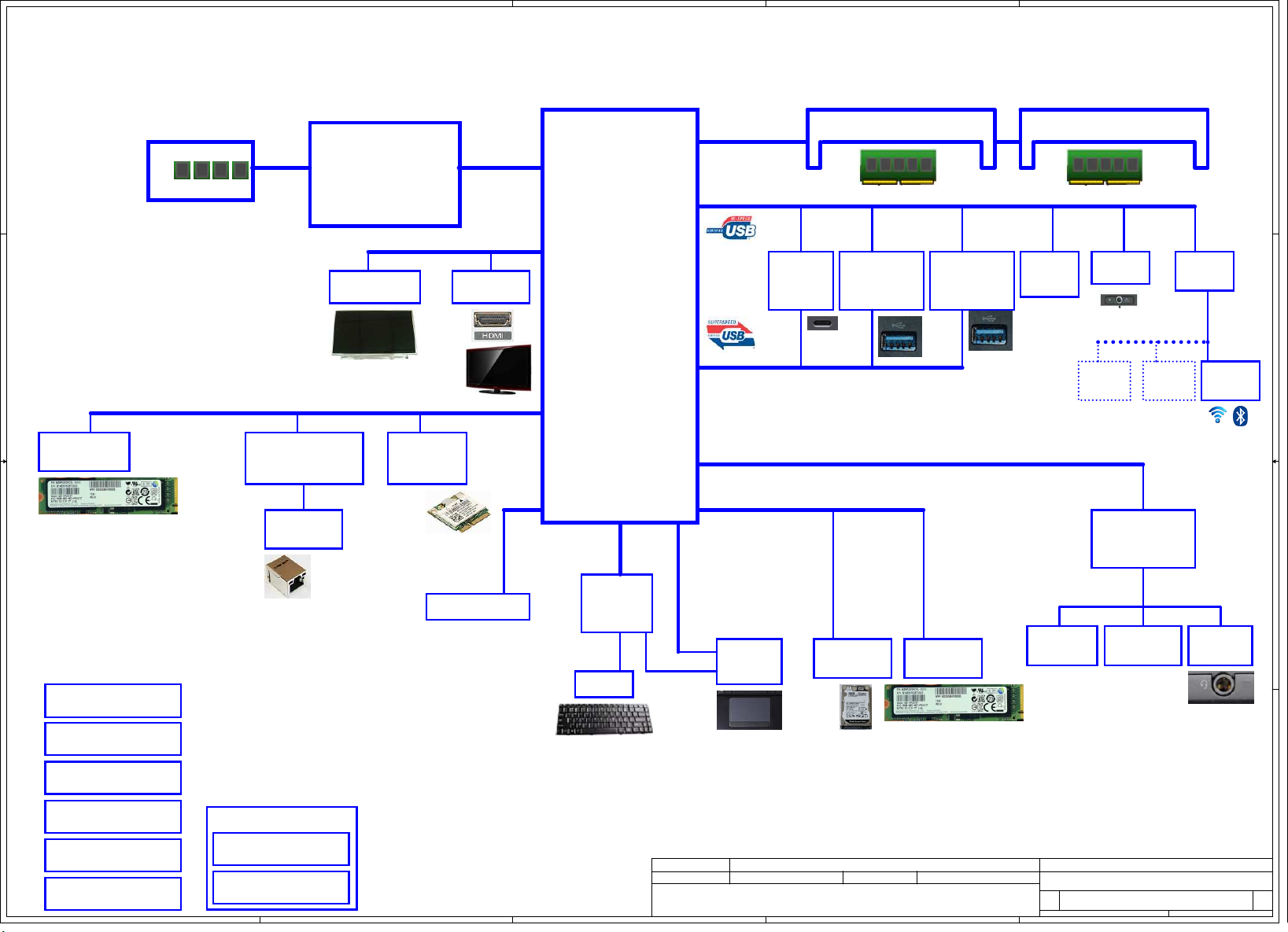

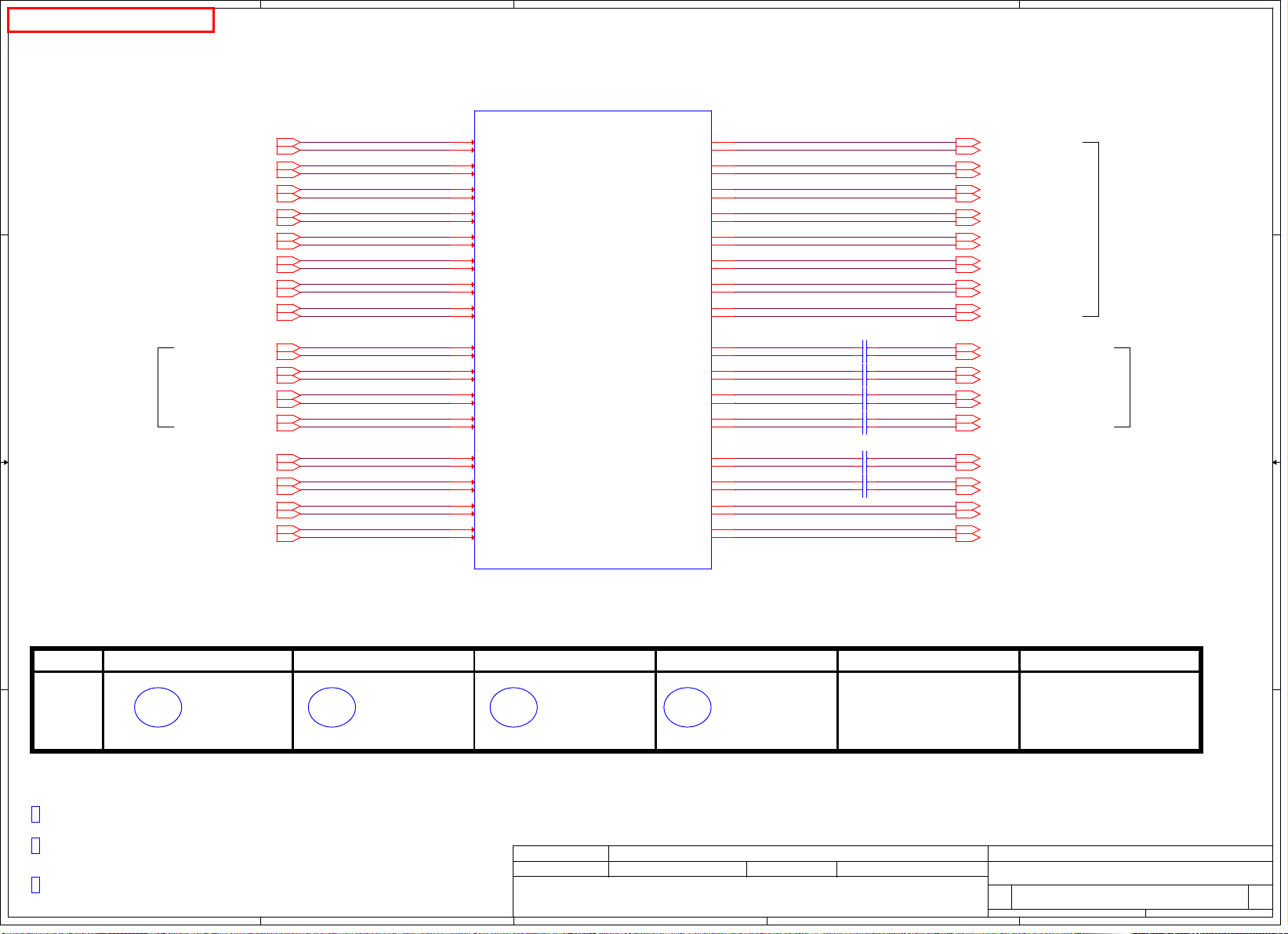

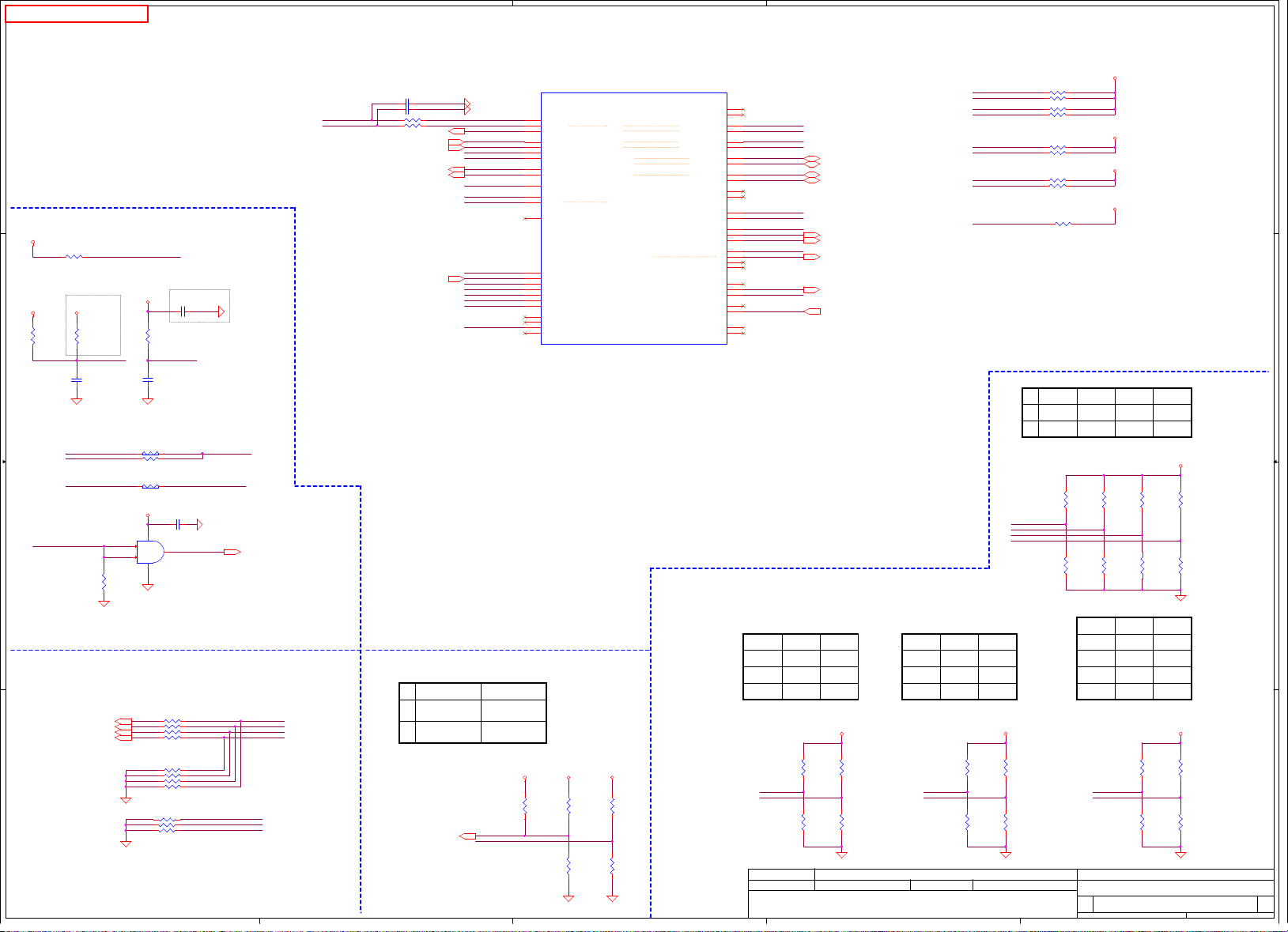

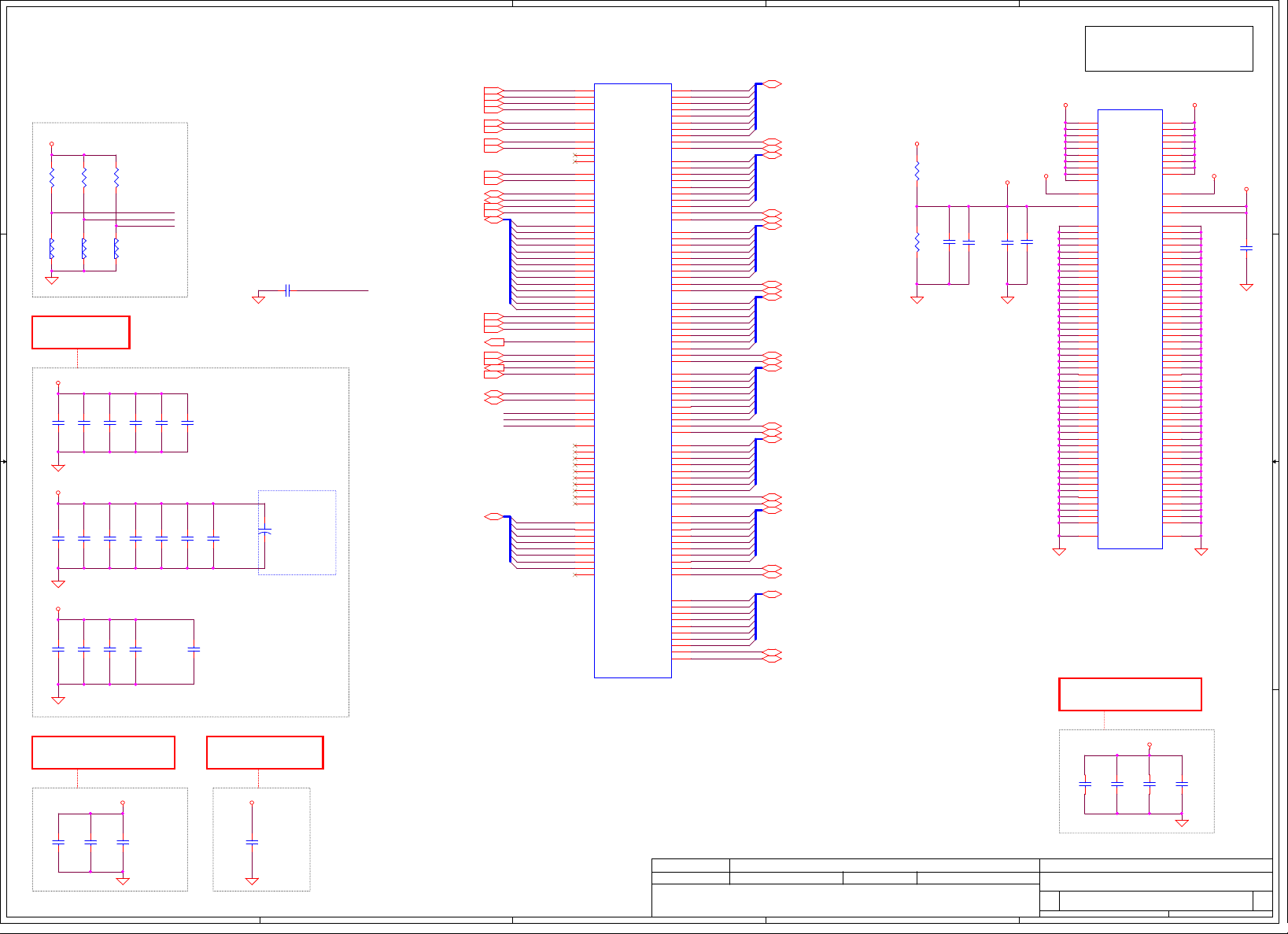

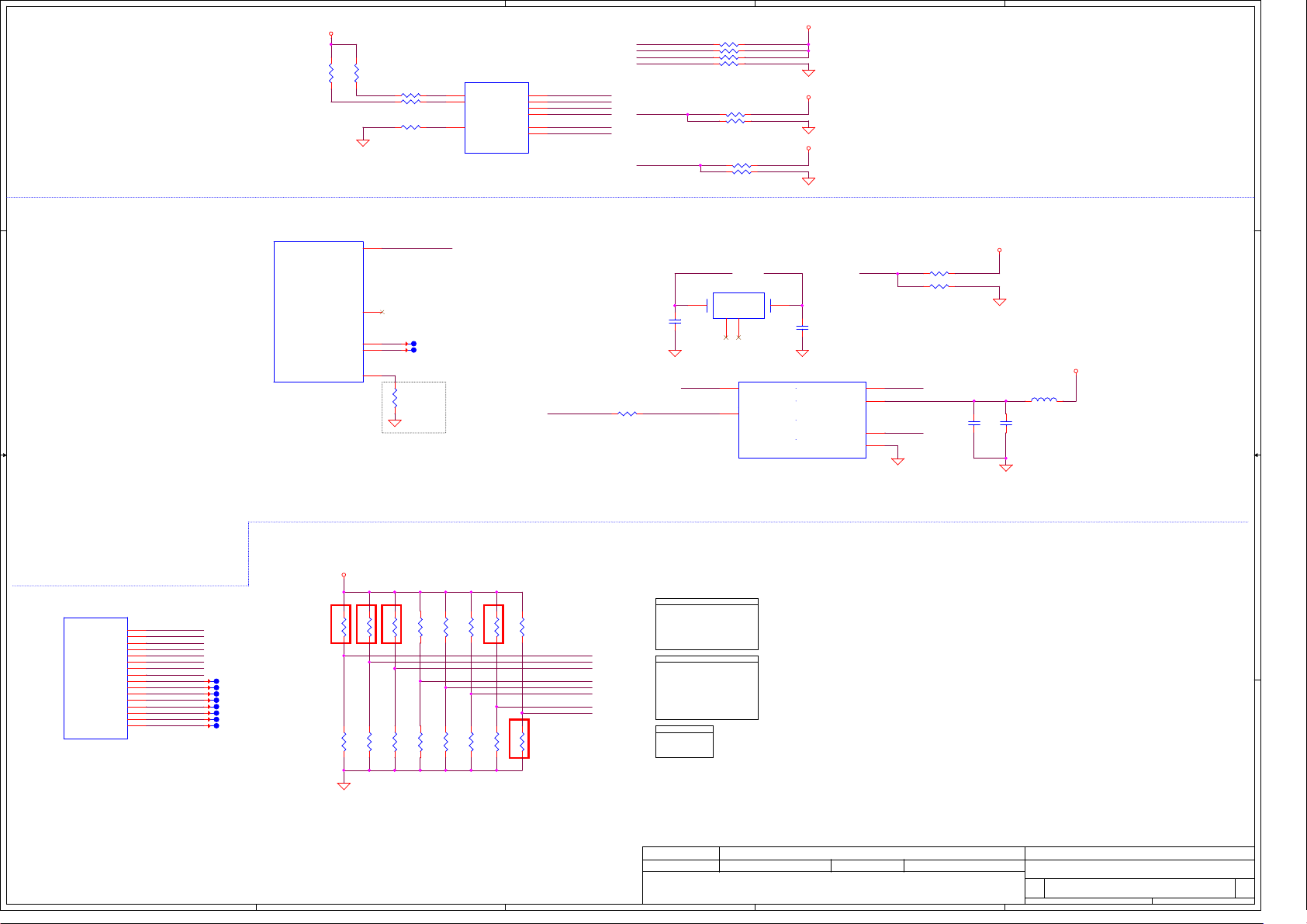

Model Name : FH50P

B

C

D

E

(Channel A)

1 1

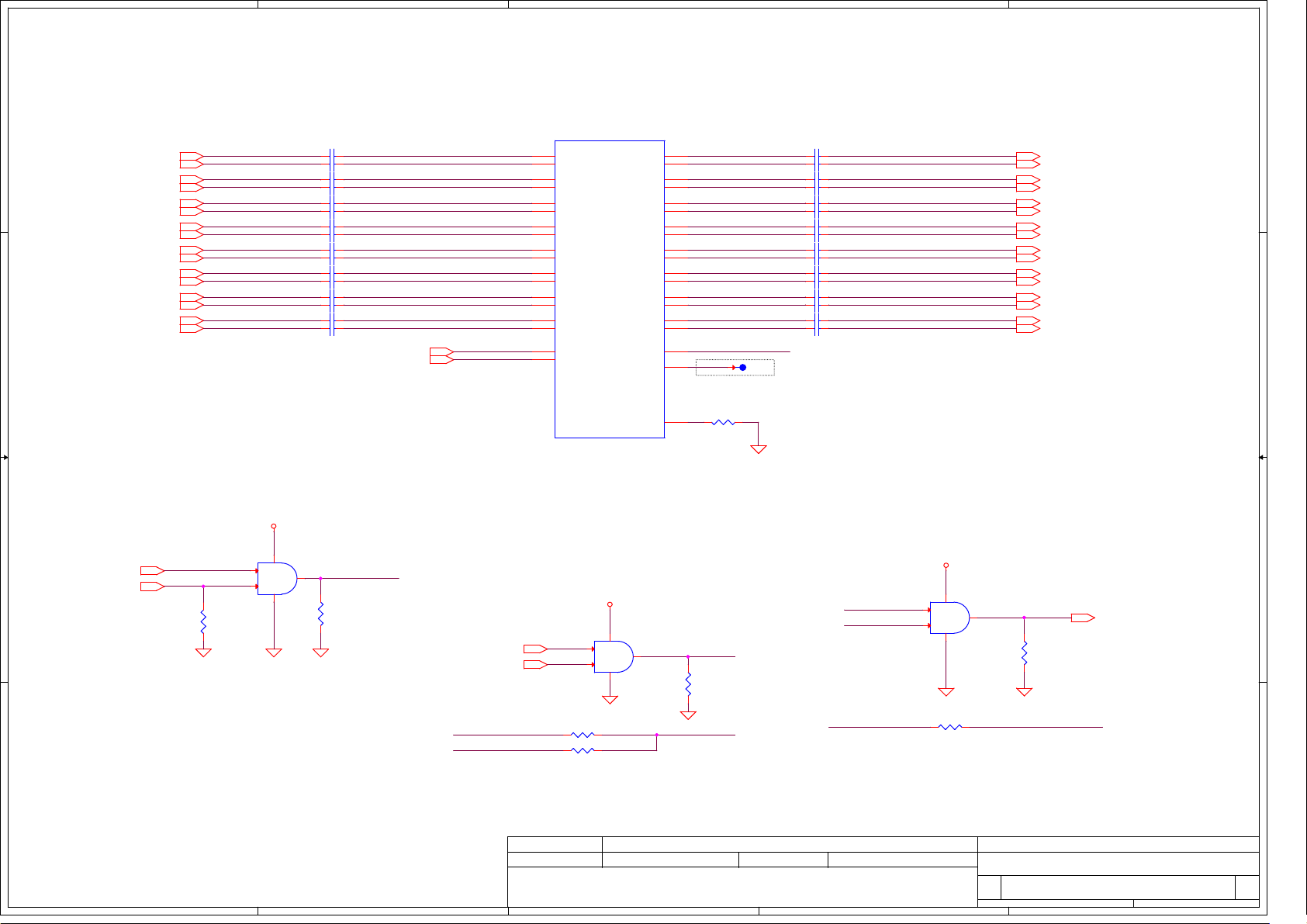

GPU

GDDR5 x4pcs

page 35~36

2 2

128-bits

S4 Package

RX560X : R18M-G1-90

page 27~33

Port 1

eDP Conn.

page 38 page 40

PEG x8

Display Port

Port 0

HDMI Conn.

AMD

Picasso

Memory BUS(DDR4)

1.2V DDRIV

2400Mhz

USB2.0

Port 3

USB3.0

260pin DDRIV SO-DIMM

Port 1

Type-C

Conn.

page 42~43

Type-A (CHG)

Conn.

Port 1

page 71

page 23

Port 2

Type-A

Conn.

Port 2Port 3

AMD FP5 APU

GA 1140-balls

PCIE

page 68~70

SSD1

NGFF Conn.

Port 4

LAN

RTL8118ASA

page 51

Port 5Port 0, 1, 2, 3

WLAN/BT

NGFF Conn.

page 52

SPI

Transformer

RJ45

page 51

3 3

page 10

BIOS (8M, 1.8V)

Fan Control

page 77

B

page 6~12

ENE

KBC9022

page 63

Int.KBD

LPC

page 58

PS2

I2C

Port 3

HD Audio

SATA III

PTP

page 63

HDD

Conn.

Port 0

page 67

Port 1

page 68

SSD2

NGFF Conn.

page 72

(Channel B)

260pin DDRIV SO-DIMM

Port 4

Type-A

(SUB)

page 38

Int. DMIC

on Camera

page 73

Port 0

Camera

Finger

Print

page 66

Audio

ALC255

page 38

Touch

Screen

Int. Speaker

Conn.

page 56

page 24

Port 5

page 38

page 56

USB2.0 Hub

page 75

WLAN/BT

NGFF Conn.

UAJ

on Sub/B

Port 1Port 2Port 3

page 52

page 73

RTC CKT.

Power On/Off CKT.

4 4

DC/DC Interface CKT.

Power Circuit DC/DC

VRAM Config Table

page 11

page 63

page 78

page 82~96

page 29

A

Sub Board

LS-H901 IO/B

LS-H502 Hall Sensor/B

page 73

page 66

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2018/ 12/18 2019/12/18

2018/ 12/18 2019/12/18

2018/ 12/18 2019/12/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

BLOCK DIAGRAMS

BLOCK DIAGRAMS

BLOCK DIAGRAMS

FH50P M/B LA-H901P

FH50P M/B LA-H901P

FH50P M/B LA-H901P

E

1A

1A

2 99Wednesday, May 15, 20 19

2 99Wednesday, May 15, 20 19

2 99Wednesday, May 15, 20 19

1A

A

B

C

D

E

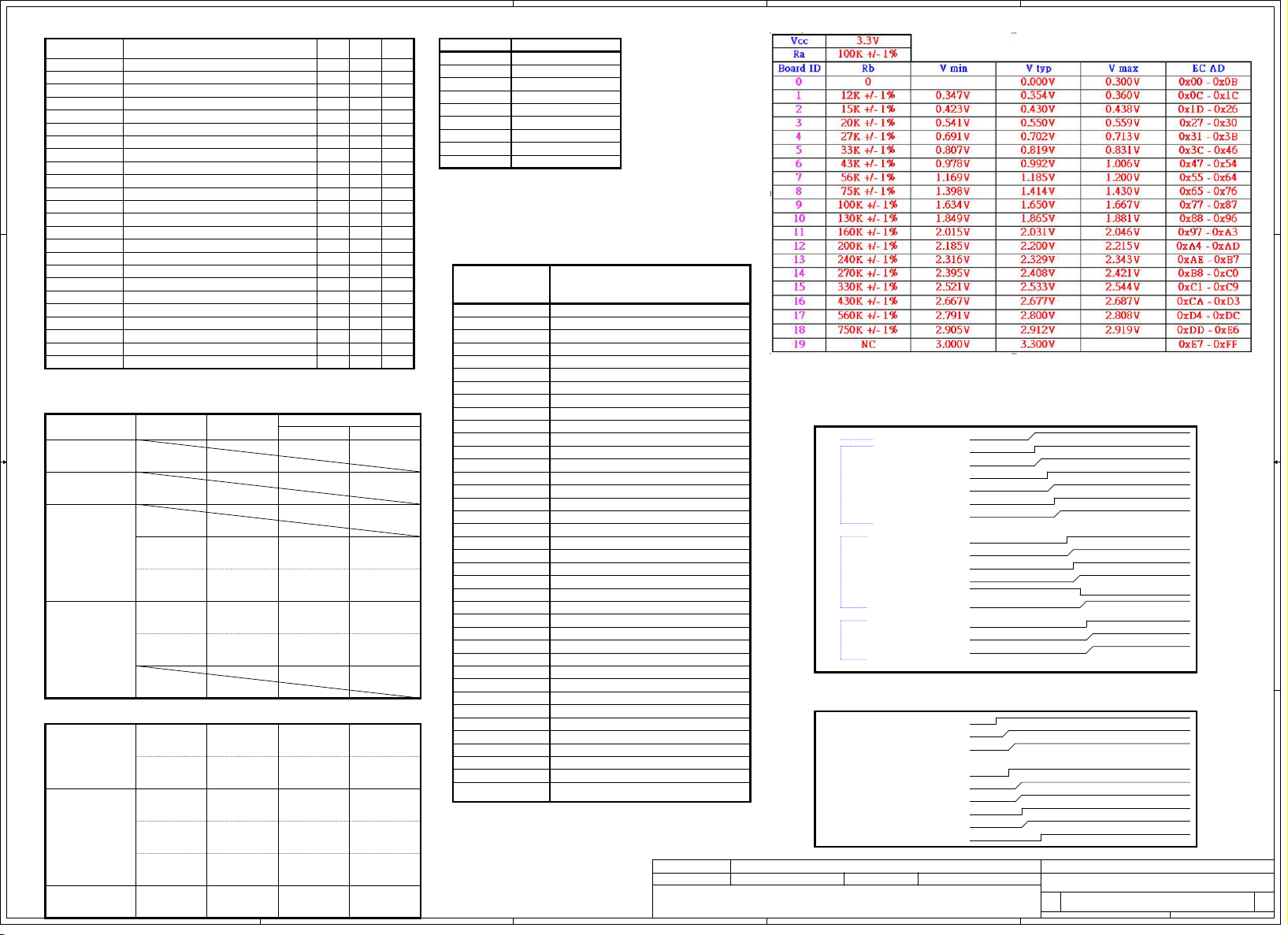

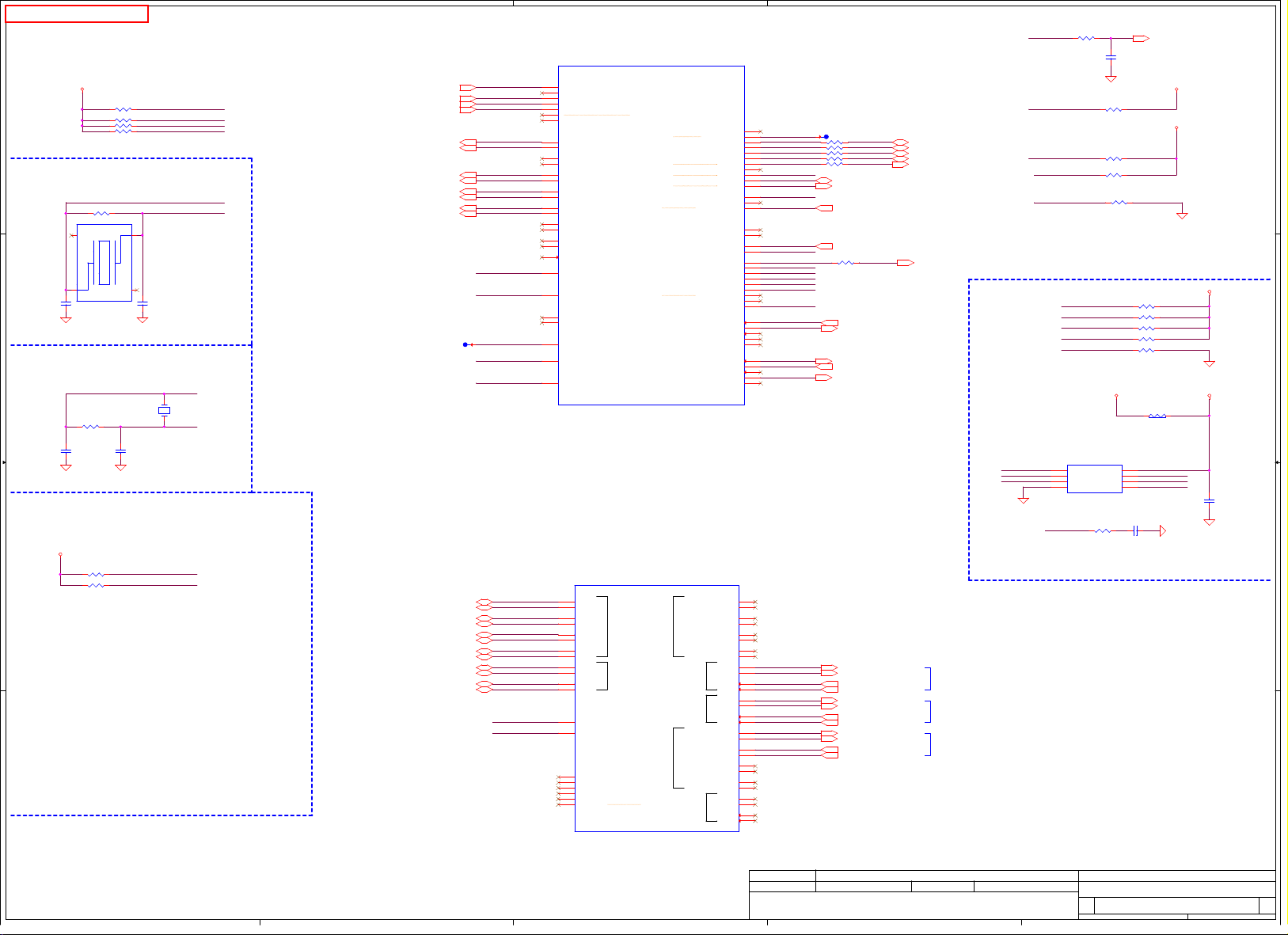

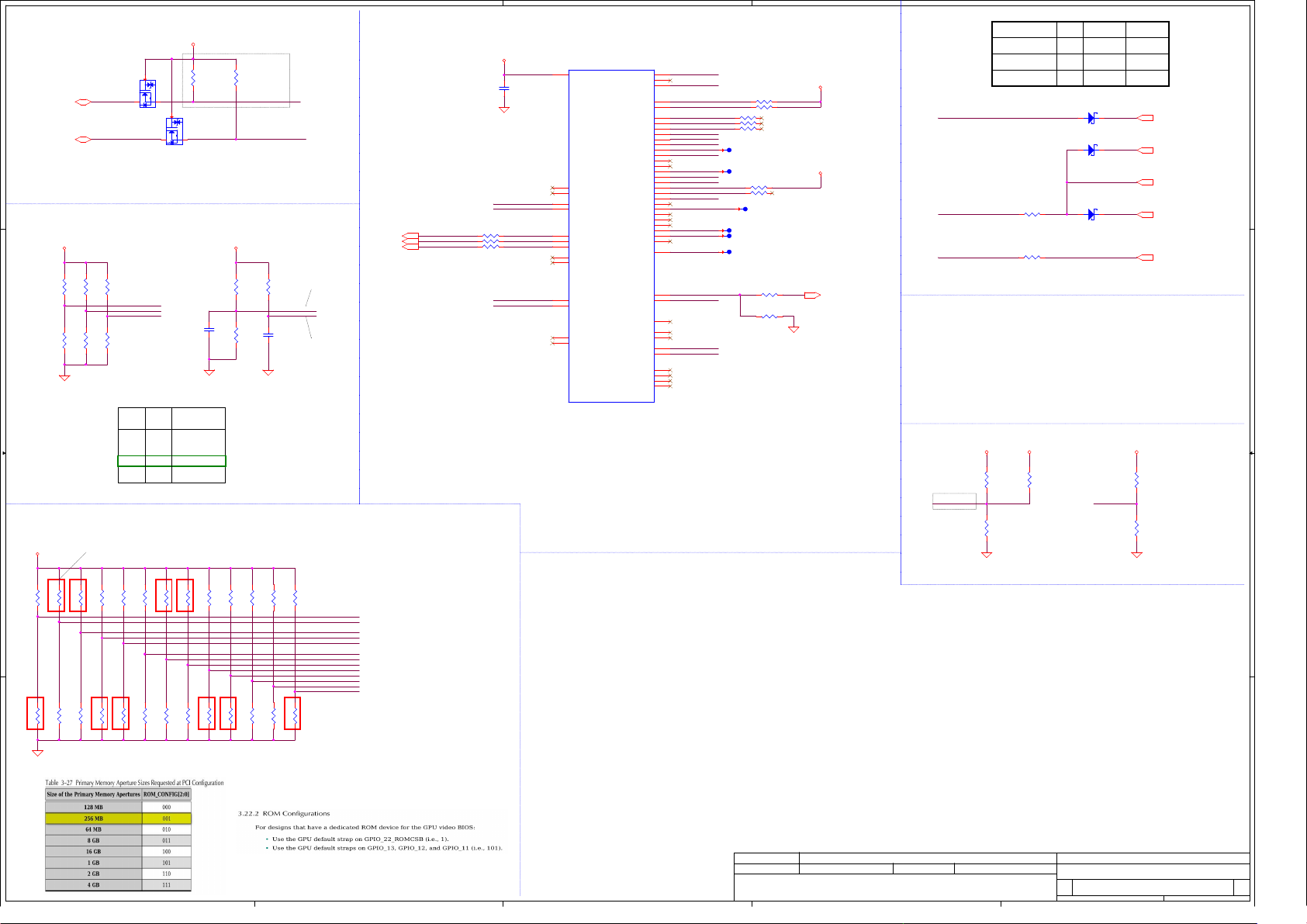

Voltage Rails

+19V_VIN

+19VB

+APU_CORE OFFON

1 1

2 2

+1.8VALW

+1.8VS

+2.5V 2.5V power rail for APU and DDR ON ON

+1.2V

+0.6VS

+3VALW

+3VS

+5VALW ONONON

+5VS

+RTC_APU

+3VSDGPU

+1.8VSDGPU

+1.5VSDGPU VGA power

+VDDCI

+VGA_CORE

APU SMBus/I2C Address Table

Master

I2C Port 0

(+1.8VS)

I2C Port 1

(+1.8VS)

I2C Port 2

(+3VS)

SBMus Port 0

3 3

(+3VS)

I2C Port 3

(+3VALW)

SMBus Port 1

(+3VALW)

DescriptionPower Plane

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for APU

Core voltage for APU ON+APU_CORE_SOC

1.8V always on power rail

1.8V switched power rail

0.6V switched power rail for DDR terminator

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

VGA power

VGA power

VGA power

VGA power

Device

JDIMM1

JDIMM2

PTP

(Synaptics)

PTP

(ELAN)

Address[7:1]

0101 0000b

50h

0101 0001b

51h

0010 1100b

2Ch

0001 1111b

15h

Address [7:0]

Write

1010 0000b

A0h

1010 0010b

A2h

0101 1000b

58h

0011 1110b

3Eh

ON

ON ON

ON

ON

ON

ON

ON

ON

ON

1010 0001b

A1h

1010 0011b

A3h

0101 1001b

59h

0011 1111b

3Fh

ON ON

OFF OFF

OFF OFF

ONON1.2V power rail for APU and DDR

OFF OFF

ONON

OFF OFF

OFF OFF

OFF OFF

Read

BOARD ID Table

S5S3S0

ONONON

OFF

OFF

OFF

OFF

OFF

ON

ONONON

OFF+3V_LAN 3.3V LAN IC power ON ON

OFF+TP_VCC 3.3V Touch Pad power ON ON

OFFOFF

OFFOFFON

OFFOFF

OFFOFF

OFFON3.3V Finger Print power+FP_VCC ON

Board ID

0

PCB Revision

EVT

1 PVT

MP2

9 With RGB BL

BOM Structure Table

BTO ItemBOM Structure

@

EMC@/@EMC@

45@

CONN@

JP@

RS@

TP@

LDO@/SWR@

R5/R7APUQC@

HDT@

DIS@

RX560@

EVT@/PVT@/MP@

TMS@

KBLED@/LED14P@

X76_S4G@

X76_H4G@

Unpop

EMI/ESD Pop/Unpop

HDMI Royalty

Mechanical Connector

Jump

R-Short

Test Point

RTL8118ASA Switching-Mode only

APU PN Refer p.6

HDT Circuits

VGA Circuits

R18M-G1-90 GPU / Circuit

Test BOM for EVT/PVT/MP

Thermal Sensor

Keyboard back light / RGB back light

VRAM Config Refer p.33

VRAM Config Refer p.33

EC SMBus Address Table

SMBus Port 1

(+3VALW)

4 4

SMBus Port 2

(+3VS)

SMBus Port 3

(+3VALW)

Smart Battery

Charger IC

(BQ24735)

APU Temp.

(TSI)

GPU Temp.

Thermal Sensor

(Remote1 GPU)

(Remote2 APU)

LED driver 1100 0000b

A

0000 1011b

0Bh

0000 1001b

09h

0100 1100b

4Ch

0100 0001b

41h

0001 0110b

16h

0001 0010b

12h

1001 1000b

98h

1000 0010b

82h

1001 1010b

9Ah

C0h

0001 0111b

17h

0001 0011b

13h

1001 1001b

99h

1000 0011b

83h

1001 1011b

9Bh

1100 0001b

C1h

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Board ID / SKU ID Table for AD channel

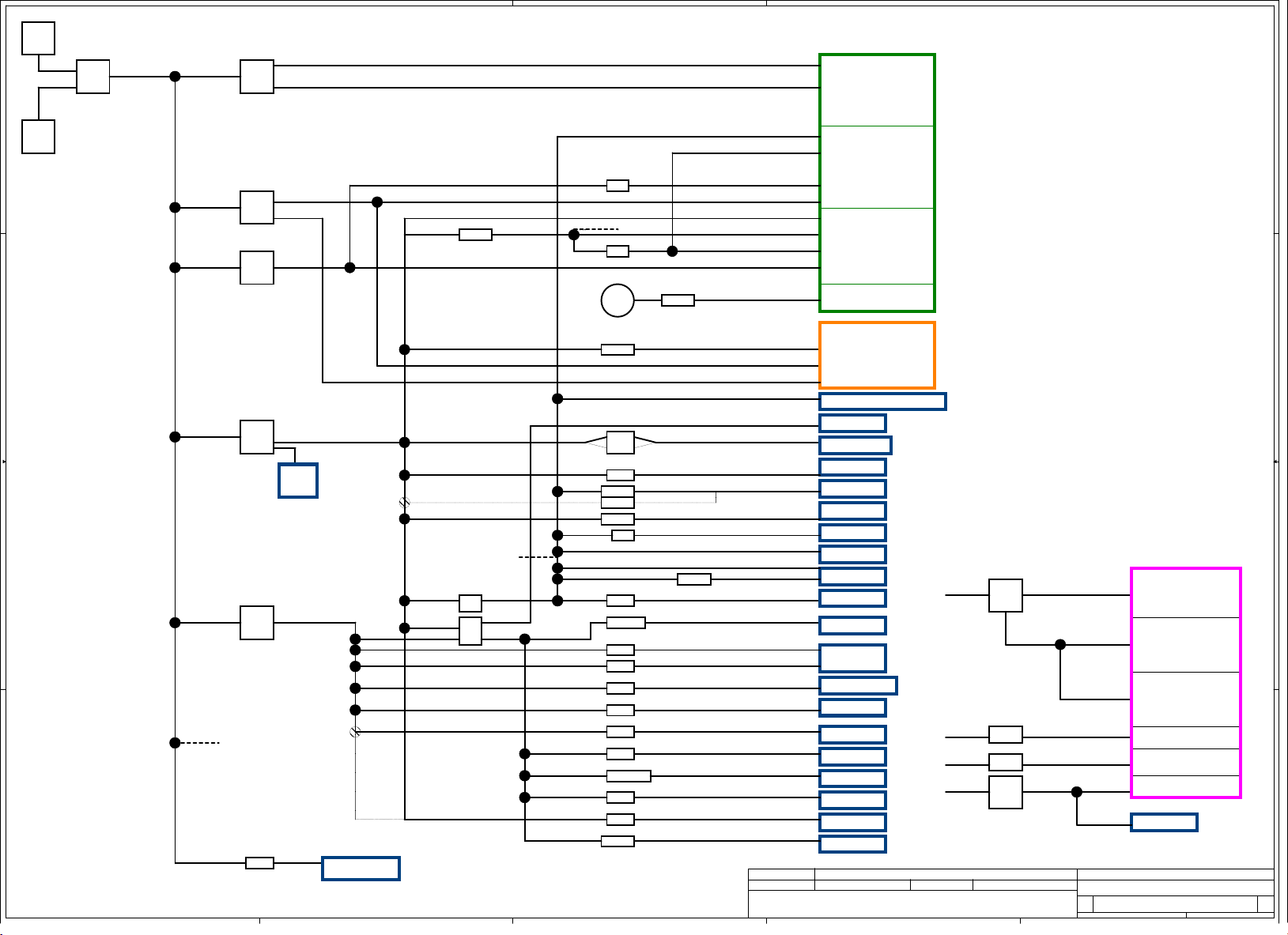

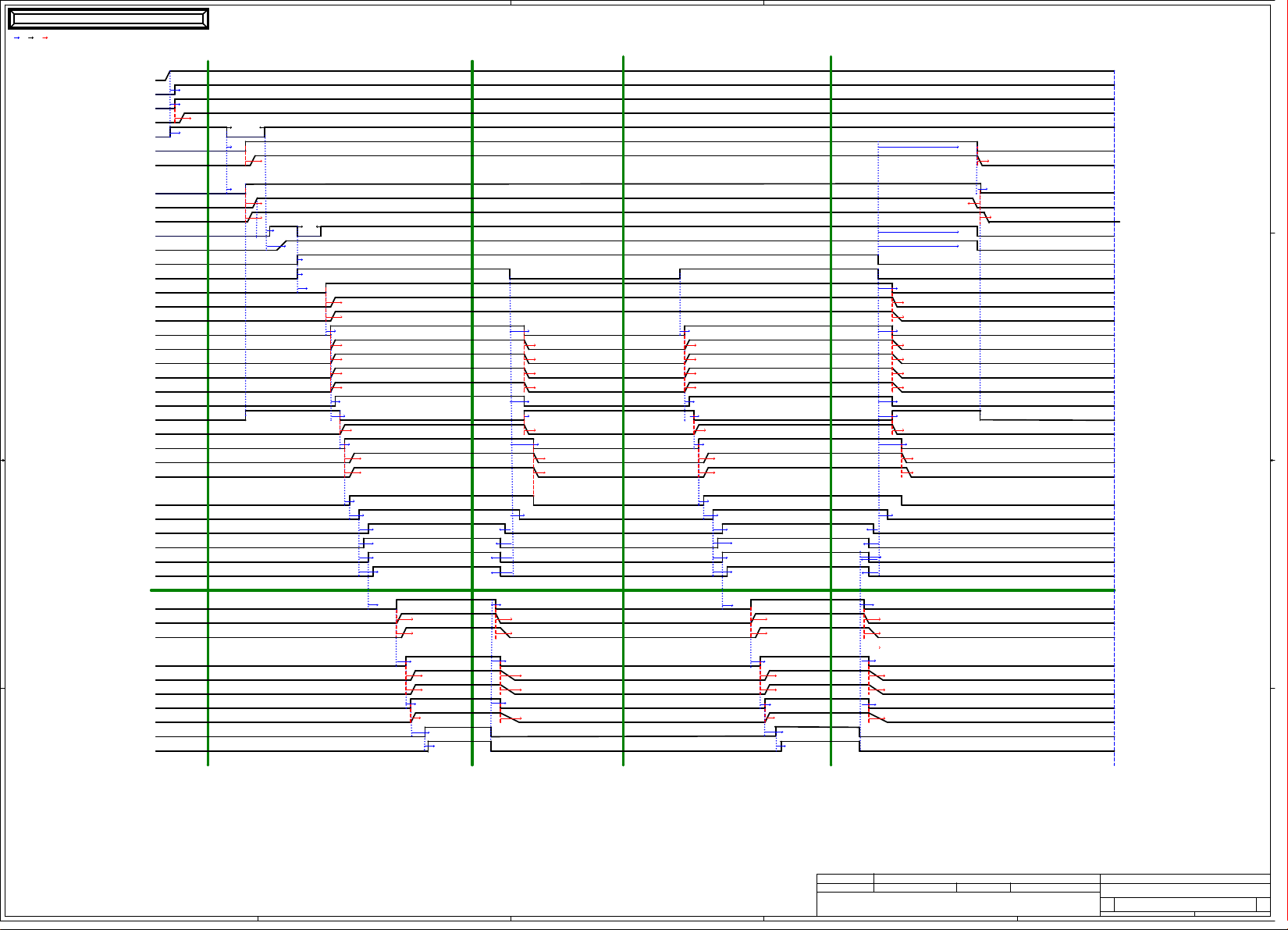

POWER SEQUENCE

G-A

G-B

G-C

G-D

+RTCBATT

EC_ON

+5VALW

3V_EN

+3VALW

0.9_1.8VALW_PWREN

+1.8VALW/+0.9VALW

SYSON

+1.2V/+2.5V

SUSP#

+5VS/+3VS/+1.8VS/+0.6VS

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_SOC

VGA POWER SEQUENCE

PE_GPIO1/VGA_ON

+3VSDGPU

+1.8VSDGPU

VGA_ON_B

+VDDCI

+VGA_CORE

DGPU_PWRGOOD

+1.5VSDGPU

PE_GPIO0

Compal Secret Data

Compal Secret Data

2018/ 12/18 2019/12/18

2018/ 12/18 2019/12/18

2018/ 12/18 2019/12/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

NOTES LIST

NOTES LIST

NOTES LIST

FH50P M/B LA-H901P

FH50P M/B LA-H901P

FH50P M/B LA-H901P

E

3 99Wednesday, May 15, 20 19

3 99Wednesday, May 15, 20 19

3 99Wednesday, May 15, 20 19

1A

1A

1A

5

PJP101

AC-IN

+19V_VIN

+17.4V_BATT

D D

P

JP201

DC-IN

C C

24810mA

+

19VB

P

U301

5243mA

638mA

237mA

2311mA

PU801

PU501

PU601

PU401

+APU_CORE

+

APU_CORE_SOC

+1.2V

+0.6VS

5000mA

+

0.9VALW

9500mA

1200mA

+3VLP

KB9022

B B

+5VALW

14700mA3869mA

PU401

To VGA

+VGA_CORE

+VDDCI/VDD_08

+1.35VSDGPU

A A

2000mA

5

3579mA

169mA

474mA

+INVPWR_B+

L

X1

Panel BackLight

13347mA

+

4

3VALW

4

2026mA

8330mA

4200mA

PU602

U2

U3

+1.8VALW

2

T

o VGA10mA

+

3VS_SSD1

+5VS

660mA

3

A

+

2.5V

+

1.2V

+0.6VS

+3VS_SSD1

+

3V_LAN

+TP_VCC

+

3VS_WLAN

+

3V_HUB

+LCDVDD

1.2V_HDMI

+3VS_CAM

+

5VS_BL

5VALW_MUX

+5VS_HDD

+VCC_FAN1

+VCC_FAN2

+5VS_PVDD

+

FP_VCC

+TS_PWR

PU Power Rail

VDDCR_VDD @0.65-TBD

VDDCR_SOC @0.72-TBD

VDD_33 @0.25A

VDD_18 @2.0A

VDDP @4.0A

VDDIO_MEM_S3 @6.0A

VDD_33_S5 @0.25A

VDD_18_S5 @0.5A

VDDIO_AUDIO @0.2A

VDDP_S5 @1.0A

VDDBT_RTC_G @0.045mA

DDR4 SO-DIMM1/SO-DIMM2

+2.5V

+1.2V

+0.6VS

S

ATA Redriver*2 (M.2 & HDD)

M

.2 PCIE SSD

LAN RTL8118ASA

Touch Pad

WLAN

U

SB HUB

P

anel Logic

M

.2 SATA SSD

H

DMI Retimer

Camera

KB Light

T

ype C

RTS5441E

USB3.0(Charger)

U

SB3.0US13

USB/B

HDD

FAN1/FAN2

Audio

Finger Print

Touch Screen

2

2

2

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

70000mA

+APU_CORE

13000mA

+APU_CORE_SOC

250mA

+3VS

2000mA

+1.8VS

4

000mA

2200mA

528mA

+

3VS

U4

T

UV8

J

RTC1

PU502

U

L1

RL2

U13

R

M101

UM3

R

S148

U

R

X18

U

2616

US14

U

S11

US12

JIO2

RO4

RF4/RF7

LA1

UK6

R

X17

o VGA

X1

+0.9VS

+

1.8VS

+

RTCVCC

+2.5V

3

1013mA

U

C8

+RTC_APU_R

U

1302

4000mA

+0.9VS

6000mA

+1.2V

250mA

+3VALW

500mA

+1.8VALW

200mA

+1.8VS

1000mA

+0.9VALW

0.045mA

+RTC_APU_R

528mA

4160mA

1500mA

280mA

2790mA

300mA

30mA

1500mA

5

9mA

1500mA

+

200mA

200mA

200mA

+

250mA

3000mA

+USB3_VCCC

2000mA

+USB3_VCCA

2

000mA +USB3_VCCB

2500mA

1500mA

1000mA

1500mA

1

00mA

100mA

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

ssued Date

ssued Date

ssued Date

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

R18M-G1-90

C

C

C

ompal Secret Data

ompal Secret Data

ompal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Group C, S0 dom ain

Group B, S0 dom ain

Group B, S3 dom ain

Group A, S5 dom ain

+19VB

PU1401

3579mA

+3VALW 10mA

U

3VALW

V8

PU701

PU1001

10mA

+

1013mA

+19VB

474mA

140000mA

12000mA

1013mA

6720mA

1

GPU Power Rail (R18M-G1-90)

+

VGA_CORE

VDDC

@140A

+

VDDCI

V

DDCI

@12A

+VDDCI

V

DD_08

@4A

+3VSDGPU

+

2000mA

+1.5VSDGPU

4

+1.5VSDGPU

T

T

T

itle

itle

itle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

ustom

ustom

ustom

Date: Sheet

Date: Sheet

Date: Sheet

VDD_GPIO33

1.8VSDGPU

VDD_18

T

SVDD

VMEMIO

720mA

V

RAM x4pcs

C

C

C

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

P

P

P

OWER MAP

OWER MAP

OWER MAP

F

F

F

H50P M/B LA-H901P

H50P M/B LA-H901P

H50P M/B LA-H901P

@0.01A

@1A

@0.013A

@2A

o

o

o

f

4 99Wednesday, May 15, 2019

f

4 99Wednesday, May 15, 2019

f

1

4 99Wednesday, May 15, 2019

1

1

1

A

A

A

5

A

MD Picasso Platform Power Sequence

A

C-IN G3 --> S0

+3VLP

ACIN

EC_ON

D D

+5VALW

ON/OFFBTN#

3

V_EN

+

3VALW

41.49ms

41.49ms

2.32ms, Tr = 555us

9.608us

197.4ms

93.85ms

1.124ms, Tr = 1.075ms

4

S

0 --> S3 S3 --> S0

3

2

1

S0 --> S5

+3VLP

ACIN

EC_ON

+5VALW

ON/OFFBTN#

8.190s

5.228ms, Tf = 4.973ms

3V_EN

+

3VALW

8.190s

8.190s

9.166ms

1.525ms, Tf = 9.252ms

0.9_1.8VALW_PWREN

+1.8VALW

+0.9VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

+2.5V

SUSP#

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_NB

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

APU_PCIE_RST#

APU_RST#

V

GA Sequence

P

E_GPIO1

+3VSDGPU

+1.8VSDGPU

0.9_1.8VALW_PWREN

+1.8VALW

+0.9VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

+2.5V

SUSP#

C C

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_SOC

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

APU_PCIE_RST#

B B

APU_RST#

V

GA Sequence

PE_GPIO1

+3VSDGPU

+1.8VSDGPU

93.9ms

2.560ms, Tr = 1.418ms

820.9us, Tr = 358us

199.4ms

99.42ms

5.422ms

132.6ms

168us

168us

119ms

721.4us, Tr = 193.8us

1.695ms, Tr = 1.431ms

19.85ms

643.7us, Tr = 540.1us

683.4us, Tr = 525.9us

321us, Tr = 205.1us

16us, Tr = 17.18us

19.92ms

39.66ms

335.9us, Tr = 132.1us 331.1us, Tr = 127.2us2.3ms, Tf = 2.246ms 2.221ms, Tf = 2.165us

19.77ms

2.186ms, Tr = 295.7us

2.212ms, Tr = 316.7us

2.393ms

41.59ms

15.02ms

10.39ms

12.24ms

21.36ms

1.93s

1.153ms, Tr = 955.4us

1.306ms

4.826ms

4.956ms

4.956ms

56.14ms

4.415ms. Tf = 4.407ms

33.12ms, Tf = 32.78ms

12.87ms, Tf = 12.59ms

2.716ms, Tf = 2.480ms 837.7us, Tf = 772.7us

60.86ms

60.92ms

90.80ms

339.7us, Tf = 267.5us

338.9us, Tf = 284.6us

27.25ms

11.1ms

77us, Tf = 266.8us

13.44ms, Tf = 3.396ms

20.48ms

696.6us, Tr = 591.2us

716.1us, Tr = 555.7us

327.7us, Tr = 211.1us

15.42us, Tr = 15.38us

19.34ms

39.45ms

19.77ms

2.190ms, Tr = 299.8us

2.210ms, Tr = 313.4us

2.391ms

41.56ms

15.10ms

10.61ms

12.64ms

21.60ms

211.1ms

1.31ms

4.837ms

4.92ms

4.92ms

1.158ms, Tr = 956.5us

4.496ms, Tr = 1.374ms4.470ms, Tr = 1.359ms

51.70ms

51.69ms

58.19ms

58.25ms

24.92ms

1

.575s

10.96ms

75.49us, Tf = 2.634ms

13.39ms, Tf = 3.463ms

7.537ms, Tf = 9.313ms

2.353ms, Tf = 38.51us

5.143ms, Tf = 20.32ms

6.756ms, Tf = 6.739ms

28.36ms, Tf = 28.04ms

13.95ms, Tf = 13.67ms

87.99ms

335.2us, Tf = 247.5us

329.9us, Tf = 273.3us

ssued Date

ssued Date

ssued Date

10.97ms

1.665ms, Tf = 19.63ms

653.5ms, Tf = 4.784ms

10.97ms

1.758ms, Tf = 17.78ms

C

C

C

ompal Secret Data

ompal Secret Data

2

2

2

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

2

ompal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

VGA_ON_B

+VDDCI

+VGA_CORE

DGPU_PWRGOOD

+1.5VSDGPU

PE_GPIO0

C

C

C

ompal Electronics, Inc.

ompal Electronics, Inc.

T

T

T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheetof

Date: Sheetof

Date: Sheetof

ompal Electronics, Inc.

itle

itle

itle

C

C

C

ustom

ustom

ustom

F

F

F

H50P M/B LA-H901P

H50P M/B LA-H901P

H50P M/B LA-H901P

1

P

P

P

OWER SEQUENCE

OWER SEQUENCE

OWER SEQUENCE

5 99Wednesday, May 15, 2019

5 99Wednesday, May 15, 2019

5 99Wednesday, May 15, 2019

1

1

1

VGA_ON_B

+

VDDCI

+VGA_CORE

DGPU_PWRGOOD

+1.5VSDGPU

PE_GPIO0

P

LT_RST_VGA# PLT_RST_VGA#

A A

5

5.351ms

6.218ms, Tr = 84.15us

6.218ms, Tr = 85.54us

6.174ms

772.6us, Tr = 416.8us 830.8us, Tr = 480.8us

139.7ms

5.036ms

4

11.1ms

1.652ms, Tf = 21.21ms

894us, Tf = 5.296ms

11.1ms

1.746ms, Tf = 18.06ms

5.354ms

6.173ms, Tr = 84.5us

6.173ms, Tr = 86.28us

6.216ms

96.42ms

5.032ms

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

A

A

5

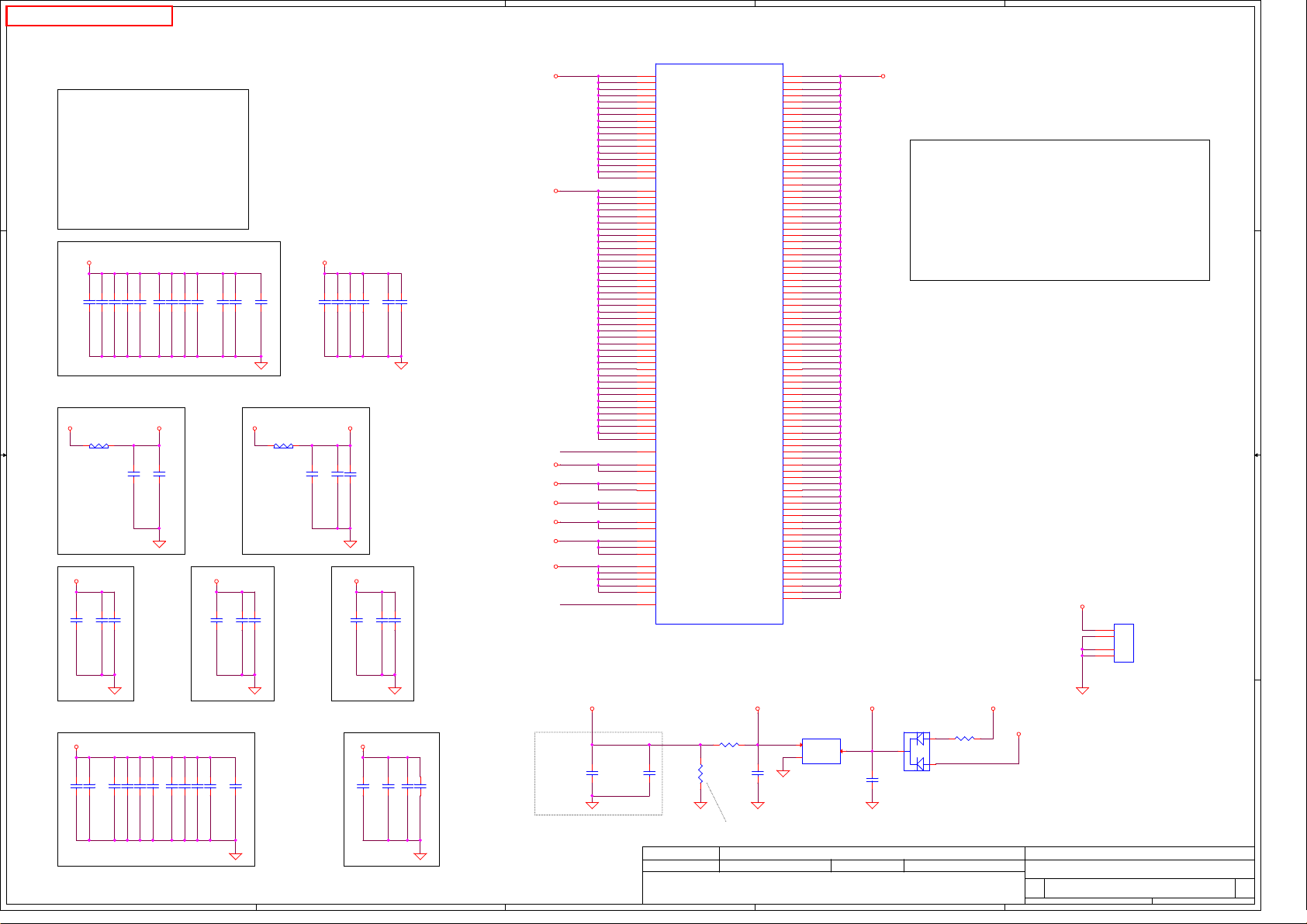

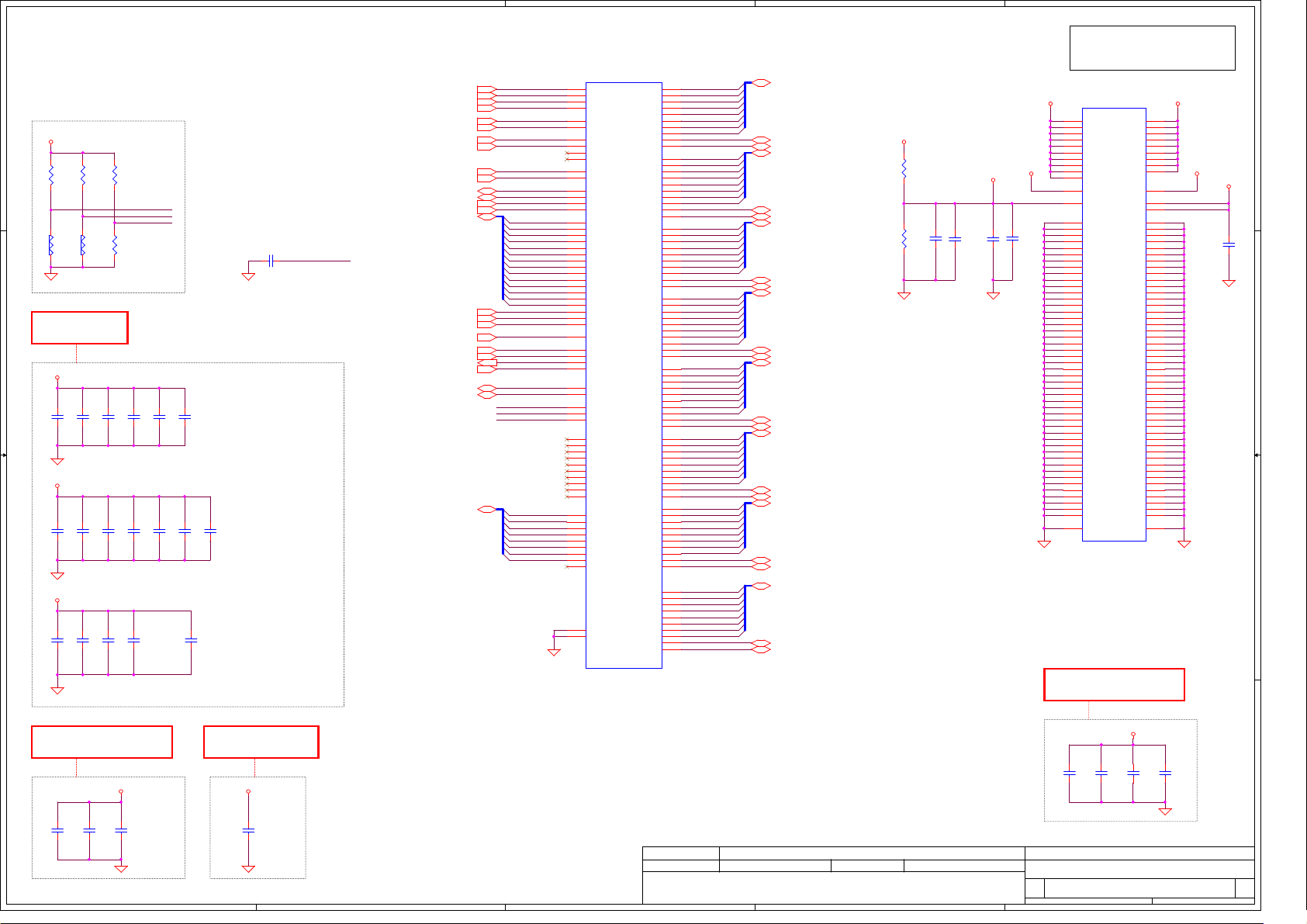

M

ain Func = CPU

4

3

2

1

UC1B

D D

P

EG_ARX_ GTX_P027

P

EG_ARX_ GTX_N027

P

EG_ARX_ GTX_P127

P

PEG

EG_ARX_ GTX_N127

P

EG_ARX_ GTX_P227

P

EG_ARX_ GTX_N227

P

EG_ARX_ GTX_P327

P

EG_ARX_ GTX_N327

P

EG_ARX_ GTX_P427

P

EG_ARX_ GTX_N427

P

EG_ARX_ GTX_P527

P

EG_ARX_ GTX_N527

P

EG_ARX_ GTX_P627

P

EG_ARX_ GTX_N627

P

EG_ARX_ GTX_P727

P

EG_ARX_ GTX_N727

EG_ARX_ GTX_P0

P

EG_ARX_ GTX_N0

P

EG_ARX_ GTX_P1

P

EG_ARX_ GTX_N1

P

EG_ARX_ GTX_P2

P

EG_ARX_ GTX_N2

P

EG_ARX_ GTX_P3

P

EG_ARX_ GTX_N3

P

EG_ARX_ GTX_P4

P

EG_ARX_ GTX_N4

P

EG_ARX_ GTX_P5

P

EG_ARX_ GTX_N5

P

EG_ARX_ GTX_P6

P

EG_ARX_ GTX_N6

P

EG_ARX_ GTX_P7

P

EG_ARX_ GTX_N7

P

P

8

P

_GFX_RXP0

P

9

P

_GFX_RXN0

N

6

P

_GFX_RXP1

N

7

P

_GFX_RXN1

M

8

P

_GFX_RXP2

M

9

P

_GFX_RXN2

L

6

P

_GFX_RXP3

L

7

P

_GFX_RXN3

K

11

P

_GFX_RXP4

J

11

P

_GFX_RXN4

H

6

P

_GFX_RXP5

H

7

P

_GFX_RXN5

G

6

P

_GFX_RXP6

F

7

P

_GFX_RXN6

G

8

P

_GFX_RXP7

F

8

P

_GFX_RXN7

PCIE

EG_ATX_ GRX_P0

P

1

N

_GFX_TXP0

P

_GFX_TXN0

P

_GFX_TXP1

P

_GFX_TXN1

P

_GFX_TXP2

P

_GFX_TXN2

P

_GFX_TXP3

P

_GFX_TXN3

P

_GFX_TXP4

P

_GFX_TXN4

P

_GFX_TXP5

P

_GFX_TXN5

P

_GFX_TXP6

P

_GFX_TXN6

P

_GFX_TXP7

P

_GFX_TXN7

P

3

N

2

M

4

M

2

L

4

L

1

L

3

L

2

K

4

K

2

J

4

J

1

H

3

H

2

H

4

H

EG_ATX_ GRX_N0

P

EG_ATX_ GRX_P1

P

EG_ATX_ GRX_N1

P

EG_ATX_ GRX_P2

P

EG_ATX_ GRX_N2

P

EG_ATX_ GRX_P3

P

EG_ATX_ GRX_N3

P

EG_ATX_ GRX_P4

P

EG_ATX_ GRX_N4

P

EG_ATX_ GRX_P5

P

EG_ATX_ GRX_N5

P

EG_ATX_ GRX_P6

P

EG_ATX_ GRX_N6

P

EG_ATX_ GRX_P7

P

EG_ATX_ GRX_N7

P

P

EG_ATX_ GRX_P0 27

P

EG_ATX_ GRX_N0 27

P

EG_ATX_ GRX_P1 27

P

EG_ATX_ GRX_N1 27

P

EG_ATX_ GRX_P2 27

P

EG_ATX_ GRX_N2 27

P

EG_ATX_ GRX_P3 27

P

EG_ATX_ GRX_N3 27

P

EG_ATX_ GRX_P4 27

P

EG_ATX_ GRX_N4 27

P

EG_ATX_ GRX_P5 27

P

EG_ATX_ GRX_N5 27

P

EG_ATX_ GRX_P6 27

P

EG_ATX_ GRX_N6 27

P

EG_ATX_ GRX_P7 27

P

EG_ATX_ GRX_N7 27

PEG

CIE_ARX_D TX_P0

P

C C

M.2 SSD1

LAN

WLAN

M.2 SSD2

B B

CIE_ARX_D TX_P068

P

CIE_ARX_D TX_N068

P

CIE_ARX_D TX_P168

P

CIE_ARX_D TX_N168

P

CIE_ARX_D TX_P268

P

CIE_ARX_D TX_N268

P

CIE_ARX_D TX_P368

P

CIE_ARX_D TX_N368

P

CIE_ARX_D TX_P451

P

CIE_ARX_D TX_N451

P

CIE_ARX_D TX_P552

P

CIE_ARX_D TX_N552

S

ATA_ARX _DTX_P067

S

ATA_ARX _DTX_N067

S

ATA_ARX _DTX_P169

S

ATA_ARX _DTX_N169

P

CIE_ARX_D TX_N0

P

CIE_ARX_D TX_P1

P

CIE_ARX_D TX_N1

P

CIE_ARX_D TX_P2

P

CIE_ARX_D TX_N2

P

CIE_ARX_D TX_P3

P

CIE_ARX_D TX_N3

P

CIE_ARX_D TX_P4

P

CIE_ARX_D TX_N4

P

CIE_ARX_D TX_P5

P

CIE_ARX_D TX_N5

P

ATA_ARX _DTX_P0

S

ATA_ARX _DTX_N0

S

ATA_ARX _DTX_P1

S

ATA_ARX _DTX_N1

S

N

10

P

_GPP_RXP0

N

9

P

_GPP_RXN0

L

10

P

_GPP_RXP1

L

9

P

_GPP_RXN1

L

12

P

_GPP_RXP2

M

11

P

_GPP_RXN2

P

12

P

_GPP_RXP3

P

11

P

_GPP_RXN3

V

6

P

_GPP_RXP4

V

7

P

_GPP_RXN4

T

8

P

_GPP_RXP5

T

9

P

_GPP_RXN5

R

6

P

_GPP_RXP6/SATA_RXP0

R

7

P

_GPP_RXN6/SATA_RXN0

R

9

P

_GPP_RXP7/SATA_RXP1

R

10

P

_GPP_RXN7/SATA_RXN1

@

FP5 REV 0.90

P

ART 2 OF 13

F

P5_BGA_ 1140P

_GPP_TXP0

P

_GPP_TXN0

P

_GPP_TXP1

P

_GPP_TXN1

P

_GPP_TXP2

P

P

_GPP_TXN2

P

_GPP_TXP3

P

_GPP_TXN3

P

_GPP_TXP4

P

_GPP_TXN4

P

_GPP_TXP5

P

_GPP_TXN5

P

_GPP_TXP6/SATA_TXP0

P

_GPP_TXN6/SATA_TXN0

P

_GPP_TXP7/SATA_TXP1

P

_GPP_TXN7/SATA_TXN1

2

N

3

P

4

P

2

P

3

R

R

1

T

4

T

2

W

2

W

4

W

3

V

2

V

1

V

3

U

2

U

4

CIE_ATX_D RX_P0

P

CIE_ATX_D RX_N0

P

CIE_ATX_D RX_P1

P

CIE_ATX_D RX_N1

P

CIE_ATX_D RX_P2

P

CIE_ATX_D RX_N2

P

CIE_ATX_D RX_P3

P

CIE_ATX_D RX_N3

P

CIE_ATX_D RX_P4

P

CIE_ATX_D RX_N4

P

CIE_ATX_D RX_P5

P

CIE_ATX_D RX_N5

P

ATA_ATX _DRX_P0

S

ATA_ATX _DRX_N0

S

ATA_ATX _DRX_P1

S

ATA_ATX _DRX_N1

S

1 2

C1204 0.22U_04 02_16V7K

C

1 2

C1203 0.22U_04 02_16V7K

C

1 2

C

C1206 0.22U_04 02_16V7K

C

C1205 0.22U_04 02_16V7K

C1212 0.22U_04 02_16V7K

C

C1211 0.22U_04 02_16V7K

C

C1214 0.22U_04 02_16V7K

C

C1213 0.22U_04 02_16V7K

C

2

1

2

1

2

1

2

1

2

1

2

1

C1 .1U_ 0402_16V7K

C

2

1

C2 .1U_ 0402_16V7K

C

2

1

C3 .1U_ 0402_16V7K

C

2

1

C4 .1U_ 0402_16V7K

C

P

CIE_ATX_C _DRX_P0 68

P

CIE_ATX_C _DRX_N0 68

P

CIE_ATX_C _DRX_P1 68

P

CIE_ATX_C _DRX_N1 68

P

CIE_ATX_C _DRX_P2 68

P

CIE_ATX_C _DRX_N2 68

P

CIE_ATX_C _DRX_P3 68

P

CIE_ATX_C _DRX_N3 68

P

CIE_ATX_C _DRX_P4 51

P

CIE_ATX_C _DRX_N4 51

P

CIE_ATX_C _DRX_P5 52

P

CIE_ATX_C _DRX_N5 52

S

ATA_ATX _DRX_P0 67

S

ATA_ATX _DRX_N0 67

S

ATA_ATX _DRX_P1 69

S

ATA_ATX _DRX_N1 69

M.2 SSD1

LAN

WLAN

HDDHDD

M.2 SSD2

APU PN Table

A

PU Platform

C1 R7APU@

U

IC RYZEN7 YM3700C4T4MFG 2.3G APU AB O!

S

A0000C7680

S

P

icasso

U

C1 R5APUQC@

S

IC RYZEN5 YM3500C4T4MFG 2.1G BGA AP U

S

A0000CCR20

U

C1 R7APUQC@

S

IC RYZEN7 YM3700C4T4MFG 2.3G BGA AP U

S

A0000C7640

U

C1 R5APU@

S

IC RYZEN5 YM3500C4T4MFG 2.1G APU AB O!

S

A0000CCR60

PCB Number

A A

ZZ

EVT@

Z

PCB 2QE L A-H901P REV0 MB 2

DA8001J M000

Z

ZZ

PVT@

PCB FH50 P LA-H901P LS-H9 01P/H502P

DAZ2QE0 0100

P

CB: DAZ2QE00100, DA8001JM010 REV: 1.0/1.0/1.0

ZZ

MP@

Z

PCB FH50 P LA-H901P LS-H9 01P/H502P

DAZ2QE0 0101

PCB: DAZ2QE00101, DA8001JM01A REV: 1.A/1.0/1.0

5

S

S

S

ecurity Classif ication

ecurity Classif ication

ecurity Classif ication

2

2

2

018/ 12/1 8 2019/12/18

018/ 12/1 8 2019/12/18

I

I

I

ssued Date

ssued Date

ssued Date

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

018/ 12/1 8 2019/12/18

3

C

C

C

ompal Secret Data

ompal Secret Data

ompal Secret Data

D

D

D

eciphered D ate

eciphered D ate

eciphered D ate

Compal PNCustomer PNCustomer PNCustomer PNCustomer PN Compal PN

C

C

T

T

Title

itle

itle

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

C

C

C

ustom

ustom

ustom

Date: Sheet

Date: Sheet

2

Date: Sheet

C

F

F

F

P5_(1/7)_PEG/PCIE/SATA

P5_(1/7)_PEG/PCIE/SATA

P5_(1/7)_PEG/PCIE/SATA

F

F

F

H50P M/B LA-H901P

H50P M/B LA-H901P

H50P M/B LA-H901P

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

6 99Wednesd ay, May 15, 2019

6 99Wednesd ay, May 15, 2019

6 99Wednesd ay, May 15, 2019

1

1

1

1

A

A

A

o

o

o

f

f

f

5

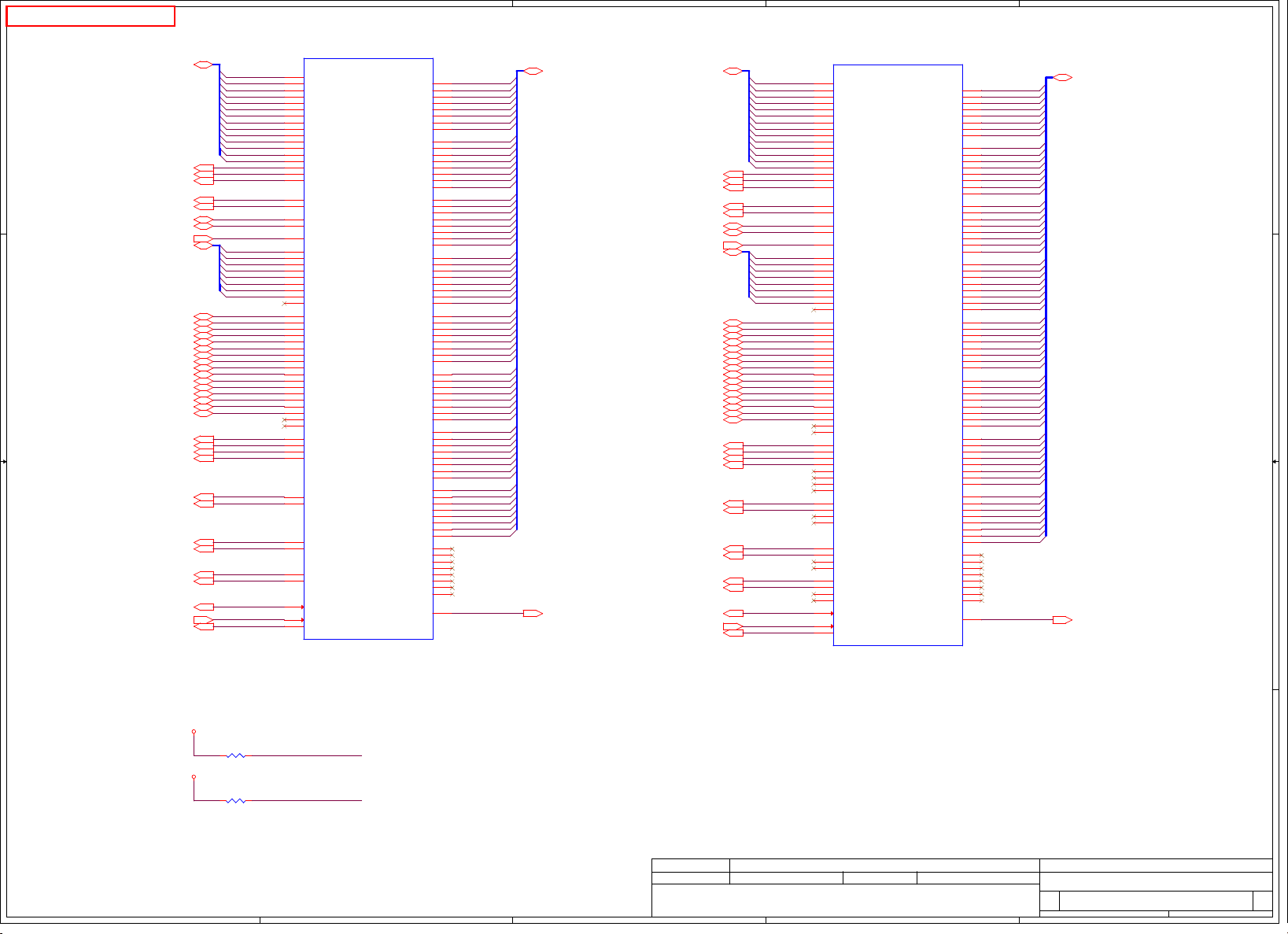

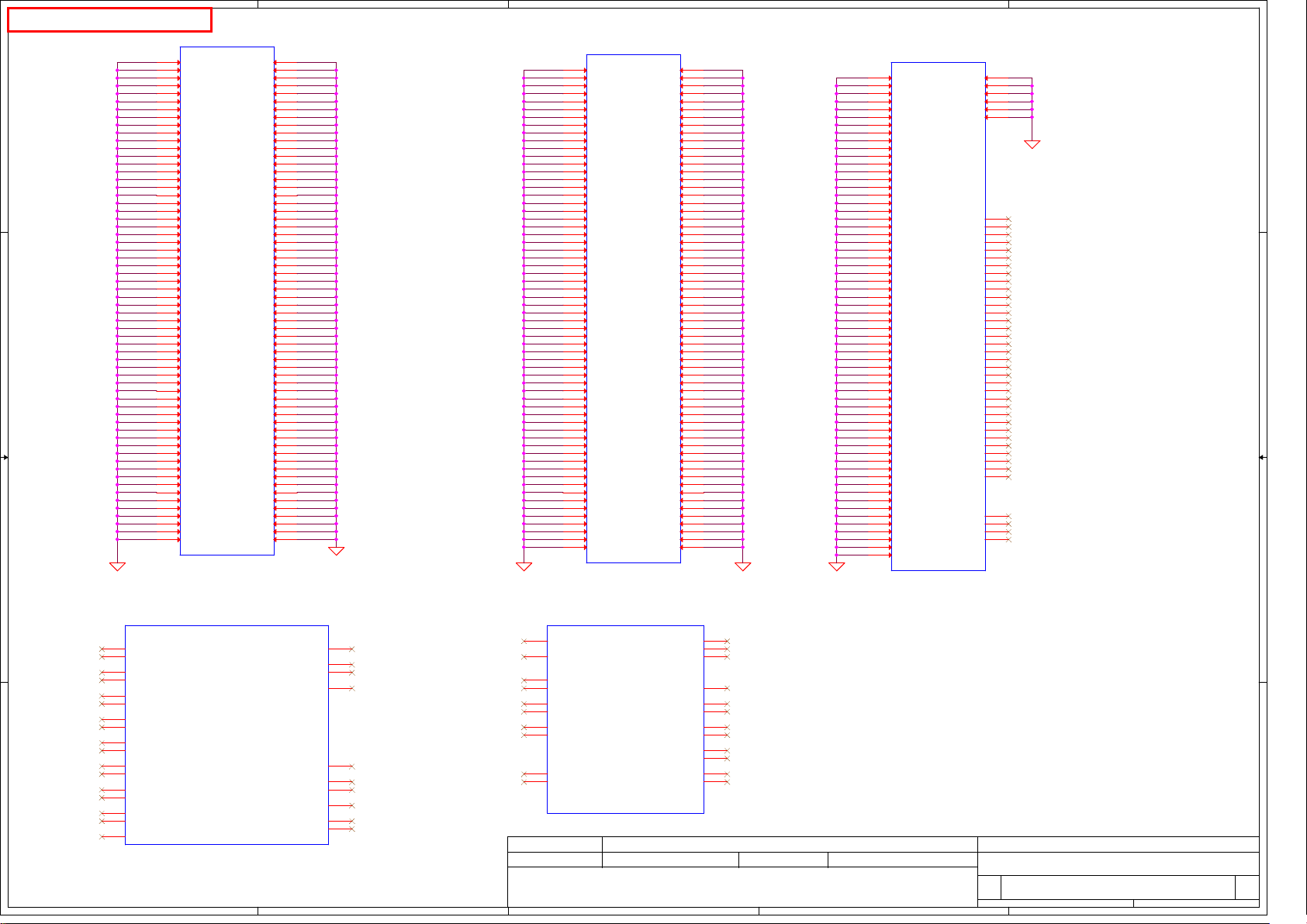

M

ain Func = CPU

4

3

2

1

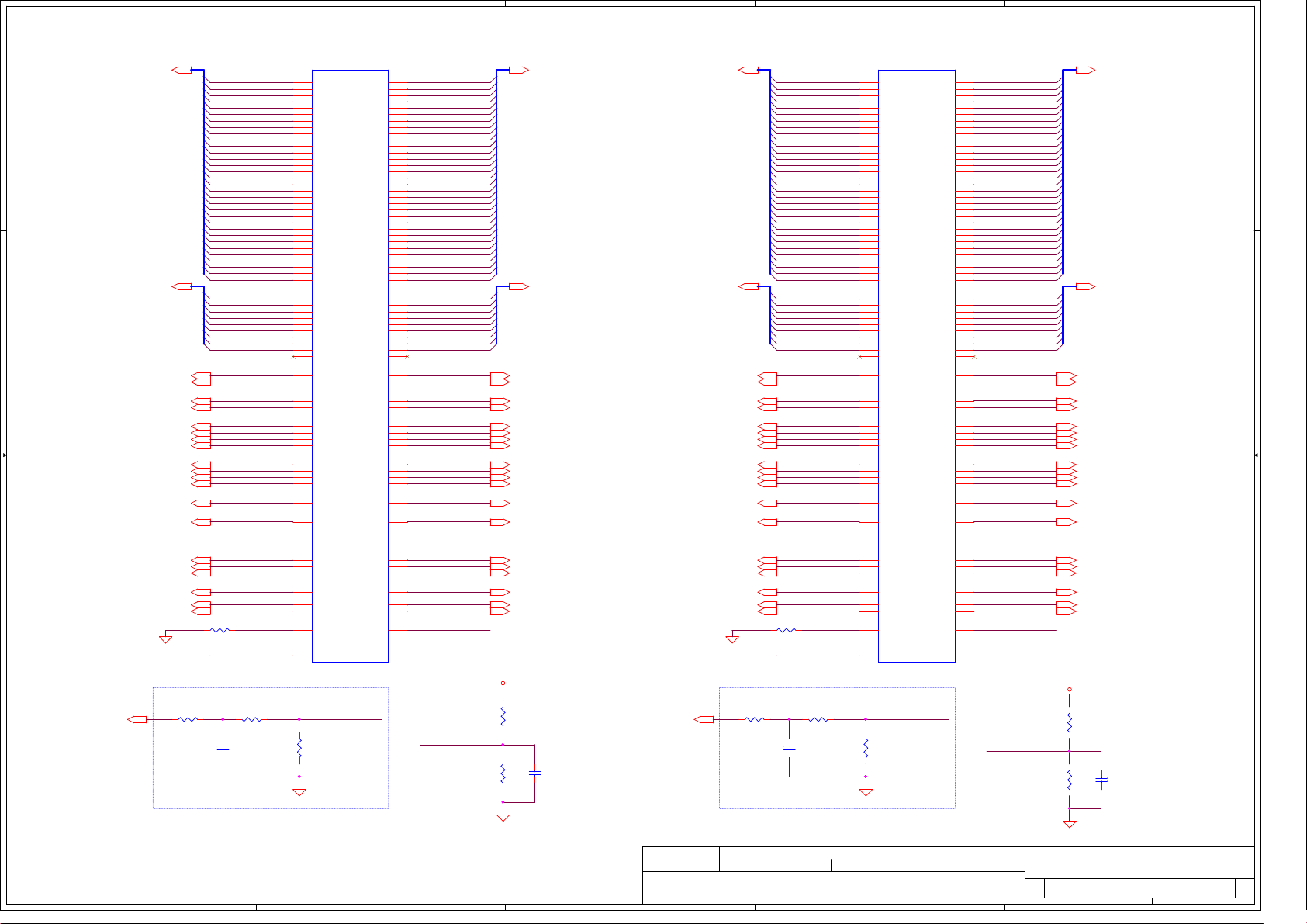

MEMORY B

FP5 REV 0.90

ART 9 OF 13

P

P5_BGA_1140P

F

UC1I

M

M

M

M

M

M

M

M

M

M

M

B_DATA10

M

B_DATA11

M

B_DATA12

M

B_DATA13

M

B_DATA14

M

B_DATA15

M

B_DATA16

M

B_DATA17

M

B_DATA18

M

B_DATA19

M

B_DATA20

M

B_DATA21

M

B_DATA22

M

B_DATA23

M

B_DATA24

M

B_DATA25

M

B_DATA26

M

B_DATA27

M

B_DATA28

M

B_DATA29

M

B_DATA30

M

B_DATA31

M

B_DATA32

M

B_DATA33

M

B_DATA34

M

B_DATA35

M

B_DATA36

M

B_DATA37

M

B_DATA38

M

B_DATA39

M

B_DATA40

M

B_DATA41

M

B_DATA42

M

B_DATA43

M

B_DATA44

M

B_DATA45

M

B_DATA46

M

B_DATA47

M

B_DATA48

M

B_DATA49

M

B_DATA50

M

B_DATA51

M

B_DATA52

M

B_DATA53

M

B_DATA54

M

B_DATA55

M

B_DATA56

M

B_DATA57

M

B_DATA58

M

B_DATA59

M

B_DATA60

M

B_DATA61

M

B_DATA62

M

B_DATA63

M

B_PAROUT

B_DATA0

B_DATA1

B_DATA2

B_DATA3

B_DATA4

B_DATA5

B_DATA6

B_DATA7

B_DATA8

B_DATA9

R

SVD_17

R

SVD_19

R

SVD_26

R

SVD_29

R

SVD_16

R

SVD_15

R

SVD_25

R

SVD_24

D

DR_B_DQ0

D

B

21

DR_B_DQ1

D

D

21

DR_B_DQ2

D

B

23

DR_B_DQ3

D

D

23

DR_B_DQ4

D

A

20

DR_B_DQ5

D

C

20

DR_B_DQ6

D

A

22

DR_B_DQ7

D

C

22

DR_B_DQ8

D

D

24

DR_B_DQ9

D

A

25

DR_B_DQ10

D

D

27

DR_B_DQ11

D

C

27

DR_B_DQ12

D

C

23

DR_B_DQ13

D

B

24

DR_B_DQ14

D

C

26

DR_B_DQ15

D

B

27

D

DR_B_DQ16

C

30

DR_B_DQ17

D

E

29

DR_B_DQ18

D

H

29

DR_B_DQ19

D

H

31

DR_B_DQ20

D

A

28

DR_B_DQ21

D

D

28

DR_B_DQ22

D

F

31

DR_B_DQ23

D

G

30

DR_B_DQ24

D

J

29

DR_B_DQ25

D

J

31

DR_B_DQ26

D

L

29

DR_B_DQ27

D

L

31

DR_B_DQ28

D

H

30

DR_B_DQ29

D

H

32

DR_B_DQ30

D

L

30

DR_B_DQ31

D

L

32

DR_B_DQ32

D

A

P29

DR_B_DQ33

D

A

P32

DR_B_DQ34

D

A

T29

DR_B_DQ35

D

A

U32

DR_B_DQ36

D

A

N30

DR_B_DQ37

D

A

P31

DR_B_DQ38

D

A

R30

DR_B_DQ39

D

A

T31

DR_B_DQ40

D

A

U29

DR_B_DQ41

D

A

V30

DR_B_DQ42

D

B

B30

DR_B_DQ43

D

B

A28

DR_B_DQ44

D

A

U30

DR_B_DQ45

D

A

U31

DR_B_DQ46

D

A

Y32

DR_B_DQ47

D

A

Y29

DR_B_DQ48

D

B

A27

DR_B_DQ49

D

B

C27

DR_B_DQ50

D

B

A24

DR_B_DQ51

D

B

C24

DR_B_DQ52

D

B

D28

DR_B_DQ53

D

B

B27

DR_B_DQ54

D

B

B25

DR_B_DQ55

D

B

D25

DR_B_DQ56

D

B

C23

DR_B_DQ57

D

B

B22

DR_B_DQ58

D

B

C21

DR_B_DQ59

D

B

D20

DR_B_DQ60

D

B

B23

DR_B_DQ61

D

B

A23

DR_B_DQ62

D

B

B21

DR_B_DQ63

D

B

A21

M

31

N

30

P

31

R

32

M

30

M

29

P

30

P

29

DR_B_PAR

D

A

G31

DR_B_DQ[63..0] 24

D

DR_B_PAR 24

UC1A

D

DR_A_MA[13..0]23

D D

D

DR_A_MA14_W E#23

D

DR_A_MA15_CAS#23

D

DR_A_MA16_RAS#23

D

DR_A_BA023

D

DR_A_BA123

D

DR_A_BG023

D

DR_A_BG123

D

DR_A_ACT#23

D

DR_A_DM[7..0]23

D

DR_A_DQS023

D

DR_A_DQS0#23

D

DR_A_DQS123

D

DR_A_DQS1#23

D

DR_A_DQS223

D

C C

B B

DR_A_DQS2#23

D

DR_A_DQS323

D

DR_A_DQS3#23

D

DR_A_DQS423

D

DR_A_DQS4#23

D

DR_A_DQS523

D

DR_A_DQS5#23

D

DR_A_DQS623

D

DR_A_DQS6#23

D

DR_A_DQS723

D

DR_A_DQS7#23

D

DR_A_CLK023

D

DR_A_CLK0#23

D

DR_A_CLK123

D

DR_A_CLK1#23

D

DR_A_CS0#23

D

DR_A_CS1#23

D

DR_A_CKE023

D

DR_A_CKE123

D

DR_A_ODT023

D

DR_A_ODT123

D

DR_A_ALERT#23

D

DR_A_EVENT#23

D

DR_A_RST#2 3

D

DR_A_MA0

D

DR_A_MA1

D

DR_A_MA2

D

DR_A_MA3

D

DR_A_MA4

D

DR_A_MA5

D

DR_A_MA6

D

DR_A_MA7

D

DR_A_MA8

D

DR_A_MA9

D

DR_A_MA10

D

DR_A_MA11

D

DR_A_MA12

D

DR_A_MA13

D

DR_A_MA14_W E#

D

DR_A_MA15_CAS#

D

DR_A_MA16_RAS#

D

DR_A_BA0

D

DR_A_BA1

DR_A_BG0

D

DR_A_BG1

D

DR_A_ACT#

D

D

DR_A_DM0

D

DR_A_DM1

D

DR_A_DM2

D

DR_A_DM3

D

DR_A_DM4

D

DR_A_DM5

D

DR_A_DM6

D

DR_A_DM7

D

DR_A_DQS0

D

DR_A_DQS0#

D

DR_A_DQS1

D

DR_A_DQS1#

D

DR_A_DQS2

D

DR_A_DQS2#

D

DR_A_DQS3

D

DR_A_DQS3#

D

DR_A_DQS4

D

DR_A_DQS4#

D

DR_A_DQS5

D

DR_A_DQS5#

D

DR_A_DQS6

D

DR_A_DQS6#

D

DR_A_DQS7

D

DR_A_DQS7#

D

DR_A_CLK0

D

DR_A_CLK0#

D

DR_A_CLK1

D

DR_A_CLK1#

D

DR_A_CS0#

D

DR_A_CS1#

D

DR_A_CKE0

D

DR_A_CKE1

D

DR_A_ODT0

D

DR_A_ODT1

D

DR_A_ALERT#

D

DR_A_EVENT#

D

DR_A_RST#

F25

A

A_ADD0

M

E23

A

A_ADD1

M

D27

A

A_ADD2

M

E21

A

A_ADD3

M

C24

A

A_ADD4

M

C26

A

A_ADD5

M

D21

A

A_ADD6

M

C27

A

A_ADD7

M

D22

A

A_ADD8

M

C21

A

A_ADD9

M

F22

A

A_ADD10

M

A24

A

A_ADD11

M

C23

A

A_ADD12

M

J25

A

A_ADD13_BANK2

M

G27

A

A_WE_L_ADD14

M

G23

A

A_CAS_L_ADD15

M

G26

A

A_RAS_L_ADD16

M

F21

A

A_BANK0

M

F27

A

A_BANK1

M

A21

A

A_BG0

M

A27

A

A_BG1

M

A22

A

A_ACT_L

M

21

F

A_DM0

M

27

G

A_DM1

M

24

N

A_DM2

M

23

N

A_DM3

M

L24

A

A_DM4

M

N27

A

A_DM5

M

W25

A

A_DM6

M

T21

A

A_DM7

M

T

27

R

SVD_36

F

22

M

A_DQS_H0

G

22

M

A_DQS_L0

H

27

M

A_DQS_H1

H

26

M

A_DQS_L1

N

27

M

A_DQS_H2

N

26

M

A_DQS_L2

R

21

M

A_DQS_H3

P

21

M

A_DQS_L3

A

M26

M

A_DQS_H4

A

M27

M

A_DQS_L4

A

N24

M

A_DQS_H5

A

N25

M

A_DQS_L5

A

U23

M

A_DQS_H6

A

T23

M

A_DQS_L6

A

V20

M

A_DQS_H7

A

W20

M

A_DQS_L7

V

24

R

SVD_41

V

23

R

SVD_40

A

D25

M

A_CLK_H0

A

D24

M

A_CLK_L0

A

E26

M

A_CLK_H1

A

E27

M

A_CLK_L1

A

G21

M

A_CS_L0

A

J27

M

A_CS_L1

Y

23

M

A_CKE0

Y

26

M

A_CKE1

A

G24

M

A_ODT0

A

J22

M

A_ODT1

A

A25

M

A_ALERT_L

A

E24

M

A_EVENT_L

Y

24

M

A_RESET_L

@

MEMORY A

FP5 REV 0.90

P

ART 1 OF 13

F

P5_BGA_1140P

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

A_PAROUT

M

A_DATA0

A_DATA1

A_DATA2

A_DATA3

A_DATA4

A_DATA5

A_DATA6

A_DATA7

A_DATA8

A_DATA9

A_DATA10

A_DATA11

A_DATA12

A_DATA13

A_DATA14

A_DATA15

A_DATA16

A_DATA17

A_DATA18

A_DATA19

A_DATA20

A_DATA21

A_DATA22

A_DATA23

A_DATA24

A_DATA25

A_DATA26

A_DATA27

A_DATA28

A_DATA29

A_DATA30

A_DATA31

A_DATA32

A_DATA33

A_DATA34

A_DATA35

A_DATA36

A_DATA37

A_DATA38

A_DATA39

A_DATA40

A_DATA41

A_DATA42

A_DATA43

A_DATA44

A_DATA45

A_DATA46

A_DATA47

A_DATA48

A_DATA49

A_DATA50

A_DATA51

A_DATA52

A_DATA53

A_DATA54

A_DATA55

A_DATA56

A_DATA57

A_DATA58

A_DATA59

A_DATA60

A_DATA61

A_DATA62

A_DATA63

SVD_34

R

SVD_35

R

SVD_51

R

SVD_52

R

SVD_27

R

SVD_28

R

SVD_43

R

SVD_42

R

D

D

DR_A_DQ0

21

J

DR_A_DQ1

D

21

H

DR_A_DQ2

D

23

F

D

DR_A_DQ3

23

H

D

DR_A_DQ4

20

G

DR_A_DQ5

D

20

F

DR_A_DQ6

D

22

J

DR_A_DQ7

D

23

J

DR_A_DQ8

D

25

G

DR_A_DQ9

D

26

F

DR_A_DQ10

D

24

L

DR_A_DQ11

D

26

L

DR_A_DQ12

D

23

L

D

DR_A_DQ13

25

F

DR_A_DQ14

D

25

K

DR_A_DQ15

D

27

K

DR_A_DQ16

D

25

M

DR_A_DQ17

D

27

M

DR_A_DQ18

D

27

P

D

DR_A_DQ19

24

R

DR_A_DQ20

D

27

L

DR_A_DQ21

D

24

M

DR_A_DQ22

D

24

P

DR_A_DQ23

D

25

P

DR_A_DQ24

D

22

M

DR_A_DQ25

D

21

N

DR_A_DQ26

D

22

T

DR_A_DQ27

D

21

V

D

DR_A_DQ28

21

L

D

DR_A_DQ29

20

M

DR_A_DQ30

D

23

R

DR_A_DQ31

D

21

T

DR_A_DQ32

D

L27

A

DR_A_DQ33

D

L25

A

D

DR_A_DQ34

P26

A

DR_A_DQ35

D

R27

A

D

DR_A_DQ36

K26

A

DR_A_DQ37

D

K24

A

DR_A_DQ38

D

M24

A

D

DR_A_DQ39

P27

A

D

DR_A_DQ40

M23

A

DR_A_DQ41

D

M21

A

DR_A_DQ42

D

R25

A

D

DR_A_DQ43

U27

A

DR_A_DQ44

D

L22

A

DR_A_DQ45

D

L21

A

D

DR_A_DQ46

P24

A

D

DR_A_DQ47

P23

A

DR_A_DQ48

D

W26

A

DR_A_DQ49

D

V25

A

DR_A_DQ50

D

V22

A

DR_A_DQ51

D

W22

A

DR_A_DQ52

D

U26

A

DR_A_DQ53

D

V27

A

DR_A_DQ54

D

W23

A

DR_A_DQ55

D

T22

A

DR_A_DQ56

D

W21

A

DR_A_DQ57

D

U21

A

DR_A_DQ58

D

P21

A

D

DR_A_DQ59

N20

A

D

DR_A_DQ60

R22

A

D

DR_A_DQ61

N22

A

DR_A_DQ62

D

T20

A

DR_A_DQ63

D

R20

A

24

T

25

T

25

W

27

W

26

R

27

R

27

V

26

V

DR_A_PAR

D

F24

A

DR_A_DQ[63..0] 23

D

DR_A_PAR 23

D

DR_B_MA[13..0]24

D

DR_B_MA14_W E#24

D

DR_B_MA15_C AS#24

D

DR_B_MA16_R AS#24

D

DR_B_BA024

D

DR_B_BA124

D

DR_B_BG024

D

DR_B_BG124

D

DR_B_ACT#2 4

D

DR_B_DM[7..0]24

D

DR_B_DQS024

D

DR_B_DQS0#24

D

DR_B_DQS124

D

DR_B_DQS1#24

D

DR_B_DQS224

D

DR_B_DQS2#24

D

DR_B_DQS324

D

DR_B_DQS3#24

D

DR_B_DQS424

D

DR_B_DQS4#24

D

DR_B_DQS524

D

DR_B_DQS5#24

D

DR_B_DQS624

D

DR_B_DQS6#24

D

DR_B_DQS724

D

DR_B_DQS7#24

D

DR_B_CLK024

D

DR_B_CLK0#24

D

DR_B_CLK124

D

DR_B_CLK1#24

D

DR_B_CS0#24

D

DR_B_CS1#24

D

DR_B_CKE024

D

DR_B_CKE124

D

DR_B_ODT024

D

DR_B_ODT124

D

DR_B_ALERT#24

D

DR_B_EVENT#24

D

DR_B_RST#2 4

DR_B_MA0

D

DR_B_MA1

D

DR_B_MA2

D

DR_B_MA3

D

DR_B_MA4

D

DR_B_MA5

D

DR_B_MA6

D

DR_B_MA7

D

DR_B_MA8

D

DR_B_MA9

D

DR_B_MA10

D

DR_B_MA11

D

DR_B_MA12

D

DR_B_MA13

D

D

DR_B_MA14_W E#

D

DR_B_MA15_C AS#

D

DR_B_MA16_R AS#

D

DR_B_BA0

D

DR_B_BA1

DR_B_BG0

D

DR_B_BG1

D

DR_B_ACT#

D

DR_B_DM0

D

DR_B_DM1

D

DR_B_DM2

D

DR_B_DM3

D

DR_B_DM4

D

DR_B_DM5

D

DR_B_DM6

D

DR_B_DM7

D

D

DR_B_DQS0

D

DR_B_DQS0#

D

DR_B_DQS1

D

DR_B_DQS1#

D

DR_B_DQS2

D

DR_B_DQS2#

D

DR_B_DQS3

D

DR_B_DQS3#

D

DR_B_DQS4

D

DR_B_DQS4#

D

DR_B_DQS5

D

DR_B_DQS5#

D

DR_B_DQS6

D

DR_B_DQS6#

D

DR_B_DQS7

D

DR_B_DQS7#

D

DR_B_CLK0

D

DR_B_CLK0#

D

DR_B_CLK1

D

DR_B_CLK1#

D

DR_B_CS0#

D

DR_B_CS1#

D

DR_B_CKE0

D

DR_B_CKE1

DR_B_ODT0

D

DR_B_ODT1

D

DR_B_ALERT#

D

DR_B_EVENT#

D

DR_B_RST#

D

A

G30

M

B_ADD0

A

C32

M

B_ADD1

A

C30

M

B_ADD2

A

B29

M

B_ADD3

A

B31

M

B_ADD4

A

A30

M

B_ADD5

A

A29

M

B_ADD6

Y

30

M

B_ADD7

A

A31

M

B_ADD8

W

29

M

B_ADD9

A

H29

M

B_ADD10

Y

32

M

B_ADD11

W

31

M

B_ADD12

A

L30

M

B_ADD13_BANK2

A

K30

M

B_WE_L_ADD14

A

K32

M

B_CAS_L_ADD15

A

J30

M

B_RAS_L_ADD16

A

H31

M

B_BANK0

A

G32

M

B_BANK1

V

31

M

B_BG0

V

29

M

B_BG1

V

30

M

B_ACT_L

C

21

M

B_DM0

C

25

M

B_DM1

E

32

M

B_DM2

K

30

M

B_DM3

A

P30

M

B_DM4

A

W31

M

B_DM5

B

B26

M

B_DM6

B

D22

M

B_DM7

N

32

R

SVD_21

D

22

M

B_DQS_H0

B

22

M

B_DQS_L0

D

25

M

B_DQS_H1

B

25

M

B_DQS_L1

F

29

B_DQS_H2

M

F

30

B_DQS_L2

M

K

31

M

B_DQS_H3

29

K

B_DQS_L3

M

R29

A

B_DQS_H4

M

R31

A

B_DQS_L4

M

W30

A

B_DQS_H5

M

W29

A

B_DQS_L5

M

C25

B

B_DQS_H6

M

A25

B

B_DQS_L6

M

C22

B

B_DQS_H7

M

A22

B

B_DQS_L7

M

31

N

SVD_20

R

29

N

SVD_18

R

C31

A

B_CLK_H0

M

D30

A

B_CLK_L0

M

D29

A

B_CLK_H1

M

D31

A

B_CLK_L1

M

E30

A

B_CLK_H2

M

E32

A

B_CLK_L2

M

F29

A

B_CLK_H3

M

F31

A

B_CLK_L3

M

J31

A

B0_CS_L0

M

M31

A

B0_CS_L1

M

J29

A

B1_CS_L0

M

M29

A

B1_CS_L1

M

29

U

B0_CKE0

M

30

T

B0_CKE1

M

32

V

B1_CKE0

M

31

U

B1_CKE1

M

L31

A

B0_ODT0

M

M32

A

B0_ODT1

M

L29

A

B1_ODT0

M

M30

A

B1_ODT1

M

30

W

B_ALERT_L

M

G29

A

B_EVENT_L

M

31

T

B_RESET_L

M

@

E

VENT# pull high

+

1.2V

D

1 2

C1 1K_0402_5%

R

+

1.2V

1 2

C2 1K_0402_5%

A A

5

R

DR_B_EVENT#

DR_A_EVENT#

D

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

ssued Date

ssued Date

ssued Date

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

2

2

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

C

C

C

ompal Secret Data

ompal Secret Data

ompal Secret Data

D

D

D

eciphered Date

eciphered Date

eciphered Date

C

C

C

ompal Electronics, Inc.

ompal Electronics, Inc.

T

T

T

itle

itle

itle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

ustom

ustom

ustom

Date: Sheet

Date: Sheet

2

Date: Sheet

ompal Electronics, Inc.

F

F

F

P5_(2/7)_DDR4

P5_(2/7)_DDR4

P5_(2/7)_DDR4

F

F

F

H50P M/B LA-H901P

H50P M/B LA-H901P

H50P M/B LA-H901P

1

7 99Wednesday, May 15, 201 9

1

1

1

A

A

A

o

o

o

f

7 99Wednesday, May 15, 201 9

f

7 99Wednesday, May 15, 201 9

f

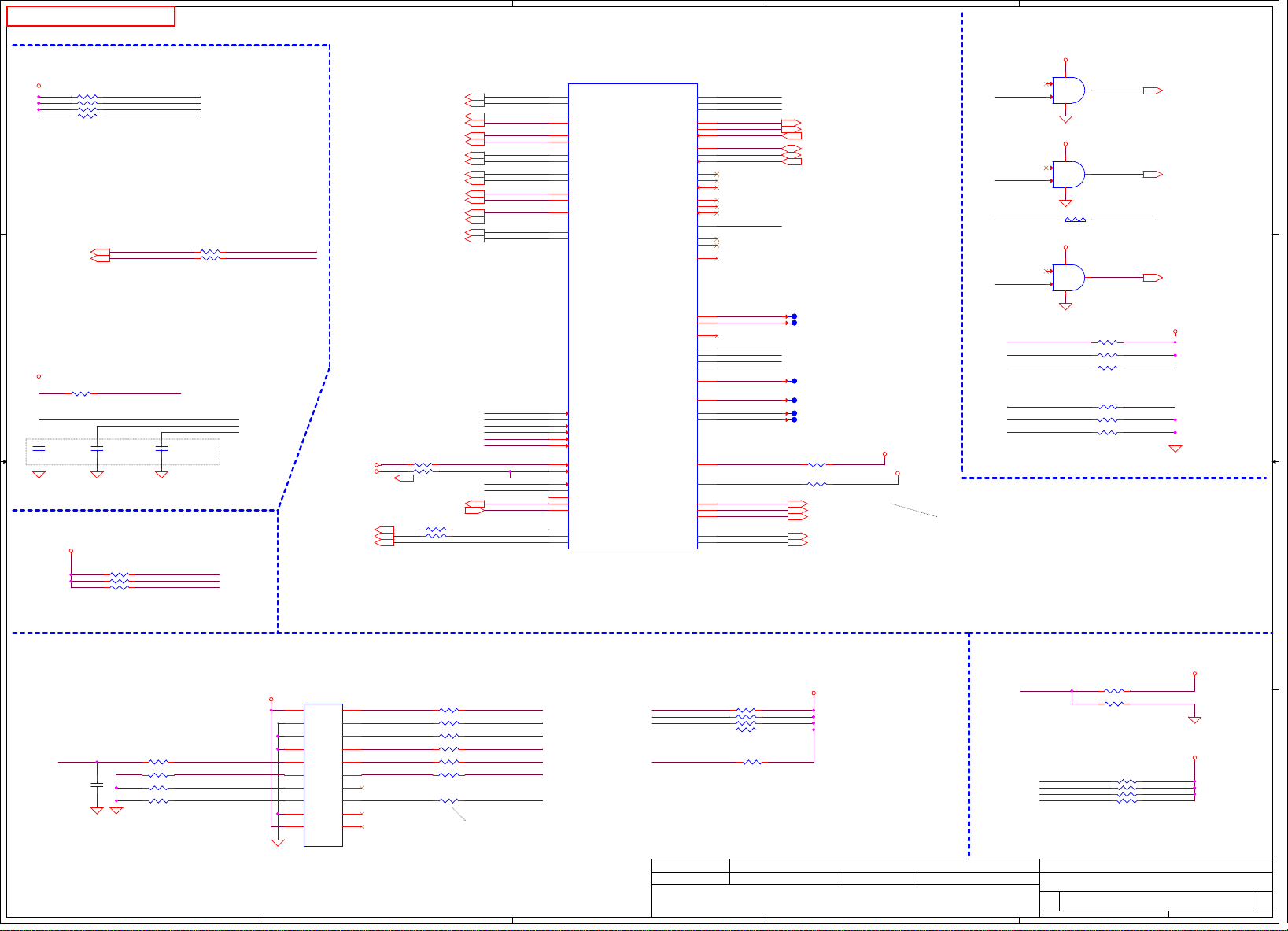

A

M

ain Func = CPU

EC/THERM

+

3VS

C105 1K_0402_ 5%

R

C106 1K_0402_ 5%

R

C107 1K_0402_ 5%

R

C108 1K_0402_ 5%

R

1 1

E

C_SMB_CK228,58,66

E

C_SMB_DA228,58,66

2 2

+

3VS

R

C664 1K_0402_5%

1

@EMC@

C1202

C

.1U_0402_1 6V7K

2

1

1 2

1 2

1 2

1

2

2

1

EMC@

C5

C

33P_0402_5 0V8J

2

C_SMB_CK2

E

C_SMB_DA2

E

A

PU_SID

A

PU_ALERT#

A

PU_SIC

A

PU_PROCHOT #

1 2

C616 0_0402_ 5%

R

1 2

R

C617 0_0402_ 5%

T

HERMTRIP#

1

EMC@

C

C6

33P_0402_5 0V8J

2

A

PU_PROCHOT #

A

PU_RST#

A

PU_PWROK

PU_SIC

A

PU_SID

A

Close to APU

SVID

+

1.8VS

A

1

1 2

1

2

2

C109 1K_0402_ 5%@

3 3

R

C110 1K_0402_ 5%@

R

C111 1K_0402_ 5%@

R

PU_SVT_R

A

PU_SVC

A

PU_SVD

A

B

A

A

PU_DP0_P040

A

PU_DP0_N040

A

PU_DP0_P140

A

H

DMI

EDP

+

1.8VS

+

1.8VS

A

PU_PWROK88

A

PU_SVC88

A

PU_SVD88

PU_SVT_R88

PU_DP0_N140

A

PU_DP0_P240

A

PU_DP0_N240

A

PU_DP0_P340

A

PU_DP0_N340

E

DP_TXP03 8

E

DP_TXN038

E

DP_TXP13 8

E

DP_TXN138

E

DP_TXP23 8

E

DP_TXN238

E

DP_TXP33 8

E

DP_TXN338

1 2

C80 300_0402_5%

R

R

2

1

C81 300_0402_5%

T

HERMTRIP#58

A

PU_PROCHOT #58,84,88

1 2

C669 0_0402_5%

R

1 2

C670 0_0402_5%

R

PU_DP0_P0

A

PU_DP0_N0

A

PU_DP0_P1

A

PU_DP0_N1

A

PU_DP0_P2

A

PU_DP0_N2

A

PU_DP0_P3

A

PU_DP0_N3

E

DP_TXP0

E

DP_TXN0

E

DP_TXP1

E

DP_TXN1

E

DP_TXP2

E

DP_TXN2

E

DP_TXP3

E

DP_TXN3

A

PU_TDI

A

PU_TDO

A

PU_TCK

A

PU_TMS

A

PU_TRST#

A

PU_DBREQ#

A

PU_RST#

A

PU_PWROK

A

PU_SIC

A

PU_SID

A

PU_ALERT#

T

HERMTRIP#

A

PU_PROCHOT #

A

PU_SVC_R

A

PU_SVD_R

A

PU_SVT_R

C

8

D

P0_TXP0

A

8

D

P0_TXN0

D

8

D

P0_TXP1

B

8

D

P0_TXN1

B

6

D

P0_TXP2

C

7

D

P0_TXN2

C

6

D

P0_TXP3

D

6

D

P0_TXN3

E

6

D

P1_TXP0

D

5

D

P1_TXN0

E

1

D

P1_TXP1

1

C

D

P1_TXN1

3

F

P1_TXP2

D

E

4

P1_TXN2

D

4

F

P1_TXP3

D

2

F

P1_TXN3

D

U2

A

DI

T

U4

A

DO

T

U1

A

CK

T

U3

A

MS

T

V3

A

RST_L

T

W3

A

BREQ_L

D

W4

A

ESET_L

R

W2

A

WROK

P

14

H

IC

S

14

J

ID

S

15

J

LERT_L

A

P16

A

HERMTRIP_L

T

19

L

ROCHOT_L

P

16

F

VC0

S

IO18

16

H

VD0

S

16

J

VT0

S

@

UC1C

DISPLAY/SVI2/JTAG/TEST

D

P3:

DP2:

DP1: eDP

DP0: HDMI

IO18S5

IO18

IO33

FP5 REV 0.90

ART 3 OF 13

P

P5_BGA_1140P

F

C

IO18

D

D

P_STEREOSYNC

V

V

DDCR_SOC_SENSE

V

DDCR_SENSE

V

SS_SENSE_A

V

SS_SENSE_B

D

P_BLON

D

P_DIGON

P_VARY_BL

D

P0_AUXP

D

P0_AUXN

D

P0_HPD

D

P1_AUXP

D

P1_AUXN

D

P1_HPD

D

P2_AUXP

D

P2_AUXN

D

P2_HPD

D

P3_AUXP

D

P3_AUXN

D

P3_HPD

R

SVD_4

R

SVD_3

R

SVD_2

T

T

T

T

EST14

T

EST15

T

EST16

T

EST17

T

EST31

T

EST41

T

EST470

T

EST471

S

MU_ZVDD

C

ORETYPE

DDP_SENSE

EST4

EST5

EST6

E

NBKL_R

G

15

E

NVDD_R

F

15

I

NVTPWM_R

L

14

A

PU_DP0_CT RL_CLK

D

9

A

PU_DP0_CT RL_DATA

B

9

A

PU_DP0_HPD

C

10

E

DP_AUXP

G

11

E

DP_AUXN

F

11

E

DP_HPD

G

13

J

12

H

12

K

13

J

10

H

10

K

8

D

P_STEREOSYNC

K

15

F

14

F

12

F

10

A

P14

A

N14

F

13

G

18

H

19

F

18

F

19

W

24

A

R11

A

J21

A

K21

S

V

4

A

W11

C

A

PU_VDDP_SEN_ H

A

N11

A

PU_CORESOC_ SEN_H

J

19

A

PU_CORE_SEN _H

K

18

A

PU_VSS_SEN_L

J

18

A

PU_VDDP_SEN_ L

A

M11

A

PU_TEST4

A

PU_TEST5

A

PU_TEST14

A

PU_TEST15

A

PU_TEST16

A

PU_TEST17

A

PU_TEST31

A

PU_TEST41

A

PU_TEST47 0

A

PU_TEST47 1

MU_ZVDDP

ORETYPE

R

R

A

PU_DP0_CT RL_CLK 40

A

PU_DP0_CT RL_DATA 40

A

PU_DP0_HPD 40

E

DP_AUXP 38

E

DP_AUXN 38

E

DP_HPD 38

TP@

T

4949

TP@

4948

T

TP@

4942

T

TP@

T

4941

TP@

4940

T

TP@

4939

T

1 2

C1682 196_0402_1 %

2

1

C1681 1K_0402_5%@

A

PU_VDDP_SEN_ H 87

A

PU_CORESOC_ SEN_H 88

A

PU_CORE_SEN _H 88

A

PU_VSS_SEN_L 88

A

PU_VDDP_SEN_ L 87

D

HDMI

EDP

+

0.9VS

+

3VALW

Leakage prevent from power side

D

ISP

E

NBKL_R

E

NVDD_R

E

NVDD_R

I

NVTPWM_R

E

NBKL

E

NVDD

I

NVTPWM

E

NBKL_R

E

NVDD_R

I

NVTPWM_R

+

1.8VALW

5

C66

U

1

P

C

N

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

A00004BV00

S

+

1.8VALW

5

U

C64

1

P

N

C

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

S

@

A00004BV00

1 2

C690 0_0402_5%RS@

R

+

1.8VALW

5

C65

U

1

P

C

N

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

A00004BV00

S

1

R

C3 4.7K_0402_5 %

1 2

R

C4 4.7K_0402_5 %@

1 2

C5 4.7K_0402_5 %

R

1 2

C6130 100K_0402_5 %

R

1 2

R

C6131 100K_0402_5 %

1 2

C6132 100K_0402_5 %@

R

E

E

NBKL

I

NVTPWM

E

NVDD

E

NBKL 58

E

NVDD 38

E

NVDD

I

NVTPWM 3 8

+

3VS

2

H

DT+

+

+

1.8VALW

J

HDT1

CONN@

PU_TCK_R

A

1

3

5

PU_TRST#

A

H2

C

0.01U_0402 _16V7K

4 4

1 2

H21 33_0402_5%

R

H38 10K_0402_5%

R

2

2

H39 10K_0402_5%

R

1

H40 10K_0402_5%

R

12

1

12

A

PU_TRST# _R

DT_P11

H

DT_P13

H

DT_P15

H

7

9

11

13

15

17

19

A

2

2

1

4

4

3

6

6

5

8

8

7

10

1

9

0

12

1

1

1

2

14

1

1

3

4

16

1

1

5

6

18

1

1

7

8

20

2

1

9

0

SAMTE_ASP-13644 6-07-B

PU_TMS_R

A

PU_TDI_R

A

PU_TDO_R

A

PU_PWROK _R

A

A

PU_RST#_R

A

PU_DBREQ#_R

H27 0_0402_5%H DT@

R

H28 0_0402_5%H DT@

R

R

H29 0_0402_5%H DT@

H30 0_0402_5%H DT@

R

H31 0_0402_5%H DT@

R

H32 0_0402_5%H DT@

R

R

H33 33_0402_5%

B

1 2

1

1 2

1 2

1

1 2

1 2

2

2

Follow C5V08

PU_TCK

A

PU_TMS

A

PU_TDI

A

PU_TDO

A

PU_PWROK

A

PU_RST#

A

PU_DBREQ#

A

A

PU_TCK

A

PU_TMS

A

PU_TDI

A

PU_DBREQ#

A

PU_TRST#

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

ssued Date

ssued Date

ssued Date

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

1

H34 1K_0402_5%

R

1 2

H35 1K_0402_5%

R

1 2

H36 1K_0402_5%

R

1 2

H37 1K_0402_5%

R

1

H26 1K_0402_5%

R

1.8VALW

2

2

C

C

C

ompal Secret Data

ompal Secret Data

2

2

2

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

018/ 12/18 2019/12/18

ompal Secret Data

D

D

D

eciphered Date

eciphered Date

eciphered Date

D

TESTPOINT

D

P_STEREOSYNC

A

PU_TEST14

A

PU_TEST15

A

PU_TEST16

A

PU_TEST17

T

T

T

itle

itle

itle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

ustom

ustom

ustom

Date: Sheet

Date: Sheet

Date: Sheet

1 2

C155 1K_0402_5%

R

1 2

C154 1K_0402_5%@

R

R

C112 10K_0402 _5%@

R

C113 10K_0402 _5%@

R

C114 10K_0402 _5%@

C115 10K_0402 _5%@

R

12

12

2

1

12

C

C

C

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

(

(

(

3/7)_DISP/MISC/HDT

3/7)_DISP/MISC/HDT

3/7)_DISP/MISC/HDT

F

F

F

H50P M/B LA-H901P

H50P M/B LA-H901P

H50P M/B LA-H901P

E

+

1.8VS

+

1.8VS

1

1

1

A

A

A

o

o

o

f

8 99Wednesday, May 15, 201 9

f

8 99Wednesday, May 15, 201 9

f

8 99Wednesday, May 15, 201 9

C28

S

YS_PWRGD_EC

C8

C6160

A

A

C700 0_0402_5%RS@

R

R

C701 0_0402_5%@

R

C30 0_0402_5%RS@

1

2

PU_PCIE_WAKE#

+

1.8VALW

1 2

1 2

1 2

+

3VALW

N1

I

N2

I

@

Reserve for MBDG/CRB

C1210

C

10U_0402_6.3V6M

1 2

@

1

R

C54

22K_0402_1%

2

E

C_RSMRST#

1

C

C16

1U_0201_6.3V6M

2

C14

C

0.1U_0201_10V6K

1 2

@

5

P

A

PU_PCIE_RST#

4

O

G

C4

U

A00000OH00

S

3

MC74VHC1G08DFT2G_SC70-5

A

PU_PCIE_RST#_U

A

PU_PCIE_RST#

A

PU_PCIE_RST# 27,51,52,68

A

PU_PCIE_RST#_C

A

PU_PCIE1_RST#_C

M

ain Func = CPU

1 1

A

CPI

+

3VALW

1 2

C6133 10K_0402_5%@

R

CRB use S0-rail

+

2 2

3 3

3VALW

12

C6165

R

10K_0402_1%@

A

PU_PCIE_RST#_U

+

3VS

12

R

10K_0402_1%

2

C

0.22U_0402_16V7K

1

A

PU_PCIE_RST#_C

A

PU_PCIE1_RST#_C

A

PU_PCIE_RST#_U

R

10K_0402_5% @

1 2

B

1 2

C

C7 150P_0402_50V 8J

1 2

C100 150P_0402_50V8J@

C

1 2

R

C29 33_0402_5%

1 2