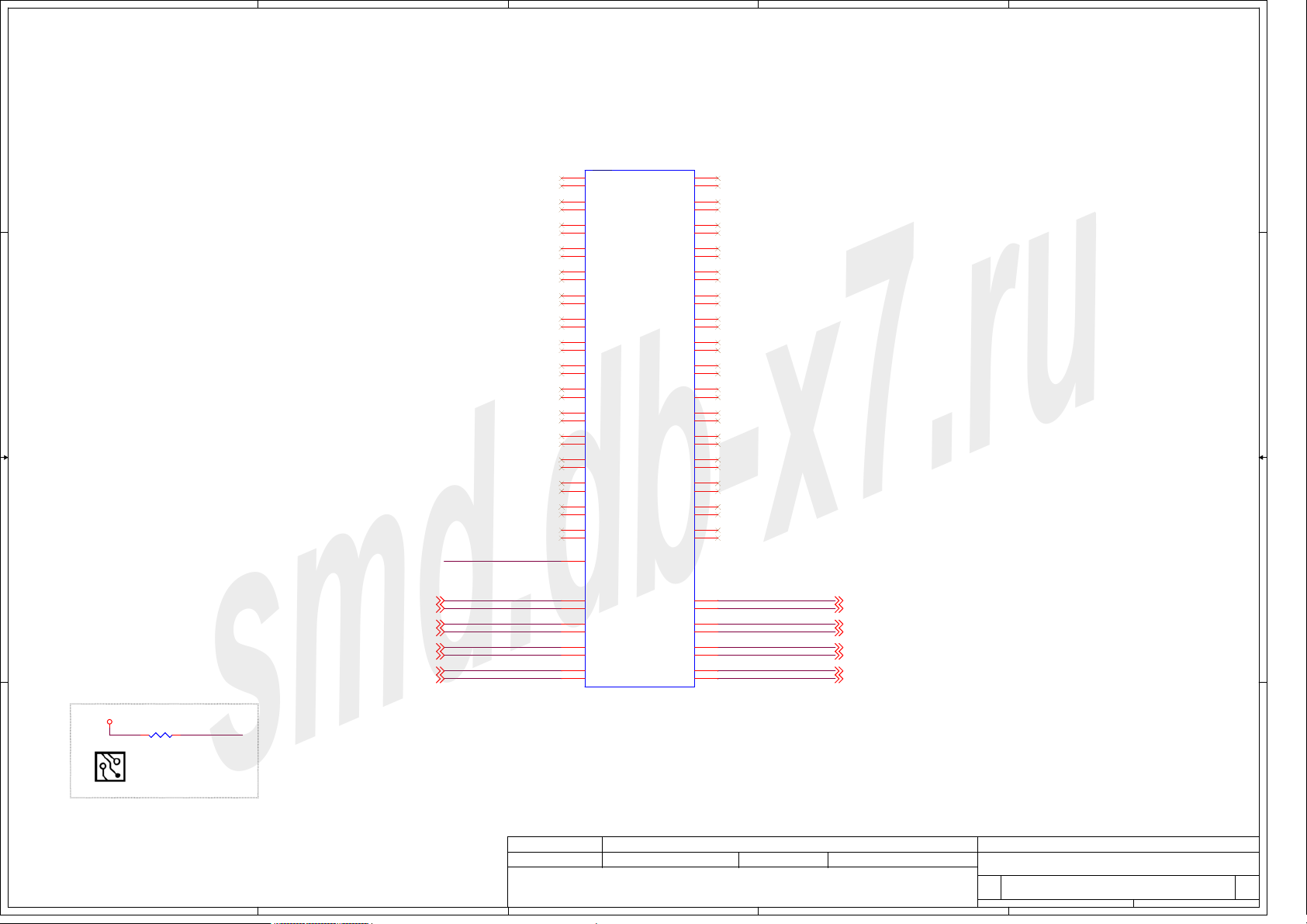

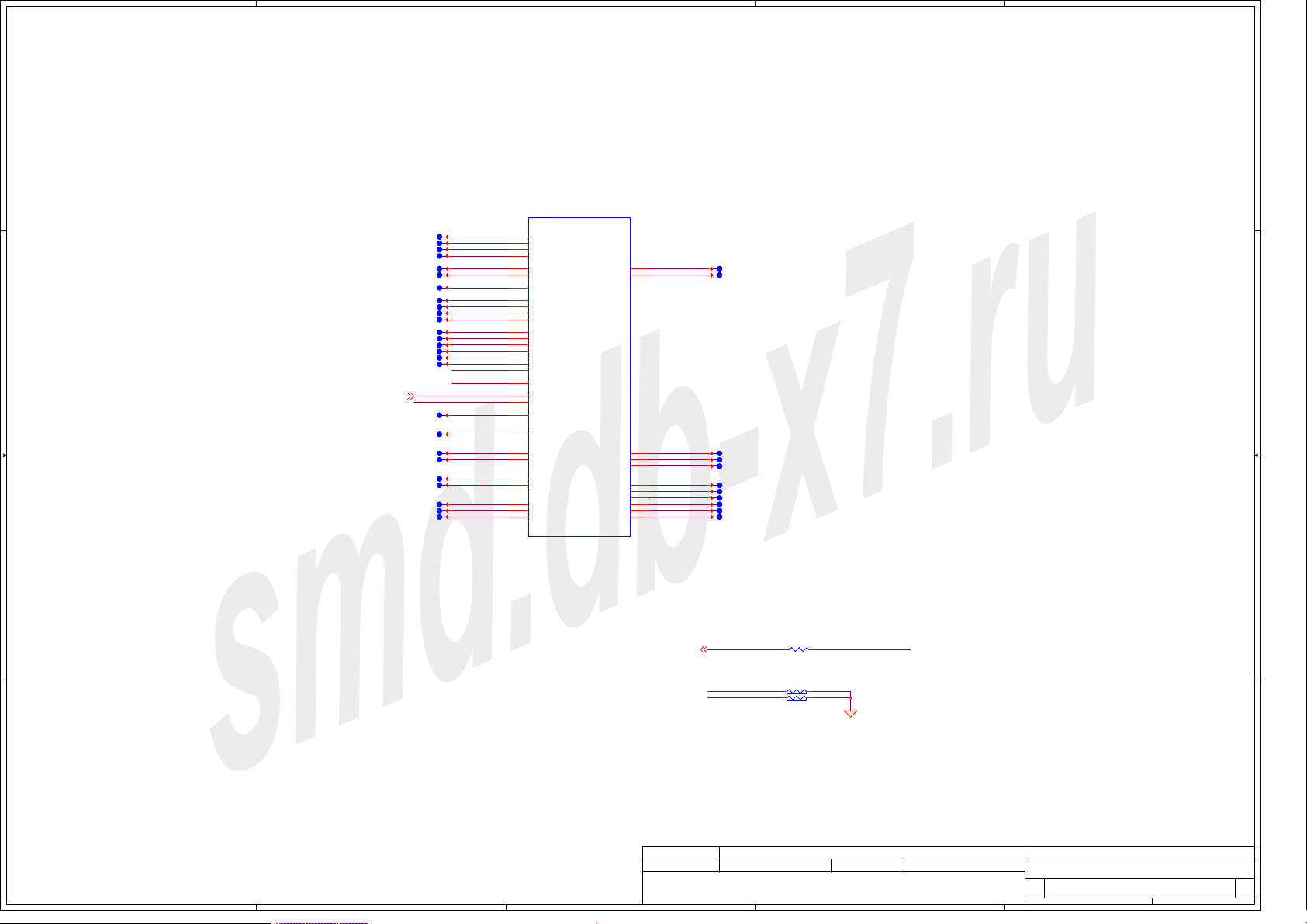

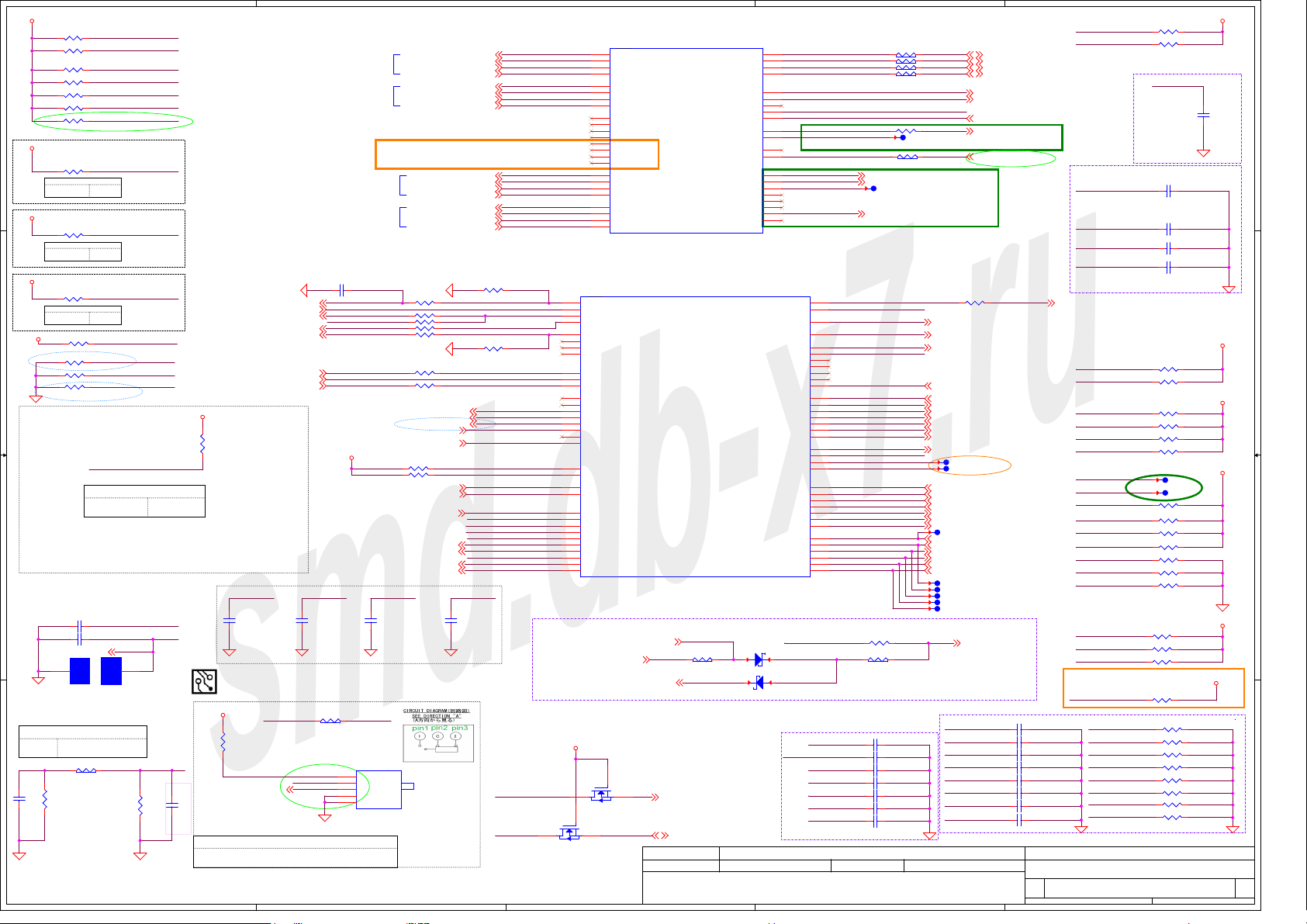

Compal LA-H171P Schematics

5

smd.db-x7.ru

4

3

2

1

COMPAL CONFIDENTIAL

MODEL NAME : EDC42

D D

PCB NO : LA-H171P

BOM P/N :

GPIO MAP: X10_WHL_KBL_CFLH_GPIO map Rev1.5_20180921

PWR Circuit: 14UMA_A00_PWR_20190308A

Brook Hollow 14 UMA (TBT)

Cof f ee Lake H

2019-03-20

C C

REV : 1.0 (A00)

@ : Nopop Component

EMI@ : EMI Component

@EMI@ : EMI Nopop Component

ESD@ : ESD Component

@ESD@ : ESD Nopop Component

RF@ : RF Component

B B

@RF@ : RF Nopop Component

XDP@ : XDP Component

CONN@ : Connector Component

MB PCB

Part Number

DAA000J2000

Description

PCB 2FB LA-H171P REV0 MB 1

Layout Dell logo

A A

5105@ : EC MEC5105 IC

5106@ : EC MEC5106 IC

WWAN@ : WWAN Component

WWANRF@ : WWAN RF Component

SATAPERI@ : Pericom SATA repeater support

eSPI@ : eSPI interface

LPC@ : LPC interface

DS3@ : Deep sleep support

NDS3@ : non Deep sleep support

RTD3@ : RTD3 support

NRTD3@ : non RTD3 support

VPRO@ : VPRO support

NVPRO@ : non VPRO support

ST33@ : ST33 TPM support

750@ : NPCT750 TPM support

JUMP@ : Jump solder and short

@JUMP@ : Jump no solder

SATAPARA@ : Parade SATA repeater support

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

A

A

A

LA-H171P

LA-H171P

LA-H171P

Wednesday, March 20, 2019

Wednesday, March 20, 2019

Wednesday, March 20, 2019

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

1

1 100

1 100

1 100

0.1

0.1

0.1

COPYRIGHT 2019

ALL RIGHT RESERVED

REV: A00

PWB: J11RG

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2018/01/01

2018/01/01

2018/01/01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

5

smd.db-x7.ru

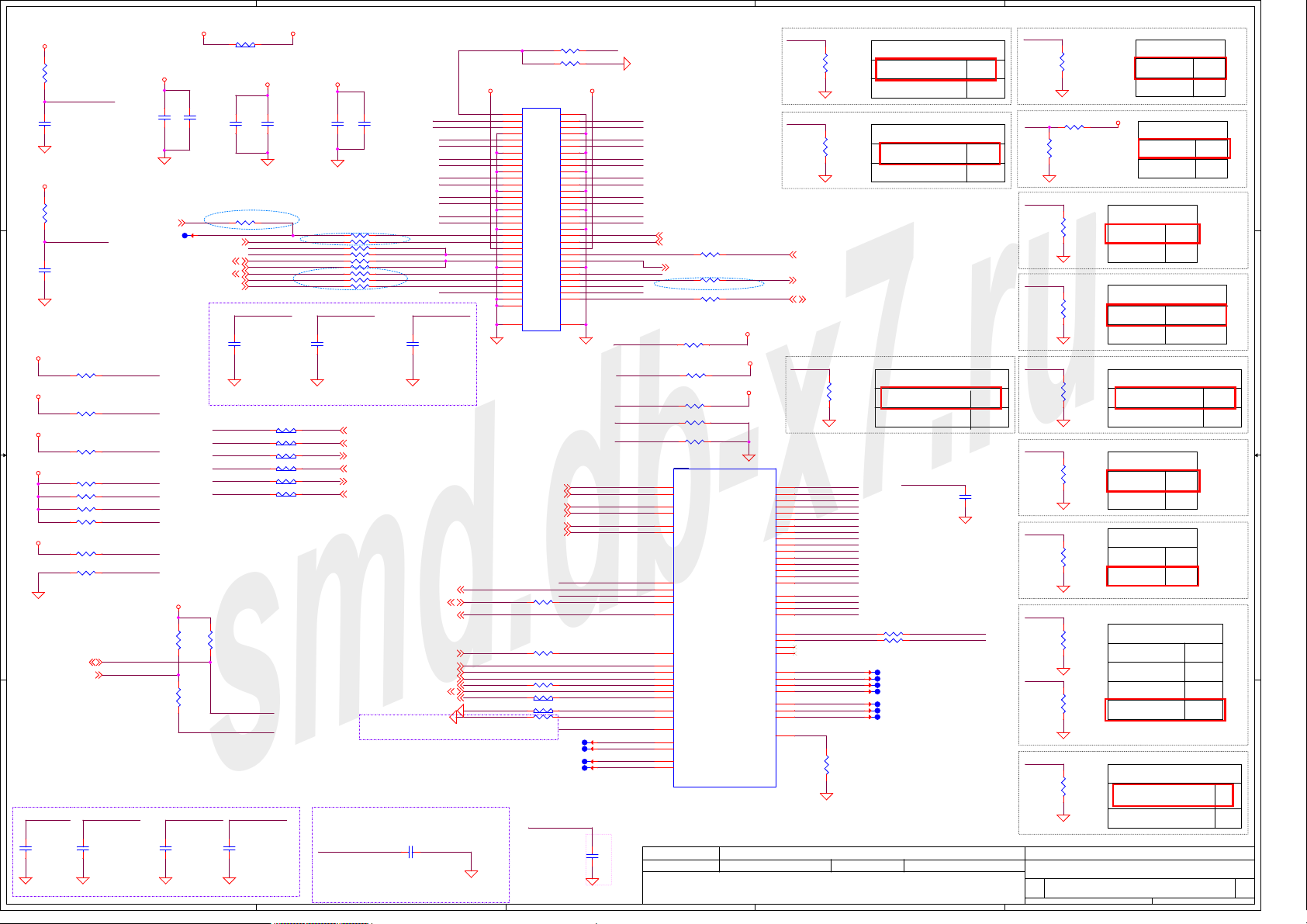

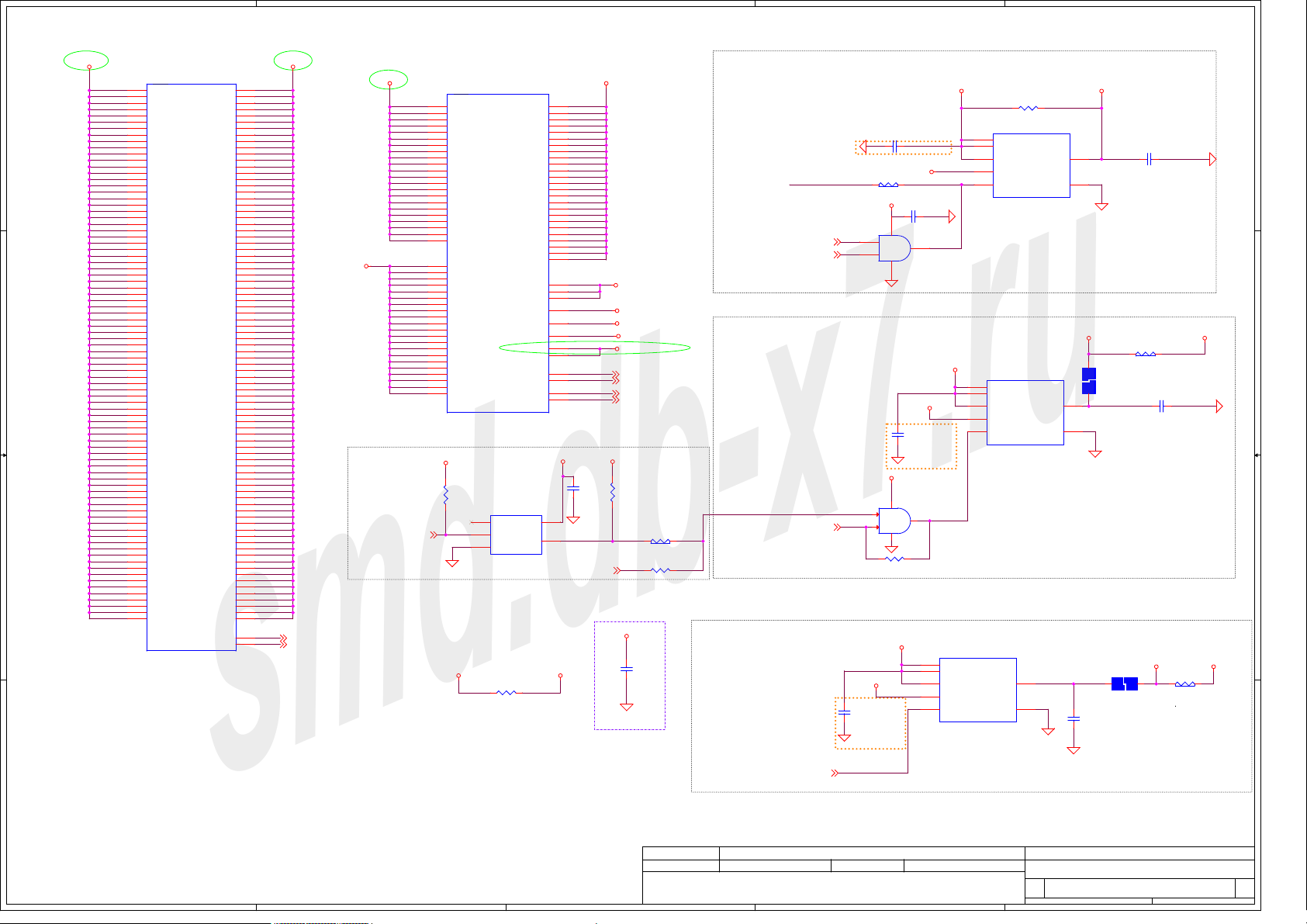

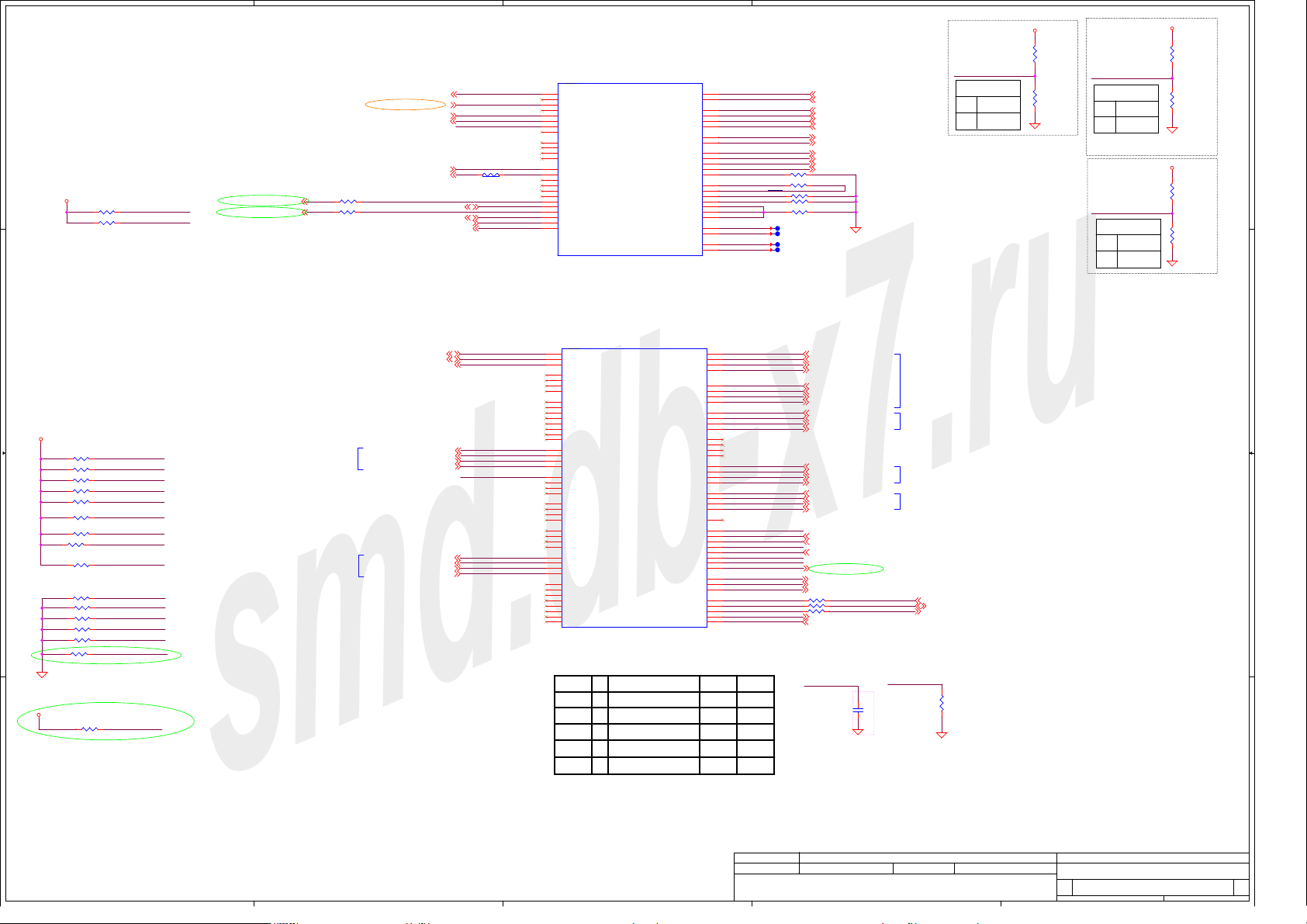

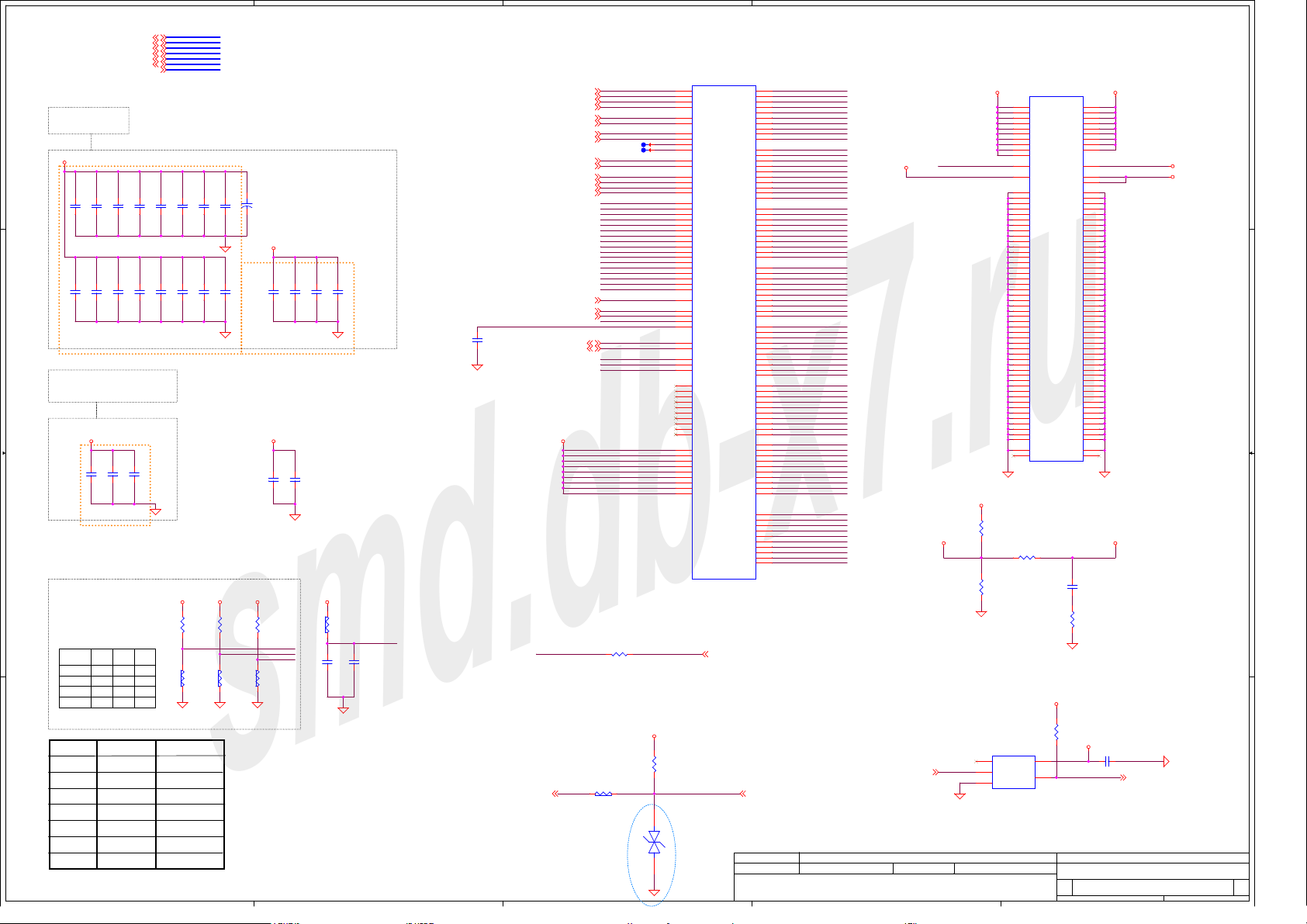

Brook Hollow 14 UMA TBT Block Diagram

4

3

2

1

Reverse Type

D D

EDP CONN

P38

eDP Lane x 2

eDP

Memory BUS (DDR4)

2400/2667 MHz

DDR4-SO-DIMM X2

BANK 0, 1, 2, 3

P.23/24

Intel

TBT_DP0

To AR

TBT_DP1

To AR

HDMI 2.0

CONN

C C

Card reader

RTS5242

SD4.0

PCIE[6]

P70

P70

Intel Jacksonville

WGI219LM(vpro)

WGI210V(non-vpro)

PCIE[1..4]

To AR

B B

TBT_DP0

TBT_DP1

P30~31

5

TBT

Port A

PCIE[1..4]

P46

TBT

AR-SP

USB2.0/SMB

AUX/POC

A A

I2C

PD

TPS65982DD

P44~45

SBU1/SBU2

CC1/CC2

USB3_TYPE C connector

DP1, DN1/DP2,DN2

P40

PCIE[5]

Transformer

RJ45

P51

P51

HDMI

P51

PCIE/USB3 Switch

PI3PCIE3212ZBEX

Smart Card

USH board(CV3)

4

DP to HDMI2.0

PS175

PCIE[17]

M.2,3042 Key B

WWAN/LTE

/HCA/SSD

USB2.0[8]

PCIE[18]

USB3.0[2]

TDA8034HN

RFID/NFC

Fingerprint

CONN

FPR IN PB MoCV

P52

P52

P40

PCIE[7]

M.2, 2230 Key E

WLAN+BT/CNVi

SPI

SPI

USB

DDI[1]

DDI[2]

DDI[3]

CNVi

P52

USB2.0[14]

USH

BCM58202

COFFEE LAKE-H

DDIB

BGA CPU

1440 Pins

DDIC

DDID

Intel

CannonLake-H

BGA PCH

874 Pins

SMSC KBC

MEC5106

USB2.0[10]

P66

3

eSPI

PAGE 6~13

USB2.0[1]

SLGC55544CVTR

USB POWER SHARE

DMI x4 Gen 3

USB

HD Audio I/F

PAGE 14~22

SATA[0]/PCIE[9..12]

SPI

P.58

SATA[2]

P.63

P.59

P.17

P.17

P.17

co- lay

P.66

2018/01/01

2018/01/01

2018/01/01

W25Q256JVEIQ

vPro use

256Mb 4K sector WSON8

W25Q64JVZEIQ

Non-vPro use

64Mb 4K sector WSON8

W25Q128JVSIQ

Non-vPro use

128Mb 4K sector SOP8

TPM2.0

ST33HTPH2E32AHC1

KB/TP CONN

FAN CONN

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PS8713

USB redriver

HDA Codec

ALC3204

SATA REPEATER

PI3EQX6741STZDEX

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

P71

P73

P.56

P67

I2C0

USB2.0[11]

USB2.0[1]_PS

USB3.0[1]

USB2.0[2]

USB3.0[3]

USB2.0[3]

USB3.0[4]

INT.Speaker

Universal Jack

Dig. MIC

2020/01/01

2020/01/01

2020/01/01

LCD Touch

USB3.0 Conn

PS(Ext Port 1)

USB3.0 Conn

(Ext Port 2)

USB3.0 Conn

(Ext Port 3)

M2 Key M

SSD Conn

Camera

P.56

P.56

P.56

P.68

SATA HDD

Conn

P38

P38

Trough eDP Cable

P71

P72

P72

Trough eDP Cable

P67

FP in PBTN CONN

CPU&PCH XDP Port

AUTOMATIC POWER

SWITCH(APS)

Free Fall sensor

DC/DC Interface

POWER ON/OFF

SW & LED

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block diagram

Block diagram

Block diagram

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

LED/B

USH CONN

2 100

2 100

2 100

P65

P62

P66

P7

P19

P67

P78

P62

0.1

0.1

0.1

5

smd.db-x7.ru

4

3

2

1

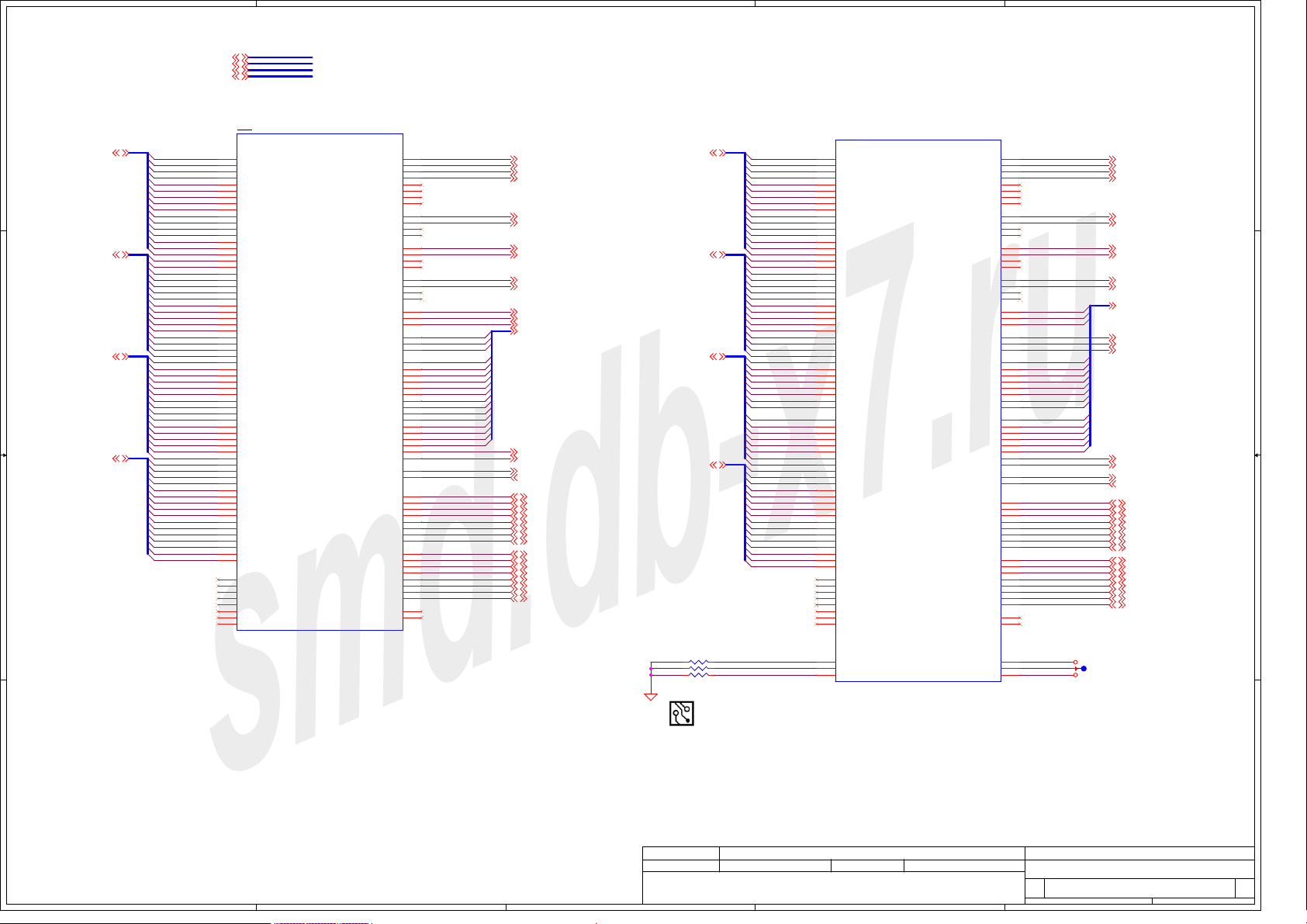

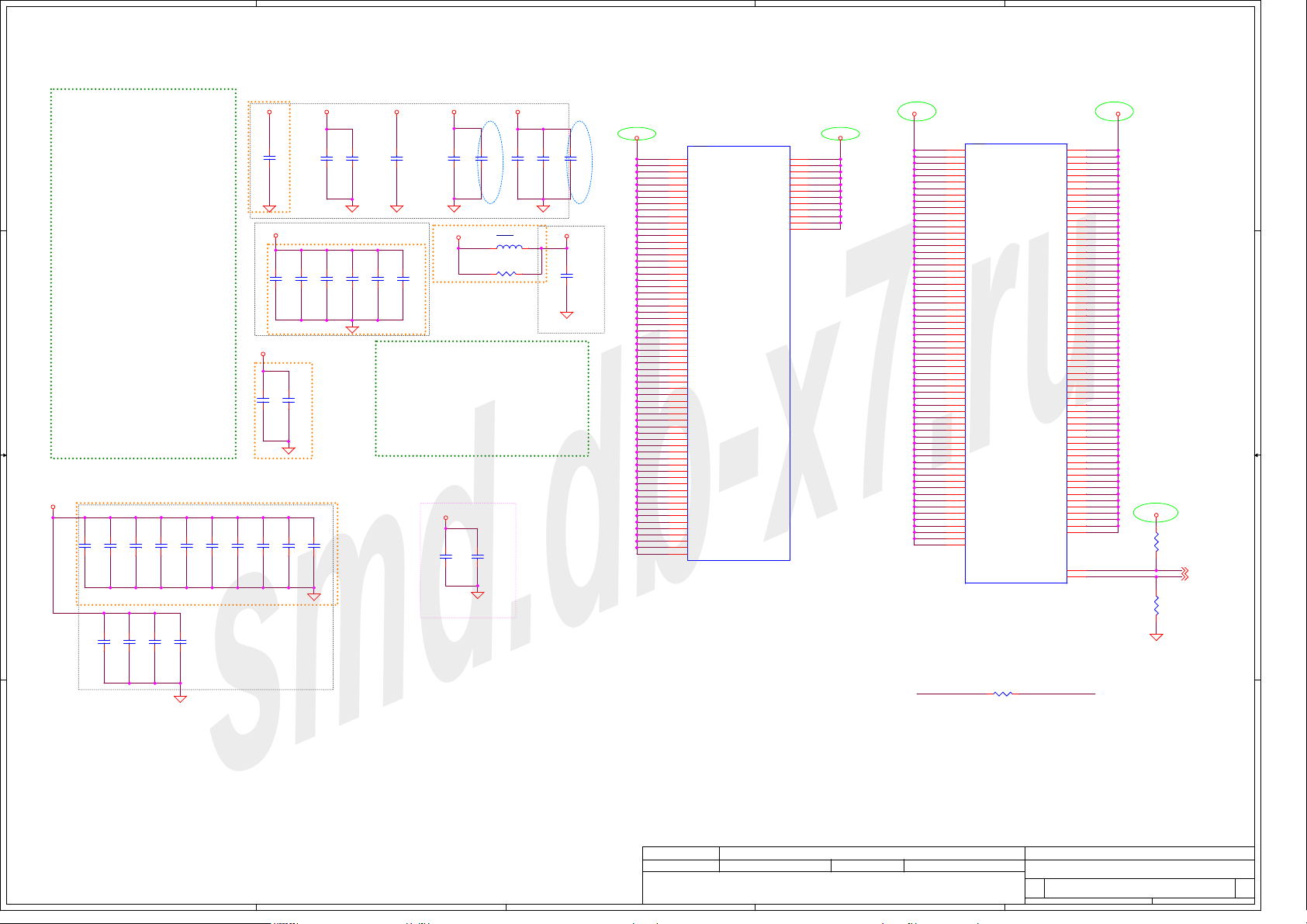

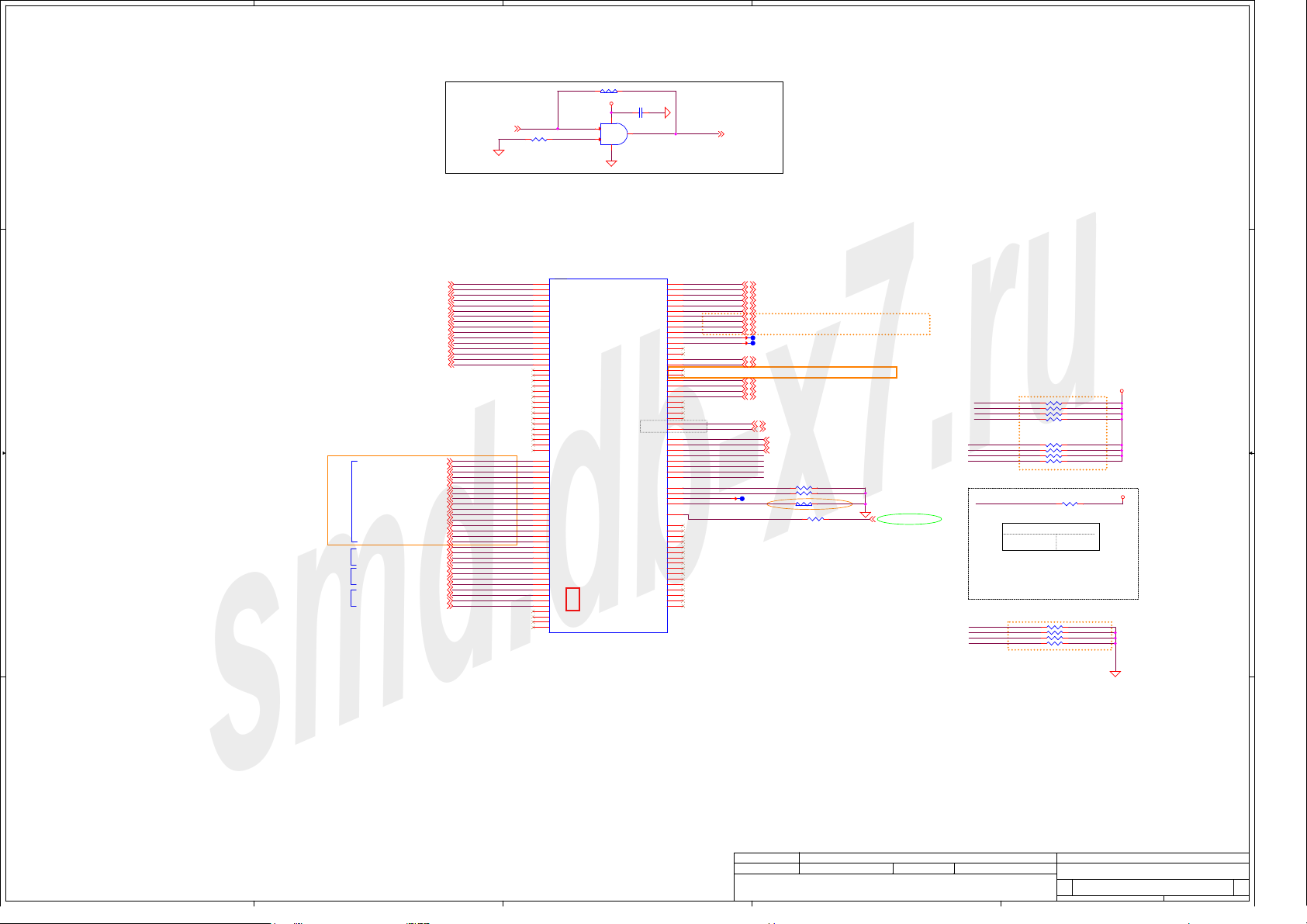

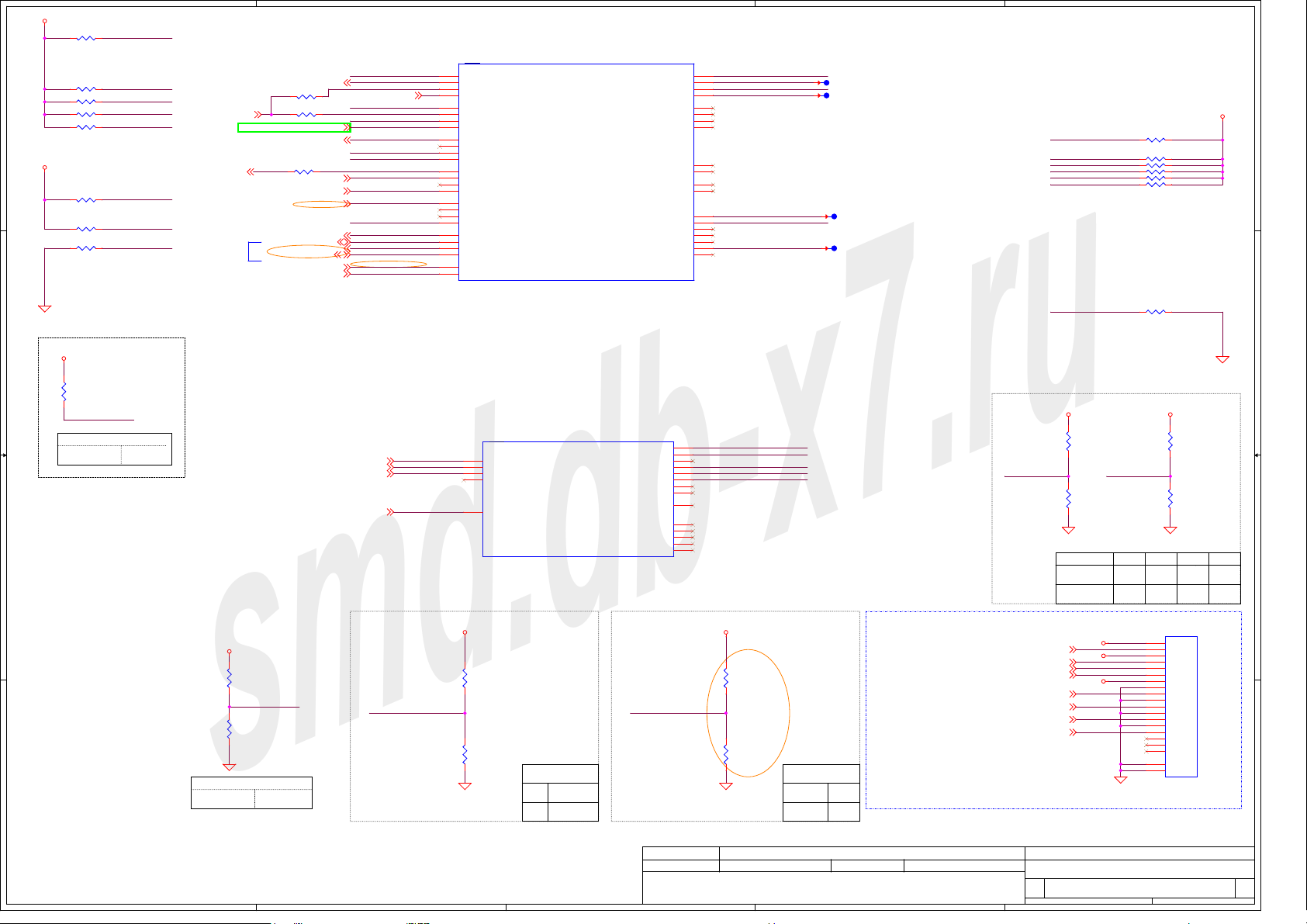

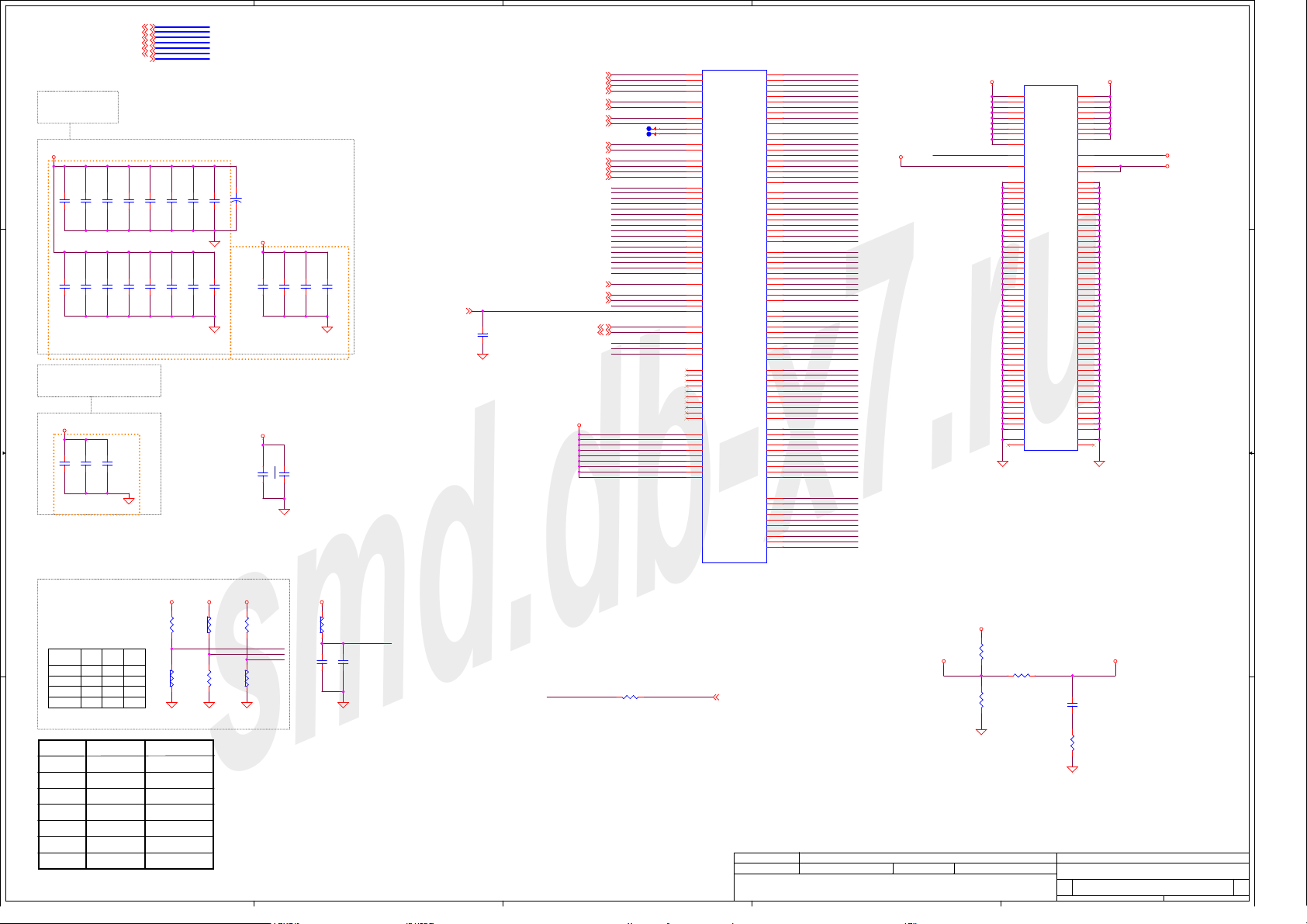

POWER STATES

RUN

Signal

State

S0 (Full ON) / M0

D D

S3 (Suspend to RAM) / M3 LOW

S4 (Suspend to DISK) / M3

S5 (SOFT OFF) / M3

SLP

S3#

HIGH

LOW

SLP

SLP

S5#

S4#

HIGH HIGH

HIGH HIGH

HIGH HIGH

LOW

LOW

LOW

SLP

A#

HIGH

HIGH

HIGH

ALWAY S

PLANE

M

PLANE

ON

ON ON ON

ON ON

ON ON

ON

SUS

PLANE

ON ON ON

OFF

OFF

PLA NE

OFF

OFF

OFFLOW

CLOCKS

OFF

OFF

OFF

USB3.0

USB3.0-1

USB3.0-2

USB3.0-3

USB3.0-4

USB3.0-5

USB3.0-6

USB3.0-7

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

HIGH HIGH

LOW

LOW LOW LOW

LOW LOW LOW LOW

LOW

HIGH

ON ON

ON

ON

OFF OFF OFF

OFF OFF OFF OFF

OFF OFF OFF OFF

USB3.0-8

USB3.0-9

USB3.0-10

PM TABLE

C C

power

plane

State

S0

B B

S3

S5 S4/AC

S5 S4/AC doesn't exist

+5V_ALW

+3.3V_ALW

+3.3V_ALW_DSW

+RTC_CELL

+1.8V_PRIM

+1.0V_PRIM

+1.0V_PRIM_CORE

+5V_ALW2

+3.3V_ALW2 +VCC_SA

+3.3V_RTC_LDO

+1.0V_MPHYGT

ON

ON

ON

OFF

+3.3V_SUS

+1.2V_MEM+3.3V_ALW_PCH

+1.0V_VCCST

+2.5V_MEM

ON

OFF

OFF

+5V_RUN

+3.3V_RUN

+0.6V_DDR_VTT

+1.2V_RUN

+VCC_CORE

+VCC_GT

+1.0VS_VCCIO

+1.8V_RUN

ONON

OFF

OFF

OFF

SSIC

SSIC-1

SSIC-2

PCIE

PCIE-1

PCIE-2

PCIE-3

PCIE-4

PCIE-5

PCIE-6

PCIE-7

PCIE-8

PCIE-9

PCIE-10

PCIE-11

PCIE-12

PCIE-13

PCIE-14

PCIE-15

PCIE-16

PCIE-17

PCIE-18

PCIE-19

PCIE-20

SATA

SATA-0A

SATA-1A

SATA-0B

SATA-1B

SATA-2

SATA-3

SATA-4

SATA-5

DESTINATION

JUSB1-->Right

JNGFF2-->M2 3042(LTE)

JUSB2-->LEFT

JUSB3-->RIGHT

NA

NA

Alpine Ridge - SP

LOM

Card Reader

JNGFF1-->M.2 2230(WLAN)

NA

M.2 Socket 3 (Key M)

M.2 2280 SSD

(PCIex4 or SATA)

NA

NA

JSATA1-->HDD SATA

NA

M.2 3042 (HCA or QCA LTE) SSD Cache

M.2 3042 (HCA or QCA LTE) SSD Cache

NA

NA

USB PORT#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

USH

VIDEO

eDP

DDI-B

DDI-C

DDI-D

DESTINATION

JUSB1-->Right

JUSB2 ->LEFT

JUSB3-->RIGHT

FP IN PB

TI PD

test point

NA

JNGFF2-->M2 3042(WWAN)

NA

JUSH1-->USH

JEDP1-->Camera

NA

NA

JNGFF1--> M.2 2230(CNVi_BT)

H BIO

DESTINATION

LCD

Alpine Ridge - SP

(Port 0)

Alpine Ridge - SP

(Port 1)

PS175 --> JHDMI1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2018/01/01

2018/01/01

2018/01/01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Port Assignment

Port Assignment

Port Assignment

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

A

A

A

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

1

3 100

3 100

3 100

0.1

0.1

0.1

5

smd.db-x7.ru

4

3

2

1

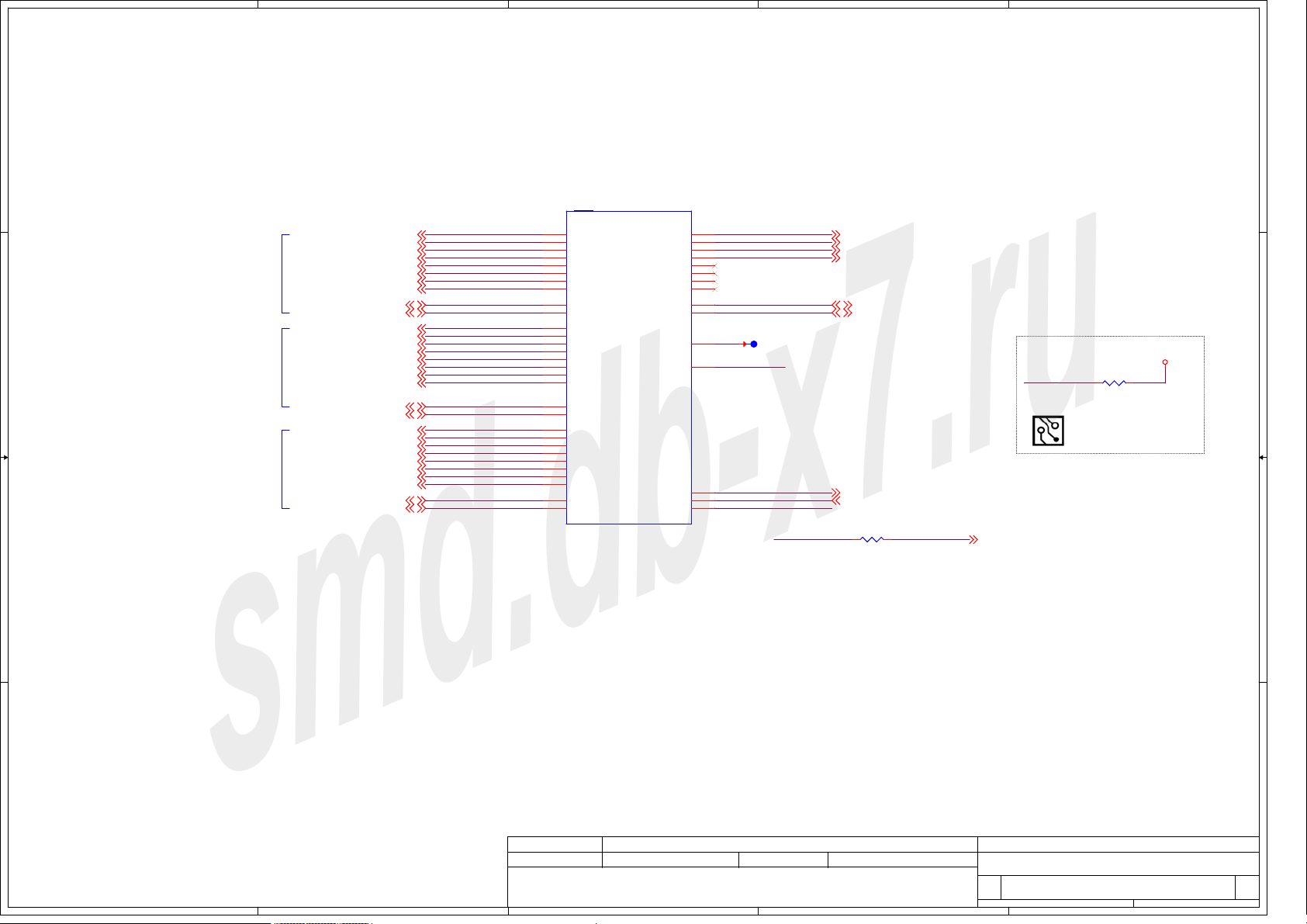

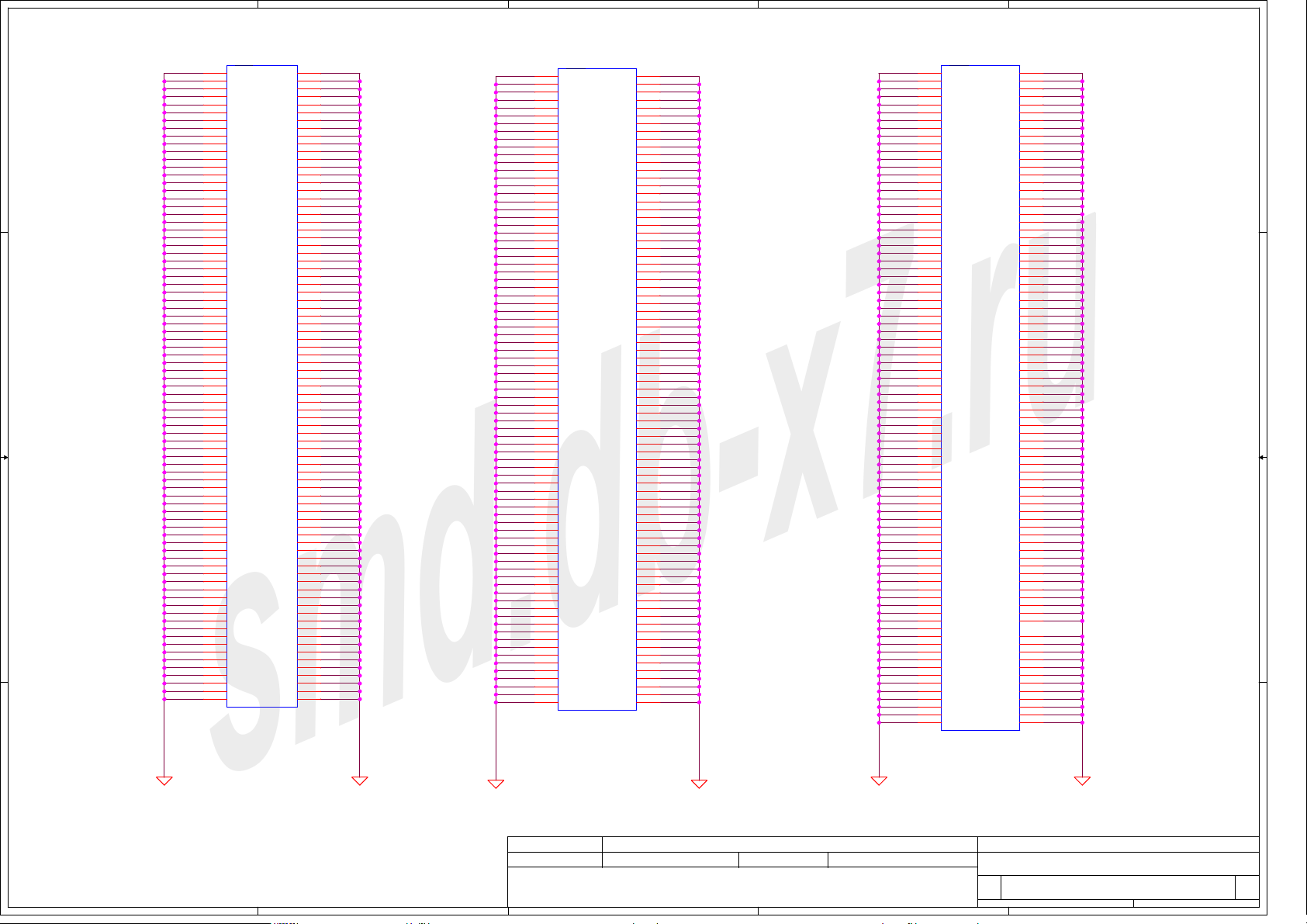

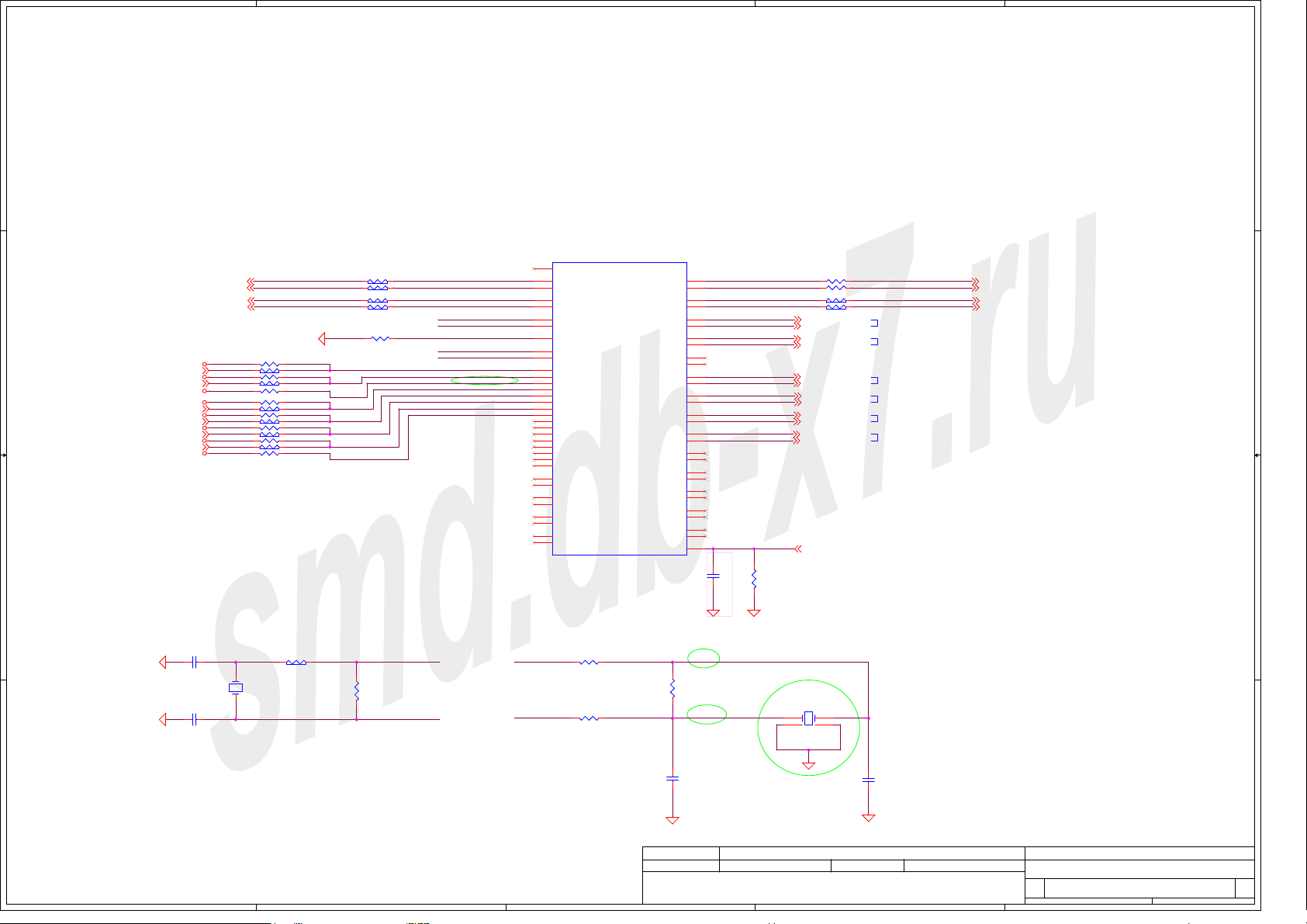

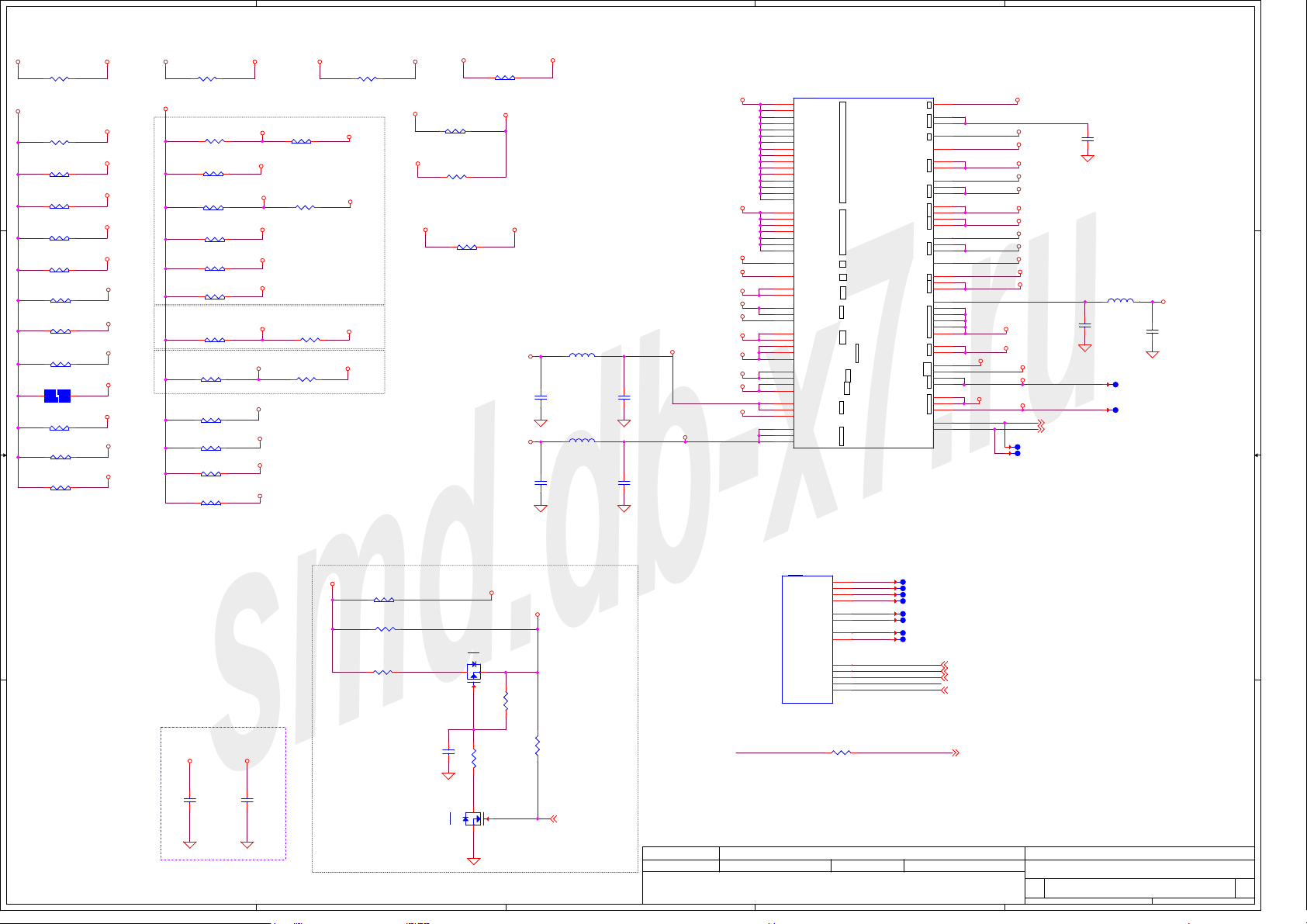

RUN_O N

3.3V_CAM_EN#

HDMI_1.2V_ EN

CPU PWR

PCH PWR

GT3 PWR

Peripheral Device PWR

TYPE-C Power

GPU PWR

+TS_PWR

+1.8V_RUN

+3.3V_CAM

+3.3V_TBT

+1.2V_RUN

@SIO_SLP_SUS#

P11

@SIO_SLP_S4#

VCCSTG_EN

SY8057QDC

(PU401)

EM5209

(UZ4)

SLGC55544C

(UI3)

SY6288D

(UI1)

SY6288D

(UI2)

RT8097ALGE

(PU501)

EM5209

(UZ2)

EM5209

(UZ3)

EM5209

(UZ4)

G524B1T11U

(UV24)

AP7361C

(PU503)

+VCC_SFR_OC

RUN_O N

P87

RUN_O N

P78

USB_PWR_S HR_EN#

P71

USB_PWR_EN 1#

P72

USB_PWR_EN 2#

P72

PCH_PRIM_ EN

@SIO_SLP_SUS#

P87

SIO_SLP_LAN#

AUX_EN_WOWL

@SIO_SLP_WLAN#

P78

PCH_PRIM_ EN

@SIO_SLP_SUS#

@PCH_ALW_O N

RUN_O N

P78

3.3V_WWAN _EN

P78

ENVDD_ PCH

P38

SIO_SLP_S4#

P87

AOZ1334DI

(UZ19)

AOZ1334DI

(UZ21)

+1.0VS_VCCIO

+5V_RUN

+5V_USB_CHG_PWR

+USB_EX2_PWR

+USB_EX3_PWR

+1.8V_PRIM

+3.3V_LAN

+3.3V_WWLAN

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_WWAN

+LCDVDD

+2.5V_MEM

for DDR4

P11

P11

RUN_O N

SIO_SLP_S0#

SIO_SLP_S4#

LP2301

(QV8)

AOZ1336

(UZ8)

LP2301A

(QZ1)

AP7361

(PU502)

+1.0V_VCCSTG

+1.0V_VCCST

3.3V_TS_EN

P38

P78

P38

P87

AOZ1334DI

(UZ26)

P86

P87

PCH_PRIM_ EN

@SIO_SLP_SUS#

P85

SIO_SLP_S4#

0.6V_DDR_VTT_ON

ALWON

D D

Barrel

ADAPTER

Type-C

ADAPTER

P82 P46

CHARGER

ISL9538

(PU700)

P84

+13.5VB

SY8210A

(PU200)

SY8286RAC

(PU301)

SY8288C

(PU102)

+1.2V_MEM

+0.6V_DDR_VTT

+1.0V_PRIM

+5V_ALW

+5V_ALW2

BATTERY

P83

C C

SY8288B

(PU100)

P85

ALWON

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

NCP81215(PUZ1)

(PUA1)

B B

+VCC_SA

NCP302045

(PUT1)

IMVP_VR_ ON

IMVP_VR_ ON

+VCC_GT

+5V_ALW

+PP_HV(5V~20V)

AP2204

(UT8)

A A

P45

(PUH1)

(PUH2)

(PUH3)

(PUH4)

P88~89

IMVP_VR_ ON

+VCC_CORE

TPS65982DC

(UT5)

+5V_ALW

+5V_TBT_VBUS

AO6405

(QV1)

+BL_PWR_SRC

P44

AP2112K

(UT7)

P38

EN_INV PWR

+TBT_VBUS(5V~20V)

P45

TYPE-C

+3.3V_TBT_SX

+3.3V_VDD_PIC

+3.3V_TBTA_FLASH

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2018/01/01

2018/01/01

2018/01/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2020/01/01

2020/01/01

2020/01/01

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Rails

Power Rails

Power Rails

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 100

4 100

4 100

0.1

0.1

0.1

5

smd.db-x7.ru

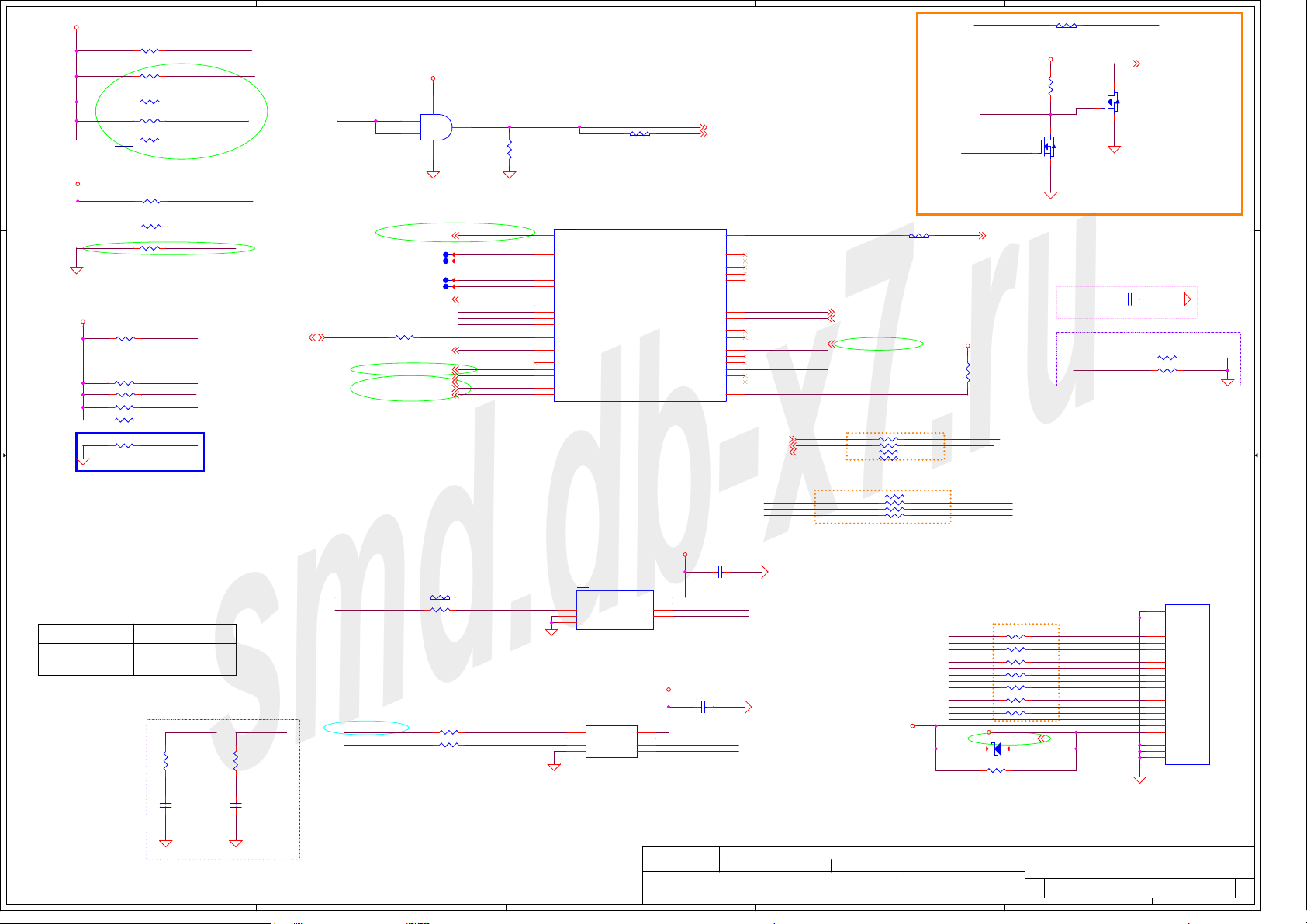

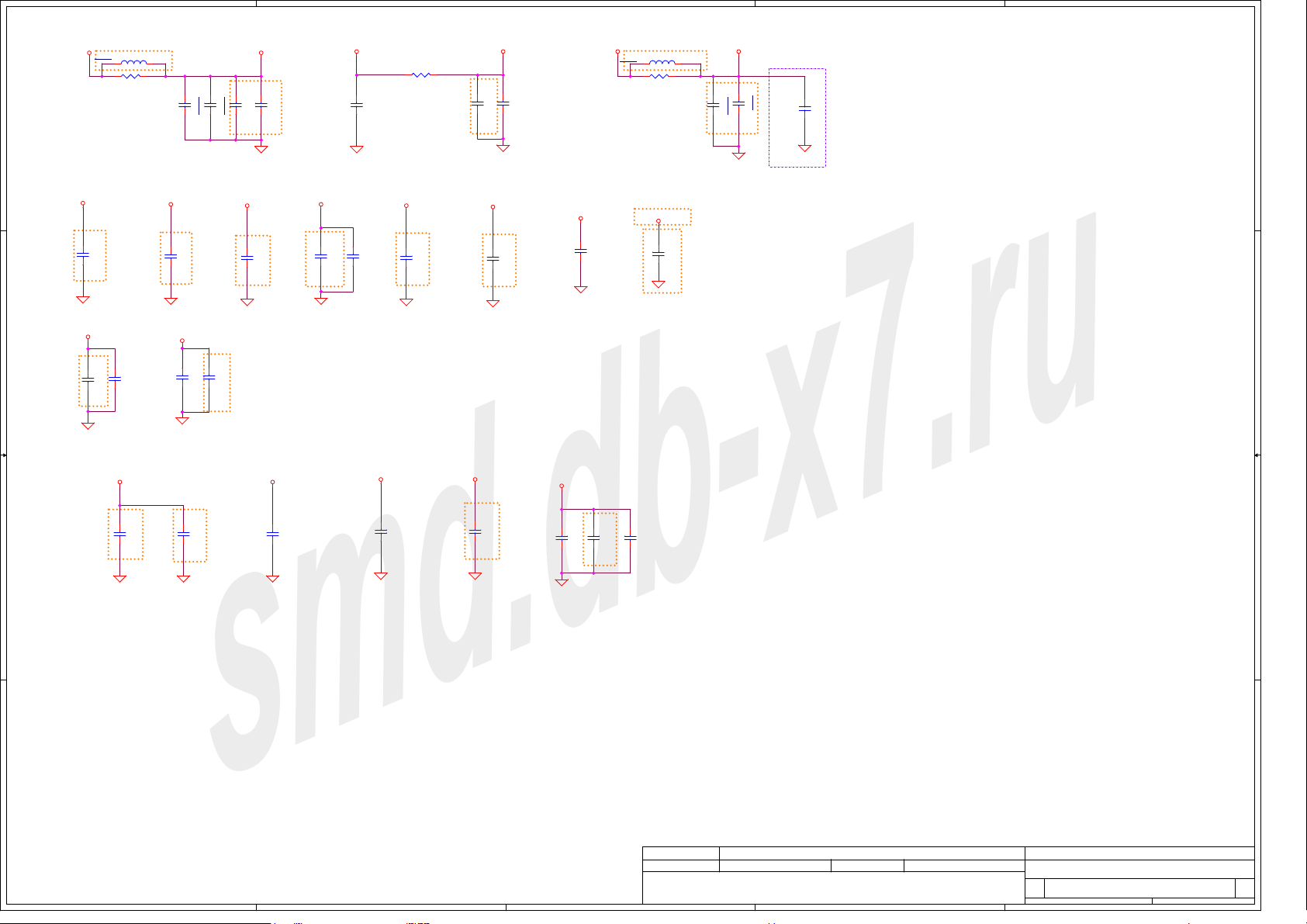

Timing Diagram for S5 to S0 mode

11

CPU

VCCST_PWRGD

PROCPWRGD

PLTRST#

DDR_VTT_CNTL

+PWR_SRC

TLV62130

+3.3V_ALW

RT8097

SIO_SLP_WLAN#

D D

C C

4

4

12

15

17

12

+1.0V_PRIM

+1.8V_PRIM

VCCST_PWRGD

H_CPUPWRGD

PCH_PLTRST#

0.6V_DDR_VTT_ON

VCCIO

VCCGT

VDDQ

VDDQC

VCCPLL_OC

VCCST

VCCSTG

VCCPLL

VCCSA

@SIO_SLP_SUS#

+VCC_CORE

VCC

+1.0VS_VCCIO

+VCC_GT

+1.35V_MEM

+1.0V_VCCST

+VCC_SA

3

PCH_PRIM_EN

EC 5105

4

+1.0V_PRIM

11

TPS22961

SIO_SLP_S0#

RUN_ON

+LCDVDD

11

+5V_TSP

+3.3V_CAM

+3.3V_SPI

3

4

4

17

7

+3.3V_ALW

AP2821K

+3.3V_ALW

EM5209VF+3.3V_LAN

+5V_RUN

LP2301ALT1G

+3.3V_RUN

LP2301ALT1G

+1.0V_PRIM

+3.3V_ALW_DSW

+3.3V_ALW_PCH

+1.8V_PRIM

+RTC_CELL

PCH_PLTRST#

PCH_DPWROK

ENVDD_PCH

SIO_SLP_LAN#

3.3V_TS_EN

3.3V_CAM_EN#

VCCPRIM_1P0

VCCPRIM_CORE

DCPDSW_1P0

VCCAPLL_1P0

VCCCLK1~6

VCCMPHYGT_1P0

VCCSRAM_1P0

VCCAMPHYPLL_1P0

VCCAPLLEBB

VCCDSW_3P3

VCCHDA

VCCSPI

VCCPRIM_3P3

VCCPGPPA~E

VCCRTCPRIM

VCCPGPPA

VCCRTC

PLTRST#

DSW_PWROK

EDP_VDDEN

SLP_LAN#

GPP_B21

GPD7

PCH

PWRBTN#

RSMRST#

SLP_SUS#

SLP_S5#

SLP_S4#

SLP_S3#

SLP_LAN#

SLP_WLAN#/GPD9

SYS_PWROK

PCH_PWROK

VCCST_PWRGD

PROCPWRGD

2

SLP_A#

Power Button

SIO_PWRBTN#

PCH_RSMRST#_AND

SIO_SLP_SUS#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

SIO_SLP_A#

SIO_SLP_LAN#

SIO_SLP_WLAN#

RESET_OUT#

PCH_PWROK

VCCST_PWRGD

H_CPUPWRGD

16

15

10

11

14

12

1

8

6

9

2AC1BAT

11

RUN_ON

+5V_ALW

EM5209VF

+3.3V_ALW

EM5209VF

+5V_RUN

+3.3V_RUN

+5V_HDD

+3.3V_HDD

ADAPTER

BATTERY

ALWON

+PWR_SRC

SYX198EC 5105

+PWR_SRC

SYX198

+5V_ALW2

+5V_ALW

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

1BAT

2AC

B B

SIO_SLP_WLAN#

+3.3V_ALW

+3.3V_WLAN EM5209VF

11

AUX_EN_WOWL

A A

5

4

+5V_ALW

SY8057QDC

+1.0VS_VCCIO

13

PCH_RSMRST#

5

RESET_OUT#

16

+3.3V_ALW

SIO_SLP_SUS#

SIO_SLP_S4#

10

SIO_SLP_S5#

9

SIO_SLP_LAN#

SIO_SLP_S3#

11

SIO_SLP_A#

+VCC_SA

+VCC_CORE

+VCC_GT

+PWR_SRC

NCP81215

PCH_PWROK

12

IMVP_VR_ON

14

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/01/01

2018/01/01

2018/01/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

3

PCH_PRIM_EN

@SIO_SLP_SUS#

EN_INVPWR

SIO_SLP_S4#

0.6V_DDR_VTT_ON

2020/01/01

2020/01/01

2020/01/01

+3.3V_ALW

EM5209VF

+PWR_SRC

AO6405

+PWR_SRC

SY8210A

+3.3V_ALW_PCH

+BL_PWR_S RC

+1.2V_MEM

+0.6V_DDR_VTT

4

Pop option

+3.3V_SPI

18

12

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

VDDQ

VTT

5 100

5 100

5 100

DDR

0.1

0.1

0.1

5

smd.db-x7.ru

D D

C C

B B

+1.0VS_VCCIO

1 2

RC2 24.9_0402_1%

Trace width=5 mils

,Spacing=15mil

A A

Max length= 600 mils.

PEG_COMP

4

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

PEG_COMP

DMI_CRX_PTX_P0<15>

DMI_CRX_PTX_N0<15> DMI_CTX_PRX_N0 <15>

DMI_CRX_PTX_P1<15>

DMI_CRX_PTX_N1<15>

DMI_CRX_PTX_P2<15>

DMI_CRX_PTX_N2<15>

DMI_CRX_PTX_P3<15>

DMI_CRX_PTX_N3<15>

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_N1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3

DMI_CRX_PTX_N3

G2

D8

E8

E6

F6

D5

E5

J8

J9

CFL-H_BGA1440

UC1C

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

PEG_RCOMP

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

3

CFL-H

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

3 OF 13

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

DMI_CTX_PRX_P0

DMI_CTX_PRX_N0

DMI_CTX_PRX_P1

DMI_CTX_PRX_N1

DMI_CTX_PRX_P2

DMI_CTX_PRX_N2

DMI_CTX_PRX_P3

DMI_CTX_PRX_N3

2

DMI_CTX_PRX_P0 <15>

DMI_CTX_PRX_P1 <15>

DMI_CTX_PRX_N1 <15>

DMI_CTX_PRX_P2 <15>

DMI_CTX_PRX_N2 <15>

DMI_CTX_PRX_P3 <15>

DMI_CTX_PRX_N3 <15>

1

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2018/01/01

2018/01/01

2018/01/01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CFL-H (1/8)

CFL-H (1/8)

CFL-H (1/8)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

A

A

A

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

1

6 100

6 100

6 100

0.1

0.1

0.1

Security Classification

DELL CONFIDENTIAL/PROPRIETARY

Security Classification

5

smd.db-x7.ru

+1.0V_PRIM

@

PAD~D

DDR_XDP_WAN_SMBDAT<18,23,24,67>

DDR_XDP_WAN_SMBCLK<18,23,24,67>

PCH_JTAG_TCK<18>

+1.0V_VCCST

+1.0V_PRIM

1 2

RC216 0_0603_1%@

@ESD@

@ESD@

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

CC334

CC335

2

2

Place near JXDP1

DVT1.0

ESD request reserve,pilot remove 0 ohm

0 ohm:RC841~RC846

1 2

RC841 0_0201_5%XDP@

PCH_RSMRST#_AND_XDP

1

SIO_PWRBTN#<18,58>

PCH_SPI_D0<17>

SYS_PWROK<18,58>

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

CPU_XDP_TCLK

CPU_XDP_PRDY#

CPU_XDP_PREQ#

56.2_0402_1%

100_0402_5%

12

12

RC152

RC157

220_0402_5%

12

RC153

VR_SVID_DATA

CPU_VIDALERT#

+3.3V_ALW_PCH

XDP@

1.5K_0402_5%

12

RC133

SYS_PWROK_R

0.1U_0402_25V6

@

1

CC33

D D

+3.3V_ALW

C C

+1.0V_PRIM_XDP

+1.0VS_VCCIO

+1.0V_VCCSTG

+1.0V_VCCST

+1.0V_VCCST

B B

Place near JXDP1.47

2

XDP@

1.5K_0402_5%

12

RC241

SIO_PWRBTN#_XDP

0.1U_0402_25V6

ESD@

1

Place near JXDP1.41

CC269

2

1 2

RC138 51_0402_5%@

1 2

RC132 150_0402_5%

1 2

RC83 1K_0402_5%

1 2

RC80 1K_0402_5%

1 2

RC166 1K_0402_5%@

1 2

RC71 1K_0402_5%

1 2

RC79 49.9_0402_1%@

1 2

RC218 150_0402_5%@

1 2

RC219 10K_0402_5%@

VR_SVID_DATA<88>

VR_SVID_ALERT#<88>

PCH_RSMRST#_AND<18,63>

T191

CPU_XDP_PREQ#

FIVR_EN_R

PROCHOT#

H_THERMTRIP#

PCH_JTAGX

VCCST_PWRGD

H_CATERR#

FIVR_EN

FIVR_EN

VR_SVID_DATA

VR_SVID_ALERT#

+1.0V_PRIM_XDP

+1.0V_PRIM_XDP

0.1U_0402_25V6

@

1

1

CC28

2

2

FIVR_EN

CFG0

CPU_XDP_TDO H_VCCST_PWRGD_XDP CPU_XDP_TRST#_XDP

0.1U_0402_25V6

@ESD@

12

CC306

1 2

RC228 0_0402_5%@

1 2

RC229 0_0402_5%@

1 2

RC230 0_0402_5%@

1 2

RC143 0_0402_5%@

1 2

RC314 0_0402_5%@

1 2

RC315 0_0402_5%@

+1.0V_VCCSTG

0.1U_0402_25V6

@

CC29

RC124 1K_0402_5%XDP@

RC842 0_0201_5%XDP@

RC217 0_0402_5%@

RC126 1K_0402_5%XDP@

RC128 1K_0402_5%XDP@

RC129 0_0402_5%@

RC846 0_0201_5%XDP@

RC845 0_0201_5%XDP@

RC843 0_0201_5%XDP@

0.1U_0402_25V6

@ESD@

12

CC307

ESD request,Place near JXDP1 side.

just remind to check layout !!

A A

H_PWRGD VCCST_PWRGD H_THERMTRIP#

100P_0402_50V8J

12

CC300ESD@

100P_0402_50V8J

12

CC301ESD@

ESD Reques t:place near CPU side

5

@ESD@

0.1U_0402_25V6

12

CC323

PROCHOT#

12

@ESD@

0.1U_0402_25V6

CC324

VR_SVID_CLK

4

change to small XDP conn,follow merion

Link FP270H-061G1AM done

XDP_PRSNT_PIN1

@ESD@

@ESD@

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

CC336

CC337

2

2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

PCH_JTAG_TMS <18>

PCH_JTAG_TDI <18>

PCH_JTAG_TDO <18>

PCH_JTAGX <18>

PCH_XDP_PRDY# <20>

PCH_XDP_PREQ# <20>

VR_SVID_CLK<88>

PROCHOT#<58,84,88>

DDR_VTT_CTRL<23>

VCCST_PWRGD<59>

H_PWRGD<18>

PLTRST_CPU#<14>

H_PM_SYNC<14>

H_PM_DOWN<14>

H_PECI<14,58>

H_THERMTRIP#<14,23,24,59>

pop RC171 for CNL

depop RC171 for SKL & KBL (CFL CRB rev0.5)

RF Request

1 2

CC325@RF@ 33P_0402_50V8J

4

+1.0V_PRIM_XDP +1.0V_PRIM_XDP

CPU_XDP_PREQ#

CPU_XDP_PRDY#

CFG0

CFG1

CFG2

CFG3

XDP_OBS0_R

XDP_OBS1_R

CFG4

CFG5

CFG6

CFG7

H_VCCST_PWRGD_XDP

SIO_PWRBTN#_XDP

FIVR_EN_R

SYS_PWROK_R

DDR_XDP_WAN_SMBDAT_XDP

DDR_XDP_WAN_SMBCLK_XDP

PCH_JTAG_TCK_XDP

CPU_XDP_TCLK

0.1U_0402_25V6

@ESD@

CC308

PCH_CPU_BCLK_R_D<16>

PCH_CPU_BCLK_R_D#<16>

PCH_CPU_PCIBCLK_R_D<16>

PCH_CPU_PCIBCLK_R_D#<16>

CPU_24MHZ_R_D<16>

CPU_24MHZ_R_D#<16>

VR_SVID_CLK

PROCHOT#

DDR_VTT_CTRL

VCCST_PWRGD VCCST_PWRGD_CPU

H_PWRGD

PLTRST_CPU#

H_PM_SYNC

H_PECI

H_THERMTRIP# H_THERMTRIP#_R

Place close CPU side

XDP@

1 2

RC121 1K_0402_5%

1 2

RC122 0_0402_5%@

CPU XDP

CONN@

JXDP1

2

112

4

334

6

556

8

778

10

9910

12

111112

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

595960

61

GND62GND

1 2

1 2

1 2

1 2

1 2

1 2

PLTRST_CPU#

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

63

PCH_CPU_BCLK_R_D

PCH_CPU_BCLK_R_D#

PCH_CPU_PCIBCLK_R_D

PCH_CPU_PCIBCLK_R_D#

CPU_24MHZ_R_D

CPU_24MHZ_R_D#

CPU_VIDALERT#

VR_SVID_DATA

H_PROCHOT#_R

T26PAD~D @

T25PAD~D @

T31PAD~D @

T32PAD~D @

ESD request 7/25

Close UC1.BP35

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

61

JXT_FP270H-061G1AM

RC84 499_0402_1%

RC78 60.4_0402_1%

RC168 20_0402_5%

RC169 0_0402_5%@

RC319 0_0402_5%@

RC171 0_0402_5%@

3

CFG3

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

PCH_XDP_CLK_DP

PCH_XDP_CLK_DN

CPU_XDP_HOOK6

XDP_DBRESET#

CPU_XDP_TDO

CPU_XDP_TRST#_XDP

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_PRS

CPU_XDP_HOOK6

XDP_DBRESET#

CPU_XDP_TDO

CPU_XDP_TRST#

CPU_XDP_TCLK

H_PM_DOWN_RH_PM_DOWN

H_SKTOCC#

SKL_CNL#

H_CATERR#

1

1

1

1

0.1U_0201_10V6K

@ESD@

1

CC549

2

3

2

CFG11

CFG12

12

@

RC441

1K_0402_5%

12

@

RC442

1K_0402_5%

DMI_ AC_c oupl ed

HALF-SWI NG

DC coupled

FULL-SWI NG

AC coupling

PMSYNC2. 0

LEGACY

PCH_XDP_CLK_DP <16>

PCH_XDP_CLK_DN <16>

RC144 0_0402_5%XDP@

XDP_DBRESET# <15>

RC844 0_0201_5%XDP@

RC127 1K_0402_5%XDP@

1 2

RC115 2.2K_0402_5%XDP@

1 2

RC137 3K_0402_5%

1 2

RC135 51_0402_5%

1 2

RC136 51_0402_5%@

1 2

RC139 51_0402_5%

UC1E

B31

BCLKP

A32

BCLKN

D35

PCI_BCLKP

C36

PCI_BCLKN

E31

CLK24P

D31

CLK24N

BH31

VIDALERT#

BH32

VIDSCK

BH29

VIDSOUT

BR30

PROCHOT#

BT13

DDR_VTT_CNTL

H13

VCCST_PWRGD

BT31

PROCPWRGD

BP35

RESET#

BM34

PM_SYNC

BP31

PM_DOWN

BT34

PECI

J31

THERMTRIP#

BR33

SKTOCC#

BN1

PROC_SELECT#

BM30

CATERR#

AT13

ZVM#

AW13

MSM#

AU13

RSVD1

AY13

RSVD2

CFL-H_BGA1440

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

1 2

1 2

CFL-H

ITP_PMODE_CPU

PCH_SPI_D2_XDP

+1.0V_PRIM_XDP

+3.3V_ALW_PCH

+1.0V_VCCSTG

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

5 OF 13

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

BPM#_0

BPM#_1

BPM#_2

BPM#_3

2018/01/01

2018/01/01

2018/01/01

ITP_PMODE_CPU <18>

CPU_XDP_TRST# <20>

PCH_SPI_D2_XDP <17>

CFG13

BN25

CFG0

BN27

CFG1

BN26

CFG2

BN28

CFG3

BR20

CFG4

BM20

CFG5

BT20

CFG6

BP20

CFG7

BR23

CFG8

BR22

CFG9

BT23

CFG10

BT22

CFG11

BM19

CFG12

BR19

CFG13

BP19

CFG14

BT19

CFG15

BN23

CFG17

BP23

CFG16

BP22

CFG19

BN22

CFG18

XDP_OBS0

BR27

XDP_OBS1

BT27

BM31

BT30

CPU_XDP_TDO

BT28

CPU_XDP_TDI

BL32

CPU_XDP_TMS

BP28

CPU_XDP_TCLK

BR28

CPU_XDP_TRST#

BP30

CPU_XDP_PREQ#

BL30

CPU_XDP_PRDY#

BP27

CFG_RCOMP

BT25

Compal Secret Data

Compal Secret Data

Compal Secret Data

12

@

RC443

1K_0402_5%

12

RC114

49.9_0402_1%

Deciphered Date

Deciphered Date

Deciphered Date

RC239 0_0402_5%@

RC240 0_0402_5%@

1

1

1

1

1

1

1

1 2

1 2

2

SYNC & AYNC MODE

ASYNCHRO NOUS

SYNCHRON OUS

XDP_DBRESET#

@

T184

PAD~D

@

T185

PAD~D

@

T180

PAD~D

@

T181

PAD~D

@

T179

PAD~D

@

T190

PAD~D

@

T189

PAD~D

XDP_OBS0_R

XDP_OBS1_R

2020/01/01

2020/01/01

2020/01/01

1

2

1

CFG10

12

@

RC440

1

1K_0402_5%

0

+1.0VS_VCCIO

RC439

@

1 2

CFG9

1K_0402_5%

12

RC438

1

@

1K_0402_5%

0

CFG8

12

@

RC437

1K_0402_5%

SAFE mode boot

active

Not active10

SVID N OT Present

Present

Not presnet10

CFG UNLOCK

disable

enable10

CFG1

12

CFG0

12

1

0

CFG2

12

0.1U_0201_10V6K

XDP@

CC32

CFG4

12

CFG5

12

CFG6

12

CFG7

12

PCHLESS MODE (CRB)

Reserved CF G lane (EDS)

@

RC436

1K_0402_5%

NORMAL

PCHLESS

Stall reset sequence after PCU

PLL lock until de-asserted

@

RC321

1K_0402_5%

No Sta ll

Stall

PEG LANE REVE RSAL

@

RC181

1K_0402_5%

NORMAL

LANE

REVERSE D

eDP enable

RC322

1K_0402_5%

Disable d

Enabled

PCI Express* Bifurcation

@

RC323

1K_0402_5%

1x8, 2 x4

Reserve d

@

RC324

1K_0402_5%

@

RC325

1K_0402_5%

2x8

1x16

PEG Training

(default) PEG Train

immediately following

RESET# de-assertion

PEG Wait for BIOS for

trai ning

1

0

1

0

1

0

1

0

[6:5 ]

00

01

10

11

1

0

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CFL-H (2/8)

CFL-H (2/8)

CFL-H (2/8)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

B

B

B

LA-H171P

LA-H171P

LA-H171P

Tuesday, March 12, 2019

Tuesday, March 12, 2019

Tuesday, March 12, 2019

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

7 100

7 100

7 100

0.1

0.1

0.1

5

smd.db-x7.ru

DDR_A_DQS#[0..7]<23>

DDR_A_DQS[0..7]<23>

DDR_B_DQS#[0..7]<24>

DDR_B_DQS[0..7]<24>

4

3

2

1

D D

DDR_A_D[0..15]<23>

DDR_A_D[32..47]<23>

C C

B B

DDR_B_D[0..15]<24>

DDR_B_D[32..47]<24>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

UC1A

DDR4(IL)/LP3-DDR4(NIL)

BR6

DDR0_DQ_0/DDR0_DQ_0

BT6

DDR0_DQ_1/DDR0_DQ_1

BP3

DDR0_DQ_2/DDR0_DQ_2

BR3

DDR0_DQ_3/DDR0_DQ_3

BN5

DDR0_DQ_4/DDR0_DQ_4

BP6

DDR0_DQ_5/DDR0_DQ_5

BP2

DDR0_DQ_6/DDR0_DQ_6

BN3

DDR0_DQ_7/DDR0_DQ_7

BL4

DDR0_DQ_8/DDR0_DQ_8

BL5

DDR0_DQ_9/DDR0_DQ_9

BL2

DDR0_DQ_10/DDR0_DQ_10

BM1

DDR0_DQ_11/DDR0_DQ_11

BK4

DDR0_DQ_12/DDR0_DQ_12

BK5

DDR0_DQ_13/DDR0_DQ_13

BK1

DDR0_DQ_14/DDR0_DQ_14

BK2

DDR0_DQ_15/DDR0_DQ_15

BG4

DDR0_DQ_16/DDR0_DQ_32

BG5

DDR0_DQ_17/DDR0_DQ_33

BF4

DDR0_DQ_18/DDR0_DQ_34

BF5

DDR0_DQ_19/DDR0_DQ_35

BG2

DDR0_DQ_20/DDR0_DQ_36

BG1

DDR0_DQ_21/DDR0_DQ_37

BF1

DDR0_DQ_22/DDR0_DQ_38

BF2

DDR0_DQ_23/DDR0_DQ_39

BD2

DDR0_DQ_24/DDR0_DQ_40

BD1

DDR0_DQ_25/DDR0_DQ_41

BC4

DDR0_DQ_26/DDR0_DQ_42

BC5

DDR0_DQ_27/DDR0_DQ_43

BD5

DDR0_DQ_28/DDR0_DQ_44

BD4

DDR0_DQ_29/DDR0_DQ_45

BC1

DDR0_DQ_30/DDR0_DQ_46

BC2

DDR0_DQ_31/DDR0_DQ_47

AB1

DDR0_DQ_32/DDR1_DQ_0

AB2

DDR0_DQ_33/DDR1_DQ_1

AA4

DDR0_DQ_34/DDR1_DQ_2

AA5

DDR0_DQ_35/DDR1_DQ_3

AB5

DDR0_DQ_36/DDR1_DQ_4

AB4

DDR0_DQ_37/DDR1_DQ_5

AA2

DDR0_DQ_38/DDR1_DQ_6

AA1

DDR0_DQ_39/DDR1_DQ_7

V5

DDR0_DQ_40/DDR1_DQ_8

V2

DDR0_DQ_41/DDR1_DQ_9

U1

DDR0_DQ_42/DDR1_DQ_10

U2

DDR0_DQ_43/DDR1_DQ_11

V1

DDR0_DQ_44/DDR1_DQ_12

V4

DDR0_DQ_45/DDR1_DQ_13

U5

DDR0_DQ_46/DDR1_DQ_14

U4

DDR0_DQ_47/DDR1_DQ_15

R2

DDR0_DQ_48/DDR1_DQ_32

P5

DDR0_DQ_49/DDR1_DQ_33

R4

DDR0_DQ_50/DDR1_DQ_34

P4

DDR0_DQ_51/DDR1_DQ_35

R5

DDR0_DQ_52/DDR1_DQ_36

P2

DDR0_DQ_53/DDR1_DQ_37

R1

DDR0_DQ_54/DDR1_DQ_38

P1

DDR0_DQ_55/DDR1_DQ_39

M4

DDR0_DQ_56/DDR1_DQ_40

M1

DDR0_DQ_57/DDR1_DQ_41

L4

DDR0_DQ_58/DDR1_DQ_42

L2

DDR0_DQ_59/DDR1_DQ_43

M5

DDR0_DQ_60/DDR1_DQ_44

M2

DDR0_DQ_61/DDR1_DQ_45

L5

DDR0_DQ_62/DDR1_DQ_46

L1

DDR0_DQ_63/DDR1_DQ_47

LP3/DDR4

BA2

NC/DDR0_ECC_0

BA1

NC/DDR0_ECC_1

AY4

NC/DDR0_ECC_2

AY5

NC/DDR0_ECC_3

BA5

NC/DDR0_ECC_4

BA4

NC/DDR0_ECC_5

AY1

NC/DDR0_ECC_6

AY2

NC/DDR0_ECC_7

CFL-H_BGA1440

CFL-H

DDR CHANNEL A

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKN_1/DDR0_CKN_1

NC/DDR0_CKP_2

NC/DDR0_CKN_2

NC/DDR0_CKP_3

NC/DDR0_CKN_3

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/DDR0_CKE_2

DDR0_CKE_3/DDR0_CKE_3

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

NC/DDR0_CS#_2

NC/DDR0_CS#_3

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_ODT_2

NC/DDR0_ODT_3

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAA_9/DDR0_BG_1

DDR0_CAA_8/DDR0_ACT#

NC/DDR0_PAR

NC/DDR0_ALERT#

DDR4(IL)/LP3-DDR4(NIL)

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSP_7/DDR1_DQSP_5

DDR0_DQSP_8/DDR0_DQSP_8

DDR0_DQSN_8/DDR0_DQSN_8

1 OF 13

LP3/DDR4

UC1B

DDR_A_CLK0

AG1

DDR_A_CLK#0

AG2

AK2

DDR_A_CLK#1 DDR_B_CLK#1

AK1

AL3

AK3

AL2

AL1

DDR_A_CKE0

AT1

DDR_A_CKE1

AT2

AT3

AT5

DDR_A_CS#0

AD5

DDR_A_CS#1

AE2

AD2

AE5

DDR_A_ODT0

AD3

DDR_A_ODT1

AE4

AE1

AD4

DDR_A_BA0

AH5

DDR_A_BA1

AH1

DDR_A_BG0

AU1

DDR_A_MA16

AH4

DDR_A_MA14

AG4

DDR_A_MA15

AD1

DDR_A_MA0

AH3

DDR_A_MA1

AP4

DDR_A_MA2

AN4

DDR_A_MA3

AP5

DDR_A_MA4

AP2

DDR_A_MA5

AP1

DDR_A_MA6

AP3

DDR_A_MA7

AN1

DDR_A_MA8

AN3

DDR_A_MA9

AT4

DDR_A_MA10

AH2

DDR_A_MA11

AN2

DDR_A_MA12

AU4

DDR_A_MA13

AE3

DDR_A_BG1

AU2

DDR_A_ACT#

AU3

DDR_A_PAR

AG3

DDR_A_ALERT#

AU5

DDR_A_DQS#0

BR5

DDR_A_DQS#1

BL3

DDR_A_DQS#4

BG3

DDR_A_DQS#5

BD3

DDR_B_DQS#0

AA3

DDR_B_DQS#1

U3

DDR_B_DQS#4

P3

DDR_B_DQS#5

L3

DDR_A_DQS0

BP5

DDR_A_DQS1

BK3

DDR_A_DQS4

BF3

DDR_A_DQS5

BC3

DDR_B_DQS0

AB3

DDR_B_DQS1

V3

DDR_B_DQS4

R3

DDR_B_DQS5

M3

AY3

BA3

DDR_A_CLK0 <23>

DDR_A_CLK#0 <23>

DDR_A_CLK1 <23>

DDR_A_CLK#1 <23> DDR_B_CLK#1 <24>

DDR_A_CKE0 <23>

DDR_A_CKE1 <23>

DDR_A_CS#0 <23>

DDR_A_CS#1 <23>

DDR_A_ODT0 <23>

DDR_A_ODT1 <23>

DDR_A_BA0 <23>

DDR_A_BA1 <23>

DDR_A_BG0 <23>

DDR_A_MA[0..16] <23>

DDR_A_BG1 <23>

DDR_A_ACT# <23>

DDR_A_PAR <23>

DDR_A_ALERT# <23>

DDR_A_DQS#0 <23>

DDR_A_DQS#1 <23>

DDR_A_DQS#4 <23>

DDR_A_DQS#5 <23>

DDR_B_DQS#0 <24>

DDR_B_DQS#1 <24>

DDR_B_DQS#4 <24>

DDR_B_DQS#5 <24>

DDR_A_DQS0 <23>

DDR_A_DQS1 <23>

DDR_A_DQS4 <23>

DDR_A_DQS5 <23>

DDR_B_DQS0 <24>

DDR_B_DQS1 <24>

DDR_B_DQS4 <24>

DDR_B_DQS5 <24>

DDR_A_D[16..31]<23>

DDR_A_D[48..63]<23>

DDR_B_D[16..31]<24>

DDR_B_D[48..63]<24>

1 2

RC5 121_0402_1%

1 2

RC6 75_0402_1%

1 2

RC7 100_0402_1%

Trace width=12-15 mils

,Spacing=20mil

Max length= 500 mils.

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

DDR4(IL)/LP3-DDR4(NIL)

BT11

DDR1_DQ_0/DDR0_DQ_16

BR11

DDR1_DQ_1/DDR0_DQ_17

BT9

DDR1_DQ_2/DDR0_DQ_18

BR8

DDR1_DQ_3/DDR0_DQ_19

BP11

DDR1_DQ_4/DDR0_DQ_20

BN11

DDR1_DQ_5/DDR0_DQ_21

BP8

DDR1_DQ_6/DDR0_DQ_22

BN8

DDR1_DQ_7/DDR0_DQ_23

BL12

DDR1_DQ_8/DDR0_DQ_24

BL11

DDR1_DQ_9/DDR0_DQ_25

BL8

DDR1_DQ_10/DDR0_DQ_26

BJ8

DDR1_DQ_11/DDR0_DQ_27

BJ11

DDR1_DQ_12/DDR0_DQ_28

BJ10

DDR1_DQ_13/DDR0_DQ_29

BL7

DDR1_DQ_14/DDR0_DQ_30

BJ7

DDR1_DQ_15/DDR0_DQ_31

BG11

DDR1_DQ_16/DDR0_DQ_48

BG10

DDR1_DQ_17/DDR0_DQ_49

BG8

DDR1_DQ_18/DDR0_DQ_50

BF8

DDR1_DQ_19/DDR0_DQ_51

BF11

DDR1_DQ_20/DDR0_DQ_52

BF10

DDR1_DQ_21/DDR0_DQ_53

BG7

DDR1_DQ_22/DDR0_DQ_54

BF7

DDR1_DQ_23/DDR0_DQ_55

BB11

DDR1_DQ_24/DDR0_DQ_56

BC11

DDR1_DQ_25/DDR0_DQ_57

BB8

DDR1_DQ_26/DDR0_DQ_58

BC8

DDR1_DQ_27/DDR0_DQ_59

BC10

DDR1_DQ_28/DDR0_DQ_60

BB10

DDR1_DQ_29/DDR0_DQ_61

BC7

DDR1_DQ_30/DDR0_DQ_62

BB7

DDR1_DQ_31/DDR0_DQ_63

AA11

DDR1_DQ_32/DDR1_DQ_16

AA10

DDR1_DQ_33/DDR1_DQ_17

AC11

DDR1_DQ_34/DDR1_DQ_18

AC10

DDR1_DQ_35/DDR1_DQ_19

AA7

DDR1_DQ_36/DDR1_DQ_20

AA8

DDR1_DQ_37/DDR1_DQ_21

AC8

DDR1_DQ_38/DDR1_DQ_22

AC7

DDR1_DQ_39/DDR1_DQ_23

DDR4(IL)/LP3-DDR4(NIL)

W8

DDR1_DQ_40/DDR1_DQ_24

W7

DDR1_DQ_41/DDR1_DQ_25

V10

DDR1_DQ_42/DDR1_DQ_26

V11

DDR1_DQ_43/DDR1_DQ_27

W11

DDR1_DQ_44/DDR1_DQ_28

W10

DDR1_DQ_45/DDR1_DQ_29

V7

DDR1_DQ_46/DDR1_DQ_30

V8

DDR1_DQ_47/DDR1_DQ_31

R11

DDR1_DQ_48/DDR1_DQ_48

P11

DDR1_DQ_49/DDR1_DQ_49

P7

DDR1_DQ_50/DDR1_DQ_50

R8

DDR1_DQ_51/DDR1_DQ_51

R10

DDR1_DQ_52/DDR1_DQ_52

P10

DDR1_DQ_53/DDR1_DQ_53

R7

DDR1_DQ_54/DDR1_DQ_54

P8

DDR1_DQ_55/DDR1_DQ_55

L11

DDR1_DQ_56/DDR1_DQ_56

M11

DDR1_DQ_57/DDR1_DQ_57

L7

DDR1_DQ_58/DDR1_DQ_58

M8

DDR1_DQ_59/DDR1_DQ_59

L10

DDR1_DQ_60/DDR1_DQ_60

M10

DDR1_DQ_61/DDR1_DQ_61

M7

DDR1_DQ_62/DDR1_DQ_62

L8

DDR1_DQ_63/DDR1_DQ_63

LP3/DDR4

AW11

NC/DDR1_ECC_0

AY11

NC/DDR1_ECC_1

AY8

NC/DDR1_ECC_2

AW8

NC/DDR1_ECC_3

AY10

NC/DDR1_ECC_4

AW10

NC/DDR1_ECC_5

AY7

NC/DDR1_ECC_6

AW7

NC/DDR1_ECC_7

G1

DDR_RCOMP_0

H1

DDR_RCOMP_1

J2

DDR_RCOMP_2

CFL-H_BGA1440

CFL-H

DDR CHANNEL B

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/DDR1_CKE_2

DDR1_CKE_3/DDR1_CKE_3

DDR1_ODT_0/DDR1_ODT_0

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSP_7/DDR1_DQSP_7

DDR1_DQSP_8/DDR1_DQSP_8

DDR1_DQSN_8/DDR1_DQSN_8

2 OF 13

LP3/DDR4

NC/DDR1_CKP_2

NC/DDR1_CKN_2

NC/DDR1_CKP_3

NC/DDR1_CKN_3

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

NC/DDR1_CS#_2

NC/DDR1_CS#_3

NC/DDR1_ODT_1

NC/DDR1_ODT_2

NC/DDR1_ODT_3

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

NC/DDR1_PAR

NC/DDR1_ALERT#

DDR4(IL)/LP3-DDR4(NIL)

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM7

AM8

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BN9

BL9

BG9

BC9

AC9

W9

R9

M9

BP9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_CLK1DDR_A_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA16

DDR_B_MA14

DDR_B_MA15

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_PAR

DDR_B_ALERT#

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#6

DDR_A_DQS#7

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#6

DDR_B_DQS#7

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS6

DDR_A_DQS7

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS6

DDR_B_DQS7

+DDR_VREF_CA

1

PAD~D

+DDR_VREF_B_DQ

DDR_B_CLK0 <24>

DDR_B_CLK#0 <24>

DDR_B_CLK1 <24>

DDR_B_CKE0 <24>

DDR_B_CKE1 <24>

DDR_B_CS#0 <24>

DDR_B_CS#1 <24>

DDR_B_ODT0 <24>

DDR_B_ODT1 <24>

DDR_B_MA[0..16] <24>

DDR_B_BA0 <24>

DDR_B_BA1 <24>

DDR_B_BG0 <24>

DDR_B_BG1 <24>

DDR_B_ACT# <24>

DDR_B_PAR <24>

DDR_B_ALERT# <24>

DDR_A_DQS#2 <23>

DDR_A_DQS#3 <23>

DDR_A_DQS#6 <23>

DDR_A_DQS#7 <23>

DDR_B_DQS#2 <24>

DDR_B_DQS#3 <24>

DDR_B_DQS#6 <24>

DDR_B_DQS#7 <24>

DDR_A_DQS2 <23>

DDR_A_DQS3 <23>

DDR_A_DQS6 <23>

DDR_A_DQS7 <23>

DDR_B_DQS2 <24>

DDR_B_DQS3 <24>

DDR_B_DQS6 <24>

DDR_B_DQS7 <24>

@

T199

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/01/01

2018/01/01

2018/01/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CFL-H (3/8)

CFL-H (3/8)

CFL-H (3/8)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

B

B

B

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

8 100

8 100

8 100

0.1

0.1

0.1

5

smd.db-x7.ru

D D

4

3

2

1

UC1D

CPU_DP1_P0<42>

CPU_DP1_N0<42>

CPU_DP1_P1<42>

CPU_DP1_N1<42>

AR P0

C C

AR P1

HDMI

B B

CPU_DP1_P2<42>

CPU_DP1_N2<42>

CPU_DP1_P3<42>

CPU_DP1_N3<42>

CPU_DP1_AUXP<42>

CPU_DP1_AUXN<42>

CPU_DP2_P0<42>

CPU_DP2_N0<42>

CPU_DP2_P1<42>

CPU_DP2_N1<42>

CPU_DP2_P2<42>

CPU_DP2_N2<42>

CPU_DP2_P3<42>

CPU_DP2_N3<42>

CPU_DP2_AUXP<42>

CPU_DP2_AUXN<42>

CPU_DP3_P0<40>

CPU_DP3_N0<40>

CPU_DP3_P1<40>

CPU_DP3_N1<40>

CPU_DP3_P2<40>

CPU_DP3_N2<40>

CPU_DP3_P3<40>

CPU_DP3_N3<40>

CPU_DP3_AUXP<40>

CPU_DP3_AUXN<40>

CPU_DP1_P0

CPU_DP1_N0

CPU_DP1_P1

CPU_DP1_N1

CPU_DP1_P2

CPU_DP1_N2

CPU_DP1_P3

CPU_DP1_N3

CPU_DP1_AUXP

CPU_DP1_AUXN

CPU_DP2_P0

CPU_DP2_N0

CPU_DP2_P1

CPU_DP2_N1

CPU_DP2_P2

CPU_DP2_N2

CPU_DP2_P3

CPU_DP2_N3

CPU_DP2_AUXP

CPU_DP2_AUXN

CPU_DP3_P0

CPU_DP3_N0

CPU_DP3_P1

CPU_DP3_N1

CPU_DP3_P2

CPU_DP3_N2

CPU_DP3_P3

CPU_DP3_N3

CPU_DP3_AUXP

CPU_DP3_AUXN

K36

DDI1_TXP_0

K37

DDI1_TXN_0

J35

DDI1_TXP_1

J34

DDI1_TXN_1

H37

DDI1_TXP_2

H36

DDI1_TXN_2

J37

DDI1_TXP_3

J38

DDI1_TXN_3

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP_0

H33

DDI2_TXN_0

F37

DDI2_TXP_1

G38

DDI2_TXN_1

F34

DDI2_TXP_2

F35

DDI2_TXN_2

E37

DDI2_TXP_3

E36

DDI2_TXN_3

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP_0

D34

DDI3_TXN_0

B36

DDI3_TXP_1

B34

DDI3_TXN_1

F33

DDI3_TXP_2

E33

DDI3_TXN_2

C33

DDI3_TXP_3

B33

DDI3_TXN_3

A27

DDI3_AUXP

B27

DDI3_AUXN

CFL-H_BGA1440

CFL-H

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXP_2

EDP_TXN_2

EDP_TXP_3

EDP_TXN_3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

DISP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

4 of 13

D29

E29

F28

E28

A29

B29

C28

B28

C26

B26

A33

D37

G27

G25

G29

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

EDP_AUXP

EDP_AUXN

1

EDP_COMP

AUD_AZACPU_SCLK

AUD_AZACPU_SDO

AUD_AZACPU_SDI

@

T194

PAD~D

AUD_AZACPU_SDI AUD_AZACPU_SDI_R

EDP_TXP0 <38>

EDP_TXN0 <38>

EDP_TXP1 <38>

EDP_TXN1 <38>

EDP_AUXP <38>

EDP_AUXN <38>

AUD_AZACPU_SCLK <18>

AUD_AZACPU_SDO <18>

1 2

RC66 20_0402_5%

EDP_COMP

min Trace width=5 mils

,Spacing=20mil

Max length= 600 mils.

AUD_AZACPU_SDI_R <18>

+1.0VS_VCCIO

1 2

RC1 24.9_0402_1%

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2018/01/01

2018/01/01

2018/01/01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CFL-H (4/8)

CFL-H (4/8)

CFL-H (4/8)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

A

A

A

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

1

9 100

9 100

9 100

0.1

0.1

0.1

5

smd.db-x7.ru

D D

C C

4

CFL-H

UC1M

1

T4PAD~D @

IST_TRIG

1

T3PAD~D @

1

T2PAD~D @

1

T1PAD~D @

1

T5PAD~D @

1

T6PAD~D @

1

T7PAD~D @

1

T9PAD~D @

1

T10PAD~D @

1

T11PAD~D @

1

T8PAD~D @

1

T14PAD~D @

1

T13PAD~D @

1

T15PAD~D @

1

T12PAD~D @

1

T28PAD~D @

1

T27PAD~D @

VSS_A36

VSS_A37

PCH_2_CPU_TRIGGER<20>

PCH_2_CPU_TRIGGER

CPU_2_PCH_TRIGGER_R

TP_SKL_F30

1

T285PAD~D @

TP_SKL_E30

1

T284PAD~D @

1

T18PAD~D @

1

T19PAD~D @

1

T21PAD~D @

1

T20PAD~D @

1

T23PAD~D @

1

T24PAD~D @

1

T22PAD~D @

BN35

BN33

BL34

AE29

AA14

AP29

AP14

BR35

BR31

BH30

E2

E3

E1

D1

BR1

BT2

J24

H24

N29

R14

A36

A37

H23

J23

F30

E30

B30

C30

G3

J3

RSVD_TP5

IST_TRIG

RSVD_TP4

RSVD_TP3

RSVD_TP1

RSVD_TP2

RSVD15

RSVD28

RSVD27

RSVD14

RSVD13

RSVD30

RSVD31

RSVD2

RSVD1

RSVD5

RSVD4

VSS_A36

VSS_A37

PROC_TRIGIN

PROC_TRIGOUT

RSVD24

RSVD23

RSVD7

RSVD21

RSVD26

RSVD29

RSVD19

RSVD18

RSVD9

CFL-H_BGA1440

13 OF 13

RSVD11

RSVD10

RSVD12

RSVD3

RSVD25

RSVD22

RSVD20

RSVD17

RSVD16

RSVD8

RSVD6

3

BK28

BJ28

BL31

AJ8

G13

C38

C1

BR2

BP1

B38

B2

1

T29 PAD~D@

1

T30 PAD~D@

1

T44 PAD~D@

1

T41 PAD~D@

1

T42 PAD~D@

1

T49 PAD~D@

1

T48 PAD~D@

1

T47 PAD~D@

1

T46 PAD~D@

1

T45 PAD~D@

1

T43 PAD~D@

2

1

B B

CPU_2_PCH_TRIGGER<20>

VSS_A36

VSS_A37

1 2

RC177 30_0402_5%

1 2

RC178 0_0402_5%@

1 2

RC179 0_0402_5%@

CPU_2_PCH_TRIGGER_RCPU_2_PCH_TRIGGER

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/01/01

2018/01/01

2018/01/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2020/01/01

2020/01/01

2020/01/01

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CFL-H (5/8)

CFL-H (5/8)

CFL-H (5/8)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

B

B

B

LA-H171P

LA-H171P

LA-H171P

Friday, March 08, 2019

Friday, March 08, 2019

Friday, March 08, 2019

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

10 100

10 100

10 100

0.1

0.1

0.1

5

smd.db-x7.ru

4

3

2

1

+GT_CORE

AT14

AT31

AT32

AT33

AT34

D D

C C

B B

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BP37

BP38

BR15

BR16

BR17

UC1K

VCCGT1

VCCGT2

VCCGT3

VCCGT4

VCCGT5

VCCGT6

VCCGT7

VCCGT8

VCCGT9

VCCGT10

VCCGT11

VCCGT12

VCCGT13

VCCGT14

VCCGT15

VCCGT16

VCCGT17

VCCGT18

VCCGT19

VCCGT20

VCCGT21

VCCGT22

VCCGT23

VCCGT24

VCCGT25

VCCGT26

VCCGT27

VCCGT28

VCCGT29

VCCGT30

VCCGT31

VCCGT32

VCCGT33