A

1 1

B

C

D

E

Compal

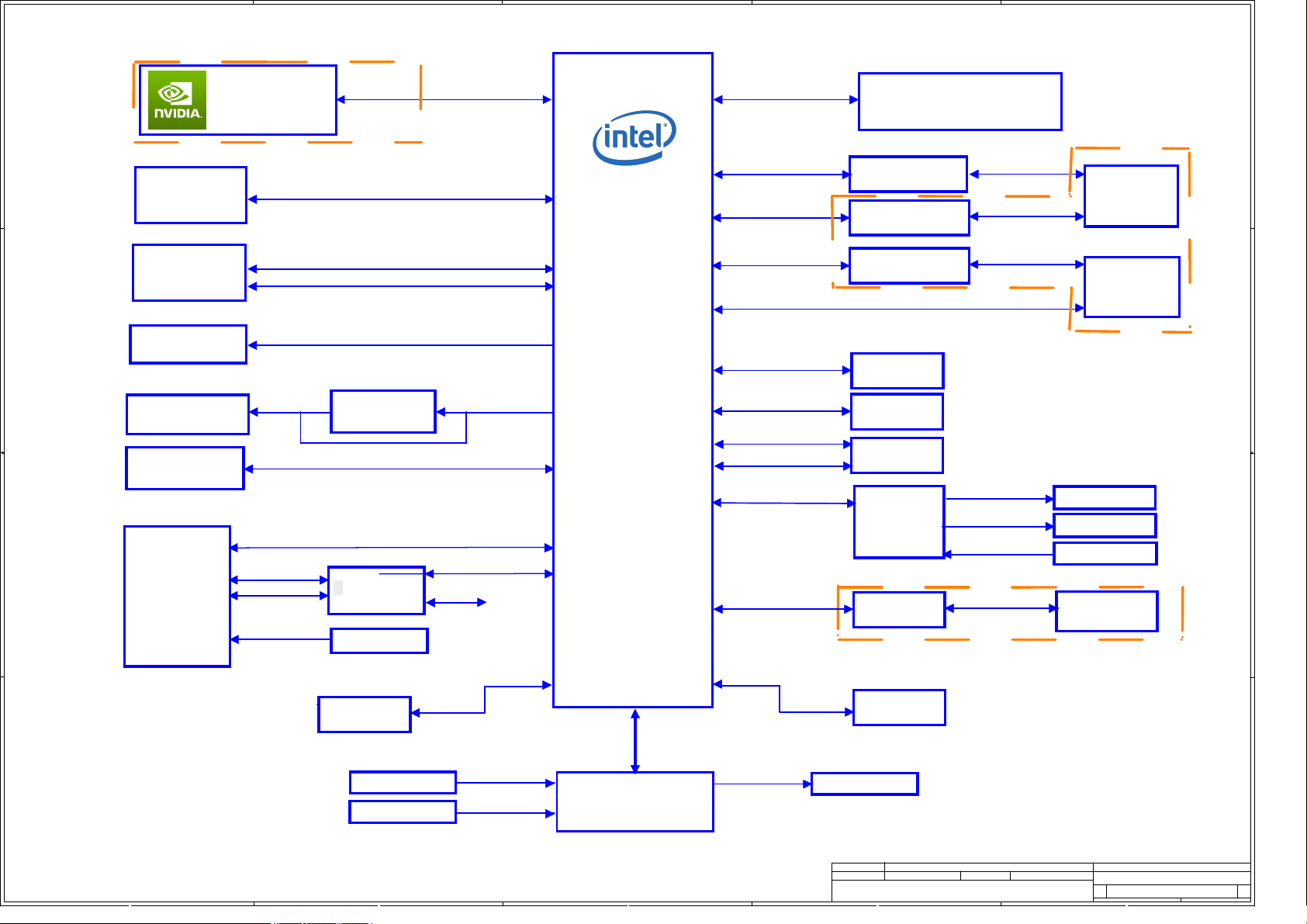

EL5C3/EL531/EL431

2 2

DIS

In

M/B Schematic Document

tel Whiskey Lake Processor with DDR4

2018-09-20

3 3

LA-H101P

REV: 0.A (EVT)

4 4

Security Classific ation

Security Classific ation

Security Classific ation

Is s u ed Date

Is s u ed Date

Is s u ed Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, IN C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, IN C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, IN C . AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

A

B

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

C

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Compal S ecret Data

Compal S ecret Data

Compal S ecret Data

Deciphered Date

Deciphered Date

Deciphered Date

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

Tit le

Tit le

Tit le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

C

LA-H101P

LA-H101P

LA-H101P

Cover Page

Cover Page

Cover Page

E

0.A0.A0.A

of

1 51Thursday, September 20, 2018

of

1 51Thursday, September 20, 2018

of

1 51Thursday, September 20, 2018

A

B

C

D

E

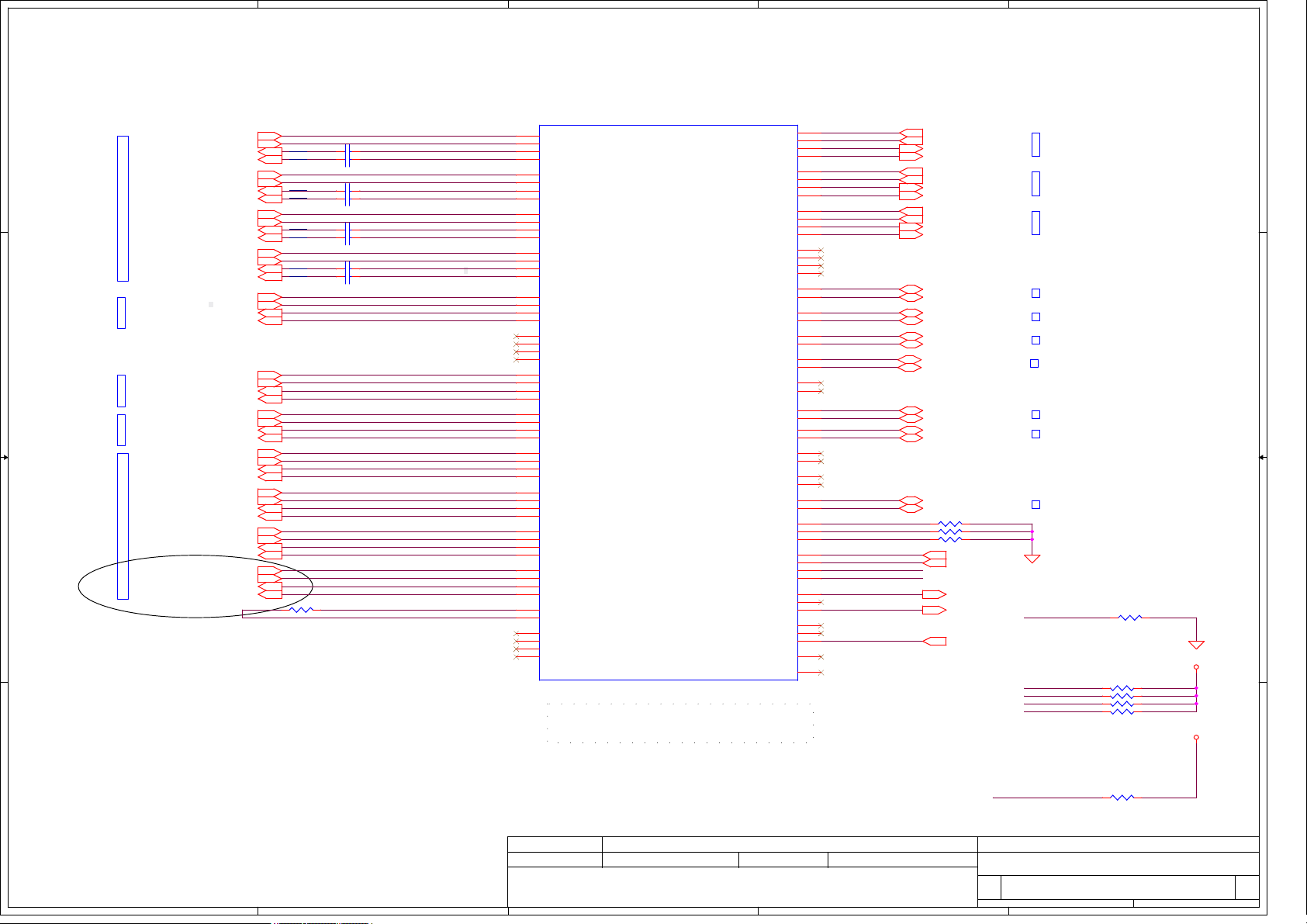

N17S-G0/G2

R4 2400MHz

PCI

TD

P:18W

1 1

FF (Key M)

NG

C

IE/SATA SSD

P

2242/2280 c o n n .

FF (Key E)

NG

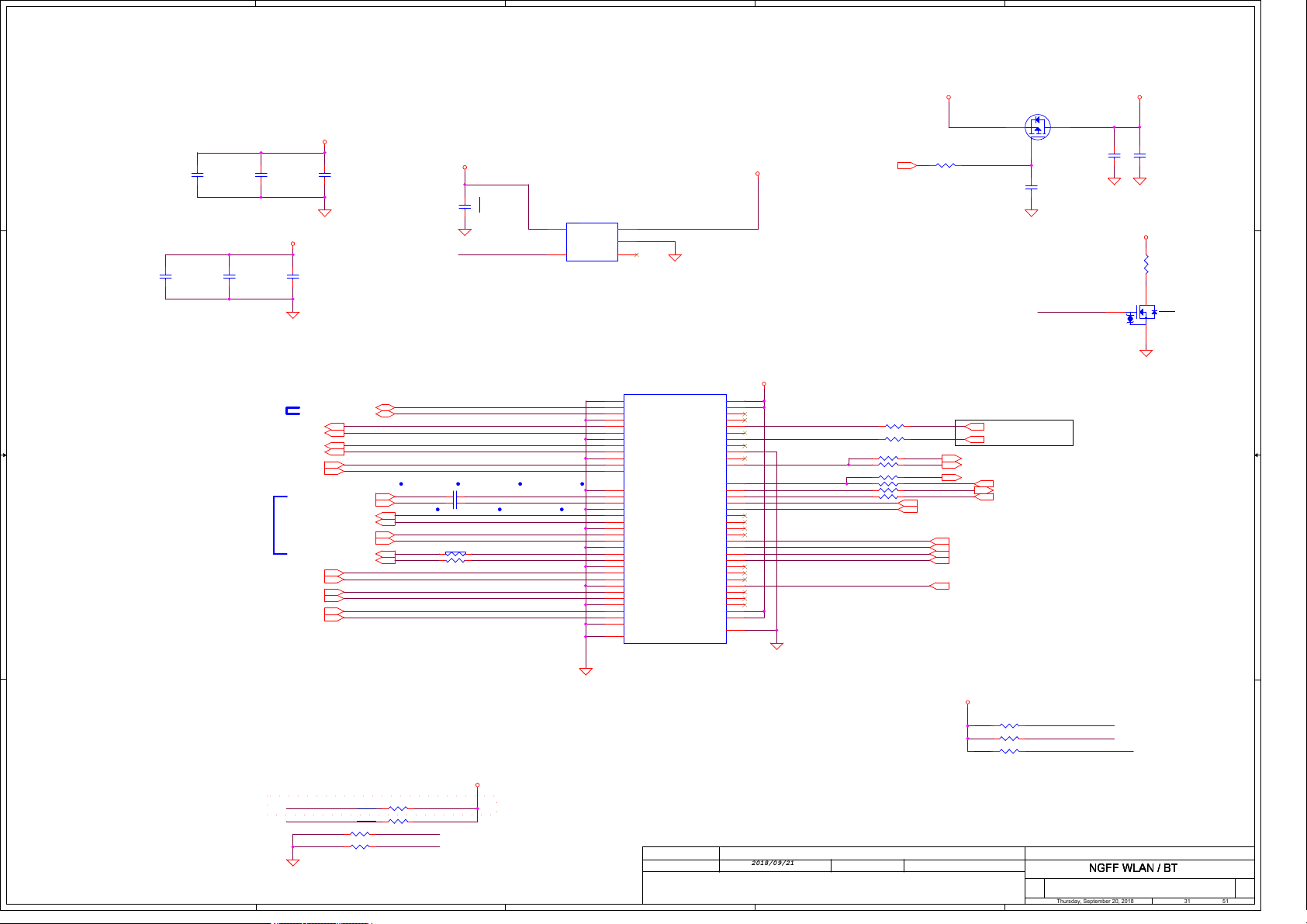

WLAN/BT

2230 c o n n .

eD

2 2

FH

P P a n e l

D L C D

HDMI Conn.

H

D Conn.

D

VRAM(GDDR5) X2

2GB

for DIS

HD

MI Re-driver

8407A

PS

e x4 , Gen3 8Gb /s

PC

Ie x4 , Gen38Gb/s

SATA , Gen3 6Gb/s

PCI e x1 , Gen12.5Gb/s

U

B2.0 x1, 480Mb/s

S

eDP x2 , HBR 2.7Gb/s

I x4 , 2.97GT/s

DD

SATA , Gen3 6Gb /s

Whiskey Lake-U

15W

USB2.0 x1, 480Mb/s

3 3

T y p e - C Conn.

US

B3. 1 Gen1

B3. 1,G en1

US

CC

/Vco nn

VBus

MUX/CC

a l t e k RTS5448

R e

w i t c h

5V S

T o

u c h P a d

I2

C_3VL P

B3.1x1,Gen1

US

EC

I2

C

FAB#TA601

1528pin

BGA

DD

USB2 .0 x1, 480Mb/s

USB3.1 x1, Gen1 5Gb/s

S

B3.1 x1, Gen1 5Gb/s

U

US

B2.0 x1, 480Mb/s

US

B2.0 x1, 480Mb/s

US

B2.0 x1, 480Mb/s

B2.0 x1, 480Mb/s

US

C

I2

A

HD

Ie x1 , Gen12.5Gb/s

PC

I

SP

-A DDR4-SO-DIMM X1

CH

CH-B o n b oa rd RAM x4

B Charge r

US

TI S

N1702001

US

B3 redriver

Pa

rade PS8713B

USB3 redriver

rade PS8713B

Pa

FingerPrint

t. C amera

In

T

h P a n e l

ouc

io Codec

Aud

a l t e k ALC3287

Re

Ca

rd Reader

Re

a l t e k RTS5232S

I R O M

SP

MB

16

US

B2.0 x1, 480Mb/s

U

B3.1 x1, Gen1 5Gb/s

S

USB3.1 x1, Gen1 5Gb/s

HP

SP

K

DMIC

IO

SD

O

ub Boa rd

n S

USB Conn.

with A O U

U

B Conn.

S

Combo Jack

Int. Speaker

t. Array Mic *2

In

SD C

ard Conn.

On S

ub Boa rd

LPC

D

4 4

A

Int. KBD

Hall Sensor

B

KB

EN

E KB9022

C

C

LE

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THISSHEET OF ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPALELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THISSHEET OF ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPALELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THISSHEET OF ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPALELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND T RADE SECRET INFORMATION. THISSHEET MAYNOT BE TRANSFERED FROM THECUSTODY OFTHECOMPET ENT DIVISIONOF R&D

AND T RADE SECRET INFORMATION. THISSHEET MAYNOT BE TRANSFERED FROM THECUSTODY OFTHECOMPET ENT DIVISIONOF R&D

AND T RADE SECRET INFORMATION. THISSHEET MAYNOT BE TRANSFERED FROM THECUSTODY OFTHECOMPET ENT DIVISIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, I N C. NEITHER THISSHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, I N C. NEITHER THISSHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, I N C. NEITHER THISSHEET NOR THE INFORMATIONIT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC .

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC .

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC .

D

CompalSecret Data

CompalSecret Data

CompalSecret Data

Deciphered Date

Deciphered Date

Deciphered Date

Com

Com

Compal Electroni cs, Inc.

pal Electronic s, Inc.

Ti t l e

Ti t l e

Ti t l e

Size

Size

Size

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

pal Electronic s, Inc.

Block Diagram

Block Diagram

Block Diagram

Document N um b e r Rev

Document N um b e r Rev

Document N um b e r Rev

LA-H101P

LA-H101P

LA-H101P

E

2 51Thursday, September 20, 2018

2 51Thursday, September 20, 2018

2 51Thursday, September 20, 2018

0.A0.A0.A

of

of

of

1

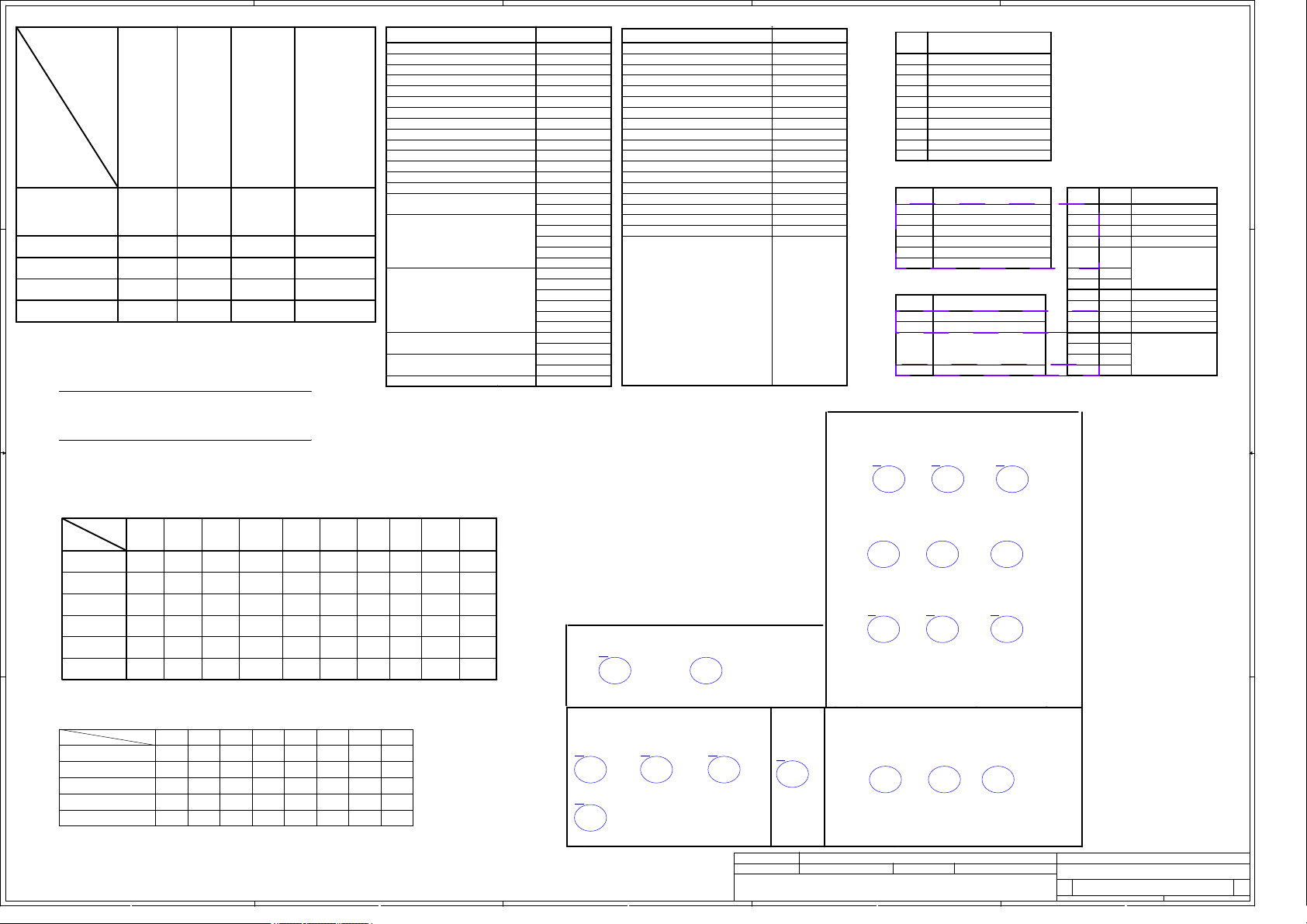

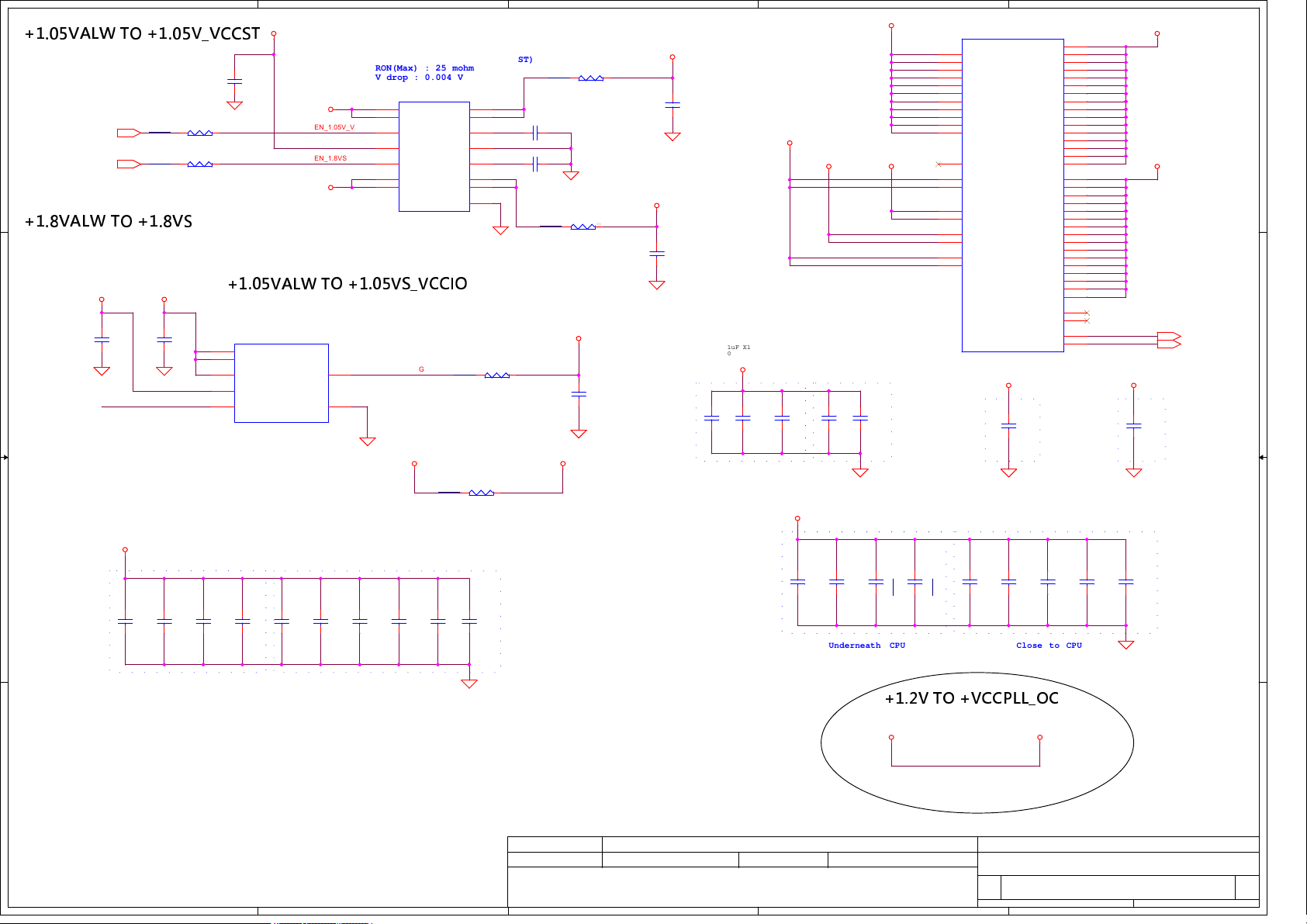

V

oltage Rails

5VS

A

d d r e s s

10

01 100x 98h

A

d d r e s s

001 111x 9Eh

1

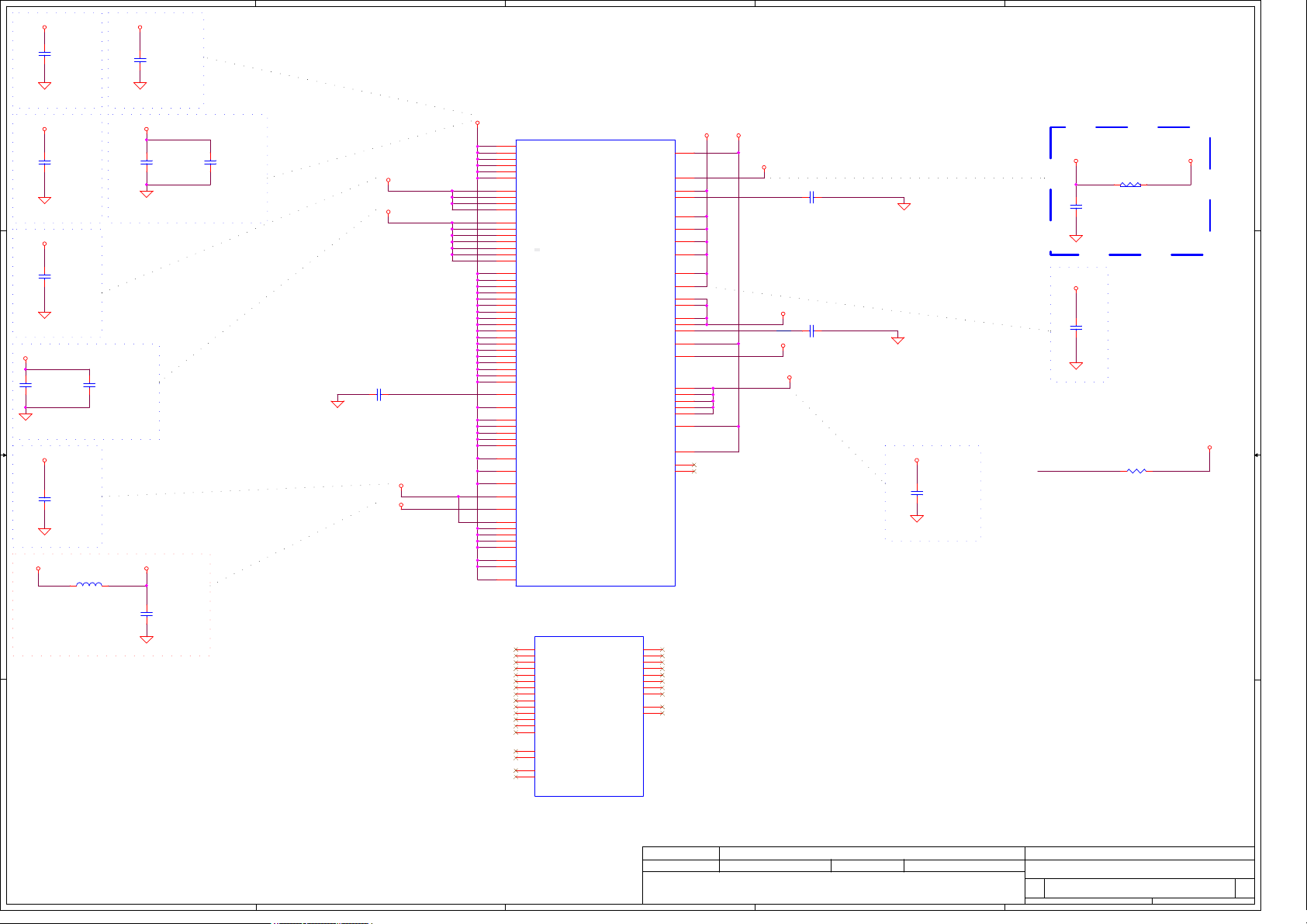

+

+

3VS

+VCCPLL_OC

1.05VS_VCCSTG

+

+

VCC_CORE

+VCC_GT

+VCC_SA

+1.05V_VCCST

+1.05VS_VCCIO

+1.8VS

+0.6VS

X

XX

X

XXX

ower

p

plane

+

CT7718W

1.2V

+2.5V

O O

O

X

+5VALW

3VALW

+

B

+

1.8VALW

A A

State

S

0

S3

S5 S4/AC

5 S4/ Battery only

S

S5 S4/AC & Battery

don't exist

B B

E

C SM Bus1 address

De vi c e

SmartBat tery

CH SM Bus address

P

De vi c e

DDR_JDIMM1

T o u c h Pad

A

d d r e s s

0001 011x 16h

Address

10 000x A0h

10

+

+1.05VALW

O

O

O

O

O

O

O

X

X

E

C SM Bus2 address

De vi c e

N

PU SM Bus address

G

De vi c e

Internalth ermal sensor

2

B

OM Structure Table

OM Structure

Item

DIS Only Components DIS@

U

MA Only Components UMA@

HDMI

Logo 45@

Memory Down - DDP Package

C

onnectors ME@

Intel CNVi

ESD Category ESD@

R

F Category RF@

Test Point TP@

Keyboard BackLight

Project select

GPU select

Memory Down select

MIC select

TypeC 20V_PRTCT 20V_PRTCT@

B

TS@Touch Screen

SDP@Memory Down - SDP Package

DDP@

GC6@GPU GC6 Components

NOGC6@Un-Mount GPU GC6 Components

CNVi@

EMI@EMI Category

KBL@

NOKBL@

S540@

S340@

C340@

S340_14@

S340_15@

N17S_G1@

N17S_G0@

N16V@

N16S@

N16@

N17@

MD@

NO_MD@

Arrary_MIC@

Single_MIC@

3

OM Structure

Item

S340_15 MD (Hynix 4GB)

S340_15 MD (Micron 4GB)

S340_15 MD (Samsung 4GB)

C340 MD (Hynix 4GB)

C340 MD (Micron 4GB)

C340 MD (Samsung 4GB)

On Board RAM X76 Resistors X76RAM@

S340_15@ VRAM (Hynix 2GB)

S340_15@ VRAM (Micron 2GB)

S340_15@ VRAM (Samsung 2GB)

C340 VRAM (Hynix 2GB)

C340 VRAM (Micron 2GB)

C340 VRAM (Samsung 2GB)

S340_14 MD (Hynix 4GB)

S340_14 MD (Micron 4GB)

S340_14 MD (Samsung 4GB)

S340_14@ VRAM (Hynix 2GB)

S340_14@ VRAM (Micron 2GB)

S340_14@ VRAM (Samsung 2GB)

B

H4G_S340_15@

M4G_S340_15@

S4G_S340_15@

H4G_C340@

M4G_C340@

S4G_C340@

VH2G_S340_15@

VM2G_S340_15@

VS2G_S340_15@

VH2G_C340@

VM2G_C340@

VS2G_C340@

H

4G_S340_14@

M4G_S340_14@

S4G_S340_14@

VH2G_S340_14@

VM2G_S340_14@

VS2G_S340_14@

4

SB 2.0 Port Table

U

External

1

SB2/3 Port (IO - 1)

U

2

USB2/3 Port (IO - 2)

3

USB2/3 Port (Type-C)

4

T

ouch Sc reen

5

6

Camer a

7

ingrt P rint

F

8

9

10

NGFF WLAN+BT

SB 3.0 Port Table PCIE Port Table

U

P

ort

1

USB2/3 Port (IO - 1)

2

USB2/3 Port (IO - 2)

3

SB2/3 Port (Type-C)

U

4

5

6

ATA Port Table

S

Port

0

1A

DD

H

1B

SSD1

USB PortPort

ON BOARD RAM * 4 (total 4GB)

340

C

ZZ

ZZ

H4G_C340@

Z

M4G_C340@

Z

ZZ

S4G_C340@

Z

5

P

ort

Lane

1

2

3

0

4

0

5

1

6

7

8

9

10

11

12

13

14

15

16

2

3

1

CardR eader

0

NG F F W L A N+ B T

0

3

2

SSD

1

0

D

GPU

X

76 SAMSUNG4GB M D

X7680538LA3

ZZZ

S4G_S340_15@ZZZ

X

76 SAMSUNG 4GB MD

X7680438L83

ZZZ

S4G_S340_14@

X76 SAMSUNG 4GB MD

XXXXXXXXX

ZZZ1

S340_14@

X4E S340-14

XXXXXXXXXX

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Ti t l e

Ti t l e

Ti t l e

otes List

otes List

otes List

N

N

N

Size

Size

Size

Document Number

Document Number

Document Number

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-H101P

LA-H101P

LA-H101P

5

3 51Thursday, September 20, 2018

3 51Thursday, September 20, 2018

3 51Thursday, September 20, 2018

Rev

Rev

Rev

0.A0.A0.A

S340_15@

X

X7680538LA2

X

76 MICRON 4GB MD

X7680438L82

ZZZ

X76 MICRON 4GB MD

XXXXXXXXX

ZZZ

X4E C340

X4EAF838L01

Deciph ered Date

Deciph ered Date

Deciph ered Date

76 MI C R O N 4G B M D

M4G_S340_15@

M4G_S340_14@

C340@

X

76 HYNIX 4GB M D

MBUS Control Tab le

S

G

T

-

DGPU

SOURCE

EC_SMB_CK1

C C

D D

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

EC_SMB_CK4

EC_SMB_DA4

SOC_SMBCLK

SOC_SMBDATA

SOC_SML0CLK

SOC_SML0DATA

EC_SMB_CK2

EC_SMB_DA2

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

NECP388

+3VL

N

+3VS

NECP388

+3VS

PCH

+3VALW

PCH

+3VALW

CH

P

+

SIGNAL

1

ECP388

3VS

VX X

+3VALW

X

V

X X X X X X

X

X

XX

V

X

+3VS

SLP_S1#

LOW

LOW

LOW LOW LOW

SLP_S4#SLP_S3# +V+VALWSLP_S5# Clock+VS

HIGHHIGHHIGH

HIGH HIGH HIGH

LOW

HIGH

LOWLOW

C

HARGER

V

+

19V_VIN

X

X

X

X

X

HIGH

HIGH

HIGH

N

EC P3 88 SODIMMBATT

X

V

+3VS+3VS

X

V

+3VS

ONONON

ON

ON

ON

ON

LOWLOW

ON

OFF

OFF

T

P

P

CH

X

X

X

ON

OFF

OFF

OFF

V

+

3VS

X

V

+

3VS

X

X

X

X

ONON

LOW

OFF

OFF

OFF

2

X

V

+

3VS

XX

X

SENSOR

X

X

V

+

3VS

X

X

X

HM

nsor

se

X

V

+

3VS

X

X

X

GPU

UV1

N17S_G0@

UV1

N17S_G2@

X

UC1

SRD1W i3_R1@

I3-8145U

SA0000C6R20

SRFG1 Pentium 5405U@

UC1

I3-8145U

SA0000C6R30

N17S-G0-A1

SA0000CC900

W

HL CPU

3

UC1

I5-8265U

SA0000C6Q20

SREJQi 5_R1@

N17S-G2-A1

SA0000CCB00

UC1

I7-8565U

SA0000C6P20

P

CB

SRFFW i7_R1@

ZZZ

PCB@

PCB

DA8001H6000

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THISSHEETOF ENGINEERING DRAWING IS THE PROPRIETARYPROPERTYOFCOMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

THISSHEETOF ENGINEERING DRAWING IS THE PROPRIETARYPROPERTYOFCOMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

THISSHEETOF ENGINEERING DRAWING IS THE PROPRIETARYPROPERTYOFCOMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THISSHEET MAY NOTBE T RANSFERED FROM THECUSTODY O F THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOTBE T RANSFERED FROM THECUSTODY O F THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOTBE T RANSFERED FROM THECUSTODY O F THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECTRONICS, INC.

X7680538LA1

S340-15

ZZZ

H4G_S340_15@

X

76 HYNI X 4G B M D

X7680438L81

S340-14

ZZZ

H4G_S340_14@

X76 HYNI X 4GB M D

XXXXXXXXX

X

4E

S340-15 C340-14 S340-14

ZZZ

X4E S340-15

X4EAF838L51

Compal Secret Data

Compal Secret Data

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Compal Secret Data

4

5

D D

C C

4

-

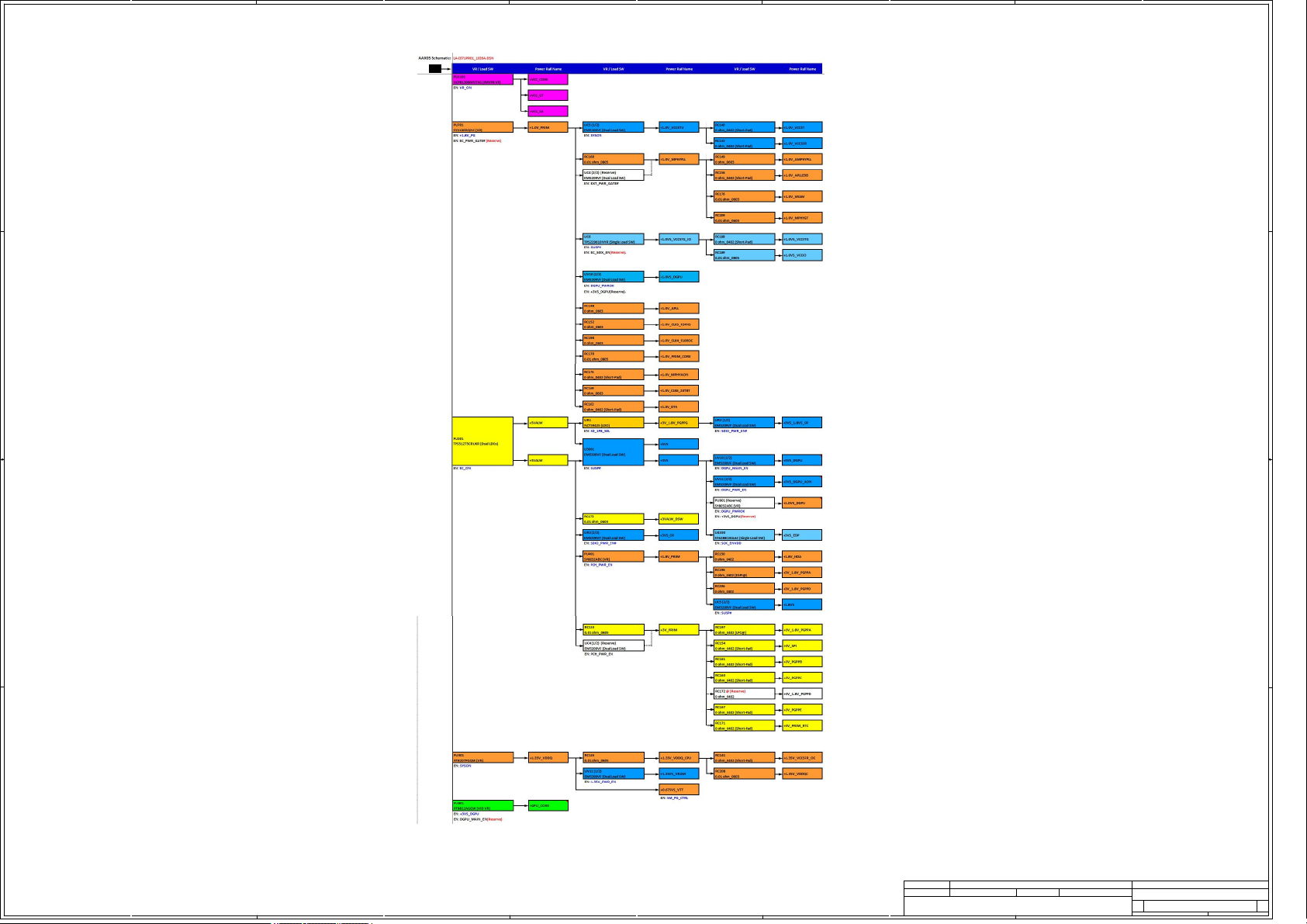

PowerMap_DDR4_Volume_NON CS]

B

+

3

2

1

B B

A A

Security Classification

Security Classification

Security Classification

IssuedDate

Issued Dat e

Issued Dat e

THISSHEETOF ENGINEE RINGD RAWING IS THE P ROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

THISSHEETOF ENGINEE RINGD RAWING IS THE P ROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

THISSHEETOF ENGINEE RINGD RAWING IS THE P ROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOTB E TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISIONOF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOTB E TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISIONOF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOTB E TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISIONOF R&D

DEPARTMENTEXCEPTA S AUTHORIZEDBY COMPAL ELECTRONICS,INC. NE ITHER THIS SHEET NOR THE IN FOR MAT ION ITCONTAINS

DEPARTMENTEXCEPTA S AUTHORIZEDBY COMPAL ELECTRONICS,INC. NE ITHER THIS SHEET NOR THE IN FOR MAT ION ITCONTAINS

DEPARTMENTEXCEPTA S AUTHORIZEDBY COMPAL ELECTRONICS,INC. NE ITHER THIS SHEET NOR THE IN FOR MAT ION ITCONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PAR TY WITHOUT PRIORWRITTENC ONSENT OF COMPALELECTRONICS,INC .

MAYBE USED BY OR DISCLOSED TO ANY THIRD PAR TY WITHOUT PRIORWRITTENC ONSENT OF COMPALELECTRONICS,INC .

5

4

3

MAYBE USED BY OR DISCLOSED TO ANY THIRD PAR TY WITHOUT PRIORWRITTENC ONSENT OF COMPALELECTRONICS,INC .

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/09/21 2019/ 09/21

2018/09/21 2019/ 09/21

2018/09/21 2019/ 09/21

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Pow er M AP

Pow er M AP

Pow er M AP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-H101P

4 51Thursday, September 20, 2018

4 51Thursday, September 20, 2018

1

4 51Thursday, September 20, 2018

0.A0.A0.A

5

4

3

2

1

3->S0 S0->S3 ->S0

G

3VL_RTC

+

OC_RTCRST#

S

B+

D D

3VLP/+5VLP

+

E

C_ON

+5VALW/+3VALW/+3VALW_DSW

PM_ BAT L OW #

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

Pull-up to DSW well if not implemented.

DS3 DS3S3/

/

PCH_PWR_EN (S LP_SUS#)

+3V_PRI M

+1.8V_PRIM

EXT_PWR_GAT E#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

tPCH06_Min : 200 us

SUSACK#

PCH_DPWROK

C_RSMRST#

E

C C

C_PRESENT

A

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

ON / O F F

P

BTN_OUT#

P

M_SLP_S5#

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

ESPI_RST#

If EXT_PWR_GATE# Toffmin is too small, Pwr

gate may choose to completely ignore it

tPCH43_Min : 95 ms

tPCH18_Min : 90 us

PM_ SL P_ S4 #

SYSON

+1.0V_VCCST/+1.0V_V CCSFR

+1.35V_VDDQ/+1.35V_VCCSF R_OC

PM_ SL P_ S3 #

SUSP#

+1.0VS_VCCST G

+1.0VS_VCCI O

B B

+5VS/+3VS/+1.5V S/+1.05 VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 10msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_GT

VR_PWRGD

PCH_PWROK

tCPU16 Min : 0 ns

H_CPUPWRGD

SYS_PWROK

A A

SUS_STAT#

SOC_PLTRST#

0->S5

S

+3VL_RTC

S

OC_RTCR ST#

B+

+3VLP/+ 5VLP

E

C_ON

+

5VALW/+ 3VALW/+3 VALW_D SW

PM_ BAT L OW #

PCH_PWR_EN (S LP_SUS#)

+3V_PRI M

+

1.8V_ PRIM

EXT_PWR_GAT E#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_P RIM

SUSACK#

PCH _DP WR OK

C_RSMR ST#

E

C_PRESENT

A

ON / O F F

P

BTN_OUT#

PM_ SL P_ S5 #

ESPI_RST#

PM_ SL P_ S4 #

SYSON

+

1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSF R_OC

PM_ SL P_ S3 #

SUSP#

+1.0VS_VCCST G

+1.0VS_VCCI O

+5VS/+3VS/+1.5 VS/+1. 05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH _PW R OK

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

SOC_PLTRST#

Com pal Secret Da ta

Com pal Secret Da ta

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET O F ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPAL ELECT RONICS, I N C. AN D CONTAINS CONFIDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPAL ELECT RONICS, I N C. AN D CONTAINS CONFIDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THEPROPRIETARY PROPERTY OF COMPAL ELECT RONICS, I N C. AN D CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION.THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THECOMPET ENT D IVISION OF R&D

AND TRADE SECRET INFORMATION.THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THECOMPET ENT D IVISION OF R&D

AND TRADE SECRET INFORMATION.THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THECOMPET ENT D IVISION OF R&D

DEPARTMENT EXCEPT AS A U T H O R IZ E D BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

DEPARTMENT EXCEPT AS A U T H O R IZ E D BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

DEPARTMENT EXCEPT AS A U T H O R IZ E D BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TOA N Y THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECT RONICS, IN C .

MAY BE USED BY OR DISCLOSED TOA N Y THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECT RONICS, IN C .

5

4

3

MAY BE USED BY OR DISCLOSED TOA N Y THIRD PA R T Y WITHOUT PRIOR WRITTENCONSENT OF COMPAL ELECT RONICS, IN C .

2

Com pal Secret Da ta

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Ti t l e

Ti t l e

Ti t l e

Size Do cument Numb e r Rev

Size Do cument Numb e r Rev

Size Do cument Numb e r Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Sequence

Power Sequence

Power Sequence

LA-H101P

1

5 51Thursday, September 20, 2018

5 51Thursday, September 20, 2018

5 51Thursday, September 20, 2018

0.A0.A0.A

A

1 1

< Compensation PU For eDP >

+1.05VS_VCCIO

2 2

1 2

RC2 24.9_0201_1%

T r a c e width=20 mils, Spacing=25mil, M ax length=600mils

EDP_COMP

B

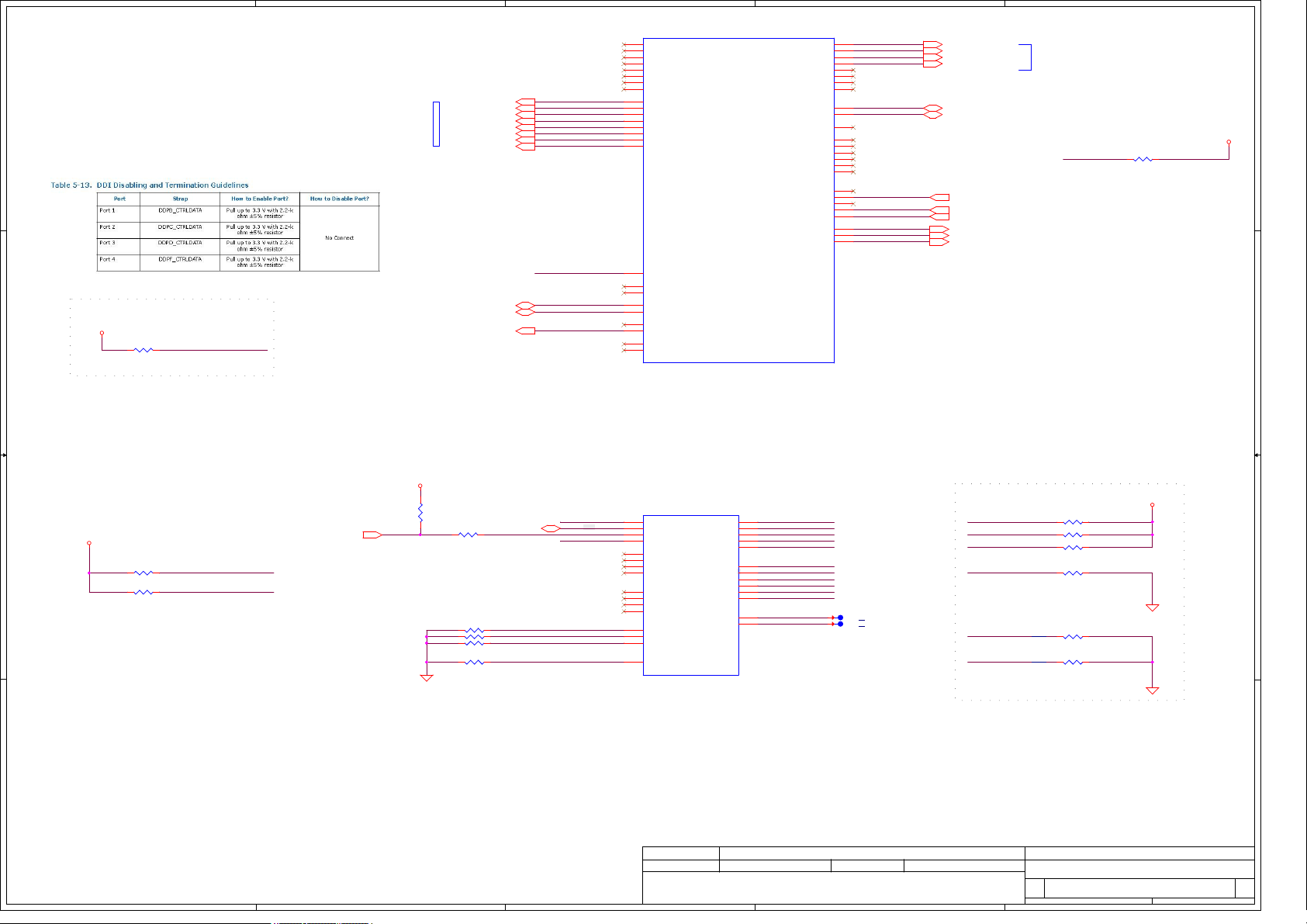

<HDMI>

HDMI DDC (Port2 )

<29>

<29>

<29>

<29>

CPU_DP2_CTRL_CLK<29,30>

CPU_DP2_CTRL_DATA<29,30>

CPU_DP2_N0<29>

CPU_DP2_P0

CPU_DP2_N1

CPU_DP2_P1<29>

CPU_DP2_N2

CPU_DP2_P2

CPU_DP2_N3<29>

CPU_DP2_P3<29>

TS_I2C_RST#<28>

EDP_COMP

C

UC1A

AL5

DDI1_TXN_0

AL6

DDI1_TXP_0

AJ5

DDI1_TXN_1

AJ6

DDI1_TXP_1

AF6

DDI1_TXN_2

AF5

DDI1_TXP_2

AE5

DDI1_TXN_3

AE6

DDI1_TXP_3

AC4

DDI2_TXN_0

AC3

DDI2_TXP_0

AC1

DDI2_TXN_1

AC2

DDI2_TXP_1

AE4

DDI2_TXN_2

AE3

DDI2_TXP_2

AE1

DDI2_TXN_3

AE2

DDI2_TXP_3

AM6

DIS P_ RCO MP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_W AKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR2 6

GPP_H16/DDPF_CTRLCLK

CP2 6

GPP_H17/DDPF_CTRLDATA

WHL-U_BGA1528

1 of 2 0

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MI SC3

GPP_E17/EDP_HPD/DISP_MIS C4

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK1 1

CG1 1

CH11

EC_SCI#

D

EDP_TXN0 <28>

EDP_TXP0 <28>

EDP_TXN1 <28>

EDP_TXP1 <28>

EDP_AUXN <28>

EDP_AUXP <28>

CPU_DP2_HPD < 29,30>

EC_SCI# <34>

EDP_HPD <28>

ENBKL <34>

PCH_ENVDD <28>

IN V P W M <28>

<e DP >

EC_SCI#

From HDMI

From eDP

E

1 2

RC1 10K_0402_5%

+3VS

+1.05 VS_VCCST G

12

RC3

1K_0402_5%

+1.05V_VCCST

3 3

4 4

1 2

RC8 1K_0402_5%

1

2

RC10 49.9_0402_1%@

A

H_THERMTRIP#

CATERR#

H_PROCHOT#<34>

B

1 2

RC4 499_0402_1%

RC11 49.9_0402_1%

RC12 49.9_0402_1%

RC14 49.9_0402_1%@

RC15 49.9_0402_1%@

If rout ed M S, PECIrequires 18mils spacingto other signals

CB3 4

CC3 5

BP27

BW25

AA4

AR1

BJ1

CE9

CN3

CATERR#

H_PECI<34>

H_PROCHOT#_R

H_THERMTRIP#

12

12

12

12

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

UC1D

CAT ER R#

PECI

Y4

PROCHOT#

THRMTRIP#

U1

BPM#_0

U2

BPM#_1

U3

BPM#_2

U4

BPM#_3

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

L5

OPCE_RCOMP

N5

OPC_RCOMP

WHL-U_BGA1528

Security Classificat ion

Security Classificat ion

Security Classificat ion

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

C

4 of 20

Is s u ed Date

Is s u ed Date

Is s u ed Date

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

PROC_PREQ#

PROC_PRDY#

CPU_XDP_TCK0

T6

SOC_XDP_TDI

U6

SOC_XDP_TDO

Y5

SOC_XDP_TMS

T5

SOC_XDP_TRST#

AB6

PCH_JTAG_TCK1

W6

SOC_XDP_TDI

U5

SOC_XDP_TDO

W5

SOC_XDP_TMS

P5

SOC_XDP_TRST#

Y6

CPU_XDP_TCK0

P6

W2

W1

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

T1TP@

T2TP@

Compal S ecret Data

Compal S ecret Data

Compal S ecret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

< PU/PD for CMC Debug >

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

SOC_XDP_TRST#

RC5 51_0402_5%CMC@

RC6 51_0402_5%CMC@

RC7 51_0402_5%DCI@

RC9 51_0402_5%DCI@

RC13 51_0402_5%@

RC16 51_0402_5%@

Tit le

Tit le

Tit le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

+1.05VS_VCCSTG

1 2

1 2

1 2

1 2

1 2

1 2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

WHL-U(1/12)DDI,EDP,MISC,CMC

WHL-U(1/12)DDI,EDP,MISC,CMC

WHL-U(1/12)DDI,EDP,MISC,CMC

LA-H101P

LA-H101P

LA-H101P

E

6 51Thursday, September 20, 2018

6 51Thursday, September 20, 2018

6 51Thursday, September 20, 2018

0.A0.A0.A

of

of

of

5

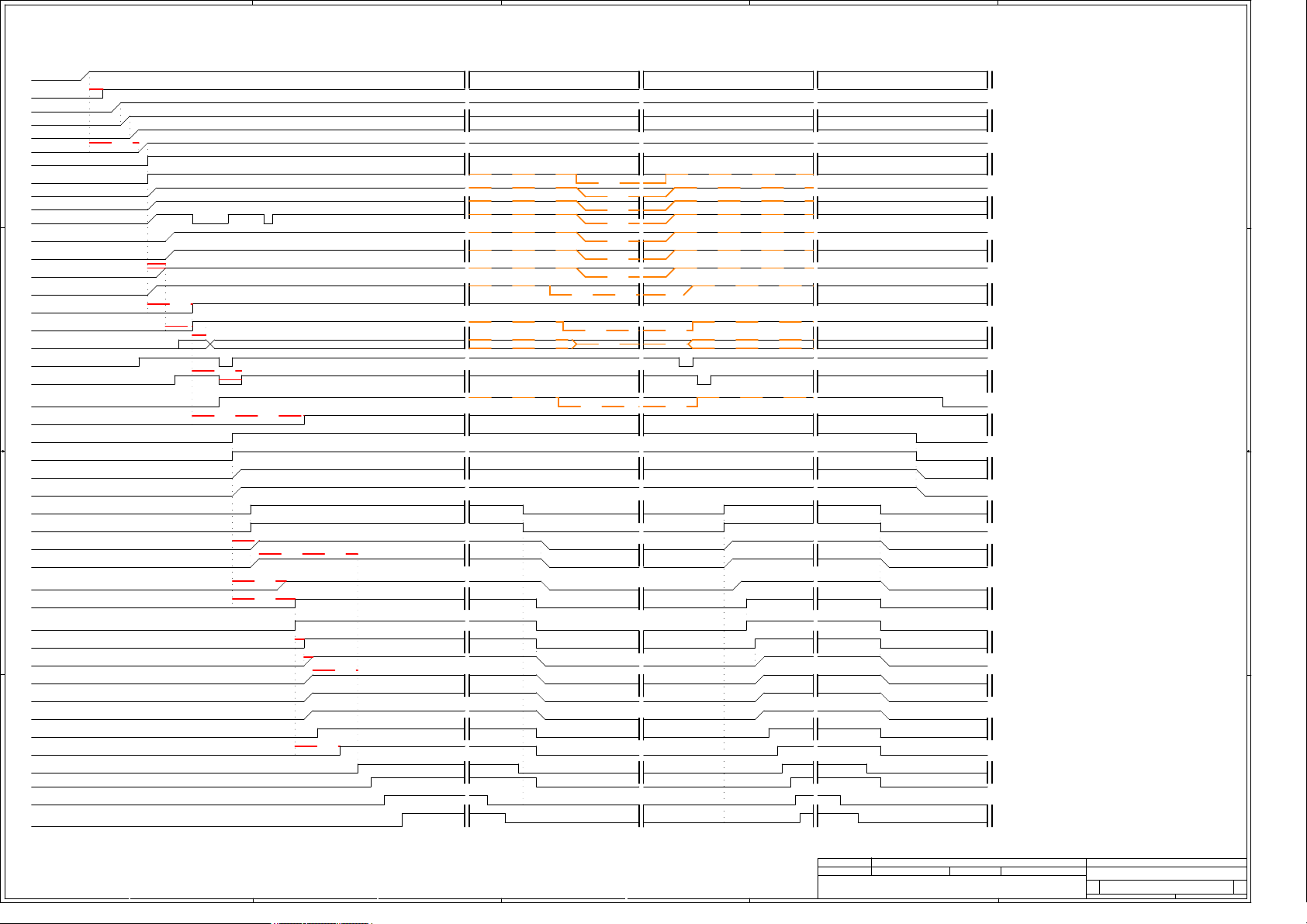

Interleaved Memory

4

3

2

1

D D

C C

B B

<18>

DDR_A_D[0..15]

DDR_A_D[16..31]<18>

DDR_A_D[32..47]<18>

DDR_A_D[48..63]<18>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

DDR0_DQ_5/DDR0_DQ_5

B28

DDR0_DQ_6/DDR0_DQ_6

A28

DDR0_DQ_7/DDR0_DQ_7

B30

DDR0_DQ_8/DDR0_DQ_8

D30

DDR0_DQ_9/DDR0_DQ_9

B33

DDR0_DQ_10/DDR0_DQ_10

D32

DDR0_DQ_11/DDR0_DQ_11

A30

DDR0_DQ_12/DDR0_DQ_12

C30

DDR0_DQ_13/DDR0_DQ_13

B32

DDR0_DQ_14/DDR0_DQ_14

C32

H37

DDR0_DQ_16/DDR0_DQ_32

H34

DDR0_DQ_17/DDR0_DQ_33

K34

DDR0_DQ_18/DDR0_DQ_34

K35

DDR0_DQ_19/DDR0_DQ_35

H36

DDR0_DQ_20/DDR0_DQ_36

H35

DDR0_DQ_21/DDR0_DQ_37

K36

DDR0_DQ_22/DDR0_DQ_38

K37

DDR0_DQ_23/DDR0_DQ_39

N36

DDR0_DQ_24/DDR0_DQ_40

N34

DDR0_DQ_25/DDR0_DQ_41

R37

DDR0_DQ_26/DDR0_DQ_42

R34

DDR0_DQ_27/DDR0_DQ_43

N37

DDR0_DQ_28/DDR0_DQ_44

N35

DDR0_DQ_29/DDR0_DQ_45

R36

DDR0_DQ_30/DDR0_DQ_46

R35

DDR0_DQ_31/DDR0_DQ_47

AN35

DDR0_DQ_32/DDR1_DQ_0

AN34

DDR0_DQ_33/DDR1_DQ_1

AR35

DDR0_DQ_34/DDR1_DQ_2

AR34

DDR0_DQ_35/DDR1_DQ_3

AN37

DDR0_DQ_36/DDR1_DQ_4

AN36

DDR0_DQ_37/DDR1_DQ_5

AR36

DDR0_DQ_38/DDR1_DQ_6

AR37

DDR0_DQ_39/DDR1_DQ_7

AU35

DDR0_DQ_40/DDR1_DQ_8

AU34

DDR0_DQ_41/DDR1_DQ_9

AW35

DDR0_DQ_42/DDR1_DQ_10

AW34

DDR0_DQ_43/DDR1_DQ_11

AU37

DDR0_DQ_44/DDR1_DQ_12

AU36

DDR0_DQ_45/DDR1_DQ_13

AW36

DDR0_DQ_46/DDR1_DQ_14

AW37

DDR0_DQ_47/DDR1_DQ_15

BA35

DDR0_DQ_48/DDR1_DQ_32

BA34

DDR0_DQ_49/DDR1_DQ_33

BC35

DDR0_DQ_50/DDR1_DQ_34

BC34

DDR0_DQ_51/DDR1_DQ_35

BA37

DDR0_DQ_52/DDR1_DQ_36

BA36

DDR0_DQ_53/DDR1_DQ_37

BC36

DDR0_DQ_54/DDR1_DQ_38

BC37

DDR0_DQ_55/DDR1_DQ_39

BE35

DDR0_DQ_56/DDR1_DQ_40

BE34

DDR0_DQ_57/DDR1_DQ_41

BG35

DDR0_DQ_58/DDR1_DQ_42

BG34

DDR0_DQ_59/DDR1_DQ_43

BE37

DDR0_DQ_60/DDR1_DQ_44

BE36

DDR0_DQ_61/DDR1_DQ_45

BG36

DDR0_DQ_62/DDR1_DQ_46

BG37

DDR0_DQ_63/DDR1_DQ_47

WHL-U_BGA1528

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_DQ_15/DDR0_DQ_15

DDR0_ODT_0/DDR0_ODT_0

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

2 of 20

DDR0_CKE_2/NC

DDR0_CKE_3/NC

NC/DDR0_ODT_1

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

DDR_VTT_CNTL

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_MA16

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_ACT#

DDR_A_BG1

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PARITY

+0.6V_A_VREFCA

+0.6V_ B_VREFDQ

DDR_PG_CTRL

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

TP@

T3

T4TP@

DDR_A_CKE0 <18,19>

DDR_A_CS#0 <18,19>

T5TP@

DDR_A_ODT0 <18,19>

T7TP@

DDR_A_MA0 <18,19>

DDR_A_MA1 <18,19>

DDR_A_MA2 <18,19>

DDR_A_MA3 <18,19>

DDR_A_MA4 <18,19>

DDR_A_MA5 <18,19>

DDR_A_MA6 <18,19>

DDR_A_MA7 <18,19>

DDR_A_MA8 <18,19>

DDR_A_MA9 <18,19>

DDR_A_MA10 <18,19>

DDR_A_MA11 <18,19>

DDR_A_MA12 <18,19>

DDR_A_MA13 <18,19>

DDR_A_MA14 <18,19>

DDR_A_MA15 <18,19>

DDR_A_MA16 <18,19>

DDR_A_BA0 <18,19>

DDR_A_BA1 <18,19>

DDR_A_BG0 <18,19>

DDR_A_ACT# <18,19>

DDR_A_BG1 <18>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

DDR_A_ALERT# <18>

DDR_A_PARITY <18,19>

+0.6V_A_VREFCA <18>

+0.6V_B_VREFDQ <20>

DDR_B_D[0..15]

<20>

DDR_B_D[16..31]<20>

DDR_B_D[32..47]<20>

DDR_B_D[48..63]<20>

Trace width/Spacing >= 20mils

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

J22

DDR1_DQ_0/DDR0_DQ_16

H25

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

DDR1_DQ_4/DDR0_DQ_20

J25

DDR1_DQ_5/DDR0_DQ_21

G25

DDR1_DQ_6/DDR0_DQ_22

F22

DDR1_DQ_7/DDR0_DQ_23

D22

DDR1_DQ_8/DDR0_DQ_24

C22

DDR1_DQ_9/DDR0_DQ_25

C24

DDR1_DQ_10/DDR0_DQ_26

D24

DDR1_DQ_11/DDR0_DQ_27

A22

DDR1_DQ_12/DDR0_DQ_28

B22

DDR1_DQ_13/DDR0_DQ_29

A24

DDR1_DQ_14/DDR0_DQ_30

B24

DDR1_DQ_15/DDR0_DQ_31

G31

DDR1_DQ_16/DDR0_DQ_48

G32

DDR1_DQ_17/DDR0_DQ_49

H29

DDR1_DQ_18/DDR0_DQ_50

H28

DDR1_DQ_19/DDR0_DQ_51

G28

DDR1_DQ_20/DDR0_DQ_52

G29

DDR1_DQ_21/DDR0_DQ_53

H31

DDR1_DQ_22/DDR0_DQ_54

H32

DDR1_DQ_23/DDR0_DQ_55

L31

DDR1_DQ_24/DDR0_DQ_56

L32

DDR1_DQ_25/DDR0_DQ_57

N29

DDR1_DQ_26/DDR0_DQ_58

N28

DDR1_DQ_27/DDR0_DQ_59

L28

DDR1_DQ_28/DDR0_DQ_60

L29

DDR1_DQ_29/DDR0_DQ_61

N31

DDR1_DQ_30/DDR0_DQ_62

N32

DDR1_DQ_31/DDR0_DQ_63

AJ29

DDR1_DQ_32/DDR1_DQ_16

AJ30

DDR1_DQ_33/DDR1_DQ_17

AM32

DDR1_DQ_34/DDR1_DQ_18

AM31

DDR1_DQ_35/DDR1_DQ_19

AM30

DDR1_DQ_36/DDR1_DQ_20

AM29

DDR1_DQ_37/DDR1_DQ_21

AJ31

DDR1_DQ_38/DDR1_DQ_22

AJ32

DDR1_DQ_39/DDR1_DQ_23

AR31

DDR1_DQ_40/DDR1_DQ_24

AR32

DDR1_DQ_41/DDR1_DQ_25

AV30

DDR1_DQ_42/DDR1_DQ_26

AV29

DDR1_DQ_43/DDR1_DQ_27

AR30

DDR1_DQ_44/DDR1_DQ_28

AR29

DDR1_DQ_45/DDR1_DQ_29

AV32

DDR1_DQ_46/DDR1_DQ_30

AV31

DDR1_DQ_47/DDR1_DQ_31

BA32

DDR1_DQ_48/DDR1_DQ_48

BA31

DDR1_DQ_49/DDR1_DQ_49

BD31

DDR1_DQ_50/DDR1_DQ_50

BD32

DDR1_DQ_51/DDR1_DQ_51

BA30

DDR1_DQ_52/DDR1_DQ_52

BA29

DDR1_DQ_53/DDR1_DQ_53

BD29

DDR1_DQ_54/DDR1_DQ_54

BD30

DDR1_DQ_55/DDR1_DQ_55

BG31

DDR1_DQ_56/DDR1_DQ_56

BG32

DDR1_DQ_57/DDR1_DQ_57

BK32

DDR1_DQ_58/DDR1_DQ_58

BK31

DDR1_DQ_59/DDR1_DQ_59

BG29

DDR1_DQ_60/DDR1_DQ_60

BG30

DDR1_DQ_61/DDR1_DQ_61

BK30

DDR1_DQ_62/DDR1_DQ_62

BK29

DDR1_DQ_63/DDR1_DQ_63

WHL-U_BGA1528

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP _0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP _1

DDR1_CKE_0/DDR1_CKE _0

DDR1_CKE_1/DDR1_CKE _1

DDR1_CKE_2/NC

DDR1_CKE_3/NC

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP _2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP _3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP _6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP _7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP _2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP _3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP _6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP _7

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_COMP_0

DDR_COMP_1

DDR_COMP_2

3 of 20

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

DDR_B_CLK#0

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_MA16

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_BG1

DDR_B_ACT#

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

#543016 PDG1.5 P.168

W=12-15 Space= 20/25 L=500mil

DDR_B_CLK#0 <20>

DDR_B_CLK0 <20>

DDR_B_CLK#1 <20>

DDR_B_CLK1 <20>

DDR_B_CKE0 <20>

DDR_B_CKE1 <20>

DDR_B_CS#0 <20>

DDR_B_CS#1 <20>

DDR_B_ODT0 <20>

DDR_B_ODT1 <20>

DDR_B_MA0 <20>

DDR_B_MA1 <20>

DDR_B_MA2 <20>

DDR_B_MA3 <20>

DDR_B_MA4 <20>

DDR_B_MA5 <20>

DDR_B_MA6 <20>

DDR_B_MA7 <20>

DDR_B_MA8 <20>

DDR_B_MA9 <20>

DDR_B_MA10 <20>

DDR_B_MA11 <20>

DDR_B_MA12 <20>

DDR_B_MA13 <20>

DDR_B_MA14 <20>

DDR_B_MA15 <20>

DDR_B_MA16 <20>

DDR_B_BA0 <20>

DDR_B_BA1 <20>

DDR_B_BG0 <20>

DDR_B_BG1 <20>

DDR_B_ACT# <20>

DDR_B_DQS#0 <20>

DDR_B_DQS0 <20>

DDR_B_DQS#1 <20>

DDR_B_DQS1 <20>

DDR_B_DQS#2 <20>

DDR_B_DQS2 <20>

DDR_B_DQS#3 <20>

DDR_B_DQS3 <20>

DDR_B_DQS#4 <20>

DDR_B_DQS4 <20>

DDR_B_DQS#5 <20>

DDR_B_DQS5 <20>

DDR_B_DQS#6 <20>

DDR_B_DQS6 <20>

DDR_B_DQS#7 <20>

DDR_B_DQS7 <20>

DDR_B_ALERT# <20>

DDR_B_PARITY <20>

DDR_DRAMRST# <18,20>

1 2

RC17 121_0402_1%

1 2

RC18 80.6_0402_1%

1 2

RC19 100_0402_1%

< F o r ODT & VTT P o we r Control >

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

UC11

DDR_PG_CTRL

A A

5

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

SA00005U600

Y

1

CC1

0.1U_0201_10V6K

@

2

5

4

+3VS+1.2V +1.2V

12

RC21

100K_0402_5%

DDR_DRAMRST#

DDR_VTT_PG_CTRL

Security Classificat ion

Security Classificat ion

Security Classificat ion

Is s u ed Date

Is s u ed Date

Is s u ed Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

4

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

3

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Compal S ecret Data

Compal S ecret Data

Compal S ecret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

12

RC20

470_0402_5%

1

CC2

100P_0402_50V8J

ESD@

2

Clo se to CPU

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

WHL-U(2/12)DDR4

WHL-U(2/12)DDR4

WHL-U(2/12)DDR4

LA-H101P

LA-H101P

Thursday, September 20, 2018

Thursday, September 20, 2018

Thursday, September 20, 2018

LA-H101P

51

51

51

7

7

7

of

of

1

of

0.A0.A0.A

5

4

3

2

1

+3VALW

1 2

RC23 100K_0201_5%

1 2

RC24 100K_0201_5%

1 2

RC25 100K_0201_5%

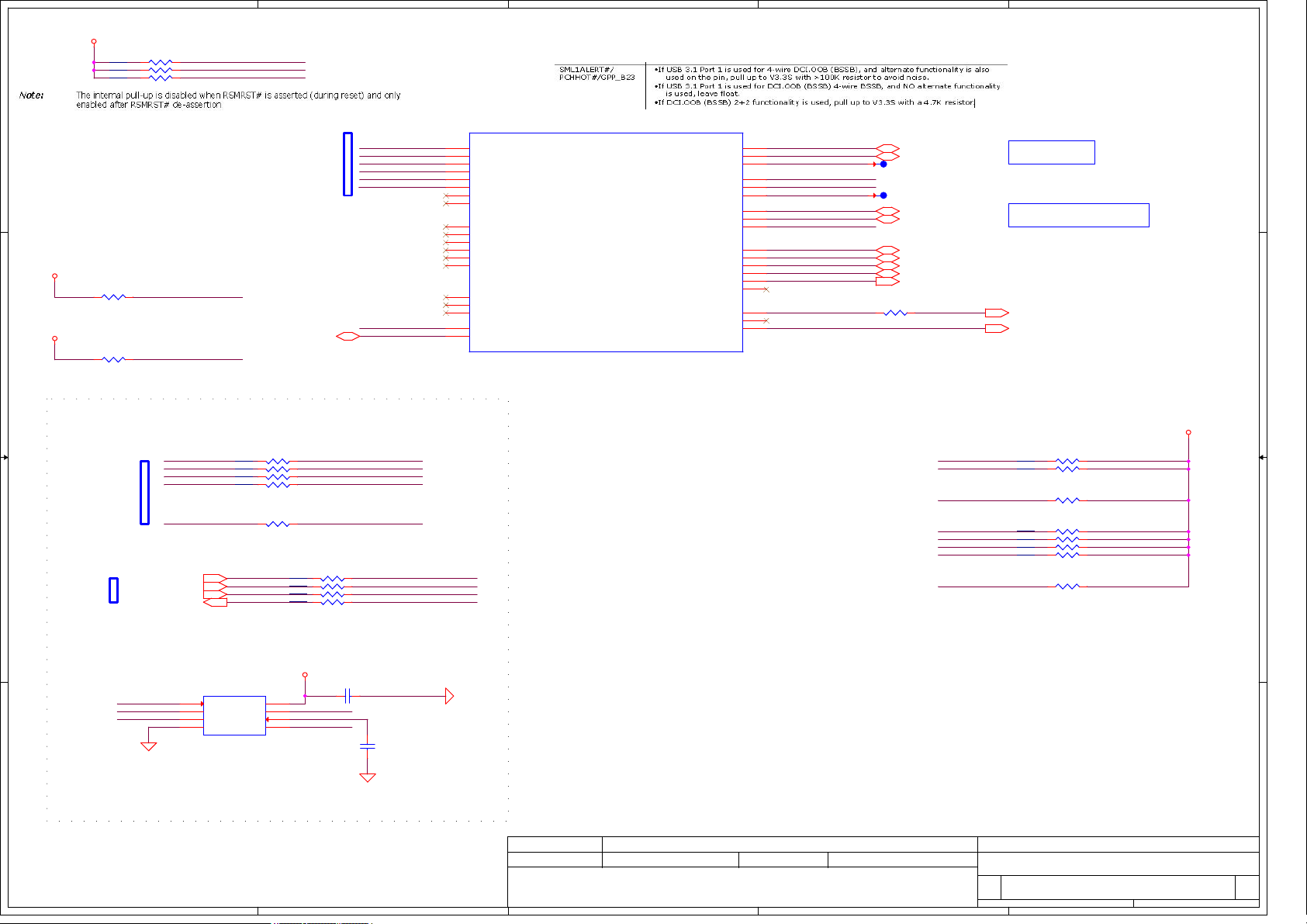

SOC_SPI_0_SI

SOC_SPI_0_IO2

SOC_SPI_0_IO3

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC ==> Default

1 = eSPI is selected for EC

D D

SOC_SPI_0_CLK

SOC_SPI_0_SO

SPI R O M

+3VS

1 2

RC26 10K_0402_5%

C C

+3VS

1 2

RC28 8.2K_0402_5%

KB_RST#

SERIRQ<34>

SERIRQ

SOC_SPI_0_SI

SOC_SPI_0_IO2

SOC_SPI_0_IO3

SOC_SPI_0_CS#0

SERIRQ

close to SPI ROM

SOC_SPI_0_SO

SOC_SPI_0_CLK SOC_SPI_0_CLK_R

SOC_SPI_0_SI

SOC_SPI_0_IO3

FromSOC

SOC_SPI_0_IO2

B B

FromE C

EC_SPI_CLK<34>

EC_SPI_MOSI<34>

EC_SPI_CS0#<34>

EC_SPI_MISO<34>

1 2

RC29 33_0402_5%

1 2

RC31 33_0402_5%EMI@

1 2

RC32 33_0402_5%

1 2

RC34 33_0402_5%

1 2

RC36 33_0402_5%

EC_SPI_CLK

EC_SPI_MOSI SOC_SPI_0_SI_R

EC_SPI_CS0#

EC_SPI_MISO

RC41 33_0402_5%EMI@

RC42 33_0402_5%

RC43 33_0402_5%

RC44 33_0402_5%

1 2

1 2

1 2

1 2

SOC_SPI_0_SO_R

SOC_SPI_0_SI_R

SOC_SPI_0_IO3_R

SOC_SPI_0_IO2_R

SOC_SPI_0_CLK_R

SOC_SPI_0_CS#0

SOC_SPI_0_SO_R

UC1E

CH37

SPI0_CLK

CF 37

SPI0_MISO

CF 36

SPI0_MOSI

CF 34

SPI 0_I O2

CG 34

SPI 0_I O3

CG 36

SPI0_CS0#

CG 35

SPI0_CS1#

CH34

SPI0_CS2#

CF 20

GPP_D1/SPI1_CLK/BK1/ SBK1

CG 22

GPP_D2/SPI1_MISO_I O1/BK2/SBK2

CF 22

GPP_D3/SPI1_MOSI_I O0/BK3/SBK3

CG 23

GPP_D21/SPI1_IO2

CH23

GPP_D22/SPI1_IO3

CG 20

GPP_D0/SPI1_CS0#/BK0/ SBK0

CH7

CL_CLK

CH8

CL_ DA TA

CH9

CL_ RS T#

BV29

GPP_A0/RCIN#/TIME_SYNC1

BV28

GPP_A6/SERIRQ

WHL-U_BGA1528

GPP_C5/SML0ALERT#

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_I O0

GPP_A2/LAD1/ESPI_I O1

GPP_A3/LAD2/ESPI_I O2

GPP_A4/LAD3/ESPI_I O3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET #

GPP_A9/CLKOUT_LPC0/ESPI _CLK

GPP_A10/CLKOUT_LPC1

5 of 20

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

CK 14

CH15

CJ 15

CH14

CF 15

CG 15

CN15

CM1 5

CC34

CA 29

BY2 9

BY2 7

BV2 7

CA 28

CA 27

BV32

BV3 0

BY30

SOC_SMBCLK

SOC_SMBDATA

SOC_SMBALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SML0ALERT#

SOC_SML1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK0

PM_CLKRUN#KB_RST#

1 2

RC27 22_0402_5%EMI@

SOC_SMBCLK <20>

SOC_SMBDATA <20>

T8TP@

T9TP@

EC_SMB_CK2 <34>

EC_SMB_DA2 <34>

LPC_AD0 < 34>

LPC_AD1 < 34>

LPC_AD2 <34>

LPC_AD3 <34>

LPC_FRAME# <34>

EC_SMB_CK2

EC_SMB_DA2

SOC_SML1ALERT#

SOC_SMBCLK

SOC_SMBDATA

SOC_SML0CLK

SOC_SML0DATA

PM_CLKRUN#

SMB

(Link to DDR)

SML1

(Link to EC, Thermal Sensor)

CLK_LPC_EC <34>

PM_CLKRUN# <34>

1 2

RC30 1K_0402_5%

1 2

RC33 1K_0402_5%

1 2

RC35 150K_0402_5%@

1 2

RC37 1K_0402_5%

1 2

RC38 1K_0402_5%

1 2

RC39 1K_0402_5%

1 2

RC40 1K_0402_5%

1 2

RC45 8.2K_0402_5%

+3VS

< SPI RO M - 16M >

SOC_SPI_0_CS#0

SOC_SPI_0_IO2_R

A A

5

UC12

1

CS#

2

DO(IO1)

3

IO2

4

DI (I O0 )

GND

XM25QH128AHIG SOP 8P

VCC

CL K

IO

+3VALW

@

1 2

CC3 0.1U_0201_10V K X5R

8

SOC_SPI_0_IO3_RSOC_SPI_0_SO_R

7

SOC_SPI_0_CLK_R

6

SOC_SPI_0_SI_R

5

1

CC4

@EMI@

10P_0402_50V8J

2

4

Security Classification

Security Classification

Security Classification

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Issued Date

Issued Date

Issued Date

THI S SHEET OF ENGINEERIN G DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THI S SHEET OF ENGINEERIN G DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THI S SHEET OF ENGINEERIN G DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

2018/09/21 2019/09/21

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

WHL-U(3/12)SPI,SMB,LPC,ESPI

WHL-U(3/12)SPI,SMB,LPC,ESPI

WHL-U(3/12)SPI,SMB,LPC,ESPI

LA-H101P

LA-H101P

LA-H101P

1

o f

o f

o f

8 51Thursday, September 20, 2018

8 51Thursday, September 20, 2018

8 51Thursday, September 20, 2018

0.A0.A0.A

5

4

3

2

1

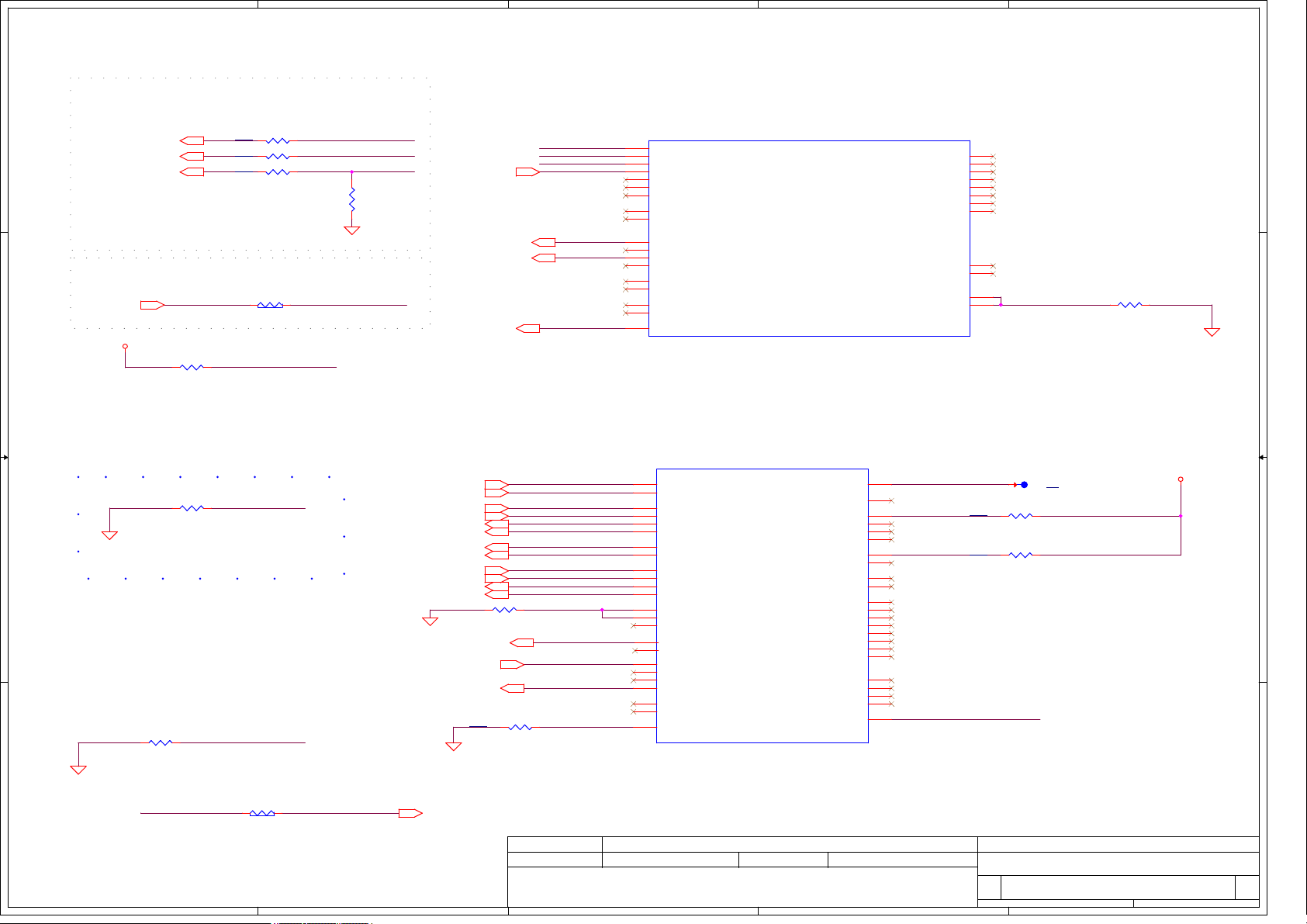

< HD A U D I O >

D D

HDA_BIT_CLK_R<33>

HDA_SYNC_R<33>

1 2

RC46 33_0402_5%

EMI@

1 2

RC48 33_0402_5%

1 2

RC47 33_0402_5%

< T o Enable ME Override>

1 2

ME_EN<34>

C C

+3VS

1 2

RC55 2.2K_0402_5%@

RC51 0_0402_5%@

HDA_SPKR

12

@

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

RC49

499_0402_1%

HDA_SDOUT

HDA_SYNC

HDA_BIT_CLK

HDA_SDIN0<33>HDA_SDOUT_R<33>

CNV_RF_RESET#<31>

CLKREQ_CNV#<31>

HDA_SPKR<33>

HDA_SDOUT

CNV_RF_RESET#

HDA_SPKR

UC1G

BN3 4

HDA_SYNC/I2S0_SFRM

BN3 7

HDA_BCLK/I2S0_SCLK

BN3 6

HDA_SDO/I2S0_TXD

BN3 5

HDA_SDI0/I2S0_RXD

BL3 6

HDA_SDI1/I2S1_ RXD/SNDW1_DATA

BL3 5

HDA_RST#/I2S1_SCLK/SNDW1_CLK

CK 23

GPP_D23/I2S_MCLK

BL3 7

I2S1_SFRM/SNDW 2_CLK

BL3 4

I2S1_TXD/SNDW2_DATA

CJ 32

GPP_H1/I2S2_SFRM/CNV_BT_I 2S_BCLK/CNV_RF_RESET#

CH32

GPP_H0/I2S2_SCLK/CNV_BT_ I2S_SCLK

CH29

GPP_H2/I2S2_TXD/CNV_BT_I 2S_SDI/MODEM_CLKREQ

CH30

GPP_H3/I2S2_RXD/CNV_BT_I2S_SDO

CP 24

GPP_D19/DMIC_CLK0/SNDW4_CLK

CN24

GPP_D20/DMIC_DATA0/SNDW4_DATA

CK 25

GPP_D17/DMIC_CLK1/SNDW3_CLK

CJ 25

GPP_D18/DMIC_DATA1/SNDW3_DATA

CF 35

GPP_B14/SPKR

WHL-U_BGA1528

7 of 20

GPP_G0/SD_CMD

GPP_G1/SD3_DATA0

GPP_G2/SD3_DATA1

GPP_G3/SD3_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_VDD1_PWR_EN# /ISH_GP7

GPP_A16/SD_1P8_SEL

SD_1P8_RCOMP

SD_3P3_RCOMP

CH36

CL 35

CL 36

CM3 5

CN35

CH35

CK 36

CK 34

BW 36

BY31

CK 33

CM3 4

SOC_SD_RCOMP

1 2

RC50 200_0402_1%

SPKR (Internal Pull Down):

TOP Swap Override

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

UC1I

CNV_CRX_DTX_N0<31>

1 2

RC5275K_0402_5% CNVi@

CNV_RF_RESET#

Follow Jefferson Peak schematic check list.

B B

1 2

RC164 1K_0402_5%@

WLBT_OFF#

CNV_CRX_DTX_P0<31>

CNV_CRX_DTX_N1<31>

CNV_CRX_DTX_P1<31>

CLK_CNV_CRX_DTX_N<31>

CLK_CNV_CRX_DTX_P<31>

CLK_CNV_CTX_DRX_N<31>

CLK_CNV_CTX_DRX_P<31>

For MX230

CNV_CTX_DRX_N0<31>

CNV_CTX_DRX_P0<31>

CNV_CTX_DRX_N1<31>

CNV_CTX_DRX_P1<31>

RC56

150_0402_1%

[11] GC6_FB_EN1V8

TP_INT#<35>

WLBT_OFF#<31>

1 2

CNVi@

1 2

RC57

10K_0402_5%

CNV_WT_RCOMP

GC6_FB_EN1V8

WLBT_OFF#

SOC_A4WP_PRESENT

CR30

CNV_WR_D0N

CP 30

CNV_WR_D0P

CM3 0

CNV_WR_D1N

CN30

CNV_WR_D1P

CN32

CNV_WT_D0N

CM3 2

CNV_WT_D0P

CP 33

CNV_WT_D1N

CN33

CNV_WT_D1P

CN31

CNV_WR_CLKN

CP 31

CNV_WR_CLKP

CP 34

CNV_WT_CLKN

CN34

CNV_WT_CLKP

CP 32

CNV_WT_RCOMP_0

CR32

CNV_WT_RCOMP_1

CP 20

GPP_F0/CNV_PA_BLANKI NG

CK 19

GPP_F1

CG 17

GPP_F2

CR14

GPP_C8/UART0_RXD

CP 14

GPP_C9/UART0_TXD

CN14

GPP_C10/UART0_RTS#

CM1 4

GPP_C11/UART0_CTS#

CJ 17

GPP_F8/CNV_MFUART2_RXD

CH17

GPP_F9/CNV_MFUART2_TXD

CF 17

GPP_F23/A4WP_ PRESENT

WHL-U_BGA1528

GPP_H18/CPU_C10_GATE#

GPP_H19/TIMESYNC_0

GPP_D4/IMGCLKOUT0/ BK4/SBK4

GPP_H20/IMGCLKOUT_1

GPP_F12/EMMC_DATA0

GPP_F13/EMMC_DATA1

GPP_F14/EMMC_DATA2

GPP_F15/EMMC_DATA3

GPP_F16/EMMC_DATA4

GPP_F17/EMMC_DATA5

GPP_F18/EMMC_DATA6

GPP_F19/EMMC_DATA7

GPP_F20/EMMC_RCLK

GPP_F21/EMMC_CLK

GPP_F11/EMMC_CMD

GPP_F22/EMMC_RESET#

EMMC_RCOMP

9 of 20

GPP_H21

GPP_H22

GPP_H23

GPP_F10

GPD7

GPP_F3

GPP_H21 XTAL frequency select.

0: 38.4 / 19.2 MHz

1: 24MHz XTAL select.

SOC_C10_GATE#

CN27

CM2 7

SOC_GPP_H21

CF 25

CN26

CM2 6

CK 17

SOC_GPD7

BV35

CN20

CG 25

XTAL INPUT MODE (HVM ONLY)

CH25

LOW: XTAL INPUT IS SINGLE ENDED

CR20

HIGH: XTAL IS ATTACHED

CM2 0

CN19

CM1 9

CN18

CR18

CP 18

CM1 8

CM1 6

CP 16

CR16

CN16

CK 15

1 2

RC53 4.7K_0201_5%

1 2

RC54 100K_0201_5%

SOC_SD_RCOMP

T10TP@

+3VALW

A A

T O D G P U

SOC_GPIO_C10 GPU_EVENT#

5

RC59

1

2

0_0402_5%

@

4

GPU_EVENT# [24 ]

Security Classification

Security Classification

Security Classification

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Issued Date

Issued Date

Issued Date

THI S SHEET OF ENG INEERI NG DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI S SHEET OF ENG INEERI NG DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI S SHEET OF ENG INEERI NG DRAWING IS TH E PROPRI ETARY PR OPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION.T HIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEE T NOR T HE INFORMATION IT CONTAINS

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

MAYBE USED B Y OR DISCLOSED TO ANY THIRD P A R T Y WITHOUTPRIO R WRITTEN CONSENT OF COM PAL ELECTRONICS, INC.

2018/09/21 2019/09/21

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-H101P

LA-H101P

Thursday, September 20, 2018

Thursday, September 20, 2018

Thursday, September 20, 2018

LA-H101P

9

9

9

1

51

51

51

o f

o f

o f

0.A0.A0.A

5

4

3

2

1

+3VS

10K_0402_5%

SE00000UC00

SE00000UC00

SYS_RESET#

EC_RSMRST#

SYS_PWROK

CLKREQ_PCIE#1

CLKREQ_PCIE#3

CLKREQ_PCIE#4

SOC_SRTCRST#

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

SYS_RESET#

PCH_PWROK

EC_RSMRST#

WAKE#

+1.05V_VCCST

1 2

RC72 0_0402_5%@

12

RC89

1K_0402_5%

1 2

RC90 60.4_0402_1%

1

CC15

100P_0402_50V8J

ESD@

2

Card Reader

EC_VCCST_PG

1 2

RC61 10K_0402_5%

1 2

RC63 10K_0402_5%

1 2

RC64

D D

+3VL_RTC

C C

B B

1 2

RC68 10K_0402_5%@

1 2

RC70 20K_0402_5%

1 2

CC5 1U_0201_6.3V6M

1 2

RC71 20K_0402_5%

1 2

CC6 1U_0201_6.3V6M

1 2

CLRP1 SHORT PADS

1 2

RC75 1M_0402_5%

+3VALW

1 2

RC77 10K_0402_5%

1 2

RC78 10K_0402_5%

1 2

RC79 10K_0402_5%

1 2

ESD@

CC10 100P_0402_50V8J

1 2

ESD@

CC11 100P_0402_50V8J

1 2

ESD@

CC12 100P_0402_50V8J

+3VALW

1 2

RC82 1K_0402_5%

Fro m EC (Open-Drain)

VCCST_PWRGD<34>

A A

5/9 Naming Rule

DGPU

SSD

[21] CLK_PEG_N0

[21] CLK_PEG_P0

[21] CLKREQ_PEG#0

<32>

WLAN

EC_CLEAR_CMOS# <34>

EC_RSMRST#<34>

T11 TP@

SYS_PWROK<34>

PCH_PWROK<34>

CLK_PCIE_N1

CLK_PCIE_P1<32>

CLKREQ_PCIE#1<32>

CLK_PCIE_N3<31>

CLK_PCIE_P3<31>

CLKREQ_PCIE#3<31>

CLK_PCIE_N4<37>

CLK_PCIE_P4<37>

CLKREQ_PCIE#4<37>

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

EC_RSMRST#

WAKE#

UC1J

AW2

CLKREQ_PEG#0

CLKREQ_PCIE#1

CLKREQ_PCIE#3

CLKREQ_PCIE#4

CF3 2

CE3 2

CF3 0

CE3 1

CE3 0

CF3 1

AY3

BC1

BC2

BD3

BC3

BH3

BH4

BA1

BA2

BE1

BE2

WHL-U_BGA1528

< PCH PLTRSTBuffer >

SOC_PLTRST#

BJ35

CN1 0

BR36

CR1 0

BP30

BV34

BY32

BU30

BU32

BU34

1 2

RC76 0_0402_5%

UC1K

GPP_B13/PLTRST#

SYS_RESET#

RSM RST #

AR2

PROCPWRGD

BJ2

VCCST_PWRGOOD

SYS_PWROK

BP31

PCH_PWROK

DSW_PWROK

GPP_A13/SUSWARN#/SUSPWRDACK

GPP_A15/SUSACK#

WAKE#

GPD2/LAN_WAKE#

GPD11/LANPHYPC

WHL-U_BGA1528

CLKOUT_PCIE_N_0

CLKOUT_PCIE_P_0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N_1

CLKOUT_PCIE_P_1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N_2

CLKOUT_PCIE_P_2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N_3

CLKOUT_PCIE_P_3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N_4

CLKOUT_PCIE_P_4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N_5

CLKOUT_PCIE_P_5

GPP_B10/SRCCLKREQ5#

10 of 2 0

12

RC80

100K_0402_5%

GPP_B11/EXT_PW R_GATE#

11 of 20

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

CLK_BIASREF

CLKIN_XTAL

12

CC9

100P_0402_50V8J

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PW RBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

INTRUDER#

GPP_B2/VRALERT#

INPUT3VSEL

XTAL_IN

XTAL_OUT

RTC X1

RTC X2

SRTCRST#

RTC RST #

PCI_RST# <31,32,34,37>

ESD@

BJ37

BU36

BU27

BT29

BU29

BT31

BT30

BU37

BU28

BU35

BV36

BR35

CC3 7

CC3 6

BT27

AU1

AU2

BT32

CK3

CK2

CJ 1

CM3

BN31

BN32

BR37

BR34

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#

AC_PRESENT_R

PM_BATLOW#

SM_INTRUDER#

SOC_VRALERT#

SOC_INPUT3VSEL

33E_SOC_XTAL24_IN_R

33E_SOC_XTAL24_OUT_R

XCLK_BIASREF

CLKIN_XTAL

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

RC83 0_0402_5%@

SUSCLK <31>

CLKIN_XTAL <31>

T12TP@

PM_SLP_S3# <34>

PM_SLP_S4# <34,42,45>

T13TP@

T14TP@

T15TP@

1 2

33E_SOC_XTAL24_IN_R

33E_SOC_XTAL24_OUT_R

XCLK_BIASREF

CLKIN_XTAL

Follow CFL-U PDG_Rev_0.7

Stuff 60.4 ohm(RC110) PD for CNL-U/ WHL-U and CFL-U

RC69 33_0201_5%EMI@

RC73 33_0201_5%EMI@

SOC_RTCX2

SOC_RTCX1

PBTN_OUT# <34>

AC_PRESENT <34>

RC60

RC65

1 2

LC1

@EMI@

1

1

4

4

DLM0NSN900HY2D_4P

1 2

1 2

60.4_0402_1%

1 2

10K_0402_5%

33E_SOC_XTAL24_IN

2

2

3

3

33E_SOC_XTAL24_OUT

1 2

RC81 10M_0402_5%

YC 2

1 2

32.768KHZ_9PF_X1A000141000200

SJ10000PW00

1

CC13

8.2P_0402_50V8B

2

PM_BATLOW#

AC_PRESENT

SOC_VRALERT#

SOC_INPUT3VSEL

1 2

RC74 200K_0402_1%

YC 1

24MHZ_18PF_XRCGB24M000F2P51R0

SJ10000UJ00

3

3

NC

NC

27P_0402_50V8J

CC7

1

2

1 2

RC84 8.2K_0402_5%

1 2

RC85 10K_0402_5%@

1 2

RC86 10K_0402_5%@

1 2

RC87 4.7K_0402_5%@

1 2

RC88 4.7K_0402_5%

2

4

1

1

1

CC14

8.2P_0402_50V8B

2

+3VALW

27P_0402_50V8J

CC8

1

2

Security Classificat ion

Security Classificat ion

Security Classificat ion

Is s u ed Date

Is s u ed Date

Is s u ed Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I N C . AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETEN T D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, IN C . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

5

4

MAY BE USED B Y OR DISCLOSED TO AN Y THIRD P A R T Y WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, IN C .

3

2018/09/21 2019/09/21

2018/09/21 2019/09/21

2018/09/21 2019/09/21

Compal S ecret Data

Compal S ecret Data

Compal S ecret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

WHL-U(5/12)CLK,PM,GPIO

WHL-U(5/12)CLK,PM,GPIO

WHL-U(5/12)CLK,PM,GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

LA-H101P

LA-H101P

LA-H101P

1

10 51Thursday, September 20, 2018

10 51Thursday, September 20, 2018

10 51Thursday, September 20, 2018

0.A0.A0.A

of

of

of

5

4

3

2

1

GSPI0_MOSI(Internal Pull Down):

No R e b o o t

0 = DisableNo R e b o o t mode. ==> Default

1 = Enable No R e b o o t Mode. (PCH will disable the TCO

Timers y s t e m re b o ot fe a t u re ) . This funct i oni s u s e f u l

when running ITP/X DP.

D D

GSPI1_MOSI (Internal Pull Down):

Boo t BI OS Strap B it

0 = SPI Mode ==> Default

1 = LPC Mode

+3VS

1 2

RC97 4.7K_0402_5%@

1 2

RC98 150K_0402_5%@

C C

+3VS

1 2

RC166 2.2K_0402_5%

1 2

RC167 2.2K_0402_5%

1 2

RC102 10K_0402_5%

1 2

RC163 4.7K_0402_5%

1 2

RC103 49.9K_0402_1%

1 2

RC108 49.9K_0402_1%

1 2

RC109 2.2K_0402_5%

1 2

RC105 2.2K_0402_5%

1 2

RC113 20K_0201_5%@

1 2

RC114 20K_0201_5%@

GSPI0_MOSI

GSPI1_MOSI

I2C1_SDA_TS

I2C1_SCL_TS

SOC_GPIO_A7

TS_INT#

UART0_RX

UART0_TX

I2C_0_SDA

I2C_0_SCL

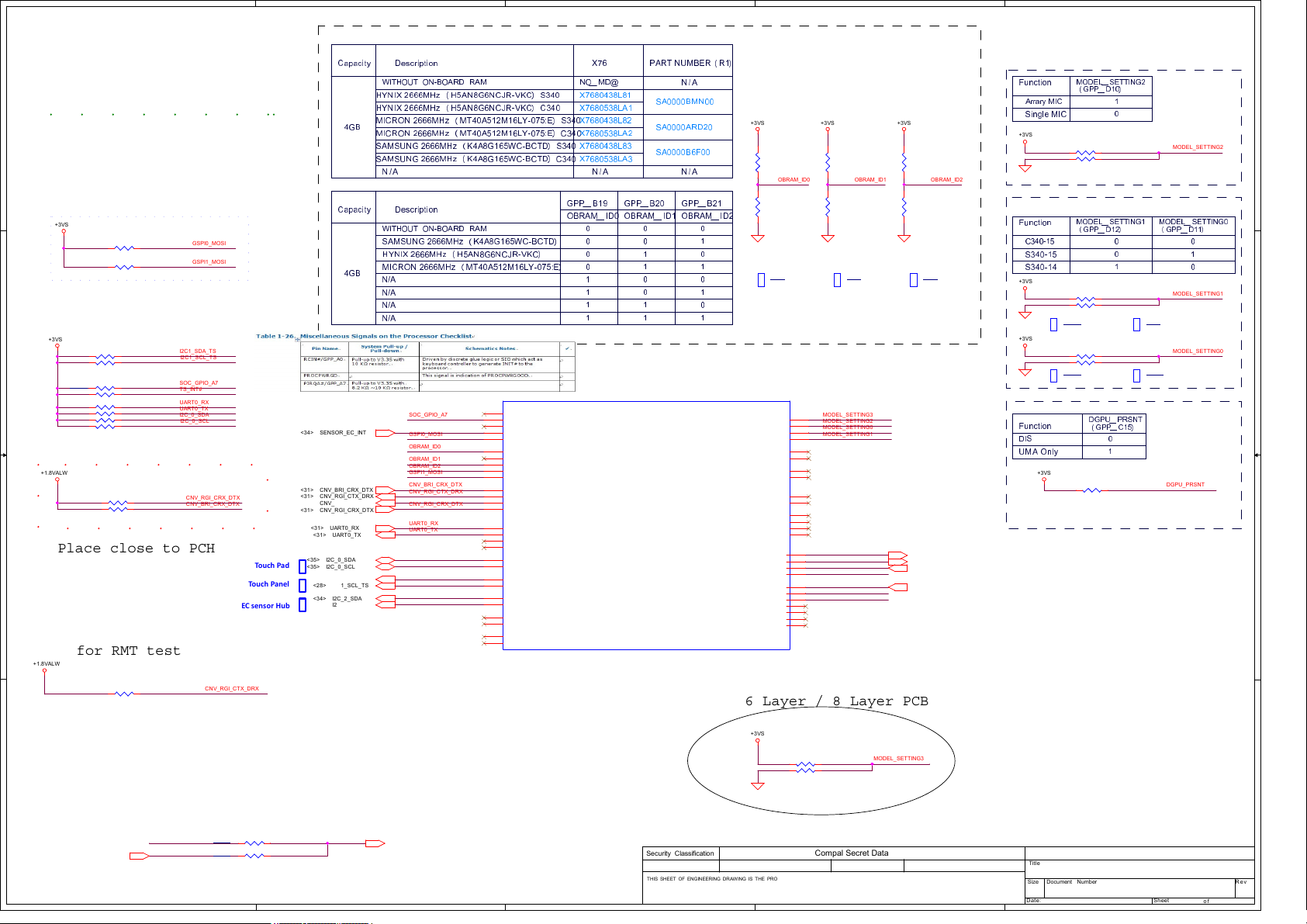

CNV_RGI_CRX_DTX

Place close to PCH

B B

for RMT test

+1.8VALW

RC162 20K_0201_5%@

12

CNV_RGI_CTX_DRX

T o u c h P ad

T o u c h P an el

E C sensor Hub

SENSOR_EC_INT<34>

CNV_BRI_CRX_DTX<31>

CNV_RGI_CTX_DRX<31>

CNV_BRI_CTX_DRX<31>

CNV_RGI_CRX_DTX<31>

UART0_RX<31>

UART0_TX<31>

I2C_0_SDA<35>

I2C_0_SCL<35>

I2C1_SDA_TS<28>

I2C1_SCL_TS<28>

I2C_2_SDA<34>

I2C_2_SCL<34>

Capacity

Description

WITHOUT ON-BOARD RAM

HYNIX 2666MHz (H5AN8G6NCJR-VKC)S340

MICRON 2666MHz (MT40A512M16LY-075:E)S340

4GB

MICRON 2666MHz (MT40A512M16LY-075:E)C340

SAMSUNG 2666MHz (K4A8G165WC-BCTD)S340

SAMSUNG 2666MHz (K4A8G165WC-BCTD)C340

N/A

Capacity

Description

WITHOUT ON-BOARD RAM

SAMSUNG 2666MHz (K4A8G165WC-BCTD)

HYNIX 2666MHz (H5AN8G6NCJR-VKC)

MICRON 2666MHz (MT40A512M16LY-075:E)

4GB

N/A

N/A

N/A

N/A

SOC_GPIO_A7

GSPI0_MOSI

OBRAM_ID0

OBRAM_ID1

OBRAM_ID2

GSPI1_MOSI

CNV_BRI_CRX_DTX

CNV_RGI_CTX_DRX

CNV_RGI_CRX_DTXCNV_BRI_CRX_DTX

UART0_RX

UART0_TX

CC2 7

CC3 2

CE2 8

CE2 7

CE2 9

CA3 1

CA3 2

CC2 9

CC3 0

CA3 0

CK2 0

CG1 9

CH1 9

CR1 2

CP1 2

CN1 2

CM1 2

CM1 1

CN1 1

CK1 2

CF2 7

CH2 7

CJ 20

CJ 12

CJ 30

X76

NO_MD@

X7680438L81

X7680538LA1HYNIX 2666MHz (H5AN8G6NCJR-VKC)C340

X7680438L82

X7680538LA2

X7680438L83

X7680538LA3

N/A N/A

GPP_B19

OBRAM_ID0 OBRAM_ID1 OBRAM_ID2

0

0 0 1

0 1 0

0 1 1

1

1 0 1

1 1 0

1 1 1

UC1F

GPP_B15/GSPI0_CS0#

GPP_A7/PIRQA#/GSPI 0_CS1#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS0#

GPP_A11/PME#/GSPI1_CS1#/ SD_VDD2_PWR_EN#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_F5/CNV_BRI_RSP

GPP_F6/CNV_RGI_DT

GPP_F4/CNV_BRI_DT

GPP_F7/CNV_RGI_RSP

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_H4/I2C2_SDA

CF2 9

GPP_H5/I2C2_SCL

GPP_H6/I2C3_SDA

CH2 8

GPP_H7/I2C3_SCL

GPP_H8/I2C4_SDA

CJ 31

GPP_H9/I2C4_SCL

WHL-U_BGA1528

PART NUMBER(R1)

N/A

SA0000BMN00

SA0000ARD20

SA0000B6F00

GPP_B20

GPP_B21

0 0

0 0

GPP_D9/ISH_SPI_CS#/GS PI2_CS0#

GPP_D10/ISH_SPI_CLK/GS PI2_CLK

GPP_D11/ISH_SPI_MISO/ GSPI2_MISO

GPP_D12/ISH_SPI_MOSI/ GSPI2_MOSI

GPP_D5/ISH_I 2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I 2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_H10/I2C5_SDA/ISH_I2C2_S DA

GPP_D13/ISH_UART0_RXD/SML0BDATA/I 2C4B_SDA

GPP_A12/ISH_GP6/BM_BUSY#/ SX_EXIT_HOLDOFF#

6 of 20

GPP_H11/I2C5_SCL/ISH_I2C2_SCL

GPP_D14/ISH_UART0_TXD/SML0BCLK/I 2C4B_SCL

GPP_D15/ISH_UART0_RTS#/GSPI 2_CS1#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A18/ISH_GP0