Page 1

5

smd.db-x7.ru

4

3

2

1

COMPAL CONFIDENTIAL

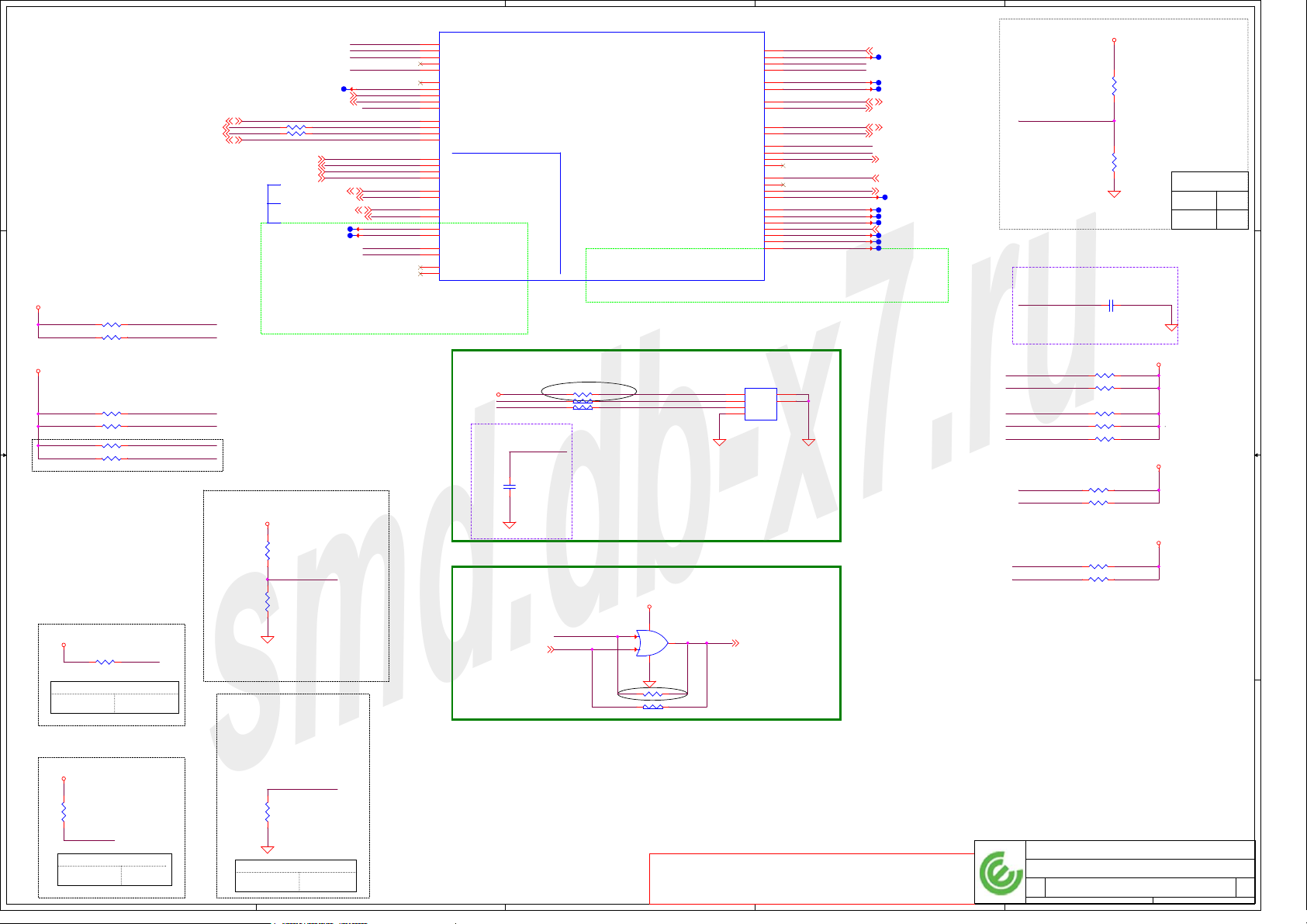

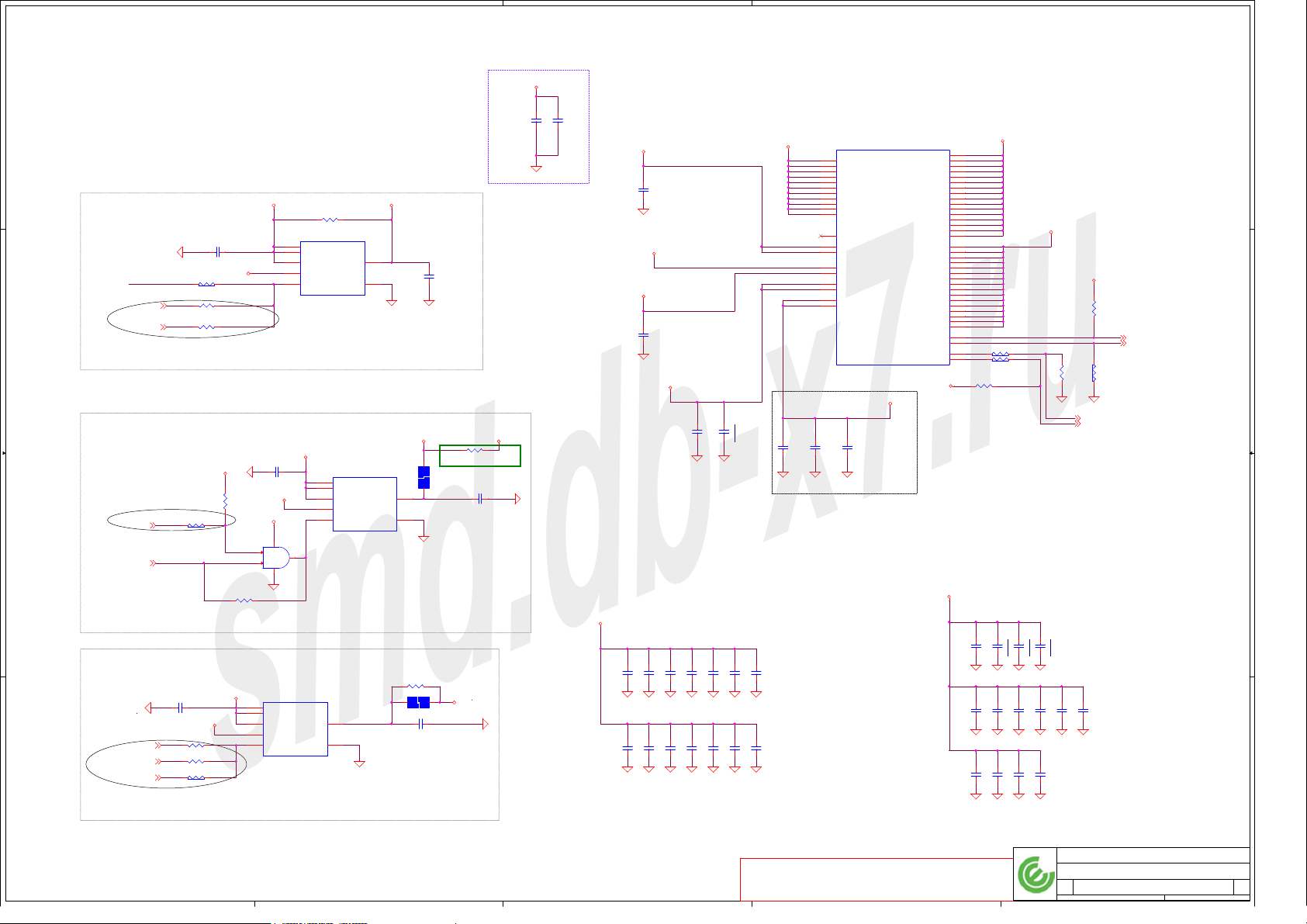

MODEL NAME :EDC40

D D

PCB NO : LA-G871P

BOM P/N : 431ADY31L0x

Merion 14 AR

Whiskey lake-U U42

2019-03-05

REV : 1.0 (A00)

@ : Nopop Component

EMI@ : EMI Component

@EMI@ : EMI Nopop Component

ESD@ : ESDComponent

@ESD@ : ESD Nopop Component

C C

RF@ : RF Component

@RF@ : RF Nopop Component

CONN@ : Connector Component

CXDP@ : XDP Component

DS3@ : Deep sleep support

NDS3@ : non Deep sleep support

750@ : NUVOTON NPCT750 TPM Component

B B

ST33@ : ST ST33HTPH TPM Component

RTD3@ : RTD3 support

@RTD3@ : RTD3 Nopop Component

NRTD3@ : non RTD3 support

MB PCB

Part Number

DAA000HW010

Description

PCB 2EE LA-G871P REV1 MB AR 1

VPRO@ : vPro Component

NVPRO@ : Non-vPro Component

Layout Dell logo

JUMP@ : Jump solder and short

A A

Power CKT : Merion 14_WHL_PWR_X02_1228a

COPYRIGHT 2018

ALL RIGHT RESERVED

REV:A00

PWB: 7YM2P

5

GPIO map : 20181221a Rev1.5

@JUMP@ : Jump no solder

i7@ : Only i7 config support 4*4 antenna

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOU T THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRIT TEN CONSENT.

4

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-G871P

LA-G871P

LA-G871P

1 109Tuesday, March 05, 2 019

1 109Tuesday, March 05, 2 019

1 109Tuesday, March 05, 2 019

1

1.0

1.0

1.0

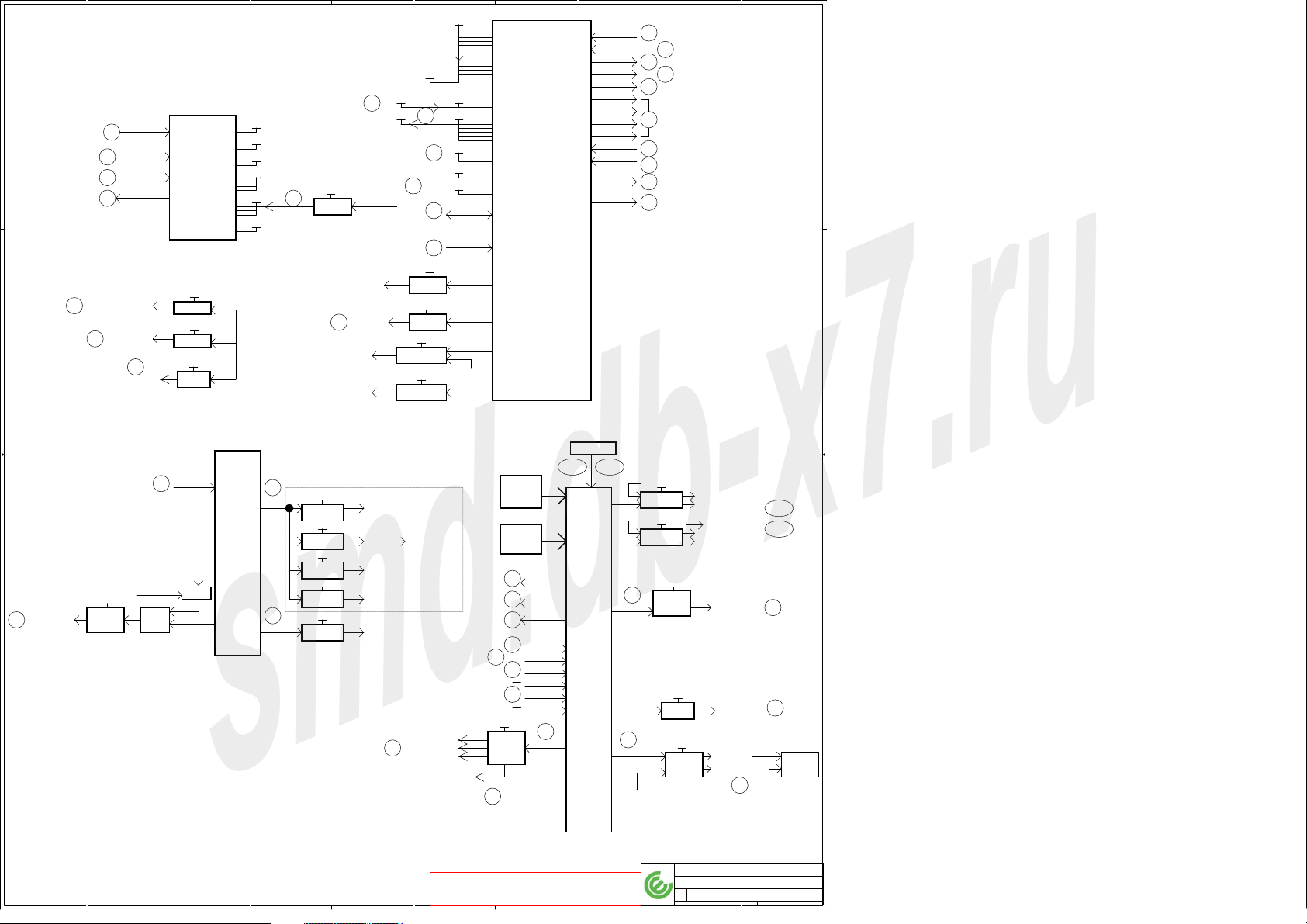

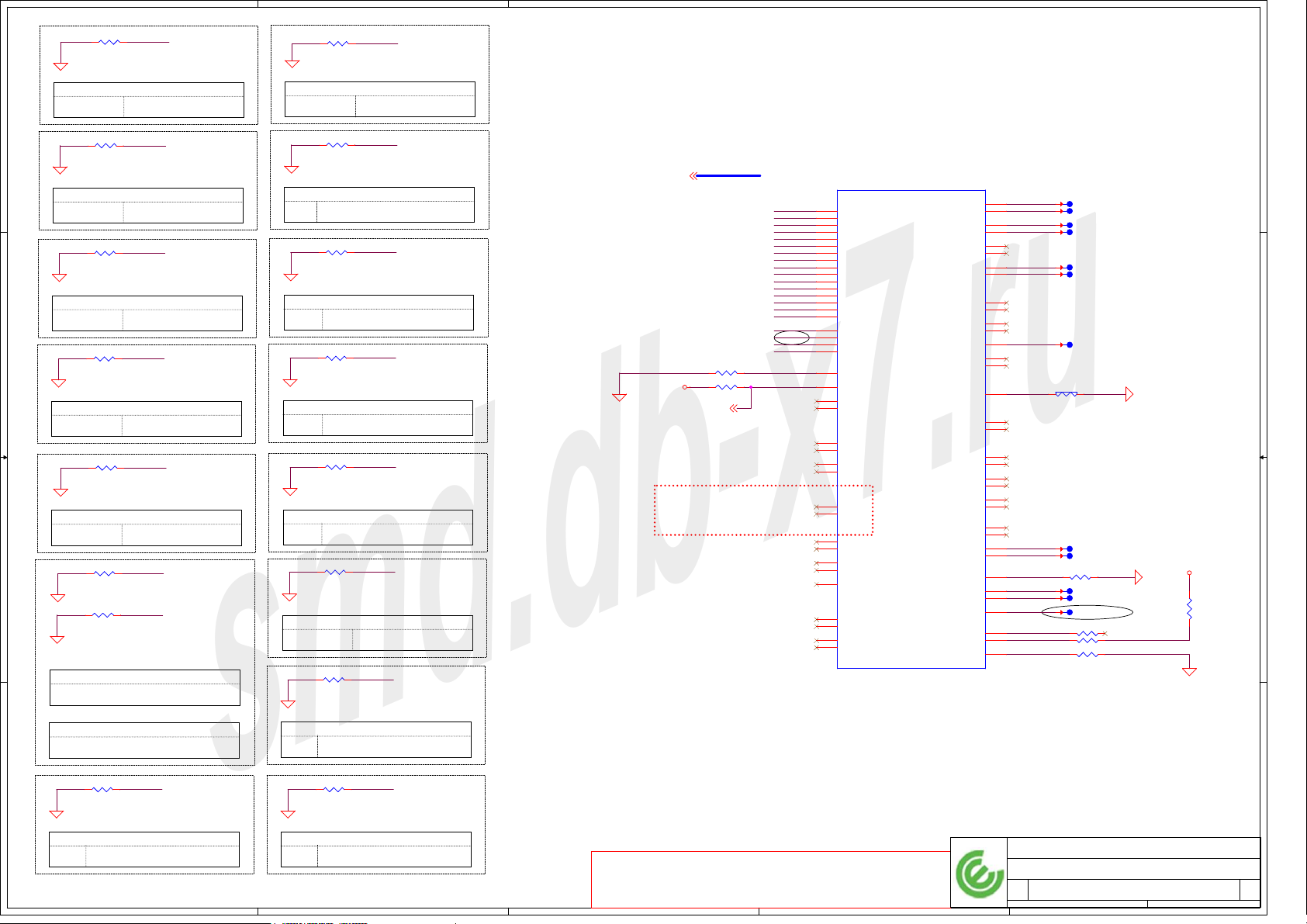

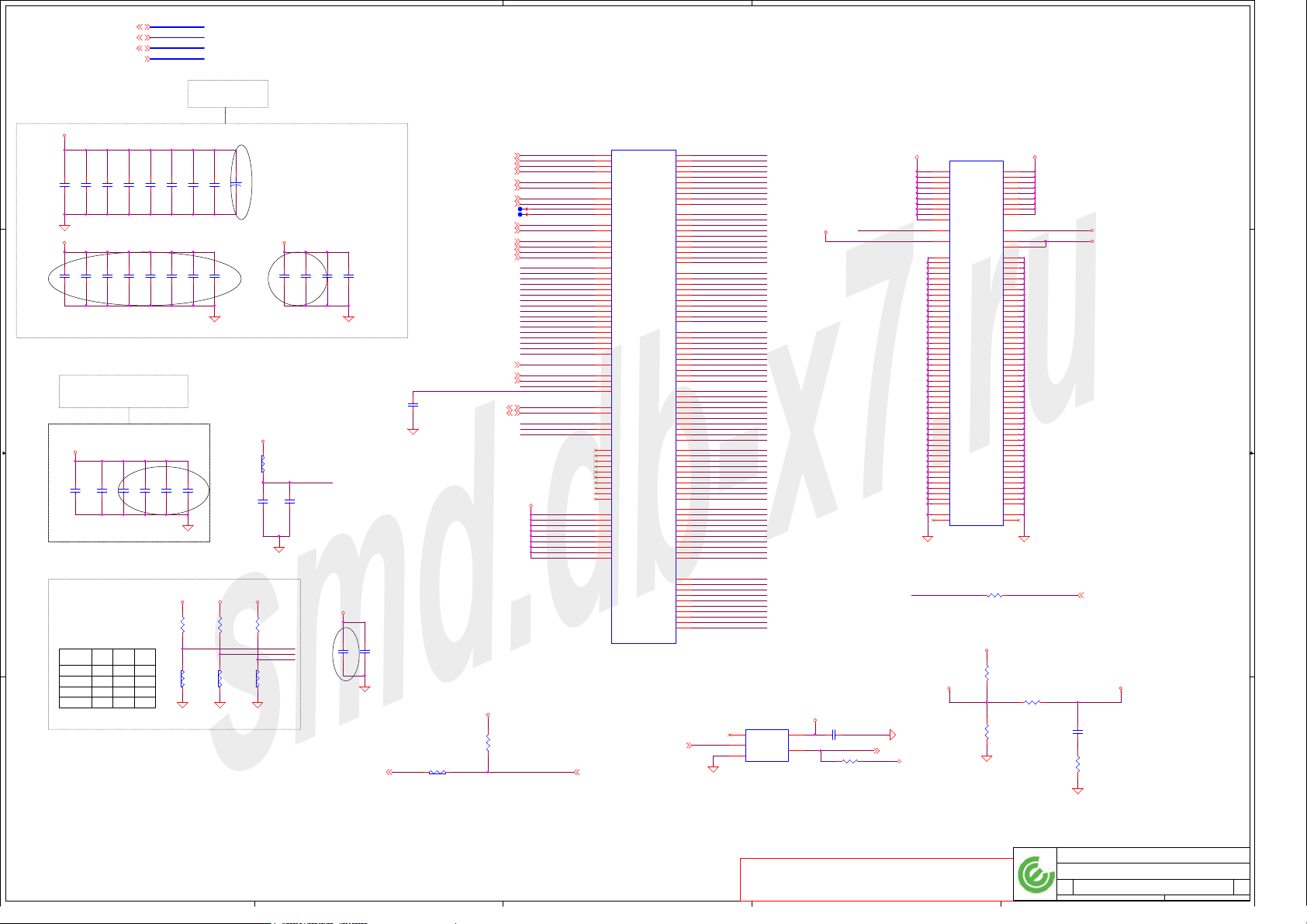

Page 2

5

smd.db-x7.ru

4

3

2

1

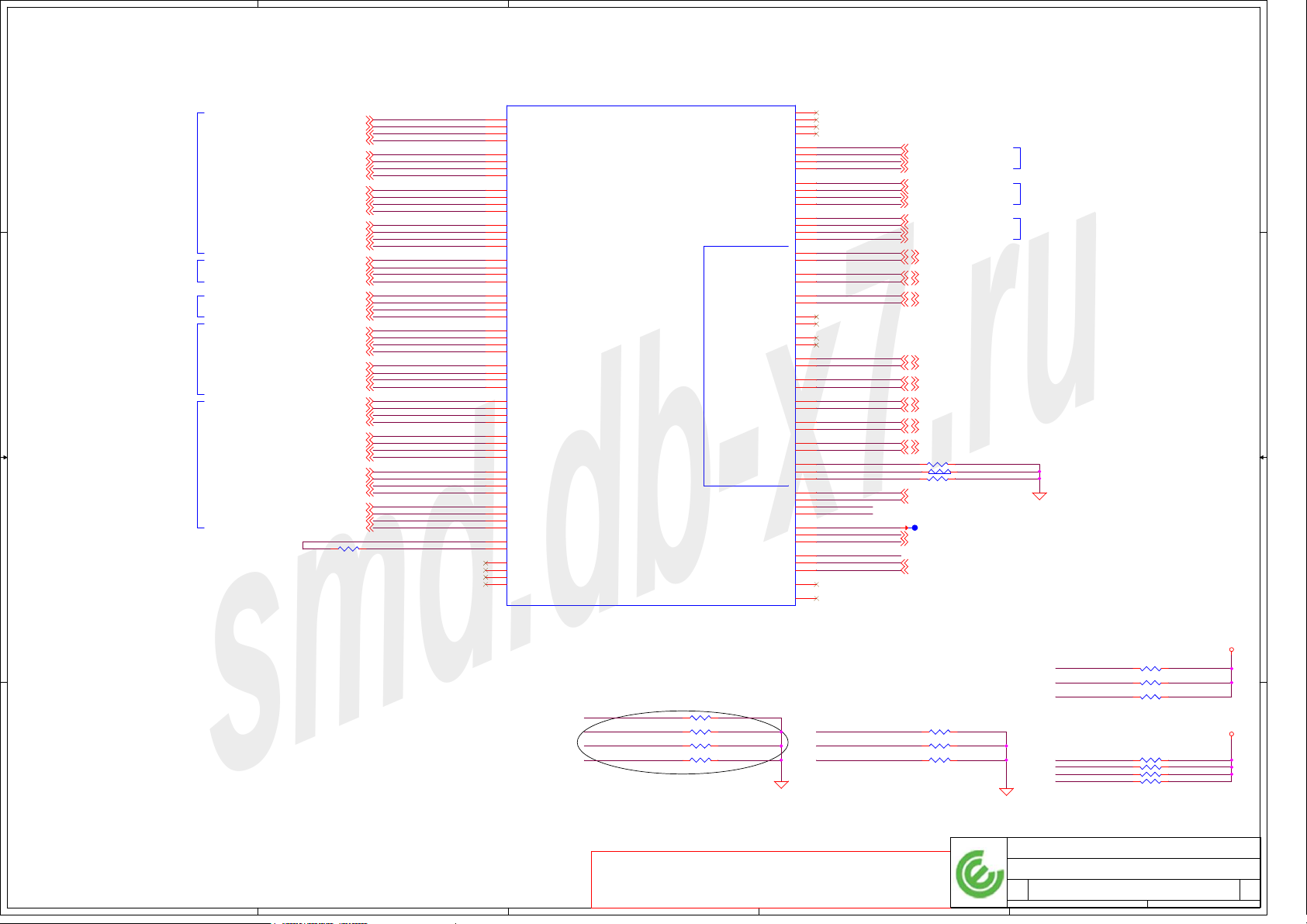

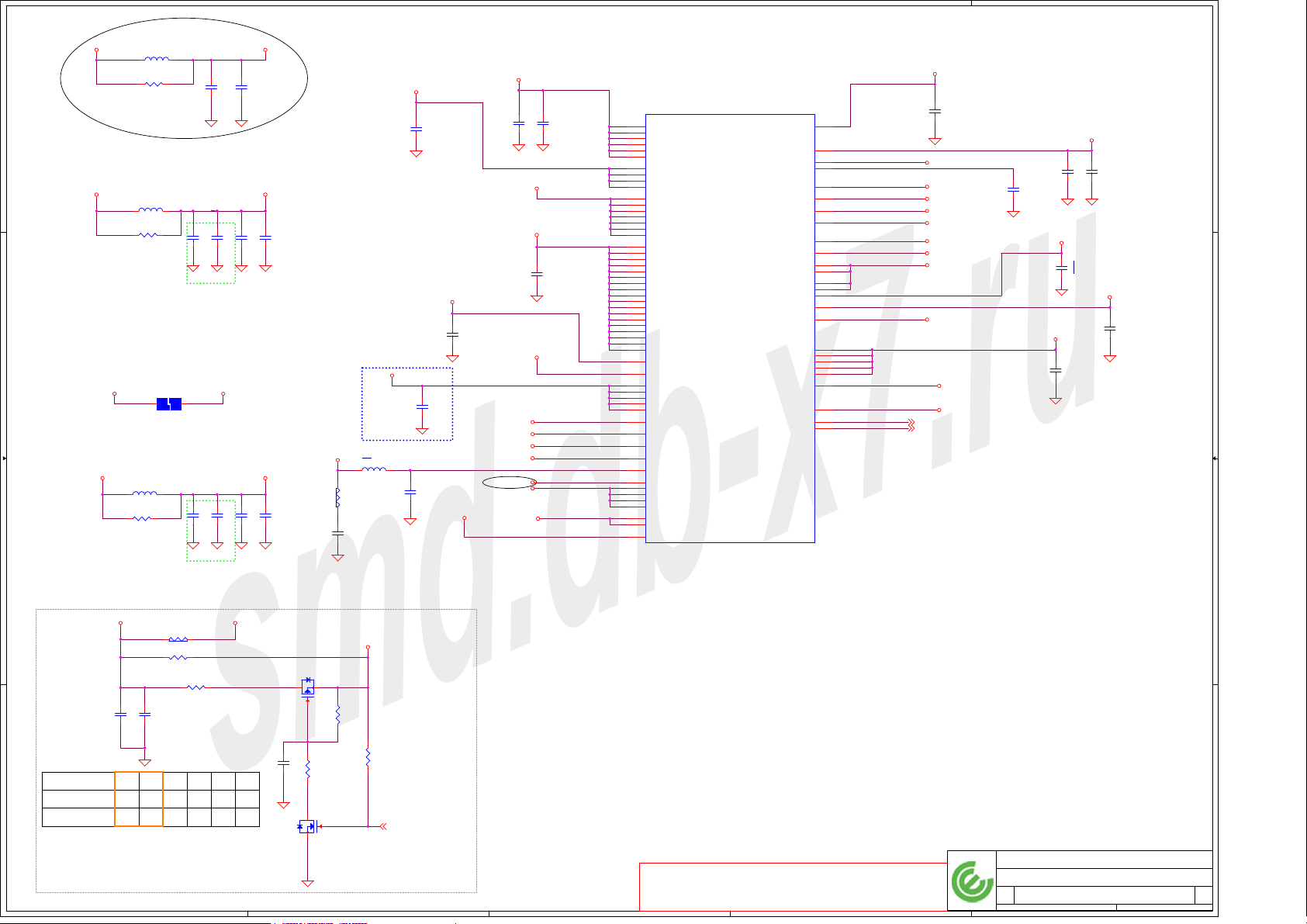

Merion14 AR Block Diagram

Memory BUS (DDR4)

DDR4 2400MHz for WHL-U

D D

2-Lane eDP1.3

P38

PCIE[5][6][7][8]

HDMI 1.4

CONN

EDP CONN

HDMI

P40

AR-SP

P42-4 3

SMBus

SATA[1]/PC IE[12]

M.2,2230 Key E

P52

USB2.0[7] USB2.0[10]

WLAN+BT/CNVi

PCIE[10]

P52

Left side TypeC

USB2.0

SD4.0

PCIE[9]

P70

P70

SMBus

Micro SIM

USB2.0[1] from PCH

C C

Card reader

RTS524 2

P45

PD Solut i on

TPS65982DD

P52

TBT

P44,50

M.2,3042 Key B

WWAN/LTE/HCA

PCIex2 for 2nd SSD and

Optane

CNVi

EDP

DDI[1]

DDI[2]

INTEL

WHL-U 42 MCP

PAGE 6~19

USB/PCIE MUX

PCIE[11]

HD3SS3212

P54

USB3.0[4]

SPI

SATA[2]/PCIE[16][15] [14][13]

Pop option

GD25B256 DYIG

B B

vPro use

256Mb 4K sector WSON8

P8

GD25B64CYIGR

Non-vPro use

64Mb 4K sector WSO N8

Smart Card

USH board

A A

TDA8034HN

RFID/NFC

Fingerprint

CONN

Fingerprint

MOCV

USH TPM1.2

BCM58202

SPI

SPI

FP-USB2.0

P66

USB2.0[8]

ESPI

SMSC KBC

MEC510 5

P58-5 9

GD25B127D SIGR

Non-vPro use

128Mb 4K sector SOP8

TPM2.0

ST-ST33HTPH 2032AHC 1

BC link

KB/TP CONN

PWM

FAN CONN

P8

P8

P63

P63

Up to 2x16GB Modules

USB

I2C

P66

USB2.0[2]

SLGC55544BVTR

USB POWER SHARE

HD Audio I/F

Reverse Type

DDR4-SO-DIMM X2

BANK 0, 1, 2, 3

P23~24

I2C[0]

USB2.0[6]

USB2.0[2]_PS

P71

USB3.0[2]

USB2.0[3]

USB3.0[3]

I2C[3]

HDA Codec

ALC3254

M.2 2280

SSD Conn

P56

P68

LCD Touch

USB3.0 Conn

PS(Ext Port 1)

USB3.0 Conn

(Ext Port 2)

Active Steering Antenna

(MB

)

INT.Speaker

Universal Jack

Dig. MIC

Camera

P38

P38

P71

P72

P56

P56

P38

Trough eDP Cable

Trough eDP Cable

Right side

Left side

P9

LED/B

Bettery LED

Breath LED

LID SWITCH

USH CONN

CPU&PCH XDP Port

AUTOMATIC POWER

SWITCH(APS)

DC/DC Interface

POWER ON/OFF SW

P64

P64

P66

P79

P79

P78

P77

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL . IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

3

PARTY WITHOUT DE LL'S EXPRESS WRITTEN CONSENT.

2

Title

Size

Size

Size

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

Document Num ber Re v

Document Num ber Re v

Document Num ber Re v

LA-G871P

LA-G871P

LA-G871P

1

2 109Tuesday, March 05, 2019

2 109Tuesday, March 05, 2019

2 109Tuesday, March 05, 2019

1.0

1.0

1.0

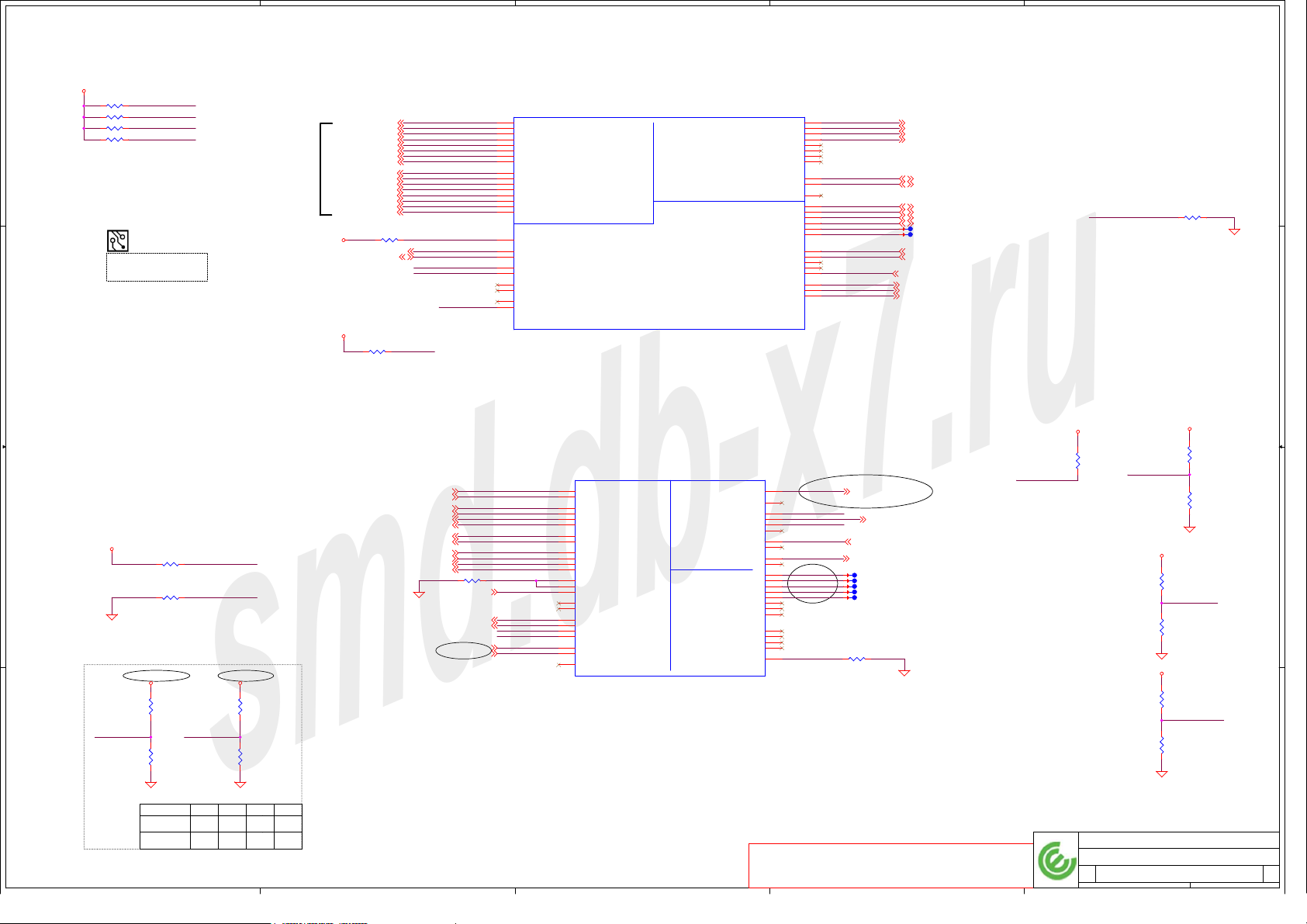

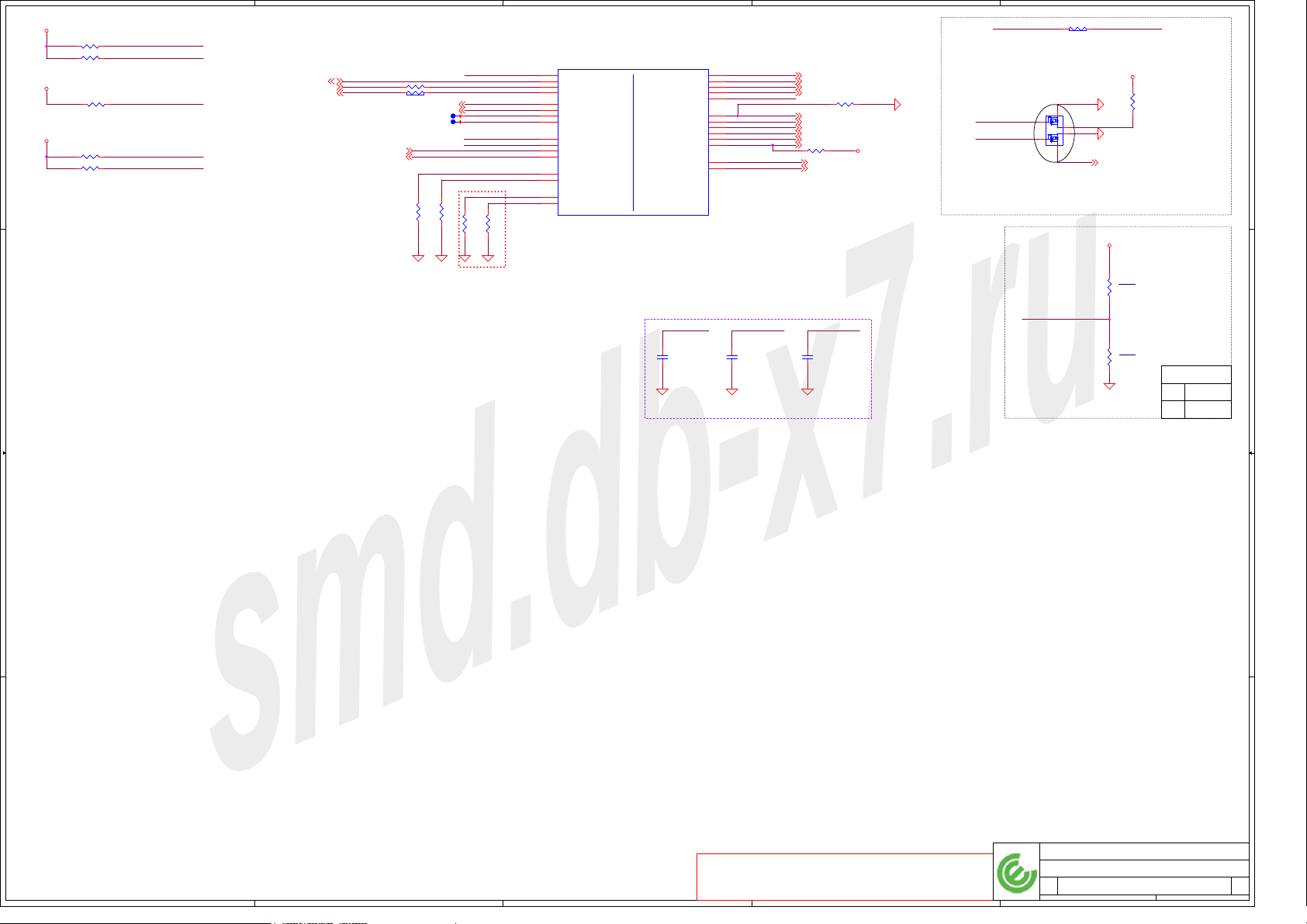

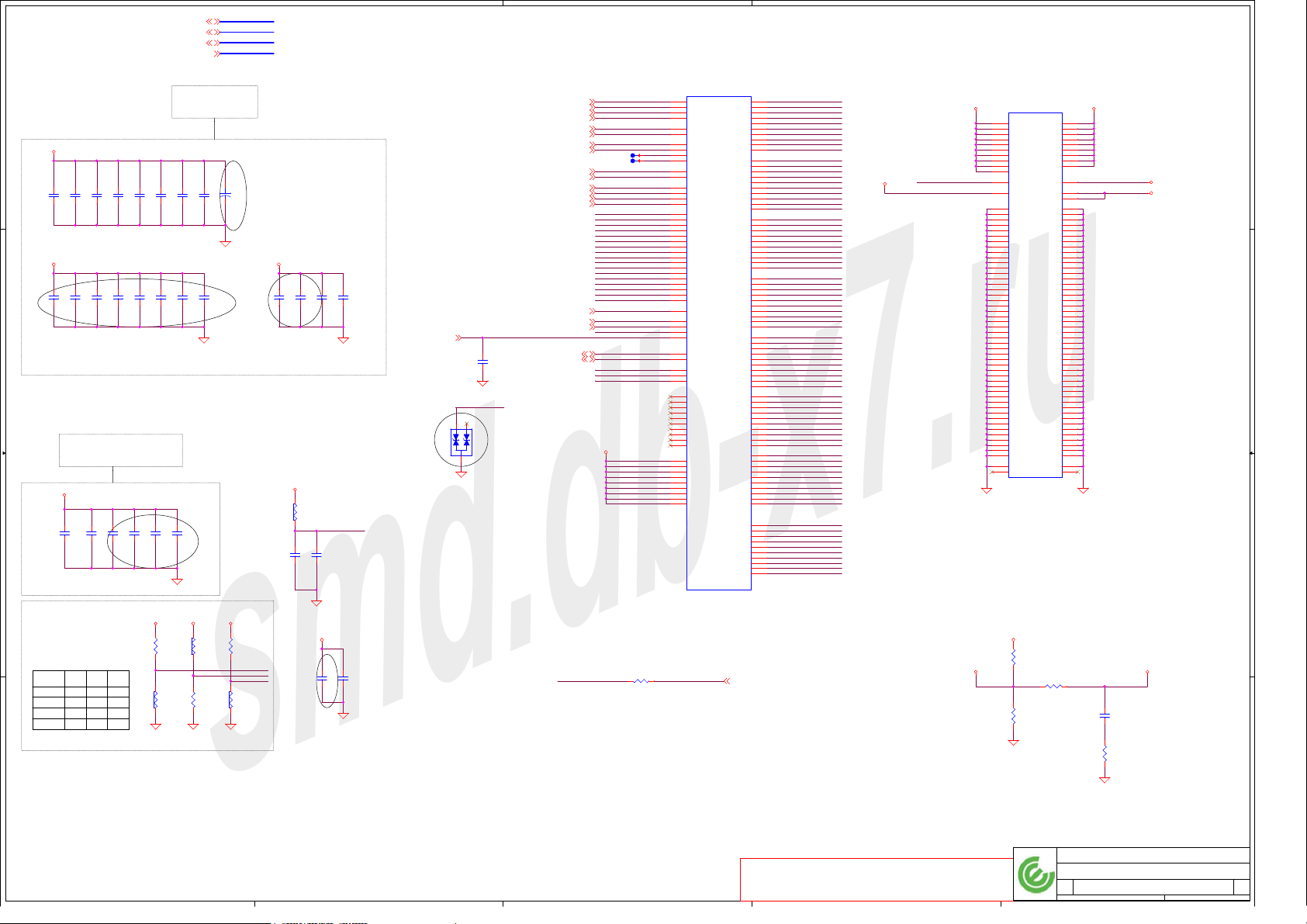

Page 3

5

smd.db-x7.ru

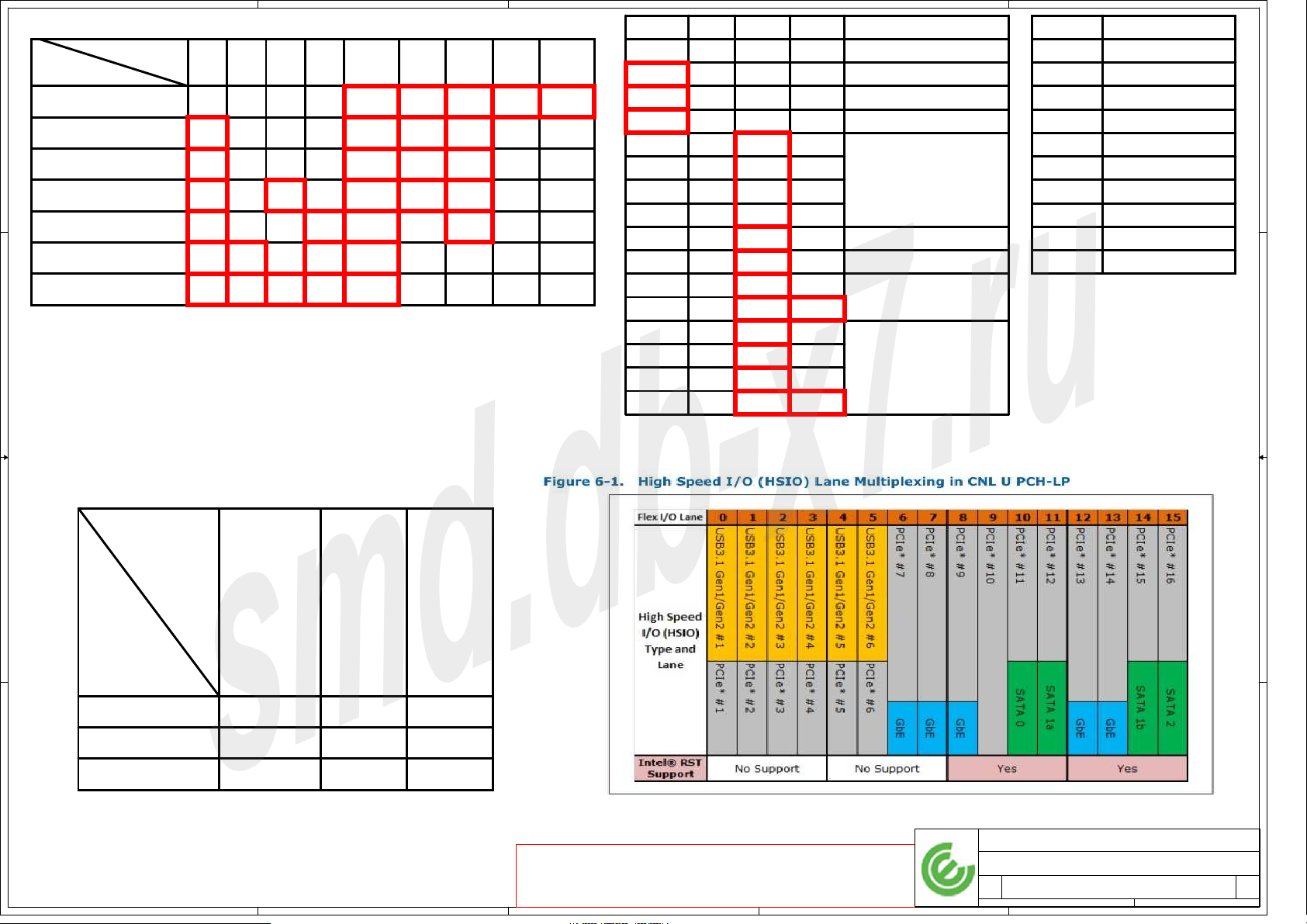

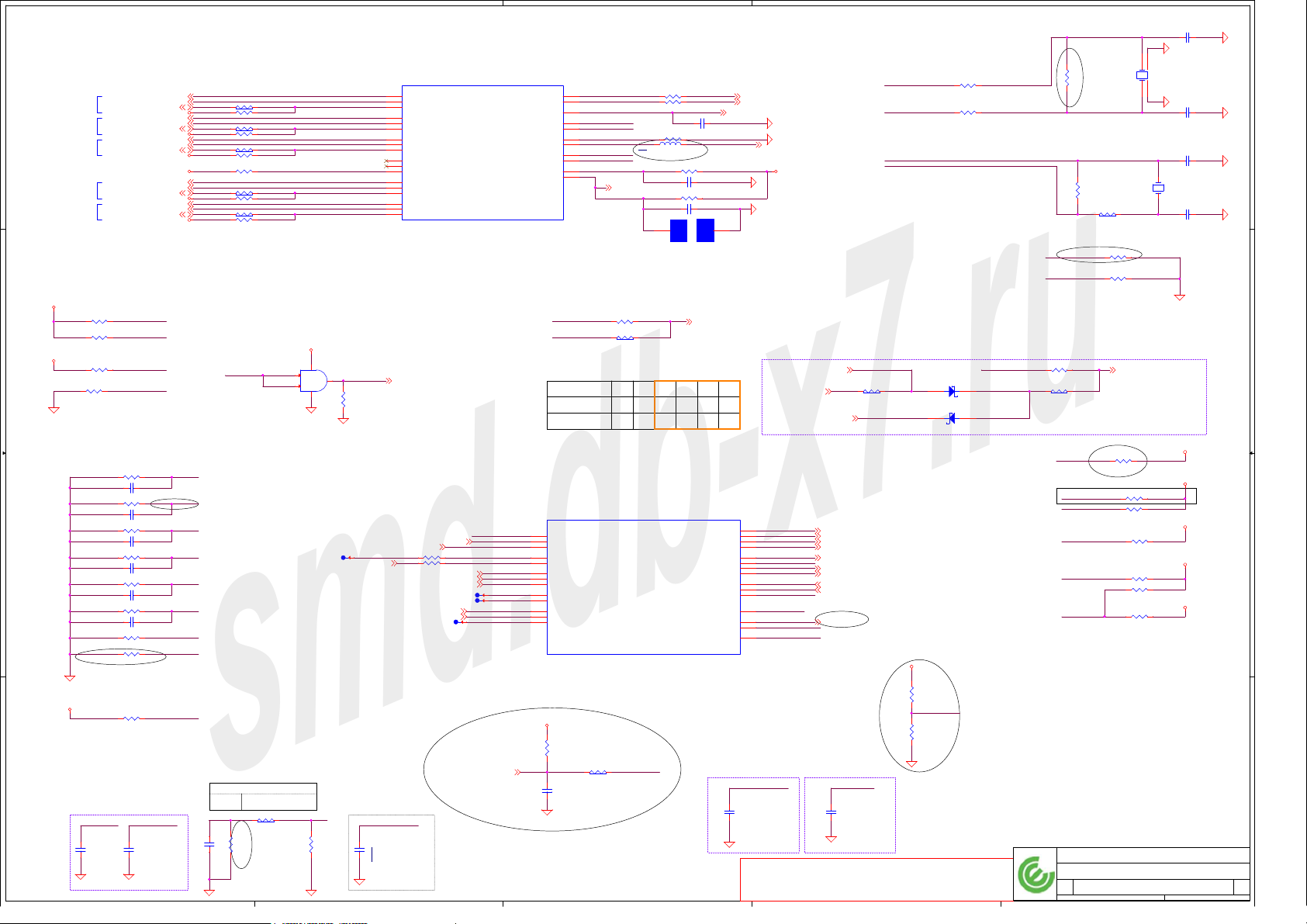

POWER STATES

Signal

State

S0 (Full ON) / M0

D D

S3 (Suspend to RAM) / M3 LOW

S4 (Suspend to DISK) / M3

S5 (SOFT OFF) / M3

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

C C

SLP

S3#

HIGH

LOW

LOW

LOW LOW LOW

LOW LOW LOW LOW

SLP

SLP

S5#

S4#

HIGH HIGH

HIGH HIGH

HIGH HIGH

LOW

LOW

LOW

HIGH HIGH

HIGH

SLP

A#

HIGH

HIGH

HIGH

LOW

4

ALW AYS

PLANE

ON

ON ON ON

ON ON

ON ON

ON ON

ON

ON

M

PLANE

ON

OFF OFF OFF

OFF OFF OFF OFF

OFF OFF OFF OFF

SUS

PLANE

RUN

PLAN E

ON ON ON

OFF

OFF

OFF

OFF

OFFLOW

CLOCKS

OFF

OFF

OFF

3

USB3.0

USB3.0-1

USB3.0-2

USB3.0-3

USB3.0-4

USB3.0-5

USB3.0-6

SSIC

2

PCIE

PCIE-1

PCIE-2

PCIE-3

PCIE-4

SATA

N/A

JUSB1-->Right

JUSB2-->Lef t

M.2 3042(LTE)

PCIE-5

PCIE-6

Alpine Ridge - SP

PCIE-7

PCIE-8

PCIE-9

PCIE-10 M.2 2230(BT)

PCIE-11

PCIE-12

SATA-0

SATA-1

Card Reader

M.2 2230(WLAN)

M.2 3042(LTE)

USB PORT#DESTINATION

1

2

3

4

5

6

7

8

9

10

1

DESTINATION

Type C

JUSB1-->Right

JUSB2-->Left

N/A

N/A

Camera

M2 3042(WWAN)

USH

Reserve for FPR in PB

PCIE-13

PCIE-14

PCIE-15

PCIE-16

SATA-1*

SATA-2

M.2 2280 SSD

(PCIex4 or SATA)

PM TABLE

+5V_ALW

+3.3V_ALW

B B

State

S0

S5 S4/AC

A A

S5 S4/AC doesn't exist OFFOFF OFF

power

plane

5

+3.3V_ALW_DSW

+3.3V_ALW_PCH

+RTC_CELL

+1.8V_PRIM

+5V_ALW2

+3.3V_ALW2

+3.3V_RTC_LDO

+1.0V_PRIM

ON

ON

+1.2V_MEM

+2.5V_MEM

+1.0V_VCCSTG

ON ON

OFF OFF

+5V_RUN

+3.3V_RUN

+0.6V_DDR_VTT

+1.8V_RUN

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOU T THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRIT TEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

LA-G871P

LA-G871P

LA-G871P

3 109Tuesday, March 05, 2 019

3 109Tuesday, March 05, 2 019

3 109Tuesday, March 05, 2 019

1

1.0

1.0

1.0

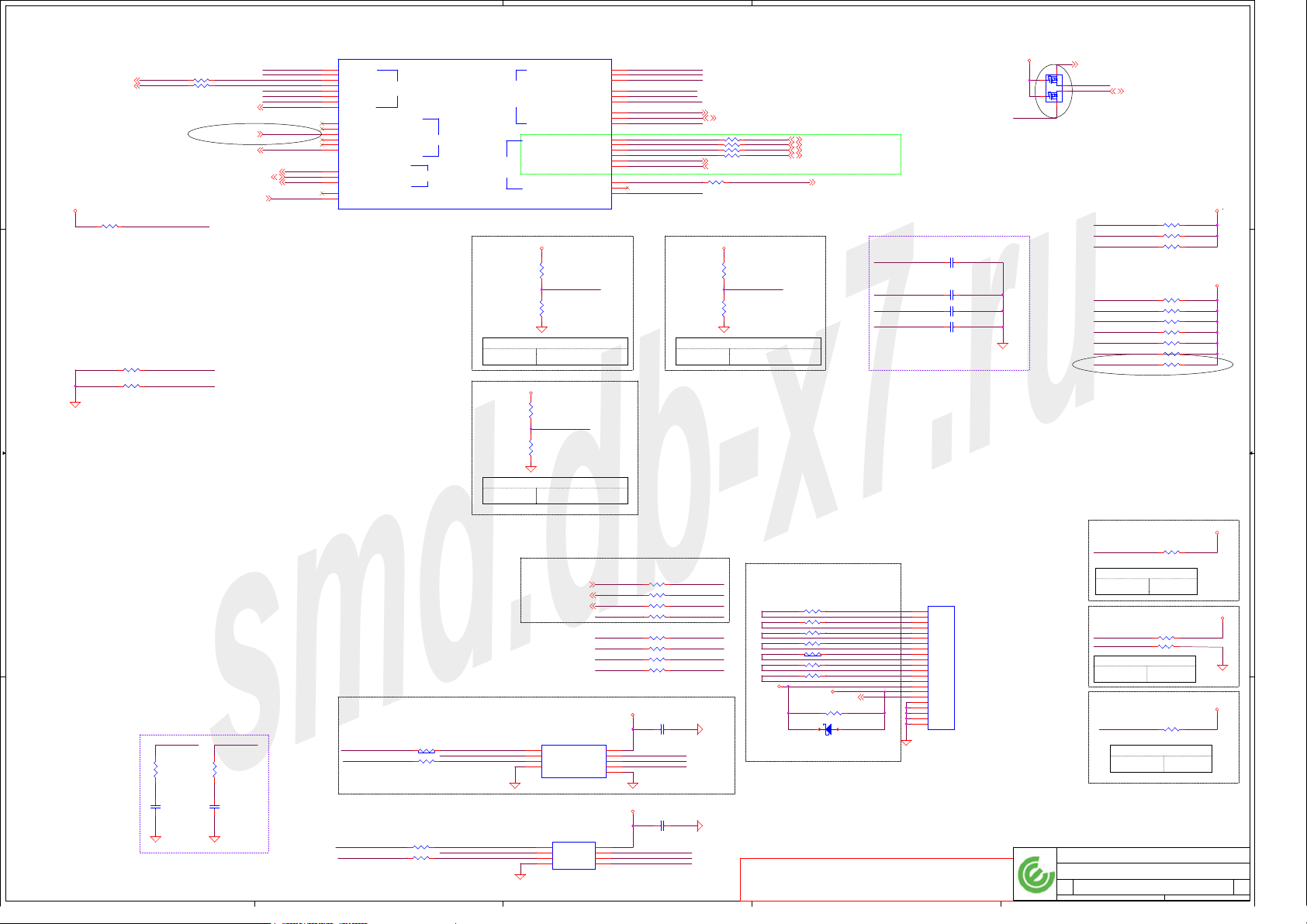

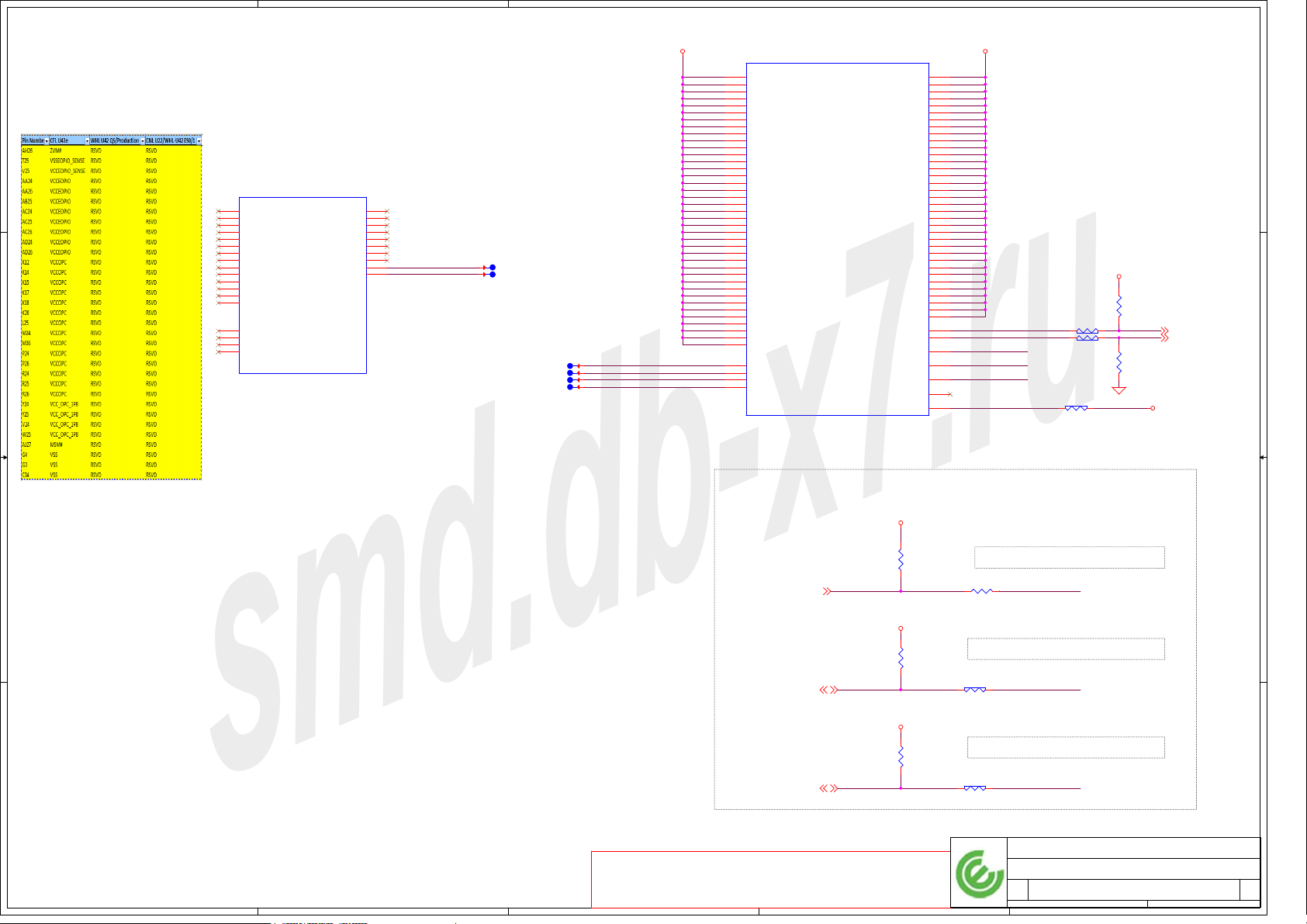

Page 4

5

smd.db-x7.ru

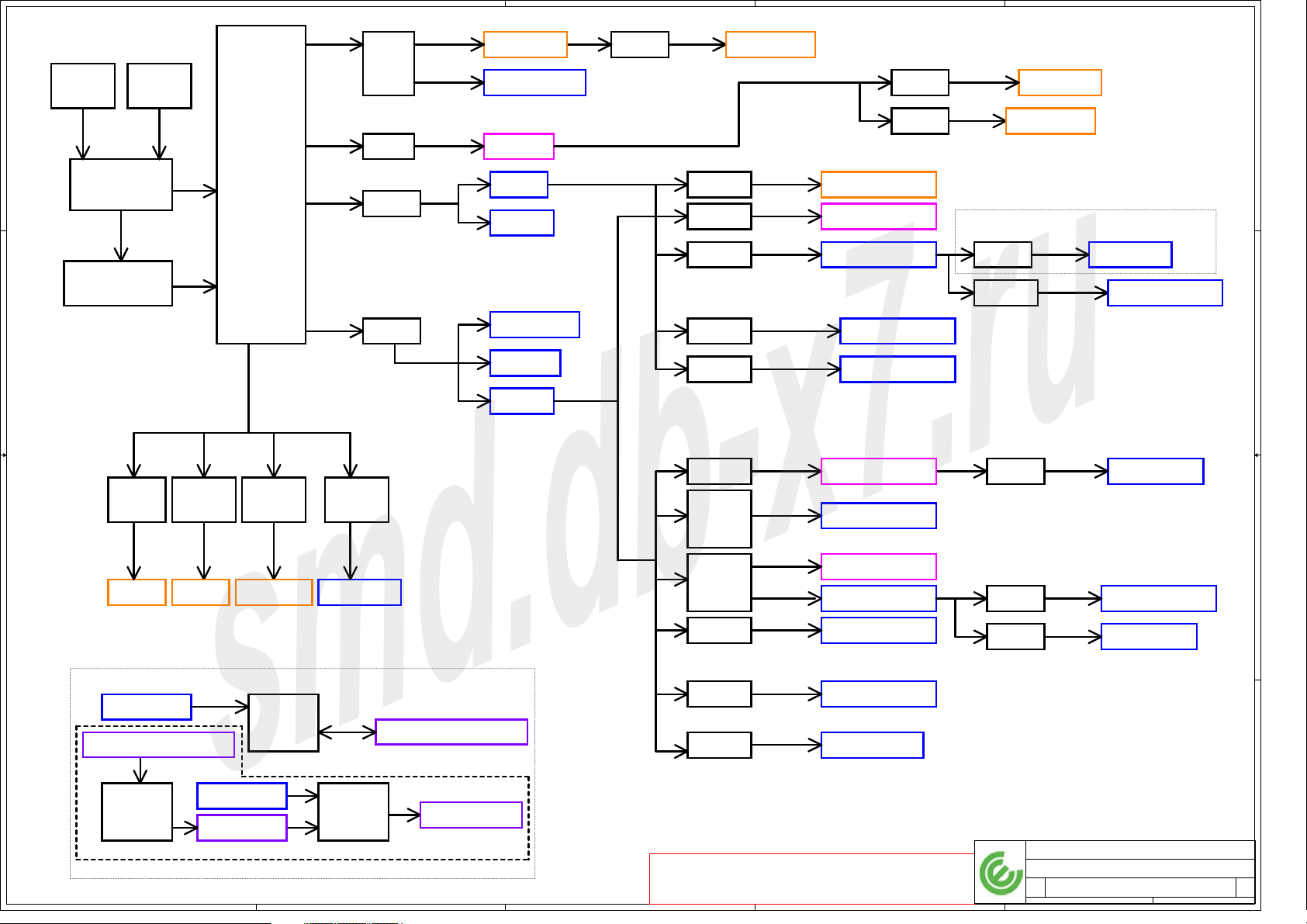

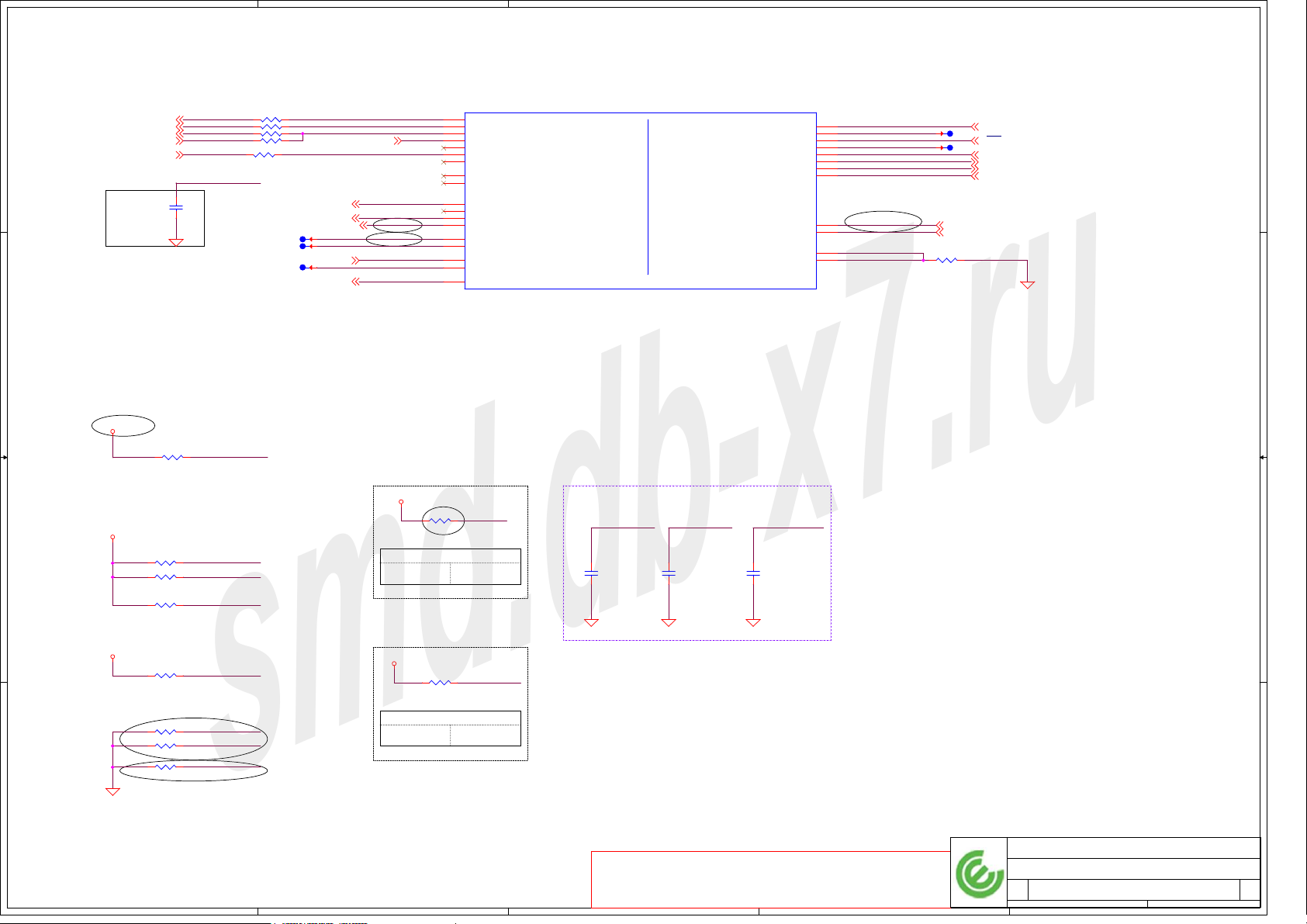

Barrel

ADAPT ER

D D

C C

Type-C

ADAPTER

CHARGER

ISL9538

(PU700)

BATTERY

+13.5VB

4

SY8210A

(PU200)

SY8286R

(PU301)

SYV828C

(PU102)

SY8288B

(PU100)

SIO_SLP_S4#

0.6V_DDR_ VTT_ON

PCH_P RIM_EN

ALWO N

ALWO N

+1.2V_MEM

+0.6V_DDR_VTT

+1.0V_PRIM

+5V_ALW

+5V_ALW2

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

3

TPS22961

(UZ27)

VCCSTG_ EN

SY8057BQ

(PU401)

SY8057CQ

(PU402)

EM5209

(UZ47)

SLGC55544C

(UI3)

SY6288

(UI1)

+VCCPLL_OC

RUN_ ON

PCH_P RIM_EN

RUN_ ON

USB_PW R_SHR_ VBUS_EN

USB_PW R_EN1#

2

TPS22961

(UZ19)

TPS22961

(UZ21)

+1.0VS_VCCIO

+1.0V_PRIM_CORE

+5V_RUN

+5V_USB_CHG_PWR

+USB_EX2_PWR

VCCSTG_ EN

RUN_ ON

+1.0V_VCCSTG

+1.0V_VCCST

Merion 14 Touch PWR is +5V

PJV1701

(QV8)

EM5209

(@UZ5)

3.3V_TS_EN

AUD_PW R_EN

+TS_PWR

+5V_RUN_AUDIO

1

CPU PWR

PCH PWR

Peripheral Device PWR

TYPE-C Power

RT8097A

FDMF3035

ISL95808

(PU614)

B B

IMVP_V R_ON

+5V_ALW

+20V_TBTA_VBUS_1(5V~20V)

FDMF3035

(PU612)

IMVP_V R_ON

+VCC_GT+VCC_SA

(PU610)

FDMF303 5

(PU613)

IMVP_V R_ON

+VCC_CORE

TPS65982DD

(UT5)

AO6405

(QV1)

EN_IN VPWR

+BL_PWR_SRC

+20V_TBTA_VBUS_1(5V~20V)

TYPE-C

(PU501)

EM5209

(UZ47)

EM5209

(UZ3)

EM5209

(UZ4)

G527ATP1U

(UV24)

AP7361C

(PU503)

PCH_P RIM_EN

WLAN_ PWR_EN

PCH_P RIM_EN

RUN_ ON

3.3V_W WAN_EN

EN_LC DPWR

SIO_SLP_S4#

+1.8V_PRIM

+3.3V_W LAN

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_W WAN

+LCDV DD

+2.5V_MEM

for D DR4

AOZ1336

(UZ8)

EM5209

(@UZ5)

PJV1701

(QZ1)

RUN_ ON

AUD_PW R_EN

3.3V_CAM_ EN#

+1.8V_RUN

+3.3V_RUN_AUDIO

+3.3V_CAM

A A

AP2204

(UT8)

5

+5V_ALW

+5V_TBT_VBUS

AP2112 K

(UT7)

4

+3.3V_VDD_PIC

Reserved

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EX PRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EX PRESS WRITTEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Re v

Size Document N umber Re v

Size Document N umber Re v

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

Power rails

Power rails

Power rails

LA-G871P

LA-G871P

LA-G871P

1

4 109Tuesday, March 05, 2019

4 109Tuesday, March 05, 2019

4 109Tuesday, March 05, 2019

1.0

1.0

1.0

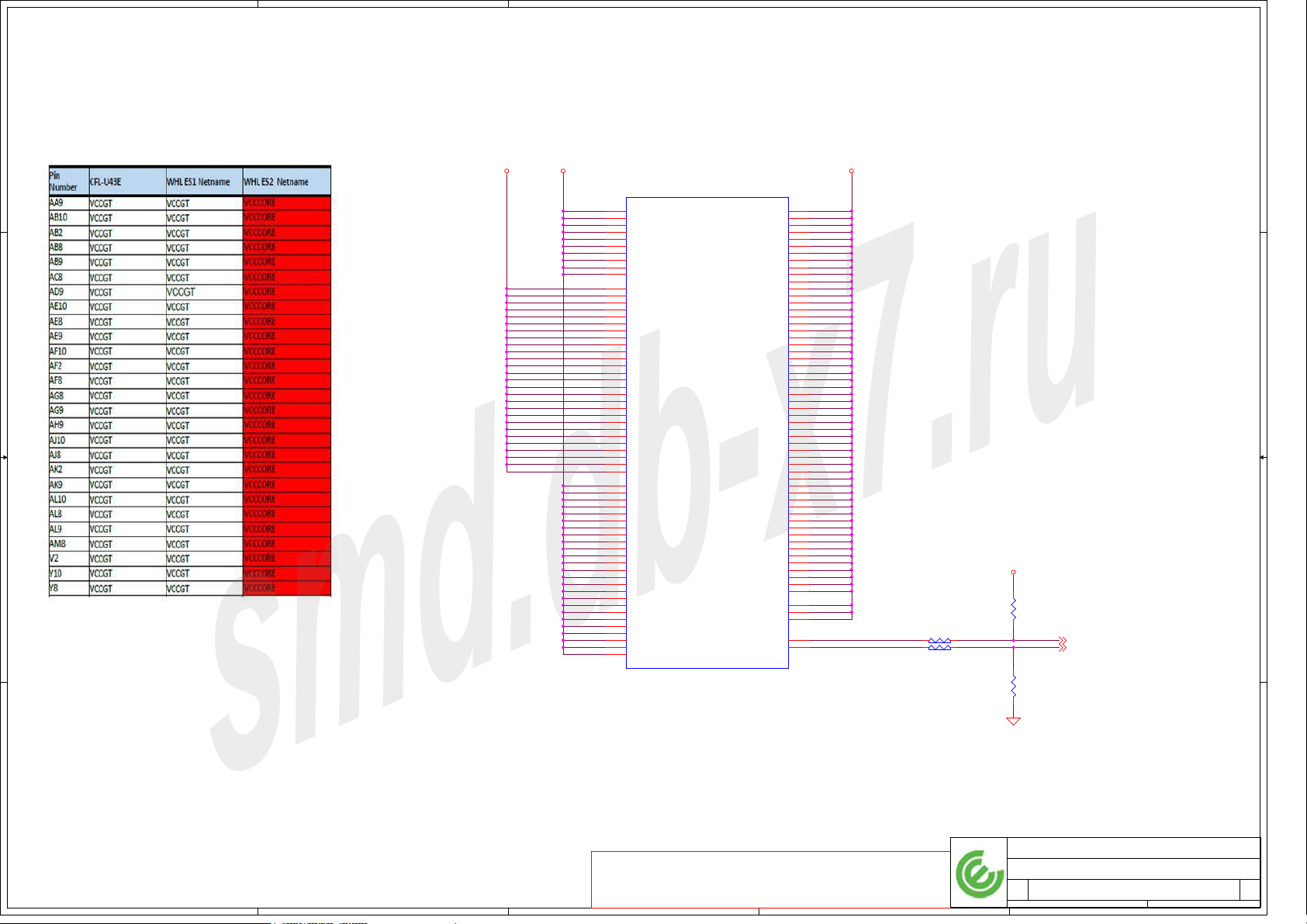

Page 5

5

smd.db-x7.ru

Timing Diagram for S5 to S0 mode

D D

6

C C

B B

+3.3V_WLAN

11

VCCST_PWRGD

12

H_CPUPWR GD

15

PCH_PLTRS T#

17

0.6V_DDR_VTT_ON

12

+1.0V_PRIM_C ORE

+1.8V_PRIM

6

6

+1.0V_PRIM SY8286

+3.3V_ALW

EM5209VF

SLP_WLAN#_GATE

OR

Gate

11

CPU

VCCST_PWRGD

PROCPWRGD

PLTRST#

DDR_VTT_CNT L

+PWR_SR C

TPS62134

+3.3V_ALW

RT8097

+PWR_SR C

SIO_SLP_WLAN#

SIO_SLP_WLAN#

NMOS

AUX_EN_WOWL

A A

4

+VCC_CO RE

VCC

+1.0VS_VCCIO

VCCIO SYS_PWROK

+VCC_GT

VCCGT

+1.2V_MEM

VDDQ

VDDQC

VCCPLL_OC

VCCST

VCCSTG

VCCPL L

VCCSA

SIO_SLP_SU S#

+1.0V_VCC ST

+VCC_S A

11

+1.0V_PRIM

TPS22961

SIO_SLP_S4 #

+LCDVD D

11

+5V_TSP

EC 5105

11

+5V_ALW

RUN_ON

11

3.3V_WWAN_EN

EM5209VF

+3.3V_ALW

EM5209VF

+1.8V_PRIM

EM5209VF +1.8V_RUN

+PWR_SR C

TLV62130

+3.3V_ALW

EM5209VF

+5V_RU N

+3.3V_RUN

+1.0VS_VCCIO

+3.3V_WWAN

3

+3.3V_ALW

+3.3V_SPI

13

3

+1.0V_MPHYGT

5

6

+1.0V_PRIM_C ORE

6

17

4

+3.3V_ALW

G524B1T11

+3.3V_ALW

EM5209VF+3.3V_LAN

+5V_RU N

LP2301ALT1G

+3.3V_RUN

LP2301ALT1G+3.3V_CAM

+3.3V_HDD_M2

+VCC_S A

+VCC_CO RE

+VCC_GT

+1.0V_PRIM

+3.3V_ALW_DSW

+3.3V_ALW_PCH

+1.8V_PRIM

+RTC_CEL L

PCH_PLTRS T#

PCH_DPWR OK

ENVDD_PCH

SIO_SLP_LAN#

@PCH_3.3V_TS _EN

3.3V_TS_EN (EC)

3.3V_CAM_EN#

PCH_PWRO K

VCCPRIM_1P0

VCCPRIM_CORE

DCPDSW _1P0

VCCMPHYAON_1P0

VCCAPLL_1P0

VCCCLK1~ 6

VCCMPHYGT_1P0

VCCSRAM_1P0

VCCAMPHYPLL_1P0

VCCAPLLEBB

VCCDSW_3P 3

VCCHDA

VCCSPI

VCCPRIM_3P3

VCCPGPPA~E

VCCRTCPRIM

VCCPGPPG

VCCATS

VCCRTC

VCCPRIM_CORE

PLTRST#

DSW_PWROK

EDP_VDDEN

SLP_LAN#

GPP_B21

GPD7

ADAPTER

BATTERY

7

4

16

5

10

9

11

+PWR_SR C

ISL95857

PCH

PCH_RSMRST #

PCH_DPWR OK

RESET_OUT#

SIO_SLP_SU S#

SIO_SLP_S4 #

SIO_SLP_S5 #

SIO_SLP_LAN#

SIO_SLP_S3 #

SIO_SLP_A#

12

IMVP_VR_ON

14

2

PWRBTN#

RSMRST#

SLP_SUS #

SLP_S5 #

SLP_S4 #

SLP_S3 #

SLP_A#

SLP_LAN#

SLP_WLAN#/GPD 9

PCH_PWRO K

VCCST_PWRGD

PROCPWRGD

Power Button

SIO_PWRBTN#

PCH_RSMRST #

SIO_SLP_SU S#

SIO_SLP_S5 #

SIO_SLP_S4 #

SIO_SLP_S3 #

SIO_SLP_A#

SIO_SLP_LAN#

SIO_SLP_WLAN#

RESET_OUT#

PCH_PWRO K

VCCST_PWRGD

H_CPUPWR GD

2AC1BAT

ALWON

PCH_PRIM_EN

EN_INVPWR

10

SIO_SLP_S4 #

0.6V_DDR_VTT_ON

10

11

16

14

12

15

+PWR_SR C

+PWR_SR C

5

8

5

SYV828EC 5105

SY8288

+3.3V_ALW

EM5209VF

7

9

+PWR_SR C

AO6405

+PWR_SR C

SY8210

+5V_ALW2

+5V_ALW

+3.3V_RTC _LDO

+3.3V_ALW2

+3.3V_ALW

+3.3V_ALW_PCH

+BL_PWR_S RC

+1.2V_MEM

+0.6V_DDR _VTT

12

1

1BAT

2AC

5

18

VDDQ

DDR

VTT

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET O F ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFO RMATION OF DELL INC. ("DELL ") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLO SED TO ANY THIRD

5

4

PARTY WITHOUT D ELL'S EXPRESS WRITTEN CONSENT.

3

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet of

Date : Sheet of

Date : Sheet of

Power Sequence

Power Sequence

Power Sequence

LA-G871P

LA-G871P

LA-G871P

1

5 109Tuesday, March 05 , 2019

5 109Tuesday, March 05 , 2019

5 109Tuesday, March 05 , 2019

1.0

1.0

1.0

Page 6

5

smd.db-x7.ru

4

3

2

1

For 2LANE EDP

+3.3V_RUN

D D

C C

CPU_DP1_CTRL_CLK

12

RC503 2.2K_0402_5%

CPU_DP1_CTRL_DATA

12

RC178 2.2K_0402_5%

CPU_DP2_CTRL_CLK

12

RC176 2.2K_0402_5%

CPU_DP2_CTRL_DATA

12

RC502 2.2K_0402_5%

All VREF traces should

have 10 mil trace width

AR

+1.0VS_VCCIO

COMPENSATION PU FOR eDP

CAD Note:

Trace width=5 mils

Isolation Spacing=25mil,

Max length=100 mils.

CPU_DP1_N0<42>

CPU_DP1_P0<42>

CPU_DP1_N1<42>

CPU_DP1_P1<42>

CPU_DP1_N2<42>

CPU_DP1_P2<42>

CPU_DP1_N3<42>

CPU_DP1_P3<42>

CPU_DP2_N0<42>

CPU_DP2_P0<42>

CPU_DP2_N1<42>

CPU_DP2_P1<42>

CPU_DP2_N2<42>

CPU_DP2_P2<42>

CPU_DP2_N3<42>

CPU_DP2_P3<42>

1 2

RC8 24.9_0402_1%

CPU_DP1_CTRL_CLK<42>

CPU_DP1_CTRL_DATA<42>

+3.3V_ALW_PCH

1 2

@

RC101

GPP_H17

20K_0402_5%

EDP_COMP

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

GPP_H17

CPU@

UC1A

AL5

DDI1_TXN_0

AL6

DDI1_TXP_0

AJ5

DDI1_TXN_1

AJ6

DDI1_TXP_1

AF6

DDI1_TXN_2

AF5

DDI1_TXP_2

AE5

DDI1_TXN_3

AE6

DDI1_TXP_3

AC4

DDI2_TXN_0

AC3

DDI2_TXP_0

AC1

DDI2_TXN_1

AC2

DDI2_TXP_1

AE4

DDI2_TXN_2

AE3

DDI2_TXP_2

AE1

DDI2_TXN_3

AE2

DDI2_TXP_3

AM6

DISP_RCOMP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR26

GPP_H16/DDPF_CTRLCLK

CP26

GPP_H17/DDPF_CTRLDATA

WHL-U42_BGA1528

DDI

DISPLAY SIDEBANDS

AG4

EDP_TXN_0

AG3

EDP_TXP_0

AG2

EDP_TXN_1

AG1

EDP_TXP_1

AJ4

EDP

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

1 of 20

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

CPU_DP1_AUXN

CPU_DP1_AUXP

CPU_DP2_AUXN

CPU_DP2_AUXP

CPU_DP3_AUXN

CPU_DP3_AUXP

CPU_DP1_HPD

CPU_DP2_HPD

EDP_HPD

EDP_TXN0 <38>

EDP_TXP0 <38>

EDP_TXN1 <38>

EDP_TXP1 <38>

EDP_AUXN <38>

EDP_AUXP <38>

CPU_DP1_AUXN <42>

CPU_DP1_AUXP <42>

CPU_DP2_AUXN <42>

CPU_DP2_AUXP <42>

1

@

PAD~D

1

@

PAD~D

CPU_DP1_HPD <42>

CPU_DP2_HPD <42>

EDP_HPD <38>

PANEL_BKLEN <38>

ENVDD_PCH <38>

EDP_BIA_PWM <38>

EDP_HPD

T1

T2

12

RC2100K_0402_5%

+3.3V_ALW_PCH

RC753

This strap should sample HIGH.

There should NOT be any on-board device

CPU@

UC1I

CR30

CNV_WR_D0N

CP30

CNV_WR_D0P

CM30

CNV_WR_D1N

CN30

CNV_WR_D1P

CN32

CNV_WT_D0N

CM32

CNV_WT_D0P

CP33

CNV_WT_D1N

CN33

CNV_WT_D1P

CN31

CNV_WR_CLKN

CP31

CNV_WR_CLKP

CP34

CNV_WT_CLKN

CN34

CNV_WT_CLKP

CP32

CNV_WT_RCOMP_0

CR32

CNV_WT_RCOMP_1

CP20

GPP_F0/CNV_PA_BLANKING

CK19

GPP_F1

CG17

GPP_F2

CR14

GPP_C8/UART0_RXD

CP14

GPP_C9/UART0_TXD

CN14

GPP_C10/UART0_RTS#

CM14

GPP_C11/UART0_CTS#

CJ17

GPP_F8/CNV_MFUART2_RXD

CH17

GPP_F9/CNV_MFUART2_TXD

CF17

GPP_F23/A4WP_PRESENT

WHL-U42_BGA1528

CNVio

9 of 20

3

GPP_H18/CPU_C10_GATE#

GPP_H19/TIMESYNC_0

GPP_H21/XTAL_FREQ_SELECT

GPP_D4/IMGCLKOUT0/BK4/SBK4

GPP_H20/IMGCLKOUT_1

GPP_F12/EMMC_DATA0

GPP_F13/EMMC_DATA1

GPP_F14/EMMC_DATA2

EMMC

GPP_F15/EMMC_DATA3

GPP_F16/EMMC_DATA4

GPP_F17/EMMC_DATA5

GPP_F18/EMMC_DATA6

GPP_F19/EMMC_DATA7

GPP_F20/EMMC_RCLK

GPP_F21/EMMC_CLK

GPP_F11/EMMC_CMD

GPP_F22/EMMC_RESET#

EMMC_RCOMP

GPP_H22

GPP_H23

GPP_F10

GPD7

GPP_F3

1 2

CNV_COEX3<52>

SBIOS_TX<79>

CNV_COEX2<52>

CNV_COEX1<52>

CNV_PRX_DTX_N0

CNV_PRX_DTX_P0

CNV_PRX_DTX_N1

CNV_PRX_DTX_P1

CNV_PTX_DRX_N0

CNV_PTX_DRX_P0

CNV_PTX_DRX_N1

CNV_PTX_DRX_P1

CLK_CNV_PRX_DTX_N

CLK_CNV_PRX_DTX_P

CLK_CNV_PTX_DRX_N

CLK_CNV_PTX_DRX_P

CNV_WT_RCOMP

RC448150_0402_1%

CNV_COEX3

PCH_TBT_PERST#

SBIOS_TX

TYPEC_CON_SEL1

TYPEC_CON_SEL2

CNV_COEX2

CNV_COEX1

CNV_PRX_DTX_N0<52>

CNV_PRX_DTX_P0<52>

CNV_PRX_DTX_N1<52>

CNV_PRX_DTX_P1<52>

CNV_PTX_DRX_N0<52>

CNV_PTX_DRX_P0<52>

CNV_PTX_DRX_N1<52>

B B

+3.3V_ALW_PCH

PCH_TBT_PERST#

12

RC557 10K_0402_5%RTD3@

PCH_TBT_PERST#

12

RC754 10K_0402_5%@

CNV_PTX_DRX_P1<52>

CLK_CNV_PRX_DTX_N<52>

CLK_CNV_PRX_DTX_P<52>

CLK_CNV_PTX_DRX_N<52>

CLK_CNV_PTX_DRX_P<52>

PCH_TBT_PERST#<42>

Reserve

+3.3V_ALW_PCH+3.3V_ALW_PCH

RC743

LOW

HIGH

@

10K_0402_5%

1 2

12

@

10K_0402_5%

LOW

RC63

HIGHHIGH

HIGH

4

RC744

@

10K_0402_5%

1 2

TYPEC_CON_SEL2TYPEC_CON_SEL1

12

RC745

@

10K_0402_5%

A A

Vendor TBDTBDFOXCONJAE

TYPEC_CON_SEL 1

TYPEC_CON_SEL 2

5

LOW

LOW

driving it to opposite direction during strap sampling.

CPU_C10_GATE#

CN27

CM27

GPP_H21

CF25

RTD3_CIO_PWR_EN

CN26

GPP_H23

CM26

CK17

TBT_RTD3_WAKE#

BV35

CN20

TBT_FORCE_PWR

CG25

CH25

MEM_CONFIG0

CR20

MEM_CONFIG1

CM20

MEM_CONFIG2

CN19

MEM_CONFIG3

CM19

MEM_CONFIG4

CN18

CR18

CP18

CM18

CM16

CP16

CR16

CN16

EMMC_RCOMP

CK15

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXP RESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

CPU_C10_GATE# <17,87>

RTD3_CIO_PWR_EN <42>

TBT_RTD3_WAKE# <42>

TBT_FORCE_PWR < 42>

1

@

T408

PAD~D

1

@

T409

PAD~D

1

@

T410

PAD~D

1

@

T411

PAD~D

1

@

T412

PAD~D

Jony_01/16 : CK15 - Keep 200 ohm

575962_WHL-U_DDR4_RVP_Sch_Rev0p5.pdf

1 2

RC10 200_0402_1%

2

RTD3_CIO_PWR_EN

@

10K_0402_5%

1 2

4.7K_0402_5%

20K_0402_5%

4.7K_0402_5%

20K_0402_5%

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

CPU(1/14)DDI,EDP,CSI2,EMMC

CPU(1/14)DDI,EDP,CSI2,EMMC

CPU(1/14)DDI,EDP,CSI2,EMMC

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

+3.3V_ALW_PCH

RC95

100K_0402_5%

TBT_RTD3_WAKE#

+3.3V_ALW_PCH

RC443

RC444

@

+3.3V_ALW_PCH

@

RC537

RC446

@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

1 2

RC454

@

20K_0402_5%

1 2

1 2

GPP_H21

LOW: 38.4/19.2MHZ (DEFAULT)

HIGH: 24MHZ

1 2

0 = Master Attached Flash Sharing

(MAFS) enabled. (Default)

1 = Slave Attached Flash Sharing

(SAFS) enabled.

1 2

GPP_H23

1 2

LA-G871P

LA-G871P

LA-G871P

1

6 109Tuesday, March 05, 2019

6 109Tuesday, March 05, 2019

6 109Tuesday, March 05, 2019

1.0

1.0

1.0

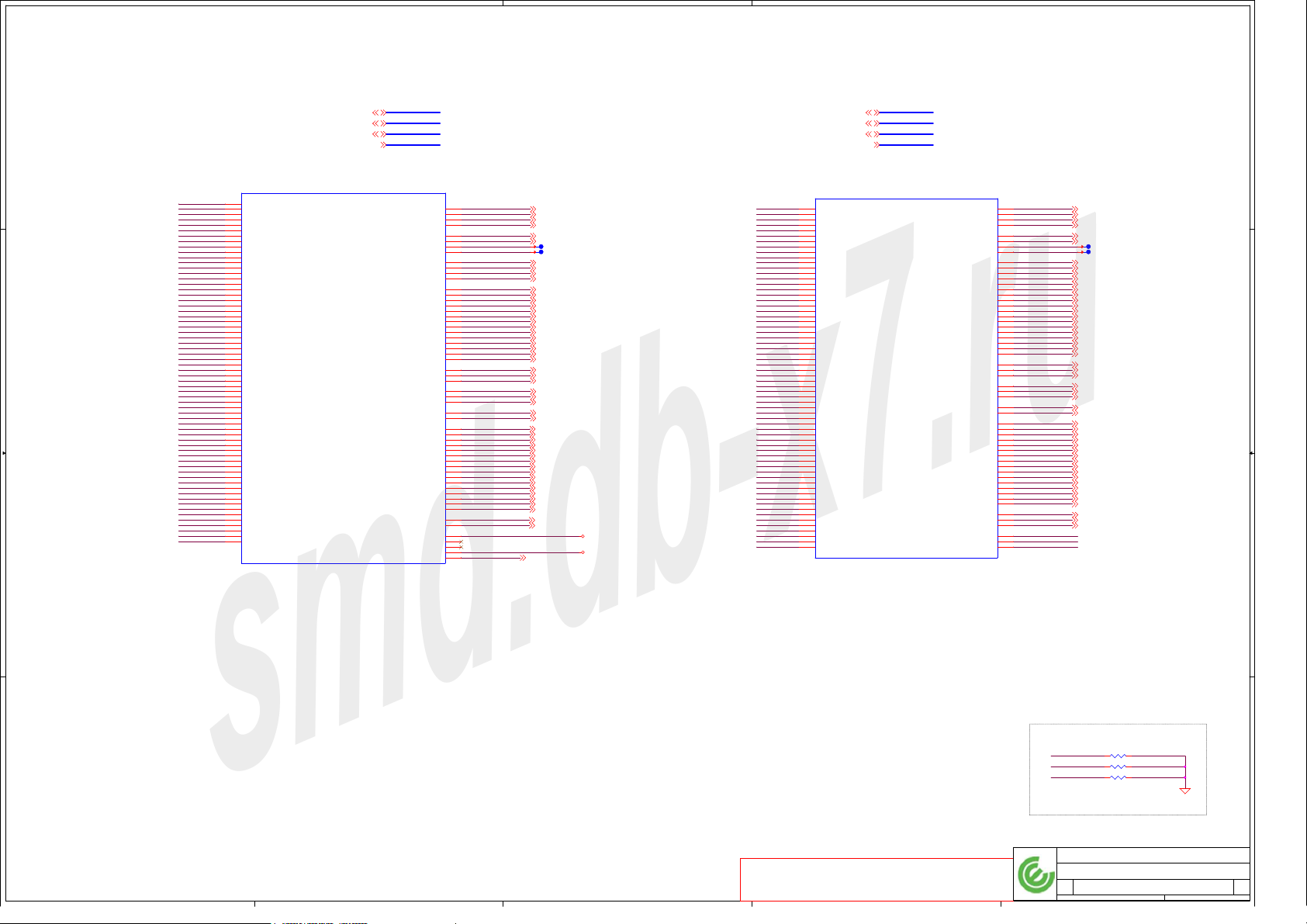

Page 7

5

smd.db-x7.ru

DDR4, Ballout for side by side(Non-Interleave)

4

3

2

1

D D

CPU@

UC1B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

C C

B B

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

Interleave / Non-Interleaved

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

DDR0_DQ_5/DDR0_DQ_5

B28

DDR0_DQ_6/DDR0_DQ_6

A28

DDR0_DQ_7/DDR0_DQ_7

B30

DDR0_DQ_8/DDR0_DQ_8

D30

DDR0_DQ_9/DDR0_DQ_9

B33

DDR0_DQ_10/DDR0_DQ_10

D32

DDR0_DQ_11/DDR0_DQ_11

A30

DDR0_DQ_12/DDR0_DQ_12

C30

DDR0_DQ_13/DDR0_DQ_13

B32

DDR0_DQ_14/DDR0_DQ_14

C32

DDR0_DQ_15/DDR0_DQ_15

H37

DDR0_DQ_16/DDR0_DQ_32

H34

DDR0_DQ_17/DDR0_DQ_33

K34

DDR0_DQ_18/DDR0_DQ_34

K35

DDR0_DQ_19/DDR0_DQ_35

H36

DDR0_DQ_20/DDR0_DQ_36

H35

DDR0_DQ_21/DDR0_DQ_37

K36

DDR0_DQ_22/DDR0_DQ_38

K37

DDR0_DQ_23/DDR0_DQ_39

N36

DDR0_DQ_24/DDR0_DQ_40

N34

DDR0_DQ_25/DDR0_DQ_41

R37

DDR0_DQ_26/DDR0_DQ_42

R34

DDR0_DQ_27/DDR0_DQ_43

N37

DDR0_DQ_28/DDR0_DQ_44

N35

DDR0_DQ_29/DDR0_DQ_45

R36

DDR0_DQ_30/DDR0_DQ_46

R35

DDR0_DQ_31/DDR0_DQ_47

AN35

DDR0_DQ_32/DDR1_DQ_0

AN34

DDR0_DQ_33/DDR1_DQ_1

AR35

DDR0_DQ_34/DDR1_DQ_2

AR34

DDR0_DQ_35/DDR1_DQ_3

AN37

DDR0_DQ_36/DDR1_DQ_4

AN36

DDR0_DQ_37/DDR1_DQ_5

AR36

DDR0_DQ_38/DDR1_DQ_6

AR37

DDR0_DQ_39/DDR1_DQ_7

AU35

DDR0_DQ_40/DDR1_DQ_8

AU34

DDR0_DQ_41/DDR1_DQ_9

AW35

DDR0_DQ_42/DDR1_DQ_10

AW34

DDR0_DQ_43/DDR1_DQ_11

AU37

DDR0_DQ_44/DDR1_DQ_12

AU36

DDR0_DQ_45/DDR1_DQ_13

AW36

DDR0_DQ_46/DDR1_DQ_14

AW37

DDR0_DQ_47/DDR1_DQ_15

BA35

DDR0_DQ_48/DDR1_DQ_32

BA34

DDR0_DQ_49/DDR1_DQ_33

BC35

DDR0_DQ_50/DDR1_DQ_34

BC34

DDR0_DQ_51/DDR1_DQ_35

BA37

DDR0_DQ_52/DDR1_DQ_36

BA36

DDR0_DQ_53/DDR1_DQ_37

BC36

DDR0_DQ_54/DDR1_DQ_38

BC37

DDR0_DQ_55/DDR1_DQ_39

BE35

DDR0_DQ_56/DDR1_DQ_40

BE34

DDR0_DQ_57/DDR1_DQ_41

BG35

DDR0_DQ_58/DDR1_DQ_42

BG34

DDR0_DQ_59/DDR1_DQ_43

BE37

DDR0_DQ_60/DDR1_DQ_44

BE36

DDR0_DQ_61/DDR1_DQ_45

BG36

DDR0_DQ_62/DDR1_DQ_46

BG37

DDR0_DQ_63/DDR1_DQ_47

WHL-U42 _BGA1528

DDR_A_DQS#[0..7]<23>

DDR_A_D[0..63]<23>

DDR_A_DQS[0..7]<23>

DDR_A_MA[0..16]<23>

2 of 20

LPDDR3 / DDR4

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/NC

DDR0_CKE_3/NC

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

Interleave / Non-Interleaved

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

LPDDR3 / DDR4

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

DDR_VTT_CTL

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_CLK#0 <23>

DDR_A_CLK0 <23>

DDR_A_CLK#1 <23>

DDR_A_CLK1 <23>

DDR_A_CKE0 <23>

DDR_A_CKE1 <23>

1

@

T351

PAD~D

1

@

T350

PAD~D

DDR_A_CS#0 <23>

DDR_A_CS#1 <23>

DDR_A_ODT0 <23>

DDR_A_ODT1 <23>

DDR_A_MA0 <23>

DDR_A_MA1 <23>

DDR_A_MA2 <23>

DDR_A_MA3 <23>

DDR_A_MA4 <23>

DDR_A_MA5 <23>

DDR_A_MA6 <23>

DDR_A_MA7 <23>

DDR_A_MA8 <23>

DDR_A_MA9 <23>

DDR_A_MA10 <23>

DDR_A_MA11 <23>

DDR_A_MA12 <23>

DDR_A_MA13 <23>

DDR_A_MA14 <23>

DDR_A_MA15 <23>

DDR_A_MA16 <23>

DDR_A_BA0 <23>

DDR_A_BA1 <23>

DDR_A_BG0 <23>

DDR_A_ACT# <23>

DDR_A_BG1 <23>

DDR_A_DQS#0 <23>

DDR_A_DQS0 <23>

DDR_A_DQS#1 <23>

DDR_A_DQS1 <23>

DDR_A_DQS#4 <23>

DDR_A_DQS4 <23>

DDR_A_DQS#5 <23>

DDR_A_DQS5 <23>

DDR_B_DQS#0 <24>

DDR_B_DQS0 <24>

DDR_B_DQS#1 <24>

DDR_B_DQS1 <24>

DDR_B_DQS#4 <24>

DDR_B_DQS4 <24>

DDR_B_DQS#5 <24>

DDR_B_DQS5 <24>

DDR_A_ALERT# <23>

DDR_A_PARITY <23>

DDR_VTT_CTRL <23>

DDR0_PAR,DDR0_ALERT#

for DDR4

+DDR_VREF_CA

+DDR_VREF_B_DQ

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_DQS#[0..7]<24>

DDR_B_D[0..63]<24>

DDR_B_DQS[0..7]<24>

DDR_B_MA[0..16]<24>

CPU@

UC1C

lnterleave /

Non-lnterle ave d

J22

DDR1_DQ_0/DDR0_DQ_16

H25

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

DDR1_DQ_4/DDR0_DQ_20

J25

DDR1_DQ_5/DDR0_DQ_21

G25

DDR1_DQ_6/DDR0_DQ_22

F22

DDR1_DQ_7/DDR0_DQ_23

D22

DDR1_DQ_8/DDR0_DQ_24

C22

DDR1_DQ_9/DDR0_DQ_25

C24

DDR1_DQ_10/DDR0_DQ_26

D24

DDR1_DQ_11/DDR0_DQ_27

A22

DDR1_DQ_12/DDR0_DQ_28

B22

DDR1_DQ_13/DDR0_DQ_29

A24

DDR1_DQ_14/DDR0_DQ_30

B24

DDR1_DQ_15/DDR0_DQ_31

G31

DDR1_DQ_16/DDR0_DQ_48

G32

DDR1_DQ_17/DDR0_DQ_49

H29

DDR1_DQ_18/DDR0_DQ_50

H28

DDR1_DQ_19/DDR0_DQ_51

G28

DDR1_DQ_20/DDR0_DQ_52

G29

DDR1_DQ_21/DDR0_DQ_53

H31

DDR1_DQ_22/DDR0_DQ_54

H32

DDR1_DQ_23/DDR0_DQ_55

L31

DDR1_DQ_24/DDR0_DQ_56

L32

DDR1_DQ_25/DDR0_DQ_57

N29

DDR1_DQ_26/DDR0_DQ_58

N28

DDR1_DQ_27/DDR0_DQ_59

L28

DDR1_DQ_28/DDR0_DQ_60

L29

DDR1_DQ_29/DDR0_DQ_61

N31

DDR1_DQ_30/DDR0_DQ_62

N32

DDR1_DQ_31/DDR0_DQ_63

AJ29

DDR1_DQ_32/DDR1_DQ_16

AJ30

DDR1_DQ_33/DDR1_DQ_17

AM32

DDR1_DQ_34/DDR1_DQ_18

AM31

DDR1_DQ_35/DDR1_DQ_19

AM30

DDR1_DQ_36/DDR1_DQ_20

AM29

DDR1_DQ_37/DDR1_DQ_21

AJ31

DDR1_DQ_38/DDR1_DQ_22

AJ32

DDR1_DQ_39/DDR1_DQ_23

AR31

DDR1_DQ_40/DDR1_DQ_24

AR32

DDR1_DQ_41/DDR1_DQ_25

AV30

DDR1_DQ_42/DDR1_DQ_26

AV29

DDR1_DQ_43/DDR1_DQ_27

AR30

DDR1_DQ_44/DDR1_DQ_28

AR29

DDR1_DQ_45/DDR1_DQ_29

AV32

DDR1_DQ_46/DDR1_DQ_30

AV31

DDR1_DQ_47/DDR1_DQ_31

BA32

DDR1_DQ_48/DDR1_DQ_48

BA31

DDR1_DQ_49/DDR1_DQ_49

BD31

DDR1_DQ_50/DDR1_DQ_50

BD32

DDR1_DQ_51/DDR1_DQ_51

BA30

DDR1_DQ_52/DDR1_DQ_52

BA29

DDR1_DQ_53/DDR1_DQ_53

BD29

DDR1_DQ_54/DDR1_DQ_54

BD30

DDR1_DQ_55/DDR1_DQ_55

BG31

DDR1_DQ_56/DDR1_DQ_56

BG32

DDR1_DQ_57/DDR1_DQ_57

BK32

DDR1_DQ_58/DDR1_DQ_58

BK31

DDR1_DQ_59/DDR1_DQ_59

BG29

DDR1_DQ_60/DDR1_DQ_60

BG30

DDR1_DQ_61/DDR1_DQ_61

BK30

DDR1_DQ_62/DDR1_DQ_62

BK29

DDR1_DQ_63/DDR1_DQ_63

WHL-U42 _BGA1528

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP_7

3 of 20

LPDDR3 / DDR4

DDR1_CKE_2/NC

DDR1_CKE_3/NC

NC/DDR1_ODT_1

NC/DDR1_MA_3

NC/DDR1_MA_4

lnterleave / Non-lnterleaved

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

DDR_B_CLK#0

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_ALE RT#

DDR_B_PAR ITY

DDR_DRAMRS T#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <24>

DDR_B_CLK0 <24>

DDR_B_CLK#1 <24>

DDR_B_CLK1 <24>

DDR_B_CKE0 <24>

DDR_B_CKE1 <24>

1

@

T353

PAD~D

1

@

T354

PAD~D

DDR_B_CS#0 <24>

DDR_B_CS#1 <24>

DDR_B_ODT0 <24>

DDR_B_ODT1 <24>

DDR_B_MA0 <24>

DDR_B_MA1 <24>

DDR_B_MA2 <24>

DDR_B_MA3 <24>

DDR_B_MA4 <24>

DDR_B_MA5 <24>

DDR_B_MA6 <24>

DDR_B_MA7 <24>

DDR_B_MA8 <24>

DDR_B_MA9 <24>

DDR_B_MA10 <24>

DDR_B_MA11 <24>

DDR_B_MA12 <24>

DDR_B_MA13 <24>

DDR_B_MA14 <24>

DDR_B_MA15 <24>

DDR_B_MA16 <24>

DDR_B_BA0 <24>

DDR_B_BA1 <24>

DDR_B_BG0 <24>

DDR_B_BG1 <24>

DDR_B_ACT# <24>

DDR_A_DQS#2 <23>

DDR_A_DQS2 <23>

DDR_A_DQS#3 <23>

DDR_A_DQS3 <23>

DDR_A_DQS#6 <23>

DDR_A_DQS6 <23>

DDR_A_DQS#7 <23>

DDR_A_DQS7 <23>

DDR_B_DQS#2 <24>

DDR_B_DQS2 <24>

DDR_B_DQS#3 <24>

DDR_B_DQS3 <24>

DDR_B_DQS#6 <24>

DDR_B_DQS6 <24>

DDR_B_DQS#7 <24>

DDR_B_DQS7 <24>

DDR_B_ALERT# <24>

DDR_B_PARITY <24>

DDR_DRAMRST# <23>

DDR1_PAR,DDR1_ALERT#

for DDR4

Hank3/5:575962_WHL_DDR4_RVP_RN_TDK_Rev0p7.pdf page12,keep setting

DDR4 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

A A

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

1 2

RC5 121_040 2_1%

1 2

RC504 80.6_0402_ 1%

1 2

RC7 100_040 2_1%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL . IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

3

PARTY WITHOUT DE LL'S EXPRESS WRITTEN CONSENT.

2

Title

Size

Size

Size

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

CPU(2/14)DDR4

CPU(2/14)DDR4

CPU(2/14)DDR4

Document Num ber Re v

Document Num ber Re v

Document Num ber Re v

LA-G871P

LA-G871P

LA-G871P

1

7 109Tuesd ay, March 05, 2 019

7 109Tuesd ay, March 05, 2 019

7 109Tuesd ay, March 05, 2 019

1.0

1.0

1.0

Page 8

5

smd.db-x7.ru

SPI_MOSI= SPI_IO0

SPI_MISO= SPI_IO1

PCH EDS R0.7 p.235~236

PCH_SPI_CLK

PCH_SPI_D1

PCH_CL_DATA1<52>

PCH_CL_CLK1<52>

PCH_CL_RST1#<52>

ESPI_ALERT#<58>

1031 change

PCH_SPI_D0

PCH_SPI_D2

PCH_SPI_D3

PCH_SPI_CS#0

PCH_SPI_CS#1

PCH_SPI_CS#2

RTC_DET#

1 2

PCH_SPI_DO_XDP<79>

PCH_SPI_DO2_XDP<79>

D D

+1.8V_PRIM

1 2

RC244 10K_040 2_1%

C C

RC833 100K_0402_ 5%@

RC96 10 0K_0402_5%

RC505 1K _0402_1%CXDP@

1 2

RC11 1K_0402_1%CXDP@

PCH_SPI_CS#2<66>

RTC_DET#<83>

MEDIACARD_IRQ#<70>

ESPI_ALERT#

ESPI_RESE T#

12

PCH_SPI_CLK

12

ESPI_ALERT#

CH37

CF37

CF36

CF34

CG34

CG36

CG35

CH34

CF20

CG22

CF22

CG23

CH23

CG20

BV29

BV28

CH7

CH8

CH9

For signal deglitch, refer to 575412_WHL_U_PDG rev0p8

4

CPU@

UC1E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI - FLASH

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

GPP_D1/SPI1_CLK/BK1/SBK1

GPP_D2/SPI1_MISO_IO1/BK2/SBK2

GPP_D3/SPI1_MOSI_IO0/BK3/SBK3

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS0#/BK0/SBK0

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#/TIME_SYNC1

GPP_A6/SERIRQ

WHL-U42 _BGA1528

SPI - TOUCH

C LINK

3

MEM_SMBCLK

CK14

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

SMBUS , SMLINK

LPC , ESPI

5 of 20

WEAK INTERNAL PU WEAK INTERNAL PU

BOOT HALT

HIGH

LOW

+3.3V_ALW _PCH

WEAK INTERNAL PU

A0 PERSONALITY STRAP

HIGH

LOW

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

+3.3V_ALW _PCH

12

RC94

100K_0402_ 5%

PCH_SPI_D0

12

RC518

@

4.7K_0402_ 5%

Disa bled

Enabled

12

RC62

100K_0402_ 5%

PCH_SPI_D3

12

RC515

@

4.7K_0402_ 5%

PLACE RC62 AND RC515 CLOS

TO THE SPI SIGNAL TO AVOID STUB

Disa bled

Enabled

MEM_SMBDATA

CH15

GPP_C2

CJ15

SML0_SMBCLK

CH14

SML0_SMBDATA

CF15

GPP_C5

CG15

SML1_SMBCLK

CN15

SML1_SMBDATA

CM15

GPP_B23

CC34

ESPI_IO0_R

CA29

ESPI_IO1_R

BY29

ESPI_IO2_R

BY27

ESPI_IO3_R

BV27

CA28

CA27

ESPI_CLK

BV32

BV30

GPP_A8

BY30

566439_CNL_PCH_UY_EDS_Vol_1_Rev_1. 1.pdf

External pull-up is required. Recommend 100K if pulled

up to 3.3V or 75K if pulled up to 1.8V. This strap should sample HIGH.

There should NOT be any on-board device driving it to opposite direction

during strap sampling.

Merion no RJ45 LAN p ort

SML1_SMBCLK <58>

SML1_SMBDATA <58>

1 2

RC366 15_0402_5%

1 2

RC367 15_0402_5%

1 2

RC368 15_0402_5%

1 2

RC369 15_0402_5%

ESPI_CS# <58,79>

ESPI_RESET# <58,79>

1 2

RC19 33 _0402_5% EMI@

+3.3V_ALW _PCH

12

RC61

100K_0402_ 5%

PCH_SPI_D2

12

RC519

@

4.7K_0402_ 5%

PLACE RC61 AND RC519 CLOS

CONSENT STRAP

HIGH

LOW

TO THE SPI SIGNAL TO AVOID STUB

Disa bled

Enabled

2

ESPI_IO0 <58,79>

ESPI_IO1 <58,79>

ESPI_IO2 <58,79>

ESPI_IO3 <58,79>

RVP 15 ohm

575962_WHL-U_DDR4_RVP_Sch_Rev0p5.pd f

ESPI_CLK_5105 <58,79>

ESPI_CLK_51 05

SML0_SMB CLK

SML1_SMB CLK

MEM_SMB CLK

RF Request

1 2

CC316@RF@ 33P_040 2_50V8J

1 2

CC318@RF@ 33P_040 2_50V8J

1 2

CC319@RF@ 33P_040 2_50V8J

1 2

CC320@RF@ 33P_040 2_50V8J

Place close CPU side

1

Merion Limit height

QC2 change to SB000014O00 H=0.6mm(MAX)

+3.3V_RUN

1219 Change

MEM_SMBDATA

QC2

2

5

1

S1

G1

D1

S2

G2

D2

PJX138K_ SOT563-6

3

MEM_SMBCLK

6

4

DDR_XDP_WAN_SMBCLK <23,24,79>

DDR_XDP_WAN_SMBDAT <23,24,79>

DDR_XDP_WAN_SMBDAT

DDR_XDP_WAN_SMBCLK

GPP_A8

MEM_SMBCLK

MEM_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

RTC_DET#

+3.3V_RUN

1 2

RC318 2.2K_0402_5%

1 2

RC319 2.2K_0402_5%

1 2

RC849 8.2K_04 02_5%@

+3.3V_ALW_PCH

1 2

RC12 1 K_0402_5%

1 2

RC14 1 K_0402_5%

1 2

RC15 1 K_0402_5%

1 2

RC507 1K_040 2_5%

1 2

RC347 499_040 2_1%@

1 2

RC348 499_040 2_1%@

1 2

RC866 10K_02 01_5%

1031 change

Follow RVP pull up change to 4.7K

B B

PCH_SPI_D1_ R1<66>

PCH_SPI_D0_ R1<66>

PCH_SPI_CLK _R1<6 6>

Pop optio n at P.102

For vPro

256Mb WSON8 Flash ROM

For Non-vPro

PCH_SPI_CLK_1_R PCH_SPI_CLK_0_R

33_0402_5%

@EMI@

12

RC289

A A

33P_0402_50V8J

12

CC1452

5

33_0402_5%

@EMI@

12

RC299

@EMI@

33P_0402_50V8J

@EMI@

12

CC1453

PCH_SPI_CS#0_R1

PCH_SPI_D2_R1

PCH_SPI_CS#1_R1 PCH_SPI_CS#1_R2

PCH_SPI_D2_R1

1 2

RC32 0_0201_5%@

1 2

RC33 49.9_0201_1%

VPRO@

NVPRO@

1 2

RC302 0_0201_5%

1 2

RC35 33 _0201_1%

NVPRO@

4

PCH_SPI_CS#0_R2

PCH_SPI_D1_0_R

PCH_SPI_D2_0_R

PCH_SPI_D1_1_R

PCH_SPI_D2_1_R

64Mb WSON8 Flash ROM

UC5VPRO@

1

CS#

2

SO(IO1)

3

IO2

4

VSS

ThemalPad

GD25B256DYIG_W SON8_8X6

For Non-vPro

128Mb SOP8 Flash ROM

UC6NVPRO@

1

CS#

2

DO(IO1)

3

IO2

4

DI(IO0)

GND

GD25B127DS IGR_SO8

SOFTWARE TAA

VPRO PDG P.296 R1 50 ohm

PCH_SPI_D1_R1

RC734 49.9_0201_ 1%VPRO@

PCH_SPI_D0_R1

RC570 49.9_0201_ 1%VPRO@

PCH_SPI_CLK_R1

RC571 49.9_0201_ 1%VPRO@

PCH_SPI_D3_R1

RC572 49.9_0201_ 1%VPRO@

NVPRO follow PDG P.298 R1 33 ohm

PCH_SPI_D1_R1 PCH_SPI_D1_1_R

RC573 33_0201_1%NVPRO@

PCH_SPI_D0_R1

RC574 33_0201_1%NVPRO@

PCH_SPI_CLK_R1

RC575 33_0201_1%NVPRO@

PCH_SPI_D3_R1

RC576 33_0201_1%NVPRO@

PDG SPI0 2 resistor 50ohm, SPI0 3 resistor 33ohm

CLOSEED TO ROM

Please place close for future replace to RP

+3.3V_SPI

8

PCH_SPI_D3_0_R

VCC

7

PCH_SPI_CLK_0_R

IO3

6

PCH_SPI_D0_0_R

SCLK

5

SI(IO0)

9

+3.3V_SPI

8

PCH_SPI_D3_1_R

VCC

7

PCH_SPI_CLK_1_R

IO

6

PCH_SPI_D0_1_R

CLK

5

3

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CC9

1 2

0.1U_0201_1 0V6K

NVPRO@

CC10

1 2

0.1U_0201_1 0V6K

PCH_SPI_D1_0_R

PCH_SPI_D0_0_R

PCH_SPI_CLK_0_R

PCH_SPI_D3_0_R

PCH_SPI_D0_1_R

PCH_SPI_CLK_1_R

PCH_SPI_D3_1_R

Pop optio n at P.102

Pop optio n at P.102

VPRO PDG P.296 R2 5 ohm

NVPRO PDG P.298 R2 10 ohm

1 2

RC24 0_ 0201_5%NVPRO@

1 2

RC25 4. 99_0201_1%

VPRO@

1 2

RC26 4. 99_0201_1%

VPRO@

1 2

RC27 4. 99_0201_1%

VPRO@

1 2

RC28 0_ 0201_5%@

1 2

RC29 4. 99_0201_1%

VPRO@

1 2

RC30 4. 99_0201_1%

VPRO@

+3.3V_SPI

+3.3V_ALW _PCH

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL . IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTEN CONSENT.

PROM_BIOS_R<63 >

1 2

RC31 0_ 0201_5%@

DC4

RB521CM-30T2R _SOD923-2

PCH_SPI_CS# 1_R1

PCH_SPI_D0_ R1

PCH_SPI_D1_ R1

PCH_SPI_CLK _R1

PCH_SPI_CS# 0_R1

PCH_SPI_D2_ R1

PCH_SPI_D3_ R1

21

PCH_SPI_CS# 1

PCH_SPI_D0

PCH_SPI_D1

PCH_SPI_CLK

PCH_SPI_CS# 0

PCH_SPI_D2

PCH_SPI_D3

JSPI1

CONN@

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

GND1

22

GND2

ACES_5050 6-02041-P01

2

DELL CONFIDENTIAL/PROPRIETARY

GPP_C2

RC266 4.7K _0402_5%

TLS CONFIDENTIALITY

HIGH

LOW(DEFAULT)

GPP_C5

RC277 4.7K _0402_5%

GPP_C5

@

RC397 20K _0402_5%

EC interface

HIGH

LOW (DEFAULT)

GPP_B23

RC317 150K_0402_5%

for DCI-OOB

EXI BOOT STALL BYPASS

HIGH

LOW(DEFAULT)

WEAK INTERNAL PD

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

CPU(3/14)SPI,ESPI,SMB,LPC

CPU(3/14)SPI,ESPI,SMB,LPC

CPU(3/14)SPI,ESPI,SMB,LPC

Document Num ber Re v

Document Num ber Re v

Document Num ber Re v

LA-G871P

LA-G871P

LA-G871P

1

1 2

ENABLE

DISABLE

1 2

1 2

ESPI

LPC

1 2

ENABLED

DIABLED

+3.3V_ALW_PCH

+3.3V_ALW_PCH

+3.3V_ALW_PCH

8 109Tuesd ay, March 05, 2 019

8 109Tuesd ay, March 05, 2 019

8 109Tuesd ay, March 05, 2 019

1.0

1.0

1.0

Page 9

5

smd.db-x7.ru

@

T12

PAD~D

TPM_PIRQ#< 66>

PCH_3.3V_TS_EN<38>

RC710,RC711 change to 33oh m from 75ohm,

D D

PU OPTION TO AVOID RSP SIGNALS

+1.8V_PRIM

C C

+3.3V_RUN

B B

FROM FLOATING IN CASE INTERNAL PUS NOT ENABLED IN A0

I2C3_A NT for ACTIVE S TEERING ANT for MERIO N

+3.3V_ALW_PC H

1 2

RC831 4.7K_0402_5 %

12

12

12

12

12

12

NRB_BIT

RC72420K _0402_5% @

RC73320K _0402_5% @

RC747100K_0402_ 5% @

RC84110K_0402_5 % @

RC5122.2K_ 0201_5%

RC5132.2K_ 0201_5%

CNV_BRI_PRX_DTX<52>

CNV_RGI_PTX_DRX_R<52>

CNV_BRI_PTX_DRX_R<52>

CNV_RGI_PRX_DTX<52>

CNV_BRI_PRX_DTX

CNV_RGI_PRX_DTX

PCH_3.3V_TS_ EN

GPP_A7

I2C3_ANT_SDA

I2C3_ANT_SCL

M.2 CNVI MODES

0 = Integrated CNVi enable.

1 = Integrated CNVi disable. (Disable CNVi for bring up)

WEAK INTERNAL PU

follow Intel MOW WW32

1 2

RC710 33_0402_5 %

1 2

RC711 33_0402_5 %

RC710,RC711 place d closer to PCH.

3MM_CAM_DET #<38>

P_SENSOR_PWR_SAVE#<38>

SMART_SPK_DET1#<56>

TS_INT#<38>

TS

TP

Follow RVP,PDG pull up change to 20K

+1.8V_PRIM

TS_I2C_SDA<38 >

TS_I2C_SCL<38>

I2C1_SDA_TP<63>

I2C1_SCK_TP<63>

@

T388

PAD~D

@

T389

PAD~D

566439_CNL_PCH_LP__EDS_Rev1p2

P.119 Primary Well Group H (Per-pad 1.8 V or 3.3 V)

Please setting 3.3V

add I2C3 TP for for sensor IC(Reserved)

add I2C3_ANT TP for ACTIVE STEERING ANT for MERION

20K_0402_5%

RC842

1 2

CNV_RGI_PTX_DRX_R

12

4.7K_0402_5%

@

RC832

NO REBOOT STRAP

HIGH

LOW(DEFAULT)

Weak IPD

No REBOOT

REBOOT ENABLE

4

PRIM_CORE_OPT_ DIS

GPP_A7

ONE_DIMM#

NRB_BIT

1

PME#

TPM_PIRQ#

PCH_3.3V_TS_ EN

GPP_B22

CNV_BRI_PRX_DTX

CNV_RGI_PTX_DRX

CNV_BRI_PTX_DRX

CNV_RGI_PRX_DTX

3MM_CAM_DET #

P_SENSOR_PW R_SAVE#

SMART_SPK_DET 1#

TS_INT#

I2C2_SDA_ALS

1

I2C2_SCL_ALS

1

I2C3_ANT_SCL

CPU@

UC1F

CC27

GPP_B15/GSPI0_CS0#

CC32

GPP_A7/PIRQA#/GSPI0_CS1#

CE28

GPP_B16/GSPI0_CLK

CE27

GPP_B17/GSPI0_MISO

CE29

GPP_B18/GSPI0_MOSI

CA31

GPP_B19/GSPI1_CS0#

CA32

GPP_A11/PME#/GSPI1_CS1#/SD_VDD2_PWR_EN#

CC29

GPP_B20/GSPI1_CLK

CC30

GPP_B21/GSPI1_MISO

CA30

GPP_B22/GSPI1_MOSI

CK20

GPP_F5/CNV_BRI_RSP

CG19

GPP_F6/CNV_RGI_DT

CJ20

GPP_F4/CNV_BRI_DT

CH19

GPP_F7/CNV_RGI_RSP

CR12

GPP_C20/UART2_RXD

CP12

GPP_C21/UART2_TXD

CN12

GPP_C22/UART2_RTS#

CM12

GPP_C23/UART2_CTS#

CM11

GPP_C16/I2C0_SDA

CN11

GPP_C17/I2C0_SCL

CK12

GPP_C18/I2C1_SDA

CJ12

GPP_C19/I2C1_SCL

CF27

GPP_H4/I2C2_SDA

CF29

GPP_H5/I2C2_SCL

CH27

GPP_H6/I2C3_SDA

CH28

GPP_H7/I2C3_SCL

CJ30

GPP_H8/I2C4_SDA

CJ31

GPP_H9/I2C4_SCL

WHL-U42 _BGA1528

+3.3V_RUN

I2C , UART

1031 change,RC435 reserve for FUSE location

I2C3_ANT_SCL

I2C3_ANT_SDA

RF Request

+3.3V_RUN_R

100P_0201_50V8J

@RF@

1

CC1466

2

place as close as JASA1

Reserved for wake on voice

SIO_SLP_S0#<11,17,66,79,87>

1218 add RC867 reserve for BITS3921 23

3

GPP_D9/ISH_SPI_CS#/GSPI2_CS0#

GPP_D10/ISH_SPI_CLK/GSPI2_CLK

ISH

6 of 20

GPP_D11/ISH_SPI_MISO/GSPI2_MISO

GPP_D12/ISH_SPI_MOSI/GSPI2_MOSI

GPP_H10/I2C5_SDA/ISH_I2C2_SDA

GPP_H11/I2C5_SCL/ISH_I2C2_SCL

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A12/ISH_GP6/BM_BUSY#/SX_EXIT_HOLDOFF#

Active Steering Antenna circuit

+3.3V_ALW_PCH

1

2

1 2

RC867 0_0201_5%@

1 2

RC660 0_0201_5%@

5

INB

INA

3

+3.3V_RUN_R

I2C3_ANT_SCL_R

I2C3_ANT_SDA_R

UC9

@

MC74VHC1G32D FT2G_SC70-5~D

P

4

O

G

1 2

RC435 0_0603_5%

1 2

RC549 0_0201_5%@

1 2

RC548 0_0201_5%@

PRIM_CORE_OPT_ DIS

SIO_SLP_S0#

IR_CAM_DET#

CN22

DGPU_HOLD_R ST#

CR22

TBT_DET#

CM22

GPP_D12

CP22

ISH_I2C0_ACC_SDA

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_D13/ISH_UART0_RXD

GPP_D14/ISH_UART0_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

CK22

CH20

CH22

CJ22

CJ27

CJ29

CM24

CN23

CM23

CR24

CG12

CH12

CF12

CG14

BW35

BW34

CA37

CA36

CA35

CA34

BW37

CONN@

JASA1

4

G2

4

3

3

G1

2

2

1

1

CVILU_CI1804M1HR G-NH

ISH_I2C0_ACC_SCL

ISH_I2C1_ALS_SDA

ISH_I2C1_ALS_SCL

ISH_I2C2_SDA

ISH_I2C2_SCL

SML0B_SMBDATA

SML0B_SMBCLK

WWAN_FULL_PWR _EN

SIO_EXT_WAKE#

LCD_CBL_D ET#

PCH_HDD_E N

ISH_ACC1

ISH_ACC2

ISH_TABLE_MODE#

ISH_ALS_INT#

ISH_NB_MODE

ISH_LID_CL#_NB

ISH_LID_CL#_TABI2C3_ANT_SDA

NB_MODE for NB13/Bandon

LID_CL#_NB for NB13/Bandon

LID_CL#_TAB for NB13/Bandon

ISH_ALS_INT# for Merion

6

5

Link CI1804M1HRG-NH done 0212

VR_LPM_R# <87>

2

IR_CAM_DET# <38>

1

@

T420

PAD~D

1

@

T415

PAD~D

1

@

T416

PAD~D

ISH_I2C1_ALS_SDA <38>

ISH_I2C1_ALS_SCL <38>

ISH_I2C2_SDA <52>

ISH_I2C2_SCL <52>

Reserve

WWAN_FULL_PWR _EN <52>

SIO_EXT_WAKE# <5 8>

LCD_CBL_DET# < 38>

1

@

T421

PAD~D

1

@

T395

PAD~D

1

@

T396

PAD~D

1

@

T397

PAD~D

ISH_ALS_INT# <38>

1

@

T375

PAD~D

1

@

T376

PAD~D

1

@

T377

PAD~D

TBT_DET#

RF Request

SML0B_SMBCL K

PRIM_CORE_OPT_ DIS

SIO_EXT_WAKE#

SML0B_SMBCLK

SML0B_SMBDATA

GPP_D12

LCD_CBL_D ET#

IR_CAM_DET#

ISH_I2C2_SDA

ISH_I2C2_SCL

1

+3.3V_ALW_PCH

@

RC400

10K_0402_5 %

1 2

12

10K_0402_5 %

RC401

1 2

CC1476@RF@ 33P _0402_50V8J

Place close CPU side

1 2

RC854 10K_04 02_5%@

1 2

RC748 10K_04 02_5%

1 2

RC829 1K_040 2_5%@

1 2

RC830 1K_040 2_5%@

1 2

RC847 100K_0 402_5%

1 2

RC749 100K_0 402_5%

RC345 100K_0 402_5%

1 2

RC363 1K_040 2_5%

1 2

RC362 1K_040 2_5%

+3.3V_ALW_PCH

12

TBT_DET#

HIG H NON AR

LOW AR

+3.3V_RUN

+3.3V_RUN

+3.3V_ALW_PC H

A A

12

2.2K_0402_5 %

RC46

@

GPP_B22

BOOT BIOS Dest i nat i on(Bi t 6)

HIGH

LOW(DEFAULT)

LPC

SPI

5

10K_0402_5%

12

DIMM Detect

HIGH

LOW

RC53

ONE_DIMM#

1 DIMM

2 DIMM

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EX PRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EX PRESS WRITTEN CONSENT.

4

3

2

Title

Size Document N umber Re v

Size Document N umber Re v

Size Document N umber Re v

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

CPU(4/14)GSPI,I2C,UART,ISH

CPU(4/14)GSPI,I2C,UART,ISH

CPU(4/14)GSPI,I2C,UART,ISH

LA-G871P

LA-G871P

LA-G871P

1

9 109Tuesday, March 05, 2019

9 109Tuesday, March 05, 2019

9 109Tuesday, March 05, 2019

1.0

1.0

1.0

Page 10

5

smd.db-x7.ru

4

3

2

1

For Merion AR (follow WHL 180416a port map)

CPU@

UC1H

D D

AR(PCIE5~8) --->

Card Reader RTS5242----->

M.2 2230(WLAN) --->

C C

M.2 3042(LTE/SATA Cache)--->

M2 2280 SSD (4 Lane) --->

B B

PCIE_PRX_DTX_N5<42>

PCIE_PRX_DTX_P5<42>

PCIE_PTX_DRX_N5<42>

PCIE_PTX_DRX_P5<42>

PCIE_PRX_DTX_N6<42>

PCIE_PRX_DTX_P6<42>

PCIE_PTX_DRX_N6<42>

PCIE_PTX_DRX_P6<42>

PCIE_PRX_DTX_N7<42>

PCIE_PRX_DTX_P7<42>

PCIE_PTX_DRX_N7<42>

PCIE_PTX_DRX_P7<42>

PCIE_PRX_DTX_N8<42>

PCIE_PRX_DTX_P8<42>

PCIE_PTX_DRX_N8<42>

PCIE_PTX_DRX_P8<42>

PCIE_PRX_DTX_N9<70>

PCIE_PRX_DTX_P9<70>

PCIE_PTX_DRX_N9<70>

PCIE_PTX_DRX_P9<70>

PCIE_PRX_DTX_N10<52>

PCIE_PRX_DTX_P10<52>

PCIE_PTX_DRX_N10<52>

PCIE_PTX_DRX_P10<52>

PCIE_PRX_DTX_N11<54>

PCIE_PRX_DTX_P11<54>

PCIE_PTX_DRX_N11<54>

PCIE_PTX_DRX_P11<54>

PCIE_PRX_DTX_N12<52>

PCIE_PRX_DTX_P12<52>

PCIE_PTX_DRX_N12<52>

PCIE_PTX_DRX_P12<52>

PCIE_PRX_DTX_N13<68>

PCIE_PRX_DTX_P13<68>

PCIE_PTX_DRX_N13<68>

PCIE_PTX_DRX_P13<68>

PCIE_PRX_DTX_N14<68>

PCIE_PRX_DTX_P14<68>

PCIE_PTX_DRX_N14<68>

PCIE_PTX_DRX_P14<68>

PCIE_PRX_DTX_N15<68>

PCIE_PRX_DTX_P15<68>

PCIE_PTX_DRX_N15<68>

PCIE_PTX_DRX_P15<68>

PCIE_PRX_DTX_N16<68>

PCIE_PRX_DTX_P16<68>

PCIE_PTX_DRX_N16<68>

PCIE_PTX_DRX_P16<68>

1 2

RC50 100_0402_1%

Jony _12/21: Refer RVP keep it setting

570990_CF L_U_DD R4_RV P_CRB_ Sch_Re v0p8. pdf

PCIE_RCOMPN

PCIE_RCOMPP

BW9

PCIE5_RXN/USB31_5_RXN

BW8

PCIE5_RXP/USB31_5_RXP

BW4

PCIE5_TXN/USB31_5_TXN

BW3

PCIE5_TXP/USB31_5_TXP

BU6

PCIE6_RXN/USB31_6_RXN

BU5

PCIE6_RXP/USB31_6_RXP

BU4

PCIE6_TXN/USB31_6_TXN

BU3

PCIE6_TXP/USB31_6_TXP

BT7

PCIE7_RXN

BT6

PCIE7_RXP

BU2

PCIE7_TXN

BU1

PCIE7_TXP

BU9

PCIE8_RXN

BU8

PCIE8_RXP

BT4

PCIE8_TXN

BT3

PCIE8_TXP

BP5

PCIE9_RXN

BP6

PCIE9_RXP

BR2

PCIE9_TXN

BR1

PCIE9_TXP

BN6

PCIE10_RXN

BN5

PCIE10_RXP

BR4

PCIE10_TXN

BR3

PCIE10_TXP

BN10

PCIE11_RXN/SATA0_RXN

BN8

PCIE11_RXP/SATA0_RXP

BN4

PCIE11_TXN/SATA0_TXN

BN3

PCIE11_TXP/SATA0_TXP

BL6

PCIE12_RXN/SATA1A_RXN

BL5

PCIE12_RXP/SATA1A_RXP

BN2

PCIE12_TXN/SATA1A_TXN

BN1

PCIE12_TXP/SATA1A_TXP

BK6

PCIE13_RXN

BK5

PCIE13_RXP

BM4

PCIE13_TXN

BM3

PCIE13_TXP

BJ6

PCIE14_RXN

BJ5

PCIE14_RXP

BL2

PCIE14_TXN

BL1

PCIE14_TXP

BG5

PCIE15_RXN/SATA1B_RXN

BG6

PCIE15_RXP/SATA1B_RXP

BL4

PCIE15_TXN/SATA1B_TXN

BL3

PCIE15_TXP/SATA1B_TXP

BE5

PCIE16_RXN/SATA2_RXN

BE6

PCIE16_RXP/SATA2_RXP

BJ4

PCIE16_TXN/SATA2_TXN

BJ3

PCIE16_TXP/SATA2_TXP

CE6

PCIE_RCOMP_N

CE5

PCIE_RCOMP_P

CR28

GPP_H12/M2_SKT2_CFG_0

CP28

GPP_H13/M2_SKT2_CFG_1

CN28

GPP_H14/M2_SKT2_CFG_2

CM28

GPP_H15/M2_SKT2_CFG_3

WHL-U42_BGA1528

PCIE / USB3.1 / SATA

8 of 20

USB_OC3#

USB_OC0#

USB_OC1#

USB_OC2# M2280_PCIE_SATA#

RC757 20K_0402_5%@

RC758 20K_0402_5%@

RC759 20K_0402_5%@

RC760 20K_0402_5%@

PCIE1_RXN/USB31_1_RXN

PCIE1_RXP/USB31_1_RXP

PCIE1_TXN/USB31_1_TXN

PCIE1_TXP/USB31_1_TXP

PCIE2_RXN/USB31_2_RXN/SSIC_1_R XN

PCIE2_RXP/USB31_2_RXP/SSIC_1_RX P

PCIE2_TXN/USB31_2_TXN/SSIC_1_TXN

PCIE2_TXP/USB31_2_TXP/SSIC_1_TXP

PCIE3_RXN/USB31_3_RXN

PCIE3_RXP/USB31_3_RXP

PCIE3_TXN/USB31_3_TXN

PCIE3_TXP/USB31_3_TXP

PCIE4_RXN/USB31_4_RXN

PCIE4_RXP/USB31_4_RXP

PCIE4_TXN/USB31_4_TXN

PCIE4_TXP/USB31_4_TXP

USB2.0

USB2_COMP

GPP_E9/USB2_OC0#/GP_BSSB_CLK

GPP_E10/USB2_OC1#/GP_BSSB_DI

1 2

1 2

1 2

1 2

USB2_VBUSSENSE

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#/SPI1_CS1#

A A

USB2_1N

USB2_1P

USB2_2N

USB2_2P

USB2_3N

USB2_3P

USB2_4N

USB2_4P

USB2_5N

USB2_5P

USB2_6N

USB2_6P

USB2_7N

USB2_7P

USB2_8N

USB2_8P

USB2_9N

USB2_9P

USB2_10N

USB2_10P

USB2_ID

RSVD_69

CB5

CB6

CA4

CA3

BY8

BY9

CA2

CA1

BY7

BY6

BY4

BY3

BW6

BW5

BW2

BW1

CE3

CE4

CE1

CE2

CG3

CG4

CD3

CD4

CG5

CG6

CC1

CC2

CG8

CG9

CB8

CB9

CH5

CH6

CC3

CC4

CC5

CE8

CC6

CK6

CK5

CK8

CK9

CP8

CR8

CM8

CN8

CM10

CP10

CN7

AR3

HDD_DET#

M3042_PCIE#_SATA

USBCOMP

USB2_ID

VBUSSENSE

USB_OC2#

Rese rve

USB_OC3#

Rese rve

HDD_DEVSLP

HDD_DET#

M3042_PCIE#_SATA

M2280_PCIE_SATA#

USB3_PRX_DTX_N2 <71>

USB3_PRX_DTX_P2 <71>

USB3_PTX_DRX_N2 <71>

USB3_PTX_DRX_P2 <71>

USB3_PRX_DTX_N3 <72>

USB3_PRX_DTX_P3 <72>

USB3_PTX_DRX_N3 <72>

USB3_PTX_DRX_P3 <72>

USB3_PRX_DTX_N4 <54>

USB3_PRX_DTX_P4 <54>

USB3_PTX_DRX_N4 <54>

USB3_PTX_DRX_P4 <54>

USB20_N1 <44>

USB20_P1 <44>

USB20_N2 <71>

USB20_P2 <71>

USB20_N3 <72>

USB20_P3 <72>

USB20_N6 <38>

USB20_P6 <38>

USB20_N7 <52>

USB20_P7 <52>

USB20_N8 <66>

USB20_P8 <66>

USB20_N9 <66>

USB20_P9 <66>

USB20_N10 <52>

USB20_P10 <52>

1 2

RC47 113_0402_1%

1 2

RC337 0_0201_5%@

1 2

RC49 1K_0402_5%

USB_OC0# <71>

USB_OC1# <72>

1

RC520 1K_0402_5%@

RC521 1K_0402_5%@

RC730 1K_0402_5%@

T417

@

PAD~D

M3042_DEVSLP <52>

M2280_DEVSLP <68>

M3042_PCIE#_SATA <58>

M2280_PCIE_SATA# <68>

1 2

1 2

1 2

-----> Ext USB3 Port 1 charge

-----> Ext USB3 Port 2

-----> M.2 3042(LTE)

-----> Type C (PD)

-----> Ext USB2 Port 1

-----> Ext USB2 Port 2

-----> UF CAM

-----> M2 3042(WWAN)

-----> USH

-----> Option to FPR in PB

-----> M.2 2230(BT)

M2280_PCIE_SATA#

HDD_DET#

M3042_PCIE#_SATA

USB_OC3#

USB_OC0#

USB_OC1#

USB_OC2#

RC764 10K_0402_5%

RC765 10K_0402_5%

RC766 10K_0402_5%

RC836

RC837 10K_0402_5%

RC839 10K_0402_5%

RC838 10K_0402_5%

12

12

12

10K_0402_5%

12

12

12

12

+3.3V_RUN

+3.3V_ALW_PCH

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WR ITTEN CONSENT.

5

4

3

2

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Compal Electronics, Inc.

CPU(5/14)PCIE,USB,SATA

CPU(5/14)PCIE,USB,SATA

CPU(5/14)PCIE,USB,SATA

LA-G871P

LA-G871P

LA-G871P

10 109Tuesday, March 05, 2019

10 109Tuesday, March 05, 2019

10 109Tuesday, March 05, 2019

1

1.0

1.0

1.0

Page 11

5

smd.db-x7.ru

CLK_PCIE_N0<52>

M.2 3042 WWAN--->

D D

M.2 2230 WLAN--->

M.2 2280 SSD--->

Card Reader --->

AR--->

+3.3V_ALW_DSW

RC323 10K_0402_5%

C C

RC67 1K _0402_5%

+1.0V_VCCST

RC71 1K _0402_5%

RC536 10K_0 402_5%@

PCH GLITCH ISSUE MIT IGATION(PDG p.130)

B B

+3.3V_ALW_PCH

A A

H_CPUPW RGD VCCST_PWRGD

100P_0402_50V8J

12

CC300ESD@

CLK_PCIE_P0<52>

CLKREQ_PCIE#0<52>

+3.3V_RUN

CLK_PCIE_N1<52>

CLK_PCIE_P1<52>

CLKREQ_PCIE#1<52>

+3.3V_RUN

CLK_PCIE_N2<68>

CLK_PCIE_P2<68>

CLKREQ_PCIE#2<68>

+3.3V_RUN

+3.3V_RUN +RTC_CELL_PCH

CLK_PCIE_N4<70>

CLK_PCIE_P4<70>

CLKREQ_PCIE#4<70>

+3.3V_RUN

CLK_PCIE_N5<42>

CLK_PCIE_P5<42>

CLKREQ_PCIE#5<42>

+3.3V_RUN

LAN_W AKE#

12

PCH_PCIE_W AKE#

12

VCCST_PW RGD

12

PCH_PW ROK

12

SIO_SLP_SUS #

12

RC229100K_0402_ 5%

12

CC14650.33U_040 2_10V6K @

SIO_SLP_S4#

12

RC232100K_0402_ 5%

12

CC14670.33U_040 2_10V6K @

SIO_SLP_S3#

12

RC231100K_0402_ 5%

12

CC14680.33U_040 2_10V6K @

SIO_SLP_A#

12

RC233100K_0402_ 5%

12

CC14690.33U_040 2_10V6K @

SIO_SLP_W LAN#

12

RC234100K_0402_ 5%

12

CC14700.33U_040 2_10V6K @

SIO_SLP_LAN #

12

RC761100K_0402_ 5%

12

CC14710.33U_040 2_10V6K @

SIO_SLP_S5#

12

RC230100K_0402_ 5% @

PCH_PLTRST#

12

RC237100K_0402_ 5% @

1211 change

Follow NB14 UU AR, Intel CNVi recommendation RC237 pop,

But measure cold reset and Global reset sequence timing fail, So depop RC237

SIO_SLP_S0#

12

RC763100K_0402_ 5%

100P_0402_50V8J

12

CC301ESD@

ESD Request:place near CPU side

5

1 2

RC297 0_0 201_5%@RF@

12

RC189 10K _0402_5%

1 2

RC526 0_0 201_5%@RF@

12

RC522 10K _0402_5%

1 2

RC727 0_0 201_5%@RF@

12

RC525 10K _0402_5%

12

RC523 10K _0402_5%

1 2

RC528 0_0 201_5%@RF@

12

RC51 10K_0402_5 %

1 2

RC529 0_0 201_5%@RF@

12

RC190 10K _0402_5%

PCH_PLTRST#

MC74VHC1G0 8DFT2G_SC70-5

S4 power side PD need @,need check

RC215

POP

NO Support Deep sleep

DE-POP

Support Deep sleep

PCH_DPW ROK PCH_ RSMRST#_AND

1 2

0.01UF_0402_25V7K

100K_0402_1%

12

1

@

CC266

RC220

2

UC7

@NDS3@

RC215

0_0201_5%

CLKREQ_PCIE #0_R

CLKREQ_PCIE #1_R

CLKREQ_PCIE #2_R

CLKREQ_PCIE #3_R

CLKREQ_PCIE #4_R

CLKREQ_PCIE #5_R

+3.3V_ALW_PCH

5

1

P

B

2

A

G

3

T355

12

4

O

@

PAD~D

10K_0402_5%

RC75

4

PCH_PLTRST#_AND

12

RC65

@

100K_0402_ 5%

1

VCCST_PWRGD<59,79>

ME_SUS_PWR_ACK is for LPC use only

PCH_PLTRST#_A ND

.047U_0402_16V7K

12

CC196ESD@

4

CPU@

UC1J

AW2

CLKOUT_PCIE_N_0

AY3

CLKOUT_PCIE_P_0

CF32

GPP_B5/SRCCLKREQ0#

BC1

CLKOUT_PCIE_N_1

BC2

CLKOUT_PCIE_P_1

CE32

GPP_B6/SRCCLKREQ1#

BD3

CLKOUT_PCIE_N_2

BC3

CLKOUT_PCIE_P_2

CF30

GPP_B7/SRCCLKREQ2#

BH3

CLKOUT_PCIE_N_3

BH4

CLKOUT_PCIE_P_3

CE31

GPP_B8/SRCCLKREQ3#

BA1

CLKOUT_PCIE_N_4

BA2

CLKOUT_PCIE_P_4

CE30

GPP_B9/SRCCLKREQ4#

BE1

CLKOUT_PCIE_N_5

BE2

CLKOUT_PCIE_P_5

CF31

GPP_B10/SRCCLKREQ5#

WHL-U42 _BGA1528

PCH_PLTRST#_AND <38 ,42,52,68,70>

SYS_RESET#<79>

PCH_RSMRST#_AND<63,79>

1 2

RC77 1K _0402_5%@

1 2

RC78 62 _0402_5%

Follow PDG P.251

SYS_PW ROK<58,79>

PCH_PWROK<88>

PCH_DPWROK<58>

T380

SUSACK# is for LPC use only

For E SD solution

T381

PCH_PCIE_WAKE#<42,58,59>

LAN_WAKE#<58>

@

T422

PAD~D

@

PAD~D

@

PAD~D

CLOCK SINGNALS

10 of 20

PCH_PLTRST#

SYS_RESET#

PCH_RSMRS T#_AND

H_CPUPW RGDH_ CPUPWRG D_R

VCCST_PW RGD_CPU

1

1

LAN_W AKE#

PM_LANPH Y_ENABLE

1

XDP_DBRESET#<79>

GPP_A13

GPP_A15

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL_IN

XTAL_OUT

XCLK_BIASREF

CLKIN_XTAL

RTCX1

RTCX2

SRTCRST#

RTCRST#

CPU@

UC1K

BJ35

GPP_B13/PLTRST#

CN10

SYS_RESET#

BR36

RSMRST#

AR2

PROCPWRGD

BJ2

VCCST_PWRGOOD

CR10

SYS_PWROK

BP31

PCH_PWROK

BP30

DSW_PWROK

BV34

GPP_A13/SUSWARN#/SUSPWRDACK

BY32

GPP_A15/SUSACK#

BU30

WAKE#

BU32

GPD2/LAN_WAKE#

BU34

GPD11/LANPHYPC

WHL-U42 _BGA1528

+3.3V_ALW_PCH

1 2

1

2

3

CLK_ITPXDP_N

AU1

CLK_ITPXDP_P

AU2

BT32

CK3

CK2

CJ1

CM3

BN31

BN32

BR37

BR34

PCH_PLTRST#

PCH_PLTRST#_A ND

Support DS3

No Support DS3

@

1 2

RC530

1 2

RC298

SUSCLK

XTAL24_IN_CPU

XTAL24_OUT_CPU

XCLK_BIASR EF

REFCLK_CNV

PCH_RTCX1

PCH_RTCX2