A

smd.db-x7.ru

B

C

D

E

COMPAL CONFIDENTIAL

MODEL NAME :

FDI40 N3-14", FDI4A V3-14", FDI43 N5-14",

FDI50 N3-15", FDI5A V3-15", FDI53 N5-15",

FDI70 N3-17"

1 1

PCB NO :

DA60027S000 (SBDR)

DA60027S100 (NBDR)

BOM P/N :

431AJ331L51

431AJ331L52

431AJ331L53

2 2

431AJ331L54

431AJ331L55

431AJ331L56

431AJ331L01

431AJ331L02

431AJ331L03

NBDR-UMASBDR-UMA

X4E

X4EAJ331L51(N3)

X4EAJ331L52(V3)

X4EAJ331L01(N5)

CML-U+MEC1418

2019-06-19

REV : 1.0 (A00)

@ : Un-pop Component

PCB R1

ZZZ

DAZ2QT00100

PCB_SBD R_R1@

PCB FDI50 LA -G717P LS-F1 12P/F114P/G 711P

PCB R3

ZZZ3

DAZ2QT00101

PCB_SBD R_R3_GCE@

PCB FDI50 LA -G717P LS-F1 12P GOLD A3 1 !

ZZZ5

DAZ2QT00102

PCB_SBD R_R3_TRI@

PCB FDI50 LA -G717P LS-F1 12P TRIPOD A31 !

ZZZ7

DAZ2QT00103

PCB_SBD R_R3_HAN@

PCB FDI50 LA -G717P LS-F1 12P HANNS A3 1 !

ZZZ9

DAZ2QT00104

PCB_SBD R_R3_TMT@

PCB FDI50 LA -G717P LS-F1 12P T-MAC A31 !

ZZZ2

DAZ2SO00100

PCB_NBR D_R1@

PCB FDI53 LA -G717P LS-G7 18P

ZZZ4

DAZ2SO00101

PCB_NBR D_R3_GCE@

PCB FDI53 LA -G717P LS-G7 18P GOLD A 31 !

ZZZ6

DAZ2SO00102

PCB_NBR D_R3_TRI@

PCB FDI53 LA -G717P LS-G7 18P TRIPOD A3 1 !

ZZZ8

DAZ2SO00103

PCB_NBR D_R3_HAN@

PCB FDI53 LA -G717P LS-G7 18P HANNS A3 1 !

ZZZ10

DAZ2SO00104

PCB_NBR D_R3_TMT@

PCB FDI53 LA -G717P LS-G7 18P T-MAC A31 !

DIS@ : GPU Support

N3@/V3@ : Inspiron/Vostro

CPU R1 CPU R3

UC12

S IC FJ80701 04307606 SRGL0 V0 2. 1G BGA

i3-10110U

SA0000CU31L

CML_2.1G _R1@

UC1

S IC FJ80701 04307606 SRGL0 V0 2. 1G A31!

i3-10110U

SA0000CU32L

CML_2.1G _R3@

CML@/CNL@ : CML/CNL

BASE@/PREM@ : (Pentium)(Celeron)i3 i5 i7

EC@ : EC Support

JP@/PJP@ : JUMP

100@/1000@: Lan

UC13

3 3

S IC FJ80701 04307504 SRGKY V0 1.6G BGA

i5-10210U

SA0000CST2L

CML_1.6G _R1@

UC1

S IC FJ80701 04307504 SRGKY V0 1.6G A31!

i5-10210U

SA0000CST3L

CML_1.6G _R3@

EMI@/ESD@/RF@ : EMI, ESD and RF Component

@EMI@/@ESD@/@RF@ : EMI, ESD and RF Un-POP Component

CMC@ : XDP Component

CONN@ : Connector Component

KBBL@ : KB Backlight

UC14

S IC FJ80701 04303905 SRGKW V 0 1.8G FCBGA

i7-10510U

SA0000CU22L

CML_1.8G _R1@

UC1

S IC FJ80701 04303905 SRGKW V 0 1.8G A31!

i7-10510U

SA0000CU21L

CML_1.8G _R3@

TPM@/FTPM@ : HW TPM/SW TPM

750_CTPM@:750 and china TPM

ST_CTPM@:ST and china TPM

CTPM@:China TPM

FFS@ : Free Fall Sensor

TYPEC@ : TypeC

TYPEC@EMI@/TYPEC@ESD@: EMI, ESD ,TypeC Component

PCB@/PCB_R1@/PCB_R3_G@/PCB_R3_T@/PCB_R3_H@/PCB_R3_TM@: PCB MB

Layout Dell logo

PCB_NBDR_R1@: PCB MB for NBDR

4 4

COPYRIGHT 2014

ALL RIGHT RESERVED

REV: X00

PWB: 9HTP8

A

B

TS_NON@/TS_USB@/TS_I2C@: Touch Screen Interface Select

SBDR@/NBDR@: SBDR/ NBDR Select

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2019/06/ 19 2020/06/ 30

2019/06/ 19 2020/06/ 30

2019/06/ 19 2020/06/ 30

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-G717P

LA-G717P

LA-G717P

1 1 00Wednesd ay, June 19, 20 19

1 1 00Wednesd ay, June 19, 20 19

1 1 00Wednesd ay, June 19, 20 19

E

1.0

1.0

1.0

A

smd.db-x7.ru

B

C

D

E

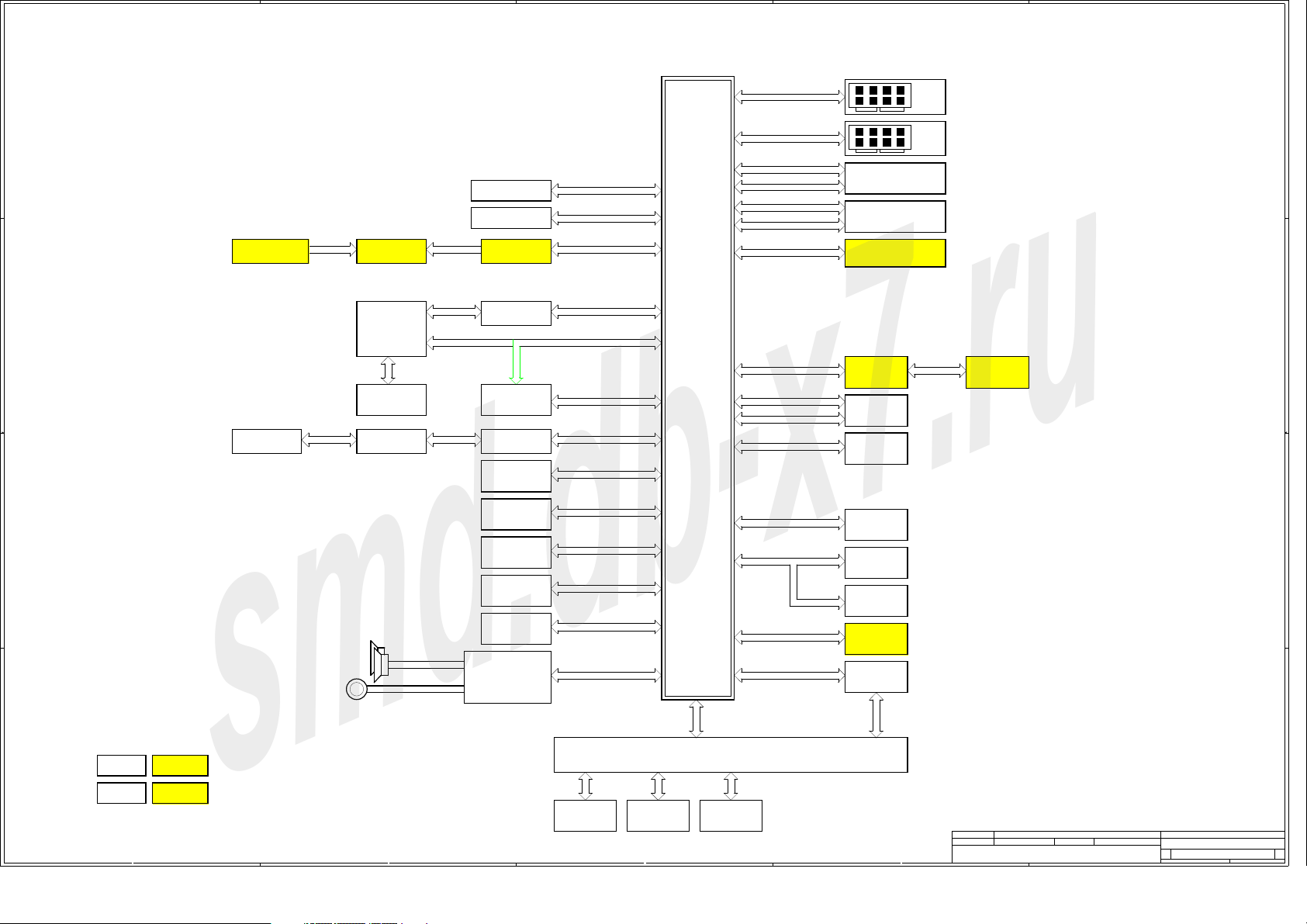

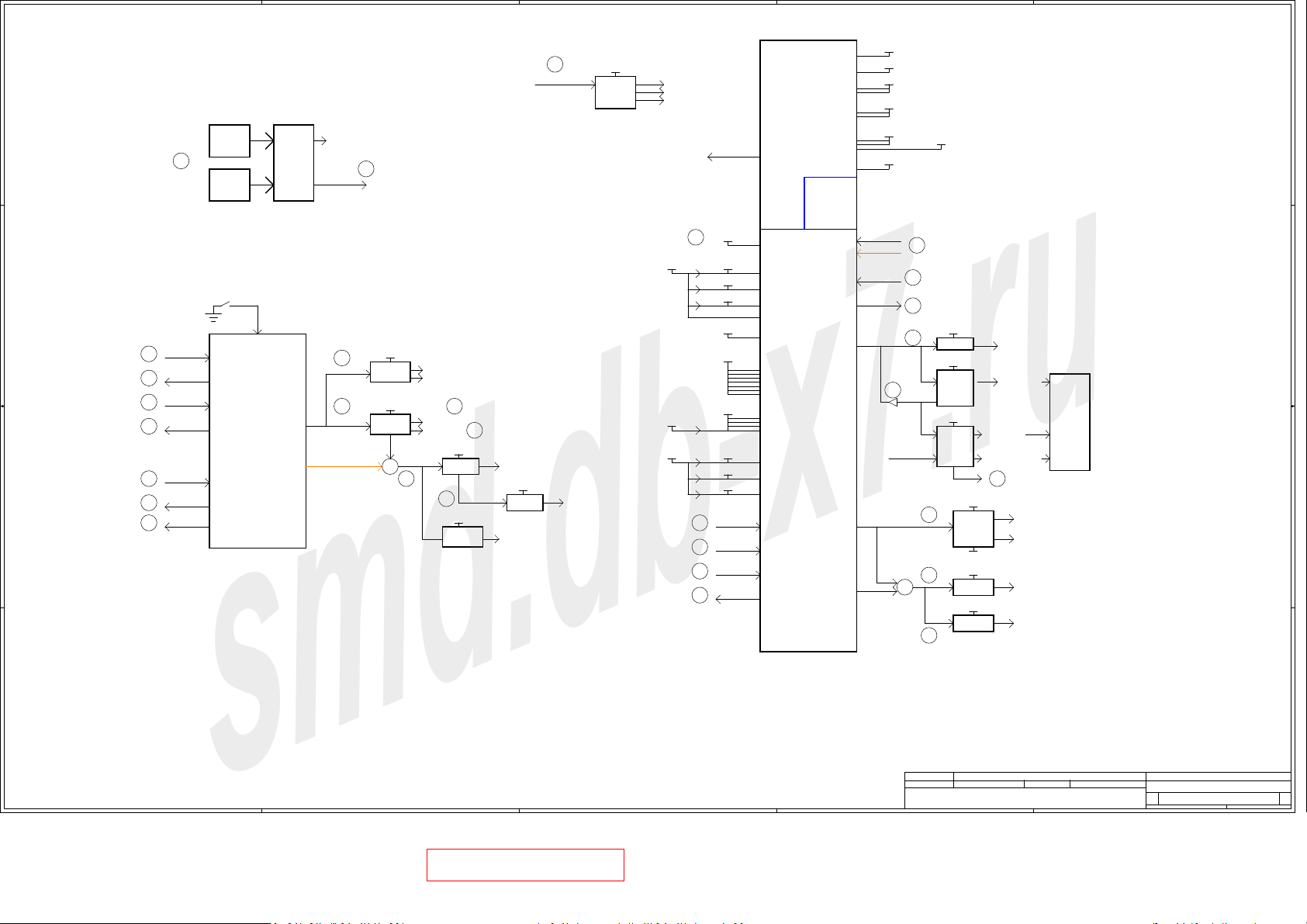

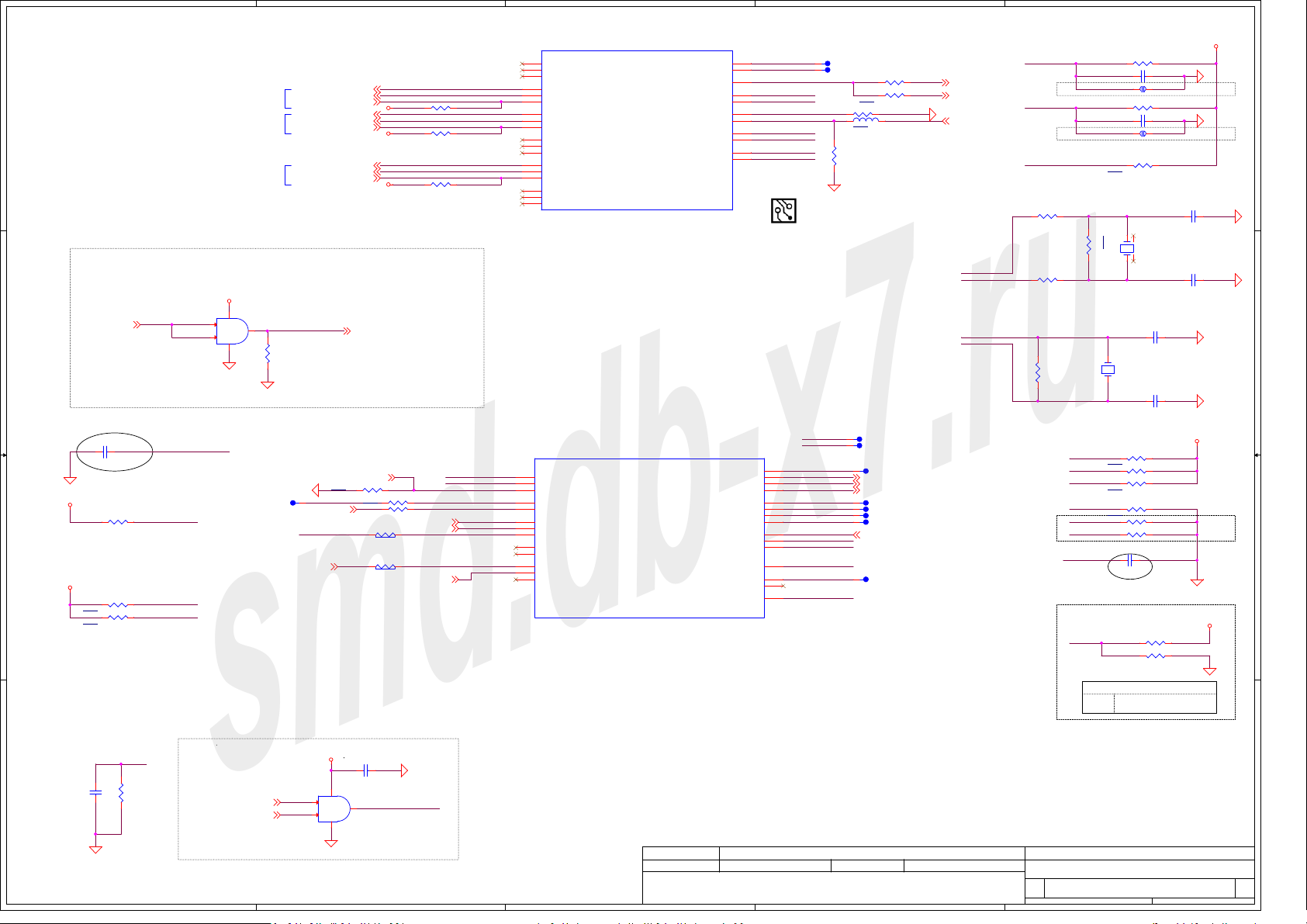

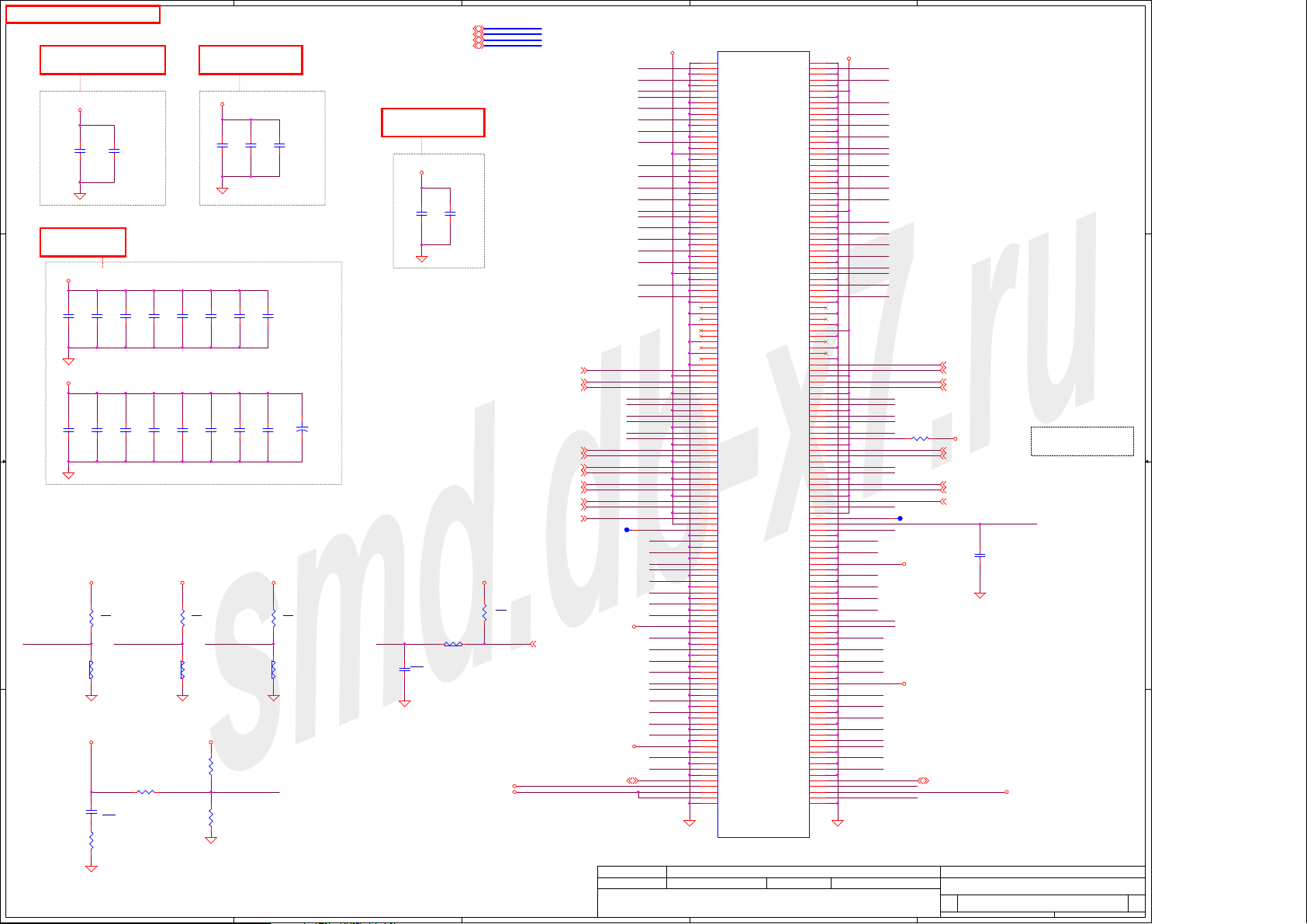

Block Diagram

DDR4

RTC

PS/2

4GB/8GB

SODIMM A

P23

DDR4

4GB/8GB

SODIMM B

P24

P71

P71

P73

P73

P52

P38

P65

P65

P8

P62

P58

D

SD Card slot

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY O F COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY O F COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY O F COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-G717P

LA-G717P

LA-G717P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

2 100Wednesday, June 19, 2019

2 100Wednesday, June 19, 2019

2 100Wednesday, June 19, 2019

1 1

DDR4 2400MHz Channel A

DDR4 2400MHz Channel B

Intel CPU

USB2.0 x 1

USB3.0 x 1 (gen1)

USB2.0 x 1

USB3.0 x 1 (gen1)

USB2.0 x 1

Port 1 (USB3.0 Type-A)

Port 2 (USB3.0 Type-A)

Port 3 (USB2.0 Type-A)

VGA

Connector

# VGA converter

RTD2166

DP x 2

eDP connector

HDMI connector , 1.4a

# DP re-driver

PS8330B

Comet Lake/

Whiskey Lake-U/

P38

P40

eDP 1.2

DDI x 4

DDI x 2

Cannon Lake-U

15W

BGA 1528 balls

Type-C MUX

TUSB542

Reserve d

*Pentium/Celeron Only

Touch screen

LAN 10/100

# LAN 10/1 00/1000

M.2 SSD (NVMe)

ODD

2.5"

HDD/SSD

# FFS

eMMC 256 GB

*UMA only

Reserve d

HDA CODEC

Realtek ALC3204-CG

P42

P38

P51P51P51

P67

P66

P66

P66

P69

P23

P43

CC

P42

2CH SPEAKER

(2CH 2W/4ohm)

RING2/SLEEVE

HP_R/L

USB3.0 x 1

Universal Ja ck

USB Type-C

Connector

Reserve d

5V@3A

TPS25810

Reserve d

Transformer

P24

2 2

RJ45

Connector

3 3

USB3.0 x 1 Gen1

USB2.0 x 1 (Port4)

USB2.0 x 1 (Port8)

PCIe x 1

PCIe x 4

SATA x 1 Gen1

SATA x 1

SMBu s

eMMC

HDA

# ----> Loki-L only

4 4

Battery

RTC

46 x 24 mm

PCH-LP

P6~1 7

eSPI

SMSC KBC 1418

MEC1418-NU

USB2.0 x 1 SD 3.0

USB2.0 x 1

PCIe x 1 / CNVi

USB2.0 x 1

USB2.0 x 1

SPI

I2C

Card reader

RTS5144

BT with WLAN

Camera

Finger print

dTPM

NPCT750

SPI ROM

16 MB

Precision

Touchpa d

Click Pad

Charger

A

Daughter board

Keyboard

B

PWM FAN

C

Thermal sensor

NCT771 8W

P65P77P62

1.0

1.0

1.0

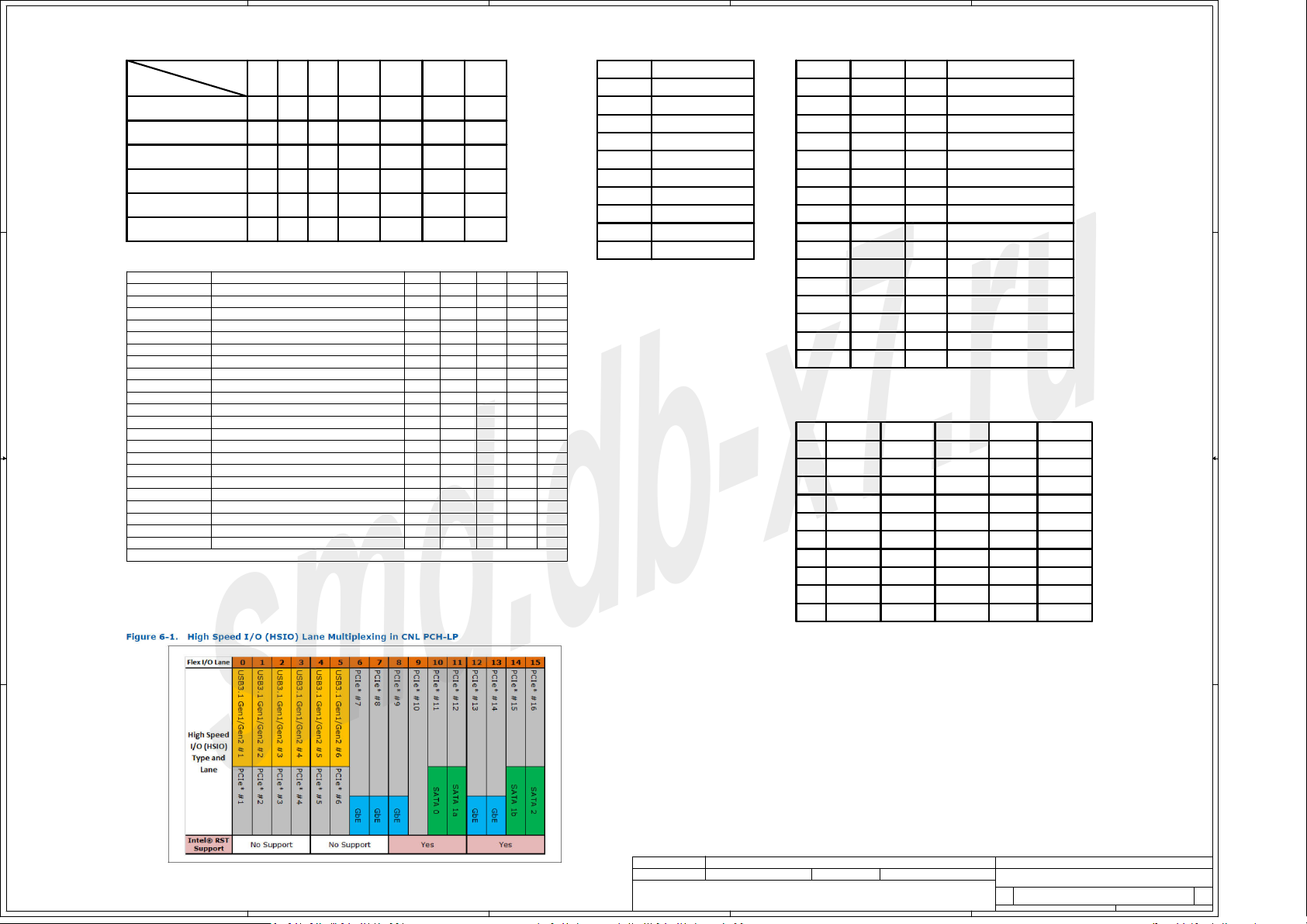

5

smd.db-x7.ru

4

3

2

1

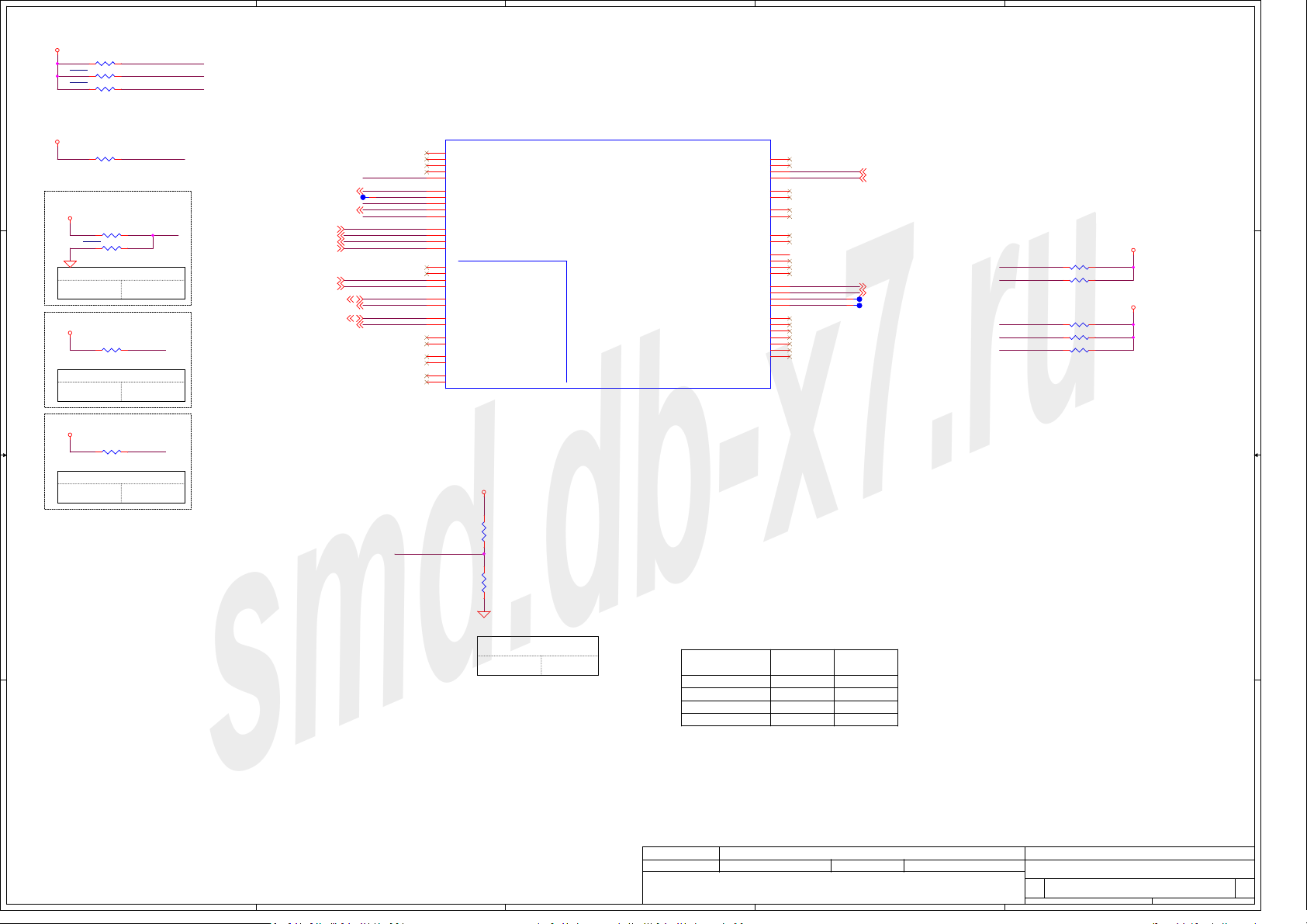

POWER STATES

Signal

State

D D

S0 (Full ON) / M0

S3 (Suspend to RAM) / M3

S4 (Suspend to DISK) / M3

S5 (SOFT OFF) / M3

G3 OFF OFF OFF OFF OFF OFF OFF

DS3

SLP

S3#

HIGH

LOW

LOW

LOW LOW

SLP

SLP

S4#

HIGH HIGH

HIGH HIGH ON

LOW

LOW

S5#

HIGH

ALWAY S

PLANE

ON

ON

ON

Voltage Rails

+19V_ADPIN

+17.4V_BATT++

+19VB

+RTC_C ELL RTC power ONONO N

C C

B B

+3VALW_DSW +3VALW power for PCH DSW rails ON*ONON

+5VALW System +5V always on power rail ON*ONON

+3VALW System +3V always on power rail ON*ONON

+1.8V_PRIM System +1.8V always on power rail

+1.0V_PRIM System +1.0V always on power rail ON*

+2.5V_MEM

+0.6V_DDR_VT T DDR +0.6VS power rail for DDR terminator OFFOFFON

+VCCST OFFONON

+VCCSTG +1.05 VCCSTG power rail ON OFF OFF

+VCCI O +1.05 VCCIO power rail ON OFF OFF

+VCC_GT Sliced graphics power rail OFFOFFON

+VCC_SA System Agent power rail OFFON OFF

+3VLP +19VB to +3VLP power rail for suspend power ONONON

+3VALW_PCH +3VALW power for PCH suspend rails

+3VS System +3VS power rail

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF

Adapter power supply

Bat t er y po wer s uppl y

AC or bat t er y p o wer r ail f or Syste m

DDR4 +1.2V power rail+1.2V_DDR

DDR4 +2.5V power rail ON OFFON

+1.05 VCCST power rail

System +5VS power rail+5VS

RUN

SUS

PLAN E

PLANE

ON

ON ON

ON

OFF

OFF

OFF

OFF OFF

OFF

S0 S3 S4/S5Power Plane Descript i on

N/A

N/A

N/A

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

ON

CLOCKS

OFF

OFF

------------------ ---

N/A

N/A

N/A

ON*

OFF

OFF+VCC_C ORE Core voltage for CPU OFFON

ON*

OFF

OFF

USB 2.0 DESTINATION

1

2

3

4*

5

6

7

8*

9

10

DESTINATION

USB2.0 port1

USB2.0 Port2

USB2.0 Port, IO/B

Touch screen

Finger printer

Camera

Card reader , IO/B

Reserved

NA

BT

USB3.0

USB3.0-1

USB3.0-2

USB3.0-3

USB3.0-4

USB3.0-5

USB3.0-6

PCIE

PCIE-1

PCIE-2

PCIE-3

PCIE-4

PCIE-5

PCIE-6

PCIE-7

PCIE-8

PCIE-9

PCIE-10

PCIE-11

PCIE-12

PCIE-13

PCIE-14

PCIE-15

PCIE-16

SATA

SATA-0

SATA-1A

SATA-1B

SATA-2

USB3.0 port1

NA

USB3.0 port2

TypeC

LOM

WLAN

SATA HDD

SATA ODD

NVME SSD

NVME SSD

NVME SSD

NVME SSD

Board ID & Model ID Table

Pull-down#Pull-up

1

100

2

100

3

100

4

100

5

100

6

100

7

100

8

100

9

100

10

100

10.0

17.8

27.0

37.4

49.9

64.9

82.5

107.0

154.0

200.0

Voltage

3.000

2.801

2.598

2.402

2.201

2.001

1.808

1.594

1.299

1.100

Board ID

EVT

DVT1

DVT2

Pilot

Model ID

SBDR-UMA

NBDR-UMA

SBDR-DSC

NBDR-DS C

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Index and Configuration

Index and Configuration

Index and Configuration

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

LA-G717P

LA-G717P

LA-G717P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

3 100Wednesday, June 19, 2019

3 100Wednesday, June 19, 2019

3 100Wednesday, June 19, 2019

1.0

1.0

1.0

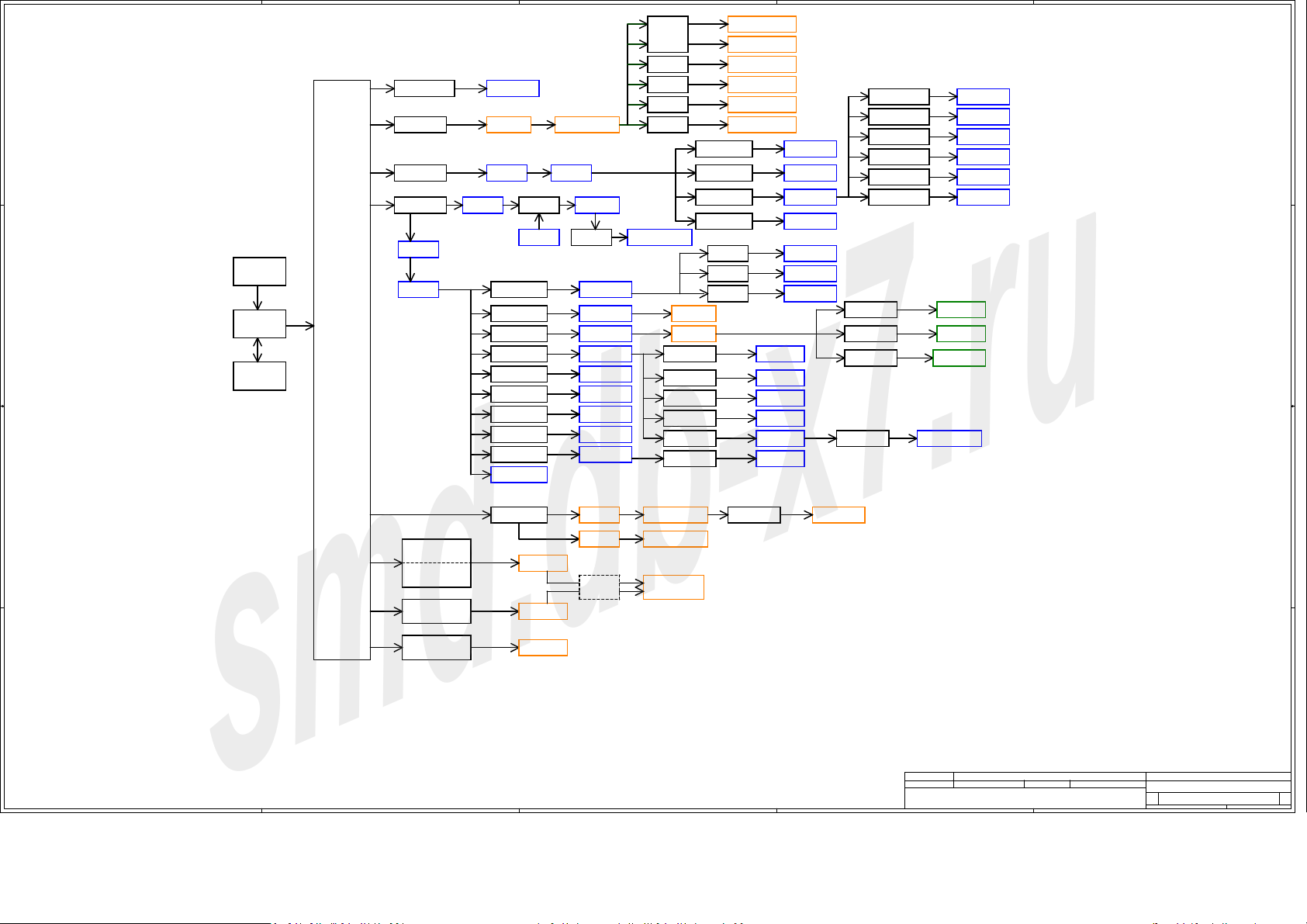

5

smd.db-x7.ru

D D

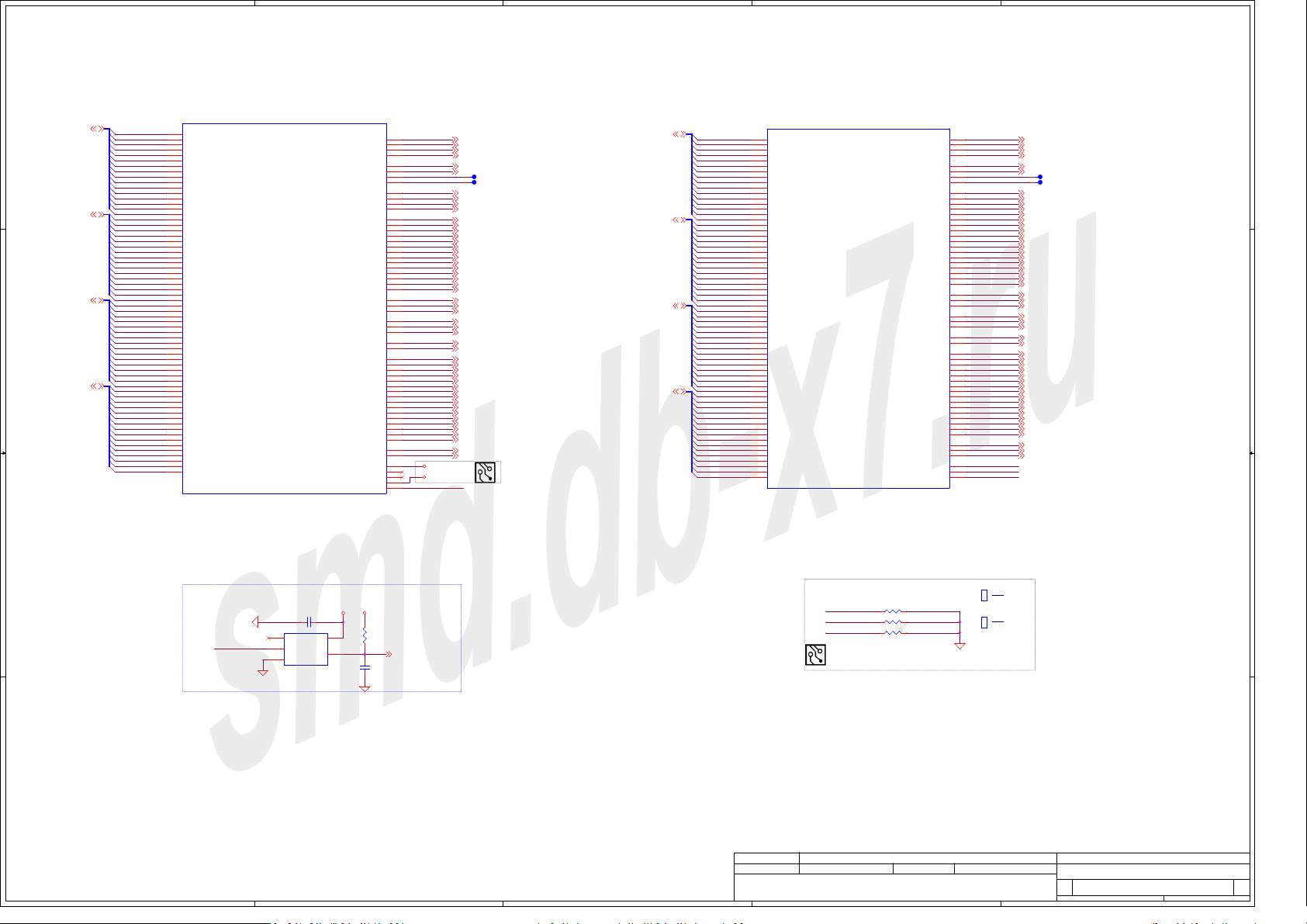

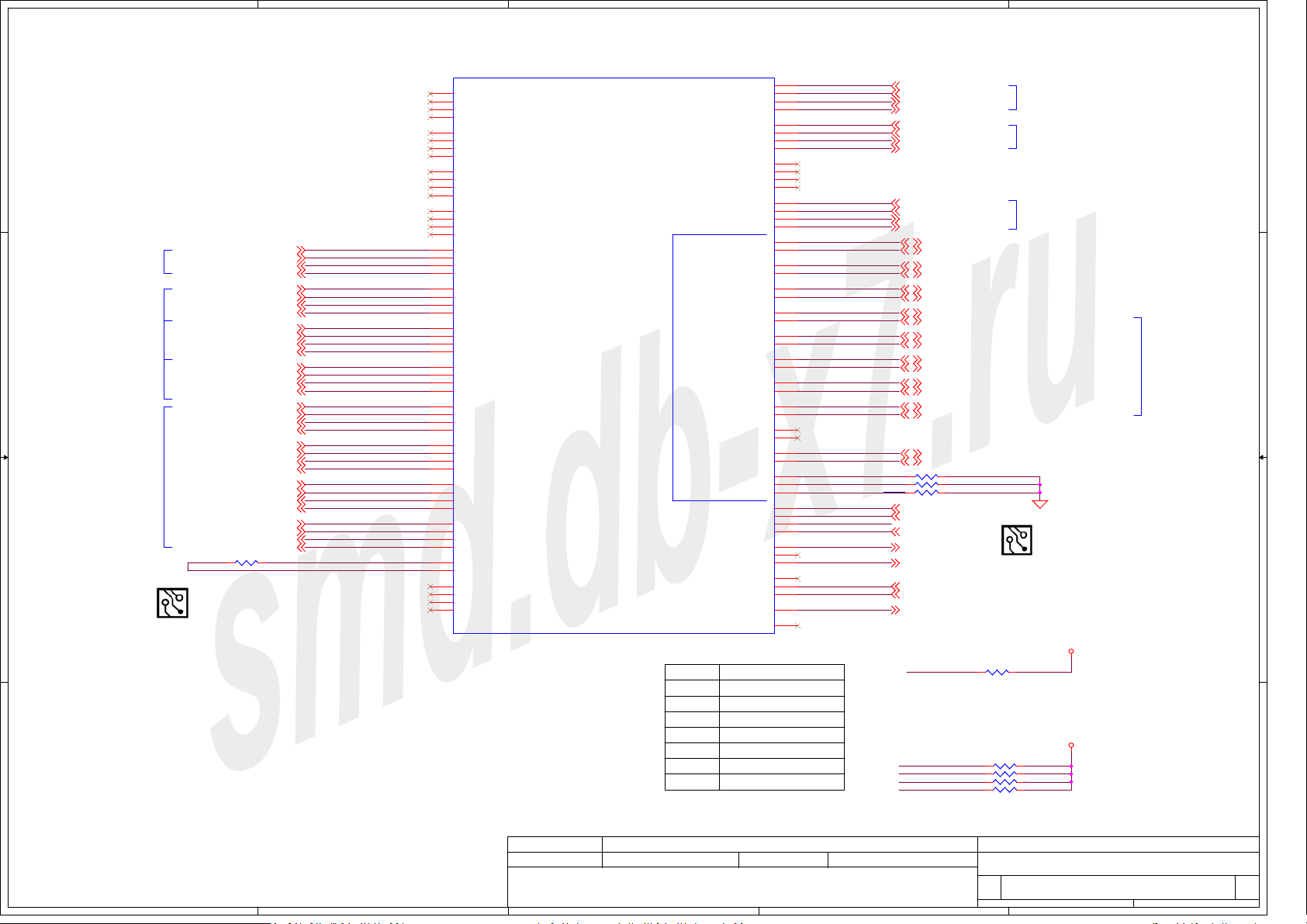

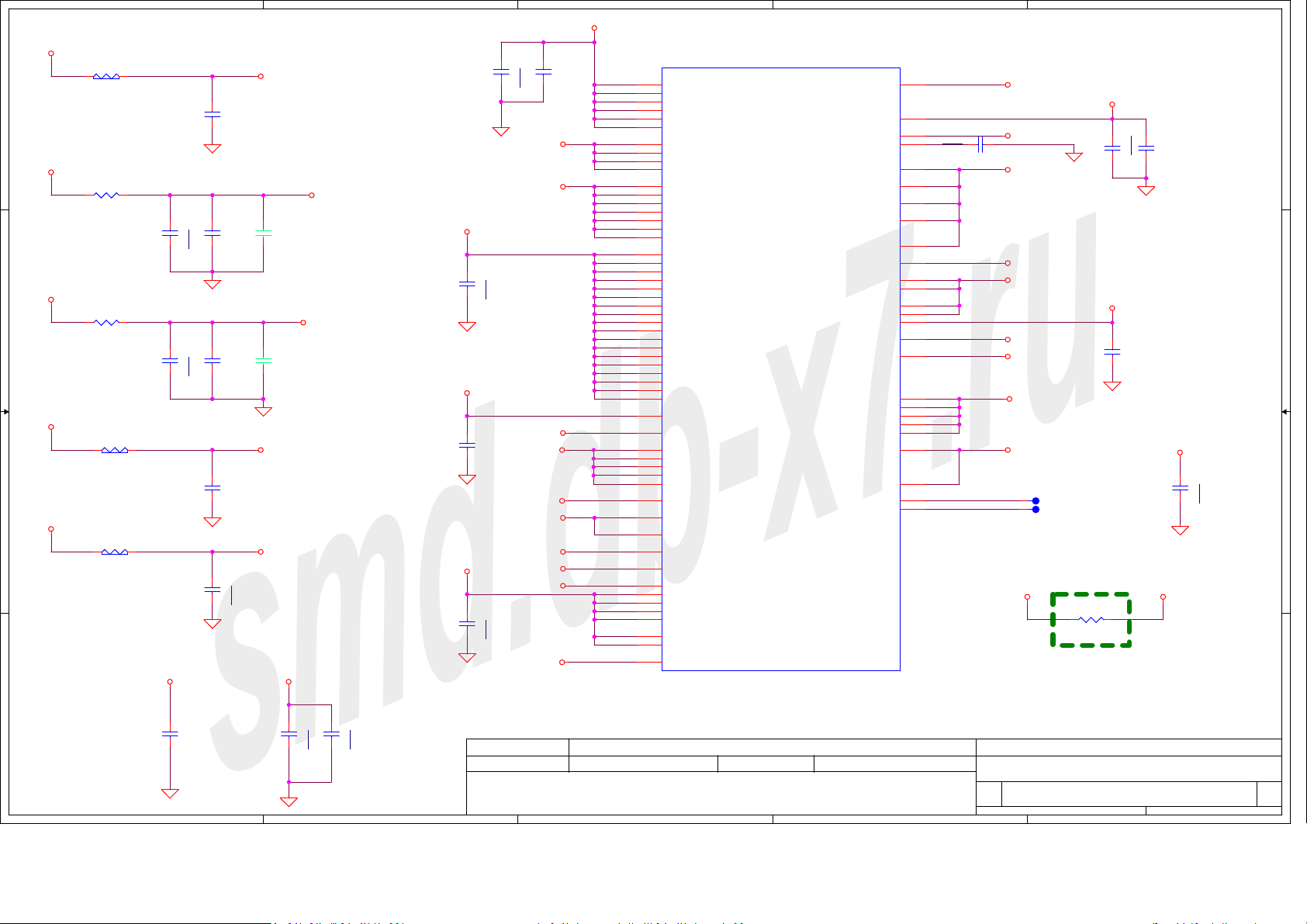

CPU PWR

GPU PWR

Peripheral Device PWR

ADAPTER

+PWR_S RC

C C

CHARGER

ISL88739HRZ-T

(PUB01)

BATTERY

(+19VB)

PJPH01

PJP501

PJP301

4

FUSE 1.5A_24V

(F1)

RT6228AGQU F

(PUH01)

SY8180CRAC

(PU501)

SY8286BRAC

(PU301)

EN_3V

+3VALWP

PJP302

+3VALW

R7

+DCBAT_LCD

PJPH02PRIM_PWR GD

PJP502

PJP503

BAS40C

(D1)

+RTC_VCC

+1.05V_PRIM

+5VALW

+RTC_CELL

0ohm 0603

(RL4)

PCH_PWR _EN

+3VALW_PCH

+2.5VP +2.5V_MEM

PCH_PRIM_ EN

+1.8VALWP

SIO_SLP _S3#

+3VS

+3VALW_EC

+3.3V_W LAN

+3V_EMMC

+3VS_MO N

+LAN_VDD33

+1.05VALWP

EN_5V

+5VALWP

+3VLP

TPS22967DSGR

(UZ4)

PJP250 1 SIO_SLP_ S4# PJP2 502

RT9059GSP

(PU2501)

PJP180 1

RT8061AZQW

(PU1801)

EM5209VF

(UZ3)

0ohm 0603

(RE5)

0ohm 0603

(RW1)

0ohm 0603

(RM1)

JP12

SY6288C20AAC

(UL2)

+TP_VDD

3

EM5209VF

(UZ1)

TPS22961

(UZ2)

0ohm 0603

(RC128)

0ohm 0603

(RC129)

0ohm 0603

(RC130)

+RTC_CELL_VB AT

PJP180 2

+1.8V_PRIM

0ohm 0402

(R5)

0ohm 0402

(RA6)

G510F51U

(U2)

RS3

SY6288C20AAC

(U1)

0ohm 0603

(RL4)

SIO_SLP _S4#

VCCSTG_IO_ EN

VCCSTG_IO_ EN

SY6288D20AAC

(UU1)

SY6288D20AAC

(UU2)

EM5209VF

(UZ3)

TPS25810RVCR

(UT1)

0ohm 0402

(RC131)

0ohm 0402

(RC132)

0ohm 0603

(RC30)

LCD_VCC_TEST_ EN

OR

EDP_VDD_ EN

+VCCST

+VCCSTG

+VCCIO

+1.05V_MPH Y

+1.05V_MPHYPLL

+1.05V_XTAL

USB_EN#

USB_EN#

SIO_SLP _S3#

OVP_TR IP_P1

+FP_VCC

+3V_DVD D

+3VS_CAM

+3VS_SSD

+LCDVD D

VDDREG

USB3_VCC

USB2_VCC

+5VS

+CCG_VBUS

+3V_HDA

+3VALW_DSW

+3.3V_SPI

+3VS

0ohm 0603

(RM2)

LN2306LT1G

(QA1)

0ohm 0603

(RE7)

0ohm 0603

(R8)

2

G510F51U

(U2)

0ohm 0805

(RA1)

RS32

JP7

FUSE 1.5A_6V

(FI1)

FUSE 0.5A_13.2V

(F3)

1

+TPAN_VDD

+5V_PVD D

+5V_HDD

+5V_ODD

+5V_HDMI

+5V_KB_B L

+1.8V_EMMC

+1.8V_AVDD

+1.8VALW_EC

+LCDVDD _LCD

B B

NCP302045MNTXG

(PUI01)

NCP302045MNTXG

(PUI02)

NCP302045MNTXG

(PUG01)

NCP81253M NTBG

(PUA01)

A A

PJPM01

DRVON

PWM1_2ph_CP U

DRVON

PWM_1a_CPU

DRVON

PWM_1b_CPU

RT8207PGQW

(PUM01)

+VCC_CORE

+VCC_GT

+VCC_S A

+.2.5V_PG

0.6V_DDR_VTT_ ON

5

4

PJPM02

+1.2VP +1.2V_DDR

PJPM03

+0.6VSP

RSHUNT

+0.6V_DDR_ VTT

+VCC_CORE_GT

3

0ohm 0402

(RZ11)

+VCCPLL_OC

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Rail

Power Rail

Power Rail

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

LA-G717P

LA-G717P

LA-G717P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 1 00Wednes day, June 19, 2 019

4 1 00Wednes day, June 19, 2 019

4 1 00Wednes day, June 19, 2 019

1.0

1.0

1.0

5

smd.db-x7.ru

4

3

2

1

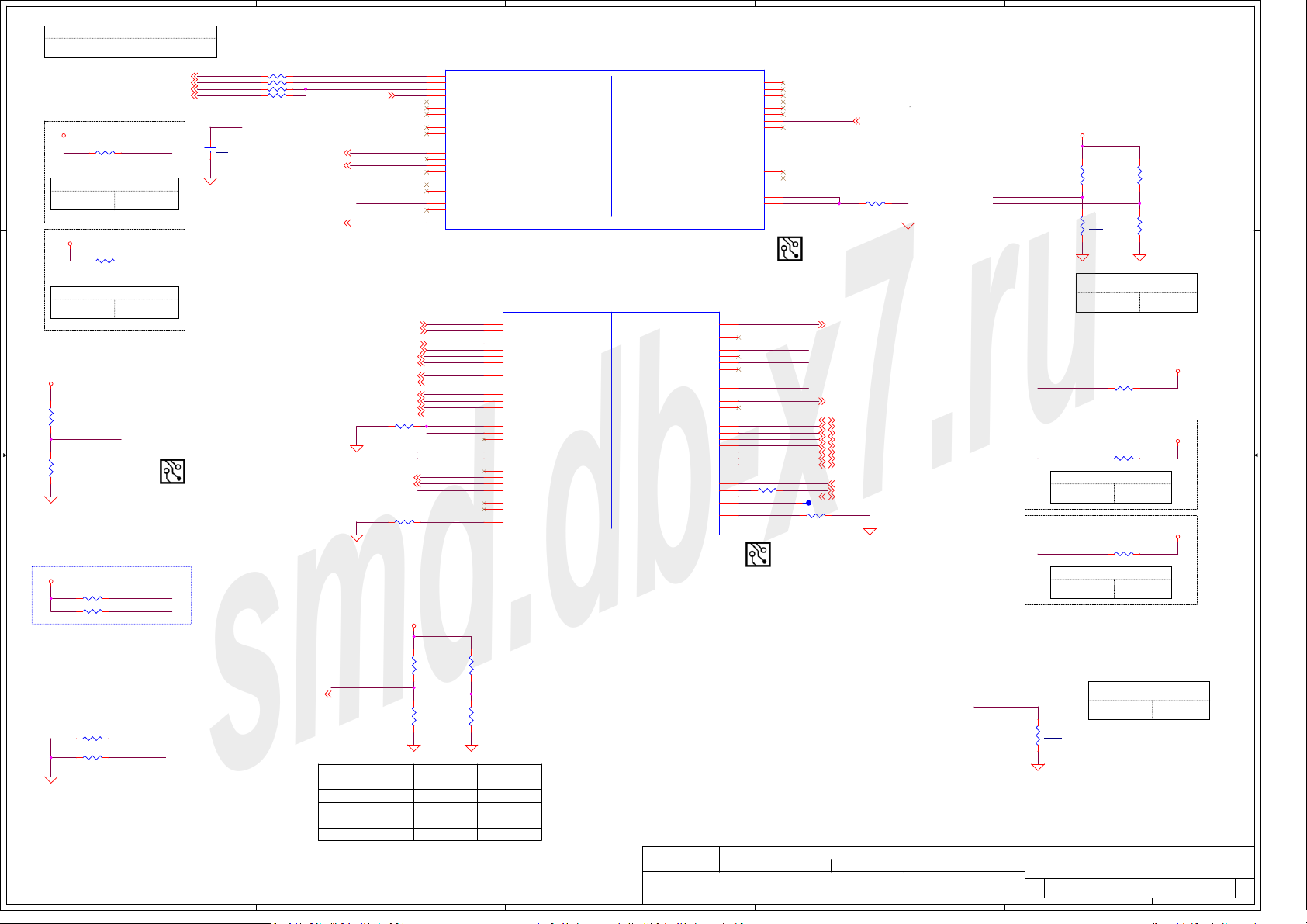

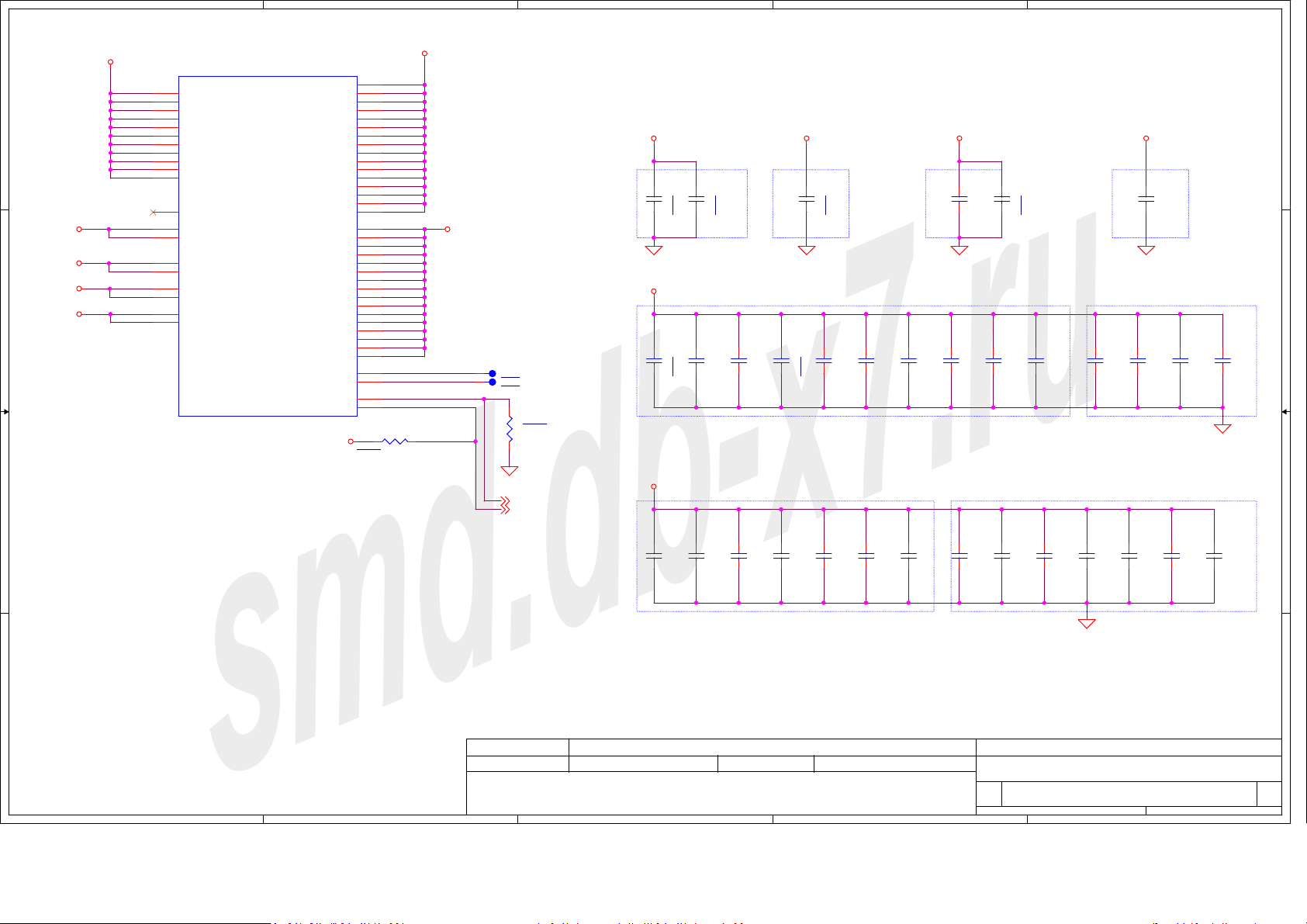

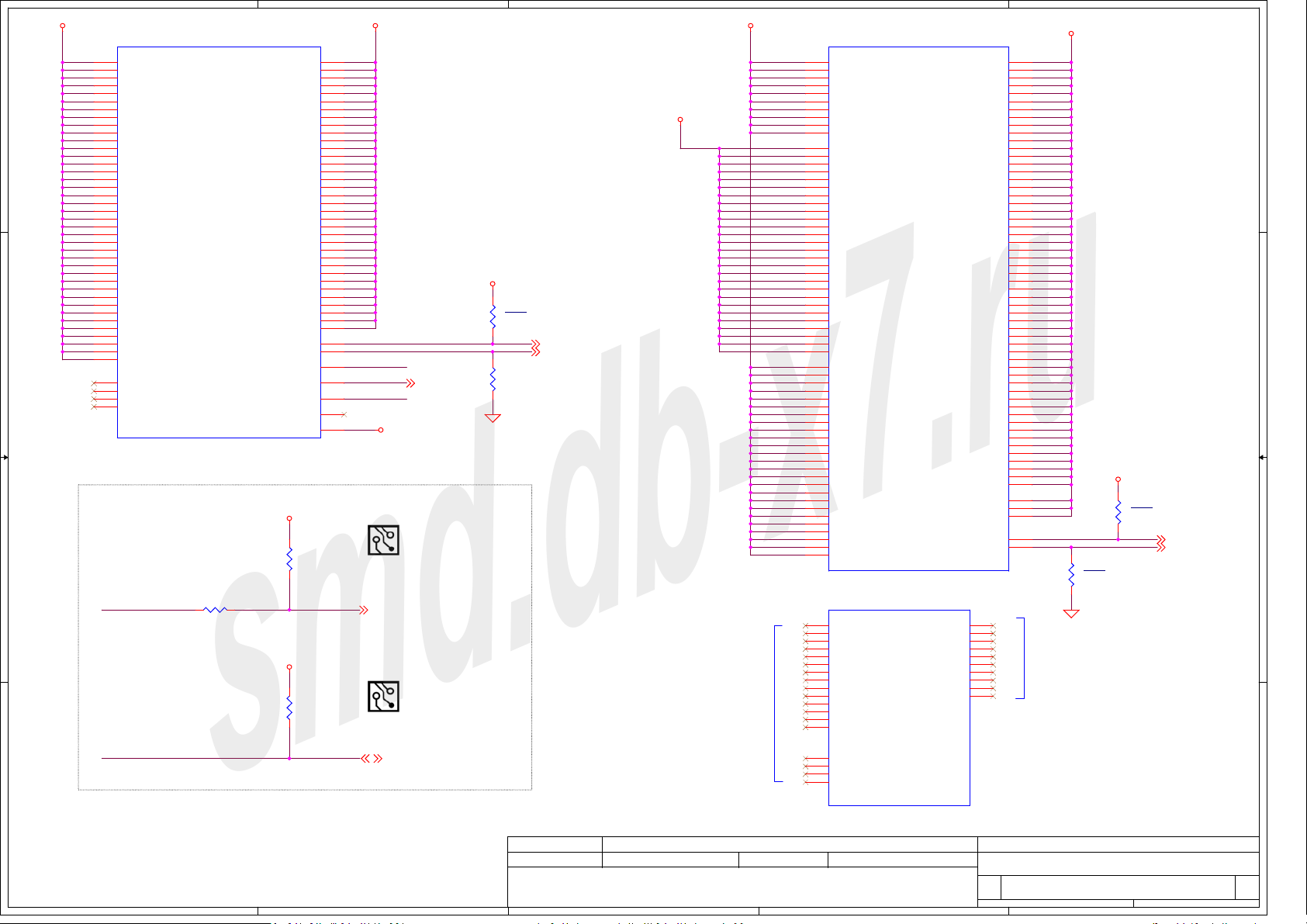

Timing Diagram for S5 to S0 mode

10b

IMVP_VR_ON

D D

ADAPTER

a

BATTERY

C C

HW_ACAV_IN

b

SIO_PWRBTN #

6

PRIM_PWRGD

5

PCH_RSM RST#

5a

RUNPWRO K

ALL_SYS_PWRG D

10a

RESET_OU T#

B B

11

12

SYS_PWROK

BAT-->1

AC-->2

POWER_SW_ IN#

EC 1416

ISL88739

ACOK

+19VB

HW_ACAV_IN

2b

EN_5V

2a

EN_3V

VCCDSW_E N

b

+19VB

AND

POK

PCH_PRIM_ EN

4

VL

+5VALW

+3VLP

+3VALW

c

+3VALW

5

+3VALW

3

PRIM_PWRGD

+1.8V_PRIMRT8061

+19VB

+3VALW_PCHTPS22967

SY8180

+19VB

SY8286

+19VB

NCP81218

+1.05V_PRIMRT6228

+VCC_S A

+VCC_COR E

+VCC_GT

DDR_VTT_ CNTL

+RTC_SOC

c

+3VALW_PCH

+1.05V_PRIM

+1.05V_PRIM +1.05V_MPHYPLL

+3VALW_DSW

+3V_HDA

+3.3V_SPI

+1.8V_PRIM

+1.05V_PRIM

+1.0V_MPHYGT

+1.05V_MPHY

+1.05V_X TAL

VCCST_PWRGD

10b

11

12

13

RESET_OU T#

SYS_PWROK

PCH_P LTRST#

CPU

DDR_VTT_ CTL

PCH

VCCRTC

VCCDSW_3 P3

VCCHDA

VCCSPI

VCCPRIM_3P3

VCCPRIM_1P8

VCCAPLL_1P 05

VCCDUSB _1P05

VCCA_BCLK_ 1P05

VCCA_SRC_ 1P05

VCCPRIM_1P0 5

VCCPRIM_CORE

VCCMPHYGT_1P0

VCCSRAM_1P0

VCCAMPHYPLL_1P0

VCCAPLLEBB

VCCAMPHYPLL_1P0 5

VCCPRIM_MPHY_1P0 5

VCCA_XTAL_1P05

VCCST_PWRGOO D

PCH_PWR OK

SYS_PWROK

PLTRST#

VDDQ

VCCPLL_OC

VCC_OPC_1 P8

VCCEOPIO

CFL-U 43e only

RSMRST#

DSW_PWROK

PWRBTN#

CPU_C1 0_GATE#

VCCIO

VCCGT

VCCGTX

VCCST

VCCPLL

VCCSTG

VCCSA

VCCOPC

SLP_S5 #

SLP_S4 #

SLP_S3 #

VCC

+VCC_COR E

+VCCIO

+VCC_GT

+1.2V_DDR

+VCCST

+VCC_S A

PCH_RSMR ST#_Q

PCH_DPW ROK

SIO_PWRBTN #

SIO_SLP_S 5#

SIO_SLP_S 4#

0.6V_DDR_V TT_ON

SIO_SLP_S 3#

8b

+2.5V_PG

AND

VCCSTG

5b

6

7

8a

+1.05V_PRIM

EM5209

+3VALW

PGOOD

+19VB

RT8207

PGOOD

1.2V_VTT_PWRGD

+5VALW

9a

EM5209

+1.05V_PRIM

9b

EM5209

+1.05V_PRIM

TPS22961 +VCCIO

+3VALW

+VCCST

+2.5V_MEMRT905 9

+1.2V_DDR

+0.6V_DDR_ VTT

8c

+5VS

+3VS

+VCCSTG

VPP

DDR4

VDDQ

VTT

9C

A A

Security C lassification

Security C lassification

5

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Platform Power Sequence

Platform Power Sequence

Platform Power Sequence

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

LA-G717P

LA-G717P

LA-G717P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 1 00Wednes day, June 19, 2 019

5 1 00Wednes day, June 19, 2 019

5 1 00Wednes day, June 19, 2 019

1.0

1.0

1.0

5

smd.db-x7.ru

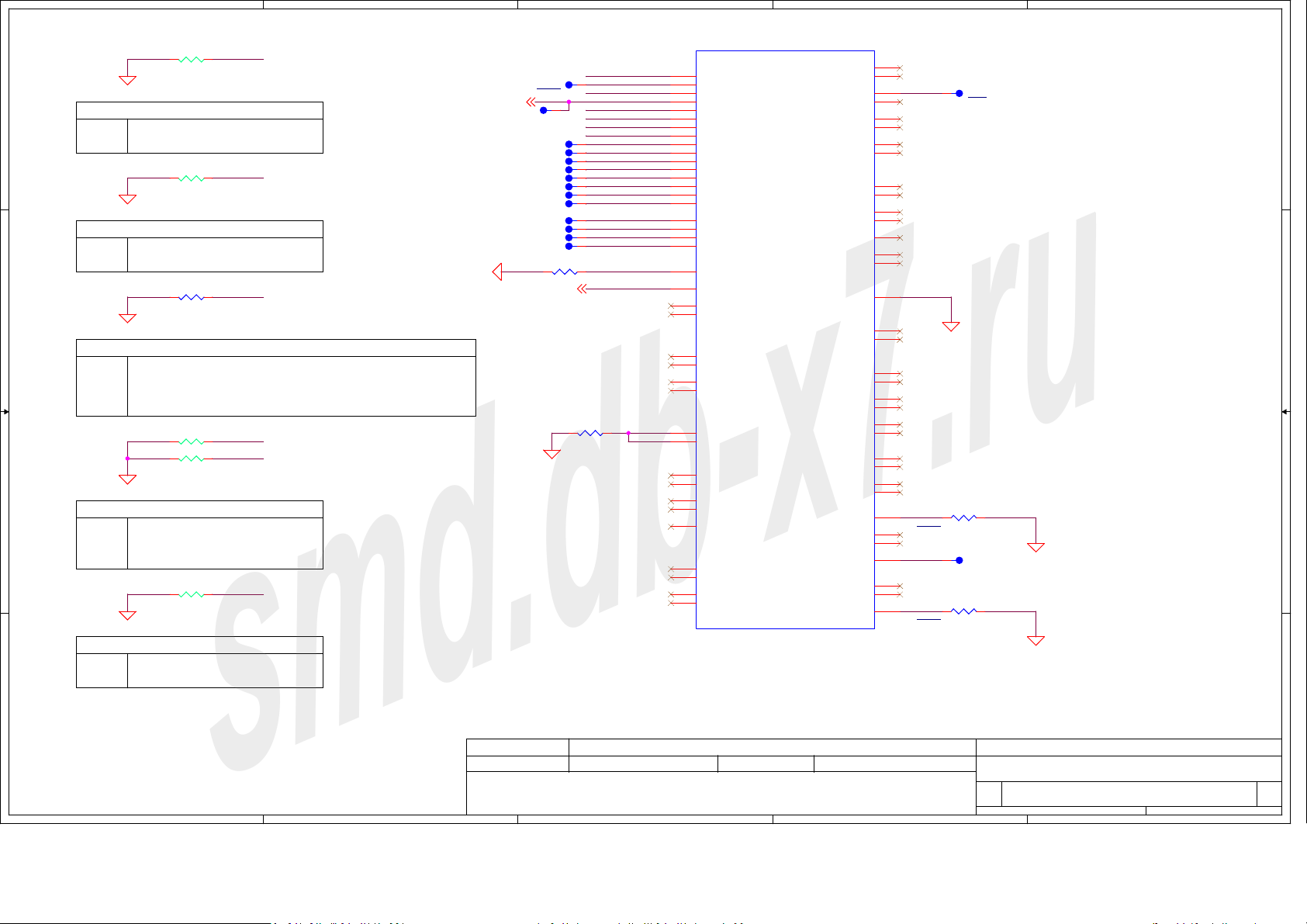

+VCCSTG

H_PROCHOT#

1 2

RC1 1K_040 2_5%

+VCCST

D D

RC2 1K_040 2_5%

RC3 49.9_04 02_1%

COMPENSATION FOR EDP_COMP

+VCCIO

RC4 24.9_0402_1%

CAD note:

Trace width=5 mils, Spacing=25mils

Max length=600mils

+3VS

RC5 10K_0402_5 %

C C

RC6 10K_0402_5 %

RC203 10K_0402_5 %

1 2

1 2

@

1 2

CML@

1 2

1 2

@

1 2

H_THERMT RIP#

CATERR#

RC4

100_0402_1%

SD0341000 80

EDP_COMP

TOUCH_PAD_INT #

TOUCH_PANEL_ PD#

TOUCH_SCR EEN_INT#

CNL@

TOUCH_SCR EEN_INT# < 38>

4

UC1A

CPU_DP1_N0<40>

CPU_DP1_P0<40>

CPU_DP1_N1<40>

CPU_DP1_P1<40>

CPU_DP1_N2<40>

CPU_DP1_P2<40>

CPU_DP1_N3<40>

CPU_DP1_P3<40>

CPU_DP2_N0<40>

CPU_DP2_P0<40>

CPU_DP2_N1<40>

CPU_DP2_P1<40>

EDP_COMP

CPU_DP1_CTRL_CLK<40>

CPU_DP1_C TRL_DATA<40>

TOUCH_SCREEN_RST<38>

CPU_DP1_C TRL_CLK

CPU_DP1_C TRL_DATA

CPU_DP2_C TRL_DATA

AL5

DDI1_TXN_0

AL6

DDI1_TXP_0

AJ5

DDI1_TXN_1

AJ6

DDI1_TXP_1

AF6

DDI1_TXN_2

AF5

DDI1_TXP_2

AE5

DDI1_TXN_3

AE6

DDI1_TXP_3

AC4

DDI2_TXN_0

AC3

DDI2_TXP_0

AC1

DDI2_TXN_1

AC2

DDI2_TXP_1

AE4

DDI2_TXN_2

AE3

DDI2_TXP_2

AE1

DDI2_TXN_3

AE2

DDI2_TXP_3

AM6

DISP_RCOMP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR26

GPP_H16/DDPF_CTRLCLK

CP26

GPP_H17/DDPF_CTRLDATA

WHL-U42 _BGA1528

DDI

DISPLAY SIDEBANDS

3

EDP

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

1 of 20

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

2

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

CPU_DP2_H PD

BKLT_IN_EC

EDP_TXN0 <38>

EDP_TXP0 <38>

EDP_TXN1 <38>

EDP_TXP1 <38>

EDP_AUXN <38>

EDP_AUXP <3 8>

TP1

CPU_DP2_AUXN <4 0>

CPU_DP2_AUXP <40>

CPU_DP1_H PD <40>

CPU_DP2_H PD <40>

EDP_HPD <38>

BKLT_IN_EC <58>

EDP_VDD_EN <38>

EDP_BKLT_CTRL <3 8>

CPU_DP1_C TRL_CLK

CPU_DP1_C TRL_DATA

CPU_DP2_C TRL_DATA

RC7 2.2K_0402 _5%

RC8 2.2K_0402 _5%

RC9 2.2K_0402 _5%

1

+3VS

12

12

12

CPU_DP2_H PD

BKLT_IN_EC

UC1D

CB34

CC35

BP27

BW25

AA4

AR1

Y4

BJ1

U1

U2

U3

U4

CE9

CN3

L5

N5

CATERR#

PECI

PROCHOT#

THRMTRIP#

BPM#_0

BPM#_1

BPM#_2

BPM#_3

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

RSVD70

RSVD71

WHL-U42 _BGA1528

CPU MISC

4 of 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

PROC_PREQ#

PROC_PRDY#

49.9_0402_1%

TP2

TP3

TP4

TP5

TP6

12

TOUCH_PANEL_ PD#

RC16

49.9_0402_1%

CATERR#

H_PROCHOT# _R

H_THERMT RIP#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

CAM_EN#

TOUCH_SCR EEN_INT#

TOUCH_PAD_INT #

CPU_POPIRCOMP

PCH_POPIRCOMP

H_PROCHOT#<58,82,84,88>

B B

TP_WAKE_KBC#<58,62>

TOUCH_SCREEN_PD#<38>

1 2

RC160 499 _0402_1%

DZ1

RB751S40T 1G_SOD523-2

1 2

TOUCH_SCR EEN_PD#

PECI_EC<58>

1 2

@

RC14 0_0201_5 %

12

RC15

T6

U6

Y5

T5

AB6

W6

U5

W5

P5

Y6

P6

W2

W1

CPU_XDP_TCK 0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST #

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK 0

XDP_PREQ#

XDP_PRDY#

CPU_XDP_TCK0 <79>

SOC_XDP_TDI <79>

SOC_XDP_TDO <79>

SOC_XDP_TMS <79>

SOC_XDP_TRST# <79>

PCH_JTAG_TCK1 <79>

TP7

TP8

RC12 100K_0 402_5%

RC13 100K_0 402_5%

12

12

L5,N5 are required for CFL U43e only.

COMPENSATION FOR OPIRCOMP

CAD Note:

Min trace width=10 mi ls, Max trace length=500 mils

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

CPU(1/12))DDI,MSIC,XDP,EDP

CPU(1/12))DDI,MSIC,XDP,EDP

CPU(1/12))DDI,MSIC,XDP,EDP

LA-G717P

LA-G717P

LA-G717P

1

6 100Wednesday, June 19, 2 019

6 100Wednesday, June 19, 2 019

6 100Wednesday, June 19, 2 019

1.0

1.0

1.0

5

smd.db-x7.ru

4

3

2

1

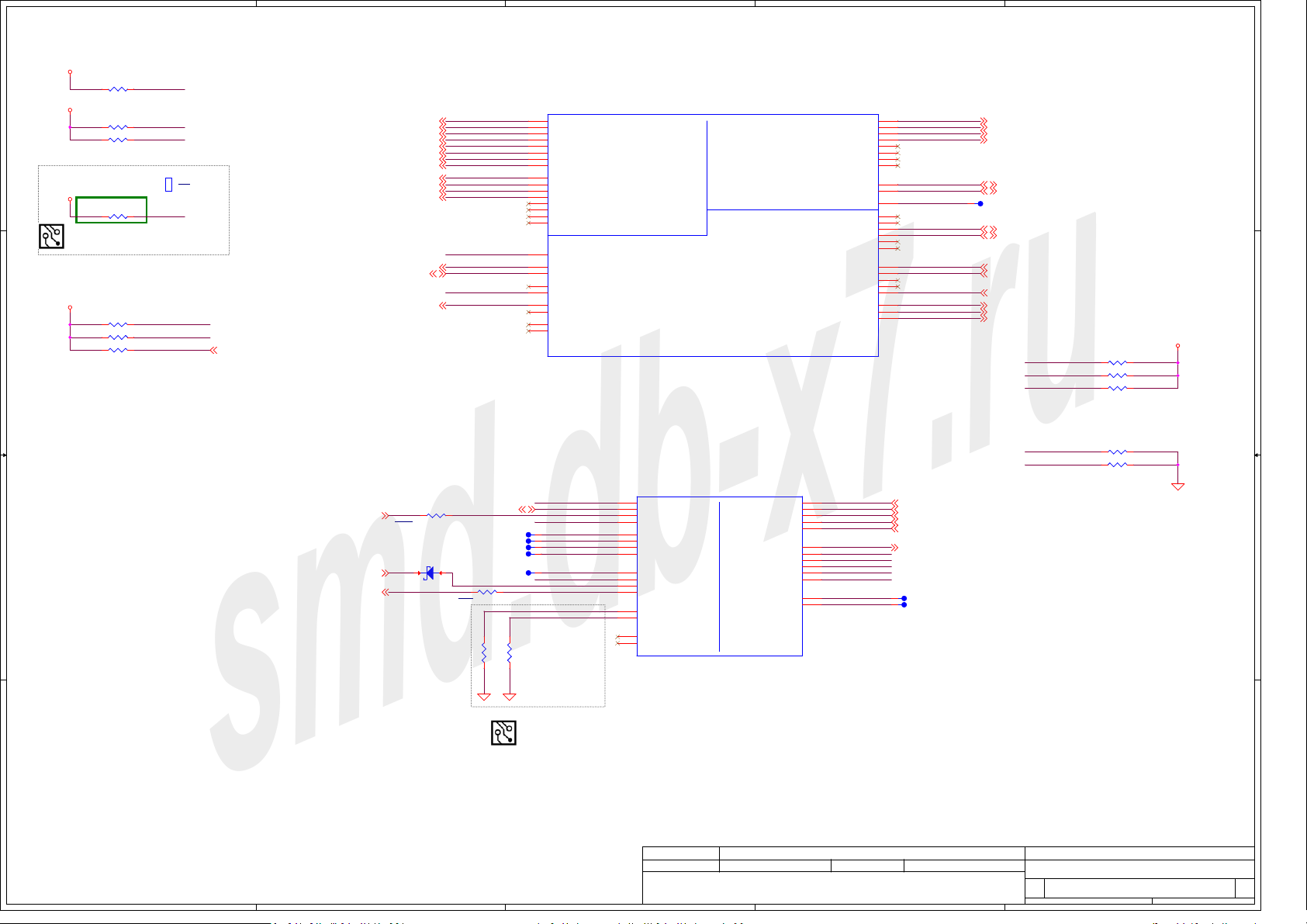

DDR4 Interleaved Memory

D D

C C

B B

DDR_A_D[0..15]<23>

DDR_A_D[16..31]<23>

DDR_A_D[32..47]<23>

DDR_A_D[48..63]<23>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

Interleave / Non-Interleaved

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

DDR0_DQ_5/DDR0_DQ_5

B28

DDR0_DQ_6/DDR0_DQ_6

A28

DDR0_DQ_7/DDR0_DQ_7

B30

DDR0_DQ_8/DDR0_DQ_8

D30

DDR0_DQ_9/DDR0_DQ_9

B33

DDR0_DQ_10/DDR0_DQ_10

D32

DDR0_DQ_11/DDR0_DQ_11

A30

DDR0_DQ_12/DDR0_DQ_12

C30

DDR0_DQ_13/DDR0_DQ_13

B32

DDR0_DQ_14/DDR0_DQ_14

C32

DDR0_DQ_15/DDR0_DQ_15

H37

DDR0_DQ_16/DDR0_DQ_32

H34

DDR0_DQ_17/DDR0_DQ_33

K34

DDR0_DQ_18/DDR0_DQ_34

K35

DDR0_DQ_19/DDR0_DQ_35

H36

DDR0_DQ_20/DDR0_DQ_36

H35

DDR0_DQ_21/DDR0_DQ_37

K36

DDR0_DQ_22/DDR0_DQ_38

K37

DDR0_DQ_23/DDR0_DQ_39

N36

DDR0_DQ_24/DDR0_DQ_40

N34

DDR0_DQ_25/DDR0_DQ_41

R37

DDR0_DQ_26/DDR0_DQ_42

R34

DDR0_DQ_27/DDR0_DQ_43

N37

DDR0_DQ_28/DDR0_DQ_44

N35

DDR0_DQ_29/DDR0_DQ_45

R36

DDR0_DQ_30/DDR0_DQ_46

R35

DDR0_DQ_31/DDR0_DQ_47

AN35

DDR0_DQ_32/DDR1_DQ_0

AN34

DDR0_DQ_33/DDR1_DQ_1

AR35

DDR0_DQ_34/DDR1_DQ_2

AR34

DDR0_DQ_35/DDR1_DQ_3

AN37

DDR0_DQ_36/DDR1_DQ_4

AN36

DDR0_DQ_37/DDR1_DQ_5

AR36

DDR0_DQ_38/DDR1_DQ_6

AR37

DDR0_DQ_39/DDR1_DQ_7

AU35

DDR0_DQ_40/DDR1_DQ_8

AU34

DDR0_DQ_41/DDR1_DQ_9

AW35

DDR0_DQ_42/DDR1_DQ_10

AW34

DDR0_DQ_43/DDR1_DQ_11

AU37

DDR0_DQ_44/DDR1_DQ_12

AU36

DDR0_DQ_45/DDR1_DQ_13

AW36

DDR0_DQ_46/DDR1_DQ_14

AW37

DDR0_DQ_47/DDR1_DQ_15

BA35

DDR0_DQ_48/DDR1_DQ_32

BA34

DDR0_DQ_49/DDR1_DQ_33

BC35

DDR0_DQ_50/DDR1_DQ_34

BC34

DDR0_DQ_51/DDR1_DQ_35

BA37

DDR0_DQ_52/DDR1_DQ_36

BA36

DDR0_DQ_53/DDR1_DQ_37

BC36

DDR0_DQ_54/DDR1_DQ_38

BC37

DDR0_DQ_55/DDR1_DQ_39

BE35

DDR0_DQ_56/DDR1_DQ_40

BE34

DDR0_DQ_57/DDR1_DQ_41

BG35

DDR0_DQ_58/DDR1_DQ_42

BG34

DDR0_DQ_59/DDR1_DQ_43

BE37

DDR0_DQ_60/DDR1_DQ_44

BE36

DDR0_DQ_61/DDR1_DQ_45

BG36

DDR0_DQ_62/DDR1_DQ_46

BG37

DDR0_DQ_63/DDR1_DQ_47

WHL-U42_BGA1528

2 of 20

Buf f er wi t h Open Drai n Out put F or VTT po wer c ontrol

0.1U_0402_16V7K

UC2

DDR_VTT_CNTL

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

LPDDR3 / DDR4

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/NC

DDR0_CKE_3/NC

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

Interleave / Non-Interleaved

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

CC1

12

Y

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

DDR_VTT_CTL

+1.2V_DDR +3VS

5

4

LPDDR3 / DDR4

12

1

2

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

RC19

200K_0402_1%

0.6V_DDR_VTT_ON <86>

@

CC2

100P_0402_50V8J

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_WE#

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_BG1

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PAR

+V_DDR_REFA_R

+V_DDR_REFB_R

DDR_VTT_CNTL

UC1C

DDR_A_CLK#0 <23>

DDR_A_CLK0 <23>

DDR_A_CLK#1 <23>

DDR_A_CLK1 <23>

DDR_A_CKE0 <23>

DDR_A_CKE1 <23>

TP9

TP11

DDR_A_CS#0 <23>

DDR_A_CS#1 <23>

DDR_A_ODT0 <23>

DDR_A_ODT1 <23>

DDR_A_MA0 <23>

DDR_A_MA1 <23>

DDR_A_MA2 <23>

DDR_A_MA3 <23>

DDR_A_MA4 <23>

DDR_A_MA5 <23>

DDR_A_MA6 <23>

DDR_A_MA7 <23>

DDR_A_MA8 <23>

DDR_A_MA9 <23>

DDR_A_MA10 <23>

DDR_A_MA11 <23>

DDR_A_MA12 <23>

DDR_A_MA13 <23>

DDR_A_WE# <23>

DDR_A_RAS# <23>

DDR_A_BA1 <23>

DDR_A_BG0 <23>

DDR_A_BG1 <23>

DDR_A_DQS#0 <23>

DDR_A_DQS0 <23>

DDR_A_DQS#1 <23>

DDR_A_DQS1 <23>

DDR_A_DQS#2 <23>

DDR_A_DQS2 <23>

DDR_A_DQS#3 <23>

DDR_A_DQS3 <23>

DDR_A_DQS#4 <23>

DDR_A_DQS4 <23>

DDR_A_DQS#5 <23>

DDR_A_DQS5 <23>

DDR_A_DQS#6 <23>

DDR_A_DQS6 <23>

DDR_A_DQS#7 <23>

DDR_A_DQS7 <23>

DDR_A_ALERT# <23>

DDR_A_PAR <23> DDR_DRAMRST# <23>

CAD Note:

Min trace width=20 mils, spacing of adjacent signal=20 mils

DDR_B_D[0..15]<24>

DDR_B_D[16..31]<24>

DDR_B_D[32..47]<24>

DDR_B_D[48..63]<24>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

lnterleave /

Non-lnterle ave d

J22

DDR1_DQ_0/DDR0_DQ_16

H25

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

DDR1_DQ_4/DDR0_DQ_20

J25

DDR1_DQ_5/DDR0_DQ_21

G25

DDR1_DQ_6/DDR0_DQ_22

F22

DDR1_DQ_7/DDR0_DQ_23

D22

DDR1_DQ_8/DDR0_DQ_24

C22

DDR1_DQ_9/DDR0_DQ_25

C24

DDR1_DQ_10/DDR0_DQ_26

D24

DDR1_DQ_11/DDR0_DQ_27

A22

DDR1_DQ_12/DDR0_DQ_28

B22

DDR1_DQ_13/DDR0_DQ_29

A24

DDR1_DQ_14/DDR0_DQ_30

B24

DDR1_DQ_15/DDR0_DQ_31

G31

DDR1_DQ_16/DDR0_DQ_48

G32

DDR1_DQ_17/DDR0_DQ_49

H29

DDR1_DQ_18/DDR0_DQ_50

H28

DDR1_DQ_19/DDR0_DQ_51

G28

DDR1_DQ_20/DDR0_DQ_52

G29

DDR1_DQ_21/DDR0_DQ_53

H31

DDR1_DQ_22/DDR0_DQ_54

H32

DDR1_DQ_23/DDR0_DQ_55

L31

DDR1_DQ_24/DDR0_DQ_56

L32

DDR1_DQ_25/DDR0_DQ_57

N29

DDR1_DQ_26/DDR0_DQ_58

N28

DDR1_DQ_27/DDR0_DQ_59

L28

DDR1_DQ_28/DDR0_DQ_60

L29

DDR1_DQ_29/DDR0_DQ_61

N31

DDR1_DQ_30/DDR0_DQ_62

N32

DDR1_DQ_31/DDR0_DQ_63

AJ29

DDR1_DQ_32/DDR1_DQ_16

AJ30

DDR1_DQ_33/DDR1_DQ_17

AM32

DDR1_DQ_34/DDR1_DQ_18

AM31

DDR1_DQ_35/DDR1_DQ_19

AM30

DDR1_DQ_36/DDR1_DQ_20

AM29

DDR1_DQ_37/DDR1_DQ_21

AJ31

DDR1_DQ_38/DDR1_DQ_22

AJ32

DDR1_DQ_39/DDR1_DQ_23

AR31

DDR1_DQ_40/DDR1_DQ_24

AR32

DDR1_DQ_41/DDR1_DQ_25

AV30

DDR1_DQ_42/DDR1_DQ_26

AV29

DDR1_DQ_43/DDR1_DQ_27

AR30

DDR1_DQ_44/DDR1_DQ_28

AR29

DDR1_DQ_45/DDR1_DQ_29

AV32

DDR1_DQ_46/DDR1_DQ_30

AV31

DDR1_DQ_47/DDR1_DQ_31

BA32

DDR1_DQ_48/DDR1_DQ_48

BA31

DDR1_DQ_49/DDR1_DQ_49

BD31

DDR1_DQ_50/DDR1_DQ_50

BD32

DDR1_DQ_51/DDR1_DQ_51

BA30

DDR1_DQ_52/DDR1_DQ_52

BA29

DDR1_DQ_53/DDR1_DQ_53

BD29

DDR1_DQ_54/DDR1_DQ_54

BD30

DDR1_DQ_55/DDR1_DQ_55

BG31

DDR1_DQ_56/DDR1_DQ_56

BG32

DDR1_DQ_57/DDR1_DQ_57

BK32

DDR1_DQ_58/DDR1_DQ_58

BK31

DDR1_DQ_59/DDR1_DQ_59

BG29

DDR1_DQ_60/DDR1_DQ_60

BG30

DDR1_DQ_61/DDR1_DQ_61

BK30

DDR1_DQ_62/DDR1_DQ_62

BK29

DDR1_DQ_63/DDR1_DQ_63

WHL-U42_BGA1528

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP_7

3 of 20

DDR4 COMPENSATION SIGNALS

SM_RCOMP0

RC17 121_ 0402_1%CML@

SM_RCOMP1

RC18 80.6 _0402_1%CML@

SM_RCOMP2

RC20 100_ 0402_1%

CAD Note:

Trace width=15 mils, Spacing=25 mils(Within Group 20mils)

Max trace length= 500 mils

LPDDR3 / DDR4

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/NC

DDR1_CKE_3/NC

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

lnterleave / Non-lnterleaved

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

1 2

1 2

1 2

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

DDR_B_CLK#0

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_WE#

DDR_B_CAS#

DDR_B_RAS#

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_BG1

DDR_B_ACT#DDR_A_ACT#

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PAR

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RC17

100_0402_1%

SD034100080

RC18

100_0402_1%

SD034100080

DDR_B_CLK#0 <24>

DDR_B_CLK0 <24>

DDR_B_CLK#1 <24>

DDR_B_CLK1 <24>

DDR_B_CKE0 <24>

DDR_B_CKE1 <24>

DDR_B_CS#0 <24>

DDR_B_CS#1 <24>

DDR_B_ODT0 <24>

DDR_B_ODT1 <24>

DDR_B_MA0 <24>

DDR_B_MA1 <24>

DDR_B_MA2 <24>

DDR_B_MA3 <24>

DDR_B_MA4 <24>

DDR_B_MA5 <24>

DDR_B_MA6 <24>

DDR_B_MA7 <24>

DDR_B_MA8 <24>

DDR_B_MA9 <24>

DDR_B_MA10 <24>

DDR_B_MA11 <24>

DDR_B_MA12 <24>

DDR_B_MA13 <24>

DDR_B_WE# <24>

DDR_B_CAS# <24>

DDR_B_RAS# <24>DDR_A_CAS# <23>

DDR_B_BA0 <24>

DDR_B_BA1 <24>DDR_A_BA0 <23>

DDR_B_BG0 <24>

DDR_B_BG1 <24>

DDR_B_ACT# <24>DDR_A_ACT# <23>

DDR_B_DQS#0 <24>

DDR_B_DQS0 <24>

DDR_B_DQS#1 <24>

DDR_B_DQS1 <24>

DDR_B_DQS#2 <24>

DDR_B_DQS2 <24>

DDR_B_DQS#3 <24>

DDR_B_DQS3 <24>

DDR_B_DQS#4 <24>

DDR_B_DQS4 <24>

DDR_B_DQS#5 <24>

DDR_B_DQS5 <24>

DDR_B_DQS#6 <24>

DDR_B_DQS6 <24>

DDR_B_DQS#7 <24>

DDR_B_DQS7 <24>

DDR_B_ALERT# <24>

DDR_B_PAR <24>

CNL@

CNL@

TP10

TP12

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(2/12)DDR4

CPU(2/12)DDR4

Size

Size

Size

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

CPU(2/12)DDR4

Document Number Re v

Document Number Re v

Document Number Re v

LA-G717P

LA-G717P

LA-G717P

1

7 100Wednesday, June 19, 2019

7 100Wednesday, June 19, 2019

7 100Wednesday, June 19, 2019

1.0

1.0

1.0

5

smd.db-x7.ru

4

3

2

1

RC21~RC25 place colse to Device

CPU_SPI_0_CLK

CPU_SPI_0_D1

CPU_SPI_0_D0

CPU_SPI_0_D2

CPU_SPI_0_D3

CPU_SPI_0_CS#0

CPU_SPI_0_CS#1

FFS_INT1

UC3

1

CS#

3

WP#

7

HOLD#

4

GND

W25Q64JVSSIQ_SO8

64Mb Flash ROM

UC3 place colse to UX1

UC11

1

CS#

3

WP#

7

HOLD#

4

GND

W25Q128JVSIQ_SO8

RC24

TPM@

10_0402_1%

SD034100A80

RC25

TPM@

10_0402_1%

SD034100A80

FFS_INT1

CPU_SPI_0_CS#0

CPU_SPI_0_D0

CPU_SPI_0_D2

CPU_SPI_0_D3

CPU_SPI_0_CLK

RC39 49.9_0402_1%FTPM@

RC41 49.9_0402_1%FTPM@

CPU_SPI_0_CS#1

RC177 49 .9_0402_1%FTPM@

RC181 49 .9_0402_1%FTPM@

CPU_SPI_CLK

CPU_SPI_D1

CPU_SPI_D0

CPU_SPI_D2

CPU_SPI_D3

1 2

1 2

1 2

1 2

CPU_SPI_CLK<65>

CPU_SPI_D1<65>

D D

C C

RC21

10_0402_1%

SD034100A80

RC22

10_0402_1%

SD034100A80

RC23

10_0402_1%

SD034100A80

+3VS

+3VALW_PCH +3.3V_SPI

+3.3V_SPI

Reserve For EC Auto Load Code

+3.3V_SPI

B B

A A

CPU_SPI_D0<65>

TPM@

TPM@

TPM@

1 2

RC27 10K_0402_5%

@

1 2

RC30 0_0603_5%

1 2

@

RC31 4.7K_0402_5%

1 2

RC35 100K_0402_5%

1 2

RC36 100K_0402_5%

1 2

RC37 100K_0402_5%

Follow 566439

1 2

RC187 100K_0402_5%

CPU_SPI_D3

+3.3V_SPI

1 2

RC207 4.7K_0402_5%

1 2

RC21 0_0402_5%

@

RC22 0_0402_5%

@

1 2

1 2

RC23 0_0402_5%

@

RC24 0_0402_5%

@

1 2

RC25 0_0402_5%

@

1 2

CPU_SPI_0_CS#2<65 >

TPM_SPI_IRQ#<65>

FFS_INT1<66>

RC21

FTPM@

S RES 1/16W 5.6 +-5% 0402

SD028560B80

RC22

FTPM@

S RES 1/16W 5.6 +-5% 0402

SD028560B80

RC23

FTPM@

S RES 1/16W 5.6 +-5% 0402

SD028560B80

RC24

FTPM@

S RES 1/16W 5.6 +-5% 0402

SD028560B80

RC25

FTPM@

S RES 1/16W 5.6 +-5% 0402

SD028560B80

CPU_SPI_0_CS#0

SPI_D2_ROMCPU_SPI_D2

SPI_D3_ROM

CPU_SPI_0_CS#1

SPI_D3_ROM2

UC1E

CH37

SPI0_CLK

CF37

SPI0_MISO

CF36

SPI0_MOSI

CF34

SPI0_IO2

CG34

SPI0_IO3

CG36

SPI0_CS0#

CG35

SPI0_CS1#

CH34

SPI0_CS2#

CF20

GPP_D1/SPI1_CLK/BK1/SBK1

CG22

GPP_D2/SPI1_MISO_IO1/BK2/SBK2

CF22

GPP_D3/SPI1_MOSI_IO0/BK3/SBK3

CG23

GPP_D21/SPI1_IO2

CH23

GPP_D22/SPI1_IO3

CG20

GPP_D0/SPI1_CS0#/BK0/SBK0

CH7

CL_CLK

CH8

CL_DATA

CH9

CL_RST#

BV29

GPP_A0/RCIN#/TIME_SYNC1

BV28

GPP_A6/SERIRQ

WHL-U42_BGA1528

XDP_HOOK3<79>

+3.3V_SPI

8

VCC

6

SCLK

5

SI/SIO0

2

SO/SIO1

+3.3V_SPI

8

VCC

6

SCLK

5

SI/SIO0

2

SO/SIO1

SPI - FLASH

SPI - TOUCH

C LINK

5 of 20

RC32 1K_0402_1%CMC@

1 2

RC40 place to within 1100 mil of SPIO_MOSI/SPI0_IO2 pin for XDP

1 2

CC4 0.1U_0402_10V7K

SPI_CLK_ROM

SPI_D0_ROM

SPI_D1_ROM

CC74 0.1U_0402_10V7K

SPI_CLK_ROM2CPU_SPI_D2 SPI_D2_ROM2

SPI_D0_ROM2

SPI_D1_ROM2

RC40 49.9_0402_1%FTPM@

RC42 49.9_0402_1%FTPM@

RC43 49.9_0402_1%FTPM@

1 2

RC178 49 .9_0402_1%FTPM@

RC180 49 .9_0402_1%FTPM@

RC179 49 .9_0402_1%FTPM@

1 2

1 2

1 2

1 2

1 2

1 2

CPU_SPI_D0

CPU_SPI_CLK

CPU_SPI_D0

CPU_SPI_D1

CPU_SPI_CLK

CPU_SPI_D0CPU_SPI_D3

CPU_SPI_D1

SMBUS , SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

LPC , ESPI

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

RC39

TPM@

33_0402_1%

SD034330A80

RC40

TPM@

33_0402_1%

SD034330A80

RC41

TPM@

33_0402_1%

SD034330A80

RC42

TPM@

33_0402_1%

SD034330A80

RC43

TPM@

33_0402_1%

SD034330A80

CK14

CH15

CJ15

CH14

CF15

CG15

CN15

CM15

CC34

CA29

BY29

BY27

BV27

CA28

CA27

BV32

BV30

BY30

MEM_SMBCLK

MEM_SMBDATA

GPP_C2

SML0_SMBCLK

SML0_SMBDATA

GPP_C5

SML1_SMBCLK

SML1_SMBDATA

GPP_B23

ESPI_IO0

ESPI_IO1

ESPI_IO2

ESPI_IO3

ESPI_CLK

RC177

TPM@

33_0402_1%

SD034330A80

RC178

TPM@

33_0402_1%

SD034330A80

RC179

TPM@

33_0402_1%

SD034330A80

RC180

TPM@

33_0402_1%

SD034330A80

RC181

TPM@

33_0402_1%

SD034330A80

SML1_SMBCLK <58,65 >

SML1_SMBDATA <58,65>

ESPI_CS# <58>

ESPI_RST# <58>

EMI@

1 2

RC26 33_0402_5%

1

CC3

10P_0402_50V8J

2

ESPI_RST#

RC205 100K_0402_5%

SPI_CLK_ROM

place colse to UC3

MEM_SMBCLK

MEM_SMBDATA

SML1 -> EC, THM

ESPI_CLK_R <58>

@RF@

12

33_0402_5%

RC45

@EMI@

1 2

33P_0402_50V8J

CC5

@EMI@

1 2

+3VS

5

3 4

ESPI_IO0

ESPI_IO1

ESPI_IO2

ESPI_IO3

SML0_SMBCLK

SML0_SMBDATA

QC1A

2

L2N7002DW1T1G_ SC88-6

1

6

QC1B

L2N7002DW1T1G_ SC88-6

1 2

1 2

RC192 15 _0402_5%

RC193 15 _0402_5%

1 2

1 2

RC194 15 _0402_5%

RC195 15 _0402_5%

PCH_SMBDATA

PCH_SMBCLK

SML1_SMBCLK

SML1_SMBDATA

MEM_SMBCLK

MEM_SMBDATA

RC196 1K_0402_5%

RC197 1K_0402_5%

RC198 1K_0402_5%

RC199 1K_0402_5%

RC33 1K_0402_5%

RC34 1K_0402_5%

Weak Int. PD.

GPP_C2

TLS CONFIDENTIALITY

LOW(DEFAULT)

HIGH

Weak Int. PD.

GPP_C5

EC interface

LOW(DEFAULT)

HIGH

GPP_B23

Intel DCI-OOB

LOW(DEFAULT)

HIGH

SMB -> DDR4, FFS, VGA

PCH_SMBCLK <23,24,40,66>

PCH_SMBDATA <23,24,40,66>

12

RC282.2 K_0402_5%

12

RC292.2 K_0402_5%

+3VALW_PCH

12

12

12

12

12

12

+3VALW_PCH

12

RC38 4.7K_0402_5%

DISABLE

ENABLE

+3VALW_PCH

12

RC44 4.7K_0402_5%

LPC

eSPI

+3VALW_PCH

CMC@

12

RC46 4.7K_0402_5%

DISABLE

ENABLE

+3VS

ESPI_IO0_R <58>

ESPI_IO1_R <58>

ESPI_IO2_R <58>

ESPI_IO3_R <58>

128Mb Flash ROM

UC11 place colse to UX1

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENT E XCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT E XCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT E XCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

CPU(3/12)SPI,ESPI,SMB,LPC

CPU(3/12)SPI,ESPI,SMB,LPC

CPU(3/12)SPI,ESPI,SMB,LPC

LA-G717P

LA-G717P

LA-G717P

1

8 1 00Wednesday, June 19, 2019

8 1 00Wednesday, June 19, 2019

8 1 00Wednesday, June 19, 2019

1.0

1.0

1.0

5

smd.db-x7.ru

ME_FWP

LOW = ENABLE -- >ME lock, can't update ME

HIGH = DISABLE -->ME un-lock, can upd ate ME

1 2

HDA_SYNC_R<56>

HDA_BIT_CLK_R<56>

HDA_SDOUT_R<56>

ME_FWP<58>

D D

+3V_HDA

Flash Descriptor Security override

LOW(DEFAULT)

HIGH

+3VALW_PCH

Weak Int. PD.

HDA_SDOUT

1 2

@

RC51 4.7K_ 0402_5%

ENABLE

DISA BLE

Weak Int. PD.

1 2

RC57 4.7K_ 0402_5%

SPKR

@

RC47 33_0402_5%

1 2

RC48 33_0402_5%

1 2

RC49 33_0402_5%

1 2

RC50 1K_0402_5%

HDA_BIT_CLK

1

@RF@

CC6

2.2P_0201_2 5V8C

2

CNV_RF_RESET#<52>

CLKREQ_CNV#<5 2>

SPKR<56>

Top Swap Override

TPM_ID

1 2

@

1 2

@

DISABLE

ENABLE

BLUETOOTH_ EN

WIFI_RF_EN

COMPENSATION FOR CNV_WT_RCOMP

CAD Note:

Min trace width=10 mils, Spacing=15 mils

Max trace length=500 mils

LOW(DEFAULT)

HIGH

C C

+3VALW_PCH

12

FTPM@

RC59

10K_0402_5 %

12

TPM@

RC63

10K_0402_5 %

B B

+3VALW

RC174 10K_0402_ 5%

RC175 10K_0402_ 5%

4

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0<56>

CNV_RF_RESET #

CLKREQ_CNV#

TPM_ID

SPKR

CNV_CRX_DTX_N0<52>

CNV_CRX_DTX_P0<52>

CNV_CRX_DTX_N1<52>

CNV_CRX_DTX_P1<52>

CNV_CTX_DRX_N0<52>

CNV_CTX_DRX_P0<52>

CNV_CTX_DRX_N1<52>

CNV_CTX_DRX_P1<52>

CLK_CNV_CRX_DTX_N<52>

CLK_CNV_CRX_DTX_P<52>

CLK_CNV_CTX_DRX_N<52>

CLK_CNV_CTX_DRX_P<52>

1 2

RC60 150_0201_ 1%

Follow RVP

BLUETOOTH_EN<52>

LCD_CBL_DET#<38>

1 2

@

RC61 10K_04 02_5%

+3VALW_PCH

UC1G

BN34

HDA_SYNC/I2S0_SFRM

BN37

HDA_BCLK/I2S0_SCLK

BN36

HDA_SDO/I2S0_TXD

BN35

HDA_SDI0/I2S0_RXD

BL36

HDA_SDI1/I2S1_RXD/SNDW1_DATA

BL35

HDA_RST#/I2S1_SCLK/SNDW1_CLK

CK23

GPP_D23/I2S_MCLK

BL37

I2S1_SFRM/SNDW2_CLK

BL34

I2S1_TXD/SNDW2_DATA

CJ32

GPP_H1/I2S2_SFRM/CNV_BT_I2S_BCLK/CNV_RF_RESET#

CH32

GPP_H0/I2S2_SCLK/CNV_BT_I2S_SCLK

CH29

GPP_H2/I2S2_TXD/CNV_BT_I2S_SDI/MODEM_CLKREQ

CH30

GPP_H3/I2S2_RXD/CNV_BT_I2S_SDO

CP24

GPP_D19/DMIC_CLK0/SNDW4_CLK

CN24

GPP_D20/DMIC_DATA0/SNDW4_DATA

CK25

GPP_D17/DMIC_CLK1/SNDW3_CLK

CJ25

GPP_D18/DMIC_DATA1/SNDW3_DATA

CF35

GPP_B14/SPKR

WHL-U42 _BGA1528

UC1I

CR30

CNV_WR_D0N

CP30

CNV_WR_D0P

CM30

CNV_WR_D1N

CN30

CNV_WR_D1P

CN32

CNV_WT_D0N

CM32

CNV_WT_D0P

CP33

CNV_WT_D1N

CN33

CNV_WT_D1P

CN31

CNV_WR_CLKN

CP31

CNV_WR_CLKP

CP34

CNV_WT_CLKN

CN34

CNV_WT_R COMP

PROJECT_ID1

PROJECT_ID2

BLUETOOTH_ EN

LCD_CBL_D ET#

BOARD_ID2

A4WP_PRESEN T

CNV_WT_CLKP

CP32

CNV_WT_RCOMP_0

CR32

CNV_WT_RCOMP_1

CP20

GPP_F0/CNV_PA_BLANKING

CK19

GPP_F1

CG17

GPP_F2

CR14

GPP_C8/UART0_RXD

CP14

GPP_C9/UART0_TXD

CN14

GPP_C10/UART0_RTS#

CM14

GPP_C11/UART0_CTS#

CJ17

GPP_F8/CNV_MFUART2_RXD

CH17

GPP_F9/CNV_MFUART2_TXD

CF17

GPP_F23/A4WP_PRESENT

WHL-U42 _BGA1528

3

AUDIO SDIO / SDXC

GPP_A17/SD_VDD1_PWR_EN#/ISH_GP7

7 of 20

CNVio

GPP_H18/CPU_C10_GATE#

GPP_H19/TIMESYNC_0

GPP_H21/XTAL_FREQ_SELECT

GPP_D4/IMGCLKOUT0/BK4/SBK4

GPP_H20/IMGCLKOUT_1

GPP_F12/EMMC_DATA0

GPP_F13/EMMC_DATA1

GPP_F14/EMMC_DATA2

EMMC

GPP_F15/EMMC_DATA3

GPP_F16/EMMC_DATA4

GPP_F17/EMMC_DATA5

GPP_F18/EMMC_DATA6

GPP_F19/EMMC_DATA7

GPP_F20/EMMC_RCLK

GPP_F21/EMMC_CLK

GPP_F11/EMMC_CMD

GPP_F22/EMMC_RESET#

9 of 20

GPP_A16/SD_1P8_SEL

GPP_H22

GPP_H23

GPP_F10

GPD7

GPP_F3

EMMC_RCOMP

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_1P8_RCOMP

SD_3P3_RCOMP

CN27

CM27

CF25

CN26

CM26

CK17

BV35

CN20

CG25

CH25

CR20

CM20

CN19

CM19

CN18

CR18

CP18

CM18

CM16

CP16

CR16

CN16

EMMC_RCOMP

CK15

CH36

CL35

CL36

CM35

CN35

CH35

CK36

CK34

BW36

BY31

CK33

SD_RCOMP

CM34

COMPENSATION FOR SD_RCOMP

CAD Note:

Min trace width=10 mils, Spacing=12 mils

Max trace length=500 mils

GPP_H21

GPP_H23

GPD7

PROJECT_ID3

WIFI_RF_EN

1 2

RM31 0_0402_5%

MMC@

EMMC_RST

TP13

1 2

RC64 200_0402_ 1%

COMPENSATION FOR EMMC_RCOMP

CAD Note:

Min trace width=10 mils, Spacing=12 mils

Max trace length=500 mils

KB_LED_BL_DET <62>

RC54 200_0402_ 1%

CPU_C10_GATE# <18>

WIFI_RF_EN <52>

EMMC_D0 <6 9>

EMMC_D1 <6 9>

EMMC_D2 <6 9>

EMMC_D3 <6 9>

EMMC_D4 <6 9>

EMMC_D5 <6 9>

EMMC_D6 <6 9>

EMMC_D7 <6 9>

EMMC_RCLK <69>

EMMC_CLK <69>

EMMC_CMD <69>

2

+1.8V_PRIM

12

PROJECT_ID1

12

PROJECT_ID3

12

RC53,RC 56

eMMC SKU Opt i onal

LOW

HIGH

GPD PU to DSW PWR rail

GPD7

Weak Int. PD.

GPP_H21

1

INSPIRON@

RC52

10K_0402_5 %

VOSTRO@

RC55

10K_0402_5 %

RC58 100K _0402_5%

12

@

RC53

10K_0402_5 %

12

RC56

10K_0402_5 %

Stand ard

Narrow Border

+3VALW_DSW

12

+3VALW_PCH

12

RC62 4.7K_0402 _5%

XTAL Frequency Select

LOW(DEFAULT)

HIGH

Weak Int. PD.

GPP_H23

eSPI Flash Sharing Mode

LOW(DEFAULT)

HIGH

38.4MHz

24MHz

+3VALW_PCH

12

@

RC65 4.7K_0402 _5%

MAF EABLE

SAF EABLE

BOARD_ID2

(GPP_C 11)

---

---

RC69

RC71

12

RC70

10K_0402_5 %

12

@

RC72

10K_0402_5 %

BOARD_ID1

(GPP_C12 )

RC70

RC72

---

---

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2019/06/19 2020/06/30

2019/06/19 2020/06/30

2019/06/19 2020/06/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

PROJECT_ID2

12

RC201

10K_0402_5 %

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

LOW(DEFAULT)

HIGH

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU(4/12)HDA,EMMC,SD

CPU(4/12)HDA,EMMC,SD

CPU(4/12)HDA,EMMC,SD

LA-G717P

LA-G717P

LA-G717P

1

PROJECT_ID2

UMA

DIS

1.0

1.0

9 100Wednesday, June 19, 2 019

9 100Wednesday, June 19, 2 019

9 100Wednesday, June 19, 2 019

1.0

12

BASE@

RC69

BOARD_ID1<11>

CNV_RF_RESET #

1 2

CNV@

RC74 75K_0402_1 %

RC73 71.5K_0402_ 1%

1 2

@

CLKREQ_CNV#

A A

BOARD_ID2

CPU ID

CML-U

10K_0402_5 %

12

PREM@

RC71

10K_0402_5 %

WHL-U(Reserved)

Pentium/Celeron

i3/i5/i7

5

4

5

smd.db-x7.ru

4

3

2

1

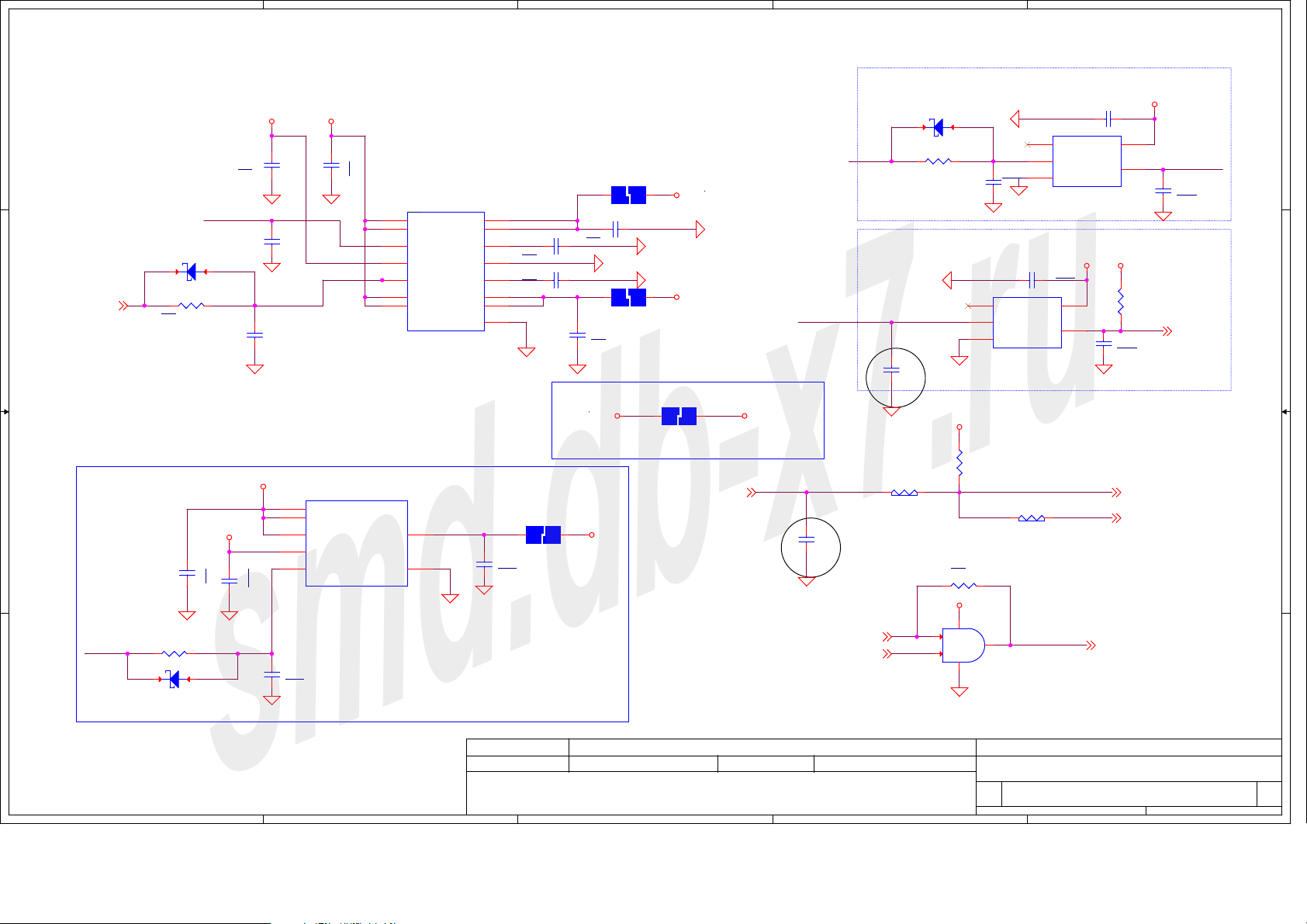

RC78,RC81.RC85,RC88 close to Device

CLK_PCIE_N1< 52>

WLAN--->

D D

LAN--->

SSD--->

CLK_PCIE_P1<52>

CLKREQ_PCIE#1<52>

CLKREQ_PCIE#2<51>

CLKREQ_PCIE#4<67>

+3VS

CLK_PCIE_N2< 51>

CLK_PCIE_P2<51>

+3VS

CLK_PCIE_N4< 67>

CLK_PCIE_P4<67>

+3VS

1 2

RC81 10K_0402_5%

1 2

RC85 10K_0402_5%

1 2

RC88 10K_0402_5%

PCH_PLTRST#

+3VS

UC4 change CPN &

Description only

5

PCH_PLTRST#<69>

C C

1 2

CC79 0.1U_ 0402_10V7K

@ESD@

+3VALW_PCH

1 2

RC100 10K_0402 _5%

B B

+3VALW_DSW

1 2

RC92 4.7K_ 0402_5%

1 2

RC93 10K_ 0402_5%

PCH_PLTRS T#

UC4

MC74VHC1G08E DFT2G_SC70

SYS_PWROK

07/4 ESD require

SYS_RESET#

PCH_PCIE_W AKE#

LANWAKE#

Jason 2019-04-26

1

P

IN1

4

O

2

12

IN2

G

3

RC94

100K_0402_ 5%

TP20

H_VCCST_PW RGD<18>

PCIE_WAKE#<51,52,58,67>

PCH_RSMRST #_Q

PLTRST# <51,52,58,65,67>

PCH_RSMRST#_Q<79>

1 2

RC75 10K_0402_5%

1 2

RC76 1K_0402_5%@

1 2

RC99 62_0402_1 %

SYS_PWROK<58>

RESET_OUT#<58>

1 2

@

RC101 0_0201_5%

1 2

@

RC102 0_0201_5%

LANWAKE#<58>

PCH_PLTRS T#

SYS_RESET#

PCH_RSMRST#_Q

H_CPUPW RGDH_CPUPW RGD_R

VCCST_PWR GD

PCH_DPWROK

PCH_PCIE_W AKE#

UC1J

AW2

CLKOUT_PCIE_N_0

AY3

CLKOUT_PCIE_P_0

CF32

GPP_B5/SRCCLKREQ0#

BC1

CLKOUT_PCIE_N_1

BC2

CLKOUT_PCIE_P_1

CE32

GPP_B6/SRCCLKREQ1#

BD3

CLKOUT_PCIE_N_2

BC3

CLKOUT_PCIE_P_2

CF30

GPP_B7/SRCCLKREQ2#

BH3

CLKOUT_PCIE_N_3

BH4

CLKOUT_PCIE_P_3

CE31

GPP_B8/SRCCLKREQ3#

BA1

CLKOUT_PCIE_N_4

BA2

CLKOUT_PCIE_P_4

CE30

GPP_B9/SRCCLKREQ4#

BE1

CLKOUT_PCIE_N_5

BE2

CLKOUT_PCIE_P_5

CF31

GPP_B10/SRCCLKREQ5#

WHL-U42 _BGA1528

UC1K

BJ35

GPP_B13/PLTRST#

CN10

SYS_RESET#

BR36

RSMRST#

AR2

PROCPWRGD

BJ2

VCCST_PWRGOOD

CR10

SYS_PWROK

BP31

PCH_PWROK

BP30

DSW_PWROK

BV34

GPP_A13/SUSWARN#/SUSPW RDACK

BY32

GPP_A15/SUSACK#

BU30

WAKE#

BU32

GPD2/LAN_WAKE#

BU34

GPD11/LANPHYPC

WHL-U42 _BGA1528

CLOCK SINGNALS

10 of 20

SYSTEM POW ER MANAGEMENT

11 of 20

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

AU1

AU2

XTAL_IN

XTAL_OUT

CLKIN_XTAL

RTCX1

RTCX2

SRTCRST#

RTCRST#

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

GPD9/SPL_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_B2/VRALERT#