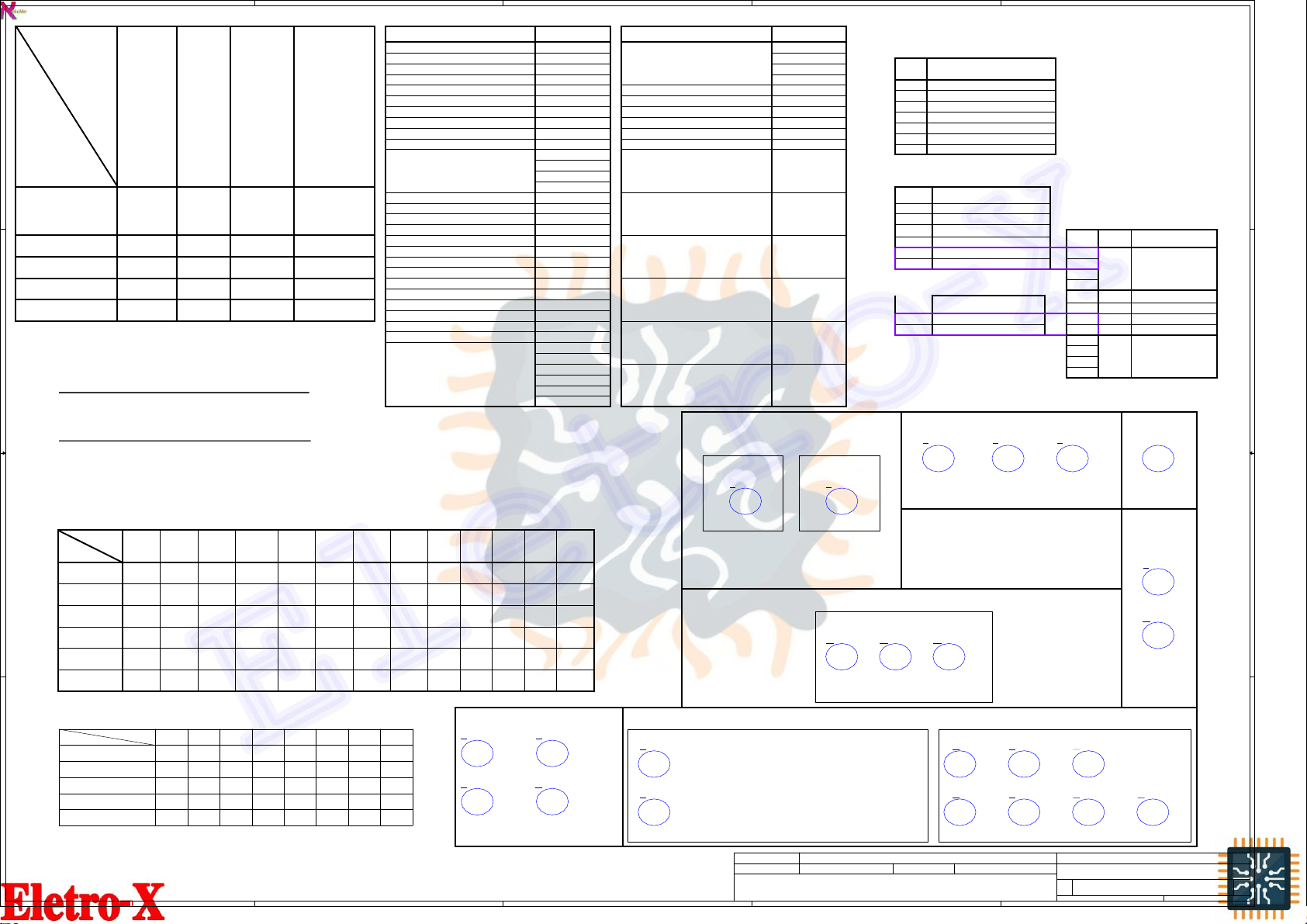

Page 1

A

1 1

B

C

D

E

Compal Confidential

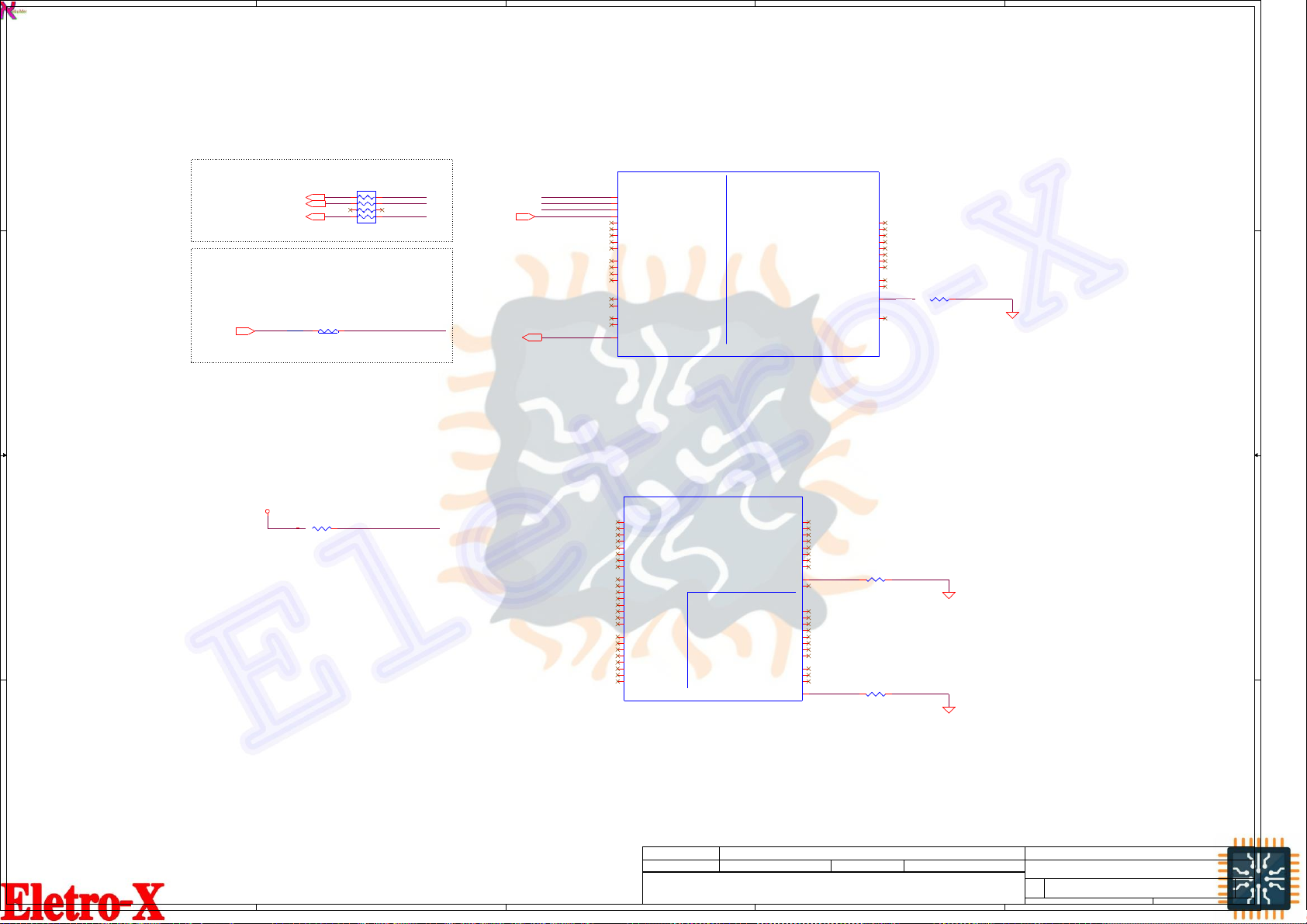

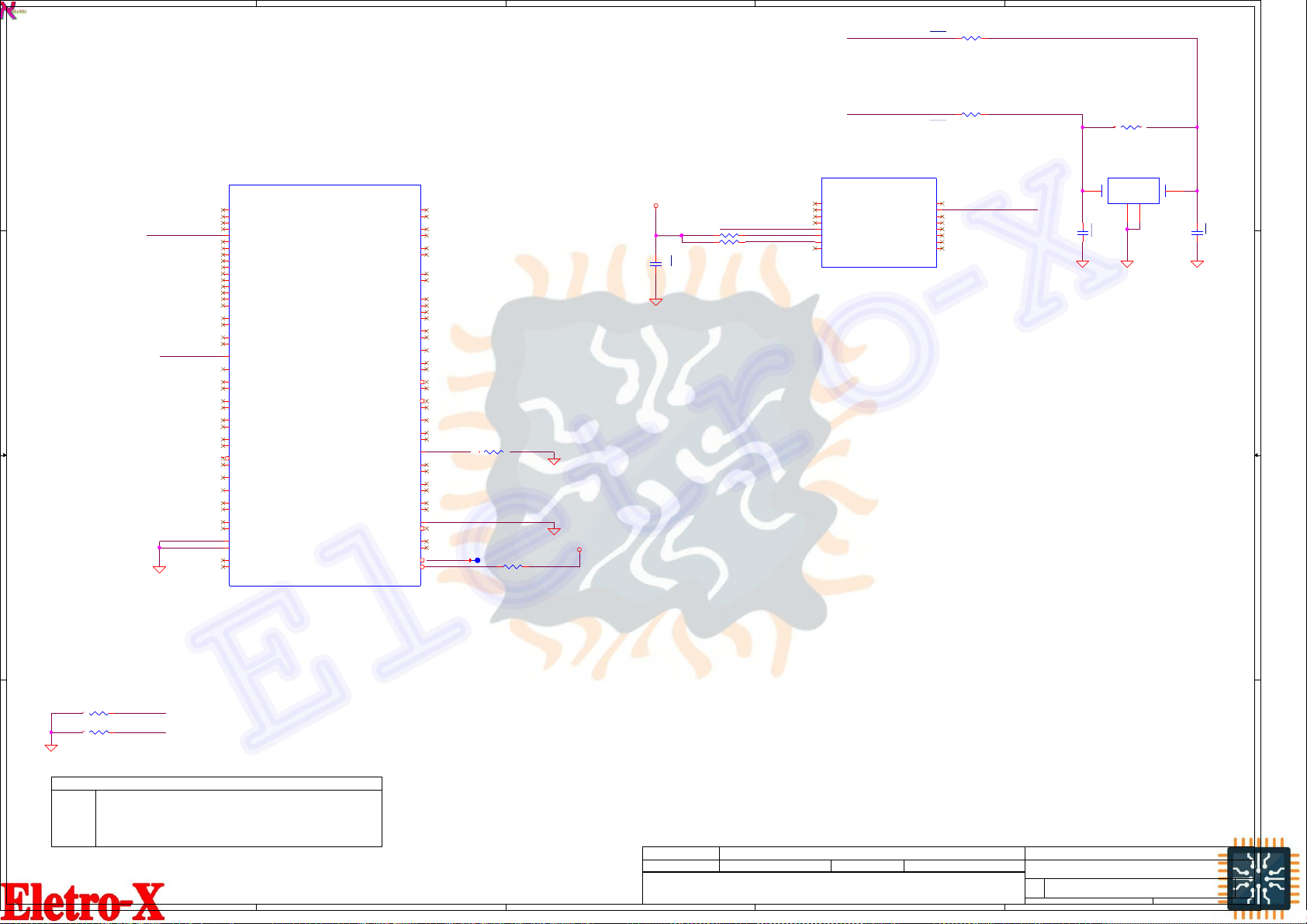

DLID4 / D5

2 2

DIS M/B Schematic Document

Intel KabyLake U/KabyLake R Processor with DDR4

3 3

LA-G202P

2018-03-09

REV 1.0

4 4

Security Classification

Issued Date Decipherii ed Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIETARY PROPERTY OF COMPAL ELECTRONIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION.. THIIS S HEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIVIIISIIION OF R&D DEPARTMENT

EXCEPT AS AUTHORIIZED BY COMPAL ELECTRONIIICS,,, IIINC.. NEIIITHER THIS SHEET NOR THE IIINFORMATIIION IIIT CONTAIIINS

A

B

MAY BE USED BY OR DIISCLOSED TO ANY THIIRD PARTY WIIITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS,,, IIINC.

C

2018/03/09 2019/03/09

Compal Secret Data

Tiiittllle

Siiize Documentt Number

Custttom

D

Compal Electronics,Inc.

Cover Page

LA-G202P

R ev

Sheett 1 off 55Date: Friiiday,,, March 09,,,2018

E

1...0

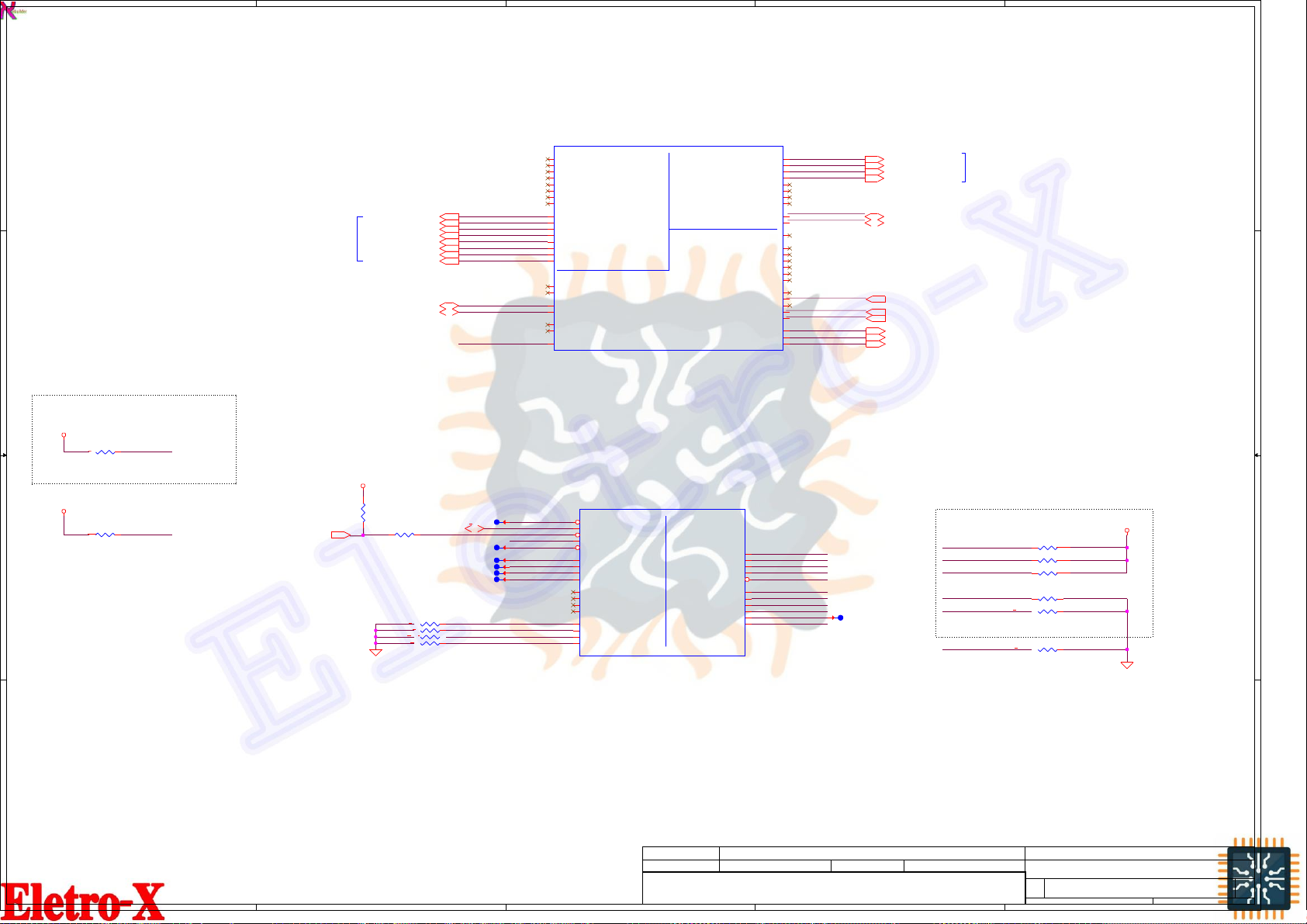

Page 2

A

B

C

D

E

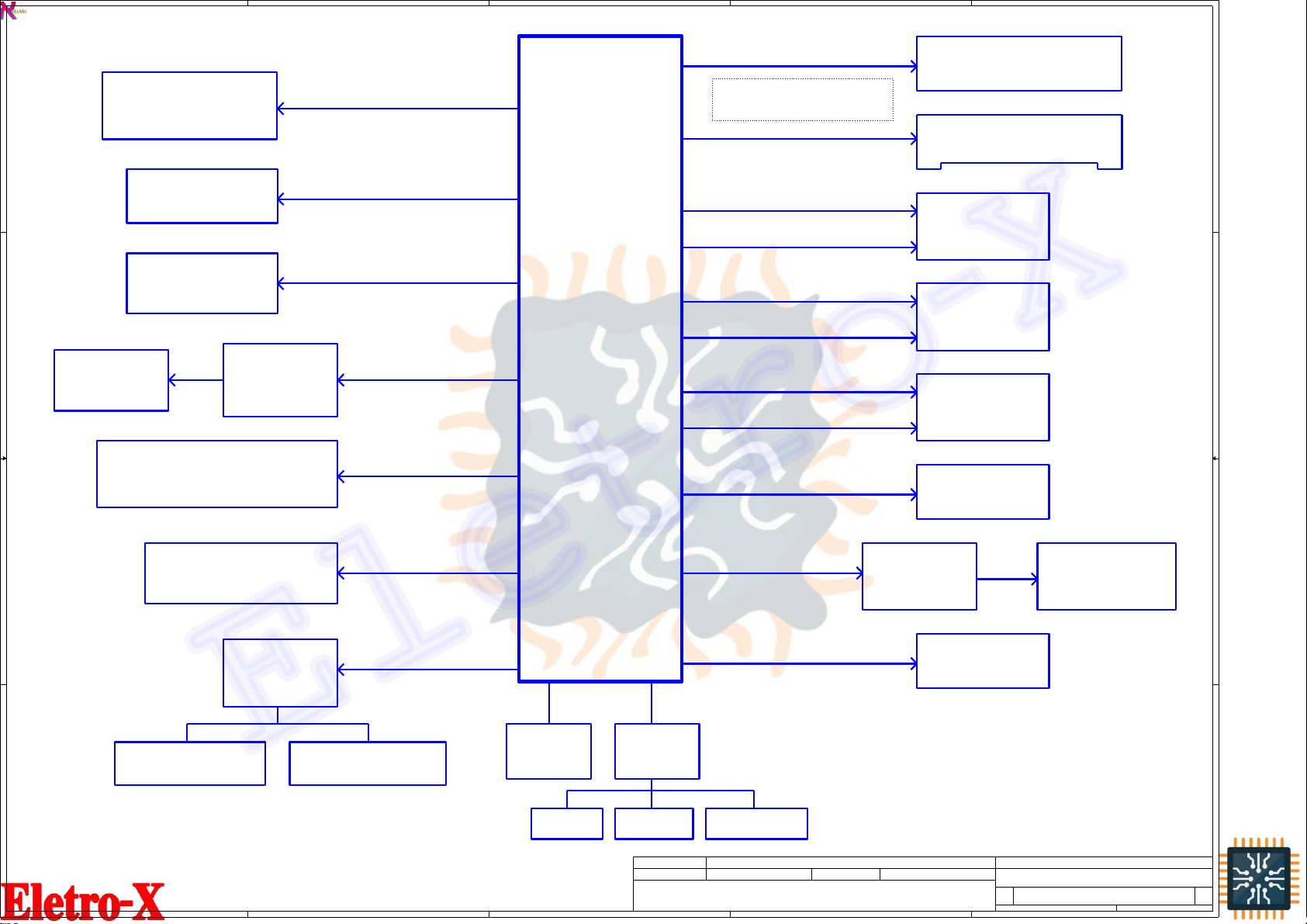

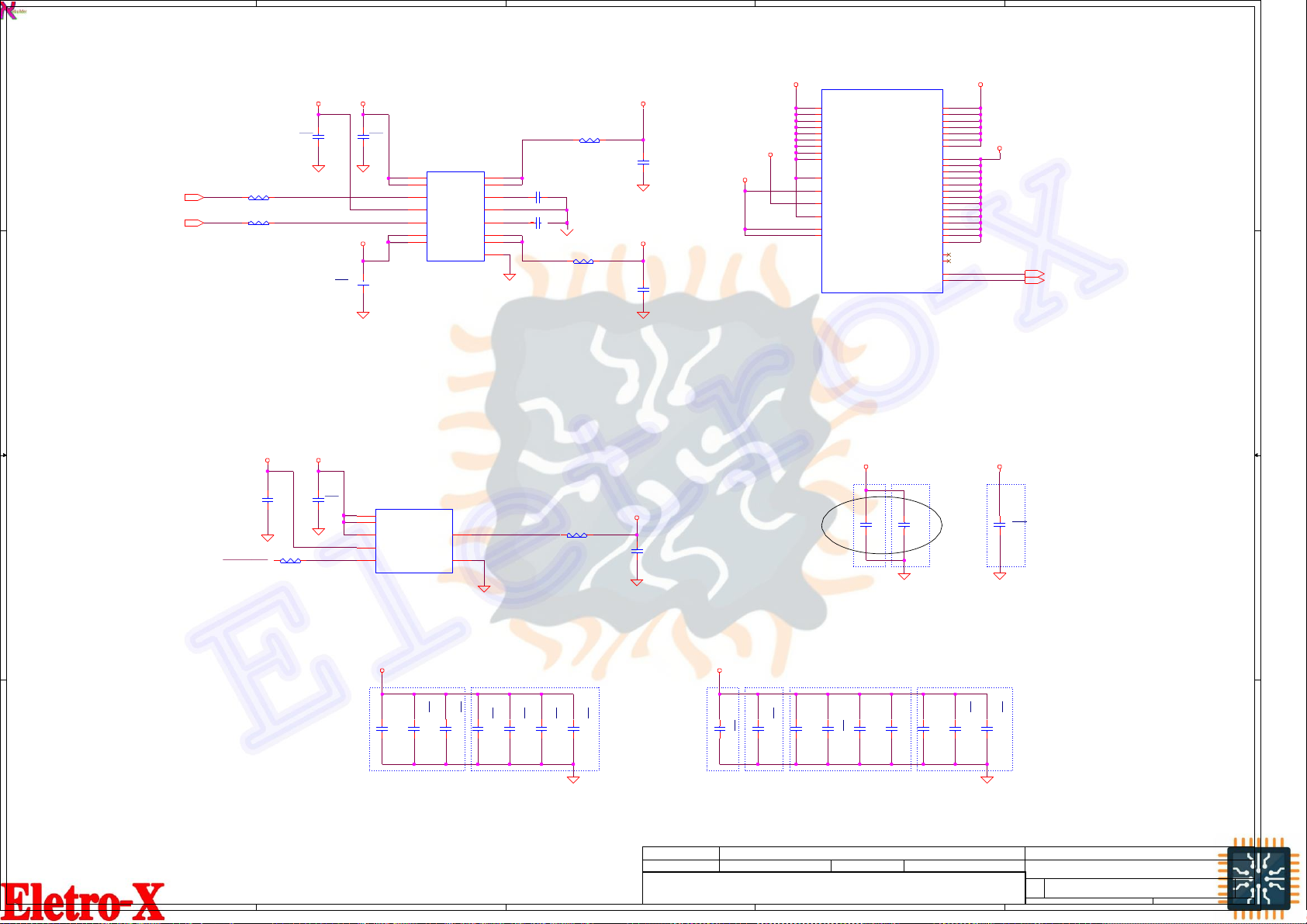

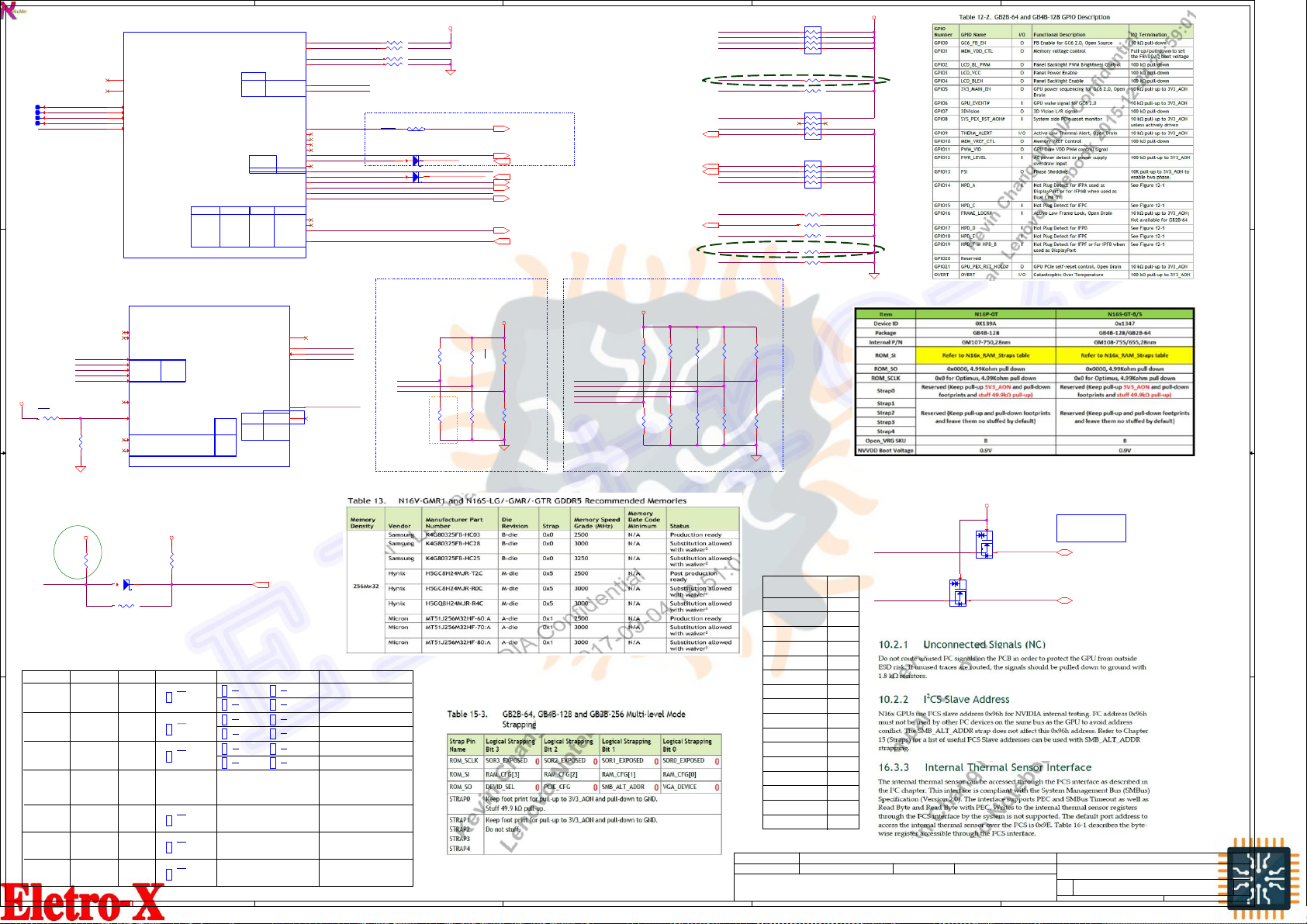

Memory Bus (Channel A)

NVIDIA MX110

(2GB GDDR5 VRAM)

1 1

(256 x 32 x 2 PCS)

PCIe X4 Gen3

*KBL-U: DDR4 (2133MHz, 1.2V)

*KBL-R: DDR4 (2400MHz, 1.2V)

Memory Bus (Channel B)

eDP Conn.

eDP X1 (2 Lanes)

PCIe X1 (1 Lanes)

USB 2.0 X1

HDMI Conn.

DDI X1 (4 Lanes)

Intel KabyLake-U

USB3.0 x1

Intel KabyLake-R

USB2.0 x1

2 2

RJ45 Conn.

LAN

RTL8106E-CG

PCIe X1 (1 Lane)

10/100

ODD Conn.

(14" -> On Mother Board)

SATA X1

(15" -> On Sub/B through FFC)

SOC

1356 PinBGA

USB3.0 x1

USB2.0 x1

USB2.0 x1

DDR4 (On Board) X4

DDR4 (SO DIMM) X1

WLAN / BT

Left USB3.0 x1

Left USB3.0 x1

Int. Camera

3 3

HDD Conn.

(On Sub/B through FFC)

SATA X1

USB2.0 x1

Card Reader

Realtek

SD Card Conn.

RTS5146-GR

Audio Codec

HDA

I2C x1

Touch Pad

Realtek

ALC3240

Int. Speaker Conn.

4 4

A

Audio Combo Jack

Headphone / Mic

B

SPI LPC

SPI ROM

8MB, 3.3V

LED

EC

ENE

KB9022QD

Int. KBD

Securiiity Clllassiiifiiicatiiion

Issued Date

THISII SHEET OF ENGINII EERINII G DRAWINII G ISII THE PROPRIEII TARY PROPERTY OF COMPAL ELECTRONICII S,,, INII C... AND CONTAINII S CONFIDII ENTIAII L AND TRADE

SECRET INII FORMATIONII ... THISII SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVII ISII IONII OF R&D DEPARTMENT EXCEPT AS

AUTHORIZEII D BY COMPAL ELECTRONICII S,,, INII C... NEITHII ER THISII SHEET NOR THE INII FORMATIONII ITII CONTAINIIS

MAY BE USED BY OR DISII CLOSED TO ANY THIRII D PARTY WITHIIOUT PRIORII WRITTEIIN CONSENTOF COMPALELECTRONICII S,,,INII C...

C

Hall Sensor

Compal SecretData

Decipherii ed Date

D

Tiiitttllle

Siiize DocumentttNumber

C

Compal Electronics, Inc.

Block Diagram

LA-G202P

Sheettt 2 o fff55Dattte::: Friiiday,,, March 09,,,2018

E

Rev

1...0

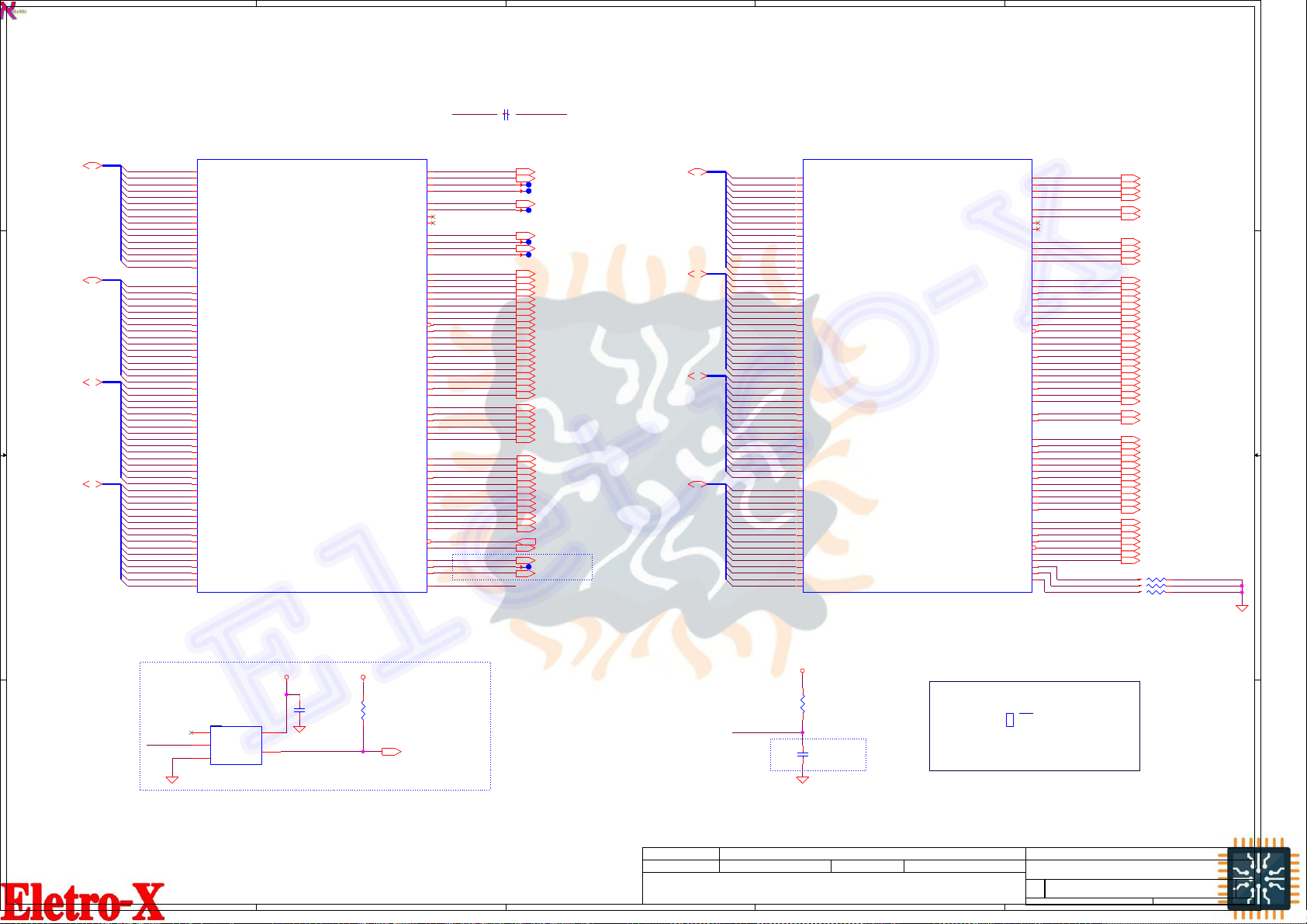

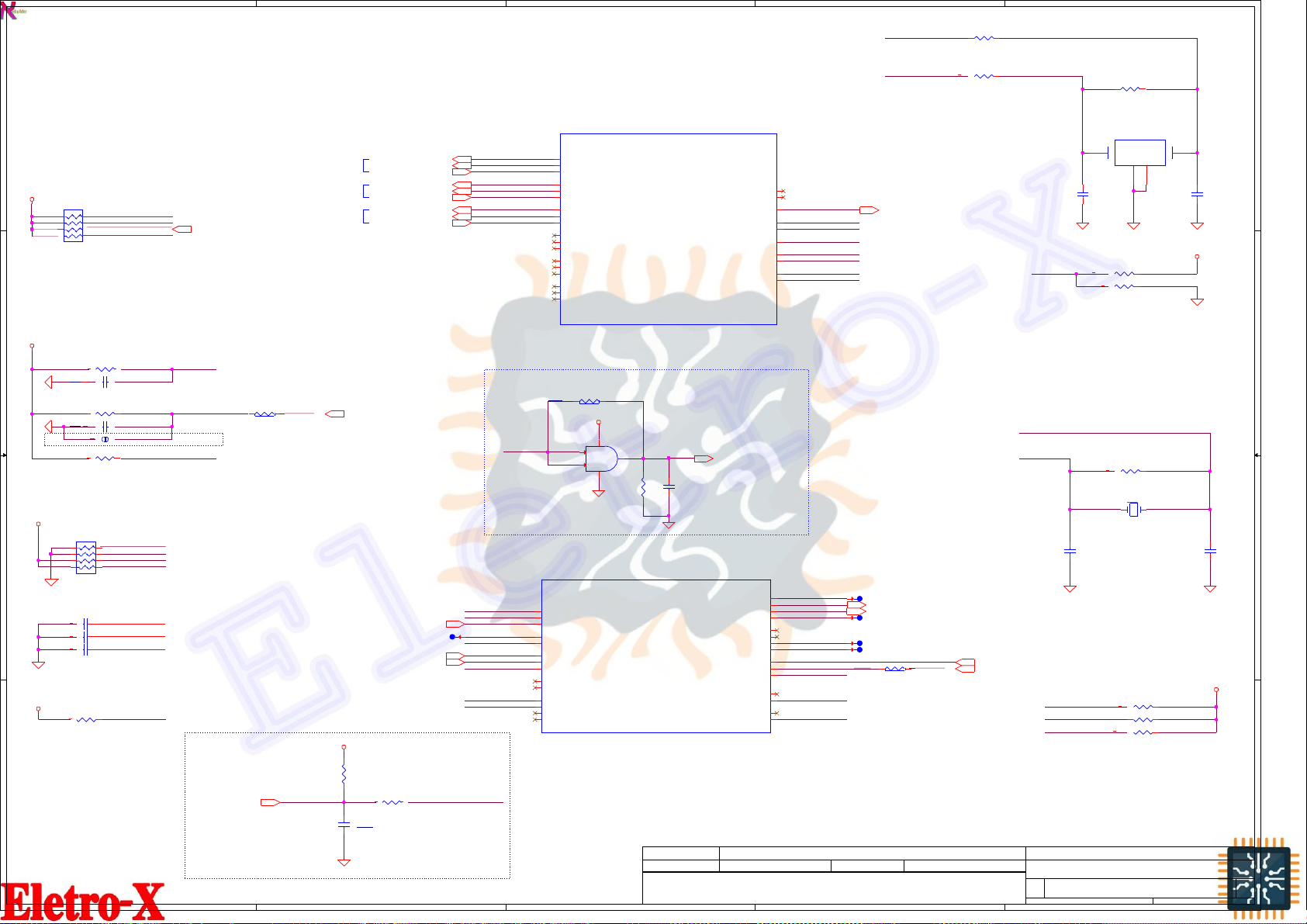

Page 3

5

4

3

2

1

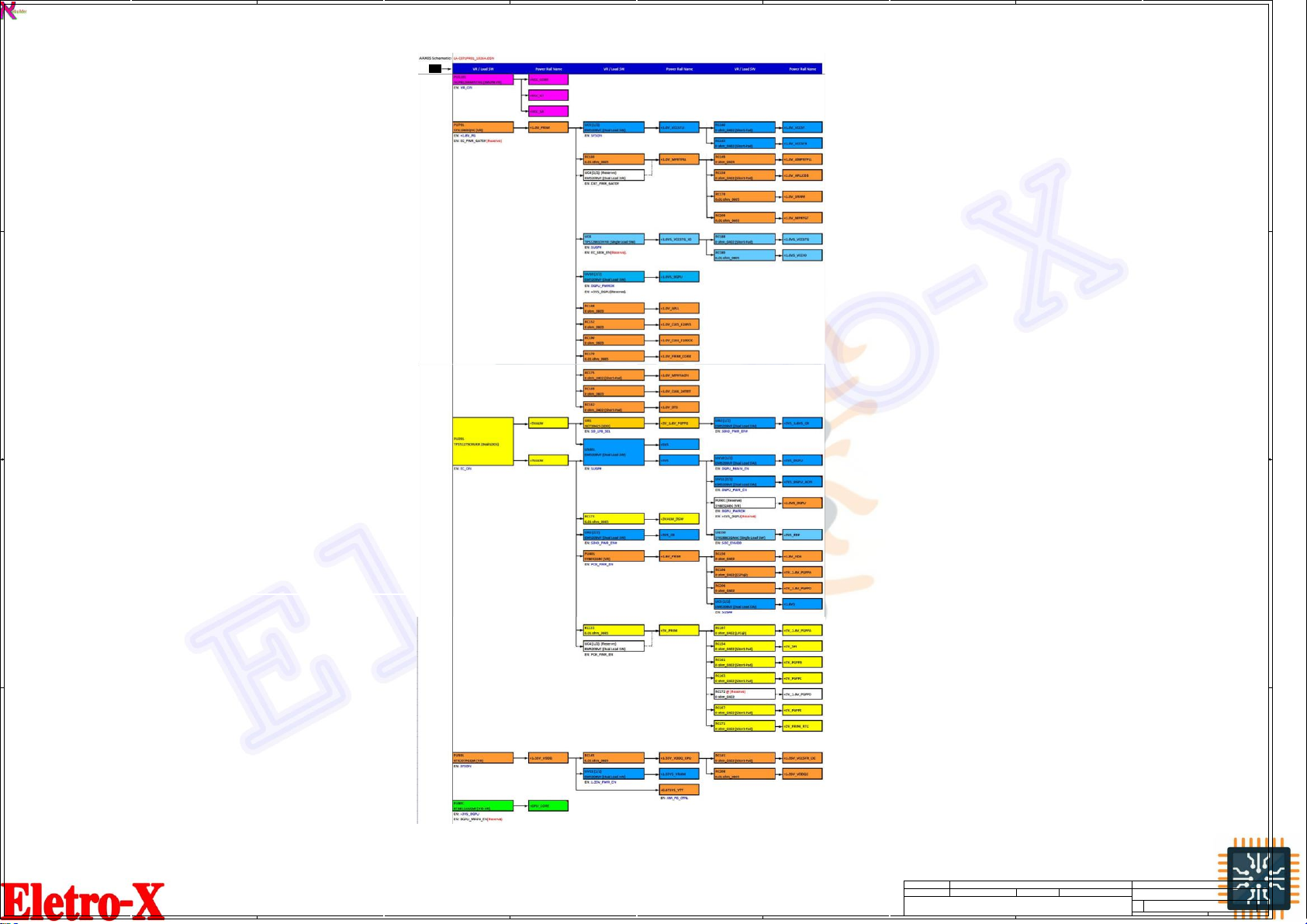

-PowerMap_KBL_DDR4_Volume_NON CS]

B+

D D

C C

B B

A A

Securiiirr tytt Classiiill fffiiicatiiitton

IIIssued Dattte

THISII SHEET OF ENGINEII ERINGII DRAWINGII ISIITHE PROPRIEII TARY PROPERTY OF COMPAL ELECTRONICII S,,, INCII ... AND CONTAINSII CONFIDII ENTIAII L AND TRADE SECRET INFII

ORMATION...II THISII SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVII ISII IONII OF R&D DEPARTMENT EXCEPT AS AUTHORIZEII D

BY COMPAL ELECTRONICII S,,, INCII ... NEITHEII R THISII SHEET NOR THE INFII ORMATIONII ITII CONTAINSII

5

4

3

MAY BE USED BY OR DISII CLOSED TO ANY THIRDII PARTY WITHOUTII PRIORII WRITTEII N CONSENT OF COMPAL ELECTRONICII S,,, INCII ...

2

2018/03/09////

Compalll SecretttDattta

Deciiipherrred Dattte

2019/03/09////

Compal Electronics,Inc.

Tiiitttllle

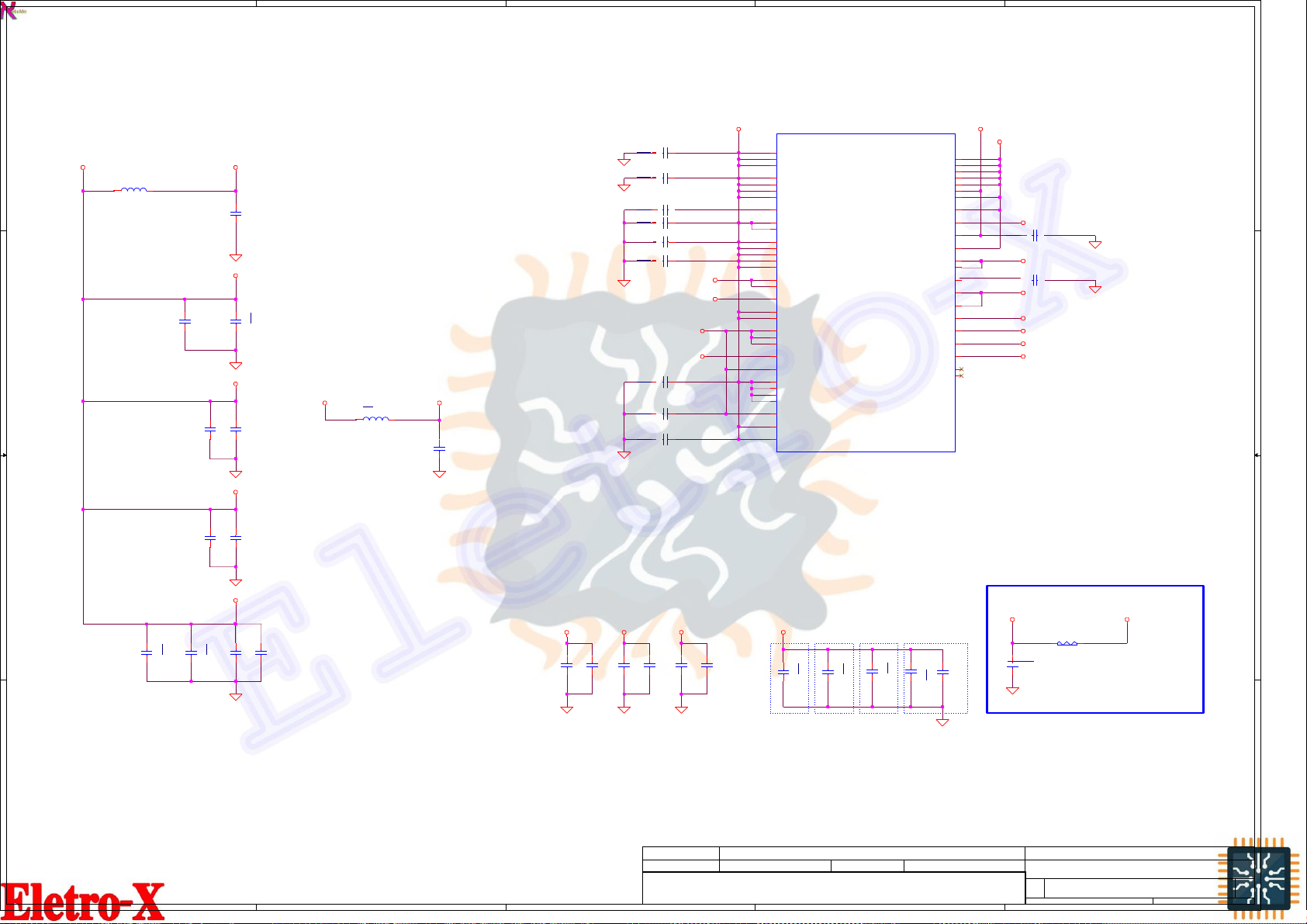

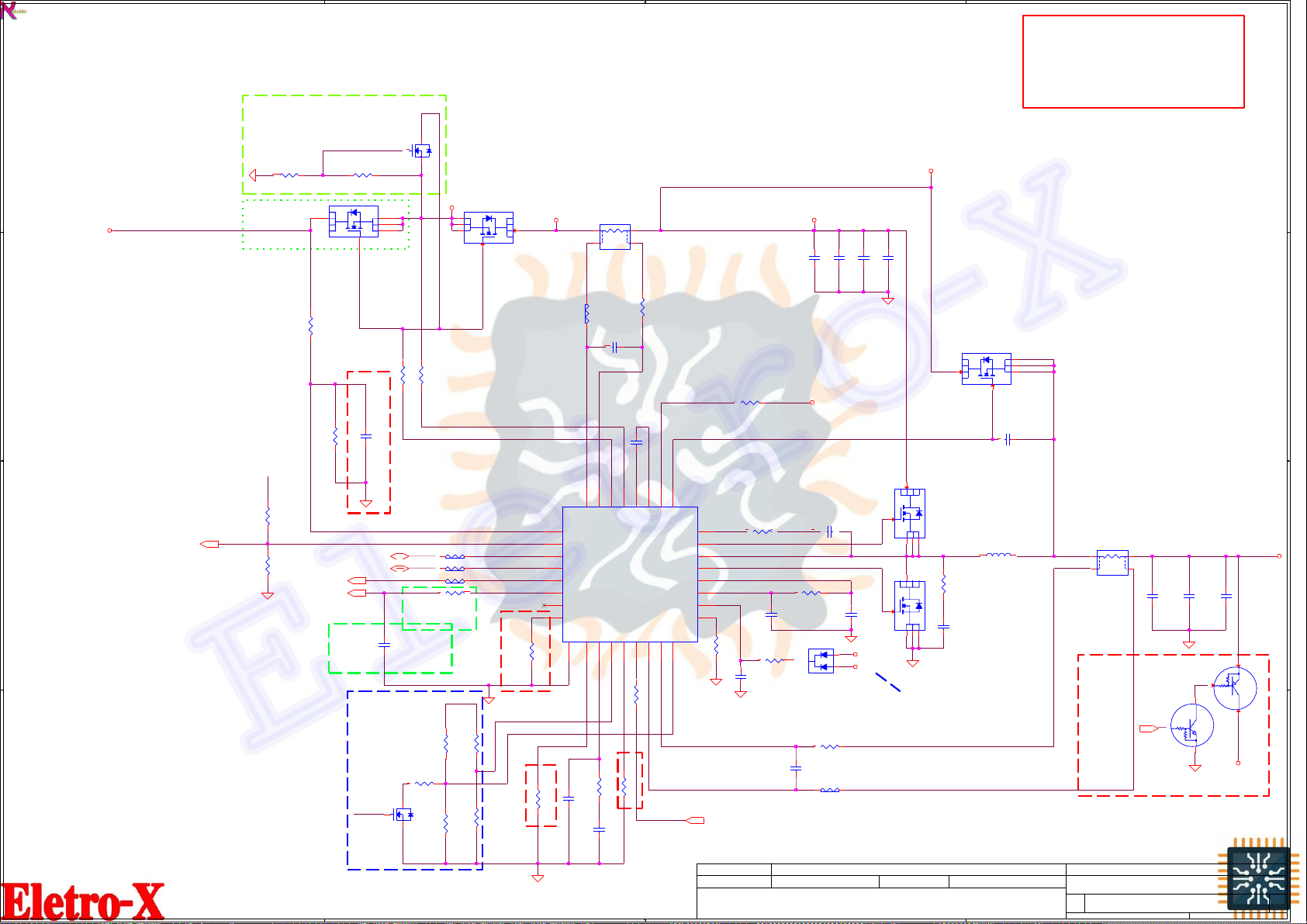

PowerMAP

Siiize Documenttt Numberrr

LA-C071P

Dattte::: Frrriiiday,,,Marrrch09,,, 2018 Sheettt 4 o fff 55

1

Rev

1...0

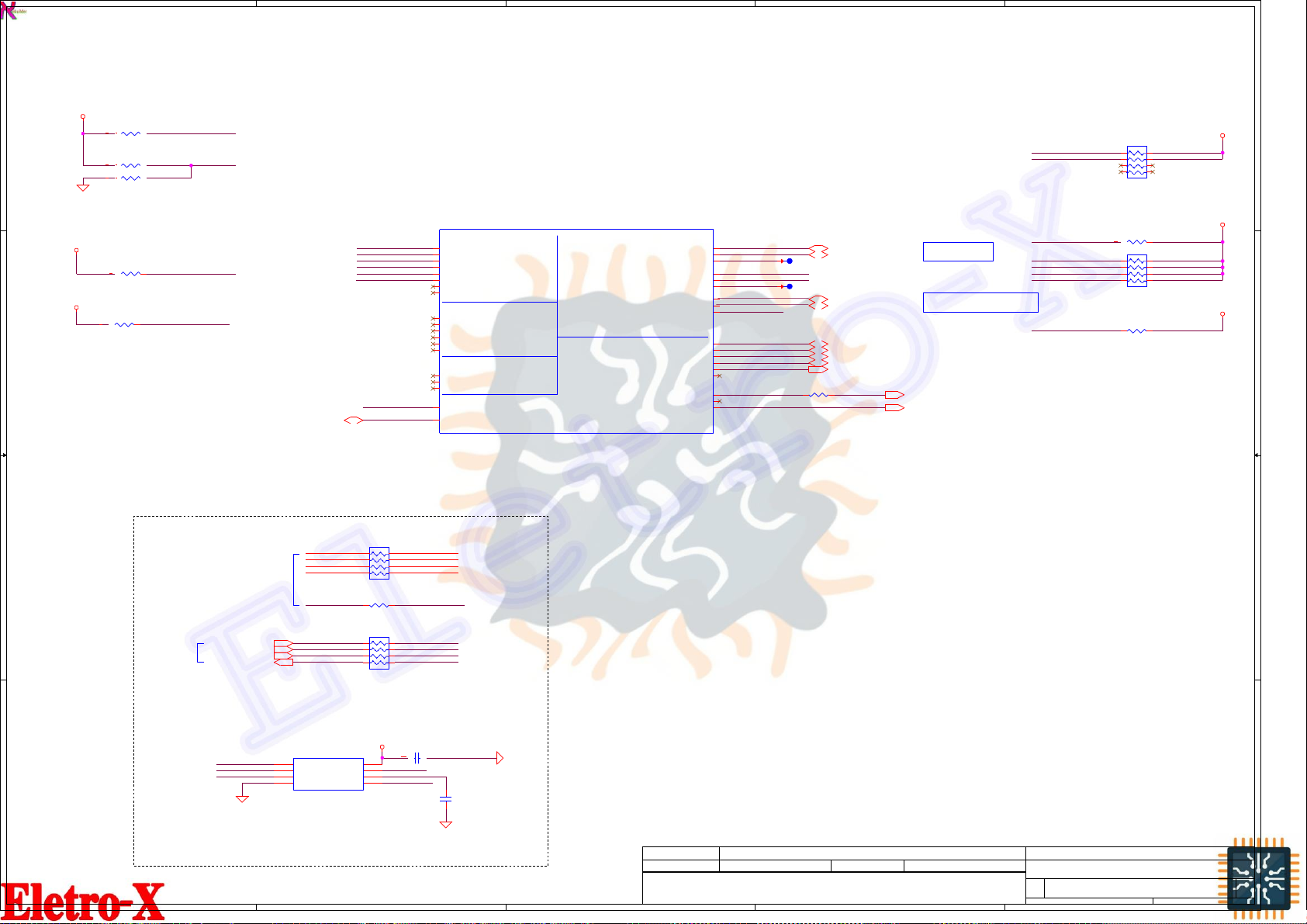

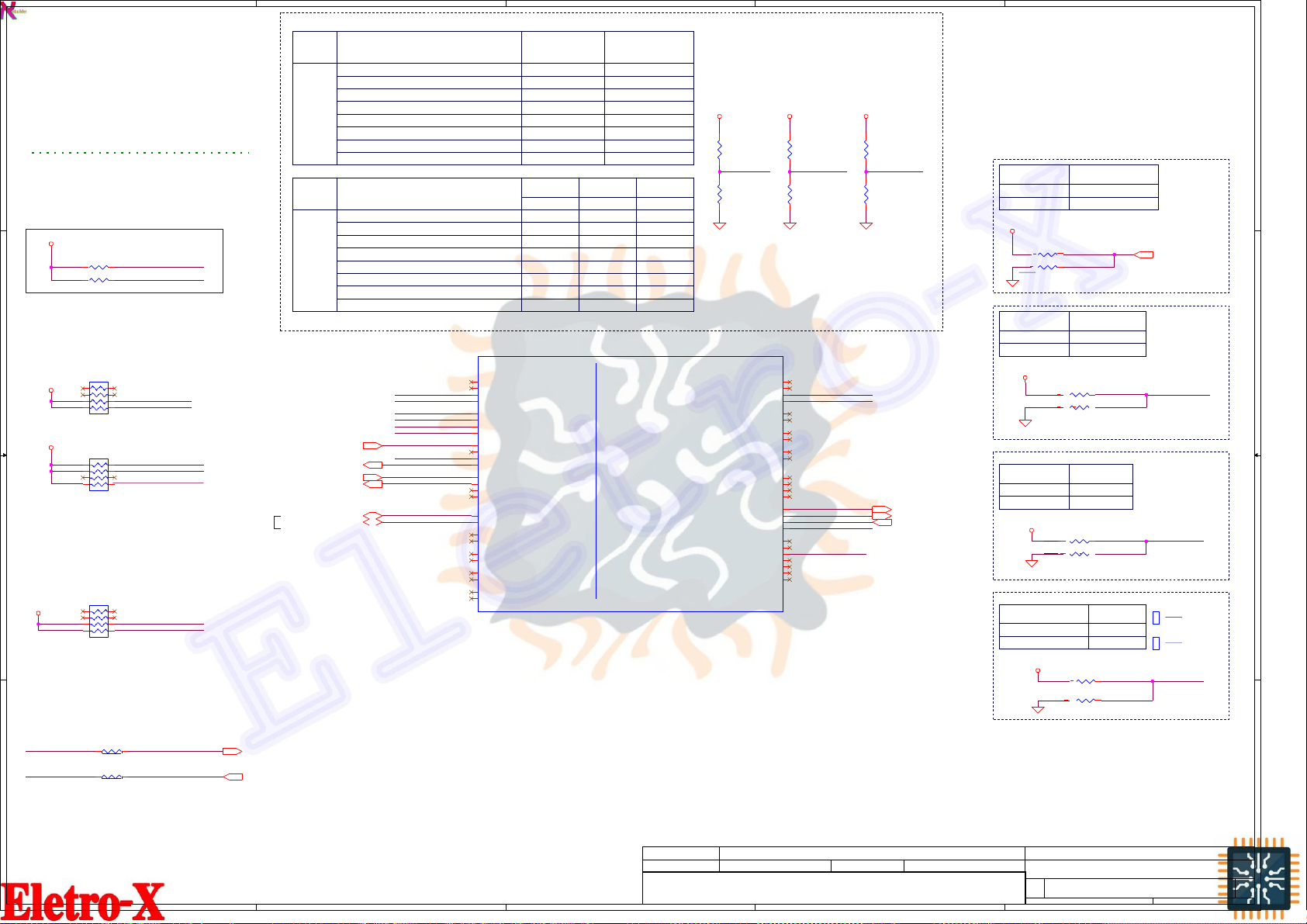

Page 4

5

4

3

2

1

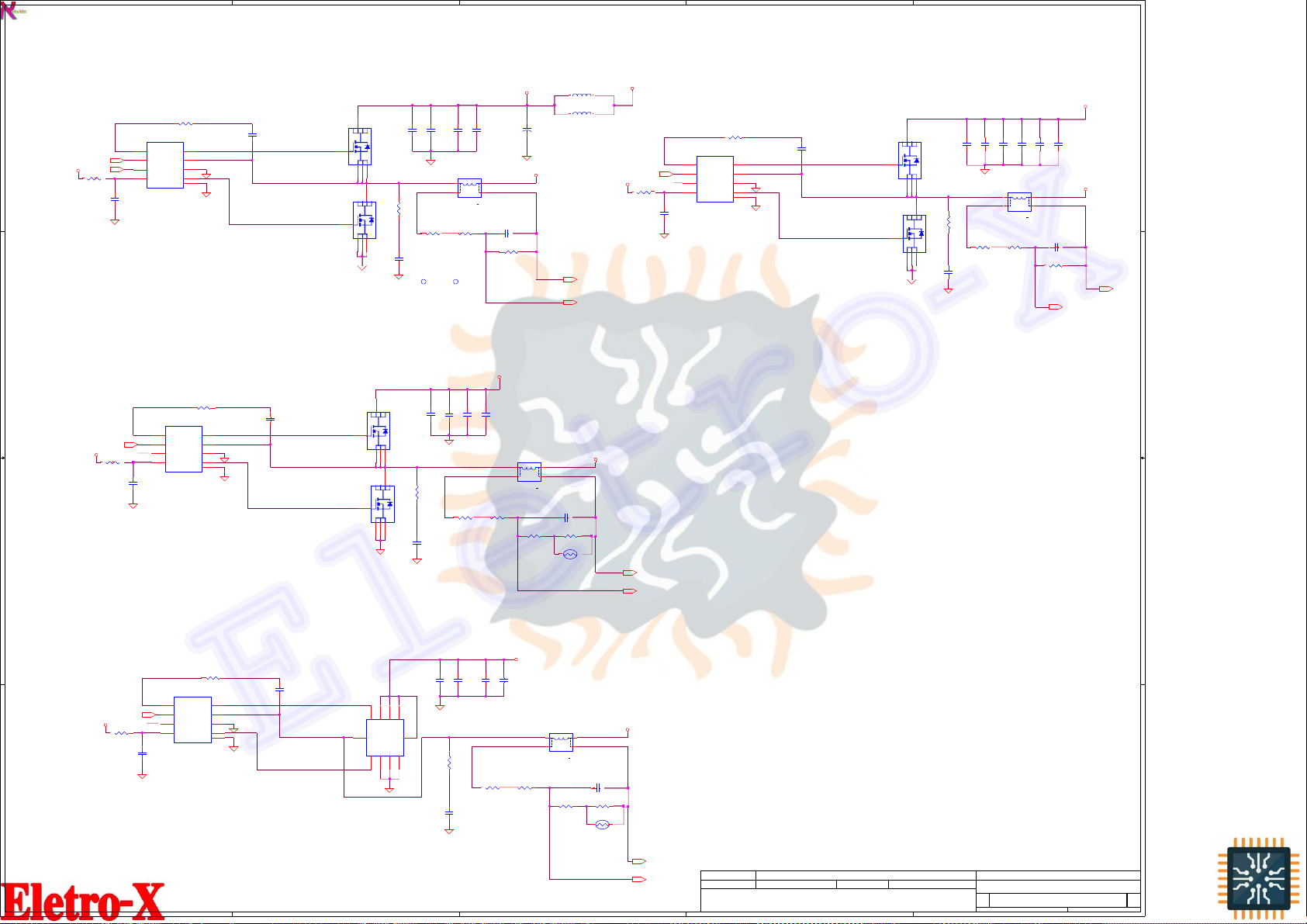

G3->S0

+3VL_RTC

SOC_RTCRST#

B+

D D

+3VLP/+ 5VLP

EC_ON

+5VALW/+ 3VALW /+3V ALW_D SW

PM_BATLOW #

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

Pull-up to D SW well if not implemented.

S0->S3/DS3 S0/DS3->S0

PCH_PWR _EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_M PHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

tPCH06_Min : 200 us

SUSACK#

PCH_DPW ROK

EC_RSMRST#

C C

AC_PRESENT

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

ON/OFF

PBTN_OUT#

Minim um duration of PWRBTN# assertion = 16m S. PW RBTN# can assert before or after RSM RST#

PM_SLP_S 5#

ESPI_RST #

If EXT_PWR _GATE# Toffmin is too small, Pwr

gate may choose to completely ignore it

tPCH43_Min : 95 ms

tPCH18_Min : 90 us

PM_SLP_S 4#

SYSON

+1.0V_VCCST/+1 .0V_VCCSFR

+1.35V_ VDDQ/+1. 35V_VC CSFR_OC

PM_SLP_S 3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

B B

+5VS/+3 VS/+1.5VS/+1. 05VS

EC_VCCST_PG

VR_ON

SM_PG_ CTRL

+0.675V S_VTT

+VCC_SA

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 10msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_CORE

+VCC_GT

VR_PWRG D

PCH_PWR OK

tCPU16 Min : 0 ns

H_CPUPW RGD

SYS_PWR OK

A A

SUS_STAT#

SOC_PLT RST#

S0->S5

+3VL_RTC

SOC_RTCRST#

B+

+3VLP/+ 5VLP

EC_ON

+5VALW/+ 3VALW /+3V ALW_D SW

PM_BATLOW #

PCH_PWR _EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_M PHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

SUSACK#

PCH_DPW ROK

EC_RSMRST#

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_SLP_S 5#

ESPI_RST #

PM_SLP_S 4#

SYSON

+1.0V_VCCST/+1 .0V_VCCSFR

+1.35V_ VDDQ/+1. 35V_VC CSFR_OC

PM_SLP_S 3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

+5VS/+3 VS/+1.5VS/+1. 05VS

EC_VCCST_PG

VR_ON

SM_PG_ CTRL

+0.675V S_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRG D

PCH_PWR OK

H_CPUPW RGD

SYS_PWR OK

SUS_STAT#

SOC_PLT RST#

Securiiittty Clllassiiifffiiicatttiiion Compalll Secret Data

IsII suedDatett

THISII SHEET OF ENGINEERINGIIII DRAWINGII ISII THE PROPRIETII ARY PROPERTY OF COMPAL ELECTRONICS,,,II INC...II AND CONTAINSII CONFIDENTII IALII AND TRADE

SECRET INFII ORMATION...II THISII SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISIONIIIIII OF R&D DEPARTMENT EXCEPT AS

AUTHORIZIIED BY COMPAL ELECTRONICS,,,II INC...II NEITII HER THISII SHEET NOR THE INFII ORMATIONII ITIICONTAINSII

5

4

3

MAY BE USED BY OR DISCLII OSED TO ANY THIRDII PARTY WITII HOUT PRIORII WRITII TEN CONSENT OF COMPAL ELECTRONICS,,,IIINC...II

2018///03///09

2

Deciiiphererr d Dattte

2019///03///09

Tiiitttllle

Siiize DocumentttNumberrr

1

Compal Electronics,Inc.

PowerSequence

Sheettt5 o fff55Dattte::: Frrriiiday,,, Marrrch 09,,,2018

Re v

1...0

Page 5

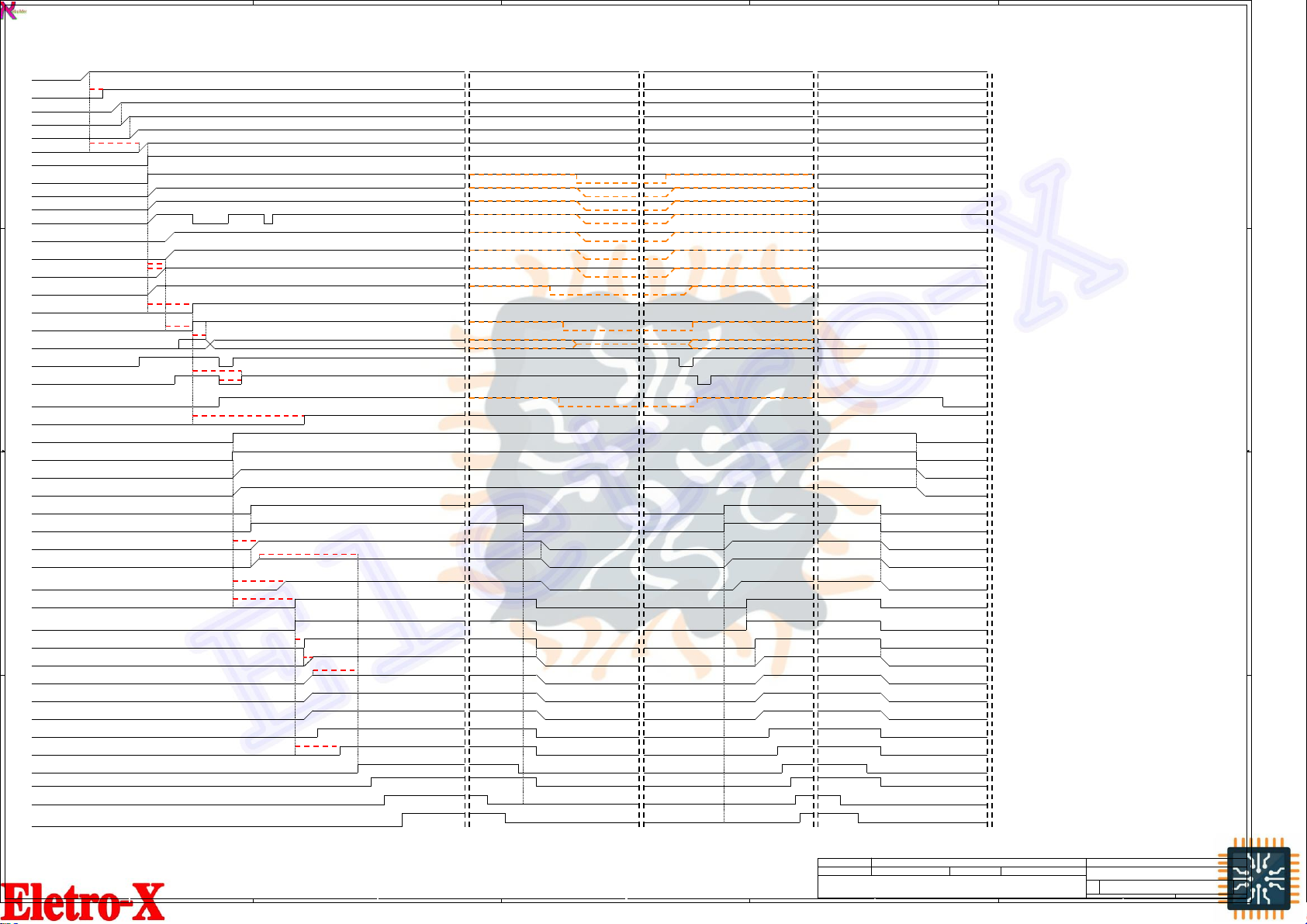

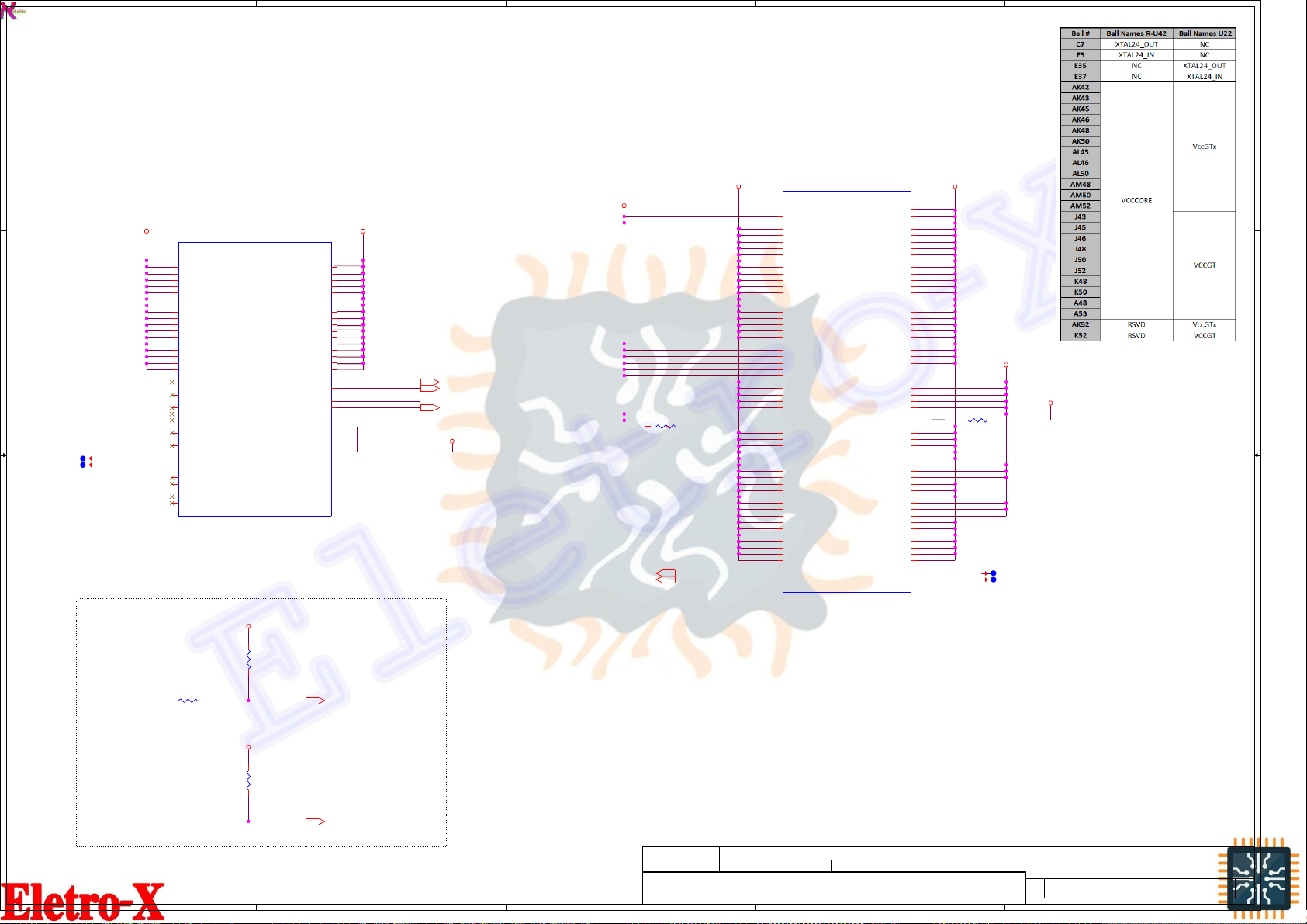

1

Voltage Rails

power

plane

+5VALW

B+

A A

State

S0

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

B B

+3VALW

O O O O

O O O

O O

O

X X X

X X X X

+1.2V

X X

+5VS

+3VS

+1.35VS

+VCC_CORE

+VGA_CORE

+VCC_GFXCORE_AXG

+1.8VS

+0.6VS

+1.0VALW

X

EC SM Bus1 address EC SM Bus2 address

Device

Smart Battery

PCH SM Bus address GPU SM Bus address

Device

DDR_J DIMM 1

Touch Pad

Address

0001 011x 16h

Address Device Address

1010 000x A0h Internal thermal sensor 1001 111x 9Eh

Device

NCT7718W

Address

1001 100x 98h

2

BOM Structure Table

Item

DIS Only Components DIS@

UMA Only Components UMA@

14" Only Components 14@

15" Only Components 15@

HDMI Logo 45@

GIGA LAN Reserved Items 8111GLDO@

Memory Down - SDP Package SDP@

Memory Down - DDP Package DDP@

GPU GC6 Components GC6@

Un-Mount GPU GC6 Components NOGC6@

GPU

EMI Category EMI@

ESD Category ESD@

RF Category RF@

EMI Un-Mount Items @EMI@

ESD Un-Mount Items @ESD@

RF Un-Mount Items @RF@

Connectors ME@

Test Point TP@

Intel Debug Components @DCI@

Un-Mount Components @

CPU Components - U22 Only U22@

CPU Components - U42 Only U42@

EMI U22 Components U22_EMI@

EMI U42 Components U42_EMI@

CPU

BOM Structure

N16S_R1@

N16S_R3@

N16V_R1@

N16V_R3@

i3_7020U_R1@

i5_8250U_R1@

i5_8250U_R3@

i7_8550U_R1@

i7_8550U_R3@

i3_8130U_R1@

3

Item

X4E

On Board RAM (Hynix 4GB) H4G_MD@

On Board RAM (Micron 4GB) M4G_MD@

On Board RAM (Samsung 4GB) S4G_MD@

On Board RAM X76 Resistors X76RAM@

Realtek Card Reader RTK_CR@

Genesys Card Reader GNS_CR@

VRAM (Hynix 2GB)

VRAM (Hynix 4GB)

VRAM (Micron 2GB)

VRAM (Micron 4GB)

VRAM (Samsung 2GB)

VRAM (Samsung 4GB)

BOM Structure

X4E_U22_14@

X4E_U22_15@

X4E_U42_14@

X4E_U42_15@

H2G_VRAM@

H2G@

H2G_R1@

H2G_R3@

H4G_VRAM@

H4G@

H4G_R1@

H4G_R3@

M2G_VRAM@

M2G@

M2G_R1@

M2G_R3@

M4G_VRAM@

M4G@

M4G_R1@

M4G_R3@

S2G_VRAM@

S2G@

S2G_R1@

S2G_R3@

S4G_VRAM@

S4G@

S4G_R1@

S4G_R3@

X4E

U42

ZZZ X4E_U42@

U22

ZZZ X4E_U22@

4

USB 2.0 Port Table

Port External USB Port

1

2

USB2/3 Port (MB-1)

3

USB2/3 Port (MB-2)

4

5

Camera

6

Card Reader

7

NGFF WLAN+BT

USB 3.0 Port Table

Port

1

2

USB2/3 Port (MB-1)

3

USB2/3 Port (MB-2)

4

5 1

6 2

SATA Port Table

Port

0

HDD

1

ODD

ON BOARD RAM * 4

ZZZ S4G_MD@ ZZZ M4G_MD@ ZZZ H4G_MD@

X76 SAMSUNG 4GB MD X76 MICRON 4GB MD X76 HYNIX 4GB MD

X7677538L13 X7677538L14 X7677538L15

5

PCIE Port Table

Lane Port

1

3

4

5

6

7

8

9

10

11

12

GPU

LAN

NGFF WLAN+BT

HDMI Logo

ZZZ 45@

HDMI Logo

RO0000003HM

X4E U42

SMBUS Control Table

X

+V3VS

X X

Thermal

DGPU

Sensor

X X

+V3VS

X X X

+V3VS

2

TP PCH

X

X X

X

X+V

X

X X

X

+V3VS

X X

+V3VS

X

X X

X

*N16V -MX110

*N16S - MX130

GPU

UV1 N16S_R1@ UV1 N16V_R1@

N16S-GTR-S-A2 BGA 595P N16V-GMR1-S-A2 BG A 595P

SA00009FP00 SA00009IT00

UV1 N16S_R3@ UV1 N16V_R3@

N16S-GTR-S-A2 BGA 595P N16V-GMR1-S-A2 BG A 595P

SA00009FP30 SA00009IT30

SOURCE VGA BATT CHARGER NECP388 SODIM M

C C

D D

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMB_EC_CK4

SMB_EC_DA4

PCH_SMBCLK

PCH_SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

STATE

Full ON HIGH HIGH HIGH HIGH ON ON ON ON

S1(Power On Suspend) LOW HIGH HIGH HIGH ON ON ON LOW

S3 (Suspend to RAM) LOW LOW HIGH HIGH ON ON OFF OFF

S4 (Suspend to Disk) LOW LOW LOW HIGH ON OFF OFF OFF

S5 (Soft OFF) LOW LOW LOW LOW ON OFF OFF OF F

NECP388

+3VALW

NECP388

+3VVGS

+3VS

NECP388

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

SIGNAL

SLP_S1# SLP_S3# SL P_S4# SLP_S5# +VALW +V +VS Clock

1

V

X

+3VALW

+19VV_VIN

X X

X X X X X

+V3VS

X X X X X X X X

X X X X

X X X X X X X X

X X X

+V3VS

3VS

X

GSENSOR

X

X

+V3VS

X

X

X

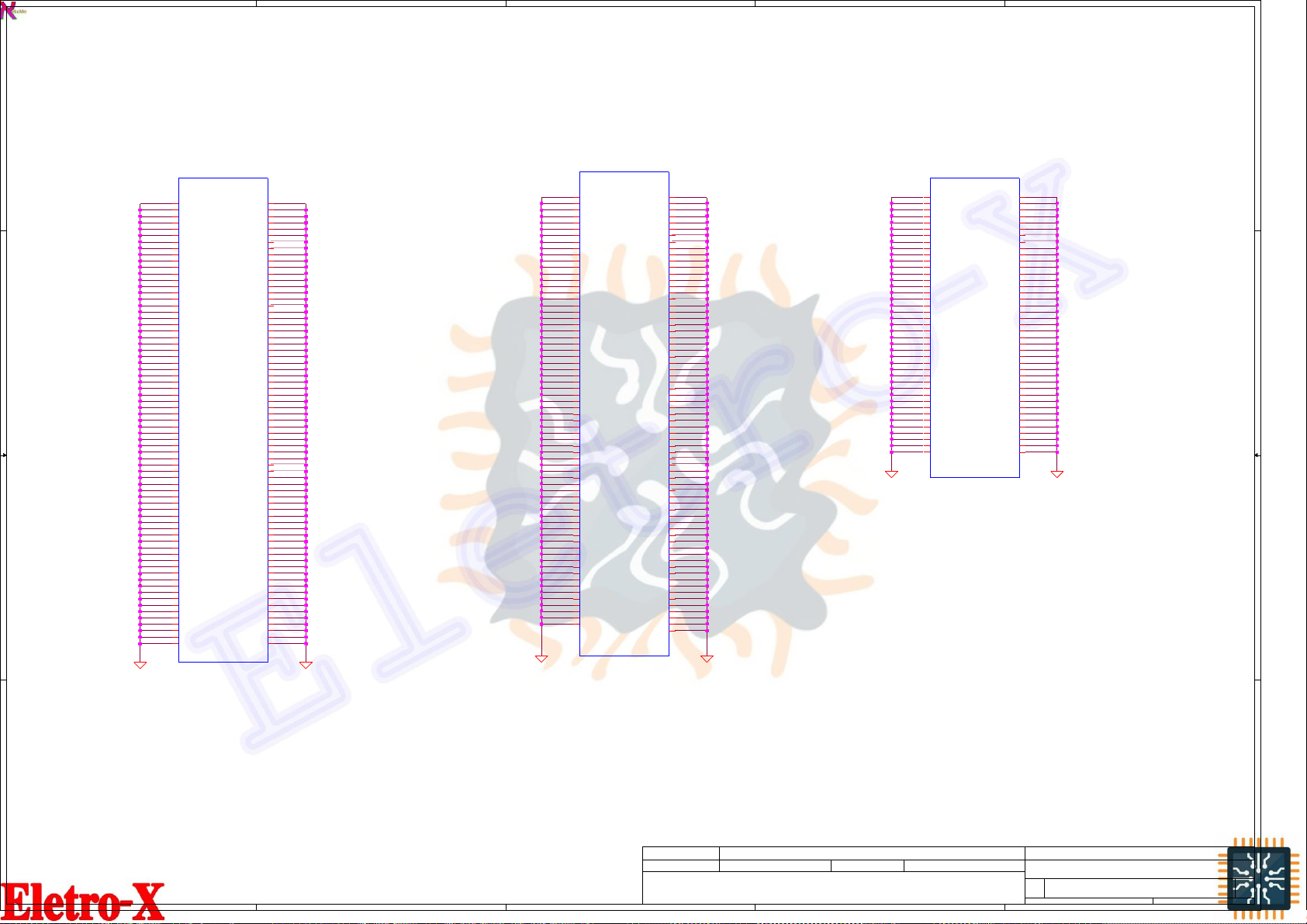

Device ID:0x174E

(

Device ID: 0x174D

(

)

CPU

)

KBL U22 (= U22@) KBL U42 (= U42@)

UC1 i3_7020U_R1@ UC1i5 _8250U_R1@ UC1i7_8550U_R1@ UC1 i3_8130U_R1@

QNZU H02.3G

SA0000BLH10

UC1 i3_7020U_U22@ UC1i5 _8250U_R3@ UC1i7_8550U_R3@ UC1 i3_8130U_R3@ UC1 i3_7020U_U42@

SR3TK H02.3G

SA0000BLH50

3

X4EABQ38L01

GDDR5 VRAM * 2

Securiiity Clllassiiifiiicatiiion

Issued Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIIIVIIISIIION OF R&D DEPARTMENT

EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIIT CONTAIIINS

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,,IIINC...

X4E U22

X4EABQ38L02

CARD READER

*Main Source - Realtek

*Substitute - Genesys

2GB

ZZZ H2G_VRAM@

X76 H YNIX 2GB

X7677538L06

2018/03/09 2019/03/09

ZZZ M2G_VRAM@

X76 MICRO N2GB

X7677538L05

Compalll Secret Data

Deciiiphered Date

4

ZZZ S2G_VRAM@

X76 SAMSUNG 2GB

X7677538L04

SR3LA Y0 1.6G FCBGA

SA0000AWB20

SR3LA Y0 1.6G FCBGA

SA0000AWB50

SR3LC Y0 1.8G FCBGA

SA0000AWC20

SR3LC Y0 1.8G FCBGA

SA0000AWC50

QP8K Y02.2G

SA0000BKN20

SR3W 0 Y02.2G

SA0000BKN30

Compal Electronics, Inc.

Tiiitttllle

NotesList

Siiize DocumentttNumberrr

Custttom

Dattte:::

PCB

ZZZ 14_DAZ@

PCB

DAZ29900201

ZZZ 15_DAZ@

PCB

DAZ29A00201

SR3LD Y02.3G

SA0000BLD60

LA-G202P

5

R e v

Sheettt 3 o fff55Frrriiiday,,, Marrrch 09,,, 2018

1...0

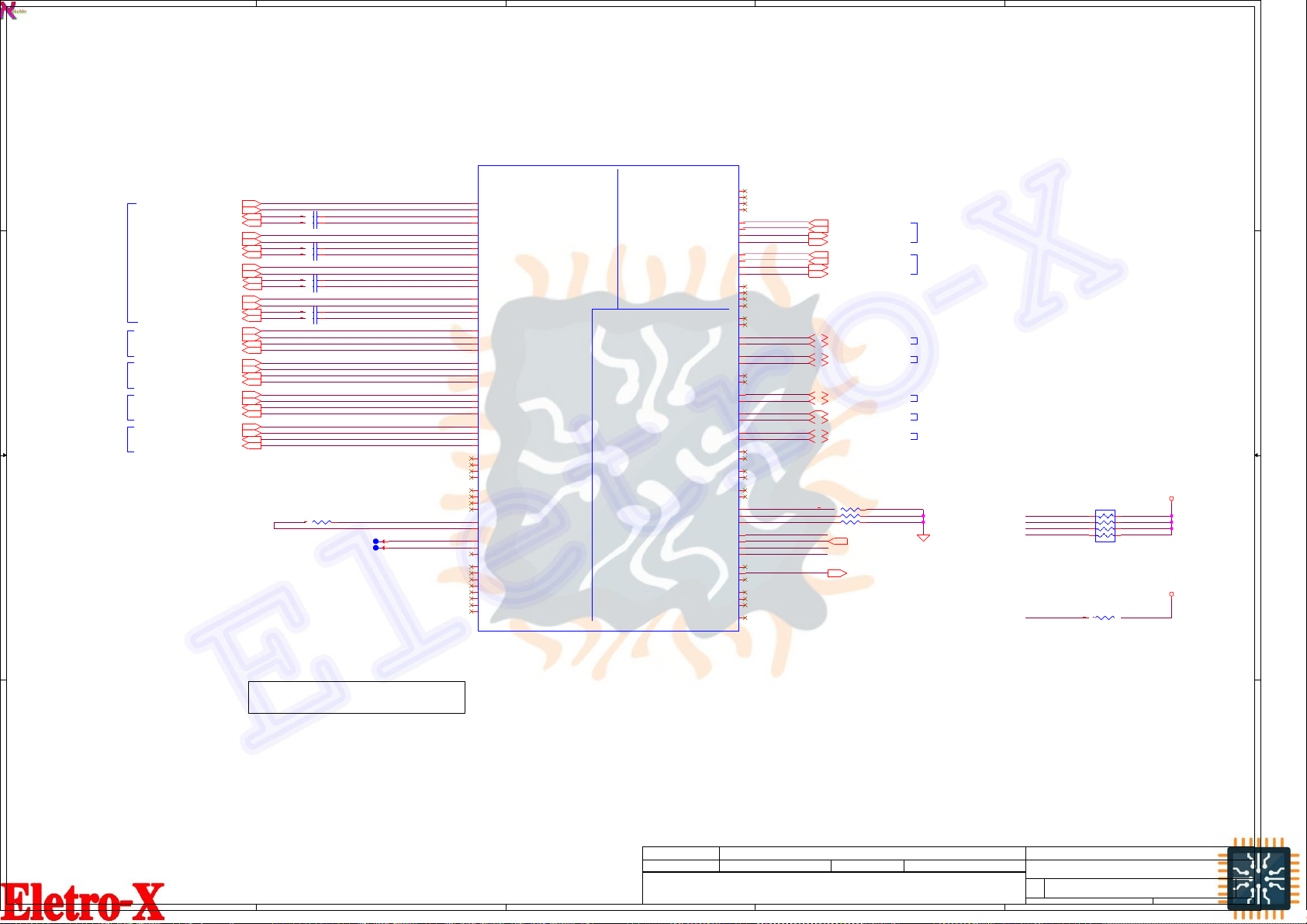

Page 6

A

1 1

<HDMI>

HDMI DDC (Port C)

2 2

B

<29> HDMI_TX2-_CK

<29> HDMI_TX2+_CK

<29> HDMI_TX1-_CK

<29> HDMI_TX1+_CK

<29> HDMI_TX0-_CK

<29> HDMI_TX0+_CK

<29> HDMI_CLK-_CK

<29> HDMI_CLK+_CK

<29> HDMICLK_NB

<29> HDMIDAT_NB

EDP_COMP

C

DDI

DISPLAY SIDEBANDS

SKL-U

1 OF20

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDAT A

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDAT A

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKL-U_BGA1356 @

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_ UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

RSVD

EDP_BKLT EN

EDP_BKLT CTL

EDP_VDDEN

B45

B47

G46

L6

R11

U13

D

C47

C46

D46

C45

A45

A47

E45

F45

B52

G50

F50

E48

F48

F46

L9

L7

N9

L10

R12

EDP_TXN0 <28>

EDP_TXP0 <28>

EDP_TXN1 <28>

EDP_TXP1 <28>

EDP_AUXN <28>

EDP_AUXP <28>

TMDS_B_HPD <29>

EC_SCI# <10,36>

EDP_HPD <28>

ENBKL <36>

INVPWM <28>

PCH_ENVDD <28>

<eDP>

From HDMI

From eD P

E

< Compensation PU For eDP >

+1.0VS_VCCIO

EDP_COMP

2

1

1 2

24.9_0402_1%

H_THERMTRIP#

<36> H_PROCHOT#

+1.0VS_VCCIO

12

If routedMS, PECIrequires 18 milsspacingto other signals

RC4

1K_0402_5%

1 2

RC6

RC7 2

RC8 2 1 49.9_040 2_1%

RC9 2@1 49.9_0402_1%

RC10 2 @

<36> H_PECI

499_0402_1%

1

49.9_0402_1%

1 49.9_0402_1%

T99 TP@

T100 TP@

T103 T P@

T105 T P@

T107 T P@

T109 TP@

EDRAM_OPIO_RCOMP

SOC_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

CPU_POPIRCOMP

PCH_OPIRCOMP

EOPIO_RCOMP

PCH_OPIRCOMP

H66

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMT RIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356 @

SKL-U

CPUMISC

4 OF20

JTAG

PROC_T CK

PROC_T DI

PROC_T DO

PROC_T MS

PROC_T RST#

PCH_JT AG_TCK

PCH_JT AG_TDI

PCH_JT AG_TDO

PCH_JT AG_TMS

PCH_TRST#

Rev_1.0

JTAGX

D60

A61

C60

B59

D59

A56

C59

C61

A59

B61

B56

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

T116 TP@

< PU/PD for CMC Debug >

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

SOC_XDP_TRST#

RC12 1 @

RC13 1 @DCI@

RC14 1 @DCI@ 2

RC15 1@

RC23 1@

+1.0VS_VCCIO

2

51_0402_5%

@RC11 1

2

51_0402_5%

2

51_0402_5%

51_0402_5%

2

51_0402_5%

2

51_0402_5%

RC3

Trace width=20 mils, Spacing=25mil, Maxlength=100mils

+1.0V_VCCST

RC5 1K_0402_5%

3 3

4 4

SecuriiityClllassiiifiiicatiiion

Issued Date Decipii hered Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS

A

B

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

C

2018/03/09 2019/03/09

Compal Secret Data

Tiiitllle

Siiize Document Number

D

Compal Electronics,Inc.

SKL-U(1/12)DDI,EDP,MISC,CMC

Custttom

LA-G202P

E

R ev

Sheet 6 o f 55Date: Friiiday,,, March 09,,,2018

1...0

Page 7

5 4 3 2 1

Interleaved Memory

@

AU53

AT53

AU55

AT55

BA56

BB56

AW 56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW 52

AY55

AW 54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW 50

AT52

AY67

AY68

BA67

AW 67

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

M_A_ACT#

DDR_A_BG1

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PARITY

+0.6V_A_VREFCA

+0.6V_B_VREFDQ

DDR_PG_CTRL

D D

<18> DDR_A_D[0..15]

<18> DDR_A_D[16..31]

C C

<18> DDR_A_D[32..47]

<18> DDR_A_D[48..63]

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW 65

DDR0_DQ[17]/DDR0_DQ[33]

AW 63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW 61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW 59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW 39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW 37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW 35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW 33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW 31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW 29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW 27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW 25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

BB25

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356 @

SKL-U

DDR3L / LPDDR3 / DDR4

DDR0_MA[5]/DDR0_CAA[0]/DDR0 _MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0 _MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0 _MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0 _MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0 _MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR 0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR 0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR 0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR 0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR 0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_ MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_ MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0 _MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR 0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0 _MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0 _MA[0]

Interleave / Non-Interl eaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2 ]/DDR0_DQ SP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3 ]/DDR0_DQ SP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4 ]/DDR1_DQ SP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5 ]/DDR1_DQ SP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6 ]/DDR1_DQ SP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH -A

2 OF20

DDR_VREF _CA

DDR0_VREF _DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

Rev_1.0

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1 ]

DDR0_ODT[0 ]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_A_CLK#0

1 2

CC110

3300P_0402_50V7-K

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

TP@ T186

TP@ T189

DDR_A_CKE0 <18,20>

TP@ T190

DDR_A_CS#0 <18,20>

TP@ T187

DDR_A_ODT0 <18,20>

TP@ T188

DDR_A_MA5 <18,20>

DDR_A_MA9 <18,20>

DDR_A_MA6 <18,20>

DDR_A_MA8 <18,20>

DDR_A_MA7 <18,20>

DDR_A_BG0 <18,20>

DDR_A_MA12 <18,20>

DDR_A_MA11 <18,20>

M_A_ACT# <18,20>

DDR_A_BG1 <18>

DDR_A_MA13 <18,20>

DDR_A_MA15 <18,20>

DDR_A_MA14 <18,20>

DDR_A_MA16 <18,20>

DDR_A_BA0 <18,20>

DDR_A_MA2 <18,20>

DDR_A_BA1 <18,20>

DDR_A_MA10 <18,20>

DDR_A_MA1 <18,20>

DDR_A_MA0 <18,20>

DDR_A_MA3 <18,20>

DDR_A_MA4 <18,20>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

DDR_A_ALERT# <18>

DDR_A_PARITY <18,20>

+0.6V_A_VREFCA <18> @

T25

+0.6V_B_VREFDQ <19>

<19> DDR_B_D[0..15]

<19> DDR_B_D[16..31]

<19> DDR_B_D[32..47]

<19> DDR_B_D[48..63]

Trace width/Spacing >= 20mils

Place componment near SODIMM

#543016 PDG0.9 P.163 RC place near SODIMM

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ [16]

AF64

DDR1_DQ[1]/DDR0_DQ [17]

AK65

DDR1_DQ[2]/DDR0_DQ [18]

AK64

DDR1_DQ[3]/DDR0_DQ [19]

AF66

DDR1_DQ[4]/DDR0_DQ [20]

AF67

DDR1_DQ[5]/DDR0_DQ [21]

AK67

DDR1_DQ[6]/DDR0_DQ [22]

AK66

DDR1_DQ[7]/DDR0_DQ [23]

AF70

DDR1_DQ[8]/DDR0_DQ [24]

AF68

DDR1_DQ[9]/DDR0_DQ [25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356 @

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1 _MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1 _MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1 _MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1 _MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1 _MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR 1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR 1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR 1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR 1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR 1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_ MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_ MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1 _MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR 1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1 _MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1 _MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0 ]/DDR0_DQ SP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1 ]/DDR0_DQ SP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2 ]/DDR0_DQ SP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3 ]/DDR0_DQ SP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4 ]/DDR1_DQ SP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1 _DQSP[3]

DDR CH- B

3 OF20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1 ]

DDR1_ODT[0 ]

DDR1_ODT[1]

DDR3L / LPDDR3 /DDR4

DDR1_MA[3]

DDR1_MA[4]

Interleave / Non- Interleaved

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_1.0

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW 42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW 44

BB44

AY47

BA44

AW 46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0DDR_B_D0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

M_B_ACT#

DDR_B_BG1

DDR_B_MA13

DDR_B_MA15

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

#543016 PDG0.9 P.117

W=12-15 Space= 20/25 L=500mil

RC16 1 SDP@ 2 200_0402_1%

RC17 1 2 80.6_0402_1%

RC18 1 2 100_0402_1 %

DDR_B_CLK#0 <19>

DDR_B_CLK#1 <19>

DDR_B_CLK0 <19>

DDR_B_CLK1 <19>

DDR_B_CKE0 <19>

DDR_B_CKE1 <19>

DDR_B_CS#0 <19>

DDR_B_CS#1 <19>

DDR_B_ODT0 <19>

DDR_B_ODT1 <19>

DDR_B_MA5 <19>

DDR_B_MA9 <19>

DDR_B_MA6 <19>

DDR_B_MA8 <19>

DDR_B_MA7 <19>

DDR_B_BG0 <19>

DDR_B_MA12 <19>

DDR_B_MA11 <19>

M_B_ACT# <19>

DDR_B_BG1 <19>

DDR_B_MA13 <19>

DDR_B_MA15 <19>

DDR_B_MA14 <19>

DDR_B_MA16 <19>

DDR_B_BA0 <19>

DDR_B_MA2 <19>

DDR_B_BA1 <19>

DDR_B_MA10 <19>

DDR_B_MA1 <19>

DDR_B_MA0 <19>

DDR_B_MA3 <19>

DDR_B_MA4 <19>

DDR_B_DQS#0 <19>

DDR_B_DQS0 <19>

DDR_B_DQS#1 <19>

DDR_B_DQS1 <19>

DDR_B_DQS#2 <19>

DDR_B_DQS2 <19>

DDR_B_DQS#3 <19>

DDR_B_DQS3 <19>

DDR_B_DQS#4 <19>

DDR_B_DQS4 <19>

DDR_B_DQS#5 <19>

DDR_B_DQS5 <19>

DDR_B_DQS#6 <19>

DDR_B_DQS6 <19>

DDR_B_DQS#7 <19>

DDR_B_DQS7 <19>

DDR_B_ALERT# <19>

DDR_B_PARITY <19>

DDR_DRAMRST# <18,19>

< For ODT & V TT Power Co ntrol >

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

UC2

1

NC

DDR_PG_CTRL

A A

VCC

2

A

3

GND

74AUP1G07SE-7 SOT353 5P LOW PW BUFF

SA00007WE00

1

CC1 RC132

0.1U_0201_10V6K 100K_0402_5%

@

2

5

4

Y

+3VS+1.2V

12

DDR_DRAMRST#

DDR_VTT_PG_CTRL <45>

Security Classification

Issued Date Decipherii ed Date

THIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIETARY P ROPERTY OF COMPAL ELECTRONIICS,,, IIINC. AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION. THIIIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIIISIIION OF R& D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONICS,,, IIINC. NEIIITHER THIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS

5 4 3 2 1

MAY BE USED BY OR DIISCLOSED TO ANY THIRD PARTY WIIITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONIIICS,,,IIINC.

+1.2V

12

RC20

470_0402_5%

@

1

CC96

100P_0402_50V8J

ESD@

2

Close t oCPU

2018/03/09 2019/03/09

Compal Secret Data

Recommended By Intel Max

RC16

SD034121090

121_0402_1%

DDP@

Compal Electronics,Inc.

Tiiittllle

Siiize Document Number

Custttom

Dattte::: Friiiday,,, March 09,2018

SKL-U(2/12)DDR3L

LA-G202P

Sheet 7

R ev

1...0

55

off

Page 8

5 4 3 2 1

L

T

L

T

T

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC ==> Default

D D

+3VALW

RC21 1 @ 2 1K_0402_5%

RC22 1 @ 2 1K_0402_5%

RC24 1 @ 2 1K_0402_5%

SOC_SPI_IO2

SOC_SPI_IO3

1 = eSPI is selected for EC

SOC_SML0CLK

SOC_SML0DATA

RPC12

1 8

2 7

346

5

499_0804_8P4R_1%

+3VS

UC1E

+3VS

RC112 1 2 10K_0 402_5%

+3VS

RC25 1 2 8.2K_04 02_5%

C C

KB_RST#

SERIRQ

<36> SERIRQ

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

KB_RST#

SERIRQ

AW 3

AW 2

AW 13

AY11

SPI - FLASH

AV2

SPI0_CLK

SPI0_MISO

AV3

SPI0_MOSI

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/ SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21 /SPI1_IO2

V2

GPP_D22 /SPI1_IO3

M1

GPP_D0/ SPI1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356 @

SKL-U

LPC

GPP_A14/SUS_ST AT#/ES PI_RESET#

5 OF20

SMBUS,SMLINK

GPP_A9/CLKOUT _LPC0/ESPI_CL K

GPP_C0/SMBC

GPP_C1/SMBDA

GPP_C2/SMBALERT

GPP_C3/SML0C

GPP_C4/SML0DA

GPP_C5/SML0ALERT

GPP_C6/SML1CL

GPP_C7/SML1DA

GPP_B23/SML1ALERT#/PCHHOT

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ ESPI_CS#

GPP_A10/CLKOUT _LPC1

GPP_A8/CLKRUN#

Rev_1.0

K

A

#

K

A

#

K

A

#

R8

R10

W2

W1

BA13

BB13

AY12

BA12

BA11

AY9

AW 11

R7

R9

W3

V3

AM7

AY13

AW 9

SOC_SMBCLK

SOC_SMBDATA

SOC_SMBALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SML0ALERT#

SOC_SML1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK0

PM_CLKRUN#

SOC_SMBCLK <19>

SOC_SMBDATA <19>

TP@ T124

TP@ T125

EC_SMB_CK2 <24,36>

EC_SMB_DA2 <24,36>

LPC_AD0 <36>

LPC_AD1 <36>

LPC_AD2 <36>

LPC_AD3 <36>

LPC_FRAME# <36>

RC26 1 EMI@ 2 22_0402_5%

SMB

(Link to DDR)

SML1

(Link to EC,DGPU,Thermal Sensor)

CLK_LPC_EC <36>

PM_CLKRUN# <36>

SOC_SML1ALERT#

SOC_SMBCLK

SOC_SMBDATA

EC_SMB_CK2

EC_SMB_DA2

PM_CLKRUN#

RC113 1 @ 2 150K_0402_5%

RC31 1 2 8.2K_0402_5%

Follow 543016_SKL_U_Y_PDG_0_9

RPC2

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

+3VS

+3VS

RPC1, RPC3 and RC30 are close to UC3

RPC1

SOC_SPI_SO

SOC_SPI_CLK

SOC_SPI_SI

SOC_SPI_IO2

EC_SPI_CLK

EC_SPI_MOSI

EC_SPI_CS0#

EC_SPI_MISO

SOC_SPI_IO3

RC30 EMI@ 33_0402_5%

B B

From EC

<36> EC_SPI_CLK

<36> EC_SPI_MOSI

<36> EC_SPI_CS0#

<36> EC_SPI_MISO

From SOC

1 8

2 7

3 6

4 5

33_0804_8P4R _5%

EMI@

2

1

RPC3

8

1

7

2

6

3

5

4

33_0804_8P4R _5%

EMI@

SOC_SPI_SO_0_R

SOC_SPI_CLK_0_R

SOC_SPI_SI_0_R

SOC_SPI_IO3_0_R

SOC_SPI_IO2_0_R

SOC_SPI_CLK_0_R

SOC_SPI_SI_0_R

SOC_SPI_CS#0

SOC_SPI_SO_0_R

< SPI ROM - 8MB > -Main Source - XMC

+3VALW

A A

5 4 3 2 1

SOC_SPI_CS#0

SOC_SPI_SO_0_R

SOC_SPI_IO2_0_R

UC3

1

/CS VCC

2

DO(IO1) /HOLD(IO3)

3

/WP( IO2) C LK

4 5

GND DI(IO0)

S IC FL 64M XM25QH64AHIG SOP 8P

SA0000B8300

@

CC2 1 2 0.1U_0201_10V K X5R

8

SOC_SPI_IO3_0_R

7

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

1

CC3

10P_0402_50 V8J

2

@EMI@

SecuriiityClllassiiifiiicatiiion

Issued Date Decipii hered Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

2018/03/09 2019/03/09

Compal Secret Data

Tiiittllle

Siiize Documentt Number

Custttom

Compal Electronics,Inc.

SKL-U(3/12)SPI,SMB,LPC,ESPI

LA-G202P

Sheett 8 o ff 55Datte:: Friiiday,,, March 09,,,2018

R ev

1...0

Page 9

5 4 3 2 1

D D

< HD AUDIO >

<30> HDA_BITCLK_AUDIO

<30> HDA_SYNC_AUDIO

<30> HDA_SDOUT_AUDIO

RPC4

8

1

7

2

3

6

4

5

33_0804_8P4R _5%

EMI@

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

<30> HDA_SDIN0

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

< To Enable ME Over ride >

HDA_SPKR

HDA_SDOUT

<30> HDA_SPKR

HDA_SPKR

C C

<36> ME_EN

RC116 1 2 0_0402_5%

+3VS

RC33 1 @ 2 2.2K_0402_5%

SPKR (Internal Pull Down):

B B

TOP Swap Override

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

UC1G

BA22

AY22

BB22

BA21

AY21

AW 22

AY20

AW 20

AK7

AK6

AK9

AK10

AW 5

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO /I2S0_T XD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST #/I2S1_SCLK

J5

GPP_D23/I2S_MC LK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356 @

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_D P0

C38

CSI2_DN1

D38

CSI2_D P1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_D P4

C33

CSI2_DN5

D33

CSI2_D P5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356 @

SKL-U

SKL-U

9 OF20

GPP_A17/SD_PW R_EN#/ISH_GP7

7 OF20

Rev_1.0

CSI2_CLKN0

CSI2_C LKP0

CSI2_CLKN1

CSI2_C LKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/ FLASHT RIG

EMMC

GPP_F13/EMMC_DAT A0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DAT A6

GPP_F20/EMMC_DAT A7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO / SDXC

GPP_G0/SD_C MD

GPP_G1/SD_D ATA0

GPP_G2/SD_D ATA1

GPP_G3/SD_D ATA2

GPP_G4/SD_D ATA3

GPP_G5/SD_CD #

GPP_G6/SD_C LK

GPP_G7/SD_W P

GPP_A16/SD_1P 8_SEL

SD_RCOMP

GPP_F23

C37

D37

C32

D32

C29

D29

B26

A26

E13

RC80 1 @ 2 100_0402_1%

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

RC129 1 @ 2 200_0402_1%

Rev_1.0

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

RC76 1 @ 2 200_0402_1%

AF13

A A

SecuriiityClllassiiifiiicatiiion

IssuedDate

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS

5 4 3 2

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

2018/03/09 2019/03/09

Compal Secret Data

Deciiiphered Date

Tiiittllle

Siiize Documentt Number

Custttom

Datte:: Friiiday,,, March 09,,,2018

Compal Electronics,Inc.

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-G202P

Sheett 9 o ff

1

R ev

1...0

55

Page 10

5 4 3 2 1

SOC_XTAL24_IN

U22_EMI@

RC154 1 2 33_040 2_1%

XTAL24_IN

SOC_XTAL24_OUT

D D

<21> CLK_PEG_VGA#

DGPU

<21> CLK_PEG_VGA

<21> VGA_CLKREQ#

<31> CLK_PCIE_LAN#

LAN

+3VS

RPC6

8

VGA_CLKREQ#

1

7

WLANCLK_REQ#

2

3

6

5

LANCLK_REQ#

4

10K_0804_8P4R_5%

+3VL_RTC

C C

RC36 1 2 20K_0402_5%

CC6 1 2 1U_0201_6.3V6M

RC37 1 2 20K_0402_5%

CC7 1 2 1U_0201_6.3V6M

CLRP2 1 2 SHORT PADS

RC39 1 2 1M_0402_5%

+3VALW

8

7

6

B B

5 4

10K_0804_8P 4R_5%

ESD@ 1

CC97

ESD@ 1

CC94

ESD@ 1

CC95

+3VALW

1 2

RC47 1K_040 2_5%

RPC7

1

2

3

2

100P_0402_5 0V8J

2

100P_0402_5 0V8J

2

100P_0402_5 0V8J

SE00000UC00

SE00000UC00

PCH_PWROK

EC_RSMRST#

LAN_WAKE#

SYS_RESET#

SYS_RESET#

EC_RSMRST#

SYS_PWROK

WAKE#

EC_SCI# <6,36>

SOC_SRTCRST#

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

RC38 1 2 0_0402_5%

Only For Power Sequ ence Debug

From EC (Open-Drain)

A A

5 4 3 2 1

<36> VCCST_PWRGD

NGFF WL+BT

+1.0V_VCCST

<31> CLK_PCIE_LAN

<31> LANCLK_REQ#

<33> CLK_PCIE_WLAN#

<33> CLK_PCIE_WLAN

<33> WLANCLK_REQ#

EC_CLEAR_CMOS# <36>

<36> EC_RSMRST#

<36> SYS_PWROK

<36> PCH_PWROK

12

RC52

1K_0402_5%

RC53 1 2 60.4_0402_1%

1

CC117

100P_0402_50V8J

2

ESD@

T132 TP@

VGA_CLKREQ#

LANCLK_REQ#

WLANCLK_REQ#

< PCH PLTRST Buffer >

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

EC_RSMRST#

WAKE#

LAN_WAKE#

EC_VCCST_PG

SOC_PLTRST#

AY17

UC1J

D42

CLKOUT _PCIE_N0

C42

CLKOUT _PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT _PCIE_N1

A42

CLKOUT _PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT _PCIE_N2

C41

CLKOUT _PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT _PCIE_N3

C40

CLKOUT _PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT _PCIE_N4

A40

CLKOUT _PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT _PCIE_N5

E38

CLKOUT _PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356 @

RC42 1 @ 2 0_0402_5%

+3VS

5

UC4@

1

B

2

A

TC7SH08FUF_SSOP5

SA007080100

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

RSMRST#

A68

PROCPW RGD

B65

VCCST_PW RGD

B6

SYS_PW ROK

BA20

PCH_PW ROK

BB20

DSW _PW ROK

AR13

GPP_A13/SUSW ARN#/SUSPWRD NACK

AP11

GPP_A15/SUSACK#

BB15

WA KE#

AM15

GPD2/LAN_WAKE#

AW 17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356 @

G P

3

SYSTEM POWERMANAGEMENT

SKL-U

CLOCKSIGNALS

10 OF20

4

Y

%

12

100K_0402_5

RC44

2 1

SKL-U

11 OF20

100P_0402_50V8

J

ESD@

CC8

GPP_B11/EXT_PW R_GATE#

GPP_B2/VRALERT #

SecuriiityClllassiiifiiicatiiion

Issued Date Decipii hered Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRADE SECRET IIINFORMATIIION... THIIIS SHEET MA Y NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS MAY BE USED

BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

Rev_1.0

CLKOUT _ITPXD P_N

CLKOUT _ITPXD P_P

GPD8/SU SCLK

XCLK_BIASREF

PCI_RST# <21,31,33,36>

GPP_B12/SLP_S0#

GPD4/SL P_S3#

GPD5/SL P_S4#

GPD10/SLP_S5#

GPD9/SL P_WLAN#

GPD6/SL P_A#

GPD3/PW RBT N#

GPD1/AC PRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

F43

E43

BA17 SUSCLK

SOC_XTAL24_IN

E37

XTAL24_IN

XTAL24_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

Rev_1.0

SLP_SUS#

SLP_LAN#

2018/03/09 2019/03/09

AP15

BA16

AY16

AW 15

AY15

AU13

AP16

AM11

E35

AM20

AM16

AT11

AN15

BB17

AN16

BA15

AU11

AM10

E42

AM18

AN18

SOC_XTAL24_OUT

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#

AC_PRESENT_R

PM_BATLOW#

SM_INTRUDER#

SOC_VRALERT#

TP@T130

PM_SLP_S3# <36>

PM_SLP_S4# <36,43,46>

TP@T131

TP@T133

TP@T134

RC103 1 @ 2 0_0402_5%

Compal Secret Data

SUSCLK <33>

RC155

U22_EMI@

1

XTAL24_OUT

2 33_0402_1%

27P_0402_50V8J

XCLK_BIASREF

U22@

RC34 1 2 1M_0402_5%

YC1 U22@

24MHZ_18PF_XRCG B24M000F2P51R0

SJ10000UJ00

1

1

NC NC

2 4

U22@

1

CC4

2

1

RC35

RC110 1 @ 2 60.4_0402_ 1%

2 2.7K_0402_1%

Follow 5 46765_20 14WW48_Skyla ke_MOW_Rev_1_0

Stuff 2.7 k ohm (RC 35) PU for S kyLake-U

Stuff 60. 4 ohm (RC 110) PD for CannonLa ke-U

SOC_RTCX2

SOC_RTCX1

PBTN_OUT# <36>

AC_PRESENT <24,36>

Tiiitllle

Siiize Document Number Rev

Custttom 1...0

Date: Friiiday,,, March 09,,,2018 Sheet 10 o ff 55

RC41 1 2 10M_0402_5 %

YC2

1 2

S CRYSTAL 32.768KHZ 9PF X1A00014100 0200

SJ10000PW00

6.8P_0402_50V8

C

1

CC9

2

PM_BATLOW #

AC_PRESENT

SOC_VRALERT#

RC46 1 2 8.2K_04 02_5%

RC48 1 @ 2 10K_0402_5%

RC50 1@

Compal Electronics,Inc.

SKL-U(5/12)CLK,PM,GPIO

LA-G202P

3

3

+1.0V_CLK5_F24NS

2 10K_0402_5%

U22@

27P_0402_50V8J

1

CC5

2

6.8P_0402_50V8

C

1

CC10

2

+3VALW

Page 11

5 4 3 2 1

GSPI0_MOSI (Internal Pull Down):

No Reboot

0 = Disable No Reboot mode. ==> Default

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This funct i oni s us ef ul

D D

when running ITP/XDP.

Capacity Description

WITHOUT ON-BOARD RAM

SAMSUNG 2666MHz K4A8G165WC-BCTD X7677538L13 SA0000B6F10

HYNIX 2666MHzH5AN8G6NCJR-VKC X7677538L15 SA0000BMN10

MICRON 2666MHzMT40A512M16LY-075:E X7677538L14 SA0000ARD30

4GB

N/A N/A N/A

( )

( )

( )

N/A N/A N/A

N/A N/A N/A

N/A N/A N/A

GSPI1_MOSI (Internal Pull Down):

Boot BI OS Strap Bit

0 = S PI Mode ==> Default

1 = LP C Mode

+3VS

RC59 1 @ 2 4.7K_0402_5%

RC60 1 @ 2 150K_0402_5%

GSPI0_MOSI

GSPI1_MOSI

Capacity Description

WITHOUT ON-BOARD RAM

SAMSUNG 2666MHz K4A8G165WC-BCTD 0 0 1

HYNIX 2666MHzH5AN8G6NCJR-VKC 0 1 0

MICRON 2666MHzMT40A512M16LY-075:E 0 1 1

4GB

N/A 1 0 0

( )

( )

( )

N/A 1 0 1

N/A 1 1 0

X76

PART NUMBER R3

N/A

GPP B19

_ _

OBRAMID

GPP B20

_

0 OBRAM ID

_ _ _

0 0 0

( )

N/A

GPP B21

1 OBRAM ID

+3VS+3VS +3VS

12

RC135

10K_0402_5%

@

OBRAM_ID0

12

RC214

2

10K_0402_5%

X76RAM@

12

RC133

10K_0402_5%

X76RAM@

12

RC134

10K_0402_5%

X76RAM@

OBRAM_ID1

12

RC215

10K_0402_5%

X76RAM@

12

RC138

10K_0402_5%

X76RAM@

OBRAM_ID2

Function

Mount ODD

Mount 2nd HDD 1

+3VS

1

RC208

1 @

RC207

HDD ODD DETECT

(

HDD_ODD_DETECT

2

10K_0402_5%

2

10K_0402_5%

_ _

GPP D11

_ )

0

HDD_ODD_DETECT <35>

N/A 1 1 1

Function

15"

C C

+3VS

RPC10

1

8

2

7

3

6

4 5

49.9K_0804_ 8P4R_1%

RPC8

18

27

6

3

5

4

10K_0804_8P4R_5%

RPC11

1

8

2

7

3

6

5 4

2.2K_0804_8 P4R_5%

UART0_RX

UART0_TX

DGPU_PWR_EN

DGPU_HOLD_RST#

WLBT _OFF#

I2C0_SCL_TP

I2C0_SDA_TP

Touch PAD

<38> TP_INT#

<33> WLBT_OFF#

<33> UART0_RX

<33> UART0_TX

<38> I2C0_SDA_TP

<38> I2C0_SCL_TP

SOC_GPIOB17

GSPI0_MOSI

OBRAM_ID0

OBRAM_ID1

OBRAM_ID2

GSPI1_MOSI

SOC_GPIOC10

+3VS

B B

+3VS

UC1F

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

AB3

AD1

AD2

AD3

AD4

AH9

AH10

AH11

AH12

AF11

AF12

W 4

U7

U6

U8

U9

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/ UART0_RXD

GPP_C9/ UART0_TXD GPP_F10/I2C5_SDA/ISH _I2C2 _SDA

GPP_C10 /UART0_RTS# GPP_F11/I2C5_SCL/ISH _I2C2_SCL

GPP_C11 /UART0_CTS#

GPP_C20 /UART2_RXD

GPP_C21 /UART2_TXD

GPP_C22/UART 2_RTS#

GPP_C23/UART 2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18 /I2C1_SD A

GPP_C19/I2C1_SCL GPP_A18/ISH_G P0

GPP_F4/I2C2_ SDA GPP_A20/ISH_GP2

GPP_F5/I2C2_ SCL G PP_A21/ISH_GP3

GPP_F6/I2C3_ SDA GPP_A23/ISH_GP5

GPP_F7/I2C3_SCL Sx_EXIT_HOLDOFF# / G PP_A12 / BM_BU SY# / ISH_GP6

GPP_F8/I2C4_ SDA

GPP_F9/I2C4_ SCL

SKL-U_BGA1356 @

SKL-U

GPP_D13/ISH_UART0_RXD/SML0BD ATA/I2C 4B_SDA

GPP_D14/ISH_UART0_T XD/SML0BCLK/I2C4B _SCL

6 OF20

GPP_D15/ISH_UART0_RT S#

GPP_D16/ISH_UART0_CT S#/SML0BALERT #

GPP_C12/UART 1_RXD/IS H_UART1_RXD

GPP_C13/UART 1_TXD/ISH_UART 1_TXD

GPP_C14/UART 1_RTS#/ISH _UART1_RTS#

GPP_C15/UART 1_CTS#/ISH _UART1_CTS#

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_A19/ISH_GP1

GPP_A22/ISH_GP4

P2

P3

HDD_ODD_DETECT

P4

MODEL_SETTING

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

DGPU_PWR_EN

AC1

DGPU_HOLD_RST#

AC2

GPU_ALL_PGOOD

AC3

DGPU_PRSNT

AB4

AY8

BA8

DGPU_SEL

BB7

BA7

AY7

AW 7

AP13

DGPU_PWR_EN <26,36>

DGPU_HOLD_RST# <21>

GPU_ALL_PGOOD <26>

14" 1

+3VS

Function

DIS

UMA Only 1

+3VS

Function DGPUSEL

N16V-GMR1 MX110

N16S-GTR M X130 1

+3VS

MODEL SETTING

GPP D12

(__ )

0

RC206 1 14@ 2 10K_0402_5%

RC205 1 15@ 2 10K_0402_5%

DGPU PRSNT

_

GPP C15

_ )

(

0

RC61 1 UMA@ 2 10K_0402_5%

RC62 1 DIS@ 2 10K_040 2_5%

GPP0A20

)

)

N16S_R1@

N16V_R1@

( _

(

(

RC210 1 2 10K_0402_5 %

RC209 1 2 10K_0402_5%

MODEL_SETTING

DGPU_PRSNT

_

)

DGPU_SEL

*N16V -MX110 Device ID: 0x174E

*N16S - MX130 Device ID:0x174D

RC210 N16S_R3@

10K_0402_5%

RC209 N16V_R3@

10K_0402_5%

(

(

)

)

SOC_GPIOC10

SOC_GPIOB17

A A

RC204

RC195

1

1

GPU_EVENT#

2

0_0402_5%

GC6_FB_EN

2 0_0402_5%

5 4 3 2

GPU_EVENT# <24>

GC6_FB_EN <24,25>

TODGPU

SecuriiityClllassiiifiiicatiiion

Issued Date Decipii hered Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRADE SECRET IIINFORMATIIION... THIIIS SHEET MA Y NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIIT CONTAIIINS MAY BE USED

BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

2018/03/09 2019/03/09

Compal Secret Data

Tiiittllle

Siiize Documentt Number Rev

Custttom 1...0

Datte:: Friiiday,,, March 09,,,2018

Compal Electronics,Inc.

SKL-U(6/12)GPIO,I2C,GSPI

LA-G202P

Sheett 11 o ff 55

1

Page 12

5 4 3 2 1

D D

UC1H @

PCIE / USB3 / SATA

<21> PCIE_PRX_DTX_N1

<21> PCIE_PRX_DTX_P1

<21> PCIE_PTX_C_DRX_N1

<21> PCIE_PTX_C_DRX_P1

<21> PCIE_PRX_DTX_N2

<21> PCIE_PRX_DTX_P2

<21> PCIE_PTX_C_DRX_N2

LAN

HDD

ODD

<21> PCIE_PTX_C_DRX_P2

<21> PCIE_PRX_DTX_N3

<21> PCIE_PRX_DTX_P3

<21> PCIE_PTX_C_DRX_N3

<21> PCIE_PTX_C_DRX_P3

<21> PCIE_PRX_DTX_N4

<21> PCIE_PRX_DTX_P4

<21> PCIE_PTX_C_DRX_N4

<21> PCIE_PTX_C_DRX_P4

<31> PCIE_PRX_DTX_N5

<31> PCIE_PRX_DTX_P5

<31> PCIE_PTX_DRX_N5

<31> PCIE_PTX_DRX_P5

<33> PCIE_PRX_DTX_N6

<33> PCIE_PRX_DTX_P6

<33> PCIE_PTX_DRX_N6

<33> PCIE_PTX_DRX_P6

<34> SATA_PRX_DTX_N0

<34> SATA_PRX_DTX_P0

<34> SATA_PTX_DRX_N0

<34> SATA_PTX_DRX_P0

<35> SATA_PRX_DTX_N1

<35> SATA_PRX_DTX_P1

<35> SATA_PTX_DRX_N1

<35> SATA_PTX_DRX_P1

dGPU

C C

NGFF WLAN+BT

B B

CC11 DIS@ 1 2 0.22U_0402_6.3V6K

CC14 DIS@ 1 2 0.22U_0402_6.3V6K

CC15 DIS@ 1 2 0.22U_0402_6.3V6K

CC16 DIS@ 1 2 0.22U_0402_6.3V6K

CC12 DIS@ 1 2 0.22U_0402_6.3V6K

CC13 DIS@ 1 2 0.22U_0402_6.3V6K

CC17 DIS@ 1 2 0.22U_0402_6.3V6K

CC18 DIS@ 1 2 0.22U_0402_6.3V6K

RC71 1 2 100_0402_1%

T147 TP@

T148 TP@

PCIE_PTX_DRX_N1

PCIE_PTX_DRX_P1

PCIE_PTX_DRX_N2

PCIE_PTX_DRX_P2

PCIE_PTX_DRX_N3

PCIE_PTX_DRX_P3

PCIE_PTX_DRX_N4

PCIE_PTX_DRX_P4

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#

XDP_PREQ#

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_R XP

B17

PCIE1_TXN/US B3_5_TXN

A17

PCIE1_T XP/USB3_ 5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_R XP

D16

PCIE2_TXN/US B3_6_TXN

C16

PCIE2_T XP/USB3_ 6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP USB2N_2

C19

PCIE5_TXN USB2P_2

D19

PCIE5_T XP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_R XP

B21

PCIE7_TXN/SATA0_T XN

A21

PCIE7_T XP/SATA0_TXP

G21

PCIE8_RXN/SATA1 A_RXN

F21

PCIE8_RXP/SATA1A _RXP USB2N_7

D21

PCIE8_TXN/SATA1A_TXN USB2P _7

C21

PCIE8_T XP/SATA 1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY# GPP_E10/USB2_OC1#

D61

PROC_PREQ# GPP_E11/U SB2_OC2#

BB11

GPP_A7/PIRQ A# GPP_E12/USB2_OC3#

E28

PCIE11_RXN/SATA1B_R XN

E27

PCIE11_RXP/SATA1B_RX P

D24

PCIE11_T XN/SAT A1B_TXN

C24

PCIE11_T XP/SAT A1B_T XP

E30

PCIE12_RXN/SATA 2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_T XN/SAT A2_TXN

B25

PCIE12_T XP/SAT A2_TXP

SKL-U_BGA1356

SKL-U

USB2

8 OF20

SSIC / USB3

GPP_E 0/SAT AXPCIE0 /SAT AGP0

GPP_E 1/SAT AXPCIE1 /SAT AGP1

GPP_E2/SATAXPC IE2/SATAGP2

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2 _RXN / SSIC_R XN

USB3_2 _RXP / SSIC_RXP

USB3_2 _TXN / SSIC_T XN

USB3_2_TXP /SSIC_TXP

USB3_3_RXN

USB3_3_RXP

USB3_3_TXN

USB3_3_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP 2

GPP_E8/SATALED #

Rev_1.0

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB20_N2

USB20_P2

USB20_N3

USB20_P3

USB20_N5

USB20_P5

USB20_N6

USB20_P6

USB20_N7

USB20_P7

USB2_COMP

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

RC70

USB3_RX2_N <37>

USB3_RX2_P <37>

USB3_TX2_N <37>

USB3_TX2_P <37>

USB3_RX3_N <37>

USB3_RX3_P <37>

USB3_TX3_N <37>

USB3_TX3_P <37>

USB20_N2 <37>

USB20_P2 <37>

USB20_N3 <37>

USB20_P3 <37>

USB20_N5 <28>

USB20_P5 <28>

USB20_N6 <32>

USB20_P6 <32>

USB20_N7 <33>

USB20_P7 <33>

1

RC104 1 2 1K_0402_5%

RC105 1 2 1K_0402_5%

2 113_0402_1%

USB_OC1# <37>

WL_OFF# <33>

USB2.0 / 3.0 Port (MB - 1)

USB2.0 / 3.0 Port (MB - 2)

USB2.0 / 3.0 Port (MB - 1)

USB2.0 / 3.0 Port (MB - 2)

Camera

Card Reader

NGFF WLAN+BT

USB_OC1#

USB_OC3#

USB_OC0#

USB_OC2#

WL_OFF#

RPC9

18

27

36

5 4

10K_0804_8P4R_5%

RC139 1 @ 2 10K_0402_5%

+3VALW

+3VS

When PCIE8/SATA1A is use d as SATA Port 1 (ODD) , then

PCIE11/SATA1B (M.2 SSD) can not be used as SATA Port 1.

A A

SecuriiityClllassiiifiiicatiiion

Issued Date Decipii hered Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRADE SECRET IIINFORMATIIION... THIIIS SHEET MA Y NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS MAY BE USED

5 4 3 2

BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

2018/03/09 2019/03/09

Compal Secret Data

Compal Electronics,Inc.

Tiiitllle

SKL-U(7/12)PCIE,USB,SATA

Siiize Document Number Rev

Custttom 1...0

Date: Friiiday,,, March 09,,,2018

LA-G202P

1

Sheet 12 o f 55

Page 13

5 4 3 2 1

+1.2V

UC1N @ SKL-U

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

SKL-U_BGA1356

+1.0V_VCCST

CC128

CPUPOWER3 OF 4

14 OF20

1

2

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

1

CC129

10U_0603_6.3V6M

2

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

10U_0603_6.3V6M

Close to A18 Close to K20 Close to A22

1U_0201_6.3V6M

SE00000UC00

1 0_040 2_5%RC74 2

1 0_040 2_5%RC75 2

0.1U_0201_10V KX5R

1

CC30

2

+VL

12

CC21

1U_0201_6.3V6M

SE00000UC00

+1.0VALW

12

1 0_040 2_5%SUSP# RC81 2

+1.8VALW

@ CC26

+1.0VALW TO +1.0VS_VCCIO

CC32

1U_0201_6.3V6M

SE00000UC00 UC6

D D

+1.0VALW TO +1.0V_VCCST

<36,45> SYSON

<36,40,45> SUSP#

+1.8VALW TO +1.8VS

C C

+VL

@

B B

I(Max) : 0.16 A(+1 .0V_VCCST)

RON(Max) : 25 mo hm

V drop : 0.004 V

12

CC22 @

1U_0201_6.3V6M

SE00000UC00

UC5

1

VOUT1

VIN1

2

VOUT1

EN_1.0V_VCCSTU

EN_1.8VS

12

I(Max) : 3.04 A( +1.0VS_VCCIO)

RON(Max) : 6.2 m ohm

V drop : 0.019 V

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

ON

AOZ1334DI-01_DFN 8P

VIN1

3

ON1

4

VBIAS

5

ON2

6

VIN2

VOUT2

7

VIN2

VOUT2

S IC JW7110DFNC#TRPBF DFN14 DUAL LOAD SW

SA0000BEL00

I(Max) : 0.2 A(+1 .8VS)

RON(Max) : 25 mo hm

V drop : 0.005 V

6

VOUT

54

GND

14

13

12 1 2

CT1

11 8200P_0402_25V7K

GND

10 1 2

CT2

9

8

15

GPAD

+1.0VS_VCCIO_STG

+1.0V_VCCST_R

CC24

CC25

1000P_0402_ 50V7K

+1.8VS_R

RC79 1 2 0_0805_5%

2

RC136 0_0402_5%

Follow 543977_SKL_PDDG_Rev0_91

CC24 10PF ->22us(Spec:<= 65us)

2

1

1 RC137

0_0402_5%

+1.0V_VCCST+1.0VALW

+1.8VS

+1.0VS_VCCIO

1

@

0.1U_0201_10V KX5R

2

0.1U_0201_10V KX5R

1

CC23

2

0.1U_0201_10V KX5R

1

CC27

2

+1.0VS_VCCIO

+1.0V_VCCST

Reserved for BSoD 0x124 Issue

CC33

+1.0VS_VCCIO

Rev_1.0

AK28

VCCIO

AK30

VCCIO

AL30

VCCIO

AL42

VCCIO

AM28

VCCIO

AM30

VCCIO

AM42

VCCIO

AK23

VCCSA

AK25

VCCSA

G23

VCCSA

G25

VCCSA

G27

VCCSA

G28

VCCSA

J22

VCCSA

J23

VCCSA

J27

VCCSA

K23

VCCSA

K25

VCCSA

K27

VCCSA

K28

VCCSA

K30

VCCSA

AM23

AM22

VSSSA_SENSE

H21

VCCSA_SENSE

H20

Trace Length Match < 25 mils

+1.0VS_VCCIO

+VCCSA

2 1

BSC SidePSC Side

CC35 @

1U_0201_6.3V6M

SE00000UC00

VSSSA_SENSE <48>

VCCSA_SENSE <48>

+1.0VS_VCCIO +1.2V

CC38 SE00000UC00

CC37 SE00000UC00

10U_0603_6.3V6

M

1

CC36

@

2

A A

5 4 3 2 1

1U_0201_6.3V6

M

1U_0201_6.3V6

M

12

12

PSC SideBSC Side BSC SidePSC Side

CC39 SE00000UC00

1U_0201_6.3V6M

12

12

CC41 SE00000UC00

1U_0201_6.3V6M

CC40 SE00000UC00

1U_0201_6.3V6M @

12

CC42 SE00000UC00

1U_0201_6.3V6M

12

@

@

BSC Side

CC43 SE00000UC00

1U_0201_6.3V6M

1U_0201_6.3V6

M

SE00000UC00

CC29

12

12

Close to CPUUnder CPU

SecuriiityClllassiiifiiicatiiion

IssuedDate

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIIONOF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATIIION IIITCONTAIIINS

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,, IIINC...

2018/03/09 2019/03/09

22U_0603_6.3V6

M

10U_0603_6.3V6

M

1

1

CC44

2

2

Close to CPU Under CPUClose to AL23 Close to AM40

Compal Secret Data

10U_0603_6.3V6

M

1

CC45

CC46

2

Deciiiphered Date

CC49 SE00000UC00

@ 1U_0201_6.3V6M

CC50 SE00000UC00

10U_0603_6.3V6

M

10U_0603_6.3V6

M

1

1

CC47

CC48

@

2

2

@ 1U_0201_6.3V6M

12

12

Compal Electronics,Inc.

Tiiittllle

Siiize Documentt Number

Custttom

Datte:: Friiiday,,, March 09,,,2018 Sheett 13 o ff 55

SKL-U(8/12)Power

LA-G202P

R ev

1...0

Page 14

5 4 3 2 1

D D

Follow 54 3016_SKL_U_ Y_PDG_1_0

+1.0VALW

LC1

MURATABLM15EG221SN1D

1 2

SM01000BV00 RF@

R_0402

+1.0V_APLL

0.1U_0201_10V KX5R

2

RF@

CC31

1

Follow 543016_SKL_U_Y_PDG_1_0

+1.0V_AMPHYPLL

SE00000UC00

CC58

12

+1.0V_CLK5_F24NS

22U_0603_6.3V6

M

1

1

CC63

@

@

2

+1.0V_CLK4_F100OC

22U_0603_6.3V6

M

1

1

CC69

@

@

2

2

+1.0V_CLK6_24TBT

1U_0201_6.3V6M

CC59 @

22U_0603_6.3V6M

CC64

2

22U_0603_6.3V6M

CC70

+3VALW

LC2

MURATABLM15EG221SN1D

1 2

SM01000BV00 RF@

R_0402

+3V_1.8V_HDA

0.1U_0201_10V KX5R

1

RF@

2

CC66

22U_0603_6.3V6

M

1

@

C C

2

Follow 543016_SKL_U_Y_PDG_1_0

Follow 543016_SKL_U_Y_PDG_1_0

B B

CC51 1 2 1U_0201_6.3V6M

@

CC54 1 2 1U_0201_6.3V6M

@

Imax : 2.57A

CC55 1 2 1U_0201_6.3V6M DCPDSW AL1

CC56 1 2 1U_0201_6.3V6M

Close toK17

CC60 1 2 22U_0603_6.3V6M

Imax : 1.54A

@

CC61 1 2 1U_0201_6.3V6M

Close to P15

+1.0V_AMPHYPLL

+1.0V_APLL

+3VALW

+3V_1.8V_HDA

CC65 1 2 1U_0201_6.3V6M

Close to AF20

@

CC67 1 2 1U_0201_6.3V6M

Close toAJ21

@

CC68 1 2 1U_0201_6.3V6M

Close toN18

Follow 543016_SKL_U_Y_PDG_1_0

22U_0603_6.3V6M

22U_0603_6.3V6

1U_0201_6.3V6M

SE00000UC00

12

1U_0201_6.3V6M

SE00000UC00

CC83 @

CC84 @

12

M

1

CC85

1

CC86

@

@

2

2

+1.0VALW +3VALW +1.8VALW

22U_0603_6.3V6M

22U_0603_6.3V6

M

22U_0603_6.3V6

M

22U_0603_6.3V6

M

1

1

CC72

CC71

@

@

@

2

2

CC74

1

1

CC73

@

2

@

2

SE00000UC00

SE00000UC00

SE00000UC00

SE00000UC00

SE00000UC00

SE00000UC00

SE00000UC00

SE00000UC00

22U_0603_6.3V6M

CC75

1

@

2

+1.0VALW

UC1O

AB19

VCCPRIM_1P0

AB20

VCCPRIM_1P0

P18

VCCPRIM_1P0

AF18

VCCPRIM_CORE

AF19

VCCPRIM_CORE

V20

VCCPRIM_CORE

V21

VCCPRIM_CORE

DCPDSW _1P0

K17

VCCMPHYAO N_1P0

L1

VCCMPHYAO N_1P0

N15

VCCMPHYG T_1P0_ N15

N16

VCCMPHYG T_1P0_ N16

N17

VCCMPHYG T_1P0_ N17

P15

VCCMPHYG T_1P0_ P15

P16

VCCMPHYG T_1P0_ P16

K15

VCCAMPHYP LL_1P0

L15

VCCAMPHYP LL_1P0

V15

VCCAPLL_1P0

AB17

VCCPRIM_1P0_AB17

Y18

VCCPRIM_1P0_Y18