Vinafix.com

A

smd.db-x7.ru

B

C

D

E

Compal Confidential

1 1

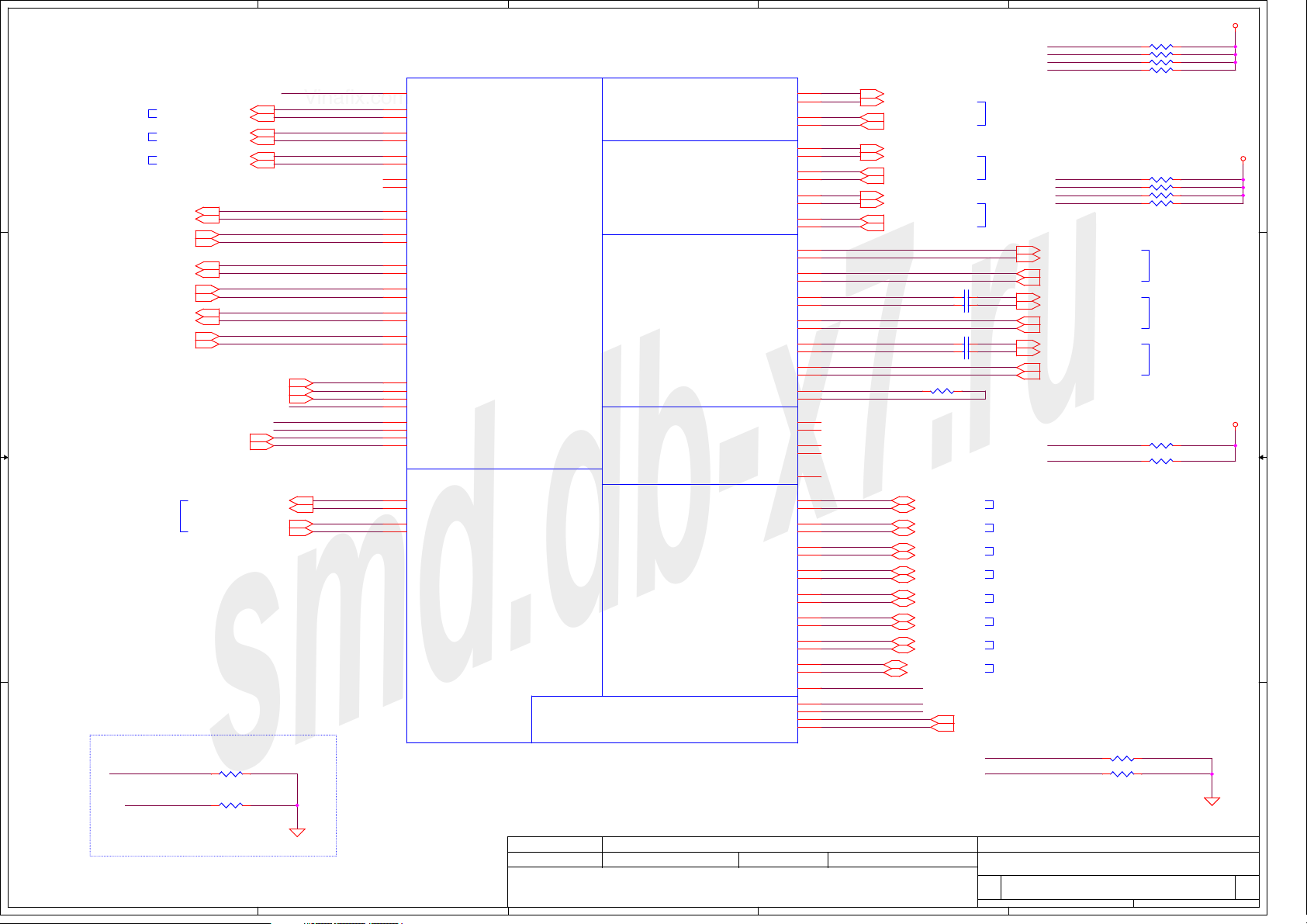

N3V3 Intel Gemini Lake Schematic

COMPAL CONFIDENTIAL

MODEL NAME : EDI55

PCB NO : DA60021O010

BOM P/N : 431ADZ31L01

2018/11/08

Rev 1.0(A00)

ZZZ

2 2

PCB

Part Number = DAZ2ED00 100

PCB EDI55 LA-G094P LS -F112P/F114P 02

PCB_DAZ_R1@

ZZZ

PCB

Part Number = DA60021 O010

PCB 2ED LA-G094P R EV1 M/B 3

PCB_R1@

DAZ R1 DAZ R3

CPU R1

SR3RZ_R1@

UC1

ZZZ

PCB

Part Number = DAZ2ED00 101

PCB EDI55 LA-G094P LS -F112P 02 GOLD A31!

PCB_DAZ_R3@

ZZZ

PCB R3PCB R1

PCB

Part Number = DA60021 O011

PCB 2ED LA-G094P R EV1 M/B GOLD 3 A31 !

PCB_R3@

CPU R3

SR3RZ_R3@

UC1

@ : Un-pop Component

EC@ : EC

EMI@/ESD@/RF@ : EMI, ESD and RF Component

@EMI@/@ESD@/@RF@ : EMI, ESD and RF Un-POP Component

ESPI@:ESPI

LPC@:LPC

PCB@:PCB

Lan@: lan component

lan@EMI@:EMI for lan pop component

1000@:Giga

CNVI@: CNVI interface

XDP@ : XDP Component

CONN@ : Connector Component

FH8068003067406 SR3RZ

Part Number = SA0000BEH 2L

3 3

S IC FH806800306 7406 SR3RZ B0 1.1G FCBGA

SR3S0_R1@

UC1

FH8068003067408 SR3S0

Part Number = SA0000BD Q1L

S IC FH806800306 7408 SR3S0 B0 1.1G FCBG A

SR3S1_R1@

UC1

FH8068003067406 SR3RZ

Part Number = SA0000BEH 3L

S IC FH806800306 7406 SR3RZ B0 1.1G A31!

SR3S0_R3@

UC1

FH8068003067408 SR3S0

Part Number = SA0000BD Q2L

S IC FH806800306 7408 SR3S0 B0 1.1G A31!

SR3S1_R3@

UC1

TP_WAKE@/NTP_WAKE@ : TouchPad wake

KBBL@ : KB Backlight

MMC@ : eMMC / NMMC@: without eMMC

FFS@ : Free Fall Sensor

45@:HDMI logo

N3@/V3@:N3000/V3000

SR3RZ_R3@/SR3S0_R3@/SR3S1_R3 : Pentium/Celeron QC/Celeron DC

S32G_R3@/S64G_R3@/H32G_R3@/H64G_R3@ : eMMC Type

FH8068003067417 SR3S1

Part Number = SA0000BEJ 0L

S IC FH806800306 7417 SR3S1 B0 1.1G

Layout Dell logo

4 4

FH8068003067417 SR3S1

Part Number = SA0000BEJ 1L

S IC FH806800306 7417 SR3S1 B0 1.1G A31!

COPYRIGHT 2014

ALL RIGHT RESERVED

REV: X00

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/09/27 2016/12/31

2017/09/27 2016/12/31

2017/09/27 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-G094PR10

LA-G094PR10

LA-G094PR10

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

E

1 39Thursday, November 08, 20 18

1 39Thursday, November 08, 20 18

1 39Thursday, November 08, 20 18

1.0

1.0

1.0

Vinafix.com

A

smd.db-x7.ru

B

C

D

E

Compal Confidential

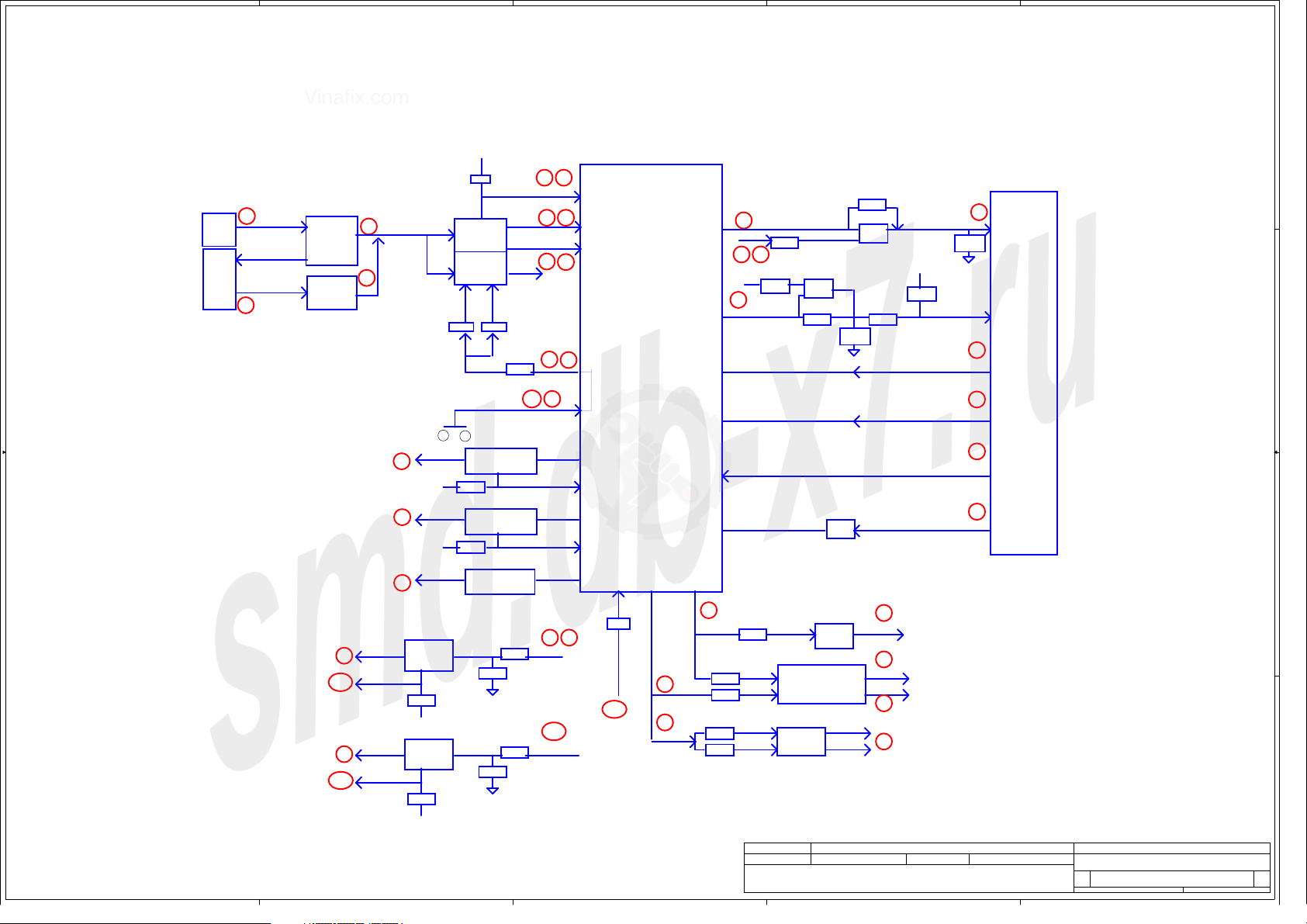

Model Name : Gemini Lake

Project Name: EDI55

File Name : LA-G094PR10

1 1

eDP panel

FHD

P16

M.2 SSD

HDMI Conn

DDI1 port

P18

P17

eDPx2

2.7Gb/s

PCI-EX4

PCIe 2.0:5Gb/s

HDMI

Gemini Lake

SOC

1090P BGA

25 x 24 mm

LAN

2 2

8106E-CG/8111H

WLAN(NGFF slot)

eMMC 32GB/64 GB

3 3

P27

On PWR board

P27

Touch Pad

Lid switch

Int.KBD

PS2

Thermal sensor

NCT7718W

PWR board for 14"

4 4

PWR board for 15/17

IO board

Port2

P19

Port3

P18

P28

ENE KB9542

P22

SMBUS

PCI-E

PCIe 1.0:2.5Gb/s

CNVI

PCI-E

PCIe 1.0:2.5Gb/s

I2C port5

100KHz

LPC

25MHz

P23

SPI ROM

16M

P6~P15

SPI

50MHz

P6

Single Channel

SATA

USB3.0

5Gb/s

USB2.0

480Mb/s

I2C Port6

100KHz

HDA

24MHz

DDR4 2400MHz 1.2V

Port 0

Port 1

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

HDA Aduio codec

ALC3204

DDR4-SO-DIMM X 1

2.5" SATA HDD

ODD

USB3.0 port

USB3.0 port

USB2.0 Port

BT(NGFF Slot)

Camera

Touch Screen

Card reader

RTS5144-GR

Finger printer

P20

P15

GEN3 6Gb/s

P24

P24

GEN1 1.5Gb/s SATA 1.0PCIe 1.0:2.5Gb/s

Port 0

P25

Port 1

P25

P27

P18

P16

P16

P27

P27

Internal SPK

Universal Jack

Digital MIC

Max Capacity :8GB

SATA 3.0

ODD board

A

IO board for V3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/09/27 2018/07/10

2017/09/27 2018/07/10

2017/09/27 2018/07/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-G094PR10

LA-G094PR10

LA-G094PR10

E

1.0

1.0

2 39Thursday, November 08, 20 18

2 39Thursday, November 08, 20 18

2 39Thursday, November 08, 20 18

1.0

Vinafix.com

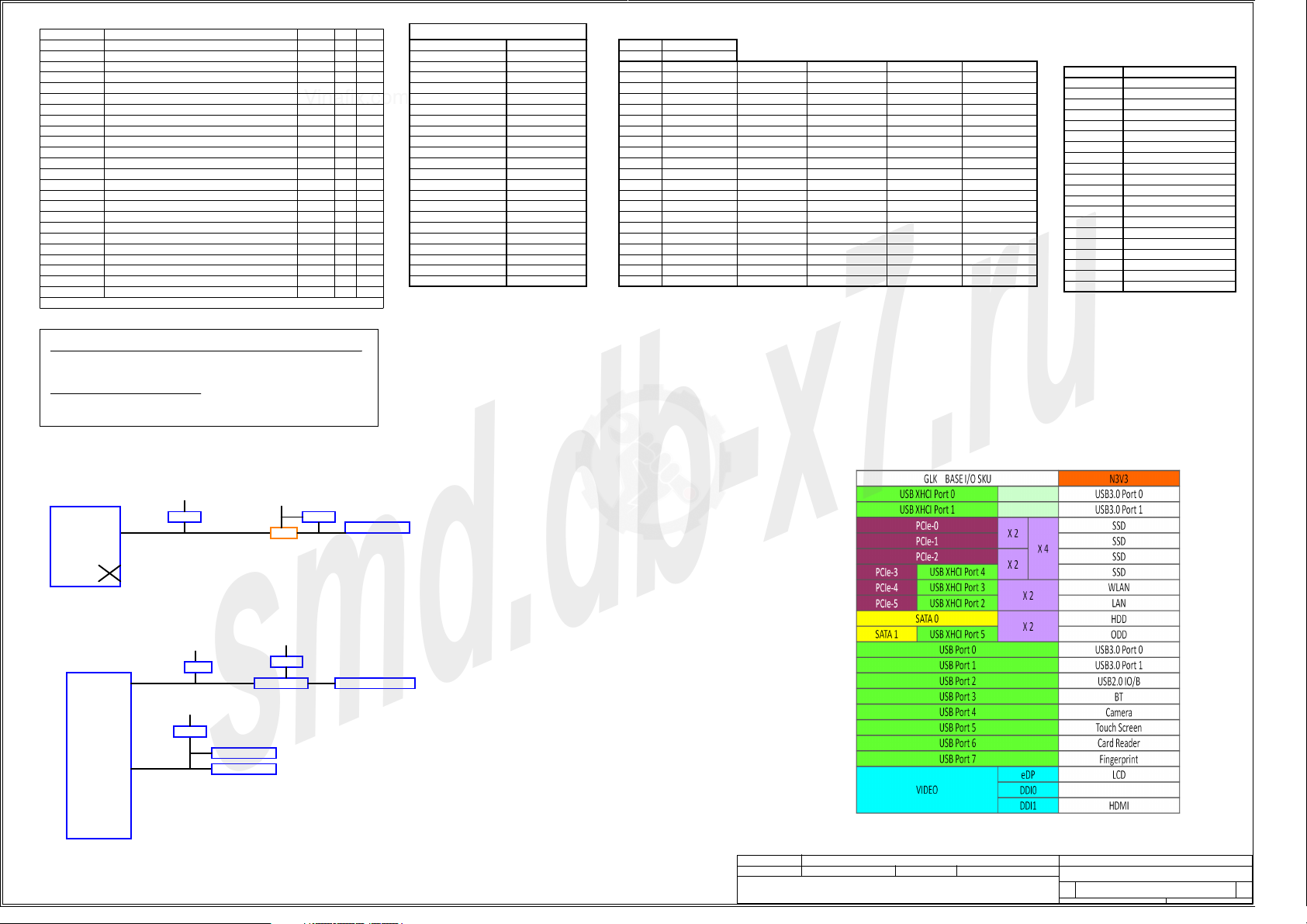

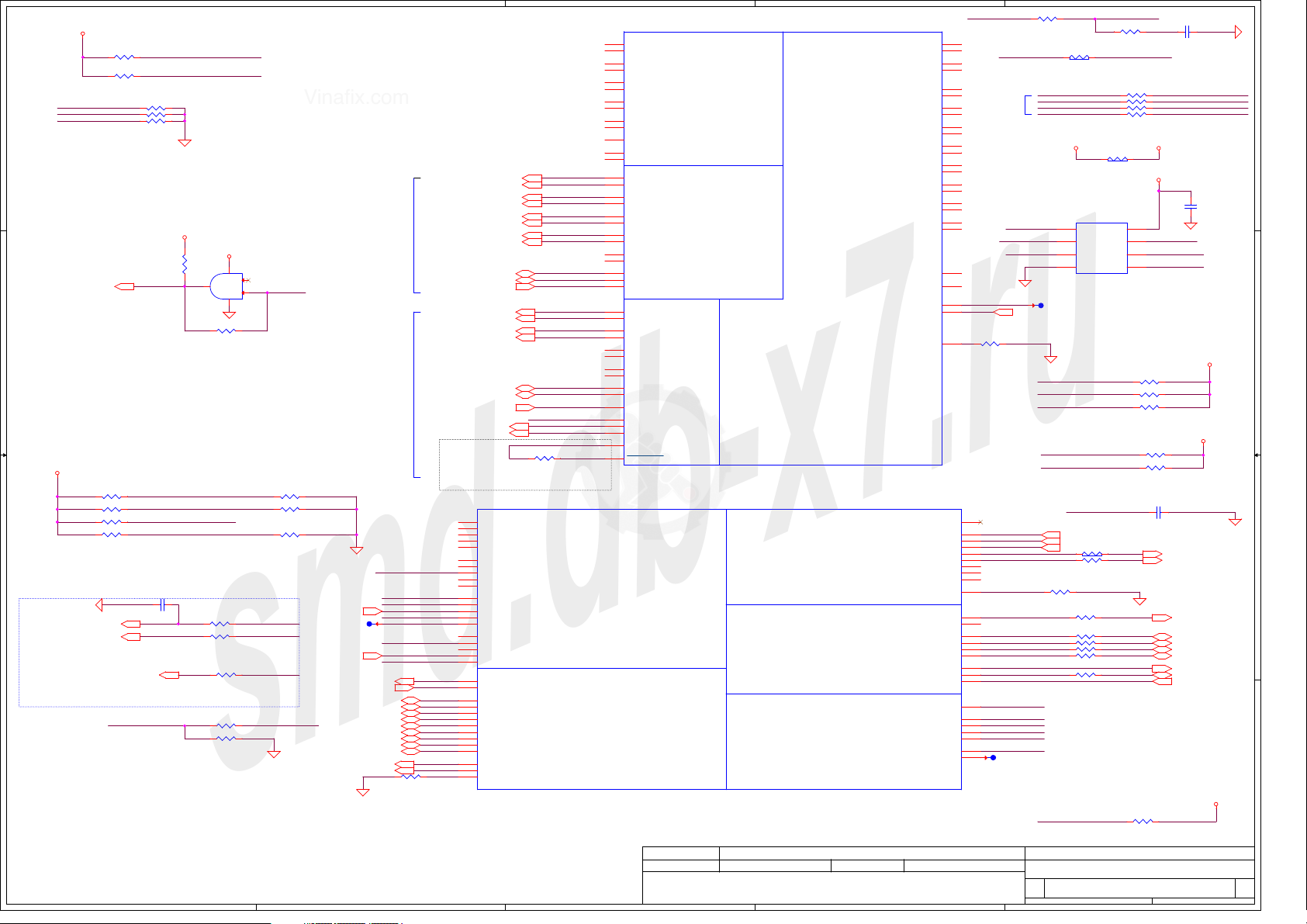

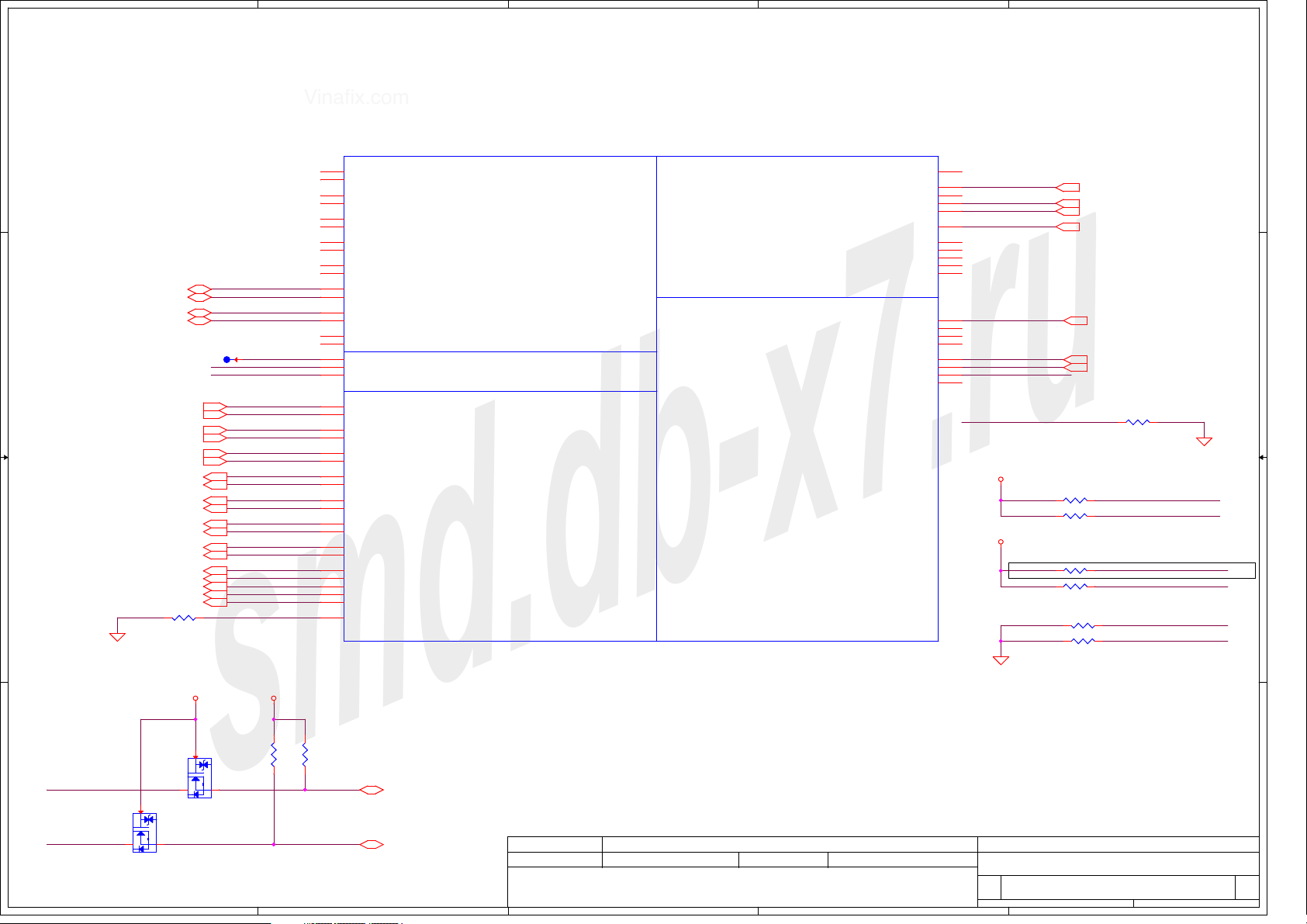

Voltage Rails

smd.db-x7.ru

VIN

BATT+ 12V Battery power supply

B+

+VSB +VSBP to +VSB always on power rail for sequence control

+RTCVCC RTC Battery Power

+1.24VALW

+1.8V_PRIM

+3VALW

+5VALW

+1.2V

+VCC_VCGI

+VNN

+0.6V_DDR_VTT

+1.05VS

+1.8VS

+3VS

+5VS

Note : ON* means that this power plane is ON only with AC power avail able, otherwise it is OFF.

19V Adapter power supply

AC or battery power rail fo r power circuit. (19V/12V)

+1.2 v Always power rail(SO C L2 , I/O Logic and PLLs)

+1.8v Always power rail(SO C all GPIOs)

+3.3v Always power rail(SO C GPIO , I/O Logic ,USB2 PHY)

+5.0v Always power rail

+1.2V power rail for DDR4

CPU , GFX and ISP logic vo ltage for SOC

non-Core Logic voltage fo r SOC

+0.6V power rail for DDR4 Terminator

+1.05v system power rail(S DRAM and I/O Logic)

+1.8v system power rail

+3.3v system power rail

+5.0v system power rail

S0 S3 S4/S5Power Plane Description

ON

ON ON

ONONOFF OFF

ON

ON OFFOFF

ON OFF OFF

ON OFF OFF

ON ON

ON ONON

ON ONON

ON ONON

ON ONON

ONON

ON

ON

ONON

ON ONON

ON ONON

ON ONON

OFF

OFF OFF

OFF OFF

BOM Option Table

BTO Item BOM Structure

Unpop @/@RF@

XDP (Debug Port)

ESD requirement ESD@

ESD requirement unpop

Board ID

N3000/V3000 N3@/V3@

CNVI CNVI@

Free fall sensor FFS@

lan 10/100 100@

lan giga 1000@

lan compoent Lan@

ESPI for EC ESPI@

TP_WAKE TP_WAKE/NTP_WAKE

eMMC MMC@

CONN@Connector

XDP@

EMI@EMI requirement

@EMI@EMI requirement unpop

@ESD@

EC@

Lan@EMI@lan EMI compoent

LPC@LPC for EC

A

Board ID Table for AD channel

Vcc 3.3V +/- 1%

Board ID

100K +/- 1%Ra

0

1

2

3

4

5

6

7 56K +/- 1%

8

9

10

11

12

13

14

15 330K +/- 1%

16

17

18

19 NC

Rb V min

0 0.000V

12K +/- 1%

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

75K +/- 1% 1.398V

100K +/- 1%

130K +/- 1%

160K +/- 1%

200K +/- 1%

240K +/- 1%

270K +/- 1%

430K +/- 1%

560K +/- 1%

750K +/- 1%

AD_BID

0.347V

0.423V 0.430V

0.541V

0.691V

0.807V

0.978V 0.992V

1.169V

1.634V

1.849V 1.865V

2.015V

2.185V

2.316V

2.395V 2.408V

2.521V

2.667V

2.791V

2.905V 2.912V

3.000V

V typ

AD_BID

0.000V 0.300V

0.354V

0.550V

0.702V

0.819V

1.185V

1.414V 1.430V

1.650V

2.031V

2.200V

2.329V

2.533V

2.677V

2.800V

3.300V

V

AD_BID

0.360V

0.438V

0.559V

0.713V

0.831V

1.006V

1.200V

1.667V

1.881V

2.046V

2.215V

2.343V

2.421V

2.544V

2.687V

2.808V

2.919V

3.300V

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x30

0x31 - 0x3A

0x3B - 0x45

0x46 - 0x54

0x55 - 0x64

0x65 - 0x76

0x77 - 0x87

0x88 - 0x96

0x97 - 0xA4

0xA5 - 0xAF

0xB0 - 0xB7

0xB8 - 0xBF

0xC0 - 0xC9

0xCA - 0xD4

0xD5 - 0xDD

0xDE - 0xF0

0xF1 - 0xFF

BOARD ID Table

Board ID

0

GLK EVT

1

GLK DVT1

2

GLK DVT2

3

GLK pilot

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

EC SM Bus1 address

Device

Smart Battery

Address Address

0001 011X b

EC SM Bus2 address

Device

SOC SM Bus address

Device Address

ChannelA JDIMM1

1 1

<SMBus Routing>

CPU

+3VALW_SOC

SMBus1

EC

+3VALW_EC

SMBus2

SMBus1

B27

C27

79

80

77

78

0xA0(1010 0000).

+3VALW_SOC

SOC_SMBCLK

SOC_SMBDATA

EC_SMB_CK2

EC_SMB_DA2

+3VALW_EC

EC_SMB_CK1

EC_SMB_DA1

R=2.2K

R=2.2K

+3VS

R=2.2K

Charger

BATT

+3VS

2N7002

+3VS

R=2.2K

DMN66D0LDW

R=2.2K

SO-DIMM A

Thermal sensor

HSIO Port Table

+3VS

+3VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/09/27 2016/12/31

2017/09/27 2016/12/31

2017/09/27 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-G094PR10

LA-G094PR10

LA-G094PR10

Date: Sheet of

Date: Sheet of

Date: Sheet of

3 39Thursday, November 08, 2018

3 39Thursday, November 08, 2018

3 39Thursday, November 08, 2018

1.0

1.0

1.0

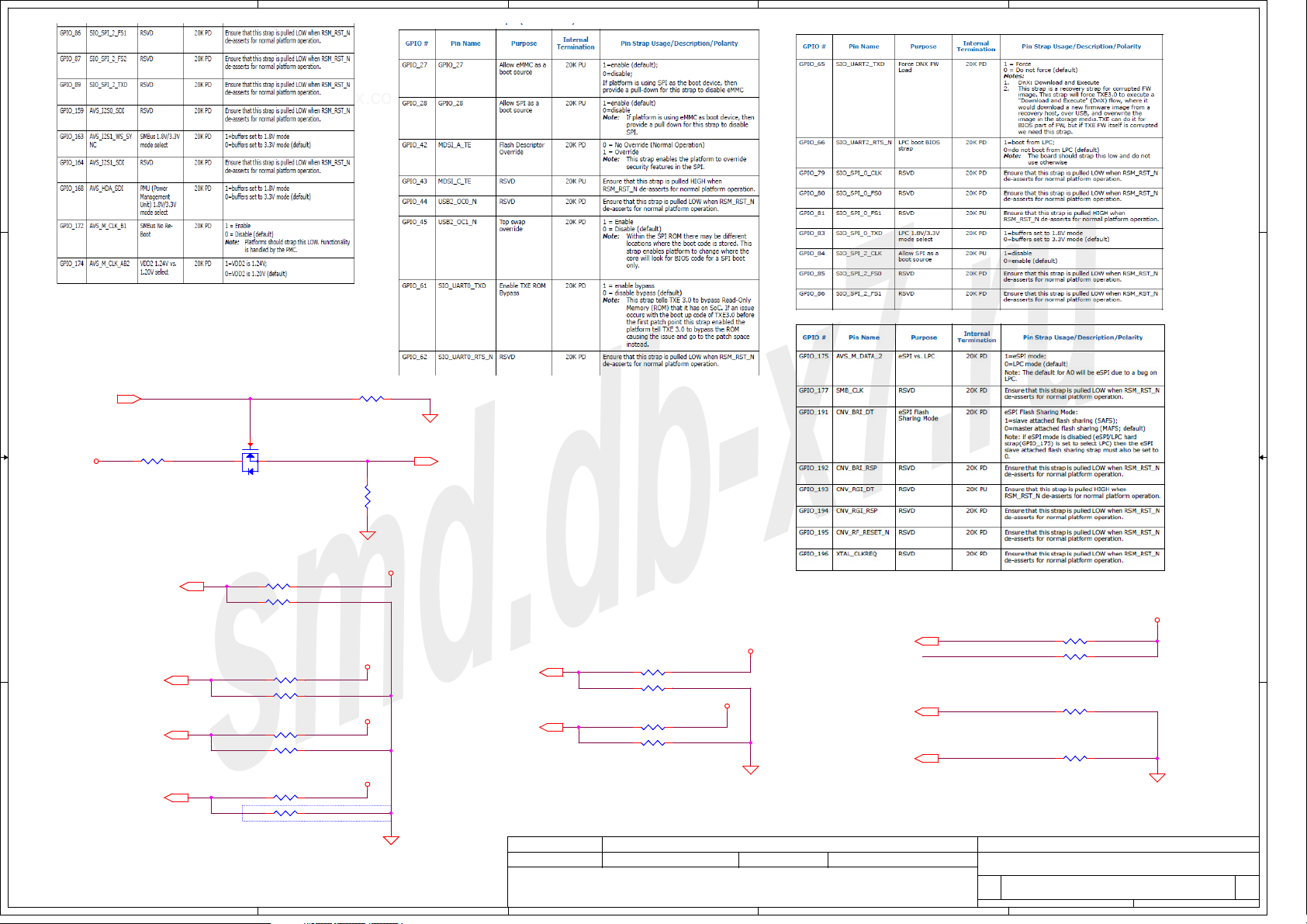

Vinafix.com

A

smd.db-x7.ru

B

C

D

E

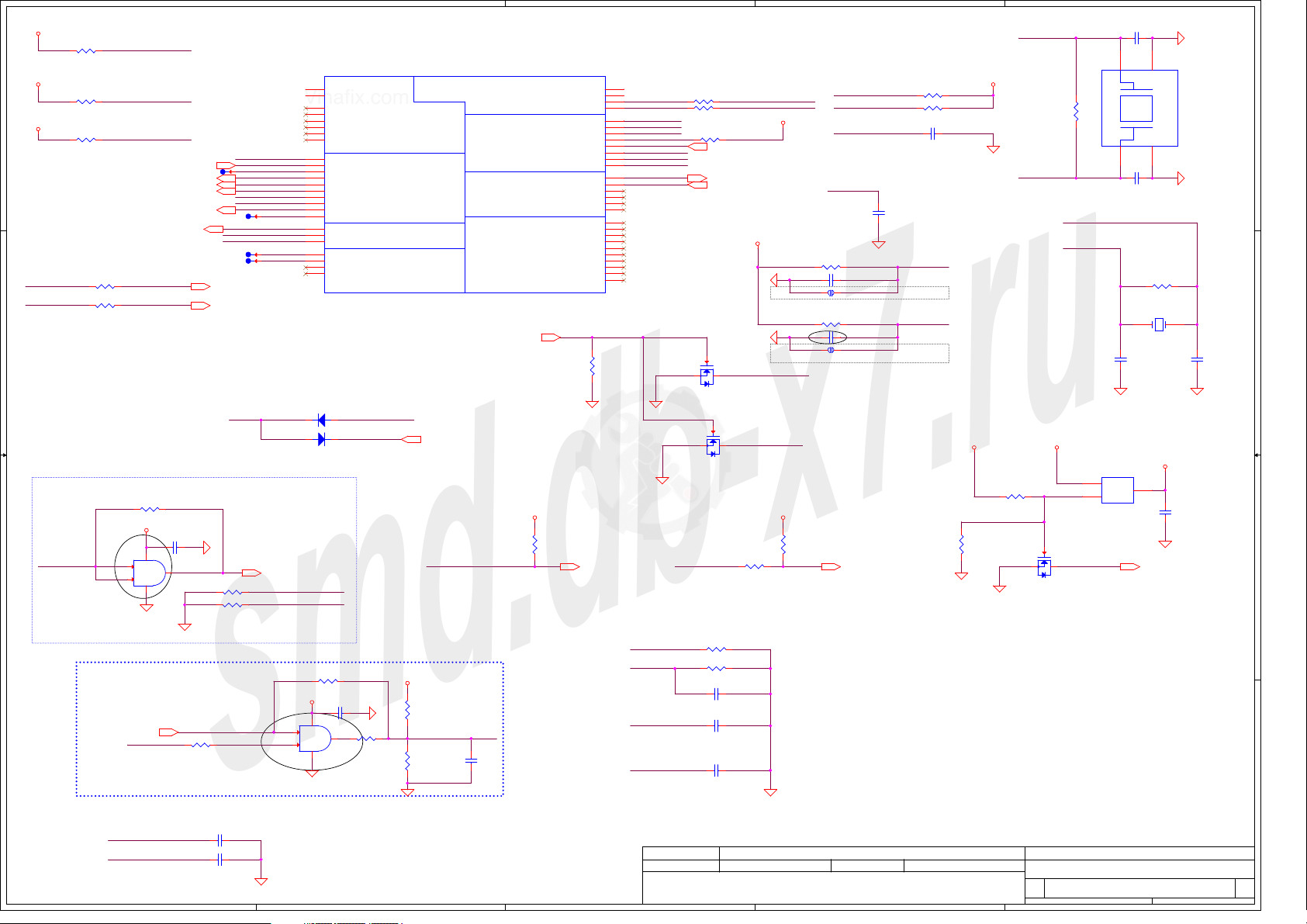

MODEL NAME:

PCB NAME:

REVISION:

+3VS

DATE:

(PJ2502)

3000mA

(PJ1202)

(R16)

(JP10)

LCDVDD_EN

(RA33)

1 1

ADAPTER

Page 30

CHARGER

SL95522HRZ

Page 31

BATTERY

2 2

3 3

4 4

+19VB

VNN_EN

VCCGI_EN

EN_1V05

850mA

(F1)

SYSON

SUSP#

EN_5V

(PJ501)

(PJ301)

EN_3V

RT3601EAGQW

Page 37

(PUZ1)

RT3601EAGQW

(PUG1)

RT6226AGQUF

(PU1051)

+DCBAT_LCD

RT8207PGQW

(PUM1)

Page 33

SY8288CRAC

(PU501)

SY8286BRAC

(PU301)

Page 36

Page 32

Page 32

Page 34

4000mA

1000mA

4500mA

8000mA

25000mA

6500mA

150mA

7000 mA

+VNN

TDC:4A

+VCC_VCGI

TDC:5.2A

+0.6VSP

TDC:1.2A

+1.2VP

TDC:6.2A

+5VALWP

TDC:6.3A

+RTC_VCC

+3VLP

+3VALWP

TDC:5A

+VCCIOA

@(RC124)

TDC:18A

+1.05VSP

1500mA

@(PJPM3)

8900mA

@(PJPM2)

(PJ502)

RC63 +RTC_CELL

(PJ302)

(PJ1052)

+1.05VS

+0.6V_DDR_VTT

+1.2V_DDR

+5VALW

BAS40C

(D1)

+3VALW

3000mA

@(JP12)

2000mA

USB_EN#

USB_EN#

SUSP#

5VS_EN

(RC122)

EN_2.5V

(PJ2501)

EN_1.8V

(PJ1801)

(RM1)

AUX_ON

(RW1)

WLAN_PWR_ EN

(RE4)

EN_1.24V

(PJ1201)

SUSP#

3VS_EN

+1.05VS_SOC_SRAM

(RC132)

+VCCIOA

(RC133)

+1.05VS_SOC_FHV0

(RC134)

+1.05VS_SOC_FUSE

(RC135)

+1.05VS_SOC_FHV1

(RC136)

+1.2V_DDR_SOC

JDIMM1

SY6288D20AAC

(UU2)

SY6288D20AAC

(UU3)

EM5209VF

(U11)

+3VALW_SOC

RT9059GSP

(PU2501)

Page 35

RT8061AZQW

(PU1801) (PJ1802)

Page 35

+3V_EMMC

SY6288C20AAC

(UL2)

SY6288C20AAC

@(UW1)

+3VALW_EC

RT80861AZQW

(PU1201)

Page 34

EM5209VF

(U11)

(JP33)

USB30_VCCA

USB20_VCC

(JP50)

+2.5VP

TDC:0.45A

+1.8VALWP

TDC:1A

+LAN_VDD33

+3.3V_WLAN

BLM15AG121

(LE1)

+1.24VALWP

TDC:2.5A

A

B

C

Power Rail Block Diagram

2018/01/22

(R12)

(JP5)

(JP51)

+5VS

+2.5V_MEM

+1.8V_PRIM

+EC_VCCA

+1.24VALW

+3VS_CAM

+3VS_SSD

AP2330W

(FG5)

SY6288C20AAC

(U1)

+3V_DVDD

(F3)

(RA1)

(RA34)

(RC123)

(RC34)

(RM2)

(RC125)

(R13)

(F11)

+3VS_TOUCH

+LCDVDD

+TPAN_VDD

+5VS_ODD

+5V_HDD

+5V_KB_BL

+5V_PVDD

+5V_AVDD

+5V_HDMI

+1.8VALW_SOC

+VCC_SPI

(RA35)

(RA36)

(RC126)

(RC127)

(RC128)

(RC129)

(RC130)

(RC131)

+1.8VS_AVDD

+1.8V_CPVDD

+1.2V_GLML

+1.2V_PLL

+1.2V_USB2

+1.2V_MPHY

+1.2V_VNNAON

+1.2V_DSI

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.8V_EMMC

LP2306LT1G

(QA2)

+1.2V_SOC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

2014/11/10 2018/01/15

2014/11/10 2018/01/15

2014/11/10 2018/01/15

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P04-Power Rail

P04-Power Rail

P04-Power Rail

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

4 39Thursday, Novemb er 08, 20 18

4 39Thursday, Novemb er 08, 20 18

4 39Thursday, Novemb er 08, 20 18

1.0

1.0

1.0

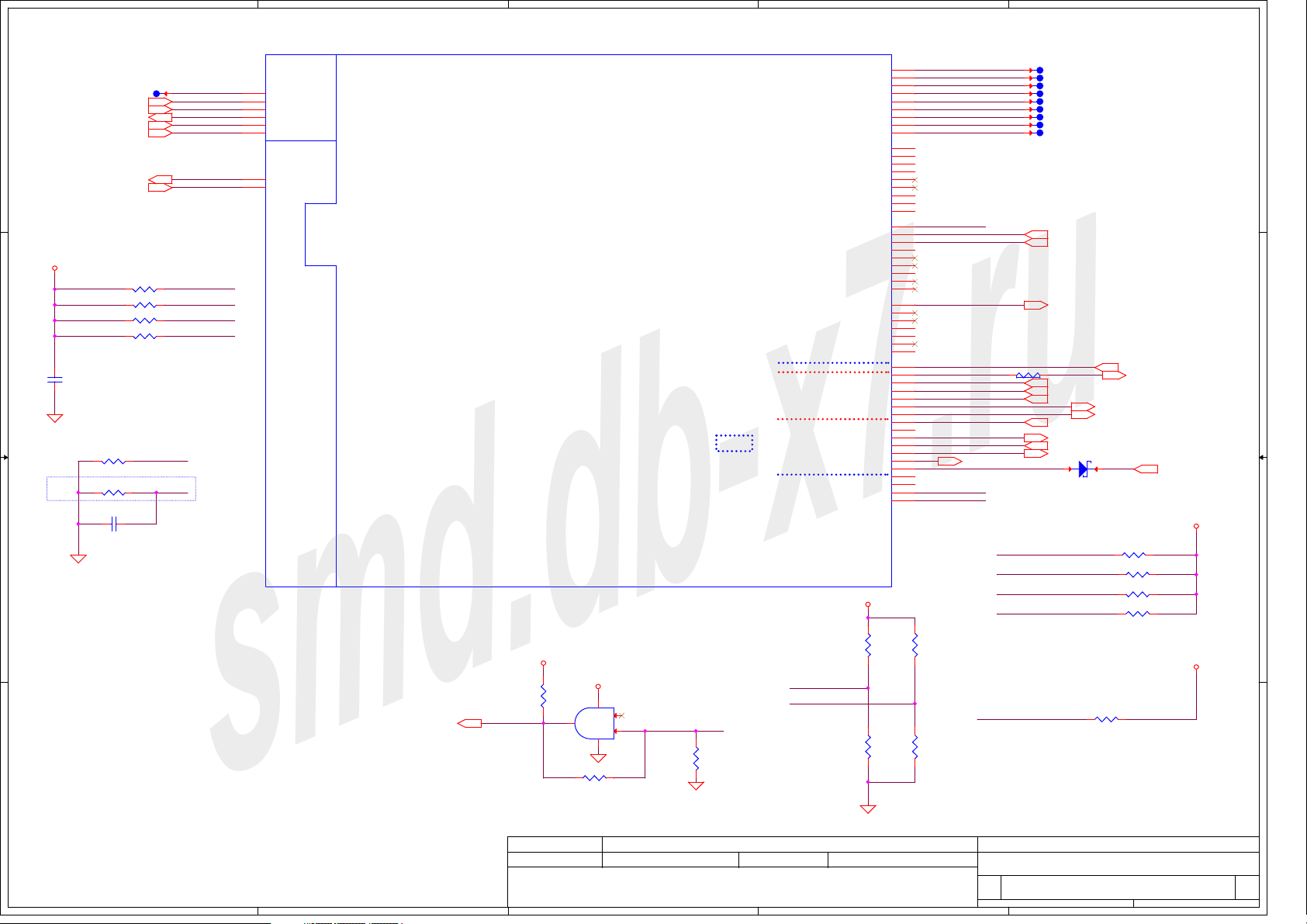

Vinafix.com

MODEL NAME:

smd.db-x7.ru

5

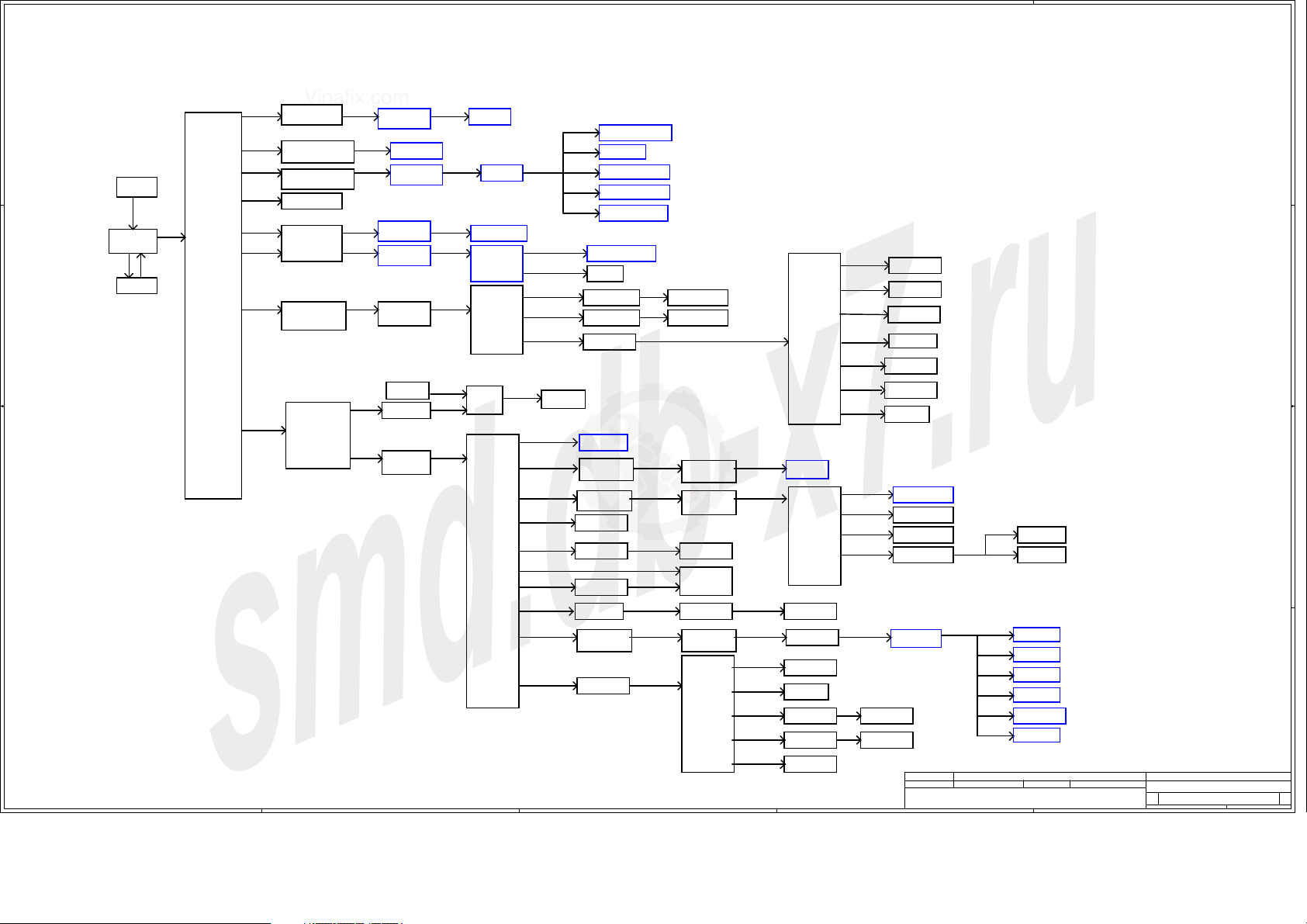

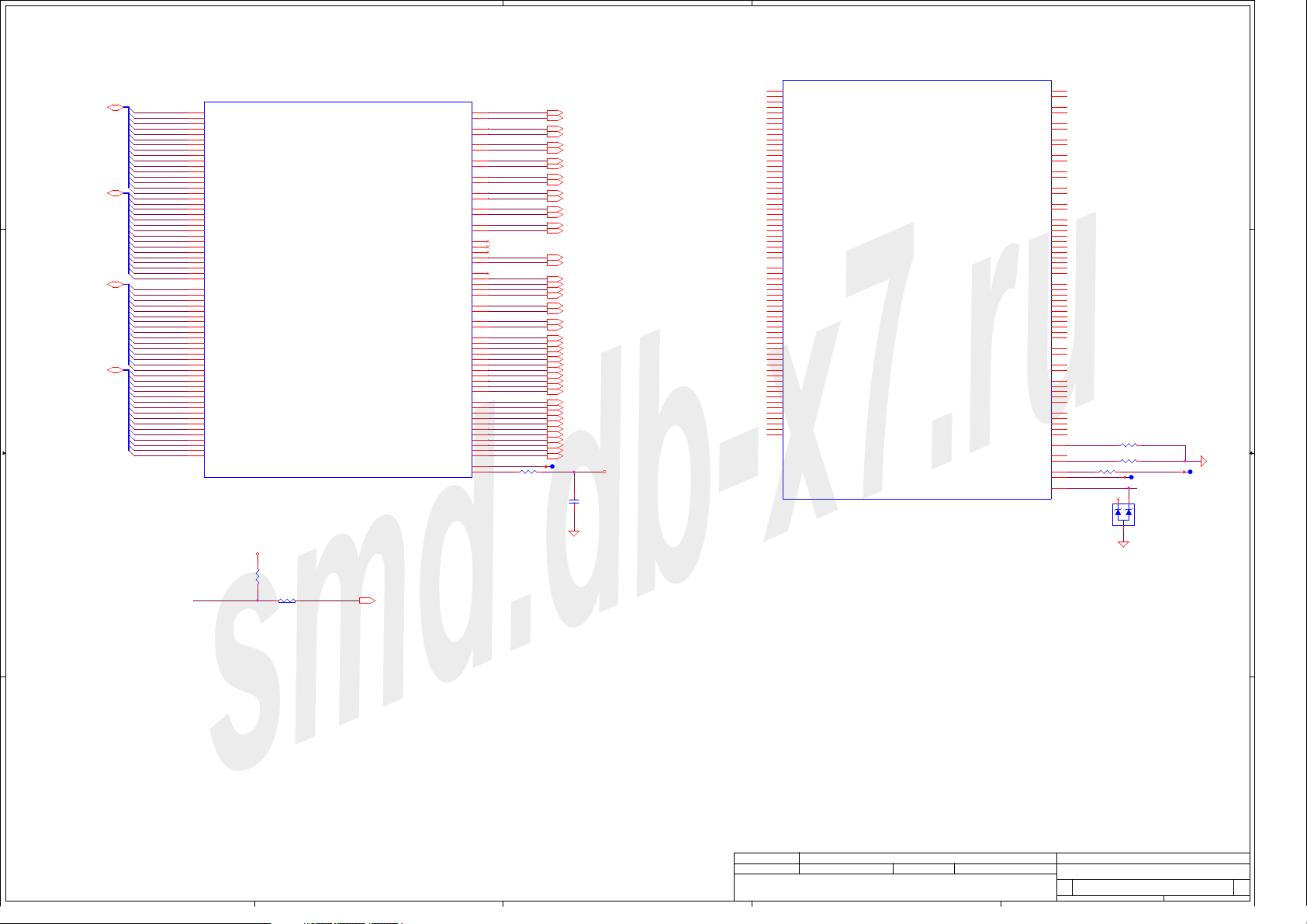

Power Sequence Block Diagram

4

3

2

1

PCB NAME:

REVISION:

DATE:

D D

C C

0.2

2018/01/29

AC

MODE

DC

MODE

A1

+19V_VIN

+17.4V_BATT+

+17.4V_BATT+

B1

PUB01

ISL88739HRZ

PQB13

+3VALWP

A10

ON/OFF#

POK

A3

+3VLP

+3VALW

A5

+5VALW

A4

EC_ON

B4

B7A6

34

B3

111

B6

UE1

B5

112

114

KB9542

11

100

EC_RSMRST#

RC53

POK

+3VALW_SOC

12

PBTN_OUT# PBTN_OUT#_SOC

15

PM_SLP_S4#

18

PM_SLP_S3#

6

B7A6

RC142

XDP@

ALW_PWRGD_3V_5V_R

UC5

(AND)

XDP@

RC143 RC144

CC11

@ESD@

RC52

UC3

(AND)

PCH_RSMRST#_AND

+3VALW_SOC

RC145

PM_SLP_S4#

PM_SLP_S3#

CC6

@ESD@

11a

F27

E54

SOC

UC1

13

J49

13

D51

PR304

A2

+19VB

B2

PU301

SY8286BRAC

PU501

SY8286BRAC

EN_5V

PR503 PR502

EN_3V

PR506

SOC_PWROK

SOC_PLTRST#

17

D25

18

D54

Compal El ectronics, Inc.

Compal El ectronics, Inc.

Compal El ectronics, Inc.

Title

Title

Title

P05-Power Sequence Block Diagram

P05-Power Sequence Block Diagram

P05-Power Sequence Block Diagram

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

LA-G094PR10

LA-G094PR10

LA-G094PR10

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 39Thursday, Novem ber 08, 2018

5 39Thursday, Novem ber 08, 2018

5 39Thursday, Novem ber 08, 2018

1.0

1.0

1.0

RT3601EAGQW

+VNN

5

5

(PUZ1)

PRZ34

(PUG1)

PRG34

RT6226AGQUF

(PUH01)

PC1805

EN_1.24V

PC1205

A7

+3VALW

+VCC_VCGI VCCGI_ENRT3601EAGQW

16

+3VALW

B B

+1.8VALW EN_1.8V

A8

A8a

PRIM_PWRGD

+1.24VALW

A9

A A

5

A9a

+1.24VALW_PG

+1.05VS

15

RT8061

2

(PU1801)

3

4

PR1803

+3VALW

RT8061

2

(PU1201)

3

4

PR1201

+3VALW

4

7

7

PR1801

PR1205

VNN_EN

2

VNN_VGATE

2 68

VCC_VGATE

EN_1.05VS

B7A6

POK

A8a

PRIM_PWRGD

86

85

17

736

29

14

RE8

+1.24VALW_PG

A9a

14

SUSP#

14

SUSP#

3

SOC_PWROK

32

PLT_RST#

13

95

13a

SYSON +2.5V_MEM

SYSON

PRM08

PRM09

R927

P926

EN_2.5V

PR2501

EN_1.2V

8

7

EN_0.6VSP

+3VS_ON

+5VS_ON

EM5209VF

(U11)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

UC2

(AND)

SY8032

(PU2501)

RT8207PGQW

(PUM1)

+3VS

+5VS

2014/11/10 2018/01/25

2014/11/10 2018/01/25

2014/11/10 2018/01/25

5

20

13b

13b

+1.2V_DDR

+0.6V_DDR_VTT

14a

14a

Compal Secret Data

Compal Secret Data

Compal Secret Data

2

Deciphered Date

Deciphered Date

Deciphered Date

Vinafix.com

A

smd.db-x7.ru

+3VS

RC4

1K_0402_5%

12

12

12

+3VS

@

1 2

SOC_DP1_CT RL_CLK

SOC_DP1_CT RL_DATA

+1.8V_PRIM

@

5

UC8

1

P

NC

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

SA00004BV00

1 2

RC5 0_0402_5%

SOC_BKLTCT L

3.3/1.8V default 3.3V

RC3 2.2K_0402_5%

RC2 2.2K_0402_5%

EDP_VDD_EN

SOC_BKLTCT L

1 1

ENBKL

12

12

RC158 100K_0402_5%@

RC159 100K_0402_5%@

RC160 100K_0402_5%@

<To Panel>

L_BKLT_CT RL[16]

2 2

3.3/1.8V default 3.3V

+1.8V_PRIM

GPIO163 SMBUS 1=1.8V 0=3.3V(default)

1 2

RC6 10K_ 0402_5%@

1 2

RC7 10K_ 0402_5%@

RC8 4.7K_0 402_5%@

RC9 4.7K_0 402_5%@

GPIO168 PMU 1=1.8V 0=3.3V(default) (HDA_SDIN0)

3 3

GPIO175 1=eSPI 0=LPC(default)

12

12

SMB_1.8V_3.3V

HDA_SDIN0

GPIO_172

GPIO_175

1 2

RC10 1K_0402_5%

1 2

RC11 4.7K_0402_5 %

1 2

RC12 10K_0402_5 %

HDA for AUDIO

1 2

CC1 10P_0402_5 0V8J@RF@

1 2

HDA_BIT_CLK_R[20]

HDA_SDOUT_R[20]

HDA_SYNC_R[20]

HDA_SDIN0 HDA_SYNC

EMI@

1 2

1 2

HDA_BIT_CLK

RC1333_0402_5 %

HDA_SDOUT

RC1433_0402_5%

HDA_SYNC

RC1533_0402_5 %

12

RC16249_0402_ 1% @

12

@

RC171K_0402_1%

4 4

HDA_SDIN0[20]

SOC_EMMC_PW R_EN#[28]

T2 @

GPIO_174[11]

<HDMI>

<eDP>

EMMC_0_CLK[28]

EMMC_0_RCL K[28]

EMMC_0_DATA0[28]

EMMC_0_DATA1[28]

EMMC_0_DATA2[28]

EMMC_0_DATA3[28]

EMMC_0_DATA4[28]

EMMC_0_DATA5[28]

EMMC_0_DATA6[28]

EMMC_0_DATA7[28]

EMMC_0_CMD[28]

PCH_PLTRS T#[28]

RC18 200_0402_1%

B

SMB_1.8V_3.3V

HDA_BIT_CLK

HDA_SYNC

HDA_SDIN0

HDA_SDOUT

HDA_RST#

GPIO_172

GPIO_175

1 2

SOC_DP1_P0[17]

SOC_DP1_N0[17]

SOC_DP1_P1[17]

SOC_DP1_N1[17]

SOC_DP1_P2[17]

SOC_DP1_N2[17]

SOC_DP1_P3[17]

SOC_DP1_N3[17]

SOC_DP1_CT RL_CLK[17]

SOC_DP1_CT RL_DATA[17]

SOC_DP1_HPD #[17]

EDP_TXP0[16]

EDP_TXN0[16]

EDP_TXP1[16]

EDP_TXN1[16]

EDP_AUXP[16]

EDP_AUXN[16]

EDP_HPD#[16]

<To EC>

ENBKL[22]

EDP_VDD_EN[16]

CAD note:

Trace width=20 mils,Spacing=25mil,Max length=100mils

UC1J

C26

AVS_I2S0_MCLK

B25

AVS_I2S0_BCLK

C25

AVS_I2S0_WS_SYNC

C24

AVS_I2S0_SDI

B23

AVS_I2S0_SDO

M23

AVS_I2S1_MCLK

L21

AVS_I2S1_BCLK

J21

AVS_I2S1_WS_SYNC

M21

AVS_I2S1_SDI

P23

AVS_I2S1_SDO

A22

AVS_HDA_BCLK

C23

AVS_HDA_WS_SYNC

B21

AVS_HDA_SDI

C22

AVS_HDA_SDO

C21

AVS_HDA_RST_N

B19

AVS_DMIC_CLK_A1

C20

AVS_DMIC_CLK_B1

C19

AVS_DMIC_DATA_1

C18

AVS_DMIC_CLK_AB2

A18

AVS_DMIC_DATA_2

J13

EMMC_CLK

L15

EMMC_RCLK

M19

EMMC_D0

H19

EMMC_D1

J19

EMMC_D2

P17

EMMC_D3

P19

EMMC_D4

J15

EMMC_D5

L17

EMMC_D6

M17

EMMC_D7

M13

EMMC_CMD

U44

EMMC_RST_N

G51

EMMC_PWR_EN_N

L13

EMMC_RCOMP

FH80680030 67411-QM_FCBGA1090~ D

SOC_BKLTCT L

EDP_RCOMP_P

EDP_RCOMP_N

1 2

RC1 100_0402_ 1%

C

UC1C

AH1

DDI0_TXP_0

AH3

DDI0_TXN_0

AE2

DDI0_TXP_1

AE3

DDI0_TXN_1

AJ2

DDI0_TXP_2

AJ3

DDI0_TXN_2

AG2

DDI0_TXP_3

AG3

DDI0_TXN_3

AC12

DDI0_AUXP

AC10

DDI0_AUXN

C39

DDI0_HPD

B43

DDI0_DDC_SCL

C43

DDI0_DDC_SDA

AA2

DDI1_TXP_0

AA3

DDI1_TXN_0

Y3

DDI1_TXP_1

Y1

DDI1_TXN_1

AD1

DDI1_TXP_2

AD3

DDI1_TXN_2

AC2

DDI1_TXP_3

AC3

DDI1_TXN_3

AC7

DDI1_AUXP

AC5

DDI1_AUXN

C42

DDI1_DDC_SCL

A42

DDI1_DDC_SDA

C38

DDI1_HPD

AE12

EDP_TXP_0

AE13

EDP_TXN_0

AC15

EDP_TXP_1

AC17

EDP_TXN_1

AE10

EDP_TXP_2

AE8

EDP_TXN_2

AE5

EDP_TXP_3

AE7

EDP_TXN_3

W17

EDP_AUXP

W15

EDP_AUXN

B39

EDP_HPD

B41

PNL0_BKLCTL

C40

PNL0_BKLTEN

C41

PNL0_VDDEN

AA5

EDP_RCOMP_P

AA7

EDP_RCOMP

FH80680030 67411-QM_FCBGA1090~ D

AUDIO-AVS

eDP/DDI_A

eMMC

7 OF 13

DDI0/DDI_B

DDI1/DDI_C

SDCARD

LPC/eSPI

FAST_SPI

3 OF 13

D

MDSI_A_CLKP

MDSI_A_CLKN

MDSI_C_CLKP

MDSI_C_CLKN

MDSI_A_DP_0

MDSI_A_DN_0

MDSI_A_DP_1

MDSI

MDSI_A_DN_1

MDSI_A_DP_2

MDSI_A_DN_2

MDSI_A_DP_3

MDSI_A_DN_3

MDSI_C_DP_0

MDSI_C_DN_0

MDSI_C_DP_1

MDSI_C_DN_1

MDSI_C_DP_2

MDSI_C_DN_2

MDSI_C_DP_3

MDSI_C_DN_3

MIPI_I2C_SCL

MIPI_I2C_SDA

MDSI_C_TE

MDSI_A_TE

MDSI_RCOMP

SDCARD_CLK

SDCARD_D0

SDCARD_D1

SDCARD_D2

SDCARD_D3

SDCARD_CMD

SDCARD_CD_N

SDCARD_LVL_WP

SDCARD_PWR_DWN_N

SDCARD_RCOMP

LPC_CLKOUT0

LPC_CLKOUT1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLKRUN_N

LPC_FRAME_N

LPC_SERIRQ

FST_SPI_CLK

FST_SPI_MOSI_IO0

FST_SPI_MISO_IO1

FST_SPI_IO2

FST_SPI_IO3

FST_SPI_CS0_N

FST_SPI_CS1_N

SOC_SPI_CLK

RC36 33_0402_5%

AL2

AM3

AG13

AG12

AN5

AN7

AJ15

AJ17

AJ7

AJ5

AJ10

AJ12

AG15

AG17

AG8

AG10

AG7

AG5

AE15

AE17

R53

R54

T53

T55

AL5

SOC

SOC_SPI_CS#0_R

SOC_SPI_SO_0_R

SOC_SPI_IO2_0_R

MDSI_C_TE_GPIO_43

L29

M29

P29

M27

P27

L27

L25

P25

L23

J25

C37

A38

A34

C34

B35

C35

C33

B33

B37

B29

B31

C30

A30

C29

C31

C32

12

CAM_DET#

LCD_CBL_D ET#_R

TOUCH_PANEL_ PD#

LPC_CLK0

LPC_AD0_R

LPC_AD1_R

LPC_AD2_R

LPC_AD3_R

LPC_FRAME#_R

SOC_SPI_CLK

SOC_SPI_SI

SOC_SPI_SO

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

RC33 150_0402_1%

1 2

EMI@

SOC_SPI_CS#0

1 2

@

RC35 0_ 0402_5%

SOC_SPI_IO3

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_SO

RC34 0_ 0402_5%

16MB SPI ROM(1.8V)

UC11

CS#1VCC

2

SO

3

IO2

4

VSS

T54TP@

ME_FWP_SOC _Q [11]

SOC_SPI_IO2_0_R

SOC_SPI_IO3_0_R

SOC_SPI_CS#0_R

CAM_DET#

TOUCH_PANEL_ PD#

LPC_CLK_EC

KB_LED_BL_D ET [27]

SATA_ODD_PRSNT [2 2,24]

CAM_DET# [16 ]

1 2

1 2

RC1149 0_0201_5%

RC1147 0_0201_5%

1 2

RC25 200_0402_ 1%

1 2

RC24 33_0402_5 %EMI@

1 2

RC23 2 0_0402_1%

1 2

RC22 2 0_0402_1%

1 2

RC21 2 0_0402_1%

1 2

RC20 2 0_0402_1%

1 2

RC19 2 0_0402_1%

T1@

SATA_ODD_PRSNT

E

SOC_SPI_CLK_R

1 2

@EMI@

RC37 33_0402_5 %

SOC_SPI_CS#0_R

CC3 22P_0201_5 0V

SPI ROM

1 2

RC16133_0402_5 %

1 2

RC16233_0402_5 %

1 2

RC16333_0402_5 %

1 2

RC16433_0402_5 %

+VCC_SPI+1.8V_PRIM

1 2

@

+VCC_SPI

8

SOC_SPI_IO3_0_R

7

IO3

SOC_SPI_CLK_R

6

SCLK

SOC_SPI_SI_0_R

5

SI

W25Q128FW SIQ SOIC

1 2

RC32 1K_0402_5%

1 2

RC31 1K_0402_5%

1 2

RC30 39K_0402_5 %

@

@

@RF@

1 2

CC2 10P_0402_50V8J

@

@

To EC

1 2

RC120 10 K_0402_5%

1 2

@EMI@

SOC_SPI_IO3_0_R

SOC_SPI_SI_0_R

SOC_SPI_IO2_0_R

SOC_SPI_SO_0_R

1

CC91

0.1U_0402_ 25V6K

2

+1.8V_PRIM

+3VS

12

RC114810K_0402_5%

12

RC114610K_0402_5 %

change to GPIO210 @2/6

LCD_CBL_D ET# [16]

TOUCH_SCR EEN_PD# [16]

LPC_CLK_EC [22]

LPC_AD0 [22]

LPC_AD1 [22]

LPC_AD2 [22]

LPC_AD3 [22]

CLKRUN# [22]

LPC_FRAME# [22]

SERIRQ [22]

change to +3VALW @2/6

+3VALW

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/09/27 2016/12/31

2017/09/27 2016/12/31

2017/09/27 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Compal Electronics, Inc.

GLK(1/9)DDI,HDA,SPI,eMMC

GLK(1/9)DDI,HDA,SPI,eMMC

GLK(1/9)DDI,HDA,SPI,eMMC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

D

LA-G094PR10

LA-G094PR10

LA-G094PR10

E

6 39Thursday, November 08, 20 18

6 39Thursday, November 08, 20 18

6 39Thursday, November 08, 20 18

1.0

1.0

1.0

5

smd.db-x7.ru

4

3

2

1

UC1B

AY3

MEM_CH1_DQ40/MEM_CH1_DQB8

BD3

MEM_CH1_D Q41/MEM_CH1_ DQB9

D D

C C

B B

DDR_M0_D[32 ..47][15]

DDR_M0_D[48 ..63][15]

DDR_M0_D[0. .15][15]

DDR_M0_D[16 ..31][15]

DDR_M0_D40

DDR_M0_D41

DDR_M0_D42

DDR_M0_D43

DDR_M0_D44

DDR_M0_D45

DDR_M0_D46

DDR_M0_D47

DDR_M0_D32

DDR_M0_D33

DDR_M0_D34

DDR_M0_D35

DDR_M0_D36

DDR_M0_D37

DDR_M0_D38

DDR_M0_D39

DDR_M0_D56

DDR_M0_D57

DDR_M0_D58

DDR_M0_D59

DDR_M0_D60

DDR_M0_D61

DDR_M0_D62

DDR_M0_D63

DDR_M0_D48

DDR_M0_D49

DDR_M0_D50

DDR_M0_D51

DDR_M0_D52

DDR_M0_D53

DDR_M0_D54

DDR_M0_D55

DDR_M0_D0

DDR_M0_D1

DDR_M0_D2

DDR_M0_D3

DDR_M0_D4

DDR_M0_D5

DDR_M0_D6

DDR_M0_D7

DDR_M0_D8

DDR_M0_D9

DDR_M0_D10

DDR_M0_D11

DDR_M0_D12

DDR_M0_D13

DDR_M0_D14

DDR_M0_D15

DDR_M0_D16

DDR_M0_D17

DDR_M0_D18

DDR_M0_D19

DDR_M0_D20

DDR_M0_D21

DDR_M0_D22

DDR_M0_D23

DDR_M0_D24

DDR_M0_D25

DDR_M0_D26

DDR_M0_D27

DDR_M0_D28

DDR_M0_D29

DDR_M0_D30

DDR_M0_D31

UC1A

BJ36

MEM_CH0_D Q40/MEM_CH0_ DQB8

BK37

MEM_CH0_DQ41/MEM_CH0_DQB9

BJ35

MEM_CH0_DQ42/MEM_CH0_DQB10

BL36

MEM_CH0_DQ43/MEM_CH0_DQB11

BJ39

MEM_CH0_DQ44/MEM_CH0_DQB12

BL40

MEM_CH0_DQ45/MEM_CH0_DQB13

BJ40

MEM_CH0_DQ46/MEM_CH0_DQB14

BK41

MEM_CH0_DQ47/MEM_CH0_DQB15

BA35

MEM_CH0_DQ32/MEM_CH0_DQB0

AY33

MEM_CH0_DQ33/MEM_CH0_DQB1

BA33

MEM_CH0_DQ34/MEM_CH0_DQB2

AY35

MEM_CH0_DQ35/MEM_CH0_DQB3

BA37

MEM_CH0_DQ36/MEM_CH0_DQB4

AY37

MEM_CH0_DQ37/MEM_CH0_DQB5

AY39

MEM_CH0_DQ38/MEM_CH0_DQB6

BA39

MEM_CH0_DQ39/MEM_CH0_DQB7

BL34

MEM_CH0_DQ56/MEM_CH0_DQB24

BL30

MEM_CH0_DQ57/MEM_CH0_DQB25

BJ29

MEM_CH0_DQ58/MEM_CH0_DQB26

BK29

MEM_CH0_DQ59/MEM_CH0_DQB27

BJ33

MEM_CH0_DQ60/MEM_CH0_DQB28

BK33

MEM_CH0_DQ61/MEM_CH0_DQB29

BJ34

MEM_CH0_DQ62/MEM_CH0_DQB30

BJ30

MEM_CH0_DQ63/MEM_CH0_DQB31

BD29

MEM_CH0_DQ48/MEM_CH0_DQB16

BF29

MEM_CH0_DQ49/MEM_CH0_DQB17

BH29

MEM_CH0_DQ50/MEM_CH0_DQB18

BF33

MEM_CH0_DQ51/MEM_CH0_DQB19

BC29

MEM_CH0_DQ52/MEM_CH0_DQB20

BD33

MEM_CH0_DQ53/MEM_CH0_DQB21

BF35

MEM_CH0_DQ54/MEM_CH0_DQB22

BH35

MEM_CH0_DQ55/MEM_CH0_DQB23

AR53

MEM_CH0_DQ0/MEM_CH0_DQA0

AP55

MEM_CH0_DQ1/MEM_CH0_DQA1

AP53

MEM_CH0_DQ2/MEM_CH0_DQA2

AN54

MEM_CH0_DQ3/MEM_CH0_DQA3

AU54

MEM_CH0_DQ4/MEM_CH0_DQA4

AV53

MEM_CH0_DQ5/MEM_CH0_DQA5

AV55

MEM_CH0_DQ6/MEM_CH0_DQA6

AW53

MEM_CH0_DQ7/MEM_CH0_DQA7

AU51

MEM_CH0_DQ8/MEM_CH0_DQA8

AU48

MEM_CH0_DQ9/MEM_CH0_DQA9

AU49

MEM_CH0_DQ10/MEM_CH0_DQA10

BA46

MEM_CH0_DQ11/MEM_CH0_DQA11

BA48

MEM_CH0_DQ12/MEM_CH0_DQA12

BA49

MEM_CH0_DQ13/MEM_CH0_DQA13

BA51

MEM_CH0_DQ14/MEM_CH0_DQA14

AR51

MEM_CH0_DQ15/MEM_CH0_DQA15

AY55

MEM_CH0_DQ16/MEM_CH0_DQA16

BA54

MEM_CH0_DQ17/MEM_CH0_DQA17

BA53

MEM_CH0_DQ18/MEM_CH0_DQA18

AY53

MEM_CH0_DQ19/MEM_CH0_DQA19

BC53

MEM_CH0_DQ20/MEM_CH0_DQA20

BD55

MEM_CH0_DQ21/MEM_CH0_DQA21

BE54

MEM_CH0_DQ22/MEM_CH0_DQA22

BD53

MEM_CH0_DQ23/MEM_CH0_DQA23

AN43

MEM_CH0_DQ24/MEM_CH0_DQA24

AN44

MEM_CH0_DQ25/MEM_CH0_DQA25

AR48

MEM_CH0_DQ26/MEM_CH0_DQA26

AU41

MEM_CH0_DQ27/MEM_CH0_DQA27

AU43

MEM_CH0_DQ28/MEM_CH0_DQA28

AN41

MEM_CH0_DQ29/MEM_CH0_DQA29

AN39

MEM_CH0_DQ30/MEM_CH0_DQA30

AU44

MEM_CH0_DQ31/MEM_CH0_DQA31

FH806800306 7411-QM_FCBGA1 090~D

DDR_M0_DRA MRST#

+1.2V_DDR

12

RC42 0_04 02_5%@

RC41

1K_0402_1%

1 2

MEM_CH0_DQS0_P/MEM_CH0_DQSA0_P

MEM_CH0_DQS0_N/MEM_CH0_DQSA0_N

MEM_CH0_DQS1_PMEM_CH0_DQSA1_P

MEM_CH0_DQS1_N/MEM_CH0_DQSA1_N

MEM_CH0_DQS2_P/MEM_CH0_DQSA2_P

MEM_CH0_DQS2_N/MEM_CH0_DQSA2_N

MEM_CH0_DQS3_P/MEM_CH0_DQSA3_P

MEM_CH0_DQS3_N/MEM_CH0_DQSA3_N

MEM_CH0_DQS4_P/MEM_CH0_DQSB0_P

MEM_CH0_DQS4_N/MEM_CH0_DQSB0_N

MEM_CH0_DQS5_P/MEM_CH0_DQSB1_P

MEM_CH0_DQS5_N/MEM_CH0_DQSB1_N

MEM_CH0_DQS6_P/MEM_CH0_DQSB2_P

MEM_CH0_DQS6_N/MEM_CH0_DQSB2_N

MEM_CH0_DQS7_P/MEM_CH0_DQSB3_P

MEM_CH0_DQS7_N/MEM_CH0_DQSB3_N

DDR0

1 OF 13

DDR4 / LPDDR4 DDR4 / LPDDR4

NCTF1/MEM_CH0_CKE1B

NCTF2/MEM_CH0_CKE0B

NCTF3/MEM_CH0_CS0B

MEM_CH0_ODT1/NCTF

MEM_CH0_CS1_N/MEM_CH0_CS1B

NCTF4/MEM_CH0_CS1A

MEM_CH0_ODT0/NCTF

MEM_CH0_CS0_N/MEM_CH0_CS0A

MEM_CH0_CKE1/MEM_CH0_CKE1A

MEM_CH0_CKE0/MEM_CH0_CKE0A

MEM_CH0_CLK0_P/MEM_CH0_CLKB_P

MEM_CH0_CLK0_N/MEM_CH0_CLKB_N

MEM_CH0_CLK1_P/MEM_CH0_CLKA_P

MEM_CH0_CLK1_N/MEM_CH0_CLKA_N

MEM_CH0_MA0/NCTF

MEM_CH0_MA1/NCTF

MEM_CH0_MA2/MEM_CH0_CAB5

MEM_CH0_MA10/NCTF

MEM_CH0_MA13/MEM_CH0_CAB0

MEM_CH0_MA16/MEM_CH0_CAB3

MEM_CH0_BA1/NCTF

MEM_CH0_BA0/MEM_CH0_CAB4

MEM_CH0_BG1/MEM_CH0_CAB2

MEM_CH0_ACT_N/MEM_CH0_CAB1

MEM_CH0_MA3/NCTF

MEM_CH0_MA4/NCTF

MEM_CH0_MA5/MEM_CH0_CAA2

MEM_CH0_MA6/MEM_CH0_CAA1

MEM_CH0_MA7/MEM_CH0_CAA3

MEM_CH0_MA8/MEM_CH0_CAA0

MEM_CH0_MA9/MEM_CH0_CAA4

MEM_CH0_MA11/NCTF

MEM_CH0_MA12/NCTF

MEM_CH0_MA14/NCTF

MEM_CH0_MA15/NCTF

MEM_CH0_BG0/MEM_CH0_CAA5

MEM_CH0_VREFDQ/NCTF

MEM_CH0_VREFCA/NCTF

DDR_M0_DRA MRST#_R [15]

AT53

AT55

AW49

AW48

BC54

BB53

AR41

AR43

AV37

AV35

BL38

BJ38

BF31

BD31

BJ32

BK31

BG54

BH54

BJ42

BF39

BK43

BL44

BD39

BJ43

BF54

BF55

BE49

BE51

BC49

BC48

BD45

BH50

BH47

BF45

BH43

BD41

BH51

BD43

BF43

BF41

BG52

BK45

BJ46

BJ44

BJ47

BJ45

BK47

BJ51

BJ52

BJ48

BJ50

BL50

AY31

AV29

+0.6V_M0_ VREFDQ

1 2

RC157 0_0402_5 %@

DDR_M0_DQS 0 [15]

DDR_M0_DQS #0 [15]

DDR_M0_DQS 1 [15]

DDR_M0_DQS #1 [15]

DDR_M0_DQS 2 [15]

DDR_M0_DQS #2 [15]

DDR_M0_DQS 3 [15]

DDR_M0_DQS #3 [15]

DDR_M0_DQS 4 [15]

DDR_M0_DQS #4 [15]

DDR_M0_DQS 5 [15]

DDR_M0_DQS #5 [15]

DDR_M0_DQS 6 [15]

DDR_M0_DQS #6 [15]

DDR_M0_DQS 7 [15]

DDR_M0_DQS #7 [15]

DDR_M0_ODT1 [15]

DDR_M0_CS #1 [15]

DDR_M0_ODT0 [15]

DDR_M0_CS #0 [15]

DDR_M0_CK E1 [15]

DDR_M0_CK E0 [15]

DDR_M0_CLK 0 [15]

DDR_M0_CLK #0 [15]

DDR_M0_CLK 1 [15]

DDR_M0_CLK #1 [15]

DDR_M0_MA 0 [15 ]

DDR_M0_MA 1 [15 ]

DDR_M0_MA 2 [15 ]

DDR_M0_MA 10 [1 5]

DDR_M0_MA 13 [1 5]

DDR_M0_MA 16_RAS# [15]

DDR_M0_BA 1 [ 15]

DDR_M0_BA 0 [ 15]

DDR_M0_BG1 [15]

DDR_M0_AC T# [15]

DDR_M0_MA 3 [15 ]

DDR_M0_MA 4 [15 ]

DDR_M0_MA 5 [15 ]

DDR_M0_MA 6 [15 ]

DDR_M0_MA 7 [15 ]

DDR_M0_MA 8 [15 ]

DDR_M0_MA 9 [15 ]

DDR_M0_MA 11 [1 5]

DDR_M0_MA 12 [1 5]

DDR_M0_MA 14_WE# [1 5]

DDR_M0_MA 15_CAS# [15]

DDR_M0_BG0 [15]

T3

@

1

ESD@

CC95

100P_0402_50V8J

2

+V_DDR_RE FA_R

BD1

MEM_CH1_DQ42/MEM_CH1_DQB10

BC3

MEM_CH1_DQ43/MEM_CH1_DQB11

AY1

MEM_CH1_DQ44/MEM_CH1_DQB12

BA3

MEM_CH1_DQ45/MEM_CH1_DQB13

BA2

MEM_CH1_DQ46/MEM_CH1_DQB14

BE2

MEM_CH1_DQ47/MEM_CH1_DQB15

AR8

MEM_CH1_DQ32/MEM_CH1_DQB0

AN15

MEM_CH1_DQ33/MEM_CH1_DQB1

AN17

MEM_CH1_DQ34/MEM_CH1_DQB2

AU12

MEM_CH1_DQ35/MEM_CH1_DQB3

AN12

MEM_CH1_DQ36/MEM_CH1_DQB4

AN13

MEM_CH1_DQ37/MEM_CH1_DQB5

AU13

MEM_CH1_DQ38/MEM_CH1_DQB6

AU15

MEM_CH1_DQ39/MEM_CH1_DQB7

AP3

MEM_CH1_DQ56/MEM_CH1_DQB24

AU2

MEM_CH1_DQ57/MEM_CH1_DQB25

AV3

MEM_CH1_DQ58/MEM_CH1_DQB26

AW3

MEM_CH1_DQ59/MEM_CH1_DQB27

AN2

MEM_CH1_DQ60/MEM_CH1_DQB28

AP1

MEM_CH1_DQ61/MEM_CH1_DQB29

AR3

MEM_CH1_DQ62/MEM_CH1_DQB30

AV1

MEM_CH1_DQ63/MEM_CH1_DQB31

AR5

MEM_CH1_DQ48/MEM_CH1_DQB16

BA8

MEM_CH1_DQ49/MEM_CH1_DQB17

AU7

MEM_CH1_DQ50/MEM_CH1_DQB18

AU5

MEM_CH1_DQ51/MEM_CH1_DQB19

BA5

MEM_CH1_DQ52/MEM_CH1_DQB20

BA7

MEM_CH1_DQ53/MEM_CH1_DQB21

AU8

MEM_CH1_DQ54/MEM_CH1_DQB22

BA10

MEM_CH1_DQ55/MEM_CH1_DQB23

BJ26

MEM_CH1_DQ0/MEM_CH1_DQA0

BL26

MEM_CH1_DQ1/MEM_CH1_DQA1

BJ27

MEM_CH1_DQ2/MEM_CH1_DQA2

BK27

MEM_CH1_DQ3/MEM_CH1_DQA3

BJ23

MEM_CH1_DQ4/MEM_CH1_DQA4

BK23

MEM_CH1_DQ5/MEM_CH1_DQA5

BJ22

MEM_CH1_DQ6/MEM_CH1_DQA6

BL22

MEM_CH1_DQ7/MEM_CH1_DQA7

BD27

MEM_CH1_DQ8/MEM_CH1_DQA8

BF27

MEM_CH1_DQ9/MEM_CH1_DQA9

BH27

MEM_CH1_DQ10/MEM_CH1_DQA10

BC27

MEM_CH1_DQ11/MEM_CH1_DQA11

BH21

MEM_CH1_DQ12/MEM_CH1_DQA12

BF23

MEM_CH1_DQ13/MEM_CH1_DQA13

BD23

MEM_CH1_DQ14/MEM_CH1_DQA14

BF21

MEM_CH1_DQ15/MEM_CH1_DQA15

BK19

MEM_CH1_DQ16/MEM_CH1_DQA16

BJ20

MEM_CH1_DQ17/MEM_CH1_DQA17

BL20

MEM_CH1_DQ18/MEM_CH1_DQA18

BJ21

MEM_CH1_DQ19/MEM_CH1_DQA19

BJ17

MEM_CH1_DQ20/MEM_CH1_DQA20

BJ16

MEM_CH1_DQ21/MEM_CH1_DQA21

BK15

MEM_CH1_DQ22/MEM_CH1_DQA22

BL16

MEM_CH1_DQ23/MEM_CH1_DQA23

BA21

MEM_CH1_DQ24/MEM_CH1_DQA24

AY23

MEM_CH1_DQ25/MEM_CH1_DQA25

BA23

MEM_CH1_DQ26/MEM_CH1_DQA26

BA17

MEM_CH1_DQ27/MEM_CH1_DQA27

AY21

MEM_CH1_DQ28/MEM_CH1_DQA28

AY17

MEM_CH1_DQ29/MEM_CH1_DQA29

AY19

MEM_CH1_DQ30/MEM_CH1_DQA30

BA19

MEM_CH1_DQ31/MEM_CH1_DQA31

FH806800306 7411-QM_FCBGA1 090~D

DDR1

2 OF 13

DDR4 / LPDDR4 DDR4 / LPDDR4

MEM_CH1_DQS0_P/MEM_CH1_DQSA0_P

MEM_CH1_DQS0_N/MEM_CH1_DQSA0_N

MEM_CH1_DQS1_P/MEM_CH1_DQSA1_P

MEM_CH1_DQS1_N/MEM_CH1_DQSA1_N

MEM_CH1_DQS2_P/MEM_CH1_DQSA2_P

MEM_CH1_DQS2_N/MEM_CH1_DQSA2_N

MEM_CH1_DQS3_P/MEM_CH1_DQSA3_P

MEM_CH1_DQS3_N/MEM_CH1_DQSA3_N

MEM_CH1_DQS4_P/MEM_CH1_DQSB0_P

MEM_CH1_DQS4_N/MEM_CH1_DQSB0_N

MEM_CH1_DQS5_P/MEM_CH1_DQSB1_P

MEM_CH1_DQS5_N/MEM_CH1_DQSB1_N

MEM_CH1_DQS6_P/MEM_CH1_DQSB2_P

MEM_CH1_DQS6_N/MEM_CH1_DQSB2_N

MEM_CH1_DQS7_P/MEM_CH1_DQSB3_P

MEM_CH1_DQS7_N/MEM_CH1_DQSB3_N

MEM_CH1_RESET_N/MEM_CH1_RESET_N

MEM_CH0_RESET_N/MEM_CH0_RESET_N

MEM_CH1_MA0/NCTF

MEM_CH1_MA1/NCTF

MEM_CH1_MA2/MEM_CH1_CAB5

MEM_CH1_MA3/NCTF

MEM_CH1_MA10/NCTF

MEM_CH1_MA13/MEM_CH1_CAB0

MEM_CH1_MA16/MEM_CH1_CAB3

MEM_CH1_BA0/MEM_CH1_CAB4

MEM_CH1_BA1/NCTF

MEM_CH1_BG1/MEM_CH1_CAB2

MEM_CH1_ACT_N/MEM_CH1_CAB1

MEM_CH1_MA11/NCTF

MEM_CH1_MA12/NCTF

MEM_CH1_MA14/NCTF

MEM_CH1_MA15/NCTF

MEM_CH1_BG0/MEM_CH1_CAA5

MEM_CH1_MA4/NCTF

MEM_CH1_MA5/MEM_CH1_CAA2

MEM_CH1_MA6/MEM_CH1_CAA1

MEM_CH1_MA7/MEM_CH1_CAA3

MEM_CH1_MA8/MEM_CH1_CAA0

MEM_CH1_MA9/MEM_CH1_CAA4

MEM_CH1_CLK0_P/MEM_CH1_CLKB_P

MEM_CH1_CLK0_N/MEM_CH1_CLKB_N

MEM_CH1_CLK1_P/MEM_CH1_CLKA_P

MEM_CH1_CLK1_N/MEM_CH1_CLKA_N

NCTF3/MEM_CH1_CKE0B

NCTF4/MEM_CH1_CKE1B

NCTF1/MEM_CH1_CS0B

MEM_CH1_CS1_N/MEM_CH1_CS1B

MEM_CH1_ODT1/NCTF

MEM_CH1_CS0_N/MEM_CH1_CS0A

MEM_CH1_ODT0/NCTF

NCTF2/MEM_CH1_CS1A

MEM_CH1_CKE0/MEM_CH1_CKE0A

MEM_CH1_CKE1/MEM_CH1_CKE1A

MEM_CH0_RCOMP/MEM_CH0_RCOMP

MEM_CH1_RCOMP/MEM_CH1_RCOMP

MEM_CH1_VREFCA/NCTF

MEM_CH1_VREFDQ/NCTF

BJ24

BK25

BD25

BF25

BL18

BJ18

AV19

AV21

AR13

AR15

BB3

BC2

AW7

AW8

AT1

AT3

BH9

BC13

BD11

BD13

BF11

BE5

BH5

BH6

BF13

BG4

BE7

BK11

BJ12

BK9

BJ11

BJ10

BJ4

BL6

BJ5

BJ9

BJ6

BJ8

BF17

BD17

BF15

BH15

BJ13

BL12

BF1

BF2

BC7

BH2

BC8

BG2

BK13

BJ14

AY29

BC15

AY27

AV27

AY25

BC43

DDR_M0_RCOM P

DDR_M1_RCOM P

1 2

RC40 0 _0402_5%@

+0.6V_M1_ VREFDQ

DDR_M0_DRA MRST#

ESD@

12

RC38 110 _0402_1%

1 2

RC39 110 _0402_1%

T4

@

2

3

D14

CEST523NC5V B 3P C/A SOT-523

1

T30

@

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/09/27 2016/12/31

2017/09/27 2016/12/31

2017/09/27 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

GLK(2/9)Memory

GLK(2/9)Memory

GLK(2/9)Memory

Size Docum ent Numbe r Rev

Size Docum ent Numbe r Rev

Size Docum ent Numbe r Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-G094PR10

LA-G094PR10

LA-G094PR10

Thursday, Novemb er 08, 2018

Thursday, Novemb er 08, 2018

Thursday, Novemb er 08, 2018

1

39

39

39

7

7

7

1.0

1.0

1.0

Vinafix.com

5

smd.db-x7.ru

+3VALW_SOC

RC43 10K _0402_5%

+3VALW_SOC +1.8V_PRIM

RC45 1 00K_0402_5%

D D

+3VALW_SOC

RC46 1 00K_0402_5%

PCH_RSMRST #_AND

SOC_PLTRST #

C C

12

12

12

@

1 2

XDP@

RC47 1K_0402_5%

1 2

XDP@

RC48 1K_0402_5%

PM_RST_BT N#

PM_BATLOW#

SUSPWRD NACK#

PBTN_OUT# _SOC[21]

PM_SLP_S3#[22]

PM_SLP_S4#[22]

SUSPWRD NACK#[2 2]

SUSCLK[18,22]

SOC_SVID_CLK[36,37]

PMU_WAKE#(AG55) ball name changed to EMMC_PWR_EN_N

refer EDS #557555

SOC_PLTRST #

T32 @

T5 @

T6 @

T7 @

XDP_RSMRST#_ B_R [21]

XDP_PLTRST# _B_R [21]

PM_BATLOW#

PM_RST_BT N#

SUSCLK

SUS_STAT#

SOC_SVID_CLK

SOC_SVID_DAT

SOC_SVID_ALERT#

UC1E

R46

PMC_I2C_SCL

R48

PMC_I2C_SDA

L48

PMC_SPI_CLK

N48

PMC_SPI_FS0

N44

PMC_SPI_FS1

L49

PMC_SPI_FS2

L51

PMC_SPI_RXD

N49

PMC_SPI_TXD

D54

PMU_PLTRST_N

E54

PMU_PWRBTN_N

C52

PMU_SLP_S0_N

D51

PMU_SLP_S3_N

J49

PMU_SLP_S4_N

F54

SUSPWRDNACK

J48

PMU_BATLOW_N

C51

PMU_RSTBTN_N

G49

PMU_SUSCLK

E52

SUS_STAT_N

F55

SVID0_CLK

G53

SVID0_DATA

G54

SVID0_ALERT_N

D1

DEBUG_PORT_A0

D2

DEBUG_PORT_A1

A54

NC2

C54

NC11

FH80680030 67411-QM_FCBGA1090~ D

DC2 C H751H-40PT_SOD3 23-2

2 1

DC3 C H751H-40PT_SOD3 23-2

PCH PLTRST Buffer

1 2

@

RC49 0 _0402_5%

+3VS

CC4

1 2

5

UC2

SOC_PLTRST #

B B

MC74VHC1G08D FT2G SC70 5P AND

change SA00000OH00 @5/3

0.1U_0402_ 25V6K

1

P

B

4

Y

2

A

G

RC50 100K_0402_ 5%@

3

RC51 100K_0402_ 5%

PLT_RST# [18,19,22,28 ]

12

12

SOC_PLTRST #

PLT_RST#

4

OSC_CLK_OUT_0

OSC_CLK_OUT_1

iCLK

RTC

PMC

Thermal

PMU

SVID

Spare

Misc

8 OF 13

EC_CLR_CM OS[22]

SOC_PWROKPCH_RSMRST #_AND

21

POK [22,30,32,35]

SVID DATA

12

OSCIN

OSCOUT

RTC_X1

RTC_X2

VCC_RTC_EXTPAD

INTRUDER

SOC_PWROK

RSM_RST_N

RTC_TEST_N

RTC_RST_N

THERMTRIP_N

PROCHOT_N

SKTOCC_N

EC_CLR_CM OS

Place the PU

resistors close to CPU

RC59

240_0402_ 1%

NC15

NC16

NC14

NC10

NC17

NC3

NC4

NC1

NC5

NC6

NC7

NC8

NC9

12

B17

C17

U2

T1

D23

F23

J23

H25

D25

F27

F25

D27

J53

J54

AG43

H53

AG44

H55

A4

BH1

A53

F37

BL2

BL3

BL53

C2

C3

R41

RC64

10K_0402_5 %

3

OSCIN

RC71 0_0402_5%EMI@

OSCOUT

RC72 0_0402_5%EMI@

SOC_RTCX1

SOC_RTCX2

INTRUDE

PCH_RSMRST #_AND

SOC_RTCTE ST#

SOC_SRTCRS T#

1 2

1 2

12

RC73 330K_0402_ 5%

SOC_PWROK [22]

H_THERMT RIP# [22]

H_PROCHOT# [22,3 0,31]

G

2

13

D

S

QC1

2N7002K_SOT 23

G

2

13

D

S

QC10

2N7002K_SOT 23

SVID ALERT

SOC_SVID_ALERT#SOC_SVID_DAT

RC60 220_0402_5%

+RTC_CEL L

@

1 2

SOC_XTAL19_IN

SOC_XTAL19_OUT

+RTC_CEL L

RC66 2 0K_0402_5%

CC12 1U_0402_6.3V6K

CLRP1 SHORT PADS

RC65 2 0K_0402_5%

CC11 1U_0402_6.3V6K

CLRP2 SHORT PADS

SOC_SRTCRS T#

SOC_RTCTE ST#

+1.05VS+1.05VS

12

RC61

68_0402_5 %

2

H_THERMT RIP#

H_PROCHOT#

VCC_RTC_EXTP ADVCC_RTC_EXTP AD

H_PROCHOT#

1 2

1 2

1 2

1 2

1 2

1 2

RC70 1K_0402_5%

RC69 1K_0402_5%

CC88 0 .1U_0402_25V6K

@ESD@

1

CC15

68P_0201_5 0V8J

2

SOC_SRTCRS T#

CLR all register bits

SOC_RTCTE ST#

CLR CMOS

From Battery

Place the PU

resistors close to CPU

SOC_SVID_ALERT#_R [36 ,37]SOC_SVID_DAT [36,3 7]

1 2

1 2

1 2

+RTC_VCC +3VLP

12

RC62

10M_0402_ 5%

SOC_XTAL19_OUT

SOC_XTAL19_IN

RC63

1K_0402_5%

RC68

200K_0402_ 5%

RTC_PWR

12

G

2

13

D

S

QC9

2N7002K_SOT 23

1 2

SOC_RTCX2

SOC_RTCX1

1

CC17 10P_0402_50V8J

3

3

YC1

11GND

CC16 10P_0 402_50V8J

RC67 10M_0 402_5%

32.768KHZ CM7 V-T1A9.0PF20PPM

SJ10000S900

1

18P_0402_50V8J

CC13

2

DC1

2

anode

1

cathode

3

anode

BAS40C_SOT23- 3

RTC_DET# [12]

12

4

GND

SJ10000BV00

2

12

1 2

YC2

1 2

+RTC_CEL L

19.2MHZ_10PF_7M19200019

1

CC10

0.47U_0402 _6.3V6K

2

1

18P_0402_50V8J

CC14

2

@

SUSCLK

RSMRST circuit

<EC>

EC_RSMRST#[22]

POK

RC53 0_0402_5%

A A

EC_RSMRST#

PLT_RST#

5

ALW_PWR GD_3V_5V_R

1 2

@

@ESD@

12

CC89 0.1 U_0402_16V7K

ESD@

12

CC90 0.1 U_0402_16V7K

change SA00000OH00 @5/3

1 2

RC52 0_0402_5%

+3VALW

CC5

1 2

5

UC3

@

0.1U_0201_ 10V6K

1

P

B

1 2

4

Y

2

A

G

0_0402_5%

3

TC7SH08FU _SSOP5

RC54

+3VALW

RC55

@

100K_0402_ 5%

1 2

4

PCH_RSMRST #_AND

RC56

@

100K_0402_ 5%

1 2

1

@ESD@

CC6

0.1U_0402_ 16V7K

2

@

SOC_PWROK

Close to CPU

SOC_PLTRST #

PM_RST_BT N#

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1 2

@

RC58 1K_0402_5%

1 2

RC57 100K_0402_ 5%

@ESD@

1 2

CC9 0.1U_0402_16V7K

@ESD@

1 2

CC8 0.1 U_0201_10V6K

@ESD@

1 2

CC7 0.1U_0402_25V6K

Issued Date

Issued Date

Issued Date

Compal Secret Data

Compal Secret Data

2017/09/27 2016/12/31

2017/09/27 2016/12/31

2017/09/27 2016/12/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

GLK(3/9)PMU,RTC,THERMAL

GLK(3/9)PMU,RTC,THERMAL

GLK(3/9)PMU,RTC,THERMAL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-G094PR10

LA-G094PR10

LA-G094PR10

1

8 39Thursday, November 08, 20 18

8 39Thursday, November 08, 20 18

8 39Thursday, November 08, 20 18

1.0

1.0

1.0

Vinafix.com

5

smd.db-x7.ru

PCIE_REF_ CLK_RCOMP

D D

SSD

WLAN

LAN

PCIE_CTX_ DRX_P0[18]

PCIE_CTX_ DRX_N0[18]

PCIE_CRX_ DTX_P0[18]

PCIE_CRX_ DTX_N0[18]

SSD

C C

B B

A A

PCIE_CTX_ DRX_P1[18]

PCIE_CTX_ DRX_N1[18]

PCIE_CRX_ DTX_P1[18]

PCIE_CRX_ DTX_N1[18]

PCIE_CTX_ DRX_P2[18]

PCIE_CTX_ DRX_N2[18]

PCIE_CRX_ DTX_P2[18]

PCIE_CRX_ DTX_N2[18]

LAN

USB2_VB USSENSE

USB2_ID

CLK_PCIE_P0[18]

CLK_PCIE_N0[18]

CLK_PCIE_P1[18]

CLK_PCIE_N1[18]

CLK_PCIE_ P2[19]

CLK_PCIE_ N2[19]

SSD

WLAN

LAN

PCIE_W AKE2#[19,22]

PCIE_W AKE3#[18]

HDD

RC75 0_0402_ 5%

RC76 0_0402_ 5%

CLKREQ_ PCIE#0[18]

CLKREQ_ PCIE#1[18]

CLKREQ_ PCIE#2[19]

SATA_CT X_DRX_P0[24]

SATA_CT X_DRX_N0[24]

SATA_CR X_DTX_P0[24]

SATA_CR X_DTX_N0[24]

1 2

1 2

@

PCIE_CTX_ DRX_P0

PCIE_CTX_ DRX_N0

PCIE_CTX_ DRX_P1

PCIE_CTX_ DRX_N1

PCIE_CTX_ DRX_P2

PCIE_CTX_ DRX_N2

CLKREQ_ PCIE#3

PCIE_W AKE0#

PCIE_W AKE1#

PCIE_W AKE2#

PCIE_W AKE3#

4

UC1D

L10

PCIE_REF_CLK_RCOMP

R12

PCIE_CLKOUT0P

R10

PCIE_CLKOUT0N

N7

PCIE_CLKOUT1P

N5

PCIE_CLKOUT1N

R7

PCIE_CLKOUT2P

R5

PCIE_CLKOUT2N

N8

PCIE_CLKOUT3P

N10

PCIE_CLKOUT3N

E2

PCIE_P0_TXP

F2

PCIE_P0_TXN

G7

PCIE_P0_RXP

H6

PCIE_P0_RXN

A7

PCIE_P1_TXP

C7

PCIE_P1_TXN

D4

PCIE_P1_RXP

E5

PCIE_P1_RXN

C9

PCIE_P2_TXP

B9

PCIE_P2_TXN

E7

PCIE_P2_RXP

F6

PCIE_P2_RXN

A46

PCIE_CLKREQ0_N

C45

PCIE_CLKREQ1_N

B45

PCIE_CLKREQ2_N

C44

PCIE_CLKREQ3_N

F47

PCIE_WAKE0_N

D47

PCIE_WAKE1_N

F45

PCIE_WAKE2_N

D50

PCIE_WAKE3_N

J3

SATA_P0_TXP

J2

SATA_P0_TXN

J7

SATA_P0_RXP

J5

SATA_P0_RXN

FH80680 03067411-QM_F CBGA1090~D

SATA

3

NC1

NC2

NC5

NC4

NC3

USB2_DP0

USB2_DN0

USB2_DP1

USB2_DN1

USB2_DP2

USB2_DN2

USB2_DP3

USB2_DN3

USB2_DP4

USB2_DN4

USB2_DP5

USB2_DN5

USB2_DP6

USB2_DN6

USB2_DP7

USB2_DN7

H1

H2

H4

G5

B15

C15

F15

D15

C14

A14

J11

H11

PCIE_CTX_ DRX_P3

C10

PCIE_CTX_ DRX_N3

A10

H9

F9

PCIE_CTX_ DRX_P4

C11

PCIE_CTX_ DRX_N4

B11

D11

F11

PCIE_CTX_ DRX_P5

B13

PCIE_CTX_ DRX_N5

C13

F13

D13

C5

C6

AA10

AA8

W13

W12

U15

U7

U5

N2

N3

L2

L3

R13

R15

M1

M3

R2

R3

P1

P3

U8

U10

U12

V1

V3

U54

U53

SATA_P1_USB3_P5_TXP

SATA/USB3

PCIe

USB3

PCIe/USB3

SSIC

USB2

4 OF 13

SATA_P1_USB3_P5_TXN

SATA_P1_USB3_P5_RXP

SATA_P1_USB3_P5_RXN

USB3_P0_TXP

USB3_P0_TXN

USB3_P0_RXP

USB3_P0_RXN

USB3_P1_TXP

USB3_P1_TXN

USB3_P1_RXP

USB3_P1_RXN

PCIE_P3_USB3_P4_TXP

PCIE_P3_USB3_P4_TXN

PCIE_P3_USB3_P4_RXP

PCIE_P3_USB3_P4_RXN

PCIE_P4_USB3_P3_TXP

PCIE_P4_USB3_P3_TXN

PCIE_P4_USB3_P3_RXP

PCIE_P4_USB3_P3_RXN

PCIE_P5_USB3_P2_TXP

PCIE_P5_USB3_P2_TXN

PCIE_P5_USB3_P2_RXP

PCIE_P5_USB3_P2_RXN

PCIE2_USB3_SATA3_RCOMP_N

PCIE2_USB3_SATA3_RCOMP_P

USB2_RCOMP

USB2_DUALROLE

USB2_VBUS_SNS

USB2_OC0_N

USB2_OC1_N

2

SATA_CT X_DRX_P1 [24]

SATA_CT X_DRX_N1 [24]

SATA_CR X_DTX_P1 [24]

SATA_CR X_DTX_N1 [24]

USB3_CT X_DRX_P0 [25]

USB3_CT X_DRX_N0 [25]

USB3_CR X_DTX_P0 [25]

USB3_CR X_DTX_N0 [25]

USB3_CT X_DRX_P1 [25]

USB3_CT X_DRX_N1 [25]

USB3_CR X_DTX_P1 [25]

USB3_CR X_DTX_N1 [25]

PCIE_RCOM PN

PCIE_RCOM PP

RCOMP close CPU side

USB20_P 0

USB20_N 0

USB20_P 1

USB20_N 1

USB20_P 2

USB20_N 2

USB20_P 3

USB20_N 3

USB20_P 4

USB20_N 4

USB20_P 5

USB20_N 5

USB20_P 6

USB20_N 6

USB20_P 7

USB20_N 7

USB2_RC OMP

USB2_ID

USB2_VB USSENSE

USB_OC0 #

USB_OC1 #

RC81

100_040 2_1%

USB20_P 0 [2 5]

USB20_N 0 [25]

USB20_P 1 [2 5]

USB20_N 1 [25]

USB20_P 2 [2 7]

USB20_N 2 [27]

USB20_P 3 [1 8]

USB20_N 3 [18]

USB20_P 4 [1 6]

USB20_N 4 [16]

USB20_P 5 [1 6]

USB20_N 5 [16]

USB20_P 6 [2 7]

USB20_N 6 [27]

USB20_P 7 [2 7]

USB20_N 7 [27]

ODD

JUSB1

JUSB2

12

CC210.1U _0402_10V7K

12

CC200.1U _0402_10V7K

12

CC190.1U _0402_10V7K

12

CC180.1U _0402_10V7K

12

JUSB1

JUSB2

JUSB S/B

BT

Camera

Touch Screen

CR

Fingerprint

USB_OC0 # [25]

USB_OC1 # [27]

PCIE_REF_ CLK_RCOMP

USB2_RC OMP

CLKREQ_ PCIE#3

CLKREQ_ PCIE#2

CLKREQ_ PCIE#1

CLKREQ_ PCIE#0

PCIE_W AKE3#

PCIE_W AKE2#

PCIE_W AKE1#

PCIE_W AKE0#

PCIE_CTX_ DRX_P3 [18]

PCIE_CTX_ DRX_N3 [18 ]

PCIE_CRX_ DTX_P3 [18]

PCIE_CRX_ DTX_N3 [18 ]

PCIE_CTX_ C_DRX_P4 [18]

PCIE_CTX_ C_DRX_N4 [18]

PCIE_CRX_ DTX_P4 [18]

PCIE_CRX_ DTX_N4 [18 ]

PCIE_CTX_ C_DRX_P5 [19]

PCIE_CTX_ C_DRX_N5 [19]

PCIE_CRX_ DTX_P5 [19]

PCIE_CRX_ DTX_N5 [19 ]

USB_OC0 #

USB_OC1 #

RC176 10K_0402_ 5%

RC165 10K_0402_ 5%

RC166 10K_0402_ 5%

RC167 10K_0402_ 5%

RC175 10K_0402_ 5%

RC168 10K_0402_ 5%

RC169 10K_0402_ 5%

RC170 10K_0402_ 5%

RC80 10K_040 2_5%

RC79 10K_040 2_5%

RC78 56_0402 _1%

1 2

RC77 113_040 2_1%

1

+3VALW

12

12

12

12

+3VALW

12

12

12

12

SSD

WLAN

LAN

+1.8V_PR IM

12

12

12

When USB OTG feature is not required

5

Security Class ification

Security Class ification

Security Class ification

2017/09/ 27 2016 /12/31

2017/09/ 27 2016 /12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/09/ 27 2016 /12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

GLK(4/9)USB2/3,PCIE,SATA

GLK(4/9)USB2/3,PCIE,SATA

GLK(4/9)USB2/3,PCIE,SATA

Size D ocument Number Rev

Size D ocument Number Rev

Size D ocument Number Rev

Custom

Custom

Custom

LA-G094PR10

LA-G094PR10

LA-G094PR10

Date: Sheet of

Thursday, November 08, 2 018

Date: Sheet of

Thursday, November 08, 2 018

Date: Sheet of

2

Thursday, November 08, 2 018

9

9

9

1

1.0

1.0

1.0

39

39

39

Vinafix.com

5

smd.db-x7.ru

D D

U49

U51

U46

U48

AA39

AA41

R44

R43

R49

R51

I2C_5_SCL[23,27]

I2C_5_SDA[2 3,27]

I2C_6_SCL[16]

I2C_6_SDA[16]

SMBus 1.8V/3.3V selection is done by

C C

B B

harware strap GPIO_163

T8 @

CNVI_W GR_CLK_DP[18]

CNVI_W GR_CLK_DN[18]

CNVI_W GR_DATA0_DP[18]

CNVI_W GR_DATA0_DN[18]

CNVI_W GR_DATA1_DP[18]

CNVI_W GR_DATA1_DN[18]

CNVI_W T_CLK_DP[18]

CNVI_W T_CLK_DN[18]

CNVI_W T_DATA0_DP[18]

CNVI_W T_DATA0_DN[18]

CNVI_W T_DATA1_DP[18]

CNVI_W T_DATA1_DN[18]

REFCLK_ CNV[18]

CLKREQ_ CNV#[18]

CNV_BRI_P TX_DRX[18]

CNV_BRI_P RX_DTX[18]

CNV_RGI_P TX_DRX[18]

CNV_RGI_P RX_DTX[18]

CNV_RF_ RESET#[18]

RC82 150_040 2_1%

12

SOC_SMB ALERT#

SOC_SMB CLK

SOC_SMB DATA

CNVI_W GR_CLK_DP

CNVI_W GR_CLK_DN

CNVI_W GR_DATA0_DP

CNVI_W GR_DATA0_DN

CNVI_W GR_DATA1_DP

CNVI_W GR_DATA1_DN

CNVI_W T_CLK_DP

CNVI_W T_CLK_DN

CNVI_W T_DATA0_DP

CNVI_W T_DATA0_DN

CNVI_W T_DATA1_DP

CNVI_W T_DATA1_DN

REFCLK_ CNV

CLKREQ_ CNV#

CNV_BRI_P TX_DRX

CNV_BRI_P RX_DTX

CNV_RGI_P TX_DRX

CNV_RGI_P RX_DTX

CNV_RF_ RESET#

CNVI_W T_RCOMP

C50

A50

C48

C47

B47

C46

A26

B27

C27

H29

H31

M31

P31

D29

F29

F35

D35

H35

F19

H17

D19

D17

F17

F33

J35

L31

J31

J29

J17

4

UC1I

SIO_I2C0_SCL

SIO_I2C0_SDA

SIO_I2C1_SCL

SIO_I2C1_SDA

SIO_I2C2_SCL

SIO_I2C2_SDA

SIO_I2C3_SCL

SIO_I2C3_SDA

SIO_I2C4_SCL

SIO_I2C4_SDA

SIO_I2C5_SCL

SIO_I2C5_SDA

SIO_I2C6_SCL

SIO_I2C6_SDA

SIO_I2C7_SCL

SIO_I2C7_SDA

SMB_ALERT_N

SMB_CLK

SMB_DATA

CNV_WGR_CLK_P

CNV_WGR_CLK_N

CNV_WGR_D0_P

CNV_WGR_D0_N

CNV_WGR_D1_P

CNV_WGR_D1_N

CNV_WT_CLK_P

CNV_WT_CLK_N

CNV_WT_D0_P

CNV_WT_D0_N

CNV_WT_D1_P

CNV_WT_D1_N

CLKIN_XTAL_LCP

XTAL_CLKREQ

CNV_BRI_DT

CNV_BRI_RSP

CNV_RGI_DT

CNV_RGI_RSP

CNV_RF_RESET_N

CNV_WT_RCOMP

FH80680 03067411-QM_F CBGA1090~D

LPSS_I2C

LPSS SMBus

CNVI

3

LPSS_SPI

LPSS_UART

6 OF 13

2

SIO_SPI_0_CLK

SIO_SPI_0_TXD

SIO_SPI_0_RXD

SIO_SPI_0_FS0

SIO_SPI_0_FS1

SIO_SPI_2_CLK

SIO_SPI_2_TXD

SIO_SPI_2_RXD

SIO_SPI_2_FS0

SIO_SPI_2_FS1

SIO_SPI_2_FS2

SIO_UART0_TXD

SIO_UART0_RXD

SIO_UART0_RTS_N

SIO_UART0_CTS_N

SIO_UART2_TXD

SIO_UART2_RXD

SIO_UART2_RTS_N

SIO_UART2_CTS_N

M39

J37

L39

L37

J39

M37

M33

P35

P33

P37

L35

N54

P53

N53

M55

L54

M53

UART_2_ CRTS#_GPIO_66

K53

L53

UART_2_ CRTS#_GPIO_66

+3VALW _SOC

+1.8V_PR IM

1

SPI_0_TX_ GPIO_83 [11]

SPI_0_FS0 _GPIO_80 [11]

SPI_0_FS1 _GPIO_81 [11,21 ]

SPI_2_CLK _GPIO_84 [11]

UART_1_ CTXD_GPIO_61 [11]

UART_2_ CTXD_GPIO_65 [11,18,2 1]

UART_2_ CRXD_GPIO_64 [18,21]

RC90 2.2K_ 0402_5%

RC89 2.2K_ 0402_5%

follow intel change to CNVI@ 4/11

RC88 20K_040 2_5%@CNVi@

RC87 10K_040 2_5%@CNVi@

RC86 75K_ 0402_5%@

RC85 10K_ 0402_5%CN Vi@

12

12

1 2

1 2

follow Intel RVP 5/25

12

12

change to CNV_RGI_PRX_DTX @04/11

12

RC9110K_0402 _5%

SOC_SMB DATA

SOC_SMB CLK

CNV_RGI_P RX_DTX

CNV_BRI_P TX_DRX

CLKREQ_ CNV#

REFCLK_ CNV

+3VS +3V S

Notice:

12

12

2

A A

SOC_SMB CLK

SOC_SMB DATA

3 4

D

6 1

5

L2N7002 DW1T1G 2N S OT-363

5

D

L2N7002 DW1T1G 2N S OT-363

G

S

QC2B

RC83

2.2K_040 2_5%

G

S

QC2A

VGS:2V

RC84

2.2K_040 2_5%

PCH_SMB _CLK [15,2 6]

PCH_SMB _DATA [15,26 ]

4

Security Class ification

Security Class ification

Security Class ification

2017/09/ 27 2016 /12/31

2017/09/ 27 2016 /12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL