A

B

C D

E

Compal Confidential

1 1

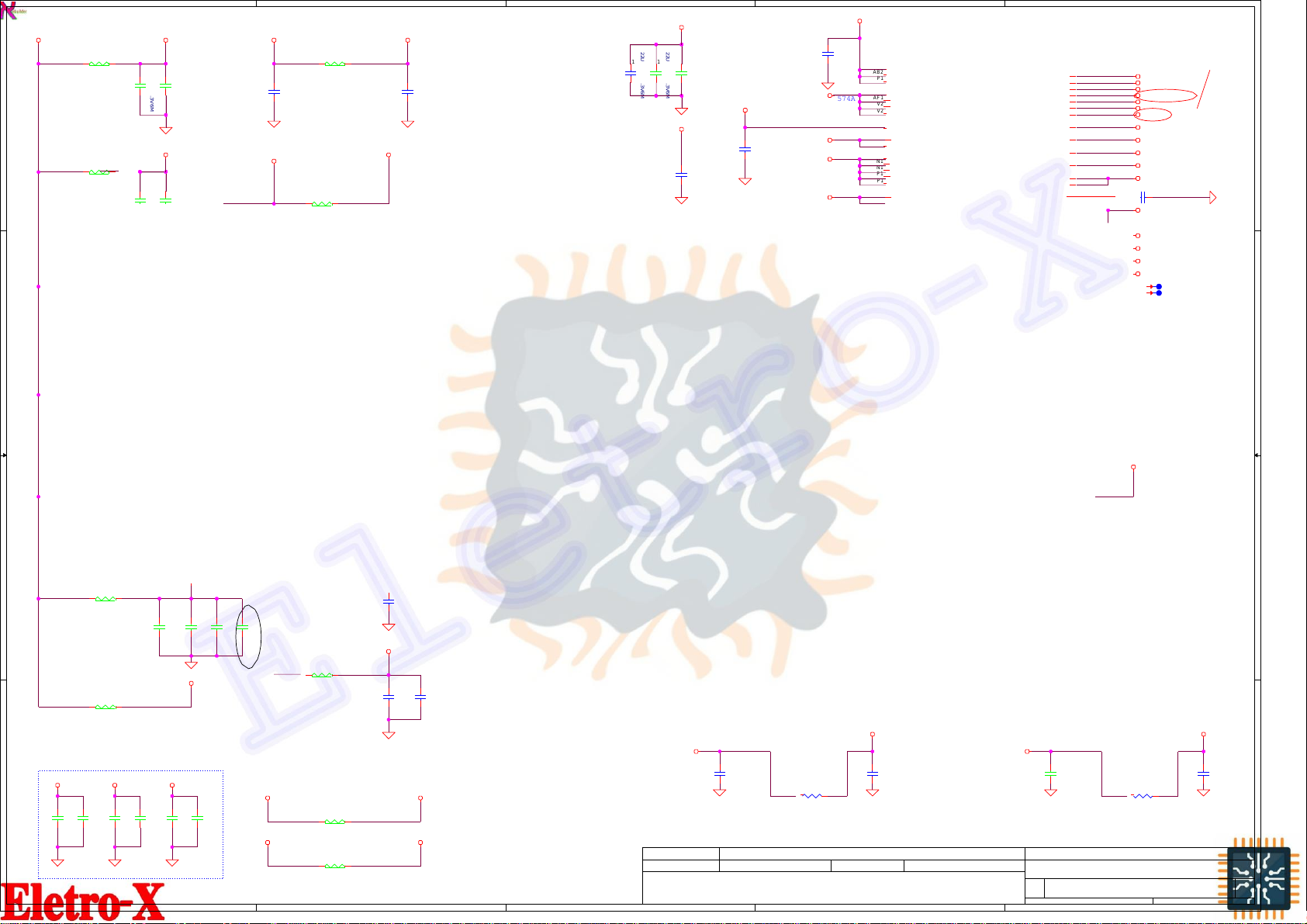

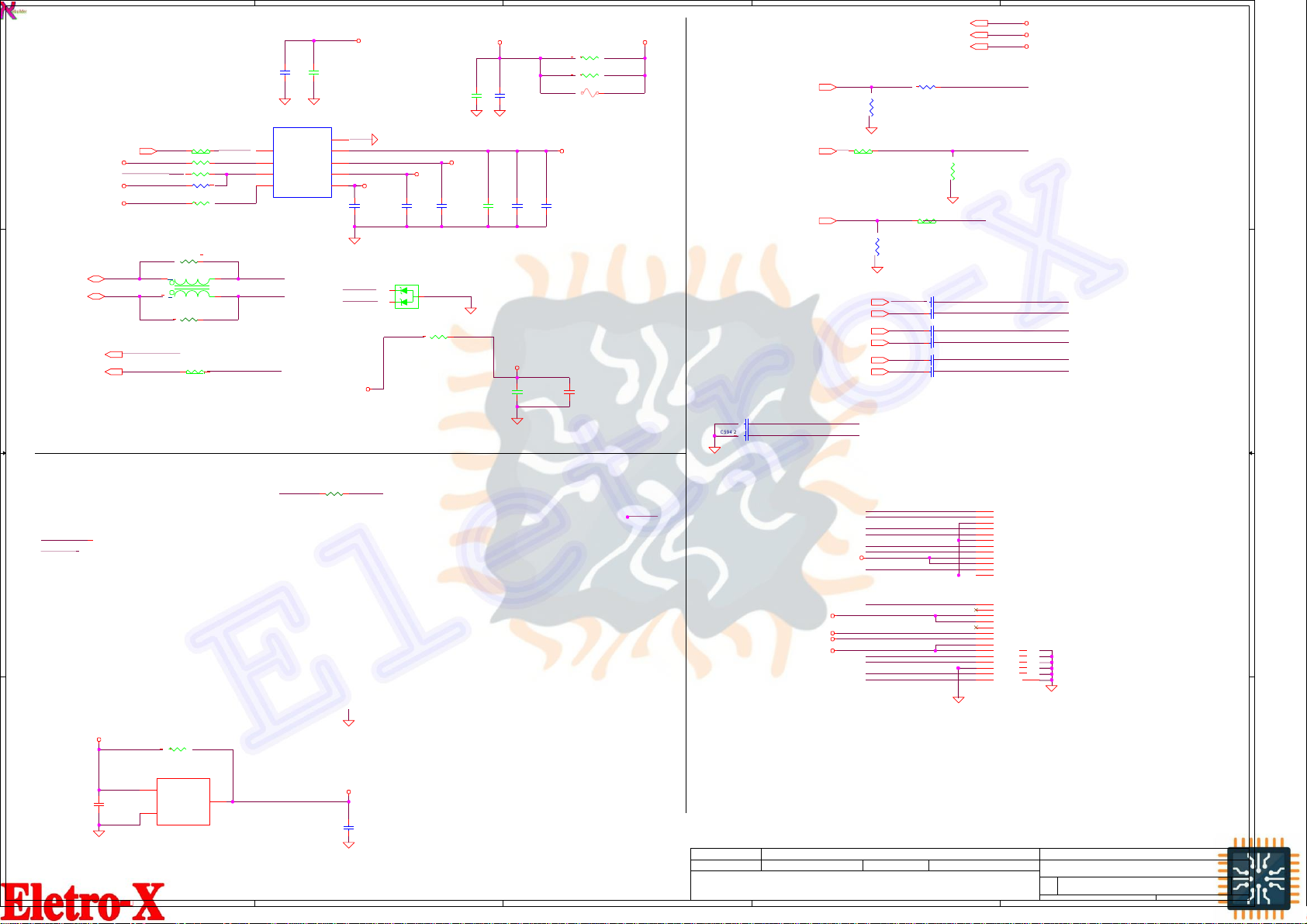

Intel M/B Schematics Document(1.2mm_6L)

Kabylake-U(2+2)-DDR4 SODIMMx2

nVidia N16 gDDR5-2GB

(N16S-GTR : GM108-670/770: GeForce MX130)

2 2

Date : 2018-01-08

(N16V-GMR1 : GM108-626/726:GeForce MX110)

Version :1.0

Project :2018OPP_Harry Potter(15.6")

3 3

(EPK52 :LA-G07EP=>v0.2 for PV)

(Modified&Ref from: 01."NFLC_KBLR_LAE802PR10_MV_FINAL")

(02."Canadiens_LA-F035P-R10_KBL-UR_2017-06-23_CPU")

(02."CNL-U ORB_DDX02_LA-F152PR01_0822B")

4 4

Security Classification

Issued Date

THIS SH EE T OF E NG IN EE RING DRAWI NG IS T HE PRO PR IE TA RY PRO PE RT Y OF C OM PA L ELECT RONIC S, INC. AN D CONTAINS CONFIDENSSTiIzAeL

AND TRADE S EC RE T INFORMA TION . THIS S HE ET MAY NO T BE T RA NS FE RE D F RO M THE CU ST ODY OF T HE CO MP ET EN T DIVIS ION OF R& D

DEPARTMENT E XC EP T AS A UT HORIZED BY C OMPA L ELECT RONIC S, INC. NEITH ER T HIS SH EE T NO R TH E IN FO RM AT IO N IT CONTAINS

A

B

MAY BE US ED BY OR DI SCLOSE D TO A NY THIRD P AR TY W ITHOU T PRIOR W RITTE N CO NS EN T OF C OM PA L ELECTRO NICS, INC.

2015/10/22 2017/10/22

C D

(EPS50 :SKLU_4G:LA-G071P)

(EPS50 :SKLU_2G:LA-G072P)

(EPK50 :KBLU_4G:LA-G079P)

(EPK50 :KBLU_2G:LA-G07AP)

(EPK52 :KBLR_4G:LA-G07BP)

(EPK52 :KBLR_2G:LA-G07CP)

(EPK50 :KBLU:LA-G07EP)

(EPK52 :KBLR:LA-G07EP)

Compal Secret Data

Deciphered Date

DIS

UMA

Title

DocumentNumber

Custom

Date: Monday, January 08, 2018 Sheet

Compal Electronics,Inc.

Cover Page

LA-G07EP(KBL-U_UMA_6L)

E

1 of 59

Rev

v0.3

A

B

C

D

E

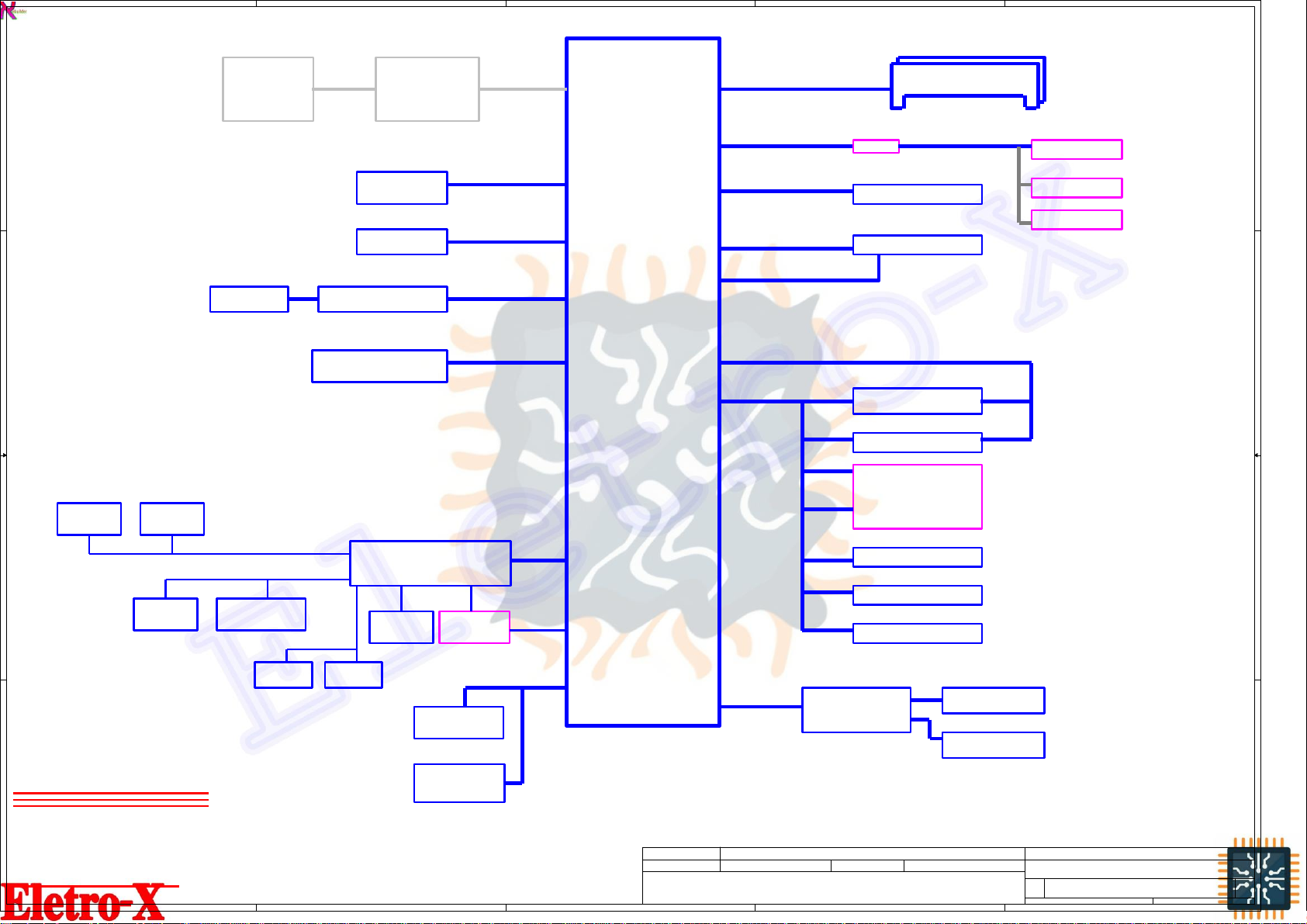

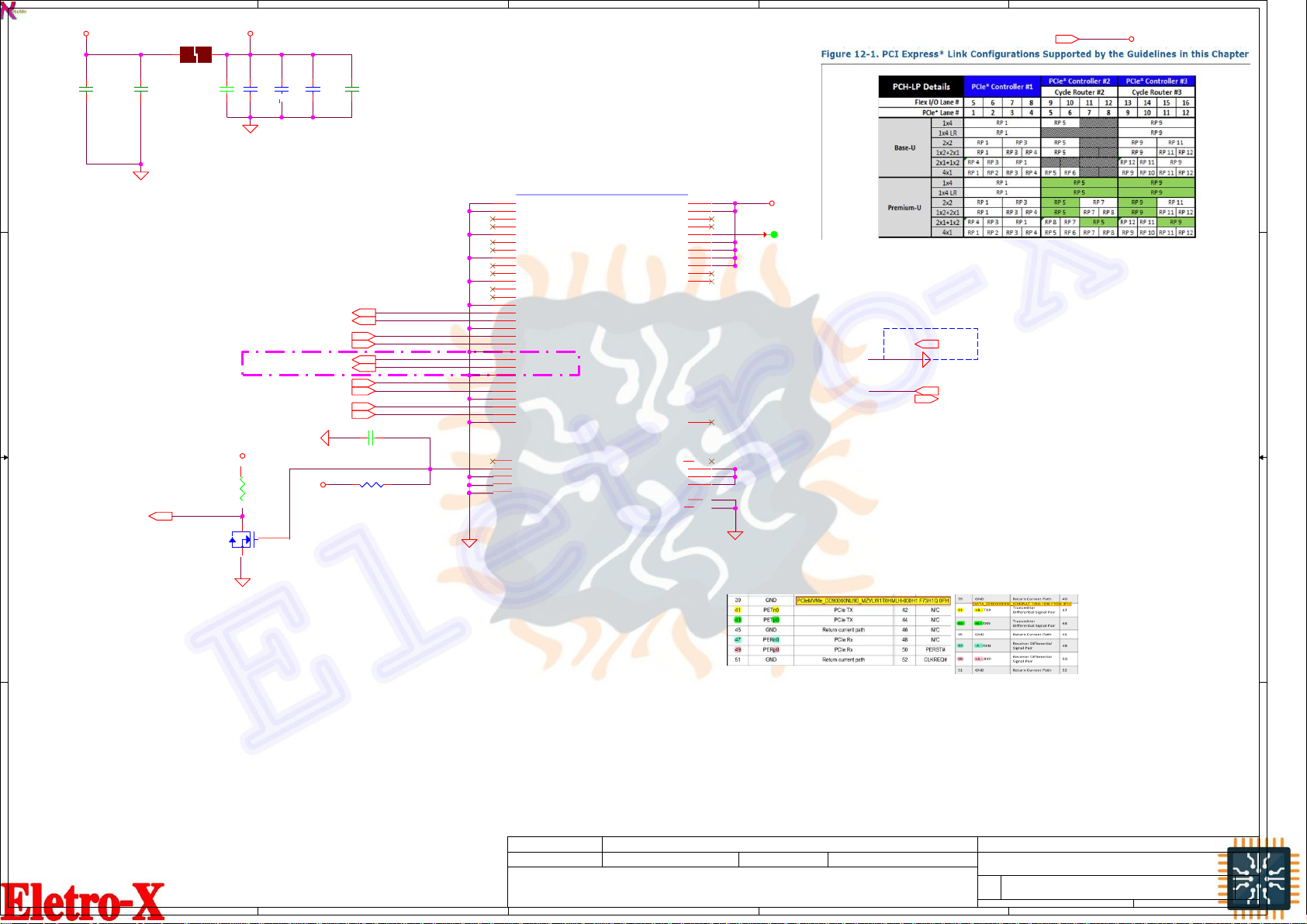

UV6 UV7

UV8 UV9(for 4GB)

VRAM

gDDR5x4pcs

256Mbx32

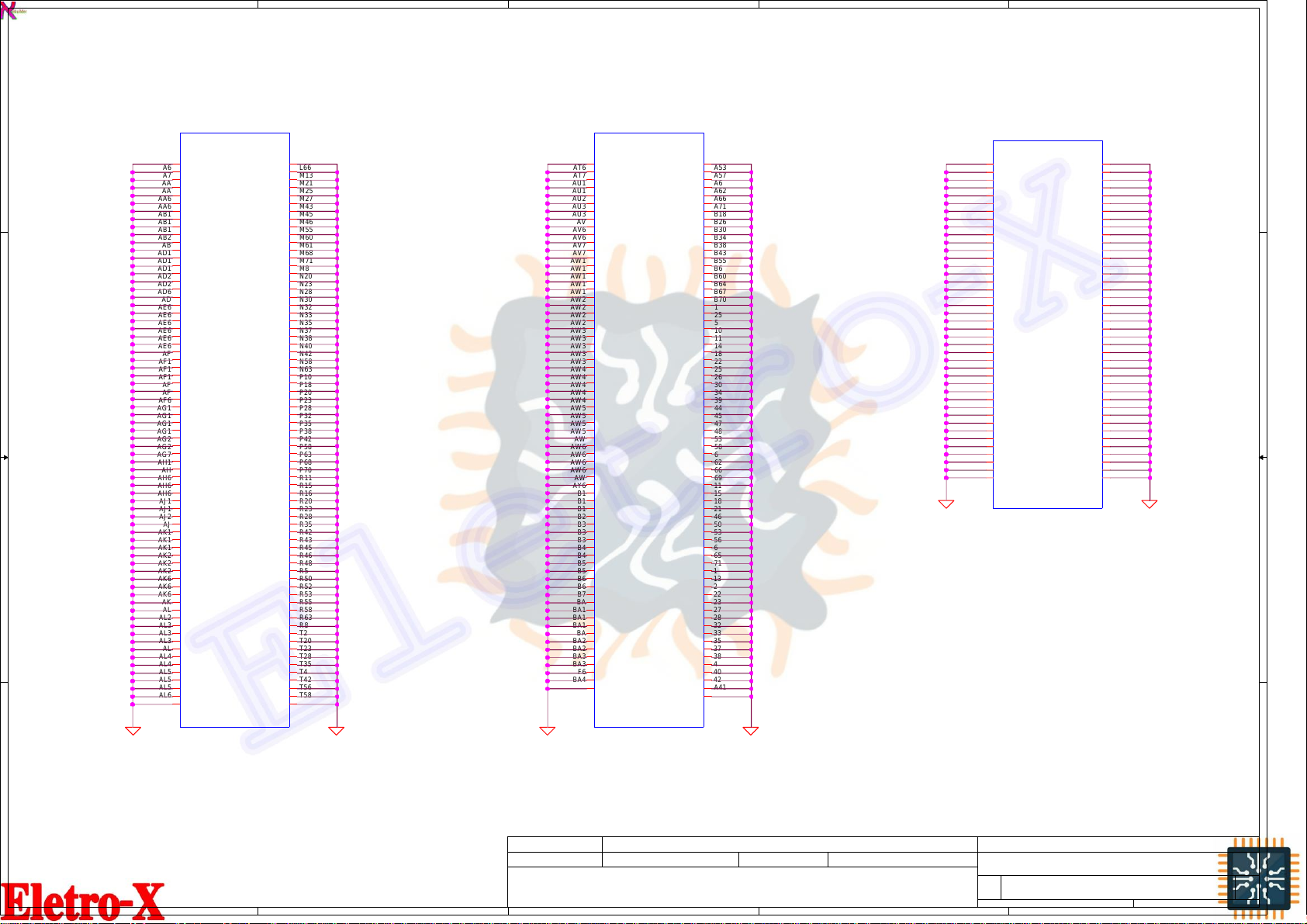

1 1

(8Gb)

P.25

nVidia

N16S-GTR

N16V-GMR1

UV1 UC1

(MX110 )

PCIex4

Port#1~#4

PCIe 3.0:8Gb/s

(MX130 )

P.19~26

Kaby Lake-RU42

Dual Channel Interleaved

DDR4 2133MHz1.2V

SATA 3.0

Port0

DDR4-SO-DIMM X 2

JHDD

P.30

JEDP

eDP CONN

P.27

eDPx2Lane

SATA 3.0

Port1

SATAODD

JHDMI

HDMI CONN

P.28

JLAN

RJ45CONN

P.29

2 2

LAN

RTL8111HSH-CG

P.29

JWLAN

NGFF WLAN+BT

(Key E)

PUB1

Charger

P.47

3 3

Battery

dGPU

P.22

PJPB1

P.46

UV1

Thermalsensor

UC3

G753T11U

Fan

75x70

P.10

P.38

SMBus1

SMBus2

JFAN

KB light

JKBL

P.34

P.30

ECENE

KB9022QD

JKB

Int.KBD

P.34 P.34

DDI x4Lane Port 1

UL1

PCIex1 Port#5

PCIe Gen1Only:2.5Gb/s

PCIex1 Port#6

PCIe Gen1Only:2.5Gb/s

UK1

P.33

PS2

JTP

TouchPad

*sub board

LS-G073PR01

DA4002M0000

UC2

SPIROM

8MBytes

P.07

LPC

33MHz

SMBus

SPI

50MHz

1356P BGA

PCIe 3.0:8Gb/s

SATA 3.0

USB3.0

5Gb/s

USB2.0

480Mb/s

HDA 24MHz

PCIe x2

Port#11~#12

Port 2

Port1

Port2

Port3

Port4

Port5

Port6

Port7

HDA Aduiocodec

ALC3247-CG

(KeyM)

M.2 SSD

*need suppor ted I ntel O ptane (3D Xpoint)

USB3.0port

USB3.0port

USB2.0Port

CardReader

AK6485RB63-GLF-GR

(sub board)

Camera

Bluetooth

Touch Screen

UA1

P.32

NVMe

UT1

TPM

B

SLB9670VQ2.0

P.35

Security Classification

Issued Date

THI S S H E ET O F E N GI NE E RI N G DR AW I NG I S TH E P R OP R IE TA R Y P RO PE R TY O F C O MP A L E LE CTR ON IC S, I NC. AN D C ON TA INS CONFIDENTSIiAzeL

AN D T RA D E SE C R ET IN FO RM AT IO N. TH IS SH E ET M A Y N OT BE TR A NS F ER E D F R OM TH E C US TO D Y OF TH E C OM P ET E NT D IV IS ION OF R &D

DE PA RTM E NT EX C E PT A S A UT HO R IZ E D B Y CO M PA L E LE CT RO NIC S , INC . N EI THE R THI S S H E ET N O R TH E I NF O RM A TI ON I T C ON TA IN S

MA Y BE U S E D BY OR D IS CL OS ED TO A N Y THI RD PA R TY W I TH O UT P R IO R W R IT TE N C ON S EN T OF CO M PA L EL EC TR ON ICS , IN C.

C

2017/08/24 2018/08/24

Compal Secret Data

DecipheredDate

D

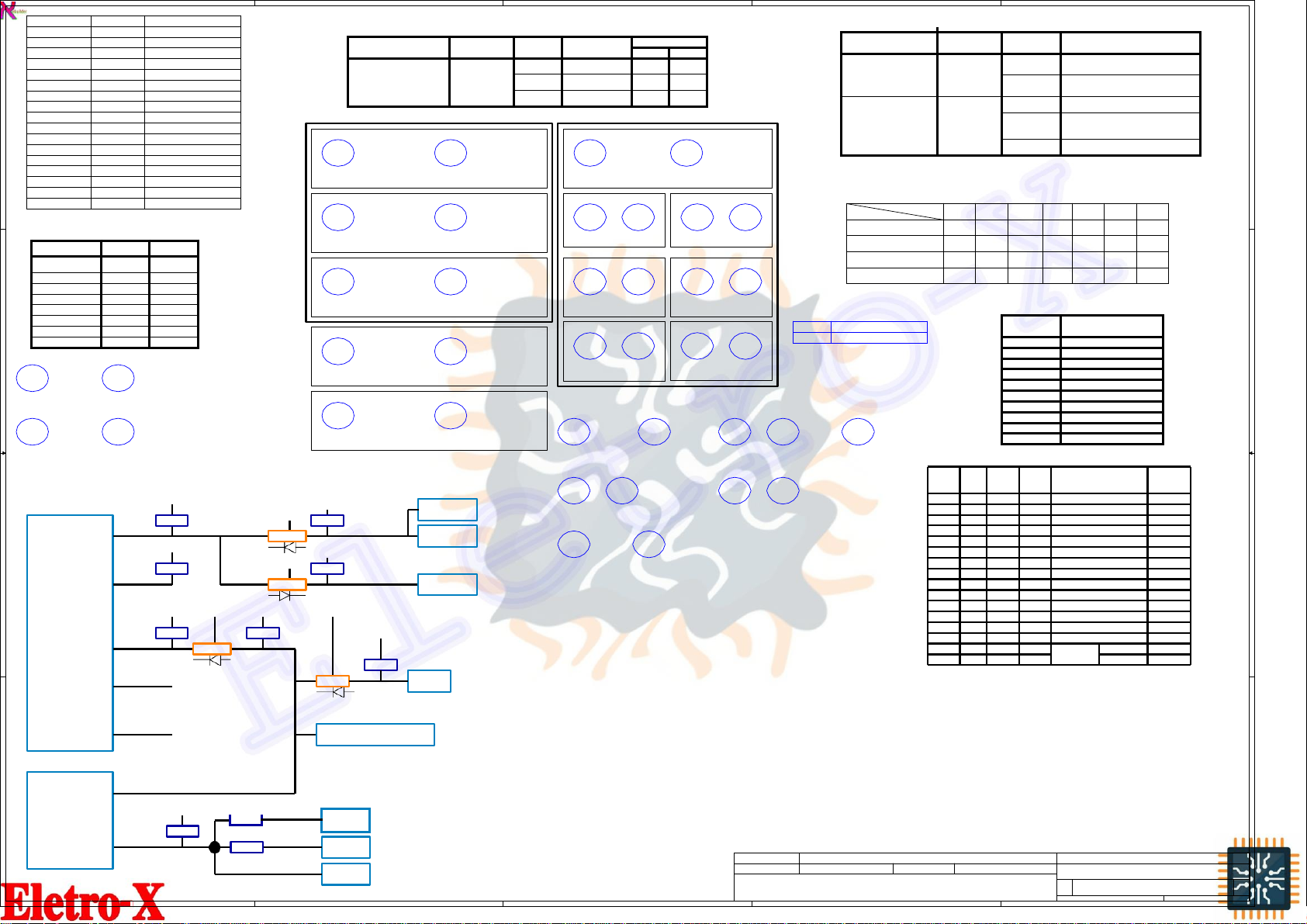

MB Board Information:

4 01.DA8001EG000, PCB 29I LA-G071P REV0 MB 3(SKLU_4G)

02.DA6001WL000, PCB 29I LA-G072P REV0 MB 3(SKLU_2G)

03.DA8001EH000, PCB 29M LA-G079P REV0 MB 3(KBLU_4G)

4. DA6001WM000, PCB 29M LA-G07AP REV0 MB 3(KBLU_2G)

5. DA8001EI000, PCB 29L LA-G07BP REV0 MB 3(KBLR_4G)

6. DA6001WI000, PCB 29L LA-G07CP REV0 MB 3(KBLR_2G)

7. DA6001YA000, PCB 29M LA-G07EP REV0 MB 3(KBLU_UMA)

8. DA6001YB000, PCB 29L LA-G07EP REV0 MB 3(KBLR_UMA)

Sub Board Information:(EPK52)

01.DA6001WJ000, PCB 29L LS-G071P REV0 IOB(435OM832L01)

02.DA4002LZ000, PCB 29L LS-G072P REV0 HDDB(435OM932L01)

3. DA4002M0000, PCB 29L LS-G073P REV0 TOUCH PADB(435OMA32L01)

4. DA6001WR00S, PCB 29L LS-G074P REV0 SSDB(435OMB32L01)

5. DA6001WS00S, PCB 29L LS-G075P REV0 eMMCB

A

ChA:JDIMM1(REV)

ChB:JDIMM2(STD)

P.17~18

JODD

P.30

JSSD

P.19

JUSB1

Port1

P.30

JUSB2

P.31

Port2

JIO

P.31

*sub board

LS-G071PR01

DA6001WJ000

P.29

JEDP

P.27

JWLAN

P.30

JEDP

P.27

InternalSPK

Combo Jack

2.5" SATA HDD

(sub board)

M.2 SATA SSD

(sub board)

eMMC

(sub board)

JSPK

P.32

JHP

P.32

Title

Document Number

Custom

*sub board

LS-G072P

DA4002LZ000

*sub board

LS-G074P

DA6001WR00S

*sub board

LS-G075P

DA6001WS00S

Compal Electronics, Inc.

Block Diagrams

LA-G07EP(KBL-U_UMA_6L)

Sheet 2 of 59Date: Monday, Ja nuary 08, 2018

E

Rev

v0.3

4

A

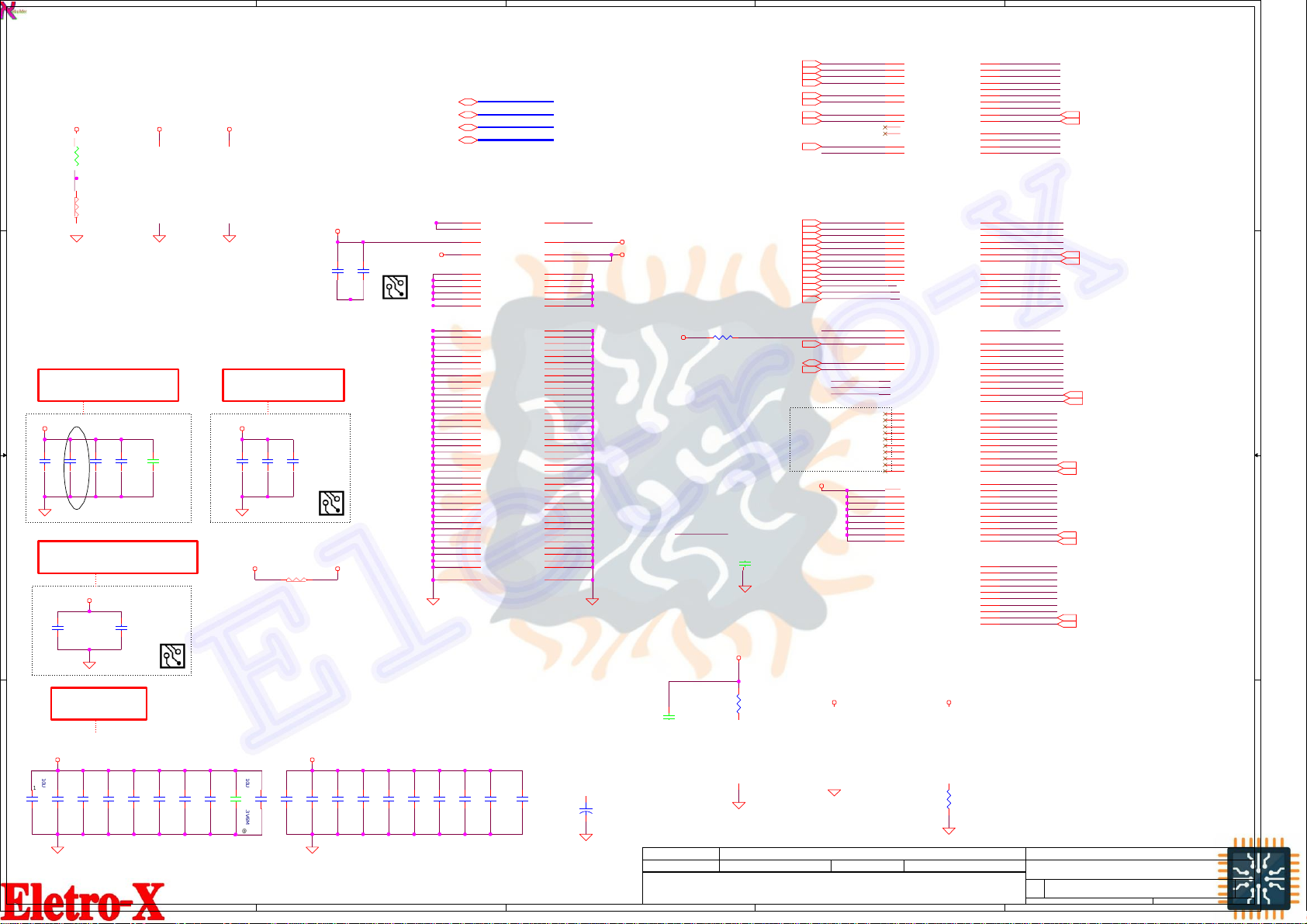

Power rail Control (EC) Source (CPU)

+RTCVCC X X

VIN X X

BATT+ X X

B+ X X

+VL X X

+3VL X X

+5VA LW EC_ON X

+3VA LW EC_ON X

+3VA LW _EC EC_ON X

1 1

+3V_PCH PCH_PWR_EN X

+1.2V_VDDQ SYSON PM_SLP_S5#/PM_SLP_S4#

+5VS SUSP# PM_SLP_S3#

+3VS SUSP# PM_SLP_S3#

+1.5VS SUSP# PM_SLP_S3#

+1.05VS SUSP# PM_SLP_S3#

+0.6V_0.6VS SUSP#

+VCC_CORE X VR12.5_VR_ON

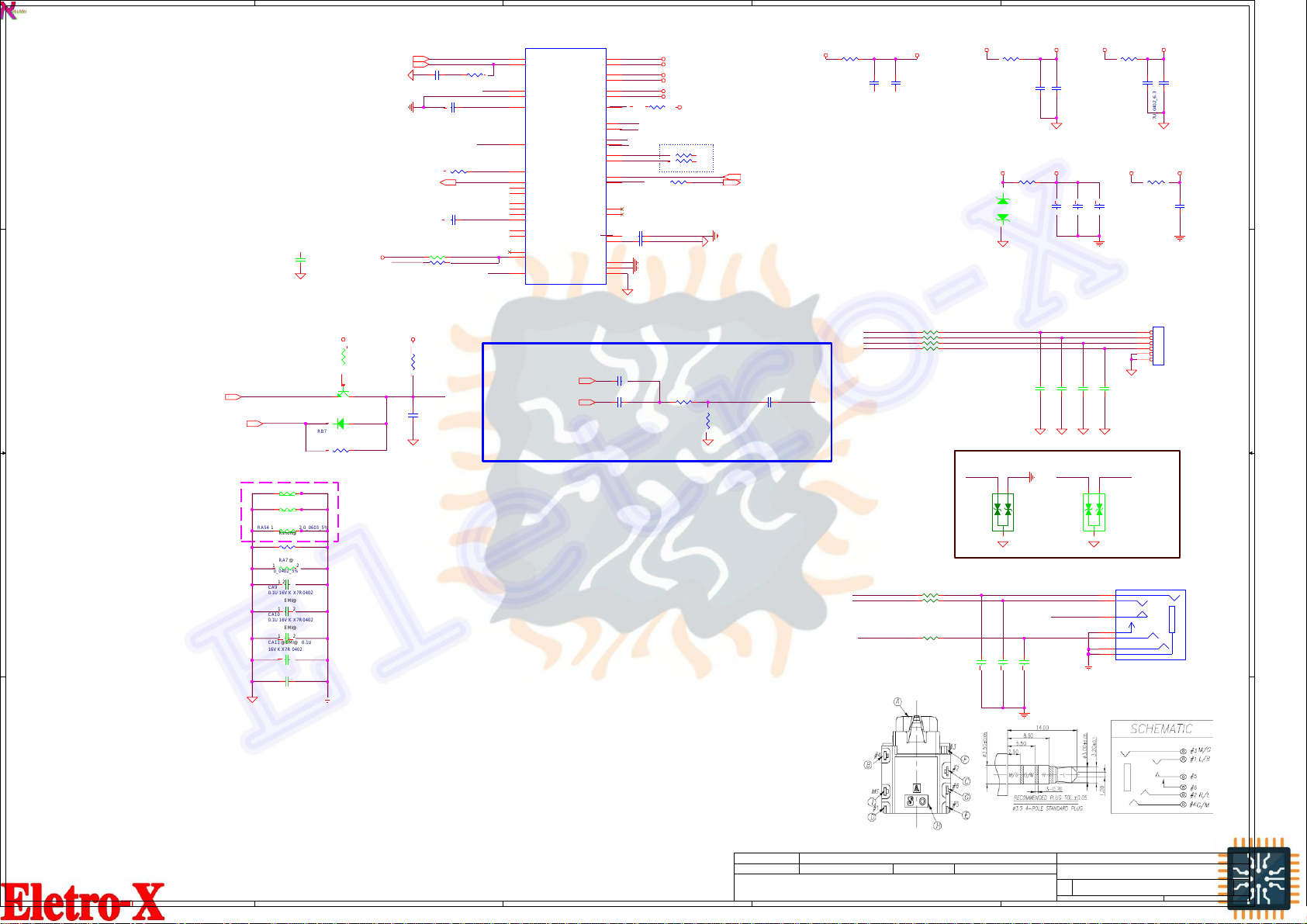

BOM Structure Table (1/2)

Function

DGPU SKU

UMA SKU UMA@

TPM TPM@

2 2

R_i3_7020U_QN96@

UC1

R_SI_i3_7020U_QN96 Y0 2.3G R_SI_i3-8130U_QP8K Y02.2G

SA0000BLD00 SA0000BKN10

S IC A3 2 FJ8067703282620 QN96 Y0 2S.3GICA32 FJ8067703282227 QP8K Y0 2.2G

R_i7_8550U_QNBF@ U_i3 _7020U_QNZU@

UC1 UC1

R_SI_i7_8550U_QNBF Y0 1.8G

SA0000AWC10

S IC A3 2 FJ8067703281816 QNBF Y0 1S.8IGCA32 FJ8067702739769 QNZU H0 2.3G

UC1

3 3

CPU

Stuff Un-Stuff

PX@

R_i3_8130U_QP8K@

UC1

U_SI_i3-7020U_QNZU H0 2.3G

SA0000BLH00

SMBCLK

R7

SMBDATA

R8

SML0CLK

R9

SML0DATA

W2

SML1CLK

W3

SML1DATA

V3

U6

U7

+3V_PRIM

R=1K

+3V_PRIM

2N7002

+3V_PRIM

@

+3V_PRIM

2N7002

+3VS

EC_SMB_CK2

EC_SMB_DA2

R=499

+3V_PRIM+3VS +3VS_DGPU_AON

R=1K R=2.2K

2N7002

i3_7100U_R1@

i3_7100U

SA0000A38H0

S IC FJ8067702739738 SR343 H0 2.4G BGA

U_i5_7200U_SR342@

U_SI_i5-7200U_SR342 H0 2.5G

SA0000A37H0

S IC FJ8067702739739 SR342 H0 2.5G BGA

U_i7_7500U_SR341@ ZZZ

U_SI_i7-7500U_SR341 H0 2.7G

SA0000A34F0

S IC FJ8067702739740 SR341 H0 2.7G BGA

R_i5_8250U_QNEF@

R_SI_i5_8250U_QNEF Y0 1.6G

SA0000AWB10

S IC FJ8067703282221 SR3LA Y0 1.6G FCBGA S IC FJ8067703282221 SR3LA Y0 1.6G A32!

R_i7_8550U_SR3LC@

R_SI_i7-8550U_SR3LC Y0 1.8G i 7_8550U

SA0000AWC20 SA0000AWC30

S IC FJ8067703281816 SR3LC Y0 1.8G FCBGA S IC FJ8067703281816 SR3LC Y0 1.8G A32!

+3VS

R=10K

+3VALW

R=10K

2N7002

B

SOC SMBUS Address Table

SOC_SMBUS Net Name Power Rai l Device Address (7bit)

SMBCLK

SMBDATA

UC1

UC1

UC1

UC1

UC1

PCH_SMBCLK

PCH_SMBDATA

TP_SMBCLK

TP_SMBDAT

+3VS_DGPU_AON

R=2.2K

PX@

I2CS_SCL

I2CS_SDA

+3V_PRIM

i3_7100U_R3@

UC1

i3_7100U

SA0000A38J0

S IC FJ8067702739738 SR343 H0 2.4G A32!

i5_7200U_R3@

i5_7200U

SA0000A37J0

S IC FJ8067702739739 SR342 H0 2.5G A32!

i7_7500U_R3@

UC1

i7_7500U

SA0000A34H0

S IC FJ8067702739740 SR341 H0 2.7G A32!

i5_8250U_R3@

UC1

i5_8250U

SA0000AWB30

i7_8550U_R3@

UC1

SO-DIMM A

SO-DIMM B

Touch Pad

DGPU

DIMM1 0x50 0xA0 0xA1

DIMM2 0x52 0xA4 0xA5

Touch PAD

KBLU_2G@

DA6001WM000

PCB 29M LA-G07AP REV0 MB 3 PCB 29L LA-G07CP REV0 MB 3

DAZ_U2G@

DAZ23T00600

KBLU_UMA@

DA6001YA000 DA6001YB000

PCB 29M LA-G07EP REV0 M/B 3 PCB 29L LA-G07EP REV0 M/B 3

C

Address (8bit)

Write Read

0x2C 0x58 0x59

MX110@

UV1

N16V-GMR1-S-A2

SA00009IT00

S IC N16V-GMR1-S-A2 BGA595P

ZZZ

2G Mi cr onUC1

M2G_R1@

X7674032L01

ZZZ

2G Hynix

H2G_R1@

X7674032L04

ZZZ

2G S ams ung

S2G_R1@

X7674032L05

DAX

KBLU -2G

ZZZ

DAZ_U2G

DAX

KBLU -UMA

M2G_R3@

X7674032L06

H2G_R3@

X7674032L07

2G S ams ung

S2G_R3@

X7674032L08

ZZZ

DAZ_R2G

DAZ_R2G@

DAZ23T00500

ZZZ

2G Mi cr on

ZZZ

2G Hynix

ZZZ

KBLR_2G@

DA6001WI000

KBLR -UMA

KBLR_UMA@

KBLR -2G

DAX

MX130@

UV1

N16S-GTR-S-A2

SA00009FP00

S IC N16S-GTR-S-A2 BGA 595P GPU

ZZZ

4G Mi cr on

M4G_R1@

X7674032L26

ZZZ

4G Hynix

H4G_R1@

X7674032L25

ZZZ

4G S ams ung

S4G_R1@

X7674032L27

DAX

ZZZ

4G Mi cr on

M4G_R3@

X7674032L29

4G Hynix

H4G_R3@

X7674032L28

ZZZ

4G S ams ung

S4G_R3@

X7674032L30

DAX

KBLU -4G

KBLU_4G@

DA8001EH000

ZZZ

DAZ_U4G

DAZ_U4G@

DAZ23T00600

Part Number Description

RO0000003HM

DAX

KBLR -4G

KBLR_4G@

DA8001EI000

ZZZ

DAZ_R4G

DAZ_R4G@

DAZ23T00500

D

EC SMBUS Address Table

EC_SMBUS Port Power Rail Device Address (7 bit)

SMBUS Port 1 +3VL_EC

SMBUS Port 2 +3VS

Power State

STATE

S0 (Full ON)

S3 (Suspend to RAM) LOW HIGH HIGH ON ON OFF OFF

S4 (Suspend to Disk)

S5 (Soft OFF)

ROYALTY HDMIW /LOGO45@

HDMI W/Logo:RO0000002HM

RO0000002HM

ZZZ

EMC for EE

X4E@

X4EABB32L01

SMT EMC FOR EE AG07C EPK52

(TBC)

BAT 0x16

CHGR 0x12

dGPU

Thermal

Sensor

PCH

SIGNAL

SLP_S3#

SLP_S4#

SLP_S5#

+VALW

HIGH HIGH HIGH ON ON ON ON

LOW LOW HIGH ON OFF OFF OFF

LOW LOW LOW ON OFF OFF OFF

<USB2.0 port>

USB2.0port DESTINATION

1 USB3.0 Type-C

2 USB2.0/USB3.0

3 USB2.0/USB3.0

4 BT

5 HD/IR_1/IR_2Camera

6 IR_2 Camera

7 Card Reader

8 X

9 X

10 X

<PCI-E,SATA,USB3.0/CLK>

Lane# PCI-E SATA USB3.0

1 1

2 2

3 3

4 4

5 1 5

6

2 6

7

3

8

4

9

5

10

6

11

7

12 1a

13

14

15

16

0

8

10

1191b*

12

2

DESTINATION

USB3.0Type-C

USB3.0Type-C

USB2.0/USB3.0

USB2.0/USB3.0

GPU(DISonly)

GPU(DISonly)

GPU(DISonly)

GPU(DISonly)

NVMex2

E

0x90

+VS Clock

+V

LAN

WLAN

HDD

ODD CLK3

X

X

X

SATA SSD

CLK

X

X

X

X

CLK0

CLK1

CLK2

X

X

X

CLK4

X

U9

U8

UK1:+3VALW_EC(+3VL)

4 4

EC

EC_SMB_CK2

EC_SMB_DA2

79

80

EC_SMB_CK1

77

EC_SMB_DA1

78

A

+3V_SMBUS

R=2.2K

R=0

R=100

GSEN_I2DAT

GSEN_I2CLK

Thermal Sensor :G753T11U

Address : 0x48

G-Sensor

HP2DC

BAT

Charger

B

Securi ty Clas sification

Issued Date

THI S SHE ET O F EN GI NEE RI NG D RA WI NG IS T HE P ROP RI ET AR Y P RO PE RT Y OF COM PA L EL EC TR ONI CS , IN C. AN D CO NTA IN S CONFIDENTSSIAizL

AND T RA DE S EC RE T I NF OR MAT IO N. T HI S S HE ET MA Y NOT BE TRA NS FE RE D F ROM T HE C UST OD Y OF TH E CO MPE TE NT DI VIS ION OF R& D

DE PAR TM ENT E XC EP T A S AU THO RI ZE D BY CO MP AL E LE CTR ON IC S, I NC. NE IT HE R TH IS S HEE T NOR THE INF OR MA TI ON I T C ON TAI NS

C

MAY BEU SE D BY OR D IS CL OS ED TO ANY THIR D PA RT Y W IT HO UT P RIO R WR IT TE N C ONS EN T OF CO MP AL E LE CT RON IC S, IN C.

2016/12/15 2019/12/15

Compal Secret Data

Deciphered Date

D

Title

e Document Number

Custom

Compal Electronics,Inc.

Notes List

LA-G07EP(KBL-U_UMA_vv60.L3)

Sheet 3 of 59Date: Friday, January 05,2018

E

Rev

5

4

3

2

1

100P_0402_50V8J

1

CN2

22U_06 03_6. 3V6K

2

+3V S

+3V ALW

100P_0402_50V8J

0.1U_0402_25V6

2 1

2 1

0.1U_0402_16V7K

CN3

1

2

<6,7, 9,10,1 1,13,1 7,18,2 7,28, 29,31, 32,33 ,36,39 ,40,52 > +3 VS

<7,13 ,29,33 ,34,35 ,40,4 8,49,5 0,51> +3VA LW

D D

+3V S_W LA N

<9, 33> E C_PC IE_W AKE #

+3V S_W LA N

RN3

10K_0 402_5%

12

<9> CL K_PCIE _P2

<9> CL K_PCIE _N2

<11 > U SB20_ P6

<11 > U SB20_ N6

<11 > PC IE_ CTX_ C_DR X_P6

<11 > PC IE_ CTX_ C_DR X_N6

<11 > PC IE_C RX_ DTX_ P6

<11 > PC IE_C RX_ DTX_ N6

CONN@

JW LAN

1 2

1_G ND

3 4

3_USB _D+

5

5_USB _D-

7

7_G ND

9

9_N/C

11

11_N/C

13

13_N/C

15

15_N/C

17

17_N/C

19

19_N/C

21

21_N/C

23

23_N/C

25

33_GND

27

35_PE Rp0

29

37_PE Rn0

31

39_GND

33

41_PE Tp0

35

43_PE Tn0

37

45_GND

39

47_REF CLKP0

41

49_REF CLKN0

43

51_GND

45

53_CLK REK0#

47

55_PE Wak e0# W_ DISA BLE2 #_54

49

57_ GND W_DI SAB LE1#_ 56

51

59_N/C N/C_ 58

53

61_N/C N/C_ 60

55

63_ GND N/C_ 62

57

65_N/C RESE RVE D_64

59

67_N/C N/C_ 66

61

69_ GND N/C_ 68

63

71_N/C N/C_ 70

65

73_N/C 3.3 V_72

67

75_ GND 3.3V_7 4

LOTES_A PCI001 9-P003 H

SP0 7001 0DA0

3.3V_2

3.3V_4

LED1#_ 6

N/C_8

N/C_10

N/C_12

N/C_14

LED2#_ 16

GND_ 18

N/C_20

N/C_22

N/C_32

N/C_34

N/C_36

CLink R eset_ 38

CLink D ATA_40

CLink CLK_ 42

COEX3_ 44

COEX2_ 46

COEX1_ 48

SUS CLK _50

PER ST0 #_52

GND

GND

NC_70

NC_71

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

69

70

71

+3V S_W LA N

R5179 R51 80

@RF @ @R F@

2 1

RN7

4.7K_0 402_5 %

1 2

2 1

+3V S_W LA N

10K_0 402_5%

BT_O N_E C

@RF@

R5181

+3V S_W LA N

1 2

RN1 5 @R F@

0.1U_0402_25V6

@RF @ @R F@ @RF@

R5182 R518 3 R5184

2 1

2 1

+3V S_W LA N

Active Low

WL _PW REN _EC # <3 3>

+3V S_W LA N

1

2

RW L1

200K_ 0402_5 %

2 2

1

QW L1

1

DGS

PJ2 301 1 PS OT23 -3

SB0 0000 T900

1 @ 2

RW L2 0_0603_5%

CW L1

1 2

0.1U_0 402_1 6V4Z

3

+3V ALW

NGFF and WLAN

Unpop QB8 and RL25 for not sup portOBFF

B B

2

G

@

<9> WA KE #

1 3 EC_ PCI E_W AKE#

D

S

SB0 0000 EN00

QB8

2N7002 H_SOT23 -3

RL25 @

100K_ 0402_5 %

+3V S_W LA N+3V S

CW L2

1 2

0.1U_0 402_1 6V4Z

A A

Security Classification

Issued Date

THIS SH EE T OF E NGI NEE RING DRA WIN G IS THE P ROP RIET ARY P ROP ER TY OF COM PA L EL ECTR ONI CS, INC. A ND CON TAIN S CONFIDENTSIiiA

AND TRA DE SE CR ET INFO RMA TION . THIS S HEE T M AY NO T BE T RAN SFE RED F ROM TH E CUS TOD Y OF THE C OMP ETE NT D IVISION OF R& D

DEP ARTM ENT EXC EPT AS A UTHO RIZE D BY C OMP AL E LEC TRON ICS, INC. NEITHE R THIS SH EET N OR T HE INF ORM ATIO N IT CO NTAINS

5

4

3

MAY BE U SE D BY OR DIS CLOS ED TO A NY THI RD PA RTY W ITHO UT PR IOR W RITTE N CON SE NT OF CO MPA L EL ECTR ONIC S, INC.

2017/08/24 2018/08/24

Compal Secret Data

Deciphered Date

2

Title

zeeLDocum ent Nu mber

Compal Electronics, Inc.

WLAN-BT

LA-G07EP(KBL-U_UMA_6L)

Rev

She et 30 of 59Date: F riday, Jan uary 05,2018

1

v0.3

5

2

+3VS_SSD

1 @1

47U_0603_6.3V6M

2

1

0.1U_0201_10V6K

10U_0603_10V6M

2

1U_0402_6.3V6K

2 1

2

+3VS

CSS5

1

18P_0201_50VNPO

RF@

D D

RF@

2

JPHW9

1

1 2

JUMP_43X79 CS27 CSS7 CS8 CS9 1 CSS6

JUMP@

10P_0201_50V

2

1

CS10

10P_0201_50V

2

RF@

4

3 2

1

+3VS<6,7,9,10,11,13,17,18,27,28,29,30,32,33,36,39,40,52>

+3VS

JSSD

<SSD>

SSD1_IF PU on CPU side RPC13.3_10K

<11> SSD1_IF

B B

@ RS21

100K_0402_5%

<11> PCIE_CRX_DTX_N11

<11> PCIE_CRX_DTX_P11

<11> PCIE_CTX_C_DRX_N11

<11> PCIE_CTX_C_DRX_P11

<11> PCIE_CRX_DTX_P12

<11> PCIE_CRX_DTX_N12

<11> PCIE_CTX_C_DRX_N12

<11> PCIE_CTX_C_DRX_P12

<9> CLK_PCIE_N4

<9> CLK_PCIE_P4

+3VS

D

S

2

1 13

SSD_PDET

+3VS

2

G

QS1 SB000009Q80

2N7002KW_SOT323-3

1 2

@EMI@ CS16

VARIST_ CK0402101V05 0402

1 2

RS22 10K_0402_5%

67

NC

69

PEDET 3P3VAUX

71

GND

73

GND

75

GND

pre PV: change to 10K for redriver detect pin voltage level

SUSCLK(32kHz)

3P3VAUX

3P3VAUX

GND1

YPCI0016-P003A 67PA32

DC04000L9A0CONN@

GND2

68

70

72

74

76

77

+3VS_SSD

TS123

TP@

DEVSLP2 <11>

PLT_RST# <9,29,30,33,35>

CLKREQ_PCIE#4 <9>

A A

Security Classification

IssuedDate

THIS SH EE T OF E NG IN EE RING DRAWI NG IS T HE PRO PR IE TA RY PRO PE RT Y OF C OM PA L ELECT RONIC S, INC. AN D CONTAINS CONFIDENSSTiIzAeL

AND TRADE S EC RE T INFORMA TION . THIS S HE ET MAY NO T BE T RA NS FE RE D F RO M THE CU ST ODY OF T HE CO MP ET EN T DIVIS ION OF R& D

DEPARTMENT E XC EP T AS A UT HORIZED BY C OMPA L ELECTRONICS, INC. NEITH ER T HIS SH EE T NO R TH E IN FO RM AT IO N IT CONTAINS

MAY BE USED BY OR DISCLOSED TO A NY THIRD PARTY WI THOUT PRIOR WRIT TE N CO NS EN T OF COMPAL ELECT RONIC S, IN C.

5

4

2017/08/24 2018/08/24

3 2

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

M.2SSD

DocumentNumber

LA-G07EP(KBL-U_UMA_6L)

Date: Friday, January 05,2018

Sheet of

1

Rev

v0.3

5931

5

4

3

2

1

UA1

<8> HDA_SYNC_R

<8> HDA_BIT_CLK_R

@EMI@

1

CA41

10P_0402_50V8J

2

C C

<8> HDA_RST#_R

<33> EC_MUTE#

B B

HDA_RST#_R

Place RA 51/RA52/RA53 on moat of UA1 BOT side

MMBT3904WH_SOT323-3

EC_MUTE# 1

RA51 1 2 0_0603_5%

Rshort@

RA52 1 2 0_0603_5%

Rshort@

RA54 1 2 0_0603_5%

Rshort@

1

2

RA6

0_0402_5%

RA7 @

1 2

0_0402_5%

1 2

CA9

0.1U 16V K X7R0402

EMI@

1 2

CA10

0.1U 16V K X7R0402

EMI@

1 2

CA11 @EMI@ 0.1U

16VK X7R 0402

1 2

CA12 @EMI@ 0.1U

16VK X7R 0402

1 2

CA13

0.1U 16V K X7R0402

EMI@

+DVDD

+3VS +DVDD

1

RA10

10K_0402_0.5%

@

B

2 2

@3QA2

E

1

C

SB000008E10

@

2

DA2 SCS00000Z00

RB751V-40SOD-323

R5260

1 2

0_0201_5%

GNDA

1 2 1 2

CA34 RA53 22_0402_5%

22P 50V J NPO 0402

EMI@

EMI@ INT_MIC

CA29

GNDA

PLUG_IN# 1 200K_0402_1%

1 2

10U 6.3V M X5R0603

2.2K_0402_5%

RA40 1 2 MIC2-VREFO 23

CA16 2 1

1U_0402_6.3V6K CBP 30

RA41

1 2 100K_0402_1%

2

RA42

12

RA9

100K_0402_5%

PDB

1

2

0.1U 16V K X7R 0402 CA23

9

SYNC

BCLK

5

BCLK

14

MIC2-R/SLEEVE

13

MIC2-L/RING2

MIC2_CAP 15

MIC2_CAP

PC_BEEP

11

PCBEEP

MIC2-VREFO

24

LINE1-VREFO-L SDA TA_IN

LDO1_CAP

21

LDO1-CAP

22

VREF

CPVEE

CPVDD

PDB

CBN 28

VREF

27

CPVEE

29

CPVDD

CBN

CBP

2

GPIO0/DMIC_DATA12

3

GPIO1/DMIC_CLK LDO2_CAP

10

DCDET

12

JD1

40

PDB THERMALPAD

ALC3247-CG_MQFN40_5X5

PC Beep

EC Beep <33>E C_BEEP#

SB Beep <8,10> HDA_SPKR

Close to C odec pin34

1

DVDD

8

DVDD_IO

20

AVDD1

33

AVDD2

34

PVDD1

39

PVDD2

16 VD33STB1 RA232

VD33STB

35 SPK _L+

SPK_OUT_L+

36 SPK_L-

SPK_OUT_L-

37 SPK_R-

SPK_OUT_R-

38 SPK_R+

SPK_OUT_R+

26

HPOUT_R

25

HPOUT_L

4

SDATA_OUT

7 HDA_SDIN0_R 1

18

LINE1_L

17

LINE1_R

32 CA27 1 2 10U 6.3V M X5R 0603

6

LDO3_CAP

19

AVSS1

31

AVSS2

41

1 2 PC_BEEP_R CA44

0.1U 16V K X7R 0402

1 2

CA43

0.1U 16V K X7R0402

GNDA

GNDA

+3VS

0_0402_5%

RA38 1

RA37 1

+DVDD

+DVDD_IO

+5VS_AVDD

+1.8VS_AVDD

+5VS_PVDD1

+5VS_PVDD2

RA26 2

22_0402_5%

RA16

47K_0402_5%

1 2

2 30_0402_1%

2 30_0402_1%

1

RA17

10K_0402_5%

2

GNDA

1 2 PC_BEEP CA42

0.1U 16V K X7R 0402

+5VS

RA8

1 2

0_0402_5%

+5VS_PVDD1

1

1

2

2

RA36 1 EMI@ 2 0_0603_5% SPK_R-_CONN

SPK_R-

RA34 1 EMI@ 2 0_0603_5% SPK_R+_CONN

SPK_R+

RA33 1 EMI@ 2 0_0603_5% SPK_L-_CONN

SPK_L-

RA35 1 EMI@ 2 0_0603_5% SPK_L+_CONN

SPK_L+

wide 40 MIL

EMI@

1 RA13 2 0_0402_5%

INT_MIC

1 RA14 2 0_0402_5%

HP_OUTL

HP_OUTR

EMI@

1 RA15 2 0_0402_5%

EMI@

+3VS +DVDD

RA1

1 2

0_0402_5%

2

4.7U_0402_6.3V6M CA36

+5VS +5VS_AV DD

RA4

1 2

0_0402_5%

@

2 1

1

2

220P_0402_50V7K

@EMI@ C11

Reserve for ESD request.

INT_MIC_R

3

GNDA

2

DA4

L03ESDL5V0CC3-2_SOT23-3

SCA00002900

ESD@

1

HP_OUTR_R HP_OUTL_R

1/20:Sw ap DA3

1

1

1

2

2

2

@EMI@

@EMI@

@EMI@

100P_0603_50V7 CA24

100P_0603_50V7 CA25

100P_0603_50V7 CA26

GNDA

1 1

2

0.1U 16V K X7R 0402 CA37

1 1

CA7

2

10U6.3V M X5R 0603

1

2

220P_0402_50V7K

INT_MIC_R

HP_OUTL_R

PLUG_IN#

HP_OUTR_R

@EMI@ C12

+3VS +DVDD_IO

1 2

0_0402_5%

1

CA5

CA6

2

2

4.7U_0402_6.3V6M

0.1U 16V KX 7R 0402

GNDA

1

1

2

2

220P_0402_50V7K

220P_0402_50V7K

@EMI@ C14

@EMI@ C13

2

3

DA5

L03ESDL5V0CC3-2_SOT23-3

SCA00002900

@ESD@

1

JHP

3 3:M/G_EARTH

1 1:L/R_TIP SPRING

5 5:TRANSFER TERMINAL

6 6:MAKE TERMINAL

2 2:R/L_RING A

4 4:G/M_RING B

7 7:MS_SHELL

SINGA_2SJ3095-067111F

DC23000DY00

GNDA

Pin6 and Pin5

Normal OPEN

RA2

1 1

2 2

4.7U_0402_6.3V6M CA32

0.1U 16V K X7R 0402 CA33

+1.8VS +1.8VS_AVDD

RA5

1 2

0_0402_5%

1

CA8

2

GNDA

CONN@

JSPK

1

1

2

2

3

3

4

4

5

G1

6

G2

ACES_50278-00401-001

4.7U_0402_6.3V6M

A A

Securi ty Clas sification

Issued Date

THI S SHE ET O F EN GI NEE RI NG D RA WI NG IS T HE P ROP RI ET AR Y P RO PE RT Y OF COM PA L EL EC TR ONI CS , IN C. AN D CO NTA IN S CONFIDENTSSIA

AND T RA DE S EC RE T I NF OR MAT IO N. T HI S S HE ET MA Y NOT BE TRA NS FE RE D F ROM T HE C UST OD Y OF TH E CO MPE TE NT DI VIS ION OF R& D

DE PAR TM ENT E XC EP T A S AU THO RI ZE D BY CO MP AL E LE CTR ON IC S, I NC. NE IT HE R TH IS S HEE T NOR THE INF OR MA TI ON I T C ON TAI NS

5

4

3

MAY BEU SE D BY OR D IS CL OS ED TO ANY THIR D PA RT Y W IT HO UT P RIO R WR IT TE N C ONS EN T OF CO MP AL E LE CT RON IC S, IN C.

2017/08/24 2018/08/24

Compal Secret Data

Deciphered Date

2

Title

iizLe Doc ument Number

Custom

Compal Electronics, Inc.

AUDIO ALC3258-CG

LA-G07EP(KBL-U_UMA_6L)

Sheet 32 of 59Date: Friday, January 05,2018

1

Rev

v0.3

5

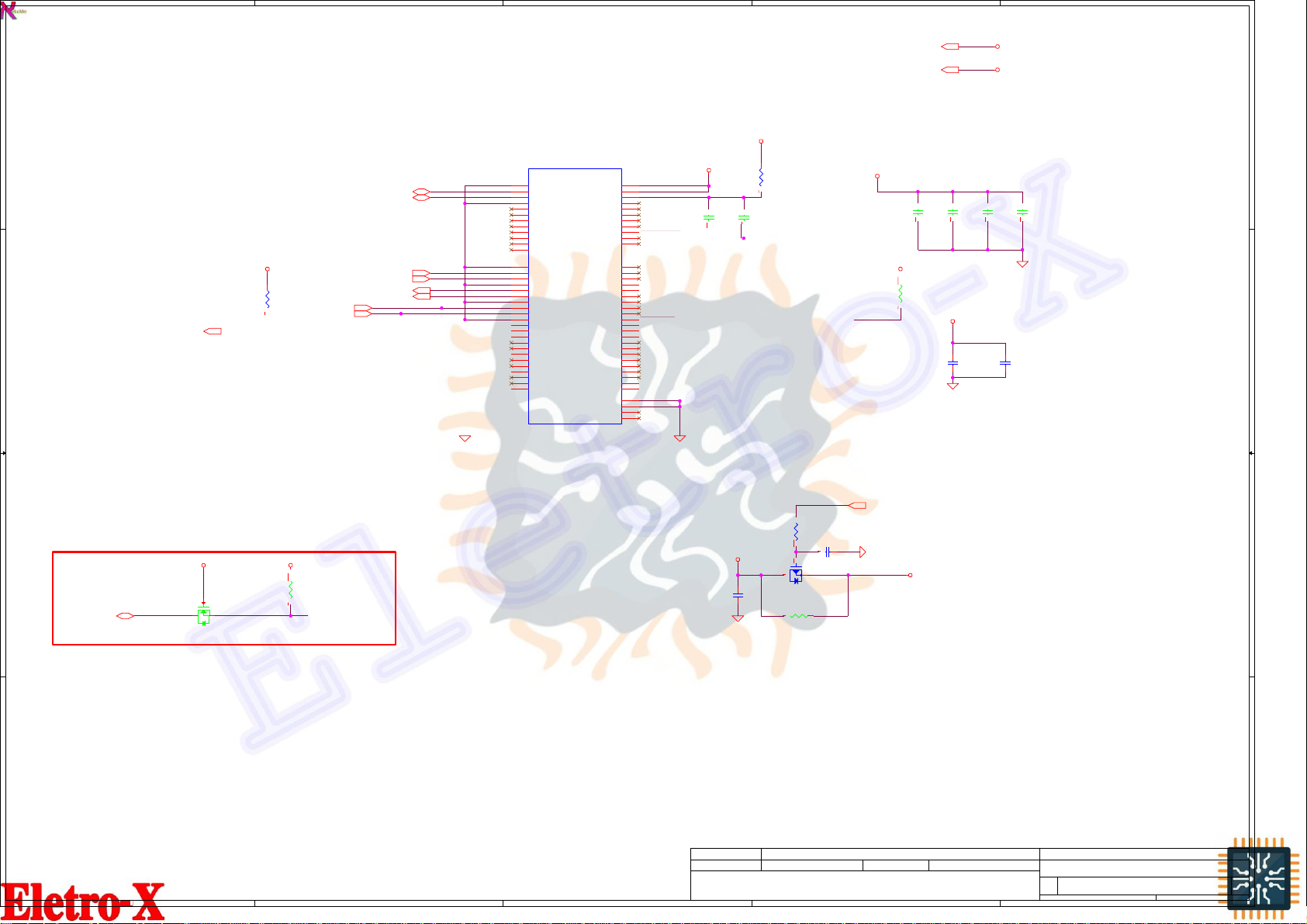

<6,7,9, 10,11,1 3,17 ,18, 19, 22,23,2 4,27,28 ,29, 30, 31,3 2,36 ,39,40, 52,55> + 3VS

D D

+3VA LW _EC

<47> VCIN 1_A COK

For Solv e tP CH0 4(M in 9m s) Seque nc e Ti mi ng

+5VS

2

2

RK20 100K_0402_5%

RK10 8 10K_04 02_5 %

A A

10K_04 02_5 %

ESD@

2

1 PLT_RST #

CK4 0.1U_04 02_2 5V6

@

2

RK7

2

@ 1

CK5

RK28

100K_0 402_ 5%

RK26

100K_0 402_ 5%

1 @ 2 PCH_PW RO K

1 2 MUT E_L ED_ IN

RK21

0.1U_04 02_ 16V7K

22P 50V J NPO 0402

VCIN 1_AC_IN 1 @ 2 V CIN1_AC _IN_R R4960

1 MUTE _LE D_O UT

1 E51 TXD _P8 0DATA

+3VA LW _EC

12

1 330K_04 02_ 5%

CK9 RK109 22_04 02_5%

EMI@

R4958

R5094

<7,10,2 2> EC _SMB_CK 2

<7,10,2 2> EC _SMB_DA 2

<22,45> +3VALW _EC

<13,39, 46, 47, 48> +3VL

EC_R ST #

CLK_ PCI_LPC

1 2 1 2

EMI@

1 @ 2 V CIN1_AC OK _R

0_0402_5%

1

2 VCIN1_AC _IN_R

0_0402_5%

0_0402_5%

<46,47> EC_ SMB_ CK 1

<46,47> EC_ SMB_ DA 1

+3VS

+3VA LW _EC

+3VL

<34> KSO[ 0.. 17]

<9,12,4 0> P M_SL P_ S3#

<9> PM_SL P_S5#

+3VL

1

RK1

T24 03 T P@

1 @ 2

1 @ 2

4

2

0_0603_5%

TOUCH_ON

EC_K BRS T#

SERI RQ

LPC_ FRAME#

LPC_AD3

LPC_AD2

LPC_AD1

LPC_AD0

CLK_ PCI_LPC

PLT _RS T#

EC_R ST #

PM_C LKRUN#_R

1

2

KSI0

KSI1

KSI2

KSI3

KSI4

KSI5

KSI6

KSI7

KSO0

KSO1

KSO2

KSO3

3 2

+3VA LW _EC

0.1U_02 01_ 10V6K

0.1U_02 01_ 10V6K

CK2

CK1

1

2

UK1

1

GAT EA2 0/G PIO0 0

2

KBRS T#/GPIO01

3

SERI RQ

4

LPC_ FRAME#

5

LPC_ AD3

7

LPC_ AD2

8

LPC_ AD1

10

PC & MISC

LPC_ADL0

12

CLK_ PCI_EC

13

PCIR ST# /GPIO0 5

37

EC_R ST #

20

EC_S CI#/GPIO0E

38

CLKR UN#/GPIO1 D

55

KSI0/GPIO30

56

KSI1/GPIO31

57

KSI2/GPIO32

58

KSI3/GPIO33

59

KSI4/GPIO34

60

KSI5/GPIO35

61

KSI6/GPIO36

62

KSI7/GPIO37

34

SUSP _LE D#/ GP IO1 9

36

NUM_ LED #/G PIO1 A

122

PBT N_O UT#/G PIO5 D

123

PM_SLP_ S4#/G PIO 5E V18R /VC C_IO2

SA00 007 5S30

LK1 SM0 100 0Q 500

S S UPPR E_ TAI -TECH HCB1005KF -22 1T1 5 0402

+3VA LW _EC

1 2 + EC_ VCCA

+3V_ LID

9

125

22

33

VCC96VCC

VCC

VCC

VCC0

Pin11 1:VC C0

VCC_LPC

PWMOutput

VCIN 1_BATT _T EMP/ AD0 /GP IO38

VCIN 1_BATT _DROP/AD1 /GPIO3 9

ADInput

DA Output

PS2Interface

Int.K/B

Matrix

GND

GND

GND

GND

11

24

35

94

113

1

CK3

0.1U_02 01_ 10V6 K

2

ECAG ND

1 RK3 2

0_0402_5%

67

AVCC

EC_V CCS T_PG/GPIO0F

BEEP #/G PIO10

EC_F AN_ PW M/G PIO1 2

AC_O FF /GP IO13

ADP_ I/AD2/G PIO 3A

AD_B ID/AD3/ GPI O3B

AD4/ GPI O42

AD5/ GPI O43

DA0/ GPI O3C

EN_D FAN 1/D A1/ GP IO3 D

DA2/ GPI O3E

EC_M UTE#/P SCL K1 /GPIO 4A

ALW _PWE _EN EC _ON /GPXIO D02

GPI

GND

DA3/GPI O3F

USB_ EN# /PSDAT 1/G PIO4B

PSCL K2/ GPIO4C

PSDA T2/GPIO4D

TP_ CLK /GP IO4E

TP_ DAT A/G PIO 4F

ENKB L/G PXI OA 00

WO L_E N/G PXIO A01

ME_EN/G PXI OA 02

VCIN 0_PH1/GPXI OD0 0

VCIN 1_AC_IN /GP XIOD01

ON/ OFF #/G PXIOD03

LID_ SW #/G PXIO D04

SUSP #/G PXI OD 05

GPXIOD0 6

PECI /GPXIOD 07

AGND

69

20mil

LK2 SM01000Q5 00

ECAG ND 2 1

TAI-TE CH HC B1005KF-22 1T15 0402

ECAG ND <4 5>

+3VL+3V_ EC_ VDD

21

23

26

27

63

64

ADP_ I

65

66

75

EC_P ME# _EC _R

76

68

70

71

72

83

84

85

86

87

88

97

98

99

109

110

112

114

115

116

117

118

124

U_PX@

RK4

56K +- 1%0402

SD03 456 028 0

R_PX@

RK4

330K + -1% 0402

SD03 433 038 0

EC_V CCS T_PG_R

EC_F AN_ PW M1

EC_C LR_ CMO S

B/I#

BOARD_ID

ADP_ ID

NMI_DBG#

VR_P WRGD

VR_O N

TP_ CLK

TP_ DAT A

ENBK L

ME_F LASH_EN

VCIN 0_PH

VCIN 1_AC_IN _R

EC_O N

ON/ OFF #

LID_SW #

SUSP #

VCIN 1_AC_IN

EC_P ECI RK1 7 1

+V18 R

1

2

+3VA LW _EC

RK2

100K_0 402_ 1%

1 2

BOARD_ID

U_UMA@

2

RK4

43K +- 1%0402

SD03 443 028 0

1

R_UMA@

111

CK8

4.7U_04 02_ 6.3V 6M

ENBK L <5 >

WL _PW RE N_EC# <3 0>

ME_F LASH_E N <8>

VCIN 0_PH <45>

+1.0VS_ PG <50>

EC_O N <39 ,48 >

ON/ OFF # <39>

LID_ SW # <39>

SUSP # <12,40,49>

2 43_040 2_1%

+3VA LW _EC

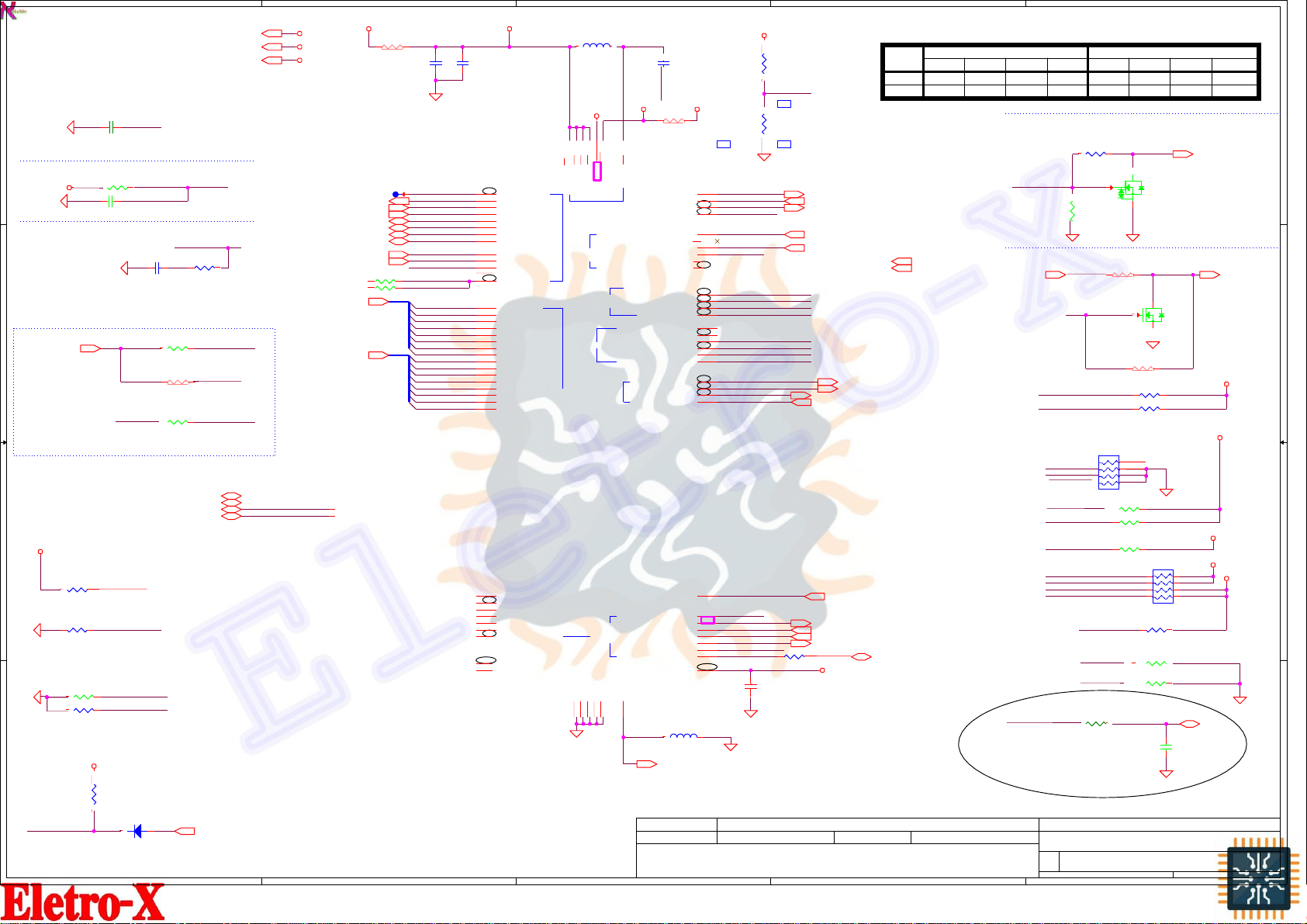

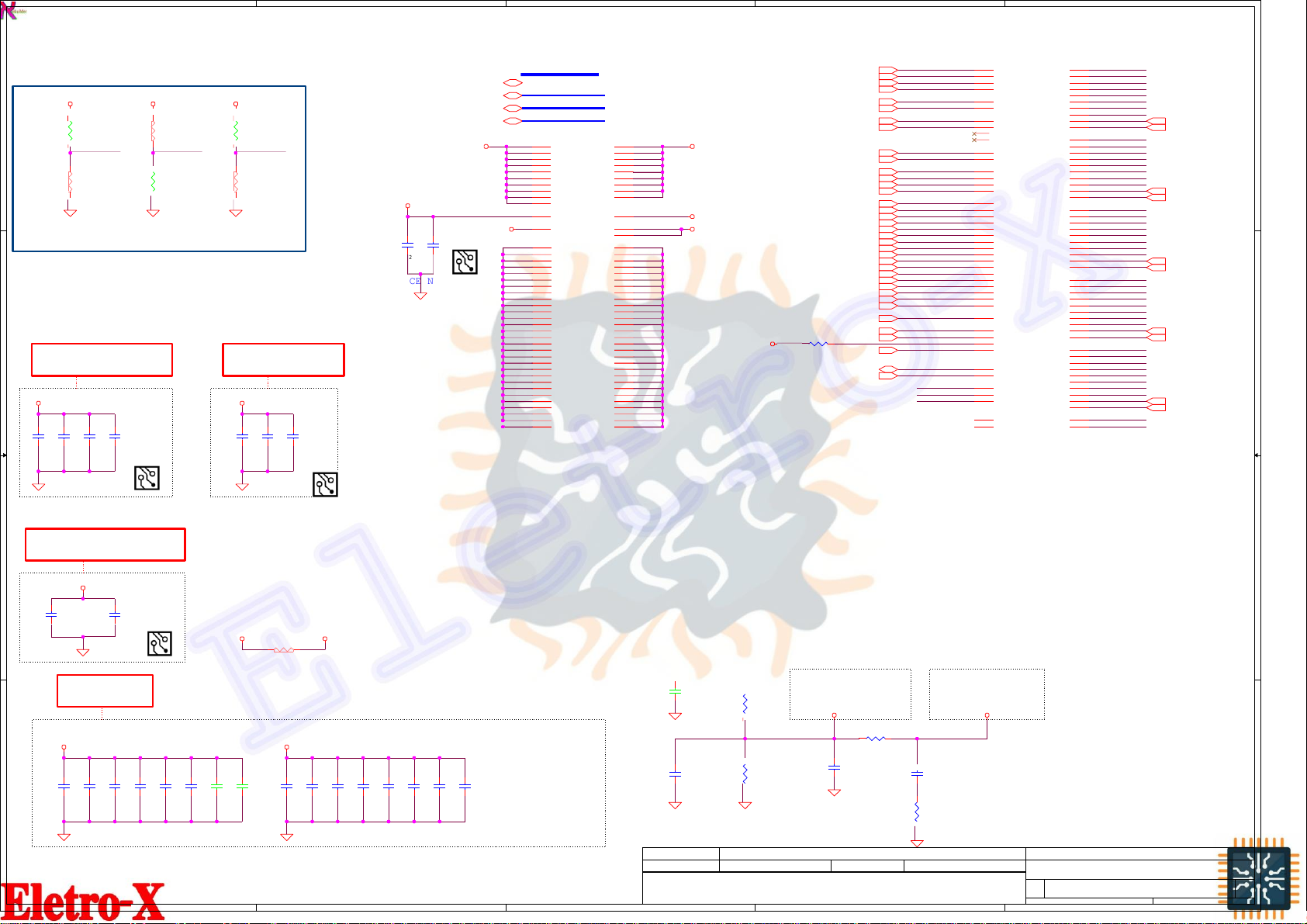

EC Board ID (UMA, DIS, phase) control table

RK4

DB SI PV MV DB SI PV MV

UMA 15K 27K 43K 75K 130K 200K 270K 430K

20K

DIS

U_DB_UMA_15kohm:SD034150280, S RES 1/16W 15K+-1% 0402

U_DB_ DIS_20kohm:SD034200280, S RES 1/16W 20K +-1% 0402

U_SI_UMA_27kohm:SD034270280, S RES 1/16W 27K +-1% 0402 (2017-10-05 : 2018OPP Add EC Clear CMOS function)

U_SI_ DIS_33kohm:SD034330280, S RES 1/16W 33K +-1%0402

U_PV_UMA_43kohm:SD034430280, S RES 116W 43K +-1% 0402

U_PV_ DIS_56kohm:SD034560280, S RES 1/16W 56K +-1% 0402

U_MV_UMA_75kohm:SD034750280, S RES 1/16W 75K +-1% 0402

U_MV_ DIS_100kohm:SD034100380, S RES 1/16W 100K+-1% 0402

R_DB_UMA_130kohm:SD034130380, S RES 116W 130K +-1%0402

R_DB_ DIS_160kohm:SD034160380, S RES 116W 160K +-1%0402

R_SI_UMA_200kohm:SD034200380, SRES 1/16W 200K +-1%0402

R_SI_ DIS_240kohm:SD000001B80, S RES 116W 240K +-1%0402

ADP_ ID <45>

EC_P ME# < 29>

H_PE CI <5>

KBL-U KBL-R

(0x02) (0x04) (0x06) (0x08 ) (0x0 A) (0x0C) (0x0E) (0x 10)

33K

56K

100K

(0x03)

(0x05)

EC_C LR_ CMO S

<52> VR_HOT #

EC_S PI_C LK R C36 9 1 2 HOST_ SPI_ 0_C LK_R

CC128 RC369 place nea r ECSide

(0x07)

(2016-03-04 :::: Confirm intel platform not support EC Clear CMOSfunction)

TP_ CLK

TP_ DAT A

EC_ON 6 3

PCH_PW R_EN 5 4

PBT N_O UT# R 295 1 @

EC_C LR_ CMO S 1 @ 2 RK 107

LID_ SW # RK18 2 @ 1 47K_0 402 _5%

EC_S MB_C K1

EC_S MB_D A1

EC_S MB_C K2

EC_S MB_D A2

EMI request

160K

(0x09)

Reserve EC_CLR_CMOS for clear CMOS

RK10 6 1 2 0_0402_ 5%

2

R483

@

10K_04 02_5 %

1

2

VR_H OT # 1

RK8

2N7002 _SOT 23-3

SB00 000 EN 00

RK12 1

RK13 1 2 4.7K_04 02_5%

RP12

8 1

PLT _RS T# 7 2

100K_0 804_ 8P4R_5%

EC_S CI# RK14 2

SYSO N RK23 1 @ 2 100K _040 2_5%

SUSP # RK 27 1

EMI@ 1 5_040 2_5%

22P 50V J NP O 0402

1

240K

(0x0D)

@

1

D

Q51

2N7002 K_SOT23- 3

SB00 000 EN00

S

2 0_0402_5%

1

D

S

3

2 4.7K_04 02_5%

2 1K_0402 _5%

10K_04 02_5 %

8

7

6 3

5 4

2.2K_0804_ 8P4R_5%

1 10K_0402_5%

2 100K_0402_5 %

CC144

330K

1 RP 11

2

(0x0B)

G

3

2

G

@QK1

RK91 2 0_0402_ 5%

@EMI@

560K

(0x0F)

CLR_CMO S# <9>

PROCHO T# <5>

+3VA LW

+3VL

+3VA LW _EC

+3V_ SMBU S

+3VS

HOST_S PI_0 _CL K_R <7 ,35>

(0x11)

NMI_DBG#

1 2

DK2 SCS 000 00Z 00

RB751V- 40 SOD-323

5

NMI_DBG#_CP U <5 ,10 >

Security Classification

Issued Date

THI S S HEET OF E NGI NEERING DR AW ING IS T HE PR OPR IET ARY PROP ERT Y OF CO MPAL ELEC TR ONICS, INC. A ND CO NT AINS CO NFID ENT IAL

AND TRADE SECRE T INF ORMATI ON. THIS SHEET MAY NO T BE TR ANSFERED FR OM T HE CUS TODY OF T HE COMPET ENT DIVISIO N OF R&SD

DEPA RT MENT EXC EPT AS AUT HO RIZE D BY CO MPAL ELECTR ONI CS, INC . NEITHER THIS S HEET NOR T HE INFO RMATIO N IT CON TAINS

4

MAY BE USED BY OR DI SCLOSED TOA NY T HIR D PARTY W IT HOUT PRIOR WR ITT EN CON SENT OF COMPAL ELEC TRONIC S, INC.

3 2

2017/04/10 2019/12/15

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Titl e

ECENE-KB9022

izeDocument Number

Custom

LA-G07EP(KBL-U_UMA_6L)

Rev

Shee t 33 of 59Date: Tuesday, J anu ary 09, 2018

1

v0.3

5

4

3 2

1

+1.0V_PRIM TO +1.0V_VCCSTU

+1.2V_VDDQ

I (Max) : 4.5 A

+1.2V_VDDQ

+1.0V_VCCST

+1.0V_PRIM

+1.2V_VCCSFR_OC

+1.0V_VCCSFR

<Cocoa_1113>

Per

543977_SKL_PDDG_Rev0_91,

change CC95 value from

1000pf to 10pf for meet

<= 65us timing for

C C

+1.0V_VCCSTU power rail.

+1.0V_VCCSTU +1.0V_VCCST

RC140 1 2 0_0402_5%

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

UC1N

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

SKL-U_BGA1356

+1.0V_PRIM TO +1.0VS_VCCSTG / +1.0VS_VCCIO

+5VALW

+1.0V_PRIM

+1.0V_PRIM

near pin A22

CPU POWER 3 OF 4

PSC Side

1

2

1U_0402_6.3V6K

SKL-U

CC48

Rev_0.53

+1.0V_PRIM

RC208 Follow 544669_SKL_U DDR3L_RVP7_Schematic_Rev1.0

+1.0V_VCCSFR

RC143 1 2 0_0402_5%

1U_0402_6.3V6K

1

CC55

2

+1.2V_VDDQ

1

CC27

2

A A

1

CC28

2

2

5

10U_0402_6.3V6M

10U_0402_6.3V6M

1

1U_0201_6.3V6K

1U_0201_6.3V6K

1

CC29

2

1U_0201_6.3V6K

1

CC30

1

CC31

2

2

1U_0402_6.3V6K

1U_0201_6.3V6K

1

CC32

2

1U_0402_6.3V6K

1

CC33

1

CC34

2

2

4

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC36

CC35

CC47 Follow 543016_SKL_U_Y_PDG_0_9

2

Security Classification

Issued Date

THIS SH EE T OF E NG IN EE RING DRAWI NG IS T HE PRO PR IE TA RY PRO PE RT Y OF C OM PA L ELECT RONIC S, INC. AN D CONTAINS CONFIDENSSTiIzAeL

AND TRADE S EC RE T INFORMA TION . THIS S HE ET MAY NO T BE T RA NS FE RE D F RO M THE CU ST ODY OF T HE CO MP ET EN T DIVIS ION OF R& D

DEPARTMENT E XC EP T AS A UT HORIZED BY C OMPA L ELECT RONIC S, INC. NEITH ER T HIS SH EE T NO R TH E IN FO RM AT IO N IT CONTAINS

MAY BE US ED BY OR DI SCLOSE D TO A NY THIRD P AR TY W ITHOU T PRIOR W RITTE N CO NS EN T OF C OM PA L ELECTRO NICS, INC.

3 2

1U_0402_6.3V6K

1

CC47

2

2017/04/10 2019/12/15

Compal Secret Data

Deciphered Date

10U_0603_6.3V6M

1

1

CC37

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC38

2

10U_0603_6.3V6M

1

CC39

1

CC40

2

2

+1.35V_VDDQ_CPU : 10UF/6.3V/0603 *6

1UF/6.3V/0402 * 4

10U_0603_6.3V6M

CC41

Title

DocumentNumber

Custom

10U_0603_6.3V6M

1

CC42

2

BSC SidePSC Side

1U_0402_6.3V6K

1

1

CC43

2

2

Compal Electronics,Inc.

SKL-U(8/12)Power

LA-G07EP(KBL-U_UMA_6L)

+1.0V_PRIM

BSC SidePSC Side

1U_0402_6.3V6K

1

CC56

2

1U_0402_6.3V6K

1

CC45

2

Sheet 12

1

1U_0402_6.3V6K

CC46

Rev

v0.3

of

59Date: Friday, January 05,2018

1U_0402_6.3V6K

1

CC44

2

5

+1.0V_PRIM

RC148 1 Rshort@2 0_0603 _5%

D D

@

+1.0V_APLL

22U_0603_6.3V6M

1

2

+3V_PRIM

22U_0603_6.3V6M

1

CC134

CC142

@

2

RC150 1 Rshort@2 0_0402 _5%

1U_0402_6.3V6K

1

CC72

2

Follow 54 3016_SKL_U_Y_PDG_1_0

+1.0V_CLK5_F24NS

RC152 1 Rshort@20_0603_5%

+3V_PRIM

RC197 1 Rshort@2 0_0402 _5%

4

+3V_HDA

+3V_PGPPA

1

CC63

1U_0201_6.3V6K

2

near pi n K15,L15

near pi n N18

3

+1.0V_PRIM

+1.0V_PRIM

+1.0V_PRIM

+1.0V_PRIM

1

2

2.574A

CC147

@

22U_0603_6.3V6M

1

CC148

@

2

+1.0V_PRIM

1U_0402_6.3V6K

1

CC61

2

+1.0VO_DSW

1U_0201_6.3V6K

1

+1.0V_MPHYAON

1U_0402_6.3V6K

CC68

1

2

CC85

2

22U_0603_6.3V6M

1

2

+1.0V_PRIM

1U_0201_6.3V6K

CC91

1.87A

2

0.69A

AB19

VCCPRIM_1P0

AB20

VCCPRIM_1P0

P18

AF18

AF19

V20

VCCPRIM_CORE

V21

AL1

DCPDSW_1P0

VCCMPHYAO N_1P0

L1

VCCMPHYAO N_1P0

N15

N16

N17

P15

VCCMPHYG T_1P0_P15

P16

UC1O

CPUPOWER 4OF 4

VCCPRIM_1P0

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCMPHYG T_1P0_N15

VCCMPHYG T_1P0_N16

VCCMPHYG T_1P0_N17

VCCMPHYG T_1P0_P16

SKL-U

Rev_0.53

VCCPGPPA

VCCPGPPB

VCCPGPPC

VCCPGPPD

VCCPGPPE

VCCPGPPF

VCCPGPPG

VCCPRIM_3P3_V19

VCCPRIM_1P0_T1

VCCATS_1P8

VCCRTCPRIM_3P3

VCCRTC_AK19

VCCRTC_BB14

DCPRTC

AK15

AG15

Y16

Y15

T16

AF16

AD15

V19

T1K17

AA1

AK17

AK19

BB14

BB10 +DCPRT C 1 2

PRIMCORE_VID0

PRIMCORE_VID1

From Bat tery

1

1209_follow G group GPIO

powe rail to +3V_PRIM

+3V_PGPPA

+3V_PGPPB

+3V_PGPPC

+3V_1.8V_PGPPD

+3V_PGPPE

+1.8V_PRIM

+3V_PRIM For SD CARD

+3V_PRIM

+1.0V_D TS

+1.8V_PRIM

+3V_PRIM_RTC

+RTCVCC

CC71 0.1U_02 01_10V6K

+1.0V_C LK6_24T BT

+1.0V_APLL

+1.0V_C LK4_F10 0OC

+1.0V_C LK5_F24 NS

+1.0V_C LK6_24T BT

T130 TP@

T131 TP@

+3V_LID

1U_0402_6.3V6K

RC169 1 Rshort@20_0603_5%

RC162 1 Rshort@20_0402 _5%

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

@

@

CC86

2

2

+1.0V_DTS

10U_0402_6.3V6M

22U_0603_6.3V6M

1

1

@

@

CC75

CC139

CC138

2

2

RC171 1 Rshort@2 0_0402 _5%

Follow 543016_SK L_U_Y_P DG _0_9

+1.0V_PRIM +3V_PRIM +1.8V_PR IM

A A

22U_0603_6.3V6M

22U_0603_6.3V6M

1

1

CC112

CC111

@

@

2

2

22U_0603_6.3V6M

22U_0603_6.3V6M

1

1

CC114

CC113

@

@

2

2

22U_0402_6.3V6M

22U_0402_6.3V6M

1

1

CC116

@

@

2

2

+3VS

CC115

RC178 1 Rshort@2 0_0402 _5%

+3VALW

RC173 1 Rshort@2 0_0603 _5%

Follow 543016_SKL_U_Y_PDG_0_9

5

1

2

+3V_PRIM_RTC

1U_0402_6.3V6K

1

2

4

CC74

1

CC77

2

+3VS_PGPPA

+3VALW _DSW

BOM

I (Max) : 0.1 A

0.1U_0201_10V6K

CC78

+1.2V_VCCSFR_OC

+1.2V_VDDQ

Security Classification

Issued Date

THI S S H E ET O F E N GI NE E RI N G DR AW I NG I S TH E P R OP R IE TA R Y P RO PE R TY O F C O MP A L E LE CTR ON IC S, I NC. AN D C ON TA INS CONFIDENTSIiiAzeL

AN D T RA D E SE C R ET IN FO RM AT IO N. TH IS SH E ET M A Y N OT BE TR A NS F ER E D F R OM TH E C US TO D Y OF TH E C OM P ET E NT D IV IS ION OF R &D

DE PA RTM E NT EX CE P T AS A UT HO R IZ ED BY C OM P AL E LE CTR ON IC S, IN C. N EI TH ER THI S S H EE T N OR T H E IN F OR M AT IO N IT C ON TAI NS

MA Y BE U S E D BY OR D IS CL OS ED TO A N Y THI RD PA R TY W I TH O UT P R IO R W R IT TE N C ON S EN T OF CO M PA L EL EC TR ON ICS , IN C.

3

1

CC150

1U_0402_6.3V6K

2

2017/04/10 2019/12/15

RC141

1

2

0_0402_5%

Compal Secret Data

1

2

DecipheredDate

2

0.1U_0201_10V6K

CC49

+3VALW TO +3V_PRIM

+3VALW

Custom

I (Max) : 0.46 A(+3V_PRIM)

RDS(Typ) : 65 mohm

V drop : 0.03 V

1

@

1U_0402_6.3V6K

CC50

2

Title

Document Number

RC393

Compal Electronics,Inc.

SKL-U(9/12)Power

LA-G07EP(KBL-U_UMA_6L)

+3V_PRIM

0.1U_0201_10V6K

1

CC51

2

1

0_0805_5%

Sheet 13 of 59Date: Friday, Janu ary 05, 2018

1

2

Rev

v0.3

5

4

3 2

1

D D

A5

A67

A70

AA2

AA4

AA65

AA68

AB15

AB16

AB18

AB21

AB8

AD13

AD16

AD19

AD20

AD21

AD62

AD8

AE64

AE65

AE66

AE67

AE68

C C

B B

AE69

AF1

AF10

AF15

AF17

AF2

AF4

AF63

AG16

AG17

AG18

AG19

AG20

AG21

AG71

AH13

AH6

AH63

AH64

AH67

AJ15

AJ18

AJ20

AJ4

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AK8

AL2

AL28

AL32

AL35

AL38

AL4

AL45

AL48

AL52

AL55

AL58

AL64

UC1P

GND 1 OF 3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-U_BGA1356

SKL-U

Rev_0.53 Rev_0.53

AL65

VSS

AL66

VSS

AM13

VSS

AM21

VSS

AM25

VSS

AM27

VSS

AM43

VSS

AM45

VSS

AM46

VSS

AM55

VSS

AM60

VSS

AM61

VSS

AM68

VSS

AM71

VSS

AM8

VSS

AN20

VSS

AN23

VSS

AN28

VSS

AN30

VSS

AN32

VSS

AN33

VSS

AN35

VSS

AN37

VSS

AN38

VSS

AN40

VSS

AN42

VSS

AN58

VSS

AN63

VSS

AP10

VSS

AP18

VSS

AP20

VSS

AP23

VSS

AP28

VSS

AP32

VSS

AP35

VSS

AP38

VSS

AP42

VSS

AP58

VSS

AP63

VSS

AP68

VSS

AP70

VSS

AR11

VSS

AR15

VSS

AR16

VSS

AR20

VSS

AR23

VSS

AR28

VSS

AR35

VSS

AR42

VSS

AR43

VSS

AR45

VSS

AR46

VSS

AR48

VSS

AR5

VSS

AR50

VSS

AR52

VSS

AR53

VSS

AR55

VSS

AR58

VSS

AR63

VSS

AR8

VSS

AT2

VSS

AT20

VSS

AT23

VSS

AT28

VSS

AT35

VSS

AT4

VSS

AT42

VSS

AT56

VSS

AT58

VSS

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV1

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8

AY66

B10

B14

B18

B22

B30

B34

B39

B44

B48

B53

B58

B62

B66

B71

BA1

BA10

BA14

BA18

BA2

BA23

BA28

BA32

BA36

F68

BA45

UC1Q

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND 2 OF 3

16 OF20

SKL-U_BGA1356

SKL-U

17 OF20

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BA49

BA53

BA57

BA6

BA62

BA66

BA71

BB18

BB26

BB30

BB34

BB38

BB43

BB55

BB6

BB60

BB64

BB67

BB70

C1

C25

C5

D10

D11

D14

D18

D22

D25

D26

D30

D34

D39

D44

D45

D47

D48

D53

D58

D6

D62

D66

D69

E11

E15

E18

E21

E46

E50

E53

E56

E6

E65

E71

F1

F13

F2

F22

F23

F27

F28

F32

F33

F35

F37

F38

F4

F40

F42

BA41

G10

G22

G43

G45

G48

G52

G55

G58

G60

G63

G66

H15

H18

H71

J11

J13

J25

J28

J32

J35

J38

J42

K16

K18

K22

K61

K63

K64

K65

K66

K67

K68

K70

K71

L11

L16

L17

F8

G5

G6

J8

UC1R

GND 3 OF 3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-U_BGA1356

SKL-U

18 OF20

Rev_0.53

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L18

L2

L20

L4

L8

N10

N13

N19

N21

N6

N65

N68

P17

P19

P20

P21

R13

R6

T15

T17

T18

T2

T21

T4

U10

U63

U64

U66

U67

U69

U70

V16

V17

V18

W13

W6

W9

Y17

Y19

Y20

Y21

A A

Security Classification

Issued Date

THIS SH EE T OF E NG IN EE RING DRAWI NG IS T HE PRO PR IE TA RY PRO PE RT Y OF C OM PA L ELECT RONIC S, INC. AN D CONTAINS CONFIDENSSTiIzAeL

AND TRADE S EC RE T INFORMA TION . THIS S HE ET MAY NO T BE T RA NS FE RE D F RO M THE CU ST ODY OF T HE CO MP ET EN T DIVIS ION OF R& D

DEPARTMENT E XC EP T AS A UT HORIZED BY C OMPA L ELECT RONIC S, INC. NEITH ER T HIS SH EE T NO R TH E IN FO RM AT IO N IT CONTAINS

5

4

MAY BE US ED BY OR DI SCLOSE D TO A NY THIRD P AR TY W ITHOU T PRIOR W RITTE N CO NS EN T OF C OM PA L ELECTRO NICS, INC.

2017/04/10 2019/12/15

3 2

Compal Secret Data

Deciphered Date

Title

DocumentNumber

Custom

Compal Electronics,Inc.

SKL-U(11/12)GND

LA-G07EP(KBL-U_UMA_6L)

Sheet

1

Rev

v0.3

15 of 59Date: Friday, January 05,2018

5

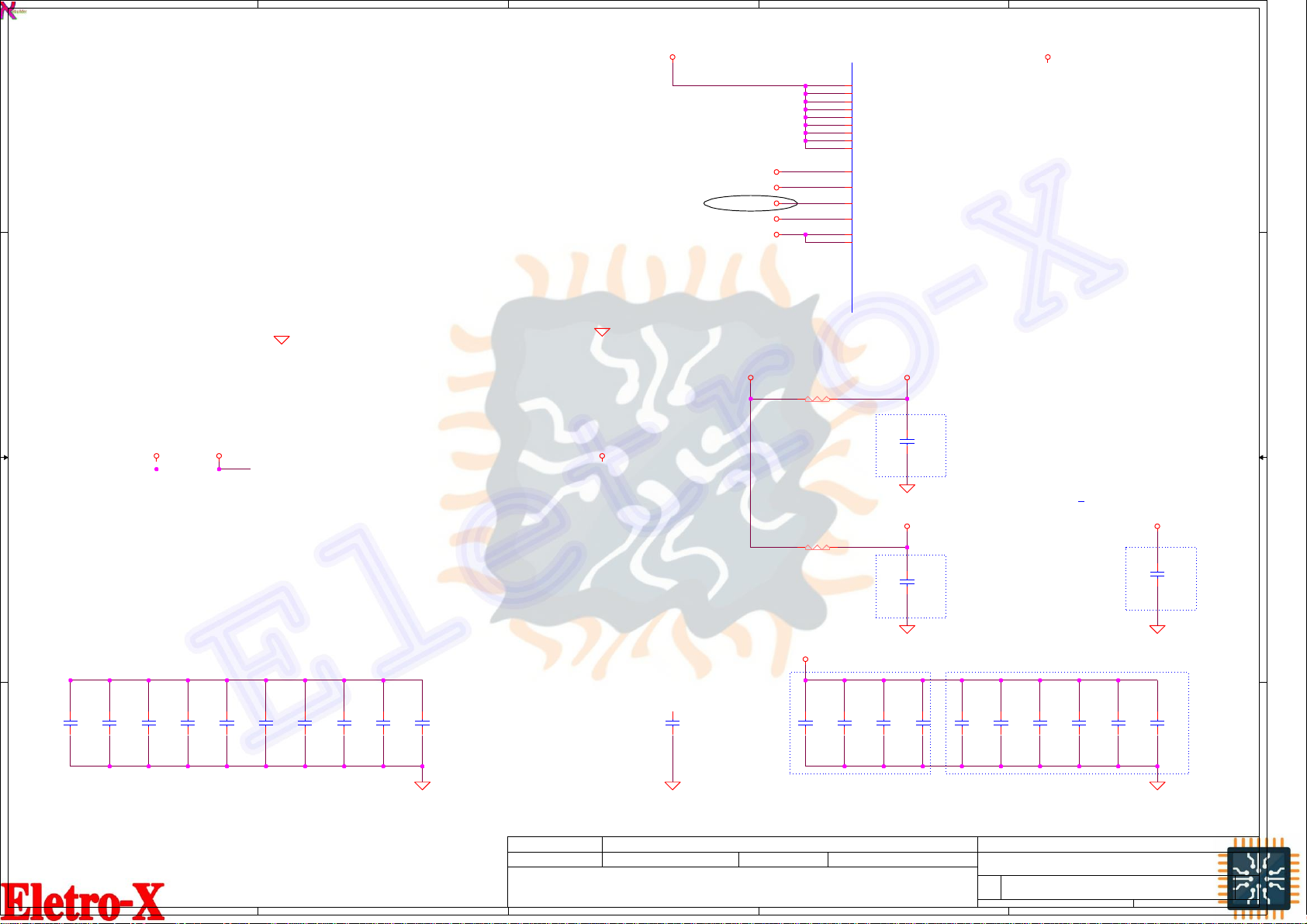

CHANNEL-A

TOP: JDIMM1 CONN Non-ECC DIMM

D D

11 2

+3VS+3VS+3VS

4

REVERSE TYPE

Interleaved Memory

<6> DDR_M0_D[0..15]

<6> DDR_M0_D[16..3 1]

<6> DDR_M0_D[32..4 7]

<6> DDR_M0_D[48..6 3]

3

<6> DDR_M0_CLK0

<6> DDR_M0_CLK#0

<6> DDR_M0_CLK1

<6> DDR_M0_CLK#1

<6> DDR_M0_CKE0

<6> DDR_M0_CKE1

<6> DDR_M0_CS#0

<6> DDR_M0_CS#1

<6> DDR_M0_ODT0

DDR_M0_CLK0

DDR_M0_CLK#0

DDR_M0_CLK1

DDR_M0_CLK#1

DDR_M0_CKE0

DDR_M0_CKE1

DDR_M0_CS#0

DDR_M0_CS#1

DDR_M0_ODT0

2

JDIMM1A

137

CK0(T)

139

CK0#(C) DQ1

138

CK1(T) DQ2

140

CK1#(C) DQ3

109

CKE0 DQ5

110

CKE1 DQ6

149

S0#

157

S1#

162

S2#/C0

165

S3#/C1

1

STD

DQ0

DQ4

DQ7

DQS0(T)

DQS0#(C)

DQ8

DQ9

DDR_M0_D0

8

DDR_M0_D4

7

DDR_M0_D3

20

DDR_M0_D7

21

DDR_M0_D1

4

DDR_M0_D5

3

DDR_M0_D2

16

DDR_M0_D6

17

DDR_M0_DQS0

13

DDR_M0_DQS#0

11

DDR_M0_D8

28

29

DDR_M0_D12

DDR_M0_D14

DDR_M0_DQS0 <6>

DDR_M0_DQS#0 <6>

10uF*2

1uF*1

10U_0603_6.3V6M

1

CD8

2

1 2

1U_0402_6.3V6K

CD9

+3V_PRIM_DA

0.1U_0201_10V6K

CD1

2

1

+3V_PRIM_DA+3V_PRIM

2.2U_0402_6.3V6M

+0.6V_D DR_VREF CA

2

CD2

1

+0.6V_0.6VS

+2.5V

+1.2V_VDDQ

PLACE N EAR TO SODIMM

FOX_AS0 A827-H2RB-7H

CONN@

Part Number:LTCX0069GA0

Part Value:S SOCKET FOX AS0A827-H2RB-7H 260P DDR4

9/8 Modify

DDR_DRAMRST#_R

2

PLACE ALL THE BELOW RESISTORS CLOSE TO SODIMM

C C

Layout Note:

Place n ear JDIMM1.257,259

+2.5V +0.6V_0.6VS

10U_0603_6.3V6M

1

1

CD3

2

2

Layout Note:

PLACE T HE CAP near JDIMM1 . 164

B B

+0.6V_D DR_VREF CA

2 2

CD11 CD12

0.1U_0201_10V 6K 12.2U_0402_6.3V6M

1

10uF*2

1uF*2

@ESD@

10U 6.3V M X5R 0603 H0.8

1U_0402_6.3V6K

1

CD4

CD5

2

0.1U_0201_10V6K

1U_0402_6.3V6K

1

1

2

CD6

CC159

2

2.2uF*1

0.1uF*1

Layout Note:

Place n ear JDIMM1.258

10U_0603_6.3V6M

1

1

CD7

2

2

RD32 0_0402_5%

<6> DDR_M0_MA5

<6> DDR_M0_MA6

<6> DDR_M0_MA7

<6> DDR_M0_MA8

<6> DDR_M0_MA9

<6> DDR_M0_MA10

<6> DDR_M0_MA11

<6> DDR_M0_MA12

<6> DDR_M0_MA13

<6> DDR_M0_MA14_WE#

<6> DDR_M0_MA15_CAS#

<6> DDR_M0_MA16_RAS#

<6,18> DDR_DRAMRST#_R

<7,18> PCH_SMBDAT A

<7,18> PCH_SMBCLK

@ESD@

CD10

0.1U_0402_25V6

2 1

+1.2V_VDDQ

DDR_M0_MA6

DDR_M0_MA7

DDR_M0_MA8

DDR_M0_MA9

DDR_M0_MA10

DDR_M0_MA11

DDR_M0_MA12

DDR_M0_MA13 158

DDR_M0_MA14_W E# 151

DDR_M0_MA15_CAS# 156

DDR_M0_MA16_RAS# 152

PCH_SMBDATA 254

PCH_SMBCLK 253

SA2_CHA_DIM1 166

SA1_CHA_DIM1 260

SA0_CHA_DIM1 256

For ECC DIMM

+1.2V_VDDQ

146

A10_AP

120

A11

119

A12

A13

A14_W E#

A15_CAS#

A16_RAS#

SDA

SCL

SA2

SA1

SA0

92

CB0_NC

91

CB1_NC

101

CB2_NC

105

CB3_NC

88

CB4_NC

87

CB5_NC

100

CB6_NC

104

CB7_NC

97

DQS8(T)

95

DQS8#(C)

12

DM0#/DBI0#

33

DM1#/DBI1#

54

DM2#/DBI2#

75

DM3#/DBI3#

178

DM4#/DBI4#

199

DM5#/DBI5#

220

DM6#/DBI6#

241

DM7#/DBI7# DQS6(T)

96

DM8#/DBI8# DQS6#(C)

FOX_AS0 A827-H2RB-7H

CONN@

DQ20

DQ21

DQ22

DQ23

DQS2(T)

DQS2#(C)

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS4(T)

DQS4#(C)

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQS5(T)

DQS5#(C)

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

219

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS7(T)

DQS7#(C)

46

45

58

59

55

53

173

187

186

170

169

183

182

179

177

195

194

207

208

191

190

203

204

200

198

215

228

229

211

212

224

225

221

237

236

249

250

232

233

245

246

242

240

174

216

DDR_M0_D16

DDR_M0_D20

DDR_M0_D19

DDR_M0_D22

DDR_M0_DQS2

DDR_M0_DQS#2

DDR_M0_D25

DDR_M0_D28

DDR_M0_D30

DDR_M0_D31

DDR_M0_D24

DDR_M0_D29

DDR_M0_D32

DDR_M0_D37

DDR_M0_D34

DDR_M0_D39

DDR_M0_D36

DDR_M0_D33

DDR_M0_D35

DDR_M0_D38

DDR_M0_DQS4

DDR_M0_DQS#4

DDR_M0_D44

DDR_M0_D45

DDR_M0_D42

DDR_M0_D43

DDR_M0_D41

DDR_M0_D40

DDR_M0_D46

DDR_M0_D47

DDR_M0_DQS5

DDR_M0_DQS#5

DDR_M0_D53

DDR_M0_D48

DDR_M0_D54

DDR_M0_D50

DDR_M0_D52

DDR_M0_D49

DDR_M0_D55

DDR_M0_D51

DDR_M0_DQS6

DDR_M0_DQS#6

DDR_M0_D60

DDR_M0_D57

DDR_M0_D59

DDR_M0_D62

DDR_M0_D56

DDR_M0_D61

DDR_M0_D58

DDR_M0_D63

DDR_M0_DQS7

DDR_M0_DQS#7

DDR_M0_DQS2 <6>

DDR_M0_DQS#2 <6>

DDR_M0_DQS4 <6>

DDR_M0_DQS#4 <6>

DDR_M0_DQS5 <6>

DDR_M0_DQS#5 <6>

DDR_M0_DQS6 <6>

DDR_M0_DQS#6 <6>

DDR_M0_DQS7 <6>

DDR_M0_DQS#7 <6>

DIMM Side

+0.6V_D DR_VREF CA

Layout Note:

Place n ear JDIMM1

10uF*6

1uF*8

330uF*1

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CD93

A A

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CD16

2

10U_0603_6.3V6M

1

1

CD18

CD17

2

2

5

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CD19

2

10U_0603_6.3V6M

1

1

1

CD21

CD20

CD22

2

2

2

@

+1.2V_VDDQ+1.2V_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CD95

CD23

2

2

1

1

CD96

CD24

2

2

1U_0402_6.3V6K

1

1

CD25

CD26

2

2

4

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CD27

CD28

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CD30

CD29

2

1U_0402_6.3V6K

1

1

CD31

2

CD94

2

330U_2.5V_M

1

+

C174

Part Number = SF00 0006S00

2

2

@

Security Classification

Issued Date

THI S S H E ET O F E N GI NE E RI N G DR AW I NG I S TH E P R OP R IE TA R Y P RO PE R TY O F C O MP A L E LE CTR ON IC S, I NC. AN D C ON TA INS CONFIDENTSIiAzeL

AN D T RA D E SE C R ET IN FO RM AT IO N. TH IS SH E ET M A Y N OT BE TR A NS F ER E D F R OM TH E C US TO D Y OF T H E C OM P ET EN T D IV ISI ON OF R &D

DE PA RTM E NT EX CE P T AS A UT HO R IZ ED BY C OM P AL E LE CTR ON IC S, IN C. N EI TH ER THI S S H E ET N OR T H E IN F OR M AT IO N IT C ON TA IN S

MA Y BE U S E D BY OR D IS CL OS ED TO A N Y T HI RD PA R TY W I TH OU T P RI O R W RI TT E N CO N SE N T OF C OM P A L E L EC TRO NI CS , INC .

3

RD8

1K_0402_1%

2017/04/10 2019/12/15

Compal Secret Data

DecipheredDate

2

CPU Side

+0.6V_VREFCA

RD11

24.9_0402_1%

Title

Compal Electronics, Inc.

P18-DDRIV_CHA: DIMM0

Document Number

LA-G07EP(KBL-U_UMA_6L)

1

Rev

Sheet 17 of 59Date: Friday, Janu ary 05, 2018

v0.3

5

4

3

2

1

STD

CHANNEL-B

Interleaved Memory

TOP: JDIMM2 CONN Non-ECC DIMM

+3VS+3VS+3VS

D D

12

@

12

RD19

0_0402_5%

RD22

0_0402_5%

12

@

2

RD20

0_0402_5%

1

RD23

0_0402_5%

PLACE ALL THE BELOW RESISTORS CLOSE TO SODIMM

SPD ADDRESS FOR CHANNEL B :

WRITE ADDRESS: 0XA4

READ ADDRESS: 0XA3

SA0 = 0; SA1 = 1; SA2 = 0.

DDR4 POR OPERATING SPEED: 1867 MT/S

STRETCH GOAL IS 2133 MT/S

C C

Layout Note:

Place n ear JDIMM2.257,259

10uF*2

1uF*2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

1U_0402_6.3V6K

1

CD62

2

1U_0402_6.3V6K

1

1

CD63

CD64

CD65

2

2

12

RD21

@

0_0402_5%

SA2_CHB_DIM2SA1_CHB_DIM2SA0_CHB_DIM2

12

RD24

0_0402_5%

Layout Note:

Place n ear JDIMM2.258

+0.6V_0.6VS+2.5V

1

2

10uF*2

1uF*1

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1

1

CD66

CD67

CD68

2

2

+3V_PRIM_DB

CD60

0.1U_0201_10V6K

<6> DDR_M1_D[0..15]

<6> DDR_M1_D[16..3 1]

<6> DDR_M1_D[32..4 7]

<6> DDR_M1_D[48..6 3]

+1.2V_VDDQ

2.2U_0402_6.3V6M

+0.6V_D DRB_VREFCA

1

2

CD61

1

2

PLACE NEAR TO PIN

JDIMM2B

STD

+1.2V_VDDQ

+0.6V_0.6VS

+2.5V

9/8 Modify

+1.2V_VDDQ

<6> DDR_M1_CLK0

<6> DDR_M1_CLK# 0

<6> DDR_M1_CLK1

<6> DDR_M1_CLK# 1

<6> DDR_M1_CKE0

<6> DDR_M1_CKE1

<6> DDR_M1_CS#0

<6> DDR_M1_CS#1

<6> DDR_M1_ODT0

<6> DDR_M1_ODT1

<6> DDR_M1_BG0

<6> DDR_M1_BG1

<6> DDR_M1_BA0

<6> DDR_M1_BA1

<6> DDR_M1_MA0

<6> DDR_M1_MA1

<6> DDR_M1_MA2

<6> DDR_M1_MA3

<6> DDR_M1_MA4

<6> DDR_M1_MA5

<6> DDR_M1_MA6

<6> DDR_M1_MA7

<6> DDR_M1_MA8

<6> DDR_M1_MA9

<6> DDR_M1_MA10

<6> DDR_M1_MA11

<6> DDR_M1_MA12

<6> DDR_M1_MA13

<6> DDR_M1_MA14_WE#

<6> DDR_M1_MA15 _CAS#

<6> DDR_M1_MA1 6_RAS#

<6> DDR_M1_ACT#

<6> DDR_M1_PAR

<6> DDR_M1_ALERT#

RD25 2 1

240<_064,1072>_1%

<7,17> PCH_SMBDATA

<7,17> PCH_SMBCLK

DDR_DRAMRST#_R

DIMM2_CHB_EVENT# 134

DDR_DRAMRST#_R

(5.2 mm)

DDR_M1_CLK0

DDR_M1_CLK#0

DDR_M1_CLK1

DDR_M1_CLK#1

DDR_M1_CKE0

DDR_M1_CKE1

DDR_M1_CS#0

DDR_M1_CS#1

DDR_M1_ODT0

DDR_M1_ODT1

DDR_M1_BG0

DDR_M1_BG1

DDR_M1_BA0

DDR_M1_BA1

DDR_M1_MA0

DDR_M1_MA1

DDR_M1_MA2

DDR_M1_MA3

DDR_M1_MA4

DDR_M1_MA5

DDR_M1_MA6

DDR_M1_MA7

DDR_M1_MA8

DDR_M1_MA9

DDR_M1_MA10

DDR_M1_MA11

DDR_M1_MA12

DDR_M1_MA13

DDR_M1_MA14_WE#

DDR_M1_MA15_CAS#

DDR_M1_MA16_RAS#

DDR_M1_ACT#

DDR_M1_PAR

DDR_M1_ALERT#

PCH_SMBDATA

PCH_SMBCLK

SA2_CHB_DIM2

SA1_CHB_DIM2

SA0_CHB_DIM2

JDIMM2A

137

CK0(T)

139

CK0#(C) DQ1

138

CK1(T) DQ2

140

CK1#(C) DQ3

109

CKE0 DQ5

110

CKE1 DQ6

149

S0#

157

S1#

162

S2#/C0

165

S3#/C1

155

ODT0

161

ODT1

115

BG0

113

BG1

150

BA0

145

BA1

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10_AP

120

A11

119

A12

158

A13

151

A14_W E#

156

A15_CAS#

152

A16_RAS#

114

ACT#

143

PARITY

116

ALERT#

EVENT#

108

RESET#

254

SDA

253

SCL

166

SA2

260

SA1

256

SA0

STD

DQ0

DQ4

DQ7

DQS0(T)

DQS0#(C)

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS1(T)

DQS1#(C)

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS2(T)

DQS2#(C)

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS3(T)

DQS3#(C)

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS4(T)

DQS4#(C)

DDR_M1_D15

8

DDR_M1_D10

7

DDR_M1_D11

20

DDR_M1_D12

21

DDR_M1_D14

4

DDR_M1_D9

3

DDR_M1_D8

16

DDR_M1_D13

17

DDR_M1_DQS1

13

DDR_M1_DQS#1

11

DDR_M1_D0

28

DDR_M1_D5

29

DDR_M1_D7

41

DDR_M1_D6

42

DDR_M1_D4

24

DDR_M1_D1

25

DDR_M1_D3

38

DDR_M1_D2

37

DDR_M1_DQS0

34

DDR_M1_DQS#0

32

DDR_M1_D20

50

49

DDR_M1_D17

62

DDR_M1_D19

63

DDR_M1_D22

46

DDR_M1_D21

45

DDR_M1_D16

58

DDR_M1_D18

59

DDR_M1_D23

55

DDR_M1_DQS2

53

DDR_M1_DQS#2

DDR_M1_D25

70

71

DDR_M1_D24

83

DDR_M1_D31

84

DDR_M1_D27

66

DDR_M1_D28

67

DDR_M1_D29

79

DDR_M1_D30

80

DDR_M1_D26

76

DDR_M1_DQS3

74

DDR_M1_DQS#3

DDR_M1_D37

174

DDR_M1_D33

173

DDR_M1_D35

187

DDR_M1_D38

186

DDR_M1_D32

170

DDR_M1_D36

169

DDR_M1_D34

183

DDR_M1_D39

182

DDR_M1_DQS4

179

DDR_M1_DQS#4

177

DDR_M1_D44

DDR_M1_DQS1 <6>

DDR_M1_DQS#1 <6>

DDR_M1_DQS0 <6>

DDR_M1_DQS#0 <6>

DDR_M1_DQS2 <6>

DDR_M1_DQS#2 <6>

DDR_M1_DQS3 <6>

DDR_M1_DQS#3 <6>

DDR_M1_DQS4 <6>

DDR_M1_DQS#4 <6>

Layout Note:

PLACE T HE CAP WITH IN 200 MILS

FROM TH E JDIMM2

+0.6V_D DRB_VREFCA

2 2

CD69 CD70

0.1U_0201_10V 6K 12.2U_0402_6.3V6M

1

Layout Note:

Place n ear JDIMM2

10U_0603_6.3V6M

1

CD73

A A

2

2.2uF*1

0.1uF*1

+3V_PRIM_DB+3V_PRIM

2

1

RD33

10uF*6

1uF*8

330uF*1

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

10U_0603_6.3V6M

1

CD74

2

10U_0603_6.3V6M

1

1

CD75

CD76

2

2

5

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CD77

2

10U_0603_6.3V6M

1

1

CD79

CD78

2

2

@

@

0_0402_5%

2

@

1

CD71

0.1U_0402_10V6K

2

1

RD26

1K_0402_1%

+1.2V_VDDQ+1.2V_VDDQ

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CD80

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

1

CD83

CD84

CD85

2

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CD87

CD86

2

2

4

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CD88

CD90

CD89

2

2

2

CD81

0.1U_0402_10V6K

1

Security Classification

Issued Date

THI S S H E ET O F E N GI NE E RI N G DR AW I NG I S TH E P R OP R IE TA R Y P RO PE R TY O F C O MP A L E LE CTR ON IC S, I NC. AN D C ON TA INS CONFIDENTSIiAzeL

AN D T RA D E SE C R ET IN FO RM AT IO N. TH IS SH E ET M A Y N OT BE TR A NS F ER E D F R OM TH E C US TO D Y OF T H E C OM P ET EN T D IV ISI ON OF R &D

DE PA RTM E NT EX CE P T AS A UT HO R IZ ED BY C OM P AL E LE CTR ON IC S, IN C. N EI TH ER THI S S H E ET N OR T H E IN F OR M AT IO N IT C ON TA IN S

MA Y BE U S E D BY OR D IS CL OS ED TO A N Y T HI RD PA R TY W I TH OU T P RI O R W RI TT E N CO N SE N T OF C OM P A L E L EC TRO NI CS , INC .

3

RD28

1K_0402_1%

1

2

2017/04/10 2019/12/15

DIMM Side

+0.6V_D DRB_VREFCA

1 RD27 2

2_0402_1%

2

CD72

0.1U_0402_10V6K

1

Compal Secret Data

DecipheredDate

1

CD82

0.022U_0402_25V7K

2

RD29

24.9_0402_1%

1 2

2

CONN@

CPU Side

+0.6V_B_VREFDQ

VREF traces should be at least 20 mils

wide with 20 mils spacing to other

signals

Title

Compal Electronics, Inc.

P19-DDRIV_CHB: DIMM0

Document Number

LA-G07EP(KBL-U_UMA_6L)

1

Rev

Sheet 18 of 59Date: Friday, Janu ary 05, 2018

v0.3

5

220P_0402_50V7K

220P_0402_50V7K

eDP Power

0.1U_0201_10V6K

4.7U_0402_6.3V6M

1

1

CG3

CG2

*UG1 +LCDVDD Current Limit : 0.8A

D D

Rshort @

<5> ENV DD_ CPU

+3V S

+3V S

+3V S

R6 1 2 EN VDD _CP U_ R 1

0_0402_5%

R5198 1 @ 2 UG2_ FLA G1 2

ENV DD_ CPU R520 0 1 @ 2 U G2_ EN2 3

100K_ 0402_5 %

0_0402_5%

2

R5201 1

100K_ 0402_5 %

R5199 1 @ 2 UG2_FLA G2

100K_ 0402_5 %

FLA G1

UG2

EN1

EN2

4

FLA G2 OUT2

G51 0F51 U_M SOP8

SA0 000B EY0 0

@

2

2

GND

8

IN1

7

OUT1

6

IN2

5

Camera

R170 E MI@ 1

<11 > U SB20_ N5

<11 > U SB20_ P5

C C

<32 > D _MIC_CL K

<32 > D_MIC _DATA

SM0 700 05U00 MURA TA DL M0N SN900 HY2D

L12

D_MIC_C LK

D_MIC_D ATA 1 Rshort@2 D_MIC _L_DATA

2

4

0_0201_5%

4

3

1 2

R171 0_0201_5%

@EM I@

1 2

EMI@

1 2

R175 0_0402_5%

3 US B20_N 5_R

USB20 _P5_R

4

SM010014520 3000ma

220ohm@100mhz

DCR 0.04

@EM I@ C117

680P_ 0402_5 0V7K

+3V S_C AME RA

0.1U_0402_16V7K

C52 32

1st:SA000080300, S IC G5250Q1T73U SOT-23 3P POWER SWITCH_0.4A

2nd:SA00004ZA00, S IC AP2330W-7 SC59 3P PWR SW_0.4A

+3V S

1U_0402_6.3V4Z

1

CG76

2

@ES D@

SCA 000 00U10

D7

1

PES D5V 0U2B T_SO T23 -3

1 @ 2

R5196 0_0603_5%

SD0 1300 0080

*FG3 Camera Current Limit : 0.4A

9

USB20 _P5_R 2

USB20 _N5_R 3

+LC DVD D

1

2

+3V S

W=60mils

+LC DVD D

0.1U_0402_16V7K

1

C52 31

2

INVP W R_B+

1

2

1

@

2

1

C118

68P_0 402_50 V8J

2

0.1U_0201_10V6K

1U_0402_6.3V4Z

1

1

CG75

CG1

2

2

+3V S_C AME RA

1 1

@

C5221 C5222

.1U _040 2_16 V7K 24.7U_0 402_6 .3V6M

2

3

W=60mils

L1 1 @ 2 0_0805_5%

SD0 0200 0080

L2 1 @ 2 0_0805_5%

SD0 0200 0080

1 2

FU1 0 .75A_ 24V_M F-MSMF 075/24

SP0 4000 9I00

+3V S

1U_0402_6.3V4Z

CG4

SE0 0000 SO0 0

+19 VB

C593 2

C594 2

<EC>

<CPU>

<CPU>

<CPU>

<6,7, 9,10,1 1,13,1 7,18,2 8,29, 30,31, 32,33 ,36,39 ,40,52 > +3 VS

<7,13 ,29,30 ,33,34 ,35,4 0,48,4 9,50,5 1> + 3V ALW

<33 > EC _BK OFF#

<5> BKL _PW M _CPU

<5> EDP _HP D

1

1

<5> ED P_A UXP

<5> ED P_A UXN

<5> EDP _TX P0

<5> EDP _TX N0

<5> EDP _TX P1

<5> EDP _TX N1

INVT PW M

DISPOFF#

R259

2

<46,4 7,48,4 9,50,5 3> +1 9VB

R5176

10K_0 402_5%

2

1

1 Rshort@2

0_0402_5%

RT34 1 Rshort@2 0_0201_5% EDP _HP D_R

RT11

100K_ 0402_5 %

2

1

1

R166233_0402_5%

@ R163

2

1

2 .1U _04 02_16 V7K EDP _AU XP_ C

CT102 1

2

.1U _040 2_16 V7K

CT101 1

2 .1U _04 02_16 V7K EDP _TXP 0_C

CT98 1

2

.1U _040 2_16 V7K

CT97 1

2 .1U _04 02_16 V7K EDP _TXP 1_C

CT103 1

2

.1U _040 2_16 V7K

CT100 1

100K_ 0402_5 %

DISPOFF#

INVT PW M

EDP _AU XN_ C

EDP _TX N0_C

EDP _TX N1_C

+3V S

+19 VB

+3V ALW

1

R5175

EDP _TX P1_C

+LC DVD D

Camera

Compal Secret Data

EDP _TX N1_C

EDP _TX P0_C

EDP _TX N0_C

EDP _AU XP_C

EDP _AU XN_C

EDP _HP D_R

USB20 _N5_R

USB20 _P5_R

D_MIC_C LK

D_MIC_L _DATA

Deciphered Date

2

TS_G PIO

USB20 _P7_R 2

USB20 _N7_R 3

INVP W R_B+

+5V S_T OUCH

+3V S_T OUCH

+3V S_C AME RA

CTS3

4.7U_0 402_6 .3V6M

+5V S_T OUCH

A A

CTS6

4.7U_0 402_6 .3V6M

TS@

RTS8 1 @ 2 0_0402_5%

TS@

1

2

3

2

5

FG2

OUT

GND

SA0 0004 ZA0 0

G5250Q1T73U SOT-23 3P POWERSWITCH

1

IN

+5VS_TOUCH only for HD with TS

+5V S

20mil

TS@

1

CTS1

0.1U_0 402_1 6V4Z

2

4

Security Classification

Issued Date

THIS SH EE T OF E NGI NEE RING DRA WIN G IS THE P ROP RIET ARY P ROP ER TY OF COM PA L EL ECTR ONI CS, INC. A ND CON TAIN S CONFIDENTSIiiA

AND TRA DE SE CR ET INFO RMA TION . THIS S HEE T M AY NO T BE TRA NSF ERE D F ROM TH E CUS TOD Y OF THE C OMP ETE NT D IVISION OF R &D

DEP ARTM ENT EXC EPT AS A UTHO RIZE D BY C OMP AL E LEC TRON ICS, INC. NEITHE R THIS SH EET N OR T HE INF ORM ATIO N IT CO NTAINS

3

MAY BE U SE D BY OR DIS CLOS ED TO A NY THI RD PA RTY W ITHO UT PR IOR W RITTE N CON SE NT OF CO MPA L EL ECTR ONIC S, INC.

2017/08/24 2018/08/24

eDP

CONN@

JED P

36

GND

35

GND

34

GND

33

GND

32

GND

ACE S_5 0203- 03001-00 2

SP0 1002 3710

Title