A

1 1

B

C

D

E

Compal Confidential

2 2

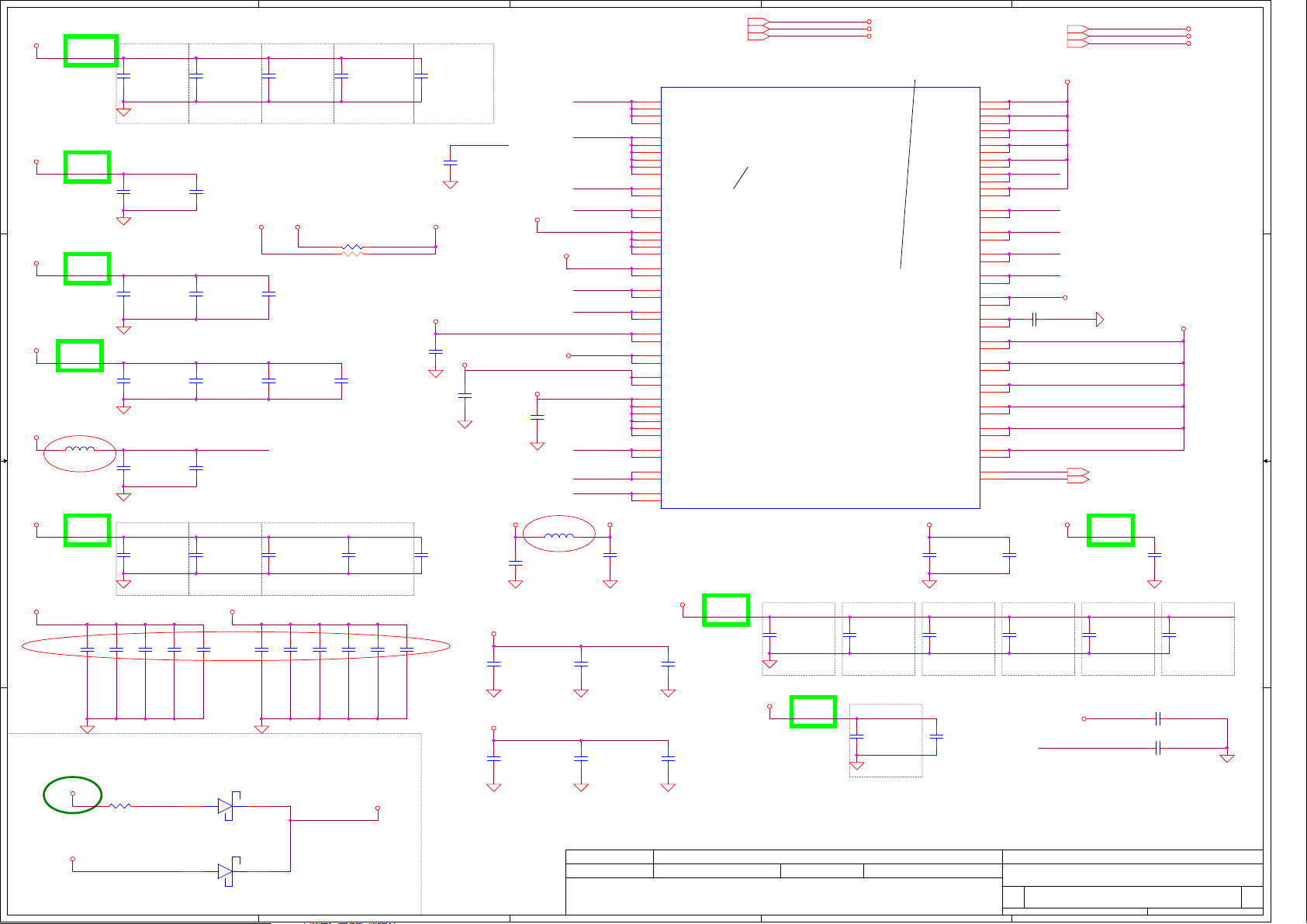

KBL-Y MB Schematic Document

EPS30 LA-F803P

3 3

4 4

Security Class ification

Security Class ification

Security Class ification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev: 0.3

2018.06.08

2017/03/ 20 2020/03/ 20

2017/03/ 20 2020/03/ 20

Issued Date

Issued Date

Issued Date

2017/03/ 20 2020/03/ 20

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

LA-F803P

LA-F803P

LA-F803P

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

1 55Friday, June 08, 201 8

1 55Friday, June 08, 201 8

1 55Friday, June 08, 201 8

E

0.1

0.1

0.1

A

Compal Confidential

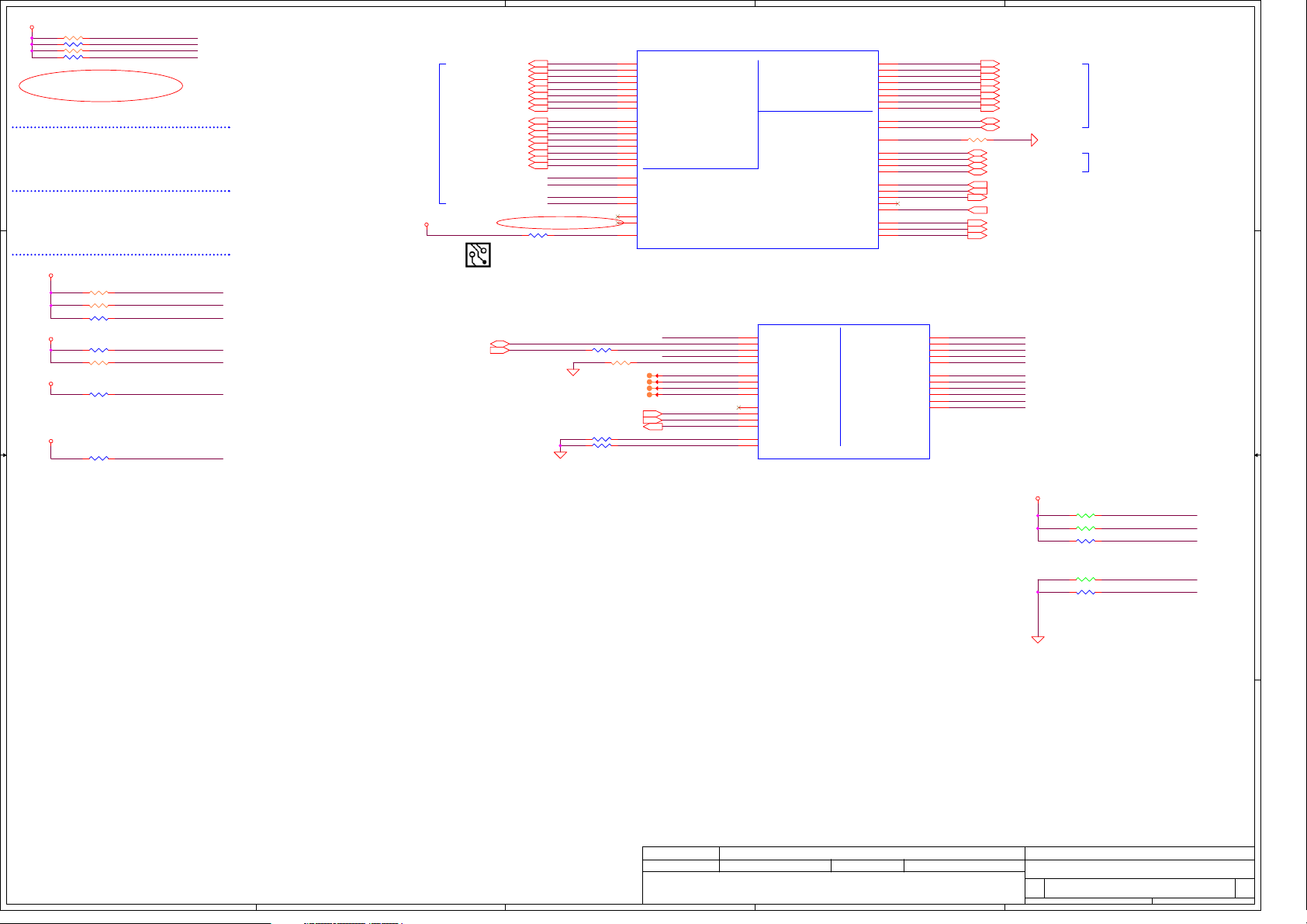

Model Name: KBL-Y

Project Name: LA-F803P

B

C

D

E

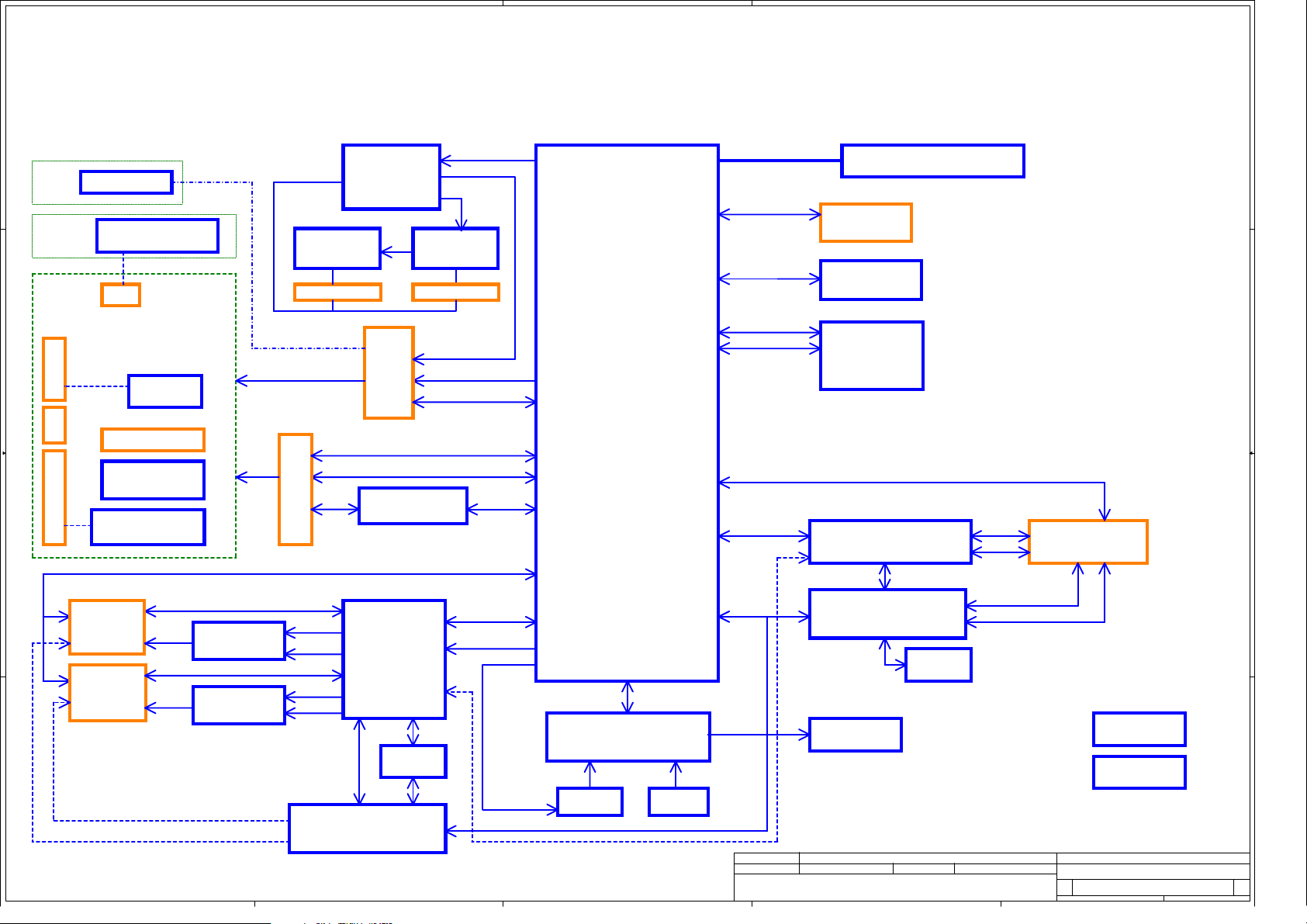

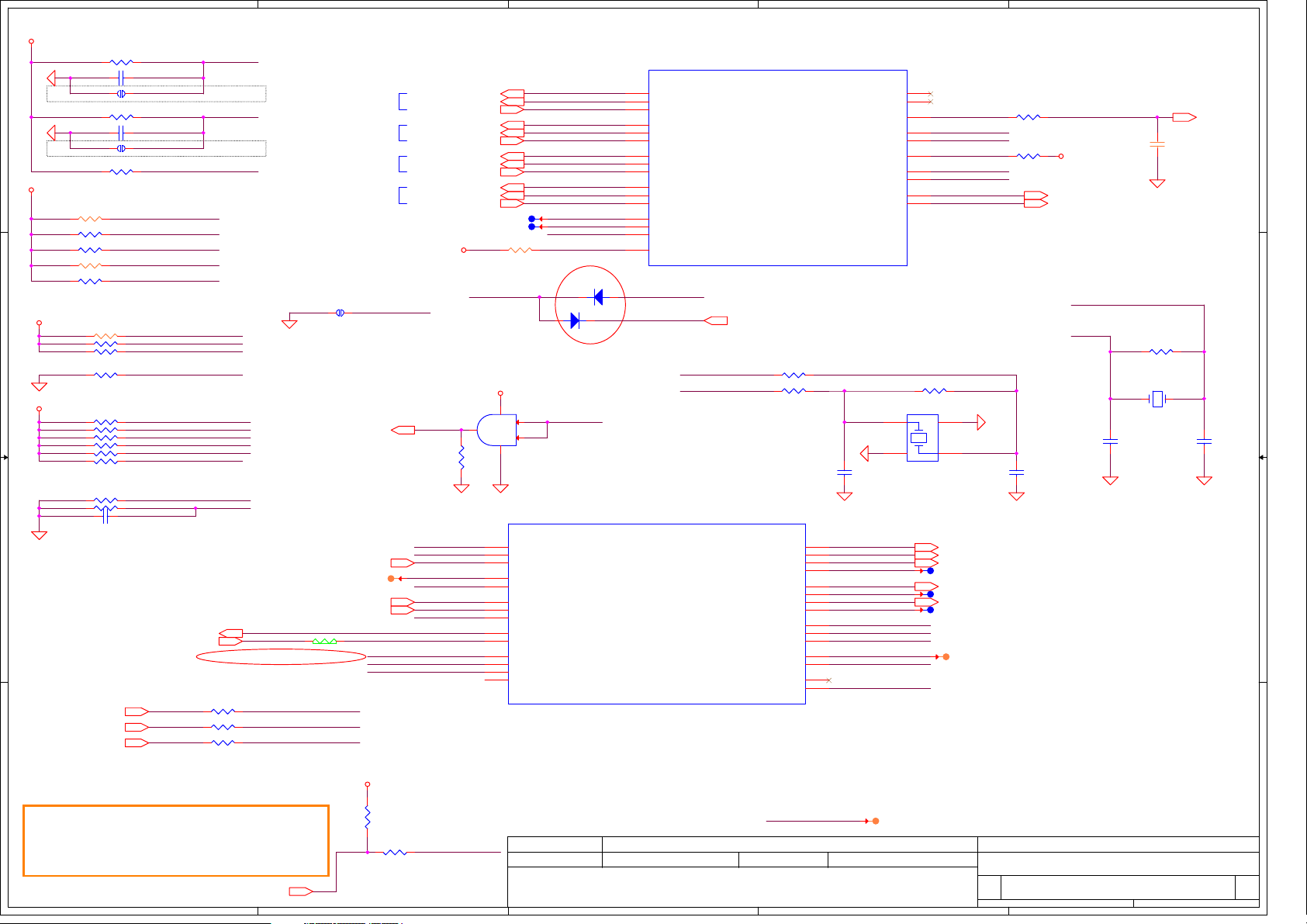

Kaby Lake Y Block Diagram

(KBL-Y 2+2 w/ LPDDR3L x64, Modern Standby )

1 1

A

FPC

Combo Jack

Sub-Board

LS-F803P

Sub-Board

LS-F801P

2 2

eDP conn

JSIM

WWAN M.2 Conn.

TouchScreen Controller

eKTH6315

JTS2

eDP Redriver

SN75DP130

HD + IR Camera

G-Sensor

Speaker AMP

TAS2557 T

Speaker_L

40 pin

40pin Conn.

40 pin

HP9DS1TR

PCIe Redriver

P. 26

udio Codec

Realtek ALC3292

P. 28

P. 28

JLCD1

P

PCIe Redriver

SN75LVPE801DRFR

SN75LVPE801DRFR

3 3

Follow Premiun Power Segment, S0ix & C10 optimized

HDA

I2S

P. 27

Speaker AMP

AS2557

P. 28

Speaker_R

. 22

P. 28

Headphone

eDP 1.3 x4

Intel Kaby Lake Y

2 + 2

I2C

Dual Core

USB2.0

ISH I2C

P. 25

USB2.0

Port 9

PCIe

Port 9

Port 1,5

TPD 4.5W

Memory Bus

Dual Channel

1866HMz

PCIe x4

Port 5 ~ 8

SPI0_CS0#

PCIe

U

SB2.0

USB2.0

USB3.1

Port 3

LPDDR3L Memory Down 64bit x 2

SSD (PCIe)

NGFF Key M

System BIOS ROM

8MB (TBD)

Port 10

Port 3

Port 7

W

LAN + BT

Windstorm Peak

SD1216

USB3.1 / DP Mux & Redriver

TI TUSB546A-DCIRNQR

DP

P. 24

I2C

P. 7

P. 23

P. 37

P. 19 ~ 21

TX/RX

SUB1/2

USB3.1 Type-C Conn.

P. 36

P. 36

t

CC1 / CC2

Power Path

DC/DC Circuit

Power Circuit

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CNL-Y_2+2 Block Diagrams

CNL-Y_2+2 Block Diagrams

CNL-Y_2+2 Block Diagrams

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F803P

LA-F803P

LA-F803P

Date: Sheet of

Date: Sheet of

Date: Sheet of

P. 39

P. 40 ~ 53

2 55Friday, June 08, 2018

2 55Friday, June 08, 2018

E

2 55Friday, June 08, 2018

0.1

0.1

0.1

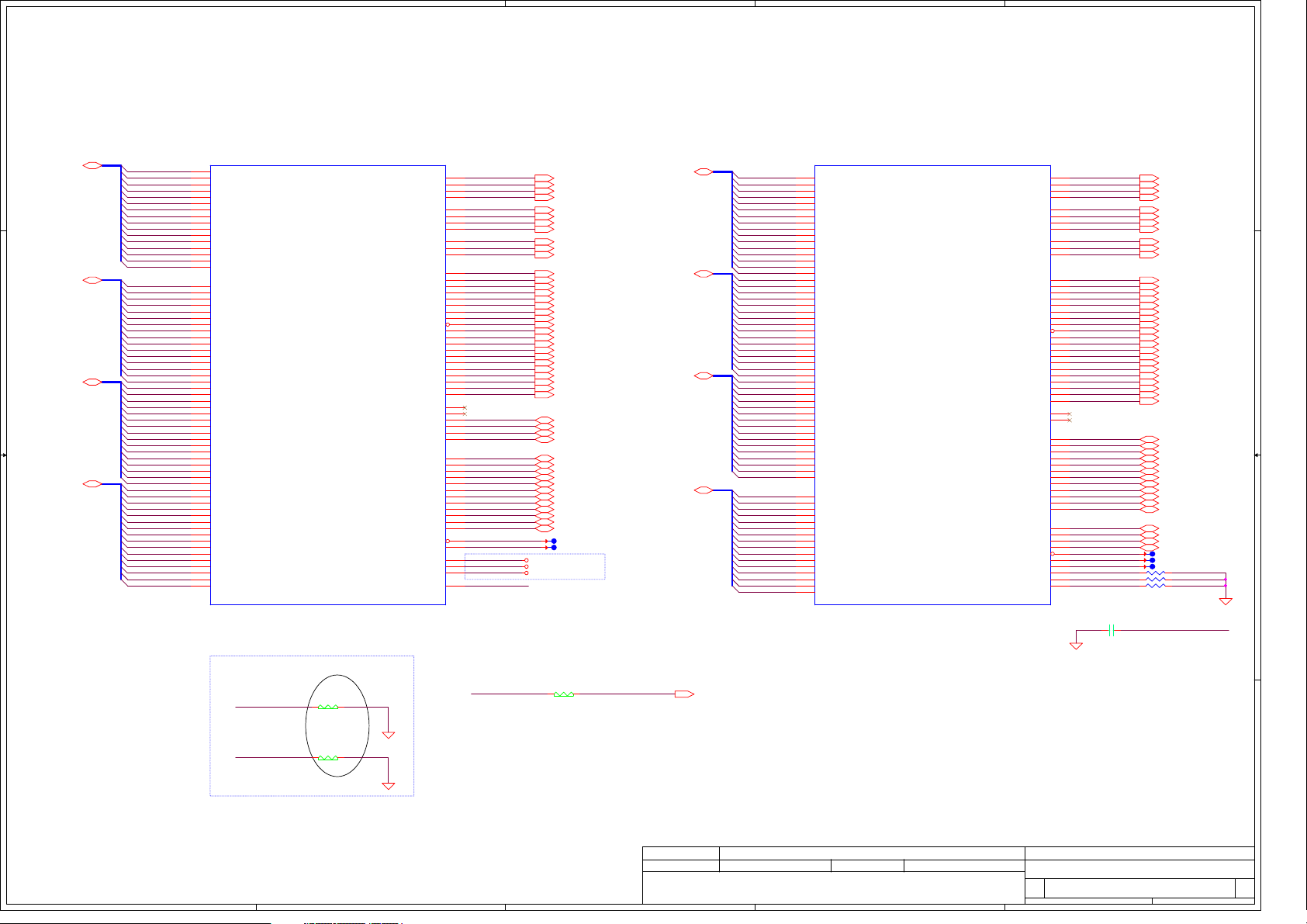

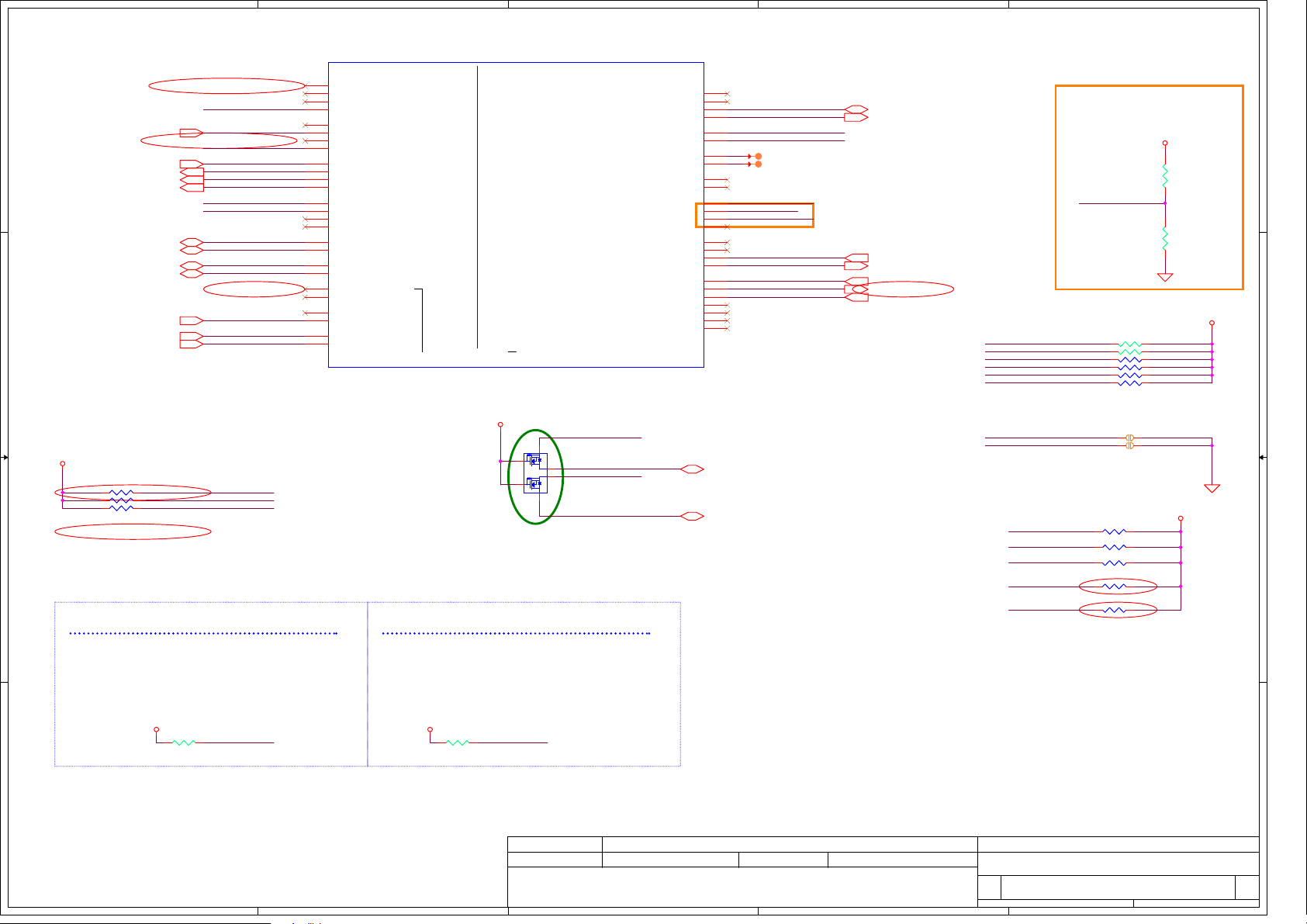

Port 1

Port 5

4 4

USB3.1

Type-C Conn.

P. 38

USB3.1

Type-C Conn.

P. 38

A

SBU1/2

SBU1/2

TX/RX

MUX/DEMUX

TS3DS10224RUKR

P. 38

TX/RX

MUX/DEMUX

TS3DS10224RUKR

P. 38

CC1/2

C1/2

C

AUX

LSTX/RX

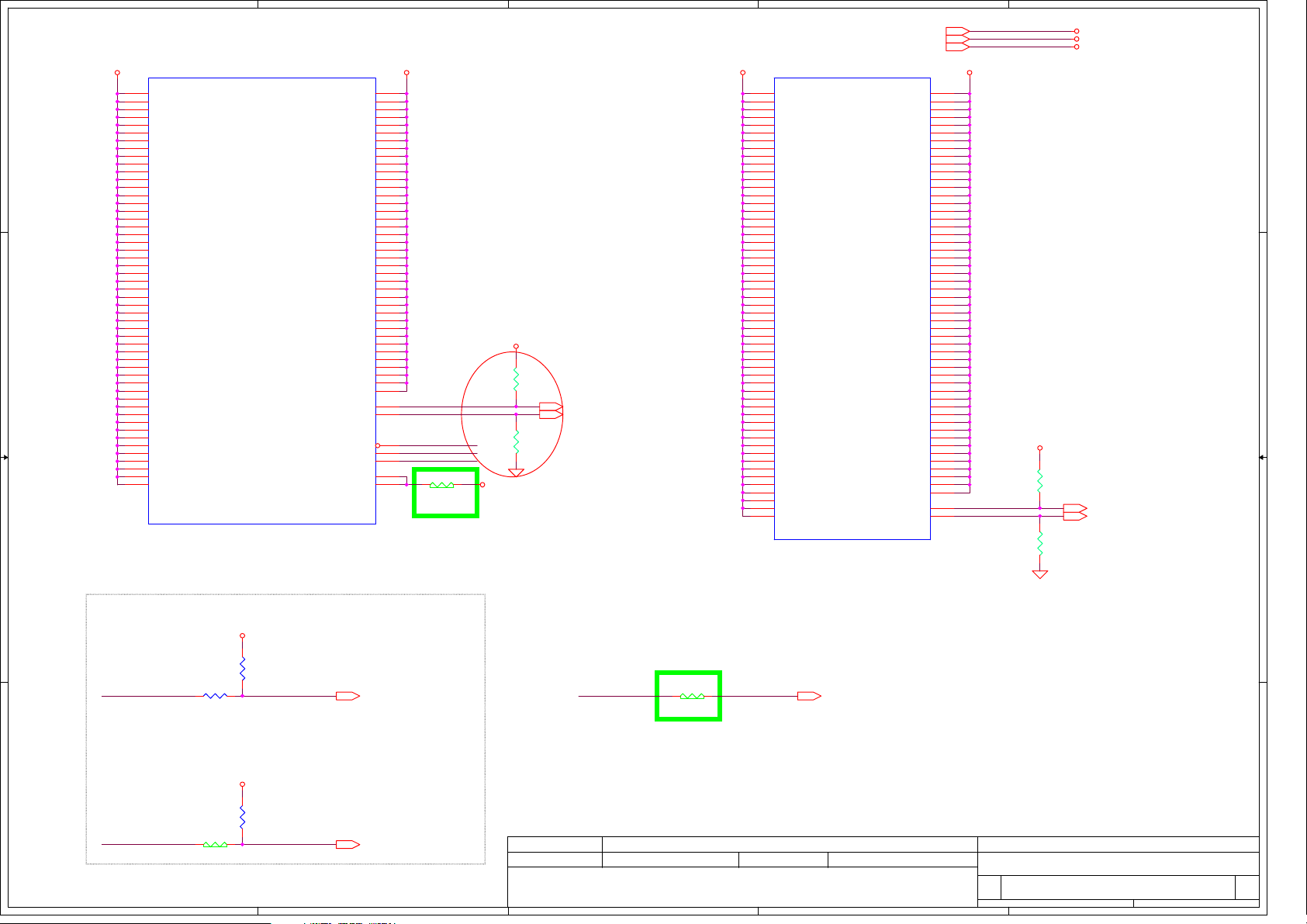

Thunderbolt 3

lpine Ridge DP

A

AUX

LSTX/RX

I2C

SB3.1 Type-C PD Controller

U

SPI ROM

8M-bi

TI TPS65988

B

P. 33~34

t

P. 35

PCIe x4

Port 1~4

DDI_1

DP

DI_2

D

I2C/SMBus

LPC

KBC

ENE KB9022

PS/2

P. 30 P

Int. KBDClickPad

C

P. 5 ~ 18

P. 29

SMBus

. 30

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

USB3.1 Type-C PD Controller

TI TPS65987D

SPI ROM

2M-bi

Thermal Sensor

F75303M

2017/03/20 2020/03/20

2017/03/20 2020/03/20

2017/03/20 2020/03/20

P. 31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

A

+3VS

(TBC)

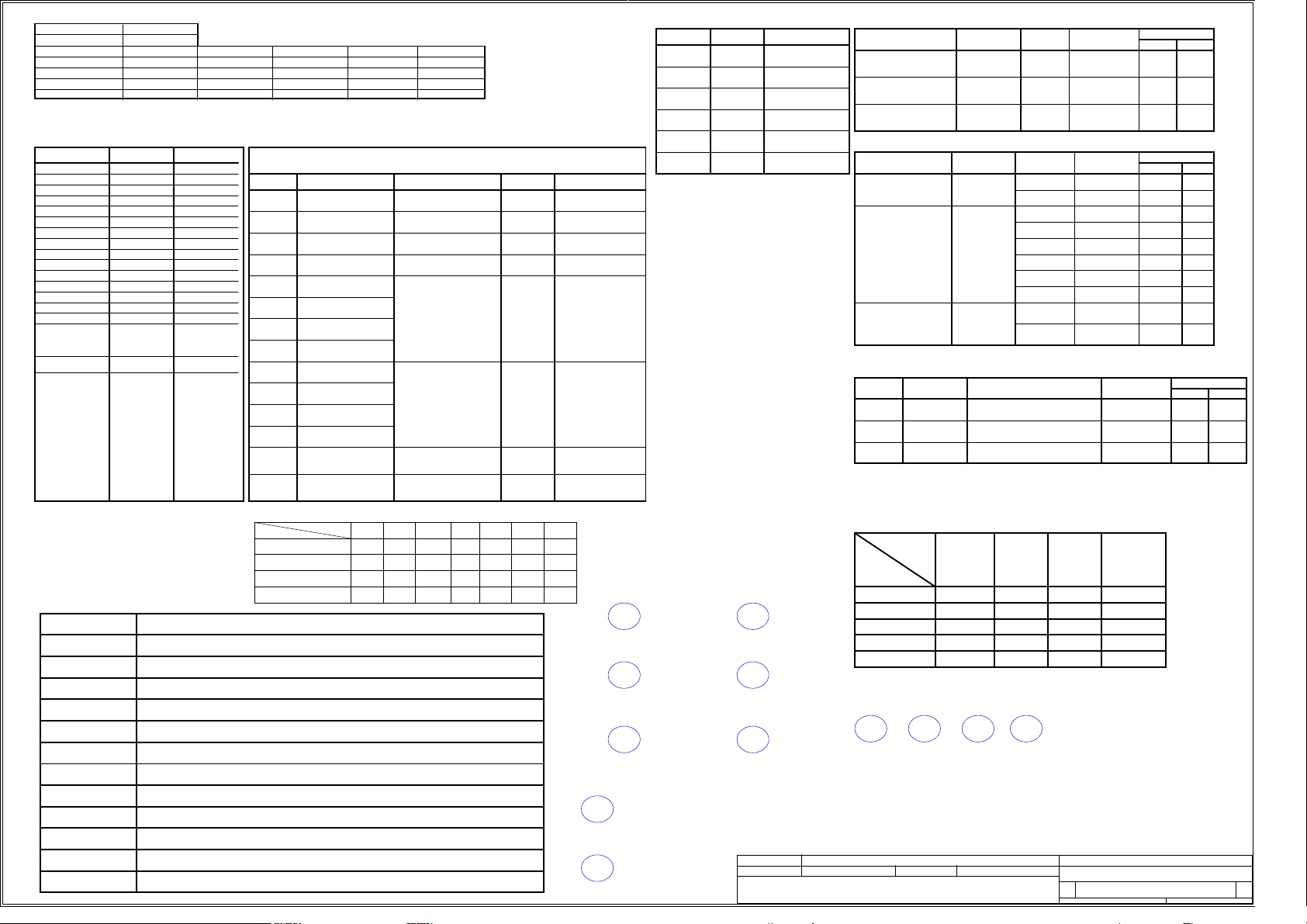

Device Address (7 bit)

Track PAD

TBC

N/A N/A N/A N/A

EC TBC TBC

TBC

(TBC)

BATT

Charger 0x09 0x12

TPS65988(1)

TPS65988(2)

TPS65987D

F75303M

Power CHIP

SN75DP130

Codec

SPK AMP

0x0B 0x16

0x25 TBC TBC

0x21

1001_101xb

TBC TBC TBC

TBC TBC TBC

(TBC)

+3V_PCH

+1.8V_PRIM+5VALW

+1.0V_PRIM

+1.0VA_GATE

+VCC_PRIM

X7676632L24

+1.2V_DDR

+3.3V_CV2

+1.8V_MEM

+

ON ON

OFF

R1Sam@

ZZZ

1.0V_VCCST

ON

ONOFF

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F803P

LA-F803P

LA-F803P

Date: Sheet of

Date: Sheet of

Date: Sheet of

0x2C

0x10b TBC

1101011xb

0011110xb

+5VS

+3VS

+1.8VS

+1.0V_VCCSTG

+0.85VS_VCCIO

+0.6VS_VTT

+VCC_SA

+VCC_GT

+VCC_CORE

ON

OFF

OFF

OFF

OFF

Address (8bit)

Read

Write

TBC TBC

Address (8bit)

Write

Read

0x17

0x13

TBC TBC

TBC0x23

TBC

TBCTBC TBC

Address (8bit)

Write Read

TBC TBC

TBC

TBC

TBC

3 55Friday, June 08, 2018

3 55Friday, June 08, 2018

3 55Friday, June 08, 2018

Board ID Table for AD channel

Vcc 3.3V

Ra

Board ID /

PCB Revision

0 / 0.2 0

1 / 0.3

2 / 0.4

4 / 1.0

100K +/- 1%

Rb

15K +/- 1%

27K +/- 1%

43K +/- 1%

BOM Structure Table

Function

S0IX Mode S0IX@ NDSX@

Non-S0IX Mode

LPC 1.8V

LPC 3.3V

RF Componets RF@ @RF@

EMI Components

ESD Components ESD@ @ESD@

ME Cnnector CONN@

Stuff

NDSX@

LPC@

@CPUPWM@Panel PWM control

EMI@ @EMI@

Un-Stuff

S0IX@

LPC@

@ECPWM@

V min

BID

0.423 V

0.978 V

V TYP

BID

0 V 0.300 V

0.430 V 0.438 V

0.702 V

0.992 V 1.006 V

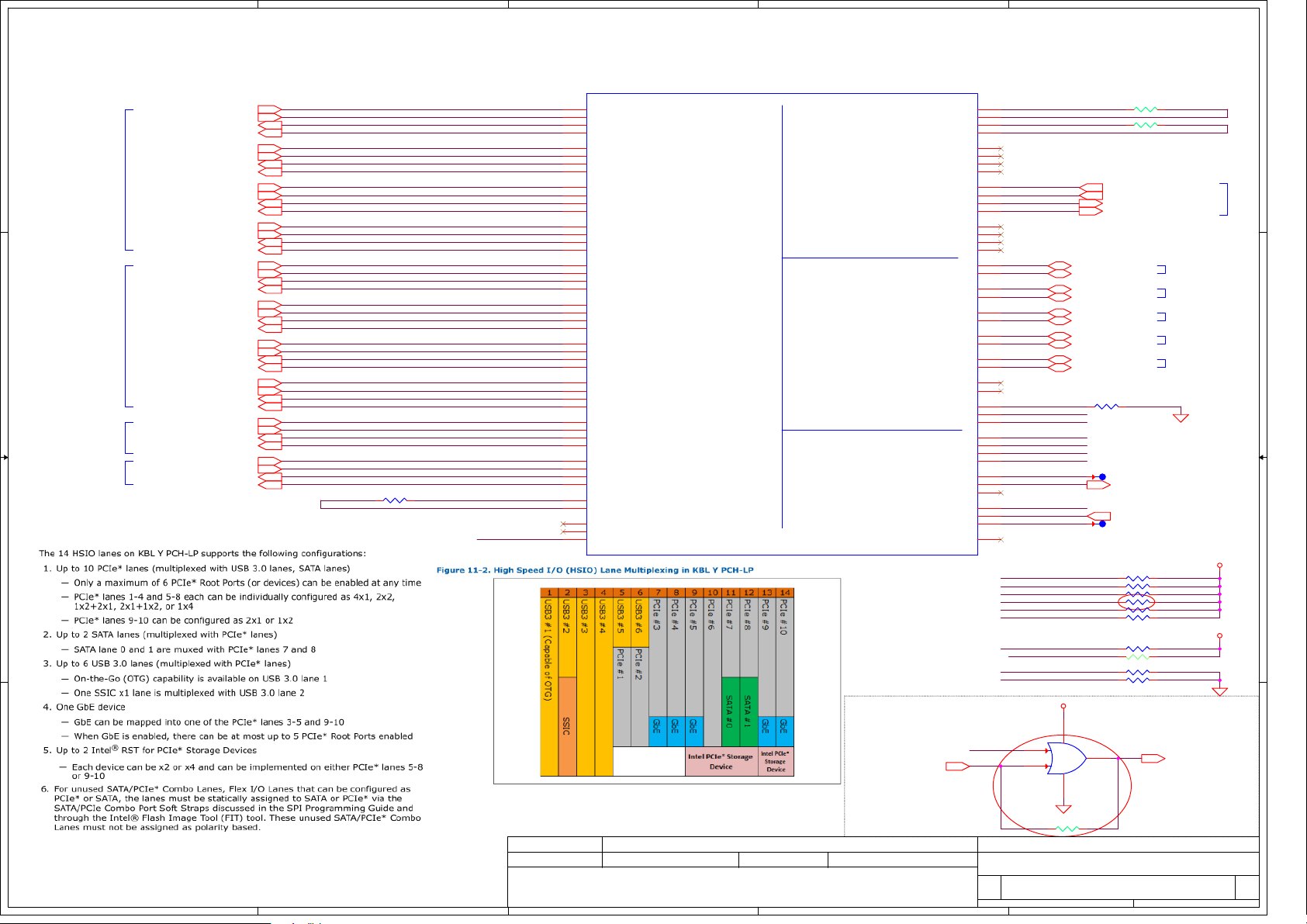

HSIO Port Table

HSIO Port Capable

0

USB3.1 #1

1

USB3.1 #2

2 USB3.1 #3

3 USB3.1 #4

V

BID

0.713 V

Max

EC AD3

0x00 - 0x0B

0x1D - 0x26

0x31 - 0x3B0.691 V

0x47 - 0x54

Device PCIe CLK

USB3.1 Type-C

NOTE

USB3.1 Type-C DP

with Mux + PD

USB2.0 Port Table

USB2.0 Port Device

USB2.0 (MB)1

5

USB2.0 (MB)

7

USB2.0 (MB)

3

Blue Tooth

9

IR Camera

2

X

NOTE

USB3.1 Type-C + PD

USB3.1 Type-C + PD

USB3.1 Type-C + PD

WLAN 8265

SOC SMBUS Address Table

SOC_SMBUS Net Name

SOC_SMBCLK

SOC_SMBDATA

SOC_SML0CLK

SOC_SML0DATA

SML1_SMBCLK

SML1_SMBDAT

Power Rail

+3V_PRIM

+3VS

EC SMBUS Address Table

EC_SMBUS Port

SMBUS Port 1

SMBUS Port 2

Power Rail Device Address (7 bit)

+3V_SMBUS

+3VL_EC

4 USB3.1 #5 / PCIE #1

5 USB3.1 #6 / PCIE #2

Un-stuff

Components

@

TP@

Rshort@

Remove in MP MP@

6 PCIE #3

7 PCIE #4

8 PCIE #5

/ GbE

/ GbE

/ GbE

9 PCIE #6

10 PCIE #7

11 PCIE #8

1 1

12 PCIE #9

13 PCIE #10 WLAN CLK3 &

Power State

STATE

/ SATA #0

/ SATA #1

/ GbE

/ GbE

SIGNAL

S0 (Full ON)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

Load BOM Option Table

S5 (Soft OFF)

BOM Number Load BOM Option

431ACZ32L01

431ACZ32L02

431ACZ32L03

431ACZ32L04

431ACZ32L05

431ACZ32L06

431ACZ32L07

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi@/R1I7@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Hy@/R1I5@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi16@/R1I7@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Sam@/R1I5@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi16@/R1I7R@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi16@/R1I5R@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Hy@/R1I7R@

431ACZ32L08 @CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi@/R1I5R@

431ACZ32L09

431ACZ32L10

431ACZ32L11

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Sam@/R1I7R@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Hy@/R1I5R@

@CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Mi@/R1I7R@

431ACZ32L12 @CPUPWM@/LPC@/MP@/S0IX@/X4E@/RF@/R1Sam@/R1I5R@

Thunderbolt, Alpine Rodge

SSD (NGFF_Key M)

WWAN CLK1 &

SLP_S4#

SLP_S3#

LOW HIGH

SLP_S5#

HIGH

LOWLOW

HIGH

+VALW

ON ON ON ONHIGH HIGH HIGH

ONONON

ON

+V

OFF

OFFLOW LOW LOW

CLK4 &

CLKREQ#4

CLK2 &

CLKREQ#2

CLKREQ#1

CLKREQ#3

+VS Clock

OFF

OFF

OFF

PCIe/SATA interface

OFF

OFF

OFF

SA0000ADW00

S IC HE8067702739826 SR345 H0 1.2G BGA

SA0000ADW10

S IC HE8067702739826 SR345 H0 1.2G A32 !

SA0000C4Q00

S IC A32 HE8067702739846 QLKW H0 1.3G BGA 1515

DAX

PCB

Part Number = DAA000H5000

PCB 2DC LA-F803P REV0 M/B

X4E@

ZZZ

X4EACZ32L01

R1I5@

UC1

R3I5@

UC1

R1I5R@

UC1

SMBUS Port 3

+3VALW

I2C/ISH Address Table

I2C Port

I2C 0

I2C 1

ISH_I2C 0

State

R1I7@

UC1

SA0000ADS30

S IC HE8067702739526 SR33X H0 1.3G BGA

R3I7@

UC1

SA0000ADS40

S IC HE8067702739526 SR33X H0 1.3G A32 !

R1I7R@

UC1

SA0000C4P00

S IC A32 HE8067702739858 QQF4 H0 1.5G BGA 1515

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

S0

S3 /AC

DS3

S5 S4/AC doesn't exist OFFO

R1Mi@

ZZZ

X7676632L21

2017/03/20 2020/03/20

2017/03/20 2020/03/20

2017/03/20 2020/03/20

Power Rail Device Address (7 bit)

+3VS

+3V_PRIM

+3VALW

Power

plane

R1Hy@

ZZZ

X7676632L22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Track PAD(Reserved)

Touch Screen

HP9DS1TR

+3VALW_D SW

+3VALW

+1.8VALW

+3VLP

ON

ON ON

ON

ONS5 S4/AC OFF

FF OFF

R1Mi16@

ZZZ

X7676632L23

0.1

0.1

0.1

5

4

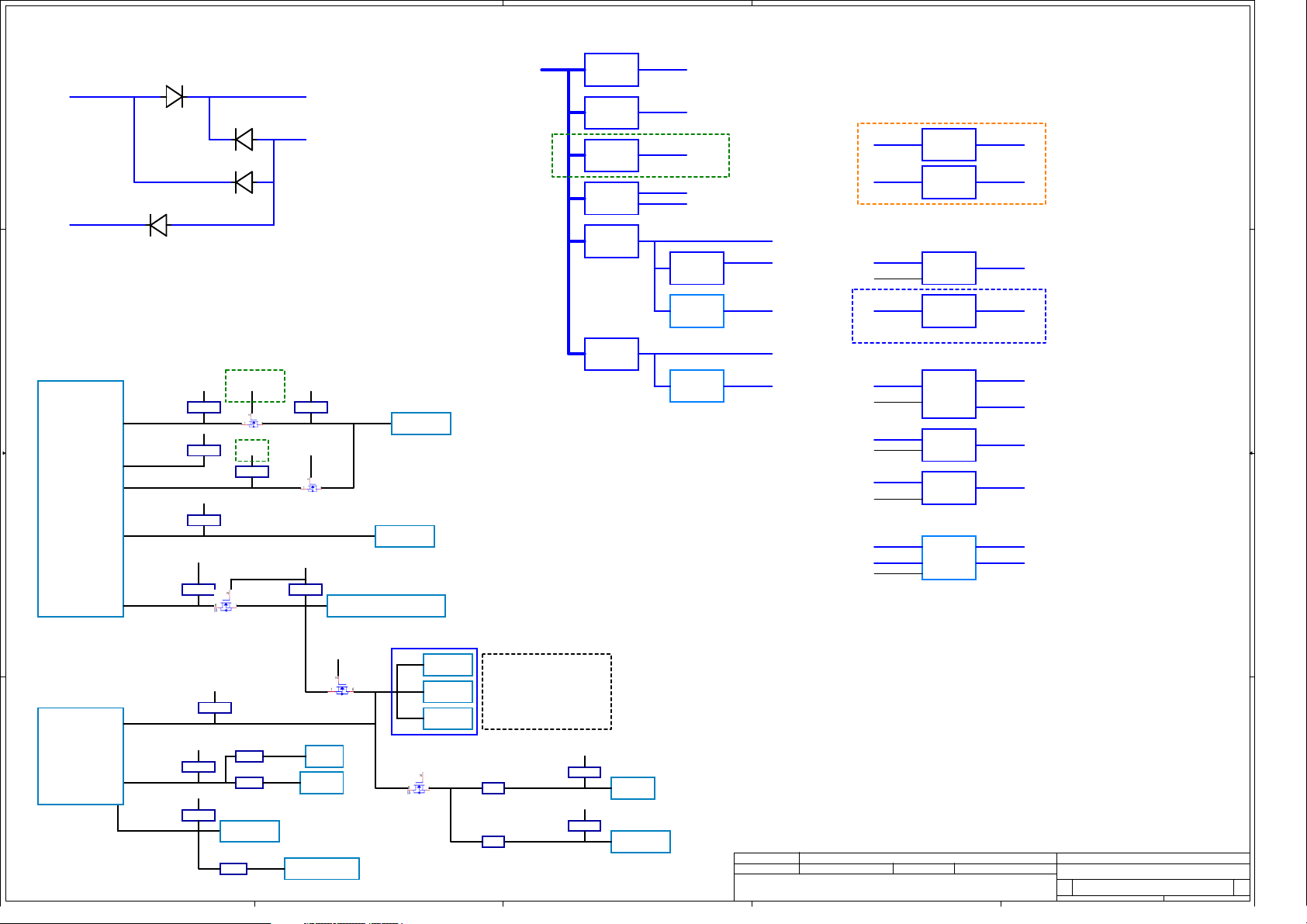

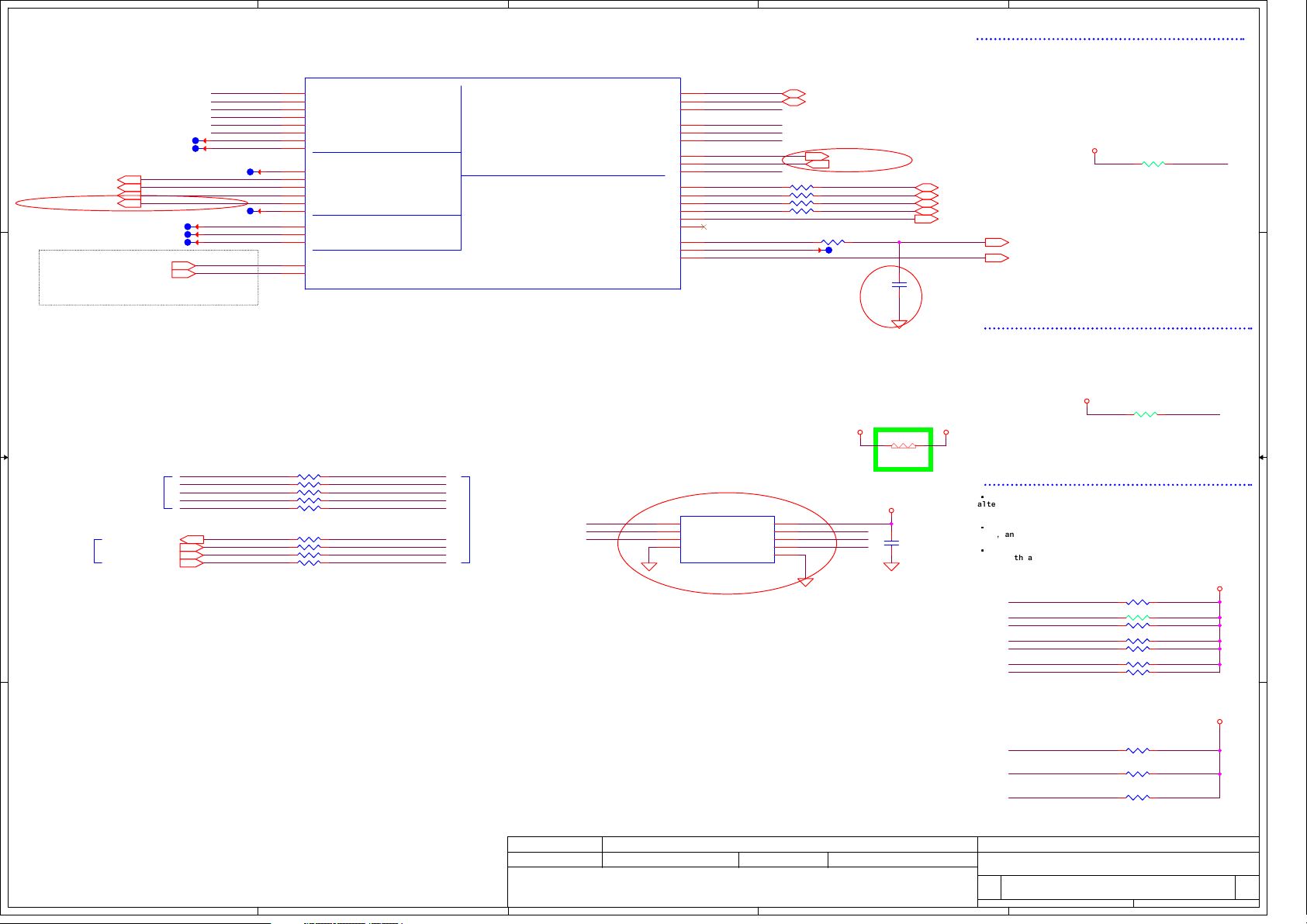

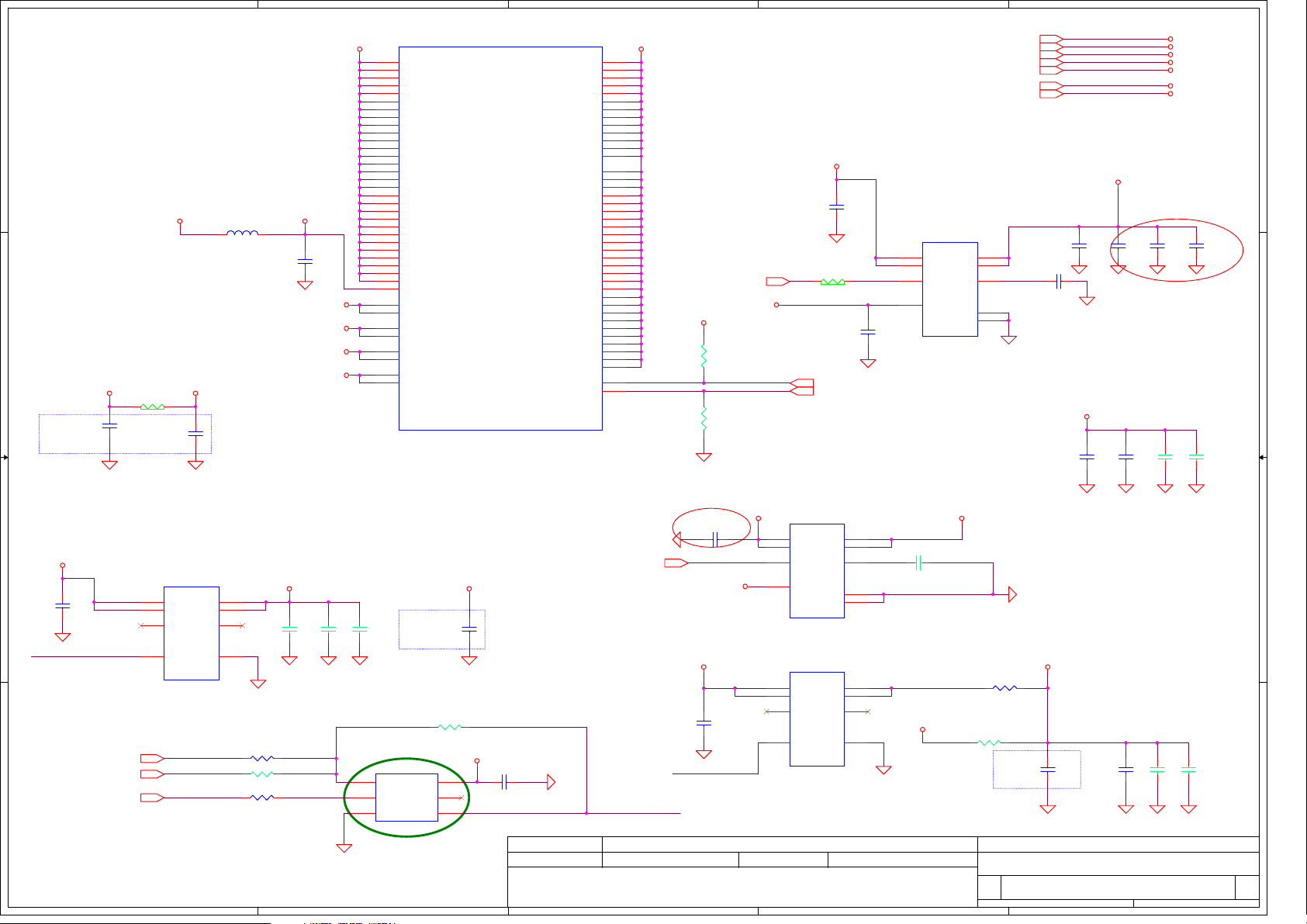

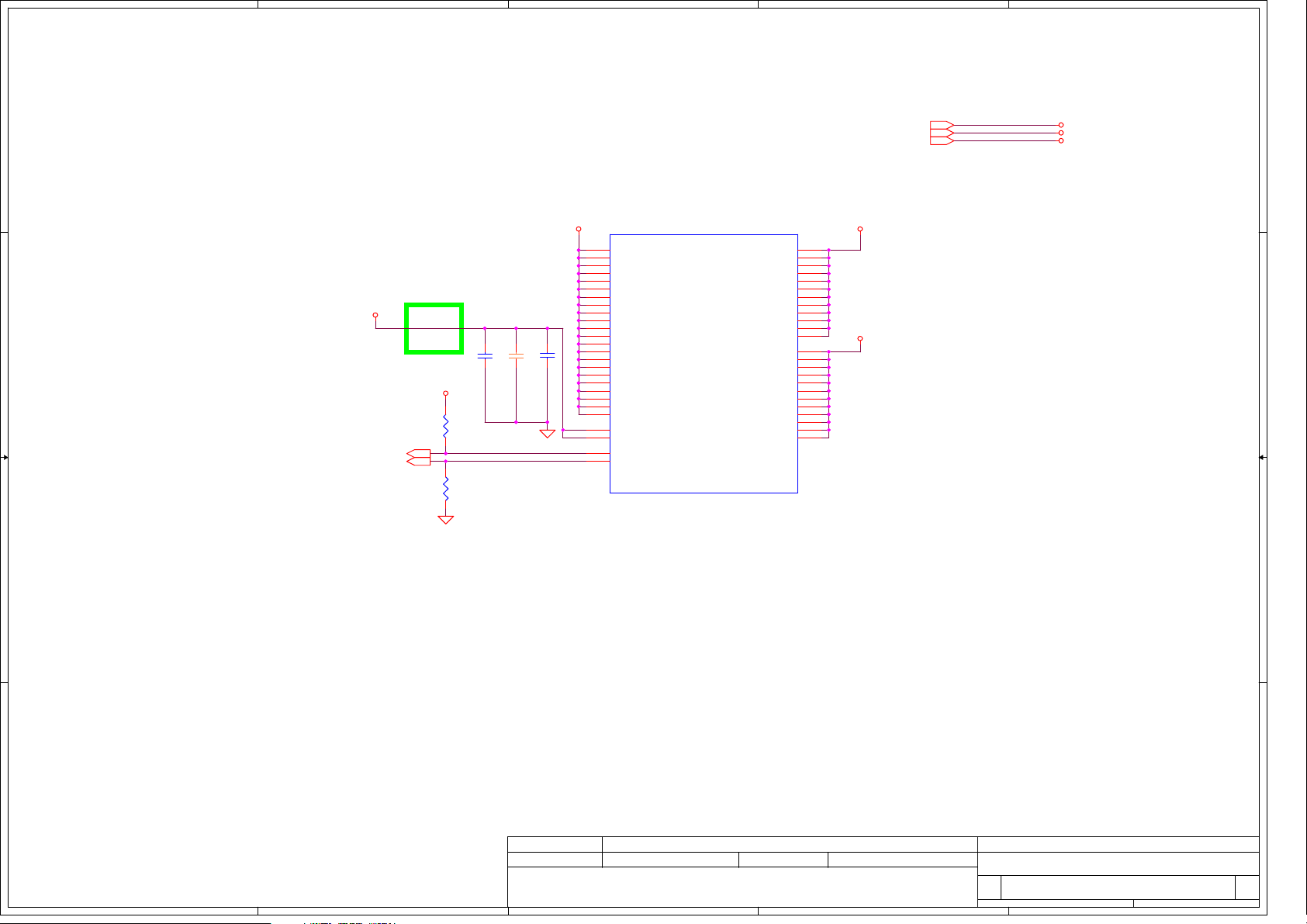

[EPDS30-Power Map_KBL-Y2+2_LPDDR3L_Premium_S0ix]

3

2

1

+8.4V PUZ1

PWM

+3V_LID(Battery Cell)

D D

DC1

DC2

+3VL_RTC

+3VL

D2

D4

+3V_SMBUS

C C

[EPS30-SMBus Map]

UC1

SOC_SMBCLK

AC12

W6

SOC_SMBDATA

CPU

B B

AA4

W10

W4

AC10

CY10

CW9

AB11

AB9

SOC_SML0CLK

SOC_SML0DATA

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL_TS

I2C_1_SDA_TS

SOC_SML1CLK

SOC_SML1DATA

+3VL

+3V_PRIM

R=1K

+3V_PRIM

R=1K

+3V_PRIM

R=1K

+3V_PRIM

R=1K

+3VALW_TP

QC3 @

Q2

+3VS

R=1K

SMB_CK2

SMB_DA2

+3VALW_TP

R=2.2K

+3VALW_TP

Q3

@

+3VS

R=2.2K

Thermal Sensor :F75303M

TP_SMBCLK

TP_SMBDAT

Address : 1001_101x b

Touch Pad

Touch Screen

MP2940-0020

PU1001

SY8286RAC

PUH1

PWM

NB681GD-Z

PUM1

PWM

SY8210DQVC

PU301

Regulator

SY8286BRAC

PU302

Regulator

SY8286BRAC

Page. 50

Page. 48

Page. 44

Page. 39

Page. 33

Page. 33

+VCCIN

(33A)

+1.05V_PRIM

(4.91A)PWM

+1.05V_PRIM_COR E

(2.31A)

Premium

+0.6VS_VTT

+1.1V_VDDQ

+3VALW

PU1801

PWM

G5719CTB1U

UC18

Loadswitch

TPS22907YZTR

+5VALW

UV2

MOSFET

G527ATP1U

Page. 40

Page. 29

Page. 29

+1.8PRIM

+3V_PRIM

(3.2A)

+5VS_SUB

(2A)

(0.15A)

+1.0V_PRIM

C10

+1.8V_PRIM

SYSON

(PM_SLP_S4#)

UC5 +1.0VS_VCCST G

Loadswitch

TPS22922YZPR

Loadswitch

TPS22907YZTR

UD5

Loadswitch

TPS22913CYZVR

UA4

+3VALW

LDO

G9090-180TO1U

Page. 12

+1.2V_VCCPLL_OCUC7+1.2V_VDDQ

Page. 12

+1.8V_MEM

Page. 21

+1.8VALW_AUDIO

Page. 28

For SPK AMP register value kee p.

Page. 39

Page. 24

Page. 23

+3VS_AUDIO

+1.8VS_AUDIO

+3VS_SSD

+3VS_WLAN

+3VALW

SUSP#

(AUDIO_PWREN)

+3VALW

NGFF_SSD_PWREN

+3VALW

WLAN_PWR_EN

U7

Loadswitch

TPS22907YZTR

US1

Loadswitch

TPS22922YZPR

UN2

Loadswitch

TPS22922YZPR

Premium

+3VS+3VALW

+5VS

+5VALW

SUSP#

(PM_SLP_S3#)

U6

Load Switch

EM5209VF

+3VS

UK1:+3VALW_EC

A A

Address : 0x1A/0X19

EC

(+3VL)

EC_SMB_CK2

B8

A6

EC_SMB_DA2

EC_SMB_CK1

A8

A7

EC_SMB_DA1

D6

E7

EC_SMB_CK3

EC_SMB_DA3

5

+3VL_EC

R=2.2K

+3V_SMBUS

R=2.2K

+3VALW

R=4.7K

EC_SMB_CK1_R

EC_SMB_DA1_R

R=100

R=0

SPK AMP*2

R=0@

SCL_CHG

SDA_CHG

QK3

BAT

Charger

Codec:ALC3292

0x09

0x09

TPS65988/TPS65987

+3VALW

4

QK5

JTYPEC1

JTYPEC2

JTYPEC3

SMB_BS_CLK

SMB_BS_DAT

Address : 0x25

Address : 0x21

Address : 0x23

SCL_P_MP2940

SDA_P_MP2940

R=0

RE_CL

RE_DA

R=0

R: Address : 0x4B

W: Address : 0x4A

R: Address : 0x43

W: Address : 0x42

R: Address : 0x47

W: Address : 0x46

+3VALW

R=10K

+3VS_EDP_RE

R=10K

MP2940

SN75DP130

3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NTDI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR WRI TTEN CONSENT OFCOMPA L ELECTRONICS, INC.

2017/03/20 2020/03/20

2017/03/20 2020/03/20

2017/03/20 2020/03/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power MAP

Power MAP

Power MAP

LA-F801P

1

4 55Friday, June 08, 2018

4 55Friday, June 08, 2018

4 55Friday, June 08, 2018

0.1

0.1

0.1

5

+3VS

1 2

RC6 2.2K_0201_5%@

1 2

RC16 2.2K_0201_5%

1 2

RC32 2.2K_0201_5%@

1 2

RC33 2.2K_0201_5%

SOC_DP1_CT RL_CLK

SOC_DP1_CT RL_DATA

SOC_DP2_CT RL_CLK

SOC_DP2_CT RL_DATA

PV: HPD double pull down

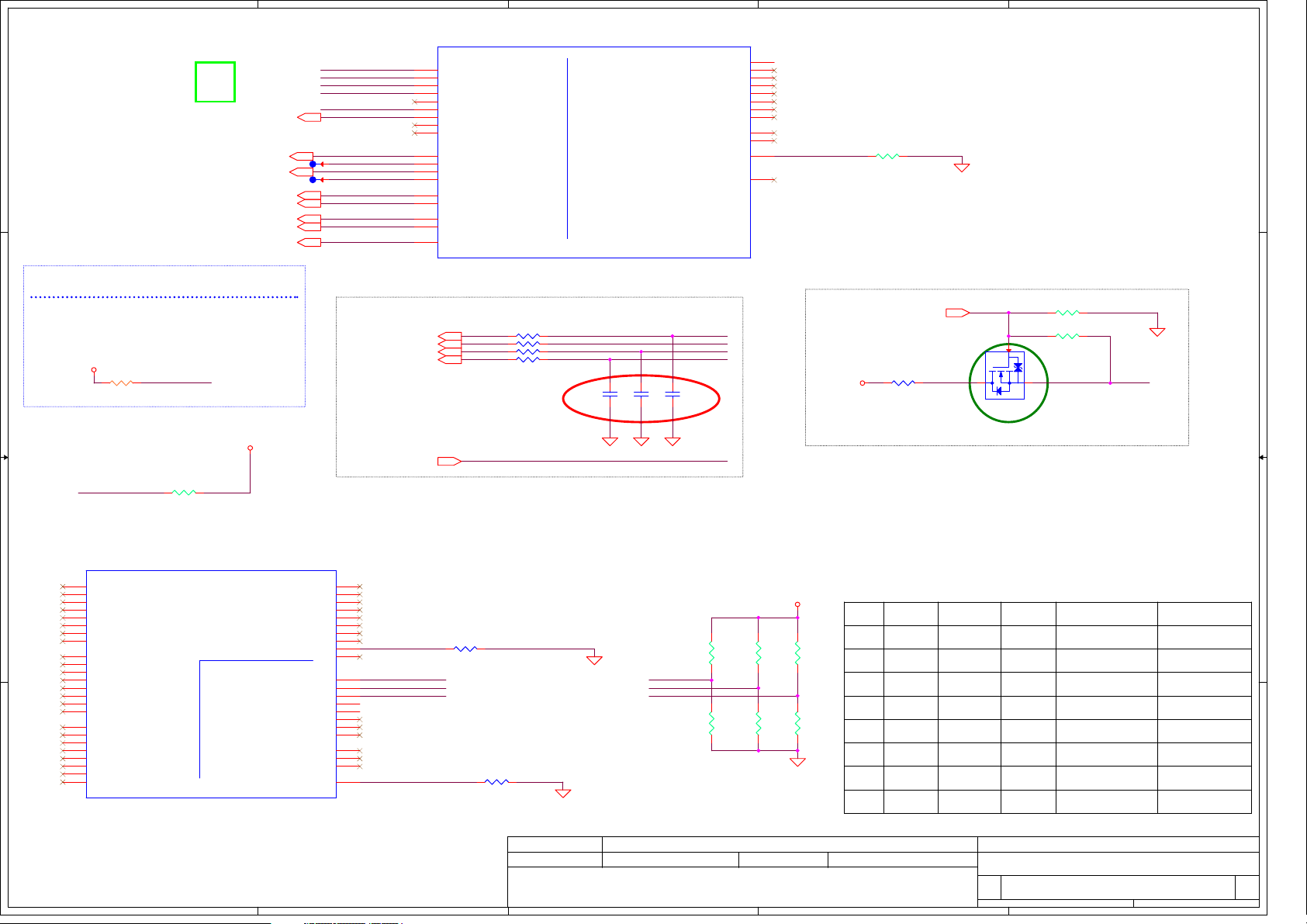

Functional Strap Definitions

D D

GPP_E19 (Internal Pull Down): DDPB_CTRLDATA

0 = Port B is not detected.

1 = Port B is detected.

GPP_E21 (Internal Pull Down): DDPC_CTRLDATA

0 = Port C is not detected.

1 = Port C is detected.

+3VS

1 2

RC1 100K_0201_5%@

1 2

RC71 10K_0201_5%@

1 2

RC485 10K_ 0201_5%

+1.0V_VCCST

C C

+1.0VS_VCCSTG

1 2

RC95 1K_0201_5%

1 2

RC80 49.9_0402_1%@

1 2

RC13 1K_0201_5%

+3V_PRIM

1 2

RC490 10K_ 0201_5%

TP_INT#

TS_INT#

EC_SCI#

H_THERMT RIP#

H_CATERR#

H_PROCHOT#

NMI_DBG#_CPU

4

Alpine Ridge

+0.85VS_VCCIO

3

PDG_Processor strap CFG[4] should be pulled

UC1A

NMI_DBG#_CPU(29)

@

A46

DDI1_TXN[0]

C46

DDI1_TXP[0]

C48

DDI1_TXN[1]

A48

DDI1_TXP[1]

B45

DDI1_TXN[2]

D45

DDI1_TXP[2]

B47

DDI1_TXN[3]

D47

DDI1_TXP[3]

A42

DDI2_TXN[0]

C42

DDI2_TXP[0]

A44

DDI2_TXN[1]

C44

DDI2_TXP[1]

B41

DDI2_TXN[2]

D41

DDI2_TXP[2]

B43

DDI2_TXN[3]

D43

DDI2_TXP[3]

L6

GPP_E18/DDPB_CTRLCLK

H6

GPP_E19/DDPB_CTRLDATA

H4

GPP_E20/DDPC_CTRLCLK

F4

GPP_E21/DDPC_CTRLDATA

M5

GPP_E22

L4

GPP_E23

A50

EDP_RCOMP

KBL-Y_BGA1515

12

@

TC69 @

TC68 @

TC6 @

TC7 @

TS_INT#(22)

TP_INT#(30)

12

12

H_CATERR#

H_PROCHOT# _R

H_THERMT RIP#

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

XDP_BPM#3_R

TS_INT#

TP_INT#

NMI_DBG#_CPU

CPU_POPIRCOMP

PCH_OPIRCOMP

SOC_DP1_N0(33)

SOC_DP1_P0(33)

SOC_DP1_N1(33)

SOC_DP1_P1(33)

SOC_DP1_N2(33)

SOC_DP1_P2(33)

SOC_DP1_N3(33)

SOC_DP1_P3(33)

SOC_DP2_N0(33)

SOC_DP2_P0(33)

SOC_DP2_N1(33)

SOC_DP2_P1(33)

SOC_DP2_N2(33)

SOC_DP2_P2(33)

SOC_DP2_N3(33)

SOC_DP2_P3(33)

P

RC4

RC4 Width 20 mils, Spacing 25 mils,

Length < 100 mil

H_PECI(29)

H_PROCHOT#(29,49)

SOC_DP1_N0

SOC_DP1_P0

SOC_DP1_N1

SOC_DP1_P1

SOC_DP1_N2

SOC_DP1_P2

SOC_DP1_N3

SOC_DP1_P3

SOC_DP2_N0

SOC_DP2_P0

SOC_DP2_N1

SOC_DP2_P1

SOC_DP2_N2

SOC_DP2_P2

SOC_DP2_N3

SOC_DP2_P3

SOC_DP1_CT RL_CLK

SOC_DP1_CT RL_DATA

SOC_DP2_CT RL_CLK

SOC_DP2_CT RL_DATA

V: delete TS_RS T#_PCH

H_PECI

H_PROCHOT#

24.9_0402_1 %

12

+EDP_COM

1 2

RC8 499_0402_1%

RC67 0_0402_5%

RC14 4 9.9_0402_1%

RC15 4 9.9_0402_1%

SKYLAKE_ULX

DDI

<DDI1>

<DDI2>

DISPLAY SIDEBANDS

SKTOCC#

low to enable embedded DisplayPort*

DISPLAY

eDP

<DDI1>

<DDI2>

<DDI1>

GPP_E13/DDPB_HPD0

<DDI2>

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

1 OF 20

SKYLAKE_ULX

UC1D

@

H49

CATERR#

F49

PECI

J48

PROCHOT#

H47

THERMTRIP#

B62

SKTOCC#

H51

BPM#[0]

J50

BPM#[1]

F51

BPM#[2]

G50

BPM#[3]

E11

GPP_E3/CPU_GP0

M9

GPP_E7/CPU_GP1

BD8

GPP_B3/CPU_GP2

BC11

GPP_B4/CPU_GP3

BN17

PROC_POPIRCOMP

BP16

PCH_OPIRCOMP

CPU MISC

KBL-Y_BGA1515

EDP_DISP_UTIL

Rev0.87

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

EDP_BKLEN

EDP_BKLCTL

EDP_VDDEN

JTAG

4 OF 20

2

EDP_TXN0

H45

EDP_TXP0

F45

EDP_TXN1

J44

EDP_TXP1

G44

EDP_TXN2

J46

EDP_TXP2

G46

EDP_TXN3

H43

EDP_TXP3

F43

EDP_AUXN

J42

EDP_AUXP

G42

EDP_DISP

A40

SOC_DP1_AUXN

H41

SOC_DP1_AUXP

F41

SOC_DP2_AUXN

J40

SOC_DP2_AUXP

G40

SOC_DP1_HPD

C11

SOC_DP2_HPD

L10

EC_SCI#

M7

F6

EDP_HPD

A7

SOC_ENBKL

D4

SOC_BKL_PW M

B6

SOC_ENVDD

D3

Rev0.87

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

1

EDP_TXN0 (22)

EDP_TXP0 (22)

EDP_TXN1 (22)

EDP_TXP1 (22)

EDP_TXN2 (22)

EDP_TXP2 (22)

EDP_TXN3 (22)

EDP_TXP3 (22)

EDP_AUXN (22)

EDP_AUXP (22)

@

0_0201_5%

CPU_XDP_TCK 0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST #

PCH_JTAG_TC K1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST #

CPU_XDP_TCK 0

12

SOC_DP1_AUXN (33)

SOC_DP1_AUXP (33)

SOC_DP2_AUXN (33)

SOC_DP2_AUXP (33)

SOC_DP1_HPD (33)

SOC_DP2_HPD (33)

EC_SCI# (29 )

EDP_HPD (22)

SOC_ENBKL ( 22,29)

SOC_BKL_PW M (22)

SOC_ENVDD (22)

RC2

D53

C54

G48

C59

F47

B53

C50

B51

A52

C52

B49

<eDP>

TBT

+1.0VS_VCCSTG

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2041/09/08 2013/10/28

2041/09/08 2013/10/28

2041/09/08 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Place to CPU si de

1

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

PCH_JTAG_TC K1

CPU_XDP_TCK 0

of

5 55Friday, June 08, 2018

5 55Friday, June 08, 2018

5 55Friday, June 08, 2018

RC390 51_0402_5 %@

RC389 51_0402_5 %@

RC391 51_0402_1 %

RC399 51_0402_5 %@

RC398 51_0402_1 %

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

12

12

12

12

12

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL Y(1/13) DDI,MSIC,XDP

SKL Y(1/13) DDI,MSIC,XDP

SKL Y(1/13) DDI,MSIC,XDP

LA-F803P

LA-F803P

LA-F803P

0.1

0.1

0.1

5

4

3

2

1

Non-Interleave Memory

D D

UC1B

DDR_A_D[0..15](19)

DDR_A_D[16..31 ](19)

C C

DDR_A_D[32..47 ](19)

DDR_A_D[48..63 ](19)

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

@

AG61

DDR0_DQ[0]

AH60

DDR0_DQ[1]

AK62

DDR0_DQ[2]

AK60

DDR0_DQ[3]

AH62

DDR0_DQ[4]

AG63

DDR0_DQ[5]

AL61

DDR0_DQ[6]

AL63

DDR0_DQ[7]

AM60

DDR0_DQ[8]

AM62

DDR0_DQ[9]

AT60

DDR0_DQ[10]

AR61

DDR0_DQ[11]

AN61

DDR0_DQ[12]

AN63

DDR0_DQ[13]

AR63

DDR0_DQ[14]

AT62

DDR0_DQ[15]

Interleave/Non-lnterleaved

AT56

DDR1_DQ[0]/DDR0_DQ[16]

AR55

DDR1_DQ[1]/DDR0_DQ[17]

AN57

DDR1_DQ[2]/DDR0_DQ[18]

AN55

DDR1_DQ[3]/DDR0_DQ[19]

AR57

DDR1_DQ[4]/DDR0_DQ[20]

AT58

DDR1_DQ[5]/DDR0_DQ[21]

AM58

DDR1_DQ[6]/DDR0_DQ[22]

AM56

DDR1_DQ[7]/DDR0_DQ[23]

AL55

DDR1_DQ[8]/DDR0_DQ[24]

AL57

DDR1_DQ[9]/DDR0_DQ[25]

AH58

DDR1_DQ[10]/DDR0_DQ[26]

AH56

DDR1_DQ[11]/DDR0_DQ[27]

AK58

DDR1_DQ[12]/DDR0_DQ[28]

AK56

DDR1_DQ[13]/DDR0_DQ[29]

AG55

DDR1_DQ[14]/DDR0_DQ[30]

AG57

DDR1_DQ[15]/DDR0_DQ[31]

BE55

DDR0_DQ[16]/DDR0_DQ[32]

BC55

DDR0_DQ[17]/DDR0_DQ[33]

BG53

DDR0_DQ[18]/DDR0_DQ[34]

BE53

DDR0_DQ[19]/DDR0_DQ[35]

BC53

DDR0_DQ[20]/DDR0_DQ[36]

BG55

DDR0_DQ[21]/DDR0_DQ[37]

BD52

DDR0_DQ[22]/DDR0_DQ[38]

BF52

DDR0_DQ[23]/DDR0_DQ[39]

BC51

DDR0_DQ[24]/DDR0_DQ[40]

BE51

DDR0_DQ[25]/DDR0_DQ[41]

BC49

DDR0_DQ[26]/DDR0_DQ[42]

BE49

DDR0_DQ[27]/DDR0_DQ[43]

BG51

DDR0_DQ[28]/DDR0_DQ[44]

BG49

DDR0_DQ[29]/DDR0_DQ[45]

BF48

DDR0_DQ[30]/DDR0_DQ[46]

BD48

DDR0_DQ[31]/DDR0_DQ[47]

BJ55

DDR1_DQ[16]/DDR0_DQ[48]

BL55

DDR1_DQ[17]/DDR0_DQ[49]

BJ53

DDR1_DQ[18]/DDR0_DQ[50]

BL53

DDR1_DQ[19]/DDR0_DQ[51]

BN55

DDR1_DQ[20]/DDR0_DQ[52]

BN53

DDR1_DQ[21]/DDR0_DQ[53]

BM52

DDR1_DQ[22]/DDR0_DQ[54]

BK52

DDR1_DQ[23]/DDR0_DQ[55]

BL51

DDR1_DQ[24]/DDR0_DQ[56]

BJ51

DDR1_DQ[25]/DDR0_DQ[57]

BL49

DDR1_DQ[26]/DDR0_DQ[58]

BJ49

DDR1_DQ[27]/DDR0_DQ[59]

BN49

DDR1_DQ[28]/DDR0_DQ[60]

BN51

DDR1_DQ[29]/DDR0_DQ[61]

BK48

DDR1_DQ[30]/DDR0_DQ[62]

BM48

DDR1_DQ[31]/DDR0_DQ[63]

KBL-Y_BGA1515

Reserve

DDR0_ALERT #

SKYLAKE_ULX

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR CH-A

2 OF 20

1 2

RC540 0_0201_5 %short@

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR3L / LPDDR3 / DDR4

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR0_ODT[0]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave/Non-lnterleaved

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

Rev0.87

DDR0_PAR

M_CLK_A_DDR #0

BC62

M_CLK_A_DDR 0

BC60

M_CLK_A_DDR #1

BA60

M_CLK_A_DDR 1

BA62

DDR_A_CKE0

BB57

DDR_A_CKE1

BC58

DDR_A_CKE2

BE57

DDR_A_CKE3

AW61

DDR_A_CS0#

AW63

DDR_A_CS1#

BJ57

DDR_A_ODT0

BN61

DDR_A_CAA_0

AW59

DDR_A_CAA_1

AW55

DDR_A_CAA_2

BF62

DDR_A_CAA_3

AV56

DDR_A_CAA_4

AW57

DDR_A_CAA_5

AV58

DDR_A_CAA_6

BA56

DDR_A_CAA_7

BD59

DDR_A_CAA_8

BD61

DDR_A_CAA_9

BG61

DDR_A_CAB_0

BK59

DDR_A_CAB_1

BL62

DDR_A_CAB_2

BJ61

DDR_A_CAB_3

AV60

DDR_A_CAB_4

BN62

DDR_A_CAB_5

BB61

DDR_A_CAB_6

BL61

DDR_A_CAB_7

BM59

DDR_A_CAB_8

BN58

DDR_A_CAB_9

AV62

BB63

BL57

DDR_A_DQS#0

AJ61

DDR_A_DQS0

AJ63

DDR_A_DQS#1

AP62

DDR_A_DQS1

AP60

DDR_A_DQS#2

AP56

DDR_A_DQS2

AP58

DDR_A_DQS#3

AJ57

DDR_A_DQS3

AJ55

DDR_A_DQS#4

BD54

DDR_A_DQS4

BF54

DDR_A_DQS#5

BF50

DDR_A_DQS5

BD50

DDR_A_DQS#6

BM54

DDR_A_DQS6

BK54

DDR_A_DQS#7

BK50

DDR_A_DQS7

BM50

DDR0_ALERT #

BG57

BM56

AR53

AN53

AW53

DDR_VTT_C NTL SM_RCOMP2

BN47

DDR_VTT_C NTL

M_CLK_A_DDR #0 (19)

M_CLK_A_DDR 0 (19)

M_CLK_A_DDR #1 (19)

M_CLK_A_DDR 1 (19)

DDR_A_CKE0 (19)

DDR_A_CKE1 (19)

DDR_A_CKE2 (19)

DDR_A_CKE3 (19)

DDR_A_CS0# (19)

DDR_A_CS1# (19)

DDR_A_ODT0 (19)

DDR_A_CAA_0 (19)

DDR_A_CAA_1 (19)

DDR_A_CAA_2 (19)

DDR_A_CAA_3 (19)

DDR_A_CAA_4 (19)

DDR_A_CAA_5 (19)

DDR_A_CAA_6 (19)

DDR_A_CAA_7 (19)

DDR_A_CAA_8 (19)

DDR_A_CAA_9 (19)

DDR_A_CAB_0 (19)

DDR_A_CAB_1 (19)

DDR_A_CAB_2 (19)

DDR_A_CAB_3 (19)

DDR_A_CAB_4 (19)

DDR_A_CAB_5 (19)

DDR_A_CAB_6 (19)

DDR_A_CAB_7 (19)

DDR_A_CAB_8 (19)

DDR_A_CAB_9 (19)

DDR_A_DQS#0 (19)

DDR_A_DQS0 (19)

DDR_A_DQS#1 (19)

DDR_A_DQS1 (19)

DDR_A_DQS#2 (19)

DDR_A_DQS2 (19)

DDR_A_DQS#3 (19)

DDR_A_DQS3 (19)

DDR_A_DQS#4 (19)

DDR_A_DQS4 (19)

DDR_A_DQS#5 (19)

DDR_A_DQS5 (19)

DDR_A_DQS#6 (19)

DDR_A_DQS6 (19)

DDR_A_DQS#7 (19)

DDR_A_DQS7 (19) DDR_B_DQS# 6 (20)

T273TP@

T86TP@

+0.6V_VREFCA

+0.6V_A_VREFDQ

+0.6V_B_VREFDQ

Trace width/Spacing >= 20mils

1 2

RC48 0_0201_5%short@

DDR_B_D[0..15 ](20)

DDR_B_D[16 ..31](20)

DDR_B_D[32 ..47](20)

DDR_B_D[48 ..63](20)

SM_PG_CTRL (44)

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

@

interleave / Non-lnterleaved

BC41

DDR0_DQ[32]/DDR1_DQ[0]

BC39

DDR0_DQ[33]/DDR1_DQ[1]

BG41

DDR0_DQ[34]/DDR1_DQ[2]

BE39

DDR0_DQ[35]/DDR1_DQ[3]

BF42

DDR0_DQ[36]/DDR1_DQ[4]

BD42

DDR0_DQ[37]/DDR1_DQ[5]

BG39

DDR0_DQ[38]/DDR1_DQ[6]

BE41

DDR0_DQ[39]/DDR1_DQ[7]

BC43

DDR0_DQ[40]/DDR1_DQ[8]

BD46

DDR0_DQ[41]/DDR1_DQ[9]

BG43

DDR0_DQ[42]/DDR1_DQ[10]

BG45

DDR0_DQ[43]/DDR1_DQ[11]

BC45

DDR0_DQ[44]/DDR1_DQ[12]

BE43

DDR0_DQ[45]/DDR1_DQ[13]

BE45

DDR0_DQ[46]/DDR1_DQ[14]

BF46

DDR0_DQ[47]/DDR1_DQ[15]

BM28

DDR1_DQ[32]/DDR1_DQ[16]

BN27

DDR1_DQ[33]/DDR1_DQ[17]

BK28

DDR1_DQ[34]/DDR1_DQ[18]

BL25

DDR1_DQ[35]/DDR1_DQ[19]

BN25

DDR1_DQ[36]/DDR1_DQ[20]

BL27

DDR1_DQ[37]/DDR1_DQ[21]

BJ25

DDR1_DQ[38]/DDR1_DQ[22]

BJ27

DDR1_DQ[39]/DDR1_DQ[23]

BM24

DDR1_DQ[40]/DDR1_DQ[24]

BK24

DDR1_DQ[41]/DDR1_DQ[25]

BN21

DDR1_DQ[42]/DDR1_DQ[26]

BJ23

DDR1_DQ[43]/DDR1_DQ[27]

BL23

DDR1_DQ[44]/DDR1_DQ[28]

BN23

DDR1_DQ[45]/DDR1_DQ[29]

BJ21

DDR1_DQ[46]/DDR1_DQ[30]

BL21

DDR1_DQ[47]/DDR1_DQ[31]

BN45

DDR0_DQ[48]/DDR1_DQ[32]

BM46

DDR0_DQ[49]/DDR1_DQ[33]

BL43

DDR0_DQ[50]/DDR1_DQ[34]

BK46

DDR0_DQ[51]/DDR1_DQ[35]

BN43

DDR0_DQ[52]/DDR1_DQ[36]

BL45

DDR0_DQ[53]/DDR1_DQ[37]

BJ45

DDR0_DQ[54]/DDR1_DQ[38]

BJ43

DDR0_DQ[55]/DDR1_DQ[39]

BM42

DDR0_DQ[56]/DDR1_DQ[40]

BN41

DDR0_DQ[57]/DDR1_DQ[41]

BJ41

DDR0_DQ[58]/DDR1_DQ[42]

BN39

DDR0_DQ[59]/DDR1_DQ[43]

BK42

DDR0_DQ[60]/DDR1_DQ[44]

BL41

DDR0_DQ[61]/DDR1_DQ[45]

BL39

DDR0_DQ[62]/DDR1_DQ[46]

BJ39

DDR0_DQ[63]/DDR1_DQ[47]

BF28

DDR1_DQ[48]

BD28

DDR1_DQ[49]

BG25

DDR1_DQ[50]

BC27

DDR1_DQ[51]

BG27

DDR1_DQ[52]

BE27

DDR1_DQ[53]

BE25

DDR1_DQ[54]

BC25

DDR1_DQ[55]

BF24

DDR1_DQ[56]

BD24

DDR1_DQ[57]

BG21

DDR1_DQ[58]

BC23

DDR1_DQ[59]

BE23

DDR1_DQ[60]

BG23

DDR1_DQ[61]

BC21

DDR1_DQ[62]

BE21

DDR1_DQ[63]

KBL-Y_BGA1515

SKYLAKE_ULX

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0] /DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

interleave / Non-lnterleaved

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH-B

3 OF 20

Rev0.87

DDR1_CKN[0]

DDR1_CKP[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

BK36

BM36

BD32

BF32

BN33

BK32

BG33

BH30

BM30

BJ33

BC35

BK30

BN31

BM32

BL37

BG31

BN37

BJ37

BJ35

BM34

BN35

BG37

BE37

BC37

BF34

BC33

BF30

BD36

BG35

BC31

BF36

BJ31

BK34

BD40

BF40

BD44

BF44

BK26

BM26

BM22

BK22

BK44

BM44

BM40

BK40

BD26

BF26

BF22

BD22

BD34

BD30

BP20

BF64

BJ64

BC64

M_CLK_B_DD R#0

M_CLK_B_DD R0

M_CLK_B_DD R#1

M_CLK_B_DD R1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS0 #

DDR_B_CS1 #

DDR_B_ODT 0

DDR_B_CAA_0

DDR_B_CAA_1

DDR_B_CAA_2

DDR_B_CAA_3

DDR_B_CAA_4

DDR_B_CAA_5

DDR_B_CAA_6

DDR_B_CAA_7

DDR_B_CAA_8

DDR_B_CAA_9

DDR_B_CAB_0

DDR_B_CAB_1

DDR_B_CAB_2

DDR_B_CAB_3

DDR_B_CAB_4

DDR_B_CAB_5

DDR_B_CAB_6

DDR_B_CAB_7

DDR_B_CAB_8

DDR_B_CAB_9

DDR_B_DQS# 0

DDR_B_DQS0

DDR_B_DQS# 1

DDR_B_DQS1

DDR_B_DQS# 2

DDR_B_DQS2

DDR_B_DQS# 3

DDR_B_DQS3

DDR_B_DQS# 4

DDR_B_DQS4

DDR_B_DQS# 5

DDR_B_DQS5

DDR_B_DQS# 6

DDR_B_DQS6

DDR_B_DQS# 7

DDR_B_DQS7

DDR1_ALERT #

DDR3_DRAMR ST#

SM_RCOMP0

SM_RCOMP1

SC03

0.1U_0201_ 16V6K

@ESD@

M_CLK_B_DD R#0 (20)

M_CLK_B_DD R0 (20)

M_CLK_B_DD R#1 (20)

M_CLK_B_DD R1 (20)

DDR_B_CKE0 (20)

DDR_B_CKE1 (20)

DDR_B_CKE2 (20)

DDR_B_CKE3 (20)

DDR_B_CS0 # (20)

DDR_B_CS1 # (20)

DDR_B_ODT 0 (20)

DDR_B_CAA_0 (20)

DDR_B_CAA_1 (20)

DDR_B_CAA_2 (20)

DDR_B_CAA_3 (20)

DDR_B_CAA_4 (20)

DDR_B_CAA_5 (20)

DDR_B_CAA_6 (20)

DDR_B_CAA_7 (20)

DDR_B_CAA_8 (20)

DDR_B_CAA_9 (20)

DDR_B_CAB_0 (20)

DDR_B_CAB_1 (20)

DDR_B_CAB_2 (20)

DDR_B_CAB_3 (20)

DDR_B_CAB_4 (20)

DDR_B_CAB_5 (20)

DDR_B_CAB_6 (20)

DDR_B_CAB_7 (20)

DDR_B_CAB_8 (20)

DDR_B_CAB_9 (20)

DDR_B_DQS# 0 (20)

DDR_B_DQS0 (20)

DDR_B_DQS# 1 (20)

DDR_B_DQS1 (20)

DDR_B_DQS# 2 (20)

DDR_B_DQS2 (20)

DDR_B_DQS# 3 (20)

DDR_B_DQS3 (20)

DDR_B_DQS# 4 (20)

DDR_B_DQS4 (20)

DDR_B_DQS# 5 (20)

DDR_B_DQS5 (20)

DDR_B_DQS6 (20)

DDR_B_DQS# 7 (20)

DDR_B_DQS7 (20)

T91

T87TP@

T274TP@

1 2

RC45 200_0402_1%

1 2

RC46 80.6_0402_1%

1 2

RC47 162_0402_1%

12

DDR3_DRAMR ST#

DDR1_ALERT #

A A

5

1 2

RC524 0_0201_5 %short@

2016-08-24

Modify-Follow TD team

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2041/09/08 2013/10/28

2041/09/08 2013/10/28

2041/09/08 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKL Y(2/13) DDRIII

SKL Y(2/13) DDRIII

SKL Y(2/13) DDRIII

LA-F803P

LA-F803P

LA-F803P

1

6 55Friday, June 08, 2018

6 55Friday, June 08, 2018

6 55Friday, June 08, 2018

0.1

0.1

0.1

5

4

3

2

1

Functional Strap Definitions

GPP_C2 (Internal Pull Down): SMBALERT#

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no confidentiality).

1 = Enable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (with confidentiality). Must be

pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

+3V_PRIM

CLK_LPC _EC_R (29)

LPC_CLK RUN# (29)

RH101

2.2K_020 1_5%

@

SOC_SMB ALERT#

12

C LINK

SKYLAKE_ULX

LPC

5 OF 20

Rev0.87

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

AC12

W6

W8

W4

AC10

AA6

AA4

W10

BB6

BK11

BJ8

BG10

BP5

BP7

BJ6

BJ10

BF5

BH11

SOC_SMB ALERT#

SOC_SML 0CLK

SOC_SML 0DATA

GPP_C5

PCH_TBT _RST#

TBT_W AKE#

SOC_SML 1ALERT#

LPC_AD0

RC446 0_0201_ 5%LPC@

LPC_AD1

RC447 0_0201_ 5%LPC@

LPC_AD2

RC448 0_0201_ 5%LPC@

LPC_AD3

RC449 0_0201_ 5%LPC@

CLK_LPC _EC

CLKOUT_ LPC1

LPC_CLK RUN#

SOC_SMB CLK (30)

SOC_SMB DATA (30)

PCH_TBT _RST# (33)

TBT_W AKE# (33)

1 2

1 2

1 2

1 2

1 2

RH20 22_0201 _5%EMI@

T23TP@

PIR29 SI: pop CH47

LPC_AD0 _R

LPC_AD1 _R

LPC_AD2 _R

LPC_AD3 _R

CH47

RF@

68P_0201_50V8J

Connect TP

P

V: modify for RTD3

LPC_AD0 _R (29)

LPC_AD1 _R (29)

LPC_AD2 _R (29)

LPC_AD3 _R (29)

LPC_FRA ME# (29)

CLK_LPC _EC_R

1

2

UC1E

50MHz

D D

T13 TP@

T369 TP@

WW AN_DISABLE#(26)

WW AN_PWRE N(26)

CAMERA_ PWREN(26)

WW AN_PREN(25 )

PV: control WWAN

To EC

T21 TP@

T22 TP@

T24 TP@

EC_KBRS T#(29)

LPC_SER IRQ(29)

PCH_SPI_C LK

PCH_SPI_S O

PCH_SPI_S I

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_C S0#

PCH_SPI_C S1#

PCH_SPI_C S2#

T15 TP@

WW AN_DISABLE#

WW AN_PWRE N

T370 TP@

CL_CK

CL_DATA

CL_RST_ N

EC_KBRS T#

LPC_SER IRQ

LPC Mode

@

AU10

SPI0_CLK

AU12

SPI0_MISO

AT3

SPI0_MOSI

AV11

SPI0_IO2

AV13

SPI0_IO3

AU4

SPI0_CS0#

AU6

SPI0_CS1#

AU8

SPI0_CS2#

P9

GPP_D1

N8

GPP_D2/SPI1_MISO

P3

GPP_D3

W12

GPP_D21

V7

GPP_D22

N6

GPP_D0

F12

CL_CLK

D12

CL_DATA

B12

CL_RST#

BL10

GPP_A0/RCIN#

BN8

GPP_A6/SERIRQ

KBL-Y_BGA1515

SPI - FLASH SMBUS, SMLINK

SPI - TOUCH

Functional Strap Definitions

C C

+3V_PRIM +3.3 V_SPI

Closed to ROM

PCH_SPI_S I

PCH_SPI_C LK

From CPU

EC_SPI_SO(29)

From EC

(For share ROM)

B B

EC_SPI_SI(29)

EC_SPI_CL K_R(29)

EC_SPI_CS #0(29)

PCH_SPI_S O

PCH_SPI_IO2

PCH_SPI_IO3

EC_SPI_SO

EC_SPI_SI

EC_SPI_CL K_R

EC_SPI_CS #0

RC454 33_02 01_5%

RC455 33_02 01_5%

RC456 33_02 01_5%

RC457 33_02 01_5%

RC539 33_02 01_5%

RC458 33_02 01_5%

RC459 33_02 01_5%

RC460 33_02 01_5%

RC461 33_02 01_5%

EMI@

LPC@

LPC@

LPC@

LPC@

12

12

12

12

12

12

12

12

12

SPI_SI_VROM0

SPI_CLK_V ROM0

SPI_SO_VR OM0

SPI_IO2_VROM 0

SPI_IO3_VROM 0

SPI_SO_VR OM0

SPI_SI_VROM0

SPI_CLK_V ROM0

PCH_SPI_C S0#

To SPI ROM

16M SPI ROM(Support ISH)

PCH_SPI_C S0#

SPI_SO_VR OM0 SPI_IO3_VROM 0

SPI_IO2_VROM 0 SPI_CLK_V ROM0

UC2

1

CS#

2

HOLD#_RESET#

DO

3

WP#

4

GND

W25 Q128FVPIQ_W SON8_6X5

SA00007 XA10

ThemalPad

VCC

CLK

8

7

6

SPI_SI_VROM0

5

DI

9

RH470

1 2

+3.3V_SP I

1

2

0_0402_ 5%@

CH35

0.1U_020 1_10V6K

GPP_B23 :SML1ALERT#

If USB 3.0 Port 1 is used for 4-wire DCI.OOB (BSSB), and

‧‧‧‧

alternate functionality is also used on the pin, pull up

to V3.3S with >100K resistor to avoid noise.

If USB 3.0 Port 1 is used for DCI.OOB (BSSB) 4-wire

‧‧‧‧

BSSB, and NO alternate functionality is used, leave float.

If DCI.OOB (BSS B) 2+2 functio nality is used, pull up to

‧‧‧‧

V3.3S with a 4.7K resistor.

PIR24 SI: Change to 16M

GPP_C5 (Internal Pull Down): SML0ALERT#

0 = LPC Is selected for EC.

1 = eSPI Is selected for EC.

SOC_SML 1ALERT#

PCH_TBT _RST#

TBT_W AKE#

SOC_SML 0CLK

SOC_SML 0DATA

SOC_SMB CLK

SOC_SMB DATA

+3V_PRIM

RH102 4.7K_040 2_5%

RH96 10K_020 1_5%@

RH97 10K_020 1_5%

RH99 1K_0201 _5%

RH100 1K_0201 _5%

RH94 1K_0201 _5%

RH95 1K_0201 _5%

RH98

@

10K_020 1_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

GPP_C5

12

+3V_PRIM

+3VS

LPC_CLK RUN#

LPC_SER IRQ

A A

Security Class ification

Security Class ification

Security Class ification

2041/09/ 08 2013/10/ 28

2041/09/ 08 2013/10/ 28

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2041/09/ 08 2013/10/ 28

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

EC_KBRS T#

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKL Y(3/13) SPI,SMB

SKL Y(3/13) SPI,SMB

SKL Y(3/13) SPI,SMB

LA-F803P

LA-F803P

LA-F803P

1 2

RH13 8.2K_020 1_5%

1 2

RH472 10K_020 1_5%

1 2

RH473 10K_020 1_5%

7 55Friday, June 08, 201 8

7 55Friday, June 08, 201 8

7 55Friday, June 08, 201 8

1

0.1

0.1

0.1

5

4

3

2

1

AUDIO

<+3V_1.8V_PGPPD>

12

EMI@

12

12

12

SKYLAKE_ULX

7 OF 20

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

MP@

MP@

1

1

CC171

2.2P_0201_25V

2.2P_0201_25V

2

2

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

HDA_BIT_C LK

HDA_SYNC

HDA_SDO UT

HDA_RST #

RF@

1

CC140

10P_0201_25V8

CC170

2

HDA_SDIN0

Rev0.87

GPP_F23

AH9

AH11

AG12

AF9

AF11

AG8

AG10

AE12

BL4

BN4

BF1

AJ8

SDIO_RCOM P

RC60 200_020 1_1%

@

12

561280_KBL UY PDG Rev2_0

if SDXC interface is not used,

the SD_RCOMP pin does not need to be connected to a RCOMP resistor.

To Enable ME Override

ME_EN(29)

+3V_HDA

1 2

RC500 1K _0201_1%

VGS(Max) : <1.5 V

HDA_SDO / I2S0_TXD (Internal Pull Down)(Primary well):

Flash Descriptor Security Override

0 = Enable (Default)

1 = Disable (Override)

The internal pull-down is disabled after PCH_PWROK is High.

1

QC1

PJE138K 1N SOT-523-3

1 2

@

RC501 100K_0201_5 %

1 2

RC507 0_0201_ 5%@

2

HDA_SDO UT

3

UC1G

A00_0906: EMI Request RH109 33chnage 56ohm

HDA_SYNC

HDA_BIT_C LK

HDA_SDO UT

HDA_SDIN0

HDA_RST #

D D

Camera

RTD3_US B_PWR_EN(33)

WLA N_TRANSMIT_OFF#(23)

T30 TP@

BT_ON(23 )

T127 TP@

SOC_DMIC_ CLK0(22)

SOC_DMIC_ DATA0(22)

AUDIO_PW REN(39)

WW AN_ASPM_CT RL(26)

SPKR(27)

RTD3_US B_PWR_EN

WLA N_TRANSMIT_OFF#

SOC_GPIOF 0

BT_ON

SOC_GPIOF 3

SOC_DMIC_ CLK0

SOC_DMIC_ DATA0

AUDIO_PW REN

WW AN_ASPM_CT RL

SPKR

@

BJ19

HDA_SYNC/I2S0_SFRM

BK18

HDA_BLK/I2S0_SCLK

BK16

HDA_SDO/I2S0_TXD

BL15

HDA_SDI0/I2S0_RXD

BL17

HDA_SDI1/I2S1_RXD

BL19

HDA_RST#/I2S1_SCLK

V5

GPP_D23/I2S_MCLK

BL12

I2S1_SFRM

BK14

I2S1_TXD

AT13

GPP_F1/I2S2_SFRM

AT11

GPP_F0/I2S2_SCLK

AP11

GPP_F2/I2S2_TXD

AT5

GPP_F3/I2S2_RXD

V3

GPP_D19/DMIC_CLK0

V11

GPP_D20/DMIC_DATA0

U12

GPP_D17/DMIC_CLK1

U8

GPP_D18/DMIC_DATA1

AV3

GPP_B14/SPKR

KBL-Y_BGA1515

Functional Strap Definitions

GPP_B14 (Internal Pull Down): SPKR

TOP Swap Override

0 = Disable TOP Swap mode.---> AAU30 Use

1 = Enable TOP Swap Mode.

C C

+3V_PRIM

RC83

1 2

@

100K_02 01_5%

RTD3_US B_PWR_EN

SPKR

+3V_PRIM

1 2

@

RC577 49 .9K_0201_1%

HDA for AUDIO

HDA_BIT_C LK_R(27)

HDA_SYNC_ R(27)

HDA_SDO UT_R(27)

HDA_RST #_R(27)

HDA_SDIN0(27)

RC462 33_0201 _5%

RC463 33_0201 _5%

RC464 33_0201 _5%

RC499 33_0201 _5%

UC1I

G30

G32

H29

F29

F33

H33

D29

B29

C32

A32

C30

A30

D33

B33

D35

B35

C36

A36

D37

B37

C38

A38

J30

J32

@

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

KBL-Y_BGA1515

B B

A A

SKYLAKE_ULX

CSI-2

eMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F12/EMMC_CMD

9 OF 20

5

Rev0.87

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

GPP_F22/EMMC_CLK

EMMC_RCOMP

H31

F31

D31

B31

C34

A34

D39

B39

A11

N4

AN12

AP9

AN10

AJ10

AM9

AL12

AJ12

AN8

AL10

AL8

AM11

BC1

CSI2_COMP

RAM_ID0

RAM_ID1

RAM_ID2

EMMC_RC OMP

4

RC64 100_020 1_1%

12

RC61 200_020 1_1%

12

Security Class ification

Security Class ification

Security Class ification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Issued Date

Issued Date

RAM ID

3

DDR Memory Configuratino Type Strap pin

+1.8V_PR IM

1K_0201_1%

RC138

@

RAM_ID0

RAM_ID1

RAM_ID2

2041/09/ 08 2013/10/ 28

2041/09/ 08 2013/10/ 28

2041/09/ 08 2013/10/ 28

1 2

1K_0201_1%

RC509

@

1 2

Compal Secret Data

Compal Secret Data

Compal Secret Data

1K_0201_1%

1K_0201_1%

RC510

@

1 2

1K_0201_1%

1K_0201_1%

RC508

@

1 2

Deciphered Date

Deciphered Date

Deciphered Date

RC511

1 2

RC512

1 2

L01

@

@

L02

L04

2

RAM_ID2/1/0

000

001

010

011L03 Micron 16G

P/N DescribtionConfig

S IC D3 512M64

Micron 8G

LPDDR3L

Hynix 8G

LPDDR3L

SAMSUNG 8GB

LPDDR3L

LPDDR3L

Micron 8GB

LPDDR3L

Hynix 4GB

LPDDR3L

SAMSUNG 4GB

LPDDR3L

R1

SA00009Z800

R1

SA000092J20

R1

SA00009DC00

SA0000C1800

R3

SA00009Z810

R3

SA000092J30

R3

SA00009DC10

Title

Title

Title

SKL Y(4/13) HDA,EMMC,SDIO

SKL Y(4/13) HDA,EMMC,SDIO

SKL Y(4/13) HDA,EMMC,SDIO

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

LA-F803P

LA-F803P

LA-F803P

Date: Sheet of

Date: Sheet of

Date: Sheet

MT52L512M64D4PQ-107WT:B

S IC D3 32G/1866

H9CCNNNCPTALBR-NUD

FBGA

S IC D3 32G/1866

K3QF4F40BM-AGCF

FBGA

S IC D3 64G/1866

MT52L1G64D8QC-107 WT:B

S IC D3

MT52L512M64D4PQ-107WT:B

A32!

S IC D3 32G/1866

H9CCNNNCPTALBR-NUD

FBGA A32 !

S IC D3 32G/1866

K3QF4F40BM-AGCF

A32 !

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Matched ResisterSKU

RC509 RC508 RC512

RC138

RC509 RC510 RC512

1

8 55Friday, June 08, 201 8

8 55Friday, June 08, 201 8

8 55Friday, June 08, 201 8

RC508 RC512

RC512RC510RC138R1

of

0.1

0.1

0.1

5

+3VL_RT C

1 2

RC514 20K_0 201_5%

1 2

CC6 1U_0201_6 .3V6M

1 2

CLRP1 S HORT PADS

1 2

D D

+3VS

+3V_PRIM

C C

+3VALW _DSW

B B

RC513 20K_0 201_5%

1 2

CC277 1U_02 01_6.3V6M

1 2

CLRP2 S HORT PADS

1 2

RC54 1M_020 1_5%

1 2

RC474 10K_020 1_5%@

1 2

RC475 10K_020 1_5%

1 2

RC476 10K_020 1_5%

1 2

RC477 10K_020 1_5%@

1 2

RC478 10K_020 1_5%

1 2

RH114 10K_020 1_5%@

1 2

RH208 10K_020 1_5%

1 2

RH132 10K_020 1_5%

1 2

RH44 100K_02 01_5%

1 2

RH115 10K_020 1_5%

1 2

RH210 10K_020 1_5%

1 2

RH117 10K_020 1_5%

1 2

RH82 10K_020 1_5%

1 2

RH471 1K_0201 _5%

1 2

RH68 2.2K_020 1_5%

1 2

RH50 100K_02 01_5%

1 2

RH49 10K_020 1_5%

1 2

CC278 100P_02 01_50V8J

ESD@

PCH_SUS WARN#(29)

SOC_SRT CRST#

SOC_RTC RST#

SM_INTRUD ER#

CLKREQ_ PCIE#1

CLKREQ_ PCIE#2

CLKREQ_ PCIE#3

CLKREQ_ PCIE#4

PCH_SUS WARN#

VRALERT #

SYS_RESET #

PCH_PW ROK

AC_PRES ENT_R

PCH_GPD 11

BATLOW #

LAN_W AKE#

SOC_PCIE_ WAKE#

PBTN_OU T#_R

PCH_DPW ROK_R

EC_RSMR ST#

SUSACK#(29 )

CLR ME

N

CLR CMOS

Wireless LAN

CLKREQ_PCIE#3 use PU RN19.

CLRP4 SHORT PA DS

1 2

RH60 0_0201_ 5%short@

PV: remove TBT_WAKE#

PBTN_OU T#(29 )

ACIN(29)

DPWR OK_EC(29 )

A A

RC516 0_020 1_5%

RC515 0_020 1_5%

RC69 0_0 201_5%

12

12

12

PBTN_OU T#_R

AC_PRES ENT_R

PCH_DPW ROK_R

RH66

1K_0201 _5%

R03_0629 For Thermal diode placement del UH2 RH4

EC_VCCS T_PG_R(29)

5

WWAN

VMe SSD

12

PLT_RST#(22,23,24,29,31,33)

EC_RSMR ST#(29)

SYS_PW ROK(29)

PCH_PW ROK(29 )

+1.0V_VC CST

4

AR

SYS_RESET #

TC67 @

12

RC79

1 2

60.4_040 2_1%

4

3

@

CLK_PCIE_ N1(26)

CLK_PCIE_ P1(26 )

CLKREQ_ PCIE#1(26)

CLK_PCIE_ N2(24)

CLK_PCIE_ P2(24 )

CLKREQ_ PCIE#2(24)

CLK_PCIE_N3(23)

CLK_PCIE_P3(23)

CLKREQ_ PCIE#3(23)

CLK_PCIE_N4(33)

CLK_PCIE_P4(33)

CLKREQ_ PCIE#4(33)

+3VS

T33 TP@

T34 TP@

1 2

RC75 10K_020 1_5%@

CLK_PCIE_ N1

CLK_PCIE_ P1

CLKREQ_ PCIE#1

CLK_PCIE_ N2

CLK_PCIE_ P2

CLKREQ_ PCIE#2

CLK_PCIE_ N3

CLK_PCIE_ P3

CLKREQ_ PCIE#3

CLK_PCIE_ N4

CLK_PCIE_ P4

CLKREQ_ PCIE#4

CLK_PCIE_ N5CLKREQ_ PCIE#5

CLK_PCIE_ P5

CLKREQ_ PCIE#5

D15

2 1

H35

F35

AV9

J36

G36

BD10

J38

G38

AV5

H37

F37

AV7

H39

F39

BC5

BB10

KBL-Y_BGA1515

D16

RB751S4 0T1G_SOD523-2

PCH_PW ROKEC_RSMR ST#

21

RB751S4 0T1G_SOD523-2

PV: D15,D16 pop

+3V_PRIM

TC7SH08 FU_SSOP5

5

UH1

P

4

O

12

BB8

BJ12

A62

B61

BP14

BN15

BL6

BF9

BP9

BE15

BC15

BB16

G

3

H2

J1

RH46

100K_02 01_5%

PCH_PLT RST#

SYS_RESET #

EC_RSMR ST#

H_CPUPW RGD_R

EC_VCCS T_PG

PCH_PW ROK

PCH_DPW ROK_R

PCH_SUS WARN#

SUSACK# _R

SOC_PCIE_ WAKE#

LAN_W AKE#

PCH_GPD 11

PDG_DPWROK connect to VccDSW3_3 power rail monitoring circuit to

support Deep Sx state.This signal can be tied to RSMRST# for platforms

that do not support the Deep Sx state.The DSW rails must be stable

for at least 10 ms before DPWROK is asserted to PCH.

PDG_SUSACK#, this signal is driven from the platform EC to PCH to acknowledge

that EC has received the SUSWARN# signals and it is preparing to go into DeepSx

mode.for at least 10 ms before DPWROK is asserted to PCH.

PDG_SLP_SUS#, a low on this signal indicates that PCH is in Deep Sx state and that

EC/platform logic does not need to keep the Primary Rails ON.

EC_VCCS T_PG

PCH_PLT RST#

1

B

2

A

UC1K

@

GPP_B13/PLTRST#

SYS_RESET#

RSMRST#

PROCPWRGD

VCCST_PWRGD

SYS_PWROK

PCH_PWROK

DSW_PWROK

GPP_A13/SUSWARN#/SUSPWRDNACK

GPP_A15/SUSACK#

WAKE#

GPD2/LAN_WAKE#

GPD11/LANPHYPC

GPD7/RSVD

KBL-Y_BGA1515

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SKYLAKE_ULX

SYSTEM POWER MANAGEMENT

11 OF 20

2041/09/ 08 2013/10/ 28

2041/09/ 08 2013/10/ 28

2041/09/ 08 2013/10/ 28

3

UC1J

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

GPP_B5/SRCCLKREQ0#

XTAL24_ OUT

XTAL24_ IN

GPP_B11/EXT_PWR_GATE#

Compal Secret Data

Compal Secret Data

Compal Secret Data

SKYLAKE_ULX

CLOCK SIGNALS

10 OF 20

PWR_ 3V5V_PG (43)

1 2

RC50

EMI@

33_0201 _1%

1 2

RC195

EMI@

33_0201 _1%

Rev0.87

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

SLP_W LAN#

Deciphered Date

Deciphered Date

Deciphered Date

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

XTAL24_ OUT_R

XTAL24_ IN_R

CC8

BC9

AY14

BF16

BH14

BN10

BP11

BH16

BE17

BF14

BD14

BD16

BF7

BG19

BC7

BD6

Rev0.87

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

22P_0402_50V8J

PM_SLP_ S0#

PM_SLP_ S3#

PM_SLP_ S4#

PM_SLP_ S5#

SLP_SUS #

SLP_LAN #

SLP_W LAN#

PM_SLP_ A#

PBTN_OU T#_R

AC_PRES ENT_R

BATLOW #

SM_INTRUD ER#

VRALERT #

2

J34

G34

BA15

M1

L2

P1

BN19

BP18

BH18

BN12

1 2

RC563

1M_0402 _1%

YC1

1

X'tal

G

2

G

X'tal

24MHZ_8 PF_8Y24080002

SJ10000 PS00

TC11@

2

1

SUSCLK_ S

XTAL24_ IN

XTAL24_ OUT

XCLK_BIAS REF

PCH_RTC X1

PCH_RTC X2

SOC_SRT CRST#

SOC_RTC RST#

RH76

1 2

0_0402_ 5%

RH78

1 2

2.7K_020 1_1%

SUSCLK

+1.0V_PR IM

SOC_SRT CRST# (29 )

SOC_RTC RST# (29)

CH46

0.1U_0201_10V6K

RTC_RST# by PWR BTN

PCH_RTC X2

PCH_RTC X1

1 2

RC58 10M_0402_5 %

1 2

YC2

4

3

PM_SLP_ S0# (11,12,29,47,49)

PM_SLP_ S3# (12,29,33,39)

PM_SLP_ S4# (21,29)

TP@

SLP_SUS # (29)

TP@

SLP_W LAN# (23)

TC63@

22P_0402_50V8J

CC7

T392

T35

T395TP@

Title

Title

Title

SKL Y(5/13) CLK,GPIO

SKL Y(5/13) CLK,GPIO

SKL Y(5/13) CLK,GPIO

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

LA-F803P

LA-F803P

LA-F803P

Date: Sheet of

Date: Sheet of

Date: Sheet

PDG_ internal pull-up resistor, nterna

16 ms de-bounce on the input.

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

6.8P_0402_50V8C

1

CC14

2

SJ10000 SK00

32.768KH Z_9PF

1

SUSCLK (23)

1

@EMI@

2

6.8P_0402_50V8C

1

CC12

2

0.1

0.1

0.1

of

9 55Friday, June 08, 201 8

9 55Friday, June 08, 201 8

9 55Friday, June 08, 201 8

5

4

3

2

1

UC1F

@

Strap Pin

Strap Pin

BC3

GPP_B15/GSPI0_CS#

AW10

GPP_B16/GSPI0_CLK

AW6

GPP_B17/GSPI0_MISO

BB4

GPP_B18/GSPI0_MOSI

BB2

GPP_B19/GSPI1_CS#

AW12

GPP_B20/GSPI1_CLK

AW4

GPP_B21/GSPI1_MISO

AW8

GPP_B22/GSPI1_MOSI

AC8

GPP_C8/UART0_RXD

AA8

GPP_C9/UART0_TXD

AA10

GPP_C10/UART0_RTS#

AA12

GPP_C11/UART0_CTS#

AD5

GPP_C20/UART2_RXD

AD7

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD9

GPP_C23/UART2_CTS#

AD11

GPP_C16/I2C0_SDA

AB3

GPP_C17/I2C0_SCL

AB9