A

1 1

B

C

D

E

Compal Confidential

2 2

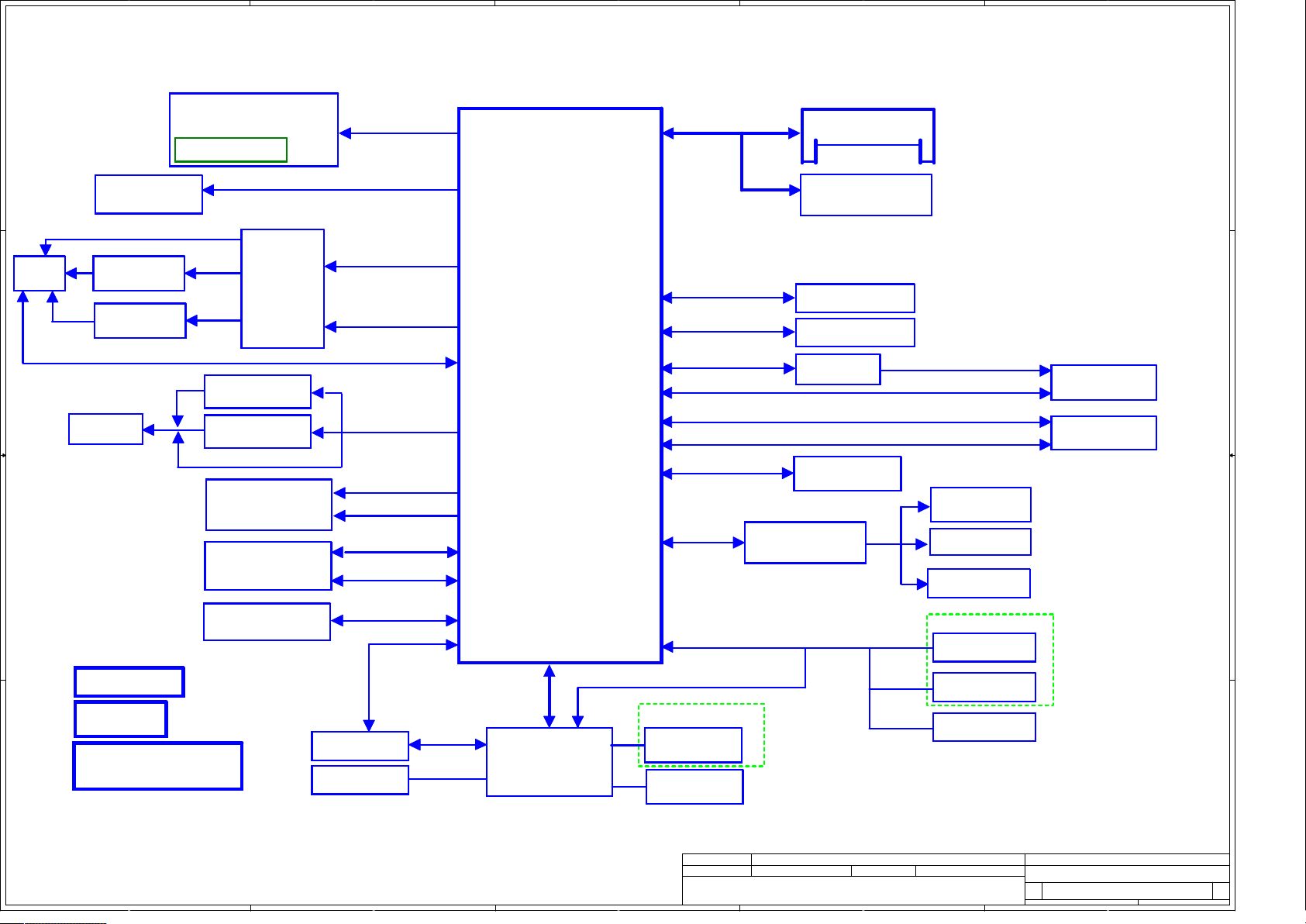

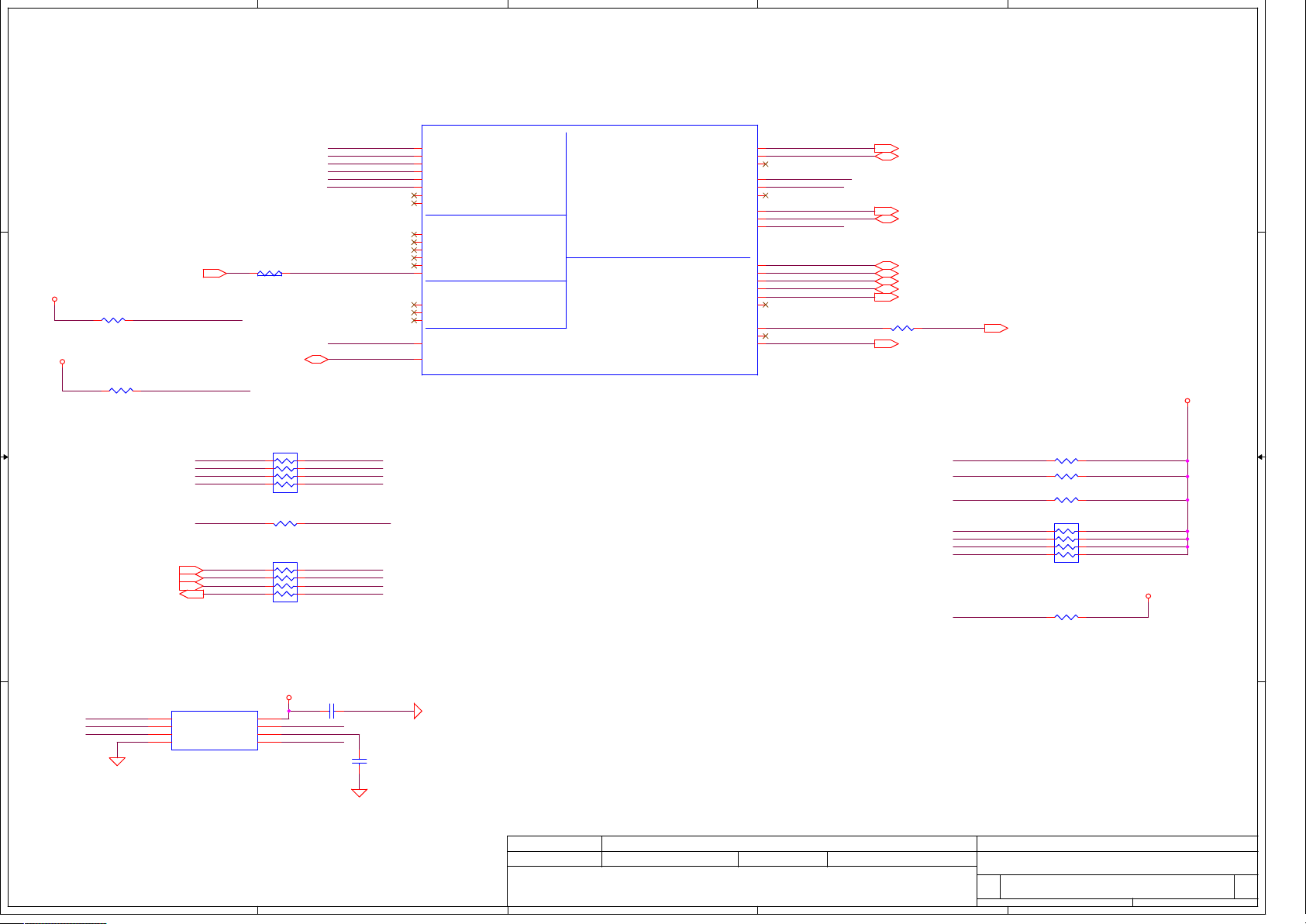

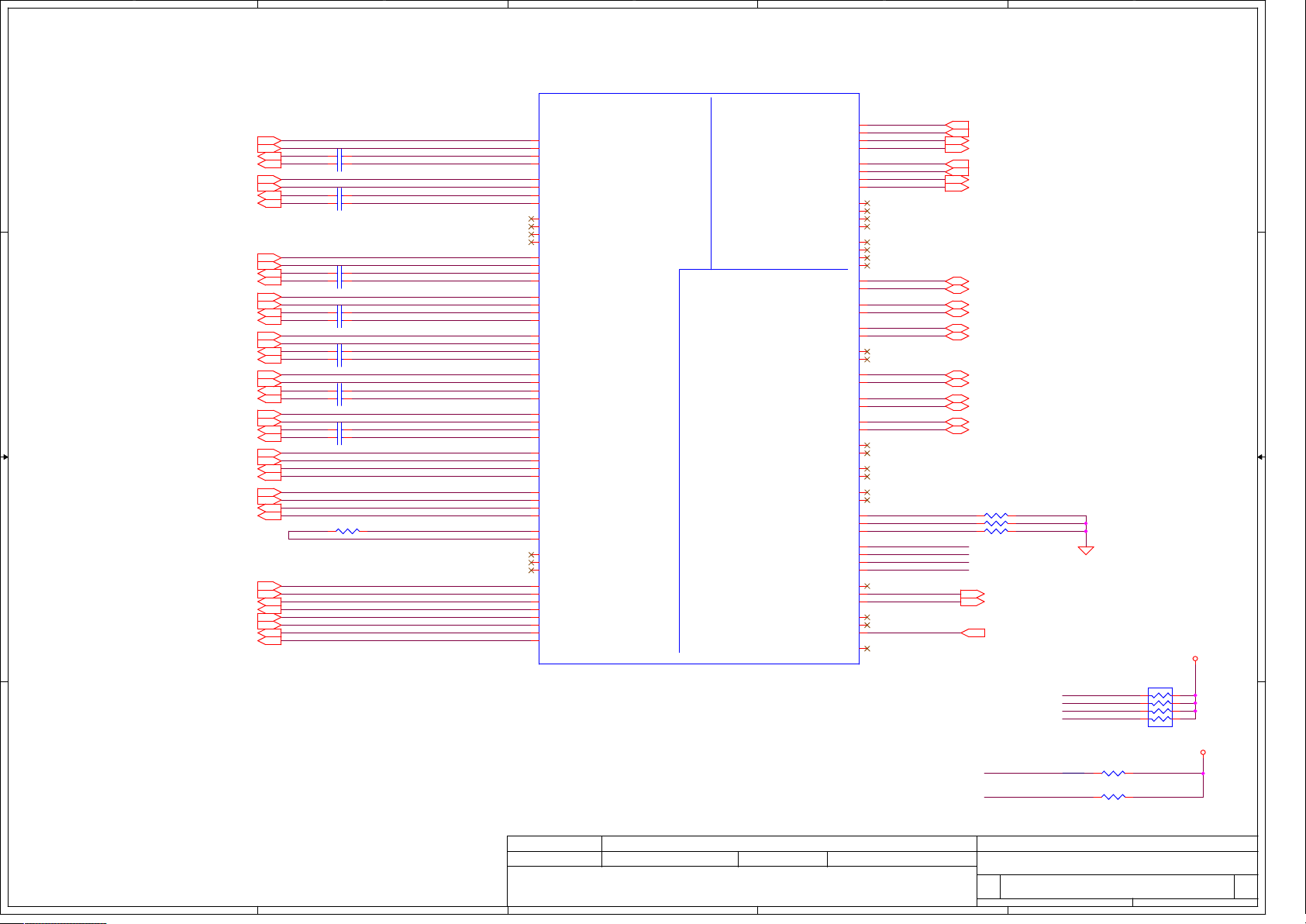

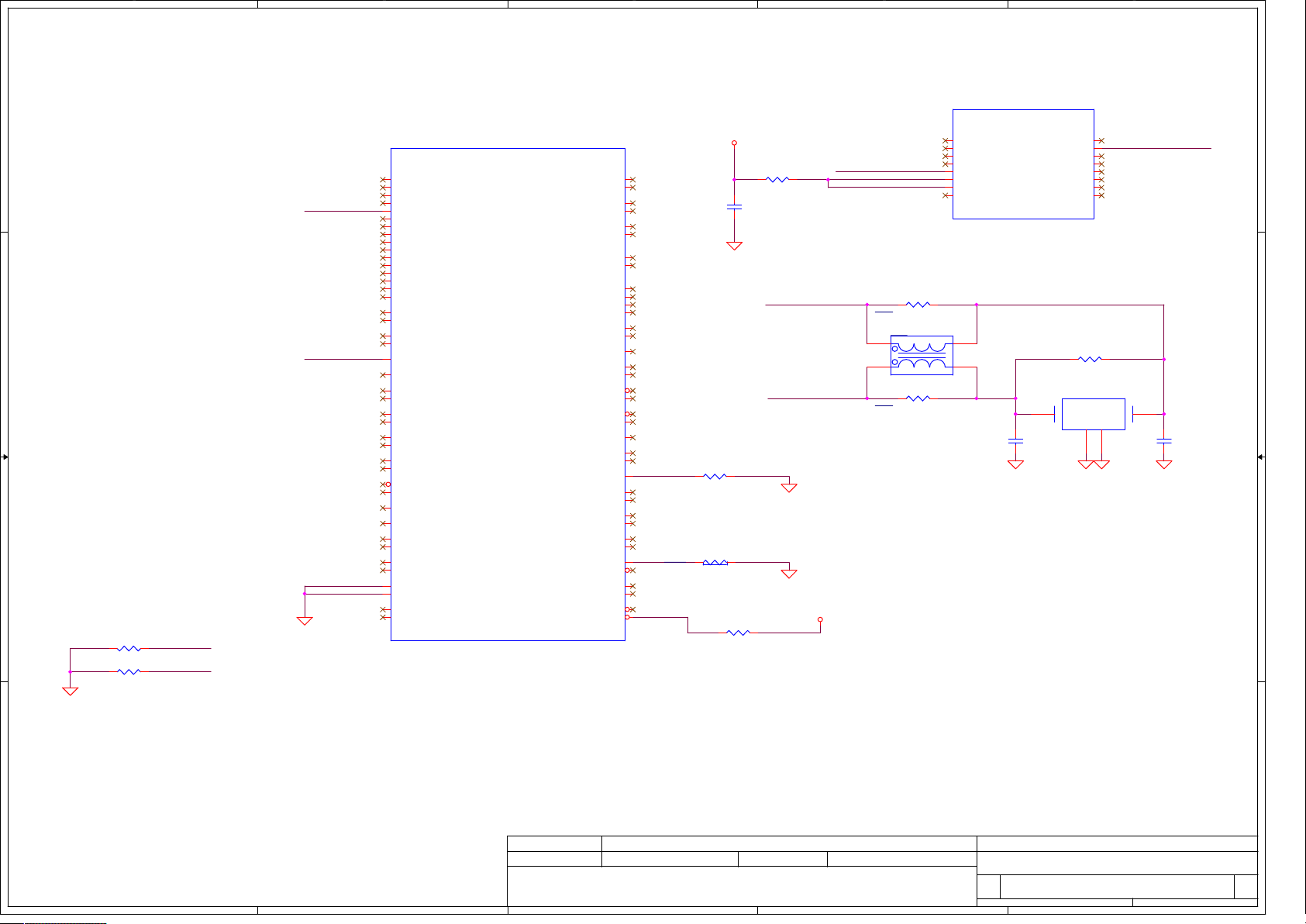

YOGA 730 15"

DIS M/B Schematics Document

Intel KabyLake R Processor with DDR4

N17P-G0-A1 (29x29mm)

2017-12-5

3 3

LA-F661P

REV:1.0

4 4

Compal Electronics, Inc.

Compal Electronics, Inc.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

C

C

C

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Document Number Re v

Document Number Re v

Document Number Re v

LA-F661P

LA-F661P

LA-F661P

E

1 61Wednesday, December 06, 2017

1 61Wednesday, December 06, 2017

1 61Wednesday, December 06, 2017

0.3

0.3

0.3

1

2

3

4

5

Compal Confidential

Pluto 5A (15")

Kabylake-R

GPU

A A

Panel FHD/UHD

IPS

N17P-G0-A1 35W

VRAM 2 56MX32

GDDR5 x 4 (2GB/4G B)

+VGA_ COR E

+1.5V GS

+1.0V GS

+1.8V GS

PEG x4

eDP x1

4 Lanes

DDR4 2400MHz

USB3.1/TBT

DDR4-SO-DIMM 1

DDR4-on board RAM

(4 DRA M Devices per channel) 8G

+1.2V, +0.6VS

Type-C

Conn

Type-C

TI TPS 65988CE

SBU Mux

I2C

AUX/TBT

Intel

Alpine Ridge

AR-LP

TS3D1 0224

B B

HDMI Re-driver

(Option)

PS8407A

HDMI Conn

HDMI2.0 Converter

(Option)

PS175

By pass for HDMI 1.4x

NGFF (TYPE E)

2230 Conn.

WLAN/BT4.0

NGFF (TYPE M)

C C

M.2 PCIE SSD(Gen3)

SPI ROM

W25Q64FVSSIQ

8MB

Power, Novo Button

Power Circuit

MIC/Sensor FPC

(Panel side MIC x2, G sensor x1,

ALS x1, Hall sensor x1)

D D

Touch Pad CONN.

Int. KBD

DDI1

PCIE x2

USB2.0 x1

DDI2

PCIE x1

USB2.0 x1

PCIE x 4

or

SATA x 1

SPI

I2C

PS2

Intel KBL-R U 15W

1356pin BGA

LPC BUS

ENE

KB9022

+3V LP

+3VA LW

+1.0V S

+3VS

+3V_P CH

+RTCV CC

I2C

I2C

MIC/Sensor FPC

Hall Sensor x1

TCS20DLR

Hall Sensor x1

TCS20DLR

USB2.0 x1

USB2.0 x1

USB2.0 x1

USB3.0 x1

USB3.0 x1

USB2.0 x1

I2C

HDA

FingerPrint

Camera

USB Charger

TPS2546

Touch Panel

Audio Codec

Realtek ALC3240

1.0M HD

USB 3.0 conn x1

USB 3.0 conn x1

Combo Jack

Int. Speaker

Int. Array Mic *2

MIC/Sensor FPC

ALS

AL3010

G Sensor x1

BMA250E

G Sensor x1

BMA250E

Compa l Electronics, Inc.

Compa l Electronics, Inc.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

1

2

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

2016/4/19 2017/4/19

2016/4/19 2017/4/19

2016/4/19 2017/4/19

Compal Secre t Data

Compal Secre t Data

Compal Secre t Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compa l Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

LA-F661P

LA-F661P

LA-F661P

Cover Page

Cover Page

Cover Page

5

2 61Tuesday, October 17, 2017

2 61Tuesday, October 17, 2017

2 61Tuesday, October 17, 2017

of

0.3

0.3

0.3

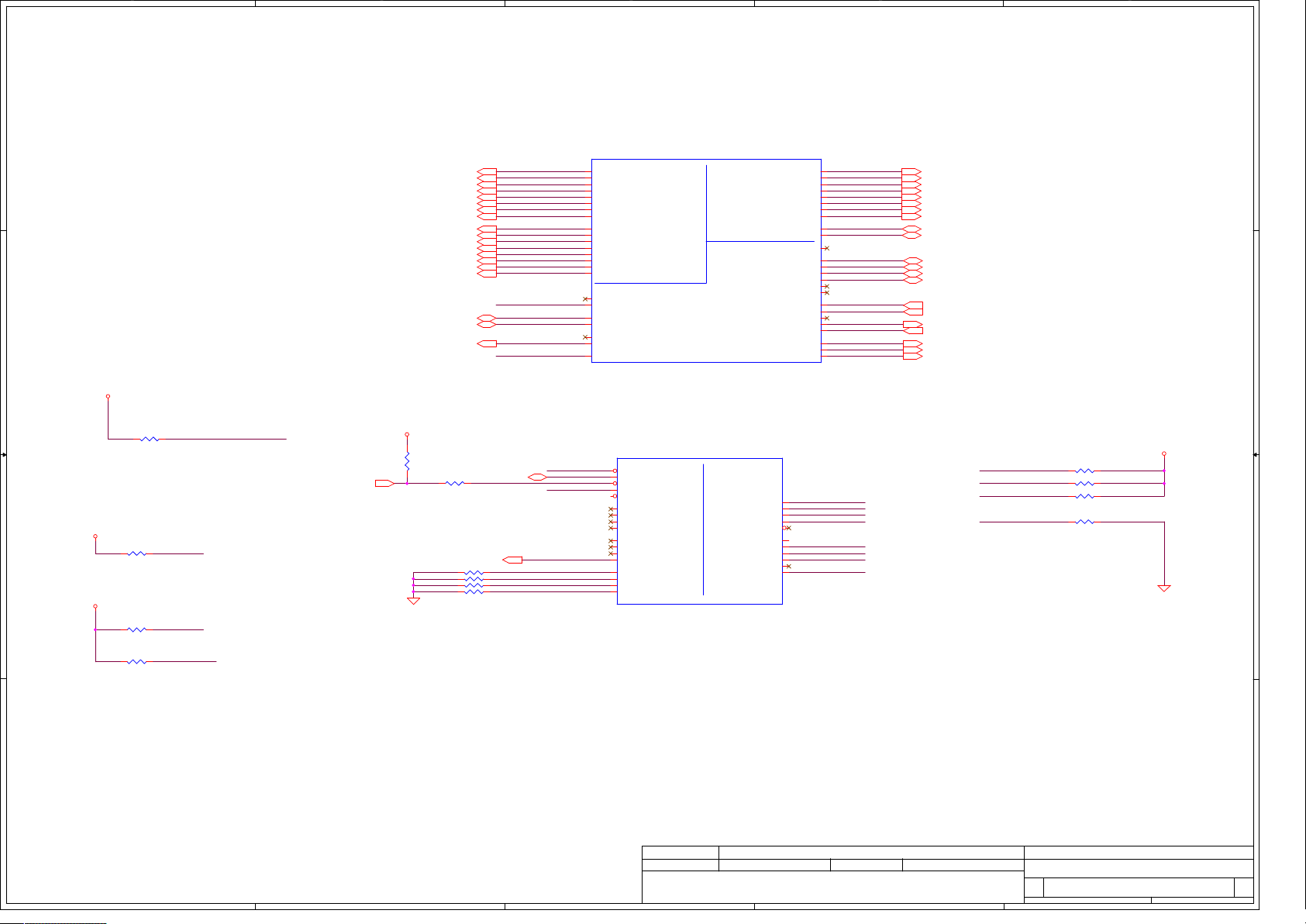

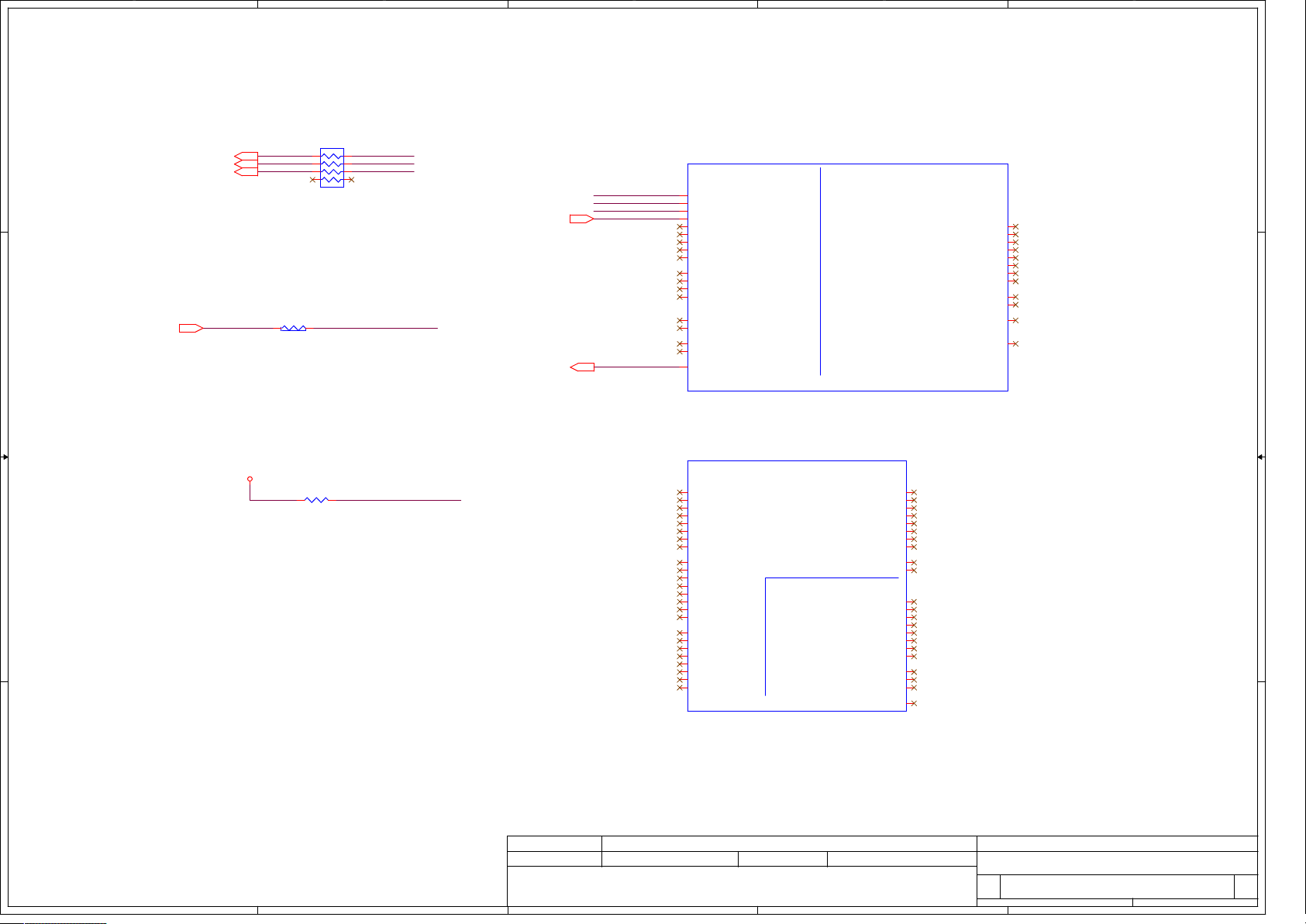

A

1 1

2 2

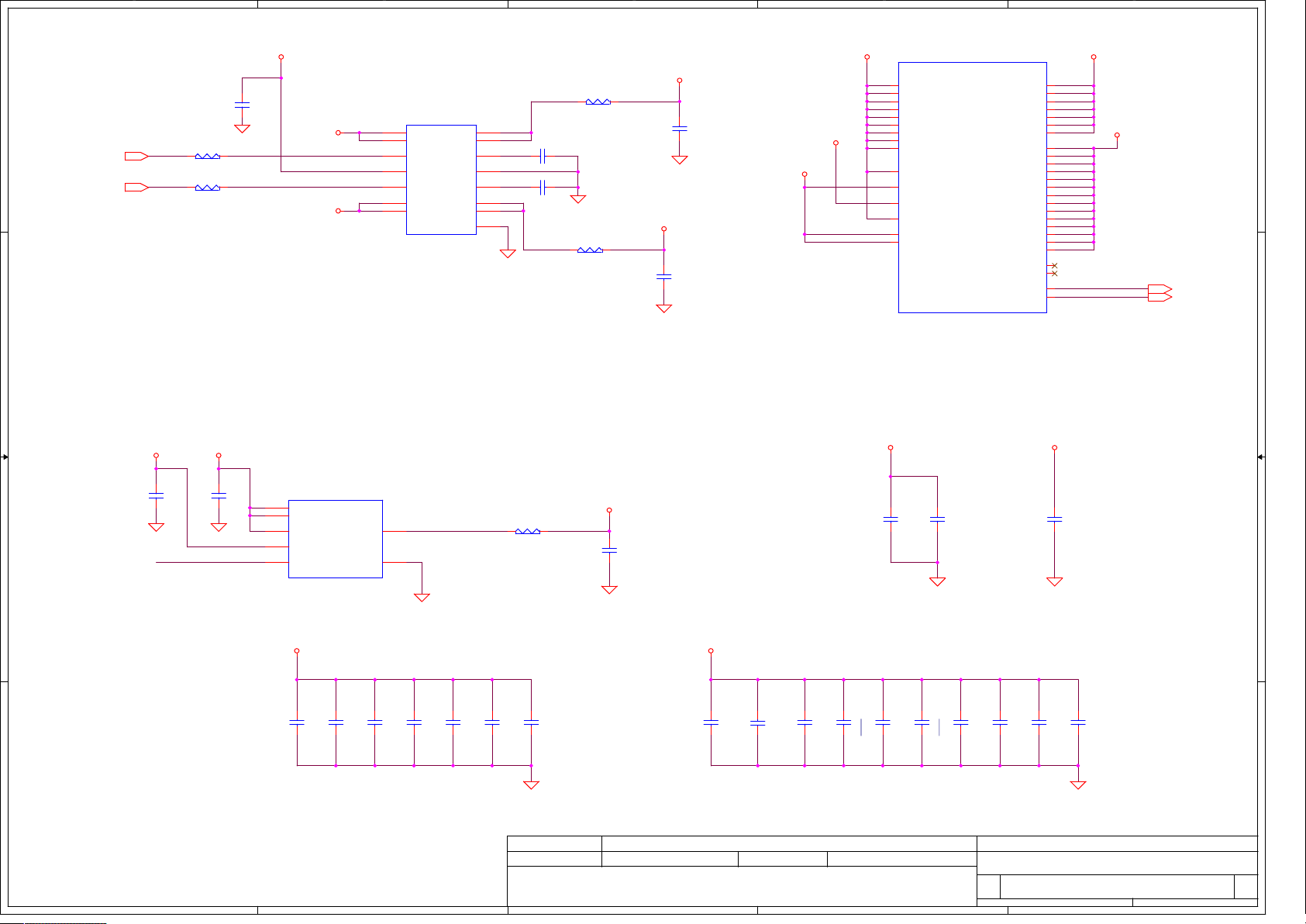

+3VS

B

CPU_DP1_ N038

CPU_DP1_ P038

CPU_DP1_ N138

CPU_DP1_ P138

CPU_DP1_ N238

CPU_DP1_ P238

CPU_DP1_ N338

CPU_DP1_ P338

CPU_DP2_ N031

CPU_DP2_ P031

CPU_DP2_ N131

CPU_DP2_ P131

CPU_DP2_ N231

CPU_DP2_ P231

CPU_DP2_ N331

CPU_DP2_ P331

CPU_DDPB _CTRL_DATA

HDMICLK_NB31,32

HDMIDAT_NB31,32

TS_I2C_RST #29

EDP_COMP

E55

F55

E58

F58

F53

G53

F56

G56

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

N7

N8

N11

N12

E52

C

UC1A

@

DDI1_TXN[0]

DDI1_TXP[0]

DDI1_TXN[1]

DDI1_TXP[1]

DDI1_TXN[2]

DDI1_TXP[2]

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

GPP_E22

GPP_E23

EDP_RCOMP

SKL-U_BGA13 56

DDI

DISPLAY SIDEBANDS

SKL-U

1 OF 20

EDP

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

RSVD

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

D

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_TXN0 29

EDP_TXP0 29

EDP_TXN1 29

EDP_TXP1 29

EDP_TXN2 29

EDP_TXP2 29

EDP_TXN3 29

EDP_TXP3 29

EDP_AUXN 29

EDP_AUXP 29

DDI1_AUX_DN 38

DDI1_AUX_DP 3 8

DDI2_AUX_DN 30

DDI2_AUX_DP 3 0

CPU_DP1_ HPD 38

CPU_DP2_ HPD 30,31,32

EC_SCI# 10,45

EDP_HPD 29

ENBKL 29,45

INVPWM 2 9

PCH_ENVDD 29

E

CPU_DDPB _CTRL_DATA

H_PROCHO T#45

1 2

1 2

@

A

12

EDP_COMP

24.9_0402 _1%

H_THERM TRIP#

12

CATERR#

RC218 2.2K_02 01_5%TBT@

+1.0VS_VCCIO

RC3

3 3

+1.0V_VCCST

RC5 1K_0402_ 5%

RC19 49.9_0402 _1%

4 4

+1.0VS_VCCIO

12

RC4

1K_0402_ 5%

RC6 499_0402 _1%

B

1 2

TBT_FORC E_PWR39

RC7 49.9_0402_ 1%

RC8 49.9_0402_ 1%

RC9 49.9_0402_ 1%@

RC10 49.9_0402 _1%@

H_PECI45

12

12

12

12

CATERR#

H_PECI

H_PROCHO T#_R

H_THERM TRIP#

CPU_POPIRCOM P

PCH_OPIRCOMP

EDRAM_OPIO_RC OMP

EOPIO_RCOMP

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

UC1D

SKL-U_BGA13 56

@

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

CPU MISC

Issued Date

Issued Date

Issued Date

SKL-U

4 OF 20

Rev_1.0

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

CPU_XDP_T CK0

B61

SOC_XDP_TD I

D60

SOC_XDP_TD O

A61

SOC_XDP_TM S

C60

B59

B56

SOC_XDP_TD I

D59

SOC_XDP_TD O

A56

SOC_XDP_TM S

C59

C61

CPU_XDP_T CK0

A59

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

+1.0VS_VCCIO

SOC_XDP_TM S

SOC_XDP_TD I

SOC_XDP_TD O

CPU_XDP_T CK0

1 2

RC11 51_0402_ 5%CMC@

1 2

RC12 51_0402_ 5%CMC@

1 2

RC13 51_0402_ 5%DCI@

1 2

RC14 51_0402_ 5%DCI@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

Size D ocument Number Re v

Size D ocument Number Re v

Size D ocument Number Re v

Custom

Custom

Custom

Dat e: Sheet of

Dat e: Sheet of

Dat e: Sheet of

LA-F661P

LA-F661P

LA-F661P

E

0.3

0.3

6 61Wednesday, October 18, 2017

6 61Wednesday, October 18, 2017

6 61Wednesday, October 18, 2017

0.3

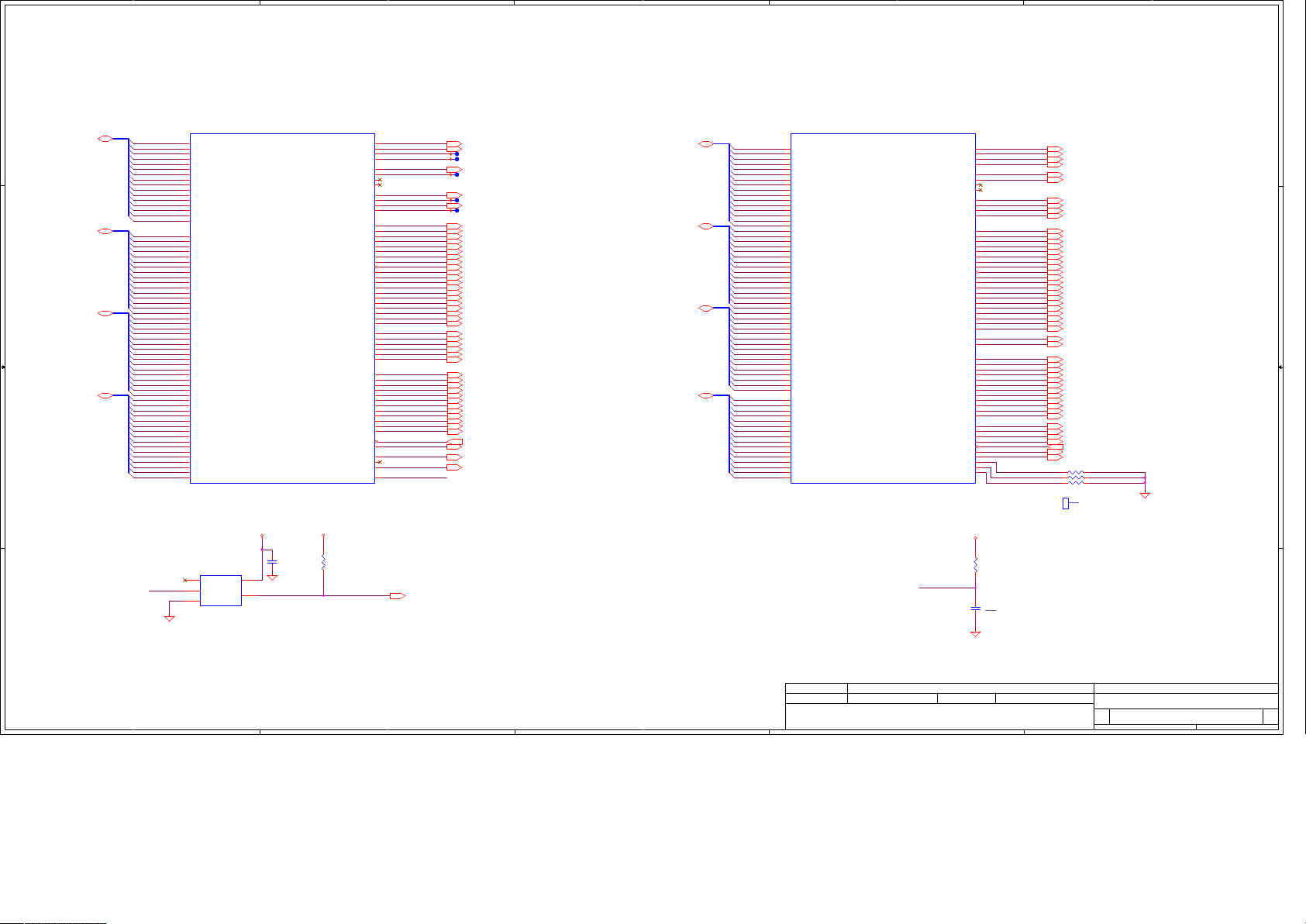

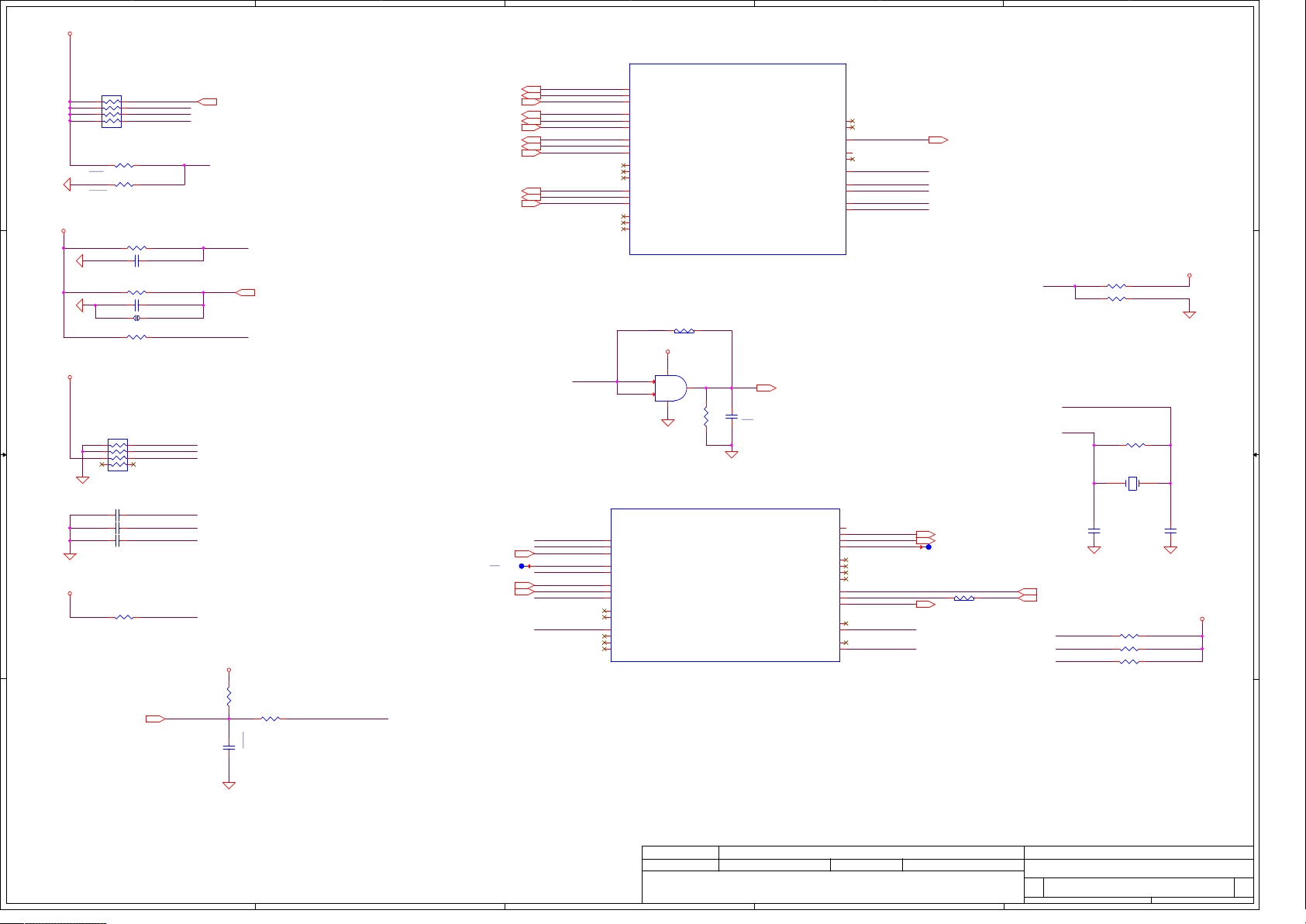

5

D D

4

3

2

1

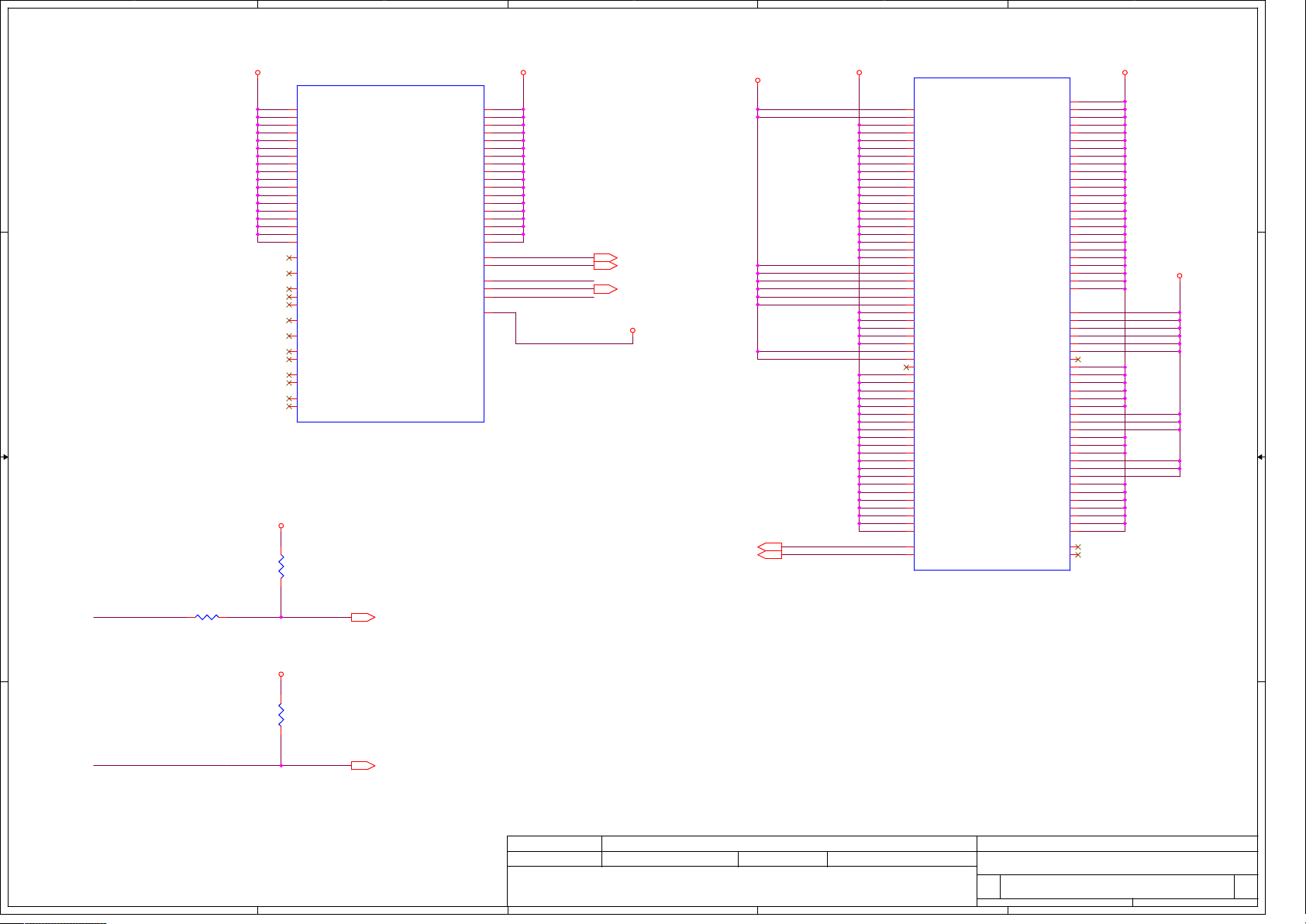

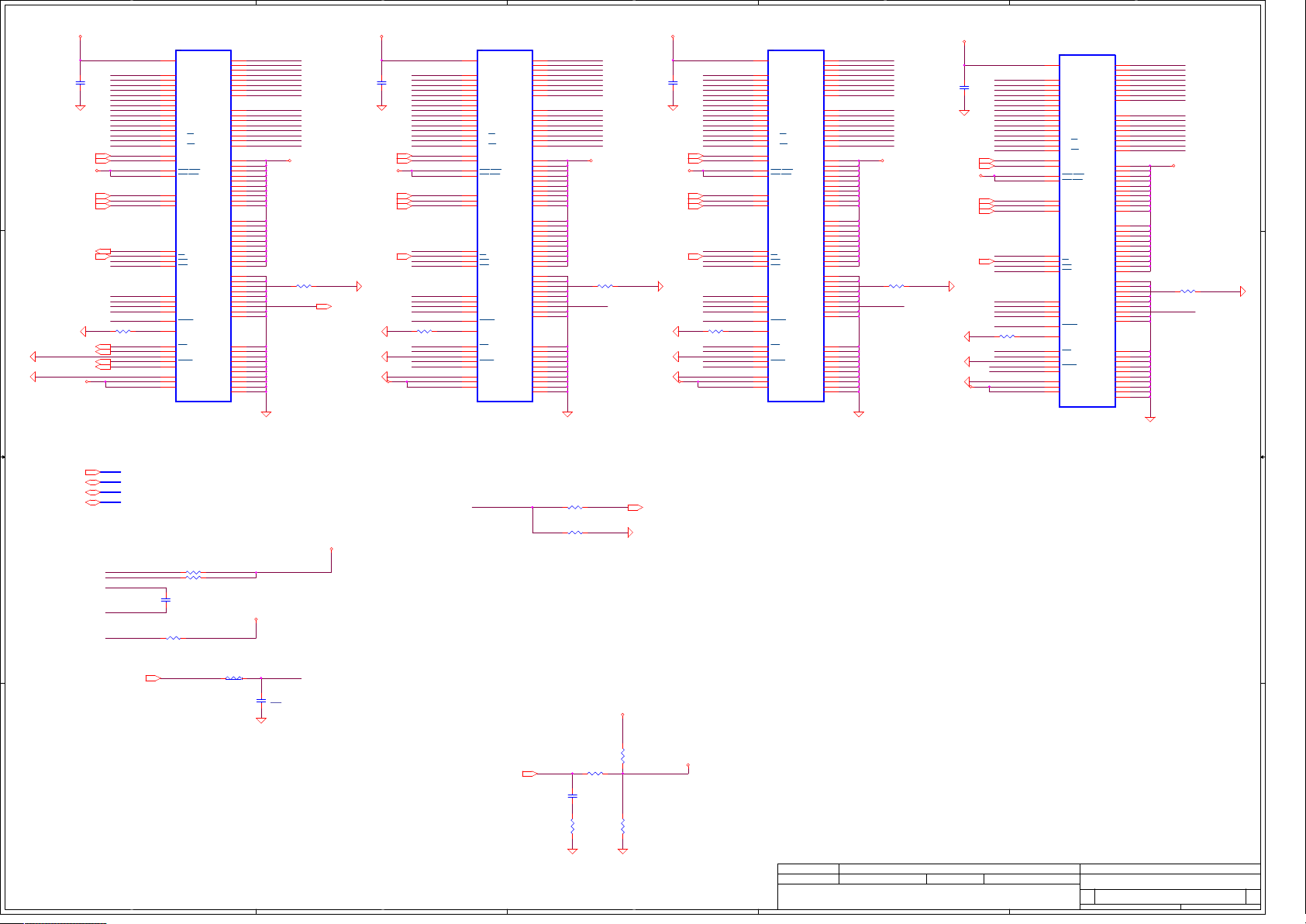

DDR_A_D[0..15]18

DDR_A_D[16..31]18

C C

DDR_A_D[32..47]18

DDR_A_D[48..63]18

B B

A A

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_PG_CTRL

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

SA00007WE00

SKL-U

DDR0_MA[5]/DDR0_CAA[0]/DD R0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DD R0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DD R0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DD R0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DD R0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DD R0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/D DR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/D DR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/D DR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/D DR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/D DR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DD R0_MA[15]

DDR0_WE#/DDR0_C AB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DD R0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DD R0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DD R0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DD R0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/D DR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DD R0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DD R0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

1

CC1

0.1U_0201_10V6K

@

2

UC2

5

4

Y

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR3L / LPDDR3 / DDR4

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

+3VS+1.2V

12

RC132

100K_0402_5%

DDR0_PAR

Rev_1.0

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

M_A_ACT#

DDR_A_BG1

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PARITY

+0.6V_A_VREFCA

+0.6V_B_VREFDQ

DDR_PG_CTRL

DDR_VTT_PG_CTRL 49

DDR_A_CLK#0 18

DDR_A_CLK0 18

T186TP@

T189TP@

DDR_A_CKE0 18,19

T190TP@

DDR_A_CS#0 18,19

T187TP@

DDR_A_ODT0 18,19

T188TP@

DDR_A_MA5 18,19

DDR_A_MA9 18,19

DDR_A_MA6 18,19

DDR_A_MA8 18,19

DDR_A_MA7 18,19

DDR_A_BG0 18,19

DDR_A_MA12 18,19

DDR_A_MA11 18,19

M_A_ACT# 18,19

DDR_A_BG1 18

DDR_A_MA13 18,19

DDR_A_MA15 18,19

DDR_A_MA14 18,19

DDR_A_MA16 18,19

DDR_A_BA0 18,19

DDR_A_MA2 18,19

DDR_A_BA1 18,19

DDR_A_MA10 18,19

DDR_A_MA1 18,19

DDR_A_MA0 18,19

DDR_A_MA3 18,19

DDR_A_MA4 18,19

DDR_A_DQS#0 18

DDR_A_DQS0 18

DDR_A_DQS#1 18

DDR_A_DQS1 18

DDR_A_DQS#2 18

DDR_A_DQS2 18

DDR_A_DQS#3 18

DDR_A_DQS3 18

DDR_A_DQS#4 18

DDR_A_DQS4 18

DDR_A_DQS#5 18

DDR_A_DQS5 18

DDR_A_DQS#6 18

DDR_A_DQS6 18

DDR_A_DQS#7 18

DDR_A_DQS7 18

DDR_A_ALERT# 18

DDR_A_PARITY 18,19

+0.6V_A_VREFCA 18

+0.6V_B_VREFDQ 20

DDR_B_D[0..15]20

DDR_B_D[16..31]20

DDR_B_D[32..47]20

DDR_B_D[48..63]20

UC1C

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45 DDR_B_DQS#2

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DD R1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DD R1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DD R1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DD R1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DD R1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DD R1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/D DR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/D DR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/D DR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/D DR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/D DR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DD R1_MA[15]

DDR1_WE#/DDR1_C AB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DD R1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DD R1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DD R1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DD R1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/D DR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DD R1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DD R1_MA[0]

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR CH - B

3 OF 20

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR_DRAMRST#

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_ALERT#

DDR1_PAR

Rev_1.0

+1.2V

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

12

RC20

470_0402_5%

1

CC96

100P_0201_25V8J

2

ESD@

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

DDR_B_ACT#

DDR_B_BG1

DDR_B_MA13

DDR_B_MA15

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 20

DDR_B_CLK#1 20

DDR_B_CLK0 20

DDR_B_CLK1 20

DDR_B_CKE0 20

DDR_B_CKE1 20

DDR_B_CS#0 20

DDR_B_CS#1 20

DDR_B_ODT0 20

DDR_B_ODT1 20

DDR_B_MA5 20

DDR_B_MA9 20

DDR_B_MA6 20

DDR_B_MA8 20

DDR_B_MA7 20

DDR_B_BG0 20

DDR_B_MA12 20

DDR_B_MA11 20

DDR_B_ACT# 20

DDR_B_BG1 20

DDR_B_MA13 20

DDR_B_MA15 20

DDR_B_MA14 20

DDR_B_MA16 20

DDR_B_BA0 20

DDR_B_MA2 20

DDR_B_BA1 20

DDR_B_MA10 20

DDR_B_MA1 20

DDR_B_MA0 20

DDR_B_MA3 20

DDR_B_MA4 20

DDR_B_DQS#0 20

DDR_B_DQS0 20

DDR_B_DQS#1 20

DDR_B_DQS1 20

DDR_B_DQS#2 20

DDR_B_DQS2 20

DDR_B_DQS#3 20

DDR_B_DQS3 20

DDR_B_DQS#4 20

DDR_B_DQS4 20

DDR_B_DQS#5 20

DDR_B_DQS5 20

DDR_B_DQS#6 20

DDR_B_DQS6 20

DDR_B_DQS#7 20

DDR_B_DQS7 20

DDR_B_ALERT# 20

DDR_B_PARITY 20

DDR_DRAMRST# 18,20

1 2

RC16 200_0402_1%SDP@

1 2

RC17 80.6_0402_1%

1 2

RC18 100_0402_1%

DDP@

RC16

SD034121090

121_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/5/3 2017/6 /2

2017/5/3 2017/6 /2

2017/5/3 2017/6 /2

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

LA-F661P

LA-F661P

LA-F661P

Wednesday, October 18, 2017

Wednesday, October 18, 2017

Wednesday, October 18, 2017

1

61

61

61

7

7

7

0.3

0.3

0.3

5

4

3

2

1

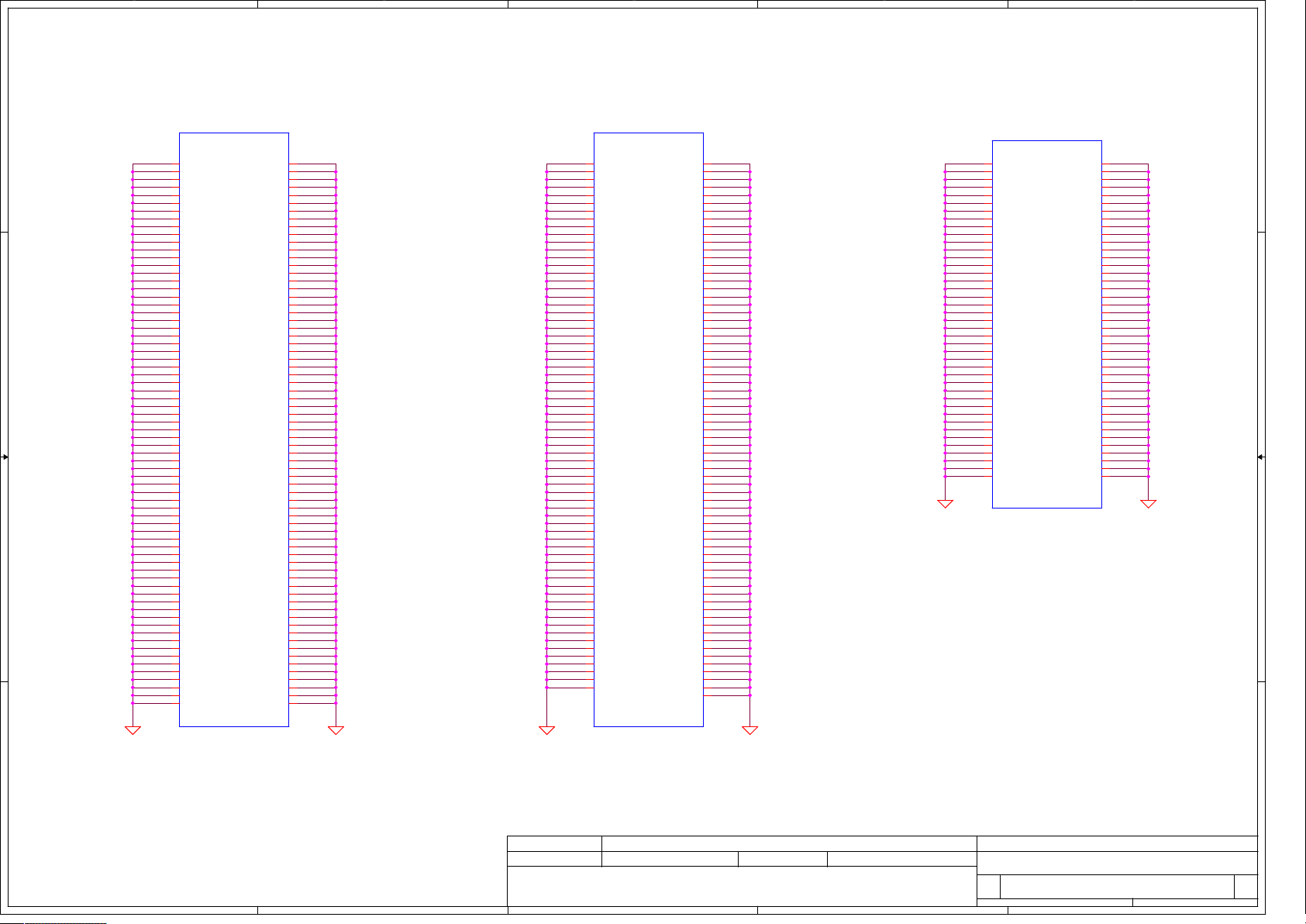

UC1E

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

SKL-U_B GA1356

@

SPI - F LASH

SPI - TOUCH

C LINK

D D

SOC_SP I_CLK

SOC_SP I_SO

SOC_SP I_SI

SOC_SP I_IO2

SOC_SP I_IO3

SOC_SP I_CS#0

RC56

TBT_CIO_ PLUG_EVENT #39

+3VS

1 2

RC25 8.2K_0402_ 5%

C C

B B

+3VS

1 2

RC112 10K_04 02_5%

EC_SPI_C LK45

EC_SPI_M OSI45

EC_SPI_C S0#45

EC_SPI_M ISO45

1 2

SERIRQ

KB_RST #

SOC_SP I_SO

SOC_SP I_CLK SOC_SP I_CLK_0_R

SOC_SP I_SI

SOC_SP I_IO3

SOC_SP I_IO2

RC30 33_0 402_5%EMI@

EC_SPI_C LK

EC_SPI_M OSI SOC_SP I_SI_0_R

EC_SPI_C S0#

EC_SPI_M ISO

TBT_CIO_ PLUG_EVENT #_R1

0_0402 _5%

SERIRQ45

RPC1

1 8

2 7

3 6

4 5

33_080 4_8P4R_5%

EMI@

1 2

RPC3

1 8

2 7

3 6

4 5

33_080 4_8P4R_5%

EMI@

SERIRQ

SOC_SP I_SO_0_R

SOC_SP I_SI_0_R

SOC_SP I_IO3_0_R

SOC_SP I_IO2_0_R

SOC_SP I_CLK_0_R

SOC_SP I_CS#0

SOC_SP I_SO_0_R

AW13

SKL-U

LPC

5 OF 20

SMBUS, SMLINK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

Rev_1.0

GPP_C0/SMBCLK

GPP_C3/SML0CLK

GPP_C6/SML1CLK

GPP_A8/CLKRUN#

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

PCH_SM B_CLK

PCH_SM B_DATA

SOC_SM L0CLK

SOC_SM L0DATA

EC_SMB _CK2

EC_SMB _DA2

SOC_SM L1ALERT#

LPC_AD 0

LPC_AD 1

LPC_AD 2

LPC_AD 3

LPC_FR AME#

LPC_CL K0

PM_CLK RUN#KB_RST #

1 2

RC26 22_0402_5 %EMI@

PCH_SM B_CLK 20

PCH_SM B_DATA 20

EC_SMB _CK2 21,35,45

EC_SMB _DA2 21,35,45

LPC_AD 0 45

LPC_AD 1 45

LPC_AD 2 45

LPC_AD 3 45

LPC_FR AME# 45

PM_CLK RUN# 45

EC_SMB _CK2

EC_SMB _DA2

SOC_SM L1ALERT#

PCH_SM B_CLK

PCH_SM B_DATA

SOC_SM L0CLK

SOC_SM L0DATA

PM_CLK RUN#

CLK_LP C_EC 45

1 2

RC28 1K_0402_5 %

1 2

RC29 1K_0402_5 %

1 2

@

RC113 150K_0 402_5%

RPC2

1 8

2 7

3 6

4 5

1K_080 4_8P4R_5%

1 2

RC31 8.2K_04 02_5%

+3VS

+3VS

+3VALW

5

UC3

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25 Q64FVSSIQ_SO 8

SA0000 39A40

VCC

/HOLD(IO3)

CLK

DI(IO0)

8

7

6

5

SOC_SP I_CS#0

SOC_SP I_IO2_0_R

A A

@

1 2

CC2 0.1U_0 201_10V K X5 R

SOC_SP I_IO3_0_RSOC_SP I_SO_0_R

SOC_SP I_CLK_0_R

SOC_SP I_SI_0_R

1

CC3

10P_04 02_50V8J

2

@EMI@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Dat e: Sh eet o f

Dat e: Sh eet o f

2

Dat e: Sh eet o f

Compal Electronics, Inc.

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

LA-F661P

LA-F661P

LA-F661P

8 61Wedn esday, October 18, 2017

8 61Wedn esday, October 18, 2017

8 61Wedn esday, October 18, 2017

1

0.3

0.3

0.3

5

D D

RPC4

HDA_BITC LK_AUDIO33

HDA_SYNC _AUDIO33

HDA_SD OUT_AUDIO33

ME_EN45

C C

RC116 0_0402 _5%

1 8

2 7

3 6

4 5

33_080 4_8P4R_5%

EMI@

12

4

HDA_BIT_ CLK

HDA_SYNC

HDA_SD OUT

HDA_SD OUT

3

UC1G

@

HDA_SYNC

HDA_BIT_ CLK

HDA_SD IN033

HDA_SP KR33

HDA_SD OUT

HDA_SP KR

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK7

AK6

AK9

AK10

AW5

J5

H5

D7

D8

C8

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_B GA1356

SKL-U

7 OF 20

2

SDIO / SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

Rev_1.0

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

1

UC1I

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_B GA1356

@

CSI-2

Compal Secret Data

Compal Secret Data

Compal Secret Data

+3VS

4

HDA_SP KR

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

3

1 2

RC33 2.2K_04 02_5%@

B B

A A

5

SKL-U

9 OF 20

Deciphered Date

Deciphered Date

Deciphered Date

Rev_1.0

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

2

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Dat e: Sh eet o f

Dat e: Sh eet o f

Dat e: Sh eet o f

Compal Electronics, Inc.

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-F661P

LA-F661P

Wedn esday, October 18, 2017

Wedn esday, October 18, 2017

Wedn esday, October 18, 2017

LA-F661P

1

61

61

61

9

9

9

0.3

0.3

0.3

+3VS

5

4

3

2

1

4

CLOCK SIGNALS

12

RC44

100K_0402_5%

SKL-U

11 OF 20

SKL-U

10 OF 20

12

CC8

100P_040 2_50V8J

ESD@

GPP_B11/EXT_PWR_GATE#

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

PCI_RST# 21,34,40,45

Rev_1.0

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

Rev_1.0

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

SUSCLK

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTC RST#

EC_CLEAR_ CMOS#

PM_SLP_S3 #

PM_SLP_S4 #

PM_SLP_S5 #

PBTN_OUT #

AC_PRESENT _R

PM_BATLOW #

SM_INTRUD ER#

SOC_VRALERT #

SUSCLK 3 4

PM_SLP_S3 # 45

PM_SLP_S4 # 45,47,49

T131TP@

1 2

RC103 0_0402 _5%

PM_BATLOW # 39

XCLK_BIASREF

RC35 2.7K_040 2_1%

RC110 60.4_04 02_1%

SOC_RTCX2

SOC_RTCX1

PBTN_OUT # 45

AC_PRESENT 21,45

PM_BATLOW #

AC_PRESENT _R

SOC_VRALERT #

1 2

1 2

@

1 2

RC41 10M_0402 _5%

1 2

32.768KHZ 9 PF 20PPM 9H0328 0012

1

CC9

6.8P_0402 _50V8C

2

1 2

RC46 8.2K_040 2_5%

1 2

@

RC48 10K_040 2_5%

1 2

@

RC50 10K_040 2_5%

+1.0VALW

YC2

1

2

CC10

6.8P_0402 _50V8C

+3VALW

UC1J

@

RPC6

18

TBTCLK_ REQ#

27

WLANCLK _REQ#

36

SSDCLK_R EQ#

D D

+3VL_RTC

C C

+3VALW

B B

+3VALW

45

10K_0804 _8P4R_5%

DIS@

1 2

RC34 10K_0402_ 5%

1 2

@

RC140 10K_0402 _5%

1 2

RC36 20K_040 2_5%

1 2

CC6 1U_0402_ 6.3V6K

1 2

RC37 20K_040 2_5%

1 2

CC7 1U_0402_ 6.3V6K

1 2

CLRP2 SHORT PADS

1 2

RC39 1M_0402 _5%

RPC7

PCH_PW ROK

18

EC_RSMRS T#

27

SYS_RESET#

36

45

10K_0804 _8P4R_5%

1 2

ESD@

CC97 100P_0402 _50V8J

1 2

ESD@

CC94 100P_0402 _50V8J

1 2

ESD@

CC95 100P_0402 _50V8J

1 2

VCCST_PW RGD45

SYS_RESET#

EC_RSMRS T#

SYS_PWRO K

RC54

1K_0402_ 5%

VGA_CLKREQ#

WAKE#

EC_SCI# 6,45

SOC_SRTC RST#

EC_CLEAR_ CMOS# 45

SM_INTRUD ER#

+1.0V_VCCST

12

RC52

1K_0402_ 5%

1 2

RC53 60.4_040 2_1%

CC126

100P_0402_50V8J

1

ESD@

2

EC_VCCST_ PG

CLK_PCIE_T BT#4 0

CLK_PCIE_T BT40

TBTCLK_ REQ#40

CLK_PEG_VGA#21

CLK_PEG_VGA21

VGA_CLKREQ#21

CLK_PCIE_W LAN#34

CLK_PCIE_W LAN34

WLANCLK _REQ#34

CLK_PCIE_SS D#34

CLK_PCIE_SS D34

SSDCLK_R EQ#34

EC_RSMRS T#45

T31 TP@

SYS_PWRO K45

PCH_PW ROK45

TBTCLK_ REQ#

VGA_CLKREQ#

WLANCLK _REQ#

SSDCLK_R EQ#

SOC_PLTR ST#

SYS_RESET#

EC_RSMRS T#

EC_VCCST_ PG

SYS_PWRO K

PCH_PW ROK

EC_RSMRS T#

WAKE#

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

SOC_PLTR ST#

TC7SH08 FUF_SSOP5

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA13 56

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

SKL-U_BGA13 56

1 2

RC55 0_0402_ 5%

+3VS

5

UC4

1

P

B

Y

2

A

G

3

@

@

SYSTEM POWER MANAGEMENT

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

Size D ocument Number Re v

Size D ocument Number Re v

Size D ocument Number Re v

Custom

Custom

Custom

Dat e: Sheet o f

Dat e: Sheet o f

2

Dat e: Sheet o f

LA-F661P

LA-F661P

LA-F661P

1

10 61Wednesday, October 18, 2017

10 61Wednesday, October 18, 2017

10 61Wednesday, October 18, 2017

0.3

0.3

0.3

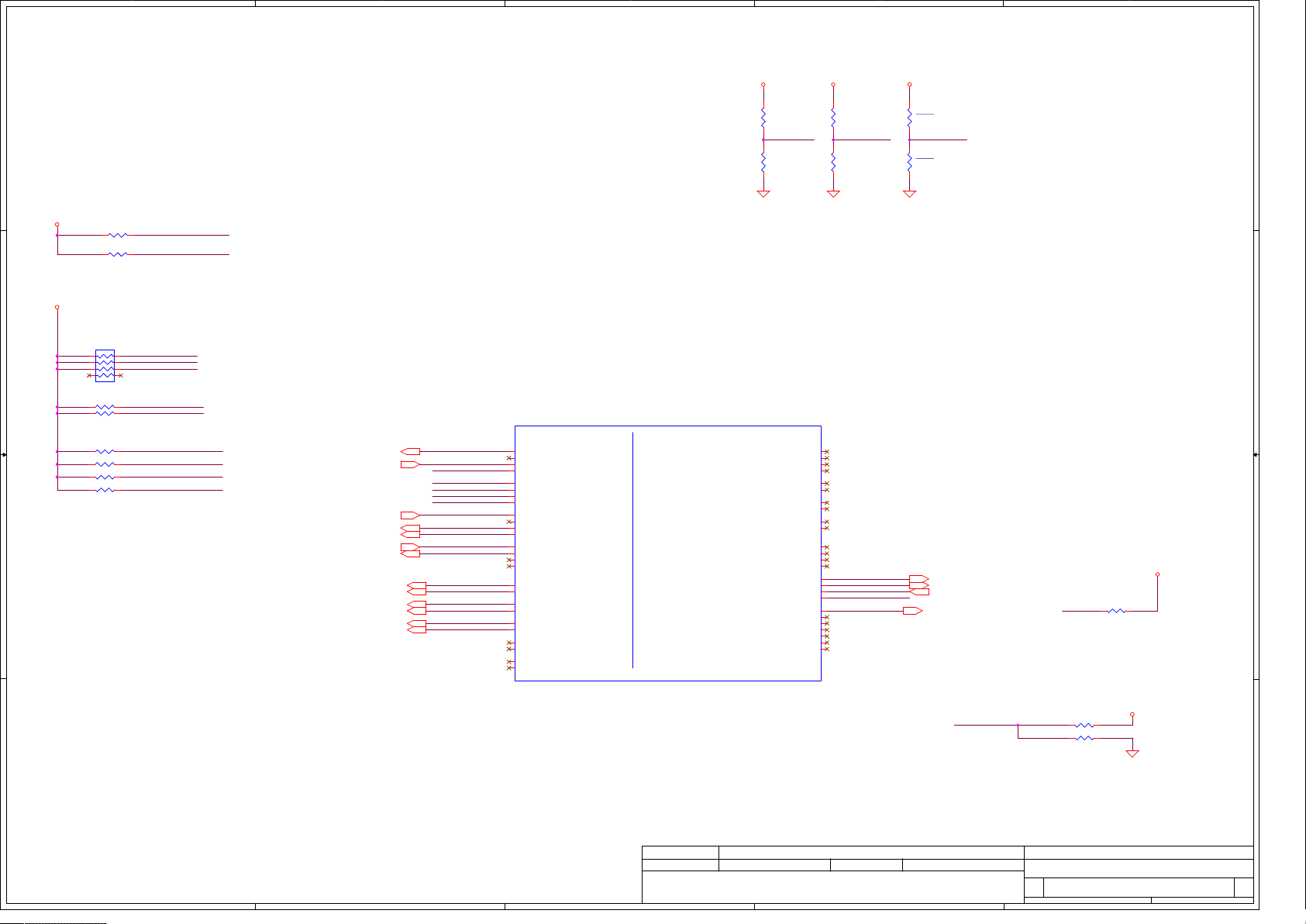

5

D D

4

3

+3VS +3VS +3VS

12

RC135

10K_0402 _5%

X76RAM@

OBRAM_ID0 OBRAM_ID1 OBRAM_ID2

12

RC136

10K_0402 _5%

X76RAM@

12

12

RC133

10K_0402 _5%

X76RAM@

RC134

10K_0402 _5%

X76RAM@

2

12

RC137

10K_0402 _5%

X76RAM@

12

RC138

10K_0402 _5%

X76RAM@

1

+3VS

+3VS

C C

B B

1 2

RC59 4.7K_04 02_5%@

1 2

RC60 150K_0 402_5%@

RPC5

18

27

36

45

10K_0804 _8P4R_5%

1 2

RC83 49.9K_04 02_1%

1 2

RC84 49.9K_04 02_1%

1 2

RC27 499_04 02_1%

1 2

RC32 499_04 02_1%

1 2

RC42 2.2K_040 2_5%

1 2

RC43 2.2K_040 2_5%

DGPU_HOLD _RST#

WLBT_ OFF#

DGPU_PW R_EN

UART0_RX

UART0_TX

I2C1_SDA_TS

I2C1_SCL_T S

I2C0_SDA_TP

I2C0_SCL_T P

GSPI0_MOSI

GSPI1_MOSI

UC1F

@

GC6_FB_EN 3V321

SENSOR_EC _INT45

TP_INT#36

GPU_EVENT#21

WLBT_ OFF#34

UART0_RX34

UART0_TX34

I2C0_SDA_TP36

I2C0_SCL_T P36

I2C1_SDA_TS29

I2C1_SCL_T S29

I2C2_SDA_SEN45

I2C2_SCL_S EN4 5

GC6_FB_EN 3V3

SENSOR_EC _INT

GSPI0_MOSI

OBRAM_ID0

OBRAM_ID1

OBRAM_ID2

GSPI1_MOSI

WLBT_ OFF#

AH10

AH11

AH12

AF11

AF12

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA13 56

SKL-U

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Sx_EXIT_HOLDOFF# / GPP_A12 / BM_BUSY# / ISH_GP6

6 OF 20

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_D15/ISH_UART0_RTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

DGPU_PW R_EN

AC1

DGPU_HOLD _RST#

AC2

GPU_ALL_PGOOD

AC3

DGPU_PRSN T#

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

DGPU_PW R_EN 21,28,45

DGPU_HOLD _RST# 21

GPU_ALL_PGOOD 21

TS_INT# 29

DGPU_PRSN T#

TS_INT#

RC64

4.7K_0402 _5%

12

R7310K_0402 _5% UMA@

12

R7410K_0402 _5% DIS@

+3VS

12

+3VS

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO AN Y THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(6/12)GPIO,I2C,GSPI

SKL-U(6/12)GPIO,I2C,GSPI

SKL-U(6/12)GPIO,I2C,GSPI

Size D ocument Number Re v

Size D ocument Number Re v

Size D ocument Number Re v

Custom

Custom

Custom

Dat e: Sheet o f

Dat e: Sheet o f

2

Dat e: Sheet o f

LA-F661P

LA-F661P

LA-F661P

1

11 61Wednesday, October 18, 2017

11 61Wednesday, October 18, 2017

11 61Wednesday, October 18, 2017

0.3

0.3

0.3

5

4

3

2

1

UC1H

@

D D

PCIE_PRX _DTX_N140

PCIE_PRX _DTX_P140

PCIE_PTX _C_DRX_N140

PCIE_PTX _C_DRX_P140

PCIE_PRX_DTX_N240

PCIE_PRX_DTX_P24 0

PCIE_PTX _C_DRX_N240

PCIE_PTX _C_DRX_P240

PCIE_PRX _DTX_N434

PCIE_PRX _DTX_P434

PCIE_PTX _C_DRX_N434

PCIE_PTX _C_DRX_P434

PCIE_PRX _DTX_N521

PCIE_PRX _DTX_P521

PCIE_PTX _C_DRX_N521

PCIE_PTX _C_DRX_P521

PCIE_PRX _DTX_N621

C C

B B

A A

PCIE_PRX _DTX_P621

PCIE_PTX _C_DRX_N621

PCIE_PTX _C_DRX_P621

PCIE_PRX _DTX_N721

PCIE_PRX _DTX_P721

PCIE_PTX _C_DRX_N721

PCIE_PTX _C_DRX_P721

PCIE_PRX _DTX_N821

PCIE_PRX _DTX_P821

PCIE_PTX _C_DRX_N821

PCIE_PTX _C_DRX_P821

PCIE_PRX _DTX_N934

PCIE_PRX _DTX_P934

PCIE_PTX _DRX_N934

PCIE_PTX _DRX_P934

PCIE_PRX _DTX_N1034

PCIE_PRX _DTX_P1034

PCIE_PTX _DRX_N1034

PCIE_PTX _DRX_P1034

PCIE_PRX _DTX_N1134

PCIE_PRX _DTX_P1134

PCIE_PTX _DRX_N1134

PCIE_PTX _DRX_P1134

SATA_P RX_DTX_N1234

SATA_P RX_DTX_P1234

SATA_P TX_DRX_N1234

SATA_P TX_DRX_P1234

1 2

CC114 0.22U _0201_6.3V 6M

1 2

CC115 0.22U _0201_6.3V 6M

1 2

CC116 0.22U _0201_6.3V 6M

1 2

CC117 0.22U _0201_6.3V 6M

1 2

CC136

CC137

CC142 0.22U _0201_6.3V 6M

CC143 0.22U _0201_6.3V 6M

CC148 0.22U _0201_6.3V 6M

CC149 0.22U _0201_6.3V 6M

CC144 0.22U _0201_6.3V 6M

CC145 0.22U _0201_6.3V 6M

CC146 0.22U _0201_6.3V 6M

CC147 0.22U _0201_6.3V 6M

RC71 100_04 02_1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

0.1U_02 01_10V K X5R

0.1U_02 01_10V K X5R

PCIE_PTX _DRX_N1

PCIE_PTX _DRX_P1

PCIE_PTX _DRX_N2

PCIE_PTX _DRX_P2

PCIE_PTX _DRX_N4

PCIE_PTX _DRX_P4

PCIE_PTX _DRX_N5

PCIE_PTX _DRX_P5

PCIE_PTX _DRX_N6

PCIE_PTX _DRX_P6

PCIE_PTX _DRX_N7

PCIE_PTX _DRX_P7

PCIE_PTX _DRX_N8

PCIE_PTX _DRX_P8

PCIE_RCO MPN

PCIE_RCO MPP

PCIE / USB3 / SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_B GA1356

SKL-U

8 OF 20

SSIC / USB3

USB3_2_RXN / SSIC_RXN

USB3_2_RXP / SSIC_RXP

USB3_2_TXN / SSIC_TXN

USB3_2_TXP / SSIC_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

Rev_1.0

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_3_RXN

USB3_3_RXP

USB3_3_TXN

USB3_3_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB20_ N1

USB20_ P1

USB20_ N2

USB20_ P2

USB20_ N3

USB20_ P3

USB20_ N5

USB20_ P5

USB20_ N6

USB20_ P6

USB20_ N7

USB20_ P7

USB2_C OMP

USB2_ID

USB2_S ENSE

USB_OC 0#

USB_OC 1#

USB_OC 2#

USB_OC 3#

WL_ OFF#

DEVSLP 2

NGFF_S SD_PEDET

USB3_R X1_N 3 7

USB3_R X1_P 37

USB3_T X1_N 37

USB3_T X1_P 37

USB3_R X2_N 3 7

USB3_R X2_P 37

USB3_T X2_N 37

USB3_T X2_P 37

USB20_ N1 3 7

USB20_ P1 37

USB20_ N2 3 7

USB20_ P2 37

USB20_ N3 4 3

USB20_ P3 43

USB20_ N5 2 9

USB20_ P5 29

USB20_ N6 3 6

USB20_ P6 36

USB20_ N7 3 4

USB20_ P7 34

1 2

RC70 113_0402_ 1%

1 2

RC104 1K_040 2_5%

1 2

RC105 1K_040 2_5%

WL_ OFF# 34

DEVSLP 2 34

NGFF_S SD_PEDET 34

NGFF_S SD_PEDET

WL_ OFF#

USB_OC 2#

USB_OC 0#

USB_OC 3#

USB_OC 1#

SSD_DE T@

1 2

RC130 1 0K_0402_5%

1 2

RC131 10K_04 02_5%

RPC9

10K_08 04_8P4R_5%

@

+3VALW

18

27

36

45

+3VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Dat e: Sh eet o f

Dat e: Sh eet o f

2

Dat e: Sh eet o f

Compal Electronics, Inc.

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

LA-F661P

LA-F661P

LA-F661P

12 61Wednesday, Octo ber 18, 2017

12 61Wednesday, Octo ber 18, 2017

12 61Wednesday, Octo ber 18, 2017

1

0.3

0.3

0.3

5

4

3

2

1

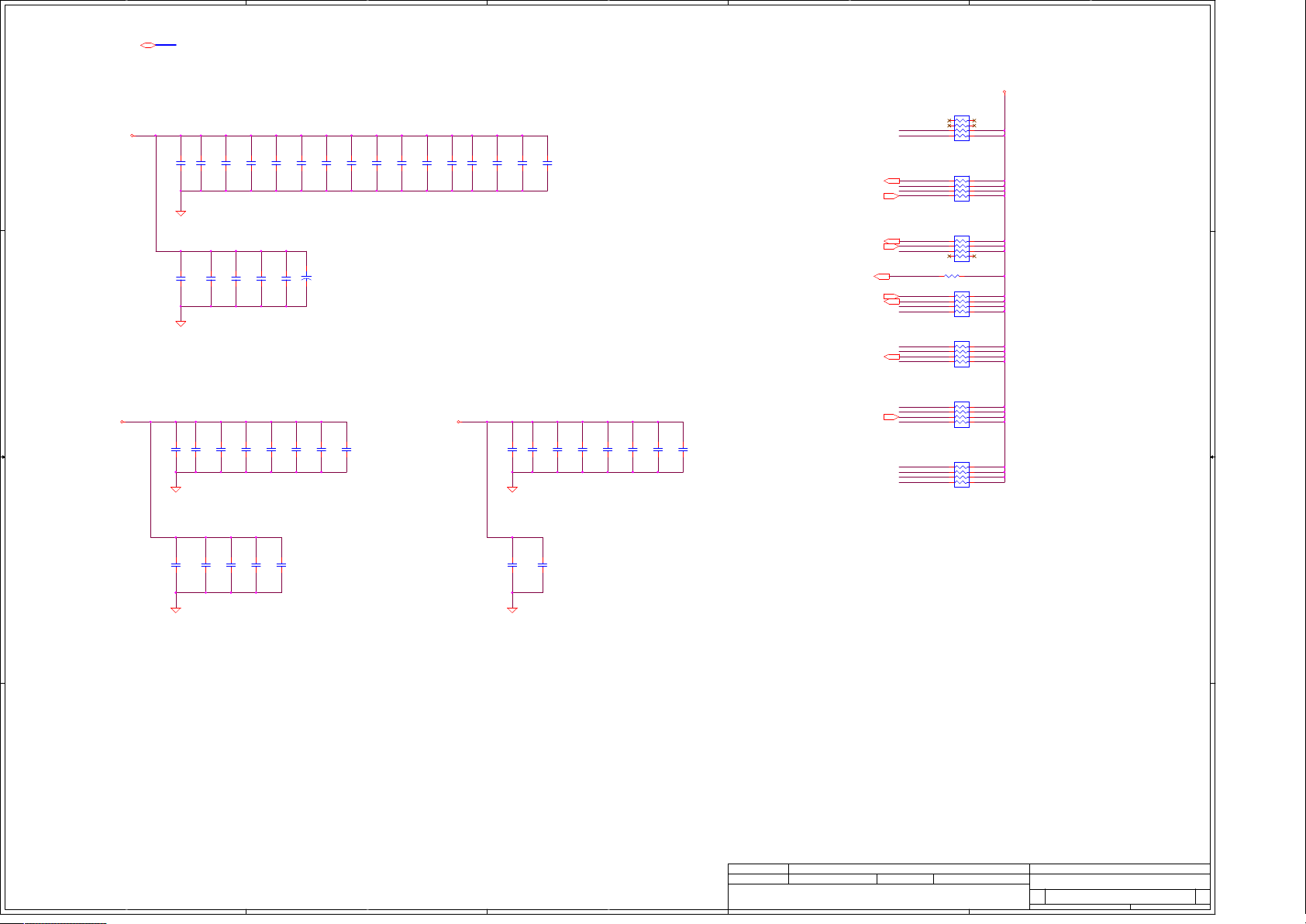

+VL

CC150

1U_0402_6.3V6K

1

+1.0VAL W

1

2

2

1U_0402_6.3V6K

CC32

+1.0VAL W

EN_1.0V _VCCSTU

EN_1.8V S

+1.8VAL W

UC6

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS229 61DNYR_WS ON8

VOUT

D D

1 2

SYSON45 ,49

SUSP#39,44 ,45,49

C C

B B

RC215 0_0402 _5%

1 2

RC216 0_0402 _5%

+VL

0.1U_0201_10V K X5R

1

CC30

@

2

SUSP#

GND

UC7

1

VIN1

2

VIN1

3

ON1

4

VBIAS

5

ON2

6

VIN2

7

VIN2

EM5209 VF_DFN14_3 X2

+1.0VS_ VCCIO_STG

6

5

VOUT1

VOUT1

CT1

GND

CT2

VOUT2

VOUT2

GPAD

14

13

12

CC152

11

8200P_ 0402_25V7K

10

CC153

9

1000P_ 0402_50V7K

8

15

RC79

1 2

0_0805 _5%

1 2

1 2

1 2

RC214 0_0402 _5%

1 2

RC217 0_0402 _5%

+1.0VS_ VCCIO

@

+1.0V_V CCST

+1.8VS

1

CC33

0.1U_02 01_10V K X5R

2

CC151

0.1U_0201_10V6K

1

@

2

CC154

0.1U_0201_10V6K

1

@

2

+1.0VS_ VCCIO

+1.0V_V CCST

+1.2V

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

AL23

+1.0V_V CCST

UC1N

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

A18

VCCST

A22

VCCSTG_A22

VCCPLL_OC

K20

VCCPLL_K20

K21

VCCPLL_K21

SKL-U_B GA1356

1U_0402_6.3V6K

1

2

SKL-U

@

CPU POWER 3 OF 4

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

14 OF 20

1U_0402_6.3V6K

1

CC28

CC34

2

Rev_1.0

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

+1.0VS_ VCCIO

@

+1.0VS_ VCCIO

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

1U_0402_6.3V6K

1

2

+VCC_S A

VSSSA_ SENSE

VCCSA_ SENSE

CC35

VSSSA_ SENSE 52

VCCSA_ SENSE 52

+1.0VS_ VCCIO

10U_0603_6.3V6M

1U_0402_6.3V6K

1

1

CC36

@

@

2

A A

5

1

CC37

@

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CC39

CC38

2

2

4

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC40

2

1U_0402_6.3V6K

1

CC41

CC42

@

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

THIS SHEET OF ENG INEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

2017/5 /3 2017/6 /2

3

+1.2V

1U_0402_6.3V6K

1

2

CC29

2

1

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

22U_0603_6.3V6M

1U_0402_6.3V6K

1

1

CC43

CC44

@

@

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

1

1

CC128

CC45

2

2

2

10U_0603_6.3V6M

10U_0402_6.3V6M

1

CC46

@

1

CC47

@

2

2

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Dat e: Sh eet o f

Dat e: Sh eet o f

Dat e: Sh eet o f

1U_0402_6.3V6K

10U_0603_6.3V6M

1

CC48

@

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

1U_0402_6.3V6K

1

CC49

CC50

@

2

SKL-U(8/12)Power

SKL-U(8/12)Power

SKL-U(8/12)Power

LA-F661P

LA-F661P

LA-F661P

1

0.3

0.3

0.3

13 61Wednesday, Octo ber 18, 2017

13 61Wednesday, Octo ber 18, 2017

13 61Wednesday, Octo ber 18, 2017

5

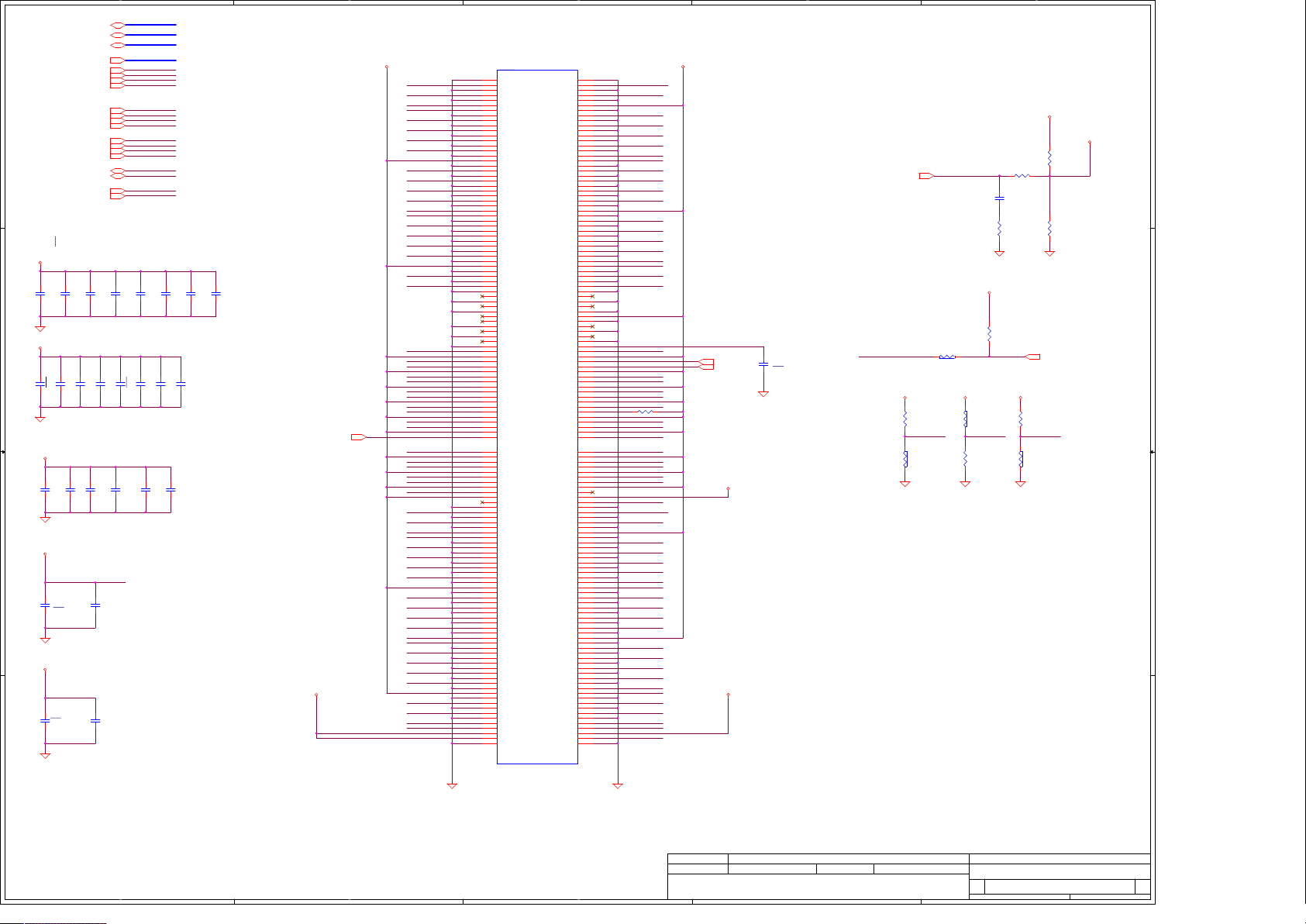

D D

CC55 1U_0402 _6.3V6K

CC56 1U_0402 _6.3V6K

CC66 1U_0402 _6.3V6K

CC59 1U_0402 _6.3V6K@

C C

+3VALW

RF@

LC4

1 2

BLM15EG22 1SN1D_2P

+3V_1.8V_HDA

1

RF@

CC52

0.1U_0402 _25V6

2

4

+1.0VALW

1 2

1 2

1 2

1 2

+1.0V_APLL

+3VALW

+3V_1.8V_HDA

+3VALW

+3VALW

1 2

CC68 1U_0402_ 6.3V6K

DCPDSW

UC1O

AB19

VCCPRIM_1P0

AB20

VCCPRIM_1P0

P18

VCCPRIM_1P0

AF18

VCCPRIM_CORE

AF19

VCCPRIM_CORE

V20

VCCPRIM_CORE

V21

VCCPRIM_CORE

AL1

DCPDSW_1P0

K17

VCCMPHYAON_1P0

L1

VCCMPHYAON_1P0

N15

VCCMPHYGT_1P0_N15

N16

VCCMPHYGT_1P0_N16

N17

VCCMPHYGT_1P0_N17

P15

VCCMPHYGT_1P0_P15

P16

VCCMPHYGT_1P0_P16

K15

VCCAMPHYPLL_1P0

L15

VCCAMPHYPLL_1P0

V15

VCCAPLL_1P0

AB17

VCCPRIM_1P0_AB17

Y18

VCCPRIM_1P0_Y18

AD17

VCCDSW_3P3_AD17

AD18

VCCDSW_3P3_AD18

AJ17

VCCDSW_3P3_AJ17

AJ19

VCCHDA

AJ16

VCCSPI

AF20

VCCSRAM_1P0

AF21

VCCSRAM_1P0

T19

VCCSRAM_1P0

T20

VCCSRAM_1P0

AJ21

VCCPRIM_3P3_AJ21

AK20

VCCPRIM_1P0_AK20

N18

VCCAPLLEBB_1P0

SKL-U_BGA13 56

@

SKL-U

CPU POWER 4 OF 4

15 OF 20

3

VCCPGPPA

VCCPGPPB

VCCPGPPC

VCCPGPPD

VCCPGPPE

VCCPGPPF

VCCPGPPG

VCCPRIM_3P3_V19

VCCPRIM_1P0_T1

VCCATS_1P8

VCCRTCPRIM_3P3

VCCRTC_AK19

VCCRTC_BB14

DCPRTC

VCCCLK1

VCCCLK2

VCCCLK3

VCCCLK4

VCCCLK5

VCCCLK6

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

Rev_1.0

AK15

AG15

Y16

Y15

T16

AF16

AD15

V19

T1

AA1

AK17

AK19

BB14

BB10

A14

K19

L21

N20

L19

A10

AN11

AN13

+1.8VALW

+3VALW

DCPRTC

+1.0VALW

1 2

CC57 1U_0402_ 6.3V6K

+3VL_RTC

1 2

CC62 0.1U_0201_ 10V K X5R

+1.0VALW

+1.0V_APLL

+1.0VALW

+1.0VALW

+1.0VALW

2

+3VALW

1U_0402_6.3V6K

1

2

+3VL_RTC +RT CVCC

1 2

RC90 0_0402 _5%

1

CC82

1U_0402_ 6.3V6K

2

0.1U_0201_10V K X5R

1

CC81

CC79

2

1

Saf t y sugges t i on r emove EE si de , Ke ep PWR s i de

+1.0VALW

1U_0402_6.3V6K

1

CC155

@

2

+1.0V_APLL

LC100

1 2

RF@

BLM15EG22 1SN1D_2P

B B

1

@

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS TH E PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS