A

B

C

D

E

Compal Confidential

Model Name : D4PB1/D5PB1

1 1

File Name : TBD

BOM P/N:43

ZZZ

LA-F241P MB REV1

DAA000EV010

DA2@

ZZZ1

LS-D303P FUN/B

DA400299000

DAS@

ZZZ2

2 2

LS-D302P USB/B

DA6001HX000

DAS@

ZZZ3

Compal Confidential

D4PB1/D5PB1

M/B Schematics Document

LS-A133P

DA600101010

DAS@

ZZZ4

LS-D301P LID/B

DA400272000

DAS@

ZZZ5

LS-B734P

3 3

DA6001B8010

DAS@

ZZZ5

HDMI LOGO

RO0000003HM

HDMI@

ZZZ

LS-B732P

DA4001YF010

DAS@

ZZZ

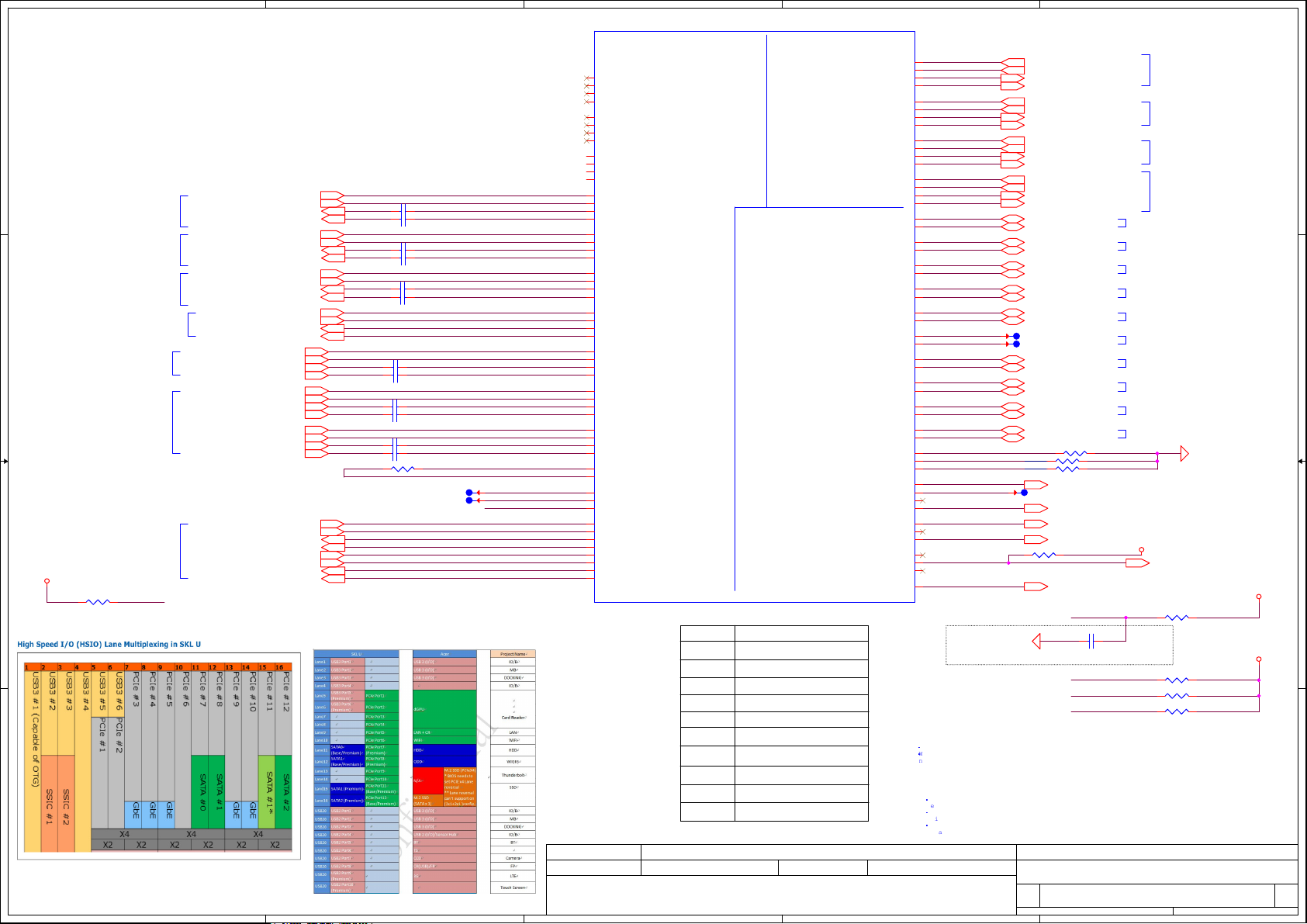

SKL U22/KBL U22 U42 Processor + DDR4

2017-02-22

Rev:1.0

UC1

FJ8067702739739 SR342 H0 2.5G

CPU_SR342@

SA0000A37N0

UC1

S IC FJ8067702739740 SR341 H0 2.7G ABO

CPU_SR341@

SA0000A34L0

UC1

S IC FJ8067703281813 QN5C Y0 1.8G

CPU_QN5C@

SA0000AQZ10

UC1

S IC FJ8067702739738 SR343 H0 2.4G ABO!

CPU_SR343@

SA0000A38M0

KBL-R U42

DAZ PCB

DAZ1IB00100

4 4

DAZ@

X4EA99BOL01 includes EMC@, EMI@ and ESD@

ZZZ

Security Cl assification

Security Cl assification

SMT EMC EE AF241 D4PB1

X4E@EMC

X4EA99BOL01

A

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

MAYBE USED BY OR DISCLOSED TOANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TOANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAYBE USED BY OR DISCLOSED TOANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

UC1

S IC FJ8067703281813 QN5C Y0 1.8G

CPU_QN5C@

SA0000AQZ10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

UC1

S IC FJ8067702739738 SR2ZW H0 2.4G ABO!

CPU_3860@

SA0000A3860

UC1

S IC FJ8067702739738 QLDP H0 2.4G BGA

CPU_3820@

SA0000A3820

UC1

S IC FJ8067702739739 SR2ZU H0 2.5G ABO!

CPU_3760@

SA0000A3760

UC1

S IC FJ8067702739739 QLDM H0 2.5G BGA

CPU_3720@

SA0000A3720

UC1

S IC FJ8066201924931 SR2F0 D1 2.4G ABO!

CPU_2T80@

SA000092T80

UC1

S IC FJ8067702739741 QLDU H0 2.6G BGA

CPU_3L20@

SA0000A3L20

UC1

S IC FJ8067702739740 SR2ZV H0 2.7G ABO!

CPU_3450@

SA0000A3450

UC1

S IC FJ8067702739633 QLYG H0 2.6G BGA

CPU_DO10@

SA0000ADO10

UC1

S IC FJ8067702739628 QLYF H0 2.8G BGA

CPU_DP10@

SA0000ADP10

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-F241P

LA-F241P

LA-F241P

E

0.1

0.1

1 54Wednesday, June 14, 2017

1 54Wednesday, June 14, 2017

1 54Wednesday, June 14, 2017

0.1

A

www.schematic-x.blogspot.com

B

C

D

E

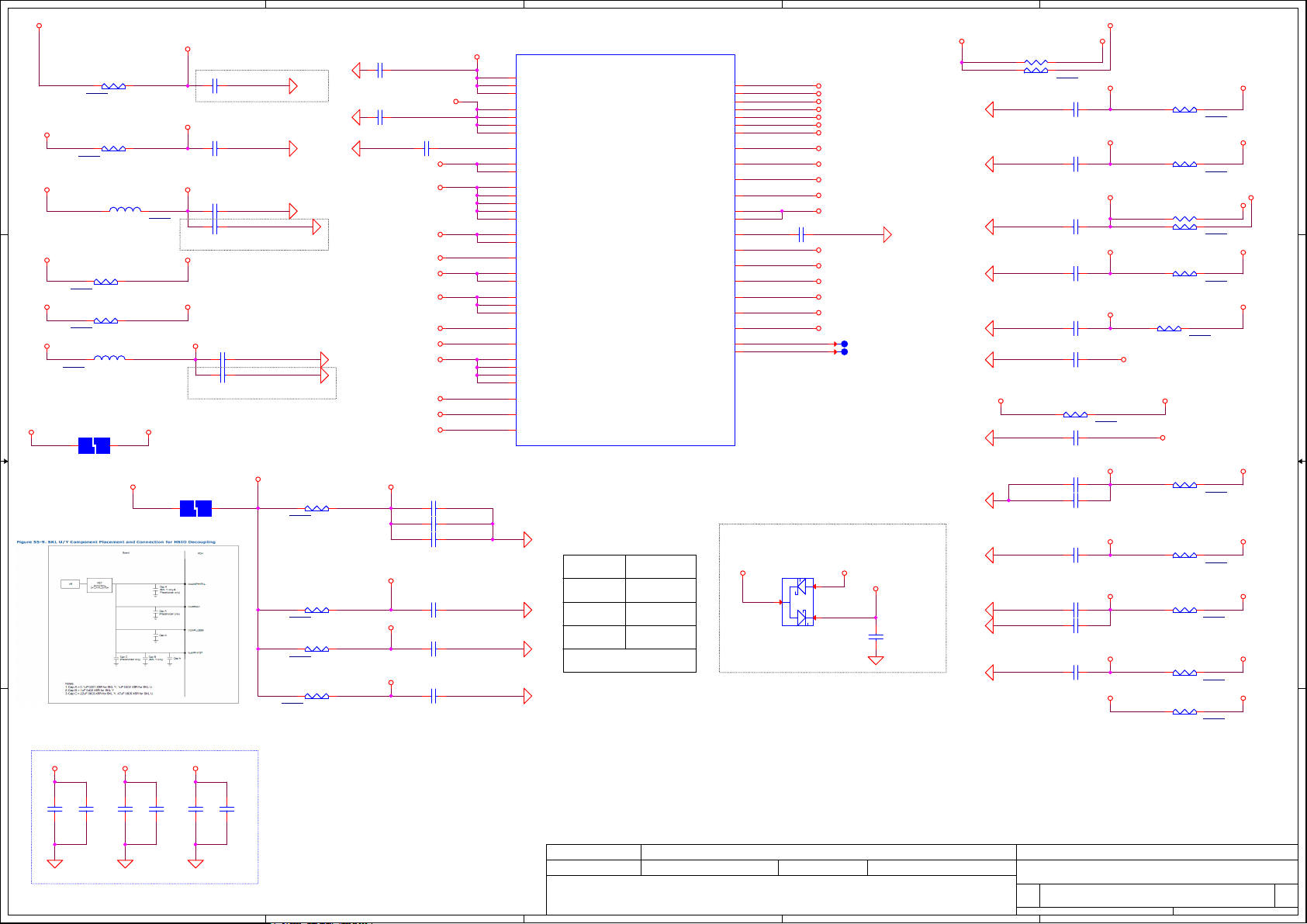

Compal Confidential

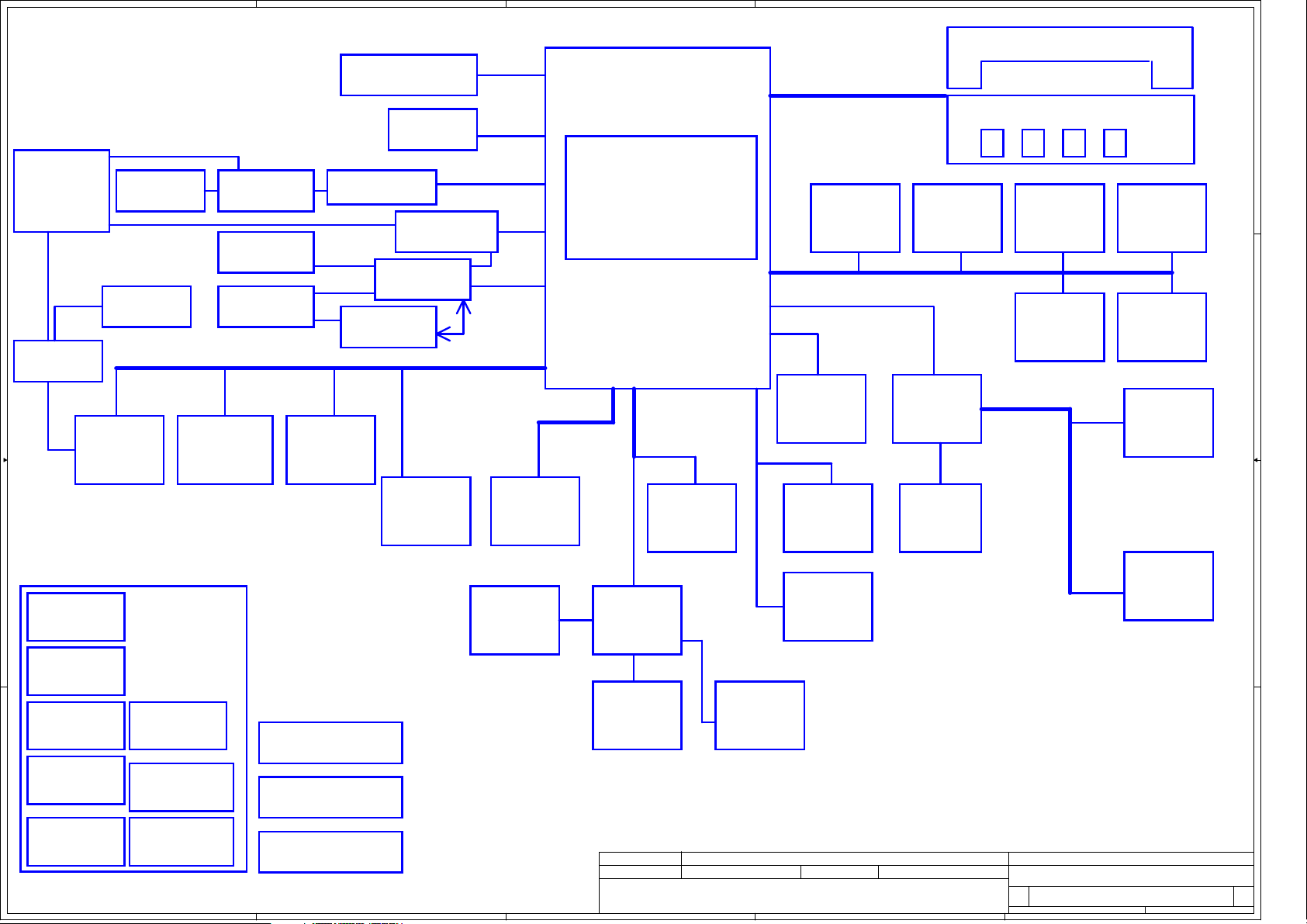

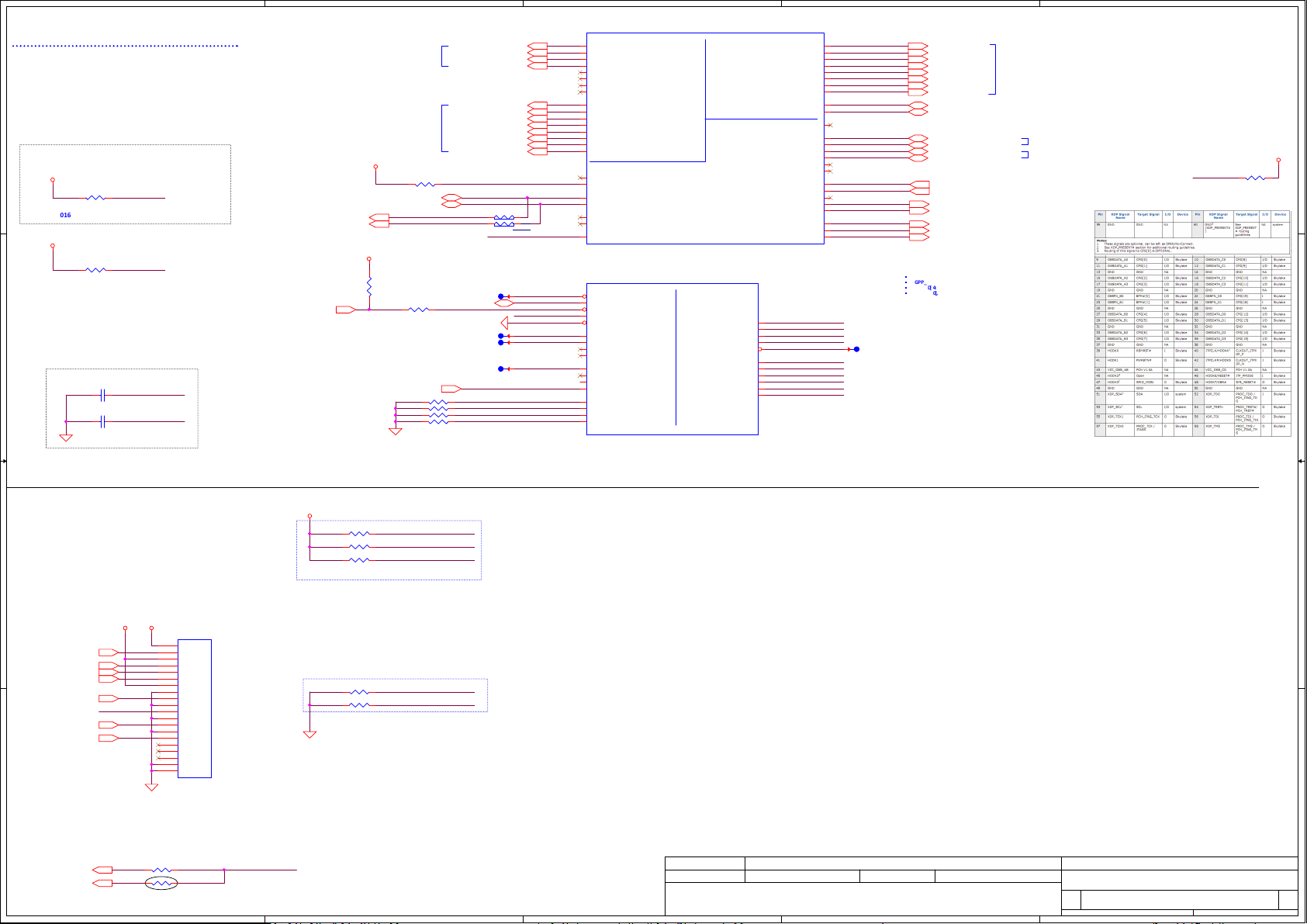

Touch Screen Conn.

page 21

USB2.0

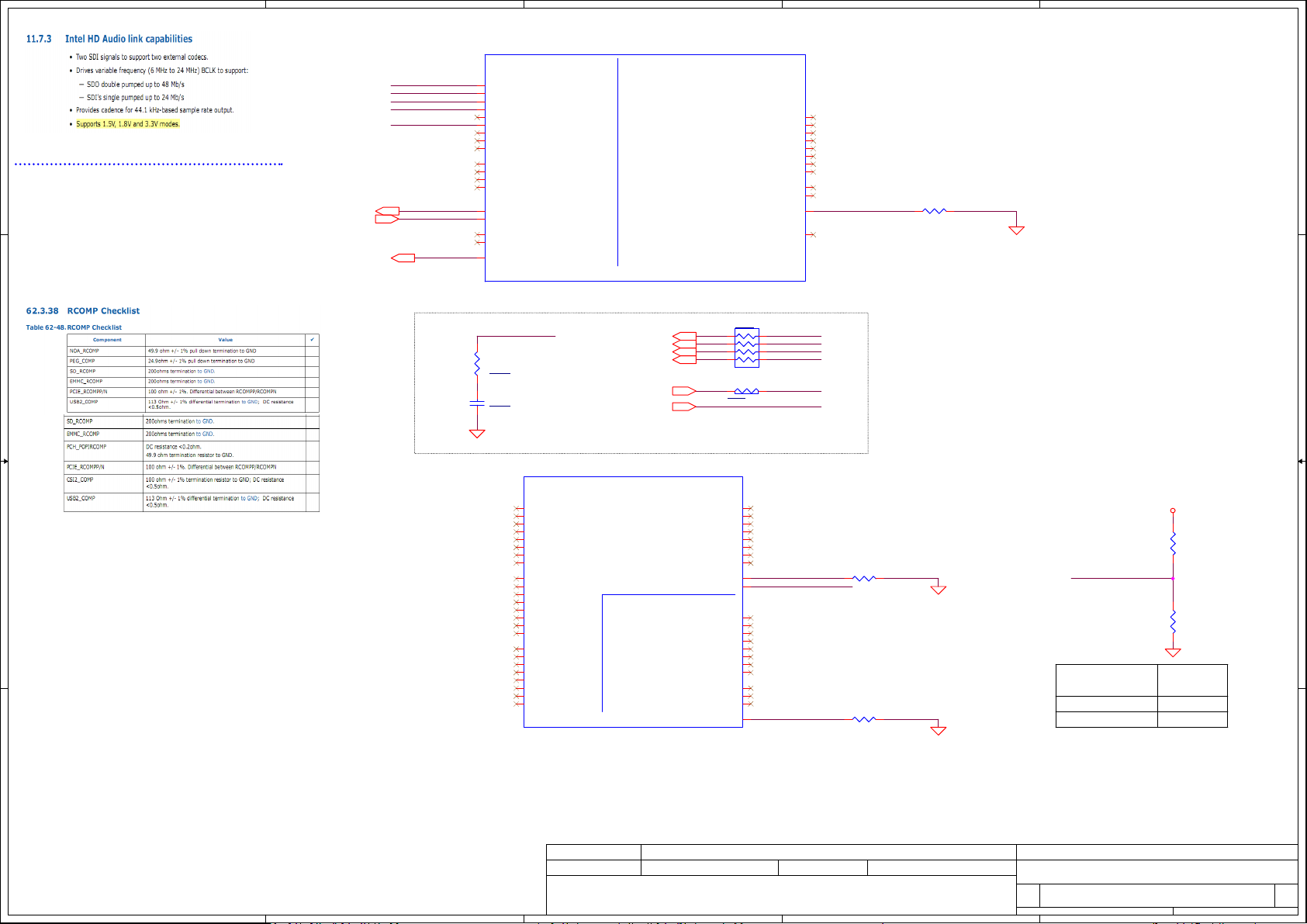

Intel Skylake U/Kabylake U

1 1

eDP Conn.

page 21

eDP

Skylake U/Kabylake U

DOCK CONN.

page 37

CRT Conn.

page 23

CRT SW.

PI3V713

page 23

HDMI CONN

page 25

MIDI

CHC

2 2

MIDI

CHB

LAN SW.

page 28

MIDI

RJ45 Conn.

PCI-Express x 8 (PCIE2.0 5GT/s)

port 5

LAN(GbE)

Intel I219

page 28

page 29

NGFF Card

WLAN+BT+Wigig

(Combo)

TYPE-C CONN

page 35

port 6,8

page 31

DP to VGA

RTD2168

HDMI/DP

Power delivery

port 4

Card reader

RTS5229

Conn.

page 38

page 22

DDI1

DP SW

PS 8338

page 24

Thunderbolt

AR4C

page 33~34

page 35

SATA x 6 (GEN2 3.0GT/S ,GEN3 6GT/S)

GEN3 GEN3

port 11,12

PCIE/SATA

SSD

NGFF Card

page 27 page 26

DDI2

PCIE

port 9,10

CLK=100MHz

CLK=100MHz

SATA

HDD

Conn.

PCH-LP(MCP)

SKL-U_2+2, KBL-U2+2,

KBL-U4+2

Processor

Dual Core + GT2

15W

1356pin BGA

page 6~17

LPC BUS

CLK=33MHz

port 0

TPM

NPCT650

page 38

Memory BUS(DDR4)

Dual Channel

1.2V DDR4 1866/2133

DOCK CONN.

USB port 3

USBx8

3.3V 48MHz

HD Audio

SPI

SPI ROM

(16M)

page 8

SM BUS

NFC

Module

page 27

page 37

3.3V 24MHz

HDA Codec

ALC3225

260pin DDR4-SO-DIMM X1

DDR4-ON BOARD 4G 8Gbx16

8G 16Gbx16

USB 3.0

conn x3

USB port 1,2,4 USB port 5

page 32 page 21

WLAN Module

for BT

page 31

LTE

Card

USB port 9

page 31

HP

page 30

MIC

LINE IN

Int.

Speaker

page 30

page 18

page 19 ,20

CMOS

Camera

USB port 7

Finger

Print

USB port 8

Combo Jack

(CTIA)

page 38

page 30

3 3

DOCK CONN.

G-Sensor

LS-A131P

FUN/B

page 38

Fan

page 39

ENE KB9022

page 36

LIS3DHTR

page 26

page 37

LS-D302

USB/B

page 32

LS-A133P

CardReader/B

page 38

LS-D301P

LID/B

4 4

page 38

LS-B734P

FP/B

page 38

LS-B732P

TP/B

LS-A136P

Docking1/B

LS-A137P

Docking2/B

A

page 38

page 37

RTC CKT.

page 14

DC/DC Interface CKT.

page 40

Power Circuit DC/DC

page 41~50

B

Touch Pad

page 38

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Int.KBD

page 38

Compal Secret Data

Compal Secret Data

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-F241P

LA-F241P

LA-F241P

2 54Friday, June 09, 2017

2 54Friday, June 09, 2017

E

2 54Friday, June 09, 2017

0.1

0.1

0.1

A

B

C

D

E

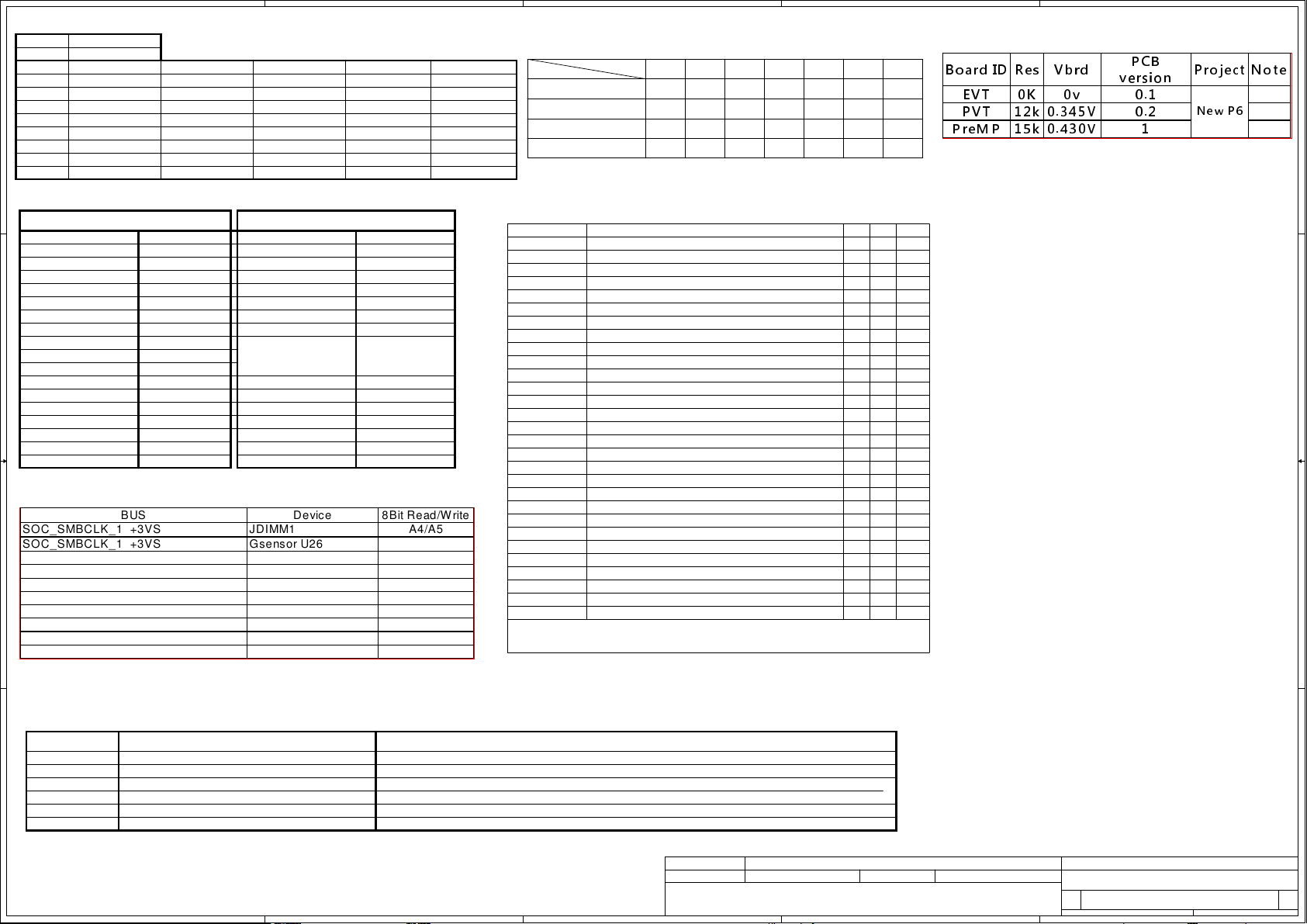

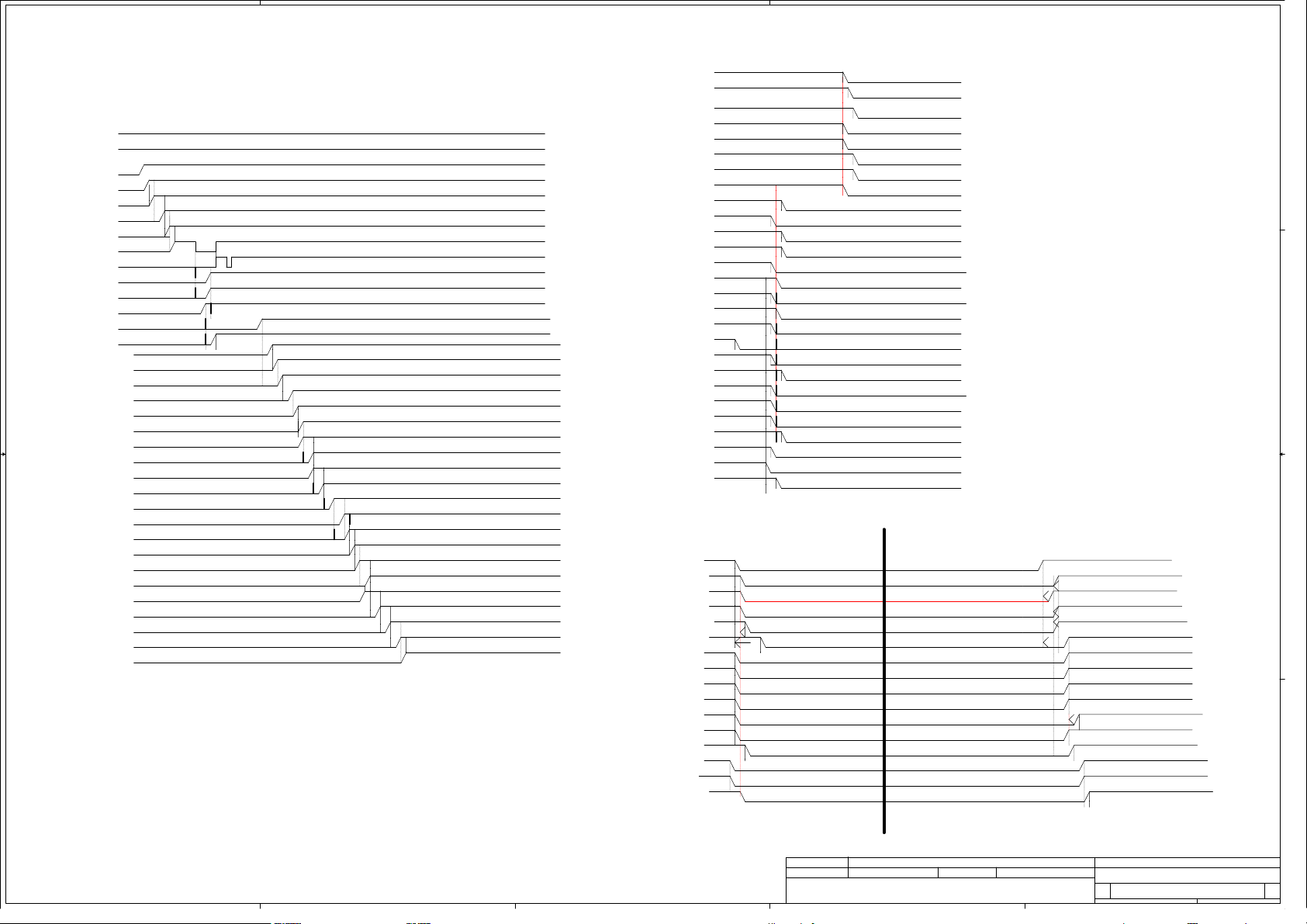

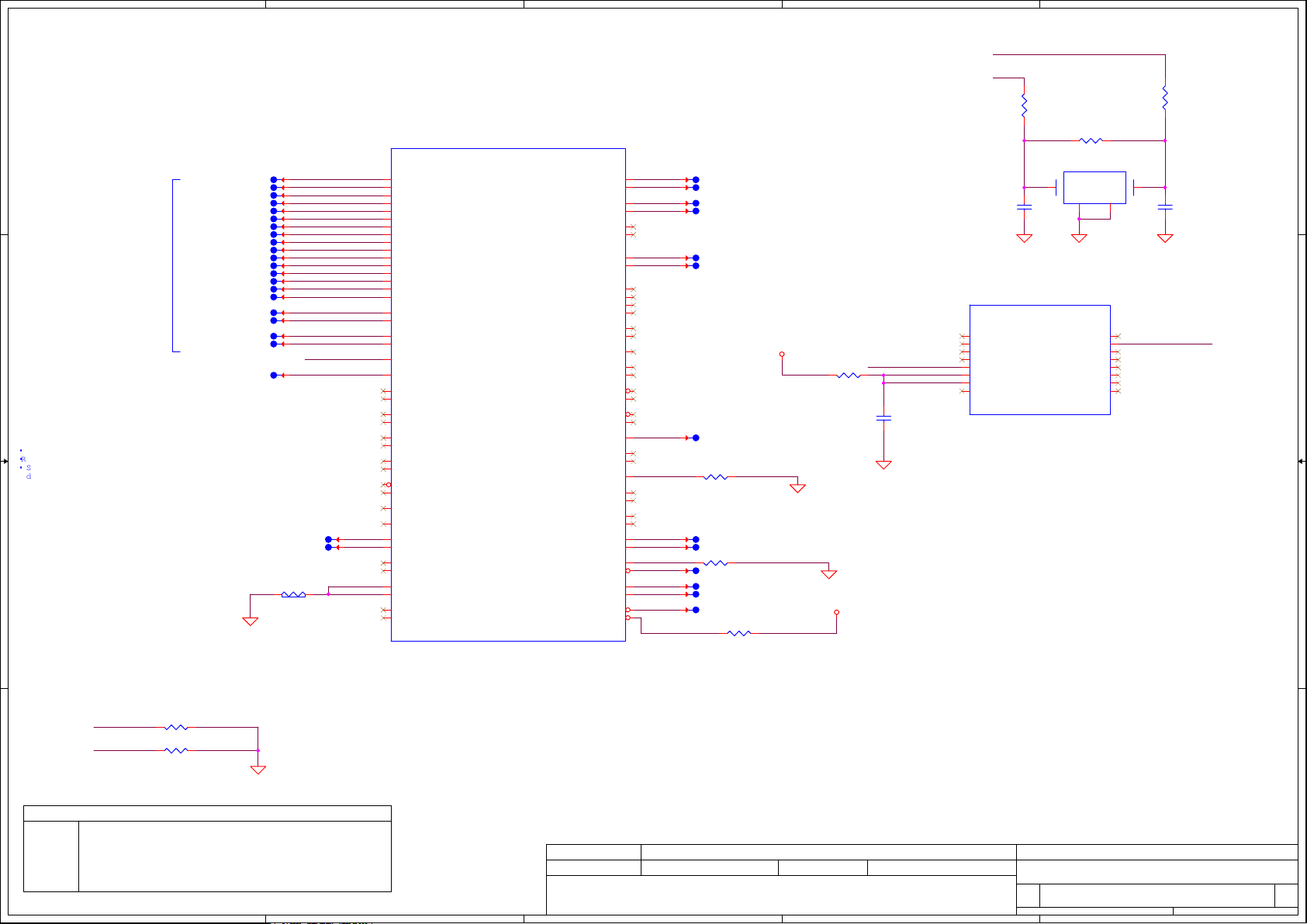

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

1 1

100K +/- 5%Ra

0

1

2

3

4

5

6

7

0 0 V

12K +/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

Rb V min

BID

0.423 V 0.430 V 0.438 V

V typ

BID

0 V 0.300 V

V

BID

max

EC AD3

0x00 - 0x0B

0x0C - 0x1C

0x1D - 0x26

0x27 - 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3B0.691 V 0.702 V 0.713 V

0x3C - 0x460.807 V 0.819 V 0.831 V

0x47 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

Power State

STATE

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspen d to R AM)

S4 (Suspen d to D isk)

S5 (Soft OFF)

SIGNAL

SLP_S3# SLP_S4# SLP_S 5# +VAL W +V +VS Cl ock

LOW HIG H

LOWLOW

HIGH

HIGH

ONONON

ON

OFF

OFFLOW LOW LOW

OFF

OFF

OFF

OFF

OFF

OFF

BOARD ID Table

Board ID Res Vb rd

EVT 0K 0v 0.1

PV T 12k 0.34 5 V 0.2

PreM P 15k 0.430V 1

versio n

PCB

Project Note

New P 6

BOM Structure Table

BOM Option Table

Item BOM Structure

Unpop

Connector

EMC requirement

EMC requirement unpop

Thunderbolt Funct i on

2 2

UMA only

VGA EMI Requirement

VGA UNPOP

VGA RF Requirement

VGA Power

GC6 Funct i on

INTEL CMC

ESPI

@

EMC@

@EMC@

@EMI@/EMI@EMI requirement

TBT@

@RF@/RF@RF requirement

3G@LTE Funct i on

UMA@

VPRO@/NOVPRO@VPRO Funct i on

@VGA_EMI@/VGA_EMI @

@VGA@

@RF@_VGA@

22@/23E@

GC6@/NOGC6@/NGC6

CMC@

ESPI @

BOM Option Table

Item BOM Structure

dGPU

ON Board DDR4

Without WiGi Funct i on

HDD Redriver

N16V-GM

VRAM BOM Select

Single/Dual Rank

PD Funct i on

ESD requirement

Touch screen reserve

KBL-R U42

KBL U22

VGA@

X76OBRAM@CONN@

SGT@N16S-GT

NOWG@

X76TI@/X76PAR@

VGM@

SR@/DR@

(DR@ is not been used

in this project)

PD@

QH7Y@CPU Code

ESD@

TS@

U42@

U22@

X76@

I2C Address Table

SO C_SMB C LK _ 1 +3 VS JD IMM1 A4 /A5

SO C_SMB C LK _ 1 +3 VS Gs ensor U26 30/31

SO C_SML 0CL K +3V S

SO C_SML 0CL K +3V _LA N

3 3

SO C_SML 1CL K _1 +3V S DGP U_ MA IN

SO C_SML 1CL K _1 +3V S

SO C_SML 1CL K _1 +3V S

EC _SMB_ C K1 +3VL P_E C

EC _SMB_ C K1 +3VL P_E C

EC _SMB_ C K1 +3VL P_E C

BUS D e vic e 8B it Read /W rite

JNF C 1 52 /53

LA N UL 1 C8 /C 9

UGPU1 9E /9F

Therm al S enso r UU24 98/99

PC H_ LP 90 /91

PD U5 007 70 /71

Battery PJ P20 1 16 /17

Charge r P U3 01 12 /13

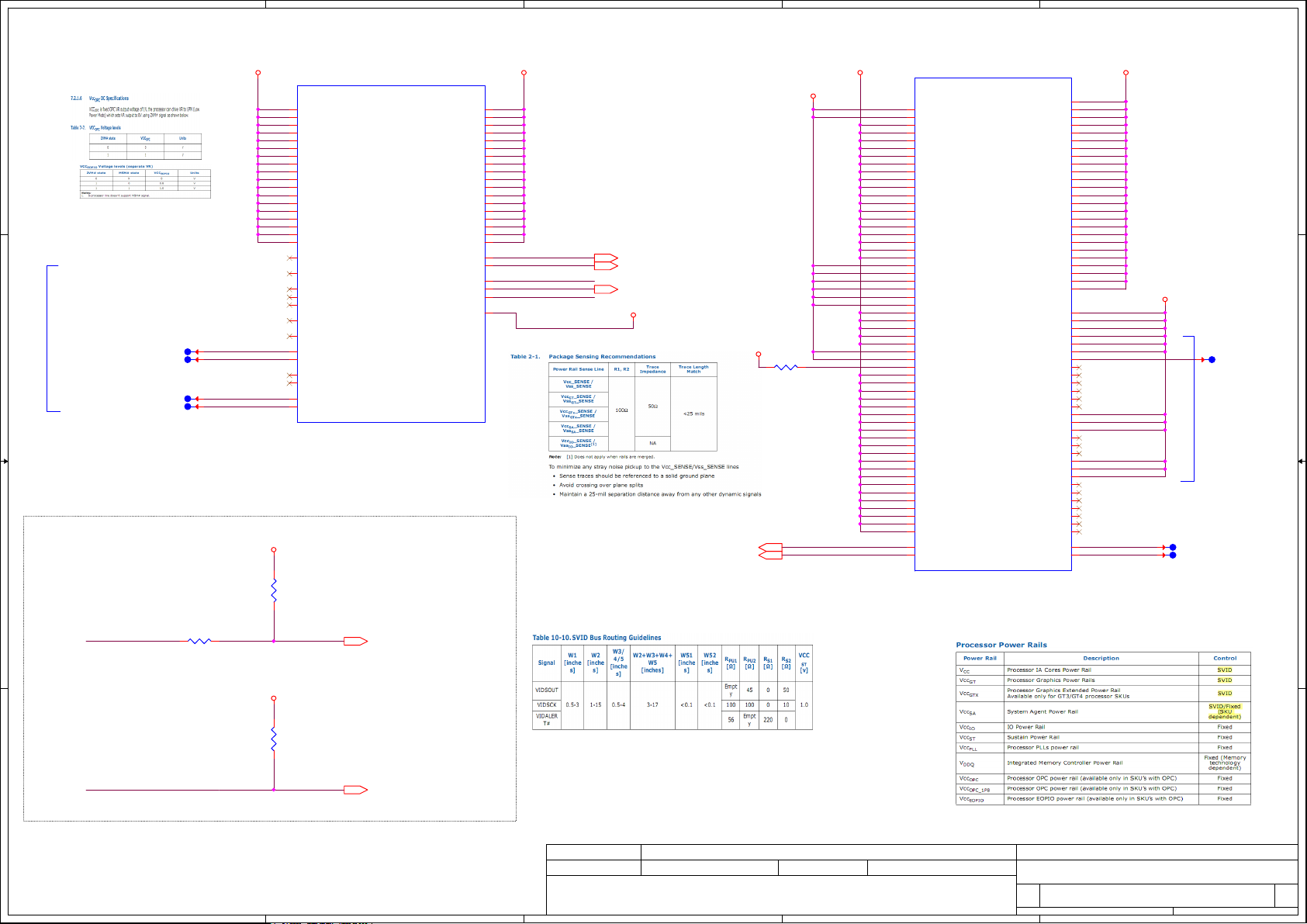

Voltage Rails

Power Plane

+19V_VIN

+17.4V_BATT

+19VB

+VCC_CORE

+VCC_GT

+VCC_SA

+0.6VS_VTT

+1.0VALW_PRIM +1.0V Always power rail

+1.0V_VCCSTU Sustain voltage for processor in Standby modes

+VCCIO

+1.0VS_VCCSTG +1.0VALW_PRIM Gated version of VCCST

+1.2V_VDDQ

+1.8VALW_PRIM +1.8V Always power rail

+1.8VS System +1.8V power rail

+3VLP +19VB to +3VLP power rail for suspend power

+3VALW System + 3VALW always on power rail

+3VS

+5VALW

+5VS System +5V power rail

+RTCVCC

+1.05VSDGPU +1.05VS power rail for GPU

+1.5VSDGPU +1.5VS power rail for GPU

+3VSDGPU_AON +3VS power rail for GPU(AON rails)

+3VSDGPU_MAIN +3VS power rail for GPU GC62.0

+VGA_CORE

+2.5V

Note : ON*1 means power plane is ON only w hen WOL enable and RTC wake at BIOS setting, otherwise it is OFF.

Description

Adapter power supply

Battery power supply

AC or battery power rail for power circuit.

Processor IA Cores Power Rail

Processor Graphics Power Rails

System Agent power rail

DDR +0.6VS power rail f or DDR terminator .

CPU IO power rail

DDR4 +1.2V Power Rail

System +3V power rail

+5V Always power rail

RTC Battery Power

Core power for descrete GPU

DDR4 +2.5V Power Rail

S0

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON ON

S3

S4/S5

N/A N /A

OFF OFF

OFF

OFF OFF

ON

ON

OFF OFF

ON

ON

OFF

ON

ON

OFF

ON

ON ON

OFF OFF

OFF OFF

OFF

N/AN/A

N/AN/A

OFF

OFFOFF

ON*1

OFF

OFFOFF

OFF

ON*1

OFF

ON

ON*1

OFF

ON

OFFOFF

OFFOFF

OFF

OFFOFF

OFF

43 level BOM table

431A0NBOL0 1

431A0NBOL0 2

431A0NBOL0 3

431A0NBOL0 4

4 4

SMT MB AD3 01 B4DBG QJFC 2.3G UMA HD MI

SMT MB AD3 01 B4DBG QJ8M 2.4G UMA HD MI

SMT MB AD3 01 B4DBG QJKP 2.3G DIS HD MI

SMT MB AD3 01 B4DBG QJKK 2.5G DIS HD MI

A

BOM Structure43 Level Descr ipt ion

3G@/CMC@/DA2@/S R@/EMC@/EMI@/ESD @/HDMI@/NOVPRO@/ PD@/TBT@/U MA@/X 76PA R@/X7 6SAM @/RF@

3G@/CMC@/DA2@/S R@/EMC@/EMI@/ESD @/HDMI@/NOVPRO@/ PD@/TBT@/U MA@/X 76PA R@/X7 6SAM @/RF@

3G@/CMC@/DA2@/S R@/EMC@/EMI@/ESD @/GC6@/HDMI@/PD@ /SGT@/TBT@/VGA@/V GA_EMI @/VP RO@/X 76PA R@/X7 6SAM @/RF@

3G@/CMC@/DA2@/S R@/EMC@/EMI@/ESD @/GC6@/HDMI@/PD@ /SGT@/TBT@/VGA@/V GA_EMI @/VP RO@/X 76PA R@/X7 6SAM @/RF@

Security Classifi cation

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

C

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

LA-F241P

LA-F241P

LA-F241P

Date : Sheet o f

Date: Sh eet o f

D

Date: Sh eet o f

E

3 54Wednesday, June 14, 2017

3 54Wednesday, June 14, 2017

3 54Wednesday, June 14, 2017

0.1

0.1

0.1

5

D D

C C

4

3

2

1

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Map

Power Map

Power Map

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

E

E

E

LA-F241P

LA-F241P

LA-F241P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 54Friday, June 09, 2017

4 54Friday, June 09, 2017

4 54Friday, June 09, 2017

0.1

0.1

0.1

A

B

C

D

E

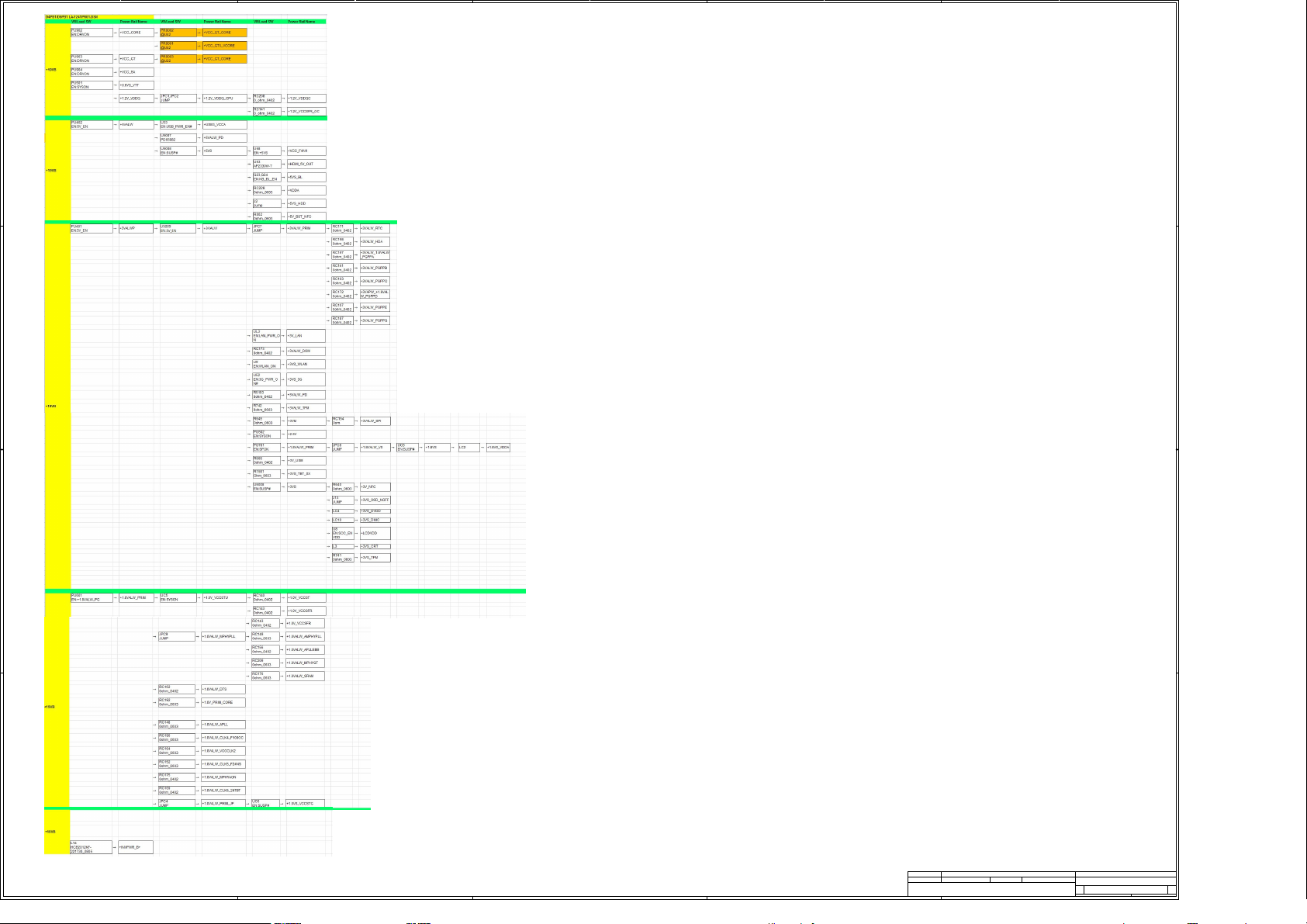

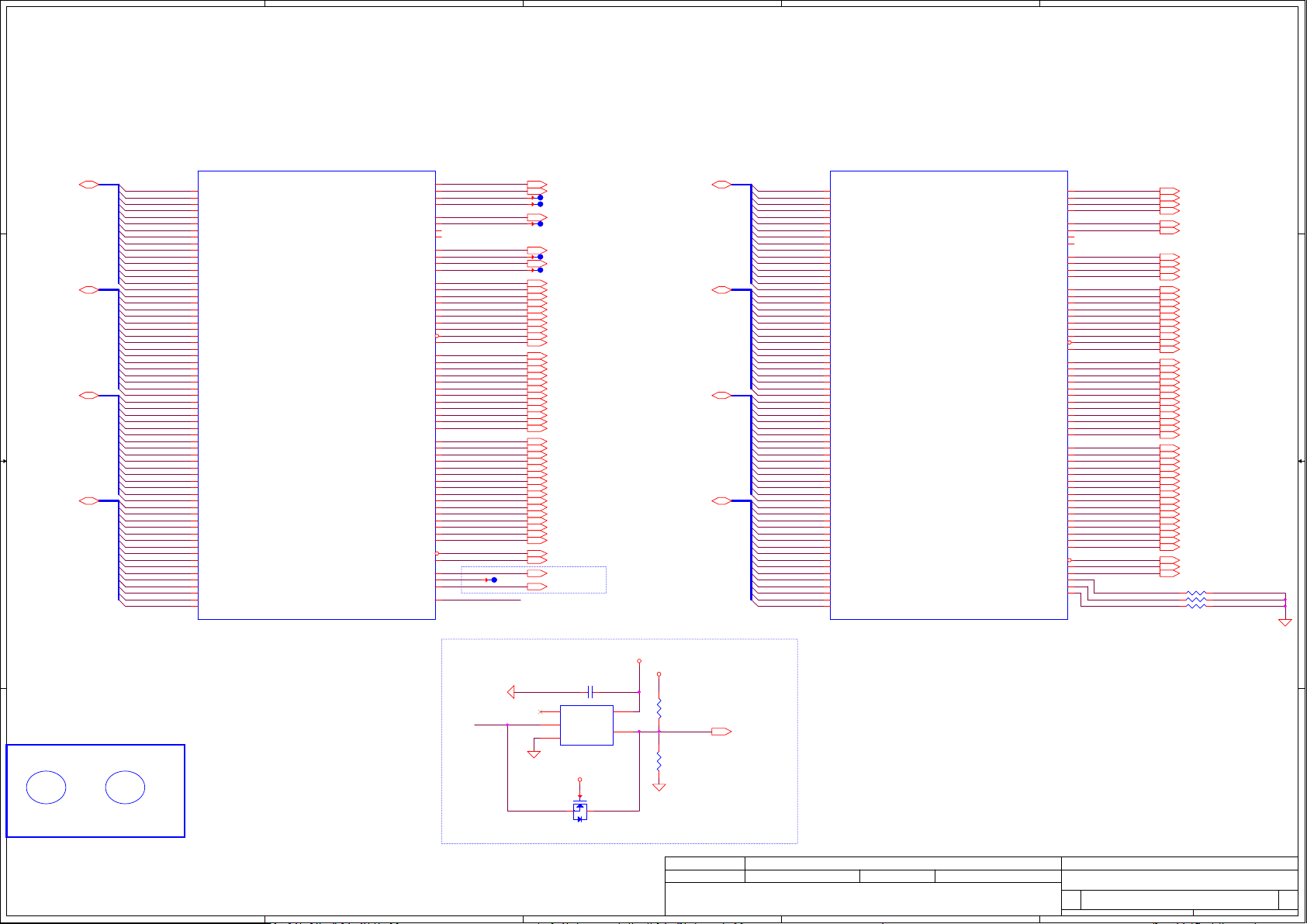

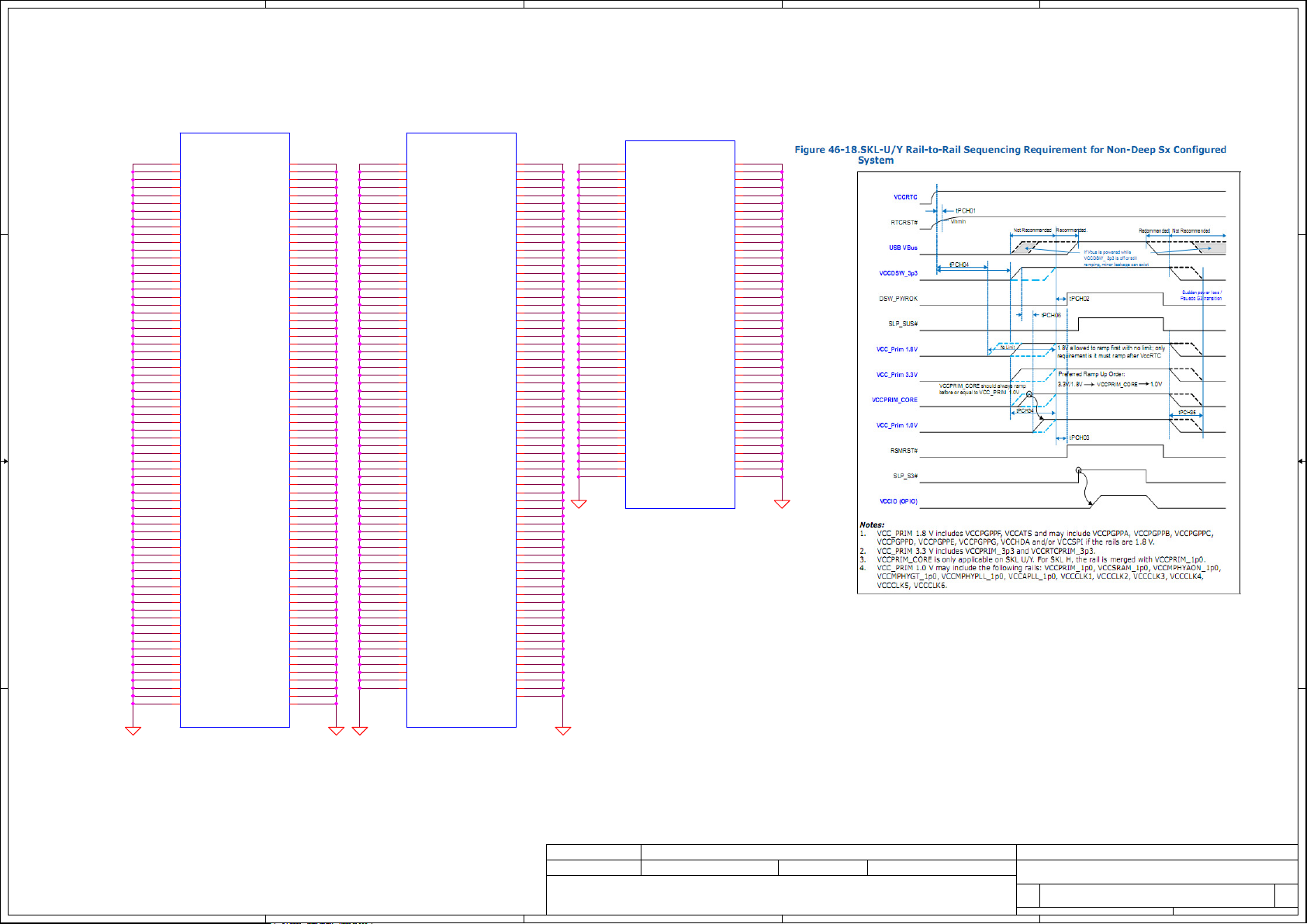

C4PB1/C5PB1 Power OFF sequence

SPOK

PBTN_OUT#

1 1

C4PB1/C5PB1 Power on sequence

+RTCVCC

SOC_RTCRST#

+19VB

+3VLP

EC_ON

+5VAL W

SPOK

ON/OFF

PBTN_OUT#

+3VAL W

+1.8VALW_P RIM

+1.8 VALW_ PG

EC_RSMRST#

+VCCPRIM_CORE

2 2

PM_SLP_S 5#

PM_SLP_S 4#

PM_SLP_S 3#

SYSON

+1.2V_VDDQ

ESPI_RST#

+1.0V_VCCS TU

+1.0VS_VC CSTG

SUSP#

+5VS/+3VS /+1.8V S

+1.5VS

EC_VCCST_PG

VR_ON

+0.6VS_V TT

3 3

SM_PG_CTRL

+VCC_SA

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

PLT_RST#

+VCC_CORE

4 4

190.0u s

2.56m s

880.0u s

910us

298ms 19ms

131ms

98ms

98ms

70.8u s

802.8u s

635.7m s

218.7m s

38us

41.06

10.12m s

720us

281.7u s

360us

9.080m s

9.72m s

1.62m s

6.160m s

6.040u s

12.4m s

12.8u s

20.8u s

2.224m s

5.26u s

8028m s

9.052m s

2.167m s

653.0u s

+3VAL W

+1.8VALW_P RIM

+1.8 VALW_ PG

EC_RSMRST#

+VCCPRIM_CORE

PM_SLP_S 5#

PM_SLP_S 4#

PM_SLP_S 3#

SYSON

+1.2V_VDDQ

+1.0V_VCCS TU

+1.0VS_VC CSTG

SUSP#

+5VS/+3VS /+1.8V S

EC_VCCST_PG

+1.5VS

VR_ON

+0.6VS_V TT

SM_PG_CTRL

+VCC_SA

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

PLT_RST#

+VCC_CORE

PM_SLP_S 3#

+1.0V_VCCS TU

+1.0VS_VC CSTG

SUSP#

+5VS/+3VS /+1.8V S

+1.5VS

EC_VCCST_PG

VR_ON

+0.6VS_V TT

SM_PG_CTRL

+VCC_SA

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

PLT_RST#

+VCC_CORE

71.68u s

39.12u s

68.48u s

130us

23.84u s

465.6u s

23.84u s

0

31.98u s

5s

29us

78us

29us

26.8u s

26.8u s

29.2u s

89.6u s

465.6u s

C4PB1/C5PB1 S3 sequence

13.46u s

39.86u s

13.46u s

68.8u s

428.3m s 36.6m s

35.68u s

33.04u s

32.4u s

32.4u s

32.4u s

20.8u s

28.2u s

376.8u s

475.2u s

0

0

6.94u s

4.294m s

0

0

4.108m s

4.108m s

8.904 s

ResumOFF

245.3u s

23.61m s

245.3u s

1.632m s

20.424 ms

20.424 ms

20.09m s

20.09m s

2.205m s

22.04m s

30.44m s

133.6m s

143.5m s

653.6u s

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

A

B

C

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

D

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F241P

LA-F241P

LA-F241P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

5 54Friday, June 09, 2017

5 54Friday, June 09, 2017

5 54Friday, June 09, 2017

0.1

0.1

0.1

A

Functional Strap Definitions

#543016 PDG0.9 P .775

DDPB_CTRLDATA/ GPP_E19 (Internal Pull Down):

DDPC_CTRLDATA/ GPP_E21 (Internal Pull Down):

DDPD_CTRLDATA/ GPP_E23 (Internal Pull Down):

(Sampled:Rising edge of P CH_PWROK)

Display Port B/C/D Detected

0 =Port is not detected.

1 1

1 =Port is detected.

!&%62!% 78!9

+VCCIO

RC1

/

2) #'$3. 4"+3.4"&5 +$34

+1.0V_VCCST

RC2 1K_0402_5%

2 2

EDP_COMP

1 2

24.9_0402_1%

/ /

:;2

7) /'+) #**# <)=>

H_THERMTRIP#

1 2

<BOM Structure>

CC52

@EMC@

.1U_0402_16V7K

H_PECI

12

CC53

ESD@

.1U_0402_16V7K

H_PROCHOT#_R

12

Reserved for ESD 2014/9/17

AR HDMI DDC

H_PROCHOT#<36,43>

PDG0.9 P.771

PROC_ POP IRC OM P/P CH_ OPI RCO MP

PD 50ohm

#544669 CRB RVP7 1.0

EDRAM _OP IO_ RCO MP/ EOP IO_ RC OMP

PD5 0oh m

Docking HDMI+TBT

PS8338 HDMI DDC

TBT_DP1_CTRL_CLK<33>

TBT_DP1_CTRL_DATA<33>

+1.0VS_VCCSTG

B

<DP to VGA>

< PS8338 >

+3VS

R4955 2.2K_0402_5%<BOM Structure>

DDI2_CTRL_CK<24>

DDI2_CTRL_DATA<24>

TBT_DP1_CTRL_CLK

TBT_DP1_CTRL_DATA

12

RC3

1K_0402_5%

1 2

RC4 499_0402_1%

DET_SIG#_R<28,37>

RC5 49.9_0402_1%

RC6 49.9_0402_1%

RC7 49.9_0402_1%

RC8 49.9_0402_1%

SOC_DP1_N0<22>

SOC_DP1_P0<22>

SOC_DP1_N1<22>

SOC_DP1_P1<22>

CPU_DP2_N0<24>

CPU_DP2_P0<24>

CPU_DP2_N1<24>

CPU_DP2_P1<24>

CPU_DP2_N2<24>

CPU_DP2_P2<24>

CPU_DP2_N3<24>

CPU_DP2_P3<24>

12

follow INTEL check list to reserve D63 test point

12

12

12

12

SOC_DP1_CTRL_DATA

DDI2_CTRL_CK

DDI2_CTRL_DATA

@

@

EDP_COMP

T167@

H_PECI<36>

T160@

T161@

T170@

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

12

12

RC2380_0402_5%

RC2450_0402_5%

CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

XDP_BPM#0

XDP_BPM#1

I2C_TS_INT#

AT16

AU16

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

@

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356

@

CPU MISC

C

DDI

DISPLAY SIDEBANDS

SKL-U

4 OF 20

SKL-U

1 OF 20

JTAG

PROC_TCK

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

EDP

Rev_0.5 3

PROC_TDI

JTAGX

Rev_0.5 3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

CPU_XDP_TCK0

B61

SOC_XDP_TDI

D60

SOC_XDP_TDO

A61

SOC_XDP_TMS

C60

SOC_XDP_TRST#

B59

PCH_JTAG_TCK1

B56

SOC_XDP_TDI

D59

SOC_XDP_TDO

A56

SOC_XDP_TMS

C59

SOC_XDP_TRST#

C61

CPU_XDP_TCK0

A59

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

D

EDP_TXN0 <21>

EDP_TXP0 <21>

EDP_TXN1 <21>

EDP_TXP1 <21>

EDP_TXN2 <21>

EDP_TXP2 <21>

EDP_TXN3 <21>

EDP_TXP3 <21>

EDP_AUXN <21>

EDP_AUXP <21>

SOC_DP1_AUXN

SOC_DP1_AUXP

SOC_DP2_AUXN

SOC_DP2_AUXP

SOC_DP1_HPD

CPU_HDMI_HPD

EC_SCI#

CPU_EDP_HPD

ENBKL

SOC_BKL_PWM

SOC_ENVDD

T3848@

SOC_DP1_AUXN <22>

SOC_DP1_AUXP <22>

DDI2_AUX_DN <24>

DDI2_AUX_DP <24>

SOC_DP1_HPD <22>

CPU_HDMI_HPD <24>

EC_SCI# <36>

CPU_EDP_HPD <21>

ENBKL <36>

SOC_BKL_PWM <21>

SOC_ENVDD <21>

!"

#$ %& ' & ' !

(# ) $ ! $ )*' +) & ) %&,

(" ( " (./

‧‧‧‧

-0. /,

‧‧‧‧

-0, 1

‧‧‧‧

-0,1" -0, /1

‧‧‧‧

<eDP>

DP Aux (Po rt B for VGA)

PS8338

From VGA Trans.

From DP MUX

From eDP

E

RC212

10K_0402_5%

EC_SCI#

1 2

EC_SCI# SOC internal PU

+3VS

@

+1.0VS_VCCSTG

RC11 51_0402_5%CMC@

Place to CPU side

3 3

RC13 51_0402_5%CMC@

RC15 51_0402_5%CMC@

12

12

12

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

APS CONN

+3VALW_PRIM+3VALW

JAPS1

1

1

A

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

ACES_50506-01841-P01

CONN@

12

12

use for iAMT Test

Place to CPU side

PBTN_OUT#_R2

RC35 51_0402_1%CMC@

RC37 51_0402_5%@

12

12

CPU_XDP_TCK0

PCH_JTAG_TCK1

Follow 544924_Skylake_EDS_Vol_1_Rev_0.93

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

C

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sh eet o f

Date: Sh eet o f

Date: Sh eet o f

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

Custom

Custom

Custom

LA-F241P

LA-F241P

LA-F241P

E

6 54Friday, June 09, 2017

6 54Friday, June 09, 2017

6 54Friday, June 09, 2017

0.1

0.1

0.1

PM_SLP_S3#<10,36,40>

PM_SLP_S5#<10>

PM_SLP_S4#<10,36,40>

PM_SLP_A#<10,36>

SOC_RTCRST#<10>

SYS_RESET#<10>

PM_SLP_S0#<10>

4 4

PBTN_OUT#<10,36>

ON/OFF#<36,38>

PBTN_OUT#_R2

RC53 0_0402_5%@

RC54 0_0402_5%@

A

B

C

D

E

)' &4)

1 1

UC1B

DDR_A_D[0..15]<19>

DDR_A_D[16..31]<19>

2 2

DDR_A_D[32..47]<19>

DDR_A_D[48..63]<19>

3 3

ES Sample

UC1

4 4

CPU_QHMF_C0_2.3G

QHMF@

SA00008M420

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1

CPU_QHMG_C0_1.6G

QHMG@

SA00008M320

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_M A[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_M A[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_M A[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_M A[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_M A[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_ MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_ MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_ BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_ MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15 ]

DDR0_WE#/DDR0_CAB[2]/DDR 0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16 ]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_M A[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_ MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_M A[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_M A[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR CH - A

2 OF 20

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

M_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#2

BA64

DDR_A_DQS2

AY64

DDR_A_DQS#3

AY60

DDR_A_DQS3

BA60

DDR_A_DQS#4

BA38

DDR_A_DQS4

AY38

DDR_A_DQS#5

AY34

DDR_A_DQS5

BA34

DDR_A_DQS#6

BA30

DDR_A_DQS6

AY30

DDR_A_DQS#7

AY26

DDR_A_DQS7

BA26

AW50

AT52

+0.6V_VREFCA

AY67

AY68

+0.6V_B_VREFDQ

BA67

DDR_PG_CTRL

AW67

DDR_ VTT_CNTL to DDR

VTT supplied ramped

<35 uS

(tC PU1 8)

DDR_PG_CTRL

Reserve for cost test.

T25@

DDR_A_CLK#0 <19>

DDR_A_CLK0 <19>

T20@

T19@

DDR_A_CKE0 <19,20>

T21@

DDR_A_CS#0 <19,20>

T23@

T22@

DDR_A_MA5 <19,20>

DDR_A_MA9 <19,20>

DDR_A_MA6 <19,20>

DDR_A_MA8 <19,20>

DDR_A_MA7 <19,20>

DDR_A_BG0 <19,20>

DDR_A_MA12 <19,20>

DDR_A_MA11 <19,20>

M_A_ACT# <19,20>

DDR_A_BG1 <19>

DDR_A_MA13 <19,20>

DDR_A_MA15 <19,20>

DDR_A_MA14 <19,20>

DDR_A_MA16 <19,20>

DDR_A_BA0 <19,20>

DDR_A_MA2 <19,20>

DDR_A_BA1 <19,20>

DDR_A_MA10 <19,20>

DDR_A_MA1 <19,20>

DDR_A_MA0 <19,20>

DDR_A_MA3 <19,20>

DDR_A_MA4 <19,20>

DDR_A_DQS#0 <19>

DDR_A_DQS0 <19>

DDR_A_DQS#1 <19>

DDR_A_DQS1 <19>

DDR_A_DQS#2 <19>

DDR_A_DQS2 <19>

DDR_A_DQS#3 <19>

DDR_A_DQS3 <19>

DDR_A_DQS#4 <19>

DDR_A_DQS4 <19>

DDR_A_DQS#5 <19>

DDR_A_DQS5 <19>

DDR_A_DQS#6 <19>

DDR_A_DQS6 <19>

DDR_A_DQS#7 <19>

DDR_A_DQS7 <19>

DDR_A_ALERT# <19>

DDR_A_PARITY <19,20>

+0.6V_VREFCA <19>

+0.6V_B_VREFDQ <18>

12

<BOM Structure>

UC7

NC1VCC

2

A

GND

Y

G

123

D

S

Q2009

@

3

74AUP1G07GW_TSSOP5

<BOM Structure>

+1.2V_VDDQ

MESS138W-G_SOT323-3

DDR_B_D[0..15]<18>

DDR_B_D[16..31]<18>

DDR_B_D[32..47]<18>

DDR_B_D[48..63]<18>

Trace width/Spacing >= 20mils

Place componment near SODIMM

#543016 PDG0.9 P.163 RC place near SODIMM

+1.2V_VDDQ

+3VS

CC57.1U_0402_16V7K

12

5

4

RC10

220K_0402_5%

<BOM Structure>

RC16

2M_0402_5%@

1 2

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

SM_PG_CTRL <45>

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_M A[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_M A[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_M A[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_M A[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_M A[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_ MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_ MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_ BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_ MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15 ]

DDR1_WE#/DDR1_CAB[2]/DDR 1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16 ]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_M A[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_ MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_M A[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_M A[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR_RCOMP[0]

DDR CH - B

3 OF 20

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_0.5 3Rev_0.5 3

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_B_CLK#0

AN45

DDR_B_CLK#1

AN46

DDR_B_CLK0

AP45

DDR_B_CLK1

AP46

DDR_B_CKE0

AN56

DDR_B_CKE1

AP55

AN55

AP53

DDR_B_CS#0

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

DDR_B_ODT1

AW42

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

M_B_ACT#

AN53

DDR_B_BG1

AN52

DDR_B_MA13

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

DDR_B_MA16

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_B_MA4

BA47

DDR_B_DQS#0

AH66

DDR_B_DQS0

AH65

DDR_B_DQS#1

AG69

DDR_B_DQS1

AG70

DDR_B_DQS#2

AR66

DDR_B_DQS2

AR65

DDR_B_DQS#3

AR61

DDR_B_DQS3

AR60

DDR_B_DQS#4

AT38

DDR_B_DQS4

AR38

DDR_B_DQS#5

AT32

DDR_B_DQS5

AR32

DDR_B_DQS#6

AR25

DDR_B_DQS6

AR27

DDR_B_DQS#7

AR22

DDR_B_DQS7

AR21

DDR_B_ALERT#

AN43

DDR_B_PARITY

AP43

DDR_DRAMRST#

AT13

AR18

AT18

SM_RCOMP0

AU18

SM_RCOMP1

SM_RCOMP2

#543016 PDG0.9 P.117

W=12-15 Space= 20/25 L=500mil

DDR_B_CLK#0 <18>

DDR_B_CLK#1 <18>

DDR_B_CLK0 <18>

DDR_B_CLK1 <18>

DDR_B_CKE0 <18>

DDR_B_CKE1 <18>

DDR_B_CS#0 <18>

DDR_B_CS#1 <18>DDR_A_ODT0 <19,20>

DDR_B_ODT0 <18>

DDR_B_ODT1 <18>

DDR_B_MA5 <18>

DDR_B_MA9 <18>

DDR_B_MA6 <18>

DDR_B_MA8 <18>

DDR_B_MA7 <18>

DDR_B_BG0 <18>

DDR_B_MA12 <18>

DDR_B_MA11 <18>

M_B_ACT# <18>

DDR_B_BG1 <18>

DDR_B_MA13 <18>

DDR_B_MA15 <18>

DDR_B_MA14 <18>

DDR_B_MA16 <18>

DDR_B_BA0 <18>

DDR_B_MA2 <18>

DDR_B_BA1 <18>

DDR_B_MA10 <18>

DDR_B_MA1 <18>

DDR_B_MA0 <18>

DDR_B_MA3 <18>

DDR_B_MA4 <18>

DDR_B_DQS#0 <18>

DDR_B_DQS0 <18>

DDR_B_DQS#1 <18>

DDR_B_DQS1 <18>

DDR_B_DQS#2 <18>

DDR_B_DQS2 <18>

DDR_B_DQS#3 <18>

DDR_B_DQS3 <18>

DDR_B_DQS#4 <18>

DDR_B_DQS4 <18>

DDR_B_DQS#5 <18>

DDR_B_DQS5 <18>

DDR_B_DQS#6 <18>

DDR_B_DQS6 <18>

DDR_B_DQS#7 <18>

DDR_B_DQS7 <18>

DDR_B_ALERT# <18>

DDR_B_PARITY <18>

follow INTEL review feedback change to 200ohm

DDR_DRAMRST# <18,19>

RC38 121_0402_1%

1 2

1 2

RC39 80.6_0402_1%

1 2

RC40 100_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF C OMPALELECTRONICS, INC.

C

2017/02/22 2018/02/22

2017/02/22 2018/02/22

2017/02/22 2018/02/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sh eet o f

Date: Sh eet o f

D

Date: Sh eet o f

SKL-U(2/12)DDR

SKL-U(2/12)DDR

SKL-U(2/12)DDR

LA-F241P

LA-F241P

LA-F241P

Friday, June 09, 2017

Friday, June 09, 2017

Friday, June 09, 2017

E

7

0.1

0.1

0.1

54

54

54

7

7

A

B

C

D

E

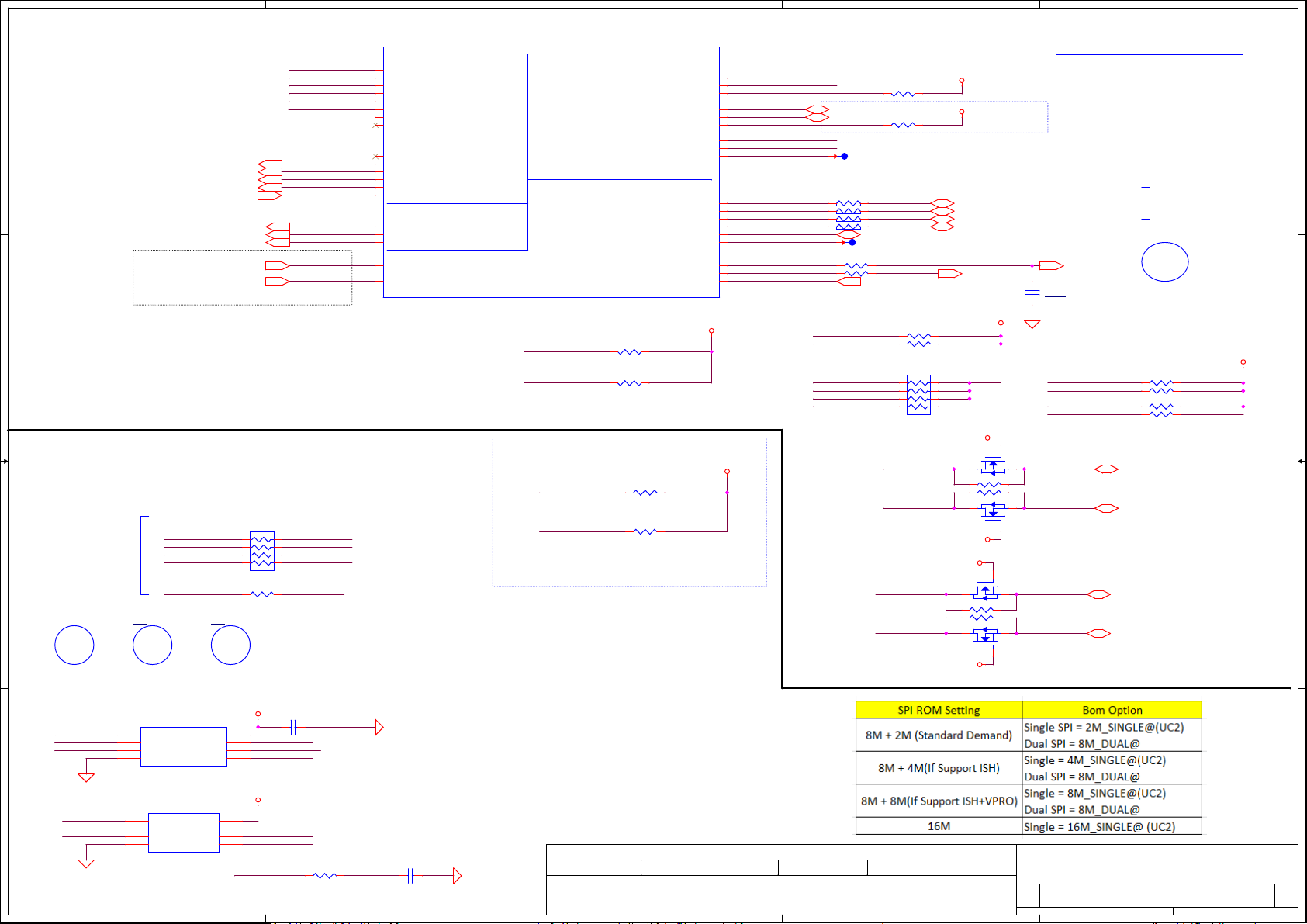

UC1E

SOC_SPI_C LK

SOC_SPI_S O

SOC_SPI_S I

SPI ROM

1 1

RTD3_US B_PWR_EN<33>

To TPM

RTD3_CIO_ PWR_EN<33>

TBT_BAT LOW#<33>

TBT_FOR CE_PWR<33>

TBT_CIO_P LUG_EVENT#<33>

CL_CLK<31>

CL_DATA<31>

CL_RST#< 31>

EC_KBRS T#_R<36>

TPM_SER IRQ<36,38>

AR GPIO

WLAN

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_C S#0

TBT_FOR CE_PWR

TBT_CIO_P LUG_EVENT#

EC_KBRS T#_R

TPM_SER IRQ

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

M2

M3

J4

V1

V2

M1

G3

G2

G1

LPC Mode

2 2

Single SPI ROM_CS0#

To SPI ROM

3 3

UC2

W25 Q128JVSIQ_SO8

ROM16M@

SA00005 VV20

SPI ROM ( 8MByte )

SOC_SPI_C S#0

SOC_SPI_IO2_ 0_R

4 4

ROM Socket

SOC_SPI_C S#0

SOC_SPI_IO2_ 0_R

SOC_SPI_IO3_ 0_R

UC2

W25 Q64FVSSIQ_SO8

ROM8M@

UC2

1

2

3

4

W25 Q64FVSSIQ_SO8

@

1

3

7

4

A

RPC5 and RC 52 are clo se UC2

RPC5

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

RC52

<BOM Struc ture>

UC9

W25 Q64FVSSIQ_SO8

ROM8M@

+3VALW _SPI

8

/CS

DO(IO1)

/WP(IO2)

GND

JC1

CS#

WP#

HOLD#

GND

ACES_91 960-0084N_MX2 5L3206EM2I

CONN@

VCC

/HOLD(IO3)

CLK

DI(IO0)

VCC

SCLK

SI/SIO0

SO/SIO1

SOC_SPI_IO3_ 0_RSOC_SPI_S O_0_R

7

SOC_SPI_C LK_0_R

6

SOC_SPI_S I_0_R

5

+3VALW _SPI

8

SOC_SPI_C LK_0_R

6

SOC_SPI_S I_0_R

5

SOC_SPI_S O_0_R

2

SOC_SPI_C LK_0_R

<BOM Struc ture>

SOC_SPI_IO3SO C_SPI_IO3_0_R

SOC_SPI_S ISOC_SPI_S I_0_R

SOC_SPI_C LKSOC_SPI_C LK_0_R

SOC_SPI_S OSOC_SPI_S O_0_R

SOC_SPI_IO2SOC_SPI_IO2_ 0_R

12

33_0402 _5%

CC8

.1U_0402 _16V7K

1 2

1 2

<BOM Struc ture>

RC24

0_0402_ 5%@EMC@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BG A1356

@

1 2

CC9

10P_040 2_50V8J

@EMC@

B

SKL-U

PM_CLKR UN#

TPM_SER IRQ

LPC

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF 20

1 2

RC107 10K_040 2_5%

1 2

RC112 10K_040 2_5%

GPP_C5/SML0ALERT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

<BOM Struc ture>

<BOM Struc ture>

Rev_0 .53

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

+1.8VS_3 VS_PGPPA

2015MOW06 no need PU 1K on SPI_IO 2/IO3

SOC_SPI_IO2

SOC_SPI_IO3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

RC47 1 K_0402_1%@

1 2

RC48 1 K_0402_1%@

2017/02/ 22 2018/02/ 22

2017/02/ 22 2018/02/ 22

2017/02/ 22 2018/02/ 22

C

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

+3VALW _SPI

SOC_SMB CLK_1

SOC_SMB DATA_1

SOC_SMB ALERT#

SOC_SML 0CLK

SOC_SML 0DATA

SOC_SML 0ALERT#

SOC_SML 1CLK_1

SOC_SML 1DATA_1

SOC_SML 1ALERT#

LPC_AD0

RC144 0_040 2_5%@

LPC_AD1

RC145 0_040 2_5%@

LPC_AD2

RC146 0_040 2_5%@

LPC_AD3

RC147 0_040 2_5%@

LPC_FRA ME#

ESPI_RST#

ESPI_CLK

CK_LPC_ TPM_R

PM_CLKR UN#

Compal Secret Data

Compal Secret Data

Compal Secret Data

RC45 22_0402_5%

R395 22_04 02_5%

SOC_SML 0CLK

SOC_SML 0DATA

SOC_SMB CLK_1

SOC_SMB DATA_1

SOC_SML 1CLK_1

SOC_SML 1DATA_1

ME2N7002D1KW use SB00000DH00 symbol

Deciphered Date

Deciphered Date

Deciphered Date

RC250 2.2K _0402_5%

SOC_SML 0CLK <27,28>

SOC_SML 0DATA <27,28>

1 2

1 2

1 2

1 2

<BOM Struc ture>

T234@

LPC_FRA ME# <36,38>

T235@

12

12

PM_CLKR UN# <38 >

1 2

RC49 4 99_0402_1%<BOM Struc ture>

1 2

RC50 4 99_0402_1%<BOM Struc ture>

1 8

2 7

3 6

4 5

SOC_SMB CLK_1

SOC_SMB DATA_1

SOC_SML 1CLK_1

SOC_SML 1DATA_1

+3VALW _PRIM

12

+3VALW _PRIM

12

RC2024.7K_040 2_5% ESPI@

LPC_AD0 _R <36,38 >

LPC_AD1 _R <36,38 >

LPC_AD2 _R <36,38 >

LPC_AD3 _R <36,38 >

CK_LPC_ TPM <38>

For TPM

+3VALW _PRIM

RPC7

2.2K_080 4_8P4R_5%

<BOM Struc ture>

RC220 0_0402_ 5%@

RC221 0_0402_ 5%@

+3VS

3 4

RC225 0_0402_ 5%@

RC224 0_0402_ 5%@

6 1

+3VS

D

Strap Pin

+3VS

5

Q2017B

3 4

6 1

+3VS

ME2N700 2D1KW-G 2N S OT363-6

12

12

Q2017A

ME2N700 2D1KW-G 2N S OT363-6

2

SB00000 SA00

5

Q2018B

ME2N700 2D1KW-G 2N S OT363-6

12

12

Q2018A

ME2N700 2D1KW-G 2N S OT363-6

2

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

SMB

(Link to DDR, G-sensor)

SML0

(Link to NFC, LAN)

SML1

(Link to EC, DGPU, DDR thermal, RTD2168)

ESPI / LPC Bus

ESPI : +1.8V

LPC : +3.3V

RC45

To EC

ESPI_CLK_ R <36>

1

@RF@

C5241

22P_040 2_50V8J

2

SOC_SMB CLK

SOC_SMB DATA

SOC_SML 1CLK

SOC_SML 1DATA

SB00000 SA00

SOC_SMB CLK

SOC_SMB DATA

SB00000 SA00

SOC_SML 1CLK

SOC_SML 1DATA

SB00000 SA00

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

LA-F241P

LA-F241P

LA-F241P

15_0402 _5%

ESPI@

1 2

RC222 2.2K_0 402_5%<BOM Struc ture>

1 2

RC223 2.2K_0 402_5%<BOM Struc ture>

1 2

RC246 2.2K_0 402_5%<BOM Struc ture>

1 2

RC247 2.2K_0 402_5%<BOM Struc ture>

SOC_SMB CLK <18,26>

SOC_SMB DATA <18,26>

SOC_SML 1CLK <19,22,36 >

SOC_SML 1DATA <19,22,36>

E

+3VS

0.1

0.1

0.1

8 54Friday, June 09, 201 7

8 54Friday, June 09, 201 7

8 54Friday, June 09, 201 7

A

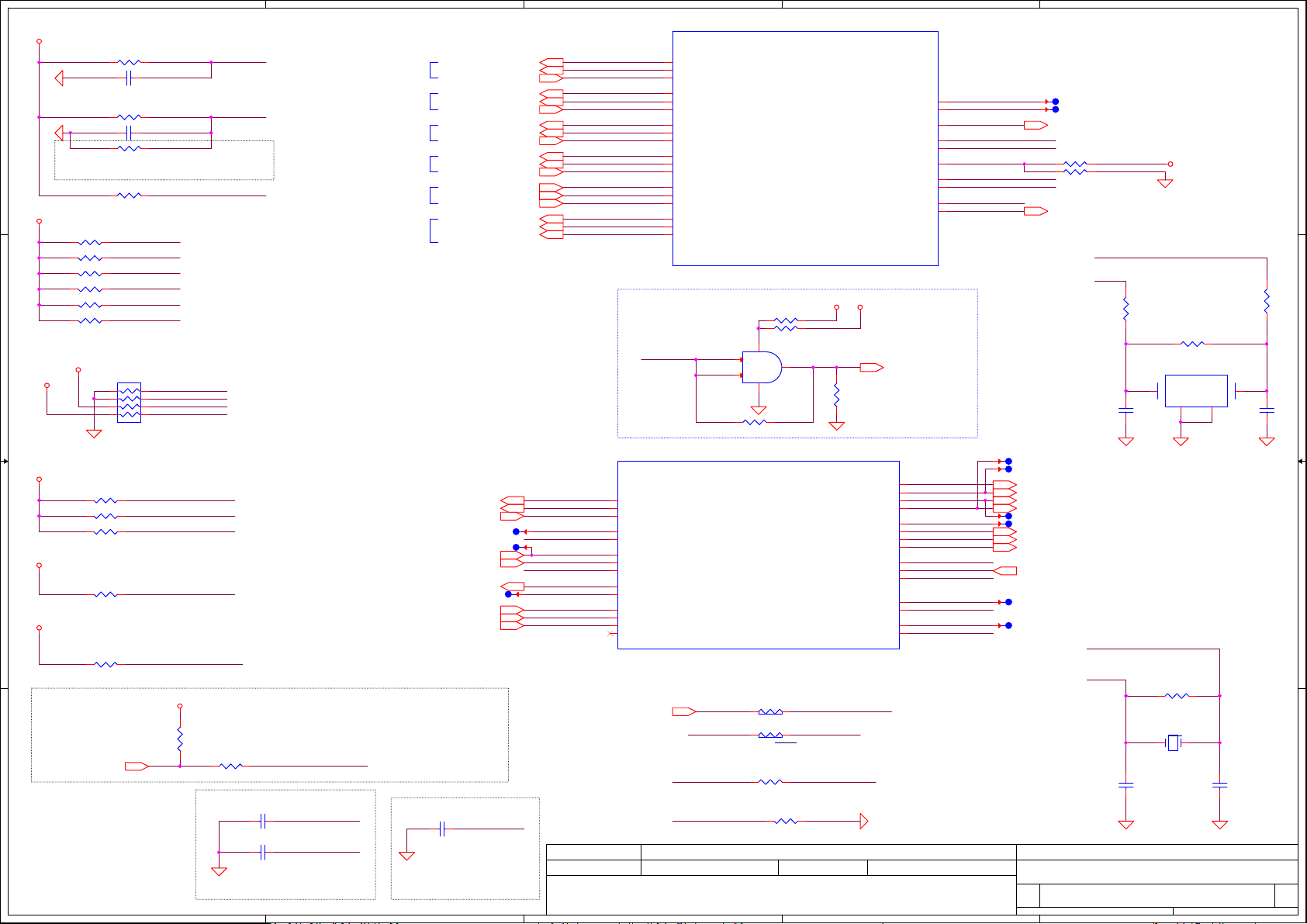

#545659 SKL_PCH_EDS_R0.7 P.84

B

C

D

E

UC1G

HDA_SYNC

HDA_BIT_C LK

HDA_SDO UT

HDA_SDIN0

1 1

HDA_RST #

Functional Strap Definitions

SPKR / GPP_B14 (Internal Pull Down):

(Sampled:Rising edge of PCH_PWROK)

TOP Swap Override

0 = Disable TOP Swap mode.---> AAX05 Use

1 = Enable TOP Swap Mode.

2 2

3 3

PCH_DMIC_ CLK<30>

PCH_DMIC_ DATA<30>

BEEP#<30>

PCH_DMIC_ CLK

PCH_DMIC_ DATA

BEEP#

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK7

AK6

AK9

AK10

AW5

J5

H5

D7

D8

C8

12

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BG A1356

@

HDA_BIT_C LK_R HDA_SYNC

RF@

0_0402_ 5%

R5253

2

RF@

C5228

22P_040 2_50V8J

1

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BG A1356

@

SKL-U

HDA for AUDIO

HDA_SYNC_ R<30>

HDA_SDO UT_R<30>

HDA_BIT_C LK_R<30>

HDA_RST #_R<30>

SKL_ULT

9 OF 20

7 OF 20

ME_EN< 36>

HDA_SDIN0<30>

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

SDIO/SDXC

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

RPC9

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

1 2

RC77 0_0402_5%

Rev_0 .53

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

Rev_0 .53

GPP_G0/SD_CMD

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_RCOMP

GPP_F23

<BOM Struc ture>

HDA_SDO UT

HDA_BIT_C LK

HDA_RST #

HDA_SDO UT

@

HDA_SDIN0

C37

D37

C32

D32

C29

D29

B26

A26

CSI2_COMP

E13

DGPU_PR SNT#

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

EMMC_RC OMP

AT1

/ /.

2)4 + 7* ' !? @ +

!+)4* 5' # $ ! '

'<* !<* A *B<

!)<*'" $+

AB11

*' !'<$ !

AB13

<* * '" $ + < =

AB12

W12

W11

W10

W8

W7

BA9

BB9

SD_RCOM P

AB7

AF13

RC80 100_040 2_1%<BOM Structu re>

RC89 200_040 2_1%

12

12

<BOM Struc ture>

RC76 2 00_0402_1%<BOM Struc ture>

12

+3VALW _1.8VALW _PGPPD

UMA@

DGPU_PR SNT#

VGA@

GPIO 67

DGPU_PRSNT#

DIS,Optimus10

UMA

12

RC133

10K_040 2_5%

12

RC134

10K_040 2_5%

4 4

Security Classification

Security Classification

Security Classification

2017/02/ 22 2018/02/ 22

2017/02/ 22 2018/02/ 22

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2017/02/ 22 2018/02/ 22

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

LA-F241P

LA-F241P

LA-F241P

Date : Sheet o f

Friday, June 09, 201 7

Date : Sheet o f

Friday, June 09, 201 7

Date : Sheet o f

D

Friday, June 09, 201 7

9

9

9

E

0.1

0.1

0.1

54

54

54

A

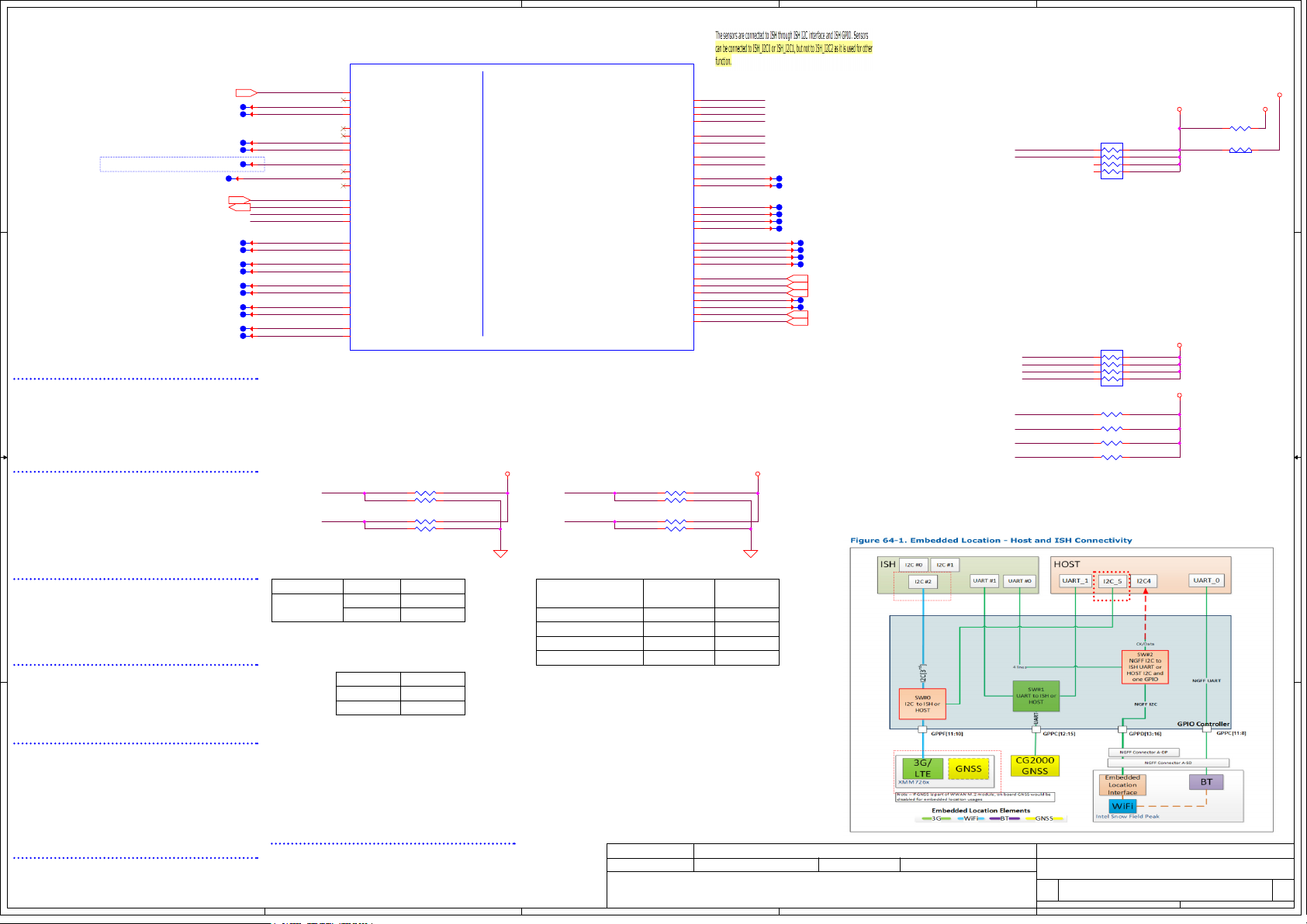

+RTCVCC

1 2

RC91 2 0K_0402_5%

1 2

CC10 1 U_0402_6.3V6K

SOC_SRT CRST#

Remove CLR ME

1 2

1 1

RC93 2 0K_0402_5%

1 2

CC11 1 U_0402_6.3V6K

1 2

JCMOS1 0_ 0603_5%@

SOC_RTC RST#

CLR CMOS

N

GFF WL+BT(KEY E)

Place at RAM DOOR

1 2

RC94 1M_040 2_5%

+3VS

1 2

RC165 10K_040 2_5%

1 2

RC105 10K_040 2_5%

1 2

RC259 10K_040 2_5%

1 2

RC121 10K_040 2_5%

1 2

RC123 10K_040 2_5%

1 2

RC124 10K_040 2_5%

2 2

+3VALW _PRIM

+3VALW _DSW

CLKREQ_ PCIE#4

CLKREQ_ PCIE#5

CLKREQ_ PCIE#0

CLKREQ_ PCIE#1

CLKREQ_ PCIE#2

CLKREQ_ PCIE#3

RPC11

18

27

36

45

10K_080 4_8P4R_5%

Follow 54 3016_SKL_U_Y_PDG _0_9

+3VALW _DSW

1 2

RC103 10K_0 402_5%

1 2

RC104 1K_04 02_5%

1 2

@

RC106 10K_0 402_5%

+3VALW _PRIM

3 3

+3VALW _DSW

1 2

RC115 10K_0 402_5%@

RC111 100K_ 0402_5%@

12

+1.0V_VC CST

From EC(open-drain)

EC_VCCS T_PG_R<36,40>

4 4

A

SM_INTRUD ER#

PCH_PW ROK

EC_RSMR ST#

SYS_RESET #

LAN_PME #

Note for PCH_PWRO K

PDG1.0 Figure43-4 note2 0: PC H_PWROK

does not glitch when RSMRS T# is

de-as ser te d

PM_BATL OW#

PCH_PCIE_ WAKE#

AC_PRES ENT

SOC_VRA LERT#

#543016 PD G0.9 P.526

PROCPWRGD is used only for power sequence

debug and is not r equired to be connected to

anything on the platform.

C6:A@#DB

: E * = * ; C/-/

2$*=* )F*)'< G )<

*' $ < ) 4

H6%C6:,H6%CD')<)4$ I

PBTN_OU T#_R

Note for VCCST_PWRGD

1. 1.0V toleran ce

2. PDG1.0 Figure4 3-4 note17: when failure events ,

VCCST_PWRGD and PCH_PWROK de-assert at the same time

12

RC113

1K_0402 _5%

1 2

RC116 60.4_0 402_1%

CC51

.1U_0402 _16V7K

CC50

.1U_0402 _16V7K

EC_VCCS T_PG

@EMC@

SYS_RESET # SYS_PW ROK

12

@EMC@

H_CPUPW RGD

12

Reserved for ESD 2014/ 9/17

B

SSD

GLAN

AR

CR

WIGI G

EC_RSMR ST#<36>

PCH_PW ROK<36>

SUSPW RDNACK<36 >

PCH_PCIE_ WAKE#<28,33>

LAN_PME #<28 >

LAN_DISAB LE_N<28>

Close to UC1

CC436 .1U_0 402_16V7K

ESD@

20 17/4/18 for MB Field

lesson learnt ESD request

B

SYS_RESET #<6>

SYS_PW ROK<36>

12

CLK_PCIE_ N0<2 7>

CLK_PCIE_ P0<27>

CLKREQ_ PCIE#0<27>

CLK_PCIE_ N1<2 8>

CLK_PCIE_ P1<28>

CLKREQ_ PCIE#1<28>

CLK_PCIE_ N2<3 1>

CLK_PCIE_ P2<31>

CLKREQ_ PCIE#2<31>

CLK_PCIE_ N3<3 3>

CLK_PCIE_ P3<33>

CLKREQ_ PCIE#3<33>

CLK_PCIE_ CARD<38>

CLK_PCIE_ CARD#<38>

CLKREQ_ PCIE#4<38>

CLK_PCIE_ N5<3 1>

CLK_PCIE_ P5<31>

CLKREQ_ PCIE#5<31>

PLT_RST #<27,33,36 ,38>

T95 @

T89 @

T92

EC_VCCS T_PG

C

UC1J

CLK_PCIE_ N0

CLK_PCIE_ P0

CLKREQ_ PCIE#0

CLK_PCIE_ N1

CLK_PCIE_ P1

CLKREQ_ PCIE#1

CLK_PCIE_ N2

CLK_PCIE_ P2

CLKREQ_ PCIE#2

CLK_PCIE_ N3

CLKREQ_ PCIE#3

CLK_PCIE_ CARD

CLK_PCIE_ CARD#

CLKREQ_ PCIE#4

CLK_PCIE_ N5

CLK_PCIE_ P5

CLKREQ_ PCIE#5

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

S

KL-U_BGA 1356

@

PCH PLTRST Buffer

PLT_RST #

UC1K

SYSTEM POWER MANAGEMENT

PLT_RST #

SYS_RESET #

EC_RSMR ST#

H_CPUPW RGD

EC_VCCS T_PG

SYS_PW ROK

PCH_PW ROK

PCH_DPW ROK

SUSPW RDNACK

@

SUSACK#

PCH_PCIE_ WAKE#

LAN_PME #

LAN_DISAB LE_N

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

S

KL-U_BGA 1356

@

PBTN_OU T#<6,36>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/02/ 22 2018/02/ 22

2017/02/ 22 2018/02/ 22

2017/02/ 22 2018/02/ 22

C

2

<BOM Struc ture>

1

UC3

MC74VHC 1G08DFT2G_SC 70-5

RC125 0_040 2_5%

RC109 0_040 2_5%

EC_RSMR ST# PCH_DPW ROK

RC122 0_040 2_5%

RC110 10K_0 402_5%<BOM Structu re>

SKL_ULT

CLOCK SIGNALS

10 OF 20

RC248 0_0 402_5%

12

@

12

RC249 0_0 402_5%

5

P

B

A

@

SKL-U

11 OF 20

PLT_RST _BUF#

4

Y

G

3

12

GPP_B11/EXT_PWR_GATE#

PBTN_OU T#_R

12

@

12

@

RC1140_ 0402_5%

PCH_PW ROKSYS_PWROK

12

@

1 2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date