A

B

C

D

E

MODEL NAME :

PCB NO :

LA-E992P

CKF50/CKA50

BOM P/N :

1 1

451A7631L51

451A7631L52

451A7631L01

451A7631L02

Dell/Compal Confidential

Schematic Document

KABYLAKE-H

2 2

N17E

Firestar/Armani

2017-07-25

Rev: 1.0 (A00)

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/08/25 2011/08/25

2011/08/25 2011/08/25

2011/08/25 2011/08/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

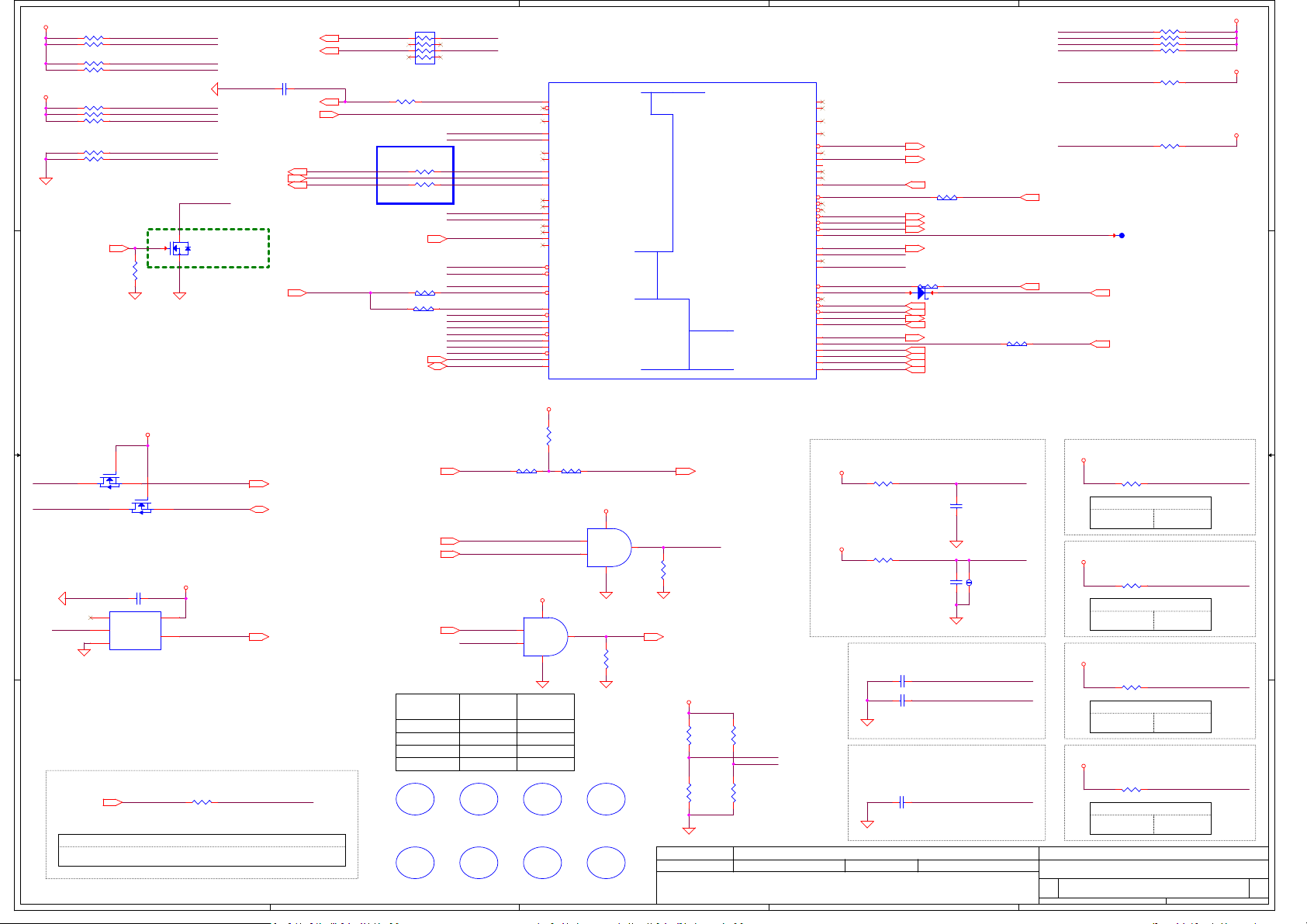

Cover Page

Cover Page

Cover Page

LA-E992P

LA-E992P

LA-E992P

E

1.0(A00)

1.0(A00)

1 77Tuesday, July 25, 2017

1 77Tuesday, July 25, 2017

1 77Tuesday, July 25, 2017

1.0(A00)

A

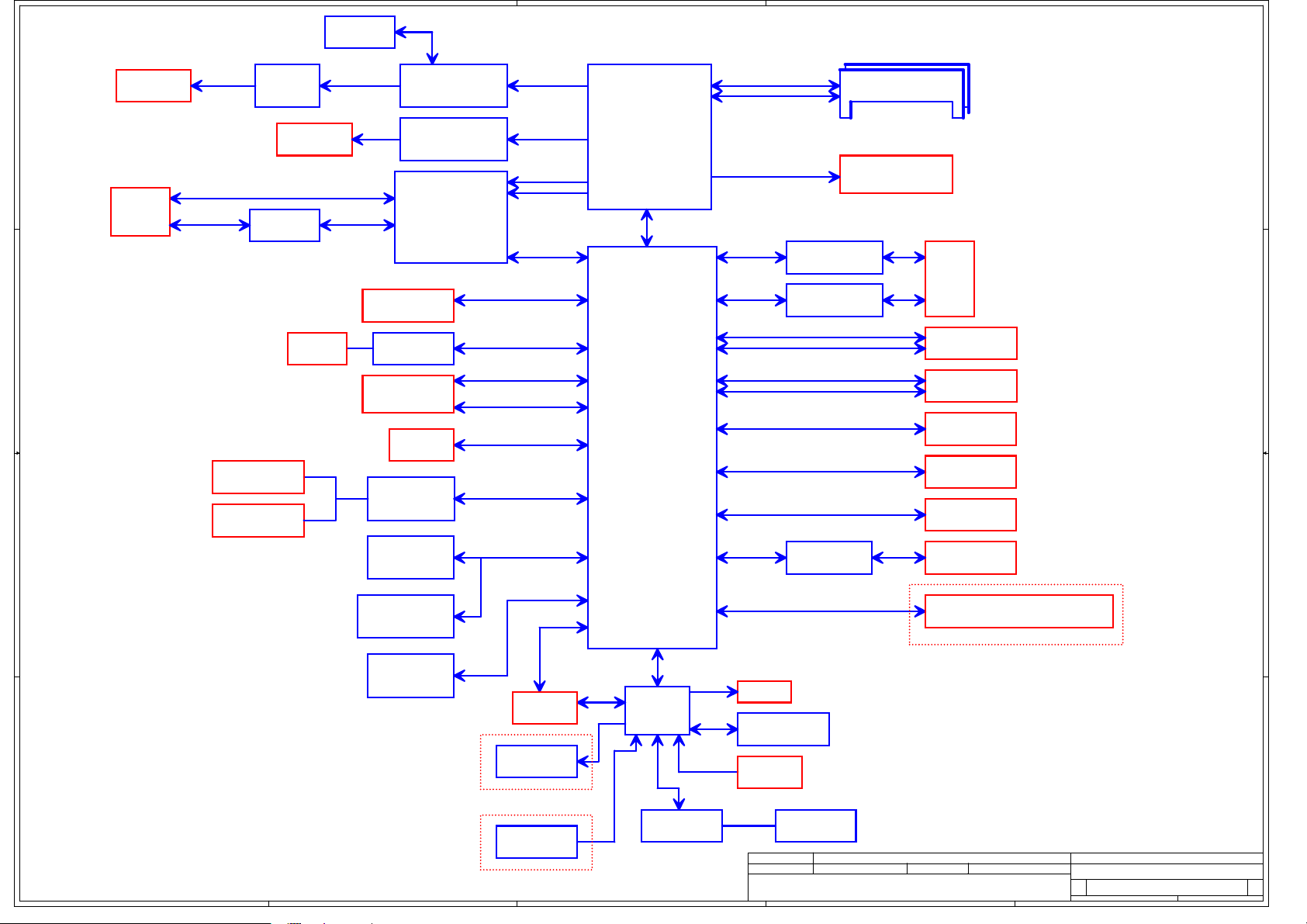

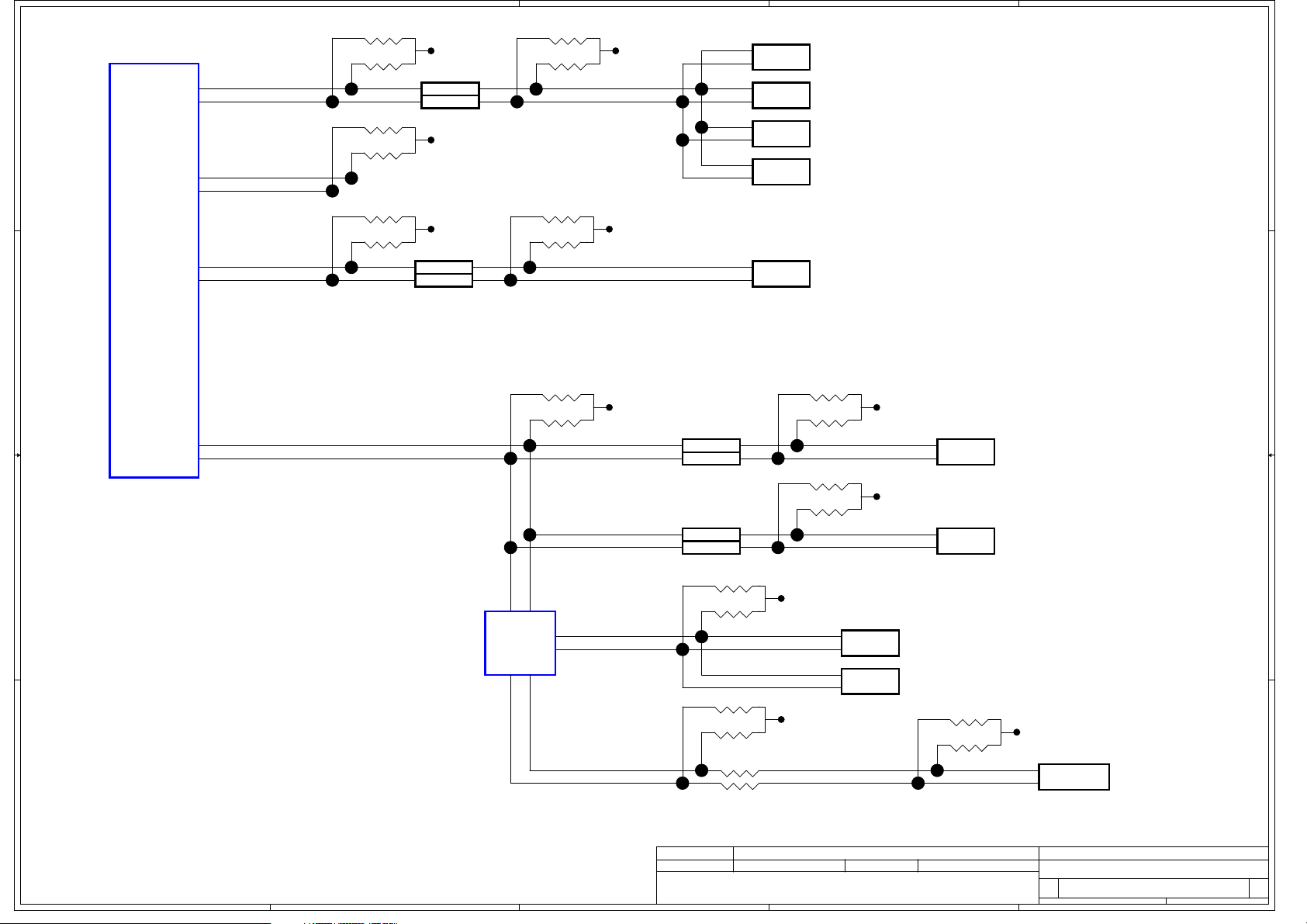

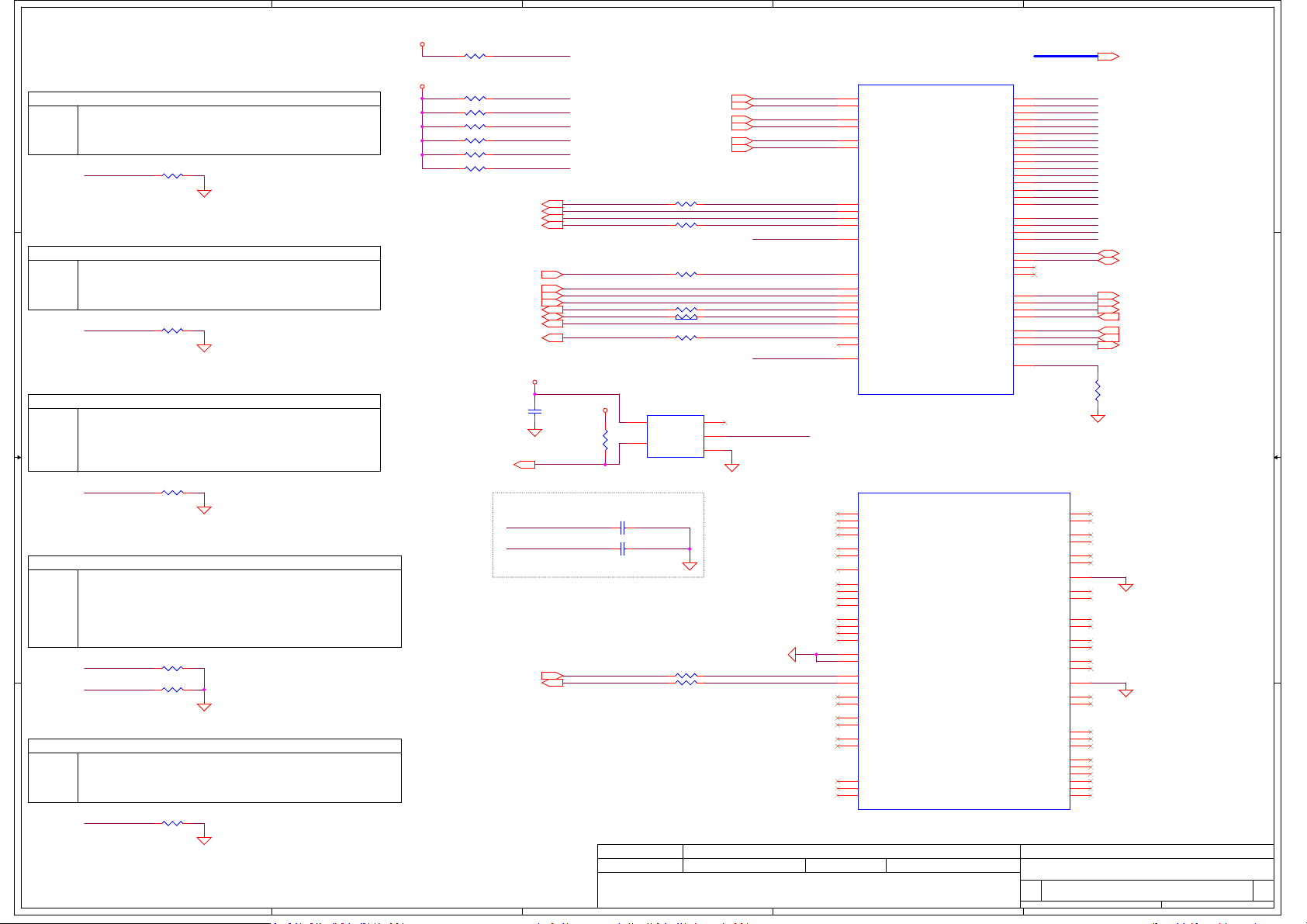

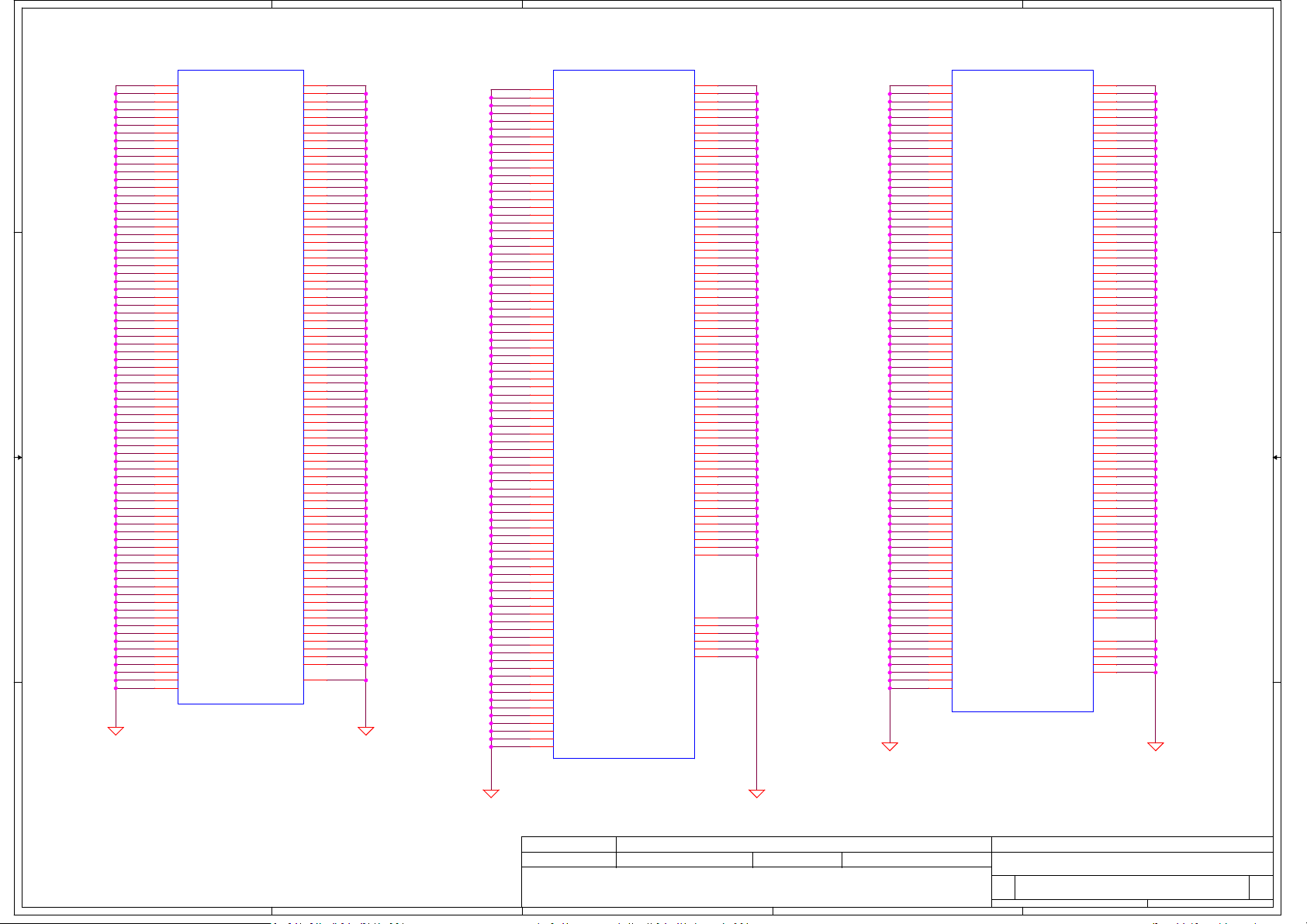

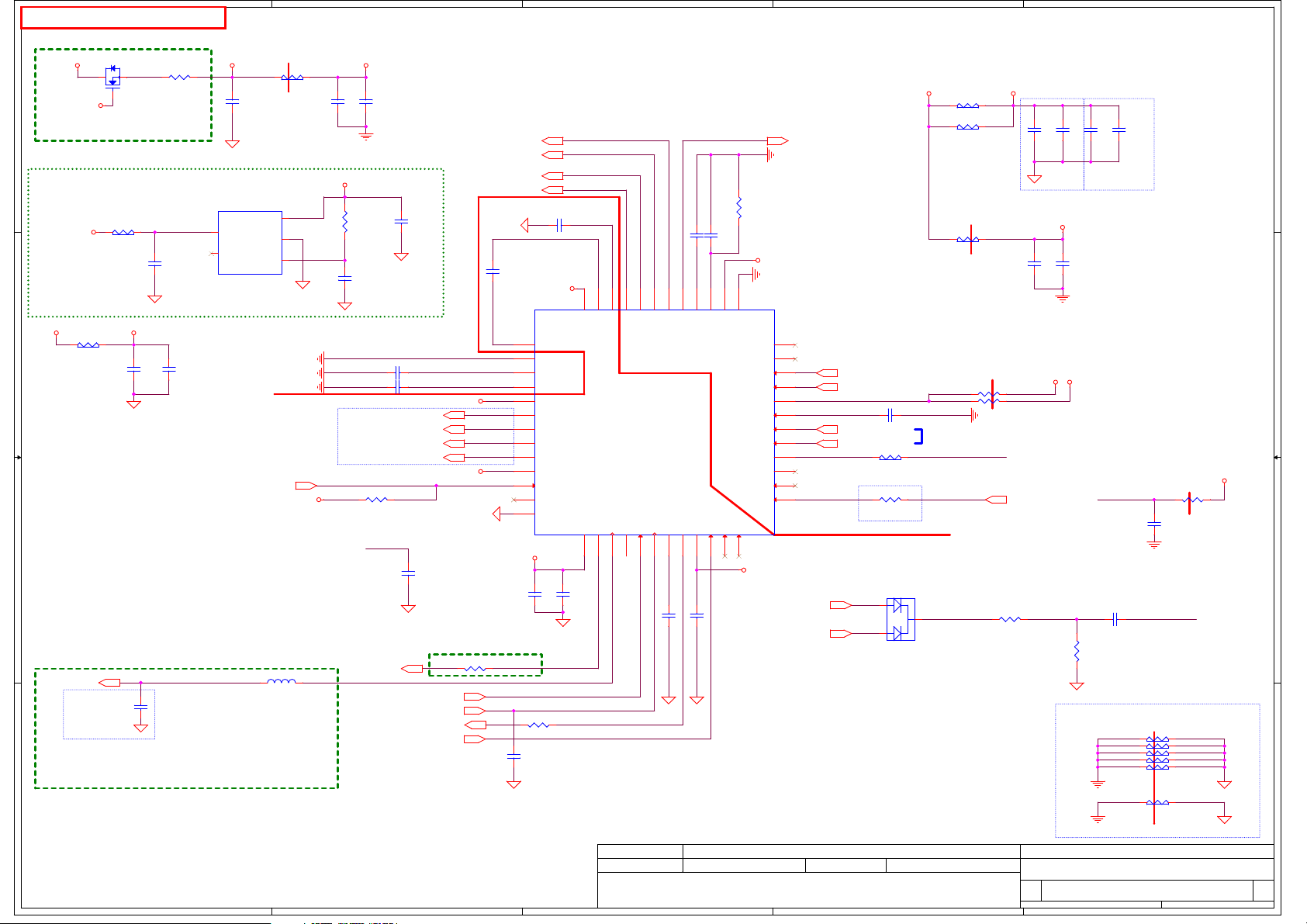

256M*32 x6 =6G

VRAM * 6

GDDR5

B

C

D

E

P28

P33P33

P29

P29

P23

P17

P27

GB4-256

P46-55

P39~40

PEG 3.0 x16

DDI3 x2

P35

DDI1 x4

DDI2 x4

PCI-E x4

Port 1-Port 4

PCI-E x1

Port 6

PCI-E x1

Port 5

PCI-E x4

Port 9-Port 12

SATA0A

SATA1B

HD Audio

SPI

SMBus

I2C

Intel

KBL-Lake-H

Processor

45W

BGA

DMI x4

100MHz

5GB/s

Intel

KBL-H-PCH

BGA 837 Balls

HM175

P7-13

P16-22

DDR4 ChannelA

DDR4 ChannelB

eDP1.4 x4

USB2.0

Port 1

USB3.0

Port 1

USB Powershare

TPS2544

USB 3.0 Re-driver

PS8713

USB2.0

USB3.0

USB2.0

USB3.0

USB2.0

USB2.0

USB2.0 SD3.0

Port 7

Card Reader 2 in 1

RTS5176E SD / MS

USB2.0

Port 8

HDMI 2.0

Conn.

1 1

P45

Retimer

PS8409A

CRT

Conn.

P44

IFPHDMI2.0

P35

GPU

N17E-G1

DP to VGA

RTD2166-CG

CIO/USB3.1

USB3.1

TypeC

2 2

3 3

P41

USB2.0/CC

Main SPKR *2

Universal

Audio Jack

TPS65982D

RJ45

P24

P24

P41

I2C/USB2.0

TPM

NPCT650VBCYX

Thunderbolt

Alpine Ridge-SP

M.2 Slot A Key-E

(WLAN+BT4.0)

LOM

RTL8111H

M.2 Slot C Key-M

(SATA/PCIe SSD)

HDD

Conn.

HDA Codec

ALC3246

SPI Flash

(BIOS 16MB)

DDRIV-DIMM X2

1.2V DDR4 2400 MHz

P14-15

32GB Max

15.6''

HD/FHD / UHD

P31

P31 P31

Port 2

Port 2

Port 3

Port 3

Port 12

Port 4

Port 9

P34 P34

P38

USB 3.0

Type-A

USB 3.0

Type-A

USB 3.0

Type-A

Digital Camera

Conn.

M.2 Slot A Key-EUSB2.0

(WLAN+BT4.0)

Touch Panel

Conn.

Touch Finger Print w/ power button

Conn.

Left

Right

P32

Right

P32

P38

P28

P38

P37

Power Button Board

MEC1416

KBC

SMBus

C

eSPI

P36

Charger &

Battery

PWM

I2C

FAN

P26

Thermal Sensor

F75303M

KB Conn.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

P27

P25

AC Adaptor

P59P59/P60

Compal Secret Data

Compal Secret Data

2011/08/25 2011/08/25

2011/08/25 2011/08/25

2011/08/25 2011/08/25

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

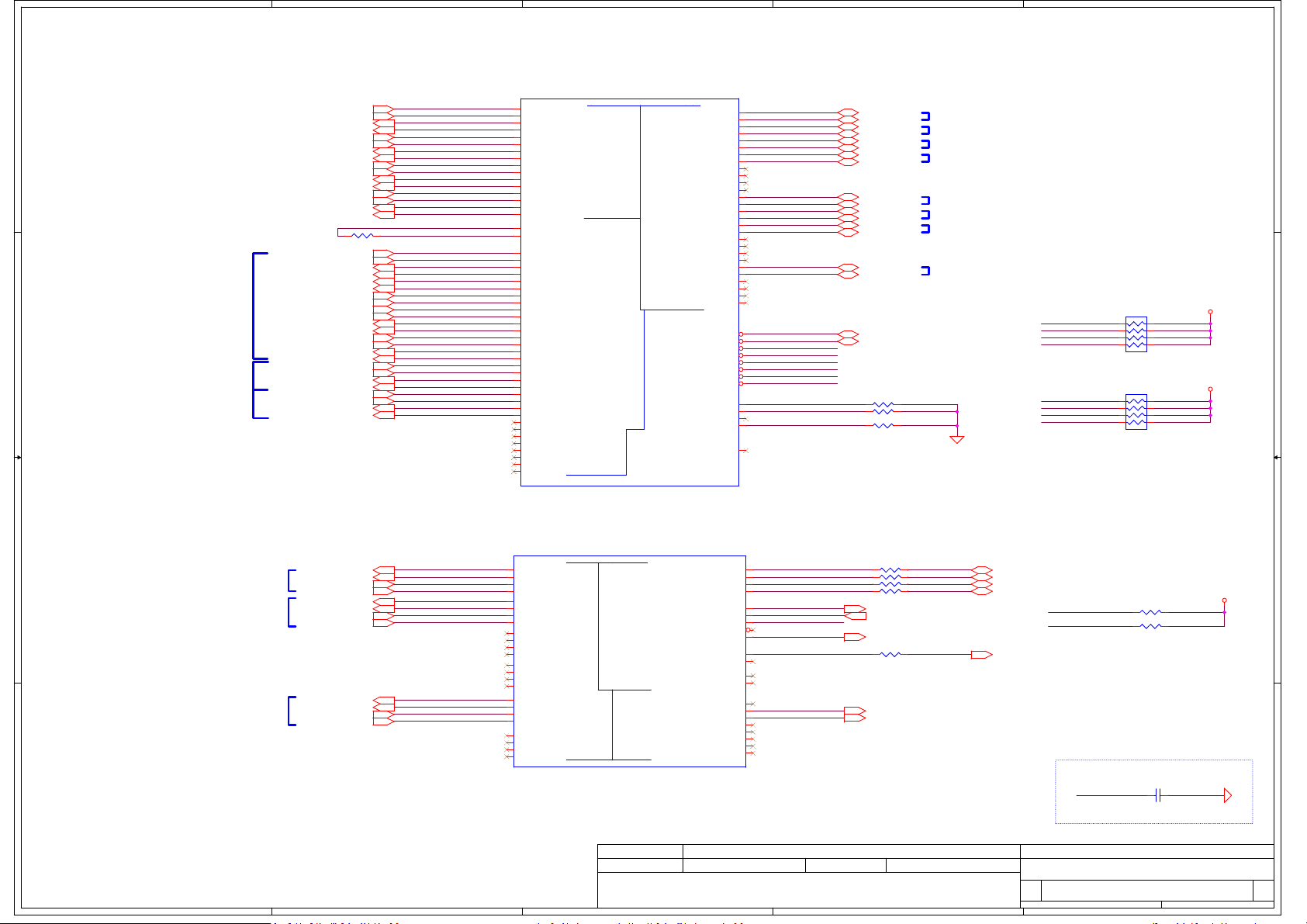

Block diagram

Block diagram

Block diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

LA-E992P

LA-E992P

LA-E992P

2 77Tuesday, July 25, 2017

2 77Tuesday, July 25, 2017

2 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

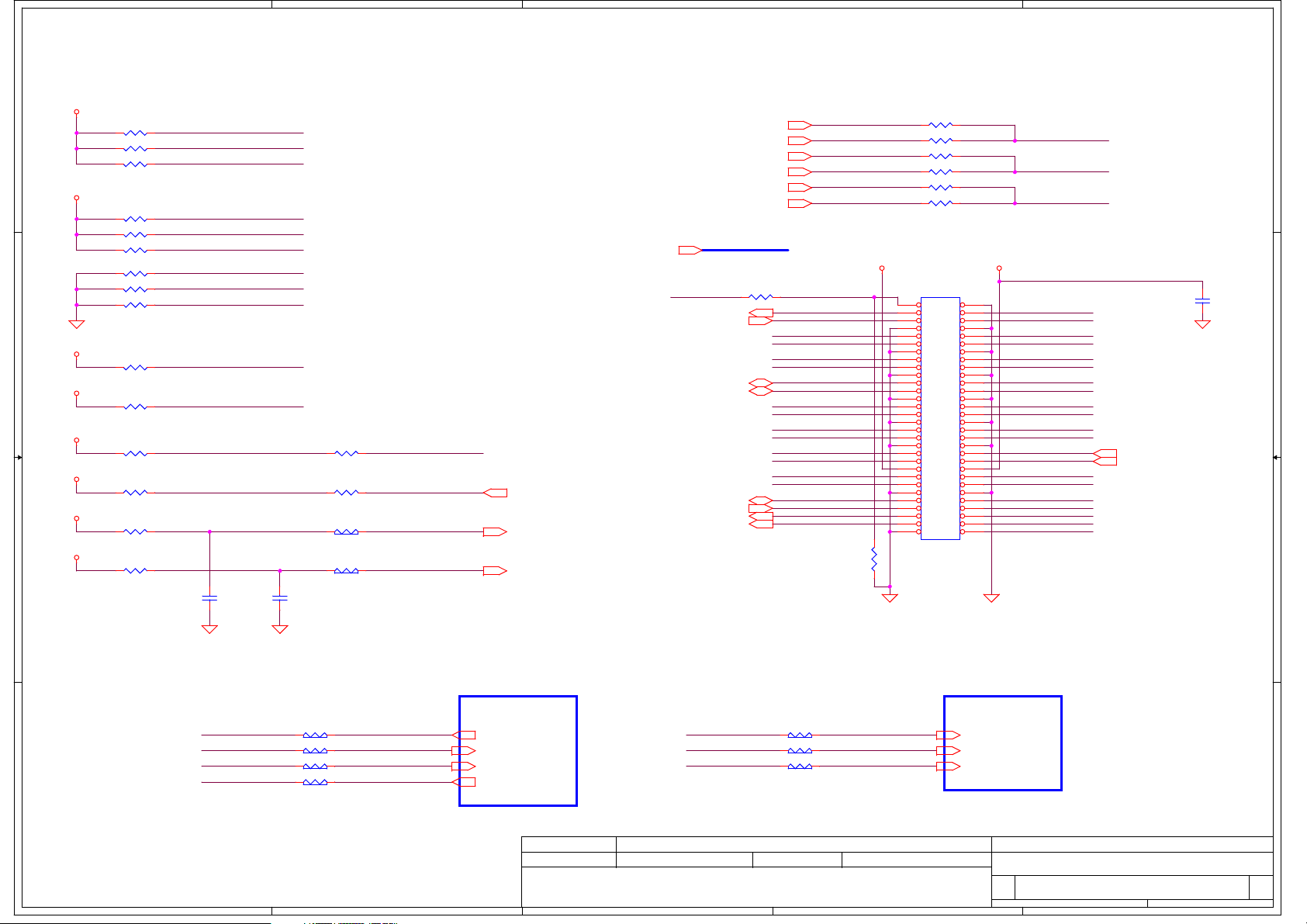

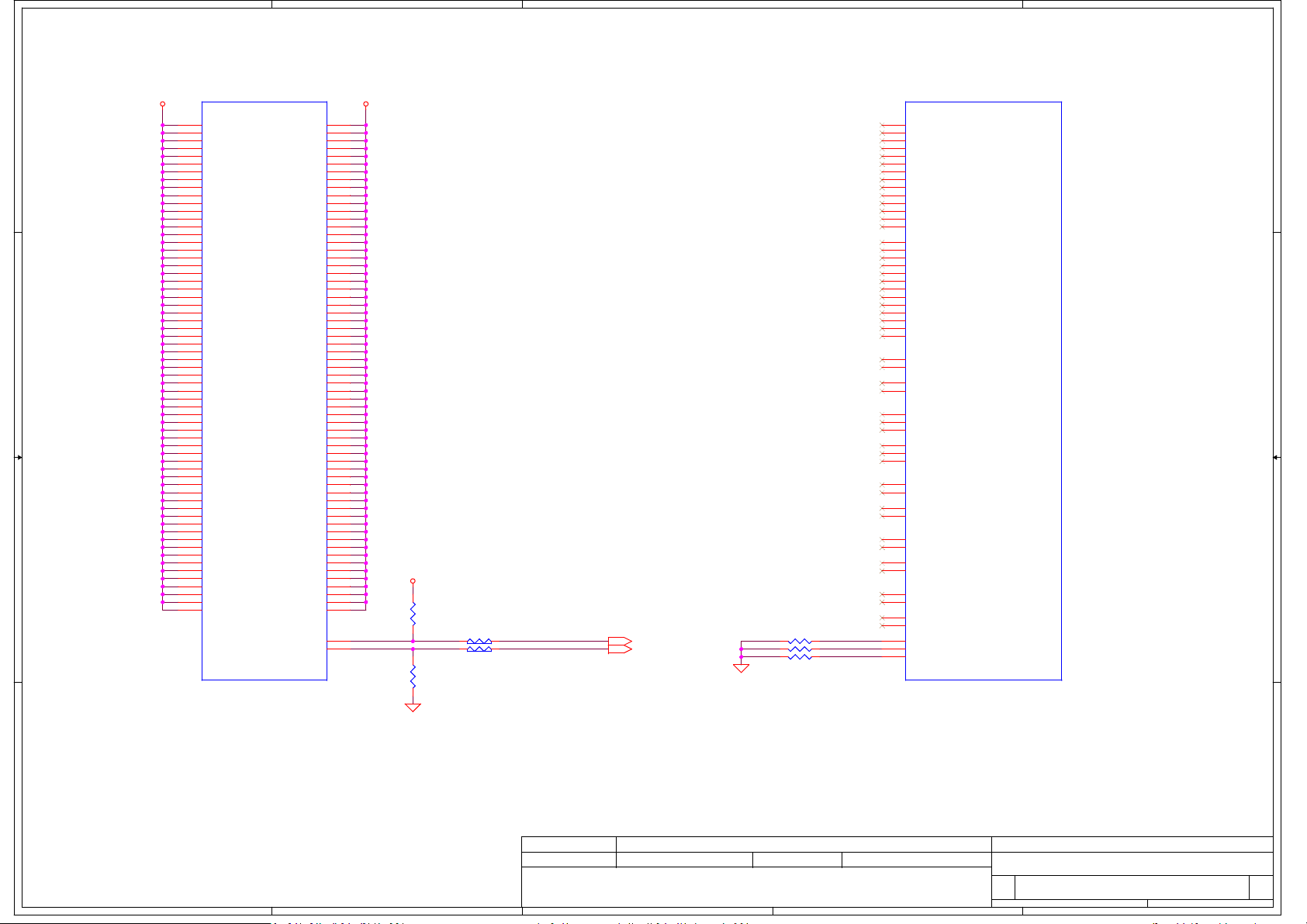

FFS

LNG2DMTR

4 4

P29

Touch Pad

LED

PS2

P26

P37

LED Board

Power Button

P37

Power Button Board

A

B

A

B

C

D

E

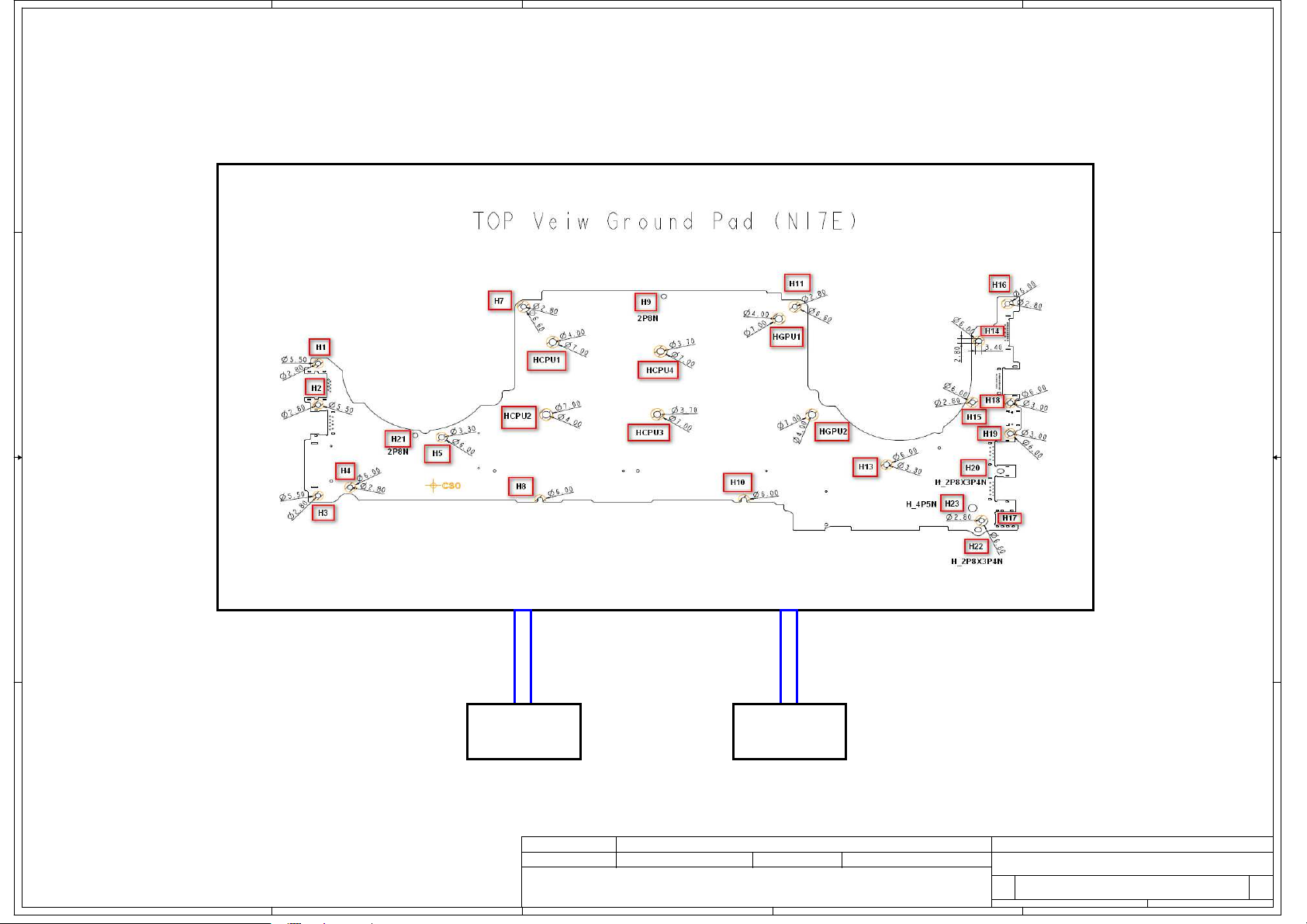

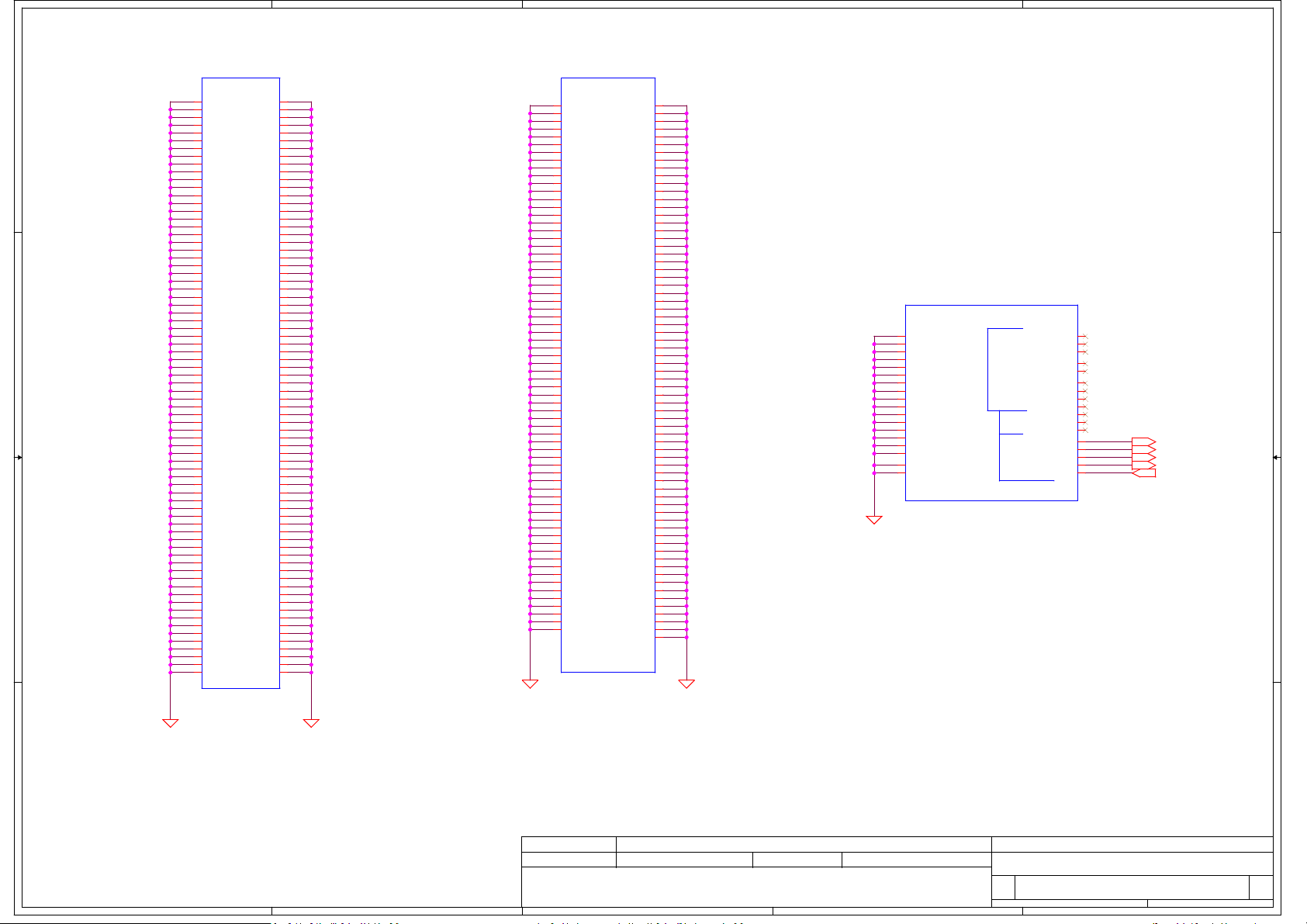

Compal Confidential

Project Code :

File Name :

1 1

ME Hole Location

M/B

2 2

3 3

Base on ME 0505

LED Board PWB Board

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

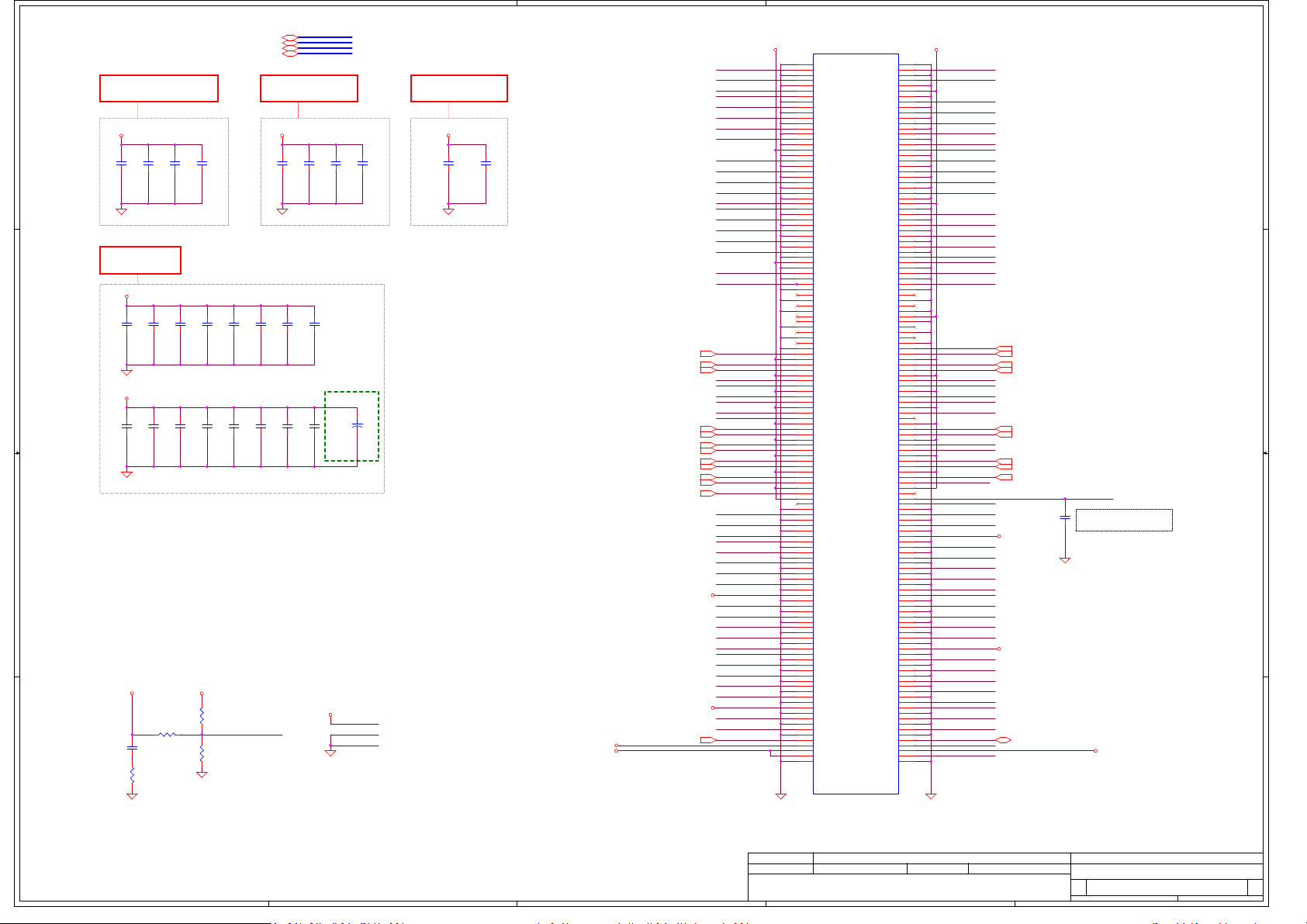

DB block diagram

DB block diagram

DB block diagram

LA-E992P

LA-E992P

LA-E992P

1.0(A00)

1.0(A00)

1.0(A00)

3 77Tuesday, July 25, 2017

3 77Tuesday, July 25, 2017

3 77Tuesday, July 25, 2017

E

Vinafix.com

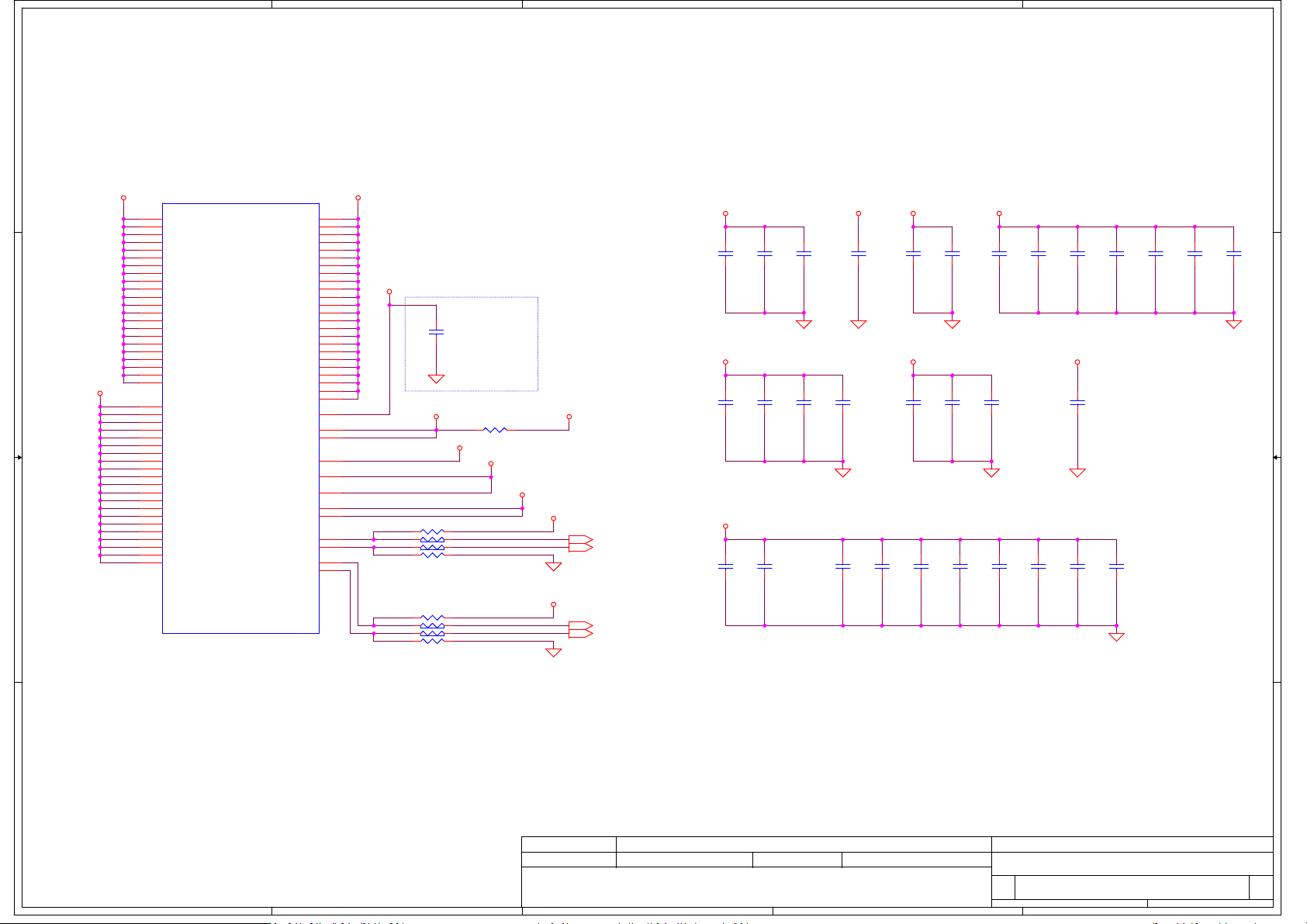

A

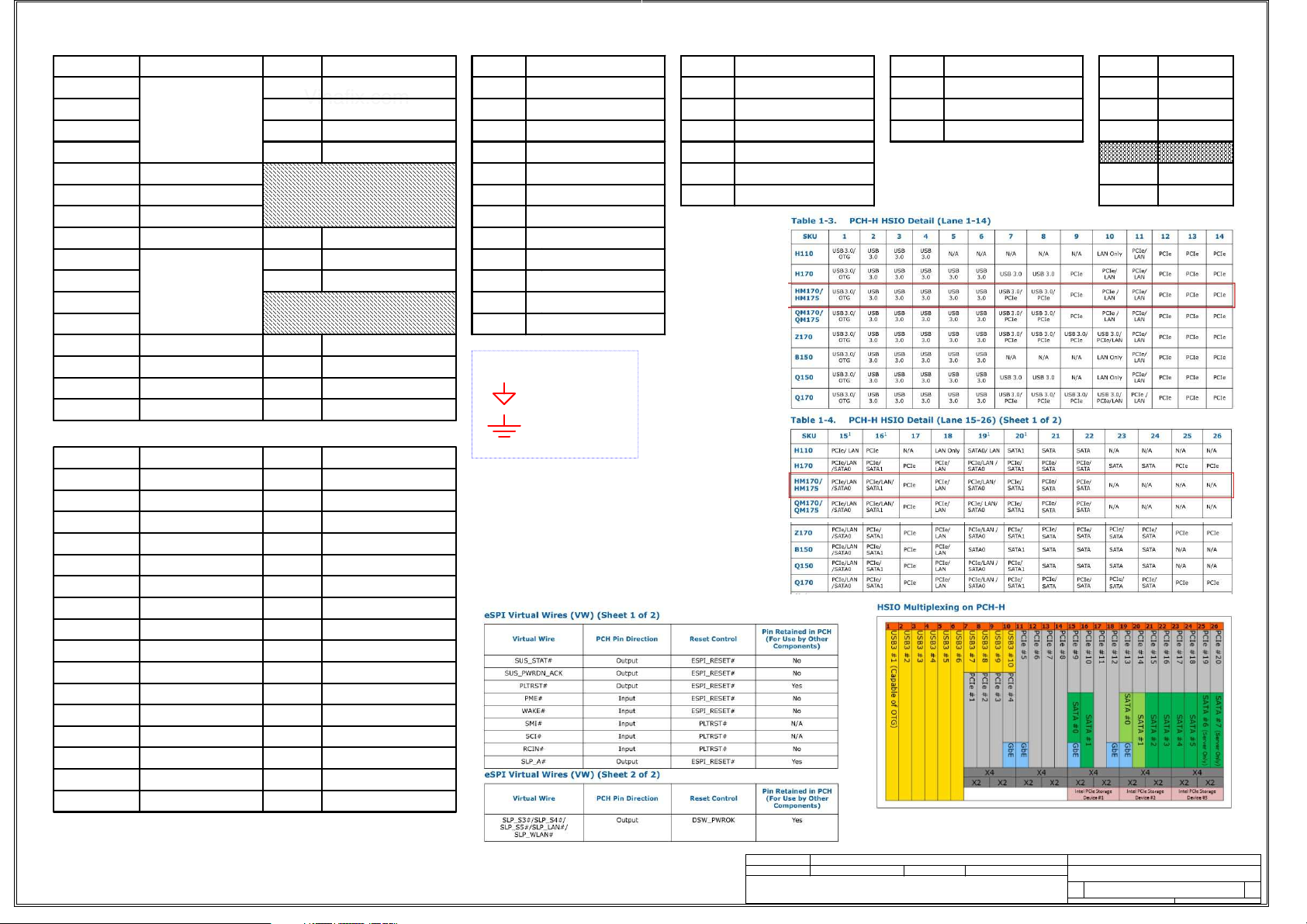

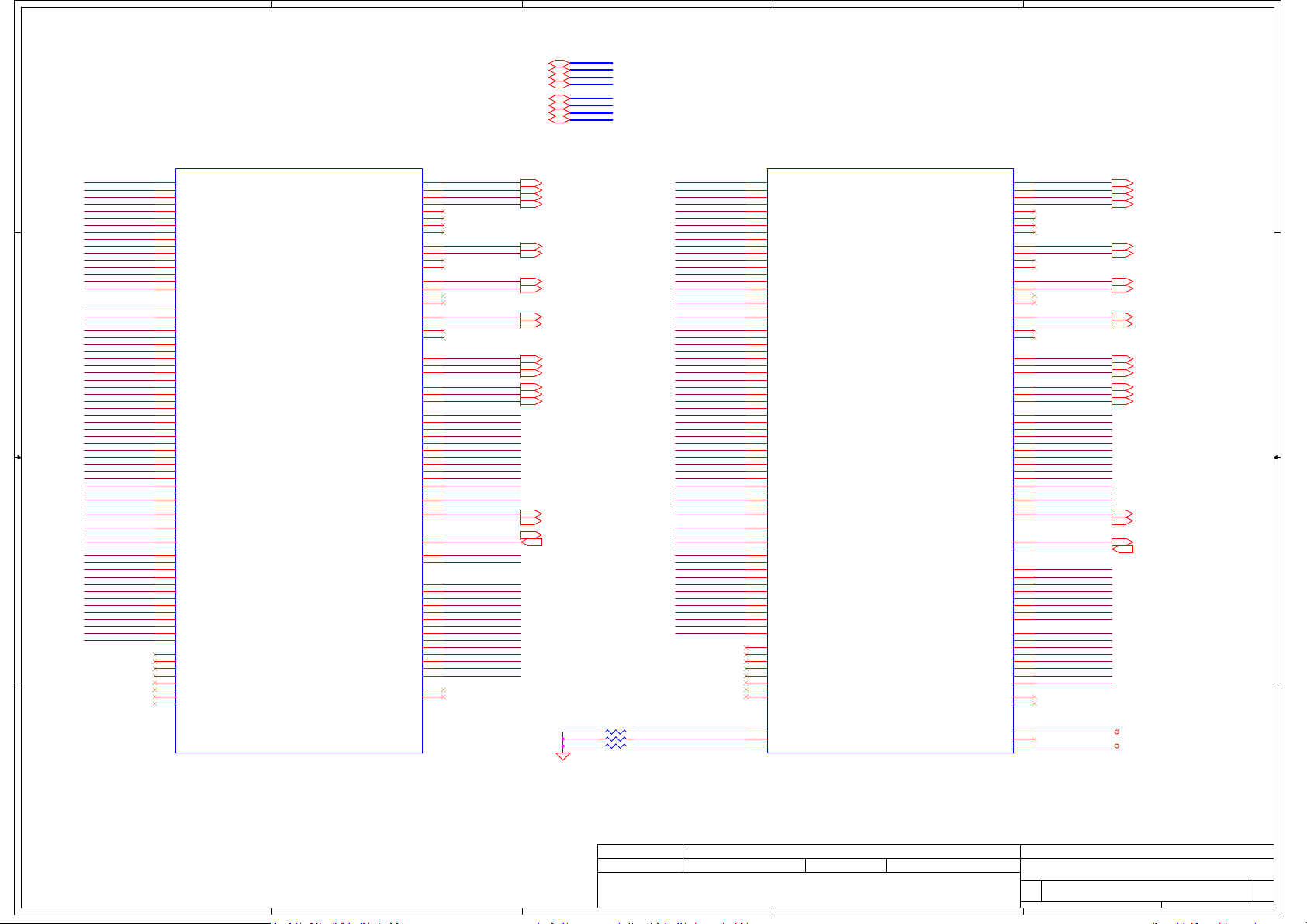

Refer Page 36

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8 None

Lane 9

Lane 10

Lane 11

DESTINATION

Alpine Ridge - SP

LOM

NGFF - WLAN + BT

None

NGFF - SSD

7

8

9

10

SATA

0A

1A

DESTINATIONUSB3

None

None

None

None

DESTINATION

NGFF - SSD

None

Lane 12

Lane 13

Lane 14

Lane 15

Lane 16

1 1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

None

None

None

None

DESTINATIONCLK_PCIE

None

None

LOM

NGFF - WLAN + BT

None

Alpine Ridge - SP

NGFF - SSD

GPU

None

None

None

None

None

None

None

None

0B

2

3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

None

HDD1B

None

None

DESTINATIONCLK_REQ

None

None

LOM

NGFF - WLAN + BT

None

Alpine Ridge - SP

NGFF - SSD

GPU

None

None

None

None

None

None

None

None

USB2 DESTINATION

1

USB JUSB3 (Left Side)

2

USB JUSB1 (Right Side)

3

USB JUSB2 (Right Side)

4

NGFF - WLAN + BT

None

5

6

None

7

CARD READER

8

Finger Print

9

Touch screen

10

11

12

None

None

CAMERA

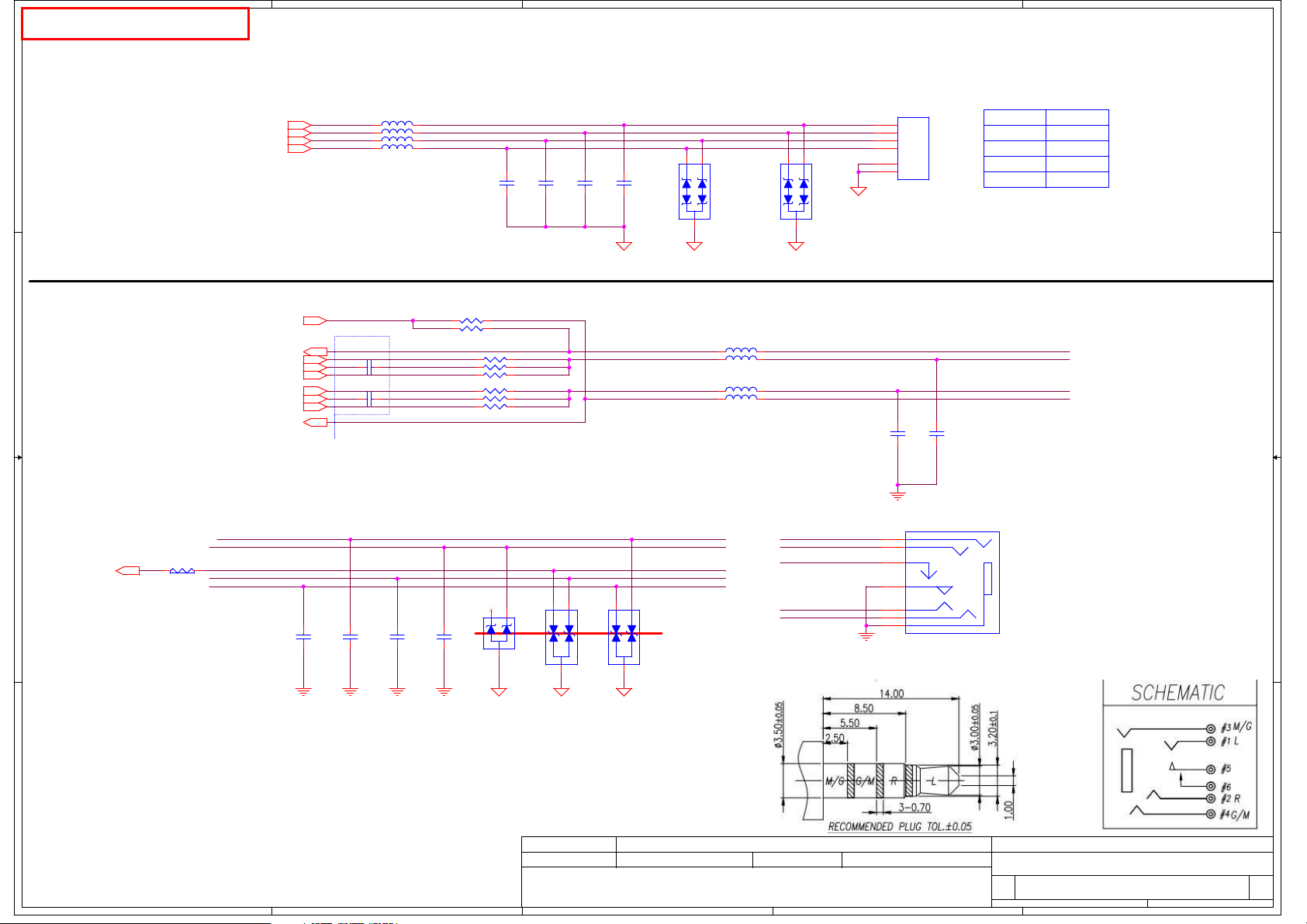

Symbol Note :

: means Digital Ground

: means Analog Ground

USB31DESTINATION

USB JUSB3 (Left Side)

2

USB JUSB1 (Right Side)

3

USB JUSB2 (Right Side)

4

None

5

None

6

None

DDI

1

2

3

DESTINATION

Alpine Ridge

Alpine Ridge

DP to VGA

Board ID

X00

X01

X02

X03

A00

Resistor

10K

17.8K

27K

37.4K

49.9K

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

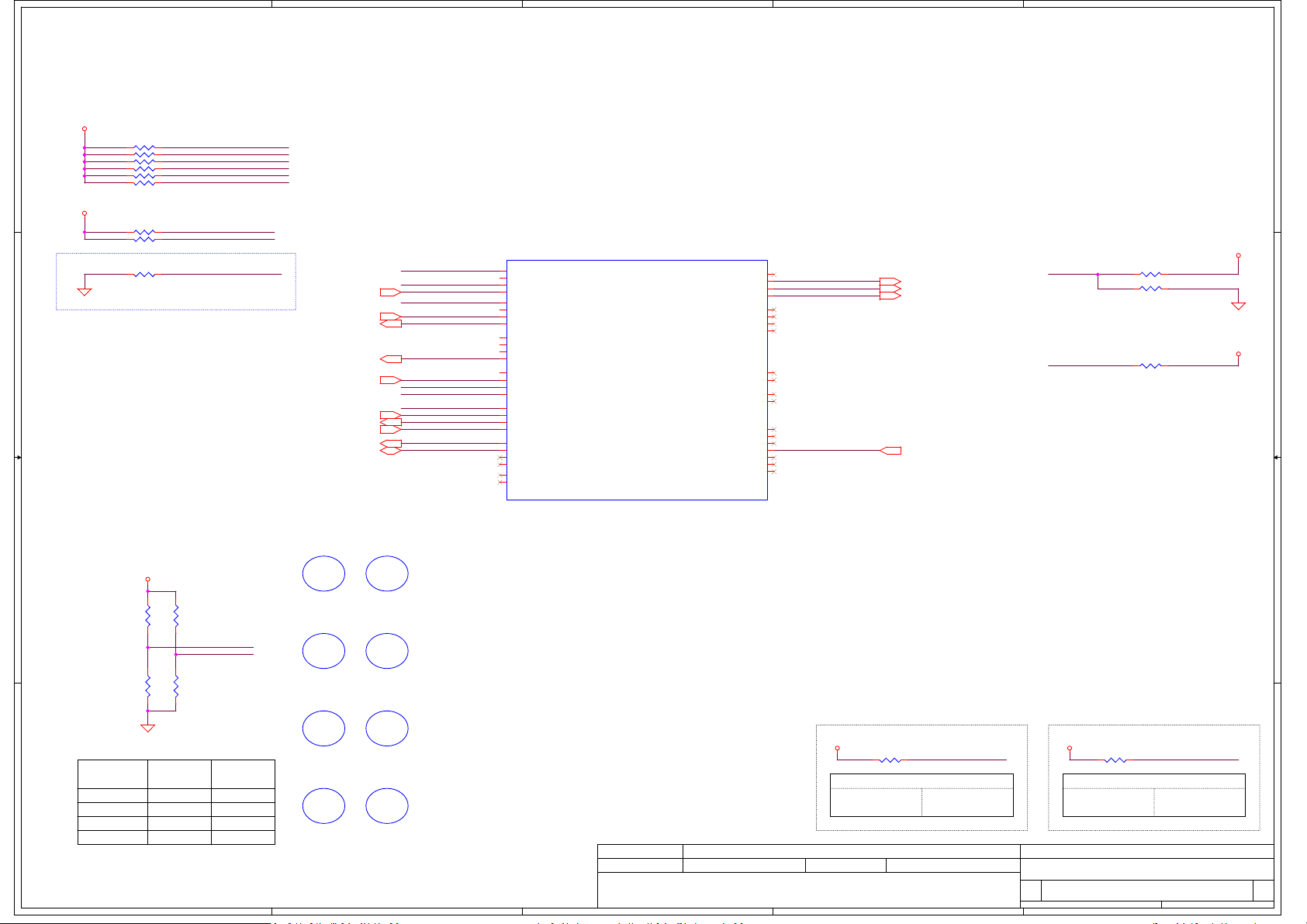

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-E992P

LA-E992P

LA-E992P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1.0(A00)

1.0(A00)

1.0(A00)

4 77Tuesday, July 25, 2017

4 77Tuesday, July 25, 2017

4 77Tuesday, July 25, 2017

5

4

3

2

1

1K

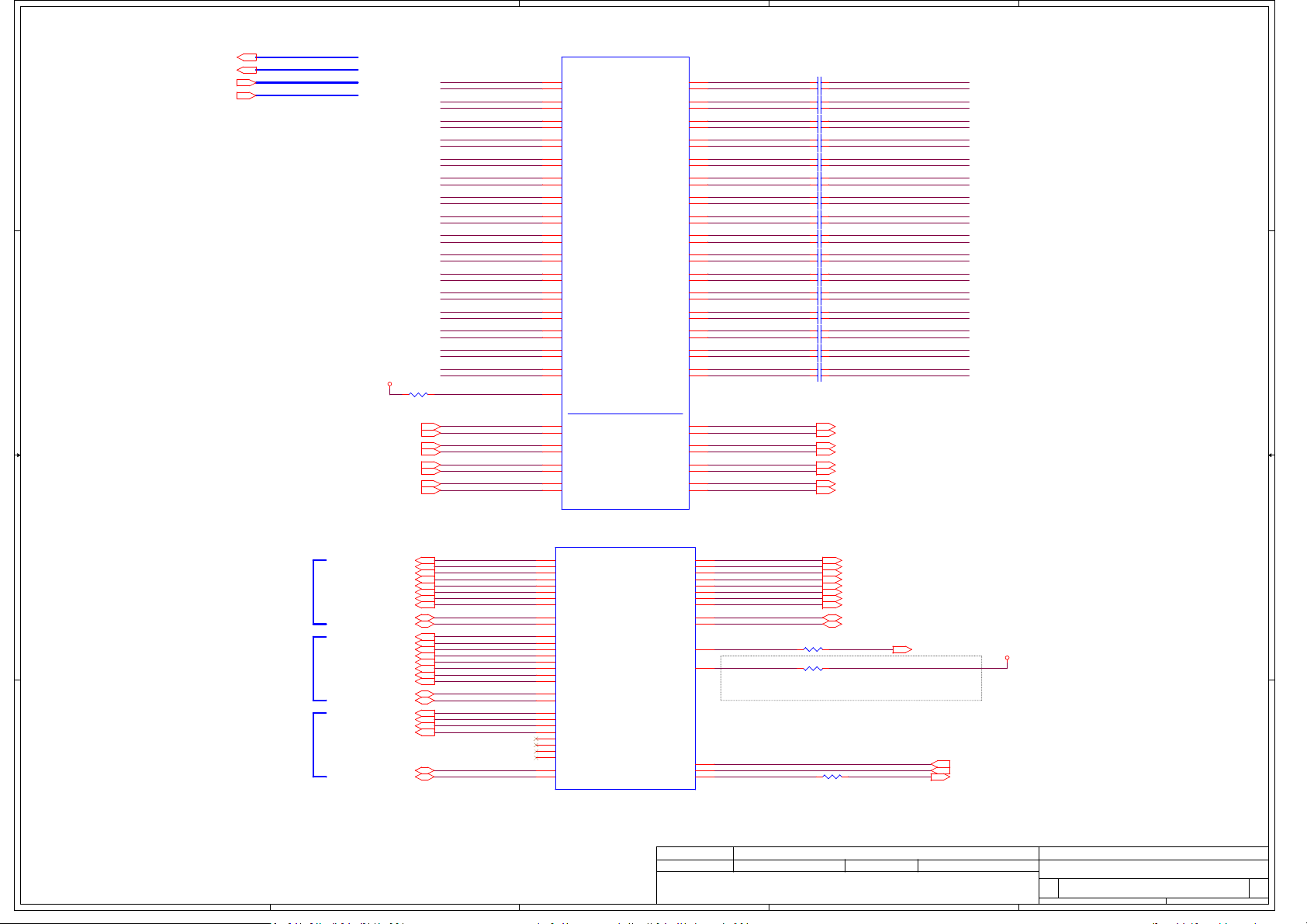

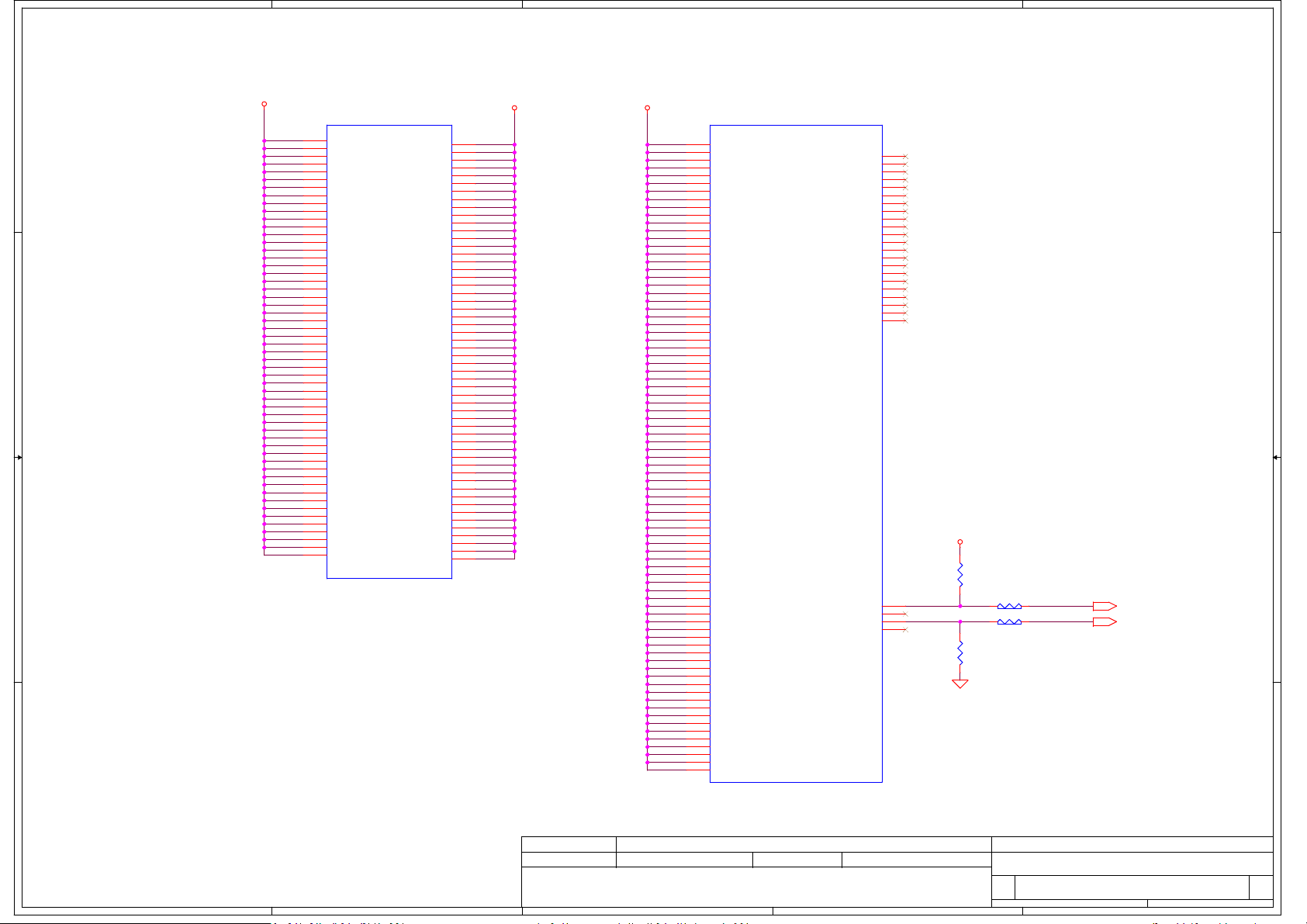

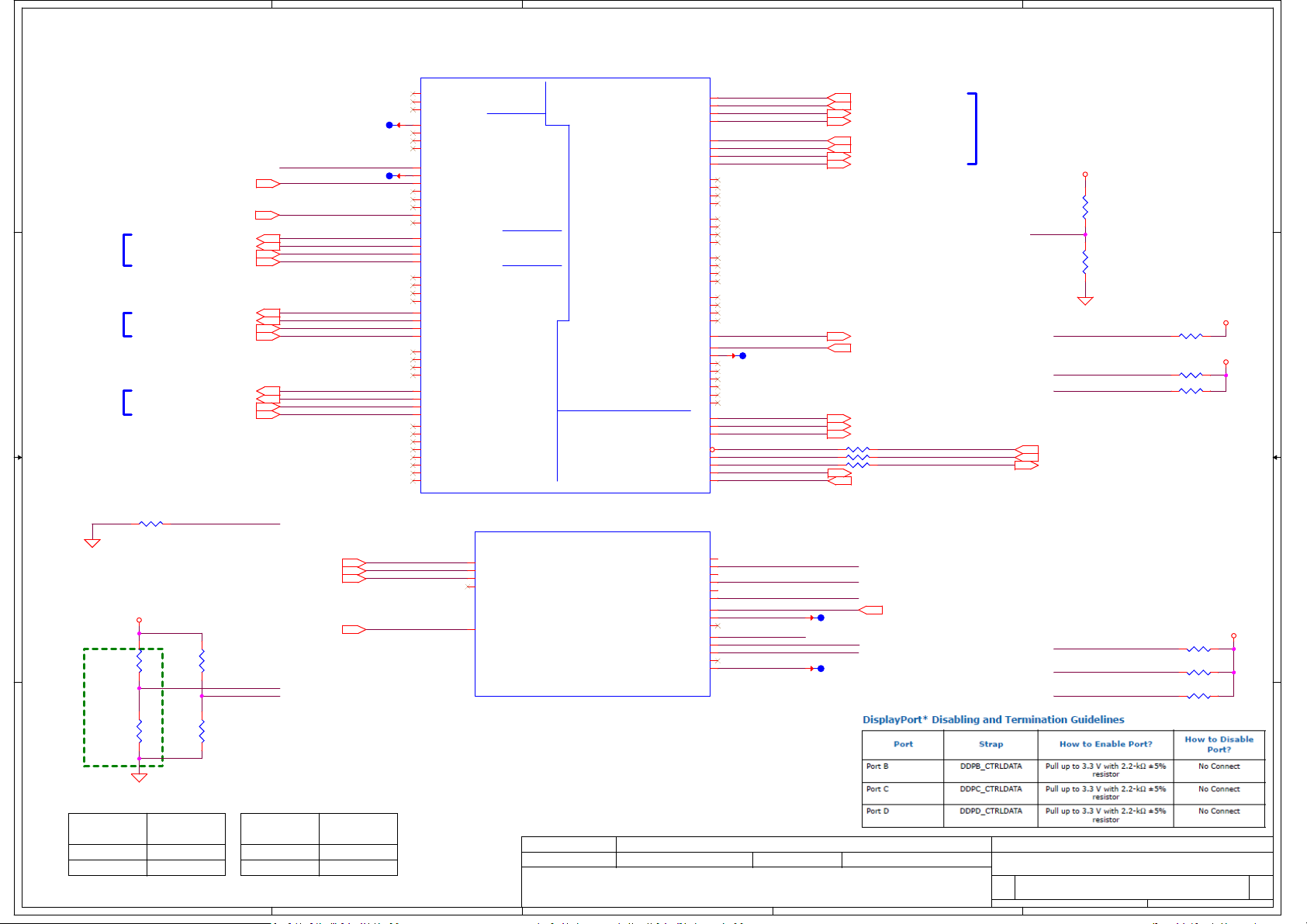

Address: 0x88/0x89

Host

AW44

BB43

D D

AY44

BB39

Host

AR41

AR44

SMBCLK

SMBDATA

SML0_SMBCLK

SML0_SMBDATA

I2C1_SCK_TP

I2C1_SDA_TP

1K

499

499

2.2K

2.2K

+3VALW

+3VS

DMN65D8L

DMN65D8L

+3VALW

+3VS

+3VS

DMN65D8L

DMN65D8L

1K

1K

PCH_SMBCLK

PCH_SMBDATA

2.4K

2.4K

I2C1_SCK_TP_C

I2C1_SDA_TP_C

+3VS

+3VS_TP

Slave

DIMMA

Slave

DIMMB

Slave

FFS

Slave

RTD2166

Slave

Touch

Pad

Address: 0xA0/0xA1

Address: 0xA4/0xA5

Address: 0x52/0x53

Address: 0x64/0x65, 0x68/0x69

Address: 0x2C/0x2D

PCH

C C

2.2K

2.2K

Slave

AW42

AW45

GPU_THM_SMBCLK

GPU_THM_SMBDAT

GPU_THM_SMBCLK

GPU_THM_SMBDAT

GPU_THM_SMBCLK

GPU_THM_SMBDAT

B B

Host

+3VALW_EC

+3VS

DMN65D8L

DMN65D8L

ALL_GPWRGD

DMN65D8L

DMN65D8L

4.7K

4.7K

PBAT_CHG_SMBCLK

MEC1416

Host

PBAT_CHG_SMBDAT

Host

TYPEC_SMBCLK

2.2K

2.2K

0 Ohm

TYPEC_SMBDA

A A

0 Ohm

10K

10K

1.8K

1.8K

+3VALW_EC

+3VALW_EC

+3VS

THM_SML1_CLK

THM_SML1_DATA

+1V8_AON

VGA_SMB_CK2

VGA_SMB_DA2

Slave

BATT

Slave

CHAGER

PD_I2C_SCL_R

PD_I2C_SDA_R

Slave

Thermal

Sensor

Slave

GPU

Address: 0x16/0x17

Address: 0x12/0x13

10K(@)

10K(@)

Address: 0x9A/0x9B

Address: 0x9E/0x9F

+3VS

Slave

TPS65982D

Address: 0x70/0x71

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/08/25 2012/07/15

2011/08/25 2012/07/15

2011/08/25 2012/07/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

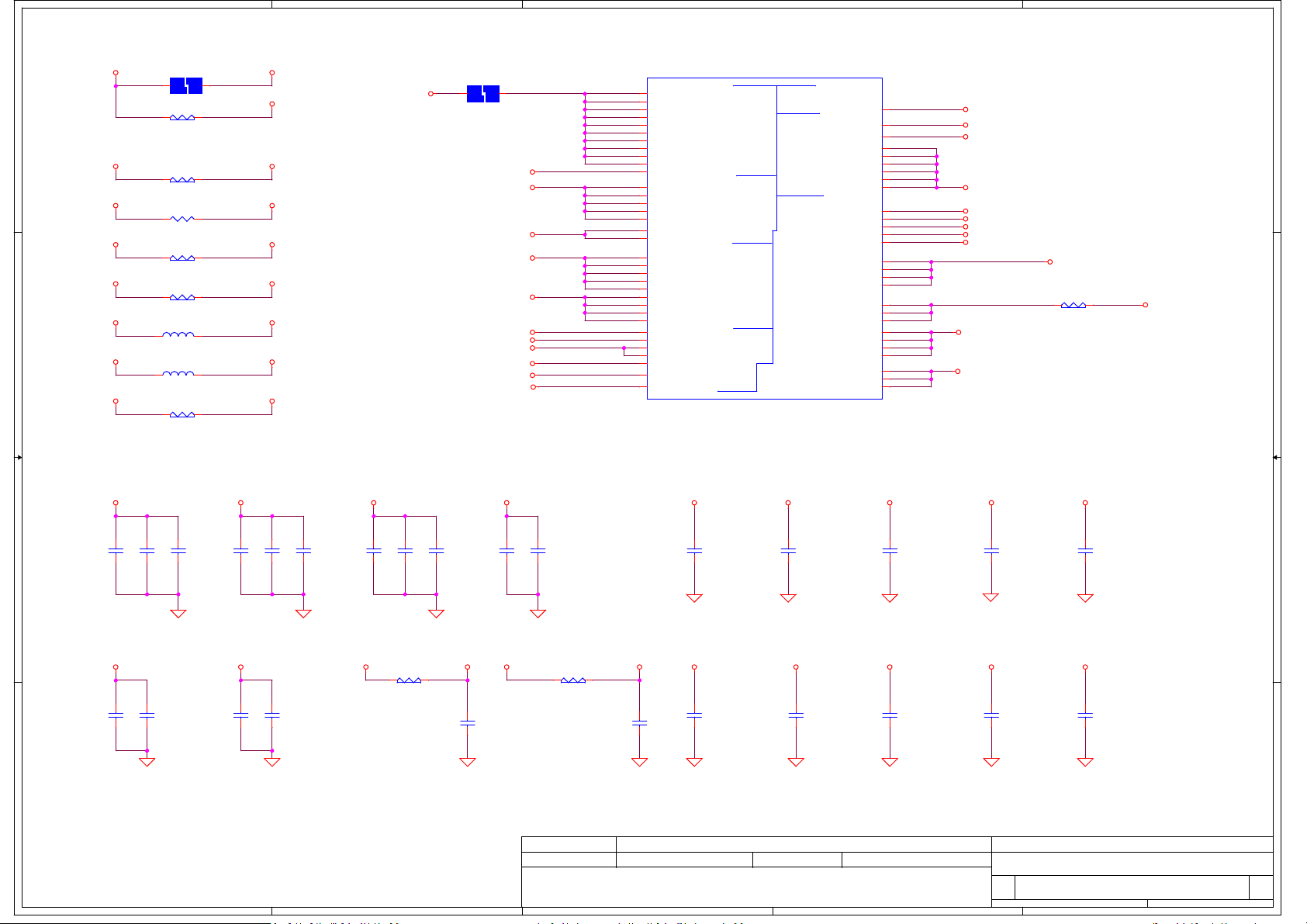

SMBus Block Diagram

SMBus Block Diagram

SMBus Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-E992P

LA-E992P

LA-E992P

1

5 77Tuesday, July 25, 2017

5 77Tuesday, July 25, 2017

5 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

5

+VCCST

D D

+VCCSTG

+1V_PCH

C C

+3VALW

+VCCIO

+3V_ROM

+3V_PCH_DSW

B B

1 2

RH97 51_0402_5%@

1 2

RH98 51_0402_5%@

1 2

RH100 51_0402_5%@

1 2

RH497 51_0402_5%

1 2

RH496 51_0402_5%

1 2

RH56 51_0402_5%

1 2

RH95 51_0402_5%

1 2

RH61 51_0402_5%

1 2

RH60 51_0402_5%

1 2

RH520 2.2K_0402_5%

1 2

RH521 2.2K_0402_5%

1 2

RH526 150_0402_5%

1 2

RH540 1K_0402_5%XDP@

1 2

RH529 1K_0402_5%XDP@

+3VS

1 2

RH531 1K_0402_5%

0.1U_0402_10V7K

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

CPU_XDP_TDO

CPU_XDP_TMS

CPU_XDP_TDI

PCH_JTAG_TCK

CPU_XDP_TCK

CPU_XDP_TRST#

XDP_PLTRST#

PCH_SYS_PWROK_XDP

PWR_DEBUG#_XDP

XDP_PRESENT#

XDP_DBRESET# SYS_RESET#

XDP@

1

CH206

2

1 2

RH528 1K_0402_5%

1 2

RH519 1K_0402_5%XDP@

1 2

RH530 0_0402_5%@

Pilot

Change RH530 to 0ohm 0402 short-pad footprint.

1 2

RH532 0_0402_5%@

XDP@

1

CH207

0.1U_0402_10V7K

2

4

CFG0

PCH_SPI_WP#

SIO_PWRBTN#PWRBTN#_XDP

DVT2.0

Change RH532 to 0ohm 0402 short-pad footprint.

PCH_SPI_WP# <17>

SIO_PWRBTN# <18,36>

SYS_RESET# <18>

3

PCH_ITP_PMODE<18>

PLTRST_CPU#<9,16>

SYS_PWROK<18,36>

PCH_SPI_SI<17,27>

PCH_RSMRST#<18,36>

H_VCCST_PWRGD<9,18>

CFG[0..19]<9>

CFG3

RH517 1K_0402_5%XDP@

XDP_PREQ#<9,22>

XDP_PRDY#<9,22>

XDP_BPM#0<9>

XDP_BPM#1<9>

PCH_SMBDATA<14,15,18,29,35>

PCH_SMBCLK<14,15,18,29,35>

PCH_JTAG_TCK<18>

CPU_XDP_TCK<9,18>

PCH_ITP_PMODE

PLTRST_CPU# XDP_PLTRST#

SYS_PWROK

PCH_SPI_SI PCH_SYS_PWROK_XDP

PCH_RSMRST#

H_VCCST_PWRGD XDP_PWRGOOD

12

XDP_PREQ#

XDP_PRDY#

CFG0

CFG1

CFG2

CFG3

XDP_BPM#0

XDP_BPM#1

CFG4

CFG5

CFG6

CFG7

XDP_PWRGOOD

PWRBTN#_XDP

PWR_DEBUG#_XDP

PCH_SYS_PWROK_XDP

PCH_SMBDATA

PCH_SMBCLK

PCH_JTAG_TCK

CPU_XDP_TCK

RH518

0_0402_5%

2

1 2

RH522 0_0402_5%XDP@

1 2

RH523 1K_0402_5%@

1 2

RH524 0_0402_5%@

1 2

RH525 1K_0402_5%XDP@

1 2

RH541 1K_0402_5%XDP@

1 2

RH542 1K_0402_5%@

+1V_PCH +1V_PCH

JXDP1

2

112

4

334

6

556

8

778

10

9910

12

111112

14

131314

16

151516

18

171718

20

191920

22

212122

24

232324

26

252526

28

272728

30

292930

32

313132

34

333334

36

353536

38

373738

40

393940

42

414142

44

434344

46

454546

48

474748

50

494950

52

515152

54

535354

56

555556

58

575758

60

12

@

595960

SAMTE_BSH-030-01-L-D-A-TR

CONN@

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

PCH_XDP_CLK_P

PCH_XDP_CLK_N

XDP_PLTRST#

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_PRESENT#

1

PCH_XDP_CLK_P <17>

PCH_XDP_CLK_N <17>

XDP@

1

CH205

0.1U_0402_10V7K

2

XDP_TDO

XDP_TDI

XDP_TMS

XDP_TRST#

A A

5

Pilot

Change RH533, RH534, RH535, RH536

to 0ohm 0402 short-pad footprint.

1 2

RH533 0_0402_5%@

1 2

RH534 0_0402_5%@

1 2

RH535 0_0402_5%@

1 2

RH536 0_0402_5%@

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TRST#

4

CPU PCH

CPU_XDP_TDO <9>

CPU_XDP_TDI <9>

CPU_XDP_TMS <9>

CPU_XDP_TRST# <9,22>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

XDP_TMS

XDP_TDI

XDP_TDO PCH_JTAG_TDO

Pilot

Change RH538, RH537, RH539 to

0ohm 0402 short-pad footprint.

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

1 2

RH538 0_0402_5%@

1 2

RH537 0_0402_5%@

1 2

RH539 0_0402_5%@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PCH_JTAG_TMS

PCH_JTAG_TDI

2

PCH_JTAG_TMS <18>

PCH_JTAG_TDI <18>

PCH_JTAG_TDO <18>

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

XDP CONN

XDP CONN

XDP CONN

LA-E992P

LA-E992P

LA-E992P

1

1.0(A00)

1.0(A00)

1.0(A00)

6 77Tuesday, July 25, 2017

6 77Tuesday, July 25, 2017

6 77Tuesday, July 25, 2017

5

4

3

2

1

PEG_HTX_C_GRX_P[0..15]<46>

PEG_HTX_C_GRX_N[0..15]<46>

PEG_GTX_C_HRX_P[0..15]<46>

PEG_GTX_C_HRX_N[0..15]<46>

D D

C C

B B

A A

PEG_HTX_C_GRX_P[0..15]

PEG_HTX_C_GRX_N[0..15]

PEG_GTX_C_HRX_P[0..15]

PEG_GTX_C_HRX_N[0..15]

TBT-AR

TBT-AR

DP to VGA

PEG_GTX_C_HRX_P15

PEG_GTX_C_HRX_N15

PEG_GTX_C_HRX_P14

PEG_GTX_C_HRX_N14

PEG_GTX_C_HRX_P13

PEG_GTX_C_HRX_N13

PEG_GTX_C_HRX_P12

PEG_GTX_C_HRX_N12

PEG_GTX_C_HRX_P11

PEG_GTX_C_HRX_N11

PEG_GTX_C_HRX_P10

PEG_GTX_C_HRX_N10

PEG_GTX_C_HRX_P9

PEG_GTX_C_HRX_N9

PEG_GTX_C_HRX_P8

PEG_GTX_C_HRX_N8

PEG_GTX_C_HRX_P7

PEG_GTX_C_HRX_N7

PEG_GTX_C_HRX_P6

PEG_GTX_C_HRX_N6

PEG_GTX_C_HRX_P5

PEG_GTX_C_HRX_N5

PEG_GTX_C_HRX_P4

PEG_GTX_C_HRX_N4

PEG_GTX_C_HRX_P3

PEG_GTX_C_HRX_N3

PEG_GTX_C_HRX_P2

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_P1

PEG_GTX_C_HRX_N1

PEG_GTX_C_HRX_P0

RH24

24.9_0402_1%

PEG_GTX_C_HRX_N0

PEG_RCOMP

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_N1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3

DMI_CRX_PTX_N3

CPU_DDI1_P0

CPU_DDI1_N0

CPU_DDI1_P1

CPU_DDI1_N1

CPU_DDI1_P2

CPU_DDI1_N2

CPU_DDI1_P3

CPU_DDI1_N3

DDI1_AUXP

DDI1_AUXN

CPU_DDI2_P0

CPU_DDI2_N0

CPU_DDI2_P1

CPU_DDI2_N1

CPU_DDI2_P2

CPU_DDI2_N2

CPU_DDI2_P3

CPU_DDI2_N3

DDI2_AUXP

DDI2_AUXN

CPU_DDI3_P0

CPU_DDI3_N0

CPU_DDI3_P1

CPU_DDI3_N1

DDI3_AUXP

DDI3_AUXN

+VCCIO

1 2

DMI_CRX_PTX_P0<19>

DMI_CRX_PTX_N0<19>

DMI_CRX_PTX_P1<19>

DMI_CRX_PTX_N1<19>

DMI_CRX_PTX_P2<19>

DMI_CRX_PTX_N2<19>

DMI_CRX_PTX_P3<19>

DMI_CRX_PTX_N3<19>

CPU_DDI1_P0<39>

CPU_DDI1_N0<39>

CPU_DDI1_P1<39>

CPU_DDI1_N1<39>

CPU_DDI1_P2<39>

CPU_DDI1_N2<39>

CPU_DDI1_P3<39>

CPU_DDI1_N3<39>

DDI1_AUXP<39>

DDI1_AUXN<39>

CPU_DDI2_P0<39>

CPU_DDI2_N0<39>

CPU_DDI2_P1<39>

CPU_DDI2_N1<39>

CPU_DDI2_P2<39>

CPU_DDI2_N2<39>

CPU_DDI2_P3<39>

CPU_DDI2_N3<39>

DDI2_AUXP<39>

DDI2_AUXN<39>

CPU_DDI3_P0<35>

CPU_DDI3_N0<35>

CPU_DDI3_P1<35>

CPU_DDI3_N1<35>

DDI3_AUXP<35>

DDI3_AUXN<35>

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

K36

K37

J35

J34

H37

H36

J37

J38

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

UH1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

SKL-H_BGA1440

@

UH1D

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

SKL-H_BGA1440

@

SKYLAKE_HALO

3 OF 14

SKYLAKE_HALO

4 OF 14

Rev_1.0

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

Rev_1.0

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

PEG_HTX_GRX_P15

B25

PEG_HTX_GRX_N15

A25

PEG_HTX_GRX_P14

B24

PEG_HTX_GRX_N14

C24

PEG_HTX_GRX_P13

B23

PEG_HTX_GRX_N13

A23

PEG_HTX_GRX_P12

B22

PEG_HTX_GRX_N12

C22

PEG_HTX_GRX_P11

B21

PEG_HTX_GRX_N11

A21

PEG_HTX_GRX_P10

B20

PEG_HTX_GRX_N10

C20

PEG_HTX_GRX_P9

B19

PEG_HTX_GRX_N9

A19

PEG_HTX_GRX_P8

B18

PEG_HTX_GRX_N8

C18

PEG_HTX_GRX_P7

A17

PEG_HTX_GRX_N7

B17

PEG_HTX_GRX_P6

C16

PEG_HTX_GRX_N6

B16

PEG_HTX_GRX_P5

A15

PEG_HTX_GRX_N5

B15

PEG_HTX_GRX_P4

C14

PEG_HTX_GRX_N4

B14

PEG_HTX_GRX_P3

A13

PEG_HTX_GRX_N3

B13

PEG_HTX_GRX_P2

C12

PEG_HTX_GRX_N2

B12

PEG_HTX_GRX_P1

A11

PEG_HTX_GRX_N1

B11

PEG_HTX_GRX_P0

C10

PEG_HTX_GRX_N0

B10

DMI_CTX_PRX_P0

B8

DMI_CTX_PRX_N0

A8

DMI_CTX_PRX_P1

C6

DMI_CTX_PRX_N1

B6

DMI_CTX_PRX_P2

B5

DMI_CTX_PRX_N2

A5

DMI_CTX_PRX_P3

D4

DMI_CTX_PRX_N3

B4

EDP_TXP0

D29

EDP_TXN0

E29

EDP_TXP1

F28

EDP_TXN1

E28

EDP_TXN2

B29

EDP_TXP2

A29

EDP_TXN3

B28

EDP_TXP3

C28

EDP_AUXP

C26

EDP_AUXN

B26

EDP_DISP_UTIL BIA_PWM_PCH

A33

EDP_COMP

D37

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

AUD_AZA_CPU_SCLK

G27

AUD_AZA_CPU_SDO

G25

AUD_AZA_CPU_SDI AUD_AZA_CPU_SDI_R

G29

1 2

CH5 0.22U_0201_6.3V6M

1 2

CH6 0.22U_0201_6.3V6M

1 2

CH7 0.22U_0201_6.3V6M

1 2

CH8 0.22U_0201_6.3V6M

1 2

CH9 0.22U_0201_6.3V6M

1 2

CH10 0.22U_0201_6.3V6M

1 2

CH11 0.22U_0201_6.3V6M

1 2

CH12 0.22U_0201_6.3V6M

1 2

CH13 0.22U_0201_6.3V6M

1 2

CH14 0.22U_0201_6.3V6M

1 2

CH15 0.22U_0201_6.3V6M

1 2

CH16 0.22U_0201_6.3V6M

1 2

CH17 0.22U_0201_6.3V6M

1 2

CH18 0.22U_0201_6.3V6M

1 2

CH19 0.22U_0201_6.3V6M

1 2

CH20 0.22U_0201_6.3V6M

1 2

CH21 0.22U_0201_6.3V6M

1 2

CH22 0.22U_0201_6.3V6M

1 2

CH23 0.22U_0201_6.3V6M

1 2

CH24 0.22U_0201_6.3V6M

1 2

CH25 0.22U_0201_6.3V6M

1 2

CH26 0.22U_0201_6.3V6M

1 2

CH27 0.22U_0201_6.3V6M

1 2

CH28 0.22U_0201_6.3V6M

1 2

CH29 0.22U_0201_6.3V6M

1 2

CH30 0.22U_0201_6.3V6M

1 2

CH31 0.22U_0201_6.3V6M

1 2

CH32 0.22U_0201_6.3V6M

1 2

CH33 0.22U_0201_6.3V6M

1 2

CH34 0.22U_0201_6.3V6M

1 2

CH35 0.22U_0201_6.3V6M

1 2

CH36 0.22U_0201_6.3V6M

DMI_CTX_PRX_P0 <19>

DMI_CTX_PRX_N0 <19>

DMI_CTX_PRX_P1 <19>

DMI_CTX_PRX_N1 <19>

DMI_CTX_PRX_P2 <19>

DMI_CTX_PRX_N2 <19>

DMI_CTX_PRX_P3 <19>

DMI_CTX_PRX_N3 <19>

EDP_TXP0 <38>

EDP_TXN0 <38>

EDP_TXP1 <38>

EDP_TXN1 <38>

EDP_TXN2 <38>

EDP_TXP2 <38>

EDP_TXN3 <38>

EDP_TXP3 <38>

EDP_AUXP <38>

EDP_AUXN <38>

1 2

RH20

@

0_0402_5%

1 2

RH30

24.9_0402_1%

1 2

RH145

20_0402_5%

Close to CPU

PEG_HTX_C_GRX_P15

PEG_HTX_C_GRX_N15

PEG_HTX_C_GRX_P14

PEG_HTX_C_GRX_N14

PEG_HTX_C_GRX_P13

PEG_HTX_C_GRX_N13

PEG_HTX_C_GRX_P12

PEG_HTX_C_GRX_N12

PEG_HTX_C_GRX_P11

PEG_HTX_C_GRX_N11

PEG_HTX_C_GRX_P10

PEG_HTX_C_GRX_N10

PEG_HTX_C_GRX_P9

PEG_HTX_C_GRX_N9

PEG_HTX_C_GRX_P8

PEG_HTX_C_GRX_N8

PEG_HTX_C_GRX_P7

PEG_HTX_C_GRX_N7

PEG_HTX_C_GRX_P6

PEG_HTX_C_GRX_N6

PEG_HTX_C_GRX_P5

PEG_HTX_C_GRX_N5

PEG_HTX_C_GRX_P4

PEG_HTX_C_GRX_N4

PEG_HTX_C_GRX_P3

PEG_HTX_C_GRX_N3

PEG_HTX_C_GRX_P2

PEG_HTX_C_GRX_N2

PEG_HTX_C_GRX_P1

PEG_HTX_C_GRX_N1

PEG_HTX_C_GRX_P0

PEG_HTX_C_GRX_N0

BIA_PWM_PCH <16,38>

+VCCIO

AUD_AZA_CPU_SCLK <18>

AUD_AZA_CPU_SDO <18>

AUD_AZA_CPU_SDI_R <18>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-E992P

LA-E992P

LA-E992P

1

7 77Tuesday, July 25, 2017

7 77Tuesday, July 25, 2017

7 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

Non-Interleave

DDR_A_D[0..63]<14>

DDR_A_MA[0..13]<14>

DDR_A_DQS#[0..7]<14>

DDR_A_DQS[0..7]<14>

DDR_B_D[0..63]<15>

DDR_B_MA[0..13]<15>

DDR_B_DQS#[0..7]<15>

D D

DDR_B_DQS[0..7]<15>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

C C

B B

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

UH1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

Interleave / Non-Interleaved

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

SKL-H_BGA1440

@

SKYLAKE_HALO

DDR3L / LPDDR3 / DDR4

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR CH - A

1 OF 14

Rev_1.0

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_BS0

DDR_A_BS1

DDR_A_BG0

DDR_A_RAS#

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_BG1

DDR_A_ACT#

DDR_A_PAR

DDR_A_ALERT#

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#4

DDR_A_DQS#5

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS4

DDR_B_DQS5

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS4

DDR_A_DQS5

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#4

DDR_B_DQS#5

DDR_A_CLK0 <14 >

DDR_A_CLK#0 <1 4>

DDR_A_CLK#1 <1 4>

DDR_A_CLK1 <14 >

DDR_A_CKE0 <14>

DDR_A_CKE1 <14>

DDR_A_CS#0 <14 >

DDR_A_CS#1 <14 >

DDR_A_ODT0 <14>

DDR_A_ODT1 <14>

DDR_A_BS0 <14>

DDR_A_BS1 <14>

DDR_A_BG0 <14>

DDR_A_RAS# <14>

DDR_A_WE# <14>

DDR_A_CAS# <14>

DDR_A_BG1 <14>

DDR_A_ACT# <14>

DDR_A_PAR <14>

DDR_A_ALERT# <14>

1 2

RH148 121_0402_1%

1 2

RH149 75_0402_1%

1 2

RH150 100_0402_1%

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

UH1B

Interleave / Non-Interleaved

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BGA1440

@

SKYLAKE_HALO

DDR3L / LPDDR3 / DDR4

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

2 OF 14

DDR0_VREF_DQ

DDR1_VREF_DQ

Rev_1.0

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BS0

DDR_B_BS1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_PAR

DDR_B_ALERT#

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#6

DDR_A_DQS#7

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#6

DDR_B_DQS#7

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS6

DDR_A_DQS7

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS6

DDR_B_DQS7

DDR_B_CLK0 <15 >

DDR_B_CLK#0 <1 5>

DDR_B_CLK#1 <1 5>

DDR_B_CLK1 <15 >

DDR_B_CKE0 < 15>

DDR_B_CKE1 < 15>

DDR_B_CS#0 <15 >

DDR_B_CS#1 <15 >

DDR_B_ODT0 <15>

DDR_B_ODT1 <15>

DDR_B_RAS# < 15>

DDR_B_WE# <15>

DDR_B_CAS# < 15>

DDR_B_BS0 <15>

DDR_B_BS1 <15>

DDR_B_BG0 <15>

DDR_B_BG1 <15>

DDR_B_ACT# <15>

DDR_B_PAR <1 5>

DDR_B_ALERT# <15>

+V_DDR_REFA_R

+V_DDR_REFB_R

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

LA-E992P

LA-E992P

LA-E992P

8 77Tuesday, July 25, 2017

8 77Tuesday, July 25, 2017

1

8 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

+VCCSTG

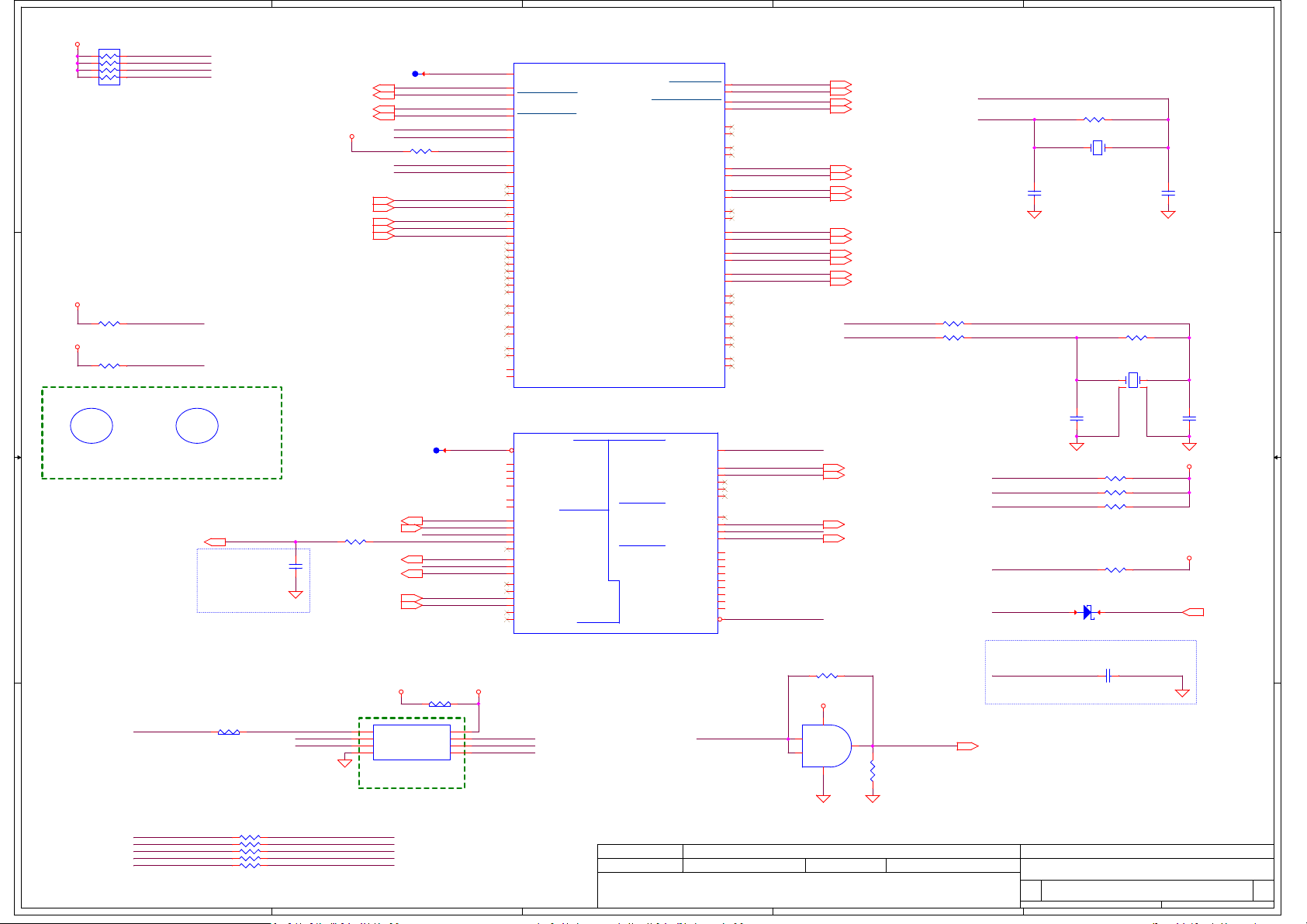

CFG Straps for Processor

+VCCST

Stall reset sequence after CPU PLL lock until de-asserted

D D

CFG0

1 = (Default) Normal Operation; No stall.

*

0 = Stall.

RH183

1 2

@

1K_0402_5%

CFG0

RH165

RH163

RH156

RH164

RH151

RH152

RH144

1 2

1K_0402_5%

1 2

1K_0402_5%

1 2

51_0402_5%

1 2

1K_0402_5%

1 2

100_0402_5%

1 2

56.2_0402_1%

1 2

49.9_0402_1%

PCI EXPRESS STATIC LANE REVERSAL FOR ALL PEG PORTS

CFG2

C C

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

RH184

1 2

1K_0402_5%

CFG2

Display Port Presence Strap

CFG4

PCIE Port Bifurcation Straps

B B

CFG[6:5]

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

*

RH185

RH186

RH187

1 2

1K_0402_5%

1 2

@

1K_0402_5%

1 2

@

1K_0402_5%

CFG4

11: (Default) x16 - Device 1 functions 1 and 2 disabled

*

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG5

CFG6

SM_PG_CTRL<62>

If change to x8, need cheange setting.

PEG DEFER TRAINING

CFG7

A A

1: (Default) PEG Train immediately following xxRESETB

de assertion

*

0: PEG Wait for BIOS for training

RH188

1 2

1K_0402_5%

5

@

CFG7

4

@

@

VR_SVID_ALERT#<71>

VR_SVID_CLK<71>

VR_SVID_DATA<71>

H_PROCHOT#<36,59,60,71>

H_VCCST_PWRGD<6,18>

H_CPUPWRGD<18>

PLTRST_CPU#< 6,16>

H_PM_SYNC_R<16>

H_PM_DOWN<16>

PECI_EC<16,36>

H_THERMTRIP#_R<16>

PROC_DETECT#<16>

0.1U_0402_10V7K

PCH_TRIGGER<22>

CPU_TRIGGER<22>

H_PROCHOT#

H_THERMTRIP#_R

XDP_PREQ#

H_VCCST_PWRGD

VR_SVID_DATA

VR_SVID_ALERT#

H_CATERR#

VR_SVID_ALERT#

VR_SVID_CLK

VR_SVID_DATA

H_VCCST_PWRGD

H_PM_DOWN

PECI_EC

PROC_DETECT#

DVT2.0

Change RH190 to 0ohm 0402 short-pad footprint.

PCH_CPU_BCLK_P<17>

PCH_CPU_BCLK_N<17>

PCH_CPU_PCIBCLK_P<17>

PCH_CPU_PCIBCLK_N<17>

CPU_24MHZ_P<17>

CPU_24MHZ_N<17>

RH153 220_0402_5%

RH158 499_0402_1%

RH154 60.4_0402_1%

RH155 20_0402_5%

RH190 0_0402_5%@

RH89 0_0402_5%@

+1.2V_DDR

@

CH197

1

2

SM_PG_CTRL

RH93

220K_0402_5%

+3VS

12

UC1

5

VCC

4

Y

74AUP1G07SE-7_SOT353

SA00007WE00

Reserve for ESD

H_VCCST_PWRGD

H_PROCHOT#_R

1 2

CH210

100P_0402_50V8J@ESD@

1 2

CH211

100P_0402_50V8J

PCH_TRIGGER PCH_TRIGGER_R

CPU_TRIGGER CPU_TRIGGER_R

RH167 30_0402_5%

RH192 30_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1 2

1 2

1 2

1 2

1 2

1 2

NC

GND

1 2

1 2

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

BM30

BN35

BN33

BL34

AE29

AA14

BR35

BR31

BH30

B31

A32

D35

C36

E31

D31

H13

J31

BN1

D1

E1

E3

E2

BR1

BT2

J24

H24

N29

R14

A36

A37

H23

J23

F30

E30

B30

C30

G3

J3

UH1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKL-H_BGA1440

@

UH1K

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PROC_TRIGIN

PROC_TRIGOUT

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

SKL-H_BGA1440

@

PCH_CPU_BCLK_P

PCH_CPU_BCLK_N

PCH_CPU_PCIBCLK_P

PCH_CPU_PCIBCLK_N

CPU_24MHZ_P

CPU_24MHZ_N

VR_SVID_ALERT#_R

H_PROCHOT#_RH_PROCHOT#

DDR_VTT_PG_CTRL

VCCST_PWRGD_CPU

H_CPUPWRGD

PLTRST_CPU#

H_PM_SYNC_R

H_PM_DOWN_R

PECI_EC_R

H_THERMTRIP#_R

H_CATERR#

1

DDR_VTT_PG_CTRL

2

A

3

Compal Secret Data

Compal Secret Data

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SKYLAKE_HALO

2

5 OF 14

SKYLAKE_HALO

11 OF 14

Rev_1.0

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

CFG[0..19] <6>

BN25

CFG0

BN27

CFG1

BN26

CFG2

BN28

CFG3

BR20

CFG4

BM20

CFG5

BT20

CFG6

BP20

CFG7

BR23

CFG8

BR22

CFG9

BT23

CFG10

BT22

CFG11

BM19

CFG12

BR19

CFG13

BP19

CFG14

BT19

CFG15

BN23

CFG17

BP23

CFG16

BP22

CFG19

BN22

CFG18

XDP_BPM#0

BR27

XDP_BPM#1

BT27

BM31

BT30

CPU_XDP_TDO

BT28

CPU_XDP_TDI

BL32

CPU_XDP_TMS

BP28

CPU_XDP_TCK

BR28

CPU_XDP_TRST#

BP30

XDP_PREQ#

BL30

XDP_PRDY#

BP27

CFG_RCOMP

BT25

Rev_1.0

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BM33

BL33

BJ14

BJ13

BK28

BJ28

BJ18

BJ16

BK16

BK24

BJ24

BK21

BJ21

BT17

BR17

BK18

BJ34

BJ33

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

XDP_BPM#0 <6>

XDP_BPM#1 <6>

CPU_XDP_TDO <6 >

CPU_XDP_TDI <6>

CPU_XDP_TMS <6>

CPU_XDP_TCK <6,18 >

CPU_XDP_TRST# <6,22>

XDP_PREQ# <6,22>

XDP_PRDY# <6,22>

12

RH59

49.9_0402_1%

LA-E992P

LA-E992P

LA-E992P

9 77Tuesday, July 25, 2017

9 77Tuesday, July 25, 2017

1

9 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

+VCC_CORE +VCC_CORE

D D

C C

B B

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

L13

SKYLAKE_HALO

UH1G

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL-H_BGA1440

@

7 OF 14

Rev_1.0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

+VCC_CORE

12

12

RH197

100_0402_1%

1 2

RH198 0_0402_5%@

1 2

RH28 0_0402_5%@

DVT2.0

Change RH198, RH28 to 0ohm 0402 short-pad footprint.

RH29

100_0402_1%

VCCSENSE

VSSSENSE

VCCSENSE <71>

VSSSENSE <71>

1 2

RH166 49.9_0402_1%@

1 2

RH57 49.9_0402_1%@

1 2

RH58 49.9_0402_1%@

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

UH1J

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

SKL-H_BGA1440

@

SKYLAKE_HALO

10 OF 14

Rev_1.0

A A

Security Classification

Security Classification

Security Classification

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/08/25 2012/07/25

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

LA-E992P

LA-E992P

LA-E992P

1

10 77Tuesday, July 25, 2017

10 77Tuesday, July 25, 2017

10 77Tuesday, July 25, 2017

1.0(A00)

1.0(A00)

1.0(A00)

5

D D

4

3

2

1

Rev_1.0

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

+1.2V_DDR

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

+1.2V_DDR

10U_0402_6.3V6M

1

CH124

Close to Ball Y12

2

+1.2V_DDR+1.2V_VCCPLL_OC

1 2

RH107 0_0402_5%@

+VCCST

+VCCSTG

+VCCST

+VCCSA

1 2

RH201 100_0402_1%

1 2

RH202 0_0402_5%@

1 2

RH31 0_0402_5%@

1 2

RH41 100_0402_1%

DVT2.0

Change RH202, RH31 to 0ohm 0402 short-pad footprint.

1 2

RH515 100_0402_1%

1 2

RH514 0_0402_5%@

1 2

RH513 0_0402_5%@

1 2

RH516 100_0402_1%

DVT2.0

Change RH514, RH513 to 0ohm 0402 short-pad footprint.

VCCSA_SENSE

VSSSA_SENSE

+VCCIO

VCCIO_SENSE

VSSIO_SENSE

VCCSA_SENSE <71>

VSSSA_SENSE <71>

VCCIO_SENSE <74>

VSSIO_SENSE <74>

CH102

10U_0603_6.3V6M

+1.2V_DDR

CH129

22U_0603_6.3V6M

+1.2V_DDR

CH118

10U_0603_6.3V6M

1

2

1

2

1

2

CH103

CH130

CH121

+VCCSTG +VCCSA

CH104

1

10U_0603_6.3V6M

2

CH131

1

22U_0603_6.3V6M

2

1

10U_0603_6.3V6M

2

CH106

1

2

1

2

CH132

CH120

1U_0402_6.3V6K

1

22U_0603_6.3V6M

2

CH119

1

10U_0603_6.3V6M

2

10U_0603_6.3V6M

22U_0603_6.3V6M

+VCCST+VCCIO

CH204

CH110

1

2

1

1U_0402_6.3V6K

2

+VCCSA +VCCSA

CH133

1

1U_0402_6.3V6K

2

CH122

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

CH134

CH123

1

2

CH111

1

2

1

2

CH135

CH125

1

2

1

10U_0603_6.3V6M

2

1

1U_0402_6.3V6K

2

1

10U_0603_6.3V6M

2

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

CH112

CH126

CH113

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

CH136

47U_0603_6.3V6M

CH127

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

2

1

2

1

2

CH114

CH128

CH115

CH116

CH117

1

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

10U_0603_6.3V6M

2

1

10U_0603_6.3V6M

2

1

10U_0603_6.3V6M

2

2

+VCCSA

C C

+VCCIO

B B

K29

K30

K31

K32

K33

K34

K35

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J30

L31

L32

L35

L36

L37

L38

J15

J16

J17

J19

J20

J21

J26

J27

UH1I

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKL-H_BGA1440

@

SKYLAKE_HALO