Page 1

A

COMPAL CONFIDENTIAL

B

C

D

E

1 1

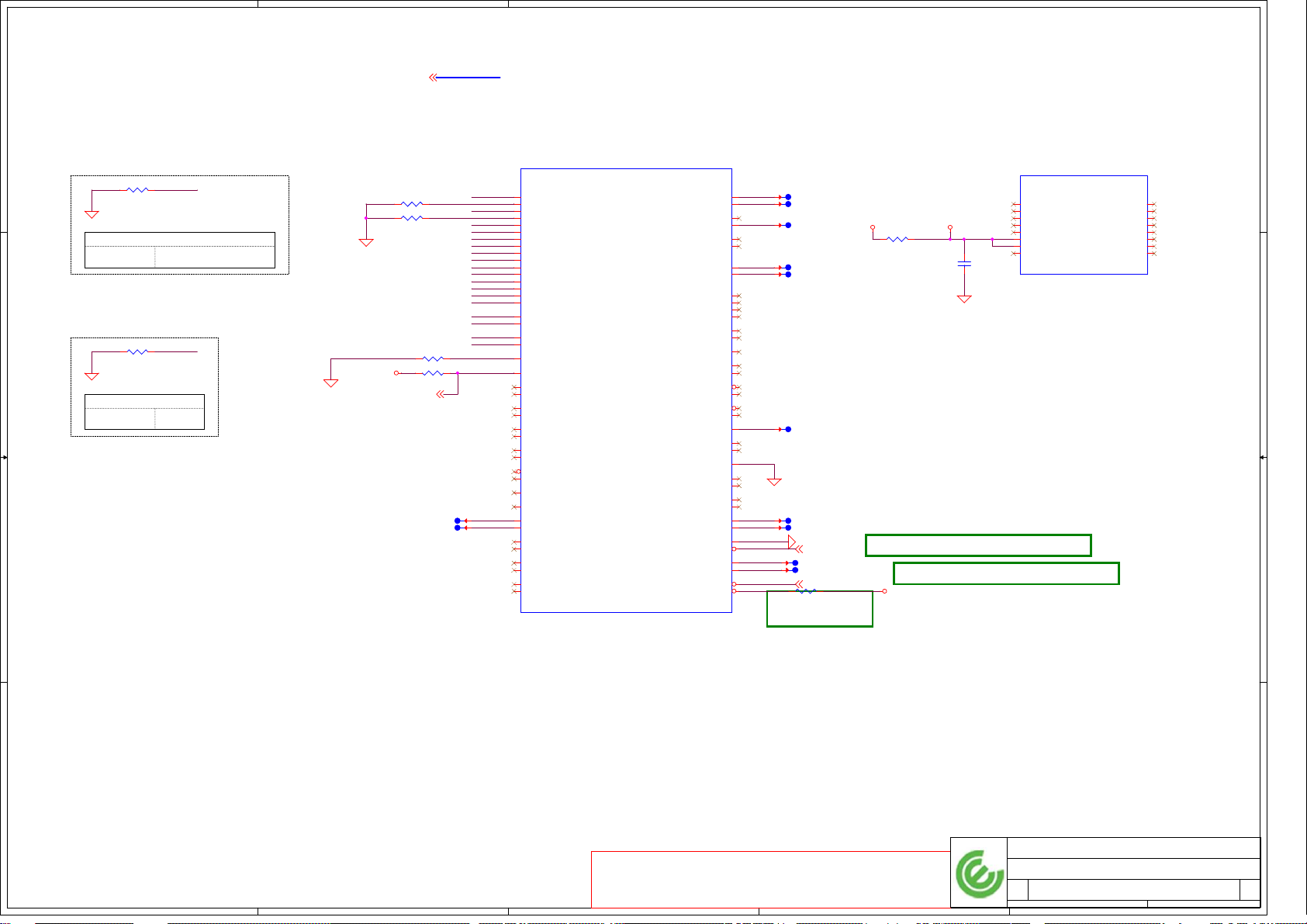

MODEL NAME : CAZ20

PCB NO : LA-E131P

BOM P/N : 431A4331L0X

Steamboat 14" AR

Kabylake U

2 2

@ : Nopop Component

EMI@ : EMI Component

@EMI@ : EMI Nopop Component

ESD@ : ESDComponent

@ESD@ : ESD Nopop Component

2016-11-9

REV : 1.0 (A00)

3 3

RF@ : RF Component

@RF@ : RF Nopop Component

CXDP@ : XDP Component

CONN@ : Connector Component

MB PCB

Part Number

DA800188010

Layout Dell logo

Description

PCB 1S1 LA-E131P REV0 MB AR 1

ESPI@ : ESPI interface Component

LPC@ : External ESPI Component (SHD)

GT3@ : KBL-U 2+3e Component

INFI@ : Infinity SKU Component

4 4

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

COPYRIGHT 2016

ALL RIGHT RESERVED

REV:A00

PWB:

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

Power CKT : 1107

A

B

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

C

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-E131P

LA-E131P

LA-E131P

1 59Wednesday, November 09, 2016

1 59Wednesday, November 09, 2016

1 59Wednesday, November 09, 2016

E

1.0

1.0

1.0

Page 2

A

B

C

D

E

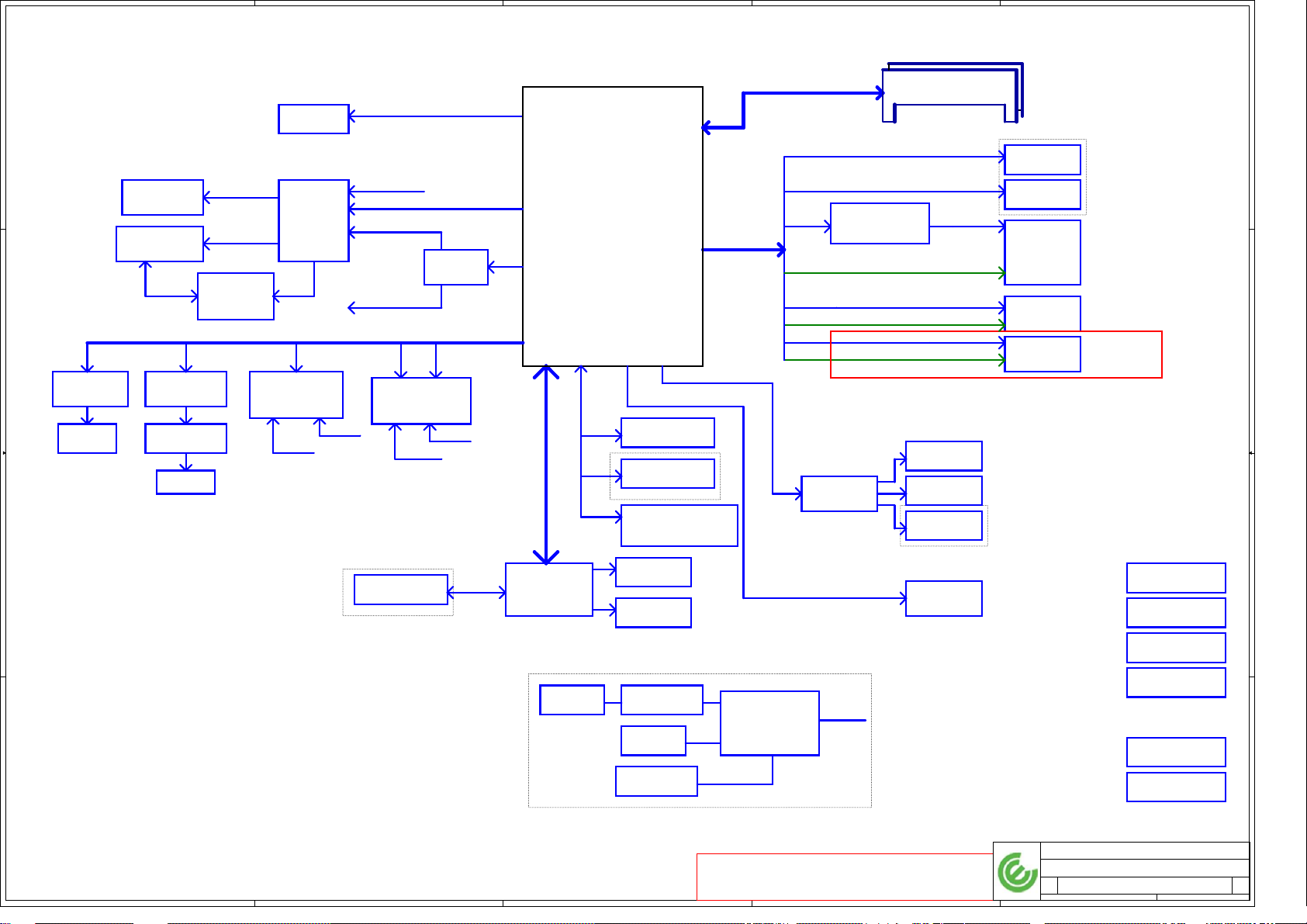

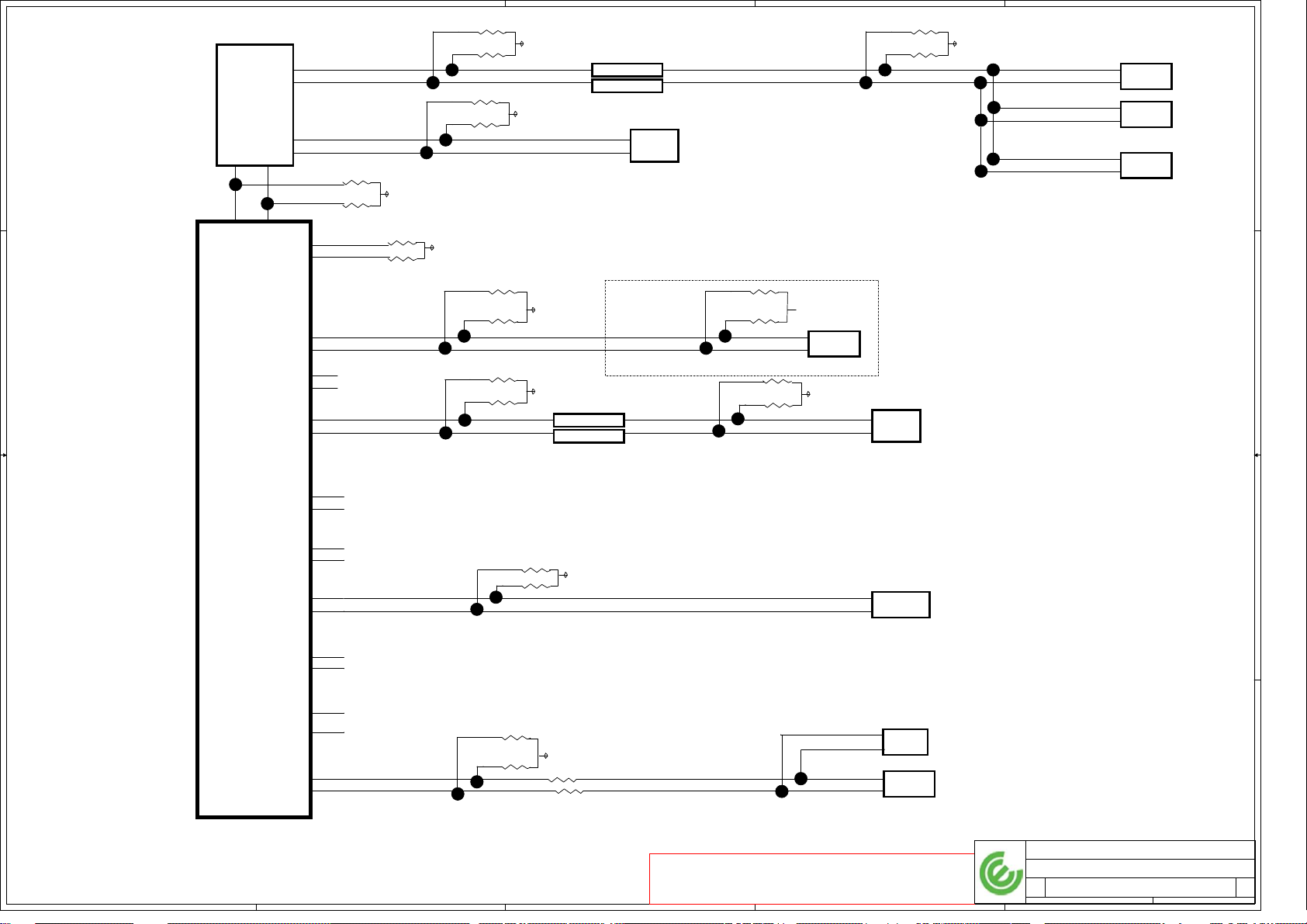

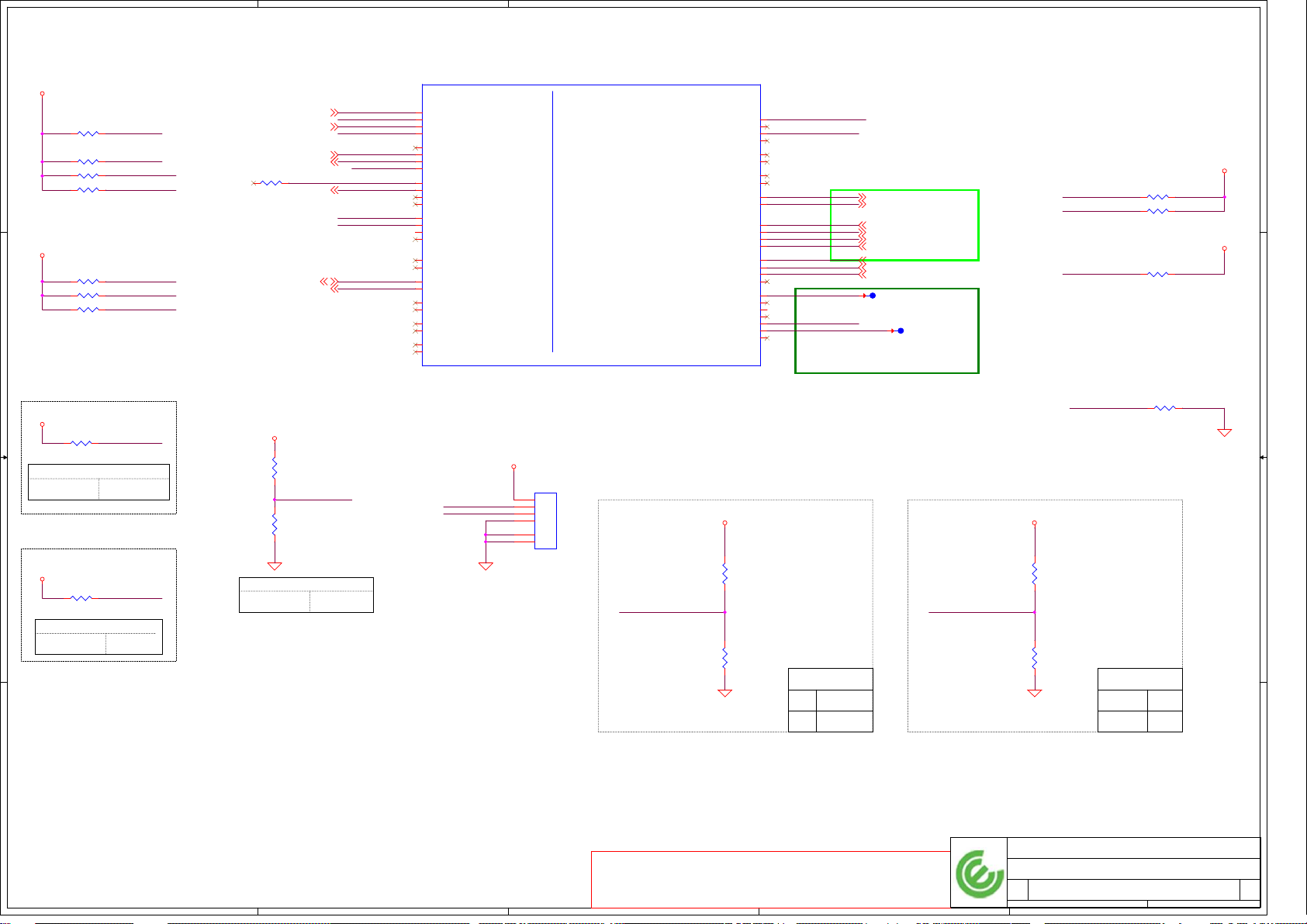

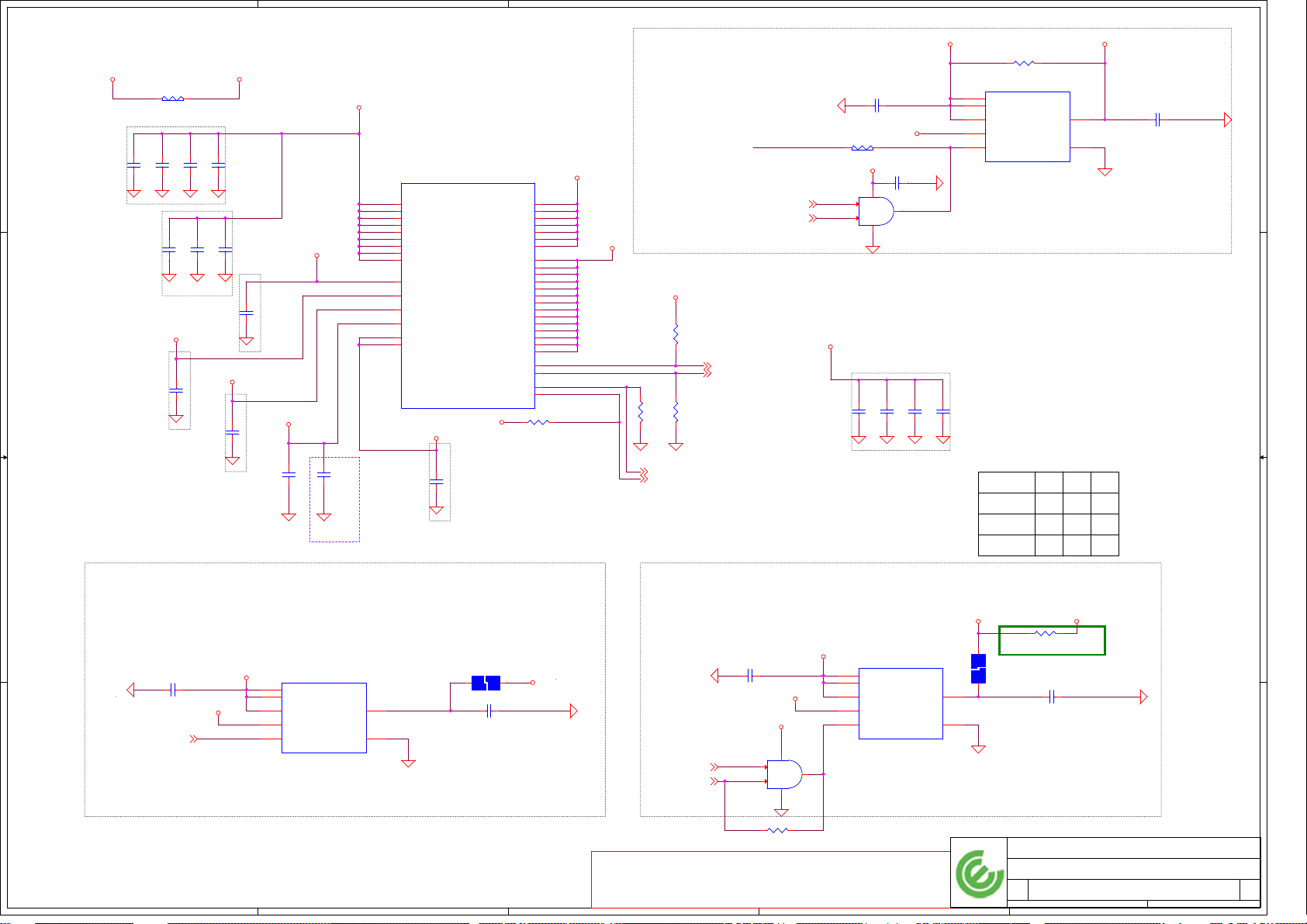

Steamboat 14 w/ AR Block Diagram

Memory BUS (DDR4)

1 1

HDMI 1.4

CONN

P23

HDMI

EDP CONN

P29

AR-SP

P28

PD Solution

TPS65982D

PCIE[9]

P30

P30

P30

TBT

P26-27

M.2,3042 Key B

USB2.0/SMBusUSB2.0/SMBus

WWAN/LTE

P32

USB2.0[4]

USB3.0[2]

TypeC

2 2

PCIE[1]

P31

P31

Intel Jacksonville

WGI219LM

Transformer

Card reader

RTS5242

SD4.0

RJ45

3 3

eDP 14": Lane x 4; 12" :Lane x 2

PCIE[5][6][7][8]

SW2_DP1

To type CP24-25

DP DeMUX

PS8338B

SW2_DP2

To M2 WiGig card

PCIE[4]

M.2,3030 Key A

WLAN+BT/WIGIG

SW1_DP2

W25Q80DVSSIG

8M 4K sector

P34

reserve

PCIE[3]

P32

USB2.0[7]

P22

SHD_IO

DDI[1]

DDI[2]

INTEL

KABYLAKE_U MCP

SPI

ESPI

SMSC KBC

MEC5105

P34-35

PAGE 6~19

HD Audio I/F

SATA[2]/PCIE[12][11]

W25Q128FVSIQ

128M 4K sector

P8

W25Q128FVSIQ

128M 4K sector

TPM1.2/2.0 Nuvoton

NPCT650VB2YX

KB/TP CONN

FAN CONN

P8

reserve

P40

P35

2133MHz

up to 16GB

USB2.0[1]

USB

USB3.0[1]

HDA Codec

ALC3246

P36

Steamboat 12 only support one DIMM

Reverse Type

DDR4-SO-DIMM X2

BANK 0, 1, 2, 3

P20~21

USB2.0[8]

USB2.0[5]

SLGC55544CVTR

USB POWER SHARE

USB2.0[1]_PS

P38

USB3.0[1]

USB2.0[2]

USB3.0[3]

USB2.0[3]

USB3.0[4]

INT.Speaker

Universal Jack

P33

Dig. MIC

P33

P33

P29

Trough eDP Cable

M.2 2280

SSD Conn

P37

LCD Touch

Camera

USB3.0 Conn

PS(Ext Port 1)

Right

USB3.0 Conn

(Ext Port 2)

Left Front

USB3.0 Conn

(Ext Port 3)

Left Rear

P29

P29

Trough eDP Cable

P38

P39

P39

only 14"

LID SWITCH

USH CONN

P41

P36

CPU&PCH XDP Port

AUTOMATIC POWER

Smart Card

4 4

TDA8034HN

RFID/NFC

Fingerprint

CONN

SPI

SPI

USH TPM1.2

BCM58102

USH board

USB2.0[10]

P36

SWITCH(APS)

DC/DC Interface

POWER ON/OFF

SW & LED

P14

P11

P42

P41

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

A

B

C

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

D

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block diagram

Block diagram

Block diagram

LA-E131P

LA-E131P

LA-E131P

E

2 59Wednesday, November 09, 2016

2 59Wednesday, November 09, 2016

2 59Wednesday, November 09, 2016

1.0

1.0

1.0

Page 3

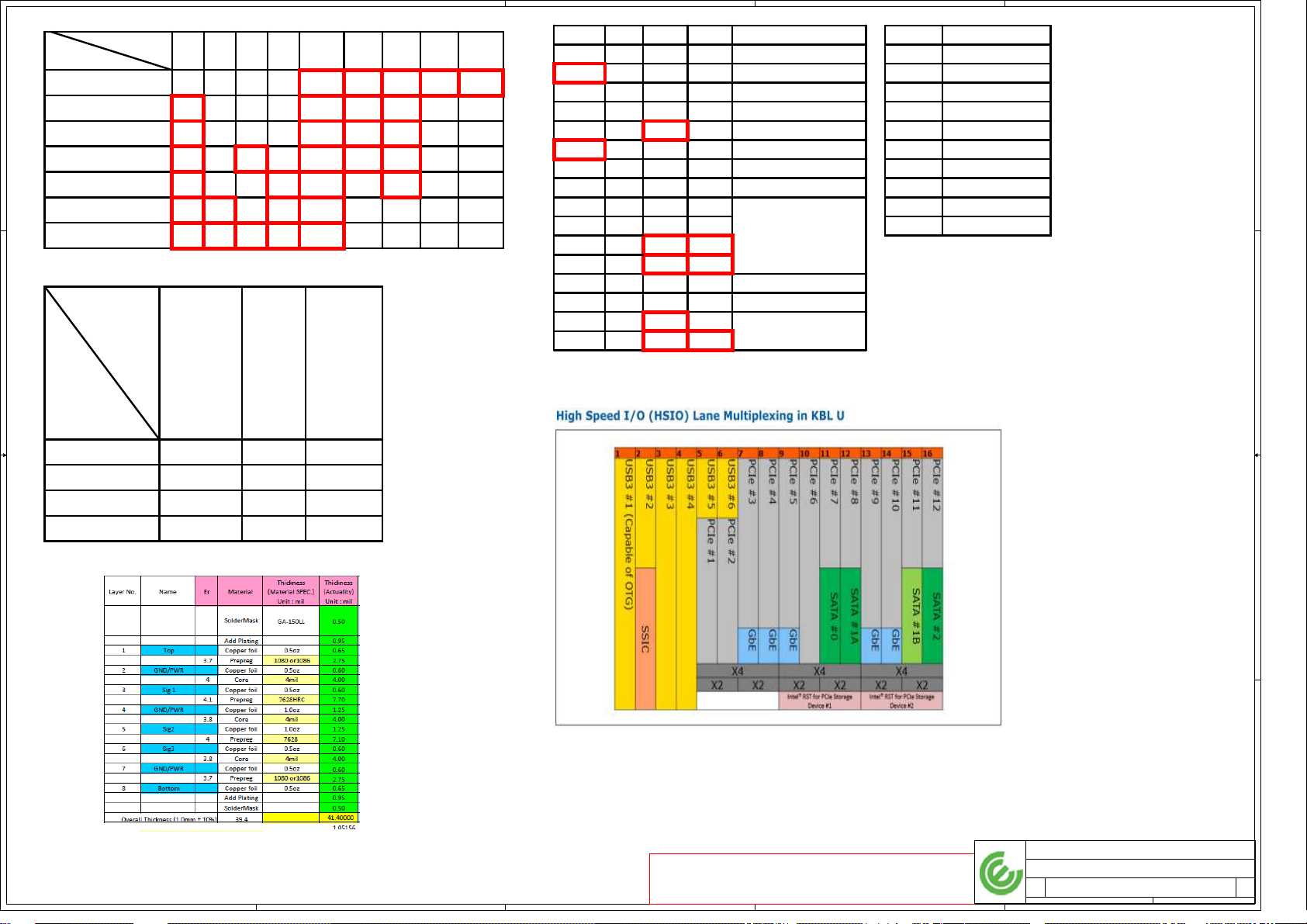

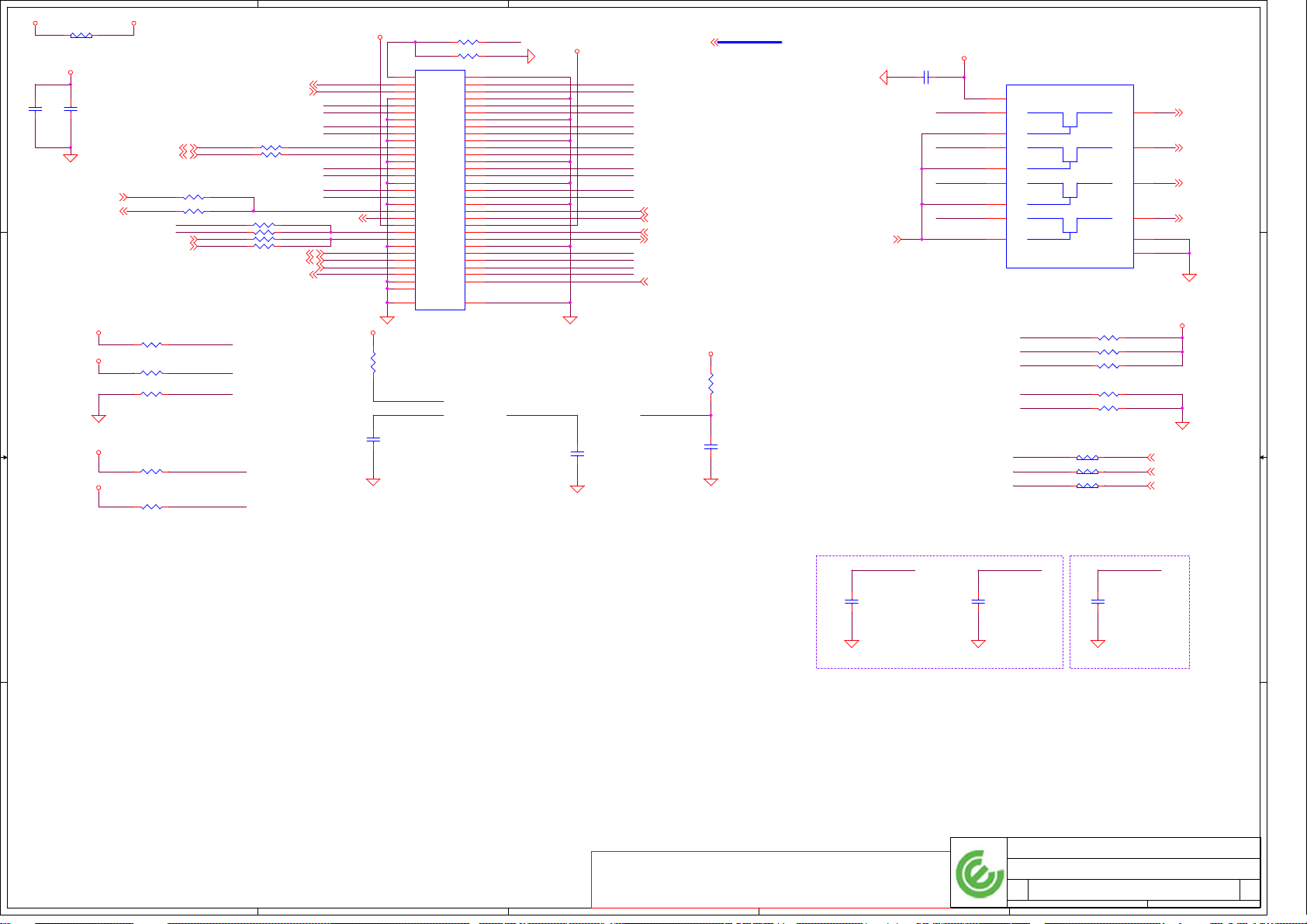

5

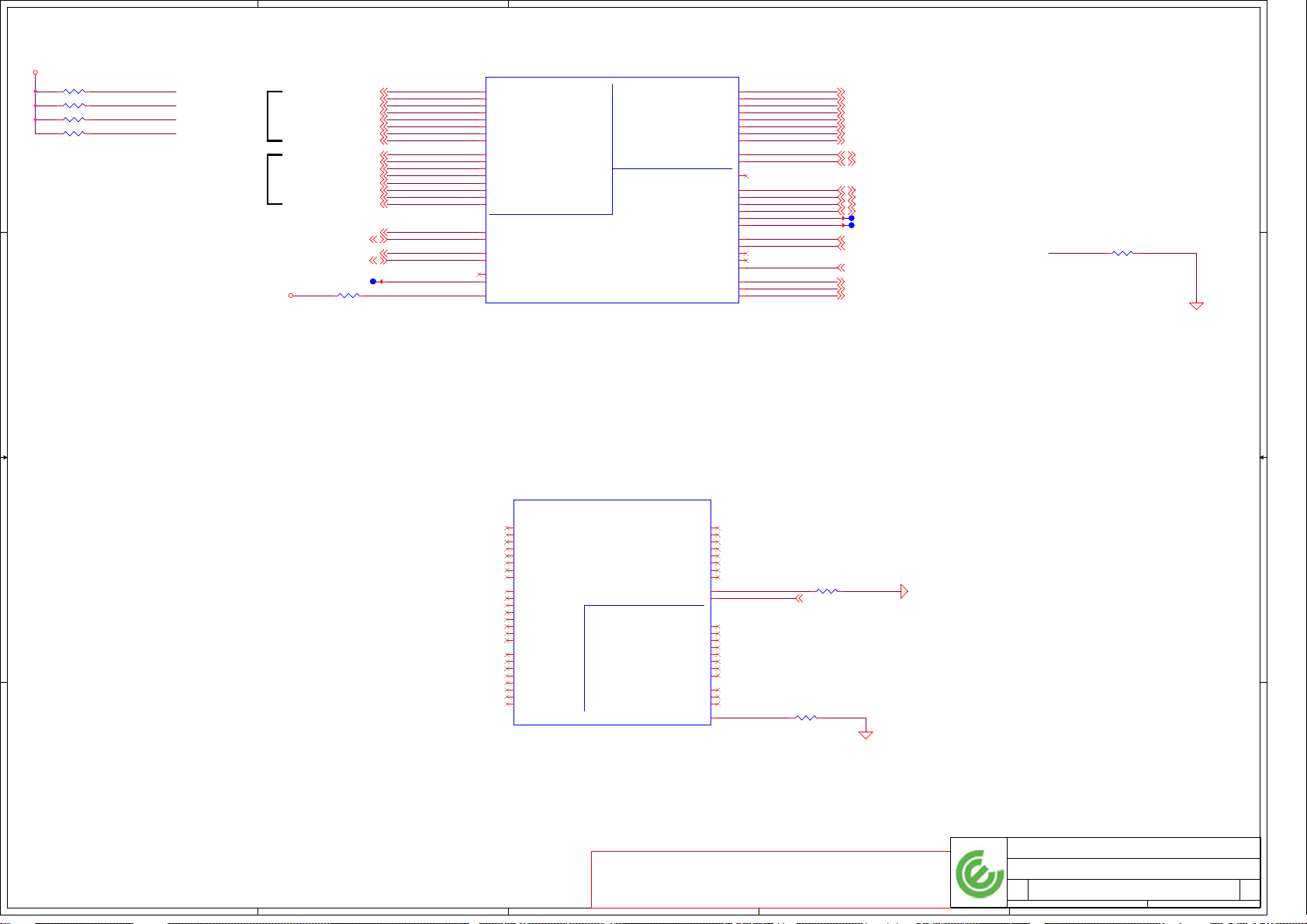

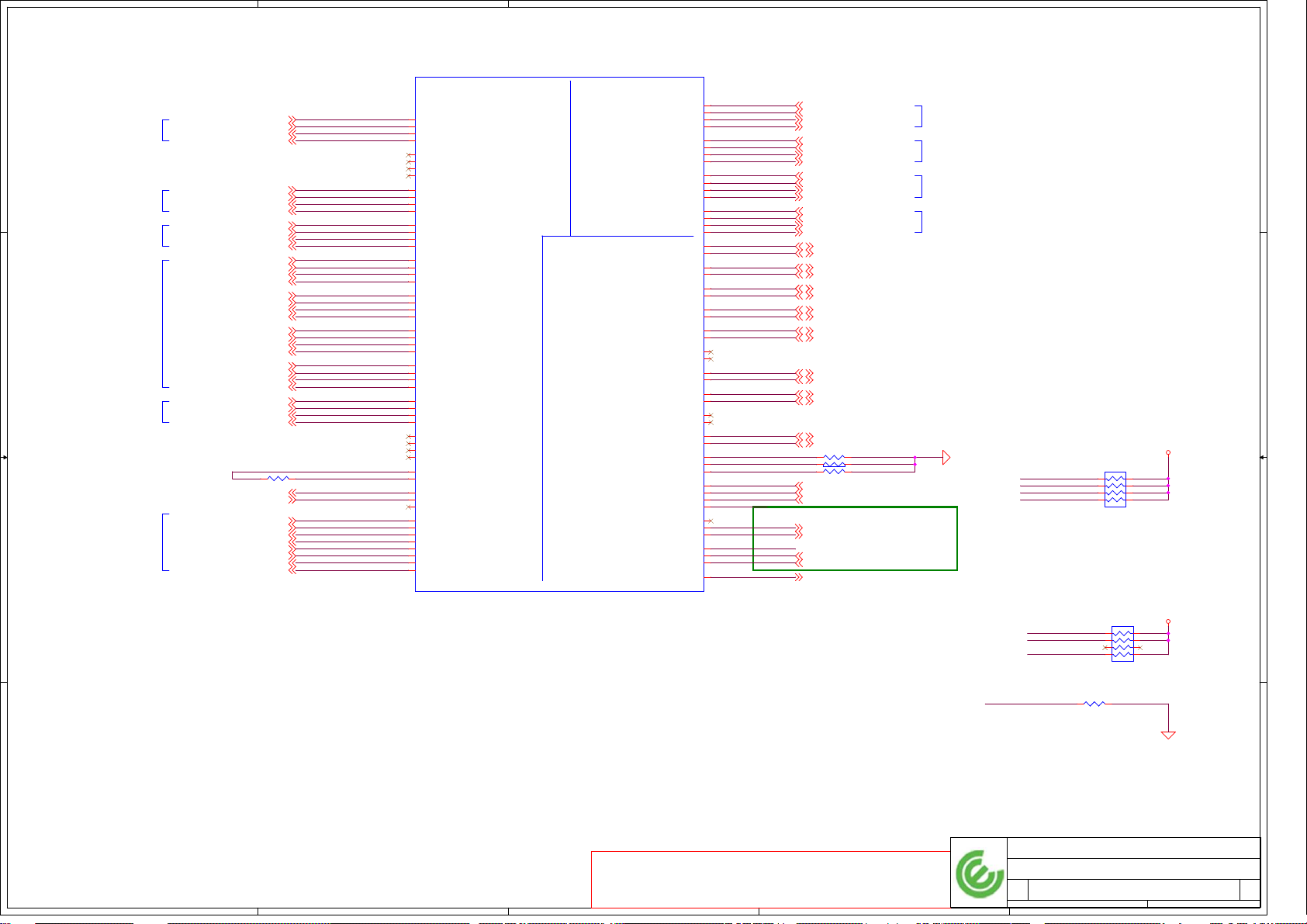

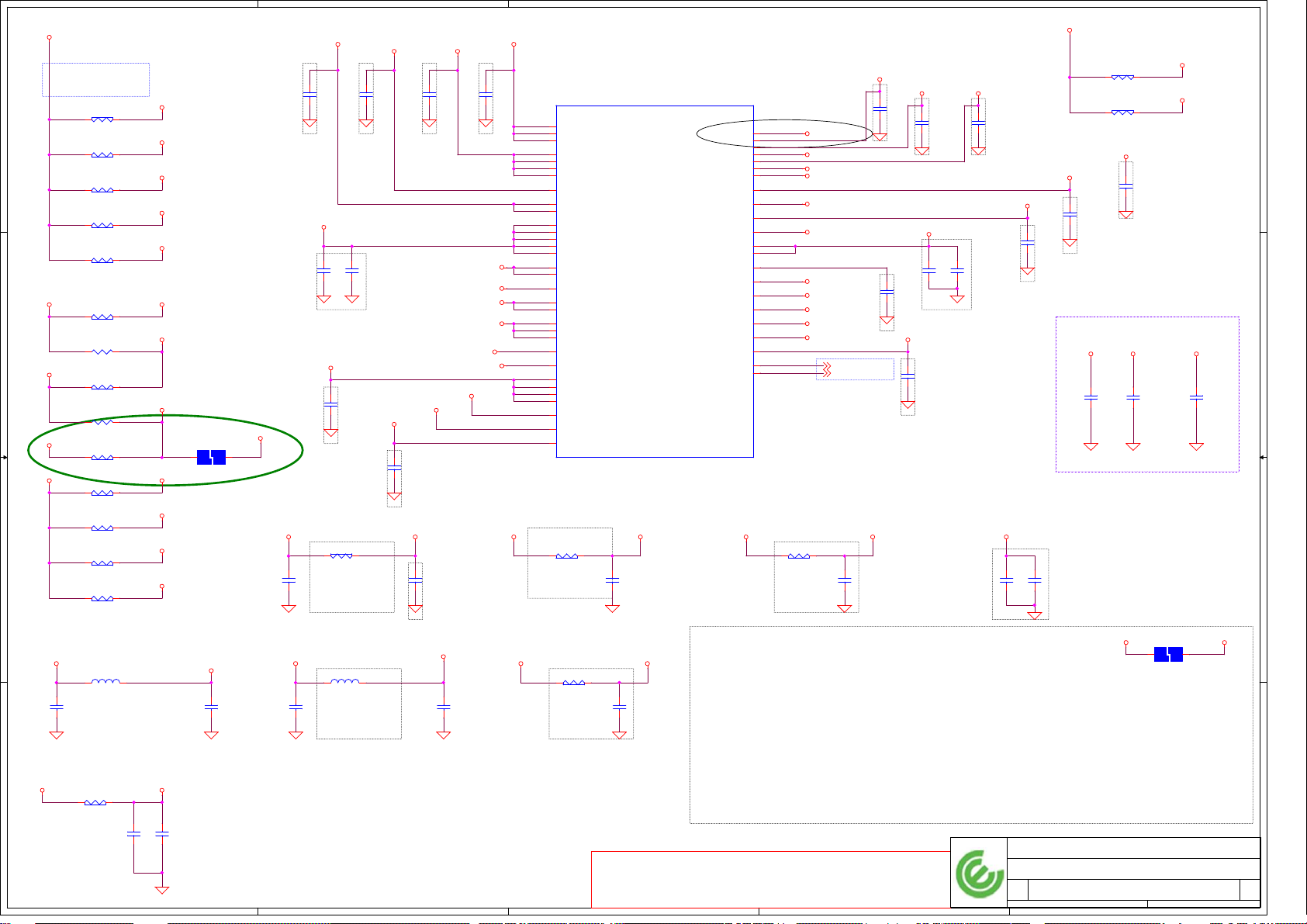

POWER STATES

Signal

State

S0 (Full ON) / M0

S3 (Suspend to RAM) / M3 LOW HIGH HIGH ON ON ON OFF

D D

S4 (Suspend to DISK) / M3 ON ON OFF

S5 (SOFT OFF) / M3 ON ON OFFLOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF HIGH

S5 (SOFT OFF) / M-OFF

SLP

S3#

HIGH

LOW HIGH HIGH

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

SLP

S5#

S4#

HIGH HIGH

LOW

LOW

SLP

A#

HIGH

HIGH

ALWAYS

PLANE

ON

PM TABLE

+5V_ALW

+3.3V_ALW

+3.3V_ALW_DSW

C C

State

S0

S3

S5 S4/AC

S5 S4/AC doesn't exist

power

plane

+3.3V_ALW_PCH +1.2V_MEM

+RTC_CELL

+1.8V_PRIM

+1.0V_PRIM

+1.0V_PRIM_CORE

+5V_ALW2

+3.3V_ALW2

+3.3V_RTC_LDO

+1.0V_MPHYGT

ON

ON

+3.3V_CV2

+2.5V_MEM

+1.0V_VCCST

+5V_RUN

+3.3V_RUN

+0.6V_DDR_VTT

+1.8V_RUN

+VCC_CORE

+VCC_GT

+VCC_SA

+1.0VS_VCCIO

ON ON

ON

OFF

OFFOFF

OFFON

OFF

OFF

M

PLANE

ON

4

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

CLOCKS

OFF

OFF

OFF

USB3.0

USB3.0-1

USB3.0-2

USB3.0-3

USB3.0-4

USB3.0-5

USB3.0-6

SSIC

SSIC

3

2

1

AR config

PCIE

PCIE-1

PCIE-2

PCIE-3

PCIE-4

PCIE-5

PCIE-6

PCIE-7

PCIE-8

PCIE-9

PCIE-10

PCIE-11

PCIE-12

SATA

JUSB3-->Left Rear (SB14 only)

SATA-0

SATA-1

SATA-1*

SATA-2

12" not support JUSB3

JUSB1-->Right

M.2 3042(LTE)

JUSB2-->Left Front

Card Reader (PCIE)

NA

M.2 3030(WLAN)

M.2 3030(WIGIG)

Alpine Ridge - SP

LOM

NA

M.2 2280 SSD

(PCIex2 or SATA)

USB PORT#DESTINATION

1

2

3

4

5

6

7

8

9

10

DESTINATION

JUSB1-->Right

JUSB2-->Left Front

JUSB3-->Left Rear (SB14 only)

M2 3042(WWAN)

Camera

NA

M.2 3030(BT)

Touch Screen

NA

USH

B B

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

AR use 1086PP

Non AR use 1080PP

5

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

LA-E131P

LA-E131P

LA-E131P

1

3 59Wednesday, November 09, 2016

3 59Wednesday, November 09, 2016

3 59Wednesday, November 09, 2016

1.0

1.0

1.0

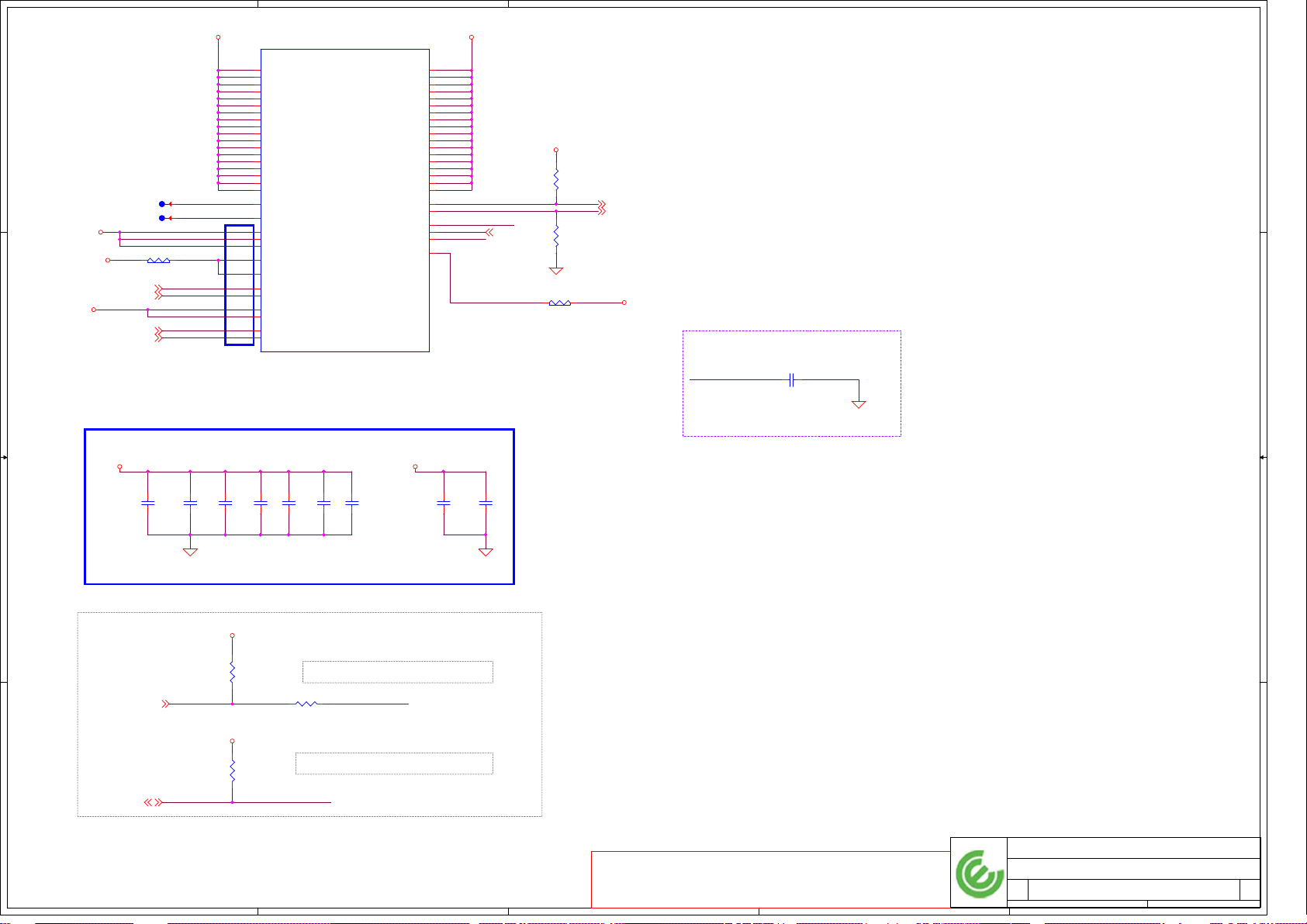

Page 4

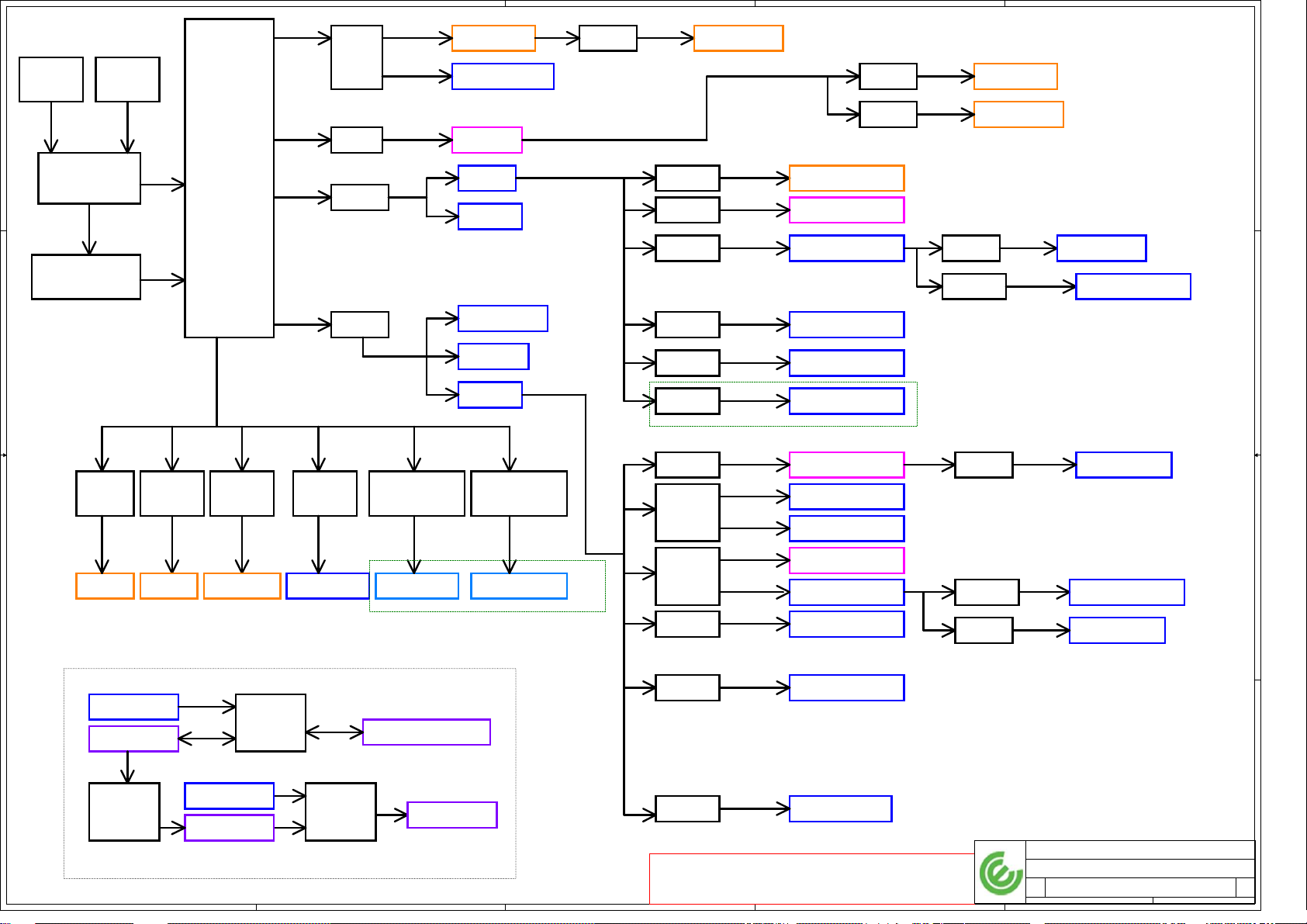

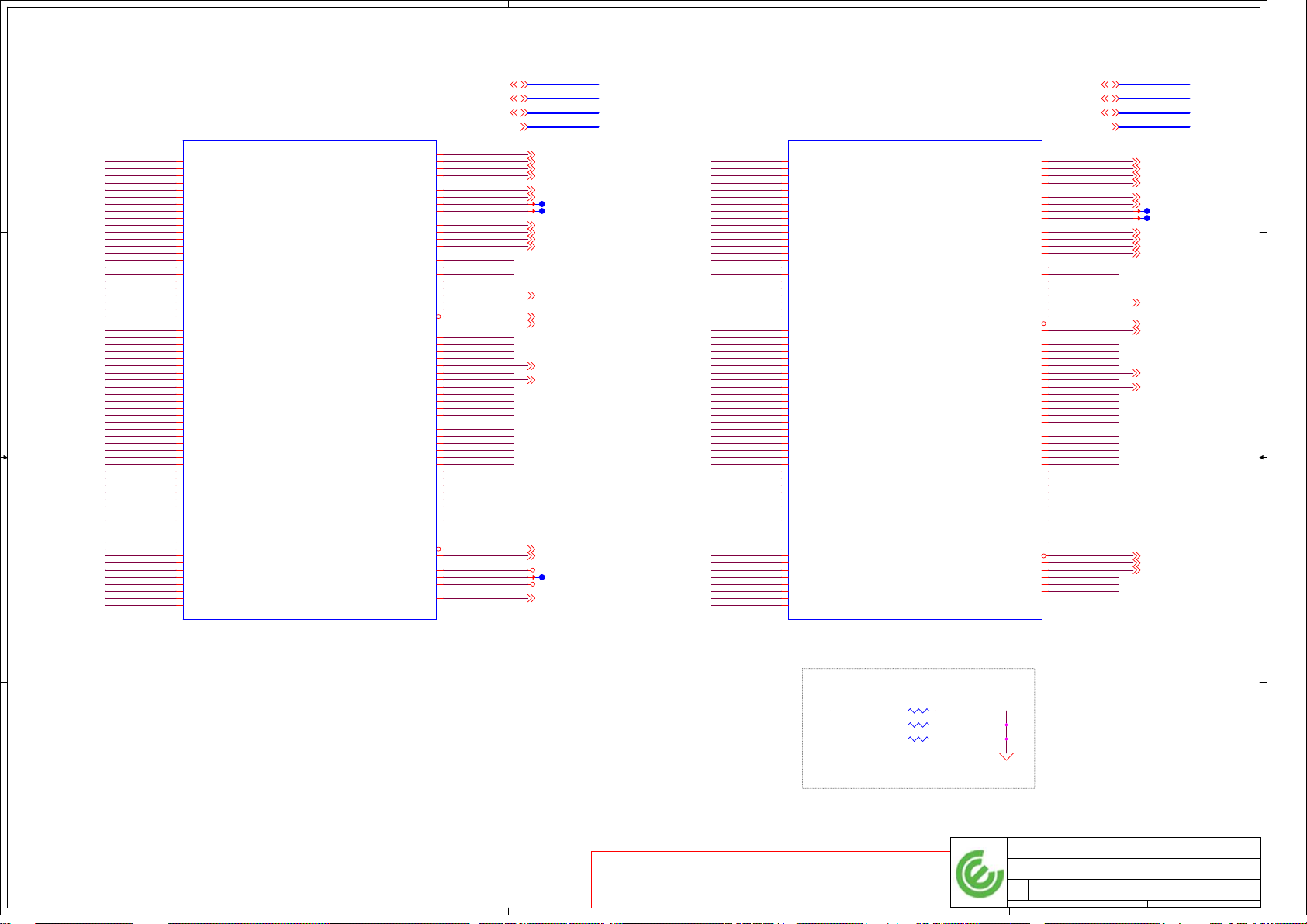

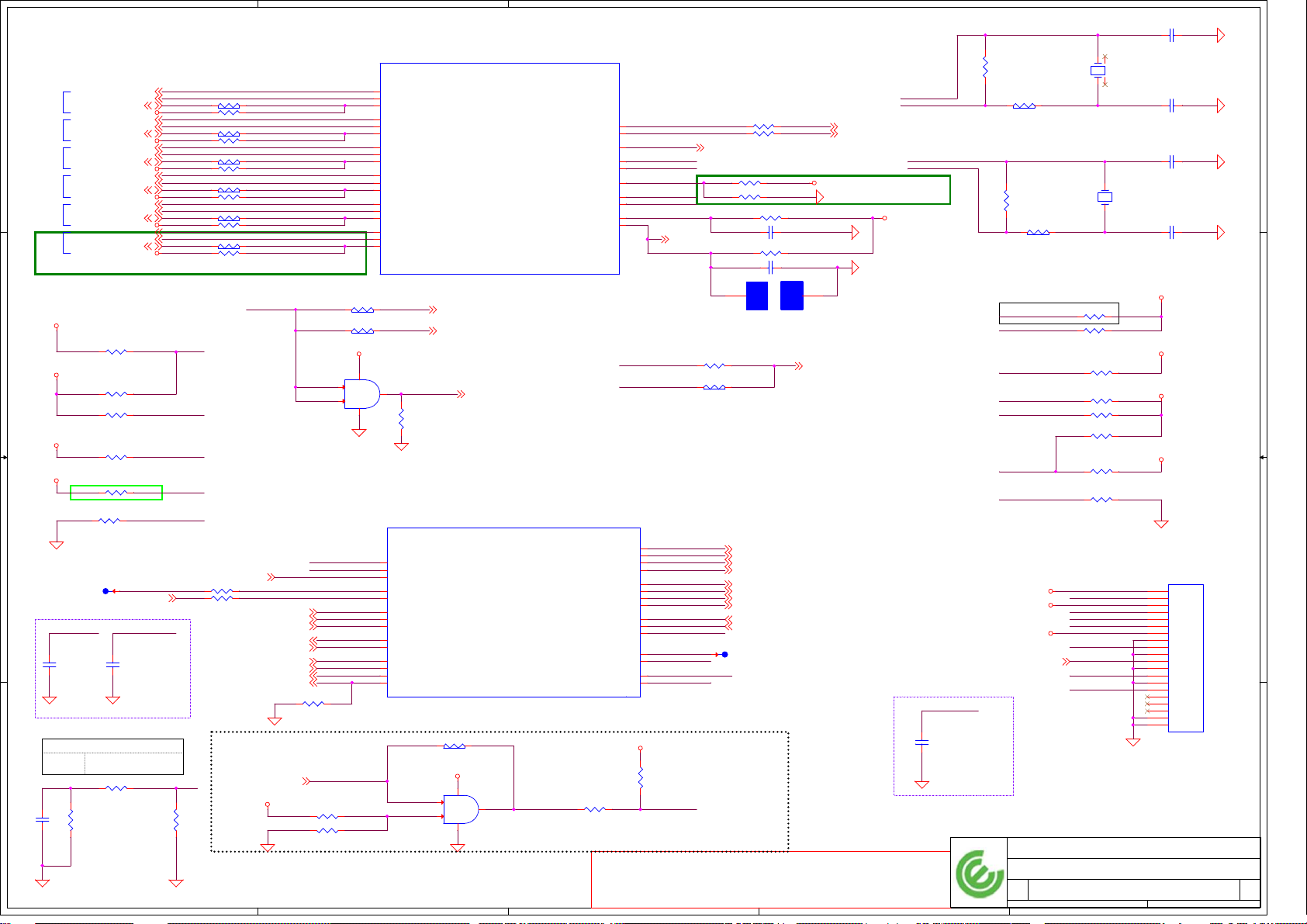

5

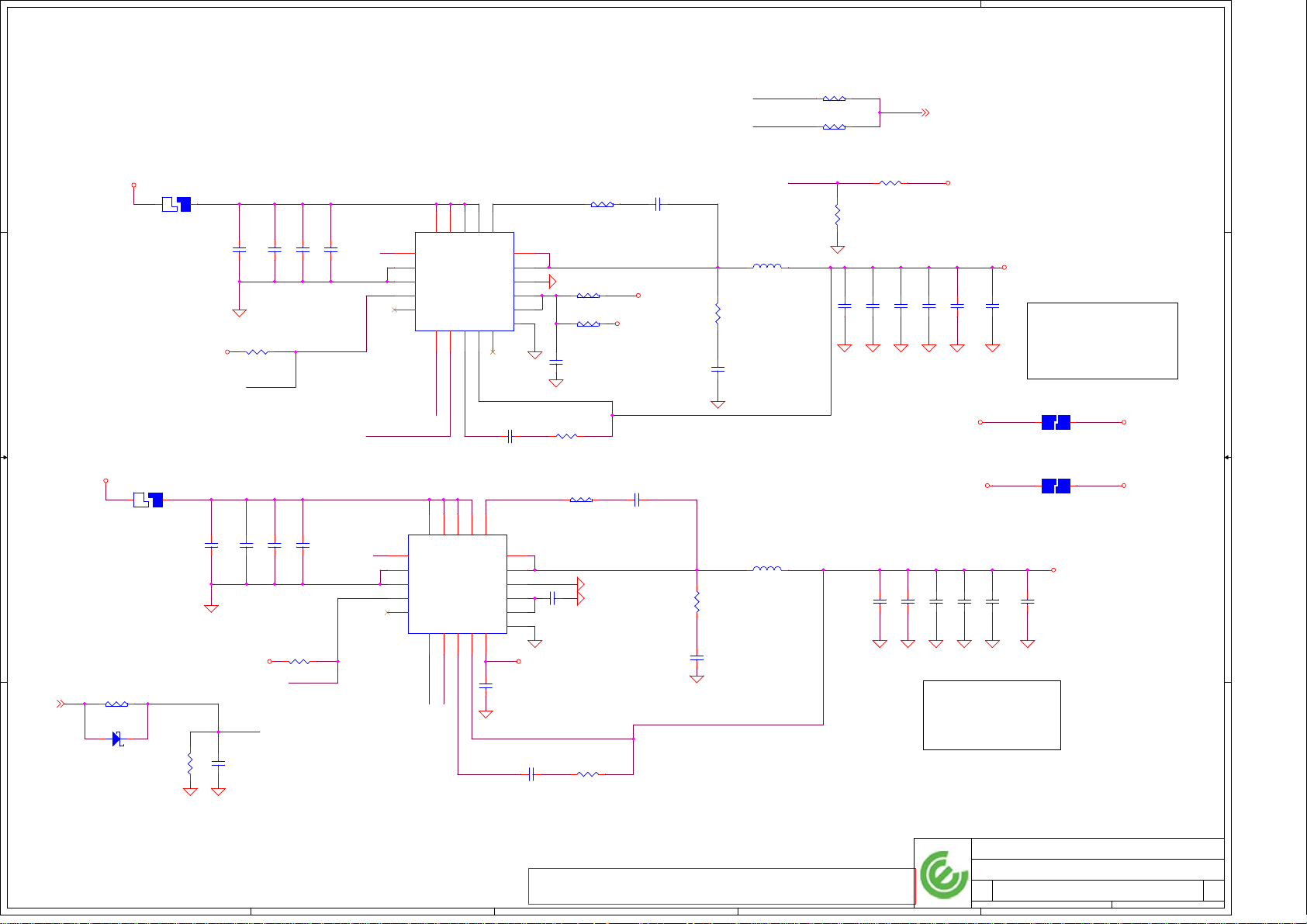

Barrel

ADAPTER

D D

CHARGER

ISL88738

(PU901)

Type-C

ADAPTER

+PWR_SRC

BATTERY

C C

SY8210A

(PU200)

SYX196D

(PU301)

SY8288C

(PU102)

SY8288B

(PU100)

4

SIO_SLP_S4#

0.6V_DDR_VTT_ON

SIO_SLP_SUS#

ALWON

ALWON

+1.2V_MEM

+0.6V_DDR_VTT

+1.0V_PRIM

+5V_ALW

+5V_ALW2

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

TPS22961

(UZ26)

3

SIO_SLP_SUS#

SIO_SLP_S4#

+VCC_SFR_OC

TPS62134C

(PU401)

TPS62134D

(PU402)

EM5209

(UZ4)

SLGC55544C

(UI3)

SY6288

(UI1)

SY6288

(UI2)

RUN_ON

SIO_SLP_SUS#

RUN_ON

USB_PWR_SHR_VBUS_EN

USB_PWR_EN1#

USB_PWR_EN2#

2

TPS22961

(UZ19)

TPS22961

(UZ21)

+1.0VS_VCCIO

+1.0V_PRIM_CORE

+5V_RUN

+5V_USB_CHG_PWR

+USB_EX2_PWR

+USB_EX3_PWR

SB14 only

RUN_ON

SIO_SLP_S0#

SIO_SLP_S4#

3V3_MAIN_EN

LP2301

(QV8)

EM5209

(@UZ5)

+1.0V_VCCSTG

+1.0V_VCCST

3.3V_TS_EN

AUD_PWR_EN

1

CPU PWR

PCH PWR

GT3 PWR

Peripheral Device PWR

TYPE-C Power

GPU PWR

+5V_TSP

+5V_RUN_AUDIO

RT8097A

(PU501)

ISL95857

(PU602)

IMVP_VR_ON

B B

CSD97374C

(PU604)

IMVP_VR_ON

+VCC_GT+VCC_SA

CSD97374C

(PU603)

IMVP_VR_ON

+VCC_CORE

AO6405

(QV1)

EN_INVPWR

+BL_PWR_SRC

TPS62134CRGT

(PU1301)

RUN_ON

+VCC_EDRAM

TYPE-C

TPS62134CRGT

(PU1302)

SIO_SLP_SUS#

+VCC_EOPIO

GT3 => SB14 only

EM5209

(UZ2)

EM5209

(UZ3)

EM5209

(UZ4)

G524B1T11U

(UV24)

SIO_SLP_SUS#

SIO_SLP_LAN#

AUX_EN_WOWL

@SIO_SLP_WLAN#

SIO_SLP_SUS#

@PCH_ALW_ON

RUN_ON

3.3V_WWAN_EN

ENVCC_PCH

+1.8V_PRIM

+3.3V_LAN

+3.3V_WLAN

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_WWAN

+LCDVDD

AOZ1336

(UZ8)

EM5209

(@UZ5)

LP2301A

(QZ1)

RUN_ON

3.3V_CAM_EN#

+1.8V_RUN

+3.3V_RUN_AUDIO

+3.3V_CAM

+5V_ALW

TPS65982D\

+5V_ALW

(UT5)

AP2112K

(UT7)

+PP_HV(5V~20V)

A A

AP2204

(UT8)

5

+5V_TBT_VBUS

+TBTA_Vbus_1(5V~20V)

+3.3V_VDD_PIC

4

AP7361C

(PU503)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

SIO_SLP_S4#

+2.5V_MEM

for DDR4

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Power rails

Power rails

Power rails

LA-E131P

LA-E131P

LA-E131P

1

4 59Wednesday, November 09, 2016

4 59Wednesday, November 09, 2016

4 59Wednesday, November 09, 2016

1.0

1.0

1.0

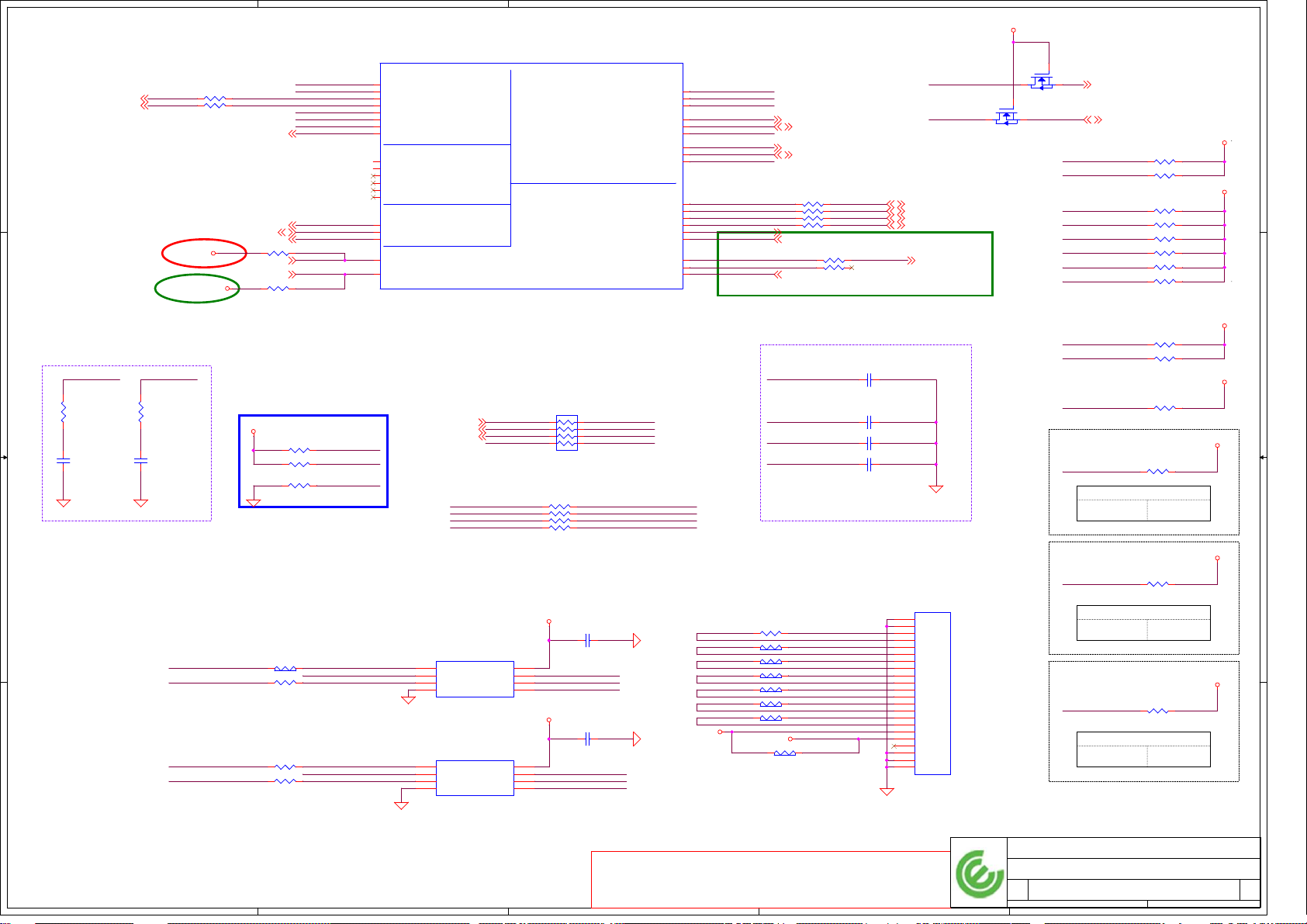

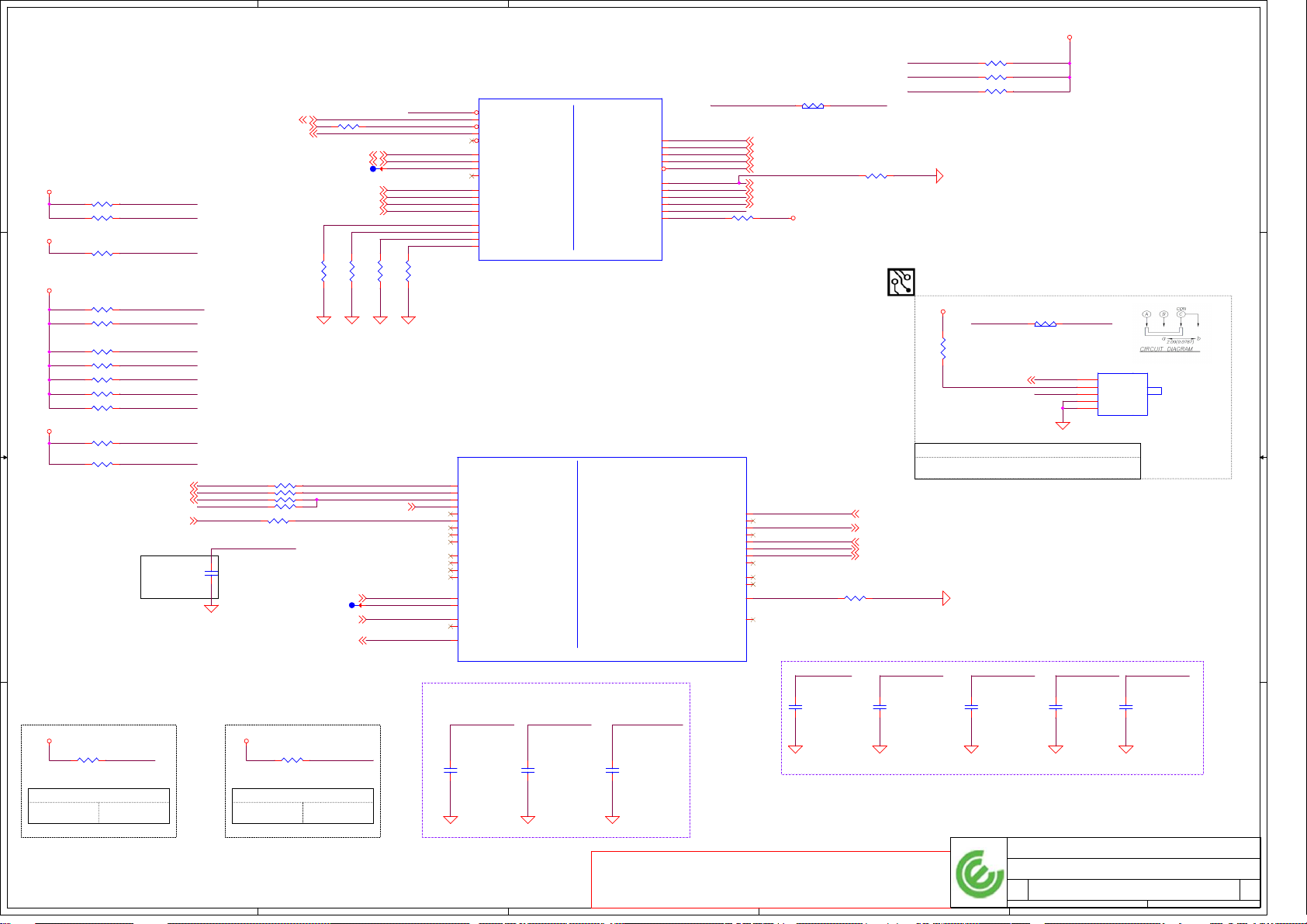

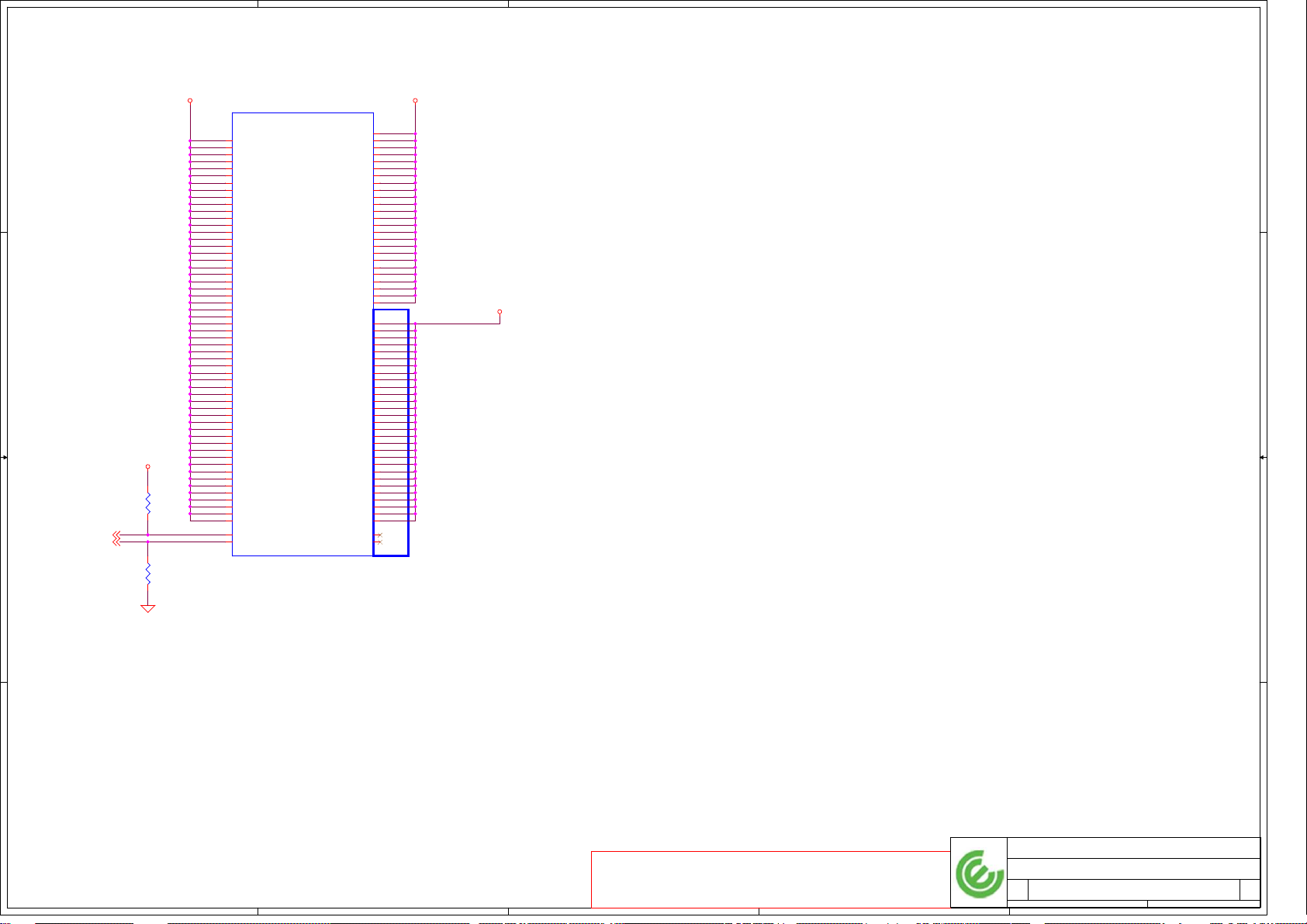

Page 5

5

AW44

BB43

KBL-U

D D

AW45 AW42

03

SML1_SMBDATA

SML1_SMBCLK

D8E11

03

00

00

AY44

BB39

UPD2_SMBCLK

D7

UPD2_SMBDAT

E7

MEM_SMBCLK

MEM_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

1K

1K

4

+3.3V_ALW_PCH

2.2K

2.2K

499

499

+3.3V_ALW

1K

1K

+3.3V_ALW_PCH

+3.3V_ALW_PCH

3

DMN65D8LDW-7

DMN65D8LDW-7

28

31

LOM

2

1

2.2K

2.2K

+3.3V_RUN

202

200

202

200

53

51

DIMMA

DIMMB

XDP

@2.2K

@2.2K

B3

E5

C12

E10

C3

B4

USH_SMBCLK

USH_SMBDAT

UPD_SMBCLK

UPD_SMBDAT

2.2K

2.2K

C C

01

01

02

02

KBC

04

04

+3.3V_ALW

+3.3V_ALW

DMN66D0LDW-7

DMN66D0LDW-7

2.2K

2.2K

2.2K

2.2K

+3.3V_CV2

M9

USH

L9

+3.3V_TBT_FLASH

USH/B

B5

A5

PD

MEC 5105

F7

05

B6

05

A12

06

N10

B B

A A

06

07

07

08 C5

08

09

09

1010M3

EXPANDER_GPU_SMCLK

M4

EXPANDER_GPU_SMDATA

M7

C8

F6

E9

N2

PBAT_CHARGER_SMBCLK

PBAT__CHARGER_SMBDAT

2.2K

2.2K

2.2K

2.2K

+3.3V_ALW

+3.3V_ALW

100 ohm

100 ohm

Expander IO

Charger

7

BATTERY

6

CONN

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

LA-E131P

LA-E131P

LA-E131P

1

5 59Wednesday, November 09, 2016

5 59Wednesday, November 09, 2016

5 59Wednesday, November 09, 2016

1.0

1.0

1.0

Page 6

5

4

3

2

1

+3.3V_RUN

CPU_DP1_CTRL_CLK

RC175 2.2K_0402_5%

RC178 2.2K_0402_5%

D D

RC176 2.2K_0402_5%

RC177 2.2K_0402_5%

12

CPU_DP1_CTRL_DATA

12

CPU_DP2_CTRL_CLK

12

CPU_DP2_CTRL_DATA

12

AR(AR)/

HDMI(Non AR)

PS8338(AR)

+1.0VS_VCCIO

C C

B B

CPU_DP1_N0<24>

CPU_DP1_P0<24>

CPU_DP1_N1<24>

CPU_DP1_P1<24>

CPU_DP1_N2<24>

CPU_DP1_P2<24>

CPU_DP1_N3<24>

CPU_DP1_P3<24>

CPU_DP2_N0<22>

CPU_DP2_P0<22>

CPU_DP2_N1<22>

CPU_DP2_P1<22>

CPU_DP2_N2<22>

CPU_DP2_P2<22>

CPU_DP2_N3<22>

CPU_DP2_P3<22>

12

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

GPP_E23

EDP_COMP

CPU_DP1_CTRL_CLK<24>

CPU_DP1_CTRL_DATA<24>

CPU_DP2_CTRL_CLK<22>

CPU_DP2_CTRL_DATA<22>

@

T120

PAD~D

RC2 24.9_0402_1%

COMPENSATION PU FOR eDP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

UC1A

CPU@

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

KBL-U_BGA1356

SKL-U Ballout Rev0.71 & INTEL symbol Rev1.0

UC1I

CPU@

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

KBL-U_BGA1356

SKL-U

DDI

DISPLAY SIDEBANDS

SKL_ULT

EDP

1 OF 20

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

EDP_DISP_UTIL

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

CSI2_COMP

EMMC_RCOMP

EDP_TXN0 <29>

EDP_TXP0 <29>

EDP_TXN1 <29>

EDP_TXP1 <29>

EDP_TXN2 <29>

EDP_TXP2 <29>

EDP_TXN3 <29>

EDP_TXP3 <29>

CPU_DP1_AUXN

CPU_DP1_AUXP

CPU_DP3_AUXN

CPU_DP3_AUXP

CPU_DP1_HPD <24>

CPU_DP2_HPD <22>

EDP_HPD <29>

PANEL_BKLEN <29>

EDP_BIA_PWM <29>

ENVDD_PCH <29,34>

1 2

RC3

1 2

RC4 200_0402_1%

100_0402_1%

TBT_FORCE_PWR <24>

EDP_AUXN <29>

EDP_AUXP <29>

CPU_DP1_AUXN <24>

CPU_DP1_AUXP <24>

CPU_DP2_AUXN <22>

CPU_DP2_AUXP <22>

@

T1

PAD~D

@

T2

PAD~D

EDP_HPD

1 2

RC1 100K_0402_5%

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (1/14)

CPU (1/14)

CPU (1/14)

LA-E131P

LA-E131P

LA-E131P

6 59Wednesday, November 09, 2016

6 59Wednesday, November 09, 2016

6 59Wednesday, November 09, 2016

1

1.0

1.0

1.0

Page 7

5

4

3

2

1

For DDR4

DDR_A_DQS#[0..7]<20>

2 OF 20

DDR_A_D[0..63]<20>

DDR_A_DQS[0..7]<20>

DDR_A_MA[0..16]<20>

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

DDR_A_CKE2

AW56

DDR_A_CKE3

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1 DDR_B_ODT0

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

DDR_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14 DDR_B_MA15

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#4

BA64

DDR_A_DQS4

AY64

DDR_A_DQS#5

AY60

DDR_A_DQS5

BA60

DDR_B_DQS#0

BA38

DDR_B_DQS0

AY38

DDR_B_DQS#1

AY34

DDR_B_DQS1

BA34

DDR_B_DQS#4

BA30

DDR_B_DQS4

AY30

DDR_B_DQS#5

AY26

DDR_B_DQS5

BA26

DDR_A_ALERT#

AW50

DDR_A_PARITY

AT52

AY67

+DDR_VREF_A_DQ

AY68

BA67

AW67

DDR_A_CLK#0 <20>

DDR_A_CLK0 <20>

DDR_A_CLK#1 <20>

DDR_A_CLK1 <20>

DDR_A_CKE0 <20>

DDR_A_CKE1 <20>

@

T3

PAD~D

@

T4

PAD~D

DDR_A_CS#0 <20>

DDR_A_CS#1 <20>

DDR_A_ODT0 <20>

DDR_A_ODT1 <20>

DDR_A_BG0 <20>

DDR_A_ACT# <20>

DDR_A_BG1 <20>

DDR_A_BA0 <20>

DDR_A_BA1 <20>

DDR0_PAR,DDR0_ALERT# for DDR4

DDR_A_ALERT# <20>

+DDR_VREF_CA

@

T132

PAD~D

+DDR_VREF_B_DQ

DDR_VTT_CTRL <20>

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

KBL-U_BGA1356

CPU@

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DRAM_RESET#

DDR_RCOMP[0]

DDR CH - B

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR4, Ballout for side by side(Non-Interleave)

D D

UC1B

CPU@

DDR_A_D0

AL71

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

C C

B B

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

KBL-U_BGA1356

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_ALERT#

DDR1_PAR

3 OF 20

DDR_B_DQS#[0..7]<21>

DDR_B_D[0..63]<21>

DDR_B_DQS[0..7]<21>

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_MA[0..16]<21>

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

DDR_B_ACT#

DDR_B_BG1

DDR_B_MA13

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <21>

DDR_B_CLK#1 <21>

DDR_B_CLK0 <21>

DDR_B_CLK1 <21>

DDR_B_CKE0 <21>

DDR_B_CKE1 <21>

@

T5

PAD~D

@

T6

PAD~D

DDR_B_CS#0 <21>

DDR_B_CS#1 <21>

DDR_B_ODT0 <21>

DDR_B_ODT1 <21>

DDR_B_BG0 <21>

DDR_B_ACT# <21>

DDR_B_BG1 <21>

DDR_B_BA0 <21>

DDR_B_BA1 <21>

DDR1_PAR,DDR1_ALERT# for DDR4

DDR_B_ALERT# <21>DDR_A_PARITY <20>

DDR_B_PARITY <21>

DDR_DRAMRST# <20>

DDR4 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

A A

1 2

RC5 121_0402_1%

1 2

RC6 80.6_0402_1%

1 2

RC7 100_0402_1%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (2/14)

CPU (2/14)

CPU (2/14)

LA-E131P

LA-E131P

LA-E131P

7 59Wednesday, November 09, 2016

7 59Wednesday, November 09, 2016

7 59Wednesday, November 09, 2016

1

1.0

1.0

1.0

Page 8

5

SPI_MOSI= SPI_IO0

SPI_MISO= SPI_IO1

PCH EDS R0.7 p.235~236

PCH_SPI_CLK

PCH_SPI_D1

CXDP@

1 2

PCH_SPI_DO_XDP<14>

D D

C C

PCH_SPI_DO2_XDP<14>

PCH_SPI_CLK_1_R PCH_SPI_CLK_0_R

33_0402_5%

@EMI@

12

RC28

33P_0402_50V8J

@EMI@

12

CC7

RC10 1K_0402_1%

CXDP@

RC11 1K_0402_1%

+1.8V?

+3.3V_RUN

+3.3V_1.8V_ESPI

33_0402_5%

@EMI@

12

RC29

33P_0402_50V8J

@EMI@

12

CC8

1 2

PCH_SPI_CS#2<36>

PCH_CL_CLK1<32>

PCH_CL_DATA1<32>

PCH_CL_RST1#<32>

RC13 10K_0402_5%LPC@

SIO_RCIN#<34>

ESPI_ALERT#<34>

RC21 8.2K_0402_1%

+3.3V_SPI

PCH_SPI_D0

PCH_SPI_D2

PCH_SPI_D3

PCH_SPI_CS#0

PCH_SPI_CS#1

PCH_SPI_CS#2

12

12

PCH_SPI_D2_R1

RC30 1K_0402_5%

@

RC31 1K_0402_5%

@

RC316 1K_0402_5%

@

12

PCH_SPI_D3_R1

12

PCH_SPI_D3_R1

12

03/02:follow Intel MOW_2015WW06

AW3

AW2

AW13

AY11

AU4

AU3

AU2

AU1

AV2

AV3

M2

M3

J4

V1

V2

M1

G3

G2

G1

4

UC1E

CPU@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

KBL-U_BGA1356

PCH_SPI_D1_R1<36>

PCH_SPI_D0_R1<36>

PCH_SPI_CLK_R1<36>

PCH_SPI_D1_R1

PCH_SPI_D0_R1

PCH_SPI_CLK_R1

PCH_SPI_D3_R1

PCH_SPI_CLK_R1

PCH_SPI_D0_R1

PCH_SPI_D1_R1

SKL-U

SMBUS, SMLINK

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

SOFTWARE TAA

RPC1

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

1 2

RC407 33_0402_5%

@

1 2

RC408 33_0402_5%

@

1 2

RC409 33_0402_5%

@

1 2

RC410 33_0402_5%

@

3

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

5 OF 20

PCH_SPI_D1_0_R

PCH_SPI_D0_0_R

PCH_SPI_CLK_0_R

PCH_SPI_D3_0_R

PCH_SPI_D3_1_RPCH_SPI_D3_R1

PCH_SPI_CLK_1_R

PCH_SPI_D0_1_R

PCH_SPI_D1_1_R

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

MEM_SMBCLK

MEM_SMBDATA

PCH_SMB_ALERT#

SML0_SMBCLK

SML0_SMBDATA

GPP_C5

SML1_SMBCLK

SML1_SMBDATA

GPP_B23

ESPI_IO0_R

ESPI_IO1_R

ESPI_IO2_R

ESPI_IO3_R

ESPI_CLK

PCI_CLK_LPC1

SML0_SMBCLK <30>

SML0_SMBDATA <30>

SML1_SMBCLK <34>

SML1_SMBDATA <34>

1 2

RC366

1 2

RC367

1 2

RC368

1 2

RC369

ESPI_CS# <34,35>

ESPI_RESET# <34>

1 2

RC16

EMI@

ESPI_CLK_5105

SML0_SMBCLK

SML1_SMBCLK

MEM_SMBCLK

1 2

RC22@ 22_0402_5%

CLKRUN# <34>

2

15_0402_5%

15_0402_5%

15_0402_5%

15_0402_5%

15_0402_5%

CHECK,LPC_CLK FOR DEBUG CARD?

ESPI_IO0 <34,35>

ESPI_IO1 <34,35>

ESPI_IO2 <34,35>

ESPI_IO3 <34,35>

ESPI_CLK_5105 <34,35>

RF Request

1 2

CC316@RF@ 33P_0402_50V8J

1 2

CC318@RF@ 33P_0402_50V8J

1 2

CC319@RF@ 33P_0402_50V8J

1 2

CC320@RF@ 33P_0402_50V8J

Place close CPU side

MEM_SMBCLK

MEM_SMBDATA

+3.3V_RUN

6

5

DMN65D8LDW-7_SOT363-6

3 4

QC2B

DMN65D8LDW-7_SOT363-6

For BR/SB

2

1

DDR_XDP_WAN_SMBCLK <14,20,21>

QC2A

DDR_XDP_WAN_SMBDAT <14,20,21>

DDR_XDP_WAN_SMBDAT

DDR_XDP_WAN_SMBCLK

MEM_SMBCLK

MEM_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

Reserve

SML0_SMBCLK

SML0_SMBDATA

CLKRUN#

PCH_SMB_ALERT#

TLS CONFIDENTIALITY

HIGH

LOW(DEFAULT)

WEAK INTERNAL 20K PD

1

+3.3V_RUN

1 2

RC318 2.2K_0402_5%

1 2

RC319 2.2K_0402_5%

1 2

RC12 1K_0402_5%

1 2

RC14 1K_0402_5%

1 2

RC15 1K_0402_5%

1 2

RC17 1K_0402_5%

1 2

RC347 499_0402_1%

1 2

RC348 499_0402_1%

1 2

RC19 499_0402_1%@

1 2

RC20 499_0402_1%@

1 2

RC27 8.2K_0402_5%LPC@

1 2

RC23 2.2K_0402_5%

ENABLE

DISABLE

+3.3V_ALW_PCH

+3.3V_LAN

+3.3V_RUN

+3.3V_ALW_PCH

+3.3V_ALW_PCH

B B

E-T_6705K-Y20N-00L

+3.3V_SPI

128Mb Flash ROM

PCH_SPI_CS#0_R1

PCH_SPI_D2_R1 PCH_SPI_CLK_0_R

@

1 2

RC37 0_0402_5%

1 2

RC39 33_0402_5%

PCH_SPI_CS#0_R2

PCH_SPI_D1_0_R

PCH_SPI_D2_0_R

UC5

1

/CS

2

IO1

3

IO2

4

GND

W25Q128FVSIQ_SO8

VCC

CLK

IO3

IO0

8

PCH_SPI_D3_0_R

7

6

PCH_SPI_D0_0_R

5

+3.3V_SPI

128Mb Flash ROM

UC6

PCH_SPI_CS#1_R1

PCH_SPI_D2_R1

A A

1 2

RC42 0_0402_5%@

1 2

RC43 33_0402_5%

@

PCH_SPI_CS#1_R2

PCH_SPI_D1_1_R

PCH_SPI_D2_1_R

@

1

/CS

2

IO1

3

IO2

4

GND

W25Q128FVSIQ_SO8

VCC

CLK

IO3

IO0

8

PCH_SPI_D3_1_R

7

PCH_SPI_CLK_1_R

6

PCH_SPI_D0_1_R

5

CC9

1 2

0.1U_0201_10V6K

CC10

@

1 2

0.1U_0201_10V6K

+3.3V_SPI

RC32 0_0402_5%

@

1 2

@

RC33 0_0402_5%

1 2

@

RC34 0_0402_5%

1 2

@

RC35 0_0402_5%

1 2

@

RC36 0_0402_5%

1 2

@

RC38 0_0402_5%

1 2

@

RC40 0_0402_5%

+3.3V_ALW_PCH

1 2

@

RC41 0_0402_5%

12

PCH_SPI_CS#1_R1

PCH_SPI_CS#1

PCH_SPI_D0_R1

PCH_SPI_D0

PCH_SPI_D1_R1

PCH_SPI_D1

PCH_SPI_CLK_R1

PCH_SPI_CLK

PCH_SPI_CS#0_R1

PCH_SPI_CS#0

PCH_SPI_D2_R1

PCH_SPI_D2

PCH_SPI_D3_R1

PCH_SPI_D3

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

GND2

GND1

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

JSPI1

CONN@

GPP_C5

EC interface

HIGH

LOW(DEFAULT)

WEAK INTERNAL 20k PD

GPP_B23

RC317 150K_0402_5%

EXI BOOT STALL BYPASS

HIGH

LOW(DEFAULT)

WEAK INTERNAL PD

1 2

RC25 4.7K_0402_5%ESPI@

1 2

ESPI

LPC

ENABLED

DIABLED

+3.3V_ALW_PCH

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (3/14)

CPU (3/14)

CPU (3/14)

LA-E131P

LA-E131P

LA-E131P

8 59Wednesday, November 09, 2016

8 59Wednesday, November 09, 2016

8 59Wednesday, November 09, 2016

1

1.0

1.0

1.0

Page 9

5

4

3

2

1

For BR/SB

UC1F

+3.3V_RUN

BBS_BIT6

AH10

AH11

AH12

AF11

AF12

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

AB3

AD1

AD2

AD3

AD4

AH9

W4

U7

U6

U8

U9

D D

RC282 100K_0402_5%

RC237 10K_0402_5%

RC402 49.9K_0402_1%@

RC403 49.9K_0402_1%@

+3.3V_ALW_PCH

RC283 10K_0402_5%

RC330 49.9K_0402_1%

RC331 49.9K_0402_1%

C C

+3.3V_RUN

RC186 4.7K_0402_5%@

12

12

12

12

12

12

12

12

3.3V_TS_EN

SIO_EXT_SCI#

NRB_BIT

LPSS_UART2_RXD

LPSS_UART2_TXD

SIO_EXT_WAKE#

LPSS_UART2_RXD

LPSS_UART2_TXD

MEDIACARD_IRQ#<31>

TPM_PIRQ#<36>

SIO_EXT_SCI#<34>

3.3V_TS_EN<29>

I2C1_SDA_TP<40>

I2C1_SCK_TP<40>

+3.3V_RUN

10K_0402_5%

12

SBIOS_TX<35>

@

RC267

RC405 100K_0402_5%@

ONE_DIMM#

NRB_BIT

GPP_C8

LPSS_UART2_RXD

LPSS_UART2_TXD

NO REBOOT STRAP

HIGH

LOW(DEFAULT)

Weak IPD

B B

+3.3V_ALW_PCH

RC184 8.2K_0402_5%

@

No REBOOT

REBOOT ENABLE

BBS_BIT6

12

1 2

10K_0402_5%

12

DIMM Detect

HIGH

LOW

RC268

ONE_DIMM#

1 DIMM

2 DIMM

CPU@

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

KBL-U_BGA1356

+5V_ALW

LPSS_UART2_TXD

LPSS_UART2_RXD

SKL-U

CONN@

JUART1

1

1

2

2

3

3

4

4

5

GND

6

GND

CVILU_CI1804M1VRA-NH

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

MEM_INTERLEAVED

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

6 OF 20

+3.3V_ALW_PCH +3.3V_ALW_PCH

RC371

@

10K_0402_5%

1 2

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

MEM_INTERLEAVED

AR_DET#

ISH_I2C2_SDA

ISH_I2C2_SCL

CLKDET#

TPM_TYPE

LID_CL#_PCH

ISH_I2C2_SDA <32>

ISH_I2C2_SCL <32>

9/24: Reserve for embedded location ,refer Intel PDG 0.9

ISH_UART0_RXD <32>

ISH_UART0_TXD <32>

ISH_UART0_RTS# <32>

ISH_UART0_CTS# <32>

SIO_EXT_WAKE# <34>

RTD3_CIO_PWR_EN <24>

LCD_CBL_DET# <29>

@

T258

PAD~D

@

T268

PAD~D

GPP_A GROUP is +1.8V

AR_DET#

WWAN

WLAN

Reserved

RC400

@

10K_0402_5%

1 2

ISH_I2C2_SDA

ISH_I2C2_SCL

LCD_CBL_DET#

TPM_TYPE

+1.8V_RUN

1 2

RC363 1K_0402_5%

1 2

RC362 1K_0402_5%

+3.3V_RUN

1 2

RC287 100K_0402_5%

1 2

RC349 100_0402_1%@

BOOT BIOS Destination(Bit 6)

HIGH

LOW(DEFAULT)

Internal 20k PD

LPC

SPI

12

10K_0402_5%

RC372

12

10K_0402_5%

DIMM TYPE

HIGH Interleave

LOW Non-Interleave LOW AR

RC401

AR_DET#

NON ARHIGH

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (4/14)

CPU (4/14)

CPU (4/14)

LA-E131P

LA-E131P

LA-E131P

9 59Wednesday, November 09, 2016

9 59Wednesday, November 09, 2016

9 59Wednesday, November 09, 2016

1

1.0

1.0

1.0

Page 10

5

4

3

2

1

For AR,Steamboat12/14

UC1H

CPU@

PCIE/USB3/SATA

D D

Card Reader RTS5242----->

M.2 3030(WLAN) --->

M.2 3030(WiGig) --->

AR(PCIE5~8) --->

C C

10/100/1G LAN --->

M2 2280 SSD --->

B B

PCIE_PRX_DTX_N1<31>

PCIE_PRX_DTX_P1<31>

PCIE_PTX_DRX_N1<31>

PCIE_PTX_DRX_P1<31>

PCIE_PRX_DTX_N3<32>

PCIE_PRX_DTX_P3<32>

PCIE_PTX_DRX_N3<32>

PCIE_PTX_DRX_P3<32>

PCIE_PRX_DTX_N4<32>

PCIE_PRX_DTX_P4<32>

PCIE_PTX_DRX_N4<32>

PCIE_PTX_DRX_P4<32>

PCIE_PRX_DTX_N5<24>

PCIE_PRX_DTX_P5<24>

PCIE_PTX_DRX_N5<24>

PCIE_PTX_DRX_P5<24>

PCIE_PRX_DTX_N6<24>

PCIE_PRX_DTX_P6<24>

PCIE_PTX_DRX_N6<24>

PCIE_PTX_DRX_P6<24>

PCIE_PRX_DTX_N7<24>

PCIE_PRX_DTX_P7<24>

PCIE_PTX_DRX_N7<24>

PCIE_PTX_DRX_P7<24>

PCIE_PRX_DTX_N8<24>

PCIE_PRX_DTX_P8<24>

PCIE_PTX_DRX_N8<24>

PCIE_PTX_DRX_P8<24>

PCIE_PRX_DTX_N9<30>

PCIE_PRX_DTX_P9<30>

PCIE_PTX_DRX_N9<30>

PCIE_PTX_DRX_P9<30>

1 2

RC45 100_0402_1%

CPU_XDP_PRDY#<14>

CPU_XDP_PREQ#<14>

PCIE_PRX_DTX_N11<37>

PCIE_PRX_DTX_P11<37>

PCIE_PTX_DRX_N11<37>

PCIE_PTX_DRX_P11<37>

PCIE_PRX_DTX_N12<37>

PCIE_PRX_DTX_P12<37>

PCIE_PTX_DRX_N12<37>

PCIE_PTX_DRX_P12<37>

PCIE_RCOMPN

PCIE_RCOMPP

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

KBL-U_BGA1356

SKL-U

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

8 OF 20

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

USBCOMP

USB2_ID

AG3

USB2_VBUSSENSE

AG4

A9

C9

D9

USB_OC3#

B9

J1

J2

J3

HDD_DET#

H2

M3042_PCIE#_SATA

H3

M2280_PCIE_SATA#

G4

H1

SATALED#

USB3_PRX_DTX_N1 <38>

USB3_PRX_DTX_P1 <38>

USB3_PTX_DRX_N1 <38>

USB3_PTX_DRX_P1 <38>

USB3_PRX_DTX_N2 <32>

USB3_PRX_DTX_P2 <32>

USB3_PTX_DRX_N2 <32>

USB3_PTX_DRX_P2 <32>

USB3_PRX_DTX_N3 <39>

USB3_PRX_DTX_P3 <39>

USB3_PTX_DRX_N3 <39>

USB3_PTX_DRX_P3 <39>

USB3_PRX_DTX_N4 <39>

USB3_PRX_DTX_P4 <39>

USB3_PTX_DRX_N4 <39>

USB3_PTX_DRX_P4 <39>

USB20_N1 <38>

USB20_P1 <38>

USB20_N2 <39>

USB20_P2 <39>

USB20_N3 <39>

USB20_P3 <39>

USB20_N4 <32>

USB20_P4 <32>

USB20_N5 <29>

USB20_P5 <29>

USB20_N7 <32>

USB20_P7 <32>

USB20_N8 <29>

USB20_P8 <29>

USB20_N10 <36>

USB20_P10 <36>

1 2

RC44 113_0402_1%

@

1 2

RC337 0_0402_5%

1 2

RC338 1K_0402_5%

USB_OC0# <38>

USB_OC1# <39>

USB_OC2# <39>

Reserve

M3042_DEVSLP <32>

M2280_DEVSLP <37>

Reserve

M3042_PCIE#_SATA <34>

M2280_PCIE_SATA# <37>

SATALED# <37,41>

-----> Ext USB3 Port 1 Charge (Right)

-----> M.2 3042(LTE)

-----> Ext USB3 Port 2 (Left Front)

-----> Ext USB3 Port 3 (Left Rear)

-----> Ext USB Port 1 Charge (Right)

-----> Ext USB Port 2 (Left Front)

-----> Ext USB Port 3 Left Rear)

-----> M2 3042(WWAN)

-----> Camera

-----> M.2 3030(BT)

-----> LCD Touch

-----> USH

USB_OC3#

USB_OC0#

USB_OC1#

USB_OC2#

NEED DOUBLE CHECK

M2280_PCIE_SATA#

HDD_DET#

SATALED#

RPC3

4 5

3

2

1

10K_8P4R_5%

RPC4

4 5

3

2

1

10K_8P4R_5%

+3.3V_ALW_PCH

6

7

8

+3.3V_RUN

6

7

8

M3042_PCIE#_SATA

A A

12

RC412 10K_0402_5%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (5/14)

CPU (5/14)

CPU (5/14)

LA-E131P

LA-E131P

LA-E131P

10 59Wednesday, November 09, 2016

10 59Wednesday, November 09, 2016

10 59Wednesday, November 09, 2016

1

1.0

1.0

1.0

Page 11

5

CLK_PCIE_N0<31>

Cardreader--->

D D

WLAN--->

WIGIG--->

M.2 SDD--->

LAN--->

AR --->

+3.3V_LAN

C C

+3.3V_ALW_DSW

+1.0V_VCCST

+3.3V_ALW_PCH

B B

H_CPUPWRGD VCCST_PWRGD

12

CLK_PCIE_P0<31>

CLKREQ_PCIE#0<31>

+3.3V_RUN

CLK_PCIE_N1<32>

CLK_PCIE_P1<32>

CLKREQ_PCIE#1<32>

+3.3V_RUN

CLK_PCIE_N2<32>

CLK_PCIE_P2<32>

CLKREQ_PCIE#2<32>

+3.3V_RUN

CLK_PCIE_N3<37>

CLK_PCIE_P3<37>

CLKREQ_PCIE#3<37>

+3.3V_RUN

CLK_PCIE_N4<30>

CLK_PCIE_P4<30>

CLKREQ_PCIE#4<30>

+3.3V_RUN

CLK_PCIE_N5<24>

CLK_PCIE_P5<24>

CLKREQ_PCIE#5<24>

+3.3V_RUN

RL70 10K_0402_5%@

RC323 10K_0402_5%

RC67 1K_0402_5%

RC71 1K_0402_5%

RC74 10K_0402_5%@

10/6 depop, prevent singal step.

RC411 10K_0402_5%@

@

T9

PAD~D

VCCST_PWRGD<14,34,35>

100P_0402_50V8J

12

CC300ESD@

ESD Request:place near CPU side

LAN_WAKE#

12

12

PCH_PCIE_WAKE#

12

VCCST_PWRGD

12

ME_SUS_PWR_ACK

12

PCH_PWROK

12

100P_0402_50V8J

CC301ESD@

@RF@

@RF@

@RF@

@RF@

@RF@

@RF@

1 2

RC373 0_0402_5%

RC189 10K_0402_5%

1 2

RC374 0_0402_5%

RC47 10K_0402_5%

1 2

RC375 0_0402_5%

RC50 10K_0402_5%

1 2

RC376 0_0402_5%

RC59 10K_0402_5%

1 2

RC377 0_0402_5%

RC51 10K_0402_5%

1 2

RC378 0_0402_5%

RC190 10K_0402_5%

PCH_RSMRST#_AND<14,40>

1 2

RC77 1K_0402_5%@

1 2

RC78 60.4_0402_1%

ME_SUS_PWR_ACK<34>

PM_LANPHY_ENABLE<30>

12

12

12

12

12

12

PCH_PLTRST#

PCH_PCIE_WAKE#<34,35>

CLKREQ_PCIE#0_R

CLKREQ_PCIE#1_R

CLKREQ_PCIE#2_R

CLKREQ_PCIE#3_R

CLKREQ_PCIE#4_R

CLKREQ_PCIE#5_R

TC7SH08FU_SSOP5~D

H_CPUPWRGDH_CPUPWRGD_R

VCCST_PWRGD_CPU

SYS_PWROK<14,34>

PCH_PWROK<49>

PCH_DPWROK<35>

SUSACK#<34>

LAN_WAKE#<30,34>

3.3V_CAM_EN#<29>

RC311 10K_0402_5%

@

RC62 0_0402_5%

@

RC244 0_0402_5%

UC7

PCH_PLTRST#

SYS_RESET#

PCH_RSMRST#_AND

12

RC215

POP

NO Support Deep sleep

DE-POP

Support Deep sleep

PCH_DPWROK PCH_RSMRST#_AND

A A

1

2

1 2

RC215 0_0402_5%@

100K_0402_1%

0.01UF_0402_25V7K

12

@

RC220

CC266

12

RC75

10K_0402_5%

5

XDP_DBRESET#<14>

+3.3V_RUN

XDP_DBRESET#

RC225@ 8.2K_0402_5%

RC227@ 8.2K_0402_5%

4

SKL_ULT

CLOCK SIGNALS

PLTRST_LAN# <30>

PCH_PLTRST#_EC <35>

PCH_PLTRST#_AND <24,31,32,36,37>

SKL-U

5

P

B

4

O

A

G

UC12@

74AHC1G09GW_TSSOP5

3

SYS_RESET#_R

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

1 2

1 2

+3.3V_ALW_PCH

5

1

P

B

2

A

G

3

AN10

AY17

BA20

BB20

AR13

AP11

BB15

AM15

AW17

AT15

12

12

UC1J

CPU@

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

KBL-U_BGA1356

PCH_PLTRST#_AND

4

O

12

RC65

@

100K_0402_5%

UC1K

CPU@

SYSTEM POWER MANAGEMENT

GPP_B13/PLTRST#

B5

SYS_RESET#

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

PCH_PWROK

DSW_PWROK

GPP_A13/SUSWARN#/SUSPW RDNACK

GPP_A15/SUSACK#

WAKE#

GPD2/LAN_WAKE#

GPD11/LANPHYPC

GPD7/RSVD

KBL-U_BGA1356

1 2

@

RC290 0_0402_5%

+3.3V_RUN

1

ME_RESET#

2

if pop UC12, RC291 also need pop(74AHC1G09GW is OD output)

4

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_OUT

XCLK_BIASREF

GPP_B11/EXT_PWR_GATE#

GPP_B2/VRALERT#

1 2

RC224 1K_0402_5%

F43

E43

BA17

E37

XTAL24_IN

E35

E42

AM18

RTCX1

AM20

RTCX2

AN18

SRTCRST#

AM16

RTCRST#

10 OF 20

PCH_PLTRST#

PCH_PLTRST#_AND

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

11 OF 20

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

CLK_ITPXDP_N

CLK_ITPXDP_P

SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

PCH_RTCX1

PCH_RTCX2

SRTCRST#

PCH_RTCRST# <34>

PCH_RTCRST#

CMOS1 must take care short & touch risk on layout placement

1 2

RC60 0_0402_5%

@

1 2

@

RC325 0_0402_5%

SIO_SLP_S0#

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

PCH_BATLOW#

AU13

AU11

PME#

AP16

INTRUDER#

MPHYP_PWR_EN

AM10

AM11

VRALERT#

+3.3V_RUN

@

RC291

10K_0402_5%

1 2

SYS_RESET#

3

1 2

RC297 0_0402_5%

@

1 2

RC298 0_0402_5%

@

SUSCLK <32,37>

1 2

RC52 2.7K_0402_1%

1 2

@

RC324 59_0402_1%

546765_546765_2014WW48_Skylake_MOW_Rev_1_0

1 2

RC56 20K_0402_5%

1 2

CC24 1U_0402_6.3V6K

1 2

RC57 20K_0402_5%

1 2

CC25 1U_0402_6.3V6K

1

1

2

SHORT PADS~D

@

CMOS1

SIO_SLP_S0# <17,36,47>

SIO_SLP_S3# <24,34,35>

SIO_SLP_S4# <17,34,45,48>

SIO_SLP_S5# <34>

SIO_SLP_SUS# <17,34,42,46,47,48,54>

SIO_SLP_LAN# <34,42>

SIO_SLP_WLAN# <34,42>

SIO_SLP_A# <34>

SIO_PWRBTN# <14,34>

AC_PRESENT <34>

@

T115

PAD~D

connect to VCCMPHYGTAON_1P0 enable pin

2

CLK_ITPXDP_N_R <14>

CLK_ITPXDP_P_R <14>

+1.0V_CLK5

For Skylake, pop RC52,depop RC324

For Cannonlake, pop RC324,depop RC52

+RTC_CELL

2

PLTRST_TPM# <36>

2

For SB/KW UMA w AR

1M_0402_1%

RC46

XTAL24_IN

XTAL24_OUT XTAL24_OUT_R

PCH_RTCX1

PCH_RTCX2

SYS_RESET#

0.1U_0402_25V6

12

ESD Request:place near CPU side

1 2

@

RC295 0_0402_5%

@

RC296 0_0402_5%

8/21 can change to 10K for merge to RP

+3.3V_ALW_PCH

+3.3V_ALW

+3.3V_ALW

@ESD@

CC302

1 2

For Skylake,YC1 24 MHz (50 Ohm ESR)

For Cannonlake,YC1 38.4 MHz (30 Ohm ESR)

546765_546765_2014WW48_Skylake_MOW_Rev_1_0

RC54

10M_0402_5%

1 2

1 2

PCH_BATLOW#

AC_PRESENT

INTRUDER#

MPHYP_PWR_EN

VRALERT#

SIO_SLP_LAN#

SUSCLK

POWER_SW#_MB<35,41>

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

3

4

YC1

24MHZ_12PF_X3G024000DC1H

1

2

12

YC2

32.768KHZ_12.5PF_9H03200042

ESR MAX=50k ohm

PCH_RTCX2_R

1 2

RC72 8.2K_0402_5%

1 2

RC243 10K_0402_5%

1 2

RC69 1M_0402_5%

1 2

RC387 10K_0402_5%@

1 2

RC73 10K_0402_5%

@

1 2

RC344 10K_0402_5%@

1 2

RC68 10K_0402_5%@

1 2

RC48 1K_0402_5%@

SIO_SLP_S3#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_A#

PCH_RTCRST#

SYS_RESET#

SIO_SLP_S0#

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU (6/14)

CPU (6/14)

CPU (6/14)

LA-E131P

LA-E131P

LA-E131P

1

CC21

1 2

12P_0402_50V8J

CC22

1 2

12P_0402_50V8J

CC23

1 2

15P_0402_50V8J

CC26

1 2

12P_0402_50V8J

+3.3V_ALW_DSW

+RTC_CELL

+3.3V_ALW_PCH

+3.3V_ALW

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

ACES_50506-01841-P01

1

JAPS1

CONN@

11 59Wednesday, November 09, 2016

11 59Wednesday, November 09, 2016

11 59Wednesday, November 09, 2016

1.0

1.0

1.0

Page 12

5

4

3

2

+1.0V_VCCSTG

1

PCH_JTAG_TDI

PCH_JTAG_TDO

D D

+1.0V_VCCST

RC79 49.9_0402_1%@

RC80 1K_0402_5%

+1.0V_VCCSTG

RC83 1K_0402_5%

+3.3V_RUN

RC414 10K_0402_5%

RC413 10K_0402_5%

C C

B B

RC278 10K_0402_5%

RC272 10K_0402_5%

@

RC279 10K_0402_5%

RC345 100K_0402_5%

RC292 10K_0402_5%

+3.3V_ALW_PCH

RC346 10K_0402_5%

RC288 10K_0402_5%

H_CATERR#

12

H_THERMTRIP#

12

H_PROCHOT#

12

TOUCHPAD_INTR#

12

CAM_MIC_CBL_DET#

12

CONTACTLESS_DET#

12

TOUCH_SCREEN_PD#

12

AUD_PWR_EN

12

IR_CAM_DET#

12

HOST_SD_WP#

12

SIO_EXT_SMI#

12

KB_DET#

12

HDA_SYNC_R<33>

HDA_BIT_CLK_R<33>

HDA_SDOUT_R<33>

HDA_RST#_R<33>

Close to RC93

TOUCH_SCREEN_PD# don't move to RPC,

ME_FWP

HDA_BIT_CLK_R

12

PECI_EC<34>

H_PROCHOT#<34,49,52>

H_THERMTRIP#<20,21,35>

TOUCH_SCREEN_DET#<29>

1 2

RC92 33_0402_5%

1 2

RC93 33_0402_5%EMI@

1 2

RC94 33_0402_5%

1 2

RC223 1K_0402_5%

1 2

RC95 33_0402_5%

47P_0402_50V8J

RF@

CC27

T269

1 2

RC84 499_0402_1%

XDP_OBS0_R<14>

XDP_OBS1_R<14>

@

T10

PAD~D

SIO_EXT_SMI#<34>

TOUCH_SCREEN_PD#<29>

TOUCHPAD_INTR#<34,40>

12

12

RC88

49.9_0402_1%

IR_CAM_DET#<29>

@

PAD~D

KB_DET#<40>

SPKR<33>

RC89

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0<33>

HDA_RST#

H_PROCHOT#_R

H_THERMTRIP#

XDP_OBS2_R

TOUCHPAD_INTR#

CPU_POPIRCOMP

PCH_POPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

12

12

RC90

49.9_0402_1%

49.9_0402_1%

IR_CAM_DET#

TBT_PWR_EN

KB_DET#

H_CATERR#

RC91

49.9_0402_1%

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

AT16

AU16

H66

H65

UC1G

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

KBL-U_BGA1356

UC1D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

KBL-U_BGA1356

CPU@

AUDIO

RF Request. Place near CPU side (Intel MOW)

+3.3V_ALW_PCH +3.3V_ALW_PCH

12

ENABLE

DISABLE

SPKR

5

RC187 4.7K_0402_5%

@

Flash Descriptor Security override

HIGH

LOW(DEFAULT)

RC183 8.2K_0402_5%

@

TOP SWAP STRAP

A A

HIGH

LOW(DEFAULT)

Internal 20k PD

HDA_SDOUT

12

DISABLE

ENABLE

4

HDA_RST# HDA_SDIN0 HDA_SDOUT

1

2

CC331

RF@

2.2P_0402_50V8C

CPU@

CPU MISC

1

2

SKL-U

JTAG

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

SKL-U

1

CC332

RF@

2.2P_0402_50V8C

2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B61

PROC_TCK

D60

PROC_TDI

A61

PROC_TDO

C60

PROC_TMS

B59

B56

D59

A56

C59

C61

PCH_TRST#

A59

JTAGX

4 OF 20

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

CC333

RF@

2.2P_0402_50V8C

3

CPU_XDP_TCLK XDP_JTAGX

@

RC328 0_0402_5%

CPU_XDP_TCLK

CPU_XDP_TDI

CPU_XDP_TDO

CPU_XDP_TMS

CPU_XDP_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

CPU_XDP_TRST#

XDP_JTAGX

RC87 1K_0402_5%@

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_RCOMP

1 2

GPP_F23

7 OF 20

CPU_XDP_TCLK <14>

CPU_XDP_TDI <14>

CPU_XDP_TDO <14>

CPU_XDP_TMS <14>

CPU_XDP_TRST# <14>

PCH_JTAG_TCK <14>

PCH_JTAG_TDI <14>

PCH_JTAG_TDO <14>

PCH_JTAG_TMS <14>

AB11

AB13

TBT_CIO_PLUG_EVENT#

AB12

W12

CONTACTLESS_DET#

W11

W10

AUD_PWR_EN

W8

W7

BA9

BB9

SD_RCOMP

AB7

AF13

1 2

1 2

RC86 51_0402_5%

@

+1.0V_VCCSTG

CAM_MIC_CBL_DET# <29>

TBT_CIO_PLUG_EVENT# <24>

CONTACTLESS_DET# <36>

AUD_PWR_EN <33>

1 2

RC96 200_0402_1%

PCH_JTAG_TDO PCH_JTAG_TDI XDP_JTAGX

@ESD@

0.1U_0402_25V6

12

CC303

ESD request,Place near CPU side.

PCH_JTAG_TMS

Service Mode Switch:

Add a switch to ME_FWP signal to unlock the ME region and

allow the entire region of the SPI flash to be updated using FPT.

+3.3V_ALW_PCH

ME_FWP PCH has internal 20K PD.

(suspend power rail)

FLASH DESCRIPTOR SECURITY OVERRIDE

LOW = ENABLE (DEFAULT) -->Pin1 & Pin3 short

HIGH = DISABLE (ME can update) -->Pin2 & Pin3 short

HOST_SD_WP# <31>

@ESD@

0.1U_0402_25V6

12

CC304

2

1 2

RC81 51_0402_5%

1 2

RC82 100_0402_5%

1 2

RC130 51_0402_5%

ME_FWPME_FW_EC

1 2

@

@

RC222

1K_0402_5%

1 2

RC221 0_0402_5%

PT,ST pop RC222 and SW1; MP pop RC221

ME_FW_EC<34>

@ESD@

0.1U_0402_25V6

12

CC305

ME_FWP

H_THERMTRIP# H_PROCHOT#

0.1U_0402_25V6

12

1

2

3

4

5

@ESD@

CC312

@

SW1

A

B

C

G1

G2

SS3-CMFTQR9_3P

12

0.1U_0402_25V6

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.