Page 1

A

B

C

D

E

1

2

1

2

Compal Confidential

B5W11 MB Schematic Document

LA-E061P

3

3

Rev: 1.0

2016.07.18

4

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

A

B

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

C

Comp al Secre t Data

Comp al Secre t Data

Comp al Secre t Data

Decipher ed Date

Decipher ed Date

Decipher ed Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Tit le

Tit le

Tit le

CoverSheet

CoverSheet

CoverSheet

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Da te : Sh eet

Da te : Sh eet

D

Da te : Sh eet

E

o f

1 44Monday, July 18, 2016

o f

1 44Monday, July 18, 2016

o f

1 44Monday, July 18, 2016

4

1.0

1.0

1.0

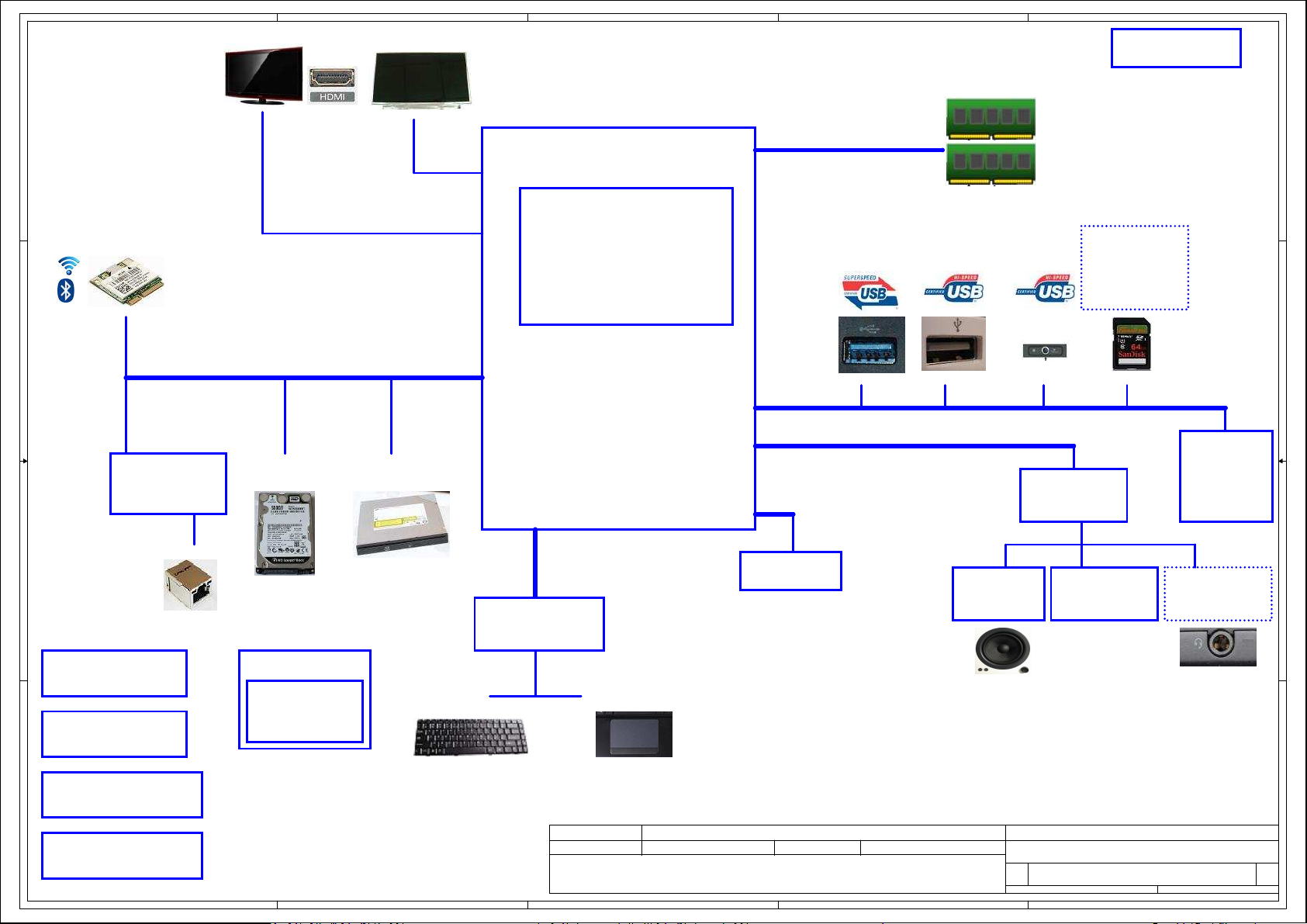

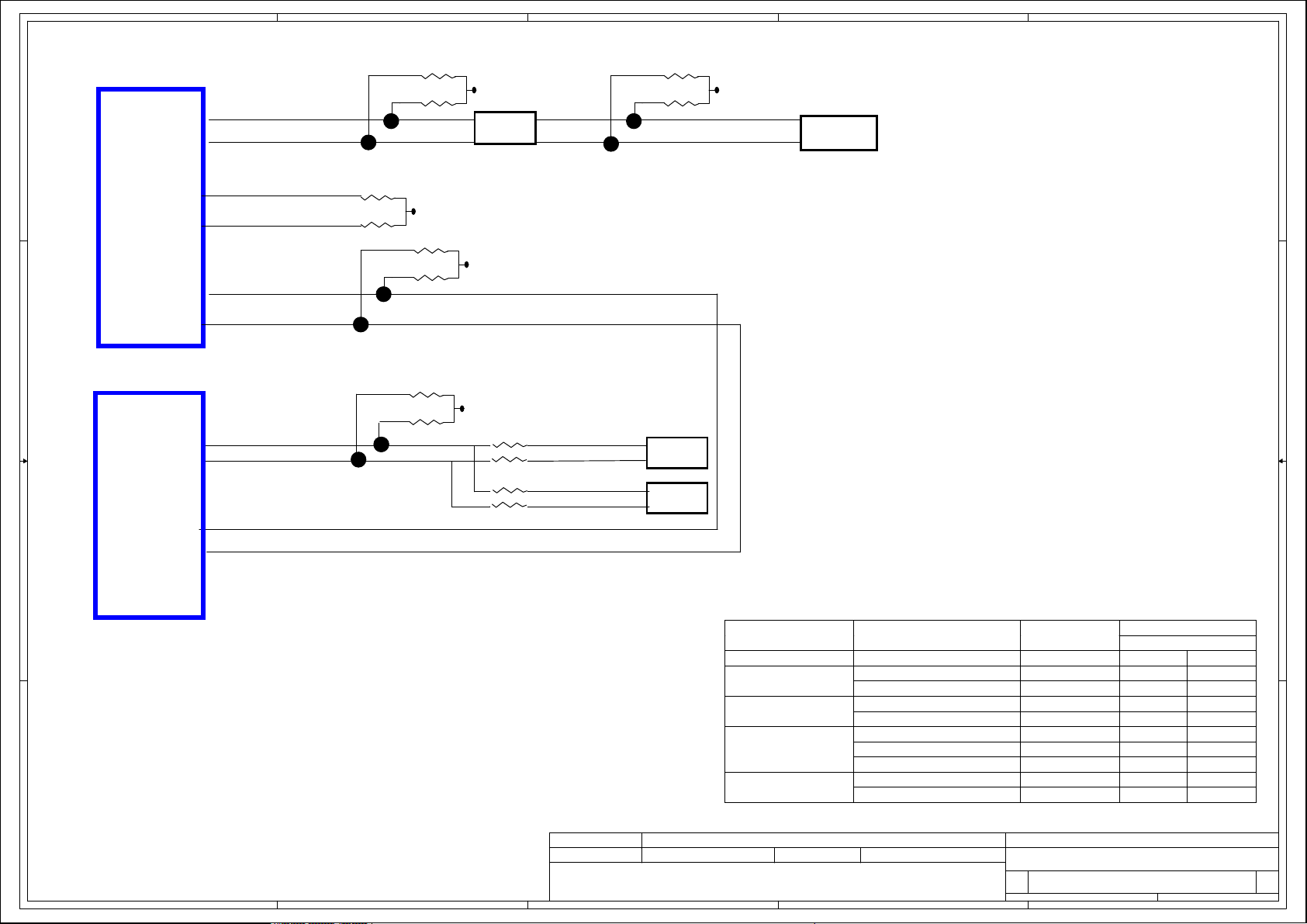

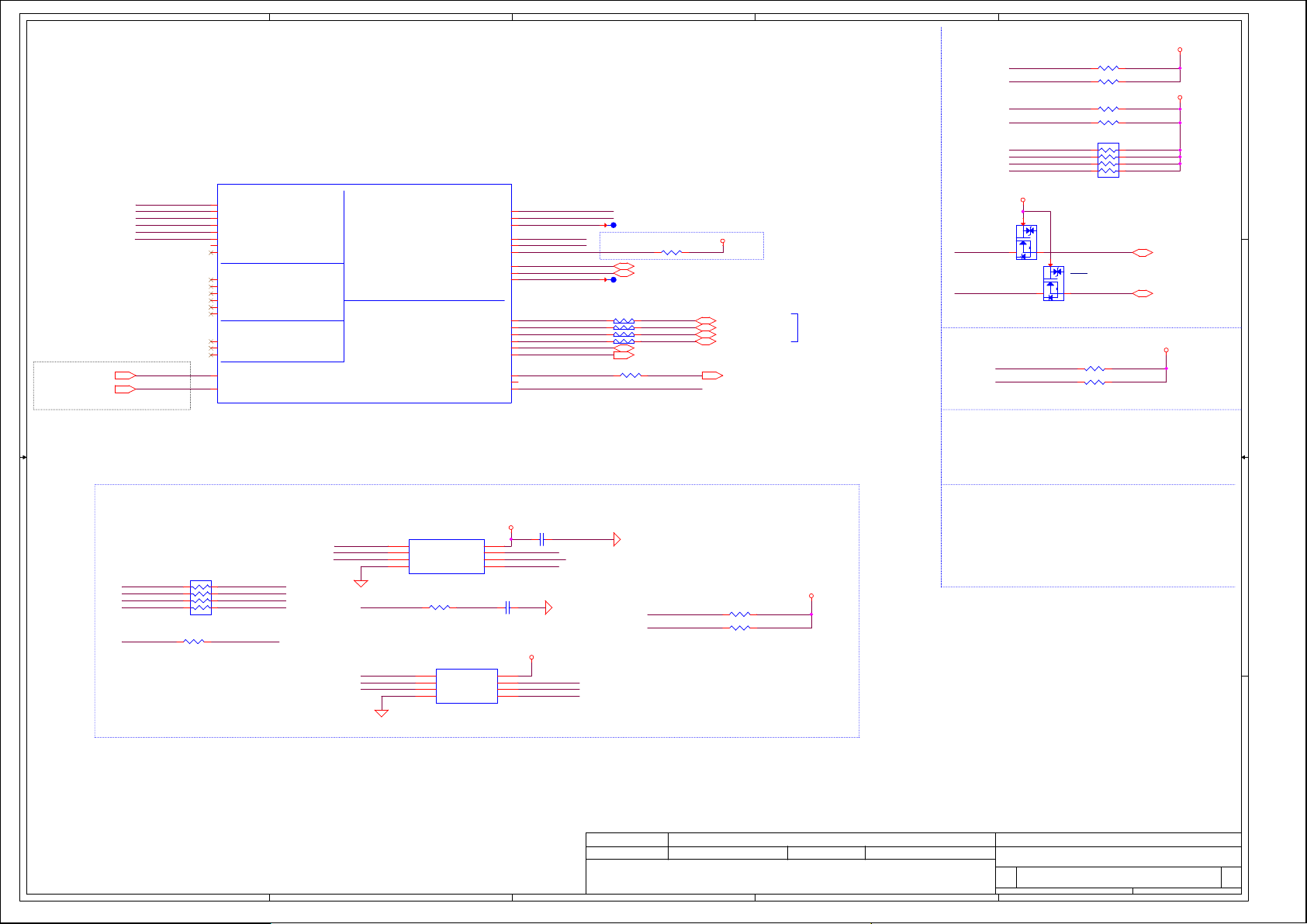

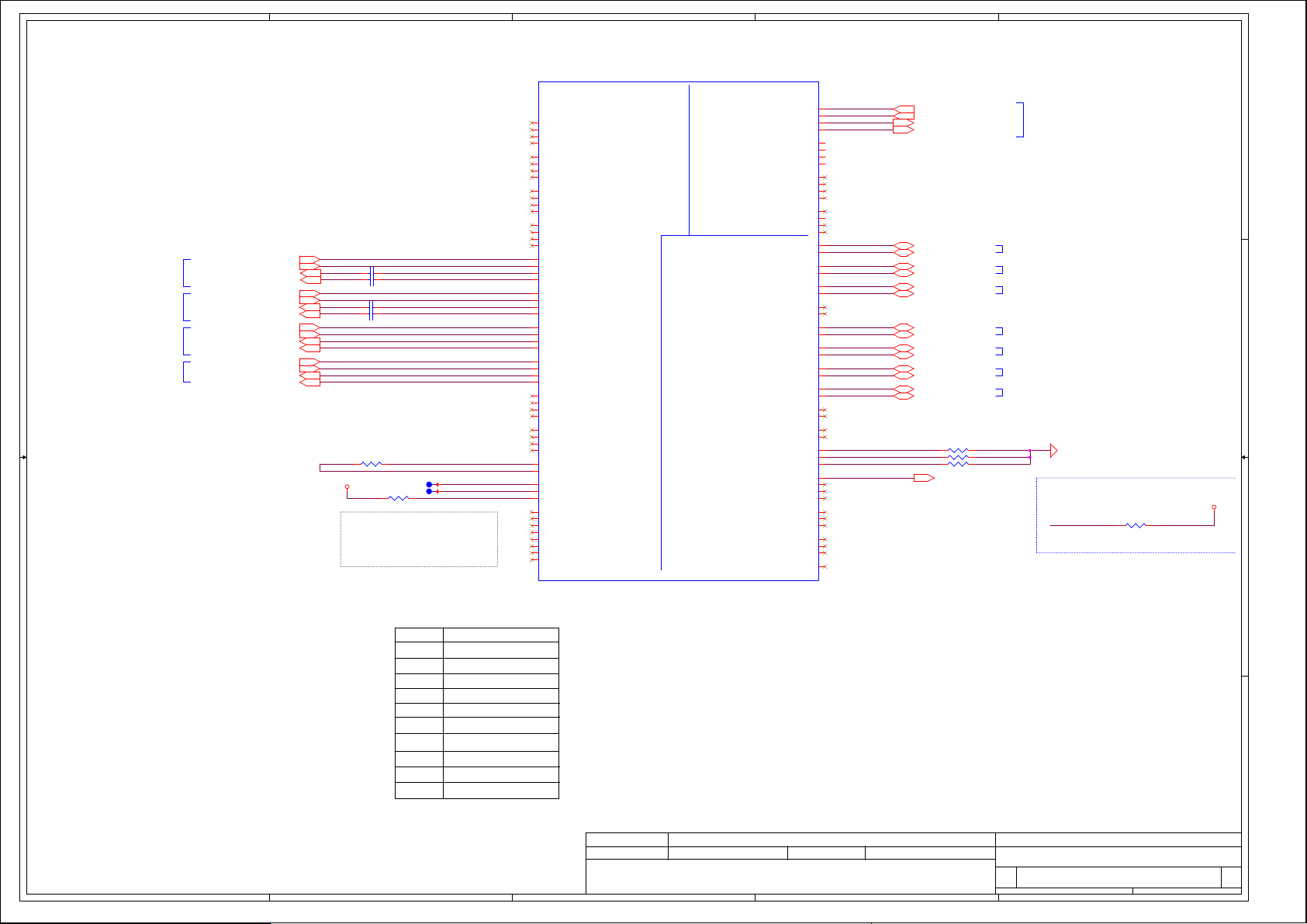

Page 2

A

B

C

D

E

1

2

NGFF

WLAN

USB port 5

page 24

PCIe 1.0

2.5G T/s

port 6

PCIe 1.0

2.5G T/s

port 5

LAN(GbE)

Realtek 8111H

page 23

HDMI Conn.

page 22

DDI2

HDMI x 4 lanes

LAN(GbE)

SATA3.0 SATA3.0

port 7

(SATA0) (SATA1)

SATA HDD

Conn.

eDP

page 21

eDP

DDI

Flexible IO

6.0 Gb/s6.0 Gb/s

port 8

SATA CDROM

Conn.

Intel Kabylake U

Kabylake U

Kabylake PCH-LP(MCP)

(KBL-U_2+2)

Processor

Dual Core + GT2

15W

1356pin BGA

page 07~18

Memory BUS

Dual Channel

1.2V DDR4 1866 /2133

USBx 8

48 M H z

HD Audio

SPI

Interleaved Memory

page 19

260pin DDR4-SO-DIMM X2

page 20

USB 2.0

USB 3.0

conn x1

USB port 1 USB port 7

page 28 page 21

conn x2

USB port2,3

Port3 on Sub/B

page 28

3.3V 2 4MH z

CMOS

Camera

HDA Codec

ALC233

Fan Control

Card Reader

RTS5170

SD only

USB port 8

on Sub/B

page 28

page 25

page 31

Touch

Screen

I2C (PORT1)

USB port 6

page 21

1

2

3

RTC CKT.

page 15

Power On/Of f CKT.

page 30

4

DC/DC Interface CKT.

Power Circuit DC/DC

page 33~43

RJ45 conn.

page 23

page 32

A

page 26

Sub Board

LS-D671

IO/B

page 28

page 26

B

Int.KBD

page 30

ENE

KB9022

LPC/eSPI BUS

CLK = 24 MHz

page 29

SPI ROM

64Mb

page 9

Touch Pad

PS2 (from EC) / I2C (from SOC)

page 30

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

C

www.schematic-x.blogspot.com

Comp al Secre t Data

Comp al Secre t Data

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

Comp al Secre t Data

Decipher ed Date

Decipher ed Date

Decipher ed Date

D

Int. Speaker

page 25

Tit le

Tit le

Tit le

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Custom

Custom

Custom

Da te : Sh eet

Da te : Sh eet

Da te : Sh eet

Int. AMIC

page 25 page 28

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

B5W11 M/B LA-E061P

B5W11 M/B LA-E061P

B5W11 M/B LA-E061P

E

UAJ

on Sub/B

o f

2 44Monday, July 18, 2016

o f

2 44Monday, July 18, 2016

o f

2 44Monday, July 18, 2016

3

4

1.0

1.0

1.0

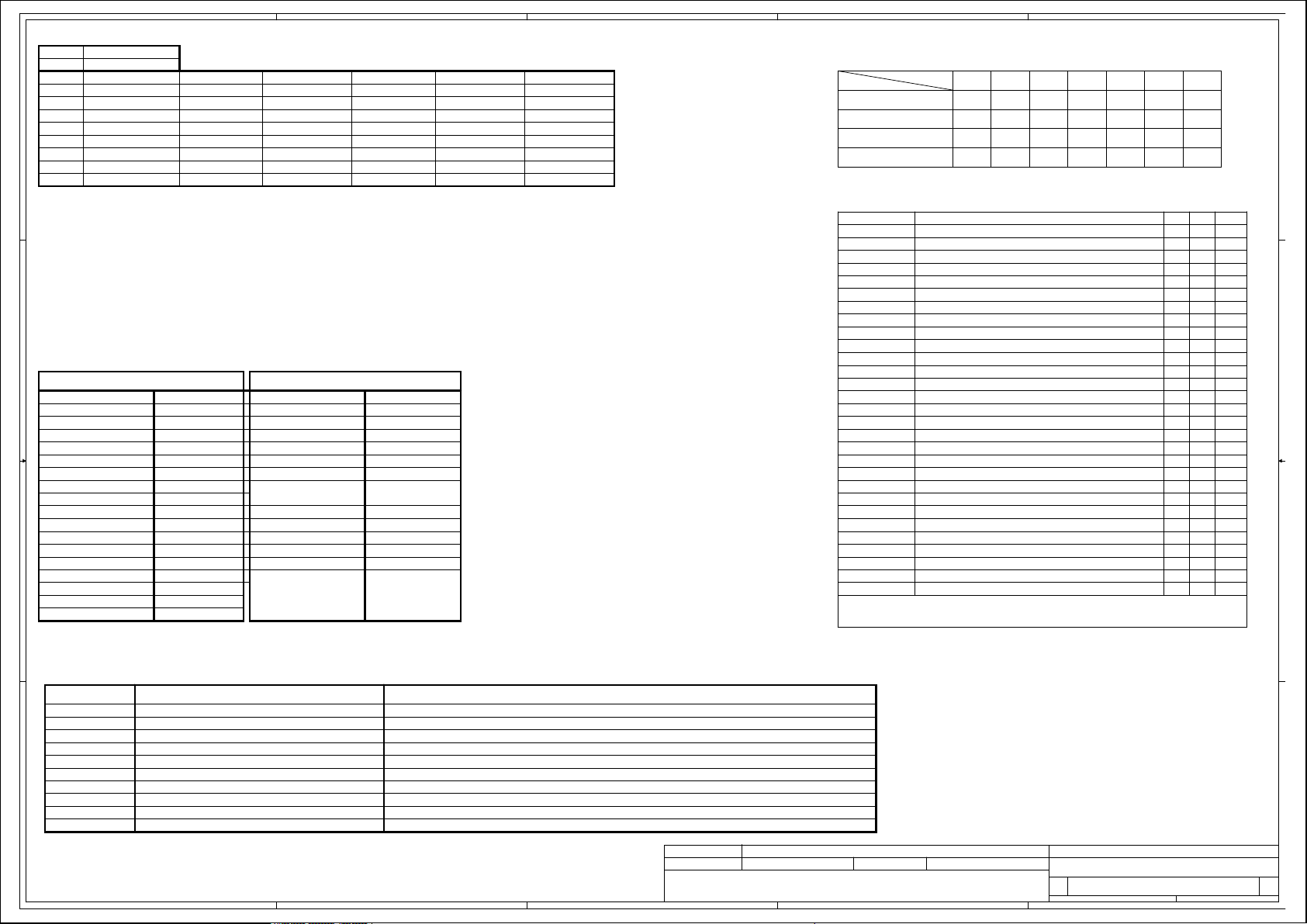

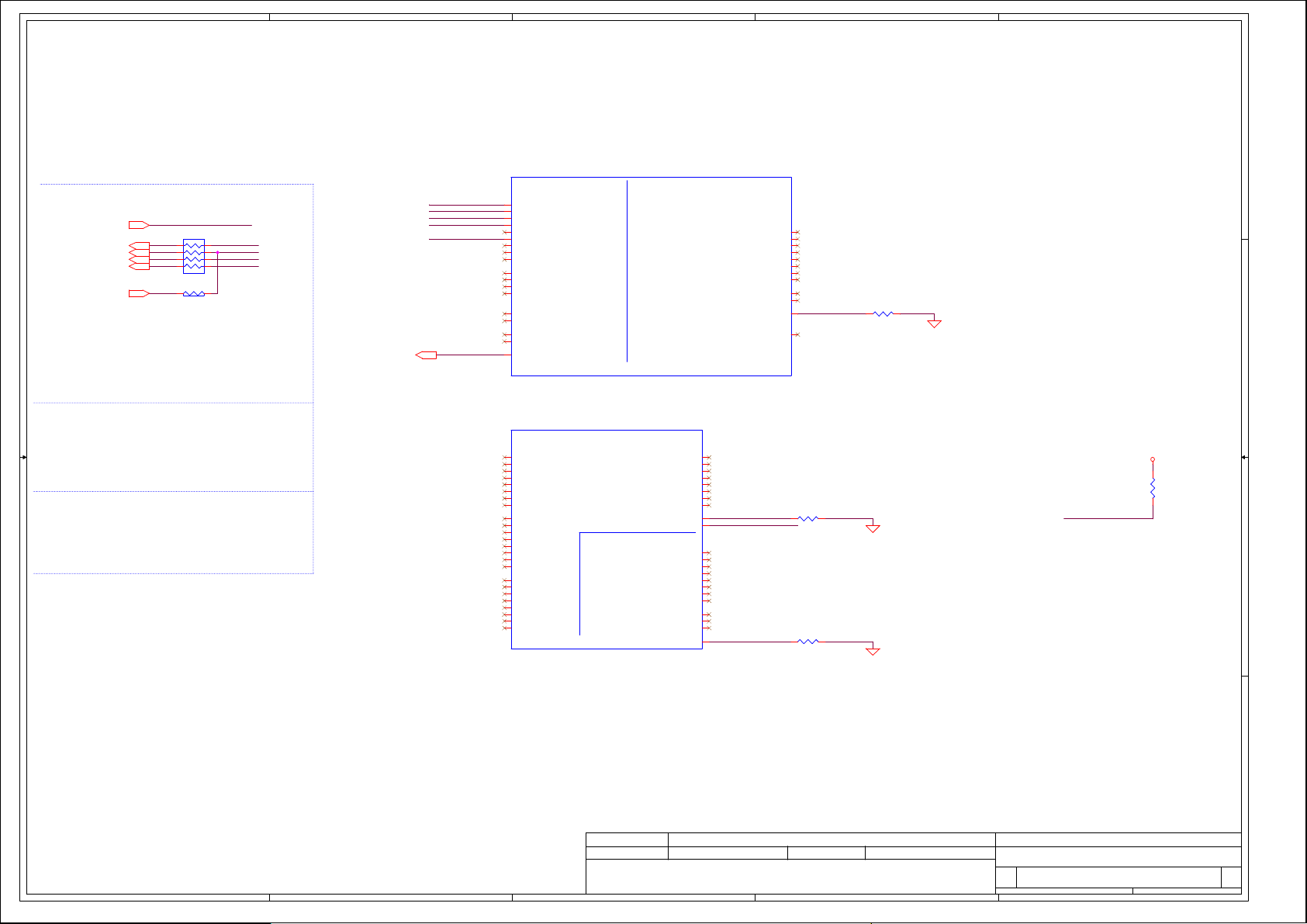

Page 3

A

Board ID Table for AD channel

Vc c 3.3V +/- 5%

Board ID

1

2

BOM Structure Table

100K +/- 1%Ra

Rb V mi n

0

1

2

3

4

5

6

7

0 0 V

12K +/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

BOM Option Table

It em BOM Structure

Unp op

Connector

For Acer BYOC B YO C@

No Acer BYOC NBYO C@

COD EC(ALC2 33) 233@

LPC MODE for EC LPC @

ESPI MODE for EC ES PI@

For Intel CMC

EMI requirement

EMI requirement depop

ESD requirement

3

ESD requirement depop

LAN(81 11GUS )

LAN(811 1H) 8 111H @

RF requirement

@

CONN @

255@COD EC(ALC2 55)

CMC @

EMI@

@EMI@

ESD@

@ESD @

8111GUS @

RF@

B

BI D

V ty p

BI D

0 V 0.300 V

V

ma x

BI D

0.423 V 0.430 V 0.438 V

BOM Option Table

It em BOM Structure

SkyLake plat f or m

KabyLake plat f or m KBL @

CPU Code

SKL@

QKJW @

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3A0.691 V 0.702 V 0.713 V

0x3B - 0x450.807 V 0.819 V 0.831 V

0x46 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

PCB Revision

0.1

0.1

C

D

E

Power State

STATE

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S3# SLP_S4# SLP _S5# +VALW +V +VS Cloc k

LOW HIGH

LOWLOW

HIGH

HIGH

ONONON

ON

OFF

OFFLOW LOW LOW

OFF

OFF

OFF

OFF

OFF

OFF

1

Voltage Rails

Power Plane

+19V_VIN

+17.4V_BATT

+19VB

+VCC _COR E

+VCC_ GT

+VCC _S A

+0.6VS_V TT

+1.0VALW_PRI M +1.0V Always power rail

+1.0 V_VCC ST U Sustain voltage f or processor in Standby modes

+VC CIO

+1. 0VS_V CCST G +1.0V ALW_PRIM G ated ver sion of V CCST

+1.2 V_V DD Q

+1.8VALW_PRI M +1.8V Always power rail

+1.8VS System +1.8V power rail

+3VLP +19VB to +3VLP power rail for suspend power

+3VALW System +3VALW always on power rail

+3VS

+5VALW

+5VS System +5V power rail

+RT CVCC

Note : ON*1 means pow er p lane is ON only when WOL enable and RT C wake at BIOS setting, other wise it is OF F.

Descr ipt ion

Adap ter pow er suppl y

Batt ery power supply

AC or batte ry power rail for power circuit.

Processor IA Cores Power Rail

Processor Graphics P ower Rails

System Agent power rail

DDR +0.6VS pow er rail for DDR termina tor .

CPU IO power ra il

DDR4 +1 .2V Power R ail

System +3V power rail

+5V Always power rail

RTC Ba ttery Pow er

S0

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

S3

S4/S5

N/AN/A

N/A N/A

N/AN/A

OF F O FF

OF F

OF F

OF F O FF

OF FOF F

ON

ON*1

OF F

ON

OF F O FF

OF FOF F

OF F

ON

ON

ON*1

OF F

OF F

ON

ON

ON

ON*1

OF F

OF F

ON

ON

OF FOF F

ON ON

2

3

43 level BOM table

431A3EBO L01

4

SMT MB AE061 B5W11 QKJW HDMI

A

BOM Structure43 Level Des cr i pti on

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SH EET OF ENGIN EERING D RAWING IS THE P ROPRIETARY PROPERT Y OF COMPAL ELECTRO NICS, INC. AND CONTAINS CONF IDENTIAL

THIS SH EET OF ENGIN EERING D RAWING IS THE P ROPRIETARY PROPERT Y OF COMPAL ELECTRO NICS, INC. AND CONTAINS CONF IDENTIAL

THIS SH EET OF ENGIN EERING D RAWING IS THE P ROPRIETARY PROPERT Y OF COMPAL ELECTRO NICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

DEPARTMENT EXCEP T AS AUTHO RIZED BY C OMPAL ELE CTRONICS, INC. NEITHE R THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHO RIZED BY C OMPAL ELE CTRONICS, INC. NEITHE R THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHO RIZED BY C OMPAL ELE CTRONICS, INC. NEITHE R THIS SHEET NOR THE I NFORMATION IT CONTAINS

MAY BE USE D BY OR DIS CLOSED TO AN Y THIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL EL ECTRONICS, INC.

MAY BE USE D BY OR DIS CLOSED TO AN Y THIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL EL ECTRONICS, INC.

B

MAY BE USE D BY OR DIS CLOSED TO AN Y THIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL EL ECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compa l Secret Dat a

Compa l Secret Dat a

Compa l Secret Dat a

Deciphered Date

Deciphered Date

Deciphered Date

CompalElectronics,Inc.

CompalElectronics,Inc.

Titl e

Titl e

Titl e

Notes List

Notes List

Notes List

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Dat e: She et

Dat e: She et

D

Dat e: She et

E

3 44Monday, July 18, 2016

3 44Monday, July 18, 2016

3 44Monday, July 18, 2016

1.0

1.0

1.0

o f

o f

o f

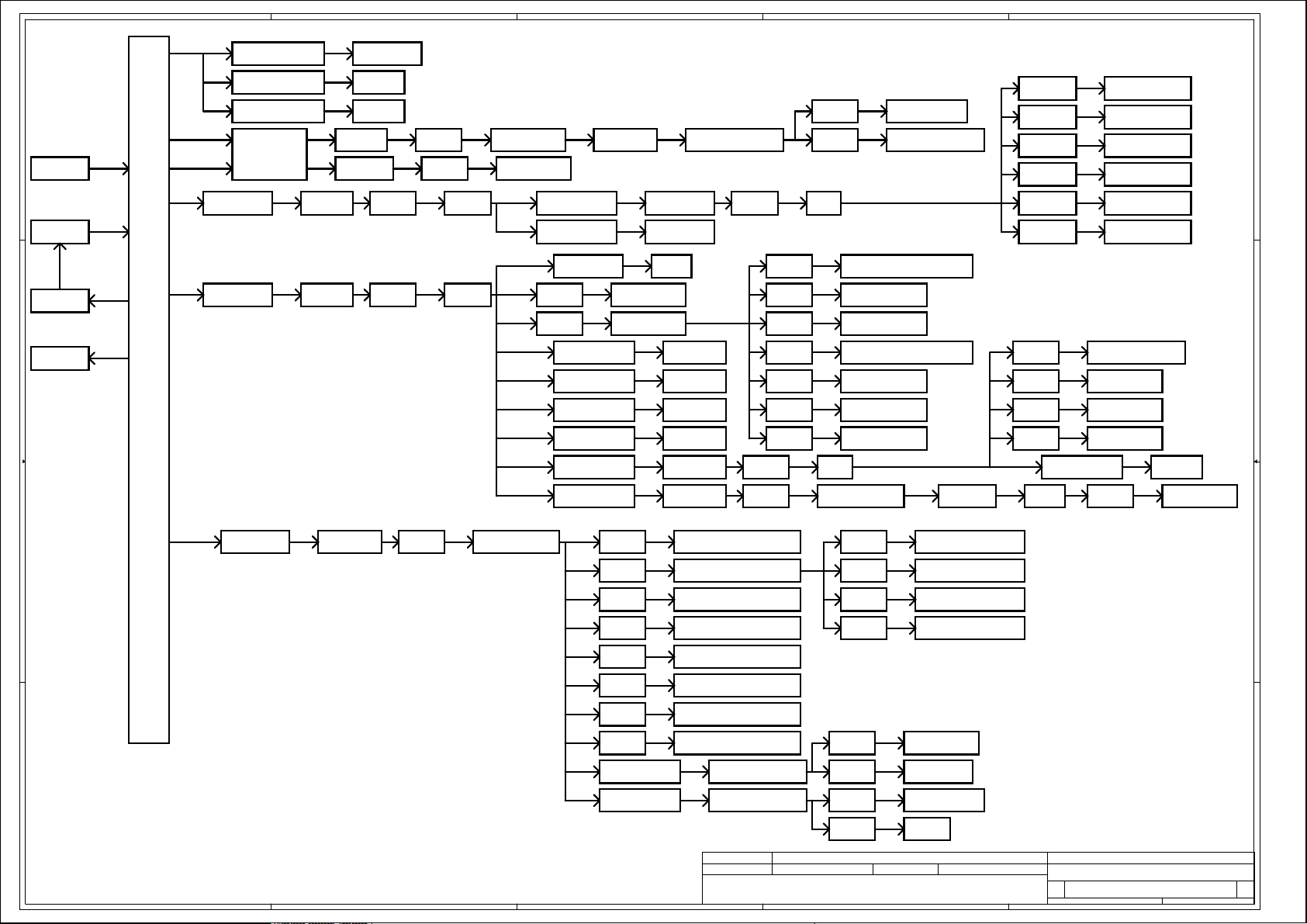

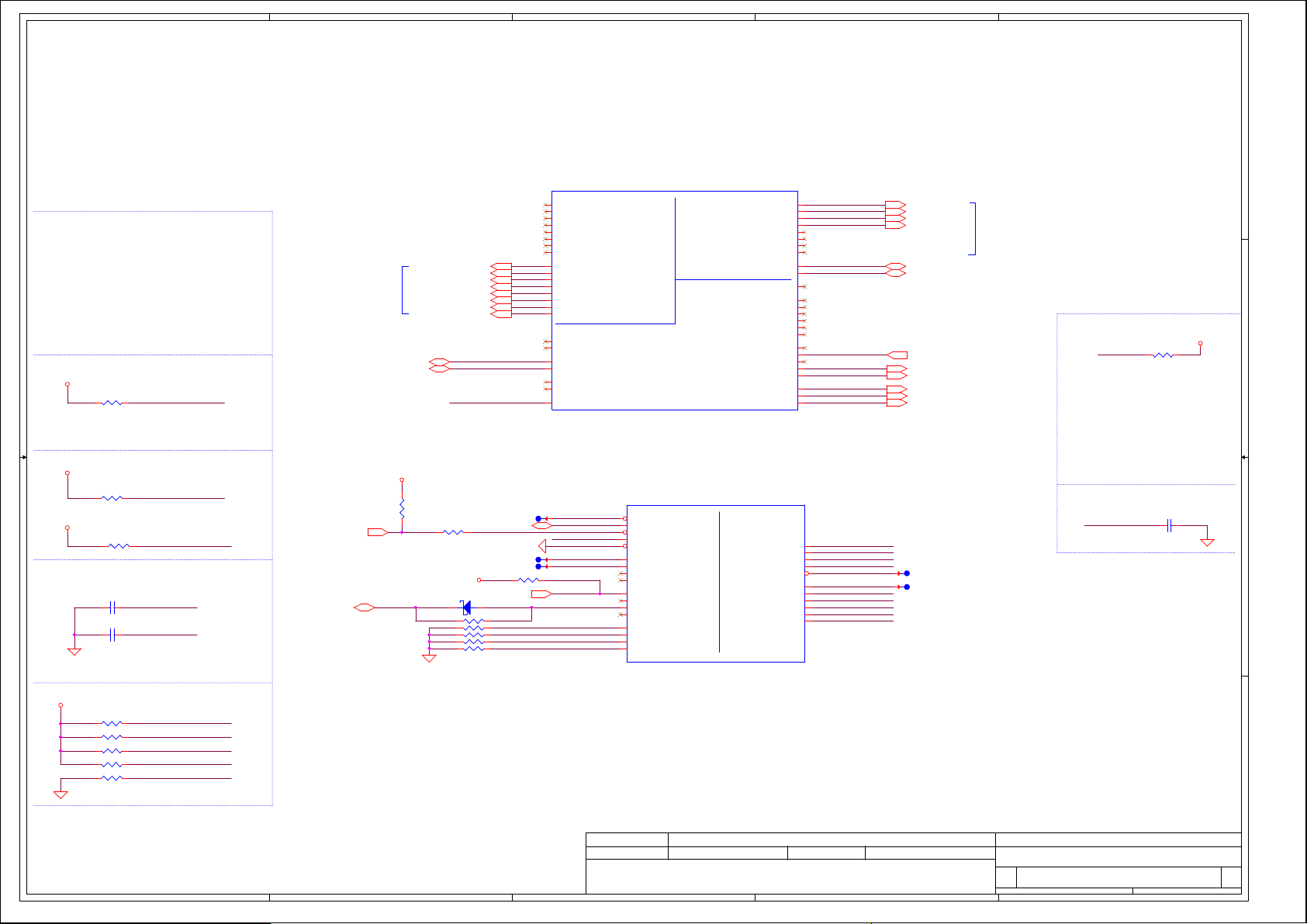

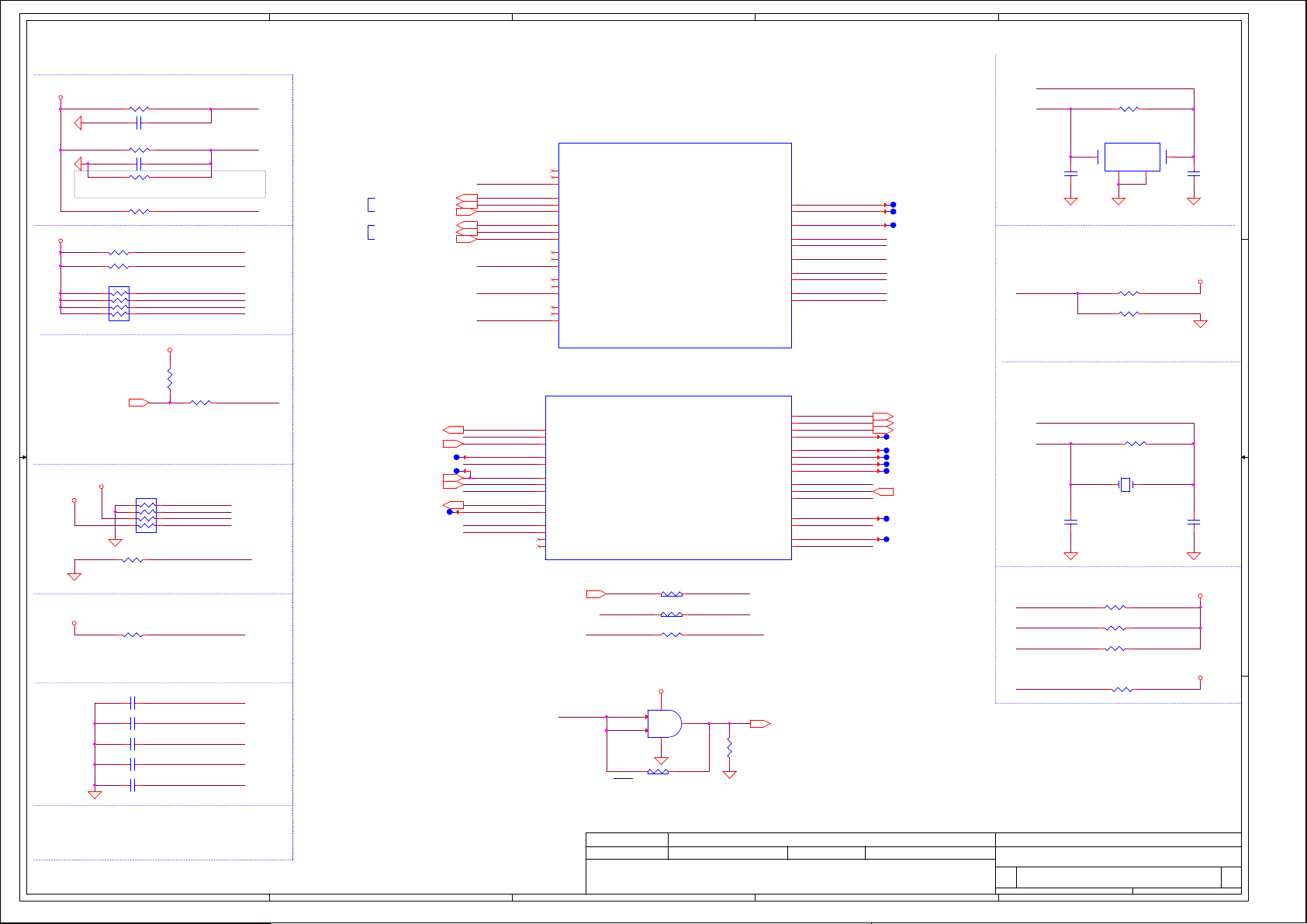

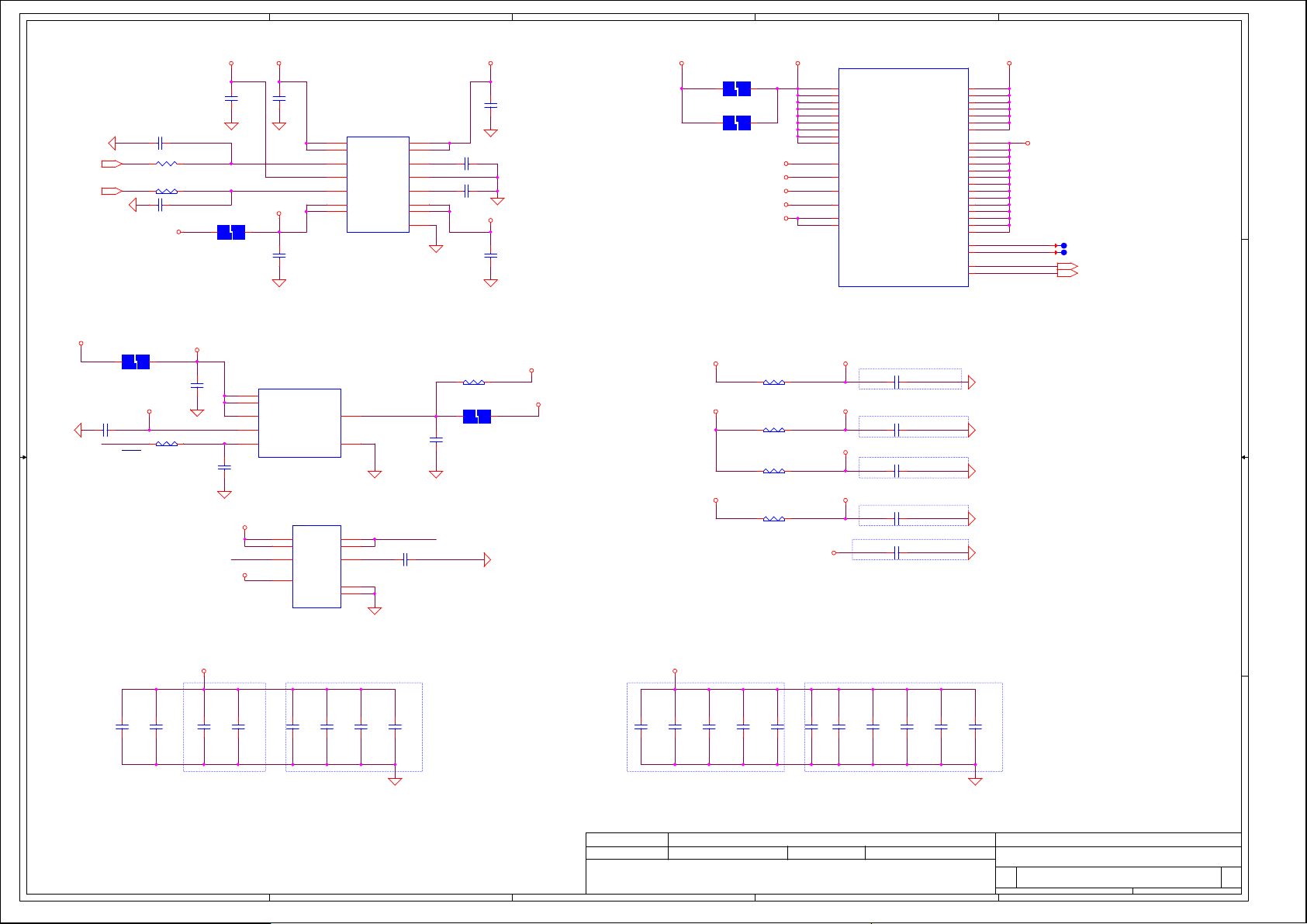

Page 4

A

B

C

D

E

1

ADAPTER

BATTE RY

CHARG ER

2

+3VLP

LD O

+19 VB

DR VON

SYS ON

SM_PG _CTR L

5V_ EN

3V_ EN

NCP 81253MNTBG

(PU9 001 )

NCP 81151MNTBG

(PU9 003 )

NCP 81253MNTBG

(PU9 004 )

RT82 07KGQW

(PU501)

SY8286C RAC

(PU402)

SY8286BR AC

(PU401)

+5VALWP

+VCC_CO RE

+VCC_GT

+VCC_SA

+1.2VP

+0.6VS P

JUMP

(PJ40 2)

JUMP

(PJ40 1)

JUMP

(PJ50 1)

JUMP

(PJ50 2)

+5VALW

+3VALW+3VALW P

+1.2V_VDDQ

+0.6VS_VTT

SUSP #

USB_E N

SYS ON

SYS ON

LAN_ PWR _EN

TP_PW R_E N

WL AN _ON

SUSP #

SPO K

JUMP

(JPC1,JPC2 )

EM5209 VF

(UQ1)

SY6288C 20AA C

(US21)

APL5 336KAI

(PU502)

R-Short

(RC 173)

JUMP

(JPC7)

APL5 336KAI

(PU502)

SY6288C 20AA C

(UL1)

SY6288C 20AA C

(UK1)

SY6288C 20AA C

(UM1)

EM5209 VF

(UQ1)

G971 ADJF11 U

(PU702)

+5VS_OUT

+USB3_VC CA

+2.5VP

+3VALW_ DSW

+3VALW_PRIM

+2.5VP

+3V_LA N

+3V_PTP

+3VS_W LAN

+3VS_OUT

+1.8VALWP

+1.2V_VDD Q_CPU

JUMP

(JPQ2)

JUMP

(JPQ1)

JUMP

(PJ70 2)

R-Short

(RC 197)

R-Short

(RC 161)

R-Short

(RC 163)

R-Short

(RC 172)

R-Short

(RC 167)

R-Short

(RC 187)

R-Short

(RC 171)

R-Short

(RC 208)

R-Short

(RC 141)

+5VS

+3VALW_1.8 VALW_ PG PPA

+3VALW_PGP PB

+3VALW_P GPP C

+3VALW_ 1.8VALW_P GPP D

+3VALW_P GPP E

+3VALW_P GPP G

+3VALW_RT C

+3VS

+1.8VALW_PRIM

+1.2V_VDDQ C

+1.2V_VCC SFR_ OC

SUSP #

EM5209 VF

(UC5)

R-Short

(RC 178)

0 ohm

(RM 1)

R-Short

(RA 2)

R-Short

(RA 5)

SOC_ ENVD D

R-Short

(RX8)

AP233 0W

(UY1)

R-Short

(RO 3)

0 ohm

(RO 2)

JUMP

(JPA1 )

R-Short

(RF1)

SY6288C 20AA C

(UX1)

+1.8VS

+TS_PWR

+HDMI_5V_OU T

+5VS_HDD

+5VS_ODD

+VDDA

+VCC_FAN 1

+1.8VS_3VS_P GPPA

+3VS_W LAN

+3VS_D VDDI O

+3VS_DVDD

+LCDVD D

R-Short

(RA 6)

+1.8VS_V DDA

1

2

EN _1V ALW

3

4

A

SY82 88 RAC

(PU601)

JUMP

(PJ60 1)

B

SYS ON

SUSP #

R-Short

(RC 148)

JUMP

(JPC9)

R-Short

(RC 162)

R-Short

(RC 169)

R-Short

(RC 164)

R-Short

(RC 190)

R-Short

(RC 152)

R-Short

(RC 175)

EM5209 VF

(UC5)

AOZ 1336

(UC8)

C

+1.0 VALW_A PLL

+1.0VALW_ MP HYP LL

+1.0VALW _DTS

+1.0VALW_C LK6_24TBT

+1.0VALW_VCC CLK 2

+1.0VALW_CLK 4_F100 OC

+1.0VALW_ CLK5_ F24NS

+1.0VALW_ MPHYAO N

+1.0V_VC CSTU

+1.0VS_VCC STG_ IO

Security Classif ication

Security Classif ication

Security Classif ication

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.0VALW_PRIM+1.0VALWP

R-Short

(RC 209)

R-Short

(RC 149)

R-Short

(RC 176)

R-Short

(RC 156)

R-Short

(RC 143)

R-Short

(RC 140)

R-Short

(RC 188)

JUMP

(JPC5)

Compal S ecret Data

Compal S ecret Data

2016/07/18 2014/04/12

2016/07/18 2014/04/12

2016/07/18 2014/04/12

Compal S ecret Data

+1.0VALW _MP HYGT

+1.0VALW_AMPH YPLL

+1.0VALW_SR AM

+1.0VALW _APLL EBB

+1.0V_VCC SFR

+1.0V_VC CST

+1.0VS_VC CSTG

+VCCIO

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Titl e

Titl e

Titl e

Size Docum ent N umb er R e v

Size Docum ent N umb er R e v

Size Docum ent N umb er R e v

Custom

Custom

Custom

Da te : She et

Da te : She et

Da te : She et

Power Rail

Power Rail

Power Rail

B5W11 M/B LA-E061P

B5W11 M/B LA-E061P

B5W11 M/B LA-E061P

E

o f

4 44Monday, July 18, 2016

o f

4 44Monday, July 18, 2016

o f

4 44Monday, July 18, 2016

3

4

1.0

1.0

1.0

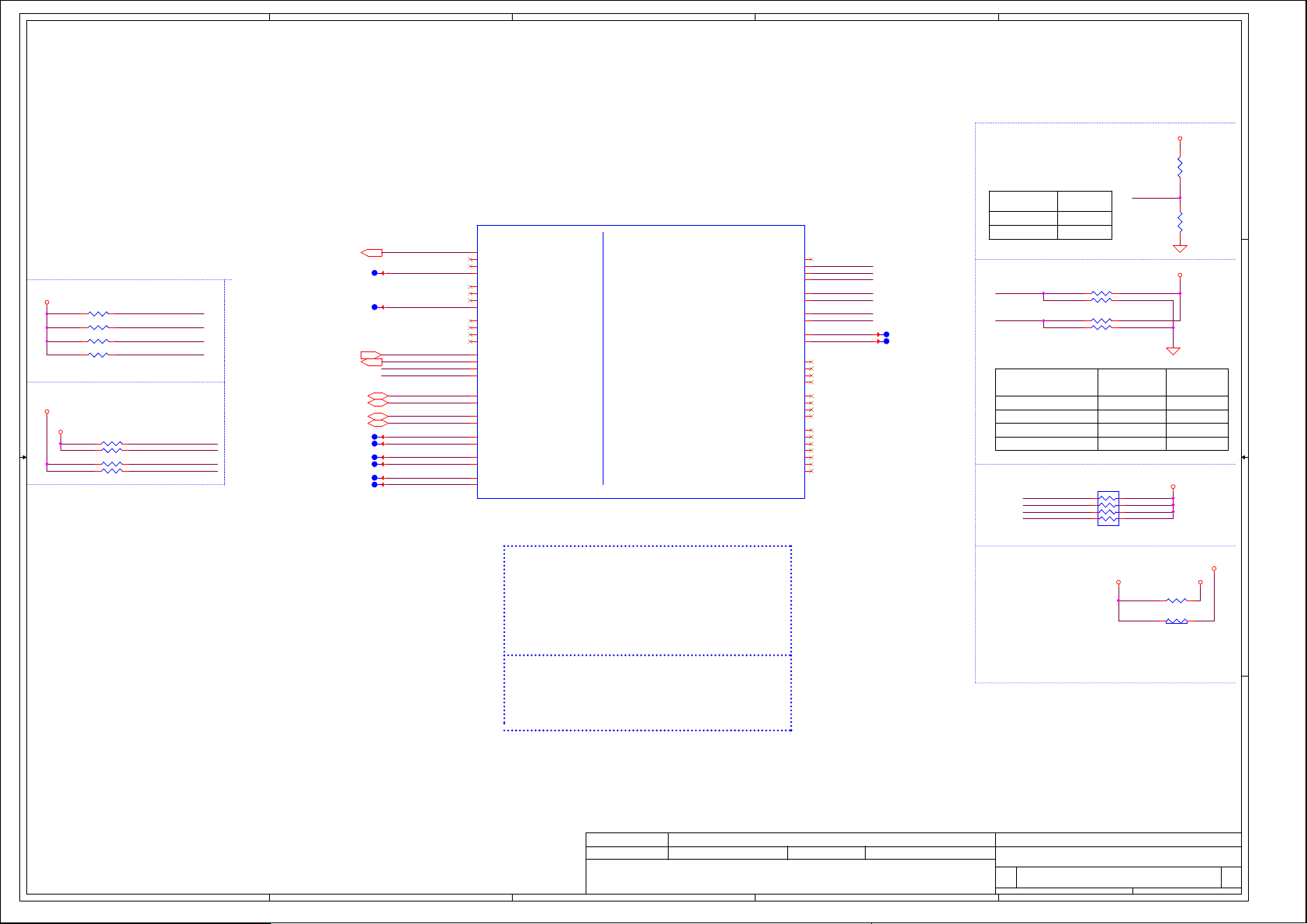

Page 5

A

B

C

D

E

2. 2 K

BH 1 0

2. 2 K

SOC_ SMBC LK

SOC_SMBDATA

1

Sk ylak e

BG 1 2

+3VALW_PRI M

2N 7002D W

2. 2 K

2. 2 K

+3VS

SO-D IMM 2

1

SOC

SOC_ SM L0C LK

SOC_SML0 DATA

SOC_ SM L1C LK

SOC_SML1 DATA

2

77

SCL 1

SDA 1

KBC

3

KB9022

SCL 2

SDA 2

78

79

80

EC_SM B_CK 1

EC_SMB _DA 1

SOC_ SM L1C LK

SOC_SML1 DATA

49 9

49 9

+3VALW_PRI M

2. 2 K

2. 2 K

2. 2 K

2. 2 K

+3VALW_PRI M

+3VLP_EC

100 ohm

100 ohm

0 ohm

0 ohm

EC_S MB_CK1 _CHGR

EC_S MB_DA1_C HGR

7

6

12

11

2

BATTE RY

CON N

Ch arge r

3

Need check

I2C Address Table

BUS

I2C_0 (+3VS)

I2C_1 (+3VS)

SOC_SMBCLK +3VS

SOC_SML1CLK

Device

Reserved (Touch Panel)

SB8787-1200 (TP-ELAN)

DIMM2

PCH-LP (SOC)

Addr ess( 7 bit)

0x2CTM-P 2969 -001 ( TP)

0x1 5

0xA4

0x9 0

+3VALW_PRIM

4

EC_SMB_CK1 +3VLP

BQ24780 (Charger IC)

BATTERY PACK

0x1 2

0x1 6

Addres s(8b it)

Wr ite

Rea d

4

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Secu rity Cl assifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

THIS SHEE T OF ENG INEERING DRAW ING I S THE P ROPRIETAR Y PRO PERTY O F CO MPAL ELE CTRONICS, INC. AND CON TAINS CON FIDENTIAL

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

AND TRA DE SE CRET INF ORMATION. THIS SHEET MAY NO T BE TRA NSFERED FRO M THE CU STODY O F THE COM PETENT DIVI SION OF R& D

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

DEPARTME NT EXC EPT AS AUTH ORIZED BY COMPAL ELE CTRONICS, INC . NE ITHER TH IS SHEE T NO R THE I NFORMATIO N IT CONTAINS

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

MAY BE USED BY O R DISCLO SED TO AN Y THIRD P ARTY WI THOUT PRI OR WR ITTEN CONSE NT OF COMP AL EL ECTRONICS, I NC.

A

B

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

2016/0 7/18 2016/1 1/10

C

Comp al Secre t Data

Comp al Secre t Data

Comp al Secre t Data

Decipher ed Date

Decipher ed Date

Decipher ed Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Tit le

Tit le

Tit le

SMBUS_Routing_Table

SMBUS_Routing_Table

SMBUS_Routing_Table

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Size Docu ment N umber R e v

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Da te : Sh eet

Da te : Sh eet

D

Da te : Sh eet

5 44Monday, July 18, 2016

5 44Monday, July 18, 2016

5 44Monday, July 18, 2016

E

1.0

1.0

1.0

o f

o f

o f

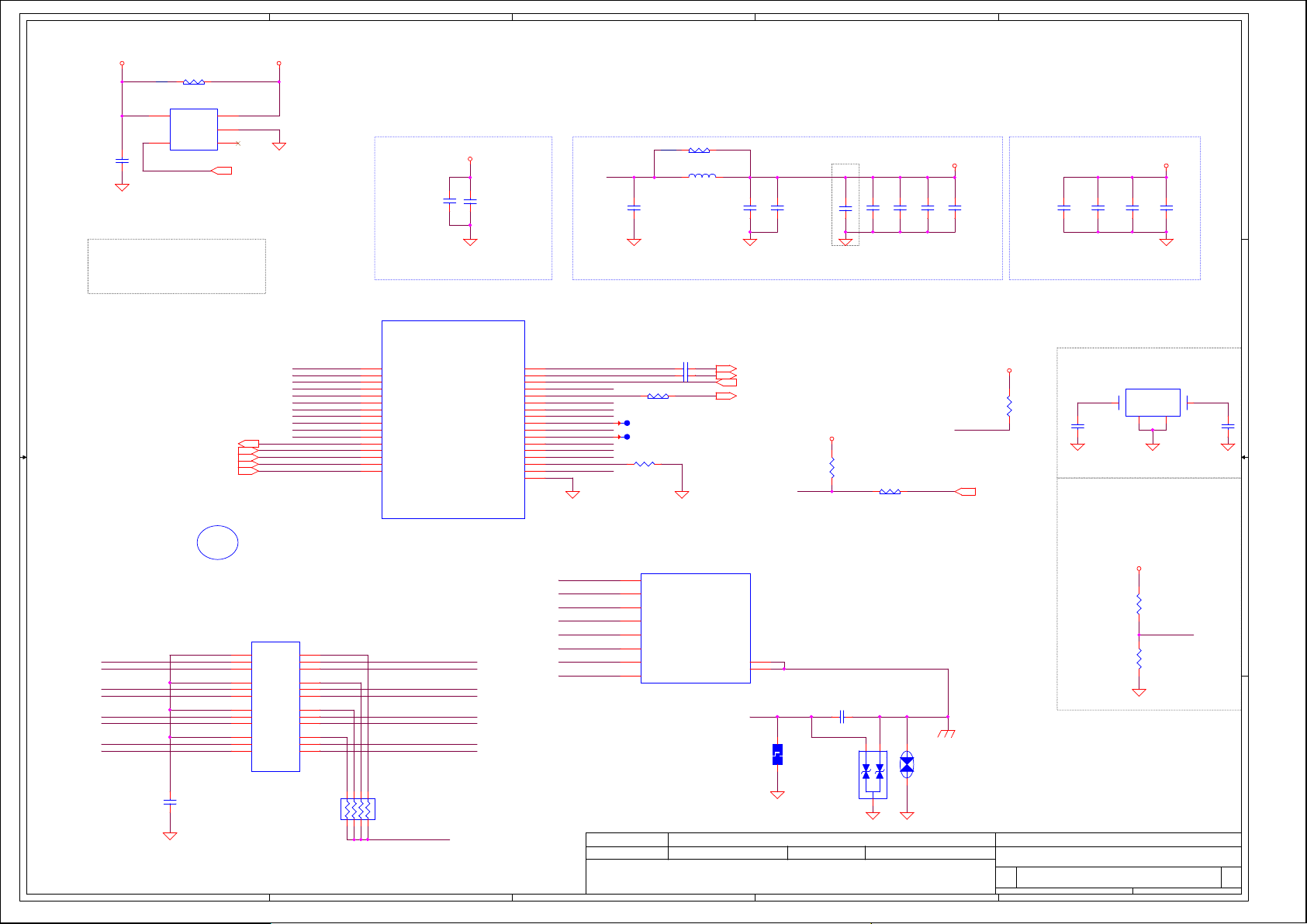

Page 6

A

B

C

D

E

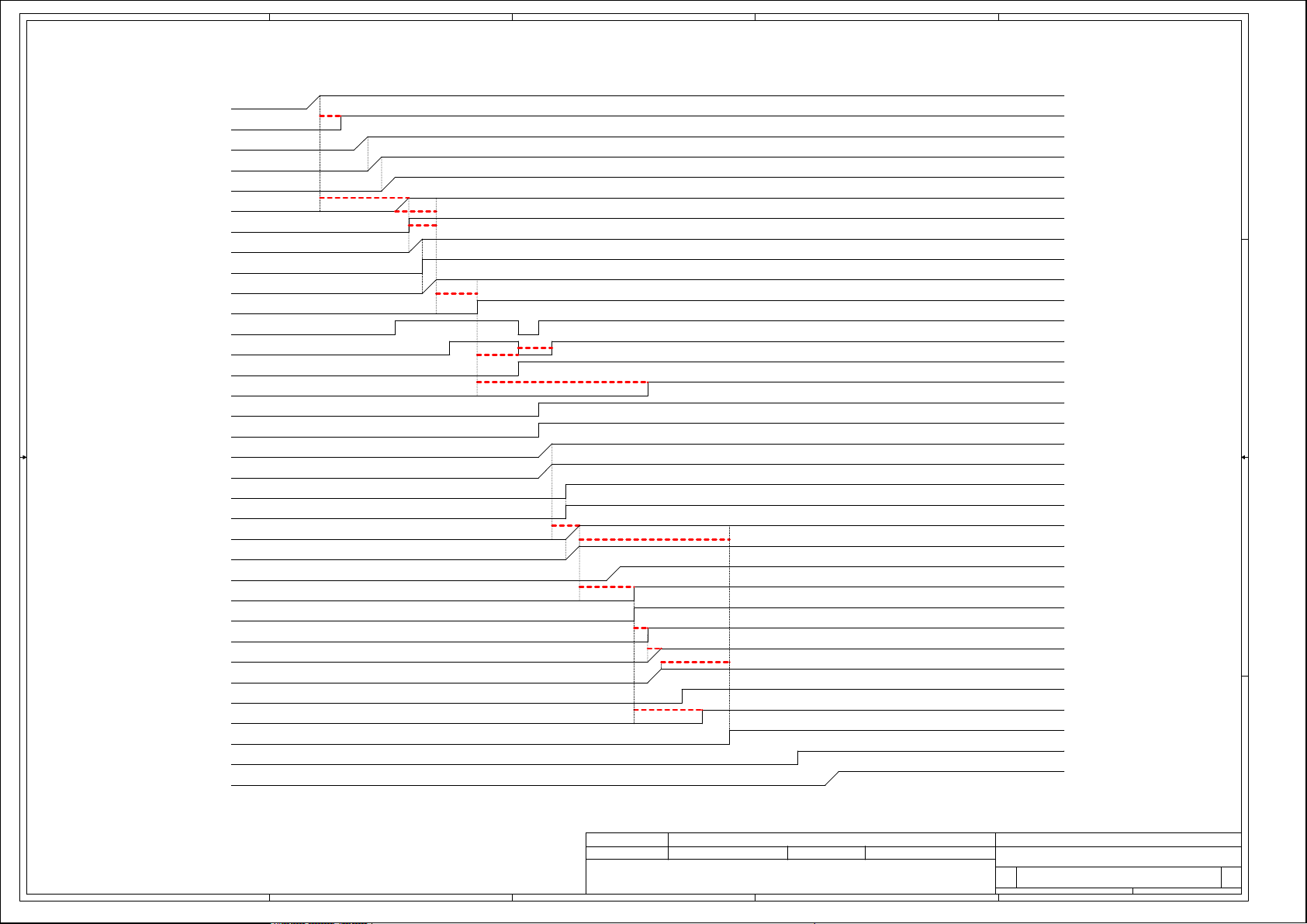

PWR Sequence_SKL-U2+2_DDR3L_Value_NON CS

+RT CVC C

1

SOC _RT CRS T#

+19 VB

+3V LP

EC_ON

+5 VALW /+3VA LW(+3 VALW _D SW. ..)

SPO K tPCH06_Min : 200 us (+3VALW stable (@95% of full value) to +1.0VALW_PRIM startin g to ramp)

+1 .8 VALW _PR IM

+1 .8VALW _PG

+VCCP RIM_ CORE/ +1 .0 VALW _P RI M

EC_R SMRST #

ON/ OFF

2

PBT N_O UT#

PM_S LP_S 5#

ESP I_R ST#

PM_S LP_S 4#

SYSO N

+1. 0V_V CCST U

+1. 2V_ VDD Q

PM_S LP_S 3#

SUSP #

+1. 0VS_ VCC STG

+VCC IO

3

+5VS/+3V S/+ 1.8 VS /+1 .5V S

EC_V CCS T_P G

VR_O N

SM_PG _C TR L

+0.6V S_ VT T

+VCC _SA

VR_ PW RGD

PCH_ PWRO K (SYS _PWR OK)

H_CP UPW RGD

PLT_R ST#

4

+VCC_C ORE / +VCC _GT

tPCH01_Min : 9 ms

tPCH43_Min : 95 ms

tPCH04_Min : 9 ms

tPCH34_M ax : 2 0 ms

tPCH03_Min : 10 ms

Minimu m duratio n of PWRBT N# assertio n = 16mS. PWRB TN# can assert befo re or after RSM RST#

tPCH18_Min : 90 us

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

tCPU00 Min : 1 ms

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

tCPU16 Min : 0 ns

tPLT05 Min : Pla tform depend ent

1

2

3

4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Title

Title

Title

PowerSequence

PowerSequence

PowerSequence

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Date : Sheet

Date : Sheet

D

Date : Sheet

E

6 44Monday, July 18, 2016

6 44Monday, July 18, 2016

6 44Monday, July 18, 2016

1.0

1.0

1.0

of

of

of

Page 7

A

B

C

D

E

1

Funct i onal Stra p Def ini t i ons

#543016 PDG2.0 P.844

DDP B_CTR LDATA

DDP C_CTR LDATA

Display Port B/C Detected

NC =Port is not detected.

PU =Port is detected.

2

+VCCIO

1

RC1 24.9_0402_1%

#543016 PDG2. 0 P.225

COMPENSATI ON PU for eDP

Trace wi dth=5 mils, Spacing= 25mil,Max len gth=600mi ls

+1.0V_VCCST

RC2 1K_0402_5%

+3VS

RC157 100K_ 0402_5%

3

+1.0VS_VCCSTG

RC11 51_0402_5%CMC@

RC13 51_0402_5%CMC@

RC15 100_0402_5%CMC@

RC17 100_0402_5%CMC@

4

RC35 51_0402_5%CMC@

2

#543016 PDG2. 0 P.857

PU 1K to VCCST

1

2

1

2

@

CC52

@ESD@

.1U_0402_16V7K

H_PECI

1

2

CC53

@ESD@

.1U_0402_16V7K

H_PROCHOT#_R

1

2

For Intel debug, place to CPU side.

#543016 PDG2. 0 P.629

1

2

1

2

1

2

1

2

1

2

EDP_COMP

H_THERMTRIP#

TP_INT#

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TDO

CPU_XDP_TCK0

CPU sid e

CMC s ide

H_PROCHOT#<29>

EC_TP_IN T#<29,30>

HDMI

HDMI DDC (Port C)

SOC_DP2_CTRL_CLK<22>

SOC_DP2_CTRL_DATA<22>

+1.0VS_VCCSTG

SPI touch INT follow CRB

SOC_DP2_N0<22>

SOC_DP2_P0<22>

SOC_DP2_N1<22>

SOC_DP2_P1<22>

SOC_DP2_N2<22>

SOC_DP2_P2<22>

SOC_DP2_N3<22>

SOC_DP2_P3<22>

SOC_DP2_CTRL_CLK

SOC_DP2_CTRL_DATA

EDP_COMP

1

RC3

1K_0402_5%

RC4

499_0402_1%

2

1

2

RC9 100K_0402_5%

+3VS

I2C_TS_INT#<21>

@

1

2

DC2RB751V-40_SOD323-2

1

2

RC137 0_0402_5%

RC5 49.9_0402_1%

RC6 49.9_0402_1%

RC7 49.9_0402_1%

RC8 49.9_0402_1%

#543016 PDG2. 0 P.873

PROC_POPIR COMP/ PCH_ OPI RCO MP

PD 50o hm

#544669 CRB1.1 P.52

EDRAM_O PIO_RCOMP/ EOPI O_R COM P

PD 50o hm

1

2

1

2

1

2

1

2

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

@

Reserve d CA TERR# for

sight i ngs i ss ue c heck

H_PECI<29>

1

T166@

T160@

T161@

2

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

XDP_BPM#0

XDP_BPM#1

I2C_TS_INT#

TP_INT#

DDI

DISPLAY SIDEBANDS

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356

@

UC1D

SKL -U

1 OF 20

CPU MISC

EDP

SKL -U

4 OF 20

Rev_ 0.5 3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

Rev_ 0.5 3

JTA G

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

SOC_DP2_HPD

EC_SCI#

CPU_EDP_HPD

ENBKL

SOC_BKL_PWM

SOC_ENVDD

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

EDP_TXN0 <21>

EDP_TXP0 <21>

EDP_TXN1 <21>

EDP_TXP1 <21>

EDP_AUXN <21>

EDP_AUXP <21>

SOC_DP2_HPD <22>

EC_SCI# <29>

CPU_EDP_ HPD <21>

ENBKL <29>

SOC_BKL_PWM <21>

SOC_ENVDD <21>

T194 @

T195 @

eDP

From HDMI

From e DP

EC_SCI#

RC212

10K_0402_5%

+3VS

1

2

@

EC_SCI# SO C in ternal PU

#545659 P CH EDS1.51 P.131

SCI capability is available on all GPIOs, while

NMI and SMI capability is available on only

select GPIO s.

Below are the PCH GPIOs that can be

routed to generate SMI# or NMI:

GPP_B14, GPP_B20, GPP_B23‧‧‧‧

GPP_C [ 23 : 22 ]‧‧‧‧

GPP_D [ 4 : 0 ]‧‧‧‧

GPP_E [ 8 : 0 ] , GPP_E [ 16 : 13 ]‧‧‧‧

CC81

@ESD@

SOC_XDP_TRST#

.1U_0402_16V7K

1

2

1

2

3

4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

CompalElectronics,Inc.

CompalElectronics,Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date : Sheet

Date : Sheet

D

Date : Sheet

CompalElectronics,Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

E

of

7 44Monday, July 18, 2016

of

7 44Monday, July 18, 2016

of

7 44Monday, July 18, 2016

1.0

1.0

1.0

Page 8

A

B

C

D

E

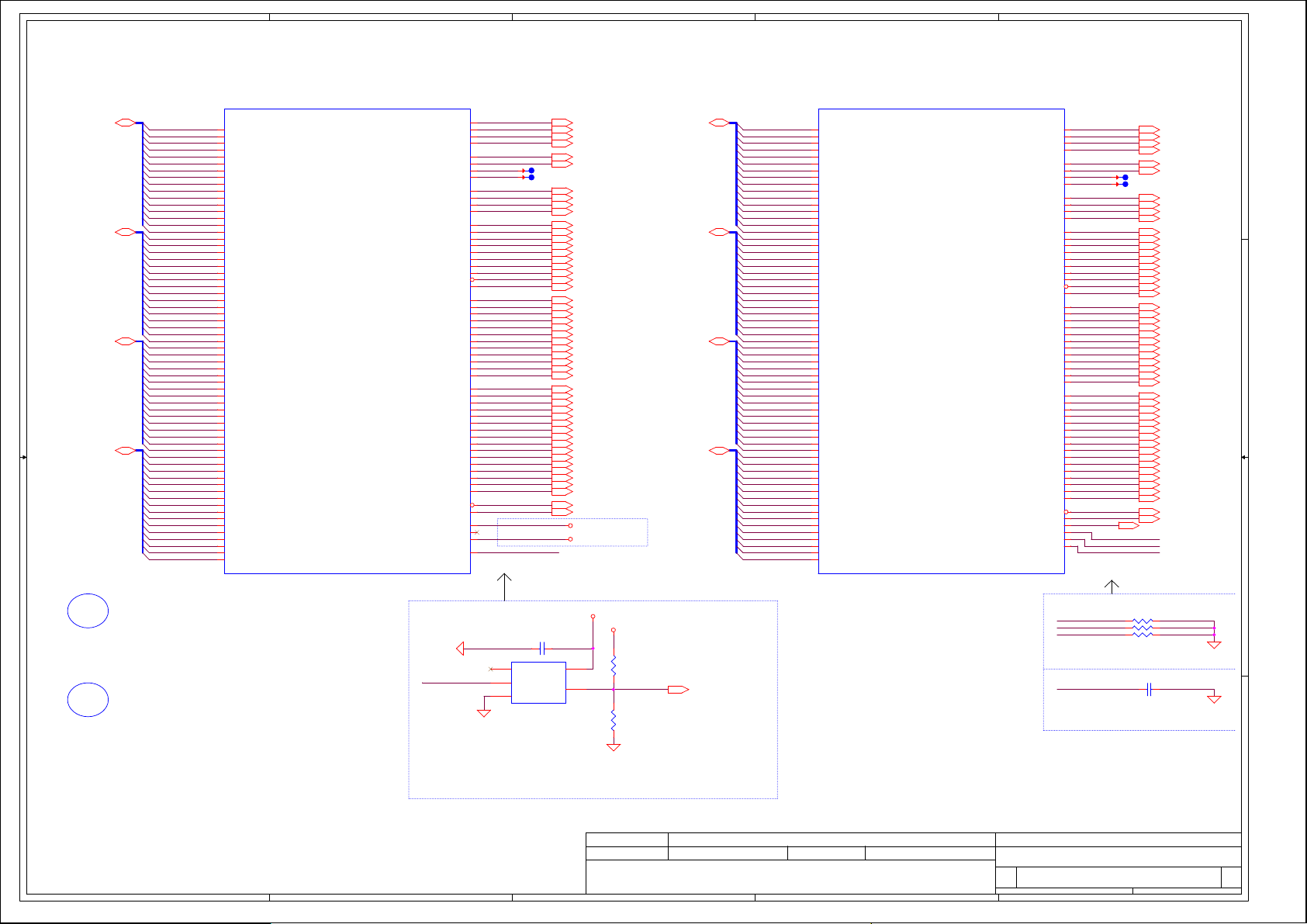

Interleaved Memory

1

2

3

DDR_A_D[0..15]<19>

DDR_A_D[16..31]<19>

DDR_A_D[32..47]<19>

DDR_A_D[48..63]<19>

ZZZ

PCB B5W11 LA-E061P LS-D671P

DAZ1P5 00100

ES Sample

UC1

CPU_G0 2.6G

QKJW@

SA0000 9UR10

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

SKL -U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR_PG_CTRL

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

DDR_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#2

BA64

DDR_A_DQS2

AY64

DDR_A_DQS#3

AY60

DDR_A_DQS3

BA60

DDR_A_DQS#4

BA38

DDR_A_DQS4

AY38

DDR_A_DQS#5

AY34

DDR_A_DQS5

BA34

DDR_A_DQS#6

BA30

DDR_A_DQS6

AY30

DDR_A_DQS#7

AY26

DDR_A_DQS7

BA26

DDR_A_ALERT#

AW50

DDR_A_PAR

AT52

+0.6V_A_VREFCA

AY67

AY68

+0.6V_B_VREFCA

BA67

DDR_PG_CTRL

AW67

1

2

3

74AUP1G07GW_TSSOP5

Change PN to SA 00007UR00.

T14@

T15@

1

2

UC7

NC

VCC

A

GND

DDR_A_CLK#0 <19>

DDR_A_CLK0 <19>

DDR_A_CLK#1 <19>

DDR_A_CLK1 <19>

DDR_A_CKE0 <19>

DDR_A_CKE1 <19>

DDR_A_CS#0 <19>

DDR_A_CS#1 <19>

DDR_A_ODT0 <19>

DDR_A_ODT1 <19>

DDR_A_MA5 <19>

DDR_A_MA9 <19>

DDR_A_MA6 <19>

DDR_A_MA8 <19>

DDR_A_MA7 <19>

DDR_A_BG0 <19>

DDR_A_MA12 <19>

DDR_A_MA11 <19>

DDR_A_ACT# <19>

DDR_A_BG1 <19>

DDR_A_MA13 <19>

DDR_A_MA15 <19>

DDR_A_MA14 <19>

DDR_A_MA16 <19>

DDR_A_BA0 <19>

DDR_A_MA2 <19>

DDR_A_BA1 <19>

DDR_A_MA10 <19>

DDR_A_MA1 <19>

DDR_A_MA0 <19>

DDR_A_MA3 <19>

DDR_A_MA4 <19>

DDR_A_DQS#0 <19>

DDR_A_DQS0 <19>

DDR_A_DQS#1 <19>

DDR_A_DQS1 <19>

DDR_A_DQS#2 <19>

DDR_A_DQS2 <19>

DDR_A_DQS#3 <19>

DDR_A_DQS3 <19>

DDR_A_DQS#4 <19>

DDR_A_DQS4 <19>

DDR_A_DQS#5 <19>

DDR_A_DQS5 <19>

DDR_A_DQS#6 <19>

DDR_A_DQS6 <19>

DDR_A_DQS#7 <19>

DDR_A_DQS7 <19>

DDR_A_ALERT# <19>

DDR_A_PAR <19>

+0.6V_A_VREFCA

+0.6V_B_VREFCA

#543016 PDG2. 0 P.190

Trace width/S pacing >= 20mils

Place com ponment nea r SODIMM

+1.2V_VDDQ

+3VS

CC57.1U_0402_16V7K

1

2

2

RC16

1M_0402_5%@

1

RC10

100K_0402_5%

5

4

Y

DDR_B_D[0..15]<20>

DDR_B_D[16..31]<20>

DDR_B_D[32..47]<20>

DDR_B_D[48..63]<20>

SM_PG_CTRL <37>

DDR_V TT_CNTL to DDR

VTT suppl ied ramped

<35u S

(tC PU18 )

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL -U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DRAM_RESET#

DDR_RCOMP[0]

DDR CH - B

3 OF 20

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_ 0.5 3Rev_ 0.5 3

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DDR_B_CLK#0

AN45

DDR_B_CLK#1

AN46

DDR_B_CLK0

AP45

DDR_B_CLK1

AP46

DDR_B_CKE0

AN56

DDR_B_CKE1

AP55

AN55

AP53

DDR_B_CS#0

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

DDR_B_ODT1

AW42

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

DDR_B_ACT#

AN53

DDR_B_BG1

AN52

DDR_B_MA13

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

DDR_B_MA16

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_B_MA4

BA47

DDR_B_DQS#0

AH66

DDR_B_DQS0

AH65

DDR_B_DQS#1

AG69

DDR_B_DQS1

AG70

DDR_B_DQS#2

AR66

DDR_B_DQS2

AR65

DDR_B_DQS#3

AR61

DDR_B_DQS3

AR60

DDR_B_DQS#4

AT38

DDR_B_DQS4

AR38

DDR_B_DQS#5

AT32

DDR_B_DQS5

AR32

DDR_B_DQS#6

AR25

DDR_B_DQS6

AR27

DDR_B_DQS#7

AR22

DDR_B_DQS7

AR21

DDR_B_ALERT#

AN43

DDR_B_PAR

AP43

AT13

AR18

SM_RCOMP0

AT18

SM_RCOMP1

AU18

SM_RCOMP2

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

#543016 PDG2. 0 P.139

W=12-1 5 Space= 20/25 L =500mil

DDR_DRAMRST#

T17@

T18@

DDR_DRAMRST# <19,20>

1

RC38 121_0402_1%

1

RC39 80.6_0402_1%

1

RC40 100_0402_1%

@ESD@

1

CC70 .1U_0402_16V7K

2015MOW02, Can't install Cap on DRAMRST

DDR_B_CLK#0 <20>

DDR_B_CLK#1 <20>

DDR_B_CLK0 <20>

DDR_B_CLK1 <20>

DDR_B_CKE0 <20>

DDR_B_CKE1 <20>

DDR_B_CS#0 <20>

DDR_B_CS#1 <20>

DDR_B_ODT0 <20>

DDR_B_ODT1 <20>

DDR_B_MA5 <20>

DDR_B_MA9 <20>

DDR_B_MA6 <20>

DDR_B_MA8 <20>

DDR_B_MA7 <20>

DDR_B_BG0 <20>

DDR_B_MA12 <20>

DDR_B_MA11 <20>

DDR_B_ACT# <20>

DDR_B_BG1 <20>

DDR_B_MA13 <20>

DDR_B_MA15 <20>

DDR_B_MA14 <20>

DDR_B_MA16 <20>

DDR_B_BA0 <20>

DDR_B_MA2 <20>

DDR_B_BA1 <20>

DDR_B_MA10 <20>

DDR_B_MA1 <20>

DDR_B_MA0 <20>

DDR_B_MA3 <20>

DDR_B_MA4 <20>

DDR_B_DQS#0 <20>

DDR_B_DQS0 <20>

DDR_B_DQS#1 <20>

DDR_B_DQS1 <20>

DDR_B_DQS#2 <20>

DDR_B_DQS2 <20>

DDR_B_DQS#3 <20>

DDR_B_DQS3 <20>

DDR_B_DQS#4 <20>

DDR_B_DQS4 <20>

DDR_B_DQS#5 <20>

DDR_B_DQS5 <20>

DDR_B_DQS#6 <20>

DDR_B_DQS6 <20>

DDR_B_DQS#7 <20>

DDR_B_DQS7 <20>

DDR_B_ALERT# <20>

DDR_B_PAR <20>

2

2

2

2

1

2

3

4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date : Sheet

Date : Sheet

D

Date : Sheet

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Monday, July 18, 2016

Monday, July 18, 2016

Monday, July 18, 2016

of

8

of

8

of

E

8

4

1.0

1.0

1.0

44

44

44

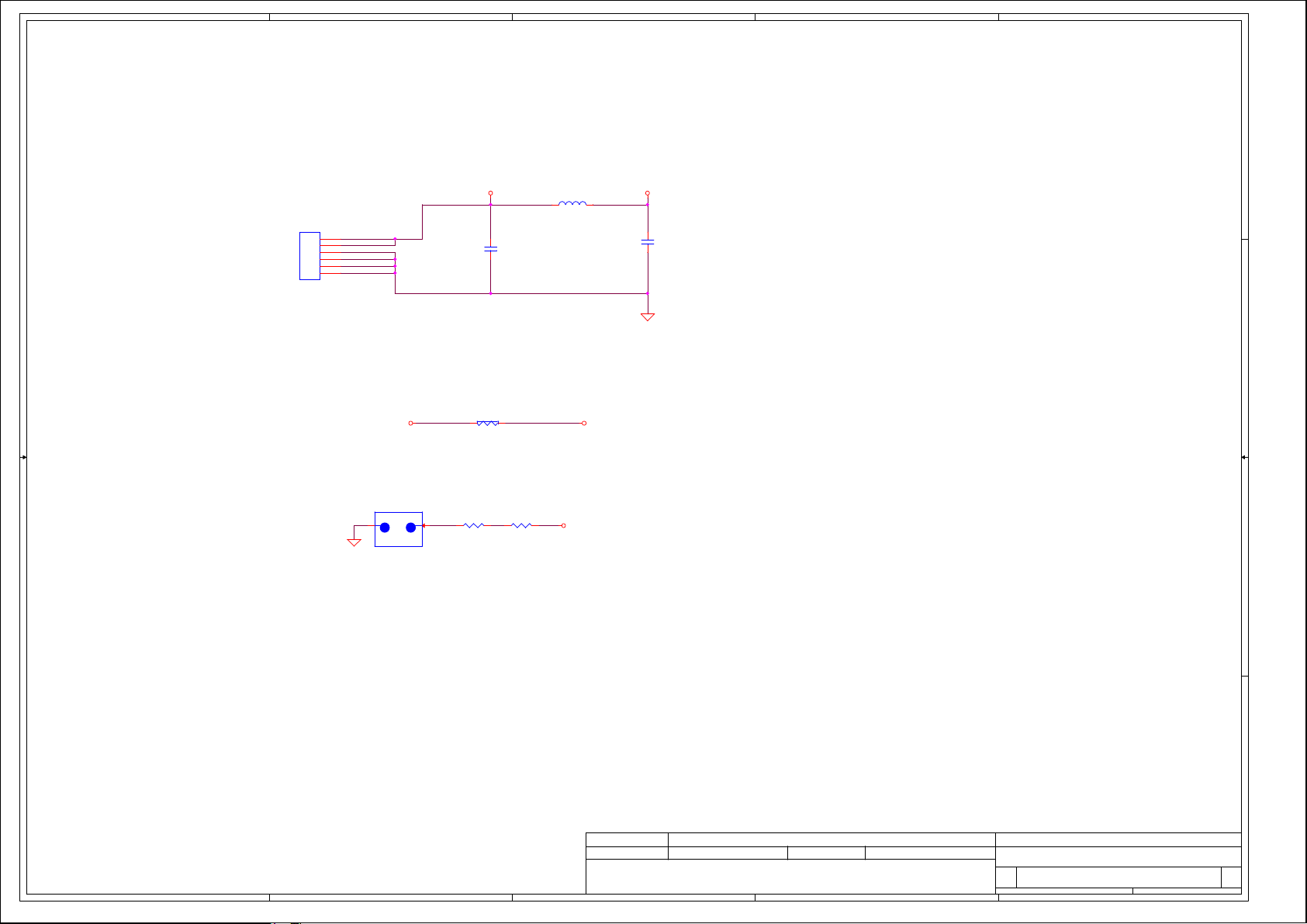

Page 9

A

1

UC1E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

@

SOC_SPI_IO3_0_R

1

SOC_SPI_SI_0_R

2

SOC_SPI_CLK_0_R

3

SOC_SPI_SO_0_R

4

SOC_SPI_IO2_0_R

1

SPI - F LASH

SPI - TOUCH

C LINK

SPI ROM

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

AW3

AW2

AV2

AV3

AU4

AU3

AU2

AU1

SPI Touch

2

EC_KBRST#_R<29>

TPM_SERIRQ<29>

3

EC_KBRST#_R

TPM_SERIRQ

LPC Mo de

RPC5 and RC52 are close UC2

SOC_SPI_IO3

SOC_SPI_SI

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_IO2

AW13

AY11

RPC5

8

7

6

5

15_0804_8P4R_5%

2

RC52 15_0402_5%

SKL -U

SOC_SPI_CS#0

SOC_SPI_SO_0_R

SOC_SPI_IO2_0_R

B

SMBUS, SMLINK

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

LPC

5 OF 20

SOC_SPI_CLK_0_R

ROM Socket, co- lay with UC2 .

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

SOC_SPI_IO3_0_R

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

SPI ROM ( 8MByte )

UC2

1

/CS

2

DO(IO1)

3

4

/HOLD(IO3)

/WP(IO2)

GND

W25Q64FVSSIQ_SO8

DI(IO0)

1

2

@EMI@

RC24 0_0402_5%

JC1

1

CS#

3

WP#

7

HOLD#

4

GND

ACES_91960-0084N_MX25L3206EM2I

CONN@

VCC

CLK

SI/SIO0

SO/SIO1

VCC

SCLK

C

SOC_SMBCLK

R7

SOC_SMBDATA

R8

SOC_SMBALERT#

R10

SOC_SML0CLK

R9

SOC_SML0DATA

W2

SOC_SML0ALERT#

W1

SOC_SML1CLK

W3

SOC_SML1DATA

V3

SOC_SML1ALERT#

AM7

Change RC 144~RC14 7, RC45 to 1 5ohm w hen use ESPI

LPC_AD0

+3VALW_SPI

8

SOC_SPI_IO3_0_R

7

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

5

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

1

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

ESPI_RST#

CLKOUT_LPC0

PM_CLKRUN#

CC8

.1U_0402_16V7K

2

RC144 0_0402_5%@

RC145 0_0402_5%@

RC146 0_0402_5%@

RC147 0_0402_5%@

T239@

Strap Pin

2

SOC_SML1CLK <29>

SOC_SML1DATA <29>

T234@

1

2

1

2

1

2

1

2

LPC_FRAME# <29>

ESPI_RST# <29>

1

2

RC45 22_0402_5%

LPC@

2015MOW06 n o need PU1K on SPI_IO2/I O3

1

2

CC9

@EMI@

10P_0402_50V8J

+3VALW_SPI

8

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

5

SOC_SPI_SO_0_R

2

SOC_SPI_IO2

SOC_SPI_IO3

1

RC2024.7K_0402_5% ESPI@

SMB

+3VALW_PRIM

SML 1

LPC_AD0_R <29>

LPC_AD1_R <29>

LPC_AD2_R <29>

LPC_AD3_R <29>

CLK_LPC_EC <29>

1

RC47 1K_0402_1%@

1

RC48 1K_0402_1%@

(to DDR, G sensor )

( to EC , Therma l se nsor)

ESPI / LPC Bus

ESPI : +1. 8V

LPC : +3.3V

*

To EC

+3VALW_SPI

2

2

D

SOC_SMBCLK_1

SOC_SMBDATA_1

SOC_SML0CLK

SOC_SML0DATA

SOC_SML1CLK

SOC_SML1DATA

SOC_SMBCLK

SOC_SMBDATA

+3VS

SOC_SMBCLK

SOC_SMBDATA

*

*

3

D

PM_CLKRUN#

TPM_SERIRQ

SML0ALERT# / GPP_C5 (Internal Pull Down):

(Sampled: Rising edge of RSMRST# )

eSPI or LPC

0 = LPC is selected for EC --> For KB9022/9032 Use

1 = eSPI is selected for EC --> For KB9032 Only.

SMBALERT# / GPP_C2 (Internal Pull Down):

(Sampled: Rising edge of RSMRST# )

TLS Conf i den tiali ty

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no conf i dent iali ty).

1 = Enable Intel ME Crypto (TLS) (with conf i dent ial i ty).

Must be pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

5

G

6

RC222 2.2K_0402_5%

RC223 2.2K_0402_5%

RC49 499_0402_1%

RC50 499_0402_1%

QC2B

2N7002KDW_SOT363-6

SOC_SMBCLK_1

4

S

2

G

QC2A

2N7002KDW_SOT363-6

1

S

D

RC107 10K_0402_5%

RC112 10K_0402_5%

1

1

1

1

RPC7

1

2

3

4

2.2K_0804_8P4R_5%

SOC_SMBDATA_1

1

2

1

2

E

2

2

2

2

8

7

6

5

+1.8VS_3VS_PGPPA

+3VS

+3VALW_PRIM

1

SOC_SMBCLK_1 <19,20>

SOC_SMBDATA_1 <19,20>

2

3

4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Title

Title

Title

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Date : Sheet

Date : Sheet

D

Date : Sheet

E

of

9 44Monday, July 18, 2016

of

9 44Monday, July 18, 2016

of

9 44Monday, July 18, 2016

4

1.0

1.0

1.0

Page 10

A

B

C

D

E

1

HDA for AUDIO

HDA_SDIN0<25>

HDA_SYNC_R<25>

HDA_SDOUT_R<25>

HDA_BIT_CLK_R<25>

HDA_RST#_R<25>

ME_EN<29>

HDA_SDO / I2S_TXD0 (Inter nal Pull Down):

(Sampled : Risi ng e dge of P CH_PWROK )

Flash D escriptor S ecurity Over ride

0 = Enable security measures def i ne d i n t he Fl ash

2

Descri pto r.

1 = Dis able Flash Descriptor Security (overrid e). T his

strap should only be assert ed h igh using external

pull-up in man ufacturing/d ebug env ironments ON LY.

SPKR / GPP_B14 (Internal Pull Down):

(Sampled:Rising edge of PCH_PWROK)

TOP Swap Override

0 = Disable TOP Swap mode.

*

1 = Enable TOP Swap Mode.

Intel HD Audio link capabilit i es

> Two SDI signals to su pport two externa l codecs.

> Drivers variable requency (5MHz to 24MHz) B CLK to support:

-- SDO double pumped up to 48 Mb/s

-- SDI's single pumped up to 24 Mb/s

> Provides cadence for 44.1 kHz based sample r ate o utput.

> Support 1.5V, 1.8V, and 3.3V modes.

3

RPC9

1

2

3

4

33_0804_8P4R_5%

1

@

RC77 0_0402_5%

HDA_SDIN0

8

7

6

5

2

HDA_SYNC

HDA_SDOUT

HDA_BIT_CLK

HDA_RST#

1

9 OF 20

SKL -U

7 OF 20

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EM M C

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO/ SDX C

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_A17/SD_PWR_EN#/ISH_GP7

Rev_ 0.5 3

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

C37

D37

C32

D32

C29

D29

B26

A26

CSI2_COMP

E13

DGPU_PRSNT#

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

EMMC_RCOMP

AT1

Rev_ 0.5 3

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

SD_RCOMP

AF13

GPP_F23

#543016 PDG2. 0 P.551

2

RC80 100_0402_1%

2

RC89 200_0402_1%

#543016 PDG2. 0 P.393

#543016 PDG2. 0 P.403

SDIO signals are mult i pl ex ed wi t h GPI Os a nd def ault

to GPIO fu nct i onalit y ( as i nput). I f S DI O i nt erf ace i s

not used, the signals can be used as GPIOs instead.

If the GPIO funct i onali t y is al s o not use d, t he si gnal s

can be lef t as no-c onnect.

RC76

200_0402_1%

SD_RCOMP

1

2

#543016 PDG2. 0 P.879

1

1

+3VALW_1.8VALW_PGPPD

DGPU_PRSNT#

2

1

RC133

10K_0402_5%

2

3

UC1G

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0

HDA_RST#

PCH_SPKR<25>

PCH_SPKR

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

AK7

AK6

AK9

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

@

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

@

AUDIO

SKL _U LT

4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USE D BY OR DISCLO SED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

2016/07/ 18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

CompalElectronics,Inc.

CompalElectronics,Inc.

CompalElectronics,Inc.

Title

Title

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

B5W11M/BLA-E061P

B5W11M/BLA-E061P

B5W11M/BLA-E061P

Date : Sheet

Date : Sheet

Monday, July 18, 2016

Date : Sheet

Monday, July 18, 2016

D

Monday, July 18, 2016

E

of

10

of

10

of

10

4

1.0

1.0

1.0

44

44

44

Page 11

A

B

C

D

E

+RTCVCC

1

1

RC91 20K_0402_5%

CC10 1U_0402_6.3V6K

RC93 20K_0402_5%

CC11 1U_0402_6.3V6K

JCMOS1 0_0603_5%@

2

1

2

1

2

1

2

1

2

SOC_SRTCRST#

SOC_RTCRST#

Place at RAM DOOR

1

RC113

1K_0402_5%

RC116

60.4_0402_1%

2

1

SM_INTRUDER#

CLKREQ_PCIE#1

CLKREQ_PCIE#2

CLKREQ_PCIE#5

CLKREQ_PCIE#4

CLKREQ_PCIE#3

CLKREQ_PCIE#0

2

PCH_PWROK

EC_RSMRST#

SYS_RESET#

LAN_WAKE#

SYS_PWROK

WAKE#

SYS_RESET#

H_CPUPWRGD

SYS_PWROK

PCH_PWROK

EC_RSMRST#

1

RPC12

2

2

1

2

3

4

+1.0V_VCCST

2

RC94 1M_0402_5%

+3VS

2

1

RC121 10K_0402_5%

1

RC123 10K_0402_5%

8

7

6

5

10K_0804_8P4R_5%

From EC(open-drain)

EC_VCCST_PG_R<29,32>

Note fo r VCCST_PWR GD

1. 1.0V to lerance

2. PDG2. 0 P.598 Figure4 3-5 note17: whe n failure eve nts,

VCCST_PW RGD and PCH_PWROK de-a ssert at the same t i me

+3VALW_PRIM

+3VALW_DSW

3

4

RC110 10K_0402_5%

+3VALW_DSW

RC104 1K_0402_5%

WAKE# (DSX wa ke event)

10 KΩ pull- up t o Vcc DS W 3_3.

The pull-up is required even if PCIe* interface

is not used on the plat f or m.

RPC11

1

8

2

7

3

6

4

5

10K_0804_8P4R_5%

1

2

1

2

@ESD@

1

2

CC51 .1U_0402_16V7K

@ESD@

1

2

CC50 .1U_0402_16V7K

@ESD@

1

2

CC66 .1U_0402_16V7K

@ESD@

1

2

CC65 .1U_0402_16V7K

@ESD@

1

2

CC69 .1U_0402_16V7K

CLR CM OS

EC_VCCST_PG

GL AN

NG FF

SOC_XTAL24_IN

SOC_XTAL24_OUT

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKREQ_PCIE#0

CLK_PCIE_N1<23>

CLK_PCIE_P1<23>

CLKREQ_PCIE#1<23>

CLK_PCIE_N2<24>

CLK_PCIE_P2<24>

CLKREQ_PCIE#2<24>

PLT_RST#<29>

EC_RSMRST#<29>

T95 @

T89 @

SYS_PWROK<29,32>

PCH_PWROK<29,32>

SUSPWRDNACK<29>

T92 @

CLK_PCIE_N1

CLK_PCIE_P1

CLKREQ_PCIE#1

CLK_PCIE_N2

CLK_PCIE_P2

CLKREQ_PCIE#2

CLKREQ_PCIE#3

CLKREQ_PCIE#4

CLKREQ_PCIE#5

PLT_RST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

PCH_DPWROK

SUSPWRDNACK

SUSACK#

WAKE#

LAN_WAKE#

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

@

UC1K

SYSTEM POWER MANAGEMENT

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

@

PBTN_OUT#<29>

SYS_PWROK

EC_RSMRST#

PCH PLTRST Buf f er

PLT_RST#

UC3

MC74VHC1G08DFT2G_SC70-5

RC125

SKL _U LT

CLOCK SIGNALS

10 OF 20

SKL -U

GPP_B11/EXT_PWR_GATE#

11 OF 20

PBTN_OUT#_R

1

2

@

RC109 0_0402_5%

RC114 0_0402_5%

RC122 0_0402_5%

2

1

2

B

A

2

2

+3VS

PCH_DPWROK

1

@

PCH_PWROK

1

@

5

P

PLT_RST_BUF#

4

Y

G

@

3

1

0_0402_5%@

Rev_ 0.5 3

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

Rev_ 0.5 3

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

PLT_RST_BUF# <23,24>

1

RC118

100K_0402_5%

2

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

CLK_CPU_ITP#

CLK_CPU_ITP

SUSCLK

SOC_XTAL24_IN

SOC_XTAL24_OUT

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_SUS#

SLP_LAN#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#_R

AC_PRESENT

PM_BATLOW#

SM_INTRUDER#

EXT_PWR_GATE#

SOC_VRALERT#

T164 @

T165 @

T185 @

PM_SLP_S0# <29>

PM_SLP_S3# <29,32>

PM_SLP_S4# <29,32>

T84@

T90@

T87@

T88@

T94@

AC_PRESENT <29>

T91@

T93@

1

2

Foll ow 2014M OW48

Skylake U PU 2.7k ohm to 1V

Cannonla ke U PD 60.4 ohm

XCLK_BIASREF

XCLK_BIA SRE F

T:50ohm S :12/15 L:1000 Via:2

201 4M OW4 8:

Skylake-U use 24M 50 oh m ESR

Cannonl ake U use 38.4M 30 o hm E SR

SOC_RTCX2

SOC_RTCX1

Change PN to SJ10000Q400

CC15

6.8P_0402_50V8C

PBTN_OUT#_R