Page 1

A

1 1

B

C

D

E

Compal Confidential

C1PR2 MB Schematic Document

2 2

LA-E051P

(Eagle 21")

Rev: 1.0

3 3

ZZZ

DA@

4 4

PCB 1SJ LA-E051P REV1 MB

DAC00006010

A

B

2017-01-09

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 103Monday, January 09, 2017

1 103Monday, January 09, 2017

1 103Monday, January 09, 2017

E

1.0

1.0

1.0

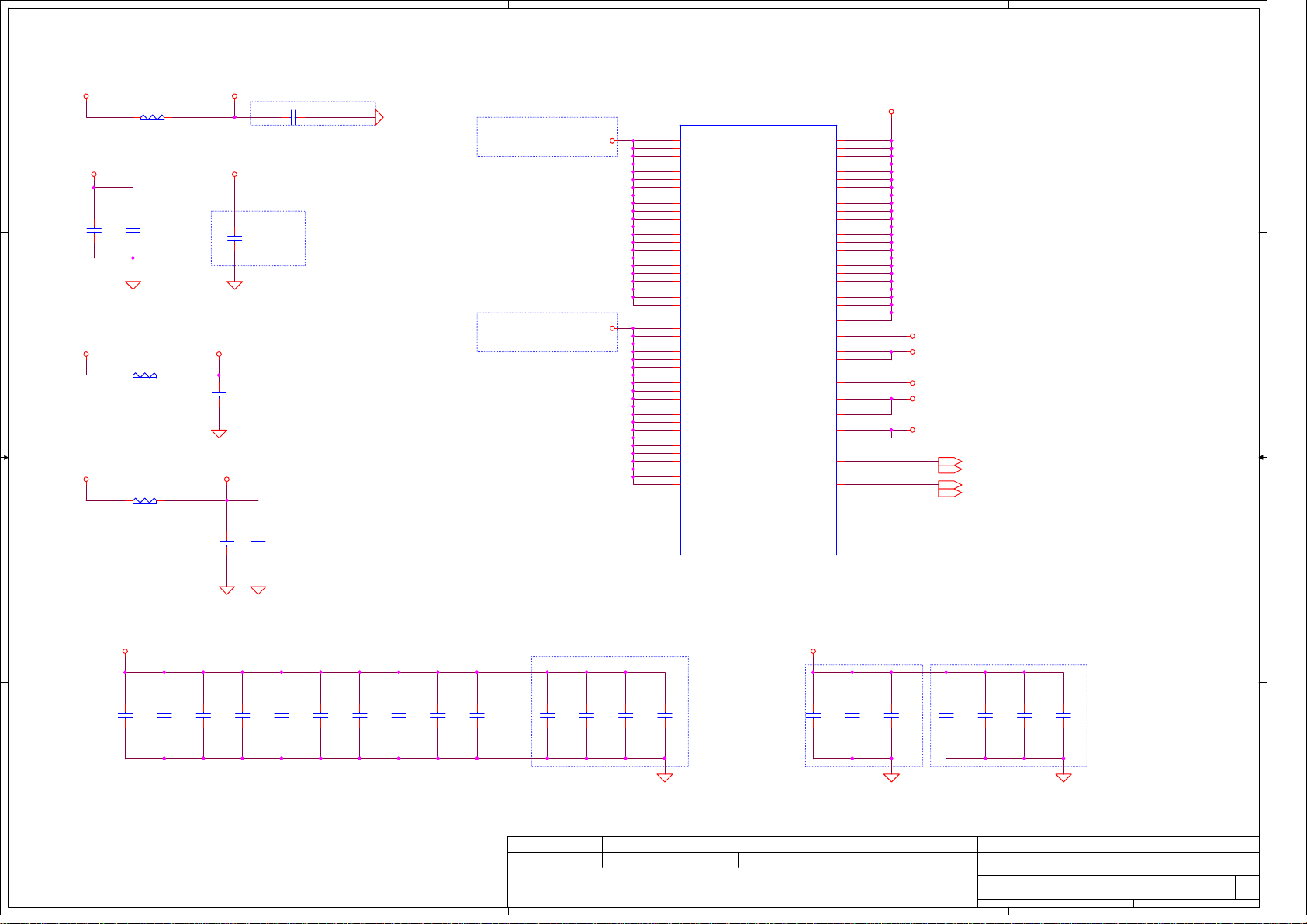

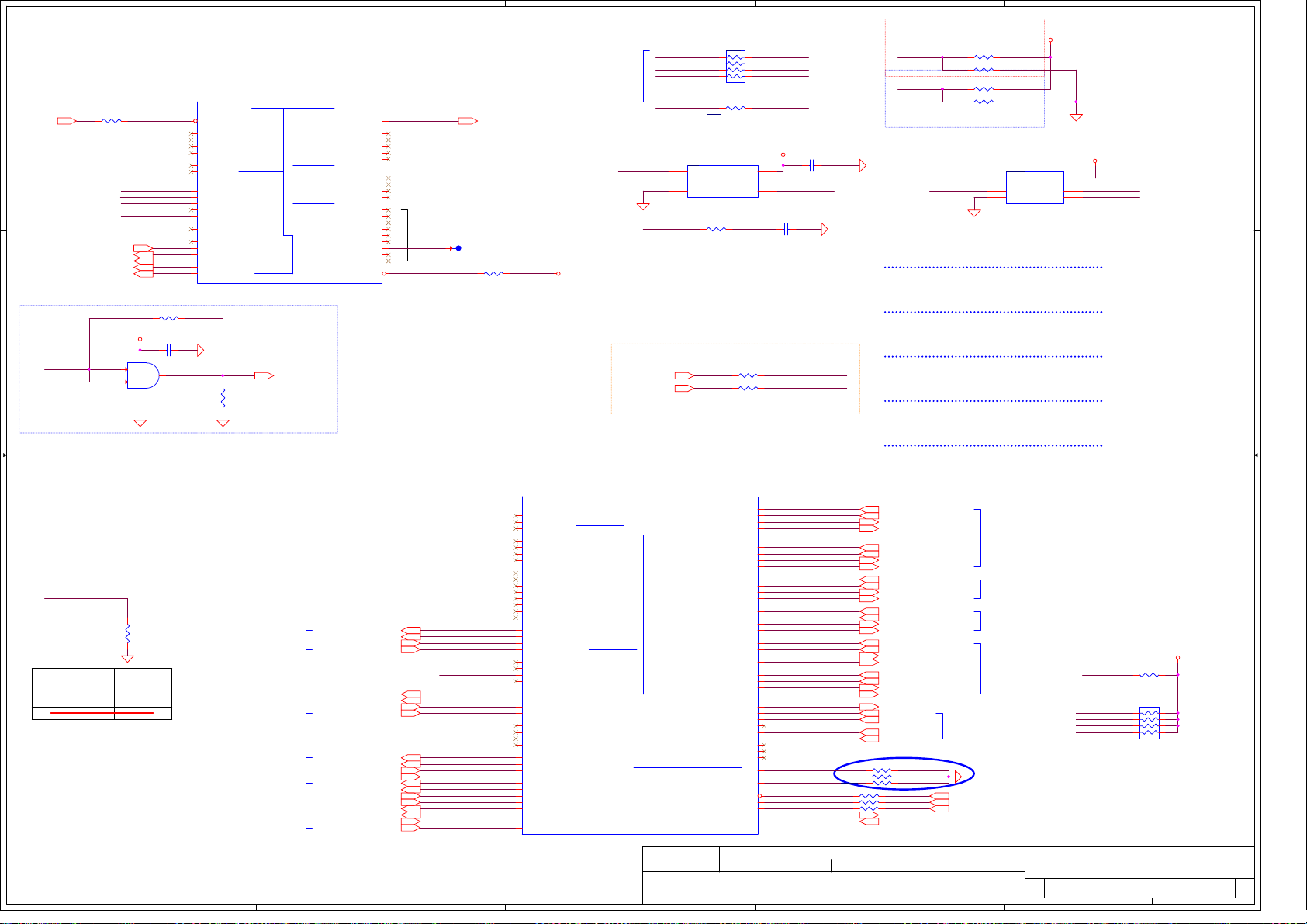

Page 2

A

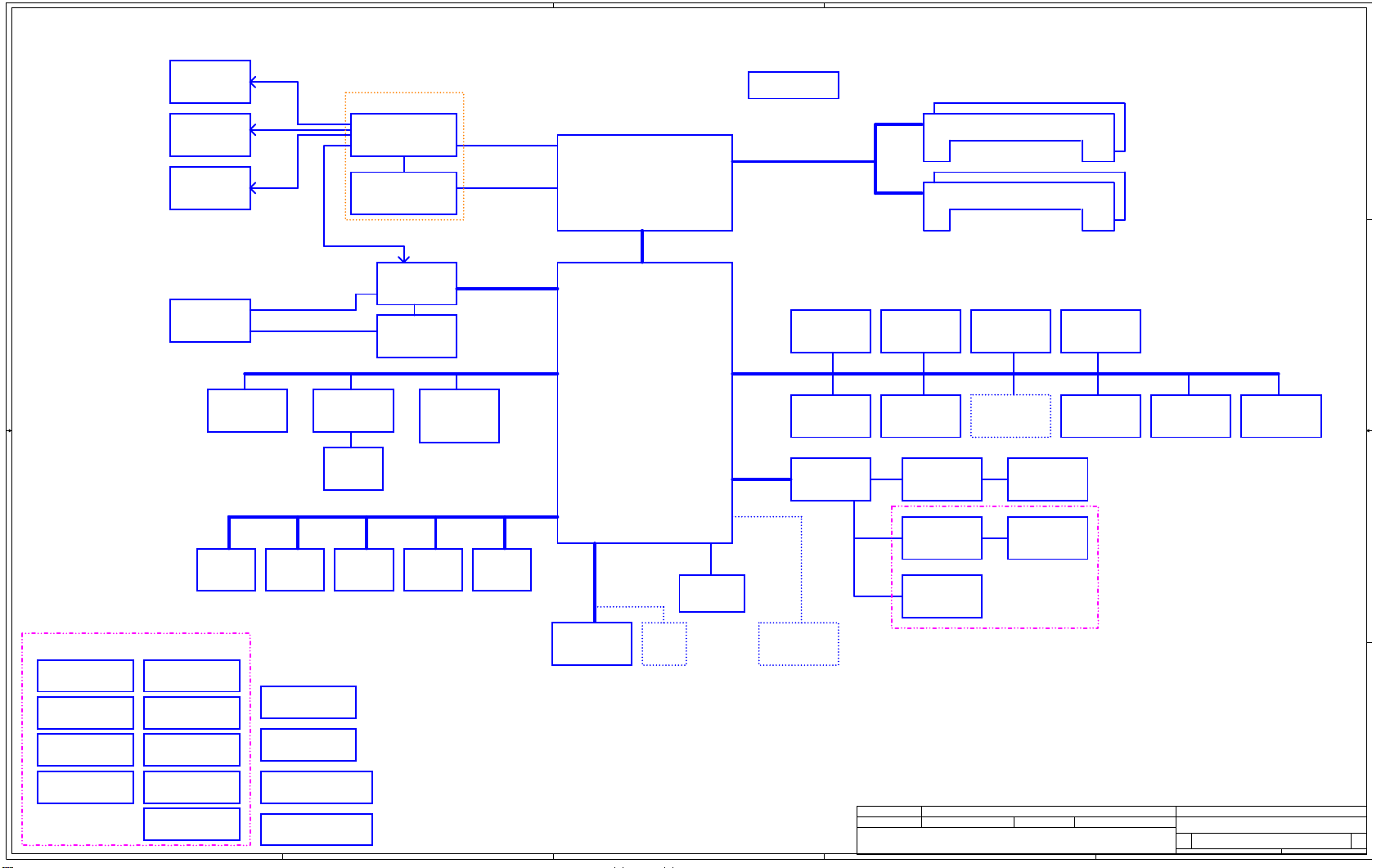

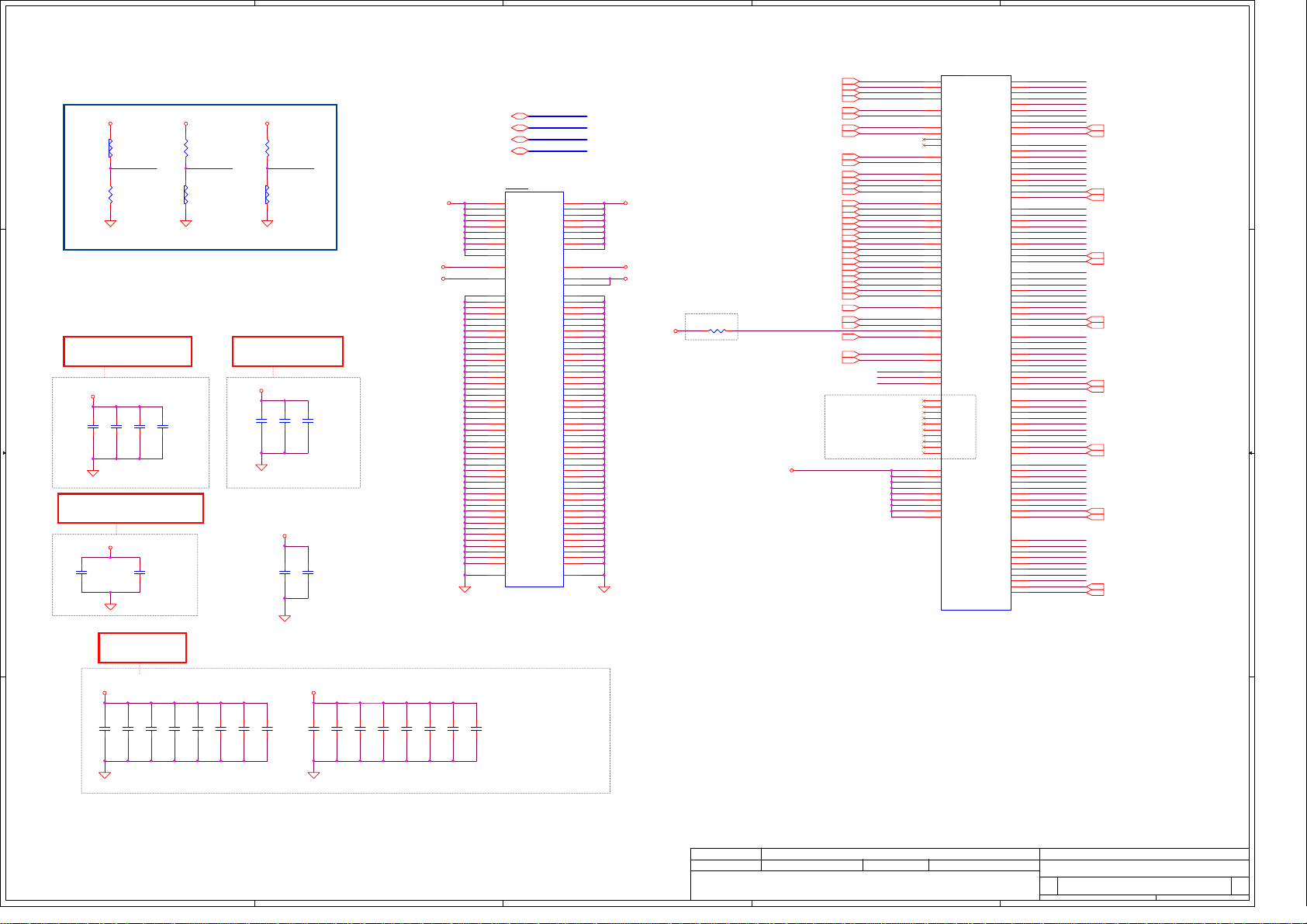

eDP

eDP Panel

Conn.

1 1

HDMI 2.0

Conn.

Display Port

Conn. x2

TYPE-C

2 2

3 3

Conn.

4 lane

page 65

HDMI

4 lane

page 66

DP

4 lane x 2

page 67

DP/USB3.1 Gen2

page 70

DP/USB3.1

M.2 WLAN

Dual Band

page 31

802.11 ac/agn

PCIe x4 PCIe x4

DDI

Nvidia N17E-G3

with GDDR5X*8

page 41~52

Nvidia N17E-G3

with GDDR5X*8

page 53~64

PCIe x1PCIe x2

LAN(GbE)

Killer Ethernet

E2500

page 30

RJ45

Conn.

page 30

M.2 SSDM.2 SSDM.2 SSD

page 28 page 28 page 29 page 29 page 27

SUB/B

USB 3.0/B

IO/B

4 4

PWR BTN/B

Marco Key/B

page 32

page 32 page 33

page 35

page 35

FAN LED/B

page 35

POGO/B

Light Bar Left/B

Light Bar Right/B

LOGO LED/B

A

page 35

page 35

page 35

RTC CKT.

Power On/Off CKT.

DC/DC Interface CKT.

Power Circuit DC/DC

page 23

page 41

page 25~26

page 72~97

MIO

DP

4 lane

Thunderbolt

AR4C

Power delivery

TPS65982

SATA3.0 SATA3.0SATA3.0 SATA3.0

B

SLI

Master GPU

Slave GPU

page 68,69

page 70

Card Reader

RTS5227

SD Conn.(IO/B)

B

PEG X8 (0~7)

8GT/s

PEG X8 (8~15)

8GT/s

PCIe x4

PCIe x1

page 32

SATA HDDM.2 SSD

Conn.Conn.Conn.Conn.Conn.

Cable Type

SATA3.0

6.0 Gb/s

SATA3.0

Kabylake H PROCESSOR

BGA1440

(42X28) (KBL-H_4+2)

Processor

PCIe

PCIe

Kabylake PCH - H

FCBGA(23X23)

837pin FCBGA

PCIe

LPC/eSPI BUS

CLK=24MHz

ENE

KB9022

page 38

C

Fan Control x5

Memory BUS

Dual Channel

1.2V DDR4 1866/2133

page 06~13

X4 DMI

USB Bus

CM238

HD Audio

3.3V 24MHz

page 08~24

SPI

SPI ROM

16M

page 19

TPM

page 40 page 40

C

G-Sensor

LIS3DHTR

D

page 39

260pin DDR4-SO-DIMM X2

260pin DDR4-SO-DIMM X2

USB3.0 USB3.0

page 32 page 32 page 32 page 32

USB3.0 USB3.0 USB3.0 USB3.0

FHD CAM Eye Tracker

Conn. Conn.

USB2.0 USB2.0 USB2.0

HDA Codec Speaker, Woofer

ALC299

page 36 page 37 page 36,37

USB3.0

Conn.(IO/B)Conn.(IO/B)

Conn.(USB/B)

Touch Screen

page 34page 65 page 65 page 33 page 33 page 31

USB/I2C

Ext Amp.

ALC1006

Head Phone

Amp.

MIC Jack

Conn.

SSSeeecccuuurrriiitttyyy CCClllaaassssssiiifffiiicccaaatttiiiooon

TTTHHHIIISSS SSSHHHEEEEEETTT OOOFFF EEENNNGGGIIINNNEEEEEERRRIIINNNGGG DDDRRRAAAWWWIIINNNGGG IIISSS TTTHHHEEE PPPRRROOOPPPRRRIIIEEETTTAAARRRYYY PPPRRROOOPPPEEERRRTTTYYY OOOFFF CCCOOOMMMPPPAAALLL EEELLLEEECCCTTTRRROOONNNIIICCCSSS,,, IIINNNCCC... AAANNNDDD CCCOOONNNTTTAAAIIINNNSSS CCCOOONNNFFFIIIDDDEEENNNTTTIIIAAALLL

AAANNNDDD TTTRRRAAADDDEEE SSSEEECCCRRREEETTT IIINNNFFFOOORRRMMMAAATTTIIIOOONNN...TTTHHHIIISSS SSSHHHEEEEEETTT MMMAAAYYY NNNOOOTTT BBBEEE TTTRRRAAANNNSSSFFFEEERRREEEDDD FFFRRROOOMMM TTTHHHEEE CCCUUUSSSTTTOOODDDYYY OOOFFF TTTHHHEEE CCCOOOMMMPPPEEETTTEEENNNTTT DDDIIIVVVIIISSSIIIOOONNN OOOFFF RRR&&&DDD

DDDEEEPPPAAARRRTTTMMMEEENNNTTT EEEXXXCCCEEEPPPTTT AAASSS AAAUUUTTTHHHOOORRRIIIZZZEEEDDD BBBYYY CCCOOOMMMPPPAAALLL EEELLLEEECCCTTTRRROOONNNIIICCCSSS,,,IIINNNCCC... NNNEEEIIITTTHHHEEERRR TTTHHHIIISSS SSSHHHEEEEEETTT NNNOOORRR TTTHHHEEE IIINNNFFFOOORRRMMMAAATTTIIIOOONNN IIITTT CCCOOONNNTTTAAAIIINNNSSS

MMMAAAYYY BBBEEEUUUSSSEEEDDD BBBYYY OOORRR DDDIIISSSCCCLLLOOOSSSEEEDDD TTTOOO AAANNNYYY TTTHHHIIIRRRDDD PPPAAARRRTTTYYY WWW IIITTTHHHOOOUUUTTT PPPRRRIIIOOORRR WWWRRRIIITTTTTTEEENNN CCCOOONNNSSSEEENNNTTT OOOFFF CCCOOOMMMPPPAAALLL EEELLLEEECCCTTTRRROOONNNIIICCCSSS,,, III NNNCCC...

IIIssussussueeeddd DDDaaattteee

nn

222000111666///000222///000111 222000111777///111222///333111

CCCooommmpppaaalll SSSeeecccrrreeettt DDDaaatttaaa

D

USB2.0

Conn.

Head Phone

Jack

Conn.

ON IO/B

DDDeeecicicippphhheeerrreeeddd DDDaaattteee

page 14,15

page 16,17

Offline USB Charger

USB3.0

Conn.(USB/B)

Key Board

page 32

E

POGO

Conn.Conn.

Touch Pad

USB2.0 USB2.0

CCCooompmpmpaaalll EEEllleeeccctttrororonnniiicccs,s,s, InInInccc...

TTTiiitttllleee

SSSiiizzzeee DDDooocucucumememennnttt NNNuuumbmbmb eeerrr RRReeevvv

CCCuuussstttooo mmm

DDDaaattt eee::: SSShhheeeeeettt ooo fff

BlBlBloooccckkk DDDiiiaaagggrrraaammmsss

C1C1C1PPPR2R2R2 LLLA-A-A-E0E0E0555111PPP

E

M.2

Blue Tooth

111...000

222 111000333MMMooonnndddaaayyy,,, JJJaaannnuuuaaarrryyy 000999,,, 222000111777

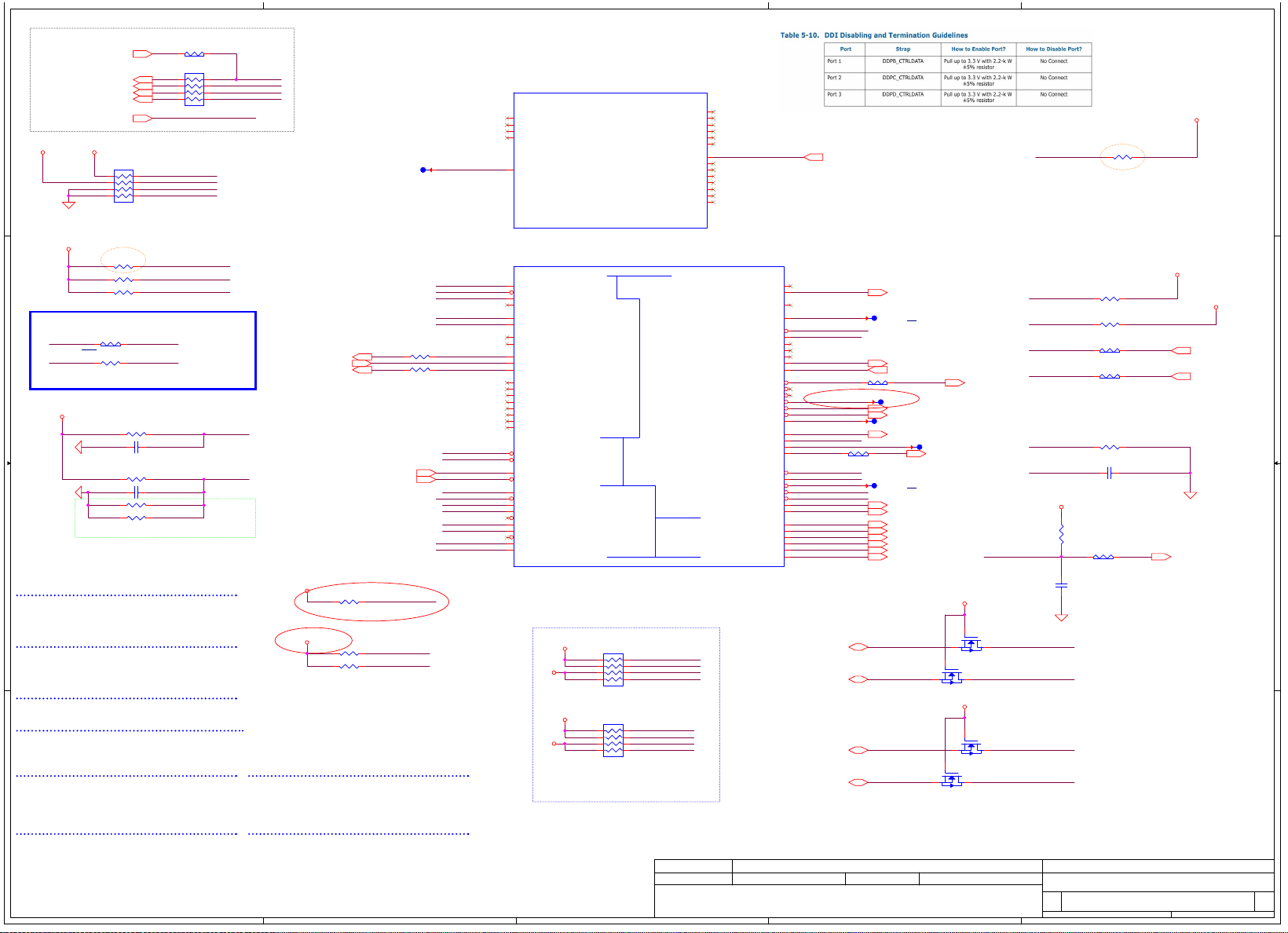

Page 3

A

B

C

D

E

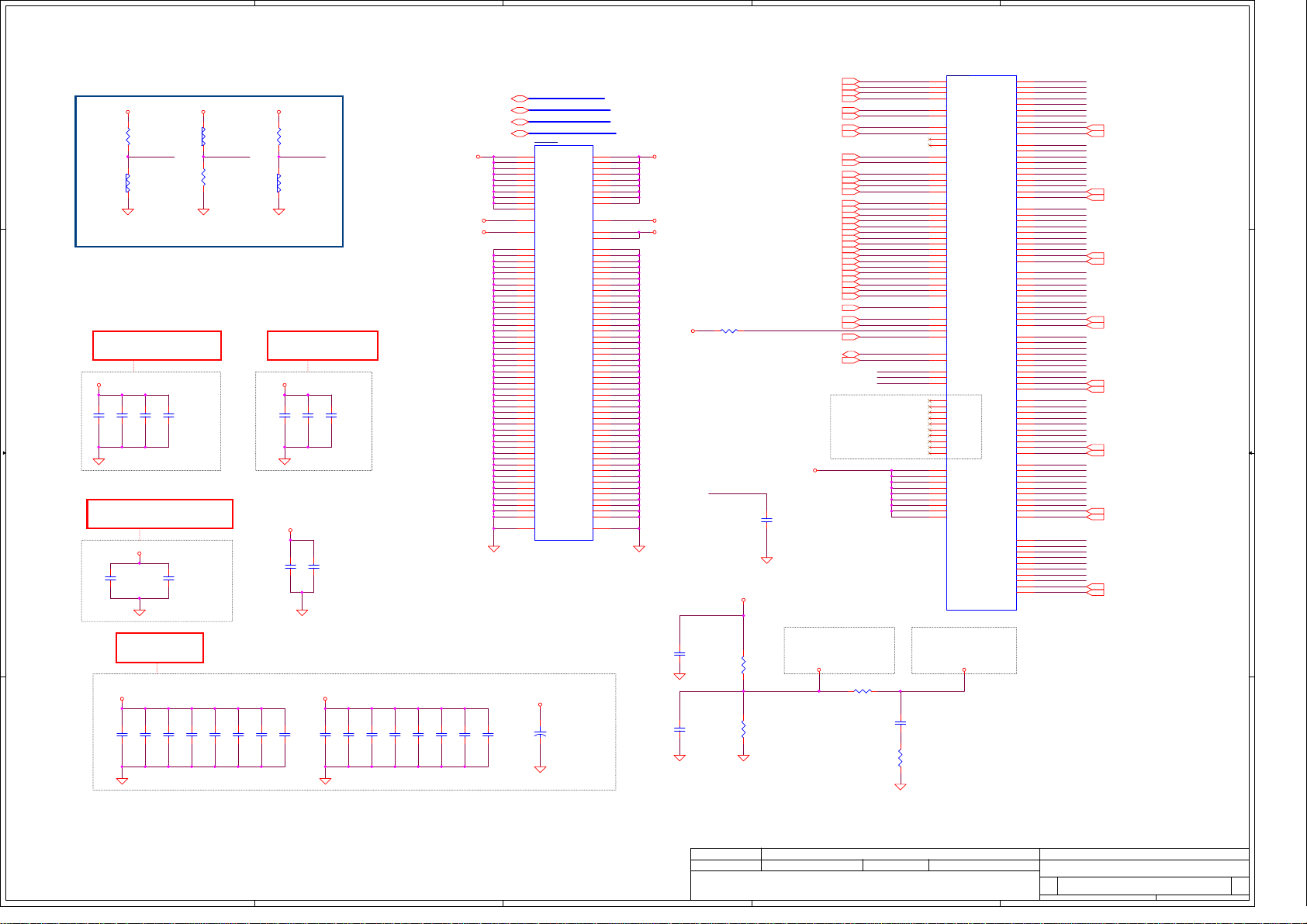

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

1 1

2 2

I2C Address Table

I2C_0 (+3VS) N/C

I2C_1 (+3VALW)

3 3

100K +/- 5%Ra

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

0

12K +/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

75K +/- 1%

100K +/- 1%

130K +/- 1%

160K +/- 1%

200K +/- 1%

240K +/- 1%

270K +/- 1%

330K +/- 1%

430K +/- 1%

560K +/- 1%

750K +/- 1%

NC

BUS

Rb V min

BID

0.423 V 0.430 V 0.438 V

1.398 V

1.634 V

1.849 V

2.015 V

2.185 V

2.316 V

2.395 V

2.521 V

2.667 V

2.791 V

2.905 V

3.000 V

Device

V typ

BID

0.000 V

1.414 V

1.650 V

1.865 V

2.031 V

2.200 V

2.329 V

2.408 V

2.533 V

2.677 V

2.800 V

2.912 V

3.000 V

Address(7 bit)

N/C

DIMM1

PCH_SMBCLK

(+3VS)

EC_SMB_CK1

(+3VLP)

EC_SMB_CK3

(+3VALW)

EC_SMB_CK2

(+3VS)

DIMM2

DIMM3

DIMM4

LIS3DHTR(G-sensor)

BQ24780 (Charger IC)

BATTERY PACK

PD(TPS65982)

9116 (LED driver, M/B)

5

59116 (LED driver, USB/B)

N17E-G3 (Master)

N17E-G3 (Slave)

0x30

0x12

0x16

0x00

0xC0

0xC2

0x9E

0x9C

AMP for SPK(ALC1006) 0x24

AMP for Woofer(ALC1006) 0x26

HP AMP (SV3S700)

External Thermal Sensor

0xE4

0x4D

V

max

BID

0.300 V

1.430 V

1.667 V

1.881 V

2.046 V

2.215 V

2.343 V

2.421 V

2.544 V

2.687 V

2.808 V

2.919 V

Address(8bit)

Write Read

EC AD

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3A0.691 V 0.702 V 0.713 V

0x3B - 0x450.807 V 0.819 V 0.831 V

0x46 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

0x65 - 0x76

0x77 - 0x87

0x88 - 0x96

0x97 - 0xA4

0xA5 - 0xAF

0xB0 - 0xB7

0xB8 - 0xBF

0xC0 - 0xC9

0xCA - 0xD4

0xD5 - 0xDD

0xDE - 0xF0

0xF1 - 0xFF

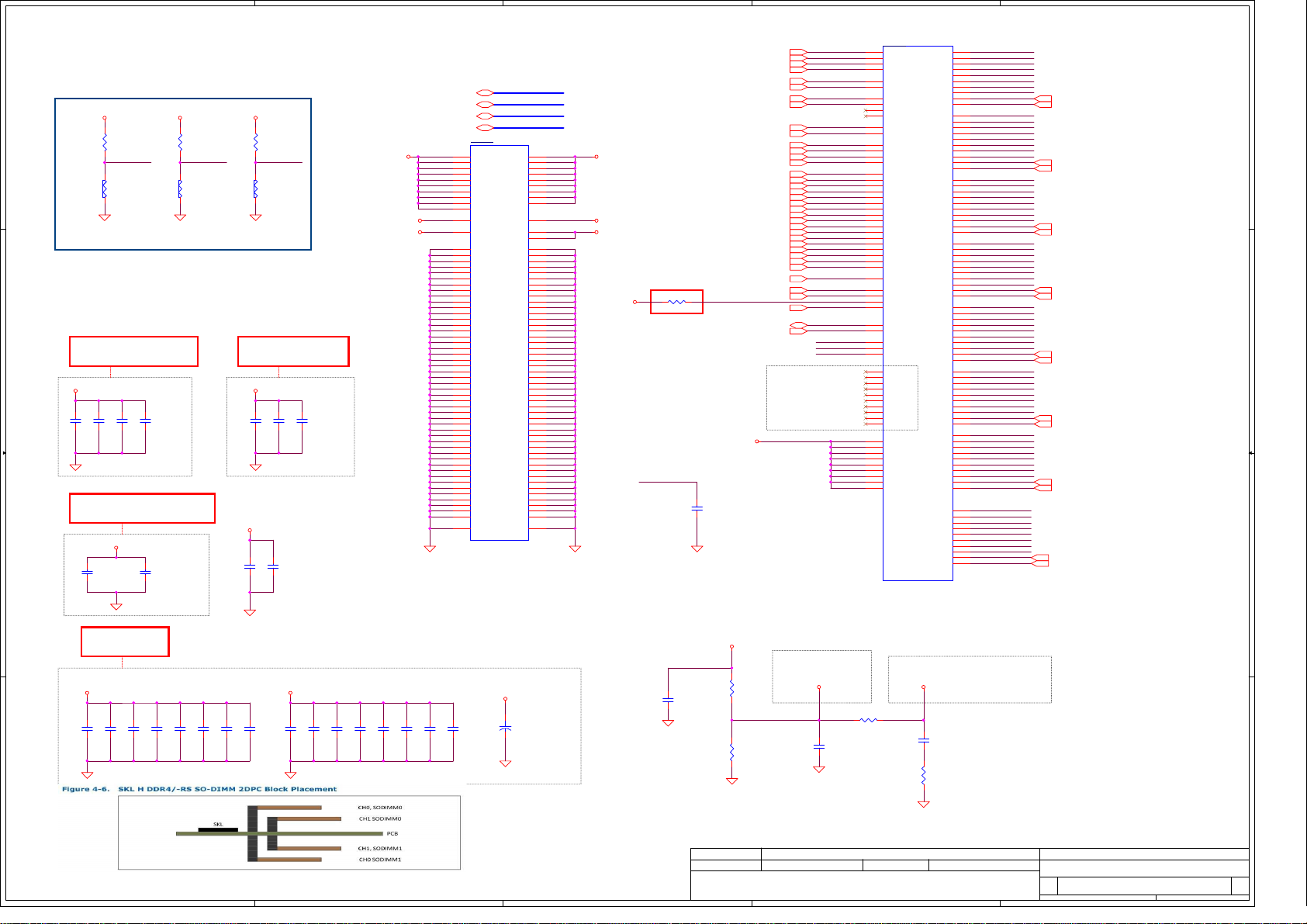

43 level BOM table

431A54BOL01

431A54BOL02 SMT MB AE051 C1PR2 G3 QL3X 2.4G HDMI

431A54BOL03 SMT MB AE051 C1PR2 G3 QLM4 2.9G HDMI QLM4@/QLF5@/CAM@/TBT@/TOBII@/CMC@/DA@

431A54BOL04 SMT MB AE051 C1PR2 I7-7820HK 2.9G HDMI SR32P@/SR30U@/CAM@/TBT@/TOBII@/CMC@/DA@

SMT MB AE051 C1PR2 G3 QL2X 2.7G HDMI QL2X@/QJGE@/CAM@/TBT@/TOBII@/CMC@/DA@

QL3X@/QJGE@/CAM@/TBT@/TOBII@/CMC@/DA@

BOM Structure43 Level Description

Power State

STATE

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW HIGH

BOM Structure Table

BOM Option Table

Item BOM Structure

Unpop @

Connector

EMC requirement depop

For EYE Tracker TOBII@

For Alpine Ridge TBT@

For HD camera power

For Intel CMC debug

TPM TPM@

For G-Sensor GSEN@

ESPI MODE for EC ESPI@

For PCB DA PN

HDMI logo P/N

For PCH

For CPU

CONN@

EMC@EMC requirement

XEMC@

CAM@

CMC@

DA@

45@

QJGE@,QLF5@,

SR30U@

QL3X@,QL2X@

QLM4@,SR32P@

ONONON

HIGH

LOWLOW

HIGH

OFF

ON

OFFLOW LOW LOW

OFF

OFF

OFF

OFF

OFF

OFF

Voltage Rails

Power Plane

+RTCVCC

+19V_VIN

+17.4V_BATT Battery power supply

+19VB

+3VLP

+5VALW

+3VALW System +3VALW always on power rail

+3VALW_DSW +3VALW power for PCH DSW rails

+3VALW_PCH_PRIM

+3VALW_SPI

+1.0VALW +1.0V Always power rail

+1.0V_VCCST

+5VS System +5V power rail

+3VS

+1.0VS_VCCSTG +1.0VALW_PRIM Gated version of VCCST

+0.6VS_VTT DDR +0.675VS power rail for DDR terminator .

+VCC_CORE

+VCC_GT

+VCCIO

+VCC_SA

+3VSDGPU

+1.8VSDGPU_AON

+NVVDD1

+NVVDD2

+1.35VSDGPU +1.5VS power rail for GPU

+1.0VSDGPU

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Description

RTC Battery Power

Adapter power supply

AC or battery power rail for power circuit.

+19VB to +3VLP power rail for suspend power

+5V Always power rail

+3VALW power for PCH power rails

+3VALW_PRIM supply for the SPI IO

DDR IV +1.2V power rail+1.2V_VDDQ

Sustain voltage for processor in Standby modes

System +3V power rail

Core voltage for CPU

Sliced graphics power rail

CPU IO power rail

System Agent power rail

+3VS power rail for GPU circuit

+1.8VALW power rail for GPU(AON rails)

+1.8VS power rail for GPU GC6+1.8VSDGPU_MAIN

Core voltage for VGA

Core voltage for VGA

+1.05VS power rail for GPU

NV name COMPAL name

NVVDD

FDVDD

FBVDDQ

VPP

IFP_IOVDD

IFPx_PLLVDD

PEX_DVDD

/

PEX_HVDD

PEX_PLL_HVDD

FBx_PLL_AVDD

GPCPLL_AVDDx/Core_PLLVDD

VID_PLLVDD

4 4

SP_PLLVDD

1V8_MAIN +1.8VSDGPU_MAIN

1V8_AON

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

0.3

1.0

+NVVDD1

+NVVDD2NVVDDS

+1.35VSDGPU

+1.35VSDGPU

+1.8VSDGPU_AON

+1.0VSDGPU

+1.8VSDGPU_MAIN

+1.0VSDGPU

+1.8VSDGPU_MAIN

+1.8VSDGPU_MAIN

+1.8VSDGPU_MAIN

+1.8VSDGPU_MAIN

+1.8VSDGPU_MAIN

+1.8VSDGPU_AON

S0

ON

N/A N/A N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

S4

S3

ON ON

ON

N/A

N/A

N/A N/A

N/A

ON ON

ON

ON ON

ON

ON

ON

ON ON

ON

ON

ON ON ONON

ON

ON

OFF

ON

OFF

OFF

OFF

OFF OFF

OFF OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF OFF OFF

OFF

OFF

OFF OFF

OFF

OFF OFF

OFF

OFF OFF

OFFOFF

OFF OFF OFF

OFF OFF OFF

S5

N/AN/AN/A

ON*

ON*ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFOFF

OFFOFF

OFF

OFF

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

E

3 103Monday, January 09, 2017

3 103Monday, January 09, 2017

3 103Monday, January 09, 2017

1.0

1.0

1.0

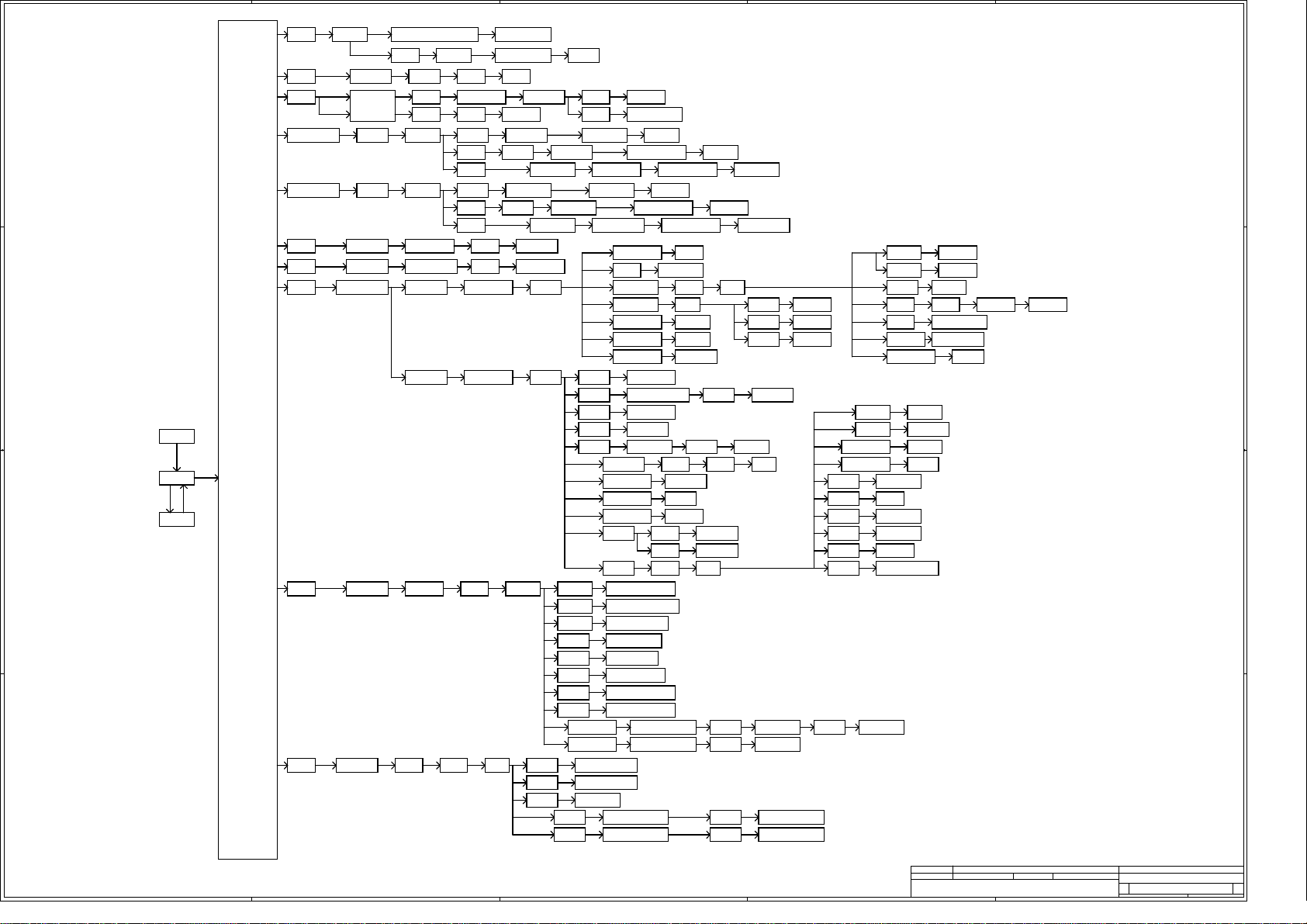

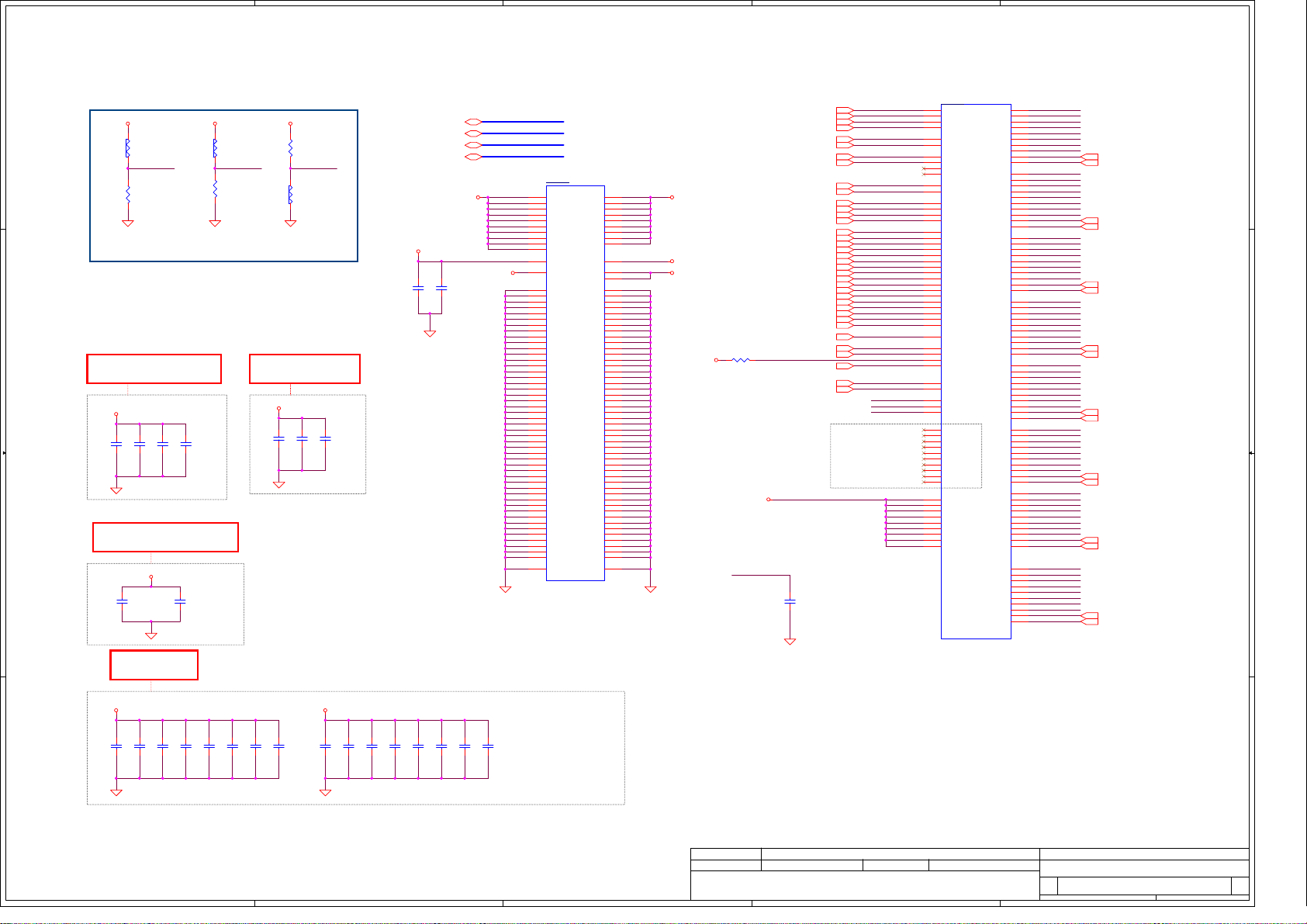

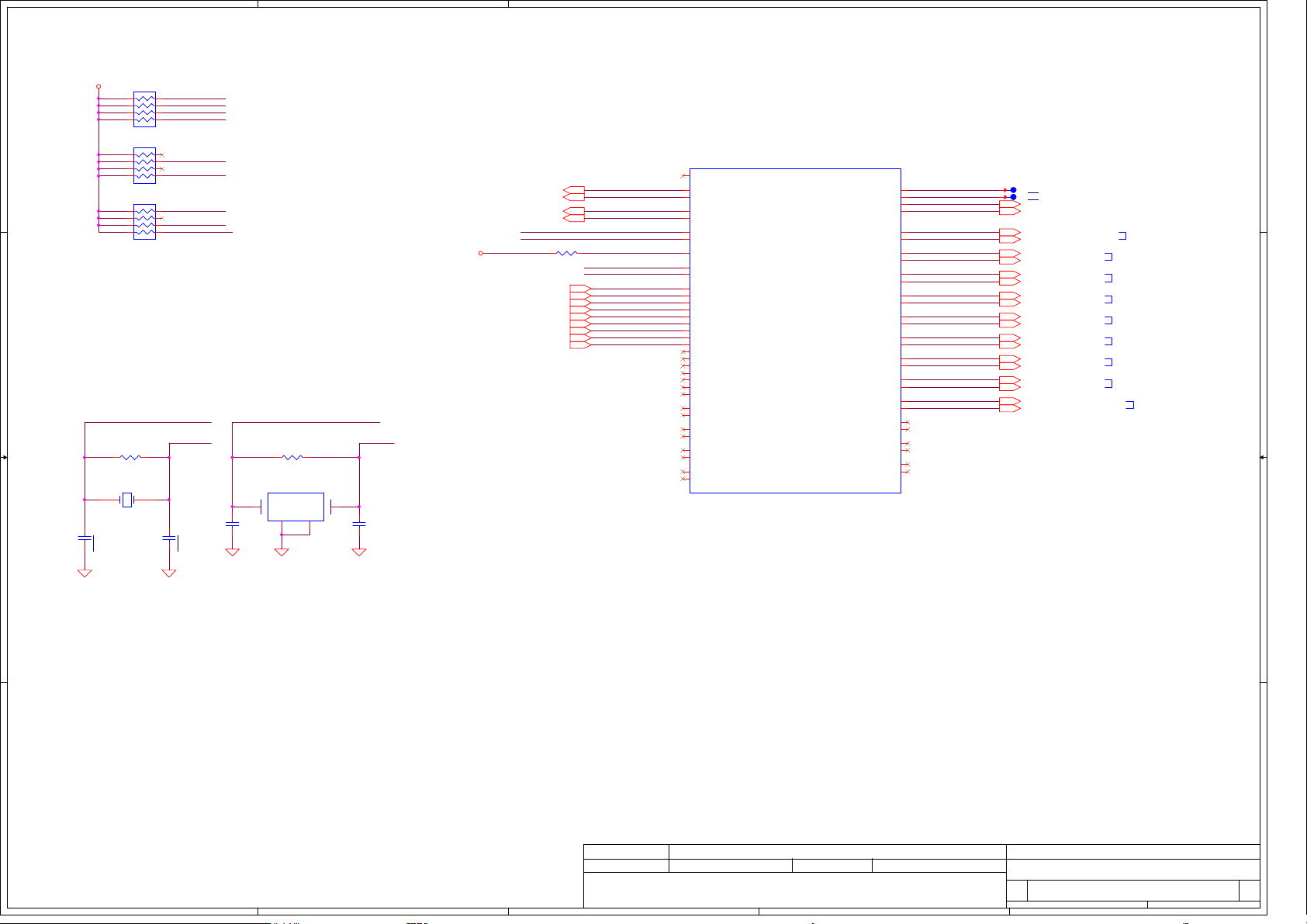

Page 4

5

4

3

2

1

JUMP

(PJ703)

+VCCIOP_EN

JUMP

(PJ701)

JUMP

(PJ506)

D D

C C

SM_PG_CTRL

JUMP

(PJ1301 ,PJ13 02)

JUMP

(PJ1901 ,PJ19 02)

EN_1VGAP

JUMP

(PJ1601 )

EN_1VGAPS

JUMP

(PJ2402 )

5V_EN

3V_EN

JUMP

(PJ401)

ADAPTER

CHARGER

B+

BATTERY

B B

EN_1VALW

JUMP

(PJ601)

SUSP#

JUMP

(PJ2201 )

A A

+CPU_B+

SYSON

TPS51225CRUKR

(PU401)

SY8286RAC

(PU2201)

DRON

SY8286RAC

(PU701)

RT8207PGQW

(PU501)

0 ohm

(PR1301 )

0 ohm

(PR1901 )

SY8288RAC

(PU1601)

SY8286RAC

(PU2405)

SY8288RAC

(PU601)

NCP81151MNT BG

(PU901,PU903,PU904,PU9 05)

JUMP

(

PJ704)

+VCCIOP

+1.2VP

+0.6VSP

GPU1_B+

GPU2_B+

+1.0VS_VGAP +1.0VS DGPU

+1.0VS_VGAP_S

+5VALWP

+3VALWP

+1.0VALWP +1.0VALW

+1.8VSP +1.8VS

SA_B+

JUMP

(PJ2202 )

DRON

JUMP

(PJ702)

JUMP

(PJ501, PJ50 2)

JUMP

(PJ503)

0 ohm

(PR1302 )

JUMP

(PJ1401 )

JUMP

(PJ1701 )

0 ohm

(PR1902 )

JUMP

(PJ2001 )

JUMP

(PJ2301 )

JUMP

(PJ1602 )

JUMP

(PJ2303 )

JUMP

(PJP404 ,PJP4 05)

JUMP

(PJP402 ,PJP4 03)

JUMP

(PJ602)

NCP81253MNT BG

(PU902)

+VCCIO

+0.6VS_VTT

0 ohm

(PR1402 )

1.35VSDGPU_EN

0 ohm

(PR2002 )

1.35VSDGPU_EN_S

+VCCCORE

+1.2V_VDDQ

NVVDD1_B+

RT8812AGQW

(PU1701)

NVVDD1_S_B+

RT8812AGQW

(PU2301)

+1.0VSDGPU_ S

+5VALW

+3VALW

R-Short

(RA71)

R-Short

(RA70)

R-Short

(RA56)

1V8_AON_EN

1V8_AON_EN_S

NVVDD1_EN

NVVDD2_B+

NVVDD1_EN_S

NVVDD2_S_B+

FBMA-L11

(LH1)

FBMA-L11

(LH2)

FBMA-L11

(LH3)

0 ohm

(RH113 )

0 ohm

(RH86)

0 ohm

(RH138 )

0 ohm

(RH140 )

0 ohm

(RH141 )

SYSON

SUSP#

AOZ1331

(UG12)

AOZ1331

(UG30)

+VCCSA

0 ohm

(RC41)

0 ohm

(RC42)

UP9511PQGJ

(PU1201)

NVVDD2_EN

+1.35VS_VGAP

UP9511PQGJ

(PU1801)

NVVDD2_EN_S

+1.35VS_VGAP_S

USBKB_EN

SUSP#

FAN_EN

TOBII_EN

POGO_EN

CAM_EN

0 ohm

(RH135 )

0 ohm

(RH89)

0 ohm

(RH136 )

R-Short

(R315)

0 ohm

(R312)

SYSON

WLAN_PW R_EN

LAN_PWR _EN

LBPWR_EN

SUSP#

SUSP#

TPS22961DNYR

(U40)

TPS22961DNYR

(U42)

+1.8VS_AVDD_AMP

+1.8VS_DVDD_AMP

+1.8VS_AVDD

+VDDQ_CLK

+1.2V_VCCPLL_O C

+NVVDD1

NCP81278MNT XG

(PU1401)

+NVVDD1_S

NCP81278MNT XG

(PU2001)

SY6288C20A AC

(U12)

JUMP

(J29)

AOZ1331

(U41)

RT8525DGQW

(PU2403)

SY6288C20A AC

(U19)

SY6288C20A AC

(U13)

SY6288C20A AC

(U18)

+3VALW_DSW

+3VALW_PCH_PRIM

+3VALW_HDA

+3VALW_PD

+3.3V_TBT_SX

SY8003ADFC

(PU502)

SY6288C20A AC

(U9)

SY6288C20A AC

(UL3)

SY6288C20A AC

(UE3)

AOZ1331

(U43)

AOZ1331

(U41)

JUMP

(J17)

JUMP

(J27)

JUMP

(J16)

+1.0VALW_AMPHYPLL

+1.0VALW_AUSB_AZPLL

+1.0VALW_VCCCLK5

+1.0VALW_MPHY

+1.0VALW_PRIM

+1.0VALW_VCCCLK

+1.0VALW_PRIMAL22

+1.0VALW_PRIMAD15

+1.0V_VCCST_OUT

+1.0VS_VCCSTG_O UT

+1.8VSDGPU_AON

+1.8VSDGPU_AON_S

+NVVDD2

JUMP

(PJP170 1,PJP 1702 )

+1.35VSDGPU

+NVVDD2_S

JUMP

(PJP230 1,PJP 2302 )

+1.35VSDGPU_S

+5V_KB

+5VALW_PD

JUMP

+5VS

(J15)

+12VS

+5V_TOBII

+5V_POGO

0 ohm

(R353)

0 ohm

(R358)

0 ohm

(R355)

+5V_3DCAM

0 ohm

+3VALW_SPI

(RH27)

0 ohm

(R313)

+2.5VP +2.5V

JUMP

(PJ505)

+3VS_TBT

+3VS_WLAN

+3V_LAN

+5V_LBPWR

+3VS_NGFF1

+3VS_NGFF2

+3VS

0 ohm

R343)

(

0 ohm

(R347)

1V8_MAIN_EN

AOZ1331

(UG12)

1V8_MAIN_EN_S

AOZ1331

(UG30)

+VCC_FAN1

+VCC_FAN2

+VCC_FAN3

+1.0V_VCCST

+1.0V_VCCSTG

+1.8VSDGPU_MAIN

+1.8VSDGPU_MAIN_S

3VSDGPU_EN_R

3VSDGPU_EN_S_R

CAM_EN

+3VS

0 ohm

(RH87)

0 ohm

(R360)

0 ohm

(R219)

0 ohm

(RA5)

0ohm

(RA1)

0 ohm

(RA72 )

0 ohm

(RC40)

EN_DFAN

DGPU_ENVDD

TPS22961

(UG14)

TPS22961

(UG29)

SY6288C20A AC

(U16)

SY6288C20A AC

(UV3)

+1.0V_VCCSFR

NCT3942S

(U29)

NCT3942S

(U46)

0 ohm

(R412)

JUMP

(J18)

JUMP

(J28)

AP2330W

(UV1)

SY6288C20A AC

(U34)

+3VSDGPU

+3VSDGPU_S

+3VS_CAM

+3VS_DP

+3VS_VCCATS

+3V_RD

+3VS_TPM

+3VS_DVDDIO

+3VS_DVDD

+3VS_DVDDIO_AMP

+VCC_FAN4

+VCC_FAN5

+5VS_HDD

+VDDA

+5VS_PVDD_AMP

+HDMI_5V_OUT

+LCDVDD

HCB2012KF

(

LA2)

+5VS_AVDD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Map

Power Map

Power Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 103Monday, January 09, 2017

4 103Monday, January 09, 2017

4 103Monday, January 09, 2017

1.0

1.0

1.0

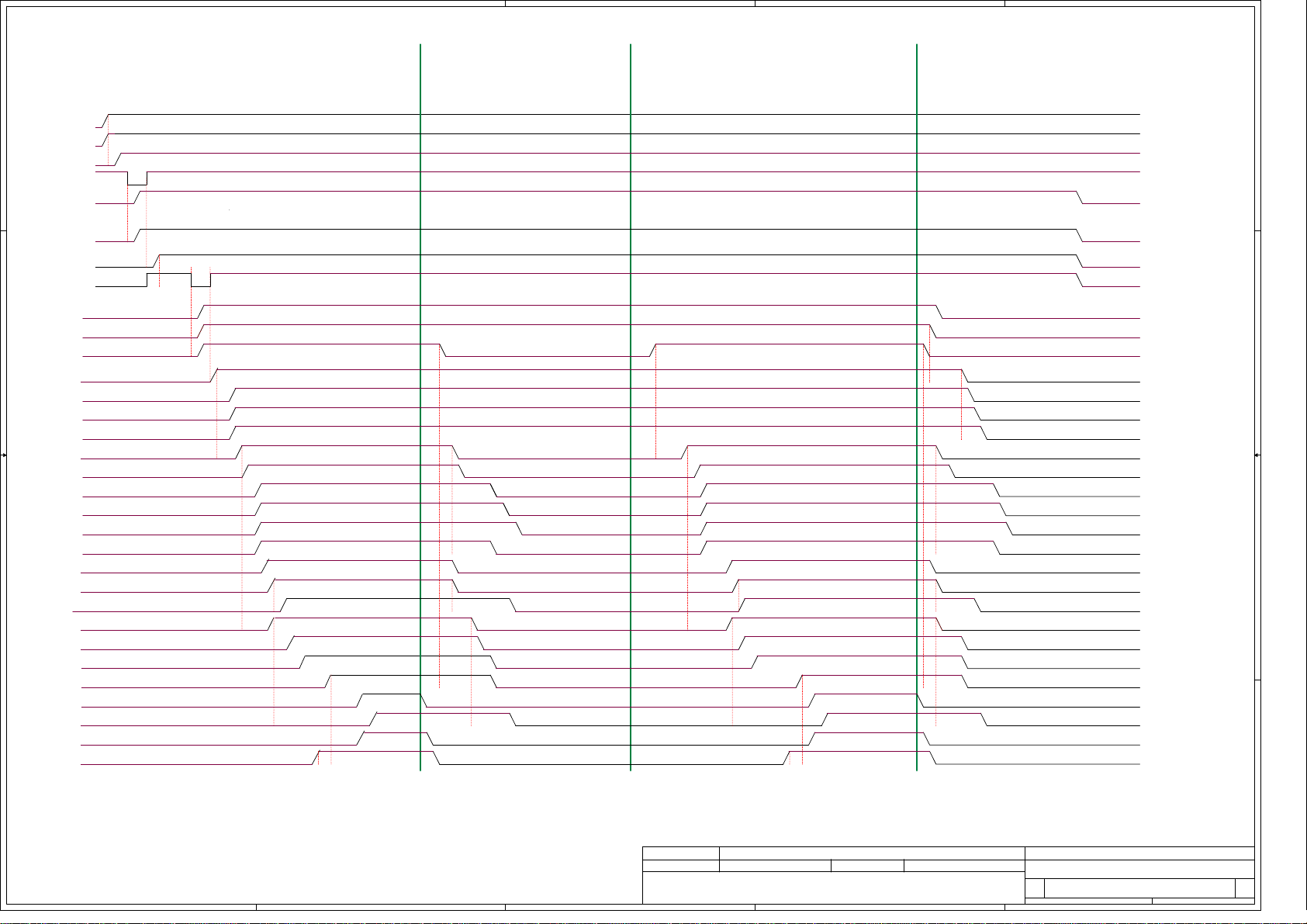

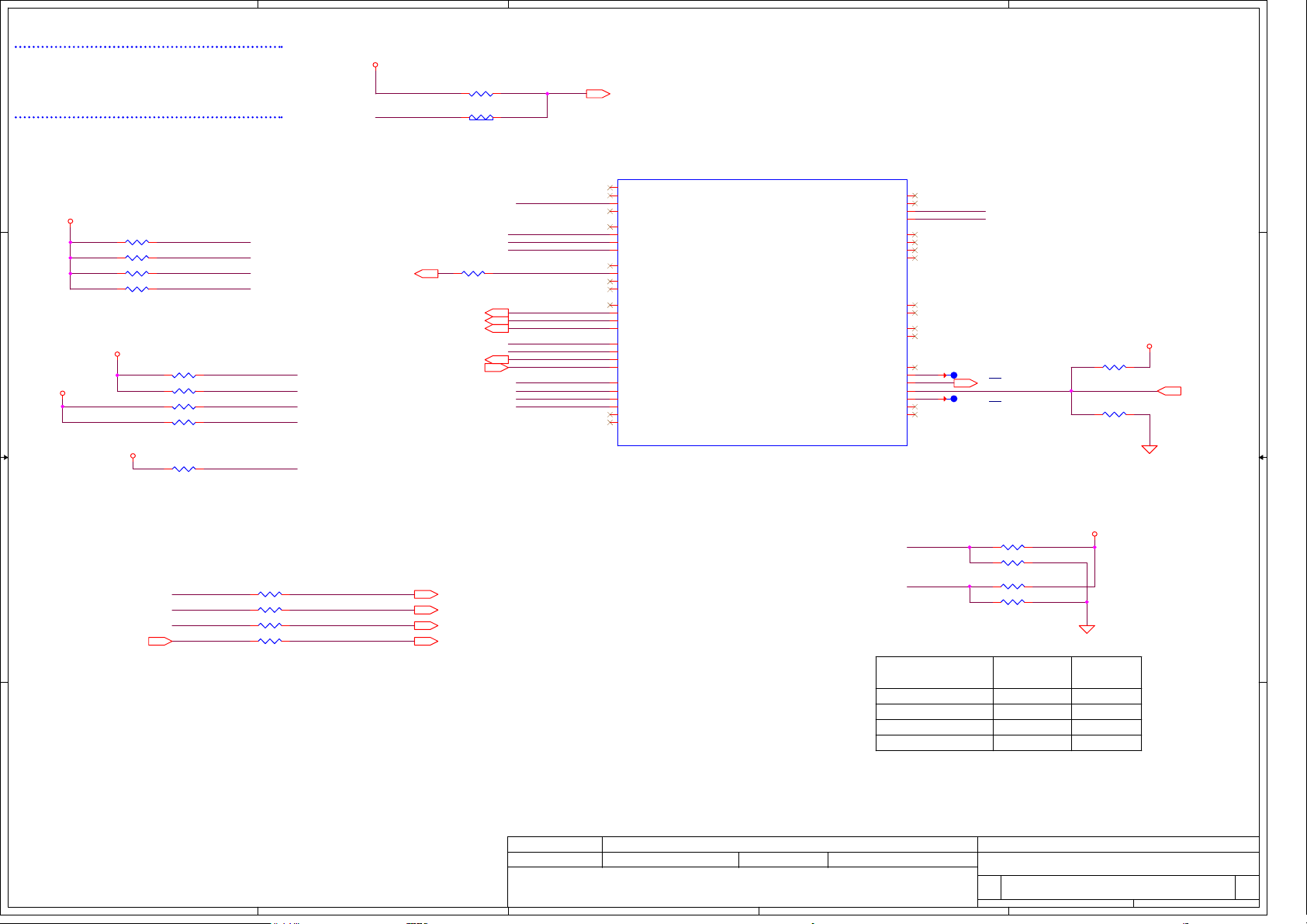

Page 5

5

4

3

2

1

BIOS : 0.04

AC mode

Power On

S3 S3 Resume

Power Off

Plug in

+3VLP

D D

EC_ON

+5VALW

→

ON/OFFBTN#

+3VALW

92.95ms

→

→

8.914

+3VLP

EC_ON

+5VALW

ON/OFFBTN#

+

3VALW

→

+1.0ALW

EC_RSMRST#

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S4#

C C

PM_SLP_S3#

SYSON

+1.0V_VCCST

+1.2V_VDDQ

+2.5V

SUSP#

+1.0VS_VCCSTG

+VCCIO

+1.8VS

+3VS

+5VS

B B

EC_VCCST_PG

DDR_PG_CTRL

+0.6VS_VTT

VR_ON

+VCCSA

PCH_PWROK

SYS_PWROK

PLT_RST#

+VCCCORE

PLTRST_CPU#

H_CPUPWRGD

93.42ms

30.4ms

→

→

121.1ms

21ms

←

←

→

16.52ms

→

16.56ms

→

16.58ms

→

→

69.64us

9.95us

→

→

584.8us

5.366ms

→

18.2ms

→

12.76us

→

287.3us

→

260.3us

→

1.431ms

→

1.372ms

→

37.63ms

→

37.63ms

→

13.03us

→

37.64ms

2.067ms

→

17.25ms

→

→

→

148.4ms

2.068ms

→

153.8ms

2.068ms

→

49.57ms

→

358.5us

→

13.85us

→

118.5us

→

1.053ms

→

→

→

→

→

→

→

→

→

11.04ns

→

83.9us

→

6.877us

7.297us

11.17us

→

→

3.84ms

3.03ms

529.6us

1.981ms

116.6us

171.6us

184us

529.4us

8.493ms

→

14us

→

258.3us

→

256.8us

→

1.288ms

→

1.389ms

→

→

→

→

28.86ms

28.86ms

→

28.86ms

→

→

→

→

12.14us

2.077ms

14.16ms

164.6ms

1.526ms

→

169ms

1.526ms

→

54.47ms

→

→

→

→

→

533.3us

→

461.6us

→

359.1us

4.51us

→

→

122.3us

→

1.079ms

→

17.87ms

→

14.02us

→

154.3us

→

→

→

→

→

7.824us

→

8.395us

→

→

11.17us

→

→

→

1.3ms

4.086ms

3.266ms

1.994ms

1.341ms

123.2us

164.9us

177.3us

8.95S

8.392S

8.392S

1.0ALW

+

EC_RSMRST#

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

S

YSON

+1.0V_VCCST

+1.2V_VDDQ

+2.5V

SUSP

+1.0VS_VCCSTG

+VCCIO

+1.8VS

+3VS

+5VS

EC_VCCST_PG

DDR_PG_CTRL

+0.6VS_VTT

VR_ON

+VCCSA

PCH_PWROK

SYS_PWROK

PLT_RST#

→

→

28.52ns

→

83.29us

569.1us

+VCCCORE

PLTRST_CPU#

H_CPUPWRGD

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

1

5 103Monday, January 09, 2017

5 103Monday, January 09, 2017

5 103Monday, January 09, 2017

1.0

1.0

1.0

Page 6

A

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

UC1

1 1

2 2

QL3X@

S IC CL8067702869811 QL3X A0 2.4G FCBGA 1440

SA0000A1520

QL2X@

UC1

S IC CL8067702869810 QL2X A0 2.7G FCBGA 1440

SA0000A1320

UC1

QLM4@

S IC CL8067702870009 QLM4 B0 2.9G BGA

SA0000ADA10

UC1

SR32P@

S IC CL8067702870009 SR32P B0 2.9G ABO!

SA0000ADA30

J34

H37

H36

J37

J38

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

S

KL-H_BGA1440

@

UC1D

B

SKYLAKE_HAL O

BGA1440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

EDP_COMP

D37

EDP_COMP

Trace = 20 mils

Spacing = 25 mils

Max lenght = 100 mils

G27

G25

G29

?REV = 1

CPU_DISPA_SDI

12

RC47 20_0402_1%

C

+VCCIO

12

RC124.9_0402_1%

CPU_DISPA_BCLK_R <20>

CPU_DISPA_SDO_R <20>

CPU_DISPA_SDI_R <20>

D

E

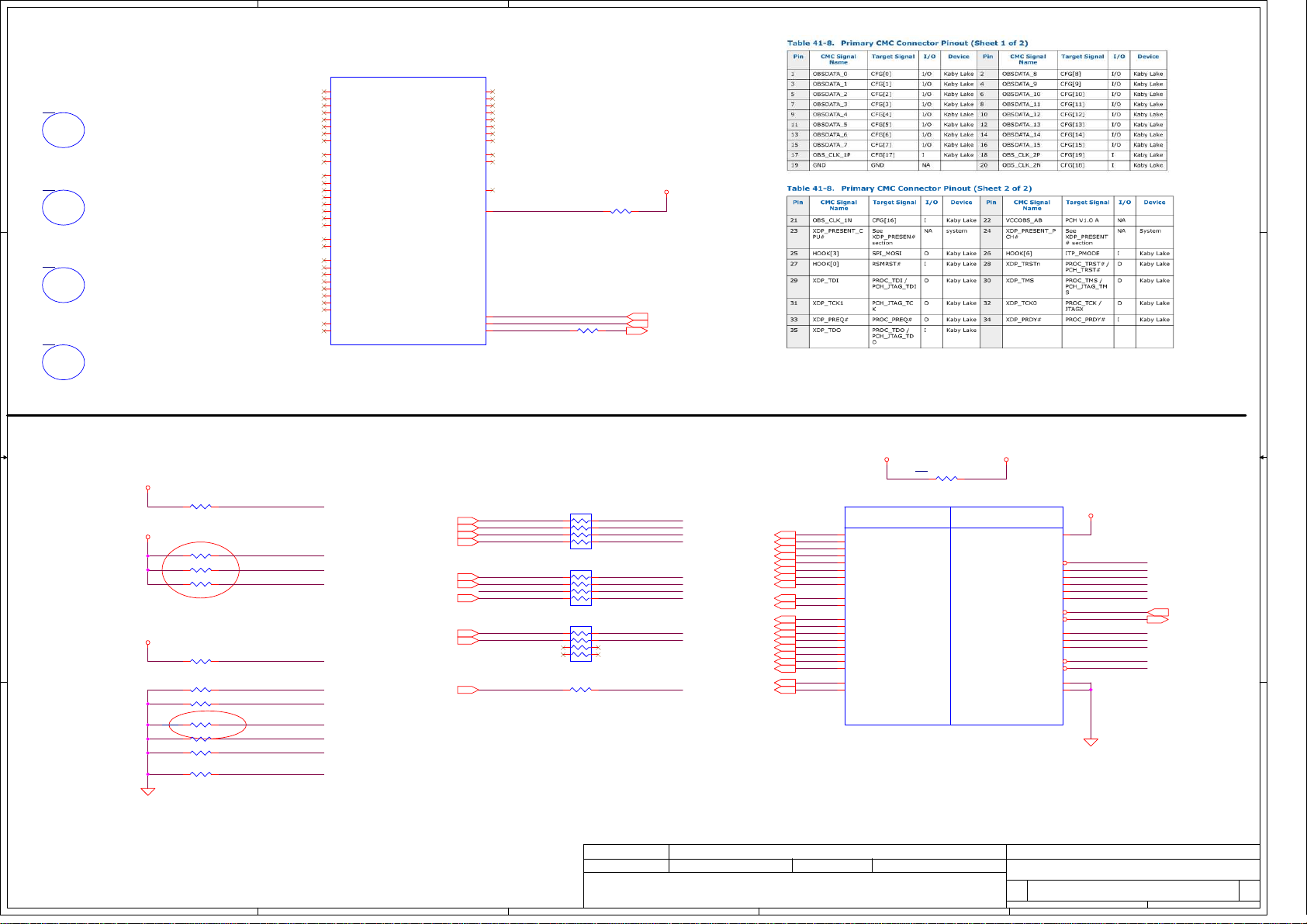

CMC CONN

RC3 0_0603_5%CMC@

+3VALW_PCH_PRIM

1 2

RC2 1K_0402_5%

+1.0VS_VCCSTG

RC4 51_0402_5%

3 3

Place to CPU side

Place to CPU side

4 4

RC5 51_0402_5%

RC6 51_0402_5%

+1.0VALW_XDP

RC8 2.2K_0402_5%CMC@

RC10 0_0402_5%@

RC11 0_0402_5%@

RC13 51_0402_5%

RC15 51_0402_5%@

RC17 51_0402_5%@

RC60 1K_0402_5%@

12

12

12

1 2

12

12

12

12

12

1 2

XDP_SPI_SI

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

XDP_ITP_PMODE

XDP_PRSENT_CPU

XDP_PRSENT_PCH

CPU_XDP_TCK0

PCH_JTAG_TCK1

CPU_XDP_TRST#

CFG0

CMC@

CPU_XDP_TDO<9,20>

CPU_XDP_TDI<9,20>

CPU_XDP_TMS<9,20>

CPU_XDP_TCK0<9,20>

CPU_XDP_TRST#<9,24>

PCH_JTAG_TCK1<20>

XDP_SPI_IO2<19>

XDP_SPI_SI<19>

XDP_ITP_PMODE<20>

EC_RSMRST#<20,38>

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TCK0

CPU_XDP_TRST#

PCH_JTAG_TCK1

CFG3

XDP_SPI_IO2

XDP_SPI_SI

XDP_ITP_PMODE XDP_HOOK6

RPC1

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

CMC@

RPC2

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

CMC@

RPC3

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

1 2

CMC@

RC56 1K_0402_5%

XDP_TDO

XDP_TDI

XDP_TMS

XDP_TCK0

XDP_TRST#

XDP_TCK1

XDP_PRSENT_CPU

XDP_PRSENT_PCH

XDP_HOOK3

XDP_HOOK0EC_RSMRST#

CFG0<9>

CFG1<9>

CFG2<9>

CFG3<9>

CFG4<9>

CFG5<9>

CFG6<9>

CFG7<9>

CFG17<9>

CFG16<9>

CFG8<9>

CFG9<9>

CFG10<9>

CFG11<9>

CFG12<9>

CFG13<9>

CFG14<9>

CFG15<9>

CFG19<9>

CFG18<9>

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG19

CFG18

JPCMC1

OBS DATA

1

DATA_0

3

DATA_1

5

DATA_2

7

DATA_3

9

DATA_4

11

DATA_5

13

DATA_6

15

DATA_7

17

DATA_CLK_1P

21

DATA_CLK_1N

2

DATA_8

4

DATA_9

6

DATA_10

8

DATA_11

10

DATA_12

12

DATA_13

14

DATA_14

16

DATA_15

18

DATA_CLK_2P

20

DATA_CLK_2N

INTEL_CMC_PRIMARY

CONN@

1 2

CMC_DEBUG_36P

+1.0VALW_XDP+1.0VALW_PRIM

JTAG/RC/HOOKS

VCCOBS_AB

XDP_TRST*

XDP_TDI

XDP_TMS

XDP_TCK0

XDP_TCK1

XDP_TDO

XDP_PREQ*

XDP_PRDY*

HOOK_0

HOOK_3

HOOK_6

XDP_PRSNT_PCH*

XDP_PRSNT_CPU*

GND

<MT> GND

+1.0VALW_XDP

22

XDP_TRST#

28

XDP_TDI

29

XDP_TMS

30

XDP_TCK0

32

XDP_TCK1

31

XDP_TDO

35

XDP_PREQ#

33

XDP_PRDY#

34

XDP_HOOK0

27

XDP_HOOK3

25

XDP_HOOK6

26

XDP_PRSENT_PCH

24

XDP_PRSENT_CPU

23

19

36

XDP_PREQ# <9,24>

XDP_PRDY# <9,24>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPALELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANYTHIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANYTHIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

A

B

MAYBE USED BY OR DISCLOSED TO ANYTHIRD PARTYWITHOUT PRIOR WRITTEN CONSENT OF COMPALELECTRONICS, INC.

C

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

D

Date: Sheet o f

Compal Electronics, Inc.

SKL-H(1/9)DDI,EDP

SKL-H(1/9)DDI,EDP

SKL-H(1/9)DDI,EDP

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

E

6 103Monday, January 09, 2017

6 103Monday, January 09, 2017

6 103Monday, January 09, 2017

1.0

1.0

1.0

Page 7

A

B

C

D

E

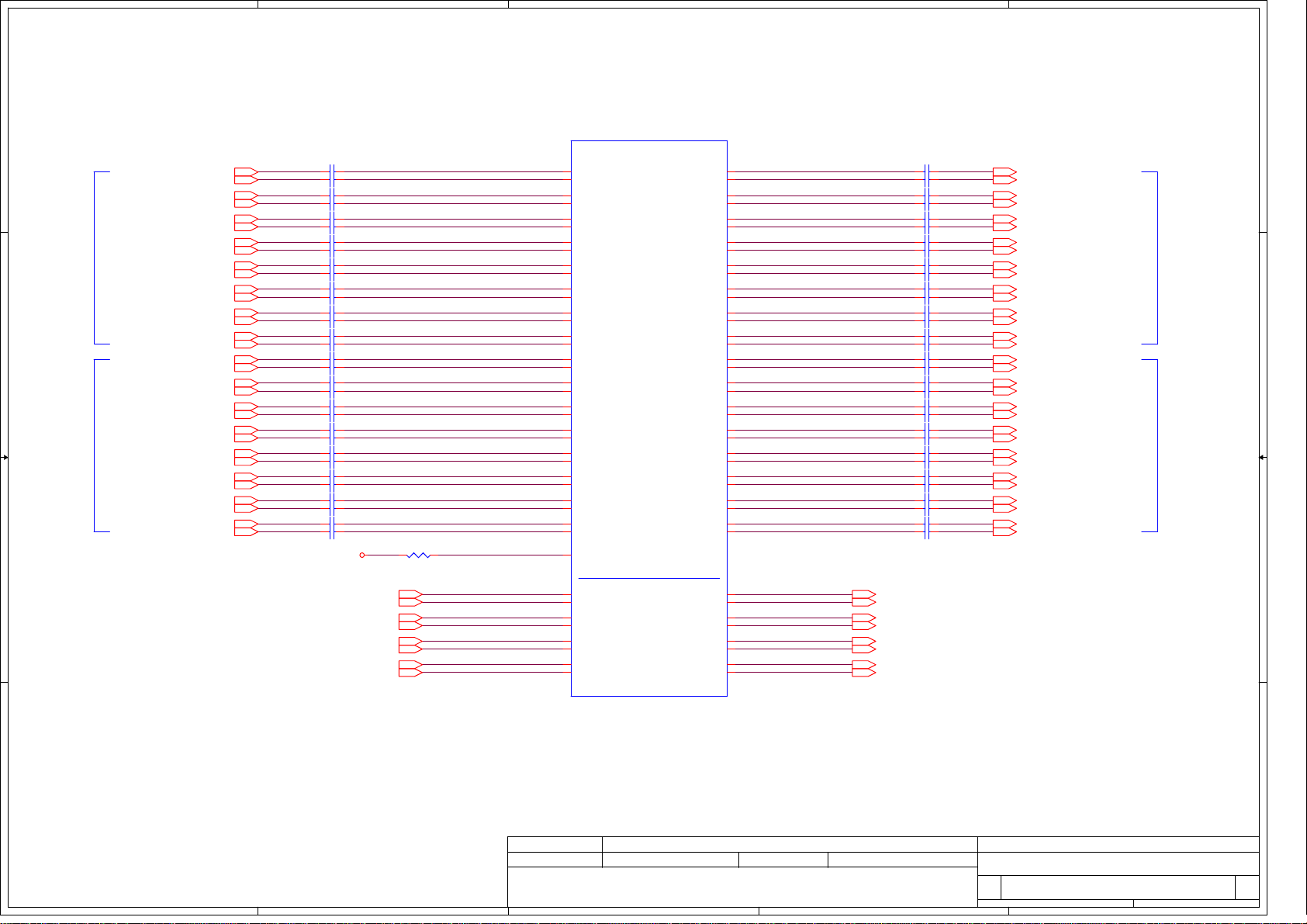

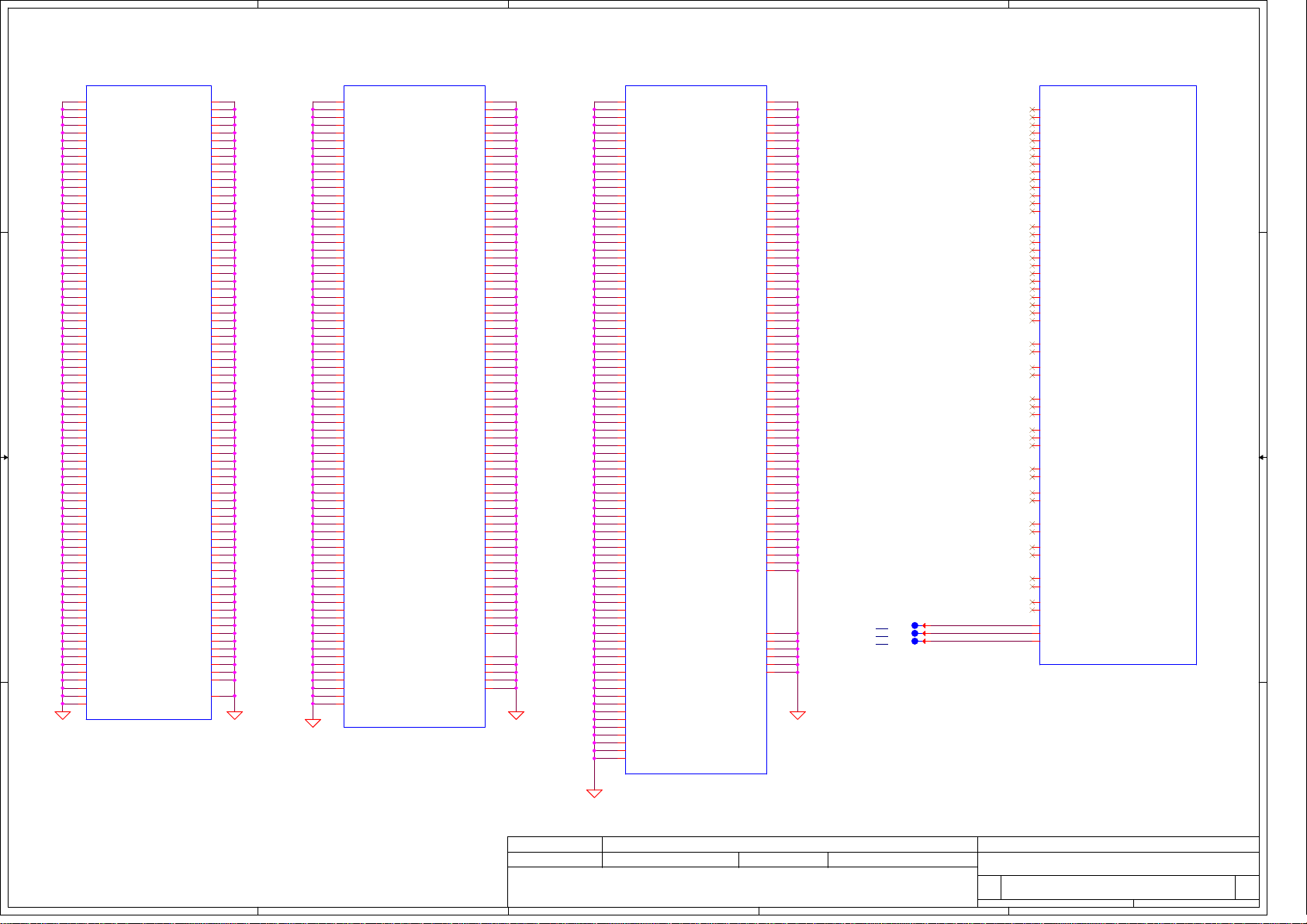

CHANNEL-A

Interleaved Memory

1 1

DDR_A_D[0..15]<14,15>

DDR_A_D[16..31]<14,15>

DDR_A_D[32..47]<14,15>

2 2

DDR_A_D[48..63]<14,15>

3 3

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

S

KL-H_BGA1440

REV = 1

@

SKYLAKE_HALO

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

?

DDR_A_CLK0

AG1

DDR_A_CLK#0

AG2

DDR_A_CLK#1

AK1

DDR_A_CLK1

AK2

DDR_A_CLK2

AL3

DDR_A_CLK#2

AK3

DDR_A_CLK3

AL2

DDR_A_CLK#3

AL1

DDR_A_CKE0

AT1

DDR_A_CKE1

AT2

DDR_A_CKE2

AT3

DDR_A_CKE3

AT5

DDR_A_CS#0

AD5

DDR_A_CS#1

AE2

DDR_A_CS#2

AD2

DDR_A_CS#3

AE5

DDR_A_ODT0

AD3

DDR_A_ODT1

AE4

DDR_A_ODT2

AE1

DDR_A_ODT3

AD4

DDR_A_BA0

AH5

DDR_A_BA1

AH1

DDR_A_BG0

AU1

DDR_A_RAS#

AH4

DDR_A_WE#

AG4

DDR_A_CAS#

AD1

DDR_A_MA0

AH3

DDR_A_MA1

AP4

DDR_A_MA2

AN4

DDR_A_MA3

AP5

DDR_A_MA4

AP2

DDR_A_MA5

AP1

DDR_A_MA6

AP3

DDR_A_MA7

AN1

DDR_A_MA8

AN3

DDR_A_MA9

AT4

DDR_A_MA10

AH2

DDR_A_MA11

AN2

DDR_A_MA12

AU4

DDR_A_MA13

AE3

DDR_A_BG1

AU2

DDR_A_ACT#

AU3

DDR_A_PAR

AG3

DDR_A_ALERT# DDR_B_PAR

AU5

DDR_A_DQS#0

BR5

DDR_A_DQS#1

BL3

DDR_A_DQS#2

BG3

DDR_A_DQS#3

BD3

DDR_A_DQS4

AB3

DDR_A_DQS5

V3

DDR_A_DQS6

R3

DDR_A_DQS7

M3

DDR_A_DQS0

BP5

DDR_A_DQS1

BK3

DDR_A_DQS2

BF3

DDR_A_DQS3

BC3

DDR_A_DQS#4

AA3

DDR_A_DQS#5

U3

DDR_A_DQS#6

P3

DDR_A_DQS#7

L3

AY3

BA3

DDR_A_CLK0 <14>

DDR_A_CLK#0 <14>

DDR_A_CLK#1 <14>

DDR_A_CLK1 <14>

DDR_A_CLK2 <15>

DDR_A_CLK#2 <15>

DDR_A_CLK3 <15>

DDR_A_CLK#3 <15>

DDR_A_CKE0 <14>

DDR_A_CKE1 <14>

DDR_A_CKE2 <15>

DDR_A_CKE3 <15>

DDR_A_CS#0 <14>

DDR_A_CS#1 <14>

DDR_A_CS#2 <15>

DDR_A_CS#3 <15>

DDR_A_ODT0 <14>

DDR_A_ODT1 <14>

DDR_A_ODT2 <15>

DDR_A_ODT3 <15>

DDR_A_BA0 <14,15>

DDR_A_BA1 <14,15>

DDR_A_BG0 <14,15>

DDR_A_RAS# <14,15>

DDR_A_WE# <14,15>

DDR_A_CAS# <14,15>

DDR_A_MA0 <14,15>

DDR_A_MA1 <14,15>

DDR_A_MA2 <14,15>

DDR_A_MA3 <14,15>

DDR_A_MA4 <14,15>

DDR_A_MA5 <14,15>

DDR_A_MA6 <14,15>

DDR_A_MA7 <14,15>

DDR_A_MA8 <14,15>

DDR_A_MA9 <14,15>

DDR_A_MA10 <14,15>

DDR_A_MA11 <14,15>

DDR_A_MA12 <14,15>

DDR_A_MA13 <14,15>

DDR_A_BG1 <14,15>

DDR_A_ACT# <14,15>

DDR_A_PAR <14,15>

DDR_A_ALERT# <14,15> DDR_B_PAR <16,17>

DDR_A_DQS#0 <14,15>

DDR_A_DQS#1 <14,15>

DDR_A_DQS#2 <14,15>

DDR_A_DQS#3 <14,15>

DDR_A_DQS4 <14,15>

DDR_A_DQS5 <14,15>

DDR_A_DQS6 <14,15>

DDR_A_DQS7 <14,15>

DDR_A_DQS0 <14,15>

DDR_A_DQS1 <14,15>

DDR_A_DQS2 <14,15>

DDR_A_DQS3 <14,15>

DDR_A_DQS#4 <14,15>

DDR_A_DQS#5 <14,15>

DDR_A_DQS#6 <14,15>

DDR_A_DQS#7 <14,15>

DDR_B_D[0..15]<16,17>

DDR_B_D[16..31]<16,17>

DDR_B_D[32..47]<16,17>

DDR_B_D[48..63]<16,17>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

SM_RCOMP0

12

RC19121_0402_1%

SM_RCOMP1

12

RC2075_0402_1%

SM_RCOMP2

12

RC21100_0402_1%

Place close to CPU

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

Trace = 12~15 mils

Spacing = 20 mils

Max lenght = 500 mils

CHANNEL-B

Interleaved Memory

UC1B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

S

KL-H_BGA1440

REV = 1 ?

@

DDR CHANNEL B

SKYLAKE_HALO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_CS#2

DDR_B_CS#3

DDR_B_ODT0

DDR_B_ODT1

DDR_B_ODT2

DDR_B_ODT3

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_ALERT#

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

+0.6V_VREFCA

+0.6V_B_VREFDQ

DDR_B_CLK0 <16>

DDR_B_CLK#0 <16>

DDR_B_CLK#1 <16>

DDR_B_CLK1 <16>

DDR_B_CLK2 <17>

DDR_B_CLK#2 <17>

DDR_B_CLK3 <17>

DDR_B_CLK#3 <17>

DDR_B_CKE0 <16>

DDR_B_CKE1 <16>

DDR_B_CKE2 <17>

DDR_B_CKE3 <17>

DDR_B_CS#0 <16>

DDR_B_CS#1 <16>

DDR_B_CS#2 <17>

DDR_B_CS#3 <17>

DDR_B_ODT0 <16>

DDR_B_ODT1 <16>

DDR_B_ODT2 <17>

DDR_B_ODT3 <17>

DDR_B_RAS# <16,17>

DDR_B_WE# <16,17>

DDR_B_CAS# <16,17>

DDR_B_BA0 <16,17>

DDR_B_BA1 <16,17>

DDR_B_BG0 <16,17>

DDR_B_MA0 <16,17>

DDR_B_MA1 <16,17>

DDR_B_MA2 <16,17>

DDR_B_MA3 <16,17>

DDR_B_MA4 <16,17>

DDR_B_MA5 <16,17>

DDR_B_MA6 <16,17>

DDR_B_MA7 <16,17>

DDR_B_MA8 <16,17>

DDR_B_MA9 <16,17>

DDR_B_MA10 <16,17>

DDR_B_MA11 <16,17>

DDR_B_MA12 <16,17>

DDR_B_MA13 <16,17>

DDR_B_BG1 <16,17>

DDR_B_ACT# <16,17>

DDR_B_ALERT# <16,17>

DDR_B_DQS#0 <16,17>

DDR_B_DQS#1 <16,17>

DDR_B_DQS#2 <16,17>

DDR_B_DQS#3 <16,17>

DDR_B_DQS#4 <16,17>

DDR_B_DQS#5 <16,17>

DDR_B_DQS#6 <16,17>

DDR_B_DQS#7 <16,17>

DDR_B_DQS0 <16,17>

DDR_B_DQS1 <16,17>

DDR_B_DQS2 <16,17>

DDR_B_DQS3 <16,17>

DDR_B_DQS4 <16,17>

DDR_B_DQS5 <16,17>

DDR_B_DQS6 <16,17>

DDR_B_DQS7 <16,17>

+0.6V_VREFCA

+0.6V_B_VREFDQ

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/02/01 2017/12/31

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

D

Date : Sheet o f

SKL-H(2/9)DDRIII

SKL-H(2/9)DDRIII

SKL-H(2/9)DDRIII

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Monday, January 09, 2017

Monday, January 09, 2017

Monday, January 09, 2017

E

7

1.0

1.0

1.0

103

103

103

7

7

Page 8

A

B

C

D

E

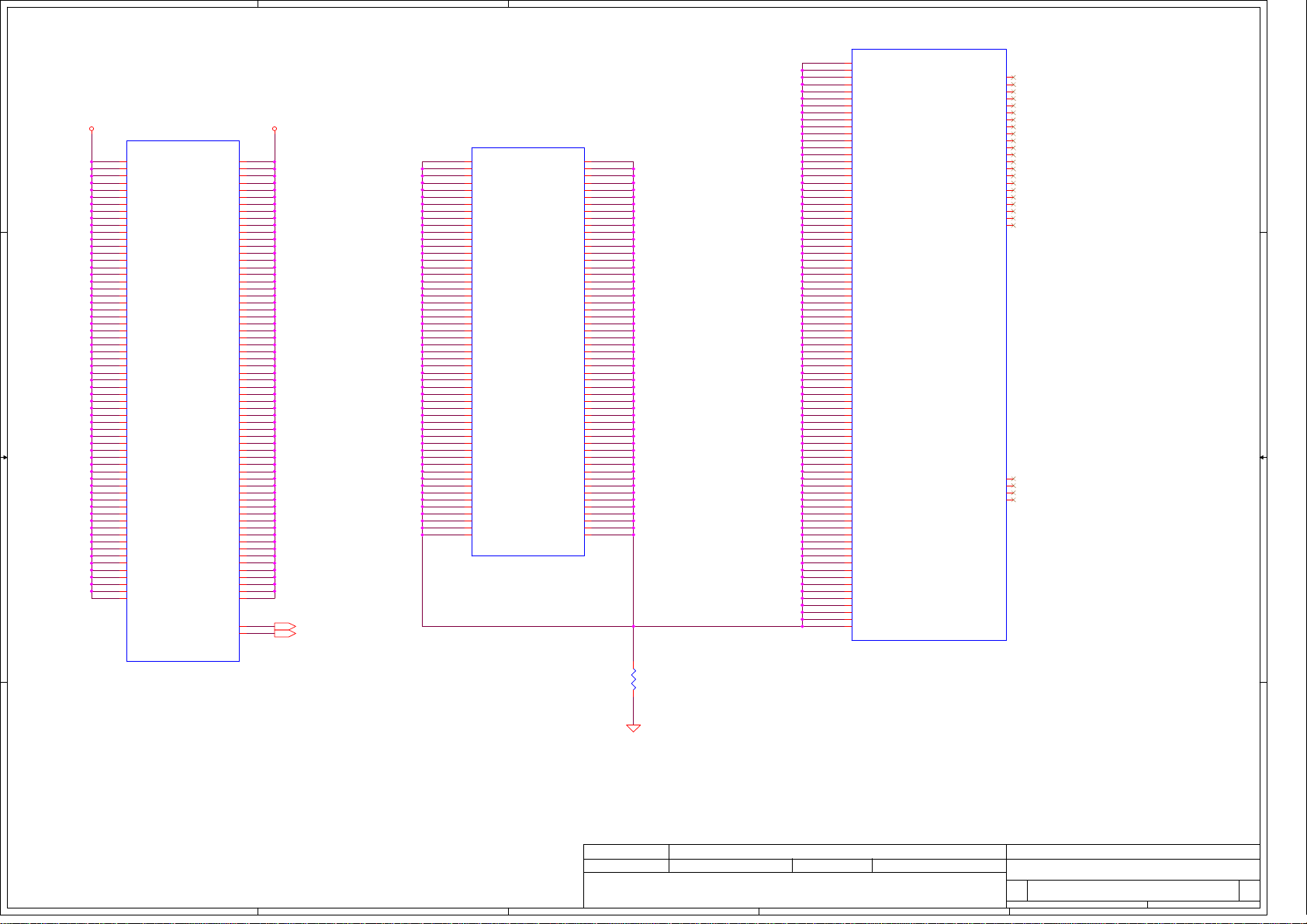

PEG 2x8 reverse

1 1

1 2

PCIE_CRX_C_GTX_P15<53>

PCIE_CRX_C_GTX_N15<53>

PCIE_CRX_C_GTX_P14<53>

PCIE_CRX_C_GTX_N14<53>

PCIE_CRX_C_GTX_P13<53>

PCIE_CRX_C_GTX_N13<53>

PCIE_CRX_C_GTX_P12<53>

Slave GPU

2 2

Master GPU

3 3

PCIE_CRX_C_GTX_N12<53>

PCIE_CRX_C_GTX_P11<53>

PCIE_CRX_C_GTX_N11<53>

PCIE_CRX_C_GTX_P10<53>

PCIE_CRX_C_GTX_N10<53>

PCIE_CRX_C_GTX_P9<53>

PCIE_CRX_C_GTX_N9<53>

PCIE_CRX_C_GTX_P8<53>

PCIE_CRX_C_GTX_N8<53>

PCIE_CRX_C_GTX_P7<41>

PCIE_CRX_C_GTX_N7<41>

PCIE_CRX_C_GTX_P6<41>

PCIE_CRX_C_GTX_N6<41>

PCIE_CRX_C_GTX_P5<41>

PCIE_CRX_C_GTX_N5<41>

PCIE_CRX_C_GTX_P4<41>

PCIE_CRX_C_GTX_N4<41>

PCIE_CRX_C_GTX_P3<41>

PCIE_CRX_C_GTX_N3<41>

PCIE_CRX_C_GTX_P2<41>

PCIE_CRX_C_GTX_N2<41>

PCIE_CRX_C_GTX_P1<41>

PCIE_CRX_C_GTX_N1<41>

PCIE_CRX_C_GTX_P0<41>

PCIE_CRX_C_GTX_N0<41>

CC87 0.22U_0402_16V7K

1 2

CC88 0.22U_0402_16V7K

1 2

CC85 0.22U_0402_16V7K

1 2

CC86 0.22U_0402_16V7K

1 2

CC83 0.22U_0402_16V7K

1 2

CC84 0.22U_0402_16V7K

1 2

CC81 0.22U_0402_16V7K

1 2

CC82 0.22U_0402_16V7K

1 2

CC80 0.22U_0402_16V7K

1 2

CC79 0.22U_0402_16V7K

1 2

CC78 0.22U_0402_16V7K

1 2

CC77 0.22U_0402_16V7K

1 2

CC76 0.22U_0402_16V7K

1 2

CC75 0.22U_0402_16V7K

1 2

CC73 0.22U_0402_16V7K

1 2

CC74 0.22U_0402_16V7K

1 2

CC49 0.22U_0402_16V7K

1 2

CC50 0.22U_0402_16V7K

1 2

CC51 0.22U_0402_16V7K

1 2

CC52 0.22U_0402_16V7K

1 2

CC57 0.22U_0402_16V7K

1 2

CC58 0.22U_0402_16V7K

1 2

CC59 0.22U_0402_16V7K

1 2

CC60 0.22U_0402_16V7K

1 2

CC61 0.22U_0402_16V7K

1 2

CC62 0.22U_0402_16V7K

1 2

CC63 0.22U_0402_16V7K

1 2

CC64 0.22U_0402_16V7K

1 2

CC65 0.22U_0402_16V7K

1 2

CC66 0.22U_0402_16V7K

1 2

CC67 0.22U_0402_16V7K

1 2

CC68 0.22U_0402_16V7K

CAD note:

Trace width=12 mils,Spacing=15mil,Max length=400mils

+VCCIO

DMI_CRX_PTX_P0<18>

DMI_CRX_PTX_N0<18>

DMI_CRX_PTX_P1<18>

DMI_CRX_PTX_N1<18>

DMI_CRX_PTX_P2<18>

DMI_CRX_PTX_N2<18>

DMI_CRX_PTX_P3<18>

DMI_CRX_PTX_N3<18>

1 2

RC22 24.9_0402_1%

PCIE_CRX_GTX_P15

PCIE_CRX_GTX_N15

PCIE_CRX_GTX_P14

PCIE_CRX_GTX_N14

PCIE_CRX_GTX_P13

PCIE_CRX_GTX_N13

PCIE_CRX_GTX_P12

PCIE_CRX_GTX_N12

PCIE_CRX_GTX_P11

PCIE_CRX_GTX_N11

PCIE_CRX_GTX_P10

PCIE_CRX_GTX_N10

PCIE_CRX_GTX_P9

PCIE_CRX_GTX_N9

PCIE_CRX_GTX_P8

PCIE_CRX_GTX_N8

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_N7

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PEG_RCOMP

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_N1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3

DMI_CRX_PTX_N3

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

UC1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

S

KL-H_BGA1440

REV = 1

@

SKYLAKE_HALO

BGA1440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

?

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

DMI_CTX_PRX_P0

DMI_CTX_PRX_N0

DMI_CTX_PRX_P1

DMI_CTX_PRX_N1

DMI_CTX_PRX_P2

DMI_CTX_PRX_N2

DMI_CTX_PRX_P3

DMI_CTX_PRX_N3

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

DMI_CTX_PRX_P0 <18>

DMI_CTX_PRX_N0 <18>

DMI_CTX_PRX_P1 <18>

DMI_CTX_PRX_N1 <18>

DMI_CTX_PRX_P2 <18>

DMI_CTX_PRX_N2 <18>

DMI_CTX_PRX_P3 <18>

DMI_CTX_PRX_N3 <18>

CC1040.22U_0402_16V7K

CC1030.22U_0402_16V7K

CC1020.22U_0402_16V7K

CC1010.22U_0402_16V7K

CC990.22U_0402_16V7K

CC1000.22U_0402_16V7K

CC970.22U_0402_16V7K

CC980.22U_0402_16V7K

CC950.22U_0402_16V7K

CC960.22U_0402_16V7K

CC940.22U_0402_16V7K

CC930.22U_0402_16V7K

CC920.22U_0402_16V7K

CC910.22U_0402_16V7K

CC900.22U_0402_16V7K

CC890.22U_0402_16V7K

CC30.22U_0402_16V7K

CC40.22U_0402_16V7K

CC50.22U_0402_16V7K

CC60.22U_0402_16V7K

CC70.22U_0402_16V7K

CC80.22U_0402_16V7K

CC90.22U_0402_16V7K

CC100.22U_0402_16V7K

CC110.22U_0402_16V7K

CC120.22U_0402_16V7K

CC130.22U_0402_16V7K

CC140.22U_0402_16V7K

CC150.22U_0402_16V7K

CC160.22U_0402_16V7K

CC170.22U_0402_16V7K

CC180.22U_0402_16V7K

PCIE_CTX_C_GRX_P15 <53>

PCIE_CTX_C_GRX_N15 <53>

PCIE_CTX_C_GRX_P14 <53>

PCIE_CTX_C_GRX_N14 <53>

PCIE_CTX_C_GRX_P13 <53>

PCIE_CTX_C_GRX_N13 <53>

PCIE_CTX_C_GRX_P12 <53>

PCIE_CTX_C_GRX_N12 <53>

PCIE_CTX_C_GRX_P11 <53>

PCIE_CTX_C_GRX_N11 <53>

PCIE_CTX_C_GRX_P10 <53>

PCIE_CTX_C_GRX_N10 <53>

PCIE_CTX_C_GRX_P9 <53>

PCIE_CTX_C_GRX_N9 <53>

PCIE_CTX_C_GRX_P8 <53>

PCIE_CTX_C_GRX_N8 <53>

PCIE_CTX_C_GRX_P7 <41>

PCIE_CTX_C_GRX_N7 <41>

PCIE_CTX_C_GRX_P6 <41>

PCIE_CTX_C_GRX_N6 <41>

PCIE_CTX_C_GRX_P5 <41>

PCIE_CTX_C_GRX_N5 <41>

PCIE_CTX_C_GRX_P4 <41>

PCIE_CTX_C_GRX_N4 <41>

PCIE_CTX_C_GRX_P3 <41>

PCIE_CTX_C_GRX_N3 <41>

PCIE_CTX_C_GRX_P2 <41>

PCIE_CTX_C_GRX_N2 <41>

PCIE_CTX_C_GRX_P1 <41>

PCIE_CTX_C_GRX_N1 <41>

PCIE_CTX_C_GRX_P0 <41>

PCIE_CTX_C_GRX_N0 <41>

Slave GPU

Master GPU

4 4

Security Classification

Security Classification

Security Classification

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/02/01 2017/12/31

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-H(3/9) PEG,DMI

SKL-H(3/9) PEG,DMI

SKL-H(3/9) PEG,DMI

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

C1PR2 LA-E051P

C1PR2 LA-E051P

C1PR2 LA-E051P

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

8 103Monday, January 09, 2017

8 103Monday, January 09, 2017

8 103Monday, January 09, 2017

E

1.0

1.0

1.0

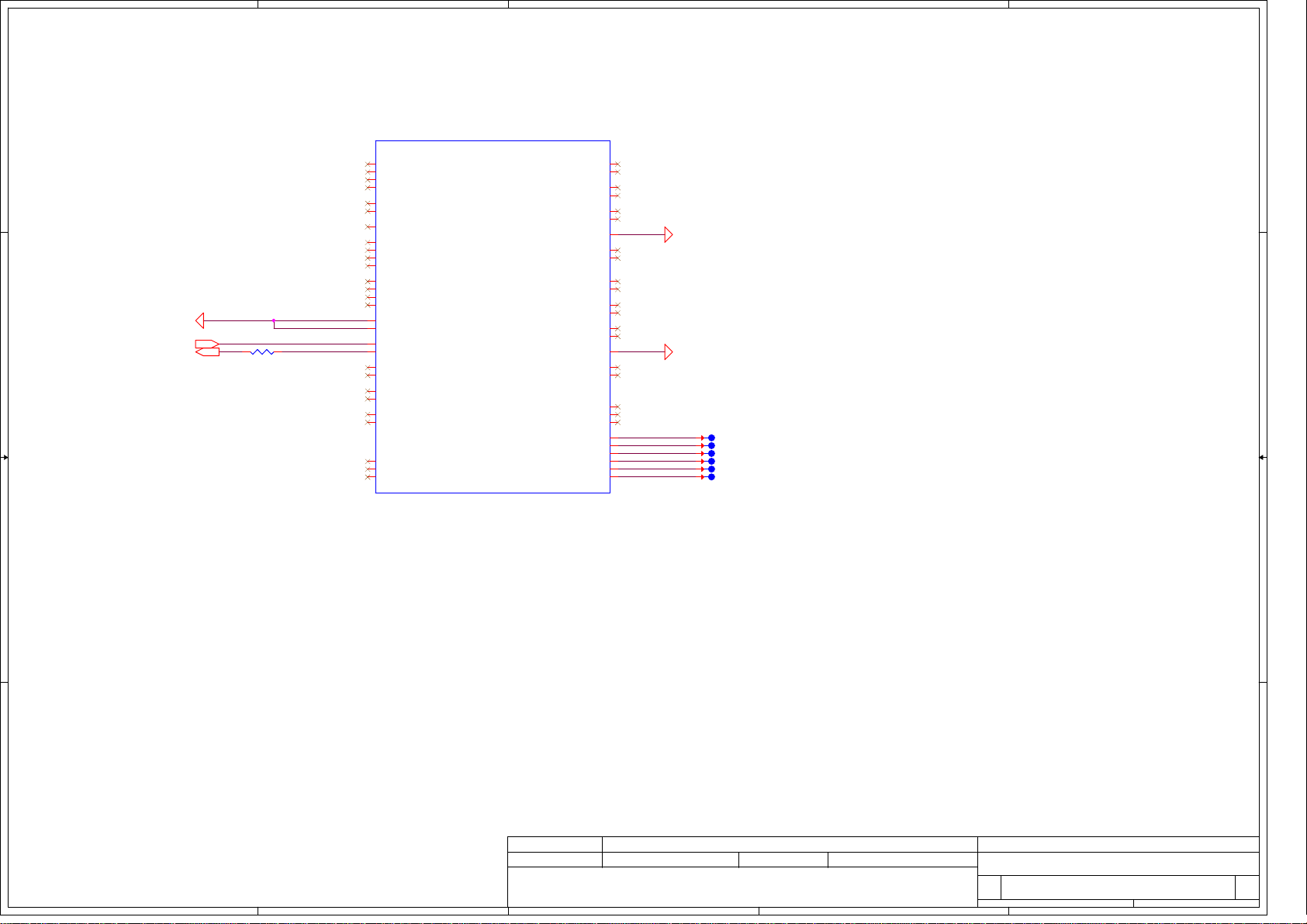

Page 9

A

B

C

D

E

SKYLAKE_HALO

BGA1440

5 OF 14

REV = 1 ?

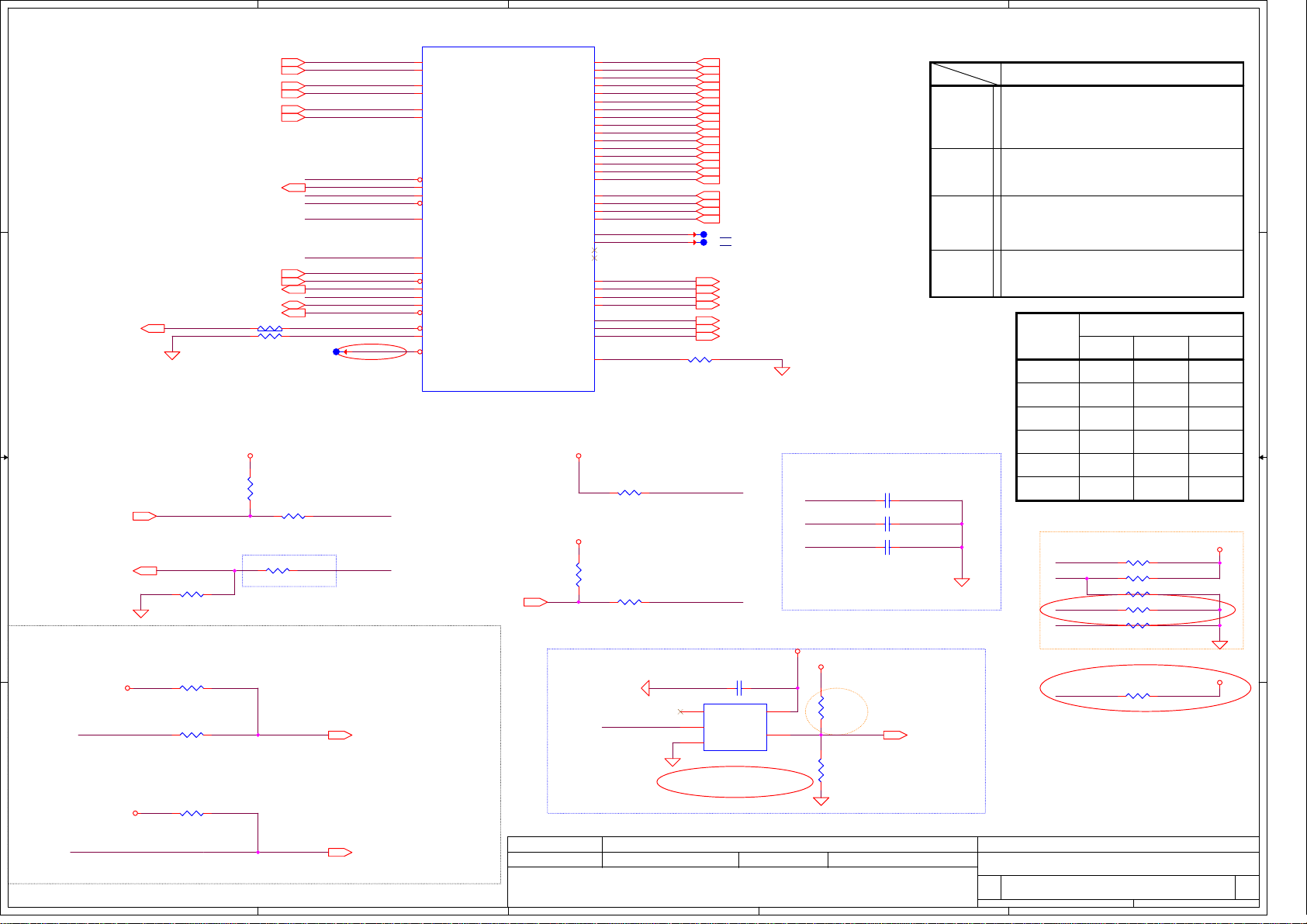

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

+1.0V_VCCST

+1.0VS_VCCSTG

From EC(open-drain)

H_PROCHOT#<38,75>

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

(To VR)

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

XDP_BPM#0

BR27

XDP_BPM#1

BT27

BM31

BT30

CPU_XDP_TDO

BT28

CPU_XDP_TDI

BL32

CPU_XDP_TMS

BP28

CPU_XDP_TCK0

BR28

CPU_XDP_TRST#

BP30

XDP_PREQ#

BL30

XDP_PRDY#SKL_CNL_N

BP27

CFG_RCOMP

BT25

1 2

RC27 1K_0402_5%

12

RC31

1K_0402_5%

1 2

RC33 499_0402_1%

DDR_PG_CTRL

CFG0 <6>

CFG1 <6>

CFG2 <6>

CFG3 <6>

CFG4 <6>

CFG5 <6>

CFG6 <6>

CFG7 <6>

CFG8 <6>

CFG9 <6>

CFG10 <6>

CFG11 <6>

CFG12 <6>

CFG13 <6>

CFG14 <6>

CFG15 <6>

CFG17 <6>

CFG16 <6>

CFG19 <6>

CFG18 <6>

PAD

T25

@

PAD

T26

@

CPU_XDP_TDO <6,20>

CPU_XDP_TDI <6,20>

CPU_XDP_TMS <6,20>

CPU_XDP_TCK0 <6,20>

CPU_XDP_TRST# <6,24>

XDP_PREQ# <6,24>

XDP_PRDY# <6,24>

1 2

RC23 49.9_0402_1%

THERMTRIP#

PROCHOT

12

UC3

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

Change PN to SA00007UR00.

H_CPUPW RGD

PROCHOT

THERMTRIP#

1 2

CH49 .1U_0402_16V7K

1 2

CH50 .1U_0402_16V7K

1 2

CH51 .1U_0402_16V7K

ESD Reserve ,place close to cpu.

+1.2V_VDDQ

+3VS

CC19.1U_0402_16V7K

5

4

Y

12

RC36

220K_0402_5%

RC38

2M_0402_5%@

1 2

CRB 330K

CPU_BCLK<21>

CPU_BCLK#<21>

CPU_PCIBCLK<21>

CPU_PCIBCLK#<21>

CPU_24M<21>

1 1

H_SKTOCC#<20>

2 2

From EC OD output

EC_VCCST_PG_R<26,38>

3 3

PM_DOW N_R<19>

H_SKTOCC# H_SKTOCC#_R

1 2

@

RC32 1K_0402_5%

CPU_24M#<21>

CPU_SVID_CLK<81>

H_CPUPW RGD<20>

PLTRST_CPU#<19>

H_PM_SYNC<19>

H_PECI<19,38>

THERMTRIP#<19>

1 2

@

1 2

RC57 0_0402_5%

RC34 0_0402_5%@

+1.0V_VCCST

PAD

12

RC25

1K_0402_5%

1 2

RC28 60.4_0402_1%

RC30 20_0402_1%

SVID ALERT

+1.0V_VCCST

CPU_SVID_ALERT#

1 2

RC35 56_0402_5%

1 2

RC37 220_0402_5%

CPU_BCLK

CPU_BCLK#

CPU_PCIBCLK

CPU_PCIBCLK#

CPU_24M

CPU_24M#

CPU_SVID_ALERT#

CPU_SVID_CLK

CPU_SVID_DAT

PROCHOT

DDR_PG_CTRL

EC_VCCST_PG

H_CPUPW RGD

PLTRST_CPU#

H_PM_SYNC

PM_DOW N

H_PECI

THERMTRIP#

CATERR#

T69

@

FLOAT FOR SKL

GND FOR CNL

EC_VCCST_PG

12

Place the PU

resistors close to CPU

PM_DOW N

CPU_SVID_ALERT#_R <81>

B31

A32

D35

C36

E31

D31

BH31

BH32

BH29

BR30

BT13

H13

BT31

BP35

BM34

BP31

BT34

BR33

BN1

BM30

J31

UC1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

S

KL-H_BGA1440

@

Follow PDG1.0

Table 12-16

SVID DATA

4 4

+1.0V_VCCST

1 2

RC39 100_0402_1%

Place the PU

resistors close to CPU

Reference SKL EDS 0.85 Table 6-8

CFG signals internal PH default value = 1

Description

Stall reset sequence after PCU PLL

CFG[0]

CFG[4]

CFG[7]

CFG[1]

CFG[3]

CFG[8:19]

XEMC@

XEMC@

XEMC@

SM_PG_CTRL <77>

lock until de-asserted

— 1 = (Default) Normal Operation;

*

No stall.

— 0 = Stall.

Enable eDP

*

— 1 = Disabled.

— 0 = Enabled.

PEG Training:

— 1 = (default) PEG Train immediately

*

following RESET# de assertion.

— 0 = PEG Wait for BIOS for training

Reserved configuration lane.

PCIE

pore

assign

1 x 16

1 x 16

reverse

2 x 8

2 x 8

reverse

1 x 8

+ 2 x 4

1x8+2x4

reverse

Config. Signals

1 1 1

1 1

1 1

*

1

0 0 0

2x8 reverse

CFG 6 int. PU 1 V

CFG6

CFG7

CFG5

CFG2

CFG4

Display Port Presence : 0 enable / 1 disable

1 2

RC61 1K_0402_1%

1 2

RC62 1K_0402_1%

1 2

@

RC66 1K_0402_1%

1 2

RC26 1K_0402_1%

1 2

RC29 1K_0402_1%

1 2

RC24 1K_0402_1%

CFG[2]CFG[5]CFG[6]

0

0 0

00

+1.0V_VCCST

+1.0V_VCCST

0

1

CPU_SVID_DAT

Security Classification

Security Classification

CPU_SVID_DAT <81>

A

B

(To VR)

Security Classification

2016/02/01 2017/12/31

2016/02/01 2017/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL