Page 1

A

1 1

2 2

B

C D E

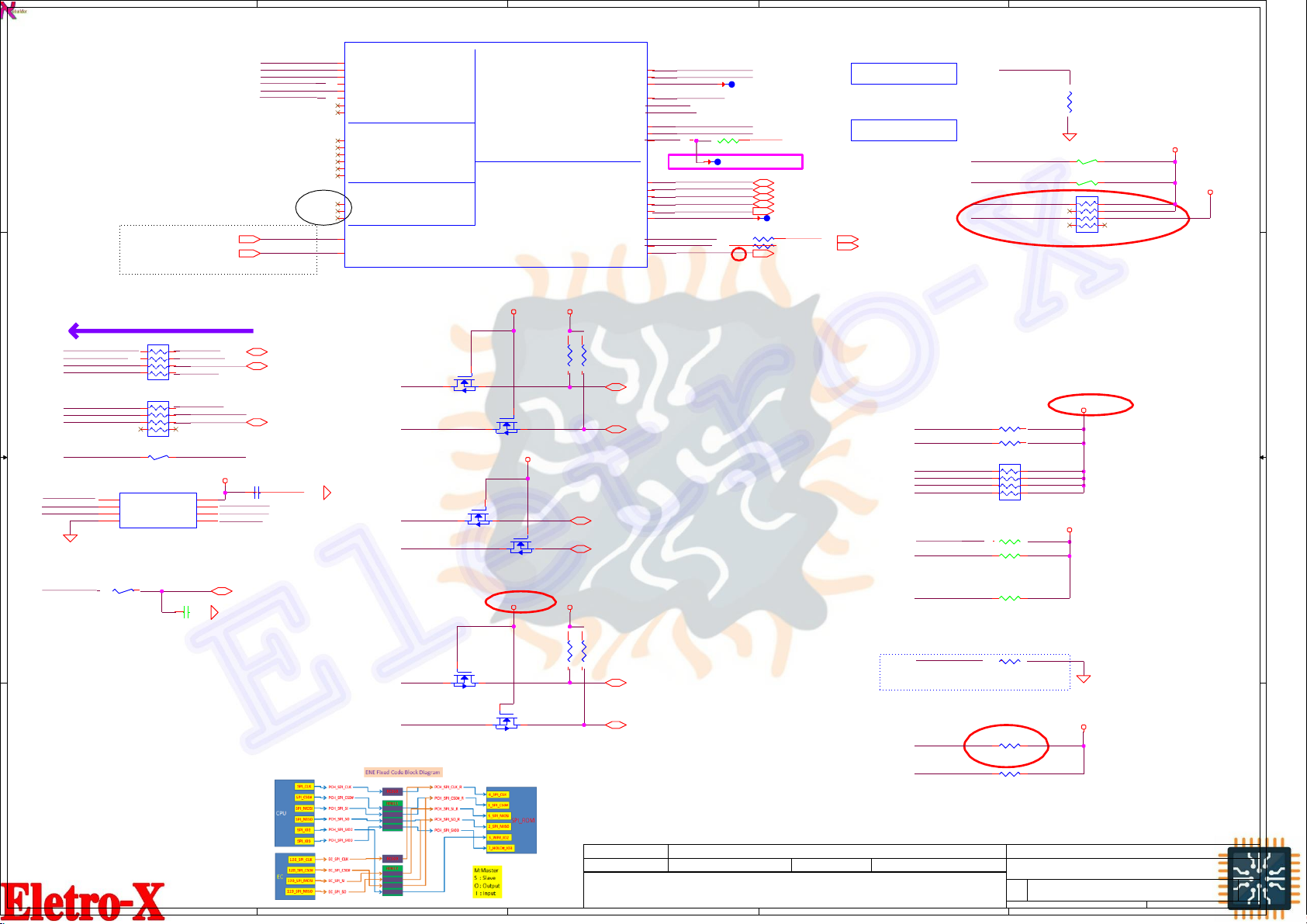

Kabylake-U M/B Schematics Document

Intel ULV Processor with DDR4 SODIMMx2

Date : 2016/05/11

3 3

Project :Diner_Crepe1.1(15")

4 4

A

B

Version : 4.0

BDL50 : LA-D704P

SecurityClassification

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C D

2011/06/29 2011/06/29

Compal Secret Data

Deciphered Date

Tiiitllle

Siiize Document Number

Custom

LA-D704P

Compal Electronics,Inc.

Cover Page

Sheet 1 of 60Date: Wednesday, May 11, 2016

E

Rev

v0.2

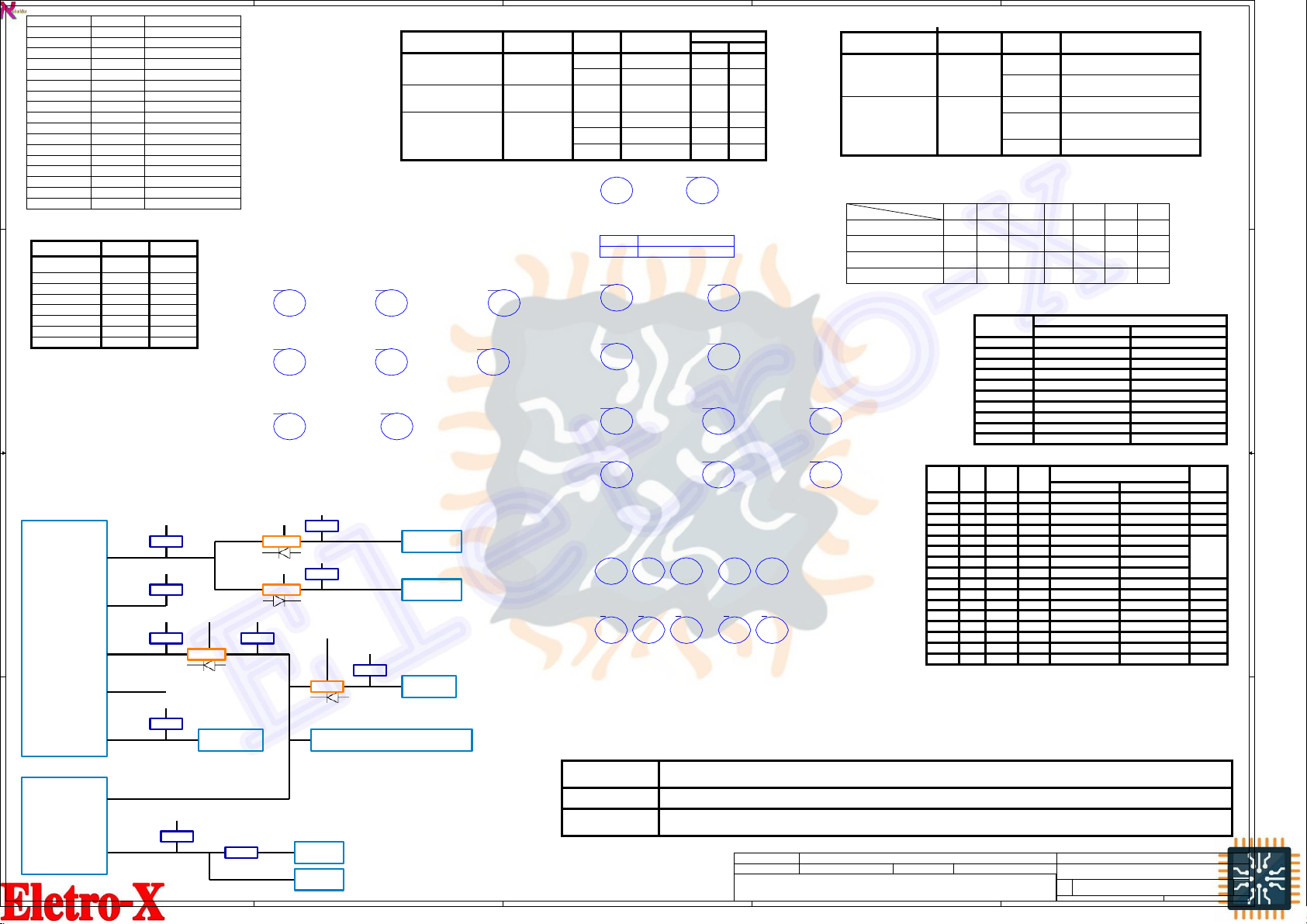

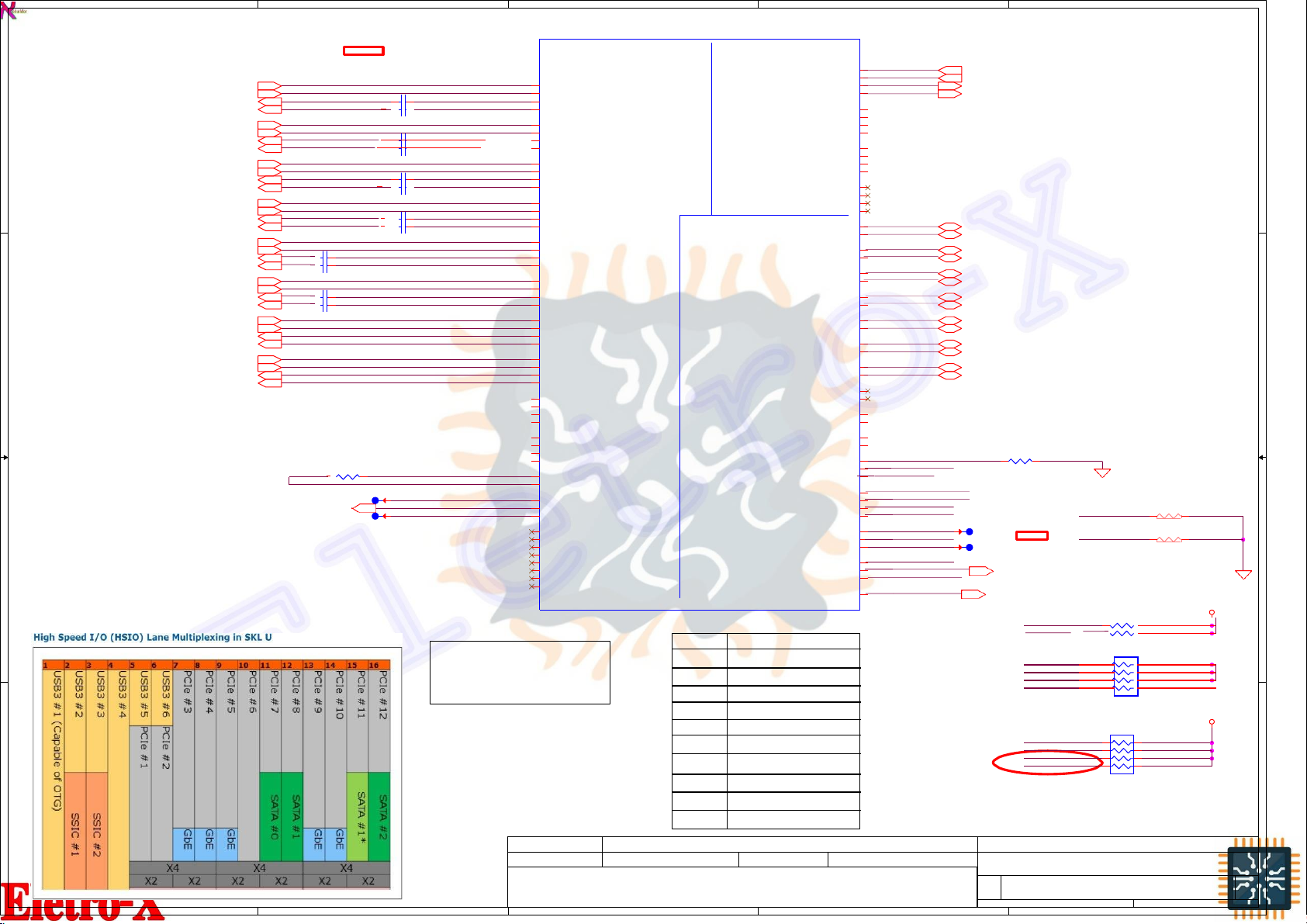

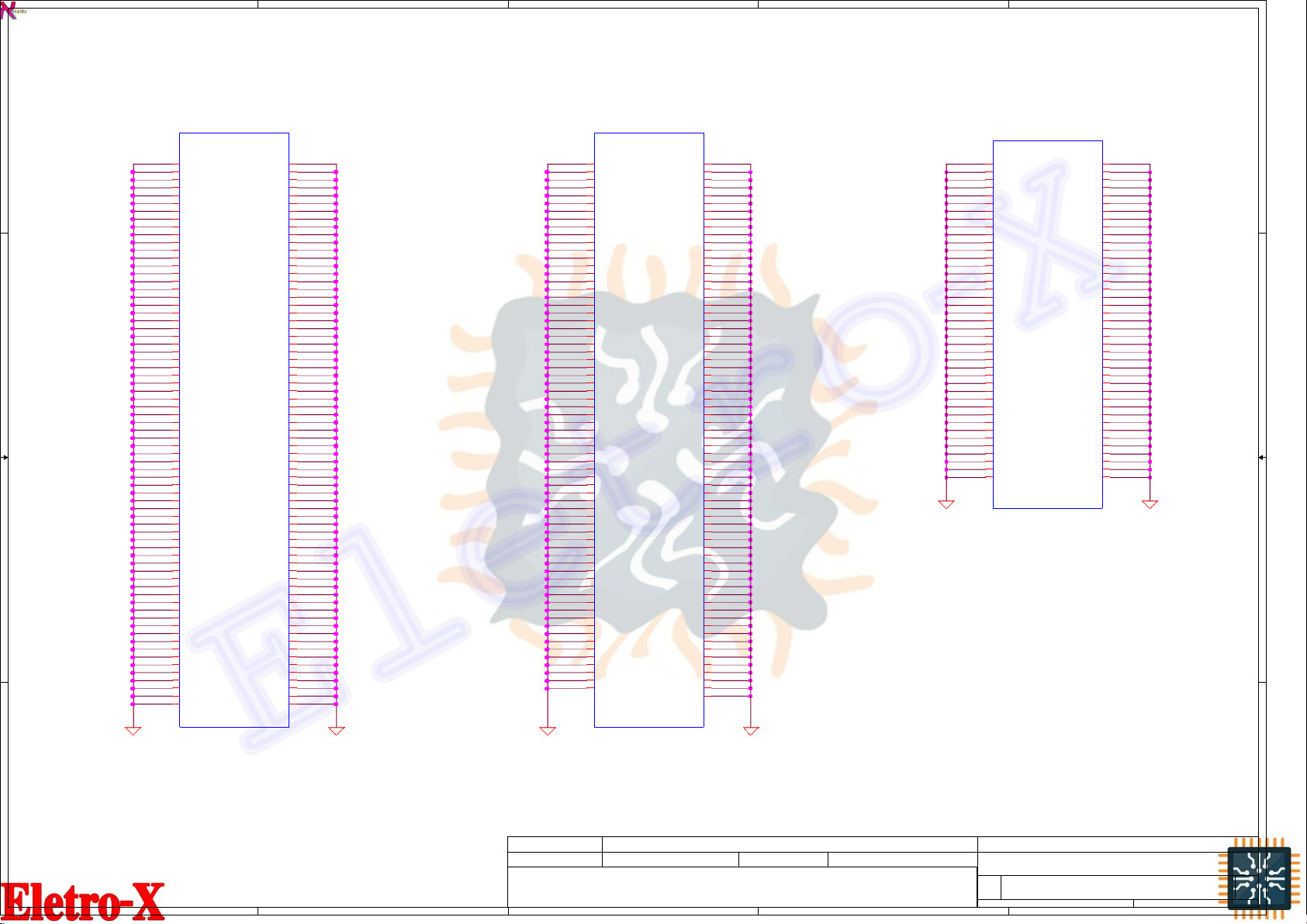

Page 2

A

B

C D E

Compal Confidential

Model Name :

File Name : LA-D704P

1 1

2 2

3 3

Diner_Crepe1.1(15")

VRAM

gDDR3 x4pcs

256Mbx16(4Gb)

512Mbx16(8Gb)

eDP/LVDS

CONN

CRT CONN

HDMI CONN

P.40~42

JL VD S1

P.20

FHD

JCR T 1

P. 22 CRT

JH DM I1

1Ch 64bits 1.5V

eDP to LVDS Transmitter

DP to VGA Transmitter

HDMI

P.21

RTL 8111HSH(Giga)

RTL8166EH(10/100)

NGFF WLAN+BT

(KeyE)

AMD

R16M-M1-70

R16M-M1-30

LVDS@

D3(R7)

D3(R5)

P.36~40

UT 1

RTD2132N P. 19

eDP@

eDP@

U410 4

RTD2168 P.22

LAN

JW LAN 1

P.32

UL1

P.23

U666

PCIex4

Port#1~#4

PCIe2.0:5Gb/s

PCIe3.0:8Gb/s

eDP x1Lane

2.7Gb/s

eDPx2Lane

2.7Gb/s

DDIx2Lane Port 2

DDIx4Lane Port 1

297MHz

PCIex1 Port #5

PCIeGen1:2.5Gb/s

PCIeGen2:5Gb/s

PCIex1 Port#6

PCIe1.0:2.5Gb/s

PCIe2.0:5Gb/s

Kabylake-U

Skylake-U

1356P BGA

KBL-U 15W2+2

SKL-U 15W 2+2

SMbus

1MHz

UC 1

Dual Channel Interleaved

DDR4 2133MHz 1.2V

SATA 3.0

GEN11.5Gb/s

GEN23Gb/s

GEN36Gb/s

USB3.0

5Gb/s

USB2.0

480Mb/s

Port0

Port1

Port1

Port2

Port3

Port4

Port5

Port6

Port7

DDR4-SO-DIMM X 2

2.5" SATA HDD

ODD

USB3.0 port

(onboard-1)

USB2.0 port

(onboard-2)

USB2.0 Port

(sub board)

Bluetooth

Camera

Touch Screen

Card reader

RTS5141

(sub board)

JHDD

P. 30

JO DD

P.30

JUS B1

P.31

JUS B2

P.31

JIO 1

P.33

JWLAN1

P.32

JL VD S1

P.20

JL VD S1

P.20

JIO 1

P.33

P.17~18

Port1

FAN

JK B1

P. 27

JT P1

P.27

P.34

JP WR

P.33

UC3

PS2

B

EC ENE

KB9022QD

SLB9665TT2.0

SPI ROM

8MBytes

Int.KBD

TouchPad

Lid switch

(sub board)

4 4

A

Thermal sensor

NCT7718W P.10

UK1

P.26

TPM

P.28

*default FWTP M

U4

UC 2

P. 07

LPC

33MHz

SPI

50MHz

UA1

HDA 24MHz

SecurityClassification

Issued Date

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS, IIINC... AND CONTAINS CONFIIIDENTIIIAL

AND TRADE SECRET IIINFORMATIIION... THIIIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS, IIINC... NEITHER THIIIS SHEET NOR THE IIINFORMATIIION IIIT CONTAINS

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS, IIINC...

C D

2011/06/29 2011/06/29

HDA Aduio codec

ALC3227

Compal Secret Data

Deciphered Date

P.24

Internal SPK

Combo Jack

Tiiitllle

Size Document Number

Custom

JSPK 1

JH P

Compal Electronics,Inc.

Block Diagrams

LA-D704P

E

Rev

v0.2

60Date: Wednesday, May 11, 2016 Sheet 2 of

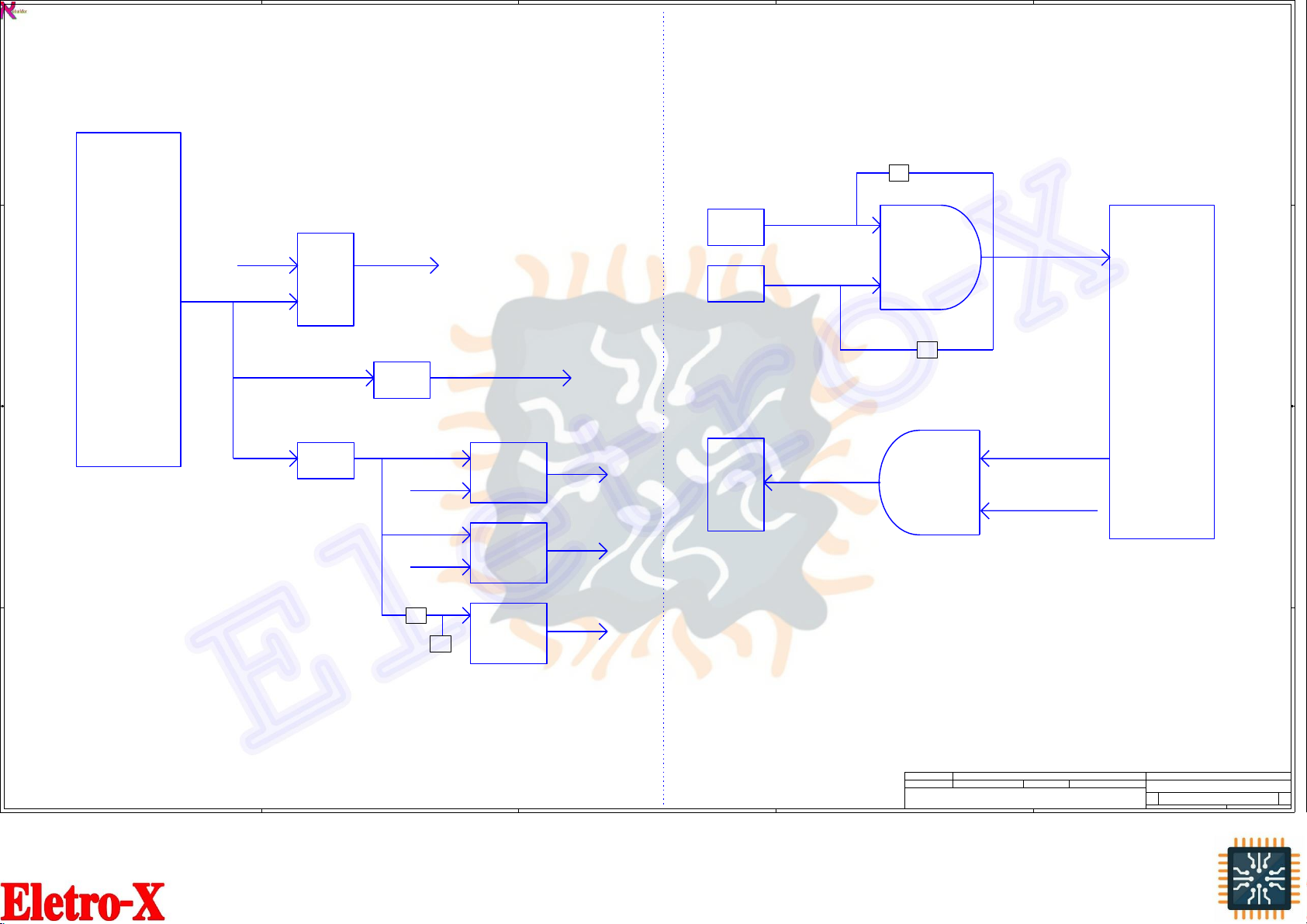

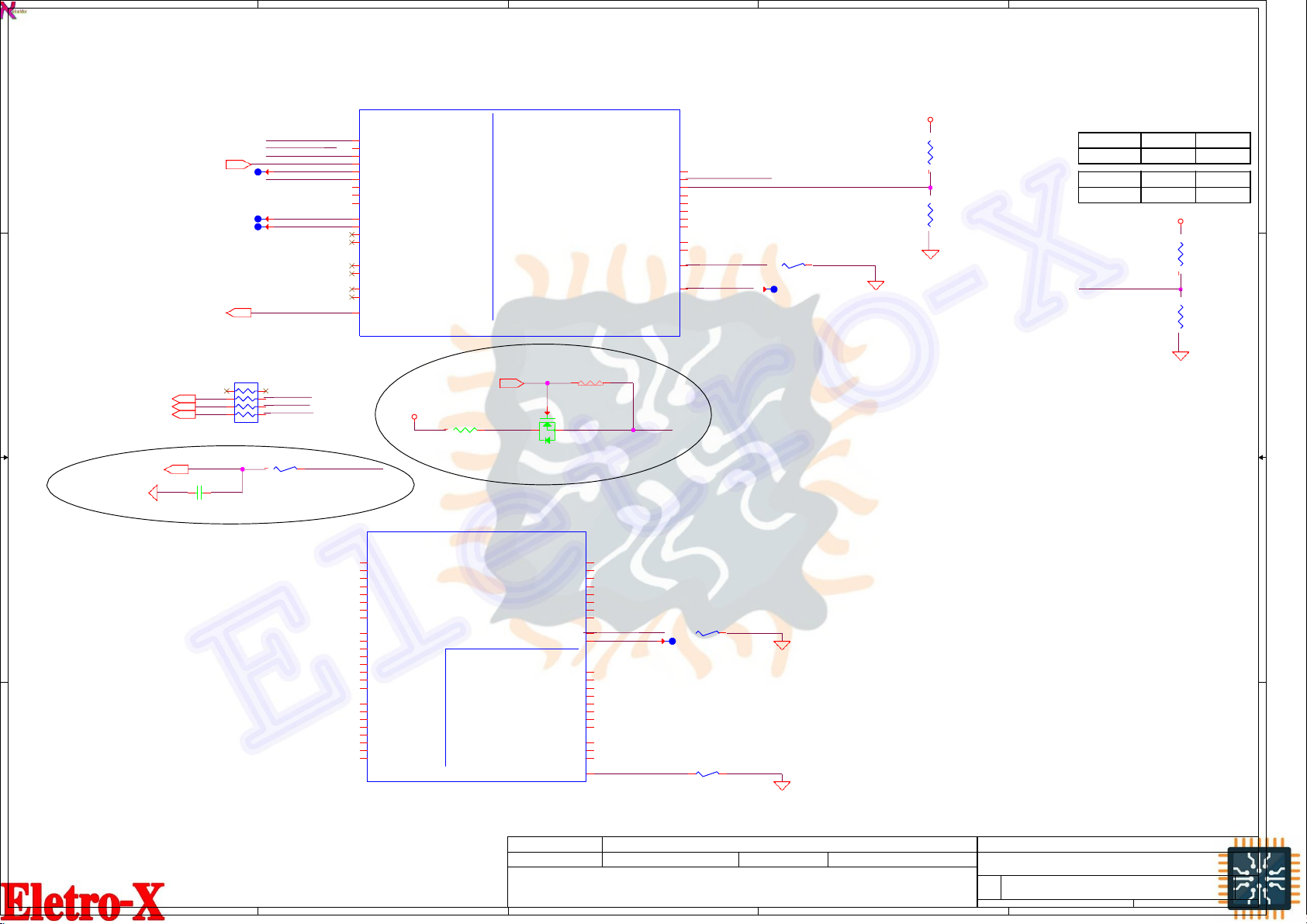

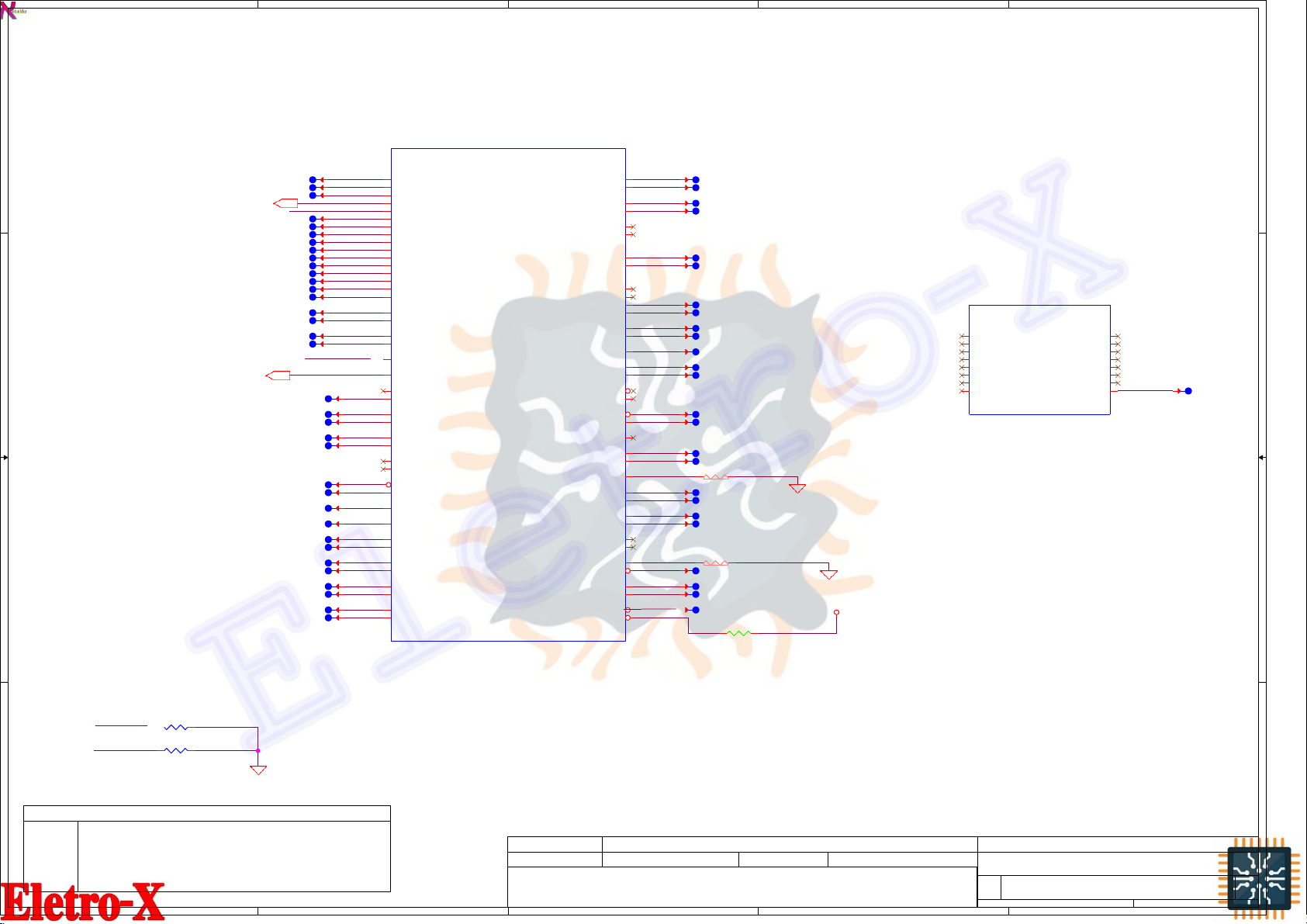

Page 3

5

D D

4

3

2

1

@ 0 ohm

R

CPU

PU801

+3VS

DGPU_PWR_EN

C C

GPIO78

U4103

EN

NMOS

B B

1. +3VS_VGA

PU801

PXS_PWREN#

+1.05VS

PU8

2. VGA_CORE

3. +1.05VS_VGA

U4102

GPU

GPU_PWRGD

1.8V_PWRGD

GPU_RST

@

R

0 ohm

DGPU_PWROK

GPIO77

CPU

DGPU_HOLD_RST#

GPIO80

PLT_RST#

4. +1.5VS_VGA

+1.5VS

EN_1.8V

R

C

U4102

5. +1.8VS_VGA

PU8

A A

SecurrriiitttyClllassiiifffiiicatttiiion

IIIssuedDate

THIIIS SHEET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIDENTIAL AND

TRADE SECRET IIINFORMATION... THIIIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIIIVIIISIIION OF R&D

DEPARTMENT EXCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NOR THE IIINFORMATION IIIT CONTAIIINS

5

4

3

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CONSENT OF COMPAL ELECTRONIIICS,,,IIINC...

2

Compalll SecretttDattta

Deciphered Date

Compal Electroni cs, Inc.

Tiiitttllle

Siiize DocumentttNumberrr

D

Dattte::: Wedne sday, M ay 11, 2016 Sheettt 43 o fff 60

1

LA-D707P

RSVD

Rev

v0.2

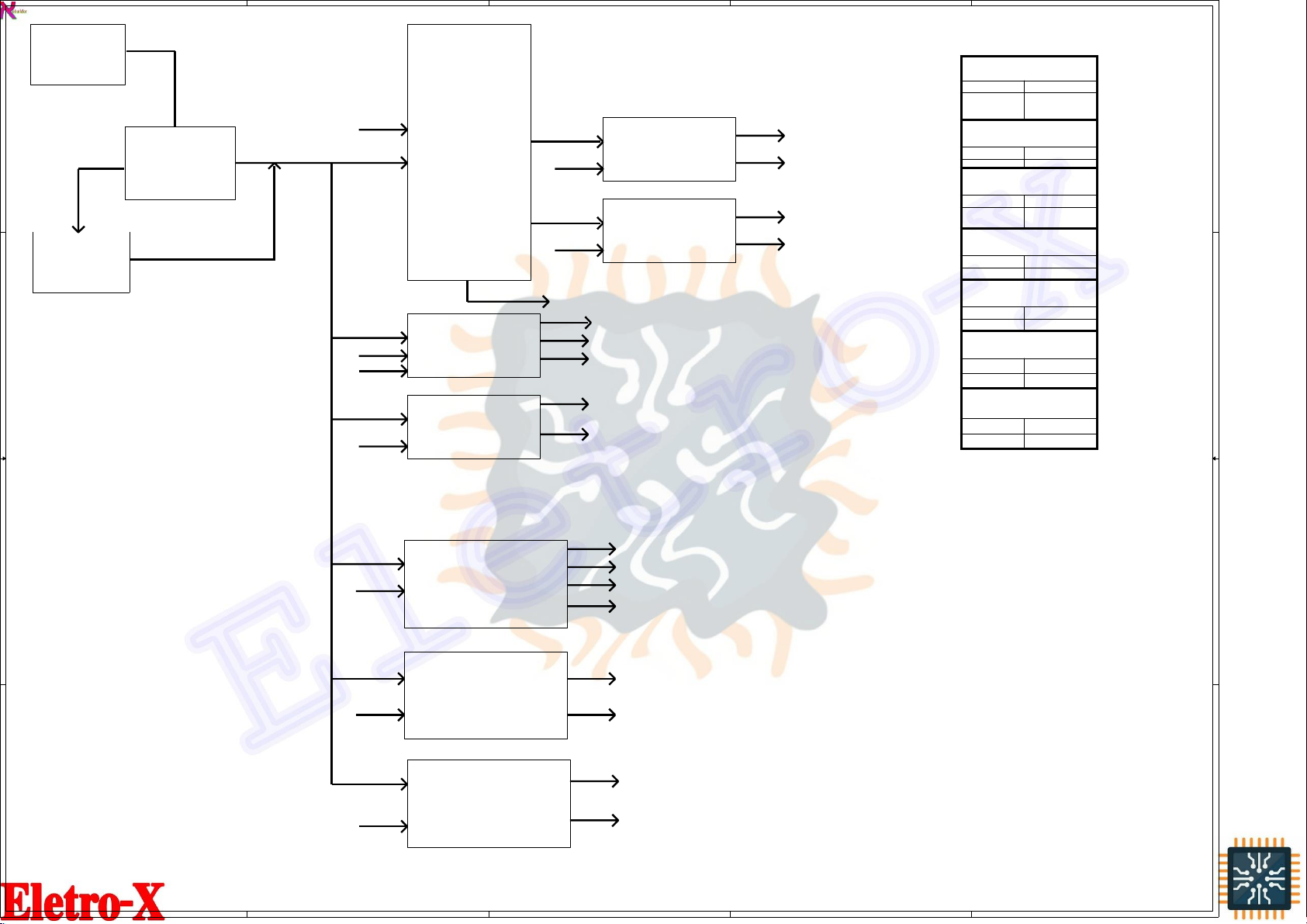

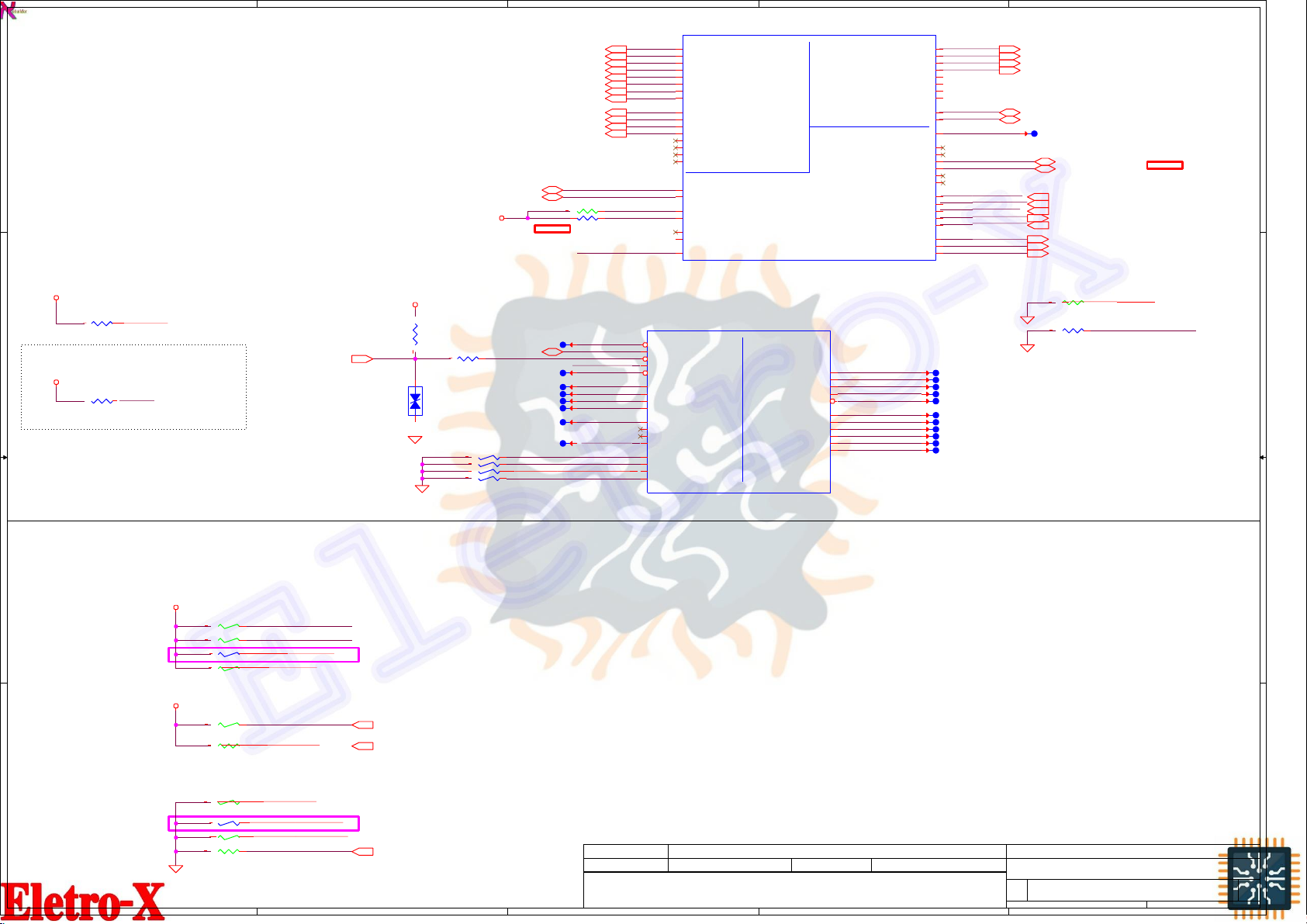

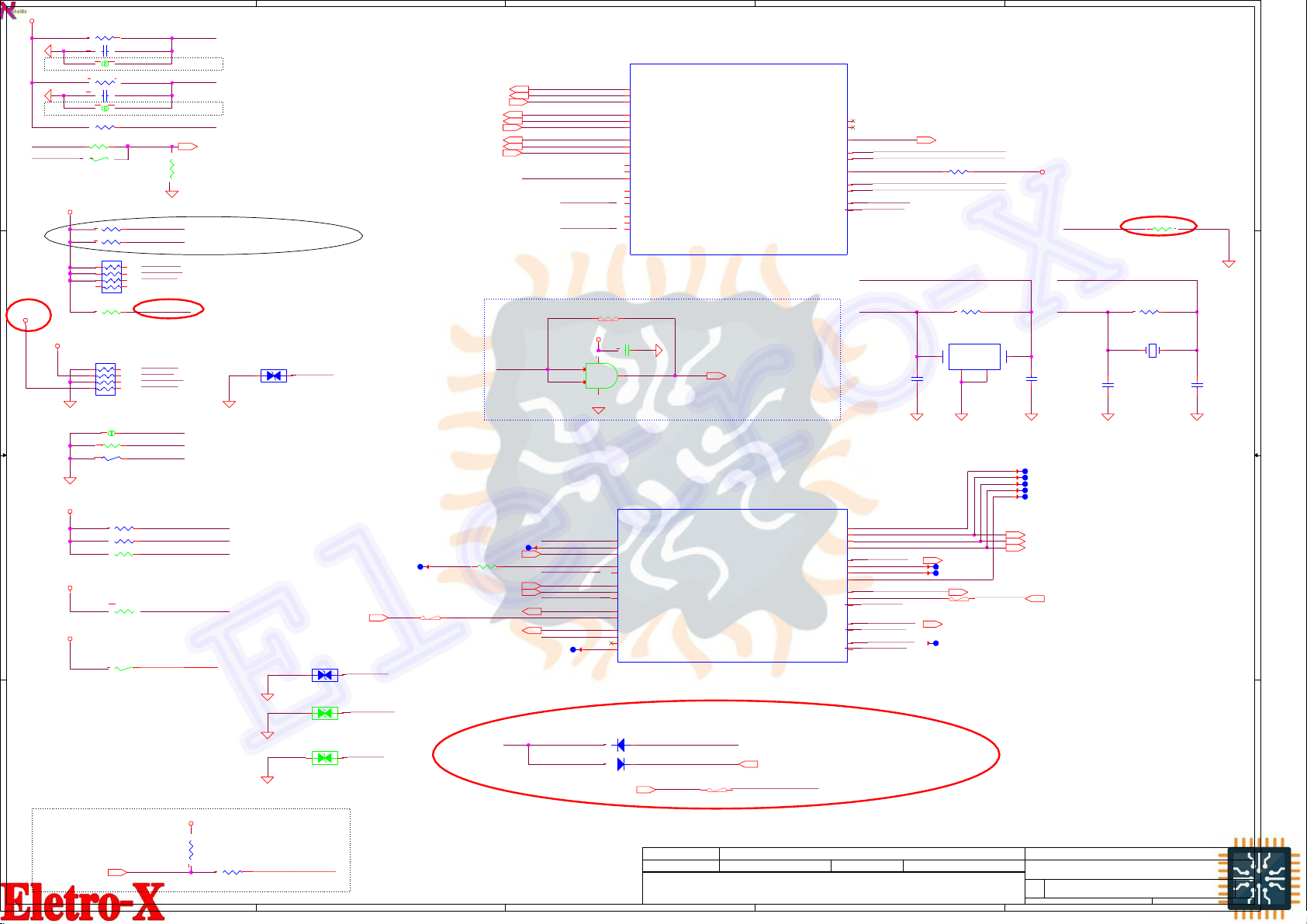

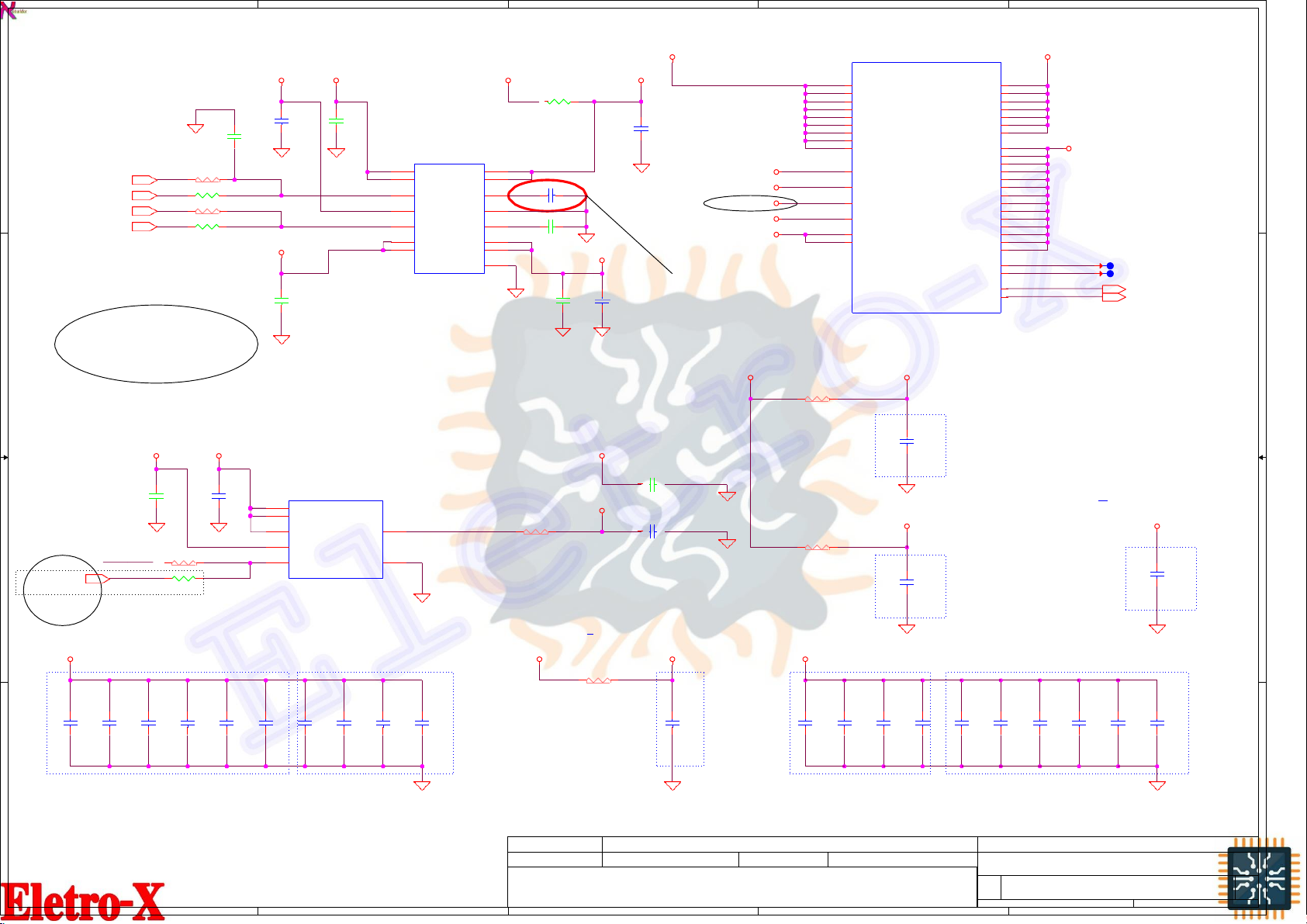

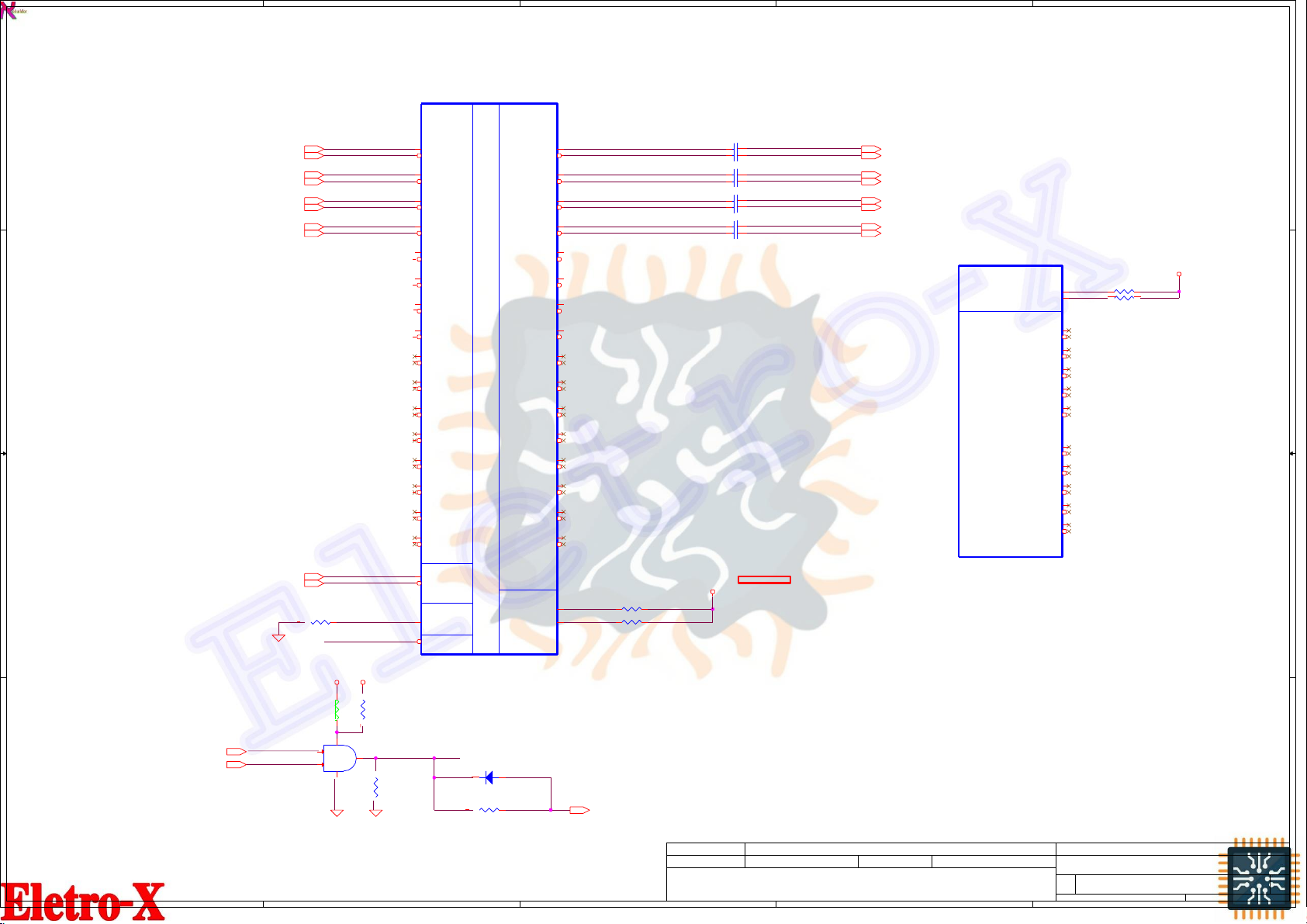

Page 4

5

AC

Adapter 19.5V

P.45

D D

Charge

Charger

+19.5VB

BQ24725

P.47

DC

Battery

3S1P

4S1P

P.46

C C

Discharge

+2.5V_PG

SM_PG_C TRL

4

3

RT8243AZQW

ECON

EN

Vout

Vin

+3VALW

PCH_PWR _EN

Vin

EN

SY8032A

DC/DC

(+5VALW/+3VALW)

Vout

PGOOD

P.48

Vin DDR4

RT8027P

EN S5

EN S3

Vin +1.0V_PRIM

+1.8V_P G +1.0V_VS_PG_PWR

SY8286

EN

PGOOD

PGOOD

PM_SLP_ S4#

Vout

Vout

P.49

Vout

P.50

+3VALW

SPOK

Vin

SY8032A

EN

+0.6V_0.6VS

+1.2V_VDDQ

DDR_PWROK

+1.0V_P RIM

Vout

PGOOD

P.51

Vout

PGOOD

P.49

+1.8V_P RIM

+1.8V_P G

+2.5V

+2.5V_P G

2

CPU DC/DC

NCP81206 52~54

INPUTS OUTP UTS

B+

SYSTEM DC/DC

RT8243AZQW

INPUTS OUTPUTS

B+ +5VALW/+3VALW

SYSTEM DC/DC

RT8207P / 8032

INPUTS OUTPUTS

B+

SYSTEM DC/DC

SY8286

VCC_SA

VCC_GT

VCC_VORE

+1.2V_VDDQ

+0.6V_0.6

INPUTS OUTPUTS

B+ +1.0V_PRIM

SYSTEM DC/DC

SY8032A

INPUTS OUTPUTS

+3VALW +1.8V_PRIM

SYSTEM DC/DC

RT8880

+2.5V

VS

56~57

1

48

49

50

51

INPUTS OUTP UTS

B+ +VGA_CORE

SYSTEM DC/DC

SY8286

55

INPUTS OUTP UTS

B+ +1.5VS_VGA

Vin

Vout

B B

VR_ON

NCP81206 Vout

VR_ON

DC/DC

(CPU_CORE)

Vout

PGOOD

+VCC_CO RE

+VCC_GT

+VCC_SA

VR_PWRGD

P.52,53

Vin RT8880

Vout

+VGA_CO RE

DC/DC

(VGA_CORE)

DGPU_PWR_EN

A A

DGPU_PWR_EN

5

EN

Vin

SY8286

DC/DC

(VGA_RAM)

EN

4

P.56

PGOOD

Vout

PGOOD

P.55

GPU_PGD

+1.5VS_ VGA

VRAM_PG

3

2

1

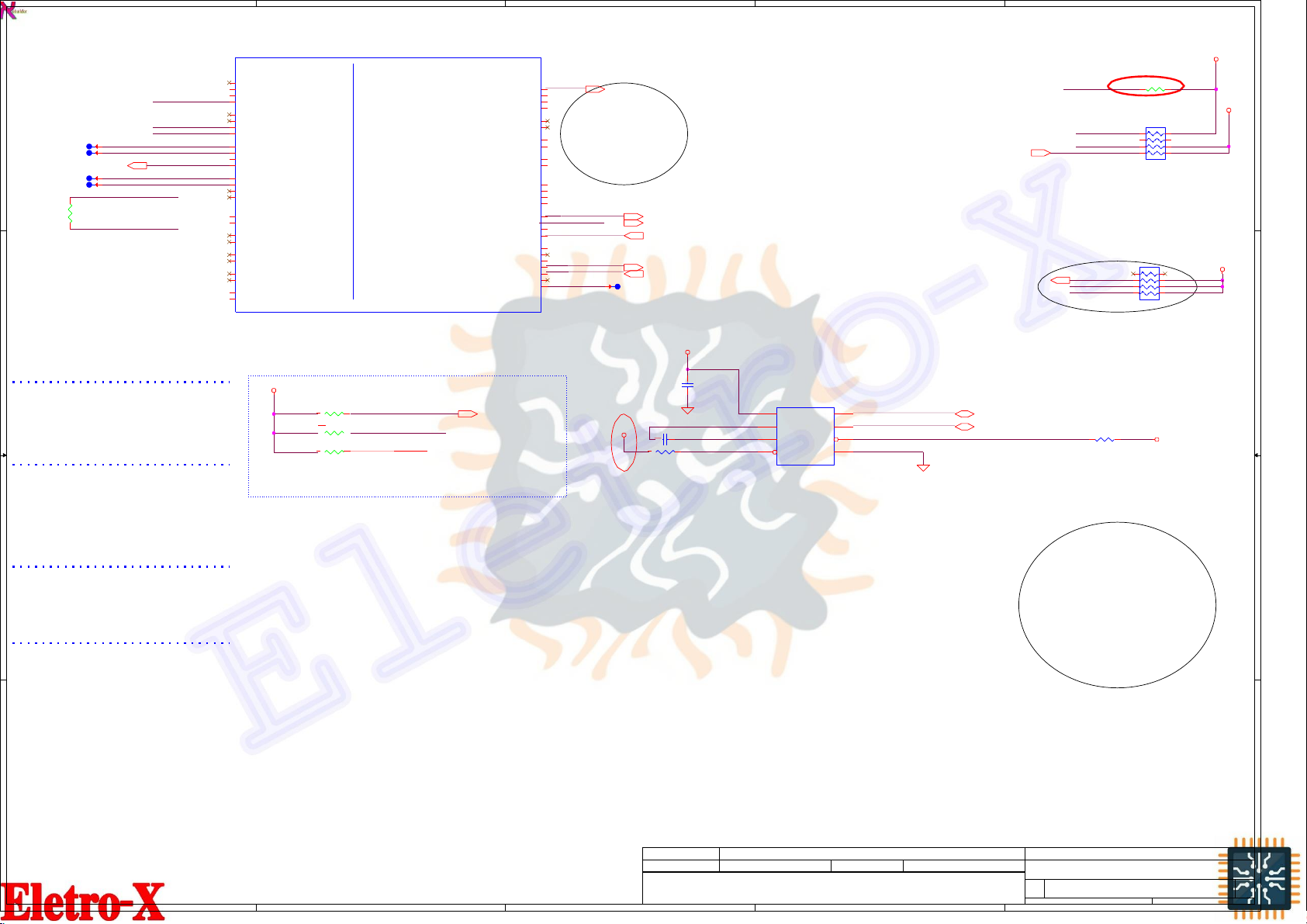

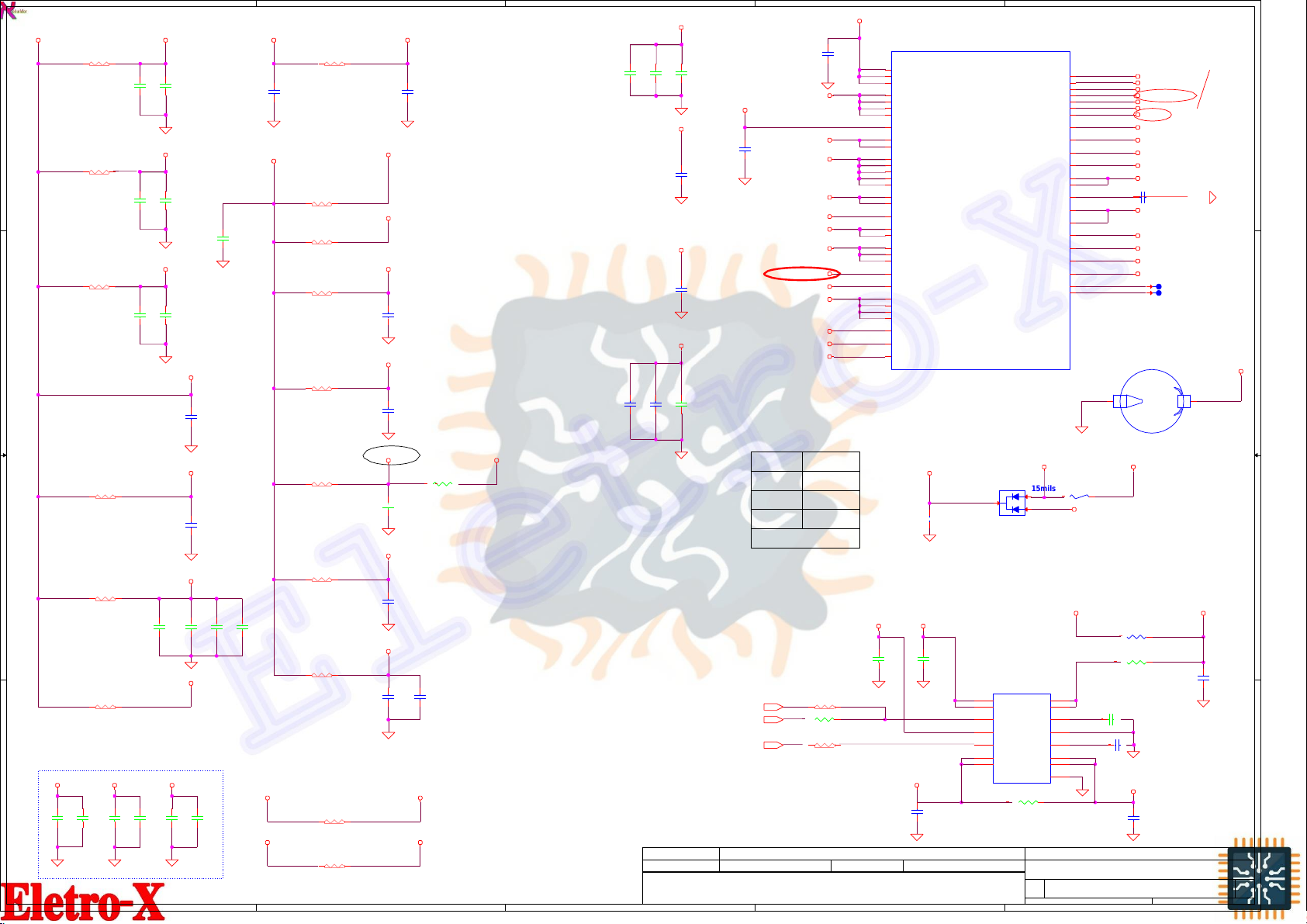

Page 5

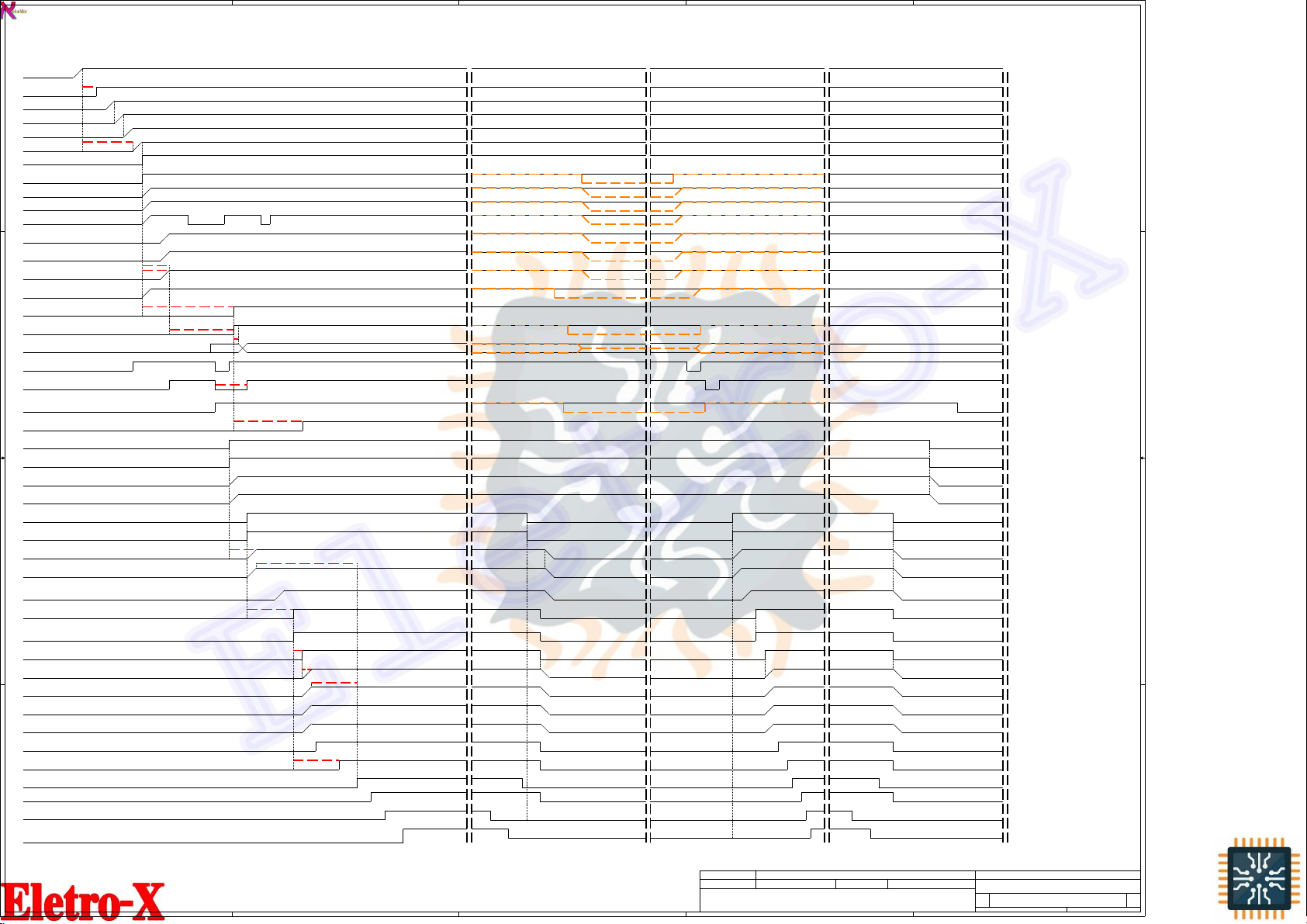

[Diner-PWR Sequence_SKL-U22_DDR3L_Volume_NON CS]

5 4 3 2 1

G3->S0

+3VL_RTC

SOC_RTC RST#

+19VB

+3VL P/+ 5VLP

D D

EC_ON

+5VAL W/+ 3VALW/+3 VALW_ DSW

PM_ BATLOW #

PCH_PWR _EN (SLP_SU S#)

+3V_ PRIM

+1.8V_PRIM

EXT_PWR_GATE #

+1.0V_M PHYPL L

+1.0V_PRIM_C ORE

+1.0V_PRIM

SUSACK#

PCH_DPW ROK

EC_RSM RST#

C C

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_ SLP_ S5#

ESPI_RST#

PM_ SLP_ S4#

SYSON

+1.0V_VCCST/ +1.0 V_VCC SFR

+1.35V_ VDDQ/ +1.3 5V_VC CSFR _OC

PM_ SLP_ S3#

SUSP #

+1. 0VS_ VCCS TG

+1.0VS_ VCCIO

B B

+5VS /+3 VS/+ 1.5VS/+ 1.05 VS

EC_VCCS T_PG

VR_ON

SM_PG_ CTRL

+0.675V S_VTT

+VCC_SA

+VCC_CORE

+VCC_G T

VR_P WRGD

PCH_PWR OK

H_CPUPW RGD

SYS_PW ROK

A A

SUS_ST AT#

SOC_PLT RST#

tPCH01_Min : 9 ms

tPCH06_Min : 200 us

tPCH04_Min : 9 ms

Pull-up to DS W w ell if notimp lement ed.

If EXT_PW R_GAT E# Tof fmin is too small, Pwr

gate m ay c hoose to completely ignore it

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02 _Min : 0 ms Max : 90 ms

Minim um duratio n of PWRBT N# assertio n = 16 mS. PWR BTN# can assert before or after RSMR ST#

tPCH18_Min : 90 us

tCPU04 Min : 100 ns

T4 = Min : 20ms Max : 3 0ms(E C Control)

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU16 Min : 0 ns

tCPU10 Min : 1ms

tCPU09 Min : 1 ms

S0->S3/DS3

S0/DS3 ->S0

S0->S5

+3VL_RTC

SOC_RTC RST#

+19VB

+3VL P/+ 5VLP

EC_ON

+5VAL W/+ 3VALW/+3 VALW_ DSW

PM_ BATLOW #

PCH_PWR _EN (SLP_SUS#)

+3V_ PRIM

+1.8V_PRIM

EXT_PWR_GATE #

+1.0V_M PHYPL L

+1.0V_PRIM_C ORE

+1.0V_PRIM

SUSACK#

PCH_DPW ROK

EC_RSM RST#

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_ SLP_ S5#

ESPI_RST#

PM_ SLP_ S4#

SYSON

+1.0V_VCCST/ +1.0 V_VCC SFR

+1.35V_ VDDQ/ +1.3 5V_VC CSFR _OC

PM_ SLP_ S3#

SUSP #

+1. 0VS_ VCCS TG

+1.0VS_ VCCIO

+5VS /+3 VS/+ 1.5VS/+ 1.05 VS

EC_VCCS T_PG

VR_ON

SM_PG_ CTRL

+0.675V S_VTT

+VCC_SA

+VCC_CORE

+VCC_G T

VR_P WRGD

PCH_PWR OK

H_CPUPW RGD

SYS_PW ROK

SUS_ST AT#

SOC_PLT RST#

SecuriiitttyClllassifffiiicatiiion

IIIssued Dattte

THIIIS SH EET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPER TY OF COMPAL ELECTRONIIICS, IIINC... AN D CONTAINS CONFIIIDENTIIIAL AND

TRADE SEC RET IIINFORMATIIION... THIIIS SHEET MAY NOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPET ENT DIIIVISION OF R&D

DEPARTME NT EXC EPT A S AUTHORIIIZED BY COMPAL ELECTRONIIICS, IIINC... NEITHER THIIIS SHEET NOR THE IIINFORMATIIION IIIT CONTAINS

5 4 3 2 1

MAY BE USED BY OR DIIISCLOSED TO ANY THIIIRD PARTY W IIITHOUT PRIIIOR WRIIITTEN CONSE NT OF COMPAL ELECTRONIIICS, IIINC...

Compalll Secret D ata

DeciiipheredDa ttte

Tiiitttllle

Siiize Documenttt Numberrr

Custom

LA-D707P

Compal Electronics,Inc.

HW Reserve

Sheettt 4 o fff60Dattte::: Wednesday, May 11, 2016

Rev

v0.2

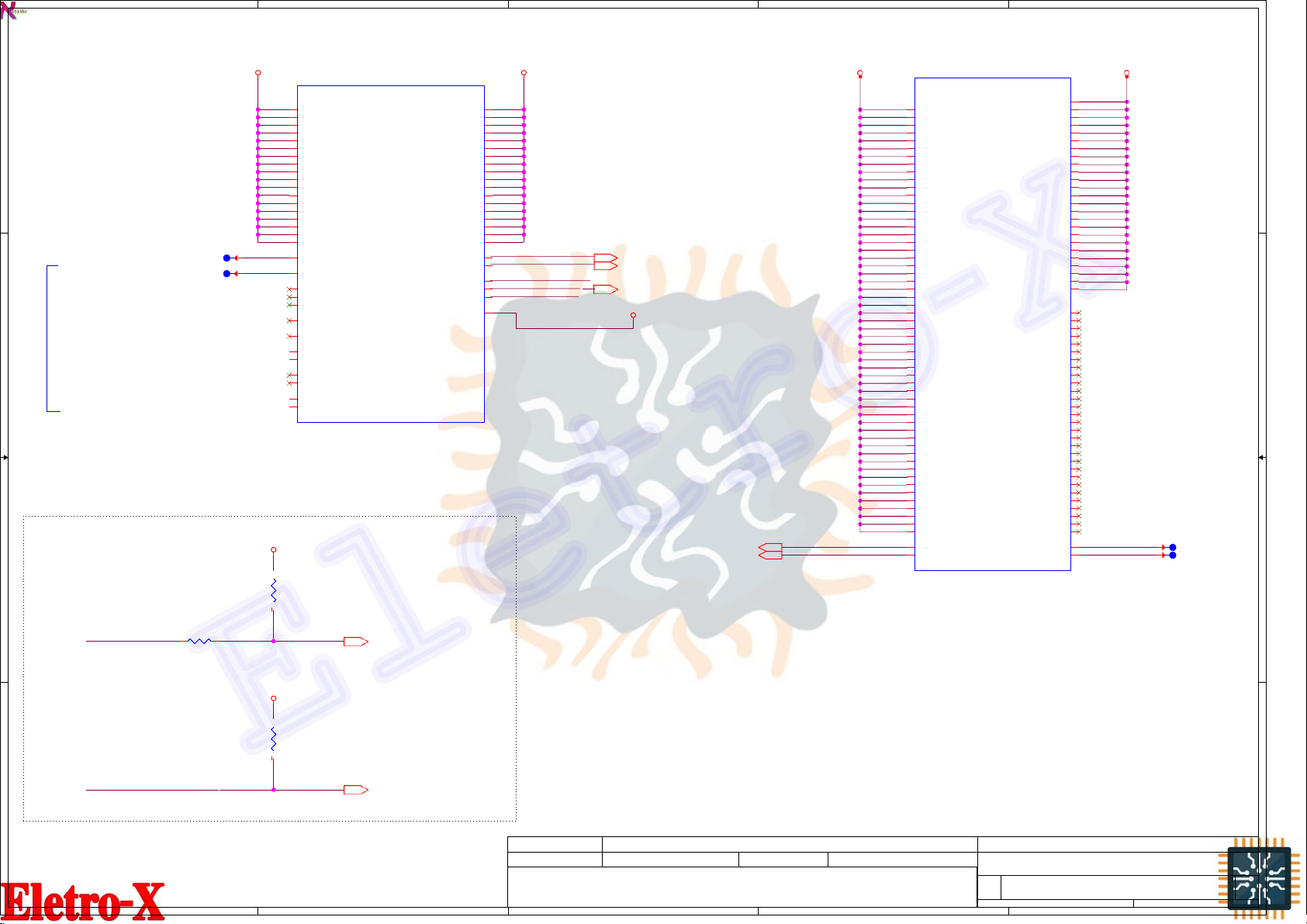

Page 6

A

Power rail

+RTCVCC

VIN

BATT+ X X

B+

+VL X X

+3VL X X

+5VALW

+3VALW

+3VALW_EC

1 1

+3V_PCH PCH_PWR_EN X

+1.2V_VDDQ

+5VS SUSP# PM_SLP_S3#

+3VS SUSP# PM_SLP_S3#

+1.5VS SUSP# PM_SLP_S3#

+1.05VS SUSP# PM_SLP_S3#

+0.6V_0.6VS SUSP#

+VCC_CORE

Control (EC)

X X

X X

X X

EC_O N

EC_O N

EC_O N

SYSON

X VR12.5_VR_ON

Source (CPU)

X

X

X

PM_SLP_S5#/PM_SLP_S4#

BOM Structure Table (1/2)

Funct i on

DGPU SKU

UMA SKU U MA@

SPI_IO3(MOW36)

Crystal (DIS) XTALPX@

Crystal XTAL@

GreenCLK(UMA) GCLK@

Green CLK(DIS) GCLKPX@

2 2

TPM T PM@

UCPU1

3 3

CPU

UK1:+3VALW_EC(+3VL)

4 4

EC

Stuf f Un-Stuff

PX@

ES@

SMBCLK

R7

SMBDATA

R8

SML0CLK

R9

SML0DATA

W2

SML1CLK

W3

SML1DATA

V3

I2C_0_SCL

I2C_0_ SDA

U6

U7

I2C_1_SCL

I2C_1_ SDA

U9

U8

EC_SMB_CK2

EC_SMB_DA2

79

80

EC_SMB_CK1

77

EC_SMB_DA1

78

A

+3VS

R=1K

+3VS

R=499

+3VS

R=1K

+3VS

R=1K

+3VL_EC

R=2.2K

+3VS

2N7002

Touch Screen

QKKS@

UC1

SA00009PJ10

ES_Q KKS

S IC A32 FJ8067702739720 QKKS G0 2.4G S IC A32 FJ8067702739718 QKJ W G0 2.6G

QS_i3@

UC1

i3_7100U_QS_QLDP

SA0000A3810

S IC A32 FJ8067702739738 QLDP H0 2.4G S IC A32 FJ8067702739739 QLDM H0 2.5G S IC A32 FJ8067702739740 QLDN H0 2.7G

R30@

U666

R16M-M1- 30 FCBG A R16M- M1-70 FCBG A

SA000087T90 SA000098V 10

S IC A32 216-0867-071 R16M-M1-30 FCBGA S IC A32 216-0864-032 R16M-M1-70FCBGA

+3VS

+3VS

R=10K

2N7002

+3VALW

+3VS

R=2.2K

2N7002

+3VS

R=2.2K

EC_SMB_CK2

EC_SMB_DA2

DGPU_PEX_RST#

2N7002

Thermal Sensor :NCT7718W_MSOP8

R=100

BAT

Charger

B

QKJW@

UC1

ES_Q KJW

QS_i5@

UC1

i5_7200U_QLDM

SA0000A3710

R70@

U666

PCH_SMBCLK

PCH_SMBDATA

TP_SMBCLK

TP_SMBDAT

+3VGS_AON

R=2.2K

I2CS_SCL

I2CS_SDA

B

SOC SMBUS Address Table

SOC_SMBUS NetName

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SA00009UR00

SO-DIMM B

Touch Pad

dGPU

Address :0x4C

i7_7500U_QLDN

SA0000A3420

PowerwRail

+3VS

+3VS ME FW 0x48/0x49

+3VS

SKLPV2@

UC1

SA000092P60

SKY_ i7_ 6500 U_SR2EZ

S IC FJ8066201930408 SR2EZ D1 2.5G BGA

QS_i7@

UC1

C

( T B C )

w

Device Ad dress (7 bit)

DIM M1

Touch PAD T BC TBC TBC

EC TBC TBC TBC

DGPU

TBC TBC

TBC TBC TBC

Address (8bit)

Write Read

0xA2

0x90/0x92

TBC

D

EC SMBUS Address Table

EC_SMBUS Port Power Rail Device Address (7 bit)

SMB US Port 1

SMBUS Port 2 +3VS

PCH TBC TBC TBC

DAX

KBL

Part Number = DA6001LS000

PCB 1RU LA-D707P REV0 M/B6

ROYALTY HDMIW /LOGO45@

Part Number Descr ipti on

HDMI W/Log o:RO 0000 002HM

RO00 00002 HM

RO0000003HM

R30R1@

U666

R16M-M1- 30 FCBG A R16M- M1-70 FCBG A

SA000087TC0 SA000098V30

S IC A32 216-0867-071 R16M-M1-30 FCBGA S IC A32 216-0864-032 R16M-M1-70FCBGA

R30R3@

U666

R16M-M1- 30 F CBG A

SA000087TB0

S IC A32 216-0867-071 R16M-M1-30 FCBGA S IC A32 216-0864-032 R16M-M1-70FCBGA

i3R1@

UC1

SA000092N70

ES_Q KKS

S IC A32 FJ8067702739720 QKKS G0 2.4G S IC A32 FJ8067702739720 QKK S G0 2.4G

i3R3@

UC1

SA000092N80

ES_Q KKS

S IC A32 FJ8067702739720 QKKS G0 2.4G S IC A32 FJ8067702739720 QKK S G0 2.4G

ZZZ

ZZZ

HY2@ MIC2@ SAM2@ HY4@ MIC4@

2G HYN IX 2G MICRON 2G SAMSUNG 4G Hynix 4G Micr on

X7667032L01 X7667032L02 X7667032L05 X7667032L03 X7667032L04

ZZZ ZZZ ZZZ

R3HY2@ R3MIC2@ R3SAM2@ R3HY4@ R3MIC4@

2G HYN IX 2G MICRON 2G SAMSUNG 4G Hynix 4G Micr on

X7667032L23 X7667032L24 X7667032L25 X7667032L21 X7667032L22

DAX

SKL

Part Number = DAZ1O200301

PCB BDL50 LA-D704P LS-C701P/C703P02

SKL@

R70R1@

U666

R70R3@

U666

R16M-M1- 70 F CBG A

SA000098V40

i5R1@

UC1

SA000092O70

ES_Q KKS

i5R3@

UC1

SA000092O80

ES_Q KKS

ZZZ

ZZZ

ZZZ ZZZ

Power State

STATE

SIGNAL

S0 (Full ON)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Sof t OFF)

i7R1@

UC1

SA000092P60

ES_Q KKS

S IC A32 FJ8067702739720 QKK S G0 2.4G

i7R3@

UC1

SA000092P70

ES_Q KKS

S IC A32 FJ8067702739720 QKK S G0 2.4G

ZZZ

Load BOM Opt i on Table

BOM Number Load BOM Opt ion

4519YN32L01(UMA)

4519YN32L02(DIS)

Securiiity Clllassiiification

Issued Date

THIS SHEE T OF ENGINE ERING DRAW ING IS THE PROPRI ETARY PROPER TY OF COMPAL ELECTRONICS,,, INC. AND CONTAINS CO NFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHE ET MAY NOT B E TRANSFERE D FROM THE CUS TODY OF THE COMPETE NT DIVISION OF R& D

DEPARTMENT E XCEPT AS AUTHORI ZED BY C OMPAL ELECTRONICS,,, INC. NEITHER THI S SHEET NOR THE INFO RMATION IT CO NTAINS

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT P RIOR WRI TTEN CONSENT OF COMP AL ELECTRONICS,,,I NC.

2011/06/29

Compalll SecretData

Deciphered Date

D

E

( T B C )

+VALW

0x16

0x12

TBC

0x4C

+VS Clock

+V

OFF OFF

OFF OFF OFF

OFF OFF OFF

+3VL_EC

BAT

CHGR

dGP U

Thermal

Sensor

PCH TBC

SLP_S4#

SLP_S3#

SLP_S5#

HIGH HIGH HIGH ON ON ON ON

LOW HIGH HIGH ON ON

LOW LOW HIGH ON

LOW LOW LOW ON

<USB2.0port>

USB2.0port

1 USB 2.0/3.0 USB 2.0/3.0

2 USB 2.0/3.0 USB 2.0/3.0

3 USB 2.0 OFFBOARD USB 2.0 OFFBOARD

4 WLAN WLAN

5 Camera Camera

6 TOUCH SCREEN TOUCH SCREEN

7 CR CR

8

9

10

DESTINATION

UMA Dis

<PCI-E,SATA,USB3.0/CLK>

PCI-E

Lane#

1 1 USB3.0 USB3.0 X

2 2 USB3.0 USB3.0 X

3 3 USB3.0(Charger) USB3.0(Charger) X

4 4 USB3.0(IOBoard )USB3.0(IOBoard ) X

5 1 5 X GPU(DIS only)

6 2 6 X GPU(DIS only)

7 3 X GPU(DIS only)

8 4 X GPU(DIS only)

9 5 LAN LAN CLK1

10 6 WLAN WLAN CLK2

11 7 0 2.5"HDD 2.5"HDD X

12 8 1 ODD ODD X

13 9

14 10 X X X

15 11 1* X X X

16 12 2 X

SATA USB3.0

2011/06/29

DESTINATION

UMA Dis

Card reader(PCI-E) Card reader(PCI-E)

Tiiitttllle

Size Documenttt Number

Custom

Compal Electronics,Inc.

Notes List

LA-D707P

E

CLK

CLK0

CLK3

Rev

v0.2

60Dattte::: W ednesday, May 11, 2016 Sheettt 3 o fff

Page 7

A

B

C D E

UC1A

UC1D

D63

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

C55

BPM#[0]

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

GPP_E3/CPU_GP0

BA5

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL-U_BGA1356

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

SKL-U

CPUMISC

4 OF20

<21> PCH_DPB_N2

<21> PCH_DPB_P2

SOC_DP1_CTRL_DATA(Internal Pull Down):

<HDMI>

Display Port B Detected

1 1

0 = Port B is not detected.

1 = Port B is detected.

<eDP to CRT>

<21> PCH_DPB_N1

<21> PCH_DPB_P1

<21> PCH_DPB_N0

<21> PCH_DPB_P0

<21> PCH_DPB_N3

<21> PCH_DPB_P3

<22> PCH_DPC_N0

<22> PCH_DPC_P0

<22> PCH_DPC_N1

<22> PCH_DPC_P1

SOC_DP2_CTRL_DATA(Internal Pull Down):

Display Port C Detected

0 = Port C is not detected.

1 = Port C is detected.

HDMI DDC (Port B)

<21> PCH_DDPB_CLK

<21> PCH_DDPB_DAT

+3VS

<DB> DP port C enable

+1.0V_VCCST

1

RC2

2 2

COMPENSATION PU FOR eDP

+1.0VS_VCCIO

RC1 1

CAD note:

Trace width=20 mils,Spacing=25mil,Maxlength=100mils

2 H_THERMTRIP#

1K_0402_5%

2EDP_COMP

24.9_0402_1%

<26> PROCHOT#

+1.0VS_VCCIO

2

1

1

RC3

1K_0402_5%

1 2

RC4

DS11

CK0402101V05_0402-2

ESD@

SCV00001K00

2

RC6 2

RC7 2

RC8 2

T248 TP@

<26> H_PECI

499_0402_1%

T25 TP@

T270 TP@

T271 TP@

T250 TP@

T249 TP@

T30 TP@

T40 TP@

1 49.9_0402_1% CPU_POPIRCOMP AT16RC5 2

1 49.9_0402_1% PCH_OPIRCOMP AU16

1 49.9_0402_1% EDRAM_OPIO_RCOMP H66

1 49.9_0402_1% EOPIO_RCOMP H65

@ RC200 1

RC199 1

PCH_DDPB_CLK

PCH_DDPB_DAT

2 2.2K_0402_5%

2 2.2K_0402_5%

CRT@

EDP_COMP

H_PECI A54

H_PROCHOT#_R C65

H_THERMTRIP# C63

SOC_OCC# A65

XDP_BPM#0

XDP_BPM#1 D55

SOC_GPIOE3 A6 A7

SOC_GPIOB4 AY5

SKL-U

DDI

DISPLA Y SIDE BANDS

JTAG

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

1 OF20

Rev_0. 53

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

JTAGX

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

B61

D60

A61

C60

B59

PCH_JTAG_TCK1

B56

SOC_XDP_TDI

D59

A56

C59

C61

A59

Rev_0. 53

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

DDI2_AUX_DN

E48

F48

DDI2_AUX_DP

G46

F46

L9 PCH_DDPB_HPD

DDI2_HPD

L7

NMI_DBG#_CPU

L6

EC_SCI#

N9

EDP_HPD

L10

R12

ENBKL

R11

ENVDD_CPU

U13

TP@ T259

TP@ T260

TP@ T261

TP@ T262

TP@ T263

TP@ T264

TP@ T265

TP@ T266

TP@ T267

TP@ T268

TP@ T269

EDP_CPU_LANE_N0_C <19>

EDP_CPU_LANE_P0_C <19>

EDP_CPU_LANE_N1_C <19>

EDP_CPU_LANE_P1_C <19>

EDP_CPU_AUX#_C <19>

EDP_CPU_AUX_C <19>

TP@ T228

DDI2_AUX_DN <22>

DDI2_AUX_DP <22>

PCH_DDPB_HPD <21>

DDI2_HPD <22>

NMI_DBG#_CPU <10,26>

EC_SCI# <10,26>

EDP_HPD <19>

ENBKL <26>

BKL_PWM_CPU <20>

ENVDD_CPU <20>

RC123 1 @ 2 100K_0402_5% ENVDD_CPU

RC124 1 2 100K_0402_5% ENBKL

<eDP>

From HDMI

From eDP to CRT

From eDP

<DB> Check

XDP CONN

3 3

+1.0VS_VCCIO

1 51_0402_5% SOC_XDP_TMSRC11 2 @

RC15 2 1 51 +-1% 0402 SOC_XDP_TDO

RC364 2 @ 1 51_0402_5% CPU_XDP_TCK0

+1.0V_PRIM

RC14 2 @ 1 51_0402_5% XDP_PREQ#

RC31 1 @ 2 1K_0402_5% XDP_ITP_PMODE

4 4

A

RC365 2 @ 1 51_0402_1% SOC_XDP_TRST#

RC35 2 1 51_0402_1% CPU_XDP_TCK0

RC37 2 @ 1 51_0402_5% PCH_JTAG_TCK1

RC366 1 @ 2 0_0402_5% CFG3

1 51_0402_5% SOC_XDP_TDIRC13 2 @

SD000008H80

XDP_PREQ# <11>

XDP_ITP_PMODE <16>

SD000008H80

CFG3 <16>

B

SecurityClassification

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C D

2014/05/19 2015/12/31

Compal Secret Data

Deciphered Date

Tiiitllle

Siiize Document Number

Custom

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

LA-D707P

Rev

Sheet 5 o f 60Date: Wednesday, May 11, 2016

E

v0.2

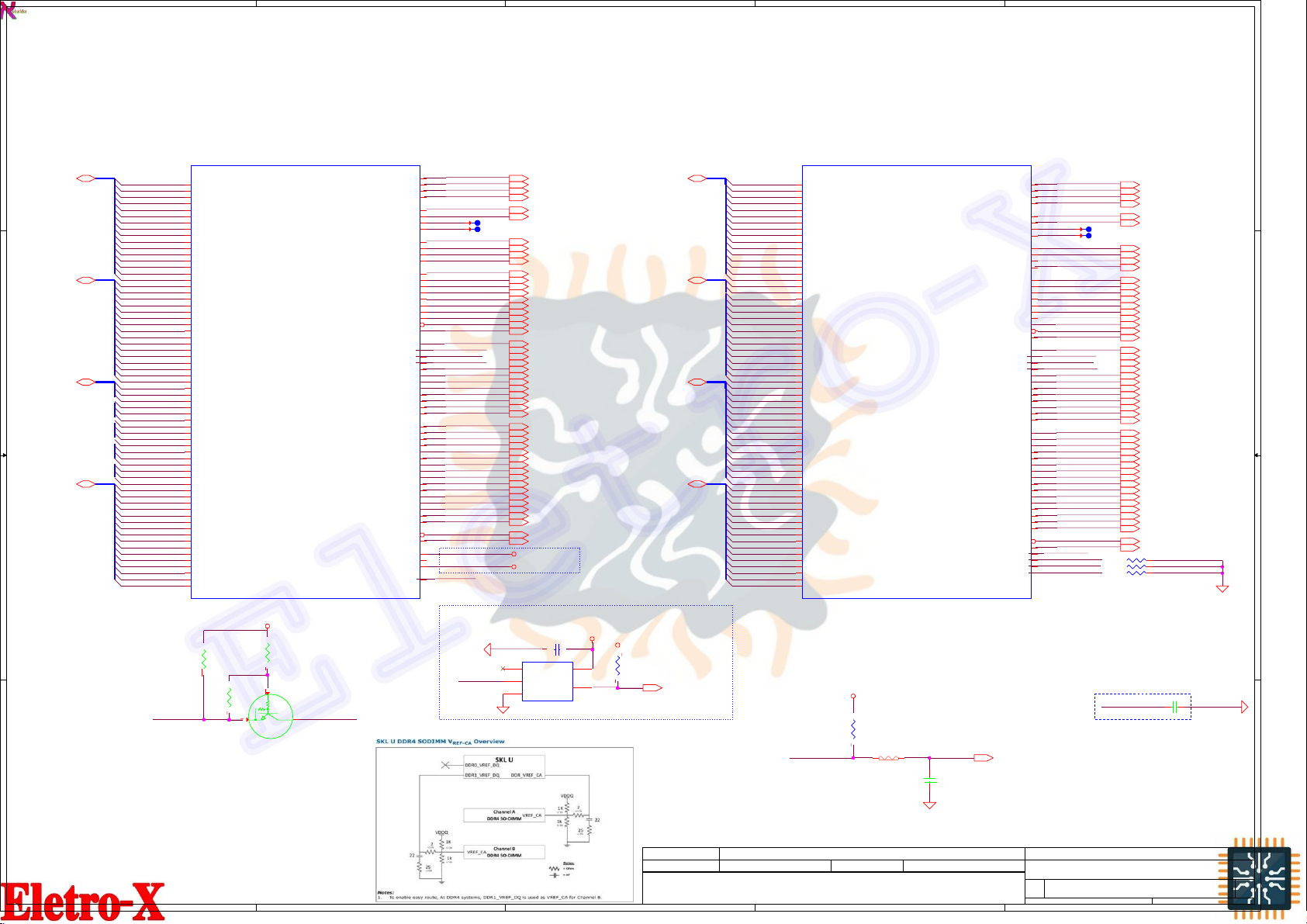

Page 8

5

Interleaved Memory

4

3

2

1

Interleaved Memory

D D

UC1B

<17> DDR_A_D[0..15]

<17> DDR_A_D[16..31]

C C

<17> DDR_A_D[32..47]

<17> DDR_A_D[48..63]

B B

A A

AL71

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22 BA63

DDR_A_D23 BB63

DDR_A_D24 BA61

DDR_A_D25 AW61

DDR_A_D26 BB59

DDR_A_D27 AW59

DDR_A_D28 BB61

DDR_A_D29 AY61

DDR_A_D30 BA59

DDR_A_D31 AY59

DDR_A_D32 AY39

DDR_A_D33 AW39

DDR_A_D34 AY37

DDR_A_D35 AW37

DDR_A_D36 BB39

DDR_A_D37 BA39

DDR_A_D38 BA37

DDR_A_D39 BB37

DDR_A_D40 AY35

DDR_A_D41 AW35

DDR_A_D42 AY33

DDR_A_D43 AW33

DDR_A_D44 BB35

DDR_A_D45 BA35

DDR_A_D46 BA33

DDR_A_D47 BB33

DDR_A_D48 AY31

DDR_A_D49 AW31

DDR_A_D50 AY29

DDR_A_D51 AW29

DDR_A_D52 BB31

DDR_A_D53 BA31

DDR_A_D54 BA29

DDR_A_D55 BB29

DDR_A_D56 AY27

DDR_A_D57 AW27

DDR_A_D58 AY25

DDR_A_D59 AW25

DDR_A_D60 BB27

DDR_A_D61 BA27

DDR_A_D62 BA25

DDR_A_D63 BB25

SB00000QJ00,S TR DRC5115E0L NPNSOT323-3

AL68

AN68

AN69

AL70

AL69

AN70

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

BB65

AW65

AW63

AY63

BA65

AY65

RC905

100K_0402_5%

DDR_PG_CTRL

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

2

1

1

RC906

100K_0402_5%

@

2

+1.2V_VDDQ

1

RC904

@

100K_0402_5%

2 2

@

UC9

SB000008 E10

MMBT3904WH NPN SOT323-3

DDRCH - A

2 OF 20

1 SM_PG_CTRL3

<Cocoa_1020>

PDG#543016, ODT: CPU side no connect, DRAM side connect to VDDQ(Memory down); FET+R(SO-DIMM)

RC32

470_0402_5%

1

RC33

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0 _DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0 _DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0 _DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0 _DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1 _DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1 _DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDRCH - B

3 OF 20

2 DDR_DRAMRST#_R

0_0402_5%

1

2

DDR_RCOMP[1]

DDR_RCOMP[2]

CC155

0.1U_0201_10V6K

@ESD@

9/8 Modify base on ESD Request

PLACE NEAR TO SoC

AN45 DDR_B_CLK#0

DDR1_CKN[0]

AN46 DDR_B_CLK#1

DDR1_CKN[1]

AP45 DDR_B_CLK0

DDR1_CKP[0]

AP46 DDR_B_CLK1

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR_DRAMRST#_R <17,18>

DDR_B_CKE0

AN56

AP55 DDR_B_CKE1

AN55

AP53

DDR_B_CS#0

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

AW42 DDR_B_ODT1

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

AN48 DDR_B_MA11

AN53 DDR_B_ACT#

AN52 DDR_B_BG1

BA43 DDR_B_MA 13

AY43 DDR_B_MA15_CAS#

AY44 DDR_B_MA14_WE#

AW44 DDR_B_MA16_RAS#

BB44 DDR_B_BA0

AY47 DDR_B_MA2

BA44 DDR_B_BA1

AW46 DDR_B_MA1 0

AY46 DDR_B_MA1

BA46 DDR_B_MA0

BB46 DDR_B_MA3

BA47 DDR_B_MA4

AH66 DDR_B_DQS#0

AH65 DDR_B_DQS0

AG69 DDR_B_DQS#1

AG70 DDR_B_DQS1

AR66 DDR_B_DQS#2

AR65 DDR_B_DQS2

AR61 DDR_B_DQS#3

AR60 DDR_B_DQS3

AT38 DDR_B_DQS#4

AR38 DDR_B_DQS4

AT32 DDR_B_DQS#5

AR32 DDR_B_DQS5

AR25 DDR_B_DQS#6

AR27 DDR_B_DQS6

AR22 DDR_B_DQS#7

AR21 DDR_B_DQS7

AN43 DDR_B_ALERT#

AP43 DDR_B_PAR

AT13 DDR_DRAMRST#

AR18 SM_RCOMP0 RC38 1

AT18 SM_RCOMP1 RC39 1

AU18 SM_RCOMP2 RC40 1 2 100_0402_1%

SKL-U

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0 _DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0 _DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1 _DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1 _DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1 _DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1 _DQSP[5]

Rev_0 .53 Rev_0 .53

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53 DDR_A_CLK#0

AT53 DDR_A_CLK0

AU55 DDR_A_CLK#1

AT55 DDR_A_CLK1

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

BA55 DDR_A_ACT#

AY54 DDR_A_BG1

AU46 DDR_A_MA13

AU48 DDR_A_MA15_CAS#

AT46 DDR_A_MA14_WE#

AU50 DDR_A_MA16_RAS#

AU52 DDR_A_BA0

AY51 DDR_A_MA2

AT48 DDR_A_BA1

AT50 DDR_A_MA10

BB50 DDR_A_MA1

AY50 DDR_A_MA0

BA50 DDR_A_MA3

BB52 DDR_A_MA4

AM70 DDR_A_DQS#0

AM69 DDR_A_DQS0

AT69 DDR_A_DQS#1

AT70 DDR_A_DQS1

BA64 DDR_A_DQS# 2

AY64 DDR_A_DQS2

AY60 DDR_A_DQS# 3

BA60 DDR_A_DQS3

BA38 DDR_A_DQS# 4

AY38 DDR_A_DQS4

AY34 DDR_A_DQS# 5

BA34 DDR_A_DQS5

BA30 DDR_A_DQS# 6

AY30 DDR_A_DQS6

AY26 DDR_A_DQS# 7

BA26 DDR_A_DQS7

AW50 DDR_A_ALERT#

AT52 DDR_A_PAR

AY67 +0.6V_VREF CA

AY68

BA67 +0.6V_B_VREFDQ

AW67 DDR_PG_CTRL

For VTT power control

DDR_PG_CTRL 2

TP@ T 14

TP@ T 15

+0.6V_VREFCA

+0.6V_B_VREFDQ

0.1U_0201_10V6K 2 1 CC57

UC7

1

NC

A

3

GND

SN74AUP1G07DCKR_SC70-5

SA00007U R00

DDR_A_CLK#0 <17 >

DDR_A_CLK0 <17>

DDR_A_CLK#1 <17 >

DDR_A_CLK1 <17>

DDR_A_CKE0 < 17>

DDR_A_CKE1 < 17>

DDR_A_CS#0 < 17>

DDR_A_CS#1 < 17>

DDR_A_ODT0 <17>

DDR_A_ODT1 <17>

DDR_A_MA5 <17>

DDR_A_MA9 <17>

DDR_A_MA6 <17>

DDR_A_MA8 <17>

DDR_A_MA7 <17>

DDR_A_BG0 <17>

DDR_A_MA12 <17>

DDR_A_MA11 <17>

DDR_A_ACT# <17>

DDR_A_BG1 <17>

DDR_A_MA13 <17>

DDR_A_MA15_CAS# <17>

DDR_A_MA14_WE# <17>

DDR_A_MA16_RAS# <17>

DDR_A_BA0 <17>

DDR_A_MA2 <17>

DDR_A_BA1 <17>

DDR_A_MA10 <17>

DDR_A_MA1 <17>

DDR_A_MA0 <17>

DDR_A_MA3 <17>

DDR_A_MA4 <17>

DDR_A_DQS#0 <17>

DDR_A_DQS0 <17>

DDR_A_DQS#1 <17>

DDR_A_DQS1 <17>

DDR_A_DQS#2 <17>

DDR_A_DQS2 <17>

DDR_A_DQS#3 <17>

DDR_A_DQS3 <17>

DDR_A_DQS#4 <17>

DDR_A_DQS4 <17>

DDR_A_DQS#5 <17>

DDR_A_DQS5 <17>

DDR_A_DQS#6 <17>

DDR_A_DQS6 <17>

DDR_A_DQS#7 <17>

DDR_A_DQS7 <17>

DDR_A_ALERT# <17>

DDR_A_PAR <17 >

+1.2V_VDDQ

5

VCC

4

Y

<18> DDR_B_D[0..15]

<18> DDR_B_D[16..31]

<18> DDR_B_D[32..47]

<18> DDR_B_D[48..63]

+3VS

1

RC394

100K_0402_5%

2

SM_PG_CT RL <49>

DDR_B_D0 AF65

DDR_B_D1 AF64

DDR_B_D2 AK65

DDR_B_D3 AK64

DDR_B_D4 AF66

DDR_B_D5 AF67

DDR_B_D6 AK67

DDR_B_D7 AK66

DDR_B_D8 AF70

DDR_B_D9 AF68

DDR_B_D10 AH71

DDR_B_D11 AH68

DDR_B_D12 AF71

DDR_B_D13 AF69

DDR_B_D14 AH70

DDR_B_D15 AH69

DDR_B_D16 AT66

DDR_B_D17 AU66

DDR_B_D18 AP65

DDR_B_D19 AN65

DDR_B_D20 AN66

DDR_B_D21 AP66

DDR_B_D22 AT65

DDR_B_D23 AU65

DDR_B_D24 AT61

DDR_B_D25 AU61

DDR_B_D26 AP60

DDR_B_D27 AN60

DDR_B_D28 AN61

DDR_B_D29 AP61

DDR_B_D30 AT60

DDR_B_D31 AU60

DDR_B_D32 AU40

DDR_B_D33 AT40

DDR_B_D34 AT37

DDR_B_D35 AU37

DDR_B_D36 AR40

DDR_B_D37 AP40

DDR_B_D38 AP37

DDR_B_D39 AR37

DDR_B_D40 AT33

DDR_B_D41 AU33

DDR_B_D42 AU30

DDR_B_D43 AT30

DDR_B_D44 AR33

DDR_B_D45 AP33

DDR_B_D46 AR30

DDR_B_D47 AP30

DDR_B_D48 AU27

DDR_B_D49 AT27

DDR_B_D50 AT25

DDR_B_D51 AU25

DDR_B_D52 AP27

DDR_B_D53 AN27

DDR_B_D54 AN25

DDR_B_D55 AP25

DDR_B_D56 AT22

DDR_B_D57 AU22

DDR_B_D58 AU21

DDR_B_D59 AT21

DDR_B_D60 AN22

DDR_B_D61 AP22

DDR_B_D62 AP21

DDR_B_D63 AN21

UC1C

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ [18]

DDR1_DQ[3]/DDR0_DQ [19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ [22]

DDR1_DQ[7]/DDR0_DQ [23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

SKL-U_BGA1356

+1.2V_VDDQ

DDR_DRAMRST#

1

2

DDR_B_CLK#0 <18>

DDR_B_CLK#1 <18>

DDR_B_CLK0 < 18>

DDR_B_CLK1 < 18>

DDR_B_CKE0 < 18>

TP@ T17

TP@ T18

DDR_B_CKE1 < 18>

DDR_B_CS#0 < 18>

DDR_B_CS#1 < 18>

DDR_B_ODT0 <18>

DDR_B_ODT1 <18>

DDR_B_MA5 <18>

DDR_B_MA9 <18>

DDR_B_MA6 <18>

DDR_B_MA8 <18>

DDR_B_MA7 <18>

DDR_B_BG0 <18>

DDR_B_MA12 <18>

DDR_B_MA11 <188>

DDR_B_ACT# <18>

DDR_B_BG1 <18>

DDR_B_MA13 <18>

DDR_B_MA15_CAS# <18>

DDR_B_MA14_WE# <18>

DDR_B_MA16_RAS# <18>

DDR_B_BA0 <18>

DDR_B_MA2 <18>

DDR_B_BA1 <18>

DDR_B_MA10 <18>

DDR_B_MA1 <18>

DDR_B_MA0 <18>

DDR_B_MA3 <18>

DDR_B_MA4 <18>

DDR_B_DQS#0 <18>

DDR_B_DQS0 <18>

DDR_B_DQS#1 <18>

DDR_B_DQS1 <18>

DDR_B_DQS#2 <18>

DDR_B_DQS2 <18>

DDR_B_DQS#3 <18>

DDR_B_DQS3 <18>

DDR_B_DQS#4 <18>

DDR_B_DQS4 <18>

DDR_B_DQS#5 <18>

DDR_B_DQS5 <18>

DDR_B_DQS#6 <18>

DDR_B_DQS6 <18>

DDR_B_DQS#7 <18>

DDR_B_DQS7 <18>

DDR_B_ALERT# <18>

DDR_B_PAR <1 8>

2 121_0402_1%

2 80.6_0402_1%

DDR_PG_CTRL 1 2

CC70 100P_040 2_50V8J

From ESD Team Request

/10 Modify for DDR4

8/10 Modify for DDR4

9/8 Modify

8/10 Modify for DDR4

@ESD@

SecurityClllassiiifiiicatiiion

Issued Date

THIIIS SHEET OF ENGIIINEERIIING D RAWING IIIS THE PROPRIIIETARY P ROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRAD E SECRE T IIINFORMATIIION... THIIIS SHE ET MAY NOT BE TRA NSFERE D FROM THE CUSTODY OF THE COMPETE NT DIIIVIIISIIION OF R&D

DEPARTMENT E XCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NO R THE IIINFORMATIIION IIIT CONTAIIINS

5

4

MAY BE US ED BY OR DIIISCLOSED TO ANY THIIIRD PARTY W ITHOUT PRIIIOR WRIIITTEN CON SENT OF COMPAL ELECTRONIIICS,,, IIINC...

3

2014/05/19 2015/12/31

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Tiiitllle

Size Document Number

Custom

2

Date: Wednesday, May 11, 2016

SKL-U(2/12)DDRIII

LA-D707P

1

Sheet 6 o f

Rev

v0.2

60

Page 9

5 4 3 2 1

UC1E

PCH_SPI_CLK

PCH_SPI_SO

PCH_SPI_SI

PCH_SPI_SIO2 AW2

PCH_SPI_SIO3

PCH_SPI_CS0# AU3

D D

AW3

AV2

AV3

AU4

AU2

AU1

12/11_Delete TP

<26> EC_KBRST#

To TPM

<26,28> SERIRQ

to SPI ROM UC2

C C

B B

A A

PCH_SPI_CS0#_R 1

PCH_SPI_CS0#_R 2

PCH_SPI_SO_R 3

PCH_SPI_SO_R 4

PCH_SPI_HOLD#

PCH_SPI_SI_R

PCH_SPI_SI_R

PCH_SPI_WP# 2 1 PCH_SPI_SIO2

SPI ROM ( 8MByte Only)

PCH_SPI_CS0#_R 1

PCH_SPI_SO_R 2

PCH_SPI_WP# 3

PCH_SPI_CLK 2

EON SA 000046 400 S IC FL 6 4M EN2 5Q64-1 04HIP SOP 8P

MXIC SA 00006N 100 S IC FL 6 4M MX25 L6473E M2I-10 G SOP 8P

WINBON D SA00 0039A3 0 S IC FL 64M W25Q64 FVSSI Q SOIC 8P SP I ROM

Micron SA000 05L100 S IC FL 64M N 25Q064 A13ES EC0F SO 8W 8P

15_0804_8P4R_5%

1

2

3

4

15_0804_8P4R_5%

RC388 15_0402_5%

UC2

/CS VCC

DO(IO1) /HOLD(IO3)

/WP(IO2) CLK

4

GND DI(IO0)

W25Q64FVSSIQ_SO8 SA000039A30

PCB Footpri nt = ACES_91960 -0084L_8P-T

Use socket footprint

RC368

15_0402_5%

1 PCH_SPI3_rCd LK:S_AR

EMI@

Source From

RPH11

8 EC_SPI_CS0#

7 PCH_SPI_CS0#

6 EC_SPI_SO

5 PCH_SPI_SO

RPH12

8 PCH_SPI_SIO3

7 PCH_SPI_SI

6 EC_SPI_SI

5

+3V_SPI

8

PCH_SPI_HOLD#

7

6

PCH_SPI_CLK_R

5

PCH_SPI_SI_R

SPI ROM:

Main:SA0 00039A3 0, S IC FL 64M W25Q64 FVSSIQ SOIC

8P SPI ROM

2nd :SA00 007LA10, S IC FL 64M GD25B64 CSIGR SOP

8P SPI ROM

000099300, S IC FL 64M N25 Q064A13E SEDFF

SO8W 8P SPI

1 2

CC9

10P_0402_50V8J

@EMI@

EC_KBRST#

SERIRQ

LPC Mode

EC_SPI_CS0# <26>

EC_SPI_SO <26>

EC_SPI_SI <26>

CC8

1 2 0.1U_0402_16V7K

PCH_SPI_CLK_R <26>

AW13

AY11

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

SPI - FLAS H

CL INK

SMBCLK

SMBDATA

2N7002DWH_SOT363-6

SML1CLK 6

SML1DATA

SMBCLK 1

2N7002DWH_SOT363-6

SMBDATA

SKL-U

LPC

2

QC1A

6 1

2N7002DWH_SOT363-6

SB00000I700

QC1B

3 4

2N7002DWH_SOT363-6

SB00000I700

2

QC2A

SB00000I700

QC2B

2N7002DWH_SOT363-6

SB00000I700

<DB> PWR Rail

2

SB00000I700

6

QC7A

QC7B SB00000I700

2N7002DWH_SOT363-6

SMBUS ,SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF20

+3VS +3VS

RC216

10K_0402_5%

5

+3VS

1

5

3 4

+3V_PRIM +3VALW

RC81

10K_0402_5%

5

34

Rev_0. 53

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

RC215

10K_0402_5%

1 2

1 2

<Co coa_ 102 0>

add leve l shift

1 2

PCH_SMBCLK <17,18,19,22>

PCH_SMBDATA <17,18,19,22>

EC_SMB_CK2 <10,19,22,26,37>

EC_SMB_DA2 <10,19,22,26,37>

RC82

10K_0402_5%

1 2

TP_SMBCLK <27>

TP_SMBDATA <27>

R7

SMBCLK

R8

SMBDATA

SMBALERT#

R10

R9

SML0CLK

W2

SML0DATA

W1

SML0ALERT#

W3

SML1CLK

V3

SML1DATA

AM7 GPP_B23 1

AY13 LPC_AD0

LPC_AD1

BA13

LPC_AD2

BB13

LPC_AD3

AY12

LPC_FRAME#

BA12

SUS_STAT#

BA11

AW9 CLK_PCI0

AY9 CLK_PCI1 RC53 1 TPM@2 22_0402_5%

AW11 PM_CLKRUN#

<SI>un -mount RC53

11/2 8 CPU side delete EC_PCIE_ WAKE#

RC387

RC902@

0_0201_5%

TP@ T234

1

TP@ T239

2 SML1ALERT#

TP@ T242

LPC_AD0 <26,28>

LPC_AD1 <26,28>

LPC_AD2 <26,28>

LPC_AD3 <26,28>

LPC_FRAME# <26,28>

2 22_0402_5%

PM_CLKRUN# <26>

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC --> For KB9022/9032 Use

1 = eSPI is selected for EC --> For KB9032 Only.

SML1ALERT#

SML0ALERT#

SMBALERT#

EC_KBRST#

SML0ALERT#

1

2

2 @ 1

150K_0402_1%

2 @ 1 10K_0402_5%

RC360

8

7

6

5

RPC19 10K_0804_8P4R_5%

RC218

1K_0402_1%

RC903

SMB

(Link to XDP , DDR, TP)

SML1

(Link to EC, DGPU, LAN, T herm al

CLK_PCI_LPC <26>

CLK_PCI_TPM <28>

To EC

Sensor)

11/28_Fo llow I ntel check list, add PU res

11/28_Change PWR rail from +3VS to +3V_PRIM

+3V_PRIM

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SMBDATA

SMBCLK

PCH_SPI_SIO2 RC3901 @ 2 1K_0402_1%

PCH_SPI_SIO3 RC3911 2 1K_0402_1%

PCH_SPI_CS0#_R

PCH_SPI_SIO3 RC51 1 ES@ 2 1K_0402_1%

From WW36 MOW for SKL-U ES sample

PM_CLKRUN#

SERIRQ

RC49 1 2 499_0402_1%

RC50 1 2 499_0402_1%

RPC7

1 8

2

7

6

3

4 5

1K_0804_8P4R_5%

@

@

2

1

RC357

RC107 8.2K_0402_5%

RC122 8.2K_0402_5%

1K_0402_5%

1 2

1 2

Follow 543016_SKL_U_Y_PDG_0_9

+3V_SPI

+3VS_PGPPA

+3V_PRIM

1

2

3

4

+3VS

SecurityClassification

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5 4 3 2 1

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/12/11 2015/12/31

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Tiiitllle

SKL-U(3/12)SPI,ESPI,SMB,LPC

Siiize Document Number

Custom

LA-D707P

Rev

Sheet 7 o f 60Date: Wednesday, May 11, 2016

v0.2

Page 10

5 4 3 2 1

UC1G

D D

<24> HDA_SDIN0

<10,24> HDA_SPKR

C C

T35 TP@

T38 TP@

T39 TP@

HDA forAUDIO

1 8

@EMI@

2

3

4

<24> HDA_SYNC_AUDIO

<24> HDA_RST_AUDIO#

<24> HDA_SDOUT_AUDIO

<24> HDA_BITCLK_AUDIO

CC143 22P_0402_50V8J

HDA_SYNC BA22

HDA_BIT_CLK AY22

HDA_SDOUT BB22

HDA_SDIN0

HDA_RST#

SOC_GPIOF1

SOC_GPIOF0

HDA_SPKR

RPC9

7 HDA_SYNC

6 HDA_RST#

5 HDA_SDOUT

33_0804_8P4R_5%

2

RC383

EMI@

BA21

AY21

AW22

AY20

AW20

AK7

AK6

AK9

AK10

AW5

1 HDA_BIT_CLK

33_0402_5%

J5

H5

D7

D8

C8

EMI request

A36

B B

A A

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

<26> ME_FLASH_EN

+3V_HDA

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

SKL_ULT

SKL-U

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

7 OF20

RC367 1 2 0_0402_5%

2

2 RC380

1

1K_0402_1%

@

G

1

D

@

3 HDA_SDOUT

QC380

S

MESS138W-G_SOT323-3

Rev_0.5 3

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_RCOMP

GPP_F23

AB11

AB13 VRAMCLK_SEL

AB12 PROJECT_ID

W12

W11

W10

W8

W7

BA9

BB9

AF13 SOC_GPIOF17

T235 TP@

+3V_PRIM

1

RC127

10K_0402_5%

PX@

2

1

RC128

10K_0402_5%

UMA@

2

1 200_0402_1%AB7 SD_RCOMP RC76 2

PROJECT_ID

VRAM Clock

VRAMCLK_SEL

UMA DIS

0

1

900MHz 1000MHz

X76@

2

RC900

10K_0402_5%

1

X76@

2

RC901

10K_0402_5%

1

1

0

+3V_PRIM

HDA_SDOUT:

ME Flash Descriptor Security Override

Low : Disabled(Default)

High : Enabled

Rev_0.5 3

C37

CSI2_CLKN0

D37

CSI2_CLKP0

C32

CSI2_CLKN1

D32

CSI2_CLKP1

C29

CSI2_CLKN2

D29

CSI2_CLKP2

B26

CSI2_CLKN3

A26

9 OF20

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMM C

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

E13 CSI2_COMP RC80 2

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

EMMC_RCOMP 2

T63 TP@

RC89

1 100_0402_1%

1

200_0402_1%

SecurityClassification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5 4 3 2 1

2014/05/19 2015/12/31

Compal SecretData

Deciphered Date

Compal Electronics,Inc.

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Siiize Document Number

Custom

LA-D707P

Date: Wednesday, May 11,2016

Sheet of

8

Rev

v0.2

60

Page 11

+RTCVCC

RC91 1 2 20K_0402_ 5% PCH_SRT CRST#

CC10 1 2 1U_0402_6 .3V6K

CLRP1 1 2 SH ORT PAD S

RC93 1 2 20K_0402_5% PCH _RTCRST#

CC11 1 2 1U_0402_6.3V6K

CLRP2 1 2 SH ORT PAD S

D D

+3V_PRIM

C C

B B

A A

RC941 2 1M_0402_5% SM_INTRUDER#

PCH_RT CRST# 2 @ 1

0_0402_5% R1088

PCH_SRT CRST# 2 @ 1

0_0402_5% R1089

+3VS

RC165

RC105

RC109 10K_0 402_5%

+3VALW _DSW

10K_0804_8P4R_5%

CLRP3 SHORTPADS

RC100 1K_0402_5%

RC101

+3VALW _DSW

+3V_PRIM

+3VALW _DSW

RC111 2 1 100K_0402_5% PBTN_OU T#

From EC (open- drain)

<26,35> EC_VCCST_P G_R

5 4 3 2 1

RC112

SKL_ULT

CLO CK SIG NALS

10 OF 20

PLT_RST# <23 ,26,28,32,36>

SKL-U

11 OF 20

2

1 PCH_DPW ROK_R

0_0402_5%

Rev_0 .53

GPD8/SU SCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

Rev_0 .53

GPD4/SL P_S3#

GPD5/SL P_S4#

SLP_SUS#

SLP_LAN#

GPD6/SL P_A#

GPP_A11/PME#

INTRUD ER#

F43

E43

BA17 SUSCLK

E37 PCH_XT AL24_IN

E35 PCH_XTAL24_OUT

E42 XCLK_BIASR EF RC96 1 2 2.7K_0402_1%

AM18 PCH_RTCX1

AM20 PCH_R TCX2

AN18 PCH_S RTCRST #

AM16 PCH_RTCRST#

PCH_XT AL24_IN

PCH_XT AL24_OU T PCH_RT CX1

AT11 PM_S LP_S0#

AP15 PM_SLP_S3#

BA16 PM_SLP_S4#

AY16 PM_SLP_S5#

AN15 PM_SLP_SUS#

AW15 SLP_LAN#

BB17 SLP_W LAN#

AN16 PM_SLP_A#

BA15 PBTN_O UT#

AY15 AC_PRESENT_R 2

AU13 PM_BATLO W# RC108

AU11 EC_PC IE_WAKE#

AP16 SM_INTRUDER #

AM10 EXT_PW R_GAT E#

AM11 SOC_VRALERT#

SUSCLK <32>

RC92 1M_0402_5%

YC1 SJ10000IZ00

24MHZ 12PF 20PPM X3G02400 0DC1H

3

3 1

22P_0402_50V8J

CC12

<Cocoa _1020>

32M use these part (SJ10000NM00, SJ10 000MH00) just can meet <50k ohm spec

24M: SJ10000DI00, SJ10000CS00

PM_SLP_SUS# <13,26>

TP@T 87

TP@T 88

EC_PCIE_WAKE# <26,32>

TP@T 298

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPP_B12/SLP_S0#

GPD10/SLP_S5#

GPD9/SL P_WLA N#

GPD3/PW RBT N#

GPD1/AC PRESENT

GPD0/BATLOW #

GPP_B11/EXT_PW R_GATE#

GPP_B2/VRALERT #

11/28 add RSMRST protect circuit

SPOK <48>

2014/05/19 2015/12/31

Compal Secret Data

Deciphered Date

1 2

GND GND

4 2

PBTN_O UT# <26>

1

1

0_0402_5%

PM_SLP_S3 # <12,2 6,35>

PM_SLP_S4 # <12,26,35,49>

PM_SLP_S5 # <26>

Tiiitllle

Size Document Number

Custom

Date: Wednesday, May 11, 2016

CLR ME

<36> CLK_PEG_VGA#

GPU

<36> CLK_PEG_VGA

CLR CMOS

CLR_CMOS# <26>

1

Clear CMOS close to RAM door

@

JCMOS1

0_0603_5%

2

CLKREQ_PCIE#4

1

2

10K_0402_5%

1

2 CLKREQ_PCIE#5

10K_0402_5%

RPC10

1 LAN_CLKREQ#

8

2 MINI1_CLKREQ#

7

3 CR_CLKREQ#

6

4

5

10K_0804_8P4R_5%

1 @ 2

RPC11

8

7

6

5

2 1 SYS_RESET#

1 @ 2 SUSCLK

2 1

RC103

RC104

RC106

RC1151 2 10K_0402_5% SOC_VRALERT#

VGA_CLKREQ#

1 PCH_PWROK

2 LAN_WAKE#

3 PCH_RSMRST #

4 SYS_RESET#

PCH_DPW ROK

100K_0402_5%

1

2

8.2K_0402_5%

1

2 W AKE#

1K_0402_5%

2 AC_PRESENT_R

1

10K_0402_5%

<DB> RC 106 unp op , f ollow m odule de sign

@

@

@

+1.0V_VCCST

5 4 3 2 1

545659_SKL_PCH_U_Y_EDS_R0_7

From

<Coc oa_10 27>

check u n-use G PIO fo r term ination guidan ce

<DB> un pop, PD at GP U si de

DS12

1 PCH_PW ROK2

CK0402101V05_0402-2

ESD@

SCV00001K00

PM_BATLOW#

Only Fo r Power Seque nce Debug

<26> SUSACK#

ESD@

DS13

SCV00001K00

1 2 H_CPUPWRGD

CK0402101V05_0402-2

DS14

1

CK0402101V05_0402-2

DS15

1

CK0402101V05_0402-2

1

RC113

1K_0402_5%

2

RC1161 2 60.4_0402_1% EC_VCCST _PG

@ESD@

SCV00001K00

2 SUSACK#

@ESD@

SCV00001K00

2 SYS_PW ROK

T95 TP@

<DB> ad d ESD p rotect ion

<37> VGA_CLKR EQ#

<23> CLK_PCIE_LAN#

LAN

<23> CLK_PCIE_LAN

<23> LAN_CLKREQ#

<32> CLK_PCIE_WLAN#

WLAN

<32> CLK_PCIE_WLAN

<32> MINI1_CLKR EQ#

CardReader

<26> PCH_RSMRST#

RC102 1 @ 2 1K_040 2_5% H_CPU PWRG D A68

<26> SYS_PW ROK

<26> PCH_PW ROK

<26> PCH_SUSW ARN#

1

2

RC110

0_0402_5%

<32> WAKE#

PCH PLTRST Buf f er<DB> Romove PLT_RST# buf fer

PLT_RST#_PCH

T296 TP@

CLK_PEG_VGA#

CLK_PEG_VGA

VGA_CLKREQ#

CLK_PCIE_LAN#

CLK_PCIE_LAN

LAN_CLKREQ#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

MINI1_CLKREQ#

CR_CLKREQ#

CLKREQ_PCIE#4 AU8

CLKREQ_PCIE#5 AU7

RC99 1 2 0_0402_5%

1

IN1

2

PLT_RST#_PCH

SYS_RESET#

PCH_RSMR ST#

EC_VCCST_PG B65

SYS_PW ROK

PCH_PW ROK

PCH_DPW ROK_R BB20

PCH_SUSWARN#

SUSACK#_ R

WAKE#

LAN_WAKE#

T94 TP@

<26> PCH_DPW ROK

IN2

SN74AHC1G08DCKR_SC70- 5

PCH_RSMR ST# PCH_PW ROK

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

GPP_B10/SRCCLKR EQ5#

SKL-U_BGA1356

+3VS

CC145

@

1 2

@

5

UC8

0.1U_0402_16V7K

4

O

G P

3

UC1K

AN10

GPP_B13/PLTRST #

B5

SYS_RESET#

AY17

RSMRST#

PROCPW RGD

VCCST_PWRG D

B6

SYS_PW ROK

BA20

PCH_PW ROK

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

DC3 SCS00003500

CH751H-40PT_SOD323-2

1 2

1

2

SCS00003500

DC4

CH751H-40PT_SOD323-2

SecurityClllassiiifiiicatiiion

THIIIS SHEET OF ENGIIINEERIIING D RAWING IIIS THE PROPRIIIETARY P ROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRAD E SECRE T IIINFORMATIIION... THIIIS SHE ET MAY NOT BE TRA NSFERE D FROM THE CUSTODY OF THE COMPETE NT DIIIVIIISIIION OF R&D

DEPARTMENT E XCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NO R THE IIINFORMATIIION IIIT CONTAIIINS

MAY BE US ED BY OR DIIISCLOSED TO ANY THIIIRD PARTY W ITHOUT PRIIIOR WRIIITTEN CON SENT OF COMPAL ELECTRONIIICS,,, IIINC...

PLT_RST#

SYS TEM POW ER MAN AGEME NT

Issued Date

+1.0V_C LK5_F24N S

XCLK_BIASREF

RC97 1 2 60.4_040 2_1%

<DB> stuf f f or cannonl ake 60oh m1 %

<SI> change to SJ10000Q300 , CL=9p

PCH_RT CX2

1 2

RC98 10M_0402_5%

YC2

32.768KHZ 9PF 10PPM 9H03200055

1 2

SJ10000Q800

6.8P_0402_50V8J

CC15

22P_0402_50V8J

TP@T254

TP@T255

TP@T256

TP@T257

TP@T 258

ACIN <26,37>

CC13

1

2

<PV> ch ange CC15,CC16 to 6.8p

<MV> change CC15,C C16 to 8.2p

Compal Electronics, Inc.

SKL-U(5/12)CLK,GPIO

LA-D707P

Sheet 9 o f 60

@

CC16

6.8P_0402_50V8J

1

2

Rev

v0.2

Page 12

5 4 3 2 1

UC1F

LPSS ISH

AN8

GPP_B15/GSPI0_ CS#

AP7

GPP_B16/GSPI0_C LK

AP8

GSPI0_MOSI

D D

C C

<DB> add TP by BIOS

TP@T129

TP@T128

<32> WL_OF F#

TP@T133

TP@T132

12

R5194

@

0_0402_5%

SOC_GPIOB21

GSPI1_MOSI

UART_0_CRXD_DTXD

UART_0_CTXD_DRXD

WL_O FF#

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

UART_2_CTXD_DRXD

UART_2_CRXD_DTXD

Functional Strap Definitions

SPKR (Internal Pull Down):

TOP Swap Override

0 = Disable TOP Swap mode.---> AAX05 Use

1 = Enable TOP Swap Mode.

GSPI0_MOSI (Internal Pull Down):

No Reboot

GPP_B17/GSPI0_ MISO

AR7

GPP_B18/GSPI0_ MOSI

AM5

GPP_B19/GSPI1_C S#

AN7

GPP_B20/GSPI1_C LK

AP5

GPP_B21/GSPI1_ MISO

AN5

GPP_B22/GSPI1_ MOSI

AB1

GPP_C8/ UART0_ RXD

AB2

GPP_C9/ UART0_ TXD

W4

GPP_C10 /UART0 _RTS#

AB3

GPP_C11 /UART0 _CTS#

AD1

GPP_C20 /UART2 _RXD

AD2

GPP_C21 /UART2 _TXD

AD3

GPP_C22 /UART2 _RTS#

AD4

GPP_C23 /UART2 _CTS#

U7

GPP_C16 /I2C0_SDA

U6

GPP_C17 /I2C0_SCL

U8

GPP_C18 /I2C1_SDA

U9

GPP_C19 /I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

Strap Pin

+3VS

RC117 1 2 100K_0402_5% HDA_SPKR

RC118 1 2 4.7K_0402_5% GSPI0_MO SI

RC201 1 2 150K_0402_1% GSPI1_MOSI

<Coc oa_10 20>

1K oh m for 40 0kHz speed/ 0.5k ohm for 1MHz s peed

SKL-U

GPP_F10/I2C5_SDA/ISH_ I2C2_SDA

GPP_F11/I2C5_SCL/ISH_ I2C2_SCL

GPP_D13 /ISH_UART0_RXD/SML0BDATA/I2C 4B_SDA

GPP_D14 /ISH_UART0_TXD/SML0BCLK/I2C 4B_SCL

6 OF 20

@

@

@

GPP_D15 /ISH_UART0_RT S#

GPP_D16 /ISH_UART0_CT S#/SML0B ALERT #

GPP_C12 /UART1 _RXD/ISH_UART1_RXD

GPP_C13 /UART1 _TXD/ISH_UART1_TXD

GPP_C14 /UART1 _RTS#/ISH_UART 1_RTS#

GPP_C15 /UART1 _CTS#/ISH_UART 1_CTS#

GPP_A12/BM_BUSY#/ISH_GP6

Rev_0 .53

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ ISH_I2C0_SDA

GPP_D6/ ISH_I2C0_SCL

GPP_D7/ ISH_I2C1_SDA

GPP_D8/ ISH_I2C1_SCL

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

HDA_SPKR <8,24>

P2

P3

P4

P1

M4

N3

12/11_Delete TP

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1 DGPU_PWR _EN

AC2 DGPU_HOLD_R ST#

AC3

AB4

AY8

BA8

BB7

BA7 ODD_PWR

AY7 ODD_DA#

AW7

AP13 SO C_GPIOA12

TS_GPIO_CPU <20>

DGPU_PWR_EN <26,38,55,56>

DGPU_HOLD_RST# <36>

GPU_PGD <56>

ODD_PW R <3 0>

ODD_DA# <30>

T122 TP@

+3VS

+3VS

CC14

1 2

2200P_0402_ 50V7K

1 2 CPU_THERM#

RC45 33K_0402_5%

1105_Mo dify sche matic

<Coc oa_10 27>

Follow #544669 GPIO I/O settin g

CPU THERMALSENSOR

0.1U_0402_16V7K

CC127

1

2

Thermalsensor:

Main:SA000067P00, S IC NCT7718W MSOP 8P THEMAL SENSOR(Nuvoton)

2nd : SA00007WP00,S IC F75397M MSOP8P THEMAL SENSOR(Fintek)

3rd : SA007810140, S IC G781P8F MSOP 8P TEMP. SENSOR(GMT)

Thermal sensor SMBus address -->100-1_100xb : 0x4C

(x=0)Write Address(0x98h)

(x=1)ReadAddress(0x99h)

UC3

1

H_THERMDA

H_THERMDC

VDD

2

D+

3 D- ALERT#

4 THERM# GND

NCT7718W_MSOP8

SA000067 P00

SCLK

SDATA

EC_SMB_CK 2

8

EC_SMB_DA 2

7

THERMAL _ALERT#

6

5

<5,26> NMI_DBG#_CPU

<5,26> EC_SCI#

<Cocoa_1127> remove EC_LID_OUT# function

<Cocoa_1020>

Follow BDW

EC_SMB_CK 2 <7,19,22,26,37>

EC_SMB_DA 2 <7,19,22,26,37>

DGPU_PWR_EN

SOC_GPIOB21

WL_O FF#

NMI_DBG#_CPU

EC_SCI#

ODD_PW R

ODD_DA#

2

RC44

<DB>

RC3821 2 10K_0402_ 5%

@

RPC14

1 8

2

3

4

10K_0804_8P4R_5%

RPC12

1

2

3

4 5

10K_0804_8P4R_5%

1

+3VS

10K_0402_5%

+3VS

+3V_PRIM

7

6

5

8

7

6

+3VS

0 = Disable No Reboot mode. --> AAX05 Use

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This function is useful

when running ITP/XDP.

B B

GSPI1_MOSI (Internal Pull Down):

<DB>

Delete Win7 de bug port

Boot BIOS Strap Bit

0 = SPI Mode --> AAX05 Use

1 = LPC Mode

A A

SecurityClllassiiifiiicatiiion

Issued Date

THIIIS SHEET OF ENGIIINEERIIING D RAWING IIIS THE PROPRIIIETARY P ROPERTY OF COMPAL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL

AND TRAD E SECRE T IIINFORMATIIION... THIIIS SHE ET MAY NOT BE TRA NSFERE D FROM THE CUSTODY OF THE COMPETE NT DIIIVIIISIIION OF R&D

DEPARTMENT E XCEPT AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SHEET NO R THE IIINFORMATIIION IIIT CONTAIIINS

5 4 3 2 1

MAY BE US ED BY OR DIIISCLOSED TO ANY THIIIRD PARTY W ITHOUT PRIIIOR WRIIITTEN CON SENT OF COMPAL ELECTRONIIICS,,, IIINC...

2014/05/19 2015/12/31

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Tiiitllle

SKL-U(6/12)GPIO

Size Document Number

Custom

LA-D707P

Date: Wednesday, May 11, 2016

Sheet 10 o f 60

Rev

v0.2

Page 13

5 4 3 2 1

UC1H

<DB> Change to 0.22uF for Gen3

<36> PEG_PRX_C_DTX_N0

<36> PEG_PRX_C_DTX_P0

<36> PEG_PTX_C_DRX_N0

D D

PEG

LAN

WLAN

HDD

C C

ODD

B B

A A

<36> PEG_PTX_C_DRX_P0

<36> PEG_PRX_C_DTX_N1

<36> PEG_PRX_C_DTX_P1

<36> PEG_PTX_C_DRX_N1

<36> PEG_PTX_C_DRX_P1

<36> PEG_PRX_C_DTX_N2

<36> PEG_PRX_C_DTX_P2

<36> PEG_PTX_C_DRX_N2

<36> PEG_PTX_C_DRX_P2

<36> PEG_PRX_C_DTX_N3

<36> PEG_PRX_C_DTX_P3

<36> PEG_PTX_C_DRX_N3

<36> PEG_PTX_C_DRX_P3

<23> PCIE_PRX_DTX_N5

<23> PCIE_PRX_DTX_P5

<23> PCIE_PTX_C_DRX_N5

<23> PCIE_PTX_C_DRX_P5

<32> PCIE_PRX_DTX_N6

<32> PCIE_PRX_DTX_P6

<32> PCIE_PTX_C_DRX_N6

<32> PCIE_PTX_C_DRX_P6

<30> SATA_PRX_DTX_N0

<30> SATA_PRX_DTX_P0

<30> SATA_PTX_DRX_N0

<30> SATA_PTX_DRX_P0

<30> SATA_PRX_DTX_N1

<30> SATA_PRX_DTX_P1

<30> SATA_PTX_DRX_N1

<30> SATA_PTX_DRX_P1

CC119 0.22U 6.3V K X5R04022 1 PX@

CC146 0.22U 6.3V K X5R 0402 2 1 PX@ PEG_PTX_DRX_P0 A17

CC128 0.22U 6.3V K X5R 0402 2 1 PX@ PEG_PTX_DRX_N1 D16

CC93 0.22U 6.3V K X5R 04022 1 PX@ PEG_PTX_DRX_P1 C16

CC124 0.22U 6.3V K X5R 04022 1 PX@ PEG_PTX_DRX_N2 D17

CC92 0.22U 6.3V K X5R 0402 2 1 PX@ PEG_PTX_DRX_P2C17

CC129 0.22U 6.3V K X5R 04022

CC118 0.22U 6.3V K X5R 04022

1 0.1U_0402_16V7K

CC18 2

1 0.1U_0402_16V7K

CC17 2

1 0.1U_0402_16V7K

CC20 2

1 0.1U_0402_16V7K

CC19 2

RC1201

<5> XDP_PREQ#

2 100_0402_1% PCIE_RCOMPN

T291 TP@

T154 TP@

XDP_PRDY#

XDP_PREQ#

SOC_GPIOA7

PEG_PRX_C_DTX_N0 H13

PEG_PRX_C_DTX_P0 G13

PEG_PTX_DRX_N0 B17

PEG_PRX_C_DTX_N1 G11

PEG_PRX_C_DTX_P1 F11

PEG_PRX_C_DTX_N2 H16

PEG_PRX_C_DTX_P2 G16

PEG_PRX_C_DTX_N3 G15

PEG_PRX_C_DTX_P3 F15

1 PX@ PEG_PTX_DRX_N3 B19

1 PX@ PEG_PTX_DRX_P3 A19

PCIE_RCOMPP

When PCIE8/SATA1A is used

as SATA Port 1 (ODD), then

PCIE11/SATA1B (M.2 SSD)

cannot be used as SATA

Port 1.

PCIE2_TXN/USB3_6_TXN

PCIE2_TXP/USB3_6_TXP

PCIE_PRX_DTX_N5F16

PCIE_PRX_DTX_P5 E16

PCIE_PTX_DRX_N5 C19

PCIE_PTX_DRX_P5 D19

PCIE_PRX_DTX_N6 G18

PCIE_PRX_DTX_P6 F18

PCIE_PTX_DRX_N6 D20

PCIE_PTX_DRX_P6 C20

PCIE/USB3 /SATA

PCIE1_RXN/USB3_5_RXN

PCIE1_RXP/USB3_5_RXP

PCIE1_TXN/USB3_5_TXN

PCIE1_TXP/USB3_5_TXP

PCIE2_RXN/USB3_6_RXN

PCIE2_RXP/USB3_6_RXP

PCIE3_RXN

PCIE3_RXP

PCIE3_TXN

PCIE3_TXP

PCIE4_RXN

PCIE4_RXP

PCIE4_TXN

PCIE4_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SecurityClassification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5 4 3 2

2014/05/19 2015/12/31

SKL-U

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

8 OF20

GPP_E8/SATALED#

GPIO DEVICE CONTROL

USB_OC0#

USB_OC1#

USB_OC2#

USB2 Port 1 and Port 2

USB2 Port 3

NA

USB_OC3# NA

DEVSLP0

NA

DEVSLP1 NGFF SSD KEY B

DEVSLP2

SATA_GP0

SATA_GP1

SATA_GP2

NA

NA

NA

ODD_PLUG#

Compal SecretData

Deciphered Date

Rev_0.5 3

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6 USB2_COMP

AG3 USB2_ID

AG4 USB2_VBUSSENSE

A9 USB_OC0#

C9 USB_OC1#

D9 USB_OC2#

B9 USB_OC3#

DEVSLP0

J1

J2 DEVSLP1

DEVSLP2

J3

H2 SATA_GP0

H3 ODD_PLUG#

SATA_GP2

G4

H1 SATA_LED#

USB3_RX1_N <31>

USB3_RX1_P <31>

USB3_TX1_N <31>

USB3_TX1_P <31>

USB20_N1 <31>

USB20_P1 <31>

USB20_N2 <31>

USB20_P2 <31>

USB20_N3 <33>

USB20_P3 <33>

USB20_N4 <32>

USB20_P4 <32>

USB20_N5 <20>

USB20_P5 <20>

USB20_N6 <20>

USB20_P6 <20>

USB20_N7 <33>

USB20_P7 <33>

RC119 1 2 113_0402_1%

USB2.0/USB3.0

USB2.0/USB3.0

USB2.0

USB2.0 ( on small board )

WLAN

Camera

Touch Screen

Card Reader

<SI> follow EDS to add 1K ohm PD

USB2_ID RC20 1 2 0_0402_5%

T243 TP@

T241 TP@ <DB> PU

ODD_PLUG# <30>

SATA_LED# <33>

DEVSLP1

SOC_GPIOA7

SATA_LED# 1 8

SATA_GP0 2 7

SATA_GP2 3 6

ODD_PLUG# 4 5

USB_OC1#

USB_OC3#

USB_OC0#

USB_OC2#

1128_Add pull high resistor

Compal Electronics, Inc.

Title

SKL-U(7/12)PCIE,USB,SATA

Siiize

Document Number

Custom

LA-D707P

Date: Wednesday, May 11, 2016 Sheet111 of 60

USB2_VBUSSENSE1

RC21

2

1

RC3621

RC361 10K_0402_5%

2 10K_0402_5%

RPC13

10K_0804_8P4R_5%

RPC20

1

8

2

7

3

6

4

5

10K_0804_8P4R_5%

2

0_0402_5%

+3V_PRIM

+3VS

Rev

v0.2

Page 14

5 4 3 2 1

+1.0V_PRIM TO +1.0V_VCCSTU

+1.2V_VDDQ

1211_Delete jump RC147

D D

<26,35,49> SYSON

<9,26,35,49> PM_SLP_S4#

<13,26,35,49> SUSP#

<9,26,35> PM_SLP_S3#

C C

1210_Delete jump RC146

RC142 1 2 0_0402_5%

RC144 1 @ 2 0_0402_5%

RC168 1 2 0_0402_5%

RC194 1 @ 2 0_0402_5%

1

2

@

CC151

+5VALW

0.1U_0402_25V6

+1.8V_PRIM

@

+1.0VS_VCCIO

@ 2 0_0603_5%

1U_0402_6.3V6K

1

CC98

2

1U_0402_6.3V6K

1

CC99

2