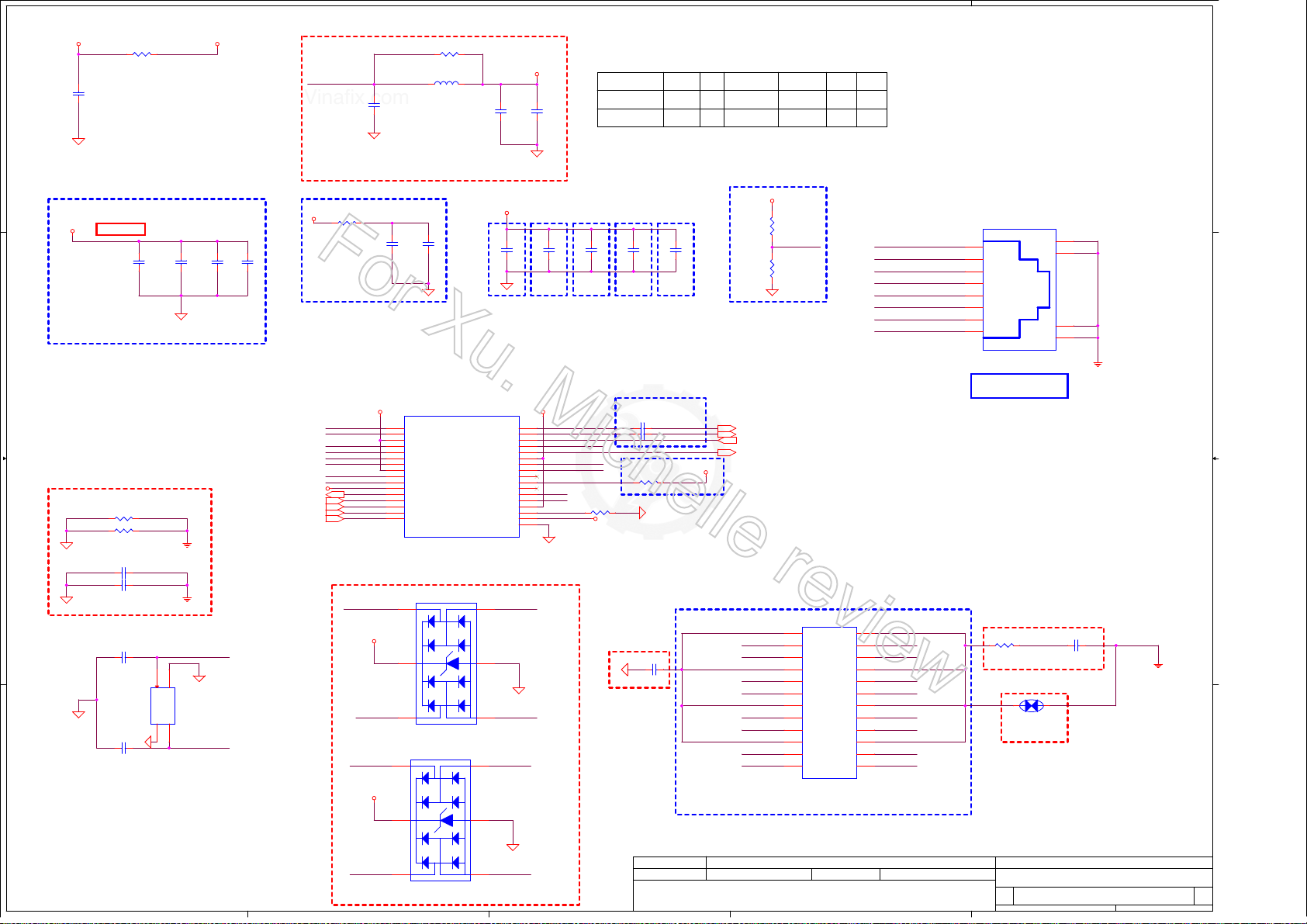

Page 1

Vinafix.com

A

1 1

2 2

B

C

D

E

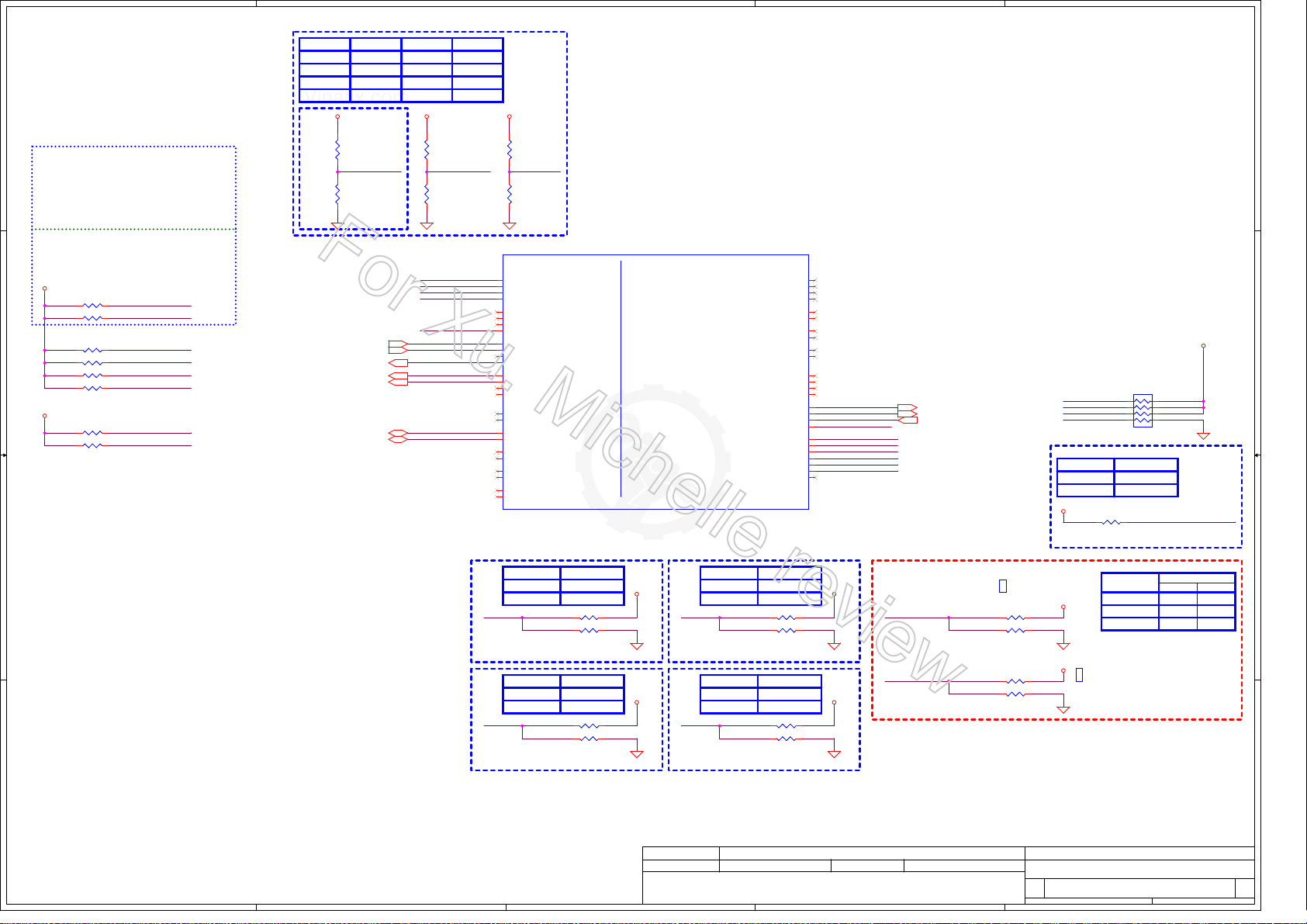

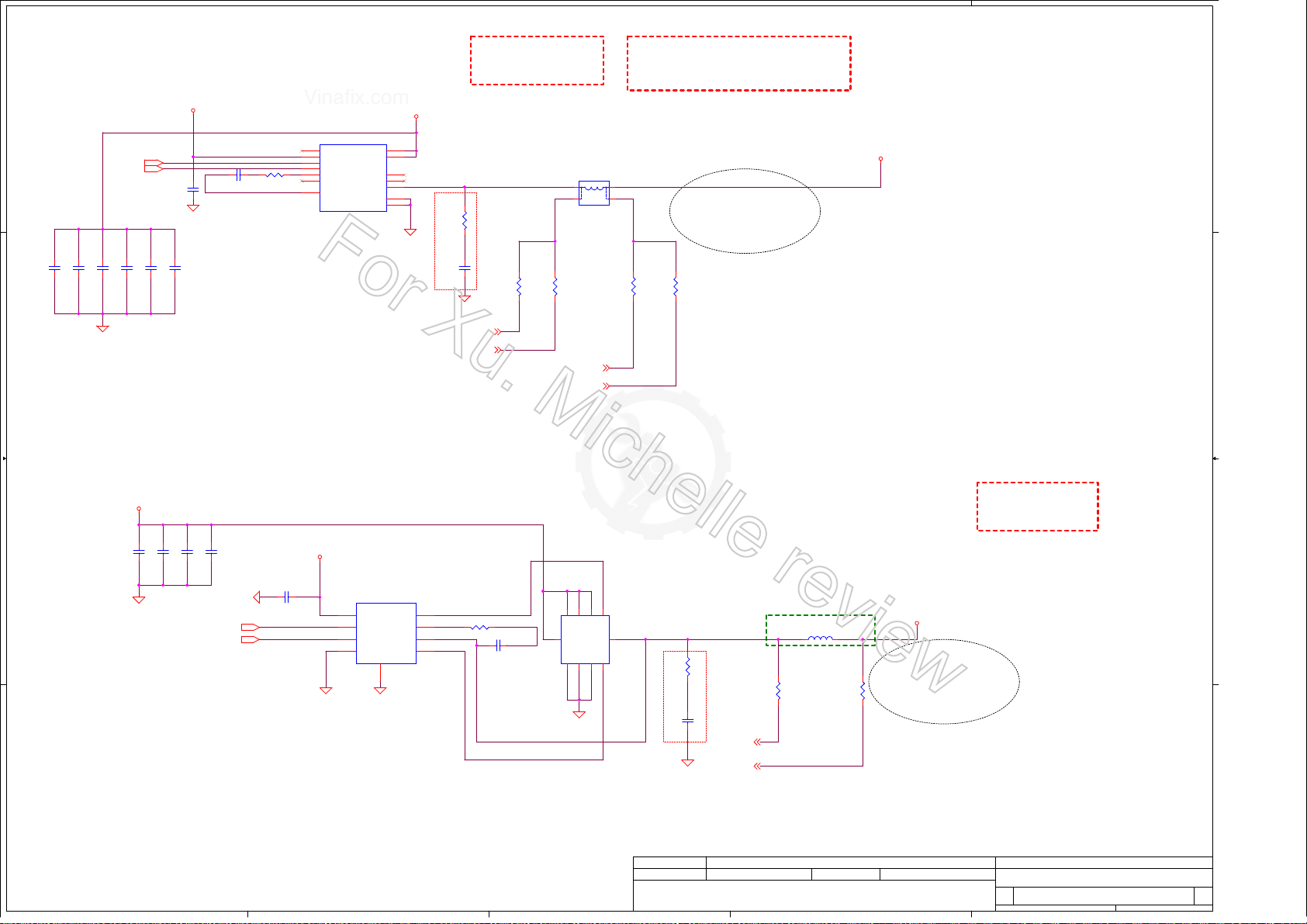

V330/V530/EX3

DIS M/B Schematics Document

Intel Kabylake RU Processor with DDR4

AMD R17M

2017-06-15

3 3

LA-F481P

R E V:0 . 2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Document Number Re v

Document Number Rev

Document Number Rev

LA-D562P

LA-D562P

LA-D562P

E

1 66Thursday, June 15, 2017

1 66Thursday, June 15, 2017

1 66Thursday, June 15, 2017

0.1

0.1

0.1

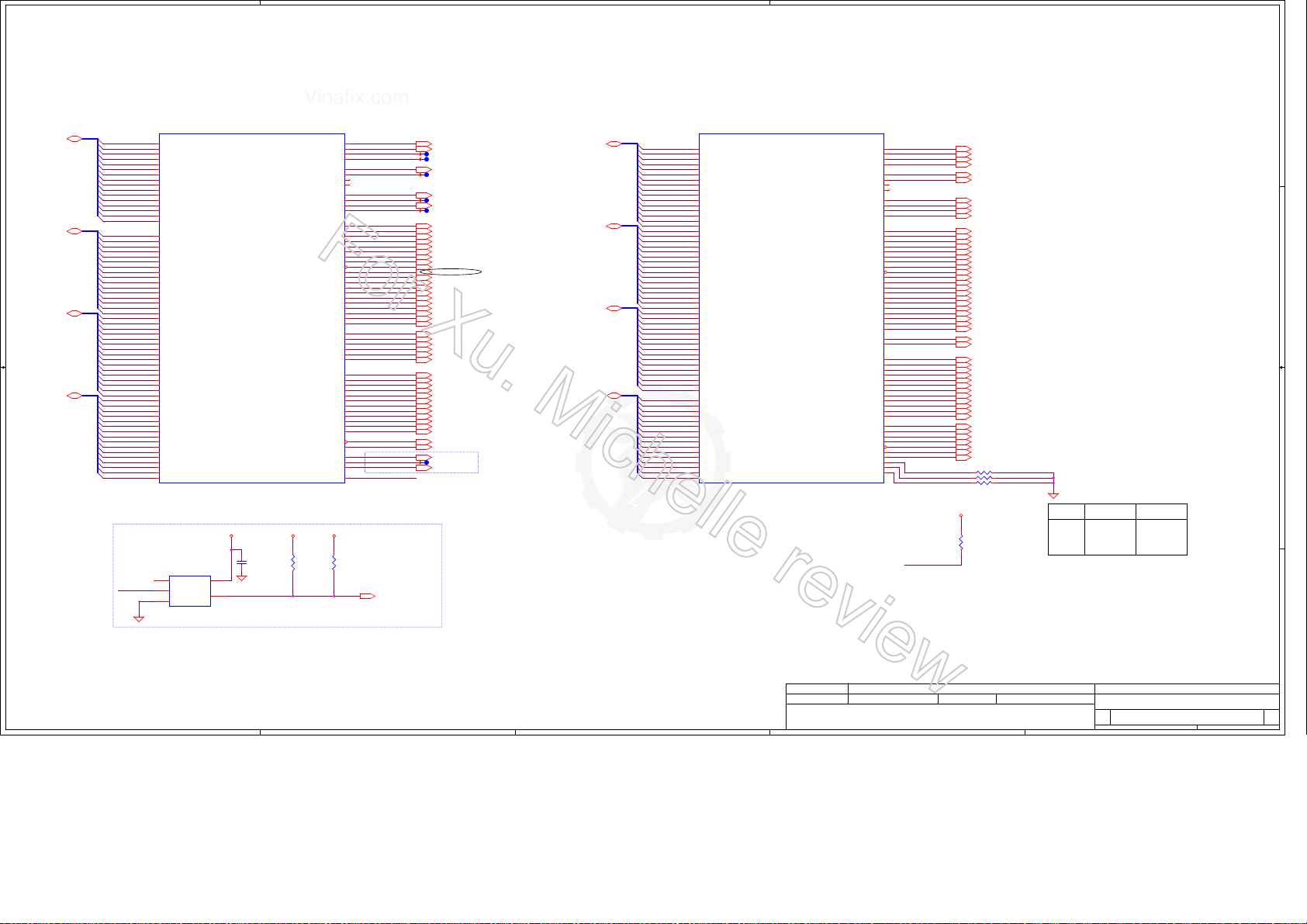

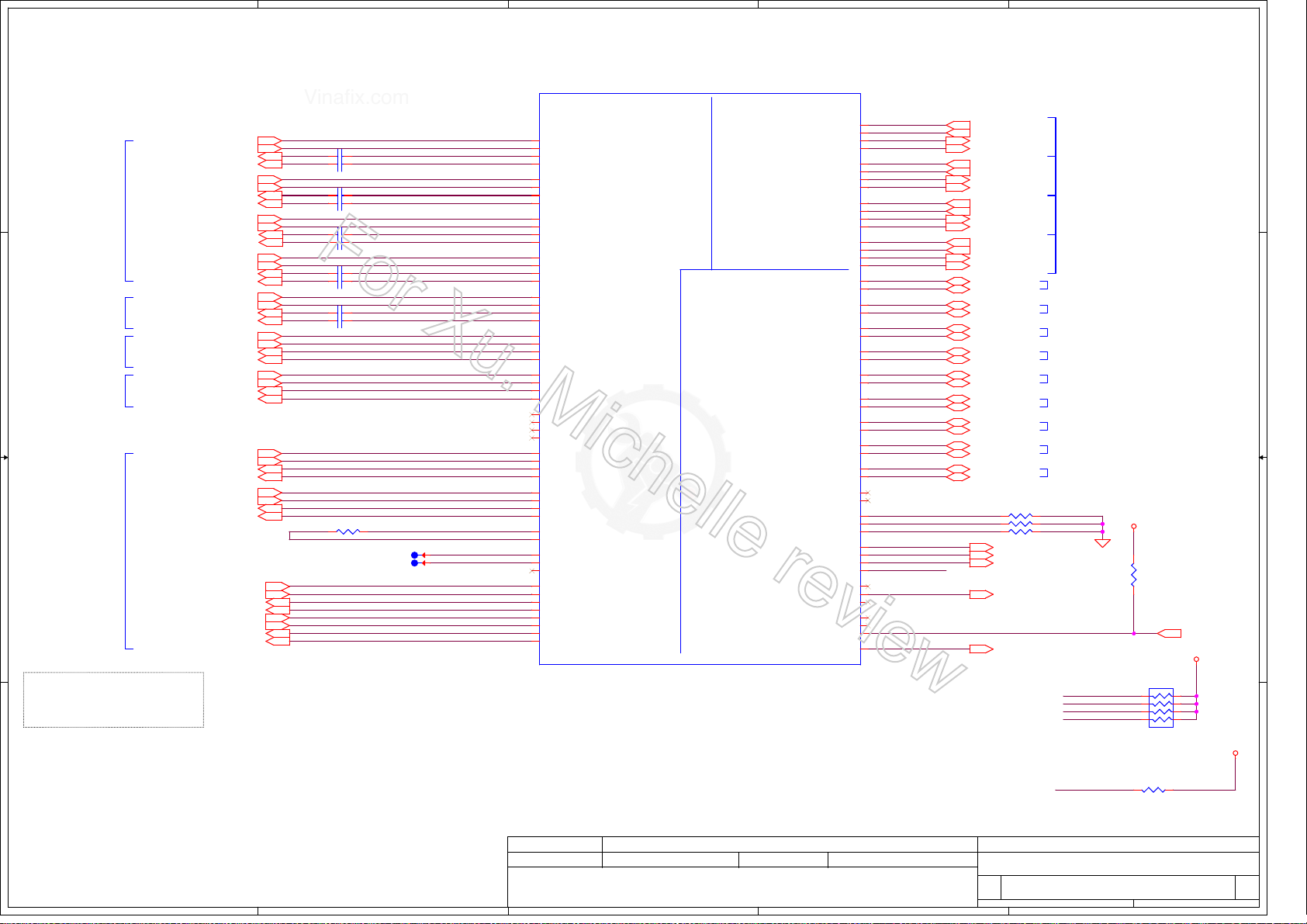

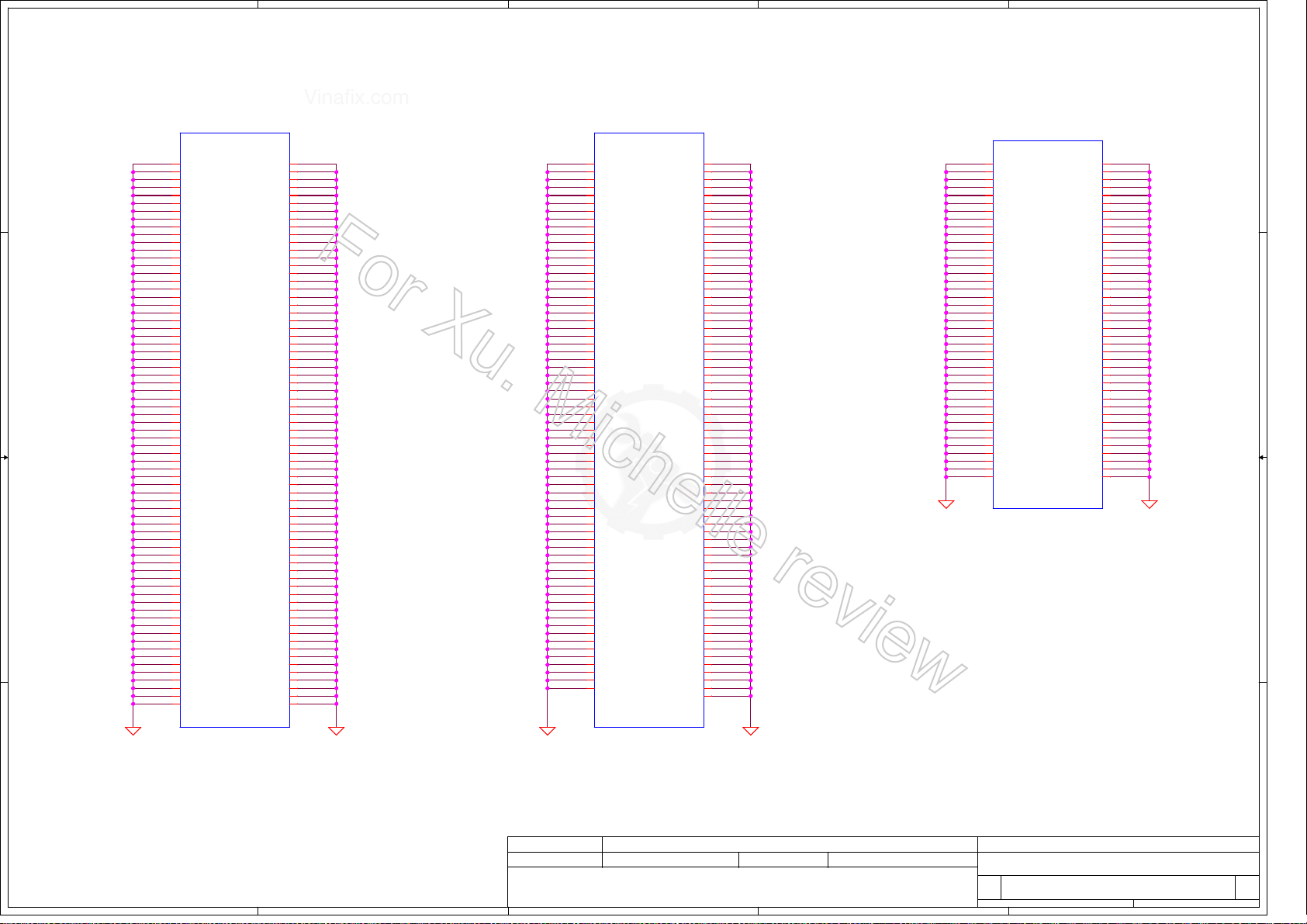

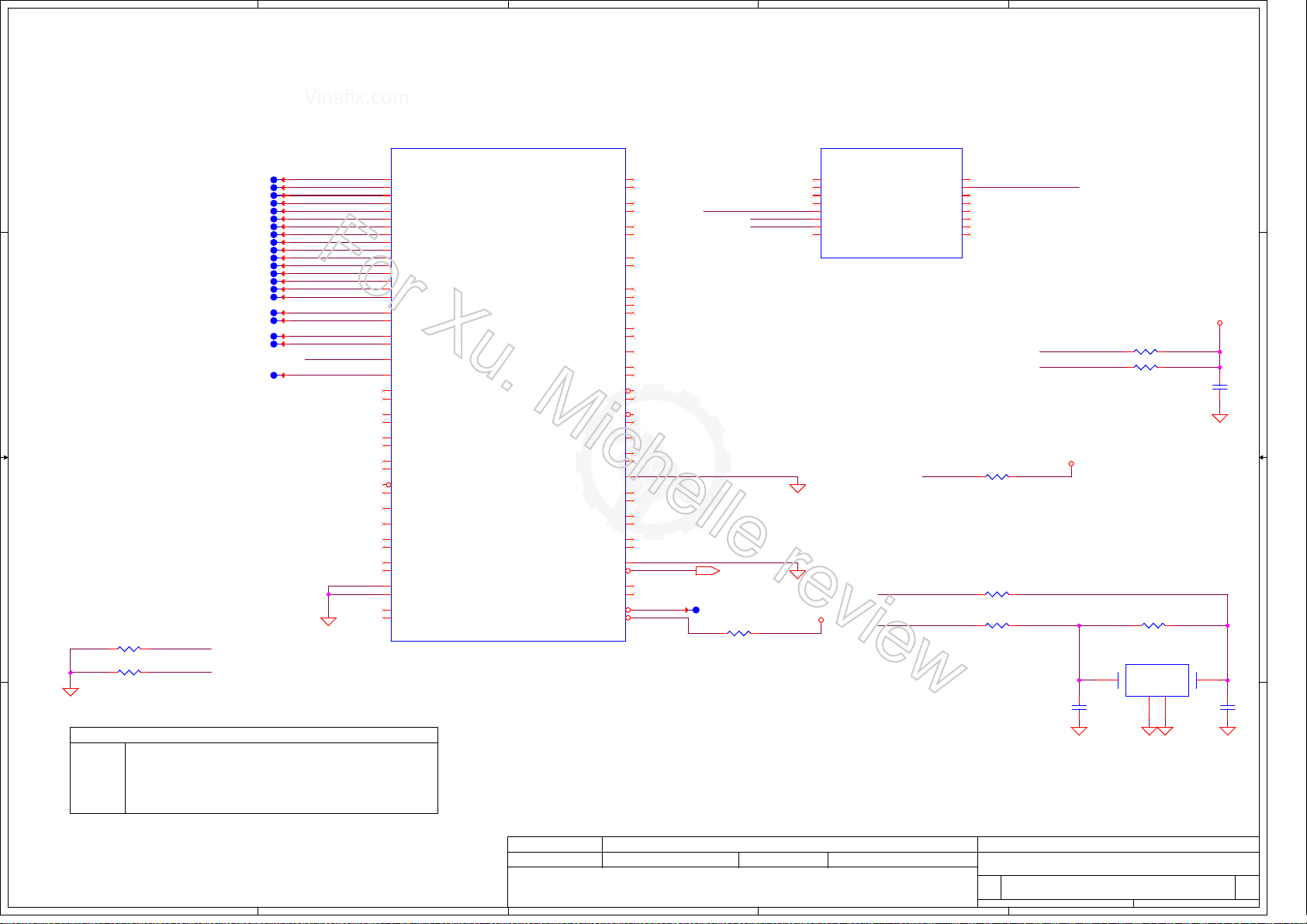

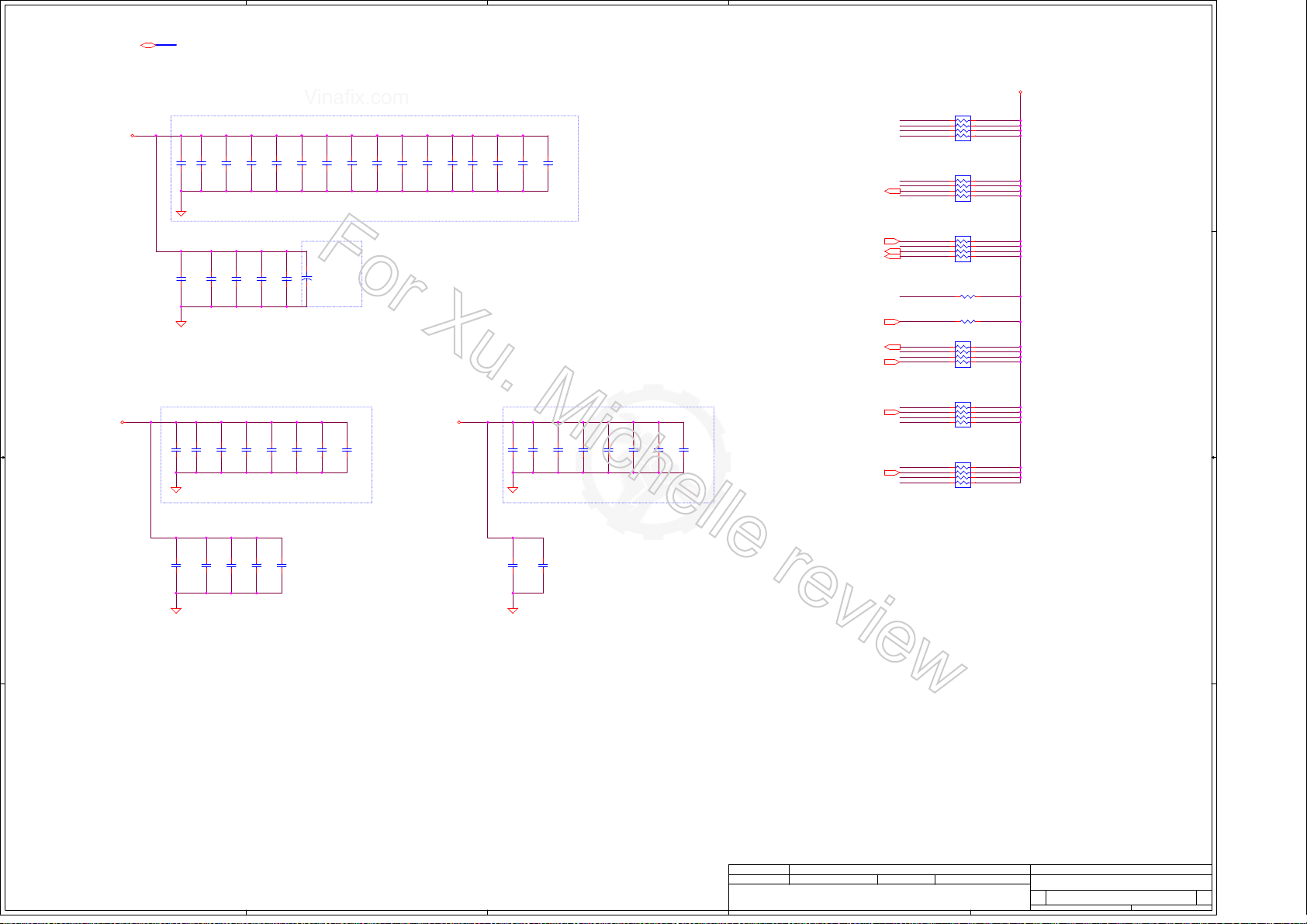

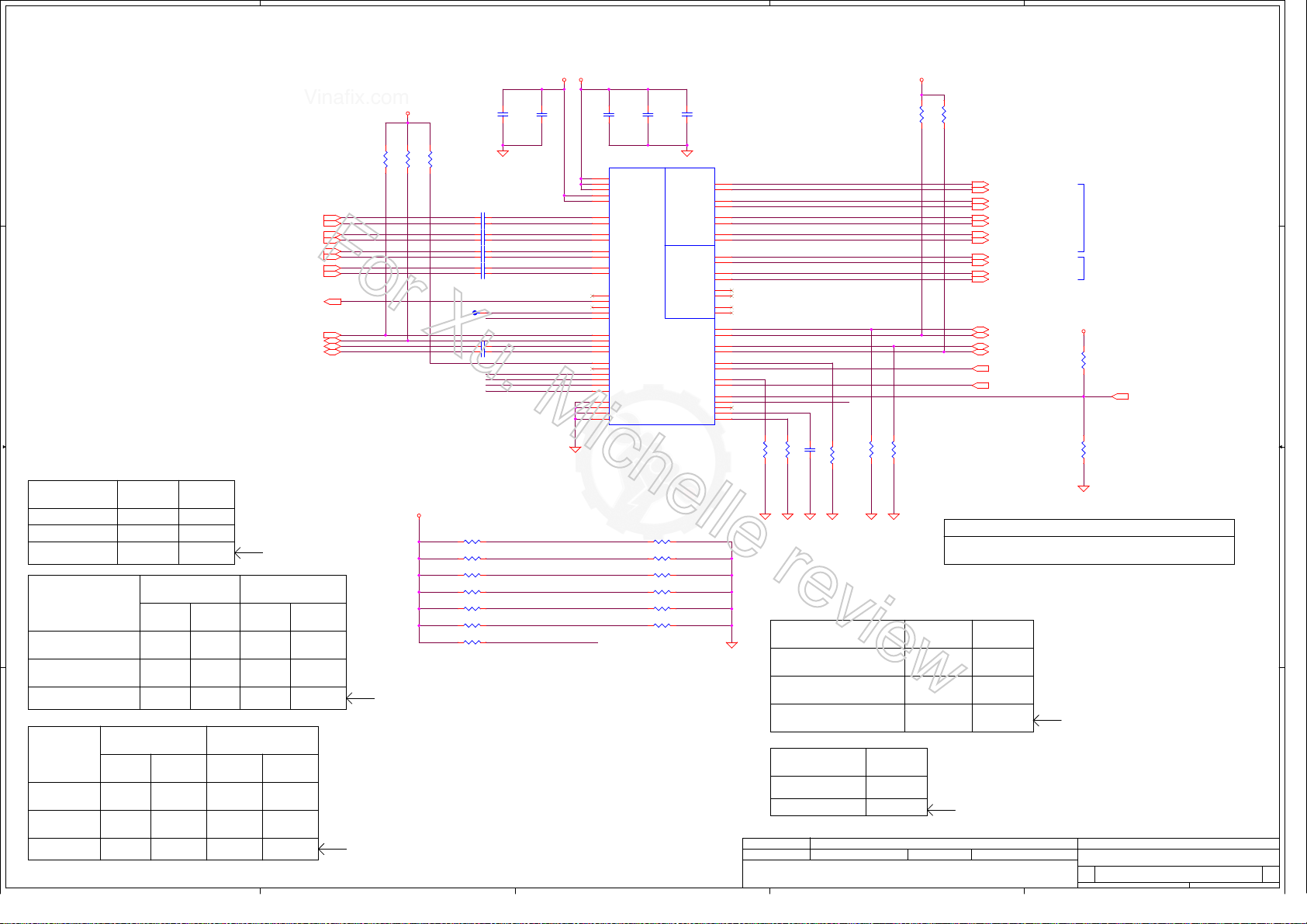

Page 2

Vinafix.com

A

B

C

D

E

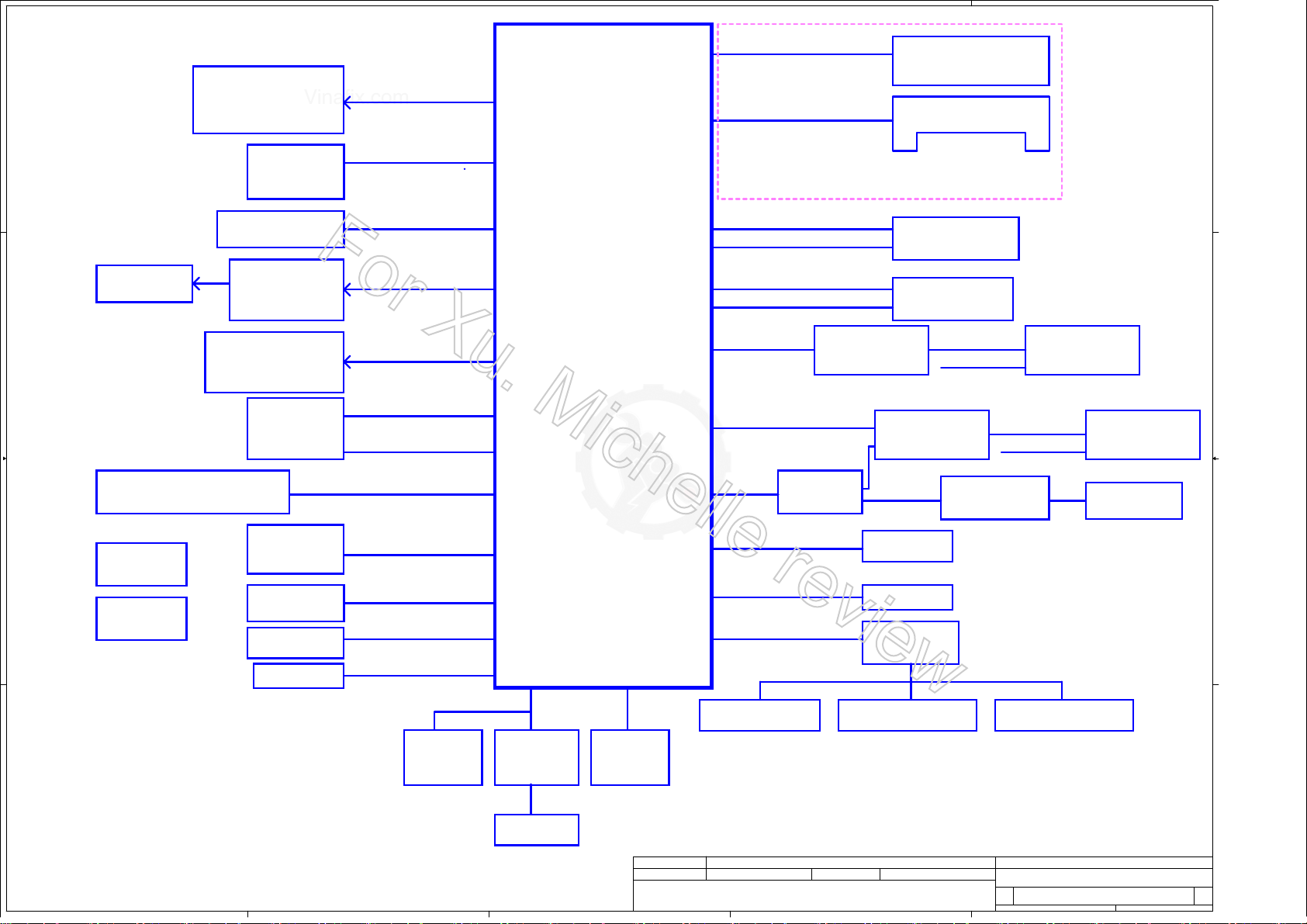

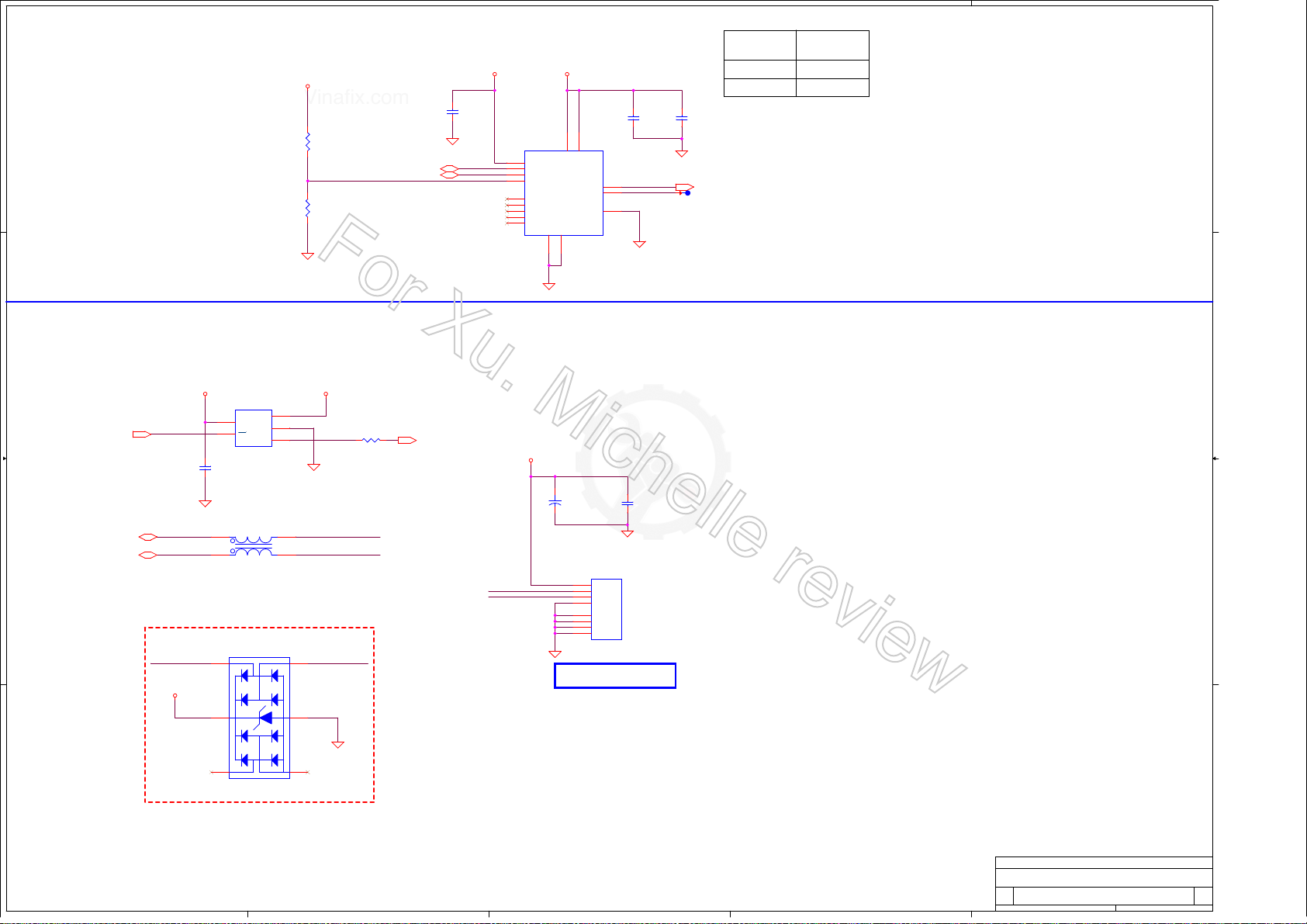

Channel A

DDR4 2133/2400MHz (1.2V , 2.5V)

AMD Radeon 530M

1 1

VRAM GDDR5 x2

P21

eDP Conn.

FHD

P28

HDMI Conn.

(HDMI 1.4)

RJ45 Conn.

2 2

LAN

RTL8111H-CG

100/1000

M.2 SSD

P29

P36

PCIe X4 / SATA X1

(TYPE M)

P32

PCIe X1 for WLAN

WLAN / BT

USB2.0 x1 for BT

P31

2nd Battery / USB2.0 conn.

(Reserve)

P46

Card Reader

Realtek

3 3

LED

RTS5146

Finger Print

DC to DC

Touch Pad

APS

4 4

A

P37

P33

P33

P46

B

PCIe X4

eDP X1

(2 Lanes)

DDI X1

PCIe X1

USB2.0 x1

USB2.0 x1

USB2.0 x1

SMBUS

TPM/TCM

Opt i on

Intel KBL-RU 15W/28W

I2C

EC

ENE

KB9022

P27 P45

Int. KBD

SOC

1356pin BGA

SPILPC

SPI ROM

16MB

P33

C

Channel B

DDR4 2133/2400MHz (1.2V , 2.5V)

DDR4 support 2133/2400MHz on KBL-RU

DDR4 support 2133MHz on SKL and KBL-U

USB3.0 x1

USB2.0 x1

USB3.0 x1

USB2.0 x1

USB3.0 x1

TypeC

RTS5448

CC+MUX

USB3.0 x1

DDI X1

DP MUX

PS8338B

P38

USB2.0 x1

SATA X1

HDA

Int. MIC Conn. Int. Speaker Conn.

P08

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

P28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

On board DDR4 X 4

DDR4 SO DIMM X1

Right USB3.0 x1

Left USB3.0 x1

With AOU

USB3.0 x1

USB2.0 x1

P42 P43

TypeC

RTL5455

PD+DP+MUX

CRT converter

RTD2166

Int. Camera

HDD Conn.

P28

P30

Audio Codec

CONEXANT

CX11802

P35

P18

P19

P34

P34

TypeC

(CC)

USB3.0 x1

USB2.0 x1

P40 P41

P39

TypeC

(CC+PD+DP)

CRT Conn.

Opt i on

Audio Combo Jack

P35

HP & MIC

P35

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

LA-D562P

LA-D562P

LA-D562P

E

2 66Thursday, June 15, 2017

2 66Thursday, June 15, 2017

2 66Thursday, June 15, 2017

P39

1.0

1.0

1.0

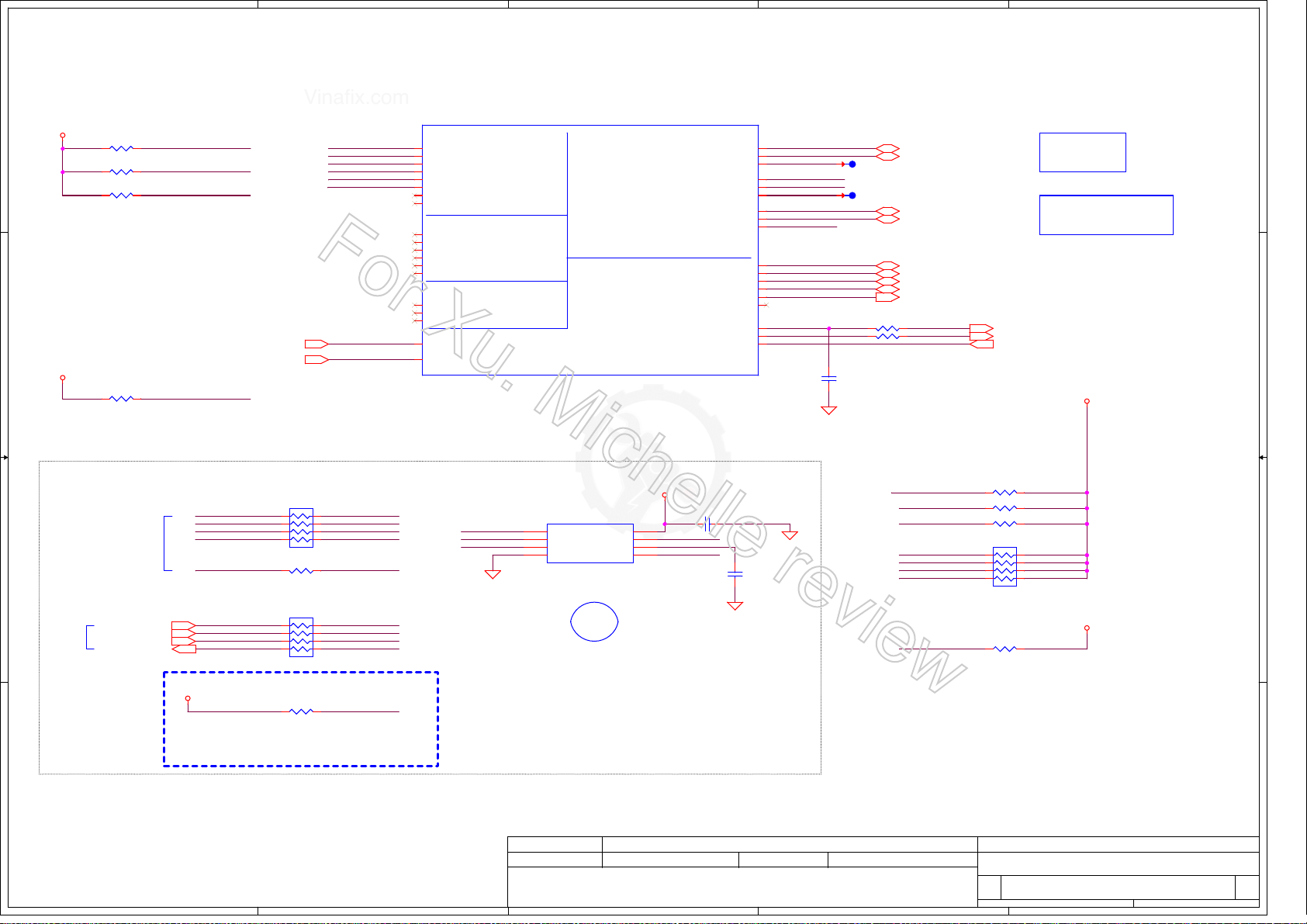

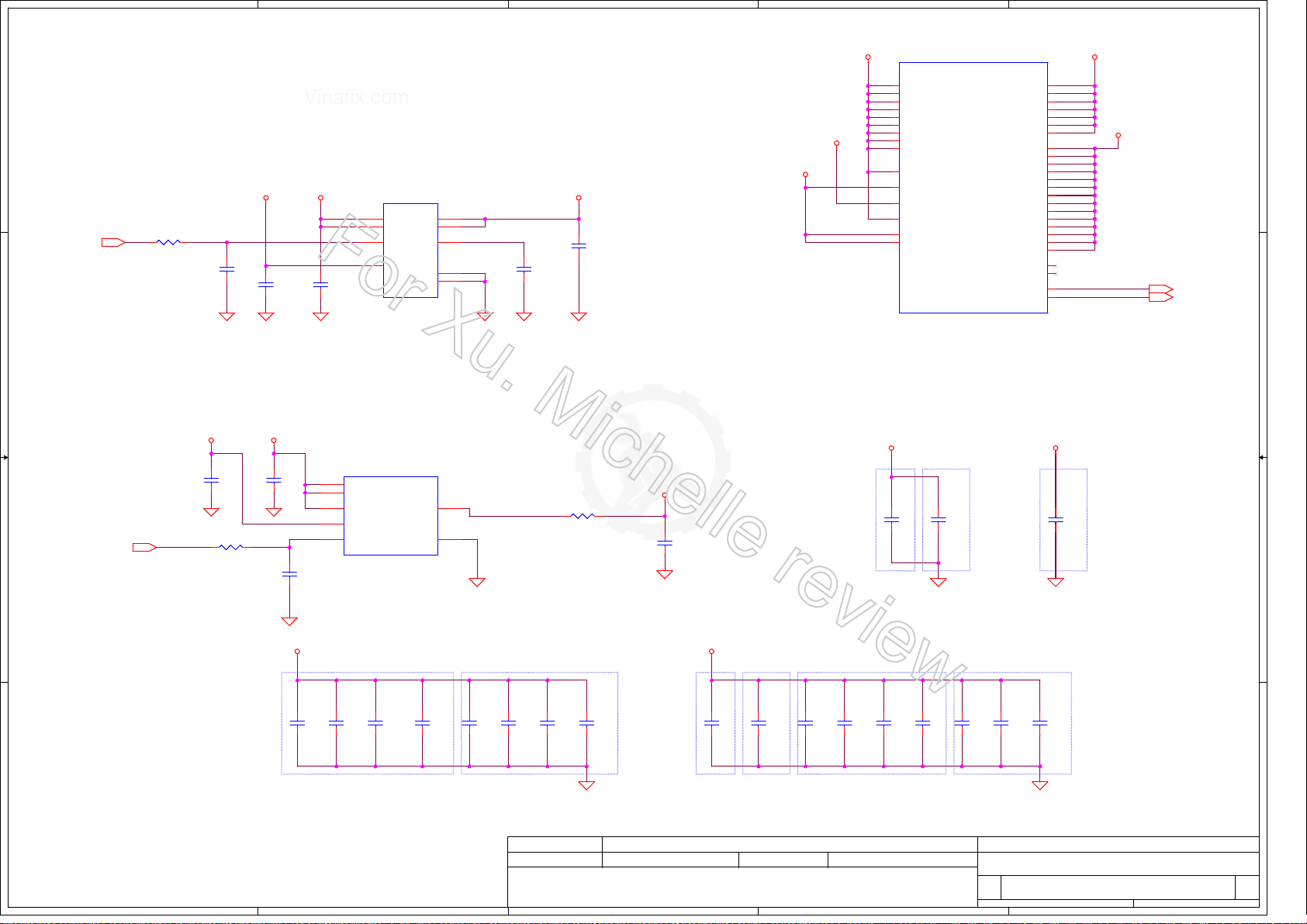

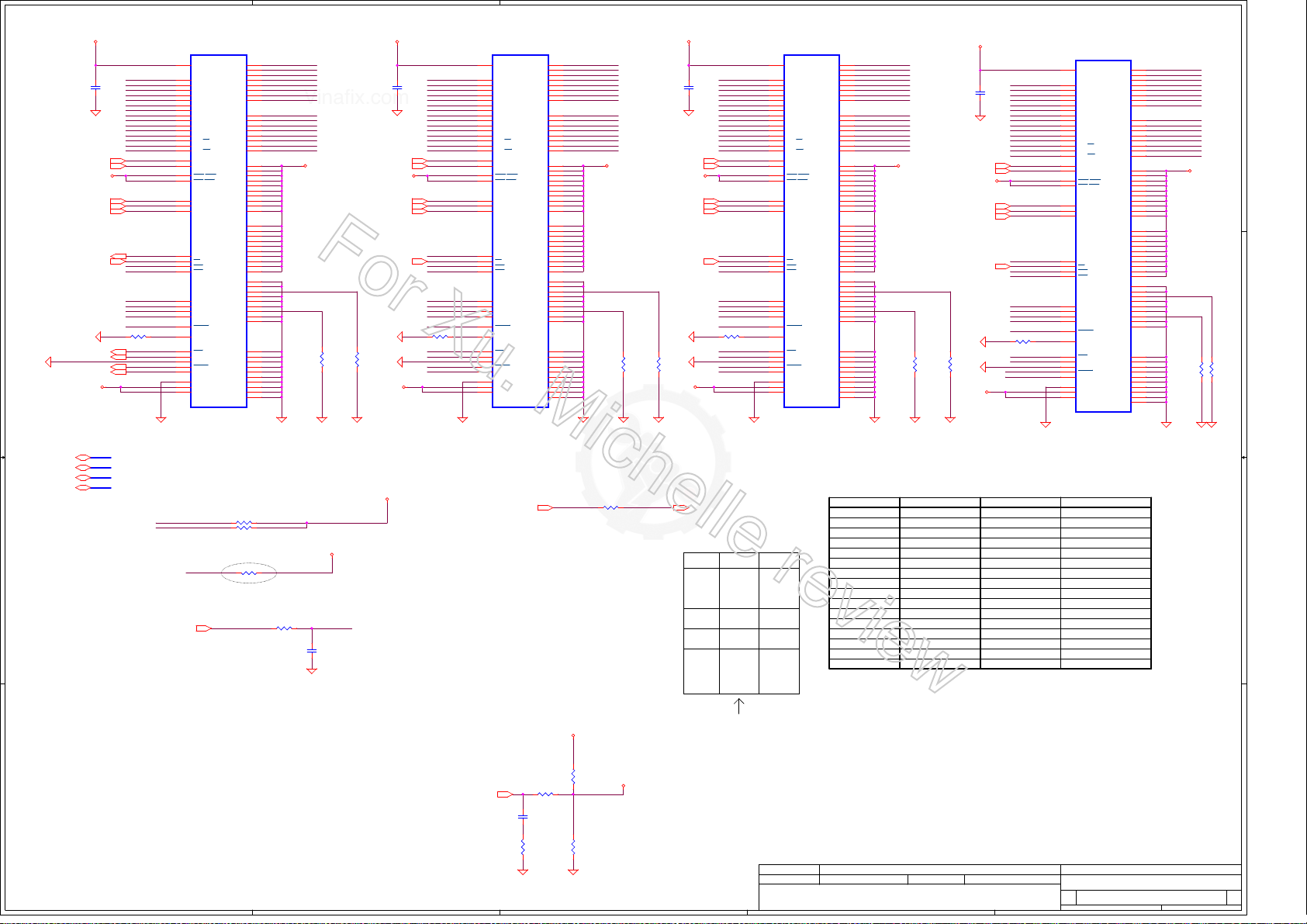

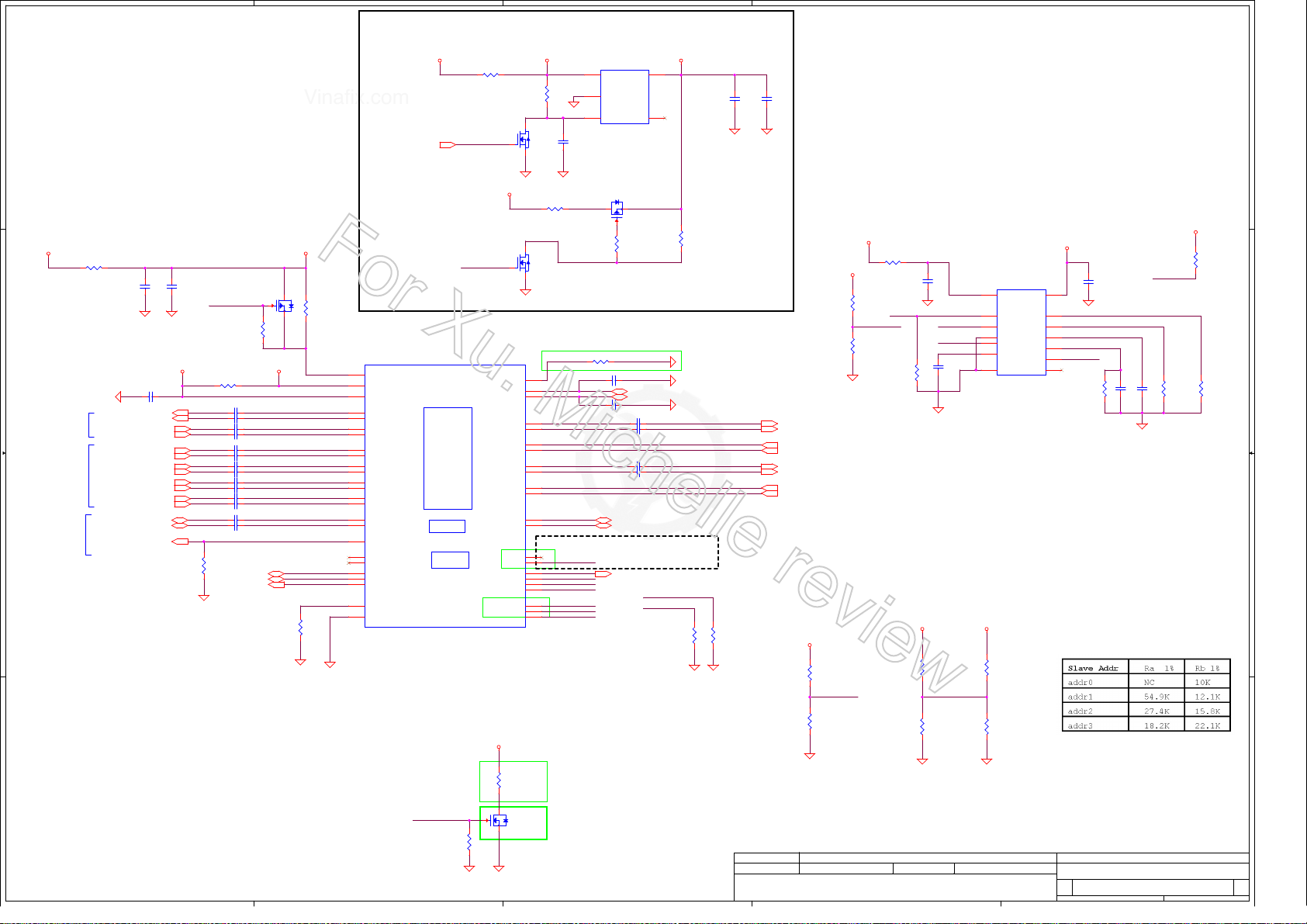

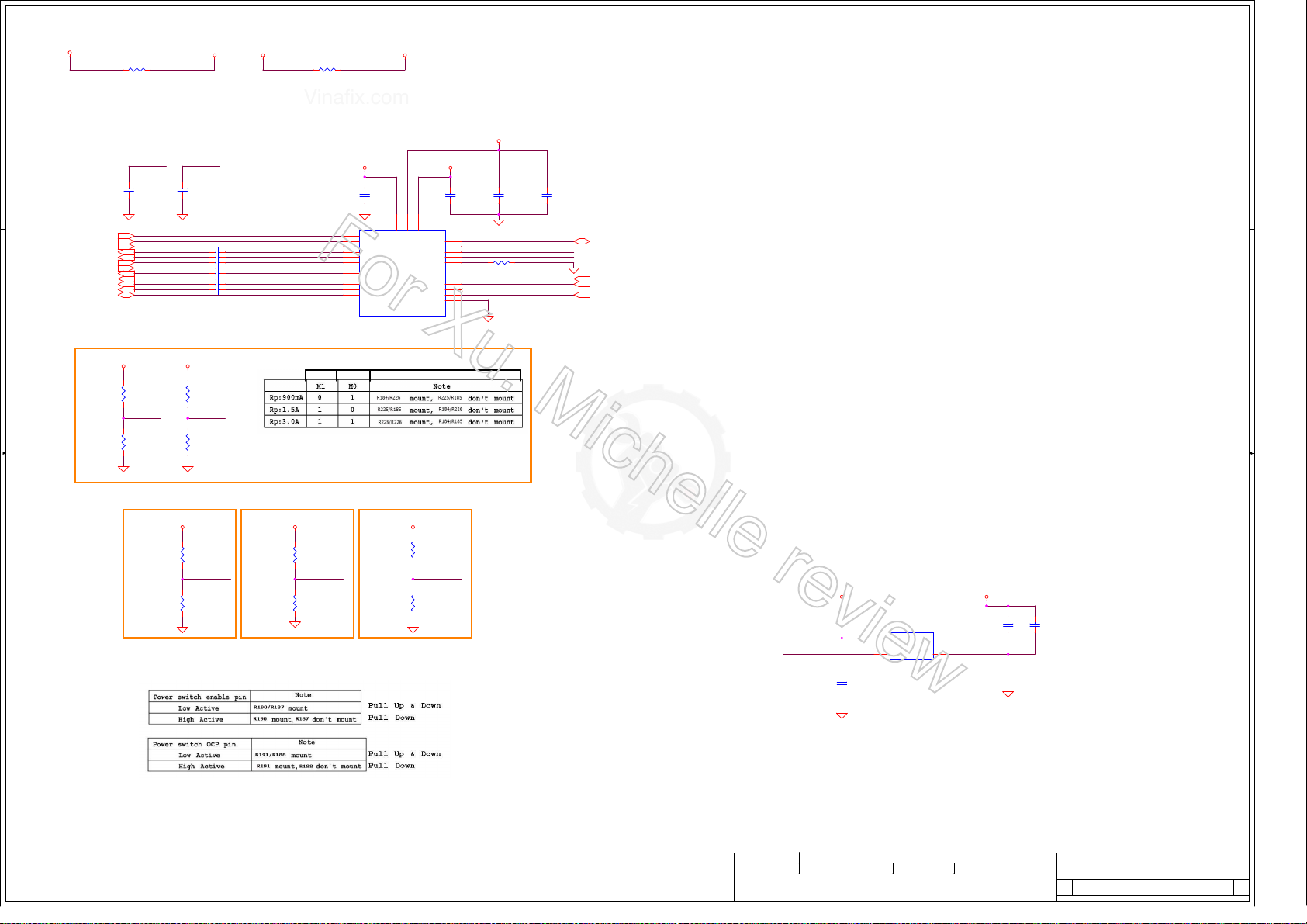

Page 3

Vinafix.com

1

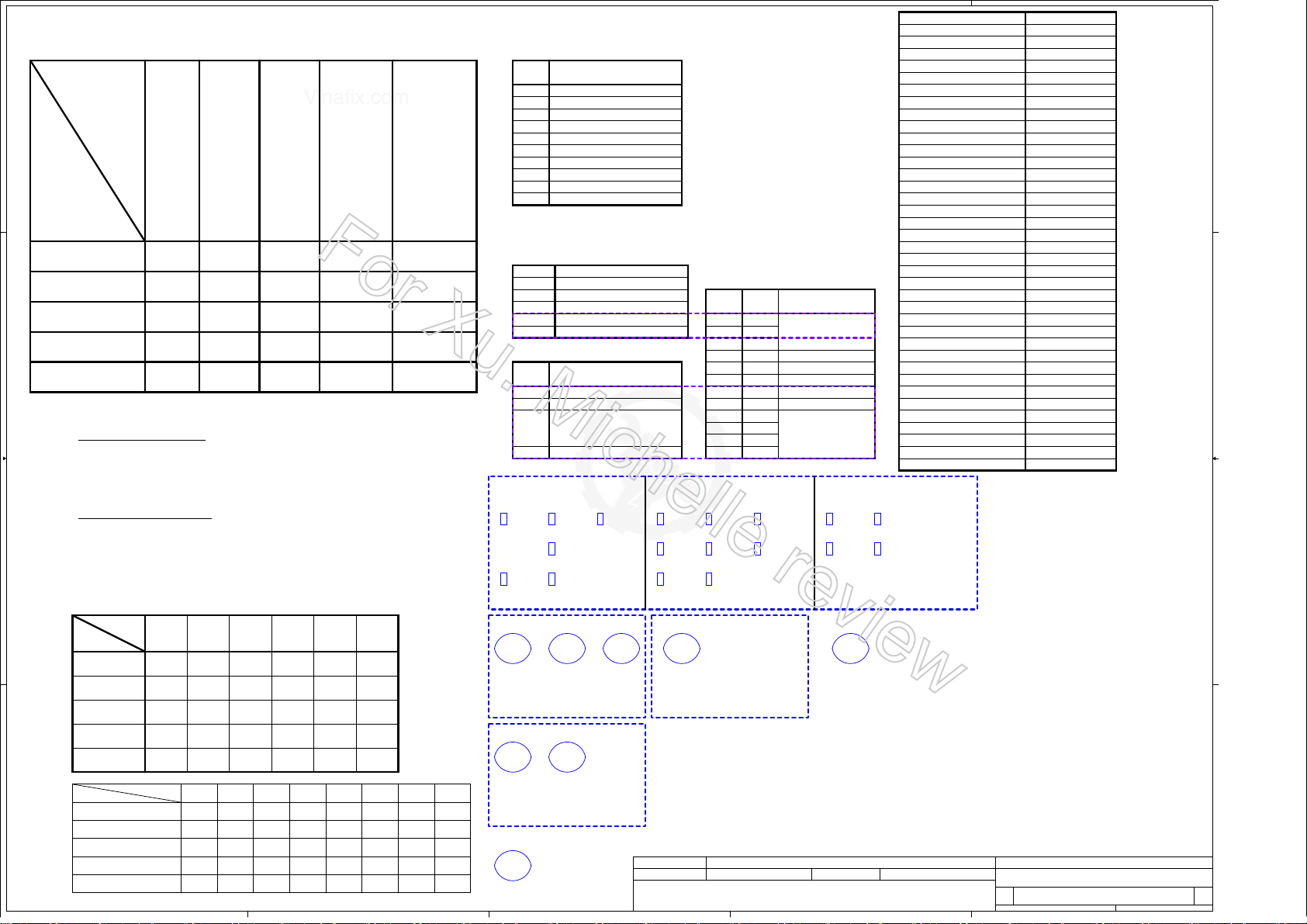

Voltage Rails

power

A A

B B

S5 and S4/Battery only

S5 and S4/AC&Battery

don't exist(Only RTC )

plane

State

S0

S3

S5 and S4/AC

+RTCBAT T

O

O

O

O

O

+B

+5VL

+3VL

+5VALW

+3VALW

+1.8VAL W

+1VALW

O

O

O

O

O

O

O

X

X

EC SM Bus1 address

Device

Smart Battery

Address

0001 011x

PCH SM Bus address

Device

DDR_JDIMM1

GPU

RTS5 455

RTD21 66

C C

APS

Address

1010 000x A0h

1000 001x A0h

1010 1100 A0h

1100 100 A0h

1111 0100 A0h

2

+1.0V_VC CST

+2.5V

+1.2V

O O

O

X

+5VS

+3VS

+3VGS

+1.8VGS

+1.0VS_V CCIO

+PCIE_VG S

+VGA_COR E

+1.35VS_ VRAM

+0.6VS

+VCCCOR E

+VCCGT

+VCCSA

X

XX

X

XXX

CPU

2+2

2+3

USB 2.0 Port Table

Port

Port

1

2

3

4

5

6

7

8

9

10

3 External

USB Port

USB 3.0 Port (AOU)

USB 3.0 Port

TYPE-C USB 3.0 Port

TYPE-C USB 3.0 Port(FULL)

Camera

M.2 BT

Card Reader

Finger Print

2nd Battery

USB 3.0 Port Table

1

USB 3.0 Port (AOU)

2

USB 3.0 Port

3

TYPE-C USB 3.0 Port

4

TYPE-C USB 3.0 Port(FULL)

5

6

SATA Port Table

Port

0

HDD

1

2

M.2 SATA SSD

SKL-U

UC1

CPU1@

SA000092P60

UC1

CPU5@

SA00009E620

i7-6500U

i7-6567U

UC1

CPU2@

i5-6300U

SA000092T40

UC1

CPU4@

i3-6006U

SA0000ACN10

UC1

CPU6@

i5-6267U

SA00009E530

3

UC1

CPU3@

i5-6200U

SA000092O70

KBL-U

UC1

CPU7@

i3-7100U

SA0000A38H0

UC1

CPU10@

i5-7300U

SA0000ADO20

UC1

CPU13@

i7-7567U

SA0000AW620

BOM Structure Table

PCIE Port Table

Port

Lane

1

1

2

2

3

3

4

4

5

6

7

8

9

10

11

12

i5-7200U

3865U

i5-7267U

UC1

CPU9@

i7-7500U

SA0000A34F0

UC1

CPU12@

4415U

SA0000ADV40

UC1

CPU8@

SA0000A37B0

UC1

CPU11@

SA0000ADL30

UC1

CPU14@

SA0000AKR20

4

GPU

LAN

M.2 WLAN+BT

M.2 PCIE*4 SSD

KBL-RU

UC1

CPU15@

KBL-R QN5D

SA0000AR010

UC1

CPU17@

KBL-R QNEF

SA0000AWB00

SKL only SKL@

For 2+2

For 2+3

For 4+2

For DIS

EMI Un-pop

ESD pop

ESD Un-pop

Finger Print

Keyboard backlight KBL@

NONA OU NONA OU@

APS

NOAP S

2nd Battery USB BATT 2@

NO 2nd Battery USB

Onboard RAM MICRON

Onboard RAM SAMSUNG

VRAM HYNIX

VRAM MICRON

VRAM SAMSUNG

CardReader RTS5146

CardReader GL835

TPM TPM@

TCM TCM@

NO TPM/TCM NOTPM@

4+2

UC1

CPU16@

KBL-R QN5C

SA0000AQZ10

UC1

CPU18@

KBL-R QNBF

SA0000AWC00

BOM StructureItem

U22@

U23@

U42@

DIS@

UMA@For UMA

CMOS @Came ra

EMI@EMI pop

@EMI @

ESD@

@ESD @

RF@RF pop

@RF@RF unpop

8M@For SPI 8M

16M@For SPI 16M

FP@

AOU@AOU

TYPE C@TYPEC FULL

NONT YPEC @NONT YPEC

APS@

NOAP S@

NOBA TT2@

X76D DRH@Onboard RAM HYNIX

X76D DRM@

X76D DRS@

X76H 2G@

X76M 4G@

X76S 2G@

X76R T@

X76G L@

ME@Conn ecto r

5

SMBUS Control Table

ZZZ

X

V

+3VS

XX

X

ONONON

ON

ON

ON

ON

SOC

X

V

+3VALW

X

X

ON

OFF

OFF

2

ON

OFF

OFF

OFF

ONON

LOW

OFF

OFF

OFF

X76DDR4H@

2G HYNIX

X7675138L01

On Board RAM

ZZZ

X76RT@

RTS5146

X7675138L61

CardReader

ZZZ

X4E@

X4E

X4EA8X38L01

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

PCH_SMBCLK

PCH_SMBDATA

PCH_SML0CLK

PCH_SML0DATA

SML1CLK

SML1DATA

D D

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

1

EC KB9022

+3VALW

EC KB9022

+3VS

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

SIGNAL

GPU

+3VALW

V

+3VGS

X

V

+3VGS

SLP_S1#

LOW

HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW

LOWLOW

SODIMMNECP388BATT

VX X

X

X

X

X

X

XX

V

X X

+3VS

SLP_S4#SLP_S3# +V (RAM)+VALWSLP_S5# Cl ock+VS

HIGHHIGHHIGH

HIGH

HIGH

HIGH

HIGH

LOWLOW

ZZZ

X76DDR4M@

2G MICRON

X7675138L02

ZZZ

X76GL@

GL835

X7675138L62

ZZZ

X76DDR4S@

2G SAMSUNG

X7675138L03

3

UV1

GPU1@

VGA

SA000098VB0

ZZZ

PCB

DA8001CE000

GPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/24 2012/07/12

2011/06/24 2012/07/12

2011/06/24 2012/07/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-D562P

LA-D562P

LA-D562P

5

3 66Thursday, June 15, 2017

3 66Thursday, June 15, 2017

3 66Thursday, June 15, 2017

0.1

0.1

0.1

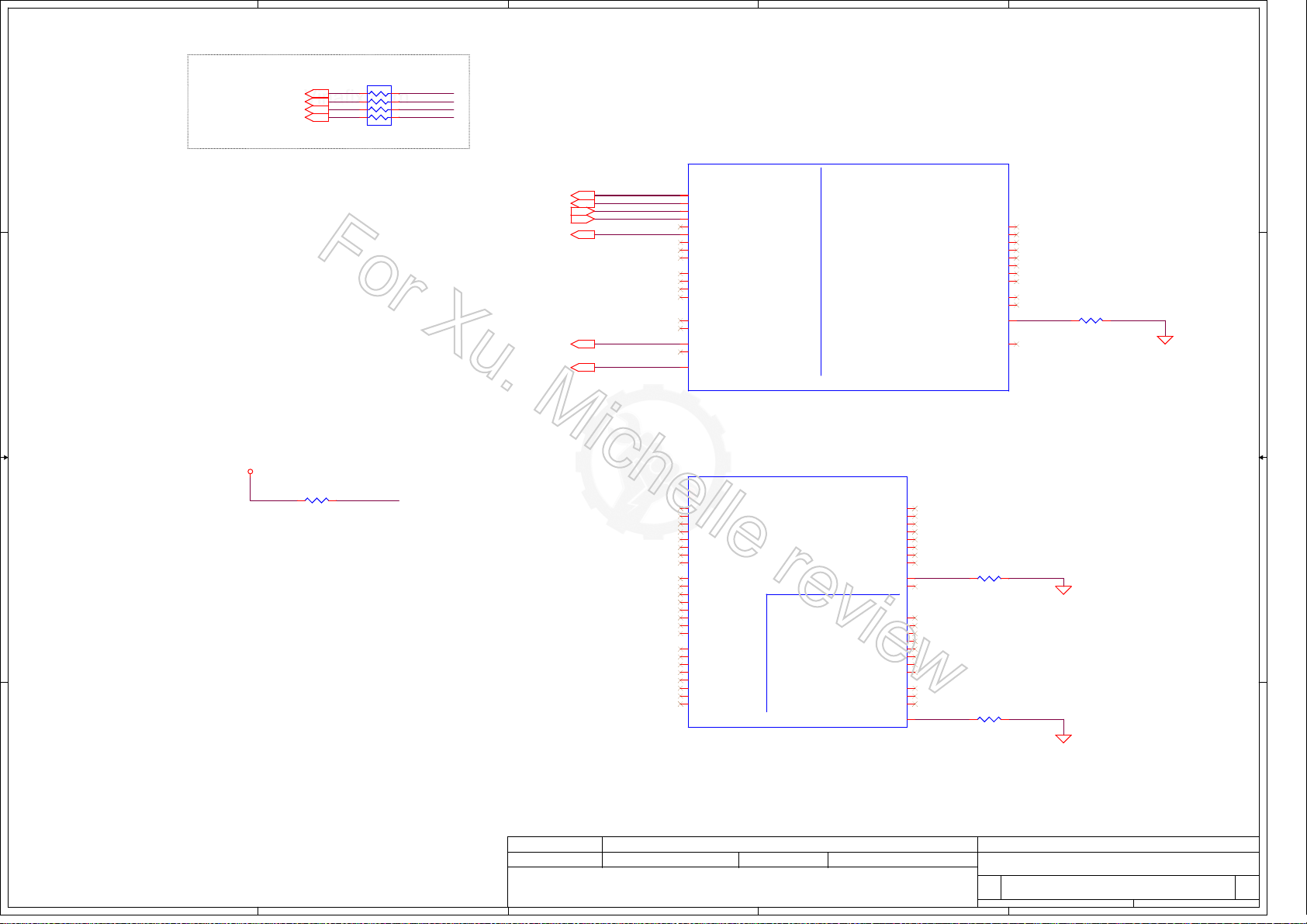

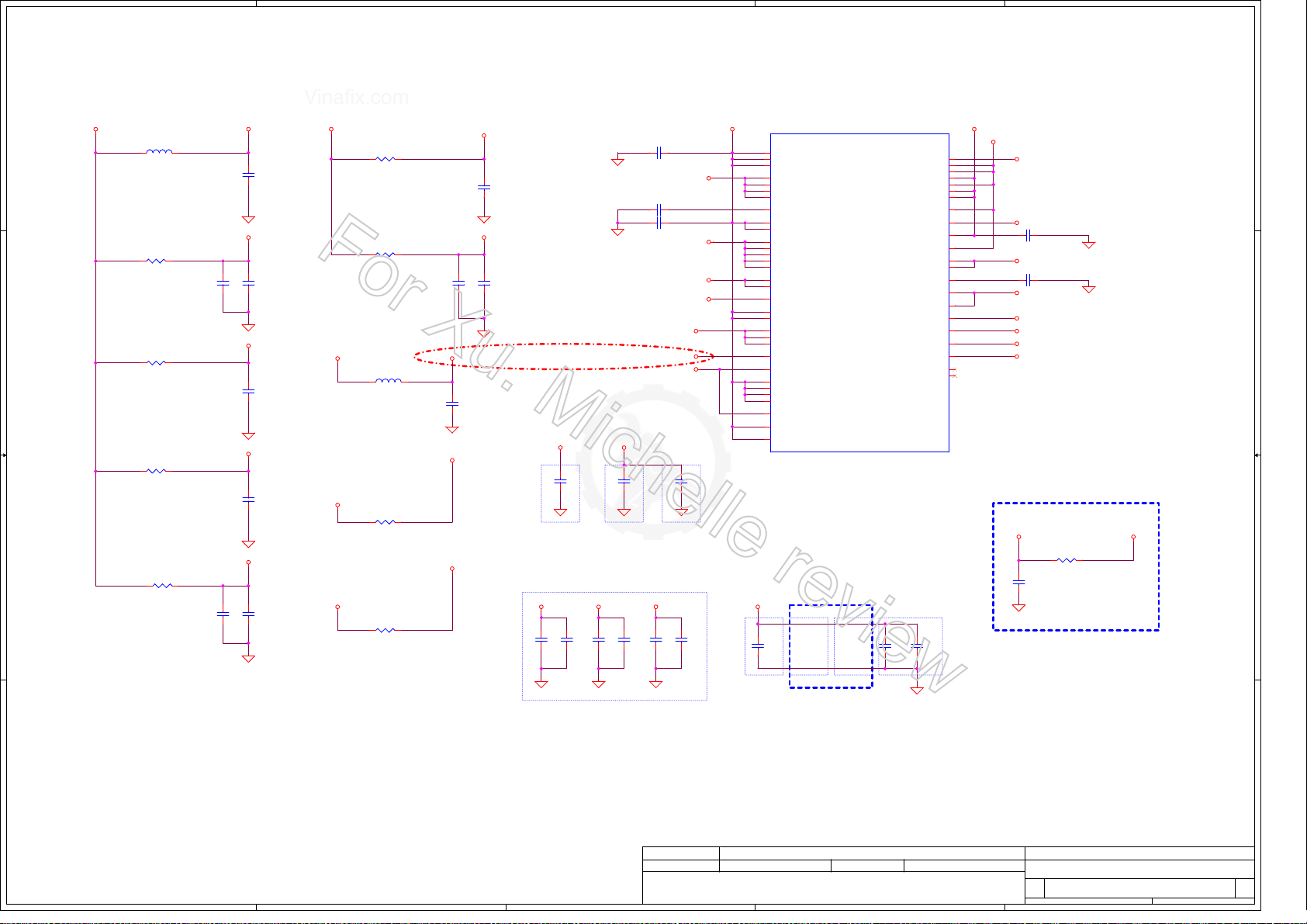

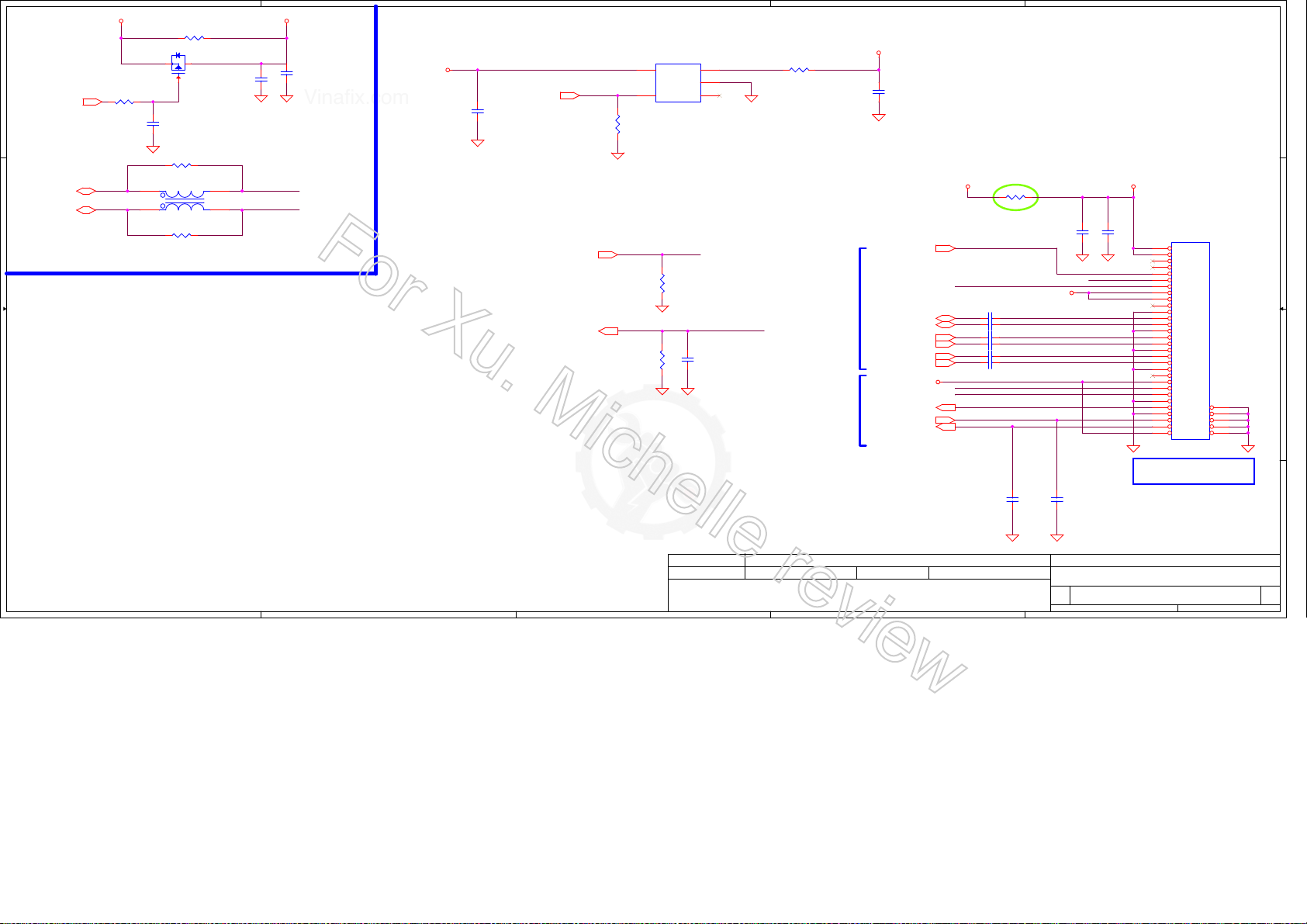

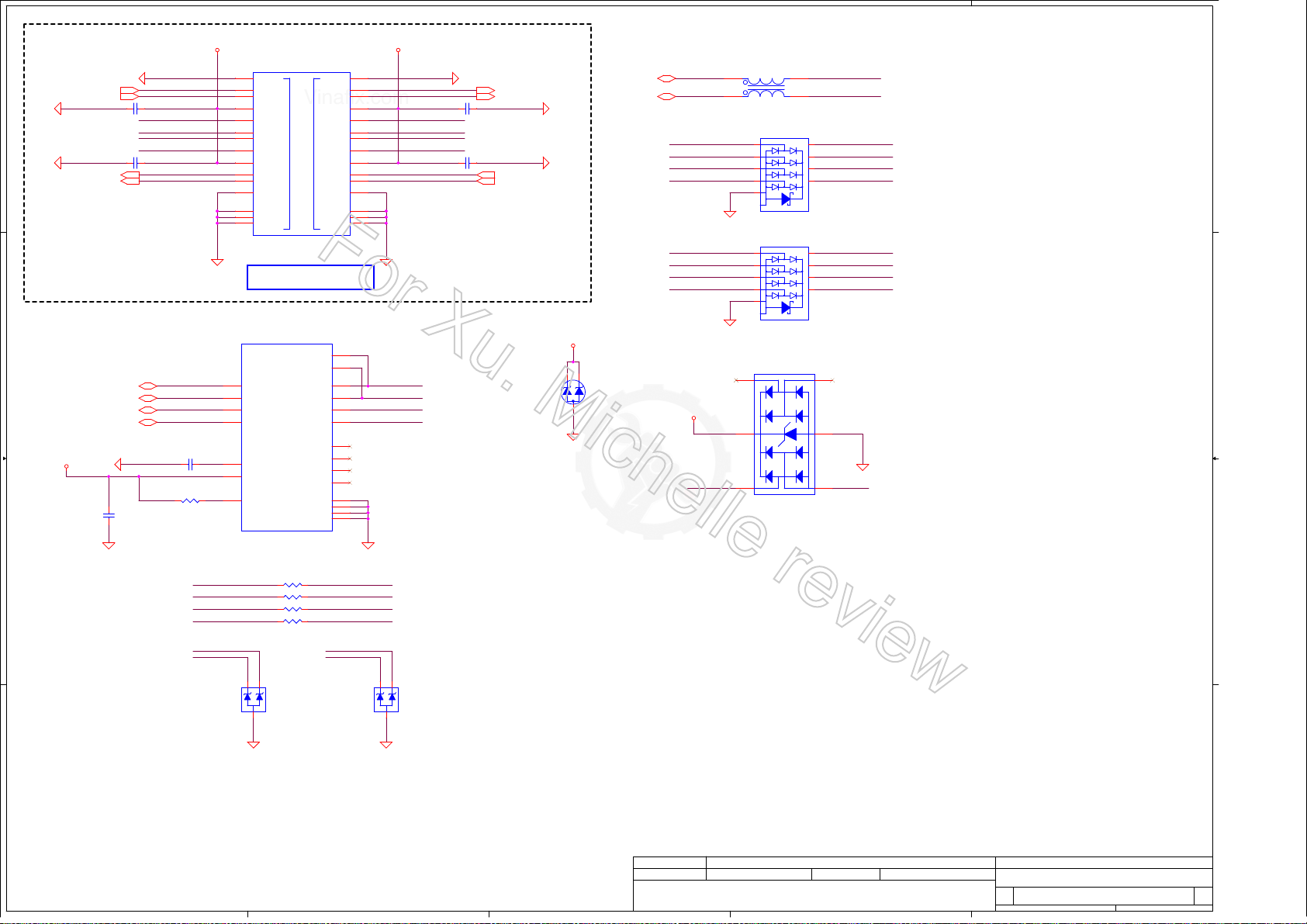

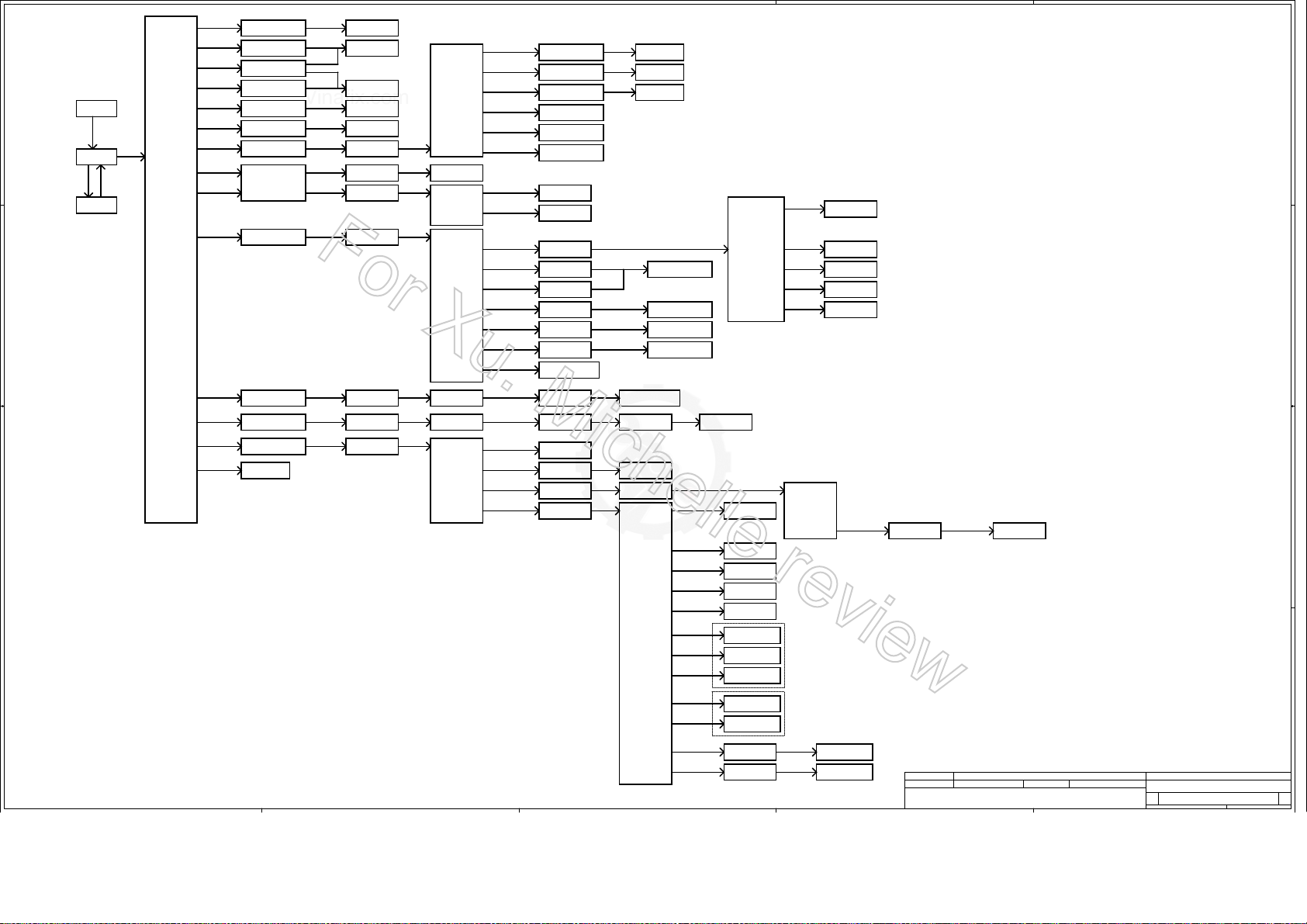

Page 4

Vinafix.com

5

[BIWB6/B7/E7/E8-PWR Sequence_SKL-U22_DDR3L_Volume_NON CS]

4

3

2

1

G3->S0 S0->S3 ->S0

+3VL_RTC

SOC_RTCRST#

B+

D D

+3VLP

EC_ON

+5VALW / +3VALW

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

Pull-up to DSW well if not implemented.

/DS3 DS3S3/

S0->S5

+3VL_RTC

SOC_RTCRST#

+19VB

+3VLP/+5VLP

EC_ON

+5VALW/+3VALW/+3 VALW_DSW

PM_BATLOW#

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8VALW

+1.0VALW

tPCH06_Min : 200 us

PCH_DPWROK

EC_RSMRST#

AC_PRESENT(VCIN1_AC_IN)

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

ON/OFF#

PBTN_OUT#

C C

PM_SLP_S5#

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

PM_SLP_S4#

SYSON

+1.0V_VCCST

+1.2V

PM_SLP_S3#

SUSP#

+1.0VS_VCCIO

+5VS / +3VS / +1.05VS

EC_VCCST_PG(VCCST_PWRGD)

VR_ON

DDR_VTT_PG_CTRL

B B

+0.675VS

tCPU04 Min : 100 ns

T4 = Min : 20ms Max : 30ms(EC Control)

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

+VCCSA

tCPU10 Min : 1 ms

tCPU09 Min : 1 ms

+VCCCORE

+VCCGT

VR_PWRGD

PCH_PWROK

tCPU16 Min : 0 ns

H_CPUPWRGD

SYS_PWROK

SOC_PLTRST#(PCIRST#)

+1.8V_PRIM

+1.0V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S4#

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3#

SUSP#

+1.0VS_VCCIO

+5VS/+3VS/+1. 5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

SYS_PWROK

SOC_PLTRST#

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2015/01/29 2016/01/29

2015/01/29 2016/01/29

2015/01/29 2016/01/29

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Sequence

Power Sequence

Power Sequence

Document Number Rev

Document Number Rev

Document Number Rev

LA-D561P

LA-D561P

LA-D561P

1

4 66Thursday, June 15, 2017

4 66Thursday, June 15, 2017

4 66Thursday, June 15, 2017

0.1

0.1

0.1

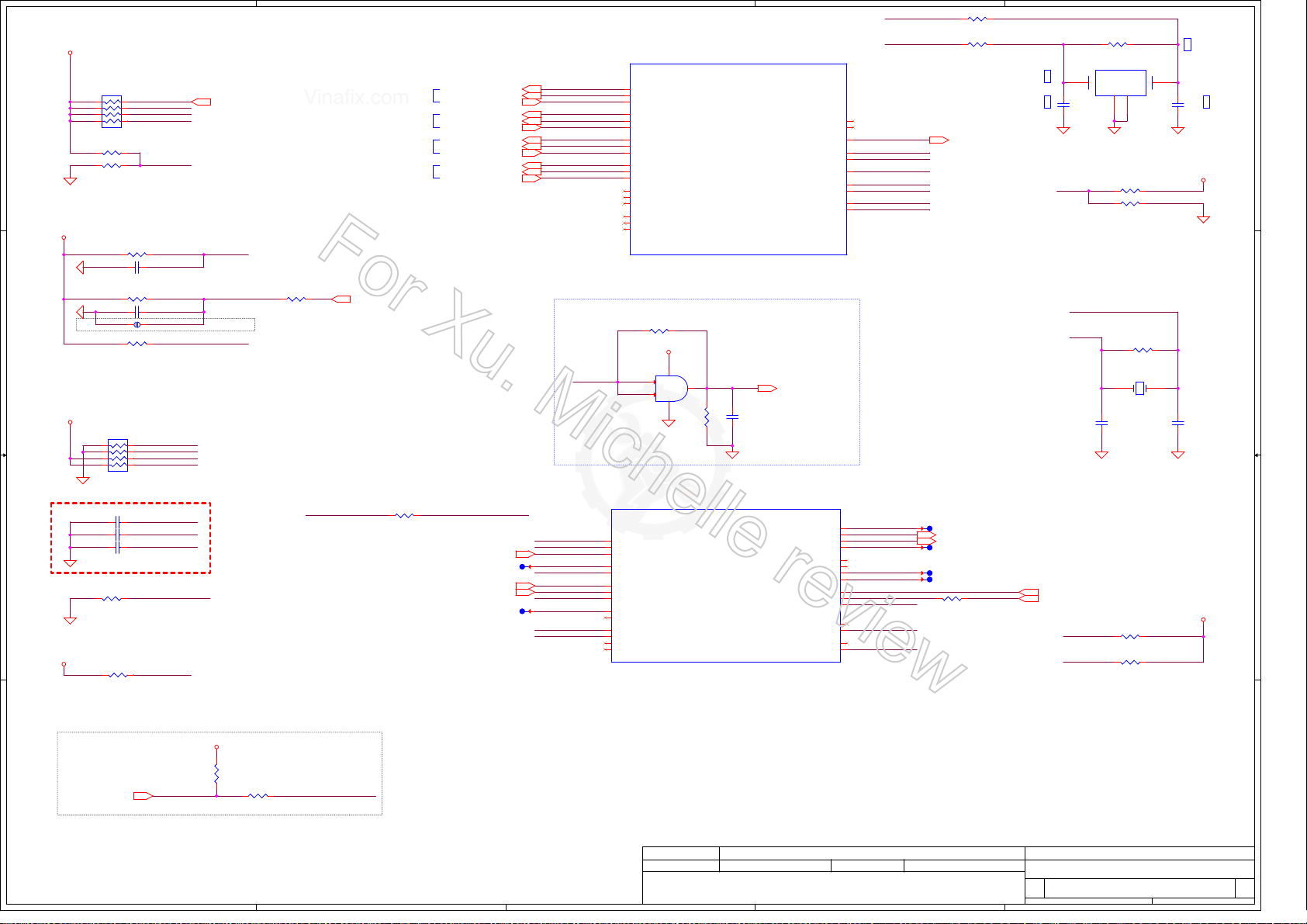

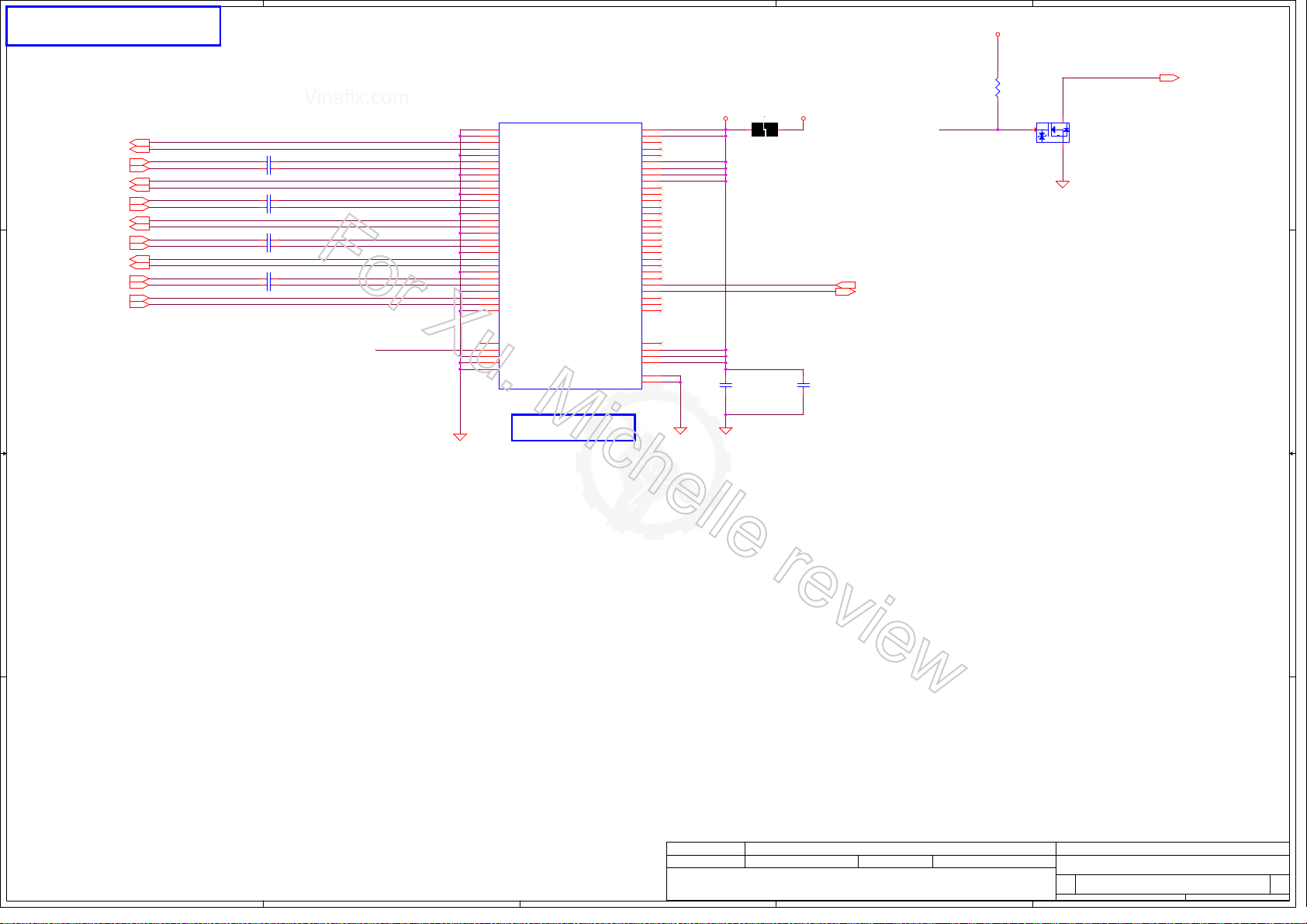

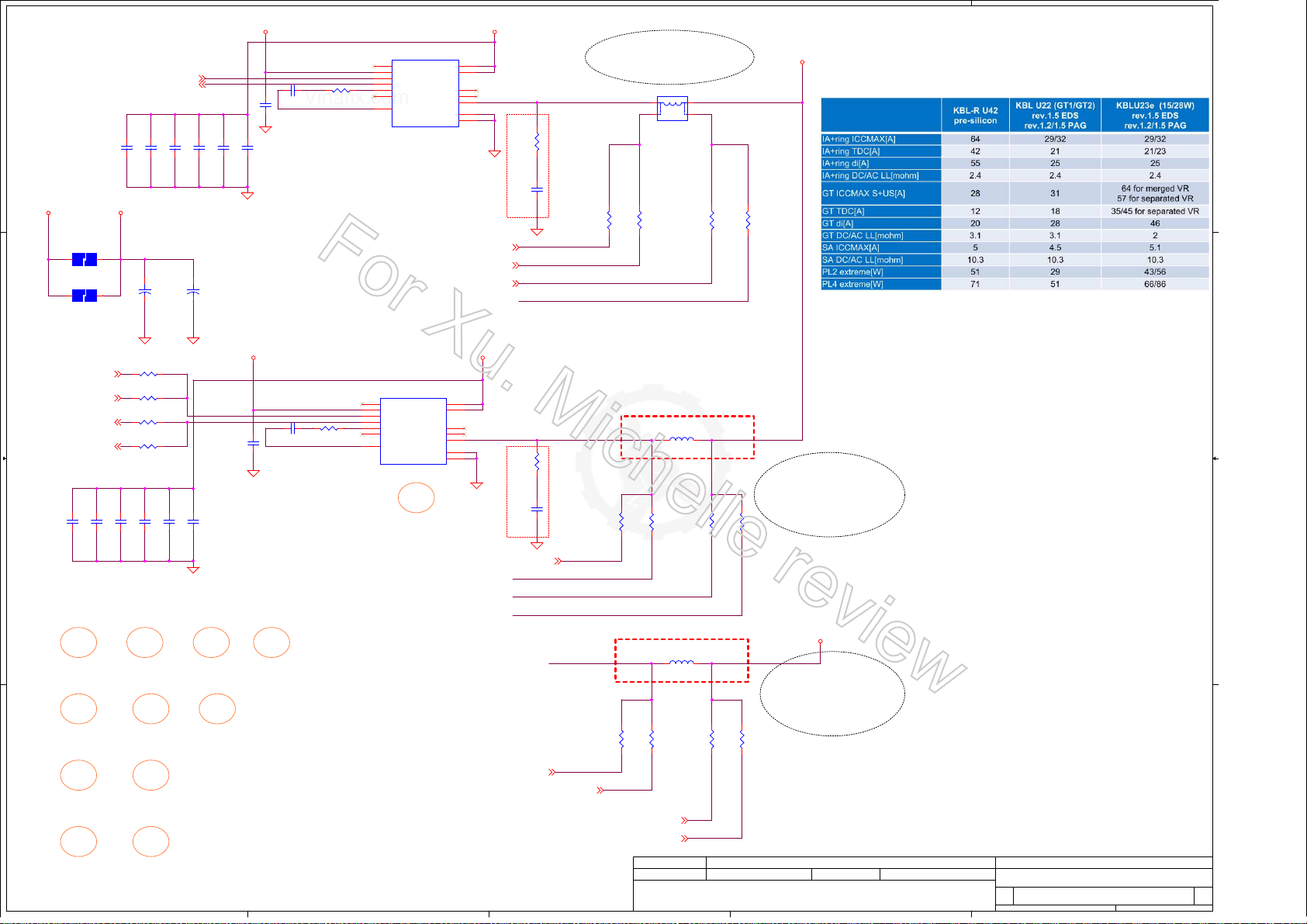

Page 5

Vinafix.com

5

4

3

2

1

M1-30 VRAM STRAP

Vendor

UV3, UV4, UV5, UV6

D D

X76H 2G@

X7667538L03

X76M 2G@

X7667538L04

X76S 2G@

X7667538L05

HYNIX 4096Mbits

SA000076P80 TEMP

256MX16 K4W4G1646E-BC1A TEMP

Micron 4096Mbits

SA00009HF00 TEMP

256Mx16 MT41J256M16LY-091G:N TEMP

SAMSUNG 4096Mbits

SA00008DN00 TEMP

256MX16 H5TC4G63CFR-N0C TEMP

2GBy tes

2GBy tes

2GBy tes

ID

0 0

0

1

2

4

PS_3[ 1 ]PS_3[ 2 ]PS_3[ 3 ]

0

10 0

00 1

001 4.99 K4.53 K

X76@X76@

R_pu

RV22 RV27

NC 4.75K

8.45 K 2K

4.53 K 2K

R_pd

Power-Up/Down Sequence

"M1" has the following requirements with regards to power-supply

sequencing to avoid damaging the ASIC:

All the ASIC supplies must reach their respective nominal voltages within 20ms

‧

of the start of the ramp-up sequence, though a shorter ramp-up duration is preferred.

The maximum slew rate on all rails is 50 mV/μ s.

It is recommended that the 3.3-V rail ramp up frist.

‧

It is recommended that the 0.95-V rail reach at least 90% of its nominal value no later

‧

than 2ms from the start of VDDC ramping up.

The power rails that are shared with other components on the system should be gated for

‧

the dGPU so that when dGPU is powered down (for example AMD PowerXpressTM idle state),

all the power rails are removed from the dGPU.

The gate circuits must meet the slew rate requirement (such as 50mV/us)

VDDC and VDD_CT should not ramp up simultaneously. For example, VDDC

‧

should reach 90% before VDD_CT starts to ramp up (or vice versa).

For power down, reversing the ramp-up sequence is recommended.

‧

≦

5 11 0 3.24 K 5.62 K

6 10K3.4K011

ZZZ

C C

X76H2G@

2G HYNIX

X7675138L04

ZZZ

X76M2G@

2G MICRON

X7675138L05

ZZZ

X76S2G@

2G SAMSUNG

X7675138L06

VDDR3(+3VGS)

PCIE_VDDC(+0.95VGS)

VDD_CT(+1.8VGS)

VDDR1(+1.35VGS)

VDDC/VDDCI(+VGA_CORE)

DGPU_PWROK

PERSTb

REFCLK

Straps Reset

B B

Straps Valid

Global ASIC Reset

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/01/07 2016/01/07

2015/01/07 2016/01/07

2015/01/07 2016/01/07

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

VGA Notes List

VGA Notes List

Document Number Rev

Document Number Rev

Document Number Rev

VGA Notes List

LA-D562P

LA-D562P

LA-D562P

1

5 66Thursday, June 15, 2017

5 66Thursday, June 15, 2017

5 66Thursday, June 15, 2017

0.1

0.1

0.1

Page 6

Vinafix.com

A

1 1

B

C

D

E

DDI

DISPLAY SIDEBANDS

SKL-U

1 OF 20

EDP

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

RSVD

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_TXN0 [28]

EDP_TXP0 [28]

EDP_TXN1 [28]

EDP_TXP1 [28]

EDP_AUXN [28]

EDP_AUXP [28]

DDIP2_AUXN [38]

DDIP2_AUXP [38]

TMDS_B_HPD [29]

DDIP2_HPD [38]

EC_SCI# [10,45]

EDP_HPD [28]

ENBKL [45]

INVPWM [28]

PCH_ENVDD [28]

From HDMI

From DP

From eDP

<eDP>

UC1A

HDMI_TX2-_CK[29]

HDMI_TX2+_CK[29]

HDMI_TX1-_CK[29]

HDMI

DP MU X

(Type-C/ VGA)

HDMI DDC

DP MUX DDC

2 2

+1.0VS_VCCIO

! "

EDP_COMP

1 2

RC1 24.9_0402_1%

HDMI_TX1+_CK[29]

HDMI_TX0-_CK[29]

HDMI_TX0+_CK[29]

HDMI_CLK-_CK[29]

HDMI_CLK+_CK[29]

DDI2_TX0-_CK[38]

DDI2_TX0+_CK[38]

DDI2_TX1-_CK[38]

DDI2_TX1+_CK[38]

DDI2_TX2-_CK[38]

DDI2_TX2+_CK[38]

DDI2_TX3-_CK[38]

DDI2_TX3+_CK[38]

HDMICLK_NB[29]

HDMIDAT_NB[29]

DDIP2_CTRLCLK[38]

DDIP2_CTRLDATA[38]

EDP_COMP

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKL-U_BGA1356

@

+1.0VS_VCCIO

12

RC2

1K_0402_5%

H_PROCHOT#_R

H_PROCHOT#[45]

3 3

1 2

RC3 499_0402_1%

+1.0V_VCCST

1 2

RC7 1K_0402_5%

H_THERMTRIP#

H_PECI[45]

RC10 49.9_0402_1%

RC11 49.9_0402_1%

RC12 49.9_0402_1%

RC14 49.9_0402_1%

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

12

12

12

12

T1 TP@

T2 TP@

T3 TP@

T4 TP@

T5 TP@

T6 TP@

T7 TP@

T8 TP@

SOC_CATERR#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

SOC_GPIOE3

SOC_GPIOB4

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

UC1D

SKL-U_BGA1356

@

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

CPU MISC

SKL-U

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

Rev_1.0

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

PCH_XDP_TRST#

CPU_XDP_TCK0

T9 TP@

#!$!%&"

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

SOC_XDP_TRST#

RC4 51_0402_5%@

RC5 51_0402_5%@

RC6 51_0402_5%@

RC8 51_0402_5%@

RC9 51_0402_5%@

RC13 51_0402_5%

+1.0VS_VCCIO

1 2

1 2

1 2

1 2

1 2

1 2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

LA-D562P

LA-D562P

LA-D562P

E

6 66Thursday, June 15, 2017

6 66Thursday, June 15, 2017

6 66Thursday, June 15, 2017

0.1

0.1

0.1

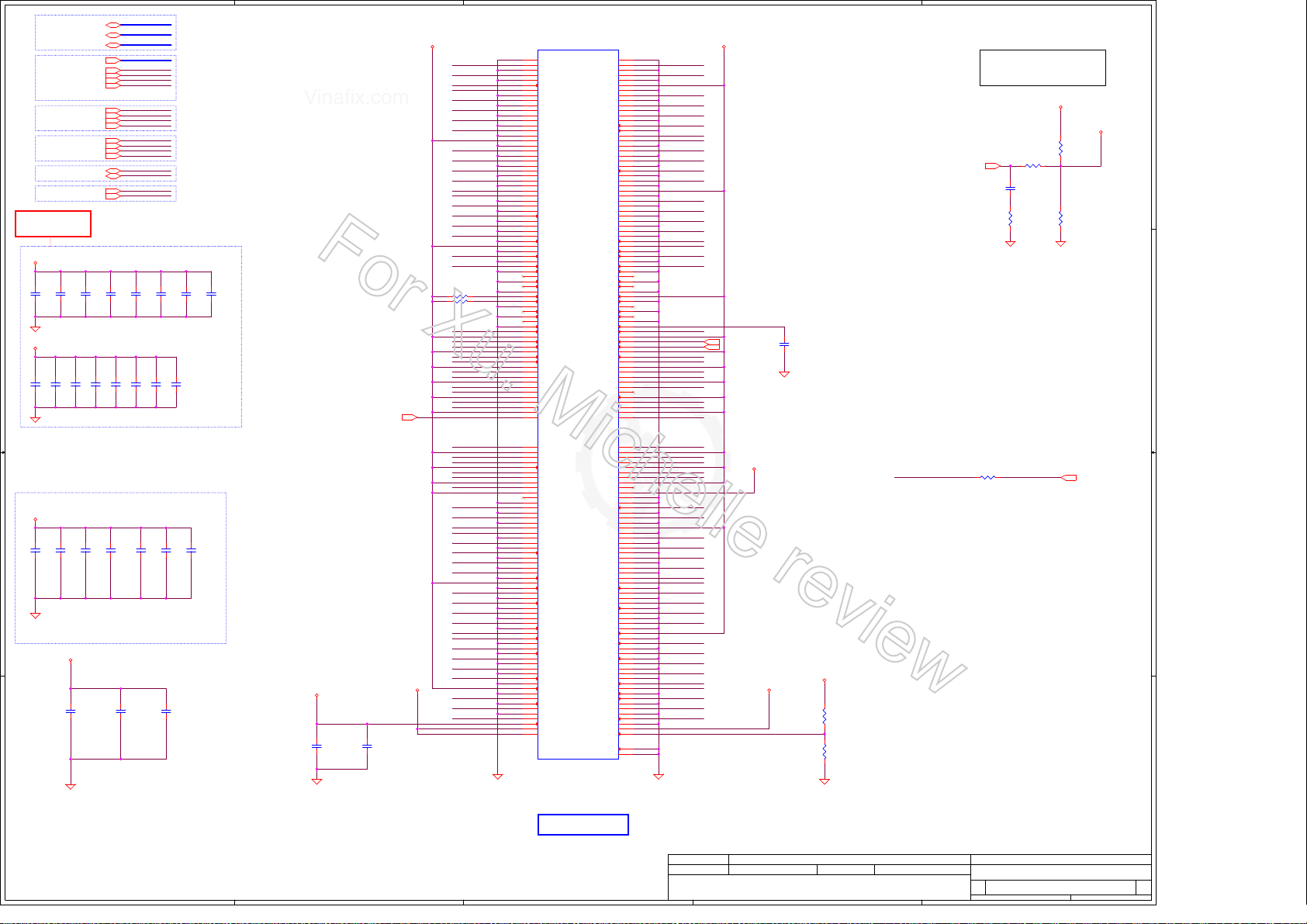

Page 7

Vinafix.com

5

4

3

2

1

'()

D D

DDR_A_D[0..15][18]

DDR_A_D[16..31][18]

C C

DDR_A_D[32..47][18]

DDR_A_D[48..63][18]

B B

UC1B

DDR_A_D0

AL71

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

*!+,"

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35u S

(tCPU 18)

DDR_PG_CTRL

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

SA00007WE00

SKL-U

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

1

CC1

0.1U_0201_10V6K

2

UC8

5

4

Y

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR3L / LPDDR3 / DDR4

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

+3VS+1.2V +3VALW

12

CRB ORB

RC19

@

220K_0402_5%

Rev_1.0

12

RC20

100K_0402_5%

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

M_A_ACT#

DDR_A_BG1

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

+0.6V_VREFCA

+0.6V_B_VREFDQ

DDR_PG_CTRL

DDR_VTT_PG_CTRL [54]

DDR_A_CLK#0 [18]

DDR_A_CLK0 [18]

T10@

T13@

DDR_A_CKE0 [18,20]

T11@

DDR_A_CS#0 [18,20]

T14@

DDR_A_ODT0 [18,20]

T12@

DDR_A_MA5 [18,20]

DDR_A_MA9 [18,20]

DDR_A_MA6 [18,20]

DDR_A_MA8 [18,20]

DDR_A_MA7 [18,20]

DDR_A_BG0 [18,20]

DDR_A_MA12 [18,20]

DDR_A_MA11 [18,20]

M_A_ACT# [18,20]

DDR_A_BG1 [18]

DDR_A_MA13 [18,20]

DDR_A_MA15 [18,20]

DDR_A_MA14 [18,20]

DDR_A_MA16 [18,20]

DDR_A_BA0 [18,20]

DDR_A_MA2 [18,20]

DDR_A_BA1 [18,20]

DDR_A_MA10 [18,20]

DDR_A_MA1 [18,20]

DDR_A_MA0 [18,20]

DDR_A_MA3 [18,20]

DDR_A_MA4 [18,20]

DDR_A_DQS#0 [18]

DDR_A_DQS0 [18]

DDR_A_DQS#1 [18]

DDR_A_DQS1 [18]

DDR_A_DQS#2 [18]

DDR_A_DQS2 [18]

DDR_A_DQS#3 [18]

DDR_A_DQS3 [18]

DDR_A_DQS#4 [18]

DDR_A_DQS4 [18]

DDR_A_DQS#5 [18]

DDR_A_DQS5 [18]

DDR_A_DQS#6 [18]

DDR_A_DQS6 [18]

DDR_A_DQS#7 [18]

DDR_A_DQS7 [18]

DDR_A_ALERT# [18]

DDR_A_PARITY [18,20]

+0.6V_VREFCA [18]

T16@

+0.6V_B_VREFDQ [19]

DDR_B_D[0..15][19]

DDR_B_D[16..31][19]

DDR_B_D[32..47][19]

DDR_B_D[48..63][19]

Trace width/Spacing >= 20mils

Place componment near SODIMM

#543016 PDG0.9 P.163 RC place near SODIMM

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_1.0

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

M_B_ACT#

DDR_B_BG1

DDR_B_MA13

DDR_B_MA15

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

#543016 PDG0.9 P.117

W=12-15 Space= 20/25 L=500mil

DDR_DRAMRST#

RC15 200_0402_1%

RC16 80.6_0402_1%

RC17 100_0402_1%

+1.2V

12

DDR_B_CLK#0 [19]

DDR_B_CLK#1 [19]

DDR_B_CLK0 [19]

DDR_B_CLK1 [19]

DDR_B_CKE0 [19]

DDR_B_CKE1 [19]

DDR_B_CS#0 [19]

DDR_B_CS#1 [19]

DDR_B_ODT0 [19]

DDR_B_ODT1 [19]

DDR_B_MA5 [19]

DDR_B_MA9 [19]

DDR_B_MA6 [19]

DDR_B_MA8 [19]

DDR_B_MA7 [19]

DDR_B_BG0 [19]

DDR_B_MA12 [19]

DDR_B_MA11 [19]

M_B_ACT# [19]

DDR_B_BG1 [19]

DDR_B_MA13 [19]

DDR_B_MA15 [19]

DDR_B_MA14 [19]

DDR_B_MA16 [19]

DDR_B_BA0 [19]

DDR_B_MA2 [19]

DDR_B_BA1 [19]

DDR_B_MA10 [19]

DDR_B_MA1 [19]

DDR_B_MA0 [19]

DDR_B_MA3 [19]

DDR_B_MA4 [19]

DDR_B_DQS#0 [19]

DDR_B_DQS0 [19]

DDR_B_DQS#1 [19]

DDR_B_DQS1 [19]

DDR_B_DQS#2 [19]

DDR_B_DQS2 [19]

DDR_B_DQS#3 [19]

DDR_B_DQS3 [19]

DDR_B_DQS#4 [19]

DDR_B_DQS4 [19]

DDR_B_DQS#5 [19]

DDR_B_DQS5 [19]

DDR_B_DQS#6 [19]

DDR_B_DQS6 [19]

DDR_B_DQS#7 [19]

DDR_B_DQS7 [19]

DDR_B_ALERT# [19]

DDR_B_PARITY [19]

DDR_DRAMRST# [18,19]

X76@

12

1 2

1 2

RC18

470_0402_5%

0606 : RC15 add X76@

!!!

- . .

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/01/29 2016/01/29

2015/01/29 2016/01/29

2015/01/29 2016/01/29

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Thursday, June 15, 2017

Thursday, June 15, 2017

Thursday, June 15, 2017

1

LA-D562P

LA-D562P

LA-D562P

7

7

7

0.1

0.1

0.1

66

66

66

Page 8

Vinafix.com

5

4

3

2

1

SMBALERT# (Internal Pull Down):

0 = Disable Intel ME TLS function ==> Default

1 = Enable Intel ME TLS function

SKL-U

LPC

5 OF 20

'-*01"

UC9

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25Q64FVSSIQ_SO8

/HOLD(IO3)

UC9

16M@

16M ROM

SA00005VV20

8M@

VCC

CLK

DI(IO0)

SMBUS, SMLINK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

8

7

6

5

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

+3VALW

CC2 0.1U_0201_10V6K

SOC_SPI_IO3_0_RSOC_SPI_SO_0_R

SOC_SPI_CLK_0_R

SOC_SPI_SI_0_R

Rev_1.0

GPP_C0/SMBCLK

GPP_C3/SML0CLK

GPP_C6/SML1CLK

GPP_A8/CLKRUN#

@

1 2

1

2

CC3 10P_0603_50V8-J

@EMI@

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

SOC_SMBCLK

SOC_SMBDATA

SOC_SMBALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SML0ALERT#

SOC_SML1CLK

SOC_SML1DATA

SOC_SML1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK0

RC24 22_0402_1%EMI@

LPC_CLK1

RC102 22_0402_1%EMI@

1

@RF@

CC95

33P_0402_50V8J

2

SOC_SMBCLK [19]

SOC_SMBDATA [19]

T17TP@

T18TP@

SOC_SML1CLK [22,39,45,46]

SOC_SML1DATA [22,39,45,46]

LPC_AD0 [27,45]

LPC_AD1 [27,45]

LPC_AD2 [27,45]

LPC_AD3 [27,45]

LPC_FRAME# [27,45]

1 2

1 2

CLKRUN#

SOC_SML1ALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SMBCLK

SOC_SMBDATA

SOC_SML1DATA

SOC_SML1CLK

CLKRUN#

RC26 150K_0402_5%@

RC27 499_0402_1%

RC28 499_0402_1%

RC30 8.2K_0402_5%

Follow 543016_SKL_U_Y_PDG_0_9

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

M2

M3

J4

V1

V2

M1

G3

G2

G1

UC1E

SKL-U_BGA1356

@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

D D

C C

+3VALW

1 2

RC21 10K_0402_5%

1 2

RC22 1K_0402_5%@

1 2

RC23 1K_0402_5%@

+1.8VS_3VS_PGPPA

1 2

RC25 8.2K_0402_5%

KB_RST#

SOC_SPI_IO2

SOC_SPI_IO3

SERIRQ

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

KB_RST#[45]

SERIRQ[27,45]

KB_RST#

SERIRQ

RPC1, RPC3 and RC30 are close to UC3

RPC1

SOC_SPI_IO2

SOC_SPI_SO

SOC_SPI_SI

B B

EC_SPI_CS0#[45]

/

EC_SPI_MOSI[45]

EC_SPI_CLK[45]

EC_SPI_MISO[45]

SOC_SPI_IO3

EC_SPI_CS0# SOC_SPI_CS#0

EC_SPI_MOSI SOC_SPI_SI_0_R

EC_SPI_CLK SOC_SPI_CLK_0_R

+3VALW

RC110

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

1 2

RC29 33_0402_5%EMI@

RPC3

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

1 2

10K_0402_5%

EMI@

SOC_SPI_IO2_0_R

SOC_SPI_SO_0_R

SOC_SPI_SI_0_R

SOC_SPI_IO3_0_R

SOC_SPI_CLK_0_RSOC_SPI_CLK

EMI@

SOC_SPI_SO_0_REC_SPI_MISO

SOC_SPI_CS#0

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC ==> Default

1 = eSPI is selected for EC

SMB

(Link to DDR)

SML1

(Link to EC,DGPU,CRT,APS,RTS5455)

CK_LPC_KBC [45]

CK_LPC_TPM [27]

CLKRUN# [45]

+3VS

12

1 2

1 2

RPC2

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

+1.8VS_3VS_PGPPA

1 2

@

For ENE auto load search code V12

A A

Security Classification

Security Classification

Security Classification

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2014/05/19 2015/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

Document Number Re v

Document Number Re v

Document Number Re v

LA-D562P

LA-D562P

LA-D562P

8 66Thursday, June 15, 2017

8 66Thursday, June 15, 2017

8 66Thursday, June 15, 2017

1

0.1

0.1

0.1

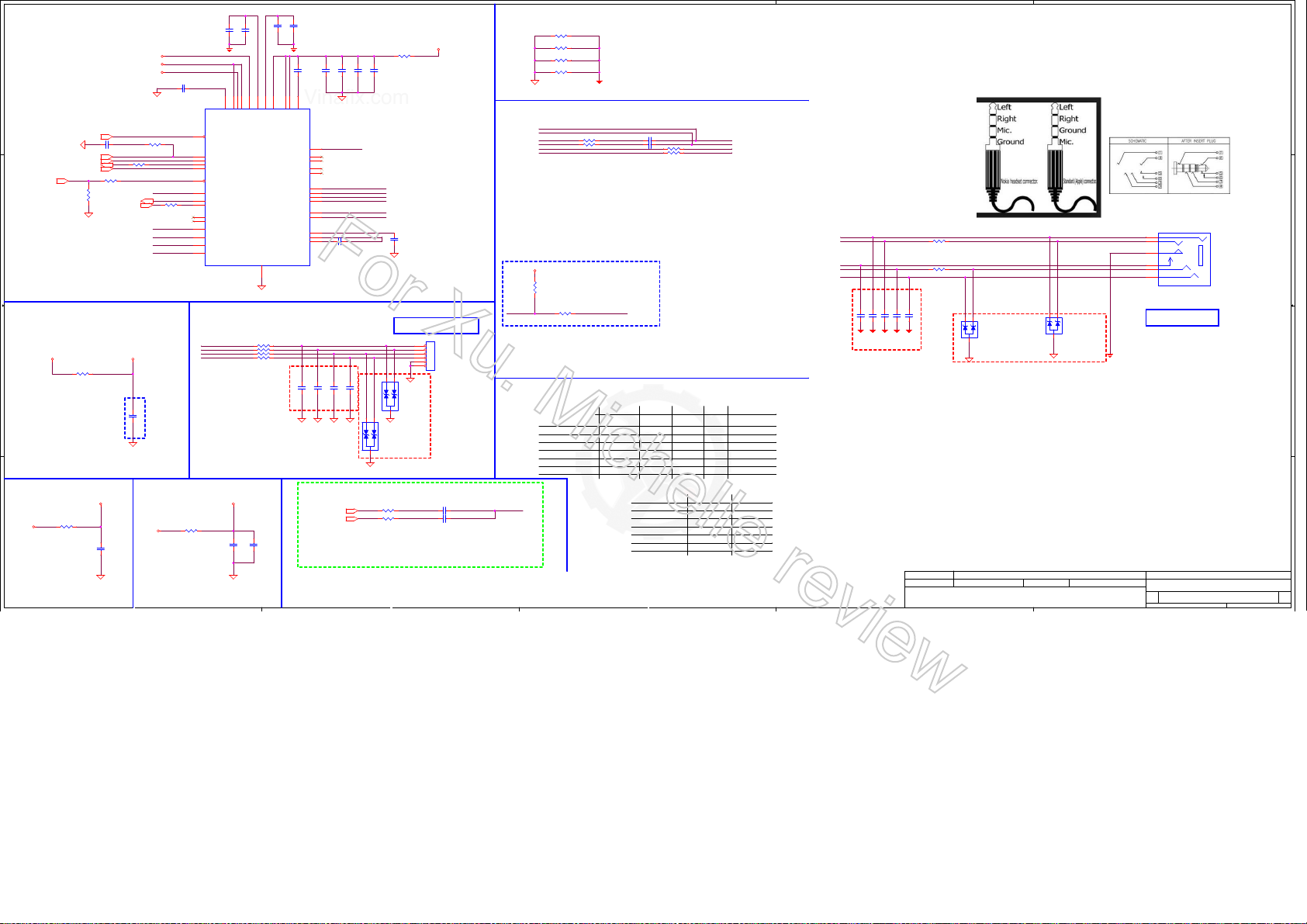

Page 9

Vinafix.com

5

4

3

2

1

2!3!'*"

RPC4

EMI@

HDA_BITCLK_AUDIO[35]

HDA_SYNC_AUDIO[35]

HDA_SDOUT_AUDIO[35]

D D

C C

HDA_RST_AUDIO#[35]

+3VS

RC32 2.2K_0402_5%

1 2

1 8

2 7

3 6

4 5

HDA_SPKR

@

SPKR (Internal Pull Down):

TOP Swap Override

B B

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

HDA_BIT_CLK

HDA_SYNC

ME_EN

HDA_RST#

33_0804_8P4R_5%

/%/*("

UC1G

HDA_SYNC[44]

HDA_BIT_CLK[44]

ME_EN[44,45]

HDA_SDIN0[35]

HDA_RST#[44]

DDI_PRIORITY[38]

HDA_SPKR[35]

HDA_SYNC

HDA_BIT_CLK

ME_EN

HDA_RST#

DDI_PRIORITY

HDA_SPKR

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK7

AK6

AK9

AK10

AW5

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

J5

H5

D7

D8

C8

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

@

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

@

SKL-U

SKL-U

9 OF 20

GPP_A17/SD_PWR_EN#/ISH_GP7

7 OF 20

Rev_1.0

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO / SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

C37

D37

C32

D32

C29

D29

B26

A26

E13

RC33 100_0402_1%@

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

RC34 200_0402_1%@

Rev_1.0

SD_RCOMP

GPP_F23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

12

12

RC31 200_0402_1%@

12

A A

Security Classification

Security Classification

Security Classification

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2014/05/19 2015/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Document Number Re v

Document Number Re v

Document Number Re v

Thursday, June 15, 2017

Thursday, June 15, 2017

Thursday, June 15, 2017

LA-D562P

LA-D562P

LA-D562P

66

66

9

9

9

1

66

0.1

0.1

0.1

Page 10

Vinafix.com

5

+3VS

RPC5

EC_SCI#

18

WLANCLK_REQ#

27

M2CLK_REQ#

36

LANCLK_REQ#

D D

RC36 10K_0402_5%UMA@

RC37 10K_0402_5%

+3VL_RTC

C C

+3VALW

45

10K_0804_8P4R_5%

1 2

1 2

GPUCLK_REQ#

DIS@

1 2

RC40 20K_0201_5%

1 2

CC6 1U_0402_6.3V6K

1 2

RC41 20K_0402_5%

1 2

CC7 1U_0402_6.3V6K

1 2

CLRP1 SHORT PADS

1 2

RC44 1M_0402_5%

RPC6

PCH_PWROK

18

EC_RSMRST#

27

LAN_WAKE#

36

SYS_RESET#

45

10K_0804_8P4R_5%

EC_SCI# [6,45]

SOC_SRTCRST#

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

RC42

1 2

0_0402_5%

/!

1 2

ESD@

CC11 100P_0402_50V8J

1 2

ESD@

CC12 100P_0402_50V8J

1 2

ESD@

CC13 100P_0402_50V8J

B B

1 2

RC107 10K_0402_5%

+3VALW

1 2

RC49 1K_0402_5%

SYS_RESET#

EC_RSMRST#

SYS_PWROK

SYS_PWROK

WAKE#

EC_RSMRST# PCH_DPWROK

Only For Power Sequence Debug

4

DGPU

LAN

NGFF WL+BT(KEY E)

M.2 PCIE SSD

EC_CLEAR_CMOS# [45]

1 2

RC47 0_0402_5%

3

0606 change

UC1J

CLK_PCIE_GPU#[21]

CLK_PCIE_GPU[21]

GPUCLK_REQ#[22]

CLK_PCIE_LAN#[36]

CLK_PCIE_LAN[36]

LANCLK_REQ#[36]

CLK_PCIE_WLAN#[31]

CLK_PCIE_WLAN[31]

WLANCLK_REQ#[31]

CLK_PCIE_M2#[32]

CLK_PCIE_M2[32]

M2CLK_REQ#[32 ]

GPUCLK_REQ#

LANCLK_REQ#

WLANCLK_REQ#

M2CLK_REQ#

2 4-5&$ $ "

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#[45]

PCH_PWROK[45]

T21 TP@

SYS_PWROK[45]

T24 TP@

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

PCH_DPWROK

SUSWARN#

WAKE#

LAN_WAKE#

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

SOC_PLTRST#

TC7SH08FUF_SSOP5

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

@

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

@

RC43

1 2

0_0402_5%

+3VS

5

UC11

1

P

B

2

A

G

3

@

SYSTEM POWER MANAGEMENT

SKL-U

CLOCK SIGNALS

10 OF 20

4

Y

12

RC46

100K_0402_5%

12

SKL-U

11 OF 20

PCIRST# [21,27,31,32,36,45]

CC8

100P_0402_50V8J

ESD@

GPP_B11/EXT_PWR_GATE#

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

Rev_1.0

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

Rev_1.0

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

2

SOC_XTAL24_IN

SOC_XTAL24_OUT

SUSCLK

SOC_XTAL24_IN

SOC_XTAL24_OUT

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#

AC_PRESENT

PM_BATLOW#

SM_INTRUDER#

SOC_VRALERT#

1 2

RC101 33_0201_1%

EMI@

1 2

RC100 33_0201_1%

EMI@

24MHZ_18PF_XRCGB24M000F2P51R0

SUSCLK [31]

T19TP@

PM_SLP_S3# [45]

PM_SLP_S4# [45,54]

T20TP@

T22TP@

T23TP@

1 2

RC48 0_0402_5%

YC1

U23@

SJ10000UJ00

CC4

27P_0402_50V8J

U23@

SE071270J80

SOC_XTAL24_IN_R

SOC_XTAL24_OUT_R

YC1

24MHZ_18PF_XRCGB24M000F2P51R0

3

CC4

27P_0402_50V8J

1

U22@

2

YC1 need to be replaced by

38.4MHz (30ohm ESR) XTAL for Cannonlake-U

XCLK_BIASREF

1

U22@

1 2

RC35 1M_0402_5%

SJ10000UJ00U22@

NC

NC

2

4

1 2

1 2

@

1

1

3

RC38 2.7K_0402_1%

RC39 60.4_0402_1%

RC35

1M_0402_5%

U23@

SD028100480

CC5

27P_0402_50V8J

1

U22@

2

+1.0V_CLK5_F24NS

Follow 546765_2014WW48_Skylake_MOW_Rev_1_0

Stuff 2.7k ohm(RC35) PU for Skylake-U

Stuff 60.4 ohm(RC110) PD for Cannonlake-U

SOC_RTCX2

SOC_RTCX1

PBTN_OUT# [45]

AC_PRESENT_R [45]

PM_BATLOW#

SOC_VRALERT#

1 2

RC45 10M_0402_5%

YC2

1 2

32.768KHZ 9PF 20PPM 9H03280012

1

CC9

4.7P_0402_50V8B

2

1 2

RC50 8.2K_0402_5%

1 2

@

RC51 10K_0402_5%

1

CC10

4.7P_0402_50V8B

2

+3VALW

CC5

27P_0402_50V8J

U23@

SE071270J80

/6*0!7

A A

VCCST_PWRGD[45]

5

+1.0V_VCCST

12

RC52

1K_0402_5%

1 2

RC53 60.4_0402_1%

EC_VCCST_PG

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

LA-D562P

LA-D562P

LA-D562P

1

10 66Thursday, June 15, 2017

10 66Thursday, June 15, 2017

10 66Thursday, June 15, 2017

0.1

0.1

0.1

Page 11

Vinafix.com

5

4

3

2

1

12

RC55

10K_0402_5%

X76@

12

RC57

10K_0402_5%

X76@

OBRAM_ID2

OBRAM_ID0

OBRAM_ID1

GSPI0_MOSI

GSPI1_MOSI

WLBT_OFF#

UART_2_CRXD_DTXDUART_2_CRXD_DTXD

UART_2_CTXD_DRXD

I2C1_SDA_TP

I2C1_SCL_TP

*5-39'!

AM5

AN7

AP5

AN5

AB1

AB2

AB3

AD1

AD2

AD3

AD4

AH9

AH10

AH11

AH12

AF11

AF12

12

RC54

10K_0402_5%

X76@

12

RC56

10K_0402_5%

X76@

UC1F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA1356

@

LPSS ISH

SKL-U

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Sx_EXIT_HOLDOFF# / GPP_A12 / BM_BUSY# / ISH_GP6

6 OF 20

GPP_D15/ISH_UART0_RTS#

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

DGPU_PWR_EN

AC1

DGPU_HOLD_RST#

AC2

DGPU_PWROK

AC3

DGPU_PRSNT#

AB4

AOU_STRAP

AY8

TPM_STRAP

BA8

TPM_STRAP2

BB7

APS_STRAP

BA7

PD_STRAP

AY7

ULTBY_STRAP

AW7

AP13

DGPU_PWR_EN [23,45,57,58]

DGPU_HOLD_RST# [21]

DGPU_PWROK [57,58]

RPC7

DGPU_HOLD_RST#

DGPU_PWR_EN

DGPU_PWROK

DGPU_PRSNT#

DIS@

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

DGPU_PRSNT# PD for DIS SKU

&

3

!'

+3VS

RC62 10K_0402_5%UMA@

89

1 2

+3VS

DGPU_PRSNT#

-3(

2)

*5-39'!

*5-39'!

&

D D

GSPI0_MOSI (Internal Pull Down):

No Reboot

0 = Disable No Reboot mode. ==> Default

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This function is useful

when running ITP/XDP.

GSPI1_MOSI (Internal Pull Down):

Boot BIOS Strap Bit

0 = SPI Mode ==> Default

+3VS

C C

+3VS

1 = LPC Mode

1 2

@

RC58 2.2K_0402_5%

1 2

@

RC59 2.2K_0402_5%

1 2

RC103 10K_0402_5%

1 2

RC106 10K_0402_5%

1 2

RC60 49.9K_0402_1%

1 2

RC61 49.9K_0402_1%

1 2

R469 2.2K_0201_ 5%

1 2

R470 2.2K_0201_ 5%

UART_2_CTXD_DRXD

GSPI0_MOSI

GSPI1_MOSI

WLBT_OFF#

DMIC_DET#

I2C1_SDA_TP

I2C1_SCL_TP

+3VS +3VS +3VS

-(

12

RC105

10K_0402_5%

X76@

OBRAM_ID2 OBRAM_ID1 OBRAM_ID0

12

RC104

10K_0402_5%

X76@

TP_INT#[33]

DMIC_DET#[28]

WLBT_OFF#[31]

UART_2_CRXD_DTXD[31]

UART_2_CTXD_DRXD[31]

I2C1_SDA_TP[33]

I2C1_SCL_TP[33]

B B

&

8931

3*

:*:3*

AOU_STRAP

&

4-353?

:*4-353?

ULTBY_STRAP PD_STRAP

A A

5

4

893>

12

RC11210K_0402_5% AOU@

12

RC11110K_0402_5% NONAOU@

+3VS +3VS

12

RC11410K_0402_5% BATT2@

12

RC11310K_0402_5% NOBATT2@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL