Page 1

A

ZZZ

PCB@

PCB 1G7 LA-D051P REV1 M/B

DA80013U010

1 1

2 2

B

C

D

E

BAV00 / BAV10

MB Schematic Document

LA-D051P

Rev: 1.0

2015.07.15

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet

Date: Sheet

D

Date: Sheet

E

1 55Tuesday, July 28, 2015

1 55Tuesday, July 28, 2015

1 55Tuesday, July 28, 2015

0.2

0.2

0.2

of

of

of

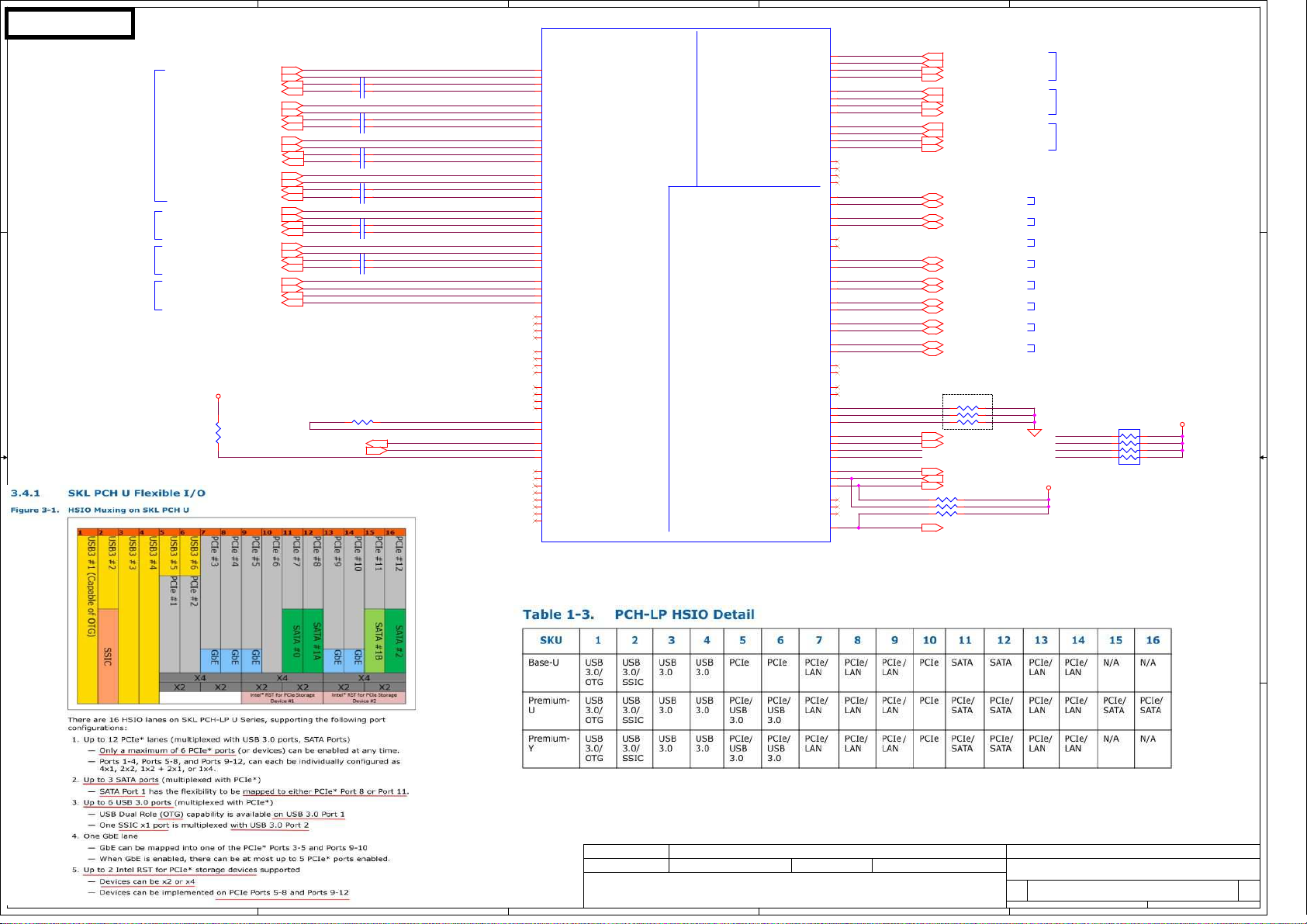

Page 2

A

B

C

D

E

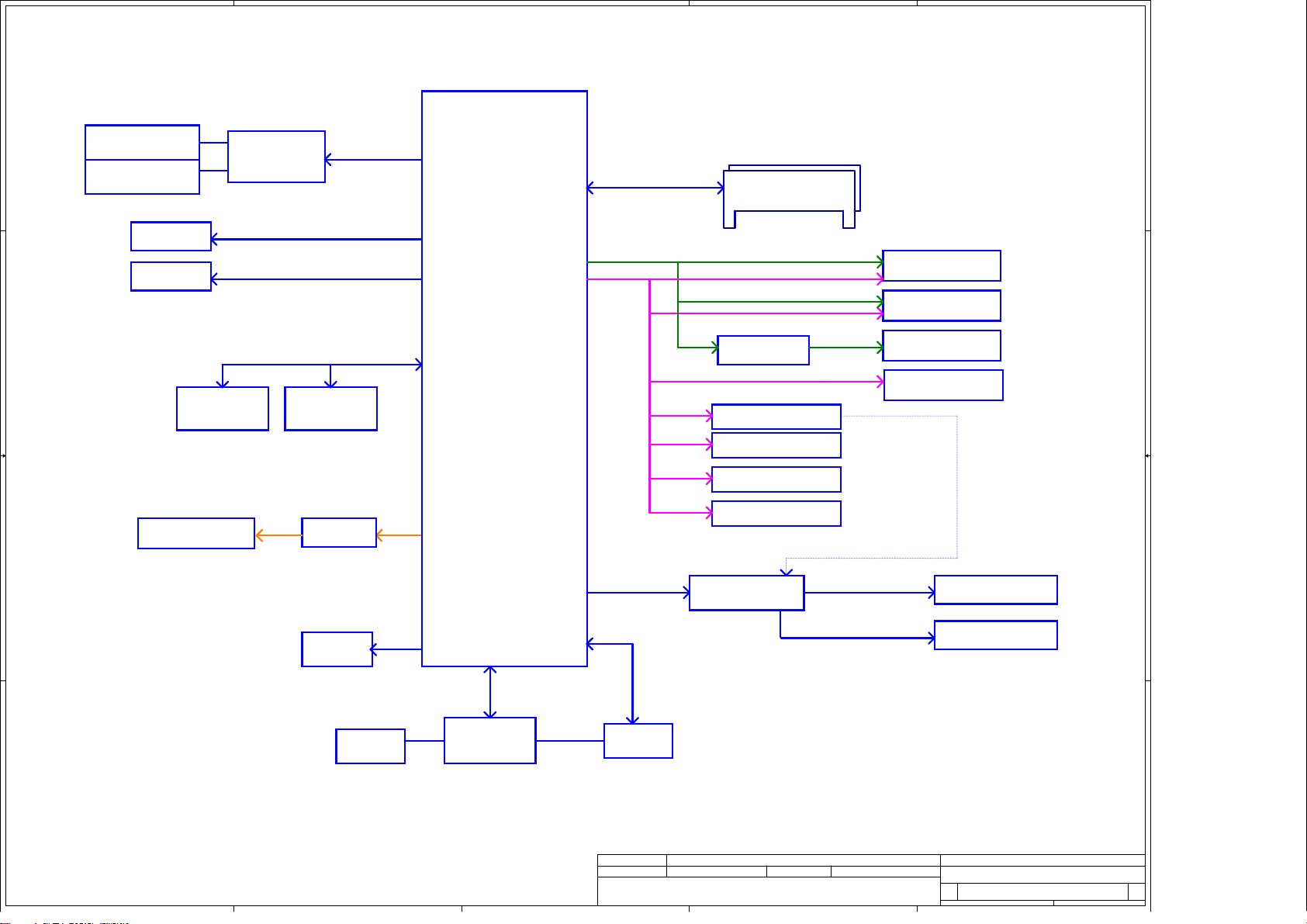

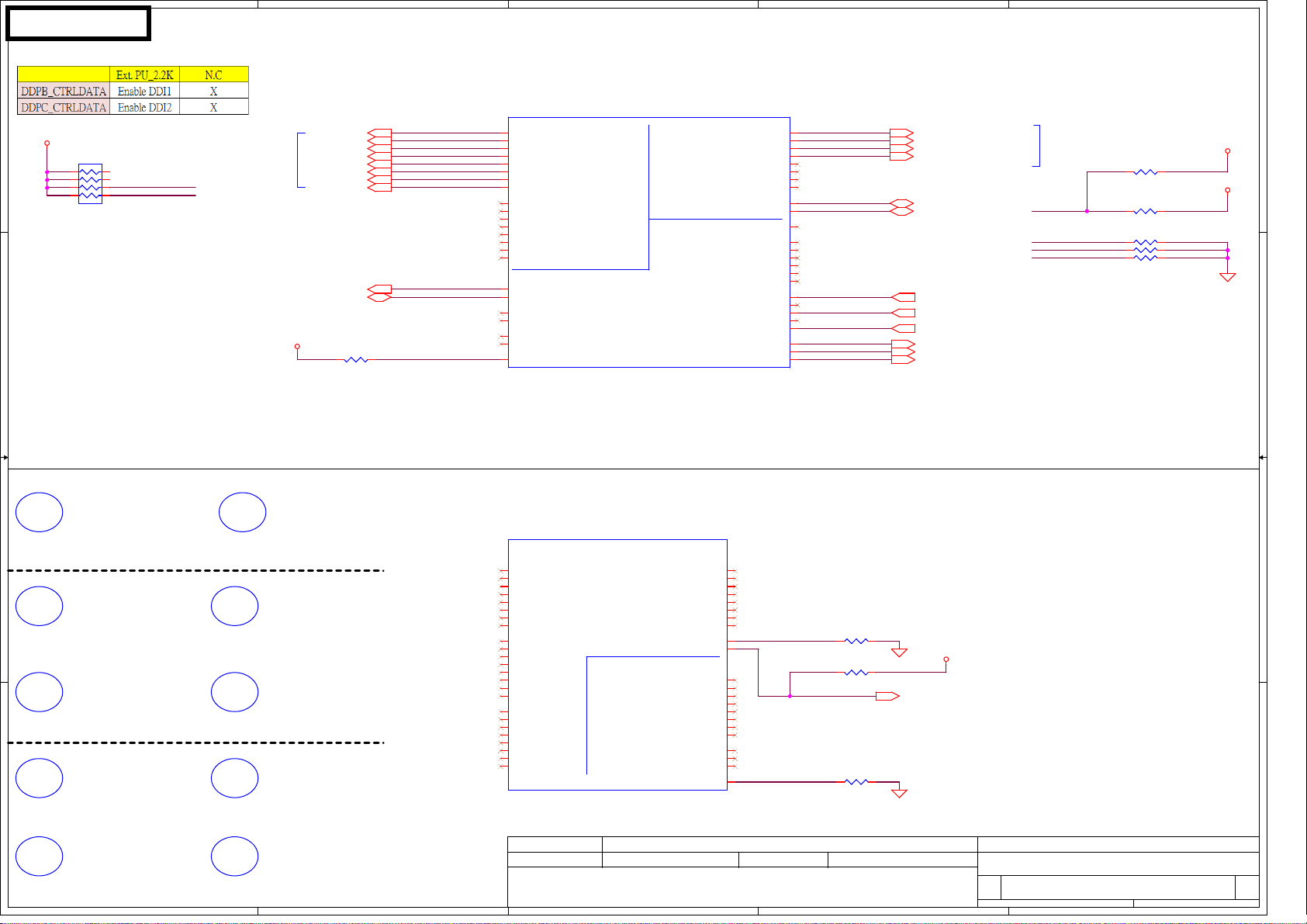

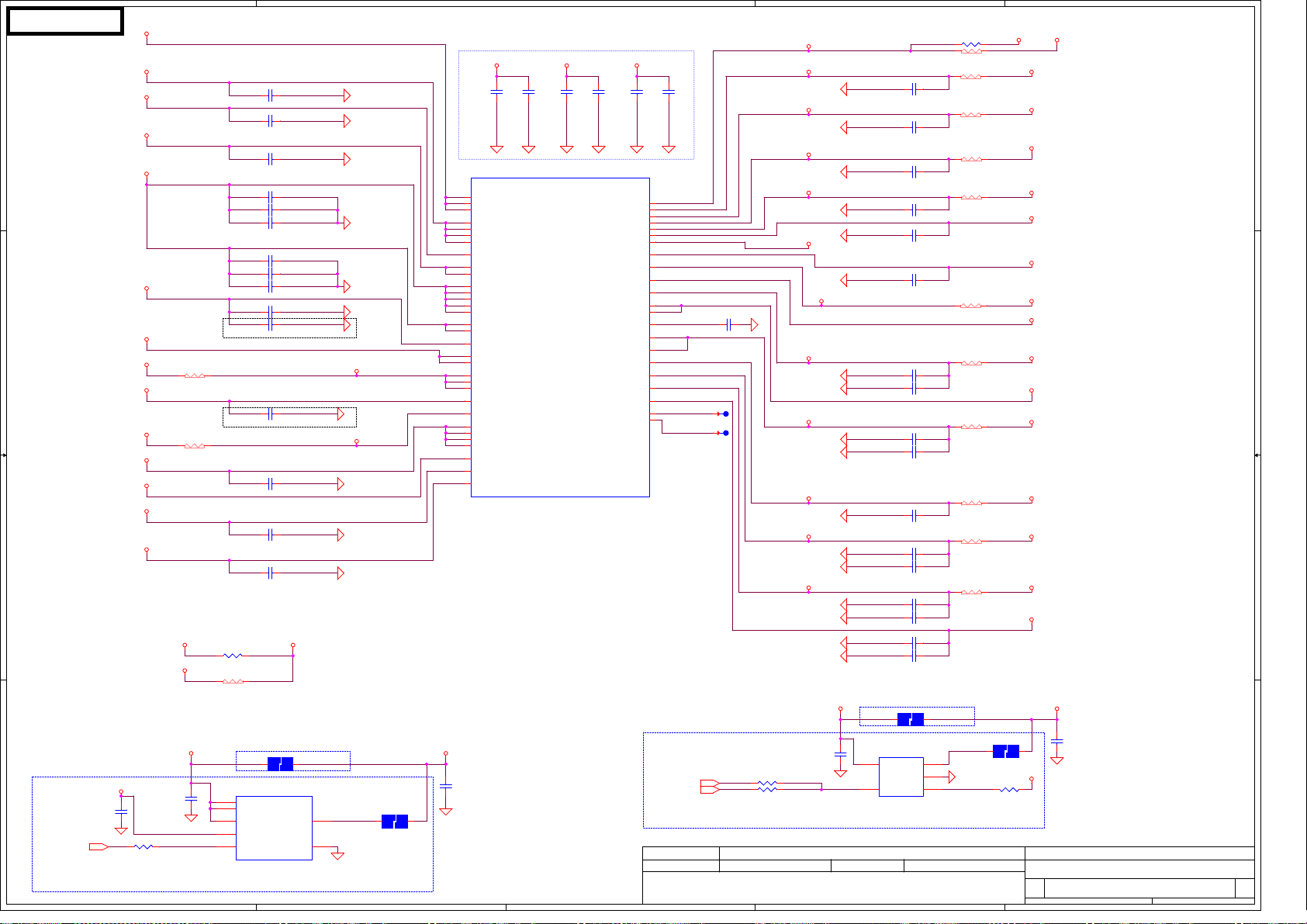

Skylake U_2+2 Block Diagram

1 1

VRAM 256M*16

DDR3L *2 / *4 pcs

VRAM 256M*16

DDR3L *2 / *4 pcs

eDP Conn.

HDMI Conn.

32bit

32bit

NV N16S-GM

PEG 3.0 _4 Lane

eDP

DDI

Skylake U

+

Skylake PCH-LP(MCP)

(SKL-U_2+2)

Memory Bus (DDR3L)

Dual Channel

1.35V DDR3L SO-DIMM

USB 3.0

USB2.0

DDR3L-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

8GB Max

(for each Channel)

USB 3.0 Conn. 1

USB 3.0 Conn. 2

2 2

PCI-E

x1x1

NGFF 2230

Ethernet

RTL8106EWiFi / BT

Dual Core

TDP : 15W

BGA 1356 balls

42 x 24 mm

USB3.0 Rediver

Digital Camera

(With Digital MIC)

NGFF 2230

WiFi/BT4.0

3D Camera

USB 2.0 Conn. 3

Touch Screen

Card Reader

SATA HDD Conn.

Port 0

SATA Rediver

SATA3.0

RTS5170

Digital Mic.

3 3

SPI ROM

SPI

16M Bytes

LPC Bus

Int.KBD

EC

MEC1404

PS/2

HD Audio

I2C

Touch Pad

Audio Codec

ALC3234

Headphone Jack /

Mic. Jack combo

Int. Speaker R / L

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U_2+2 Block Diagrams

SKL-U_2+2 Block Diagrams

SKL-U_2+2 Block Diagrams

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet

Date: Sheet

Date: Sheet

E

of

of

of

2 55Tuesday, July 28, 2015

2 55Tuesday, July 28, 2015

2 55Tuesday, July 28, 2015

0.2

0.2

0.2

Page 3

A

1 1

(Blanking)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

A

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet of

Date: Sheet of

Date: Sheet of

3 55Tuesday, July 28, 2015

3 55Tuesday, July 28, 2015

3 55Tuesday, July 28, 2015

0.2

0.2

0.2

Page 4

5

D D

C C

4

3

2

1

(Blanking)

B B

A A

Security Classification

Security Classification

Security Classification

2013/11/19 2015/12/31

2013/11/19 2015/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/11/19 2015/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Power MAP

Power MAP

Power MAP

4 55Tuesday, July 28, 2015

4 55Tuesday, July 28, 2015

4 55Tuesday, July 28, 2015

1

0.2

0.2

0.2

Page 5

5

D D

C C

4

3

2

1

(Blanking)

B B

A A

Security Classification

Security Classification

Security Classification

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/05/19 2015/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Power Sequence

Power Sequence

Power Sequence

5 55Tuesday, July 28, 2015

5 55Tuesday, July 28, 2015

5 55Tuesday, July 28, 2015

1

0.2

0.2

0.2

Page 6

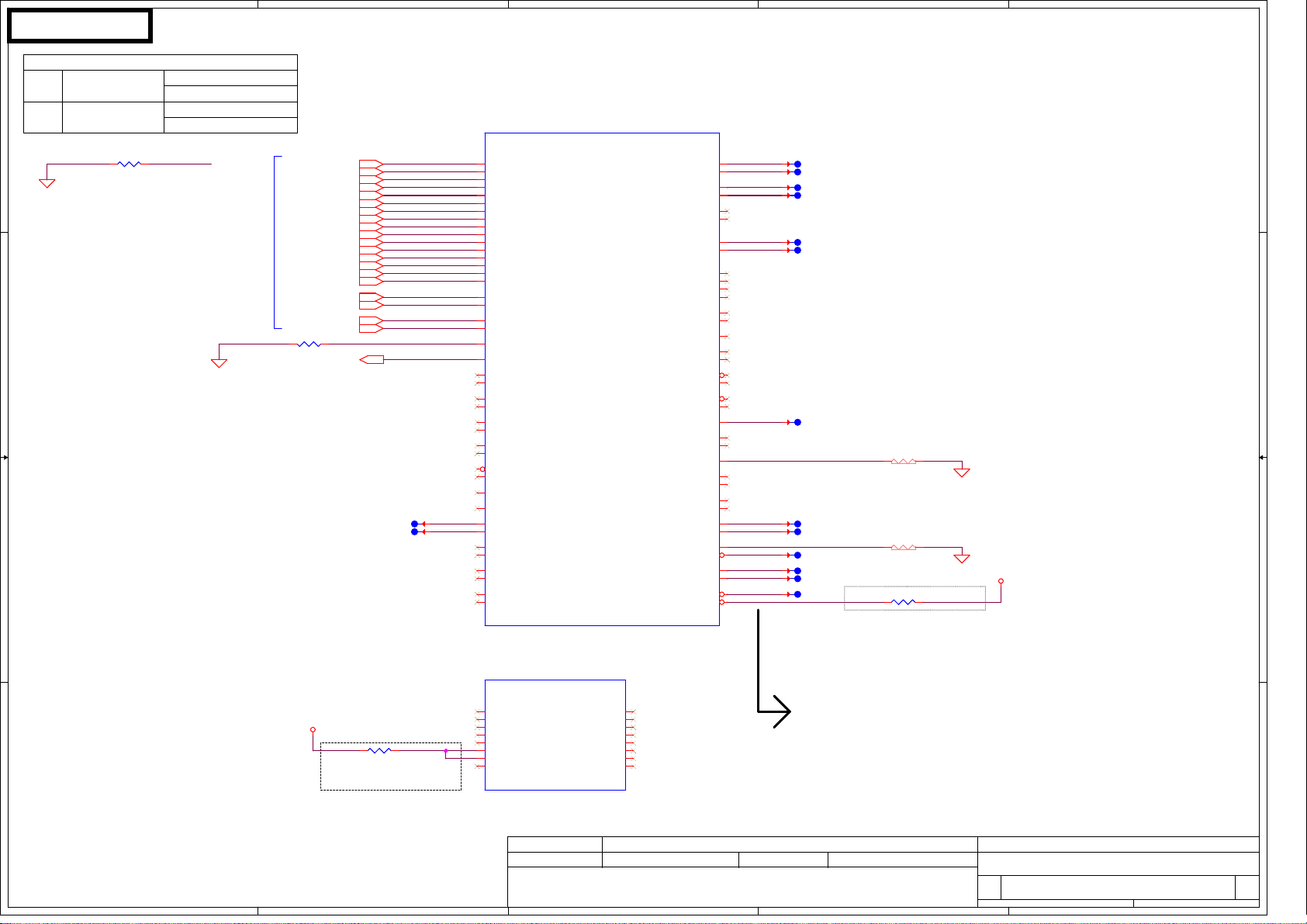

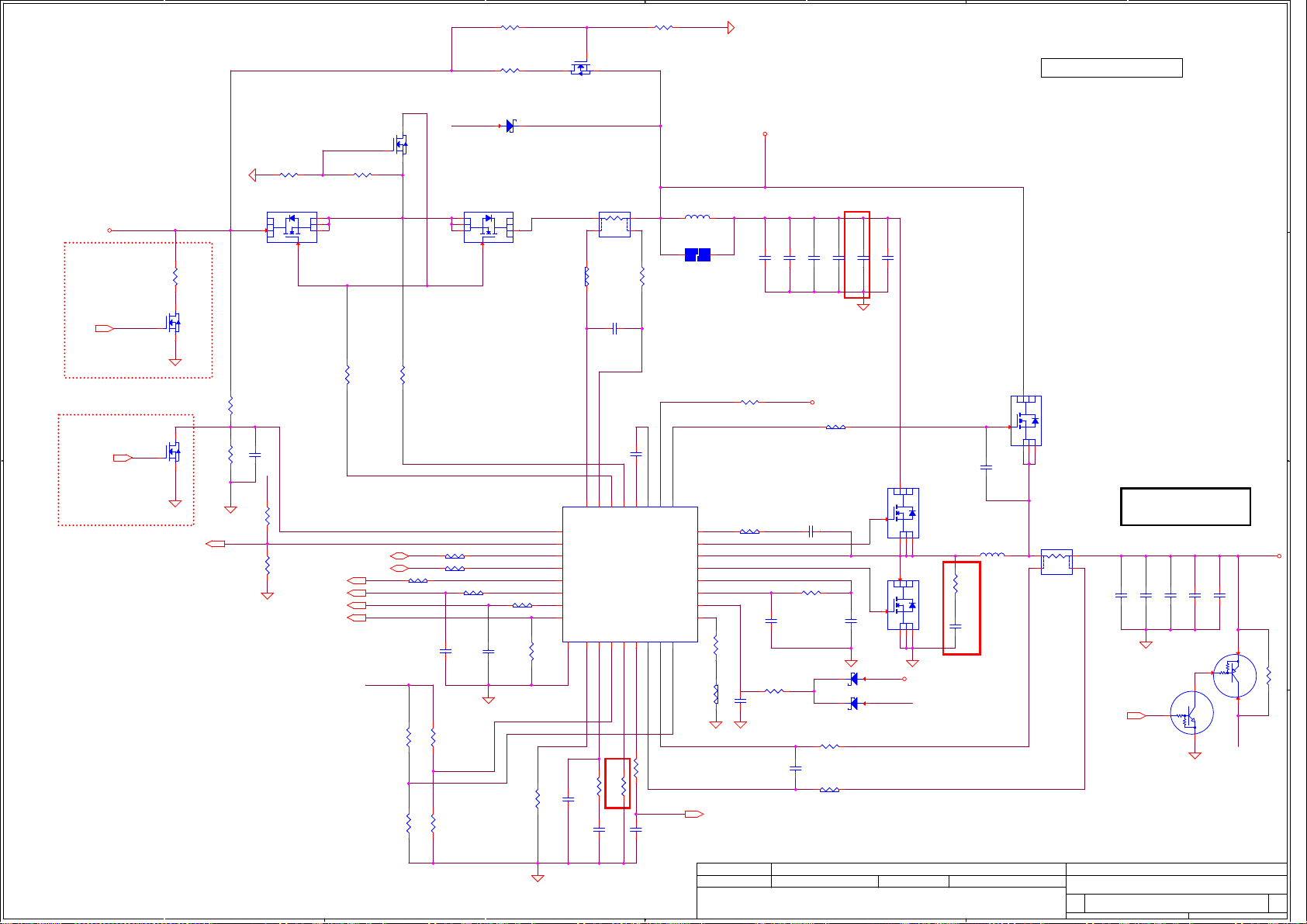

Main Func : CPU

A

B

C

D

E

UC1A

1 1

+3VS

RPC1

1 8

2 7

3 6

4 5

2 2

UC1

ES_2.3G@

PCH_HDMI_CLK

PCH_HDMI_DATA

2.2K_0804_8P4R_5%

S IC A31 FJ8066201924925 QHMF C0 2.3G

SA00008M40L

3 3

UC1

QS_i5@

S IC A31 FJ8066201930409 QJ8N D0 2.3G

SA000092O0L

UC1

QS_i7@

S IC A31 FJ8066201930408 QJ8L D0 2.5G

SA000092P0L

UC1

MP_i5@

4 4

S IC FJ8066201930409 SR2EY D1 2.3G A31!

SA000092O3L

UC1

SQS_2.1G@

S IC A31 FJ8066201930905 QJKT D1 2.1G

SA00009420L

A

<HDMI>

<HDMI DDC>

CAD note:

Trace width=5 mils,Spacing=25mil,Max length=600mils

( PDG_V1.2_Update)

UC1

ES_1.6G@

S IC A31 FJ8066201924932 QHMG C0 1.6G

SA00008M30L

UC1

SQS_i5@

S IC A31 FJ8066201930409 QJKP D1 2.3G

SA000092O1L

UC1

SQS_i7@

S IC A31 FJ8066201930408 QJKK D1 2.5G

SA000092P1L

UC1

MP_i7@

S IC FJ8066201930408 SR2EZ D1 2.5G A31!

SA000092P3L

UC1

MP_2.1G@

S IC FJ8066201930905 SR2EX D1 2.1G BGA 1356 A31 !

SA00009422L

HDMI_DATA2#<26>

HDMI_DATA2<26>

HDMI_DATA1#<26>

HDMI_DATA1<26>

HDMI_DATA0#<26>

HDMI_DATA0<26>

HDMI_CLK#<26>

HDMI_CLK<26>

PCH_HDMI_CLK<26>

PCH_HDMI_DATA<26>

+1.0VS_VCCIO

RC1 24.9_0402_1%

1 2

B

PCH_HDMI_CLK

PCH_HDMI_DATA

EDP_COMP

E55

F55

E58

F58

F53

G53

F56

G56

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

N11

N12

E52

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

N7

N8

@

DDI1_TXN[0]

DDI1_TXP[0]

DDI1_TXN[1]

DDI1_TXP[1]

DDI1_TXN[2]

DDI1_TXP[2]

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

GPP_E22

GPP_E23

EDP_RCOMP

SKL-U_BGA1356

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDI

DISPLAY SIDEBANDS

@

SKL-U

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

1 OF 20

SKL-U

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

9 OF 20

GPP_F12/EMMC_CMD

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

C

Rev_1.0

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

EMMC_RCOMP

Compal Secret Data

Compal Secret Data

Compal Secret Data

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

RSVD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C37

D37

C32

D32

C29

D29

B26

A26

E13

CSI2_COMP

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

EMMC_RCOMP

Deciphered Date

Deciphered Date

Deciphered Date

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

RC80 100_0402_1%

RC224 10K_0402_5%

RC89 200_0402_1%

HDMI_DET

SIO_EXT_SMI#

EDP_HPD

EDP_TX0_DN <25>

EDP_TX0_DP <25>

EDP_TX1_DN <25>

EDP_TX1_DP <25>

EDP_AUX_DN <25>

EDP_AUX_DP <25>

HDMI_DET <26>

SIO_EXT_SMI# <23>

EDP_HPD <25>

L_BKLT_EN_EC <23>

L_BKLT_CTRL <25>

EDP_VDD_EN <25>

12

12

12

D

+3VS

WLAN_RADIO_DIS# <28>

<eDP_FHD>

RC234 10K_0402_5%

SIO_EXT_SMI#

HDMI_DET

EDP_HPD

L_BKLT_EN_EC

From HDMI

From eDP

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

LA-C071P

LA-C071P

LA-C071P

RC222 10K_0402_5%@

RC312 100K_0402_5%@

RC220 100K_0402_5%

RC223 100K_0402_5%

E

+3V_PRIM

12

12

12

12

12

+3VS

6 55Tuesday, July 28, 2015

6 55Tuesday, July 28, 2015

6 55Tuesday, July 28, 2015

0.2

0.2

0.2

Page 7

5

4

3

2

1

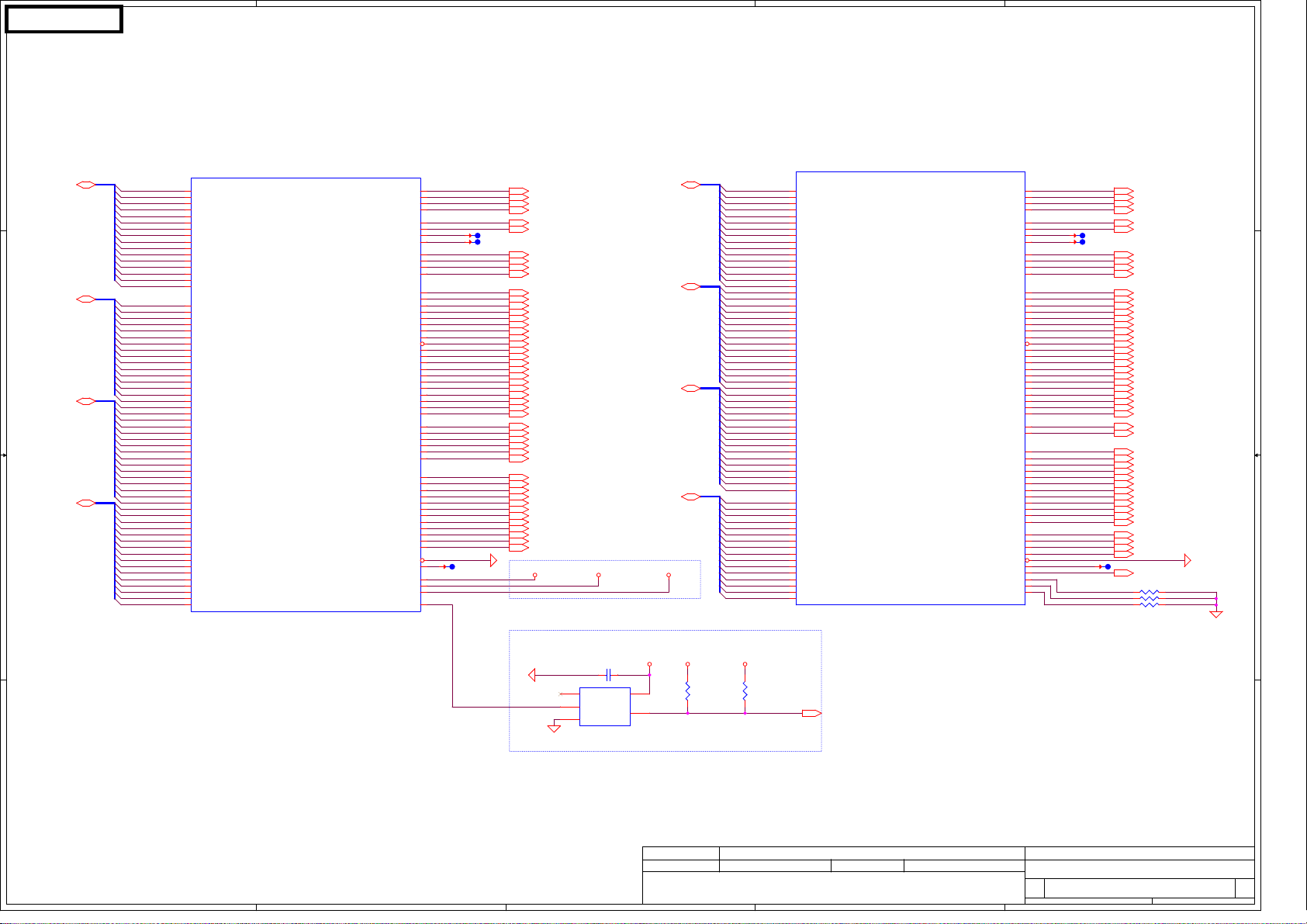

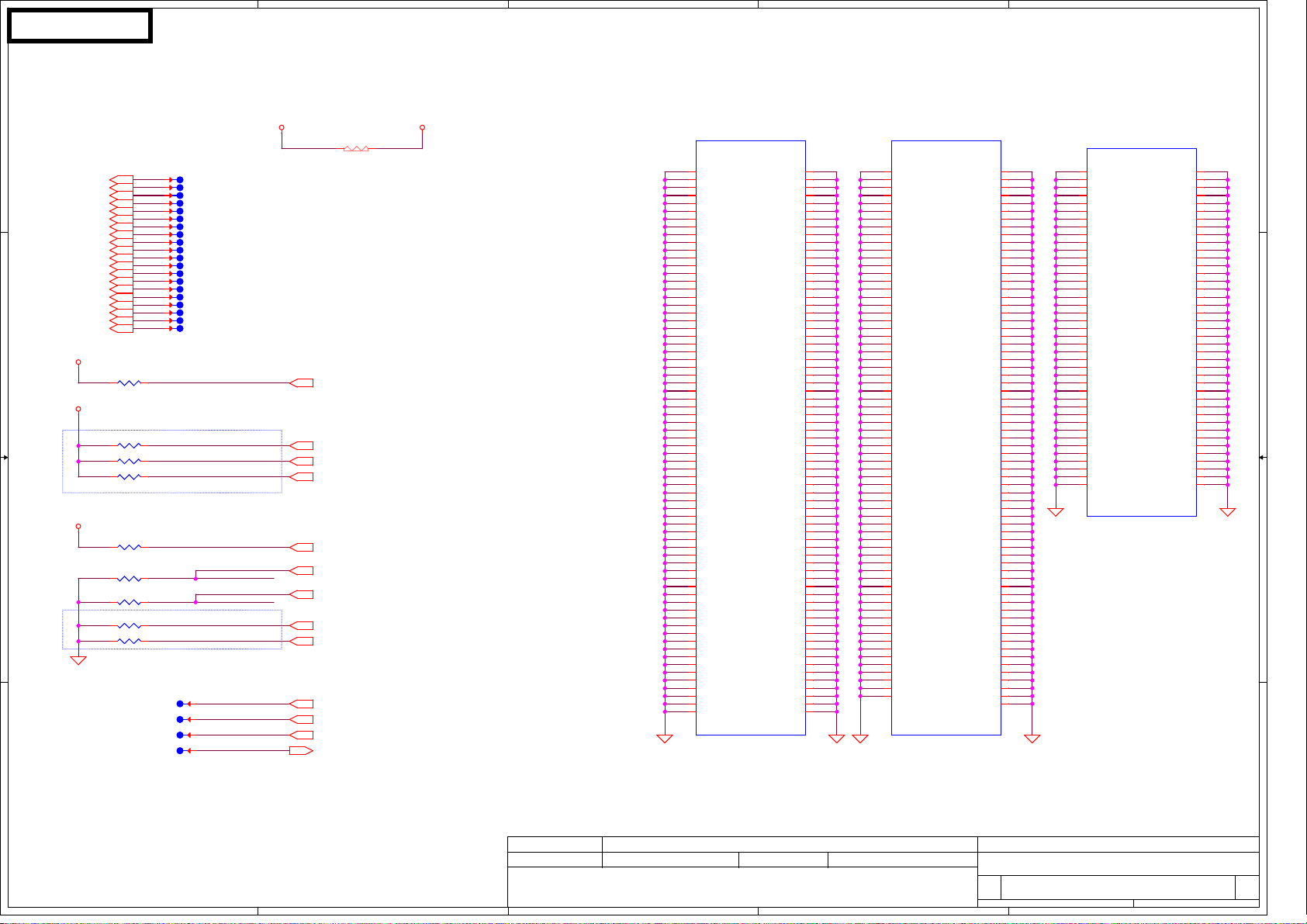

Main Func : CPU

Interleaved Memory

D D

DDR_A_D[0..15]

DDR_A_D[16..31]

C C

DDR_A_D[32..47]

DDR_A_D[48..63]

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR CH - A

2 OF 20

DDR3L / LPDDR3 / DDR4

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

Rev_1.0

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BS2

DDR_A_MA12

DDR_A_MA11

DDR_A_MA15

DDR_A_MA14

DDR_A_MA13

DDR_A_CAS#

DDR_A_WE#

DDR_A_RAS#

DDR_A_BS0

DDR_A_MA2

DDR_A_BS1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

T22TP@

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

DDR_A_CLK#1 <18>

DDR_A_CLK1 <18>

DDR_A_CKE0 <18>

DDR_A_CKE1 <18>

T14TP@

T15TP@

DDR_A_CS#0 <18>

DDR_A_CS#1 <18>

DDR_A_ODT0 <18>

DDR_A_ODT1 <18>

DDR_A_MA5 <18>

DDR_A_MA9 <18>

DDR_A_MA6 <18>

DDR_A_MA8 <18>

DDR_A_MA7 <18>

DDR_A_BS2 <18>

DDR_A_MA12 <18>

DDR_A_MA11 <18>

DDR_A_MA15 <18>

DDR_A_MA14 <18>

DDR_A_MA13 <18>

DDR_A_CAS# <18>

DDR_A_WE# <18>

DDR_A_RAS# <18>

DDR_A_BS0 <18>

DDR_A_MA2 <18>

DDR_A_BS1 <18>

DDR_A_MA10 <18>

DDR_A_MA1 <18>

DDR_A_MA0 <18>

DDR_A_MA3 <18>

DDR_A_MA4 <18>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

+0.675V_VREFCA +0.675V_A_VREFDQ +0.675V_B_VREFDQ

Trace width/Spacing >= 20mils

DDR_B_D[0..15]<19>

DDR_B_D[16..31]<19>

DDR_B_D[32..47]<19>

DDR_B_D[48..63]<19>

Buffer with Open Drain Output

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

Rev_1.0

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BS2

DDR_B_MA12

DDR_B_MA11

DDR_B_MA15

DDR_B_MA14

DDR_B_MA13

DDR_B_CAS#

DDR_B_WE#

DDR_B_RAS#

DDR_B_BS0

DDR_B_MA2

DDR_B_BS1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_PAR

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <19>

DDR_B_CLK#1 <19>

DDR_B_CLK0 <19>

DDR_B_CLK1 <19>

DDR_B_CKE0 <19>

DDR_B_CKE1 <19>

T17TP@

T18TP@

DDR_B_CS#0 <19>

DDR_B_CS#1 <19>

DDR_B_ODT0 <19>

DDR_B_ODT1 <19>

DDR_B_MA5 <19>

DDR_B_MA9 <19>

DDR_B_MA6 <19>

DDR_B_MA8 <19>

DDR_B_MA7 <19>

DDR_B_BS2 <19>

DDR_B_MA12 <19>

DDR_B_MA11 <19>

DDR_B_MA15 <19>

DDR_B_MA14 <19>

DDR_B_MA13 <19>

DDR_B_CAS# <19>

DDR_B_WE# <19>

DDR_B_RAS# <19>

DDR_B_BS0 <19>

DDR_B_MA2 <19>

DDR_B_BS1 <19>

DDR_B_MA10 <19>

DDR_B_MA1 <19>

DDR_B_MA0 <19>

DDR_B_MA3 <19>

DDR_B_MA4 <19>

DDR_B_DQS#0 <19>

DDR_B_DQS0 <19>

DDR_B_DQS#1 <19>

DDR_B_DQS1 <19>

DDR_B_DQS#2 <19>

DDR_B_DQS2 <19>

DDR_B_DQS#3 <19>

DDR_B_DQS3 <19>

DDR_B_DQS#4 <19>

DDR_B_DQS4 <19>

DDR_B_DQS#5 <19>

DDR_B_DQS5 <19>

DDR_B_DQS#6 <19>

DDR_B_DQS6 <19>

DDR_B_DQS#7 <19>

DDR_B_DQS7 <19>

T23TP@

DDR_DRAMRST# <18,19>

1 2

RC38 121_0402_1%

1 2

RC39 80.6_0402_1%

1 2

RC40 100_0402_1%

For VTT power control

+3VALW

12

5

4

RC123

100K_0402_5%

@

12

RC129

100K_0402_5%

0.675V_DDR_VTT_ON <37>

DDR_VTT_CNTL

12

CC570.1U_0201_10V6K

UC7

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

+1.35V_VDDQ +3VS

Y

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

SKL-U(2/12)DDRIII

SKL-U(2/12)DDRIII

SKL-U(2/12)DDRIII

LA-C071P

LA-C071P

LA-C071P

Tuesday, July 28, 2015

Tuesday, July 28, 2015

Tuesday, July 28, 2015

1

0.2

0.2

0.2

55

55

55

of

of

of

7

7

7

Page 8

5

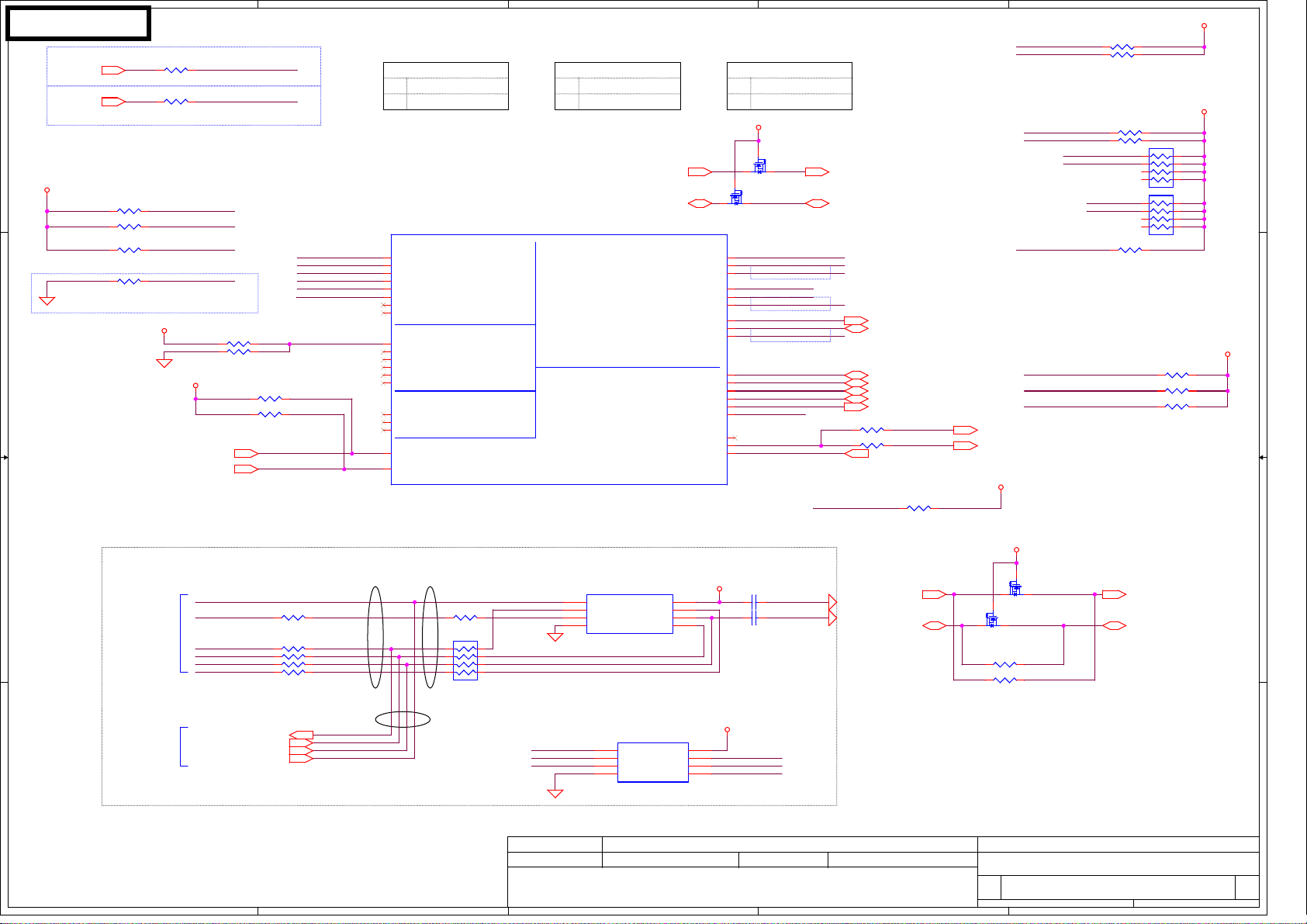

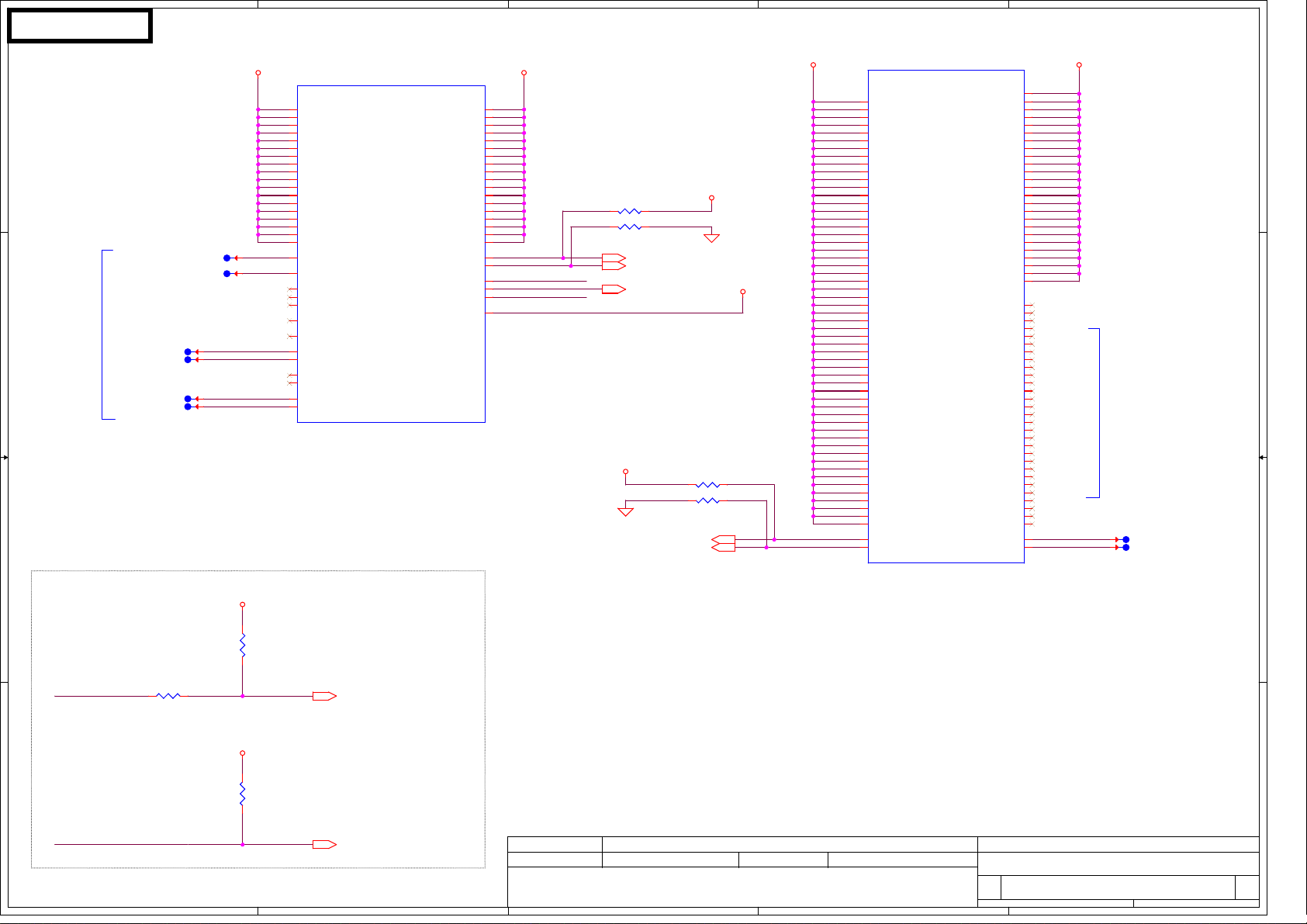

Main Func : CPU

From WW48 MOW for PCH SPI0_MOSI Pin

XDP_SPI_SI<14>

XDP_SPI_IO2<14>

D D

C C

RC21/44 place to within 1100 mil of SPIO_MOSI/SPI0_IO2 pin for CMC

+3V_SPI

*****ONLY*****

From WW36 MOW for SKL-U ES sample

RC44 1K_0402_5%CMC@

RC21 1K_0402_5%CMC@

12

12

12

12

12

12

PCH_SPI_D2

RC471K_0402_1%

PCH_SPI_D3

RC481K_0402_1% @

PCH_SPI_CS#0

RC534.7K_0402_5%

PCH_SPI_D3

RC511K_0402_1% ES@

+3VS

+1.8VS_3VS_PGPPA

*** Not Strap Pin ***

High --> 1 DIMM

Low --> 2 DIMM

PCH_SPI_D0

PCH_SPI_D2

12

12

Follow 543016_SKL_U_Y_PDG_0_9

SIO_RCIN#<23>

SERIRQ<23>

RC23110K_0402_5% @

RC23210K_0402_5%

12

12

SIO_RCIN#

SERIRQ

PCH_SPI_CLK

PCH_SPI_D1

PCH_SPI_D0

PCH_SPI_D2

PCH_SPI_D3

PCH_SPI_CS#0

ONE_DIMM#

RC22510K_0402_5%

RC12210K_0402_5%

4

SMB_ALERT#

TLS Confidentiality

Enable ( for iAMT )

1

0 Disable ( Default )

UC1E

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

SKL-U_BGA1356

@

SPI - FLASH

SML0_ALERT#

EC interface

ESPI mode

1

0 LPC mode ( Default )

SKL-U

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

LPC

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF 20

3

SML1_ALERT#

EXI BOOT STALL BYPASS

Enable

1

0 Disable ( Default )

+3VS

2

G

6 1

S

D

QC2B

5

DMN66D0LDW-7_SOT363-6

3 4

SMBDATA PCH_SMBDAT <18,19>

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

SGD

DMN66D0LDW-7_SOT363-6

Rev_1.0

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

QC2A

SMBCLK

SMBDATA

SMB_ALERT#

SML0_SMBCLK

SML0_SMBDATA

SML0_ALERT#

SML1CLK

SML1DATA

SML1_ALERT#

SUS_STAT#

PCI_CLK_LPC1

CLKRUN#

PCH_SMBCLK <18,19>SMBCLK

1 2

RC45 22_0402_5%EMI@

1 2

RC54 22_0402_5%EMI@

CLKRUN#

SML1CLK <8>

SML1DATA <8>

LPC_LAD0 <23>

LPC_LAD1 <23>

LPC_LAD2 <23>

LPC_LAD3 <23>

LPC_LFRAME# <23>

CLKRUN# <23>

RC107 8.2K_0402_5%

2

1 2

PCH_SMBCLK

PCH_SMBDAT

SML0_SMBCLK

SML0_SMBDATA

SUS_STAT#

SMB -> XDP, DDR

Strap Pin

Strap Pin

SML1 -> EC,DGPU

Strap Pin

SML0_ALERT#

SMB_ALERT#

SML1_ALERT#

CLK_PCI_LPC_MEC <23>

CLK_PCI_LPDEBUG <23>

+1.8VS_3VS_PGPPA

1

1 2

1 2

DSX@

SMBCLK

SMBDATA

1 2

12

12

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RC390 1K_0402_5%

RC391 1K_0402_5%

RC49 499_0402_1%

RC50 499_0402_1%

SML1CLK

SML1DATA

RC110 8.2K_0402_5%@

To EC

To Debug

+3VS

+3V_PRIM

RPC71K_0804_8P4R_5%

RPC181K_0804_8P4R_5%

12

12

12

+3V_PRIM

RC2024.7K_0402_5% @

RC22910K_0402_5% @

RC2214.7K_0402_5% @

+3V_PRIM

B B

To SPI ROM

From EC

(For share ROM)

A A

5

Single SPI ROM_CS0#

PCH_SPI_CS#0

PCH_SPI_D2

PCH_SPI_D1

PCH_SPI_D0

PCH_SPI_CLK

PCH_SPI_D3 PCH_SPI_D3_R

1 2

RC52 33_0402_5%

1 2

RC57 33_0402_5%

1 2

RC58 33_0402_5%

1 2

RC59 33_0402_5%

1 2

RC60 33_0402_5%

Layout need meet L1 = L2 = L3

EC_MISO_R<23>

EC_MOSI_R<23>

EC_SPICLK_R<23>

EC_SPICS#_R<23>

EC_MISO_R

EC_MOSI_R

EC_SPICLK_R

EC_SPICS#_R

L1 Routing

L2 Routing

RC61

1 2

15_0402_1%

RPC5

15_0804_8P4R_5%

L3 Routing

4

16M SPI ROM (Confirmed by BIOS RD)

UC2

1

/CS

PCH_SPI_D1_R

PCH_SPI_D2_R

18

27

PCH_SPI_D0_R

36

PCH_SPI_CLK_R

45

2

IO1

3

IO2

4

GND

W25Q128FVSIQ_SO8

VCC

CLK

+3V_SPI

8

7

IO3

6

5

IO0

1 2

CC8 0.1U_0201_10V6K

1 2

CC9 10P_0402_50V8J

@EMI@

SML1CLK<8>

SML1DATA<8>

<< JC1 colay UC2 >>

VCC

SCLK

+3V_SPI

8

6

PCH_SPI_CLK_R

5

PCH_SPI_D0_R

2

PCH_SPI_D1_R

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

ROM Socket

JC1

PCH_SPI_CS#0

PCH_SPI_D2_R

PCH_SPI_D3_R

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

CS#

3

WP#

7

HOLD#

4

SI/SIO0

SO/SIO1

GND

ACES_91960-0084N_MX25L3206EM2I

CONN@

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

3

5

34

SGD

QC3A

2

DMN66D0LDW-7_SOT363-6

G

DSX@

61

S

D

QC3B

DSX@

DMN66D0LDW-7_SOT363-6

1 2

NDSX@

RC397 0_0402_5%

1 2

NDSX@

RC399 0_0402_5%

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet of

Date: Sheet of

Date: Sheet of

GPU_THM_SMBCLK <23,30,48>

GPU_THM_SMBDAT <23,30,48>

8 55Tuesday, July 28, 2015

8 55Tuesday, July 28, 2015

8 55Tuesday, July 28, 2015

1

0.2

0.2

0.2

Page 9

5

Main Func : CPU

+3VS

1 2

RC118 4.7K_0402_5%@

NRB_BIT

D D

NO REBOOT

Reboot Disable

1

0 Reboot Enable (Default)

Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This function is useful

when running ITP/XDP.

GSPI1_MOSI (AN5)

BOOT BIOS STRAP (BBS)

LPC mode

1

SPI mode (Default)

0

+3VS

1 2

RC394 1K_0402_5%

1 2

RC395 1K_0402_5%

RC329 10K_0402_5%

RC322 10K_0402_5%

C C

RC62 49.9K_0402_1%

RC63 49.9K_0402_1%

RC65 49.9K_0402_1%

RC330 10K_0402_5%

+3V_PRIM

RC64 10K_0402_5%

RC68 49.9K_0402_1%@

12

12

12

12

12

12

12

12

NRB_BIT

3D Camera

I2C_SDA_TP

I2C_SCL_TP

DBC_EN

BLUETOOTH_EN

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

LPSS_UART2_CTS#

CAM_DETECT

SIO_EXT_WAKE#

UART_2_CTXD_DRXD

DBC_EN<25>

BLUETOOTH_EN<28>

Win7 Debug

SIO_EXT_WAKE#<23>

I2C_SDA_TP<29>

I2C_SCL_TP<29>

TO DGPU

SOC_GPIOC10 GPU_EVENT#

SOC_GPIOB16 GC6_FB_EN

1 2

RC204 0_0402_5%GC6@

1 2

RC195 0_0402_5%

GPU_EVENT# <48>

GC6_FB_EN <48,49>

SOC_GPIOB16

VRAM_ID1

NRB_BIT

DBC_EN

3D_CAM_EN_R

FW_UPDATE_R

BLUETOOTH_EN

SOC_GPIOC10

BOARD_ID2

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

SIO_EXT_WAKE#

LPSS_UART2_CTS#

4

UC1F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

@

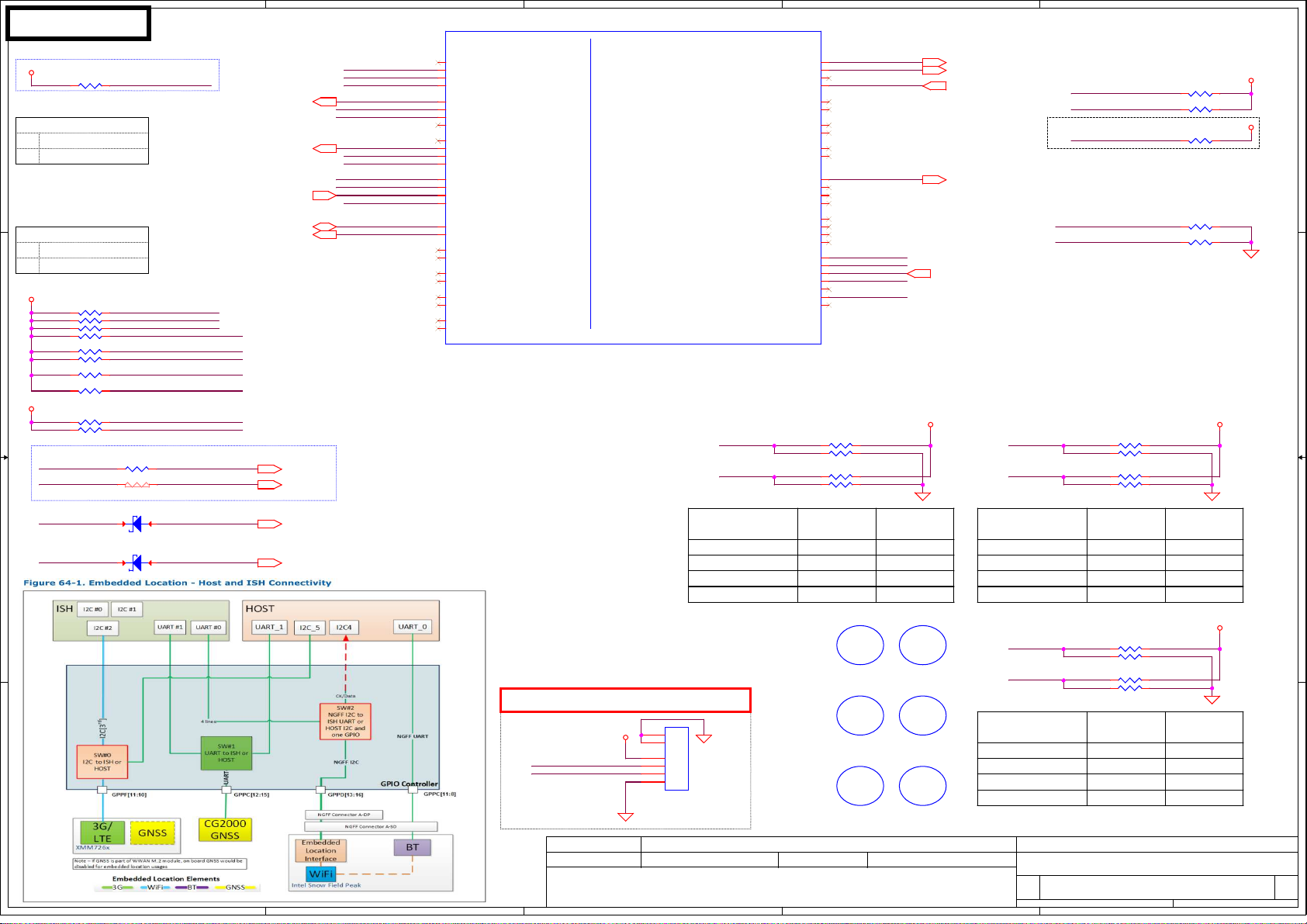

LPSS ISH

SKL-U

3

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Sx_EXIT_HOLDOFF# / GPP_A12 / BM_BUSY# / ISH_GP6

6 OF 20

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

PROJECT_ID2

PROJECT_ID1

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

RC318 10K_0402_5%@

1 2

RC315 10K_0402_5%

RC314 10K_0402_5%@

1 2

RC319 10K_0402_5%

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

CAM_DETECT

DGPU_HOLD_RST#

DGPU_PWR_EN

PROJECT_ID1

PROJECT_ID2

BOARD_ID3

VRAM_ID2

12

12

2

CAM_DETECT <33>

DGPU_HOLD_RST# <45>

RTC_DET# <20>

DGPU_PWR_EN <50>

KB_DET# <29>

Need " PANEL_SIZE_ID " ?

+3VS

BOARD_ID2

BOARD_ID3

RTC_DET#

KB_DET#

Reseve PU by NV

DGPU_PWR_EN

DGPU_HOLD_RST#

DGPU_PWR_EN

RC325 10K_0402_5%@

1 2

RC324 10K_0402_5%

RC323 10K_0402_5%@

1 2

RC326 10K_0402_5%

1

+3V_PRIM

1 2

1 2

1 2

1 2

1 2

12

12

RC23310K_0402_5%

RC32710K_0402_5%

+3VS

RC23010K_0402_5% DIS@

RC21410K_0402_5% DIS@

RC21110K_0402_5% @

+3VS

3D_CAM_EN_R

RB751S40T1G_SOD523-2

FW_UPDATE_R

B B

A A

RB751S40T1G_SOD523-2

21

DC4

21

DC5

3D_CAM_EN <23,33>

FW_UPDATE <23,33>

PROJECT ID

*

BAV00

Reserved

Reserved

Reserved

*** Pin defintion was defined by Customer ***

Win7 Debug solution

+5VALW

UART_2_CTXD_DRXD

UART_2_CRXD_DTXD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

JWDB1

6

GND

5

GND

4

4

3

3

2

2

1

1

CVILU_CI1804M1VRA-NH

CONN@

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

PROJECT_ID2

0 0

0

1

1 1

RC316

10K_0402_5%

SD028100280

RC316

10K_0402_5%

SD028100280

RC321

10K_0402_5%

SD028100280

Deciphered Date

Deciphered Date

Deciphered Date

PROJECT_ID1 BOARD_ID2

1

0

BOARD ID

*

BAV00

Reserved

Reserved

BOARD_ID3

0

1

Reserved

RC317

UMA@

2G@

4G@

UMA@

10K_0402_5%

SD028100280

RC320

2G@

10K_0402_5%

SD028100280

4G@

RC317

10K_0402_5%

SD028100280

2

VRAM_ID2

VRAM_ID1

VRAM ID

(PCBA VRAM Size Config.)

UMA

2G

4G

Reserved

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(6/12)GPIO

SKL-U(6/12)GPIO

SKL-U(6/12)GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet

Date: Sheet of

Date: Sheet of

1 2

RC321 10K_0402_5%@

1 2

RC316 10K_0402_5%@

1 2

RC320 10K_0402_5%@

1 2

RC317 10K_0402_5%@

VRAM_ID2

VRAM_ID1

0 0

0

1

1 1

1

00

1

0

11

+3VS

1

0

0.2

0.2

0.2

of

9 55Tuesday, July 28, 2015

9 55Tuesday, July 28, 2015

9 55Tuesday, July 28, 2015

Page 10

5

Main Func : CPU

PCIE_CRX_GTX_N1<45>

PCIE_CRX_GTX_P1<45>

PCIE_CTX_C_GRX_N1<45>

PCIE_CTX_C_GRX_P1<45>

PCIE_CRX_GTX_N2<45>

RC201

10K_0402_5%

PCIE_CTX_C_GRX_N2<45>

PCIE_CTX_C_GRX_P2<45>

PCIE_CRX_GTX_N3<45>

PCIE_CRX_GTX_P3<45>

PCIE_CTX_C_GRX_N3<45>

PCIE_CTX_C_GRX_P3<45>

PCIE_CRX_GTX_N4<45>

PCIE_CRX_GTX_P4<45>

PCIE_CTX_C_GRX_N4<45>

PCIE_CTX_C_GRX_P4<45>

PCIE_PRX_WLANTX_N5<28>

PCIE_PRX_WLANTX_P5<28>

PCIE_PTX_WLANRX_N5_C<28>

PCIE_PTX_WLANRX_P5_C<28>

PCIE_PRX_LANTX_N6<22>

PCIE_PRX_LANTX_P6<22>

PCIE_PTX_LANRX_N6_C<22>

PCIE_PTX_LANRX_P6_C<22>

SATA3_PRX_HDDTX_N0<27>

SATA3_PRX_HDDTX_P0<27>

SATA3_PTX_HDDRX_N0<27>

SATA3_PTX_HDDRX_P0<27>

+3VS

1 2

D D

DGPU

(x4 Lane)

NGFF WLAN+BT

LAN

For selected technology

please use 100nF for PCIE.

please use 10nF for SATA.

C C

HDD

Follow 545659_SKL_PCH_LP_EDS_Rev1_0

CC17 0.22U_0402_16V7KDIS@

CC21 0.22U_0402_16V7KDIS@

CC18 0.22U_0402_16V7KDIS@

CC19 0.22U_0402_16V7KDIS@

CC20 0.22U_0402_16V7KDIS@

CC22 0.22U_0402_16V7KDIS@

CC23 0.22U_0402_16V7KDIS@

CC24 0.22U_0402_16V7KDIS@

CC25 0.1U_0402_10V7K

CC26 0.1U_0402_10V7K

CC135 0.1U_0402_10V7K

CC136 0.1U_0402_10V7K

RC120 100_0402_1%

XDP_PRDY#<14>

XDP_PREQ#<14>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

4

UC1H

@

PCIE / USB3 / SATA

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P1

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P2

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P3

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_P4

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_P4

PCIE_PRX_WLANTX_N5

PCIE_PRX_WLANTX_P5

PCIE_PTX_WLANRX_N5

PCIE_PTX_WLANRX_P5

PCIE_PRX_LANTX_N6

PCIE_PRX_LANTX_P6

PCIE_PTX_LANRX_N6

PCIE_PTX_LANRX_P6

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#

XDP_PREQ#

SOC_GPIOA7

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

3

SKL-U

8 OF 20

SSIC / USB3

USB3_2_RXN / SSIC_RXN

USB3_2_RXP / SSIC_RXP

USB3_2_TXN / SSIC_TXN

USB3_2_TXP / SSIC_TXP

USB2

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

Rev_1.0

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_3_RXN

USB3_3_RXP

USB3_3_TXN

USB3_3_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

2

USB20_N1

USB20_P1

USB20_N2

USB20_P2

USB20_N4

USB20_P4

USB20_N5

USB20_P5

USB20_N6

USB20_P6

USB20_N7

USB20_P7

USB20_N8

USB20_P8

USB2_COMP

USB2_ID

USB2_VBUSSENSE

USB_OC#0_1

USB_OC#2_3

USB_OC#4_5

USB_OC#6_7

DEVSLP0

SIO_EXT_SCI#

GC6_THM_DIS#

SATA_LED#

USB3_CRX_DTX_N1 <24>

USB3_CRX_DTX_P1 <24>

USB3_CTX_DRX_N1 <24>

USB3_CTX_DRX_P1 <24>

USB3_CRX_DTX_N2 <24>

USB3_CRX_DTX_P2 <24>

USB3_CTX_DRX_N2 <24>

USB3_CTX_DRX_P2 <24>PCIE_CRX_GTX_P2<45>

USB3_CRX_DTX_N3 <33>

USB3_CRX_DTX_P3 <33>

USB3_CTX_DRX_N3 <33>

USB3_CTX_DRX_P3 <33>

USB20_N1 <24>

USB20_P1 <24>

USB20_N2 <24>

USB20_P2 <24>

USB20_N4 <31>

USB20_P4 <31>

USB20_N5 <25>

USB20_P5 <25>

USB20_N6 <31>

USB20_P6 <31>

USB20_N7 <25>

USB20_P7 <25>

USB20_N8 <28>

USB20_P8 <28>

Intel NOW update design :

Unused USBID, VBUSSEBSE need PD_1K ohm

1 2

RC119 113_0402_1%

1 2

RC10 1K_0402_5%

1 2

RC16 1K_0402_5%

USB_OC#0_1 <24>

USB_OC#2_3 <31>

DEVSLP0 <27>

SIO_EXT_SCI# <23>

GC6_THM_DIS# <23>

1 2

RC20610K_0402_5% @

1 2

RC20010K_0402_5%

1 2

RC19910K_0402_5%

SATA_LED# <23,31>

USB3.0 MB_PORT1

USB3.0 MB_PORT2

3D CAMERA

USB2.0 MB_PORT1

USB2.0 MB_PORT2

NC

USB2.0 IO_PORT3

USB2.0 Camera

Card Reader

TOUCH SCREEN

NGFF WLAN+BT

USB_OC#2_3

USB_OC#6_7

USB_OC#0_1

USB_OC#4_5

+3VS

10K_0804_8P4R_5%

1

RPC14

1 8

2 7

3 6

4 5

+3V_PRIM

B B

Follow 545659_SKL_PCH_LP_EDS_Rev1_0

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-C071P

LA-C071P

LA-C071P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

10 55Tuesday, July 28, 2015

10 55Tuesday, July 28, 2015

10 55Tuesday, July 28, 2015

0.2

0.2

0.2

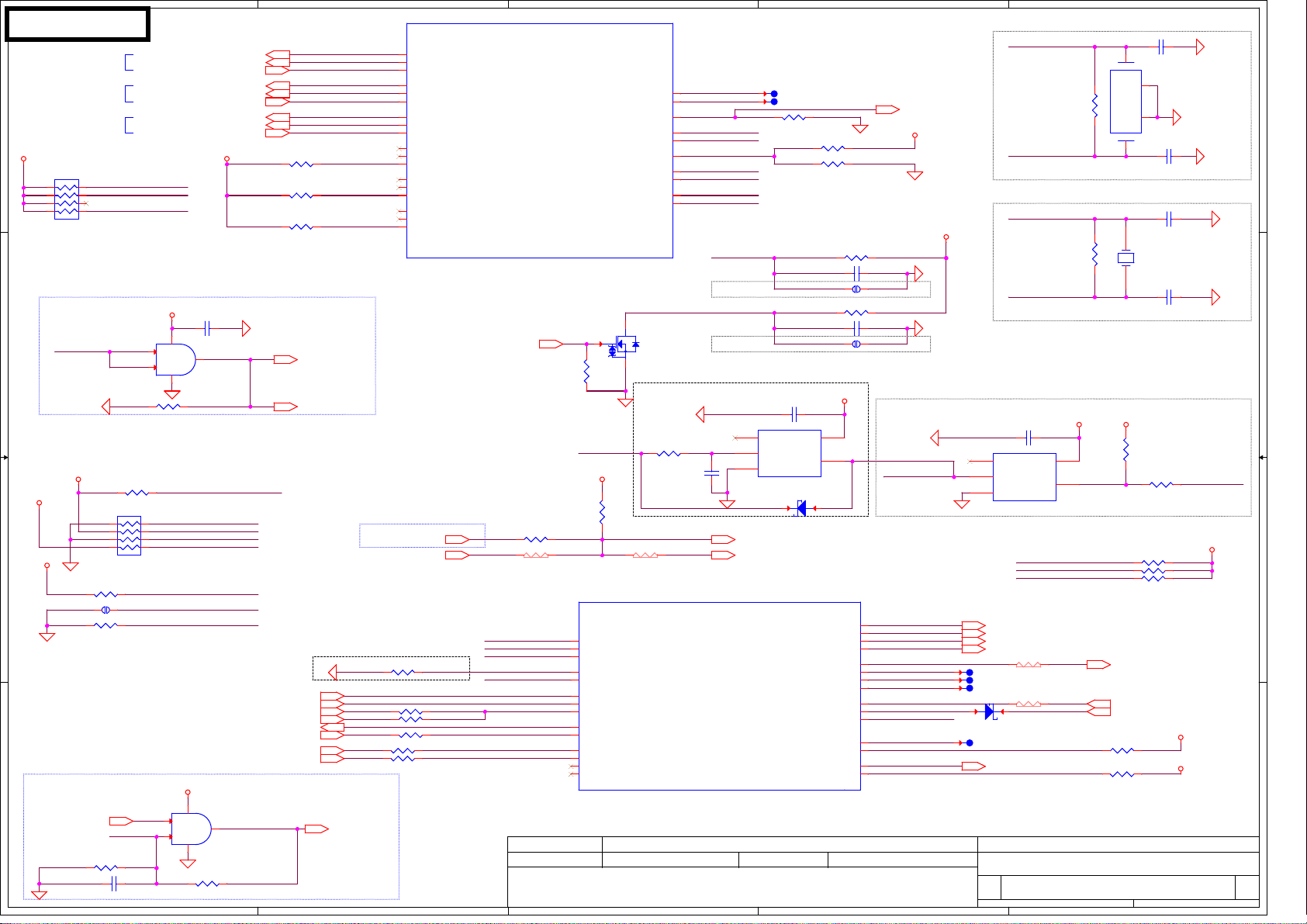

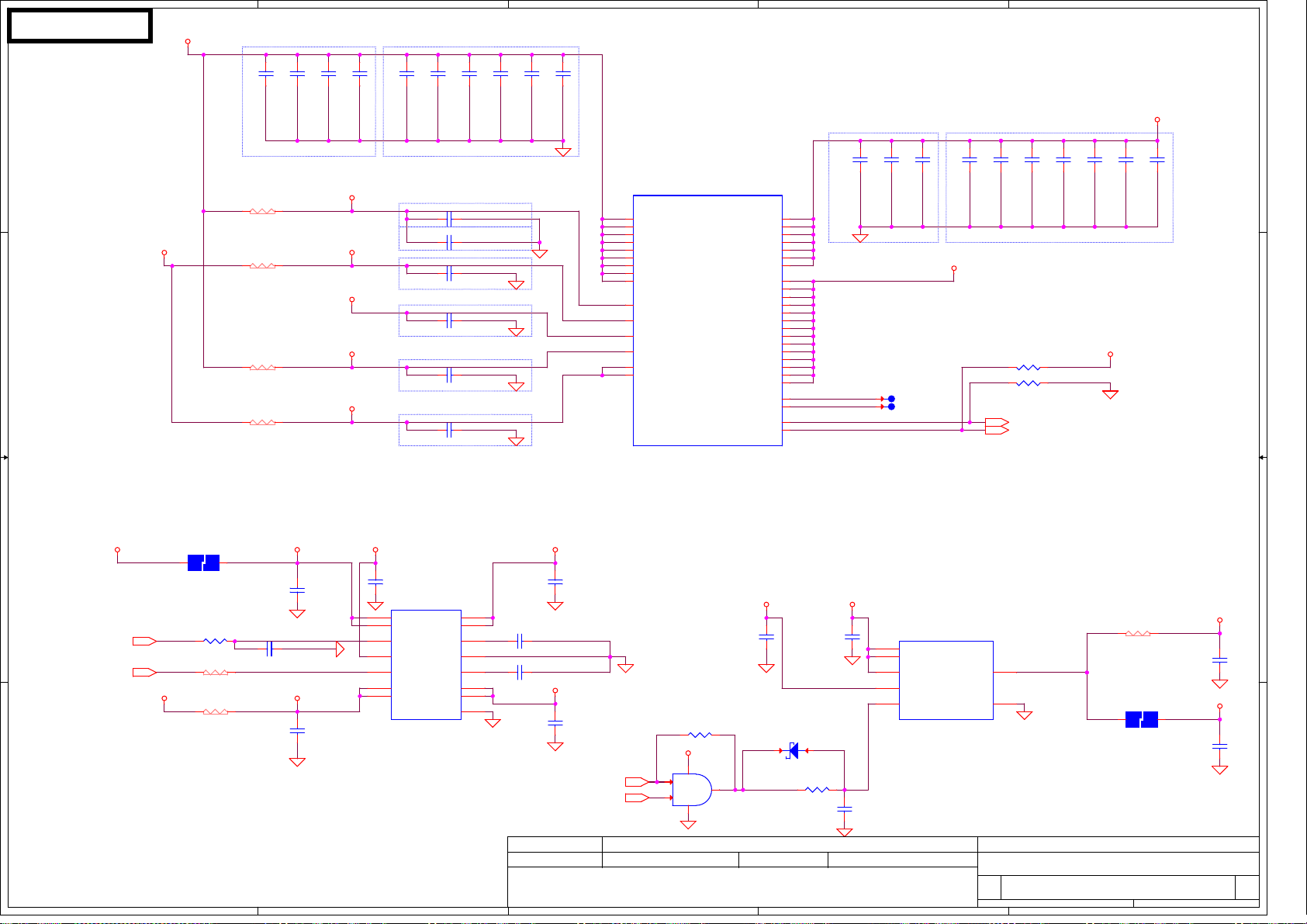

Page 11

5

Main Func : CPU

DGPU

NGFF WALN+BT

D D

+3VS +3VS

RPC10

10K_0804_8P4R_5%

LAN

18

CLK_PCIE_WLAN_REQ#

27

CLK_PCIE_LAN_REQ#

36

45

PEG_CLKREQ#

CLK_PEG_VGA#<45>

CLK_PEG_VGA<45>

PEG_CLKREQ#<45>

CLK_PCIE_WLAN_N1<28>

CLK_PCIE_WLAN_P1<28>

CLK_PCIE_WLAN_REQ#<28>

CLK_PCIE_LAN_N2<22>

CLK_PCIE_LAN_P2<22>

CLK_PCIE_LAN_REQ#<22>

RC127 10K_0402_5%@

RC126 10K_0402_5%@

RC125 10K_0402_5%@

From 545659_SKL_PCH_U_Y_EDS_R0_7

PCH PLTRST Buffer

C C

B B

A A

PCH_PLTRST#

+3VALW_DSW

+3VS

+3V_PRIM

RC104 1K_0402_5%@

1 2

RC108 10K_0402_5%@

CLRP3 SHORT PADS

RC101 100K_0402_5%@

REMRST Circuit

PCH_RSMRST#<23>

1 2

1 2

10K_0804_8P4R_5%

12

POK

+3VS

CC14

1 2

5

UC3

1

2

1 2

RC99 100K_0402_5%

RPC11

18

27

36

45

12

RC951M_0402_5%

12

CC1421U_0402_6.3V6K

5

0.1U_0201_10V6K

P

B

4

Y

A

G

TC7SH08FUF_SSOP5

3

PCH_PCIE_WAKE#

From 543016_SKL_PDG_UY_v1.0

RESET_OUT#

LAN_WAKE#

PCH_RSMRST#_Q

SYS_RESET#

ME_SUS_PWR_ACK

SYS_RESET#

PCH_DPWROK

+3VALW

5

UC11

1

P

B

4

PCH_RSMRST#_Q

Y

2

A

G

TC7SH08FUF_SSOP5

3

RC55 0_0402_5%@

12

PCH_RSMRST#_Q<11,14>

ME_SUS_PWR_ACK<23>

CLK_PEG_VGA#

CLK_PEG_VGA

PEG_CLKREQ#

CLK_PCIE_WLAN_N1

CLK_PCIE_WLAN_P1

CLK_PCIE_WLAN_REQ#

CLK_PCIE_LAN_N2

CLK_PCIE_LAN_P2

CLK_PCIE_LAN_REQ#

1 2

1 2

1 2

PLT_RST# <22,23,25,28,45>

PCH_PLTRST#_EC <22,23,25,28,45>

Only For Power Sequence Debug

SYS_PWROK<23>

RESET_OUT#<23>

POK<36,38,39>

SUSACK#<23>

PCIE_WAKE#<22,23,28>

EC_WAKE#<23>

PCH_RSMRST#_Q <11,14>

4

UC1J

@

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

Unused for PWR sequence.

1VS_VCCIO_PWRGD

1.35V_VTT_PWRGD<37>

1 2

RC102 1K_0402_5%@

1 2

4

12

12

12

12

RC112 0_0402_5%DSX@

RC396 0_0402_5%NDSX@

RC398 0_0402_5%DSX@

RC66 0_0402_5%

RC56 0_0402_5%@

SKL-U

CLOCK SIGNALS

10 OF 20

3

Rev_1.0

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

CLK_CPU_ITP#

CLK_CPU_ITP

SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

PCH_RTCX1

PCH_RTCX2

SRTCRST#

PCH_RTCRST#

SRTCRST#

T89TP@

T90TP@

1 2

RC105 1K_0402_5%@

1 2

RC96 2.7K_0402_1%

1 2

RC124 60.4_0402_1%@

Follow 546765_2014WW48_Skylake_MOW_Rev_1_0

Stuff 2.7k ohm(RC96) PH for Skylake U

Stuff 60.4 ohm(RC124) PD for Cannonlake U

CLR ME

13

D

RTCRST_ON<23>

10K_0402_5%

1 2

@

RC389 0_0402_5%

1 2

RC392 0_0402_5%

PCH_PLTRST#

SYS_RESET#

PCH_RSMRST#_Q

H_CPUPWRGD

VCCST_PWRGD

RESET_OUT#

PCH_DPWROK

ME_SUS_PWR_ACK

SUSACK#_R

PCH_PCIE_WAKE#

LAN_WAKE#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

12

RC121

SIO_SLP_S3#

+3VS

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

QC1

G

2N7002K_SOT23-3

S

2.2U_0402_6.3V6M

RC388

1K_0402_5%

1 2

ALL_SYS_PWRGD

1 2

RC345 0_0402_5%

@

SYSTEM POWER MANAGEMENT

2014/05/19 2015/12/31

2014/05/19 2015/12/31

2014/05/19 2015/12/31

3

1 2

RC130

10K_0402_5%

PCH_RTCRST#

CLR CMOS

For S3 timing issue

CC93

74AUP1G07GW_TSSOP5

1 2

ALL_SYS_PWRGD <23>

IMVP_VR_ON <40,41>

SKL-U

11 OF 20

Compal Secret Data

Compal Secret Data

Compal Secret Data

12

CC920.1U_0201_10V6K

UC13

NC1VCC

2

A

3

GND

DC6

GPP_B11/EXT_PWR_GATE#

Deciphered Date

Deciphered Date

Deciphered Date

Y

RB751S40T1G_SOD523-2

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

+3VALW

5

4

21

@

SLP_SUS#

SLP_LAN#

2

SUSCLK <28>

+1.0V_CLK5

+3VL_RTC

12

RC9120K_0402_5%

12

CC101U_0402_6.3V6K

12

CLRP1SHORT PADS

12

RC9320K_0402_5%

12

CC111U_0402_6.3V6K

12

CLRP2SHORT PADS

Buffer with Open Drain Output For VTT power control

ALL_SYS_PWRGD

Rev_1.0

AT11

SIO_SLP_S0#

AP15

SIO_SLP_S3#

BA16

SIO_SLP_S4#

AY16

SIO_SLP_S5#

AN15

SIO_SLP_SUS#_R

AW15

SIO_SLP_LAN#

BB17

SIO_SLP_WLAN#

AN16

SIO_SLP_A#

BA15

SIO_PWRBTN#_R

AY15

AC_PRESENT

AU13

PCH_BATLOW#

AU11

PME#

AP16

INTRUDER#

AM10

MPHYP_PWR_EN

AM11

VRALERT#

2

1

Closed to CPU

XTAL24_IN

RC92

1M_0402_5%

XTAL@

1 2

XTAL24_OUT

Closed to CPU

PCH_RTCX2

RC98

10M_0402_5%

XTAL@

1 2

PCH_RTCX1

+1.0V_VCCST

+3VALW

12

CC830.1U_0201_10V6K

1

2

3

74AUP1G07GW_TSSOP5

SIO_SLP_S0# <16>

SIO_SLP_S3# <16,23,32,34,41>

SIO_SLP_S4# <16,23,37>

SIO_SLP_S5# <35>

TP@

2 1

DC2

RB751S40T1G_SOD523-2

TP@

MPHYP_PWR_EN <17>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

UC12

VCC

Y

SIO_PWRBTN#

AC_PRESENT

PCH_BATLOW#

RC1280_0402_5%

RC1090_0402_5%

5

4

NC

A

GND

1 2

T87

T88TP@

T93TP@

1 2

T91

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

LA-C071P

LA-C071P

LA-C071P

XTAL@

CC1315P_0402_50V8J

1

1

2

YC1

GND

GND

3

3

YC2

32.768KHZ_12.5PF_9H03280012

1 2

12

RC113

1K_0402_5%

1 2

RC116 60.4_0402_1%

1 2

SIO_SLP_SUS# <17,23,38,39>

SIO_PWRBTN# <23>

ACAV_IN <23,35>

12

12

RC11510K_0402_5%

1

XTAL@

24MHZ_12PF_7V24000020

4

CC1218P_0402_50V8J

XTAL@

XTAL@

1 2

CC165.6P_0402_50V8J

XTAL@

1 2

CC155.6P_0402_50V8J

XTAL@

VCCST_PWRGD

+3VALW_DSW

RC111100K_0402_5% @

12

RC10610K_0402_5%

12

RC1038.2K_0402_5%

+3VL_RTC

RC941M_0402_5%

+3VALW

11 55Tuesday, July 28, 2015

11 55Tuesday, July 28, 2015

11 55Tuesday, July 28, 2015

0.2

0.2

0.2

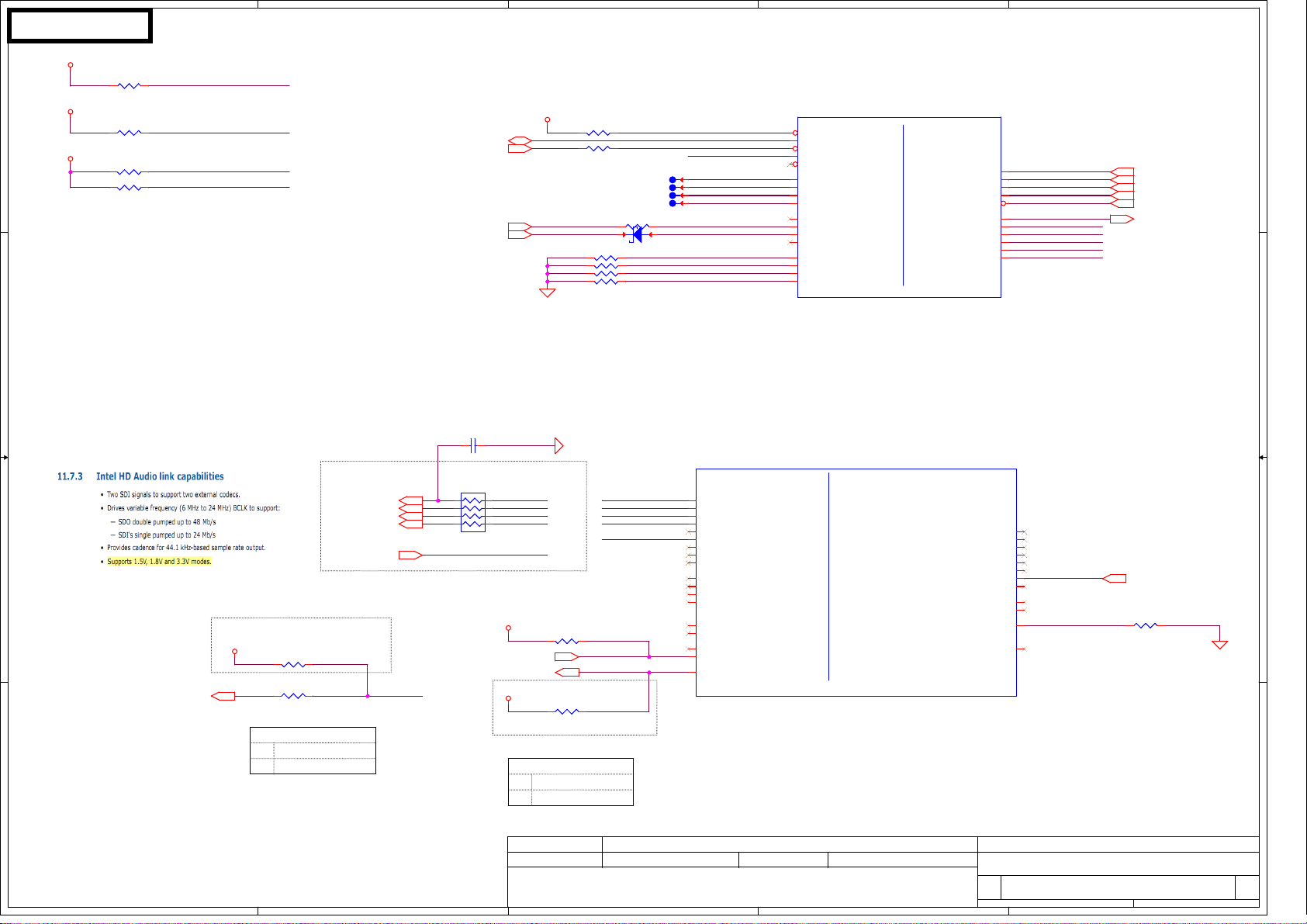

Page 12

5

4

3

2

1

Main Func : CPU

+1.0V_VCCST

1 2

RC2 1K_0402_5%

+1.0VS_VCCSTG

D D

+3VS

C C

1 2

RC3 1K_0402_5%

1 2

RC215 10K_0402_5%

1 2

RC216 10K_0402_5%

#545659 SKL_PCH_EDS_R0.7 P.84

B B

ME_FWP_EC<23>