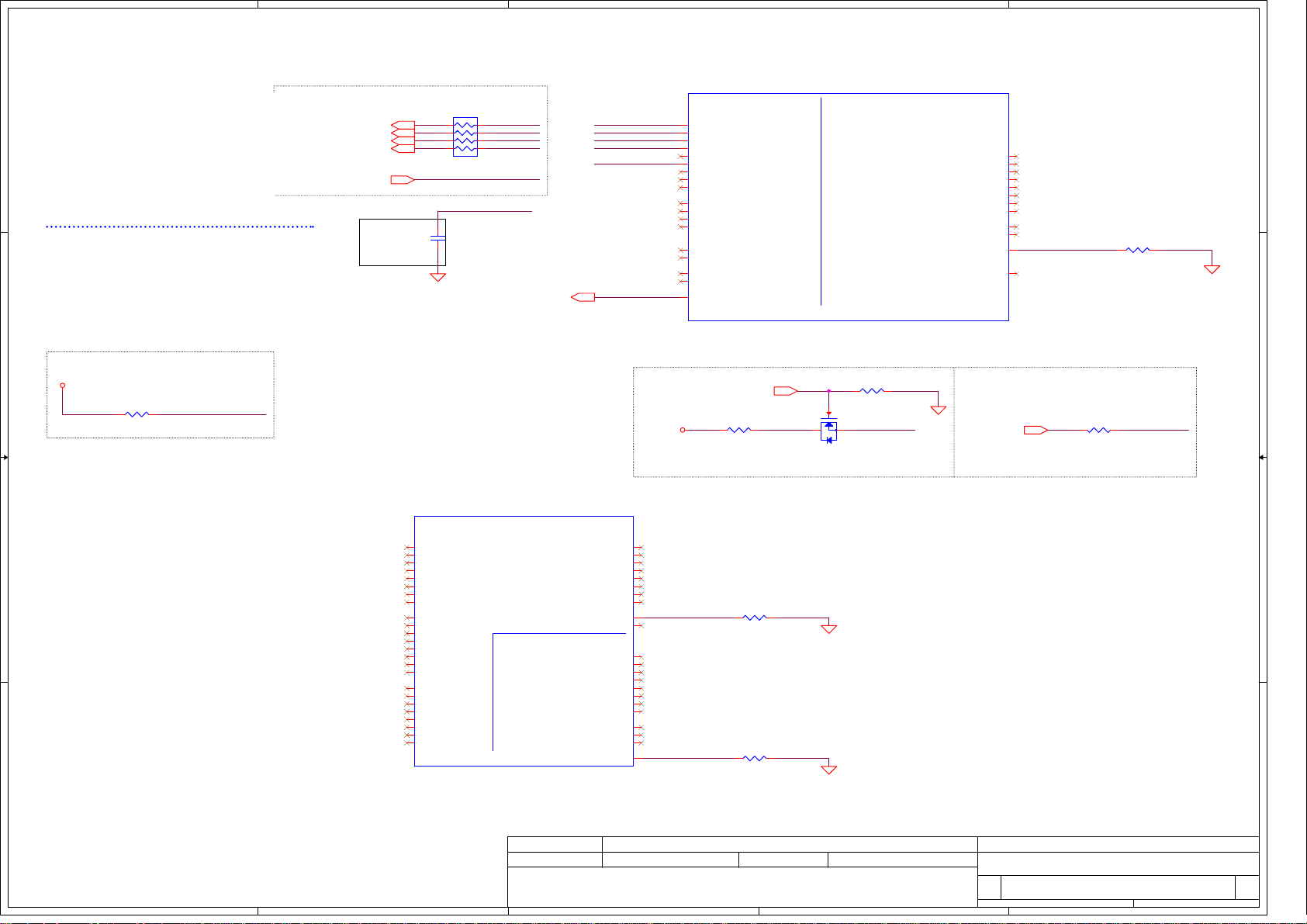

Page 1

A

B

C

D

E

MODEL NAME : AAP01

PROJECT CODE : ANRAAP0100

PCB NO :

DAA000AK000 LA-C901P M/B

1 1

DA400237000 LS-C901P SSD/B

DA40023X000 LS-C902P SSD/B (w/o redriver)

DA40023Y000 LS-C904P LOGO/B

ZZZ

PCB@

PCB 1FU LA-C901P REV0 M/B MLK 3

DAA000AK000

ZZZ

PCBR1@

2 2

PCB 1FU LA-C901P REV1 M/B MLK 3

DAA000AK010

ZZZ

PCBR3@

PCB 1FU LA-C901P REV1 MB MLK TRIP 3 A31!

DAA000AK011

ZZZ

DAZR1@

Echo MLK 13" SKL-U

Skylake U-type (1 chip_DSC)

REV : 1.0 (A00)

2015.07.14

@ : Nopop Component

PCB AAP01 LA-C901P LS-A302P/A303P/C904P 02

DAZ1FU00100

ZZZ

DAZR3@

EMI@,ESD@ : EMI/ESD/RF part

CONN@ : Connector Component

PCB AAP01 LA-C901P LS-A302P/A303P/C904P 02 TRIPOD A31 !

DAZ1FU00101

3 3

ROYALTY HDMI W/LOGOHDMI@

Part Number Description

HDMI W/Logo:RO0000002HM

RO0000002HM

Layout Dell logo

COPYRIGHT 2015

ALL RIGHT RESERVED

4 4

REV: X00

PWB: XXXXX

DATE: 1450-06

CMC@ : Total debug Component

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover page

Cover page

Cover page

LA-C901P

LA-C901P

LA-C901P

E

1 63Tuesday, August 04, 2015

1 63Tuesday, August 04, 2015

1 63Tuesday, August 04, 2015

1.0

1.0

1.0

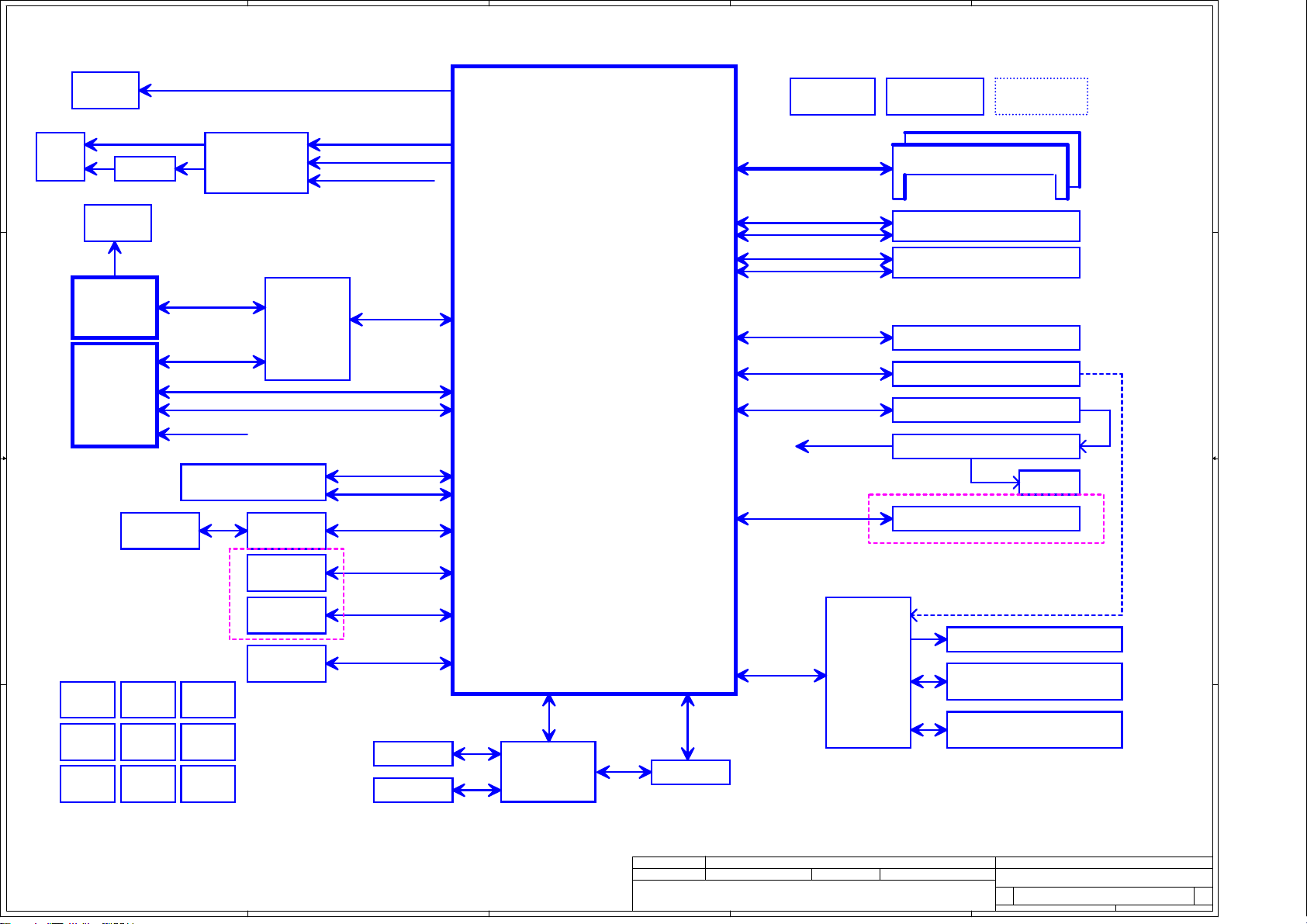

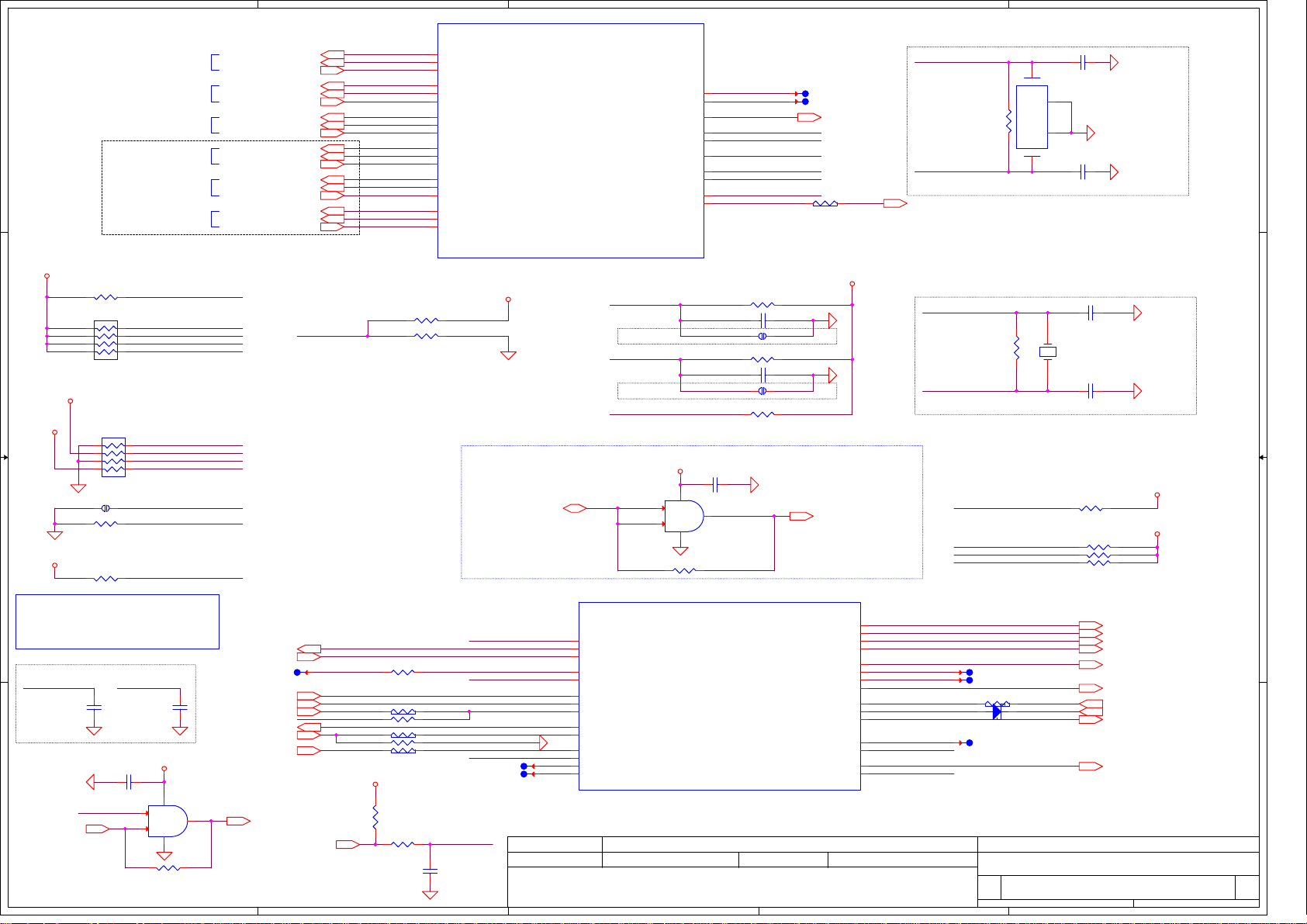

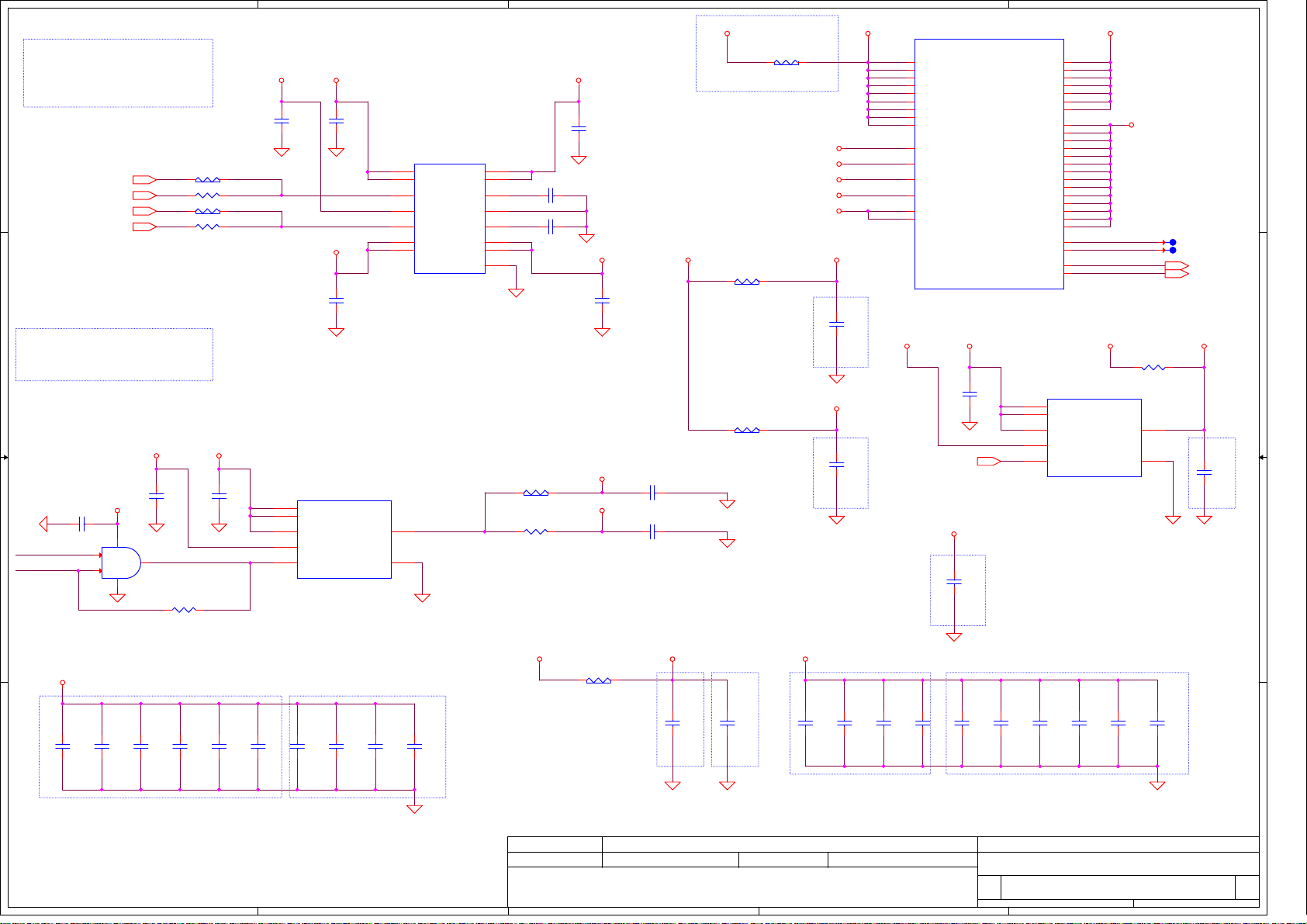

Page 2

A

B

C

D

E

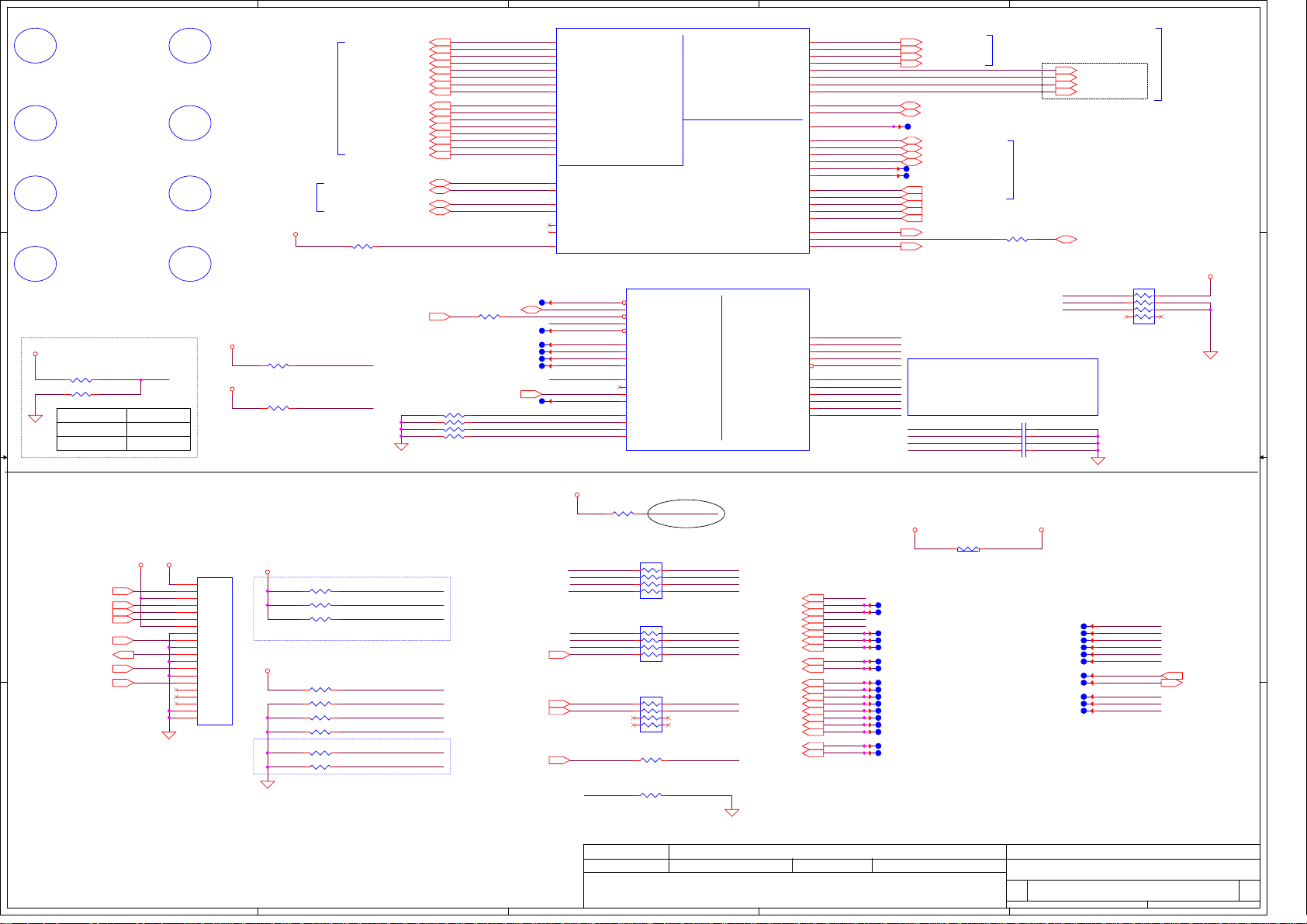

eDP

P.20

eDP 1.3

panel

1 1

P.47

USB3

TypeC

USB PD I2C/USB2

HDMI

TPS65982

P.21

P.46

ThunderBolt

Alpine Ridge-SP

P.44,45

DP 1.2 (DDI1)

DP 1.2 (DDI2)

PCI-E x2(port9,port10)

connector

HDMI 2.0

dGPU

nVIDIA

N16P-GX,50W

4pcs GDDR5

2 2

P.34

PCI-E x4 (Gen3)

PCIE MUX

PERICOM

PI3PCIE3415

PCI-E x4 (Gen3)

Video

Docking

Caldera

P.34P.22~29

USB3.0 port3

USB2.0 port3

PCI-E(Gen3)x4

po

rt1~port4

Skylake U

+

Skylake PCH-LP (MCP)

(SKL-U_2+2)

15W BGA 1356 balls

CDR_I2C

P.32

P.30P.30

P.08

PCI-E3.0 port5

USB2.0 port8

PCI-E3.0 port6

PCI-E3.0 port7,8

SATA3.0 port0,1

PC

I-E3.0 port11,12

SATA3.0 port1,2

SPI

NGFF (M.2)WLAN+BT

QCA killer 1535(A Key)

RJ45

connector

3 3

Storage Option2

Dual M.2 DB

LAN(Gigabit)

Killer E2400

NGFF (M.2)

SSD 1

NGFF (M.2)

SSD 2

SPI ROM

16MB

DC in

1.0V

Battery

3V/5V

System

4 4

1.35V

1.5V

CPU

Vcore

dGPU

Core

Charger

dGPU

1.35V

Int. KBD

ENE KC3810

P.40

P.41

LPC Bus

ENE KB9022

P.41

PS2

P.06~17

I2C(400KHz)

Touch pad

Memory Bus Dual Channel

35V,DDR3L,1600 MHz

1.

US

B3.0 port2

SB2.0 port2

U

USB3.0 port1

USB2.0 port1

USB2.0 port5

USB2.0 port6

USB2.0 port7

SATA3.0 port0 ; option

HD Audio

P.38

FFS

KXCNL-1010

CDR_I2C

Audio codec

Realtek

ALC3234

P.36 P.40 P.06

Fan control

NCT7718W

W83L771AWG-2

CMC connector

(Reserve)

P.18,19

204pin SO-DIMM x2

P.38,39

P.38,39

LED SET

P.33

P.33

P.20

P.20

P.37

P.36

USB connector 1 , Left side

USB power share

USB connector 2 , Right side 1

Touch screen

Digital camera(with digital MIC)

AlienFX / ELC , C8051F383-GQ

ELC PWM expander , TLC59116F

2.5”HDD

Storage Option1

P.31

digital MIC

Speaker

Headphone/MIC Global headset

combo JACK

Headphone/MIC Retaskable

combo JACK

P.31

P.31

P.31

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block diagram

Block diagram

Block diagram

LA-C901P

LA-C901P

LA-C901P

E

2 63Tuesday, August 04, 2015

2 63Tuesday, August 04, 2015

2 63Tuesday, August 04, 2015

1.0

1.0

1.0

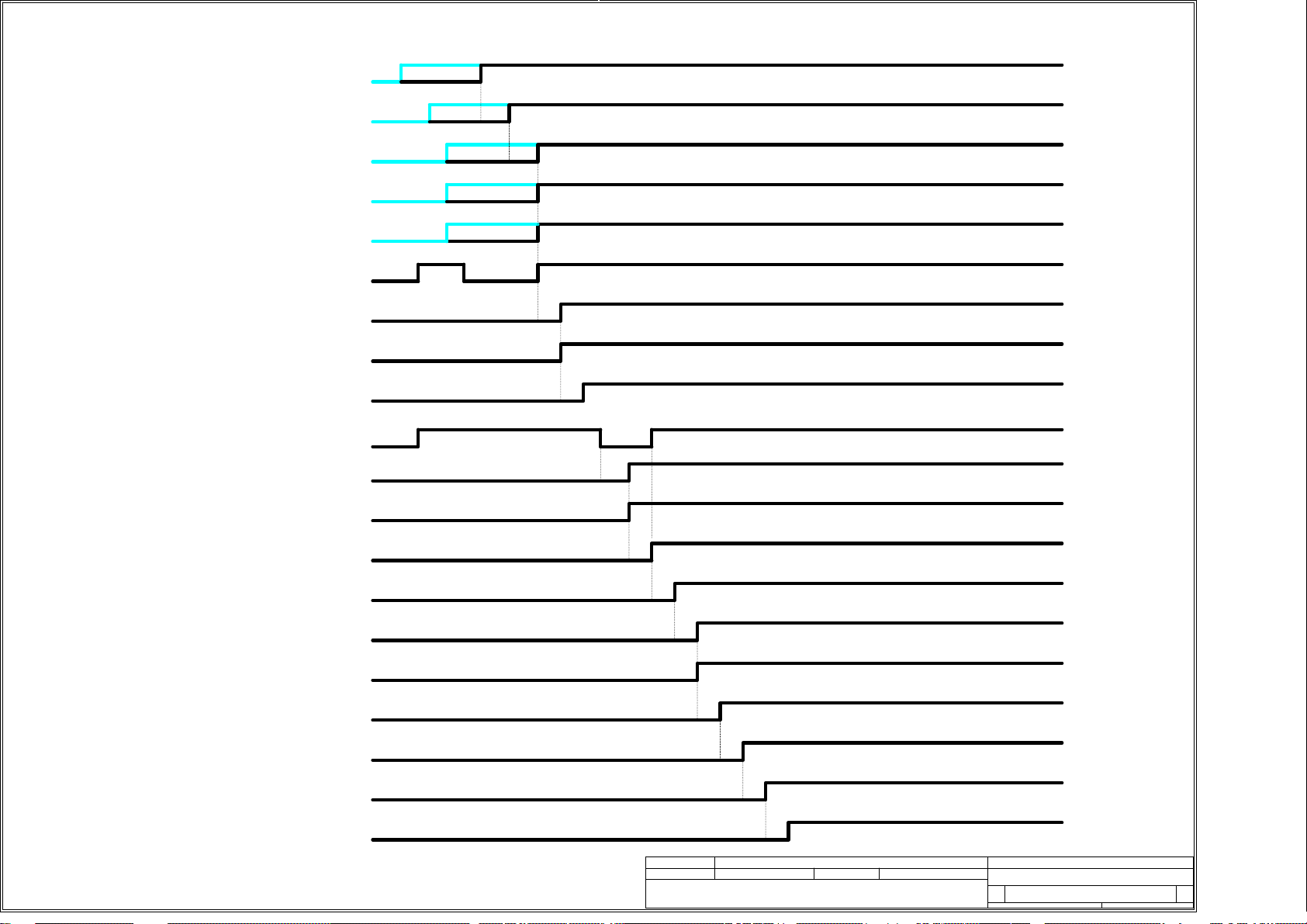

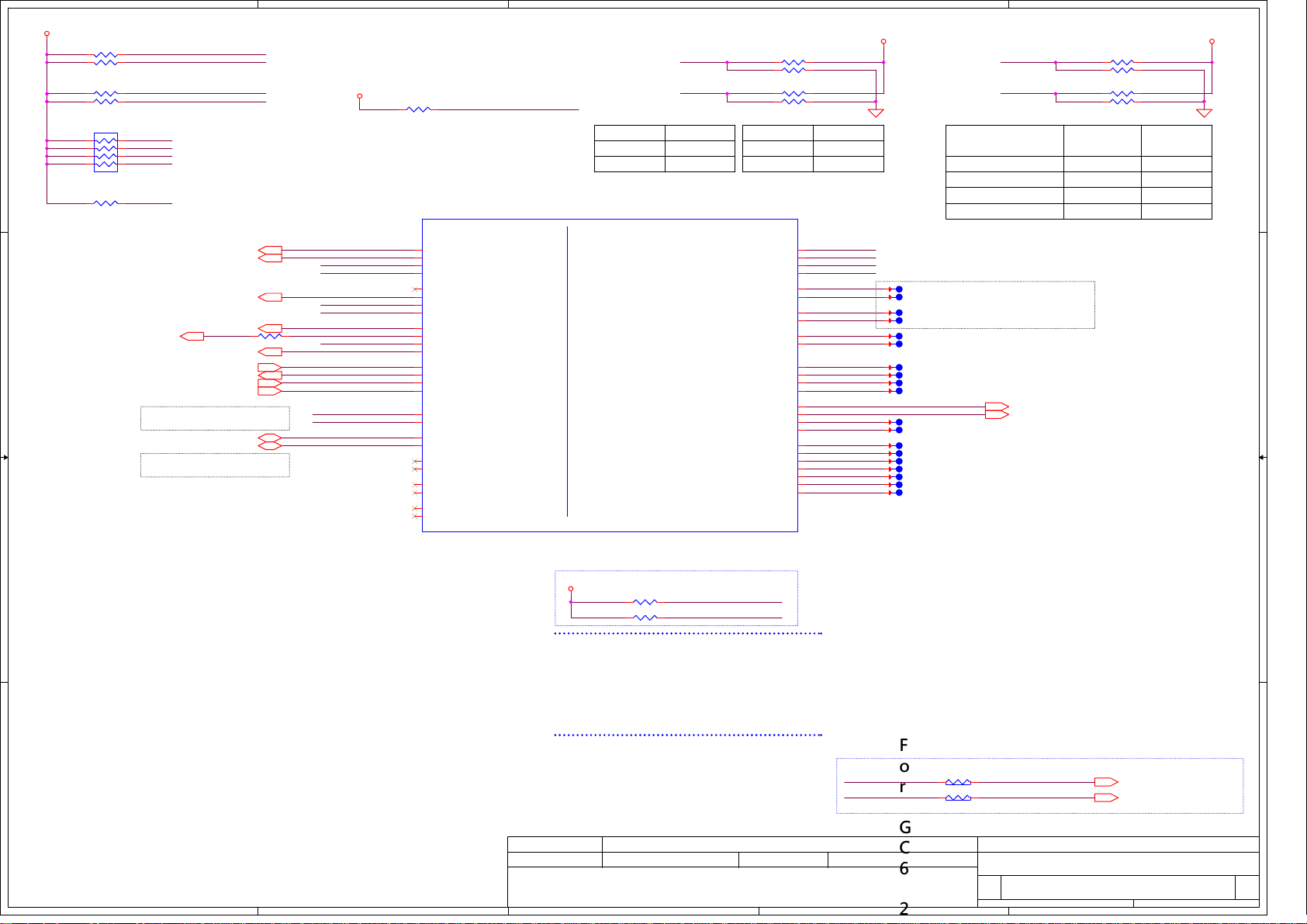

Page 3

A

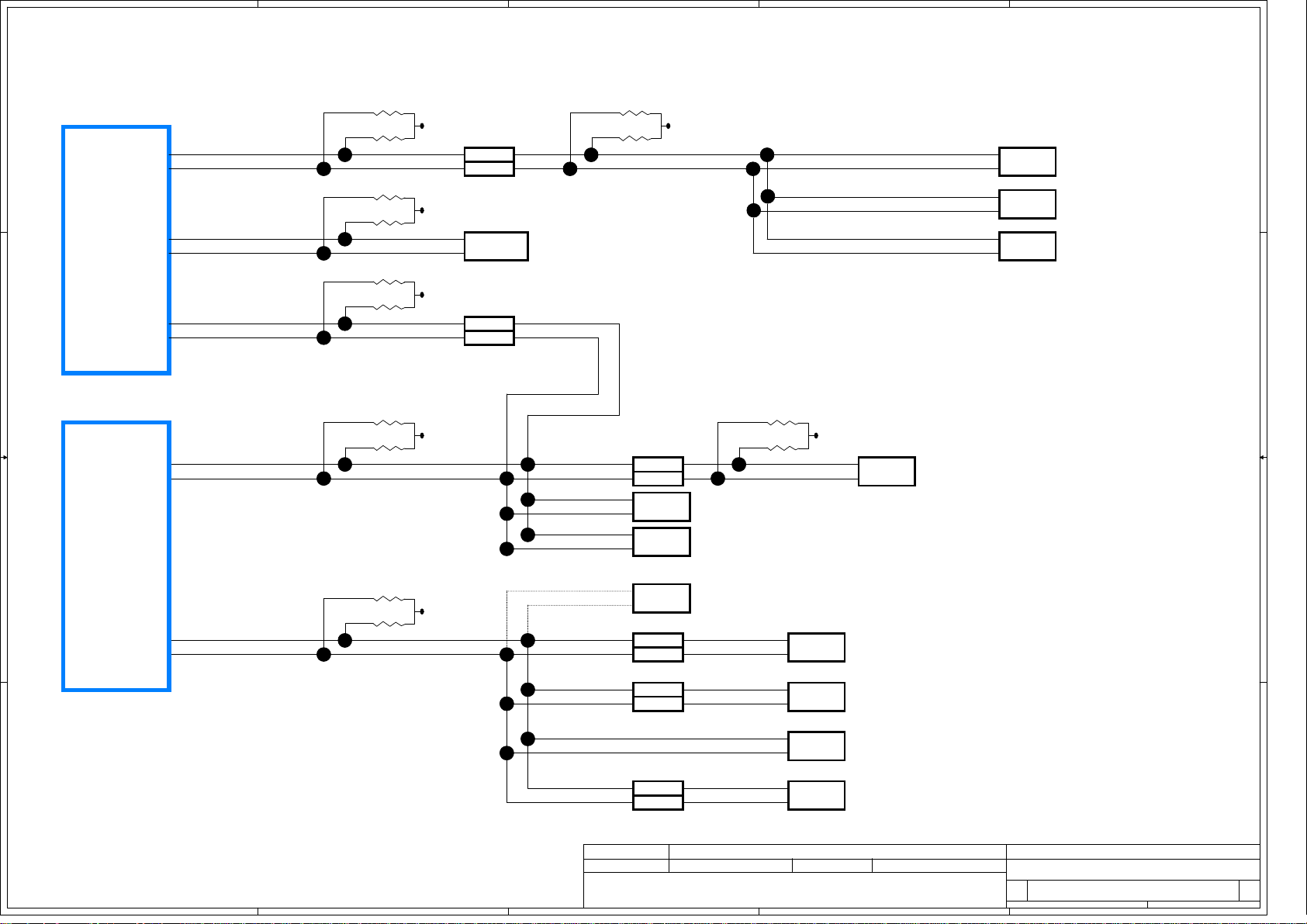

Power on sequence

DCACEC_ON

DCACVCCDSW(+3VALW)

DCACPCH_PWR_EN(SLP_SUS#)

+3V/+1.8V_PRIM

SUSACK#

DCAC

DCAC

Power Button

DPWROK_EC

EC_RSMRST#

AC_Present

Power Button Out

1 1

PM_SLP_S4# (Input)

PM_SLP_S3# (Input)

SYSON

SUP#

VCCST_PG_EC

VR_ON

VR_PWRGD

PCH_PWROK

SYS_PWROK

T_RST#

PL

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFOR MATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITH OUT PRIOR WRITT EN CONSENT OF C OMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITH OUT PRIOR WRITT EN CONSENT OF C OMPAL ELECTRONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITH OUT PRIOR WRITT EN CONSENT OF C OMPAL ELECTRONICS, INC.

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Power on sequence

Power on sequence

Power on sequence

LA-C901P

LA-C901P

LA-C901P

3 63Tuesday, August 04, 2015

3 63Tuesday, August 04, 2015

3 63Tuesday, August 04, 2015

1.0

1.0

1.0

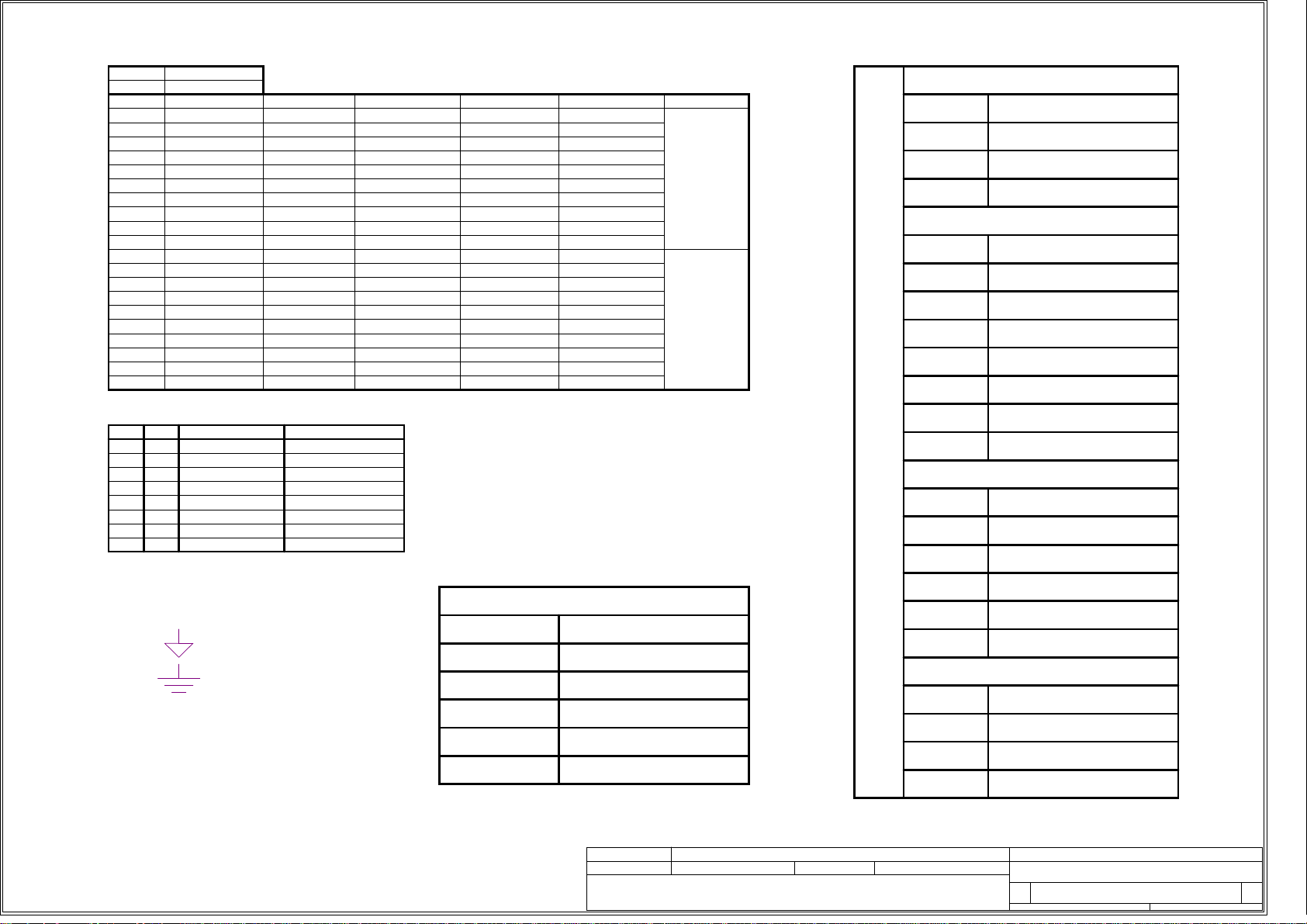

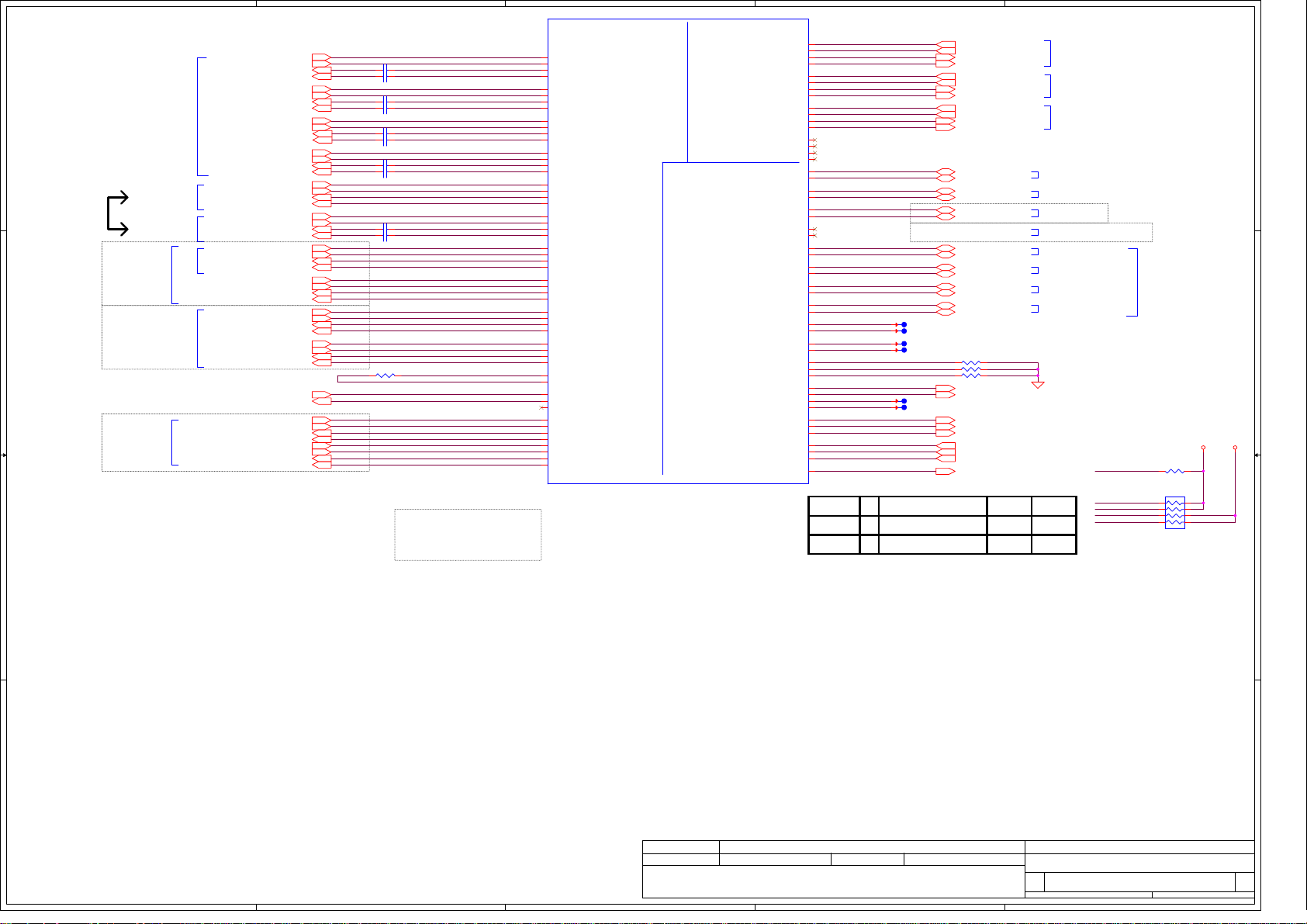

Page 4

A

Board ID Table for AD channel

Vcc 3.3V

Board ID

10

11

12

13

14

15

16

17

18

19

Board ID table and PCB version

ID

1 1

0

1

2

3

4

5 33K

6

7 56K

100K +/- 1%Ra

0

1

0

12K +/- 1% 0.354V

2

Rb V min

3

20K +/- 1%

4

27K +/- 1%

5

33K +/- 1%

6

43K +/- 1%

7

56K +/- 1%

8

75K +/- 1%

9

100K +/- 1%

130K +/- 1%

160K +/- 1%

200K +/- 1%

240K +/- 1%

270K +/- 1%

330K +/- 1%

430K +/- 1%

560K +/- 1%

750K +/- 1%

NC

AD_BID

0.347V

0.423V 0.430V

0.541V 0.559V

0.691V

0.807V

0.978V

1.169V

1.398V

1.634V

1.849V

2.015V

2.185V

2.316V

2.395V

2.521V

2.667V

2.791V

2.905V

3.000V 3.000V

Rb

0

12K

15K

20K

27K

EVT(R0.1)

DVT-1(R0.2)

DVT-1.1(R0.3)

DVT-2(R0.4)

Pilot(R1.0)

43K

V typ

AD_BID

V

AD_BID

0.000V 0.300V

0.360V

0.438V15K +/- 1%

0.550V

0.702V

0.819V

0.992V

1.185V

1.414V

1.650V

1.865V

2.031V

2.200V

2.329V

2.408V

2.533V

2.677V

2.800V

2.912V

0.713V

0.831V

1.006V

1.200V

1.430V

1.667V

1.881V

2.046V

2.215V

2.343V

2.421V

2.544V

2.687V

2.808V

2.919V

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x30

0x31 - 0x3A

0x3B - 0x45

0x46 - 0x54

0x55 - 0x64

0x65 - 0x76

0x77 - 0x87

0x88 - 0x96

0x97 - 0xA4

0xA5 - 0xAF

0xB0 - 0xB7

0xB8 - 0xBF

0xC0 - 0xC9

0xCA - 0xD4

0xD5 - 0xDD

0xDE - 0xF0

0xF1 - 0xFF

ULT

Port1

Port2

Port3

Port4

Port1

Port2

Port3

Port4

Port5

Port6

Port7

Port8

Lane 1~4

Lane 5

Lane 6

USB3.0

Right side 1

Left side (power share)

Caldera

USB2.0

Right side 1

Left side (power share)

Caldera

Touch screen

Camera

ELC

BT

PCI EXPRESS

MUX for dGPU & Caldera

WLAN(M.2 Card)

10/100/1000 LAN

Symbol Note :

: means Digital Ground

: means Analog Ground

CLOCK SIGNAL

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

Lane 7~8

Lane 9~10

N16P-GX +Caldera

Lane 11~12

M.2 Card WLAN+BT

Giga LAN

M.2 NGFF SSD

SATA1

Thunderbolt

SATA2

M.2 NGFF SSD

SATA3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

M.2 SATA+PCIeX2

Alpine Ridge SP

M.2 SATA+PCIeX2

SATA

HDD or SSD1SATA0

SSD2

SSD2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes list

Notes list

Notes list

LA-C901P

LA-C901P

LA-C901P

4 63Tuesday, August 04, 2015

4 63Tuesday, August 04, 2015

4 63Tuesday, August 04, 2015

1.0

1.0

1.0

of

of

of

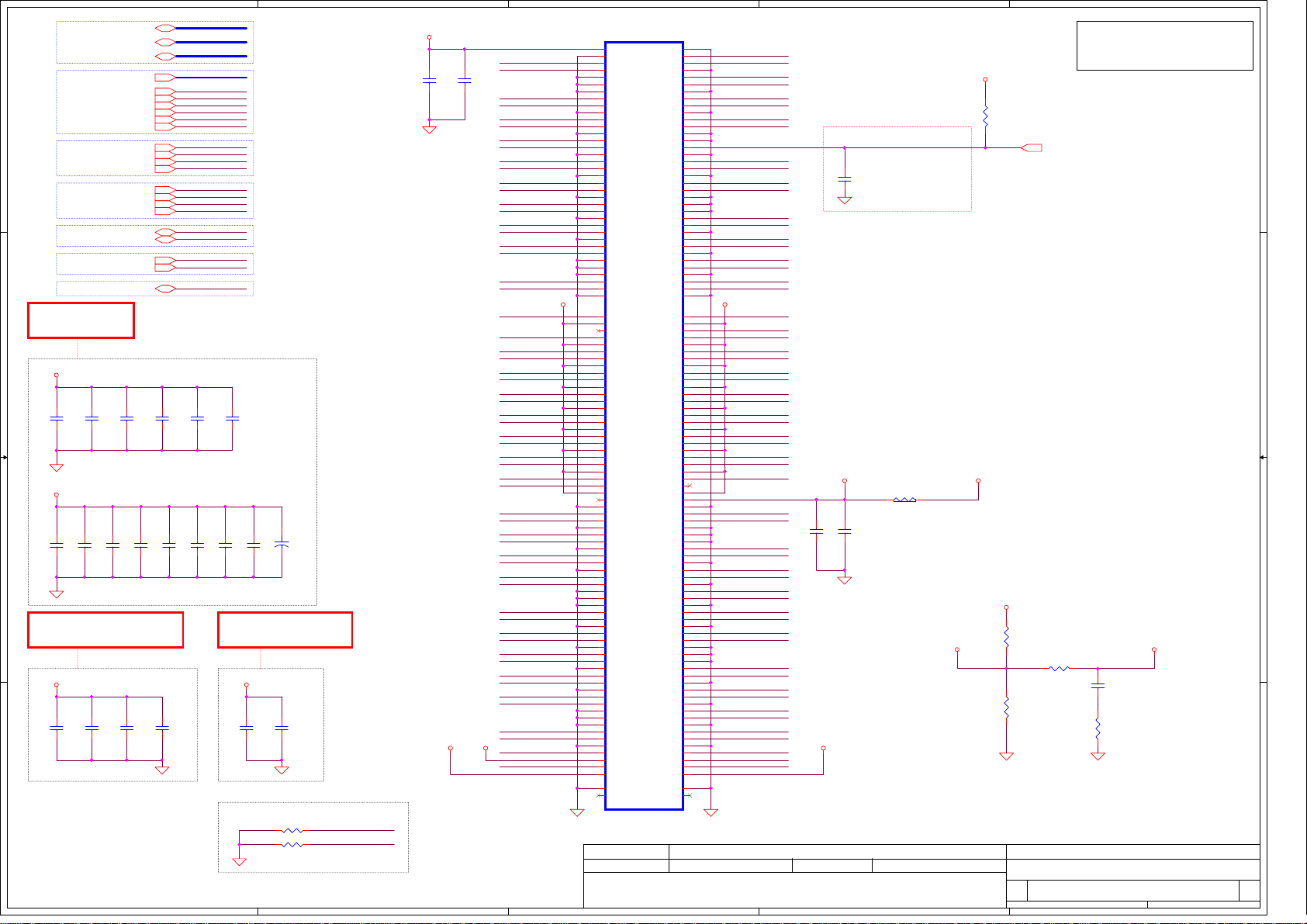

Page 5

5

4

3

2

1

1K

D D

MEM_SMBCLK

R7

MEM_SMBDATA

R8

SKYLAKE

ULT

C C

R9

W2

W3

V3

79

80

SOC_SML0CLK

SOC_SML0DATA

SOC_SML1CLK

EC_SMB_CK2

EC_SMB_DA2

1K

2.2K

2.

1K

1K

2.2K

2.2K

+3V_PRIM

N-MOS

N-MOS

+3VS

2K

CLK BUFFER

11

10

+3V_PRIM

N-MOS

N-MOS

EC_SMB_CK2

EC_SMB_DA2SOC_SML1DATA

+3VS

KBC

B B

KB9022QD

77

78

EC_SMB_CK1

EC_SMB_DA1

2.2K

2.2K

+3VALW_EC

10K

10K

SOC_SMBCLK

SOC_SMBDATA

N-MOS

N-MOS

UF18

7

UF28

7

UF3

8

(On SSD/B)

7

0 ohm

0 ohm

+3VS

VGA_SMB_CK2

VGA_SMB_DA2T4T3

SMBUS Address [0x98]

SMBUS Address [0x9A]

SMBUS Address [0X98]

<Reserve>

SCL

SDA

1.8K

1.8K

12

11

PU700

Charger

+3VS_VGA

UV1

GPU

SMBUS Address [0x12]

DIMMA

202

200

DIMMB

202

200

FFS

4

6

SMBUS Address [0x9E]

SMBUS Address [0x00]

SMBUS Address [0x01]

SMBUS Address [0x1D]

100 ohm

100 ohm

CLK_SMB

DAT_SMB

EC_SMB_CK1 50

EC_SMB_DA1

0 ohm

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

0 ohm

TBTA_I2C_SCL1_R B5

TBTA_I2C_SDA1_R

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

PBATT1

7

6

PCI-E

Re-Driver

49

Power

Deliver

A5

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SMBUS Address [0x16]

SMBUS Address [RX:0xB2 / TX:0xB6]

SMBUS Address [0x70]

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SMBus block diagram

SMBus block diagram

SMBus block diagram

LA-C901P

LA-C901P

LA-C901P

1

1.0

1.0

1.0

of

5 63Tuesday, August 04, 2015

of

5 63Tuesday, August 04, 2015

of

5 63Tuesday, August 04, 2015

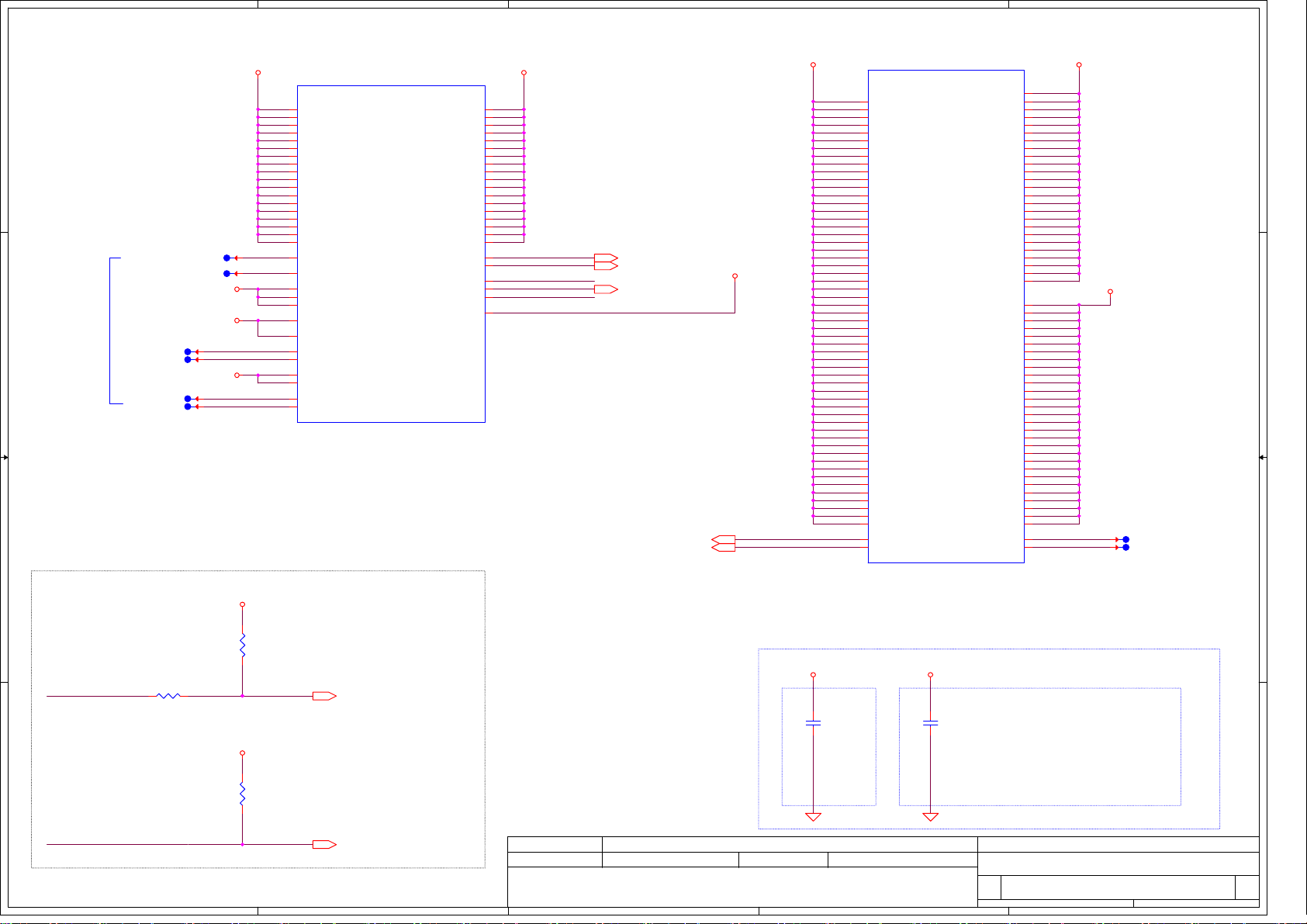

Page 6

A

UC1

S IC A31 FJ8066201924932 QHMG C0 1.6G

SA00008M30L

1.6GES@

UC1

I5-6200U I7-6500U

1 1

S IC A31 FJ8066201930409 QJ8N D0 2.3G

SA000092O0L

i5QS@

UC1

I5-6200U I7-6500U

S IC A31 FJ8066201930409 QJKP D1 2.3G

SA000092O1L

i5QS'@

UC1

I5-6200U I7-6500U

S IC FJ8066201930409 SR2EY D1 2.3G A31!

SA000092O3L

i5R3@

+3VS

2 2

For BIOS Verify UMA/DIS SKU

1 2

RC212 10K_0402_5%

1 2

RC213 10K_0402_5%

UMA@

DIS@

DGPU_PRSNT#

GPP_E15

DIS,Optimus

UMA

UC1

S IC A31 FJ8066201924925 QHMF C0 2.3G

SA00008M40L

2.3GES@

UC1

S IC A31 FJ8066201930408 QJ8L D0 2.5G

SA000092P0L

i7QS@

UC1

S IC A31 FJ8066201930408 QJKK D1 2.5G

SA000092P1L

i7QS'@

UC1

S IC FJ8066201930408 SR2EZ D1 2.5G A31!

SA000092P3L

i7R3@

Pull High at TBT side

+1.0V_VCCST

+1.0VS_VCCSTG

DGPU_PRSNT#

0

1

<Thunderbolt>

Thunderbolt

+1.0VS_VCCIO

CAD note:

Trace width=20 mils,Spacing=25mil,Max length=100mils

1 2

RC2 1K_0402_5%

1 2

RC3 1K_0402_5%

H_THERMTRIP#

H_PROCHOT#

RC1

SOC_DP1_CTRL_CLK<44>

SOC_DP1_CTRL_DATA<44>

SOC_DP2_CTRL_CLK<44>

SOC_DP2_CTRL_DATA<44>

1 2

B

SOC_DP1_N0<44>

SOC_DP1_P0<44>

SOC_DP1_N1<44>

SOC_DP1_P1<44>

SOC_DP1_N2<44>

SOC_DP1_P2<44>

SOC_DP1_N3<44>

SOC_DP1_P3<44>

SOC_DP2_N0<44>

SOC_DP2_P0<44>

SOC_DP2_N1<44>

SOC_DP2_P1<44>

SOC_DP2_N2<44>

SOC_DP2_P2<44>

SOC_DP2_N3<44>

SOC_DP2_P3<44>

24.9_0402_1%

H_PROCHOT#<41,51,52>

RC5 49.9_0402_1%

RC6 49.9_0402_1%

RC7 49.9_0402_1%

RC8 49.9_0402_1%

SOC_DP1_CTRL_CLK

SOC_DP1_CTRL_DATA

SOC_DP2_CTRL_CLK

SOC_DP2_CTRL_DATA

EDP_COMP

T26 TP@

H_PECI<41>

1 2

RC4 499_0402_1%

T25 TP@

T16 TP@

T19 TP@

T10 TP@

T11 TP@

TS_INT# is not Used at Echo

PCH_TP_INT#<41>

T40 TP@

12

12

12

12

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

DGPU_PRSNT#

PCH_TP_INT#

SOC_GPIOB4

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

AT16

AU16

UC1D

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

C

SKL-U

DDI

DISPLAY SIDEBANDS

1 OF 20

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

EDP

SKL-U

4 OF 20

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

RSVD

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

L-U_BGA1356@

SK

Rev_1.0

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

L-U_BGA1356@

SK

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

D

EDP_DISP_UTIL

SOC_DP1_HPD

SOC_DP2_HPD

HDMI_HPD

EC_SCI#

EDP_HPD

EDP_BKLTEN

EDP_BKLT_PWM

EDP_VDDEN

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

EDP_TXN0 <20>

EDP_TXP0 <20>

EDP_TXN1 <20>

EDP_TXP1 <20>

EDP_AUXN <20>

EDP_AUXP <20>

T9TP@

SOC_DP1_AUXN <44>

SOC_DP1_AUXP <44>

SOC_DP2_AUXN <44>

SOC_DP2_AUXP <44>

T7TP@

T8TP@

SOC_DP1_HPD <44>

SOC_DP2_HPD <44>

HDMI_HPD <21>

EC_SCI# <41>

EDP_HPD <20>

EDP_BKLTEN <41>

EDP_VDDEN <20>

SOC_XDP_TDO

SOC_XDP_TDI

SOC_XDP_TRST#

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TRST#

CPU_XDP_TCK0

eDP_FHD>

<

Thunderbolt

From dGPU

From eDP

12

RC10 0_0402_5%

As Short As Possible

1 2

1 2

CC64 0.1U_0402_16V7K@ESD@

1 2

CC65 0.1U_0402_16V7K@ESD@

1 2

CC69 0.1U_0402_16V7K@ESD@

CC70 0.1U_0402_16V7K@ESD@

EDP_TXN2 <20>

EDP_TXP2 <20>

EDP_TXN3 <20>

EDP_TXP3 <20>

EDP_BIA_PWM <20>

EC_SCI#

EDP_HPD

EDP_VDDEN

E

RPC16

1 8

2 7

3 6

4 5

100K_8P4R_5%

<eDP_4K2K>

+3VS

+3V_PRIM

Change from +3VALW to +3V_PRIM to fix leakage on S5

APS CONN

3 3

PM_SLP_S3#<10,13,37,41>

PM_SLP_S5#<10,37,41>

PM_SLP_S4#<10,13,37,41,54>

PM_SLP_A#<10>

SOC_RTCRST#_R<10>

PBTN_OUT#<10,41>

SYS_RESET#<10>

PM_SLP_S0#<10,41>

4 4

+3VALW +3V_PRIM

A

JAPS1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

ACES_50506-01841-P01

CONN@

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

GND

GND

+1.0VS_VCCSTG

RC11 51_0402_5%CMC@

RC13 51_0402_5%CMC@

RC15 51_0402_5%CMC@

+1.0V_XDP

RC31 1K_0402_5%CMC@

RC32 1K_0402_5%@

RC43 0_0402_5%@

RC46 0_0402_5%@

RC35 51_0402_1%CMC@

RC37 51_0402_5%@

Place to CPU side

12

12

12

1 2

1 2

12

12

12

12

Place to CPU side

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

XDP_ITP_PMODE

CFG0

XDP_PRSENT_CPU

XDP_PRSENT_PCH

CPU_XDP_TCK0

PCH_JTAG_TCK1

B

XDP_SPI_IO2<8>

XDP_SPI_SI<8>

XDP_ITP_PMODE<17>

EC_RSMRST#<10,41>

1 2

RC9 1K_0402_5%

SOC_XDP_TDO XDP_TDO

SOC_XDP_TDI XDP_TDI

SOC_XDP_TMS XDP_TMS

CPU_XDP_TCK0 XDP_TCK0

SOC_XDP_TRST#

PCH_JTAG_TCK1

CFG3 XDP_PRSENT_CPU

XDP_SPI_IO2 XDP_PRSENT_PCH

XDP_SPI_SI

XDP_ITP_PMODE

RC158 1K_0402_5%

CFG4

RC193 1K_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

@

RPC2

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

@

RPC4

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

@

RPC15

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

1 2

CMC@

1 2

C

XDP_SPI_SI

CFG0<17>

CFG1<17>

CFG2<17>

CFG3<17>

XDP_TRST#

XDP_TCK1

XDP_HOOK3

XDP_HOOK6

XDP_HOOK0EC_RSMRST#

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

CFG4<17>

CFG5<17>

CFG6<17>

CFG7<17>

CFG17<17>

CFG16<17>

CFG8<17>

CFG9<17>

CFG10<17>

CFG11<17>

CFG12<17>

CFG13<17>

CFG14<17>

CFG15<17>

CFG19<17>

CFG18<17>

Compal Secret Data

Compal Secret Data

Compal Secret Data

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG19

CFG18

Deciphered Date

Deciphered Date

Deciphered Date

PRIMARY CMC CONN

+1.0V_XDP+1.0V_PRIM

1 2

RC12 0_0603_1%@

T37TP@

T38TP@

T47TP@

T48TP@

T49TP@

T50TP@

T51TP@

T52TP@

T53TP@

T54TP@

T55TP@

T56TP@

T57TP@

T58TP@

T59TP@

T60TP@

T61TP@

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

T13 TP@

T20 TP@

T21 TP@

T24 TP@

T27 TP@

T28 TP@

T29 TP@

T30 TP@

T31 TP@

T32 TP@

T33 TP@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_TCK0

XDP_TCK1

XDP_TDO

XDP_PREQ#

XDP_PRDY#

XDP_HOOK0

XDP_HOOK3

XDP_HOOK6

LA-C901P

LA-C901P

LA-C901P

XDP_PREQ# <12>

XDP_PRDY# <12>

of

6 63Tuesday, August 04, 2015

of

6 63Tuesday, August 04, 2015

of

E

6 63Tuesday, August 04, 2015

1.0

1.0

1.0

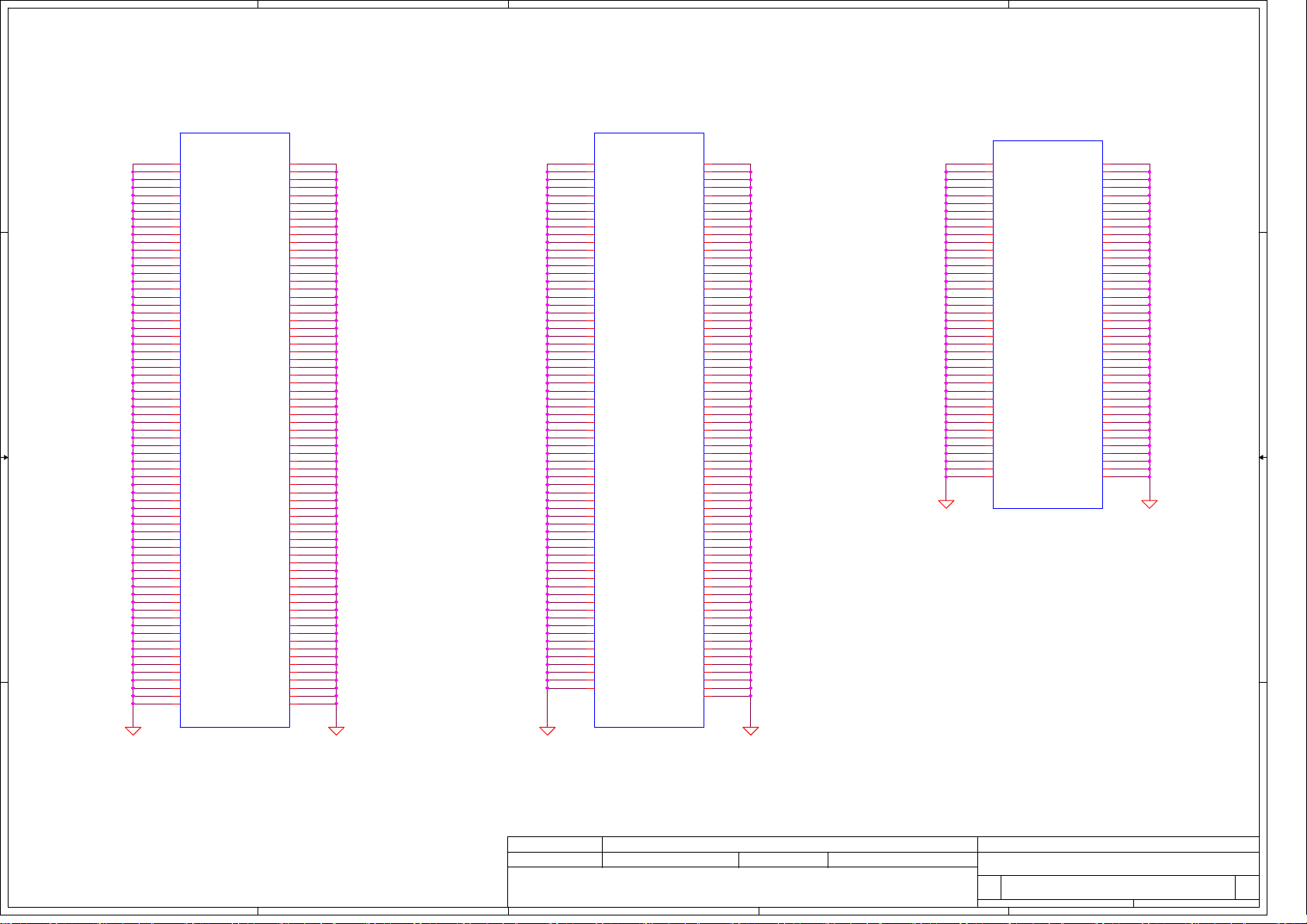

Page 7

5

4

3

2

1

Non-Interleaved Memory

D D

DDR_A_D[0..15]<18>

DDR_A_D[32..47]<18>

C C

DDR_B_D[0..15]<19>

DDR_B_D[32..47]<19>

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR3L / LPDDR3 / DDR4

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR CH - A

2 OF 20

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

SK

Rev_1.0

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

L-U_BGA1356@

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BS2

DDR_A_MA12

DDR_A_MA11

DDR_A_MA15

DDR_A_MA14

DDR_A_MA13

DDR_A_CAS#

DDR_A_WE#

DDR_A_RAS#

DDR_A_BS0

DDR_A_MA2

DDR_A_BS1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

+0.675V_VREFCA

+0.675V_A_VREFDQ

+0.675V_B_VREFDQ

T14TP@

T22TP@

+0.675V_VREFCA

+0.675V_A_VREFDQ

+0.675V_B_VREFDQ

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

DDR_A_CLK#1 <18>

DDR_A_CLK1 <18>

DDR_A_CKE0 <18>

DDR_A_CKE1 <18>

DDR_A_CS#0 <18>

DDR_A_CS#1 <18>

DDR_A_ODT0 <18>

DDR_A_ODT1 <18>

DDR_A_MA5 <18>

DDR_A_MA9 <18>

DDR_A_MA6 <18>

DDR_A_MA8 <18>

DDR_A_MA7 <18>

DDR_A_BS2 <18>

DDR_A_MA12 <18>

DDR_A_MA11 <18>

DDR_A_MA15 <18>

DDR_A_MA14 <18>

DDR_A_MA13 <18>

DDR_A_CAS# <18>

DDR_A_WE# <18>

DDR_A_RAS# <18>

DDR_A_BS0 <18>

DDR_A_MA2 <18>

DDR_A_BS1 <18>

DDR_A_MA10 <18>

DDR_A_MA1 <18>

DDR_A_MA0 <18>

DDR_A_MA3 <18>

DDR_A_MA4 <18>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_B_DQS#0 <19>

DDR_B_DQS0 <19>

DDR_B_DQS#1 <19>

DDR_B_DQS1 <19>

DDR_B_DQS#4 <19>

DDR_B_DQS4 <19>

DDR_B_DQS#5 <19>

DDR_B_DQS5 <19>

DDR_A_D[16..31]<18>

DDR_A_D[48..63]<18>

DDR_B_D[16..31]<19>

DDR_B_D[48..63]<19>

Trace width/Spacing >= 20mils

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

Rev_1.0

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

L-U_BGA1356@

SK

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BS2

DDR_B_MA12

DDR_B_MA11

DDR_B_MA15

DDR_B_MA14

DDR_B_MA13

DDR_B_CAS#

DDR_B_WE#

DDR_B_RAS#

DDR_B_BS0

DDR_B_MA2

DDR_B_BS1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_DRAMRST #

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <19>

DDR_B_CLK#1 <19>

DDR_B_CLK0 <19>

DDR_B_CLK1 <19>

DDR_B_CKE0 <19>

DDR_B_CKE1 <19>

T17TP@

T18TP@T15TP@

DDR_B_CS#0 <19>

DDR_B_CS#1 <19>

DDR_B_ODT0 <19>

DDR_B_ODT1 <19>

DDR_B_MA5 <19>

DDR_B_MA9 <19>

DDR_B_MA6 <19>

DDR_B_MA8 <19>

DDR_B_MA7 <19>

DDR_B_BS2 <19>

DDR_B_MA12 <19>

DDR_B_MA11 <19>

DDR_B_MA15 <19>

DDR_B_MA14 <19>

DDR_B_MA13 <19>

DDR_B_CAS# <19>

DDR_B_WE# <19>

DDR_B_RAS# <19>

DDR_B_BS0 <19>

DDR_B_MA2 <19>

DDR_B_BS1 <19>

DDR_B_MA10 <19>

DDR_B_MA1 <19>

DDR_B_MA0 <19>

DDR_B_MA3 <19>

DDR_B_MA4 <19>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

DDR_B_DQS#2 <19>

DDR_B_DQS2 <19>

DDR_B_DQS#3 <19>

DDR_B_DQS3 <19>

DDR_B_DQS#6 <19>

DDR_B_DQS6 <19>

DDR_B_DQS#7 <19>

DDR_B_DQS7 <19>

T23TP@

DDR_DRAMRST # <18,19>

1 2

RC38 121_0402_1%

1 2

RC39 80.6_0402_1%

1 2

RC40 100_0402_1%

Buffer with Open Drain Output

For VTT power control

+3VALW

+1.35V_VDDQ +3VS

12

DDR_PG_CTRL

CC570.1U_0201_10V6K

UC7

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

12

5

4

Y

RC123

100K_0402_5%

@

12

RC129

100K_0402_5%

0.675V_DDR_VTT_ON <54>

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

SKL-U(2/12)DDRIII

SKL-U(2/12)DDRIII

SKL-U(2/12)DDRIII

LA-C901P

LA-C901P

LA-C901P

Tuesday, August 04, 2015

Tuesday, August 04, 2015

Tuesday, August 04, 2015

1

1.0

1.0

1.0

63

63

63

of

7

of

7

of

7

Page 8

5

SOC_SMBALERT# SOC_SML0ALERT#

TLS CONFIDENTIALITY

HIGH

LOW(DEFAULT)

UC1E

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

CMC@

CMC@

O2 pin for CMC

12

12

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

SOC_SPI_CS#1

FFS_INT1

FFS_INT2

EC_KBRST#

SERIRQ

SERIRQ

SOC_SPI_SI

SOC_SPI_IO2

C21/44 place to within 1100 mil of SPIO_MOSI/SPI0_I

R

XDP_SPI_SI<6>

XDP_SPI_IO2<6>

+3VS

D D

RC32410K_0402_5%

RC32510K_0402_5%

RC32610K_0402_5% @

C C

+3VS

LPC Mode

12

12

12

FFS_INT2

FFS_INT1

EC_KBRST#

RC44 1K_0402_1%

RC21 1K_0402_1%

T41 TP@

FFS_INT1<36>

FFS_INT2<36>

T42 TP@

T43 TP@

T44 TP@

EC_KBRST#<41>

SERIRQ<41>

12

RC1228.2K_0402_5%

Follow 543016_SKL_U_Y_PDG_0_9

B B

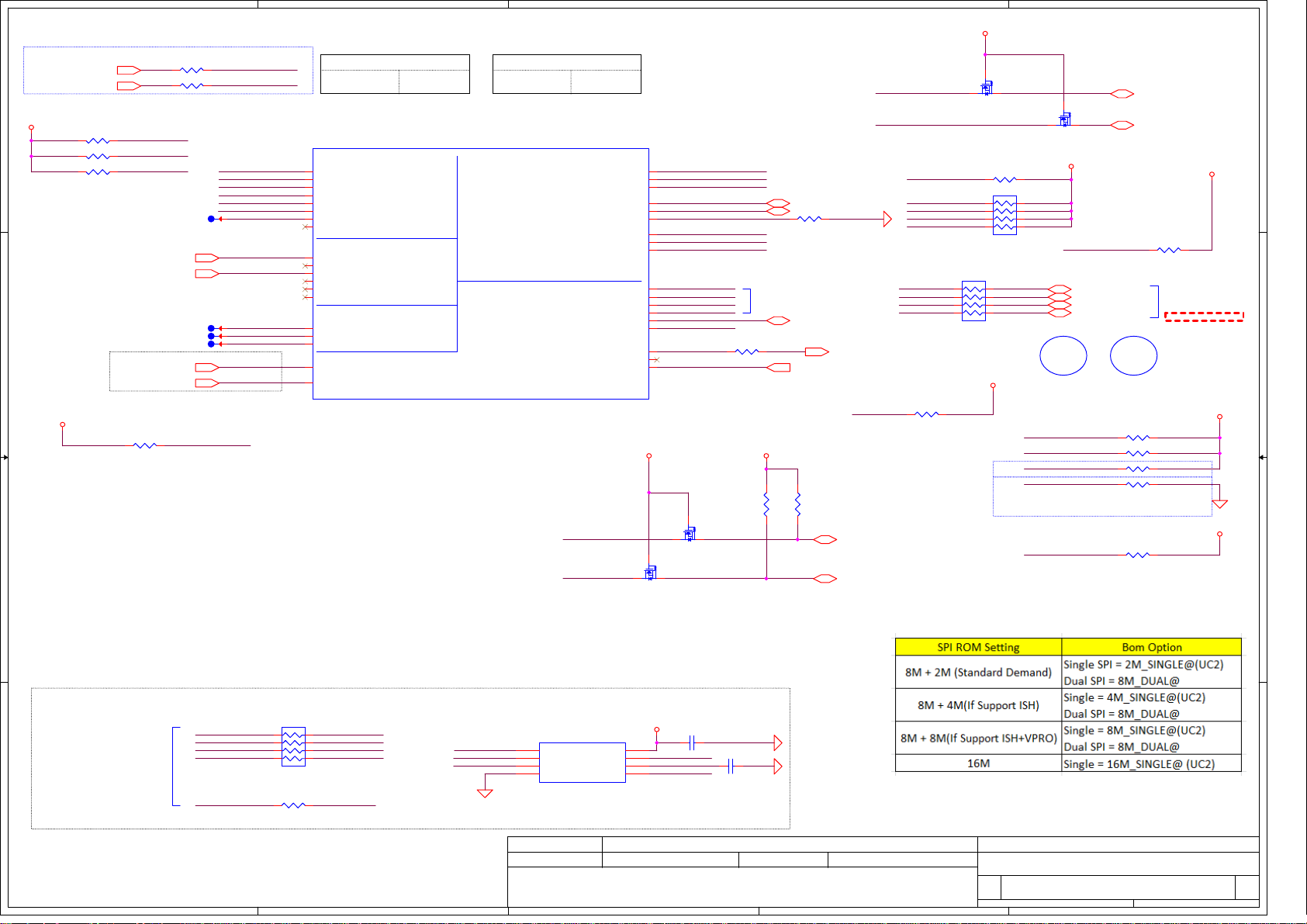

SPI - FLASH

SPI - TOUCH

C LINK

4

EC interface

ENABLE

DISABLE

SKL-U

LPC

5 OF 20

HIGH

LOW(DEFAULT)

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

ESPI

LPC

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

MEM_SMBCLK

MEM_SMBDATA

3

----->For KB9032 Only.

----->For KB9022/9032 Use

Rev_1.0

R7

MEM_SMBCLK

R8

MEM_SMBDATA

R10

SOC_SMBALERT#

R9

SOC_SML0CLK

W2

SOC_SML0DATA

W1

SOC_SML0ALERT#

W3

SOC_SML1CLK

V3

SOC_SML1DATA

AM7

SOC_SML1ALERT# SOC_SML1ALERT#

AY13

ESPI_IO0

BA13

ESPI_IO1

BB13

ESPI_IO2

AY12

ESPI_IO3

BA12

ESPI_CS#

BA11

SUS_STAT#

<Echo13>

AW9

ESPI_CLK

AY9

AW11

PM_CLKRUN#

L-U_BGA1356@

SK

SMB Bus : DDR/WLAN/FFS

2

G

6 1

S

D

5

DMN66D0LDW-7_SOT363-6

3 4

SGD

QC3A

DMN66D0LDW-7_SOT363-6

LPC@

1 2

RC45 22_0402_5%

RC66

10K_0402_5%

QC3B

2

SML1 Bus : EC/dGPU/THERMAL

SOC_SML1CLK

SOC_SML1DATA

SMB -> DDR , WLAN , FFS

SML0 -> PCIE CLK BUFFER

SOC_SML0CLK <34>

SOC_SML0DATA <34>

RC202 4.7K_0402_5%

12

SML1 -> EC , dGPU , THERMAL , TBT

To EC

ESPI_CS# <41>

ESPI_CLK_R <41>

PM_CLKRUN# <41>

SUS_STAT#

+3VS+3VS

12

12

RC67

10K_0402_5%

SOC_SMBCLK <18,19,36>

SOC_SMBDATA <18,19,36>

SOC_SMBALERT#

MEM_SMBCLK

MEM_SMBDATA

SOC_SML1CLK

SOC_SML1DATA

ESPI_IO0 ESPI_IO0_R

ESPI_IO2 ESPI_IO2_R

ESPI_IO1 ESPI_IO1_R

ESPI_IO3

To EC

For TPM

1 2

@

RC36 10K_0402_5%

+3VS

2

G

6 1

S

D

QC2B

DMN66D0LDW-7_SOT363-6

1 2

RC130 8.2K_0402_5%

RPC12

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

RPC8

1 8

2 7

3 6

4 5

ESPI_IO3_R

0_0804_8P4R_5%

LPC@

+3V_PRIM

*****ONLY*****

From WW36 MOW for SKL-U ES sample

1

5

3 4

SGD

QC2A

DMN66D0LDW-7_SOT363-6

+3V_PRIM

ESPI_IO0_R <41>

ESPI_IO2_R <41>

ESPI_IO1_R <41>

ESPI_IO3_R <41>

RC45

15_0402_5%

ESPI@

EC_SMB_CK2 <22,40,41,46>

EC_SMB_DA2 <22,40,41,46>

1 2

RC41 150K_0402_1%@

ESPI / LPC Bus

ESPI : +1.8V

LPC : +3.3V

RPC8

15_0804_8P4R_5%

ESPI@

Echo MLK use LPC

Reserve For EC Auto Load Code

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

SOC_SPI_IO3

PM_CLKRUN#

1 2

RC47 1K_0402_1%@

1 2

RC48 1K_0402_1%@

1 2

RC53 1K_0402_1%@

1 2

RC51 1K_0402_1%@

1 2

RC107 8.2K_0402_5%

Follow TD team

+3VS

+3V_SPI

+3VS

Single SPI ROM_CS0#

To SPI ROM

A A

5

RPC5 and RC52 are close UC2

RPC5

1 8

2 7

3 6

4 5

SOC_SPI_SOSOC_SPI_SO_0_R

SOC_SPI_SISOC_SPI_SI_0_R

SOC_SPI_CLKSOC_SPI_CLK_0_R

SOC_SPI_IO3SOC_SPI_IO3_0_R

15_0804_8P4R_5%

RC52

12

SOC_SPI_IO2SOC_SPI_IO2_0_R

15_0402_5%

16M SPI ROM(Support ISH)

UC2

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

4

1

/CS

2

DO(IO1)

3

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

/HOLD(IO3)

/WP(IO2)

GND

W25Q128FVSIQ_SO8

+3V_SPI

1 2

CC8 0.1U_0201_10V6K

8

VCC

7

SOC_SPI_IO3_0_RSOC_SPI_SO_0_R

6

SOC_SPI_CLK_0_R

CLK

5

DI(IO0)

SOC_SPI_SI_0_R

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

3

1 2

CC9

10P_0402_50V8J

@EMI@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-C901P

LA-C901P

LA-C901P

Date: Sheet

Date: Sheet

2

Date: Sheet

1

of

8 63Tuesday, August 04, 2015

of

8 63Tuesday, August 04, 2015

of

8 63Tuesday, August 04, 2015

1.0

1.0

1.0

Page 9

5

4

3

2

1

#545659 SKL_PCH_EDS_R0.7 P.84

HDA for AUDIO

RPC9

CC53

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

1 8

2 7

3 6

4 5

1

2

D D

HDA_BIT_CLK_R<31>

HDA_RST#_R<31>

HDA_SDOUT_R<31>

HDA_SYNC_R<31>

HDA_SDIN0<31>

Functional Strap Definitions

SPKR / GPP_B14 (Internal Pull Down):

(Sampled:Rising edge of PCH_PWROK)

TOP Swap Override

0 = Disable TOP Swap mode. -->AAX05 use

1 = Enable TOP Swap Mode.

TOP Swap Override

C C

+3VS

1 2

RC117 2.2K_0402_5%@

B B

SPKR

22P_0402_50V8J

Close to RPC9

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

HDA_BIT_CLK

HDA_RST#

HDA_SDOUT

HDA_SYNC

33_0804_8P4R_5%

HDA_SDIN0

HDA_BIT_CLK_R

SKL-U

9 OF 20

SPKR<31>

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F12/EMMC_CMD

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0

HDA_RST#

SPKR

Rev_1.0

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

GPP_F22/EMMC_CLK

EMMC_RCOMP

L-U_BGA1356@

SK

To Enable ME Override

TD Team Solution A

+3V_PRIM

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

UC1G

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

AW22

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

AW20

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

1 2

RC77 1K_0402_1%

CSI2_COMP

EMMC_RCOMP

RC80 100_0402_1%

RC89 200_0402_1%

AUDIO

ME_EN<9,41>

SKL-U

GPP_A17/SD_PWR_EN#/ISH_GP7

7 OF 20

eserve RC229 follow TD team dat.04/23

R

1 2

@

RC229 100K_0402_5%

2

G

12

12

1 3

QC1

BSS138W -7-F_SOT323-3

HDA_SDOUT

D

S

Rev_1.0

SDIO / SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

L-U_BGA1356@

SK

BO Solution

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

SD_RCOMP

AF13

ME_EN<9,41>

RC76 200_0402_1%

1 2

@

RC313 0_0402_5%

12

HDA_SDOUT

A A

Security Classification

Security Classification

Security Classification

2015/01/06 2016/01/06

2015/01/06 2016/01/06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/01/06 2016/01/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-C901P

LA-C901P

LA-C901P

Date: Sheet

Date: Sheet

Date: Sheet

Tuesday, August 04, 2015

Tuesday, August 04, 2015

2

Tuesday, August 04, 2015

1

of

9

of

9

of

9

1.0

1.0

1.0

63

63

63

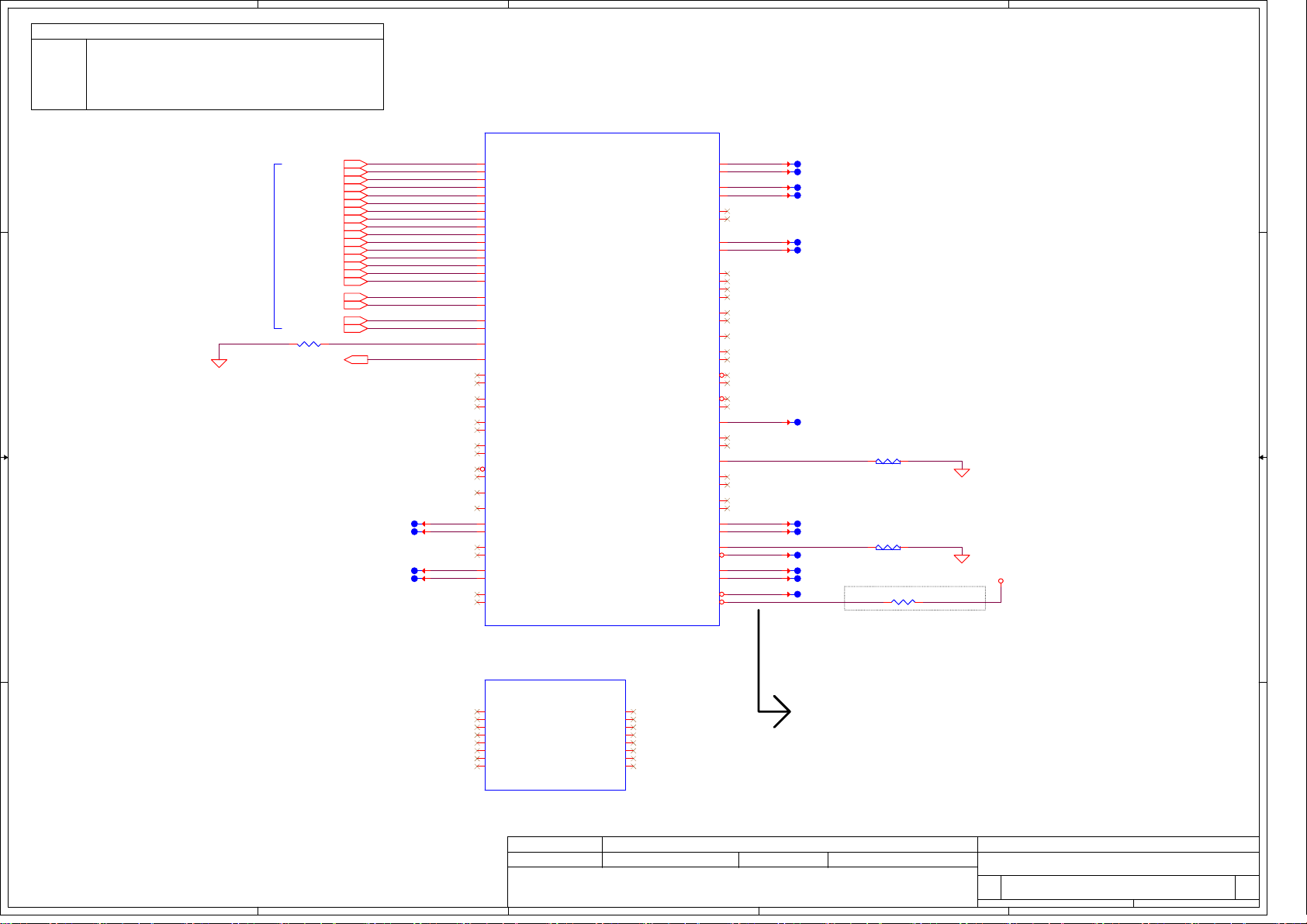

Page 10

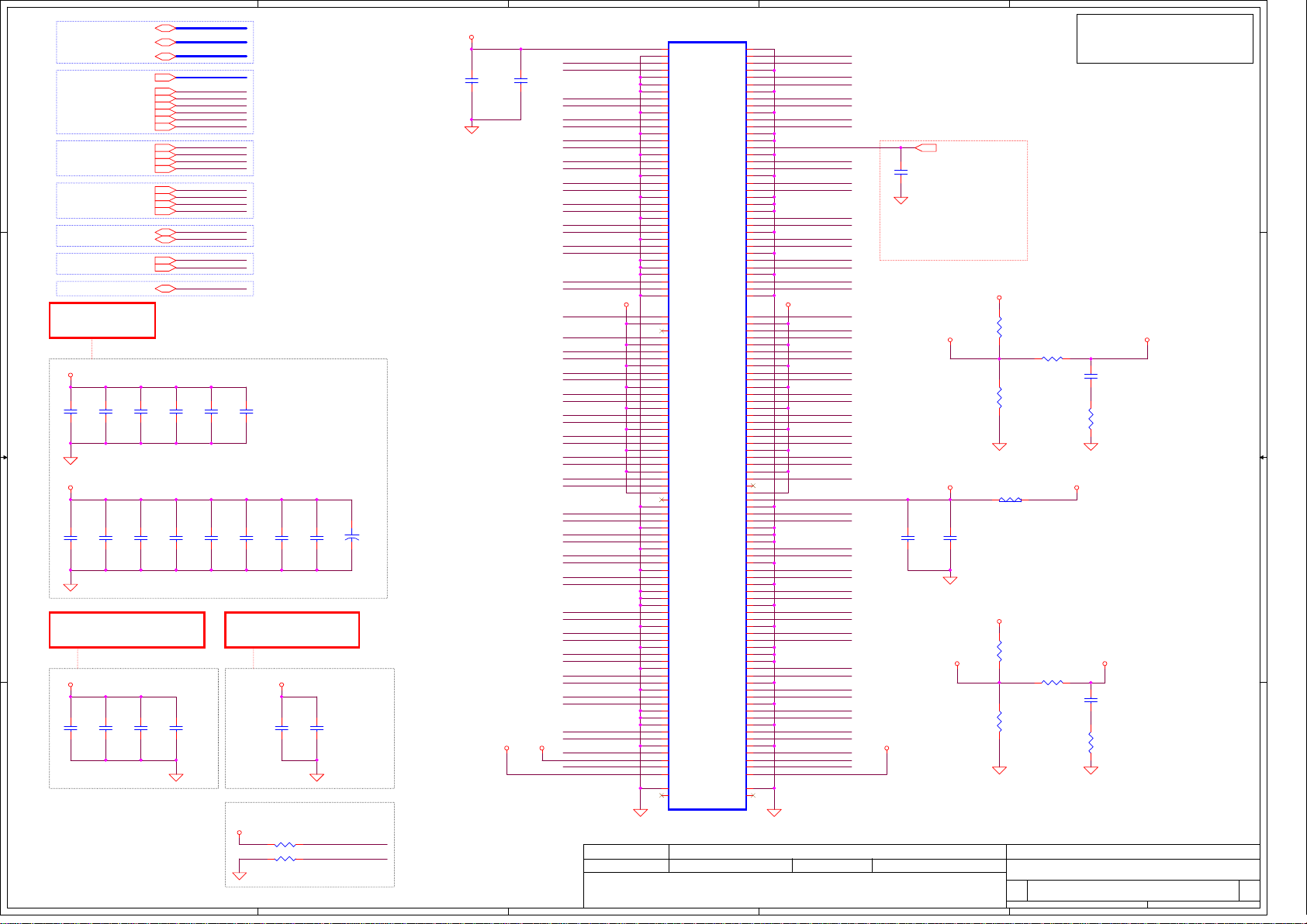

5

DGPU

NGFF WALN+BT

D D

NG

LAN

FF SSD

Thunderbolt

NGFF SSD

+3VS

1 2

RC105 10K_0402_5%

RPC10

18

27

C C

From 545659_SKL_PCH_U_Y_EDS_R0_7

+3VALW _DSW

+3V_PRIM

CLRP3 SHORT PADS

RC101 100K_0402_5%

+3VALW _DSW

B B

RC108 10K_0402_5%

36

45

10K_0804_8P4R_5%

RPC11

18

27

36

45

10K_0804_8P4R_5%

12

12

1 2

CLKREQ_PCIE#5

CLKREQ_PCIE#1

CLKREQ_PCIE#2

CLKREQ_PCIE#3

CLKREQ_PCIE#0

From 543016_SKL_PDG_UY_v1.0

PCH_PW ROK

LAN_WAKE#

EC_RSMRST#

SYS_RESET#

SYS_RESET#

PCH_DPW ROK

WAKE_PCH#_R

CLK_PCIE_N0<34>

CLK_PCIE_P0<34>

CLKREQ_PCIE#0<22,34>

CLK_PCIE_N1<32>

CLK_PCIE_P1<32>

CLKREQ_PCIE#1<32>

CLK_PCIE_N2<30>

CLK_PCIE_P2<30>

CLKREQ_PCIE#2<30>

CLK_PCIE_N3<36>

CLK_PCIE_P3<36>

CLKREQ_PCIE#3<36>

CLK_PCIE_N4<44>

CLK_PCIE_P4<44>

CLKREQ_PCIE#4<44>

CLK_PCIE_N5<36>

CLK_PCIE_P5<36>

CLKREQ_PCIE#5<36>

XCLK_BIASREF

Follow 546765_2014WW48_Skylake_MOW_Rev_1_0

Stuff 2.7k ohm(RC96) PH for Skylake U

Stuff 60.4 ohm(RC124) PD for Cannonlake U

EC_VCCST_PG

H_CPUPWRGD

SYS_RESET#

H_CPUPW RGD SYS_RESET#

100P_0402_50V8J

@ESD@

A A

VR_ON_EC<41>

For meet tPLT17 & tCPU28 power down sequence.

tPLT17 : 1us (Max)

tCPU28 : 1us (Max)

CC60

1

2

0.1U_0201_10V6K

PM_SLP_S3#

As Short As Possible

1

CC63

0.1U_0402_16V7K

@ESD@

2

+3V_PRIM

CC83

1 2

UC9

5

TC7SH08FU_SSOP5~D

1

P

B

4

O

2

A

G

3

1 2

@

RC127 0_0402_5%

5

SYS_RESET#<6>

EC_RSMRST#<6,41>

T95 TP@

Only For Power Sequence Debug

SYS_PWROK<41>

PCH_PW ROK<41>

DPWROK_EC<41>

SUSWARN#<41>

SUSACK#<41>

WAKE_PCH#<41>

VR_ON <58>

H_CPUPW RGD_R

EC_RSMRST#

1K_0402_5%

VCCST_PG_EC<41>

4

UC1J

CLK_PCIE_N0

CLK_PCIE_P0

CLKREQ_PCIE#0

CLK_PCIE_N1

CLK_PCIE_P1

CLKREQ_PCIE#1

CLK_PCIE_N2

CLK_PCIE_P2

CLKREQ_PCIE#2

CLK_PCIE_N3

CLK_PCIE_P3

CLKREQ_PCIE#3

CLK_PCIE_N4

CLK_PCIE_P4

CLKREQ_PCIE#4

CLK_PCIE_N5

CLK_PCIE_P5

CLKREQ_PCIE#5

RC102 1K_0402_5%@

RC112 0_0402_1%

RC114 0_0402_5%

RC110 0_0402_1%

RC100 1K_0402_5%

RC68 0_0402_1%

+1.0V_VCCST

RC113

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

1 2

RC96 2.7K_0402_1%

1 2

RC124 60.4_0402_1%@

1 2

1 2

@

1 2

@

1 2

@

1 2

@

1 2

@

12

From EC(open-drain)

RC116

1 2

60.4_0402_1%

4

EC_VCCST_PG

1

CC54

100P_0402_50V8J

@ESD@

2

3

SKL-U

CLOCK SIGNALS

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

10 OF 20

+1.0V_CLK5_F24NS

SOC_SRTCRST#

CLR ME

SOC_RTCRST#

CL

SM_INTRUDER#

PCH PLTRST Buffer

SOC_PLTRST#<22,34>

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPW RGD

EC_VCCST_PG

SYS_PWROK

PCH_PW ROK

PCH_DPW ROK

SUSWARN#

SUSACK#_R

WAKE_PCH#_R

LAN_WAKE#

T92 TP@

T94 TP@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SOC_PLTRST#

RC99 0_0402_5%@

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SYSTEM POWER MANAGEMENT

3

Rev_1.0

F43

CLK_CPU_ITP#

E43

CLK_CPU_ITP

BA17

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

L-U_BGA1356@

SK

R CMOS

+3VS

5

UC3

1

P

B

2

A

G

TC7SH08FU_SSOP5~D

3

1 2

2015/01/06 2016/01/06

2015/01/06 2016/01/06

2015/01/06 2016/01/06

SUSCLK

E37

SOC_XTAL24_IN

E35

SOC_XTAL24_OUT

E42

XCLK_BIASREF

AM18

SOC_RTCX1

AM20

SOC_RTCX2

AN18

SOC_SRTCRST#

AM16

SOC_RTCRST#

CC14

1 2

0.1U_0201_10V6K

4

O

SKL-U

11 OF 20

Compal Secret Data

Compal Secret Data

Compal Secret Data

RC104 0_0201_1%

12

12

12

CLRP1SHORT PADS

12

12

12

CLRP2SHORT PADS

12

RC941M_0402_5%

GPP_B11/EXT_PWR_GATE#

Deciphered Date

Deciphered Date

Deciphered Date

T89TP@

T90TP@

SUSCLK <32,36>

1 2

@

+3VL_RTC

RC9120K_0402_5%

CC101U_0402_6.3V6K

RC9320K_0402_5%

CC111U_0402_6.3V6K

PLT_RST# <30,32,36,41,44>

Rev_1.0

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

L-U_BGA1356@

SK

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

2

**Avoid Sub-trace**

Closed to CPU

SOC_XTAL24_IN

SOC_XTAL24_OUT

SOC_RTCRST#_R <6>

Closed to CPU

SOC_RTCX2

SOC_RTCX1

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_SUS#

SLP_LAN#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#_R

AC_PRESENT_R

PM_BATLOW#

SM_INTRUDER#

EXT_PW R_GATE#

SOC_VRALERT#

2

RC109 0_0402_1%@

1

XTAL@

GND

GND

1

1

2

4

3

3

1 2

CC13

YC1

XTAL@

24MHZ_12PF_7V24000020

XTAL@

1 2

CC1215P_0402_50V8J

RC92

1M_0402_5%

XTAL@

15P_0402_50V8J

1 2

**Avoid Sub-trace**

XTAL@

1 2

CC164.7P_0402_50V8C

RC98

10M_0402_5%

XTAL@

SOC_VRALERT#

PM_BATLOW#

AC_PRESENT_R

PBTN_OUT#_R

T87

TP@

T88TP@

1 2

12

DC2 RB751V-40_SOD323-2

T91

TP@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-C901P

LA-C901P

LA-C901P

Date: Sheet

Date: Sheet

Date: Sheet

YC2

32.768KHZ 9PF 20PPM 9H03280012

1 2

1 2

XTAL@

1 2

CC154.7P_0402_50V8C

XTAL@

12

RC11510K_0402_5% @

+3VALW _DSW

12

RC1038.2K_0402_5%

12

1 2

RC10610K_0402_5%

RC111100K_0402_5% @

PM_SLP_S0# <6,41>

PM_SLP_S3# <6,13,37,41>

PM_SLP_S4# <6,13,37,41,54>

PM_SLP_S5# <6,37,41>

SLP_SUS# <14,41>

PM_SLP_A# <6>

PBTN_OUT# <6,41>

ACIN <22,37,41,51,52>

PM_BATLOW# <44>

EXT_PW R_GATE# <14>

1

+3V_PRIM

Follow Echo

of

10 63Tuesday, August 04, 2015

of

10 63Tuesday, August 04, 2015

of

10 63Tuesday, August 04, 2015

1.0

1.0

1.0

Page 11

5

+3VS

RC203 10K_0402_5%

RC205 10K_0402_5%

RC62 49.9K_0402_1%

RC63 49.9K_0402_1%

D D

RC126 8.2K_0402_5%

C C

12

12

12

12

RPC7

18

I2C_1_SDA

27

I2C_1_SCL

36

I2C_0_SDA

45

I2C_0_SCL

10K_0804_8P4R_5%

12

WL_OFF#

@

PD_PWR_EN<41,46>

C10 for GC6_EVENT#

nsor

Se

Touch PAD/Panel

SOC_GPIOB21

EC_SMI#

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

Echo13

RTD3_CIO_PWR_EN<44>

RTD3_USB_PWR_EN<44>

B17 for GPU_GC6_FB_EN

PCIE_SEL<34>

WL_OFF#<32>

1 2

RC128 0_0201_5%

BT_OFF#<32>