Page 1

A

Compal Confidential

Model Name : A5WAH/A5WAB

1

File Name : LA-B991P

B

C

D

Compal Confidential

E

1

2

2

EA50_HB M/B Schematics Document

Intel Broadwell ULT (Broadwell + Wildcat point)

Nvidia N15S-GT / N15V-GM / N15V-GL

3

2014-08-27

REV:1.0

3

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

E

1 54Friday, October 17, 2014

of

1 54Friday, October 17, 2014

of

1 54Friday, October 17, 2014

of

4

1.0

1.0

1.0

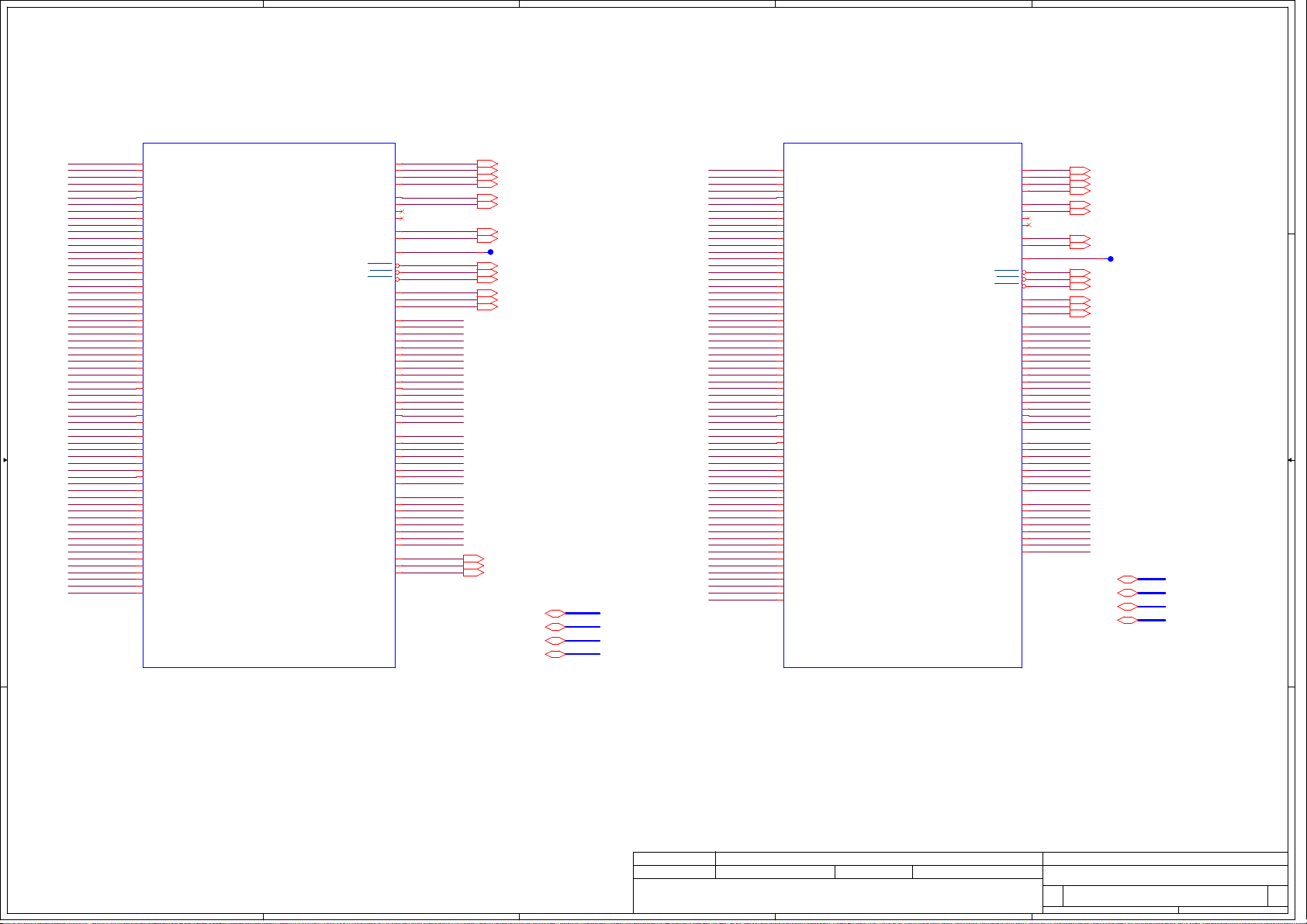

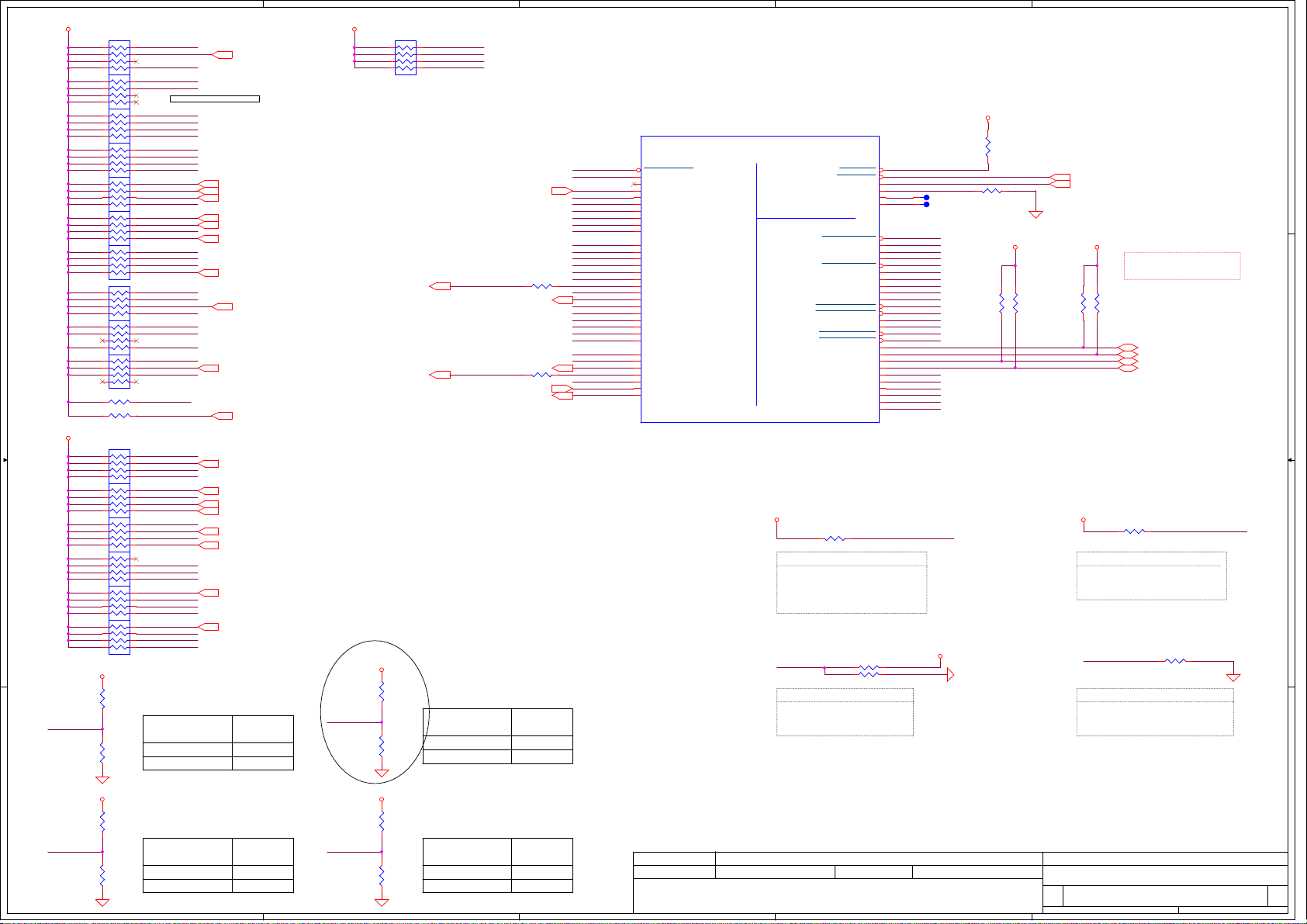

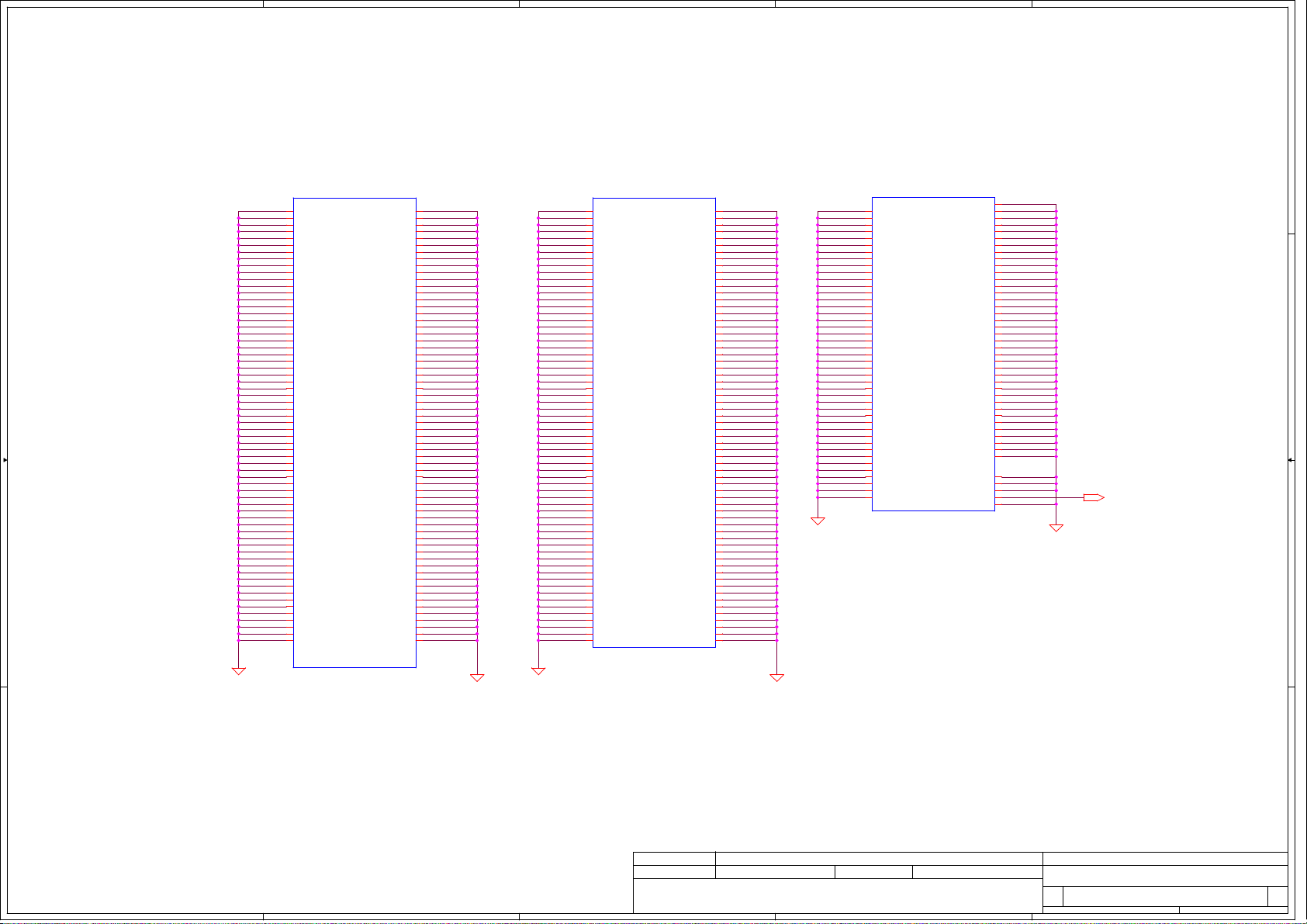

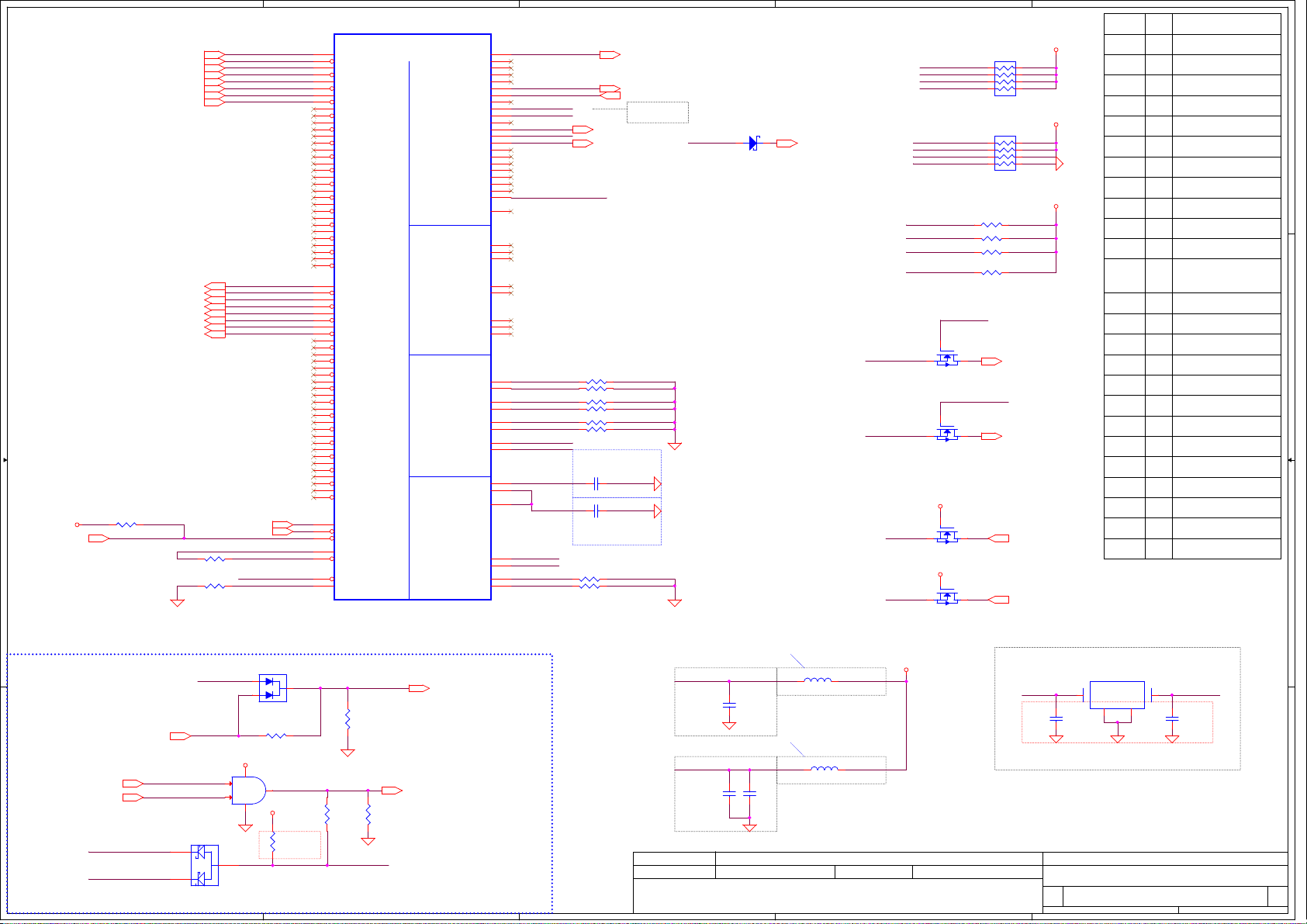

Page 2

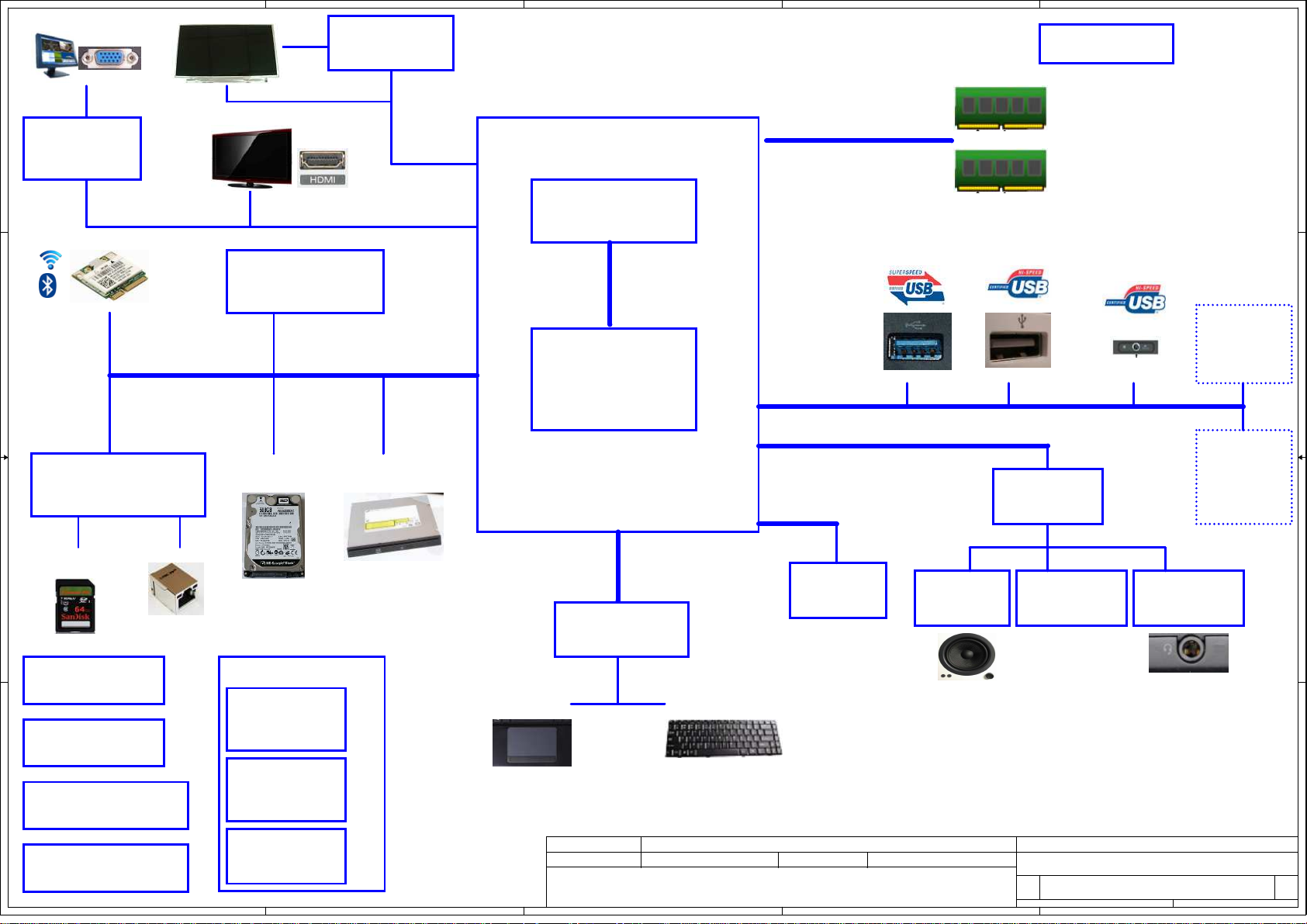

VGA

A

B

C

D

E

eDP

LVDS-Translator

LVDS

RTD2132R

page 24

Fan Control

page 36

page 28

1

DP to VGA

ITE IT6513FN

page 27

DP x 2 lanes

MINI Card

WLAN

USB port 4

2

LAN(GbE)/ Card Reader

Realtek 8411B

page 31

PCIe 2.0

5GT/s

port 4

PCIe 2.0

5GT/s

port 3

page 29

page 25

HDMI Conn.

page 26

HDMI x 4 lanes

Nvidia N15x

with DDR3 x4 or 8

page 17~23

PCIe 2.0 x4

5GT/s

port 5

SATA3.0 SATA3.0

port 0

SATA HDD

Conn.

Flexible IO

6.0 Gb/s6.0 Gb/s

port 1

SATA CDROM

Conn.

eDP

DDI

Intel Broadwell ULT

Broadwell ULT

Processor

OPI

Wildcat point

PCH

1168pin BGA

page 04~14

Memory BUS

Dual Channel

1.35V DDR3L 1333/1600

USBx8

HD Audio

SPI

48MHz

204pin DDR3L-SO-DIMM X1

BANK 0, 1, 2, 3

204pin DDR3L-SO-DIMM X1

BANK 4, 5, 6, 7

USB 3.0

conn x1

USB port 0

USB 2.0

conn x2

(port 1,2)

USB/B

CMOS

Camera

USB port 7

page 33 page 25

3.3V 24MHz

page 33

HDA Codec

ALC283

page 36

page 15

page 16

Finger

Print

USB

(port 5)

page 33

Touch

Screen

I2C (PORT1)

USB (port 6)

page 25

1

2

Card Reader

3

2 in 1 (SD)

page 30

RTC CKT.

Power On/Off CKT.

4

DC/DC Interface CKT.

Power Circuit DC/DC

RJ45 conn.

page 30

page 6

page 35

page 38

page 39~50

A

page 32

Sub Board

LS-B161P

PWR/B

page 33

LS-B162P

USB/B

(port 1,2)

page 33

LS-B163P

BATT/B (UMA)

page 32

B

LPC BUS

CLK=24MHz

ENE

KB9012/9022

Touch Pad Int.KBD

PS2 / I2C

page 35

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

page 34

C

page 35

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

SPI ROM x2

www.schematic-x.blogspot.com

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

page 7

Int. Speaker Combo Jack

page 36

D

Int. MIC

page 36 page 36

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

E

3

4

1.0

1.0

1.0

2 54Friday, October 17, 2014

of

2 54Friday, October 17, 2014

of

2 54Friday, October 17, 2014

of

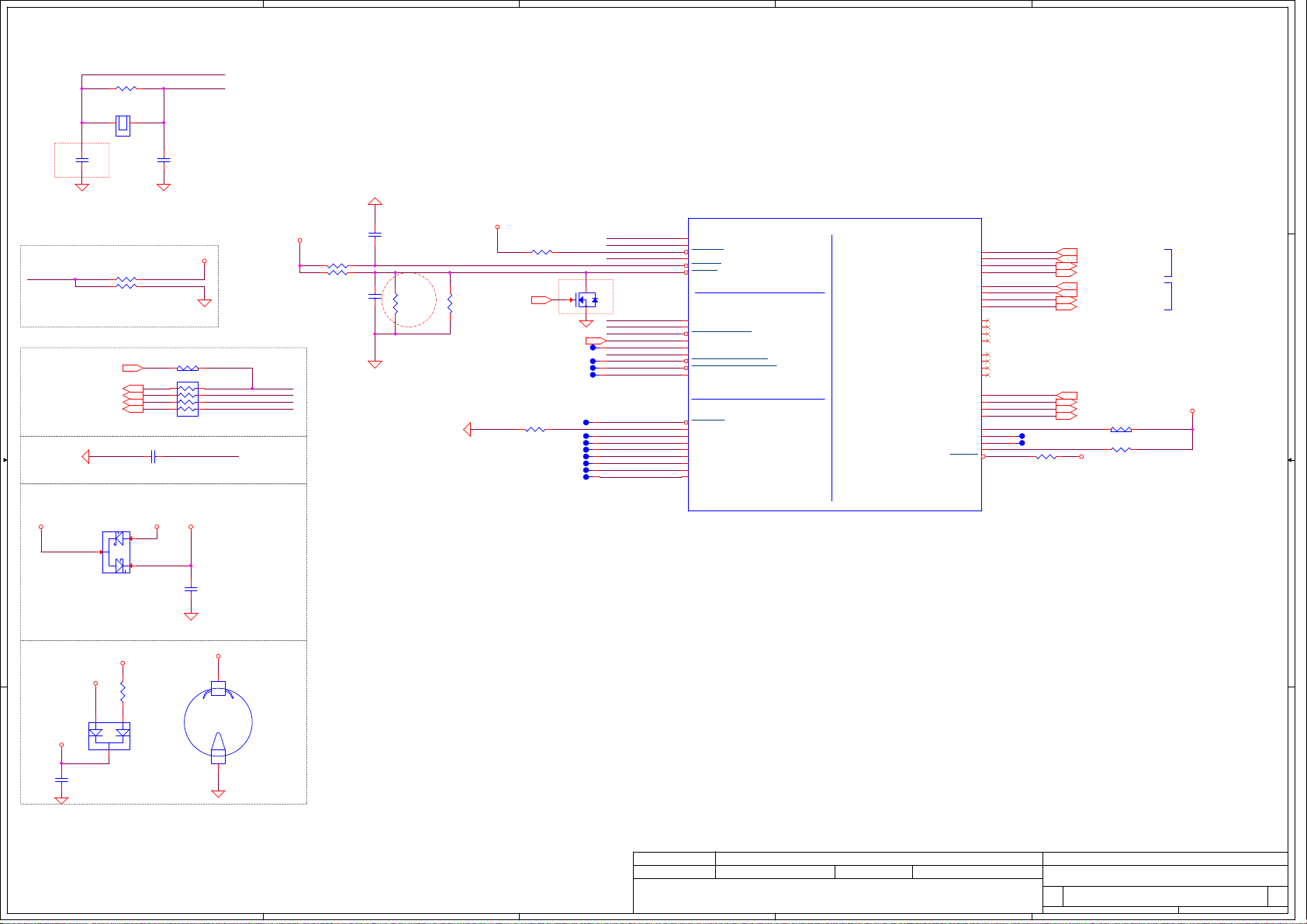

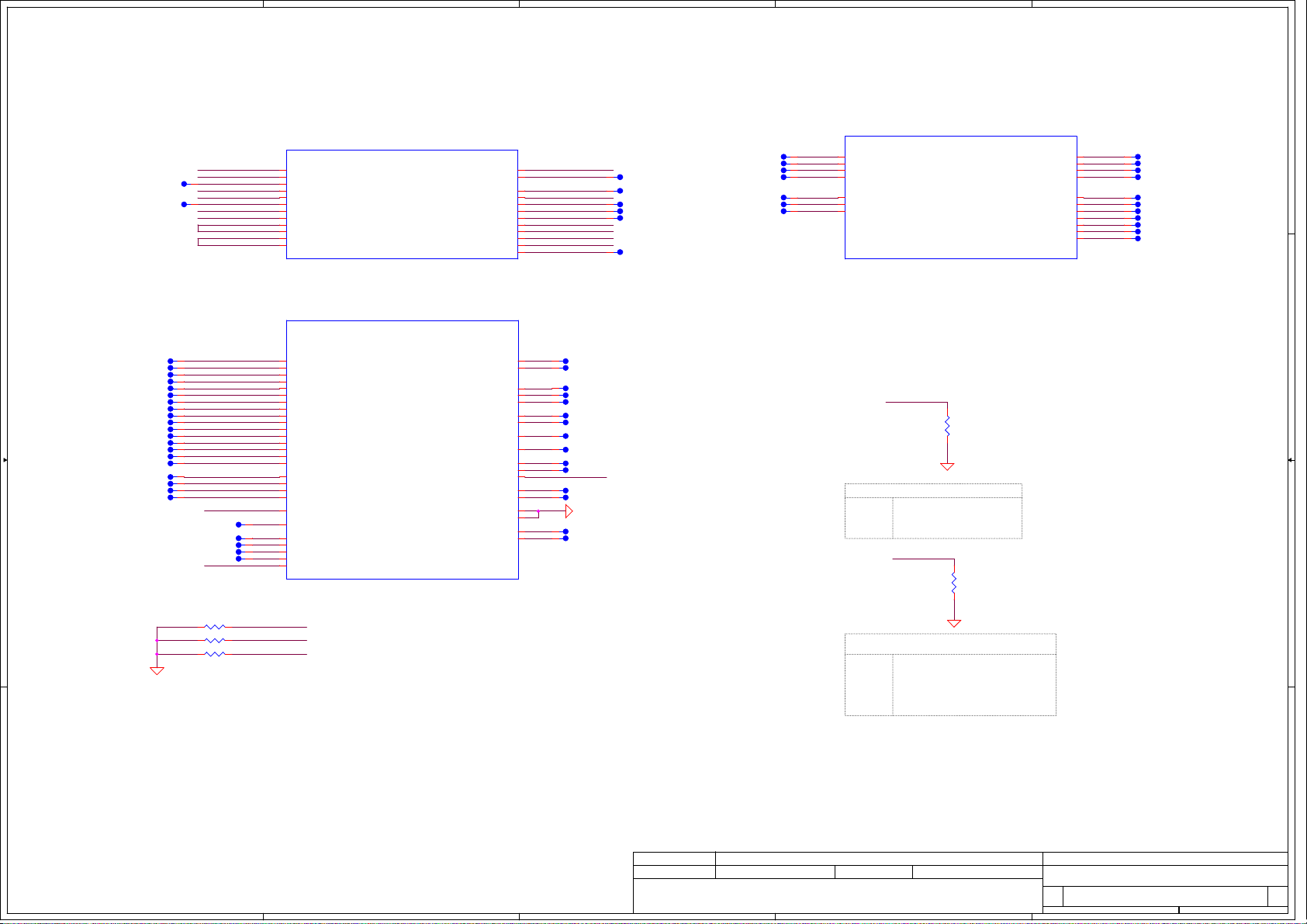

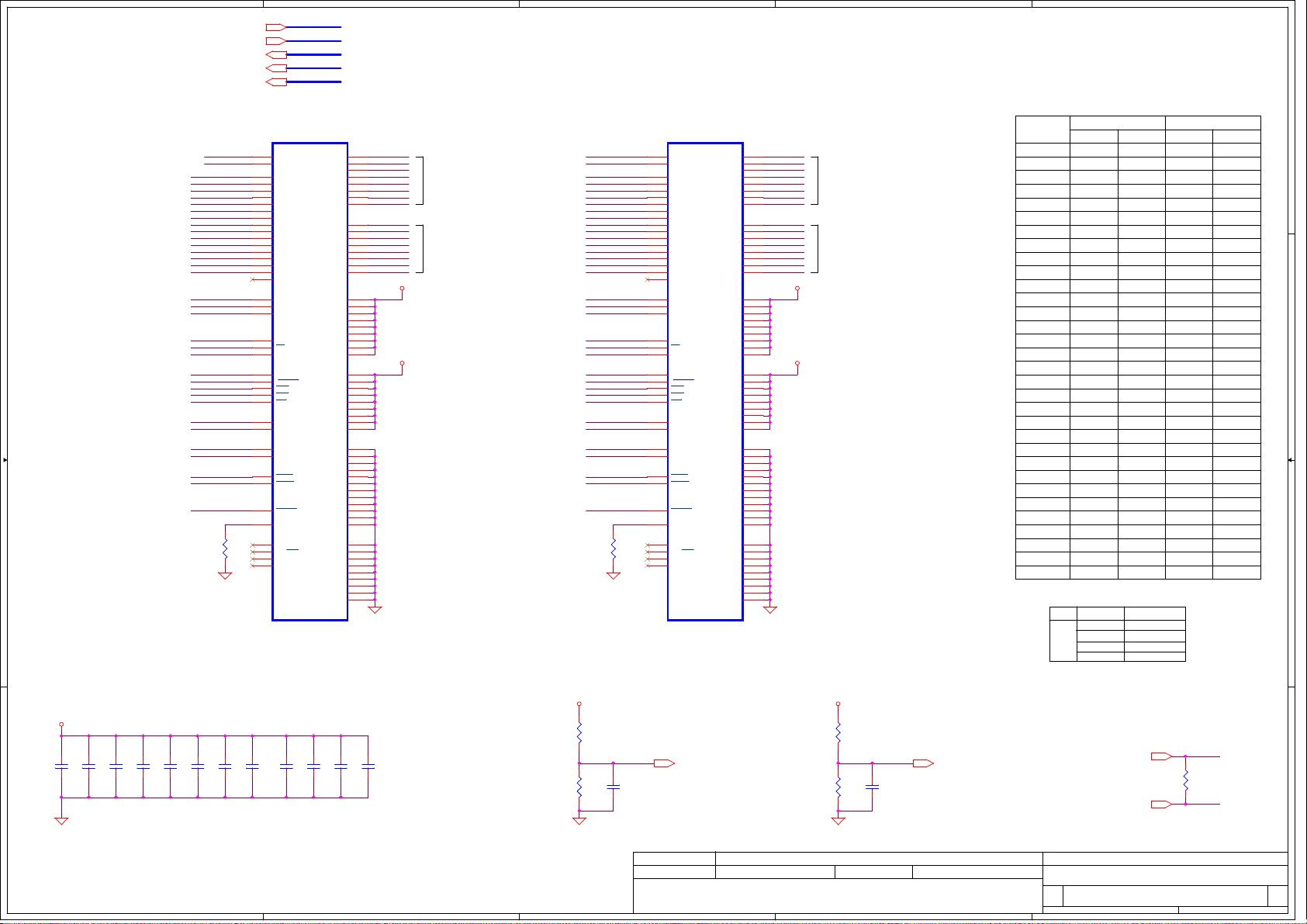

Page 3

A

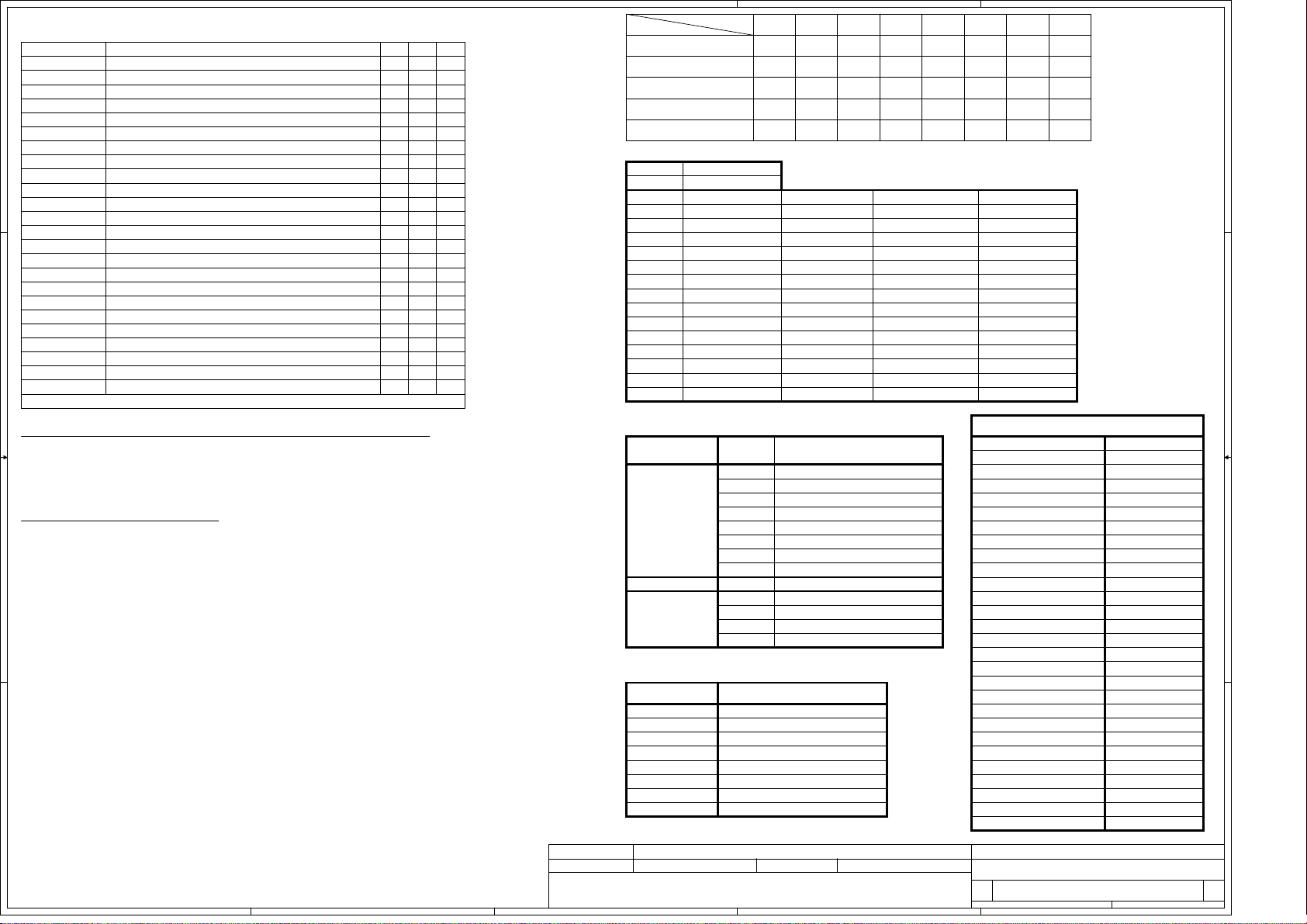

Voltage Rails

Power Plane Description

VIN

BATT+

B+

+CPU_CORE

+VGA_CORE

1

+0.675VS +0.675VS power rail for DDR3L terminator

+1.05VS_VTT

+1.05VSDGPU +1.05VSDGPU switched power rail for GPU

+1.35V

+1.5VSDGPU +1.5VSDGPU power rail for GPU

+1.5VS

+3VALW +3VALW always on power rail

+3VLP B+ to +3VLP power rail for suspend power

+3VS

+3VSDGPU

+5VALW

+5VS +5VALW to +5VS power rail

+RTCVCC

2

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

Battery power supply (12.6V)

AC or battery power rail for power circuit.

Core voltage for CPU

Core voltage for GPU

+1.05V power rail for CPU

+1.35V power rail for DDR3L

+1.5V power rail for CPU

+3VALW to +3VS power rail

+3VS to +3VSDGPU power rail for GPU

+5VALWP to +5VALW power rail

RTC power

B

S1 S3 S5

N/A N/A N/A

N/A N/A N/A

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

ON ON

ON

ON

ON

N/AN/AN/A

OFFOFF

OFF

OFF

OFF OFF

OFF OFF

OFF OFF

OFF

OFF OFF

OFF OFF

ON

ON*

ON

OFF

OFF

OFFOFF

ON

ON*

OFFONOFF

ONONON

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

D

HIGH

LOWLOWLOW

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 56K +/- 5%

8

9

10

11

12

13

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

12K +/- 5%

15K +/- 5%

20K +/- 5%

27K +/- 5%

33K +/- 5%

43K +/- 5%

AD_B ID

0 V

0.347 V 0.354 V 0.360 V

0.423 V

0.541 V

0.691 V

0.807 V 0.819 V 0.831 V

0.978 V

1.169 V

75K +/- 5%

100K +/- 5%

130K +/- 5%

160K +/- 5%

200K +/- 5%

240K +/- 5%

1.398 V

1.634 V

1.849 V 1.865 V 1.881 V

2.015 V 2.031 V 2.046 V

2.185 V 2.200 V 2.215 V

2.316 V 2.329 V 2.343 V

ON

ONONON ON

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

V typ

AD_B ID

ON

OFF

OFF

V

AD_B ID

0 V 0 V

0.430 V

0.550 V

0.702 V 0.713 V

0.992 V

1.185 V

1.414 V 1.430 V

1.650 V 1.667 V

ON

OFF

OFF

OFF

max

0.438 V

0.559 V

1.006 V

1.200 V

LOW

OFF

OFF

OFF

E

1

2

EC SM Bus1 address

Device

Smart Battery

PCH SM Bus address

Device

ChannelA DIMM 0

3

4

DIMM 1ChannelB JDIMM2

EC SM Bus2 address

Address Address

0x16

Address

1010 0000

1010 0010

A

JDIMM1

Device

On Board Thermal Senser

VGA Internal Thermal Senser

0x96

0x9E

B

USB Port Table

USB 2.0 Port

0

1

2

EHCI1

3

4

5

6

7

PortUSB 3.0

0

XHCI

1

2

3

3 External

USB Port

USB Port(Left 3.0)

USB Port(Right 2.0)

USB Port(Right 2.0)

Mini Card (WLAN+BT)

Touch Screen

Camera

Finger Print

USB Port(Left 3.0)

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

PCB Revision

0.1

0.2

0.3

1.0

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

BTO Option Table

BTO Item BOM Structure

Unpop @

EC 9022 9022@

EC 9012 9012@

UMA Component

GPU

On Board HDD

EDP panel EDP@

eDP to LVDS LVDS@

EMC Reserve XEMC@

TPM Module TPM@

G-Sensor BA@

Redriver HDD

Touch Screen TS@

DGPU_IDEN

CPU_IDEN

GC6 2.0

non GC6

One DMIC

Two DMIC

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

CONN@Connector

UMA@

VGA@

HDD@

EMC@EMC Component

BA@

X76@VRAM Selection

VGL@, VGM@, SGT@

HW@, BW@

GC6@

NGC6@

EA50@

2MIC@

3 54Friday, October 17, 2014

3 54Friday, October 17, 2014

3 54Friday, October 17, 2014

E

of

of

of

3

4

1.0

1.0

1.0

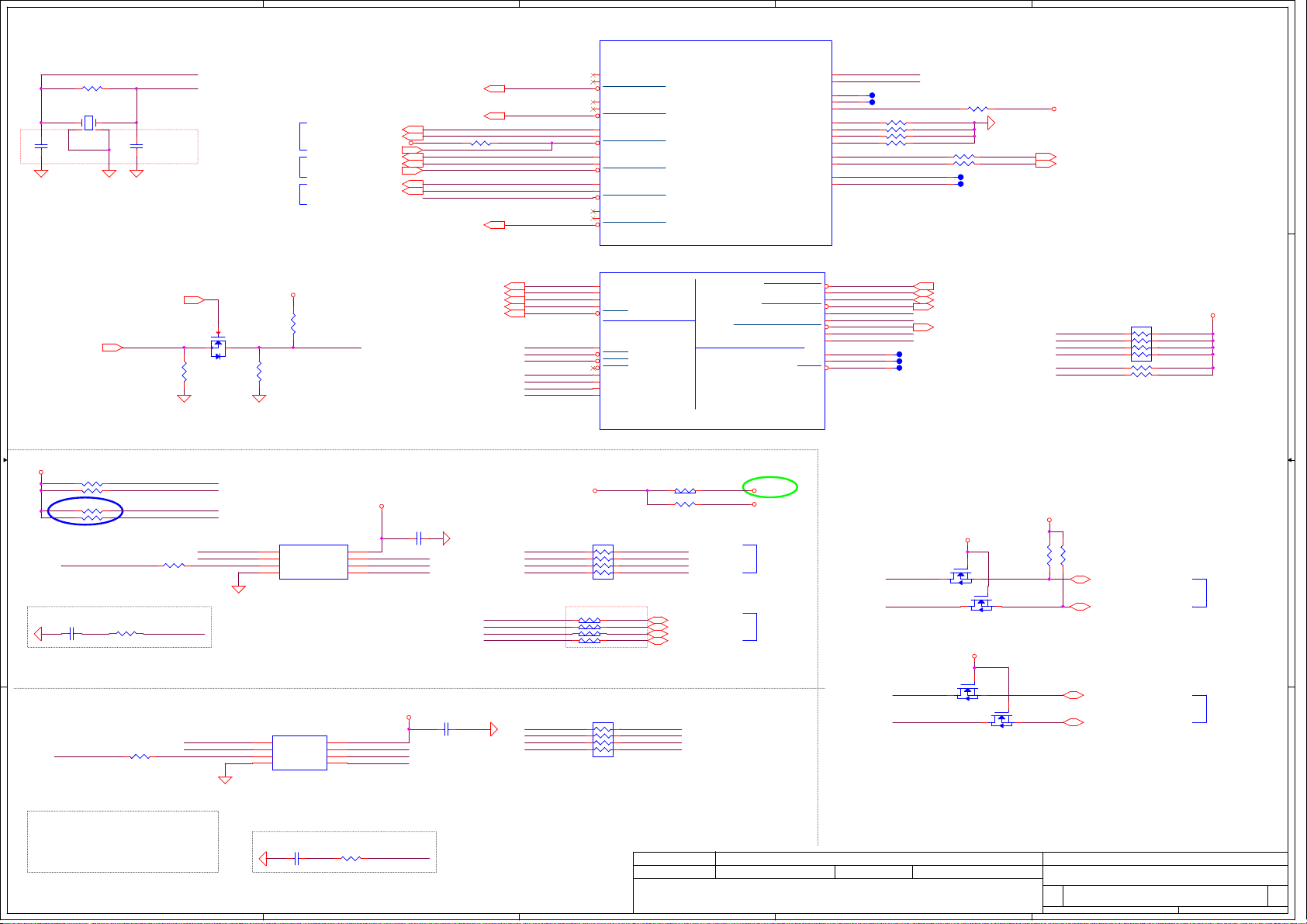

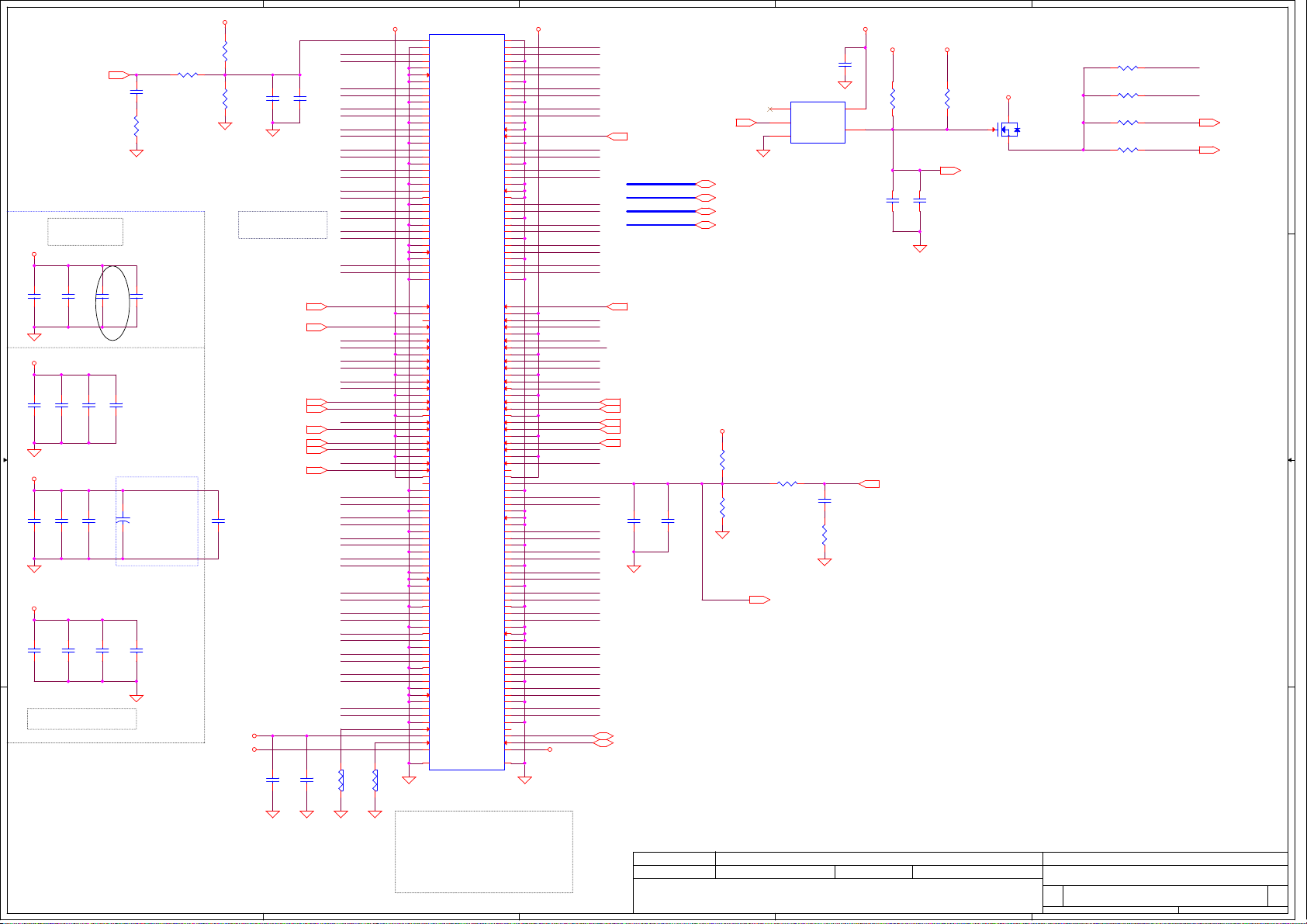

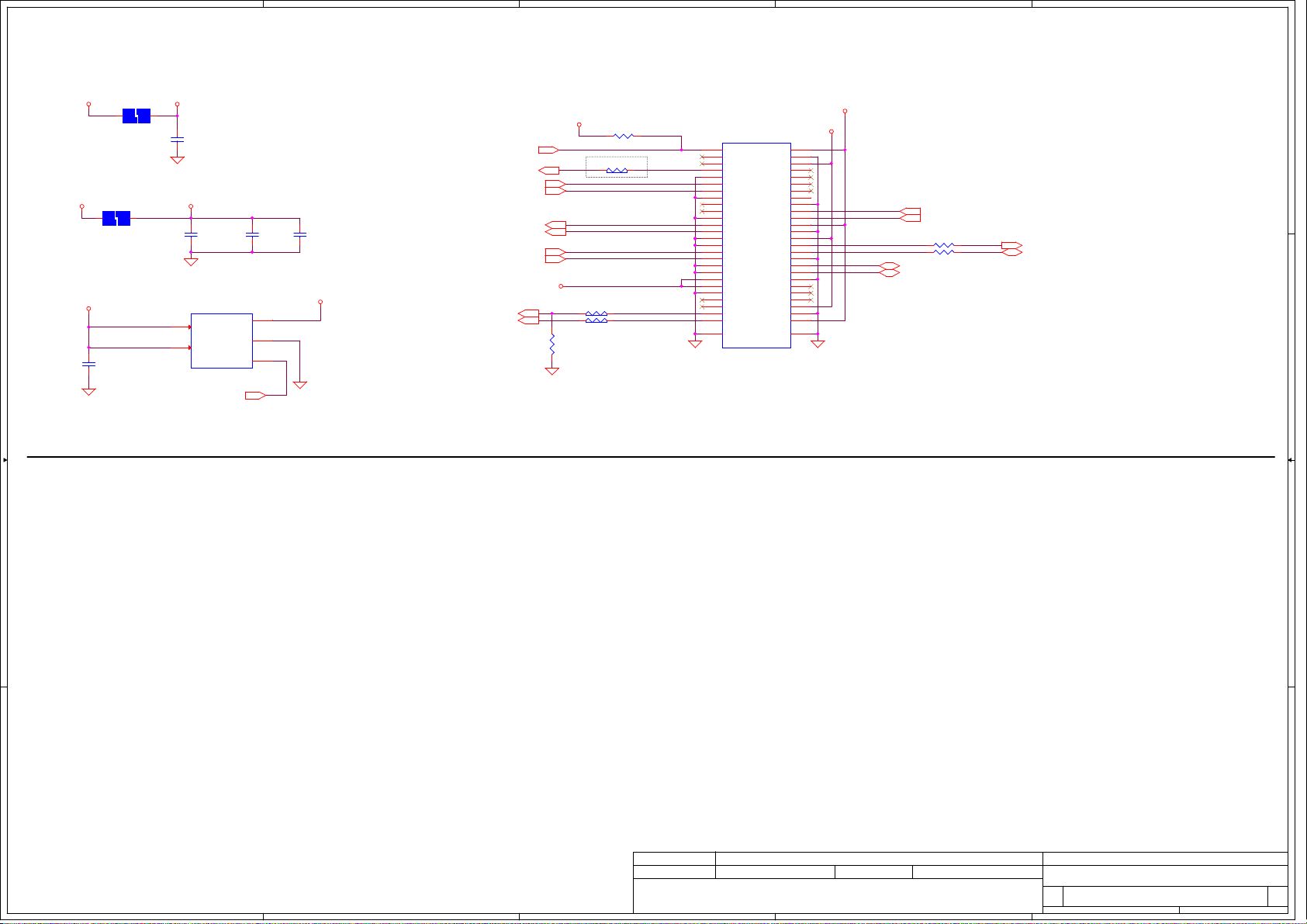

Page 4

5

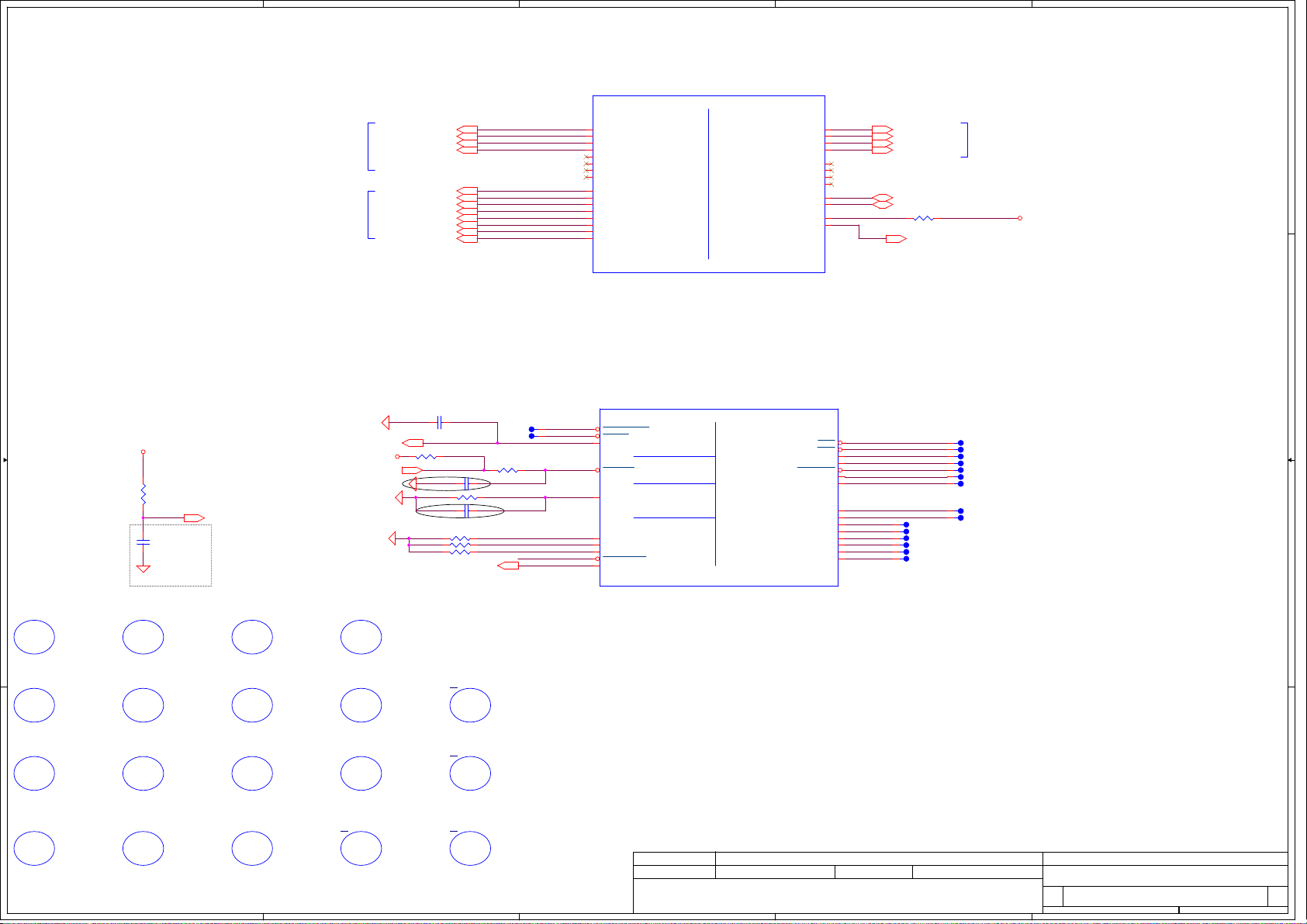

DDR3 Compensat i on Si gnal s

4

3

2

1

U1A

D

DP to CRT

HDMI

C

+1.35V

1

R184

470_0603_5%

2

2

C96

6.8P_0402_50V8C

1

XEMC@

B

U1

Close to AV15

PVT2 ,Replace i3-4030 to i3-4020

U1

DIMM_DRAMRST# <15,16>

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 m il

U1

+1.05VS_VTT

H_PROCHOT#<36,41>

A5WAH PVT: ESD request add

U1

CPU_DP1_N0<29>

CPU_DP1_P0<29>

CPU_DP1_N1<29>

CPU_DP1_P1<29>

CPU_DP2_N0<28>

CPU_DP2_P0<28>

CPU_DP2_N1<28>

CPU_DP2_P1<28>

CPU_DP2_N2<28>

CPU_DP2_P2<28>

CPU_DP2_N3<28>

CPU_DP2_P3<28>

1

C94 6.8P_0402_50V8C

XEMC@

H_PECI<36>

2

C95 6.8P_0402_50V8C

EMC@

R6 10K_0402_5%

C60 6.8P_0402_50V8C

EMC@

R11 200_0402_1%

R13 120_0402_1%

R41 100_0402_1%

2

1

R68

62_0402_5%

1

1

1

1

1

1

DDR_PG_CTRL<15>

2

2

2

2

2

2

R8

56_0402_5%

1

T20 @

T2 @

2

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DIMM_DRAMRST#

DDR_PG_CTRL

H_PROCHOT#_R

H_CPUPWRGD

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

HASWELL-MCP-E-ULT_BGA1168

@

U1B

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

DDI EDP

1 OF 19

HASWELL_MCP_E

MISC

JTAG

THERMAL

PWR

DDR3

2 OF 19

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

Rev1p2

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

PRDY

PREQ

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

Rev1p2

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

EDP_TXN0 <27>

EDP_TXP0 <27>

EDP_TXN1 <27>

EDP_TXP1 <27>

EDP_AUXN <27>

EDP_AUXP <27>

EDP_COMP

Trace width=20 mils,Spacing=25mil,Max length=100mils

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

XDP_TDI_R

XDP_TDO_R

XDP_BPM#0_R

XDP_BPM#1_R

1

R1 24.9_0402_1%

EDP_DISP_UTIL <27>

T148@

T149@

T150@

T151@

T152@

T153@

2

eDP Panel

T157@

T158@

T159@

T160@

T161@

T162@

T163@

T164@

T165@

D

+VCCIOA_OUT

C

B

CPU_Haswell intel PMD3558U 1.7G

3558@

SA00007G260

U1

CPU_Haswell intel I5-4210 1.7G

4210@

SA00007LO70

U1

CPU_Haswell intel I3-4020 1.9G

4020@

A

SA00007MG50

ZZZ

PCB A5WAH LA-B991P LS-B161P/B162P

DAZ1A400100

CPU_Haswell intel I3-4030 1.9G

4030@

SA00007TA60

U1

CPU_Haswell intel I7-4510 2G

4510@

SA00007M760

U1

CPU_Haswell intel PMD3556U 1.7G

3556@

SA000072Y70

U1

CPU_Boardwell intel QG21 1.2G

QG21@

SA00007OS10

5

CPU Haswell InteI I5-4200U 1.6G

4200@

SA00006SMB0

U1

CPU Haswell Intel I7-4500U 1.8G

4500@

SA00006SLB0

U1

CPU_Haswell intel I7-4550U 1.5G

4550@

SA00006SJA0

U1

CPU_Boardwell intel QG22 1.2G

QG22@

SA00007OT10

CPU Haswell Intel I3-4010U 1.7G

4010@

SA00006SX70

U1

CPU_Haswell intel I3-4158U 2G

4158@

SA00006VW40

U1

CPU_Haswell intel PDC2957 1.4G

2957@

SA00007G060

U1

CPU_Boardwell intel QGH9 1.8G

QGH9@

SA00007U920

4

U1

CPU Haswell InteI I3-4005 1.7G

4005@

SA000072QD0

U1

CPU_Boardwell intel QGHB 1.6G

QGHB@

SA00007UH20

U1

CPU_Boardwell intel QGHA 1.6G

QGHA@

SA00007UG20

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet

Compal Electronics, Inc.

BDW MCP(1/11) DDI,MSIC,XDP

BDW MCP(1/11) DDI,MSIC,XDP

BDW MCP(1/11) DDI,MSIC,XDP

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

1

4 54Friday, October 17, 2014

4 54Friday, October 17, 2014

4 54Friday, October 17, 2014

of

of

of

A

1.0

1.0

1.0

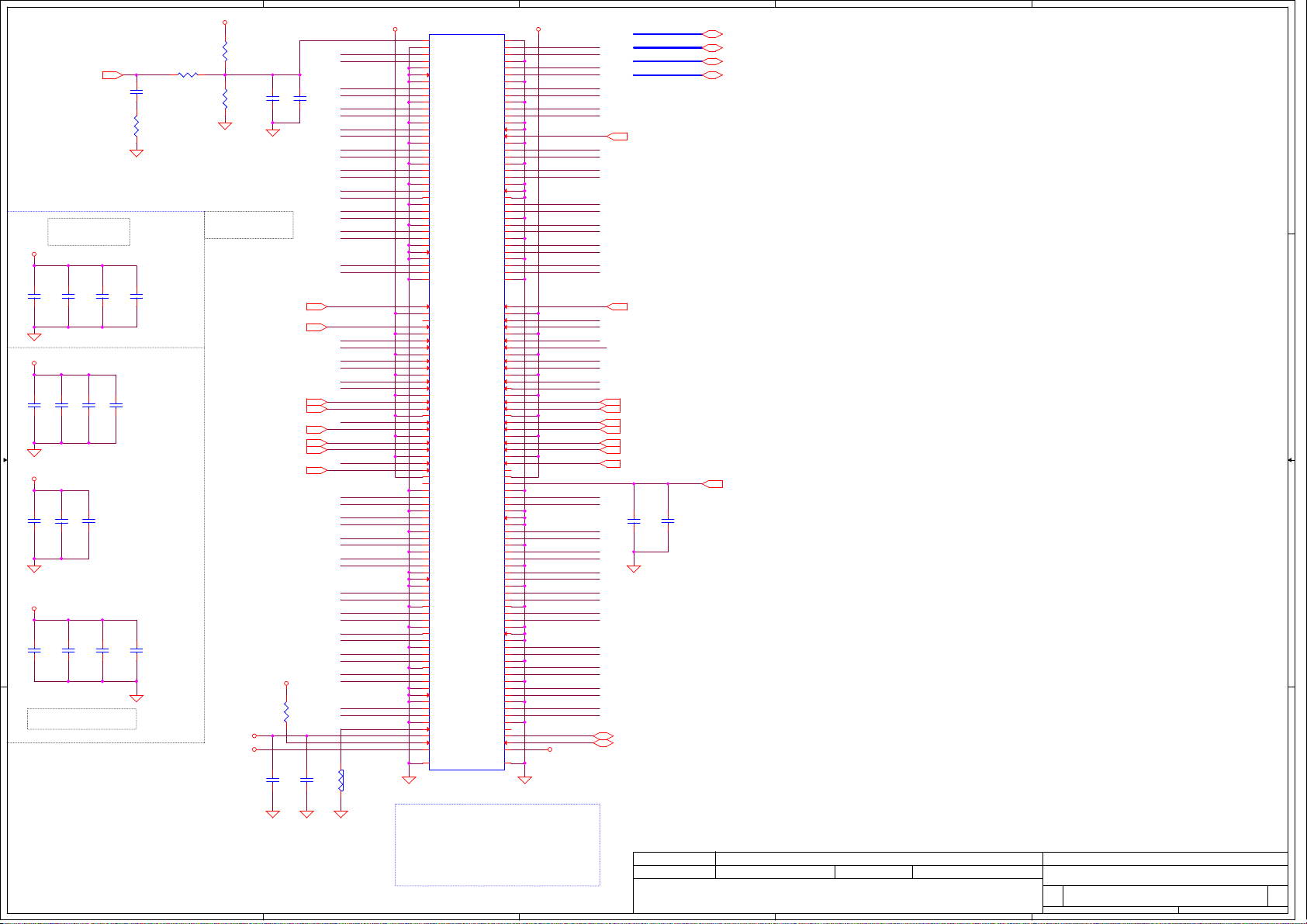

Page 5

5

4

3

2

1

D

U1C

DDR_A_D0

AH63

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

C

B

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

SA_DQ0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ10

AP62

SA_DQ11

AM61

SA_DQ12

AM60

SA_DQ13

AP61

SA_DQ14

AP60

SA_DQ15

AP58

SA_DQ16

AR58

SA_DQ17

AM57

SA_DQ18

AK57

SA_DQ19

AL58

SA_DQ20

AK58

SA_DQ21

AR57

SA_DQ22

AN57

SA_DQ23

AP55

SA_DQ24

AR55

SA_DQ25

AM54

SA_DQ26

AK54

SA_DQ27

AL55

SA_DQ28

AK55

SA_DQ29

AR54

SA_DQ30

AN54

SA_DQ31

AY58

SA_DQ32

AW58

SA_DQ33

AY56

SA_DQ34

AW56

SA_DQ35

AV58

SA_DQ36

AU58

SA_DQ37

AV56

SA_DQ38

AU56

SA_DQ39

AY54

SA_DQ40

AW54

SA_DQ41

AY52

SA_DQ42

AW52

SA_DQ43

AV54

SA_DQ44

AU54

SA_DQ45

AV52

SA_DQ46

AU52

SA_DQ47

AK40

SA_DQ48

AK42

SA_DQ49

AM43

SA_DQ50

AM45

SA_DQ51

AK45

SA_DQ52

AK43

SA_DQ53

AM40

SA_DQ54

AM42

SA_DQ55

AM46

SA_DQ56

AK46

SA_DQ57

AM49

SA_DQ58

AK49

SA_DQ59

AM48

SA_DQ60

AK48

SA_DQ61

AM51

SA_DQ62

AK51

SA_DQ63

HASWELL-MCP-E-ULT_BGA1168

@

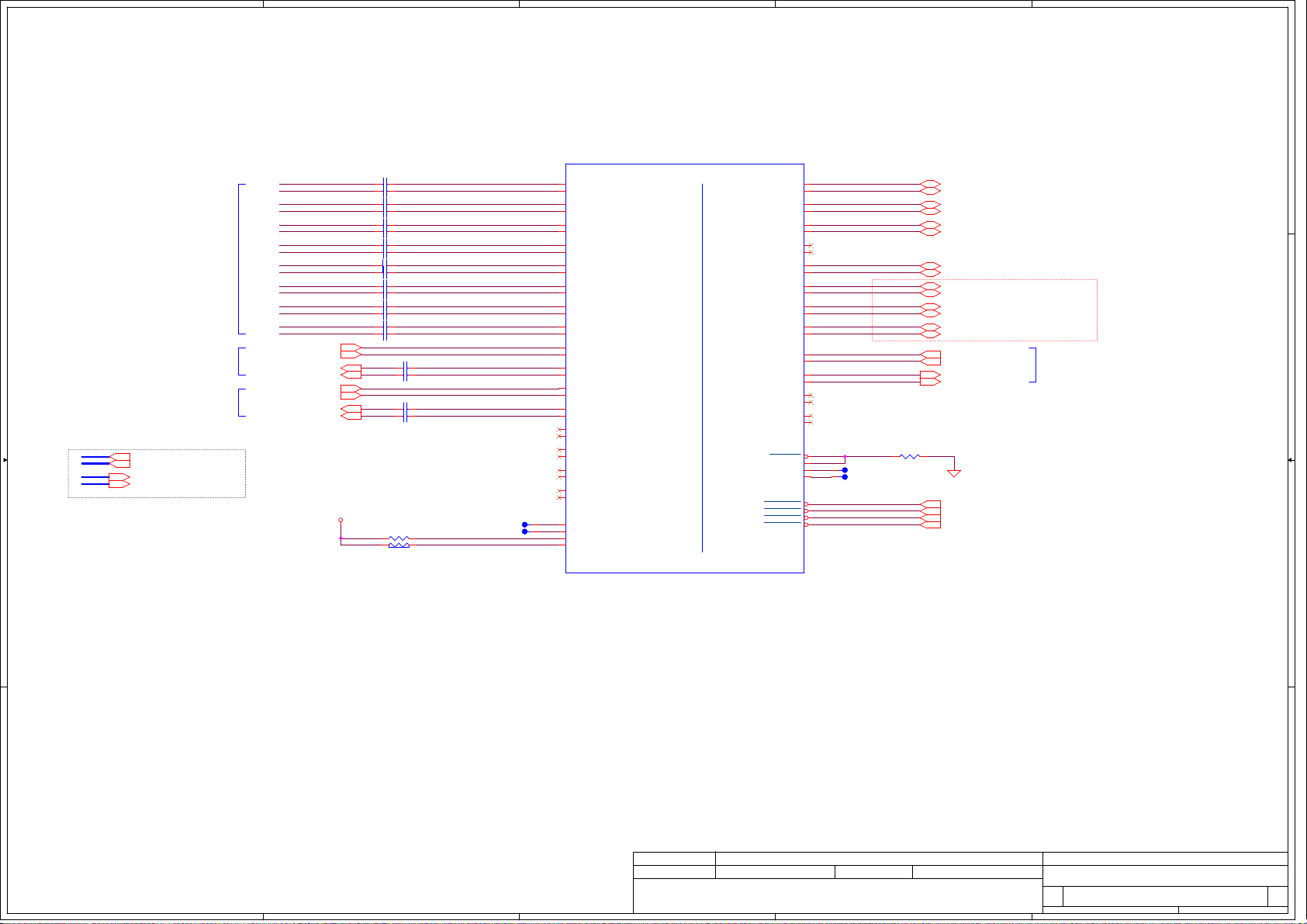

HASWELL_MCP_E

DDR CHANNEL A

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

Rev1p2

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

DDRA_ODT0

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

SA_CLK_DDR#0 <15>

SA_CLK_DDR0 <15>

SA_CLK_DDR#1 <15>

SA_CLK_DDR1 <15>

DDRA_CKE0_DIMMA <15>

DDRA_CKE1_DIMMA <15>

DDRA_CS0_DIMMA# <15>

DDRA_CS1_DIMMA# <15>

T4@

DDR_A_RAS# <15>

DDR_A_WE# <15>

DDR_A_CAS# <15>

DDR_A_BS0 <15>

DDR_A_BS1 <15>

DDR_A_BS2 <15>

SM_DIMM_VREFCA <15>

SA_DIMM_VREFDQ <15>

SB_DIMM_VREFDQ <16>

DDR_A_D[0..63]<15>

DDR_A_MA[0..15]<15>

DDR_A_DQS#[0..7]<15>

DDR_A_DQS[0..7]<15>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

U1D

AY31

SB_DQ0

AW31

SB_DQ1

AY29

SB_DQ2

AW29

SB_DQ3

AV31

SB_DQ4

AU31

SB_DQ5

AV29

SB_DQ6

AU29

SB_DQ7

AY27

SB_DQ8

AW27

SB_DQ9

AY25

SB_DQ10

AW25

SB_DQ11

AV27

SB_DQ12

AU27

SB_DQ13

AV25

SB_DQ14

AU25

SB_DQ15

AM29

SB_DQ16

AK29

SB_DQ17

AL28

SB_DQ18

AK28

SB_DQ19

AR29

SB_DQ20

AN29

SB_DQ21

AR28

SB_DQ22

AP28

SB_DQ23

AN26

SB_DQ24

AR26

SB_DQ25

AR25

SB_DQ26

AP25

SB_DQ27

AK26

SB_DQ28

AM26

SB_DQ29

AK25

SB_DQ30

AL25

SB_DQ31

AY23

SB_DQ32

AW23

SB_DQ33

AY21

SB_DQ34

AW21

SB_DQ35

AV23

SB_DQ36

AU23

SB_DQ37

AV21

SB_DQ38

AU21

SB_DQ39

AY19

SB_DQ40

AW19

SB_DQ41

AY17

SB_DQ42

AW17

SB_DQ43

AV19

SB_DQ44

AU19

SB_DQ45

AV17

SB_DQ46

AU17

SB_DQ47

AR21

SB_DQ48

AR22

SB_DQ49

AL21

SB_DQ50

AM22

SB_DQ51

AN22

SB_DQ52

AP21

SB_DQ53

AK21

SB_DQ54

AK22

SB_DQ55

AN20

SB_DQ56

AR20

SB_DQ57

AK18

SB_DQ58

AL18

SB_DQ59

AK20

SB_DQ60

AM20

SB_DQ61

AR18

SB_DQ62

AP18

SB_DQ63

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

DDR CHANNEL B

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

Rev1p2

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDRB_ODT0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_D[0..63]<16>

DDR_B_MA[0..15]<16>

DDR_B_DQS#[0..7]<16>

DDR_B_DQS[0..7]<16>

SB_CLK_DDR#0 <16>

SB_CLK_DDR0 <16>

SB_CLK_DDR#1 <16>

SB_CLK_DDR1 <16>

DDRB_CKE0_DIMMB <16>

DDRB_CKE1_DIMMB <16>

DDRB_CS0_DIMMB# <16>

DDRB_CS1_DIMMB# <16>

T5@

DDR_B_RAS# <16>

DDR_B_WE# <16>

DDR_B_CAS# <16>

DDR_B_BS0 <16>

DDR_B_BS1 <16>

DDR_B_BS2 <16>

D

C

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

2

Date : Sheet

Compal Electronics, Inc.

BDW MCP(2/11) DDRIII

BDW MCP(2/11) DDRIII

BDW MCP(2/11) DDRIII

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

1

5 54Friday, October 17, 2014

of

5 54Friday, October 17, 2014

of

5 54Friday, October 17, 2014

of

A

1.0

1.0

1.0

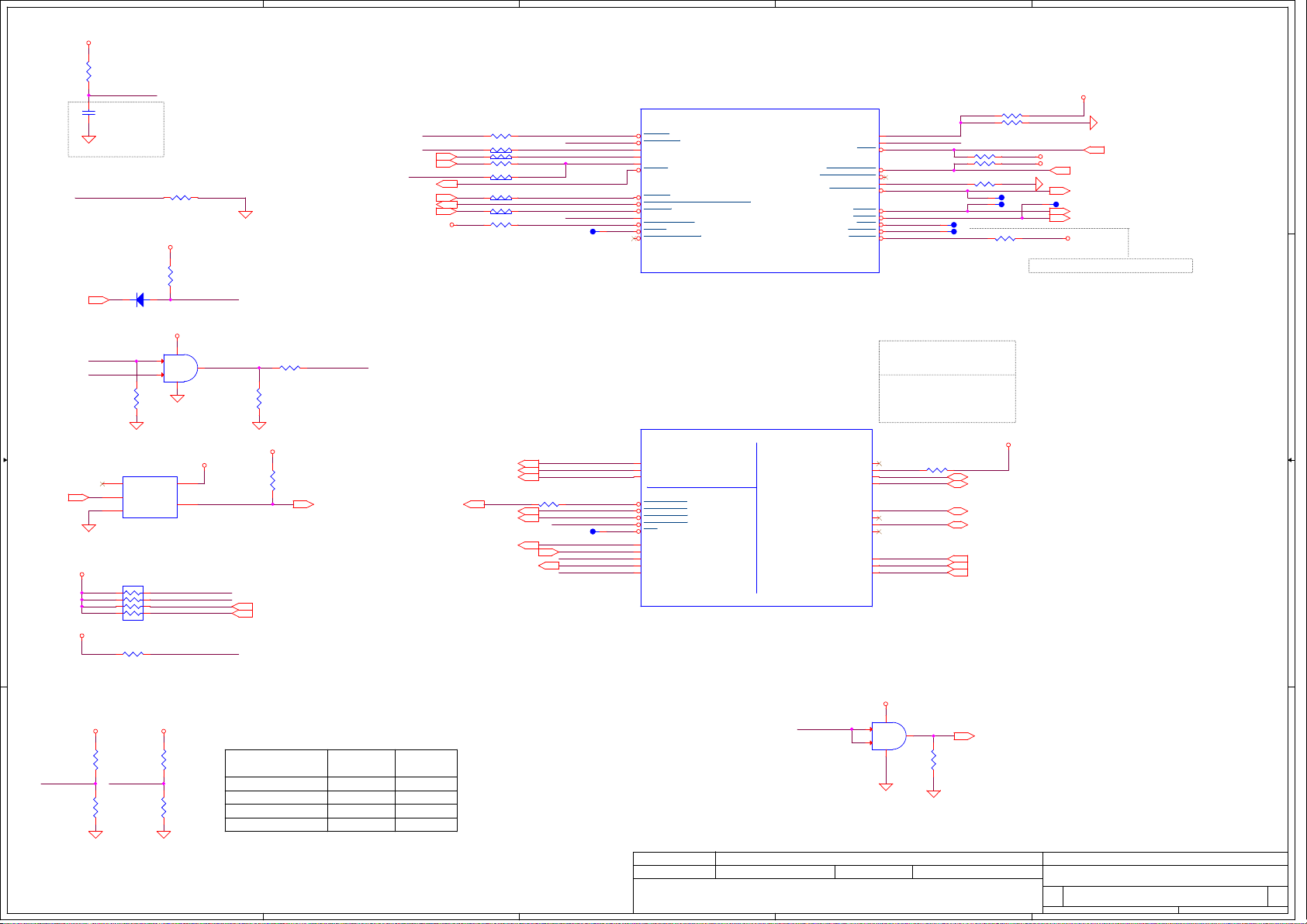

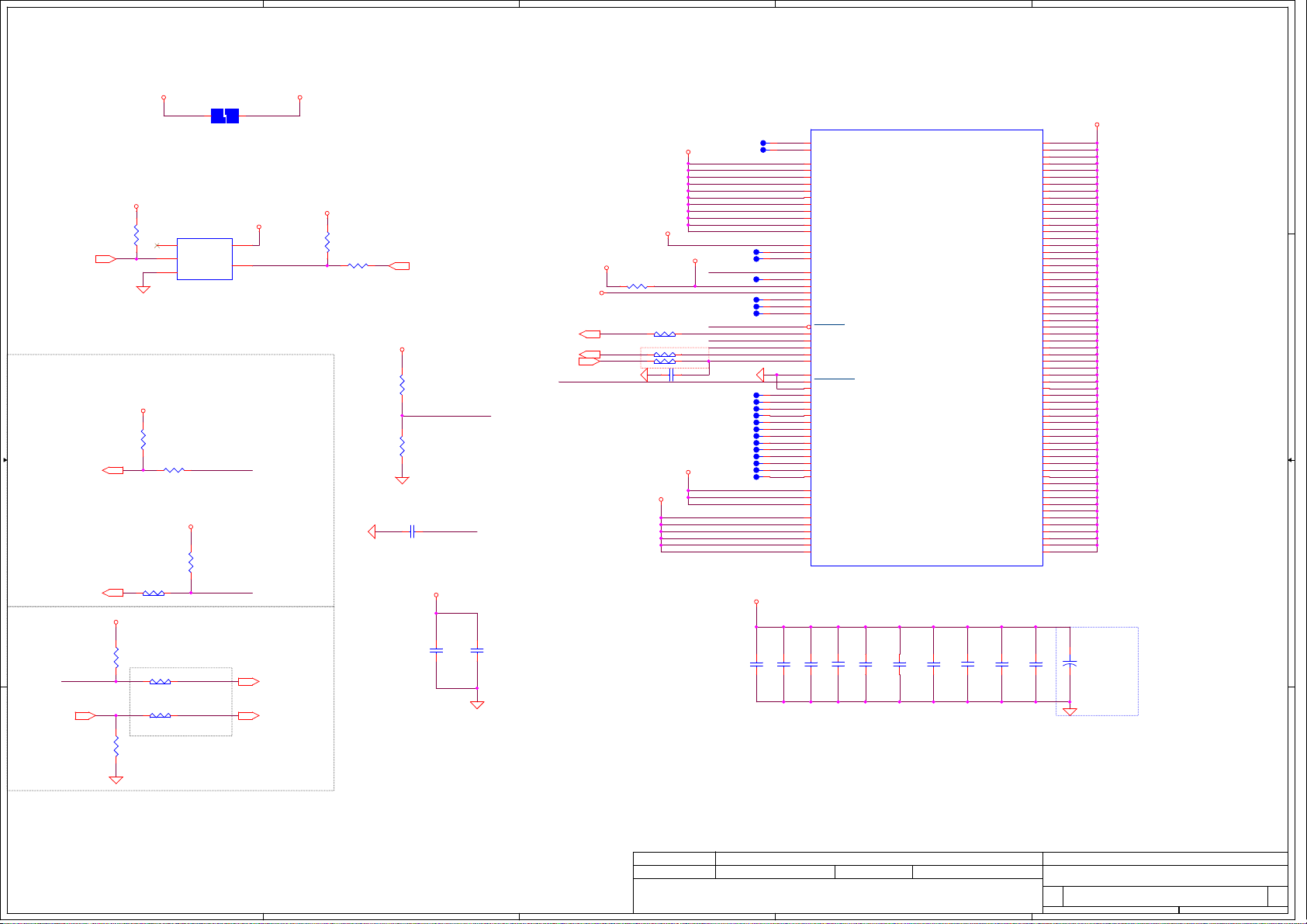

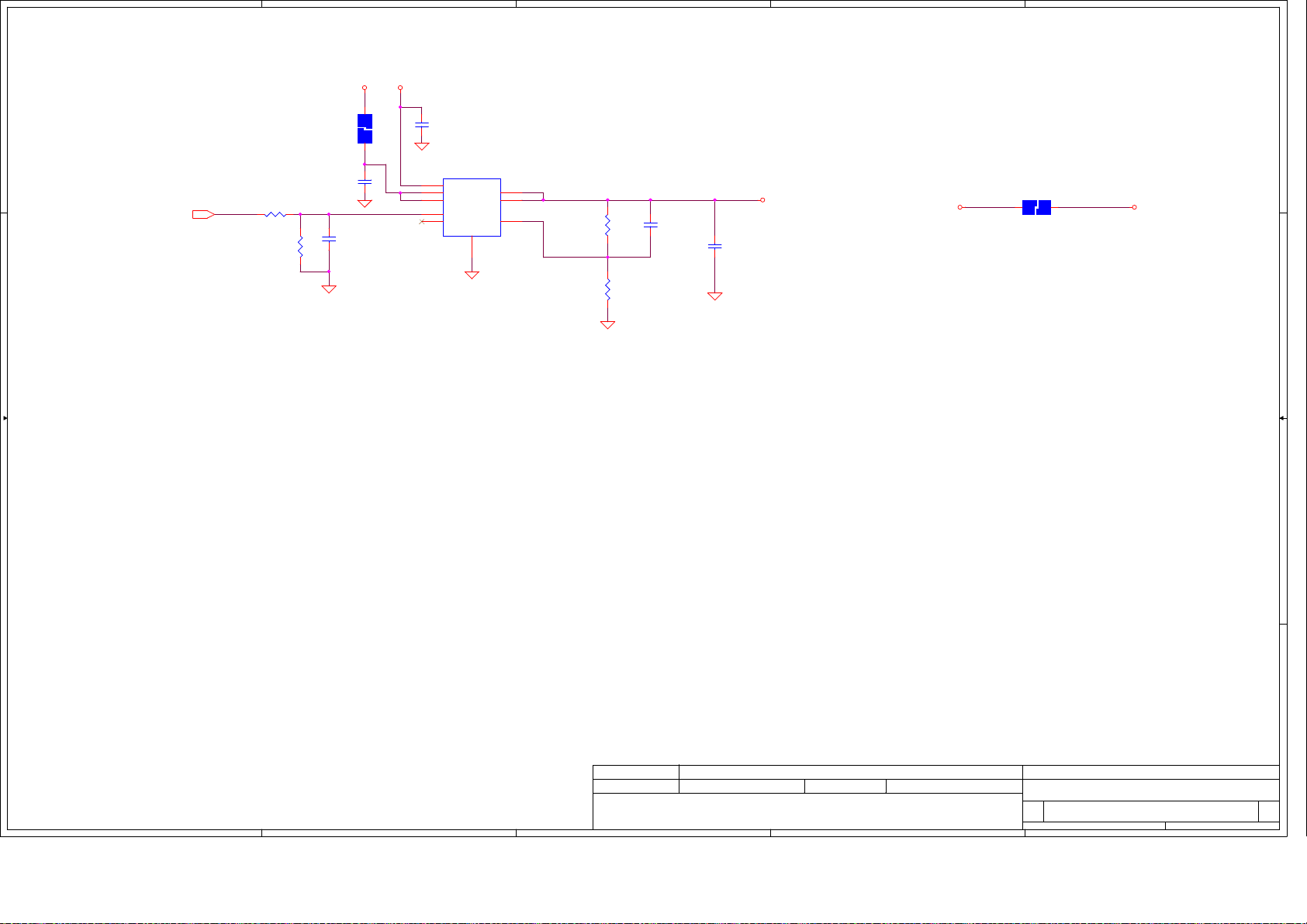

Page 6

5

2

1

R101 10M_0402_5%

Y1

32.768KHZ_12.5PF_Q13FC135000040

2

15P_0402_50V8J

1

R73 330K_0402_5%

1

R74 330K_0402_5%@

HDA_SDO<36>

trace width 10mil

D23

1

BAS40-04_SOT23-3

1

C154

2

2

R122 0_0402_5%@

C519

1

0.1U_0402_16V4Z

XEMC@

+CHGRTC

2

3

D

1

C153

2

DVT modify 11/27

TXC recommend from 18P change to 15P

PCH_INTVRMEN

INTVRMEN

HI nt egr ated VR M enabl e

*

LI nt egr ated VR M di s abl e

C

HDA for AUDIO

HDA_SDOUT_AUDIO<38>

HDA_RST_AUDIO#<38>

HDA_SYNC_AUDIO<38>

HDA_BITCLK_AUDIO<38>

EMI Request

W=20mils W=20mils

+RTCBATT

B

PCH_RTCX1

PCH_RTCX2

1

2

18P_0402_50V8J

1

RP14

1

2

3

4

33_0804_8P4R_5%

2

+RTCVCC

+RTCVCC

2

EMC@

8

7

6

5

PCH_RTCRST#

1

C151

0.1U_0402_16V4Z

2

+RTCVCC

ME Debug

HDA_SDOUT

HDA_SDOUT

HDA_RST#

HDA_SYNC

HDA_BIT_CLK

PVT modify 12/31

EMI reserved C519

4

1

C149

1U_0402_6.3V6K

R69

20K_0402_1%

1

1

R70

20K_0402_1%

1U_0402_6.3V6K

ME CMOS

2

2

2

1

C150

2

RTCRST close RAM door

1

2

JME1

0_0603_5%

@

1

2

JME2

0_0603_5%

@

+RTCVCC

1

R72 1M_0402_5%

EC_RTCRST#<36>

DVT modify 11/12

add Q19 for EC_RTCRST#

pull low on EC side

1

3

U1E

PCH_RTCX1

PCH_RTCX2

2

G

T95 @

T21 @

T19 @

T15 @

T10 @

T11 @

T22 @

T12 @

T6 @

T7 @

T8 @

T9 @

SM_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST#

PCH_RTCRST#

1

D

Q52

L2N7002LT1G_SOT23-3

@

S

3

HDA_BIT_CLK

HDA_SYNC

HDA_RST#

HDA_SDIN0

HDA_SDOUT

PCH_JTAG_RST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TCK_JTAGX

2

HDA_SDIN0<38>

2

R9751_0402_5% @

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

RTC

JTAG

5 OF 19

2

SATA_IREF

RSVD

RSVD

SATALED

Rev1p2

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

PCH_GPIO34

PCH_GPIO35

PCH_GPIO36

PCH_GPIO37

SATA_IREF

T13@

T14@

SATA_RCOMP

1

R10

10K_0402_5%

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATAAUDIO

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_RCOMP

SATA_PRX_DTX_N0 <34>

SATA_PRX_DTX_P0 <34>

SATA_PTX_DRX_N0 <34>

SATA_PTX_DRX_P0 <34>

SATA_PRX_DTX_N1 <34>

SATA_PRX_DTX_P1 <34>

SATA_PTX_DRX_N1 <34>

SATA_PTX_DRX_P1 <34>

PCH_GPIO34 <9>

PCH_GPIO35 <9>

PCH_GPIO36 <9>

PCH_GPIO37 <9>

1

R75 0_0603_5%@

1

R2 3.01K_0402_1%

2

+3VS

1

HDD

ODD

+1.05VS_ASATA3PLL

2

2

SATA_RCOMP, IREF

Trace width=12~15 mil, Spcing=12 mils

Max trace length= 500 m il

D

C

B

+RTCBATT

2

+CHGRTC

20mil

+RTCVCC

1

C168

0.1U_0402_16V4Z

@

A

2

2

D32

1

CHN202UPT_SC70-3

@

R446

1K_0402_5%

@

1

+RTCBATT_R

3

20mil

5

+RTCBATT

1

+

-

JBATT1

LOTES_AAA-BAT-054-K01

2

CONN@

SP07000H700

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

3

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

2

Date : Sheet

Compal Electronics, Inc.

BDW MCP(3/11) RTC,SATA,XDP

BDW MCP(3/11) RTC,SATA,XDP

BDW MCP(3/11) RTC,SATA,XDP

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

1

6 54Friday, October 17, 2014

6 54Friday, October 17, 2014

6 54Friday, October 17, 2014

1.0

1.0

1.0

of

of

of

Page 7

5

4

3

2

1

2

1

R481M_0402_5%

Y2

D

C

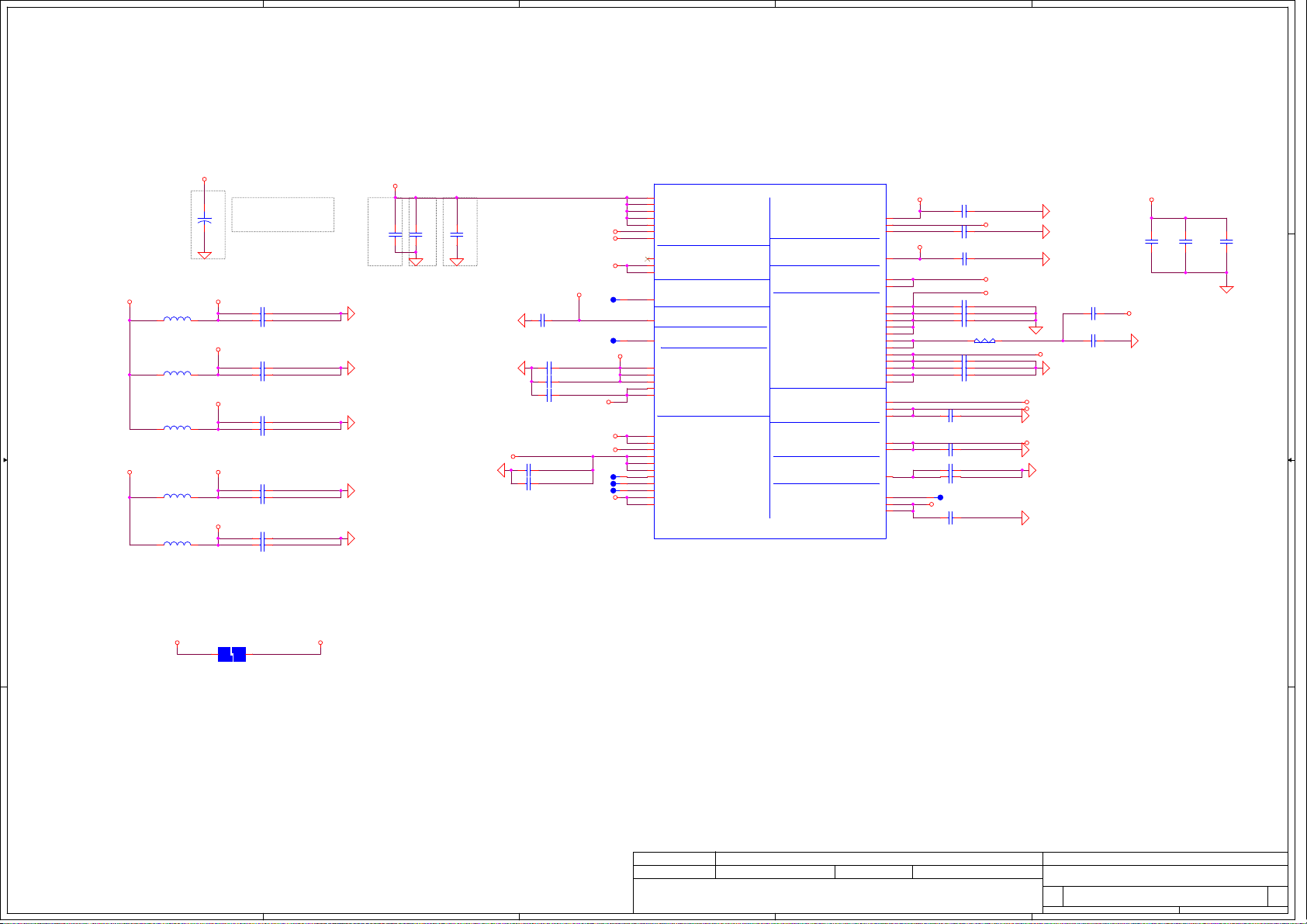

+3V_SPI

B

A

24MHZ_12PF_X3G024000DC1H

1

C2

15P_0402_50V8J

2

Pull high @ VGA side

PEG_CLKREQ#<17>

3

1

4

2

DVT modify 11/27

TXC recommend from 10P change to 15P

1

R105 1K_0402_5%

1

R106 1K_0402_5%

1

R103 1K_0402_5%@

1

R102 1K_0402_5%@

2ROM pop

PCH_SPI_WP1#

Reserve for EMI(Near SPI ROM)

C152

10P_0402_50V8J

2

1

XEMC@

PCH_SPI_WP1#

DGPU_PWR_EN<8,9,40,51>

2

2

2

2

2

R104 33_0402_5%XEMC@

2

@

33_0402_5%

1

2

R108 15_0402_5%

2ROM is SPI ROM 2M + 4M Byte

2ROM POP

U6 - EN25QH16-104HIP_SO8 (SA00004UG00)

RP19 - 33_0804_8P4R_5% (SD309330A80)

R108 - 33_0402_5% (SD028330A80)

5

XTAL24_IN

XTAL24_OUT

C3

15P_0402_50V8J

PCH_SPI_IO2_1

PCH_SPI_IO3_1

PCH_SPI_HOLD1#

PCH_SPI_WP1#

2

PCH_SPI_CLK_1

1

1

R109

PCIE LAN

WLAN

VGA

+3VS

1

VGA@

G

2

1

R107

2.2K_0402_5%

@

2

Q2L2N7002LT1G_SOT23-3

3

1

D

S

1

R112

2.2K_0402_5%

@

2

2

SPI ROM ( 8MByte )

PCH_SPI_CS0#

PCH_SPI_MISO_1

PCH_SPI_IO2_1

1

U6

1

CS#

2

DO(IO1)

3

WP#(IO2)

4

GND

EN25QH64-104HIP_SO8

SPI ROM ( 4MByte ) 2ROM pop

PCH_SPI_CS1#

PCH_SPI_MISO_2

PCH_SPI_IO2_2

U7

1

CS#

2

DO

3

WP#

4

GND

EN25QH32-104HIP_SO8

@

C453

10P_0402_50V8J

1

XEMC@

CLK_PCIE_LAN#<31>

CLK_PCIE_LAN<31>

LAN_CLKREQ#<31>

CLK_PCIE_MINI1#<33>

CLK_PCIE_MINI1<33>

MINI1_CLKREQ#<8,33>

CLK_PEG_VGA#<17>

CLK_PEG_VGA<17>

R115

10K_0402_5%

VGA_CLKREQ#

+3V_SPI

8

VCC

PCH_SPI_IO3_1

7

HOLD#(IO3)

VCC

HOLD#

CLK

DI

DI(IO0)

CLK

8

7

6

5

PCH_SPI_CLK_1

6

PCH_SPI_MOSI_1

5

PCH_SPI_IO3_2

PCH_SPI_CLK_2

PCH_SPI_MOSI_2

Reserve for EMI(Near SPI ROM)

2

R402 33_0402_5%XEMC@

PCH_SPI_CLK_2

2

1

+3VS

1

C66

0.1U_0402_16V4Z

+3V_SPI

C67

0.1U_0402_16V4Z

4

PCH_GPIO18<9>

PCH_GPIO19<9>

CLK_PCIE_LAN#

CLK_PCIE_LAN

R52 10K_0402_5%

CLK_PCIE_MINI1

MINI1_CLKREQ#

CLK_PEG_VGA#

CLK_PEG_VGA

VGA_CLKREQ#

PCH_GPIO23<9>

2

1

1

CLK_PCIE_MINI1#

LPC_AD0<36,37>

LPC_AD1<36,37>

LPC_AD2<36,37>

LPC_AD3<36,37>

LPC_FRAME#<36,37>

2

@

PCH_GPIO18

PCH_GPIO19

2

PCH_GPIO23

PCH_SPI_HOLD1#

PCH_SPI_MISO_1

PCH_SPI_IO3_1

PCH_SPI_CLK_1

PCH_SPI_MOSI_1

PCH_SPI_MOSI_1

PCH_SPI_CLK_1

PCH_SPI_MISO_1

PCH_SPI_CS0#

PCH_SPI_MOSI_2

PCH_SPI_CLK_2

PCH_SPI_IO3_2

PCH_SPI_MISO_2

HASWELL_MCP_E

CLOCK

SIGNALS

6 OF 19

HASWELL_MCP_E

LPC

SMBUS

SPI C-LINK

7 OF 19

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_MOSI

PCH_SPI_MISO

PCH_SPI_WP1#

U1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

HASWELL-MCP-E-ULT_BGA1168

@

U1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

HASWELL-MCP-E-ULT_BGA1168

@

for Share EC ROM, +3VS change to +3VALW

+3V_SPI

1

R498 0_0402_5%@

1

R500 0_0402_5%@

1

R502 0_0402_5%@

1

R505 0_0402_5%@

DVT modify 11/15

pop share rom

PVT modify 01/06

change to R-short

+3V_SPI

RP19

1

2

3

4

15_0804_8P4R_5%

2

2

2

2

RP20

1

2

3

4

PCH_SPI_MISO

8

PCH_SPI_HOLD1#

7

PCH_SPI_CLK

6

PCH_SPI_MOSI

5

PCH_SPI_MOSI

8

PCH_SPI_CLK

7

PCH_SPI_HOLD1#

6

PCH_SPI_MISO

5

33_0804_8P4R_5%

@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

R126

2

1

0_0402_5%@

R123

2

1

0_0402_5%@

EC_SPI_SO <36>

EC_SPI_CLK <36>

EC_SPI_SI <36>

EC_SPI_CS# <36>

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

Rev1p2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

CL_CLK

CL_DATA

CL_RST

Rev1p2

PVT modify 1/20

chang R126 to R-short

Compal Secret Data

Compal Secret Data

Compal Secret Data

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

SMBALERT/GPIO11

SML0ALERT/GPIO60

SML1ALERT/PCHHOT/GPIO73

SML1CLK/GPIO75

SML1DATA/GPIO74

+3VALW

+3VS

SPI ROM

From EC

(For share ROM)

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

B25

K21

M21

C26

C35

R140 10K_0402_5%

R141 10K_0402_5%

C34

AK8

R142 10K_0402_5%

AL8

R148 10K_0402_5%

CLKOUT_LPC0

AN15

CLKOUT_LPC1

AP15

B35

A35

PCH_GPIO11

PCH_SMBCLK

PCH_SMBDATA

PCH_GPIO60

SML0CLK

SML0DATA

PCH_GPIO73

SML1CLK

SML1DATA

Deciphered Date

Deciphered Date

Deciphered Date

XTAL24_OUT

T16@

T17@

XCLK_BIASREF

2

1

2

1

2

1

2

1

R390 22_0402_5%

R395 22_0402_5%

CLK_BCLK_ITP#

CLK_BCLK_ITP

T23@

T24@

T25@

DMN66D0LDW-7_SOT363-6

PCH_SMBDATA

PCH_SMBCLK

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

SML1CLK

SML1DATA

DMN66D0LDW-7_SOT363-6

2

XTAL24_IN

A25

2

1

R78 3.01K_0402_1%

2

1

EMC@

2

1

TPM@

T184@

T183@

PCH_GPIO11 <9>

PCH_SMBCLK <33>

PCH_SMBDATA <33>

PCH_GPIO60 <9>

PCH_GPIO73 <9>

+3VS

Q7A

6

Q8A

6

4.7K_0402_5%

2

D_CK_SDATA

1

5

D_CK_SCLK

4

3

Q7B

+3VS

2

1

5

4

3

Q8B

+1.05VS_AXCK_LCPLL

CLK_PCI_LPC <36>

CLK_PCI_TPM <37>

+3VALW_PCH

8

1

RP8 2.2K_0804_8P4R_5%

SML0CLK

R116

+3VS

2

1

PCH_SMBCLK

PCH_SMBDATA

SML0DATA

SML1CLK

SML1DATA

2

R119

4.7K_0402_5%

1

D_CK_SDATA <15,16,39>

R114 2.2K_0402_5%

R113 2.2K_0402_5%

7

2

6

3

5

4

2

1

2

1

DDR, G-sensor

D_CK_SCLK <15,16,39>

PU 2.2K at EC side (+3VS)

EC_SMB_CK2 <17,36>

VGA, EC

EC_SMB_DA2 <17,36>

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet

Compal Electronics, Inc.

BDW MCP(4/11) CLK,SPI,SMBUS

BDW MCP(4/11) CLK,SPI,SMBUS

BDW MCP(4/11) CLK,SPI,SMBUS

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

1

7 54Friday, October 17, 2014

7 54Friday, October 17, 2014

7 54Friday, October 17, 2014

D

C

B

A

1.0

1.0

1.0

of

of

of

Page 8

5

ACPRESENT funct i on

+3VS

1

R227

10K_0402_5%

2

SYS_RESET#

2

C513

D

0.01U_0402_16V7K

1

XEMC@

place near AC3

PCH_RSMRST#

ACIN<36,41,43>

C

VGATE<11,48>

B

PCH_PWROK

VGATE_3V

10K_0402_5%

+3VS

RP27

+3VS

R210

R117 10K_0402_5%

D21

@

1

RB751V-40 SOD-323

1

R208

2

U17

1

NC

2

A

3

GND

74AUP1G07GW_TSSOP5

@

8

1

7

2

6

3

5

4

2

1

NGC6@

10K_0402_5%

2

1

+3VALW_PCH

1

R245

10K_0402_5%

BW@

2

+3VS

5

P

B

A

G

3

+1.05VS_VTT

5

VCC

4

Y

G_SEN_INT

PCH_GPIO80

MINI1_CLKREQ#

DEVSLP0

PCH_ACIN

4

Y

VGATE_3V

PCH_GPIO77

SYS_PWROK

2

2

1

U43

MC74VHC1G08DFT2G_SC70-5

@

10K_0804_8P4R_5%

Note: Deep Sx need use EC GPIO for

R65

0_0402_5%

1

1

R207

10K_0402_5%

@

2

+3VS

1

R310

10K_0402_5%

@

2

MINI1_CLKREQ# <7,33>

DEVSLP0 <9,34>

PCH_PWROK

2

VGATE_3V <36>

4

PCH_PWROK<36>

VCCST_PG_EC<11,36>

PCH_RSMRST#<36>

PBTN_OUT#<36>

PCH_PWROK_R

PLT_RST#<17,36,37>

SUSWARN#<9>

+3VALW_PCH

GC6_FB_EN<17>

SUSWARN#

SYS_PWROK

PVT modify 01/06

R62, R64 change to R-short

2

1

2

1

R61 0_0402_5%@

R62 0_0402_5%@

R63 0_0402_5%@

R64 0_0402_5%@

R79 0_0402_5%@

R110 0_0402_5%@

R156 8.2K_0402_5%

PCH_INV_PWM<26,27>

ENBKL<36>

PCH_ENVDD<27>

DGPU_PWR_EN<7,9,40,51>

DGPU_HOLD_RST#<9,17>

1

1

1

1

1

1

GC6_FB_EN

TP_INT#<9,37>

2

2

2

2

2

2

G_SEN_INT<39>

PCH_GPIO51<9>

R206

0_0402_5%@

R2057 0_0402_5%

2

GC6@

DGPU_PWR_EN

DGPU_HOLD_RST#

SUSACK#

SYS_RESET#

SYS_PWROK_R

PCH_PWROK_R

PM_APWROK

PLT_RST#

PCH_RSMRST#_R

SUSWARN#

PBTN_OUT#_R

PCH_ACIN

PCH_BATLOW#

T31 @

PCH_GPIO77

1

PCH_GPIO80

T26 @

TP_INT#

G_SEN_INT

Project_ID1

PCH_GPIO51

Project_ID0

3

U1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

HASWELL-MCP-E-ULT_BGA1168

@

U1I

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

SYSTEM POWER MANAGEMENT

HASWELL_MCP_E

eDP SIDEBAND

GPIO

8 OF 19

9 OF 19

DISPLAY

DSWVRMEN

DPWROK

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_SUS

SLP_LAN

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

Rev1p2

2

AW7

DSWODVREN

PCH_RSMRST#_R

AV5

PCH_PCIE_WAKE#

AJ5

WAKE

V5

CLKRUN#

AG4

AE6

SUSCLK

PM_SLP_S5#

AP5

PM_SLP_S4#

AJ6

PM_SLP_S3#

AT4

AL5

SLP_A

AP4

PM_SLP_LAN#

AJ7

Rev1p2

DDPB_CTRLDATA: Port B Detected

DDPC_CTRLDATA: Port C Detected

1: Port B or C is detected

*

0: Port B or C is not detected

(Have internal PD)

B9

1

R271 2.2K_0402_5%

C9

DDI2_CTRL_CK

D9

DDI2_CTRL_DATA

D11

DDI1_AUX_DN

C5

B6

DDI1_AUX_DP

B5

A6

C8

A8

D6

DSWODVREN - On Die DSW VR Enable

HEna bl e( DEF AULT)

*

LDi s a bl e

1

R124 330K_0402_5%

1

R125 330K_0402_5%@

2

1

R1201K_0402_5%

2

1

R1578.2K_0402_5%

2

1

R127

@

10K_0402_5%

T30@

T96@

2

T27@

T28@

2

1

R118

@

10K_0402_5%

+3VS

DDI2_CTRL_CK <28>

DDI2_CTRL_DATA <28>

DDI1_AUX_DN <29>

DDI1_AUX_DP <29>

CPU_DP_HPD <29>

CPU_HDMI_HPD <28>

CPU_EDP_HPD <27>

+RTCVCC

2

2

+3VALW_PCH

+3VS

CLKRUN# <37>

PM_SLP_S5# <36>

T29@

PM_SLP_S4# <36>

PM_SLP_S3# <36>

+3VALW_PCH

not support Deep S4,S5 can NC

PCH_PCIE_WAKE# <31>

1

D

C

B

10K_0402_5%

Project_ID1

A

R205

BA50@

R214

10K_0402_5%

EA50@

+3VS

1

2

2

1

10K_0402_5%

Project_ID0

10K_0402_5%

5

R204

@

R215

+3VS

+3VS

5

U30

PLT_RST#

1

2

2

1

Project ID

*

Z5WAH

Z5W1H

Z5WBH

Reserved

Project_ID0Project_ID1

GPIO53GPIO54

0 0

0

1

1 1

4

1

0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MC74VHC1G08DFT2G_SC70-5

Compal Secret Data

Compal Secret Data

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

P

B

4

Y

1

A

G

3

2

1

R416

100K_0402_5%

2

PLT_RST_BUF# <31,33>

Custom

Custom

Custom

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet

Date : Sheet

Date : Sheet

Compal Electronics, Inc.

BDW MCP(5/11) PM,GPIO,DDI

BDW MCP(5/11) PM,GPIO,DDI

BDW MCP(5/11) PM,GPIO,DDI

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

1

8 54Friday, October 17, 2014

8 54Friday, October 17, 2014

8 54Friday, October 17, 2014

of

of

of

A

1.0

1.0

1.0

Page 9

1

GPIO15 : TLS Conf i dent ial i t y

0: Intel ME TLS with no conf i dent ial i ty

PVT modify 01/06

change PCH GPIO4/GPIO5 to

PCH_I2C0_SDA/PCH_I2C0_S CL

PCH_I2C0_SDA <27>

PCH_I2C0_SCL <27>

PCH_I2C1_SDA <37>

PCH_I2C1_SCL <37>

2

1

(Have internal PD)

1

R270 1K_0402_5%@

1

2

PCH_SPKR

9 54Friday, October 17, 2014

9 54Friday, October 17, 2014

9 54Friday, October 17, 2014

Touch Screen

Touch Pad

of

of

of

D

C

B

A

1.0

1.0

1.0

RSVD

RSVD

Rev1p2

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

2

2

2

H_THERMTRIP#

SERIRQ

PCH_OPIRCOMP

T106@

T32@

PCH_GPIO83

PCH_GPIO84

PCH_GPIO85

PCH_GPIO86

PCH_GPIO87

PCH_GPIO88

PCH_GPIO89

PCH_GPIO90

PCH_GPIO91

PCH_GPIO92

PCH_GPIO93

PCH_GPIO94

PCH_GPIO0

PCH_GPIO1

PCH_GPIO2

PCH_GPIO3

PCH_I2C0_SDA

PCH_I2C0_SCL

PCH_I2C1_SDA

PCH_I2C1_SCL

PCH_GPIO64

PCH_GPIO65

PCH_GPIO66

PCH_GPIO67

PCH_GPIO68

PCH_GPIO69

EC_LID_OUT#

+3VS

2

+1.05VS_VTT

1

R275

2.2K_0402_5%

1

R144

1K_0402_5%

2

2

49.9_0402_1%

+3VS

2

1

EC_KBRST# <36>

R277

2.2K_0402_5%

SERIRQ <36,37>

+3VS

2

2

1

1

+3VS

R269 1K_0402_5%@

R276

2.2K_0402_5%

R145

R274

2

2.2K_0402_5%

1

SPKR / GPIO81 : NO REBOOT

1: ENABLED

0: DISABLED

*

PCH_GPIO66

SDIO_D0 / GPIO66 : Top-Block Swap Override

1: ENABLED

0: DISABLED*(Have internal PD)

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet

Compal Electronics, Inc.

BDW MCP(6/11) GPIO,LPIO

BDW MCP(6/11) GPIO,LPIO

BDW MCP(6/11) GPIO,LPIO

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

A5WAH M/B LA-B991P

3

U1J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

GPIO

10 OF 19

CPU/

MISC

LPIO

+3VALW_PCH

PCH_OPI_RCOMP

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

1

R247 10K_0402_5%@

THERMTRIP

RCIN/GPIO82

SERIRQ

2

1: Intel ME TLS wi th conf i dent ial i ty

*

(Have internal PD)

PCH_GPIO86

1

R272 1K_0402_5%@

1

R273 1K_0402_5%

GSPI0_MOSI / GPIO86 : Boot BIOS Strap

1: ENABLED

0: SPI ROM

*

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2013/10/01 2014/05/24

2013/10/01 2014/05/24

2013/10/01 2014/05/24

(Have internal PD)

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

RP36

R2605

SR@

R2604

DR@

R312

BW@

R221

HW@

1

2

3

4

DGPU_AC_DETECT<17,36>

GPU_EVENT#<17>

+3VALW_PCH

1

2

2

1

+3VALW_PCH

1

2

2

1

4

EC_SMI#_SCI#

8

PCH_GPIO85

7

PCH_GPIO92

6

PCH_GPIO88

5

10K_0804_8P4R_5%

Dual Rank

Single Rank 1

Haswell

Boradwell

4

DGPU_AC_DETECT

GPU_EVENT#

A5WAH Pre MP 0819

SR for PU, DR for PD

EC_LID_OUT#<36>

R71

0_0402_5%

1

TS_INT#<27>

DEVSLP0<8,34>

2

R2058 0_0402_5%GC6@

EC_SMI#_SCI#<36>

PCH_SPKR<38>

GPIO28

CPU INFO

0

GPIO27

CPU INFO

0

1

PCH_GPIO76

PCH_GPIO8

EC_LID_OUT#

PCH_GPIO16

PCH_GPIO17

PCH_GPIO24

CPU_IDEN

PCH_GPIO28

DGPU_IDEN

PCH_GPIO56

PCH_GPIO57

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

PCH_GPIO47

PCH_GPU_ACIN

2

@

DGPU_PRSNT#

TS_INT#

PCH_GPIO71

PCH_GPIO13

PCH_GPIO14

PCH_GPIO25

PCH_GPIO45

PCH_GPIO46

PCH_GPIO9

PCH_GPIO10

DEVSLP0

PCH_GPIO70

1

PCH_GPIO38

EC_SMI#_SCI#

PCH_SPKR

5

+3VS

PCH_GPIO87

8

1

RP23

2

3

4

1

RP24

2

3

4

1

RP25

R216

R217

+3VALW_PCH

RP34

RP35

R306

10K_0402_5%

UMA@

R219

10K_0402_5%

VGA@

R311

10K_0402_5%

VGM@

R220

10K_0402_5%

VGL@

RP26

RP16

RP28

RP29

RP30

RP31

RP32

RP37

RP38

RP39

RP40

+3VS

+3VALW_PCH

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

8

7

6

5

8

7

6

5

8

7

6

5

1

10K_0402_5%

1

10K_0402_5%

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

2

1

1

2

2

1

D

C

B

DGPU_PRSNT#

A

DGPU_IDEN

NGC6@

PCH_GPIO51

7

6

PCH_GPIO83

5

10K_0804_8P4R_5%

PCH_GPIO68

8

PCH_GPIO69

7

6

change to I2C0 for TS use

5

10K_0804_8P4R_5%

PCH_GPIO1

8

PCH_GPIO94

7

PCH_GPIO93

6

PCH_GPIO2

5

10K_0804_8P4R_5%

PCH_GPIO91

8

PCH_GPIO0

7

PCH_GPIO90

6

PCH_GPIO38

5

10K_0804_8P4R_5%

PCH_GPIO19

8

PCH_GPIO36

7

TP_INT#

6

5

SERIRQ

10K_0804_8P4R_5%

PCH_GPIO18

8

PCH_GPIO35

7

PCH_GPU_ACIN

6

PCH_GPIO34

5

10K_0804_8P4R_5%

PCH_GPIO71

8

PCH_GPIO16

7

EC_KBRST#

6

PCH_GPIO37

5

10K_0804_8P4R_5%

PCH_GPIO67

1

PCH_GPIO65

2

DGPU_HOLD_RST#

3

PCH_GPIO64

4

10K_0804_8P4R_5%

PCH_GPIO84

1

PCH_GPIO3

2

3

PCH_GPIO89

4

10K_0804_8P4R_5%

PCH_GPIO17

1

PCH_GPIO23

2

PCH_GPIO76

3

4

10K_0804_8P4R_5%

PCH_GPIO70

2

DGPU_PWR_EN

2

PCH_GPIO10

8

PCH_GPIO11

7

PCH_GPIO57

6

PCH_GPIO13

5

10K_0804_8P4R_5%

USB_OC1#

8

PCH_GPIO8

7

PCH_GPIO73

6

5

SUSWARN#

10K_0804_8P4R_5%

PCH_GPIO46

8

PCH_GPIO42

7

PCH_GPIO14

6

PCH_GPIO60

5

10K_0804_8P4R_5%

8

PCH_GPIO47

7

PCH_GPIO45

6

PCH_GPIO24

5

10K_0804_8P4R_5%

PCH_GPIO43

8

PCH_GPIO59

7

PCH_GPIO25

6

PCH_GPIO58

5

10K_0804_8P4R_5%

USB_OC0#

8

PCH_GPIO56

7

PCH_GPIO44

6

PCH_GPIO9

5

10K_0804_8P4R_5%

DIS,Optimus

UMA

N15V-GL

N15V-GM

5

PCH_GPIO51 <8>

PCH_GPIO19 <7>

PCH_GPIO36 <6>

TP_INT# <8,37>

PCH_GPIO18 <7>

PCH_GPIO35 <6>

PCH_GPIO34 <6>

PCH_GPIO37 <6>

DGPU_HOLD_RST# <8,17>

PCH_GPIO23 <7>

DGPU_PWR_EN <7,8,40,51>

Pre MP modify 03/10

solve VGA sequence error issue

PCH_GPIO11 <7>

USB_OC1# <10>

PCH_GPIO73 <7>

SUSWARN# <8>

PCH_GPIO42 <10>

PCH_GPIO60 <7>

PCH_GPIO43 <10>

USB_OC0# <10,35>

GPIO49

DGPU_PRSNT#

0

1

GPIO26

VGA INFO

0

1

+3VS

10K_0402_5%

PCH_GPIO28

10K_0402_5%

10K_0402_5%

CPU_IDEN

10K_0402_5%

Page 10

5

4

3

2

1

D

U1K

PEG_GTX_HRX_N0

PEG_GTX_HRX_P0

PEG_HTX_C_GRX_N0

PEG_HTX_C_GRX_P0

PEG_GTX_HRX_N1

PEG_GTX_HRX_P1

PEG_HTX_C_GRX_N1

VGA

C

PCIE LAN

WLAN

PEG_GTX_HRX_N[0..3] <17>

PEG_GTX_HRX_P[0..3] <17>

PEG_HTX_C_GRX_N[0..3] <17>

PEG_HTX_C_GRX_P[0..3] <17>

B

PEG_HTX_C_GRX_P1

PEG_GTX_HRX_N2

PEG_GTX_HRX_P2

PEG_HTX_C_GRX_N2

PEG_HTX_C_GRX_P2

PEG_GTX_HRX_N3

PEG_GTX_HRX_P3

PEG_HTX_C_GRX_N3

PEG_HTX_C_GRX_P3

PCIE_PRX_DTX_N3<31>

PCIE_PRX_DTX_P3<31>

PCIE_PTX_C_DRX_N3<31>

PCIE_PTX_C_DRX_P3<31>

PCIE_PRX_DTX_N4<33>

PCIE_PRX_DTX_P4<33>

PCIE_PTX_C_DRX_N4<33>

PCIE_PTX_C_DRX_P4<33>

+1.05VS_AUSB3PLL

Trace width=12~15 mil, Spcing=12 mils

Max trace length= 500 m il

2

1

C76 0.22U_0402_10V6KVGA@

2

1

C77 0.22U_0402_10V6KVGA@

2

1

C78 0.22U_0402_10V6KVGA@

2

1

C79 0.22U_0402_10V6KVGA@

2

1

C80 0.22U_0402_10V6KVGA@

2

1

C81 0.22U_0402_10V6KVGA@

2

1

C82 0.22U_0402_10V6KVGA@

2

1

C83 0.22U_0402_10V6KVGA@

2

1

C84 0.22U_0402_10V6KVGA@

2

1

C85 0.22U_0402_10V6KVGA@

2

1

C86 0.22U_0402_10V6KVGA@

2

1

C87 0.22U_0402_10V6KVGA@

2

1

C88 0.22U_0402_10V6KVGA@

2

1

C89 0.22U_0402_10V6KVGA@

2

1

C90 0.22U_0402_10V6KVGA@

2

1

C91 0.22U_0402_10V6KVGA@

2

1

C155 0.1U_0402_16V7K

2

1

C160 0.1U_0402_16V7K

C156 0.1U_0402_16V7K

C157 0.1U_0402_16V7K

R232 3.01K_0402_1%

R155 0_0603_5%@

2

1

2

1

2

1

2

1

PEG_GTX_C_HRX_N0

PEG_GTX_C_HRX_P0

PEG_HTX_GRX_N0

PEG_HTX_GRX_P0

PEG_GTX_C_HRX_N1

PEG_GTX_C_HRX_P1

PEG_HTX_GRX_N1

PEG_HTX_GRX_P1

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_P2

PEG_HTX_GRX_N2

PEG_HTX_GRX_P2

PEG_GTX_C_HRX_N3

PEG_GTX_C_HRX_P3

PEG_HTX_GRX_N3

PEG_HTX_GRX_P3

PCIE_PRX_DTX_N3

PCIE_PRX_DTX_P3

PCIE_PTX_DRX_N3

PCIE_PTX_DRX_P3

PCIE_PRX_DTX_N4

PCIE_PRX_DTX_P4

PCIE_PTX_DRX_N4

PCIE_PTX_DRX_P4

T33 @

T34 @

PCIE_RCOMP

PCIE_IREF

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

HASWELL-MCP-E-ULT_BGA1168

@

HASWELL_MCP_E

PCIe

USB3.0 P3 / PCIE P1

USB3.0 P4 / PCIE P2

11 OF 19

USB

USB3.0 P1

USB3.0 P2

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS