Page 1

A

1 1

B

C D

E

Compal Confidential

2 2

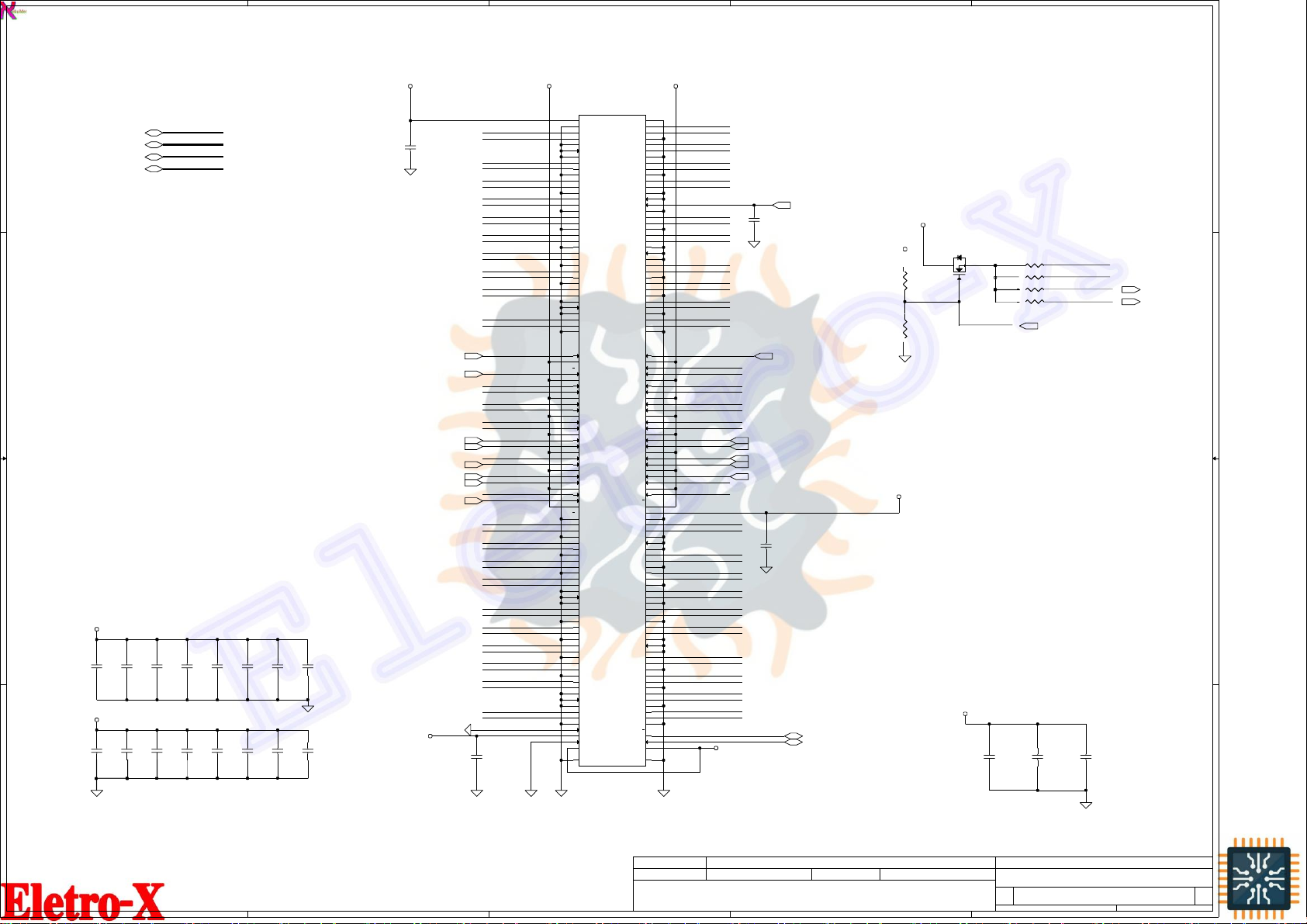

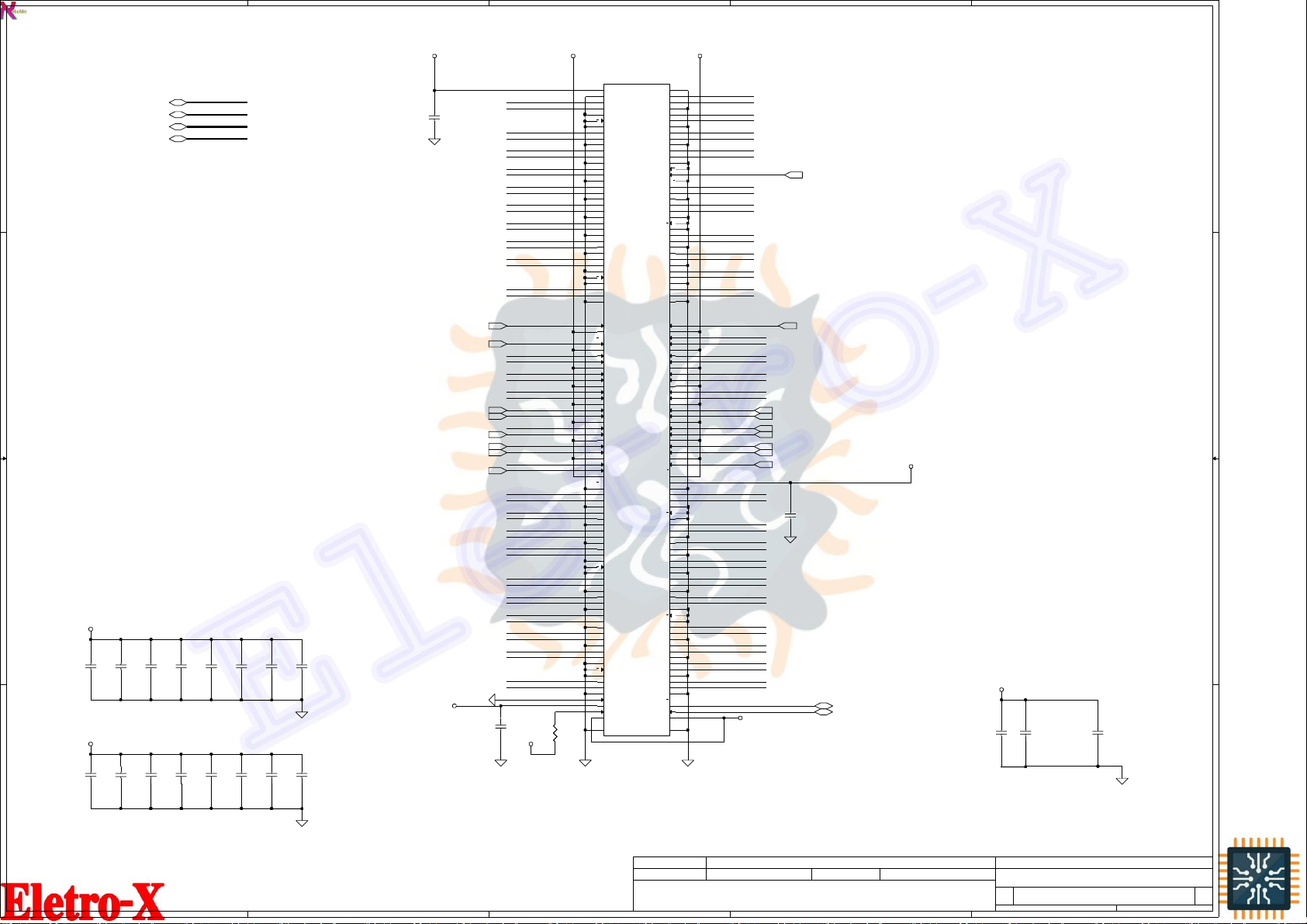

Hasswell M/B Schematics Document

Intel ULV Processor with DDRIIIL

Date : 2014/02/08

3 3

VER 1.0

4 4

Security Classification

Issued Date

TH IS SH E ET OF ENG I NEE RI N G DR A W IN G IS TH E P ROP R IE T AR Y P ROP ERT Y O F COM PAL E L EC T RON I CS , IN C. A N D C ON TAI NS CONFIDENTISSAiL

AN D T RAD E S ECR ET IN FO RMATI ON . THIS S HEE T MAY N O T BE T R AN S FER ED FR O M TH E CU S TOD Y OF T H E COM PET E NT DIVI SION OF R&D

DE P ART MEN T EX CEP T AS A U THO R IZE D BY C O MP A L EL E CT R ONI CS, IN C. N EIT HE R THI S SH E ET N O R T HE I N FO R MAT ION IT CO NT AIN S

A

B

MA Y BE US ED BY OR D IS CLOSE D TO AN Y TH IRD P ART Y W IT H OUT PRI O R WRI TTE N CON SEN T OF C O MP A L EL E CT R ONI CS, IN C.

2011/06/29 2011/06/29

C D

Compal Secret Data

Deciphered Date

Title

ze Document Number

B

Compal Electronics,Inc.

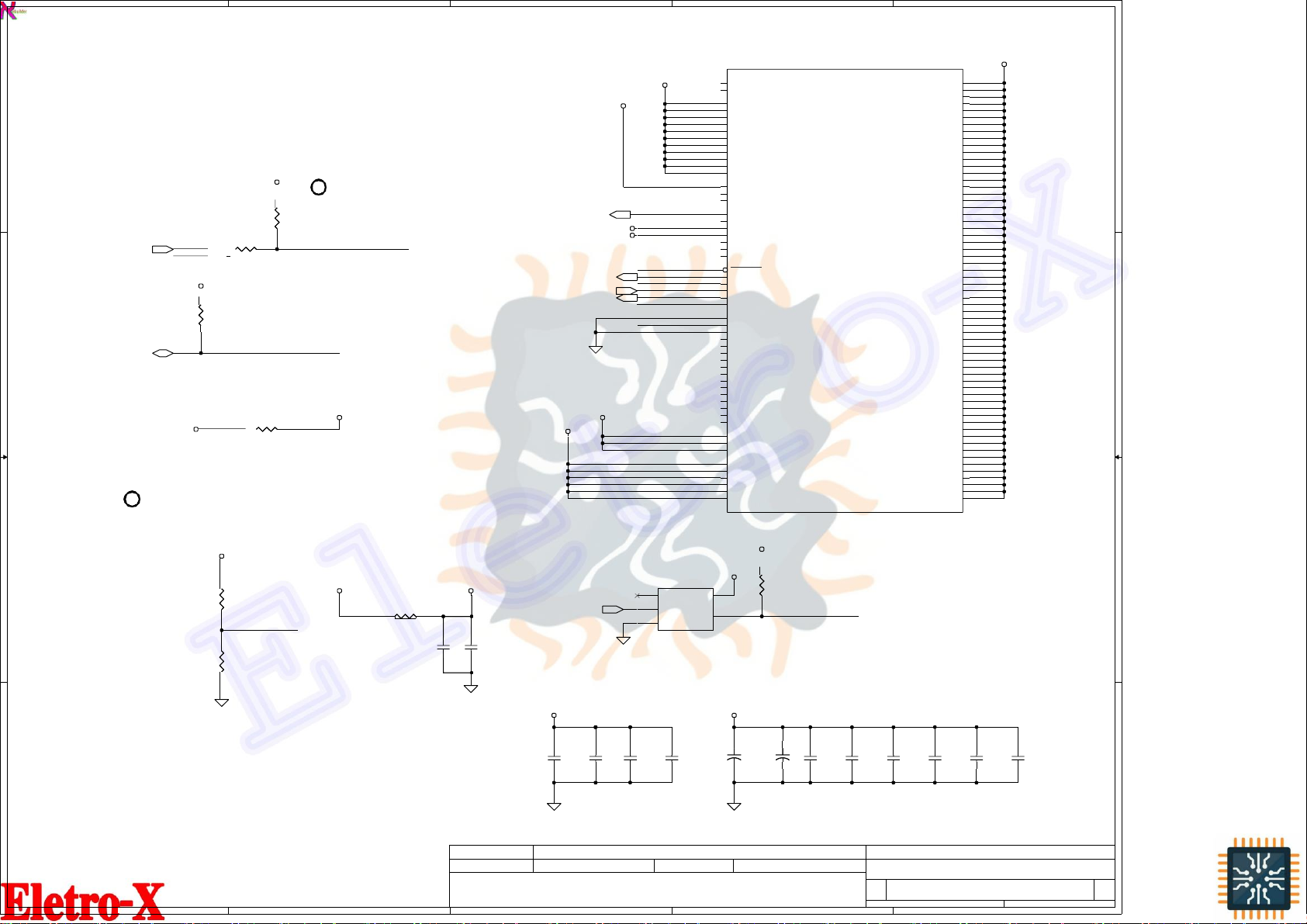

Cover Page

LA-B972P

Sheet

E

Rev

of

1 54Date: Thursday, March 20, 2014

0.1

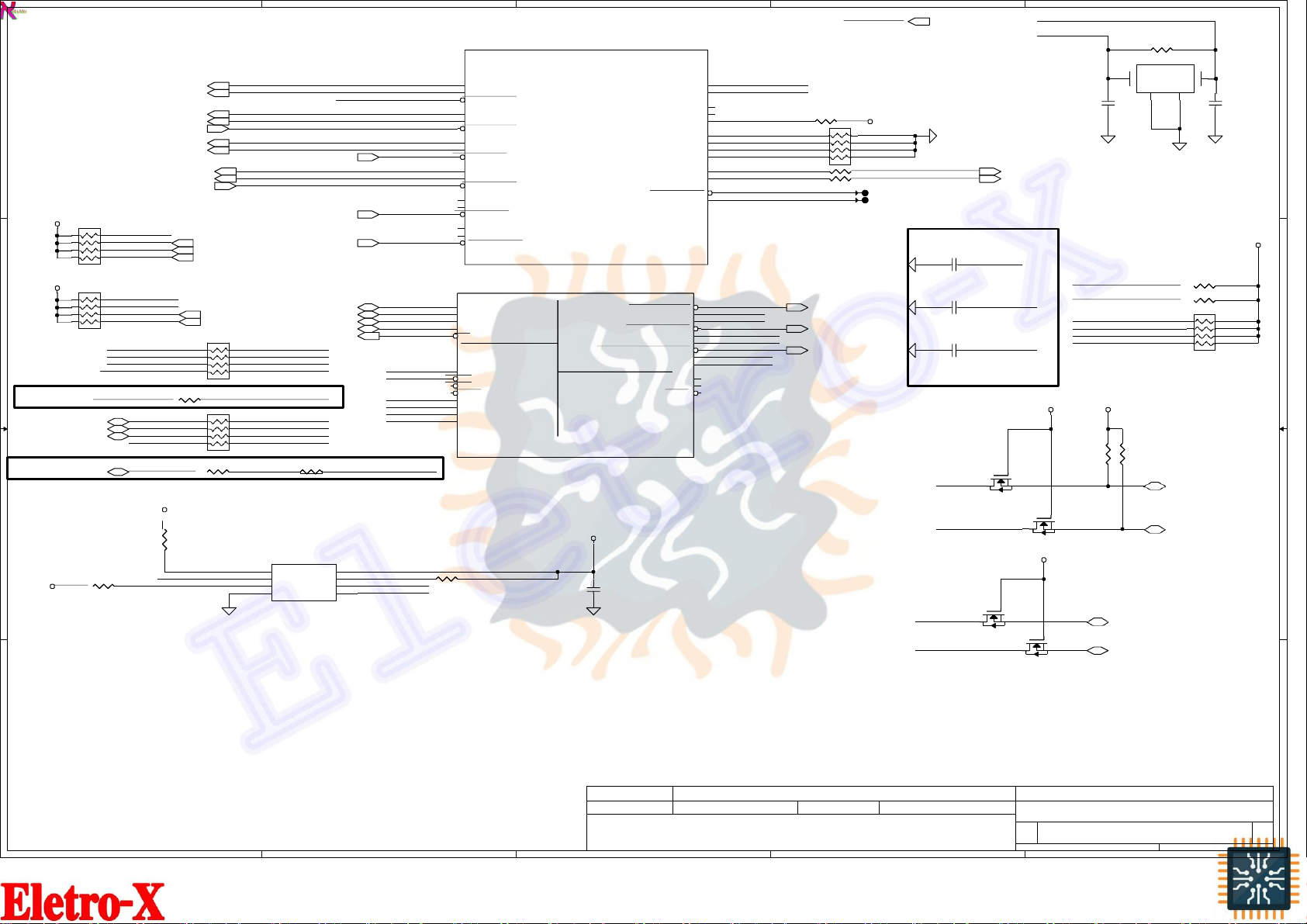

Page 2

A

CompalConfidential

Model Name : Haswell

B

C D

E

PCI-Ex4

Lane7-Lane10

PCIe2.0:5Gb/s

PCIe3.0:8Gb/s

P18

P29

eDPx2

2.7Gb/s

DDI

Haswell

Ultra Light & Thin

DualChannel

DDR3L 1600MHz1.35V

SATA3.0

GEN11.5Gb/s

GEN23Gb/s

GEN36Gb/s

Port 0

Port 1

DDR3-SO-DIMM X2

2.5" SATAHDD

ODD

P15,16

P22

P22

File Name :

1 LA-B972PR10

VRAM*4

SingleRank

P37~P40

LVDS panel

CRT Conn

P20

P29

Nvidia

N15V-GM

17W

P32~P36

RTD2132R

IT6513

1168P BGA

HDMI Conn

DDPB port P19 222.75MHz

2 2

PCI-E Card reader

RTS5239

10/100 1GLAN

8151/8166Option

WLAN(MiniPCIe slot)

Port 3

3 3

P23

Lane4

P25

Lane5

P24

Lane 11 PCIe1.0:2.5Gb/s

Port 3 (Reserved) USB2.0

HDMI

(USW ULT)

PCI-E

PCIe 1.0:2.5Gb/s

PCIe 2.0:5Gb/s

PCIe2.0:5Gb/s

PCI-E

480Mb/s

SMBUS

1MHz

USB3.0

5Gb/s

USB2.0

480Mb/s

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

USB3.0port

USB2.0port

USB2.0Port

WLAN

Camera

TouchScreen

Port 0

P26

P26

P27

P20

P19

P19

1

Int.KBD

TouchPad

PS2

FAN

Lidswitch

4 4

ENEKB9012

TPM 1.2@

SLB 9656

P28

P30

LPC

33MHz

SPI

50MHz

HDA 24MHz

HDA Aduiocodec

ALC3227

P25

InternalSPK

Combo Jack

SPIROM

8M

A

B

P7

Security Classification

Issued Date

THI S SH EET O F E NGIN EERING DR AW ING IS T HE PROPRIET ARY PROP ERT Y OF COMPAL ELECTRONICS, INC. AND C ONT AINS CONFIDENTSSIAizL

AND TR ADE SECRET INFORMAT ION. T HIS SHEET MAY NOT BE T RANS FERED FROM TH E CU STO DY OF TH E C OMPET ENT DIVIS ION OF R &D

DEPA RTMENT EXC EPT A S A UTH ORIZ ED BY COMP AL ELE CTR ONIC S, IN C. NEIT HER THIS SH EET NO R T HE I NFORMAT ION IT CONTAI NS

MAY BE USED BY OR D ISCLOSED TO ANY T HIR D PARTY W ITH OUT PRIOR W RITTEN C ONSE NT OF COMPAL ELE CTR ONIC S, INC .

C D

2011/06/29 2011/06/29

Compal SecretData

Deciphered Date

Titl e

eDo cum ent N umb er

Cus tom

Compal Electronics,Inc.

Block Diagrams

LA-B972P

Shee t 2 of 54Date: Thurs day, Marc h 20, 2014

E

Rev

0.1

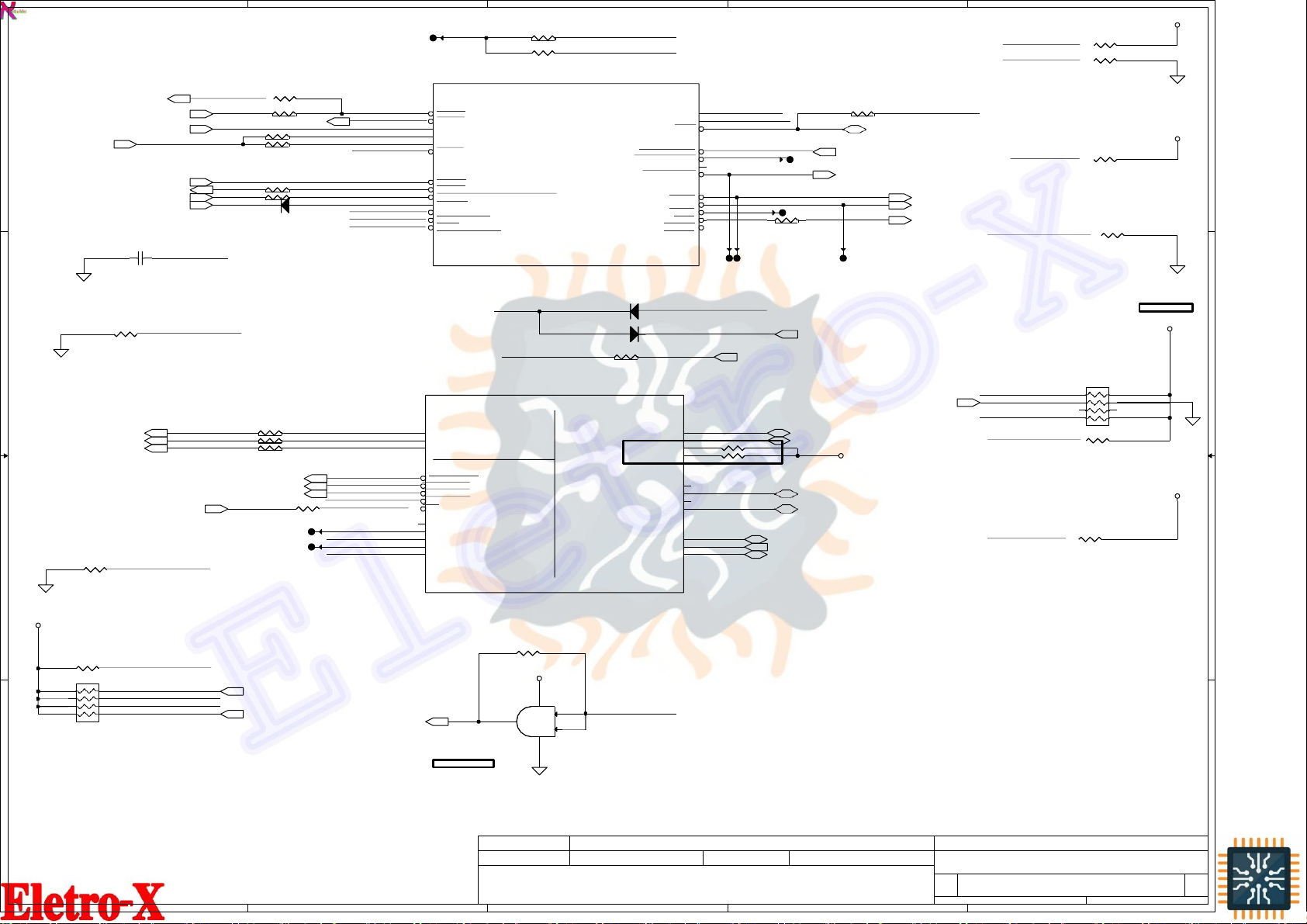

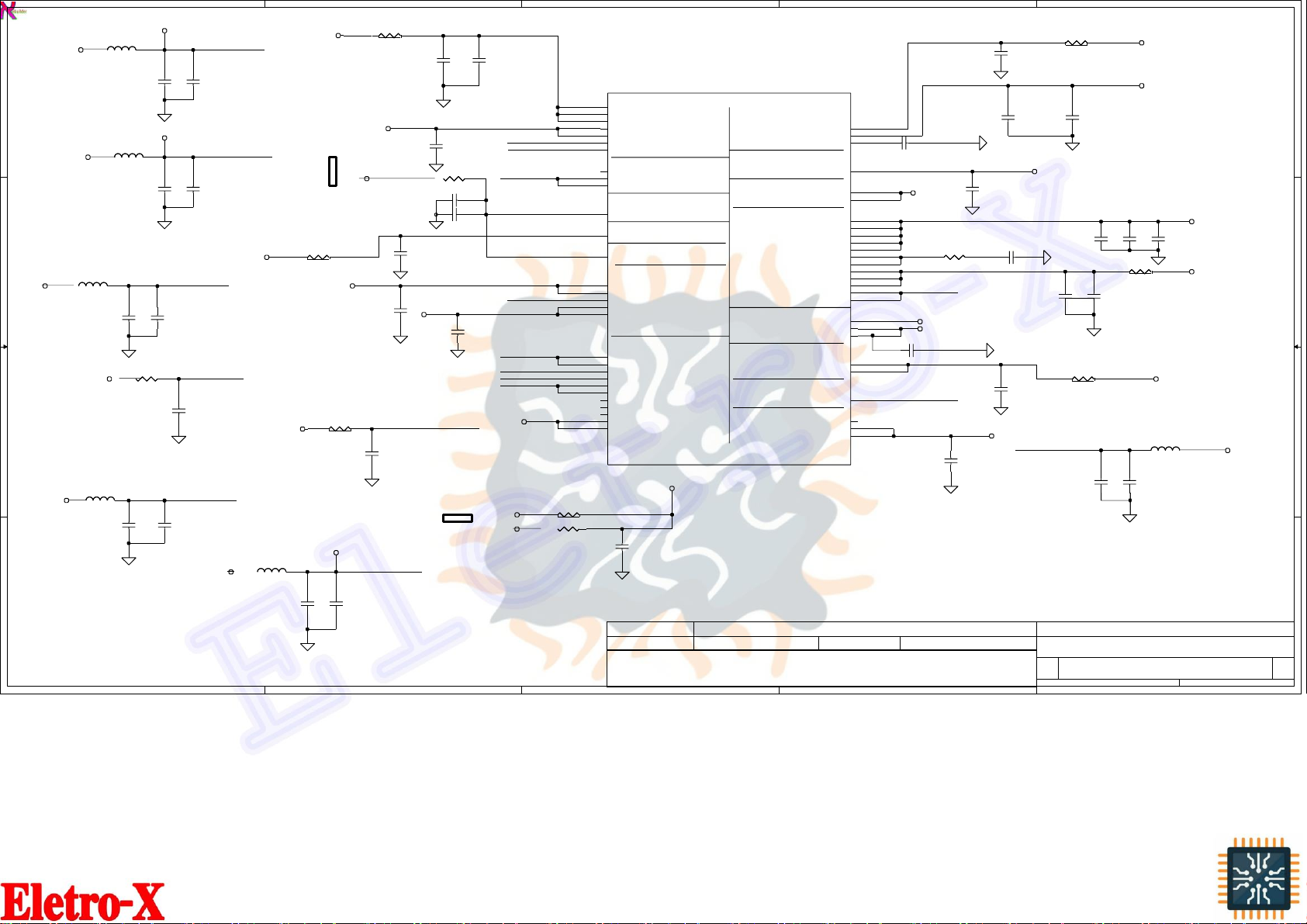

Page 3

5

4

3 2

1

CMSRC ACDRV

DC IN

D D

Battery

C C

B B

ACFET RBFET

BATDRV

RBFET

BATT

Charger

BQ24738

B+

Jumper

+3VALW

Jumper

+5VALW

+1.35V_VDDQ

Jumper

+0.6V_0.675VS

umper

Jumper

+1.05VS

SUSP#

SY8003 UMA only

EN

+1.5VSP

Jumper

+1.5VS

EC_ON

SYSON

SUSP#

SUSP#

VR12.5_VR_ON

RT8243

EN

RT8207M

EN

SY8208D

EN

TPS51622

EN

+3VALWP

+5VALWP

+1.35V_VDDQP

+0.6V_0.675VSJP

+1.05VSP

+VCC_CORE

RT8813 DIS only

GPU_PWR_EN

EN

SY8208D DIS only

SUSP#

A A

5

EN

4

+VGA_CORE

Jumper

+1.5VDIS

Security Classification

IssuedDate

THIS SHEET OF ENGINEERING DR AWING IS T HE PRO PRIETAR Y PROPERTY OF COMPAL ELECT RONICS, I NC. AND CO NTAINS CONFIDENTIASL

AND TRADE SECRET INFORMAT ION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUS TOD Y OF TH E COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RON ICS, INC. NEITHER TH IS SHEET NOR T HE INFORMATI ON IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WIT HOU T PRIOR WRITTEN CONSENT OF C OMPAL ELECTRONIC S, INC.

+1.5VS

Compal Secret Data

2013/08/07 2016/08/06

3 2

DecipheredDate

Compal Electronics, Inc.

Title

Power Block Diagram

ize DocumentNumber

LA-B972P

Thursday, March 20,2014

Date: Sheet of

1

Rev

0.4

5543

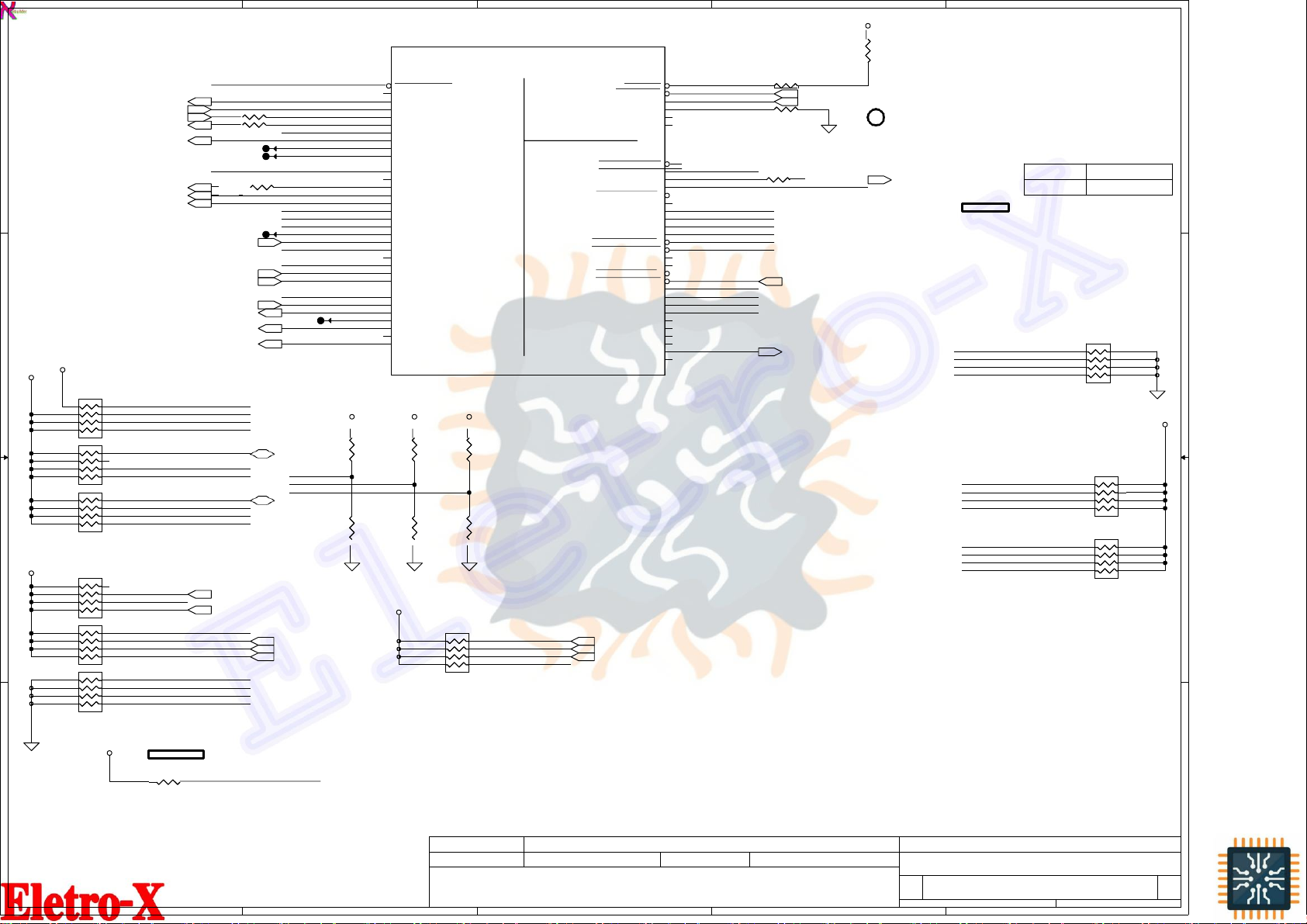

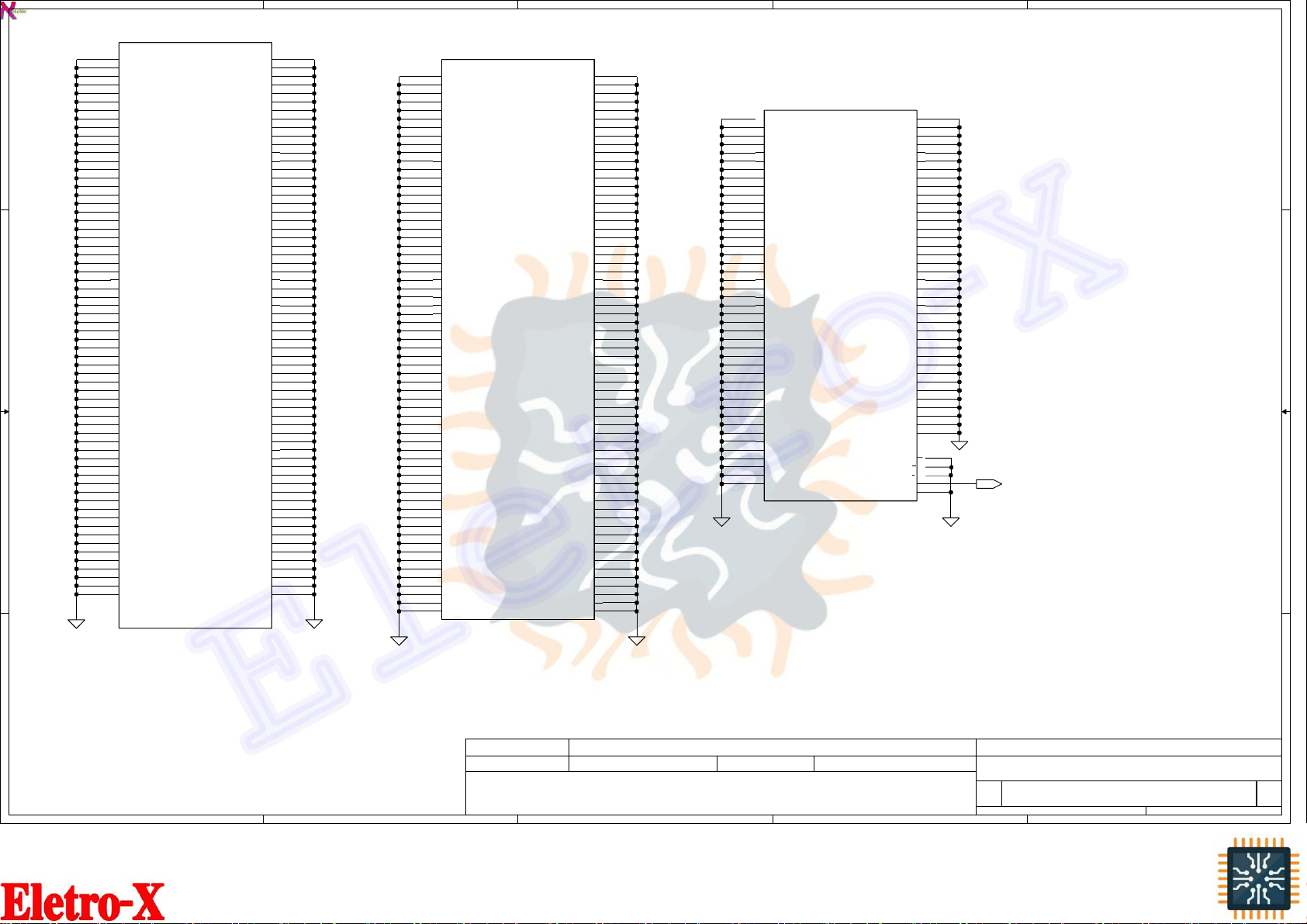

Page 4

A

Power rail Control (EC) Source (CPU)

+RTCVCC X X

VIN X X

BATT+ X X

B+ X X

+VL X X

+3VL X X

+5VALW EC_ON X

1 1

+3VALW EC_ON X

+3VALW_EC EC_ON X

+3V_PCH PCH_PWR_EN X

+1.35V_VDDQ SYSON PM_SLP_S5#/PM_SLP_S4#

+5VS SUSP# PM_SLP_S3#

+3VS SUSP# PM_SLP_S3#

+1.5VS SUSP# PM_SLP_S3#

+1.05VS SUSP# PM_SLP_S3#

+0.6V_0.675VS SUSP#

+VCC_CORE X VR12.5_VR_ON

@ is NO SMT part (empty)

short@ : short pad , don't pop.

@EMI@,@ESD@,@RF@ : Reserve , don't pop.

RF@ : RF team request, must add.

EMI@ : EMI team request, must add.

ESD@ : ESD team request, must add.

LVDS@ : Support LVDS panel.

GCLK@ : Support GCLK

CRT@,CRTEMI@ : Support CRT port

eDP@,eDPEMI@ : Support eTP panel

B

C

DAX

<BOM Structure>

PCB

Part Number = DAZ14Z00100

PCB 14Z LA-B972P REV0 M/B 3

45@

ZZZ1

ROYALTY HDMIW/LOGO+HDCP

Part Number = RO0000003HM

ROYALTY HDMI W/LOG O+HDCP

D

<USB2.0 port>

USB2.0 port

E

DESTINATION

UMA Dis

0 USB 2.0/3.0(leftside) USB 2.0/3.0(leftside)

ZSO40@,ZSO56@ : Board ID config.

DIS@ : GPU BOM config.

1 USB 2.0(rightside) USB 2.0(right side)

2 USB 2.0(rightside) USB 2.0(right side)

3 WLAN/BT

WLAN/BT

4 Camera Camera

5

Touch screen(Options) Touch screen(Options)

6 X X

7 X X

2 2

3 3

UCPU1

CPU

UK1:+3V ALW_EC

EC

AP2 SMBCLK

SMBDATA

AH1

SML0CLK

AN1

SML0DATA

AK1

AU3 SML1CLK

SML1DATA

AH3

79 EC_SMB_CK2

EC_SMB_DA2

80

77 EC_SMB_CK1

EC_SMB_DA1

78

+3V_PCH

R=2.2K

+3V_PCH

R=1K

+3V_PCH

R=2.2K

+3VL

R=2.2K

2N7002

2N7002

+3VS

R=2.2K

EC_SMB_CK2

EC_SMB_DA2

R=100

+3VS

R=10K

PCH_SMBCLK

PCH_SMBDATA

+3VS

Thermal Sensor @

+3VS

eDP to LVDS bridge RTD2132R

BAT

SO‐DIMM A

SO‐DIMM B

<PCI-E,SATA,USB3.0>

Lane# PCI-E SATA USB3.0

1 1 USB3.0 USB3.0

2 2 X X

3 1 3 X X

4 2 4

5 3 10/100/1000LAN10/100/1000LAN

6 4

7

8 GPU(DISonly)

5

9 GPU(DISonly)

10 GPU(DISonly)

116L3 3 WLAN WLAN

12 L2 2 X X

13 L1 1 ODD ODD

14 L0 0 2.5"HDD 2.5"HDD

DESTINATION

UMA Dis

Cardreader(PCI-E) Cardreader(PCI-E)

GPU(DISonly)

Charger

4 4

G‐Sensor @

Security Classification

Issued Date

THI S SH EE T OF E NG INE ER ING DR AW IN G IS TH E PR OPR IE TAR Y PRO PE R TY OF COM PA L EL EC TRO NIC S, IN C. AN D CO NTA INS CONFIDENTISSAiL

AN D T RA DE S EC RE T IN FO RMA TI ON . TH IS SH EET M AY NOT BE TR A NS FE RE D F R OM THE CU STO DY OF THE COM PE TEN T DIV IS ION OF R &D

DE PA RTM ENT EX CE PT AS A UT HOR IZ ED BY CO MPA L EL EC TRO NIC S, IN C. NE ITH ER TH IS S HE ET N OR T HE I NFO RM ATI ON IT CO NTA IN S

A

B

MA Y BE USE D BY OR D IS CLO SE D TO AN Y T HIR D PAR TY WI THO UT P RIO R WR ITTE N CO NSE NT OF C OM PAL EL EC TRO NIC S, I NC .

C

2011/06/29 2011/06/29

Compal Secret Data

DecipheredDate

D

Title

ze Document Number

Custom

Compal Electronics, Inc.

Notes List

LA-B972P

Sheet 3 of 54Date: Thursday, March 20, 2014

E

Rev

0.1

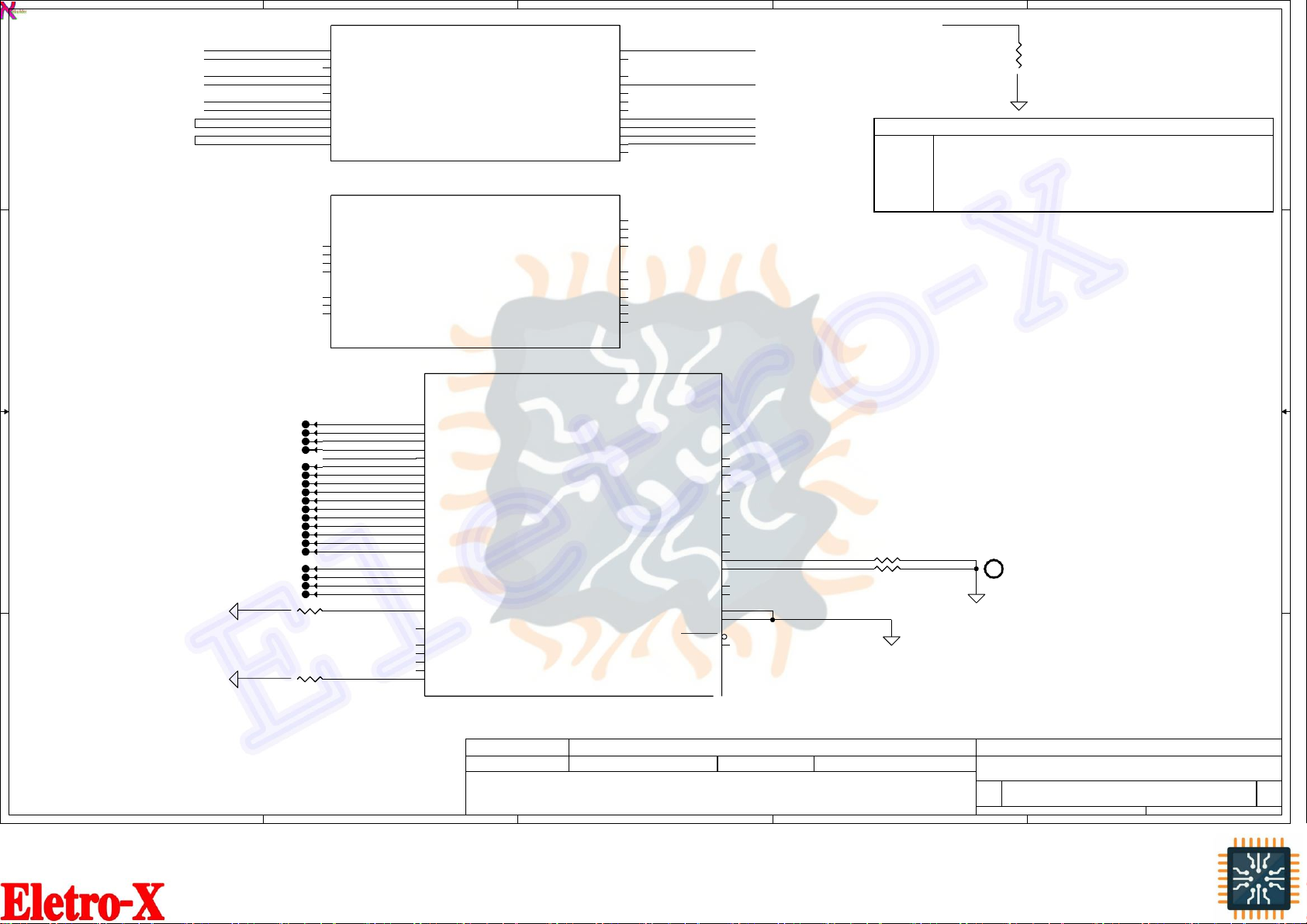

Page 5

5

4

UCPU1A

HASW ELL _MCP _E

3

CC97~CC102 must closed to connector not CPU

L

2

1

C45

EDP_TXN0

B46

EDP_TXP0

A47

EDP_TXN1

B47

EDP_TXP1

C47

EDP_TXN2

C46

EDP_TXP2

A49

EDP_TXN3

B49

EDP_TXP3

A45

EDP_AUXN

B45

EDP_AUXP

D20

EDP_RCO MP

A43

PRDY

PREQ

PROC_T CK

PROC_T MS

PROC_T RST

PROC_T DI

PROC_T DO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

UC10

5

VCC

4

Y

74AUP1G07GW_TSSOP5

GND

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

NC

A

RC1 1 @ 2 0_0201_5%

RC2 1 @ 2 0_0201_5%

XDP_PRDY#

XDP_PREQ #

XDP_TC K

XDP_TMS_CPU

XDP_TR ST#_CPU

XDP_TD I_CPU

XDP_TD O_CPU

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

XDP_OBS4_R

XDP_OBS5_R

XDP_OBS6_R

XDP_OBS7_R

1

2

DDR_PG_CNTL

3

EDP_CPU_LANE_N0_ C <18>

EDP_CPU_LANE_P0_C <18>

EDP_CPU_AUX#_C <18>

EDP_CPU_AUX_C <18>

EDP_COMP

COMPENSATION PU FOR eDP

EDP_COMP 2

24.9_0402_1%

T58 @ PAD

XDP_TC K <6>

XDP_TMS_CPU <6>

XDP_TD I_CPU <6>

XDP_TD O_CPU <6>

T80 @ PAD

T79 @ PAD

T52 @ PAD

T53 @ PAD

T54 @ PAD

T55 @ PAD

T56 @ PAD

T57 @ PAD

<eDP>

<eDP>

BKL_PW M_CPU <18,8>

+VCCIOA_OUT

1

RC3

DG V0.9 PEG_COMP

L

Trace width=20mil and spacing=25mil

Max length=100mil

XDP_TD I_CPU @ RC12 2

XDP_PREQ # @ RC13 2

XDP_TR ST#_CPU

1

@ESD@

CC99

0.1U_0402_16V7K

2

XDP_TR ST#_CPU <6>

+1.05VS_VCCST

1 51_0402_1%

1 51_0402_1%

RC234

10K_0402_5%

PROC_DETECT# D61

+1.35V_VDDQ

1 2

RC308

470_0402_5%

1

0.1U_0402_16V7K

2

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

UCPU1B

PROC_D ETECT

K61

CATERR

N62

PECI

PROCHO T

PROCPW RGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CN TL1

DDR3_DRAMRST# <15,16>

DDI EDP

1 OF19

HASW ELL _MCP _E

MIS C

THER MAL

PW R

DDR3

2 OF19

<15> SM_PG_CTRL

EDP_DISP_ UTIL

JTAG

+1.35V_VDDQ

<20> PC H_DPB_N2

<20> PC H_DPB_P2

<20> PC H_DPB_N1

<20> PC H_DPB_P1

<30> H_PECI

1

1K_0402_1%

RC7 1

<20> PC H_DPB_N0

<20> PC H_DPB_P0

<20> PC H_DPB_N3

<20> PC H_DPB_P3

<29> PC H_DPC_N0

<29> PC H_DPC_P0

<29> PC H_DPC_N1

<29> PC H_DPC_P1

+3V_PCH

1 2

PAD T51@

2 56_0402_5% H_PROCHOT #_R K63

@

2 H_CPUPWRGD_R C61

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2 AU61

DDR3_DRAMRST# AV15

DDR_PG_CNTL AV61

DDR3_DRAMRST#

@ESD@ CC88

D D

<HDMI>

<DP TOCRT>

RC11 2 1 10K_0402_5% H_CPUPW RGD_R

+VCCIO_OUT

1 2

C C

<30,44> PROC HOT#

DG V0.5 Trace width=12~15 mil

L

DDR3 COMPENSATION SIGNALS

200_0402_1% 2 1 RC18 SM_RCOMP0

120_0402_1% 2

100_0402_1% 2

B B

PROCHO T#

Max length=500mil

1 RC19 SM_RCOMP1

1 RC20 SM_RCOMP2

62_0402_5%

@ESD@

10P_0402_50V8J

RC4

C295

1

2

RC6

<11,6> +1.05VS_PG

A A

Security Classification

Issued Date

THI S SH EE T OF E NG INE ER ING DR AW IN G IS TH E PR OPR IE TAR Y PRO PE R TY OF COM PA L EL EC TRO NIC S, IN C. AN D CO NTA INS CONFIDENTISSAiL

AN D T RA DE S EC RE T I NFO RM AT ION . TH IS SH EET M AY NOT BE TR A NS FE RE D FRO M THE CU STO DY OF T HE COM PE TE NT DI VIS ION OF R &D

DE PA RTM ENT EX CE PT AS A UT HOR IZ ED BY CO MPA L EL EC TRO NIC S, IN C. NE ITH ER TH IS S HE ET N OR T HE I NFO RM ATI ON IT CO NTA IN S

5

4

MA Y BE USE D BY OR DISC LO SE D TO AN Y TH IR D PA RTY W ITHO UT P RIO R WR ITT EN CO NS ENT OF COMP AL EL EC TRO NIC S, I NC .

3

2011/06/29 2011/06/29

Compal Secret Data

DecipheredDate

2

Title

DDI,MSIC,XDP

ze Document Number

Custom

Date:

LA-B972P

Rev

Sheet 4 of 54Thursday, March 20, 2014

1

0.1

Compal Electronics,Inc.

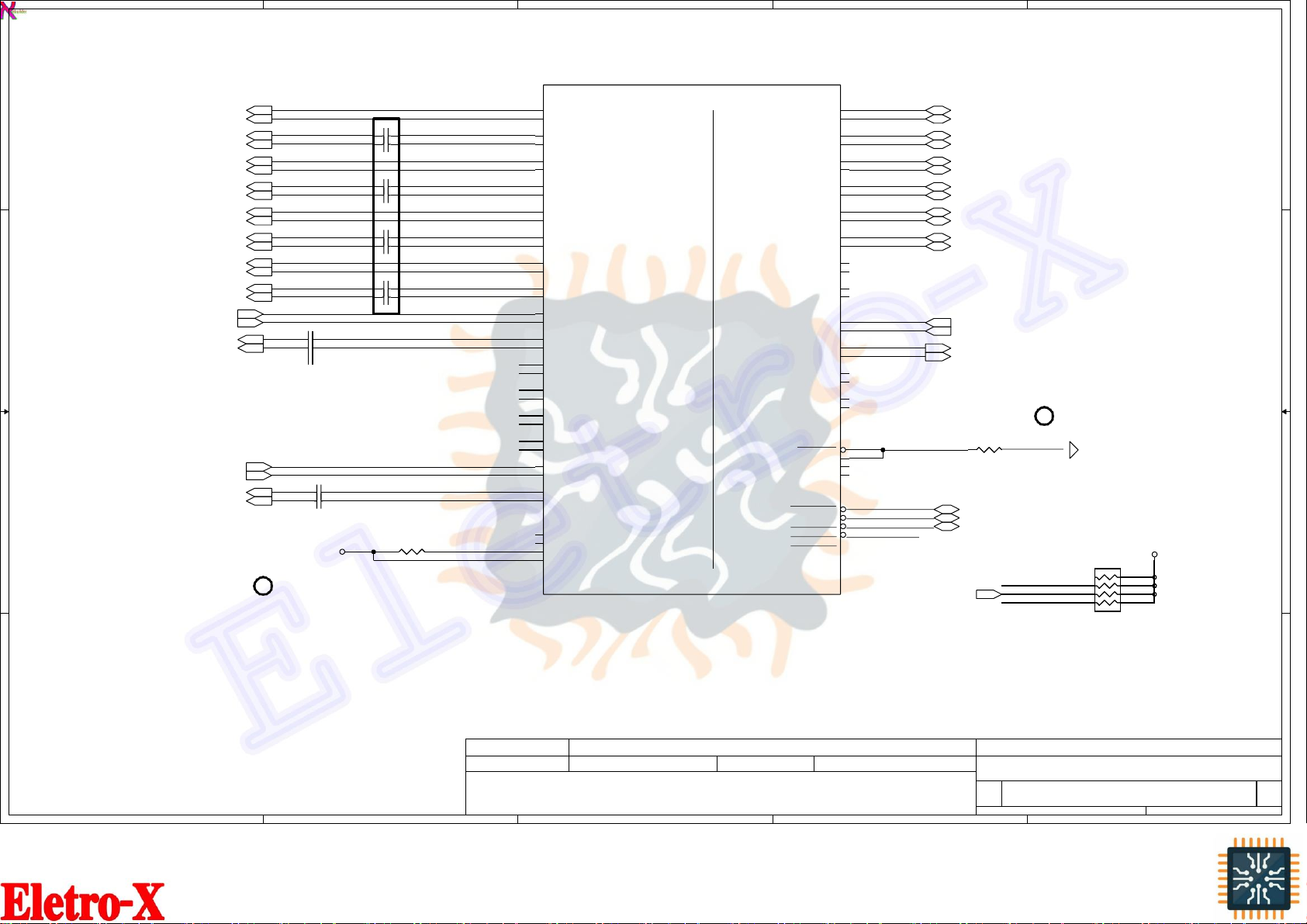

Page 6

5

4

3

2

1

<15> DDR_A_D[0..63]

UCPU1C

D D

C C

B B

DDR_A_ D0

DDR_A_ D1

DDR_A_ D2

DDR_A_ D3

DDR_A_ D4

DDR_A_ D5

DDR_A_ D6

DDR_A_ D7

DDR_A_ D8

DDR_A_ D9

DDR_A_ D10

DDR_A_ D11

DDR_A_ D12

DDR_A_ D13

DDR_A_ D14

DDR_A_ D15

DDR_A_ D16

DDR_A_ D17

DDR_A_ D18

DDR_A_ D19

DDR_A_ D20

DDR_A_ D21

DDR_A_ D22

DDR_A_ D23

DDR_A_ D24

DDR_A_ D25

DDR_A_ D26

DDR_A_ D27

DDR_A_ D28

DDR_A_ D29

DDR_A_ D30 AR54

DDR_A_ D31 A N54

DDR_A_ D32 AY58

DDR_A_ D33A W58

DDR_A_ D34 AY56

DDR_A_ D35A W56

DDR_A_ D36 AV58

DDR_A_ D37 AU58

DDR_A_ D38 A V56

DDR_A_ D39 AU56

DDR_A_ D40 A Y54

DDR_A_ D41 AW54

DDR_A_ D42 AY52

DDR_A_ D43A W52

DDR_A_ D44 AV54

DDR_A_ D45 AU54

DDR_A_ D46 AV52

DDR_A_ D47 AU52

DDR_A_ D48 A K40

DDR_A_ D49 AK42

DDR_A_ D50 AM 43

DDR_A_ D51 AM4 5

DDR_A_ D52 AK45

DDR_A_ D53 A K43

DDR_A_ D54 AM40

DDR_A_ D55 AM 42

DDR_A_ D56 AM4 6

DDR_A_ D57 AK46

DDR_A_ D58 AM 49

DDR_A_ D59 AK49

DDR_A_ D60 AM 48

DDR_A_ D61 AK48

DDR_A_ D62 AM51

DDR_A_ D63 A K51

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ1 0

SA_DQ1 1

SA_DQ1 2

SA_DQ1 3

SA_DQ1 4

SA_DQ1 5

SA_DQ1 6

SA_DQ1 7

SA_DQ1 8

SA_DQ1 9

SA_DQ2 0

SA_DQ2 1

SA_DQ2 2

SA_DQ2 3

SA_DQ2 4

SA_DQ2 5

SA_DQ2 6

SA_DQ2 7

SA_DQ2 8

SA_DQ2 9

SA_DQ3 0

SA_DQ3 1

SA_DQ3 2

SA_DQ3 3

SA_DQ3 4

SA_DQ3 5

SA_DQ3 6

SA_DQ3 7

SA_DQ3 8

SA_DQ3 9

SA_DQ4 0

SA_DQ4 1

SA_DQ4 2

SA_DQ4 3

SA_DQ4 4

SA_DQ4 5

SA_DQ4 6

SA_DQ4 7

SA_DQ4 8

SA_DQ4 9

SA_DQ5 0

SA_DQ5 1

SA_DQ5 2

SA_DQ5 3

SA_DQ5 4

SA_DQ5 5

SA_DQ5 6

SA_DQ5 7

SA_DQ5 8

SA_DQ5 9

SA_DQ6 0

SA_DQ6 1

SA_DQ6 2

SA_DQ6 3

HASWELL_MCP_E

DDR CHANNELA

3 OF19

SA_CL K#0

SA_CL K0

SA_CL K#1

SA_CL K1

SA_CK E0

SA_CK E1

SA_CK E2

SA_CK E3

SA_CS #0

SA_CS #1

SA_ODT0

SA_RA S

SA_W E

SA_CA S

SA_BA0

SA_BA1

SA_BA 2

SA_MA 0

SA_MA 1

SA_MA 2

SA_MA 3

SA_MA 4

SA_MA 5

SA_MA 6

SA_MA 7

SA_MA 8

SA_MA 9

SA_MA 10

SA_MA 11

SA_MA 12

SA_MA 13

SA_MA 14

SA_MA 15

SA_DQS N0

SA_DQS N1

SA_DQS N2

SA_DQS N3

SA_DQS N4

SA_DQS N5

SA_DQS N6

SA_DQS N7

SA_DQS P0

SA_DQS P1

SA_DQS P2

SA_DQS P3

SA_DQS P4

SA_DQS P5

SA_DQS P6

SA_DQS P7

SM_VR EF_CA

SM_VR EF_DQ0

SM_VR EF_DQ1

<DDR3L>

AU37AH63

AV37

AW3 6

AY36

AU43

AW4 3

AY42

AY43

AP33

AR32

AP32

AY34

AW3 4

AU34

AU35

AV35

AY41

AU36

DDR_A_ MA0

DDR_A_ MA1

AY37

DDR_A_ MA2

AR38

DDR_A_ MA3

AP36

DDR_A_ MA4

AU39

DDR_A_ MA5

AR36

DDR_A_ MA6

AV40

AW3 9 DDR_A_ MA7

AY39 DDR_A_MA8

AU40 D DR_A_M A9

AP35 DDR_A_MA 10

AW4 1 DDR_A_M A11

AU41 DDR _A_MA12

AR35 DDR _A_MA13

AV42 DDR_A_MA 14

AU42 DDR _A_MA15

AJ61 DD R_A_DQS# 0

AN62 DDR_A_D QS#1

AM58DD R_A_DQS#2

AM55DD R_A_DQS#3

AV57 DDR_A_ DQS#4

AV53 DDR_A_ DQS#5

AL43 DDR_A _DQS#6

AL48 DDR_A _DQS#7

AJ62 DD R_A_DQS0

AN61 DDR_A_ DQS1

AN58 DDR_ A_DQS2

AN55 DDR_A_ DQS3

AW5 7DDR_A_DQS4

AW5 3DDR_A_DQS5

AL42 DD R_A_DQS6

AL49 DDR_A_DQS 7

AP49 +V_SM_ VREF_CN T

AR51 + V_DDR_ REFA_R

AP51 +V_DD R_REFB_ R

M_CLK_ DDR#0 <15>

M_CLK_ DDR0 <15>

M_CLK_ DDR#1 <15>

M_CLK_ DDR1 <15>

DDR_CK E0_DIMMA <15>

DDR_CK E1_DIMMA <15>

DDR_CS 0_DIMMA# <15>

DDR_CS 1_DIMMA# <15>

DDR_A_ RAS# < 15>

DDR_A_W E# < 15>

DDR_A_ CAS# < 15>

DDR_A_ BS0 <15 >

DDR_A_ BS1 <15 >

DDR_A_ BS2 <15 >

DDR_A_MA[0..15] <15>

DDR_A_DQS#[0..7] <15>

DDR_A_DQS[0..7] <15>

+V_SM _VREF_C NT

+V_DD R_REFA_ R

+V_DD R_REFB_ R

<16> DDR_B_D[0..63]

DDR_B_ D0 AY31

DDR_B_ D1 AW 31

DDR_B_ D2 A Y29

DDR_B_ D3 AW29

DDR_B_ D4 AV 31

DDR_B_ D5 AU31

DDR_B_ D6 AV 29

DDR_B_ D7 AU2 9

DDR_B_ D8 AY27

DDR_B_ D9 AW 27

DDR_B_ D10 AY25

DDR_B_ D11A W25

DDR_B_ D12 AV27

DDR_B_ D13 AU27

DDR_B_ D14 A V25

DDR_B_ D15 AU25

DDR_B_ D16 AM 29

DDR_B_ D17 AK29

DDR_B_ D18 AL28

DDR_B_ D19 A K28

DDR_B_ D20 AR29

DDR_B_ D21 AN29

DDR_B_ D22 A R28

DDR_B_ D23 AP28

DDR_B_ D24 AN26

DDR_B_ D25 AR26

DDR_B_ D26 AR25

DDR_B_ D27 AP25

DDR_B_ D28 AK26

DDR_B_ D29 AM 26

DDR_B_ D30 AK25

DDR_B_ D31 AL2 5

DDR_B_ D32 AY23

DDR_B_ D33 AW23

DDR_B_ D34 A Y21

DDR_B_ D35 AW21

DDR_B_ D36 A V23

DDR_B_ D37 A U23

DDR_B_ D38 AV21

DDR_B_ D39 AU21

DDR_B_ D40 AY19

DDR_B_ D41A W19

DDR_B_ D42 AY17

DDR_B_ D43 AW17

DDR_B_ D44 A V19

DDR_B_ D45 AU19

DDR_B_ D46 A V17

DDR_B_ D47 A U17

DDR_B_ D48 AR21

DDR_B_ D49 AR22

DDR_B_ D50 AL21

DDR_B_ D51 AM 22

DDR_B_ D52 A N22

DDR_B_ D53 AP21

DDR_B_ D54 A K21

DDR_B_ D55 AK22

DDR_B_ D56 AN20

DDR_B_ D57 A R20

DDR_B_ D58 AK18

DDR_B_ D59 AL1 8

DDR_B_ D60 AK20

DDR_B_ D61 AM 20

DDR_B_ D62 AR18

DDR_B_ D63 A P18

UCPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ1 0

SB_DQ1 1

SB_DQ1 2

SB_DQ1 3

SB_DQ1 4

SB_DQ1 5

SB_DQ1 6

SB_DQ1 7

SB_DQ1 8

SB_DQ1 9

SB_DQ2 0

SB_DQ2 1

SB_DQ2 2

SB_DQ2 3

SB_DQ2 4

SB_DQ2 5

SB_DQ2 6

SB_DQ2 7

SB_DQ2 8

SB_DQ2 9

SB_DQ3 0

SB_DQ3 1

SB_DQ3 2

SB_DQ3 3

SB_DQ3 4

SB_DQ3 5

SB_DQ3 6

SB_DQ3 7

SB_DQ3 8

SB_DQ3 9

SB_DQ4 0

SB_DQ4 1

SB_DQ4 2

SB_DQ4 3

SB_DQ4 4

SB_DQ4 5

SB_DQ4 6

SB_DQ4 7

SB_DQ4 8

SB_DQ4 9

SB_DQ5 0

SB_DQ5 1

SB_DQ5 2

SB_DQ5 3

SB_DQ5 4

SB_DQ5 5

SB_DQ5 6

SB_DQ5 7

SB_DQ5 8

SB_DQ5 9

SB_DQ6 0

SB_DQ6 1

SB_DQ6 2

SB_DQ6 3

HASWELL_MCP_E

DDR CHANNELB

4 OF19

SB_CK #0

SB_CK 0

SB_CK #1

SB_CK 1

SB_CK E0

SB_CK E1

SB_CK E2

SB_CK E3

SB_CS #0

SB_CS #1

SB_ODT0

SB_RA S

SB_W E

SB_CA S

SB_BA0

SB_BA1

SB_BA 2

SB_MA 0

SB_MA 1

SB_MA 2

SB_MA 3

SB_MA 4

SB_MA 5

SB_MA 6

SB_MA 7

SB_MA 8

SB_MA 9

SB_MA 10

SB_MA 11

SB_MA 12

SB_MA 13

SB_MA 14

SB_MA 15

SB_DQS N0

SB_DQS N1

SB_DQS N2

SB_DQS N3

SB_DQS N4

SB_DQS N5

SB_DQS N6

SB_DQS N7

SB_DQS P0

SB_DQS P1

SB_DQS P2

SB_DQS P3

SB_DQS P4

SB_DQS P5

SB_DQS P6

SB_DQS P7

AM38

AN38

AK38

AL38

AY49

AU50

AW4 9

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40 DDR_B_MA 0

AR40 DDR _B_MA1

AP42 DDR_B_MA 2

AR42 DDR _B_MA3

AR45 DDR _B_MA4

AP45 DDR_B_MA 5

AW4 6 DDR_B_ MA6

AY46 DDR_B_MA 7

AY47 DDR_B_MA 8

AU46 DDR _B_MA9

AK36 DDR_B_MA 10

AV47 DDR_B_MA 11

AU47 D DR_B_M A12

AK33 DDR_B_MA 13

AR46 D DR_B_M A14

AP46 DDR_B_MA 15

AW3 0DDR_B_DQS#0

AV26 DDR_B _DQS#1

AN28 DDR_ B_DQS#2

AN25 DDR_B_ DQS#3

AW2 2DDR_B_DQS#4

AV18 DDR_B _DQS#5

AN21 DDR_B_ DQS#6

AN18 DDR_ B_DQS#7

AV30 DDR_ B_DQS0

AW2 6DDR_B_DQS1

AM28 DDR_B_DQS 2

AM25 DDR_B_ DQS3

AV22 DDR_B _DQS4

AW1 8DDR_B_DQS5

AM21 DDR_B_DQS 6

AM18 DDR_B_DQS 7

<DDR3L>

M_CLK_ DDR#2 <16>

M_CLK_ DDR2 <16>

M_CLK_ DDR#3 <16>

M_CLK_ DDR3 <16>

DDR_CK E0_DIMMB <16>

DDR_CK E1_DIMMB <16>

DDR_CS 0_DIMMB# <16>

DDR_CS 1_DIMMB# <16>

DDR_B_ RAS# < 16>

DDR_B_W E# < 16>

DDR_B_ CAS# < 16>

DDR_B_ BS0 <16 >

DDR_B_ BS1 <16 >

DDR_B_ BS2 <16 >

DDR_B_MA[0..15] <16>

DDR_B_DQS#[0..7] <16>

DDR_B_DQS[0..7] <16>

A A

Security Classification

Issued Date

THI S S HE ET O F E NG INE E RI NG D RA WI NG I S T HE P R OP RI ET AR Y P RO PE R TY O F C OM PA L EL EC TR ON IC S, IN C. AN D C ONT AIN S CONFIDENSSTiIzAeL

AN D T RA DE SE CR E T I NF OR MA TI ON . T HIS S HE ET MA Y N OT BE T RAN SF E RE D F R OM TH E C US TO DY OF T HE CO MP E TEN T D IVI SI ON OF RC&uD

DE PA RT ME NT EXC E PT AS A UT HOR I ZE D BY COM PA L E L EC TR ONI C S, I NC . NEI THE R THIS S HE ET NOR T HE IN FO RM AT IO N I T CON TAI NS

5

4

3

MA Y BEU SE D BY ORD IS CLO SE D TO ANY TH IR D P AR TY W IT HOU T PR IO R W R IT TE N CO NS EN T OF COM PA L E L EC TR ON IC S, I NC.

2011/06/29 2011/06/29

Compal Secret Data

Deciphered Date

2

Title

Docum ent Number

stom

DDRIII

LA-B972P

Rev

Sheet 5 of 54Date: Thurs day, Mar ch 20,2014

1

0.1

Compal Electronics,Inc.

Page 7

5

+RTCVCC

330K_ 0402_5% 1 2 RC23 6 PCH_ INTVRMEN

INTVRMEN

H:Integrated VRM enable

*

L:Integrated VRM disable

D D

HDA_SY NC_R HDA_SY NC

Intel ME update

<30> HDA_SDO

C C

B B

+3V_P CH

12

RC283 @

210_0402_5%

R3d

12

RC304 @

100_0402_1%

+3V_P CH +3V_P CH

12

RC41 @

210_0402_5%

R4

12

RC301 @

100_0402_1%

<XDP>

<PCH site>

<XDP>

<PCH site>

<XDP>

<PCH site>

<XDP>

A A

<PCH site>

<PCH site>

<PCH site>

RC353 short@

1 2

0_0402_5%

short@

RC356 1 20_0201_5% HDA_SDOUT

PCH_J TAG_TDO

PCH_J TAG_TDI

Contact ok

R8

XDP_TRS T# 1

PCH_J TAG_TMS

XDP_TMS

XDP_TDI_ SWITCH RC1 99 1 @ 2 0_0201_5% XDP_TDI_C PU

PCH_J TAG_TDO RC307 1 @ 2 0_0201_5% XD P_TDI_SW ITCH

XDP_TDI

PCH_J TAG_TDI

XDP_TDO

XDP_TCK:XDP contact with CPU No 0ohm(RS5)

PCH_J TAG_TCK

XDP_TCK _JTAGX

XDP_TCK _JTAGX RC30 6 1 @ 2 0_0201_5% XD P_TDO

5

9/17 add RF solution

12

RC46

210_0402_5%

@

12

RC302

100_0402_1%

RC37 @

RC196 1 @ 2 0_0201_5% XDP_ TMS_CPU

RC200 1 2 0_0201_5% X DP_TDI_S WITCH

short@

RC195 1 2 0_0201_5% XDP_TDI

short@

RC198 1 @ 2 0_0201_5% X DP_TDO_C PU

RC194 1 2 0_0201_5% PCH_JTAG_TDO

short@

J1S

RC197 1 @ 2 0_0201_5% XDP _TCK

J2D

RC193 1 2 0_0201_5%

short@

J2S

<25> HDA_BITCL K_AUDIO

<25> HDA_R ST_AUDIO#

<25> HDA_SY NC_AUDIO

<25> HDA_S DOUT_AUDIO

CM28

@

2 HD A_BITCLK_ AUDIO

1

22P_0 402_50V8J

CM29

@

2

1

22P_0 402_50V8J

XDP_TCK _JTAGX

@

S1

2 0_0201_5%

S2

S3

J3S

J4d

S4

J3D

+RTCVCC

RC32 20K _0402_ 5%

RC34 20K _0402_ 5%

HDA_RS T_AUDIO#

PCH_J TAG_RST#

4

1

12

CC2

1U_0402 _6.3V6K

1 2

1 2

1U_0402 _6.3V6K

R5

XDP_TRS T#_CPU

2

1

12

CC5

2

EMI@ R C367

HDA_BITC LK_AUDIO 2 1 HDA_ BIT_CLK

33_0402_5%

HDA_RS T_AUDIO# 2

+3V_P CH

12

RC45 @

210_0402_5%

12

RC303 @

100_0402_1%

Contact ok

<CPU site>

XDP_TCK <4>

4

JCMOS1

SHORT PADS

PCH_RTC RST#

PCH_SR TCRST#

JME1

SHORT PADS

RP1

1

8

7 HD A_RST#

3

6 HDA _SYNC_R

5 HDA_S DOUT

4

33_0804_8P4R_5%

PCH_J TAG_TMS

XDP_TDI_ CPU <4>

XDP_TDO _CPU <4 >

<PCH site>

<CPU andXDP>

<XDP>

CMOS

XTAL@

CC3

18P_0 402_50V8J

MECMOS

+RTCVCC

<25> HDA_SDIN 0

2

RC35 1

SI# 2012.1 1.1 Add RC367 EMI@ toisolate

Audio Clock by EM Irequest

<CPU site>

<PCH site>

<CPU>

XDP_TRS T#_CPU RC16 2 @ 1 51_0402_1%

<XDP>

XDP_TDO _CPU RC10 2 1 51_0402_1%

XDP_TDO RC14 2

XDP_TCK R C15 2

XTAL@

1 2

RC31 10M_0402_5%

XTAL@

YC1

1 2

32.768 KHZ Q13FC13501000500

1

2

1M_0402_5%

PCH_J TAG_RST#

PCH_J TAG_TCK

PCH_J TAG_TDI

PCH_J TAG_TDO

PCH_J TAG_TMS

T156PAD

XDP_TCK _JTAGX

T157PAD

<CPU site>

<4> XDP_TRST#_ CPU

R1d

R7

R2

PCH_RTC X1

PCH_RTC X1

PCH_RTC X2

SM_INTRU DER#

PCH_INTV RMEN

PCH_SR TCRST#

PCH_RTC RST#

HDA_BIT_CLK

HDA_SY NC

HDA_RS T#

HDA_SD IN0

HDA_SD OUT

<4> XDP_TMS_C PU

R6

51_0402_5%PCH_JTAG_TCK

1 @

R9

@

1 51_0402_1%

1 51_0402_1%

3

PCH_RTC X1

PCH_RTC X2

CC4 XTAL @

18P_0 402_50V8J

2

EC_+1 .05VS_P G

XDP_TDO _CPU

XDP_TDI_ CPU

2 RC38

+1.05 VS_VCCS T

+1.05 VS_VCCS T

3

+RTCVCC

CC6

1U_0402 _6.3V6K

PCH_RTC X1 <31>

UCPU1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BC LK/I2S0_SC LK

AV11

HDA_SY NC/I2S0_SF RM

AU8

HDA_RS T/I2S_MC LK

AY10

HDA_SD I0/I2S0_R XD

AU12

HDA_SD I1/I2S1_R XD

AU11

HDA_SD O/I2S0_TX D

AW10

DOCKEN /I2S1_TX D

AV10

HDA_DOCK _RST/I2S1 _SFRM

AY8

I2S1_S CLK

AU62

PCH_TRS T

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

TP5

AC4

TP6

AE63

JTAGX

AV2

RSVD

XDP_TRS T#_CPU

<EC output>

Topolog

Default Setting: Dual

TCK S ca n Chains

(also kn own as

"Shared JTAG" in

other do cum ent)

Single T CK scan chain

(also kn own as "Com m on

JTAG" in other docum

ent)

Security Classification

THI S SHE ET OF E NG IN EE RI NG DR AW I NG IS THE PR OP R IE TA RY P RO P ER TY OF C OM PA L EL EC TR ONI C S, I NC . A ND CON TAI NS CO NF IDE NTI AL

AN D T RA DE SE CR E T I NF OR MA TI ON. TH IS SH EE T M A Y N OT BE T RA NS FE RE D FR OM TH E C US TO DY OF T HE CO MP ET EN T D IVI SI ON OF R& D

DE PA RT ME NT E X CE PT AS AU TH OR IZ ED BY C OM PA L E L EC TR ONI C S, I NC . NE IT HER TH IS SH EE T NOR TH E INF O RM ATI ON IT C ONT AIN S

MA Y BE US ED BY OR D IS CL OSE D TO ANY TH IR D PAR TY WI TH OU T PR IO R W R IT TE N CO NS EN T OF COM PA L E L EC TR ON IC S, INC.

15mils

1

2

RTC

AUDIO

JTAG

2 1

10K_0 402_5%

@ UC5

2

1OE V CC

3

1A 1B

5

2OE

6

2A

12

3OE

11

3A

15

4OE

14

4A

8

GND

74CBTLV 3126DS _SSOP16

Issued Date

1

BAV70 W 3PC/ C_SOT-323

HASWELL_MCP_E

5 OF19

RC240

@

2B

3B

4B

NC

NC

<30> EC_+1.05 VS_PG

+RTCBATT_ R

1K_04 02_5%

3

SATA

+3VS

XDP_TDO

XDP_TDI_ SWITCH

XDP_TMS

XDP_TRS T#

RC33

12 2

+3VL

SATA_ RN0/PER N6_L3

SATA_ RP0/PE RP6_L3

SATA_ TN0/PE TN6_L3

SATA_TP 0/PETP6 _L3

SATA_ RN1/PER N6_L2

SATA_ RP1/PE RP6_L2

SATA_ TN1/PE TN6_L2

SATA_TP 1/PETP6 _L2

SATA_ RN2/PER N6_L1

SATA_ RP2/PE RP6_L1

SATA_ TN2/PE TN6_L1

SATA_TP 2/PETP6 _L1

SATA_ RN3/PER N6_L0

SATA_ RP3/PE RP6_L0

SATA_ TN3/PE TN6_L0

SATA_TP 3/PETP6 _L0

SATA0 GP/GP IO34

SATA1 GP/GP IO35

SATA2 GP/GP IO36

SATA3GP /GPIO37

@CC8 6

1 2

.1U_04 02_16V7K

EC_+1 .05VS_P G

DC1

16

4

7

10

13

1

9

Description

In this topology, the

CPU JTAG chain will be

controlled by TCK0 and

TCK1 wil l control

the PCH JTAG chain.

In th is topolog y, PCH

TDI- TD O and CPU TDI-TDO

will be chained to form

one JTAG scan chain

controlled by TCK0

2011/06/29

Compal Secret Data

2

+RTCBATT

15mils15mils

SATA_IR EF

SATA_RCOMP

SATALE D

Deciphered Date

2

RTC BAT conn

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17 PCIE _PTX_DRX _N6 CC71

D17 PCIE _PTX_DRX _P6 CC81

V1

U1 ODD_PL UG#

V6 PC H_GPIO36 T159

AC1 mSATA_DE T#

A12

L11

TP7

K10

TP8

C12

SATA_C OMP 1

U3

SATA_L ED#

U16

1 5

NC V CC

2

A

3

GND

74AUP 1G07GW _TSSOP5

2

-

JRTC1

LOTES_A AA-BAT-054-K01

CONN@

<9> MPHY_PW REN

2 0.1U_040 2_16V7K

2 0.1U_040 2_16V7K

ODD_PL UG# <22>

PAD

mSATA _DET# <7>

SATA_L ED# <27,9>

+1.05 VS_VCCS T

12

R511

10K_0 402_5%

+1.05 VS_VCCS ATA3PLL <Page 12>

RC39

3K_04 02_1%

4

Y

2

+3V_P CH

Be st Us e for

- Run control oper.

- ME/S x debug

-B oundary Scan/

Manufacturing est

Compal Electronics, Inc.

2011/06/29 Title

Siz e Do cument Num ber

Custo m

1

+RTCBATT

15mils

1

+

MPHY_P WREN RC217 1 2 1 0K_0402 _5%

ODD_PL UG# R C218 1 2 1 00K_040 2_5%

SATA_P RX_DTX_N 0 <2 2>

SATA_P RX_DTX_P 0 <22>

SATA_P TX_DRX_N 0 <2 2>

SATA_P TX_DRX_P 0 <22>

SATA_P RX_DTX_N 1 <2 2>

SATA_P RX_DTX_P 1 <22>

SATA_P TX_DRX_N 1 <2 2>

SATA_P TX_DRX_P 1 <22>

PCIE_P RX_DTX_N 6 <21>

PCIE_P RX_DTX_P 6 < 21>

PCIE_P TX_C_DRX _N6 <21>

PCIE_P TX_C_DRX _P6 <21>

DG V0.9 SATA_COMP

L

Width=12mil

Max length=500mil

+1.05 VS_PG <11,4> <CPU,XDP,XDP Switch>

Resistors

Stuffed

R1d,R2,R3d,

R4,R5,J1d

J2d,J3d*

J4d and Rs5*

J1s,J2s,J3s**

R2,R4,R5,R5s**

2.5" HDD

ODD

WLAN

Resistors

ufStuffed

J1s, J2s,

J3s

R6,R7,R8,R9

R1d,r3 d,J1d,J2 d

J3d**,J 4d,

R6,R7, R8,R9

RTC,SATA,HDA,JTAG

LA-B972P

Sheet 6 of 54Date: Thurs day, Mar ch 20, 2014

1

+3VS

Rev

0.1

Page 8

5

PCIELAN

D

PCIE Cardreader

WLAN

GPU

+3VS

4 5

3 6 SYS_RESET#

2 7 EC_KBRST#

1 8 MSATA_DET#

+3VS

4 5 PCIECLKREQ0#

3 6 MINI1_CLKREQ#

2 7 PCI_PIRQB#

C C

1 8 PCH_GPIO33

DB# 2013.08.27 RC368 place near CPU

<30> EC_SPI_SI

<30> EC_SPI_SO

<30> EC_SPI_CS0#

<30> EC_SPI_CLK

B B

+3V_PCH

RC85

<23> CLK_PCIE_LAN#

<23> CLK_PCIE_LAN

<23> CLK_PCIE_CR#

<23> CLK_PCIE_CR

<23,9> CR_CLKREQ#

<21> CLK_PCIE_MINI1#

<21> CLK_PCIE_MINI1

<32> CLK_PCIE_GPU#

<32> CLK_PCIE_GPU

<32,8> GPU_CLKREQ#

RPH11

LAN_CLKREQ#

10K_0804_8P4R_5%

RPH12

10K_0804_8P4R_5%

PCH_SPI_CS0#

PCH_SPI_SO 7 2 PCH_SPI_SO_R

PCH_SPI_SI 6 3 PCH_SPI_SI_R

PCH_SPI_HOLD# 5 4 PCH_SPI_SIO3

PCH_SPI_CLK RC368 1 2 PCH_SPI_CLK_R

EMI@ 15_0402_5%

PCH_SPI_SIO2 5

1

2

3.3K_0402_5%

SYS_RESET# <8>

EC_KBRST# <30,9>

MSATA_DET# <6>

PCI_PIRQB# <8>

PCH_GPIO33 <9>

RPH19

1 PCH_SPI_CS0#_R

8

15_0804_8P4R_5%

RPH20

18

2

7

3

6

15_0804_8P4R_5%

EMI@ RC369 1 2 short@ RC56 1 2 0_0402_5% PCH_SPI_CLK_R

DB# 2013.08.27 RC369 place near SPI ROM

+3V_PCH

@

RC80

3.3K_0402_5%

1 2

4

15_0402_5%

PCH_SPI_CS0#_R 1

PCH_SPI_SO_R 2

PCH_SPI_WP# 3

SPI ROM8M

4

<23> LAN_CLKREQ#

<9> PCIECLKREQ4#

<21> MINI1_CLKREQ#

<28,30> LPC_AD0

<28,30> LPC_AD1

<28,30> LPC_AD2

<28,30> LPC_AD3

<28,30> LPC_FRAME#

PCH_SPI_SI_R PCH_SPI_SIO3 AF1

PCH_SPI_SO_R

PCH_SPI_CS0#_R

PCH_SPI_WP#

UC2

CS# VCC

SO/SIO1 HOLD#

WP# SCLK

GND SI/SIO0

EN25Q64-104HIP

SI# 2012.11.1 Add RC368 ,RC369to

Isolate SPI Clock by EMI request

8

7

6

5

4

UCPU1F

CLK_PCIE_LAN# C43

CLK_PCIE_LAN

PCIECLKREQ0#

CLK_PCIE_CR# B41

CLK_PCIE_CR

CR_CLKREQ#

CLK_PCIE_MINI1# C41

CLK_PCIE_MINI1 B42

LAN_CLKREQ#

CLK_PCIE_GPU# B38

CLK_PCIE_GPU

GPU_CLKREQ#

PCIECLKREQ4# U5

MINI1_CLKREQ#

LPC_AD0

LPC_AD1

LPC_AD2 AY12

LPC_AD3 AW 11

LPC_FRAME# AV12

PCH_SPI_CLK AA3

PCH_SPI_CS0# Y7

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_SIO2

EON SA000046400 S IC FL 64M EN25Q64-104HIP SOP 8P MXIC

SA00006N100 S IC FL 64M MX25L6473EM2I-10G SOP 8P

WINBOND SA000039A30 S IC FL 64M W25Q64FVSSIQ SOIC 8P SPI ROM

Micron SA00005L100 S IC FL 64M N25Q064A13ESEC0F SO8W 8+P3V_PCH

PCH_SPI_HOLD# 2

PCH_SPI_CLK_R

PCH_SPI_SI_R

C42

U2

A41

Y5

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

AD1

CLKOUT_PCIE_N3

C37

N1

A39

B39

CLKOUT_PCIE_P4

B37

A37

T2

AU14

LAD0

AW12

LAD1

LAD2

LAD3

LFRAME

SPI_CLK

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

SPI_IO3

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

PCIECLKRQ0/GPIO18

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

PCIECLKRQ1/GPIO19

PCIECLKRQ2/GPIO20

CLKOUT_PCIE_P3

PCIECLKRQ3/GPIO21

CLKOUT_PCIE_N4

PCIECLKRQ4/GPIO22

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

PCIECLKRQ5/GPIO23

UCPU1G

LPC

SPI C-LINK

3.3K_0402_5%1 RC84

HASW ELL_MCP_E

7 OF19

HASW ELL_MCP_E

CLOCK

SIGNALS

6 OF19

SMBUS

3 2

XTAL24_IN

XTAL24_OUT

DIFFCLK_BIASREF

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML1ALERT/PCHHOT/GPIO73

1

CC11

0.1U_0402_16V7K

2

@

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

A25

CPU_XTAL24_IN

B25

CPU_XTAL24_OUT

K21

TP15

M21

TP16

C26 PCH_CLK_BIASREF

C35 TESTLOW1

TP19

C34 TESTLOW2

TP20

AK8 TESTLOW 3

TP21

AL8 TESTLOW4

TP22

AN15 CLK_PCI0

AP15 CLK_PCI1

B35

CLK_CPU_ITP#

A35

CLK_CPU_ITP

AN2 SMBALERT#

AP2 SMBCLK

AH1 SMBDATA

AL2 USB_CR_PWREN

AN1 SML0CLK

AK1 SML0DATA

AU4 SML1ALERT#

AU3 SML1CLK

AH3 SML1DATA

AF2

AD2

AF4

3K_0402_1%

1

EMI@ RC61 1

EMI@ RC62 1

CPU_XTAL24_IN

RC52

2

4

5 RPH22

3

6

217

8

2 22_0402_5% CLK_PCI_LPC

2 22_0402_5% CLK_PCI_TPM

SMBALERT# <9>

USB_CR_PWREN <8>

SML1ALERT# <9>

+1.05VS_AXCK_LCPLL

10K_0804_8P4R_5%

T82 @ PAD

T81 @ PAD

9/17 add RFsolution

2N7002DWH_SOT363-6

SML1CLK 6

SML1DATA

CPU_XTAL24_IN <31>

<Page12>

<PV>PRH13 change to RPH22.

CLK_PCI_LPC <30>

CLK_PCI_TPM <28>

<XDP CLK reserveTP>

@RF@

CM30

1

2 CLK_PCI_LPC

22P_0402_50V8J

@RF@

CM31

1 2 CLK_PCI_TPM

22P_0402_50V8J

@RF@

CM33

1

2 PCH_SPI_CLK_R

22P_0402_50V8J

2

QC2A 2N7002DWH_SOT363-6

6 1

SMBCLK

QC2B

SMBDATA

QC6A

3 4

2

1

3 4

2N7002DWH_SOT363-6

QC6B

CPU_XTAL24_IN

CPU_XTAL24_OUT

XTAL@

CC9

18P_0402_50V8J

1

XTAL@

2

1M_0402_5%

3

3 1

GND GND

1

4

2

XTAL@

24MHZ 12PF 5YEA24000122IF240Q3

<EC>

SML0CLK 1K_0402_5% 1 2 RC72

SML0DATA 1K_0402_5% 1 2 RC73

SMBCLK

SMBDATA

SML1CLK

SML1DATA

+3VS +3VS

10K_0402_5%

5

2N7002DWH_SOT363-6

+3VS

5

RC78

RC79

10K_0402_5%

1 2

1 2

EC_SMB_CK2 <18,30,32>

EC_SMB_DA2 <18,30,32>

1

RC48

1

1

2

YC2

RP2 1

2

3

4

PCH_SMBCLK <15,16>

PCH_SMBDATA <15,16>

XTAL@

CC10

18P_0402_50V8J

+3V_PCH

8 2.2K_0804_8P4R_5%

7

6

5

D

A A

remove thernal sensor 10/14

Security Classification

Issued Date

THI S SHE ET O F ENG IN EER ING DR AW IN G IS T HE PR OP RIE TA RY P ROPER TY O F CO MPA L EL ECT RO NI CS, INC. AN D CO NTA INS CONFIDENTIASSL

AND T RADE SECRE T INF ORMAT ION . THI S SHEE T MAY NOT BE T RANSF ERED FRO M THE CUST OD Y OF T HE COMPETEN T DIVIS ION OF R&D

DEPAR TMENT EX CEPT AS A UT HO RIZ ED BY C OMPAL E LEC TR ON ICS , INC. NEIT HER THIS SH EET N OR TH E INFO RM ATION IT CONTAIN S

5

4

MAY BE USE D BY OR DI SCLOSE D TO A NY TH IRD PA RT Y WITHOUT PRIO R WR IT TEN CON SE NT OF CO MPAL ELE CT RO NIC S, INC.

3 2

2011/06/29 2011/06/29

Compal Secret Data

DecipheredDate

Compal Electronics, Inc.

Title

CLK,SPI,SMB,LPC

ize Document Number

Custom

LA-B972P

Rev

Sheet 7 of 54Date: Thursday, March 20, 2014

1

0.1

Page 9

5 4 3 2 1

T83

Non Deep S3RC91-->SMT

Deep S3 RC93-->SMT

<9> SUSWARN#_R

D D

<30> PCH _PW ROK

Deep S3

C C

<30> SUSACK#

<30> SYS_PWROK

<30> P CH_RSMRST#

<30> PCH_SUSWARN#

<30> PBT N_O UT#

<30,44,45,46> AC IN

C70 ES D@

1 2 PCH_PWROK

0.047U_0402_16V7K

1 100K_0402_5% SYS_PWROKRC112 2

SUSW ARN#_R RC91 1

short@ RC93 1

PCH_PW ROK short@ RC1001 2 0_0402_5%

short@ RC99 1

short@ RC1041

short@ RC1031

@

2 0_0201 _5%

20_0201_5%

<7> SYS _RESET#

2 0_0402_5%

2 0_0402_ 5%

2 0_0402_ 5%

2 DC2

1

SUSACK#_R AK2

SYS_RESE T# AC3

SYS_PWR OK AG2

PM_P WROK_R AY7

APW ROK_R AB5

PLT_RST #_PCH AG7

PCH_RSMRST# A W6

SUSWARN#_R AV4

PBTN_OUT#_R AL7

ACIN_R AJ8

PM_B ATLOW# AN4

PM_S LP_S0#_R AF3

PCH_SLP_WLAN# AM5

short@ RC268 1 20_0201_5%

PAD

RC269 1 2 0_0201_5%

@

UCPU1H

SUSACK

SYS_RESE T

SYS_PWROK

PCH_PW ROK

APWR OK

PLTRST

RSMRST

SUSW ARN/SUSPW RDN ACK/GPIO30

PW RB TN SLP_ S4

ACPRESENT/GPI O31 SLP_ S3

BATLOW /GP IO72 SLP_ A

SLP_ S0 SLP_S US

SLP_ WLAN/G PIO29 SLP_ LAN

UCPU1I

HASWELL_MCP_E

SYSTEM POWERMANAGEMENT

8 OF 19

PCH_RSMRST#

PCH_DPW ROK_R RC316 1

short@

HASWELL_MCP_E

PANEL_BKEN_CPU PD 100K on Page20

<18,4> BKL_PWM_CPU

<30> E NBKL

<19> ENVDD _CPU

<30> AOAC_PME#

RC120 1 2 100K_0402_5% ENVDD _CPU

B B

short@ RC114 1 2 0_0402_5% BKL_PW M_CPU_R B8

short@ RC115 1

ENVDD_CPU RC116 1

short@

AOAC_PME# 1 2 AOAC_PME#_R AD4

<9> EC_SMI#

<7> PCI_PIRQB#

<9> PCI_PIRQC#

RC305 0_0402_5%

PAD T146

PAD T154

2 0_0402_5% ENBKL_CPU

2 0_0402_5% ENVDD_CPU_R

PCI_PIRQB# P4

PCI_PIRQC# N4

@ P CH_GPIO 80 N2

TS_RST#

@

PCH_MC_WAKE#

PCH_MIC_DET

@

PCH_HP_DET

EC_SMI# U6

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/G PIO79

PIRQD/G PIO80

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

eDPSIDEBAND

GP IO

9 OF 19

PM_S LP_S0#_R

PM_S LP_S3#

SUS_STA T/GPIO61

CH751H-40PT_SOD323-2

1

CH751H-40PT_SOD323-2

DC4 2 1

DDPB_CT RLCLK

DDPB_CT RLDATA

DDPC_CT RLCLK

DDPC_CT RLDATA

DDPB_AUXN

DISPLAY

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPC_HPD

DPWROK

WAKE

PAD PAD

B9 PCH_DDPB _CLK

C9 P CH_DDPB _DAT

D9 @ 1RC107

D11 1

C5

B6

B5

A6

C8

A8

D6

AW 7 D SWODVRE N

AV5 PCH_DPW ROK_R

AJ5 WAKE#

V5 PM_CLKRUN #

AG4 SU S_ST AT#

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

T142 T143

@ @

RC102 2.2K_0402_5%

DDI1_AUX_DN

DDI1_AUX_DP

DSW VRMEN

CLKRUN/GPIO32

SUSCLK/GPIO 62

SLP_ S5/G PIO63

2 DC3 PCH_P WROK

20_0201_5%

DDPB_HPD

EDP_HPD

RC371 1

short@

T147

PAD

@

PM_S LP_S3#

T145PAD @CH751H-40PT_SOD323-2

1

short@ RC286

Non Deep S3RC286-->@

Deep S3 RC286-->SMT

PCH_DPW ROK <30>

2 2.2K_0402_5%

2

2 0_0201_5%

SPOK <47>

PCH_DDPB_CL K <20>

PCH_DDPB_DA T <20>

T144

2 0_0402_5%

WAKE# <41>

PM_C LKRUN# <30>

PM_S LP_S5# <30>

PAD

@

<7> USB_CR_PWREN

+3VS

<SI>Displayport Port C Enable pin RC102 pull high +3VS

DDI1_AUX_DN <29>

DDI1_AUX_DP <29>

PCH_DDPB_HP D <20>

DDI1_HPD <29>

EDP_HPD <18>

<DP TO CRT HPD>

<HDMI>

<DP TO CRT HPD>

<eDP HPD>

DSWODVREN - On Die DSW VR Enable

H:Enable

*

L:Disable

AOAC_PME#

WAKE# RC98 1 2 1K_0402_5%

PM_S LP_S4# <30>

PM_S LP_S3# <30>

PM_S LP_SUS# <30>

Deep S3:DSW power choose onpage12

PM_B ATLOW#

USB_CR_PWREN

PCH_SLP_WLAN# 4

<HDMI>

ACIN_R RC101 1 2 10K_0402_5%

@

RPH15

1 8

2

7

3

6

5

10K_0804_8P4R_5%

1 8.2K_0402_5%PM_C LKRUN# RC110 2

+RTCVCC

1 330K_0402_5%DSW ODVREN RC254 2

1 330K_0402_5%DSW ODVREN RC255 2

+3V_DSW _P

1 10K_0402_5%PCH_RSMRST# RC106 2

+3V_DSW _P

+3VS

+3VS

@

1

2

RC300

UC9

O

Issued Date

+3VS

5

3

0_0402_5%

1

IN1

IN2

G P

SN74AHC1G08DCKR _SC70-5

PLT_RST #_PCH

2

2011/06/29 2011/06/29

<CPU>

Compal Secret Data

Deciphered Date

Title

PM,GPIO,DDI

ize Document Number

Custom

LA-B972P

Sheet

Rev

0.1

8 of 54Date: T hursday, March 20, 2014

1 10K_0402_5% PCH_MC_WAKE#RC125 2

RPH27 4

3

2

1

5

6

7

8

10K_0804_8P4R_5%

GPU_CLKREQ#

PCH_GPIO80

PCH_HP_DET

DEVSLP1

GPU_CLKREQ# <32,7>

DEVSLP1 <22,9>

<21,23,28,30,32> PLT_RST#

PLT_RST # 4

<PV>PRH18 change to RPH27.

A A

5 4 3 2 1

PD on KBCpage

Security Classification

TH IS S H EE T O F EN GI NE ER IN G DR AW ING I S T HE P R OPR IE T A RY P R O PE R TY OF CO MPA L E LE CT R ON IC S, I NC. AN D C ONT AI NS CONFIDENTIASL

AN D T RA D E SE CR E T INF O RM AT IO N. TH IS S HE E T MA Y NOT BE TR AN S FER ED F R OM T H E CU STO D Y OFT H E CO MP ET EN T D IVI SION OF R& D

DE PA RT ME NT EXC EPT AS AU T HO R IZ E D BY C O MP AL ELEC TR ONICS, IN C. N EITH ER T HI S SH EE T N O R TH E INF O RM AT IO N IT CO NT A IN S

MA Y BE U S ED BY OR D IS CL OS ED TO AN Y THIR D PAR T Y WI T HO UT PR IO R W R IT T EN CON S EN T OF COM PAL E LE CT RON IC S, INC.

Page 10

5 4 3 2 1

GPIO

HASWELL_MCP_E

10 OF19

CPU/

MISC

LPIO

THRMTRIP

RCIN/GPIO82

SERIRQ

OPI_COMP2

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

short@RC129

D60 H_THERMTRIP#_C 1 2 H_THEMTRIP#

V4 EC_KBRST#

SERIRQ

T4

AW15PCH_OPIRCOMP

AF20

AB21

R6

NGFF_WIFI_3.3_PWREN

WWAN_PWREN

L6

N6

PCH_GPIO85RC1081@ 2

MSATA_SSD_PWREN

L8

R7

L5

N7 TOUCH_PANEL_PWREN

K2 SATA1_PWREN

J1 PCH_LAN_RST#

K3 PCH_LAN_WAKE#

J2 PCH_CR_RST#

G1PCH_CR_WAKE#

K4

G2

J3

J4 ODD_DA#

I2C_0_SDA

F2

I2C_0_SCL

F3

I2C_1_SDA

G4

I2C_1_SCL

F1

E3

F4

D3

E4

ODD_PWR

C3

E2

0_0402_5%

2 1

RC131

49.9_0402_1%

ODD_DA# <22>

ODD_PWR <22>

EC_KBRST#<30,7>

SERIRQ <28,30>

0_0201_5%

UCPU1J

PCH_AUDIO_PWREN P1

<23> LAN_PWR_EN

<30> EC_LID_OUT#

D D

C C

+3V_PCH

<30> EC_FB_CLAMP_TGL_REQ#

<34> DGPU_GC6_EN

<23,30> EC_PME#

<30,32>DGPU_HOLD_RST#

<10,21>WL_OFF#

<30> NMI_DBG#_CPU

+3VS

RC1221@

RC1231@

EC_PME#

PAD

PAD

RC1191@

PAD T150

<6> MPHY_PWREN

<19> TS_GPIO_CPU

<28> ACCEL_INT#

<30> EC_SCI#

<7> PCH_GPIO33

<22,8> DEVSLP1

<25> HDA_SPKR

LAN_PWR_EN

EC_LID_OUT#

2 0_0201_5% PCH_GPIO16

2 0_0201_5% PCH_GPIO17

UART_WAKE#

T148

T149

BT_ON

2 PCH_GPIO58

0_0201_5% WL_OFF#

NMI_DBG#_CPU

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

MPHY_PWREN

USB32_P0_PWREN_R# AT3

USB_CAM_PWREN

TS_GPIO_CPU

ACCEL_INT#

PCH_GPIO9

EC_SCI#

PCH_GPIO33

PAD T158

DEVSLP1

HDA_SPKR

Dummy

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

<SI> PRH14.4 change from +3V_PCH to +3VS for S3 leakage

3

2

1

3

2

1

3 6

2

1

RPH13

4

3

2

1

10K_0804_8P4R_5%

3

2

1

3

2

1

+3V_DSW_P

5

6

7

8

10K_0804_8P4R_5%

5

6

7

8

10K_0804_8P4R_5%

5

7

8

10K_0804_8P4R_5%

<PV>PRH14 change to RPH23.

5

6 CR_CLKREQ#

7 SERIRQ

8 SATA_LED#

5

6

7

8

10K_0804_8P4R_5%

5

6

7

8

10K_0804_8P4R_5%

ODD_DA#

EC_LID_OUT#

UART_WAKE#

BT_ON

USB_OC2#

ACCEL_INT#

PCH_GPIO58

USB_OC0#

USB32_P0_PWREN_R#

PCH_GPIO9

NMI_DBG#_CPU

PRH15 change to RPH24.

PRH16 change toRPH25.

PCH_GPIO17

EC_SMI#

PCIECLKREQ4#

PCI_PIRQC#

SATA1_PWREN

PCH_AUDIO_PWREN

USB_CAM_PWREN

LAN_PWR_EN

CR_CLKREQ#<23,7>

SATA_LED#<27,6>

<PV>PRH10 change to RPH10.

+3V_PCH +3VS +3VS

12

USB_OC2# <10>

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

USB_OC0# <10,24>

EC_SMI# <8>

PCIECLKREQ4# <7>

PCI_PIRQC#<8>

RC135

10K_0402_5%

@

12

@RC263

10K_0402_5%

PRH17 change toRPH26.

12

RC261 RC262

10K_0402_5%10K_0402_5%

12

@RC264 @RC265

10K_0402_5%10K_0402_5%

+3V_PCH

RPH14 4

12

@ @

12

5

6

3

7

2

8

1

10K_0804_8P4R_5%

SUSWARN#_R

SML1ALERT#

SMBALERT#

EC_SCI#

SUSWARN#_R<8>

SML1ALERT# <7>

SMBALERT# <7>

RPH23 4

RPH24 4

RPH25 4

+3VS

B B

RPH26 4

RPH10 4

+1.05VS_VCCST

12

RC242

1K_0402_5%

DG V0.9 PCH_OPIRCOMP

Width=12mil,spacing=12mil

L

Max length=500mil

DGPU_PWR_EN <30,35,53>

Boot BIOS Strap

PCH_GPIO86 Boot BIOSLocation

SPI

0

*

9/12 reserve DGPU_PWR_EN on GPIO85

NGFF_WIFI_3.3_PWREN 4 5 RPH21

WWAN_PWREN 3 6

MSATA_SSD_PWREN 2 7

TOUCH_PANEL_PWREN 1 8

10K_0804_8P4R_5%

<PV>PRH12 change to RPH21.

<PV>PRH19 change to RPH28.

PCH_CR_WAKE#

PCH_CR_RST#

PCH_LAN_WAKE#

PCH_LAN_RST#

I2C_1_SDA

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL

10K_0804_8P4R_5%

4

5 RPH28

3 6

2

7

1

8

@

8

1 RPH18

7

2

3

6

4

5

1K_0804_8P4R_5%

@

+3VS

DSW power choose onpage12

*

GPIO27

A A

RC277 1 2 10K_0402_5% EC_PME#

PCH_GPIO27 (Have internal Pull-High)

High: VCCVRM VR Enable

Low: VCCVRM VR Disable

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DR AWING IS T HE PRO PRIETAR Y PR OPERTY OF COMPAL ELECT RONICS, I NC. AND CO NTA INS CONFIDENTIASL

AND TRADE SECRET INFORMAT ION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUS TOD Y OF TH E COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, INC. NEITHER TH IS SHEET NOR T HE INFORMATI ON IT CONTAINS

5 4 3 2 1

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WIT HOUT PRIOR WRITTEN CONSENT OF C OMPAL ELECTRONIC S, INC.

2011/06/29 2011/06/29

Compal Secret Data

DecipheredDate

Title

GPIO,UART,I2C

ize DocumentNumber

Custom

LA-B972P

Sheet

Rev

9 of 54Date: Thursday, March 20,2014

0.1

Page 11

5

USB2N4

USB2N5

USB2N6

USB2N7

USB3RN0

USB3RN1

USB3TN1

USBRBIAS

4

3 2

1

HASWELL_MCP_ E

PC Ie

11 OF19

AN8

USB2N0

AM8

USB2P0

AR7

USB2N1

AT7

USB2P1

AR8

USB2N2

AP8

USB2P2

AR10

USB2N3

AT10

USB2P3

AM15

AL15

USB2P4

AM13

AN13

USB2P5

AP11

AN11

USB2P6

AR13

AP13

USB2P7

G20

H20

USB3RP0

USB

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

USB3TN0

USB3TP0

USB3RP1

USB3TP1

TP13

TP14

C33

B34

E18

F18

B33

A33

USBRBIAS

AJ10

AJ11

AN10

AM10

AL3 USB_OC0#

AT1 USB_OC1#

AH2 USB_OC2#

AV3 USB1_PWR_EN

<21,9> WL_OFF#

USB20_N0 <24>

USB20_P0 <24>

USB20_N1 <24>

USB20_P1 <24>

USB20_N2 <24>

USB20_P2 <24>

USB20_N3 <21>

USB20_P3 <21>

USB20_N4 <19>

USB20_P4 <19>

USB20_N5 <19>

USB20_P5 <19>

USB3_RX0_N <24>

USB3_RX0_P <24>

USB3_TX0_N <24>

USB3_TX0_P<24>

USB2.0/USB3.0

USB2.0

USB2.0

WLAN/BT

Camera

Touch screen

USB2.0/USB3.0

L

RC148 1 2 22.6_0402_1%

USB_OC0# <24,9>

USB_OC1# <24>

USB_OC2# <9>

USB_OC1# 3 6

WL_OFF# 2 7

USB1_PWR_EN 1 8

DG V0.9 USBRBIAS

Trace width=50ohm and spacing=15mil

Max length=500mil

+3V_PCH

RPH17

4 5

10K_0804_8P4R_5%

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

F13

G13

PERN4

PERP4

B29

A29

PETN4

PETP4

G17

F17

PERN1/USB3RN

2

C30

C31

PERP1/USB3RP2

PETN1/USB3TN

2

PETP1/USB3TP2

PERN2/USB3RN

3

PERP2/USB3RP3

PETN2/USB3TN

3

PETP2/USB3TP3

B27

TP3

TP4

PCIE_RCOMP

PCIE_IREF

UCPU1K

<DB>change AC cap to 0.22uF review by Nvidia

D D

C C

10/100/1G LAN

PCI-E Cardreader

B B

<32> PEG_GTX_C_HRX_N7

<32> PEG_GTX_C_HRX_P7

<32> PEG_HTX_C_GRX_N7

<32> PEG_HTX_C_GRX_P7

<32> PEG_GTX_C_HRX_N8

<32> PEG_GTX_C_HRX_P8

<32> PEG_HTX_C_GRX_N8

<32> PEG_HTX_C_GRX_P8

<32> PEG_GTX_C_HRX_N9

<32> PEG_GTX_C_HRX_P9

<32> PEG_HTX_C_GRX_N9

<32> PEG_HTX_C_GRX_P9

<32> PEG_GTX_C_HRX_N10

<32> PEG_GTX_C_HRX_P10

<32> PEG_HTX_C_GRX_N10

<32> PEG_HTX_C_GRX_P10

<23> PCIE_PRX_DTX_N3

<23> PCIE_PRX_DTX_P3

<23> PCIE_PTX_C_DRX_N3

<23> PCIE_PTX_C_DRX_P3

<23> PCIE_PTX_C_DRX_N2

<23> PCIE_PTX_C_DRX_P2

<23> PCIE_PRX_DTX_N2

<23> PCIE_PRX_DTX_P2

<Page12>

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

0.22U_0402_6.3V6K DIS@ 1

CC12 2 1 PCIE_PTX_DRX_N3 C29

CC13 2 1 0.1U_0402_16V7K PCIE_PTX_DRX_P3 B30

CC16 2

CC17 2

+1.05VS_VCCUSB3PLL

DG V0.9 PCIE_RCOMP

L

Width=12mil,spacing=12mil

0.1U_0402_16V7K

1 0.1U_0402_16V7K

1 0.1U_0402_16V7K

3K_0402_1% E13

PEG_GTX_C_HRX_N7 F10

PEG_GTX_C_HRX_P7 E10

2 CC90

2 CC91

2 CC89

2 CC92

2 CC93

2 CC94

2 CC95

2 CC96

RC151 E15

1 2 PCH_PCIE_RCOMP A27

PEG_HTX_GRX_NC723

PEG_HTX_GRX_PC722

PEG_GTX_C_HRX_N8

PEG_GTX_C_HRX_P8

PEG_HTX_GRX_NB823

PEG_HTX_GRX_PA823

PEG_GTX_C_HRX_N9 H10

PEG_GTX_C_HRX_P9 G10

PEG_HTX_GRX_N9 B21

PEG_HTX_GRX_P9 C21

PEG_GTX_C_HRX_N10 E6

PEG_GTX_C_HRX_P10 F6

PEG_HTX_GRX_N10 B22

PEG_HTX_GRX_P10 A21

PCIE_PRX_DTX_N3 G11

PCIE_PRX_DTX_P3 F11

PCIE_PRX_DTX_N2 F15

PCIE_PRX_DTX_P2 G15

PCIE_PTX_DRX_N2 B31

PCIE_PTX_DRX_P2 A31

Max length=500mil

<PV>PRH11 change to RPH17.

A A

Security Classification

Issued Date

TH IS SH E ET OF ENG I NEE RI N G DR A W IN G IS TH E P ROP R IE T AR Y P ROP ERT Y O F COM PAL E L EC T RON I CS , IN C. A N D C ON TAI NS CONFIDENTISSAiL

AN D T RAD E S ECR ET IN FO RMATI ON . TH IS S H EE T MAY N O T BE T R AN S FER ED FRO M TH E CUS T OD Y OF TH E CO M PE T ENT D IVISI ON OF R& D

DE P ART MEN T EXC EPT AS A U THO R IZE D BY CO MPA L E LEC T RON ICS , IN C. NE IT HE R T HIS S H EE T N O R T H E IN F ORM ATI O N IT C ONT AI NS

5

4

MA Y BE US ED BY OR D ISC LO SE D TO AN Y T HI RD PA RT Y W ITH OUT P R IO R W RI T TEN C ONS EN T OF CO MP A L EL E CT R O NI C S, IN C.

2011/06/29 2011/06/29

3 2

Compal Secret Data

Deciphered Date

Title

PCIE,USB

ze Document Number

B

LA-B972P

Sheet of

10 54Date: Thursday, March 20, 2014

1

Rev

0.1

Page 12

5

4

3 2

1

+VCC_CORE@10000mA

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

+VCC_CORE

G33

RC288

10K_0402_5%

HASWELL_MCP_E

HSW ULT POWE R

12 OF19

VR12.6PG_MCP

+1.35V_VDDQ

+VCC_CORE

D D

<PWR VR12.6>

SVID ALERT

<50> VR_SVID_ALRT#

SVID DATA

RC1551

+1.05VS_VCCST

12

RC156

110_0402_1%

43_0402_1%

+1.05VS_VCCST

12

RC154

75_0402_5%

2

DG V0.5 H_CPU_SVIDALRT#

L RC154 close to CPU<300mil

Max length=1000~2000mil

H_CPU_SVIDALRT#

VCC_SENSE

<PWR VR12.6>

<VR IV and CPU>

<EDP_COMP power rail>

<50> VR12.5_VR_ON

PH on power page

<50> VCCSENSE

+VCCIO_OUT

+VCCIOA_OUT

<50> VR_SVID_CLK

<4,6> +1.05VS_PG

<PWR VR12.6>

C C

B B

<CPU>

<50> VR_SVID_DAT

L

+1.05VS

DG V0.5 VIDSOUT

RC156 close to CPU<500mil

Max length=1000~2000mil

VR_SVID_DAT

RC294 1 2 0_0402_5%

+1.05VS_VCCST

150_0402_5

%

12 1 2

RC166

CPU_PWR_DEBUG

7

10K_0402_5

%

@

RC16

@

+VCCIO_OUT

+1.05VS +1.05VS_VCCST

short@

RC223

1 2

0_0805_5%

1

1

CC7

CC72

2

2

1U_0402_6.3V6

K

1

22U_0805_6.3V6

M

<50> VGATE

@

+1.05VS_VCCST

+VCC_CORE

2500mA

VCCSENSE

H_CPU_SVIDALRT# L62

VR_SVID_CLK

VR_SVID_DAT

VR12.6PG_MCP

CPU_PWR_DEBUG H59

600mA

UC8

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

L59

RSVD

J58

RSVD

AH26

VDDQ

AJ31

VDDQ

AJ33

VDDQ

AJ37

VDDQ

AN33

VDDQ

AP43

VDDQ

AR48

VDDQ

AY35

VDDQ

AY40

VDDQ

AY44

VDDQ

AY50

VDDQ

F59

N58

RSVD

AC58

RSVD

E63

VCC_SENSE

AB23

A59

VCCIO_OUT

E20

VCCIOA_OUT

AD23

RSVD

AA23

RSVD

AE59

RSVD

N63

VIDSCLK

L63

VIDSOUT

B59

VCCST_PWRGD

F60

VR_EN

C59

VR_READY

D63

VSS

PWR_DEBUG

P62

VSS

P60

RSVD_TP

P61

RSVD_TP

N59

RSVD_TP

N61

RSVD_TP

T59

VSS

AD60

AD59

AA59

AE60

AC59

AG58

U59

VSS

V59

AC22

VCCST

AE22

VCCST

AE23

AB57

VCC

AD57

VCC

AG57

VCC

C24

VCC

C28

VCC

C32

+3V_PCH

5

4

Y

UCPU1L

VCCIN

RSVD

VIDALERT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCCST

VCC

+1.05VS_VCCST

12

+1.35V_VDDQ+1.35V_VDDQ

10U_0603_6.3V6

CC20

2.2U_0402_6.3V6

M

1

2

A A

Security Classification

Issued Date

THI S SH EET OF E NGIN EERING DR AWING IS T HE PROPRIET ARY PROP ERT Y OF COMPAL ELECTRO NICS, INC. AND C ONT AINS CONFIDENTIAL

AND TR ADE SECRET INFO RMAT ION. T HIS SHEET MAY NOT BE TRANS FERE D FROM THE CU STO DY OF T HE COMPETENT DIVISION OF R&D

DEPA RTMENT EXC EPT A S A UTH ORIZ ED BY COMP AL ELE CTR ONIC S, IN C. NEIT HER THIS SH EET NO R T HE I NFORMAT ION IT CONTAI NS

5

4

MAY BE USED BY OR D ISCLOSED TO ANY T HIR D PARTY W ITH OUT PRIOR W RITT EN C ONSE NT OF COMPAL ELE CTR ONIC S, INC .

3 2

CC21

2.2U_0402_6.3V6

M

1

2

2011/06/29 2011/06/29

2.2U_0402_6.3V6

M

1

@

2

Compal SecretData

CC22

1

2

Deciphered Date

CC23

2.2U_0402_6.3V6

M

CC24

330U_2.5V_M 330U_2.5V_M

CC25

1

+

2

@

1

+

2

M

10U_0603_6.3V6

M

@

1

1

CC26

2

1

CC27

2

2

Compal Electronics, Inc.

Title

Power

Size DocumentNumber

Custom

Date:

10U_0603_6.3V6

M

CC28

LA-B972P

10U_0603_6.3V6

M

@

1

2

10U_0603_6.3V6

M

1

CC29

2

10U_0603_6.3V6

M

@

1

CC30

CC31

2

Rev

Sheet 11 of 54Thursday, March 20, 2014

1

0.1

Page 13

5

+1.05VS_VCCUSB3PLL

RC170

+1.05VS_MODPHY

2.2UH_LQM2MPN2R2NG0L_30%

D D

+1.05VS_MODPHY

C C

+1.05VS

2.2UH_LQM2MPN2R2NG0L_30%

B B

+1.05VS

2.2UH_LQM2MPN2R2NG0L_30%

A A

1 2

+1.05VS_VCCSATA3PLL

RC171

2.2UH_LQM2MPN2R2NG0L_30%

1 2

<DB>Aduio code powerrail

RC176

2

1

1

2

+1.05VS

1 2

1 RC280 2

0_0603_5%

RC179

1

2

5

CC57

CC63

1

CC35

2

1

CC42

2

+1.05VS_APPLOPI

1

CC58

2

22U_0805_6.3V6M

1U_0402_6.3V6K

+1.05VS_AXCKDCB

1

CC64

2

47U_0805_6.3V6M

+1.05VS_VCCUSB3PLL

41mA

1

CC36

2

47U_0805_6.3V6M

1U_0402_6.3V6K

+1.05VS_VCCSATA3PLL

42mA

1

CC43

2

47U_0805_6.3V6M

1U_0402_6.3V6K

57mA

+V1.05S_SSCF100

62mA

1

CC61

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+1.05VS

2.2UH_LQM2MPN2R2NG0L_30%

+1.05VS_MODPHY

Use+1.05V

RC172 1 2 0_0402_5%

+1.5VS

+1.05VS

RC181

1

short@

2

1

2

+1.05V

+3V_PCH

RC281

1 2

short@

0_0603_5%

+1.05VS_AXCK_LCPLL

+1.05VS_AXCK_LCPLL

1

CC68

2

47U_0805_6.3V6M

short@

RC1681 2

0_0805_5%

+1.05VS

10U_0603_6.3V6M

1U_0402_6.3V6K

CC5

5

1

CC62

2

1U_0402_6.3V6K

31mA

CC69

1U_0402_6.3V6K

4

1.838A

1

CC33

2

1

CC41

2

RC173

0_0402_5% 1 @

1

2

1

+3VS

2

22U_0805_6.3V6M

2

2

CC51

1U_0402_6.3V6K

CC5

+V1.05S_SSCFF

124mA

1U_0402_6.3V6K

9

Deep S3 and Non Deep S3

4

1U_0402_6.3V6K

1

CC45

1

CC46

1

2

22U_0805_6.3V6M

1

CC34

2

2

+3VALW

+3V_PCH

+1.05VS_VCCHSIO

1U_0402_6.3V6K

+1.05VS_APPLOPI

+1.05V_DCPSUS

+VCCSUSHDA

+1.05VS_AXCKDCB

+1.05VS_AXCK_LCPLL

+V1.05S_SSCF100

+V1.05S_SSCFF

+3V_PCH

+1.05VS_VCCUSB3PLL

+1.05VS_VCCSATA3PLL B11

+3V_DSW_P

short@

RC285 1 2 0_0402_5%

RC182 1

@

3 2

65mA

+3V_DSW_PRTCSUS

UCPU1M

K9

VCCHSIO

L10

VCCHSIO

M9

VCCHSIO

N8

VCCIO

P9

VCCIO

B18

VCCUSB3PLL

VCCSAT A3PLL

Y20

VCCAPLL

AA21

VCCAPLL

W21

VCCAPLL

J13

DCPSUS3

AH14

VCCSUSHDA

AH13

DCPSUS2

AC9

VCCSUS3_3

AA9

VCCSUS3_3

AH10

VCCDSW 3_3

V8

VCC3_3

W9

VCC3_3

J18

VCC1P05

K19

VCC1P05

A20

VCCACLKPLL

J17

VCCCLK

R21

VCCCLK

T21

VCCCLK

K18

VCCCLK

M20

VCCCLK

V21

VCCCLK

AE20

VCCSUS3_3

AE21

VCCSUS3_3

2 0_0402_5% +3V_DSW_P

1

CC70

2

1U_0402_6.3V6K

HASW ELL_MCP_E

mPHY

OPI

USB3

AXALIA /HDA

VRM/US B2/AZA LIA

GPIO/LCC

ICC

LPT LP POW ER

+3V_DSW_P

Deep S3RC285-->SMT

Non Deep S3 RC182-->SMT

13 OF 19

RTC

SPI

CORE

THERMAL SENSOR

SDIO/PL SS

SUS OSCILL ATOR

USB2

AH11

VCCSUS3

AG10

VCCRTC

AE7 CC40 1 2 0.1U_0402_16V7K

DCPRTC

Y8

VCCSPI

AG14

VCCASW

AG13

VCCASW

J11

VCC1P05

H11

VCC1P05

H15

VCC1P05

AE8

VCC1P05

AF22

VCC1P05

AG19

DCPSUSBYP

AG20

DCPSUSBYP

AE9

VCCASW

AF9

VCCASW

AG8

VCCASW

AD10

DCPSUS1

AD8

DCPSUS1

J15

VCCTS1_5

K14

VCC3_3

K16

VCC3_3

CC76

U8

VCCSDIO

T9

VCCSDIO

+1.05V_AOSCSUS

AB8

DCPSUS4

AC20

VCCAPLL

AG16

VCCIO

AG17

VCCIO

Total1.05VS=1838+2274=4111mA

Total 1.5VS=3mA

Total 1.8VS=7mA

Total3VS=0mA

Total3VALW=200+62=262mA

Total3V_PCH=99mA

+RTCVCC

18mA

+1.05VS

+1.05VS_VCCASW

+1.05V_DCPSUS

+1.5VS

+3VS

2

1

0.1U_0402_16V7K

1

2

RC174 CC52

5.11_0402_1% 1U_0402_6.3V6K

2

1 1 2

+3V_1V8_SDIO

1

CC65

2

1U_0402_6.3V6K

Total1.05V=540+109=649mA

Security Classification

Issued Date

THI S SHE ET O F ENG IN EER ING DR AW IN G IS T HE PR OP RIE TA RY P ROPER TY O F CO MPA L EL ECT RO NI CS, INC. AN D CO NTA INS CONFIDENTIASSL

AND T RADE SECRE T INF ORMAT ION . THI S SHEE T MAY NOT BE T RANSF ERED FRO M THE CUST OD Y OF T HE COMPETEN T DIVIS ION OF R&D

DEPAR TMENT EX CEPT AS A UT HO RIZ ED BY C OMPAL E LEC TR ON ICS , INC. NEIT HER THIS SH EET N OR TH E INFO RM ATION IT CONTAIN S

MAY BE USE D BY OR DI SCLOSE D TO A NY TH IRD PA RT Y WITHOUT PRIO R WR IT TEN CON SE NT OF CO MPAL ELE CT RO NIC S, INC.

3 2

2011/06/29 2011/06/29

Compal Secret Data

DecipheredDate

1

CC32

2

1

2

CC44@

0.1U_0402_16V7K

1

CC60

2

+1.05VS

+1.05V_AOSCSUS

short@

RC1692 1 0_0402_5%

1U_0402_6.3V6K

0.1U_0402_16V7K

CC37

@

+3V_PCH

1

CC39

2

1.6A

0.658A

1

CC5

CC53

2

1U_0402_6.3V6K

4

RC178 short@

1 2 0_0603_5%

1U_0402_6.3V6K

@

1U_0402_6.3V6K

Title

ize Document Number

Custom

+3V_PCH

+RTCVCC

1U_0402_6.3V6K

SPI ROM powerrail

1

1

CC48

CC49

2 2

1U_0402_6.3V6K

1U_0402_6.3V6K

short@

2

0_0805_5%

1

1

CC67

100U_1206_6.3V6K

1

2

22U_0805_6.3V6M

CC66

RC1751

1

2 2

Power

LA-B972P

1

+1.05VS

1

CC50

2

10U_0603_6.3V6M

+1.05VS

+3VS

@

RC180

2

2.2UH_LQM2MPN2R2NG0L_30%

@

1

+1.05V

Sheet 12 of 54Date: Thursday, March 20, 2014

Rev

0.1

Page 14

5 4 3 2 1

HASWELL_MCP_E

UCPU1N

A11

VSS

A14

VSS

A18

VSS

A24

VSS

A28

VSS

A32

VSS

A36

D D

C C

B B

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

14 OF19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS