Page 1

A

B

C

D

E

Model Name : Z5W1M

File Name : LA-B511P

1 1

Compal Confidential

2 2

EA52_BM UMA M/B Schematics Document

Intel Bay Trail M

2014-03-13

3 3

REV:1.0

4 4

PCB@

PCB@

PCB 12R LA-B211P REV0 M/B

DAX

PCB 12R LA-B211P REV0 M/B

DAX

Part Number

Part Number

DA60016I000 PCB 12R LA-B511P REV0 M/B

DA60016I000 PCB 12R LA-B511P REV0 M/B

Description

Description

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

E

0.3

0.3

1 39Thursday, March 13, 2014

1 39Thursday, March 13, 2014

1 39Thursday, March 13, 2014

0.3

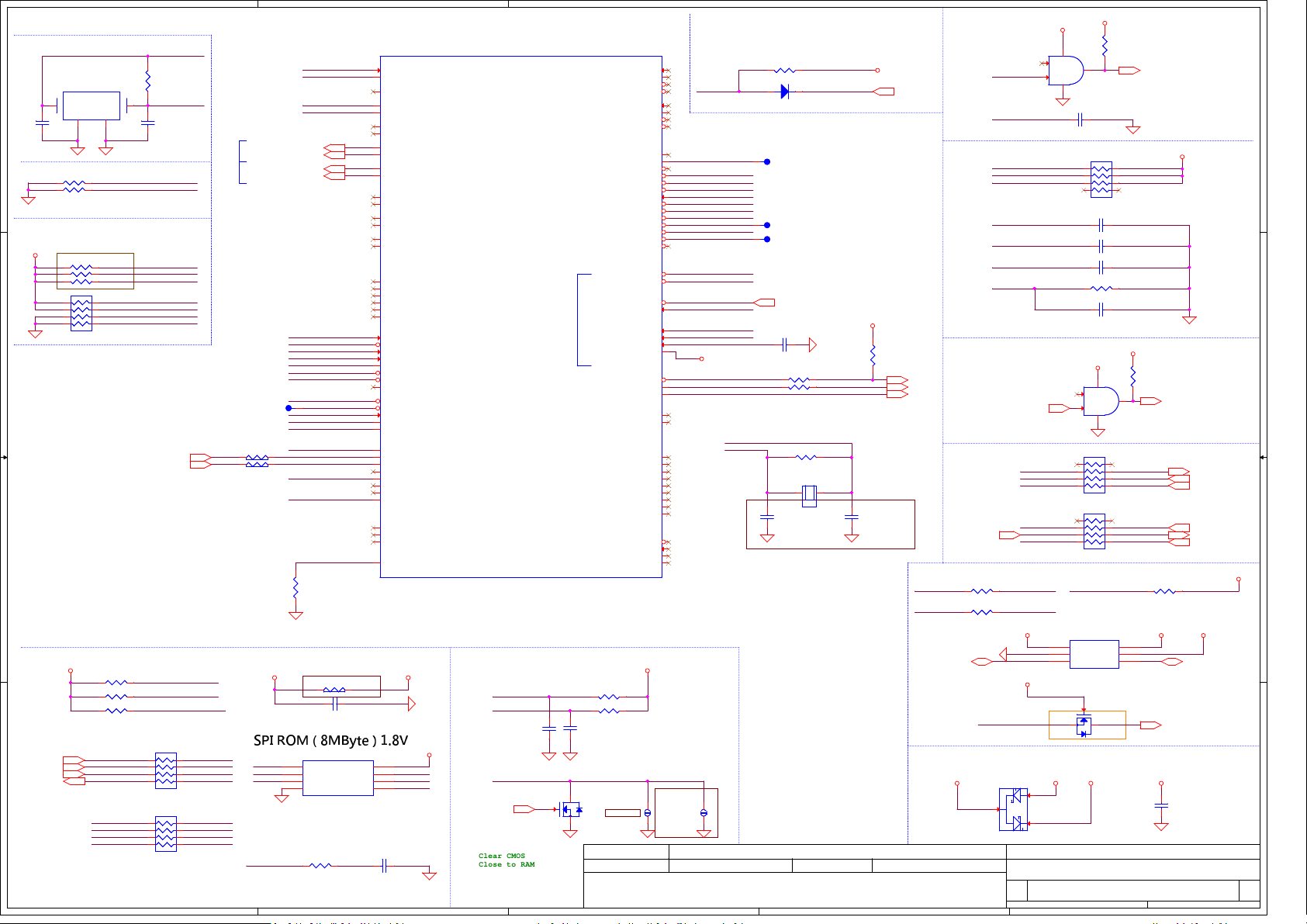

Page 2

A

B

C

D

E

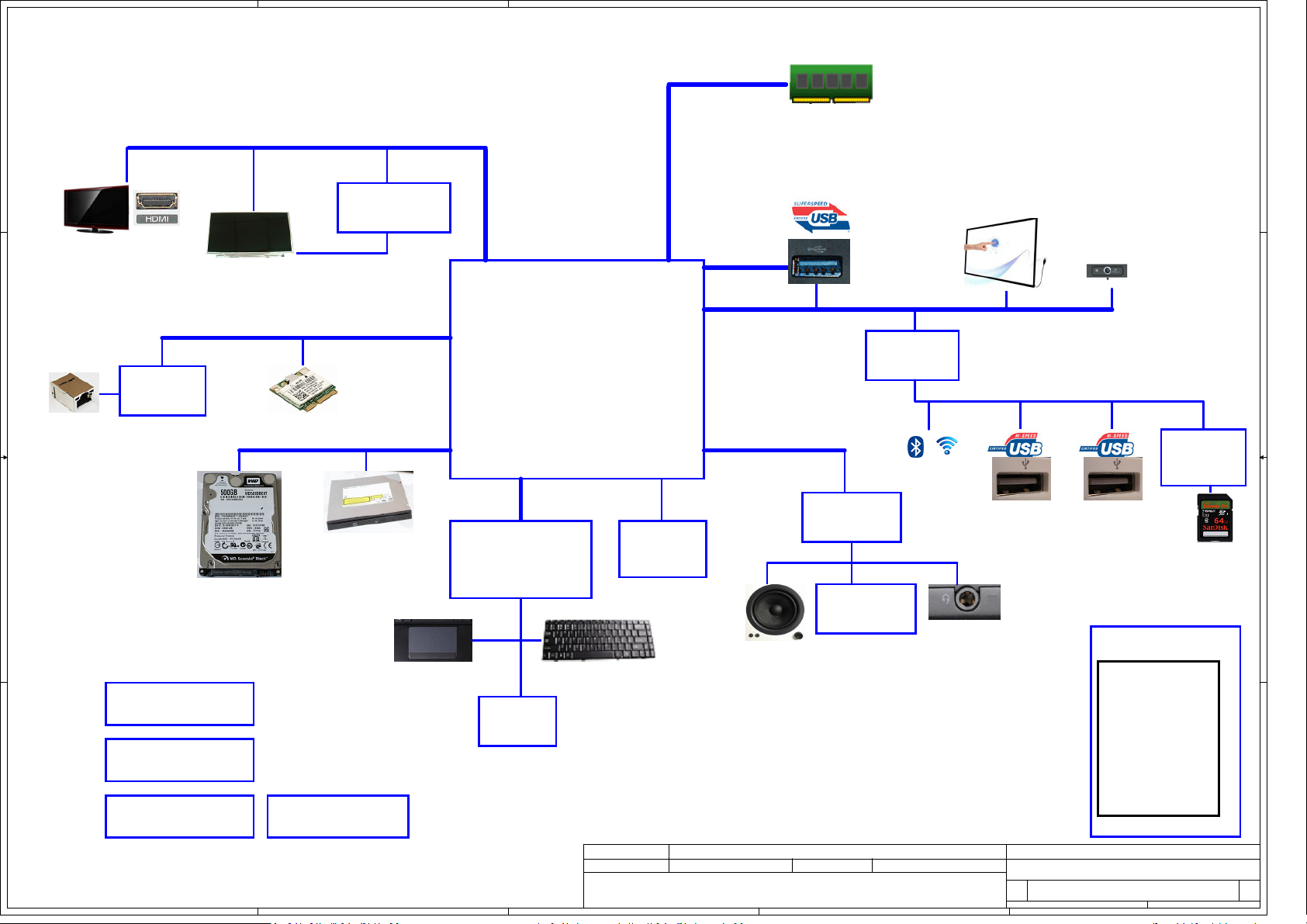

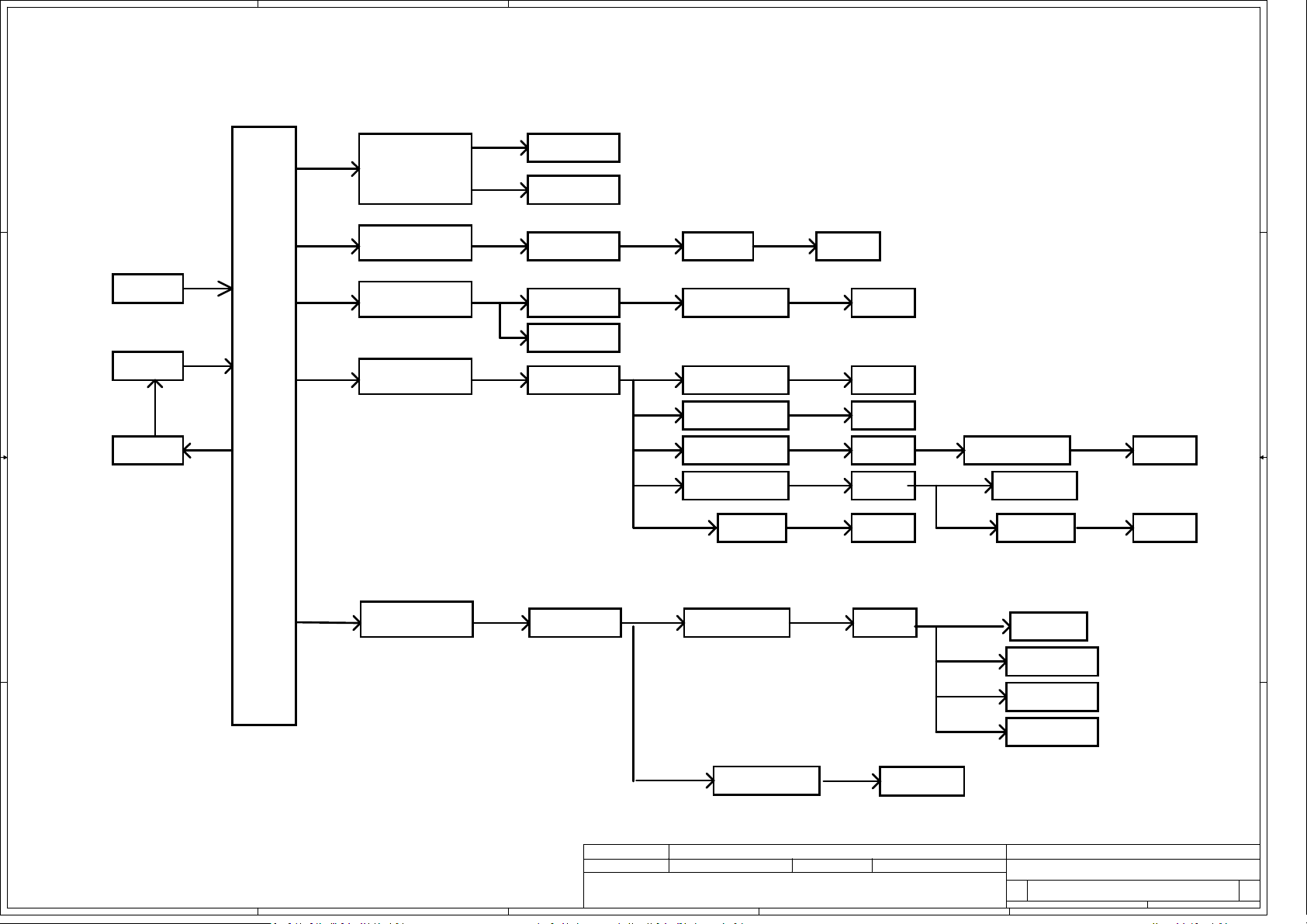

Memory BUS

One Channel

1.35V DDR3L 1066/1333

1 1

Max speed of DDR3L to 1333MT/s for M sku. -- EDS

204pin DDR3L-SO-DIMM X1

P.13

port 1port 0

EDP

LVDS-Translator

RTD2132N

P.16

HDMI Conn.

LCD Conn.

P.15

LVDS

eDP/LVDS

2 2

RJ45 conn.

P.17

port 0 port 1

LAN(GbE)

RTL8111GUS

P.17

WLAN

MINI CARD

P.18

port 0

SATA ODD Conn.

3 3

SATA HDD Conn.

P.20

RTC CKT.

P.08

port 1

P.14

DDI x2

PCIe 2.0 x4

VALLEYVIEW-M

FCBGA 1170 Pin

SATA II x2

port 1

LPC BUS

EC

P.20

Touch Pad Int.KBD

ENE KB9022

P.23

TPM

NPCT650

P.18

SOC

P.22

page 05~12

SPI

SPI ROM

1.8V (8MB)

P.23

P.08

USB3.0 x1

USB2.0 x4

HD Audio

Int. Speaker

P.19

USB 3.0 Conn

P.21

port 0 port 2 port 3

HDA Codec

ALC283

Int. Analog MIC

port 1

USB HUB

GL850G

BT

MINI CARD

P.19

P.19

Touch Panel

Conn.

P.15

CMOS Camera

P.15

P.21

HUB port1 HUB port2 HUB port3

P.20

USB 2.0 Conn

Universal Jack

P.19

P.21

USB 2.0 Conn

Sub Board

LS-B471P

Card Reader

RTS5170

2 in 1 (SD)

HUB port4

Card Reader

RTS5170

SD only

DC/DC Interface CKT.

P.24

4 4

Power Circuit DC/DC

P.25~P.35

A

LED/Power On/Off

P.23

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

USB 2.0

conn x1

USB port 2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

E

P.21

1.0

1.0

2 39Thursday, March 13, 2014

2 39Thursday, March 13, 2014

2 39Thursday, March 13, 2014

1.0

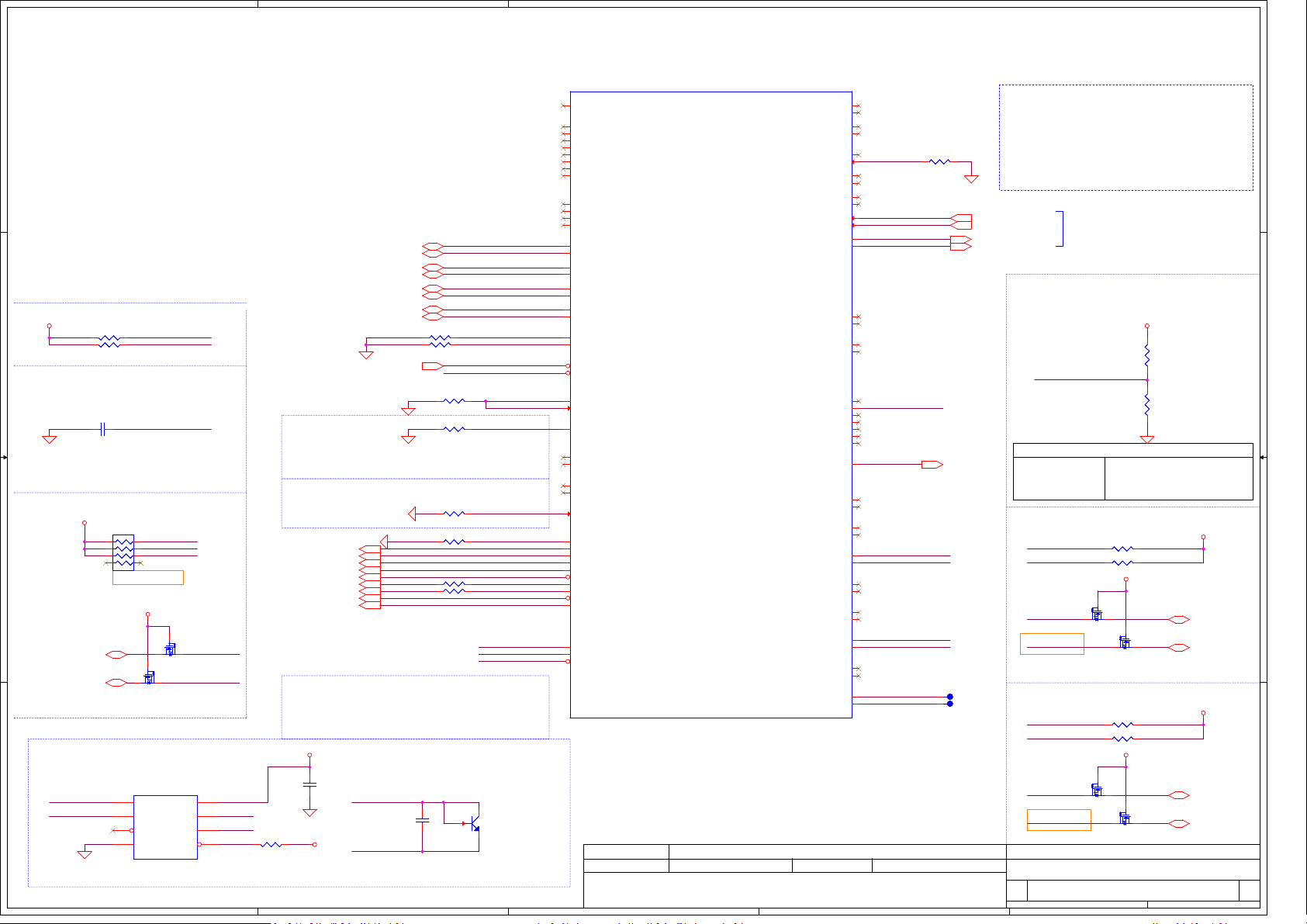

Page 3

A

B

C

D

E

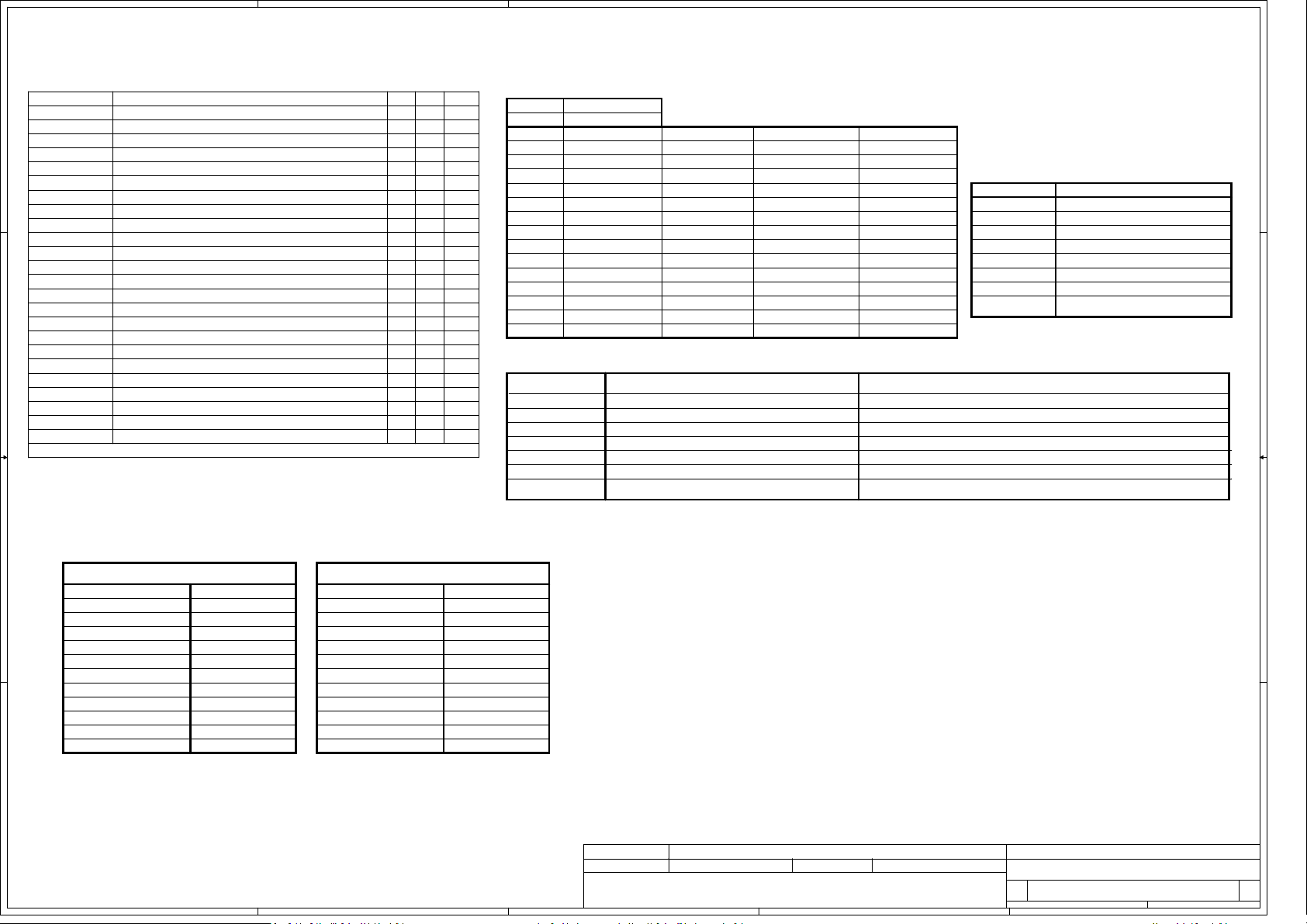

Voltage Rails

VIN

1 1

BATT+ 12V Battery power supply

B+

+RTCVCC RTC Battery Power

+1.0VALW

+1.8VALW +1.8v Always power rail

+3VALW +3.3v Always power rail

+5VALW

+SOC_VCC Core voltage for SOC

+SOC_VNN GFX voltage for SOC

+0.675VS +0.675V power rail for DDR3L Terminator

+1.0VS

+1.05VS

+1.35VS

+1.5VS

+1.8VS

2 2

+3VS

+5VS

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

19V Adapter power supply

AC or battery power rail for power circuit. (19V/12V)

+1.0v Always power rail

+5.0v Always power rail

+1.35V power rail for DDR3L+1.35V

+1.0v system power rail

+1.05v system power rail

+1.35v system power rail

+1.5v system power rail

+1.8v system power rail

+3.3v system power rail

+5.0v system power rail

S0 S3 S4/S5Power Plane Description

ON

ON ON

ON ONON

ON ONON

ON ONON

ON ONON

ON ONON

ON ONON

ON ONON

ON ON

ON

ON

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

OFF

OFF OFF

OFF OFF

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 56K +/- 5%

8

9

10

11

12

13

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

12K +/- 5%

15K +/- 5%

20K +/- 5%

27K +/- 5%

33K +/- 5%

43K +/- 5%

AD_BID

0 V

0.347 V 0.354 V 0.360 V

0.423 V

0.541 V

0.691 V

0.807 V 0.819 V 0.831 V

0.978 V

1.169 V

75K +/- 5%

100K +/- 5%

130K +/- 5%

160K +/- 5%

200K +/- 5%

240K +/- 5%

1.398 V

1.634 V

1.849 V 1.865 V 1.881 V

2.015 V 2.031 V 2.046 V

2.185 V 2.200 V 2.215 V

2.316 V 2.329 V 2.343 V

V typ

AD_BID

0 V 0 V

0.430 V

0.550 V

0.702 V 0.713 V

0.992 V

1.185 V

1.414 V 1.430 V

1.650 V 1.667 V

43 level BOM table

4319TDBOL01

4319TDBOL02

4319TDBOL03

4319TDBOL04

4319TDBOL05

4319TDBOL06

435MNVBOL01 SMT IO/B SB471 Z5W1M EMC@

SMT MB AB511 Z5W1M UMA 2.17G N3520@/EMC@/AMIC@/EDP@/DBG@/TPM@/PCB@/TS@

SMT MB AB511 Z5W1M UMA 1.86G N2920@/EMC@/AMIC@/LVDS@/DBG@/TPM@/PCB@/TS@

SMT MB AB511 Z5W1M UMA 1.86G EPD HDMI

SMT MB AB511 Z5W1M UMA 2.17G LVDS HDMI

SMT MB AB511 Z5W1M UMA 2.13G EPD HDMI

SMT MB AB511 Z5W1M UMA 2.13G LVDS HDMI

V

max

AD_BID

0.438 V

0.559 V

BOARD ID Table

Board ID

0

1

1.006 V

1.200 V

2

3

4

5

6

BOM Structure43 Level Description

N2920@/EMC@/AMIC@/EDP@/DBG@/TPM@/PCB@/TS@

N3520@/EMC@/AMIC@/LVDS@/DBG@/TPM@/PCB@/TS@

N2820@/EMC@/AMIC@/EDP@/DBG@/TPM@/PCB@/TS@

N2820@/EMC@/AMIC@/LVDS@/DBG@/TPM@/PCB@/TS@

PCB Revision

EVT

DVT

PVT

Pre-MP & MP

3 3

BOM Option Table

Item BOM Structure

Unpop @

CONN@Connector

EMC@EMC requirement

@EMC@EMC requirement unpop

AC@IOAC support

Choose Analog MIC pop AMIC@

BL@Backlight Keyboard

EDP panel select EDP@

BOM Option Table

Item BOM Structure

CPU for N2920 pop N2920@

N3520@CPU for N3520 pop

TPM@TPM support

NTPM@No supoort TPM

PCB@PCB PN

SP@CLEAN CMOS JUMP

TS@Touch Screen function

EDP + Touch Screen ETS@

LVDS panel select LVDS@

Power Switch on board DBG@

JP@Jump for transfer power

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

E

1.0

1.0

3 39Thursday, March 13, 2014

3 39Thursday, March 13, 2014

3 39Thursday, March 13, 2014

1.0

Page 4

A

B

C

D

E

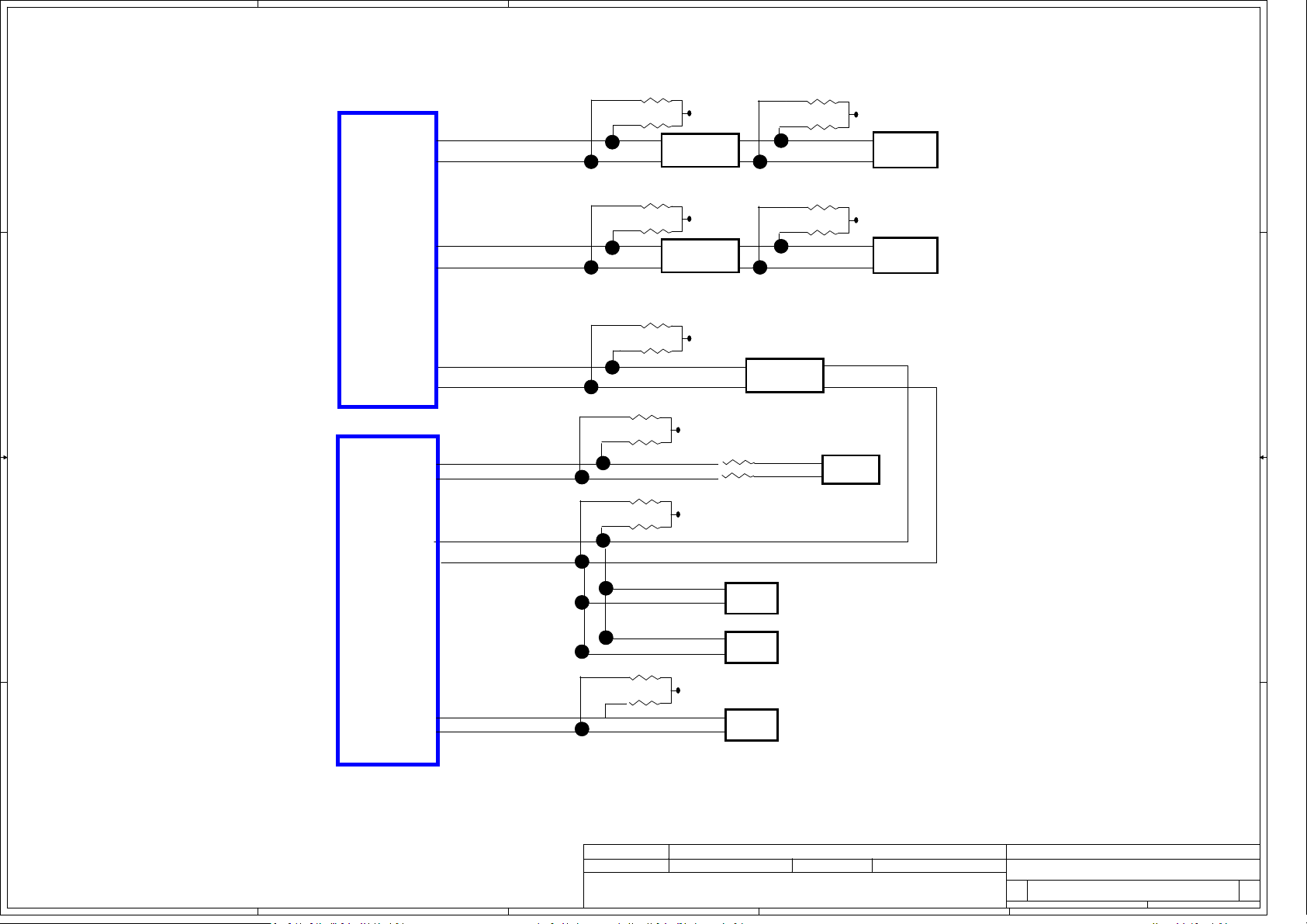

2.2K

1 1

BG25

BJ25

SOC_I2C2_DATA

SOC_I2C2_CLK

2.2K

+1.8VS

DMN63D8LDW

4.7K

4.7K

I2C2_SDA_TP

I2C2_SCL_TP

+3V_TP

Touch Pad

Dual channel NMOS

SOC

BH28

BG28

SOC_I2C5_DATA

SOC_I2C5_CLK

2.2K

2.2K

+1.8VS

DMN63D8LDW

2.2K

2.2K

I2C5_SDA_PNL

I2C5_SCL_PNL

+5VS_TS

Touch Panel

Dual channel NMOS

2.2K

2 2

BH10

BG12

PCU_SMB_CLK

PCU_SMB_DATA

2.2K

2.2K

2.2K

77

SCL1

SDA1

EC_SMB_CK1

78

EC_SMB_DA1

2.2K

2.2K

79

SCL2

3 3

KBC

SDA2

EC_SMB_CK2

80

EC_SMB_DA2

KB9022

4.7K

4.7K

SCL3

SDA3

85

86

EC_SMB_CK3

EC_SMB_DA3

+1.8VS

+3VALW_EC

100 ohm

100 ohm

+3VS

200

202

DIMMA

30

32

WLAN

+3VS_TL

9

10

DP-LVDS

DMN63D8LDW

Dual channel NMOS

7

6

SMBUS Address [A0h]

SMBUS Address [TBD]

SMBUS Address [TBD]

BATTERY

CONN

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

SMB/I2C

SMB/I2C

SMB/I2C

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

E

1.0

1.0

4 39Thursday, March 13, 2014

4 39Thursday, March 13, 2014

4 39Thursday, March 13, 2014

1.0

Page 5

A

1 1

VR_ON

B

ISL95833HRTZ-T

(PU801)

12000mA

14000mA

+SOC_VNN

+SOC_VCC

C

D

E

SPOK

ADAPTER

2 2

BATTERY

B+

SYSON

EC_ON

CHARGER

3 3

EC_ON

SY8208DQNC

(PU601)

RT8207MZQW

(PU501)

SY8208BQNC

(PU401)

SY8208BQNC

(PU402)

325mA

5250mA

4850mA

10050mA

+1.0VALWP

+1.35VP

+0.675VSP

+3VALWP

+5VALWP

(U67)

2750mA

458mA

1000mA

110mA

+1.0VS

+1.35VS

+1.5VSP

+1.05VSP

+1.8VALWP

+3VS

+3V_LAN

+5VS

SUSP#

1000mA

1050mA

SUSP

ME4856-G

(U25)

SUSP# 420mA

TPS22966DPUR

(U26)

SUSP#

SY8003DFC_DFN8

(PU701)

SUSP#

APL5930KAI-TRG

(PU602)

SPOK

APL5930KAI-TRG

(PU702)

SUSP#

TPS22966DPUR

(U24)

LAN_PWR_EN ENVDD

SUSP# 1000mA

G5243AT11U

TPS22966DPUR

(U24)

TPS22966DPUR

(U26)

+3VS_WLAN

G5243AT11U

(U8)

+VDDA

10mA

+1.8VS

+LCDVDD

1500mA

+5VS_HDD

1500mA

+5VS_ODD

500mA

+HDMI_5V_OUT

USB_PWR_EN#

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

SY6288D10CAC

(U17)

Compal Secret Data

Compal Secret Data

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

1500mA

Deciphered Date

Deciphered Date

Deciphered Date

+USB3_VCCA

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Power Rail

Power Rail

Power Rail

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

E

5 39Thursday, March 13, 2014

5 39Thursday, March 13, 2014

5 39Thursday, March 13, 2014

1.0

1.0

1.0

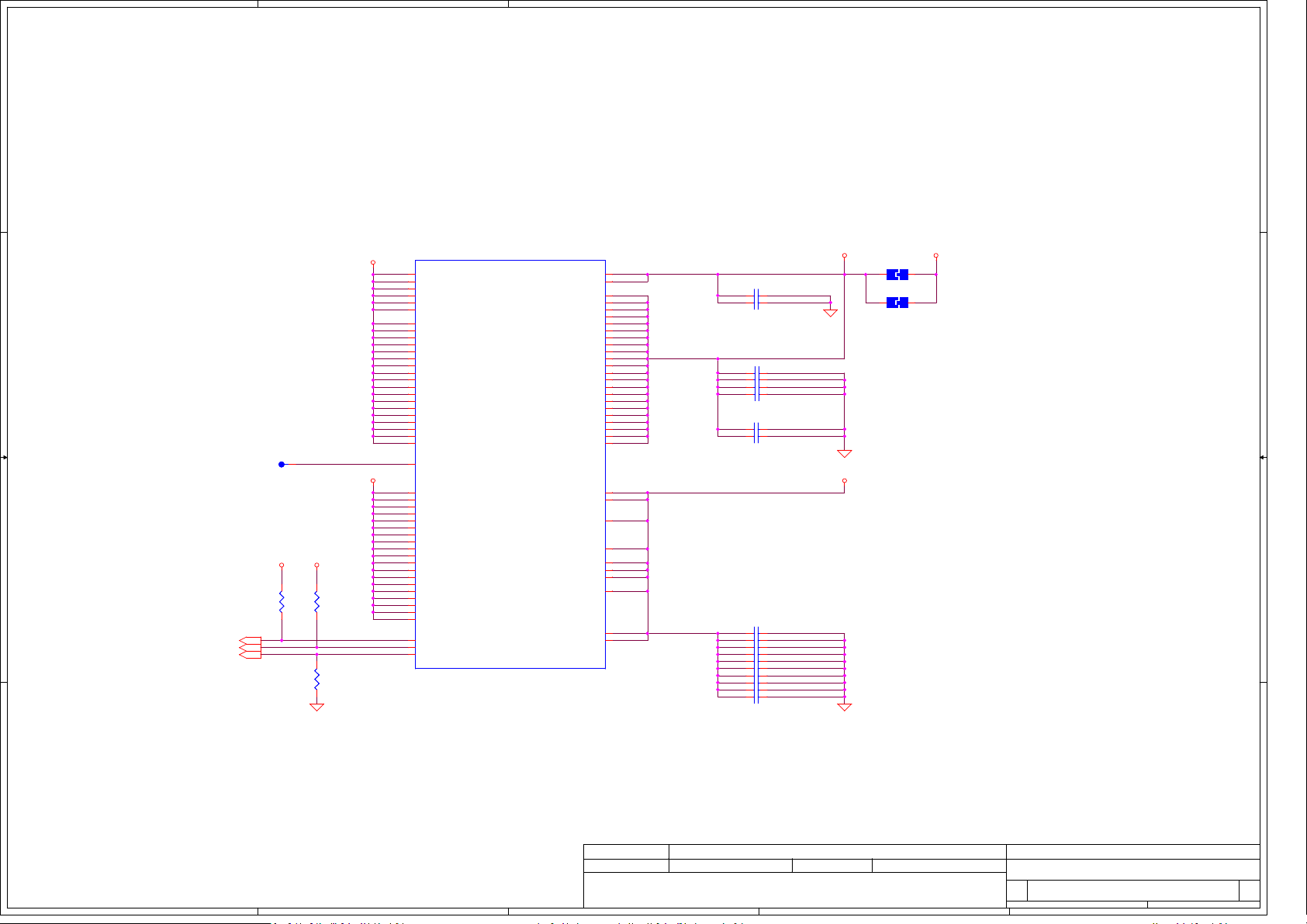

Page 6

5

USOC1A

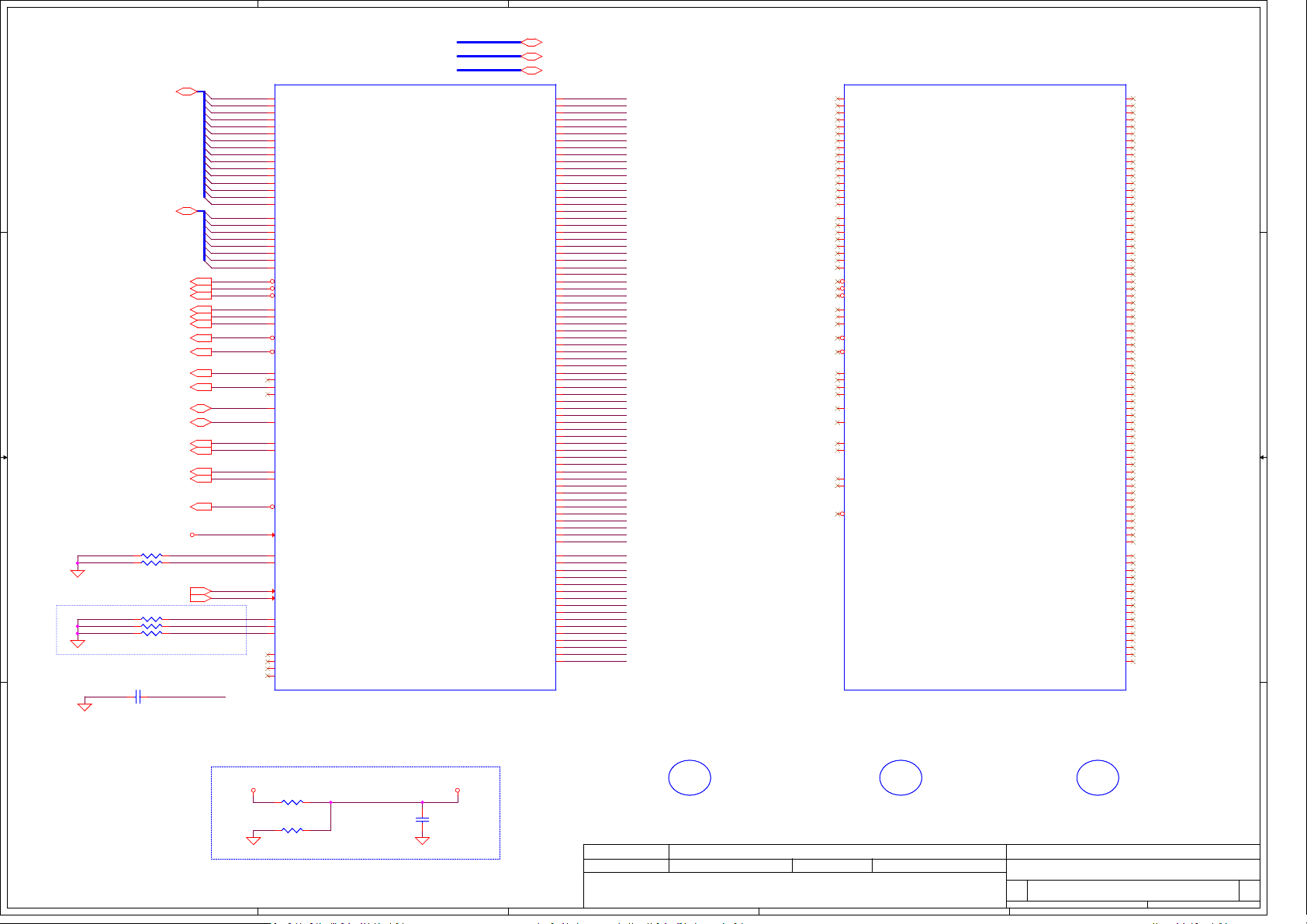

DDR_A_MA[0..15]<14>

D D

DDR_A_DM[0..7]<14>

DDR_A_RAS#<14>

DDR_A_CAS#<14>

DDR_A_WE#<14>

DDR_A_BS0<14>

DDR_A_BS1<14>

DDR_A_BS2<14>

C C

B B

DDR_A_CS0#<14>

DDR_A_CS2#<14>

DDR_A_CKE0<14>

DDR_A_CKE2<14>

DDR_A_ODT0<14>

DDR_A_ODT2<14>

DDR_A_CLK0<14>

DDR_A_CLK0#<14>

DDR_A_CLK2<14>

DDR_A_CLK2#<14>

DDR_A_RST#<14>

+DDR_SOC_VREF

1 2

1 2

DDR_PWROK<30>

DDR_CORE_PWROK<9>

1 2

1 2

1 2

R1100K_0402_5% R1100K_0402_5%

R2100K_0402_5% R2100K_0402_5%

R323.2_0402_1% R323.2_0402_1%

R429.4_0402_1% R429.4_0402_1%

R5162_0402_1% R5162_0402_1%

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_TERMN0

DDR_TERMN1

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

Follow CRB v2.0

12

DDR_CORE_PWROK

C1

EMC@ C1

EMC@

0.01U_0402_16V7K

0.01U_0402_16V7K

USOC1A

K45

DRAM0_MA_0

H47

DRAM0_MA_1

L41

DRAM0_MA_2

H44

DRAM0_MA_3

H50

DRAM0_MA_4

G53

DRAM0_MA_5

H49

DRAM0_MA_6

D50

DRAM0_MA_7

G52

DRAM0_MA_8

E52

DRAM0_MA_9

K48

DRAM0_MA_10

E51

DRAM0_MA_11

F47

DRAM0_MA_12

J51

DRAM0_MA_13

B49

DRAM0_MA_14

B50

DRAM0_MA_15

G36

DRAM0_DM_0

B36

DRAM0_DM_1

F38

DRAM0_DM_2

B42

DRAM0_DM_3

P51

DRAM0_DM_4

V42

DRAM0_DM_5

Y50

DRAM0_DM_6

Y52

DRAM0_DM_7

M45

DRAM0_RAS#

M44

DRAM0_CAS#

H51

DRAM0_WE#

K47

DRAM0_BS_0

K44

DRAM0_BS_1

D52

DRAM0_BS_2

P44

DRAM0_CS_0#

P45

DRAM0_CS_2#

C47

DRAM0_CKE_0

D48

RESERVED_D48

F44

DRAM0_CKE_2

E46

RESERVED_E46

T41

DRAM0_ODT_0

P42

DRAM0_ODT_2

M50

DRAM0_CKP_0

M48

DRAM0_CKN_0

P50

DRAM0_CKP_2

P48

DRAM0_CKN_2

P41

DRAM0_DRAMRST#

AF44

DRAM_VREF

AF42

ICLK_DRAM_TERMN_AF4 2

AH42

ICLK_DRAM_TERMN_AH 42

AD42

DRAM_VDD_S4_PW ROK

AB42

DRAM_CORE_PWR OK

AD44

DRAM_RCOMP_0

AF45

DRAM_RCOMP_1

AD45

DRAM_RCOMP_2

AF40

RESERVED_AF40

AF41

RESERVED_AF41

AD40

RESERVED_AD40

AD41

RESERVED_AD41

FH8065301546401_FCBGA131170

FH8065301546401_FCBGA131170

@

@

0.675V

4

DDR_A_D[0..63] <14>

DDR_A_DQS[0..7] <14>

DDR_A_DQS#[0..7] <14>

M36

J36

P40

M40

P36

N36

K40

K42

B32

C32

C36

A37

C33

A33

C37

B38

F36

G38

F42

J42

G40

C38

G44

D42

A41

C41

A45

B46

C40

B40

B48

B47

K52

K51

T52

T51

L51

L53

R51

R53

T47

T45

Y40

V41

T48

T50

Y42

AB40

V45

V47

AD48

AD50

V48

V50

AB44

Y45

V52

W51

AC53

AC51

W53

Y51

AD52

AD51

J38

K38

C35

B34

D40

F40

B44

C43

N53

M52

T42

T44

Y47

Y48

AB52

AA51

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

1 OF 13

1 OF 13

DRAM0_DQ_0

DRAM0_DQ_1

DRAM0_DQ_2

DRAM0_DQ_3

DRAM0_DQ_4

DRAM0_DQ_5

DRAM0_DQ_6

DRAM0_DQ_7

DRAM0_DQ_8

DRAM0_DQ_9

DRAM0_DQ_10

DRAM0_DQ_11

DRAM0_DQ_12

DRAM0_DQ_13

DRAM0_DQ_14

DRAM0_DQ_15

DRAM0_DQ_16

DRAM0_DQ_17

DRAM0_DQ_18

DRAM0_DQ_19

DRAM0_DQ_20

DRAM0_DQ_21

DRAM0_DQ_22

DRAM0_DQ_23

DRAM0_DQ_24

DRAM0_DQ_25

DRAM0_DQ_26

DRAM0_DQ_27

DRAM0_DQ_28

DRAM0_DQ_29

DRAM0_DQ_30

DRAM0_DQ_31

DRAM0_DQ_32

DRAM0_DQ_33

DRAM0_DQ_34

DRAM0_DQ_35

DRAM0_DQ_36

DRAM0_DQ_37

DRAM0_DQ_38

DRAM0_DQ_39

DRAM0_DQ_40

DRAM0_DQ_41

DRAM0_DQ_42

DRAM0_DQ_43

DRAM0_DQ_44

DRAM0_DQ_45

DRAM0_DQ_46

DRAM0_DQ_47

DRAM0_DQ_48

DRAM0_DQ_49

DRAM0_DQ_50

DRAM0_DQ_51

DRAM0_DQ_52

DRAM0_DQ_53

DRAM0_DQ_54

DRAM0_DQ_55

DRAM0_DQ_56

DRAM0_DQ_57

DRAM0_DQ_58

DRAM0_DQ_59

DRAM0_DQ_60

DRAM0_DQ_61

DRAM0_DQ_62

DRAM0_DQ_63

DRAM0_DQSP_0

DRAM0_DQSN_0

DRAM0_DQSP_1

DRAM0_DQSN_1

DRAM0_DQSP_2

DRAM0_DQSN_2

DRAM0_DQSP_3

DRAM0_DQSN_3

DRAM0_DQSP_4

DRAM0_DQSN_4

DRAM0_DQSP_5

DRAM0_DQSN_5

DRAM0_DQSP_6

DRAM0_DQSN_6

DRAM0_DQSP_7

DRAM0_DQSN_7

3

AY45

BB47

AW41

BB44

BB50

BC53

BB49

BF50

BC52

BE52

AY48

BE51

BD47

BA51

BH49

BH50

BD38

BH36

BC36

BH42

AT51

AM42

AK50

AK52

AV45

AV44

BB51

AY47

AY44

BF52

AT44

AT45

BG47

BE46

BD44

BF48

AP41

AT42

AV50

AV48

AT50

AT48

AT41

2

USOC1B

USOC1B

DRAM1_MA_0

DRAM1_MA_1

DRAM1_MA_2

DRAM1_MA_3

DRAM1_MA_4

DRAM1_MA_5

DRAM1_MA_6

DRAM1_MA_7

DRAM1_MA_8

DRAM1_MA_9

DRAM1_MA_10

DRAM1_MA_11

DRAM1_MA_12

DRAM1_MA_13

DRAM1_MA_14

DRAM1_MA_15

DRAM1_DM_0

DRAM1_DM_1

DRAM1_DM_2

DRAM1_DM_3

DRAM1_DM_4

DRAM1_DM_5

DRAM1_DM_6

DRAM1_DM_7

DRAM1_RAS#

DRAM1_CAS#

DRAM1_WE#

DRAM1_BS_0

DRAM1_BS_1

DRAM1_BS_2

DRAM1_CS_0#

DRAM1_CS_2#

DRAM1_CKE_0

RESERVED_BE46

DRAM1_CKE_2

RESERVED_BF48

DRAM1_ODT_0

DRAM1_ODT_2

DRAM1_CKP_0

DRAM1_CKN_0

DRAM1_CKP_2

DRAM1_CKN_2

DRAM1_DRAMRST#

FH8065301546401_FCBGA131170

FH8065301546401_FCBGA131170

@

@

2 OF 13

2 OF 13

DRAM1_DQ_0

DRAM1_DQ_1

DRAM1_DQ_2

DRAM1_DQ_3

DRAM1_DQ_4

DRAM1_DQ_5

DRAM1_DQ_6

DRAM1_DQ_7

DRAM1_DQ_8

DRAM1_DQ_9

DRAM1_DQ_10

DRAM1_DQ_11

DRAM1_DQ_12

DRAM1_DQ_13

DRAM1_DQ_14

DRAM1_DQ_15

DRAM1_DQ_16

DRAM1_DQ_17

DRAM1_DQ_18

DRAM1_DQ_19

DRAM1_DQ_20

DRAM1_DQ_21

DRAM1_DQ_22

DRAM1_DQ_23

DRAM1_DQ_24

DRAM1_DQ_25

DRAM1_DQ_26

DRAM1_DQ_27

DRAM1_DQ_28

DRAM1_DQ_29

DRAM1_DQ_30

DRAM1_DQ_31

DRAM1_DQ_32

DRAM1_DQ_33

DRAM1_DQ_34

DRAM1_DQ_35

DRAM1_DQ_36

DRAM1_DQ_37

DRAM1_DQ_38

DRAM1_DQ_39

DRAM1_DQ_40

DRAM1_DQ_41

DRAM1_DQ_42

DRAM1_DQ_43

DRAM1_DQ_44

DRAM1_DQ_45

DRAM1_DQ_46

DRAM1_DQ_47

DRAM1_DQ_48

DRAM1_DQ_49

DRAM1_DQ_50

DRAM1_DQ_51

DRAM1_DQ_52

DRAM1_DQ_53

DRAM1_DQ_54

DRAM1_DQ_55

DRAM1_DQ_56

DRAM1_DQ_57

DRAM1_DQ_58

DRAM1_DQ_59

DRAM1_DQ_60

DRAM1_DQ_61

DRAM1_DQ_62

DRAM1_DQ_63

DRAM1_DQSP_0

DRAM1_DQSN_0

DRAM1_DQSP_1

DRAM1_DQSN_1

DRAM1_DQSP_2

DRAM1_DQSN_2

DRAM1_DQSP_3

DRAM1_DQSN_3

DRAM1_DQSP_4

DRAM1_DQSN_4

DRAM1_DQSP_5

DRAM1_DQSN_5

DRAM1_DQSP_6

DRAM1_DQSN_6

DRAM1_DQSP_7

DRAM1_DQSN_7

1

BG38

BC40

BA42

BD42

BC38

BD36

BF42

BC44

BH32

BG32

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT36

AV40

AT40

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

Close To SOC Pi n

USOC1

USOC1

N3530@

A A

5

+1.35V

1 2

R6

4.7K_0402_1%

4.7K_0402_1%

1 2

R7

R7

4.7K_0402_1%

4.7K_0402_1%

4

+DDR_SOC_VREF

1

C2

C2

.1U_0402_16V7K

.1U_0402_16V7K

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

N3530@

S IC FH8065301728500 QG9T C0 2.17G FCBGA

S IC FH8065301728500 QG9T C0 2.17G FCBGA

Part Number = SA00007QQ70

Part Number = SA00007QQ70R6

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

USOC1

USOC1

N2830@

N2830@

S IC FH8065301729601 QG9V C0 2.17G ABO!

S IC FH8065301729601 QG9V C0 2.17G ABO!

Part Number = SA00007QR30

Part Number = SA00007QR30

2

USOC1

USOC1

N2930@

N2930@

S IC FH8065301729501 QG9U C0 1.83G FCBGA

S IC FH8065301729501 QG9U C0 1.83G FCBGA

Part Number = SA00007RV70

Part Number = SA00007RV70

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

VLV-M SOC Memory DDR3L

VLV-M SOC Memory DDR3L

VLV-M SOC Memory DDR3L

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

1

6 39Thursday, March 13, 2014

6 39Thursday, March 13, 2014

6 39Thursday, March 13, 2014

1.0

1.0

1.0

Page 7

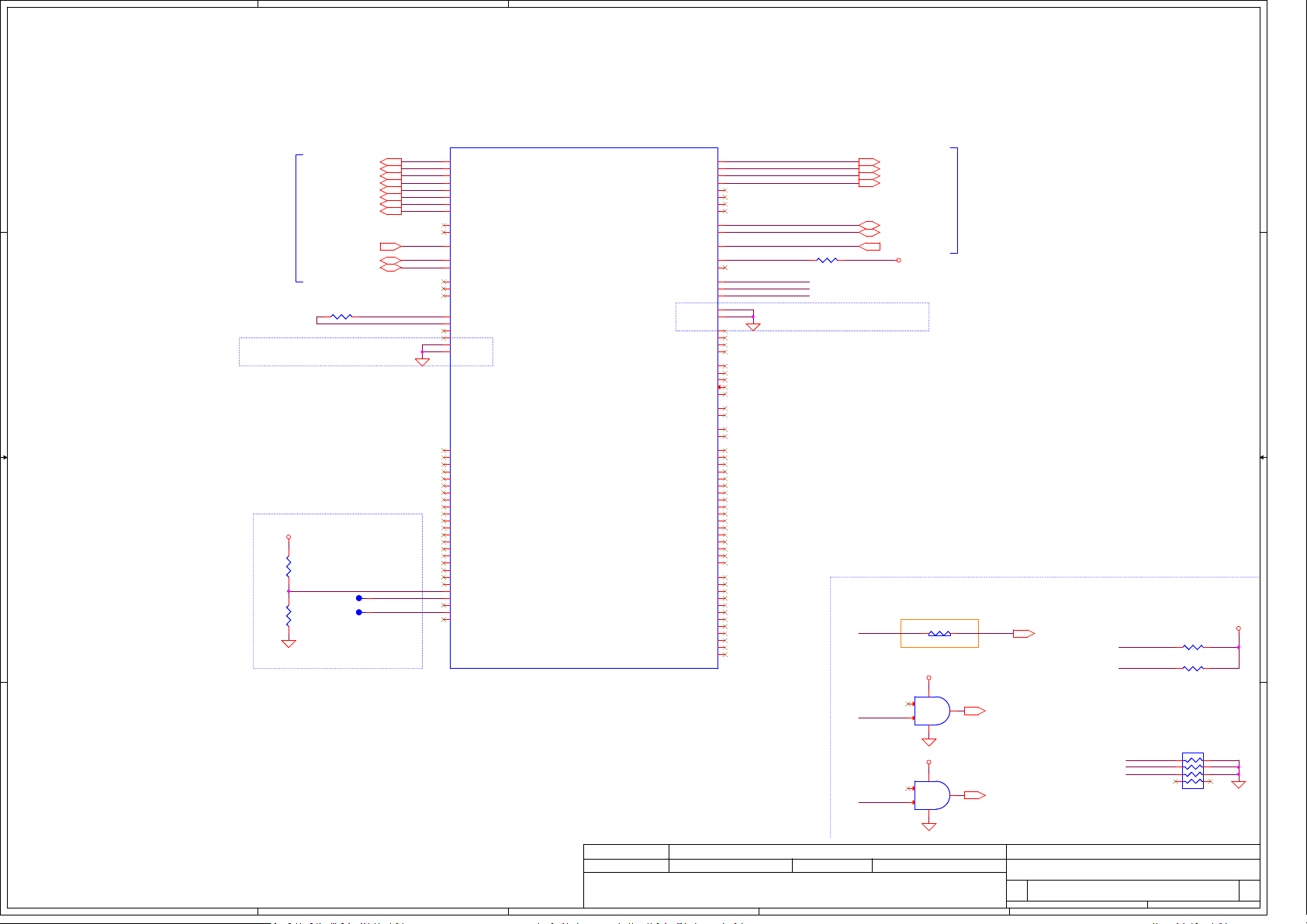

5

D D

HDMI

HDMI_HPD#<17>

HDMI_DDCDATA<17>

HDMI_DDCCLK<17>

1 2

R9

R9

402_0402_1%

402_0402_1%

C C

B B

A A

Follow CRB v2.0 0ohm till to GND

+1.8VS

12

@

@

R10

R10

10K_0402_5%

10K_0402_5%

@

12

@

R11

R11

10K_0402_1%

10K_0402_1%

Follow CRB v2.0

From check list:

GPIO_S0_NC[13] Multiplexed with Hardware Straps Pin:MDSI_DDCDATA

HDMI_TX2+<17>

HDMI_TX2-<17>

HDMI_TX1+<17>

HDMI_TX1-<17>

HDMI_TX0+<17>

HDMI_TX0-<17>

HDMI_CLK+<17>

HDMI_CLK-<17>

T1@T1

T2@T2

4

DDI0_RCOMPP

DDI0_RCOMPN

GPIO_NC13

GPIO_NC14

GPIO_NC12

USOC1C

USOC1C

AV3

DDI0_TXP_0

AV2

DDI0_TXN_0

AT2

DDI0_TXP_1

AT3

DDI0_TXN_1

AR3

DDI0_TXP_2

AR1

DDI0_TXN_2

AP3

DDI0_TXP_3

AP2

DDI0_TXN_3

AL3

DDI0_AUXP

AL1

DDI0_AUXN

D27

DDI0_HPD

C26

DDI0_DDCDATA

C28

DDI0_DDCCLK

B28

DDI0_VDDEN

C27

DDI0_BKLTEN

B26

DDI0_BKLTCTL

AK12

DDI0_RCOMP_P

AK13

DDI0_RCOMP_N

AM14

RESERVED_AM14

AM13

RESERVED_AM13

AM3

VSS_AM3

AM2

VSS_AM2

T2

RESERVED_T2

T3

RESERVED_T3

AB3

RESERVED_AB3

AB2

RESERVED_AB2

Y3

RESERVED_Y3

Y2

RESERVED_Y2

W3

RESERVED_W3

W1

RESERVED_W1

V2

RESERVED_V2

V3

RESERVED_V3

R3

RESERVED_R3

R1

RESERVED_R1

AD6

RESERVED_AD6

AD4

RESERVED_AD4

AB9

RESERVED_AB9

AB7

RESERVED_AB7

Y4

RESERVED_Y4

Y6

RESERVED_Y6

V4

RESERVED_V4

V6

RESERVED_V6

A29

GPIO_S0_NC_13

C29

GPIO_S0_NC14

AB14

RESERVED_AB14

B30

GPIO_S0_NC_12

C30

RESERVED_C30

FH8065301546401_FCBGA131170

FH8065301546401_FCBGA131170

1.8V

1.8V

1.8V

3 OF 10

3 OF 10

3

1.0V1.0V

1.0V

1.0V

1.8V

1.8V

1.8V

1.8V

1.8V

1.8V

3.3V

3.3V

3.3V

3.3V

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_DDCDATA

DDI1_DDCCLK

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

VSS_AH3

VSS_AH2

RESERVED_AH14

RESERVED_AH13

RESERVED_AF14

RESERVED_AF13

VGA_RED

VGA_BLUE

VGA_GREEN

VGA_IREF

VGA_IRTN

VGA_HSYNC

VGA_VSYNC

VGA_DDCCLK

VGA_DDCDATA

RESERVED_T7

RESERVED_T9

RESERVED_AB13

RESERVED_AB12

RESERVED_Y12

RESERVED_Y13

RESERVED_V10

RESERVED_V9

RESERVED_T12

RESERVED_T10

RESERVED_V14

RESERVED_V13

RESERVED_T14

RESERVED_T13

RESERVED_T6

RESERVED_T4

RESERVED_P14

GPIO_S0_NC_15

GPIO_S0_NC_16

GPIO_S0_NC_17

GPIO_S0_NC_18

GPIO_S0_NC_19

GPIO_S0_NC_20

GPIO_S0_NC_21

GPIO_S0_NC_22

GPIO_S0_NC_23

GPIO_S0_NC_24

GPIO_S0_NC_25

GPIO_S0_NC_26

@

@

AG3

AG1

AF3

AF2

AD3

AD2

AC3

AC1

AK3

AK2

K30

P30

DDI1_ENABLE

G30

N30

DDI1_ENVDD

J30

DDI1_ENBKL

M30

DDI1_PWM

AH3

AH2

Follow CRB v2.0 0ohm till to G ND

AH14

AH13

AF14

AF13

BA3

AY2

BA1

AW1

AY3

BD2

BF2

BC1

BC2

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

F34

M32

D28

J28

K34

D34

F32

F28

K28

J34

N32

D32

1 2

R8 2.2K_0402_5%R8 2.2K_0402_5%

eDP

DDI1_ENBKL

DDI1_ENVDD

DDI1_PWM

2

EDP_TXP0 <15,16>

EDP_TXN0 <15,16>

EDP_TXP1 <16>

EDP_TXN1 <16>

EDP_AUXP <15,16>

EDP_AUXN <15,16>

EDP_HPD# <16>

+1.8VS

1 2

+1.8VS

5

1

P

NC

2

A

G

3

+1.8VS

5

1

P

NC

2

A

G

3

eDP Panel

@

R130_0402_5%@R130_0402_5%

Modify R02

U2

U2

4

4

ENVDD <16>

INVT_PWM_SOC <15,16>

Y

NL17SZ07DFT2G_SC70-5

NL17SZ07DFT2G_SC70-5

SA00004BV00

SA00004BV00

U3

U3

Y

NL17SZ07DFT2G_SC70-5

NL17SZ07DFT2G_SC70-5

SA00004BV00

SA00004BV00

ENBKL <2 3>

1

ENVDD

INVT_PWM_SOC

DDI1_ENBKL

DDI1_ENVDD

DDI1_PWM

1 2

R144.7K_0402_5% R144.7K_0402_5%

1 2

R154.7K_0402_5% R154.7K_0402_5%

RP1

RP1

18

27

36

45

100K_0804_8P4R_5%

100K_0804_8P4R_5%

+3VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

VLV-M SOC Display

VLV-M SOC Display

VLV-M SOC Display

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

1

1.0

1.0

7 39Thursday, March 13, 2014

7 39Thursday, March 13, 2014

7 39Thursday, March 13, 2014

1.0

Page 8

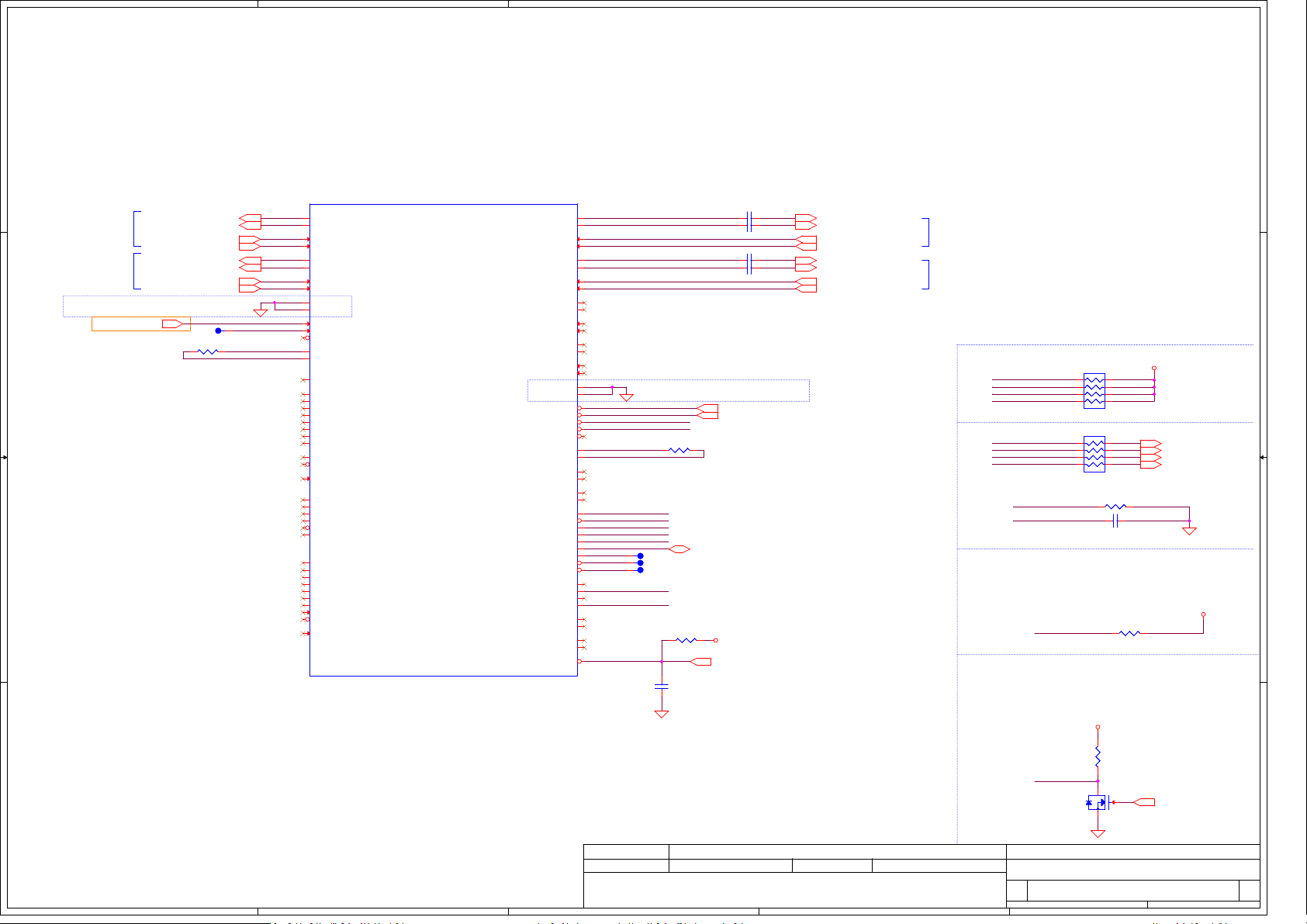

5

D D

USOC1D

USOC1D

SATA_PTX_DRX_P0<21>

HDD

ODD

Follow CRB V2.0 0ohm till to GND

SOC_SCI#<9>

C C

B B

A A

Modify R02

SATA_PTX_DRX_N0<21>

SATA_PRX_DTX_P0<21>

SATA_PRX_DTX_N0<21>

SATA_PTX_DRX_P1<21>

SATA_PTX_DRX_N1<21>

SATA_PRX_DTX_P1<21>

SATA_PRX_DTX_N1<21>

@

T3@T3

1 2

R16

R16

402_0402_1%

402_0402_1%

SOC_SCI#

DEVSLP_SOC

SATA_RCOMPP

SATA_RCOMPN

BF6

SATA_TXP_0

BG7

SATA_TXN_0

AU16

SATA_RXP_0

AV16

SATA_RXN_0

BD10

SATA_TXP_1

BF10

SATA_TXN_1

AY16

SATA_RXP_1

BA16

SATA_RXN_1

BB10

VSS_BB10

BC10

VSS_BC10

BA12

SATA_GP0 / GPIO_S0_SC_0

AY14

SATA_GP1 / SATA_DEVSLP_0 / GPIO_S0_SC_1

AY12

SATA_LED# / GPIO_S0_SC_2

AU18

SATA_RCOMP_P

AT18

SATA_RCOMP_N

AT22

MMC1_CLK / GPIO_S0_SC_16

AV20

MMC1_D0 / GPIO_S0_SC_17

AU22

MMC1_D1 / GPIO_S0_SC_18

AV22

MMC1_D2 / GPIO_S0_SC_19

AT20

MMC1_D3 / GPIO_S0_SC_20

AY24

MMC1_D4 / GPIO_S0_SC_21

AU26

MMC1_D5 / GPIO_S0_SC_22

AT26

MMC1_D6 / GPIO_S0_SC_23

AU20

MMC1_D7 / GPIO_S0_SC_24

AV26

MMC1_CMD / GPIO_S0_SC_25

BA24

MMC1_RST# / SATA_DEVSLP_0 / GPIO_S0_SC_26

AY18

MMC1_RCOMP

BA18

SD2_CLK / GPIO_S0_SC_27

AY20

SD2_D0 / GPIO_S0_SC_28

BD20

SD2_D1 / GPIO_S0_SC_29

BA20

SD2_D2 / GPIO_S0_SC_30

BD18

SD2_D3_CD# / GPIO_S0_SC_31

BC18

SD2_CMD / GPIO_S0_SC_32

AY26

SD3_CLK / GPIO_S0_SC_33

AT28

SD3_D0 / GPIO_S0_SC_34

BD26

SD3_D1 / GPIO_S0_SC_35

AU28

SD3_D2 / GPIO_S0_SC_36

BA26

SD3_D3 / GPIO_S0_SC_37

BC24

SD3_CD# / GPIO_S0_SC_38

AV28

SD3_CMD / GPIO_S0_SC_39

BF22

SD3_1P8EN / GPIO_S0_SC_40

BD22

SD3_PWREN# / GPIO_S0_SC_41

BF26

SD3_RCOMP

FH8065301546401_FCBGA131170 @

FH8065301546401_FCBGA131170 @

4

PCIE_CLKREQ_0# / GPIO_S0_SC_3

PCIE_CLKREQ_1# / GPIO_S0_SC_4

PCIE_CLKREQ_2# / GPIO_S0_SC_5

PCIE_CLKREQ_3# / GPIO_S0_SC_6

SD3_WP / GPIO_S0_SC_7

PCIE_RCOMP_P

PCIE_RCOMP_N

RESERVED_BB4

RESERVED_BB3

RESERVED_AV10

RESERVED_AV9

HDA_RST# / LPE_I2S0_CLK / GPIO_S0_SC_8

HDA_SYNC / LPE_I2S0_FRM / GPIO_S0_SC_9

HDA_CLK / LPE_I2S0_DATAOUT / GPIO_S0_SC_10

HDA_SDO / LPE_I2S0_DATAIN / GPIO_S0_SC_11

HDA_SDI0 / LPE_I2S1_CLK / GPIO_S0_SC_12

HDA_SDI1 / LPE_I2S1_FRM / GPIO_S0_SC_13

HDA_DOCKRST# / LPE_I2S1_DATAOUT / GPIO_S0_SC_14

HDA_DOCKEN# / LPE_I2S1_DATAIN / GPIO_S0_SC_15

LPE_I2S2_CLK / SATA_DEVSLP_1 / GPIO_S0_SC_62

4 OF 10

4 OF 10

LPE_I2S2_DATAIN / GPIO_S0_SC_64

LPE_I2S2_DATAOUT / GPIO_S0_SC_65

HDA_LPE_RCOMP

LPE_I2S2_FRM / GPIO_S0_SC_63

RESERVED_P34

RESERVED_N34

RESERVED_AK9

RESERVED_AK7

PCIE_TXP_0

PCIE_TXN_0

PCIE_RXP_0

PCIE_RXN_0

PCIE_TXP_1

PCIE_TXN_1

PCIE_RXP_1

PCIE_RXN_1

PCIE_TXP_2

PCIE_TXN_2

PCIE_RXP_2

PCIE_RXN_2

PCIE_TXP_3

PCIE_TXN_3

PCIE_RXP_3

PCIE_RXN_3

VSS_BB7

VSS_BB5

PROCHOT#

AY7

PCIE_PTX_DRX_P0

AY6

PCIE_PTX_DRX_N0

AT14

PCIE_PRX_DTX_P0

AT13

PCIE_PRX_DTX_N0

AV6

PCIE_PTX_DRX_P1

AV4

PCIE_PTX_DRX_N1

AT10

PCIE_PRX_DTX_P1

AT9

PCIE_PRX_DTX_N1

AT7

AT6

AP12

AP10

AP6

AP4

AP9

AP7

BB7

BB5

BG3

LAN_CLKREQ#

BD7

WLAN_CLKREQ#

BG5

PCIE_CLKREQ_2#

BE3

PCIE_CLKREQ_3#

BD5

AP14

PCIE_RCOMPP

AP13

PCIE_RCOMPN

BB4

BB3

AV10

AV9

BF20

HDA_RCOMP

BG22

HDA_RST#

BH20

HDA_SYNC

BJ21

HDA_BIT_CLK

BG20

HDA_SDOUT

BG19

HDA_SDIN0

BG21

BH18

BG18

BF28

BA30

GPIO_S0_SC_63

BD28

BC30

GPIO_S0_SC_65

P34

N34

AK9

AK7

C24

Internal PD 2K

3

1 2

1 2

1 2

1 2

Follow CRB V2.0 0ohm till to G ND

LAN_CLKREQ# <18>

WLAN_CLKREQ# <19>

1 2

R17

R17

402_0402_1%

402_0402_1%

HDA_SDIN0 <20>

@

T4@T4

@

T5@T5

@

T6@T6

Follow CRB v2.0

R20

R20

73.2_0402_1%

73.2_0402_1%

1 2

2

@EMC@

@EMC@

1

C8

C8

10P_0402_50V8J

10P_0402_50V8J

+1.0VS

H_PROCHOT# <23>

2

C5.1U_0402_16V7K C5.1U_0402_16V7K

C3.1U_0402_16V7K C3.1U_0402_16V7K

C4.1U_0402_16V7K C4.1U_0402_16V7K

C6.1U_0402_16V7K C6.1U_0402_16V7K

PCIE_PTX_C_DRX_P0 <18>

PCIE_PTX_C_DRX_N0 <18>

PCIE_PRX_DTX_P0 <18>

PCIE_PRX_DTX_N0 <18>

PCIE_PTX_C_DRX_P1 <19>

PCIE_PTX_C_DRX_N1 <19>

PCIE_PRX_DTX_P1 <19>

PCIE_PRX_DTX_N1 <19>

PCIE LAN

WLAN

RP2

RP2

LAN_CLKREQ#

PCIE_CLKREQ_2#

PCIE_CLKREQ_3#

WLAN_CLKREQ#

HDA_SYNC

HDA_SDOUT

HDA_BIT_CLK

HDA_RST#

HDA_RCOMP

HDA_BITCLK_AUDIO

GPIO_S0_SC_65:

Security Flash Descriptors

0 = Override

1 = Normal Operation (Internal PU)

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RP3

RP3

33_0804_8P4R_5%

33_0804_8P4R_5%

EMC@

EMC@

R18 49.9_0402_1%R18 49.9_0402_1%

C7 22P_0402_50V8J

C7 22P_0402_50V8J

GPIO_S0_SC_63:

BIOS/EFI Boot Strap (BBS)

0 = LPC

1 = SPI

GPIO_S0_SC_63

R21

R21

10K_0402_5%

10K_0402_5%

GPIO_S0_SC_65

1

+1.8VS

18

27

36

45

1 2

1 2

@EMC@

@EMC@

R19 10K_0402_5%R19 10K_0402_5%

+1.8VS

12

EC programing :

"High"for Flash BIOS

1

D

D

2

G

G

Q1

Q1

S

S

3

MESS138W-G_SOT323-3

MESS138W-G_SOT323-3

HDA_SYNC_AUDIO <20>

HDA_SDOUT_AUDIO <20>

HDA_BITCLK_AUDIO <20>

HDA_RST_AUDIO# <20>

12

TXE_DBG <23>

+1.8VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

VLV-M SOC SATA/PCI-E/HDA

VLV-M SOC SATA/PCI-E/HDA

VLV-M SOC SATA/PCI-E/HDA

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

1

8 39Thursday, March 13, 2014

8 39Thursday, March 13, 2014

8 39Thursday, March 13, 2014

1.0

1.0

1.0

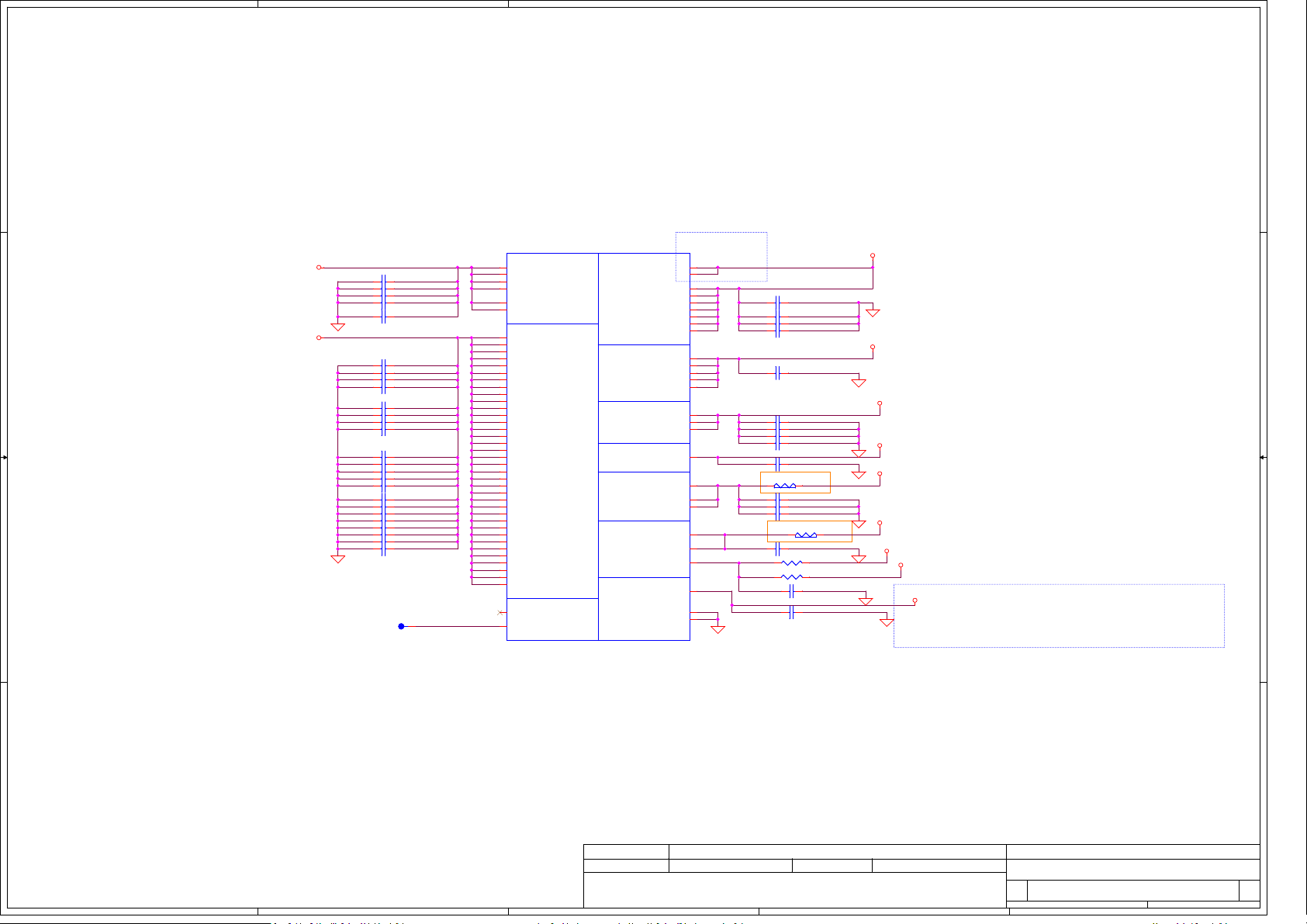

Page 9

5

XTAL_25M_IN

12

R23

3

3

R23

1M_0402_5%

1M_0402_5%

XTAL_25M_OUT

1

C9

C9

10P_0402_25V8J

10P_0402_25V8J

2

Y1

Y1

25MHZ_10PF_7V25000014

25MHZ_10PF_7V25000014

10P_0402_25V8J

10P_0402_25V8J

1

1

C11

C11

1

GND

D D

2

GND

2

4

LAN

1 2

R25 4.02K_0402_1%R25 4.02K_0402_1%

1 2

R26 47.5_0402_1%R26 47.5_040 2_1%

+1.8VALW

R27 51_0402_5%@R27 51_0402_5%@

R28 51_0402_5%R28 51_0402_5%

R29 200_0402_5%@R29 200_0402_5%@

C C

B B

From EC

(For share ROM)

EC_SPICS#<23>

EC_SPICLK<23>

EC_MOSI<23>

EC_MISO<23>

A A

From CPU

R03 modify

1 2

1 2

1 2

RP5

@RP5

@

4 5

3 6

2 7

1 8

51_0804_8P4R_5%

51_0804_8P4R_5%

+BIOS_SPI

1 2

R39 3.3K_0402_5%R39 3.3K_0402_5%

1 2

R41 3.3K_0402_5%R41 3.3K_0402_5%

1 2

R43 3.3K_0402_5%R43 3.3K_0402_5%

EC_SPICS#

EC_SPICLK

EC_MOSI

EC_MISO RTC_TEST#

SOC_SPI_CLK

SOC_SPI_MOSI

SOC_SPI_MISO

SOC_SPI_CS0# SPI_CS0#

ICLK_ICOMP

ICLK_RCOMP

For XDP use

XDP_H_PRDY#

XDP_H_TDO

XDP_H_PREQ_BUF#

XDP_H_TDI

XDP_H_TMS

XDP_H_TCK

XDP_H_TRST#

TS_INT_R#<16>

PCH_TP_INT#<24>

RP8

RP8

1 8

2 7

3 6

4 5

22_0804_8P4R_5%

22_0804_8P4R_5%

EMC@

EMC@

RP9

RP9

1 8

2 7

3 6

4 5

22_0804_8P4R_5%

22_0804_8P4R_5%

EMC@

EMC@

5

WLAN

SPI_CS0#

SPI_WP#

SPI_HOLD#

SPI_CS0#

SPI_CLK

SPI_MOSI

SPI_MISO

SPI_CLK

SPI_MOSI

SPI_MISO

1 2

@

1 2

@

modify R02

SPI ROM ( 8MByte ) 1.8V

SPI_CS0#

SPI_MISO

SPI_WP#

SPI_CLK

XTAL_25M_IN

XTAL_25M_OUT

ICLK_ICOMP

ICLK_RCOMP

CLK_PCIE_LAN#<18>

CLK_PCIE_LAN<18>

CLK_PCIE_WLAN#<19>

CLK_PCIE_WLAN<19>

XDP_H_TCK

XDP_H_TRST#

XDP_H_TMS

XDP_H_TDI

XDP_H_TDO

XDP_H_PRDY#

XDP_H_PREQ_BUF#

SOC_SPI_CS0#

T10@T10@

SOC_SPI_MISO

SOC_SPI_MOSI

SOC_SPI_CLK

SOC_KBRST#

SOC_TS_INT#

SOC_TP_INT#

R340_0402_5%@R340_0402_5%

R360_0402_5%@R360_0402_5%

SOC_LID_OUT#

SOC_SMI#

GPIO_RCOMP

R37

R37

49.9_0402_1%

49.9_0402_1%

1 2

Modify R03

@

@

R40 0_0402_5%

R40 0_0402_5%

C19 .1U_0402_16V7KC19 .1U_0402_16V7K

U7

U7

1

CS#

2

DO(IO1)

HOLD#(IO3)

3

WP#(IO2)

4

GND

W25Q64DWSSIG_SO8

W25Q64DWSSIG_SO8

Reserve for EMI(Near SPI ROM)

1 2

R47

@EMC@ R47

@EMC@

33_0402_5%

33_0402_5%

4

USOC1E

USOC1E

AH12

ICLK_OSCIN

AH10

ICLK_OSCOUT

AD9

RESERVED_AD9

AD14

ICLK_ICOMP

AD13

ICLK_RCOMP

AD10

RESERVED_AD10

AD12

RESERVED_AD12

AF6

PCIE_CLKN_0

AF4

PCIE_CLKP_0

AF9

PCIE_CLKN_1

AF7

PCIE_CLKP_1

AK4

PCIE_CLKN_2

AK6

PCIE_CLKP_2

AM4

PCIE_CLKN_3

AM6

PCIE_CLKP_3

AM9

RESERVED_AM9

AM10

RESERVED_AM10

BH7

PMC_PLT_CLK_0 / GPIO_S0_SC_96

BH5

PMC_PLT_CLK_1 / GPIO_S0_SC_97

BH4

PMC_PLT_CLK_2 / GPIO_S0_SC_98

BH8

PMC_PLT_CLK_3 / GPIO_S0_SC_99

BH6

PMC_PLT_CLK_4 / GPIO_S0_SC_100

BJ9

PMC_PLT_CLK_5 / GPIO_S0_SC_101

D14

TAP_TCK

G12

TAP_TRST#

F14

TAP_TMS

F12

TAP_TDI

G16

TAP_TDO

D18

TAP_PRDY#

F16

TAP_PREQ#

AT34

RESERVED_AT34

C23

PCU_SPI_CS_0#

C21

PCU_SPI_CS_1# / GPIO_S5_21

B22

PCU_SPI_MISO

A21

PCU_SPI_MOSI

C22

PCU_SPI_CLK

B18

GPIO_S5_0

B16

GPIO_S5_1 / PMC_WAKE_PCIE_1

C18

GPIO_S5_2 / PMC_WAKE_PCIE_2

A17

GPIO_S5_3 / PMC_WAKE_PCIE_3

C17

GPIO_S5_4

C16

GPIO_S5_5 / PMU_SUSCLK_1

B14

GPIO_S5_6 / PMU_SUSCLK_2

C15

GPIO_S5_7 / PMU_SUSCLK_3

C13

GPIO_S5_8

A13

GPIO_S5_9

C19

GPIO_S5_10

N26

GPIO_RCOMP

FH8065301546401_FCBGA131170

FH8065301546401_FCBGA131170

+1.8VALW+BIOS_SPI

12

12

8

VCC

7

SPI_HOLD#

6

SPI_CLK

CLK

5

SPI_MOSI

DI(IO0)

12

C23

@EMC@ C23

@EMC@

10P_0402_50V8J

10P_0402_50V8J

4

+BIOS_SPI

RTC domain

5 OF 13

5 OF 13

RTC_TEST#

RTC_RST#

C20

C20

1U_0402_6.3V6K

1U_0402_6.3V6K

CL_CMOS<23>

MESS138W-G_SOT323-3

MESS138W-G_SOT323-3

Clear CMOS

Close to RAM do or

3

GPIO_S5_14

GPIO_S5_17

ILB_RTC_X1

ILB_RTC_X2

SVID_DATA

SVID_CLK

GPIO_S5_22

GPIO_S5_23

GPIO_S5_24

GPIO_S5_25

GPIO_S5_26

GPIO_S5_27

GPIO_S5_28

GPIO_S5_29

GPIO_S5_30

+RTCVCC

12

12

SP@

SP@

3

@

@

12

SHORT PADS

SHORT PADS

AU34

AV34

BA34

AY34

BF34

BD34

BD32

BF32

D26

G24

F18

F22

D22

J20

D20

F26

K26

J26

BG9

F20

J24

G18

C11

C12

B10

B7

C9

A9

B8

P22

B24

A25

C25

AU32

AT32

K24

N24

M20

J18

M18

K18

K20

M22

M24

AV32

BA28

AY28

AY30

PMC_ACIN

PMC_SUSCLK

PMC_SLP_S4#

PMC_SLP_S3#

GPIO_S5_14

PMC_ACIN

PMC_PCIE_WAKE#

PMC_BATLOW#

PMC_PWRBTN#

PMC_RSTBTN#

PMC_PLTRST#

GPIO_S5_17

RTC_TEST#

RTC_RST#

EC_RSMRST#

PMC_CORE_PWROK

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

VR_SVID_ALERT#_SOC

VR_SVID_DATA_SOC

SP@

SP@

JCMOS2

JCMOS2

SIO_UART1_RXD / GPIO_S0_SC_70

SIO_UART1_TXD / GPIO_S0_SC_71

SIO_UART1_RTS# / GPIO_S0_SC_72

SIO_UART1_CTS# / GPIO_S0_SC_73

SIO_UART2_RXD / GPIO_S0_SC_74

SIO_UART2_TXD / GPIO_S0_SC_75

SIO_UART2_RTS# / GPIO_S0_SC_76

SIO_UART2_CTS# / GPIO_S0_SC_77

PMC_SUSPWRD NACK / GPIO_S5_11

PMC_SUSCLK_0 / GPIO_S5_12

PMC_SLP_S0IX# / GPIO_S5_13

PMC_WAKE_PCIE_0# / GPIO_S5_15

PMC_PWRBTN# / GPIO_S5_16

PMC_SUS_STAT# / GPIO_S5_18

SIO_PWM_0 / GPIO_S0_SC_94

SIO_PWM_1 / GPIO_S0_SC_95

SIO_SPI_CS# / GPIO_S0_SC_66

SIO_SPI_MISO / GPIO_S0_SC_67

SIO_SPI_MOSI / GPIO_S0_SC_68

SIO_SPI_CLK / GPIO_S0_SC_69

2

1

2

G

G

@

@

Q19

Q19

PMC_SLP_S4#

PMC_SLP_S3#

PMC_ACPRESENT

PMC_BATLOW#

PMC_RSTBTN#

PMC_PLTRST#

ILB_RTC_TEST#

ILB_RTC_RST#

PMC_RSMRST#

PMC_CORE_PWROK

ILB_RTC_EXTPAD

RTC_VCC_P22

SVID_ALERT#

R42

R42

20K_0402_1%

20K_0402_1%

R44 20K_0402_1%R44 20K_0402_1%

1

C21

C21

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

D

D

JCMOS1

JCMOS1

SHORT PADS

SHORT PADS

S

S

3

Modify R03

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

R24 2.2K_0402_5%R24 2.2K_0402_5%

D1 RB751V40_S C76-2D1 RB751V40_S C76-2

+RTCVCC

ILB_RTC_X1

ILB_RTC_X2

Modify R03

12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

12

12

T7 @T7 @

32.768k output

T8 @T8 @

T9 @T9 @

EC_RSMRST# <2 3>

1 2

C16

C16

.1U_0402_16V7K

.1U_0402_16V7K

1 2

R32 20_0402_1%R32 20_0402_1%

1 2

R33 16.9_0402_1%R33 16.9_0402_1%

1 2

R35

R35

10M_0402_5%

10M_0402_5%

32.768KHZ_12.5PF_Q13FC135000040

32.768KHZ_12.5PF_Q13FC135000040

1 2

Y2

Y2

1

C17

C17

18P_0402_50V8J

18P_0402_50V8J

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.8VALW

+1.0VS

12

R31

R31

73.2_0402_1%

73.2_0402_1%

1

C18

C18

18P_0402_50V8J

18P_0402_50V8J

2

2

ACIN <23,28>

VR_SVID_ALERT# <33>

VR_SVID_DATA <33>

VR_SVID_CLK <33>

PMC_SLP_S3# EC_SLP_S3#

2

1.8V 3.3V

PMC_PLTRST#

PLT_RST_BUF#

PMC_PCIE_WAKE#

PMC_BATLOW#

GPIO_S5_14

PMC_CORE_PWROK

DDR_CORE_PWROK

PMC_PLTRST#

EC_RSMRST#

PMC_CORE_PWROK<23>

SOC_SCI#<8>

R213

R213

0_0402_5%

0_0402_5%

1 2

NTPM@

NTPM@

NTPM@

NTPM@

1 2

R214

R214

0_0402_5%

0_0402_5%

+1.8VALW

SOC_SERIRQ<10>

+1.8VALW

PMC_SLP_S3#

+RTCBATT +RTC VCC+CHGRTC

trace width 10milW=20mils W=20mils

D2

D2

1

BAS40-04_SOT23-3

BAS40-04_SOT23-3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3VS

+1.8VS

1

NC

2

A

C10

0.01U_0402_16V7K

0.01U_0402_16V7K

C15 .1U_0402_16V7K

C15 .1U_0402_16V7K

PMC_SLP_S4#

SOC_KBRST#

SOC_LID_OUT#

SOC_SMI#

SOC_SCI#

PMC_PWRBTN#

SOC_SERIRQ

MESS138W-G_SOT323-3

MESS138W-G_SOT323-3

2

3

VLV-M SOC CLK/PMU/SPI

VLV-M SOC CLK/PMU/SPI

VLV-M SOC CLK/PMU/SPI

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

12

R22

5

3

R30 100K_0402_5%R30 100K_0402_5%

1

2

3

G2129TL1U_SC70-6

G2129TL1U_SC70-6

Q21

Q21

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

R22

U4

U4

4.7K_0402_5%

4.7K_0402_5%

P

4

Y

G

NL17SZ07DFT2G_SC70-5

NL17SZ07DFT2G_SC70-5

SA00004BV00

SA00004BV00

1 2

@EMC@C 10

@EMC@

RP4

RP4

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

10K_0804_8P4R_5%

EMC@

EMC@

1 2

C12 0.01U_0402_16V7K

C12 0.01U_0402_16V7K

EMC@

EMC@

1 2

C13 0.01U_0402_16V7K

C13 0.01U_0402_16V7K

EMC@

EMC@

1 2

C14 .1U_0402_16V7K

C14 .1U_0402_16V7K

1 2

EMC@

EMC@

1 2

+1.35VS

+3VALW

5

U6

U6

1

P

NC

Y

2

A

G

NL17SZ07DFT2G_SC70-5

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

SA00004BV00

RP6

RP6

1 8

2 7

EC_SLP_S4#

3 6

EC_KBRST#

4 5

EC_LID_OUT#

0_0804_8P4R_5%

0_0804_8P4R_5%

RP7

RP7

1 8

2 7

EC_SMI#

3 6

EC_SCI#

4 5

PBTN_OUT#

0_0804_8P4R_5%

0_0804_8P4R_5%

PMC_SLP_S3#SOC_SERIRQ EC_SERIRQ

U27

U27

VCCA

VCCB

GND

EO

A4

B4

TPM@

TPM@

G

G

2

1

3

D

S

D

S

TPM@

TPM@

1

PLT_RST_BUF# <18,19,21,23>

PLT_RST Buffer

+1.8VALW

12

R38

R38

10K_0402_5%

10K_0402_5%

1.35V3.3V

4

DDR_CORE_PWROK <6>

EC_SLP_S4# <23>

EC_KBRST# < 23>

EC_LID_OUT# <23>

EC_SMI# <2 3>

EC_SCI# <23>

PBTN_OUT# <23>

+3VALW_EC

+RTCVCC

1

12

TPM@

TPM@

EC_SLP_S3# <23>

1

C22

C22

.1U_0402_16V7K

.1U_0402_16V7K

2

9 39Thursday, March 13, 2014

9 39Thursday, March 13, 2014

9 39Thursday, March 13, 2014

+1.8VALW

EC_SERIRQ <21,23>

R116 2.2K_0402_5%

R116 2.2K_0402_5%

6

5

4

Modify R02

+1.8VALW

1.0

1.0

1.0

Page 10

5

D D

USB3.0 Connector

USB Hub

Touch Panel

+1.8VALW

C C

B B

Pull High at EC side

1 2

R49 10K_0402_5%R49 10K_0402_5%

1 2

R51 10K_0402_5%R51 10K_0402_5%

@EMC@

@EMC@

12

C24 10P_0402_50V8J

C24 10P_0402_50V8J

+1.8VS

RP10

RP10

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

EMC@

EMC@

R02 modify

EC_SMB_CK2<14,19,23>

EC_SMB_DA2<14,19,23>

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

45

PCU_SMB_CLK

36

PCU_SMB_DATA

27

PCU_SMB_ALERT#

18

+1.8VS

5

3 4

2

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

G

G

6 1

S

D

S

D

Q4B

Q4B

USB_OC0#

USB_OC1#

LPC_CLK_0

PCU_SMB_CLK

SGD

SGD

Q4A

Q4A

PCU_SMB_DATA

CPU Thermal sensor

U28

@ U28

A A

EC_SMB_CK2

EC_SMB_DA2 REMOTE1+

ADM1032ARMZ-2REEL_MS OP8

ADM1032ARMZ-2REEL_MS OP8

@

8

SCLK

7

SDATA

6

ALERT#

5

GND

5

VDD

D+

D-

THERM#

Modify R03

1

2

3

4

REMOTE1-

THERM#

Camera

NOTE: Ref checklist rev1.2 p.24

USB_PLL_MON is a single ended signal and should follow

single ended signal routing requirements.

NOTE: Ref checklist rev1.2 p.25

USB_HSIC_RCOMP must NOT float if they are not being used.

LPC_AD0<21,23>

LPC_AD1<21,23>

LPC_AD2<21,23>

LPC_AD3<21,23>

LPC_FRAME#<21,23>

LPC_CLK_EC<23>

CLK_PCI_TPM<21>

LPC_CLKRUN#<21>

SOC_SERIRQ<9>

ILB_LPC_CLK_0 : Output of 25MHz,

Need Check with EC

ILB_LPC_CLK_1 is for CLK_0 feedback.(Input)

Set to Outpot for Normal Usage

+3VS

C275

0.1U_0402_16V4Z@C275

0.1U_0402_16V4Z

1

@

2

1 2

@

@

R258 10K_0402_5%

R258 10K_0402_5%

+3VS

4

USB20_P0<22>

USB20_N0<22>

USB20_P1<22>

USB20_N1<22>

USB20_P2<16>

USB20_N2<16>

USB20_P3<16>

USB20_N3<16>

USB_OC0#<22>

REMOTE1+

@C276

@

2200P_0402_50V7K

2200P_0402_50V7K

REMOTE1-

4

1 2

1 2

1 2

R54

R54

45.3_0402_1%

45.3_0402_1%

1 2

R56

@R56

@

0_0402_5%

0_0402_5%

1 2

R57 45.3_0402_1%R57 45.3_0402_1%

1 2

1 2

1 2

2

C276

2

B

B

1

ICLK_USB_TERMP

R501K_0402_1% R501K_0402_1%

ICLK_USB_TERMN

R521K_0402_1% R521K_0402_1%

USB_OC1#

USB_RCOMP

USB_PLL_MON

HSIC_RCOMP

LPC_RCOMP

R5849.9_0402_1% R5849.9_0402_1%

LPC_CLK_0

R6122_0402_5% EMC@ R6122_0402_5% EMC@

LPC_CLK_1

R6222_0402_5% EMC@ R6222_0402_5% EMC@

LPC_CLKRUN#

PCU_SMB_DATA

PCU_SMB_CLK

PCU_SMB_ALERT#

C

C

@

@

Q22

Q22

MMST3904-7-F_SOT323-3

MMST3904-7-F_SOT323-3

E

E

3 1

3

USOC1F

USOC1F

G2

GPIO_S5_31

M3

GPIO_S5_32

L1

GPIO_S5_33

K2

GPIO_S5_34

K3

GPIO_S5_35

M2

GPIO_S5_36

N3

GPIO_S5_37

P2

GPIO_S5_38

L3

GPIO_S5_39

J3

GPIO_S5_40

P3

GPIO_S5_41

H3

GPIO_S5_42

B12

GPIO_S5_43

M16

USB_DP0

K16

USB_DN0

J14

USB_DP1

G14

USB_DN1

K12

USB_DP2

J12

USB_DN2

K10

USB_DP3

H10

USB_DN3

D10

ICLK_USB_TERMP

F10

ICLK_USB_TERMN

C20

USB_OC_0# / GPIO_S5_19

B20

USB_OC_1# / GPIO_S5_20

D6

USB_RCOMPO

C7

USB_RCOMPI

M13

USB_PLL_MON

B4

USB_HSIC0_DATA

B5

USB_HSIC0_STROBE

E2

USB_HSIC1_DATA

D2

USB_HSIC1_STROBE

A7

USB_HSIC_RCOMP

BF18

LPC_RCOMP / VGA_RCOMP

BH16

ILB_LPC_AD_0 / GPIO_S0_SC_42

BJ17

ILB_LPC_AD_1 / GPIO_S0_SC_43

BJ13

ILB_LPC_AD_2 / GPIO_S0_SC_44

BG14

ILB_LPC_AD_3 / GPIO_S0_SC_45

BG17

ILB_LPC_FRAME# / GPIO_S0_SC_46

BG15

ILB_LPC_CLK_0 / GPIO_S0_SC_47

BH14

ILB_LPC_CLK_1 / GPIO_S0_SC_48

BG16

ILB_LPC_CLKRUN# / GPIO_S0_SC_49

BG13

ILB_LPC_SERIRQ / GPIO_S0_SC_50

BG12

PCU_SMB_DATA / GPIO_S0_SC_51

BH10

PCU_SMB_CLK / GPIO_S0_SC_52

BG11

PCU_SMB_ALERT# / GPIO_S0_SC_53

FH8065301546401_FCBGA131170

FH8065301546401_FCBGA131170

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

GPIO_S0_SC_57 / PCU_UART_TXD

GPIO_S0_SC_61 / PCU_UART_RXD

ILB_8254_SPKR / GPIO_S0_SC_54

SIO_I2C0_DATA / GPIO_S0_SC_78

SIO_I2C0_CLK / GPIO_S0_SC_79

SIO_I2C1_DATA / GPIO_S0_SC_80

SIO_I2C1_CLK / GPIO_S0_SC_81

SIO_I2C2_DATA / GPIO_S0_SC_82

SIO_I2C2_CLK / GPIO_S0_SC_83

SIO_I2C3_DATA / GPIO_S0_SC_84

SIO_I2C3_CLK / GPIO_S0_SC_85

SIO_I2C4_DATA / GPIO_S0_SC_86

SIO_I2C4_CLK / GPIO_S0_SC_87

SIO_I2C5_DATA / GPIO_S0_SC_88

SIO_I2C5_CLK / GPIO_S0_SC_89

SIO_I2C6_DATA / GPIO_S0_SC_90

SIO_I2C6_CLK / GPIO_S0_SC_91 / SD3_WP

6 OF 13

6 OF 13

2013/04/12 2014/04/12

2013/04/12 2014/04/12

2013/04/12 2014/04/12

RESERVED_M10

RESERVED_M9

RESERVED_P6

RESERVED_P7

RESERVED_M7

USB3_REXT0

RESERVED_P10

RESERVED_P12

RESERVED_M4

RESERVED_M6

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

RESERVED_H8

RESERVED_H7

RESERVED_H4

RESERVED_H5

GPIO_S0_SC_55

GPIO_S0_SC_56

GPIO_S0_SC_58

GPIO_S0_SC_59

GPIO_S0_SC_60

GPIO_S0_SC_092

GPIO_S0_SC_093

PDA (Platform D ebug Assistant) Test Points

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

@

@

M10

M9

P6

P7

M7

M12

P10

P12

M4

M6

D4

E3

K6

K7

H8

H7

H4

H5

BD12

BC12

BD14

BC14

BF14

BD16

BC16

BH12

BH22

BG23

BG24

BH24

BG25

BJ25

BG26

BH26

BF27

BG27

BH28

BG28

BJ29

BG29

BH30

BG30

2

USB3_REXT0

GPIO_S0_SC_56

SOC_SPKR

SOC_I2C2_DATA

SOC_I2C2_CLK

SOC_I2C5_DATA

SOC_I2C5_CLK

GPIO_S0_SC_92

GPIO_S0_SC_93

2

R48

R48

1.24K_0402_1%

1.24K_0402_1%

1 2

PCH_USB3_RX0_P <22>

PCH_USB3_RX0_N <22>

PCH_USB3_TX0_P <22>

PCH_USB3_TX0_N <22>

SOC_SPKR <20>

T14 @T14 @

T15 @T15 @

1

BIOS/EFI Top Swap

While updating the BIOS/EFI boot sector in

flash, unexpected system power loss can

cause an incomplete write resulting in a

corrupt boot sector.

Reference EDS v1.5 Page2294

USB3 Port 0

BIOS/EFI Top Swap

+1.8VS

Modify R02

12

R53

R53

10K_0402_5%

10K_0402_5%

GPIO_S0_SC_56

BIOS/EFI Top Swap

GPIO_S0_SC_56

For Touch Screen

SOC_I2C5_DATA

SOC_I2C5_CLK

SOC_I2C5_DATA

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

SOC_I2C5_CLK

Modify R02

R59 2.2K_0402_5%

R59 2.2K_0402_5%

R60 2.2K_0402_5%EDP@R60 2.2K_0402_5%EDP@

5

SGD

SGD

Q2A

EDP@

Q2A

EDP@

EDP@

EDP@

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

For Touch Pad

SOC_I2C2_DATA

SOC_I2C2_CLK

SOC_I2C2_DATA

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

SOC_I2C2_CLK

Modify R02

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Bay Trail M LA-B511P

Date: Sheet of

Date: Sheet of

Date: Sheet of

R63 2.2K_0402_5%R63 2.2K_0402_5%

R64 2.2K_0402_5%R64 2.2K_0402_5%

5

SGD

SGD

Q3A

Q3A

Q3B

Q3B

DMN63D8LDW_SOT363-6

DMN63D8LDW_SOT363-6

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

VLV-M SOC USB/LPC/SMBus

VLV-M SOC USB/LPC/SMBus

VLV-M SOC USB/LPC/SMBus

1: DISABLED

*

0: ENABLED

EDP@

EDP@

1 2

1 2

+1.8VS

34

2

G

G

S

D

S

D

Q2B

Q2B

1 2

1 2

+1.8VS

34

2

G

G

S

D

S

D

1

12

61

61

R55

@R55

@

10K_0402_5%

10K_0402_5%

10 39Thursday, March 13, 2014

10 39Thursday, March 13, 2014

10 39Thursday, March 13, 2014

+1.8VS

I2C5_SDA_PNL <16>

I2C5_SCL_PNL <16>

+1.8VS

I2C2_SDA_TP <24>

I2C2_SCL_TP <24>

1.0

1.0

1.0

Page 11

5

D D

4

3

2

1

+SOC_VCC

12A

C C

TP2_CORE_VCC_S0iX

T16@ T16@

B B

VGFX_VSNS<33>

VCORE_VSNS<33>

VCORE_GSNS<33>