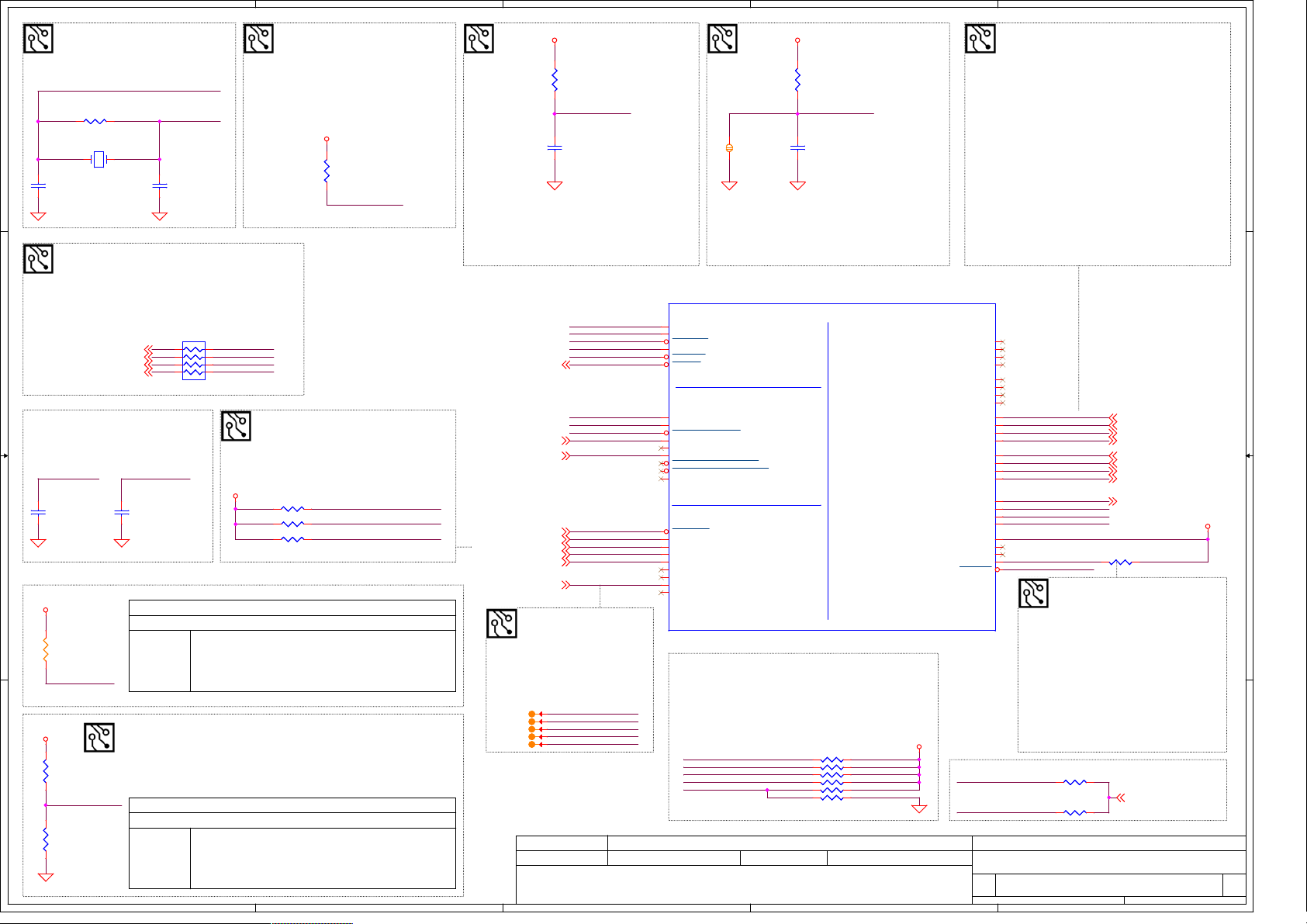

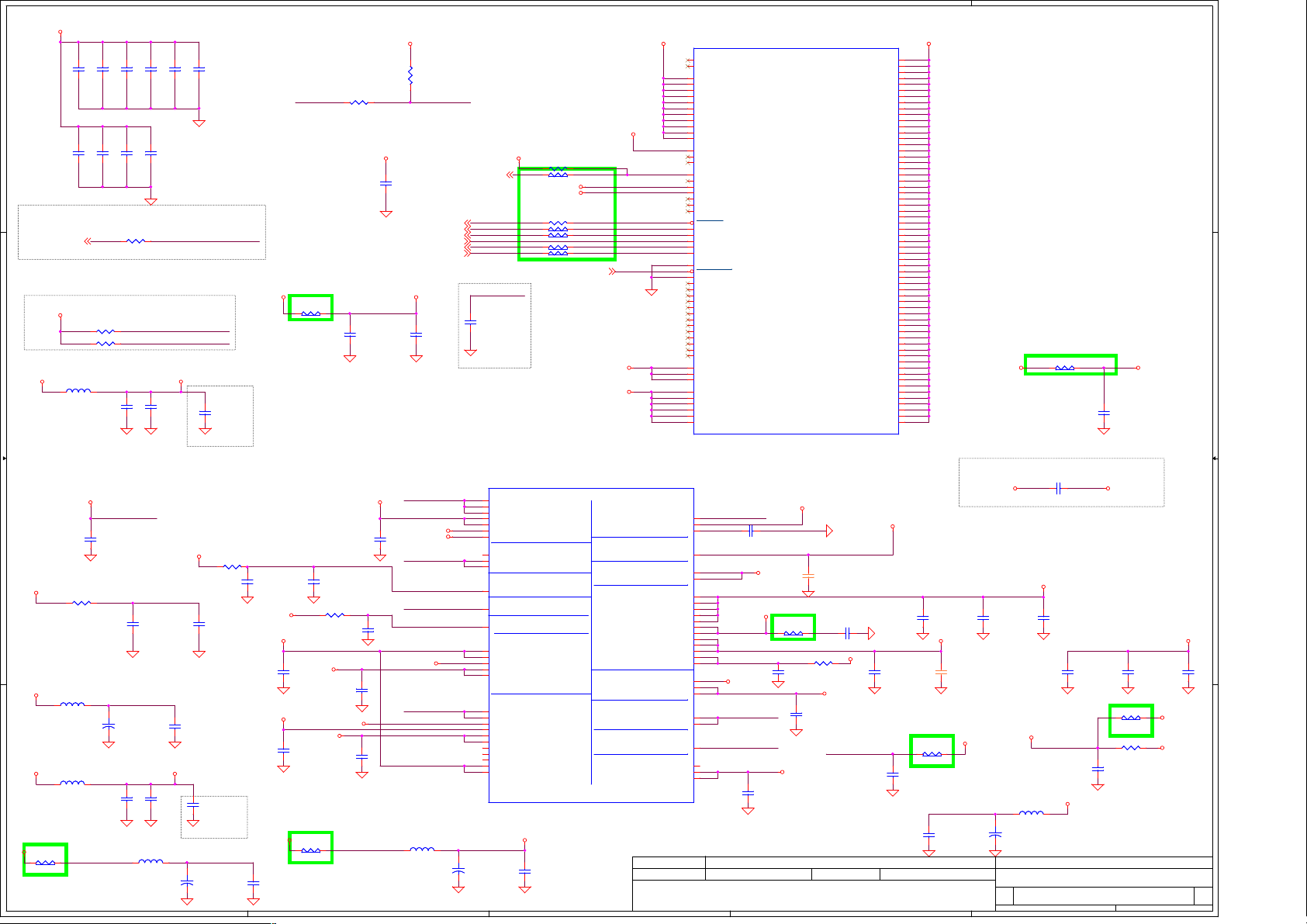

Page 1

A

B

C

D

E

MODEL NAME :

PCB NO :

BOM P/N :

ZZZ

ZZZ

1 1

MB_PCB

MB_PCB

DAA0008I000

DAA0008I000

LA-B441P

TBD

ZAZ00

Dell/Compal Confidential

2 2

Schematic Document

Dino (Broadwell ULT)

3 3

2014-10-16

Rev: 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

C

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secr et Data

Compal Secr et Data

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P01-Cover Page

P01-Cover Page

P01-Cover Page

LA-B441P

LA-B441P

LA-B441P

E

150Thursday, October 16, 2014

150Thursday, October 16, 2014

150Thursday, October 16, 2014

1.0

1.0

1.0

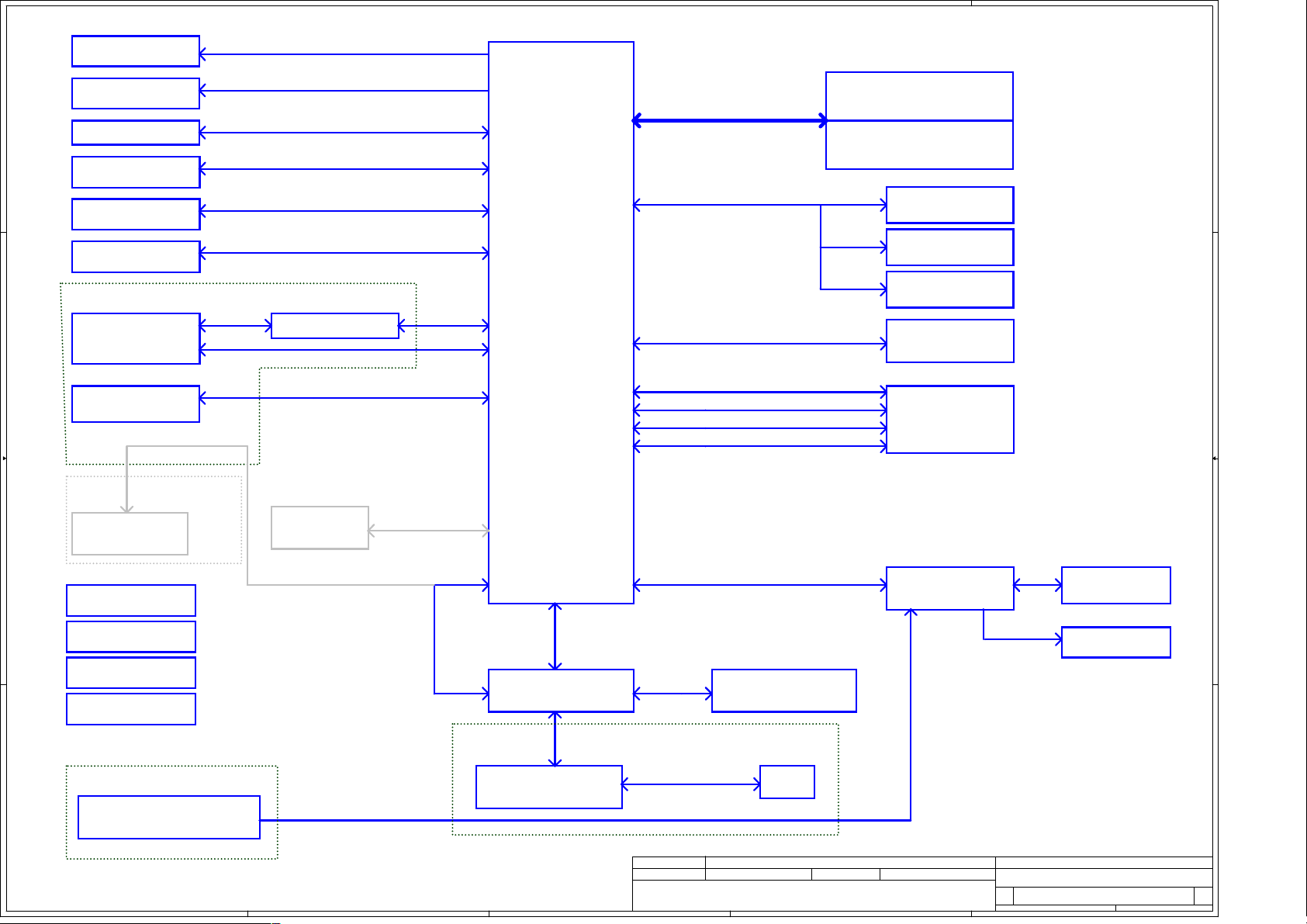

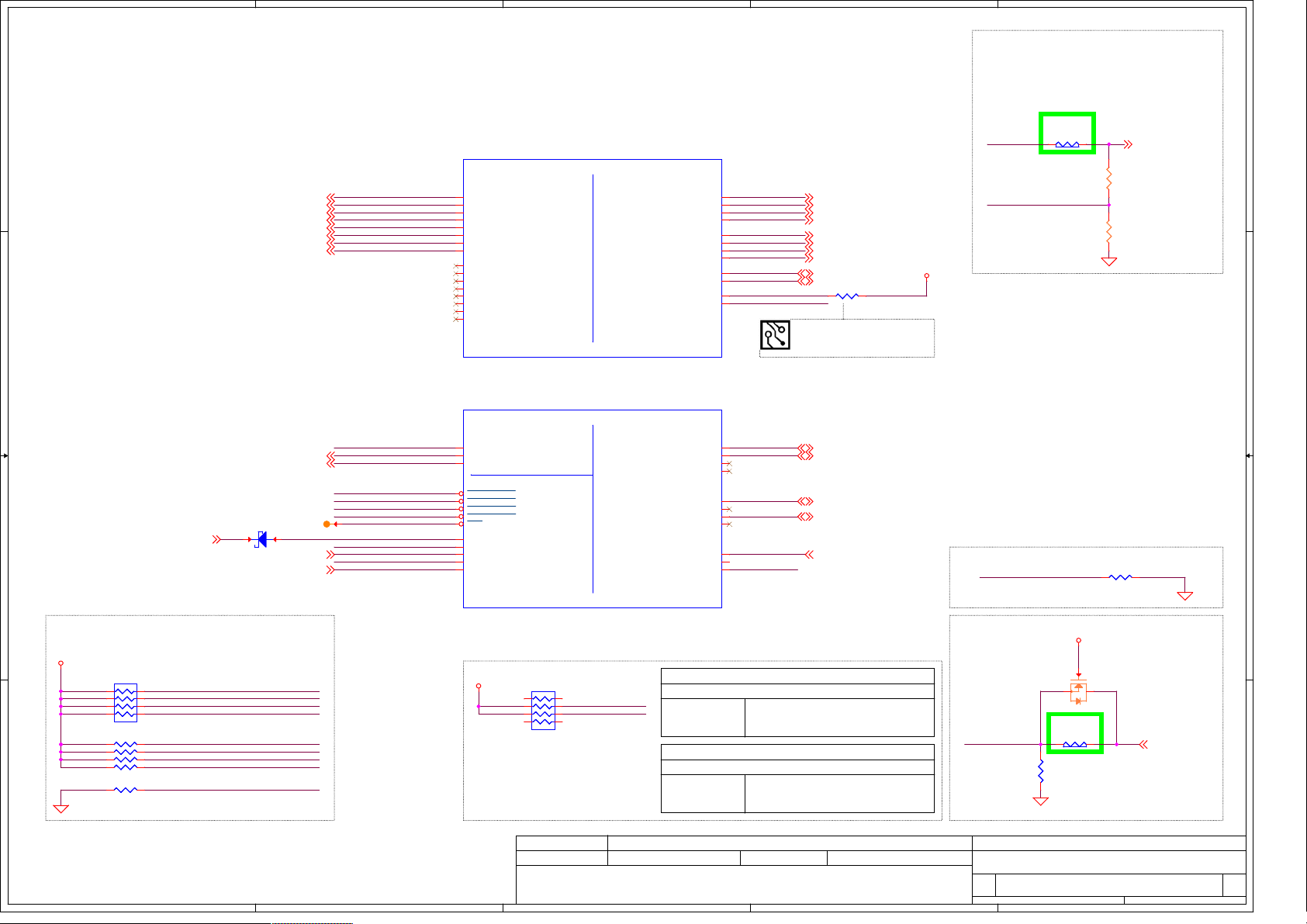

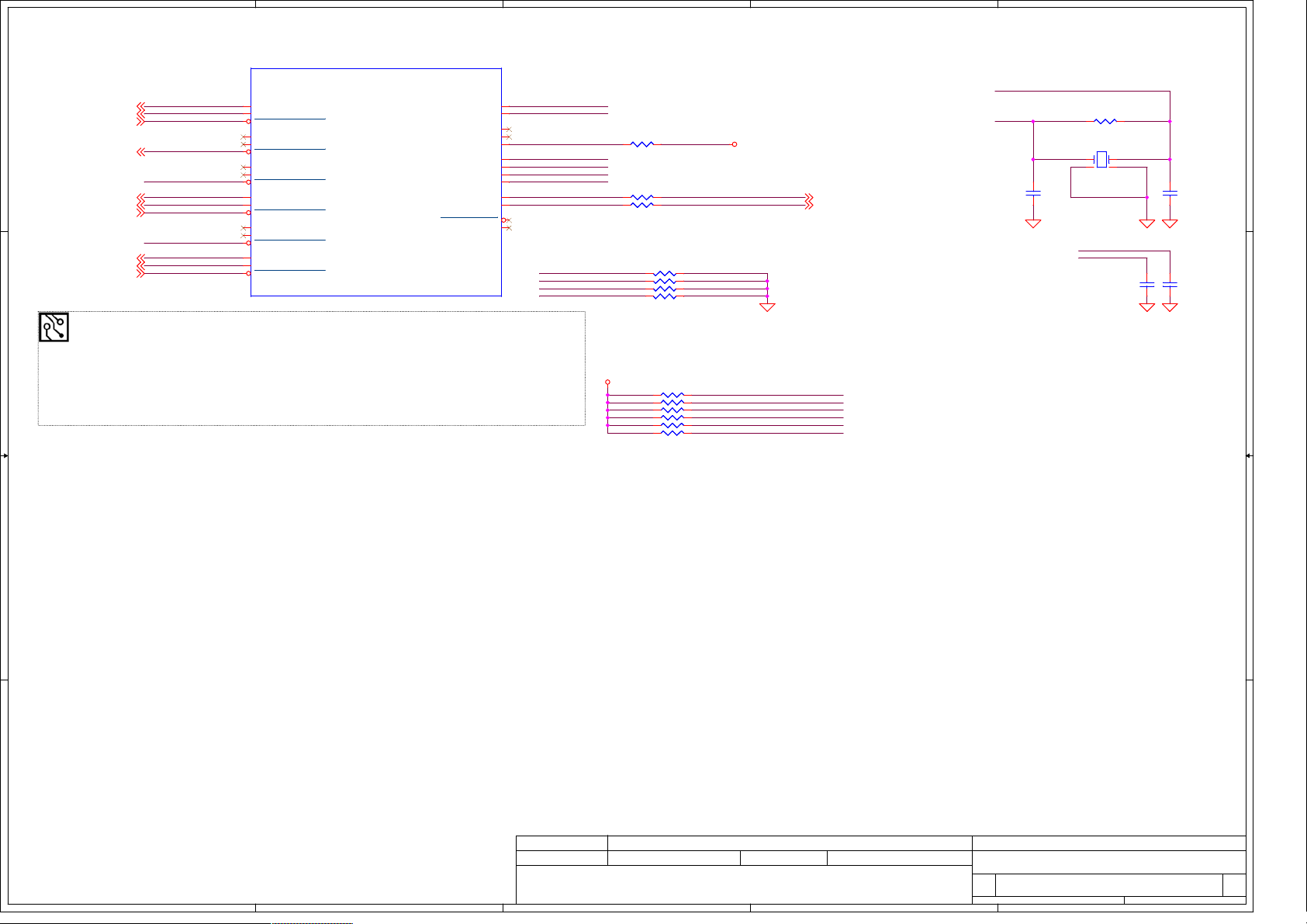

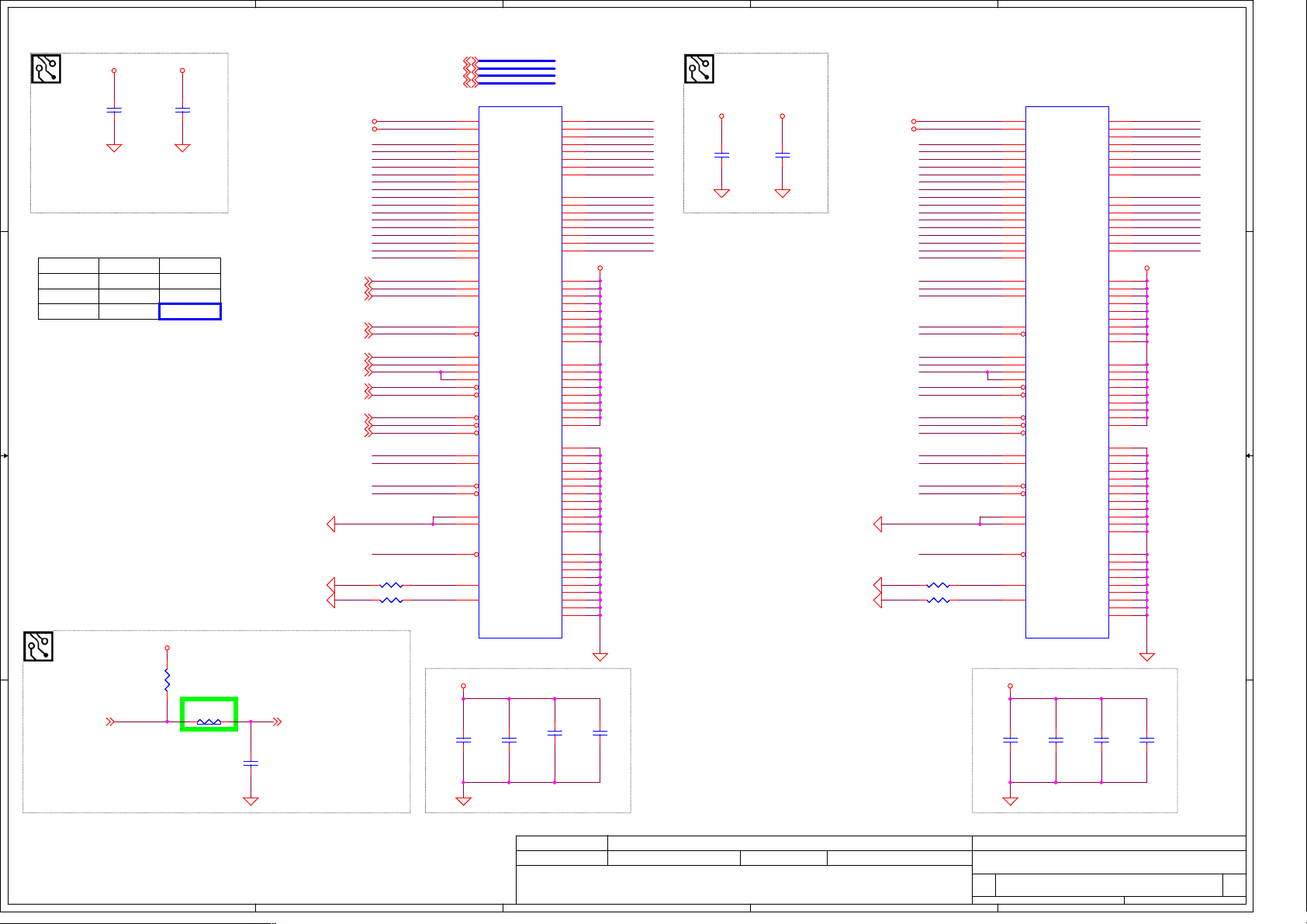

Page 2

A

www.vinafix.vn

B

C

D

E

eDP Panel

miniDP Conn.

1 1

USB 3.0 Conn.

Precision Touch Pad

Digital Camera

Touch Screen

P.22

P.26

P.30

P.35

P.22

P.22

Daughter/B (LS-B441P)

USB 3.0 Conn.

2 2

( Power Share)

CardReader

RTS5249

USB3.0

USB3.0 Re-Driver

eDP 1.3

DP 1.2

USB3.0/USB2.0

I2C / PS2

USB2.0

USB2.0

USB3.0

USB2.0

PCIE

Intel

Broadwell ULT

BGA 1168 Balls

15W TDP

Memory Bus (DDR3L-RS)

Dual Channel

1.35V DDR3L-RS 1600 MHz

SPI

SATA3 / PCIE *2

USB2.0

PCIE

UART

SDIO

Channel A

DDR3L-RS 4Gb or 8Gb (x16) * 4

P.15,16

Channel B

DDR3L-RS 4Gb or 8Gb (x16) * 4

P.17,18

SPI ROM

8MB

SPI ROM(vPRO)

4MB

TPM

AT97SC3205

M.2 Slot B Key-B

# mSATA

M.2 Slot A-SD

WLAN

BT

P.08

P.08

P.27

P.29

P.28

ALS/B (LS-B444P)

(Reserved ALS)

TCS3472

Reserved NFC

Module Conn

(Reserved SMLink)

P.29

3 3

Fan conn.

P.29

(Reserve ALS SM BUS)

RTC conn.

DC/DC Interface CKT.

Power Circuit DC/DC

4 4

LED/B (LS-B443P)

P.32~33

P.38~48

Front Side LED+DMICx2 Board

A

B

SMBus

ECE1117

LPC Bus

MEC 5085

BCBUS

Page 5 ~ 14

C

HDA / I2S

Audio Codec

ALC3263

P.36

I2C

MCP 23017

P.37

KBC/B (LS-B442P)

KSIO

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

Int.KBDKeyboard Controller

DMIC

Compal Secr et Data

Compal Secr et Data

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Headphone Jack

( iPhone & Nokia compatible)

P.24

Int. Speaker

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P02-Block Diagram

P02-Block Diagram

P02-Block Diagram

LA-B441P

LA-B441P

LA-B441P

E

P.25

P.25

250Saturday, October 04, 2014

250Saturday, October 04, 2014

250Saturday, October 04, 2014

1.0

1.0

1.0

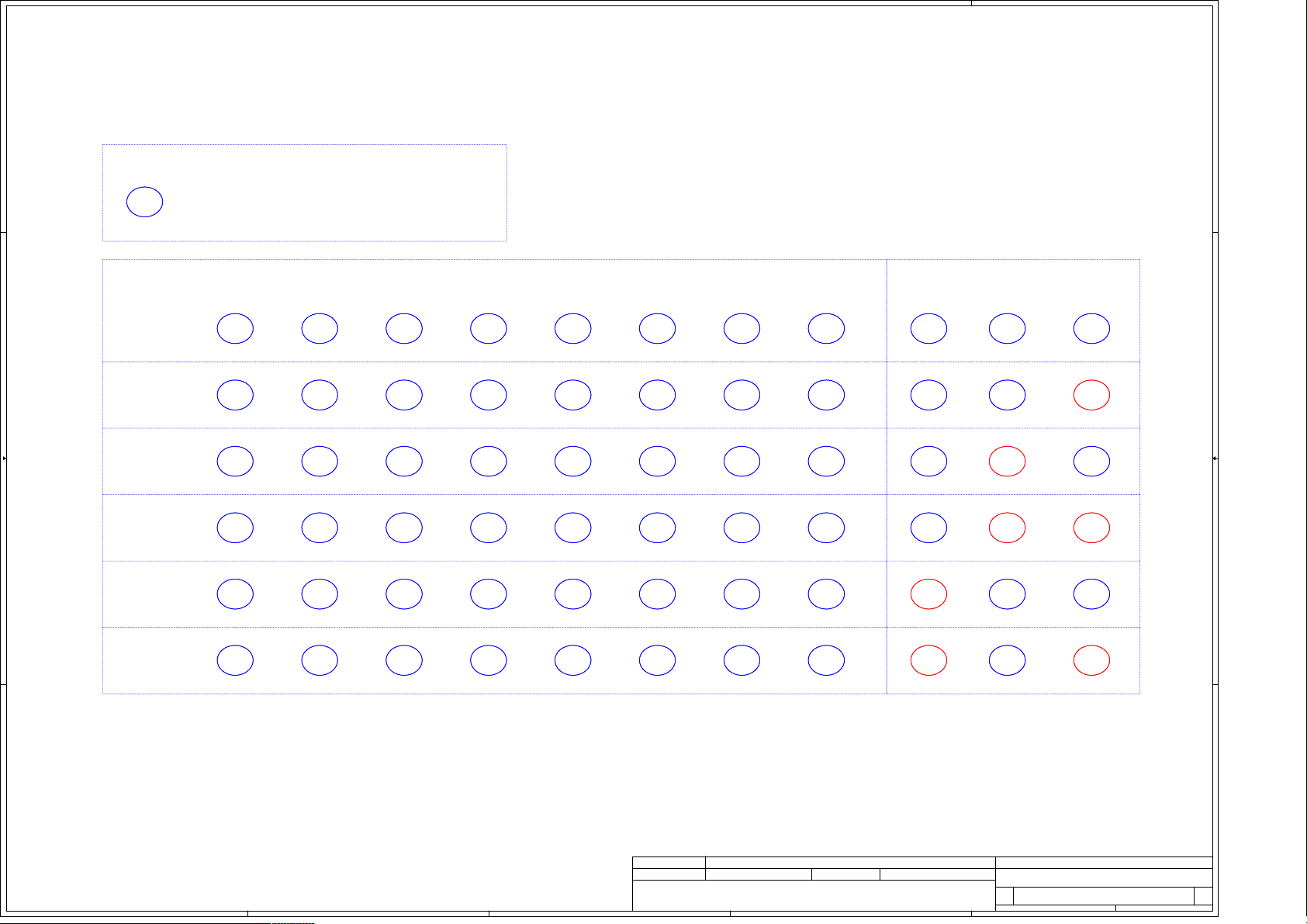

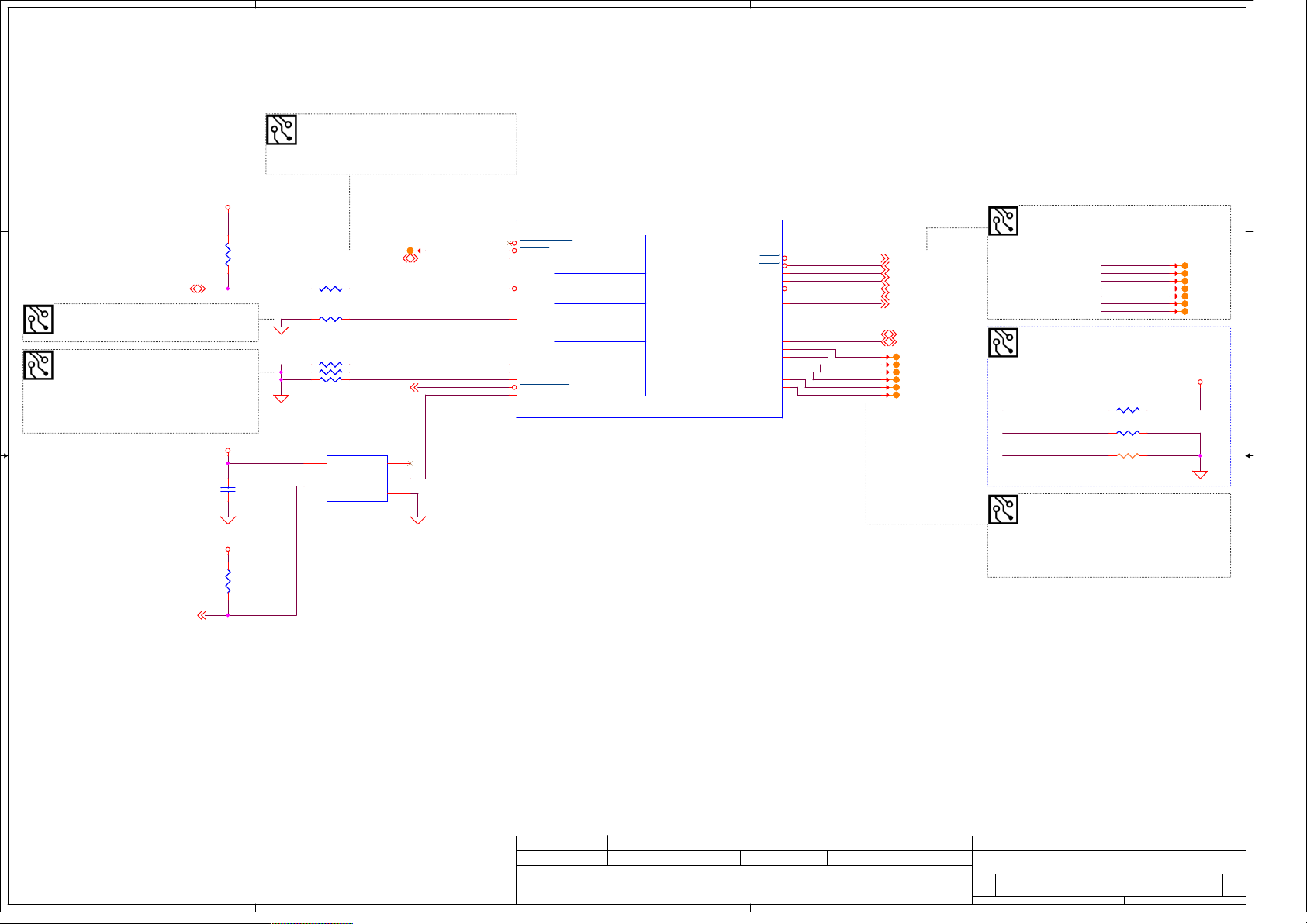

Page 3

A

1 1

B

C

D

E

CPU Option

UCPU1

BDW_TBD@

UCPU1

BDW_TBD@

SA00006G10L

SA00006G10L

CL8064701325204 QDJ9

CL8064701325204 QDJ9

DRAM Option DRAM Config Option

UD32

Micron_4G@

UD32

UD28

UD28

Micron_4G@

Micron_4G@

UD29

UD29

Micron_4G@

Micron_4G@

UD31

UD31

Micron_4G@

Micron_4G@

Micron_4G@

UD4

Micron_4G@

UD4

UD7

Micron_4G@

UD7

UD1

Micron_4G@

UD1

Micron_4G@

Micron_4G@

UD3

Micron_4G@

UD3

Micron_4G@

Micron_4G@

Micron 4G

SA00005TH0L

SA00005TH0L

2 2

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD28

Micron_8G@

UD28

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD29

Micron_8G@

UD29

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD31

Micron_8G@

UD31

Micron_8G@

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD32

Micron_8G@

UD32

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD1

Micron_8G@

UD1

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD7

Micron_8G@

UD7

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD3

Micron_8G@

UD3

Micron_8G@

SA00005TH0L

SA00005TH0L

MT41K256M16HA-125M:E

MT41K256M16HA-125M:E

UD4

Micron_8G@

UD4

Micron_8G@

Micron 8G

SA00006FB0L

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD28

Hynix_4G@

UD28

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD29

Hynix_4G@

UD29

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD31

Hynix_4G@

UD31

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD32

Hynix_4G@

UD32

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD1

Hynix_4G@

UD1

Hynix_4G@

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD7

Hynix_4G@

UD7

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD3

Hynix_4G@

UD3

Hynix_4G@

SA00006FB0L

SA00006FB0L

MT41K512M16TNA-125M:E

MT41K512M16TNA-125M:E

UD4

Hynix_4G@

UD4

Hynix_4G@

Hynix 4G

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD28

Hynix_8G@

UD28

Hynix_8G@

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD29

Hynix_8G@

UD29

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD31

Hynix_8G@

UD31

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD32

Hynix_8G@

UD32

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD1

Hynix_8G@

UD1

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD7

Hynix_8G@

UD7

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD3

Hynix_8G@

UD3

Hynix_8G@

SA00006JF0L

SA00006JF0L

H5TC4G63AFR-PBR

H5TC4G63AFR-PBR

UD4

Hynix_8G@

UD4

Hynix_8G@

SA00006JF0L

Hynix 8G

SA00006Q90L

SA00006Q90L

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

3 3

UD28

UD28

Elpida_4G@

Elpida_4G@

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD29

Elpida_4G@

UD29

Elpida_4G@

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD31

Elpida_4G@

UD31

Elpida_4G@

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD32

Elpida_4G@

UD32

Elpida_4G@

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD1

Elpida_4G@

UD1

Elpida_4G@

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD7

Elpida_4G@

UD7

Elpida_4G@

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD3

Elpida_4G@

UD3

Elpida_4G@

SA00006Q90L

SA00006Q90L

H5TC8G63AMR-PBR

H5TC8G63AMR-PBR

UD4

Elpida_4G@

UD4

Elpida_4G@

Elpida 4G

SA00005HT0L

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD28

Elpida_8G@

UD28

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD29

Elpida_8G@

UD29

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD31

Elpida_8G@

UD31

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD32

Elpida_8G@

UD32

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD1

Elpida_8G@

UD1

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD7

Elpida_8G@

UD7

Elpida_8G@

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD3

Elpida_8G@

UD3

Elpida_8G@

SA00005HT0L

SA00005HT0L

K4B4G1646B-HKK0

K4B4G1646B-HKK0

UD4

Elpida_8G@

UD4

Elpida_8G@

Elpida 8G

SA00006O90L

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

SA00006O90L

SA00006O90L

K4B8G1646B-MKK0

K4B8G1646B-MKK0

MEM_CONFIG2 MEM_CONFIG1 MEM_CONFIG0

RH316

Micron_4G@

RH316

RH314

Micron_4G@

RH314

Micron_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH314

Micron_8G@

RH314

Micron_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH314

Hynix_4G@

RH314

Hynix_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH314

Hynix_8G@

RH314

Hynix_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH271

Elpida_4G@

RH271

Elpida_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH271

Elpida_8G@

RH271

Elpida_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH315

Micron_4G@

RH315

Micron_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH315

Micron_8G@

RH315

Micron_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH180

Hynix_4G@

RH180

Hynix_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH180

Hynix_8G@

RH180

Hynix_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH315

Elpida_4G@

RH315

Elpida_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH315

Elpida_8G@

RH315

Elpida_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

Micron_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH303

Micron_8G@

RH303

Micron_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH316

Hynix_4G@

RH316

Hynix_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH303

Hynix_8G@

RH303

Hynix_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH316

Elpida_4G@

RH316

Elpida_4G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

RH303

Elpida_8G@

RH303

Elpida_8G@

SD028100280

SD028100280

10K_0402_5%~D

10K_0402_5%~D

4 4

LA-B441P

LA-B441P

LA-B441P

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

C

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secr et Data

Compal Secr et Data

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P03-BoM Option

P03-BoM Option

P03-BoM Option

E

350Saturday, October 04, 2014

350Saturday, October 04, 2014

350Saturday, October 04, 2014

1.0

1.0

1.0

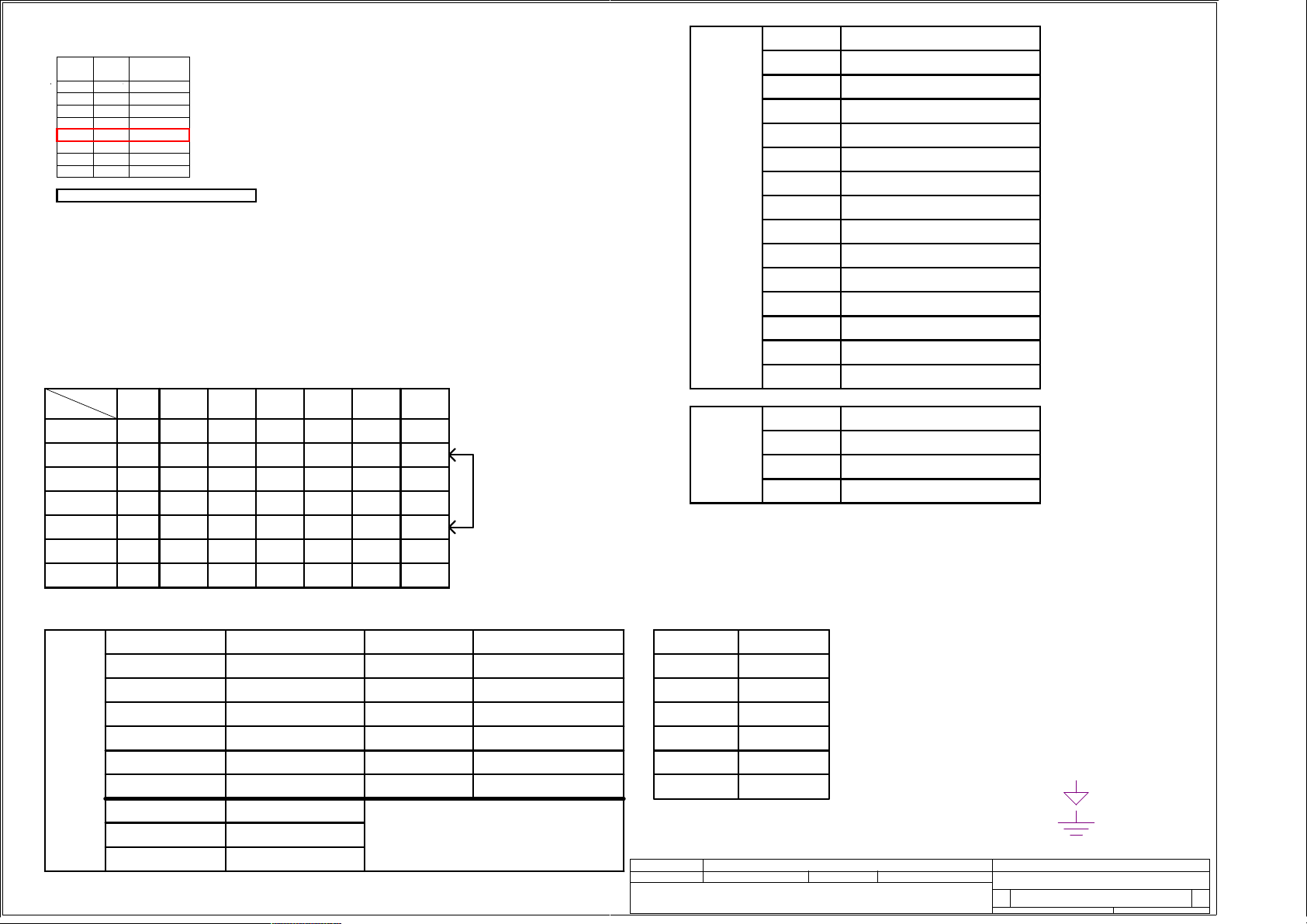

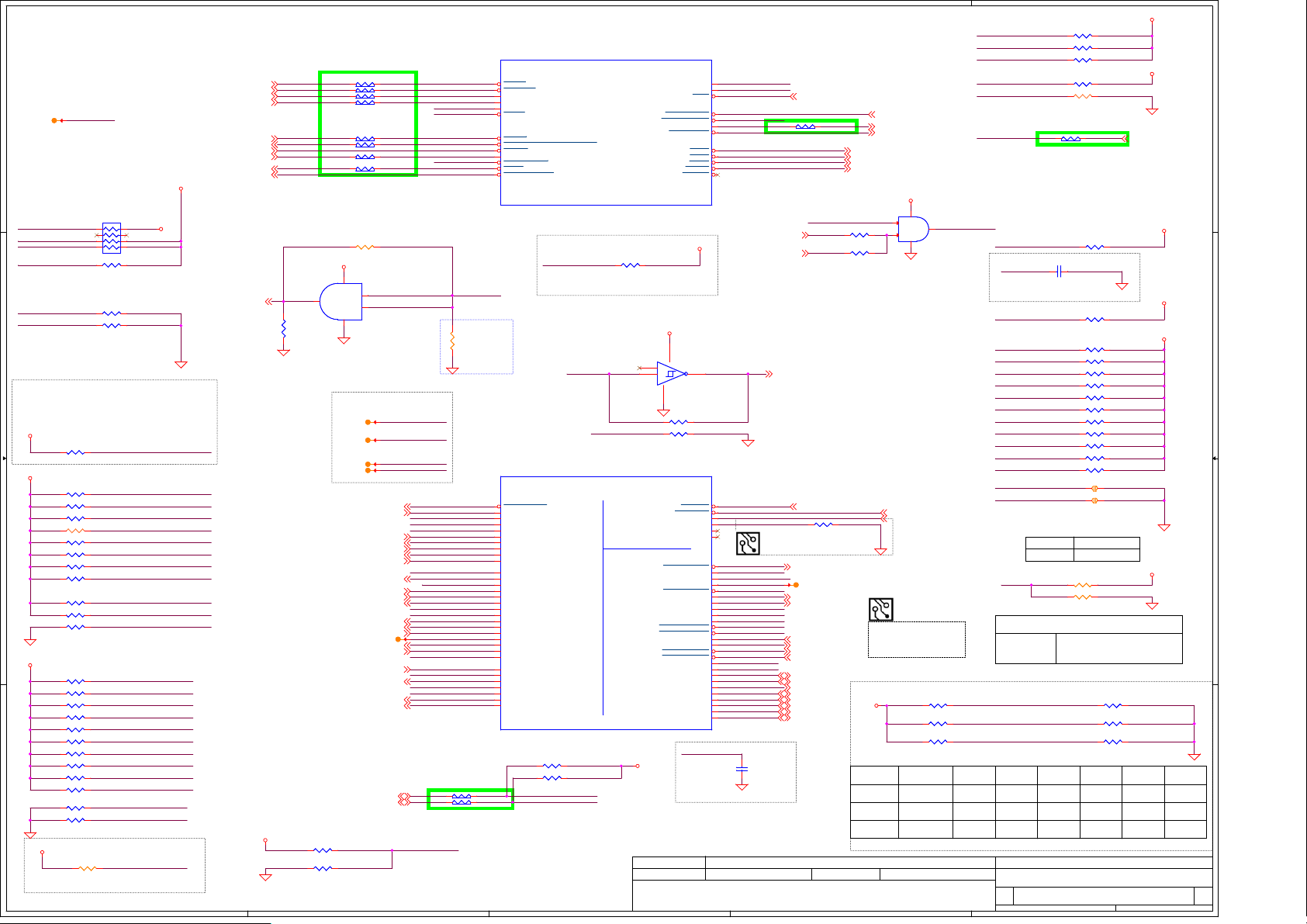

Page 4

A

Board ID Table for AD channel

X01

X03

X04

A00

REV

CE54RE79

4700p130K

4700p

62K X02

4700p

33K

4700p

8.2K

4700p4.3K

4700p

2K

1K

4700p

BOARD_ID rise time is measured from 5%~68%.

PCH

USB

Port

Mapping

USB PORT#

0

1

2

3

4

5

6

DESTINATION

External USB3(On IOB)

External USB3(On MB)

NGFF CARD WLAN

Touch Panel

Camera

7

SMBUS Control Table

SOURCE

I2C1C_CLK

I2C1C_DATA

1 1

I2C1D_CLK

I2C1D_DATA

I2C1G_CLK

I2C1G_DATA

PCH_SML0CLK PCH

PCH_SML0DATA

PCH_SML1CLK

PCH_SML1DATA

SMBCLK

SMBDATA

I2C1_DATA

MEC5085

MEC5085

MEC5085

PCH

PCH

PCHI2C1_CLK

BATTERY

V

Reserve ALS SMBUS

ALS

V

NFCCharger

XDP

Touch Pad

PCH

DDI

Port

V

Link

Mapping

DDI PORT# DESTINATION

1

mini-DP

2

V

V

V

CLK

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

FLEX CLK#

CLKOUT_LPC_0

CLKOUT_LPC_1

DESTINATIONDIFFERENTIAL CLK#

Card Reader

NGFF CARD WLAN

mSATA/ PCIe

DESTINATION

EC LPC

TPM

PCI EXPRESS PORT#

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

DESTINATION

Card Reader

NGFF CARD WLAN

mSATA/ PCIe(Port0+Port1)

SATA PORT#

DESTINATION

SATA0

SATA1

SATA2

SATA3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

A

m-SATA

Compal Secr et Data

Compal Secr et Data

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

Symbol Note :

: means Digital Ground

: means Analog Ground

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P04-Notes List

P04-Notes List

P04-Notes List

LA-B441P

LA-B441P

LA-B441P

450Saturday, October 04, 2014

450Saturday, October 04, 2014

450Saturday, October 04, 2014

1.0

1.0

1.0

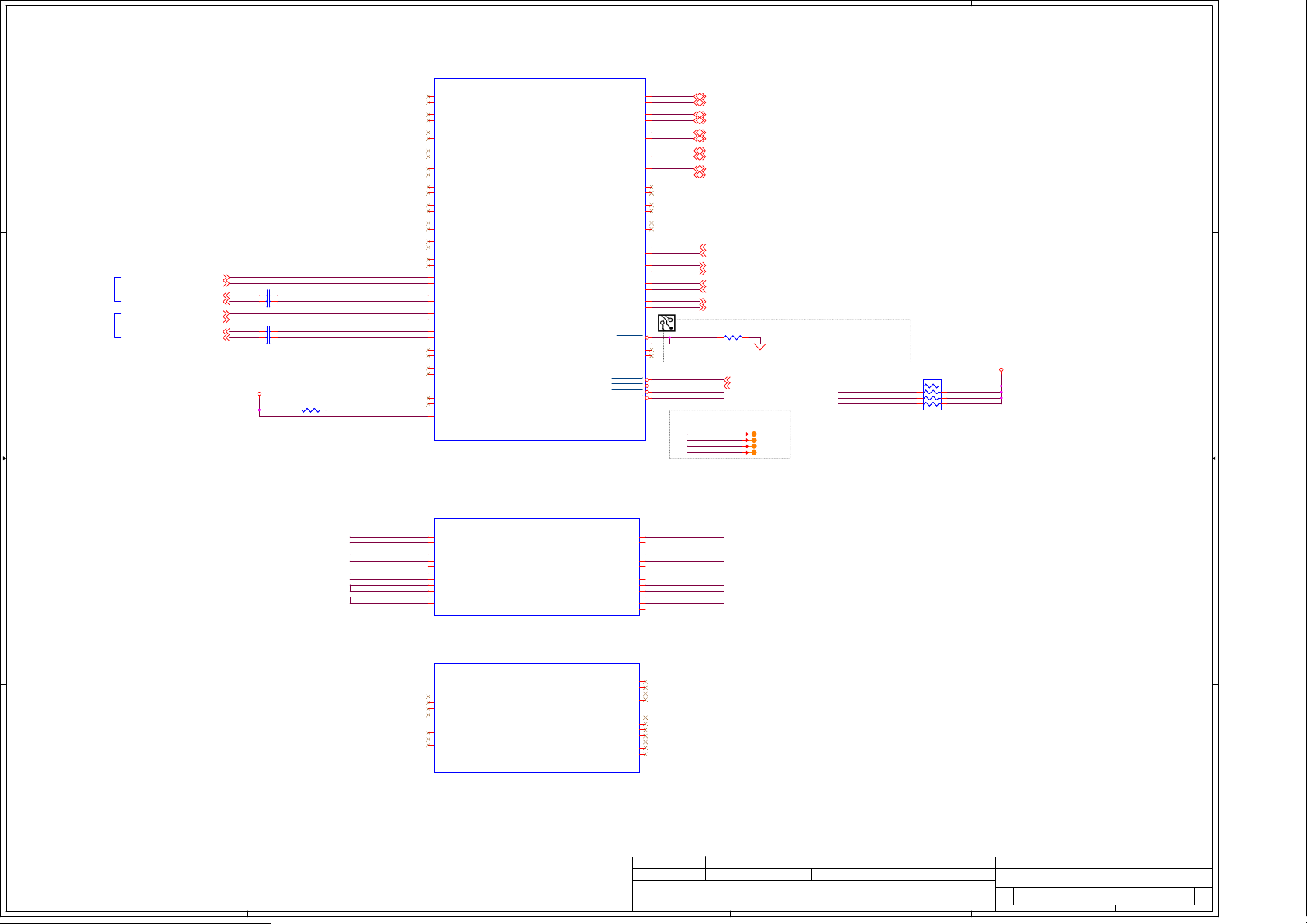

Page 5

5

D D

DP Port

PCH_DP_N0[26]

PCH_DP_P0[26]

PCH_DP_N1[26]

PCH_DP_P1[26]

PCH_DP_N2[26]

PCH_DP_P2[26]

PCH_DP_N3[26]

PCH_DP_P3[26]

C C

4

BDW_ULT_DDR3L

BDW_ULT_DDR3L

BDW_ULT_DDR3L

BDW_ULT_DDR3L

C54

C55

C58

C51

C50

C53

C49

B58

B55

A55

A57

B57

B54

B50

A53

B53

UCPU1A@

UCPU1A@

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

UCPU1I@

UCPU1I@

1 OF 19

1 OF 19

3

C45

EDP_TXN0

B46

EDP_TXP0

A47

EDP_TXN1

B47

EDP_TXP1

C47

EDP_TXN2

C46

EDP_TXP2

A49

EDPDDI

EDPDDI

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

B49

A45

B45

D20

A43

EDP_COM

EDP_DISP

eDP_TXN_P0 [22]

eDP_TXP_P0 [22]

eDP_TXN_P1 [22]

eDP_TXP_P1 [22]

eDP_TXN_P2 [22]

eDP_TXP_P2 [22]

eDP_TXN_P3 [22]

eDP_TXP_P3 [22]

eDP_AUXN [22]

eDP_AUXP [22]

1 2

RC36 24.9_0402_1%RC36 24.9_0402_1%

EDP_COM

Width 20 mils, Spacing 25 mils,

Length < 100 mil

2

+VCCIOA_OUT

1

Low voltage multipurpose DISP_UTIL pin on the

processor for backlight modulation control of

embedded panels and S3D device control for active

shutter glasses. This pin will co-exist with

functionality similar to existing BKLTCTL pin on the

PCH.

A00_1004: Change to short pad.

RC147

RC147

0_0402_1%

0_0402_1%

EDP_BKLCTL

EDP_DISP

12

@

@

RC146

RC146

0_0402_5%~D

0_0402_5%~D

@

@

1 2

RC158

RC158

0_0402_5%~D

0_0402_5%~D

@

@

1 2

EDP_BIA_PWM [22]

EDP_HPD

Compal Secret Data

Compal Secret Data

Compal Secret Data

B9

PCH_DP_CLK

C9

PCH_DP_DAT

D9

D11

C5

B6

B5

A6

C8

PCH_DP_HPD

A8

D6

CPU_EDP_HPD

Enable : Pull up to 3.3V with 2.2K+-5% ohm

Disable : No connect

Enable : Pull up to 3.3V with 2.2K+-5% ohm

Disable : No connect

Deciphered Date

Deciphered Date

Deciphered Date

PCH_DP_CLK [26]

PCH_DP_DAT [26]

PCH_DP_AUXN [26]

PCH_DP_AUXP [26]

PCH_DP_HPD [26]

PCH_DP_HPD

+5VS

G

G

2

D

S

D

S

RC148

RC148

0_0402_1%

CPU_EDP_HPD

Title

Title

Title

P05-MCP(1/10) DDI,EDP

P05-MCP(1/10) DDI,EDP

P05-MCP(1/10) DDI,EDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-B441P

LA-B441P

LA-B441P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

0_0402_1%

@

@

12

A00_1004: Change to short pad.

RC160

RC160

100K_0402_5%~D

100K_0402_5%~D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

12

QC5

@

QC5

@

DII-DMN65D8LW-7~D

DII-DMN65D8LW-7~D

13

12

1

RH300100K_0402_5%~D RH300100K_0402_5%~D

EDP_HPD [22]

550Sunday, October 05, 2014

550Sunday, October 05, 2014

550Sunday, October 05, 2014

1.0

1.0

1.0

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

9 OF 19

9 OF 19

DISPLAY

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

PANEL_BKLEN[22]

ENVDD_PCH[32,36]

@

DZ3

DZ3

RB751S40T1G_SOD523-2

RB751S40T1G_SOD523-2

PTP_INT#[35,36]

B B

1 2

T123@T123

SDIO_WAKE#[28]

CODEC_IRQ[24]

EDP_BKLCTL

PCH_GPIO77

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

TOUCHPAD _INTR#

TOUCH_R ST_N_GYRO_IN T1

SDIO_WAKE#

PCH_GPIO51

CODEC_IRQ

GPIO Signals

+3VS

RP4

RP4

1 8

2 7

3 6

4 5

10K_8P4R_5%

10K_8P4R_5%

1 2

RH3547 10K_0402_5%~DRH3547 10K_0402_5%~D

1 2

RH3545 10K_0402_5%~DRH3545 10K_0402_5%~D

1 2

RH397 10K_0402_5%~DRH397 10K_0402_5%~D

1 2

RH3532 10K_0402_5%~D@RH3532 10K_0402_5%~D@

1 2

A A

RH3544 10K_0402_5%~D@RH3544 10K_0402_5%~D@

5

PCH_GPIO79

PCH_GPIO80

TOUCHPAD _INTR# PCH_DP_CLK

PCH_GPIO78

PCH_GPIO77

TOUCH_R ST_N_GYRO_IN T1

SDIO_WAKE#

CODEC_IRQ

PCH_GPIO51

4

+3VS

RP14

RP14

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

Security Classifi cation

Security Classifi cation

Security Classifi cation

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Issued Date

Issued Date

PCH_DP_DAT

Functional Strap Definitions

DDI Port 1 Disabling

DDPB_CTRLDATA

Functional Strap Definitions

DDI Port 2 Disabling

DDPC_CTRLDATA

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

3

Page 6

5

4

3

2

1

D D

+1.05VS_VCCST

12

RC43

RC43

62_0402_5%~D

62_0402_5%~D

H_PROCHOT#[36,39,40,42,47]

Avoid stub in the PWRGD path

while placing resistors RC44 & RC53

C C

SM_RCOMP

1. Total Width : 12-15 mils.

2. Min Trace spacing for Group : 20 mils

3. Min Trace spacing for Group to Group :25

mils

4. Max Length : 500 mils

+1.35V_DDR

1

@

@

CC240

CC240

0.1U_0402_10V7K

0.1U_0402_10V7K

2

+3VALW

B B

12

RC161

RC161

220K_0402_5%~D

220K_0402_5%~D

H_PECI

1. Total Length : 15 inchs

2. Resistor Value (±5%) : 43 ohm

3. Breakin/Breakout Length Max :0.4 ~ 1 inchs

1

2

3

H_CATERR#

H_PROCHOT#_RH_PROCHOT#

H_CPUPWRGD_R

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

T2@T2@

PECI_EC[36]

1 2

RC41 56_0402_5%RC41 56_0402_5%

1 2

RC44 10K_0402_5%~DRC44 10K_0402_5%~D

1 2

RC55 200_0402_1%~DRC55 200_0402_1%~D

1 2

RC58 121_0402_1%~DRC58 121_0402_1%~D

1 2

RC60 100_0402_1%~DRC60 100_0402_1%~D

H_DRAMRST#[15]

UC1

UC1

5

4

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

VCC

Y

NC

GND

A

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

UCPU1B@

UCPU1B@

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

BDW_ULT_DDR3L

BDW_ULT_DDR3L

JTAG

JTAG

2 OF 19

2 OF 19

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

XDP_PRD Y#

K62

XDP_PRE Q#

E60

CPU_XDP_TCK

E61

CPU_XDP_TMS

E59

CPU_XDP_TRST#

F63

CPU_XDP_TDI

F62

CPU_XDP_TDO

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PRD Y# [20]

XDP_PRE Q# [20]

CPU_XDP_TCK [20]

CPU_XDP_TMS [20]

CPU_XDP_TRST# [20]

CPU_XDP_TDI [20]

CPU_XDP_TDO [20]

XDP_BPM0 # [20]

XDP_BPM1 # [20]

T226@T22 6@

T227@T22 7@

T228@T22 8@

T229@T22 9@

T230@T23 0@

T231@T23 1@

Place a test point pad to within 250 ps of the

ROC_TCK pin.and the maximum distance of

test point pad to the termination must not

be over 200 ps.

The Pull Up/Pull down terminations

(R1d,R2,R9) should be placed to within 200 ps

(1100 mils) of respective Broadwell pins.

CPU_XDP_TDO

CPU_XDP_TCK

CPU_XDP_TRST#

BPM

1. Length match these signals within 360 mils.

2. Stubs on these nets should be limited to less

than 1400 mils (35.5 mm) in length.

3. Routing Recommendation :1-6 inchs

4. Impedance : 50 ohm.

XDP_PRD Y#

XDP_PRE Q#

CPU_XDP_TCK

CPU_XDP_TMS

CPU_XDP_TRST#

CPU_XDP_TDI

CPU_XDP_TDO

R1d

R2

R9

12

12

12

RC48 51_0402_5%RC48 51_0402_5%

RC52 51_0402_5%RC52 51_0402_5%

RC54 51_0402_5%@ RC54 51_0402_5%@

T263@T26 3@

T264@T26 4@

T265@T26 5@

T266@T26 6@

T267@T26 7@

T268@T26 8@

T269@T26 9@

+1.05VS_VCCST

SM_PG_CTRL[46]

A A

Security Classifi cation

Security Classifi cation

Security Classifi cation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P06-MCP(2/10) PM,XDP

P06-MCP(2/10) PM,XDP

P06-MCP(2/10) PM,XDP

LA-B441P

LA-B441P

LA-B441P

1

1.0

1.0

650Saturday, October 04, 2014

650Saturday, October 04, 2014

650Saturday, October 04, 2014

1.0

Page 7

5

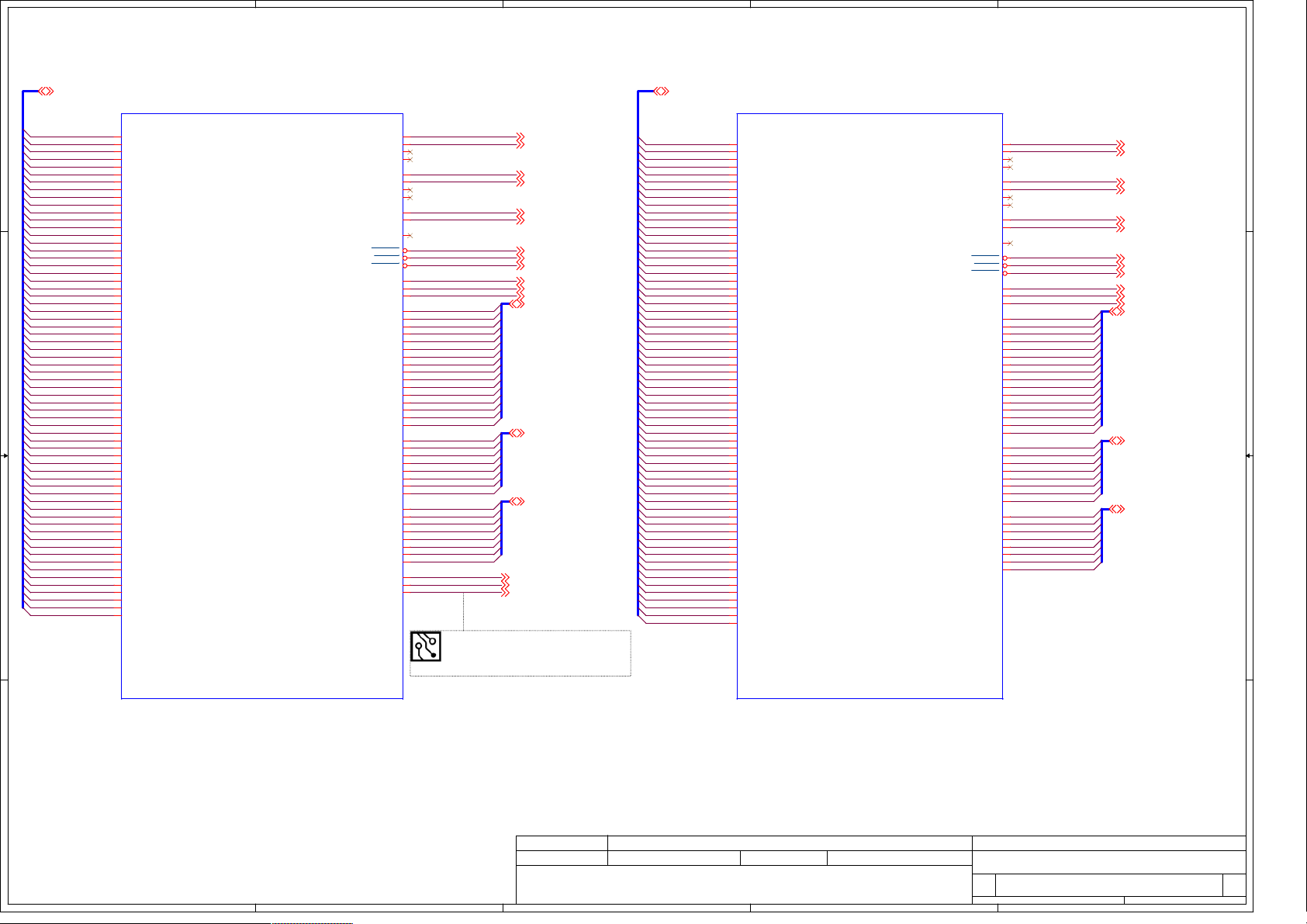

DDR_A_D[0..63] [15,16] DDR_B_D[0..63] [17,18]

BDW_ULT_DDR3L

UCPU1C@

D D

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

C C

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

B B

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

UCPU1C@

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

BDW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

3 OF 19

4

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

DDR_A_MA0

AY37

DDR_A_MA1

AR38

DDR_A_MA2

AP36

DDR_A_MA3

AU39

DDR_A_MA4

AR36

DDR_A_MA5

AV40

DDR_A_MA6

AW39

DDR_A_MA7

AY39

DDR_A_MA8

AU40

DDR_A_MA9

AP35

DDR_A_MA10

AW41

DDR_A_MA11

AU41

DDR_A_MA12

AR35

DDR_A_MA13

AV42

DDR_A_MA14

AU42

DDR_A_MA15

AJ61

DDR_A_DQS#0

AN62

DDR_A_DQS#1

AM58

DDR_A_DQS#2

AM55

DDR_A_DQS#3

AV57

DDR_A_DQS#4

AV53

DDR_A_DQS#5

AL43

DDR_A_DQS#6

AL48

DDR_A_DQS#7

AJ62

DDR_A_DQS0

AN61

DDR_A_DQS1

AN58

DDR_A_DQS2

AN55

DDR_A_DQS3

AW57

DDR_A_DQS4

AW53

DDR_A_DQS5

AL42

DDR_A_DQS6

AL49

DDR_A_DQS7

AP49

AR51

AP51

at least 20 mils wide with 20 mils spacing to

other signals/planes. Short violations are

acceptable if required due to tight routing

constraints.

M_CLK_A_ DDR#0 [1 5,16,19]

M_CLK_A_ DDR0 [15 ,16,19]

DDR_A_CKE0 [15,16,19]

DDR_A_CKE1 [15,16,19]

DDR_A_CS0# [15,16,19]

DDR_A_RAS# [15,16,19]

DDR_A_WE# [15,16,19]

DDR_A_CAS# [15,16,19]

DDR_A_BA0 [15,16,19]

DDR_A_BA1 [15,16,19]

DDR_A_BA2 [15,16,19]

DDR_A_MA[0..15] [15,16,19]

DDR_A_DQS#[0..7] [15,16]

DDR_A_DQS[0..7] [15,16]

V_DDR_REF_CA [19]

V_DDR_REF_DQA [19]

V_DDR_REF_DQB [19]

3

UCPU1D@

UCPU1D@

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

2

BDW_ULT_DDR3L

BDW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

1

M_CLK_B _DDR#0 [1 7,18,19]

M_CLK_B _DDR0 [17 ,18,19]

DDR_B_CKE0 [17,18,19]

DDR_B_CKE1 [17,18,19]

DDR_B_CS0# [17,18,19]DDR_A_CS1# [15,16,19]

DDR_B_CS1# [17,18,19]

DDR_B_RAS# [17,18,19]

DDR_B_WE# [17,18,19]

DDR_B_CAS# [17,18,19]

DDR_B_BA0 [17,18,19]

DDR_B_BA1 [17,18,19]

DDR_B_BA2 [17,18,19]

DDR_B_MA[0..15] [17,18,19]

DDR_B_DQS#[0..7] [17,18]

DDR_B_DQS[0..7] [17,18]

A A

Security Classifi cation

Security Classifi cation

Security Classifi cation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P07-MCP(3/10) DDRIII

P07-MCP(3/10) DDRIII

P07-MCP(3/10) DDRIII

LA-B441P

LA-B441P

LA-B441P

1

1.0

1.0

750Saturday, October 04, 2014

750Saturday, October 04, 2014

750Saturday, October 04, 2014

1.0

Page 8

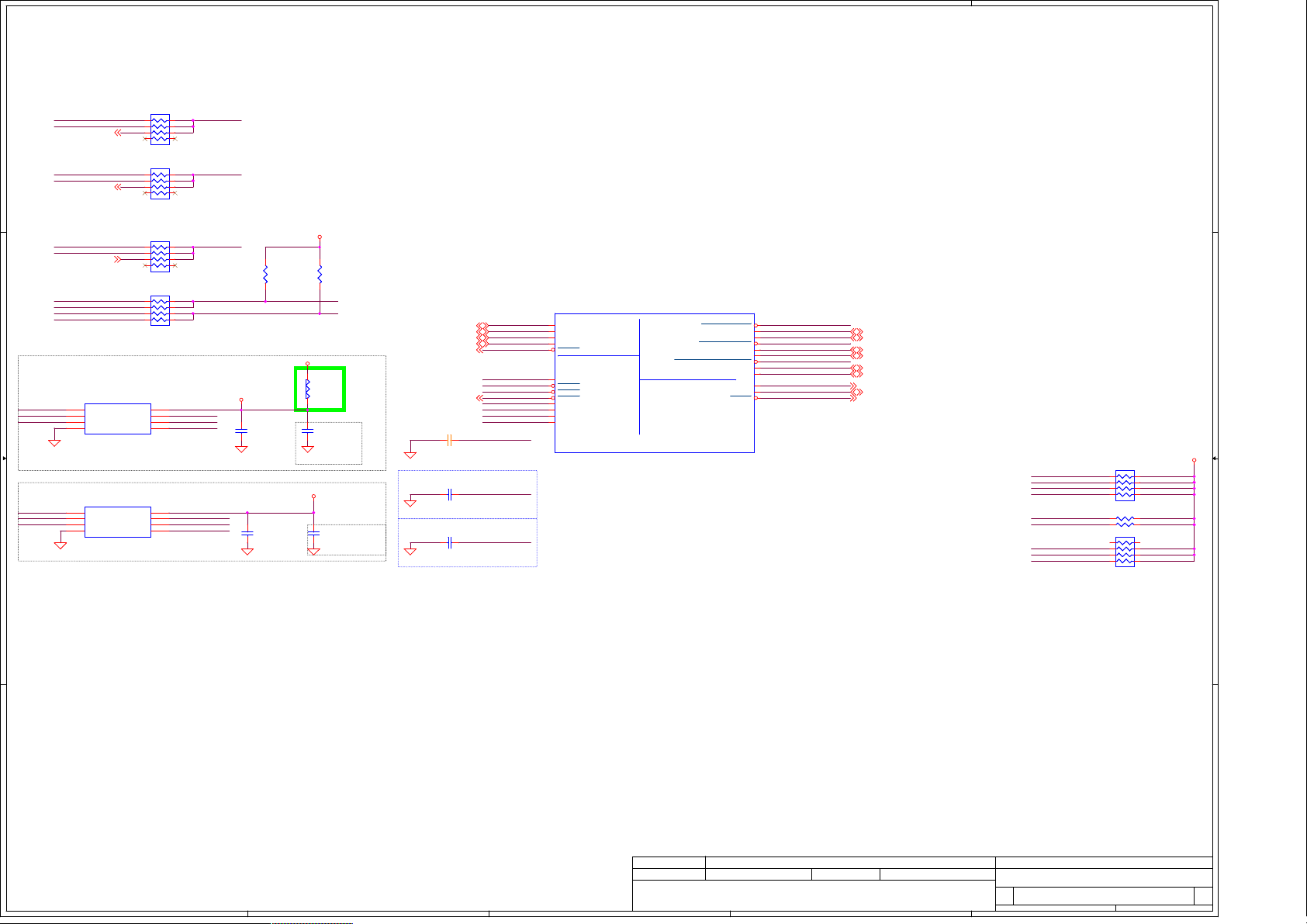

5

RP5

RP5

D D

SPI_CLK_VROM

PCH_SPI_CLK_TPM[27]

SPI_SI_VROM

PCH_SPI_SI_TPM[27]

1 8

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

1 8

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

PCH_SPI_CLKSPI_CLK_ROM

RP6

RP6

PCH_SPI_SISPI_SI_ROM

4

3

2

1

12

RH55

RH55

1K_0402_5%~D

1K_0402_5%~D

+3.3V_M

12

RH57

RH57

1K_0402_5%~D

1K_0402_5%~D

+3.3V_M

12

RH3527

RH3527

@0_0603_5%

@0_0603_5%

1

EMI@

EMI@

CH1245

CH1245

15P_0402_50V8J

15P_0402_50V8J

2

RF Reserved.

+3V_ROM

1

vpro@

vpro@

CH1249

CH1249

15P_0402_50V8J

15P_0402_50V8J

2

RF Reserved.

LPC_AD0[36]

LPC_AD1[36]

LPC_AD2[36]

LPC_AD3[36]

LPC_FRAME#[36]

A00_1004: Change to short pad.

PCH_SPI_CS2#[27]

MC29

@MC29

@

1 2

12P_0402_50V8J~D

12P_0402_50V8J~D

EMI@

EMI@

MC30

MC30

12

22P_0402_50V8J~D

22P_0402_50V8J~D

Reserve for EMI please close to U48

@

@

MC32

MC32

12

22P_0402_50V8J~D

22P_0402_50V8J~D

Reserve for EMI please close to U727

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CLK

SPI_CLK_ROM

SPI_CLK_VROM

AU14

AW12

AY12

AW11

AV12

BDW_ULT_DDR3L

UCPU1G@

UCPU1G@

LAD0

LAD1

LAD2

LAD3

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

BDW_ULT_DDR3L

LPC

LPC

SMBUS

SMBUS

SML1ALERT/PCHHOT /GPIO73

C-LINKSPI

C-LINKSPI

SMBALERT/GPIO11

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_DATA

7 OF 19

7 OF 19

SMBCLK

CL_CLK

CL_RST

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

PCH_SMB_ALERT#

PCH_SMBCLK

PCH_SMBDATA

PCH_SML0ALERT

SML0CLK

SML0DATA

PCH_GPIO73

SML1_SMBCLK

SML1_SMBDAT

PCH_SMBCLK [20]

PCH_SMBDATA [20]

SML0CLK [29]

SML0DATA [29]

SML1_SMBCLK [36]

SML1_SMBDAT [36]

CL_CK [28]

CL_DAT [28]

CL_RST# [28]

Connect XDP

Connect NFC

Connect EC

PCH_SMBCLK

PCH_SMBDATA

SML1_SMBCLK

SML1_SMBDAT

SML0CLK

SML0DATA

PCH_SMB_ALERT#

PCH_SML0ALERT

PCH_GPIO73

RP2

RP2

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

1 2

RH70 499_0402_1%~DRH70 499_0402_1%~D

1 2

RH72 499_0402_1%~DRH72 499_0402_1%~D

RP16

RP16

1 8

2 7

3 6

4 5

10K_8P4R_5%

10K_8P4R_5%

+3V_PCH

RP7

RP7

1 8

SPI_SO_VROM

PCH_SPI_SO_TPM[27]

SPI_IO3_VROM

SPI_IO3_ROM

SPI_IO2_VROM

C C

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

1 8

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

PCH_SPI_SOSPI_SO_ROM

RP8

RP8

PCH_SPI_IO3

PCH_SPI_IO2SPI_IO2_ROM

SPI ROM FOR ME ( 8MByte )

U48

U48

PCH_SPI_CS0#

SPI_SO_ROM

4MB SPI ROM for Vpro

PCH_SPI_CS1#

SPI_SO_VROM

SPI_IO2_VROM

B B

1

/CS

2

DO(IO1)

3

/WP(IO2)

GND4DI(IO0)

W25Q64FVSSIQ_SO8

W25Q64FVSSIQ_SO8

U727

vpro@U727

vpro@

1

/CS

2

DO/IO1

3

/WP/IO2

4

GND

W25Q32FVSSIQ_SO8

W25Q32FVSSIQ_SO8

/HOLD(IO3)

/HOLD/IO3

DI/IO0

8

VCC

7

SPI_IO3_ROM

6

SPI_CLK_ROMSPI_IO2_ROM

CLK

5

SPI_SI_ROM

8

VCC

7

SPI_IO3_VROM

6

SPI_CLK_VROM

CLK

5

SPI_SI_VROM

+3V_ROM

1

CH6

CH6

.1U_0402_16V7K~D

.1U_0402_16V7K~D

2

vpro@

vpro@

1

CH7

CH7

.1U_0402_16V7K~D

.1U_0402_16V7K~D

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRONI CS, INC.

3

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secr et Data

Compal Secr et Data

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P08-MCP(4/10) LPC,SPI,SMBUS,CL

P08-MCP(4/10) LPC,SPI,SMBUS,CL

P08-MCP(4/10) LPC,SPI,SMBUS,CL

LA-B441P

LA-B441P

LA-B441P

1

850Sunday, October 05, 2014

850Sunday, October 05, 2014

850Sunday, October 05, 2014

1.0

1.0

1.0

Page 9

5

4

3

2

1

RTCX1 RTCX2

1. Total Length : 1000 mils

2. Space > 15 mils

3. Resistor Value (±5%) : 10M

RH2

RH2

10M_0402_5%

10M_0402_5%

D D

C C

1 2

YH1

YH1

32.768KHZ_X1A000141000300

32.768KHZ_X1A000141000300

1 2

1

Max Crystal ESR

= 50k Ohm.

CH2

CH2

15P_0402_50V8J~D

15P_0402_50V8J~D

2

HDA_SDIN/HDA_SDO/HDA_SYNC/HDA_BCLK/HDA_RST#

1. BO < 500 mils

2. 1000 mils < M1 < 14000 mils.

3. Trace Length Matching

(HDA_SDIO,HDA_BCLK,HDA_SDOUT)

4. Resistor Value : 33 ohm

I2S_RST_ AUDIO#[24]

I2S_BITCL K_AUDIO[24]

I2S_SDO UT_AUDIO[24]

I2S_SYNC _AUDIO[24]

PCH_RTCX1

PCH_RTCX2

1

CH3

CH3

15P_0402_50V8J~D

15P_0402_50V8J~D

2

RP15

RP15

1 8

2 7

3 6

4 5

33_8P4R_5%

33_8P4R_5%

B0M1

I2S_RST#

I2S_BIT_C LK

I2S_SDO UT

I2S_SYNC

RF Reserved.

I2S_BIT_C LK

1

EMI@

EMI@

CH1242

CH1242

15P_0402_50V8J

15P_0402_50V8J

2

B B

+3VS_AUDIO

12

@

@

RH42

RH42

1K_0402_5%~D

1K_0402_5%~D

I2S_SDO UT

+RTCVCC

12

RH31

RH31

330K_0402_5%~D

330K_0402_5%~D

A A

PCH_INTVRMEN

12

RH34

RH34

330K_0402_5%~D

330K_0402_5%~D

@

@

I2S_SDO UT

12

EMI@

EMI@

MC31

MC31

10P_0402_50V8J~D

10P_0402_50V8J~D

+1.05V_M

Functional Strap Definitions

Flash Descriptor Security Override

HDA_SDO/

I2S0_TXD

INTRUDER#

1. Critical Low Speed Signal

2. Space > 15 mils

3. Frequency to Avoid 32K

4. All critical signals must stay away from potential glitch or noise sources on the

platform.

0 = Enable security measures defined in the Flash Descriptor.

1 = Disable Flash Descriptor Security (override). This strap

should only be asserted high using external pull-up in

manufacturing/debug environments ONLY.

Functional Strap Definitions

Integrated VRM

INTVRMEN

5

0 = DCPSUS1, DCPSUS2, DCPSUS3 and DCPSUS4 are powered

from an external power source (should be connected to an

external VRM).

1 = Integrated VRMs enabled. DCPSUS1, DCPSUS2 and

DCPSUS3 can be left as No Connect.

INTRUDER#

1. Critical Low Speed Signal

2. Space > 15 mils

3. Frequency to Avoid 32K

4. All critical signals must stay away from

potential glitch or noise sources on the

platform.

+RTCVCC

12

RH11

RH11

1M_0402_5%~D

1M_0402_5%~D

SM_INTRUDER#

PCH JTAG

The Pull Up/Pull down terminations

(R4,R3d,R5) should be placed to within 200ps

of the respective Broadwell pin.

R4

1 2

RH40 51_0402_5%RH40 51_0402_5%

R3d

1 2

RH445 51_0402_5%RH445 51_0402_5%

R5

1 2

RH39 51_0402_5%RH39 51_0402_5%

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

4

ME Reset

SRTCRST#

1. Total Length : 8000 mils

2. Space > 15 mils

3. Impedance Target 50 Ω ±15% for Microstrip.

4. RC time delay between 18 ms - 25 ms must be met.

5. There must not be a jumper for SRTCRST# pin.

+RTCVCC +RTCVCC

12

RH23

RH23

20K_0402_5%~D

20K_0402_5%~D

PCH_SRTCRST# PCH_RTCRST#

1

CH5

CH5

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

2

UCPU1E

UCPU1E

PCH_RTCX1

PCH_RTCX2

SM_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST#

PCH_JTAG_JTAGX

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TCK

PCH_JTAG_TDI

Issued Date

Issued Date

Issued Date

PCH_RTCRST#

I2S_BIT_C LK

I2S_SYNC

I2S_RST#

I2S_SDO UT

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_JTAGX

PCH_RTCRST#[21]

I2S_SDIN 0[24]

I2S_SDO UT[21]

PCH_JTAG_TRST#[20]

PCH_JTAG_TCK[20]

PCH_JTAG_TDI[20]

PCH_JTAG_TDO[20]

PCH_JTAG_TMS[20]

PCH_JTAG_JTAGX[20]

TP should be placed to with

250ps (1380 mils) of the

respetive Haswell ULT pins,

and the distance between TP

and termination (if any) must

be within 200ps (1100 mils).

T273@T27 3@

T275@T27 5@

T276@T27 6@

T277@T27 7@

T278@T27 8@

Security Classifi cation

Security Classifi cation

Security Classifi cation

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

AW5

RTCX1

AY5

RTCX2

AU6

INTR UDER

AV7

INTV RMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1 _SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

GPIO Signals

SATA0GP,SATA1GP,SATA2GP,SATA3GP

1. Needs a weak pull-up:10 KΩ ±10% pull-up to V3.3.

2. Unused SATA[3:0]GP pins must be terminated to either

3.3V rail or GND using 8.2–10 KΩ on the motherboard.

Either pull-up or pull-down is acceptable.

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

3

RTC Reset

12

@

@

CLRP1

CLRP1

SHORT PADS

SHORT PADS

RTCRST#

1. Total Length : 8000 mils

2. Space > 15 mils

3. Impedance Target 50 Ω ±15% for Microstrip.

4. RC time delay between 18 ms - 25 ms must be met.

MPCIE_RS T#

HDD_DET#

PCH_SATALED#

SATA2_PCIE6_L1

mCARD_PCIE#_SATA_R

Compal Secret Data

Compal Secret Data

Compal Secret Data

12

RH25

RH25

20K_0402_5%~D

20K_0402_5%~D

1

CH4

CH4

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

2

BDW_ULT_DDR3L

BDW_ULT_DDR3L

RTC

RTC

AUDIO SATA

AUDIO SATA

JTAG

JTAG

5 OF 19

5 OF 19

1 2

RH393 10K_0402_5%~DRH393 10K_0402_5%~D

1 2

RH466 10K_0402_5%~DRH466 10K_0402_5%~D

RH35 10K_0402_5%~DRH35 10K_0402_5%~D

RH467 10K_0402_5%~D@RH467 10K_0402_5%~D@

RH392 10K_0402_5%~DRH392 10K_0402_5%~D

RH395 10K_0402_5%~D@RH395 10K_0402_5%~D@

Deciphered Date

Deciphered Date

Deciphered Date

1 2

12

12

12

+3VS

2

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

mCARD_PCIE#_SATA_R

SATA2_PCIE6_L1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1.When SATA and PCIe are muxed, always route according

to SATA design guidelines.

2. Breakout < 600 mils

3. Zdiff : 85 ohm

4. Isolation to Other Signal Groups: Breakout : 8 mils/

Main routing : 20 mils in MS, 15 mils in SL,DSL

5. Max Length : 2 via Max 8", 3 vias Max 7"

6. Within Layer Max Mismatch : 15 mils.

7. Total Length Max Mismatch : 10 mils.

8. AC capacitors to be placed as close as possible to the

connector. Maximum distance from AC capacitors to

connector is 500 mils.

9. Minimum breakout pair-to-pair spacing of 3.5 mils is

allowed for a maximum length of 20 mils within the 600

mils breakout.

10. Design constraint: breakout routing should be

non-interleaved to mitigate concerns on near-end

crosstalk.

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

MPCIE_RS T#

U1

HDD_DET#

V6

SATA2_PCIE6_L1

AC1

mCARD_PCIE#_SATA_R

A12

L11

K10

C12

SATA_RCOMP

U3

PCH_SATALED#

SATA_RCOMP, SATA_IREF

1. Break-out : 4 mils

2. 12-15 mil trace with <0.2 Ω.

3. Length total <= 500 mils.

4. Requires 12 mils isolation from all

High Speed I/O and clocks.

SATA_RCOMP

1. Tied up to a clean 1.05V source

(VCCASATA3PLL) with no capacitor on

the net.

2. 3 KΩ ±1% precision pull-up resistor

SATA_IREF

1. Pull-up direct to 1.05V

(VCCASATA3PLL).

R1020

R1020

0_0402_5%~D

0_0402_5%~D

1 2

R1021

R1021

0_0402_5%~D

0_0402_5%~D

1 2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

P09-MCP(4/10) RTC,AUDIO,SATA

P09-MCP(4/10) RTC,AUDIO,SATA

P09-MCP(4/10) RTC,AUDIO,SATA

LA-B444P

LA-B444P

LA-B444P

SATA_RN2/PERN6_L1 [29]

SATA_RP2/PERP6_L1 [29]

SATA_TN2/PETN6_L1 [29]

SATA_TP2/PETP6_L1 [29]

SATA_RN3/PERN6_L0 [29]

SATA_RP3/PERP6_L0 [29]

SATA_TN3/PETN6_L0 [29]

SATA_TP3/PETP6_L0 [29]

MPCIE_RS T# [ 28]

RH43

RH43

3K_0402_1%~D

3K_0402_1%~D

1 2

mCARD_PCIE#_SATA [29]

950Saturday, October 04, 2014

950Saturday, October 04, 2014

950Saturday, October 04, 2014

1

+V1.05S_ASATA3PLL

1.0

1.0

1.0

Page 10

5

UCPU1F@

UCPU1F@

CLK_PCIE_MMI#[23]

CLK_PCIE_MMI[23]

D D

C C

MMICLK_RE Q#[23]

USB1_PWR_EN[30]

CLK_PCIE_WLAN#[28]

CLK_PCIE_WLAN[28]

WLANCLK_REQ#[28]

CLK_PCIE_mSATA#[29]

CLK_PCIE_mSATA[29]

mSATACLK_REQ#[29]

1. Breakout Routing Length Max : 500 mils.

2. Breakin Routing Length Max : 1500 mils

3. Routing Min and Max Length : 2"~9"

4. Differential Pair Length Matching. <25 mils for PCIe, <20 mils for ITP

6. Max Vias : 4

5. Stitching vias should be placed with this spacing:

a).30-mils pitch between differential clock via and closest stitching GND-via.

b). Every differential clock via must have at least one GND stitching via with a maximum spacing of 30 mils (0.762 mm).

6. Placement of additional stitching vias, where possible, is recommended.

MMICLK_RE Q#

USB1_PWR_EN

LANCLK_REQ#

WLANCLK_REQ#

PEG_WIGIGCLK_REQ#

mSATACLK_REQ#

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

CardReader

BDW_ULT_DDR3L

BDW_ULT_DDR3L

CLOCK

CLOCK

SIGNALS

SIGNALS

WiFi/BT

SSD

6 OF 19

6 OF 19

4

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

XTAL24_IN

XTAL24_OU T

XCLK_BIASREF <100 MILS

XCLK_BIAS REF

TESTLOW 1

TESTLOW 2

TESTLOW 3

TESTLOW 4

CLKOUT_LPC0

CLKOUT_LPC1

TESTLOW 1

TESTLOW 2

TESTLOW 3

TESTLOW 4

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

3

1 2

RH113 3K_0402_1%~DRH113 3K_0402_1%~D

1 2

RH360 22_0402_5%~DRH360 22_0402_5%~D

1 2

RH428 22_0402_5%~DRH428 22_0402_5%~D

RH36 10K_0402_5%~DRH36 10K_0402_5%~D

RH41 10K_0402_5%~DRH41 10K_0402_5%~D

RH44 10K_0402_5%~DRH44 10K_0402_5%~D

RH45 10K_0402_5%~DRH45 10K_0402_5%~D

12

12

12

12

+V1.05S_AXCK_LCPLL

CLK_PCI_MEC

CLK_LPC_DEBUG

2

CLK_PCI_MEC [36]

CLK_LPC_DEBUG [36]

XTAL24_IN

XTAL24_OU T

RH117 1M_0402_5%~DRH117 1M_0402_5%~D

24MHZ_12PF_7V24000020

24MHZ_12PF_7V24000020

1

CH24

CH24

15P_0402_50V8J~D

15P_0402_50V8J~D

2

15P_0402_50V8J

15P_0402_50V8J

1

1 2

YH2

YH2

123

4

CLK_LPC_DEBUG

CLK_PCI_MEC

CH1243

@ CH1243

@

1

2

1

CH23

CH23

15P_0402_50V8J~D

15P_0402_50V8J~D

2

1

CH1244

@CH1244

@

15P_0402_50V8J

15P_0402_50V8J

2

RF Reserved.

+3VS

1 2

RH100 10K_0402_5%~DRH100 10K_0402_5%~D

1 2

RH95 10K_0402_5%~DRH95 10K_0402_5%~D

1 2

RH91 10K_0402_5%~DRH91 10K_0402_5%~D

1 2

RH103 10K_0402_5%~DRH103 10K_0402_5%~D

1 2

RH107 10K_0402_5%~DRH107 10K_0402_5%~D

1 2

RH110 10K_0402_5%~DRH110 10K_0402_5%~D

MMICLK_RE Q#

USB1_PWR_EN

LANCLK_REQ#

WLANCLK_REQ#

PEG_WIGIGCLK_REQ#

mSATACLK_REQ#

B B

A A

Security Classifi cation

Security Classifi cation

Security Classifi cation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

P10-MCP(5/10) CLOCKS

P10-MCP(5/10) CLOCKS

P10-MCP(5/10) CLOCKS

LA-B444P

LA-B444P

LA-B444P

1

1.0

1.0

10 50Saturday, October 04, 2014

10 50Saturday, October 04, 2014

10 50Saturday, October 04, 2014

1.0

Page 11

5

Deep S3 support, connect to EC

SIO_PWRBTN#

T281@T281@

D D

NON-Deep S3 Support

Deep S3 support, connect to DSW power rail

+3V_PCH_DSW

RP20

RP20

SYS_RESET#

EC_WAKE#

PCH_BATLOW#

AC_PRESENT

PCH_RSMRST#

RESET_OUT#_R

C C

TLS Confidentiality

Low - Intel ME Crypto Transport Layer Security (TLS)

cipher suite with no confidentiality

High - Intel ME Crypto Transport Layer Security (TLS)

*

cipher suite with confidentiality

+3V_PCH

RH270 1K_0402_5%~DRH270 1K_0402_5%~D

+3V_PCH

RH3538 10K_0402_5%~DRH3538 10K_0402_5%~D

RH3536 10K_0402_5%~DRH3536 10K_0402_5%~D

RH382 100K_0402_5%~DRH382 100K_0402_5%~D

RH294 10K_0402_5%~D@ RH294 10K_0402_5%~D@

RH3537 10K_0402_5%~DRH3537 10K_0402_5%~D

RH3533 10K_0402_5%~DRH3533 10K_0402_5%~D

RH3535 10K_0402_5%~DRH3535 10K_0402_5%~D

B B

RH3541 10K_0402_5%~DRH3541 10K_0402_5%~D

RH3546 10K_0402_5%~DRH3546 10K_0402_5%~D

RH465 1M_0402_5%~DRH465 1M_0402_5%~D

RH400 100K_0402_5%~DRH400 100K_0402_5%~D

+3VS

RH3534 10K_0402_5%~DRH3534 10K_0402_5%~D

RH3543 10K_0402_5%~DRH3543 10K_0402_5%~D

RH383 100K_0402_5%~DRH383 100K_0402_5%~D

RH3540 10K_0402_5%~D@RH3540 10K_0402_5%~D@

RH3539 10K_0402_5%~DRH3539 10K_0402_5%~D

RH457 49.9K_0402_1%~DRH457 49.9K_0402_1%~D

RH458 49.9K_0402_1%~DRH458 49.9K_0402_1%~D

RH459 49.9K_0402_1%~DRH459 49.9K_0402_1%~D

RH460 49.9K_0402_1%~DRH460 49.9K_0402_1%~D

RH3548 10K_0402_5%~DRH3548 10K_0402_5%~D

A A

RH3530 10K_0402_5%~DRH3530 10K_0402_5%~D

RH3531 10K_0402_5%~DRH3531 10K_0402_5%~D

+3VS

1 8

2 7

3 6

4 5

10K_8P4R_5%

10K_8P4R_5%

RH12 10K_0402_5%~DRH12 10K_0402_5%~D

RH159 10K_0402_5%~DRH159 10K_0402_5%~D

RH394 10K_0402_5%~DRH394 10K_0402_5%~D

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

1 2

RH37 1K_0402_5%~D@ RH37 1K_0402_5%~D@

LOW=Default

*

HIGH=No Reboot

12

12

12

5

+3VS

HOST_ALERT1_R_N

PCH_GPIO12

SIO_EXT_SMI#

UART_WAKE#

NFC_IRQ

SIO_EXT_WAKE#

MEDIACARD_IRQ#

MEDIACARD_RST#

CAM_CBL_DET#

PCH_GPIO58

NFC_DET#

USB0_PWR_EN

TPM_PIRQ#

PCH_GPIO49

SIO_EXT_SCI#

PCH_GPIO38

PCH_GPIO16

UART1_RXD

UART1_TXD

UART1_RTS#

UART1_CTS#

TOUCH_PANEL_INTR#

PCH_GPIO48

PCH_GPIO87

SPKR

SUSACK#[36]

PM_SYS_RESET#[20,21]

SYS_PWROK[20,36]

RESET_OUT#[35,36]

PCH_RSMRST#[36]

ME_SUS_PWR_ACK[36]

SIO_PWRBTN#[20,36]

AC_PRESENT[36]

PM_SLP_S0#[21,45]

SIO_SLP_WLAN#[36]

PCH_PLTRST#_EC[20,23,27,28,36]

PCH_RSMRST# PCH_RSMRST#_R

A00_1004: Change to short pad.

4

12

RH171

RH171

100K_0402_5%~D

100K_0402_5%~D

Audio CODEC

+3V_PCH

BC@

BC@

RH3542 10K_0402_5%~D