Page 1

A

B

C

D

E

MODEL NAME :

PCB NO :

BOM P/N :

1 1

LA-6961P ( DA********** )

TBD

PAP00

Schematic Document

2 2

Phantom(Huron River)

Sandy Bridge(BGA1023) + Cougar Point(SFF)

DISCRETE VGA N12P-GS(optimus)

3 3

2010-11-29

Rev: 0.4

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-6961P

LA-6961P

LA-6961P

E

0.4

0.4

0.4

of

of

of

154Monday, January 24, 2011

154Monday, January 24, 2011

154Monday, January 24, 2011

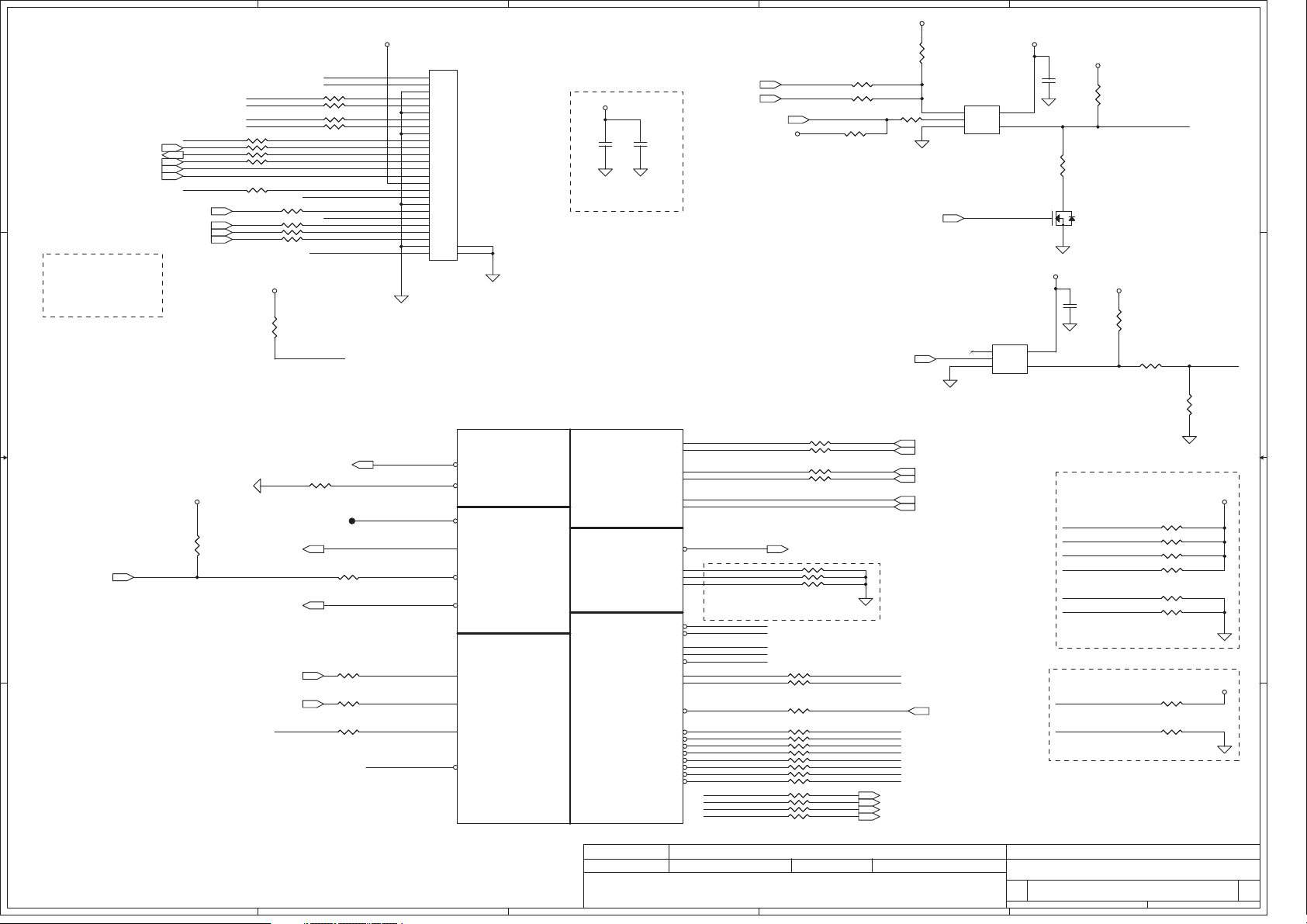

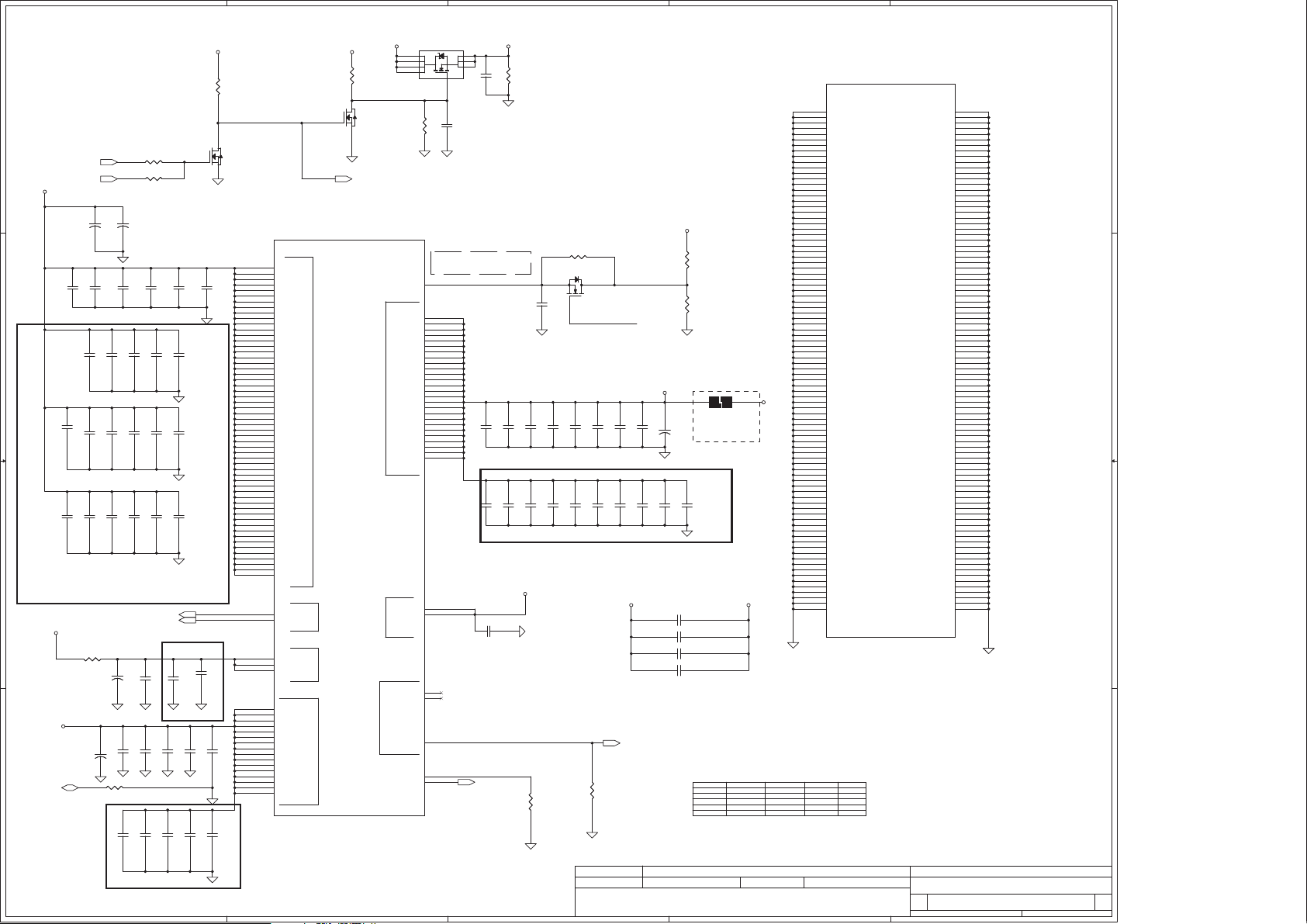

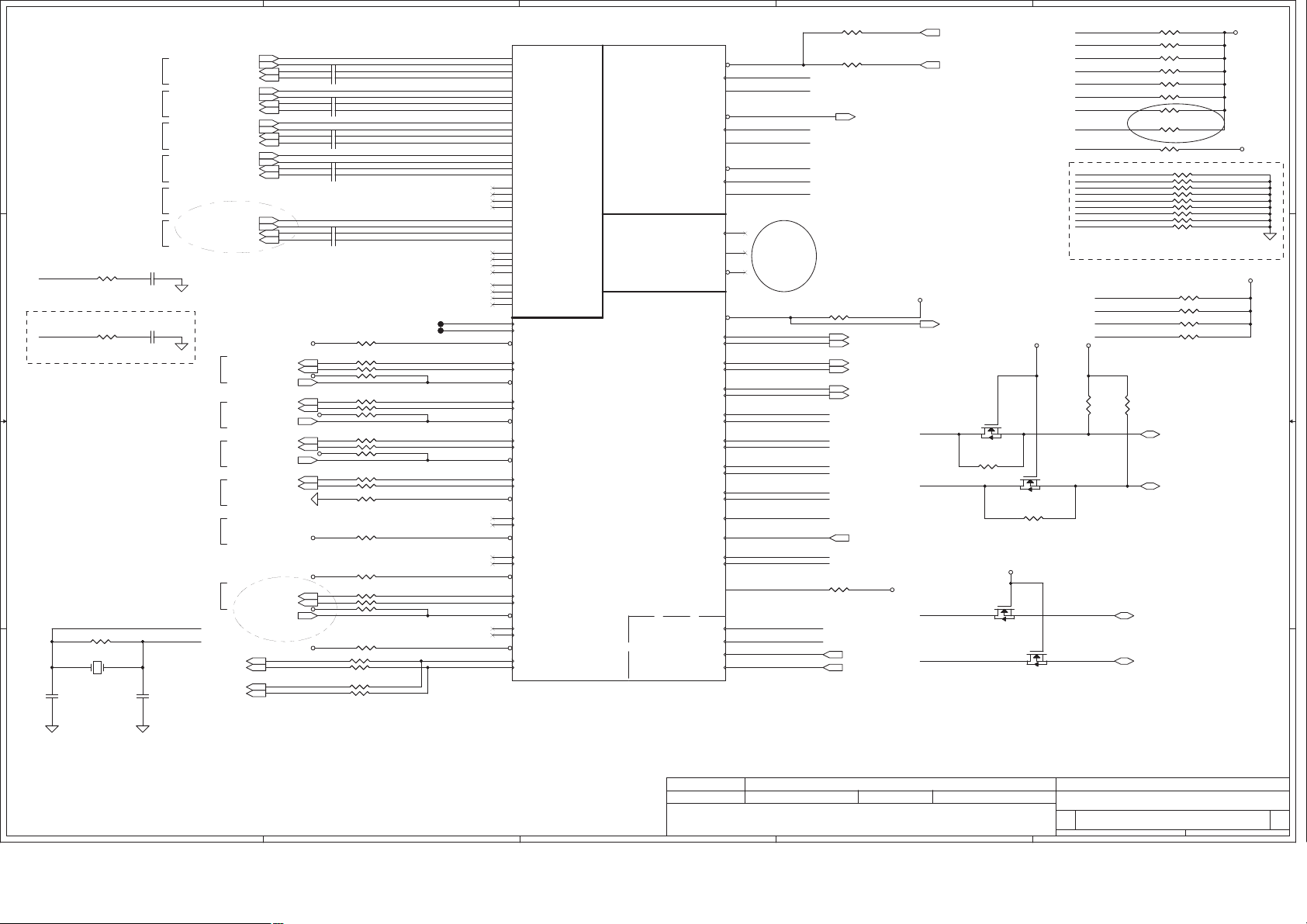

Page 2

A

B

C

D

E

Compal Confidential

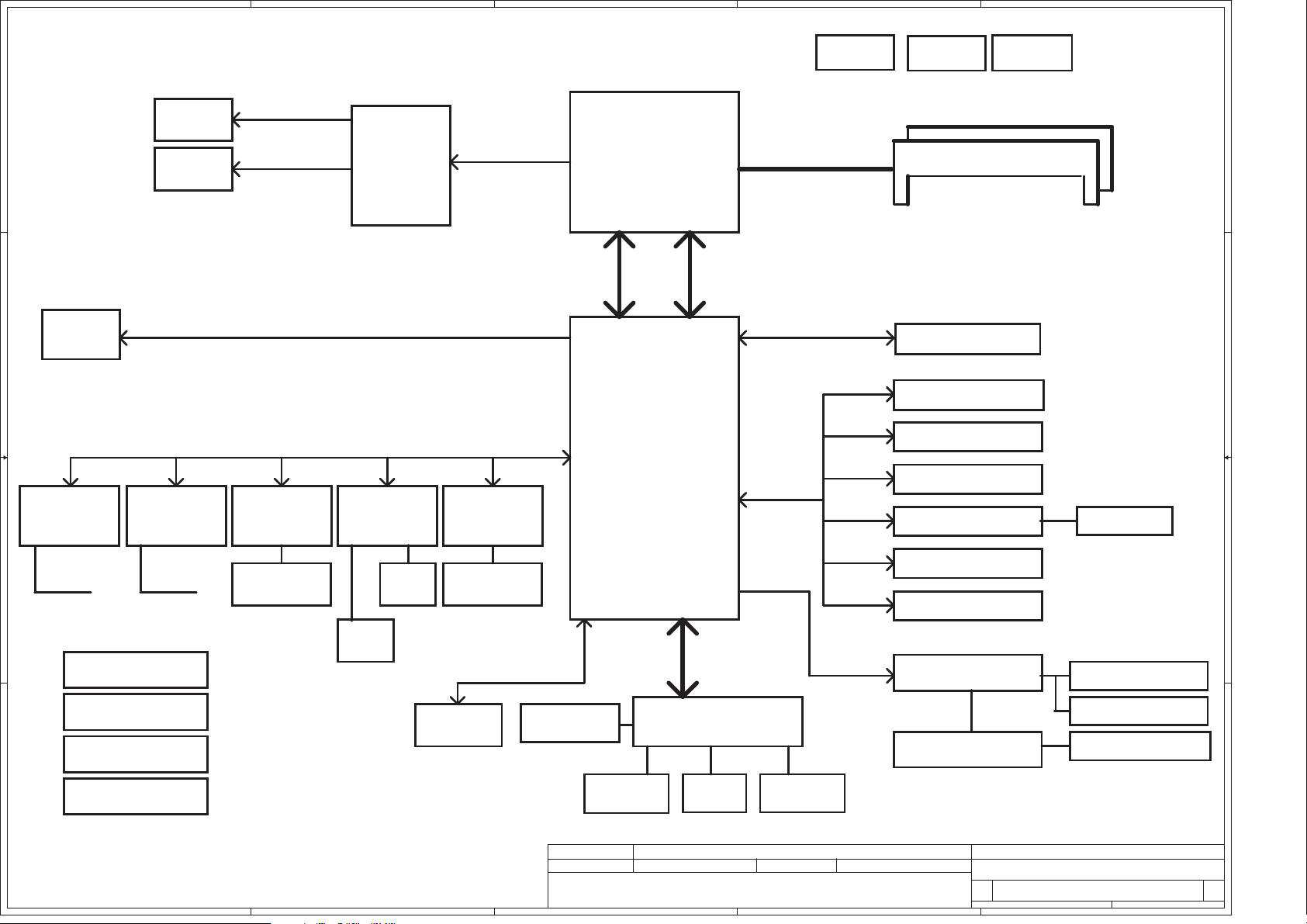

Project Code : PAP00

FFS

Small card

Fan Control

P.31

CPU XDP

Conn.

P.5

File Name : LA-6961P

1 1

HDMI

Conn.

DP Conn.

HDMI

DisplayPort

GPU

N12P-GS

PEG x16 (DIS)

P.30~41

Intel

Sandy Bridge

Processor

2C 17W ULV

Memory Bus (DDRIII)

Dual Channel

1.5V DDRIII 1066/1333 MHz

204pin DDRIII SO-DIMM x2

BANK 0, 1, 2, 3

P.10,11

BGA 1023

P.4~9

DMI x4FDI x8

(UMA)

100MHz

2.7GT/s

LVDS

2 2

Conn.

P.20

LVDS

Intel

PCI-E x1

Port 3 Port 2 Port 1 Port 4

Mini Card-2

WLAN (Half)

USB[x]

3 3

port4

WWAN (Full)

P.23 P.23 P.21 P.22

USB[x]

port5

LAN(GbE)

AR8151-BL1A

RJ45

Card ReaderMini Card-1

JMB380

3 in 1

Socket

P.22P.21

USB 3.0/2.0

Host Ctrl.

USB 3.0/2.0

Combo Conns x2

Port 6

Small card

Small card

1394

Conn.

RTC CKT.

Power On/Off CKT.

DC/DC Interface CKT.

P.12

P.27

P.43

SPI ROM

ENE 3810

P.12 P.32

Cougar Point

PCH SFF

BGA 1017 Balls

SPI

P.32

100MHz

5GB/s

HD Audio

P12~19

LPC Bus

ENE KB930

SATA3.0

USB2.0

Port 0

Port 1

Port 3

Port 4

Port 5

Port 6

Port 2

SATA HDD-1 Conn.

USB 2.0

( USB Charger )

Digital Camera

Mini Card-1 (WLAN)

( Half )

Mini Card-2 (WWAN)

( Full )

AlienFX/ELC

BT 2.1 /BT 3.0

P.26

P.24

P.20

P.23

P.23 P.23

P.27

P.34

Audio Codec

ALC665-GR

Small card

Small card

SIM Card

Audio Jack x3

( HeadPhone x2, MIC)

Digital MIC

Int. SpeakerAMP. APA2031RI

Small card

Small card

Small card

4 4

Power Circuit DC/DC

A

P.43

B

Touch Pad Int.KBD

P.33

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/06/10 2011/07/06

2010/06/10 2011/07/06

2010/06/10 2011/07/06

BIOS ROM

P.33 P.33

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics,Inc.

Title

Title

Title

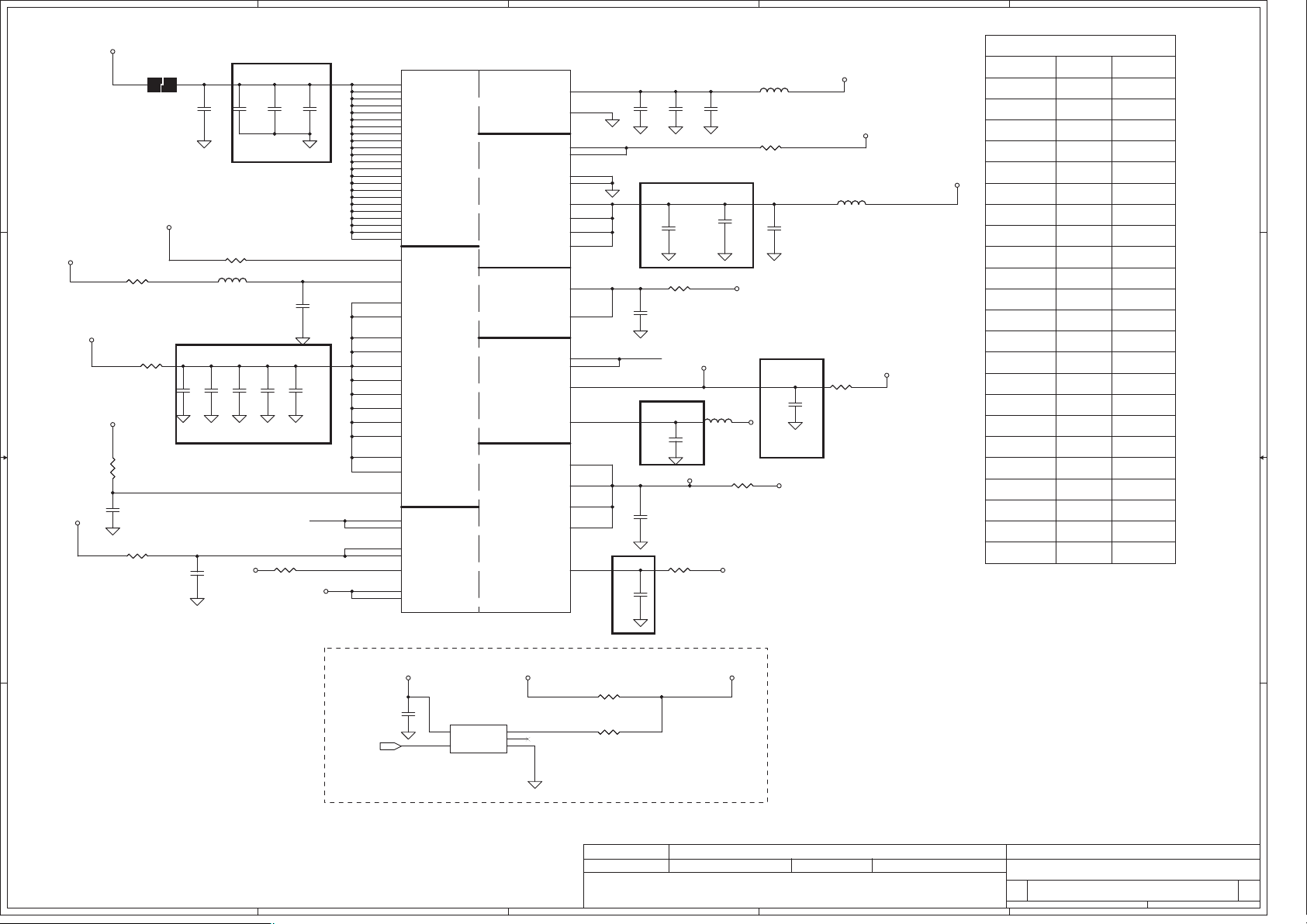

PCH (6/8) PWR

PCH (6/8) PWR

PCH (6/8) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

254Monday, January 24, 2011

254Monday, January 24, 2011

254Monday, January 24, 2011

E

0.4

0.4

0.4

of

of

of

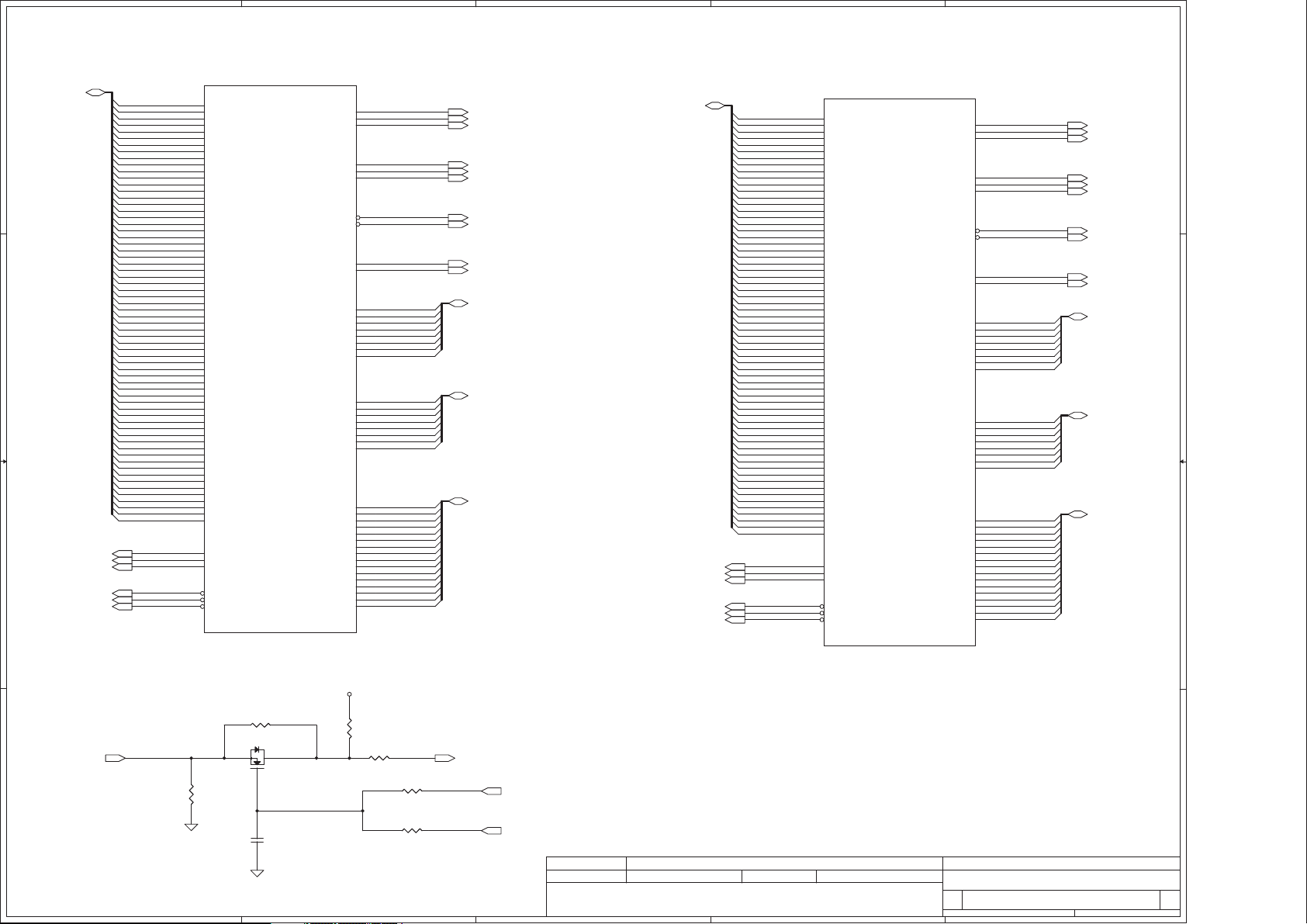

Page 3

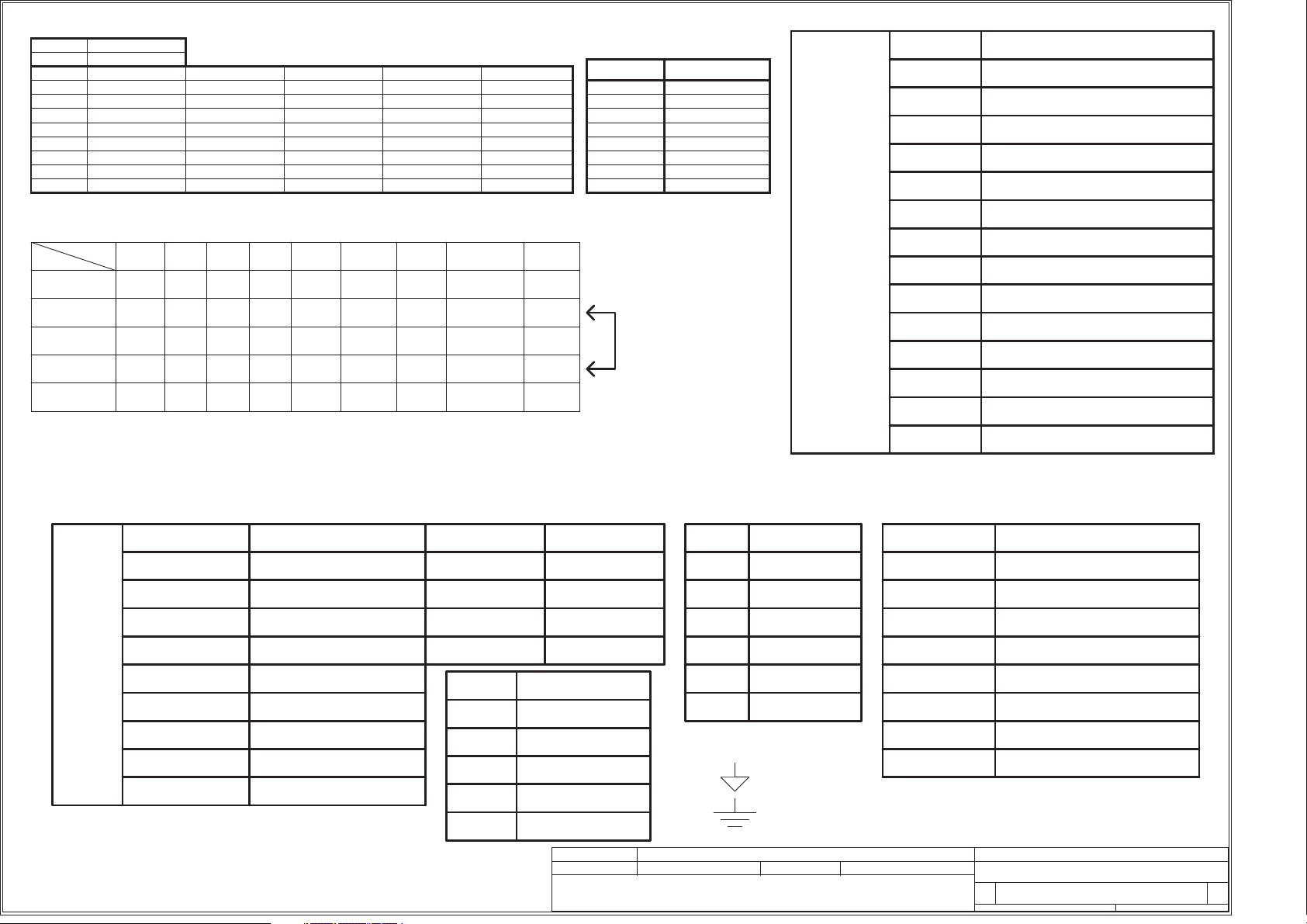

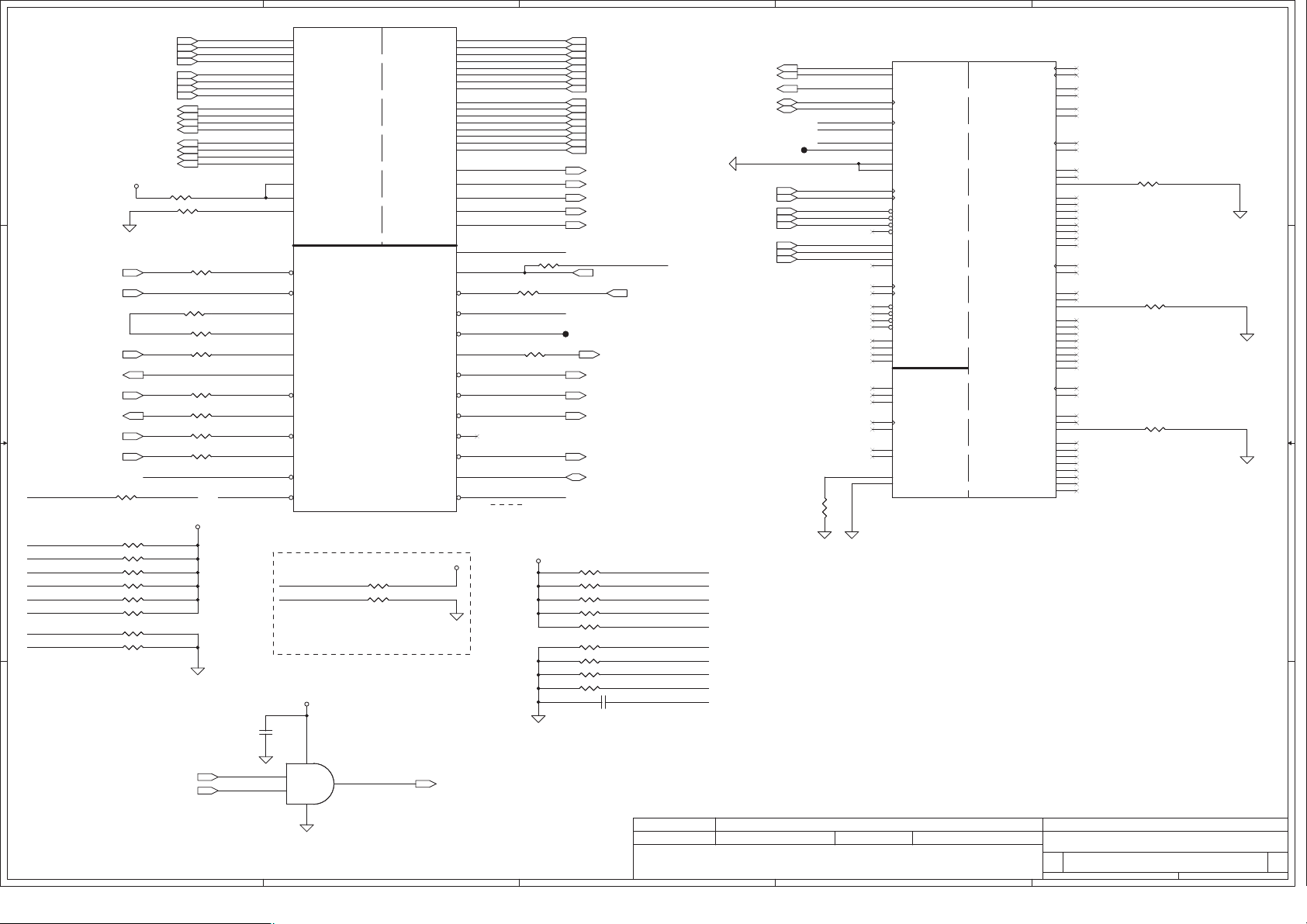

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7NC

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SML0CLK PCH

PCH_SML0DATA

PCH_SML1CLK

PCH_SML1DATA

MEM_SMBCLK

MEM_SMBDATA

100K +/- 5%Ra

Rb V min

00 V

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

SOURCE

KB930

KB930

PCH

PCH

AD_BID

0.168 V

0.375 V 0.503 V

0.634 V

0.958 V

1.372 V

1.851 V 2.200 V

2.433 V

MINI2

MINI1 BATT SODIMM

VV

V

V typ

AD_BID

0 V 0.155 V

0.250 V

0.819 V

1.185 V

1.650 V

3.300 V

Thermal

Sensor 1

V

V

AD_BID

0.362 V

0.621 V

0.945 V

1.359 V

1.838 V

2.420 V

3.300 V

FFS

VV

max

VGA Thermal

Sensor

V

EC AD3

0x00-0x0C

0x0D-0x1C

0x1D-0x30

0x31-0x49

0x4A-0x69

0x6A-0x8E

0x8F-0xBB

0xBC-0xFF

SMSC

BOARD ID Table

Board ID

V

A

0

1

2

3

4

5

6

7

Link

PCB Revision

0.1

0.2

0.3

0.4

0.5

PCH

USB PORT#

0

1

2

3

4

5

6

7

8

9

10

11

12

DESTINATION

None

JUSB1 (Ext Left Side)

Bluetooth

CAMERA

JMINI1 (WLAN)

JMINI2 (WWAN)

ELC

None

None

None

None

None

None

1 1

13

DESTINATION

HDD

None

None

None

None

None

Symbol Note :

: means Digital Ground

: means Analog Ground

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8 None

CLK

DESTINATIONDIFFERENTIAL

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

CLKOUT_PCIE6

10/100/1G LAN

MINI CARD-2 WWAN

MINI CARD-1 WLAN

CARD READER

None

USB 3.0

CLKOUT_PCIE7 None

CLKOUT_PEG_B

None

FLEX CLOCKS DESTINATION

CLKOUTFLEX0None

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

CLKOUT

PCI0

PCI1

PCI2

PCI3

PCI4

None

None

None

None

DESTINATION

PCH_LOOPBACK

EC

None

None

None

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

None

DESTINATION

10/100/1G LAN

MINI CARD-2 WWAN/DMC

MINI CARD-1 WLAN

CARD READER and 1394

None

USB 3.0

None

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-6961P

LA-6961P

LA-6961P

of

of

of

354Monday, January 24, 2011

354Monday, January 24, 2011

354Monday, January 24, 2011

0.4

0.4

0.4

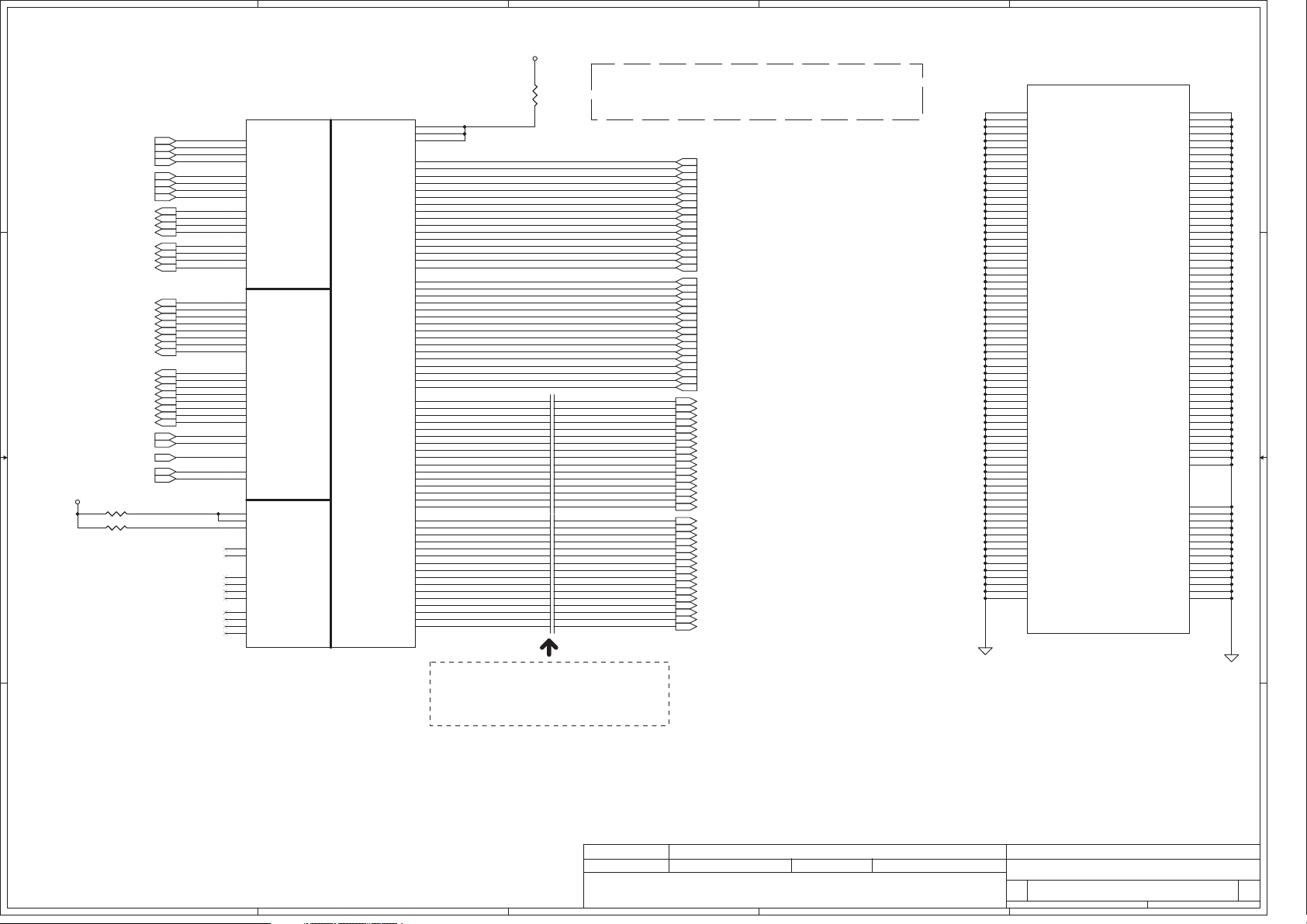

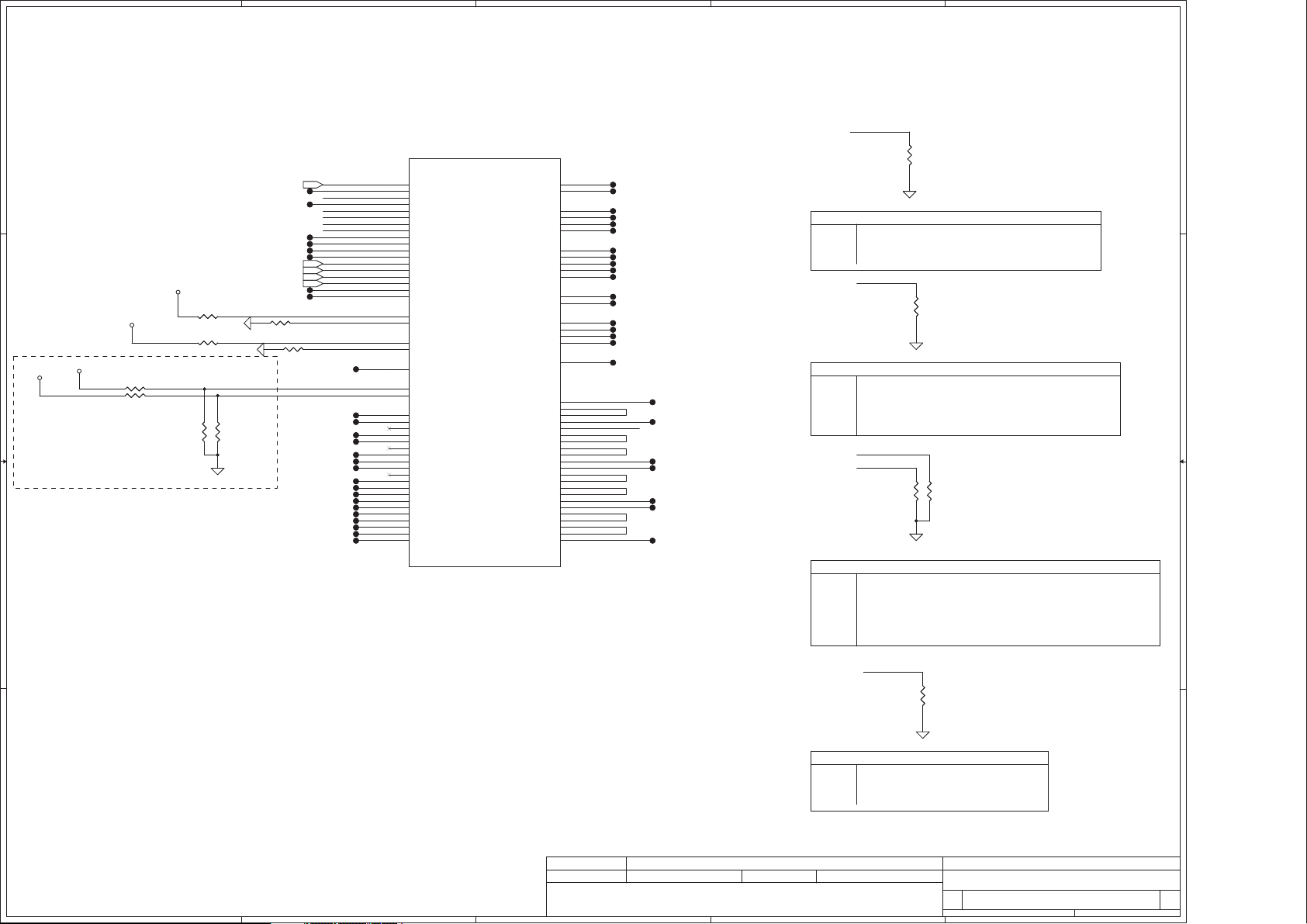

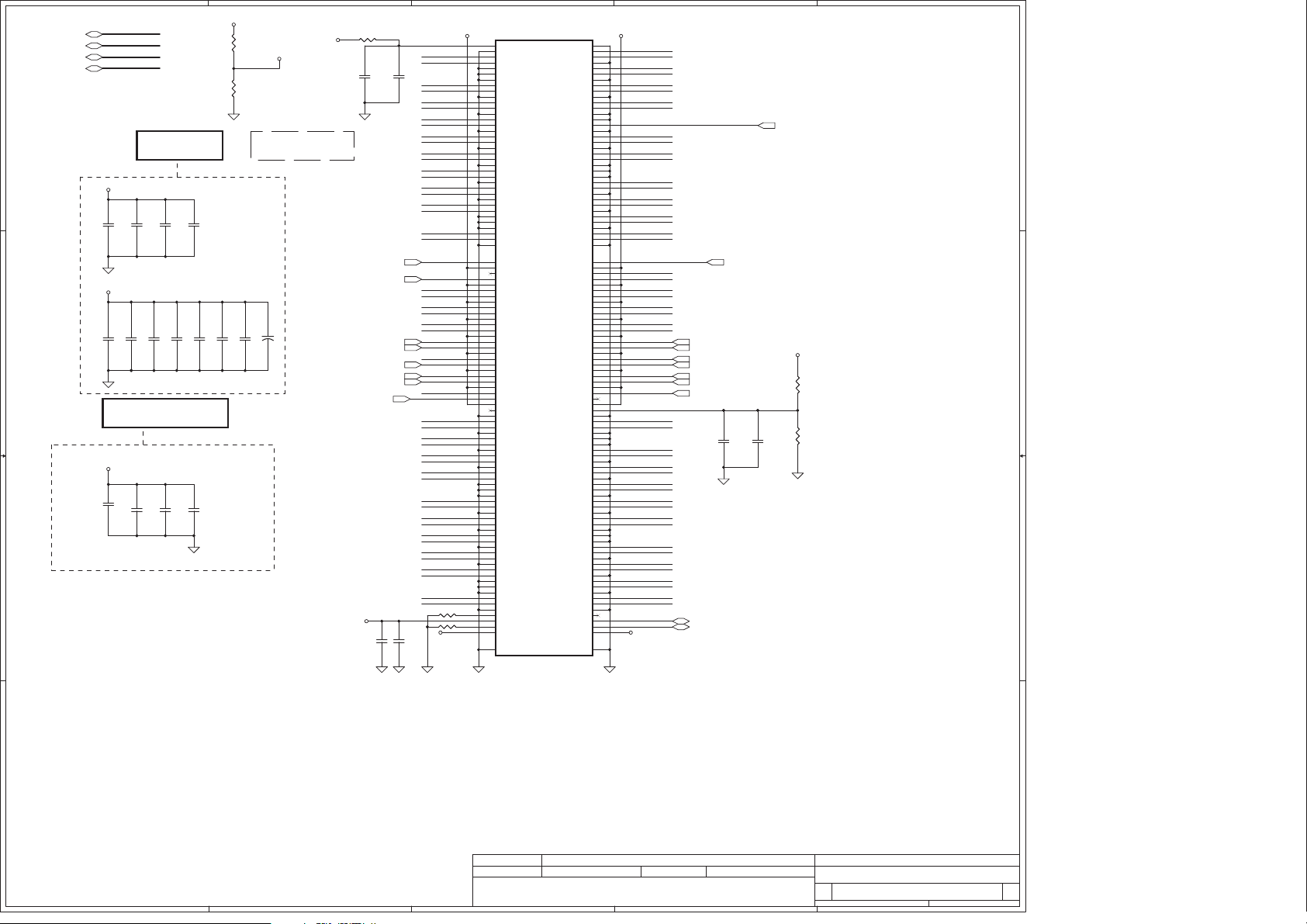

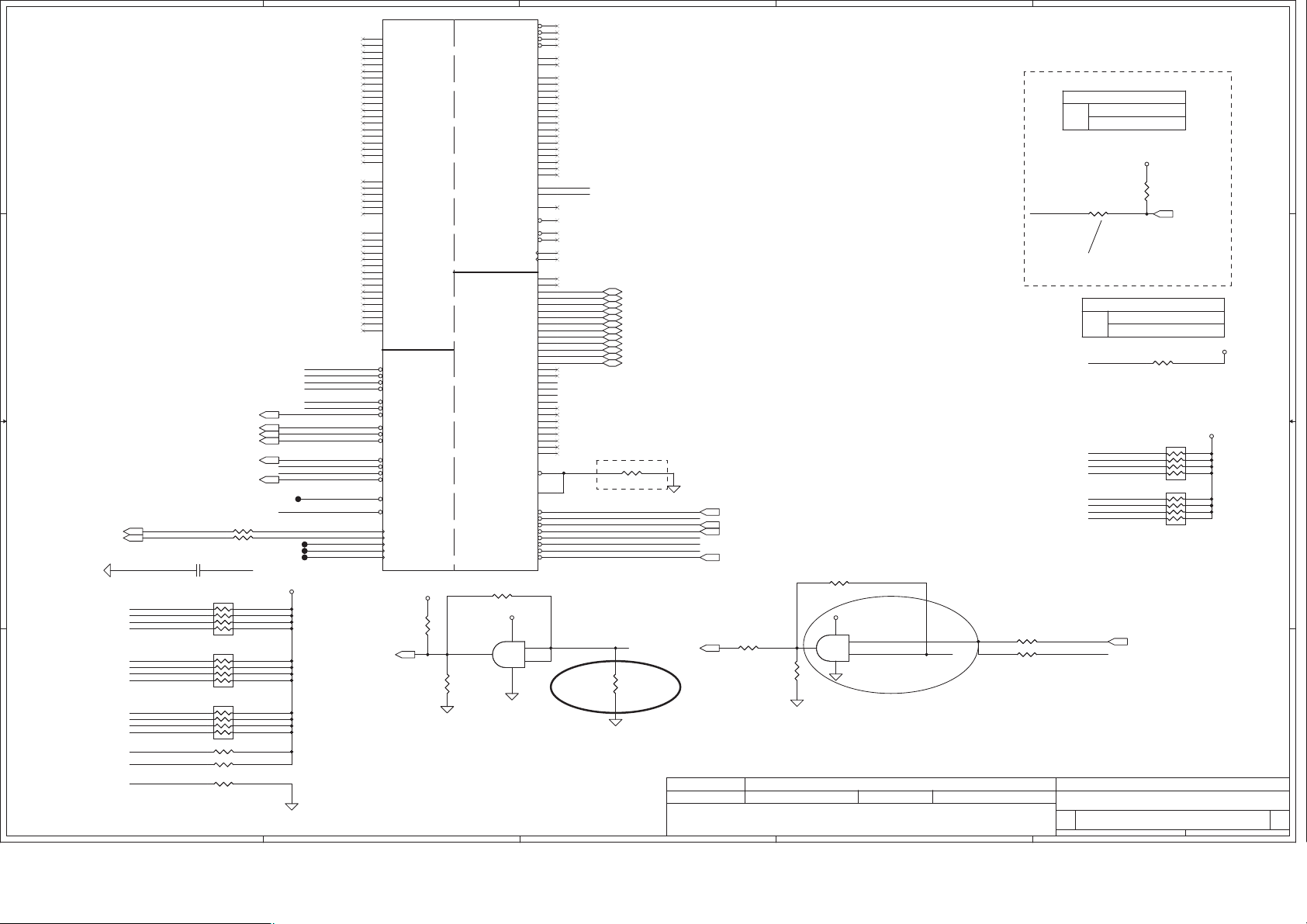

Page 4

5

UCPU1A

D D

DMI_CRX_PTX_N014

DMI_CRX_PTX_N114

DMI_CRX_PTX_N214

DMI_CRX_PTX_N314

DMI_CRX_PTX_P014

DMI_CRX_PTX_P114

DMI_CRX_PTX_P214

DMI_CRX_PTX_P314

DMI_CTX_PRX_N014

DMI_CTX_PRX_N114

DMI_CTX_PRX_N214

DMI_CTX_PRX_N314

DMI_CTX_PRX_P014

DMI_CTX_PRX_P114

DMI_CTX_PRX_P214

DMI_CTX_PRX_P314

10K_0402_5%

10K_0402_5%

12

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

+EDP_COM

FDI_CTX_PRX_N014

FDI_CTX_PRX_N114

FDI_CTX_PRX_N214

FDI_CTX_PRX_N314

FDI_CTX_PRX_N414

FDI_CTX_PRX_N514

C C

B B

FDI_CTX_PRX_N614

FDI_CTX_PRX_N714

FDI_CTX_PRX_P014

FDI_CTX_PRX_P114

FDI_CTX_PRX_P214

FDI_CTX_PRX_P314

FDI_CTX_PRX_P414

FDI_CTX_PRX_P514

FDI_CTX_PRX_P614

FDI_CTX_PRX_P714

FDI_FSYNC014

FDI_FSYNC114

FDI_INT14

FDI_LSYNC014

FDI_LSYNC114

+1.05VS

1 2

RC36 24.9_0402_1%RC36 24.9_0402_1%

RC126

RC126

UCPU1A

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

DMI Intel(R) FDI DP

DMI Intel(R) FDI DP

4

+1.05VS

12

PEG_COMP

CC185 0.1U_0402_10V7K~DCC185 0.1U_0402_10V7K~D

CC186 0.1U_0402_10V7K~DCC186 0.1U_0402_10V7K~D

CC187 0.1U_0402_10V7K~DCC187 0.1U_0402_10V7K~D

CC188 0.1U_0402_10V7K~DCC188 0.1U_0402_10V7K~D

CC189 0.1U_0402_10V7K~DCC189 0.1U_0402_10V7K~D

CC190 0.1U_0402_10V7K~DCC190 0.1U_0402_10V7K~D

CC191 0.1U_0402_10V7K~DCC191 0.1U_0402_10V7K~D

CC192 0.1U_0402_10V7K~DCC192 0.1U_0402_10V7K~D

CC193 0.1U_0402_10V7K~DCC193 0.1U_0402_10V7K~D

CC194 0.1U_0402_10V7K~DCC194 0.1U_0402_10V7K~D

CC195 0.1U_0402_10V7K~DCC195 0.1U_0402_10V7K~D

CC196 0.1U_0402_10V7K~DCC196 0.1U_0402_10V7K~D

CC197 0.1U_0402_10V7K~DCC197 0.1U_0402_10V7K~D

CC198 0.1U_0402_10V7K~DCC198 0.1U_0402_10V7K~D

CC199 0.1U_0402_10V7K~DCC199 0.1U_0402_10V7K~D

CC200 0.1U_0402_10V7K~DCC200 0.1U_0402_10V7K~D

CC201 0.1U_0402_10V7K~DCC201 0.1U_0402_10V7K~D

CC202 0.1U_0402_10V7K~DCC202 0.1U_0402_10V7K~D

CC203 0.1U_0402_10V7K~DCC203 0.1U_0402_10V7K~D

CC204 0.1U_0402_10V7K~DCC204 0.1U_0402_10V7K~D

CC205 0.1U_0402_10V7K~DCC205 0.1U_0402_10V7K~D

CC206 0.1U_0402_10V7K~DCC206 0.1U_0402_10V7K~D

CC207 0.1U_0402_10V7K~DCC207 0.1U_0402_10V7K~D

CC208 0.1U_0402_10V7K~DCC208 0.1U_0402_10V7K~D

CC209 0.1U_0402_10V7K~DCC209 0.1U_0402_10V7K~D

CC210 0.1U_0402_10V7K~DCC210 0.1U_0402_10V7K~D

CC211 0.1U_0402_10V7K~DCC211 0.1U_0402_10V7K~D

CC212 0.1U_0402_10V7K~DCC212 0.1U_0402_10V7K~D

CC213 0.1U_0402_10V7K~DCC213 0.1U_0402_10V7K~D

CC214 0.1U_0402_10V7K~DCC214 0.1U_0402_10V7K~D

CC215 0.1U_0402_10V7K~DCC215 0.1U_0402_10V7K~D

CC216 0.1U_0402_10V7K~DCC216 0.1U_0402_10V7K~D

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G3

G1

G4

PEG_GTX_C_HRX_N0

H22

PEG_GTX_C_HRX_N1

J21

PEG_GTX_C_HRX_N2

B22

PEG_GTX_C_HRX_N3

D21

PEG_GTX_C_HRX_N4

A19

PEG_GTX_C_HRX_N5

D17

PEG_GTX_C_HRX_N6

B14

PEG_GTX_C_HRX_N7

D13

PEG_GTX_C_HRX_N8

A11

PEG_GTX_C_HRX_N9

B10

PEG_GTX_C_HRX_N10

G8

PEG_GTX_C_HRX_N11

A8

PEG_GTX_C_HRX_N12

B6

PEG_GTX_C_HRX_N13

H8

PEG_GTX_C_HRX_N14

E5

PEG_GTX_C_HRX_N15

K7

PEG_GTX_C_HRX_P0

K22

PEG_GTX_C_HRX_P1

K19

PEG_GTX_C_HRX_P2

C21

PEG_GTX_C_HRX_P3

D19

PEG_GTX_C_HRX_P4

C19

PEG_GTX_C_HRX_P5

D16

PEG_GTX_C_HRX_P6

C13

PEG_GTX_C_HRX_P7

D12

PEG_GTX_C_HRX_P8

C11

PEG_GTX_C_HRX_P9

C9

PEG_GTX_C_HRX_P10

F8

PEG_GTX_C_HRX_P11

C8

PEG_GTX_C_HRX_P12

C5

PEG_GTX_C_HRX_P13

H6

PEG_GTX_C_HRX_P14

F6

PEG_GTX_C_HRX_P15

K6

PEG_HTX_GRX_N0

G22

PEG_HTX_GRX_N1

C23

PEG_HTX_GRX_N2

D23

PEG_HTX_GRX_N3

F21

PEG_HTX_GRX_N4

H19

PEG_HTX_GRX_N5

C17

PEG_HTX_GRX_N6

K15

PEG_HTX_GRX_N7

F17

PEG_HTX_GRX_N8

F14

PEG_HTX_GRX_N9

A15

PEG_HTX_GRX_N10

J14

PEG_HTX_GRX_N11

H13

PEG_HTX_GRX_N12

M10

PEG_HTX_GRX_N13

F10

PEG_HTX_GRX_N14

D9

PEG_HTX_GRX_N15

J4

PEG_HTX_GRX_P0

F22

PEG_HTX_GRX_P1

A23

PEG_HTX_GRX_P2

D24

PEG_HTX_GRX_P3

E21

PEG_HTX_GRX_P4

G19

PEG_HTX_GRX_P5

B18

PEG_HTX_GRX_P6

K17

PEG_HTX_GRX_P7

G17

PEG_HTX_GRX_P8

E14

PEG_HTX_GRX_P9

C15

PEG_HTX_GRX_P10

K13

PEG_HTX_GRX_P11

G13

PEG_HTX_GRX_P12

K10

PEG_HTX_GRX_P13

G10

PEG_HTX_GRX_P14

D8

PEG_HTX_GRX_P15

K4

Typ- suggest 220nF. The change in AC capacitor

value from 100nF to 220nF is to enable

compatibility with future platforms having PCIE

Gen3 (8GT/s)

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

RC2

RC2

24.9_0402_1%

24.9_0402_1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

3

PEG_ICOMPI and RCOMPO signals should be shorted and routed

with - max length = 500 mils - typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with - max length = 500 mils

- typical impedance = 14.5 mohms

PEG_GTX_C_HRX_N0 30

PEG_GTX_C_HRX_N1 30

PEG_GTX_C_HRX_N2 30

PEG_GTX_C_HRX_N3 30

PEG_GTX_C_HRX_N4 30

PEG_GTX_C_HRX_N5 30

PEG_GTX_C_HRX_N6 30

PEG_GTX_C_HRX_N7 30

PEG_GTX_C_HRX_N8 30

PEG_GTX_C_HRX_N9 30

PEG_GTX_C_HRX_N10 30

PEG_GTX_C_HRX_N11 30

PEG_GTX_C_HRX_N12 30

PEG_GTX_C_HRX_N13 30

PEG_GTX_C_HRX_N14 30

PEG_GTX_C_HRX_N15 30

PEG_GTX_C_HRX_P0 30

PEG_GTX_C_HRX_P1 30

PEG_GTX_C_HRX_P2 30

PEG_GTX_C_HRX_P3 30

PEG_GTX_C_HRX_P4 30

PEG_GTX_C_HRX_P5 30

PEG_GTX_C_HRX_P6 30

PEG_GTX_C_HRX_P7 30

PEG_GTX_C_HRX_P8 30

PEG_GTX_C_HRX_P9 30

PEG_GTX_C_HRX_P10 30

PEG_GTX_C_HRX_P11 30

PEG_GTX_C_HRX_P12 30

PEG_GTX_C_HRX_P13 30

PEG_GTX_C_HRX_P14 30

PEG_GTX_C_HRX_P15 30

PEG_HTX_C_GRX_N0 30

PEG_HTX_C_GRX_N1 30

PEG_HTX_C_GRX_N2 30

PEG_HTX_C_GRX_N3 30

PEG_HTX_C_GRX_N4 30

PEG_HTX_C_GRX_N5 30

PEG_HTX_C_GRX_N6 30

PEG_HTX_C_GRX_N7 30

PEG_HTX_C_GRX_N8 30

PEG_HTX_C_GRX_N9 30

PEG_HTX_C_GRX_N10 30

PEG_HTX_C_GRX_N11 30

PEG_HTX_C_GRX_N12 30

PEG_HTX_C_GRX_N13 30

PEG_HTX_C_GRX_N14 30

PEG_HTX_C_GRX_N15 30

PEG_HTX_C_GRX_P0 30

PEG_HTX_C_GRX_P1 30

PEG_HTX_C_GRX_P2 30

PEG_HTX_C_GRX_P3 30

PEG_HTX_C_GRX_P4 30

PEG_HTX_C_GRX_P5 30

PEG_HTX_C_GRX_P6 30

PEG_HTX_C_GRX_P7 30

PEG_HTX_C_GRX_P8 30

PEG_HTX_C_GRX_P9 30

PEG_HTX_C_GRX_P10 30

PEG_HTX_C_GRX_P11 30

PEG_HTX_C_GRX_P12 30

PEG_HTX_C_GRX_P13 30

PEG_HTX_C_GRX_P14 30

PEG_HTX_C_GRX_P15 30

2

UCPU1I

UCPU1I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G48

VSS[221]

G51

VSS[222]

G6

VSS[223]

G61

VSS[224]

H10

VSS[225]

H14

VSS[226]

H17

VSS[227]

H21

VSS[228]

H4

VSS[229]

H53

VSS[230]

H58

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

K11

VSS[235]

K21

VSS[236]

K51

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

M11

VSS[249]

M15

VSS[250]

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

VSS

VSS

1

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS[301]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

NCTF

NCTF

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

LA-6961P

LA-6961P

LA-6961P

1

of

of

of

454Monday, January 24, 2011

454Monday, January 24, 2011

454Monday, January 24, 2011

0.4

0.4

0.4

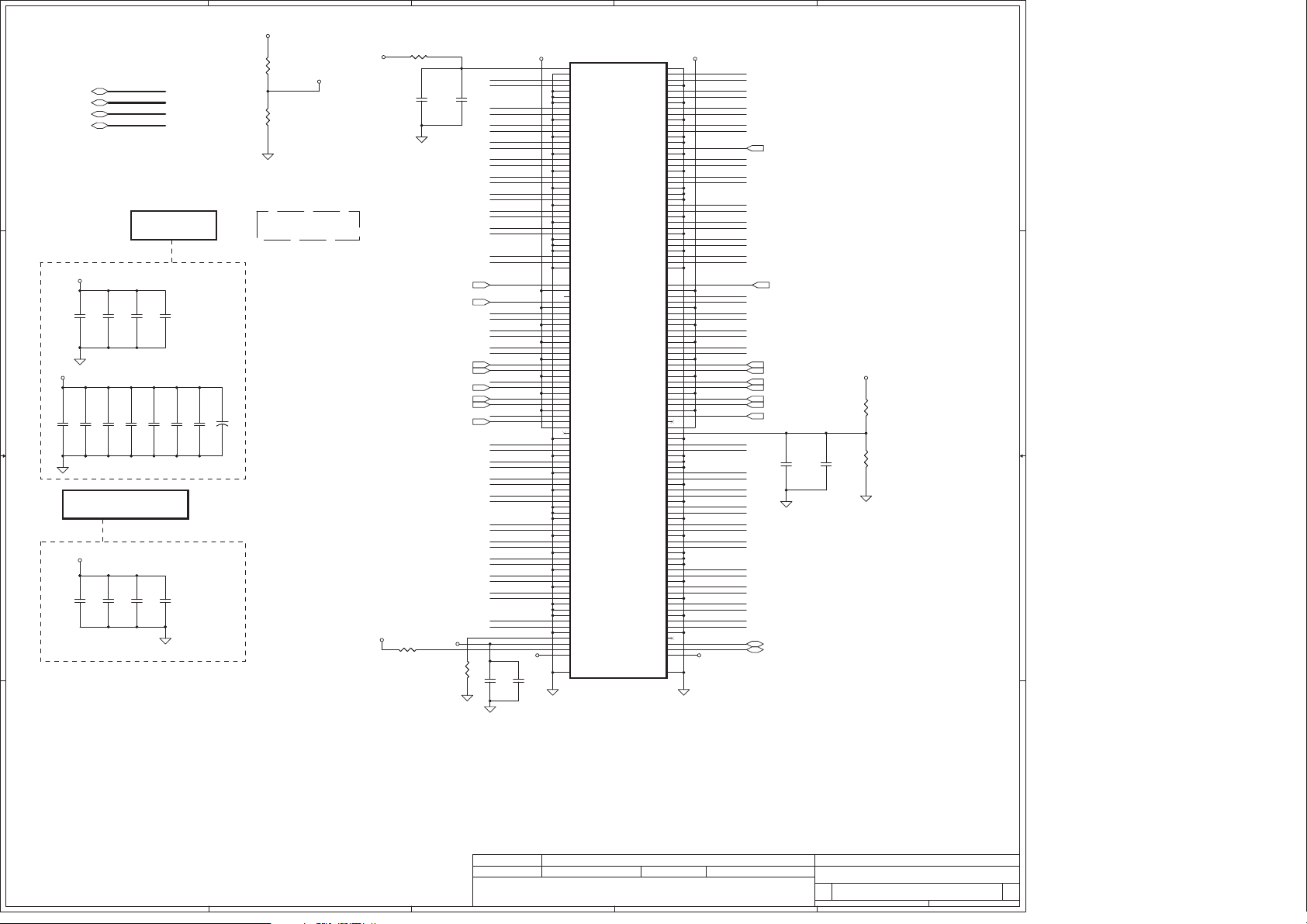

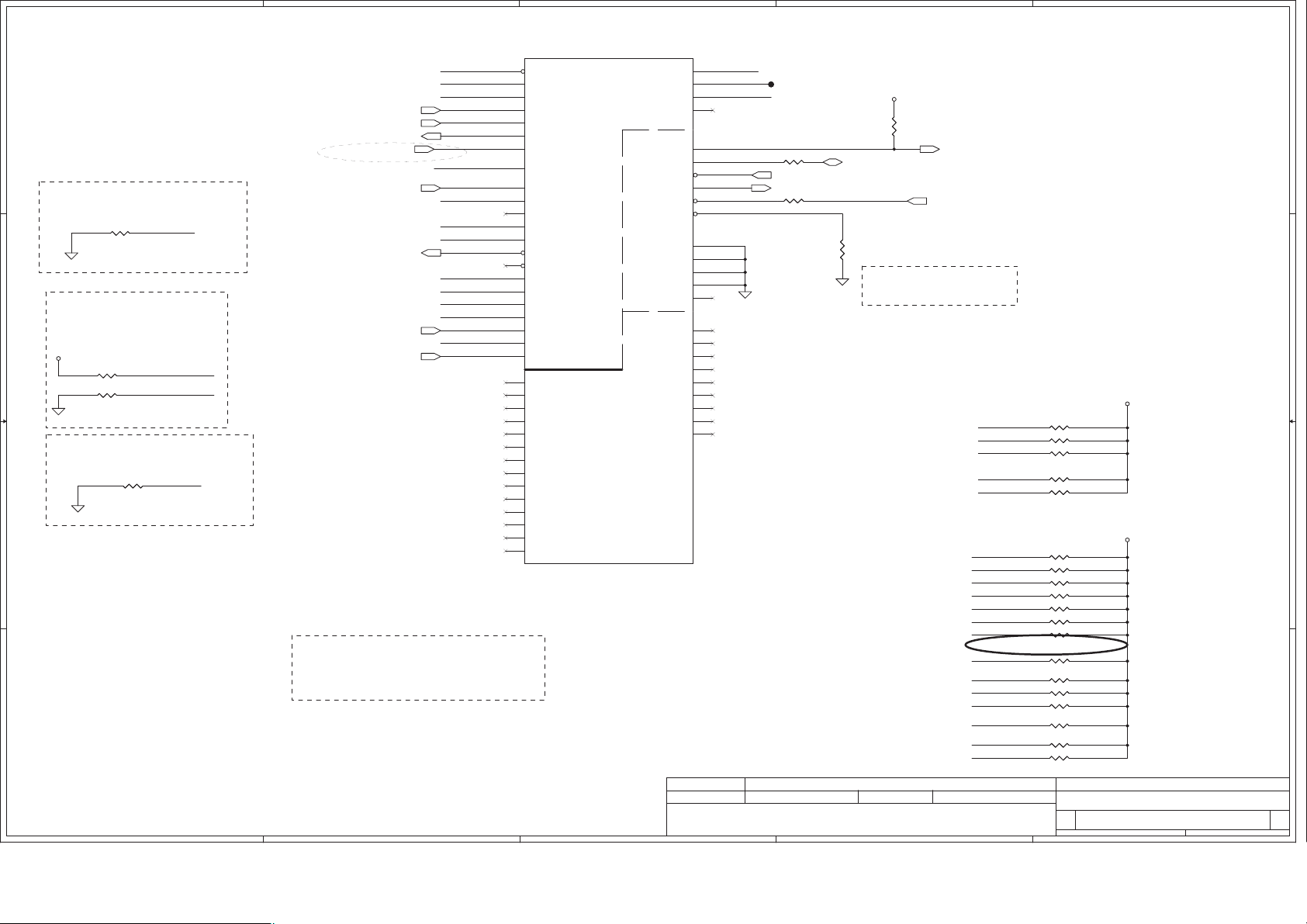

Page 5

5

XDP_PREQ#

XDP_BPM#0

XDP_BPM#1

D D

PBTN_OUT#14,25

CFG07

VGATE14,25,54

CLK_CPU_ITP13

CLK_CPU_ITP#13

The resistor

for HOOK2 should be

placed such that the

stub is very small

on CFG0 net

C C

PROC_DETECT (Processor Detect): pulled to

ground on the processor package. There is no

connection to the processor silicon for this

signal. System board designers may use this

signal to determine if the processor is present

B B

A A

H_PROCHOT#25,44

5

PLT_RST# XDP_RST#_R

PCH_JTAG_TDO12

PCH_JTAG_TDI12

PCH_JTAG_TMS12

PCH_JTAG_TCK12

+1.05VS

RC43

RC43

62_0402_5%

62_0402_5%

1 2

XDP_BPM#2

XDP_BPM#3

1K_0402_5%~D

1K_0402_5%~D

1 2

1 2

1 2

1 2

1K_0402_5%

1K_0402_5%

12

0_0402_5% @

0_0402_5% @

1 2

+3VALW

12

RC121 10K_0402_5%

RC121 10K_0402_5%

H_PECI16,25

H_THERMTRIP#16

H_PM_SYNC14

H_CPUPWRGD16

VDDPWRGOOD

XDP_PRDY#

RC35 0_0402_5%

RC35 0_0402_5%

RC114 0_0402_5%@RC114 0_0402_5%@

RC117 0_0402_5%@RC117 0_0402_5%@

RC115 0_0402_5%@RC115 0_0402_5%@

H_CPUPWRGD_XDPH_CPUPWRGD

RC22

RC22

CFD_PWRBTN#_XDP

RC230_0402_5%~D @ RC230_0402_5%~D @

CFG0_R

RC71K_0402_5%~D RC71K_0402_5%~D

SYS_PWROK_XDP

RC260_0402_5%~D @ RC260_0402_5%~D @

CLK_CPU_ITP

CLK_CPU_ITP#

RC25

RC25

XDP_DBRESET#

XDP_TDO

RC280_0402_5% @ RC280_0402_5% @

12

XDP_TRST#

XDP_TDI

RC310_0402_5% @ RC310_0402_5% @

12

XDP_TMS

RC290_0402_5% @ RC290_0402_5% @

12

XDP_TCK1

RC30

RC30

XDP_TCK

@

@

RC27

RC27

1K_0402_5%~D

1K_0402_5%~D

SYS_PWROK_XDP

H_SNB_IVB#15

12

@

@

T1PAD~D @T1PAD~D @

1 2

56_0402_5%

56_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

130_0402_1%

130_0402_1%

@

@

RC41

RC41

RC49

RC49

RC53

RC53

RC57

RC57

12

12

12

12

4

+1.05VS

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#

H_PM_SYNC_R

H_CPUPWRGD_R

VDDPWRGOOD_R

BUF_CPU_RST#

4

JXDP

@ JXDP

@

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

G1

26

26

G2

ACES_87152-26051

ACES_87152-26051

UCPU1B

UCPU1B

F49

C57

C49

A48

C45

D45

C48

B46

BE45

D44

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

27

28

PROC_SELECT#

PROC_DETECT#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

+1.05VS

1

2

3

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

CC67

CC67

CC66

CC66

2

RC127

RC4

RC4

RC127

RC128

1 2

SYSTEM_PWROK14

PCH_PWROK14,25

PM_DRAM_PWRGD14

+3V_PCH

2

0_0402_5%~D

0_0402_5%~D

12

12

0_0402_5%~D

0_0402_5%~D

RC11 0_0402_5%RC11 0_0402_5%

200_0402_1%

200_0402_1%

Place near JXDP1

RUN_ON_CPU1.5VS3#9,43

PLT_RST#15,21,22,23,24,25

MISC THERMAL PWR MANAGEMENT

MISC THERMAL PWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

BCLK_ITP

BCLK_ITP#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

3

CLK_CPU_DMI#_R

H2

CLK_CPU_DPLL_R

AG3

CLK_CPU_DPLL#_R

AG1

N59

N58

H_DRAMRST#

AT30

SM_RCOMP0

BF44

SM_RCOMP1

BE43

SM_RCOMP2

BG43

DDR3 Compensation Signals

XDP_PRDY#

N53

XDP_PREQ#

N55

XDP_TCK

L56

TCK

XDP_TMS

L55

TMS

XDP_TRST#

J58

XDP_TDI_R

M60

TDI

XDP_TDO_R

L59

TDO

XDP_DBRESET#_R

K58

XDP_BPM#0_R

G58

XDP_BPM#1_R

E55

XDP_BPM#2_R

E59

XDP_BPM#3_R

G55

XDP_BPM#4_R

G59

XDP_BPM#5_R

H60

XDP_BPM#6_R

J59

XDP_BPM#7_R

J61

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

CLK_CPU_DMI_R

J3

RC37 0_0402_5%RC37 0_0402_5%

1 2

RC38 0_0402_5%RC38 0_0402_5%

1 2

RC39 0_0402_5%RC39 0_0402_5%

1 2

RC40 0_0402_5%RC40 0_0402_5%

1 2

H_DRAMRST# 6

RC55140_0402_1% RC55140_0402_1%

1 2

RC5825.5_0402_1% RC5825.5_0402_1%

1 2

RC60200_0402_1% RC60200_0402_1%

1 2

RC50 0_0402_5%RC50 0_0402_5%

1 2

RC51 0_0402_5%RC51 0_0402_5%

1 2

RC56

RC56

0_0402_5%

0_0402_5%

1 2

RC59 0_0402_5%RC59 0_0402_5%

1 2

RC61 0_0402_5%RC61 0_0402_5%

1 2

RC62 0_0402_5%RC62 0_0402_5%

1 2

RC63 0_0402_5%RC63 0_0402_5%

1 2

RC64 0_0402_5%RC64 0_0402_5%

1 2

RC65 0_0402_5%RC65 0_0402_5%

1 2

RC66 0_0402_5%RC66 0_0402_5%

1 2

RC67 0_0402_5%RC67 0_0402_5%

1 2

RC68 0_0402_5%RC68 0_0402_5%

1 2

RC69 0_0402_5%RC69 0_0402_5%

1 2

RC70 0_0402_5%RC70 0_0402_5%

1 2

RC71 0_0402_5%RC71 0_0402_5%

1 2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

CFG12 7

CFG13 7

CFG14 7

CFG15 7

2

+3VS

@RC128

@

1 2

CLK_CPU_DMI 13

CLK_CPU_DMI# 13

CLK_CPU_DPLL 13

CLK_CPU_DPLL# 13

CLK_RES_ITP 13

CLK_RES_ITP# 13

12

RC6

RC6

10K_0402_5%

10K_0402_5%

@

@

1

D_PWG

2

XDP_DBRESET# 14

1

+3VALW

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

+1.5V_CPU_VDDQ

CC65

CC65

UC1

UC1

5

B

VCC

A

4

GND3Y

MC74VHC1G09DFT2G_SC70-5

MC74VHC1G09DFT2G_SC70-5

RUN_ON_CPU1.5VS3#

UC2

UC2

1

2

SN74LVC1G07DCKR_SC70-5~D

SN74LVC1G07DCKR_SC70-5~D

NC

VCC

A

GND3Y

2

G

G

5

4

1

2

+3VS

12

@

@

RC19

RC19

39_0402_1%

39_0402_1%

1 2

13

D

D

@

@

QC1

QC1

2N7002_SOT23

2N7002_SOT23

S

S

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

CC68

CC68

2

BUFO_CPU_RST#

RC8

RC8

200_0402_1%

200_0402_1%

VDDPWRGOOD

RC8

CRB 1.1K

CHECK LIST 0.7 --> 4.75K

INTEL recommand 1.1K

PDG 0.71 rev -->200

+1.05VS

12

RC32

RC32

75_0402_5%

75_0402_5%

RC33

RC33

1 2

43_0402_1%

43_0402_1%

PU/PD for JTAG signals

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO

XDP_TCK

XDP_TRST#

XDP_DBRESET#

H_CPUPWRGD_R

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

LA-6961P

LA-6961P

LA-6961P

1

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

BUF_CPU_RST#

12

@

@

RC34

RC34

0_0402_5%

0_0402_5%

+1.05VS

RC4551_0402_5% RC4551_0402_5%

RC4651_0402_5% RC4651_0402_5%

RC4751_0402_5% @ RC4751_0402_5% @

RC4851_0402_5% RC4851_0402_5%

RC5251_0402_5% RC5251_0402_5%

RC5451_0402_5% RC5451_0402_5%

+3VS

RC421K_0402_5% RC421K_0402_5%

RC4410K_0402_5% RC4410K_0402_5%

of

of

of

554Monday, January 24, 2011

554Monday, January 24, 2011

554Monday, January 24, 2011

0.4

0.4

0.4

Page 6

5

UCPU1C

DDR_A_D[0..63]10

D D

C C

DDR_A_BS010

DDR_A_BS110

B B

A A

DDR_A_BS210

DDR_A_CAS#10

DDR_A_RAS#10

DDR_A_WE#10

H_DRAMRST#5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

H_DRAMRST#

4.99K_0402_1%~D

4.99K_0402_1%~D

5

UCPU1C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

AP11

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

AR11

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

AT13

SA_DQ[14]

AU13

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

BA13

SA_DQ[18]

BB11

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

AY13

SA_DQ[23]

AV14

SA_DQ[24]

AR14

SA_DQ[25]

AY17

SA_DQ[26]

AR19

SA_DQ[27]

BA14

SA_DQ[28]

AU14

SA_DQ[29]

BB14

SA_DQ[30]

BB17

SA_DQ[31]

BA45

SA_DQ[32]

AR43

SA_DQ[33]

AW48

SA_DQ[34]

BC48

SA_DQ[35]

BC45

SA_DQ[36]

AR45

SA_DQ[37]

AT48

SA_DQ[38]

AY48

SA_DQ[39]

BA49

SA_DQ[40]

AV49

SA_DQ[41]

BB51

SA_DQ[42]

AY53

SA_DQ[43]

BB49

SA_DQ[44]

AU49

SA_DQ[45]

BA53

SA_DQ[46]

BB55

SA_DQ[47]

BA55

SA_DQ[48]

AV56

SA_DQ[49]

AP50

SA_DQ[50]

AP53

SA_DQ[51]

AV54

SA_DQ[52]

AT54

SA_DQ[53]

AP56

SA_DQ[54]

AP52

SA_DQ[55]

AN57

SA_DQ[56]

AN53

SA_DQ[57]

AG56

SA_DQ[58]

AG53

SA_DQ[59]

AN55

SA_DQ[60]

AN52

SA_DQ[61]

AG55

SA_DQ[62]

AK56

SA_DQ[63]

BD37

SA_BS[0]

BF36

SA_BS[1]

BA28

SA_BS[2]

BE39

SA_CAS#

BD39

SA_RAS#

AT41

SA_WE#

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

12

RC77

RC77

@

@

1 2

RC74 0_0402_5%~D

RC74 0_0402_5%~D

QC2

QC2

BSS138_SOT23

BSS138_SOT23

D

S

D

S

13

G

G

2

DRAMRST_CNTRL

1

CC69

CC69

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

2

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

DDR3_DRAMRST#_R

4

AU36

SA_CLK[0]

AV36

SA_CLK#[0]

AY26

SA_CKE[0]

AT40

SA_CLK[1]

AU40

SA_CLK#[1]

BB26

SA_CKE[1]

BB40

SA_CS#[0]

BC41

SA_CS#[1]

AY40

SA_ODT[0]

BA41

SA_ODT[1]

AL11

SA_DQS#[0]

AR8

SA_DQS#[1]

AV11

SA_DQS#[2]

AT17

SA_DQS#[3]

AV45

SA_DQS#[4]

AY51

SA_DQS#[5]

AT55

SA_DQS#[6]

AK55

SA_DQS#[7]

AJ11

SA_DQS[0]

AR10

SA_DQS[1]

AY11

SA_DQS[2]

AU17

SA_DQS[3]

AW45

SA_DQS[4]

AV51

SA_DQS[5]

AT56

SA_DQS[6]

AK54

SA_DQS[7]

BG35

SA_MA[0]

BB34

SA_MA[1]

BE35

SA_MA[2]

BD35

SA_MA[3]

AT34

SA_MA[4]

AU34

SA_MA[5]

BB32

SA_MA[6]

AT32

SA_MA[7]

AY32

SA_MA[8]

AV32

SA_MA[9]

BE37

SA_MA[10]

BA30

SA_MA[11]

BC30

SA_MA[12]

AW41

SA_MA[13]

AY28

SA_MA[14]

AU26

SA_MA[15]

+1.5V

12

RC75

RC75

1K_0402_5%~D

1K_0402_5%~D

1 2

RC76 1K_0402_5%RC76 1K_0402_5%

DG 1.0 Figure 61 RC76=1K

4

3

M_CLK_DDR0

M_CLK_DDR#0

DDR_CKE0_DIMMA M_CLK_DDR2

M_CLK_DDR1

M_CLK_DDR#1

DDR_CKE1_DIMMA

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

M_ODT0

M_ODT1

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

1 2

RC72 0_0402_5%~DRC72 0_0402_5%~D

@

@

1 2

RC73 0_0402_5%~D

RC73 0_0402_5%~D

M_CLK_DDR0 10

M_CLK_DDR#0 10

DDR_CKE0_DIMMA 10 M_CLK_DDR2 11

M_CLK_DDR1 10

M_CLK_DDR#1 10

DDR_CKE1_DIMMA 10

DDR_CS0_DIMMA# 10

DDR_CS1_DIMMA# 10

M_ODT0 10

M_ODT1 10

DDR_A_DQS#[0..7] 10

DDR_A_DQS[0..7] 10

DDR_A_MA[0..15] 10

DDR3_DRAMRST# 10,11

DRAMRST_CNTRL_PCH 13

DRAMRST_CNTRL_EC 25

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

DDR_B_D[0..63]11

DDR_B_BS011

DDR_B_BS111

DDR_B_BS211

DDR_B_CAS#11

DDR_B_RAS#11

DDR_B_WE#11

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

UCPU1D

UCPU1D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

SB_DQ[57]

AG58

SB_DQ[58]

AG59

SB_DQ[59]

AM60

SB_DQ[60]

AL59

SB_DQ[61]

AF61

SB_DQ[62]

AH60

SB_DQ[63]

BG39

SB_BS[0]

BD42

SB_BS[1]

AT22

SB_BS[2]

AV43

SB_CAS#

BF40

SB_RAS#

BD45

SB_WE#

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

2

BA34

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

M_CLK_DDR#2

AY34

DDR_CKE2_DIMMB

AR22

M_CLK_DDR3

BA36

M_CLK_DDR#3

BB36

DDR_CKE3_DIMMB

BF27

DDR_CS2_DIMMB#

BE41

DDR_CS3_DIMMB#

BE47

M_ODT2

AT43

M_ODT3

BG47

DDR_B_DQS#0

AL3

DDR_B_DQS#1

AV3

DDR_B_DQS#2

BG11

DDR_B_DQS#3

BD17

DDR_B_DQS#4

BG51

DDR_B_DQS#5

BA59

DDR_B_DQS#6

AT60

DDR_B_DQS#7

AK59

DDR_B_DQS0

AM2

DDR_B_DQS1

AV1

DDR_B_DQS2

BE11

DDR_B_DQS3

BD18

DDR_B_DQS4

BE51

DDR_B_DQS5

BA61

DDR_B_DQS6

AR59

DDR_B_DQS7

AK61

DDR_B_MA0

BF32

DDR_B_MA1

BE33

DDR_B_MA2

BD33

DDR_B_MA3

AU30

DDR_B_MA4

BD30

DDR_B_MA5

AV30

DDR_B_MA6

BG30

DDR_B_MA7

BD29

DDR_B_MA8

BE30

DDR_B_MA9

BE28

DDR_B_MA10

BD43

DDR_B_MA11

AT28

DDR_B_MA12

AV28

DDR_B_MA13

BD46

DDR_B_MA14

AT26

DDR_B_MA15

AU22

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

LA-6961P

LA-6961P

LA-6961P

1

1

M_CLK_DDR#2 11

DDR_CKE2_DIMMB 11

M_CLK_DDR3 11

M_CLK_DDR#3 11

DDR_CKE3_DIMMB 11

DDR_CS2_DIMMB# 11

DDR_CS3_DIMMB# 11

M_ODT2 11

M_ODT3 11

DDR_B_DQS#[0..7] 11

DDR_B_DQS[0..7] 11

DDR_B_MA[0..15] 11

654Monday, January 24, 2011

654Monday, January 24, 2011

654Monday, January 24, 2011

of

of

of

0.4

0.4

0.4

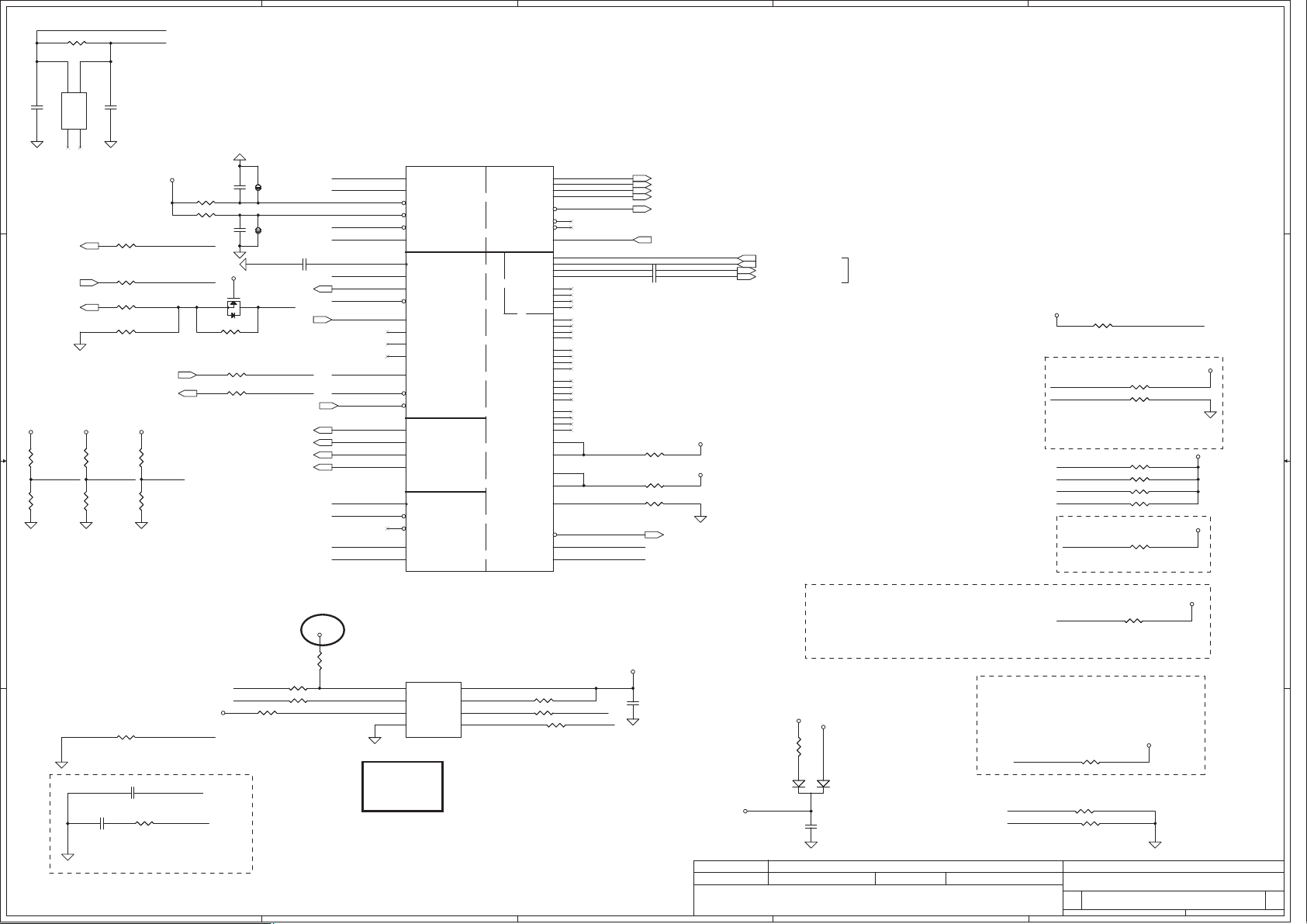

Page 7

5

4

3

2

1

CFG Straps for Processor

D D

UCPU1E

UCPU1E

CFG05

T51PAD~D@T51PAD~D

T53PAD~D@T53PAD~D

T59PAD~D@T59PAD~D

T60PAD~D@T60PAD~D

T61PAD~D@T61PAD~D

T62PAD~D@T62PAD~D

CFG125

CFG135

CFG145

+VCC_CORE

RC80

@RC80

@

50_0402_1%

50_0402_1%

+VCC_GFXCORE_AXG

C C

B B

+V_DDR_REFB

+V_DDR_REFA

RC82 0_0402_5%~D@RC82 0_0402_5%~D@

1 2

RC83 0_0402_5%~D@RC83 0_0402_5%~D@

1 2

RC84

RC84

1K_0402_1%

1K_0402_1%

INTEL 12/28 recommand

to add 1k pull down

RC79

12

12

@RC79

@

50_0402_1%

50_0402_1%

12

12

RC85

RC85

1K_0402_1%

1K_0402_1%

CFG155

T64PAD~D@T64PAD~D

T63PAD~D@T63PAD~D

1 2

RC91 50_0402_1%@RC91 50_0402_1%@

@

@

1 2

RC90 50_0402_1%

RC90 50_0402_1%

+V_DDR_REFA_R

+V_DDR_REFB_R

CFG0

CFG1

@

CFG2

CFG3

@

CFG4

CFG5

CFG6

CFG7

CFG8

@

CFG9

@

CFG10

@

CFG11

@

CFG12

CFG13

CFG14

CFG15

CFG16

@

CFG17

@

VCC_VAL_SENSE

VSS_VAL_SENSE

VCC_AXG_VAL_SENSE

VSS_AXG_VAL_SENSE

T19PAD~D @T19PAD~D @

T25PAD~D @T25PAD~D @

T26PAD~D @T26PAD~D @

T28PAD~D @T28PAD~D @

T30PAD~D @T30PAD~D @

T33PAD~D @T33PAD~D @

T34PAD~D @T34PAD~D @

T35PAD~D @T35PAD~D @ T29 PAD~D@ T29 PAD~D@

T38PAD~D @T38PAD~D @

T39PAD~D @T39PAD~D @

T40PAD~D @T40PAD~D @

T41PAD~D @T41PAD~D @

T42PAD~D @T42PAD~D @

T43PAD~D @T43PAD~D @

T44PAD~D @T44PAD~D @

T45PAD~D @T45PAD~D @

T46PAD~D @T46PAD~D @

T47PAD~D @T47PAD~D @

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

T2 PAD~D@T2 PAD~D@

T3 PAD~D@T3 PAD~D@

T4 PAD~D@T4 PAD~D@

T5 PAD~D@T5 PAD~D@

T6 PAD~D@T6 PAD~D@

T7 PAD~D@T7 PAD~D@

T8 PAD~D@T8 PAD~D@

T9 PAD~D@T9 PAD~D@

T10 PAD~D@ T10 PAD~D@

T11 PAD~D@ T11 PAD~D@

T12 PAD~D@ T12 PAD~D@

T13 PAD~D@ T13 PAD~D@

T14 PAD~D@ T14 PAD~D@

T15 PAD~D@ T15 PAD~D@

T16 PAD~D@ T16 PAD~D@

T17 PAD~D@ T17 PAD~D@

T204 PAD~D@T204 PAD~D@

T20 PAD~D@ T20 PAD~D@

T21 PAD~D@ T21 PAD~D@

T22 PAD~D@ T22 PAD~D@

T24 PAD~D@ T24 PAD~D@

T31 PAD~D@ T31 PAD~D@

T36 PAD~D@ T36 PAD~D@

T48 PAD~D@ T48 PAD~D@

PEG Static Lane Reversal - CFG2 is for the 16x

Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5]

CFG2

12

RC78

@RC78

@

1K_0402_1%~D

1K_0402_1%~D

1:(Default) Normal Operation; Lane #

*

CFG2

definition matches socket pin map definition

0:Lane Reversed

CFG4

12

RC81

@RC81

@

1K_0402_1%~D

1K_0402_1%~D

1 : Disabled; No Physical Display Port

*

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

12

12

RC87

@RC87

@

1K_0402_1%~D

1K_0402_1%~D

11: (Default) x16 - Device 1 functions 1 and 2 disabled

*

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

RC86

@RC86

@

1K_0402_1%~D

1K_0402_1%~D

CFG7

12

RC89

@RC89

@

1K_0402_1%~D

1K_0402_1%~D

PEG DEFER TRAINING

1: (Default) PEG Train immediately

*

CFG7

following xxRESETB de assertion

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

0: PEG Wait for BIOS for training

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

LA-6961P

LA-6961P

LA-6961P

754Monday, January 24, 2011

754Monday, January 24, 2011

754Monday, January 24, 2011

1

0.4

0.4

0.4

of

of

of

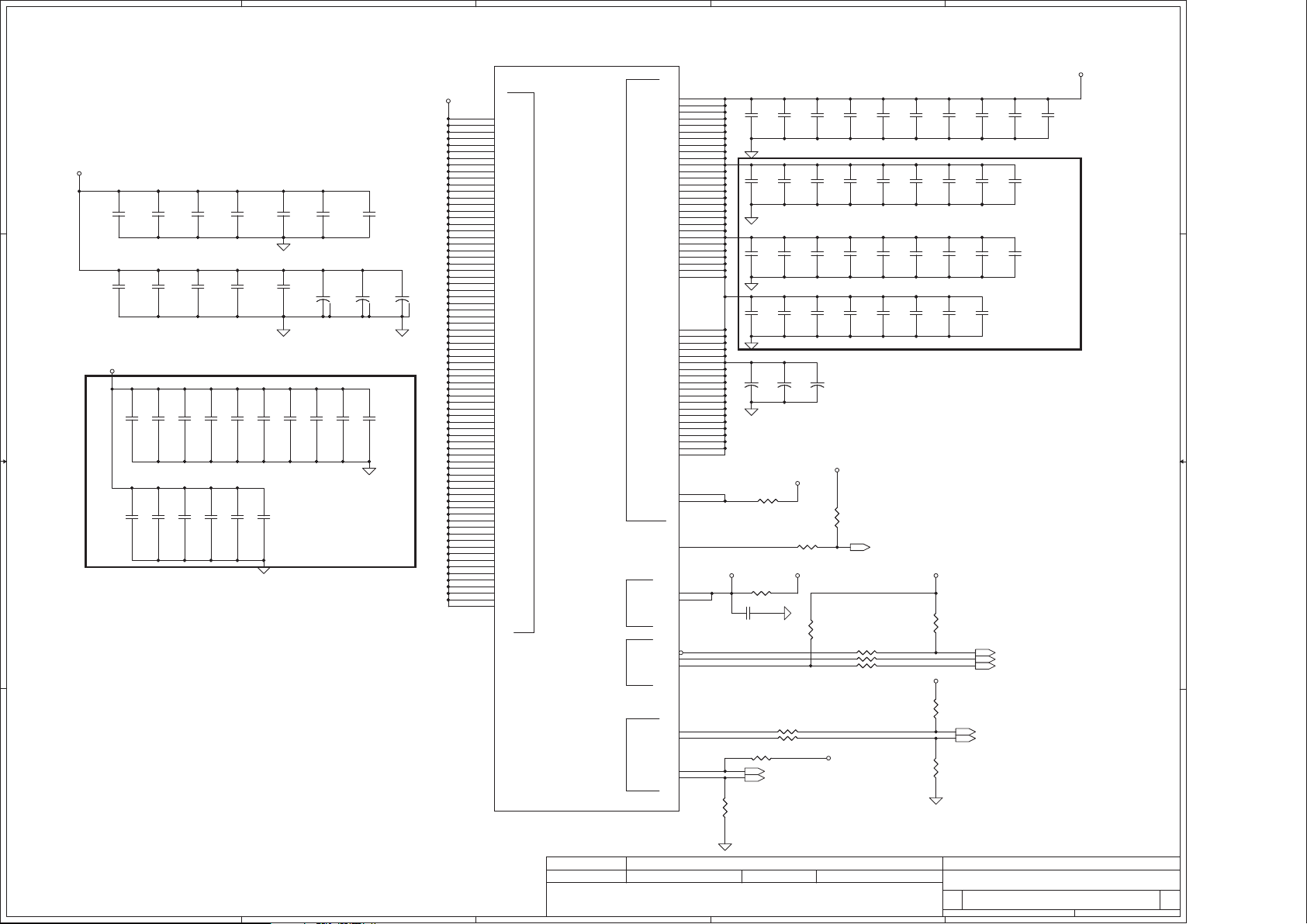

Page 8

5

D D

+VCC_CORE

CC242

22U_0805_6.3V6M

CC242

CC241

22U_0805_6.3V6M

CC241

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

1

2

C C

+VCC_CORE

B B

A A

22U_0805_6.3V6M

1

2

CC252

22U_0805_6.3V6M

CC252

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

,ŝŐŚͲ&ƌĞƋƵĞŶĐLJĞĐŽƵƉůŝŶŐ

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC266

CC266

CC265

CC265

1

1

2

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC275

CC275

CC276

CC276

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

CC230

CC230

1

2

CC253

CC253

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC267

CC267

1

1

2

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC277

CC277

1

1

2

2

CC231

CC231

1

2

CC254

CC254

1

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC268

CC268

1

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC278

CC278

1

2

CC232

22U_0805_6.3V6M

CC232

22U_0805_6.3V6M

1

2

CC255

22U_0805_6.3V6M

CC255

22U_0805_6.3V6M

1

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC269

CC269

CC270

CC270

1

2

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC279

CC279

CC280

CC280

1

2

22U_0805_6.3V6M

CC256

22U_0805_6.3V6M

CC256

22U_0805_6.3V6M

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC271

CC271

1

2

CC233

22U_0805_6.3V6M

CC233

22U_0805_6.3V6M

1

2

1

C106

C106

+

+

2 3

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC272

CC272

1

2

4

1

2

1

C107

C107

+

+

2 3

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC273

CC273

1

1

2

2

placed internal

DC=33A

CC234

22U_0805_6.3V6M

CC234

22U_0805_6.3V6M

1

C108

C108

+

+

2 3

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

2.2U_0402_6.3V6K

2.2U_0402_6.3V6K

CC274

CC274

+VCC_CORE

UCPU1F

UCPU1F

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

SANDY-BRIDGE_BGA1023~D

SANDY-BRIDGE_BGA1023~D

@

@

3

CORE SUPPLY

CORE SUPPLY

POWER

POWER

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

VCCIO[33]

PEG AND DDRSENSE LINES SVID QUIET RAILS

PEG AND DDRSENSE LINES SVID QUIET RAILS

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

8.5A

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

+VCCP_VCCPQ +1.05VS

AM25

AN22

H_CPU_SVIDALRT#

A44

H_CPU_SVIDCLK

B43

H_CPU_SVIDDAT

C44

VCCSENSE_R

F43

VSSSENSE_R

G43

AN16

AN17

@

@

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

330U_D2_2VM_R6M~D

330U_D2_2VM_R6M~D

1

+

+

@

@

2

RC122

RC122

1 2

0_0805_5%

0_0805_5%

H_VCCP_SEL

RC123

RC123

1 2

0_0805_5%

0_0805_5%

1 2

CC281

CC281

1U_0402_6.3V6K

1U_0402_6.3V6K

RC98 0_0402_5%~DRC98 0_0402_5%~D

RC99 0_0402_5%~DRC99 0_0402_5%~D

@

@

RC124

RC124

1 2

12

RC125

RC125

10_0402_1%

10_0402_1%

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC235

CC235

CC236

CC236

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC238

CC238

CC224

CC224

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC243

CC243

CC244

CC244

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC258

CC258

CC257

CC257

2

330U_D2_2VM_R6M~D

330U_D2_2VM_R6M~D

1

CC110

CC110

CC111

CC111

+

+

2

+1.05VS

1 2

1 2

10_0402_1%

10_0402_1%

VCCIO_SENSE 50

VSSIO_SENSE 50

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC217

CC217

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CC239

CC239

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CC245

CC245

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

CC259

CC259

2

2

330U_D2_2VM_R6M~D

330U_D2_2VM_R6M~D

1

CC112

CC112

+

+

2

+1.05VS

12

RC113

RC113

75_0402_5%

75_0402_5%

10U_0603_6.3V6M

CC237

CC237

1U_0402_6.3V6K

1U_0402_6.3V6K

CC225

CC225

1U_0402_6.3V6K

1U_0402_6.3V6K

CC246

CC246

1U_0402_6.3V6K

1U_0402_6.3V6K

CC260

CC260

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC218

CC218

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC226

CC226

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC247

CC247

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC261

CC261

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC219

CC219

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC240

CC240

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC248

CC248

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC262

CC262

2

Need PWR add new circuit on 1.05V(refer CRB)

12

RC880_0402_5%~D RC880_0402_5%~D

12

RC95

RC95

130_0402_1%~D

130_0402_1%~D

RC94 43_0402_1%RC94 43_0402_1%

RC92 0_0402_5%~DRC92 0_0402_5%~D

RC96 0_0402_5%~DRC96 0_0402_5%~D

+1.05VS

1 2

1 2

1 2

VCCP_PWRCTRL 50

+1.05VS

+VCC_CORE

12

RC93

RC93

75_0402_5%

75_0402_5%

12

RC97

RC97

100_0402_1%~D

100_0402_1%~D

12

RC100

RC100

100_0402_1%~D

100_0402_1%~D

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

1

2

1

2

1

2

CC221

CC221

CC220

CC220

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC228

CC228

CC227

CC227

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC249

CC249

CC250

CC250

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC263

CC263

CC264

CC264

2

placed internal

Place the PU

resistors close to CPU

VR_SVID_ALRT# 54

VR_SVID_CLK 54

VR_SVID_DAT 54

Place the PU

resistors close to CPU

VCCSENSE 54

VSSSENSE 54

Place the PU

resistors close to VR

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC222

CC222

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC229

CC229

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC251

CC251

2

1

+1.05VS

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC223

CC223

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/07/06 2011/07/06

2010/07/06 2011/07/06

2010/07/06 2011/07/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

LA-6961P

LA-6961P

LA-6961P

854Monday, January 24, 2011

854Monday, January 24, 2011

854Monday, January 24, 2011

of

of

1

of

0.4

0.4

0.4

Page 9

5

4

3

2

1

+1.5V_CPU_VDDQ Source

+1.5V +1.5V_CPU_VDDQ

B+_BIAS+3VALW

12

RC102

RC102

100K_0402_5%~D

100K_0402_5%~D

2

22U_0805_6.3V6M

22U_0805_6.3V6M

CC288

CC288

1

1

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC328

CC328

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC318

CC318

2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC301

CC301

1

2

VCC_AXG_SENSE

VSS_AXG_SENSE

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D