Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

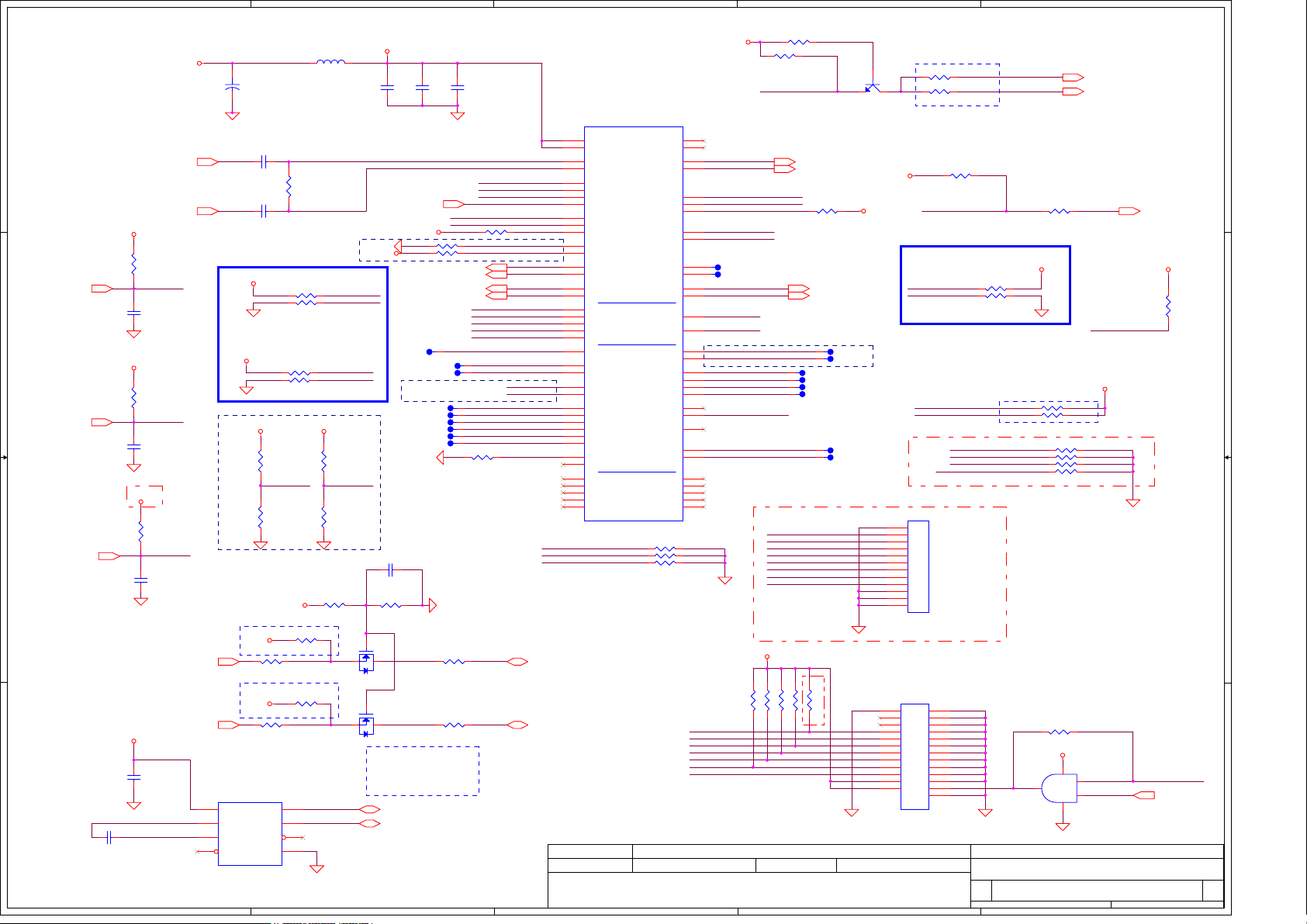

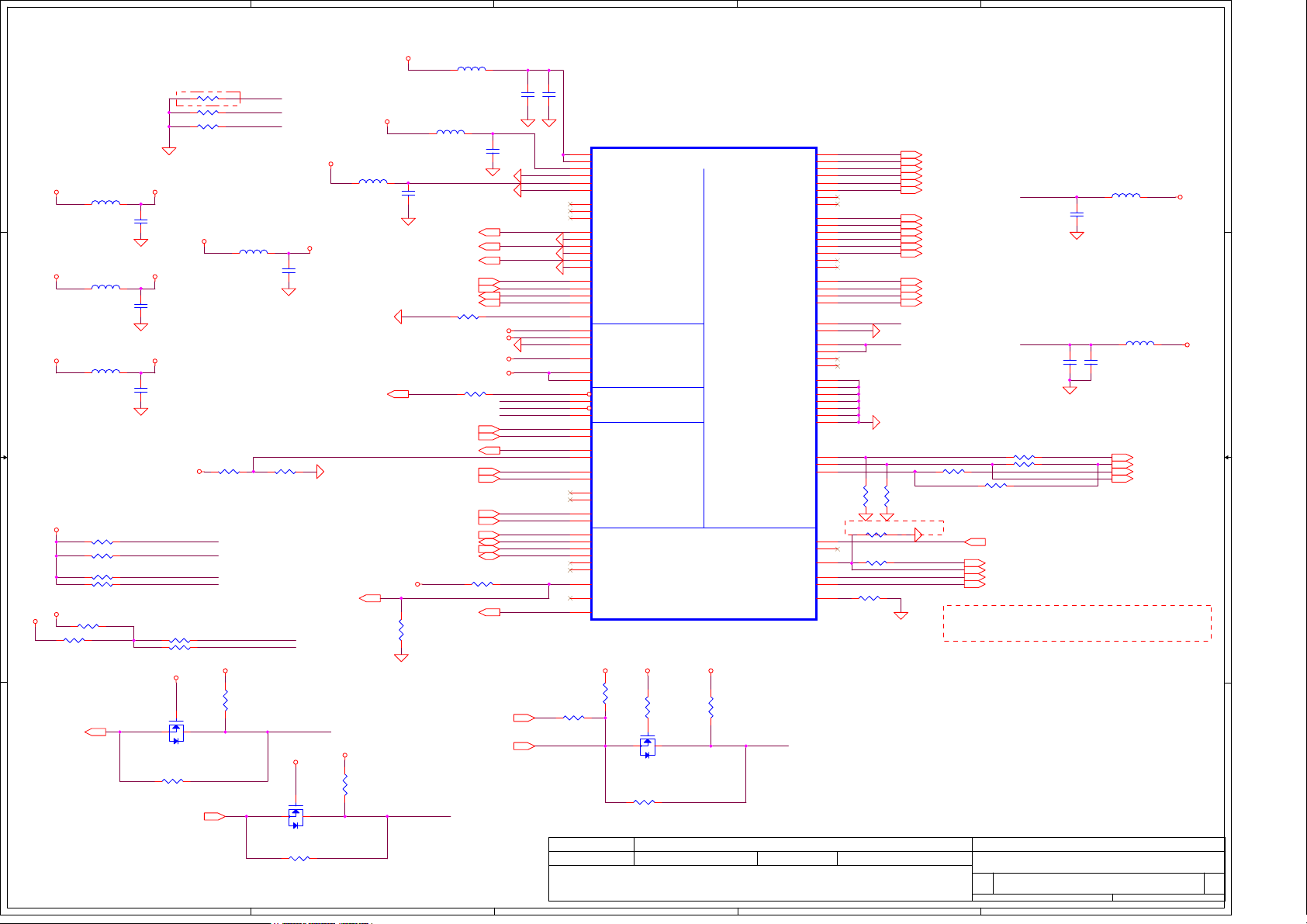

KBYF0 Schematics Document

AMD Griffin Processor with RS780M+SB700

(With ATI MXM/B)

3 3

2009-01-22

REV:0.3

ZZZ1

PCB

DA60000B600-*

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

KBYF0 LA-5051P

146Tuesday, Fe b r u a r y 03, 2009

E

0.3

of

Page 2

A

Compal Confidential

B

C

D

E

Model Name : KBYF0

File Name: LA-5051P

1 1

HDMI Conn.

page 17

LCD Conn.

Clock Generator

ICS9LPRS488B

page 16

page 15

CRT Conn.

page 18

Thermal Sensor

ADM1032

page 5

Fan Control

page 36

AMD S1G2 Processor

uPGA-638 Package

page 4,5,6,7

Hyper Transport Link

16 x 16

Memory BUS(DDRII)

Dual Channel

1.8V DDRII 667/800

200pin DDRII-SO-DIMM X2

BANK 0, 1, 2, 3

page 8,9

ATI RS780M

MXM III VGA/B

page 14

2 2

MINI Card x2

TV-Tuner WLAN

page 28

LAN(GbE)

B5784M

page 26

PCI-Express 16x

PCI-Express 1x

port 3port 1,2

BGA-528

page 10,11,12,13

A link

Express2

3.3V 48MHz

USB Conn

x4

page 29 page 16 page 29

USB port 0,1,2,6

CMOS

Camera

USB port 3 USB port 12 USB port4

Bluetooth

Conn

USB

Card Reader

RTS5159

page 25

5 in 1

Socket

page 25

ATI SB700

RJ45

page 27

SPI

RTC CKT.

3 3

page 19

BTN/B Conn.

page 31

BIOS ROM

page 21

BGA-528

page 19,20,21,22,23

LPC BUS

Power On/Off CKT.

page 32

LED/B Conn.

page 31

ENE KB926

page 30

3.3V 24MHz

S-ATA

SATA HDD

Conn.

page 24

port 0

DC/DC Int erface CKT.

page 37

Media/B Conn.

page 31

Touch Pad

page 31

Int.KBD

page 31

HD Audio

Second SATA

HDD Conn.

page 24

port1

SATA ODD

Conn.

page 24

port 2

MDC 1.5

Conn

page 32

HDA Codec

ALC272

page 33

Audio AMP

TPA6017

page 34

Phone Jack x2

page 34

Int. MIC

page 33

Digital/Analog MIC.

Mono AMP

(for Woofer)

page 34

FUN/B Conn.

page 31

4 4

Power Circuit DC/DC

page 39,40,41

42,43,44,45

A

USB/B Conn.

USB port 0,1,2,6

page 28

B

CIR

page 32

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

EC ROM

page 31

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Block Diagrams

KBKC0 LA-5051P

0.3

of

246Tuesday, Fe b r u a r y 03, 2009

E

Page 3

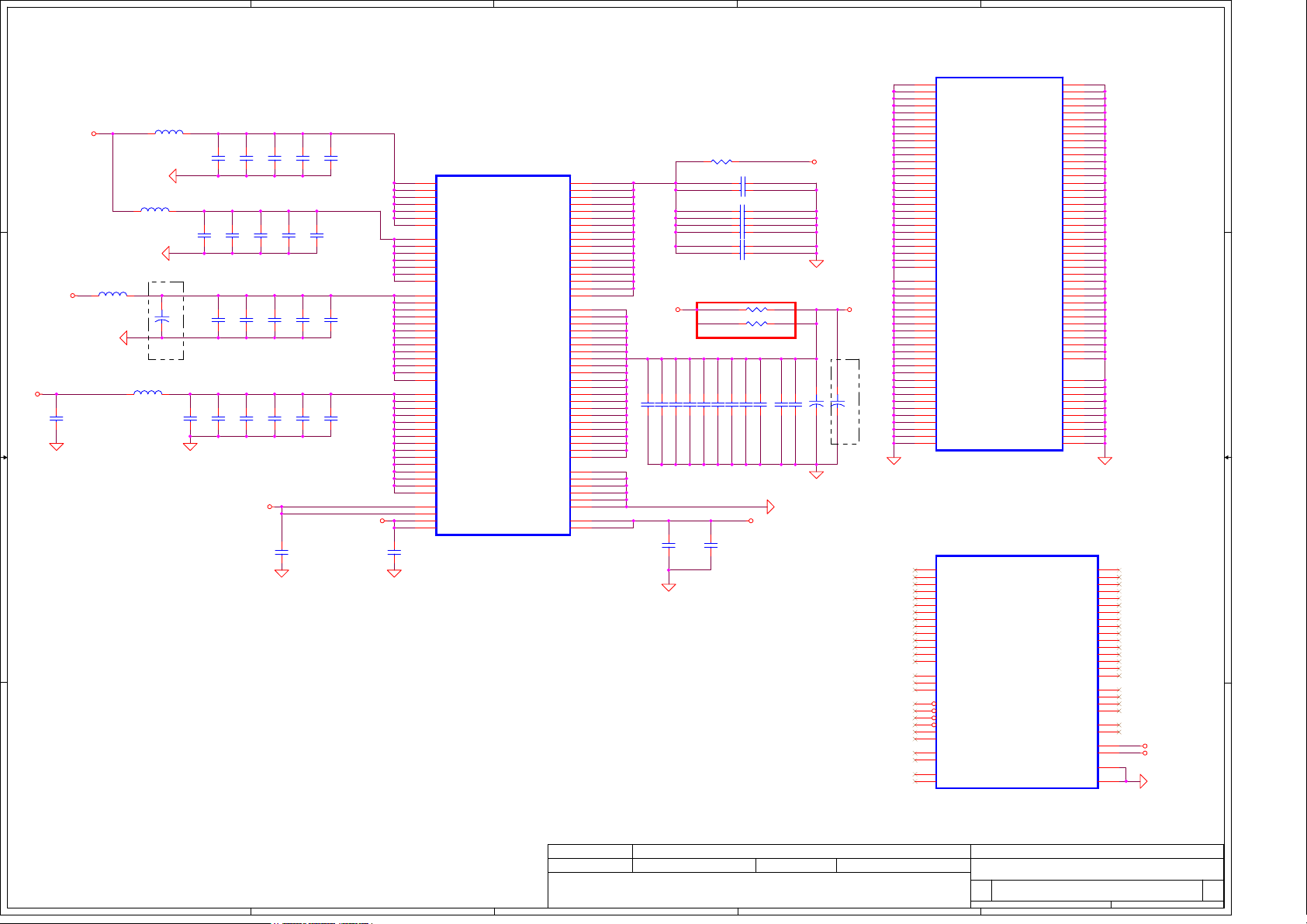

A

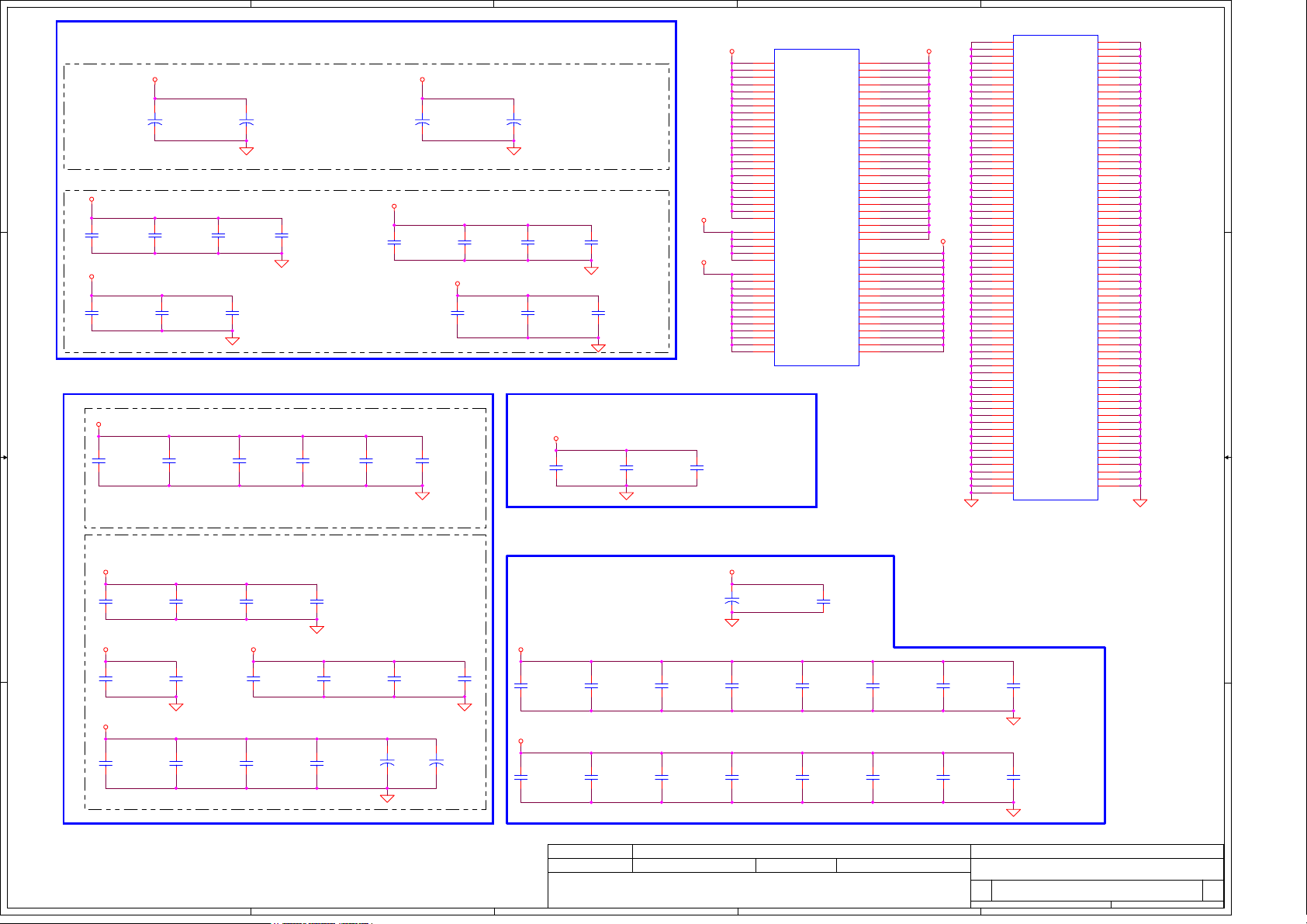

Voltage Rails

Power Pl ane Description

VIN

B+

1 1

2 2

+CPU_CORE_0

+CPU_CORE_1 Core voltage for CPU ON OFF OFF

+CPU_CORE_NB Core voltage for CPU

+0.9V 0.9V switched power rail for DDR terminator

+1.1VS

+1.2V_HT 1.25V switched power rail ON OFF OFF

+NB_CORE

+1.5VS

+1.8V

+1.8VS 1.8V switched power rail

+2.5VS

+3VALW

+3V_LAN 3.3V power rail for LAN ON ON ON

+3VS

+5VALW

+5VS

+VSB VSB always on power rail ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise i t is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.05V switched power rail

1.5V power rail for PCIE Card

1.8V power rail for CPU VDDIO and DDR

2.5V for CPU_VDDA and MXM/B

3.3V always on power rail

3.3V switched power r ail

5V always on power rail

5V switched power rail

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupt s

No PCI device

B

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF OFF

ON

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

ON

OFFOFFON1.0V~1.1V switched power rail for NB VDDC

OFF OF F

ON

OFF

OFF

OFF

OFF

OFF

ON ON *

OFF

OFF

ON*

ON

OFFON

OFF

ONON

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW

HIGH

LOWLOWLOW

D

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ONONON ON

ON

OFF

ON

OFF

OFF

OFF

OFF

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

Vtyp

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

BOARD ID Table BTO Option Table

Board ID

0

1

2

PCB Revision

0.1

0.2

0.3 0.4 1.0*

BTO Item BOM Structure

Discrete

UMA

VGA@

UMA@

E

LOW

OFF

OFF

OFF

3

4

5

6

7

EC SM Bus1 address

3 3

Device

Smart Battery

EEPROM(24C16/02)

MXM GMT G781-1

Address Address

1010 000X b

1001 101X b

EC SM Bus2 address

Device

ADI ADM1032

CPU SB

1001 100X b0001 011X b

1001 101X b

PROJECT ID Table

Board ID

0

1

2

PROJECT

KBKC0 (SJM70)

KBYF0 (SJV70)

3

SB700

SM Bus 0 address

Device

Clock Generator

(ICS9LPRS365)

DDR DIMM0

DDR DIMM2

Minicard

4 4

Minicard

A

Address

1101 001Xb

1001 000Xb

1001 010Xb

SB700

SM Bus 1 address

Device Address

Lan

B

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

5

6

7

2008/11/03 2009/11/03

C

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

Notes List

KBYF0 LA-5051P

346Tuesday, Fe b r u a r y 03, 2009

E

0.3

of

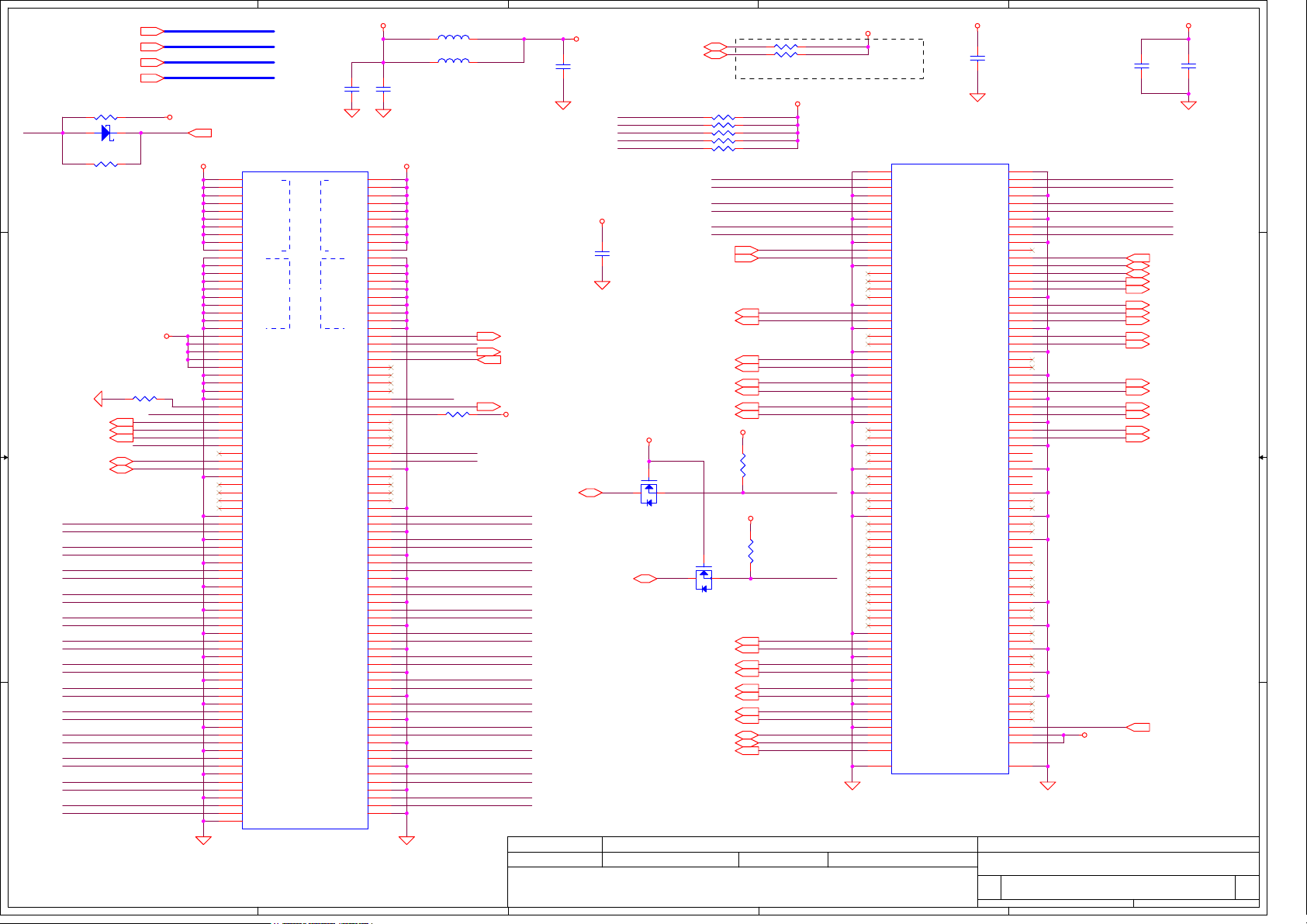

Page 4

A

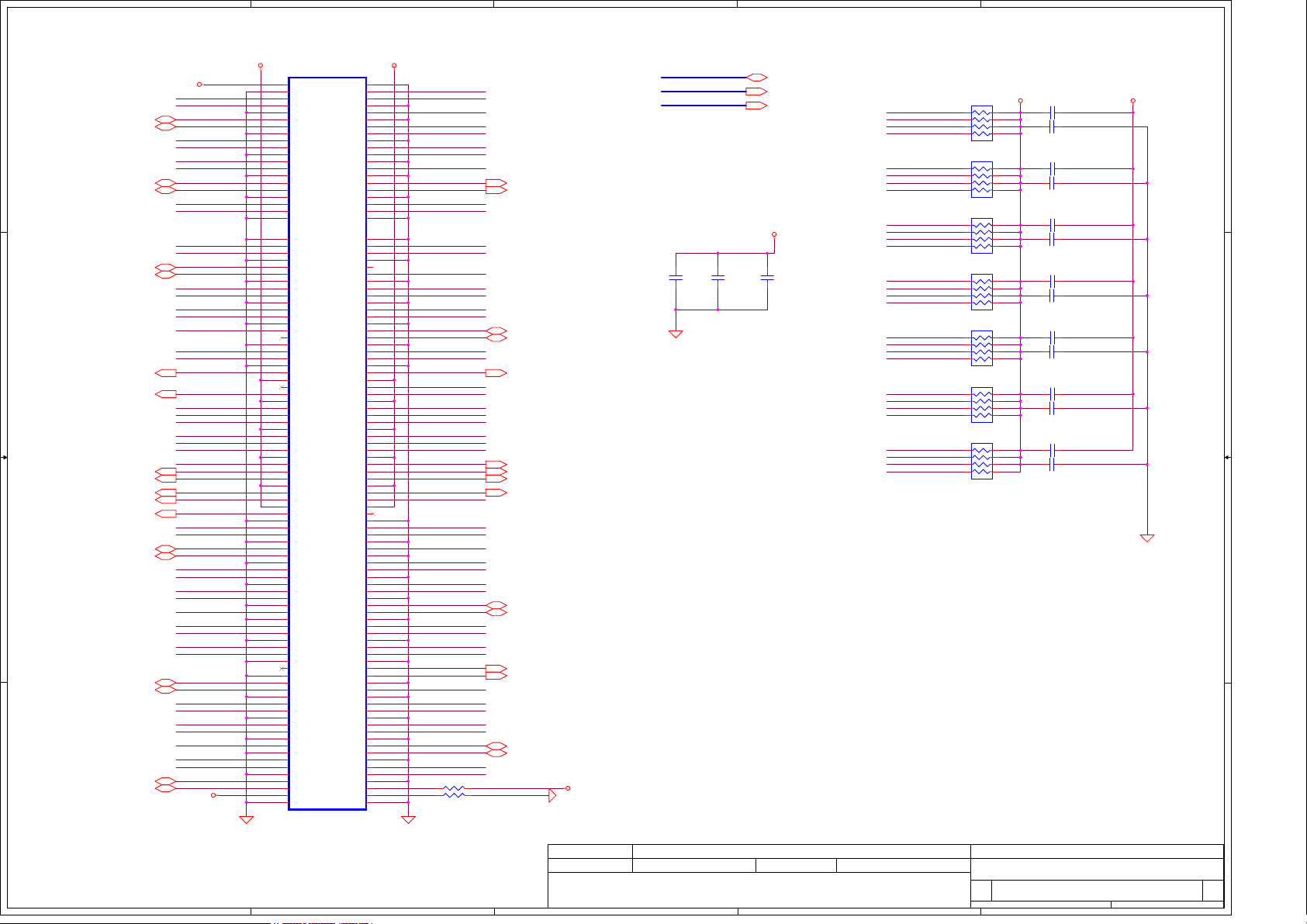

1 1

B

C

D

E

+1.2V_HT

250 mil

1

H_CADIP[0..15]<10>

H_CADIN[0..15]<10>

H_CADIP[0..15]

H_CADIN[0..15]

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP[0..15] <10>

H_CADON[0..15] <10>

C535

4.7U_0805_10V4Z

2

1

C534

4.7U_0805_10V4Z

2

VLDT CAP.

1

C520

0.22U_0603_16V4Z

2

1

2

C518

0.22U_0603_16V4Z

1

C516

180P_0402_50V8J

2

1

C517

180P_0402_50V8J

2

Near CPU Socket

+1.2V_HT

2 2

3 3

H_CLKIP0<10>

H_CLKIN0<10>

H_CLKIP1<10>

H_CLKIN1<10>

H_CTLIP0<10>

H_CTLIN0<10>

H_CTLIP1<10>

H_CTLIN1<10>

VLDT=500mA

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

H_CTLIN0

H_CTLIP1

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

6090022100G_B

Athlon 64 S1

Processor Socket

CONN@

JCPU1A

HT LINK

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

+1.2V_HT

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

1 2

C533 4.7U_0805_10V4Z

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

H_CTLOP0H_CTLIP0

H_CTLON0

H_CTLOP1

H_CTLON1H_CTLIN1

H_CLKOP0 <10>

H_CLKON0 <10>

H_CLKOP1 <10>

H_CLKON1 <10>

H_CTLOP0 <10>

H_CTLON0 <10>

H_CTLOP1 <10>

H_CTLON1 <10>

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G2 HT I/F

KBYF0 LA-5051P

446Tuesday, F e b r u a r y 03, 2009

E

0.3

of

Page 5

A

B

C

D

E

PLACE CLOSE TO PROCESSOR

Processor DDR2 Memory Interface

WITHIN 1.5 INCH

AD10

AF10

AE10

AA16

D10

C10

B10

H16

T19

V22

U21

V19

T20

U19

U20

V20

J22

J20

N19

N20

E16

F16

Y16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

J21

R19

T22

T24

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

VTT1

MEM:CMD/CTRL/CLK

VTT2

VTT3

VTT4

MEMZP

MEMZN

RSVD_M1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CLK_H2

MA_CLK_L2

MA_CLK_H3

MA_CLK_L3

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

Athlon 64 S1

Processor

Socket

CONN@

JCPU1B

1

2

1

2

1

2

1

2

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

C244

1.5P_0402_50V9C

C178

1.5P_0402_50V9C

C509

1.5P_0402_50V9C

C447

1.5P_0402_50V9C

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

+0.9V+0.9V

+MCH_REF

DDRB_ODT0

DDRB_ODT1

DDRB_SCS1#

DDRB_CKE0

DDRB_CKE1

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#DDRA_CLK1#

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_SMA14

DDRB_SMA15

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

@

@

DDRB_SBS0# <9>

DDRB_SBS1# <9>

DDRB_SBS2# <9>

DDRB_SRAS# <9>

DDRB_SCAS# <9>

DDRB_SWE# <9>

T2PAD

T17PAD

DDRB_ODT0 <9>

DDRB_ODT1 <9>

DDRB_SCS0# <9>

DDRB_SCS1# <9>

DDRB_CKE0 <9>

DDRB_CKE1 <9>

DDRB_CLK0 <9>

DDRB_CLK0# <9>

DDRB_CLK1 <9>

DDRB_CLK1# <9>

DDRB_SMA[15..0] <9>

1 1

2 2

R79

1K_0402_1%

R78

1K_0402_1%

+1.8V

1 2

1 2

+MCH_REF

1

C181

2

1

C189

2

0.1U_0402_16V4Z

1000P_0402_50V7K

Place them close to CPU within 1"

R343 39.2_0402_1%

1 2

+1.8V

DDRA_ODT0<8>

DDRA_ODT1<8>

DDRA_SCS0#<8>

DDRA_SCS1#<8>

DDRA_CKE0<8>

DDRA_CKE1<8>

DDRA_CLK0<8>

DDRA_CLK0#<8>

DDRA_CLK1<8>

DDRA_CLK1#<8>

3 3

4 4

DDRA_SMA[15..0]<8>

DDRA_SBS0#<8>

DDRA_SBS1#<8>

DDRA_SBS2#<8>

DDRA_SRAS#<8>

DDRA_SCAS#<8>

DDRA_SWE#<8>

1 2

R352 39.2_0402_1%

T5 PA D

DDRA_SCS0#

DDRA_SCS1# DDRB_SCS0#

DDRA_CKE0

DDRA_CKE1

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

MBMZP

MBMZN VTT_SENSE

@

DDRA_ODT0

DDRA_ODT1

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

DDRB_SDQ[63..0]<9>

DDRB_SDM[7..0]<9>

DDRB_SDQS0<9>

DDRB_SDQS0#<9>

DDRB_SDQS1<9>

DDRB_SDQS1#<9>

DDRB_SDQS2<9>

DDRB_SDQS2#<9>

DDRB_SDQS3<9>

DDRB_SDQS3#<9>

DDRB_SDQS4<9>

DDRB_SDQS4#<9>

DDRB_SDQS5<9>

DDRB_SDQS5#<9>

DDRB_SDQS6<9>

DDRB_SDQS6#<9>

DDRB_SDQS7<9>

DDRB_SDQS7#<9>

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

JCPU1C

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

6090022100G_B

CONN@

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

Athlon 64 S1

Processor Socket

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_SDQ[63..0] <8>

DDRA_SDM[7..0] <8>

DDRA_SDQS0 <8>

DDRA_SDQS0# <8>

DDRA_SDQS1 <8>

DDRA_SDQS1# <8>

DDRA_SDQS2 <8>

DDRA_SDQS2# <8>

DDRA_SDQS3 <8>

DDRA_SDQS3# <8>

DDRA_SDQS4 <8>

DDRA_SDQS4# <8>

DDRA_SDQS5 <8>

DDRA_SDQS5# <8>

DDRA_SDQS6 <8>

DDRA_SDQS6# <8>

DDRA_SDQS7 <8>

DDRA_SDQS7# <8>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G2 DDRII I/F

KBYF0 LA-5051P

546Tuesday, F e b r u a r y 03, 2009

E

0.3

of

Page 6

A

B

C

D

E

+2.5VDDA

L33

1 2

FBM_L11_201209_300L_0805

3900P_0402_50V7K

12

R409

169_0402_1%

CPU_VDD0_FB_H

1 2

CPU_VDD0_FB_L

1 2

Close to CPU

CPU_VDD1_FB_H

1 2

CPU_VDD1_FB_L

1 2

R107

@

300_0402_5%

1 2

R105

@

300_0402_5%

1 2

R351

@

20K_0402_5%

R361

12

390_0402_5%

CPU_SID

390_0402_5%

CPU_SIC

8

7

6

5

R365

12

EC_SMB_CK2

EC_SMB_DA2

Q31 FDV301N_NL_SOT23-3@

12

G

S

G

S

Q30

CLK_CPU_BCLK<15>

CLK_CPU_BCLK#<15>

R420

300_0402_5%

1 2

LDT_RST#

1

C554

0.01U_0402_16V7K

@

2

R419

300_0402_5%

1 2

H_PWRGD

1

C553

0.01U_0402_16V7K

@

2

+1.8VS

R113

300_0402_5%

1 2

LDT_STOP#

1

C245

0.01U_0402_16V7K

@

2

1

C446

2

THERMDA_CPU

THERMDC_CPU

+2.5VS

1

+

C282

150U_D2_6.3VM

2

1 2

C531

1 2

C532 3900P_0402_50V7K

Place close to CPU wihtin 1.5"

+CPU_CORE_0

R92 10_0402_5%

R95 10_0402_5%

+CPU_CORE_1

R80 10_0402_5%

R81 10_0402_5%

+1.8VS +1.8VS

R108

300_0402_5% @

1 2

TEST25_H TEST25_L

R98

300_0402_5%@

1 2

+3VS

+1.8V

CPU_SID_SB<20>

CPU_SIC_SB<20>

Address:100_1101

1 2

R564 0_0402_5%@

+1.8V

1 2

R565 0_0402_5%@

U27

1

VDD

2

3

SCLK

D+

SDATA

ALERT#

DTHERM#4GND

ADM1032ARMZ_MSOP8

EC is PU to 5VALW

A:Need to re-Link "SGN00000200"

1 1

+1.8VS

LDT_RST#<19>

2 2

H_PWRGD<19>

LDT_STOP#<11,19>

3 3

4 4

C449 3300p for tigris

2200p change to

1000p for ADT7421

+1.8VS

+3VS

0.1U_0402_16V4Z

C449

1 2

2200P_0402_50V7K

A

VDDA=300mA

3300P_0402_50V7K

1

1

C2644.7U_0805_10V4Z

C255

2

2

<BOM Structure>

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_LDT_REQ#<11>

Address:100_1100

+1.2V_HT

C436 0.1U_0402_16V4Z

34.8K_0402_1%~N

2

2

FDV301N_NL_SOT23-3@

B

+1.8V

R82 44.2_0402_1%

1 2

R86 44.2_0402_1%

1 2

CPU_VDD0_FB_H<44>

CPU_VDD0_FB_L<44>

CPU_VDD1_FB_H<44>

CPU_VDD1_FB_L<44>

T10 PAD @

T27 PAD

T28 PAD

T21 PAD

T22 PAD

T23 PAD

T24 PAD

T25 PAD

T26 PAD

@

1 2

R360

@

12

13

D

R567 0_0402_5%@

13

D

R569 0_0402_5%@

FDV301N, the Vgs is:

min = 0.65V

Typ = 0.85V

Max = 1.5V

EC_SMB_CK2 <30>

EC_SMB_DA2 <30>

1

C261

0.22U_0603_16V4Z

2

LDT_RST#

H_PWRGD

LDT_STOP#

CPU_LDT_REQ#

CPU_SIC

CPU_SID

@

1 2

R356 1K_0402_5%

CPU_TEST23_TSTUPD

@

@

CPU_TEST21_SCANEN

@

CPU_TEST20_SCANCLK2

@

CPU_TEST24_SCANCLK1

@

CPU_TEST22_SCANSHIFTEN

@

CPU_TEST12_SCANSHIFTENB

@

CPU_TEST27_SINGLECHAIN

@

1 2

CPU_HTREF0

CPU_HTREF1

CPU_VDD0_FB_H

CPU_VDD0_FB_L

CPU_VDD1_FB_H

CPU_VDD1_FB_L

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

TEST25_H

TEST25_L

R418 0_0402_5%

CPU intern al thermal sensor

2.09V for Gate

1 2

1 2

JCPU1D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

6090022100G_B

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST22_SCANSHIFTEN

EC_SMB_DA1 <14,30,38>

EC_SMB_CK1 <14,30,38>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

KEY1

KEY2

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

1 2

R531 300_0402_5% @

1 2

R532 300_0402_5% @

1 2

R533 300_0402_5% @

2008/11/03 2009/11/03

+1.8V

M11

W18

CPU_SVC

A6

CPU_SVD

A4

CPU_THERMTRIP#_R

AF6

H_PROCHOT#

AC7

CPU_MEMHOT#_1.8V

AA8

THERMDC_CPU

W7

THERMDA_CPU

W8

T30

+1.8V sense no support

T29

PAD@

W9

PAD@

Y9

CPU_VDDNB_FB_H

H6

CPU_VDDNB_FB_L

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST17_BP3

D7

CPU_TEST16_BP2

E7

CPU_TEST15_BP1

F7

CPU_TEST14_BP0

C7

C3

CPU_TEST10

K8

C4

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

H18

H19

AA7

D5

C5

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

1 2

R364 10K_0402_5%

1 2

R358 300_0402_5%

CPU_SVC <44>

CPU_SVD <44>

@

@

@

@

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

HDT_RST#

+1.8V

R118220_0402_5%

R112220_0402_5%

R115220_0402_5%

R119220_0402_5%

12

12

12

12

@

@

@

@

Compal Secret Data

Deciphered Date

B

E

3 1

MMBT3904_NL_SOT23-3

R353

12

300_0402_5%

CPU_VDDNB_FB_H <44>

CPU_VDDNB_FB_L <44>

@

@

@

@

R129300_0402_5%

12

+1.8V

T3PAD

T4PAD

T16PAD

T7PAD

T6PAD

T9PAD

T8PAD

T15PAD

D

2

Q32

C

1 2

1 2

+1.8V

CPU_VDDNB_FB_H

CPU_VDDNB_FB_L

R335

R334

1 2

R357 300_0402_5%

H_PROCHOT#

Close to CPU

route as differential

as short as possible

testpoint under package

CPU_SVC

CPU_SVD

CPU_TEST23_TSTUPD

JP29

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

GND

12

GND

ACES_85201-1005N

@

HDT Connector

JP1

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

@

MAINPWON

0_0402_5%@

H_THERMTRIP#CPU_THERMTRIP#_R

0_0402_5%

1 2

+CPU_CORE_NB

R101 10_0402_5%

1 2

1 2

R106 10_0402_5%

0718 AMD --> 1K ohm

1 2

R415 1K_0402_5%

1 2

R416 1K_0402_5%

CPU_TEST20_SCANCLK2

CPU_TEST21_SCANEN

CPU_TEST24_SCANCLK1

HDT_RST#

Title

Size Document Number Rev

Custom

Date: Sheet of

R537 300_0402_5%

R538 300_0402_5%

R539 300_0402_5%

R535 300_0402_5%

1 2

U8

4

Y

Compal Electronics, Inc.

AMD CPU S1G2 CTRL

MAINPWON <38,39>

H_THERMTRIP# <20>

R370

0_0402_5%

CPU_TEST10

+1.8V

@

1 2

1 2

1 2

1 2

@

R93

0_0402_5%

+3VS

5

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5@

3

KBYF0 LA-5051P

E

H_PROCHOT# <19>

+1.2V_HT

SB_PWRGD <20,32>

646Tuesday, F e b r u a r y 03, 2009

12

R337

0_0402_5%

@

LDT_RST#

0.3

Page 7

A

VDD(+CPU_CORE) decoupling.

+CPU_CORE_0

1

C221

22U_0805_6.3V6M

2

1

2

1

+

C79

330U_X_2VM_R6M

2

C219

180P_0402_50V8J

Near CPU Socket

1

C224

22U_0805_6.3V6M

2

Under CPU Socket

1

+

1 1

+CPU_CORE_0

1

C214

22U_0805_6.3V6M

2

+CPU_CORE_0

1

C220

0.22U_0603_16V4Z

2

2 2

C80

330U_X_2VM_R6M

2

1

C225

22U_0805_6.3V6M

2

1

C217

0.01U_0402_25V4Z

2

VDDIO decoupling.

+1.8V

1

C206

22U_0805_6.3V6M

2

1

C226

22U_0805_6.3V6M

2

Under CPU Socket

1

C216

0.22U_0603_16V4Z

2

1

C230

0.22U_0603_16V4Z

2

B

+CPU_CORE_1

1

C191

180P_0402_50V8J

2

+CPU_CORE_1

1

+

2

1

C196

22U_0805_6.3V6M

2

1

2

C77

330U_X_2VM_R6M

1

2

+CPU_CORE_1

1

C195

0.22U_0603_16V4Z

2

C182

180P_0402_50V8J

C

+CPU_CORE_0

1

+

C78

330U_X_2VM_R6M

2

+CPU_CORE_NB

C200

22U_0805_6.3V6M

1

C186

22U_0805_6.3V6M

2

1

C184

0.01U_0402_25V4Z

2

1

C201

22U_0805_6.3V6M

2

1

C179

180P_0402_50V8J

2

+1.8V

+CPU_CORE_NB decoupling.

+CPU_CORE_NB

1

C198

22U_0805_6.3V6M

2

1

C207

22U_0805_6.3V6M

2

1

C223

22U_0805_6.3V6M

2

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

6090022100G_B

Athlon 64 S1

Processor Socket

JCPU1E

VDD0_1

VDD0_2

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

VDD0_11

VDD0_12

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

D

JCPU1F

AA4

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

+CPU_CORE_1

+1.8V

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AB2

AB7

AB9

AD6

AD8

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

6090022100G_B

Athlon 64 S1

Processor Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

E

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3 3

4 4

+1.8V

1

C235

0.22U_0603_16V4Z

2

+1.8V +1.8V

1

C162

0.01U_0402_25V4Z

2

+1.8V

1

2

Between CPU Socket and DIMM

1

C165

0.22U_0603_16V4Z

2

180PF Qt'y follow the distance between

CPU socket and DIMM0. <2.5inch>

1

C164

180P_0402_50V8J

2

1

C169

4.7U_0805_10V4Z

2

C167

4.7U_0805_10V4Z

1

C234

0.22U_0603_16V4Z

2

1

C163

0.01U_0402_25V4Z

2

1

C168

4.7U_0805_10V4Z

2

1

C166

0.22U_0603_16V4Z

2

1

C237

180P_0402_50V8J

2

A: Add C165 and C176

to follow AMD Layout

review recommand for

EMI

1

C170

4.7U_0805_10V4Z

2

1

C238

180P_0402_50V8J

2

1

+

C233

220U_D2_4VM_R15

2

1

2

1

+

C218

220U_D2_4VM_R15

2

@

C: Change to NBO CAP

C239

180P_0402_50V8J

VTT decoupling.

+0.9V

1

C141

4.7U_0805_10V4Z

2

+0.9V

1

C541

4.7U_0805_10V4Z

2

1

C146

4.7U_0805_10V4Z

2

Near CPU Socket Right side.

1

C530

4.7U_0805_10V4Z

2

1

C144

0.22U_0603_16V4Z

2

1

C514

0.22U_0603_16V4Z

2

+0.9V

Near Power Supply

1

C: Change to NBO CAP

+

C281

220U_D2_4VM_R15

2

1

C148

0.22U_0603_16V4Z

2

1

C515

0.22U_0603_16V4Z

2

1

C273

22U_0805_6.3V6M

2

1

C174

1000P_0402_50V7K

2

1

C528

1000P_0402_50V7K

2

1

C173

1000P_0402_50V7K

2

1

C537

1000P_0402_50V7K

2

1

C172

180P_0402_50V8J

2

1

C540

180P_0402_50V8J

2

1

C175

180P_0402_50V8J

2

1

C543

180P_0402_50V8J

2

Near CPU Socket Left side.

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G2 PWR & GND

KBYF0 LA-5051P

E

of

746Tuesday, F e b r u a r y 03, 2009

0.3

Page 8

A

B

C

D

E

+1.8V +1.8V

JDIMM1

+V_DDR_MCH_REF

DDRA_SDQS0#<5>

1 1

2 2

3 3

4 4

DDRA_SDQS0<5>

DDRA_SDQS1#<5>

DDRA_SDQS1<5>

DDRA_SDQS2#<5>

DDRA_SDQS2<5>

DDRA_CKE0<5>

DDRA_SBS2#<5>

DDRA_SBS0#<5>

DDRA_SWE#<5>

DDRA_SCAS#<5>

DDRA_SCS1#<5>

DDRA_ODT1<5>

DDRA_SDQS4#<5>

DDRA_SDQS4<5>

DDRA_SDQS6#<5>

DDRA_SDQS6<5>

ICH_SMBDATA0<9,15,20,28>

ICH_SMBCLK0<9,15,20,28>

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQS0#

DDRA_SDQS0

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25 DDRA_SDQ29

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS#

DDRA_SCS1#

DDRA_ODT1

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

ICH_SMBDATA0

ICH_SMBCLK0

+3VS

+3VS

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

203

GND

FOX_AS0A426-M2RN-7F

CONN@

DQ12

DQ13

CK0#

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQS3#

DQS3

DQ30

DQ31

NC/CKE1

NC/A15

NC/A14

RAS#

ODT0

NC/A13

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQS5#

DQS5

DQ46

DQ47

DQ52

DQ53

CK1#

DQ54

DQ55

DQ60

DQ61

DQS7#

DQS7

DQ62

DQ63

GND

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

VSS

DM1

VSS

CK0

VSS

VSS

VSS

VSS

DM2

VSS

VSS

VSS

VSS

VSS

VDD

VDD

VDD

VDD

BA1

VDD

VDD

VSS

VSS

DM4

VSS

VSS

VSS

VSS

VSS

VSS

CK1

VSS

DM6

VSS

VSS

VSS

VSS

VSS

SAO

SA1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

NC

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

A11

92

A7

94

A6

96

98

A4

100

A2

102

A0

104

106

108

110

S0#

112

114

116

118

120

NC

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

204

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDM0

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDM1

DDRA_CLK0

DDRA_CLK0#

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDM2

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ28

DDRA_SDQS3#

DDRA_SDQS3

DDRA_SDQ30

DDRA_SDQ31

DDRA_CKE1DDRA_CKE0

DDRA_SMA15

DDRA_SMA14

DDRA_SMA11

DDRA_SMA7

DDRA_SMA6

DDRA_SMA4

DDRA_SMA2

DDRA_SMA0

DDRA_SBS1#

DDRA_SRAS#

DDRA_SCS0#

DDRA_ODT0

DDRA_SMA13

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDM4

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQS5#

DDRA_SDQS5

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ52

DDRA_SDQ53

DDRA_CLK1

DDRA_CLK1#

DDRA_SDM6

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQS7#

DDRA_SDQS7

DDRA_SDQ62

DDRA_SDQ63

R314 10K_0402_5%

1 2

R315 10K_0402_5%

1 2

DDRA_CLK0 <5>

DDRA_CLK0# <5>

DDRA_SDQS3# <5>

DDRA_SDQS3 <5>

DDRA_CKE1 <5>

DDRA_SBS1# <5>

DDRA_SRAS# <5>

DDRA_SCS0# <5>

DDRA_ODT0 <5>

DDRA_SDQS5# <5>

DDRA_SDQS5 <5>

DDRA_CLK1 <5>

DDRA_CLK1# <5>

DDRA_SDQS7# <5>

DDRA_SDQS7 <5>

DDRA_SDQ[63..0]

DDRA_SDM[7..0]

DDRA_SMA[15..0]

+V_DDR_MCH_REF

1

C256

2

1000P_0402_50V7K

0.1U_0402_16V4Z

+1.8V

1 2

1

C257

2

1 2

1U_0402_6.3V4Z

+1.8V

0.1U_0402_16V4Z

1

C155

2

0.1U_0402_16V4Z

1

C113

2

0.1U_0402_16V4Z

DDRA_SDQ[63..0] <5>

DDRA_SDM[7..0] <5>

DDRA_SMA[15..0] <5>

R148

1K_0402_1%

R141

1K_0402_1%

1

1

C128

C151

2

2

0.1U_0402_16V4Z

+0.9V

1

1

C119

2

2

0.1U_0402_16V4Z

+V_DDR_MCH_REF

0.1U_0402_16V4Z

1

C124

2

0.1U_0402_16V4Z

1

C55

C197

2

RESERVE

+V_DDR_MCH_REF BUFFER CIRCUIT

+0.9V

DDRA_SMA6

DDRA_SMA7

DDRA_SMA11

DDRA_SMA15

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA14

DDRA_CKE1

DDRA_SBS1#

DDRA_SMA0

DDRA_SMA2

DDRA_SMA4

DDRA_SMA5

DDRA_SMA8

DDRA_SMA9

DDRA_SMA12

DDRA_SBS0#

DDRA_SMA10

DDRA_SMA1

DDRA_SMA3

DDRA_SCS1#

DDRA_ODT1

DDRA_SWE#

DDRA_SCAS#

DDRA_SMA13

DDRA_ODT0

DDRA_SCS0#

DDRA_SRAS#

RP20

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP23

47_0804_8P4R_5%

RP17

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP18

47_0804_8P4R_5%

RP15

47_0804_8P4R_5%

RP9

47_0804_8P4R_5%

RP12

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

1 2

C187 0.1U_0402_16V4Z

1 2

C213 0.1U_0402_16V4Z

1 2

18

C194 0.1U_0402_16V4Z

27

1 2

36

C222 0.1U_0402_16V4Z

45

1 2

C157 0.1U_0402_16V4Z

1 2

C152 0.1U_0402_16V4Z

18

1 2

C190 0.1U_0402_16V4Z

27

36

1 2

C211 0.1U_0402_16V4Z

45

1 2

18

C180 0.1U_0402_16V4Z

27

1 2

36

C199 0.1U_0402_16V4Z

45

1 2

18

C161 0.1U_0402_16V4Z

27

36

1 2

C156 0.1U_0402_16V4Z

45

1 2

C159 0.1U_0402_16V4Z

1 2

C154 0.1U_0402_16V4Z

+1.8V

1

C413

0.1U_0402_16V4Z

2

4.7U_0805_10V4Z

A

C414

1

2

DIMM1 REV H:5.2mm (BOT)

B

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/11/03 2009/11/03

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

DDRII SO-DIMM 0

KBYF0 LA-5051P

846Tuesday, F e b r u a r y 03, 2009

E

of

0.3

Page 9

A

B

C

D

E

+1.8V +1.8V

JDIMM2

+V_DDR_MCH_REF

1 1

2 2

3 3

4 4

DDRB_SDQS0#<5>

DDRB_SDQS0<5>

DDRB_SDQS1#<5>

DDRB_SDQS1<5>

DDRB_SDQS2#<5>

DDRB_SDQS2<5>

DDRB_CKE0<5>

DDRB_SBS2#<5>

DDRB_SBS0#<5>

DDRB_SWE#<5>

DDRB_SCAS#<5>

DDRB_SCS1#<5>

DDRB_ODT1<5>

DDRB_SDQS4#<5>

DDRB_SDQS4<5>

DDRB_SDQS6#<5>

DDRB_SDQS6<5>

ICH_SMBDATA0<8,15,20,28>

ICH_SMBCLK0<8,15,20,28>

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQS0#

DDRB_SDQS0

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQS1#

DDRB_SDQS1

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQS2#

DDRB_SDQS2

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDM3

DDRB_SDQ26 DDRB_SDQ30

DDRB_SDQ27

DDRB_CKE0

DDRB_SBS2#

DDRB_SMA12

DDRB_SMA9

DDRB_SMA8

DDRB_SMA5

DDRB_SMA3

DDRB_SMA1

DDRB_SMA10

DDRB_SBS0#

DDRB_SWE#

DDRB_SCAS#

DDRB_SCS1#

DDRB_ODT1

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQS4#

DDRB_SDQS4

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDM5

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQS6#

DDRB_SDQS6

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDM7

DDRB_SDQ58

DDRB_SDQ59

ICH_SMBDATA0

ICH_SMBCLK0

+3VS

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

201

GND

FOX_AS0A426-MARG-7F

CONN@

DIMM1 REV H:9.2mm (BOT)

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

VDD

VDD

RAS#

VDD

ODT0

NC/A13

VDD

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

GND

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

CK0

32

34

36

38

40

42

44

46

48

50

NC

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

A11

92

A7

94

A6

96

98

A4

100

A2

102

A0

104

106

BA1

108

110

S0#

112

114

116

118

120

NC

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

CK1

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

SA1

202

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDM0

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDM1

DDRB_CLK0

DDRB_CLK0#

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDM2

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQS3#

DDRB_SDQS3

DDRB_SDQ31

DDRB_CKE1

DDRB_SMA15

DDRB_SMA14

DDRB_SMA11

DDRB_SMA7

DDRB_SMA6

DDRB_SMA4

DDRB_SMA2

DDRB_SMA0

DDRB_SBS1#

DDRB_SRAS#

DDRB_SCS0#

DDRB_ODT0

DDRB_SMA13

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDM4

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQS5#

DDRB_SDQS5

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ52

DDRB_SDQ53

DDRB_CLK1

DDRB_CLK1#

DDRB_SDM6

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQS7#

DDRB_SDQS7

DDRB_SDQ62

DDRB_SDQ63

R331 10K_0402_5%

1 2

R327 10K_0402_5%

1 2

DDRB_SDQS3# <5>

DDRB_SDQS3 <5>

DDRB_SDQS5# <5>

DDRB_SDQS5 <5>

DDRB_SDQS7# <5>

DDRB_SDQS7 <5>

DDRB_CLK0 <5>

DDRB_CLK0# <5>

DDRB_CKE1 <5>

DDRB_SBS1# <5>

DDRB_SRAS# <5>

DDRB_SCS0# <5>

DDRB_ODT0 <5>

DDRB_CLK1 <5>

DDRB_CLK1# <5>

+3VS

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

DDRB_SDQ[63..0]

DDRB_SDM[7..0]

DDRB_SMA[15..0]

+V_DDR_MCH_REF

1

1

C202

2

2

1000P_0402_25V8J

2008/11/03 2009/11/03

DDRB_SDQ[63..0] <5>

DDRB_SDM[7..0] <5>

DDRB_SMA[15..0] <5>

+V_DDR_MCH_REF

1

C3388

22U_0805_6.3V6M

C292

@

2

0.1U_0402_16V4Z

Compal Secret Data

Deciphered Date

D

DDRB_SRAS#

DDRB_SMA0

DDRB_SMA2

DDRB_SMA4

DDRB_SMA6

DDRB_SMA7

DDRB_SMA11

DDRB_SMA14

DDRB_CKE0

DDRB_SBS2#

DDRB_SMA15

DDRB_CKE1

DDRB_SMA8

DDRB_SMA5

DDRB_SMA12

DDRB_SMA9

DDRB_SBS0#

DDRB_SMA10

DDRB_SMA3

DDRB_SMA1

DDRB_ODT1

DDRB_SCS1#

DDRB_SWE#

DDRB_SCAS#

DDRB_SMA13

DDRB_ODT0

DDRB_SCS0#

DDRB_SBS1#

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP19

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP22

18

27

36

45

47_0804_8P4R_5%

RP21

18

27

36

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

45

RP16

18

27

36

45

RP10

18

27

36

45

RP11

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

Title

Size Document Number Rev

Custom

Date: Sheet

12

C185 0.1U_0402_16V4Z

1 2

C176 0.1U_0402_16V4Z

12

C188 0.1U_0402_16V4Z

1 2

C193 0.1U_0402_16V4Z

12

C203 0.1U_0402_16V4Z

1 2

C215 0.1U_0402_16V4Z

12

C205 0.1U_0402_16V4Z

1 2

C210 0.1U_0402_16V4Z

12

C204 0.1U_0402_16V4Z

1 2

C209 0.1U_0402_16V4Z

12

C171 0.1U_0402_16V4Z

1 2

C153 0.1U_0402_16V4Z

12

C158 0.1U_0402_16V4Z

1 2

C160 0.1U_0402_16V4Z

Compal Electronics, Inc.

DDRII SO-DIMM 1

KBYF0 LA-5051P

+0.9V

RP14

+1.8V

E

0.3

of

946Tuesday, F e b r u a r y 03, 2009

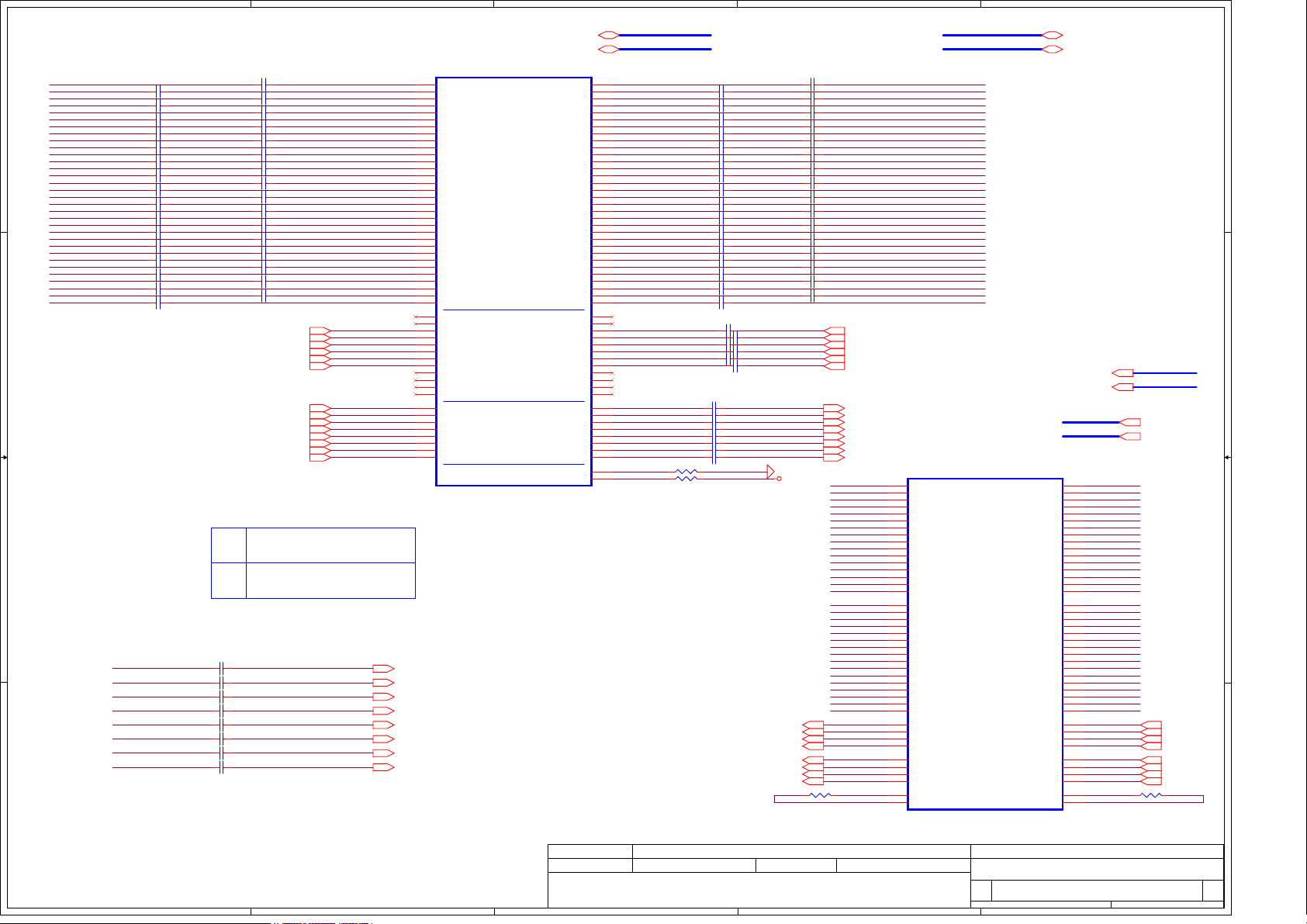

Page 10

A

B

C

D

E

PCIE_GTX_C_MRX_P[0..15]<14>

PCIE_GTX_C_MRX_N[0..15]<14>

PCIE_GTX_C_MRX_P0

PCIE_GTX_C_MRX_N0

PCIE_GTX_C_MRX_P1

PCIE_GTX_C_MRX_N1

PCIE_GTX_C_MRX_P2

1 1

2 2

PCIE_GTX_C_MRX_N2

PCIE_GTX_C_MRX_P3

PCIE_GTX_C_MRX_N3 PCIE_GTX_MRX_N3

PCIE_GTX_C_MRX_P4

PCIE_GTX_C_MRX_N4

PCIE_GTX_C_MRX_P5

PCIE_GTX_C_MRX_N5

PCIE_GTX_C_MRX_P6 PCIE_GTX_MRX_P6

PCIE_GTX_C_MRX_N6

PCIE_GTX_C_MRX_P7

PCIE_GTX_C_MRX_N7 PCIE_GTX_MRX_N7

PCIE_GTX_C_MRX_P8

PCIE_GTX_C_MRX_N8

PCIE_GTX_C_MRX_P9

PCIE_GTX_C_MRX_N9 PCIE_GTX_MRX_N9

PCIE_GTX_C_MRX_P10

PCIE_GTX_C_MRX_N10

PCIE_GTX_C_MRX_P11

PCIE_GTX_C_MRX_N11 PCIE_GTX_MRX_N11

PCIE_GTX_C_MRX_P12

PCIE_GTX_C_MRX_N12

PCIE_GTX_C_MRX_P13

PCIE_GTX_C_MRX_N13

PCIE_GTX_C_MRX_P14 PCIE_GTX_MRX_P14

PCIE_GTX_C_MRX_N14

PCIE_GTX_C_MRX_P15 PCIE_GTX_MRX_P15

PCIE_GTX_C_MRX_N15

C681 0.1U_0402_16V7K VGA@

1 2

C683 0.1U_0402_16V7K VGA@

1 2

C685 0.1U_0402_16V7K VGA@

1 2

C687 0.1U_0402_16V7K VGA@

1 2

C689 0.1U_0402_16V7K VGA@

1 2

C691 0.1U_0402_16V7K VGA@

1 2

C693 0.1U_0402_16V7K VGA@

1 2

C695 0.1U_0402_16V7K VGA@

1 2

C697 0.1U_0402_16V7K VGA@

1 2

C699 0.1U_0402_16V7K VGA@

1 2

C701 0.1U_0402_16V7K VGA@

1 2

C703 0.1U_0402_16V7K VGA@

1 2

C705 0.1U_0402_16V7K VGA@

1 2

C707 0.1U_0402_16V7K VGA@

1 2

C709 0.1U_0402_16V7K VGA@

1 2

C711 0.1U_0402_16V7K VGA@

1 2

C680 0.1U_0402_16V7K VGA@

1 2

C682 0.1U_0402_16V7K VGA@

1 2

C684 0.1U_0402_16V7K VGA@

1 2

C686 0.1U_0402_16V7K VGA@

1 2

C688 0.1U_0402_16V7K VGA@

1 2

C690 0.1U_0402_16V7K VGA@

1 2

C692 0.1U_0402_16V7K VGA@

1 2

C694 0.1U_0402_16V7K VGA@

1 2

C696 0.1U_0402_16V7K VGA@

1 2

C698 0.1U_0402_16V7K VGA@

1 2

C700 0.1U_0402_16V7K VGA@

1 2

C702 0.1U_0402_16V7K VGA@

1 2

C704 0.1U_0402_16V7K VGA@

1 2

C706 0.1U_0402_16V7K VGA@

1 2

C708 0.1U_0402_16V7K VGA@

1 2

C710 0.1U_0402_16V7K VGA@

1 2

PCIE_PTX_C_IRX_P1<28>

PCIE_PTX_C_IRX_N1<28>

PCIE_PTX_C_IRX_P2<28>

PCIE_PTX_C_IRX_N2<28>

PCIE_PTX_C_IRX_P3<26>

PCIE_PTX_C_IRX_N3<26>

SB_RX0P<19>

SB_RX0N<19>

SB_RX1P<19>

SB_RX1N<19>

SB_RX2P<19>

SB_RX2N<19>

SB_RX3P<19>

SB_RX3N<19>

PCIE_GTX_MRX_P0

PCIE_GTX_MRX_N0

PCIE_GTX_MRX_P1

PCIE_GTX_MRX_N1

PCIE_GTX_MRX_P2

PCIE_GTX_MRX_N2

PCIE_GTX_MRX_P3

PCIE_GTX_MRX_P4

PCIE_GTX_MRX_N4

PCIE_GTX_MRX_P5

PCIE_GTX_MRX_N5

PCIE_GTX_MRX_N6

PCIE_GTX_MRX_P7

PCIE_GTX_MRX_P8

PCIE_GTX_MRX_N8

PCIE_GTX_MRX_P9

PCIE_GTX_MRX_P10

PCIE_GTX_MRX_N10

PCIE_GTX_MRX_P11

PCIE_GTX_MRX_P12

PCIE_GTX_MRX_N12

PCIE_GTX_MRX_P13

PCIE_GTX_MRX_N13

PCIE_GTX_MRX_N14

PCIE_GTX_MRX_N15

PCIE_PTX_C_IRX_P1

PCIE_PTX_C_IRX_N1

PCIE_PTX_C_IRX_P2

PCIE_PTX_C_IRX_N2

PCIE_PTX_C_IRX_P3

PCIE_PTX_C_IRX_N3

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

RS780M Display Port Support (muxed on GFX)

DP0

3 3

PCIE_MTX_GRX_P0

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_P3 HDMI_CLK+_UMA

PCIE_MTX_GRX_N3

4 4

DP1

C897 0.1U_0402_10V7KUMA@

1 2

C898 0.1U_0402_10V7KUMA@

1 2

C899 0.1U_0402_10V7KUMA@

1 2

C900 0.1U_0402_10V7KUMA@

1 2

C901 0.1U_0402_10V7KUMA@

1 2

C902 0.1U_0402_10V7KUMA@

1 2

C903 0.1U_0402_10V7KUMA@

1 2

C904 0.1U_0402_10V7KUMA@

1 2

GFX_TX0,TX1,TX2 and TX3

AUX0 and HPD0

GFX_TX4,TX5,TX6 and TX7

AUX1 and HPD1

HDMI_TX2+_UMA

HDMI_TX2-_UMA

HDMI_TX1+_UMA

HDMI_TX1-_UMA

HDMI_TX0+_UMA

HDMI_TX0-_UMA

HDMI_CLK-_UMA

U25B

D4

GFX_RX0P

C4

GFX_RX0N

A3

GFX_RX1P

B3

GFX_RX1N

C2

GFX_RX2P

C1

GFX_RX2N

E5

GFX_RX3P

F5

GFX_RX3N

G5

GFX_RX4P

G6

GFX_RX4N

H5

GFX_RX5P

H6

GFX_RX5N

J6

GFX_RX6P

J5

GFX_RX6N

J7

GFX_RX7P

J8

GFX_RX7N

L5

GFX_RX8P

L6

GFX_RX8N

M8

GFX_RX9P

L8

GFX_RX9N

P7

GFX_RX10P

M7

GFX_RX10N

P5

GFX_RX11P

M5

GFX_RX11N

R8

GFX_RX12P

P8

GFX_RX12N

R6

GFX_RX13P

R5

GFX_RX13N

P4

GFX_RX14P

P3

GFX_RX14N

T4

GFX_RX15P

T3

GFX_RX15N

AE3

GPP_RX0P

AD4

GPP_RX0N

AE2

GPP_RX1P

AD3

GPP_RX1N

AD1

GPP_RX2P

AD2

GPP_RX2N

V5

GPP_RX3P

W6

GPP_RX3N

U5

GPP_RX4P

U6

GPP_RX4N

U8

GPP_RX5P

U7

GPP_RX5N

AA8

SB_RX0P

Y8

SB_RX0N

AA7

SB_RX1P

Y7

SB_RX1N

AA5

SB_RX2P

AA6

SB_RX2N

W5

SB_RX3P

Y5

SB_RX3N

RS780M_FCBGA528

HDMI_TX2+_UMA <17>

HDMI_TX2-_UMA <17>

HDMI_TX1+_UMA <17>

HDMI_TX1-_UMA <17>

HDMI_TX0+_UMA <17>

HDMI_TX0-_UMA <17>

HDMI_CLK+_UMA <17>

HDMI_CLK-_UMA <17>

PART 2 OF 6

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

PCIE I/F GFX

PCIE I/F GPP

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PCIE_GTX_C_MRX_P[0..15]

PCIE_GTX_C_MRX_N[0..15]

A5

PCIE_MTX_GRX_N0

B5

PCIE_MTX_GRX_P1

A4

B4

PCIE_MTX_GRX_P2

C3

PCIE_MTX_GRX_N2

B2