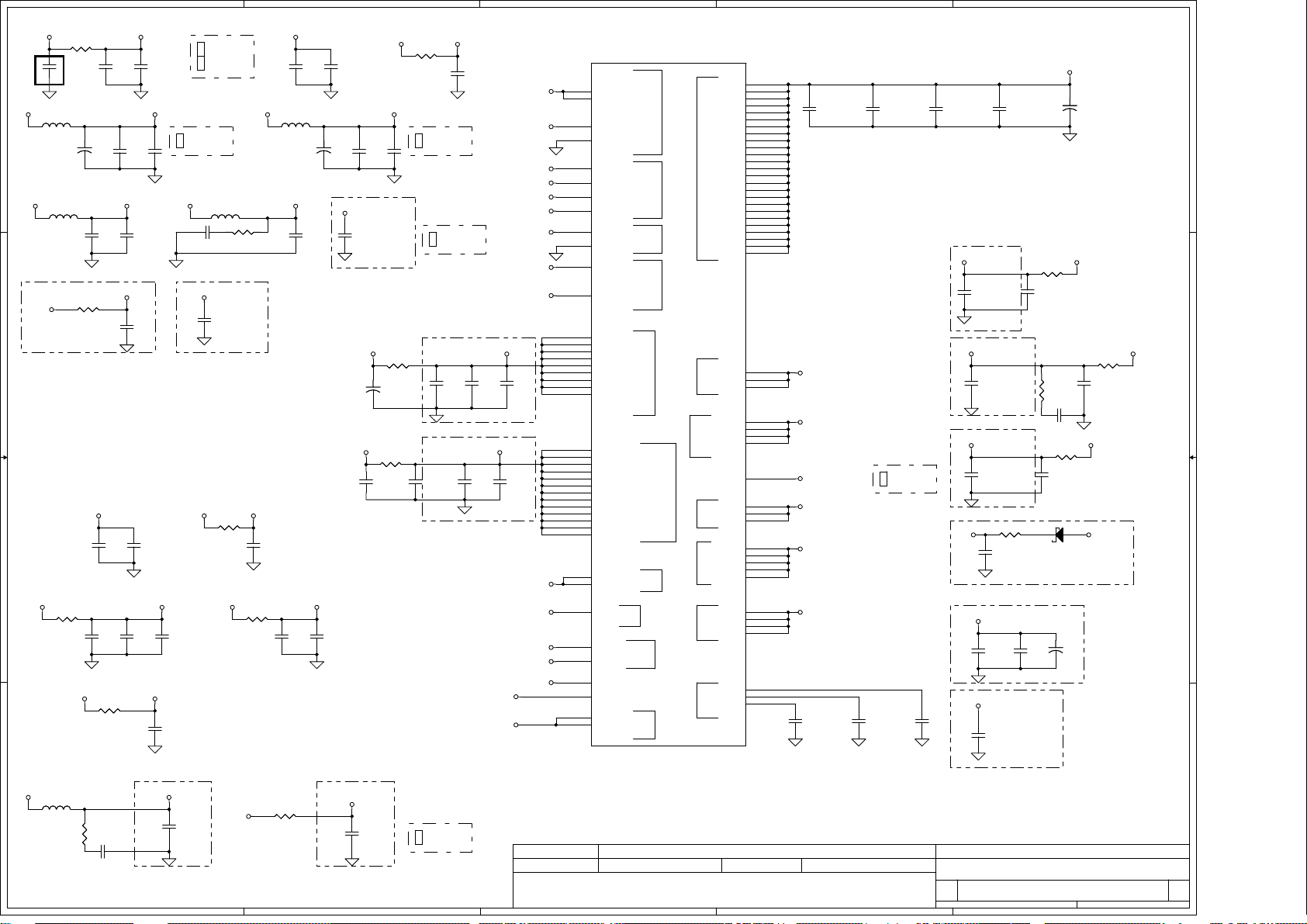

Page 1

A

1 1

B

C

D

E

KSKAA

2 2

LA-4993P

3 3

Bradford 10M/10MG

REV 1.0

Intel Penryn/ Cantiga/ ICH9M

Schematic

2009-07-23 Rev. 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

146Tuesday, August 18, 2009

146Tuesday, August 18, 2009

146Tuesday, August 18, 2009

E

A

A

A

of

of

of

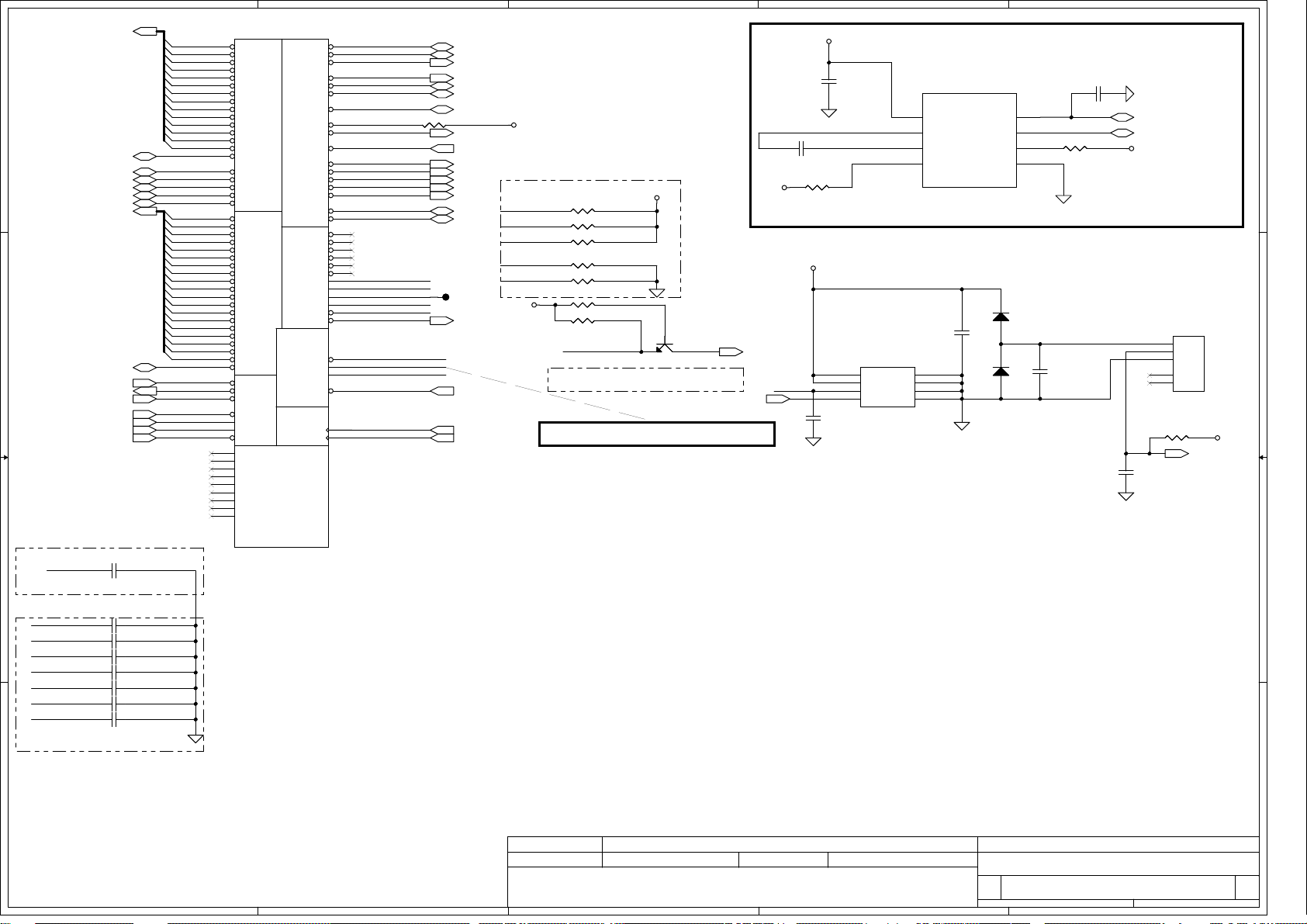

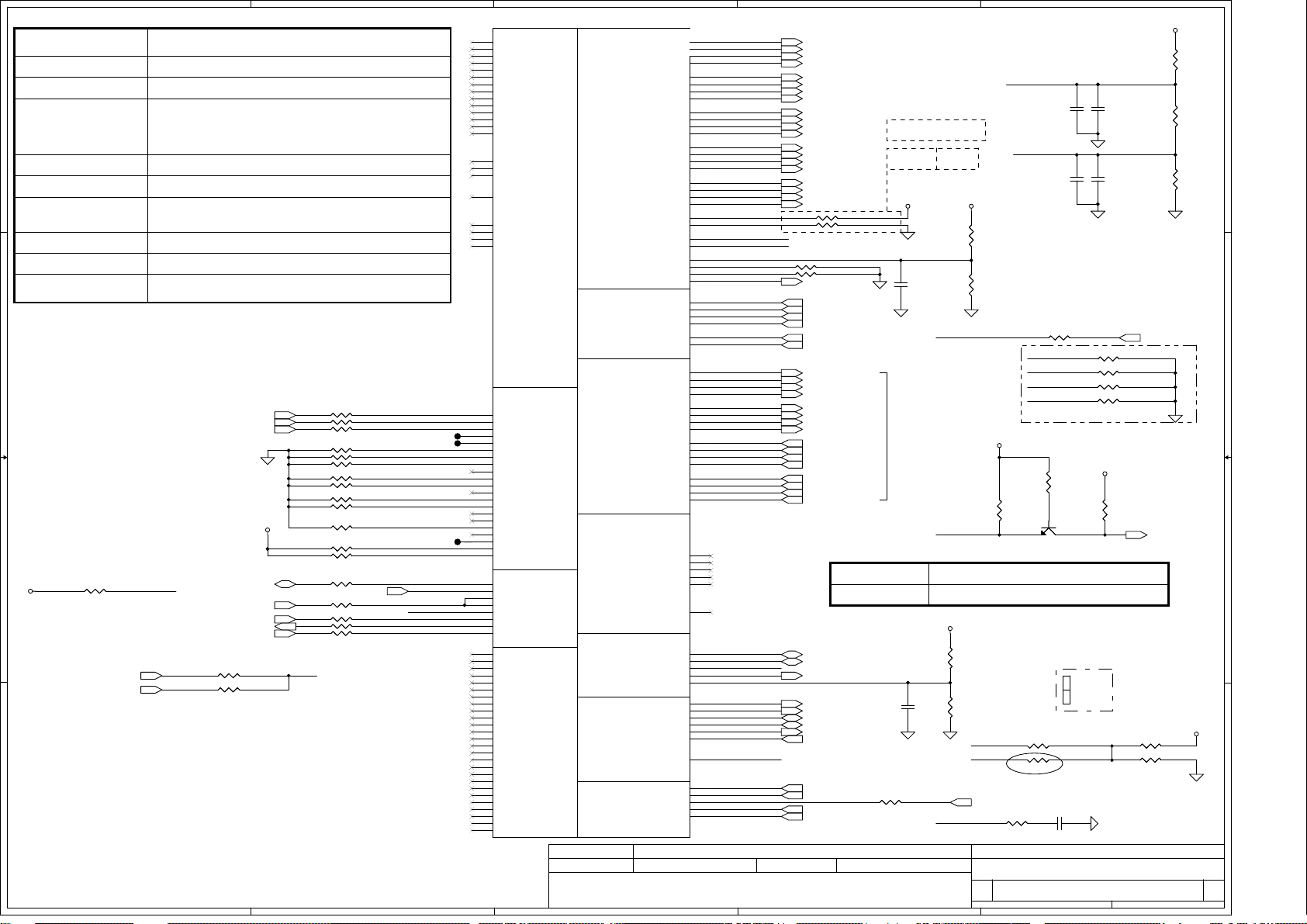

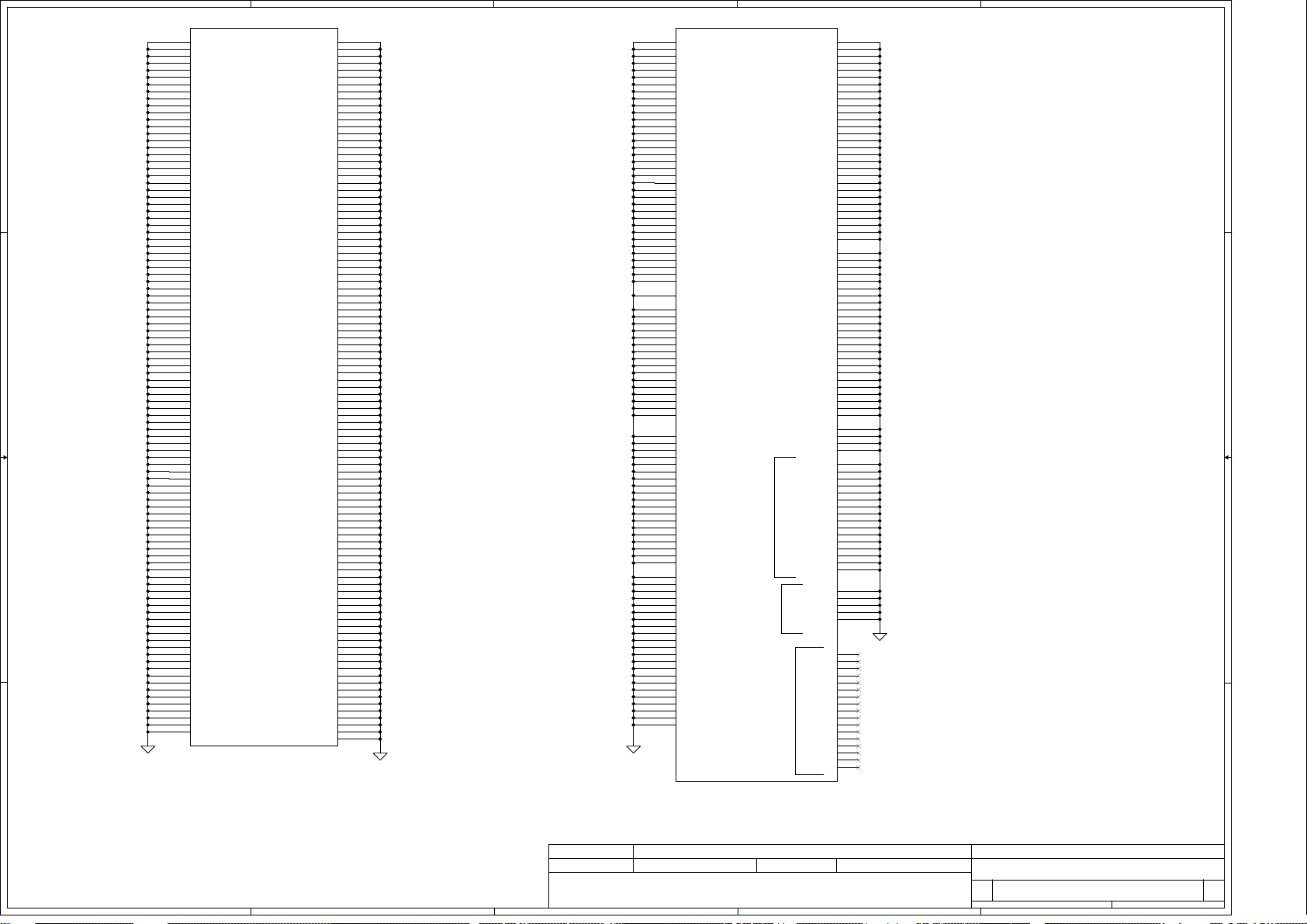

Page 2

A

Compal Confidential

B

C

D

E

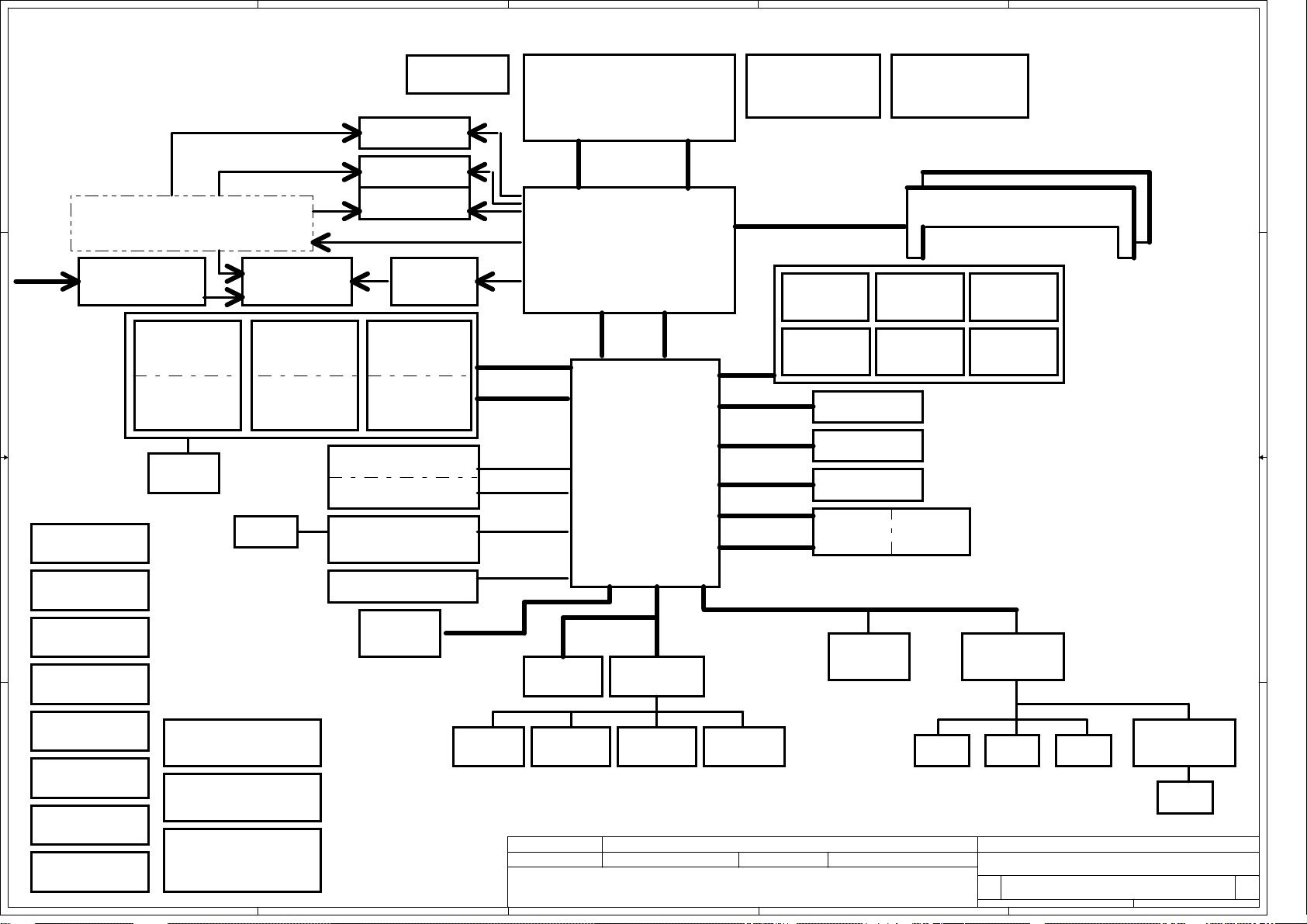

Model Name : KSKAA

File Name : LA-4993P

1 1

Fan Control

Display Port

page 19

CRT

page 18

page 4

Intel Penryn Processor

uPGA-478 Package

(Socket P)

H_A#(3..35) H_D#(0..63)

FSB

667/800/1066MHz

page 4,5,6

Thermal Sensor

EMC1402

page 4

Memory BUS(DDRII)

VGA MXM/B

ATI M92XT,64bit with 256M/512MB

ATI M96,128bit with 512M/1GB

EC

SMBUS

2 2

USB/B-1

3 3

USB/B-2

Finger print/B

Power/B

HDMI CEC Controller

R5F211A4SP

page 20

PCIeMini Card

3G/GPS/TV Tuner

PCIeMini Card

Reserve

BCAS

page 26

page 25

page 27

page 27

page 35

USB port 6

page 28

PCIe port 5

page 28

HDMI Conn.

PCIeMini Card

WiMax

PCIeMini Card

WLAN

RJ45

page 29

page 20

USB port 7

page 28

PCIe port 4

page 28

Express Card

Express Card

RTL8103EL 10/100M

RTL8111DL Giga

LCD Conn.

page 18

PCIE-Express 16X

Level Shifter

page 20

PCIeMini Card

Reserve

PCIe port 11

page 28

PCIeMini Card

UWB/JET

PCIe port 2

page 28

USB port 4

PCIe port 1

PCIe port 3

JMB380

PCIe port 6

FM tuner Conn

page 26

page 29

5IN1

page 32

page 27

5V 480MHz

PCIe 1x [2,4,5]

1.5V 2.5GHz(250MB/s)

5V 480MHz

PCIe 1x

1.5V 2.5GHz(250MB/s)

PCIe 1x

1.5V 2.5GHz(250MB/s)

PCIe 1x

1.5V 2.5GHz(250MB/s)

I2C from SB

USB

USB

Intel Cantiga

GM45/PM45/GL40

GM47/GM49

uFCBGA-1329

page 7,8,9,10,11,12,13

DMI x 4

Intel ICH9-M

BGA-676

LPC BUS

3.3V 33 MHz

Debug Port

page 34

C-Link

page 20,21,22,23

ENE KB926 D3

page 33

USB

5V 480MHz

SATA port 1

5V 1.5GHz(150MB/s)

SATA port 0

5V 1.5GHz(150MB/s)

SATA port 4

5V 1.5GHz(150MB/s)

SATA port 5

5V 1.5GHz(150MB/s)

USB port 3

5V 480MHz

HD Audio

Dual Channel

1.5V DDRIII 800/1066

USB/B Right

USB port 0,1

page 27

BT conn

USB port 5

page 27

SATA HDD0

SATA ODD

eSATA

page 26

3.3V 24.576MHz/48Mhz

MDC 1.5 Conn

SSD

page 27 page 30

Clock Generator

SLG8SP556VTR

page 16

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

USB Left

USB port 2

page 27

Felica

USB port 9

page 27

page 25

page 25

page 25

USB Left

USB port 3

page 26

FP conn

USB port 8

page 27

Int. Camera

USB port 11

page 27

HDA Codec

ALC272

page 15,16

CAP SENSOR/B

LIGTH PIPE/B

4 4

LED/B

Touch Pad/B

page 35

page 35

page 35

page 35

RTC CKT.

DC/DC Interface CKT.

Power Circuit DC/DC

page 36,37,38,39

40,41,42

A

page 21

page 35

Int.KBD

page 34

B

SPI ROM

page 34

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CIR

page 34

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

C

GSENSOR

page 34

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Int.

MIC CONN

page 31

MIC CONN

page 31 page 31

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

HP CONN

page 31

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

TPA6017

SPK CONN

E

AMP.

page 31

246Tuesday, August 18, 2009

246Tuesday, August 18, 2009

246Tuesday, August 18, 2009

A

A

A

of

of

of

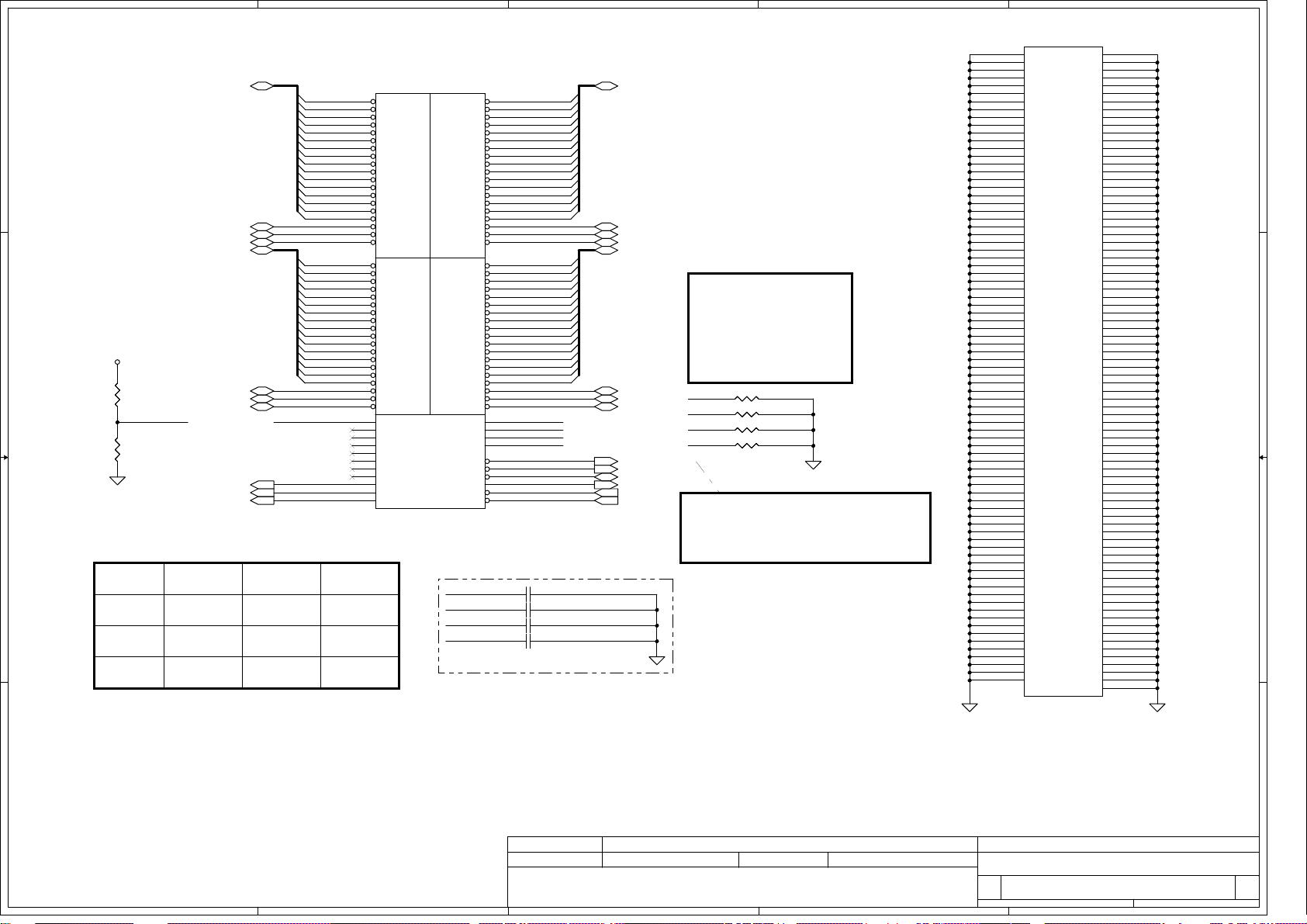

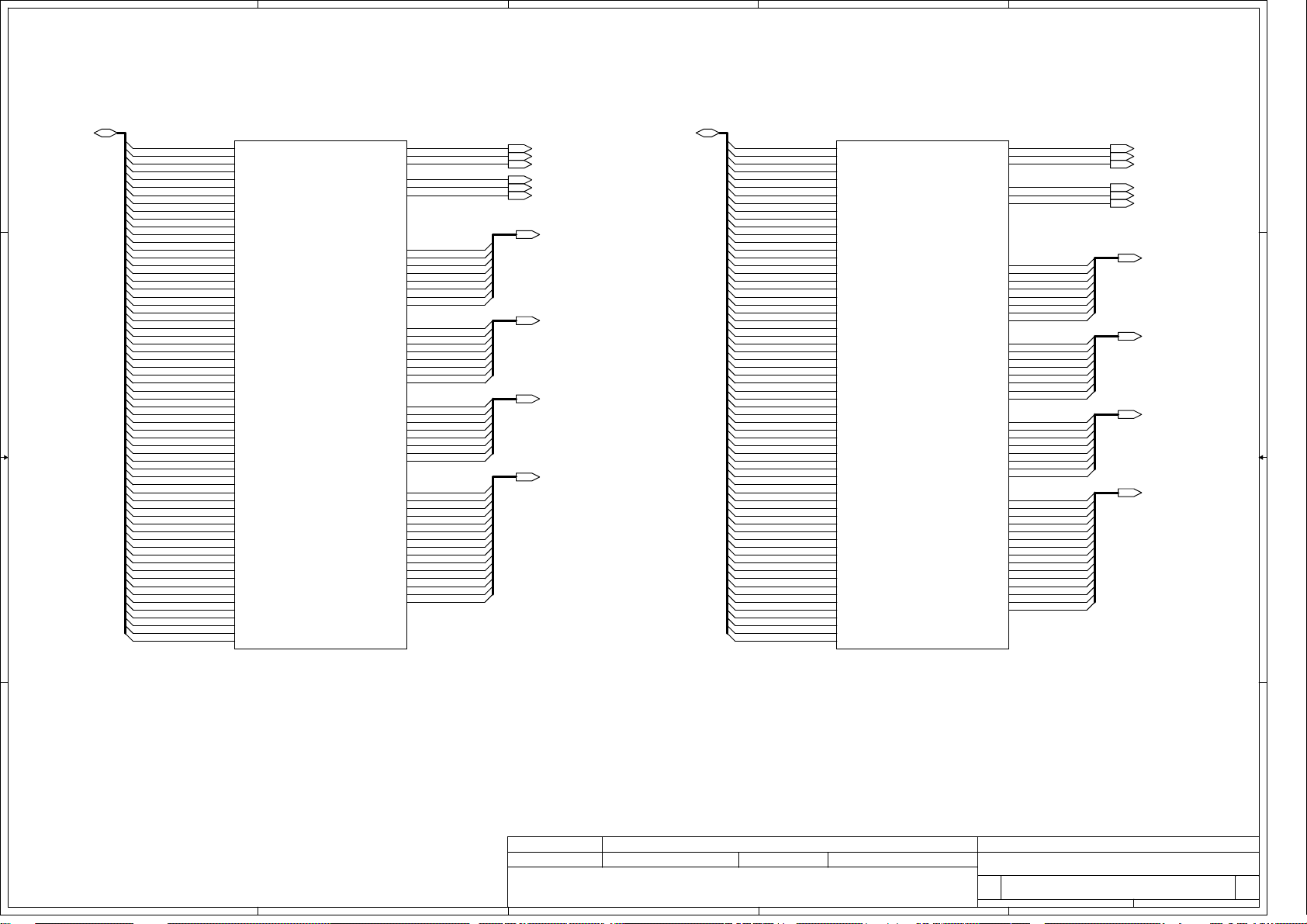

Page 3

5

4

3

2

1

DESIGN CURRENT 0.1A

B+

TPS51125RGER

D D

N-CHANNEL

KSKAA/Bradford Intel

N-CHANNEL

C C

N-CHANNEL

N-CHANNEL

SI4800

2N7002

SI3456

SI4800

SUSP

SBPWR_EN#

RUNON

SUSP

P-CHANNEL

AO-3413

P-CHANNEL

AO-3413

N-CHANNEL

SI3456

P-CHANNEL

BCPWON

FELICA_PWR

SUSP

ENVDD

DESIGN CURRENT 0.1A

DESIGN CURRENT 0.1A

DESIGN CURRENT 3A

DESIGN CURRENT 2A

DESIGN CURRENT 0.5A

DESIGN CURRENT 0.5A

DESIGN CURRENT 0.5A

DESIGN CURRENT 0.5A

DESIGN CURRENT 0.5A

DESIGN CURRENT 0.5A

DESIGN CURRENT 2A

DESIGN CURRENT 1A

+3VL

+5VL

+VSB

+5VALW

+5VS

+5VS_L_BCAS

+FLICA_VCC

+HDMI_5V_OUT

+5V_SB

+3VALW

+3VS_DP

+3VS

+LCD_VDD

AO-3413

WOL_EN#

P-CHANNEL

DESIGN CURRENT 330mA

+3V_LAN

AO-3413

BT_PWR#

P-CHANNEL

DESIGN CURRENT 180mA

+BT_VCC

AO-3413

B B

VR_ON

P-CHANNEL

SBPWR_EN#

AO-3413

ISL6262

SYSON

TPS51117RGYR

SUSP

N-CHANNEL

SUSP

SUSP#

SI4856

APL5331KAC

TPS51117RGYR

SUSP#

TPS51117RGYR

A A

DESIGN CURRENT 750mA

DESIGN CURRENT 35A

DESIGN CURRENT 7A

DESIGN CURRENT 1A

DESIGN CURRENT 2A

DESIGN CURRENT 2A

DESIGN CURRENT 10A

+3V_SB

+CPU_CORE

+1.8V

+1.8VS

+0.9VS

+1.5VS

+1.05VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

346Tuesday, August 18, 2009

346Tuesday, August 18, 2009

346Tuesday, August 18, 2009

1

A

A

A

of

of

of

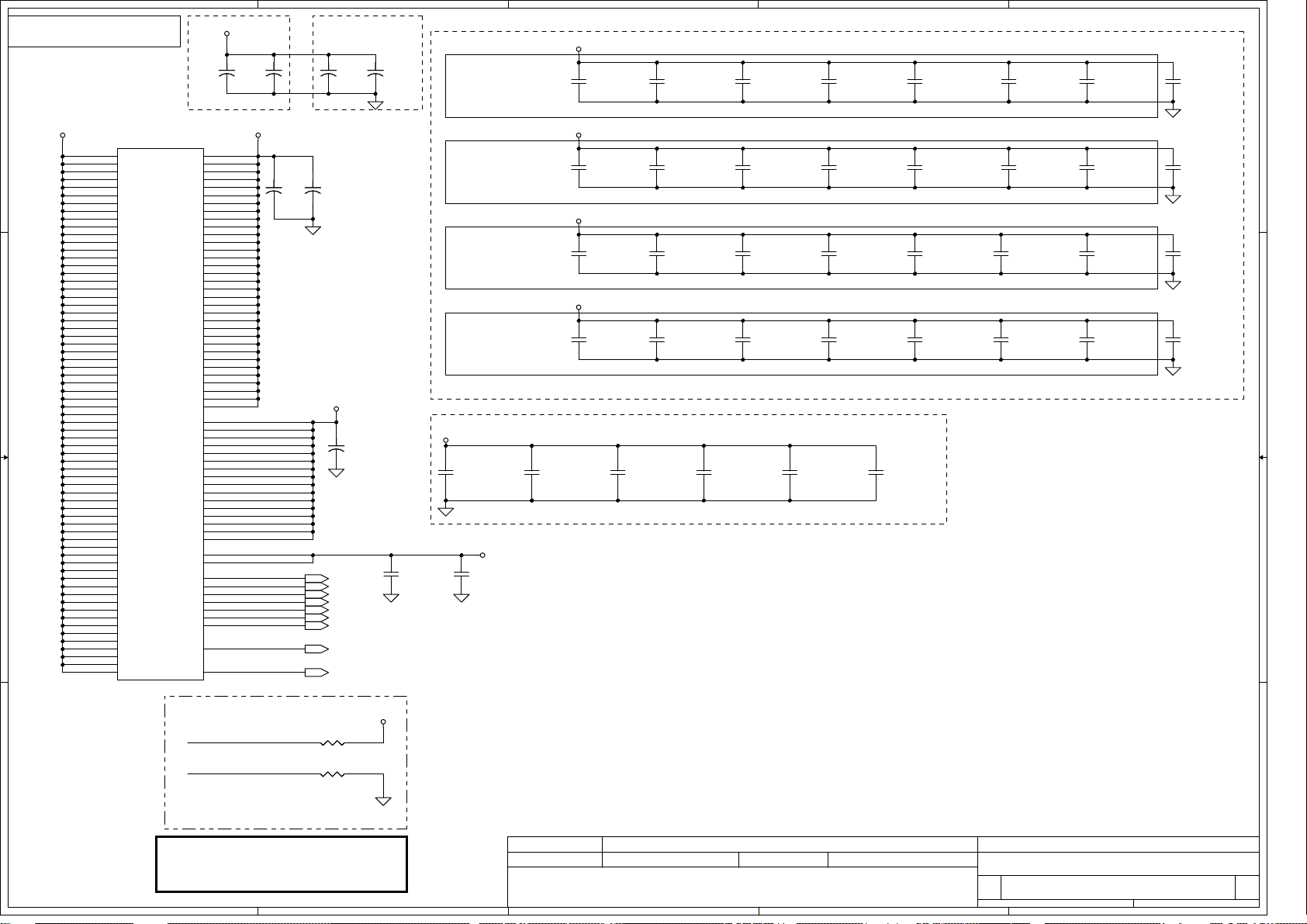

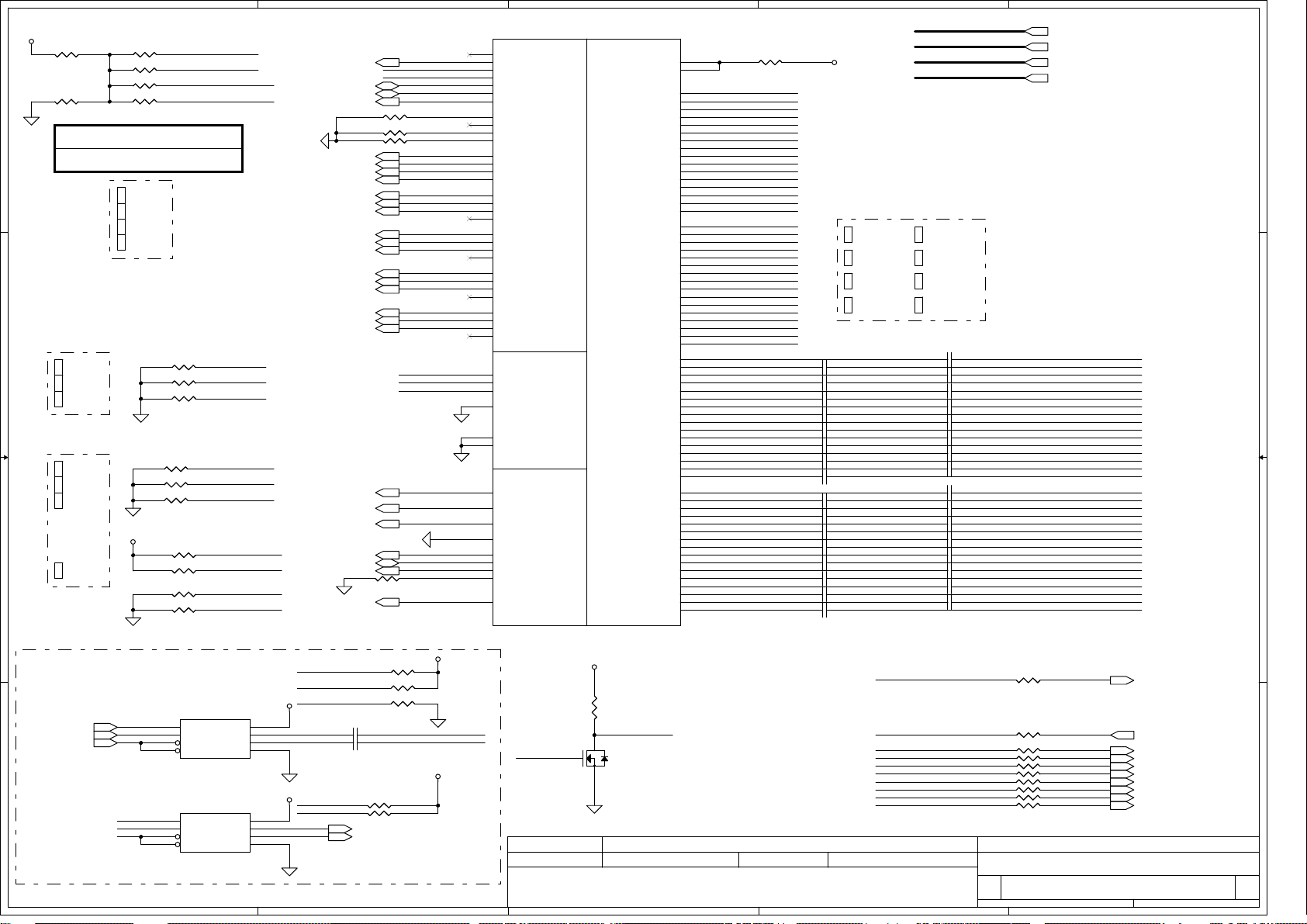

Page 4

A

B

C

D

E

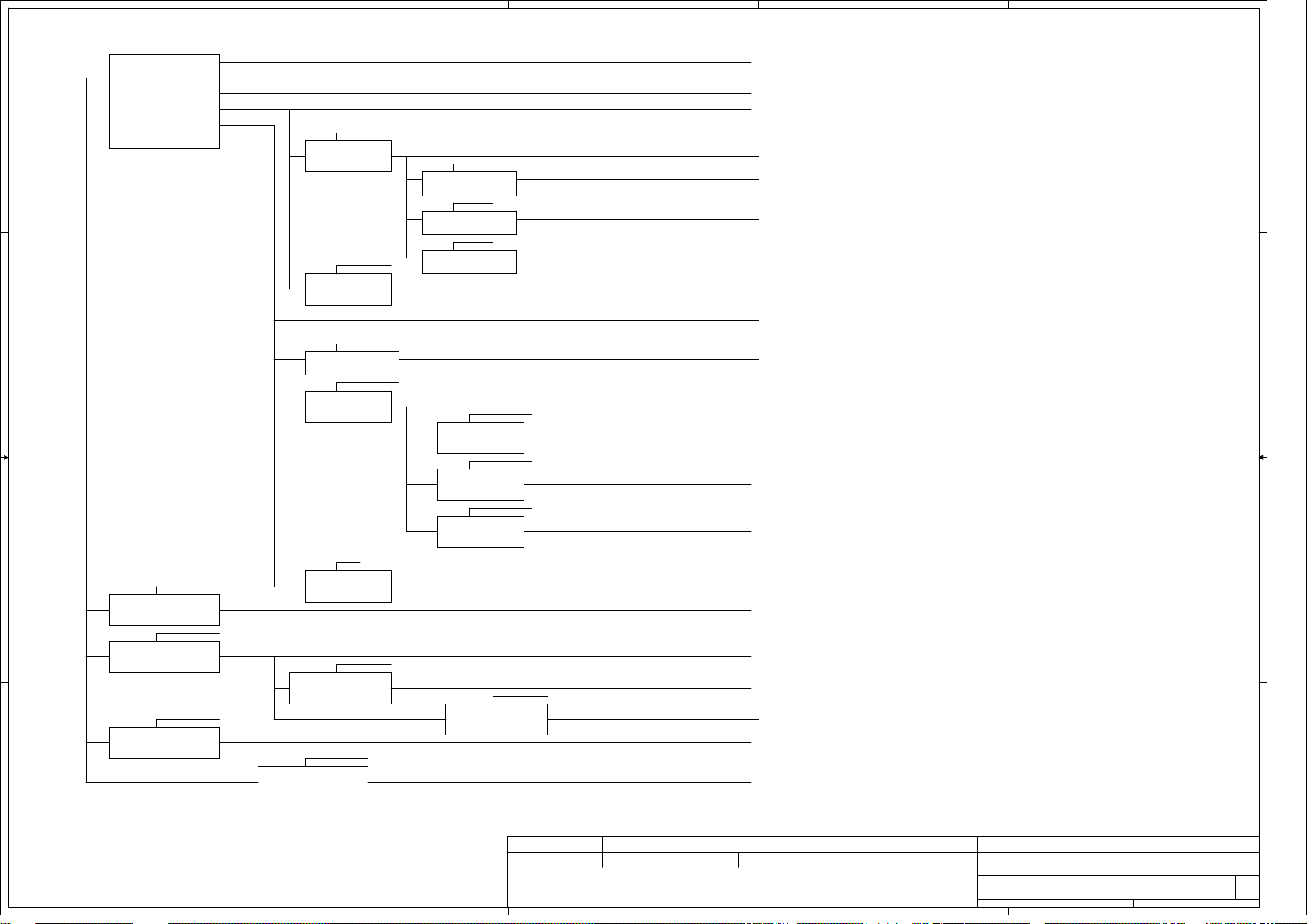

Voltage Rails

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON ON

OFF OFF+5V_SB 5V power rail for SB ON ON

OFF

OFFON

OFF

ONON

ON

OFF

OFF

OFF

OFF

OFF

OFF

G3

BTO Option Table

Function

description

explain

BTO

Function

Power Plane Description

1 1

VIN

B+

+CPU_CORE

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

+0.9VS 0.9V switched power rail for DDR terminator

+1.05VS

+1.5VS

+1.8V

+3VALW

1.05V switched power rail

1.5V switched power rail

1.8V power rail for DDR

3.3V always on power rail

S1 S3 S5

ON ON ON OFF

ON ON ON ON

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON OFF

ON

ON ON

ON

+3VL 3.3V always on power rail ONON

+3V_SB 3.3V power rail for LAN ON ON

+3V_LAN 3.3V power rail for LAN ON ON

+3V_WLAN 3.3V power rail for LAN ON ON

+3VS

+5VALW

3.3V switched power rail

5V always on power rail

ON

ON

OFF

ON ON

+5VL 5V always on power rail ON ON

2 2

+5VS

+VSB VSB always on power rail ON ON

+RTCVCC RTC power

+CPU_CORE

+VGA_PCIE_1.1VS

+1.8VS

5V switched power rail

Core voltage for VGA chip

1.1V switched power rail for VGA PCIE

1.8V power rail for VRAM

ON

ON

ON

ON

ON

OFF

ON

ON

ON

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

G3 LOWLOWLOWLOW

Intel(UMA)

IHDMI@

3G SIM slot

description

explain

External PCI Devices

BTO

(3)

3G@

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

HDMI

(Y)

ATI MXM/B

NIHDMI@ HDMI@

Mini card

(D2)

Two Cards

3G@

SLP_S4# SLP_S5#

HIGHHIGHHIGH

LOW

HIGH

COMMON

H@

Felica BLUE TOOTH

(J)

HIGH

LOWLOWLOW

HIGH

CRT

(Q)

CRT@

Finger printer

(F)

Display

(Z)

DP@

CIR

(I)

LAN

(E) (C)

10/100M Giga

8103EL@ 8111DL@

CAMERA & MIC

(X)

(B)

CAMERA MIC

FP@FLICA@

CIR@

CAM@ MIC@

BT@

EC SM Bus1 address

3 3

Device

EC KB926 D3+3VL EC KB926 D3+3VS

Smart Battery+5VL

HDMI-CEC

+5VL

+3VL

FUN/B (CAP Sensor)

Address Address

0001 011X b

0011 010x b

EC SM Bus2 address

Device

PowerPower

CPU THM Sen

+3VS

SMSC SMC1402

0100 110x b

ICH9M SM Bus address

Power

+3V_SB

4 4

+3VS

+3VS

+3VS

+3VS

+3VS

Device

ICH9M

Clock Generator

(SLG8SP556V)

DDR DIMM0

DDR DIMM1

Express

FM Module

A

Address

1101 001Xb

1001 000Xb

1001 010Xb

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

446Tuesday, August 18, 2009

446Tuesday, August 18, 2009

446Tuesday, August 18, 2009

E

A

A

A

of

of

of

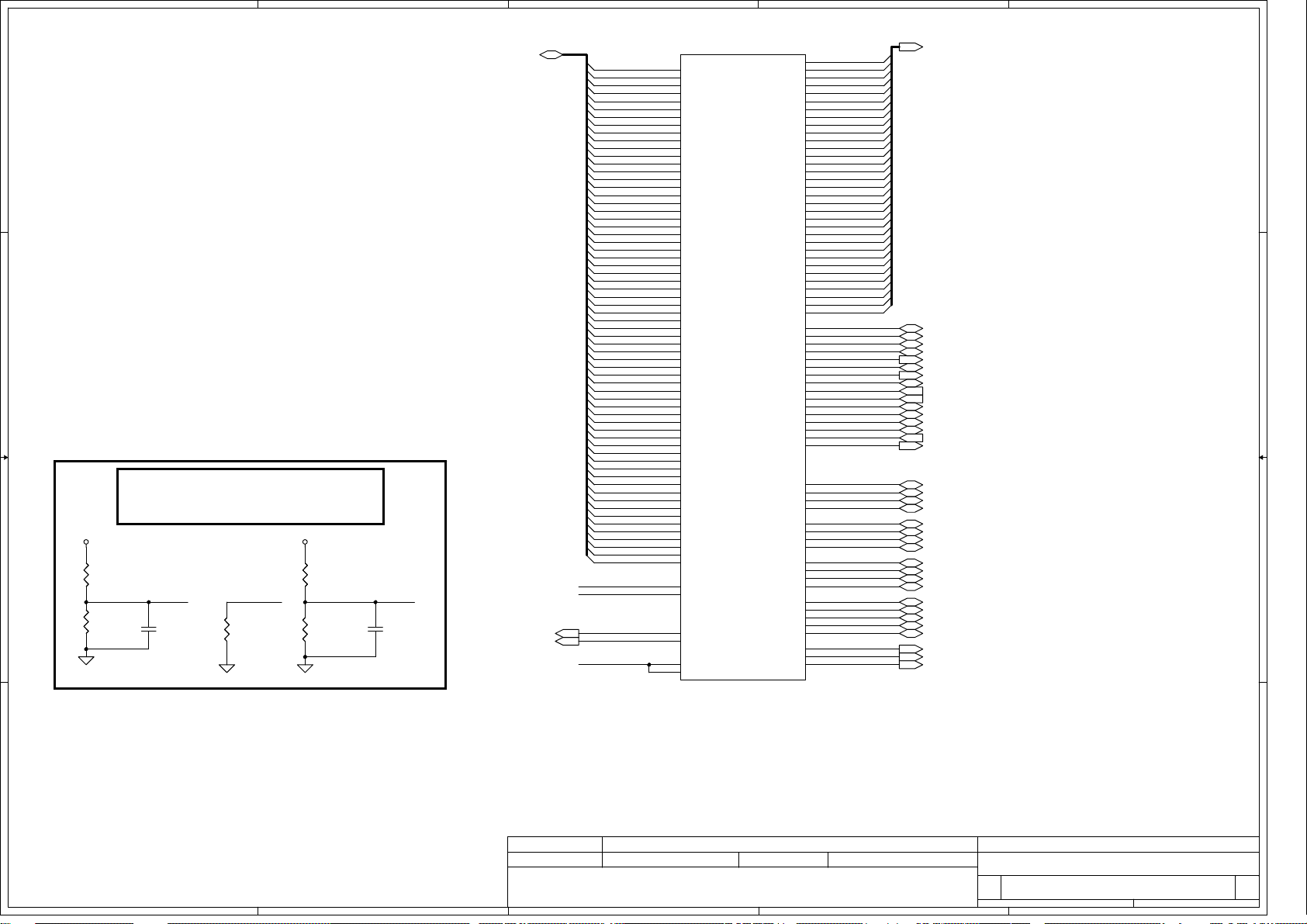

Page 5

5

@

AA4

AB2

AA3

D22

K5

M3

N2

N3

P5

P2

P4

P1

R1

M1

K3

H2

K2

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

D2

D3

F6

J4

L5

L4

J1

L2

J3

L1

@

JCPUA

JCPUA

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

Penryn

Penryn

ADDR GROUP_0

ADDR GROUP_0

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

ADDR GROUP_1

ADDR GROUP_1

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

H_A#[3..16]8

D D

H_ADSTB#08

H_REQ#08

H_REQ#18

H_REQ#28

H_REQ#38

H_REQ#48

H_A#[17..35]8

C C

H_ADSTB#18

H_A20M#23

H_FERR#23

H_IGNNE#23

H_STPCLK#23

H_INTR23

H_NMI23

H_SMI#23

Reserve for

debug

close to South

Bridge

B B

H_FERR#

C596 180P_0402_50V8J@C596 180P_0402_50V8J@

12

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

4

H_IERR#

R1 56_0402_5%R1 56_0402_5%

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT#

H_THERMDA

H_THERMDC

1 2

H_INIT#

H_RESET#

H_ADS# 8

H_BNR# 8

H_BPRI# 8

H_DEFER# 8

H_DRDY# 8

H_DBSY# 8

H_BR0# 8

H_INIT# 23

H_LOCK# 8

H_RESET# 8

H_RS#0 8

H_RS#1 8

H_RS#2 8

H_TRDY# 8

H_HIT# 8

H_HITM# 8

XDP_DBRESET# 24

H_THERMTRIP# 9,23

CLK_CPU_BCLK 17

CLK_CPU_BCLK# 17

+1.05VS

if use XDP,these resistor are 51ohm

XDP_TDO

XDP_TMS

XDP_TDI

XDP_TCK

XDP_TRST#

T13PAD T13PAD

+1.05VS

3

+1.05VS

1 2

R14 54.9_0402_1%R14 54.9_0402_1%

1 2

R4 54.9_0402_1%R4 54.9_0402_1%

1 2

R5 54.9_0402_1%R5 54.9_0402_1%

1 2

R6 54.9_0402_1%R6 54.9_0402_1%

1 2

R7 54.9_0402_1%R7 54.9_0402_1%

1 2

R8 56_0402_5%@R8 56_0402_5%@

1 2

R9 56_0402_5%R9 56_0402_5%

H_PROCHOT#

PROCHOT# PU: 68Ohm near CPU and MVP6.

56Ohm near CPU if no used.

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

B

B

2

E

E

3 1

Q6

Q6

MMBT3904_SOT23@

MMBT3904_SOT23@

C

C

EN_DFAN134

+3VS

OCP# 24

+FAN1

10mil

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C2

C2

1 2

2200P_0402_50V7K

2200P_0402_50V7K

R3

R3

1 2

10K_0402_5%

10K_0402_5%

+5VS

1A

1

2

1

C1

C1

2

H_THERMDA

H_THERMDC

CPU_THERM#

U2

U2

1

EN

2

VIN

3

VOUT

4

VSET

APL5607KI-TRG_SO8

APL5607KI-TRG_SO8

C5

C5

10U_0805_10V4Z

10U_0805_10V4Z

2

U1

U1

1

VDD

2

DP

3

DN

4

THERM#

EMC1402-1-ACZL-TR_MSOP8

EMC1402-1-ACZL-TR_MSOP8

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

SMCLK

SMDATA

ALERT#

GND

8

7

6

5

1 2

R2 10K_0402_5%

R2 10K_0402_5%

FAN Control Circuit

12

1SS355_SOD323-2

1SS355_SOD323-2

D1

D1

@

@

12

D2

D2

@

@

BAS16_SOT23-3

BAS16_SOT23-3

2

1

+FAN1

C4

1000P_0402_25V8J@C41000P_0402_25V8J@

10U_0805_10V4Z

10U_0805_10V4Z

8

GND

7

GND

6

GND

5

GND

2

C3

C3

1

1

C64 33P_0402_50V8KC64 33P_0402_50V8K

1 2

EC_SMB_CK2 18,34,35,36

EC_SMB_DA2 18,34,35,36

@

@

Reserve for source control

+3VS

1

2

3

4

5

ACES_85204-0300N

ACES_85204-0300N

R10 10K_0402_5%R10 10K_0402_5%

1

C6

@C6

@

0.01U_0402_25V7K

0.01U_0402_25V7K

2

JFAN

JFAN

@

@

1

2

3

GND

GND

12

FAN_SPEED1 34

+3VS

H_SMI#

H_INIT#

H_NMI

H_A20M#

H_INTR

H_IGNNE#

H_STPCLK#

A A

12

C597 180P_0402_50V8J@C597 180P_0402_50V8J@

12

C598 180P_0402_50V8J@C598 180P_0402_50V8J@

12

C599 180P_0402_50V8J@C599 180P_0402_50V8J@

12

C600 180P_0402_50V8J@C600 180P_0402_50V8J@

12

C601 180P_0402_50V8J@C601 180P_0402_50V8J@

12

C602 180P_0402_50V8J@C602 180P_0402_50V8J@

12

C603 180P_0402_50V8J@C603 180P_0402_50V8J@

Reserve for

debug

close to CPU

5

Security Classification

Security Classification

Security Classification

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

1

A

A

A

of

546Tuesday, August 18, 2009

of

546Tuesday, August 18, 2009

of

546Tuesday, August 18, 2009

Page 6

5

H_D#[0..15]8

D D

H_DSTBN#08

H_DSTBP#08

H_DINV#08

H_D#[16..31]8

C C

R11

R11

1K_0402_1%

1K_0402_1%

R17

R17

2K_0402_1%

2K_0402_1%

+1.05VS

12

12

Close to

CPU pin

AD26

within

500mils.

+CPU_GTLREF

H_DSTBN#18

H_DSTBP#18

H_DINV#18

CPU_BSEL09,17

CPU_BSEL19,17

CPU_BSEL29,17

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

+CPU_GTLREF

layout note: Route TEST3 & TEST5 traces on ground referenced layer to the TPs

B B

CPU_BSEL CPU_BSEL2 CPU_BSEL1

166

200

01

0

1

CPU_BSEL0

266 0 0 0

G22

G25

G24

H26

H25

M24

M23

R24

N25

M26

N24

AD26

C23

D25

C24

AF26

AF1

C21

1

0

E22

F24

E26

F23

E25

E23

K24

H22

F26

K22

H23

N22

K25

P26

R23

L23

L22

P25

P23

P22

T24

L25

T25

L26

A26

B22

B23

J24

J23

J26

C3

4

@

@

JCPUB

JCPUB

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

BSEL[0]

BSEL[1]

BSEL[2]

Penryn

Penryn

DATA GRP 0

DATA GRP 0

MISC

MISC

DATA GRP 1

DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

H_CPUSLP#

H_PWRGOOD

H_DPRSTP#

H_DPSLP#

H_D#32

Y22

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

AE25

AF24

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

H_DPRSTP#

E5

H_DPSLP#

B5

D24

H_PWRGOOD

D6

H_CPUSLP#

D7

AE6

12

C650 180P_0402_50V8J@C650 180P_0402_50V8J@

12

C651 180P_0402_50V8J@C651 180P_0402_50V8J@

12

C652 180P_0402_50V8JC652 180P_0402_50V8J

12

C653 180P_0402_50V8J@C653 180P_0402_50V8J@

3

H_D#[32..47] 8

H_DSTBN#2 8

H_DSTBP#2 8

H_DINV#2 8

H_D#[48..63] 8

H_DSTBN#3 8

H_DSTBP#3 8

H_DINV#3 8

H_DPRSTP# 9,23,44

H_DPSLP# 23

H_DPWR# 8

H_PWRGOOD 23

H_CPUSLP# 8

H_PSI# 44

2

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

COMP0

1 2

R12 27.4_0402_1%R12 27.4_0402_1%

COMP1

1 2

R13 54.9_0402_1%R13 54.9_0402_1%

COMP2

1 2

R15 27.4_0402_1%R15 27.4_0402_1%

COMP3

1 2

R18 54.9_0402_1%R18 54.9_0402_1%

layout note: Please use "Daisy Chain"

to layout and the signal (H_DPRSTP#)

is routed from ICH9 to power IC,

then to NB and CPU

Reserve for

debug

close to CPU

@

@

JCPUD

JCPUD

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Penryn

Penryn

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

1

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

.

A A

Security Classification

Security Classification

Security Classification

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

646Tuesday, August 18, 2009

646Tuesday, August 18, 2009

646Tuesday, August 18, 2009

1

A

A

A

of

of

of

Page 7

5

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

+CPU_CORE

330U_D2_2VY_R7M

330U_D2_2VY_R7M

1

+

+

C8

C7

C7

.

.

VCCSENSE

C8

2

330U_D2_2VY_R7M

330U_D2_2VY_R7M

change highly to H1.9 for thermal type issue.

AB20

AB7

AC7

AC9

AC12

C79

C79

AC13

AC15

AC17

AC18

330U_6.3V_M_R15

330U_6.3V_M_R15

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VCCSENSE

AF7

VSSSENSE

AE7

330U_D2_2VY_R7M

330U_D2_2VY_R7M

1

+

+

2

330U_6.3V_M_R15

330U_6.3V_M_R15

1

+

+

@

@

2

reserve for test

please co-layout with C7~C10

C80

C80

@

@

1

+

+

C9

C9

2

1

+

+

2

+1.05VS

1

2

CPU_VID0 44

CPU_VID1 44

CPU_VID2 44

CPU_VID3 44

CPU_VID4 44

CPU_VID5 44

CPU_VID6 44

VCCSENSE 44

VSSSENSE 44

Near CPU CORE regulator

ESR <= 1.5m ohm

Capacitor > 1980uF

D D

+CPU_CORE +CPU_CORE

C C

B B

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

@

@

JCPUC

JCPUC

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

Penryn

Penryn

4

1

+

+

C10

C10

2

330U_D2_2VY_R7M

330U_D2_2VY_R7M

+

+

C43

C43

330U_D2_2VY_R7M

330U_D2_2VY_R7M

Near pin B26

1

2

+CPU_CORE

R19100_0402_1% R19100_0402_1%

12

Mid Frequence Decoupling

+1.05VS

1

2

C50

C50

0.01U_0402_25V7K

0.01U_0402_25V7K

+CPU_CORE

Place these capacitors on L8

(North side,Secondary Layer)

+CPU_CORE

Place these capacitors on L8

(North side,Secondary Layer)

+CPU_CORE

Place these capacitors on L8

(Sorth side,Secondary Layer)

+CPU_CORE

Place these capacitors on L8

(Sorth side,Secondary Layer)

Place these inside socket cavity on L8

(North side Secondary)

1

C45

C44

C44

0.1U_0402_10V6K

0.1U_0402_10V6K

+1.5VS

1

C51

C51

10U_0805_6.3V6M

10U_0805_6.3V6M

2

C45

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

C11

C11

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C19

C19

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C27

C27

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C35

C35

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

2

3

1

C12

C12

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C20

C20

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C28

C28

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C36

C36

10U_0805_6.3V6M

10U_0805_6.3V6M

2

C46

C46

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C47

C47

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

C13

C13

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C21

C21

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C29

C29

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C37

C37

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C48

C48

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

C14

C14

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C22

C22

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C30

C30

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C38

C38

10U_0805_6.3V6M

10U_0805_6.3V6M

2

2

1

C49

C49

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

C15

C15

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C23

C23

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C31

C31

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C39

C39

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C16

C16

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C24

C24

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C32

C32

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C40

C40

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C17

C17

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C25

C25

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C33

C33

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C41

C41

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

1

C18

C18

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C26

C26

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C34

C34

10U_0805_6.3V6M

10U_0805_6.3V6M

2

1

C42

C42

10U_0805_6.3V6M

10U_0805_6.3V6M

2

VSSSENSE

A A

Close to CPU pin

R20100_0402_1% R20100_0402_1%

12

within 500mils.

Security Classification

Security Classification

Length match within 25 mils.

The trace width/space/other is

14/7/25.

5

Security Classification

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

746Tuesday, August 18, 2009

746Tuesday, August 18, 2009

746Tuesday, August 18, 2009

1

A

A

A

of

of

of

Page 8

5

4

3

2

1

U3A

H_D#[0..63]6

D D

C C

Layout Note:

H_RCOMP / +H_VREF / H_SWNG

trace width and spacing is 10/20

within 100 mils from NB

+1.05VS+1.05VS

12

B B

R21

R21

1K_0402_1%

1K_0402_1%

12

R23

R23

2K_0402_1%

2K_0402_1%

1

C52

C52

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

2

H_RCOMP+H_VREF

12

R24

R24

24.9_0402_1%

24.9_0402_1%

12

R22

R22

221_0402_1%

221_0402_1%

H_SWING=0.3125*VCCP

12

R25

R25

100_0402_1%

100_0402_1%

H_SWNG

1

2

C53

C53

0.1U_0402_16V4Z

0.1U_0402_16V4Z

H_RESET#5

H_CPUSLP#6

Near B3 pin

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWNG

H_RCOMP

+H_VREF

U3A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

G7R3@

G7R3@

H_ADSTB#_0

H_ADSTB#_1

H_BREQ#

H_DEFER#

HOST

HOST

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_HIT#

H_HITM#

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A#[3..35] 5

H_ADS# 5

H_ADSTB#0 5

H_ADSTB#1 5

H_BNR# 5

H_BPRI# 5

H_BR0# 5

H_DEFER# 5

H_DBSY# 5

CLK_MCH_BCLK 17

CLK_MCH_BCLK# 17

H_DPWR# 6

H_DRDY# 5

H_HIT# 5

H_HITM# 5

H_LOCK# 5

H_TRDY# 5

H_DINV#0 6

H_DINV#1 6

H_DINV#2 6

H_DINV#3 6

H_DSTBN#0 6

H_DSTBN#1 6

H_DSTBN#2 6

H_DSTBN#3 6

H_DSTBP#0 6

H_DSTBP#1 6

H_DSTBP#2 6

H_DSTBP#3 6

H_REQ#0 5

H_REQ#1 5

H_REQ#2 5

H_REQ#3 5

H_REQ#4 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

A A

Security Classification

Security Classification

Security Classification

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/10/06 2009/10/06

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

846Tuesday, August 18, 2009

846Tuesday, August 18, 2009

846Tuesday, August 18, 2009

1

A

A

A

of

of

of

Page 9

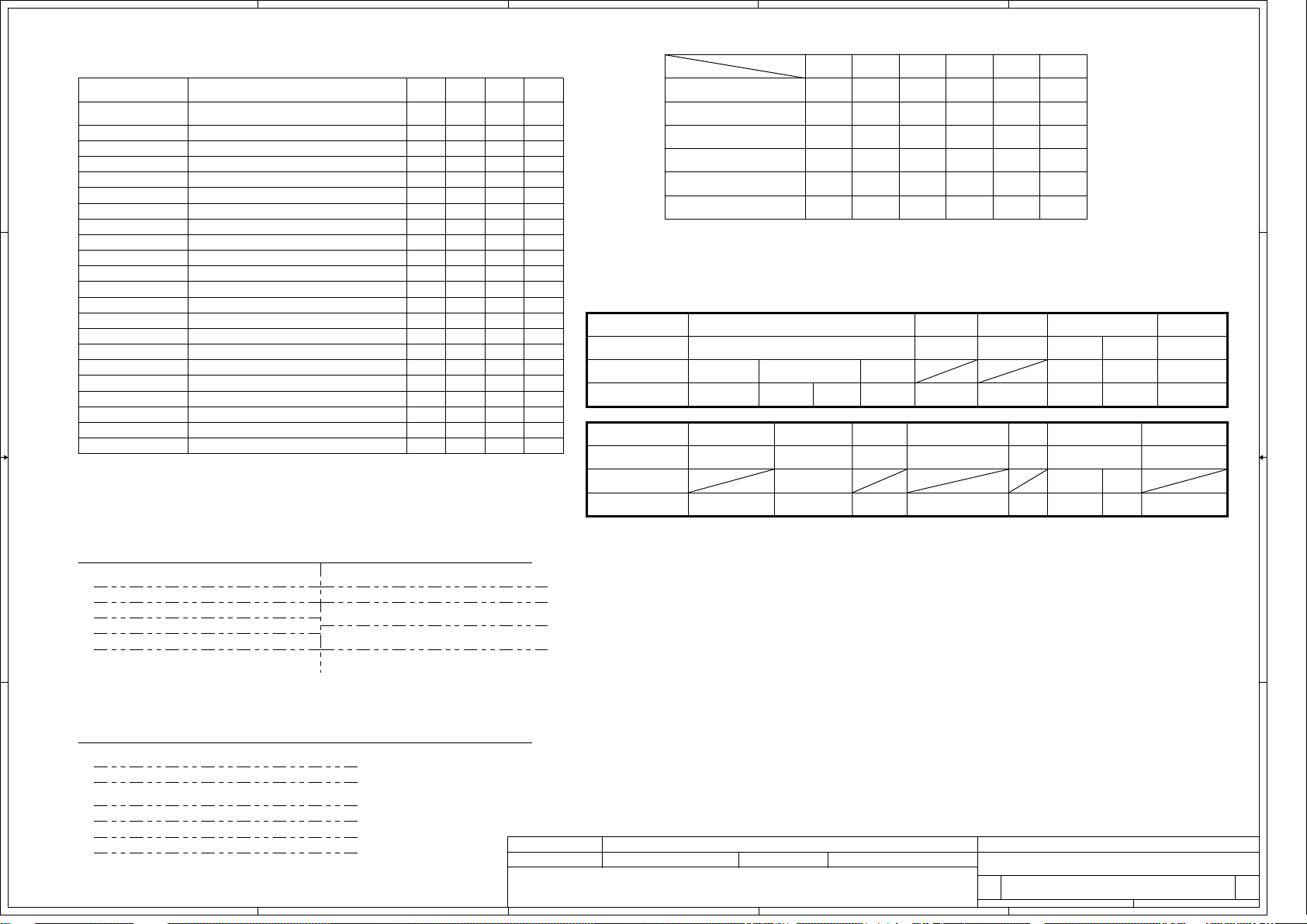

Strap Pin Table

5

011 = FSB667

CFG[2:0]

Internal pull-up

CFG5

Internal pull-up

CFG6

D D

C C

B B

+3VS

A A

Internal pull-up

CFG7

Internal pull-up

CFG9

Internal pull-up

CFG10

CFG[13:12]

Internal pull-up

Internal pull-up

CFG16

Internal pull-down

CFG19

CFG20

Internal pull-down

(PCIE/SDVO select)

1 2

R52 10K_0402_5%R52 10K_0402_5%

ICH_PWROK24

010 = FSB800

000 = FSB1067

0 = DMI x 2

1 = DMI x 4

0 = iTPM Host Interface is enabled

1 = iTPM Host Interface is Disabled

0 = Intel Management Engine Crypto Transport Layer Security

(TLS) cipher suite with no confidentiality

1 = Intel Management Engine Crypto TLS cipher suite with

confidentiality

0 = Lane Reversal Enable

0 = PCIe Loopback Enable

1 = Disable

01 = All Z Mode Enabled

00 = Reserved

10 = XOR Mode Enabled

11 = Normal Operation

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = Normal Operation

1 = DMI Lane Reversal Enable

(Default)

*

(Default)

*

(Default)

*

(Default)1 = Normal Operation

*

(Default)

*

*

can support disble by SW.

(Default)

*

(Default)

(Default)

*

0 = Only PCIE or [SDVO/DP/HDMI] is operational.

1 = PCIE/[SDVO/DP/HDMI] are operating simu.

R35 1K_0402_5%R35 1K_0402_5%

R36 1K_0402_5%R36 1K_0402_5%

R37 1K_0402_5%R37 1K_0402_5%

R39 2.21K_0402_1%@R39 2.21K_0402_1%@

R40 2.21K_0402_1%@R40 2.21K_0402_1%@

R43 2.21K_0402_1%@R43 2.21K_0402_1%@

R44 2.21K_0402_1%@R44 2.21K_0402_1%@

R45 2.21K_0402_1%@R45 2.21K_0402_1%@

R46 2.21K_0402_1%@R46 2.21K_0402_1%@

R47 2.21K_0402_1%@R47 2.21K_0402_1%@

+3VS

R48 2.21K_0402_1%@R48 2.21K_0402_1%@

R49 4.02K_0402_1%R49 4.02K_0402_1%

R50 4.02K_0402_1%@R50 4.02K_0402_1%@

R51 0_0402_5%R51 0_0402_5%

R53 0_0402_5%R53 0_0402_5%

R54 100_0402_5%R54 100_0402_5%

R55 0_0402_5%R55 0_0402_5%

R56 0_0402_5%R56 0_0402_5%

GMCH_PWROK

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PM_EXTTS#_R

Use VGATE for GMCH_PWROK

VGATE24,34,44

5

CPU_BSEL06,17

CPU_BSEL16,17

CPU_BSEL26,17

PM_SYNC#24

PM_EXTTS#15,16

PLT_RST#18,22,27,29,30,33,34,35

H_THERMTRIP#5,23

PM_DPRSLPVR24,44

1 2

R58 0_0402_5%@R58 0_0402_5%@

1 2

R59 0_0402_5%R59 0_0402_5%

4

U3B

U3B

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

AL34

RSVD10

AK34

RSVD11

AN35

RSVD12

AM35

RSVD13

T24

RSVD14

B31

RSVD15

B2

RSVD16

M1

RSVD17

AY21

RSVD20

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

(Default)

*

4

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

T1 PADT1 PAD

T2 PADT2 PAD

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

T12 PADT12 PAD

MCH_CFG_19

MCH_CFG_20

PM_SYNC#_R

PM_EXTTS#_R

GMCH_PWROK

MCH_RSTIN#

NB_THERMTRIP#

DPRSLPVR

12

12

12

H_DPRSTP#6,23,44

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC_1

BF48

NC_2

BD48

NC_3

BC48

NC_4

BH47

NC_5

BG47

NC_6

BE47

NC_7

BH46

NC_8

BF46

NC_9

BG45

NC_10

BH44

NC_11

BH43

NC_12

BH6

NC_13

BH5

NC_14

BG4

NC_15

BH3

NC_16

BF3

NC_17

BH2

NC_18

BG2

NC_19

BE2

NC_20

BG1

NC_21

BF1

NC_22

BD1

NC_23

BC1

NC_24

F1

NC_25

A47

NC_26

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

G7R3@

G7R3@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

RSVD CFG PM NC

RSVD CFG PM NC

3

DDR CLK/ CONTROL/ COMPENSATIONHDA

DDR CLK/ CONTROL/ COMPENSATIONHDA

DPLL_REF_SSCLK#

CLKDMIGRAPHICS VIDMEMISC

CLKDMIGRAPHICS VIDMEMISC

3

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

BB36

SB_CKE_1

BA17

SA_CS#_0

AY16

SA_CS#_1

AV16

SB_CS#_0

AR13

SB_CS#_1

BD17

SA_ODT_0

AY17

SA_ODT_1

BF15

SB_ODT_O

AY13

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

SMRCOMP

BG22

SMRCOMP#

BH21

+SM_RCOMP_VOH

BF28

+SM_RCOMP_VOL

BH28

+SM_VREF

AV42

SM_PWROK

AR36

SM_REXT

BF17

SM_DRAMRST#

BC36

CLK_DREF_96M

B38

CLK_DREF_96M#

A38

CLK_DREF_SSC

E41

CLK_DREF_SSC#

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

ICH_PWROK

AN36

AJ35

+CL_VREF

AH34

+CL_VREF=0.355V

DP_CLK

N28

DP_DATA

M28

SDVO_SCLK

G36

SDVO_SDATA

E36

K36

H36

MCH_TSATN#

B12

B28

B30

AZ_SDIN2_MCH_R

B29

C29

A28

Compal Secret Data

Compal Secret Data

Compal Secret Data

DDRA_CLK0 15

DDRA_CLK1 15

DDRB_CLK0 16

DDRB_CLK1 16

DDRA_CLK0# 15

DDRA_CLK1# 15

DDRB_CLK0# 16

DDRB_CLK1# 16

DDRA_CKE0 15

DDRA_CKE1 15

DDRB_CKE0 16

DDRB_CKE1 16

DDRA_SCS0# 15

DDRA_SCS1# 15

DDRB_SCS0# 16

DDRB_SCS1# 16

DDRA_ODT0 15

DDRA_ODT1 15

DDRB_ODT0 16

DDRB_ODT1 16

R29 80.6_0402_1%R29 80.6_0402_1%

1 2

R30 80.6_0402_1%R30 80.6_0402_1%

1 2

R32 10K_0402_1%@R32 10K_0402_1%@

1 2

R33 499_0402_1%R33 499_0402_1%

1 2

SM_DRAMRST# 15,16

CLK_DREF_96M 17

CLK_DREF_96M# 17

CLK_DREF_SSC 17

CLK_DREF_SSC# 17

CLK_MCH_3GPLL 17

CLK_MCH_3GPLL# 17

DMI_ITX_MRX_N0 22

DMI_ITX_MRX_N1 22

DMI_ITX_MRX_N2 22

DMI_ITX_MRX_N3 22

DMI_ITX_MRX_P0 22

DMI_ITX_MRX_P1 22

DMI_ITX_MRX_P2 22

DMI_ITX_MRX_P3 22

DMI_MTX_IRX_N0 22

DMI_MTX_IRX_N1 22

DMI_MTX_IRX_N2 22

DMI_MTX_IRX_N3 22

DMI_MTX_IRX_P0 22

DMI_MTX_IRX_P1 22

DMI_MTX_IRX_P2 22

DMI_MTX_IRX_P3 22

CL_CLK0 24

CL_DATA0 24

CL_RST#0 24

DP_CLK 11

DP_DATA 11

SDVO_SCLK 21

SDVO_SDATA 21

CLKREQ_3GPLL# 17

MCH_ICH_SYNC# 24

AZ_BITCLK_MCH 23

AZ_RST_MCH# 23

AZ_SDOUT_MCH 23

AZ_SYNC_MCH 23

Deciphered Date

Deciphered Date

Deciphered Date

2

SM_DRAMRST# would be

needed for DDR3 only

For Cantiga 80 Ohm

+1.5V

1

C58

C58

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

@

@

Lane reversal

SDVO_CTRLDATA

(Internal pull-down)

DDPC_CTRLDATA

(Internal pull-down)

Width:Spacing

12mil:12mil

1

C59

C59

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

1 2

R63 33_0402_5%

R63 33_0402_5%

IHDMI@

IHDMI@

1

+SM_RCOMP_VOH

1

0.01U_0402_25V7K

0.01U_0402_25V7K

+SM_RCOMP_VOL

0.01U_0402_25V7K

0.01U_0402_25V7K

+1.5V

R31

R31

1K_0402_1%

1K_0402_1%

20mil

1 2

R34

R34

1K_0402_1%

1K_0402_1%

1 2

SM_PWROK

CLK_DREF_96M

CLK_DREF_96M#

CLK_DREF_SSC

CLK_DREF_SSC#

Please place these resistors close to related balls

+1.05VS

12

R41

R41

54.9_0402_1%

54.9_0402_1%

MCH_TSATN#

Strap Pin Table

0 = SDVO interface disabled

1 = SDVO interface enabled

0 = Digital display (iHDMI/DP) interface disabled

1 = Digital display (iHDMI/DP) interface enabled

+1.05VS

R57

R57

1K_0402_1%

1K_0402_1%

CL_VREF

1 2

should be

0.35 V

R60

R60

499_0402_1%

499_0402_1%

1 2

SDVO_SCLK

R61

GM@R61

SDVO_SDATA

GM@

R62

IHDMI@R62

IHDMI@

1

C54

C54

2

1

C56

C56

2

R105

R105

1 2

R575 0_0402_5%

R575 0_0402_5%

R576 0_0402_5%

R576 0_0402_5%

R577 0_0402_5%

R577 0_0402_5%

R578 0_0402_5%

R578 0_0402_5%

12

R38

R38

1K_0402_5%

1K_0402_5%

B

B

2

E

E

3 1

C

C

Q7

Q7

MMBT3904_SOT23-3

MMBT3904_SOT23-3

(Default)

*

R61

R61

0_0402_5%

0_0402_5%

R62

R62

0_0402_5%

0_0402_5%

2.2K_0402_5%

2.2K_0402_5%

12

2.2K_0402_5%

2.2K_0402_5%

12

2

1

2

0_0402_5%

0_0402_5%

PM@

PM@

1 2

PM@

PM@

1 2

PM@

PM@

1 2

PM@

PM@

1 2

+3VS

PM@

PM@

PM@

PM@

the strap pin will impact no IHDMI SKU if mount R62

AZ_SDIN2_MCH 23

IHDMI@ RA35

IHDMI@

AZ_BITCLK_MCH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C66

IHDMI@C66

RA35

1 2

0_0402_5%

0_0402_5%

IHDMI@

12

33P_0402_50V8K

33P_0402_50V8K

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

SCHEMATIC,MB A4993

401781

401781

401781

1

1K_0402_1%

1K_0402_1%

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

C55

C55

3.01K_0402_1%

3.01K_0402_1%

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

C57

C57

1K_0402_1%

1K_0402_1%

DDR3_SM_PWPOK 43

12

R42

R42

1K_0402_5%

1K_0402_5%

(Default)

*

GM@

GM@

1 2

R579 0_0402_5%

R579 0_0402_5%

PM@

PM@

1 2

R580 0_0402_5%

R580 0_0402_5%

946Tuesday, August 18, 2009

946Tuesday, August 18, 2009

946Tuesday, August 18, 2009

+1.5V

12

R26

R26

12

R27

R27

12

R28

R28

MCH_TSATN_EC# 34

+3VS

of

of

of

A

A

A

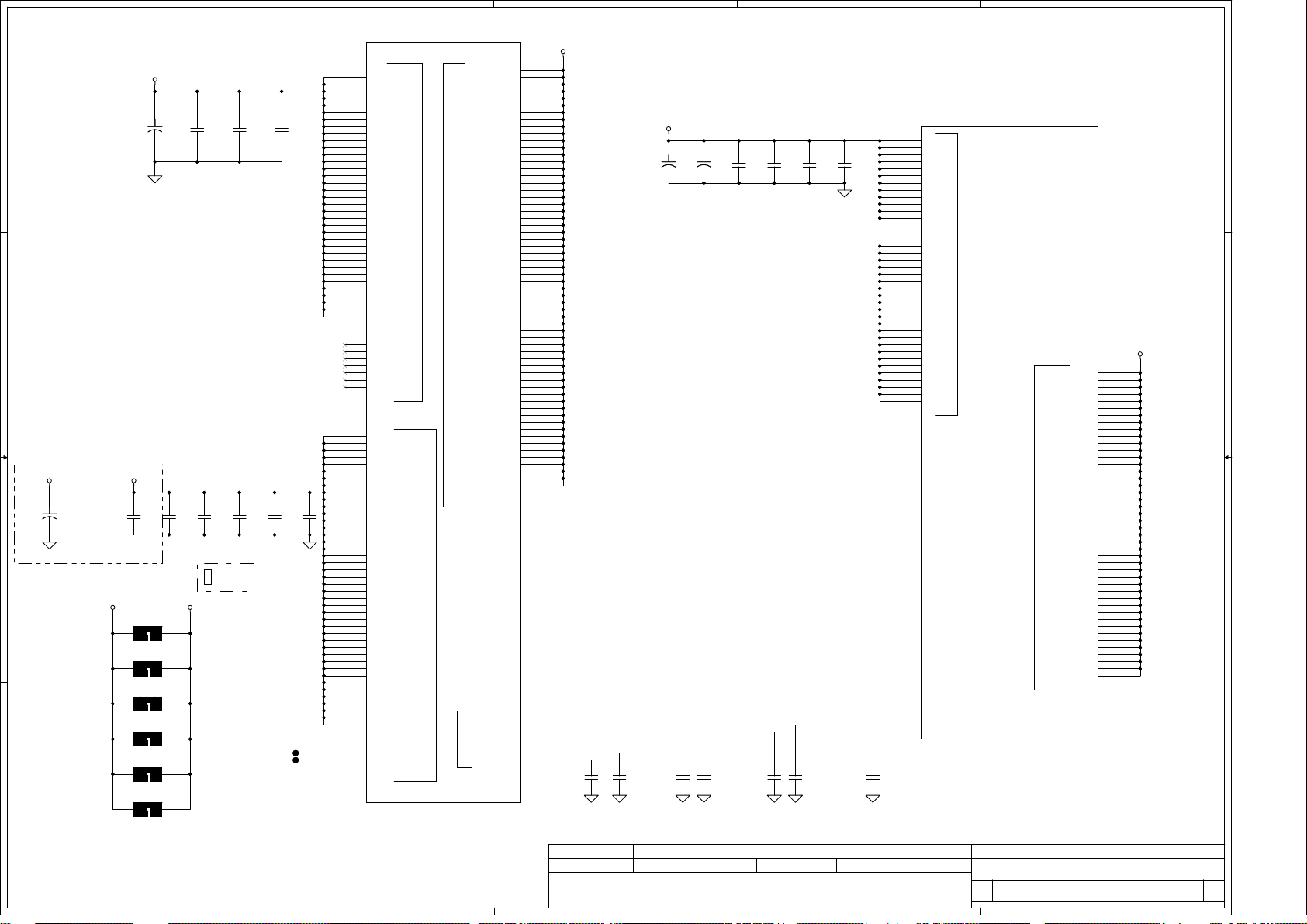

Page 10

5

D D

DDR_A_D[0..63]15 DDR_B_D[0..63]16

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

U3D

U3D

AJ38

SA_DQ_0

AJ41

SA_DQ_1

AN38

SA_DQ_2

AM38

SA_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_10

AT38

SA_DQ_11

AN41

SA_DQ_12

AN39

SA_DQ_13

AU44

SA_DQ_14

AU42

SA_DQ_15

AV39

SA_DQ_16

AY44

SA_DQ_17

BA40

SA_DQ_18

BD43

SA_DQ_19

AV41

SA_DQ_20

AY43

SA_DQ_21

BB41

SA_DQ_22

BC40

SA_DQ_23

AY37

SA_DQ_24

BD38

SA_DQ_25

AV37

SA_DQ_26

AT36

SA_DQ_27

AY38

SA_DQ_28

BB38

SA_DQ_29

AV36

SA_DQ_30

AW36

SA_DQ_31

BD13

SA_DQ_32

AU11

SA_DQ_33

BC11

SA_DQ_34

BA12

SA_DQ_35

AU13

SA_DQ_36

AV13

SA_DQ_37

BD12

SA_DQ_38

BC12

SA_DQ_39

BB9

SA_DQ_40

BA9

SA_DQ_41

AU10

SA_DQ_42

AV9

SA_DQ_43

BA11

SA_DQ_44

BD9

SA_DQ_45

AY8

SA_DQ_46

BA6

SA_DQ_47

AV5

SA_DQ_48

AV7

SA_DQ_49

AT9

SA_DQ_50

AN8

SA_DQ_51

AU5

SA_DQ_52

AU6

SA_DQ_53

AT5

SA_DQ_54

AN10

SA_DQ_55

AM11

SA_DQ_56

AM5

SA_DQ_57

AJ9

SA_DQ_58

AJ8

SA_DQ_59

AN12

SA_DQ_60

AM13

SA_DQ_61

AJ11

SA_DQ_62

AJ12

SA_DQ_63

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

G7R3@

G7R3@

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4

SA_BS_0

SA_BS_1