Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

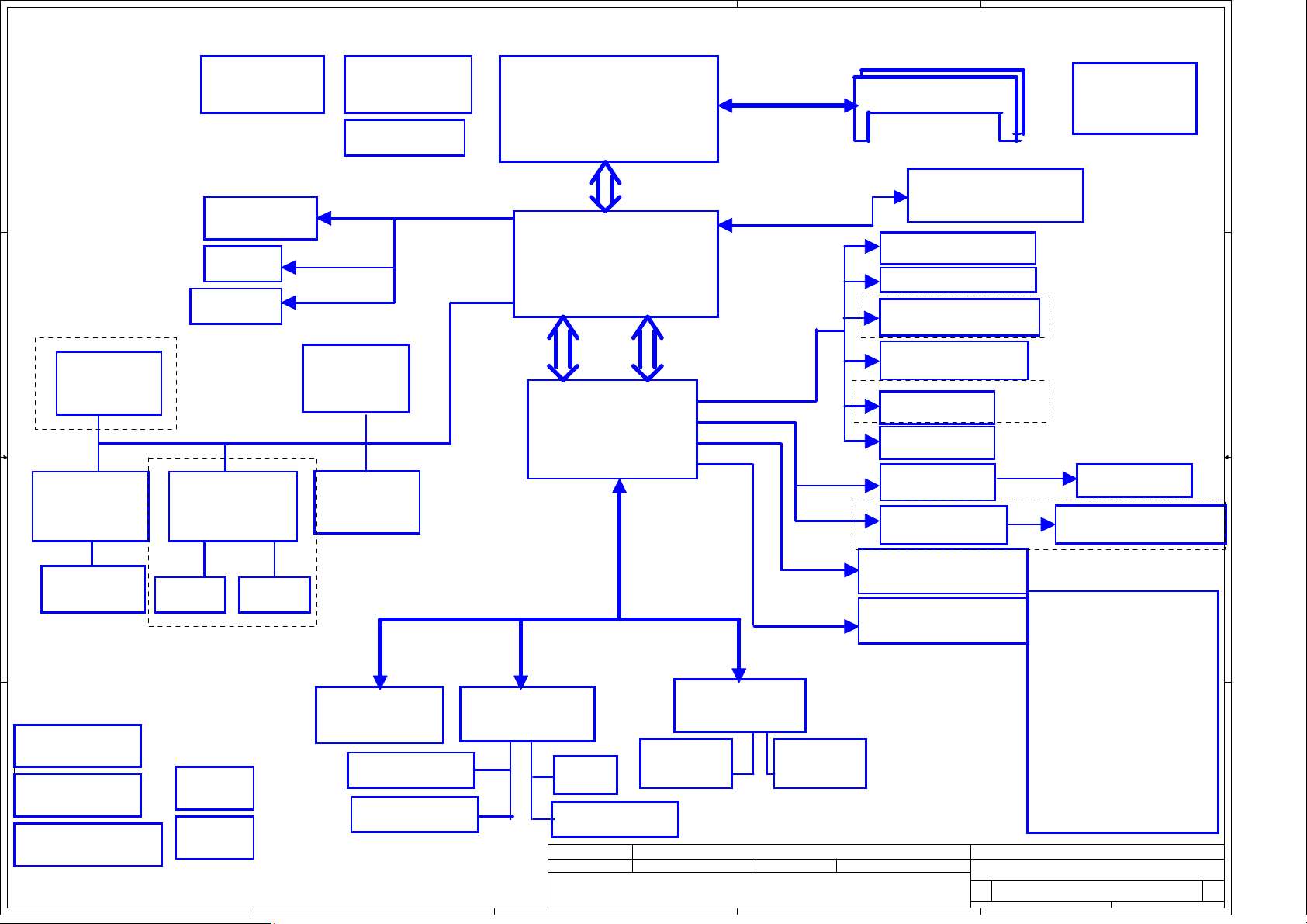

Schematics Document

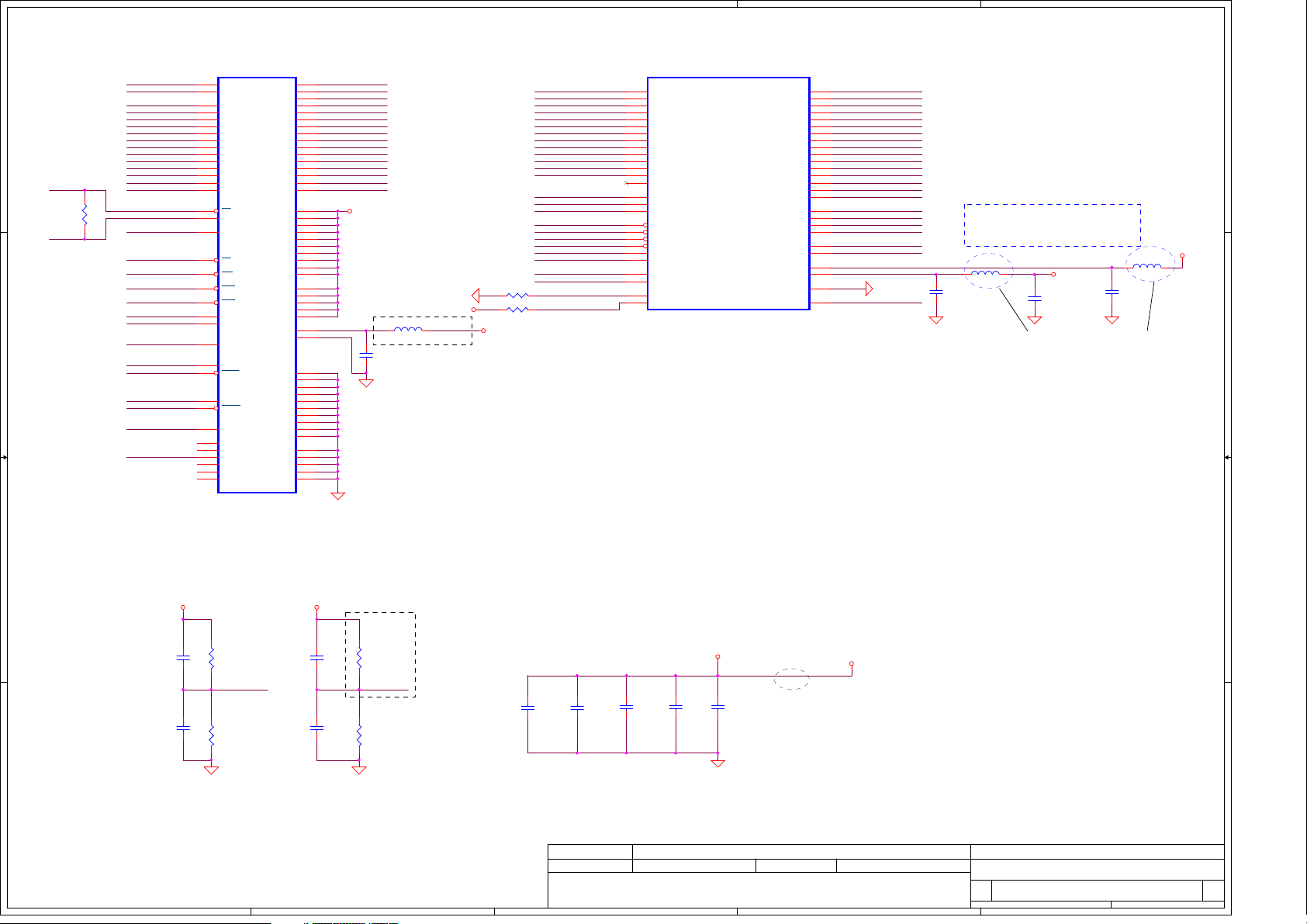

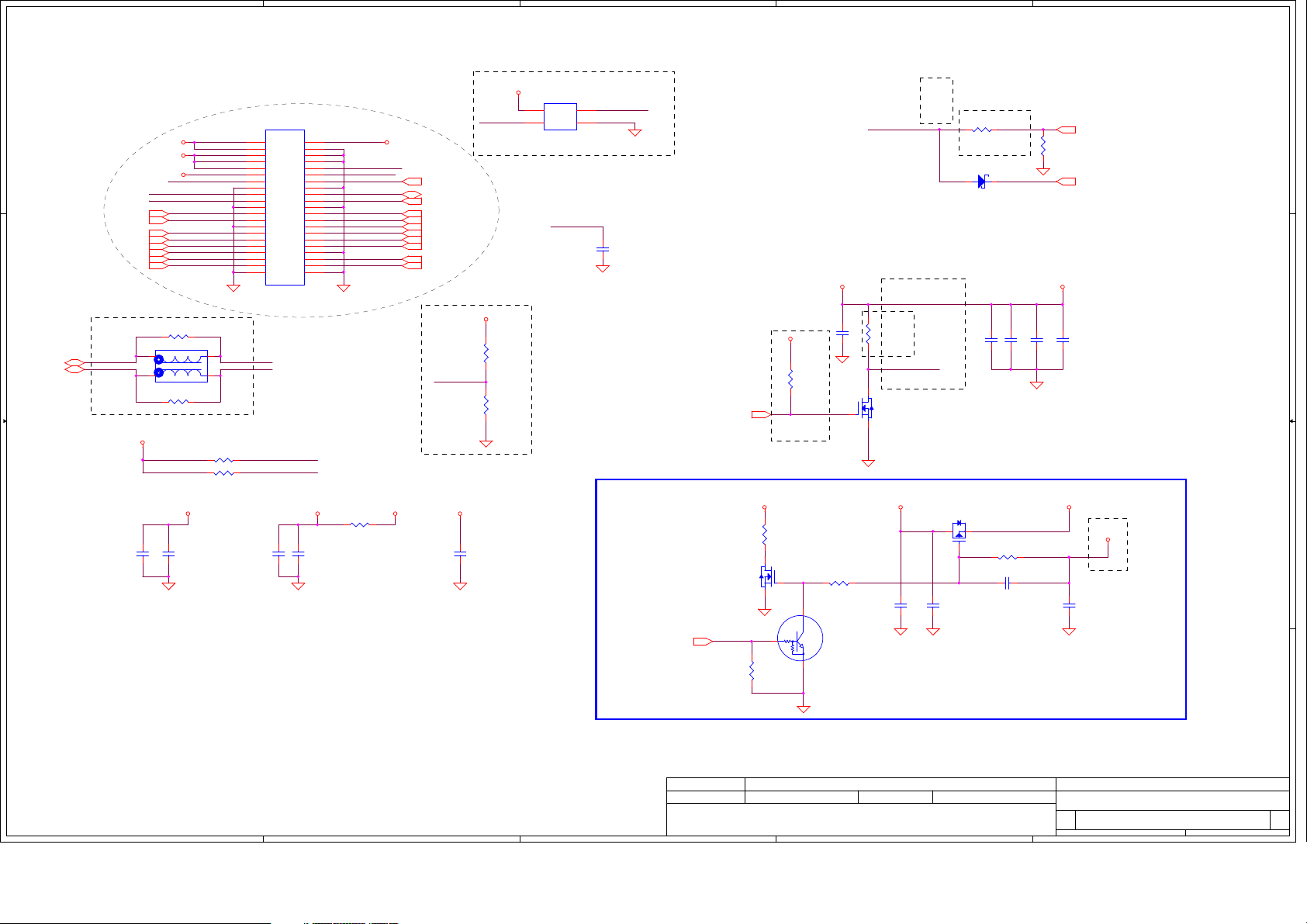

Mobile AMD S1G3 CPU with ATI

RS880M(NB) & SB710(SB) core logic

3 3

2009-08-27

REV:1.0

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/03/23 2010/03/23

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

LA-4961P

1 54Thursday , August 27, 2009

E

1.0

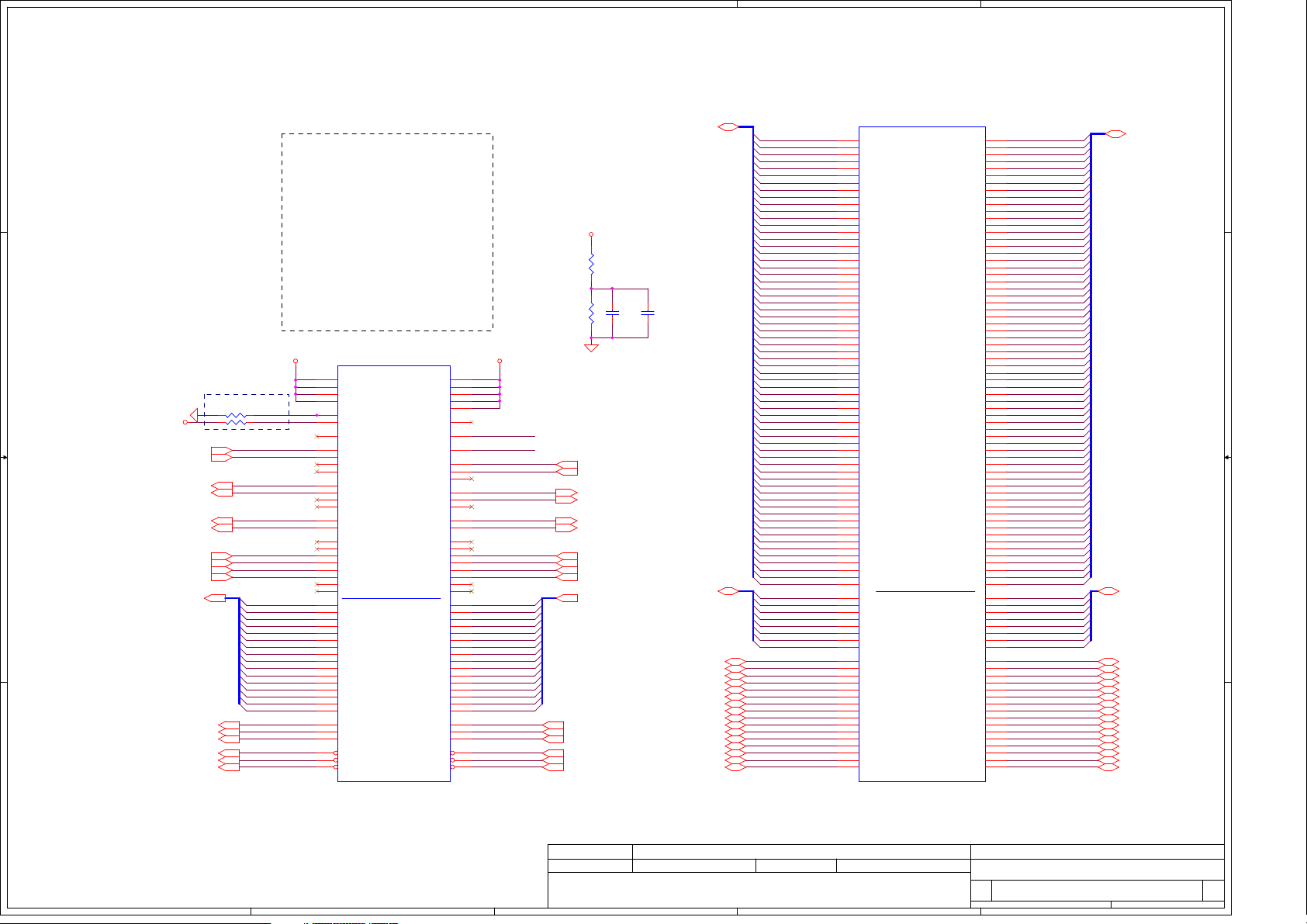

Page 2

A

Compal Confidential

B

C

D

E

TAG UMA

Accelerometer

ST LIS302DL TR

1 1

Page 3 0

LVDS Panel

Interface

CRT

Display Port

Page 1 7

Page 1 6

Page 1 8

daughter board

2 2

Express Card 54

PCIE X1 + USB X1

Page 3 1

10/100/1 000 LAN

88 E 8 072

Page 25

3 3

RJ45 CONN

Page 26

Ri co R5U230

Controller

1394 port

Page 3 1 Page 3 1 Page 3 1

Smart Card

Mini Card UWB

PCIE X 1

daughter board

Thermal Se nsor

ADM1032

Fan c onn

Page 27

PCI-E BUS

WLAN Card

USB + PCIE X1

Page 27

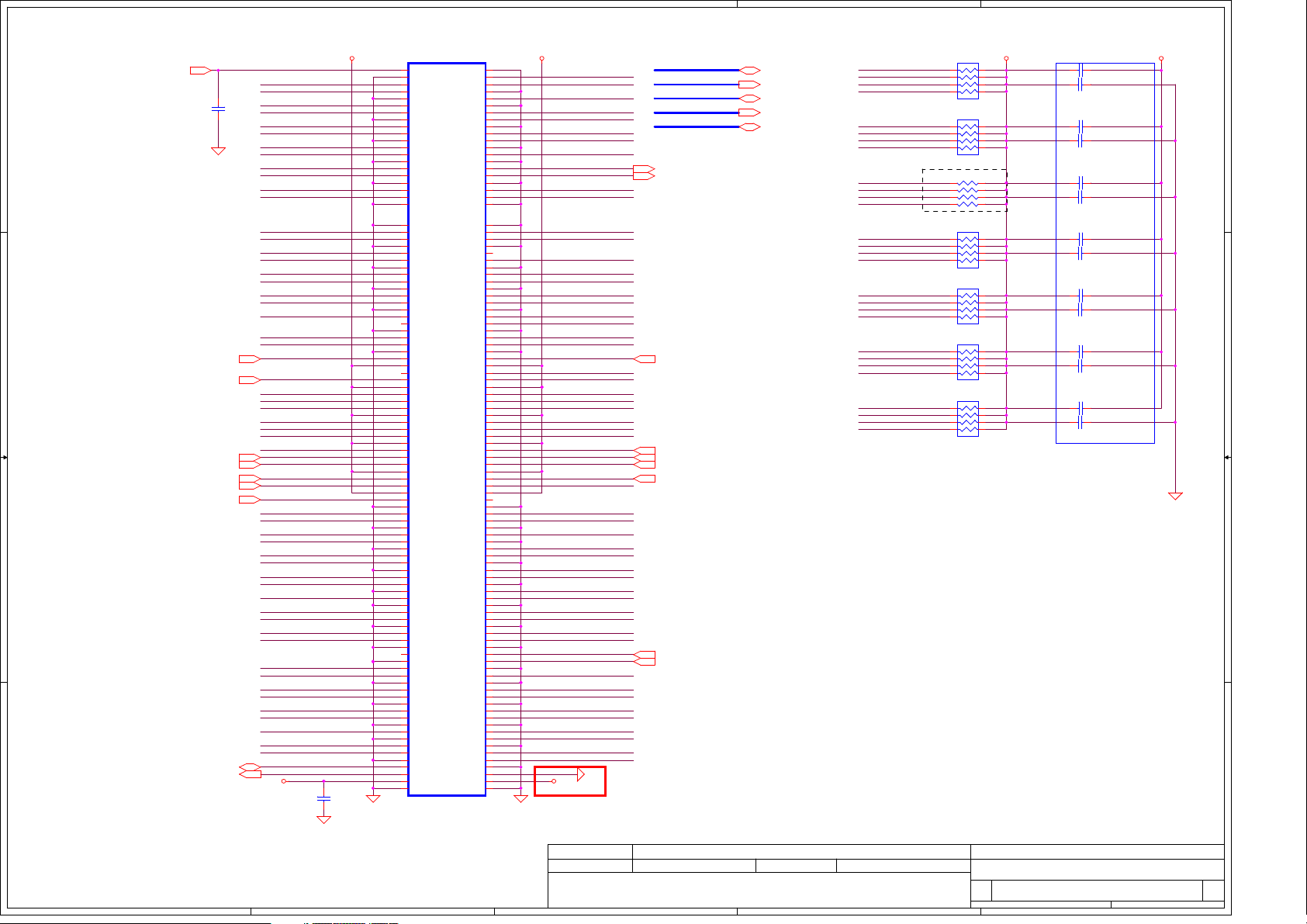

Page 4

Page 4

Caspian

AMD S1G3 CPU

638-PIN uFCPGA 638

Hyper Transport Link

16X16

ATI RS880M

Page 10, 11, 12, 13, 14

A- Li nk Expre ss II

4X P CI-E

ATI SB710

Page 19, 20, 21 ,22, 23

LPC BUS

Page 4, 5, 6, 7

DDR2 800MHz 1.8V

Dual Channel

DDR2 4 00MHz

USB2.0

Azalia

SATA0

SATA1

DDR2- SO-DIMM X2

BANK 0 , 1, 2, 3

Page 8, 9

Side-Port DDR2 SDRAM

512Mbits (32Mbx16)-64MB

WWAN USB X 1

Page 27

USB x2(Docking)

FingerPrinter VFM451

USBx1

USB conn x 2(For I/O)

BT Conn USB x 1

USB ConnX2

sub BD

USB x1(Camara)

MD C V1.5

Audio CKT

92HD75

SATA ODD Connector

2.5" SAT A HDD Connector

Page 33

Page 30

Page 30

Page 3 1

Page 17

Page 28

Page 24

Page 24

72QFN

Clock Generator

IC S9L PRS4 76E

Page 15

Page 13

daughter board

daughter board

RJ11

Page 28

TPA6041A

AMP & Audio Jack

daughter board

P38

Docking CONN.

(1) PCI Express x1 channels

(2) PS/2 Interf aces

(2) USB 2.channels

(2) SATA Channels

(2) Display Port Channels

TPM1.2

SLB9635TT

Page 29 page 34

SMSC KBC 1098

SMSC Super I/O

ITE IT8305

Page 35

Power OK CKT.

page 36

Power On/Off CKT.

4 4

page 28

DC/DC Interface CKT.

Page 3 3

A

LED CKT.

Page 3 1

RTC CKT.

Page 3 1

TrackPoint CONN.

Page 28

Touch Pad CONN.

B

Page 3 1

Int.KBD

Page 28

SP I ROM

2 M B

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

COM1 LPT

( Docking ) ( Docking )

Page 33 Page 33

Page 29

2007/08/02 2008/08/02

C

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

(1) Serial P ort

(1) Parallel Port

(1) Line In

(1) Line Out

(1) RJ45 (10/100/1000)

(1) V GA

(1) 2 LAN indicator LED's

(1) Power Button

(1) I2C interface

Compal Electronics, Inc.

Block Diagram

LA-4961P

2 54Thursday , August 27 , 2009

E

1.0

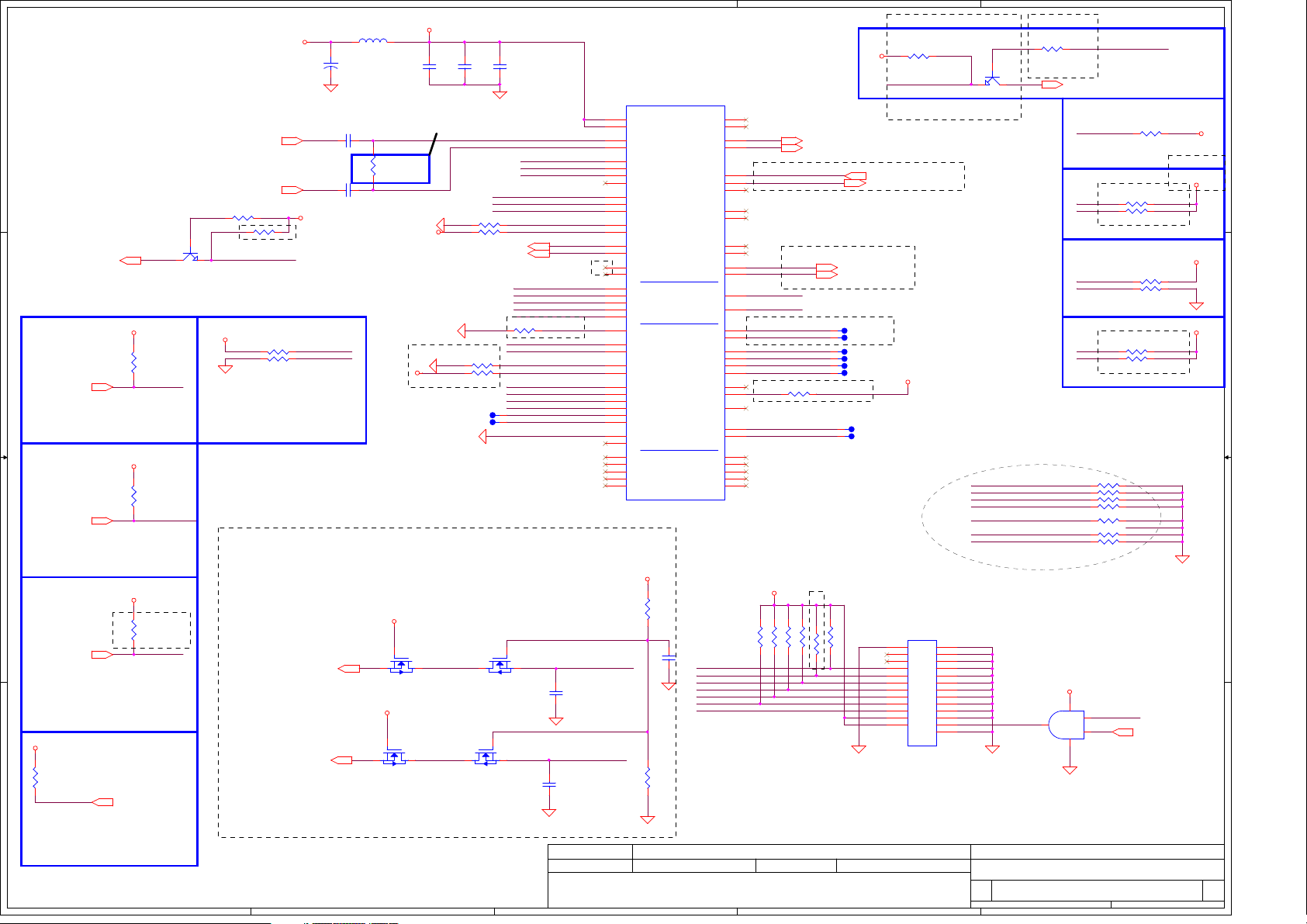

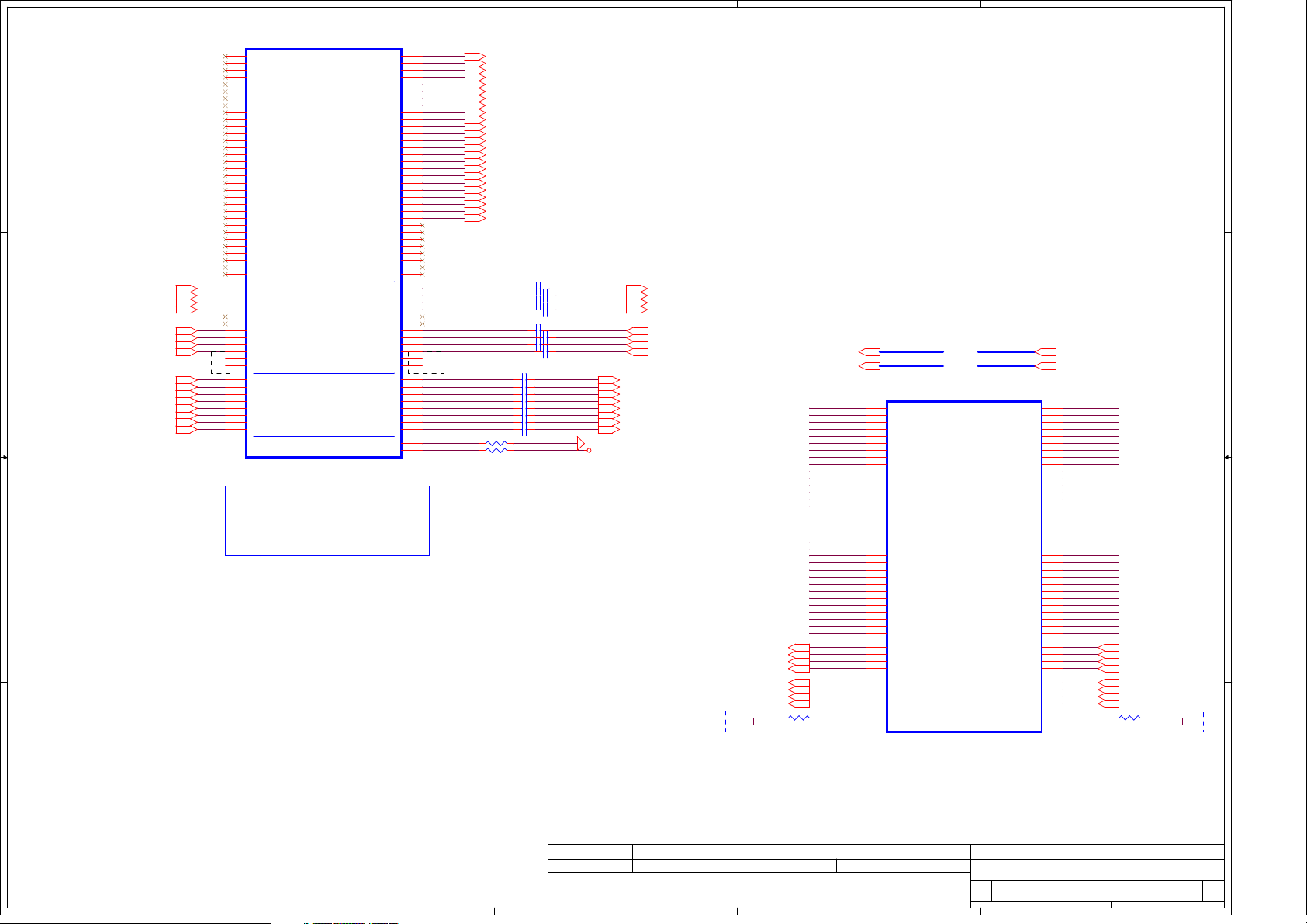

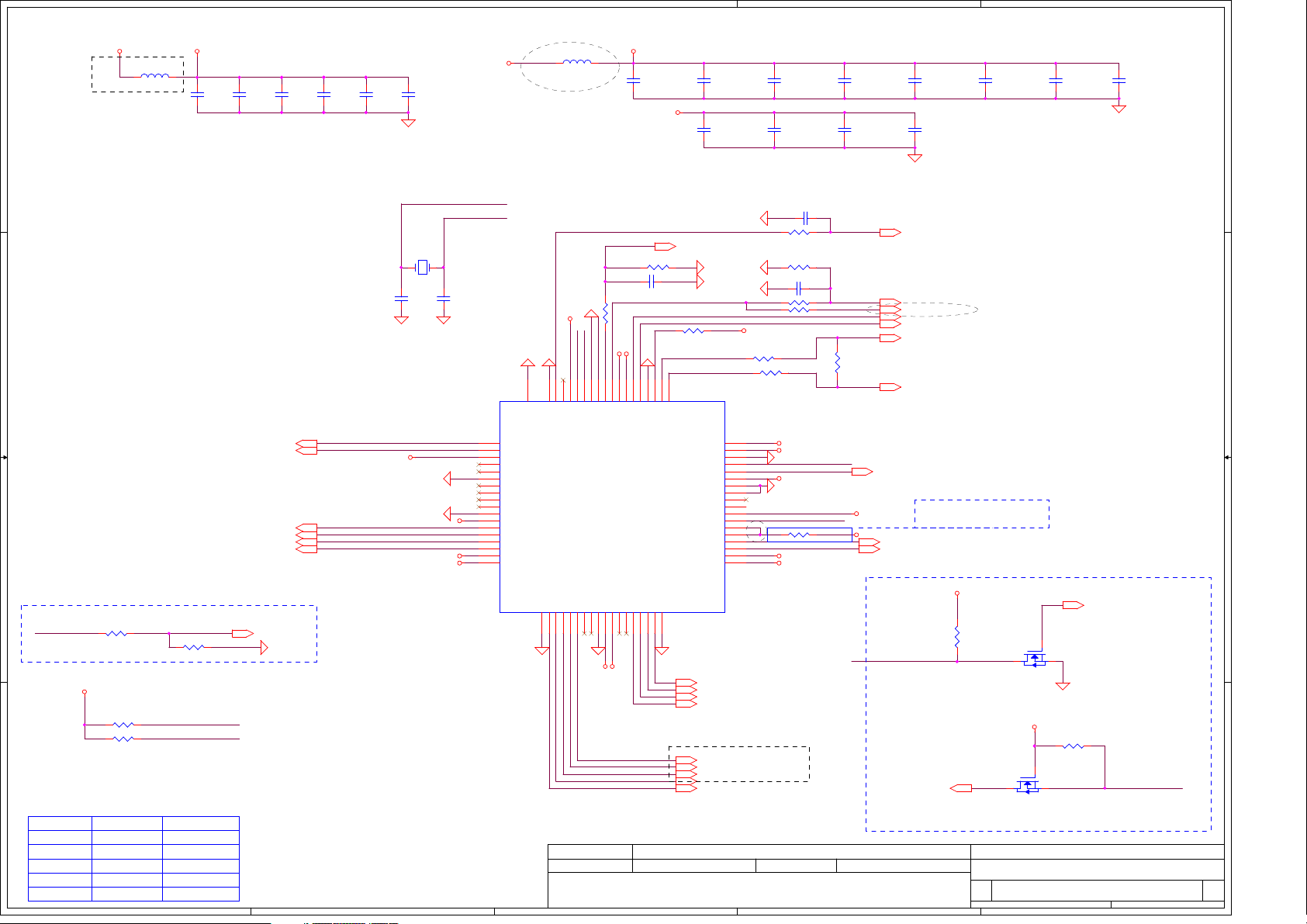

Page 3

A

B

C

D

E

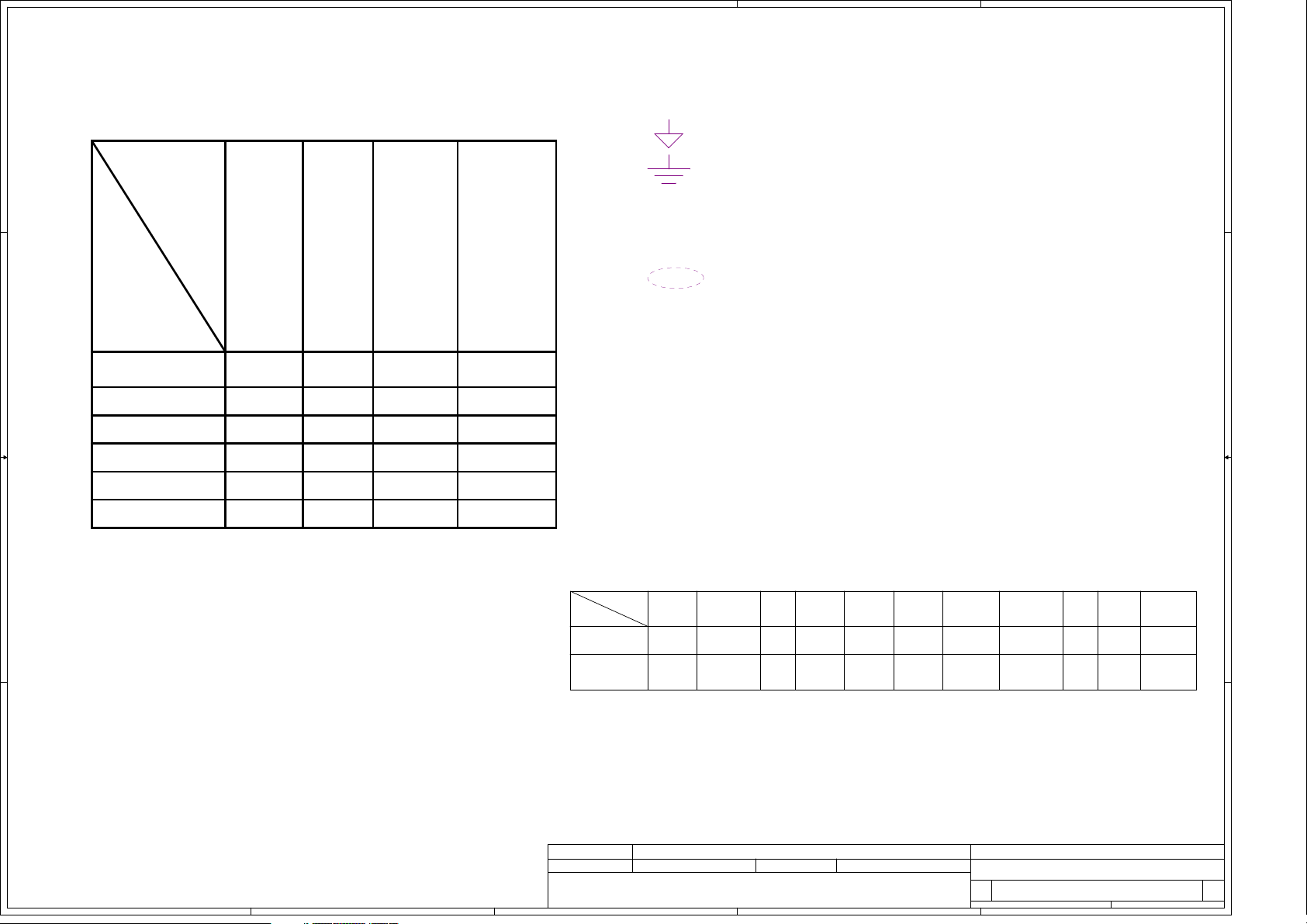

Voltage Rails

1 1

O MEANS ON X MEANS OFF

Symbol Note :

: means Digital Ground

+5VS

State

power

plane

+B

VL

+3VL

+5VALW

+3VALW

+1.8V

+3VS

+1.5VS

+0.9V

+CPU_CORE_0

+2.5VS

+1.8VS

+NB_VDDC

+VDDA11PCIE

: means Analog Ground

Lay out Note s

: Q ues ti on Are a Mark. (Wa it ch eck )

"*" as default BOM setting

@ : means just reserve , no build

45@ : Install when 45 level Assy.

2 2

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O

O

O

O

O

X

O

O

O

O

X

O

X X

X

X X X

OO

OO

X

X

CONN@:means ME part

3 3

4 4

A

B

SMBUS Control Table

THERMAL

SOURCE INVERTER BATT EEPROM

SMB_CK_CLK0

SMB_CK_DAT0

SMB_CK_CLK1

SMB_CK_DAT1

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SB710

SB710

2007/08/02 2008/08/02

C

X X X X X X

X X X X X X X X X X

Compal Secret Data

SERIAL

Deciphered Date

SENSOR

CPU &

ADM103 2

D

SODIMM CLK CHIP

V

MINI CARD LCD

Slot 2I / II

X

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Notes List

LA-4961P

E

HDMI

G-Sensor

VV

3 54Thursday , August 27 , 2009

1.0

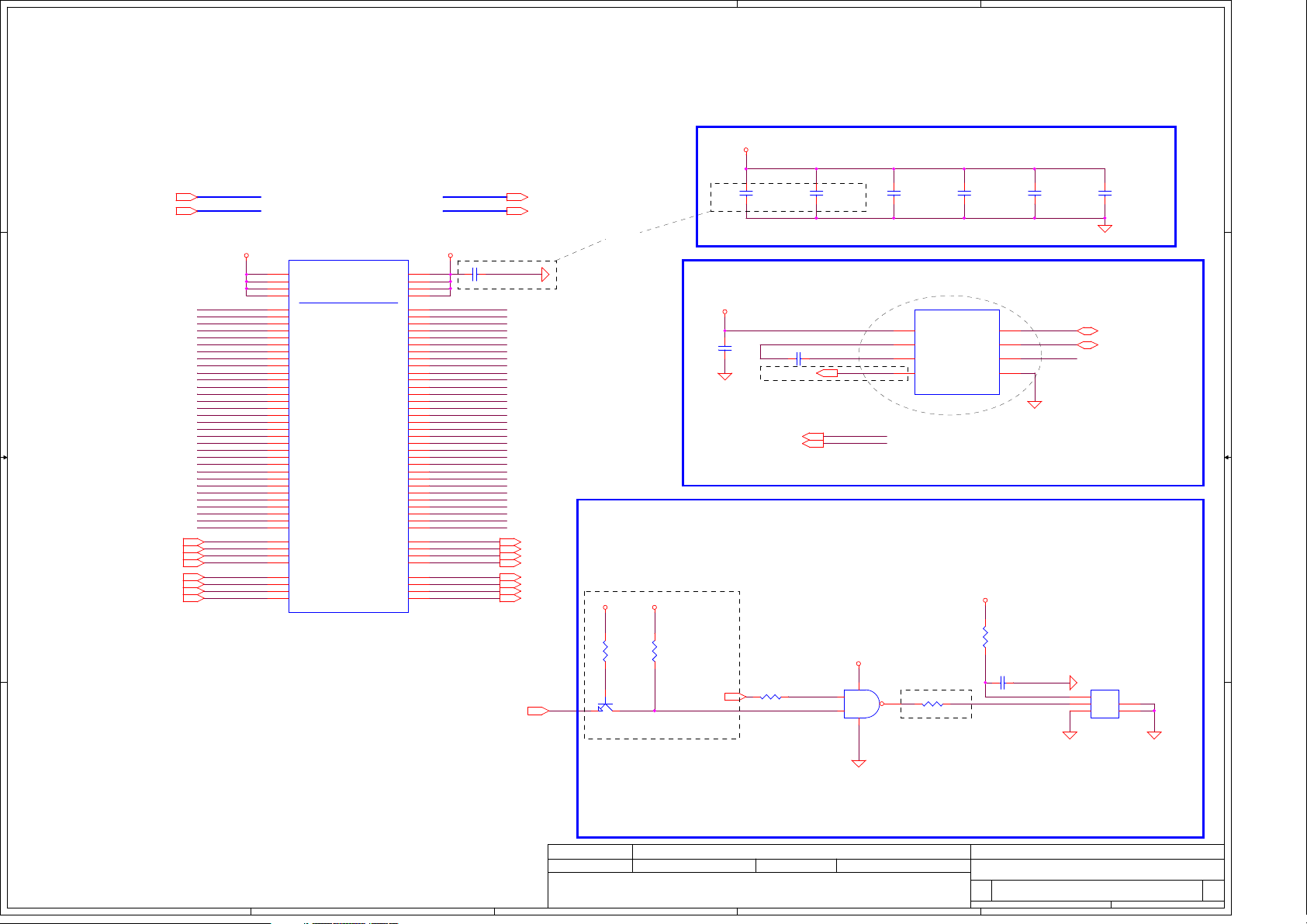

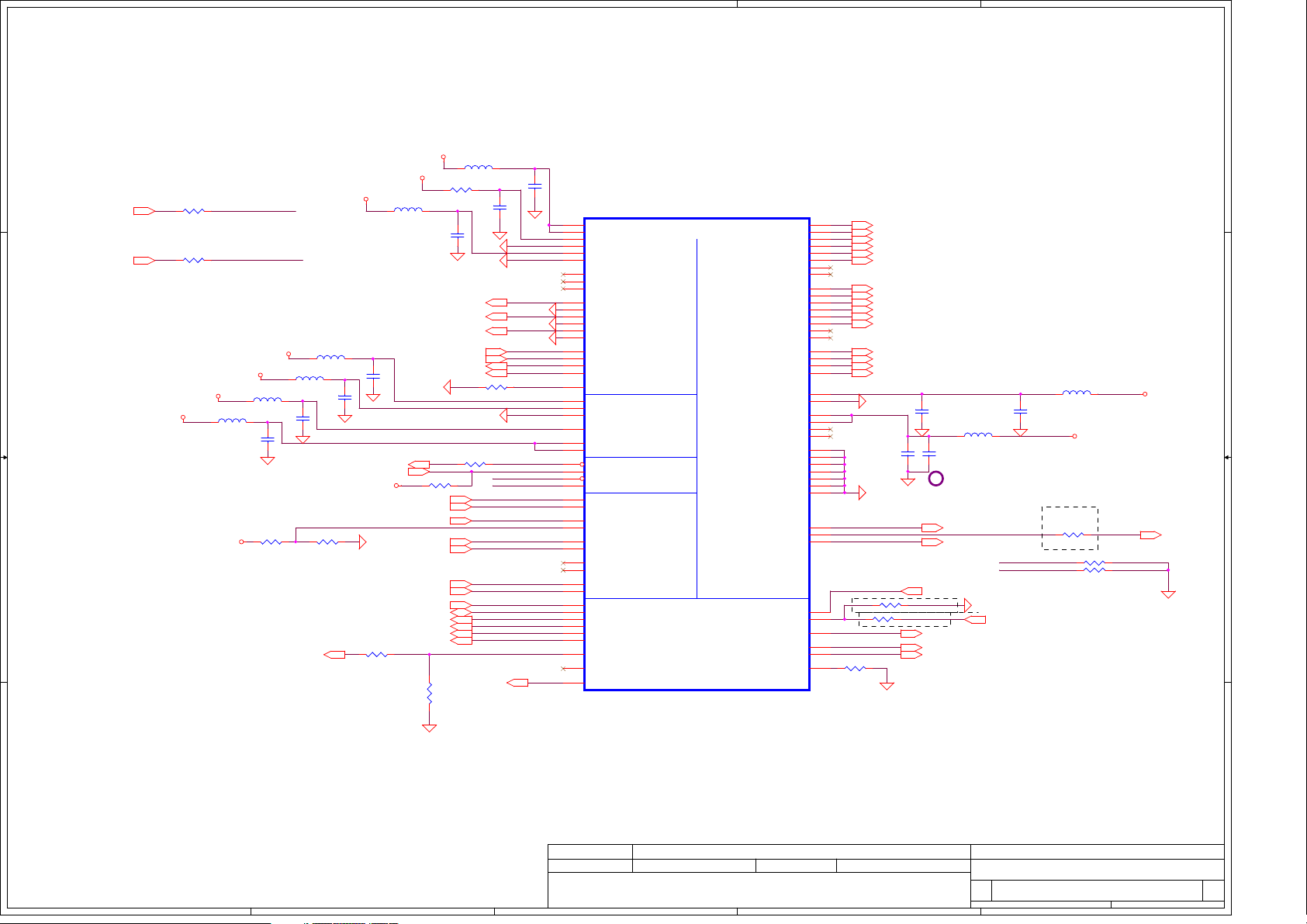

Page 4

A

1 1

H_C ADIP[0..15 ]<10>

2 2

H_CLKIP0<10>

H_CLK IN0<10>

H_CLKIP1<10>

3 3

H_CLK IN1<10>

H_CTLIP0<10>

H_CTLIP1<10> H_CTLOP1 <10>

H_CTLIN1<10>

H_ CADIP[0..1 5]

H_C ADIN[0 ..15]

VLDT= 500mA

H_CAD IP0

H_C ADIN0

H_CAD IP1

H_C ADIN1

H_CAD IP2

H_C ADIN2

H_CAD IP3

H_C ADIN3

H_CAD IP4

H_C ADIN4

H_CAD IP5

H_C ADIN5

H_CAD IP6

H_C ADIN6

H_CAD IP7

H_C ADIN7

H_CAD IP8

H_C ADIN8

H_CAD IP9

H_C ADIN9

H_CAD IP10

H_CAD IN10

H_CAD IP11

H_CAD IN11

H_CAD IP12

H_CAD IN12

H_CAD IP13

H_CAD IN13

H_CAD IP14

H_CAD IN14

H_CAD IP15

H_CAD IN15

+1.2V_HT

JCPU1A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

FOX_P Z6382A-284S-41F_GRIFFIN

CONN@

Athlon 64 S1

Processor Socket

9/2 0 SP0 70 00D M0 0/SP 07000 EQ00

HT LINK

B

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

H_CAD OP[0..15]

H_ CADON[0..1 5]

+1.2V_HT

1 2

C7 10U_0805_10V4Z

H_CAD OP0

H_CAD ON0

H_CAD OP1

H_CAD ON1

H_CAD OP2

H_CAD ON2

H_CAD OP3

H_CAD ON3

H_CAD OP4

H_CAD ON4

H_CAD OP5

H_CAD ON5

H_CAD OP6

H_CAD ON6

H_CAD OP7

H_CAD ON7

H_CAD OP8

H_CAD ON8

H_CAD OP9

H_CAD ON9

H_CAD OP10

H_CAD ON10

H_CAD OP11

H_CAD ON11

H_CAD OP12

H_CAD ON12

H_CAD OP13

H_CAD ON13

H_CAD OP14

H_CAD ON14

H_CAD OP15

H_CAD ON15

H_PROCH OT#<6,46>

C

H_CAD OP[0..15] <10>

H_C ADON[0..15 ] <10>H_C ADIN[0..1 5]<10>

chang e 4.7 U to 1 0U fo r AMD S1G3 requ est. HP 12/8

H_CLKOP0 <10>

H_CLKON0 <10>

H_CLKOP1 <10>

H_CLKON1 <10>

H_CTLOP0 <10>

H_CTLON0 <10>H_CTLIN0<10>

H_CTLON1 <10>

12

30K_0402_5%

R556

Q108

CBE

123

PMBT3904_SOT23

for F an sh ake i ss ue wh en in 7 0 de gree . Co mpal 3/23

+5VS+1.8V

12

+1.2V_HT

1

2

+3VS

1

C8

2

CPU_THER MTRIP#_R<6>

0.1U_0402_16V4Z

NB_THERMAL_DA<11>

NB_THERMAL_DC<11>

PWM Fan Control

circuit

10K_0402_5%

R557

FAN_PWM<33>

R1 3K_0402_5%

250 mi l

C1

10U_0805_10V4Z

C9

1 2

HP 3/ 30

12

D

VLDT CAP.

1

C2

10U_0805_10V4Z

2

Thermal Sensor EMC1402

NB_THERMAL_DA

NB_THERMAL_DC

2200P_0402_50V7K

CPU_THER MTRIP#_R

NB_THERMAL_DA

NB_THERMAL_DC

FAN_PWM_R

1

2

1

C3

0.22U_0603_16V4 Z

2

Near CPU Socket

U1

1

VDD

2

DP

3

DN

4

THERM#

EMC1402-1-ACZL-TR_MSOP8

chang e fro m ADM1 032 t o EMC 1402 12/1

addre ss: 4 C

+3VS

5

U2

P

INB

4

O

G

TC7SH00FU_SSOP5

R534 2.2K_0402_5%

INA

3

for R F, HP 12/10

1

2

SMDATA

12

C4

0.22U_0603_16V4 Z

8

SMCLK

7

6

ALERT#

5

GND

+5VS

12

0_0603_5%

R471

C10

1 2

0.1U_0402_10V6K@

1

C5

180P_0402_50V8J

2

FAN_PWM_R

E

1

2

SMB_CK_CLK0 <6,8,9,1 5,21,30>

SMB_CK_DAT0 < 6,8,9,15,21,30>

conn@

JP1

1

1

2

2

G1

3

3

G2

ACES_85204-03001

C6

180P_0402_50V8J

4

5

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/08/02 2008/08/02

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

AMD CPU S1G2 HT I/F

LA-4961P

4 54Thursday , August 27 , 2009

E

1.0

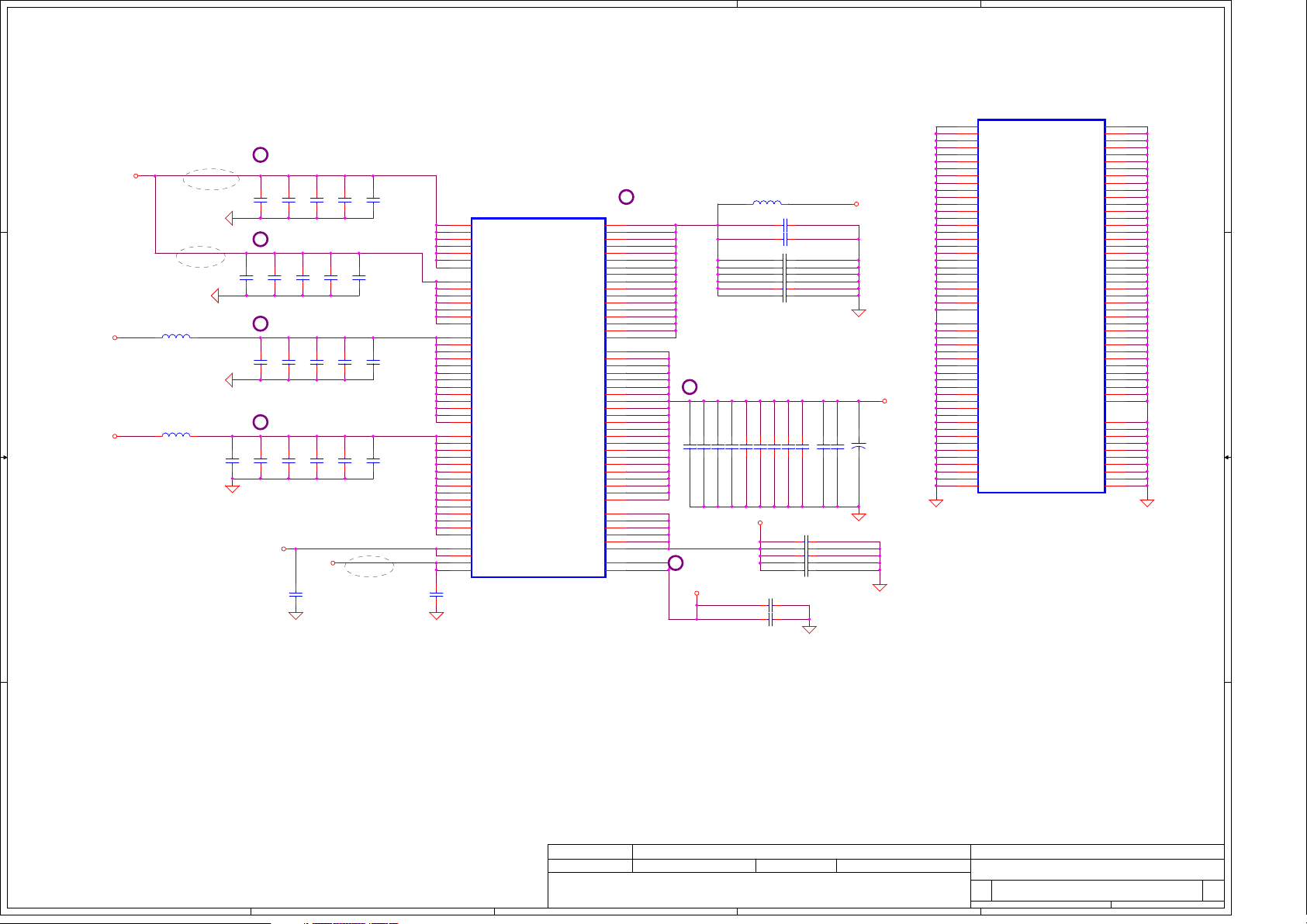

Page 5

A

B

C

D

E

Processor DDR2 Memory Interface

1 1

+1.8V

9/2 3 HP

R2

1K_0402_1%

1 2

+MCH_REF

C12

R3

1K_0402_1%

1 2

2 2

JCPU1B

D10

VTT1

Pla ce th em cl os e t o CP U wi thin 1"

R4 39.2_0402_1%

1 2

DDR_A_BS #0<8>

DDR_A_BS #1<8>

DDR_A_BS #2<8>

DDR_A _RAS#<8>

DDR_A _CAS#<8>

DDR_A_W E#<8>

1 2

R5 39.2_0402_1%

+1.8V

DDR_A _ODT0<8>

DDR_A _ODT1<8>

DDR_CS0_D IMMA#<8>

DDR_CS1_D IMMA#<8> DDR_CS0_D IMMB# <9>

DDR_CKE 0_DIMMA<8>

DDR_CKE 1_DIMMA<8>

DDR_A _CLK0<8>

DDR_A _CLK#0<8>

3 3

4 4

DDR_A _CLK1<8>

DDR_A _CLK#1<8>

DDR_A _MA[15..0]<8> DDR_B _MA[15..0] <9>

MEMZP

MEMZN

DDR_A _ODT0

DDR_A _ODT1

DDR_C S0_DIMMA#

DDR_C S1_DIMMA# DDR_C S0_DIMMB#

DDR_CKE 0_DIMMA

DDR_CKE 1_DIMMA

DDR_A _CLK0

DDR_A _CLK#0

DDR_A _CLK1

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS #0

DDR_A_BS #1

DDR_A_BS #2

DDR_A _RAS#

DDR_A _CAS#

DDR_A_W E#

AD10

AF10

AE10

AA16

MEM:CMD /CTRL/CLK

C10

VTT2

B10

VTT3

VTT4

MEMZP

MEMZN

H16

RSVD_M1

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

FOX_P Z6382A-284S-41F_GRIFFIN

Athlo n 64 S1

Proce ssor

Socke t

CONN@

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

+0.9V+0.9V

+MCH_REF

DDR_B _ODT0

DDR_B _ODT1

DDR_C S1_DIMMB#

DDR_CKE 0_DIMMB

DDR_CKE 1_DIMMB

DDR_B _CLK0

DDR_B _CLK#0

DDR_B _CLK1

DDR_B _CLK#1DDR_A _CLK#1

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_BS #0

DDR_B_BS #1

DDR_B_BS #2

DDR_B _RAS#

DDR_B _CAS#

DDR_B_W E#

0.1U_0402_16V4Z

DDR_B _ODT0 <9>

DDR_B _ODT1 <9>

DDR_CS1_D IMMB# <9>

DDR_CKE 0_DIMMB <9>

DDR_CKE 1_DIMMB <9>

DDR_B _CLK0 <9>

DDR_B _CLK#0 <9>

DDR_B _CLK1 <9>

DDR_B _CLK#1 <9>

DDR_B_BS #0 <9>

DDR_B_BS #1 <9>

DDR_B_BS #2 <9>

DDR_B _RAS# <9>

DDR_B _CAS# <9>

DDR_B_W E# <9>

1

C13

2

1000P_0402_25V8J

DDR _B_D[63.. 0]<9>

1

2

DDR_B _DM[7..0]<9> DDR_A _DM[7..0] <8>

DDR_B _DQS0<9>

DDR_B _DQS#0<9>

DDR_B _DQS1<9>

DDR_B _DQS#1<9>

DDR_B _DQS2<9>

DDR_B _DQS#2<9>

DDR_B _DQS3<9>

DDR_B _DQS#3<9>

DDR_B _DQS4<9>

DDR_B _DQS#4<9>

DDR_B _DQS5<9>

DDR_B _DQS#5<9>

DDR_B _DQS6<9>

DDR_B _DQS#6<9>

DDR_B _DQS7<9>

DDR_B _DQS#7<9>

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D10

DDR_B _D11

DDR_B _D12

DDR_B _D13

DDR_B _D14

DDR_B _D15

DDR_B _D16

DDR_B _D17

DDR_B _D18

DDR_B _D19

DDR_B _D20

DDR_B _D21

DDR_B _D22

DDR_B _D23

DDR_B _D24

DDR_B _D25

DDR_B _D26

DDR_B _D27

DDR_B _D28

DDR_B _D29

DDR_B _D30

DDR_B _D31

DDR_B _D32

DDR_B _D33

DDR_B _D34

DDR_B _D35

DDR_B _D36

DDR_B _D37

DDR_B _D38

DDR_B _D39

DDR_B _D40

DDR_B _D41

DDR_B _D42

DDR_B _D43

DDR_B _D44

DDR_B _D45

DDR_B _D46

DDR_B _D47

DDR_B _D48

DDR_B _D49

DDR_B _D50

DDR_B _D51

DDR_B _D52

DDR_B _D53

DDR_B _D54

DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B _D58

DDR_B _D59

DDR_B _D60

DDR_B _D61

DDR_B _D62

DDR_B _D63

DDR_B_DM 0

DDR_B_DM 1

DDR_B_DM 2

DDR_B_DM 3

DDR_B_DM 4

DDR_B_DM 5

DDR_B_DM 6

DDR_B_DM 7

DDR_B _DQS0

DDR_B _DQS#0

DDR_B _DQS1

DDR_B _DQS#1

DDR_B _DQS2

DDR_B _DQS#2

DDR_B _DQS3

DDR_B _DQS#3

DDR_B _DQS4

DDR_B _DQS#4

DDR_B _DQS5

DDR_B _DQS#5

DDR_B _DQS6

DDR_B _DQS#6

DDR_B _DQS7

DDR_B _DQS#7

JCPU 1C

C11

MB_DATA0

A11

MB_DATA1

A14

MB_DATA2

B14

MB_DATA3

G11

MB_DATA4

E11

MB_DATA5

D12

MB_DATA6

A13

MB_DATA7

A15

MB_DATA8

A16

MB_DATA9

A19

MB_DATA10

A20

MB_DATA11

C14

MB_DATA12

D14

MB_DATA13

C18

MB_DATA14

D18

MB_DATA15

D20

MB_DATA16

A21

MB_DATA17

D24

MB_DATA18

C25

MB_DATA19

B20

MB_DATA20

C20

MB_DATA21

B24

MB_DATA22

C24

MB_DATA23

E23

MB_DATA24

E24

MB_DATA25

G25

MB_DATA26

G26

MB_DATA27

C26

MB_DATA28

D26

MB_DATA29

G23

MB_DATA30

G24

MB_DATA31

AA24

MB_DATA32

AA23

MB_DATA33

AD24

MB_DATA34

AE24

MB_DATA35

AA26

MB_DATA36

AA25

MB_DATA37

AD26

MB_DATA38

AE25

MB_DATA39

AC22

MB_DATA40

AD22

MB_DATA41

AE20

MB_DATA42

AF20

MB_DATA43

AF24

MB_DATA44

AF23

MB_DATA45

AC20

MB_DATA46

AD20

MB_DATA47

AD18

MB_DATA48

AE18

MB_DATA49

AC14

MB_DATA50

AD14

MB_DATA51

AF19

MB_DATA52

AC18

MB_DATA53

AF16

MB_DATA54

AF15

MB_DATA55

AF13

MB_DATA56

AC12

MB_DATA57

AB11

MB_DATA58

Y11

MB_DATA59

AE14

MB_DATA60

AF14

MB_DATA61

AF11

MB_DATA62

AD11

MB_DATA63

A12

MB_DM0

B16

MB_DM1

A22

MB_DM2

E25

MB_DM3

AB26

MB_DM4

AE22

MB_DM5

AC16

MB_DM6

AD12

MB_DM7

C12

MB_DQS_H0

B12

MB_DQS_L0

D16

MB_DQS_H1

C16

MB_DQS_L1

A24

MB_DQS_H2

A23

MB_DQS_L2

F26

MB_DQS_H3

E26

MB_DQS_L3

AC25

MB_DQS_H4

AC26

MB_DQS_L4

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF12

MB_DQS_H7

AE12

MB_DQS_L7

FOX_P Z6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor Socket

CONN@

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D10

DDR_A _D11

DDR_A _D12

DDR_A _D13

DDR_A _D14

DDR_A _D15

DDR_A _D16

DDR_A _D17

DDR_A _D18

DDR_A _D19

DDR_A _D20

DDR_A _D21

DDR_A _D22

DDR_A _D23

DDR_A _D24

DDR_A _D25

DDR_A _D26

DDR_A _D27

DDR_A _D28

DDR_A _D29

DDR_A _D30

DDR_A _D31

DDR_A _D32

DDR_A _D33

DDR_A _D34

DDR_A _D35

DDR_A _D36

DDR_A _D37

DDR_A _D38

DDR_A _D39

DDR_A _D40

DDR_A _D41

DDR_A _D42

DDR_A _D43

DDR_A _D44

DDR_A _D45

DDR_A _D46

DDR_A _D47

DDR_A _D48

DDR_A _D49

DDR_A _D50

DDR_A _D51

DDR_A _D52

DDR_A _D53

DDR_A _D54

DDR_A _D55

DDR_A _D56

DDR_A _D57

DDR_A _D58

DDR_A _D59

DDR_A _D60

DDR_A _D61

DDR_A _D62

DDR_A _D63

DDR_A_DM 0

DDR_A_DM 1

DDR_A_DM 2

DDR_A_DM 3

DDR_A_DM 4

DDR_A_DM 5

DDR_A_DM 6

DDR_A_DM 7

DDR_A _DQS0

DDR_A _DQS#0

DDR_A _DQS1

DDR_A _DQS#1

DDR_A _DQS2

DDR_A _DQS#2

DDR_A _DQS3

DDR_A _DQS#3

DDR_A _DQS4

DDR_A _DQS#4

DDR_A _DQS5

DDR_A _DQS#5

DDR_A _DQS6

DDR_A _DQS#6

DDR_A _DQS7

DDR_A _DQS#7

DDR_ A_D[63..0 ] <8>

DDR_A _DQS0 <8>

DDR_A _DQS#0 <8>

DDR_A _DQS1 <8>

DDR_A _DQS#1 <8>

DDR_A _DQS2 <8>

DDR_A _DQS#2 <8>

DDR_A _DQS3 <8>

DDR_A _DQS#3 <8>

DDR_A _DQS4 <8>

DDR_A _DQS#4 <8>

DDR_A _DQS5 <8>

DDR_A _DQS#5 <8>

DDR_A _DQS6 <8>

DDR_A _DQS#6 <8>

DDR_A _DQS7 <8>

DDR_A _DQS#7 <8>

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/08/02 2008/08/02

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

AMD CPU S1G2 DDRII I/F

LA-4961P

5 54Thursday , August 27 , 2009

E

1.0

Page 6

A

+2.5VS

C14

@

100U_D2_10VM

1 1

CLK_CP U_BCLK<15>

Plac e cl ose to C PU wihtin 1.5"

C18

0718 Silego -- 216 ohm

CLK_CP U_BCLK#<15>

12

R1210K_0402_5%

Q11

CBE

THERM_SC#<21>

+1.8VS

2 2

LDT_RST#<19>

+1.8VS

H_PW RGD_CPU<19>

PMBT3904_SOT23

R19

300_0402_5%

1 2

LDT_RST#

R25

300_0402_5%

1 2

H_PW RGD_CPU

123

+CPU_C ORE_0

R141K_0402_5%

ALERT

R18 10_0402_ 5%

1 2

1 2

R20 10_0402_ 5%

+1.8V

12

10/ 29 HP

CPU_V DD0_FB_L

Close to CPU

C19 3900P_0402_50V7K

9/2 3 H P

3 3

+1.8VS

HP 4/ 6

R35

560_0402_5%

1 2

LDT_STOP#<11,19>

+1.8VS

R42

1K_0402_5%

1 2

4 4

CPU_LDT_R EQ#

LDT_STOP#

SMB_CK_CLK0<4,8,9 ,15,21,30>

SMB_CK_DAT0<4,8,9,15,21,30>

CPU_LD T_REQ# <11,19>

B

L1

1 2

FBM_L11_201209_300L_0805

1

+

2

3900P_0402_50V7K

1 2

12

R9

169_0402_1%

1 2

+1.8V

+5VS

2

Q4A

DMN66D0LDW-7_SOT363-6

+5VS

2

Q5A

DMN66D0LDW-7_SOT363-6

+2.5VDDA

+1.2V_HT

11/ 6 H P

61

CPU_SMDATA

61

1

C154.7U_0805_10V4Z

2

10/ 29 HP

CPU_SMCLK

VDDA= 300mA

3300P_0402_50V7K

1

1

C17

C16

0.22U_0603_16V4 Z

2

2

CPU_C LKIN_SC_P

CPU_C LKIN_SC_N

LDT_RST#

H_PW RGD_CPU

LDT_STOP#

CPU_S IC

CPU_S ID

R13 44.2_0402_1%

R15 44.2_0402_1%

R509

R510 300_0402_5%

ALERT

1 2

1 2

CPU_V DD0_FB_H<45>

CPU_V DD0_FB_L<45>

AMD r eco mm end NC 10/15

CPU _DBRD Y

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_T DI

R489 300_0402_5%

1 2

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1CPU_V DD0_FB_H

510_0402_5%

CPU_T EST25_H_BYPASSCLK_H

1 2

CPU_TEST25_L_BYPASSCLK_L

1 2

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_T EST22_SCANSHIFTEN

T17 PAD

T18 PAD

CPU_T EST12_SCANSHIFTENB

CPU_T EST27_SINGLECHAIN

5

3

4

Q4B

DMN66D0LDW-7_SOT363-6

5

3

4

Q5B

DMN66D0LDW-7_SOT363-6

C21 220P_0402_25V8J

F10

AF4

AF5

AE6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

AB8

AF7

AE7

AE8

AC8

AF8

AA6

R34

1.5K_0402_5%

CPU_S IC

CPU_S ID

4.7K_0402_5%

CPU_HTREF0

CPU_HTREF1

CPU_V DD0_FB_H

CPU_V DD0_FB_L

1

C20 220P_0402_25V8J

2

1

2

C

JCPU 1D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

LDTSTOP_L

C6

LDTREQ_L

SIC

SID

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

C2

TEST9

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

FOX_P Z6382A-284S-41F_GRIFFIN

CONN@

R43

+3VS

12

12

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

TEST28_H

TEST29_H

1

C705

0.1U_0402_25V6

2

KEY1

KEY2

SVC

SVD

DBREQ_L

TDO

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

D

Q10

CBE

123

HDT_RST#

R572

1K_0402_1%

11/ 6 H P

U3

4

Y

R7

1 2

+1.8V

M11

W18

CPU_SVC

A6

CPU_SVD

A4

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

CPU_D BREQ#

E10

CPU_TDO

AE9

CPU_T EST28_H_PLLCHRZ_P

J7

CPU_T EST28_L_PLLCHRZ_N

H8

CPU_TEST17_BP3

D7

CPU_TEST16_BP2 CPU_S ID

E7

CPU_TEST15_BP1

F7

CPU_TEST14_BP0

C7

C3

K8

C4

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

H18

H19

AA7

D5

C5

CPU_SVC <45>

CPU_SVD <45>

CPU_THER MTRIP#_R

H_PROCH OT#

VDD_N B_FB_H <45>

VDD_N B_FB_L <45>

10/ 29 HP

10/ 29 HP

@

R508 590_0402_1%

1 2

11/ 6 H P

11/ 6 HP

+1.8V

R39220_0402_5%@

R38220_0402_5%@

R40300_0402_5%

R41220_0402_5%@

12

12

12

12

220_0402_5%@ R3 7

220_0402_5%@ R3 6

12

12

H_PROCH OT# <4,46>

PAD

HDT Connector

680_0402_5%

CPU_THER MTRIP#_R

CPU_THER MTRIP#_R <4>

rou te as d iff eren tial

as sh ort a s po ssib le

tes t poi nt un der the pac kage

T9PAD

T10PAD

T11PAD

T12PAD

T1PAD

T2PAD

+1.2V_HT

T15PAD

T16

JP2

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

PMBT3904_SOT23

HP 3/ 30

HP 3/ 30

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_T EST22_SCANSHIFTEN

CPU_TEST15_BP1

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

E

HP, 6 /12

12

H_THERMTRIP# <21>

H_PROCH OT#

chang e fro m +1.8 VS to +1.8V

for l ekage issue HP 12/18

CPU_SVC

CPU_SVD

VDD_N B_FB_H

VDD_N B_FB_L

LDT_RST#

1 2

R8 300_0402_5%

R10 1K_0402_5%

1 2

1 2

R11 1K_0402_5%

10/ 29 HP

R16 10_0402_5%

1 2

1 2

R17 10_0402_5%

Close to CPU

R490 390_0402_5%

CPU_S IC

1 2

1 2

R491 390_0402_5%

10/ 29 HP

R24 300_0402_5%

1 2

R26 300_0402_5%

R27 300_0402_5%

R28 300_0402_5%@

R30 300_0402_5%@

R32 300_0402_5%@

R33 300_0402_5%@

+3VS

5

LDT_RST#

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5

3

12

12

12

12

12

12

SB_PW RGD <21,33,45>

+1.8V

+1.8V

+CPU_ CORE_NB

+1.8V

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/08/02 2008/08/02

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

AMD CPU S1G2 CTRL

LA-4961P

6 54Thursday , August 27 , 2009

E

1.0

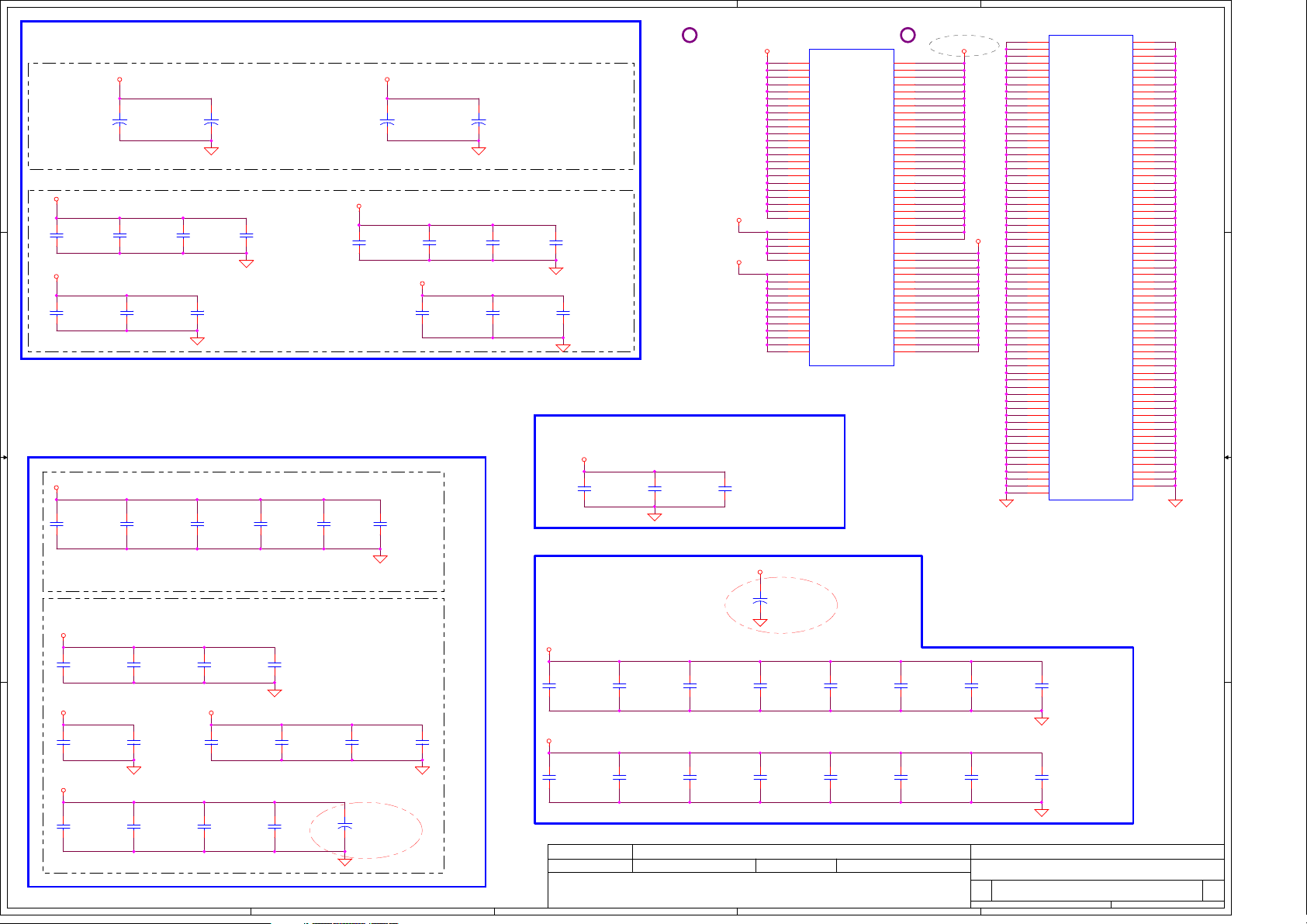

Page 7

A

VDD(+CPU_CORE) decoupling.

+CPU_C ORE_0

1

+

1 1

C22

330U_X_2VM_R6M

2

1

+

C23

330U_X_2VM_R6M

2

Near CPU Socket

+CPU_C ORE_0

1

C26

22U_0805_6.3V6M

2

+CPU_C ORE_0

1

C34

0.22U_0603_16V4 Z

2

2 2

1

C27

22U_0805_6.3V6M

2

1

C35

0.01U_0402_25V4 Z

2

1

C28

22U_0805_6.3V6M

2

1

2

C36

180P_0402_50V8J

1

C29

22U_0805_6.3V6M

2

Under CPU Socket

VDDIO decoupling.

+1.8V

1

C43

22U_0805_6.3V6M

2

3 3

+1.8V

1

C50

0.22U_0603_16V4 Z

2

+1.8V +1.8V

1

C62

0.01U_0402_25V4 Z

2

4 4

+1.8V

1

C77

4.7U_0805_10V4Z

2

1

C44

22U_0805_6.3V6M

2

1

C45

0.22U_0603_16V4 Z

2

1

C46

0.22U_0603_16V4 Z

2

Under CPU Socket

Between CPU Socket and DIMM

1

C51

0.22U_0603_16V4 Z

2

1

C63

0.01U_0402_25V4 Z

2

1

2

A

C78

4.7U_0805_10V4Z

1

C52

0.22U_0603_16V4 Z

2

180 PF Qt 'y fo ll ow the dis tanc e be twee n

CPU s ock et an d DIMM 0. < 2.5i nch>

1

C64

180P_0402_50V8J

2

1

C79

4.7U_0805_10V4Z

2

1

C53

0.22U_0603_16V4 Z

2

1

2

1

2

C65

180P_0402_50V8J

C80

4.7U_0805_10V4Z

1

180P_0402_50V8J

2

B

+CPU_C ORE_0

1

+

2

+CPU_C ORE_0

1

C30

22U_0805_6.3V6M

2

1

C47

C48

180P_0402_50V8J

2

1

C66

180P_0402_50V8J

2

1

C: Ch ang e to N BO C AP

+

C76

220U_Y_4VM

@

2

B

C24

330U_X_2VM_R6M

1

C31

22U_0805_6.3V6M

2

+CPU_C ORE_0

1

C37

0.22U_0603_16V4 Z

2

1

C67

180P_0402_50V8J

2

1

+

C25

330U_X_2VM_R6M

2

1

C32

22U_0805_6.3V6M

2

1

C38

0.01U_0402_25V4 Z

2

1

C33

22U_0805_6.3V6M

2

1

C39

180P_0402_50V8J

2

C

L

+0. 8V ~+1 .1V , 3A

(+- 25 mV_ dc , + -125 mV_ac )

2A , (+- 100 mV_d c,

+- 15 0mV_ ac)

18A /72 0mil /36v ias

+CPU_ CORE_NB

+1.8V

JCPU1E

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

FOX_P Z6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor Socket

CONN@

VDD0_1

VDD0_2

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

VDD0_11

VDD0_12

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

D

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

+CPU_CORE_NB decoupling.

+CPU_ CORE_NB

1

C40

22U_0805_6.3V6M

2

VTT decoupling.

+0.9V

1

C54

4.7U_0805_10V4Z

2

+0.9V

1

C68

4.7U_0805_10V4Z

2

Secur ity Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Near CPU Socket Right side.

Near CPU Socket Left side.

Issued Date

1

C55

4.7U_0805_10V4Z

2

1

C69

4.7U_0805_10V4Z

2

C

1

C41

22U_0805_6.3V6M

2

2007/08/02 2008/08/02

1

2

1

C56

0.22U_0603_16V4 Z

2

1

C70

0.22U_0603_16V4 Z

2

C42

22U_0805_6.3V6M

+0.9V

Near Power Supply

1

C: Ch ang e to N BO C AP

+

C49

220U_Y_4VM

2

1

C57

0.22U_0603_16V4 Z

2

1

C71

0.22U_0603_16V4 Z

2

Compal Secret Data

Deciphered Date

1

C58

1000P_0402_25V8J

2

1

C72

1000P_0402_25V8J

2

D

L

10/6 HP

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

1

C59

1000P_0402_25V8J

2

1

C73

1000P_0402_25V8J

2

18A /72 0mil /36v ias

+CPU_C ORE_0+CPU_C ORE_0

+1.8V

1

C60

180P_0402_50V8J

2

1

C74

180P_0402_50V8J

2

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet

E

JCPU 1F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_P Z6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor Socket

CONN@

1

C61

180P_0402_50V8J

2

1

C75

180P_0402_50V8J

2

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

Compal Electronics, Inc.

AMD CPU S1G2 PWR & GND

LA-4961P

E

of

7 54Thursday , August 27 , 2009

1.0

Page 8

A

B

C

D

E

+V_DD R_MCH_REF

JDIMMA

1

VREF

3

DDR_A _D0

DDR_A _D1

1 1

2 2

DDR_CKE 0_DIMMA<5>

DDR_A_BS #2<5>

DDR_A_BS #0<5>

DDR_A_W E#<5>

DDR_A _CAS#<5>

DDR_C S1_DIMMA#<5>

DDR_A _ODT1<5>

3 3

SMB_CK_DAT0<4,6,9,15,21,30>

SMB_CK_CLK0<4,6,9 ,15,21,30>

4 4

A

+3VS

DDR_A _DQS#0

DDR_A _DQS0

DDR_A _D2

DDR_A _D3

DDR_A _D8

DDR_A _D9

DDR_A _DQS#1

DDR_A _DQS1

DDR_A _D10

DDR_A _D11

DDR_A _D16 DDR_A _D20

DDR_A _D17

DDR_A _DQS#2

DDR_A _DQS2

DDR_A _D18

DDR_A _D19

DDR_A _D24

DDR_A _D25

DDR_A_DM 3

DDR_A _D26

DDR_A _D27

DDR_CKE 0_DIMMA

DDR_A_BS #2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1 DDR_A_MA0

DDR_A_MA10

DDR_A_BS #0

DDR_A_W E#

DDR_A _CAS# DDR_A _ODT0

DDR_C S1_DIMMA#

DDR_A _ODT1

DDR_A _D32

DDR_A _D33

DDR_A _DQS#4

DDR_A _DQS4

DDR_A _D34

DDR_A _D35

DDR_A _D40

DDR_A _D41

DDR_A_DM 5

DDR_A _D42

DDR_A _D43

DDR_A _D48

DDR_A _D49

DDR_A _DQS#6

DDR_A _DQS6

DDR_A _D50

DDR_A _D51

DDR_A _D56

DDR_A _D57

DDR_A_DM 7

DDR_A _D58

DDR_A _D59

1

C97

0.1U_0402_16V4Z

2

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

201

GND

TYCO_292527-4

CONN@

9/2 0 SP0 70 00B Z0 0/SP 07000 EU00

DDR 2 SOC KE T H 9.2 (REV)

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

NC

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

A11

A7

A6

VDD

A4

A2

A0

VDD

BA1

RAS#

S0#

VDD

ODT0

NC/A13

VDD

NC

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

SA1

GND

B

+1.8V+1.8V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

DDR_A _D4

DDR_A _D5

DDR_A_DM 0

DDR_A _D6

DDR_A _D7

DDR_A _D12

DDR_A _D13

DDR_A_DM 1

DDR_A _D14

DDR_A _D15

DDR_A _D21

DDR_A_DM 2

DDR_A _D22

DDR_A _D23

DDR_A _D28

DDR_A _D29

DDR_A _DQS#3

DDR_A _DQS3

DDR_A _D30

DDR_A _D31

DDR_CKE 1_DIMMA

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_BS #1

DDR_A _RAS#

DDR_C S0_DIMMA#

DDR_A_MA13

DDR_A _D36

DDR_A _D37

DDR_A_DM 4

DDR_A _D38

DDR_A _D39

DDR_A _D44

DDR_A _D45

DDR_A _DQS#5

DDR_A _DQS5

DDR_A _D46

DDR_A _D47

DDR_A _D52

DDR_A _D53

DDR_A_DM 6

DDR_A _D54

DDR_A _D55

DDR_A _D60

DDR_A _D61

DDR_A _DQS#7

DDR_A _DQS7

DDR_A _D62

DDR_A _D63

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDR _A_D[0..6 3]

DDR_A _DM[0..7]

DDR _A_DQS[0. .7]

DDR_A _MA[0..15]

DDR_A _DQS#[0.. 7]

DDR_A _CLK0 <5>

DDR_A _CLK#0 <5>

+V_DD R_MCH_REF

1

C90

2

1000P_0402_25V8J

0.1U_0402_16V4Z

DDR_CKE 1_DIMMA <5>

DDR_A_BS #1 <5>

DDR_A _RAS# <5>

DDR_CS0_D IMMA# <5>

DDR_A_ODT0 <5>

DDR_A _CLK1 <5>

DDR_A _CLK#1 <5>

C

D

DDR_A_MA6

DDR_A_MA7

DDR_A_MA11

DDR_A_MA14

DDR_CKE 0_DIMMA

DDR_CKE 1_DIMMA

DDR_A_MA15

DDR_A_BS #2

DDR_A_BS #1

DDR_A_MA0

DDR_A_MA2

DDR_A_MA4

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS #0

DDR_A_W E#

DDR_A _CAS#

DDR_C S1_DIMMA#

DDR_A _ODT1

DDR_A_MA13

DDR_A _ODT0

DDR_C S0_DIMMA#

DDR_A _RAS#

DDR _A_D[0..6 3] <5>

DDR_A _DM[0..7] <5>

DDR_ A_DQS[0.. 7] <5>

DDR_A _MA[0..15] <5>

DDR_A _DQS#[0.. 7] <5>

+1.8V

R44

@

1K_0402_1%

1 2

1

C91

@

2

2007/08/02 2008/08/02

+V_DD R_MCH_REF <9,44>

R45

1K_0402_1%

1 2

Compal Secret Data

Deciphered Date

47_0804_8P4R_5%

R478 47_0402_5%

R479 47_0402_5%

R480 47_0402_5%

R481 47_0402_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

Size Doc ument Number Re v

Cus tom

Date: Sheet of

+0.9V

RP1

18

27

36

45

12

12

12

12

RP3

18

27

36

45

RP4

18

27

36

45

RP5

18

27

36

45

RP6

18

27

36

45

RP7

18

27

36

45

Cross between +1.8V and +0.9V power plan

C720

@

0.1U_0402_16V4Z

Title

Compal Electronics, Inc.

1 2

C81 0.1U_0402_16V4Z

1 2

C82 0.1U_0402_16V4Z

1 2

C83 0.1U_0402_16V4Z

1 2

C84 0.1U_0402_16V4Z

1 2

C85 0.1U_0402_16V4Z

1 2

C86 0.1U_0402_16V4Z

1 2

C87 0.1U_0402_16V4Z

1 2

C88 0.1U_0402_16V4Z

1 2

C89 0.1U_0402_16V4Z

1 2

C92 0.1U_0402_16V4Z

1 2

C93 0.1U_0402_16V4Z

1 2

C94 0.1U_0402_16V4Z

1 2

C95 0.1U_0402_16V4Z

1 2

C96 0.1U_0402_16V4Z

+1.8V

2

2

C721

@

1

0.1U_0402_16V4Z

1

Compa l EMI 6/11

DDRII SO-DIMM 1

LA-4961P

E

8 54Thursday , August 27 , 2009

+1.8V

1.0

Page 9

A

B

C

D

E

JDIMMB

+V_DD R_MCH_REF<8,44>

1

C100

1 1

2 2

3 3

4 4

1000P_0402_25V8J

DDR_CKE 0_DIMMB<5>

DDR_B_BS #2<5>

DDR_B_BS #0<5>

DDR_B_W E#<5>

DDR_B _CAS#<5>

DDR_C S1_DIMMB#<5>

DDR_B _ODT1<5>

SMB_CK_DAT0<4,6,8,15,21,30>

SMB_CK_CLK0<4,6,8 ,15,21,30>

2

DDR_B _D0

DDR_B _D1

DDR_B _DQS#0

DDR_B _DQS0

DDR_B _D2

DDR_B _D3

DDR_B _D8

DDR_B _D13

DDR_B _DQS#1

DDR_B _DQS1

DDR_B _D10

DDR_B _D11

DDR_B _D21

DDR_B _D17

DDR_B _DQS#2

DDR_B _DQS2

DDR_B _D18 DDR_B _D22

DDR_B _D19

DDR_B _D24

DDR_B _D25

DDR_B_DM 3

DDR_B _D26

DDR_B _D27

DDR_CKE 0_DIMMB

DDR_B_BS #2

DDR_B_MA12

DDR_B_MA9

DDR_B_MA5

DDR_B_MA3

DDR_B_MA1

DDR_B_MA10

DDR_B_BS #0

DDR_B_W E#

DDR_B _CAS# DDR_B _ODT0

DDR_C S1_DIMMB#

DDR_B _ODT1

DDR_B _D32

DDR_B _D33

DDR_B _DQS#4

DDR_B _DQS4

DDR_B _D34

DDR_B _D35

DDR_B _D40

DDR_B _D41

DDR_B_DM 5

DDR_B _D42

DDR_B _D43 DDR_B _D47

DDR_B _D48

DDR_B _D49 DDR_B _D53

DDR_B _DQS#6

DDR_B _DQS6

DDR_B _D50

DDR_B _D51 DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B_DM 7

DDR_B _D58

DDR_B _D59

+3VS

0.1U_0402_16V4Z

C113

1

2

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

201

GND

TYCO_292527-4

CONN@

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

A11

VDD

VDD

BA1

RAS#

S0#

VDD

ODT0

NC/A13

VDD

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

SA1

GND

NC

A7

A6

A4

A2

A0

NC

9/2 0 SP0 70 00E T0 0/SP 07000 GN00

+1.8V+1.8V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

DDR_B _D4

DDR_B _D5

DDR_B_DM 0

DDR_B _D6

DDR_B _D7

DDR_B _D12

DDR_B _D9

DDR_B_DM 1

DDR_B _D14

DDR_B _D15

DDR_B _D20

DDR_B _D16

DDR_B_DM 2

DDR_B _D23

DDR_B _D28

DDR_B _D29

DDR_B _DQS#3

DDR_B _DQS3

DDR_B _D30

DDR_B _D31

DDR_CKE 1_DIMMB

DDR_B_MA15

DDR_B_MA14

DDR_B_MA11

DDR_B_MA7

DDR_B_MA6DDR_B_MA8

DDR_B_MA4

DDR_B_MA2

DDR_B_MA0

DDR_B_BS #1

DDR_B _RAS#

DDR_C S0_DIMMB#

DDR_B_MA13

DDR_B _D36

DDR_B _D37

DDR_B_DM 4

DDR_B _D38

DDR_B _D39

DDR_B _D44

DDR_B _D45

DDR_B _DQS#5

DDR_B _DQS5

DDR_B _D46

DDR_B _D52

DDR_B_DM 6

DDR_B _D54

DDR_B _D60

DDR_B _D61

DDR_B _DQS#7

DDR_B _DQS7

DDR_B _D62

DDR_B _D63

+3VS

DDR _B_D[0..6 3]

DDR_B _DM[0..7]

DDR _B_DQS[0. .7]

DDR_B _MA[0..15]

DDR_B _DQS#[0.. 7]

DDR_B _CLK0 <5>

DDR_B _CLK#0 <5>

DDR_CKE 1_DIMMB <5>

DDR_B_BS #1 <5>

DDR_B _RAS# <5>

DDR_C S0_DIMMB# <5>

DDR_B _ODT0 <5>

DDR_B _CLK1 <5>

DDR_B _CLK#1 <5>

DDR_ B_D[0..63 ] <5>

DDR_B _DM[0..7] <5>

DDR_B _DQS[0..7 ] <5>

DDR_B _MA[0..15] <5>

DDR_B _DQS#[0.. 7] <5>

DDR_B_MA6

DDR_B_MA2

DDR_B_MA0

DDR_C S0_DIMMB#

DDR_B_MA14

DDR_B_MA11

DDR_B_MA7

DDR_B_MA4

DDR_CKE 1_DIMMB

DDR_B_MA15

DDR_CKE 0_DIMMB

DDR_B_BS #2

chang e 8P4 R to 0 402 f or im prove layo ut pl aceme nt. C ompal 12/5

DDR_B_MA8

DDR_B_MA5

DDR_B_MA12

DDR_B_MA9

DDR_B_MA10

DDR_B_BS #0

DDR_B_MA1

DDR_B_MA3

DDR_B _ODT1

DDR_C S1_DIMMB#

DDR_B _CAS#

DDR_B_W E#

DDR_B_BS #1

DDR_B _RAS#

DDR_B _ODT0

DDR_B_MA13

47_0804_8P4R_5%

47_0804_8P4R_5%

R524 47_0402_5%

R525 47_0402_5%

R526 47_0402_5%

R527 47_0402_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

+0.9V

RP8

RP9

RP11

RP12

RP13

RP14

18

27

36

45

18

27

36

45

12

12

12

12

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

12

C98 0.1U_0402_16V4Z

1 2

C99 0.1U_0402_16V4Z

12

C101 0.1U _0402_16V4Z

1 2

C102 0.1U _0402_16V4Z

12

C103 0.1U _0402_16V4Z

1 2

C104 0.1U _0402_16V4Z

12

C105 0.1U _0402_16V4Z

1 2

C106 0.1U _0402_16V4Z

12

C107 0.1U _0402_16V4Z

1 2

C108 0.1U _0402_16V4Z

12

C109 0.1U _0402_16V4Z

1 2

C110 0.1U _0402_16V4Z

12

C111 0.1U _0402_16V4Z

1 2

C112 0.1U _0402_16V4Z

Cross between +1.8V and +0.9V power plan

+1.8V

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/08/02 2008/08/02

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

DDRII SO-DIMM 2

LA-4961P

9 54Th urs day, Au gust 27, 2009

E

1.0

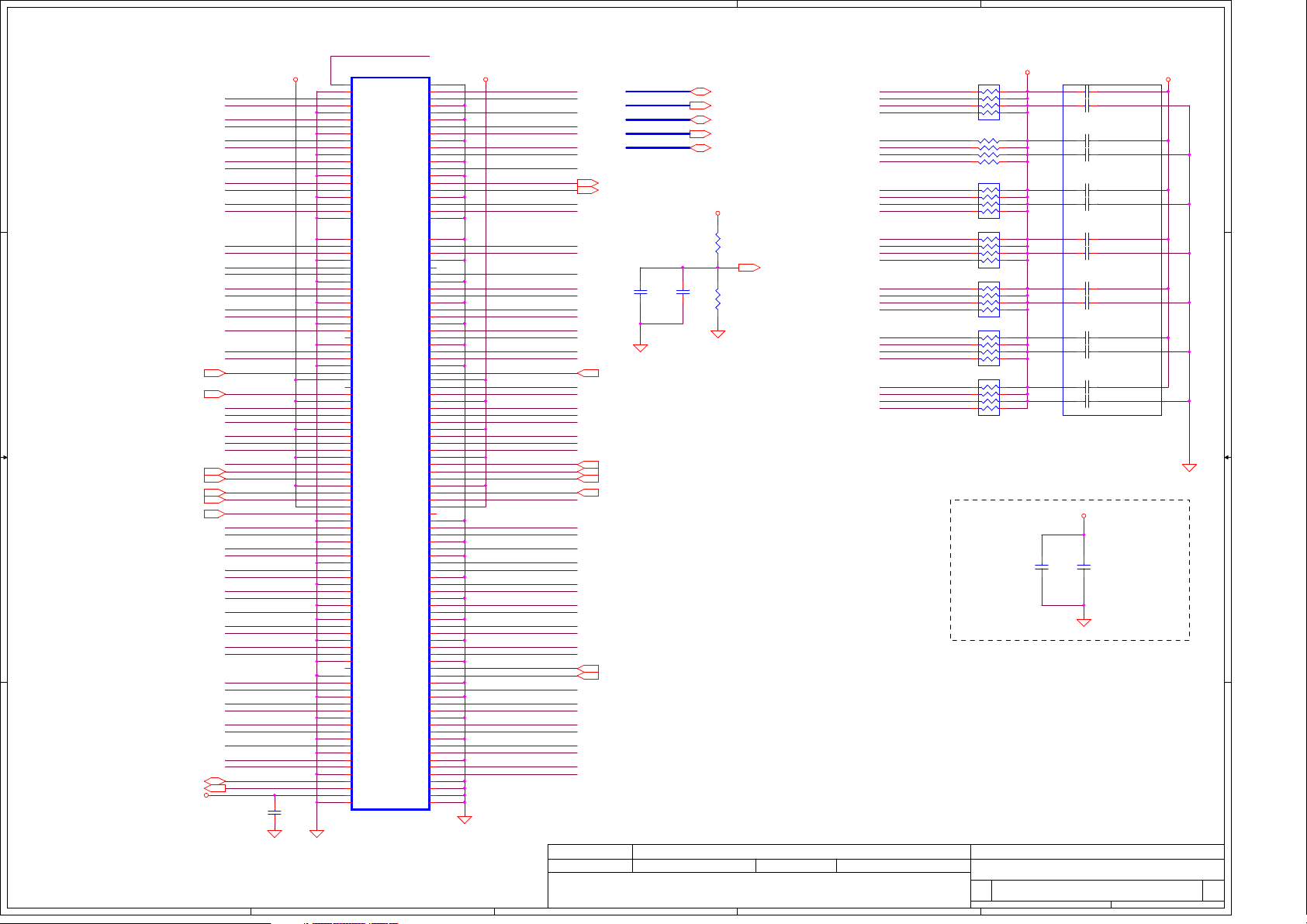

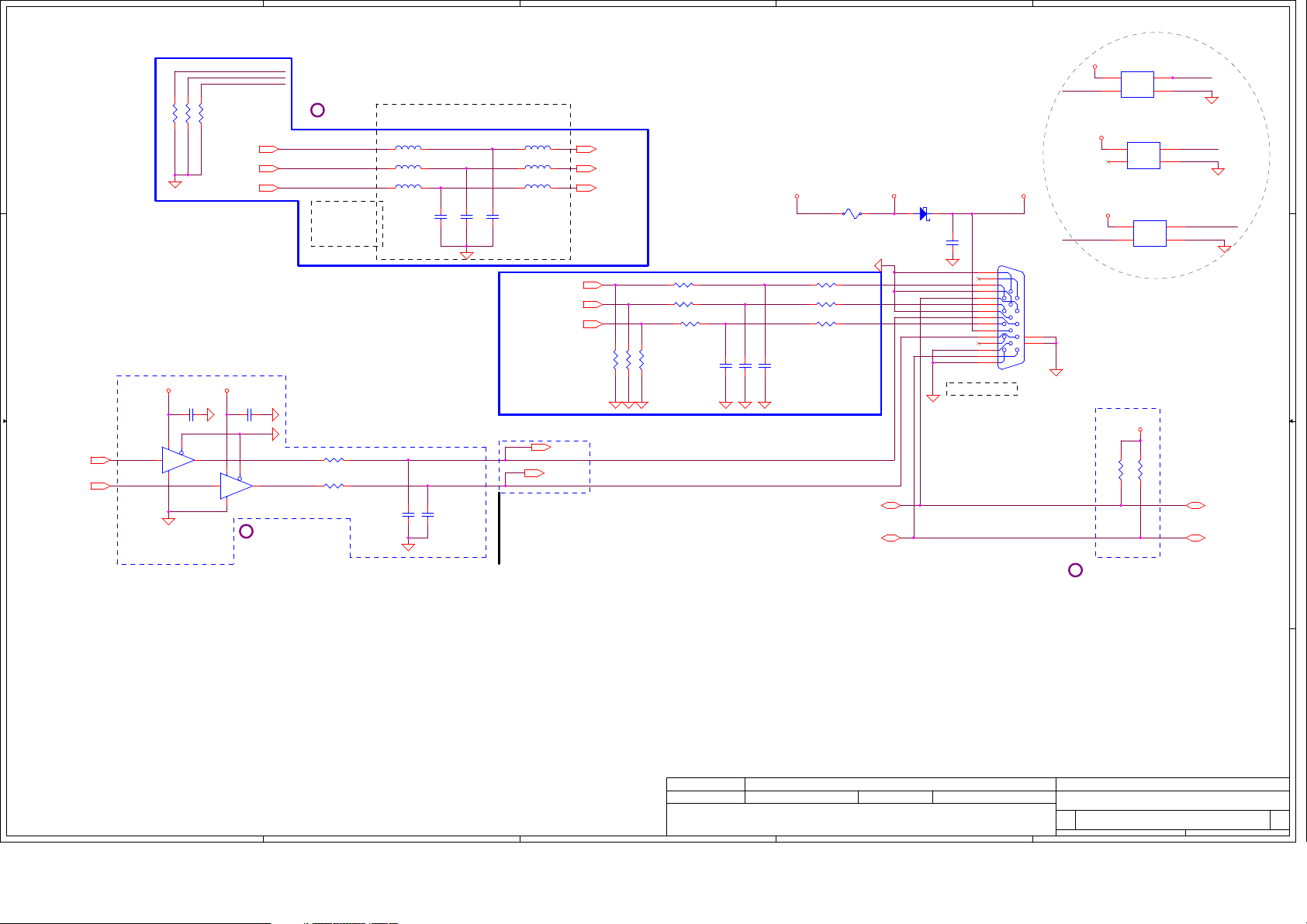

Page 10

A

U4B

D4

GFX_RX0P

C4

GFX_RX0N

A3

GFX_RX1P

B3

GFX_RX1N

C2

GFX_RX2P

C1

GFX_RX2N

E5

GFX_RX3P

F5

GFX_RX3N

G5

GFX_RX4P

G6

AE3

AD4

AE2

AD3

AD1

AD2

AA8

AA7

AA5

AA6

H5

H6

M8

M7

M5

R8

R6

R5

W6

U5

U6

U8

U7

W5

J6

J5

J7

J8

L5

L6

L8

P7

P5

P8

P4

P3

T4

T3

V5

Y8

Y7

Y5

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

1 1

PCIE_PRX_DTX_P0<25>

PCIE_PRX_DTX_N0<25>

PCIE_PRX_DTX_P1<31>

PCIE_PRX_DTX_N1<31>

PCIE_PRX_DTX_P3<31>

PCIE_PRX_DTX_N3<31>

2 2

PCIE_PRX_DTX_P4<27>

PCIE_PRX_DTX_N4<27>

SB_RX0P<19>

SB_RX0N<19>

SB_RX1P<19>

SB_RX1N<19>

SB_RX2P<19>

SB_RX2N<19>

SB_RX3P<19>

SB_RX3N<19>

PAR T 2 O F 6

PCIE I/F GFX

PC IE I/ F GP P

PCI E I/F SB

PCE_CALRP(PCE_BCALR P)

PCE_CALRN(PCE_BCALR N)

RS880MN_FCBGA528

RS780 M Displa y Port Suppo rt (muxed on GFX)

DP0

DP1

3 3

9/2 0 SA0 00 01Z G0 0( A11 ) S I C 216 -067 4001 -00/ RS78 0M F CBGA5 28P 0FH

GFX_TX0,TX1,TX2 and TX3

AUX0 and HPD0

GFX_TX4,TX5,TX6 and TX7

AUX1 and HPD1

B

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

PCIE_PTX_DRX_P0

AC1

PCIE_PTX_DRX_N0

AC2

PCIE_PTX_DRX_P1

AB4

PCIE_PTX_DRX_N1

AB3

AA2

AA1

PCIE_PTX_DRX_P3

Y1

PCIE_PTX_DRX_N3

Y2

PCIE_PTX_DRX_P4

Y4

PCIE_PTX_DRX_N4

Y3

V1

V2

SB_TX0P_C

AD7

SB_TX0N_C

AE7

SB_TX1P_C

AE6

SB_TX1N_C

AD6

SB_TX2P_C

AB6

SB_TX2N_C

AC6

SB_TX3P_C

AD5

SB_TX3N_C

AE5

AC8

AB8

DPA_TXP0 <18>

DPA_TXN0 <18>

DPA_TXP1 <18>

DPA_TXN1 <18>

DPA_TXP2 <18>

DPA_TXN2 <18>

DPA_TXP3 <18>

DPA_TXN3 <18>

DPB_TXP0 <32>

DPB_TXN0 <32>

DPB_TXP1 <32>

DPB_TXN1 <32>

DPB_TXP2 <32>

DPB_TXN2 <32>

DPB_TXP3 <32>

DPB_TXN3 <32>

DPC_TXP0 <32>

DPC_TXN0 <32>

DPC_TXP1 <32>

DPC_TXN1 <32>

DPC_TXP2 <32>

DPC_TXN2 <32>

DPC_TXP3 <32>

DPC_TXN3 <32>

rem ov e U WB , 1 0/21 HPrem ov e U WB , 1 0/21 HP

C124 0.1U_0402_16V7K

C125 0.1U_0402_16V7K

C126 0.1U_0402_16V7K

C127 0.1U_0402_16V7K

C128 0.1U_0402_16V7K

C129 0.1U_0402_16V7K

C130 0.1U_0402_16V7K

C131 0.1U_0402_16V7K

R46 1.27K_0402_1%

1 2

R47 2K_0402_1%

1 2

C114 0.1U_0402_16V7K

1 2

C115 0.1U_0402_16V7K

1 2

C116 0.1U_0402_16V7K

1 2

C117 0.1U_0402_16V7K

1 2

C118 0.1U_0402_16V7K

1 2

C119 0.1U_0402_16V7K

1 2

C120 0.1U_0402_16V7K

1 2

C121 0.1U_0402_16V7K

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C

Display Port

PCIE_PTX_C_DRX_P0 <25>

PCIE_PTX_C_DRX_N0 <25>

PCIE_PTX_C_DRX_P1 <31>

PCIE_PTX_C_DRX_N1 <31>

PCIE_PTX_C_DRX_P3 <31>

PCIE_PTX_C_DRX_N3 <31>

PCIE_PTX_C_DRX_P4 <27>

PCIE_PTX_C_DRX_N4 <27>

SB_TX0P <19>

SB_TX0N <19>

SB_TX1P <19>

SB_TX1N <19>

SB_TX2P <19>

SB_TX2N <19>

SB_TX3P <19>

SB_TX3N <19>

+1.1VS

NIC

Media Card

EXP

WLAN

H_CLKOP0<4>

H_CLKON0<4>

H_CLKOP1<4>

H_CLKON1<4>

H_CTLOP0<4>

H_CTLON0<4>

H_CTLON1<4>

Place within 1"

layout 1:2 (W/S=5mil/10mil)

H_CAD OP[0..15]<4>

H_C ADON[0..15 ]<4> H_C ADIN[0. .15] <4>

H_CAD OP0

H_CAD ON0

H_CAD OP1

H_CAD ON1

H_CAD OP2

H_CAD ON2

H_CAD OP3

H_CAD ON3

H_CAD OP4

H_CAD ON4

H_CAD OP5

H_CAD ON5

H_CAD OP6

H_CAD ON6

H_CAD OP7

H_CAD ON7

H_CAD OP8

H_CAD ON8

H_CAD OP9

H_CAD ON9

H_CAD OP10

H_CAD ON10

H_CAD OP11

H_CAD ON11

H_CAD OP12

H_CAD ON12

H_CAD OP13

H_CAD ON13

H_CAD OP14

H_CAD ON14

H_CAD OP15

H_CAD ON15

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

R48 301_0402_1%

1 2

D

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

M22

M23

R21

R20

C23

A24

H_ CADON[0..1 5]

U4A

HT_RXCAD0P

PAR T 1 O F 6

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS880MN_FCBGA528

H_ CADIP[0..1 5]H _CADOP[0. .15]

H_C ADIN[0 ..15]

HYPER TRANSPORT CPU I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

E

H_C ADIP[0..15 ] <4>

H_CAD IP0

D24

H_C ADIN0

D25

H_CAD IP1

E24

H_C ADIN1

E25

H_CAD IP2

F24

H_C ADIN2

F25

H_CAD IP3

F23

H_C ADIN3

F22

H_CAD IP4

H23

H_C ADIN4

H22

H_CAD IP5

J25

H_C ADIN5

J24

H_CAD IP6

K24

H_C ADIN6

K25

H_CAD IP7

K23

H_C ADIN7

K22

H_CAD IP8

F21

H_C ADIN8

G21

H_CAD IP9

G20

H_C ADIN9

H21

H_CAD IP10

J20

H_CAD IN10

J21

H_CAD IP11

J18

H_CAD IN11

K17

H_CAD IP12

L19

H_CAD IN12

J19

H_CAD IP13

M19

H_CAD IN13

L18

H_CAD IP14

M21

H_CAD IN14

P21

H_CAD IP15

P18

H_CAD IN15

M18

H24

H25

L21

L20

H_CTLIP0

M24

H_CTLIN0

M25

H_CTLIP1

P19

H_CTLIN1

R18

B24

B25

Place within 1"

layout 1:2 (W/S=5mil/10mil)

H_CLK IP0 <4>

H_CLK IN0 <4>

H_CLK IP1 <4>

H_CLK IN1 <4>

H_CTLIP0 <4>

H_CTL IN0 <4>

H_CTLIP1 <4>H_CTLOP1<4>

H_CTL IN1 <4>

R49 301_0402_1%

1 2

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/08/02 2008/08/02

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

RS880-HT/PCIE

LA-4961P

10 54Thu rsd ay, Aug ust 27, 2009

E

1.0

Page 11

A

1 1

R50

LDT_STOP#<6,19>

CPU_LDT_R EQ#<6,19>

2 2

3 3

1 2

0_0402_5%

R51

1 2

0_0402_5%

+1.8VS

FBMA-L11-160808-221LMT_0603

NB_LDTSTOP#

NB_ALLOW_LDTSTOP

+1.1VS

FBMA-L11-160808-221LMT_0603

+1.8VS

FBMA-L11-160808-221LMT_0603

+1.8VS

FBMA-L11-160808-221LMT_0603

1 2

2.2U_0 603_6.3V4Z

+1.8VS

1 2

L9

L8

1

C140

2

1 2