Page 1

A

1 1

B

C

D

E

Compal Confidential

Schematics Document

2 2

AUBURNDALE/CLARKSFIELD with

Intel IBEX PEAK-M core logic

Versace

3 3

2009-07-24

REV:0.4

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR DISCL OSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/09/15 2009/09/15

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-4951P

E

0.4

of

148Tuesday, July 28, 2009

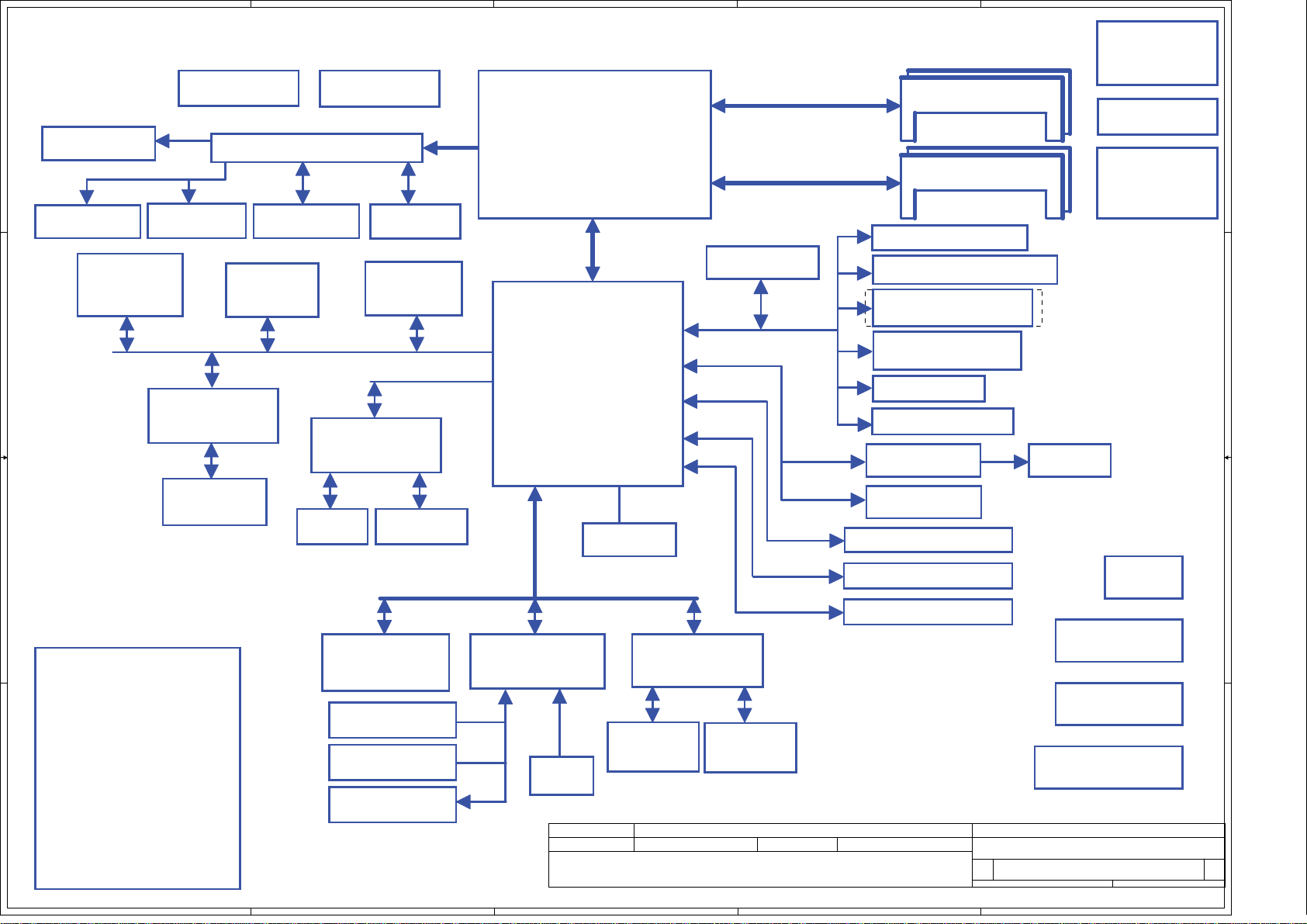

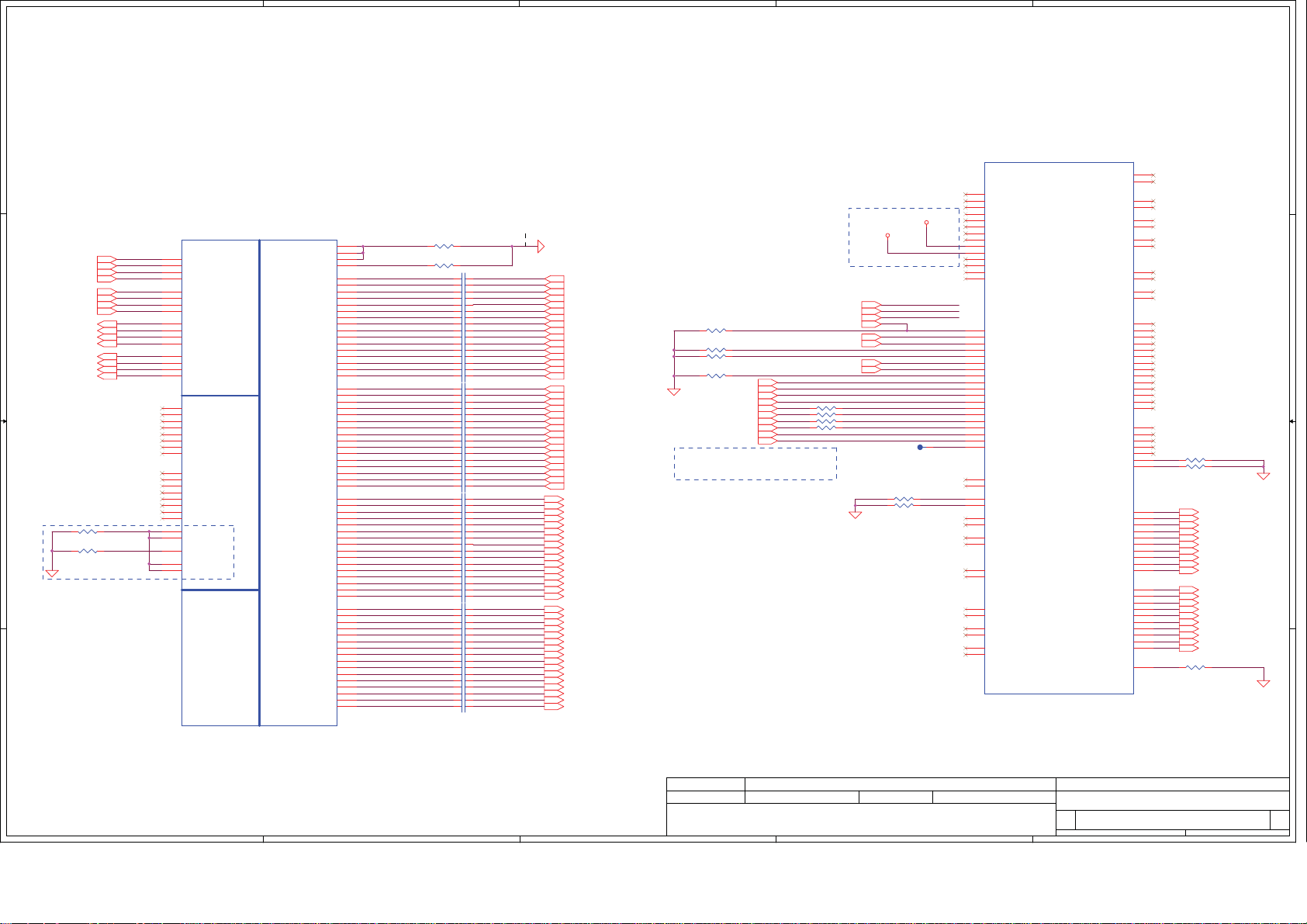

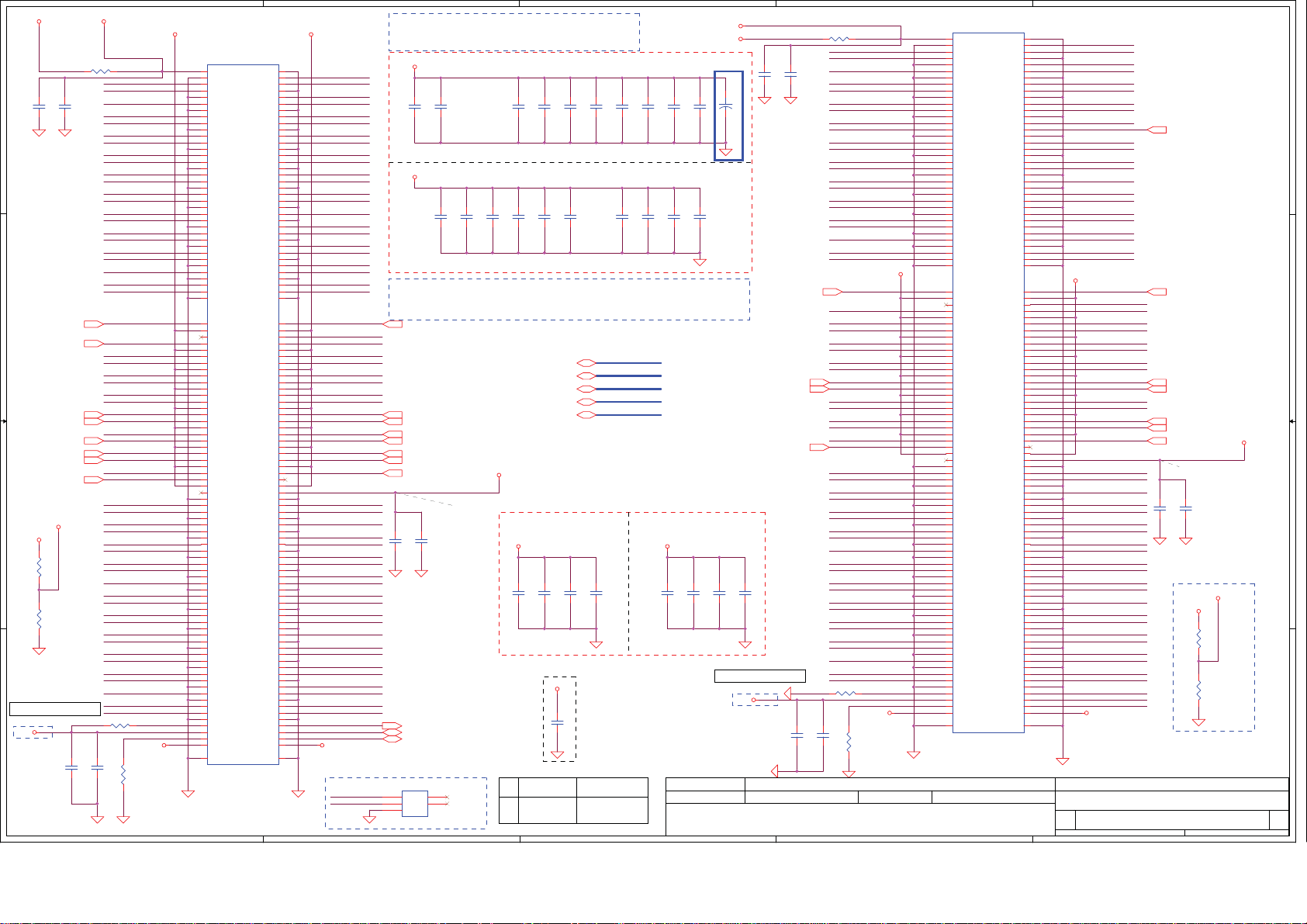

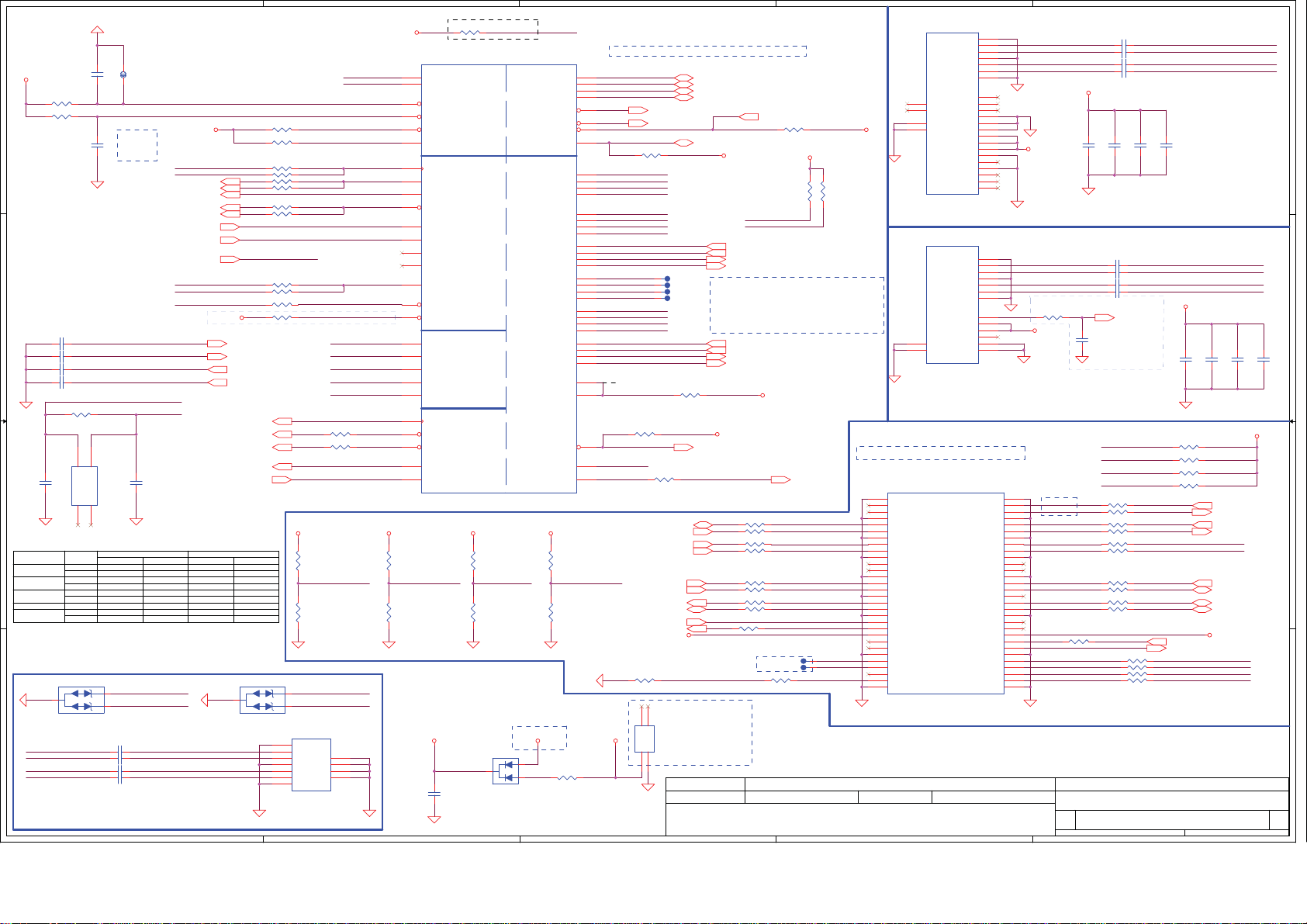

Page 2

A

Compal Confidential

File Name : Versace

Thermal Sensor

ADM1032

1 1

Display Port X 2

(Docking)

CRT to Docking

Page 29

Page 29

CRT+USB X

2 CONN

Express Card 54

& Card Reader

Sub-board

Page 30

*

2 2

PCI-E BUS

10/100/1000 LAN

Intel Hanksville-LM

82577LM

RJ45 CONN

3 3

MXM 3.0 Type A Connector

Page 21

**

DP conn

Page 20

WLAN Card

Page 24

PCI BUS

Page 22

Page 23

1394 port

B

Fan Control

Page 4Page 4

LCD conn

USB3.0 X 2

UPD720200F1

RICOH 835

Page 32

Card Reader

Conn

Page 20Page 19

Page 27

C

Versace

Mobile

PEG

LPC BUS

CPU Qual Core

Clarkesfield

Socket-rPGA989

37.5mm*37.5mm

Page 4,5,6,7,8

DMI X4

Intel Ibex Peak M

1071pins

25mm*27mm

Page 13,14,15,16,17,18

ONFI Interface

Braidwood

Page 28

Mini-Card

NAND Flash

Channel A

Channel B

USB X 2 (For I/O)

Page 19

USB2.0

Azalia

SATA0

SATA1

SATA2

USB2.0

D

DDR3-SO-DIMM X 2DDR3 1066/1333MHz 1.5V

BANK 0, 1, 2, 3

DDR3-SO-DIMM X 2DDR3 1066/1333MHz 1.5V

BANK 0, 1, 2, 3

USB x2(Docking)

*

USB x1(Sub/B for Exp Card)

Page 9

Page 10

Page 33

FingerPrinter VFM451

USBx1

Page 28

USB conn x 1 (For I/O)

BT Conn USB x 1

USB x1(Camera)

USB X1(WWAN Card)

Page 26

Page 20

Page 24

MDC V1.5

92HD75

*

Audio CKT

Sub-board

SATA ODD Connector

2.5" SATA HDD Connector

ESATA Connector

Page 25

Page 30

Page 13

Page 13

Page 13

Page 34

daughter board

RJ11 CONN

E

Accelerometer

LIS302DLTR

Page 31

XDP Conn.

Page 4

CK505

Clock Generator

ICS9LPRS397

Page 12

Page 23

LED

Page 29

Power OK CKT.

Docking CONN.

(2) PS/2 Interfaces

(2) USB 2.channels

(2) SATA Channels (SATA3&4)

(2) Display Port Channels

(1) Seria

(1) Parallel Port

(1) Line In

(1) Line Out

(1) RJ45 (10/100/1000)

4 4

(1) VGA

(1) 2 LAN indicator LED's

(1) Power Button

(1) I2C interface

l Port

Page. 27

SLB9635TT

Page 28 page 31

Touch Pad CONN.

Page 25

TrackPoint CONN.

Page 25

SPI ROM

4MB X 2

Page 27

TPM1.2

SMSC KBC

1098

Int.KBD

Page 25

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR DISCL OSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Super I/O

LPC47N217

COM1

( Docking )

Page 28

2008/09/15 2009/09/15

Page 33

LPT

( Docking )

*:

**:

Page 28

Compal Secret Data

Deciphered Date

We will inatll them on same sub

board via a board to board

connector.

Daughtor board for stack-up

USB CONN and VGA CONN.

Title

Size Document Number Rev

Custom

Date: Sheet

Power On/Off CKT.

DC/DC Interface CKT.

Compal Electronics, Inc.

Block Diagram

LA-4951P

Page 33

Page 25

Page 34

248Tuesday, July 28, 2009

0.4

of

A

B

C

D

E

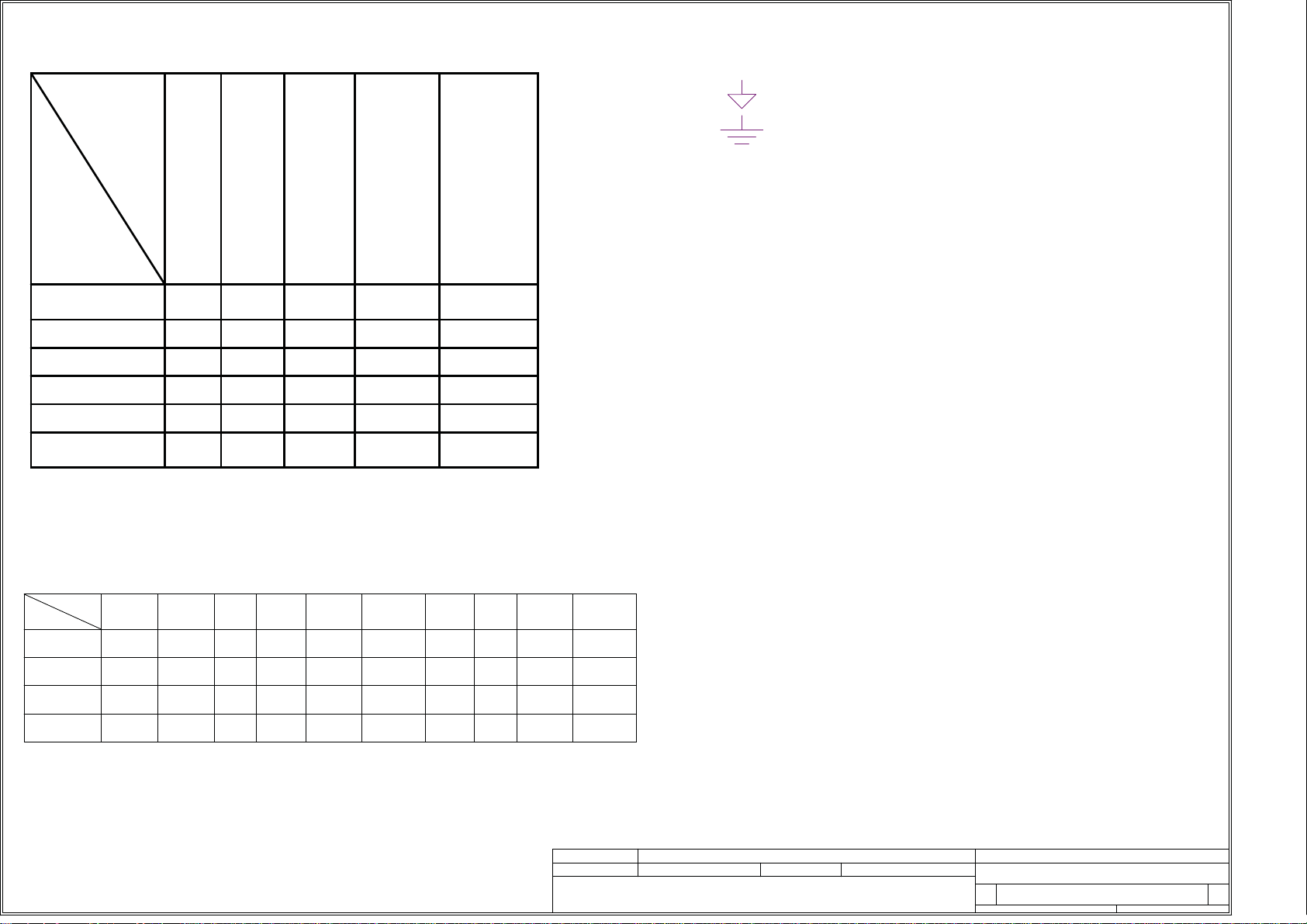

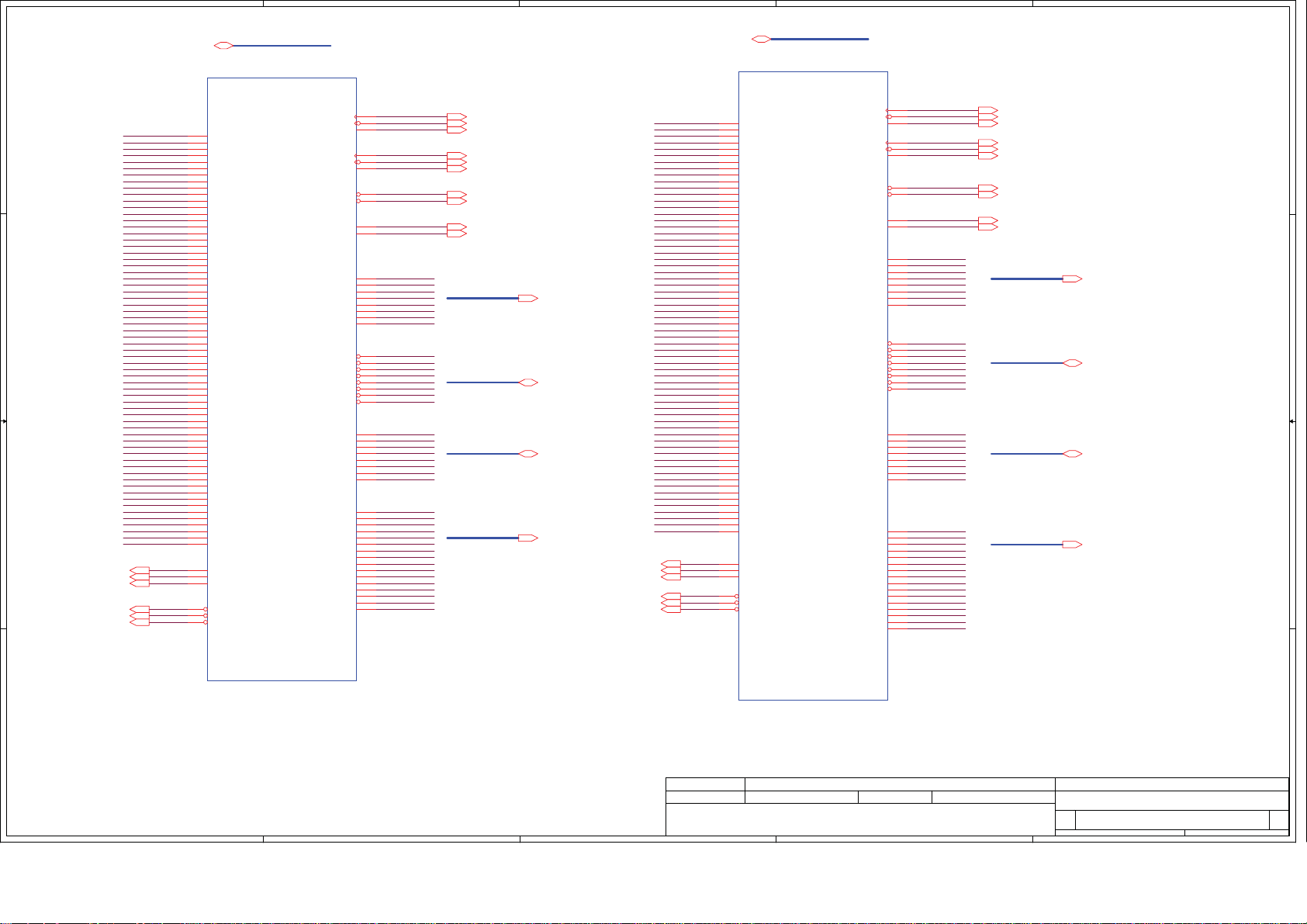

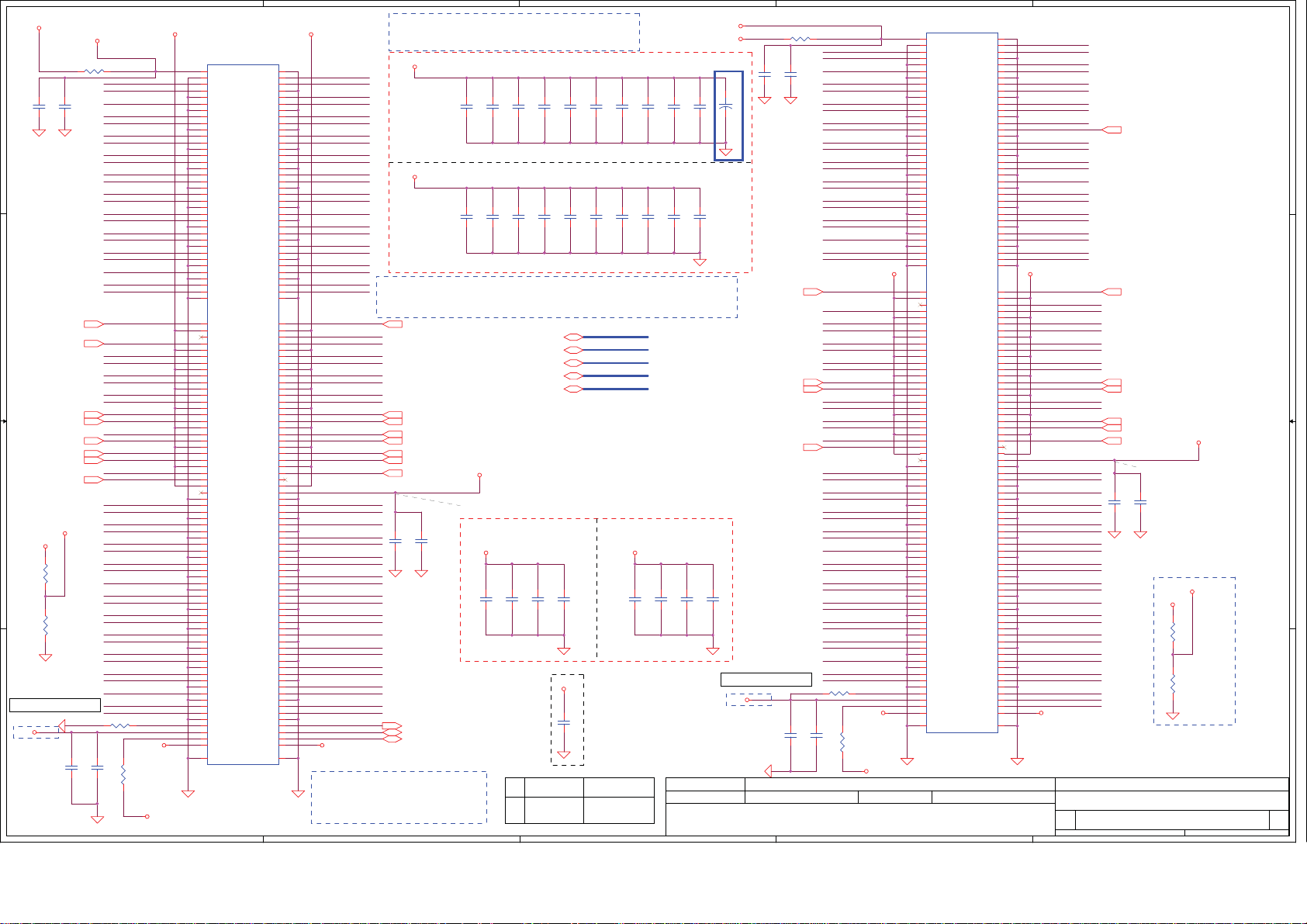

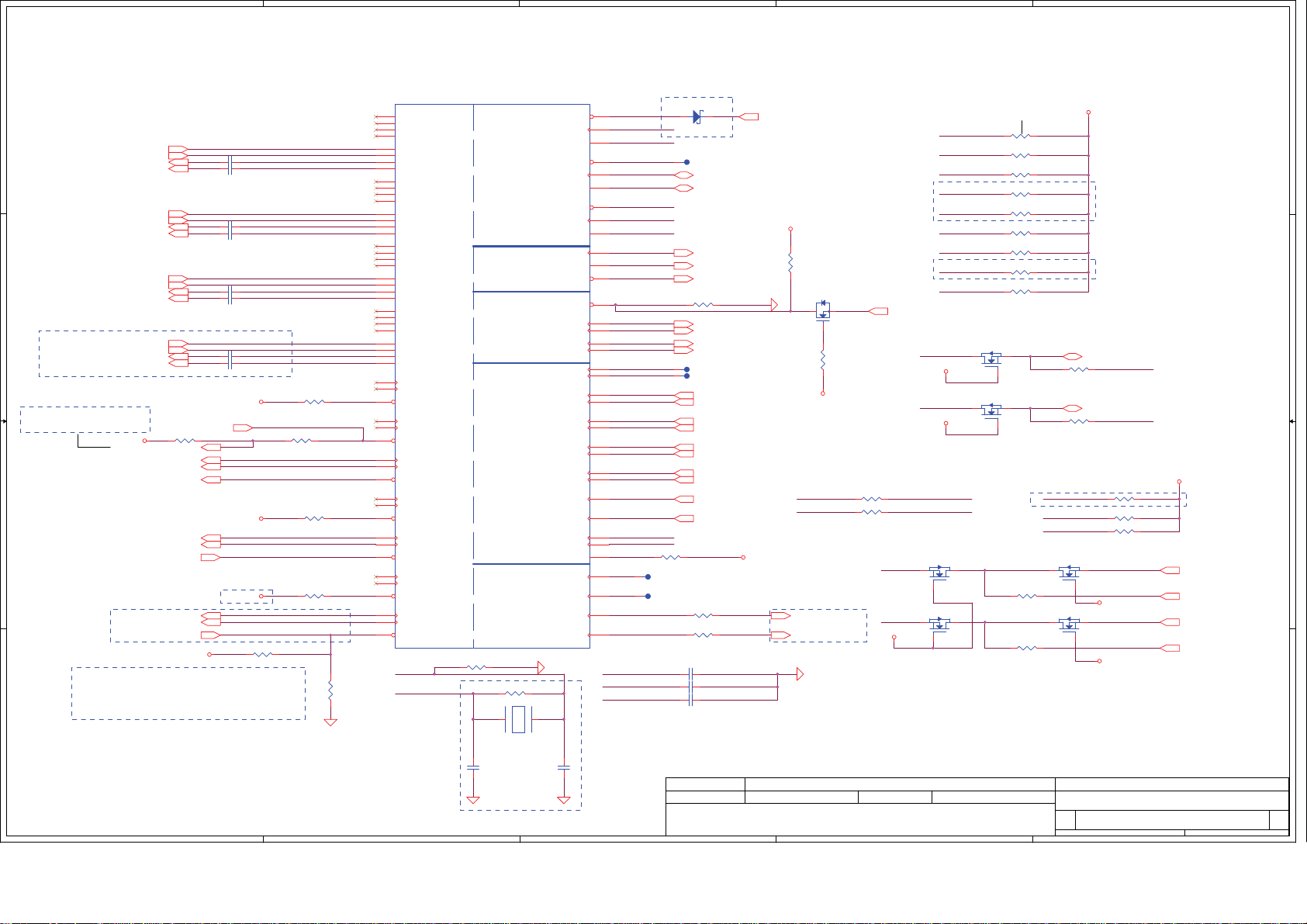

Page 3

A

Voltage Rails

power

plane

State

( O MEANS ON X MEANS OFF )

+RTCVCC

+B

+3VL +0.75V

+5VALW

+3VALW

+1.5V

+5VS

+3VS

+1.5VS

+NVVDD

+VCCP

+CPU_CORE

+1.05VS

+1.8VS

Symbol Note :

: means Digital Ground

: means Analog Ground

Install below 43 level BOM structure for ver. 0.1

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

O

O

O

O

O

O

O

O

O

O

O

X

O

O

O

O

X

O

XX

X

OO

OO

X

X

XX X

DEBUG@ : means just b uild when PCI E po rt 80 CARD function enable.

M92@ : Install for M92 Graphic controller

8072@ : Install for 8072 NIC controller

1098@ : Install for 1098 KBC controller

CK32@ : Ins ta ll for 32 pin CLOCK GEN

Install below 45 level BOM structure for ver. 0.1

45@ : means just put it in the BOM of 45 level.

Remove before MP

Reserve below BOM structure for ver. 0.1

@ : means just reserve , no build

CONN@ : means ME part.

M93@ : Install for M93 Graphic controller

8075@ : Install for 8075 NIC controller

SMBUS Control Table

SOURCE

BATT

THERMAL

SODIMM CLK CHIP

XDP G-SENSOR

MINI CARD

DOCK

NIC

SENSOR

1091@ : Install for 1091 KBC controller

CK72@ : Ins ta ll for 72 pin CLOCK GEN

SMB_EC_CK1

SMB_EC_DA1

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SMSC1098

Calpella

Calpella

Calpella

V

X

X

X

X

XX

VV

X

X

XX

X

VV

X

X

XX

X

V

X

X

XX

X

V

X

X

X

V

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

X

X

X

V

2008/09/15 2009/09/15

A

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Notes List

LA-4951P

0.4

of

348Tuesday, July 28, 2009

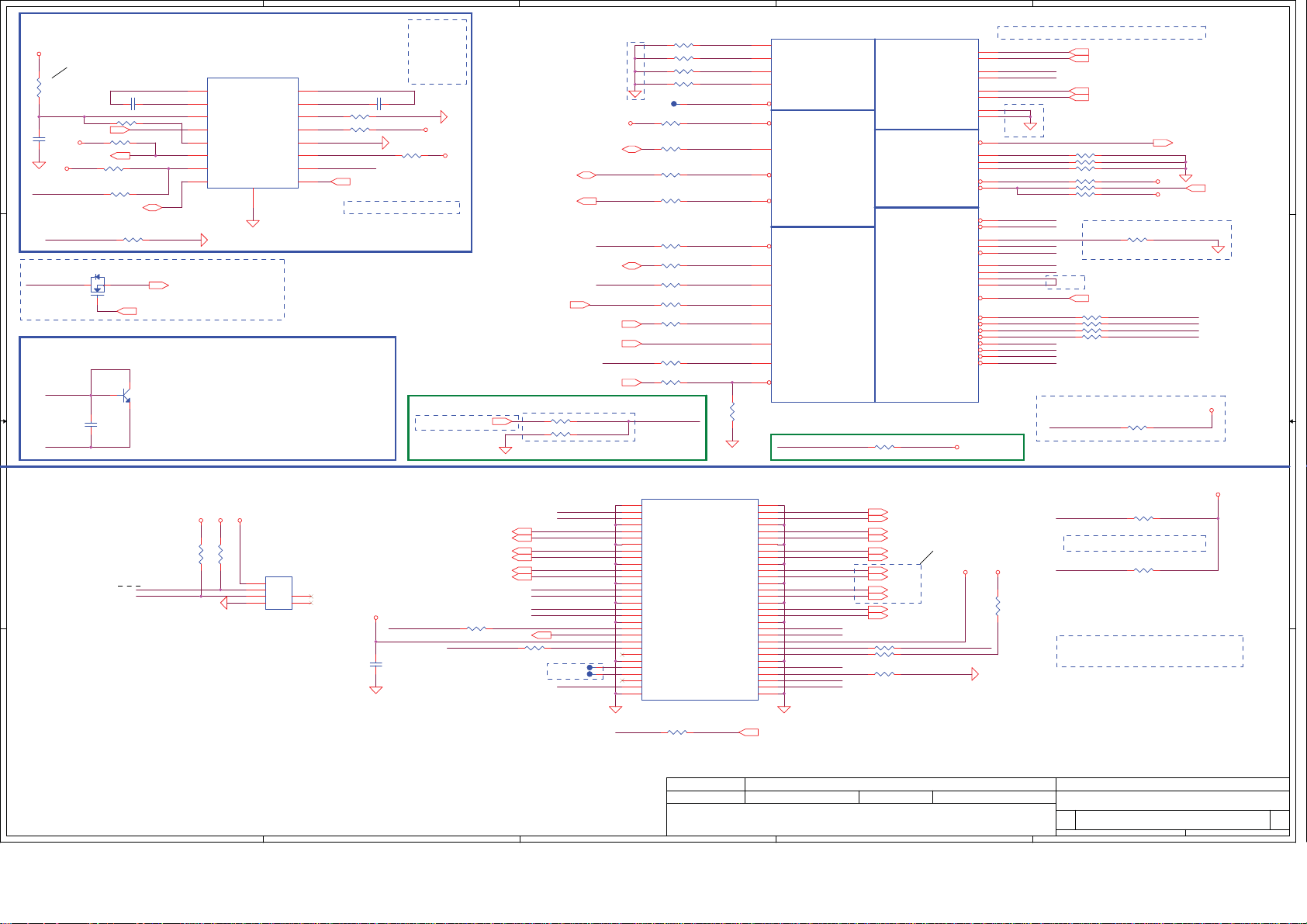

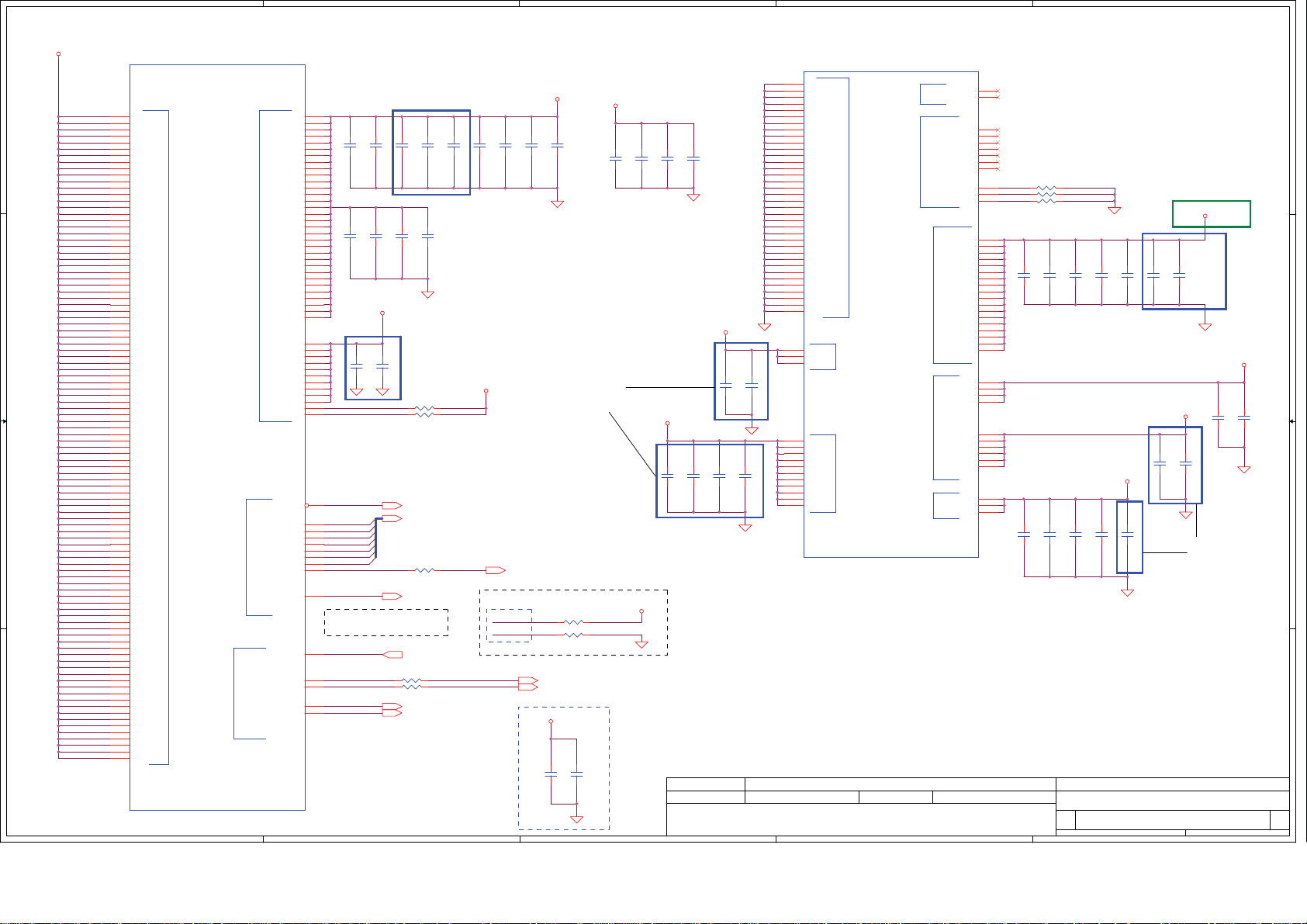

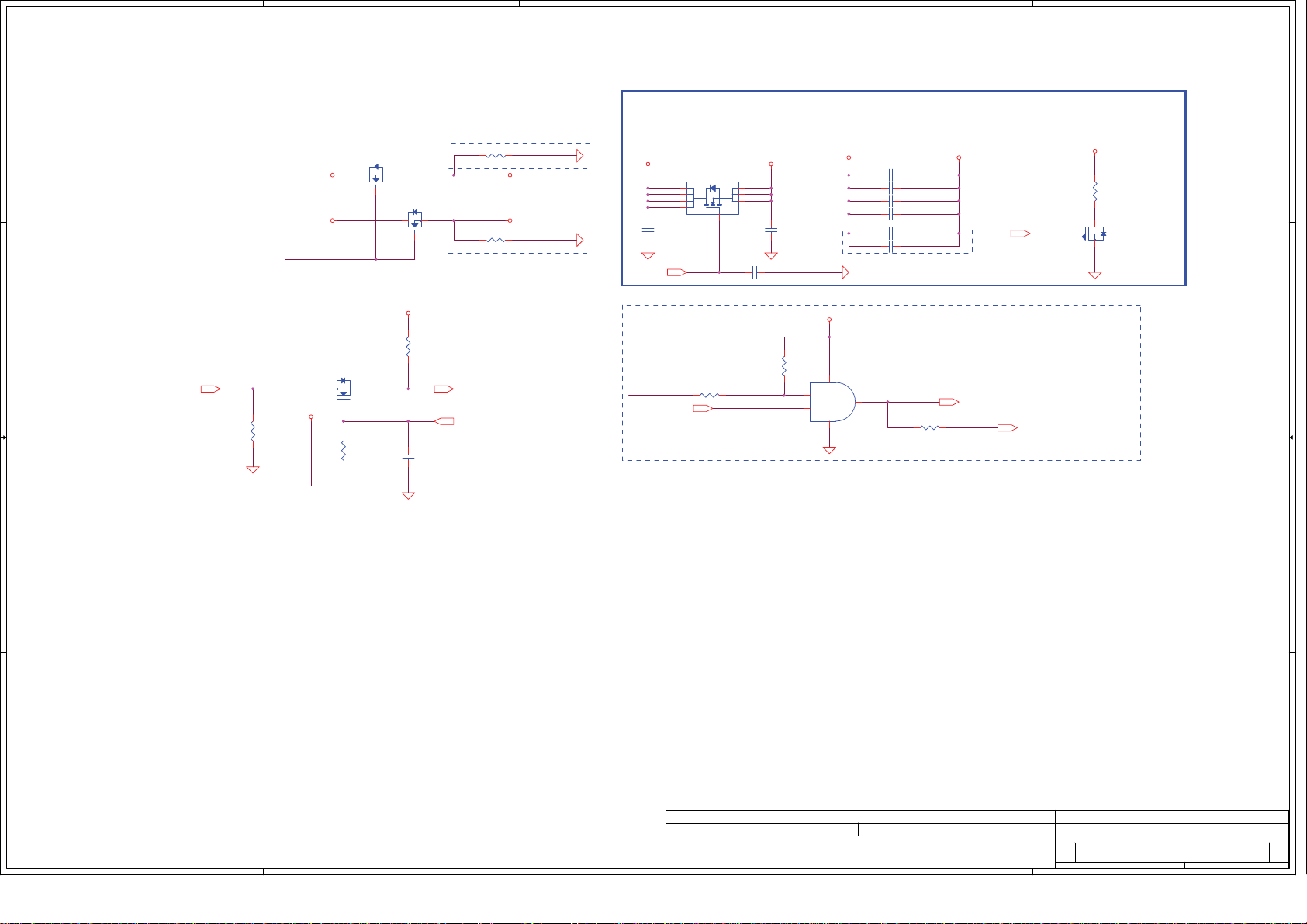

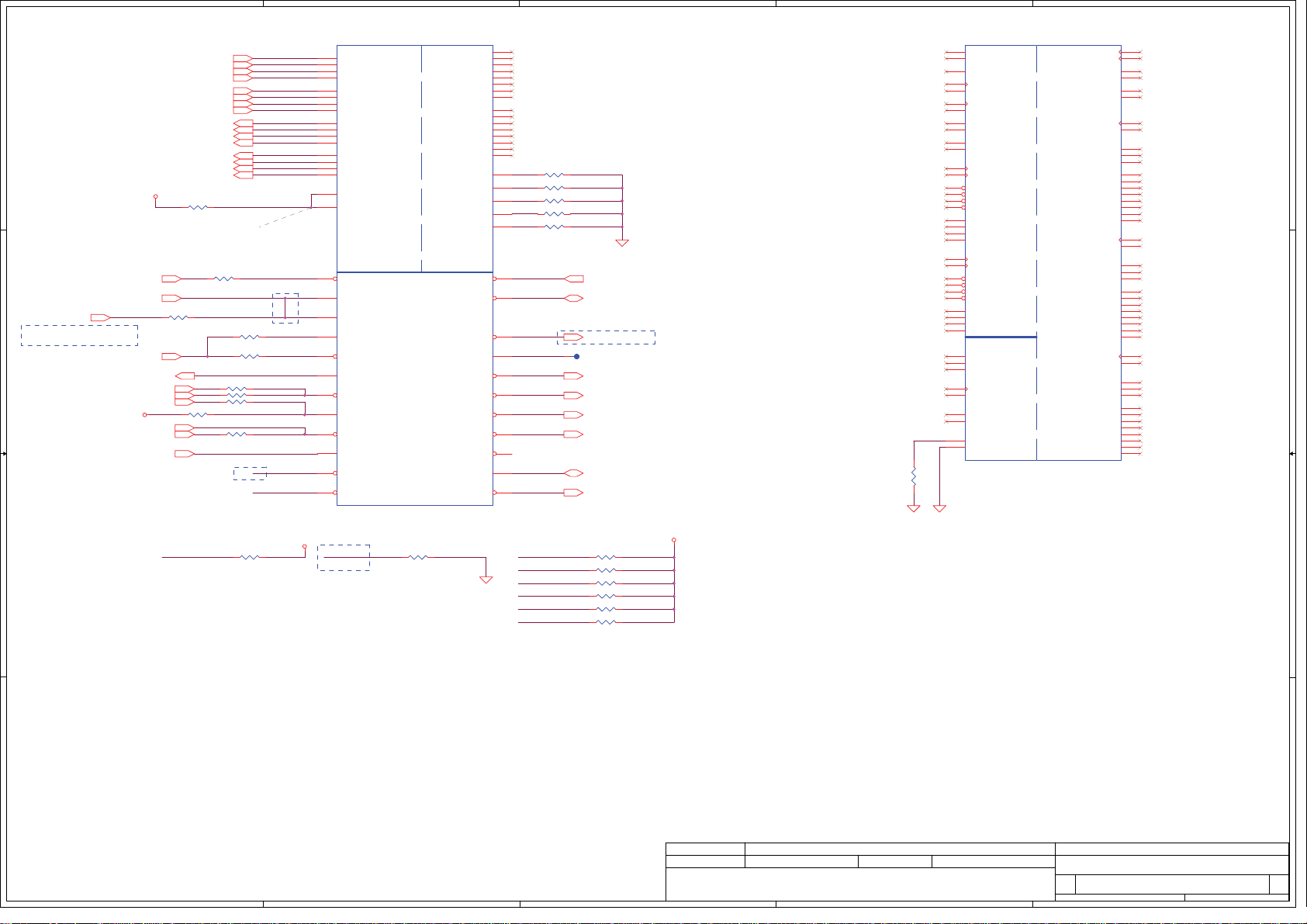

Page 4

5

Thermal Sensor EMC2113 with CPU PWM FAN

+3VS

Change R5 to 22ohm

from 68ohm. 11/30

R5

22_0402_5%

1 2

D D

+3VS_THER

1

C2

2

H_THERMTRIP#

H_THERMTRIP#

C C

Change Q24.2 connect from +3VS to PWR_GD. 12/11

R35 10K_0402_5%

FAN_PWM31

R13 10K_0402_5%

+3VS

THERM_SCI#16,21

0.1U_0402_16V4Z

R18

1 2

+3VS

10K_0402_5%@

Add PD R211 for FAN_PWM. 11/30

FAN_PWM

Q24

2N7002_SOT23-3

D

1 3

Layout note:

1. Place C1 & C408 close to U1 pin.

2. Place U1 close to JCFAN1.

H_THERMDA

1 2

C1 2200P_0402_50V7K

1 2

FAN_PWM

1 2

1 2

R21 0_0402_5%

SMB_DATA_S39,10,12,14,26

R211 10K_0402_5%

1 2

S

G

2

H_THERMTRIP#_U1 21

PWR_GD 11,13,31,34

U1

EMC2113-2-AX_QFN16_4X4

1

DN

2

DP

3

VDD

4

PWM_IN

5

ADDR_SEL

6

ALERT#

7

SYS_SHDN#

8

SMDATA

17

SHDN_SEL

GND

DP2/DN3

DN2/DP3

TRIP_SET

GND

PWM

TACH

SMCLK

Add C408. 11/30

REMOTE2+H_THERMDC

16

REMOTE2-

15

R9 2.05K_0402_1%

14

1 2

R10 6.8K_0402_5%

13

1 2

12

FAN_PWM_OUT

11

TACH

10

9

REMOTE thermal sensor

Layout note:

1. Place Q1 close to bottom DDR DIMM.

1 2

C

Q1

2

B

MMBT3904W_SOT323-3

E

3 1

Layout Note:

place near the hottest spot area for

NB & top SODIMM.

H_THERMDA

100P_0402_50V8J

H_THERMDC

C3

4

Change

R10 to

6.8K to

setup Q1

E-diode1.

12/04

1 2

C4082200P_0402_50V7K

+3VS

R133

1 2

10K_0402_5%

SMB_CLK_S3 9,10,12,14,26

Install R133. 7/14

Intel S3

Change from +1.5V. 7/8

VCCP_1.5VSPWRGD11

+3VS

Layout rule 10mil wi:dth trace

length < 0.5", spacing 20mil

+VCCP

H_PECI16

H_PROCHOT#43

H_THERMTRIP#16

H_CPUPWRGD16

R33 1.5K_0402_1%

R34 750_0402_1%

H_PROCHOT#

H_CPURST#

H_PM_SYNC15

H_CPUPWRGD

H_CPUPWRGD

PM_DRAM_PWRGD15

VTTPWRGOOD34

BUF_PLT_RST#16

12

12

VDDPWRGOOD_R

Change R33, R34 value. 7/10

3

R1 20_0402_1%

1 2

R2 20_0402_1%

1 2

R3 49.9_0402_1%

1 2

R4 49.9_0402_1%

1 2

TP_SKTOCC#

T1PAD

H_CATERR#

1 2

R8 49.9_0402_1%

1 2

R11 0_0402_5%

1 2

R16 0_0402_5%

1 2

R22 0_0402_5%

1 2

R24 0_0402_5%

1 2

R25 0_0402_5%

1 2

R26 0_0402_5%

1 2

R27 0_0402_5%

1 2

R28 0_0402_5%

1 2

R30 0_0402_5%

1 2

R31 1.5K_0402_1%

H_PECI_ISO

H_PROCHOT#_D

H_THERMTRIP#_RH_THERMTRIP#

H_CPURST#_R

H_PM_SYNC_R

VCCPWRGOOD_1

VCCPWRGOOD_0

VDDPWRGOOD_R

H_PWRGD_XDP_RH_PWRGD_XDP

PLT_RST#_R

12

R32

750_0402_1%

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

JCPU1B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

Intel S3

VDDPWRGOOD_R

MISC THERMAL

CLOCKS

DDR3

PWR MANAGEMENT

JTAG & BPM

R751 1.1K_0402_1%@

12

2

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

MISC

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

IC,AUB_CFD_rPGA,R1P0

+1.5VS_CPU_VDDQ

Removed RP1 & RP3 connect to U3. 10/27

A16

B16

CLK_CPU_XDP

AR30

CLK_CPU_XDP#

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

Intel doc 395136:

Remove R6 & R7 connect to GND directly. 11/06

SM_RCOMP0

R12 100_0402_1%

SM_RCOMP1

R14 24.9_0402_1%

SM_RCOMP2

R15 130_0402_1%

PM_EXTTS#0

R17 10K_0402_5%

PM_EXTTS#1

R19 0_0402_5%

R20 10K_0402_5%

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

XDP_BPM#3_R

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

CLK_CPU_BCLK_P 16

CLK_CPU_BCLK#_P 16

CLK_EXP 14

CLK_EXP# 14

1 2

1 2

1 2

1 2

1 2

1 2

Place close to JCPU1.

R23 51_0402_5%@

Follow DIOR's design. 2/20

XDP_DBRESET# 13,15

R126 0_0402_5%

1 2

R127 0_0402_5%

1 2

R141 0_0402_5%

1 2

R142 0_0402_5%

1 2

Place close to JCPU1.

H_PROCHOT#_D

R29 68_0402_5%

1 2

1 2

1

SM_DRAMRST# 11

+VCCP

+VCCP

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

PM_EXTTS#1_R 9,10

+VCCP

FAN Connector

+5VS

R40

1 2

+5VS+3VS

No install R41. 7/14

R41

1 2

10K_0402_5%

10K_0402_5%

@

4

3

2

1

JCFAN1

4

3

2

GND

1

GND

ACES_50273-0040N-001CONN@

XDP_BPM#05

XDP_BPM#15

XDP_BPM#25

XDP_BPM#35

CFG175

CFG165

6

5

+VCCP

H_CPUPWRGD

1

C4

0.1U_0402_16V4Z@

2

4

R45 1K_0402_5%

1 2

PM_PWRBTN#_R13,15

H_PWRGD_XDP

Disconnect from

SMB_DATA/CLK_S3. 0206

R47 0_0402_5%

1 2

B B

Remove D29 to

prevent FAN fully

turn issue. 7/2

A A

FAN_PWM_OUT

TACH

5

XDP_PREQ#

XDP_PRDY#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

H_CPUPWRGD_R

T90PAD

T91PAD

XDP_TCK

XDP Connector

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A CONN@

XDP_RST#_R

1 2

R54 0_0402_5%@

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

OBSFN_C0

OBSFN_C1

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSFN_D0

OBSFN_D1

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

PLT_RST#

2

GND1

4

6

8

GND3

10

12

14

GND5

16

18

20

GND7

22

24

26

GND9

28

30

32

GND11

34

36

38

GND13

GND15

TRST#

GND17

TD0

TMS

CLK_CPU_XDP

40

CLK_CPU_XDP#

42

44

XDP_RST#_R

46

XDP_DBRESET#_R

48

50

XDP_TDO

52

XDP_TRST#

54

XDP_TDI

56

TDI

XDP_TMS

58

60

PLT_RST# 13,16,21,22,24,27,28,30

2008/09/15 2009/09/15

Compal Secret Data

CFG8 5

CFG9 5

CFG0 5

CFG1 5

CFG2 5

CFG3 5

CFG10 5

CFG11 5

CFG4 5

CFG5 5

CFG6 5

CFG7 5

R48 1K_0402_5%

1 2

R49 0_0402_5%

1 2

R51 51_0402_5%

1 2

Deciphered Date

Swap. 02/25

2

+VCCP

H_CPURST#

XDP_DBRESET#

+3VS

R43

1K_0402_5%

1 2

H_CPURST#_R

R36 68_0402_5%@

1 2

Remove R37, R38, R39. 2/17

XDP_TDO

R42 51_0402_5%

1 2

2/20.

Delete R44, R46, R52, R53, R50 and

short XDP_TDI_M to XDP_TDO_M (pins

AR29 and AP29 of JCPU1) like DIOR

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Clarksfield(1/5)-Thermal/XDP

LA-4951P

+VCCP

1

448Tuesday, July 28, 2009

0.4

of

Page 5

5

D D

4

3

2

1

JCPU1E

AP25

RSVD1

CFG7

CFG4

CFG3

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

IC,AUB_CFD_rPGA,R1P0

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RESERVED

Change net name. 7/9

JCPU1A

DMI_CRX_PTX_N015

DMI_CRX_PTX_N115

DMI_CRX_PTX_N215

DMI_CRX_PTX_N315

DMI_CRX_PTX_P015

DMI_CRX_PTX_P115

DMI_CRX_PTX_P215

DMI_CRX_PTX_P315

C C

DMI_CTX_PRX_N015

DMI_CTX_PRX_N115

DMI_CTX_PRX_N215

DMI_CTX_PRX_N315

DMI_CTX_PRX_P015

DMI_CTX_PRX_P115

DMI_CTX_PRX_P215

DMI_CTX_PRX_P315

B B

R61 1K_0402_5%

R65 1K_0402_5%

12

12

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

Intel doc 395136:

Tie FDI_F(L)SYNC[0:1]

via 1 1K to GND. (11/05)

A A

IC,AUB_CFD_rPGA,R1P0

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

Layout rule trace len:gth < 0.5"

EXP_ICOMPI

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

R55 49.9_0402_1%

EXP_RBIAS

R56 750_0402_1%

PCIE_CRX_GTX_C_N0

PCIE_CRX_GTX_C_N1

PCIE_CRX_GTX_C_N2

PCIE_CRX_GTX_C_N3

PCIE_CRX_GTX_C_N4

PCIE_CRX_GTX_C_N5

PCIE_CRX_GTX_C_N6

PCIE_CRX_GTX_C_N7

PCIE_CRX_GTX_C_N8

PCIE_CRX_GTX_C_N9

PCIE_CRX_GTX_C_N10

PCIE_CRX_GTX_C_N11

PCIE_CRX_GTX_C_N12

PCIE_CRX_GTX_C_N13

PCIE_CRX_GTX_C_N14

PCIE_CRX_GTX_C_N15

PCIE_CRX_GTX_C_P0

PCIE_CRX_GTX_C_P1

PCIE_CRX_GTX_C_P2

PCIE_CRX_GTX_C_P3

PCIE_CRX_GTX_C_P4

PCIE_CRX_GTX_C_P5

PCIE_CRX_GTX_C_P6

PCIE_CRX_GTX_C_P7

PCIE_CRX_GTX_C_P8

PCIE_CRX_GTX_C_P9

PCIE_CRX_GTX_C_P10

PCIE_CRX_GTX_C_P11

PCIE_CRX_GTX_C_P12

PCIE_CRX_GTX_C_P13

PCIE_CRX_GTX_C_P14

PCIE_CRX_GTX_C_P15

PCIE_CTX_GRX_C_N0

PCIE_CTX_GRX_C_N1

PCIE_CTX_GRX_C_N2

PCIE_CTX_GRX_C_N3

PCIE_CTX_GRX_C_N4

PCIE_CTX_GRX_C_N5

PCIE_CTX_GRX_C_N6

PCIE_CTX_GRX_C_N7

PCIE_CTX_GRX_C_N8

PCIE_CTX_GRX_C_N9

PCIE_CTX_GRX_C_N10

PCIE_CTX_GRX_C_N11

PCIE_CTX_GRX_C_N12

PCIE_CTX_GRX_C_N13

PCIE_CTX_GRX_C_N14

PCIE_CTX_GRX_C_N15

PCIE_CTX_GRX_C_P0

PCIE_CTX_GRX_C_P1

PCIE_CTX_GRX_C_P2

PCIE_CTX_GRX_C_P3

PCIE_CTX_GRX_C_P4

PCIE_CTX_GRX_C_P5

PCIE_CTX_GRX_C_P6

PCIE_CTX_GRX_C_P7

PCIE_CTX_GRX_C_P8

PCIE_CTX_GRX_C_P9

PCIE_CTX_GRX_C_P10

PCIE_CTX_GRX_C_P11

PCIE_CTX_GRX_C_P12

PCIE_CTX_GRX_C_P13

PCIE_CTX_GRX_C_P14

PCIE_CTX_GRX_C_P15

1 2

1 2

C662 0.1U_0402_16V4Z

1 2

C663 0.1U_0402_16V4Z

1 2

C664 0.1U_0402_16V4Z

1 2

C665 0.1U_0402_16V4Z

1 2

C666 0.1U_0402_16V4Z

1 2

C667 0.1U_0402_16V4Z

1 2

C668 0.1U_0402_16V4Z

1 2

C669 0.1U_0402_16V4Z

1 2

C670 0.1U_0402_16V4Z

1 2

C671 0.1U_0402_16V4Z

1 2

C672 0.1U_0402_16V4Z

1 2

C673 0.1U_0402_16V4Z

1 2

C674 0.1U_0402_16V4Z

1 2

C675 0.1U_0402_16V4Z

1 2

C676 0.1U_0402_16V4Z

1 2

C677 0.1U_0402_16V4Z

1 2

C678 0.1U_0402_16V4Z

1 2

C679 0.1U_0402_16V4Z

1 2

C680 0.1U_0402_16V4Z

1 2

C681 0.1U_0402_16V4Z

1 2

C682 0.1U_0402_16V4Z

1 2

C683 0.1U_0402_16V4Z

1 2

C684 0.1U_0402_16V4Z

1 2

C685 0.1U_0402_16V4Z

1 2

C686 0.1U_0402_16V4Z

1 2

C687 0.1U_0402_16V4Z

1 2

C688 0.1U_0402_16V4Z

1 2

C689 0.1U_0402_16V4Z

1 2

C690 0.1U_0402_16V4Z

1 2

C691 0.1U_0402_16V4Z

1 2

C692 0.1U_0402_16V4Z

1 2

C693 0.1U_0402_16V4Z

1 2

C5 0.1U_0402_16V4Z

1 2

C6 0.1U_0402_16V4Z

1 2

C7 0.1U_0402_16V4Z

1 2

C8 0.1U_0402_16V4Z

1 2

C9 0.1U_0402_16V4Z

1 2

C10 0.1U_0402_16V4Z

1 2

C11 0.1U_0402_16V4Z

1 2

C12 0.1U_0402_16V4Z

1 2

C13 0.1U_0402_16V4Z

1 2

C14 0.1U_0402_16V4Z

1 2

C15 0.1U_0402_16V4Z

1 2

C16 0.1U_0402_16V4Z

1 2

C17 0.1U_0402_16V4Z

1 2

C18 0.1U_0402_16V4Z

1 2

C19 0.1U_0402_16V4Z

1 2

C20 0.1U_0402_16V4Z

1 2

C21 0.1U_0402_16V4Z

1 2

C22 0.1U_0402_16V4Z

1 2

C23 0.1U_0402_16V4Z

1 2

C24 0.1U_0402_16V4Z

1 2

C25 0.1U_0402_16V4Z

1 2

C26 0.1U_0402_16V4Z

1 2

C27 0.1U_0402_16V4Z

1 2

C28 0.1U_0402_16V4Z

1 2

C29 0.1U_0402_16V4Z

1 2

C30 0.1U_0402_16V4Z

1 2

C31 0.1U_0402_16V4Z

1 2

C32 0.1U_0402_16V4Z

1 2

C33 0.1U_0402_16V4Z

1 2

C34 0.1U_0402_16V4Z

1 2

C35 0.1U_0402_16V4Z

1 2

C36 0.1U_0402_16V4Z

1 2

PCIE_CRX_GTX_N0 21

PCIE_CRX_GTX_N1 21

PCIE_CRX_GTX_N2 21

PCIE_CRX_GTX_N3 21

PCIE_CRX_GTX_N4 21

PCIE_CRX_GTX_N5 21

PCIE_CRX_GTX_N6 21

PCIE_CRX_GTX_N7 21

PCIE_CRX_GTX_N8 21

PCIE_CRX_GTX_N9 21

PCIE_CRX_GTX_N10 21

PCIE_CRX_GTX_N11 21

PCIE_CRX_GTX_N12 21

PCIE_CRX_GTX_N13 21

PCIE_CRX_GTX_N14 21

PCIE_CRX_GTX_N15 21

PCIE_CRX_GTX_P0 21

PCIE_CRX_GTX_P1 21

PCIE_CRX_GTX_P2 21

PCIE_CRX_GTX_P3 21

PCIE_CRX_GTX_P4 21

PCIE_CRX_GTX_P5 21

PCIE_CRX_GTX_P6 21

PCIE_CRX_GTX_P7 21

PCIE_CRX_GTX_P8 21

PCIE_CRX_GTX_P9 21

PCIE_CRX_GTX_P10 21

PCIE_CRX_GTX_P11 21

PCIE_CRX_GTX_P12 21

PCIE_CRX_GTX_P13 21

PCIE_CRX_GTX_P14 21

PCIE_CRX_GTX_P15 21

PCIE_CTX_GRX_N0 21

PCIE_CTX_GRX_N1 21

PCIE_CTX_GRX_N2 21

PCIE_CTX_GRX_N3 21

PCIE_CTX_GRX_N4 21

PCIE_CTX_GRX_N5 21

PCIE_CTX_GRX_N6 21

PCIE_CTX_GRX_N7 21

PCIE_CTX_GRX_N8 21

PCIE_CTX_GRX_N9 21

PCIE_CTX_GRX_N10 21

PCIE_CTX_GRX_N11 21

PCIE_CTX_GRX_N12 21

PCIE_CTX_GRX_N13 21

PCIE_CTX_GRX_N14 21

PCIE_CTX_GRX_N15 21

PCIE_CTX_GRX_P0 21

PCIE_CTX_GRX_P1 21

PCIE_CTX_GRX_P2 21

PCIE_CTX_GRX_P3 21

PCIE_CTX_GRX_P4 21

PCIE_CTX_GRX_P5 21

PCIE_CTX_GRX_P6 21

PCIE_CTX_GRX_P7 21

PCIE_CTX_GRX_P8 21

PCIE_CTX_GRX_P9 21

PCIE_CTX_GRX_P10 21

PCIE_CTX_GRX_P11 21

PCIE_CTX_GRX_P12 21

PCIE_CTX_GRX_P13 21

PCIE_CTX_GRX_P14 21

PCIE_CTX_GRX_P15 21

R57 3.01K_0402_1%@

R58 3.01K_0402_1%@

R59 3.01K_0402_1%@

R60 3.01K_0402_1%

12

12

12

12

CFG84

CFG94

CFG104

CFG114

XDP_BPM#04

XDP_BPM#14

XDP_BPM#24

XDP_BPM#34

CFG164

Add per XDP DG. 11/13

Change R120, R122, R123,

R125 to NI. 11/30

CFG174

R120 0_0402_5%@

1 2

R122 0_0402_5%@

1 2

R123 0_0402_5%@

1 2

R125 0_0402_5%@

1 2

CFG74

CFG44

CFG34

CFG04

CFG14

CFG24

CFG54

CFG64

V_CPU_DDR_REF0

V_CPU_DDR_REF1

T16 PAD

R68 0_0402_5%@

1 2

R69 0_0402_5%@

1 2

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

KEY

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

R63 0_0402_5%@

AJ15

R64 0_0402_5%@

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

R70 0_0402_5%@

AP34

1 2

1 2

M_CLK_A_DDR2 9

M_CLK_A_DDR#2 9

DDR_CKE2_DIMMA 9

DDR_CS2_DIMMA# 9

M_A_ODT2 9

M_CLK_A_DDR3 9

M_CLK_A_DDR#3 9

DDR_CKE3_DIMMA 9

DDR_CS3_DIMMA# 9

M_A_ODT3 9

M_CLK_B_DDR2 10

M_CLK_B_DDR#2 10

DDR_CKE2_DIMMB 10

DDR_CS2_DIMMB# 10

M_B_ODT2 10

M_CLK_B_DDR3 10

M_CLK_B_DDR#3 10

DDR_CKE3_DIMMB 10

DDR_CS3_DIMMB# 10

M_B_ODT3 10

1 2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/09/15

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Clarksfield(2/5)-DMI/PEG/FDI

LA-4951P

1

548Tuesday, July 28, 2009

of

0.4

Page 6

5

4

3

2

1

DDR_B_D[0..63]

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_B_DDR0 10

M_CLK_B_DDR#0 10

DDR_CKE0_DIMMB 10

M_CLK_B_DDR1 10

M_CLK_B_DDR#1 10

DDR_CKE1_DIMMB 10

DDR_CS0_DIMMB# 10

DDR_CS1_DIMMB# 10

M_B_ODT0 10

M_B_ODT1 10

DDR_B_D M[0..7]

DDR_B_D QS#[0..7]

DDR_B_DQS[0..7]

DDR_B_MA[0..15]

DDR_B_DM[0..7] 10

DDR_B_DQS#[0..7] 10

DDR_B_DQS[0..7] 10

DDR_B_MA[0..15] 10

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63]10

JCPU1D

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

AR10

SB_DQ[62]

AT10

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

JCPU1C

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR_A_D[0..63]

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_A_DDR0 9

M_CLK_A_DDR#0 9

DDR_CKE0_DIMMA 9

M_CLK_A_DDR1 9

M_CLK_A_DDR#1 9

DDR_CKE1_DIMMA 9

DDR_CS0_DIMMA# 9

DDR_CS1_DIMMA# 9

M_A_ODT0 9

M_A_ODT1 9

DDR_A_DM[0..7]

DDR_A_DQS#[0..7]

DDR_A_DQ S[0..7]

DDR_A_MA[0..15]

DDR_A_DM[0..7] 9

DDR_A_DQS#[0..7] 9

DDR_A_DQ S [0..7] 9

DDR_A_MA[0..15] 9

DDR_B_BS010

DDR_B_BS110

DDR_B_BS210

DDR_B_CAS#10

DDR_B_RAS#10

DDR_B_WE#10

DDR_A_D[0..63]9

D D

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

C C

B B

DDR_A_CAS#9

DDR_A_RAS#9

DDR_A_WE#9

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_BS09

DDR_A_BS19

DDR_A_BS29

AG5

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AM9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

C10

C7

A7

B10

D10

E10

A8

D8

F10

E6

F7

E9

B7

E7

C6

H10

G8

K7

J8

G7

G10

J7

J10

L7

M6

M8

L9

L6

K8

N8

P9

AH5

AF5

AK6

AK7

AF6

AJ7

AJ6

AJ9

AK8

AL7

AL8

AN8

AN9

AC3

AB2

U7

AE1

AB3

AE9

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PR OPERTY OF COMPAL ELECTRONICS, INC . AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/09/15

Compal Secret Data

Deciphered Date

2

Title

Size Document Number R ev

Custom

Date: Sheet

Compal Electronics, Inc.

Clarksfield(2/6)-DDR3 A/B CH

LA-4951P

1

648Tuesday, July 28, 2009

of

0.4

Page 7

5

4

3

2

1

+CPU_CORE

D D

C C

B B

A A

JCPU1F

48A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,AUB_CFD_rPGA,R1P0

5

CPU CORE SUPPLY

POWER

CPU VIDS

SENSE LINES

1.1V RAIL POWER

PROC_DPRSLPVR

VTT_SELECT

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

18A

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

ISENSE

PSI#

Chnage 10uF to 22uF for DB1.

12/03

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

C37

@

10U_0805_6.3V6M

1

2

10U_0805_6.3V6M

C50

1

2

22U_0805_6.3V6M

C62

1

2

+VTT_43

+VTT_44

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

PM_DPRSLPVR_R

C38

@

10U_0805_6.3V6M

1

2

10U_0805_6.3V6M

C51

1

2

+VCCP

22U_0805_6.3V6M

C63

1

2

R74 0_0603_5%

R75 0_0603_5%

R76 0_0402_5%

H_VTTVID1 = Low, 1.1V

H_VTTVID1 = High, 1.05V

AN35

VCC_SENSE

VSS_SENSE

R79 0_0402_5%

1 2

R80 0_0402_5%

1 2

4

AJ34

AJ35

B15

A15

22U_0805_6.3V6M

22U_0805_6.3V6M

C40

C39

1

1

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C52

C53

1

1

2

2

Chnage 10uF

to 22uF for

DB1. 12/03

1 2

1 2

PSI# 43

H_VID[0..6] 43

1 2

H_VTTVID1 40

IMVP_IMON 43

VTT_SENSE 40

VSS_SENSE_VTT 40

C41

1

2

10U_0805_6.3V6M

22U_0805_6.3V6M

C42

1

2

+VCCP

Close to CPU

Update 10/27

VCCSENSE

VSSSENSE

10U_0805_6.3V6M

C43

C44

1

1

2

2

PROC_DPRSLPVR 43

VCC_SENSE

R77 100_0402_1%

VSS_SENSE

R78 100_0402_1%

Del C81, C82. 5/15

+CPU_CORE

+VCCP

10U_0805_6.3V6M

10U_0805_6.3V6M

C45

1

2

Chnage 10uF

to 22uF for

DB1. 12/03

1 2

1 2

VCCSENSE 43

VSSSENSE 43

C79

12

@

47P_0402_50V8J

C80

12

@

47P_0402_50V8J

+VCCP

C46

12

@

47P_0402_50V8J

+CPU_CORE

JCPU1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

C48

C47

12

C49

12

12

@

@

3

@

47P_0402_50V8J

47P_0402_50V8J

+VCCP

47P_0402_50V8J

+VCCP

22U_0805_6.3V6M

C64

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C70

1

2

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C71

1

2

Issued Date

C72

1

2

22U_0805_6.3V6M

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

22U_0805_6.3V6M

VTT1_46

H25

C65

C73

1

2

1

2

22U_0805_6.3V6M

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,AUB_CFD_rPGA,R1P0

2008/09/15 2009/09/15

15A

GRAPHICS

FDI PEG & DMI

Compal Secret Data

Deciphered Date

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

GFX_DPRSLPVR

GRAPHICS VIDs

3A

POWER

DDR3 - 1.5V RAILS

1.1V1.8V

0.6A

2

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

R71 4.7K_0402_5%

AR25

1 2

R72 10K_0402_5%@

AT25

1 2

R73 1K_0402_5%

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

1U_0603_10V4Z

C55

1

2

1U_0402_6.3V4Z

C74

1

2

1

2

1U_0603_10V4Z

C60

22U_0805_6.3V6M

1

2

Intel S3

+1.5VS_CPU_VDDQ

22U_0805_6.3V6M

C61

1

2

12

1U_0603_10V4Z

1U_0603_10V4Z

C56

1

2

1U_0603_10V4Z

C57

C58

1

2

C59

1

2

Remove C54. 7/14

Chnage 10uF to 22uF DB1. 12/16

+VCCP

10U_0805_6.3V6M

C67

C66

1

+VCCP

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C69

C68

1

1

2

2

+1.8VS

22U_0805_6.3V6M

4.7U_0603_6.3V6K

2.2U_0603_6.3V4Z

1U_0402_6.3V4Z

C77

C76

C75

1

2

Title

Size Document Number Re v

Custom

Date: Sheet

C78

1

1

2

1

2

2

Compal Electronics, Inc.

Clarksfield(4/5)-PWR

LA-4951P

1

Chnage 10uF

to 22uF for

DB1. 12/03

748Tuesday, July 28, 2009

of

10U_0805_6.3V6M

1

2

0.4

Page 8

5

4

3

2

1

T17

T18

T19

T20

T21

T22

T23

+CPU_CORE

C83

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C84

1

2

10U_0805_6.3V6M

C85

1

2

10U_0805_6.3V6M

C86

1

2

+CPU_CORE

C105

1

2

10U_0805_6.3V6M

C87

C88

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C106

1

2

22U_0805_6.3V6M

C89

1

2

10U_0805_6.3V6M

C107

1

2

22U_0805_6.3V6M

C90

1

2

10U_0805_6.3V6M

C108

1

2

+CPU_CORE

C115

22U_0805_6.3V6M

C91

1

2

10U_0805_6.3V6M

C109

1

2

330U_X_2VM_R6M

C116

1

+

2

10U_0805_6.3V6M

C92

1

2

10U_0805_6.3V6M

C110

1

2

C117

330U_X_2VM_R6M

1

+

2

10U_0805_6.3V6M

C93

1

2

10U_0805_6.3V6M

C111

1

2

330U_X_2VM_R6M

C118

1

+

2

10U_0805_6.3V6M

C94

1

2

10U_0805_6.3V6M

C112

1

2

330U_X_2VM_R6M

1

+

2

22U_0805_6.3V6M

1

2

C113

1

2

Install for

DB1. 12/03

C119

1

2

22U_0805_6.3V6M

C95

1

2

10U_0805_6.3V6M

C114

C120

330U_X_2VM_R6M

+

10U_0805_6.3V6M

C96

1

2

Add for debug. 5/13

10U_0805_6.3V6M

1

2

330U_X_2VM_R6M

1

+

2

Chnage 330uF ESR from 7m to 6m for DB1. 12/16

10U_0805_6.3V6M

C97

1

2

22U_0805_6.3V6M

C712

1

2

10U_0805_6.3V6M

C98

1

2

22U_0805_6.3V6M

C713

1

2

10U_0805_6.3V6M

C99

1

2

22U_0805_6.3V6M

C714

1

2

22U_0805_6.3V6M

C100

1

2

22U_0805_6.3V6M

C101

1

2

22U_0805_6.3V6M

C102

1

2

22U_0805_6.3V6M

C103

1

2

22U_0805_6.3V6M

C104

1

2

JCPU1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

D D

C C

B B

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

VSS8

VSS9

VSS10

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

VSS15

VSS16

VSS17

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

VSS80

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

JCPU1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

VSS

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

NCTF

AT1

AR34

B34

B2

B1

A35

VSS_NCTF2_R

VSS_NCTF3_R

VSS_NCTF4_R

VSS_NCTF5_R

VSS_NCTF6_R

VSS_NCTF7_R

VSS_NCTF1_R

AT35

IC,AUB_CFD_rPGA,R1P0

A A

5

IC,AUB_CFD_rPGA,R1P0

4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/09/15

Compal Secret Data

Deciphered Date

2

Title

Size Document Number R e v

Custom

Date: Sheet

Compal Electronics, Inc.

Clarksfield(5/5)-GND/Bypass

LA-4951P

1

848Tuesday, July 28, 2009

of

0.4

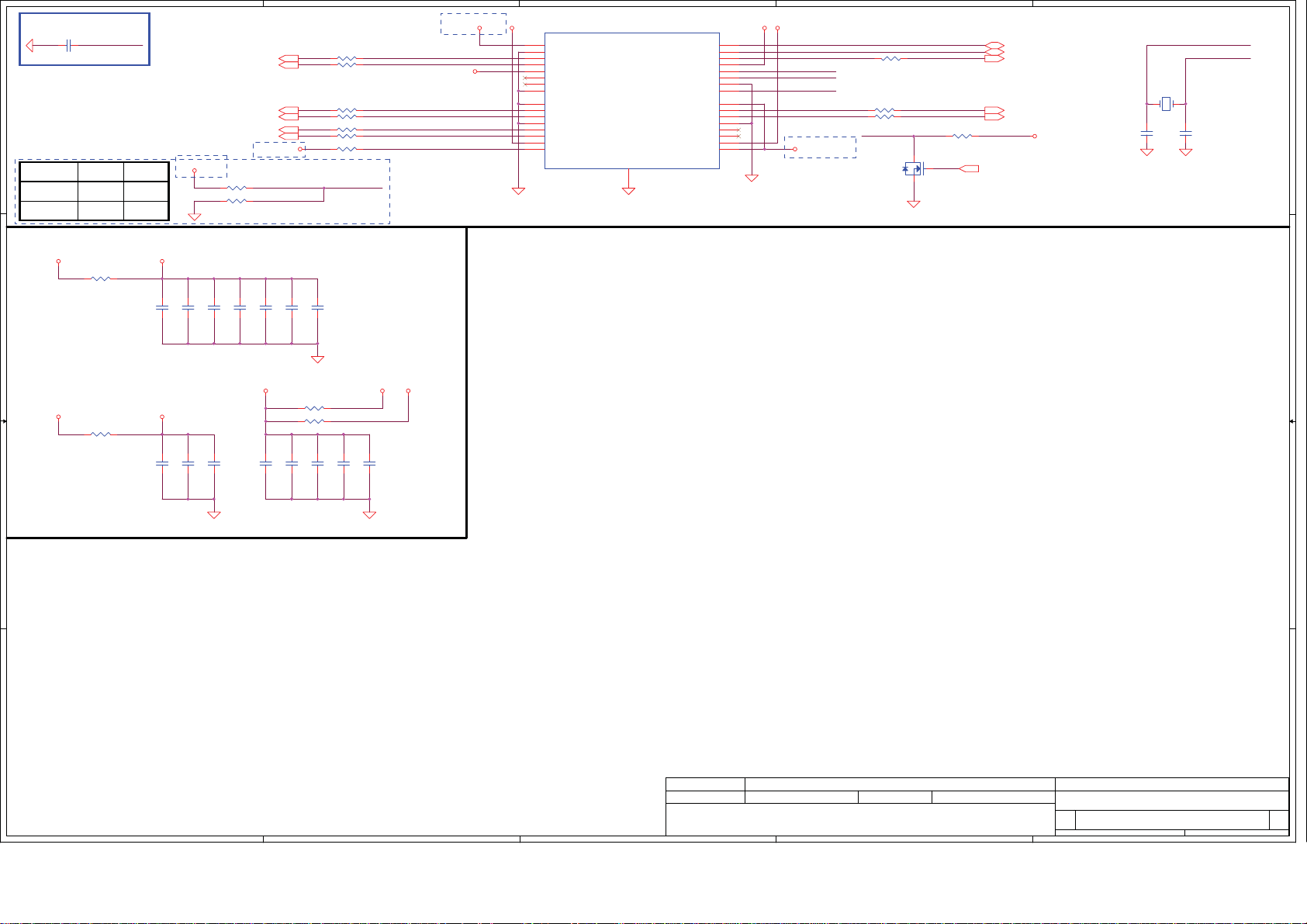

Page 9

V_DDR_CPU_REF0

3A @ 1 . 5 V

0.6 5 A @ 0 . 7 5 V

3A @ 1 . 5 V

0.6 5 A @ 0 . 7 5 V

R84 0_0402_5%

1 2

C124

2.2U_0402_6.3V6M

C123

0.1U_0402_16V4Z

1

1

D D

C C

B B

2

2

DDR_CKE2_DIMMA5

DDR_A_BS26

M_CLK_A_DDR25

M_CLK_A_DDR#25

DDR_A_BS06

DDR_A_WE#6

DDR_A_CAS#6

DDR_CS3_DIMMA#5

V_DDR_CPU_REF _A

+1.5V

12

R85

1K_0402_1%

12

R86

1K_0402_1%

SPD address 0xA2

+3VS

A A

Change. 2/17

R88 10K_0402_5%

C165

2.2U_0402_6.3V6M

1

2

5

V_DDR_CPU_REF_DA

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

1 2

C166

0.1U_0402_16V4Z

+0.75VS

10K_0402_5%

1

12

R90

2

5

+1.5V +1.5V

DDR3 SO-DIMM A

JDIMM2

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

VSS49DQS#0

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

A12/BC#83A11

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

VDD999VDD10

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

FOX_AS0A626-U4SG-7HCONN@

DQ4

DQ5

VSS3

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

DQ14

DQ15

DQ20

DQ21

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

CK1

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

A15

80

A14

82

84

86

A7

88

90

A6

92

A4

94

96

A2

98

A0

100

102

104

106

108

BA1

110

112

114

S0#

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

G2

TOP SIDE STD

(LOW)

DDR_A_D4

DDR_A_D5

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A_DM1

DRAMRST#

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_D30

DDR_A_D31

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_BS1

DDR_A_RAS#

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_D62

DDR_A_D63

PM_EXTTS#1_R

SMB_DATA_S3

SMB_CLK_S3

+0.75VS

ME/iAMT debug

SMB_DATA_S3

SMB_CLK_S3

4

1. Remove R682, R683.

2. Change R81 & R83 to 1K to another divider.

3. Install R82, R84.

+1.5V

Layout Note: Place near JDIMM1

C126

10U_0603_6.3V6M

1

@

2

C127

10U_0603_6.3V6M

1

@

2

C130

10U_0603_6.3V6M

1

@

2

C131

10U_0603_6.3V6M

1

2

C132

10U_0603_6.3V6M

1

2

C133

1

2

4/30

C134

0.1U_0201_6.3V6K

10U_0603_6.3V6M

1

2

3

C135

0.1U_0201_6.3V6K

1

2

V_DDR_CPU_REF_DA

V_DDR_CPU_REF0

C136

0.1U_0201_6.3V6K

C137

0.1U_0201_6.3V6K

1

1

2

2

C125

1

+

2

Remove C128, C129, C138, & C145. 5/11

+1.5V

Layout Note: Place near JDIMM2

C144

C139

10U_0603_6.3V6M

C141

10U_0603_6.3V6M

C140

10U_0603_6.3V6M

C142

1

1

@

@

2

2

1027: Change JDIMM1.1 and JDIMM2.1 to connect to V_DDR_CPU_REF_A via

R682 & R683 and move V_DDR_CPU_REF0 option and resistors R82 and R84

to JDIMM1.1 and JDIMM2.1. (Will check with Intel whether we should

use separate divider for VREF_DQ and VREF_CA for M1 solution?)

DDR_CKE3_DIMMA 5

M_CLK_A_DDR3 5

M_CLK_A_DDR#3 5

DDR_A_BS1 6

DDR_A_RAS# 6

DDR_CS2_DIMMA# 5

M_A_ODT2 5

M_A_ODT3 5

C152

0.1U_0402_16V4Z

C153

1

1

2

2

PM_EXTTS#1_R 4,10

SMB_DATA_S3 4,10,12,14,26

SMB_CLK_S3 4,10,12,14,26

As short as possible

2.2U_0402_6.3V6M

V_DDR_CPU_REF _A

10U_0603_6.3V6M

1

1

2

2

DDR_A_D[0..63]6

DDR_A_DM[0..7]6

DDR_A_DQS[0..7]6

DDR_A_DQS#[0..7]6

DDR_A_MA[0..15]6

Layout Note: Place near

JDIMM3.203 & JDIMM3.204

+0.75VS +0.75VS

C154

1U_0603_10V4Z

1

@

2

10U_0603_6.3V6M

C143

10U_0603_6.3V6M

1

1

@

2

2

C156

C155

1

@

2

C157

1U_0603_10V4Z

1U_0603_10V4Z

1

1

2

2

+0.75VS

C162

10U_0603_6.3V6M

1

Layout Note: Place between

JDIMM3 & JDIMM3.

2

Change ESR to 6m for DB1. 12/16

C149

C146

0.1U_0201_6.3V6K

C147

0.1U_0201_6.3V6K

1

1

2

2

Layout Note: Place near

JDIMM4.203 & JDIMM4.204

1U_0603_10V4Z

@

0.1U_0201_6.3V6K

C148

0.1U_0201_6.3V6K

1

1

2

2

C158

1U_0603_10V4Z

C159

1U_0603_10V4Z

1

1

2

2

C160

1U_0603_10V4Z

1

2

SPD address 0xA0

Change. 2/17

VREFDQ

JiAMT1

3

3

2

2

1

1

4

2/10

5

G2

4

G1

ACES_85204-03001CONN@

V_DDR_CPU_REF_AM1

M3 V_DDR_CPU_REF0

R81, R83, R682, R683

R82, R84

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PR OPERTY OF COMPAL ELECTRONICS, INC . AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

R82 0_0402_5%

1 2

C121

0.1U_0402_16V4Z

C122

1

1

330U_X_2VM_R6M

2

2

DDR_CKE0_DIMMA6

M_CLK_A_DDR06

M_CLK_A_DDR#06

DDR_CS1_DIMMA#6

C161

1U_0603_10V4Z

1

@

2

+3VS

C163

1

2

2008/09/15 2009/09/15

DDR_A_D0

2.2U_0402_6.3V6M

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

R87 10K_0402_5%

1 2

C164

0.1U_0402_16V4Z

2.2U_0402_6.3V6M

+0.75VS

10K_0402_5%

1

12

R89

2

Compal Secret Data

Deciphered Date

+1.5V

2

DDR3 SO-DIMM A

JDIMM1

FOX_AS0A626-J8SG-7HCONN@

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

VSS49DQS#0

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

DQS247VSS17

VSS1849DQ22

51

DQ18

53