A

1 1

2 2

B

C

D

E

Compal confidential

Schematics Document

Mobile Arrandale rPGA989 with

3 3

4 4

A

Intel PCH(Ibex Peak-M) core logic

2009-09-10

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2007/08/28 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

Calpella DIS LA4743P

1 52Friday, September 11, 2009

E

0.4

A

B

C

D

E

Compal confidential

1 1

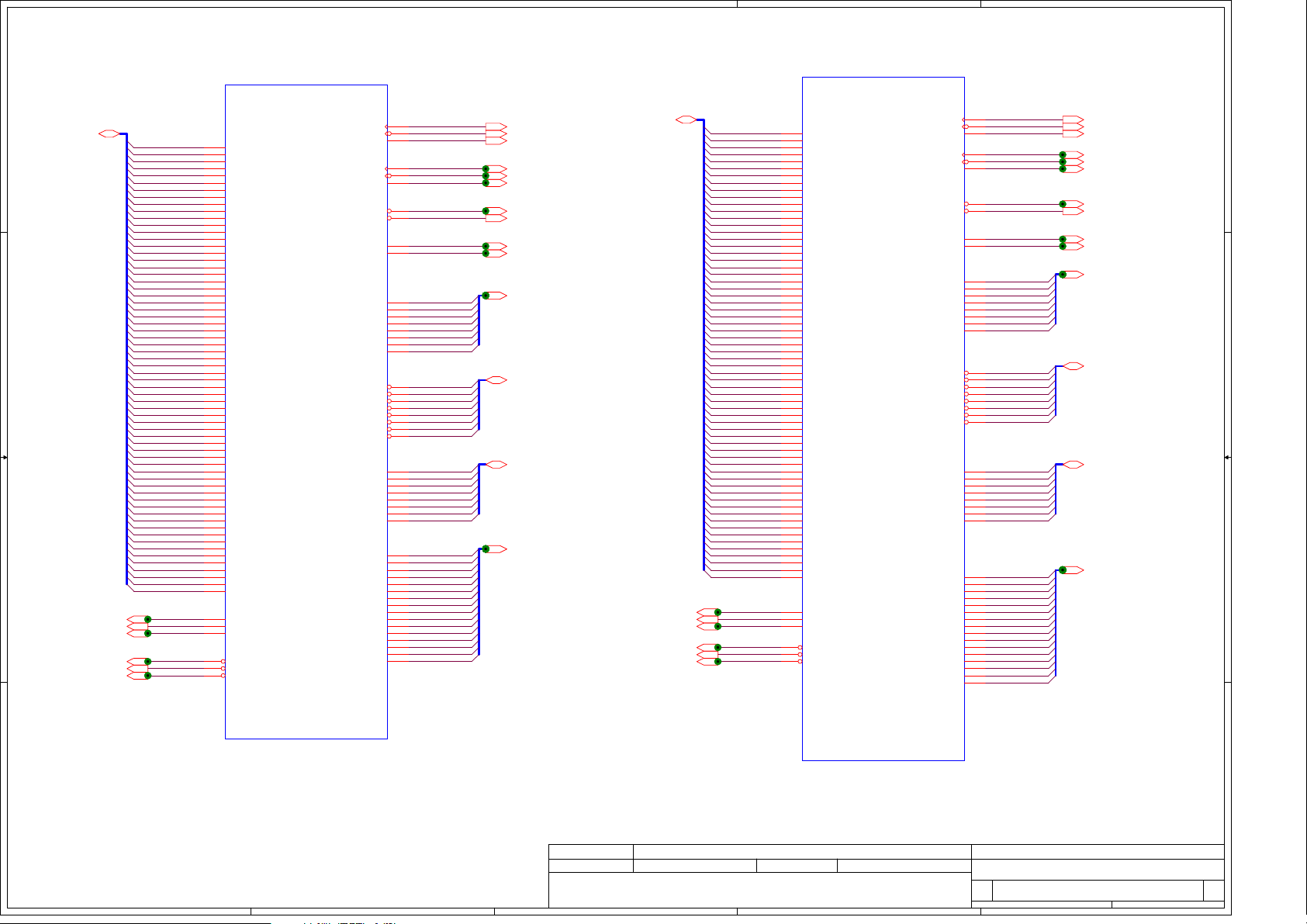

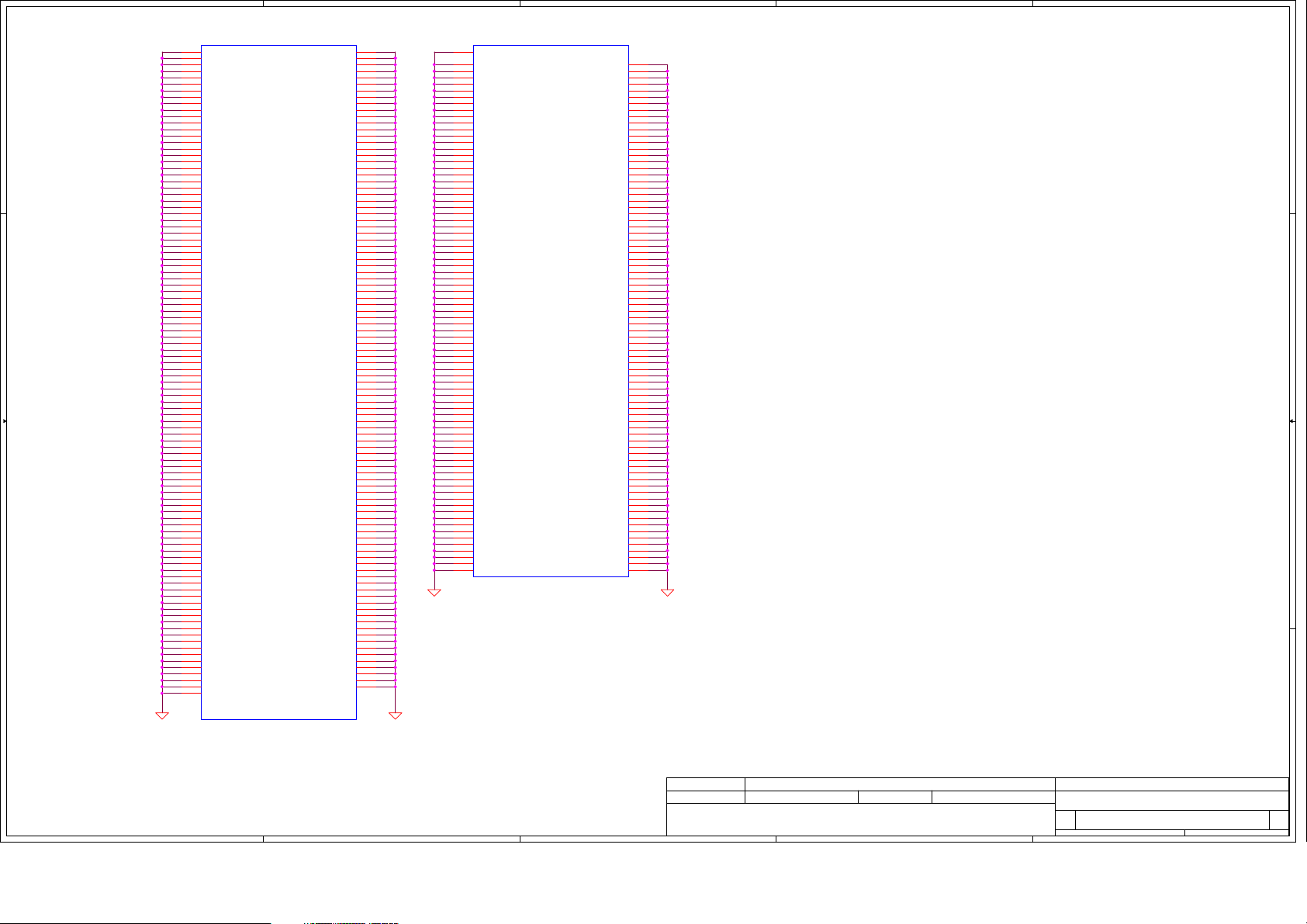

ATI M93

VRAM DDR3

128/512MB

page 29

Fan conn

page 24,25 ,26,27,28

Dis Dis(UMA)

Page 6

LCD Conn.

page 21

MUX

PCIE-Express 16X

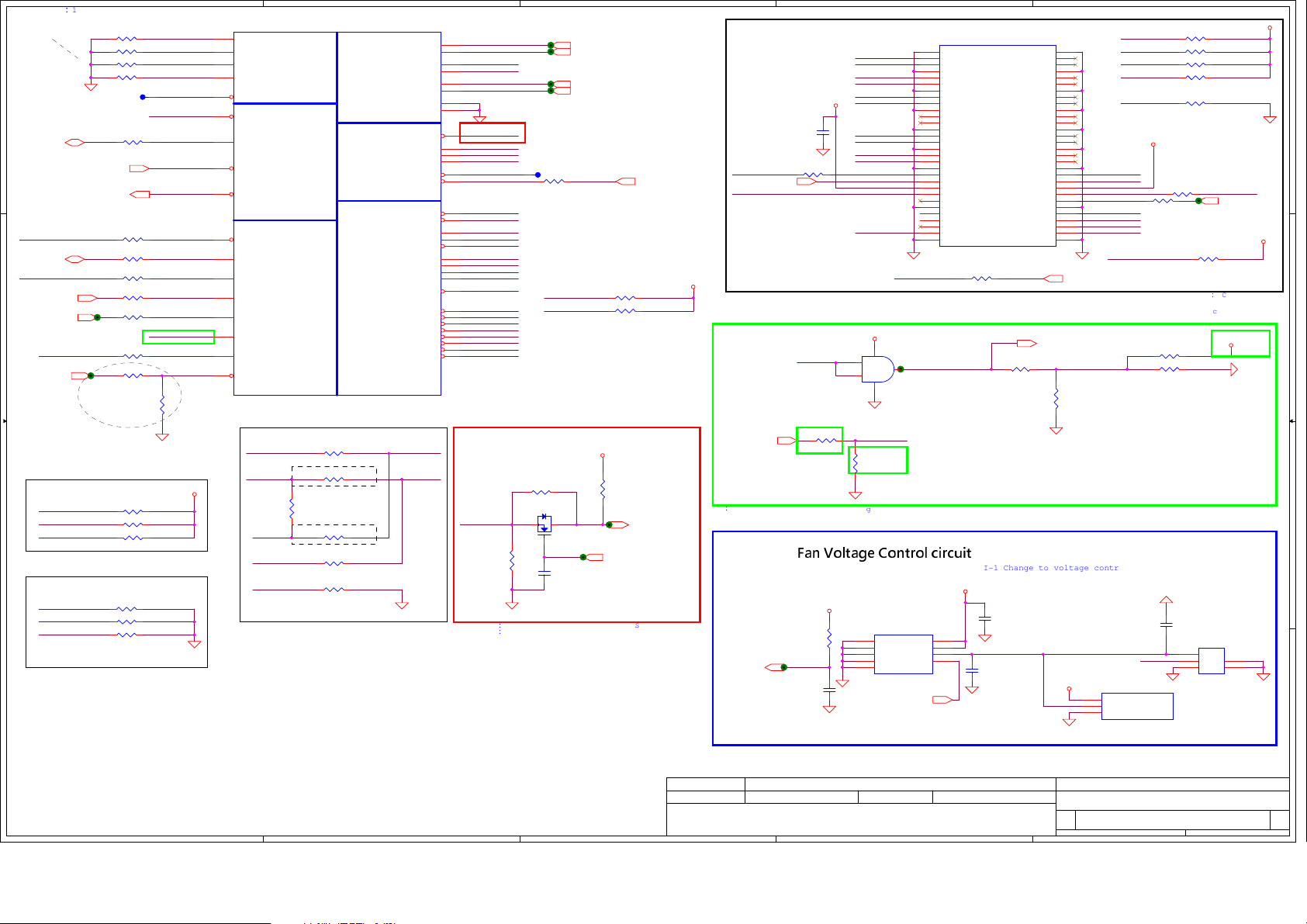

Calpella Consumer 13.3" UMA +Switchable

32QFN

P19

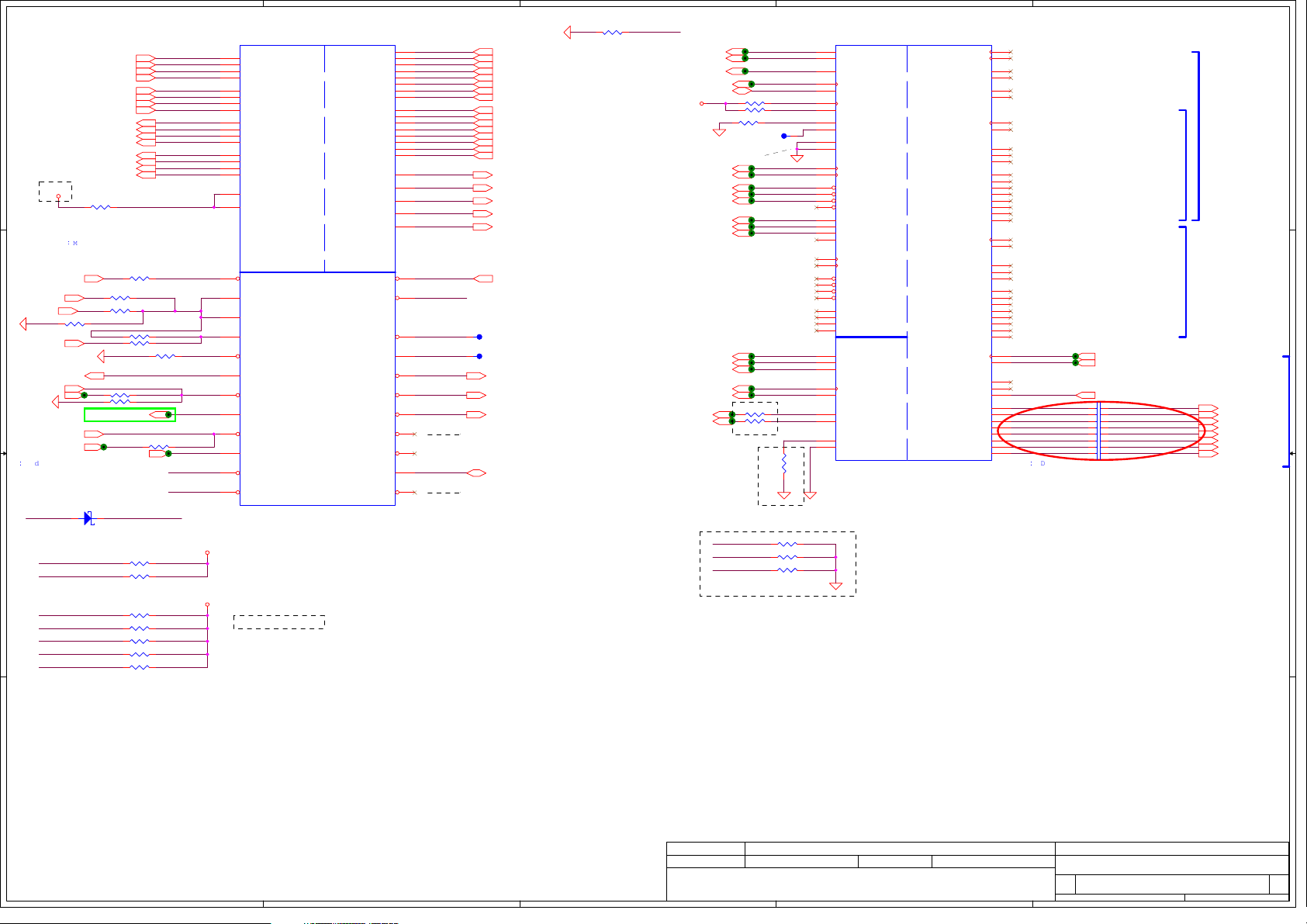

DDR3 SO-DIMM X2

BANK 0, 1, 2, 3

UMA

Mobile Arrandale

2C CPU + GMCH

Socket-rPGA989

Page 6,7,8,9,10

CK505

Clock Generator

SLG8SP585VTR

DDR3 1066/1333 MHz 1.5V

Dual Channel

P17, 18

USB Card reader

RTS 5138

CRT

page 20

MUX

2 2

Dis

HDMI Conn.

page 23

Level Shifter

UMA

Dis(UMA)Dis

UMA

page 23

FDI

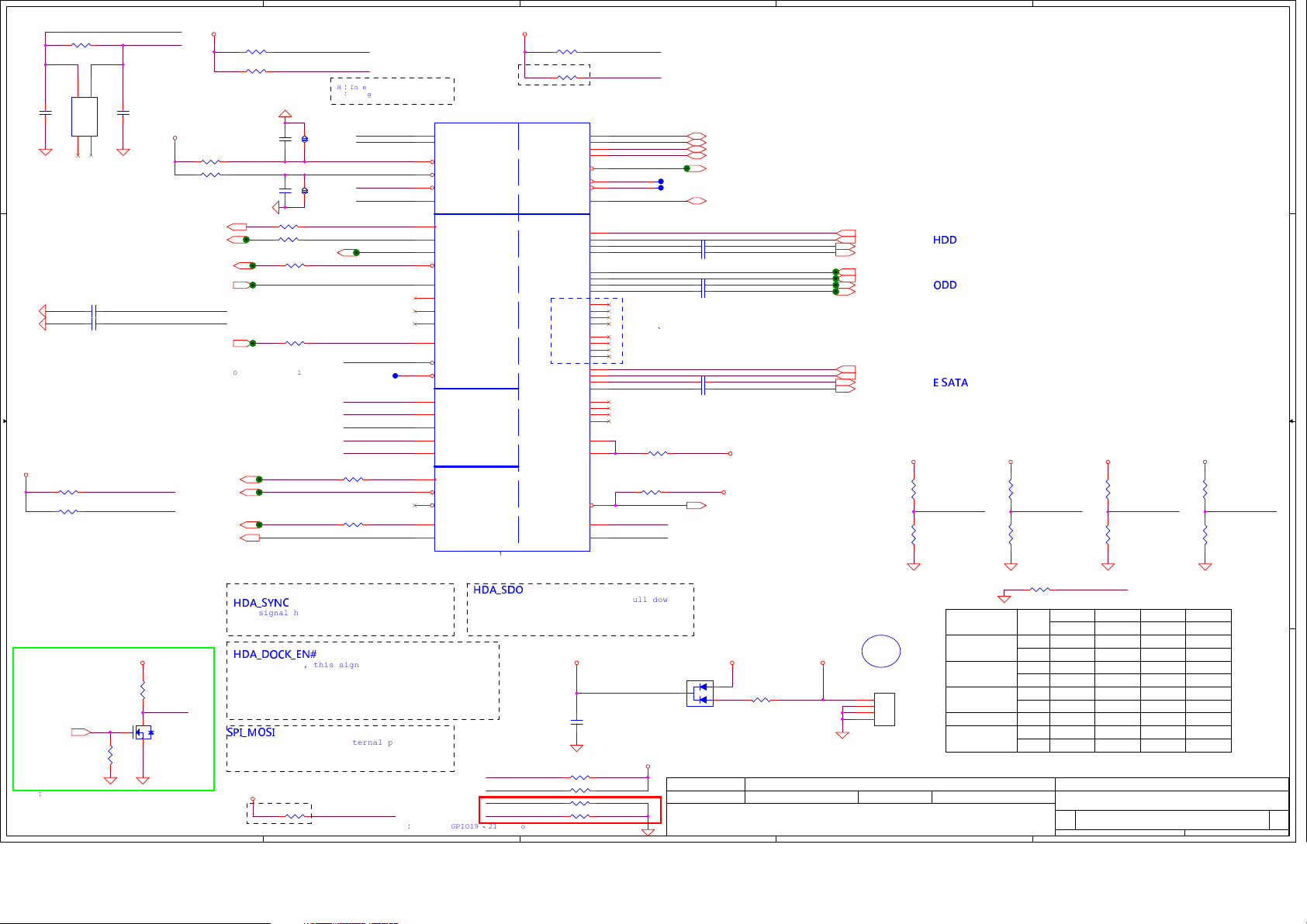

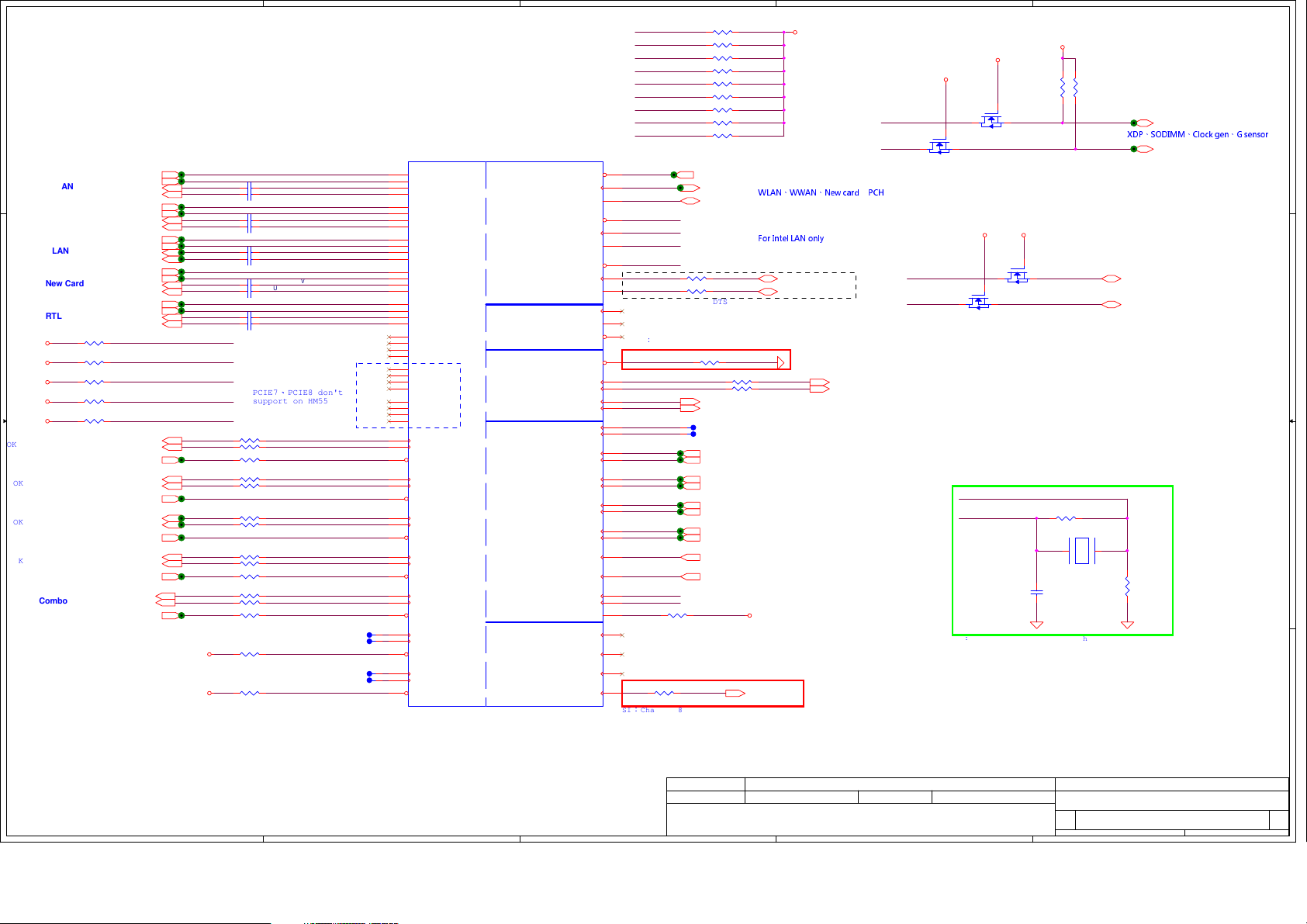

Intel PCH

Ibex Peak-M

PCI-E BUS*4

Realtek 8401

(10/100 LAN +Card

reader)

UMA only

3 3

P33

(Giga LAN)

DIS only

P32

Mini-Card

WLAN

Mini-CardRealtek 8111DL

WWAN

P31P31 P31

New Card

FCBGA 951

Page 11,12,13,14,15,16

RJ45/11 CONN

P31

ENE

DMI X4

LPC BUS

USB2.0 X12

Azalia

SATA Master-1

SATA Slave

SPI

SPI ROM 16M

P34

MX25L1605AM2C-15G

4M Bytes

KB926

Version D2

P38

DIS only

USB conn x3

BT Conn

USB Camera

Finger print

Touch Screen

Audio CKT

Codec_IDT92HD80

SATA HDD Connector

SATA ODD Connector

P33

P36

P36

P21

P36

P21

P34 P35

Audio Jack

P30

P30

RTC CKT.

P11

LED

P39

ACCELEROMETER

ST

4 4

P30

Touch Pad CONN.

P39

SPI ROM

SST25VF080

256K bits

K/B backlight Conn

P36

Security Classification

DC/DC Interface CKT.

A

P40

B

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

Int.KBD

P38

USB Board Conn

P37

USB conn x2

Capsense switch Conn

2006/02/13 2006/03/10

C

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

Calpella DIS LA4743P

E

2 52Friday, September 11, 2009

P36

P36

0.4

A

Symbol Note :

Voltage Rails

power

plane

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

KB926

KB926

PCH

PCH

PCH

NB10M-GE SMBUS Control Table

D_EDID_DATA

D_EDID_CLK

D_CRT_DDC_DATA

D_CRT_DDC_DATA

HDMIDAT_VGA

HDMICLK_VGA

O MEANS ON X MEANS OFF

+B

O

O

O

O

O

XDP BATT

X V

X

V

X

SOURCE LVDS CRT

M93

M93

M93

X X

V

X

V

X

X

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

+5VALW

+3VALW

+1.8V

+5VS

+3VS

+1.5VS

+0.9V

+VCCP

+CPU_CORE

+2.5VS

+1.8VS

45@ : means need be mounted when 45 level assy or rework stage.

BATT @ : means need be mounted when 45 level assy or rework stage.

CONN@ : means ME part

SG@ : means stuff when Switchable graphic

UMA@ : means stuff when UMA skus

X76@ : X76 level

PA@ : Only For PA

O

O

O

O

X

XX

Thermal

Sensor

X

X

X

X

X

X

X

HDMI

X

V

O

O

O

X

X

X

SODIMM CLK CHIP

X

X

X

X

V V V

X

X

O

O

X

X

PR@ : Only For PR

8111@ : Only DIS Giga LAN use

5138@ : Only DIS card reader use

8401@ : Only UMA (LAN + Card reader) use

Park@ : Only for Park use

X

X

WLAN

WWAN

+3VALW +3VALW+3VS+3VS+3VS +3VS+5VL +5VL

M93

NB10M-GE

Thermal

Sensor

X

X

X

X X

X

X

X

X

Cap sensor

board

X

X

X

X

X

X

X

X XXX X X X X X X

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

NEW

CARD

X X

X

V V

X

A

G sensor

PCH I2C / SMBUS ADDRESSING

DEVICE

DDR SO-DIMM 0

DDR SO-DIMM 1

X

X

2007/08/28 2006/03/10

Compal Secret Data

CLOCK GENERATOR (EXT.)

NBW10 SKUs

43172932L01:PA Switchable graphic

3172932L02:PA UMA

4

43172932L03:PR Switchable graphic

43172932L04:PR UMA

PCB part number

CB:DA80000EW00

P

PA:DAZ09A00800

PR:DAZ09A00900

PCH version

A1 QV73 SA00002KV10

B0 QLLT SA00002KV30

B1 QMGS SA00002KV60

B3 QMNT SA00003N730

Deciphered Date

PA@

ZZZ1

PCB-MB

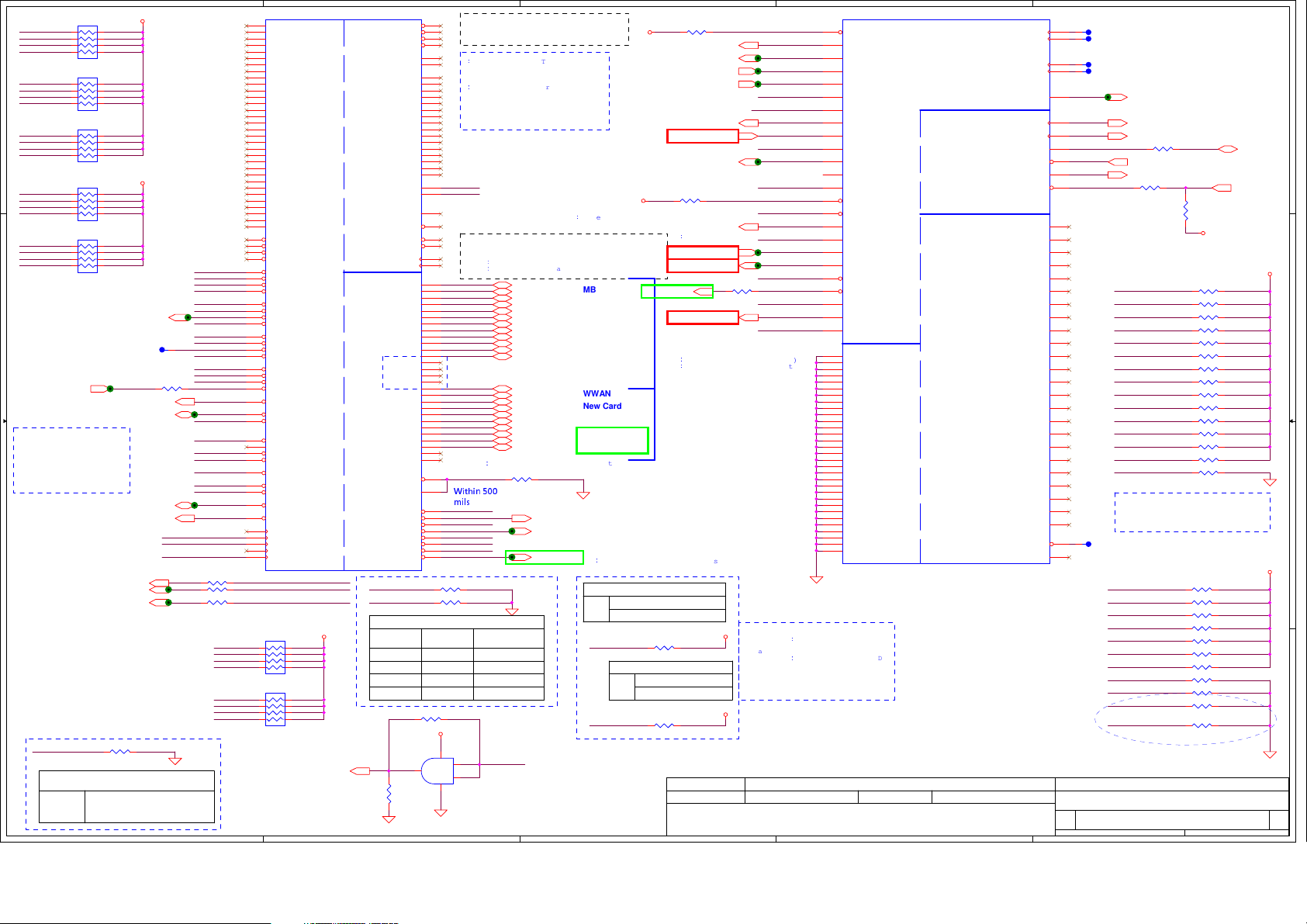

USB assignment:

USB-0 Right side

USB-1 Right side

USB-2 Left side(with ESATA)

USB-3 Touch Screen

USB-4 Camera

USB-5 WLAN

USB-6 X

USB-7 X

USB-8 MiniCard(WWAN/TV)

USB-9 New card

USB-10 USB Card reader

USB-11 Finger Print

USB-12 Bluetooth

USB-13 X

PCIe assignment:

PCIe-1 WWAN

PCIe-2 WLAN

PCIe-3 LAN

PCIe-4 New card

PCIe-5 RTL8401 Combo

PCIe-6 X

PCIe-7 X

PCIe-8 X

SATA assignment:

SATA0 HDD

SATA1 ODD

SATA2 X

SATA3 X

SATA4 ESATA

SATA5 X

HEX

A0

D2

1DG sensor 0 0 0 1 1 1 0 1

PA@/SG@/8111@/8401@

PA@/UMA@/8401@

PR@/SG@/8111@/8401@

PR@/UMA@/8401@

PR@

ZZZ2

PCB-MB

Title

Size Document Number Rev

Custom

Date: Sheet of

ADDRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 1 0 0A4

1 1 0 1 0 0 1 0

Compal Electronics, Inc.

Notes List

Calpella DIS LA4743P

3 52Friday, September 11, 2009

0.4

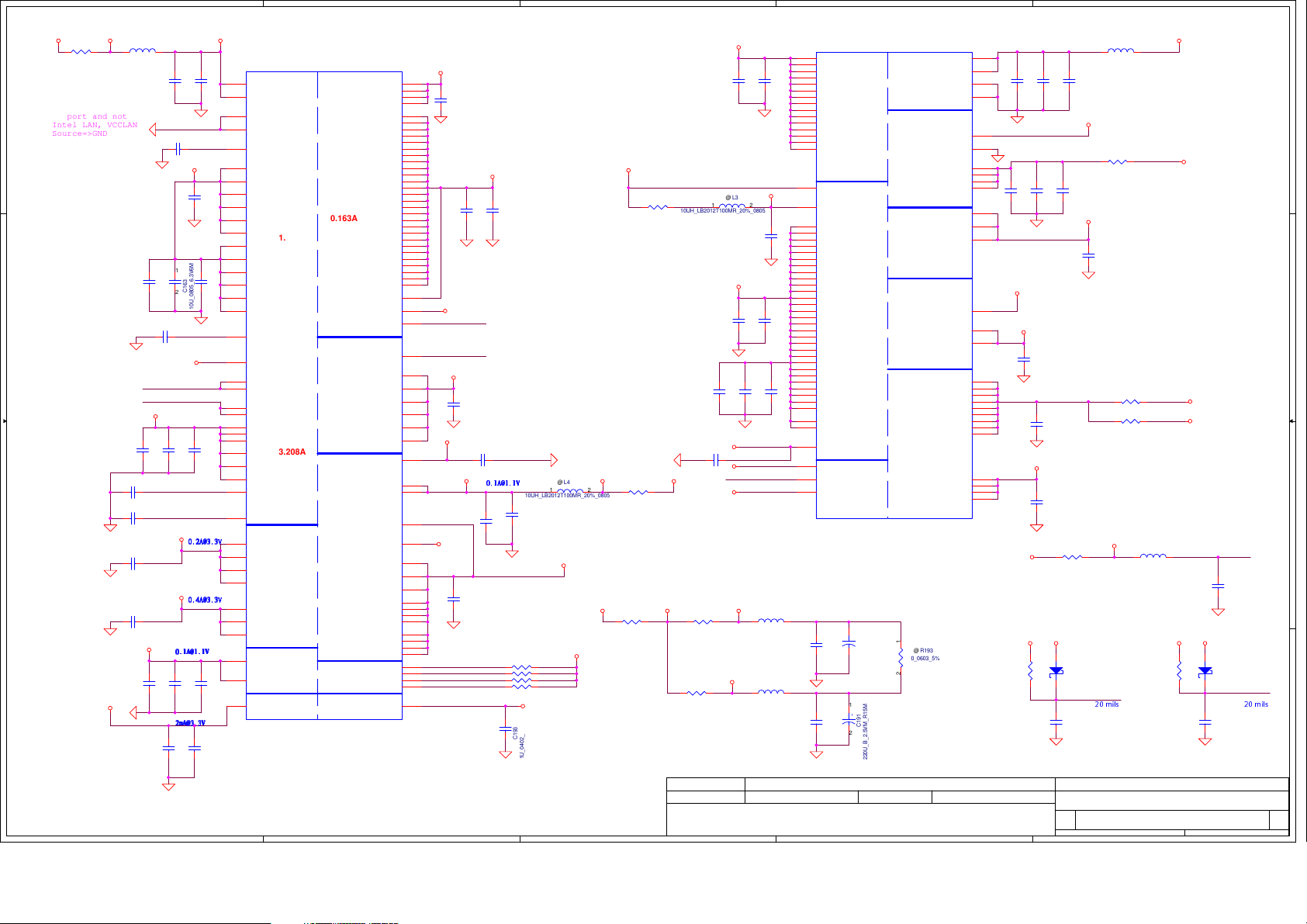

5

4

3

2

60mA

+3VAUX_BT

1

50mA

1A

D D

VIN

AC

C C

B+

7A

+V_BATTERY Dock con

0.3A

INVPWR_B+

2A

B++

LVDS CON

1.7A

+3VALW

+1.5VS

+5VALW

35mA

169mA

300mA

MDC 1.5

ICH9

LAN

3.39A5.89A

+3VS

RT5158

??mA

???A

1.3A0.58A

Mini card

New card

+5VS

35mA

10mA

25mA

20mA

10mA

1A

811mA

1.5A

250mA

1A

1A

+VDDA

IDT 9271B7

+5VAMP

Finger printer

+3VS_DVDD

ALC268

+3VALW_EC

SPI ROM

New card

PCH

+LCDVDD

LVDS CON

+3VS_CK505

Mini card (WLAN)

Mini card (TV tu/WWAN/Robeson)

1.8A

B B

3.7 X 3=11.1V

BATT

DC

B+++

A A

CPU_B+ +VCC_CORE

5

11.05A1.9A

4.7A

+1.5V

1.05V_B+

+1.05VS PCH

10mA2A

4

38A/1.05V

3A

8 A

50mA

+VCCP

2.59A

CPU

CPU

DDR3 800Mhz 4G x2

+0.75V

162mA

??A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

PCH

CPU

2007/08/28 2006/03/10

700mA

50mA

Compal Secret Data

Deciphered Date

ODD

SATA

PC Camera(4.75V)

2

Compal Electronics, Inc.

Title

Size Document Number Rev

C

Calpella DIS LA4743P

Date: Sheet of

Power delevry

1

4 52Friday, September 11, 2009

0.4

A

1 1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

2007/08/28 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

Date: Sheet of

Compal Electronics, Inc.

Notes List

Calpella DIS LA4743P

5 52Friday, September 11, 2009

0.4

Layout rule:10mil

width trace length <

0.5", spacing 20mil

D D

H_PECI<14>

H_PROCHOT#<47>

H_THERMTRIP#<14,26>

H_CPURST#

H_PM_SYNC<13>

H_CPUPWRGD

H_CPUPWRGD<14>

PM_DRAM_PWRGD<13>

C C

BUF_PLT_RST#<14>

Design guide

1.11update,PLTR ST series

resittor 1.5K, PL

resistor 750 oh m

Processor Pullups

H_CATERR#

H_CPURST#_R

B B

H_PROCHOT#

DDR3 Compensation Signals

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

Layout Note:Please these

resistors near Processor

A A

5

R1 20_0402_1%

1 2

R3 20_0402_1%

1 2

R5 49.9_0402_1%

1 2

R7 49.9_0402_1%

1 2

TP_SKTOCC#

T1PAD

H_CATERR#

R1063

H_PECI_ISO

0_0402_5%

H_PROCHOT#

H_THERMTRIP#

H_CPURST#_R

0_0402_5%

H_PM_SYNC_R

0_0402_5%

SYS_AGENT_PWROK

0_0402_5%

VCCPWRGOOD_0

0_0402_5%

VDDPWRGOOD_R

VTTPWRGOOD_R

H_PWRGD_XDP_RH_PWRGD_XDP

0_0402_5%

PLT_RST#_R

12

R28

12

R10

1 2

R19

1 2

R20

1 2

R21

1 2

R23

1 2

1 2

0_0402_5%

R25

1 2

R26

1 2

1.5K_0402_1%

750_0402_1%

R35 49.9_0402_1%

1 2

R36 68_0402_5%@

1 2

R11 68_0402_5%

R40 100_0402_1%

1 2

R41 24.9_0402_1%

1 2

R42 130_0402_1%

1 2

COMP3

COMP2

COMP1

COMP0

+VCCP

JCPU1B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,AUB_CFD_rPGA,R1P0

CONN@

JTAG MAPPING

XDP_TDI_R

XDP_TDI_M

XDP_TDO_R

XDP_TRST#

MISC THERMAL

PWR MANAGEMENT

R30 0_0402_5%

1 2

R32 0_0402_5%@

1 2

R34

0_0402_5%

1 2

R37 0_0402_5%@

1 2

R38 0_0402_5%

1 2

R39 51_0402_1%

1 2

4

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

MISC

JTAG & BPM

PRDY#

PREQ#

TRST#

TDO_M

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

XDP_TDI

XDP_TDOXDP_TDO_M

TCK

TMS

TDO

TDI_M

DBR#

TDI

CLK_CPU_BCLK

A16

CLK_CPU_BCLK#

B16

CLK_CPU_XDP

AR30

CLK_CPU_XDP#

AT30

CLK_EXP

E16

CLK_EXP#

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

eDP

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PM_EXTTS#0

PM_EXTTS#1

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

SM_DRAMRST#

R1065

100K_0402_5%

SI:Reserve Reset I C for DRAM RESE T

PV:Add Intel S3 re duce circuit

T63 PAD

R14 0_0402_5%

1 2

PM_EXTTS#0

PM_EXTTS#1

R1073

@

0_0402_5%

1 2

Q87

2N7002_SOT23-3

S

G

2

12

1

2

CLK_CPU_BCLK <14>

CLK_CPU_BCLK# <14>

CLK_EXP <12>

CLK_EXP# <12>

R27 10K_0402_5%

R29 10K_0402_5%

+1.5V

D

13

C1298

470P_0402_50V7K

3

OK

PM_EXTTS#1_R <17,18>

1 2

1 2

12

R1064

1K_0402_1%

DRAMRST# <17,18>

PCH_DDR_RST <14>

from DDR

+VCCP

XDP_PREQ#

XDP_PRDY#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

+VCCP

XDP_BPM#3

1

R1084

2

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

H_CPUPWRGD_R

PM_PWRBTN#_R

2

1

VTTPWRGOOD_R

12

C1

@

0.1U_0402_16V4Z

R13

H_CPUPWRGD

PM_PWRBTN#_R<13>

H_PWRGD_XDP

VTTPWRGOOD<45>

PV

:

Change solutio n for S3 leakag e issue.

1K_0402_5%

1 2

VTTPWRGOOD

1 2

2K_0402_1%

Fan Voltage Control circuit

+3VS

R678

10K_0402_5%

1 2

FAN_SPEED<38>

FAN_SPEED

C775

1000P_0402_50V7K

1

2

2

XDP_RST#_R

+3VALW

5

U54

P

B

4

Y

A

G

NC7SZ08P5X_NL_SC70-5

3

R1085

1.5K_0402_1%

U32

9

Thermal Pad

8

GND

7

GND

6

GND

5

GND

G996RD1U_TDFN8_3X3

FAN_SET<38>

XDP Connector

JP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

R22 0_0402_5%@

1 2

1.5VSCPU_DRAM_PWRGD

+5VS

1

VEN

2

VIN

3

VO

4

VSET

XDP_TDI

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND15

TRST#

GND17

CONN@

1.5VSCPU_DRAM_PWRGD <46>

R1072

12

1.5K_0402_1%

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

TD0

54

56

TDI

58

TMS

60

PLT_RST# <14,24,31,32,33>

VDDPWRGOOD_R

12

R117

750_0402_1%

XDP_TMS

XDP_PREQ#

XDP_TDO

This shall place near CPU

XDP_TCK

+VCCP

CLK_CPU_XDP

CLK_CPU_XDP#

XDP_RST#_R

XDP_DBRESET#_R

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMSXDP_TCK

XDP_DBRESET#

R31 1.1K_0402_1%@

R33 3K_0402_1%@

SI-1 Change to voltage control circuit

1

C2

2.2U_0603_6.3V4Z

2

1

C774

2.2U_0603_6.3V4Z

2

+5VS_FAN

+5VS

3

2

1

FAN_SPEED

D1

Vcc

Line to be protected

GND

DLPT05-7-F_SOT23-3

1

R2 51_0402_1%@

1 2

R4 51_0402_1%@

1 2

R6 51_0402_1%@

1 2

R8 51_0402_1%

1 2

R9 51_0402_1%@

1 2

R17

1K_0402_5%

1 2

1 2

R18

0_0402_5%

R603 1K_0402_5%

1 2

PV: Change to

+1.5VS_CPU, fol low

checklist

1 2

1 2

1

C3

0.1U_0402_16V4Z

2

CONN@

JFAN1

1

2

3

ACES_85204-03001

H_CPURST#

XDP_DBRESET# <13>

+1.5VS_CPU

1

4

2

G1

5

3

G2

+VCCP

+3VS

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/03/13 2009/05/11

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Rev

Custom

Date: Sheet of

Compal Electronics, Inc.

Auburndale(1/5)-Thermal/XDP

Calpella DIS LA4743P

1

6 52Friday, September 11, 2009

0.4

5

JCPU1A

DMI_CRX_PTX_N0<13>

DMI_CRX_PTX_N1<13>

DMI_CRX_PTX_N2<13>

DMI_CRX_PTX_N3<13>

DMI_CRX_PTX_P0<13>

DMI_CRX_PTX_P1<13>

D D

DMI_CRX_PTX_P2<13>

DMI_CRX_PTX_P3<13>

DMI_CTX_PRX_N0<13>

DMI_CTX_PRX_N1<13>

DMI_CTX_PRX_N2<13>

DMI_CTX_PRX_N3<13>

DMI_CTX_PRX_P0<13>

DMI_CTX_PRX_P1<13>

DMI_CTX_PRX_P2<13>

DMI_CTX_PRX_P3<13>

FDI_CTX_PRX_N0<13>

FDI_CTX_PRX_N1<13>

FDI_CTX_PRX_N2<13>

FDI_CTX_PRX_N3<13>

FDI_CTX_PRX_N4<13>

FDI_CTX_PRX_N5<13>

FDI_CTX_PRX_N6<13>

FDI_CTX_PRX_N7<13>

FDI_CTX_PRX_P0<13>

FDI_CTX_PRX_P1<13>

FDI_CTX_PRX_P2<13>

FDI_CTX_PRX_P3<13>

FDI_CTX_PRX_P4<13>

FDI_CTX_PRX_P5<13>

C C

FDI_CTX_PRX_P6<13>

FDI_CTX_PRX_P7<13>

FDI_FSYNC0<13>

FDI_FSYNC1<13>

FDI_INT<13>

FDI_LSYNC0<13>

FDI_LSYNC1<13>

B B

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

IC,AUB_CFD_rPGA,R1P0

CONN@

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

4

EXP_ICOMPI

B26

A26

B27

EXP_RBIAS

A25

PCIE_CRX_GTX_N0

K35

PCIE_CRX_GTX_N1

J34

PCIE_CRX_GTX_N2

J33

PCIE_CRX_GTX_N3

G35

PCIE_CRX_GTX_N4

G32

PCIE_CRX_GTX_N5

F34

PCIE_CRX_GTX_N6

F31

PCIE_CRX_GTX_N7

D35

PCIE_CRX_GTX_N8

E33

PCIE_CRX_GTX_N9

C33

PCIE_CRX_GTX_N10

D32

PCIE_CRX_GTX_N11

B32

PCIE_CRX_GTX_N12

C31

PCIE_CRX_GTX_N13

B28

PCIE_CRX_GTX_N14

B30

PCIE_CRX_GTX_N15

A31

PCIE_CRX_GTX_P0

J35

PCIE_CRX_GTX_P1

H34

PCIE_CRX_GTX_P2

H33

PCIE_CRX_GTX_P3

F35

PCIE_CRX_GTX_P4

G33

PCIE_CRX_GTX_P5

E34

PCIE_CRX_GTX_P6

F32

PCIE_CRX_GTX_P7

D34

PCIE_CRX_GTX_P8

F33

PCIE_CRX_GTX_P9

B33

PCIE_CRX_GTX_P10

D31

PCIE_CRX_GTX_P11

A32

PCIE_CRX_GTX_P12

C30

PCIE_CRX_GTX_P13

A28

PCIE_CRX_GTX_P14

B29

PCIE_CRX_GTX_P15

A30

PCIE_CTX_GRX_C_N0

L33

PCIE_CTX_GRX_C_N1

M35

PCIE_CTX_GRX_C_N2

M33

PCIE_CTX_GRX_C_N3

M30

PCIE_CTX_GRX_C_N4

L31

PCIE_CTX_GRX_C_N5

K32

PCIE_CTX_GRX_C_N6

M29

PCIE_CTX_GRX_C_N7

J31

PCIE_CTX_GRX_C_N8

K29

PCIE_CTX_GRX_C_N9

H30

PCIE_CTX_GRX_C_N10

H29

PCIE_CTX_GRX_C_N11

F29

PCIE_CTX_GRX_C_N12

E28

PCIE_CTX_GRX_C_N13

D29

PCIE_CTX_GRX_C_N14

D27

PCIE_CTX_GRX_C_N15

C26

PCIE_CTX_GRX_C_P0

L34

PCIE_CTX_GRX_C_P1

M34

PCIE_CTX_GRX_C_P2

M32

PCIE_CTX_GRX_C_P3

L30

PCIE_CTX_GRX_C_P4

M31

PCIE_CTX_GRX_C_P5

K31

PCIE_CTX_GRX_C_P6

M28

PCIE_CTX_GRX_C_P7

H31

PCIE_CTX_GRX_C_P8

K28

PCIE_CTX_GRX_C_P9

G30

PCIE_CTX_GRX_C_P10

G29

PCIE_CTX_GRX_C_P11

F28

PCIE_CTX_GRX_C_P12

E27

PCIE_CTX_GRX_C_P13

D28

PCIE_CTX_GRX_C_P14

C27

PCIE_CTX_GRX_C_P15

C25

R44 49.9_0402 _1%

1 2

R45 750_ 0402_1%

1 2

PCIE_CRX_GTX_N[0..15] <24>

PCIE_CRX_GTX_P[0..15] <24>

C4 0.1U_0402_16V4ZSG@

1 2

C5 0.1U_0402_16V4ZSG@

1 2

C6 0.1U_0402_16V4ZSG@

1 2

C7 0.1U_0402_16V4ZSG@

1 2

C8 0.1U_0402_16V4ZSG@

1 2

C9 0.1U_0402_16V4ZSG@

1 2

C10 0.1U_0402_16V 4ZSG@

1 2

C11 0.1U_0402_16V 4ZSG@

1 2

C12 0.1U_0402_16V 4ZSG@

1 2

C13 0.1U_0402_16V 4ZSG@

1 2

C14 0.1U_0402_16V 4ZSG@

1 2

C15 0.1U_0402_16V 4ZSG@

1 2

C16 0.1U_0402_16V 4ZSG@

1 2

C17 0.1U_0402_16V 4ZSG@

1 2

C18 0.1U_0402_16V 4ZSG@

1 2

C19 0.1U_0402_16V 4ZSG@

1 2

C20 0.1U_0402_16V 4ZSG@

1 2

C21 0.1U_0402_16V 4ZSG@

1 2

C22 0.1U_0402_16V 4ZSG@

1 2

C23 0.1U_0402_16V 4ZSG@

1 2

C24 0.1U_0402_16V 4ZSG@

1 2

C25 0.1U_0402_16V 4ZSG@

1 2

C26 0.1U_0402_16V 4ZSG@

1 2

C27 0.1U_0402_16V 4ZSG@

1 2

C28 0.1U_0402_16V 4ZSG@

1 2

C29 0.1U_0402_16V 4ZSG@

1 2

C30 0.1U_0402_16V 4ZSG@

1 2

C31 0.1U_0402_16V 4ZSG@

1 2

C32 0.1U_0402_16V 4ZSG@

1 2

C33 0.1U_0402_16V 4ZSG@

1 2

C34 0.1U_0402_16V 4ZSG@

1 2

C35 0.1U_0402_16V 4ZSG@

1 2

3

Layout rule:trace

length < 0.5"

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P15

+V_DDR_CPU_REF1

PCIE_CTX_GRX_N[0..15] <24>

PCIE_CTX_GRX_P[0..15] <24>

R50 0_04 02_5%@

R51 0_04 02_5%@

1 2

1 2

2

+V_DDR_CPU_REF0

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

H17

G25

G17

AC9

L28

J17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

JCPU1E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

SA_DIMM_VREF

SB_DIMM_VREF

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

KEY

RSVD62

RSVD63

RSVD64

RSVD65

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

1

R48 0_04 02_5%@

1 2

R49 0_04 02_5%@

1 2

IC,AUB_CFD_rPGA,R1P0

CONN@

CFG Straps for PROCESSOR

CFG0

R52 3.01K_0402_1%@

1 2

PCI-Express Configuration Select

1: Single PEG

CFG0

A A

Not applicable for Clarksfield Processor

CFG3

0: Bifurcation enabled

R54 3.01K_0 402_1%

1 2

CFG3-PCI Expres s Static Lane R eversal

1: Normal Opera tion

CFG3

0: Lane Numbers Reversed

15 -> 0, 14 ->1 , .....

5

*

CFG4

R53 3.01K_0402_1%@

1 2

CFG4-Display Po rt Presence

1: Disabled; No Physical

Display Port

attached to Emb edded Display P ort

0: Enabled; An external

CFG4

Display Port

device is conne cted to the

Embedded Displa y Port

CFG7

R55 3.01K_0 402_1%@

Only temporary for early

CFD samples (rPGA/BGA)

Only for pre ES1 sample

1 2

4

**

CFG7

WW33:PD 3.01K on CFG7 for PCIE Jitter

WW41:don't staff

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2008/03/13 2009/05/11

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet of

Compal Electronics, Inc.

Auburndale(2/5)-DMI/PEG/FDI

Calpella DIS LA4743P

CRB 0.9 change to GND

7 52Friday, September 11, 2009

1

0.4

5

4

3

2

1

AG1

AG4

AG3

AH4

AM6

AN2

AM4

AM3

AN5

AN6

AN4

AN3

AN7

AR10

AT10

AC5

AC6

JCPU1D

W8

SB_CK[0]

W9

SB_CK#[0]

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

AJ4

SB_DQ[38]

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

AP3

SB_DQ[48]

SB_DQ[49]

AT4

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

SB_CAS#

Y7

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY - B

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_DDR2 <18>

M_CLK_DDR#2 <18>

DDR_CKE2_DIMMB <18>

M_CLK_DDR3 <18>

M_CLK_DDR#3 <18>

DDR_CKE3_DIMMB <18>

DDR_CS2_DIMMB# <18>

DDR_CS3_DIMMB# <18>

M_ODT2 <18>

M_ODT3 <18>

DDR_B_DM[0..7] <18>

DDR_B_DQS#[0..7] <18>

DDR_B_DQS[0..7] <18>

DDR_B_MA[0..15] <18>

JCPU1C

D D

DDR_A_D[0..63]<17>

C C

B B

DDR_A_BS0<17>

DDR_A_BS1<17>

DDR_A_BS2<17>

DDR_A_CAS#<1 7>

DDR_A_RAS#<1 7>

DDR_A_WE#<17>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

AJ7

AJ6

AJ9

AL7

AL8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

G7

J10

M6

M8

K8

N8

P9

U7

J8

J7

L7

L9

L6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DDR0 <17>

M_CLK_DDR#0 <17>

DDR_CKE0_DIMMA <17>

M_CLK_DDR1 <17>

M_CLK_DDR#1 <17>

DDR_CKE1_DIMMA <17>

DDR_CS0_DIMMA# <17>

DDR_CS1_DIMMA# <17>

M_ODT0 <17>

M_ODT1 <17>

DDR_A_DM[0..7] <17>

DDR_A_DQS#[0..7] <17>

DDR_A_DQS[0..7] <17>

DDR_A_MA[0..15] <17>

DDR_B_D[0..63]<18>

DDR_B_BS0<18>

DDR_B_BS1<18>

DDR_B_BS2<18>

DDR_B_CAS#<1 8>

DDR_B_RAS#<1 8>

DDR_B_WE#<18>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

IC,AUB_CFD_rPGA,R1P0

CONN@

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2008/03/13 2009/05/11

Compal Secret Data

IC,AUB_CFD_rPGA,R1P0

CONN@

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet of

Compal Electronics, Inc.

Cantiga(2/6)-DDR3 A/B CH

Calpella DIS LA4743P

1

8 52Friday, September 11, 2009

0.4

5

+VCC_CORE

JCPU1F

D D

C C

B B

A A

48A 15A18A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,AUB_CFD_rPGA,R1P0

CONN@

CPU CORE SUPPLY

5

1.1V RAIL POWER

POWER

PROC_DPRSLPVR

CPU VIDS

VTT_SELECT

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

ISENSE

AH14

AH12

AH11

AH10

1

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

C40

2

10U_0805_6.3V6M

1

C48

2

10U_0805_6.3V6M

1

C67

2

+VTT_43

+VTT_44

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

PM_DPRSLPVR_R

H_VTTVID1 = Low, 1.1V(Clarksfield)

H_VTTVID1 = High, 1.05V(Arrandale)

AN35

VCCSENSE_R

AJ34

VSSSENSE_R

AJ35

B15

VSS_SENSE_VTT

A15

Near Processor

VCCSENSE

VSSSENSE

R61 100_ 0402_1%

R62 100_ 0402_1%

4

1

1

C41

2

10U_0805_6.3V6M

1

C49

2

@

10U_0805_6.3V6M

1

2

22U_0805_6.3V6M

+VTT_44

+VTT_43

to power

R58 0_0402_5%

to power

R59 0_0402_5%

1 2

R60 0_0402_5%

1 2

R203 0_0402_ 5%

1 2

1 2

1

C42

2

2

10U_0805_6.3V6M

1

1

C50

2

2

@

10U_0805_6.3V6M

+VCCP

C68

22U_0805_6.3V6M

R56 0_06 03_5%

1 2

R57 0_06 03_5%

1 2

H_PSI# <47>

H_VID[0..6] <47>

to power

1 2

VTT_SELECT <45>

IMVP_IMON <47>

1 2

+VCC_CORE

4

C43

C51

3

+GFX_CORE

22U_0805_6.3V6M

22U_0805_6.3V6M

C988

+VCCP

10U_0805_6.3V6M

1

C52

2

10U_0805_6.3V6M

1

2

+VCCP

10U_0805_6.3V6M

1

1

C63

C62

C61

22U_0805_6.3V6M

2

+VCCP

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C987

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C993

C991

1

1

@

@

2

330U_D2_2VY_R7M

C995

1

1

+

+

2

2

+VCCP

1

2

@

2

330U_D2_2VY_R7M

C996

+VCCP

1

C73

C74

2

22U_0805_6.3V6M

22U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

C990

C989

1

1

2

2

22U_0805_6.3V6M

C994

1

2

1

1

C69

2

2

22U_0805_6.3V6M

1

1

C75

2

2

22U_0805_6.3V6M

CPU

H_DPRSLPVR <47>

to power

J7

1 2

VCCSENSE

VSSSENSE

VCCSENSE <47>

VSSSENSE <47>

VTT_SENSE <45>

+1.5V +1.5VS_CPU

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

PAD-OPEN 4x4m

C1299 0.1U_0402_10 V6K

1 2

C1301 0.1U_0402_10 V6K

1 2

C1304 0.1U_0402_10 V6K

1 2

C1305 0.1U_0402_10 V6K

1 2

2008/03/13 2009/05/11

JCPU1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

C70

22U_0805_6.3V6M

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

H27

G28

G27

G26

22U_0805_6.3V6M

F26

E26

E25

+1.5VS_CPU+1.5V

VTT1_51

VTT1_52

VTT1_53

VTT1_54

VTT1_55

VTT1_56

VTT1_57

VTT1_58

IC,AUB_CFD_rPGA,R1P0

CONN@

C76

Compal Secret Data

B+

12

SUSP<40,46>

Deciphered Date

2

VCC_AXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

U53

2N7002DW-7-F_SOT363-6

AR22

VSS_AXG_SENSE

AT22

GFXVR_VID_0

AM22

GFXVR_VID_1

AP22

GFXVR_VID_2

AN22

GFXVR_VID_3

AP23

GFXVR_VID_4

AM23

GFXVR_VID_5

AP24

GFXVR_VID_6

AN24

R43 4.7K_04 02_5%

GFXVR_EN

AR25

GFXVR_DPRSLPVR

AT25

GFXVR_IMON

AM24

R128 1K_04 02_5%@

AJ1

AF1

AE7

1

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

4

12

1

2

C56

2

1

+

C64

2

1

C71

2

1

C77

2

1

1

C79

2

2

1U_0603_10V4Z

1

2

35

1

2

R1069

1K_0402_5%

C1306

0.1U_0402_25V4K

Title

Size Document Number Rev

Custom

Calpella DIS LA4743P

Date: Sheet of

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

GRAPHICS

GFX_VR_EN

GFX_DPRSLPVR

GRAPHICS VIDs

3A

FDI PEG & DMI

POWER

DDR3 - 1.5V RAILS

1.1V1.8V

0.6A

+1.5V to +1.5VS_CPU Transfer

+1.5V +1.5VS_CPU

R1068

330K_0402_5%

RUNON_1.5VS_CPU

SUSP

2

SI7326DN-T1-E3_PAK1212-8

1

C1300

2

10U_0805_10V4Z

61

Q88A

2

1

VCC_AXG_SENSE <44>

VSS_AXG_SENSE <44>

GFXVR_VID_0 <44>

GFXVR_VID_1 <44>

GFXVR_VID_2 <44>

GFXVR_VID_3 <44>

GFXVR_VID_4 <44>

GFXVR_VID_5 <44>

1 2

1U_0603_10V4Z

330U_D2_2VY_R7M

10U_0805_6.3V6M

22U_0805_6.3V6M

GFXVR_VID_6 <44>

GFXVR_EN <44>

GFXVR_DPRSLPVR < 44>

1

C57

2

1

C65

2

1

C72

2

1

C78

2

1

C80

2

1U_0603_10V4Z

C1302

0.1U_0402_16V4Z

GFXVR_IMON <44>

12

1

1

C58

2

2

1U_0603_10V4Z

1U_0603_10V4Z

1

C66

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+VCCP

10U_0805_6.3V6M

+VCCP

22U_0805_6.3V6M

1

C81

C82

2

22U_0805_6.3V6M

2.2U_0603_6.3V4Z

1

C1303

2

10U_0805_10V4Z

PV:change discharge

resistor to 220 follow

checkist

1

C60

C59

2

1U_0603_10V4Z

1U_0603_10V4Z

C83

SUSP

4.7U_0603_6.3V6K

R1067

220_0402_5%

+1.8VS

Q88B

5

1

2

Compal Electronics, Inc.

Auburndale(4/5)-PWR

1

+1.5VS_CPU

+1.5VS_CPU

12

3

4

2N7002DW-7-F_SOT363-6

0.4

9 52Friday, September 11, 2009

5

4

3

2

1

JCPU1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

D D

C C

B B

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

JCPU1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

VSS

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

+VCC_CORE

1

C982

@

2

VSS_NCTF1_R

VSS_NCTF2_R

VSS_NCTF3_R

VSS_NCTF4_R

VSS_NCTF5_R

VSS_NCTF6_R

VSS_NCTF7_R

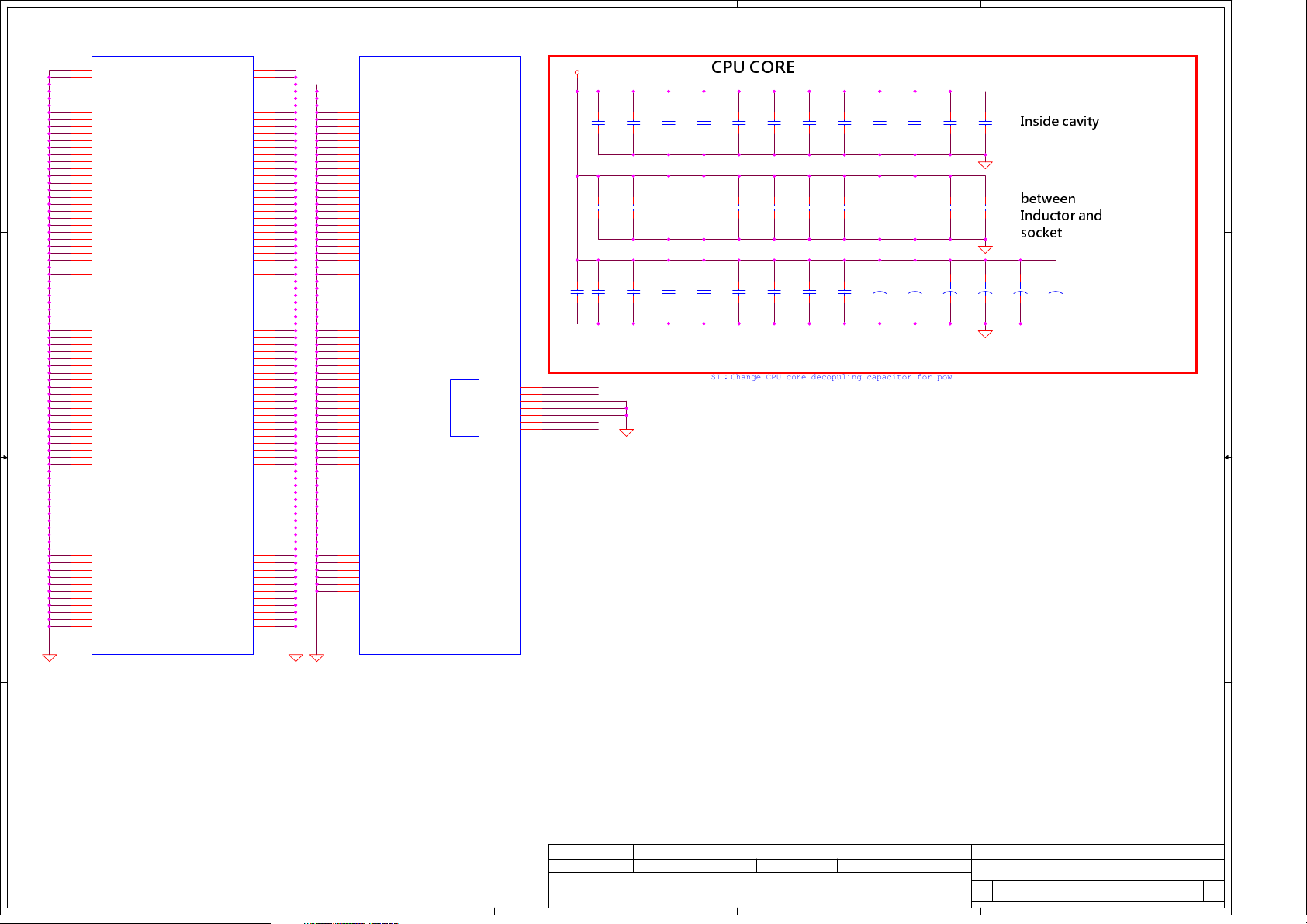

CPU CORE

1

1

2

1

2

1

2

47P_0402_50V8J

C86

C84

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C115

C114

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C95

C103

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

2

1

2

1

2

C96

C91

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C117

C116

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C105

C106

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

2

1

2

1

2

C98

C97

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C87

C85

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C118

C119

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

2

1

2

1

2

C100

C99

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C88

C89

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C120

C121

2

10U_0805_6.3V6M

10U_0805_6.3V6M

SI:Change CPU core decopuling capacitor for power Transient

1

1

2

1

2

1

+

2

C102

C101

2

22U_0805_6.3V6M

1

C90

C92

2

10U_0805_6.3V6M

1

+

C108

C109

2

470U_D2_2VM_R4.5M

470uF 4.5mohm

1

1

C107

2

22U_0805_6.3V6M

1

C94

2

10U_0805_6.3V6M

1

+

C111

2

470U_D2_2VM_R4.5M

Inside cavity

between

Inductor and

socket

1

1

+

+

C1287

2

C1288

2

@

@

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

C104

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C93

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

+

C110

2

470U_D2_2VM_R4.5M

470U_D2_2VM_R4.5M

IC,AUB_CFD_rPGA,R1P0

CONN@

A A

5

IC,AUB_CFD_rPGA,R1P0

CONN@

4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2008/03/13 2009/05/11

Compal Secret Data

Deciphered Date

Custom

2

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

Auburndale(5/5)-GND/Bypass

Calpella DIS LA4743P

10 52Friday, September 11, 2009

1

0.4

5

ICH_RTCX1

R63 10M_0402_5%

1 2

1

1

D D

2

C C

+3VS

R656 10K_0402_5%

R657 10K_0402_5%

B B

C122

18P_0402_50V8J

C53 22P_0402_50V8J@

C54 22P_0402_50V8J@

1 2

1 2

2

OSC4OSC

NC3NC

1 2

1 2

ICH_RTCX2

1

C123

2

Y1

18P_0402_50V8J

32.768KHZ_12.5PF_Q13MC14610002

SPI_SB_CS#

SPI_SO_R

+RTCVCC

R65 1M_0402_5%

R66 330K_0402_5%

+RTCVCC

R69 20K_0402_1%

1 2

R70 20K_0402_1%

1 2

HDA_BITCLK_CODEC<34>

HDA_SYNC_CODEC<34>

HDA_RST#_CODEC<34,38>

HDA_SDIN0<34>

HDA_BITCLK_CODEC

HDA_SDOUT_CODEC

HDA_SDOUT_CODEC<34>

GPIO33 can not pull down

(manufacturing environments)

SPI_CLK_PCH<37>

SPI_SB_CS#<37>

SPI_SI<37>

SPI_SO_R<37>

1 2

1 2

1

C124

1U_0603_10V4Z

1U_0603_10V4Z

2

1

C125

2

R73 33_0402_5%

1 2

R75 33_0402_5%

1 2

1 2

R78 33_0402_5%

R82 33_0402_5%

1 2

SPI_CLK_PCH

SPI_SB_CS#

SPI_SI

SPI_SO_R

SM_INTRUDER#

PCH_INTVRMEN

INTVRMEN

H:Integrated VRM enable

L:Integrated VRM disable

12

CLRP1

SHORT PADS

12

CLRP2

SHORT PADS

SB_SPKR<34>

R654 15_0402_5%

1 2

R655 15_0402_5%

1 2

ICH_RTCX1

ICH_RTCX2

ICH_RTCRST#

ICH_SRTCRST#

SM_INTRUDER#

PCH_INTVRMEN

HDA_BIT_CLK

HDA_SYNC

SB_SPKR

HDA_RST#

HDA_SDIN0

HDA_SDOUT

ME_EN#

T16PAD

PCH_JTAG_TCK

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_RST#

4

*

U1A

B13

RTCX1

D13

RTCX2

C14

RTCRST#

D17

SRTCRST#

A16

INTRUDER#

A14

INTVRMEN

A30

HDA_BCLK

D29

HDA_SYNC

P1

SPKR

C30

HDA_RST#

G30

HDA_SDIN0

F30

HDA_SDIN1

E32

HDA_SDIN2

F32

HDA_SDIN3

B29

HDA_SDO

H32

HDA_DOCK_EN# / GPIO33

J30

HDA_DOCK_RST# / GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

BA2

SPI_CLK

AV3

SPI_CS0#

AY3

SPI_CS1#

AY1

SPI_MOSI

AV1

SPI_MISO

IBEXPEAK-M_FCBGA1071

+3VS

R64 10K_0402_5%

1 2

R67 1K_0402_5%@

1 2

LOW=Default

HIGH=No Reboot

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

FWH4 / LFRAME#

LDRQ1# / GPIO23

LPC

RTCIHDA

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

SATA0GP / GPIO21

SATA1GP / GPIO19

SPI JTAG

LDRQ0#

SERIRQ

SIRQ

SB_SPKR

*

D33

B33

C32

A32

C34

LDRQ0#

A34

LDRQ1#

F34

SIRQ

AB9

AK7

AK6

SATA_TXN0_C

AK11

SATA_TXP0_C

AK9

AH6

AH5

SATA_TXN4_C

AH9

SATA_TXP4_C

AH8

AF11

AF9

AF7

AF6

SATA2、SATA3 don't

AH3

support on HM55

AH1

AF3

AF1

AD9

AD8

SATA_TXN2_C

AD6

SATA_TXP2_C

AD5

AD3

AD1

AB3

AB1

AF16

R89 37.4_0402_1%

AF15

1 2

R91 10K_0402_1%

1 2

T3

GPIO21

Y9

GPIO19

V1

3

LPC_AD0 <31,38>

LPC_AD1 <31,38>

LPC_AD2 <31,38>

LPC_AD3 <31,38>

LPC_FRAME# <31,38>

T13 PAD

T14 PAD

SIRQ <38>

C126 0.01U_0402_50V7K

1 2

C127 0.01U_0402_50V7K

1 2

C130 0.01U_0402_50V7K

1 2

C131 0.01U_0402_50V7K

1 2

C128 0.01U_0402_50V7K

1 2

C129 0.01U_0402_50V7K

1 2

SATA_LED# <39>

+3VS

+1.05VS

SATA_RXN0_C

SATA_RXP0_C

SATA_TXN0

SATA_TXP0

SATA_RXN4_C

SATA_RXP4_C

SATA_TXN4

SATA_TXP4

SATA_RXN2_C

SATA_RXP2_C

SATA_TXN2

SATA_TXP2

SATA_RXN0_C <30>

SATA_RXP0_C <30>

SATA_TXN0 <30>

SATA_TXP0 <30>

SATA_RXN4_C <30>

SATA_RXP4_C <30>

SATA_TXN4 <30>

SATA_TXP4 <30>

SATA_RXN2_C <36>

SATA_RXP2_C <36>

SATA_TXN2 <36>

SATA_TXP2 <36>

2

12

R86

@

200_0402_5%

12

R684

@

100_0402_1%

HDD

ODD

E SATA

1

+3VALW+3VALW +3VALW +3VALW

12

R84

@

200_0402_5%

PCH_JTAG_TMS PCH_JTAG_RST#PCH_JTAG_TDO PCH_JTAG_TDI

12

R683

@

100_0402_1%

R85

20K_0402_5%

1 2

R685

10K_0402_1%

1 2

@

1 2

12

@

R87

20K_0402_5%

R88

10K_0402_5%

HDA_SDO

HDA_SYNC

This signal has a weak internal pull down.

H=>On Die PLL is supplied by 1.5V

L=>On Die PLL is supplied by 1.8V

*

+3VS

12

R670

100K_0402_5%

ME_EN<38>

A A

R1086

100K_0402_5%

ME_EN#

13

D

Q89

2

G

12

2N7002_SOT23

S

PV:Add ME_EN

5

HDA_DOCK_EN#

ME debug mode , this signal has a weak internal PU

H=>security measures defined in the Flash

*

Descriptor will be in effect (default)

L=>Flash Descriptor Security will be overridden

SPI_MOSI

This signal has a weak internal pull down.

Disable iTPM=No Stuff

*

Enable iTPM=Stuff

iTPM ENABLE/DISABLE

+3VS

R68 1K_0402_5%@

1 2

SPI_SI

SI:Reserve GPIO19、21 PD for LPM e nable power sav ing

4

This signal has a weak internal pull down.

This signal can't PU

Disable iTPM=No Stuff

*

Enable iTPM=Stuff

W=20milsW=20mils

1

C132

2.2U_0603_6.3V4Z

2

Place near IBEX-M

GPIO21

GPIO19

GPIO21

GPIO19

R92 10K_0402_5%

R93 10K_0402_5%

R230 10K_0402_5%@

R232 10K_0402_5%@

12

12

1 2

1 2

+3VS

3

BATT1

@

BATT1.1+3VL+RTCVCC

D3

2

1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DAN202U_SC70

R94 1K_0402_5%

1 2

3

W=20mils

2008/03/13 2009/05/11

CR2032 RTC BATTERY

JBATT1

1

1

2

2

3

GND

4

GND

ACES_85205-02001

CONN@

Compal Secret Data

Deciphered Date

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TCK

PCH_JTAG_RST#

2

1 2

R90 51_0402_5%

RefDesPCH Pin

R86

R684

R84

R683

R685

R90

R87

R88

PCH_JTAG_TCK

PCH JTAG Enable PCH JTAG Disable

ES1 ES1ES2 ES2

200ohm

No Install

No Install

200ohm

100ohm

200ohm

No Install

100ohm 100ohm

200ohm

200ohm

100ohm 100ohm

51ohm 51ohm 51ohm

20Kohm 20Kohm

10Kohm 10Kohm

Title

Size Document Number Rev

Custom

Date: Sheet of

Compal Electronics, Inc.

IBEX-M(1/6)-HDA/JTAG/SATA

Calpella DIS LA4743P

No Install

No Install

No Install

20Kohm

10Kohm

No Install

1

No Install

No Install

No Install

No Install

No InstallR85

No Install

51ohm

No Install

No InstallNo Install

11 52Friday, September 11, 2009

0.4

5

D D

PCIE_RXN1<31>

1 2

1 2

1 2

1 2

1 2

CLK_PCIE_WWAN#<31>

CLK_PCIE_WWAN<31>

CLKREQ_WWAN#<31>

CLK_PCIE_WLAN#<31>

CLK_PCIE_WLAN<31>

CLKREQ_WLAN#<31>

CLK_PCIE_LAN#<32>

CLK_PCIE_LAN<32>

CLKREQ_LAN#<32>

CLK_PCIE_EXP#<31>

CLK_PCIE_EXP<31>

CLKREQ_EXP#<31>

CLK_PCIE_COMBO#<33>

CLK_PCIE_COMBO<33>

CLKREQ_COMBO#<33>

PCIE_RXP1<31>

PCIE_TXN1<31>

PCIE_TXP1<31>

PCIE_RXN2<31>

PCIE_RXP2<31>

PCIE_TXN2<31>

PCIE_TXP2<31>

PCIE_RXN3<32>

PCIE_RXP3<32>

PCIE_TXN3<32>

PCIE_TXP3<32>

PCIE_RXN4<31>

PCIE_RXP4<31>

PCIE_TXN4<31>

PCIE_TXP4<31>

PCIE_RXN5<33>

PCIE_RXP5<33>

PCIE_TXN5<33>

PCIE_TXP5<33>

CLKREQ_WWAN#_R

CLKREQ_WLAN#

CLKREQ_LAN#

CLKREQ_EXP#_R

PCIECLKREQ4#

WWAN

WLAN

LAN

New Card

RTL 8401

C C

R405 10K_0402_5%

+3VALW

R411 10K_0402_5%

+3VS

R677 10K_0402_5%

+3VS

R415 10K_0402_5%

+3VALW

R503 10K_0402_5%

+3VALW

OK

WWAN

OK

WLAN

OK

LAN

B B

OK

New Card

Combo

A A

C133 0.1U_0402_16V4Z@

C134 0.1U_0402_16V4Z@

C135 0.1U_0402_16V4Z

C136 0.1U_0402_16V4Z

C137 0.1U_0402_16V4Z8111@

C138 0.1U_0402_16V4Z8111@

C139 0.1U_0402_16V4Z

C140 0.1U_0402_16V4Z

C1277 0.1U_0402_16V4Z8401@

C1278 0.1U_0402_16V4Z8401@

R107 0_0402_5%@

R108 0_0402_5%@

R80 100_0402_5%@

R109 0_0402_5%

R110 0_0402_5%

R111 0_0402_5%

R112 0_0402_5%

R114 0_0402_5%

R115 0_0402_5%

R83 100_0402_5%

R501 0_0402_5%

R502 0_0402_5%

R756 100_0402_5%

R757 10K_0402_5%

+3VALW

R606 10K_0402_5%