Page 1

A

B

C

D

E

1 1

Compal Confidential

2 2

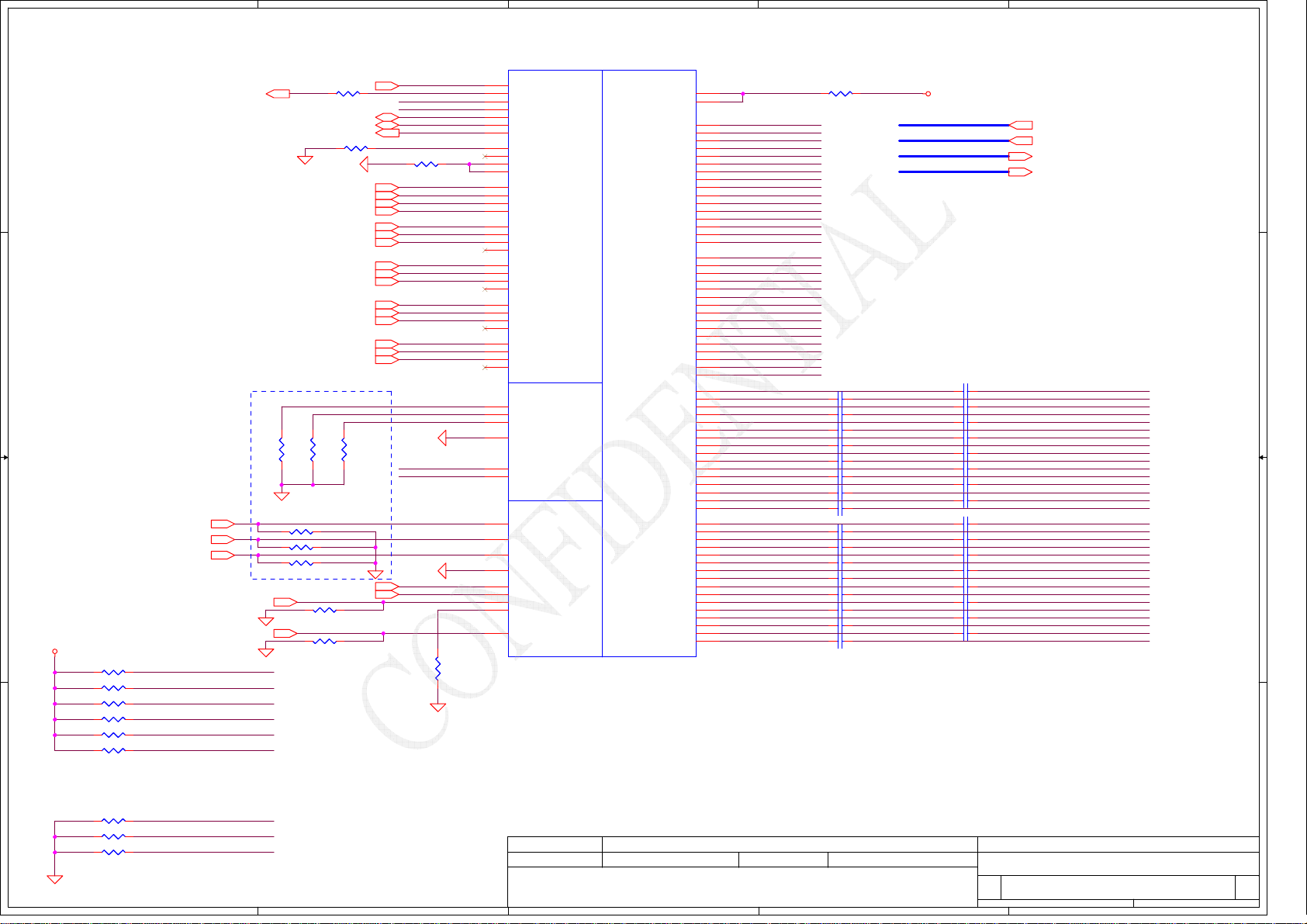

JAL90 M/B Schematics Document

Intel Penryn Processor with Cantiga + DDRII + ICH9M

3 3

2008-07-04

REV:1.0

4 4

A

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/09/20 2008/09/20

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

401551

401551

401551

150Monday, July 21, 2008

150Monday, July 21, 2008

150Monday, July 21, 2008

E

of

of

of

I

I

I

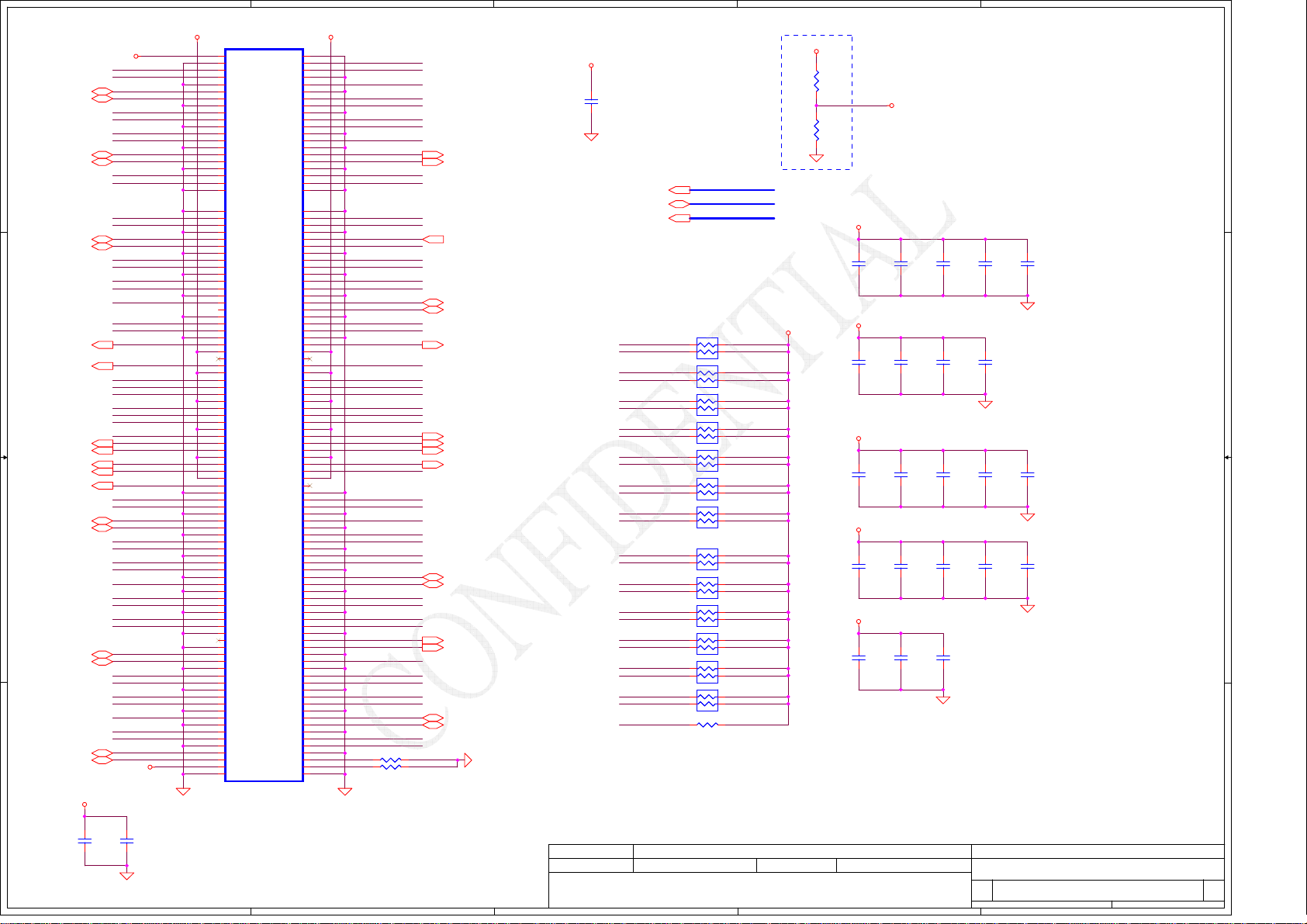

Page 2

A

B

C

D

E

Compal Confidential

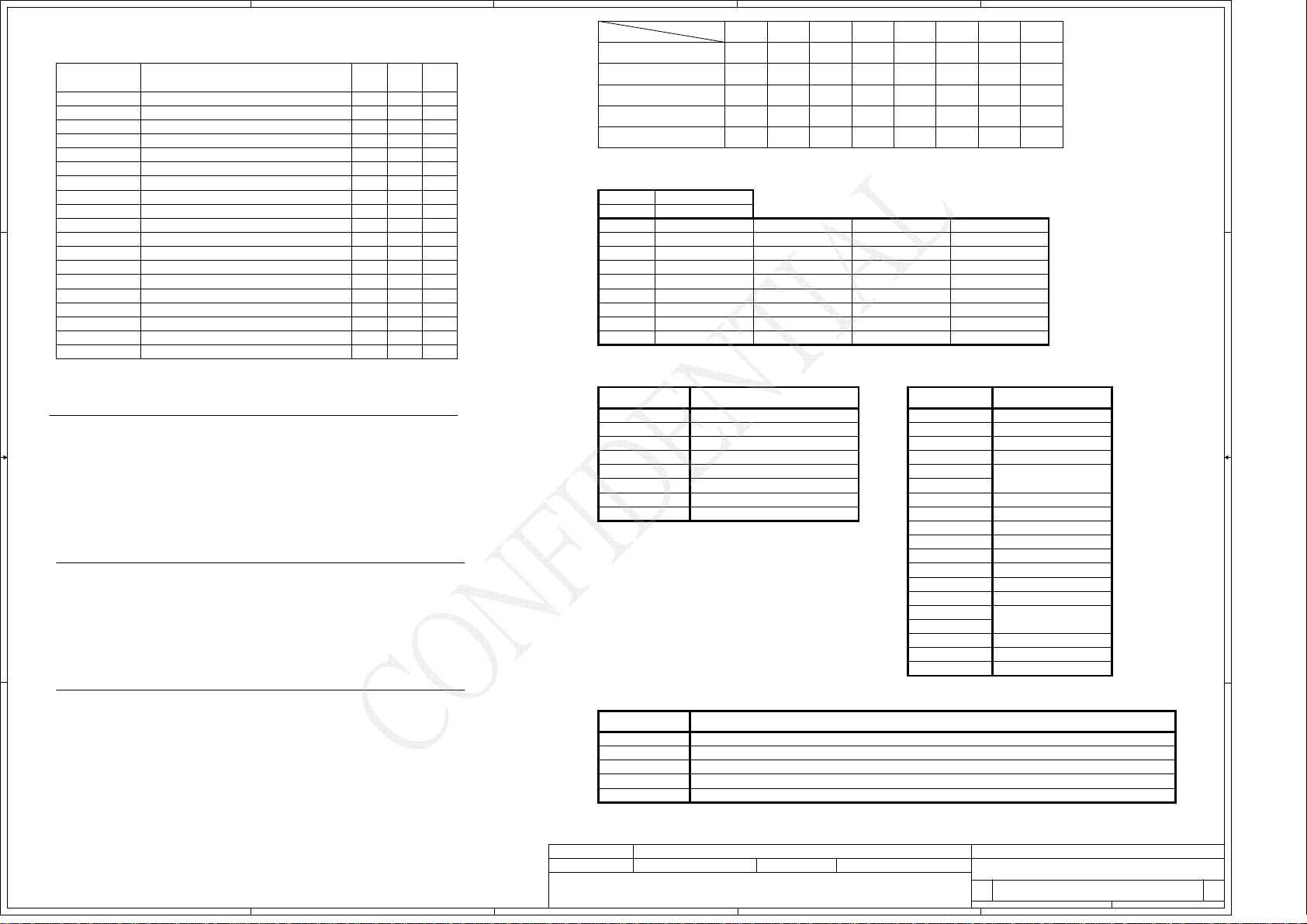

Model Name : JAL90

File Name : LA-4201P

1 1

HDMI Conn.

page 20

Fan Control

LCD Conn.

page 18

page 36

CRT Conn.

page 19

LVDS

LVDSTMDS

PCI-Express

Card Reader

JMB385

page 26

2 2

New Card

Socket

MINI Card x2

WLAN, Robson2

page 29page 30

LAN(GbE)

Realtek RTL8111C

MXM II VGA/B

page 27

page 17

port 0

16X

PCI-Express

SATA HDD

Conn.

DOCKING

RJ45

page 28

Intel Penryn Processor

uPGA-478 Package

(Socket P)

H_A#(3..35) H_D#(0..63)

667/800/1066MHz

page 4,5,6

FSB

Intel Cantiga

uFCBGA-1329

page 7,8,9,10,11,12,13

DMI

C-Link

Intel ICH9-M

S-ATA

port 1

CDROM

Conn.

page 25page 25

BGA-676

page 21,22,23,24

Thermal Sensor

EMC1402-1-ACZL

page 4

Memory BUS(DDRII)

Dual Channel

1.8V DDRII 533/667

USB conn x2

USB port 0, 2

3.3V 48MHz

3.3V 24.576MHz/48Mhz

USB

GMCH HDA

page 08

(DVI/LAN/

CRT/USB/AUDIO)

3 3

page 38

RTC CKT.

page 22

Power On/Off CKT.

page 33

DC/DC Interface CKT.

page 37

LS-4208P

Media/B Conn.

page 32

LS-4202P

BTN/B Conn.

page 32

LS-4204P

PWR/B Conn.

page 32

LS-4205P

USB/B Conn.

USB port 4

page 29

Touch Pad

page 32

EC I/O Buffer

page 32

LPC BUS

ENE KB926

page 31

Int.KBD

page 32

BIOS

page 32

CIR

Power Circuit DC/DC

4 4

page 39,40,41,42

43,44,45,46

LS-4206P

UMA HDMI/B

page 33

Clock Generator

ICS9LPRS387

page 16

200pin DDRII-SO-DIMM X2

BANK 0, 1, 2, 3

Bluetooth

Conn

page 30

MDC 1.5

Conn

page 33

HD Audio

page 14,15

CMOS

Camera

HDA Codec

ALC888S-VC

page 34

Audio AMP

page 35

Phone Jack x3

page 35

LS-4201P

Finger Print

AES1610

page 30page 30 page 18

MXM HDA

page 17

A

LS-4205P

COVER LIGHT

Conn

page 36

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/09/20 2008/09/20

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

401551

401551

401551

250Monday, July 21, 2008

250Monday, July 21, 2008

250Monday, July 21, 2008

E

I

I

I

of

of

of

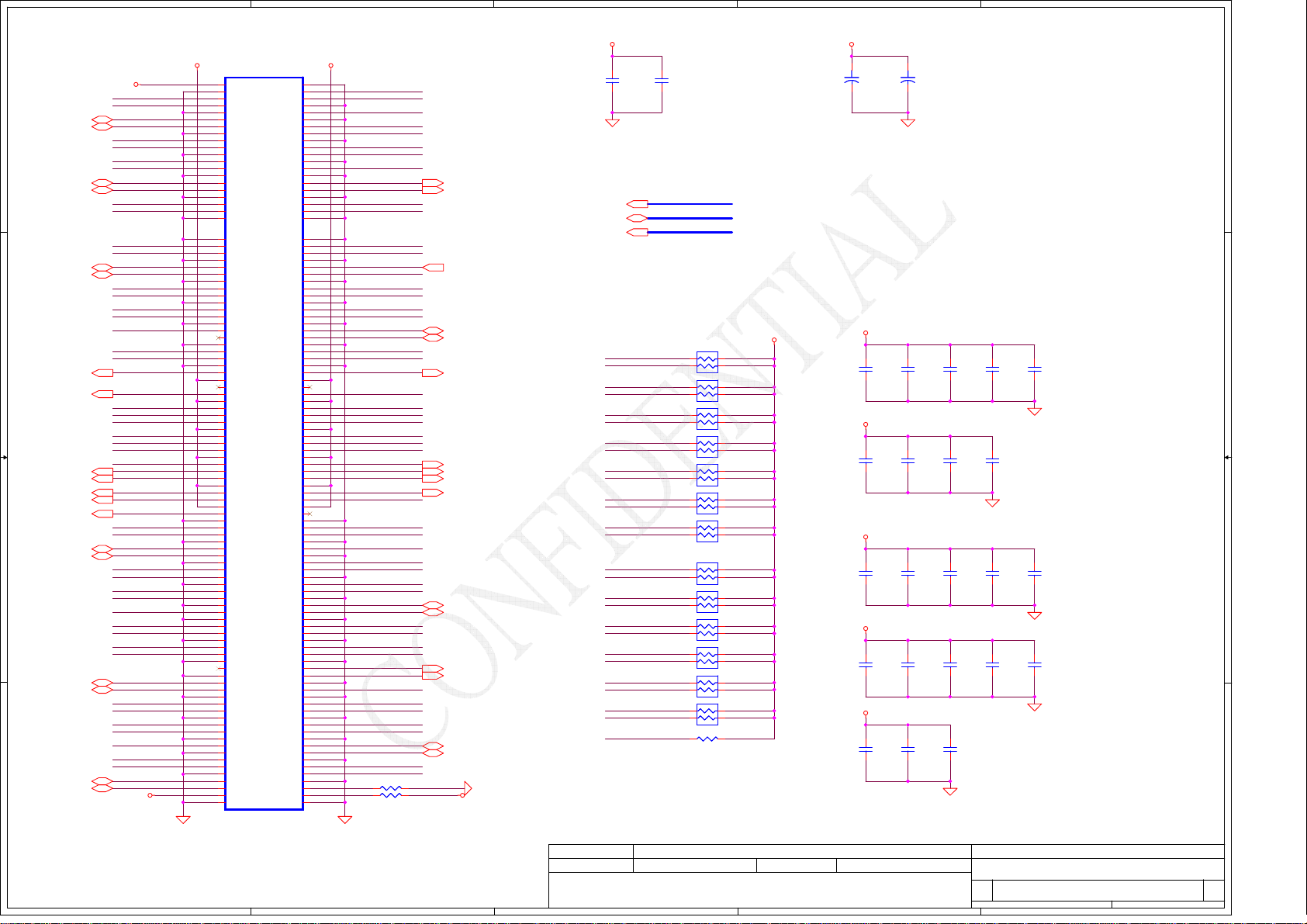

Page 3

A

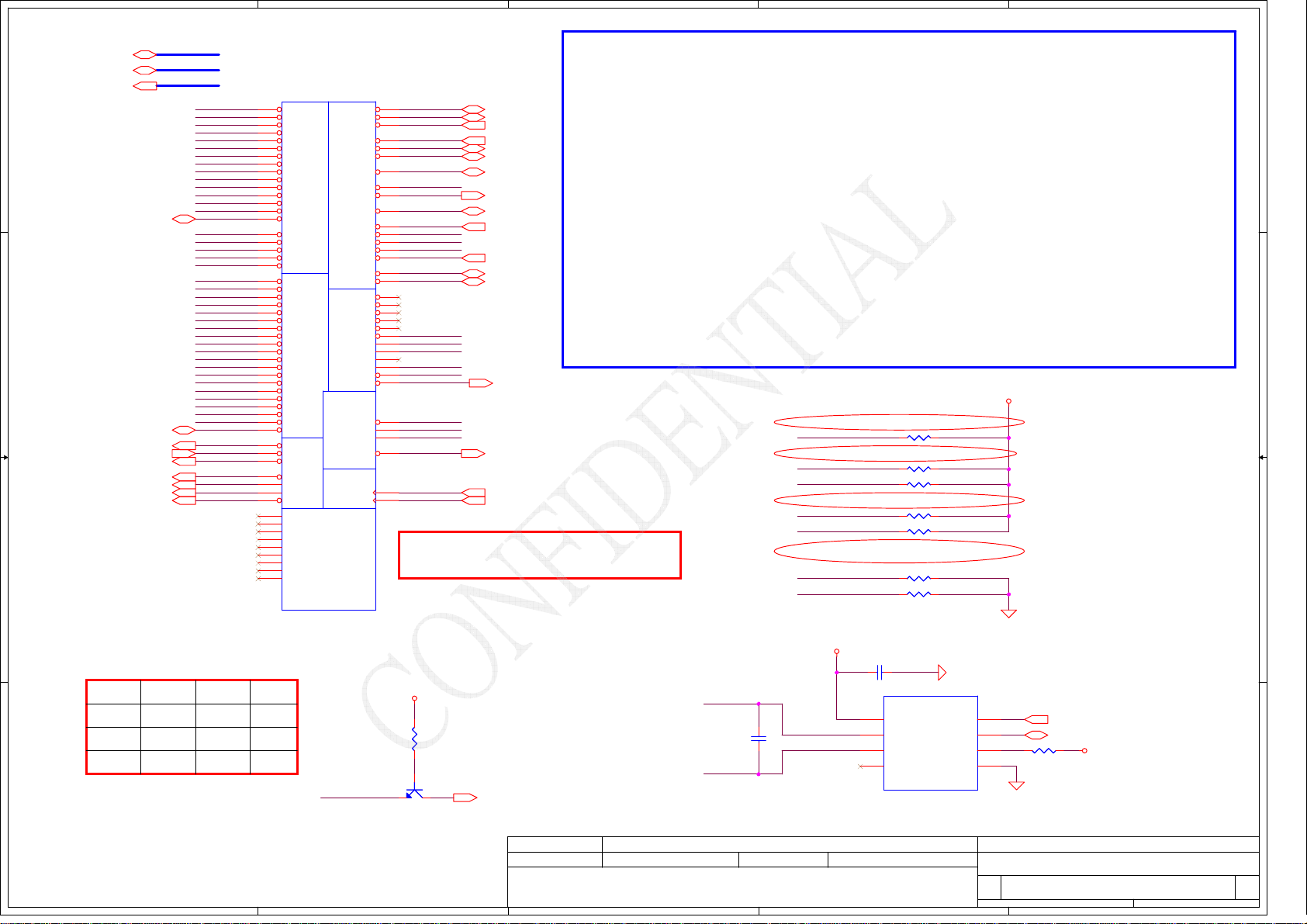

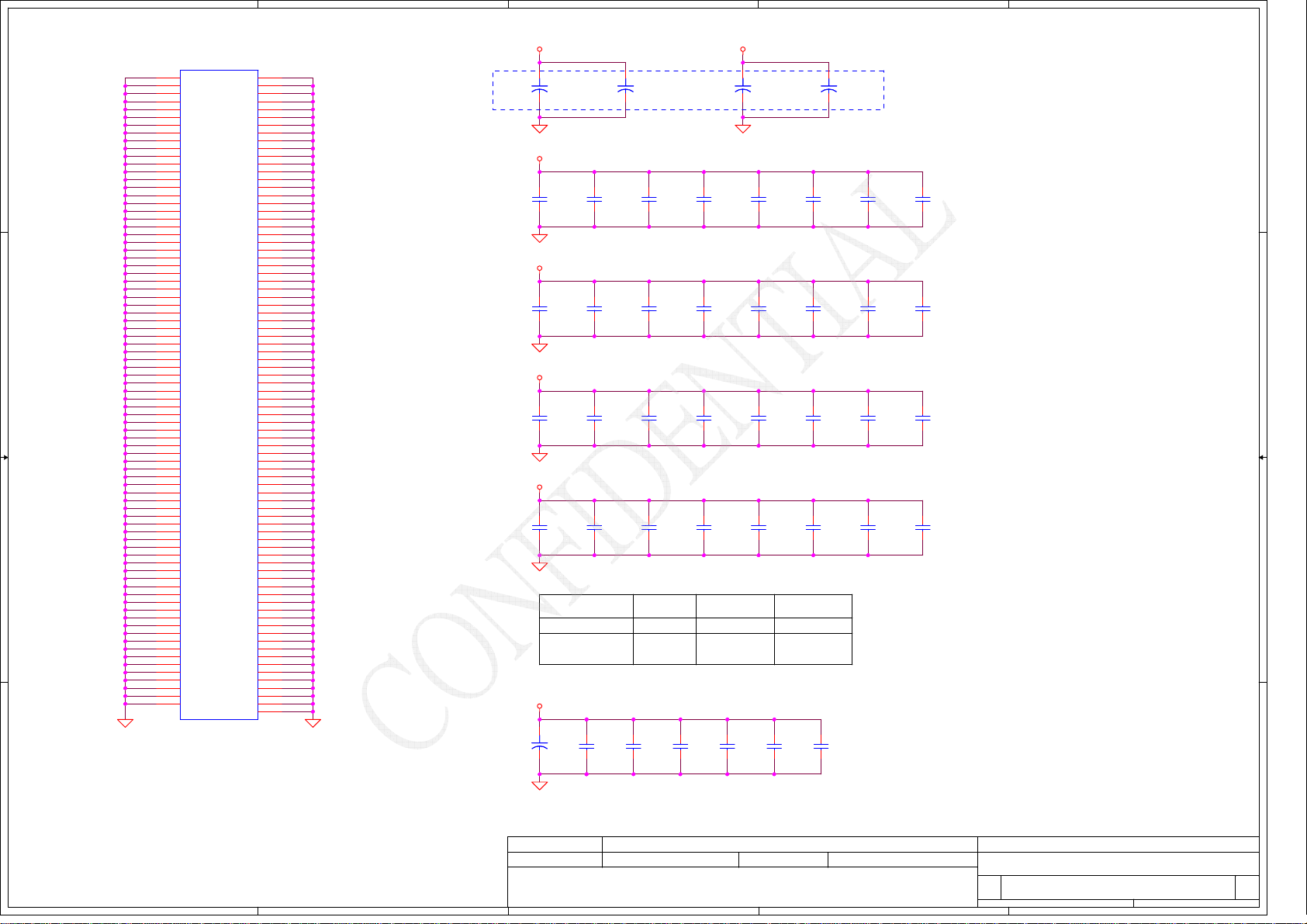

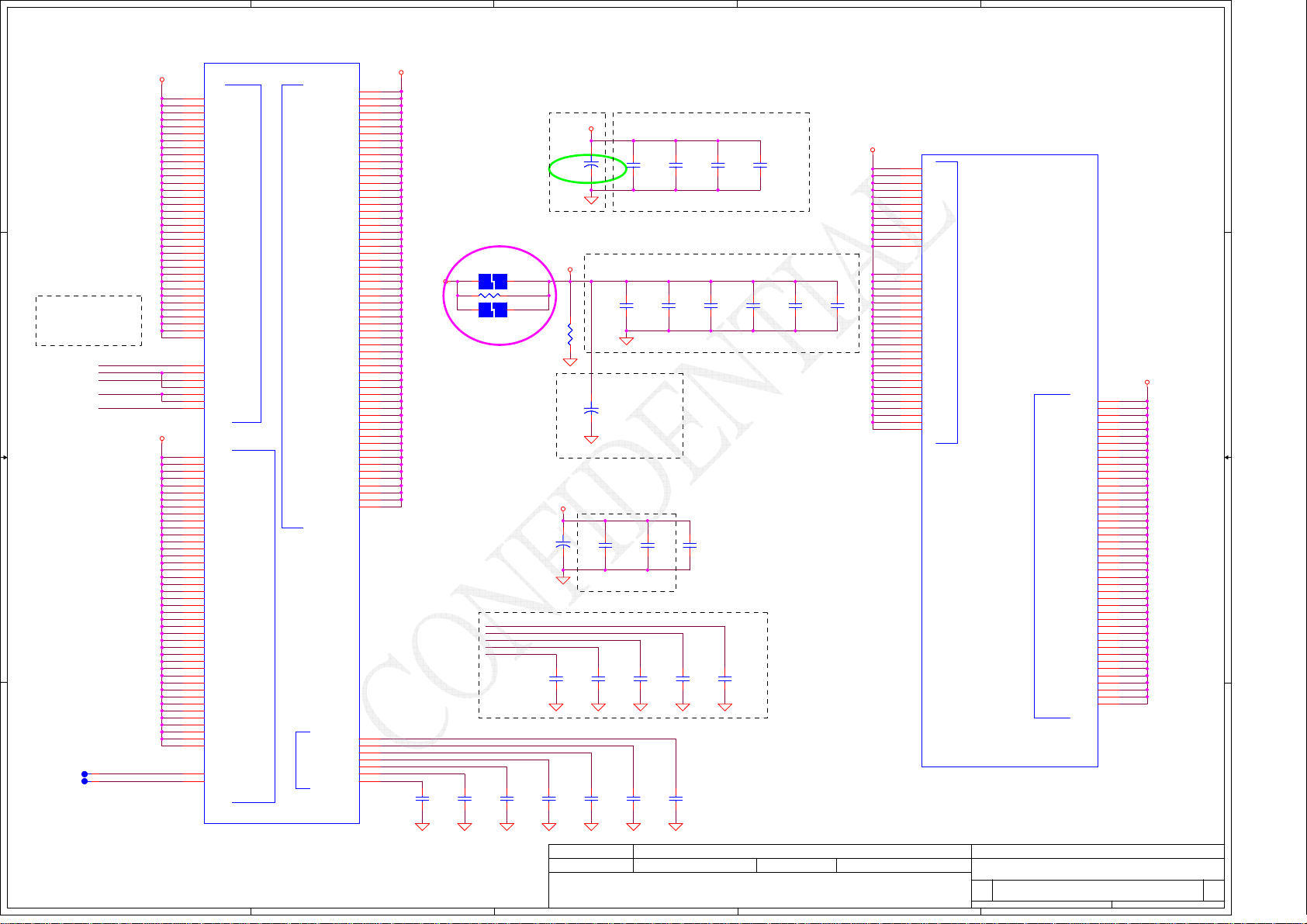

Voltage Rails

Power Plane Description

VIN

1 1

2 2

B+

+CPU_CORE

+0.9VS 0.9V switched power rail for DDR terminator

+1.05VS

+1.25VS 1.25V switched power rail ON OFF OFF

+1.5V 1.5V power rail for HDA ON ON OFF

+1.5VS

+1.8V

+1.8VS 1.8V switched power rail

+2.5VS

+3VALW

+3V

+3V_LAN

+3VS

+5VALW

+5VS

+VSB VSB always on power rail ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.05V switched power rail

1.5V switched power rail

1.8V power rail for DDR

2.5V switched power rail

3.3V always on power rail

3.3V power rail for SB

3.3V power rail for LAN

3.3V switched power rail

5V always on power rail

5V switched power rail

B

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON

ON

ON ON

ON ONXX

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

ON

OFF

OFF

OFF

OFF

OFF

ON ON*

OFF

OFF

ON*

ON

OFFON

OFF

ONON

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW

HIGH

LOWLOWLOW

D

HIGHHIGHHIGH

HIGH

HIGH

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.168 V 0.250 V 0.362 V

0.375 V

0.634 V

0.958 V

1.372 V 1.650 V 1.838 V

1.851 V

2.433 V

V typ

ON

ON

ON

OFF

OFF

V

AD_BID

ON ON

ON

OFF

OFF

OFF

ON

ON

ON

ON

ON

AD_BID

0 V 0.155 V

0.503 V

0.819 V

0.621 V

0.945 V

1.185 V 1.359 V

2.200 V

3.300 V

2.420 V

3.300 V

E

LOW

OFF

OFF

OFF

max

BOARD ID Table BTO Option Table

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

Board ID

0

1

2

3

4

5

6

7

EC SM Bus1 address

3 3

Device

Smart Battery

EEPROM(24C16/02)

GMT G781-1

Address Address

1010 000X b

1001 101X b

EC SM Bus2 address

Device

ADI ADT7421

1001 100X b0001 011X b

ICH9M SM Bus address

Device

Clock Generator

(ICS9LPRS387, SLG8SP556V)

DDR DIMM0

DDR DIMM2

4 4

Address

1101 001Xb

1001 000Xb

1001 010Xb

BOM Configuration Table

JAL90-UMA 431551BOL01:JAL90GM@/JAL9050@/JAL90@/GM@/888VC@/8111C@/ABO@

KAW00 431551BOL31:JAW50@/JAW50GL@/JAL9050@/GM@/GLPM@/8111C@/268@/EM@

PCB Revision

431551BOL02:PM@/JAL90PM@/JAL9050@/JAL90@/GLPM@/888VC@/8111C@/ABO@JAL90-Dis

431551BOL11:JAW50@/JAW50GL@/JAL9050@/GM@/GLPM@/8111C@/268@/ABO@JAW50-UMA

431551BOL12:PM@/JAW50@/JAW50PM@/JAL9050@/GLPM@/8111C@/268@/ABO@JAW50-DIS

0.1

0.2

0.3

1.0

1A

BTO Item BOM Structure

JAL90@JAL90

JAW50@JAW50/KAW00

UMA

GM@

JAL90GM@JAL90-UMA

JAW50/KAW00

Discrete

Discrete

ALC888VC

ALC888VB

GLPM@

PM@

888VC@

888VB@

8111C 8111C@

8102E 8102E@

ALC268

268@

ABO@JAL90/JAW50

EM@KAW00

JAL90/JAW50

KAW00

JAL90-DIS

JAW50-DIS

JAW50-UMA

JAL9050@

JAL90PM@

JAW50PM@

JAW50GL@

BOM ConfigurationProject

A

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2007/09/20 2008/09/20

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

401551

401551

401551

of

of

of

350Monday, July 21, 2008

350Monday, July 21, 2008

350Monday, July 21, 2008

E

I

I

I

Page 4

5

4

3

2

1

H_A#[3..35]7

H_REQ#[0..4]7

H_RS#[0..2]7

D D

C C

B B

BSEL2 BSEL1 BSEL0 BCLK

000266

010200

A A

H_A#[3..35]

H_REQ#[0..4]

H_RS#[0..2]

JCPU1A

AA4

AB2

AA3

D22

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

D2

D3

F6

16601

JCPU1A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

Penryn

Penryn

CONN@

CONN@

ADDR GROUP_0

ADDR GROUP_0

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

ADDR GROUP_1

ADDR GROUP_1

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

H_PROCHOT#

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

B3

H4

H_RESET#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

XDP_DBRESET#

C20

H_PROCHOT#

D21

H_THERMDA

A24

H_THERMDC

B25

C7

A22

A21

Layout Note:

H_THERMDA&H_THERMDC Trace / Space = 10 / 10 mil

+1.05VS

12

R39

R39

56_0402_5%

56_0402_5%

@

@

B

B

2

E

E

3 1

C

C

Q2

Q2

MMBT3904_SOT23-3

MMBT3904_SOT23-3

@

@

4

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

H_INIT# 22

H_LOCK# 7

H_RESET# 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

XDP_DBRESET# 23

H_THERMTRIP# 8,22

CLK_CPU_BCLK 16

CLK_CPU_BCLK# 16

OCP# 23

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

XDP_TDI

XDP_TMS

XDP_BPM#5

H_PROCHOT#

H_IERR#

XDP_TRST#

XDP_TCK

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

H_THERMDA

1

C94

C94

2200P_0402_50V7K

2200P_0402_50V7K

2

H_THERMDC

Compal Secret Data

Compal Secret Data

2007/09/20 2008/09/20

2007/09/20 2008/09/20

2007/09/20 2008/09/20

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1

2

3

4

R17 54.9_0402_1%

R17 54.9_0402_1%

1 2

R16 54.9_0402_1%

R16 54.9_0402_1%

1 2

R8 54.9_0402_1%

R8 54.9_0402_1%

1 2

@

@

R32 56_0402_5%

R32 56_0402_5%

R31 56_0402_5%

R31 56_0402_5%

R13 54.9_0402_1%

R13 54.9_0402_1%

R7 54.9_0402_1%

R7 54.9_0402_1%

C95

C95

U8

U8

VDD

DP

DN

THERM#

EMC1402-1-ACZL-TR_MSOP8

EMC1402-1-ACZL-TR_MSOP8

2

1 2

12

12

12

8

SMCLK

7

SMDATA

6

ALERT#

5

GND

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

+1.05VS

left NC if no ITP

39Ohm

1 2

R541

R541

10K_0402_5%

10K_0402_5%

401551

401551

401551

EC_SMB_CK2 31,32

EC_SMB_DA2 31,32

+3VS

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

450Monday, July 21, 2008

450Monday, July 21, 2008

450Monday, July 21, 2008

1

I

I

I

of

of

of

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_ADSTB#07

H_ADSTB#17

H_A20M#22

H_FERR#22

H_IGNNE#22

H_STPCLK#22

H_INTR22

H_NMI22

H_SMI#22

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

1

5

Page 5

5

4

3

2

1

JCPU1B

G22

G25

G24

H22

H23

H26

H25

N22

R23

M24

M23

R24

N25

M26

N24

AD26

C23

D25

C24

AF26

AF1

C21

E22

F24

E26

F23

E25

E23

K24

J24

J23

F26

K22

J26

K25

P26

L23

L22

P25

P23

P22

T24

L25

T25

L26

A26

B22

B23

C3

JCPU1B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

BSEL[0]

BSEL[1]

BSEL[2]

Penryn

Penryn

CONN@

CONN@

DATA GRP 0

DATA GRP 0

MISC

MISC

DATA GRP 1

DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

H_D#0

PAD

PAD

PAD

PAD

PAD

PAD

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTL_REF0

@

@

@

@

@

@

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

D D

H_DSTBN#07 H_DSTBN#2 7

H_DSTBP#07 H_DSTBP#2 7

H_DINV#07

C C

Trace Close CPU < 0.5'

Width=4 mil ,

Spacing: 15mil

(55Ohm)

B B

R287

R287

1K_0402_1%

1K_0402_1%

R289

R289

2K_0402_1%

2K_0402_1%

+1.05VS

1 2

1 2

H_DSTBN#17 H_DSTBN#3 7

H_DSTBP#17 H_DSTBP#3 7

H_DINV#17

R317 1K_0402_5%@R317 1K_0402_5%@

R316 1K_0402_5%@R316 1K_0402_5%@

C381 0.1U_0402_16V4Z@C381 0.1U_0402_16V4Z@

1 2

12

12

T4

T4

T2

T2

T13

T13

CPU_BSEL016

CPU_BSEL116

CPU_BSEL216

H_D#32

Y22

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

AE25

AF24

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

E5

B5

D24

H_PWRGOOD

D6

H_CPUSLP#

D7

AE6

TRACE CLOSELY CPU < 0.5'

COMP0, COMP2 layout : Width 18mils and Space 25mils (27.4Ohms)

COMP1, COMP3 layout : Width 4mils and Space 25mils (55Ohms)

H_D#[0..63]

H_DINV#2 7

R295 27.4_0402_1%

R295 27.4_0402_1%

R291 54.9_0402_1%

R291 54.9_0402_1%

R10 27.4_0402_1%

R10 27.4_0402_1%

R12 54.9_0402_1%

R12 54.9_0402_1%

H_DINV#3 7

1 2

1 2

1 2

1 2

H_DPRSTP# 8,22,46

H_DPSLP# 22

H_DPWR# 7

H_PWRGOOD 22

H_CPUSLP# 7

PSI# 46

H_D#[0..63] 7

+CPU_CORE

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

JCPU1C

JCPU1C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

Penryn

Penryn

CONN@

CONN@

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

.

+CPU_CORE

VCCSENSE

VSSSENSE

C85

CPU_VID0 46

CPU_VID1 46

CPU_VID2 46

CPU_VID3 46

CPU_VID4 46

CPU_VID5 46

CPU_VID6 46

R286 100_0402_1%

R286 100_0402_1%

R285 100_0402_1%

R285 100_0402_1%

0.01U_0402_16V7K

0.01U_0402_16V7K

1 2

1 2

C85

+1.05VS

1

2

20mils

1

C93

C93

2

10U_0805_10V4Z

10U_0805_10V4Z

+CPU_CORE

VCCSENSE 46

VSSSENSE 46

+1.5VS

A A

5

4

Security Classification

Security Classification

Security Classification

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/09/20 2008/09/20

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

401551

401551

401551

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

550Monday, July 21, 2008

550Monday, July 21, 2008

550Monday, July 21, 2008

of

of

1

of

I

I

I

Page 6

5

4

3

2

1

+CPU_CORE +CPU_CORE

JCPU1D

JCPU1D

D D

C C

B B

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Penryn

Penryn

CONN@

CONN@

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

.

.

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

1

+

+

C378

C378

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

+CPU_CORE

1

C409

C409

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU_CORE

1

C21

C21

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU_CORE

1

C78

C78

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU_CORE

1

C395

C395

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU-CORE

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

+1.05VS

1

+

+

C73

C73

330U_D2E_2.5VM_R15

330U_D2E_2.5VM_R15

2

2 x 330uF(6mOhm/2) 2 x 330uF(6mOhm/2)

1

+

+

C377

C377

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

1

+

+

C98

C98

@

@

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

South Side Secondary North Side Secondary

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C413

C413

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

C390

C390

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C68

C68

2

1

C70

C70

2

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C7

C7

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

1

C64

C64

2

(Place these capacitors on South side,Secondary Layer)

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C20

C20

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

C19

C19

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C18

C18

2

1

C17

C17

2

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C394

C394

2

(Place these capacitors on North side,Secondary Layer)

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C77

C77

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C76

C76

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C75

C75

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

C386

C386

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C382

C382

2

(Place these capacitors on South side,Primary Layer)

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C391

C391

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

C384

C384

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C385

C385

2

1

C410

C410

2

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C383

C383

2

(Place these capacitors on North side,Primary Layer)

C,uF ESR, mohm ESL,nH

4X330uF 6m ohm/4 1.8nH/6

32X22uF 3m ohm/32 0.6nH/32

32X10uF 3m ohm/32 0.6nH/32

C30

C30

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C16

C16

2

1

C13

C13

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C31

C31

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C29

C29

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C61

C61

2

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+

+

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C60

C60

C403

C403

C65

C65

C411

C411

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C402

C402

2

1

C69

C69

2

1

C59

C59

2

1

C412

C412

2

A A

5

4

Security Classification

Security Classification

Security Classification

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/09/20 2008/09/20

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

401551

401551

401551

650Monday, July 21, 2008

650Monday, July 21, 2008

650Monday, July 21, 2008

of

of

1

of

I

I

I

Page 7

5

4

3

2

1

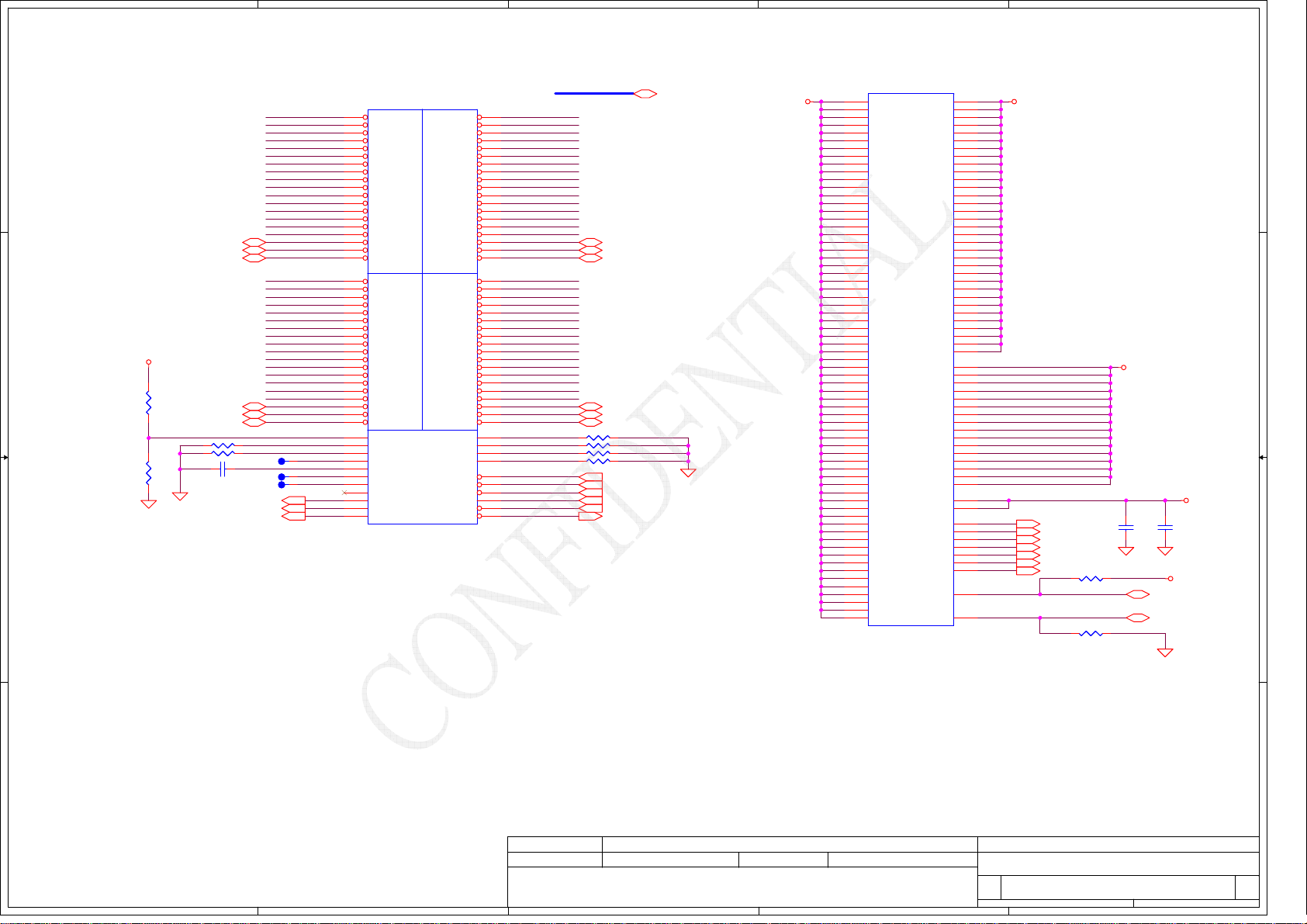

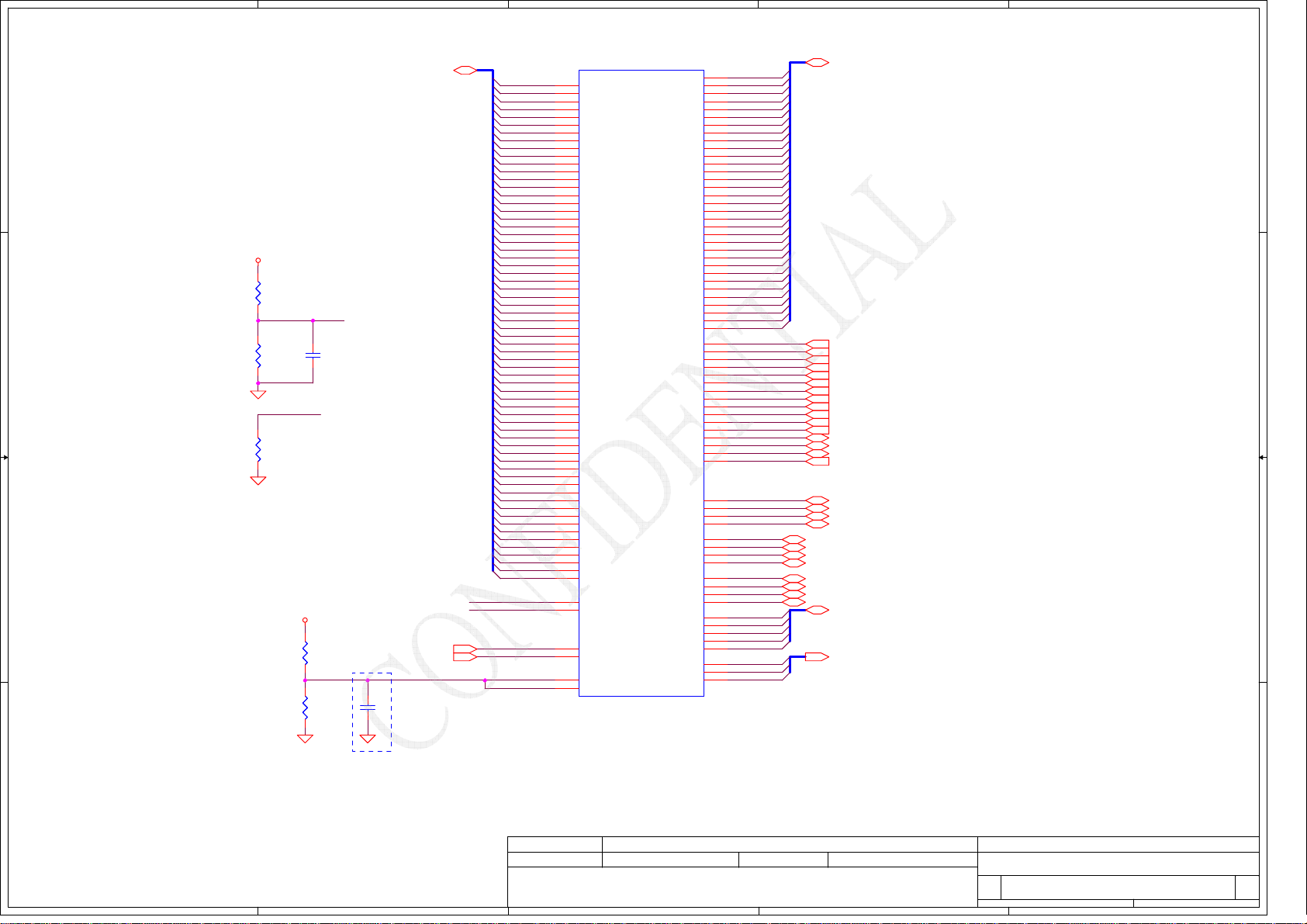

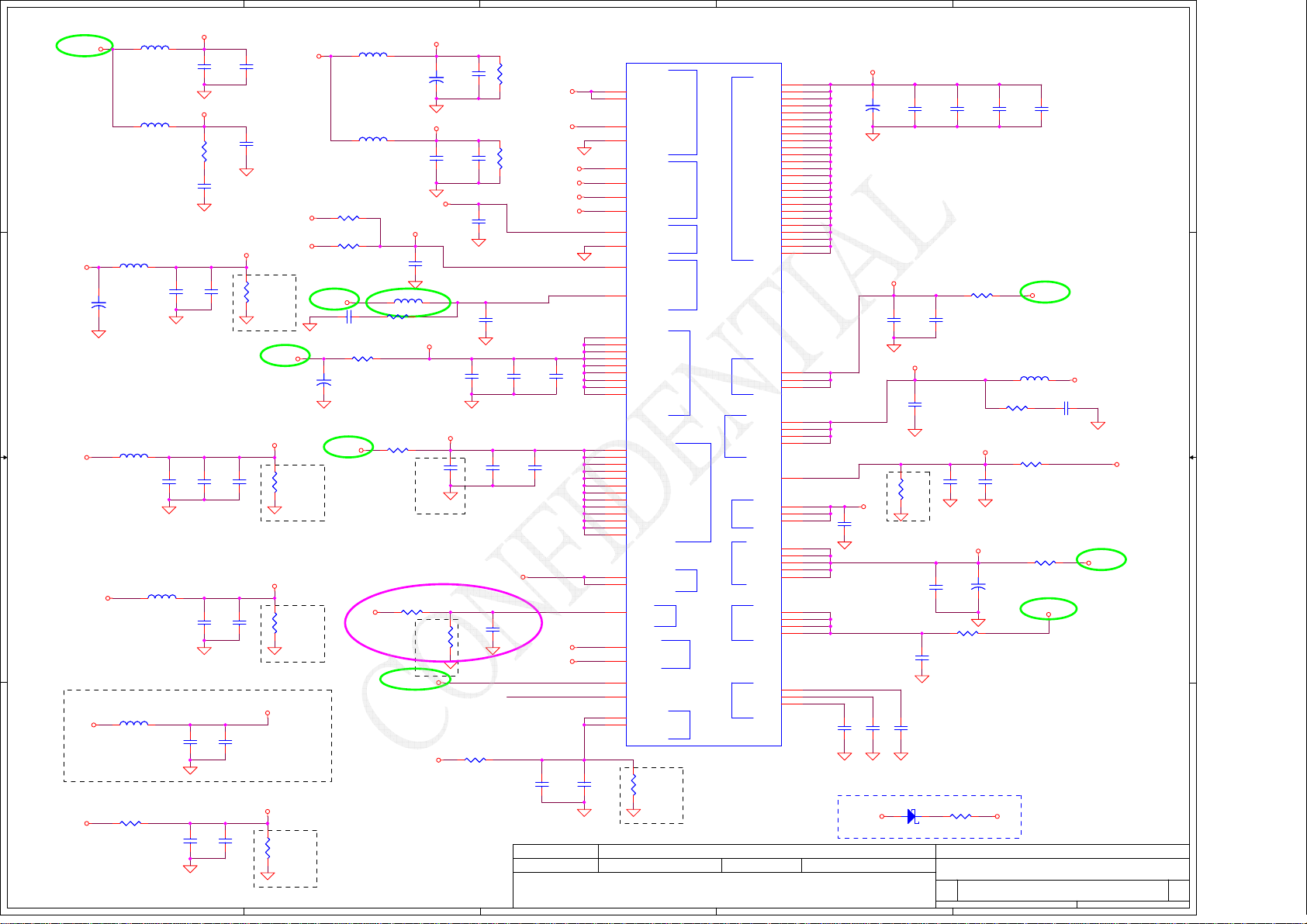

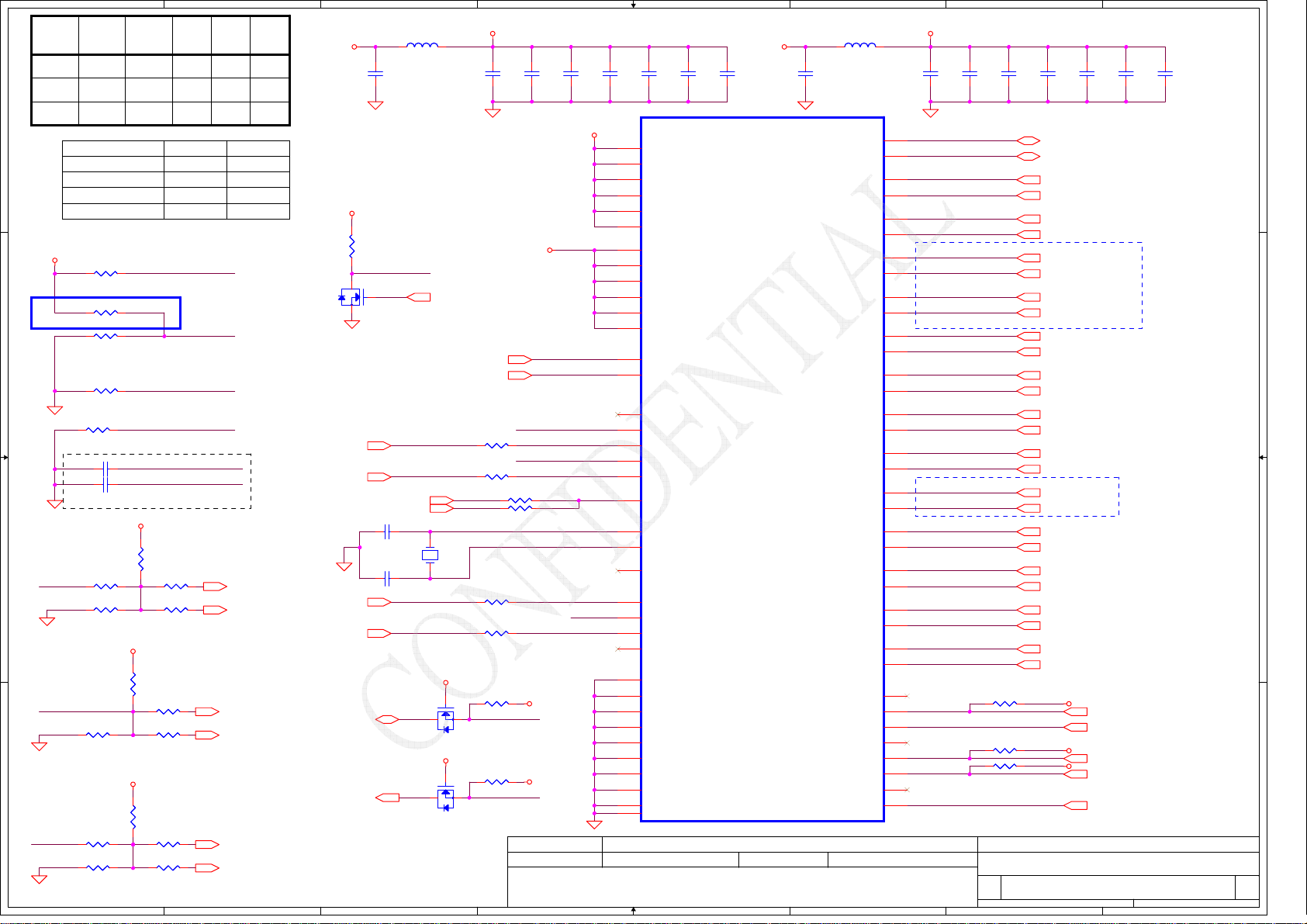

U31A

D D

+1.05VS

12

R69

R69

221_0402_1%

221_0402_1%

H_SWING

width=10mil

C C

1 2

12

B B

width:spacing=10mil:20mil (<0.5")

R68

R68

100_0402_1%

100_0402_1%

H_RCOMP

R334

R334

24.9_0402_1%

24.9_0402_1%

+1.05VS

1

C155

C155

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

width=10mil

R77

R77

1K_0402_1%

1K_0402_1%

1 2

12

R74

R74

2K_0402_1%

2K_0402_1%

1

2

H_D#[0..63]5

H_RESET#4

H_CPUSLP#5

C161

C161

@

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_RESET#

H_CPUSLP#

H_AVREF

U31A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

JAL90GM@

JAL90GM@

H_ADSTB#_0

H_ADSTB#_1

H_BREQ#

H_DEFER#

HOST

HOST

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_HIT#

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_A#[3..35] 4

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BR0# 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 16

CLK_MCH_BCLK# 16

H_DPWR# 5

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#0 5

H_DINV#1 5

H_DINV#2 5

H_DINV#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_REQ#[0..4] 4

H_RS#[0..2] 4

within 100mil to Ball A9,B9

A A

5

4

Security Classification

Security Classification

Security Classification

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/09/20 2008/09/20

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

401551

401551

401551

750Monday, July 21, 2008

750Monday, July 21, 2008

750Monday, July 21, 2008

of

of

1

of

I

I

I

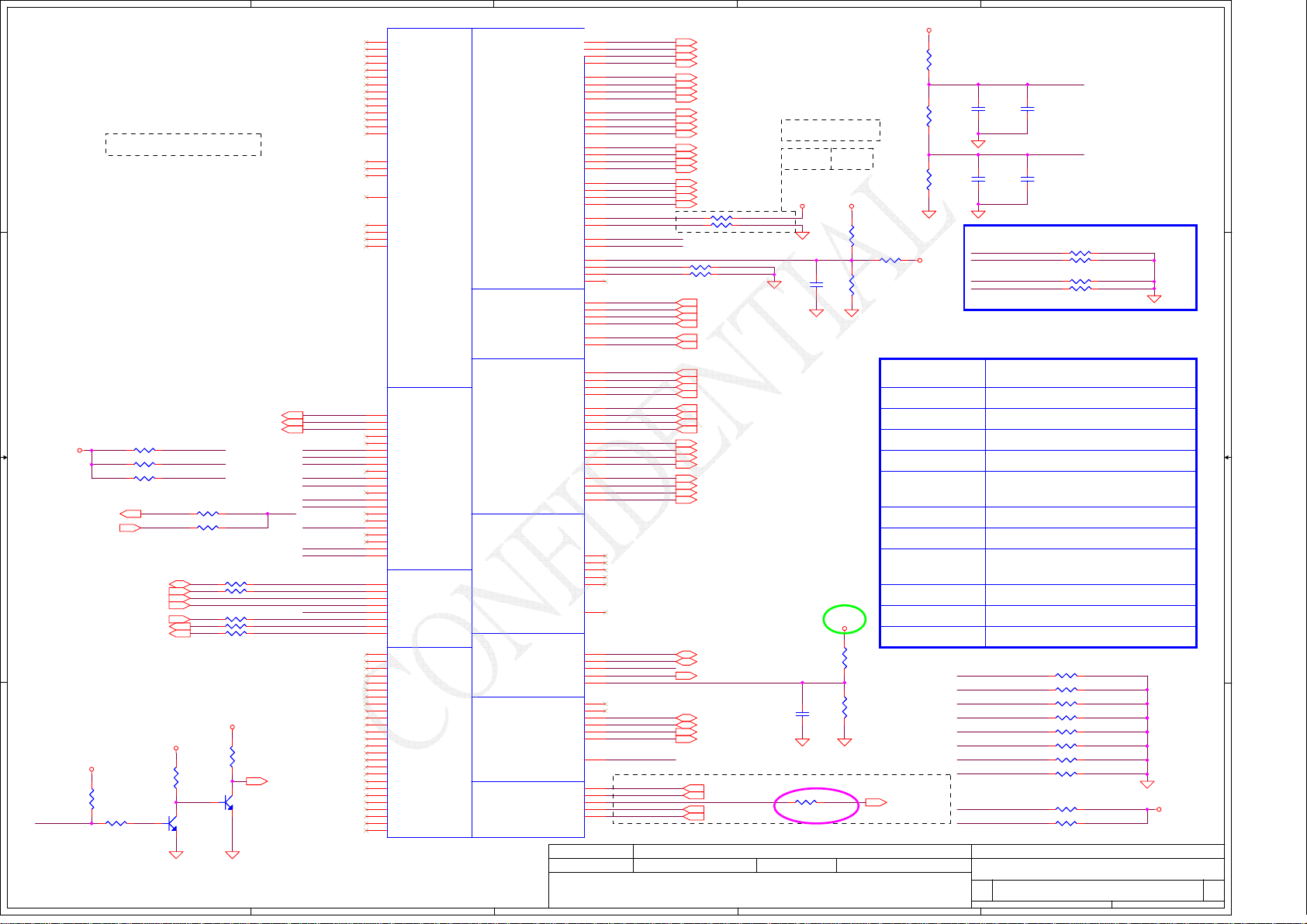

Page 8

5

D D

All RSVD balls on GMCH should be left No

Connect.

C C

MCH_CLKSEL016

MCH_CLKSEL116

MCH_CLKSEL216

PM_EXTTS#0

VGATE16,23,46

+1.05VS

12

1 2

R118 10K_0402_5% R118 10K_0402_5%

R121 10K_0402_5% R121 10K_0402_5%

R126 10K_0402_5% R126 10K_0402_5%

H_THERMTRIP#4,22

PM_DPRSLPVR23,46

R371

R371

54.9_0402_1%

54.9_0402_1%

R366

R366

1 2

330_0402_5%

330_0402_5%

PM_EXTTS#1

1 2

MCH_CLKREQ#

1 2

Use VGATE for GMCH_PWROK

VGATE

ICH_PWROK

PM_SYNC#23

H_DPRSTP#5,22,46

PM_EXTTS#014

PM_EXTTS#115

PLT_RST#21,23,26,27,31

+3VS

2

B

B

E

E

5

1 2

R143 0_0402_5%@R143 0_0402_5%@

1 2

R144 0_0402_5% R144 0_0402_5%

R82 0_0402_5% R82 0_0402_5%

1 2

R73 0_0402_5% R73 0_0402_5%

1 2

R75 100_0402_5% R75 100_0402_5%

1 2

R85 0_0402_5% R85 0_0402_5%

1 2

R80 0_0402_5% R80 0_0402_5%

1 2

12

R202

R202

1K_0402_5%

1K_0402_5%

2

B

B

C

C

Q18

Q18

MMBT3904_SOT23-3

MMBT3904_SOT23-3

3 1

GMCH_PWROK

+3VS

12

R210

R210

1K_0402_5%

1K_0402_5%

C

C

Q21

Q21

MMBT3904_SOT23-3

MMBT3904_SOT23-3

E

E

3 1

+3VS

ICH_PWROK23

B B

A A

MCH_TSATN#

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_19

MCH_CFG_20

PM_SYNC#_R

PM_DPRSTP#_R

PM_EXTTS#0

PM_EXTTS#1

GMCH_PWROK

MCH_RSTIN#

THERMTRIP#_R

DPRSLPVR_R

MCH_TSATN_EC# 31

4

U31B

U31B

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

AL34

RSVD10

AK34

RSVD11

AN35

RSVD12

AM35

RSVD13

T24

RSVD14

B31

RSVD15

B2

RSVD16

M1

RSVD17

AY21

RSVD20

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC_1

BF48

NC_2

BD48

NC_3

BC48

NC_4

BH47

NC_5

BG47

NC_6

BE47

NC_7

BH46

NC_8

BF46

NC_9

BG45

NC_10

BH44

NC_11

BH43

NC_12

BH6

NC_13

BH5

NC_14

BG4

NC_15

BH3

NC_16

BF3

NC_17

BH2

NC_18

BG2

NC_19

BE2

NC_20

BG1

NC_21

BF1

NC_22

BD1

NC_23

BC1

NC_24

F1

NC_25

A47

NC_26

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

JAL90GM@

JAL90GM@

4

RSVD CFG PM NC

RSVD CFG PM NC

DDR CLK/ CONTROL/ COMPENSATIONHDA

DDR CLK/ CONTROL/ COMPENSATIONHDA

CLKDMIGRAPHICS VIDMEMISC

CLKDMIGRAPHICS VIDMEMISC

3

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

BB36

SB_CKE_1

BA17

SA_CS#_0

AY16

SA_CS#_1

AV16

SB_CS#_0

AR13

SB_CS#_1

BD17

SA_ODT_0

AY17

SA_ODT_1

BF15

SB_ODT_O

AY13

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

Issued Date

Issued Date

Issued Date

SMRCOMP

SMRCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_PWROK

SM_REXT

CLK_DREF_96M

CLK_DREF_96M#

CLK_DREF_SSC

CLK_DREF_SSC#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

DMI_ITX_MRX_N0

DMI_ITX_MRX_N1

DMI_ITX_MRX_N2

DMI_ITX_MRX_N3

DMI_ITX_MRX_P0

DMI_ITX_MRX_P1

DMI_ITX_MRX_P2

DMI_ITX_MRX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

ICH_PWROK

CL_VREF

SDVO_SCLK

SDVO_SDATA

MCH_CLKREQ#

MCH_TSATN#

HDA_BITCLK_MCH

HDA_RST_MCH#

HDA_SDIN2_MCH

HDA_SDOUT_MCH

HDA_SYNC_MCH

Notice: Please check HDA power rail to select HDA controller.

3

DDRA_CLK0 14

DDRA_CLK1 14

DDRB_CLK0 15

DDRB_CLK1 15

DDRA_CLK0# 14

DDRA_CLK1# 14

DDRB_CLK0# 15

DDRB_CLK1# 15

DDRA_CKE0 14

DDRA_CKE1 14

DDRB_CKE0 15

DDRB_CKE1 15

DDRA_SCS0# 14

DDRA_SCS1# 14

DDRB_SCS0# 15

DDRB_SCS1# 15

DDRA_ODT0 14

DDRA_ODT1 14

DDRB_ODT0 15

DDRB_ODT1 15

R386 80.6_0402_1% R386 80.6_0402_1%

1 2

R383 80.6_0402_1% R383 80.6_0402_1%

1 2

SM_VREF

R125 0_0402_5% R125 0_0402_5%

1 2

R375 499_0402_1%

R375 499_0402_1%

1 2

CLK_DREF_96M 16

CLK_DREF_96M# 16

CLK_DREF_SSC 16

CLK_DREF_SSC# 16

CLK_MCH_3GPLL 16

CLK_MCH_3GPLL# 16

DMI_ITX_MRX_N0 23

DMI_ITX_MRX_N1 23

DMI_ITX_MRX_N2 23

DMI_ITX_MRX_N3 23

DMI_ITX_MRX_P0 23

DMI_ITX_MRX_P1 23

DMI_ITX_MRX_P2 23

DMI_ITX_MRX_P3 23

DMI_MTX_IRX_N0 23

DMI_MTX_IRX_N1 23

DMI_MTX_IRX_N2 23

DMI_MTX_IRX_N3 23

DMI_MTX_IRX_P0 23

DMI_MTX_IRX_P1 23

DMI_MTX_IRX_P2 23

DMI_MTX_IRX_P3 23

CL_CLK0 23

CL_DATA0 23

CL_RST#0 23

SDVO_SCLK 17

SDVO_SDATA 17

MCH_CLKREQ# 16

MCH_ICH_SYNC# 23

HDA_BITCLK_MCH 22

HDA_RST_MCH# 22

HDA_SDOUT_MCH 22

HDA_SYNC_MCH 22

Compal Secret Data

Compal Secret Data

2007/09/20 2008/09/20

2007/09/20 2008/09/20

2007/09/20 2008/09/20

Compal Secret Data

SM_DRAMRST# would be

needed for DDR3 only

For Cantiga 80 Ohm

+1.8V +1.8V

20mil

C212

C212

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C198

C198

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

R102 33_0402_5%

R102 33_0402_5%

JAL90GM@

JAL90GM@

Deciphered Date

Deciphered Date

Deciphered Date

1 2

1

2

1 2

+1.05VS

R128

R128

1K_0402_1%

1K_0402_1%

1 2

R129

1

2

R129

511_0402_1%

511_0402_1%

1 2

2

+1.8V

R392

R392

1K_0402_1%

1K_0402_1%

R390

R390

3.01K_0402_1%

3.01K_0402_1%

R389

R389

1K_0402_1%

1K_0402_1%

R146

R146

1K_0402_1%

1K_0402_1%

@

@

1 2

R147

0_0402_5%

0_0402_5%

R145

R145

1K_0402_1%

1K_0402_1%

@

@

R147

+DIMM_VREF

Strap Pin Table

CFG[2:0]

CFG5

CFG6

CFG9

CFG10

CFG[13:12]

CFG16

CFG19

CFG20

(PCIE/SDVO select)

SDVO_CTRLDATA

L_DDC_DATA

DDPC_CTRLDATA

HDA_SDIN2 22

2

1

12

SM_RCOMP_VOH

SM_RCOMP_VOH

12

12

1

C491

C491

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

2

1

C483

C483

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

2

CLK_DREF_96M

CLK_DREF_96M#

CLK_DREF_SSC

CLK_DREF_SSC#

1

C492

C492

0.01U_0402_16V7K

0.01U_0402_16V7K

2

SM_RCOMP_VOL

1

C482

C482

0.01U_0402_16V7K

0.01U_0402_16V7K

2

R483 0_0402_5%PM@R483 0_0402_5%PM@

1 2

R482 0_0402_5%PM@R482 0_0402_5%PM@

1 2

R481 0_0402_5%PM@R481 0_0402_5%PM@

1 2

R480 0_0402_5%PM@R480 0_0402_5%PM@

1 2

as close as possible to the related balls

011 = FSB667

010 = FSB800

000 = FSB1067

0 = DMI x 2

1 = DMI x 4

0 = iTPM Host Interface is enabled

1 = iTPM Host Interface is Disabled

0 = Lane Reversal Enable

1 = Normal Operation (Default)

0 = PCIe Loopback Enable

1 = Disable

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = Normal Operation

1 = DMI Lane Reversal Enable

0 = Only PCIE or SDVO is operational.

1 = PCIE/SDVO are operating simu.

0 = No SDVO Card Present

1 = SDVO Card Present

0 = LFP Disable

1 = LFP Card Present; PCIE disable

0 = Digital DisplayPort Disable

1 = Digital DisplayPort Device Present

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_19

MCH_CFG_20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

401551

401551

401551

Date: Sheet

Date: Sheet

Date: Sheet

*

(Default)

*

(Default)

*

(Default)

*

*

*

*

(Default)

R110 2.21K_0402_1%@R110 2.21K_0402_1%@

R86 4.02K_0402_1%@R86 4.02K_0402_1%@

R92 2.21K_0402_1%@R92 2.21K_0402_1%@

R103 2.21K_0402_1%@R103 2.21K_0402_1%@

R98 2.21K_0402_1%@R98 2.21K_0402_1%@

R89 2.21K_0402_1%@R89 2.21K_0402_1%@

R90 2.21K_0402_1%@R90 2.21K_0402_1%@

R88 2.21K_0402_1%@R88 2.21K_0402_1%@

R96 4.02K_0402_1%@R96 4.02K_0402_1%@

R95 4.02K_0402_1%@R95 4.02K_0402_1%@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

SCHEMATIC,LA-4201P

12

12

12

12

12

12

12

12

12

12

1

(Default)

(Default)

*

*

*

(Default)

*

(Default)

(Default)

(Default)

+3VS

850Monday, July 21, 2008

850Monday, July 21, 2008

850Monday, July 21, 2008

I

I

I

of

of

of

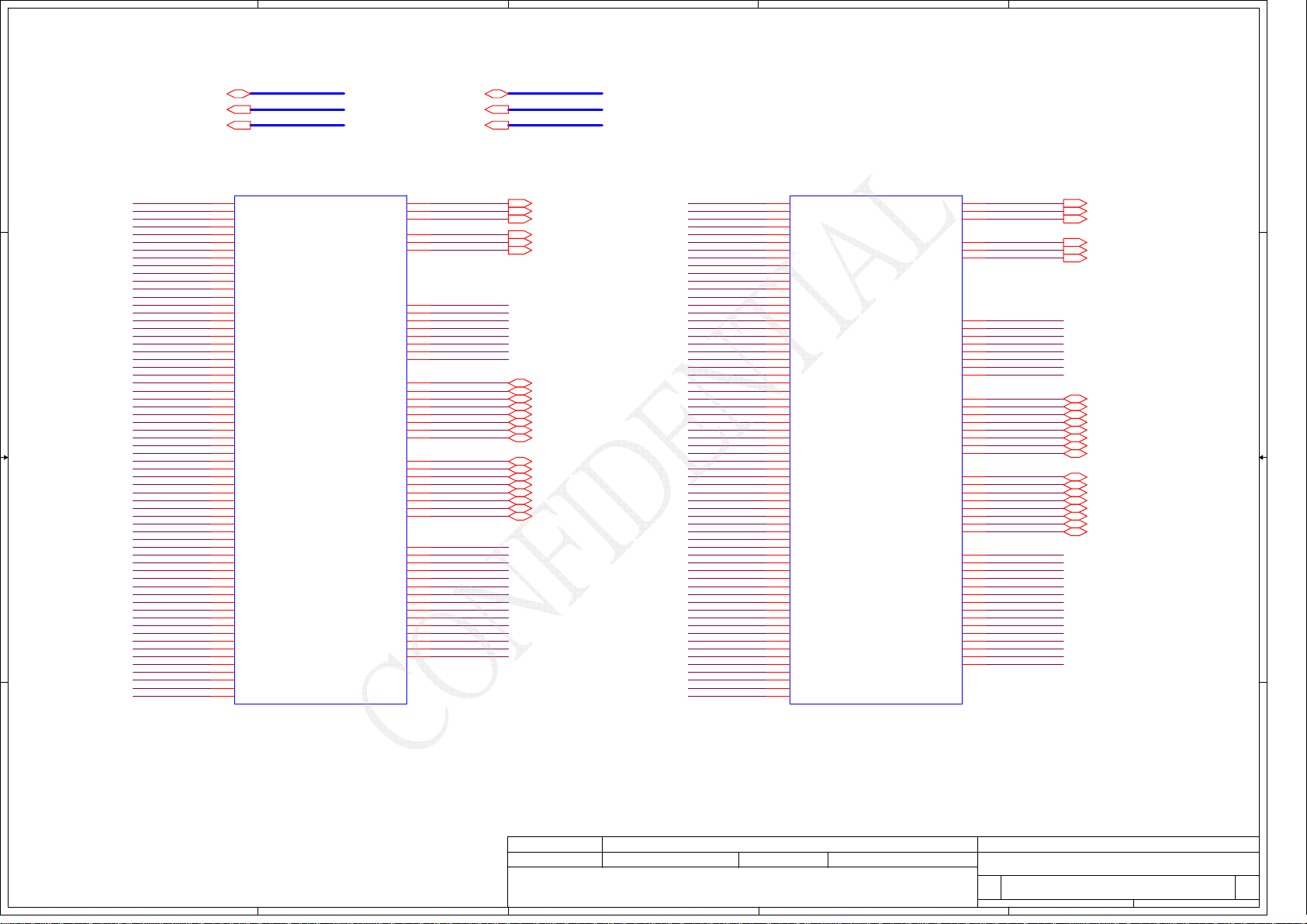

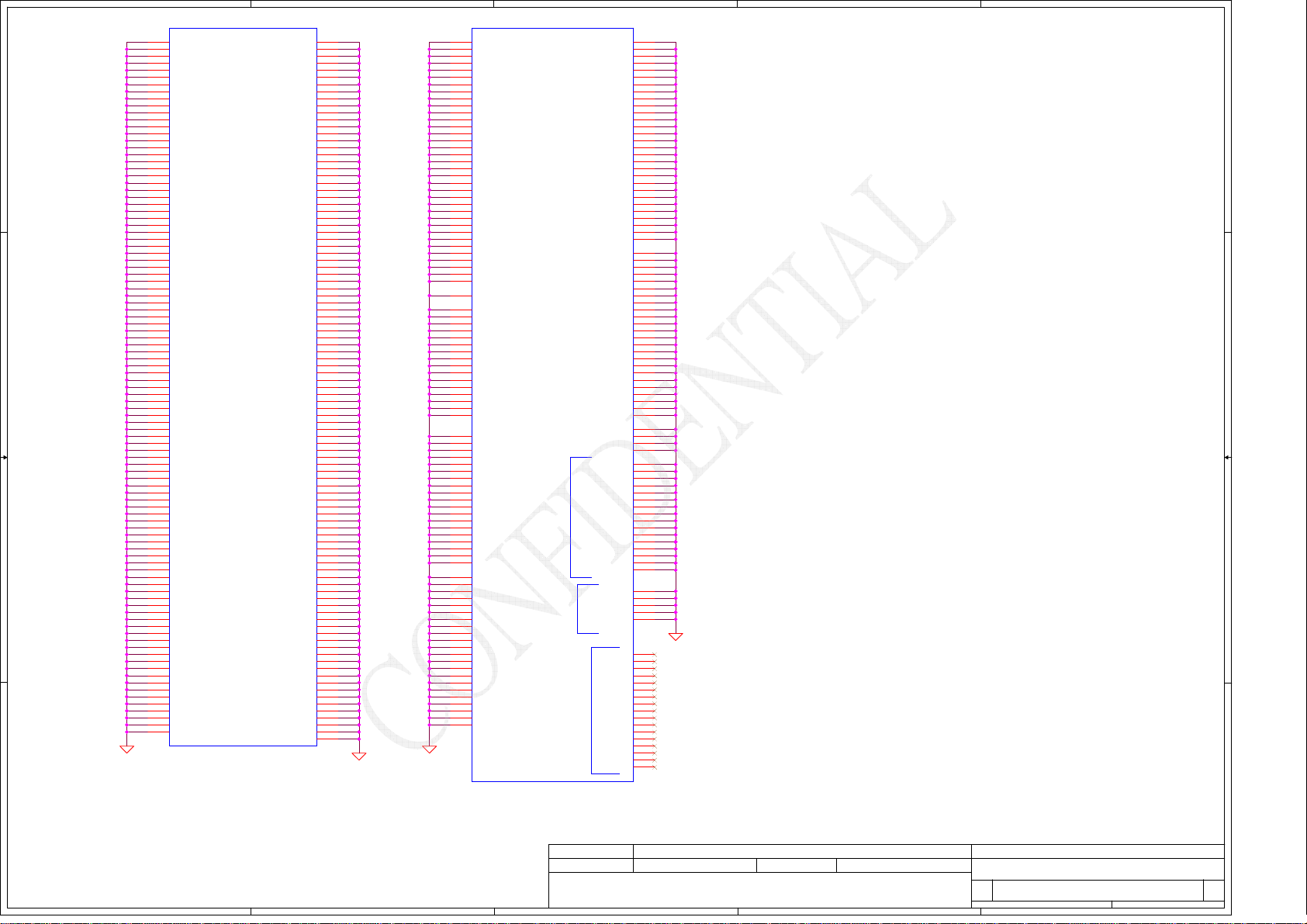

Page 9

5

4

3

2

1

DDRA_SDQ[0..63]14

D D

DDRA_SDM[0..7]14

DDRA_SMA[0..14]14

DDRA_SDQ[0..63]

DDRA_SDM[0..7]

DDRA_SMA[0..14]

DDRB_SDQ[0..63]15

DDRB_SDM[0..7]15

DDRB_SMA[0..14]15

DDRB_SDQ[0..63]

DDRB_SDM[0..7]

DDRB_SMA[0..14]

U31E

U31D

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

C C

B B

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

AJ38

AJ41

AN38

AM38

AJ36

AJ40

AM44

AM42

AN43

AN44

AU40

AT38

AN41

AN39

AU44

AU42

AV39

AY44

BA40

BD43

AV41

AY43

BB41

BC40

AY37

BD38

AV37

AT36

AY38

BB38

AV36

AW36

BD13

AU11

BC11

BA12

AU13

AV13

BD12

BC12

BB9

BA9

AU10

AV9

BA11

BD9

AY8

BA6

AV5

AV7

AT9

AN8

AU5

AU6

AT5

AN10

AM11

AM5

AN12

AM13

AJ11

AJ12

AJ9

AJ8

U31D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

BD21

SA_BS_0

BG18

SA_BS_1

AT25

SA_BS_2

BB20

SA_RAS#

BD20

SA_CAS#

AY20

SA_WE#

DDRA_SDM0

AM37

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

JAL90GM@

JAL90GM@

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS1

DDRA_SDQS2

DDRA_SDQS3

DDRA_SDQS4

DDRA_SDQS5

DDRA_SDQS6

DDRA_SDQS7

DDRA_SDQS0#

DDRA_SDQS1#

DDRA_SDQS2#

DDRA_SDQS3#

DDRA_SDQS4#

DDRA_SDQS5#

DDRA_SDQS6#

DDRA_SDQS7#

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SBS0# 14

DDRA_SBS1# 14

DDRA_SBS2# 14

DDRA_SRAS# 14

DDRA_SCAS# 14

DDRA_SWE# 14

DDRA_SDQS0 14

DDRA_SDQS1 14

DDRA_SDQS2 14

DDRA_SDQS3 14

DDRA_SDQS4 14

DDRA_SDQS5 14

DDRA_SDQS6 14

DDRA_SDQS7 14

DDRA_SDQS0# 14

DDRA_SDQS1# 14

DDRA_SDQS2# 14

DDRA_SDQS3# 14

DDRA_SDQS4# 14

DDRA_SDQS5# 14

DDRA_SDQS6# 14

DDRA_SDQS7# 14

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

AK47

AH46

AP47

AP46

AJ46

AJ48

AM48

AP48

AU47

AU46

BA48

AY48

AT47

AR47

BA47

BC47

BC46

BC44

BG43

BF43

BE45

BC41

BF40

BF41

BG38

BF38

BH35

BG35

BH40

BG39

BG34

BH34

BH14

BG12

BH11

BG8

BH12

BF11

BF8

BG7

BC5

BC6

AY3

AY1

BF6

BF5

BA1

BD3

AV2

AU3

AR3

AN2

AY2

AV1

AP3

AR1

AL1

AL2

AJ1

AH1

AM2

AM3

AH3

AJ3

U31E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

BC16

SB_BS_0

BB17

SB_BS_1

BB33

SB_BS_2

AU17

SB_RAS#

BG16

SB_CAS#

BF14

SB_WE#

DDRB_SDM0

AM47

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

CANTIGA ES_FCBGA1329

CANTIGA ES_FCBGA1329

JAL90GM@

JAL90GM@

AY47

BD40

BF35

BG11

BA3

AP1

AK2

AL47

AV48

BG41

BG37

BH9

BB2

AU1

AN6

AL46

AV47

BH41

BH37

BG9

BC2

AT2

AN5

AV17

BA25

BC25

AU25

AW25

BB28

AU28

AW28

AT33

BD33

BB16

AW33

AY33

BH15

AU33

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS1

DDRB_SDQS2

DDRB_SDQS3

DDRB_SDQS4

DDRB_SDQS5