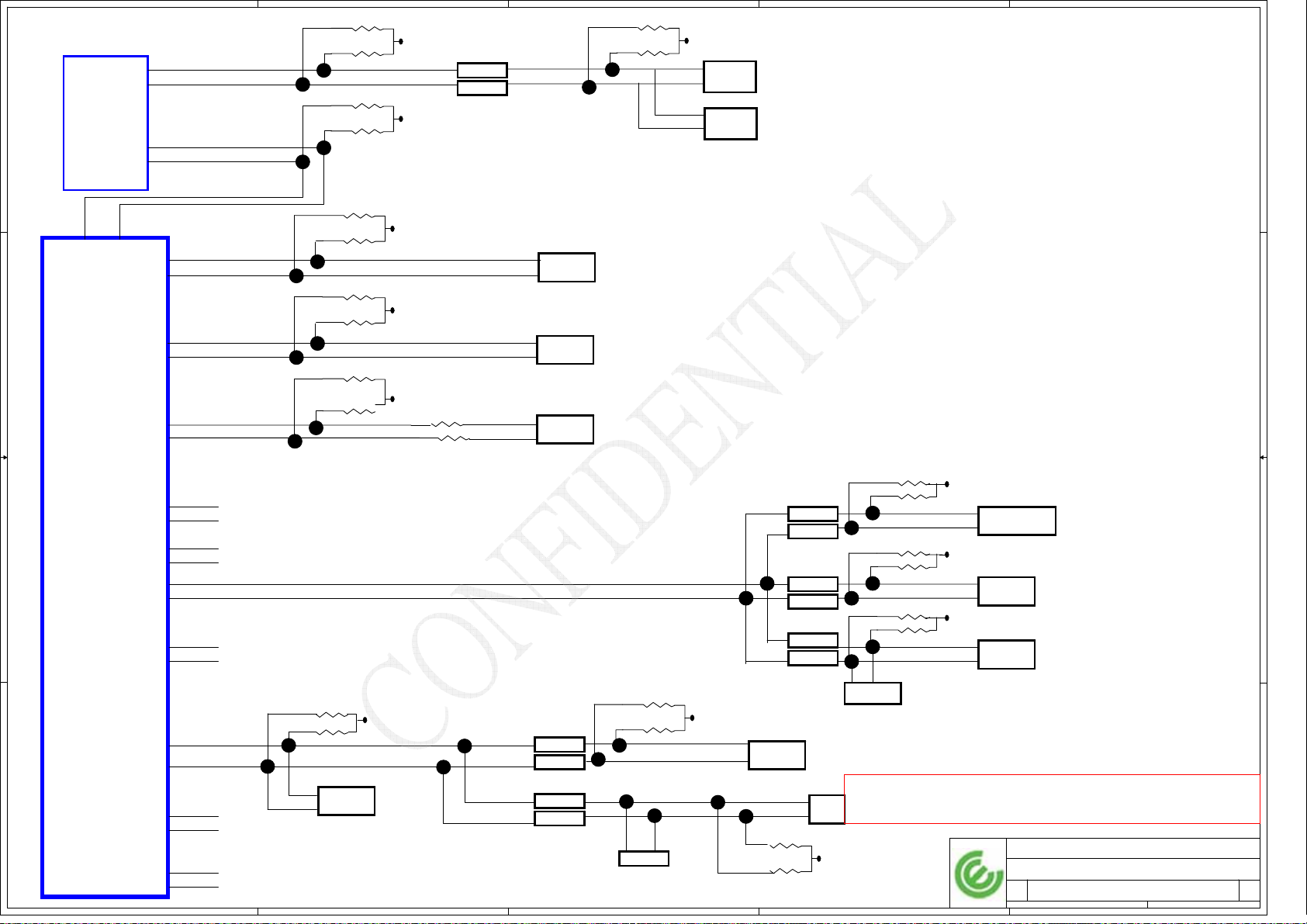

Page 1

A

B

C

D

E

COMPAL CONFIDENTIAL

MODEL NAME :

1 1

PCB NO :

BOM P/N :

JAL21

LA-4042P (DAA00000T0L)

43153331L01

M09 Maybach DIS

2 2

uFCPGA Mobile Penryn

Intel Cantiga PM + ICH9M

2007-10-30

REV : 0.1

3 3

4 4

MB PCB

MB PCB

Part Number Description

Part Number Description

PCB 03P LA-4051P REV0 M/B

PCB 03P LA-4051P REV0 M/B

DAA00000R0L

DAA00000R0L

A

B

@ : Nopop Component

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

C

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

156Monday, December 17, 2007

156Monday, December 17, 2007

156Monday, December 17, 2007

E

A

A

A

of

of

of

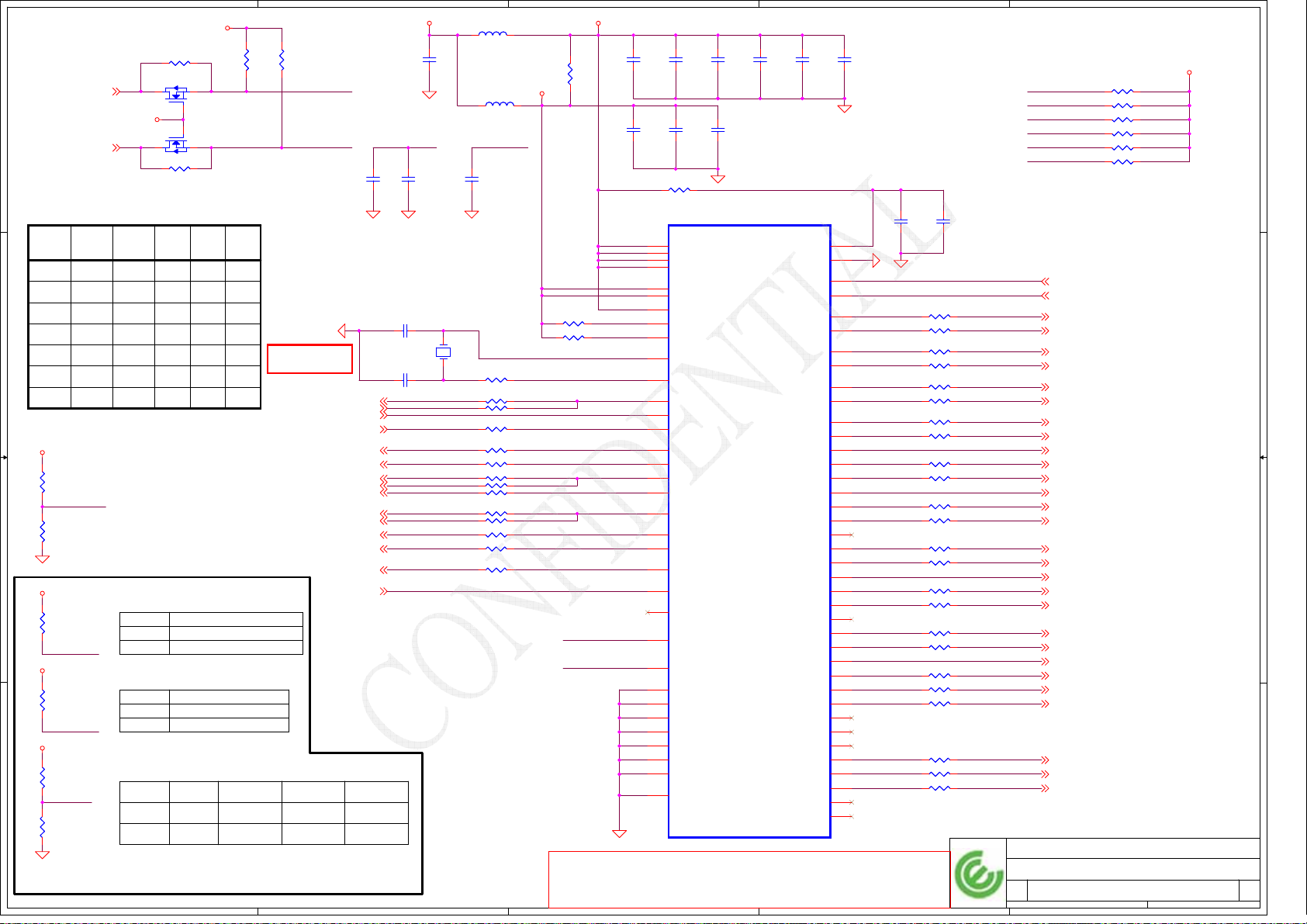

Page 2

A

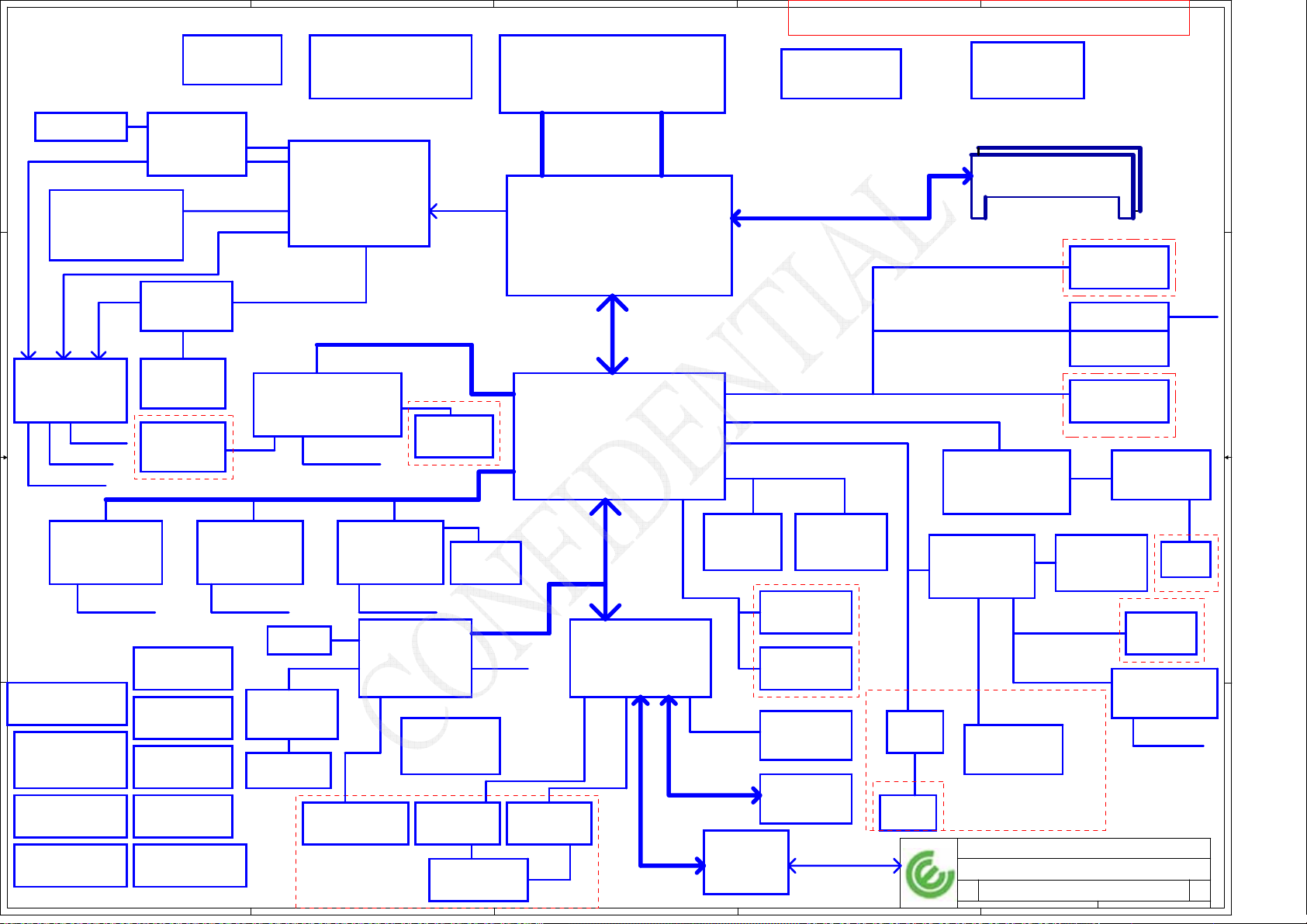

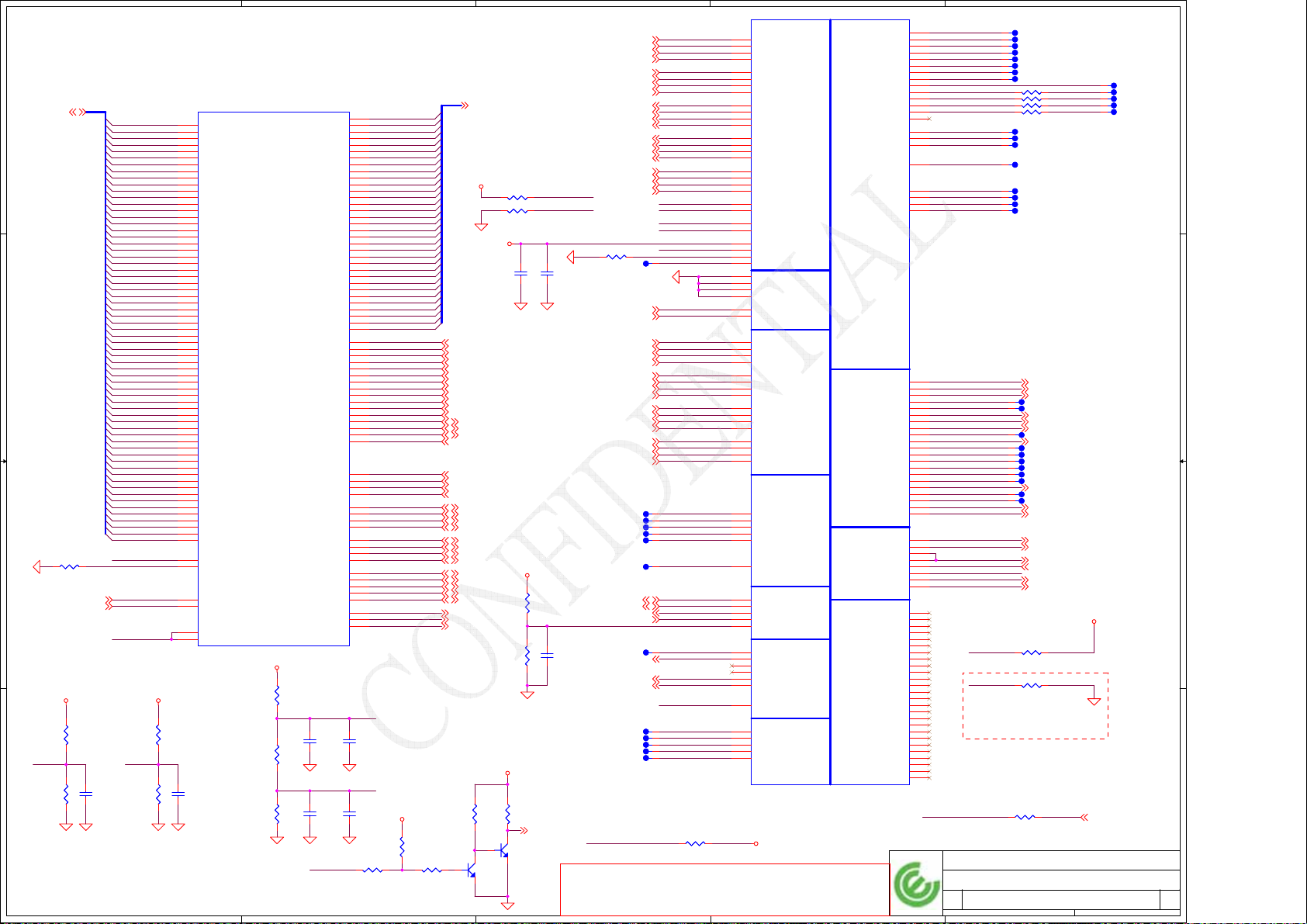

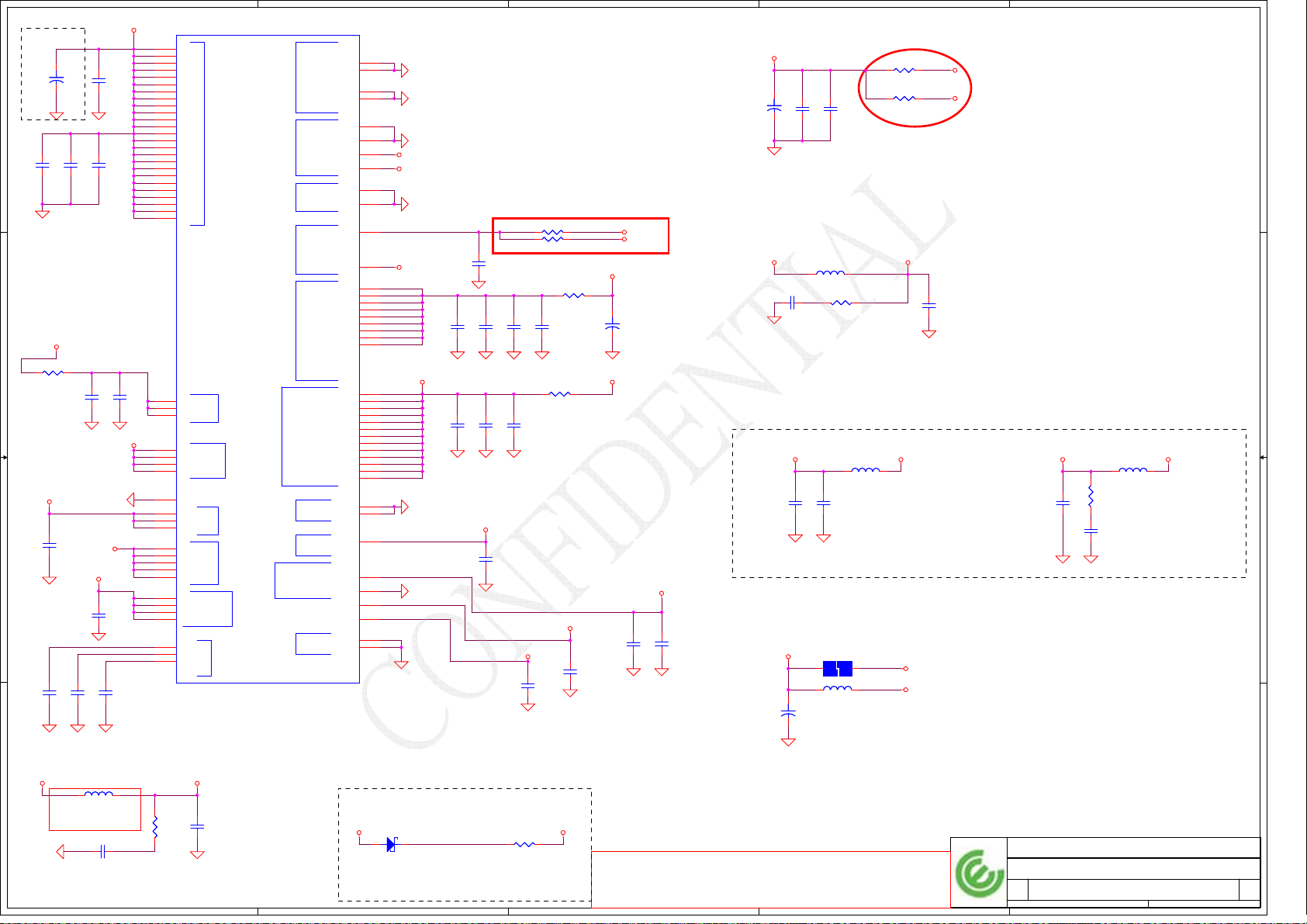

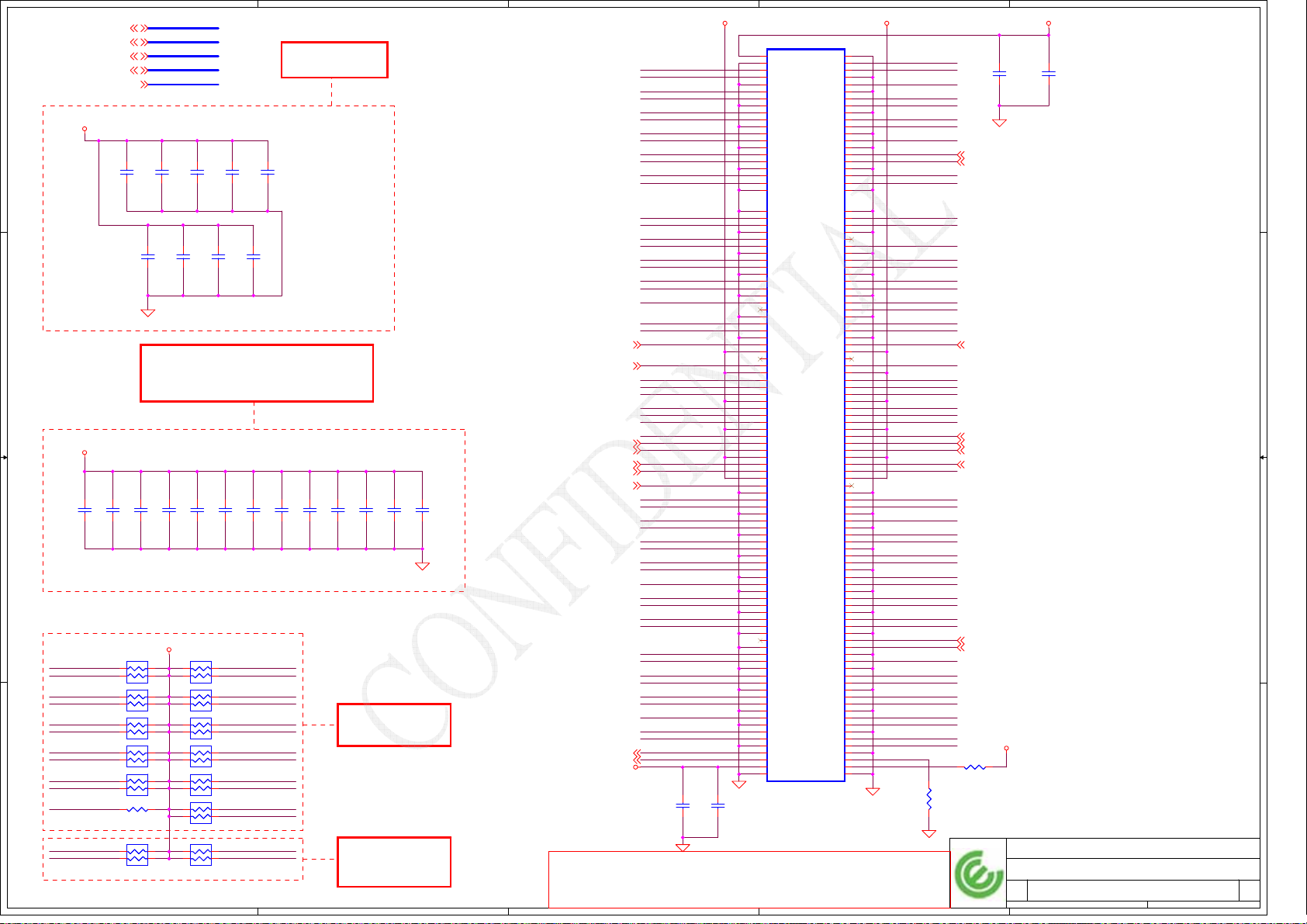

Block Diagram

Compal confidential

Model : JAL22

1 1

CRT CONN

+5V_RUN

page 20

VGA/SVID

Video Switch

+3.3V_RUN

LVDS CONN

+5V_ALW

+3.3V_RUN

+PWR_SRC

2 2

DOCKING

PORT

+PWR_SRC

+1.8V_LAN_M

USB[8,9]

Mini Card 3

WPAN/BT/Robson

3 3

+3.3V_RUN

SCREW HOLE

LED

GPUCORE / 1.1V

4 4

Selector

page 35

DAI

SATA5

page 42

page 41

page 40

on M/B Board

page 19

DP Switch

+5V_RUN

DP CONN

+5V_RUN

SD CONN

+3.3V_RUN

Through FPC to SD Board

DC IN

BATT IN

1.5V/1.05V

1.8V/0.9V

VCORE (IMVP-6)CHARGER

A

FAN

+FAN1_VOUT

TS3DV520

page 20

TS2DP512

page 21

page 21

page 31

Mini Card 2

+3.3V_WLAN

+1.5V_RUN+1.5V_RUN

page 43

3V/5V

page 44

page 45

page 46

page 47page 48

page 18

DPC

WLAN

USB[4]

VGA

SVID

+FBVDDQ

+3.3V_RUN

LVDS

+1.1V_GFX_PCIE

+GPU_CORE

CardBus

R5C847

+3.3V_RUN

PCI Express BUS

page 34page 34

RFID

page 36

73S8009CN

+3.3V_RUN

page 36

Smart Card

page 36

+3.3V_SUS

NV G98

IDSEL:AD17

(GNT#1,REQ#1)

(PIRQD#,PIRQB#,PIRQC#)

USB[7]

+3.3V_RUN

Trough Cable

B

Thermal

GUARDIAN III

EMC4002

page 51,52,53,54,55,56

DPB

PCI BUS

page 31,32

+3VRUN 33MHz

Through FPC to IO Board

PCIE1PCIE2PCIE3

Mini Card 1

WWAN

+3.3V_RUN

+1.5V_RUN

page 34

USB[5]USB[6]

USH I/F

BCM5880

+3.3V_RUN

+2.5V_AVDD_5880

+1.2V_AVDD_5880

USBH

Biometric

TPM 1.2

ME & LED

B

page 18

PCIE-E 16X

SNIFFER

IEEE1394

page 31

SIM card

USB[10]

page 36

page 42

ECE1077

+3.3V_ALW

Int.KBD &

Stick

C

Pentium-M

+1.5V_RUN

+1.05V_VCCP

+VCC_CORE

H_A#(3..35) H_D#(0..63)

Penryn -4MB (Socket P)

uFCPGA CPU

478pin

page 7,8,9

System Bus

FSB 1066 MHz

INTEL

Cantiga

+1.5V_RUN

+1.8V_MEM

+1.05V_VCCP

+3.3V_RUN

+1.05V_M

1329pin BGA

page 10,11,12,13,14,15

DMI

+1.5V_RUN

100MHz

+5V_ALW

+5V_RUN

+RTC_CELL

+3.3V_RUN

+3.3V_ALW_ICH

+1.5V_RUN

+1.05V_VCCP

INTEL

ICH9-M

676pin BGA

page 22,23,24,25

LPC BUS

+3V_RUN

page 34

33MHz

LPC BUS

SMSC KBC

+RTC_CELL

+3.3V_ALW

BC

MEC5035

page 38

SMBus

Touch Pad

page 39

page 39page 33

Stick

BC BUS

C

E-Module

+5V_MOD

SPI

SPI

BC BUS

SMSC SIO

ECE5028

+3.3V_ALW

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

D

CPU ITP Port

+1.05V_VCCP

Memory BUS (DDR2)

+1.8V_MEM 667/800 MHz

48MHz

GLCI/LCI

Azalia I/F

S-ATA(4)

SATA0SATA1

S-HDD

+3.3V_RUN

page 26 page 26

+5V_HDD

W25X32VSSIG

+3.3V_LAN

page 24

32Mbit

W25X32VSSIG

+3.3V_LAN

+3.3V_ALW

page 24

SST25VF

16Mbit

page 38

Expend GPIO

ECE1088

+3.3V_ALW

page 39

DOCK LPC BUS

page 37

D

Clock Generator

SLG8LP554

+3.3V_M

DDRII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7 ,8

+0.9V_DDR_VTT

+1.8V_MEM

USB[11]

USB[2,3]

LEFT SIDE

USB[0,1] RIGHT SIDE

Intel Boazman

+3.3V_ALW

+1.8V_LAN_M

+1V_LAN_M

Azalia Codec

92HD71B

+3.3V_RUN

+VDDA

MDC

+3V_SUS

RJ11

page 27

HeadPhone &

MIC Jack

+3.3V_RUN

Through Cable

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

E

CK505

page6page 7

page 16,17

USB Port

Camera

E-SATA

USB Port1 X1

Charger USB Port X1

+5V_ALW

USB Ports X2

+5V_ALW

82567LF

page 29

AMP & INT.

Speaker

+5V_RUN

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

page 28

On IO/B

E

Trough LVDS Cable

page 19

SATA4

page 33

On IO/B

LAN Switch

P13L500

+3.3V_LAN

page 30

RJ45

On IO/B

Trough LVDS Cable

Dig. MIC

+VDDA

DAI

SSM2602

+3.3V_RUN

256Monday, December 17, 2007

256Monday, December 17, 2007

256Monday, December 17, 2007

page 27

DOCKING

of

of

of

A

A

A

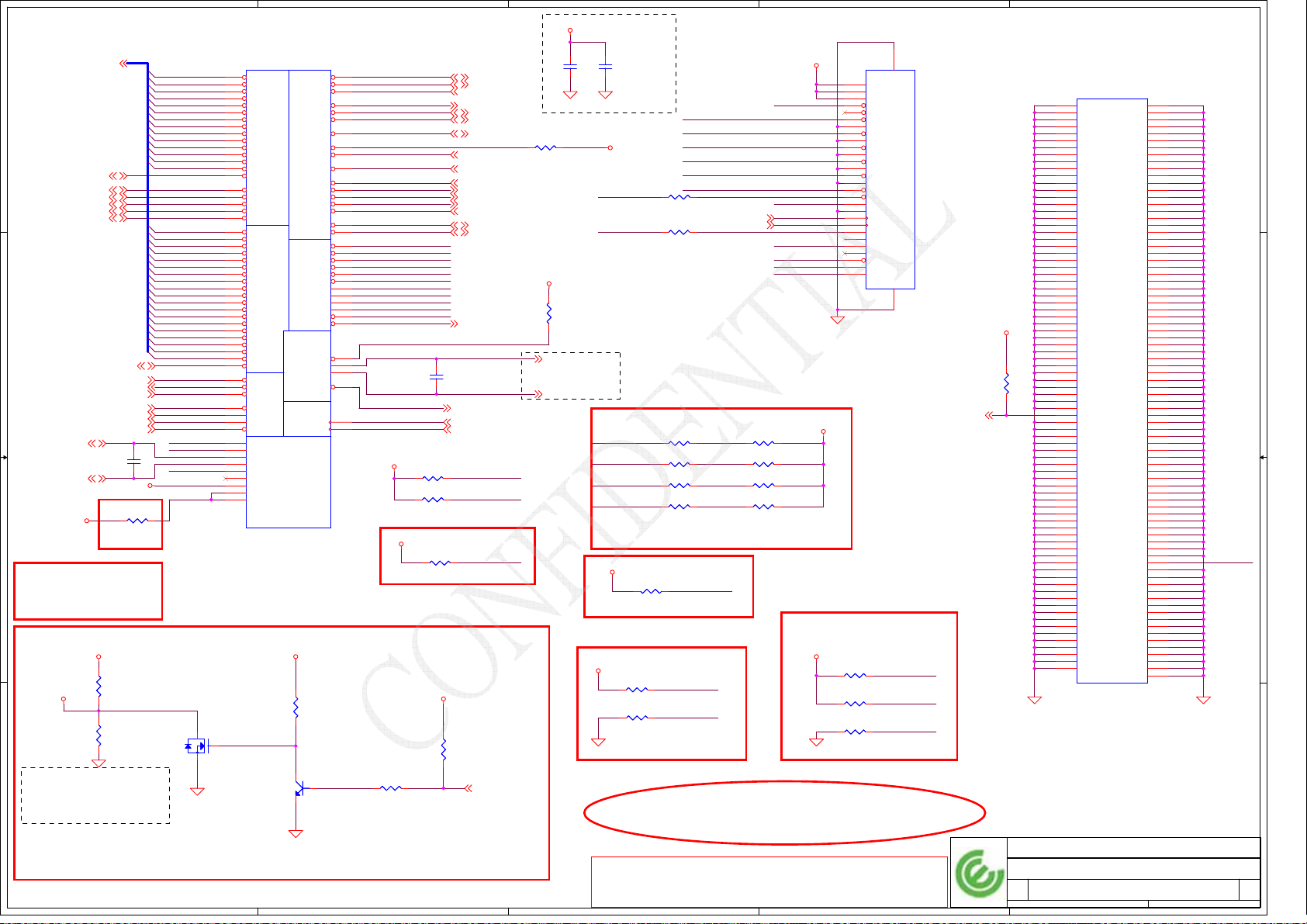

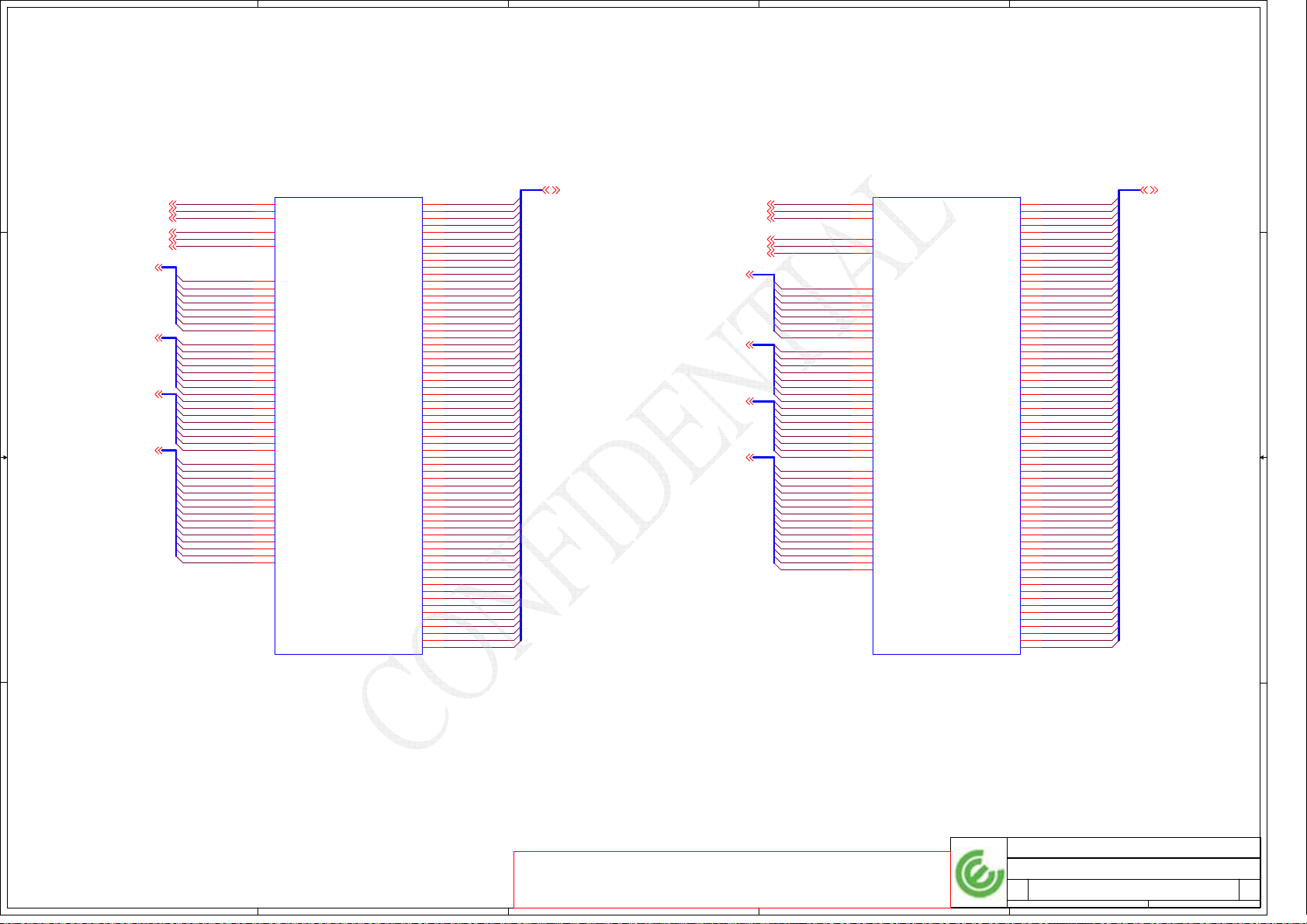

Page 3

5

4

3

2

1

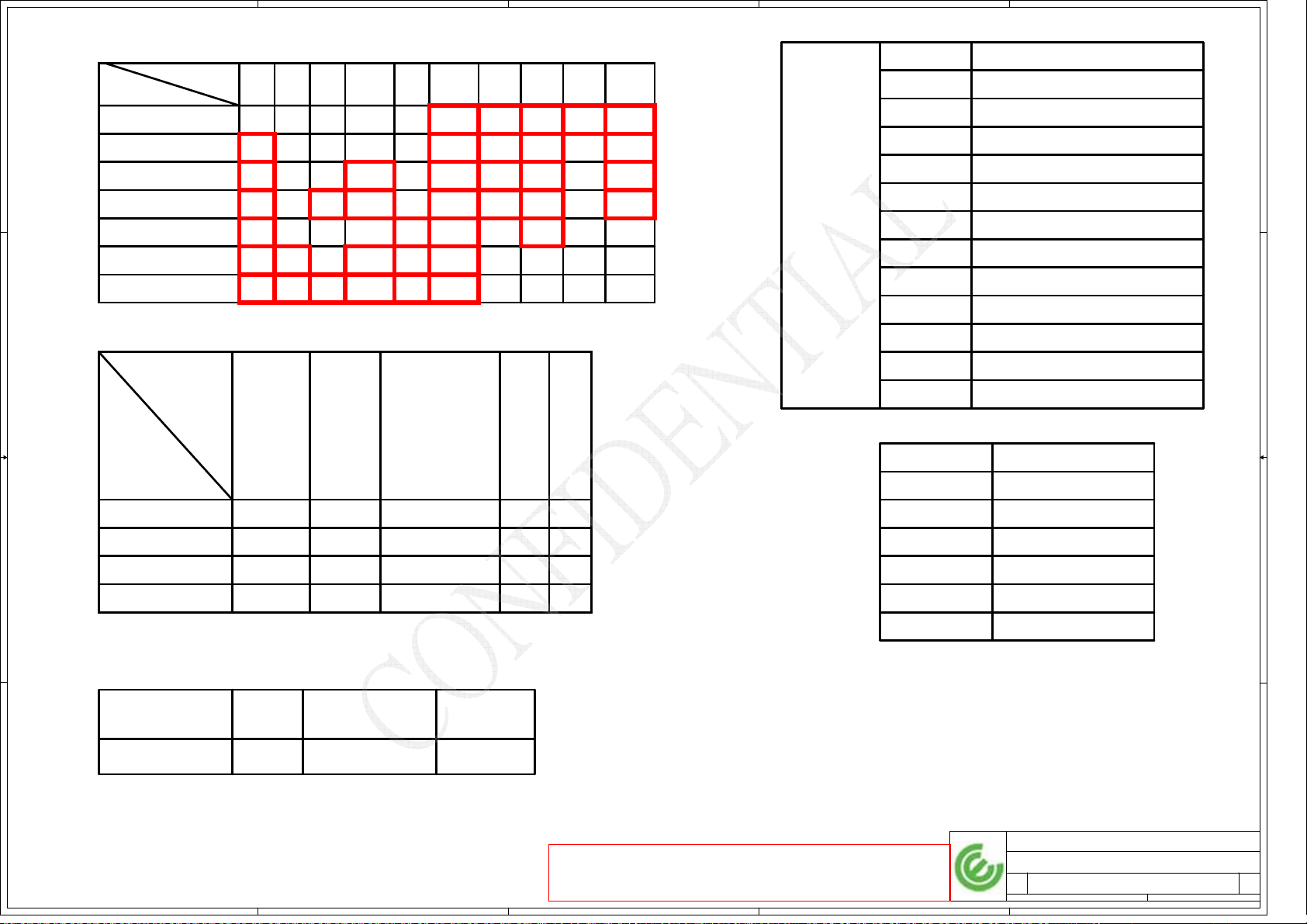

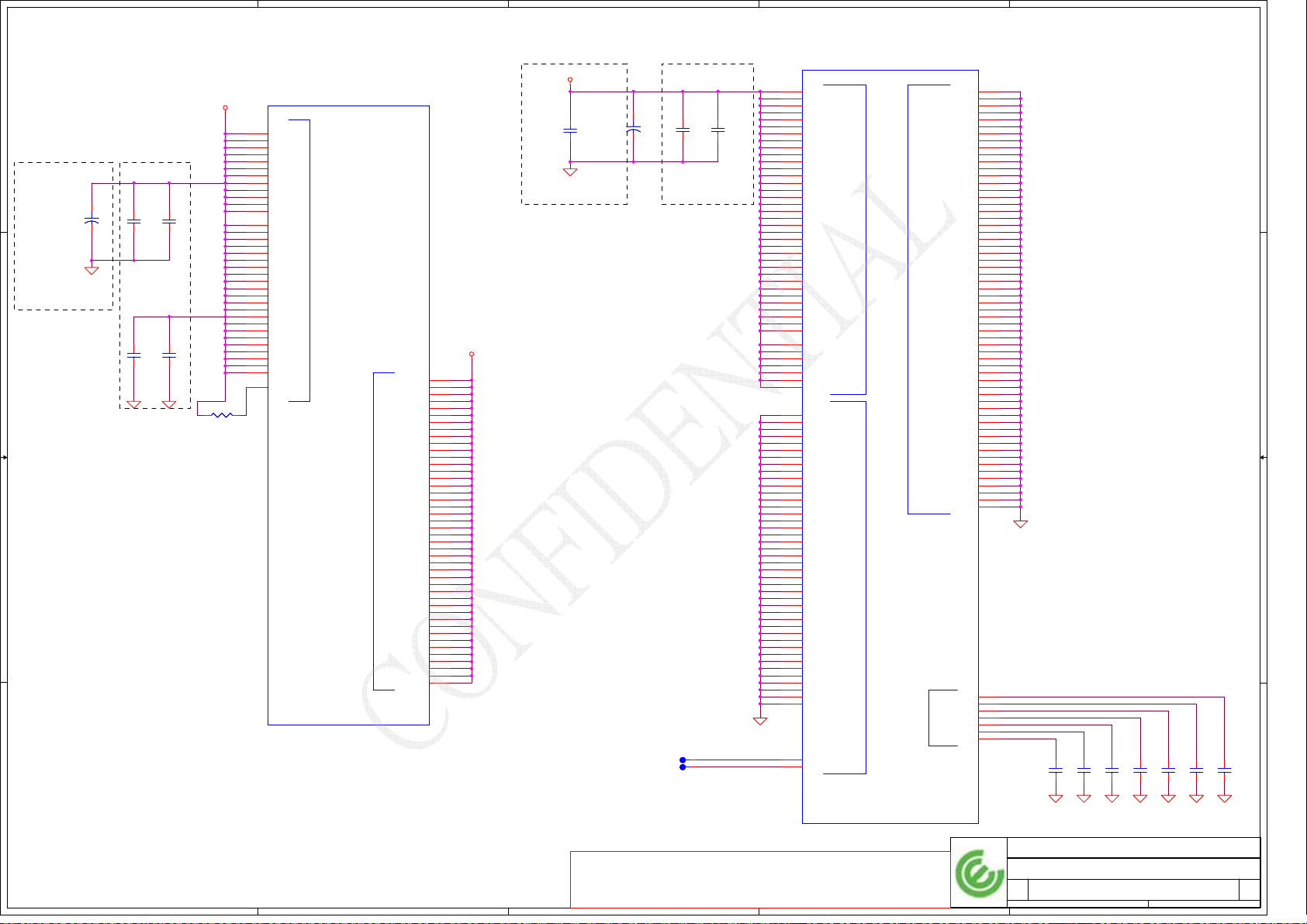

POWER STATES

State

D D

S0 (Full ON) / M0

S3 (Suspend to RAM) / M1

S4 (Suspend to DISK) / M1 ON ON ON ONOFF

S5 (SOFT OFF) / M1 ON ON ON ONOFFLOW HIGH LOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

Signal

SLP

SLP

S3#

S4#

HIGH HIGH HIGH

HIGH

LOW HIGH HIGH HIGH ON ON ON ONOFF

LOW HIGH HIGH HIGHLOW

LOW HIGH HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

S5#

HIGH

S4

STATE#

SLP

M#

HIGH

HIGH

ALWAYS

PLANE

ON

M

PLANE

ON

SUS

RUN

PLANE

PLANE

ON ON ON

CLOCKS

ICH9-M

USB PORT#

0

1

2

3

4

5

6

7

DESTINATION

JUSB1 (Ext Right Side Top)

JUSB1 (Ext Right Side Bottom)

JESA1 (Ext Left Side Bottom)

JESA1 (Ext Left Side TOP)

WLAN

WWAN

WPAN

Card Bus/Express card

DOCKING8

C C

B B

PM TABLE

State

S0

S3

S5 S4/AC

S5 S4/AC don't exist

power

plane

+15V_ALW

+5V_ALW

+3.3V_ALW_ICH

+3.3V_RTC_LDO

ON

ON

+3.3V_SUS

+1.8V_MEM

ON ON

ON

OFF

OFFOFF

+5V_RUN

+3.3V_RUN

+2.5V_RUN

+1.5V_RUN

+0.9V_DDR_VTT

+GPU_CORE

+VCC_CORE

+1.05V_VCCP

+FBVDDQ

+1.1V_GFX_PCIE

OFFON

OFF

OFF

ON

ON

ON

+3.3V_M

(M-OFF)

ON

OFF

OFF

OFFOFF

+3.3V_M

+1.05V_M +1.05V_M

9

11

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

DOCKING

USH->BIO10

Camera

DESTINATION

MINI CARD-1 WWAN

MINI CARD-2 WLAN

MINI CARD-3 BT/UWB

EXPRESS CARD

None

Lane 6

10/100/1G LAN

PCI TABLE

PCI DEVICE IDSEL

REQ#/GNT#

PIRQ

R5C847 REQ#1 / GNT#1AD17 PIRQ[B..D]

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

356Monday, December 17, 2007

356Monday, December 17, 2007

356Monday, December 17, 2007

1

A

A

A

of

of

of

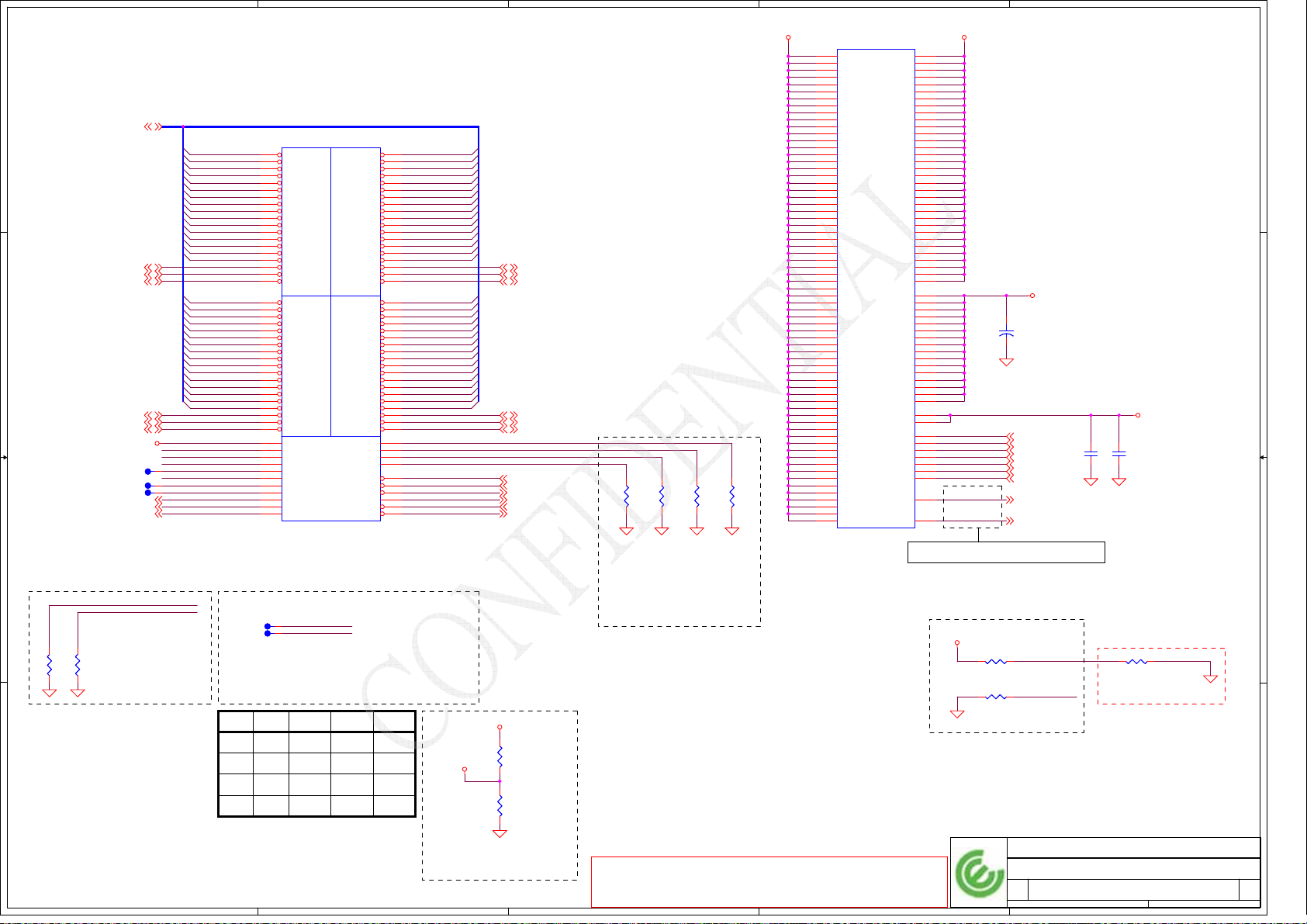

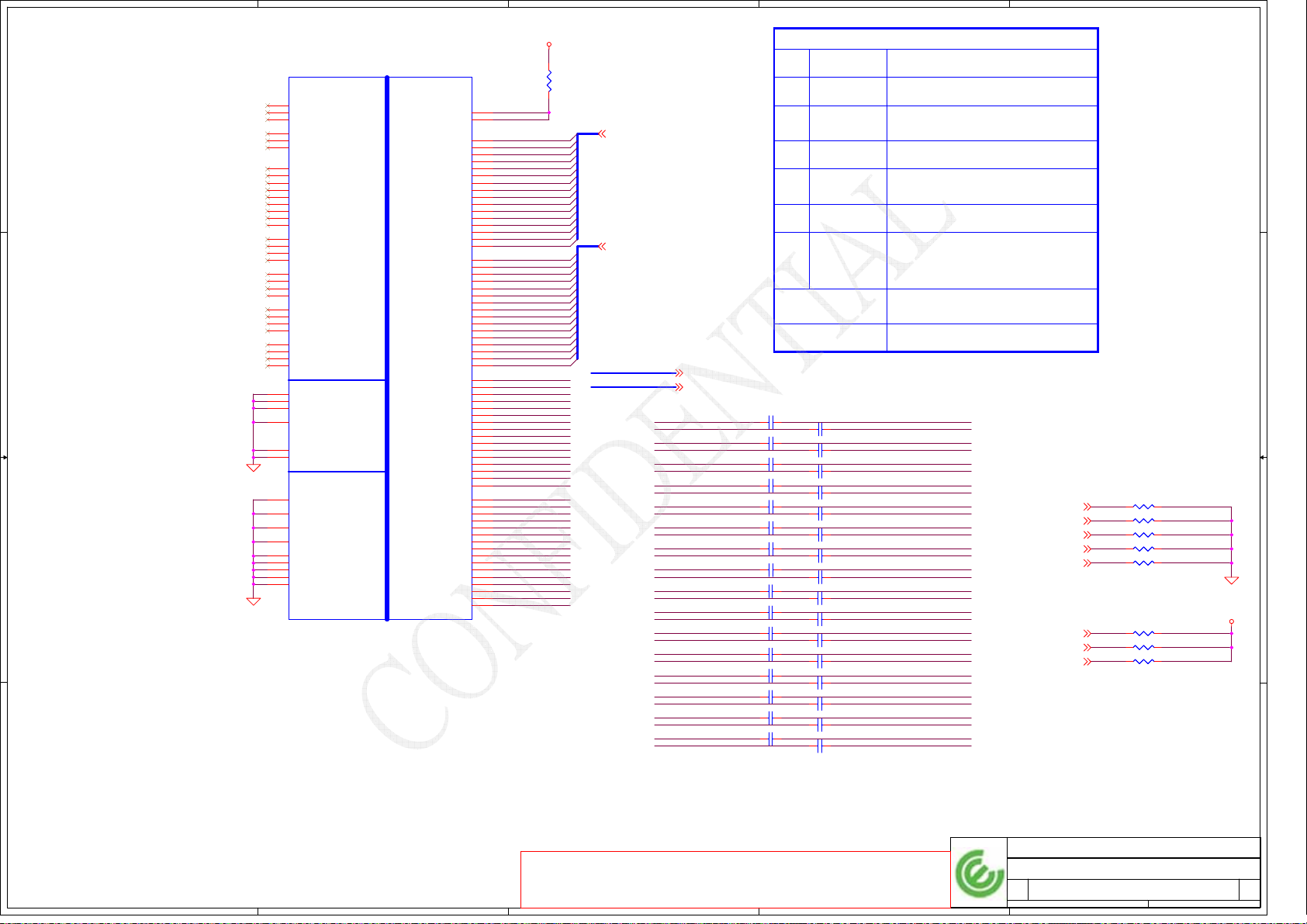

Page 4

5

4

3

2

1

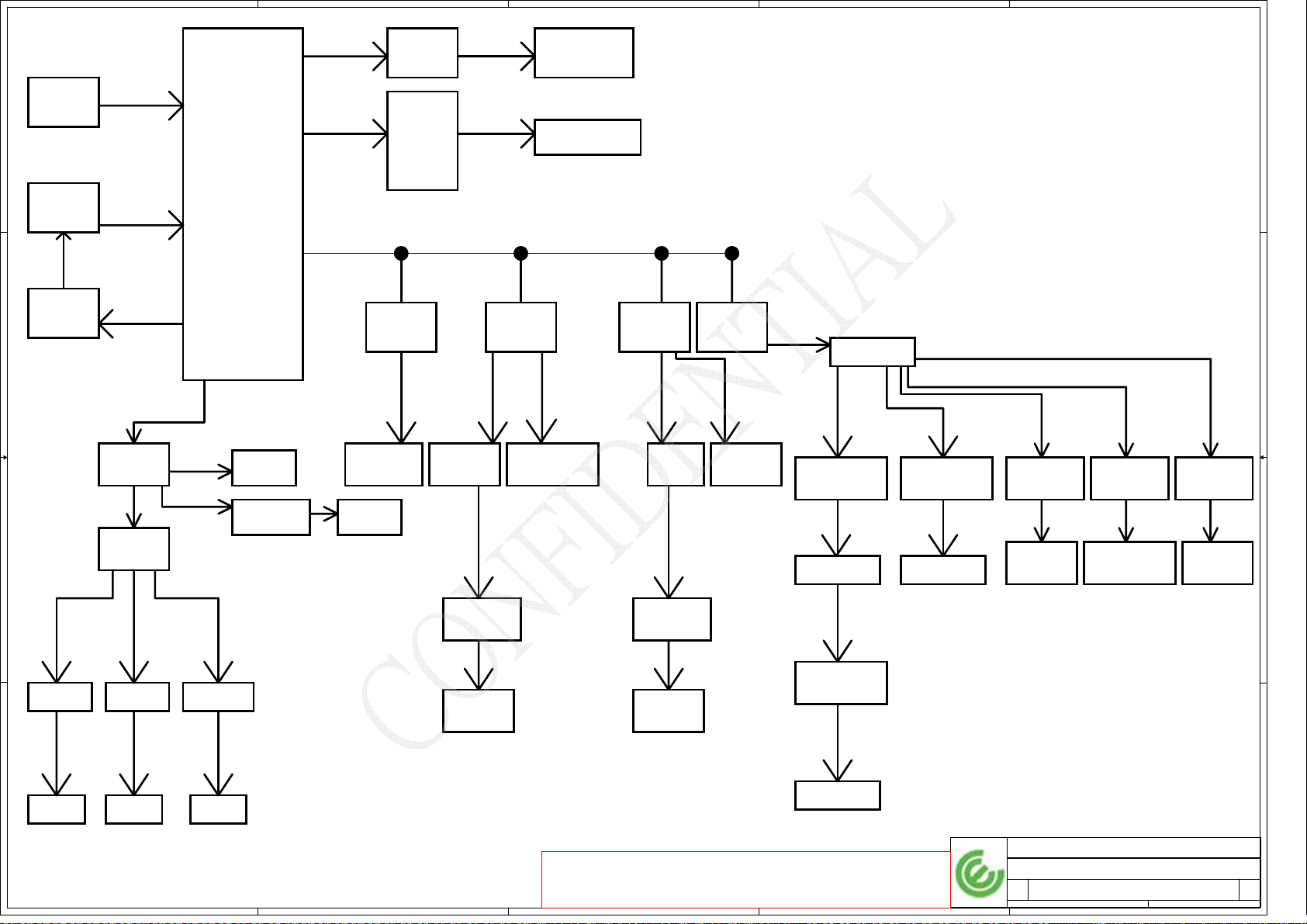

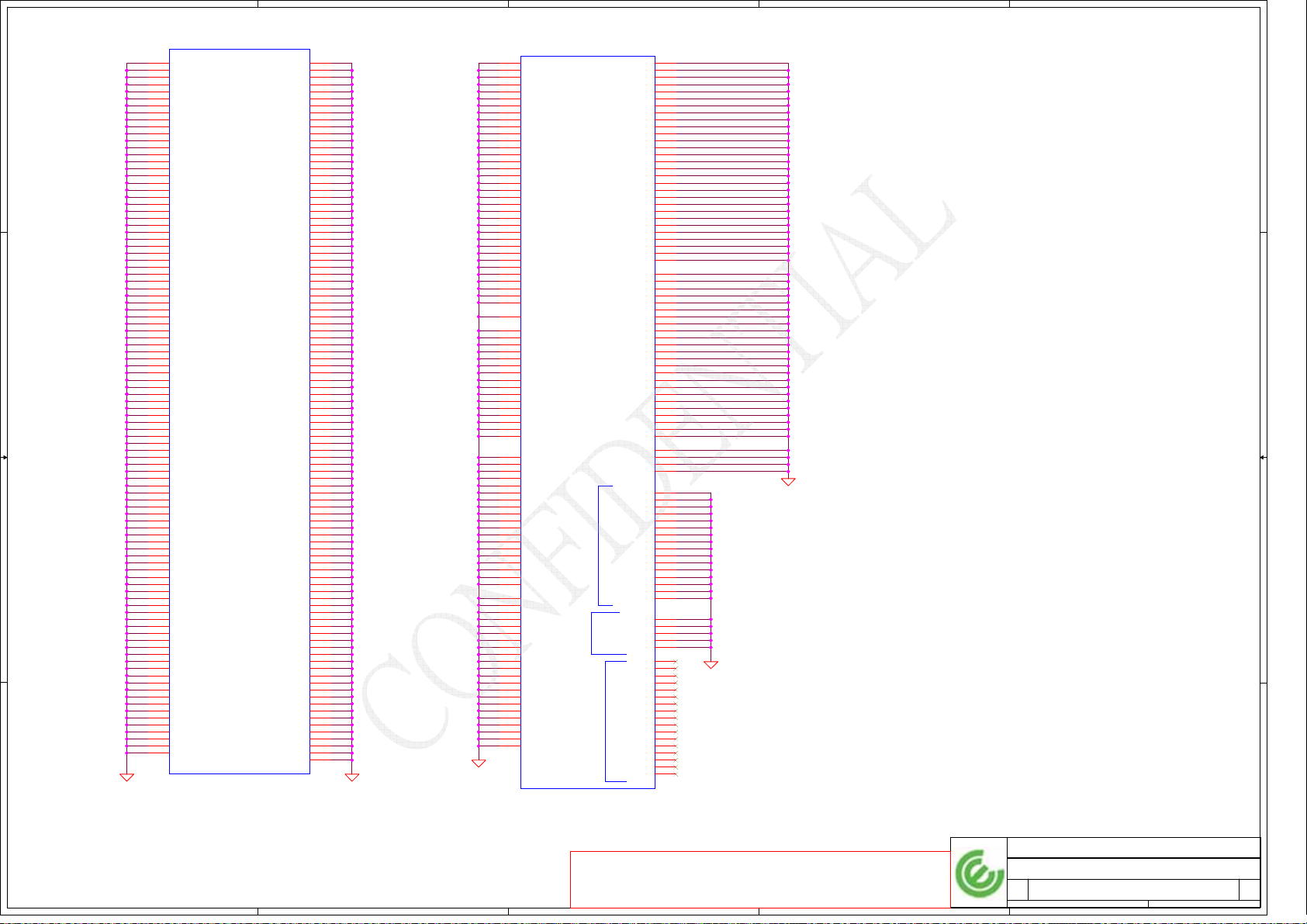

RUN_ON

SI3457

( Q17 )

+INV_PWR_SRC

ADAPTER

D D

GFX_CORE_CNTRL

MAX17007

(PU13)

+GPU_COREP

RUN_ON

+PWR_SRC

+15V_ALW

(Q55)

ISL6260

(PU7)

IMVP_VR_ON

+VCC_CORE

+5V_RUNSTS11NF30L

DDR_ON

+1.8V_MEM

GFX_CORE_PWRGD

TPS51116

(PU4)

+0.9V_DDR_VTT

SN0608098

0.9V_DDR_VTT_ON

(PU3)

M_ON

(PU2)

1.5V_RUN_ON

+1.05V_M +1.5V_RUN

1.05V_RUN_ON

SN0608098

ALWON

+3.3V_ALW

ENAB_3VLAN

STS11NF30L

(Q44)

+3.3V_LAN

3.3V_RUN_ON

SI4336DY

+3.3V_RUN

(Q61)

SUS_ON

STS11NF30L

(Q60)

+3.3V_SUS

ICH_ALW_ON

SI3456BDV

(Q54)

+3.3V_ALW_ICH

M_ON

SI3456BDV

(Q54)

+3.3V_M

BATTERY

CHARGER

C C

ALW_ON

SN0608098

(PU2)

+5V_ALW

B B

HDDC_EN

MODC_EN

STS11NF30L

(Q116)

RUN_ON

SI4336DY

(Q67)

REGCTL_PNP18

BCP69

SI3456BDVSI3456BDV

(Q29)(Q32)

A A

+5V_HDD

+5V_MOD

MAX9789A

(U22)

+VDDA

+FBVDDQ

(Q45)

+1.05V_VCCP

+1.8V_LAN_M

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

456Monday, December 17, 2007

456Monday, December 17, 2007

456Monday, December 17, 2007

1

A

A

A

of

of

of

Page 5

5

G16

A13

ICH_SMBCLK

ICH_SMBDATA

ICH9-M

D D

C17

B18

AMT_SMBCLK

AMT_SMBDAT

2.2K

2.2K

10K

10K

4

+3.3V_ALW_ICH

+3.3V_ALW_ICH

2N7002

2N7002

MEM_SCLK

MEM_SDATA

3

2.2K

2.2K

+3.3V_M

197

195

197

195

DIMMA

DIMMB

SMBUS Address [TBD]

SMBUS Address [TBD]

2

1

8.2K

9493

2A 2A

6

5

DOCK_SMB_CLK

DOCK_SMB_DAT

1A

1A

8.2K

8.2K

8.2K

8

7

LCD_SMBCLK

LCD_SMDATA

C C

1B

1B

+5V_ALW

+3.3V_ALW

6

5

6

5

DOCKING

INVERTER

(JLVDS)

SMBUS Address [TBD]

SMBUS Address [TBD]

2.2K

PBAT_SMBCLK

112

10

9

100

99

97

PBAT_SMBDAT

CARD_SMBCLK

CARD_SMBDAT

SIO

B B

1C1C111

1D

1D

1E

1E

1F1F98

2.2K

MEC 5035

96

1G

95

1H

2.2K

12

1H

1H

A A

1J

1J

CKG_SMBDAT

13

CKG_SMBCLK

106

105

Dedicated JTAG

2.2K

9

Charger

10

SMBUS Address [TBD]

103

1K

102

1K

5

Dedicated JTAG

+3.3V_ALW

+3.3V_ALW

4

100 ohm

100 ohm

3

BATTERY

4

CONN

2N7002

2N7002

2N7002

2N7002

SMBUS Address [TBD]

2.2K

2.2K

CLK_SDATA

CLK_SCLK

DAI

SMBUS Address [TBD]

3

+3.3V_M

17

16

CLK GEN

2.2K

2.2K

2N7002

2N7002

2N7002

2N7002

2N7002

2N7002

3032

WWAN

SMBUS Address [TBD]

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

USH

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

SMBUS Address [TBD]

+3.3V_RUN

2.2K

2.2K

EXP_SMBCLK

EXP_SMBDATA

2.2K

2.2K

WLAN_SMBCLK

WLAN_SMBDATA

2.2K

2.2K

MINI_SMBCLK

MINI_SMBDATA

SMBUS Address [TBD]

2

+3.3V_SUS

7

8

Express card

+3.3V_WLAN

30

32

WLAN

+3.3V_RUN

30

32

BT/UWB

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

556Monday, December 17, 2007

556Monday, December 17, 2007

556Monday, December 17, 2007

1

of

of

of

A

A

A

Page 6

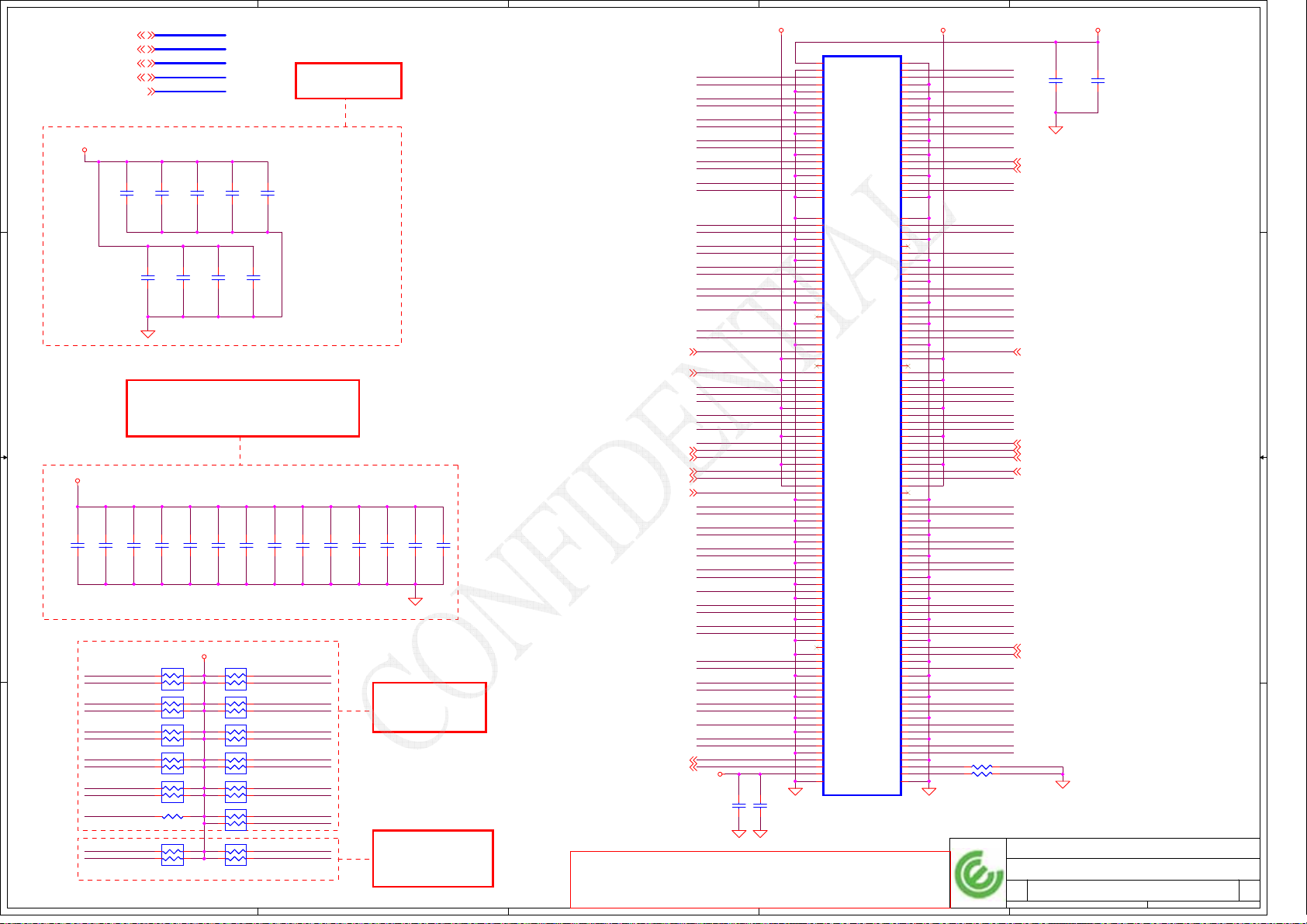

5

+3.3V_M

1 2

R3

@R3

@

0_0402_5%~D

0_0402_5%~D

CKG_SMBDAT<27,38,48>

D D

CKG_SMBCLK<27,38,48>

FSC FSB FSA CPU

CLKSEL2 CLKSEL0CLKSEL1

000

*

00

1

0

11

C C

0

1

1

0

11

+3.3V_M

12

R51

@R51

@

10K_0402_5%~D

10K_0402_5%~D

FSA

12

R55

@R55

@

10K_0402_5%~D

10K_0402_5%~D

B B

+3.3V_RUN

10K_0402_5%~D

10K_0402_5%~D

R43

R43

1 2

PCI_PCM

R46

R46

PCI_ICH

R50

R50

R54

R54

*

*

+3.3V_RUN

10K_0402_5%~D

10K_0402_5%~D

1 2

+3.3V_RUN

10K_0402_5%~D

10K_0402_5%~D

1 2

A A

PCI_SIO

10K_0402_5%~D

10K_0402_5%~D

12

@

@

*

6 1

Q1A

Q1A

2N7002DW-T/R7_SOT363-6~D

2N7002DW-T/R7_SOT363-6~D

+3.3V_M

2

5

Q1B

Q1B

2N7002DW-T/R7_SOT363-6~D

2N7002DW-T/R7_SOT363-6~D

3

1 2

R9

@R9

@

0_0402_5%~D

0_0402_5%~D

4

SRC

MHz

MHz

100

266

1

0

00

1

0

TME PIN 32

0

1

ITP_EN

0

1 Pin 5/6 as CPU_ITP

0=UMA

1=DIS

100

133

100

200

100

166

100

333

100

100

100

400

overclocking enabled

overclocling disabled

PIN 37

Pin 5/6 as SRC_10

PIN43FCTSEL1 PIN48PIN47PIN44

27M_out

2.2K_0402_5%~D

2.2K_0402_5%~D

2.2K_0402_5%~D

2.2K_0402_5%~D

12

12

R1

R1

R2

R2

CLK_SDATA

CLK_SCLK

PCI

MHz

33.3

33.3

33.3

33.3

Place crystal within

33.3

500 mils of CK505

33.3

33.3

CLK_ICH_48M<24>

CPU_MCH_BSEL0<8,10>

CPU_MCH_BSEL1<8,10>

CPU_MCH_BSEL2<8,10>

CLK_PCI_5028<37>

CLK_PCI_TPM<36>

CLK_PCI_PCM<31>

CLK_PCI_DOCK<35>

CLK_PCI_5035<38>

CLK_ICH_14M<24>

CLK_SIO_14M<37>

CLK_NV_27M<51>

CLK_NVSS_27M<51>

CLK_PCI_ICH<22>

CLK_PWRGD<24>

96/100M_TDOT96CDOT96T

0=UMA

1=Disc. GRFX down

5

4

1 2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

L1

L1

BLM21AG601SN1D_0805~D

BLM21AG601SN1D_0805~D

1

C1

C1

2

4.7U_0603_6.3V4Z~D

4.7U_0603_6.3V4Z~D

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

1

1

@

@

C11

C11

C12

C12

2

2

X1

X1

14.31818MHz_20P_1BX14318CC1A~D

33P_0402_50V8J~D

33P_0402_50V8J~D

33P_0402_50V8J~D

33P_0402_50V8J~D

14.31818MHz_20P_1BX14318CC1A~D

12

C16

C16

C17

C17

12

CLK_ICH_48M FSA

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

CLK_PCI_5028

CLK_PCI_TPM PCI_TPM

CLK_PCI_PCM PCI_PCM

CLK_PCI_DOCK

CLK_PCI_5035 PCI_EC

CLK_ICH_14M

CLK_SIO_14M

CLK_NV_27M

CLK_NVSS_27M

CLK_PWRGD

12

R17 0_0402_5%~DR17 0_0402_5%~D

R19 33_0402_5%~D

R19 33_0402_5%~D

R22 2.2K_0402_5%~D

R22 2.2K_0402_5%~D

R24 10K_0402_5%~D

R24 10K_0402_5%~D

R26 33_0402_5%~D

R26 33_0402_5%~D

R29 22_0402_5%~D

R29 22_0402_5%~D

R30 22_0402_5%~D

R30 22_0402_5%~D

R27 22_0402_5%~D

R27 22_0402_5%~D

R32 33_0402_5%~D

R32 33_0402_5%~D

R33 22_0402_5%~D

R33 22_0402_5%~D

R35 22_0402_5%~D

R35 22_0402_5%~D

R37 33_0402_5%~DR37 33_0402_5%~D

R38 33_0402_5%~DR38 33_0402_5%~D

R41 33_0402_5%~D

R41 33_0402_5%~D

+CK_VDD_MAIN2

1 2

L2

@L2

@

BLM21PG600SN1D_0805~D

BLM21PG600SN1D_0805~D

+CK_VDD_REF+CK_VDD_48

0.047U_0402_16V7K~D

0.047U_0402_16V7K~D

1

C13

C13

2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

12

12

12

12

96/100M_C

SRCC0SRCT027M SSout

4

+CK_VDD_MAIN+3.3V_M

0_0805_5%~D

0_0805_5%~D

R851

R851

1 2

1 2

R12 0_0603_5%~D R12 0_0603_5%~D

1 2

R14 0_0603_5%~D R14 0_0603_5%~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

+CK_VDD_MAIN

1

2

1

2

+CK_VDD_REF

+CK_VDD_48

CLK_XTAL_IN

CLK_XTAL_OUT

FSC

PCI_SIO

CLKREF

CLK_NV

CLK_NVSS

PCI_ICHCLK_PCI_ICH

CLK_SCLK

CLK_SDATA

3

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

10U_0805_10V4Z~D

10U_0805_10V4Z~D

1

C3

C3

C2

C2

2

10U_0805_10V4Z~D

10U_0805_10V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

@

@

C8

C8

C9

C9

2

1 2

R10 2.2_0603_5%~D

R10 2.2_0603_5%~D

U1

U1

1

VDD_SRC

49

VDD_SRC

54

VDD_SRC

65

VDD_SRC

30

VDD_PCI

36

VDD_PCI

12

VDD_CPU

18

VDD_REF

40

VDD_48

20

XTAL_IN

19

XTAL_OUT

41

USB_48MHz/FSLA

45

FSL_B/TEST_MODE

23

REF_0/FSL_C/TEST_SEL

34

PCICLK4/FCT_SEL

33

PCICLK3

32

PCICLK2/TME

27

PCICLK1

22

REF_1

43

DOT_96/27M

44

DOT_96#/27M_SS

37

PCICLK_F0/ITP_EN

39

CKPWRGD/PD#

9

NC

16

SMBCLK

17

SMBDAT

4

VSS_SRC

15

VSS_CPU

21

VSS_REF

31

VSS_PCI

35

VSS_PCI

42

VSS_48

68

VSS_SRC

73

THRM_PAD

SLG8LP554VTR_QFN72_10X10~D

SLG8LP554VTR_QFN72_10X10~D

1

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

SLG8LP554VTR

SLG8LP554VTR

C4

C4

C10

C10

C5

C5

2

CPU_STP#

CPU_ITP/SRC_10

CPU_ITP#/SRC_10#

CLKREQ_9#

CLKREQ_8#

CLKREQ_7#

CLKREQ_6#

CLKREQ_5#

CLKREQ_4#

CLKREQ_3#

CLKREQ_2#

SRC_1/SATA

SRC_1#/SATA#

CLKREQ_1#

LCD_CLK/SRC_0

LCD_CLK#/SRC_0#

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

+CK_VDD_A

VDD_A

VSS_A

PCI_STP#

CPU_1

CPU_1#

CPU_0

CPU_0#

SRC_9

SRC_9#

SRC_8

SRC_8#

SRC_7

SRC_7#

SRC_6

SRC_6#

SRC_5

SRC_5#

SRC_4

SRC_4#

SRC_3

SRC_3#

SRC_2

SRC_2#

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

C7

C7

C6

C6

2

7

8

H_STP_PCI#

25

H_STP_CPU#

24

MCH_BCLK CLK_MCH_BCLK

11

MCH_BCLK#

10

CPU_BCLK

14

CPU_BCLK#

13

CPU_ITP

6

CPU_ITP#

5

PCIE_MINI1

3

PCIE_MINI1#

2

MINI1CLK_REQ#

72

PCIE_MINI2

70

PCIE_MINI2#

69

MINI2CLK_REQ#

71

PCIE_ICH

66

PCIE_ICH#

67

38

63

64

MINI3CLK_REQ#

62

PCIE_VGA CLK_PCIE_VGA

60

PCIE_VGA# CLK_PCIE_VGA#

61

29

PCIE_EXP CLK_PCIE_EXP

58

PCIE_EXP# CLK_PCIE_EXP#

59

EXPCLK_REQ#

57

MCH_3GPLL

55

56

CLK_3GPLLREQ#_R

28

52

53

26

PCIE_SATA CLK_PCIE_SATA

50

PCIE_SATA#

51

SATA_CLKREQ#_R

46

47

48

2

4.7U_0603_6.3V4Z~D

4.7U_0603_6.3V4Z~D

1

C14

C14

2

1 2

R11 33_0402_5%~D

R11 33_0402_5%~D

1 2

R13 33_0402_5%~D

R13 33_0402_5%~D

1 2

R15 33_0402_5%~D

R15 33_0402_5%~D

1 2

R16 33_0402_5%~D

R16 33_0402_5%~D

1 2

R18 33_0402_5%~D

R18 33_0402_5%~D

1 2

R21 33_0402_5%~D

R21 33_0402_5%~D

1 2

R23 33_0402_5%~D

R23 33_0402_5%~D

1 2

R25 33_0402_5%~D

R25 33_0402_5%~D

1 2

R28 33_0402_5%~D

R28 33_0402_5%~D

1 2

R31 33_0402_5%~D

R31 33_0402_5%~D

1 2

R34 33_0402_5%~D

R34 33_0402_5%~D

1 2

R36 33_0402_5%~D

R36 33_0402_5%~D

1 2

R39 33_0402_5%~D

R39 33_0402_5%~D

1 2

R40 33_0402_5%~D

R40 33_0402_5%~D

1 2

R42 33_0402_5%~DR42 33_0402_5%~D

1 2

R44 33_0402_5%~DR44 33_0402_5%~D

1 2

R408 33_0402_5%~DR408 33_0402_5%~D

1 2

R415 33_0402_5%~DR415 33_0402_5%~D

1 2

R45 33_0402_5%~D

R45 33_0402_5%~D

1 2

R47 33_0402_5%~D

R47 33_0402_5%~D

1 2

R48 475_0402_1%~D

R48 475_0402_1%~D

1 2

R49 33_0402_5%~D

R49 33_0402_5%~D

1 2

R52 33_0402_5%~D

R52 33_0402_5%~D

1 2

R53 475_0402_1%~D

R53 475_0402_1%~D

2

1

+3.3V_RUN

MINI1CLK_REQ#

MINI2CLK_REQ#

CLK_3GPLLREQ#

SATA_CLKREQ#

MINI3CLK_REQ#

EXPCLK_REQ#

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

1

C15

C15

2

H_STP_PCI# <24>

H_STP_CPU# <24>

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

CLK_PCIE_MINI2

CLK_PCIE_MINI2#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_MINI3PCIE_MINI3

CLK_PCIE_MINI3#PCIE_MINI3#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#MCH_3GPLL#

CLK_3GPLLREQ#

CLK_PCIE_SATA#

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CLK_CPU_BCLK <7>

CLK_CPU_BCLK# <7>

CLK_CPU_ITP <7>

CLK_CPU_ITP# <7>

CLK_PCIE_MINI1# <34>

MINI1CLK_REQ# <34>

CLK_PCIE_MINI2 <34>

CLK_PCIE_MINI2# <34>

MINI2CLK_REQ# <34>

CLK_PCIE_ICH <24>

CLK_PCIE_ICH# <24>

CLK_PCIE_MINI3 <34>

CLK_PCIE_MINI3# <34>

MINI3CLK_REQ# <34>

CLK_PCIE_VGA <51>

CLK_PCIE_VGA# <51>

CLK_PCIE_EXP <32>

CLK_PCIE_EXP# <32>

EXPCLK_REQ# <32>

CLK_MCH_3GPLL <10>

CLK_MCH_3GPLL# <10>

CLK_3GPLLREQ# <10>

CLK_PCIE_SATA <23>

CLK_PCIE_SATA# <23>

SATA_CLKREQ# <24>

1 2

R4 10K_0402_5%~D

R4 10K_0402_5%~D

1 2

R5 10K_0402_5%~D

R5 10K_0402_5%~D

1 2

R6 10K_0402_5%~D

R6 10K_0402_5%~D

1 2

R7 10K_0402_5%~D

R7 10K_0402_5%~D

1 2

R8 10K_0402_5%~D

R8 10K_0402_5%~D

1 2

R356 10K_0402_5%~D

R356 10K_0402_5%~D

CLK_PCIE_MINI1 <34>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

656Tuesday, December 18, 2007

656Tuesday, December 18, 2007

656Tuesday, December 18, 2007

1

A

A

A

of

of

of

Page 7

5

H_A#[3..35]<10>

D D

H_ADSTB#0<10>

H_REQ#0<10>

H_REQ#1<10>

H_REQ#2<10>

H_REQ#3<10>

H_REQ#4<10>

C C

H_ADSTB#1<10>

H_A20M#<23>

H_FERR#<23>

H_IGNNE#<23>

H_STPCLK#<23>

H_INTR<23>

H_NMI<23>

H_THERMDA1<18>

width / Spacing = 10 / 10 mil

H_THERMDC1<18>

+1.05V_VCCP

B B

Pin D22

Dual Core: 0 V

Quad Core: 2/3 VTT

+V_CPU_GTLREF_2

H_SMI#<23>

C227

C227

100P_0402_50V8K~D

100P_0402_50V8K~D

+V_CPU_GTLREF_2

51_0402_5%~D

51_0402_5%~D

QC: POP

DC: DEPOP

+1.05V_VCCP

12

@

@

R942

R942

1K_0402_1%~D

1K_0402_1%~D

12

@

@

R944

R944

2K_0402_1%~D

2K_0402_1%~D

@

@

1 2

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25 ITP_TCK

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

ITP_BPM2#1

ITP_BPM2#0

2

@

@

ITP_BPM2#2

1

R984

R984

13

D

D

S

S

Layout close CPU PIN D22

50 ohm, 0.5 inch (max)

A A

JCPU1A

JCPU1A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

D2

RSVD[06]

D22

RSVD[07]

D3

RSVD[08]

F6

RSVD[09]

TYCO_1-1674770-2_Penryn~D

TYCO_1-1674770-2_Penryn~D

Q129

Q129

BSS138_SOT23~D

BSS138_SOT23~D

@

@

2

G

G

ADDR GROUP_0

ADDR GROUP_0

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

ADDR GROUP_1

ADDR GROUP_1

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

+3.3V_ALW

12

R943

R943

100K_0402_5%~D

100K_0402_5%~D

@

@

C

C

2

B

B

E

E

MMST3904-7-F_SOT323-3~D

MMST3904-7-F_SOT323-3~D

3 1

@

@

Q14

Q14

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

4

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#H_REQ#3

H_HIT#

H_HITM#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_DBRESET#

EC_CPU_PROCHOT#

H_THERMDA

H_THERMDC

H_THERMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

+1.05V_VCCP

R973

R973

1 2

R61 56_0402_5%~D

R61 56_0402_5%~D

+1.05V_VCCP

51_0402_5%~D

51_0402_5%~D

1 2

@

@

H_ADS# <10>

H_BNR# <10>

H_BPRI# <10>

H_DEFER# <10>

H_DRDY# <10>

H_DBSY# <10>

H_BR0# <10>

H_INIT# <23>

H_LOCK# <10>

H_RESET# <10>

H_RS#0 <10>

H_RS#1 <10>

H_RS#2 <10>

H_TRDY# <10>

H_HIT# <10>

H_HITM# <10>

ITP_DBRESET# <24,37>

2

C18

@C18

@

100P_0402_50V8K~D

100P_0402_50V8K~D

1

H_THERMTRIP# <18>

CLK_CPU_BCLK <6>

CLK_CPU_BCLK# <6>

H_RESET#

51_0402_1%~D

51_0402_1%~D

H_THERMTRIP#

R785

R785

ITP_BPM#5

Place close to CPU within 200 mil

+3.3V_ALW

12

R945

R945

100K_0402_5%~D

100K_0402_5%~D

@

R946

R946

10K_0402_5%~D

10K_0402_5%~D

@

@

12

@

QUAD_REF_EN <37>

+1.05V_VCCP

Place near JITP

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

1

2

12

R56 56_0402_5%~D

R56 56_0402_5%~D

+1.05V_VCCP

12

H_THERMDA <18>

R59

R59

56_0402_5%~D

56_0402_5%~D

C19

C19

C20

C20

2

+1.05V_VCCP

H_RESET#

ITP_TDO

width / Spacing = 10 / 10 mil

H_THERMDC <18>

ITP_BPM#0 ITP_BPM2#0

ITP_BPM#1 ITP_BPM2#1

ITP_BPM#2 ITP_BPM2#2

ITP_BPM#3 ITP_BPM2#3

QC:

ES1: POP ALL

ES2: POP 0 ohm ONLY

DC: DEPOP ALL

+3.3V_ALW_ICH

R60 10K_0402_5%~D

R60 10K_0402_5%~D

Place close to JITP within 1ns = 5000 mil

+1.05V_VCCP

51_0402_5%~D

51_0402_5%~D

1 2

51_0402_5%~D

51_0402_5%~D

1 2

Place close to CPU within 200ps = 1000 mil

Depop JITP1,C19,C20,R64,R67,R785,R65,R66 when not supported for cost saving.

3

1 2

R57 1K_0402_5%~DR57 1K_0402_5%~D

1 2

R989 22.6_0402_1%~DR989 22.6_0402_1%~D

R976

R976

0_0402_5%~D

0_0402_5%~D

1 2

R978

R978

0_0402_5%~D

0_0402_5%~D

1 2

R980

R980

0_0402_5%~D

0_0402_5%~D

1 2

R982

R982

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R65

R65

R66

R66

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

@

@

@

@

@

@

@

@

ITP_DBRESET#

ITP_TDI

ITP_TRST#

CLK_CPU_ITP<6>

CLK_CPU_ITP#<6>

2

R977

R977

51_0402_1%~D

51_0402_1%~D

@

@

R979

R979

51_0402_1%~D

51_0402_1%~D

@

@

R981

R981

51_0402_1%~D

51_0402_1%~D

@

@

R983

R983

51_0402_1%~D

51_0402_1%~D

@

@

+1.05V_VCCP

ITP_DBRESET#

ITP_TCK

CLK_CPU_ITP

CLK_CPU_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

+1.05V_VCCP

+1.05V_VCCP

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

R62

R62

51_0402_5%~D

51_0402_5%~D

1 2

R64

R64

51_0402_5%~D

51_0402_5%~D

1 2

R67

R67

51_0402_5%~D

51_0402_5%~D

1 2

JITP1

JITP1

VTT1

VTT0

VTAP

DBR#

DBA#

BPM0#

GND5

BPM1#

GND4

BPM2#

GND3

BPM3#

GND2

BPM4#

GND1

BPM5#

RESET#

FBO

GND0

BCLKP

BCLKN

TDO

NC2

TCK

NC1

TRST#

TMS

TDI

Place close to JITP within 200ps = 1000 mil

29

GND6

GND7

MOLEX_52435-2891_28P~D

MOLEX_52435-2891_28P~D

30

100K_0402_5%~D

100K_0402_5%~D

QUAD_DET<37>

Pin F8

Dual Core: GND (internal)

Quad Core: Floating (internal)

ITP_TDO

ITP_TMS

ITP_TCK

+3.3V_ALW

R941

R941

@

@

1

JCPU1D

JCPU1D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

12

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

TYCO_1-1674770-2_Penryn~D

TYCO_1-1674770-2_Penryn~D

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

ITP_BPM2#3

Quad Core support circuit

5

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

756Monday, December 17, 2007

756Monday, December 17, 2007

756Monday, December 17, 2007

1

A

A

A

of

of

of

Page 8

5

4

3

2

1

+VCC_CORE +VCC_CORE

D D

C C

B B

1 2

A A

1K_0402_5%~D

1K_0402_5%~D

@R72

@

R72

+V_CPU_GTLREF

CPU_MCH_BSEL0<6,10>

CPU_MCH_BSEL1<6,10>

CPU_MCH_BSEL2<6,10>

1K_0402_5%~D

1K_0402_5%~D

@R73

@

R73

1 2

H_D#[0..63]<10>

JCPU1B

JCPU1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

C3

TEST7

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

TYCO_1-1674770-2_Penryn~D

TYCO_1-1674770-2_Penryn~D

T154PAD~D T154PAD~D

T3PAD~D T3PAD~D

TEST3

TEST5

DATA GRP 0

DATA GRP 0

DATA GRP 1

DATA GRP 1

MISC

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

BCLK BSEL2 BSEL1 BSEL0

133

001

166

200

100

TEST1

TEST2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

For the purpose of testability, route these signals

through a ground referenced Z0 = 50ohm trace that

ends in a via that is near a GND via and is

accessible through an oscilloscope connection.

H_DSTBN#0<10>

H_DSTBP#0<10>

H_DINV#0<10>

H_DSTBN#1<10>

H_DSTBP#1<10>

H_DINV#1<10>

T153PAD~D T153PAD~D

T138PAD~D T138PAD~D

T4PAD~D T4PAD~D

FSB

533

667

800

1067 266 0 0 0

5

4

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

110

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54H_D#22

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

COMP1

COMP2

COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGOOD

H_CPUSLP#

H_PSI#

+V_CPU_GTLREF

H_DPRSTP# <10,23,47>

H_DPWR# <10>

H_PWRGOOD <23>

H_CPUSLP# <10>

+1.05V_VCCP

12

R77

R77

1K_0402_1%~D

1K_0402_1%~D

12

R78

R78

2K_0402_1%~D

2K_0402_1%~D

H_PSI# <47>

Layout close CPU PIN AD26

50 ohm, 0.5 inch (max)

H_DSTBN#2 <10>

H_DSTBP#2 <10>

H_DINV#2 <10>

H_DSTBN#3 <10>

H_DSTBP#3 <10>

H_DINV#3 <10>

H_DPSLP# <23>

24.9_0402_1%~D

24.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

12

12

Resistor placed within 0.5" of

CPU pin.Trace should be at least

25 mils away from any other

toggling signal. COMP0, COMP2

trace should be 25 ohm. COMP1,

COMP3 should be 50 ohm.

(Quad Core design)

R69

R69

R68

R68

24.9_0402_1%~D

24.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

12

12

R71

R71

R70

R70

Dual Core Should follow Quad Core value

Avia should support Quad / Dual Core CPU

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

JCPU1C

JCPU1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

TYCO_1-1674770-2_Penryn~D

TYCO_1-1674770-2_Penryn~D

AB20

VCC[068]

AB7

VCC[069]

AC7

VCC[070]

AC9

VCC[071]

AC12

VCC[072]

AC13

VCC[073]

AC15

VCC[074]

AC17

VCC[075]

AC18

VCC[076]

AD7

VCC[077]

AD9

VCC[078]

AD10

VCC[079]

AD12

VCC[080]

AD14

VCC[081]

AD15

VCC[082]

AD17

VCC[083]

AD18

VCC[084]

AE9

VCC[085]

AE10

VCC[086]

AE12

VCC[087]

AE13

VCC[088]

AE15

VCC[089]

AE17

VCC[090]

AE18

VCC[091]

AE20

VCC[092]

AF9

VCC[093]

AF10

VCC[094]

AF12

VCC[095]

AF14

VCC[096]

AF15

VCC[097]

AF17

VCC[098]

AF18

VCC[099]

AF20

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

VSSSENSE

+1.05V_VCCP

220U_D2_4VY_R15M~D

220U_D2_4VY_R15M~D

1

+

+

C21

C21

2

CRB was 270uF

VID0 <47>

VID1 <47>

VID2 <47>

VID3 <47>

VID4 <47>

VID5 <47>

VID6 <47>

VCCSENSE <47>

VSSSENSE <47>

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

10U_0805_10V4Z~D

10U_0805_10V4Z~D

1

1

C22

C22

C23

C23

2

2

Length match within 25 mils, Z0=27.4 ohm

Place R75 and R76 near CPU

+VCC_CORE

1 2

R75 100_0402_1%~D

R75 100_0402_1%~D

1 2

R76 100_0402_1%~D

R76 100_0402_1%~D

Route VCCSENSE and VSSSENSE trace at

27.4 ohms, 7 mils spacing and the placement should be within 1 inch (max)

VCCSENSE

VSSSENSE

1 2

R833 27.4_0402_1%~D@R833 27.4_0402_1%~D@

Reserve for testing

only

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

1

+1.5V_RUN

A

A

856Monday, December 17, 2007

856Monday, December 17, 2007

856Monday, December 17, 2007

A

of

of

of

Page 9

5

4

3

2

1

+VCC_CORE

Place these inside

socket cavity on L8

(North side

Secondary)

D D

+VCC_CORE

Place these inside

socket cavity on L8

(Sorth side

Secondary)

+VCC_CORE

Place these inside

socket cavity on L8

(North side

Primary)

+VCC_CORE

Place these inside

socket cavity on L8

(Sorth side

C C

Primary)

1

C24

C24

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C34

C34

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C44

C44

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C50

C50

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C25

C25

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C35

C35

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C45

C45

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C51

C51

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C26

C26

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C36

C36

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C46

C46

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C52

C52

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C27

C27

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C37

C37

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C47

C47

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C53

C53

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C28

C28

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C38

C38

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C48

C48

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C54

C54

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C29

C29

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C39

C39

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C49

C49

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C55

C55

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C30

C30

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C40

C40

10U_0805_4VAM~D

10U_0805_4VAM~D

2

10uF 0805 X6S -> 85 degree C

1

C31

C31

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C41

C41

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C32

C32

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C42

C42

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C33

C33

10U_0805_4VAM~D

10U_0805_4VAM~D

2

1

C43

C43

10U_0805_4VAM~D

10U_0805_4VAM~D

2

High Frequence Decoupling

Near VCORE regulator.

+VCC_CORE

220U_X_2VM_R7M~D

1

+

+

2

220U_X_2VM_R7M~D

@

@

C58

C58

1

+

+

2

220U_X_2VM_R7M~D

220U_X_2VM_R7M~D

@

@

C61

C61

220U_X_2VM_R7M~D

220U_X_2VM_R7M~D

1

+

+

2

220U_X_2VM_R7M~D

220U_X_2VM_R7M~D

1

1

+

+

+

C56

C56

+

C59

C59

2

2

220U_X_2VM_R7M~D

220U_X_2VM_R7M~D

C60

C60

1

+

+

2

220U_X_2VM_R7M~D

220U_X_2VM_R7M~D

C57

C57

ESR <= 1.5m ohm

Capacitor > 1320uF

B B

+1.05V_VCCP

1

C62

C62

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

A A

Board Bottom Side Board Top Side

1

C63

C63

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

1

C64

C64

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

5

1

C65

C65

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

1

C66

C66

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

4

1

C67

C67

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

Place these inside

socket cavity on L8

(North side

Secondary)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

SCHEMATIC, MB A4042

401533

401533

401533

956Tuesday, December 18, 2007

956Tuesday, December 18, 2007

956Tuesday, December 18, 2007

1

A

A

A

of

of

of

Page 10

5

U2A

M11

N12

P13

N10

AD14

Y10

Y12

Y14

W2

AA8

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

AA2

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

AE11

AE8

AG2

AD6

C12

E11

A11

B11

12

R91

R91

221_0402_1%~D

221_0402_1%~D

12

1

2

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

M9

P2

R2

N9

M5

N2

R1

N5

N6

N8

M3

Y3

Y6

Y7

Y9

C5

E3

U2A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

J1

H_D#_12

J2

H_D#_13

H_D#_14

J6

H_D#_15

H_D#_16

L2

H_D#_17

H_D#_18

H_D#_19

L6

H_D#_20

H_D#_21

J3

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

L7

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CANTIGA ES_FCBGA1329~D

CANTIGA ES_FCBGA1329~D

3.01K_0402_1%~D

3.01K_0402_1%~D

0.1U_0402_16V7K~D

0.1U_0402_16V7K~D

C74

C74

1K_0402_1%~D

1K_0402_1%~D

+1.8V_MEM

R93

R93

R97

R97

HOST

HOST

12

R88

R88

1K_0402_1%~D

1K_0402_1%~D

12

12

H_ADSTB#_0

H_ADSTB#_1

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

1

2

1

2

H_D#[0..63]<8>

D D

C C

1 2

R82 24.9_0402_1%~D

R82 24.9_0402_1%~D

B B

A A

+H_VREF

R94

2K_0402_1%~D

2K_0402_1%~D

R94

H_RESET#<7>

H_CPUSLP#<8>

12

R90

R90

1K_0402_1%~D

1K_0402_1%~D

12

0.1U_0402_16V7K~D

0.1U_0402_16V7K~D

@C73

@

1

C73

2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWNG

+H_RCOMP

H_RESET#

H_CPUSLP#

+H_VREF

+1.05V_VCCP+1.05V_VCCP

H_SWNG

100_0402_1%~D

100_0402_1%~D

R95

R95

5

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

SMRCOMP_VOH

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

C71

C71

SMRCOMP_VOL

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

C75

C75

MCH_TSATN#

4

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

2.2U_0603_6.3V6K~D

2.2U_0603_6.3V6K~D

1

C72

C72

2

2.2U_0603_6.3V6K~D

2.2U_0603_6.3V6K~D

1

C76

C76

2

R103

R103

0_0402_5%~D

0_0402_5%~D

4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

+1.05V_VCCP

12

R101

R101

54.9_0402_1%~D

54.9_0402_1%~D

1 2

12

R104

R104

330_0402_5%~D

330_0402_5%~D

MMST3904-7-F_SOT323-3~D

MMST3904-7-F_SOT323-3~D

H_A#[3..35] <7>

+1.8V_MEM

R79 80.6_0402_1%~DR79 80.6_0402_1%~D

R80 80.6_0402_1%~DR80 80.6_0402_1%~D

+V_DDR_MCH_REF

H_ADS# <7>

H_ADSTB#0 <7>

H_ADSTB#1 <7>

H_BNR# <7>

H_BPRI# <7>

H_BR0# <7>

H_DEFER# <7>

H_DBSY# <7>

CLK_MCH_BCLK <6>

CLK_MCH_BCLK# <6>

H_DPWR# <8>

H_DRDY# <7>

H_HIT# <7>

H_HITM# <7>

H_LOCK# <7>

H_TRDY# <7>

H_DINV#0 <8>

H_DINV#1 <8>

H_DINV#2 <8>

H_DINV#3 <8>

H_DSTBN#0 <8>

H_DSTBN#1 <8>

H_DSTBN#2 <8>

H_DSTBN#3 <8>

H_DSTBP#0 <8>

H_DSTBP#1 <8>

H_DSTBP#2 <8>

H_DSTBP#3 <8>

H_REQ#0 <7>

H_REQ#1 <7>

H_REQ#2 <7>

H_REQ#3 <7>

H_REQ#4 <7>

H_RS#0 <7>

H_RS#1 <7>

H_RS#2 <7>

499_0402_1%~D

499_0402_1%~D

+3.3V_RUN

1K_0402_5%~D

1K_0402_5%~D

12

R98

R98

2

B

B

C

C

2

B

B

Q3

Q3

E

E

MMST3904-7-F_SOT323-3~D

MMST3904-7-F_SOT323-3~D

3 1

Q4

Q4

E

E

+1.05V_M

R87

R87

12

C

C

3 1

1

2

12

1 2

1K_0402_5%~D

1K_0402_5%~D

R99

R99

3

M_ODT0<16>

M_ODT1<16>

M_ODT2<17>

M_ODT3<17>

T13PAD~D T13PAD~D

T25PAD~D T25PAD~D

T26PAD~D T26PAD~D

T27PAD~D T27PAD~D

T28PAD~D T28PAD~D

T29PAD~D T29PAD~D

T30PAD~D T30PAD~D

T31PAD~D T31PAD~D

T32PAD~D T32PAD~D

T33PAD~D T33PAD~D

T34PAD~D T34PAD~D

T35PAD~D T35PAD~D

T36PAD~D T36PAD~D

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMP

SMRCOMP#

SMRCOMP_VOH

SMRCOMP_VOL

+V_DDR_MCH_REF

SM_PWROK

TP_SM_DRAMRST#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VR_ON

CL_CLK0

CL_DATA0

ICH_CL_PWROK

CL_RST0#

+CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

CLK_3GPLLREQ#

MCH_ICH_SYNC#

MCH_TSATN#

ICH_AZ_MCH_BITCLK

ICH_AZ_MCH_RST#

ICH_AZ_MCH_SDIN2

ICH_AZ_MCH_SDOUT

ICH_AZ_MCH_SYNC

1 2

R102 56_0402_5%~D R102 56_0402_5%~D

M_CLK_DDR0<16>

M_CLK_DDR1<16>

M_CLK_DDR2<17>

M_CLK_DDR3<17>

M_CLK_DDR#0<16>

M_CLK_DDR#1<16>

M_CLK_DDR#2<17>

M_CLK_DDR#3<17>

DDR_CKE0_DIMMA<16>

DDR_CKE1_DIMMA<16>

DDR_CKE2_DIMMB<17>

DDR_CKE3_DIMMB<17>

DDR_CS0_DIMMA#<16>

DDR_CS1_DIMMA#<16>

DDR_CS2_DIMMB#<17>

DDR_CS3_DIMMB#<17>

SMRCOMP

12

SMRCOMP#

12

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

MCH_TSATN_EC <37>

R81 499_0402_1%~D

R81 499_0402_1%~D

1 2

1

C69

C69

C68

C68

2

CLK_MCH_3GPLL<6>

CLK_MCH_3GPLL#<6>

DMI_MRX_ITX_N0<24>

DMI_MRX_ITX_N1<24>

DMI_MRX_ITX_N2<24>

DMI_MRX_ITX_N3<24>

DMI_MRX_ITX_P0<24>

DMI_MRX_ITX_P1<24>

DMI_MRX_ITX_P2<24>

DMI_MRX_ITX_P3<24>

DMI_MTX_IRX_N0<24>

DMI_MTX_IRX_N1<24>

DMI_MTX_IRX_N2<24>

DMI_MTX_IRX_N3<24>

DMI_MTX_IRX_P0<24>

DMI_MTX_IRX_P1<24>

DMI_MTX_IRX_P2<24>

DMI_MTX_IRX_P3<24>

1K_0402_1%~D

1K_0402_1%~D

R83

R83

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

CL_CLK0<24>

CL_DATA0<24>

ICH_CL_PWROK<24,38>

CL_RST0#<24>

C70

C70

DDPC_CTRLDATA<12>

CLK_3GPLLREQ#<6>

MCH_ICH_SYNC#<24>

THERMTRIP_MCH#

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

AP24

AT21

AV24

AU20

AR24

AR21

AU24

AV20

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

AH37

AH36

AN36

AJ35

AH34

U2B

U2B

B38

A38

E41

F41

F43

E43

B33

B32

G33

F33

E33

C34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

+1.05V_VCCP

2

TP_MCH_RSVD1

M36

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD

RSVD

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

CLK

CLK

CFG

CFG

DMI

DMI

PM

PM

GRAPHICS VID

GRAPHICS VID

MEHDA

MEHDA

NC

NC

MISC

MISC

CANTIGA ES_FCBGA1329~D

CANTIGA ES_FCBGA1329~D

RSVD14

RSVD15

RSVD16

RSVD17

RSVD20

RSVD22

RSVD23

RSVD24

RSVD25

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

NC_26

N36

R33

T33

AH9

AH10

AH12

AH13

K12

AL34

AK34

AN35

AM35

T24

B31

B2

M1

AY21

BG23

BF23

BH18

BF18

T25

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

P29

R28

T28

R29

B7

N33

P32

AT40

AT11

T20

R32

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

A47

TP_MCH_RSVD2

TP_MCH_RSVD3

TP_MCH_RSVD4

TP_MCH_RSVD5

TP_MCH_RSVD6

TP_MCH_RSVD7

TP_MCH_RSVD8

TP_MCH_RSVD9

ME_JTAG_TCK

ME_JTAG_TDI

ME_JTAG_TDO

ME_JTAG_TMS

TP_MCH_RSVD15