Page 1

5

4

COMPAL CONFIDENTIAL

3

2

1

D D

PCB NO :

LA-3954P

COMPAL P/N :

MODEL NAME :

E-Docking (For APR)

TBD

E-Docking Schematics Document

C C

E-APR

2008-04-18

REV : 0.4 (DELL: X03)

B B

A A

MB PCB

MB PCB

Part Number Description

Part Number Description

DA40000930L

DA40000930L

PCB LA-3954P

PCB LA-3954P

REV0.3 MB

REV0.3 MB

5

BOM NO:

TBD

PCB P/N: TBD

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-3954P

LA-3954P

LA-3954P

129Friday, April 18, 2008

129Friday, April 18, 2008

129Friday, April 18, 2008

1

X03

X03

X03

of

of

of

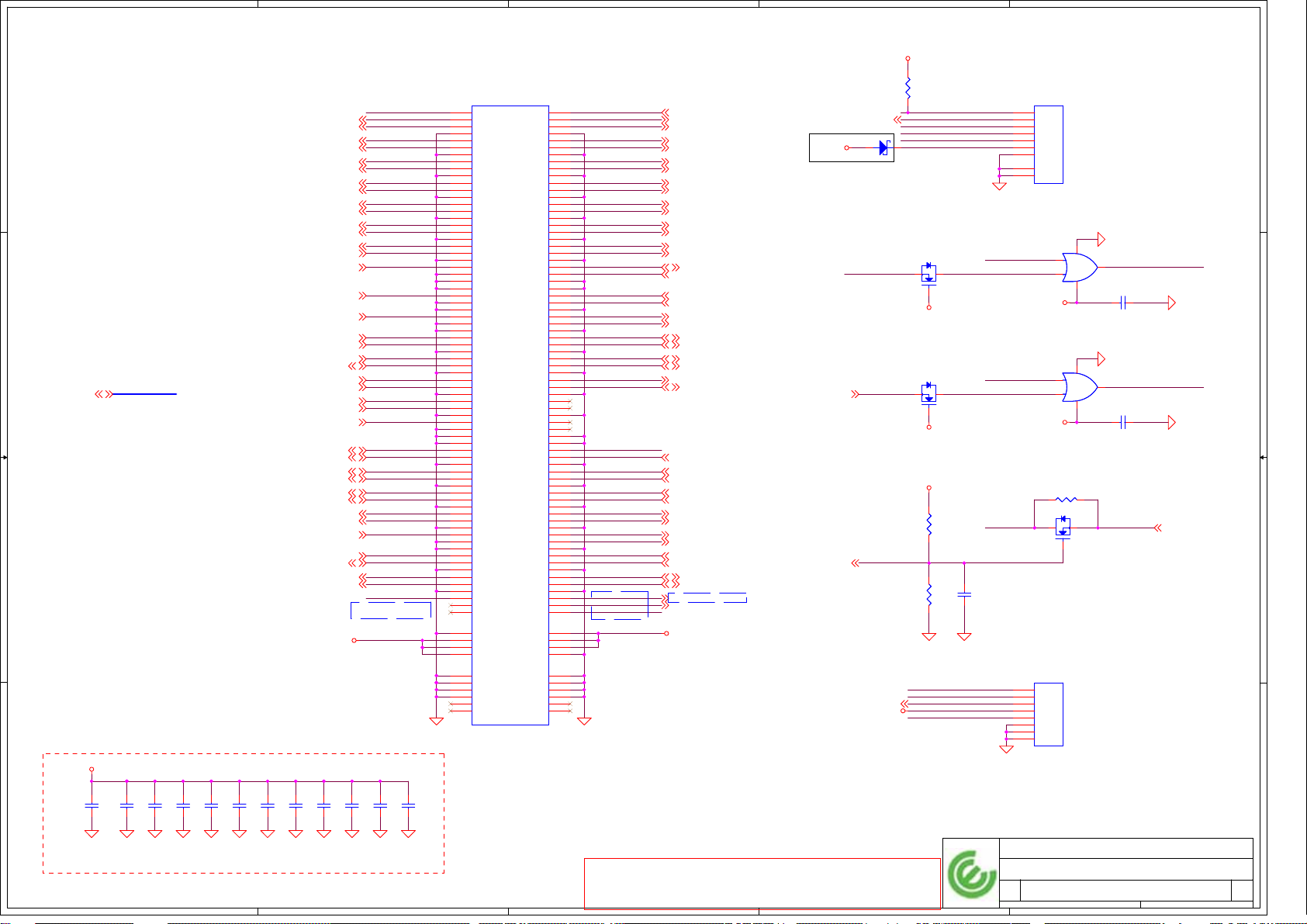

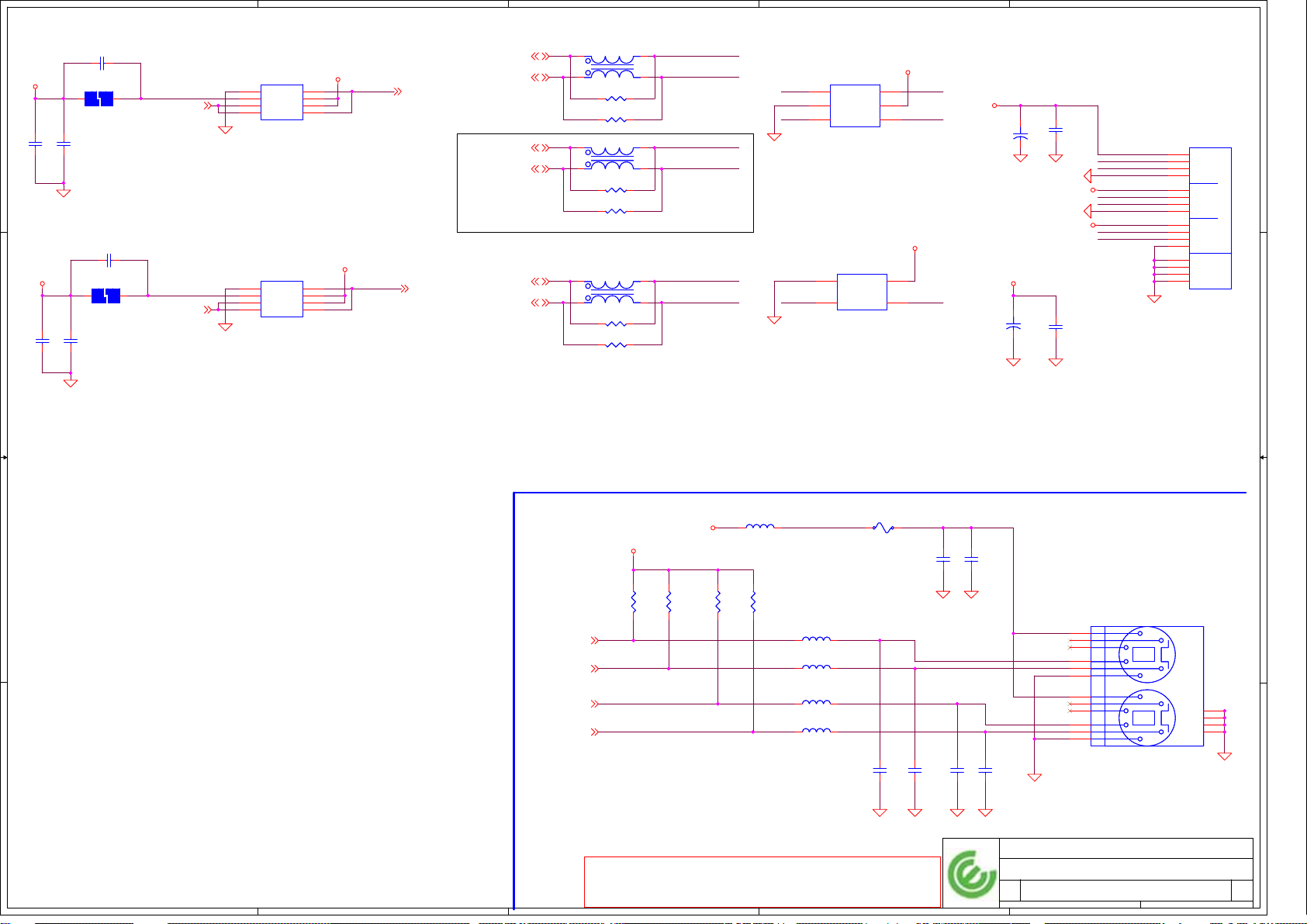

Page 2

5

Compal confidential

Model : E-Docking

4

3

2

1

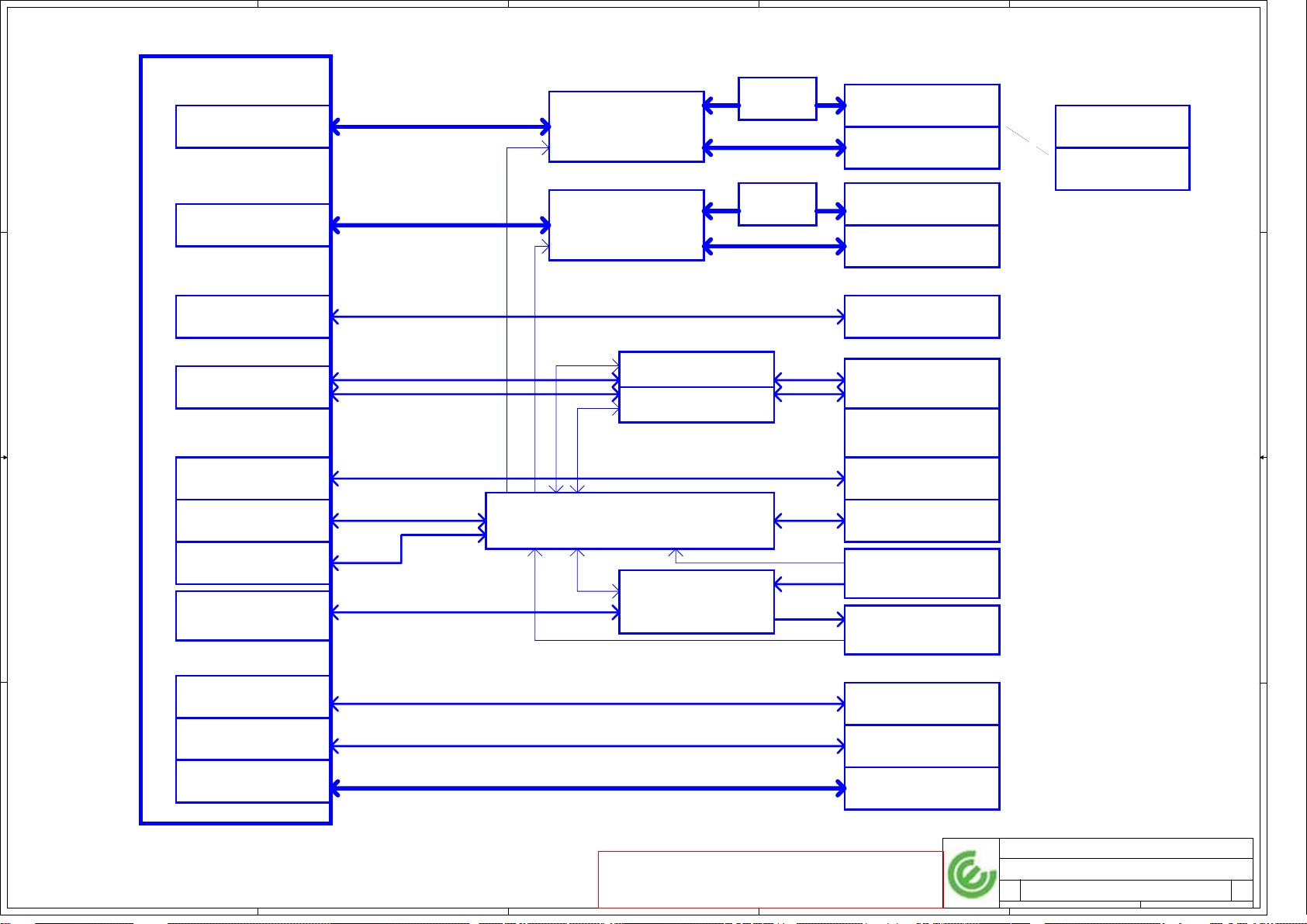

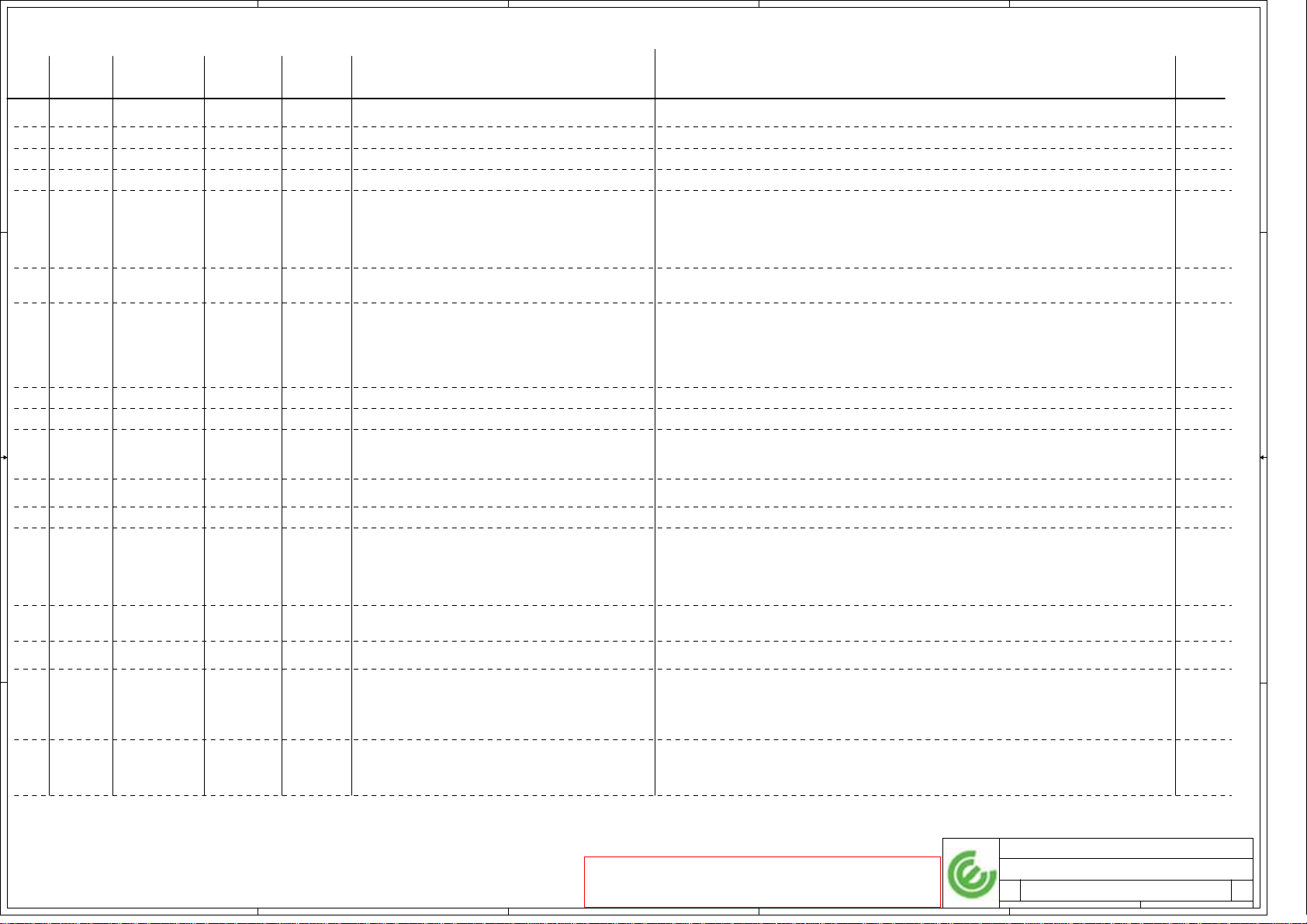

Block Diagram

E Docking Connector

Display Port/

D D

Display Port #1

DVI -VS

w/ port sel

TI SN75DP122

Page 13

PS8121E

Repeater

Display Port

w/buffer

Page 13

DVI

Page 13

Adapters

HDMI

PS8121E

Repeater

Display Port #2

Display Port/

DVI -VS

w/ port sel

TI SN75DP122

Page 14

VGA

C C

USB (2)

SMBUS#1

USB 2.0 HUB

SMSC USB2513

USB 2.0 HUB

SMSC USB2513

Page 8

Page 8

SATA

LPC

B B

SMBUS

SMBUS

LIO

SMBUS#1

SMSC 47N237

Page 6

Mic Detect

Dock Audio

Dock Audio Intf.

HCP Detect

Interface

Page 15

Display Port

w/buffer

Page 14

DVI

Page 14

VGA

Page 12

USB 2.0

(6) User Ports

Page 9,10,11

Monitor Stand

interface

Page 5

P -ESATA

Page 10

LPT/RS232

Page 7

MIC In

Page 16

Audio Conns

Page 16

LOM

PS2 (x2)

Power

A A

Page 5

RJ45

Page 11

PS2 (x2)

Page 9

Power

Page TBD

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-3954P

LA-3954P

LA-3954P

229Friday, April 18, 2008

229Friday, April 18, 2008

229Friday, April 18, 2008

1

X03

X03

X03

of

of

of

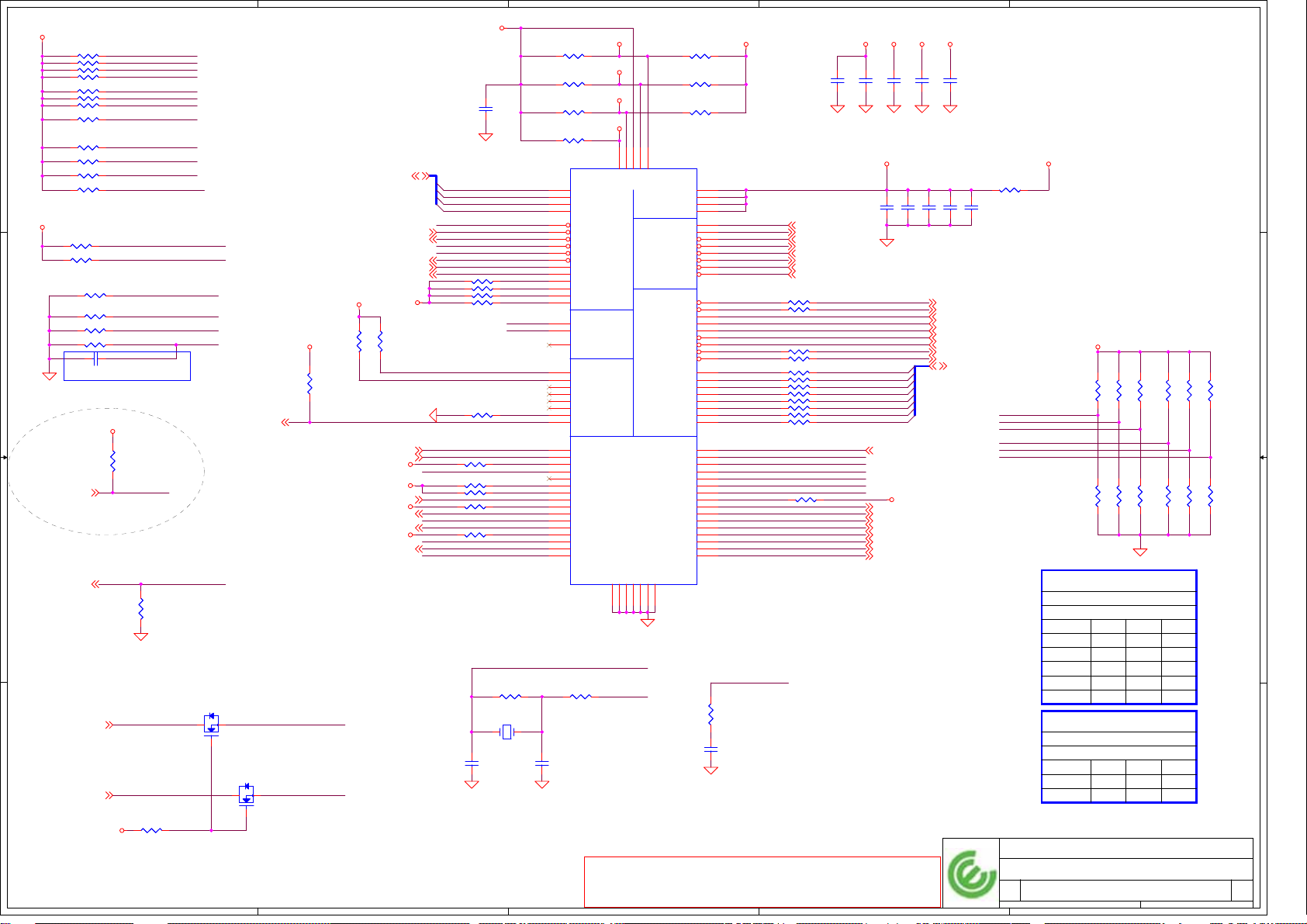

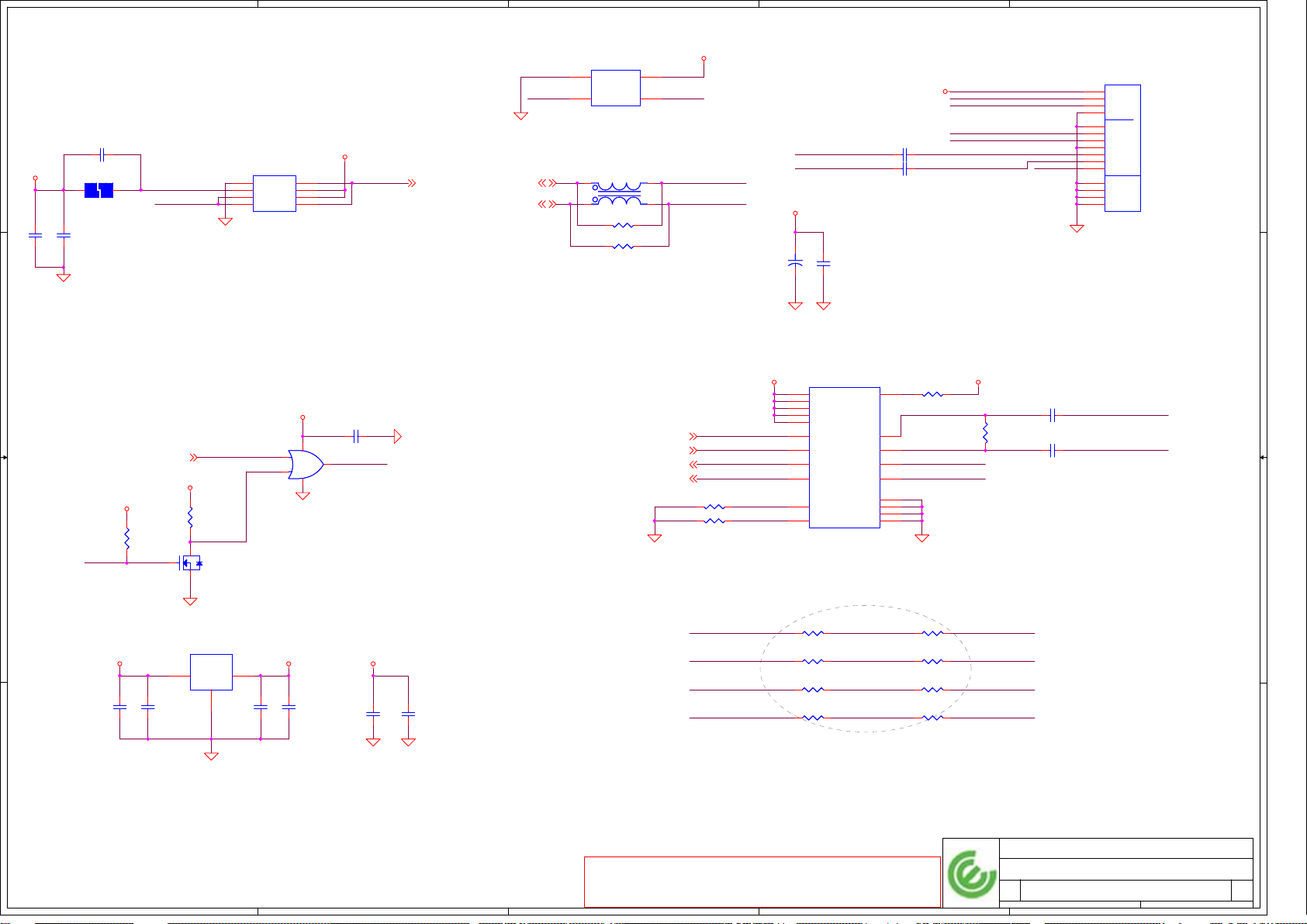

Page 3

5

4

3

2

1

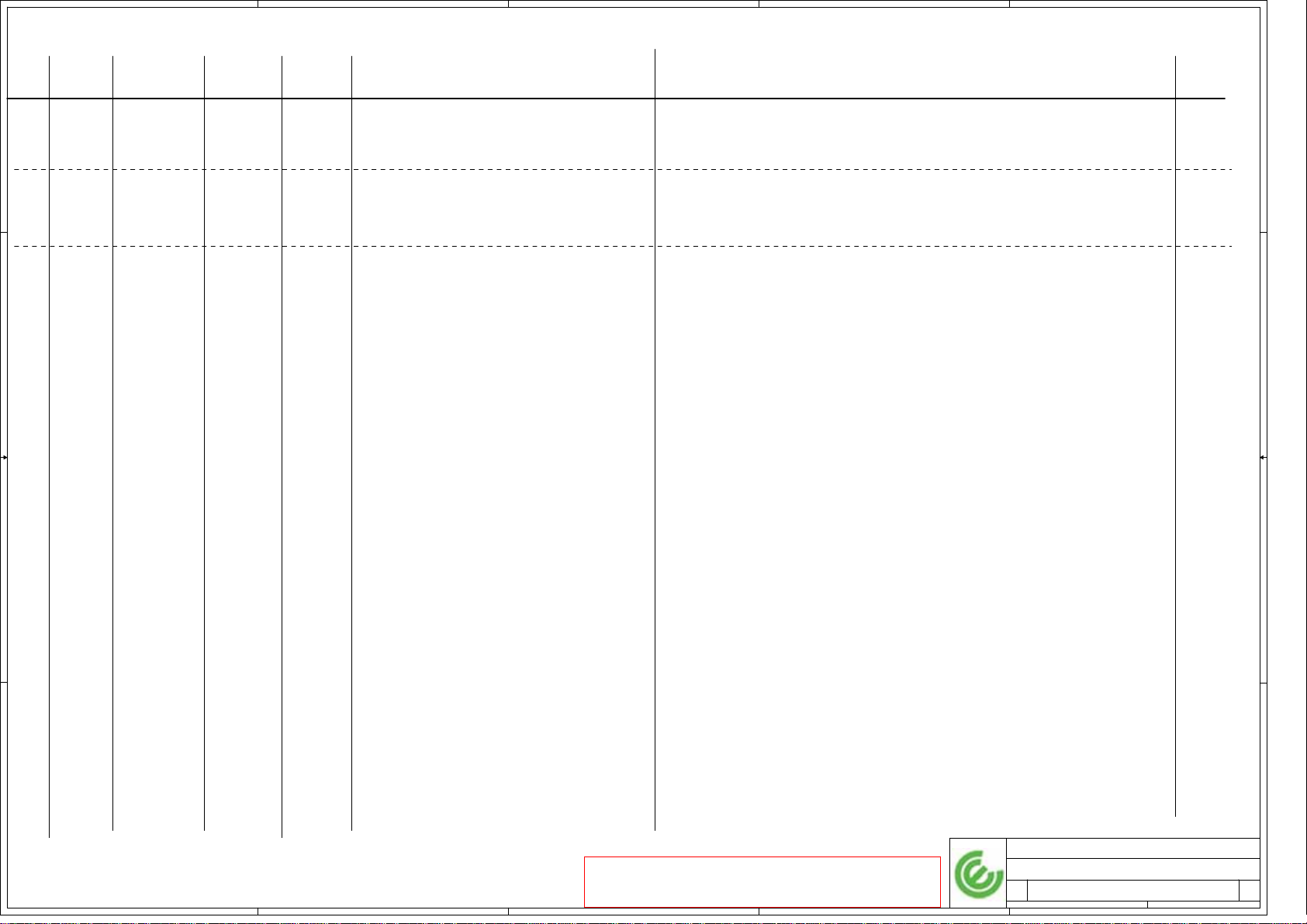

+3.3V_ALW

10K

D D

2N7002

2N7002

10K

48 (0100 1000)

SMSC 47N237

+3.3V_SUS

2.2K

2.2K

USB_HUB1_RST#

DOCK_SMB_ALERT#

C C

DOCK_SMB_DAT

DOCK_SMB_CLK

2N7002

2N7002

USB2513

Port 4/5/6

58/59 (0101-100x)

+3.3V_SUS

USB_HUB2_RST#

2.2K

2.2K

USB2513

Port 1/2/3

58/59 (0101-100x)

+3.3V_RUN

B B

2.2K

2.2K

2N7002

2N7002

Audio

SSM2603

34/35 (0011-010X)

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SMBus Block Diagram

SMBus Block Diagram

SMBus Block Diagram

LA-3954P

LA-3954P

LA-3954P

329Friday, April 18, 2008

329Friday, April 18, 2008

329Friday, April 18, 2008

1

X03

X03

X03

of

of

of

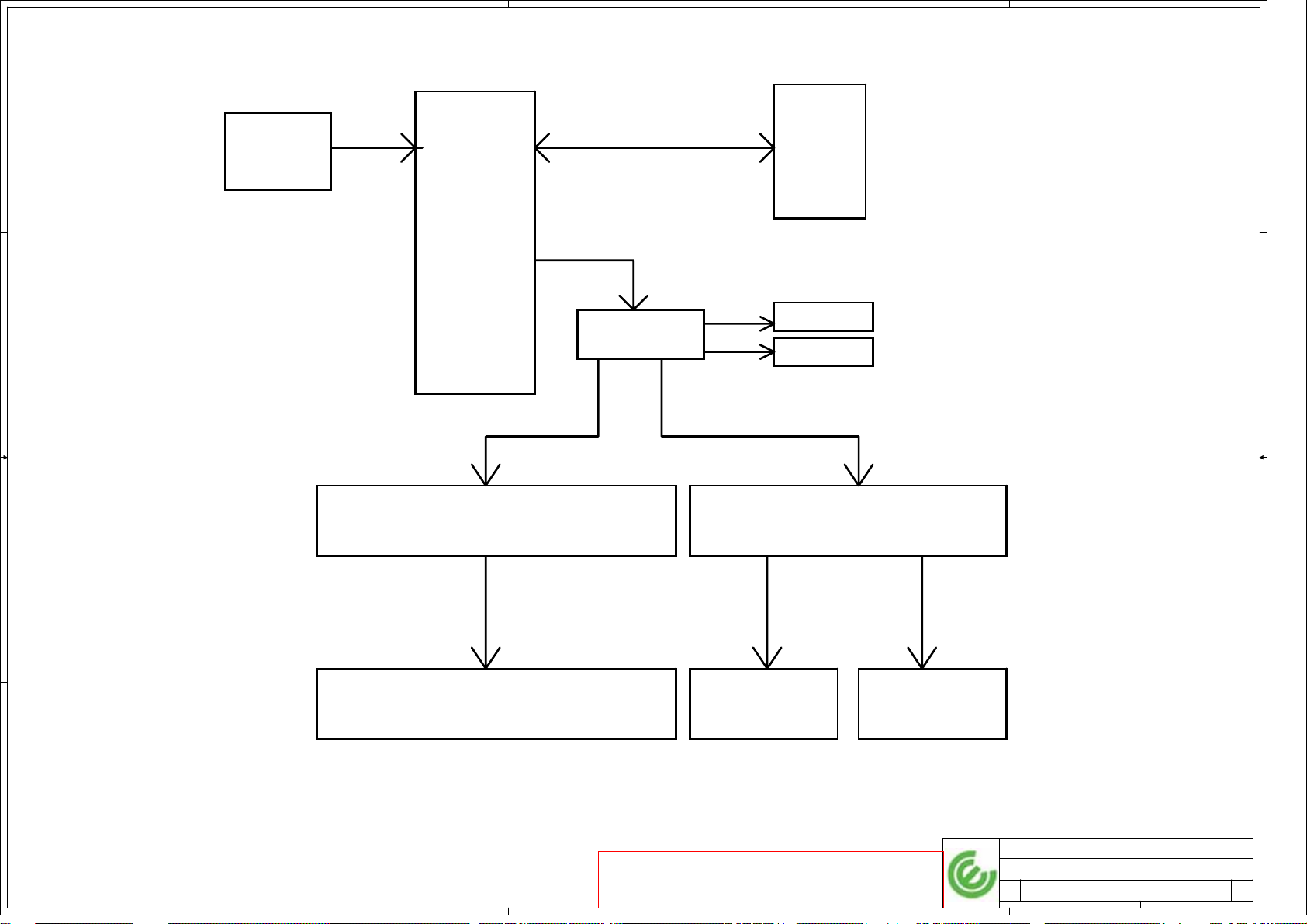

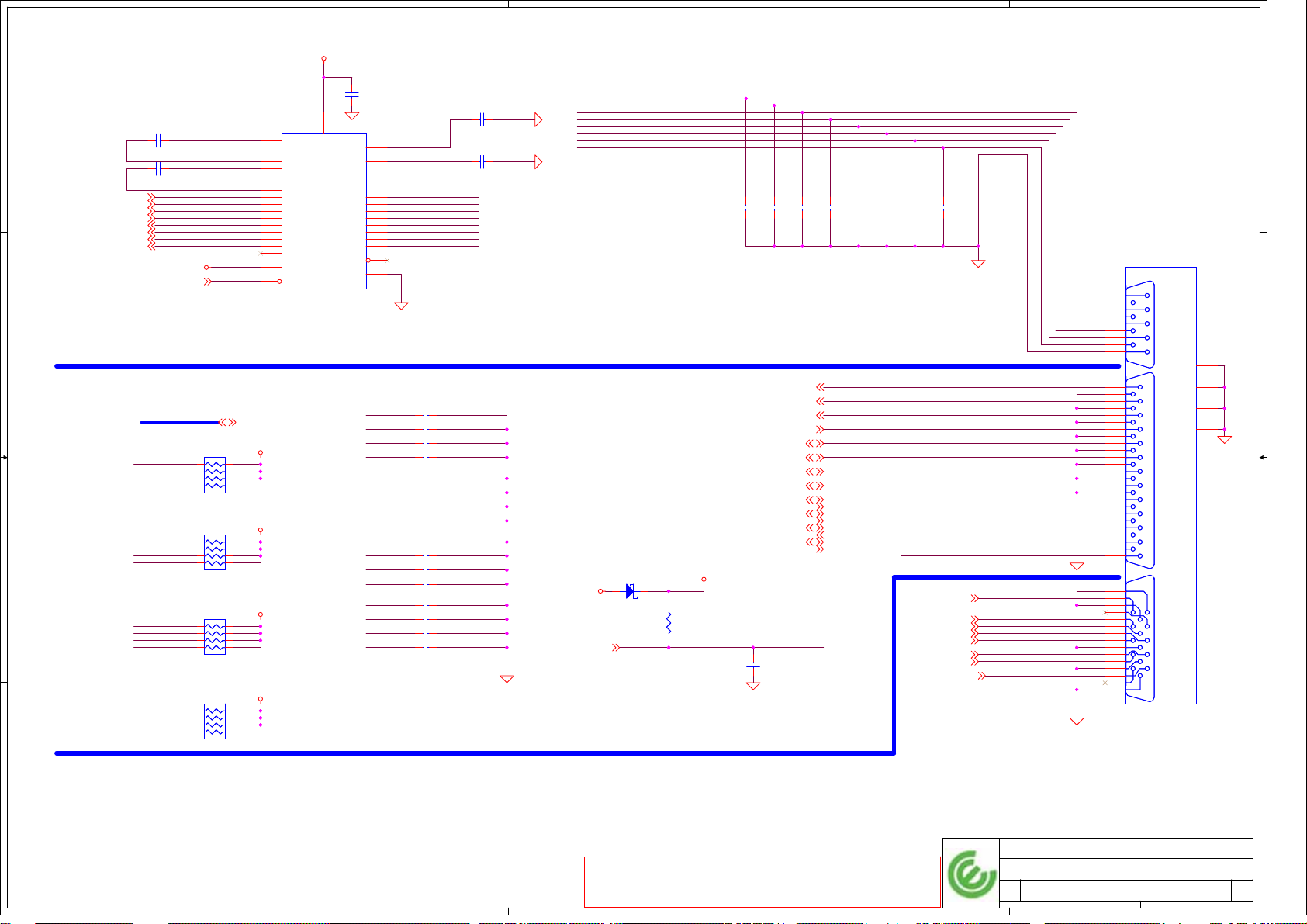

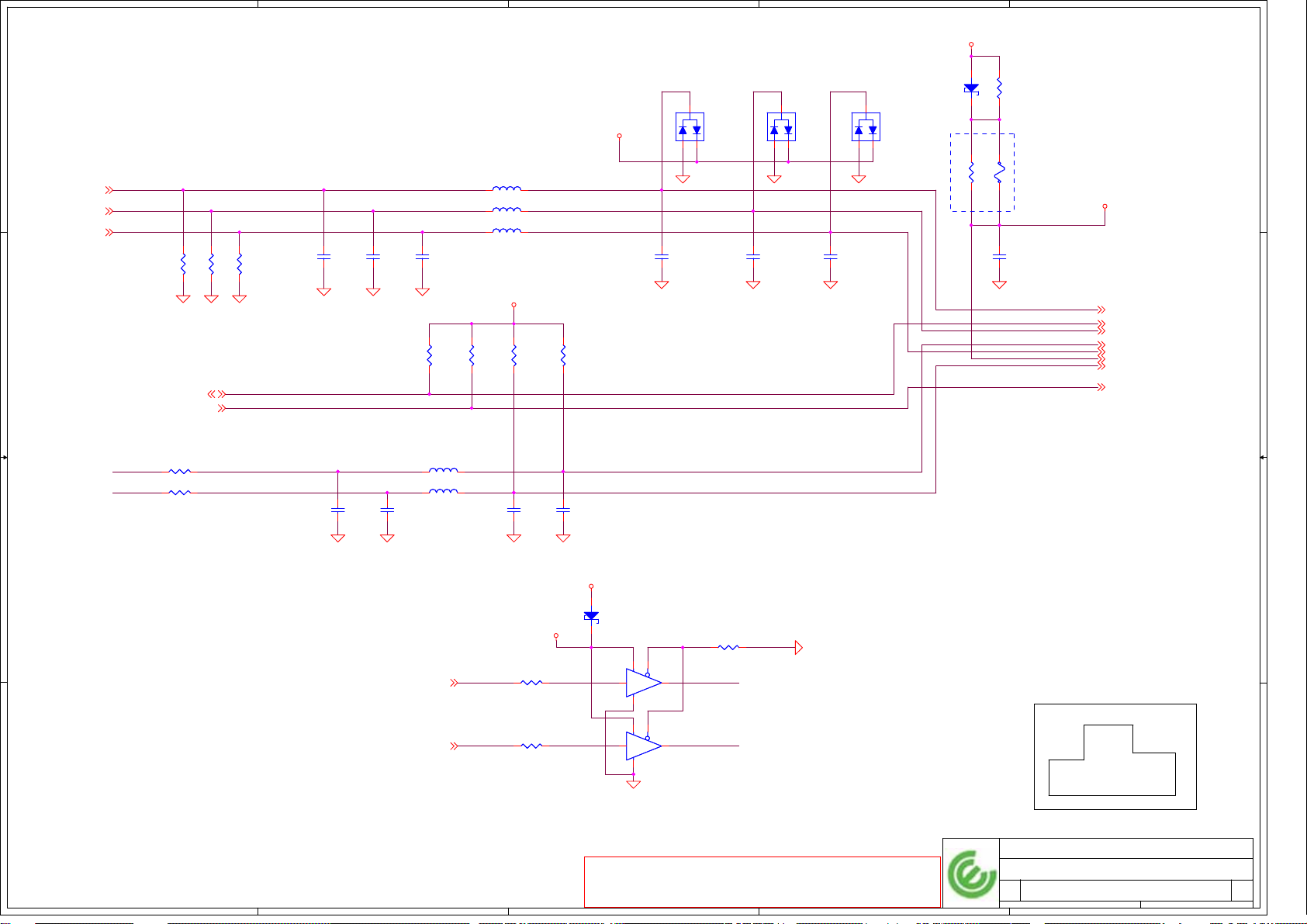

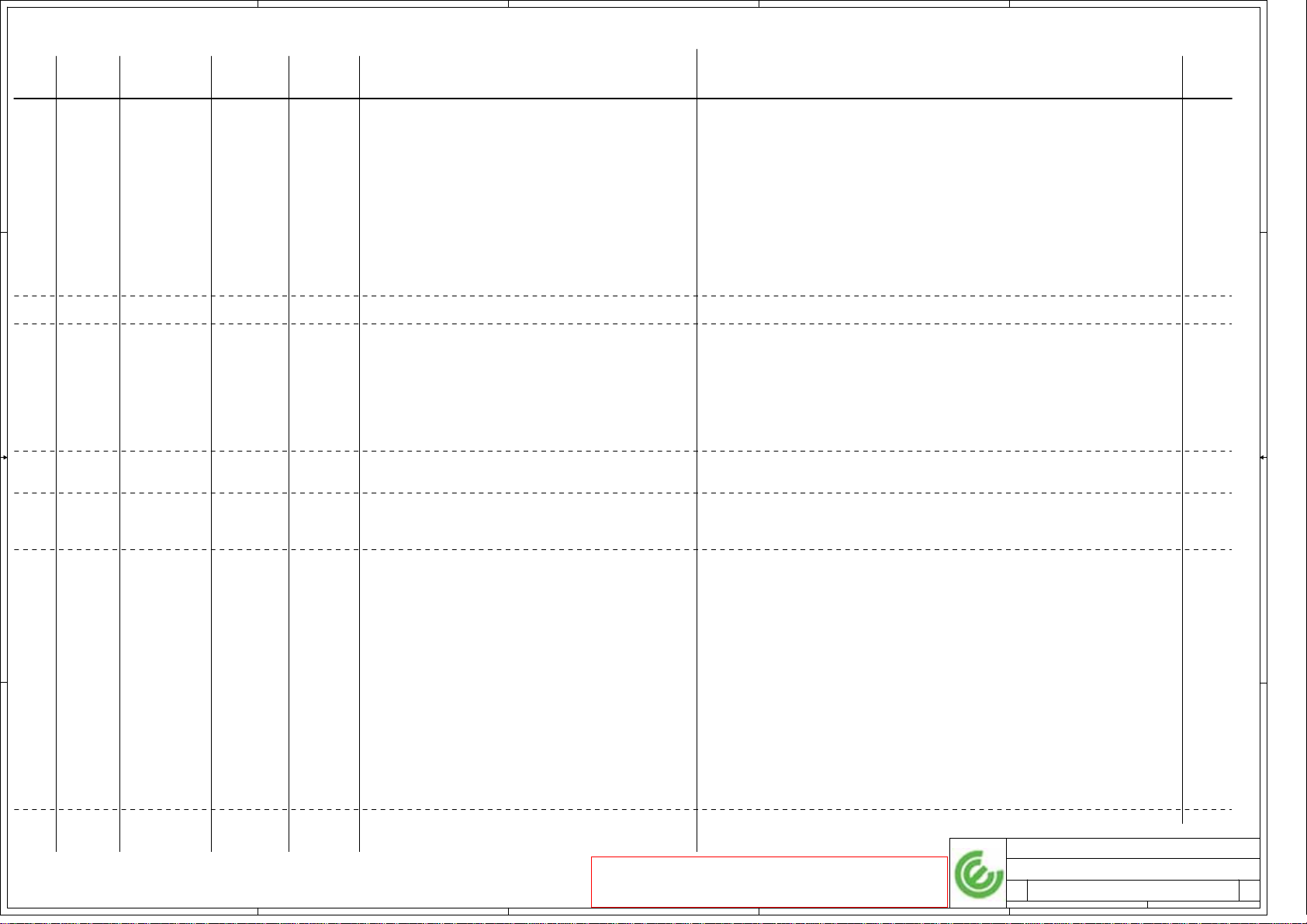

Page 4

5

D D

ADAPTER

4

3

2

1

+PWR_SRC

Docking

+PWR_SRC

NB_DET#

C C

MAX8778ETJ

NB_DET#

NB_DET#

+5V_ALW

+3V_ALW2

+15V_ALW

+5V_ALW +3.3V_ALW

B B

DK_RUNON

+5V_RUN

DK_SUSON

+3.3V_SUS

DK_RUNON

+3.3V_RUN

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Power Rail Block Diagram

Power Rail Block Diagram

Power Rail Block Diagram

LA-3954P

LA-3954P

LA-3954P

429Friday, April 18, 2008

429Friday, April 18, 2008

429Friday, April 18, 2008

1

X03

X03

X03

of

of

of

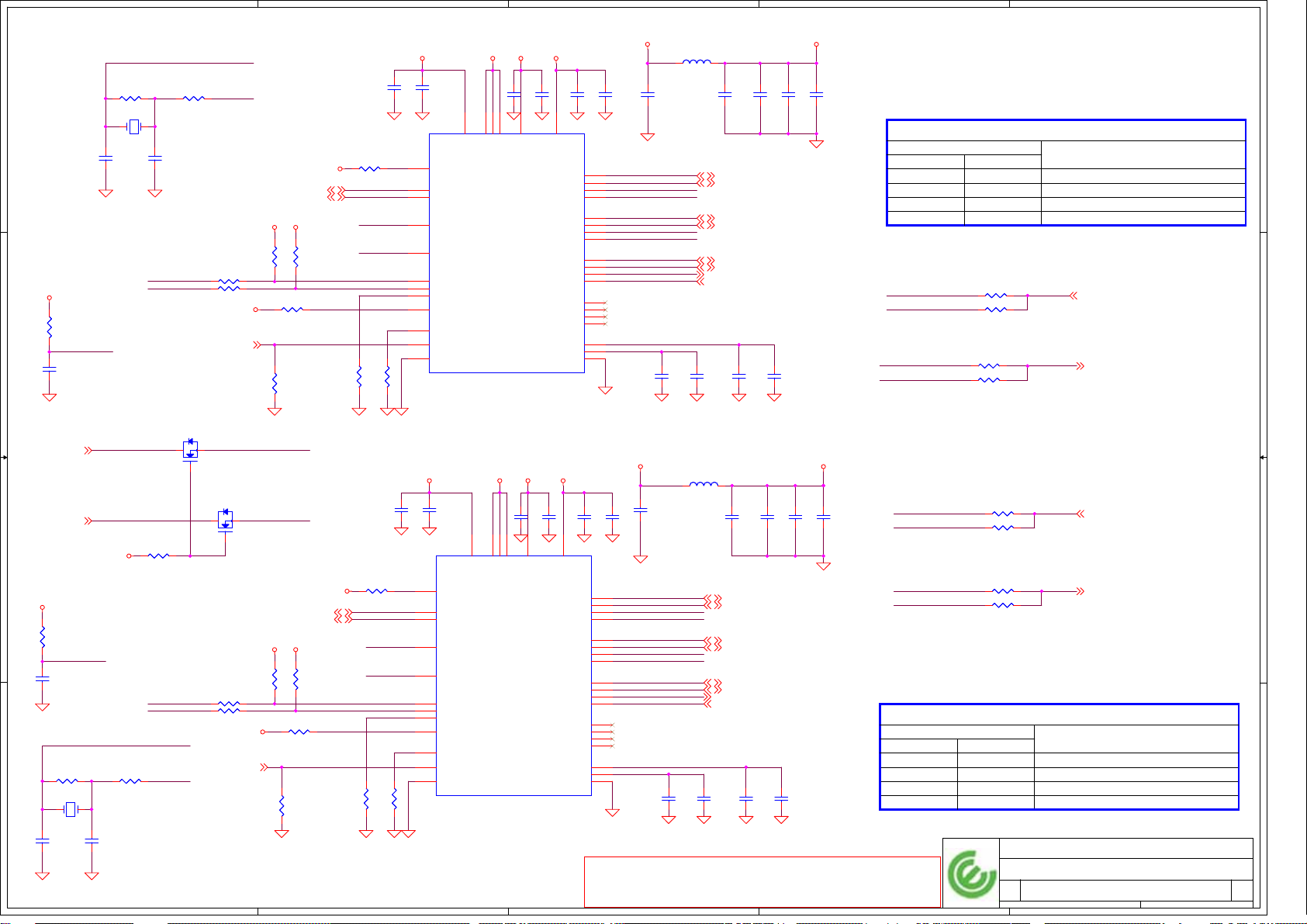

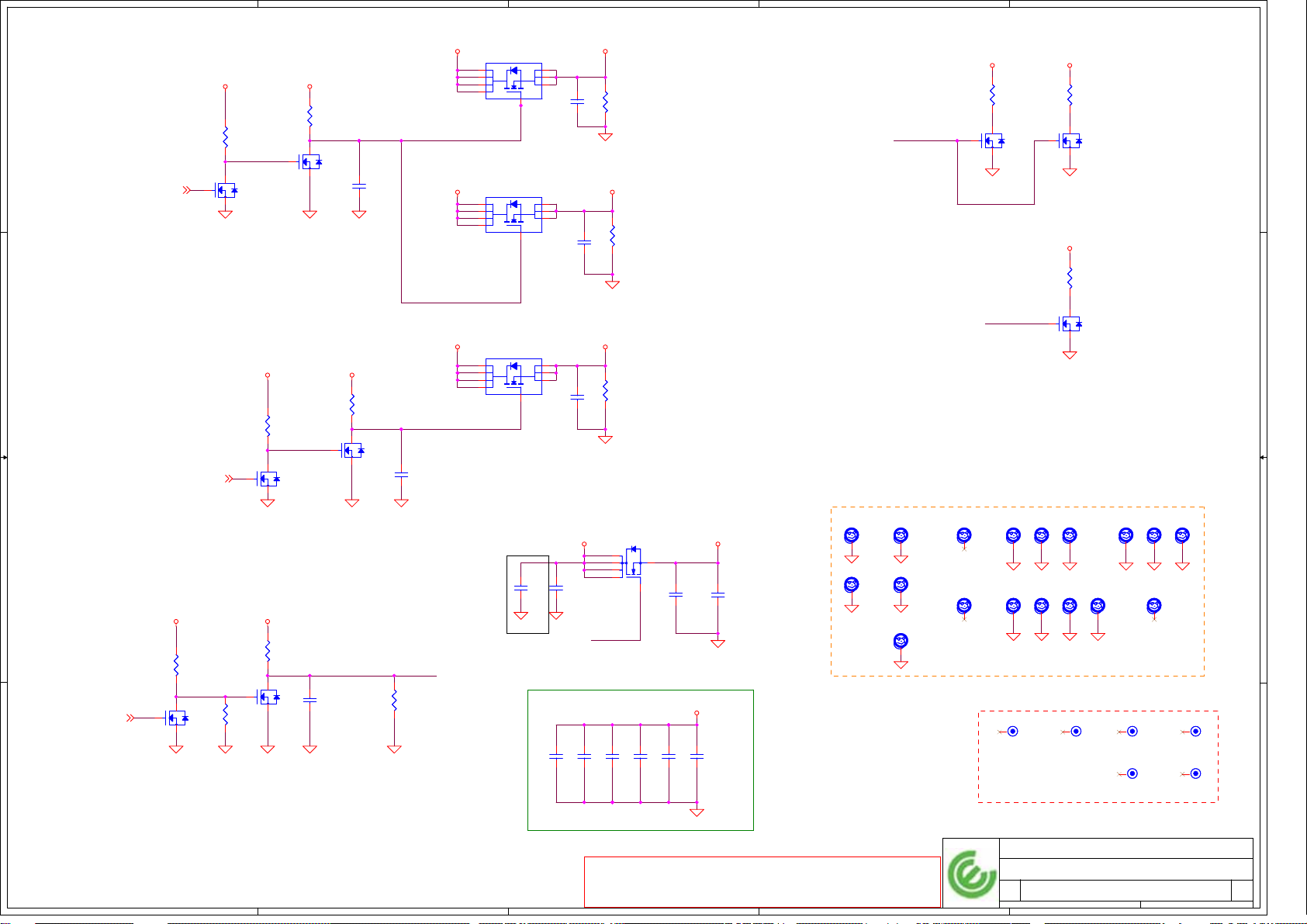

Page 5

5

D D

C C

D_LAD[0..3]<6>

B B

+DOCK_PWR_BAR

DOCK_LOM_SPD10LED_GRN#<11>

DP_A_CA_DET1<13>

DP_A_L0+<13>

DP_A_L0-<13>

DP_A_L1+<13>

DP_A_L1-<13>

DP_A_L2+<13>

DP_A_L2-<13>

DP_A_L3+<13>

DP_A_L3-<13>

DP_A_AUX+<13>

DP_A_AUX-<13>

DP_A_HP<13>

+NBDOCK_DC_IN_SS<18>

VGA_B<12>

VGA_R<12>

VGA_G<12>

VGA_HS<12>

VGA_VS<12>

CLK_MSE<9>

DAT_MSE<9>

DAI_BCLK<15>

DAI_LRCK<15>

DAI_DI<15>

DAI_DO<15>

DAI_12MHZ<15>

D_LAD0<6>

D_LAD1<6>

D_LAD2<6>

D_LAD3<6>

D_LFRAME#<6>

D_CLKRUN#<6>

D_SERIRQ<6>

D_DLDRQ1#<6>

CLK_PCI_DOCK<6>

DOCK_SMB_CLK<6,8,16>

DOCK_SMB_DAT<6,8,16>

DOCK_SMB_ALERT#<6>

DOCK_PS_ID<18>

+DOCK_PWR_BAR

4

DOCK_DET_1

DOCK_PWR_BTN#

SLICE_BAT_PRES#

SLICE_CONN_LOOP#

JP1

JP1

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

33

33

35

35

37

37

39

39

41

41

43

43

45

45

47

47

49

49

51

51

53

53

55

55

57

57

59

59

61

61

63

63

65

65

67

67

69

69

71

71

73

73

75

75

77

77

79

79

81

81

83

83

85

85

87

87

89

89

91

91

93

93

95

95

97

97

99

99

101

101

103

103

105

105

107

107

109

109

111

111

113

113

115

115

117

117

119

119

121

121

123

123

125

125

127

127

129

129

131

131

133

133

135

135

137

137

139

139

141

141

143

143

145

PWR1

146

PWR2

147

PWR2

148

PWR2

153

Shield_G1

154

Shield_G2

155

Shield_G3

156

Shield_G4

161

Shield_G9

162

Shield_G10

JAE_WD2M144WB1

JAE_WD2M144WB1

PWR3

PWR3

PWR3

PWR4

Shield_G5

Shield_G6

Shield_G7

Shield_G8

Shield_G11

Shield_G12

3

DOCK_AC_OFF

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

62

62

64

64

66

66

68

68

70

70

72

72

74

74

76

76

78

78

80

80

82

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

149

150

151

152

157

158

159

160

163

164

RESV_011

RESV_010

RESV_021

RESV_020

BREATH_PWR_LED#

TRCT0_1_DOCK

TRCT2_3_DOCK

NB_DET#

DOCK_DET_2

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

DOCK_AC_OFF <18>

DOCK_LOM_SPD100LED_ORG# <11>

DP_B_CA_DET1 <14>

DP_B_L0+ <14>

DP_B_L0- <14>

DP_B_L1+ <14>

DP_B_L1- <14>

DP_B_L2+ <14>

DP_B_L2- <14>

DP_B_L3+ <14>

DP_B_L3- <14>

DP_B_AUX+ <14>

DP_B_AUX- <14>

DP_B_HP <14>

ACAV_DOCK_SRC# <18>

VGA_DDC_DAT <7,12>

VGA_DDC_CLK <7,12>

SATA_SBRX_DTX_P <10>

SATA_SBRX_DTX_N <10>

SATA_SBTX_DRX_P <10>

SATA_SBTX_DRX_N <10>

USB_A_+ <8>

USB_A_- <8>

USB_B_+ <8>

USB_B_- <8>

CLK_KBD <9>

DAT_KBD <9>

DOCK_LOM_ACTLED_YEL# <11>

DOCK_LOM_TRD0+ <11>

DOCK_LOM_TRD0- <11>

DOCK_LOM_TRD1+ <11>

DOCK_LOM_TRD1- <11>

TRCT0_1_DOCK <11>

TRCT2_3_DOCK <11>

DOCK_LOM_TRD2+ <11>

DOCK_LOM_TRD2- <11>

DOCK_LOM_TRD3+ <11>

DOCK_LOM_TRD3- <11>

DOCK_DCIN_IS+ <18>

DOCK_DCIN_IS- <18>

DOCK_POR_RST# <19>

NB_DET# <18>

+DOCK_PWR_BAR

Add net at 12/27.

DOCK_PWR_BTN#

+5V_ALW

DOCKED_LED#<6>

HOT_UNDOCK#<6>

2

+5V_ALW

12

BREATH_PWR_MS_LED#

DOCKED_MS_LED#

D10

D10

+5V_ALW_MS

2 1

RB500V-40 TE-17_SOD323-2~D

RB500V-40 TE-17_SOD323-2~D

2N7002W-7-F_SOT323-3~D

BREATH_PWR_LED# BREATH_PWR_LED_1#

DOCK_PWR_BTN#

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

DOCKED_LED#

HOT_UNDOCK#

+5V_ALW

+DOCK_PWR_BAR

Monitor Stand

R253

R253

10K_0402_5%~D

10K_0402_5%~D

MS_ENABLE#

DOCK_PWR_BTN#

HOT_UNDOCK#

Q7

Q7

D

S

D

S

13

G

G

2

+3.3V_ALW

Q6

Q6

D

S

D

S

13

G

G

2

+3.3V_ALW

12

R238

100K_0402_5%~D

100K_0402_5%~D

@ R238

@

12

1

C202

@ C202

@

100K_0402_5%~D

100K_0402_5%~D

HOT_UNDOCK#

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

2

R239

@ R239

@

DOCKED_LED_1#

BREATH_PWR_LED_1#

DOCK_PWR_BTN#

MS_ENABLE#

MS_ENABLE#

DOCKED_LED_1#

DOCK_DET_2

JMS1

JMS1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

Shield

9

Shield

MOLEX_53398-0719

MOLEX_53398-0719

2

INB

1

INA

+5V_ALW

2

INB

1

INA

+5V_ALW

R297

R297

0_0402_5%~D

0_0402_5%~D

1 2

D

D

1 3

2

JP2

JP2

1

1

2

2

3

3

4

4

5

5

6

6

7

Shield

8

Shield

MOLEX_48227-0611

MOLEX_48227-0611

3

U39

U39

G

BREATH_PWR_MS_LED#

4

O

P

SN74AHC1G32DCKR_SC70-5~D

SN74AHC1G32DCKR_SC70-5~D

5

C204

C204

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

3

U40

U40

G

DOCKED_MS_LED#

4

O

P

SN74AHC1G32DCKR_SC70-5~D

SN74AHC1G32DCKR_SC70-5~D

5

C203

C203

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

S

S

DOCK_DET_1

Q25

Q25

2N7002W-7-F_SOT323-3~D@

2N7002W-7-F_SOT323-3~D@

G

G

1

12

12

DOCK_DET_1 <18>

1

A A

C158

C158

1

C159

C159

2

2

C205

C205

1

1

2

C206

C206

1

C218

C218

2

2

C219

C219

1

1

2

C207

C207

1

C208

C208

2

2

C160

C160

1

C161

C161

1

1

C220

C220

C221

C221

2

2

2

1

2

DELL CONFIDENTIAL/PROPRIETARY

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

5

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

Close to connector

0.1U_0603_50V4Z~D

0.1U_0603_50V4Z~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

100P_0402_50V8J~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Docking Connector

Docking Connector

Docking Connector

LA-3954P

LA-3954P

LA-3954P

X03

X03

529Friday, April 18, 2008

529Friday, April 18, 2008

529Friday, April 18, 2008

1

X03

of

of

of

Page 6

5

+3.3V_RUN

R177

R177

10K_0402_5%~D

10K_0402_5%~D

12

R190

R190

2.7K_0402_5%~D

2.7K_0402_5%~D

R65

R65

0_0402_5%~D

0_0402_5%~D

1 2

5

D_LAD0

D_LAD1

D_LAD2

D_LAD3

D_LFRAME#

D_CLKRUN#

D_SERIRQ

D_DLDRQ1#

TXD1

RTS1#

DTR1#

HP_SHTDN#

DOCK_SIO_ALERT#

DOCKED_LED#

LPCPD#

DK_RUNON

DK_SUSON

SIO_RESET#SIO_RESET#

AUX_ON

D

D

1 3

DOCK_SMB_ALERT#<5>

S

S

Q1

Q1

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

G

G

2

D

D

1 3

G

G

2

+3.3V_ALW

12

@

@

R231

R231

10K_0402_5%~D

10K_0402_5%~D

SMB_DATDOCK_SMB_DAT

S

S

SMB_CLK

Q3

Q3

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

R2 100K_0402_1%~DR2 100K_0402_1%~D

1 2

R3 100K_0402_1%~DR3 100K_0402_1%~D

1 2

R4 100K_0402_1%~DR4 100K_0402_1%~D

1 2

R5 100K_0402_1%~DR5 100K_0402_1%~D

1 2

R6 100K_0402_1%~DR6 100K_0402_1%~D

1 2

R7 100K_0402_1%~D@R7 100K_0402_1%~D@

1 2

R8 100K_0402_1%~D@R8 100K_0402_1%~D@

1 2

R9 100K_0402_1%~D@R9 100K_0402_1%~D@

D D

C C

B B

A A

1 2

R228 100K_0402_1%~D@R228 100K_0402_1%~D@

1 2

R229 100K_0402_1%~D@R229 100K_0402_1%~D@

1 2

R230 100K_0402_1%~D@R230 100K_0402_1%~D@

1 2

R240 10K_0402_5%~DR240 10K_0402_5%~D

+3.3V_ALW

R10 100K_0402_1%~DR10 100K_0402_1%~D

R185 10K_0402_5%~DR185 10K_0402_5%~D

R227 47K_0402_5%~DR227 47K_0402_5%~D

R241 100K_0402_1%~DR241 100K_0402_1%~D

R242 100K_0402_1%~DR242 100K_0402_1%~D

R183 10K_0402_5%~DR183 10K_0402_5%~D

HOT_UNDOCK#<5>

DOCK_SMB_DAT<5,8,16>

DOCK_SMB_CLK<5,8,16>

12

1 2

12

12

1 2

1 2

C165 0.1U_0402_16V4Z~DC165 0.1U_0402_16V4Z~D

AUX_ON<17>

12

12

+3.3V_ALW

12

HOT_UNDOCK#

+3.3V_ALW

DOCK_SMB_CLK

4

+3.3V_RUN

1

C188

C188

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

D_LAD[0..3]<5>

D_LFRAME#<5>

D_DLDRQ1#<5>

D_CLKRUN#<5>

CLK_PCI_DOCK<5>

D_SERIRQ<5>

+3.3V_ALW

+3.3V_RUN

R27

R27

R28

R28

1 2

1 2

10K_0402_5%~D

10K_0402_5%~D

10K_0402_5%~D

10K_0402_5%~D

0100 1000

MIC_DET<16> VTT_PWRGD <19>

ACAV_IN_DOCK<18>

+3.3V_ALW

+3.3V_ALW

HP_DET<16>

+3.3V_ALW

PS_ID_DISABLE#<18>

+3.3V_ALW

DOCKED_LED#<5>

4

D_LAD0

D_LAD1

D_LAD2

D_LAD3

DOCK_SIO_ALERT#

D_LFRAME#

D_DLDRQ1#

SIO_RESET#

LPCPD#

D_CLKRUN#

CLK_PCI_DOCK

D_SERIRQ

R15 10K_0402_5%~DR15 10K_0402_5%~D

R17 10K_0402_5%~DR17 10K_0402_5%~D

R18 10K_0402_5%~DR18 10K_0402_5%~D

R19 10K_0402_5%~DR19 10K_0402_5%~D

R38 10K_0402_5%~DR38 10K_0402_5%~D

MIC_DET

ACAV_IN_DOCK DTYPE2

R184 10K_0402_5%~DR184 10K_0402_5%~D

HOT_UNDOCK#

R179 10K_0402_5%~DR179 10K_0402_5%~D

R180 10K_0402_5%~DR180 10K_0402_5%~D

HP_DET

R182 10K_0402_5%~DR182 10K_0402_5%~D

LPCPD#

HP_SHTDN#

R178 10K_0402_5%~DR178 10K_0402_5%~D

AUX_ON

DOCKED_LED#

SIO_RESET#

C27

C27

15P_0402_50V8J~D

15P_0402_50V8J~D

12

12

12

12

SMB_DAT

SMB_CLK

12

DOCK_SMB_ALERT#

12

12

12

12

12

R269

1M_0402_5%~D

1M_0402_5%~D

1 2

Y1

Y1

R149

R149

0_0402_5%~D

0_0402_5%~D

1 2

R151

R151

0_0402_5%~D

0_0402_5%~D

1 2

R153

R153

0_0402_5%~D

0_0402_5%~D

1 2

R155

R155

0_0402_5%~D

0_0402_5%~D

1 2

20

21

22

23

17

24

25

26

27

28

29

30

44

45

46

47

SIO_XTAL1

61

SIO_XTAL2

62

64

3

9

2

8

4

10

5

6

15

49

50

51

52

54

55

16

57

58

59

14

40

41

42

43

@R269

@

0_0402_5%~D

0_0402_5%~D

1 2

12

24MHZ_12PF_1BX24000CE1B~D

24MHZ_12PF_1BX24000CE1B~D

C28

C28

12P_0402_50V8J~D

12P_0402_50V8J~D

U1

U1

LAD0

LAD1

LAD2

LAD3

nIO_PME#

nLFRAME#

nLDRQ#

nPCIRST#

nLPCPD#

nCLKRUN#

PCICLK

SER_IRQ

LGP44

LGP45

LGP46

SYSOPT/LGP47

XTAL1

XTAL2

24MHZ_OUT

SDAT

SCLK

SDAT_1

SCLK_1

SDAT_2

SCLK_2

SMB_A0

nSMBINT

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

R41

R41

3

+VTR3

+VTR2

+VTR1

+VR_CAP

13

VCC

VCC48VCC53VCC65VCC

CLK

CLK

SMBUS LPC & GPIO

SMBUS LPC & GPIO

GPIO PORT

GPIO PORT

VSS7VSS19VSS31VSS39VSS56VSS60VSS

SIO_XTAL1

SIO_XTAL2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

R150

R150

0_0402_5%~D@

0_0402_5%~D@

R152

R152

0_0402_5%~D@

0_0402_5%~D@

R154

R154

0_0402_5%~D@

0_0402_5%~D@

93

POWER

POWER

VTR

VTR

VTR

VTR

RXD

SERIAL PORT

SERIAL PORT

TXD

nDSR#

nRTS#

nCTS#

nDTR#

nRI#

nDCD#

nINIT#

nSLCTIN#

SLCT

PE

BUSY

nACK#

PARALLEL PORT

PARALLEL PORT

nERROR#

nALF#

nSTROBE#

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO50

GPIO51

GPIO52

GPIO53

GPIO54

GPIO55

GPIO56

GPIO57

76

LPC47N237-MT_TQFP100~D

LPC47N237-MT_TQFP100~D

note: R60 and C29 are placed near U1 chip

12

12

12

1

18

32

63

84

85

86

87

88

89

90

91

66

67

77

78

79

80

81

82

83

68

69

70

71

72

73

74

75

11

33

34

35

36

37

38

12

92

94

95

96

97

98

99

100

CLK_PCI_DOCK

1 2

1

2

33_0402_5%~D

33_0402_5%~D

+VTR

RXD1

TXD1

DSR1#

RTS1#

CTS1#

DTR1#

RI1#

DCD1#

VTT_PWRGD

DOCK_ID0

DOCK_ID1

DOCK_ID2

DTYPE0

DTYPE1

DTYPE2

DPB_LP

DPB_PRI

DPA_LP

DPA_PRI

USB_HUB2_RST#

USB_HUB1_RST#

DK_RUNON

DK_SUSON

R60

R60

C29

C29

10P_0402_50V8J~D

10P_0402_50V8J~D

RXD1 <7>

DSR1# <7>

CTS1# <7>

RI1# <7>

DCD1# <7>

R20 33_0402_5%~DR20 33_0402_5%~D

1 2

R21 33_0402_5%~DR21 33_0402_5%~D

1 2

R30 33_0402_5%~DR30 33_0402_5%~D

1 2

R31 33_0402_5%~DR31 33_0402_5%~D

1 2

R32 33_0402_5%~DR32 33_0402_5%~D

1 2

R33 33_0402_5%~DR33 33_0402_5%~D

1 2

R34 33_0402_5%~DR34 33_0402_5%~D

1 2

R35 33_0402_5%~DR35 33_0402_5%~D

1 2

R36 33_0402_5%~DR36 33_0402_5%~D

1 2

R37 33_0402_5%~DR37 33_0402_5%~D

1 2

R39 33_0402_5%~DR39 33_0402_5%~D

1 2

R40 33_0402_5%~DR40 33_0402_5%~D

1 2

R181 10K_0402_5%~DR181 10K_0402_5%~D

1

C153

C153

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

TXD1 <7>

RTS1# <7>

DTR1# <7>

12

1

C154

C154

C155

C155

2

4.7U_0603_6.3V6K~D@

4.7U_0603_6.3V6K~D@

C21

C21

DPB_LP <14>

DPB_PRI <14>

DPA_LP <13>

DPA_PRI <13>HP_SHTDN#<15>

USB_HUB2_RST# <8>

USB_HUB1_RST# <8>

DK_RUNON <7,17>

DK_SUSON <17>

2

+VTR1 +VTR2 +VTR3+VR_CAP

1

1

C156

C156

2

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

C23

C23

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

1

2

2

C22

C22

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

INIT#

SLCT_IN#

SLCT

PE

BUSY

ACK#

ERROR#

AFD#

STRB#

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

+3.3V_ALW

2

1

C157

C157

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

1

2

2

C24

C24

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

INIT# <7>

SLCT_IN# <7>

SLCT <7>

PE <7>

BUSY <7>

ACK# <7>

ERROR# <7>

AFD# <7>

STRB# <7>

PD[0..7] <7>

1

R156

R156

0_0402_5%~D

0_0402_5%~D

DOCK_ID0

DOCK_ID1

DOCK_ID2

DTYPE0

DTYPE1

+3.3V_ALW+VTR

12

+3.3V_ALW

R44

R44

R45

R45

R42

R42

R43

R43

@

@

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

1 2

1 2

R53

R53

R52

R51

R51

@

@

@ R52

@

1 2

1 2

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

R46

@ R46

@

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

1 2

1 2

R55

R55

R54

@ R54

@

1 2

1 2

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

47K_0402_1%~D

C25

C25

10U_0805_10V4Z~D

10U_0805_10V4Z~D

1

2

Dock ID

ID2 ID1 ID0

X00

X01 0

X02

X03

A00

A01

000

0

0

100

GP31GP32GP33

1

0

0

1

1

1

1

01

Dock Type ID

GP34GP35GP36

1

001

E-APR

E-LIO

ID2 ID1 ID0

00

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SMSC 47N237

SMSC 47N237

SMSC 47N237

LA-3954P

LA-3954P

LA-3954P

629Friday, April 18, 2008

629Friday, April 18, 2008

629Friday, April 18, 2008

1

R236

@R236

@

47K_0402_1%~D

47K_0402_1%~D

1 2

1 2

R237

R237

1 2

1 2

47K_0402_1%~D

47K_0402_1%~D

*

*

X03

X03

X03

of

of

of

Page 7

5

+5V_RUN

D D

1 2

C33 0.1U_0402_16V4Z~DC33 0.1U_0402_16V4Z~D

1 2

C35 0.47U_0402_10V4Z~DC35 0.47U_0402_10V4Z~D

TXD1<6>

RTS1#<6>

DTR1#<6>

DCD1#<6>

RI1#<6>

RXD1<6>

CTS1#<6>

DSR1#<6>

C C

PD0

PD1

PD2

PD3

PD4

PD5

PD6

B B

PD7

AFD#

ERROR#

INIT#

SLCT_IN#

SLCT

PE

BUSY

ACK#

+3.3V_RUN

DK_RUNON<6,17>

3243C1+

3243C13243C2+

3243C2TXD1

RTS1#

DTR1#

DCD1#

RI1#

RXD1

CTS1#

DSR1#

PD[0..7] <6>

+LPT5V

RP1

RP1

1 8

2 7

3 6

4 5

4.7K_1206_8P4R_5%~D

4.7K_1206_8P4R_5%~D

+LPT5V

RP2

RP2

1 8

2 7

3 6

4 5

4.7K_1206_8P4R_5%~D

4.7K_1206_8P4R_5%~D

+LPT5V

RP3

RP3

1 8

2 7

3 6

4 5

4.7K_1206_8P4R_5%~D

4.7K_1206_8P4R_5%~D

+LPT5V

RP4

RP4

1 8

2 7

3 6

4 5

4.7K_1206_8P4R_5%~D

4.7K_1206_8P4R_5%~D

28

24

1

2

14

13

12

19

18

17

16

15

20

23

22

26

U2

U2

C1+

VCC

C1C2+

C2T1IN

T2IN

T3IN

R1OUT

R2OUT

R3OUT

R4OUT

R5OUT

R2OUTB

FORCEON

FORCEOFF#

MAX3243ECUI+T_TSSOP28~D

MAX3243ECUI+T_TSSOP28~D

INVALID#

1

C31

C31

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

2

27

V+

3

V-

9

T1OUT

10

T2OUT

11

T3OUT

4

R1IN

5

R2IN

6

R3IN

7

R4IN

8

R5IN

21

25

GND

SLCT_IN#

ERROR#

4

3243V-

TXD1#

RTS1

DTR1

DCD1

RI1

RXD1#

CTS1

DSR1

PD3

C259 270P_0402_50V7K~DC259 270P_0402_50V7K~D

1 2

PD2

C260 270P_0402_50V7K~DC260 270P_0402_50V7K~D

1 2

PD1

C261 270P_0402_50V7K~DC261 270P_0402_50V7K~D

1 2

PD0

C262 270P_0402_50V7K~DC262 270P_0402_50V7K~D

1 2

PD7

C263 270P_0402_50V7K~DC263 270P_0402_50V7K~D

1 2

PD6

C264 270P_0402_50V7K~DC264 270P_0402_50V7K~D

1 2

PD5

C265 270P_0402_50V7K~DC265 270P_0402_50V7K~D

1 2

PD4

C266 270P_0402_50V7K~DC266 270P_0402_50V7K~D

1 2

ACK#

C267 270P_0402_50V7K~DC267 270P_0402_50V7K~D

1 2

BUSY

C268 270P_0402_50V7K~DC268 270P_0402_50V7K~D

1 2

PE

C269 270P_0402_50V7K~DC269 270P_0402_50V7K~D

1 2

SLCT

C270 270P_0402_50V7K~DC270 270P_0402_50V7K~D

1 2

C271 270P_0402_50V7K~DC271 270P_0402_50V7K~D

1 2

INIT#

C272 270P_0402_50V7K~DC272 270P_0402_50V7K~D

1 2

C273 270P_0402_50V7K~DC273 270P_0402_50V7K~D

1 2

AFD#

C274 270P_0402_50V7K~DC274 270P_0402_50V7K~D

1 2

C32

C32

0.47U_0402_10V4Z~D

0.47U_0402_10V4Z~D

1 2

C34

C34

0.47U_0402_10V4Z~D

0.47U_0402_10V4Z~D

1 2

+5V_RUN

DCD1

DSR1

RXD1#

RTS1

TXD1#

CTS1

DTR1

RI13243V+

D1

D1

2 1

RB751V_SOD323-2~D

RB751V_SOD323-2~D

STRB#<6>

3

12

R67

R67

1K_0402_5%~D

1K_0402_5%~D

+LPT5V

1

1

C36

C36

2

2

270P_0402_50V7K~D

270P_0402_50V7K~D

SLCT_IN#<6>

ERROR#<6>

STRB#

1

C30

C30

270P_0402_50V7K~D

270P_0402_50V7K~D

2

1

1

C38

C38

C37

C37

2

2

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

SLCT<6>

PE<6>

BUSY<6>

ACK#<6>

PD7<6>

PD6<6>

PD5<6>

PD4<6>

PD3<6>

PD2<6>

INIT#<6>

PD1<6>

PD0<6>

AFD#<6>

2

1

1

C39

C39

C40

C40

2

2

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

1

1

C43

2

STRB#

VGA_DDC_CLK<5,12>

VGA_DDC_DAT<5,12>

C43

C42

C42

2

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

270P_0402_50V7K~D

VGA_DDC_CLK

JVGA_VS<12>

+CRT_VCC<12>

BLUE<12>

JVGA_HS<12>

GREEN<12>

RED<12>

JVGA_VS

+CRT_VCC

BLUE

JVGA_HS

GREEN

VGA_DDC_DAT

RED

C41

C41

270P_0402_50V7K~D

270P_0402_50V7K~D

1

JP5

JP5

41

42

43

44

45

46

47

48

49

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

1

11

6

2

12

7

3

13

8

4

14

9

5

15

10

TYCO_2-1734198-1

TYCO_2-1734198-1

Serial

Serial

Print

Print

VGA

VGA

50

51

52

53

DELL CONFIDENTIAL/PROPRIETARY

A A

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

LPT and RS232

LPT and RS232

LPT and RS232

LA-3954P

LA-3954P

LA-3954P

X03

X03

729Friday, April 18, 2008

729Friday, April 18, 2008

729Friday, April 18, 2008

1

X03

of

of

of

Page 8

5

4

3

2

1

1

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

C47

C47

1

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

C59

C59

1

2

C55

C55

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

+3.3VDDA_USB1

1

C48

C48

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

1U_0603_10V6K~D

1U_0603_10V6K~D

+3.3VDDA_USB2

1

C60

C60

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

C67

C67

2

1U_0603_10V6K~D

1U_0603_10V6K~D

1

C49

C49

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

SMBUS or EEPROM INTERFACE BEHAVIOR

CFG_SEL1 CFG_SEL0

Pin24Pin25

0

0

*

0

1

01

11

R263

R263

0_0402_5%~D

S_USB_OC1#

S_USB_OC2#

S_USB1_EN

S_USB2_EN

1

1

C61

C61

2

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

S_USB_OC4#

S_USB_OC5#

S_USB4_EN

S_USB5_EN

0_0402_5%~D

1 2

1 2

R265

R265

0_0402_5%~D@

0_0402_5%~D@

R264

R264

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R266

R266

0_0402_5%~D@

0_0402_5%~D@

R298

R298

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R299

R299

0_0402_5%~D@

0_0402_5%~D@

R301

R301

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R300

R300

0_0402_5%~D@

0_0402_5%~D@

Internal Default Configuration

SMBus slave address 58 (0101100x)

Bus Power Operation / LED Mode = USB

2-Wire I2C EEPROMS are support

S_USB_OC12# <9>

S_USB12_EN <9>

S_USB_OC45# <11>

S_USB45_EN <11>

SMBUS or EEPROM INTERFACE BEHAVIOR

CFG_SEL1 CFG_SEL0

0

0

*

11

Pin24Pin25

0

1

01

Internal Default Configuration

SMBus slave address 58 (0101100x)

Bus Power Operation / LED Mode = USB

2-Wire I2C EEPROMS are support

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SMSC USB2513

SMSC USB2513

SMSC USB2513

LA-3954P

LA-3954P

LA-3954P

X03

X03

829Friday, April 18, 2008

829Friday, April 18, 2008

829Friday, April 18, 2008

1

X03

of

of

of

P_XTAL1

R69

12

C51

C51

FX_SMB_CLK

FX_SMB_DAT

R66

R66

0_0402_5%~D

0_0402_5%~D

1 2

FX_SMB_CLK

FX_SMB_DAT

S_XTAL1

S_XTAL2

R69

0_0402_5%~D

0_0402_5%~D

1 2

15P_0402_50V8J~D

15P_0402_50V8J~D

USB_HUB1_RST#<6>

D

S

D

S

1 3

G

G

2

P_XTAL2

+3.3V_SUS +3.3V_SUS

R72

@ R72

@

2.2K_0402_5%~D

2.2K_0402_5%~D

R162

R162

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R163

R163

0_0402_5%~D

0_0402_5%~D

+3.3V_SUS

S

S

Q4

Q4

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

G

G

2

+3.3V_SUS +3.3V_SUS

R81

R81

2.2K_0402_5%~D

2.2K_0402_5%~D

+3.3V_SUS

FX_SMB_DATDOCK_SMB_DAT

FX_SMB_CLKDOCK_SMB_CLK

Q2

Q2

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

D

D

1 3

R166

R166

0_0402_5%~D

0_0402_5%~D

1 2

1 2

R167

R167

0_0402_5%~D

0_0402_5%~D

USB_HUB2_RST#<6>

+3.3V_SUS

USB_A_+<5>

USB_A_-<5>

R73

2.2K_0402_5%~D

2.2K_0402_5%~D

1 2

1 2

1 2

R74

R74

10K_0402_5%~D

10K_0402_5%~D

USB_HUB1_RST#

12

R215

@R215

@

47K_0402_5%~D

47K_0402_5%~D

+3.3V_SUS

USB_B_+<5>

USB_B_-<5>

R82

R82

2.2K_0402_5%~D

2.2K_0402_5%~D

1 2

1 2

1 2

R83

R83

10K_0402_5%~D

10K_0402_5%~D

USB_HUB2_RST#

12

R216

@R216

@

47K_0402_5%~D

47K_0402_5%~D

R70

R70

1K_0402_5%~D

1K_0402_5%~D

@R73

@

R75

R75

1 2

100K_0402_5%~D

100K_0402_5%~D

R80

R80

1K_0402_5%~D

1K_0402_5%~D

R84

R84

R68

R68

1M_0402_5%~D

1M_0402_5%~D

1 2

Y2

Y2

24MHZ_12PF_1BX24000CE1B~D

D D

+3.3V_SUS

12

R221

R221

4.7K_0402_5%~D

4.7K_0402_5%~D

C C

B B

A A

USB_HUB1_RST#

1

C75

C75

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

2

DOCK_SMB_DAT<5,6,16>

DOCK_SMB_CLK<5,6,16>

+3.3V_SUS

12

R222

R222

4.7K_0402_5%~D

4.7K_0402_5%~D

USB_HUB2_RST#

1

C81

C81

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

2

R77

R77

1M_0402_5%~D

1M_0402_5%~D

1 2

Y3

Y3

24MHZ_12PF_1BX24000CE1B~D

24MHZ_12PF_1BX24000CE1B~D

1

C62

C62

2

18P_0402_50V8J~D

18P_0402_50V8J~D

24MHZ_12PF_1BX24000CE1B~D

1

C50

C50

2

18P_0402_50V8J~D

18P_0402_50V8J~D

+3.3V_SUS

R78

R78

0_0402_5%~D

0_0402_5%~D

1 2

12

C63

C63

15P_0402_50V8J~D

15P_0402_50V8J~D

5

+3.3V_SUS +3.3V_SUS

1

C44

C44

C189

C189

2

1U_0603_10V6K~D

1U_0603_10V6K~D

P_XTAL1

P_XTAL2

FX1_SMB_CLK

FX1_SMB_DAT

PCFG_SEL1

12

12

R76

R76

12K_0402_1%~D

12K_0402_1%~D

+3.3V_SUS +3.3V_SUS

1

C192

C192

2

1U_0603_10V6K~D

1U_0603_10V6K~D

1 2

S_XTAL1

S_XTAL2

FX2_SMB_CLK

FX2_SMB_DAT

SCFG_SEL1

12

12

R85

R85

12K_0402_1%~D

12K_0402_1%~D

100K_0402_5%~D

100K_0402_5%~D

4

+3.3VDDA_USB1

1

2

5

23

U3

U3

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

VDD33

27

VBUS_DET

31

USBUP_DP

30

USBUP_DM

33

XTAL1/CLKIN

32

XTAL2

24

SCL/SMBCLK/CFG_SEL0

22

SDA/SMBDATA/NON_REM1

25

HS_IND/CFG_SEL1

28

SUSP_IND/LOCAL_PWR/NON_REM0

35

RBIAS

26

RESET_N

11

TEST

1

C56

C56

2

U5

U5

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

27

VBUS_DET

31

USBUP_DP

30

USBUP_DM

33

XTAL1/CLKIN

32

XTAL2

24

SCL/SMBCLK/CFG_SEL0

22

SDA/SMBDATA/NON_REM1

25

HS_IND/CFG_SEL1

28

SUSP_IND/LOCAL_PWR/NON_REM0

35

RBIAS

26

RESET_N

11

TEST

VDDA33

USB2513-AEZG_QFN36_6X6~D

USB2513-AEZG_QFN36_6X6~D

+3.3VDDA_USB2

23

VDD33

10

29

VDDA33

5

10

VDDA33

USB2513-AEZG_QFN36_6X6~D

USB2513-AEZG_QFN36_6X6~D

1

C190

C190

2

1U_0603_10V6K~D

1U_0603_10V6K~D

VDDA33

29

1U_0603_10V6K~D

1U_0603_10V6K~D

VDDA33

VDDA33

C193

C193

+3.3V_SUS

1

C180

C180

2

36

15

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

VDD33PLL

USBDN1_DM

USBDN1_DP

PRTPWR1

OCS1_N

USBDN2_DM

USBDN2_DP

PRTPWR2

OCS2_N

USBDN3_DM

USBDN3_DP

PRTPWR3

OCS3_N

VDD18PLL

Thermal Slug(VSS)

+3.3V_SUS

1

1

C57

C57

2

2

36

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

VDD33PLL

USBDN1_DM

USBDN1_DP

PRTPWR1

USBDN2_DM

USBDN2_DP

PRTPWR2

USBDN3_DM

USBDN3_DP

PRTPWR3

VDD18PLL

Thermal Slug(VSS)

C45

C45

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

VDD33CR

VDD18

C181

C181

15

VDD33CR

OCS1_N

OCS2_N

OCS3_N

VDD18

1

2

NC

NC

NC

NC

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

NC

NC

NC

NC

+3.3V_SUS

1

1

C184

C184

C191

C191

1U_0603_10V6K~D

1U_0603_10V6K~D

1

2

12

13

3

4

16

17

6

7

18

19

8

9

20

21

34

14

37

1

C194

C194

2

1

2

12

13

3

4

16

17

6

7

18

19

8

9

20

21

34

14

37

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

2

+VDD18PLL_1

+VDD18_1

+3.3V_SUS

1

2

1U_0603_10V6K~D

1U_0603_10V6K~D

+VDD18PLL_2

+VDD18_2

1U_0603_10V6K~D

1U_0603_10V6K~D

S_USBP1S_USBP1+

S_USB1_EN

S_USB_OC1#

S_USBP2S_USBP2+

S_USB2_EN

S_USB_OC2#

S_USBP3S_USBP3+

S_USB3_EN

S_USB_OC3#

1

C185

C185

2

1U_0603_10V6K~D

1U_0603_10V6K~D

S_USBP4S_USBP4+

S_USB4_EN

S_USB_OC4#

S_USBP5S_USBP5+

S_USB5_EN

S_USB_OC5#

S_USBP6S_USBP6+

S_USB6_EN

S_USB_OC6#

3

2

C52

C52

L1

L1

BLM18PG181SN1_0603~D

BLM18PG181SN1_0603~D

1 2

C46

C46

10U_0805_10V4Z~D

10U_0805_10V4Z~D

1

1

C53

C53

2

2

1U_0603_10V6K~D

1U_0603_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

BLM18PG181SN1_0603~D

BLM18PG181SN1_0603~D

1 2

10U_0805_10V4Z~D

10U_0805_10V4Z~D

1

C65

C65

C64

C64

2

1U_0603_10V6K~D

1U_0603_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

S_USBP1- <9>

S_USBP1+ <9>

S_USBP2- <9>

S_USBP2+ <9>

S_USBP3- <9>

S_USBP3+ <9>

S_USB3_EN <9>

S_USB_OC3# <9>

C54

C54

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

L2

L2

1

C58

C58

2

S_USBP4- <11>

S_USBP4+ <11>

S_USBP5- <11>

S_USBP5+ <11>

S_USBP6- <10>

S_USBP6+ <10>

S_USB6_EN <10>

S_USB_OC6# <10>

1

C66

C66

2

Page 9

5

FUSE1

@FUSE1

@

L0603

L0603

1 2

+5V_ALW

D D

1

2

+5V_ALW

C C

@

@

1

2

C71

C71

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

C77

C77

@

@

PAD-OPEN 4x4m

PAD-OPEN 4x4m

1

C72

C72

2

10U_1206_16V4Z~D

10U_1206_16V4Z~D

1

C76

C76

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

PJP8

PJP8

12

Short mode

FUSE3

@FUSE3

@

L0603

L0603

1 2

PJP10

PJP10

PAD-OPEN 4x4m

PAD-OPEN 4x4m

Short mode

10U_1206_16V4Z~D

10U_1206_16V4Z~D

S_USB12_EN<8>

12

S_USB3_EN<8>

U7

U7

1

GND

2

IN

3

EN1

EN24OC2#

TPS2066ADR_SO8~D

TPS2066ADR_SO8~D

U37

U37

1

GND

2

IN

3

EN1

EN24OC2#

TPS2066ADR_SO8~D

TPS2066ADR_SO8~D

OC1#

OUT1

OUT2

OC1#

OUT1

OUT2

+USB_A_PWR

8

7

6

5

+USB_B_PWR

8

7

6

5

4

S_USB_OC12#

S_USB_OC3#

S_USB_OC12# <8>

S_USB_OC3# <8>

3

L3 DLW21SN900SQ2_0805~D@L3 DLW21SN900SQ2_0805~D@

S_USBP2+<8>

S_USBP2-<8>

S_USBP1-<8>

S_USBP1+<8>

S_USBP3-<8>

S_USBP3+<8>

1

1

4

4

R86 0_0402_5%~DR86 0_0402_5%~D

R87 0_0402_5%~DR87 0_0402_5%~D

L4 DLW21SN900SQ2_0805~D@L4 DLW21SN900SQ2_0805~D@

1

1

4

4

R89 0_0402_5%~DR89 0_0402_5%~D

R88 0_0402_5%~DR88 0_0402_5%~D

2008.03.12 modify

L5 DLW21SN900SQ2_0805~D@L5 DLW21SN900SQ2_0805~D@

1

1

4

4

R90 0_0402_5%~DR90 0_0402_5%~D

R91 0_0402_5%~DR91 0_0402_5%~D

2

3

12

12

2

3

12

12

2

3

12

12

USBP2_D+

2

USBP2_D-

3

USBP1_D-

2

USBP1_D+

3

USBP3_D-

2

USBP3_D+ USBP3_D-USBP3_D+

3

USBP1_D+ USBP2_D+

USBP2_D-

U10

1

D1+

2

GND

3

D2-

IP4220CZ6_SO6~D

IP4220CZ6_SO6~D

1

2

2

+USB_A_PWR

@U10

@

4

D2+

5

VCC

6

D1-

+USB_B_PWR

D25

@D25

@

VCC

4

3

IO2

GND

IO1

PRTR5V0U2X_SOT143-4~D

PRTR5V0U2X_SOT143-4~D

USBP1_D-

+USB_A_PWR

1

+

+

C68

C68

2

150U_D_6.3VM_R18M~D

150U_D_6.3VM_R18M~D

+USB_B_PWR

Need close JUSB1.

1

+

+

C73

C73

2

150U_D_6.3VM_R18M~D

150U_D_6.3VM_R18M~D

1

C69

C69

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

+USB_A_PWR

+USB_B_PWR

1

C74

C74

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

USBP2_DUSBP2_D+

USBP1_DUSBP1_D+

USBP3_DUSBP3_D+

1

JUSB1

JUSB1

USB

USB

1

VBUS

2

D-

PORT1

PORT1

3

D+

4

GND

5

VBUS

6

D-

PORT2

PORT2

7

D+

8

GND

9

VBUS

10

D-

PORT3

PORT3

11

D+

12

GND

13

SHLD1

14

SHLD2

15

SHLD3

16

SHLD4

FOX_UB11123-M4-4F

FOX_UB11123-M4-4F

L9

L9

BLM21PG600SN1D_0805~D

BLM21PG600SN1D_0805~D

12

@

@

1 2

R107

R107

10K_0402_5%~D

10K_0402_5%~D

+5V_RUN

B B

DAT_KBD<5>

CLK_KBD<5>

DAT_MSE<5>

CLK_MSE<5>

A A

+5V_RUN

12

12

@

@

@

@

R105

R105

R106

R106

10K_0402_5%~D

10K_0402_5%~D

10K_0402_5%~D

10K_0402_5%~D

+5V_RUN_PS2_A +5V_RUN_PS2

12

@

@

R108

R108

L10

L10

BLM18AG601SN1D_0603~D

BLM18AG601SN1D_0603~D

10K_0402_5%~D

10K_0402_5%~D

1 2

L11

L11

BLM18AG601SN1D_0603~D

BLM18AG601SN1D_0603~D

1 2

L12

L12

BLM18AG601SN1D_0603~D

BLM18AG601SN1D_0603~D

1 2

L13

L13

BLM18AG601SN1D_0603~D

BLM18AG601SN1D_0603~D

1 2

F1

F1

3A_6VDC_2920SMD300

3A_6VDC_2920SMD300

21

DAT_KBD_1

CLK_KBD_1

DAT_MSE_1

CLK_MSE_1

1

1

C93

C93

2

2

270P_0402_50V7K~D

270P_0402_50V7K~D

1

1

C92

C92

C213

C213

2

2

10U_0805_10V4Z~D

10U_0805_10V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

1

C95

C95

C96

C94

C94

270P_0402_50V7K~D

270P_0402_50V7K~D

C96

2

2

270P_0402_50V7K~D

270P_0402_50V7K~D

PS2 Connector

JPS1

JPS1

3

5

1

2

6

4

9

11

7 13

8

12

10

TYCO_1734336-6

TYCO_1734336-6

270P_0402_50V7K~D

270P_0402_50V7K~D

KEYBOARD

KEYBOARD

PURPLE

PURPLE

MOUSE

MOUSE

GREEN

GREEN

14

15

16

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

USB Port x3 and PS2x2

USB Port x3 and PS2x2

USB Port x3 and PS2x2

LA-3954P

LA-3954P

LA-3954P

X03

X03

929Friday, April 18, 2008

929Friday, April 18, 2008

929Friday, April 18, 2008

1

X03

of

of

of

Page 10

5

D D

+5V_ALW

1

2

C C

@

@

C197

C197

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

FUSE9

@FUSE9

@

L0603

L0603

PJP7

PJP7

PAD-OPEN 4x4m

PAD-OPEN 4x4m

Short mode

1

C198

C198

2

10U_1206_16V4Z~D

10U_1206_16V4Z~D

1 2

+USB_D_PWR

U33

U33

1

12

S_USB6_EN_1

2

3

8

GND

OC1#

7

IN

OUT1

6

EN1

OUT2

5

EN24OC2#

TPS2066ADR_SO8~D

TPS2066ADR_SO8~D

4

S_USB_OC6#

S_USB_OC6# <8>

3

+USB_D_PWR

D34

@D34

@

1

GND

USBP6_D+ USBP6_D- USBP6_D-

S_USBP6+<8>

S_USBP6-<8>

2

IO1

PRTR5V0U2X_SOT143-4~D

PRTR5V0U2X_SOT143-4~D

L33 DLW21SN900SQ2_0805~D@L33 DLW21SN900SQ2_0805~D@

1

1

4

4

R302 0_0402_5%~DR302 0_0402_5%~D

R303 0_0402_5%~DR303 0_0402_5%~D

VCC

4

3

IO2

SATA_SBRX_C_DTX_N_1

USBP6_D+

2

2

USBP6_D-

3

3

12

12

SATA_SBRX_C_DTX_P_1

+USB_D_PWR

Need close JESATA.

1

+

+

C255

C255

C256

C256

2

150U_D_6.3VM_R18M~D

150U_D_6.3VM_R18M~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

2

+USB_D_PWR

12

C83 0.01U_0402_16V7K~DC83 0.01U_0402_16V7K~D

12

C84 0.01U_0402_16V7K~DC84 0.01U_0402_16V7K~D

USBP6_D+

SATA_SBTX_C_DRX_P

SATA_SBTX_C_DRX_N

SATA_SBRX_C_DTX_N

SATA_SBRX_C_DTX_P

ESATA_DET

JESATA

JESATA

1

VBUS

2

D-

USB

USB

3

D+

4

GND

5

GND

6

T+

ESATA

ESATA

7

T-

8

GND

9

R-

10

R+

11

GND

12

SHLD1

13

SHLD2

14

SHLD3

15

SHLD4

TYCO_1909573-3

TYCO_1909573-3

1

+1.8V_RUN +1.8V_RUN

+5V_ALW

S_USB6_EN<8>

+5V_ALW

12

R187

R187

10K_0402_5%~D

10K_0402_5%~D

B B

A A

ESATA_DET

+3.3V_RUN +1.8V_RUN

1

1

C238

C238

@

@

2

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

5

S_USB6_EN

+5V_ALW

12

R188

R188

10K_0402_5%~D

10K_0402_5%~D

13

D

D

Q5

Q5

2

G

G

2N7002W-7-F_SOT323-3~D

2N7002W-7-F_SOT323-3~D

S

S

NCP1117ST18T3G_SOT223-3~D

NCP1117ST18T3G_SOT223-3~D

3

OUT

IN

ADJ/GND

U43

U43

10U_0805_6.3V6M~D

10U_0805_6.3V6M~D

1

C239

C239

1

INA

2

INB

2

1

1

C240

C240

@

@

2

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

C211

C211

5

3

C241

C241

P

G

10U_0805_6.3V6M~D

10U_0805_6.3V6M~D

O

12

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

SN74AHC1G32DCKR_SC70-5~D

SN74AHC1G32DCKR_SC70-5~D

S_USB6_EN_1

4

U41

U41

+1.8V_RUN

Need close U42 pin 6, 19.

1

1

2

C254

C254

C253

C253

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

4

SATA_SBTX_DRX_P<5>

SATA_SBTX_DRX_N<5>

SATA_SBRX_DTX_P<5>

SATA_SBRX_DTX_N<5>

SATA_SBTX_DRX_P

SATA_SBTX_DRX_N

SATA_SBRX_DTX_P

SATA_SBRX_DTX_N

R267 1K_0402_5%~DR267 1K_0402_5%~D

1 2

R268 1K_0402_5%~DR268 1K_0402_5%~D

1 2

SATA_SBRX_DTX_P

SATA_SBRX_DTX_N

SATA_SBTX_DRX_P

SATA_SBTX_DRX_N

Bill0703: Please place under U42. (co-layout..)

Benson0912: If populate R287~290 and R293~R296,

the U42,R262, R267, R268 ,U43, C239, C241

is no-stuff and C244,C245 will change to 0ohm.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

U42

U42

2

VDD

6

VDD

11

VDD

15

VDD

19

VDD

3

AI+

4

AI-

7

BO+

8

BO-

1

EQA

10

EQB

PI2EQX3211BHE_SSOP20~D

PI2EQX3211BHE_SSOP20~D

R293

R293

0_0402_5%~D@

0_0402_5%~D@

1 2

R294

R294

0_0402_5%~D@

0_0402_5%~D@

1 2

R295

R295

0_0402_5%~D@

0_0402_5%~D@

1 2

R296

R296

0_0402_5%~D@

0_0402_5%~D@

1 2

20

EN

18

AO+

17

AO-

14

BI+

13

BI-

5

GND

9

GND

12

GND

16

GND

SATA_SBRX_P

SATA_SBRX_N

SATA_SBTX_P

SATA_SBTX_N

2

1 2

R262 10K_0402_5%~DR262 10K_0402_5%~D

SATA_SBTX_C_DRX_P_1

SATA_SBTX_C_DRX_N_1

SATA_SBRX_C_DTX_P_1

SATA_SBRX_C_DTX_N_1

R287

R287

0_0402_5%~D@

0_0402_5%~D@

SATA_SBRX_C_DTX_P_1

1 2

R288

R288

0_0402_5%~D@

0_0402_5%~D@

SATA_SBRX_C_DTX_N_1

1 2

R289

R289

0_0402_5%~D@

0_0402_5%~D@

SATA_SBTX_C_DRX_P_1

1 2

R290

R290

0_0402_5%~D@

0_0402_5%~D@

SATA_SBTX_C_DRX_N_1

1 2

SATA_SBTX_C_DRX_P

12

C244 0.01U_0402_16V7K~DC244 0.01U_0402_16V7K~D

R308

R308

470_0402_5%~D

470_0402_5%~D

C245 0.01U_0402_16V7K~DC245 0.01U_0402_16V7K~D

12

SATA_SBTX_C_DRX_N

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

E-SATA+USB Port x1

E-SATA+USB Port x1

E-SATA+USB Port x1

LA-3954P

LA-3954P

LA-3954P

10 29Friday, April 18, 2008

10 29Friday, April 18, 2008

10 29Friday, April 18, 2008

of

of

1

of

X03

X03

X03

Page 11

5

4

3

2

1

LED2_+

VBUS0

GND

VBUS1

GND

+3.3V_LAN

R102

D2+

VCC

D1-

R102

1 2

150_0402_5%~D

150_0402_5%~D

R103

R103

1 2

150_0402_5%~D

150_0402_5%~D

R104

R104

1 2

150_0402_5%~D

150_0402_5%~D

+USB_C_PWR

4

5

6

LED_10_GRN_R#

LED_100_ORG_R#

USBP4_D-

LED_10_GRN_R#

13

14

LED_100_ORG_R#

15

12

LED_1000_YEL_R#

11

16

USBP4_D-

17

D0-

D0+

D1-

D1+

USBP4_D+

18

19

20

USBP5_D-

21

USBP5_D+

22

23

S_USBP4+<8>

S_USBP4-<8>

S_USBP5+<8>

S_USBP5-<8>

+USB_C_PWR

L34 DLW21SN900SQ2_0805~D@L34 DLW21SN900SQ2_0805~D@

1

1

4

4

R304 0_0402_5%~DR304 0_0402_5%~D

R305 0_0402_5%~DR305 0_0402_5%~D

L35 DLW21SN900SQ2_0805~D@L35 DLW21SN900SQ2_0805~D@

1

1

4

4

R306 0_0402_5%~DR306 0_0402_5%~D

R307 0_0402_5%~DR307 0_0402_5%~D

USBP4_D+

2

2

USBP4_D-

3

3

12

12

USBP5_D+

2

2

USBP5_D-

3

3

12

12

DOCK_LOM_ACTLED_YEL#<5>

DOCK_LOM_SPD10LED_GRN#<5>DOCK_LOM_TRD0-<5>

DOCK_LOM_SPD100LED_ORG#<5>

Need close JP3.

+USB_C_PWR

C78

C78

1

+

+

2

150U_D_6.3VM_R18M~D

150U_D_6.3VM_R18M~D

DOCK_LAN_ACTLED_YEL# LED_1000_YEL_R#

DOCK_LED_10#

DOCK_LED_100#

1

C79

C79

2

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

U44

@U44

USBP4_D+ USBP5_D+

USBP5_D-

@

1

D1+

2

GND

3

D2-

IP4220CZ6_SO6~D

IP4220CZ6_SO6~D

JP3

TRCT0_1_2_3

1 2

DOCK_LOM_TRD0+

DOCK_LOM_TRD0DOCK_LOM_TRD1+

DOCK_LOM_TRD1DOCK_LOM_TRD2+

DOCK_LOM_TRD2DOCK_LOM_TRD3+

DOCK_LOM_TRD3-

12

+USB_C_PWR

U45

U45

1

2

S_USB45_EN<8>

3

8

GND

OC1#

7

IN

OUT1

6

EN1

OUT2

5

EN24OC2#

TPS2066ADR_SO8~D

TPS2066ADR_SO8~D

DOCK_LOM_TRD0+<5>

+5V_ALW

1

2

@

@

DOCK_LOM_TRD1+<5>

DOCK_LOM_TRD1-<5>

DOCK_LOM_TRD2+<5>

DOCK_LOM_TRD2-<5>

C257

C257

DOCK_LOM_TRD3+<5>

DOCK_LOM_TRD3-<5>

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

FUSE10

@FUSE10

@

L0603

L0603

PJP11

PJP11

PAD-OPEN 4x4m

PAD-OPEN 4x4m

Short mode

C258

C258

10U_1206_16V4Z~D

10U_1206_16V4Z~D

D D

C C

B B

JP3

6

VCC

2

MD1+

3

MD1-

4

MD2+

5

MD2-

7

MD3+

8

MD3-

9

MD4+

10

MD4-

1

CH_GND

24

SHLD1

25

SHLD2

26

SHLD3

27

SHLD4

TYCO_1840015-1

TYCO_1840015-1

Modify symbol at 12/19

S_USB_OC45#

LED2_GREEN-

LED2_ORANGE-

LED1_YELLOW+

LED1_YELLOW-

S_USB_OC45# <8>

L31

L31

0_0603_5%~D

0_0603_5%~D

TRCT2_3_DOCK<5>

TRCT0_1_DOCK<5>

A A

1 2

@

@

Close to JP3 connector

C209

C209

TRCT0_1_2_3

1

1

C210

C210

@

@

2

2

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

RJ45+USB Portx2

RJ45+USB Portx2

RJ45+USB Portx2

LA-3954P

LA-3954P

LA-3954P

X03

X03

11 29Friday, April 18, 2008

11 29Friday, April 18, 2008

11 29Friday, April 18, 2008

1

X03

of

of

of

Page 12

5

4

3

2

+5V_RUN

1

D2

D2

RB500V-40 TE-17_SOD323-2~D

RB500V-40 TE-17_SOD323-2~D

R109

R109

0_1206_5%~D

0_1206_5%~D

+CRTVCC

21

12

@

@

1 2

F4

F4

1 2

1.1A_6V_1812L110PR~D

1.1A_6V_1812L110PR~D

1

C103

C103

2

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

RED

VGA_DDC_DAT

GREEN

JVGA_HS

BLUE

+CRT_VCC

JVGA_VS

VGA_DDC_CLK

@R243

@

R243

0_1206_5%~D

0_1206_5%~D

+CRT_VCC

RED <7>

VGA_DDC_DAT <5,7>

GREEN <7>

JVGA_HS <7>

BLUE <7>

+CRT_VCC <7>

JVGA_VS <7>

VGA_DDC_CLK <5,7>

D3

DA204U_SOT323-3~D@D3DA204U_SOT323-3~D@

1

D D

L14

L14

BK1608HS220T_0603~D

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

L17

L17

L18

L18

BK1608HS220T_0603~D

1 2

BK1608HS220T_0603~D

BK1608HS220T_0603~D

1 2

BK1608HS220T_0603~D

BK1608HS220T_0603~D

1 2

12

R292

R292

2.2K_0402_5%~D

2.2K_0402_5%~D

L15

L15

L16

L16

+5V_SYNC

12

@R110

@

R110

1K_0402_5%~D

1K_0402_5%~D

1

C106

C106

2

@R111

@

R111

C107

C107

1K_0402_5%~D

1K_0402_5%~D

VGA_R<5>

VGA_G<5>

VGA_B<5>

C C

VGA_R

VGA_G

VGA_B

HSYNC_BUF

VSYNC_BUF

12

12

R270

R270

R271

R271

150_0402_1%~D

150_0402_1%~D

150_0402_1%~D

150_0402_1%~D

VGA_DDC_DAT<5,7>

VGA_DDC_CLK<5,7>

HSYNC_BUF_1

1 2

R273 10_0402_5%~DR273 10_0402_5%~D

R274 10_0402_5%~DR274 10_0402_5%~D

1 2

VSYNC_BUF_1

R272

R272

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

1

2

1

C98

C98

2

@

@

C105

C105

12

150_0402_1%~D

150_0402_1%~D

1

C97

C97

2

@

@

C104

C104

1

C99

C99

2

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

12

R291

R291

2.2K_0402_5%~D

2.2K_0402_5%~D

68NH_LQW18AN68NJ00D_5%_0603

68NH_LQW18AN68NJ00D_5%_0603

1 2

68NH_LQW18AN68NJ00D_5%_0603

68NH_LQW18AN68NJ00D_5%_0603

1 2

1

2

+5V_RUN

2

3

1

C100

C100

2

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

12

1

2

C101

C101

D4

DA204U_SOT323-3~D@D4DA204U_SOT323-3~D@

1

2

3

1

2

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

C102

C102

D5

DA204U_SOT323-3~D@D5DA204U_SOT323-3~D@

1

2

3

1

2

2.2P_0402_50V8C~D

2.2P_0402_50V8C~D

10P_0402_50V8J~D

22P_0402_50V8J~D

22P_0402_50V8J~D

B B

22P_0402_50V8J~D

22P_0402_50V8J~D

VGA_HS<5>

VGA_VS<5>

10P_0402_50V8J~D

R114 39_0402_5%~DR114 39_0402_5%~D

R116 39_0402_5%~DR116 39_0402_5%~D

10P_0402_50V8J~D

10P_0402_50V8J~D

+5V_SYNC

1 2

VSYNC_LVGA_VS VSYNC_BUF

1 2

+5V_RUN

21

D6

D6

RB500V-40 TE-17_SOD323-2~D

RB500V-40 TE-17_SOD323-2~D

+5V_SYNC

A2Y

A2Y

1

5

U13

U13

P

4

OE#

G

74AHCT1G125GW_SOT353-5~D

74AHCT1G125GW_SOT353-5~D

3

5

1

U14

U14

P

4

OE#

G

74AHCT1G125GW_SOT353-5~D

74AHCT1G125GW_SOT353-5~D

3

1 2

R113

R113

HSYNC_BUFVGA_HS HSYNC_L

1K_0402_5%~D

1K_0402_5%~D

DA204U

K1 A2

A1 K2

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

CRT

CRT

CRT

LA-3954P

LA-3954P

LA-3954P

X03

X03

12 29Friday, April 18, 2008

12 29Friday, April 18, 2008

12 29Friday, April 18, 2008

1

X03

of

of

of

Page 13

5

U15

R247 0_0402_5%~DR247 0_0402_5%~D

+3.3V_RUN_DPA

D D

DPA_PRI<6>

DPA_LP<6>

C C

1 2

R248 0_0402_5%~DR248 0_0402_5%~D

1 2

R249 0_0402_5%~DR249 0_0402_5%~D

1 2

+5V_RUN_DPA

+3.3V_RUN_DPA

DP_A_L0+

DP_A_L0-

DP_A_L1+

DP_A_L1-

DP_A_L2+

DP_A_L2-

DP_A_L3+

DP_A_L3-

DP_A_AUX+

DP_A_AUX-

DP_A_HP

DP_A_CA_DET1

DPA_PRI

DPA_LP

12

R201

R201

12

R202

R202

4.7K_0402_1%~D

4.7K_0402_1%~D

3.48K_0402_1%~D

3.48K_0402_1%~D

R199

R199

DP_A_L0+<5>

DP_A_L0-<5>

DP_A_L1+<5>

DP_A_L1-<5>

DP_A_L2+<5>

DP_A_L2-<5>

DP_A_L3+<5>

DP_A_L3-<5>

DP_A_AUX+<5>

DP_A_AUX-<5>

100K_0402_5%~D

100K_0402_5%~D

12

U15

14

VCC

17

VCC

23

VCC

2

VDD

8

VDD

34

VDD

48

VDD

54

VDD

38

VDD*1

3

ML_IN0 (p)

4

ML_IN0 (n)

6

ML_IN1(p)

7

ML_IN1(n)

9

ML_IN2(p)

10

ML_IN2(n)

12

ML_IN3(p)

13

ML_IN3(n)

36

AUX(p)_I2C_SCL

35

AUX(n)_I2C_SDA

37

HPD

39

CAD

33

Priority

30

LP

26

VSadj

1

DPVadj

57

Thermal

4

DP_SINK0(p)

DP_SINK0(n)

DP_SINK1(p)

DP_SINK1(n)

DP_SINK2(p)

DP_SINK2(n)

DP_SINK3(p)

DP_SINK3(n)

AUX_SINK(p)

AUX_SINK(n)

DP_HPD_SINK

CAD_SINK

TMDS_HPD_SINK

TMDS_SINK0(p)

TMDS_SINK0(n)

TMDS_SINK1(p)

TMDS_SINK1(n)

TMDS_SINK2(p)

TMDS_SINK2(n)

TMDS_SINK_CLK(p)

TMDS_SINK_CLK(n)

I2C_SCL

I2C_SDA

GND

GND

GND

GND

GND

GND

GND

SN75DP122_QFN56~D

SN75DP122_QFN56~D

GND

DPA_DOCK_RP1_LANE0

56

DPA_DOCK_RP1_LANE0#

55

DPA_DOCK_RP1_LANE1

53

DPA_DOCK_RP1_LANE1#

52

DPA_DOCK_RP1_LANE2

50

DPA_DOCK_RP1_LANE2#

49

DPA_DOCK_RP1_LANE3

47

DPA_DOCK_RP1_LANE3#

46

DPA_DOCK_AUX

45

DPA_DOCK_AUX#

43

DP_HPD1_SINK

40

DPA_DOCK_CA_DET

41

DPA_DVI_DETECT

32

DPA_DVI_LANE0

19

DPA_DVI_LANE0#

18

DPA_DVI_LANE1

22

DPA_DVI_LANE1#

21

DPA_DVI_LANE2

25

DPA_DVI_LANE2#

24

DPA_DVI_CLK

16

DPA_DVI_CLK#

15

DPA_DVI_SCLK

29

DPA_DVI_SDAT

28

5

11

20

27

31

42

44

51

R275

R275

3

DPA_DVI_LANE0#

DPA_DVI_LANE0

DPA_DVI_LANE1#

DPA_DVI_LANE1

DPA_DVI_LANE2#

DPA_DVI_LANE2

DPA_DVI_CLK

DPA_DVI_CLK#

DPA_DVI_DETECT

DPA_DVI_SCLK

DPA_DVI_SDAT

12

100K_0402_5%~D

100K_0402_5%~D

+3.3V_RUN_DPA

R328 4.7K_0402_5%~DR328 4.7K_0402_5%~D

R211 4.7K_0402_5%~DR211 4.7K_0402_5%~D

R317 500_0402_1%R317 500_0402_1%

C275 2.2U_0603_10V6K~DC275 2.2U_0603_10V6K~D

JP4

JP4

1

1

3

3

5

5

7

7

9

9

111112

131314

151516

171718

191920

212122

232324

252526

272728

292930

313132

333334

353536

373738

393940

TYCO_1775729-1

TYCO_1775729-1

2

2

4

4

6

6

8

8

10

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

PS_I2C_CTL_EN#

DPB_DVI_CLK

DPB_DVI_CLK#

DPB_DVI_LANE2

DPB_DVI_LANE2#

DPB_DVI_LANE1

DPB_DVI_LANE1#

DPB_DVI_LANE0

DPB_DVI_LANE0#

DPB_DVI_DETECT

DPB_DVI_SCLK

DPB_DVI_SDAT

PS_MODE

PS_REXT

PS_CEXT

+5V_RUN_DPB+5V_RUN_DPA

2

DPB_DVI_CLK <14>

DPB_DVI_CLK# <14>

DPB_DVI_LANE2 <14>

DPB_DVI_LANE2# <14>

DPB_DVI_LANE1 <14>

DPB_DVI_LANE1# <14>

DPB_DVI_LANE0 <14>

DPB_DVI_LANE0# <14>

DPB_DVI_DETECT <14>

DPB_DVI_SCLK <14>

DPB_DVI_SDAT <14>

DPA_DOCK_HPD DPA_DOCK_HPD_1

12

R232

R232

5.1M_0402_5%~D

5.1M_0402_5%~D

F2

L29

L29

0_0402_5%~D

0_0402_5%~D

1 2

R119

R119

1 2

1M_0402_5%~D

1M_0402_5%~D

+3.3V_RUN_DPA

@

@

D7

D7

SDM10U45-7_SOD523-2~D

SDM10U45-7_SOD523-2~D

21

3A_6VDC_2920SMD300F23A_6VDC_2920SMD300

21

+DPA_VCC

+3.3V_RUN_AR

@

@

R117

R117

0_1206_5%~D

0_1206_5%~D

1 2

DPA_DOCK_AUX#

DPA_DOCK_AUX

DPA_DOCK_CA_DET

DPA_DOCK_LANE3#_C

DPA_DOCK_LANE3_C

DPA_DOCK_LANE2#_C

DPA_DOCK_LANE2_C

DPA_DOCK_LANE1#_C

DPA_DOCK_LANE1_C

DPA_DOCK_LANE0#_C

DPA_DOCK_LANE0_C

1

R244

R244

0_1206_5%~D

0_1206_5%~D

1 2

1

1

C108

C108

C128

C128

10U_0805_10V4Z~D

10U_0805_10V4Z~D

12

@

@

R276

R276

100K_0402_5%~D

100K_0402_5%~D

JDP1

JDP1

20

DP_PWR

19

RTN

18

HP_DET

17

AUX_CH-

16

GND

15

AUX_CH+

14

GND

13