Page 1

5

4

3

2

1

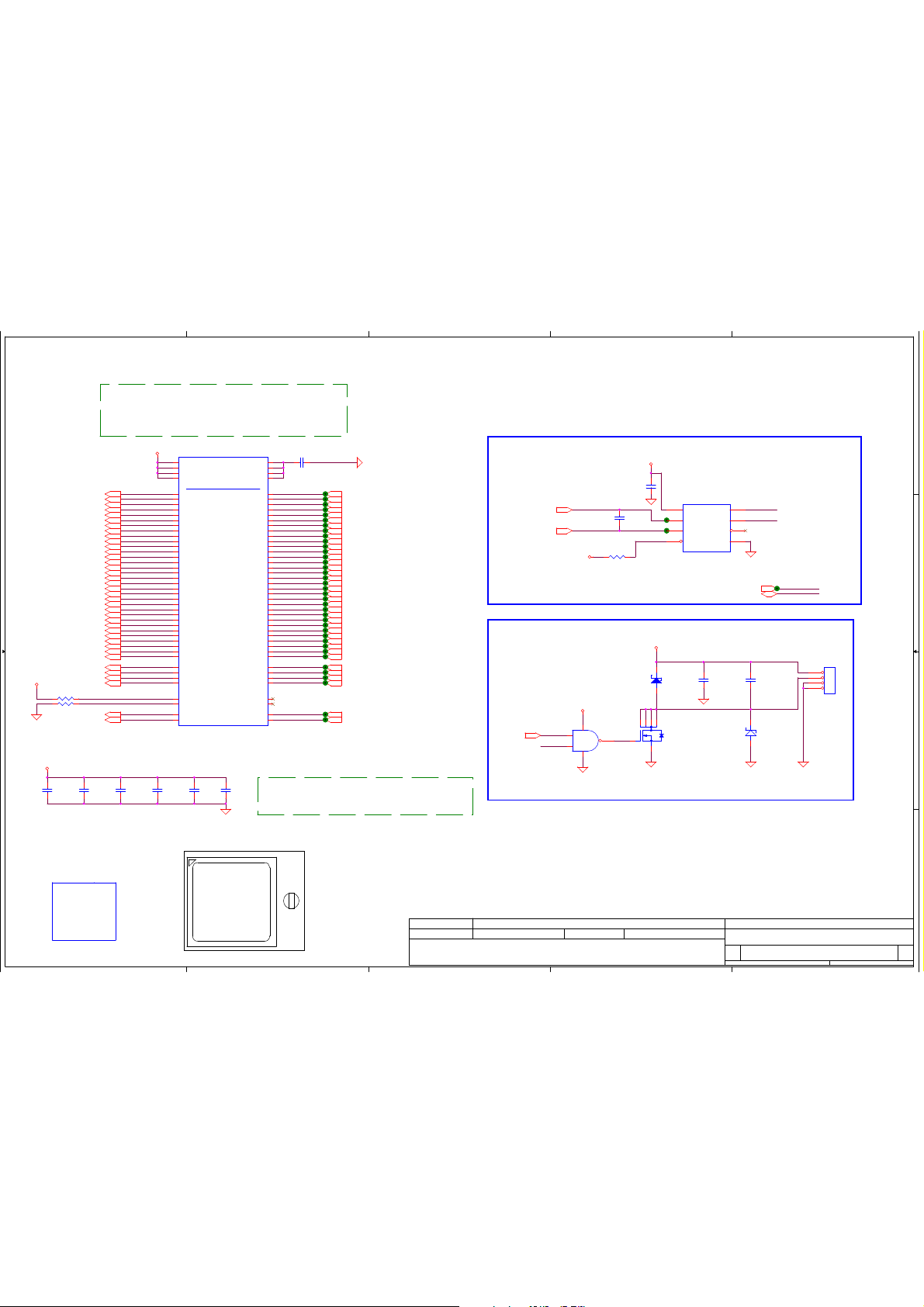

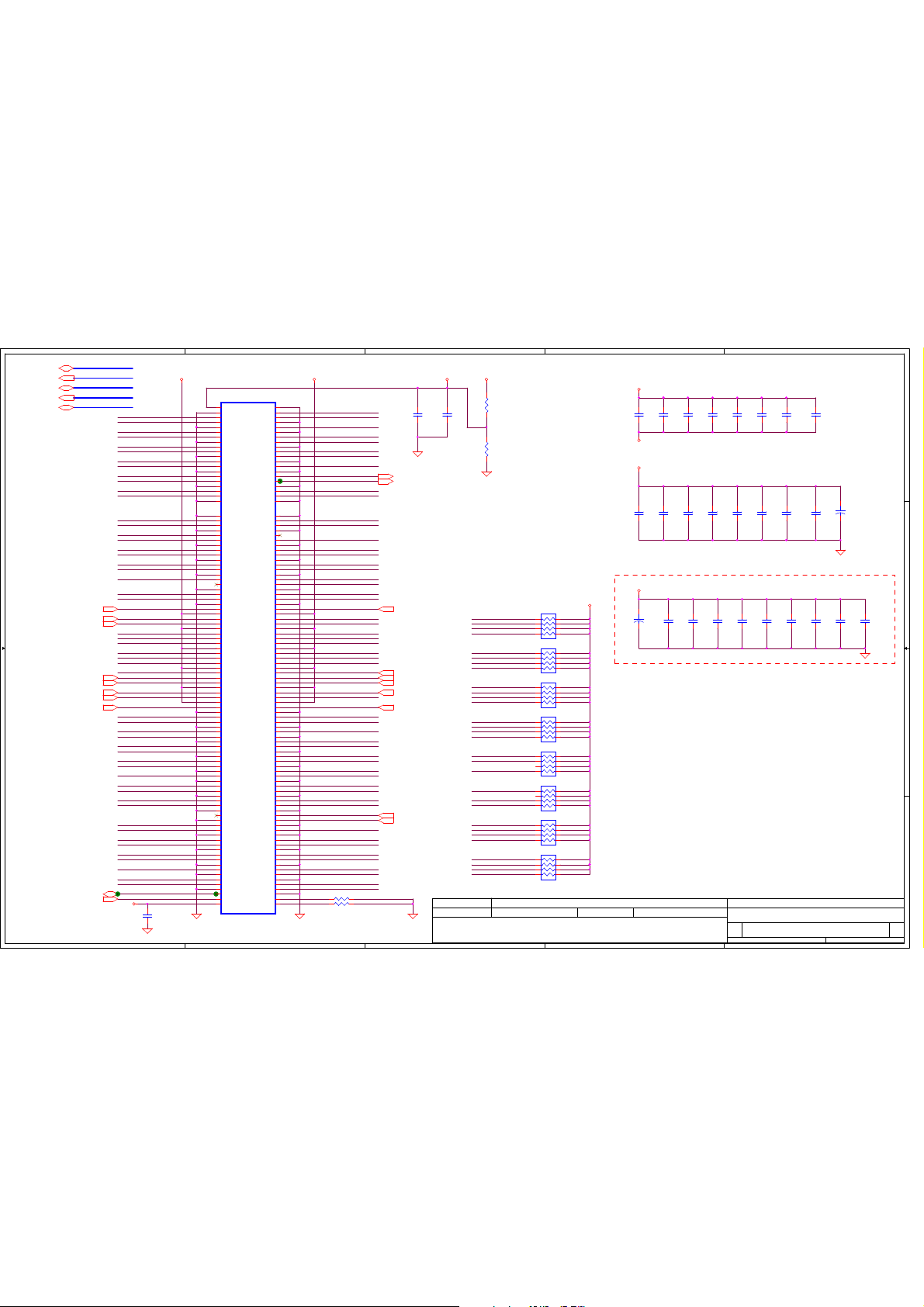

Power On Sequence (AC IN mod e)

ACIN

+5VA LW/+3V ALW

-->E C

+1.2 VALW

EC_R SMRST#

(PWR GD_SB)

ON_O FF

PWRB TN_OUT #

(PWR BTN#)

SLP_ S5#MCP6 7-->EC

SYS_ ONEC-- >PWR

+1.8 V/+0.9 V

MEM_ VLD

SLP_ S3#

SUSP #

+5VS /+3VS

+1.8 VS/+1. 2VS

MCP_ PWRGD

(PWR GD)

VR_O N

(CPU VDD_EN )

CPU_ CORE

VGAT E

(CPU _VLD)

VLDT _EN

(MCP VDD/HT _EN)

+1.2 V_HT

HT_V LD

(MCP VLD/HT _VLD)

CPUC LK/#

HT_C PU_PWR GD

(HT_ MCP_PW RGD)

KB_R ST#

LPC_ RST#

HTCP U_RST#

(HT_ MCP_RS T#)

10~1 2ms

>0ms

10~1 5ms

>0ms

>0ms

>0ms

50~7 3ms

>0ms

10~1 5ms

>0ms

>0ms

>0ms

max :70ms

1~12 8ms

1~10 0ms

D D

EC-- >MCP67

EC-- >MCP67

PU6- ->MCP6 7

C C

MCP6 7-->EC

EC-- >PWR

EC-- >MCP67

MCP6 7-->PU 11

B B

PU11 -->MCP 67

MCP6 7-->PW R

PWR- ->MCP6 7

MCP6 7-->CP U

EC-- >MCP67

A A

MCP6 7-->LP C

MCP6 7-->CP U

5

4

3

2

1

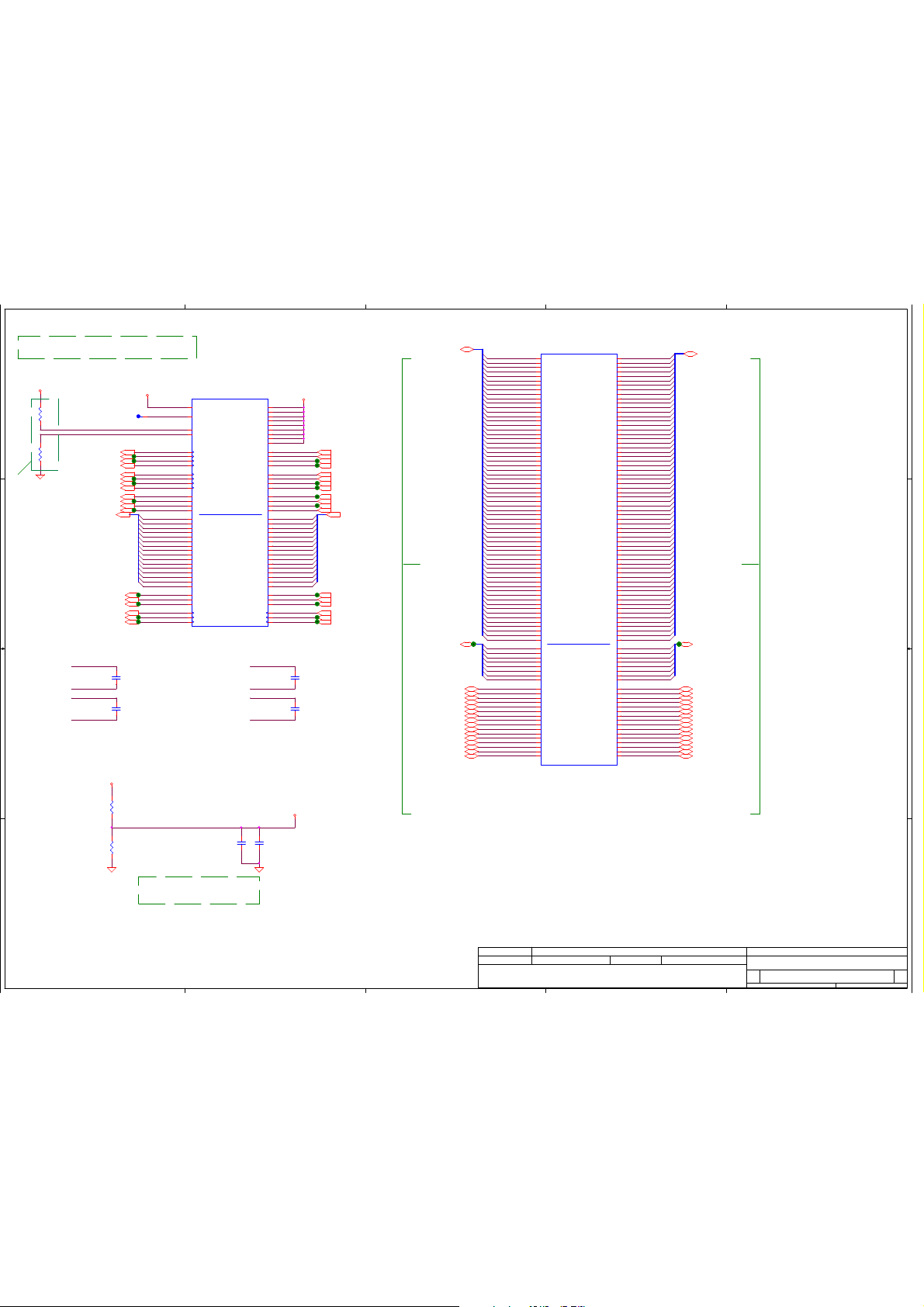

Page 2

A

1 1

B

C

D

E

2 2

Compal Confidential

Schematics Document

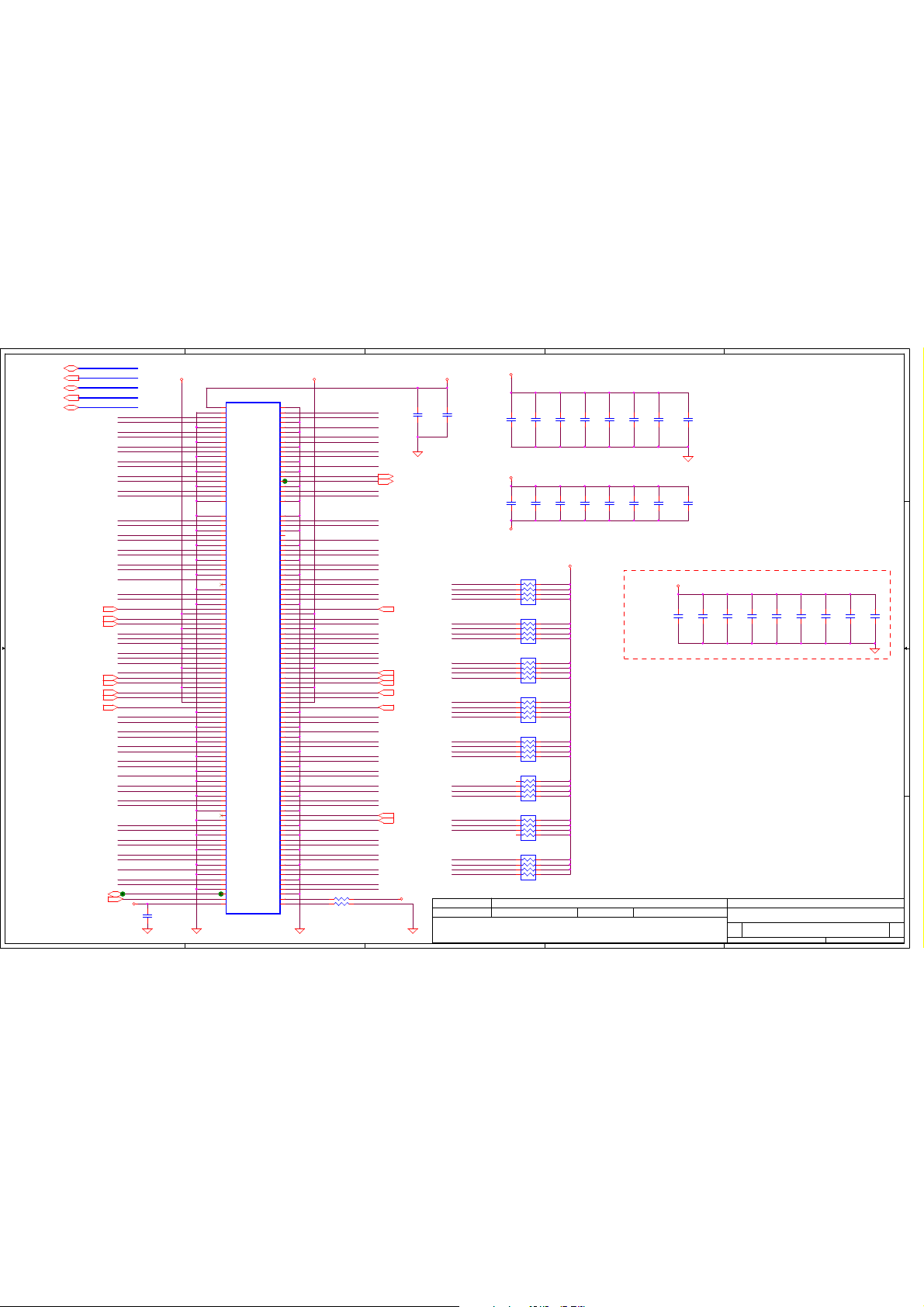

AMD Turion/Sempron + Nvidia MCP67-MV

2007-01-12

3 3

4 4

A

B

Rev:0.1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/01/07 2008/01/12

C

Compal Secret Data

Deciphered Date

D

Compal Electr onics, Inc.

Title

Cover Sheet

Size Docume nt Number Re v

Cus tom

LA- 3733P

Date: Sheet of

1 36Monday , Marc h 05, 2007

E

0.1

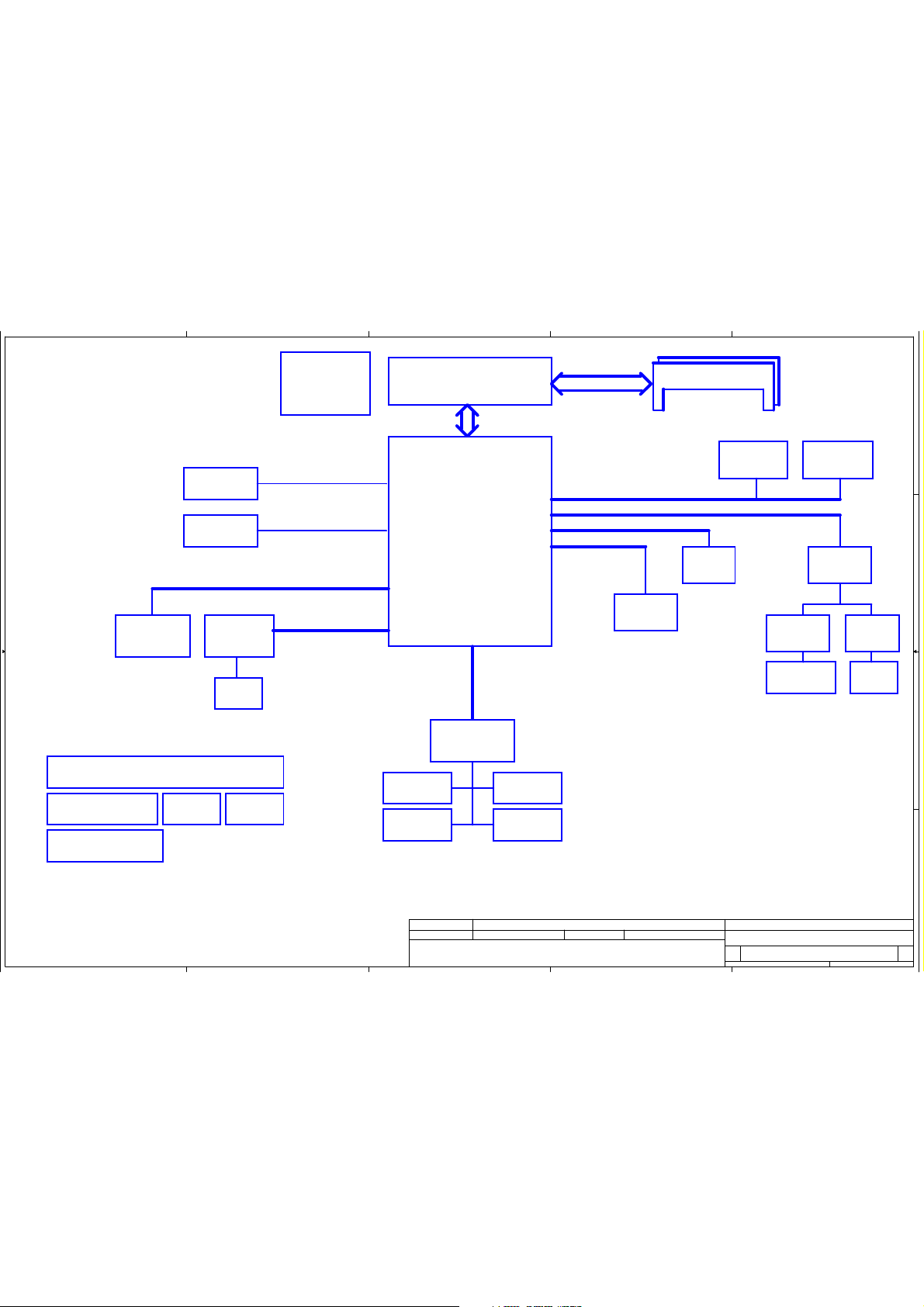

Page 3

5

4

3

2

1

Compal confidential

533/667/800

Project Code: IBL80

File Name : LA-3733P

D D

Therm al S ensor

AD M 10 32AR M

page 4

AMD Turion/Sempron CPU

So ck et S1 638 P

page 4 ,5,6,7

HT L INK

200-800MHz

DD RI I DD RI I-SO-DIM M X2

page 08,09

Dual Channel

USB con n x1

CRT & TV-ou t

page 19

LCD Co nn. 2C H LVDS

page 18

Nvidia

MCP67-MV

836 BGA

USB 2.0 BUS

HD Audio

IDE BUS

SATA2.0 BUS

3.3V 2 4.576MHz/48Mhz

3.3V A TA-100

CD RO M

C C

PCI- Express

port 1

Co nn.

page 20

USB SU B/ B

page 26page 26

HD A Codec

CX20549

page 22

S- ATA HDD

MI NI C ard

WLAN

page 20

B B

Po wer On /Of f C KT / L ID swi tch / Power O K CKT

DC /DC Inter face CKT.

Power Circu it DC/ DC

A A

page 28

page 29~36

L ED

page 25

LAN (10/100)

RTL8201CL

page 21

RJ -4 5

page 21

page 25

RTC CKT.

page 16

MI I

page 1 0,11,12 ,13,14,15,16,17

LP C BUS

ENE KB926

page 27

To uc h P ad

page 25

EC I/ O Buffer SP I RO M

page 26

Int. KBD

page 27

page 26

Co nn.

page 20

Audio A MP

TI6017 CX20548

page 24

Phone Jack

page 24

AM O M

page 24

RJ -1 1

page 21

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/01/07 2008/01/12

3

Compal Secret Data

Deciphered Date

Title

BLOCK D IAGRAM

Size Docume nt Number Re v

Custo m

LA- 3733P

2

Date: Sheet of

2 36Monda y, Marc h 05, 2007

1

0.1

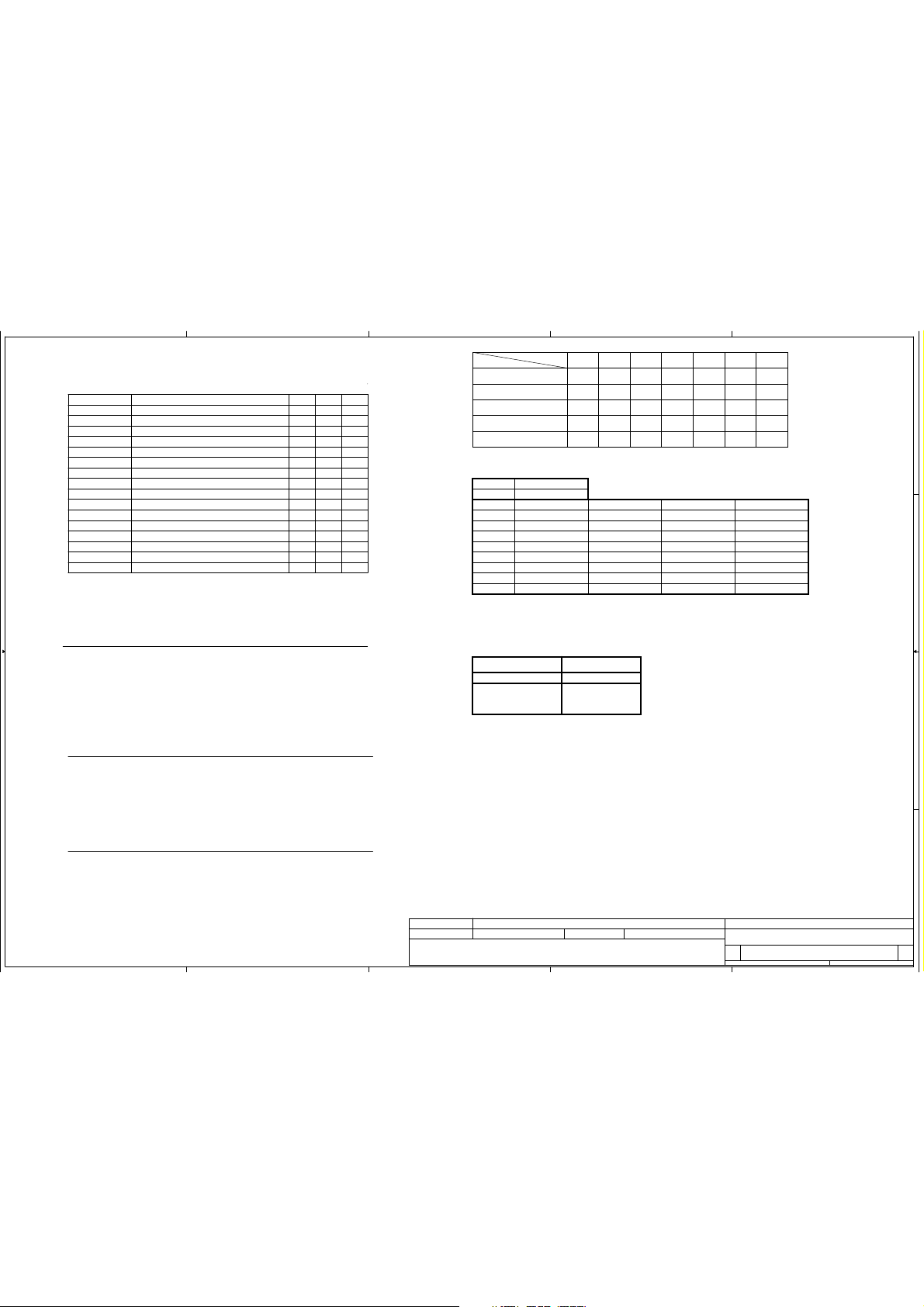

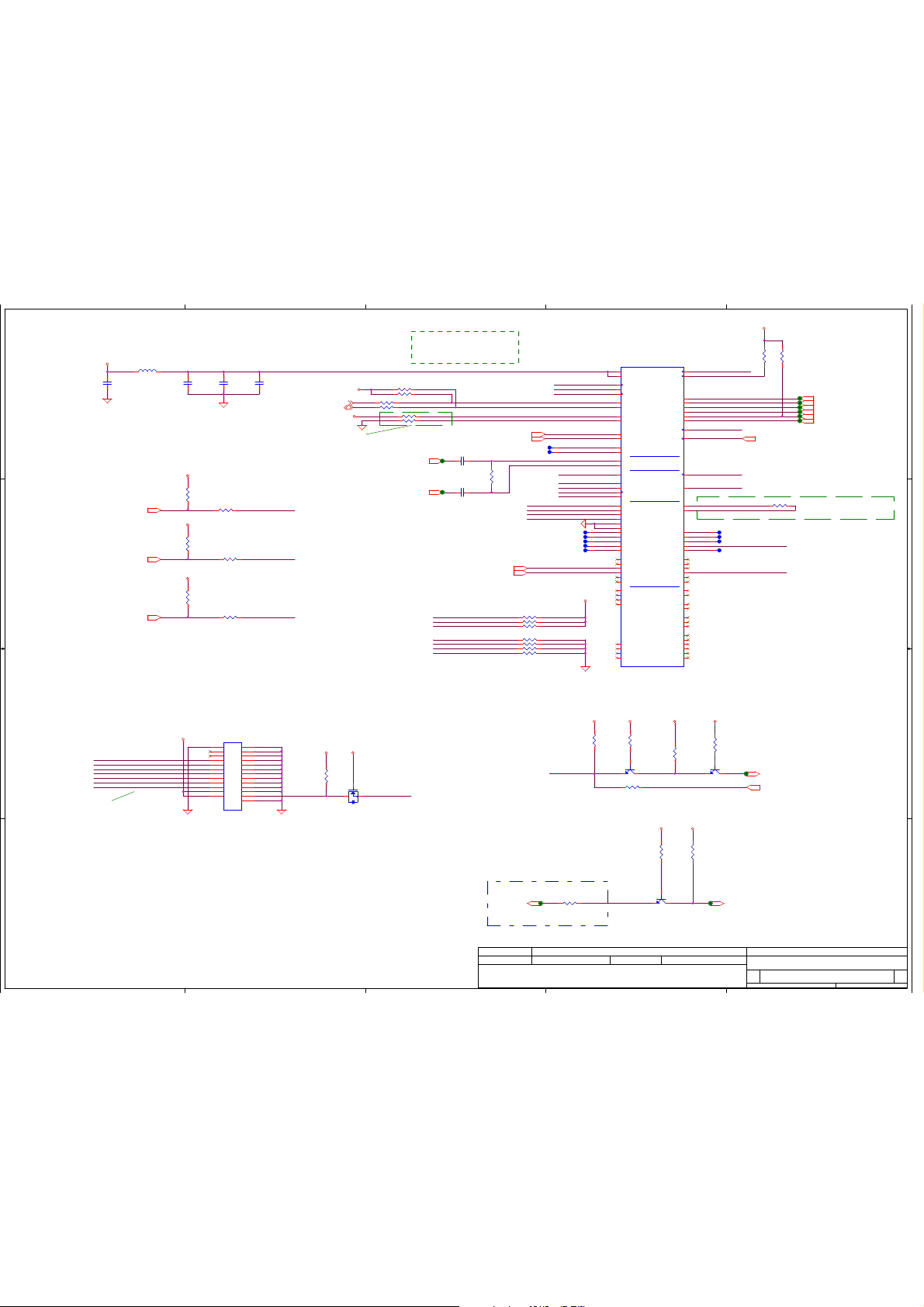

Page 4

5

Voltage Rails

Power Plane Description

D D

C C

VIN

B+

+CPU_CORE

+0.9V 0.9V switch ed power rail for DDR terminator

+1.5VS

+1.2VALW ON ON ON*

+1.2VS ON OFF OFF

+1.2V_HT

+1.8V 1.8V power rail for DDR

+1.8VS 1.8V switch ed power rail

+3VALW

+3VS

+5VALW

+5VS

Note : ON* m eans that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or batt ery power rail for power circuit.

Core voltage for CPU

1.5V switch ed power rail

1.2V alway s on power rail

1.2V switch ed power rail

1.2V switch ed power rail ON OFF OFF

2.5V switch ed power rail+2.5VS OFFON OFF

3.3V alway s on power rail

3.3V switch ed power rail

5V always on power rail

5V switched power rail

4

S1 S3 S5

N/A N/A N/A

ON OFF

ON ON

ON OFFOFF

ON

ON OFF

ON

ON

ON

ON OFF

ON+RTCVCC

3

STATE

Full ON

S1(P ower On Suspend)

N/AN/AN/A

OFF

OFF

S3 ( Suspe nd to RAM)

S4 ( Suspe nd to Disk)

S5 ( Soft OFF)

SIGNAL

SLP_S1# SLP_S3# SLP_S5# +VALW +V +VS Clock

HIGH HIGH H IGH

LOW

LOW

LOW LOW LOW

2

ON

ONONON ON

ON

HIGHHIGH

HIGH

HIGH

ON

ON

LOW

LOWLOW

ON

ON

LOW

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

1

Board ID / SKU ID Table for AD channel

OFF

ON

OFF

ON*

ON

OFF

OFF

ON

ON*

OFF

ON

ONRTC power

Vcc 3.3V +/- 5%

100K +/- 5%Ra/Rc/Re

Board ID

Rb / Rd / Rf V min

0

1

2

3

4

5

6

7 NC

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

V typ

AD_BID

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

V

max

0 V 0 V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

B B

EC SM Bus1 address

Device

Smart Battery

Address Address

EC SM Bus2 address

Device

ADM1032

1001 10 0X b0001 01 1X b

BTO Option Table

BTO Item BOM Structure

45@DIP CAP & RTC

MCP67 SM Bus address

Device Address

DDR DIMM0

A A

DDR DIMM2

MINI CARD

5

1001 00 0Xb

1001 001Xb

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/01/07 2008/01/12

3

Compal Secret Data

Deciphered Date

Title

TABLE OF CONTENTS

Size Docume nt Number Re v

Custo m

LA- 3733P

2

Date: Sheet of

3 36Monda y, Marc h 05, 2007

1

0.1

Page 5

5

4

3

2

1

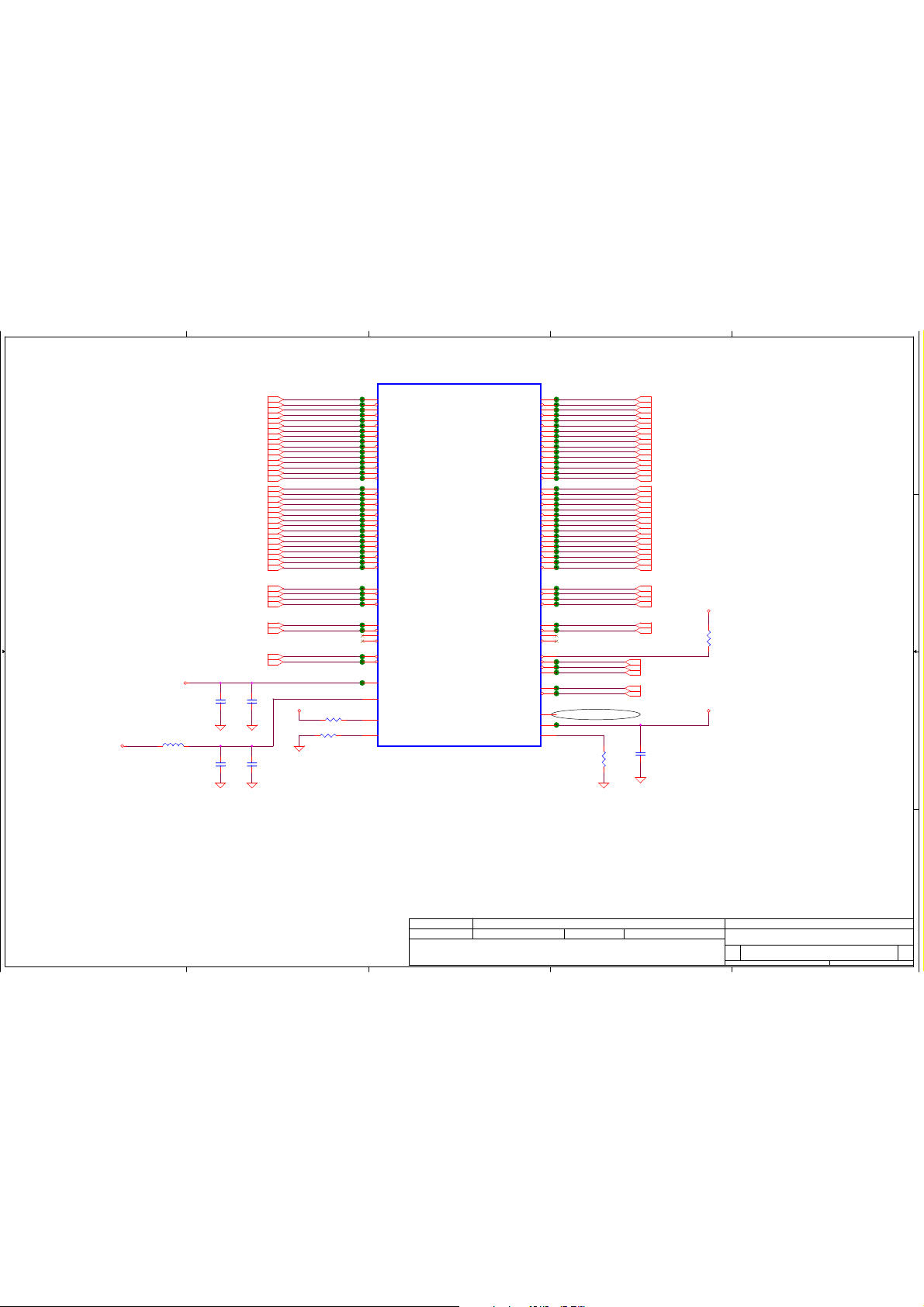

PROCESS OR HYPE RTRANSPORT INTERFACE

D D

H_CAD IP1510 H_CAD OP15 10

H_CA DIN1510

H_CAD IP1410

H_CA DIN1410

H_CAD IP1310

H_CA DIN1310

H_CAD IP1210

H_CA DIN1210

H_CAD IP1110

H_CA DIN1110

H_CAD IP1010

H_CA DIN1010

H_CA DIP910

H_C ADIN910

H_CA DIP810

C C

B B

H_C ADIN810

H_CA DIP710

H_C ADIN710

H_CA DIP610

H_C ADIN610

H_CA DIP510

H_C ADIN510

H_CA DIP410

H_C ADIN410

H_CA DIP310

H_C ADIN310

H_CA DIP210

H_C ADIN210

H_CA DIP110

H_C ADIN110

H_CA DIP010

H_C ADIN010

+1.2V_HT

R2 51_0402_1%

1 2

R3 51_0402_1%

1 2

+1.2V_HT

1

C6

2

4.7U_0 805_10V4Z

H_CLK IP110

H_CLK IN110

H_CLK IP010

H_CLK IN010

H_CTLIP010

H_CTL IN010

4.7U_0 805_10V4Z

1

2

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+1.2V_HT

JP1A

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

FOX_PZ63823-284S-41F

0.22U_ 0402_10V4Z

1

C9

2

180P_0402_50V8J

1

2

C10

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

ace

ace

ace

ace

HT T In te r f

HT T In te r f

HT T In te r f

HT T In te r f

Athlon 64 S1

Processor Socket

180P_0402_50V8J

1

2

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

C11

C7

H_CAD IP15

H_CAD IP14

H_C ADIN14

H_CAD IP13

H_C ADIN13

H_CAD IP12

H_C ADIN12

H_CAD IP11

H_C ADIN11

H_CAD IP10

H_C ADIN10

H_CA DIP9

H_C ADIN9

H_CA DIP8

H_C ADIN8

H_CA DIP7

H_C ADIN7

H_CA DIP6

H_C ADIN6

H_CA DIP5

H_C ADIN5

H_CA DIP4

H_C ADIN4

H_CA DIP3

H_C ADIN3

H_CA DIP2

H_C ADIN2

H_CA DIP1

H_C ADIN1

H_CA DIP0

H_C ADIN0

H_CLK IP1

H_CL KIN1

H_CLK IP0

H_CL KIN0

H_CTLIP1

H_CTL IN1

H_CTLIP0

H_CTL IN0

1

C8

2

0.22U_ 0402_10V4Z

C1

AE5

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

1 2

4.7U_0 805_10V4Z

AE4

AE3

AE2

H_CAD OP15

T4

H_CAD ON15H_C ADIN15

T3

H_CAD OP14

V5

H_CAD ON14

U5

H_CAD OP13

V4

H_CAD ON13

V3

H_CAD OP12

Y5

H_CAD ON12

W5

H_CAD OP11

AB5

H_CAD ON11

AA5

H_CAD OP10

AB4

H_CAD ON10

AB3

H_CAD OP9

AD5

H_CA DON9

AC5

H_CAD OP8

AD4

H_CA DON8

AD3

H_CAD OP7

T1

H_CA DON7

R1

H_CAD OP6

U2

H_CA DON6

U3

H_CAD OP5

V1

H_CA DON5

U1

H_CAD OP4

W2

H_CA DON4

W3

H_CAD OP3

AA2

H_CA DON3

AA3

H_CAD OP2

AB1

H_CA DON2

AA1

H_CAD OP1

AC2

H_CA DON1

AC3

H_CAD OP0

AD1

H_CA DON0

AC1

H_CLKOP1

Y4

H_CLK ON1

Y3

H_CLKOP0

Y1

H_CLK ON0

W1

T5

R5

H_CTLOP0

R2

H_CTLON0

R3

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

H_CAD ON15 10

H_CAD OP14 10

H_CAD ON14 10

H_CAD OP13 10

H_CAD ON13 10

H_CAD OP12 10

H_CAD ON12 10

H_CAD OP11 10

H_CAD ON11 10

H_CAD OP10 10

H_CAD ON10 10

H_CAD OP9 10

H_CA DON9 10

H_CAD OP8 10

H_CA DON8 10

H_CAD OP7 10

H_CA DON7 10

H_CAD OP6 10

H_CA DON6 10

H_CAD OP5 10

H_CA DON5 10

H_CAD OP4 10

H_CA DON4 10

H_CAD OP3 10

H_CA DON3 10

H_CAD OP2 10

H_CA DON2 10

H_CAD OP1 10

H_CA DON1 10

H_CAD OP0 10

H_CA DON0 10

H_CLK OP1 10

H_CLK ON1 10

H_CLK OP0 10

H_CLK ON0 10

H_CTLOP0 10

H_CTLON 0 10

Thermal Sensor ADM1032ARMZ

C2

0.1U_0 402_16V4Z

H_THERM DA

H_THERM DC

+3VS

R1

1 2

10K_0402_5%

2

C3

2200P_0402_50V7K

1

H_THERM DA6

H_THERM DC6

PWM Fan Control circuit

+3VS

5

U2

1

THERM#

INB

2

INA

P

4

O

G

TC7SH00 FU_SSOP5

3

3

FAN_PWM27

G

+3VS

THERM#

2

1

2

1

+5VS

2 1

6

S

4 5

U1

1

VDD

2

D+

3

D-

THERM#4GND

ADM10 32ARMZ-2REEL_MSOP8

Addres s:100_1100

1

D1

RB751 V_SOD323

2

D

Q1

SI3456 BDV-T1-E3_TSOP6

CLOSE CPU,

CPU_THERMDA&CPU_THERMDC PLACE

CLOSE TO PROCESSOR WITHIN 1" INCH

SMB_EC_CK2

8

SCLK

SMB_EC_DA2

7

SDATA

6

ALERT#

5

1

C5

0.1U_0 402_16V4Z

2

12

ZD1

@

RLZ5.1B _LL34

SMB_EC_DA2

SMB_EC_CK2

SMB_EC_DA227

SMB_EC_CK227

SP02000D000 S W-CONN ACES 85204-02001 2P P1.25

ACES_85204-02001_2P

C4

4.7U_0 805_10V4Z

FAN

JP2

1

1

2

2

3

G1

4

G2

ACES_85204-02001

CONN @

A1

A26

ZZZ1

A A

PCB

LA-3733P

DA600005I00

5

AF1

Athlon 64 S1g1

uPGA638

Top View

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/01/07 2008/01/12

3

Compal Secret Data

Deciphered Date

Title

AMD CPU HT I/F

Size Docume nt Number Re v

Custo m

LA- 3733P

2

Date: Sheet of

4 36Monda y, Marc h 05, 2007

1

0.1

Page 6

A

B

C

D

E

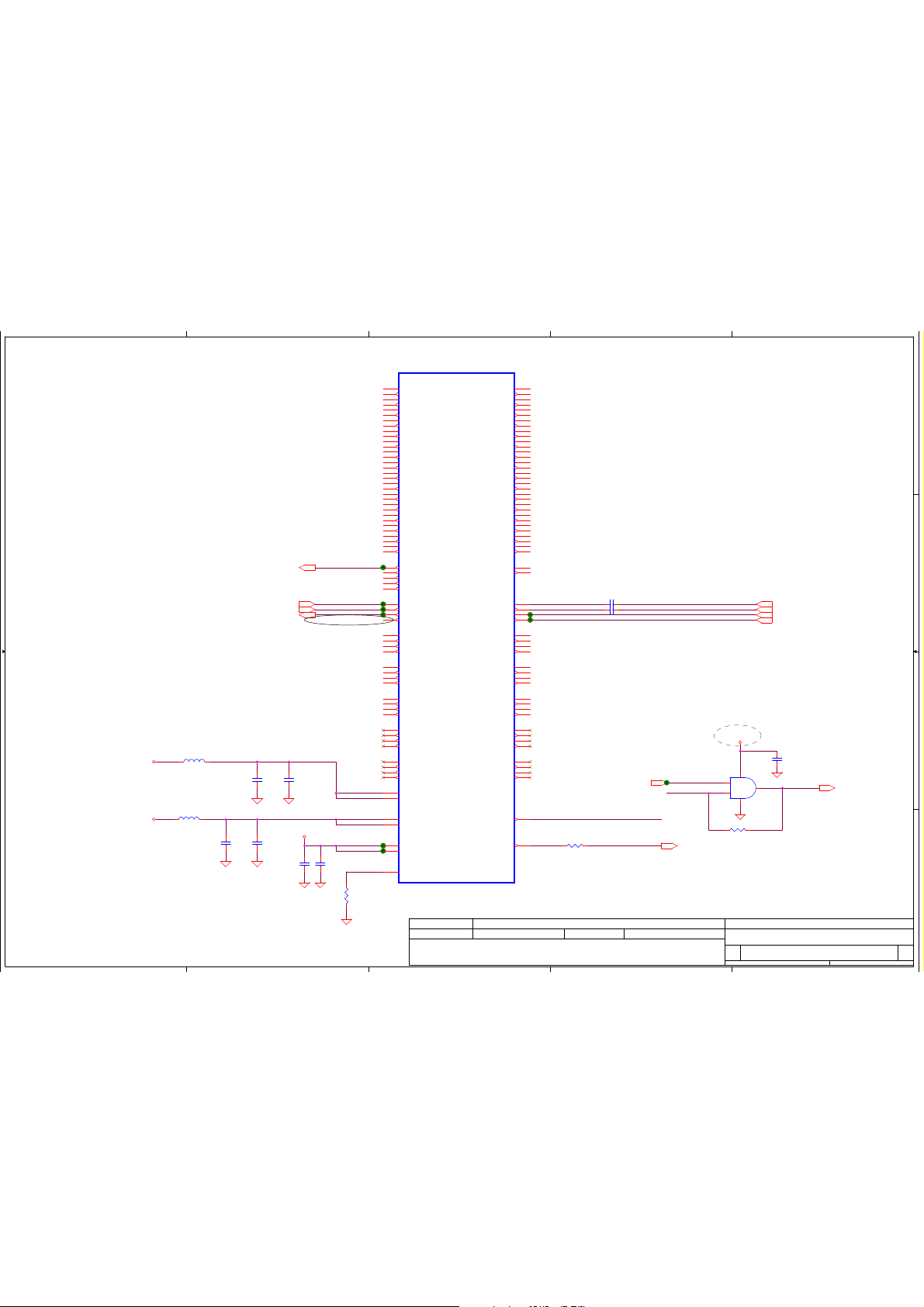

Processor DDR2 Memory Interface

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+1.8V

4 4

12

R4

39.2_ 0402_1%~D

R5

12

39.2_ 0402_1%~D

DDR_ CS3_ DIMMA#8

DDR_ CS2_ DIMMA#8

DDR_ CS1_ DIMMA#8

DDR_ CS0_ DIMMA#8

DDR_ CS3_ DIMMB#9

DDR_ CS2_ DIMMB#9

PLACE THEM CLOSE TO

CPU WITHIN 1"

3 3

2 2

DDR_ CS1_ DIMMB#9

DDR_ CS0_ DIMMB#9

DDR_ CKE1 _DIMMB9

DDR_ CKE0 _DIMMB9

DDR_ CKE1 _DIMMA8

DDR_ CKE0 _DIMMA8

DDR_ A_MA[1 5..0 ]8

DDR_ A_BS#28

DDR_ A_BS#18

DDR_ A_BS#08

DDR_ A_RAS #8

DDR_ A_CAS #8

DDR_ A_WE #8

DDR_ A_CLK 2

DDR_ A_CLK #2

DDR_ A_CLK 1

DDR_ A_CLK #1

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

1K_0402_1 %

1K_0402_1 %

R6

R7

10:8:1 0:8:10

1

2

1

2

+1.8V

12

12

+0.9 VREF_ CPU

TP1PAD

M_Z N

M_ZP

DDR_ CS3_ DIMMA#

DDR_ CS2_ DIMMA#

DDR_ CS1_ DIMMA#

DDR_ CS0_ DIMMA#

DDR_ CS3_ DIMMB#

DDR_ CS2_ DIMMB#

DDR_ CS1_ DIMMB#

DDR_ CS0_ DIMMB#

DDR_ CKE1 _DIMMB

DDR_ CKE0 _DIMMB

DDR_ CKE1 _DIMMA

DDR_ CKE0 _DIMMA

DDR_ A_MA15

DDR_ A_MA14

DDR_ A_MA13

DDR_ A_MA12

DDR_ A_MA11

DDR_ A_MA10

DDR_ A_MA9

DDR_ A_MA8

DDR_ A_MA7

DDR_ A_MA6

DDR_ A_MA5

DDR_ A_MA4

DDR_ A_MA3

DDR_ A_MA2

DDR_ A_MA1

DDR_ A_MA0

DDR_ A_BS#2

DDR_ A_BS#1

DDR_ A_BS#0

DDR _A_RA S#

DDR _A_CA S#

DDR_ A_WE #

C12

1.5P _0402_50 V8C

C14

1.5P _0402_50 V8C

VTT_SE NSE

JP1B

W17

M_VREF

Y10

VTT_SENSE

AE10

M_ZN

AF10

M_ZP

V19

MA0_CS_L3

J22

MA0_CS_L2

V22

MA0_CS_L1

T19

MA0_CS_L0

Y26

MB0_CS_L3

J24

MB0_CS_L2

W24

MB0_CS_L1

U23

MB0_CS_L0

H26

MB_CKE1

J23

MB_CKE0

J20

MA_CKE1

J21

MA_CKE0

K19

MA_ADD15

K20

MA_ADD14

V24

MA_ADD13

K24

MA_ADD12

L20

MA_ADD11

R19

MA_ADD10

L19

MA_ADD9

L22

MA_ADD8

L21

MA_ADD7

M19

MA_ADD6

M20

MA_ADD5

M24

MA_ADD4

M22

MA_ADD3

N22

MA_ADD2

N21

MA_ADD1

R21

MA_ADD0

K22

MA_BANK2

R20

MA_BANK1

T22

MA_BANK0

T20

MA_RAS_L

U20

MA_CAS_L

U21

MA_WE_L

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor

Socket

CPU _VRE F_RE F

0.1U_ 0402 _16V4Z

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

Cm d/ Ctr l/ /C lk

Cm d/ Ctr l/ /C lk

MB_ADD14

Cm d/ Ctr l/ /C lk

Cm d/ Ctr l/ /C lk

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

DD RI I

DD RI I

DD RI I

DD RI I

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

DDR_ B_CL K2

DDR_ B_CL K#2

DDR_ B_CL K1

DDR_ B_CL K#1

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

1

1

C16

C17

2

2

1000P_040 2_50V7K

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

DDR_ A_CLK 2

DDR_ A_CLK #2

DDR_ A_CLK 1

DDR_ A_CLK #1

DDR_ B_CL K2

DDR_ B_CL K#2

DDR_ B_CL K1

DDR_ B_CL K#1

DDR_ B_ODT1

DDR_ B_ODT0

DDR_ A_ODT1

DDR_ A_ODT0

DDR_ B_MA15

DDR_ B_MA14

DDR_ B_MA13

DDR_ B_MA12

DDR_ B_MA11

DDR_ B_MA10

DDR_ B_MA9

DDR_ B_MA8

DDR_ B_MA7

DDR_ B_MA6

DDR_ B_MA5

DDR_ B_MA4

DDR_ B_MA3

DDR_ B_MA2

DDR_ B_MA1

DDR_ B_MA0

DDR_ B_BS#2

DDR_ B_BS#1

DDR_ B_BS#0

DDR_ B_RAS #

DDR_ B_CAS #

DDR_ B_W E#

1

2

1

2

+0.9 VREF_ CPU

+0.9V

C13

1.5P _0402_50 V8C

C15

1.5P _0402_50 V8C

DDR_ A_CLK 2 8

DDR_ A_CLK #2 8

DDR_ A_CLK 1 8

DDR_ A_CLK #1 8

DDR_ B_CL K2 9

DDR_ B_CL K#2 9

DDR_ B_CL K1 9

DDR_ B_CL K#1 9

DDR_ B_ODT1 9

DDR_ B_ODT0 9

DDR_ A_ODT1 8

DDR_ A_ODT0 8

DDR_ B_MA[ 15..0 ] 9

DDR_ B_BS#2 9

DDR_ B_BS#1 9

DDR_ B_BS#0 9

DDR_ B_RAS # 9

DDR_ B_CAS # 9

DDR_ B_W E# 9

DDR_ B_D[ 63.. 0]9

To reverse SODIMM socket

DDR_ B_DM[ 7..0 ]9 DDR_ A_DM[ 7..0 ] 8

DDR_ B_DQS 79

DDR_ B_DQS #79

DDR_ B_DQS 69

DDR_ B_DQS #69

DDR_ B_DQS 59

DDR_ B_DQS #59

DDR_ B_DQS 49

DDR_ B_DQS #49

DDR_ B_DQS 39

DDR_ B_DQS #39

DDR_ B_DQS 29

DDR_ B_DQS #29

DDR_ B_DQS 19

DDR_ B_DQS #19

DDR_ B_DQS 09

DDR_ B_DQS #09

DDR_ B_D6 3

DDR_ B_D6 2

DDR_ B_D6 1

DDR_ B_D6 0

DDR_ B_D5 9

DDR_ B_D5 8

DDR_ B_D5 7

DDR_ B_D5 6

DDR_ B_D5 5

DDR_ B_D5 4

DDR_ B_D5 3

DDR_ B_D5 2

DDR_ B_D5 1

DDR_ B_D5 0

DDR_ B_D4 9

DDR_ B_D4 8

DDR_ B_D4 7

DDR_ B_D4 6

DDR_ B_D4 5

DDR_ B_D4 4

DDR_ B_D4 3

DDR_ B_D4 2

DDR_ B_D4 1

DDR_ B_D4 0

DDR_ B_D3 9

DDR_ B_D3 8

DDR_ B_D3 7

DDR_ B_D3 6

DDR_ B_D3 5

DDR_ B_D3 4

DDR_ B_D3 3

DDR_ B_D3 2

DDR_ B_D3 1

DDR_ B_D3 0

DDR_ B_D2 9

DDR_ B_D2 8

DDR_ B_D2 7

DDR_ B_D2 6

DDR_ B_D2 5

DDR_ B_D2 4

DDR_ B_D2 3

DDR_ B_D2 2

DDR_ B_D2 1

DDR_ B_D2 0

DDR_ B_D1 9

DDR_ B_D1 8

DDR_ B_D1 7

DDR_ B_D1 6

DDR_ B_D1 5

DDR_ B_D1 4

DDR_ B_D1 3

DDR_ B_D1 2

DDR_ B_D1 1

DDR_ B_D1 0

DDR _B_D 9

DDR _B_D 8

DDR _B_D 7

DDR _B_D 6

DDR _B_D 5

DDR _B_D 4

DDR _B_D 3

DDR _B_D 2

DDR _B_D 1

DDR _B_D 0

DDR_ B_DM7

DDR_ B_DM6

DDR_ B_DM5

DDR_ B_DM4

DDR_ B_DM3

DDR_ B_DM2

DDR_ B_DM1

DDR_ B_DM0

DDR_ B_DQS 7

DDR_ B_DQS #7

DDR_ B_DQS 6

DDR_ B_DQS #6

DDR_ B_DQS 5

DDR_ B_DQS #5

DDR_ B_DQS 4

DDR_ B_DQS #4

DDR_ B_DQS 3

DDR_ B_DQS #3

DDR_ B_DQS 2

DDR_ B_DQS #2

DDR_ B_DQS 1

DDR_ B_DQS #1

DDR_ B_DQS 0

DDR_ B_DQS #0

JP1C

AD11

MB_DATA63

AF11

MB_DATA62

AF14

MB_DATA61

AE14

MB_DATA60

Y11

MB_DATA59

AB11

MB_DATA58

AC12

MB_DATA57

AF13

MB_DATA56

AF15

MB_DATA55

AF16

MB_DATA54

AC18

MB_DATA53

AF19

MB_DATA52

AD14

MB_DATA51

AC14

MB_DATA50

AE18

MB_DATA49

AD18

MB_DATA48

AD20

MB_DATA47

AC20

MB_DATA46

AF23

MB_DATA45

AF24

MB_DATA44

AF20

MB_DATA43

AE20

MB_DATA42

AD22

MB_DATA41

AC22

MB_DATA40

AE25

MB_DATA39

AD26

MB_DATA38

AA25

MB_DATA37

AA26

MB_DATA36

AE24

MB_DATA35

AD24

MB_DATA34

AA23

MB_DATA33

AA24

MB_DATA32

G24

MB_DATA31

G23

MB_DATA30

D26

MB_DATA29

C26

MB_DATA28

G26

MB_DATA27

G25

MB_DATA26

E24

MB_DATA25

E23

MB_DATA24

C24

MB_DATA23

B24

MB_DATA22

C20

MB_DATA21

B20

MB_DATA20

C25

MB_DATA19

D24

MB_DATA18

A21

MB_DATA17

D20

MB_DATA16

D18

MB_DATA15

C18

MB_DATA14

D14

MB_DATA13

C14

MB_DATA12

A20

MB_DATA11

A19

MB_DATA10

A16

MB_DATA9

A15

MB_DATA8

A13

MB_DATA7

D12

MB_DATA6

E11

MB_DATA5

G11

MB_DATA4

B14

MB_DATA3

A14

MB_DATA2

A11

MB_DATA1

C11

MB_DATA0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MB_DQS_L2

D16

MB_DQS_H1

C16

MB_DQS_L1

C12

MB_DQS_H0

B12

MB_DQS_L0

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

DR II Da t a

DR II Da t a

DR II Da t a

DR II Da t a

MA_DATA15

MA_DATA14

D

D

D

D

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

DDR _A_D6 3

DDR _A_D6 2

DDR _A_D6 1

DDR _A_D6 0

DDR _A_D5 9

DDR _A_D5 8

DDR _A_D5 7

DDR _A_D5 6

DDR _A_D5 5

DDR _A_D5 4

DDR _A_D5 3

DDR _A_D5 2

DDR _A_D5 1

DDR _A_D5 0

DDR _A_D4 9

DDR _A_D4 8

DDR _A_D4 7

DDR _A_D4 6

DDR _A_D4 5

DDR _A_D4 4

DDR _A_D4 3

DDR _A_D4 2

DDR _A_D4 1

DDR _A_D4 0

DDR _A_D3 9

DDR _A_D3 8

DDR _A_D3 7

DDR _A_D3 6

DDR _A_D3 5

DDR _A_D3 4

DDR _A_D3 3

DDR _A_D3 2

DDR _A_D3 1

DDR _A_D3 0

DDR _A_D2 9

DDR _A_D2 8

DDR _A_D2 7

DDR _A_D2 6

DDR _A_D2 5

DDR _A_D2 4

DDR _A_D2 3

DDR _A_D2 2

DDR _A_D2 1

DDR _A_D2 0

DDR _A_D1 9

DDR _A_D1 8

DDR _A_D1 7

DDR _A_D1 6

DDR _A_D1 5

DDR _A_D1 4

DDR _A_D1 3

DDR _A_D1 2

DDR _A_D1 1

DDR _A_D1 0

DD R_A_D 9

DD R_A_D 8

DD R_A_D 7

DD R_A_D 6

DD R_A_D 5

DD R_A_D 4

DD R_A_D 3

DD R_A_D 2

DD R_A_D 1

DD R_A_D 0

DDR_ A_DM7

DDR_ A_DM6

DDR_ A_DM5

DDR_ A_DM4

DDR_ A_DM3

DDR_ A_DM2

DDR_ A_DM1

DDR_ A_DM0

DDR _A_DQ S7

DDR_ A_DQS #7

DDR _A_DQ S6

DDR_ A_DQS #6

DDR _A_DQ S5

DDR_ A_DQS #5

DDR _A_DQ S4

DDR_ A_DQS #4

DDR _A_DQ S3

DDR_ A_DQS #3

DDR _A_DQ S2

DDR_ A_DQS #2

DDR _A_DQ S1

DDR_ A_DQS #1

DDR _A_DQ S0

DDR_ A_DQS #0

DDR_ A_D[6 3..0 ] 8

DDR_ A_DQS 7 8

DDR_ A_DQS #7 8

DDR_ A_DQS 6 8

DDR_ A_DQS #6 8

DDR_ A_DQS 5 8

DDR_ A_DQS #5 8

DDR_ A_DQS 4 8

DDR_ A_DQS #4 8

DDR_ A_DQS 3 8

DDR_ A_DQS #3 8

DDR_ A_DQS 2 8

DDR_ A_DQS #2 8

DDR_ A_DQS 1 8

DDR_ A_DQS #1 8

DDR_ A_DQS 0 8

DDR_ A_DQS #0 8

To normal SODIMM socket

VDD_VREF_SUS_CPU

1 1

A

LAYOUT:PLACE CLOSE TO CPU

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

2007/01/07 2008/01/12

Deciphered Date

D

Title

AMD CPU DDRII MEMORY I/F

Size Docume nt Numb er Rev

Cus tom

LA-3 733P

Date : Sheet o f

5 36Monda y, M arch 05, 2007

E

0.1

Page 7

5

+2.5VS

1

C18

22U_0 805_6.3 V6M

2

D D

C C

HTCP U_PW RGD10

HTCPU_ STOP#10

HTCPU_ RST#10

1 2

FCM2 012C-800_ 0805

L1

1

C19

2

4.7U_ 0805 _10V4Z

+1.8V

12

R17

300_0402_ 5%

+1.8V

12

R20

300_0402_ 5%

+1.8V

12

R22

300_0402_ 5%

1

C20

2

0.22 U_0603_ 16V7K

1 2

R19 0_0402_5%

1 2

R21 0_0402_5%

1 2

R23 0_0402_5%

4

W=50mils

1

C21

3300P_040 2_50V7K

2

CPU_ SIC15

CPU_ SID15

+1.8V

+1.2 V_HT

R10 300_0402_ 5%

1 2

R11 300_0402_ 5%

1 2

R12 0_0402_5%

1 2

R13 0_0402_5%

1 2

R14 44.2_0603 _1%

1 2

R15 44.2_0603 _1%

1 2

place t hem to CPU within 1"

CPU CLK10

CPUC LK#10

CPU_AL L_P WROK

CPU_L DTSTOP#

CPU_HT _RES ET#

3

ATHLON Control and Debug

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

+2.5 VS_VDD A

CP U_SIC _R

CP U_SID _R

CP U_HTRE F1

CP U_HTRE F0 VID0

5:10

CPU _VCC_ SENS E34

CPU_VS S_SE NSE34

C22

1 2

12

3900P_040 2_50V7K

R16

169_0402_ 1%

1 2

H_T HERMD C4

H_T HERMDA4

R24 300_0402_ 5%

R25 1K_0402_5 %

R26 510_0402_ 5%

R27 300_0402_ 5%

R28 510_0402_ 5%

R29 300_0402_ 5%

R30 300_0402_ 5%

C23

3900P_040 2_50V7K

CPU_ TEST2 6_B URNIN#

CPU_P RESE NT#

CPU_TE ST25 _H_B YPASS CLK_H

CPU_TE ST21 _SCAN EN

CPU_TE ST25 _L_ BYPASSCLK_L

CPU_TE ST19_PLL TEST0

CPU_TE ST18_PLL TEST1

TP2PAD

TP3PAD

CPU_ CLKI N_SC _P

CPU _CL KIN_S C_N

CPU_TE ST25 _H_B YPASS CLK_H

CPU_TE ST25 _L_ BYPASSCLK_L

CPU_TE ST19_PLL TEST0

CPU_TE ST18_PLL TEST1

H_T HERMD C

H_T HERMD A

10:10

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CPU_HT _RES ET#

CPU_AL L_P WROK

CPU_L DTSTOP#

CP U_VCC_ SENS E

CPU_VS S_SE NSE

CPU _DB RD Y

CPU_TMS

CPU_ TCK

CPU_TR ST#

CP U_TDI

TP4

TP6

TP8

TP10

TP11

+1.8V

JP1D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

SID

P6

HTREF1

R6

HTREF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

TEST25_HE9TEST29_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

THERMDC

W8

THERMDA

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

FOX_PZ63823-284S-41F

2

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

SC

SC

SC

SC

MI

MI

MI

MI

AMD NPT S1 SOCKET

Processor Socket

DBREQ_L

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

TEST8

AF6

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

AC6

A3

PSI_L

E10

AE9

TDO

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

R8

300_0402_ 5%

H_THER MTRIP_ S#

CPU_P ROCHO T#_1. 8

VID5

VID4

VID3

VID2

VID1

CPU_P RESE NT#

PSI#

CPU_ DBRE Q#

CP U_TDO

CPU_TE ST29 _H_F BCLKOUT_P

CPU_TE ST29 _L_ FBCLKOUT_N

5:5:5

TP5

TP7

TP9

CPU_TE ST21 _SCAN EN

TP12

CPU_ TEST2 6_B URNIN#

+1.8V

12

PSI# 34

1 2

80.6_0402 _1%

R18

12

R9

300_0402_ 5%

1

VID5 34

VID4 34

VID3 34

VID2 34

VID1 34

VID0 34

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

HDT Connector

B B

CPU_ DBRE Q#

CPU _DB RD Y

CPU_ TCK

CP U_TDI

CPU_TR ST#

CP U_TDO

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

A A

+1.8V

JP3

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC _ASP-68200-0 7

@

R35

220_0402_ 5%@

3V_L DT_RST# CPU_HT_R ESET#

+3VALW+3VS

12

2

G

1 3

D

S

Q4

2N700 2_SOT23@

PRO CHOT#10

+1.8V + 1.8V +3VALW +3VAL W

12

@

Q2

3 1

MMBT3904_SOT23

1 2

R36 0_0402_5%

CPU_P ROCHO T#_1. 8

12

2

10K_0402_ 5%

R31

300_0402_ 5%

H_THER MTRIP_ S# H_THER MTRIP#CPU_TMS

1 2

R39 0_0402_5%

R32

1K_0402_5 %

@

R37

+1.8V +3VS

12

CP U_PH_G

B

2

Q5

E

3 1

C

MMBT3904_SOT23

12

R34

10K_0402_ 5%

@

12

12

2

3 1

R38

4.7K_0402_ 5%

R33

1K_0402_5 %@

Q3

MMBT3904_SOT23

@

EC_THE RM# 15,27

MAI NPWO N 31,35

H_THER MTRIP# 10

Connect to MCP67

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

2007/01/07 2008/01/12

Deciphered Date

2

Title

AMD CPU CTRL & DEBUG

Size Docume nt Numb er Rev

C

LA-3 733P

Date : Sheet o f

6 36Monda y, M arch 05, 2007

1

0.1

Page 8

5

4

3

2

1

+CPU_ CORE

1

+

C24

330U_ 4V_M

D D

PROCESSOR POWER AND GROUND

JP1F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_PZ63823-284S-41F

er

er

er

er

Po w

Po w

Po w

Po w

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

+CP U_COR E+CP U_COR E

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

+1.8V

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

JP1E

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

C C

B B

VDD17

M6

VDD18

M8

VDD19

M10

VDD20

N7

VDD21

N9

VDD22

N11

VDD23

P8

VDD24

P10

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

R11

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

U11

VDD38

U13

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor Socket

Athlon 64 S1

Processor Socket

J6

VSS66

J8

VSS67

J10

VSS68

J12

VSS69

J14

VSS70

J16

VSS71

J18

VSS72

K2

VSS73

K7

VSS74

K9

VSS75

K11

VSS76

K13

VSS77

K15

VSS78

K17

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L12

VSS83

L14

VSS84

L16

VSS85

L18

VSS86

M7

VSS87

M9

VSS88

M11

VSS89

M17

VSS90

N4

VSS91

N8

VSS92

N10

VSS93

N16

VSS94

N18

VSS95

P2

VSS96

P7

VSS97

P9

und

und

VSS98

und

und

P11

VSS99

P17

VSS100

R8

VSS101

R10

Gr o

Gr o

VSS102

Gr o

Gr o

R16

VSS103

R18

VSS104

T7

VSS105

T9

VSS106

T11

VSS107

T13

VSS108

T15

VSS109

T17

VSS110

U4

VSS111

U6

VSS112

U8

VSS113

U10

VSS114

U12

VSS115

U14

VSS116

U16

VSS117

U18

VSS118

V2

VSS119

V7

VSS120

V9

VSS121

V11

VSS122

V13

VSS123

V15

VSS124

V17

VSS125

W6

VSS126

Y21

VSS127

Y23

VSS128

N6

VSS129

2

+CPU_ CORE

1

2

C29

10U_0 805_10V6M

CPU SOCKET S1 DECOUPLING

+CP U_COR E

22U_0 805_6.3 V

+CP U_COR E

0.22 U_0603_ 10V7K

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8V

1

2

1

2

+0.9V

1

2

C30

10U_0 805_10V6M

1

2

22U_0 805_6.3 V

1

1

C36

2

2

0.22 U_0603_ 10V7K

1

1

C45

2

2

C54

4.7U_ 0805 _10V4Z

C61

0.22 U_040 2_10V4Z

C66

4.7U_ 0805 _10V4Z

0125 Cost down $0.155

1

+

C25

330U_ 4V_M

2

1

2

C31

10U_0 805_10V6M

1

C38

C37

2

22U_0 805_6.3 V

180P _0402_50V8J

1

C46

C47

2

0.01 U_0402_ 16V7K

1

C55

4.7U_ 0805 _10V4Z

2

1

C62

0.01 U_0402_ 16V7K

2

1

C67

4.7U_ 0805 _10V4Z

2

C32

10U_0 805_10V6M

1

2

22U_0 805_6.3 V

1

C39

2

1

C48

2

1

+

C26

330U_ 4V_M

2

1

2

C33

10U_0 805_10V6M

1

C40

2

22U_0 805_6.3 V

1

C49

180P _0402_50V8J

2

1

C56

4.7U_ 0805 _10V4Z

2

1

C63

0.01 U_0402_ 16V7K

2

1

C68

4.7U_ 0805 _10V4Z

2

C34

10U_0 805_10V6M

1

2

22U_0 805_6.3 V

1

C41

2

1

2

1

2

1

+

2

1

2

C35

10U_0 805_10V6M

1

2

22U_0 805_6.3 V

C57

4.7U_ 0805 _10V4Z

1

C64

180P_0402 _50V8J

2

C69

4.7U_ 0805 _10V4Z

C27

330U_ 4V_M

22U_0 805_6.3 V

C42

1

C43

2

+1.8V

10U_0 805_10V6M

1

2

1

C58

0.22 U_040 2_10V4Z

2

1

2

1

C70

0.22 U_040 2_10V4Z

2

1

C44

22U_0 805_6.3 V

2

C50

C65

180P_0402 _50V8J

+CPU_ CORE

1

+

2

1

C51

2

10U_0 805_10V6M

1

C59

0.22 U_040 2_10V4Z

2

1

C71

0.22 U_040 2_10V4Z

2

C28

820U_ E9_2 .5V_M_R7

45@

0.22 U_040 2_10V4Z

1

C52

2

1

C60

0.22 U_040 2_10V4Z

2

1

C72

0.22 U_040 2_10V4Z

2

1

C53

0.22 U_040 2_10V4Z

2

1

C73

0.22 U_040 2_10V4Z

2

1

C76

1000P_040 2_50V7K

2

Compal Secret Data

Deciphered Date

2

1

C77

1000P_040 2_50V7K

2

1

1

2

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

C75

C74

1000P_040 2_50V7K

1000P_040 2_50V7K

2

2007/01/07 2008/01/12

1

C78

180P_0402 _50V8J

2

1

C79

180P_0402 _50V8J

2

Title

Size Docume nt Numb er Rev

C

Date : Sheet o f

1

1

C80

180P_0402 _50V8J

2

2

AMD CPU PWR & GND

LA-3 733P

C81

180P_0402 _50V8J

1

0.1

7 36Monda y, M arch 05, 2007

Page 9

5

DDR_ CKE0_ DIMMA5

DDR_ CS2_D IMMA#5

DDR_ A_BS#25

DDR_ A_BS#05

DDR_ A_WE #5

DDR_ A_CAS #5

DDR_ CS1_D IMMA#5

DDR_ A_ODT15

MEM_SMBDATA9,15

MEM_SMBCL K9,15

DD R_A_D [0..6 3]

DD R_A_D M[0..7 ]

DDR _A_ DQS[0 ..7]

DDR_ A_MA[0 ..15]

DD R_A_D QS#[0 ..7]

DDR_ A_D0

DDR_ A_D1

DDR_ A_DQS #0

DDR_ A_DQS 0

DDR_ A_D2

DDR_ A_D3

DDR_ A_D8

DDR_ A_D9

DDR_ A_DQS #1

DDR_ A_DQS 1

DDR_ A_D10

DDR_ A_D11

DDR_ A_D16

DDR_ A_D17

DDR_ A_DQS #2

DDR_ A_DQS 2

DDR_ A_D18 DDR_ A_D22

DDR_ A_D19

DDR_ A_D24

DDR_ A_D25

DDR_ A_DM3

DDR_ A_D26

DDR_ A_D27

DDR_ CKE0_ DIMMA

DDR_ CS2_D IMMA#

DDR_ A_BS#2

DDR_ A_MA12

DDR_ A_MA9

DDR_ A_MA5

DDR_ A_MA3

DDR_ A_MA1

DDR_ A_MA10

DDR_ A_BS#0

DDR_ A_WE#

DDR_ A_CAS #

DDR_ CS1_D IMMA#

DDR_ A_ODT1

DDR_ A_D32

DDR_ A_D33

DDR_ A_DQS #4

DDR_ A_DQS 4

DDR_ A_D34

DDR_ A_D35

DDR_ A_D40

DDR_ A_D41

DDR_ A_DM5

DDR_ A_D42

DDR_ A_D43 DDR_ A_D47

DDR_ A_D48

DDR_ A_D49 DDR_ A_D53

DDR_ A_DQS #6

DDR_ A_DQS 6

DDR_ A_D50

DDR_ A_D51 DDR_ A_D55

DDR_ A_D56

DDR_ A_D57

DDR_ A_DM7

DDR_ A_D58

DDR_ A_D59

MEM_SMBDATA

MEM_SMBCL K

+3VS

1

C111

0.1U_ 0402_1 6V4Z

2

5

JP4

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

FOX_A S0A426-M2RN -7F

<BOM S tructure>

DIMM1 REV H:4mm (BOT)

DDR _A_D [0..6 3]5

DDR _A_DM [0..7]5

DDR _A_D QS[0. .7]5

DDR_ A_MA[0 ..15]5

DDR _A_D QS#[0. .7]5

D D

C C

B B

A A

DQS3#

NC/CKE1

NC/A15

NC/A14

NC/A13

DQS5#

DQS7#

4

2

VSS

4

DQ4

6

DQ5

8

VSS

10

DM0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

VSS

30

CK0

32

CK0#

34

VSS

36

DQ14

38

DQ15

40

VSS

42

VSS

44

DQ20

46

DQ21

48

VSS

50

NC

52

DM2

54

VSS

56

DQ22

58

DQ23

60

VSS

62

DQ28

64

DQ29

66

VSS

68

70

DQS3

72

VSS

74

DQ30

76

DQ31

78

VSS

80

82

VDD

84

86

88

VDD

90

A11

92

A7

94

A6

96

VDD

98

A4

100

A2

102

A0

104

VDD

106

BA1

108

RAS#

110

S0#

112

VDD

114

ODT0

116

118

VDD

120

NC

122

VSS

124

DQ36

126

DQ37

128

VSS

130

DM4

132

VSS

134

DQ38

136

DQ39

138

VSS

140

DQ44

142

DQ45

144

VSS

146

148

DQS5

150

VSS

152

DQ46

154

DQ47

156

VSS

158

DQ52

160

DQ53

162

VSS

164

CK1

166

CK1#

168

VSS

170

DM6

172

VSS

174

DQ54

176

DQ55

178

VSS

180

DQ60

182

DQ61

184

VSS

186

188

DQS7

190

VSS

192

DQ62

194

DQ63

196

VSS

198

SAO

200

SA1

4

DDR_ A_D4

DDR_ A_D5

DDR_ A_DM0

DDR_ A_D6

DDR_ A_D7

DDR_ A_D12

DDR_ A_D13

DDR_ A_DM1

DDR_ A_CLK1

DDR_ A_CLK #1

DDR_ A_D14

DDR_ A_D15

DDR_ A_D20

DDR_ A_D21

DDR_ A_DM2

DDR_ A_D23

DDR_ A_D28

DDR_ A_D29

DDR_ A_DQS #3

DDR_ A_DQS 3

DDR_ A_D30

DDR_ A_D31

DDR_ CKE1_ DIMMA

DDR_ A_MA15

DDR_ A_MA14

DDR_ A_MA11

DDR_ A_MA7

DDR_ A_MA6DDR_ A_MA8

DDR_ A_MA4

DDR_ A_MA2

DDR_ A_MA0

DDR_ A_BS#1

DDR_ A_RAS #

DDR_ CS0_D IMMA#

DDR_ A_ODT0

DDR_ A_MA13

DDR_ CS3_D IMMA#

DDR_ A_D36

DDR_ A_D37

DDR_ A_DM4

DDR_ A_D38

DDR_ A_D39

DDR_ A_D44

DDR_ A_D45

DDR_ A_DQS #5

DDR_ A_DQS 5

DDR_ A_D46

DDR_ A_D52

DDR_ A_CLK2

DDR_ A_CLK #2

DDR_ A_DM6

DDR_ A_D54

DDR_ A_D60

DDR_ A_D61

DDR_ A_DQS #7

DDR_ A_DQS 7

DDR_ A_D62

DDR_ A_D63

R42 10K_0402_5 %

1 2

R43 10K_0402_5 %

1 2

DDR_ A_CLK1 5

DDR_ A_CLK# 1 5

DDR_ CKE1_ DIMMA 5

DDR_ A_BS#1 5

DDR_ A_RAS # 5

DDR_ CS0_D IMMA# 5

DDR_ A_ODT0 5

DDR_ CS3_D IMMA# 5

DDR_ A_CLK2 5

DDR_ A_CLK# 2 5

3

+1.8V+DIMM_ VREF+1.8V+1.8V

C83 0 .1U_04 02_16V4Z

C82 4 .7U_08 05_10V4Z

1

2

12

R40

1

1K_0402_ 1%

2

12

R41

1K_0402_ 1%

2

+1.8V

0.1U_ 0402_1 6V4Z

1

2

C84

+0.9V

+0.9V

0.1U_ 0402_1 6V4Z

1

2

C93

+1.8V

+0.9V

DDR_ A_MA8

DDR_A _MA9

DDR_ A_MA3

DDR_ A_MA5

DDR_ CKE0_ DIMMA

DDR_ CS2_D IMMA#

DDR_ A_MA12

DDR_ A_BS#2

DDR_ A_BS#1

DDR_ A_MA0

DDR_ A_RAS #

DDR_ CS0_D IMMA#

DDR_ A_MA7

DDR_A _MA6

DDR_ A_MA4

DDR_ A_MA2

DDR_ A_ODT0

DDR_ A_MA13

DDR_ CS3_D IMMA#

DDR_ A_CAS #

DDR_ CS1_D IMMA#

DDR_ A_ODT1

DDR_ A_MA1

DDR_ A_MA10

DDR_ A_BS#0

DDR_ A_WE#

DDR_ A_MA15

DDR_ A_MA14

DDR_ CKE1_ DIMMA

DDR_A _MA11

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

RP1

18

27

36

45

47_0 804_8P4R_5%

RP2

18

27

36

45

47_0 804_8P4R_5%

RP3

45

36

27

18

47_0 804_8P4R_5%

RP4

45

36

27

18

47_0 804_8P4R_5%

RP5

45

36

27

18

47_0 804_8P4R_5%

RP6

18

27

36

45

47_0 804_8P4R_5%

RP7

18

27

36

45

47_0 804_8P4R_5%

RP8

45

36

27

18

47_0 804_8P4R_5%

2007/01/07 2008/01/12

Compal Secr et Data

Deciphered Date

220U_ D2_4V M_R15

1

C101

+

2

2

Layout Note:

Plac e one ca p close to every 2 pul lup

resi stors term inated to + 0.9V

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

2

C85

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

2

C94

2.2U_ 0805_ 16V4Z

C102

1

2

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

2

C86

Layout Note:

Plac e one ca p close to every 2 pul lup

resi stors term inated to + 0.9V

0.1U_ 0402_1 6V4Z

1

2

C95

2.2U_ 0805_ 16V4Z

C103

1

2

0.1U_ 0402_1 6V4Z

1

1

2

C87

1

2

C96

2.2U_ 0805_ 16V4Z

1

2

2

C88

C89

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

1

2

2

C98

C97

2.2U_ 0805_ 16V4Z

2.2U_ 0805_ 16V4Z

C104

C105

1

1

2

2

Title

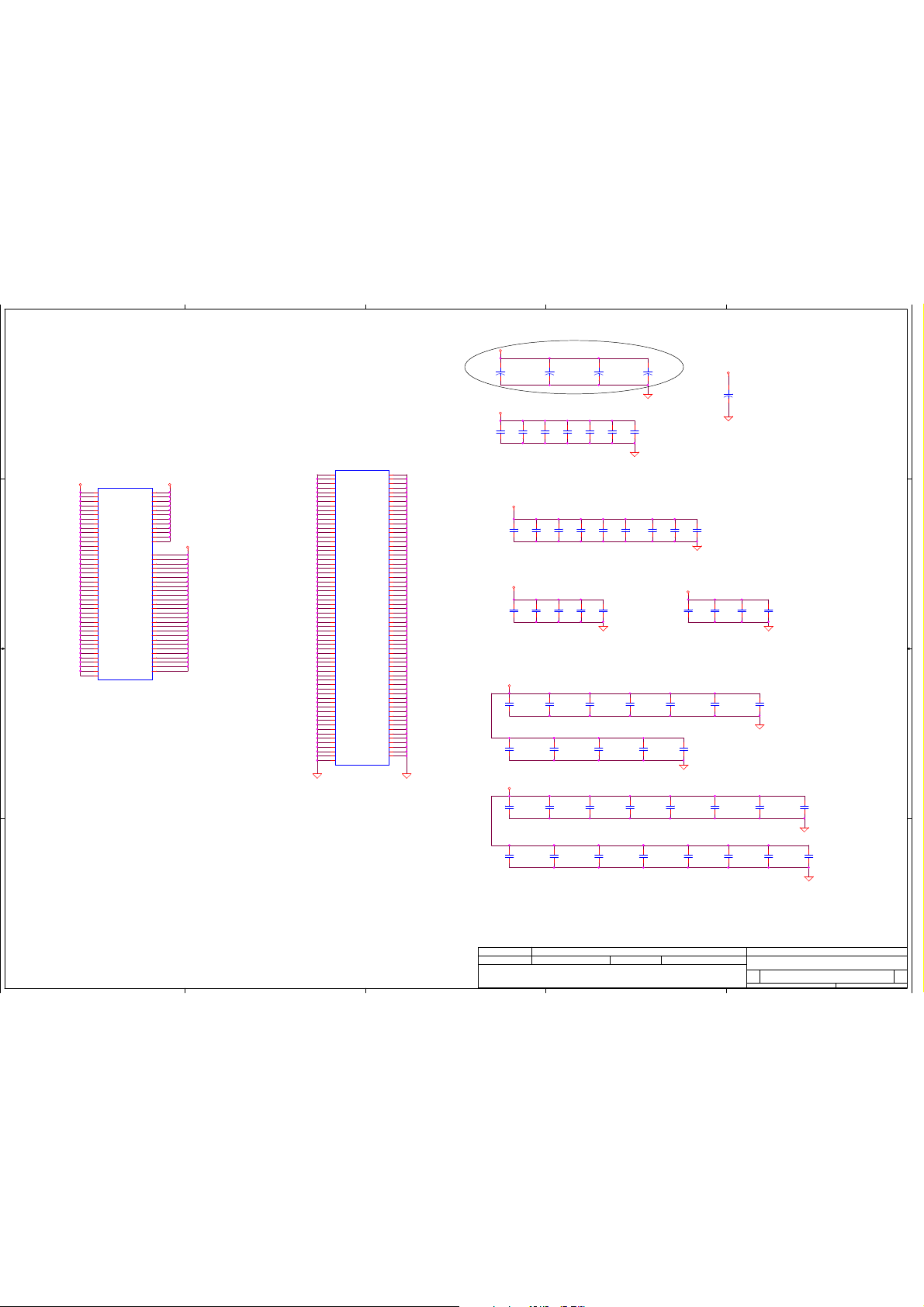

DDR2 SO-DIMM I

Size Doc ument Number Re v

Cus tom

LA- 3733P

Date : Sheet of

1

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

1

2

2

C90

C91

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

1

2

C99

0.1U_ 0402_ 16V4Z

C106

C107

1

1

2

2

C92

1

+

150U _D2_6.3VM

2

2

C100

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

C108

C109

1

2

1

C110

1

1

2

2

0.1

8 36Monday, Marc h 05, 2 007

Page 10

5

DDR _B_D [0..6 3]5

DDR _B_DM [0..7]5

DDR _B_D QS[0. .7]5

DDR_ B_MA[0 ..15]5

DDR _B_D QS#[0. .7]5

D D

C C

B B

A A

DD R_B_D [0..6 3]

DD R_B_D M[0..7 ]

DDR _B_ DQS[0 ..7]

DDR_ B_MA[0 ..15]

DD R_B_D QS#[0 ..7]

DDR_ B_D0

DDR_ B_D1

DDR_ B_DQS #0

DDR_ B_DQS 0

DDR_ B_D2

DDR_ B_D3

DDR_ B_D8

DDR_ B_D9

DDR_ B_DQS #1

DDR_ B_DQS 1

DDR_ B_D10

DDR_ B_D11

DDR_ B_D16

DDR_ B_D17

DDR_ B_DQS #2

DDR_ B_DQS 2

DDR_ B_D18 DDR_ B_D22

DDR_ B_D19

DDR_ B_D24

DDR_ B_D25

DDR_ B_DM3

DDR_ B_D26

DDR_ B_D27

DDR_ CKE0_ DIMMB5

DDR_ CS2_D IMMB#5

DDR_ B_BS#25

DDR_ B_BS#05

DDR_ B_WE #5

DDR_ B_CAS #5

DDR_ CS1_D IMMB#5

DDR_ B_ODT15

MEM_SMBDATA8,15

MEM_SMBCL K8,15

DDR_ CKE0_ DIMMB

DDR_ CS2_D IMMB#

DDR_ B_BS#2

DDR_ B_MA12

DDR_ B_MA9

DDR_ B_MA5

DDR_ B_MA3

DDR_ B_MA1

DDR_ B_MA10

DDR_ B_BS#0

DDR_ B_WE#

DDR_ B_CAS #

DDR_ CS1_D IMMB#

DDR_ B_ODT1

DDR_ B_D32

DDR_ B_D33

DDR_ B_DQS #4

DDR_ B_DQS 4

DDR_ B_D34

DDR_ B_D35

DDR_ B_D40

DDR_ B_D41

DDR_ B_DM5

DDR_ B_D42

DDR_ B_D43 DDR_ B_D47

DDR_ B_D48

DDR_ B_D49 DDR_ B_D53

DDR_ B_DQS #6

DDR_ B_DQS 6

DDR_ B_D50

DDR_ B_D51 DDR_ B_D55

DDR_ B_D56

DDR_ B_D57

DDR_ B_DM7

DDR_ B_D58

DDR_ B_D59

MEM_SMBDATA

MEM_SMBCL K

+3VS

1

C139

0.1U_ 0402_1 6V4Z

2

5

JP5

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

FOX_A S0A426-MARG- 7F

Change PCB Footprint

DIMM0 REV H:8mm (BOT)

DQS3#

NC/CKE1

NC/A15

NC/A14

NC/A13

DQS5#

DQS7#

4

2

VSS

4

DQ4

6

DQ5

8

VSS

10

DM0

12

VSS

14

DQ6

16

DQ7

18

VSS

20

DQ12

22

DQ13

24

VSS

26

DM1

28

VSS

30

CK0

32

CK0#

34

VSS

36

DQ14

38

DQ15

40

VSS

42

VSS

44

DQ20

46

DQ21

48

VSS

50

NC

52

DM2

54

VSS

56

DQ22

58

DQ23

60

VSS

62

DQ28

64

DQ29

66

VSS

68

70

DQS3

72

VSS

74

DQ30

76

DQ31

78

VSS

80

82

VDD

84

86

88

VDD

90

A11

92

A7

94

A6

96

VDD

98

A4

100

A2

102

A0

104

VDD

106

BA1

108

RAS#

110

S0#

112

VDD

114

ODT0

116

118

VDD

120

NC

122

VSS

124

DQ36

126

DQ37

128

VSS

130

DM4

132

VSS

134

DQ38

136

DQ39

138

VSS

140

DQ44

142

DQ45

144

VSS

146

148

DQS5

150

VSS

152

DQ46

154

DQ47

156

VSS

158

DQ52

160

DQ53

162

VSS

164

CK1

166

CK1#

168

VSS

170

DM6

172

VSS

174

DQ54

176

DQ55

178

VSS

180

DQ60

182

DQ61

184

VSS

186

188

DQS7

190

VSS

192

DQ62

194

DQ63

196

VSS

198

SAO

200

SA1

4

DDR_ B_D4

DDR_ B_D5

DDR_ B_DM0

DDR_ B_D6

DDR_ B_D7

DDR_ B_D12

DDR_ B_D13

DDR_ B_DM1

DDR_ B_CLK1

DDR_ B_CLK #1

DDR_ B_D14

DDR_ B_D15

DDR_ B_D20

DDR_ B_D21

DDR_ B_DM2

DDR_ B_D23

DDR_ B_D28

DDR_ B_D29

DDR_ B_DQS #3

DDR_ B_DQS 3

DDR_ B_D30

DDR_ B_D31

DDR_ CKE1_ DIMMB

DDR_ B_MA15

DDR_ B_MA14

DDR_ B_MA11

DDR_ B_MA7

DDR_ B_MA6DDR_ B_MA8

DDR_ B_MA4

DDR_ B_MA2

DDR_ B_MA0

DDR_ B_BS#1

DDR_ B_RAS #

DDR_ CS0_D IMMB#

DDR_ B_ODT0

DDR_ B_MA13

DDR_ CS3_D IMMB#

DDR_ B_D36

DDR_ B_D37

DDR_ B_DM4

DDR_ B_D38

DDR_ B_D39

DDR_ B_D44

DDR_ B_D45

DDR_ B_DQS #5

DDR_ B_DQS 5

DDR_ B_D46

DDR_ B_D52

DDR_ B_CLK2

DDR_ B_CLK #2

DDR_ B_DM6

DDR_ B_D54

DDR_ B_D60

DDR_ B_D61

DDR_ B_DQS #7

DDR_ B_DQS 7

DDR_ B_D62

DDR_ B_D63

R44 10K_0 402_5%

1 2

R45 10K_0 402_5%

1 2

4.7U_ 0805_1 0V4Z

DDR_ B_CLK1 5

DDR_ B_CLK# 1 5

DDR_ CKE1_ DIMMB 5

DDR_ B_BS#1 5

DDR_ B_RAS # 5

DDR_ CS0_D IMMB# 5

DDR_ B_ODT0 5

DDR_ CS3_D IMMB# 5

DDR_ B_CLK2 5

DDR_ B_CLK# 2 5

+3VS

3

+DIMM_ VREF+1.8V+1.8V

0.1U_ 0402_1 6V4Z

C113

C112

1

1

2

2

DDR_ B_RAS #

DDR_ CS0_D IMMB#

DDR_ B_BS#1

DDR_ B_MA0

DDR_ B_MA2

DDR_ B_MA4

DDR_B _MA6

DDR_ B_MA7

DDR_ CKE0_ DIMMB

DDR_ CS2_D IMMB#

DDR_ B_BS#2

DDR_ B_MA12

DDR_B _MA8

DDR_ B_MA3

DDR_ B_MA9

DDR_ B_MA5

DDR_ B_MA1

DDR_ B_WE#

DDR_ B_BS#0

DDR_ B_MA10

DDR_ CS1_D IMMB#

DDR_ B_CAS #

DDR_ B_ODT1

DDR_ CS3_D IMMB#

DDR_ B_MA13

DDR_ B_ODT0

DDR_B _MA11

DDR_ B_MA14

DDR_ B_MA15

DDR_ CKE1_ DIMMB

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+0.9V

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

2

C114

+1.8V

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

1

2

C122

+0.9V

RP9

47_0 804_8P4R_5%

RP10

47_0 804_8P4R_5%

RP11

47_0 804_8P4R_5%

RP12

47_0 804_8P4R_5%

RP13

47_0 804_8P4R_5%

RP14

47_0 804_8P4R_5%

RP15

47_0 804_8P4R_5%

RP16

47_0 804_8P4R_5%

2007/01/07 2008/01/12

1

2

C115

1

2

C123

45

36

27

18

45

36

27

18

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

45

36

27

18

45

36

27

18

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

2

C116

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

1

2

C124

+0.9V

Compal Secr et Data

1

2

C117

1

2

C125

Deciphered Date

2

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

1

1

2

2

C119

C118

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

0.1U_ 0402_ 16V4Z

1

1

2

2

C127

C126

2

1

0.1U_ 0402_1 6V4Z

1

1

2

C120

1

2

C128

Layout Note:

Plac e one ca p close to every 2 pul lup

2

resi stors term inated to + 0.9V

C121

0.1U_ 0402_ 16V4Z

Layout Note:

1

Plac e one ca p close to every 2 pul lup

resi stors term inated to + 0.9V

2

C129

+1.8V

2.2U_ 0805_1 6V4Z

2.2U_ 0805_1 6V4Z

2.2U_ 0805_1 6V4Z

C130

C131

1

1

2

2

2.2U_ 0805_1 6V4Z

2.2U_ 0805_1 6V4Z

C132

C133

1

1

2

2

Title

DDR2 SO-DIMM II

Size Doc ument Number Re v

Cus tom

LA- 3733P

Date : Sheet of

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

C134

C135

1

1

2

2

1

0.1U_ 0402_1 6V4Z

0.1U_ 0402_1 6V4Z

C138

C137

C136

1

1

1

2

2

2

0.1

9 36Monday, Marc h 05, 2 007

Page 11

5

4

3

2

1

U3A

AF16

HT_MCP_RXD0_P

AG16

HT_MCP_RXD0_N

AH16

HT_MCP_RXD1_P

AJ16

HT_MCP_RXD1_N

AJ15

HT_MCP_RXD2_P

AK15

HT_MCP_RXD2_N

AK16

HT_MCP_RXD3_P

AL16

HT_MCP_RXD3_N

AG17

HT_MCP_RXD4_P

AF17

HT_MCP_RXD4_N

AL17

HT_MCP_RXD5_P

AK17

HT_MCP_RXD5_N

AL18

HT_MCP_RXD6_P

AK18

HT_MCP_RXD6_N

AJ19

HT_MCP_RXD7_P

AK19

HT_MCP_RXD7_N

AD14

HT_MCP_RXD8_P

AE14

HT_MCP_RXD8_N

AF14

HT_MCP_RXD9_P

AG14

HT_MCP_RXD9_N

AH14

HT_MCP_RXD10_P

AJ14

HT_MCP_RXD10_N

AL13

HT_MCP_RXD11_P

AK13

HT_MCP_RXD11_N

AC15

HT_MCP_RXD12_P

AD15

HT_MCP_RXD12_N

AD16

HT_MCP_RXD13_P

AE16

HT_MCP_RXD13_N

AE17

HT_MCP_RXD14_P

AD17

HT_MCP_RXD14_N

AB17

HT_MCP_RXD15_P

AC17

HT_MCP_RXD15_N

AJ17

HT_MCP_RX_CLK0_P

AH17

HT_MCP_RX_CLK0_N

AL14

HT_MCP_RX_CLK1_P

AK14

HT_MCP_RX_CLK1_N

AH19

HT_MCP_RXCTL0_P

AG19

HT_MCP_RXCTL0_N

AC18

HT_MCP_RXCTL1_P/RESERVED

AD18

HT_MCP_RXCTL1_N/RESERVED

AC13

THERMTRIP#/GPIO_58

AB13

PROCHOT#/GPIO_20

AB16

+3.3V_PLL_CPU

AB15

+1.2V_PLL_CPU_HT

AM12

HT_MCP_COMP_VDD

AL12

HT_MCP_COMP_GND

MCP67-MV_PBGA836

0.1U_0 402_16V4Z

C141

C144

0.1U_0 402_16V4Z

H_CAD OP0

H_CA DON0

H_CAD OP1

H_CA DON1

H_CAD OP2

H_CA DON2

H_CAD OP3

H_CA DON3

H_CAD OP4

H_CA DON4

H_CAD OP5

H_CA DON5

H_CAD OP6

H_CA DON6

H_CAD OP7

H_CA DON7

H_CAD OP8

H_CA DON8

H_CAD OP9

H_CA DON9

H_CAD OP10

H_CAD ON10

H_CAD OP11

H_CAD ON11

H_CAD OP12

H_CAD ON12

H_CAD OP13

H_CAD ON13

H_CAD OP14

H_CAD ON14

H_CAD OP15

H_CAD ON15

H_CLKOP0

H_CLK ON0

H_CLKOP1

H_CLK ON1

H_CTLOP0

H_CTLON0

+1.2V _PLL_CPU_HT

+1.2V_HT

1 2

R47 150_0402_1%

1 2

R48 150_0402_1%

H_CAD OP04

H_CAD ON04

H_CAD OP14

D D

C C

+3.3V_PLL

4.7U_0 805_10V4Z

B B

+1.2V_HT

L2

1 2

MBK16 08121YZF_0603

10U_0805_10V 4Z

H_CAD ON14

H_CAD OP24

H_CAD ON24

H_CAD OP34

H_CAD ON34

H_CAD OP44

H_CAD ON44

H_CAD OP54

H_CAD ON54

H_CAD OP64

H_CAD ON64

H_CAD OP74

H_CAD ON74

H_CAD OP84

H_CAD ON84

H_CAD OP94

H_CAD ON94

H_CAD OP104

H_CAD ON104

H_CAD OP114

H_CAD ON114

H_CAD OP124

H_CAD ON124

H_CAD OP134

H_CAD ON134

H_CAD OP144

H_CAD ON144

H_CAD OP154

H_CAD ON154

H_CLKOP04

H_CLK ON04

H_CLKOP14

H_CLK ON14

H_CTLOP04

H_CTLON04

H_THERM TRIP#6

PROCHO T#6

1

1

C140

2

2

1

1

C143

2

2

MC P67

PA RT 1 OF 8

HT

RESERVED/HT_MCP_TXCTL1_P

RESERVED/HT_MCP_TXCTL1_N

HT_MCP_TXD0_P

HT_MCP_TXD0_N

HT_MCP_TXD1_P

HT_MCP_TXD1_N

HT_MCP_TXD2_P

HT_MCP_TXD2_N

HT_MCP_TXD3_P

HT_MCP_TXD3_N

HT_MCP_TXD4_P

HT_MCP_TXD4_N

HT_MCP_TXD5_P

HT_MCP_TXD5_N

HT_MCP_TXD6_P

HT_MCP_TXD6_N

HT_MCP_TXD7_P

HT_MCP_TXD7_N

HT_MCP_TXD8_P

HT_MCP_TXD8_N

HT_MCP_TXD9_P

HT_MCP_TXD9_N

HT_MCP_TXD10_P

HT_MCP_TXD10_N

HT_MCP_TXD11_P

HT_MCP_TXD11_N

HT_MCP_TXD12_P

HT_MCP_TXD12_N

HT_MCP_TXD13_P

HT_MCP_TXD13_N

HT_MCP_TXD14_P

HT_MCP_TXD14_N

HT_MCP_TXD15_P

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL0_P

HT_MCP_TXCTL0_N

HT_MCP_REQ#

HT_MCP_STOP#

HT_MCP_RST#

HT_MCP_PWRGD

CLKOUT_200MHZ_P

CLKOUT_200MHZ_N

CLKOUT_25MHZ

CPU_SBVREF

CLK200_TERM_GND

H_CA DIP0

AK27

H_C ADIN0

AJ27

H_CA DIP1

AK26

H_C ADIN1

AL26

H_CA DIP2

AK25

H_C ADIN2

AL25

H_CA DIP3

AL24

H_C ADIN3

AK24

H_CA DIP4

AK22

H_C ADIN4

AL22

H_CA DIP5

AK21

H_C ADIN5

AL21

H_CA DIP6

AH21

H_C ADIN6

AJ21

H_CA DIP7

AL20

H_C ADIN7

AM20

H_CA DIP8

AG27

H_C ADIN8

AH27

H_CA DIP9

AF25

H_C ADIN9

AG25

H_CAD IP10

AH25

H_C ADIN10

AJ25

H_CAD IP11

AE23

H_C ADIN11

AF23

H_CAD IP12

AD21

H_C ADIN12

AE21

H_CAD IP13

AF21

H_C ADIN13

AG21

H_CAD IP14

AC20

H_C ADIN14

AD20

H_CAD IP15

AE19

H_C ADIN15

AF19

H_CLK IP0

AK23

H_CL KIN0

AJ23

H_CLK IP1

AG23

H_CL KIN1

AH23

H_CTLIP0

AK20

H_CTL IN0

AJ20

AD19

AC19

HTCPU_R EQ#

AD23

HTCPU_S TOP#

AB20

HTCPU_R ST#

AC21

HTCPU_P WRGD

AD22

AL28

AM28

0208 _chan ge to page 12

AK28

AG28

CLK20 0_TERM_GND

AJ28

R49

2.37K_0402_1%

H_CA DIP0 4

H_C ADIN0 4

H_CA DIP1 4

H_C ADIN1 4

H_CA DIP2 4

H_C ADIN2 4

H_CA DIP3 4

H_C ADIN3 4

H_CA DIP4 4

H_C ADIN4 4

H_CA DIP5 4