Page 1

A

1 1

B

C

D

E

2 2

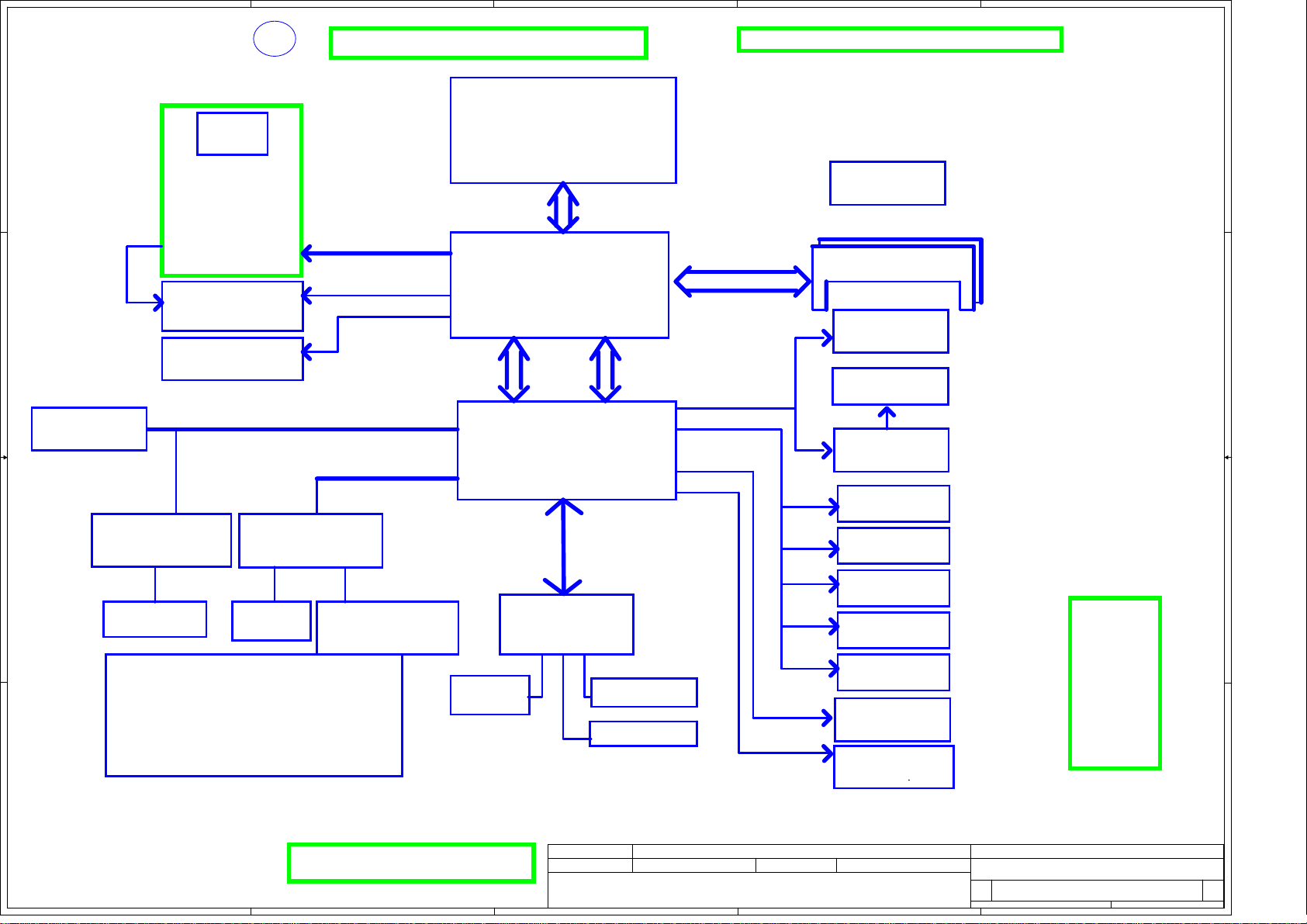

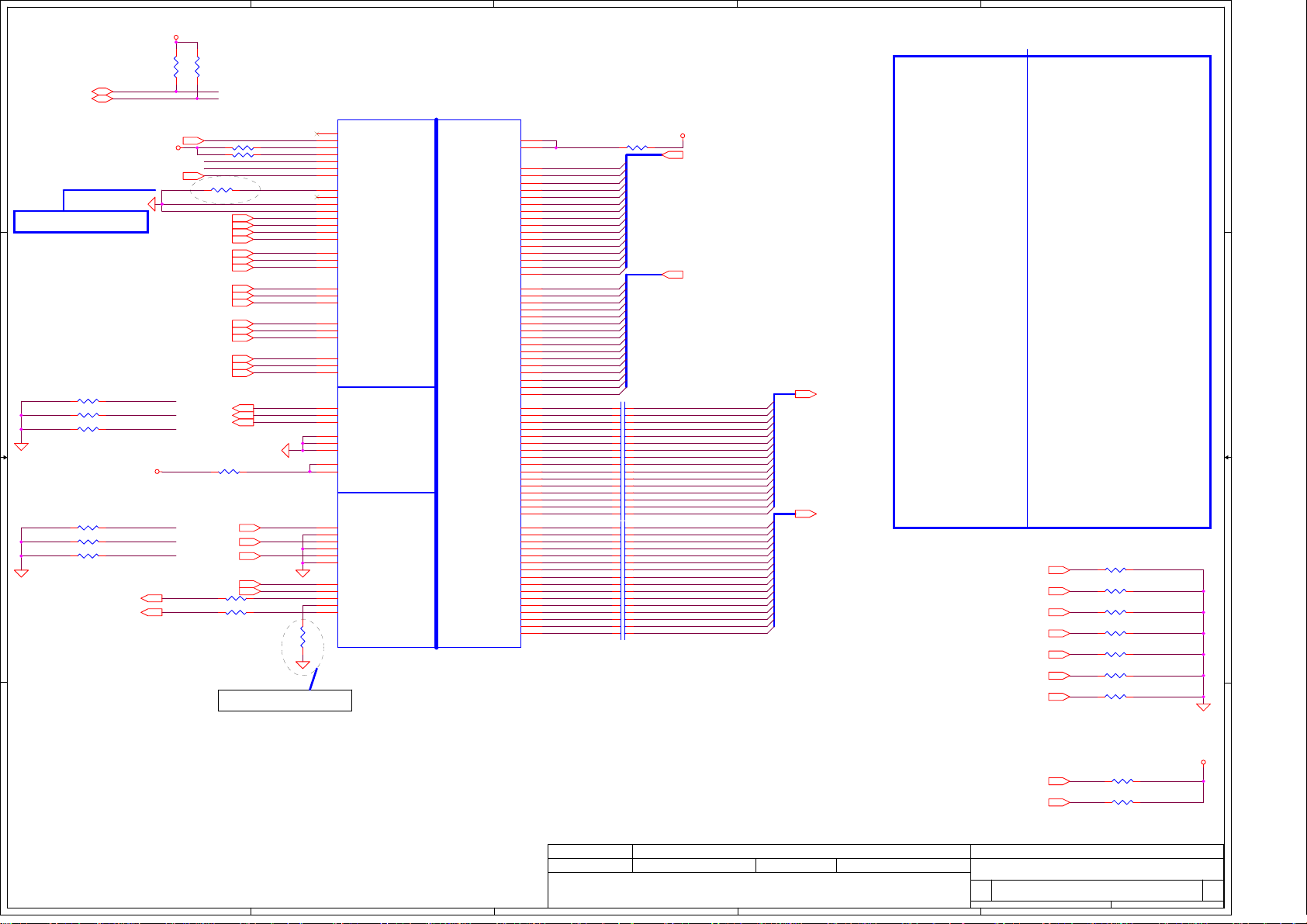

IGT30

Schematics Document

Compal confidential

Mobile Merom uFCPGA with Intel

3 3

Crestline_GM/PM+ICH8-M core logic

Monday, December 25, 2006

REV:0.1

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

IGT30 LA-3571P

E

0.1

of

147

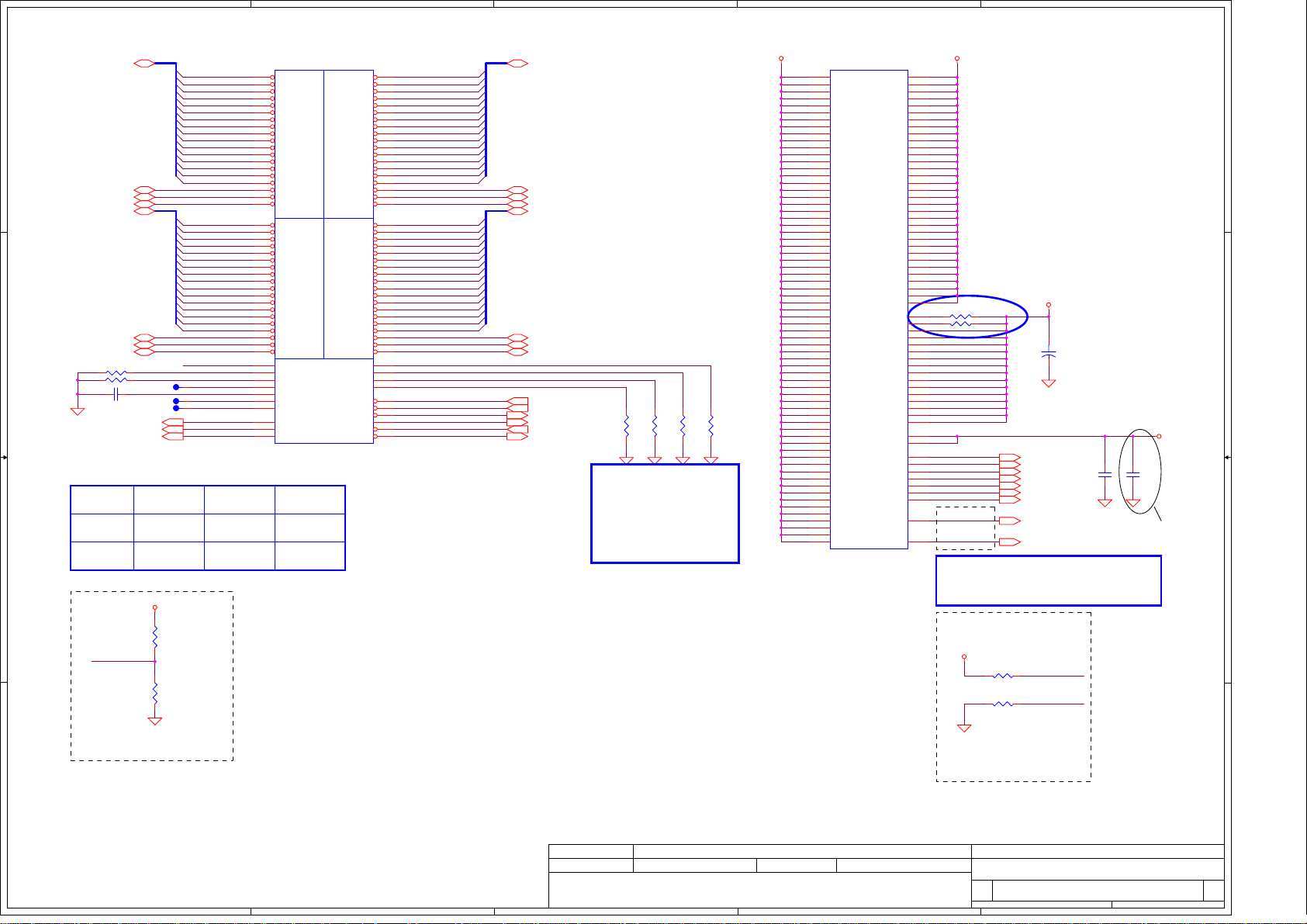

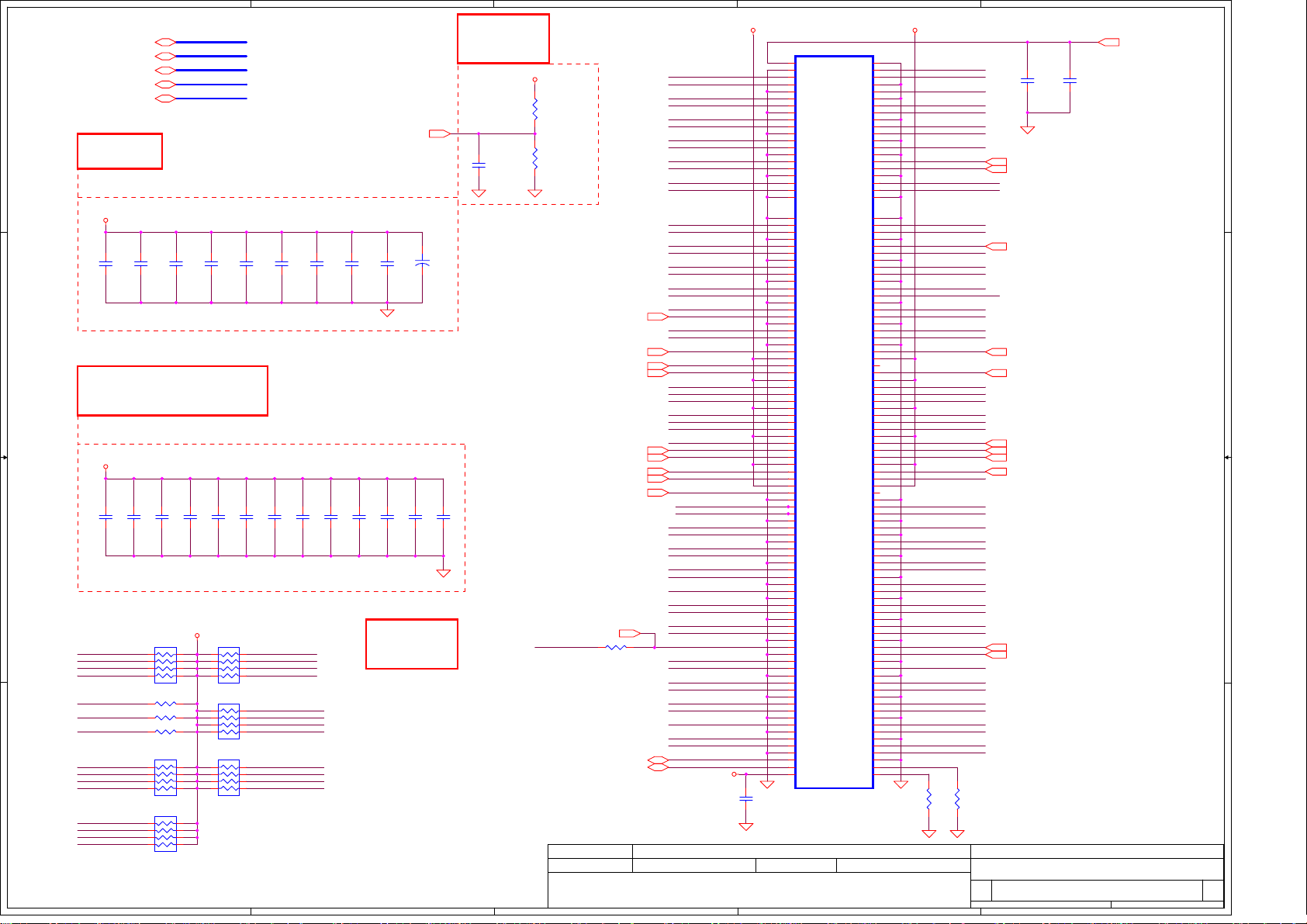

Page 2

A

Compal confidential

File Name : LA-3451P

ZZZ1

14W_PCB

B

LEFT SWITCH Board

C

D

E

LEDs Board

1 1

LVDS

Mobile Merom

uFCPGA-478 CPU

Connector

Nvidia N8M

H_A#(3..35)

H_D#(0..63)

page4,5,6

FSB

667/800MHz

Clock Gen.

ICS9LPRS355

page15

PCI-E X16

Intel Crestline GMCH

CRT & TV OUT

page17

2 2

LVDS

Connector

page16

LVDS I/F

PCBGA 1299

page7,8,9,10,11,12

DMI

C-Line

DDR2 -667

Dual Channel

DDR2-SO-DIMM X2

BANK 0, 1, 2, 3

page 13,14

MODEM

Ver 1.5

page 28

AMP&Audio Jack

AZALIA

PCI Express

Mini card Slot

page28

BCM5906 BCM5787

10/100/1G LAN

3 3

page27

RJ45 CONN

page27

SUB Board

*RJ45 CONN

*RJ11 CONN

*MIC IN JACK

*HP OUT JACK

*LED

page32,36

PCI-E BUS

3.3V / 33 MHz

1394+Card Reader

RICOH R5C832

1394 Conn

page26

*1394 CONN

*DC JACK

*TVOUT CONN

*USB CONN

*SWITCH

Card reader(XD/SD

MMC/MS/MS-Pro

HD SD)

page26

PCI BUS

page26

Intel ICH8-M

mBGA-676

EC

ENE KB925/KB926

Touch Pad

page32

page19,20,21,22

LPC BUS

page33

Int.KBD

BIOS

*SWITCH

page32

page34

USB2.0

SATA

ATA100

Audio Codec

ALC 262H

Finger printer

CMOS Camera

BlueTooth Conn

USB conn X4

USB 3G

SATA HDD

Connector

PATA CDROM

Connector

4 4

page30

page29

page36

page36

page28

page31

page31

USB Board

page23

page23

Security Classification

TP Board

A

B

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

Block Diagram

IGT30 LA-3571P

E

0.1

of

247Monday, December 25, 2006

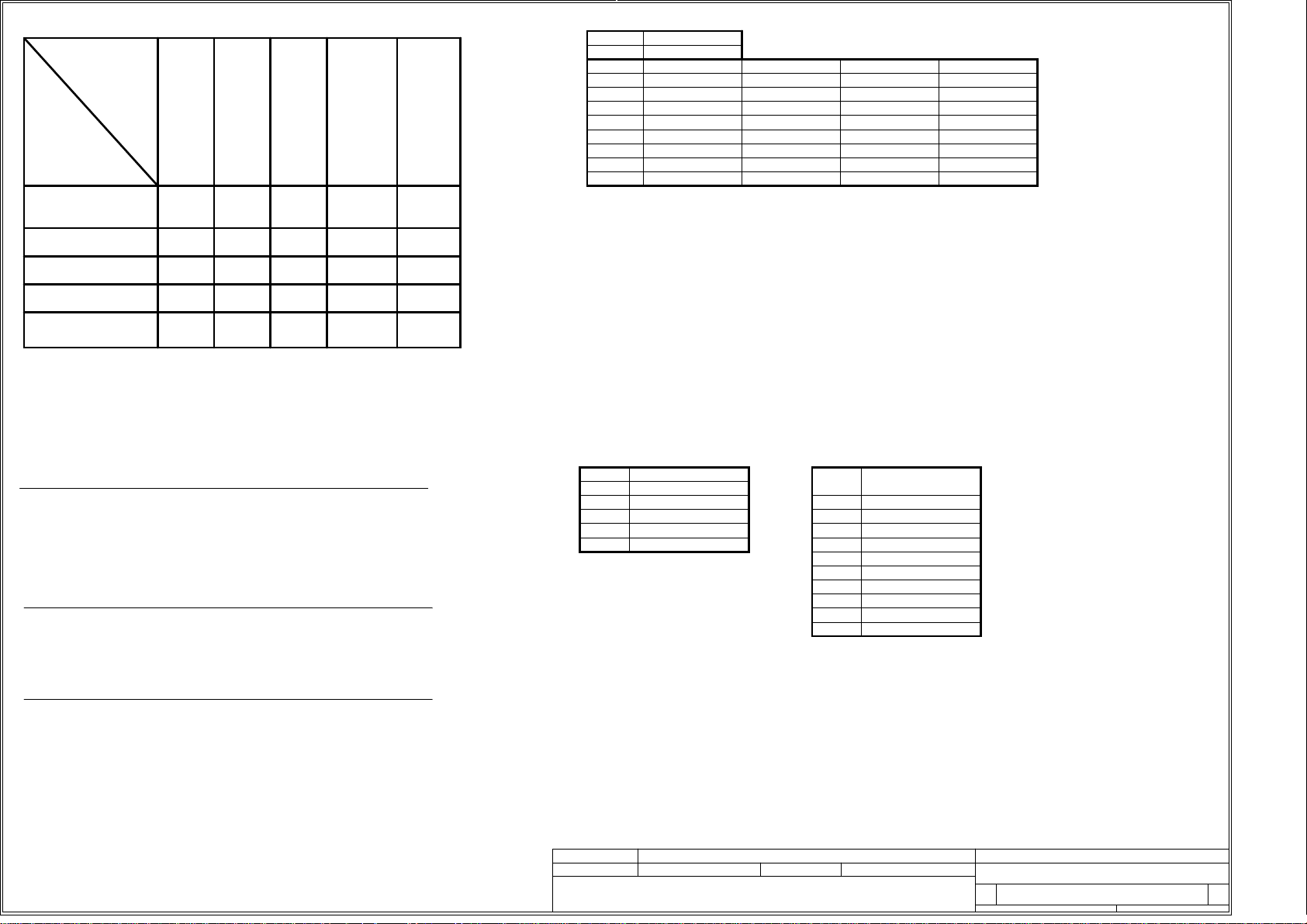

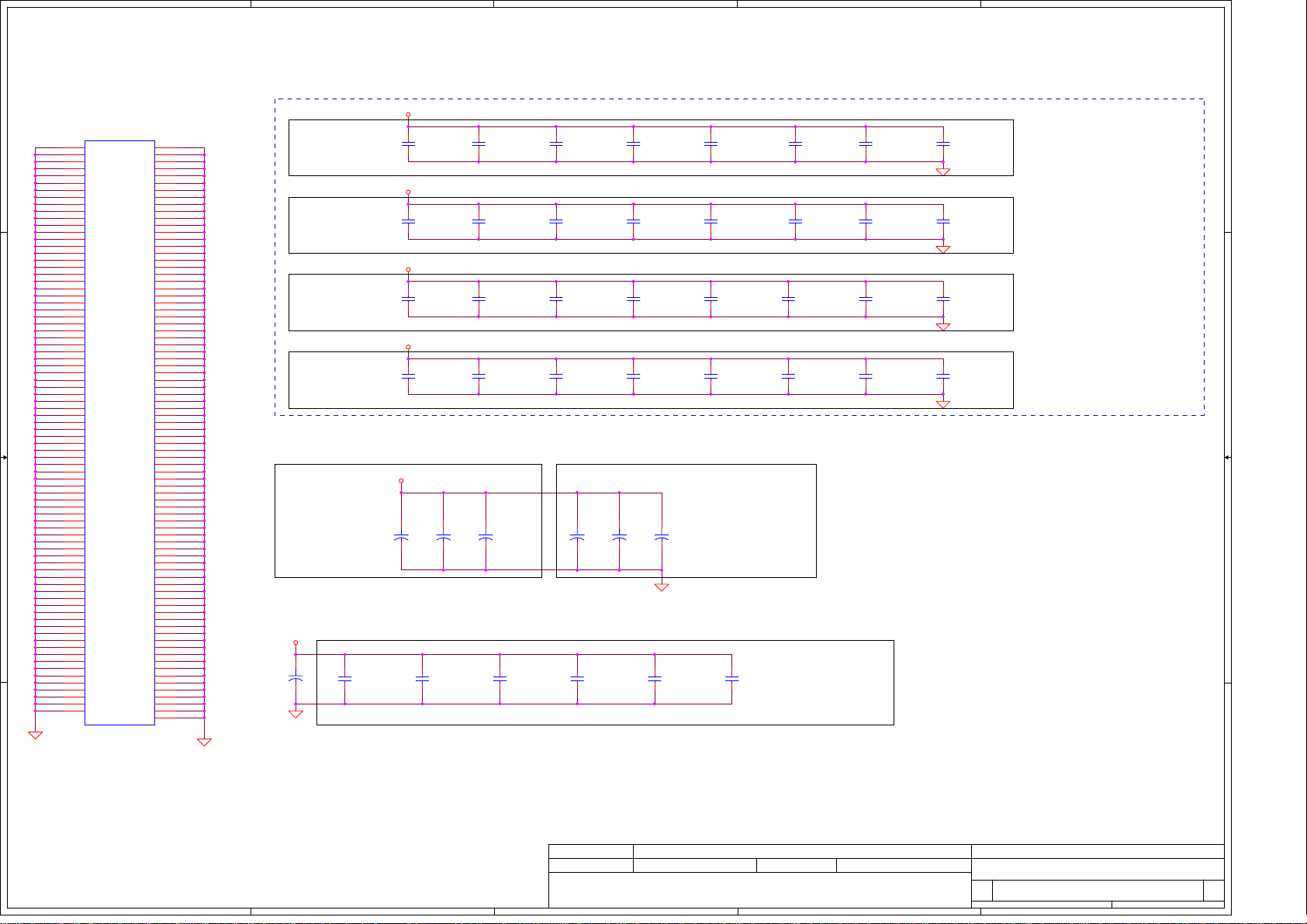

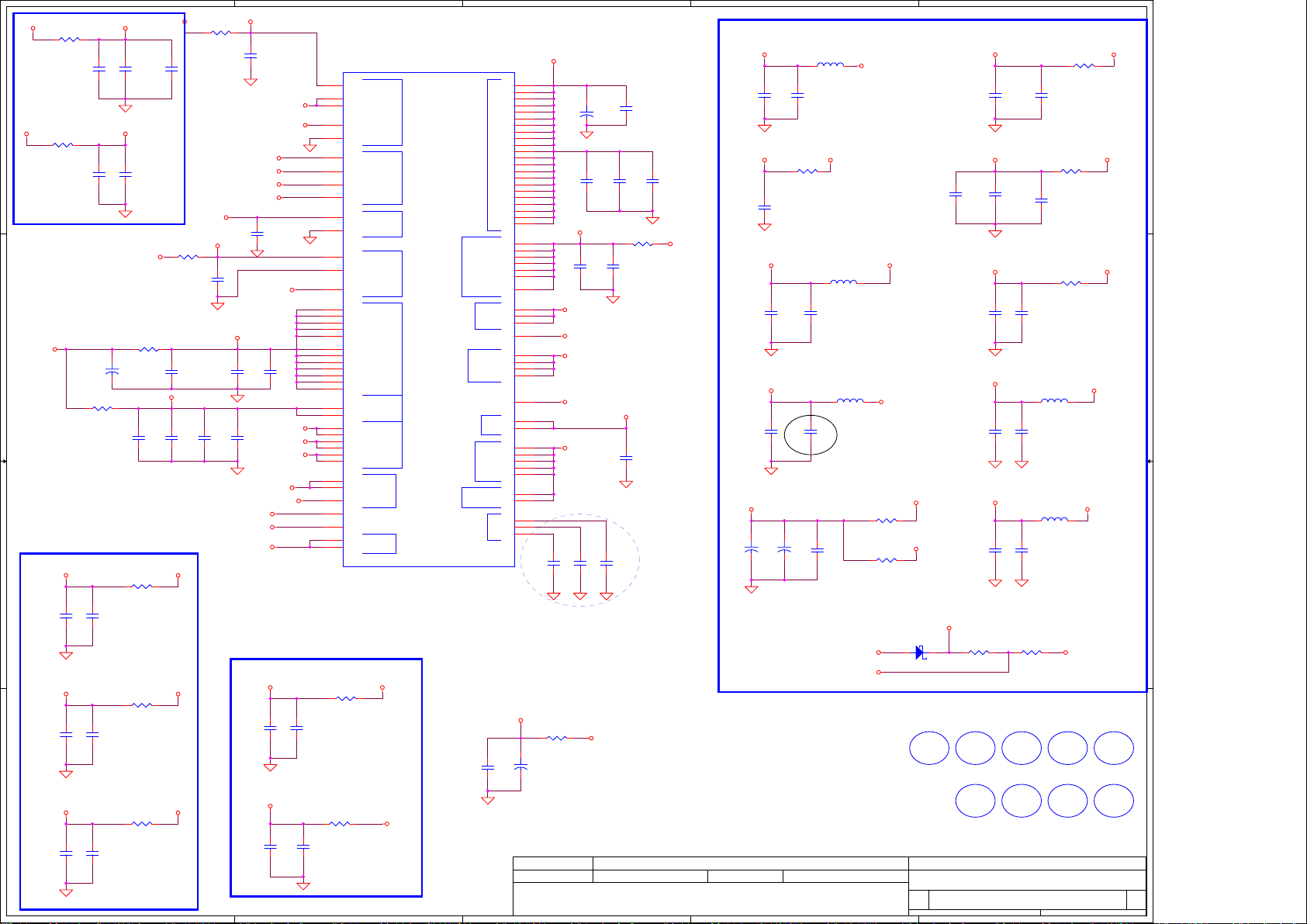

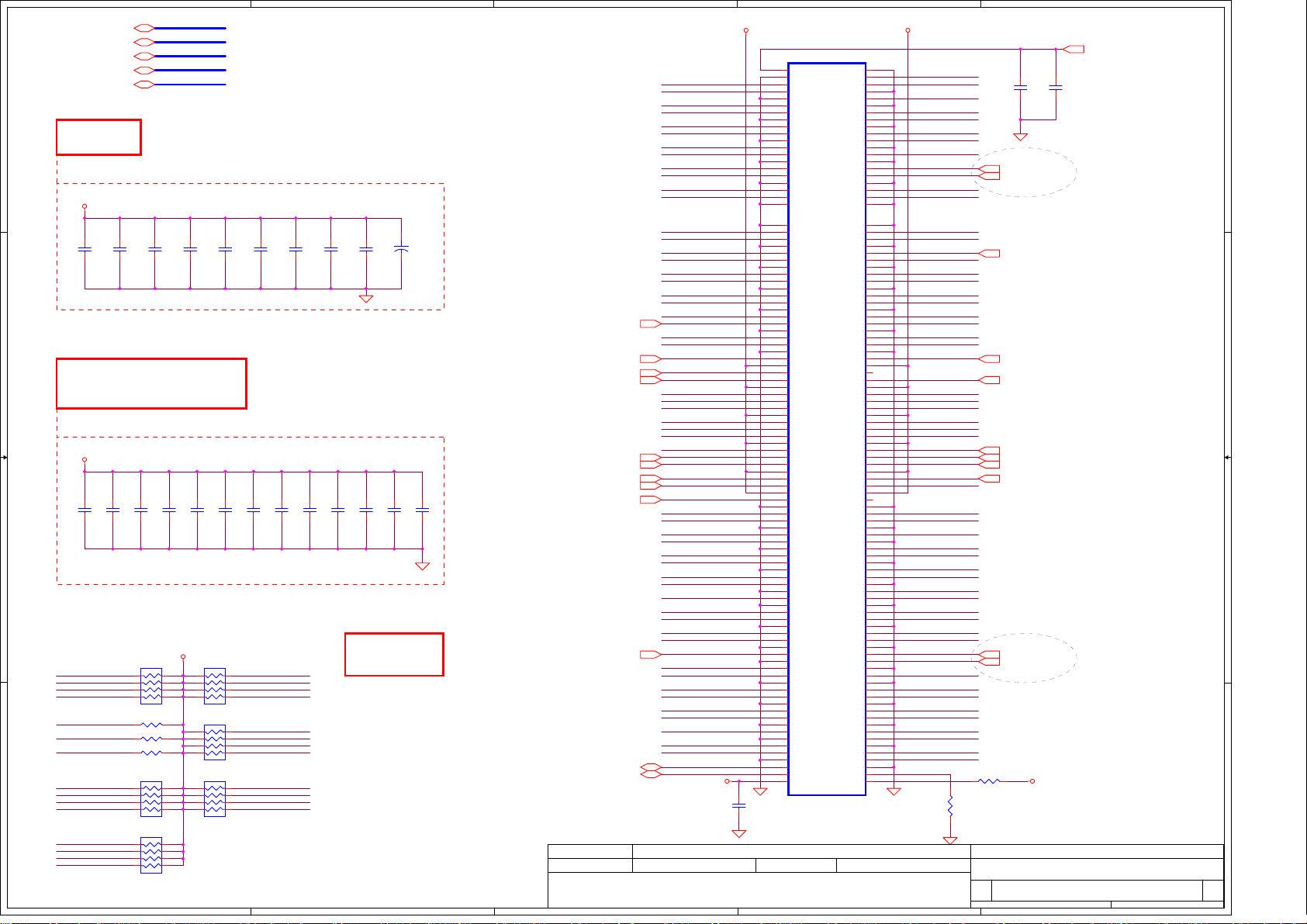

Page 3

Voltage Rails

power

plane

State

O MEANS ON X MEANS OFF

+B

LDO3

LDO5

+5VALW

+3VALW

+1.8V

+5V

+0.9V

+5VS

+3VS

+2.5VS

+1.8VS

+1.5VS

+1.25VS

+VGA_CORE

+CPU_CORE

+VCCP

CLOCK

A

SKU ID Table

Vcc 3.3V +/- 5%

Board ID

0

*

1

2

3

4

5

6

7 NC

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

Vtyp

AD_BID

0 V 0 V

V

AD_BID

max

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

S0

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O MEANS ON

X MEANS OFF

O

O

O

O

X

S3 : STR

S4 : STD

O

O

O

X

O

XX

X

XXX

OO

X

O

O

O

X

X

X

S5 : SOFT OFF

1 1

External PCI Devices

Device IDSEL # REQ # / GN T # Interrupts

1394 PIRQG/H

AD22

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

Address

0001 011X b

1010 000X b

0

EC SM Bus2 address

Device

ADM1032

Address

1001 100X b

BOM Structure USB PORT LIST

MARK FUNCTION

GIGA@

Address

100@

UMA@

VGA@

NC FOR ALL@

BCM5787

BCM5906

Internal 965GM

965PM + Ext VGA

PORT DEVICE

0

LEFT SIDE

1

WIRELESS

2

RIGHT SIDE

CMOS

3

4

RIGHT SIDE

NEW CARD

5

6

BT(HDL20)

7

8

93G

ICH8 SM Bus address

Device

Clock Generator

( ICS954226)

DDRII DIMM0

DDRII DIMM1

Address

1101 001Xb

1010 000Xb

1010 010Xb

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Notes List

IGT30 LA-3571P

347Monday, December 25, 2006

of

0.1

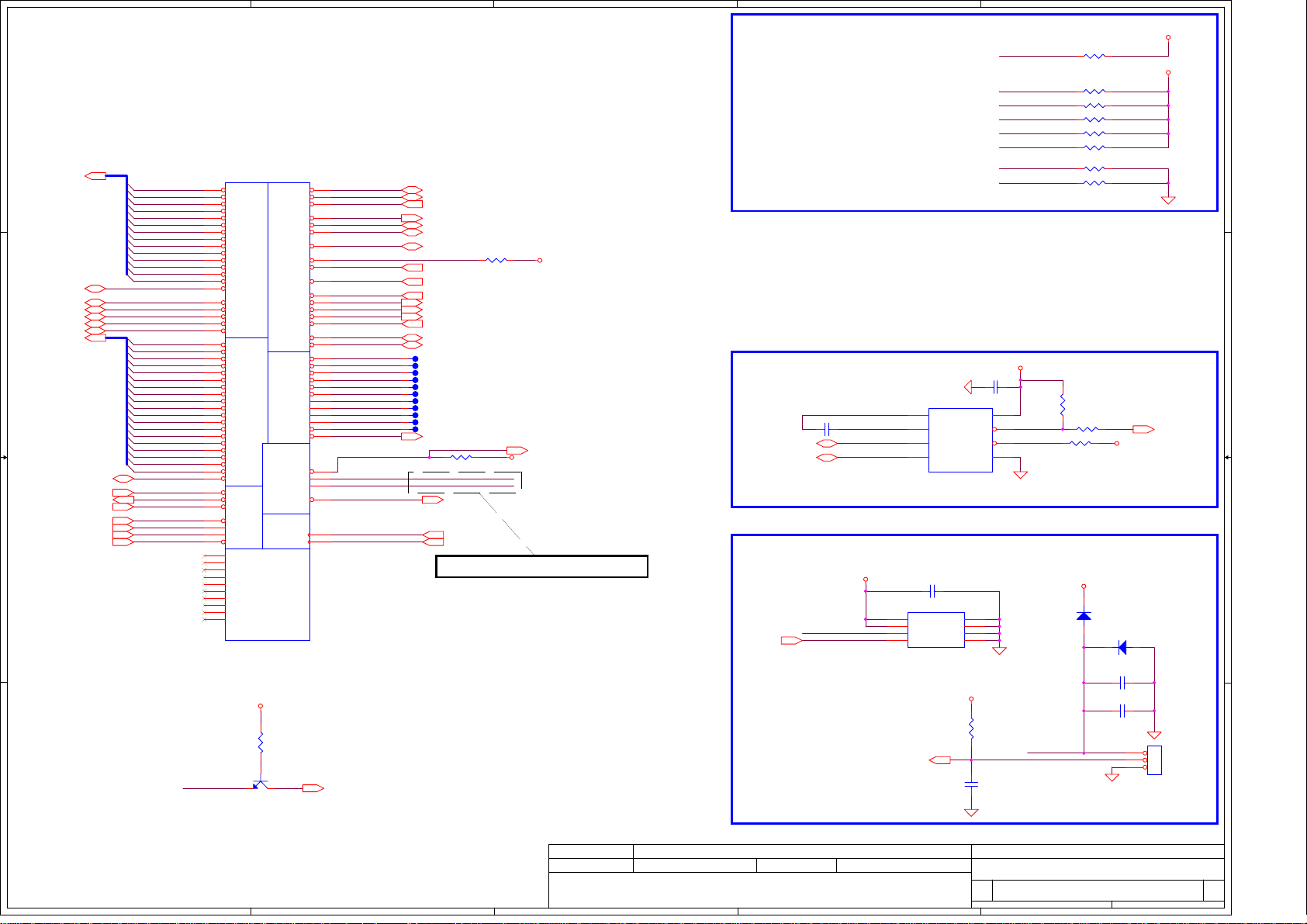

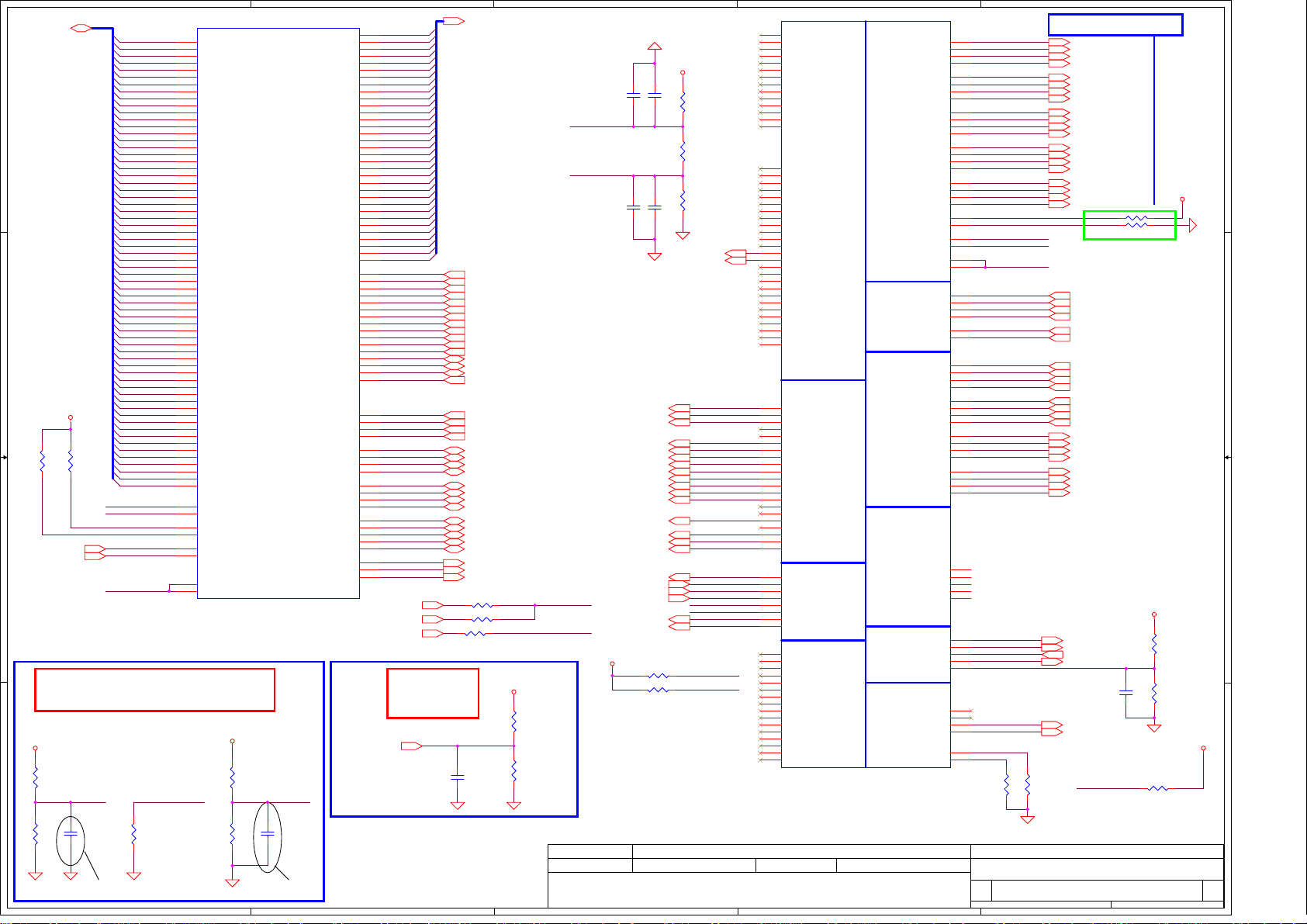

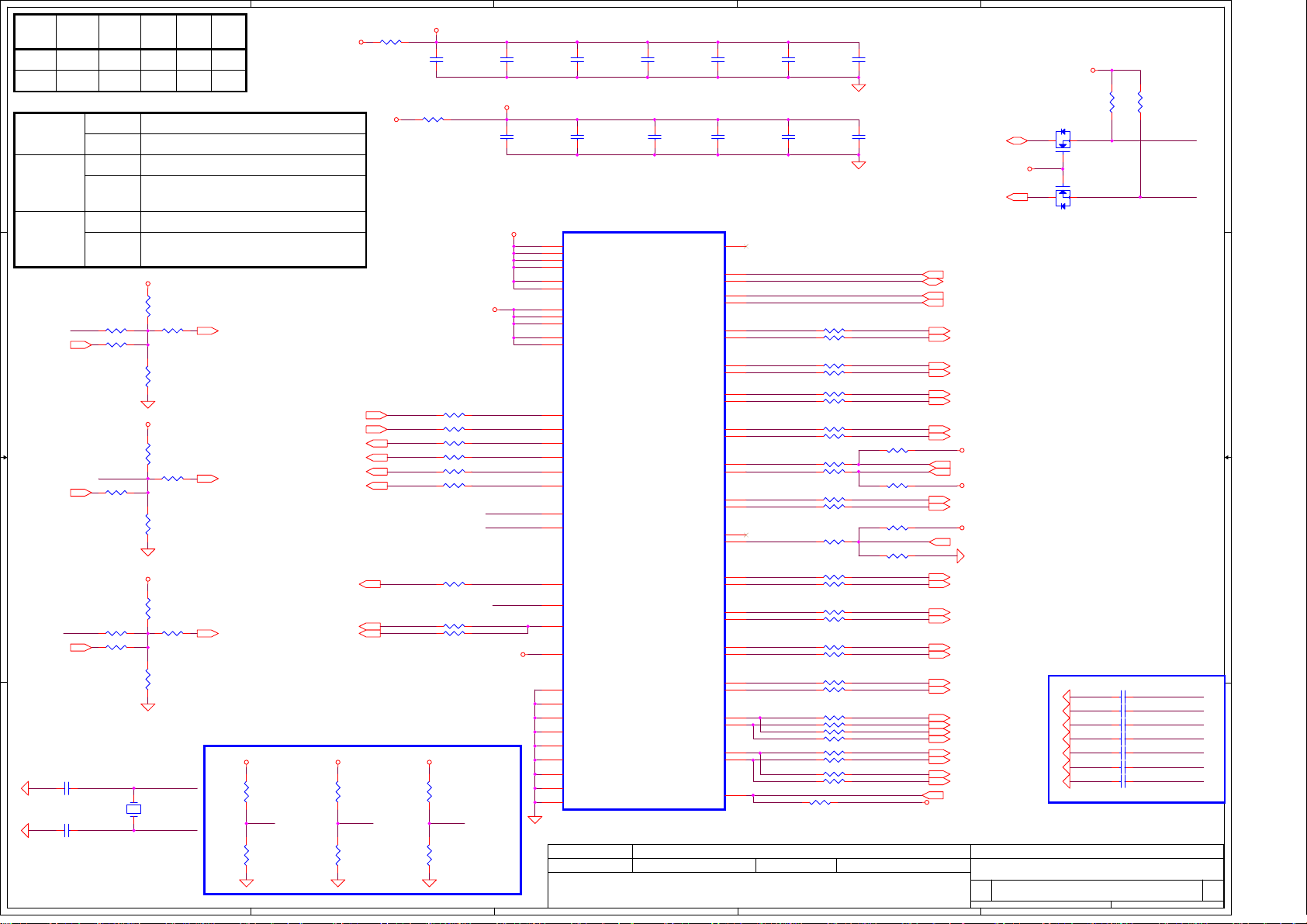

Page 4

5

4

3

2

1

XDP Reserve

D D

H_A#[3..16]7

H_ADSTB#07

H_REQ#07

H_REQ#17

H_REQ#27

H_REQ#37

H_REQ#47

H_A#[17..35]7

C C

H_ADSTB#17

H_A20M#20

H_FERR#20

H_IGNNE#20

H_STPCLK#20

H_INTR20

H_NMI20

H_SMI#20

B B

A A

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

JP1A

J4

ADDR GROUP 0 ADDR GROUP 1

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

H_PROCHOT# OCP#

XDP/ITP SIGNALS

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

THERMTRIP#

H CLK

RESERVED

+VCCP

12

R85

56_0402_5%@

B

2

E

3 1

C

Q4

@

MMBT3904_SOT23

BPRI#

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

BCLK[0]

BCLK[1]

ME@

ADS#

BNR#

BR0#

INIT#

HIT#

TCK

TDO

TMS

DBR#

H_ADS#

H1

H_BNR#

E2

H_BPRI#

G5

H_DEFER#

H5

H_DRDY#

F21

H_DBSY#

E1

H_BR0#

F1

H_IERR#

D20

H_INIT#

B3

H_LOCK#

H4

H_RESET#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

H_TRDY#

G2

H_HIT#

G6

H_HITM#

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

OCP# 21

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT#

H_THERMDA

H_THERMDC

H_THERMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

H_INIT# 20

H_LOCK# 7

H_RESET# 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

T17

T6

T13

T15

T12

T14

T7

T9

T16

T11

T5

XDP_DBRESET# 21

R87 56_0402_5%

CLK_CPU_BCLK 15

CLK_CPU_BCLK# 15

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

R92

56_0402_5%

12

H_THERMTRIP# 7,20

12

H_PROCHOT# 45

+VCCP

+VCCP

1

2

3

4

FAN_SPEED133

C528 10U_1206_16V4Z

U23

VEN

VIN

VO

VSET

G993P1UF_SOP8

U24

2

D+

3

D-

8

SCLK

7

SDATA

G781F_SOP8

Address:100_1100

1 2

GND

GND

GND

GND

H_THERMDA

C536

H_THERMDC

1 2

+VCC_FAN1

EN_FAN1

2200P_0402_50V7K

EC_SMB_DA2

+5VS

EC_SMB_CK233

EC_SMB_DA233

EN_FAN133

XDP_DBRESET#

XDP_TDI

XDP_TMS

XDP_TDO

XDP_BPM#5

XDP_HOOK1

XDP_TRST#

XDP_TCK

+3VS

C535

1 2

0.1U_0402_16V4Z

1

VDD1

THERM_SCI#

6

ALERT#

THERM#

GND

THERM#EC_SMB_CK2

4

5

FAN1 Conn

8

7

6

5

+3VS

12

R427

10K_0402_5%

1

C531

1000P_0402_50V7K

2

1 2

R157

R158 150_0402_1%

1 2

R159 39_0402_1%

1 2

R163 54.9_0402_1%@

1 2

R162 54.9_0402_1%

1 2

R161 54.9_0402_1%@

1 2

R155 560_0402_5%

1 2

R156 27_0402_5%

1 2

R445

10K_0402_5%

1 2

12

R442 0_0402_5%@

12

R44810K_0402_5%

+5VS

12

D17

1SS355_SOD323@

D18

1N4148_SOT23@

1 2

C532

10U_1206_16V4Z

1 2

C529

1000P_0402_50V7K

1 2

40mil

+VCC_FAN1

+3VS

1K_0402_5%@

+VCCP

EC_THERM# 21,33

+3VS

Check : to sb

JP61

1

2

3

ACES_85205-03001

ME@

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Merom(1/3)-AGTL+/XDP

IGT30 LA-3571P

1

0.1

of

447Monday, December 25, 2006

Page 5

5

4

3

2

1

H_D#[0..15]7

D D

H_DSTBN#07

H_DSTBP#07

H_DINV#07

H_D#[16..31]7

H_DSTBN#17

C C

H_DSTBP#17

H_DINV#17

R94 1K_0402_5%@

1 2

R93 1K_0402_5%@

1 2

C237 0.1U_0402_16V4Z@

1 2

CPU_BSEL015

CPU_BSEL115

CPU_BSEL215

T4

T8

T3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

+CPU_GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

CPU_BSEL0 H_PWRGOOD

CPU_BSEL1

CPU_BSEL2

JP1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

ME@

DATA GRP 0

DATA GRP 1

MISC

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP 2DATA GRP 3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

COMP1

COMP2

COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_CPUSLP#

H_PSI#

layout note: Route TEST3 & TEST5 traces on ground referenced layer to the TPs

CPU_BSEL CPU_BSEL2 CPU_BSEL1

166

200

B B

+CPU_GTLREF

01

+VCCP

0

12

R89

1K_0402_1%

12

R95

2K_0402_1%

1

CPU_BSEL0

1

0

H_D#[32..47] 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#2 7

H_D#[48..63] 7

H_DSTBN#3 7

H_DSTBP#3 7

H_DINV#3 7

H_DPRSTP# 7,20,45

H_DPSLP# 20

H_DPWR# 7

H_PWRGOOD 20

H_CPUSLP# 7

H_PSI# 45

12

12

12

R153

R154

27.4_0402_1%

54.9_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

R96

54.9_0402_1%

12

R97

27.4_0402_1%

JP1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

ME@

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

+CPU_CORE+CPU_CORE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

For testing purpose only

R91 0_0402_5%

12

12

R164 0_0402_5%

VCCSENSE

VSSSENSE

+VCCP

1

+

C214

2

CPU_VID0 45

CPU_VID1 45

CPU_VID2 45

CPU_VID3 45

CPU_VID4 45

CPU_VID5 45

CPU_VID6 45

VCCSENSE 45

VSSSENSE 45

330U_D2E_2.5VM_R7

Length match within 25 mils.

The trace width/space/other is

20/7/25.

+CPU_CORE

R483

100_0402_1%

1 2

R486

100_0402_1%

1 2

VCCSENSE

VSSSENSE

C231

1

C238

2

10U_0805_10V4Z

+1.5VS

1

2

0.01U_0402_16V7K

Near pin B26

Close to CPU pin AD26

within 500mils.

Close to CPU pin

within 500mils.

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Merom(2/3)-AGTL+/PWR

IGT30 LA-3571P

1

0.1

of

547Monday, December 25, 2006

Page 6

5

4

3

2

1

1

C324

0.1U_0402_16V4Z

2

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

1

+

C561

2

330U_V_2.5VK_R9

1

C546

10U_0805_6.3V6M

2

1

C549

10U_0805_6.3V6M

2

1

C321

10U_0805_6.3V6M

2

1

C267

10U_0805_6.3V6M

2

C312

330U_V_2.5VK_R9

1

C272

0.1U_0402_16V4Z

2

1

+

C548

2

330U_V_2.5VK_R9

C271

0.1U_0402_16V4Z

1

C289

10U_0805_6.3V6M

2

1

C297

10U_0805_6.3V6M

2

1

C547

10U_0805_6.3V6M

2

1

C292

10U_0805_6.3V6M

2

1

C562

2

330U_V_2.5VK_R9

1

2

+

C323

0.1U_0402_16V4Z

1

C564

10U_0805_6.3V6M

2

1

C542

10U_0805_6.3V6M

2

1

C291

10U_0805_6.3V6M

2

1

C298

10U_0805_6.3V6M

2

1

2

1

2

North Side Secondary

1

C325

0.1U_0402_16V4Z

2

1

C287

10U_0805_6.3V6M

2

1

C327

10U_0805_6.3V6M

2

C554

10U_0805_6.3V6M

C296

10U_0805_6.3V6M

1

C545

10U_0805_6.3V6M

2

1

C286

10U_0805_6.3V6M

2

1

C314

10U_0805_6.3V6M

2

1

C543

10U_0805_6.3V6M

2

ESR <= 1.5m ohm

Capacitor > 1980uF

Place these inside

socket cavity on L8

(North side

Secondary)

1

C322

10U_0805_6.3V6M

2

1

C559

10U_0805_6.3V6M

2

1

C295

10U_0805_6.3V6M

2

1

C315

10U_0805_6.3V6M

2

Mid Frequence Decoupling

C273

0.1U_0402_16V4Z

1

C268

10U_0805_6.3V6M

2

1

C558

10U_0805_6.3V6M

2

1

C555

10U_0805_6.3V6M

2

1

C563

10U_0805_6.3V6M

2

1

+

C557

2

330U_V_2.5VK_R9

1

2

1

C551

10U_0805_6.3V6M

2

1

C328

10U_0805_6.3V6M

2

1

C288

10U_0805_6.3V6M

2

1

C285

10U_0805_6.3V6M

2

1

1

+

+

C313

@

2

@

2

330U_V_2.5VK_R9

1

2

D D

C C

B B

JP1D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

220U_D2_4VM

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(Sorth side,Secondary Layer)

Place these capacitors on L8

(Sorth side,Secondary Layer)

South Side Secondary

+VCCP

1

+

C229

2

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Merom(3/3)-GND&Bypass

IGT30 LA-3571P

1

0.1

of

647Monday, December 25, 2006

Page 7

5

M10

W10

AD12

AC14

AD11

AC11

AG3

AJ14

AE11

AH12

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

N12

N9

H5

P13

K9

M2

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AE3

AD9

AC9

AC7

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AJ9

AH8

AE9

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

B3

C2

W1

W2

B6

E5

B9

A9

U22A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

HOST

H_ADSTB#_0

H_ADSTB#_1

H_BREQ#

H_DEFER#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_D#[0..63]5

D D

C C

+VCCP

12

12

R15

R18

54.9_0402_1%

54.9_0402_1%

H_RESET#4

H_CPUSLP#5

B B

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWNG

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#

H_CPUSLP#

H_VREF

layout note:

Route H_SCOMP and H_SCOMP# with trace width, spacing and impedance (55 ohm) same as FSB data traces

Layout Note:

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

+VCCP

R16

R17

12

221_0603_1%

12

100_0402_1%

H_SWNGH_VREF

1

C15

2

0.1U_0402_16V4Z

+VCCP

12

R411

1K_0402_1%

A A

0.1U_0402_16V4Z

12

1

C23

R412

2

2K_0402_1%

12

R399

24.9_0402_1%

H_RCOMP

Near B3 pinwithin 100 mils from NB

5

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_DBSY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_RS#_0

H_RS#_1

H_RS#_2

+DDR_MCH_REF

4

H_A#3

J13

H_A#4

B11

H_A#5

C11

H_A#6

M11

H_A#7

C15

H_A#8

F16

H_A#9

L13

H_A#10

G17

H_A#11

C14

H_A#12

K16

H_A#13

B13

H_A#14

L16

H_A#15

J17

H_A#16

B14

H_A#17

K19

H_A#18

P15

H_A#19

R17

H_A#20

B16

H_A#21

H20

H_A#22

L19

H_A#23

D17

H_A#24

M17

H_A#25

N16

H_A#26

J19

H_A#27

B18

H_A#28

E19

H_A#29

B17

H_A#30

B15

H_A#31

E17

H_A#32

C18

H_A#33

A19

H_A#34

B19

H_A#35

N19

H_ADS#

G12

H_ADSTB#0

H17

H_ADSTB#1

G20

H_BNR#

C8

H_BPRI#

E8

H_BR0#

F12

H_DEFER#

D6

H_DBSY#

C10

CLK_MCH_BCLK

AM5

CLK_MCH_BCLK#

AM7

H_DPWR#

H8

H_DRDY#

K7

H_HIT#

E4

H_HITM#

C6

H_LOCK#

G10

H_TRDY#

B7

H_DINV#0

K5

H_DINV#1

L2

H_DINV#2

AD13

H_DINV#3

AE13

H_DSTBN#0H_D#58

M7

H_DSTBN#1

K3

H_DSTBN#2

AD2

H_DSTBN#3

AH11

H_DSTBP#0

L7

H_DSTBP#1

K2

H_DSTBP#2

AC2

H_DSTBP#3

AJ10

H_REQ#0

M14

H_REQ#1

E13

H_REQ#2

A11

H_REQ#3

H13

H_REQ#4

B12

H_RS#0

E12

H_RS#1

D7

H_RS#2

D8

ICH_POK21,33

VGATE21,45

PLT_RST#18,19,21,23,24,26,27

Layout Note:

V_DDR_MCH_REF

trace width and

spacing is 20/20.

4

H_A#[3..35] 4

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BR0# 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 15

CLK_MCH_BCLK# 15

H_DPWR# 5

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#0 5

H_DINV#1 5

H_DINV#2 5

H_DINV#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_REQ#0 4

H_REQ#1 4

H_REQ#2 4

H_REQ#3 4

H_REQ#4 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

R436 0_0402_5%

R438 0_0402_5%@

1 2

R449 100_0402_5%

+DDR_MCH_REF

1

C161

2

0.1U_0402_16V4Z

3

SMRCOMP_VOH

SMRCOMP_VOL

2.2U_0603_10V6K

2.2U_0603_10V6K

MCH_CLKSEL015

MCH_CLKSEL115

MCH_CLKSEL215

Check : different from hdl00

12

12

PM_POK_R PM_POK_R

H_THERMTRIP#4,20

+3VS

+1.8V

12

12

R67

R68

0309 add

PLT_RST#_R

1K_0402_1%

1K_0402_1%

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

U22B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

+1.8V

2

2

C73

1

1

2

C91

PM_BMBUSY#21

H_DPRSTP#5,20,45

PM_EXTTS#013

PM_EXTTS#114

DPRSLPVR21,45

R57 10K_0402_5%

R64 10K_0402_5%

C83

1

1

2

C84

CFG59

CFG6

CFG79

CFG89

CFG99

CFG10

CFG11

CFG129

CFG139

CFG169

CFG18

CFG199

CFG209

1 2

1 2

0.01U_0402_25V7K

0.01U_0402_25V7K

DDR_A_MA1413

DDR_B_MA1414

12

R31

1K_0402_1%

12

R38

3.01K_0402_1%

NA lead free

12

R45

1K_0402_1%

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

CFG5

CFG6

CFG7

CFG9

CFG10

CFG11

CFG12

CFG13

CFG16

CFG18

CFG19

CFG20

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PLT_RST#_R

H_THERMTRIP#

DPRSLPVR

PM_EXTTS#0

PM_EXTTS#1

2006/08/04 2006/10/06

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

RSVD32

BE24

RSVD33

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

RSVD37

D47

RSVD38

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

C21

CFG_3

C23

CFG_4

F23

CFG_5

N23

CFG_6

G23

CFG_7

J20

CFG_8

C20

CFG_9

R24

CFG_10

L23

CFG_11

J23

CFG_12

E23

CFG_13

E20

CFG_14

K23

CFG_15

M20

CFG_16

M24

CFG_17

L32

CFG_18

N33

CFG_19

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

BL2

NC_7

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2

NC_16

CRESTLINE_1p0

Compal Secret Data

Deciphered Date

2

DDR MUXINGCLK

CFGRSVD

DMI

PM

GRAPHICS VID

ME

NC

MISC

2

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

TEST_2

1

For Crestline: 20ohm

M_CLK_DDR0

AV29

M_CLK_DDR1

BB23

M_CLK_DDR2

BA25

M_CLK_DDR3

AV23

M_CLK_DDR#0

AW30

M_CLK_DDR#1

BA23

M_CLK_DDR#2

AW25

M_CLK_DDR#3

AW23

DDR_CKE0_DIMMA

BE29

DDR_CKE1_DIMMA

AY32

DDR_CKE2_DIMMB

BD39

DDR_CKE3_DIMMB

BG37

DDR_CS0_DIMMA#

BG20

DDR_CS1_DIMMA#

BK16

DDR_CS2_DIMMB#

BG16

DDR_CS3_DIMMB#

BE13

M_ODT0

BH18

M_ODT1

BJ15

M_ODT2

BJ14

M_ODT3

BE16

SMRCOMP

BL15

SMRCOMP#

BK14

SMRCOMP_VOH

BK31

SMRCOMP_VOL

BL31

AR49

+DDR_MCH_REF

AW4

CLK_MCH_DREFCLK

B42

CLK_MCH_DREFCLK#

C42

MCH_SSCDREFCLK

H48

MCH_SSCDREFCLK#

H47

CLK_MCH_3GPLL

K44

CLK_MCH_3GPLL#

K45

DMI_TXN0

AN47

DMI_TXN1

AJ38

DMI_TXN2

AN42

DMI_TXN3

AN46

DMI_TXP0

AM47

DMI_TXP1

AJ39

DMI_TXP2

AN41

DMI_TXP3

AN45

DMI_RXN0

AJ46

DMI_RXN1

AJ41

DMI_RXN2

AM40

DMI_RXN3

AM44

DMI_RXP0

AJ47

DMI_RXP1

AJ42

DMI_RXP2

AM39

DMI_RXP3

AM43

E35

A39

C38

B39

E36

For AMT function

CL_CLK0

AM49

CL_DATA0

AK50

AT43

CL_RST#

AN49

CL_VREF

AM50

H35

K36

CLKREQ_3GPLL#

G39

MCH_ICH_SYNC#

G40

A37

R32

12

R47

20K_0402_5%

Title

CRESTLINE(1/6)-AGTL+/DMI/DDR2

Size Document Number Rev

Custom

IGT30 LA-3571P

Date: Sheet

For Calero: 80.6ohm

M_CLK_DDR0 13

M_CLK_DDR1 13

M_CLK_DDR2 14

M_CLK_DDR3 14

M_CLK_DDR#0 13

M_CLK_DDR#1 13

M_CLK_DDR#2 14

M_CLK_DDR#3 14

DDR_CKE0_DIMMA 13

DDR_CKE1_DIMMA 13

DDR_CKE2_DIMMB 14

DDR_CKE3_DIMMB 14

DDR_CS0_DIMMA# 13

DDR_CS1_DIMMA# 13

DDR_CS2_DIMMB# 14

DDR_CS3_DIMMB# 14

M_ODT0 13

M_ODT1 13

M_ODT2 14

12

R423

0_0402_5%

M_ODT3 14

CLK_MCH_DREFCLK 15

CLK_MCH_DREFCLK# 15

MCH_SSCDREFCLK 15

MCH_SSCDREFCLK# 15

CLK_MCH_3GPLL 15

CLK_MCH_3GPLL# 15

DMI_TXN0 21

DMI_TXN1 21

DMI_TXN2 21

DMI_TXN3 21

DMI_TXP0 21

DMI_TXP1 21

DMI_TXP2 21

DMI_TXP3 21

DMI_RXN0 21

DMI_RXN1 21

DMI_RXN2 21

DMI_RXN3 21

DMI_RXP0 21

DMI_RXP1 21

DMI_RXP2 21

DMI_RXP3 21

CL_CLK0 21

CL_DATA0 21

M_PWROK 21

CL_RST# 21

0.1U_0402_16V4Z

CLKREQ_3GPLL# 15

MCH_ICH_SYNC# 21

CLKREQ_3GPLL#

20_0402_1%

R23

R22 20_0402_1%

+1.25VS

1

C167

2

R63

10K_0402_5%

Compal Electronics, Inc.

747Monday, December 25, 2006

1

12

12

12

R71

1K_0402_1%

12

R75

392_0402_1%

+1.8V

+3VS

12

0.1

of

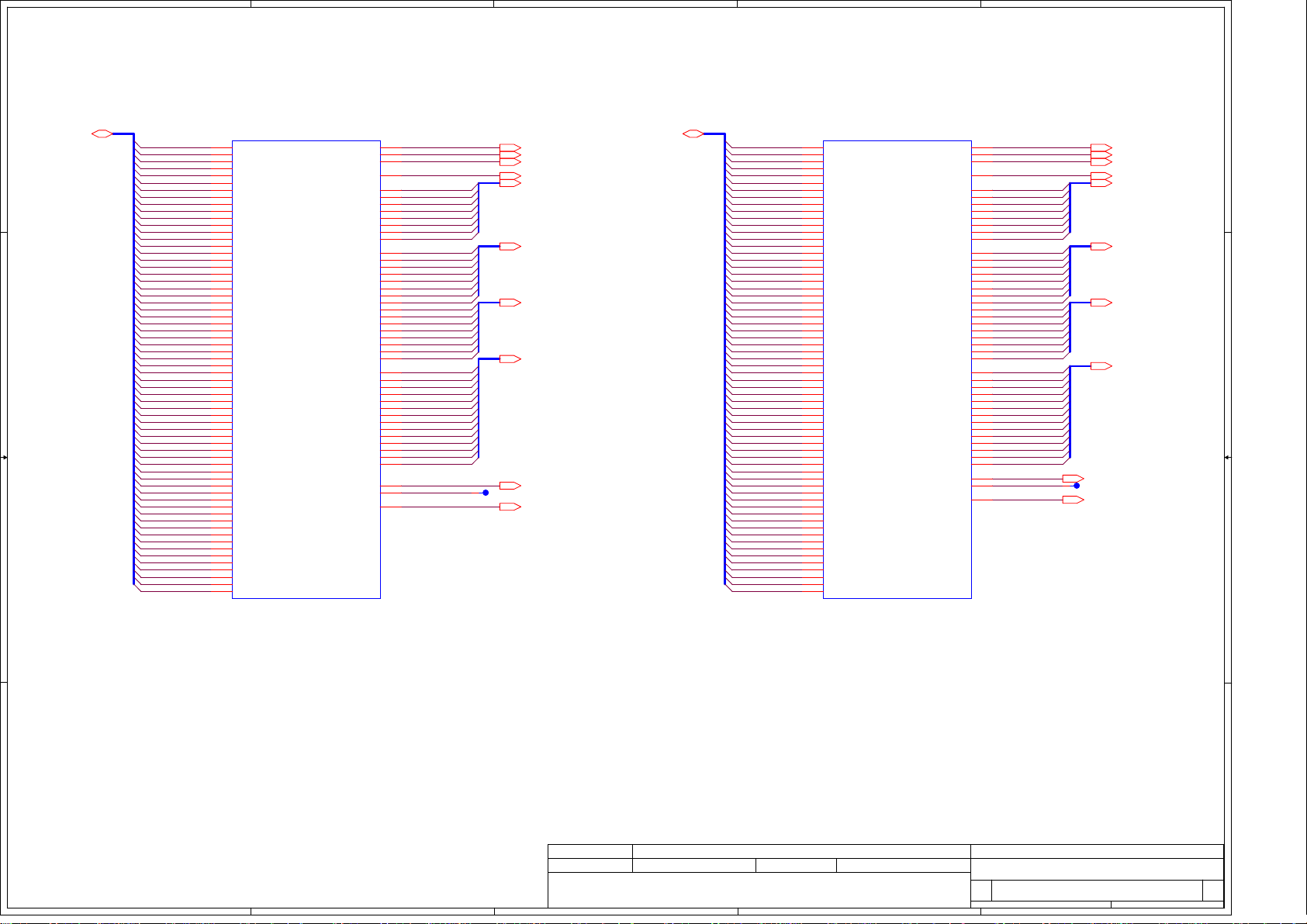

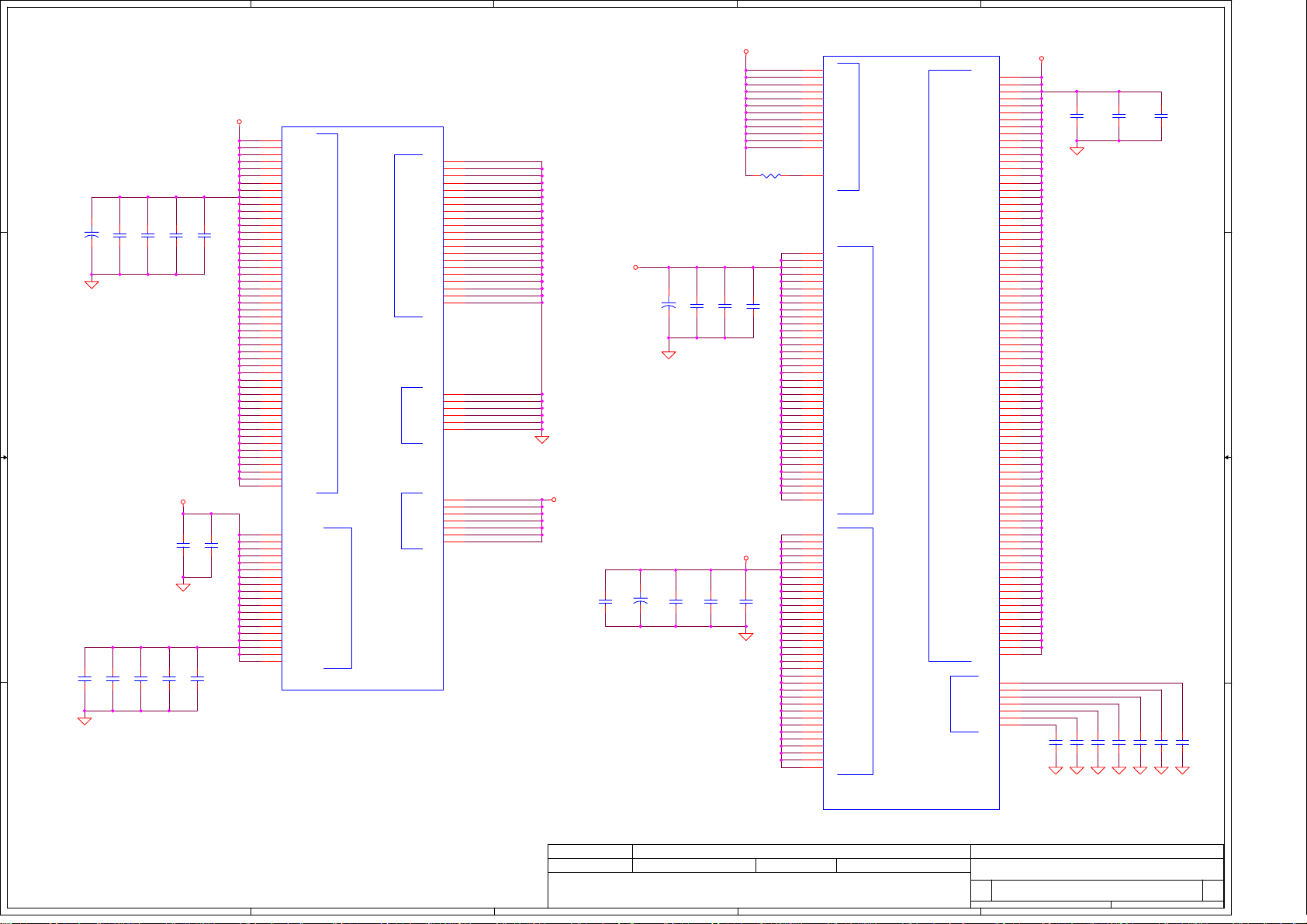

Page 8

5

D D

DDR_A_D[0..63]13

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BG10

AW9

AN10

AN11

AM8

AM9

BD8

AY9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AT9

AN9

U22D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

DDR SYSTEM MEMORY A

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

SA_WE#

4

DDR_A_BS#0

BB19

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

DDR_A_BS#1

DDR_A_BS#2

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_RAS#

SA_RCVEN#

DDR_A_WE#

DDR_A_BS#0 13

DDR_A_BS#1 13

DDR_A_BS#2 13

DDR_A_CAS# 13 DDR_B_CAS# 14

DDR_A_DM[0..7] 13

DDR_A_DQS[0..7] 13

DDR_A_DQS#[0..7] 13

DDR_A_MA[0..13] 13

DDR_A_RAS# 13

T2

DDR_A_WE# 13

3

DDR_B_D[0..63]14

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18DDR_A_DQS3

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK10

BG1

BC2

BK3

BE4

BD3

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

BL9

BK5

BL5

BK9

BJ8

BJ6

BF4

BH5

BJ2

2

U22E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

1

DDR_B_BS#0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS#1

DDR_B_BS#2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10DDR_B_D42

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

SB_RCVEN#

DDR_B_WE#

DDR_B_RAS# 14

T1

DDR_B_WE# 14

DDR_B_BS#0 14

DDR_B_BS#1 14

DDR_B_BS#2 14

DDR_B_DM[0..7] 14

DDR_B_DQS[0..7] 14

DDR_B_DQS#[0..7] 14

DDR_B_MA[0..13] 14

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

CRESTLINE((2/6)-DDR2 A/B CH

IGT30 LA-3571P

1

of

847Monday, December 25, 2006

0.1

Page 9

5

4

3

2

1

+3VS

12

+3VS

12

R56

2.2K_0402_5%

UMA@

R425 10K_0402_5%

1 2

R429 10K_0402_5%

1 2

EDID_CLK_LCD

EDID_DAT_LCD

GMCH_LVDDEN

R62 2.4K_0402_1%

LVDSAC-37

LVDSAC+37

LVDSBC-37

LVDSBC+37

LVDSA0-37

LVDSA1-37

LVDSA2-37

LVDSA0+37

LVDSA1+37

LVDSA2+37

LVDSB0-37

LVDSB1-37

LVDSB2-37

LVDSB0+37

LVDSB1+37

LVDSB2+37

TV_COMPS17

TV_LUMA17

TV_CRMA17

1 2

R52 2.2K_0402_5%

CRT_B17

CRT_G17

CRT_R17

3VDDCCL17

3VDDCDA17

CRT_HSYNC

1 2

R424 39_0402_1%

CRT_VSYNC

1 2

R422 39_0402_1%

For Crestline:1.3kohm

For Calero: 255ohm

12

GMCH_ENBKL

LVDSACLVDSAC+

LVDSBCLVDSBC+

LVDSA0LVDSA1LVDSA2-

LVDSA0+

LVDSA1+

LVDSA2+

LVDSB0LVDSB1LVDSB2-

LVDSB0+

LVDSB1+

LVDSB2+

TV_COMPS

TV_LUMA

TV_CRMA

CRT_B

CRT_G

CRT_R

3VDDCCL

3VDDCDA

HSYNC_R

VSYNC_R

R417

1.3K_0402_1%

12

U22C

J40

H39

E39

E40

C37

D35

K40

L41

L43

N41

N40

D46

C45

D44

E42

G51

E51

F49

G50

E50

F48

G44

B47

B45

E44

A47

A45

E27

G27

K27

F27

J27

L27

M35

P33

H32

G32

K29

J29

F29

E29

K33

G35

F33

C32

E33

CRESTLINE_1p0

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

TVA_DAC

TVB_DAC

TVC_DAC

TVA_RTN

TVB_RTN

TVC_RTN

TV_DCONSEL_0

TV_DCONSEL_1

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

LVDS

TV VGA

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PCI-EXPRESS GRAPHICS

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEGCOMP tr ace width

and spacing is 20/25 mils.

N43

PEGCOMP

M43

PEG_RXN0

J51

PEG_RXN1

L51

PEG_RXN2

N47

PEG_RXN3

T45

PEG_RXN4

T50

PEG_RXN5

U40

PEG_RXN6

Y44

PEG_RXN7

Y40

PEG_RXN8

AB51

PEG_RXN9

W49

PEG_RXN10

AD44

PEG_RXN11

AD40

PEG_RXN12

AG46

PEG_RXN13

AH49

PEG_RXN14

AG45

PEG_RXN15

AG41

PEG_RXP0

J50

PEG_RXP1

L50

PEG_RXP2

M47

PEG_RXP3

U44

PEG_RXP4

T49

PEG_RXP5

T41

PEG_RXP6

W45

PEG_RXP7

W41

PEG_RXP8

AB50

PEG_RXP9

Y48

PEG_RXP10

AC45

PEG_RXP11

AC41

PEG_RXP12

AH47

PEG_RXP13

AG49

PEG_RXP14

AH45

PEG_RXP15

AG42

PEG_TXN0

N45

PEG_TXN1

U39

PEG_TXN2

U47

PEG_TXN3

N51

PEG_TXN4

R50

PEG_TXN5

T42

PEG_TXN6

Y43

PEG_TXN7

W46

PEG_TXN8

W38

PEG_TXN9

AD39

PEG_TXN10

AC46

PEG_TXN11

AC49

PEG_TXN12

AC42

PEG_TXN13

AH39

PEG_TXN14

AE49

PEG_TXN15

AH44

PEG_TXP0

M45

PEG_TXP1

T38

PEG_TXP2

T46

PEG_TXP3

N50

PEG_TXP4

R51

PEG_TXP5

U43

PEG_TXP6

W42

PEG_TXP7

Y47

PEG_TXP8

Y39

PEG_TXP9

AC38

PEG_TXP10

AD47

PEG_TXP11

AC50

PEG_TXP12

AD43

PEG_TXP13

AG39

PEG_TXP14

AE50

PEG_TXP15

AH43

R66

24.9_0402_1%

1 2

C277 0.1U_0402_16V4ZVGA@

C234 0.1U_0402_16V4ZVGA@

C259 0.1U_0402_16V4ZVGA@

C218 0.1U_0402_16V4ZVGA@

C279 0.1U_0402_16V4ZVGA@

C236 0.1U_0402_16V4ZVGA@

C264 0.1U_0402_16V4ZVGA@

C221 0.1U_0402_16V4ZVGA@

C282 0.1U_0402_16V4ZVGA@

C242 0.1U_0402_16V4ZVGA@

C257 0.1U_0402_16V4ZVGA@

C223 0.1U_0402_16V4ZVGA@

C284 0.1U_0402_16V4ZVGA@

C239 0.1U_0402_16V4ZVGA@

C262 0.1U_0402_16V4ZVGA@

C225 0.1U_0402_16V4ZVGA@

C276 0.1U_0402_16V4ZVGA@

C233 0.1U_0402_16V4ZVGA@

C258 0.1U_0402_16V4ZVGA@

C217 0.1U_0402_16V4ZVGA@

C278 0.1U_0402_16V4ZVGA@

C235 0.1U_0402_16V4ZVGA@

C263 0.1U_0402_16V4ZVGA@

C219 0.1U_0402_16V4ZVGA@

C281 0.1U_0402_16V4ZVGA@

C241 0.1U_0402_16V4ZVGA@

C256 0.1U_0402_16V4ZVGA@

C222 0.1U_0402_16V4ZVGA@

C283 0.1U_0402_16V4ZVGA@

C243 0.1U_0402_16V4ZVGA@

C261 0.1U_0402_16V4ZVGA@

C224 0.1U_0402_16V4ZVGA@

+VCC_PEG

PEG_RXN[0..15] 18

PEG_RXP[0..15] 18

PEG_M_TXN0

PEG_M_TXN1

PEG_M_TXN2

PEG_M_TXN3

PEG_M_TXN4

PEG_M_TXN5

PEG_M_TXN6

PEG_M_TXN7

PEG_M_TXN8

PEG_M_TXN9

PEG_M_TXN10

PEG_M_TXN11

PEG_M_TXN12

PEG_M_TXN13

PEG_M_TXN14

PEG_M_TXN15

PEG_M_TXP0

PEG_M_TXP1

PEG_M_TXP2

PEG_M_TXP3

PEG_M_TXP4

PEG_M_TXP5

PEG_M_TXP6

PEG_M_TXP7

PEG_M_TXP8

PEG_M_TXP9

PEG_M_TXP10

PEG_M_TXP11

PEG_M_TXP12

PEG_M_TXP13

PEG_M_TXP14

PEG_M_TXP15

PEG_M_TXN[0..15] 18

PEG_M_TXP[0..15] 18

CFG[2:0] FSB Freq select

CFG5 (DMI select)

CFG7 (CPU Strap)

CFG8 (Low power PCIE)

(PCIE Graphics Lane Reversal)

CFG[13:12] (XOR/ALLZ)

CFG[15:14] Reserved

CFG16 (FSB Dynamic ODT)

SDVO_CTRLDATA

CFG19 (DMI Lane Reversal)

CFG20 (PCIE/SDVO concurrent)

R59

2.2K_0402_5%

UMA@

12

12

12

12

12

12

CRT_HSYNC17

CRT_VSYNC17

EDID_CLK_LCD

EDID_DAT_LCD

GMCH_ENBKL16

GMCH_LVDDEN16

TV_COMPS

TV_LUMA

TV_CRMA

+3VS

CRT_R

CRT_G

CRT_B

EDID_CLK_LCD37

EDID_DAT_LCD37

D D

For Crestline:2.4kohm

For Calero: 1.5Kohm

C C

R414 150_0603_1%UMA@

R415 150_0603_1%UMA@

R416 150_0603_1%UMA@

R421 150_0603_1%UMA@

R419 150_0603_1%UMA@

B B

R418 150_0603_1%UMA@

Strap Pin Table

010 = FSB 800MHz

011 = FSB 667MHz

Others = Reserved

0 = DMI x 2

1 = DMI x 4

CFG6

CFG9

CFG[11:10]

CFG[18:17] Reserved

Reserved

0 = Reserved

1 = Mobile CPU

0 = Normal mode

1 = Low Power mode

0 = Reverse Lane

1 = Normal Operation

Reserved

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

0 = Disabled

1 = Enabled

0 = No SDVO Device Present

1 = SDVO Device Present

0 = Normal Operation

(Lane number in Order)

1 = Reverse Lane

0 = Only PCIE or SDVO is operational.

1 = PCIE/SDVO a r e o p e r a t ing simu.

CFG57

CFG77

CFG87

CFG97

CFG127

CFG137

CFG167

*

*

*

R32 4.02K_0402_1%@

1 2

R33 4.02K_0402_1%@

1 2

R26 4.02K_0402_1%@

1 2

R413 4.02K_0402_1%@

1 2

R25 4.02K_0402_1%@

1 2

R29 4.02K_0402_1%@

1 2

R27 4.02K_0402_1%@

1 2

*

*

(Default)

*

*

*

*

CFG[17:3] have internal pull up

CFG[19:18] have internal pull down

+3VS

R55 4.02K_0402_1%@

CFG197

A A

CFG207

1 2

R58 4.02K_0402_1%@

1 2

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/04 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

CRESTLINE((3/6)-VGA/LVDS/TV

IGT30 LA-3571P

1

of

947Monday, December 25, 2006

0.1

Page 10

5

0.1U_0402_16V4Z

UMA@

0.1U_0402_16V4Z

UMA@

C8

150U_D_6.3VM

R37

0_0603_5%

0316 add

1

1

C64

2

2

UMA@

1

1

C54

2

2

UMA@

1

1

C65

2

2

UMA@

+3VS_DAC_BG

1

1

C96

2

2

+3VS_DAC_CRT

1

1

C117

2

2

1

+

22U_0805_6.3V4Z

2

+1.25VS_A_SM_CK

12

C75

R49

0_0603_5%

0.1U_0402_16V4Z

R35

0_0603_5%

0.1U_0402_16V4Z

UMA@

R36

0_0603_5%

0.1U_0402_16V4Z

UMA@

5

+3VS

R39

1 2

0_0603_5%

UMA@

D D

+3VS

R54

1 2

0_0603_5%

UMA@

+1.25VS

C C

+3VS_TVDACC

B B

0.022U_0402_16V7K

C76

UMA@

+3VS_TVDACA

0.022U_0402_16V7K

C56

UMA@

A A

+3VS_TVDACB

0.022U_0402_16V7K

C66

UMA@

0.022U_0402_16V7K

C97

UMA@

C92

0.022U_0402_16V7K

C116

UMA@

+3VS

0.1U_0402_16V4Z

R21

1 2

0_0805_5%

C28

1U_0402_6.3V4Z

C55

1

2

0317 change value

12

UMA@

12

12

+3VS

4.7U_0805_10V4Z

1

2

R72

0_0603_5%

0317 change value

1

4.7U_0805_6.3V6K

2

22U_0805_6.3V4Z

1

2

+3VS

+3VS

+3VS

R51

0_0603_5%

+1.8V_TXLVDS

+3VS_PEG_BG

12

C165

C29

C77

1

2

VCCSYNC

12

C94

+1.25VS_DPLLA

+1.25VS_DPLLB

+1.25VS_HPLL

+1.25VS_MPLL

1000P_0402_50V7K

C154

1

+1.25VS_PEGPLL

2

+1.25VS_A_SM

1

2

1U_0603_10V4Z

C82

1

2

+1.25VS_HPLL

+1.25VS_PEGPLL

+1.8V_LVDS

0.1U_0402_16V4Z

1

2

+3VS_DAC_CRT

+3VS_DAC_BG

1

2

1

2

1U_0603_10V4Z

0.1U_0402_16V4Z

+3VS_TVDACA

+3VS_TVDACB

+3VS_TVDACC

+1.5VS_TVDAC

+1.5VS_QDAC

+1.5VS_QDAC

0.022U_0402_16V7K

1

C58

2

UMA@

+1.8V_LVDS

10U_0805_10V6K

C155

1

2

UMA@

C34

C46

1U_0603_10V4Z

20 mils

1

2

UMA@

C152

AW18

AV19

AU19

AU18

AU17

AT22

AT21

AT19

AT18

AT17

AR17

AR16

BC29

BB29

0.1U_0402_16V4Z

0_0603_5%

UMA@

1

2

UMA@

J32

A33

B33

A30

B32

B49

H49

AL2

AM2

A41

B41

K50

K49

U51

C25

B25

C27

B27

B28

A28

M32

L29

N28

AN2

U48

J41

H42

R43

0_0603_5%

UMA@

R69

U22H

CRESTLINE_1p0

4

VCCSYNC

VCCA_CRT_DAC_1

VCCA_CRT_DAC_2

VCCA_DAC_BG

VSSA_DAC_BG

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_LVDS

VSSA_LVDS

VCCA_PEG_BG

VSSA_PEG_BG

VCCA_PEG_PLL

VCCA_SM_1

VCCA_SM_2

VCCA_SM_3

VCCA_SM_4

VCCA_SM_5

VCCA_SM_7

VCCA_SM_8

VCCA_SM_9

VCCA_SM_10

VCCA_SM_11

VCCA_SM_NCTF_1

VCCA_SM_NCTF_2

VCCA_SM_CK_1

VCCA_SM_CK_2

VCCA_TVA_DAC_1

VCCA_TVA_DAC_2

VCCA_TVB_DAC_1

VCCA_TVB_DAC_2

VCCA_TVC_DAC_1

VCCA_TVC_DAC_2

VCCD_CRT

VCCD_TVDAC

VCCD_QDAC

VCCD_HPLL

VCCD_PEG_PLL

VCCD_LVDS_1

VCCD_LVDS_2

+1.5VS

12

12

4

CRTPLLA PEGA SMTV

POWER

A CK A LVDS

D TV/CRTLVDS

+1.8V

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VCC_AXD_1

VCC_AXD_2

VCC_AXD_3

VCC_AXD_4

VCC_AXD_5

AXD

VCC_AXD_6

VCC_AXD_NCTF

VCC_AXF_1

VCC_AXF_2

VCC_AXF_3

AXF

VCC_DMI

VCC_SM_CK_1

VCC_SM_CK_2

VCC_SM_CK_3

VCC_SM_CK_4

SM CK

VCC_TX_LVDS

VCC_HV_1

VCC_HV_2

HV

VCC_PEG_1

VCC_PEG_2

VCC_PEG_3

VCC_PEG_4

PEG

VCC_PEG_5

VCC_RXR_DMI_1

VCC_RXR_DMI_2

DMI

VTTLF1

VTTLF2

VTTLF3

VTTLF

40 mils

1000P_0402_50V7K

1

C158

UMA@

2

3

+VCCP

330U_D2E_2.5VM_R7

U13

U12

U11

U9

U8

U7

U5

U3

U2

U1

T13

T11

T10

T9

T7

T6

T5

T3

T2

R3

R2

R1

AT23

AU28

AU24

AT29

AT25

AT30

AR29

B23

B21

A21

AJ50

BK24

BK23

BJ24

BJ23

A43

C40

B40

AD51

W50

W51

V49

V50

AH50

AH51

A7

F2

AH1

+1.8V_TXLVDS

1

220U_D2_4VM_R15

+

2

C14

C156

UMA@

+1.25VS_AXD

0.47U_0603_10V7K

1

2

R74

0_0603_5%

UMA@

C198

C135

1U_0603_10V4Z

1

2

+V1.25VS_AXF

+1.25VS_DMI

+1.8V_SM_CK

+1.8V_TXLVDS

+VCC_PEG

20mils

0.47U_0603_10V7K

C12

1

2

12

1

+

2

1

2

C68

C21

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

4.7U_0805_10V4Z

1

C24

2

0316 add

0.47U_0603_10V7K

C129

C87

1

2

+3VS_HV

C139

0.47U_0603_10V7K

1

2

+1.8V

2.2U_0805_16V4Z

4.7U_0805_10V4Z

1

1

C138

2

2

R34

1 2

10U_0805_10V6K

1

2

2006/08/04 2006/10/06

0_0805_5%

0.1U_0402_16V4Z

+1.25VS

Compal Secret Data

+1.25VS_DPLLB

0.1U_0402_16V4Z

+1.25VS_DMI

+1.25VS_PEGPLL

+1.25VS_DPLLA

+VCC_PEG

1

C199

+

2

0316 add

Deciphered Date

C164

1

2

0.1U_0402_16V4Z

C166

1

2

0.1U_0402_16V4Z

C168

1

2

0.1U_0402_16V4Z

C163

1

2

220U_D2_4VM

C181

2

R433

1 2

10U_0805_10V4Z

10U_FLC-453232-100K_0.25A_10%

1

C534

2

1 2

R73

0_0603_5%

BLM18PG121SN1D_0603

10U_0805_10V4Z

C162

1

2

10U_0805_10V6K

C533

1

2

220U_D2_4VM

1

C179

1

+

2

2

2

+1.25VS

0316 add

+1.25VS

+1.25VS

L4

12

R431

1 2

10U_FLC-453232-100K_0.25A_10%

0316 add

+1.25VS

04/10 stuff

R76

0_0805_5%

10U_0805_10V4Z

R435

@

0_0805_5%

04/10 no stuff

+VCCP

CH751H-40PT_SOD323-2

+3VS

1

+V1.25VS_AXF

10U_0805_10V4Z

+1.8V_SM_CK

22U_0805_6.3V4Z

22U_0805_6.3V4Z

1

C47

2

+1.5VS_TVDAC

C78

+1.25VS_HPLL