Page 1

5

4

COMPAL CONFIDENTIAL

3

2

1

D D

COMPAL P/N :

MODEL NAME :

PCB NO :

Revision :

C C

LA-3091P

1.0

Biathlon (IBM 15R)

HEL00

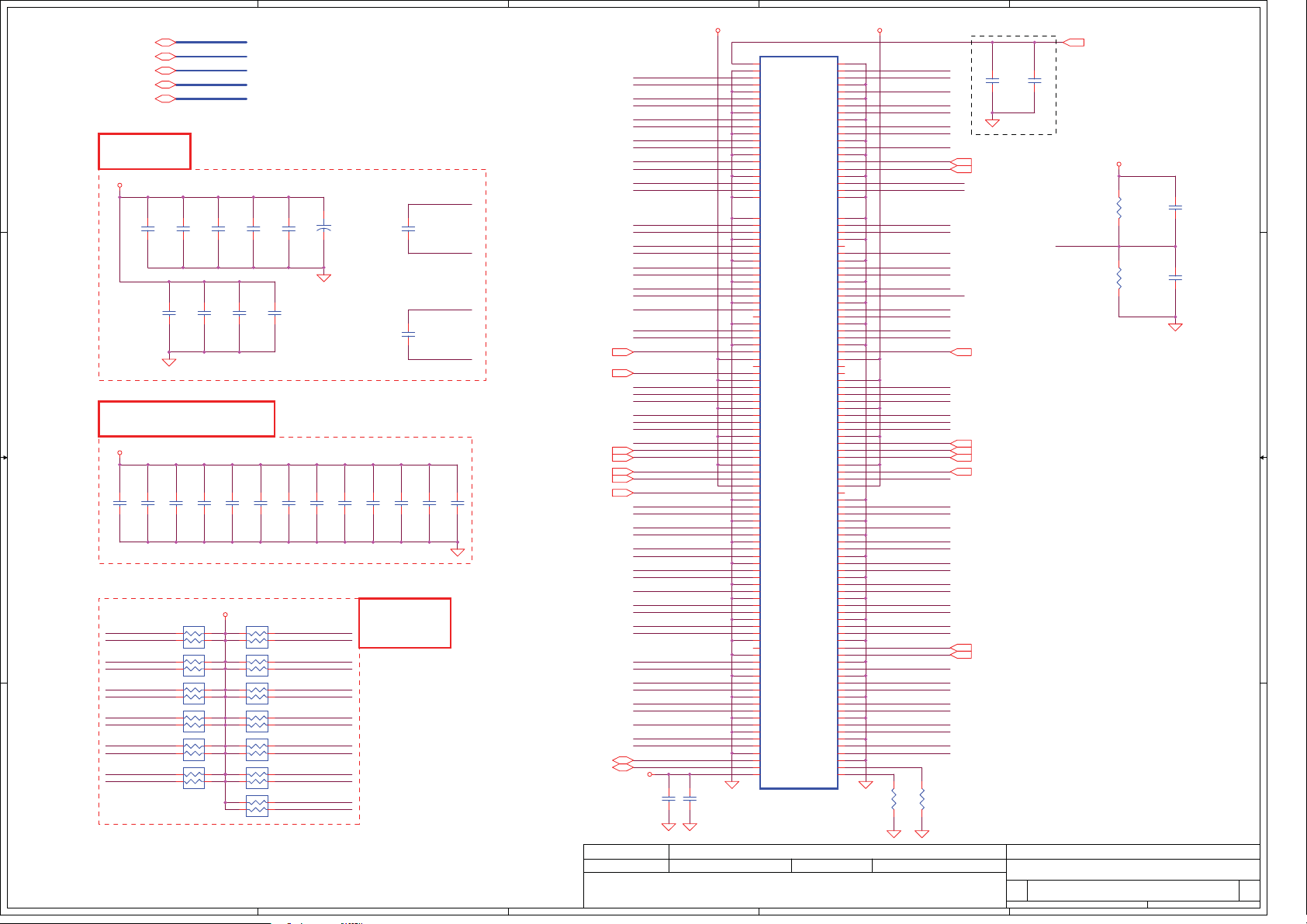

IBM 15R Schematics Document

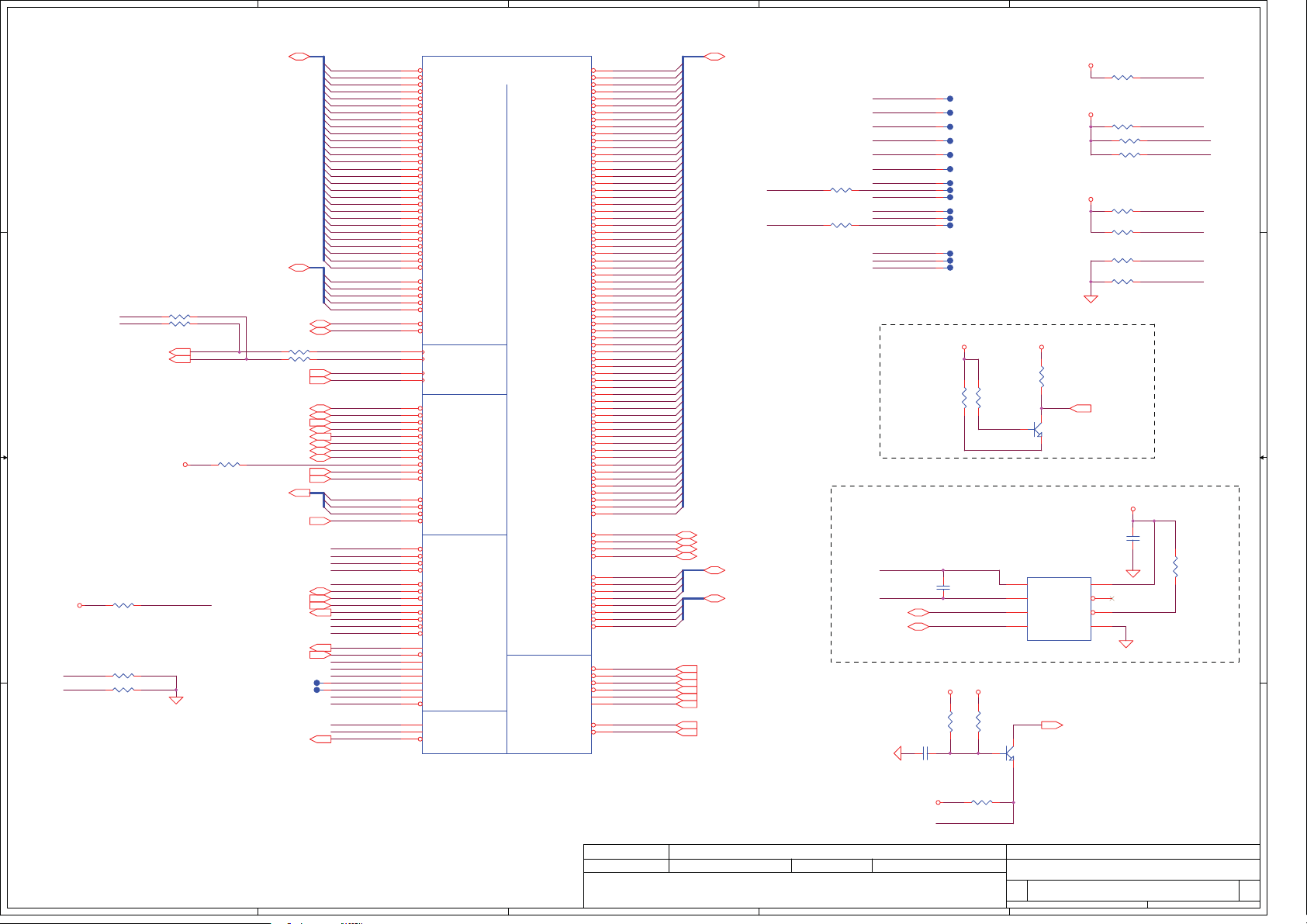

uFCBGA/uFCPGA Mobile Dothan

Alviso 915+ ICH6-M

2 Channel DDR2

B B

2005-12-20

REV : 1.0

SW LED/B

LS-3093P

M/B LA-3091P

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

Title

Bithlon LA3091 Schematic

Size Document Number Rev

LA-3091 1.0

Custom

2

Date: Sheet

TP/B

LS-3094P

Tuesday, Janua ry 10, 2006

1

LED/B

LS-3092P

144

of

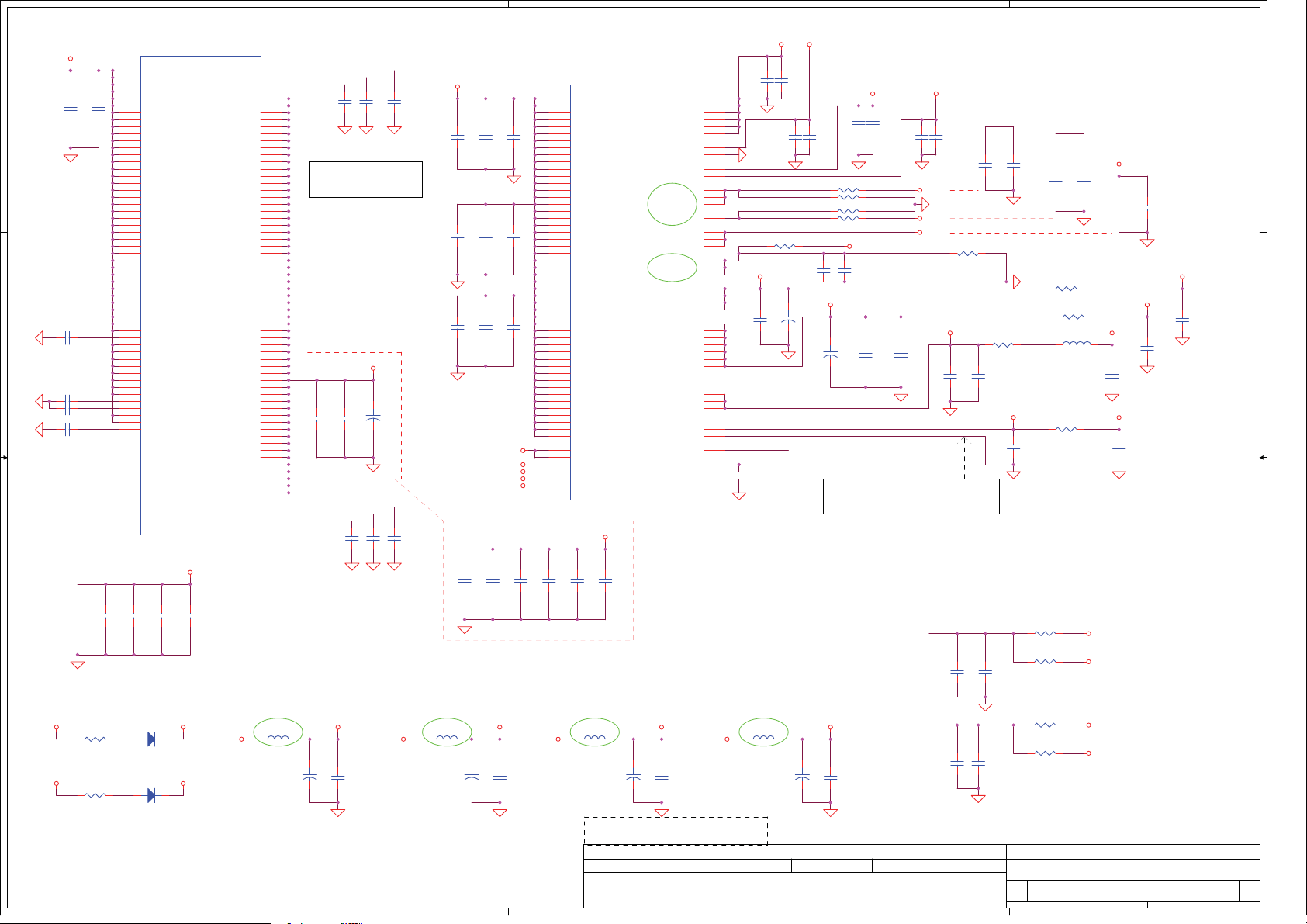

Page 2

5

4

3

2

1

Compal confidential

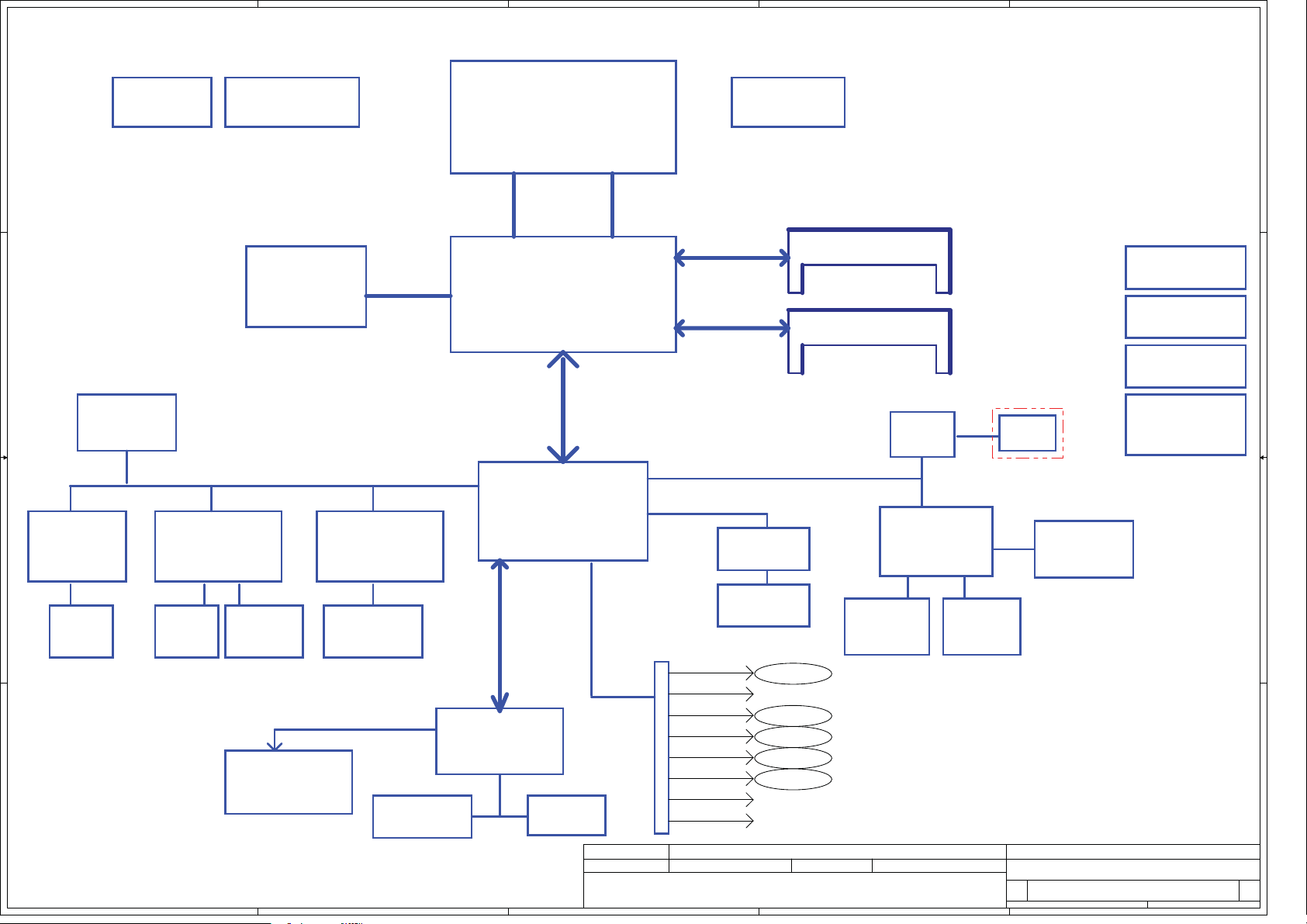

Block Diagram

Dothan

FAN

+12VALW

+5VALW

D D

+3V

page 33

Thermal(CPU)

ADM1032ARZ

+3VS

page 5

+VCCP (1.05V)

+VCC_CORE

+3V

+3VS

uFCPGA CPU

page 6,7,8

Clock Generator

ICS954226AG

+3VS

page 17

Memory

HA#(3..31)

LVDS Conn

B+

CRT Conn

+3VS

+5VS

TV-OUT

+2.5VS

C C

IDSEL:AD18

(PIRQG,H#,GNT3#,REQ3#)

page 15,16

Internal GM

Alviso Intel 915 GM

GMCH-M

page 8,9,10,11,12

Mini PCI Conn

+3VS

+3V

+5VS

IDSEL:AD16

(PIRQE#,GNT2#,REQ2#)

VIA6311S

1394

+3VS

B B

page 26

page 27

IDSEL:AD20

(PIRQA,B#,GNT1#,REQ1#),SIRQ

CardBus

Controller

ENE CB714

+3VS

+CBS_VCC

page 25

PCI BUS

3.3V 33MHz

IDSEL:AD17

(PIRQF#,GNT0#,REQ0#)

RTL 8100CL/100

+3VALW

page 23

System Bus

400 / 533MHz

1257 FC-BGA

DMI

1.5V

100MHz

+3VS

+3V

+1.5VS

+1.5V

+2.5VS

HD#(0..63)

+1.5VS

+1.8V

+VCCP

+3VS

+2.5VS

ICH6

609 BGA

page 18,19,20,21

BUS(DDR2)

Dual Channel

1.8V 266MHz

Channel A

1.8V 266MHz

Channel B

AC97'

ATA100

Parallel ATA

+5VS

3.3V 24.576MHz

page 22

SO-DIMM X 1

BANK 0, 1

+0.9VS

+1.8V

SO-DIMM X 1

BANK 2, 3

+0.9VS

+1.8V

AC97 CODEC

+3VS

+5VS

page 13

page 14

MDC

+5VS

+3VS

+3V

RTL 250

Cable

page 28

RJ11

page 36

HeadPhone &

MIC Conn

+5VAMP

page 29

LED/ BD

+5VALW

+3VALW

SW LED/ BD

+3VALW

+3VS

T/P BD

+5VS

LS-3092

page 32

LS-3093

page 32

LS-3094

page 32

POWER Circuit

IDE

1394

CONN.

page 26

SDIO

CONN.

PCMCIA

Slot 0

+CBS_VCC

+CBS_VPP

page 25page 25

Transformer

& RJ45

page 24

LPC BUS

3.3V 33MHz

USB2.0

48MHz / 480Mb

USBPORT 0

USBPORT 1

X BUS

SST39VF040

A A

5

+3VALW

page 32

Touch Pad

+5VS

4

+5VALW

+3VALW

+3VS

page 32

KB910L

page 31

Int.KBD

page 32

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

http://hobi-elektronika.net

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

USBPORT 6

USBPORT 7

3

CD-ROM

+5VCD

page 22

JUSBP2

BT

JUSBP1

JUSBP1

JUSBP3

2005/03/01 2006/03/01

Compal Secret Data

+5VS

page 34

page 33

page 34

page 34

page 34

Deciphered Date

AMP & INT.

Speaker

page 29

2

INT. MIC

Conn

+AUD_VREF

page 29

Custom

Title

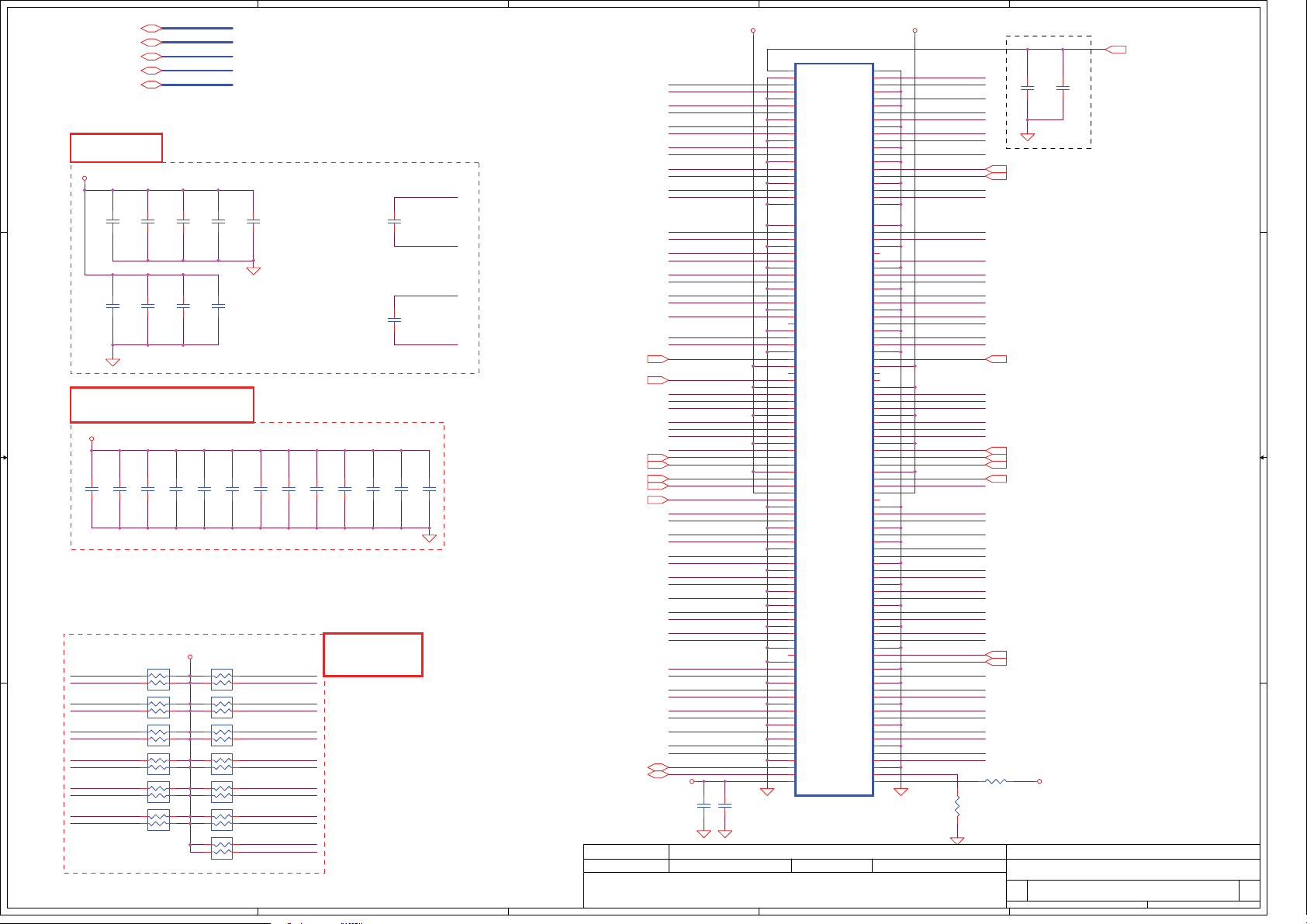

Functional Block

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

244

Page 3

5

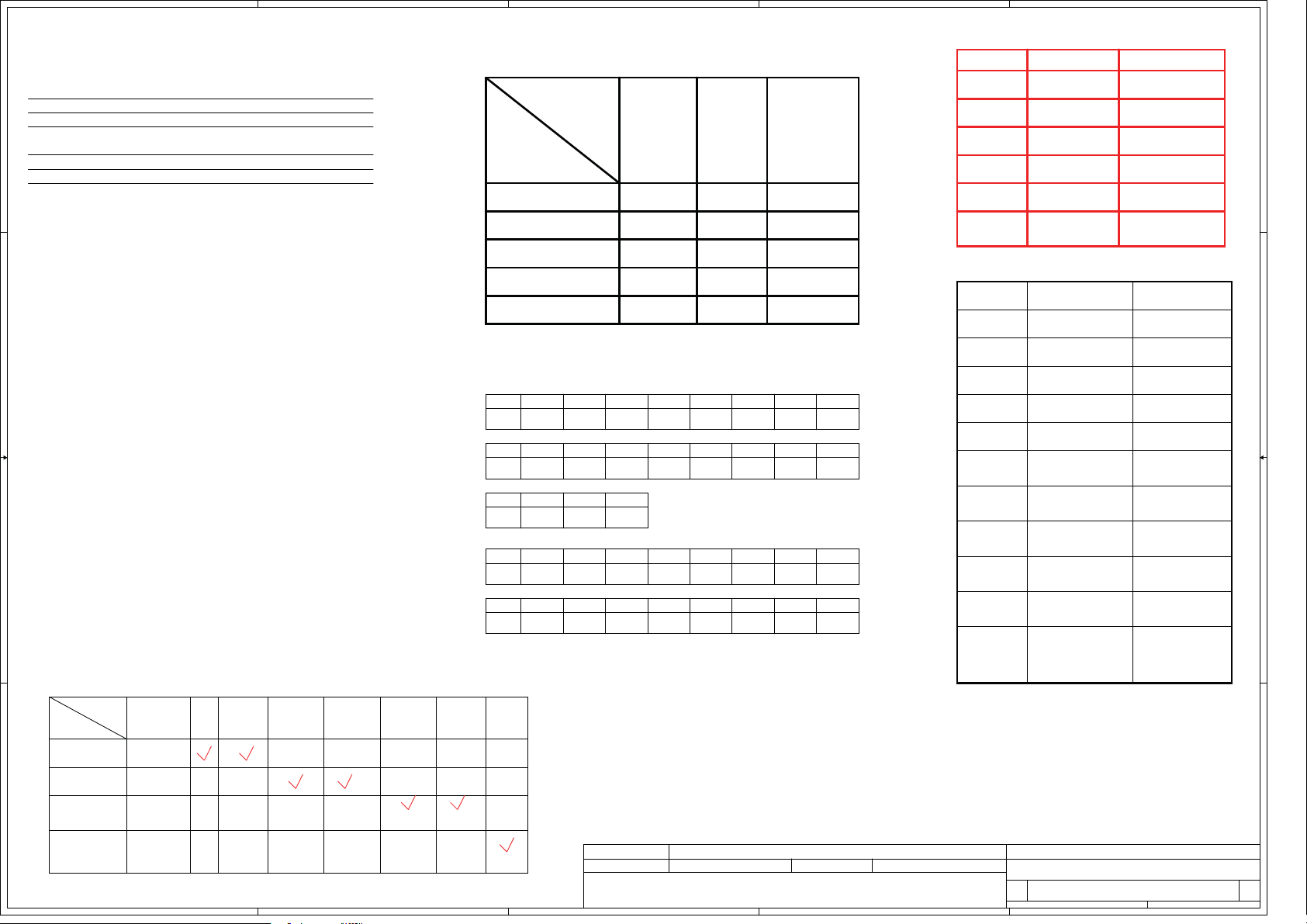

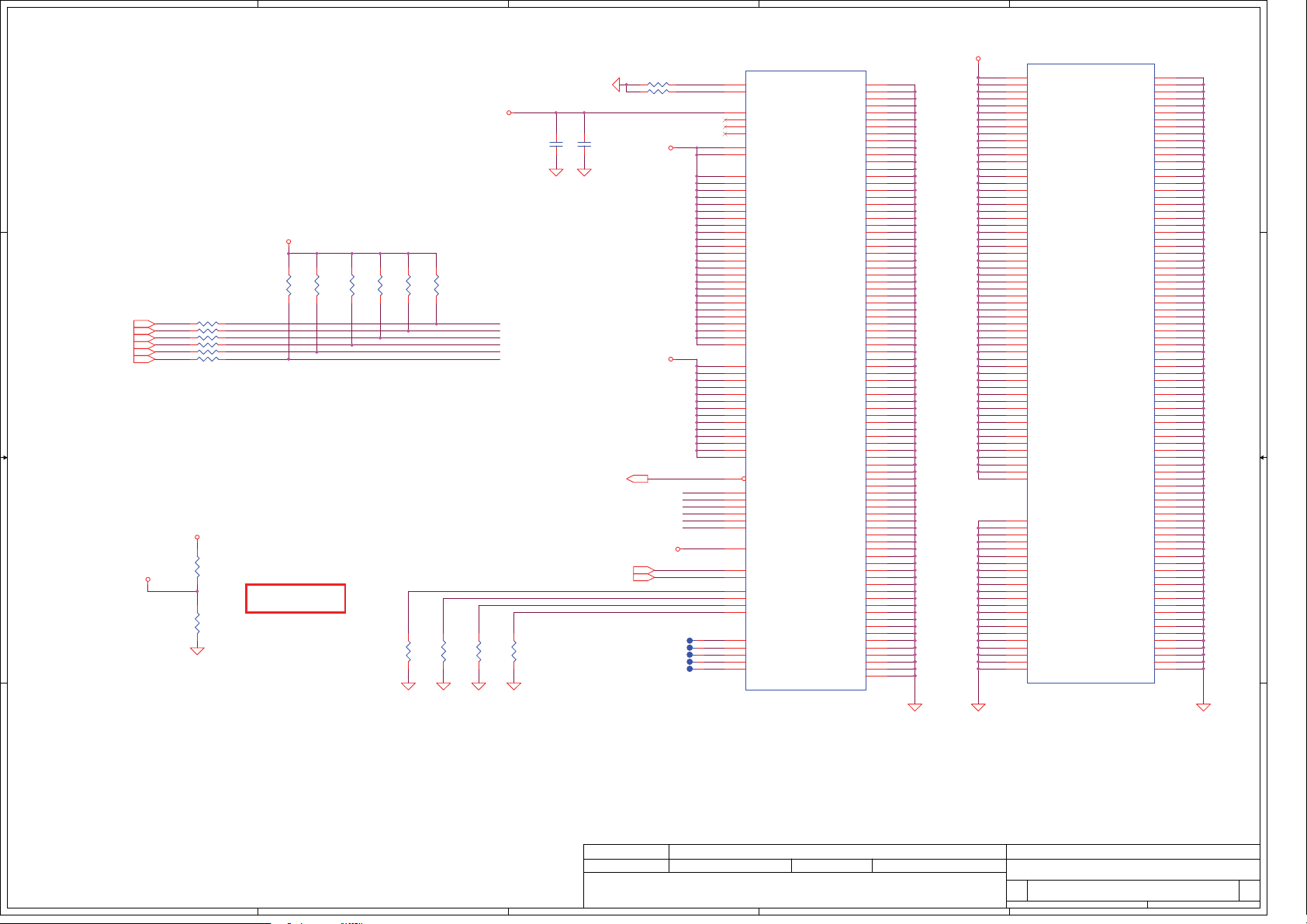

I2C / SMBUS ADDRESSING

4

3

2

1

External PCI Devices

LAN

D D

CARD BUS

Cardreader

1394

Wireless LAN(MINI PCI)

@ Depop

AD17

AD20

AD16 2

AD18

0

1

3

F

A

B

E

G,H

State

S0

S1

S3

S5 S4/AC

IDSEL # PIRQREQ/GNT #DEVICE

Signal

+12VALW

+5VALW

+3VALW

+12V

+5V

+3V

+1.8V

ON

ON ON

ON ON ON

ON ON

ON OFF

+CPU_CORE

+VCCP

+5VS

+3VS

+2.5VS

+1.8VS

+1.25VS

+1.5VS

OFF

OFF

1@ IBM 15R (UMA)

2@ (Discrete)

C C

S5 S4/AC don't exist

Ceramic Capacitor Spec

Guide:

Temperature Characteristics:

Symbol

0

CODE

Z5U

8

NP0 SH

H

UK

UJ

9

C0G

I

1

Z5V

A

J

SL

OFF OFF OFF

2

Z5P

B

BJ

3

Y5U

C

CH

4

5

Y5V Y5P

E

D

CK

CJ

X5R

7

6

X7R

F

G

SJ

EVT-Build

DVT-Build

PVT-Build

MP-Build

SCHEMATICS VERSION LIST

VERSION ISSUE DATE REMARK

0.1

0.2

Power Managment table

PCB Rev

0.1

0.2

Data

EVT-Build

DVT-Build

PVT-Build

MP-Build

Tolerance:

CODE

A

+-0.05PF

B B

Symbol

B

+-0.1PF

C

+-0.25PF

D

+-0.5PF +-1PF

F

+-2%

H

G

+-3%

J

+-5%

M

+-20%

N

+-30%

+100,-0%

+30,-10%

V

+20,-10%

+40,-20%

KQ

+-10%

X

Z

+80,-20%

P

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

A A

SMB_EC_DA2

ICH_SMBCLK

ICH_SMBDATA

LCD_CLK

LCD_DAT

KB910L

PU +5VALW

KB910L

PU +5VALW

ICH6-M

PU +3VALW PU +3VS

Alviso

GM-GP

PU +2.5VS PU +3VS

5

BATT

SERIAL SENSOR

EEPROM

THERMAL

CPU

(ADM1032)

Intel

PCI WLAN

SO-DIMM1 CLK CHIP

SO-DIMM2

4

LCD

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

Title

Design Note

Size Document Number Rev

LA-3091 1.0

Custom

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

344

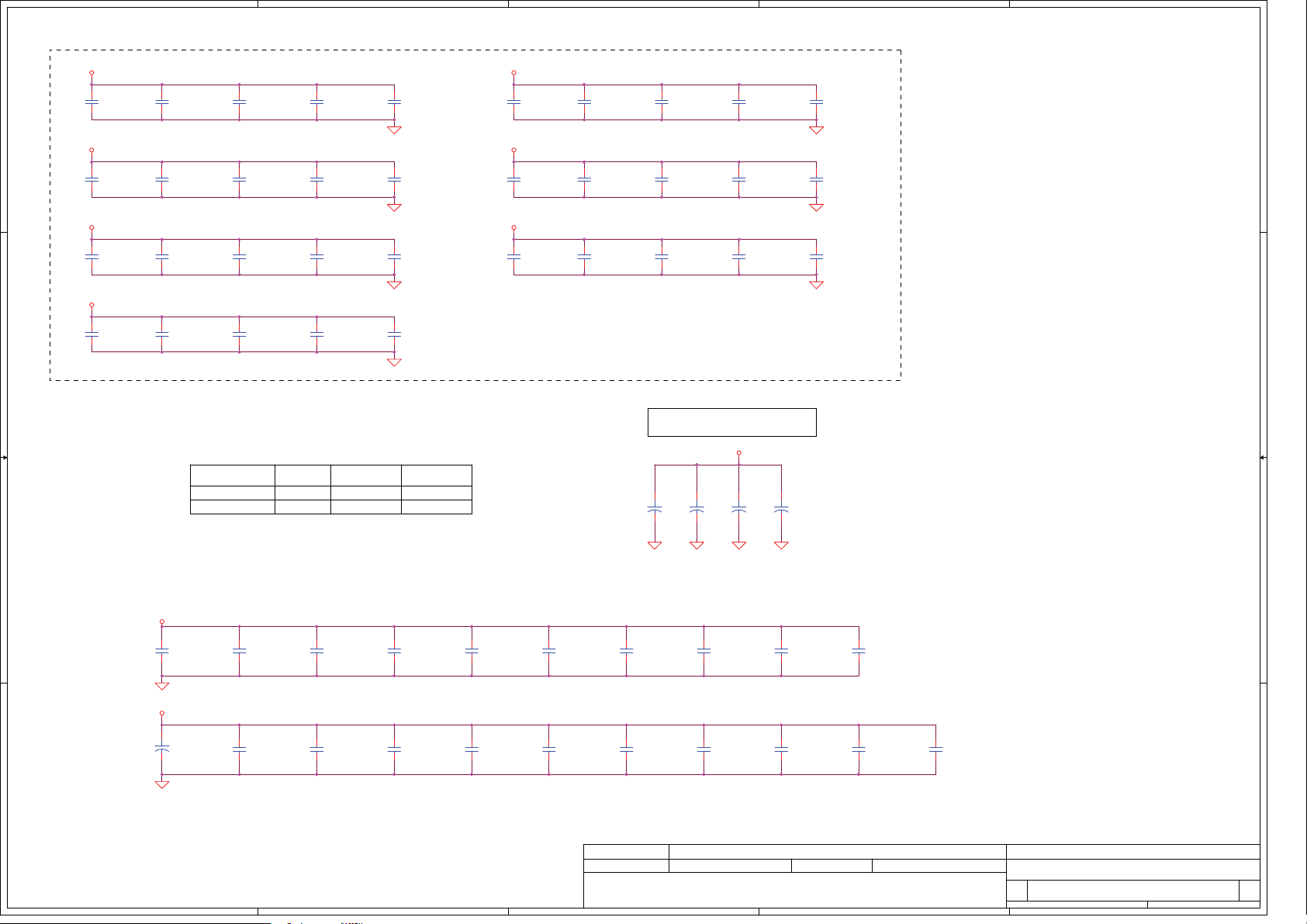

Page 4

5

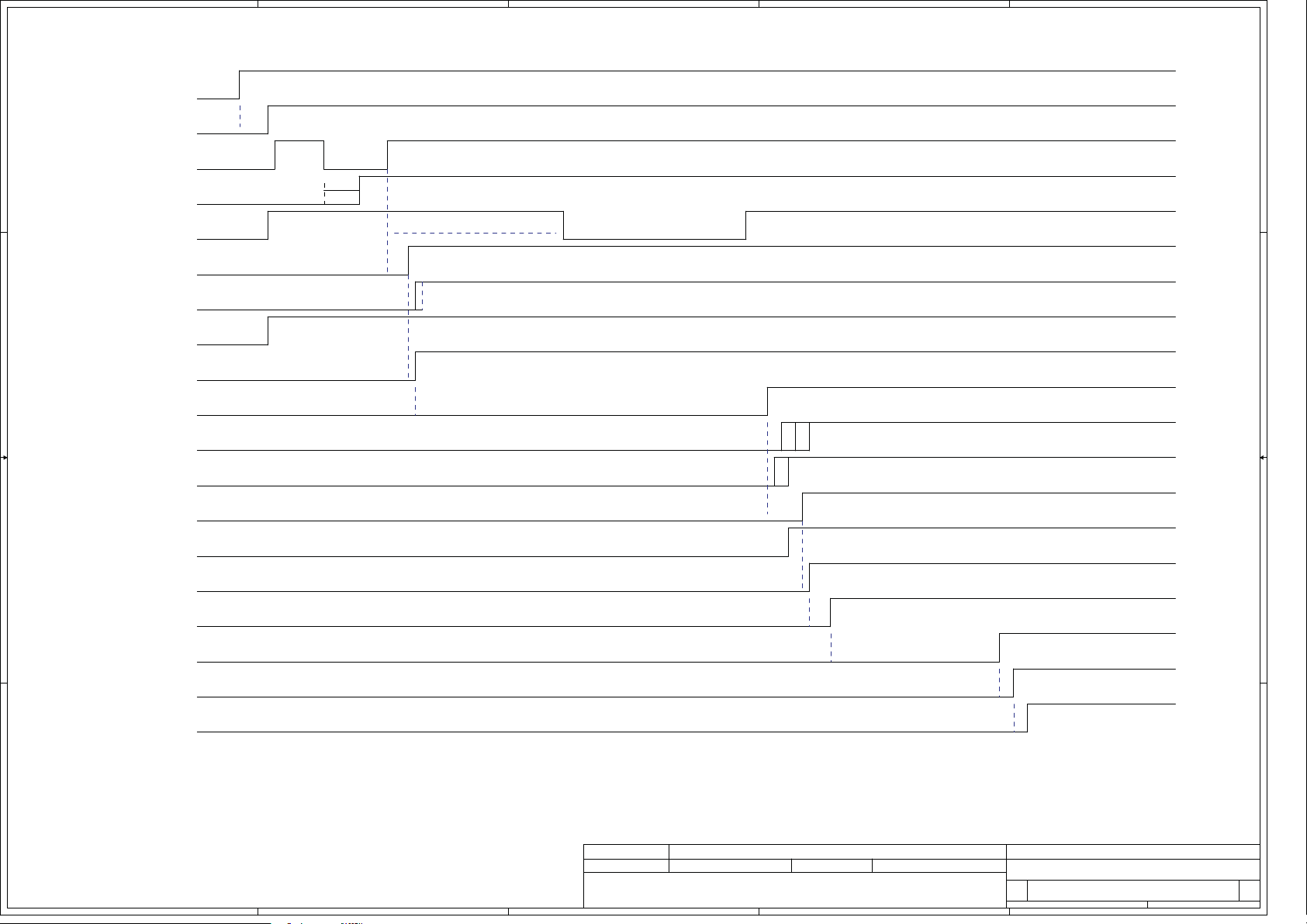

ACIN

4

3

2

1

D D

+3/5/12VALW

32ms

ON/OFF#

EC_ON#

8.5/2.44/3.792ms

PWRBTN_OUT#

SYSON

+1.8/3/5/12V

C C

RSMRST#

t<=10 ms

112ms

8.4ms

3V(370us)5V (450us) 1.8V(1.3ms)

164us

t=100 ms

SLP_S3/4/5#

SUSP#

+1.25/1.5/1.8/3/5VS

+VCCP

VR_ON#

1.25VS(140us) 1.5VS(2.8ms) 3VS(7.44ms) 5VS(11.3ms) 1.8VS(5.48ms)

216ms

t>0

210us 1.3ms PGD

9.2ms

CPU_VID

B B

+CPU_CORE

Vgate

ICHPWRGD

PCIRST/PLTRST#

CPU_RST#

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

960us

1.820ms

Compal Secret Data

Deciphered Date

t<110 ms

99ms

2

2<t<3 RTCCLK

1.036ms

61us

Custom

Title

Power Rail

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

444

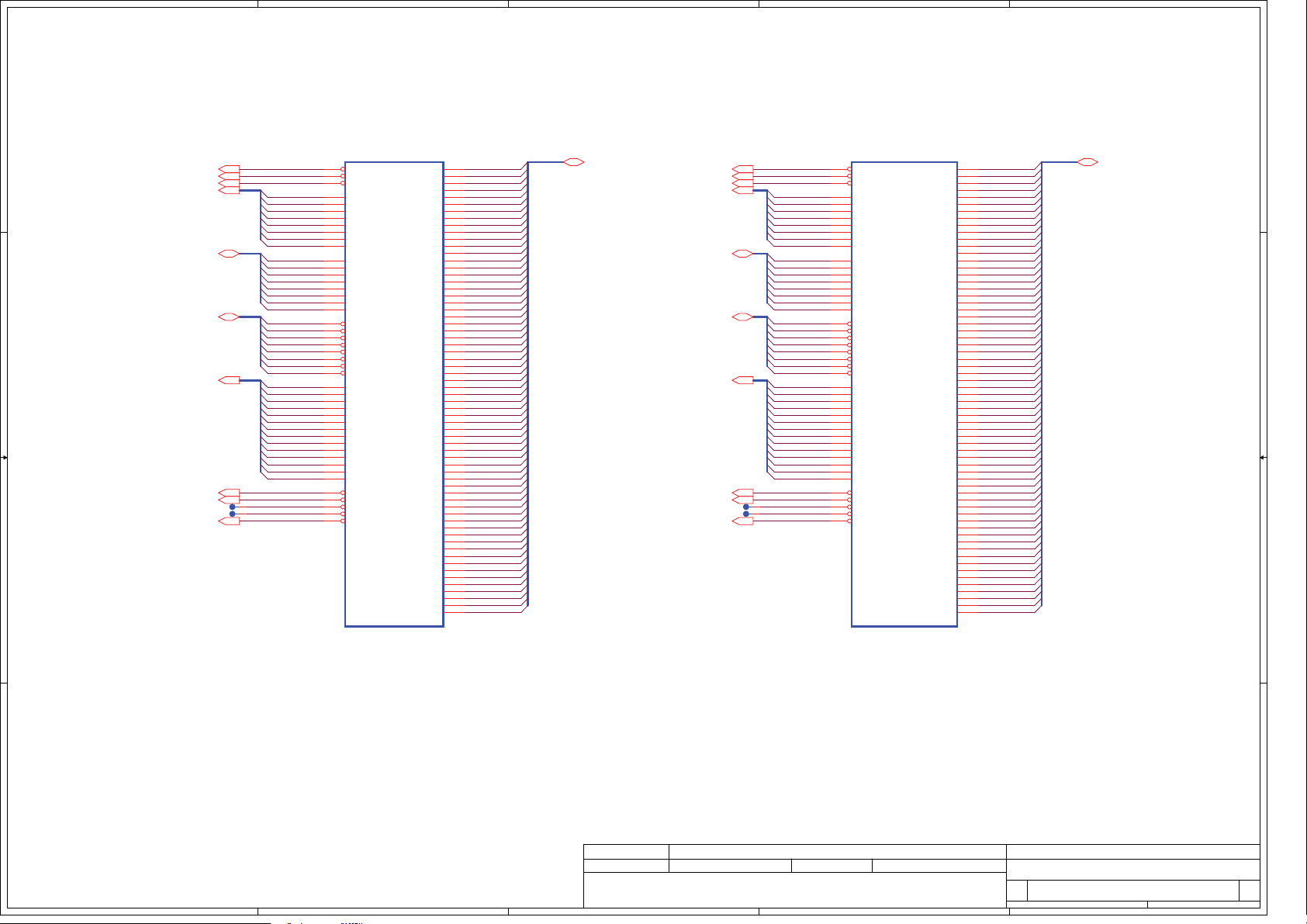

Page 5

5

4

3

2

1

H_A#[3..31]8

D D

H_REQ#[0..4]8

CLK_ITP_R#

CLK_ITP_R

C C

B B

A A

Add pullup s fo r PWRGOOD and

THERMTRIP per INTEL

+VCCP

R458 200_0402_5%

TEST2

R530 1K_0402_5%@

TEST1

R464 1K_0402_5%@

1 2

1 2

1 2

CLK_ITP17

CLK_ITP#17

H_PWRGOOD

R110 0_0402_5%@

1 2

1 2

R112 0_0402_5%@

+VCCP

CLK_ITP

CLK_ITP#

R78 56_0402_5%

1 2

R111 0_0402_5%@

R109 0_0402_5%@

CLK_CPU_BCLK17

CLK_CPU_BCLK#17

H_RS#[0..2]8

H_PWRGOOD19

H_CPUSLP#8,19

H_THERMTRIP#8,19

H_ADSTB#08

H_ADSTB#18

1 2

1 2

H_ADS#8

H_BNR#8

H_BPRI#8

H_BR0#8

H_DEFER#8

H_DRDY#8

H_HIT#8

H_HITM#8

H_LOCK#8

H_RESET#8

H_TRDY#8

H_DBSY#8

H_DPSLP#19

H_DPRSLP#19

H_DPWR#8

T5 PAD

T39 PAD

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_CK_ITP

CPU_CK_ITP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSLP#

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

JCPU1A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

ADDR GROUP

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

TYCO_1612365-1_Dothan

Dothan

DATA GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_D#0

A19

H_D#[0..63] 8

H_DINV#0 8

H_DINV#1 8

H_DINV#2 8

H_DINV#3 8

H_DSTBN#[0..3] 8

H_DSTBP#[0..3] 8

H_A20M# 19

H_FERR# 19

H_IGNNE# 19

H_INIT# 19

H_INTR 19

H_NMI 19

H_STPCLK# 19

H_SMI# 19

Place near JITP 0.5"

H_RESET#

ITP_TDO

Test pad as closed as posible

R74

22.6_0402_1%

1 2

R87

22.6_0402_1%

1 2

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CLK_ITP_R#

CLK_ITP_R

ITP_TRST#

ITP_TMS

ITP_TDI

T7PAD

T6PAD

T8PAD

T10PAD

T9PAD

T12PAD

T11PAD

T4PAD

T17PAD

T42PAD

T19PAD

T15PAD

T16PAD

T13PAD

T14PAD

Check ITP connector.

CPU HOT

R123

56_0402_5%

+VCCP

12

12

R124

56_0402_5%

H_PROCHOT#

CPU Thermal Sensor

H_THERMDA

H_THERMDC

SMB_EC_CK215,27,31

SMB_EC_DA215,27,31

+VCCP

R561

@

47K_0402_5%

1 2

C526

0.68U_0603_10V6K

+VCCP

1

C141

2200P_0402_50V7K

2

SMB_EC_CK2

SMB_EC_DA2

+CPU_CORE

12

@

R494

75_0402_1%

1 2

H_THERMTRIP#

12

R762

47K_0402_5%

2

B

+3VS

C

2

B

E

U9

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARMZ_RM8

1

C

Q39

2SC2411KT146_SC59

E

3

+3V

+VCCP

+VCCP

12

R132

1K_0402_5%

1

Q6

2SC2411KT146_SC59

3

0.1U_0603_25V7K

VDD1

ALERT#

THERM#

GND

MAINPWRON 36,38,41

1 2

1 2

or 39.4Ohm

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_BPM#5

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

1 2

R79 150_0402_5%

1 2

R90 54.9_0603_1%

R76 54.9_0603_1%

R745 56_0402_5%

1 2

R479 37.4_0402_1%

1 2

R85 150_0402_5%

1 2

R100 680_0402_5%

1 2

R106 27.4_0402_1%

PROCHOT# 31

+3VS

1

C132

2

1

6

4

5

12

R149

10K_0402_5%

This shall place near CPU

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

Custom

Title

Dothan(1/2)-GTL/ITP

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

544

Page 6

5

4

3

2

1

R470

@

54.9_0402_1%

R465

D D

CPU Voltage ID

VID042

VID142

VID242

C C

VID342

VID442

VID542

R433 0_0402_5%

R434 0_0402_5%

R435 0_0402_5%

R436 0_0402_5%

R437 0_0402_5%

R438 0_0402_5%

12

12

12

12

12

12

+VCCP

12

12

12

12

@

R413

10K_0402_5%

@

R412

10K_0402_5%

@

R411

@

10K_0402_5%

R410

12

@

10K_0402_5%

R409

10K_0402_5%

+1.5VS

1

1

C516

C150

2

2

10U_1206_6.3V6M

0.01U_0402_16V7K

12

R408

@

10K_0402_5%

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

54.9_0402_1%

+CPU_CORE

PSI#42

+VCCP

R_A

12

B B

+V_CPU_GTLREF

12

R155

1K_0402_1%

R_B

R153

2K_0402_1%

Layout close CPU

Layout Note:

500 mil max length

20 mils

12

27.4_0402_1%

R156

5 mils

12

54.9_0402_1%

R157

20 mils

12

27.4_0402_1%

R416

5 mils

12

54.9_0402_1%

R417

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

miles away from any

other toggling signal.

+V_CPU_GTLREF

CPU_BSEL017

CPU_BSEL117

1 2

1 2

@

+VCCP

T3 PAD

T2 PAD

T20 PAD

T31 PAD

T29 PAD

VCCSENSE

VSSSENSE

H_PSI#

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

JCPU1B

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

B2

RSVD

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

TYCO_1612365-1_Dothan

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Dothan

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

+CPU_CORE

JCPU1C

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA19

VCC

AA21

VCC

AB6

VCC

AB8

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

TYCO_1612365-1_Dothan

Dothan

POWER, GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

Custom

Title

Dothan(2/2)-PWR/GND

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

644

Page 7

5

4

3

2

1

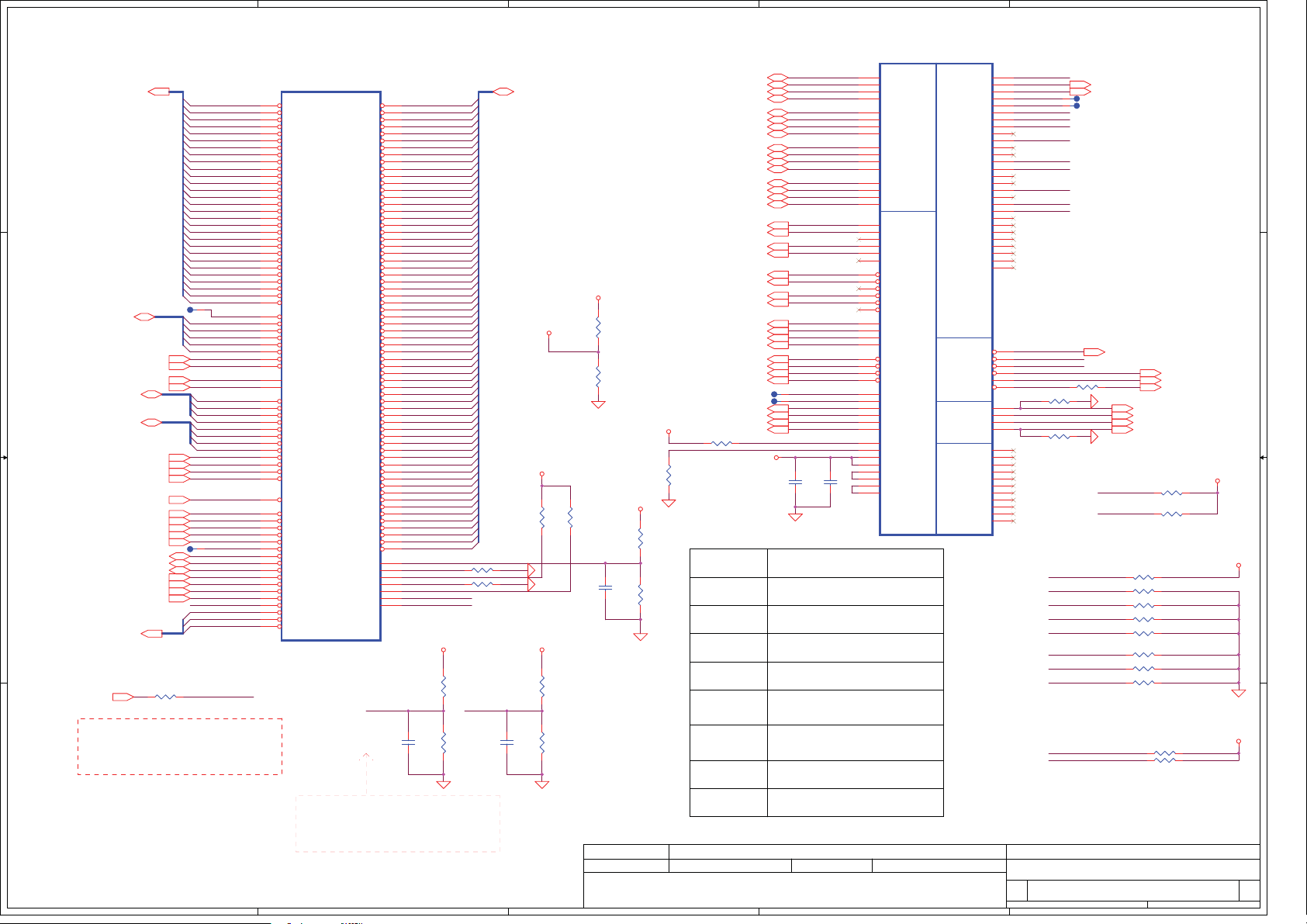

+CPU_CORE

1

C482

10U_0805_6.3V6M

D D

C C

2

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

C430

10U_0805_6.3V6M

C100

10U_0805_6.3V6M

C512

10U_0805_6.3V6M

1

C483

10U_0805_6.3V6M

2

1

C421

10U_0805_6.3V6M

2

1

C105

10U_0805_6.3V6M

2

1

C507

10U_0805_6.3V6M

2

1

C460

10U_0805_6.3V6M

2

1

C415

10U_0805_6.3V6M

2

1

C109

10U_0805_6.3V6M

2

1

C502

10U_0805_6.3V6M

2

1

C446

10U_0805_6.3V6M

2

1

C416

10U_0805_6.3V6M

2

1

C114

10U_0805_6.3V6M

2

1

C469

10U_0805_6.3V6M

2

1

C431

10U_0805_6.3V6M

2

1

C480

10U_0805_6.3V6M

2

1

C91

10U_0805_6.3V6M

2

1

C442

10U_0805_6.3V6M

2

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

C422

10U_0805_6.3V6M

C481

10U_0805_6.3V6M

C92

10U_0805_6.3V6M

1

C518

10U_0805_6.3V6M

2

1

C113

10U_0805_6.3V6M

2

1

C121

10U_0805_6.3V6M

2

10uF 1206 X5R -> 85 degree

1

C470

10U_0805_6.3V6M

2

1

C108

10U_0805_6.3V6M

2

1

C120

10U_0805_6.3V6M

2

1

C459

10U_0805_6.3V6M

2

1

C104

10U_0805_6.3V6M

2

1

C383

10U_0805_6.3V6M

2

X7R

High Frequence Decoupling

1

C445

10U_0805_6.3V6M

2

1

C99

10U_0805_6.3V6M

2

1

C522

10U_0805_6.3V6M

2

Near VCORE regulator.

+CPU_CORE

Vcc-core

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

C,uF ESL,nH

ESR, mohm

3X330uF 9m ohm/3 3.5nH/4

35X10uF

5m ohm/35 0.6nH/35

C358

1

C378

+

2

1

C377

+

+

2

2

330U_D2_2.5VM_R9

330U_D2_2.5VM_R9

1

@

330U_D2_2.5VM_R9

330U_D2_2.5VM_R9

1

C357

+

2

ESR <= 3m ohm

Capacitor > 880 uF

B B

+VCCP

1

C664

0.1U_0402_10V6K

2

+VCCP

1

+

C525

150U_D2_6.3VM_R15

2

A A

1

C665

0.1U_0402_10V6K

2

1

C498

0.1U_0402_10V6K

2

1

C666

0.1U_0402_10V6K

2

1

C499

0.1U_0402_10V6K

2

1

C667

0.1U_0402_10V6K

2

1

C504

0.1U_0402_10V6K

2

1

C668

0.1U_0402_10V6K

2

1

C500

0.1U_0402_10V6K

2

1

C669

0.1U_0402_10V6K

2

1

C503

0.1U_0402_10V6K

2

1

C670

0.1U_0402_10V6K

2

1

C463

0.1U_0402_10V6K

2

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

1

C671

0.1U_0402_10V6K

2

1

C441

0.1U_0402_10V6K

2

2005/03/01 2006/03/01

1

C672

0.1U_0402_10V6K

2

1

C424

0.1U_0402_10V6K

2

Compal Secret Data

Deciphered Date

1

C673

0.1U_0402_10V6K

2

1

C450

0.1U_0402_10V6K

2

2

1

C398

0.1U_0402_10V6K

2

Custom

Title

Dothan Bypass

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

744

Page 8

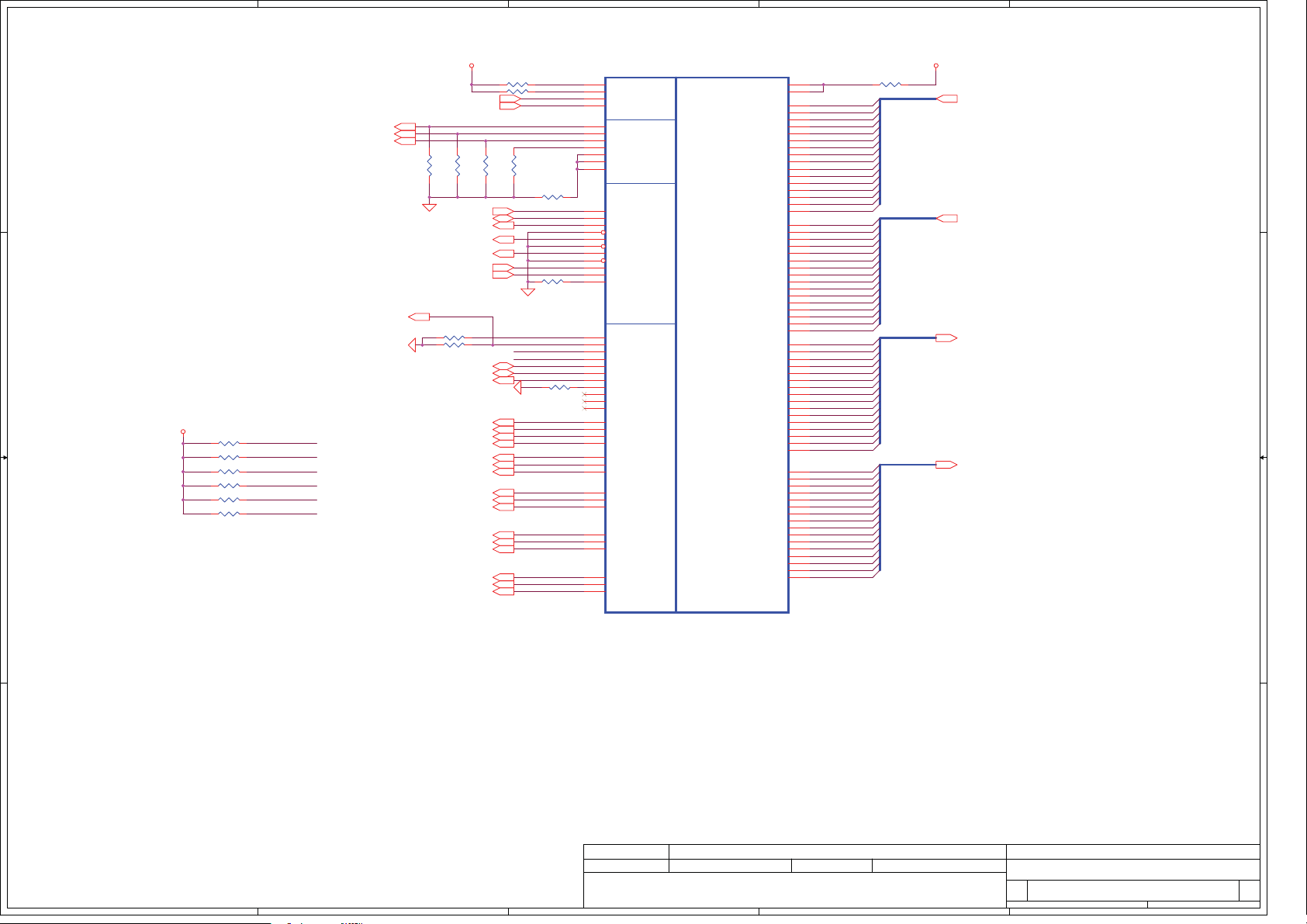

5

4

3

2

1

Layout Guide will show these

signals routed differentially.

DMI_TXN020

H_A#[3..31]5

D D

H_REQ#[0..4]5

C C

Layout Guide will show

these signals routed

differentially.

H_DSTBN#[0..3]5

H_DSTBP#[0..3]5

B B

H_RS#[0..2]5

H_CPUSLP#5,19

Note:

"Do not install R418 for Dothan-A,

Install R418 for Dothan-B"

A A

T1 PAD@

H_ADSTB#05

H_ADSTB#15

CLK_MCH_BCLK#17

CLK_MCH_BCLK17

H_DINV#05

H_DINV#15

H_DINV#25

H_DINV#35

H_RESET#5

H_ADS#5

H_TRDY#5

H_DPWR#5

H_DRDY#5

H_DEFER#5

@

T27 PAD

H_HITM#5

H_HIT#5

H_LOCK#5

H_BR0#5

H_BNR#5

H_BPRI#5

H_DBSY#5

R418

0_0402_5%

1 2

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_EDRDY#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_R_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

H_R_CPUSLP#

U5A

G9

HA3#

Alviso

C9

HA4#

E9

HA5#

B7

HA6#

A10

HA7#

F9

HA8#

D8

HA9#

B10

HA10#

E10

HA11#

G10

HA12#

D9

HA13#

E11

HA14#

F10

HA15#

G11

HA16#

G13

HA17#

C10

HA18#

C11

HA19#

D11

HA20#

C12

HA21#

B13

HA22#

A12

HA23#

F12

HA24#

G12

HA25#

E12

HA26#

C13

HA27#

B11

HA28#

D13

HA29#

A13

HA30#

F13

HA31#

A11

HPCREQ#

A7

HREQ#0

D7

HREQ#1

B8

HREQ#2

C7

HREQ#3

A8

HREQ#4

B9

HADSTB#0

E13

HADSTB#1

AB1

HCLKN

AB2

HCLKP

G4

HDSTBN#0

K1

HDSTBN#1

R3

HDSTBN#2

V3

HDSTBN#3

G5

HDSTBP#0

K2

HDSTBP#1

R2

HDSTBP#2

W4

HDSTBP#3

H8

HDINV#0

K3

HDINV#1

T7

HDINV#2

U5

HDINV#3

H10

HCPURST#

F8

HADS#

B5

HTRDY#

G6

HDPWR#

F7

HDRDY#

E6

HDEFER#

F6

HEDRDY#

D6

HHITM#

D4

HHIT#

B3

HLOCK#

E7

HBREQ0#

A5

HBNR#

D5

HBPRI#

C6

HDBSY#

G8

HCPUSLP#

A4

HRS0#

C5

HRS1#

B4

HRS2#

ALVISO_BGA1257

Layout Note:

H_XRCOMP & H_YRCOMP trace width

and spacing is 10/20

HOST

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

H_SWNG0

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

J11

C1

C2

T1

L1

D1

P1

C362

0.1U_0402_16V4Z

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_SWNG0

H_SWNG1

R397

1

R388

2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

12

221_0603_1%

12

100_0402_1%

1 2

R44 24.9_0402_1%

1 2

R77 24.9_0402_1%

10/20 mils

H_SWNG1

1

2

C385

0.1U_0402_16V4Z

H_D#[0..63] 5

+SDREF_DIMM

+VCCP

12

R41

R66

54.9_0402_1%

54.9_0402_1%

+VCCP+VCCP

12

R67

221_0603_1%

12

R73

100_0603_1%

+1.8V

R835

1K_0402_5%

1 2

R836

1K_0402_5%

1 2

+1.8V

12

R489

80.6_0402_1%

12

+VCCP

12

R372

100_0402_1%

1

12

C379

R376

2

200_0402_1%

0.1U_0402_16V7K

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

DMI_TXN120

DMI_TXN220

DMI_TXN320

DMI_TXP020

DMI_TXP120

DMI_TXP220

DMI_TXP320

DMI_RXN020

DMI_RXN120

DMI_RXN220

DMI_RXN320

DMI_RXP020

DMI_RXP120

DMI_RXP220

DMI_RXP320

DDR_CLK013

DDR_CLK113

DDR_CLK314

DDR_CLK414

DDR_CLK0#13

DDR_CLK1#13

DDR_CLK3#14

DDR_CLK4#14

DDR_CKE0_DIMMA13

DDR_CKE1_DIMMA13

DDR_CKE2_DIMMB14

DDR_CKE3_DIMMB14

DDR_SCS#013

DDR_SCS#113

DDR_SCS#214

DDR_SCS#314

@

T43 PAD

@

T44 PAD

M_ODT013

M_ODT113

M_ODT214

M_ODT314

1 2

R484 80.6_0402_1%

+SDREF_DIMM

CFG[2:0]

CFG5

CFG6

CFG7

CFG9

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

CFG18

(VCC Select)

CFG19

(VTT Select)

2005/03/01 2006/03/01

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DDR_CLK0

DDR_CLK1

DDR_CLK3

DDR_CLK4

DDR_CLK0#

DDR_CLK1#

DDR_CLK3#

DDR_CLK4#

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

M_OCDOCMP0

M_OCDOCMP1

SMRCOMPN

SMRCOMPP

1

1

C428

C419

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Refer to sheet 6 for FSB

frequenc y select

Low = DMI x 2

High = DMI x 4

Low = DDR-II

High = DDR-I

Low = DT/Transportable CPU

High = Mobile CPU

Low = Reverse Lane

High = Normal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation (Default)

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

Low = 1.05V (Default)

High = 1.2V

Compal Secret Data

Deciphered Date

AA31

AB35

AC31

AD35

AA35

AB31

AC35

AA33

AB37

AC33

AD37

AA37

AB33

AC37

AM33

AE11

AJ34

AC10

AN33

AE10

AJ33

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AE27

AE28

AF10

*

*

*

Y31

Y33

AL1

AF6

AK1

AF5

AD1

AF9

U5B

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO_BGA1257

*

*

*

*

2

DMIDDR MUXING

DREF_SSCLKP

CLK

DREF_SSCLKN

*

Alviso CFG[17:3] has internal pull-up

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

CFG/RSVD

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

PM

DREF_CLKN

DREF_CLKP

NC10

NC

NC11

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

D37

C37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

MCH_CLKSEL1

MCH_CLKSEL0

CFG5

CFG6

CFG7

CFG9

CFG12

CFG13

CFG16

CFG18

CFG19

PM_EXTTS#0

PM_EXTTS#1

PLTRST_R#

R384

10K_0402_5%@

R387

10K_0402_5%

MCH_CLKSEL1 17

MCH_CLKSEL0 17

1 2

R492 100_0402_1%

12

12

@

T25PAD

T26PAD

CFG0

G16

CFG[17:3] have internal pull-up

CFG0

R367 10K_0402_5%

CFG6

R369 2.2K_0402_5%

CFG5

R370 2.2K_0402_5%@

CFG7

R368 2.2K_0402_5%@

CFG9

R394 2.2K_0402_5%@

CFG12

R374 2.2K_0402_5%@

CFG13

R375 2.2K_0402_5%@

CFG16

R430 2.2K_0402_5%@

CFG[19:18] have internal pull-down

3.5 k reserve for choose

CFG18

CFG19

Custom

Title

Alviso(1/5)-GTL/DMI/DDR-MUX

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

@

@

PM_BMBUSY# 20

PM_EXTTS#0

PM_EXTTS#1

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R36 1K_0402_5%@

R37 1K_0402_5%@

1

H_THERMTRIP# 5,19

VGATE 17,20,42

PLTRST_MCH# 18

DREFCLK# 17

DREFCLK 17

SSC_DREFCLK 17

SSC_DREFCLK# 17

R366 10K_0402_5%

12

R365 10K_0402_5%

12

12

1 2

1 2

844

+2.5VS

+VCCP

+2.5VS

of

Page 9

5

D D

4

3

2

1

DDR_A_BS#013

DDR_A_BS#113

DDR_A_BS#213

DDR_A_DM[0..7]13

DDR_A_DQS[0..7]13

DDR_A_DQS#[0..7]13

C C

DDR_A_MA[0..13]13

DDR_A_CAS#13

DDR_A_RAS#13

@

T36 PAD

@

T35 PAD

DDR_A_WE#13

B B

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

DDR_A_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AK36

AP33

AN29

AP23

AM8

AM4

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

AP9

AP4

AJ2

AD3

AJ1

AE5

AE4

U5C

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

ALVISO_BGA1257

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

DDR MEMORY SYSTEM A

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_D0

AG35

DDR_A_D[0..63] 13

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

DDR_B_BS#014

DDR_B_BS#114

DDR_B_BS#214

DDR_B_DM[0..7]14

DDR_B_DQS[0..7]14

DDR_B_DQS#[0..7]14

DDR_B_MA[0..13]14

DDR_B_CAS#14

DDR_B_RAS#14

@

T33 P AD

@

T34 P AD

DDR_B_WE#14

DDR_B_BS#0

DDR_B_BS#1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

TP_MB_RCVENIN#

TP_MB_RCVENOUT#

DDR_B_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

U5D

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

ALVISO_BGA1257

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

DDR SYSTEM MEMORY B

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

DDR_B_D1DDR_B_D1

DDR_B_D2DDR_B_D2

DDR_B_D3DDR_B_D3

DDR_B_D4DDR_B_D4

DDR_B_D5DDR_B_D5

DDR_B_D6DDR_B_D6

DDR_B_D7DDR_B_D7

DDR_B_D8DDR_B_D8

DDR_B_D9DDR_B_D9

DDR_B_D10DDR_B_D10

DDR_B_D11DDR_B_D11

DDR_B_D12DDR_B_D12

DDR_B_D13DDR_B_D13

DDR_B_D14DDR_B_D14

DDR_B_D15DDR_B_D15

DDR_B_D16DDR_B_D16

DDR_B_D17DDR_B_D17

DDR_B_D18DDR_B_D18

DDR_B_D19DDR_B_D19

DDR_B_D20DDR_B_D20

DDR_B_D21DDR_B_D21

DDR_B_D22DDR_B_D22

DDR_B_D23DDR_B_D23

DDR_B_D24DDR_B_D24

DDR_B_D25DDR_B_D25

DDR_B_D26DDR_B_D26

DDR_B_D27DDR_B_D27

DDR_B_D28DDR_B_D28

DDR_B_D29DDR_B_D29

DDR_B_D30DDR_B_D30

DDR_B_D31DDR_B_D31

DDR_B_D32DDR_B_D32

DDR_B_D33DDR_B_D33

DDR_B_D34DDR_B_D34

DDR_B_D35DDR_B_D35

DDR_B_D36DDR_B_D36

DDR_B_D37DDR_B_D37

DDR_B_D38DDR_B_D38

DDR_B_D39DDR_B_D39

DDR_B_D40DDR_B_D40

DDR_B_D41DDR_B_D41

DDR_B_D42DDR_B_D42

DDR_B_D43DDR_B_D43

DDR_B_D44DDR_B_D44

DDR_B_D45DDR_B_D45

DDR_B_D46DDR_B_D46

DDR_B_D47DDR_B_D47

DDR_B_D48DDR_B_D48

DDR_B_D49DDR_B_D49

DDR_B_D50DDR_B_D50

DDR_B_D51DDR_B_D51

DDR_B_D52DDR_B_D52

DDR_B_D53DDR_B_D53

DDR_B_D54DDR_B_D54

DDR_B_D55DDR_B_D55

DDR_B_D56DDR_B_D56

DDR_B_D57DDR_B_D57

DDR_B_D58DDR_B_D58

DDR_B_D59DDR_B_D59

DDR_B_D60DDR_B_D60

DDR_B_D61DDR_B_D61

DDR_B_D62DDR_B_D62

DDR_B_D63DDR_B_D63

DDR_B_D0DDR_B_D0

AE31

DDR_B_D[0..63] 14

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

Custom

Title

Alviso(2/5)-DDR A/B

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

944

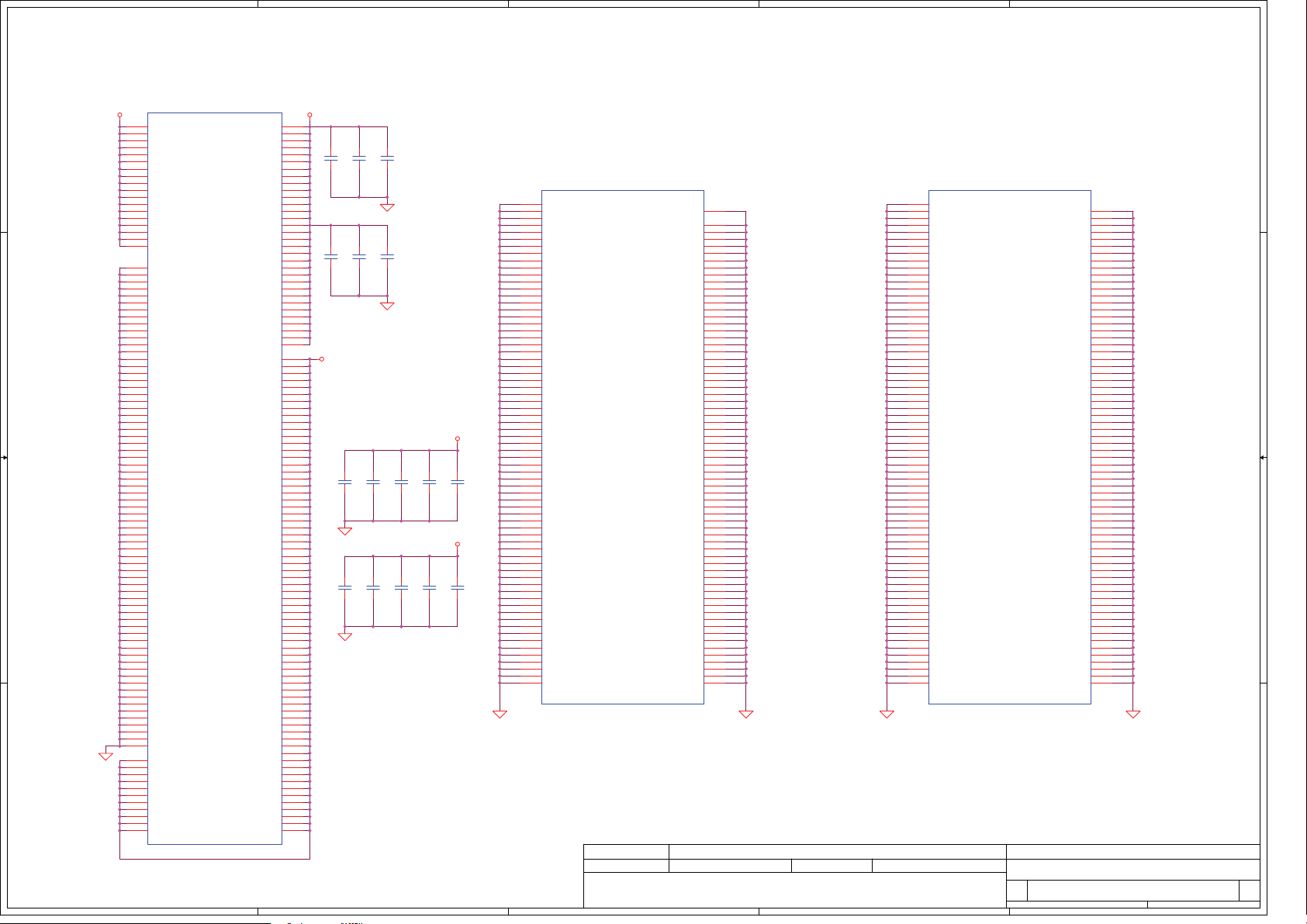

Page 10

5

4

3

2

1

+1.5VS_PCIE+2.5VS

PEGCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

R40 24.9_0603_1%

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

This Symbol as same as Intel CRB

schematic, So Layout Guide will show

these signals routed differentially.

PEG_TXN[0..15]

PEG_TXP[0..15]

PEG_RXN[0..15] 15

PEG_RXP[0..15] 15

PEG_TXN[0..15] 15

PEG_TXP[0..15] 15

0_0402_5%

12

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

U5G

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO_BGA1257

EXP_RXN0/SDVO_TVCLKIN#

EXP_RXN1/SDVO_INT#

MISCTVVGALVDS

EXP_RXN2/SDVO_FLDSTALL#

EXP_RXP0/SDVO_TVCLKIN

EXP_RXP1/SDVO_INT

EXP_RXP2/SDVO_FLDSTALL

EXP_TXN0/SDVOB_RED#

EXP_TXN1/SDVOB_GREEN#

EXP_TXN2/SDVOB_BLUE#

EXP_TXN3/SDVOB_CLKN

EXP_TXN4/SDVOC_RED#

EXP_TXN5/SDVOC_GREEN#

EXP_TXN6/SDVOC_BLUE#

EXP_TXN7/SDVOC_CLKN

PCI - EXPRESS GRAPHICS

EXP_TXP0/SDVOB_RED

EXP_TXP1/SDVOB_GREEN

EXP_TXP2/SDVOB_BLUE

EXP_TXP3/SDVOB_CLKP

EXP_TXP4/SDVOC_RED

EXP_TXP5/SDVOC_GREEN

EXP_TXP6/SDVOC_BLUE

EXP_TXP7/SDVOC_CLKP

EXP_COMPI

EXP_ICOMPO

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

R29 3K_0402_5%@

1 2

R30 3K_0402_5%@

12

R34

150_0402_1%

1@

12

1 2

12

R428

4.99K_0603_1%

BIA

BK_EN

LCTLA_CLK

LCTLB_DAT

LCD_CLK

LCD_DAT

EN_LCDVDD

LVDS_ACLVDS_AC+

LVDS_BCLVDS_BC+

LVDS_A0LVDS_A1LVDS_A2-

LVDS_A0+

LVDS_A1+

LVDS_A2+

LVDS_B0LVDS_B1LVDS_B2-

LVDS_B0+

LVDS_B1+

LVDS_B2+

R392

1@

1 2

CLK_DDC2

DAT_DDC2

1 2

R429

255_0402_1%

R378

1.5K_0402_1%

CLK_MCH_3GPLL#17

CLK_MCH_3GPLL17

D D

C C

+2.5VS

1 2

R362 2.2K_0402_5%

1 2

R363 2.2K_0402_5%

1 2

R385 2.2K_0402_5%

1 2

R364 2.2K_0402_5%

1 2

R360 2.2K_0402_5%

1 2

R361 2.2K_0402_5%

B B

LCD_CLK

LCD_DAT

LCTLA_CLK

LCTLB_DAT

CLK_DDC2

DAT_DDC2

COMP/B16

Y/G16

C/R16

BK_EN15

12

R33

R32

150_0402_1%

1@

1@

R396 100K_0402_1%

1 2

1 2

R404 100K_0402_1%

150_0402_1%

CLK_DDC216

DAT_DDC216

CRT_BLU16

CRT_GRN16

CRT_RED16

VSYNC16

HSYNC16

LCD_CLK15

LCD_DAT15

EN_LCDVDD15

LVDS_AC-15

LVDS_AC+15

LVDS_BC-15

LVDS_BC+15

LVDS_A0-15

LVDS_A1-15

LVDS_A2-15

LVDS_A0+15

LVDS_A1+15

LVDS_A2+15

LVDS_B0-15

LVDS_B1-15

LVDS_B2-15

LVDS_B0+15

LVDS_B1+15

LVDS_B2+15

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

http://hobi-elektronika.net

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

Custom

Title

Alviso(3/5)-PCI-E/LVDS/TV

Size Document Number Rev

LA-3091 1.0

Tuesday, Janua ry 10, 2006

Date: Sheet

1

of

10 44

Page 11

5

+VCCP

1

C392

C391

D D

C C

B B

2

2.2U_0805_10V6K

4.7U_0805_6.3V6K

C29

0.47U_0603_16V7K

12

C28

0.47U_0603_16V7K

12

12

C74

0.22U_0603_10V7K

12

C52

0.22U_0603_10V7K

0.1U_0402_16V4Z

1

C674

2

U5F

K13

VTT0

J13

VTT1

K12

VTT2

W11

VTT3

V11

1

VTT4

U11

VTT5

T11

VTT6

R11

VTT7

2

P11

POWER

VTT8

N11

VTT9

M11

VTT10

L11

VTT11

K11

VTT12

W10

VTT13

V10

VTT14

U10

VTT15

T10

VTT16

R10

VTT17

P10

VTT18

N10

VTT19

M10

VTT20

K10

VTT21

J10

VTT22

Y9

VTT23

W9

VTT24

U9

VTT25

R9

VTT26

P9

VTT27

N9

VTT28

M9

VTT29

L9

VTT30

J9

VTT31

N8

VTT32

M8

VTT33

N7

VTT34

M7

VTT35

N6

VTT36

M6

VTT37

A6

VTT38

N5

VTT39

M5

VTT40

N4

VTT41

M4

VTT42

N3

VTT43

M3

VTT44

N2

VTT45

M2

VTT46

B2

VTT47

V1

VTT48

N1

VTT49

M1

VTT50

G1

VTT51

ALVISO_BGA1257

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

Note : All VCCSM pin

shorted internally.

Note: Place near chip.

10U_1206_6.3V6M

C127

1

2

C429

+VCCP

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C675

C676

2

2

0.1U_0402_16V4Z

1

1

C677

C678

2

2

C478

4

W=20 mils

C468

+VCCP

1

1

1

C393

0.1U_0402_16V7K

C855

4.7U_0805_6.3V6K

0.1U_0402_16V4Z

C680

0.1U_0402_16V4Z

C683

C388

2

2

2

0.1U_0402_16V4Z

4.7U_0805_6.3V6K

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C681

2

1

C684

2

1

C682

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C685

2

2

1

1

1

C443

2

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

+1.8V

10U_1206_6.3V6M

330U_D2_3VM

1

C135

C130

1

+

2

2

+1.5VS

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+1.5VS_MPLL

0.1U_0402_16V7K

0.1U_0402_16V7K

C465

1

2

0.1U_0402_16V7K

C475

1

1

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

1

C413

C412

2

2

2

C408

0.1U_0402_16V4Z

T29

R29

N29

M29

K29

J29

V28

U28

T28

R28

P28

N28

M28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

K20

V19

U19

K19

W18

V18

T18

K18

K17

AC1

AC2

B23

C35

AA1

AA2

0.1U_0402_16V4Z

1

C411

2

U5E

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCD_HMPLL1

VCCD_HMPLL2

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

ALVISO_BGA1257

1

2

POWER

+1.8V

0.1U_0402_16V4Z

1

C418

2

C420

0.1U_0402_16V4Z

3

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCDQ_TVDAC

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

VCC_SYNC

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

H20

F19

E19

G19

+3VS

1

C355

2

0.1U_0402_16V4Z

+1.5VS_PM

+2.5VS_PM

R740 0_0603_5%1@

1 2

4.7U_0805_6.3V6K

1

C473

C131

2

0.1U_0402_16V4Z

VCC_SYNC

+2.5VS_CRT

1

2

C372

0.1U_0402_16V4Z

1

2

100U_D2_10VM

2

+3VS

C366

0.022U_0402_16V7K

1

1

2

2

R736 0_0603_5%1@

R737 0_0603_5%2@

R738 0_0603_5%2@

R739 0_0603_5%1@

C329

C353

0.022U_0402_16V7K

1 2

1 2

1 2

1 2

1

2

+1.5VS

1

1

2

2

C341

0.1U_0402_16V4Z

+2.5VS

1

C340

0.1U_0402_16V4Z

2

C339

0.022U_0402_16V7K

+2.5VS_LVDSPM

+1.5VS_PCIE

+

1

1

+

C380

2

C452

220U_D2_4VM

Route VSSA3GBG gnd from GMCH to

decoupling cap ground lead and

then conne c t to the gnd plane.

1

C433

2

2

10U_1206_6.3V6M

10U_1206_6.3V6M

+1.5VS

Close B26,B25,A25

C336

0.022U_0402_16V7K

R741

0_0603_5%

1

2

0.1U_0402_16V4Z

1

C30

2

10U_1206_6.3V6M

2@

C126

10U_1206_6.3V6M

C371

C354

1

2

0.1U_0402_16V4Z

+1.5VS_PM

0.1U_0402_16V4Z

1

2

12

R134

0.5_0805_1%

1 2

1

2

10U_1206_6.3V6M

1

2

L14 0_0603_5%

L26 0_0603_5%

3GRLL_R

1

C365

0.1U_0402_16V4Z

2

R838

0_0603_5%

1 2

R31

0_0402_5%

1

1

2

2

C349

0.1U_0402_16V4Z

+1.5VS

+2.5VS

+2.5VS

+1.5VS_3GPLL

C399

Note : R31, R837 stuff for Ext. VGA.

R28, R838 no stuff for Int. VGA.

VCC_SYNC

+2.5VS_PM

1

1

C352

C346

2

2

0.1U_0402_16V4Z

0.01U_0402_16V7K

12

L13

MBK1608301YZF_0603

C128

0.1U_0402_16V4Z

L9

12

0_0603_5%

12

1@

2@

12

+1.5VS

12

+2.5VS

+VCCP

+2.5VS

C334

10U_1206_6.3V6M

1

2

+2.5VS+2.5VS_3GBG

1

1

1

C342

2

2

0.1U_0402_16V4Z

+1.5VS

1

C438

2

0.1U_0402_16V4Z

1

C31

0.1U_0402_16V4Z

2

+1.5VS+1.5VS_DDRDLL

1

C140

2

0.1U_0402_16V4Z

+1.5VS_DPLLA

0.1U_0402_16V4Z

330U_D2_3VM

1

C345

C330

Note : C330, C348 No stuff for Ext. VGA.

Stuff for Int. VGA.

1

+

2

2

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS