Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

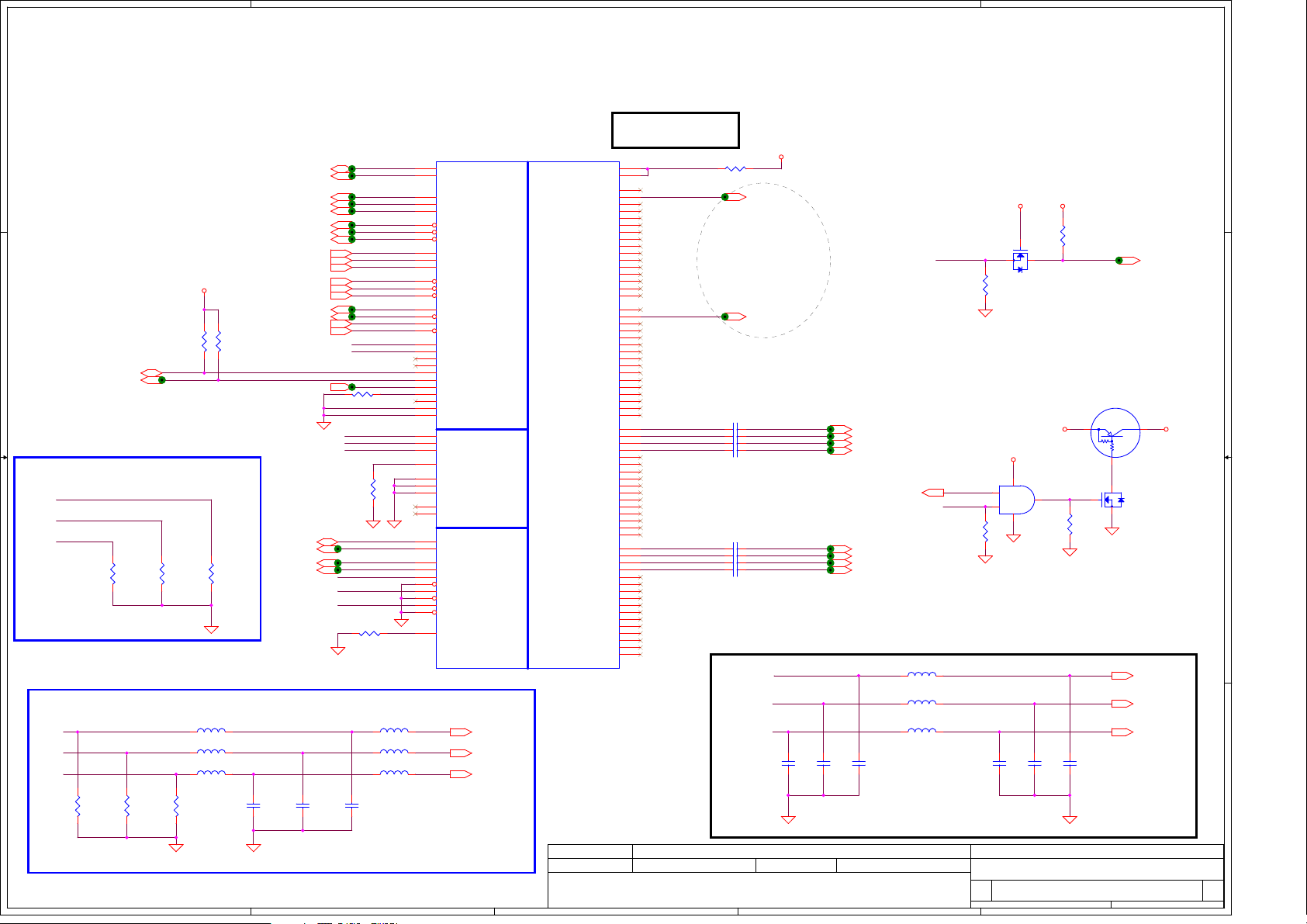

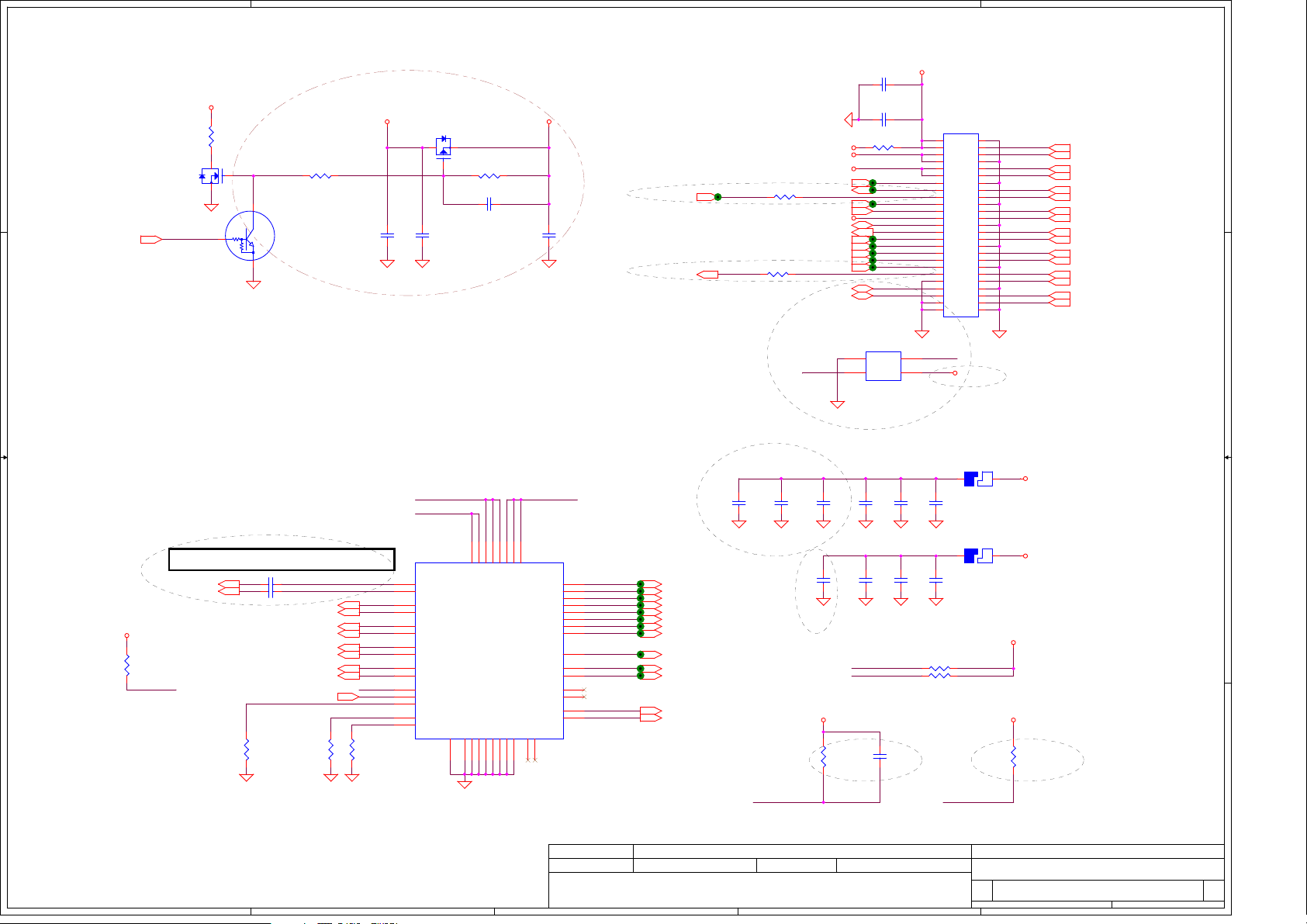

Schematics Document

Mobile Yonah uFCPGA with Intel

Calistoga_GM+ICH7-M core logic

3 3

4 4

A

B

2006-02-27

REV:0.5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

Feb 27, 2007

Title

Size Docume nt Number Re v

D

Date : Sheet o f

Compal Electronics, Inc.

Cover Sheet

LA-3031P

1 49Tuesd ay, Febru ary 28, 2006

E

0.5

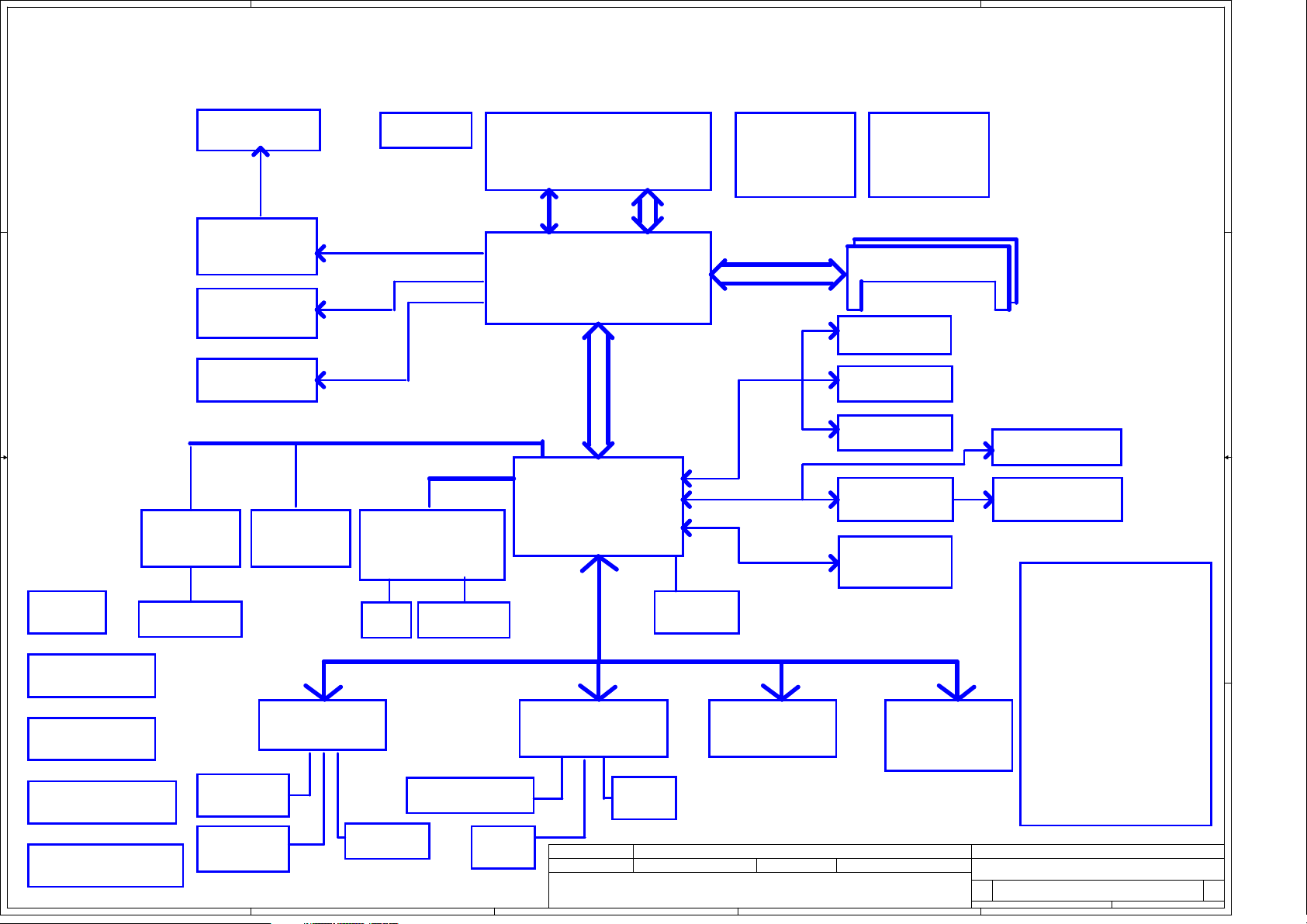

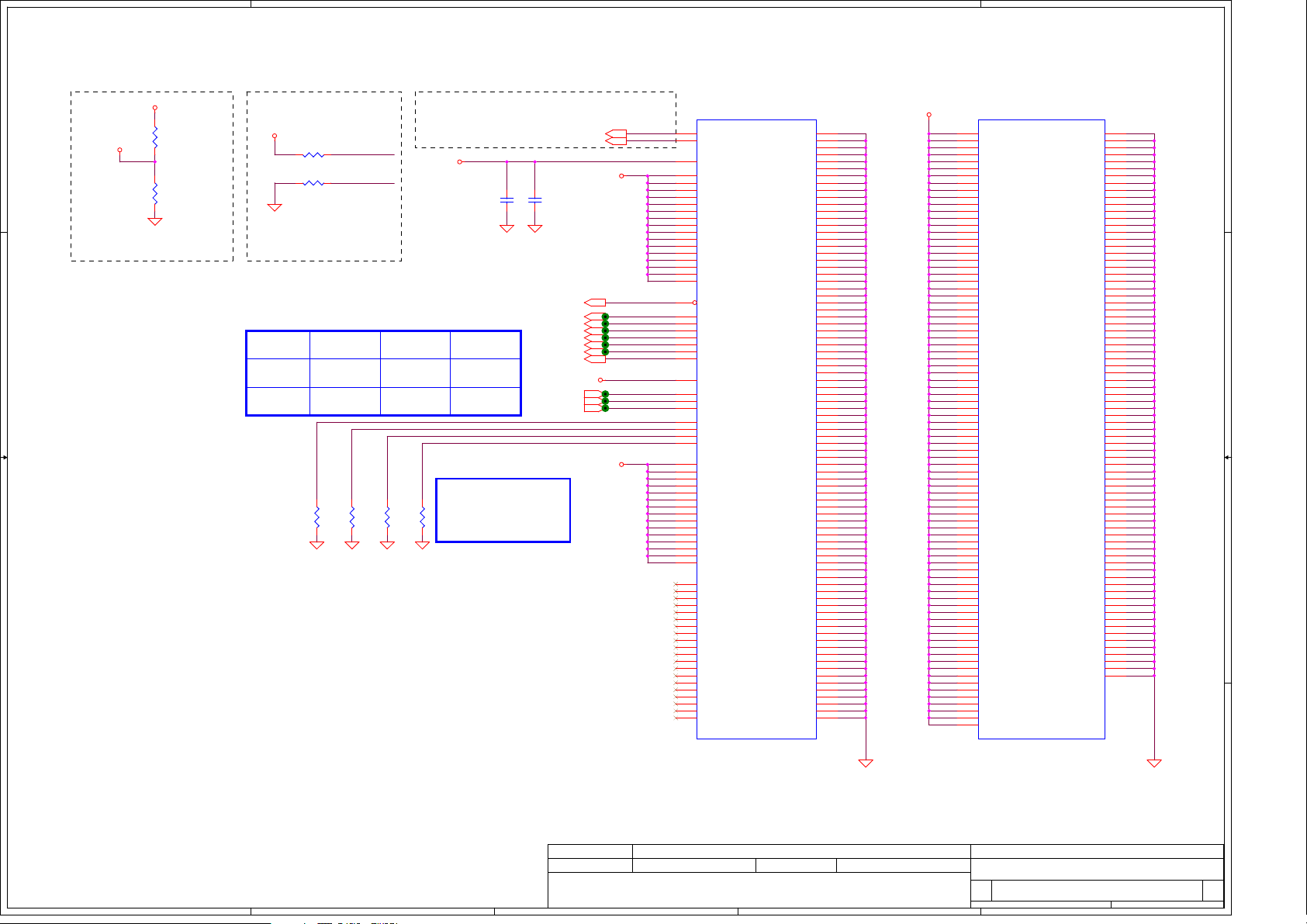

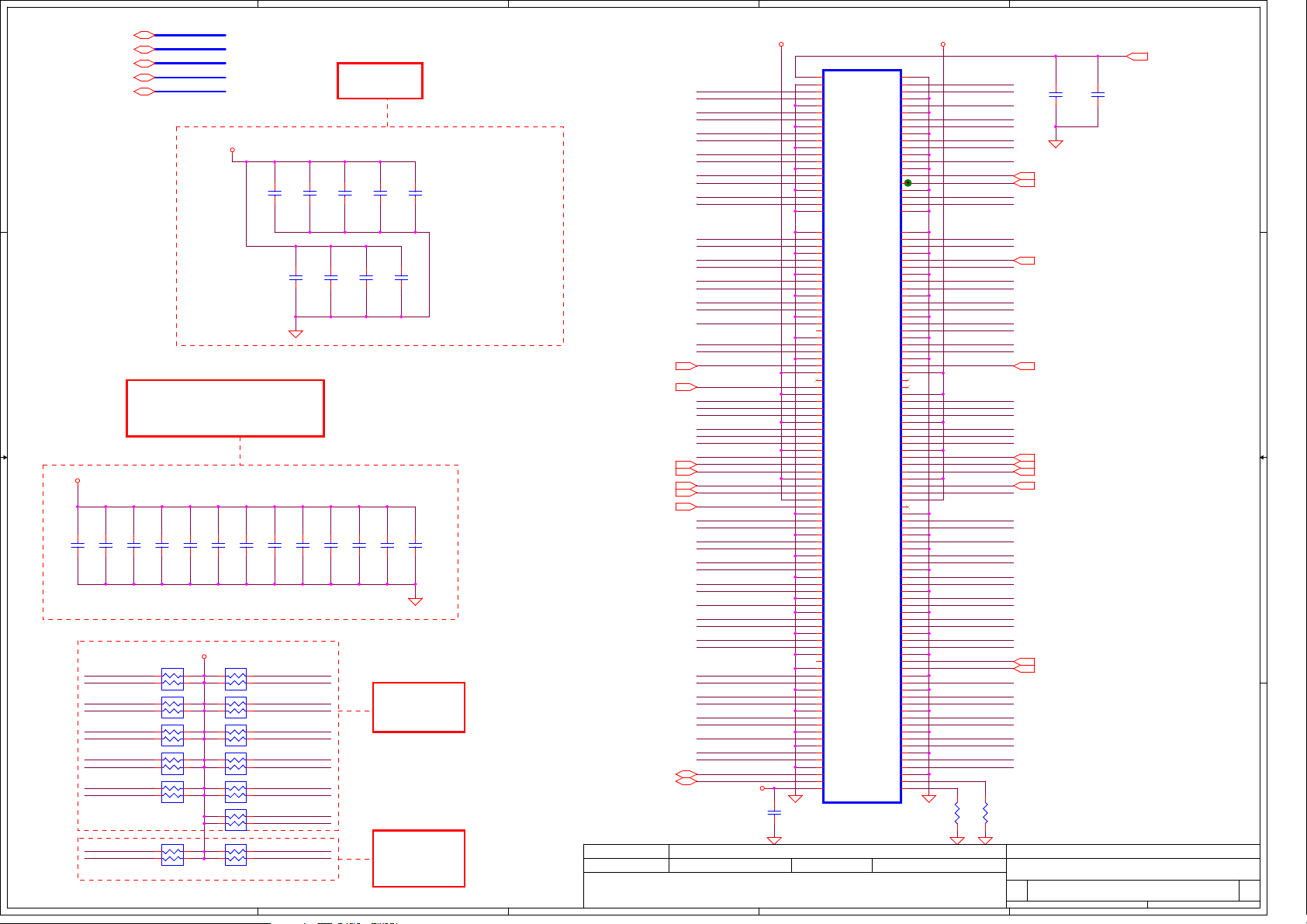

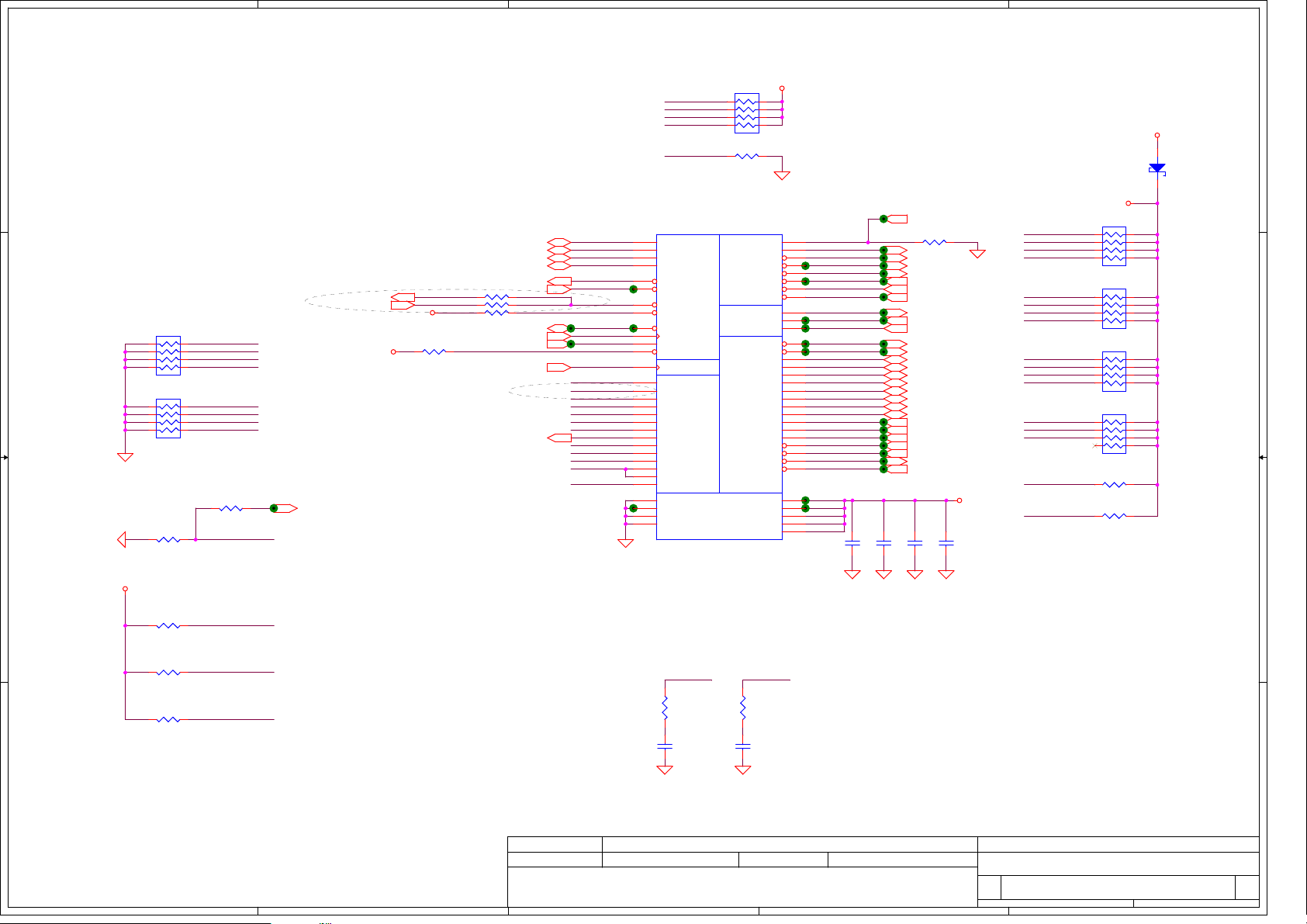

Page 2

A

Compal confidential

File Name : LA-3031

B

C

Heavenly 2.0

D

E

1 1

2 2

DOCK/DVI

page 34

DVI controller

CH 7307C- DE

page 17

CRT/TV-OUT

pag e 16

LCD CONN

page 17 page 29

Fan Control

SD VO

PCI-E BUS

page 4

Mobile Yonah & Merom

uF CPGA-478 CPU

page 4,5,6

H_ A# (3.. 31)

FSB

533/667MHz

Intel Calistoga GMCH

945GM

PCBG A 1466

page 7,8,9,10,11,12

DM I

H_ D#( 0..6 3)

Thermal Sensor

ADM1032AR

page 4

DDR2 -400/533/667

Dual Channel

USB2.0

Clock Generator

IC S9L P306

DDR- SO-DIMM X2

BAN K 0, 1, 2, 3

FingerPrinter

AES2501

page 13,14

page 29

USB conn x3

BT Conn

page 29

page 15

MDC1. 5

page 31

PCI BUS

Intel ICH7-M

Gigabit LAN

BC M 5 75 3M

page 24

3 3

RTC CKT.

page 19

RJ45 /11 CONN

page 25

Mini C ard

socket

page 26

CardBus Controller

TI PCI6 612

page 22,23

Slot 0

page 23

SD/SDIO Slot

page 22

mBGA-652

page 18,19,20,21

SPI ROM

25LF080A

AC-LINK/Azalia

SATA Master

SPI

page 31

LPC BUS

Power OK C KT.

page 36

SMSC Super I/O

Power On/Off CKT.

page 33

4 4

DC/DC Interface CKT.

page 35

COM1 on

Docking side

LPC47N217

page 30

page 30

Touch Pad CONN. Int.KBD

page 33

SMSC KBC 1021

page 32

page 33

page 31

Audio CKT

AD1981HD

page 27

SATA HDD

Co nnector

page 19

SST49LF008A

AMP & Audio Jack

page 28

Docking CONN.

*RJ-45(LED*2)

*RJ-11(Pass Through)

*CRT

*COMPOSITE Video Out

*TVOUT

*DVI

*LINE IN

*LINE OUT

*PCI-E x2

Flash ROMSecurity Module

page 31

*Serial Port

*Parallel Port

*PS/2 x2

*USB x2

*DC JACK

page 34

Power Circuit DC/DC

36,37,38,39,40,41,42,43

A

LPT on

Docking side

page 30

FIR

B

page 30

Digitizer

page 17

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

D

Title

Size Docume nt Number Re v

Date : Sheet o f

Compal Electronics, Inc.

Block Diagram

LA-3031P

2 49Tuesd ay, Febru ary 28, 2006

E

0.5

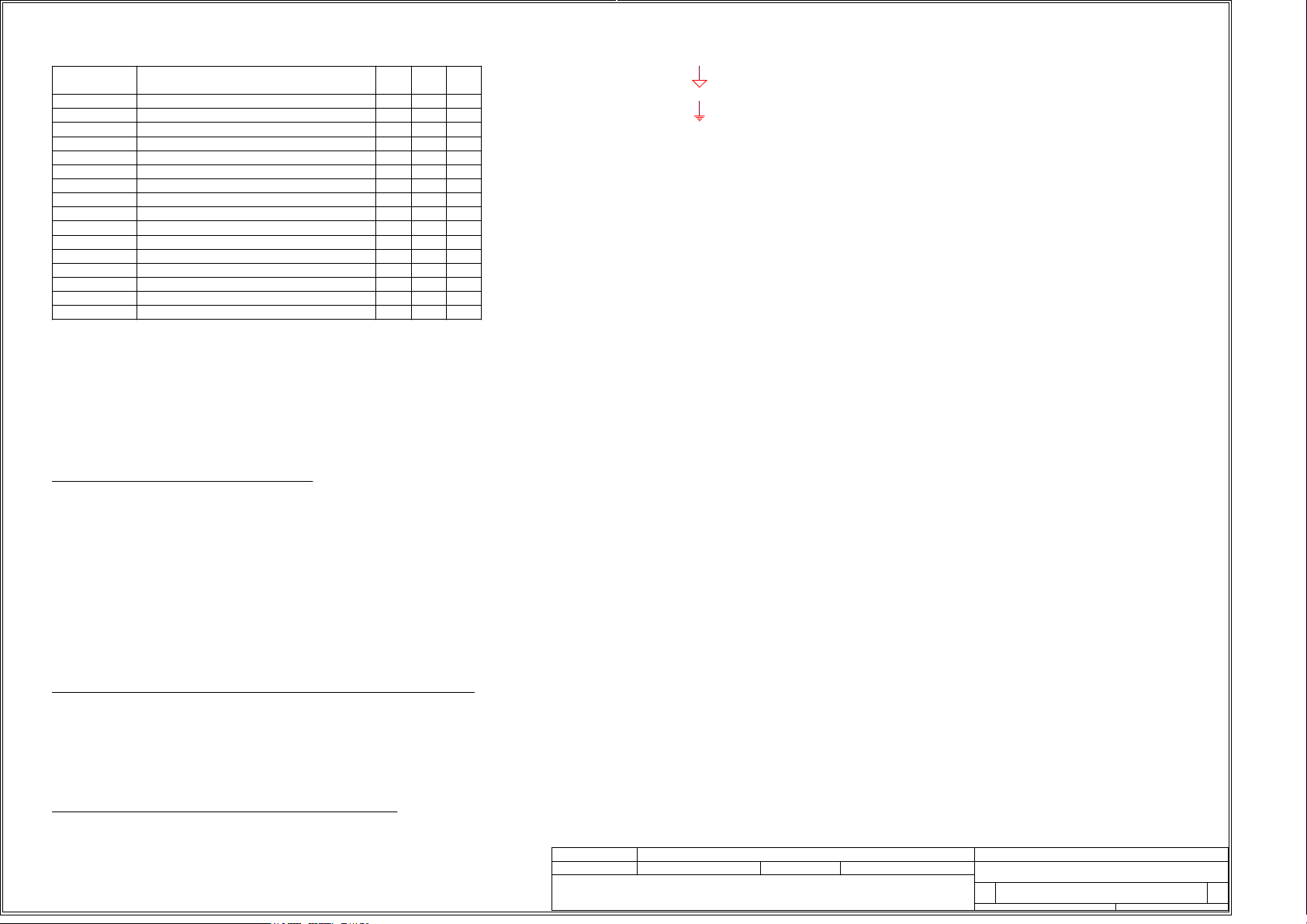

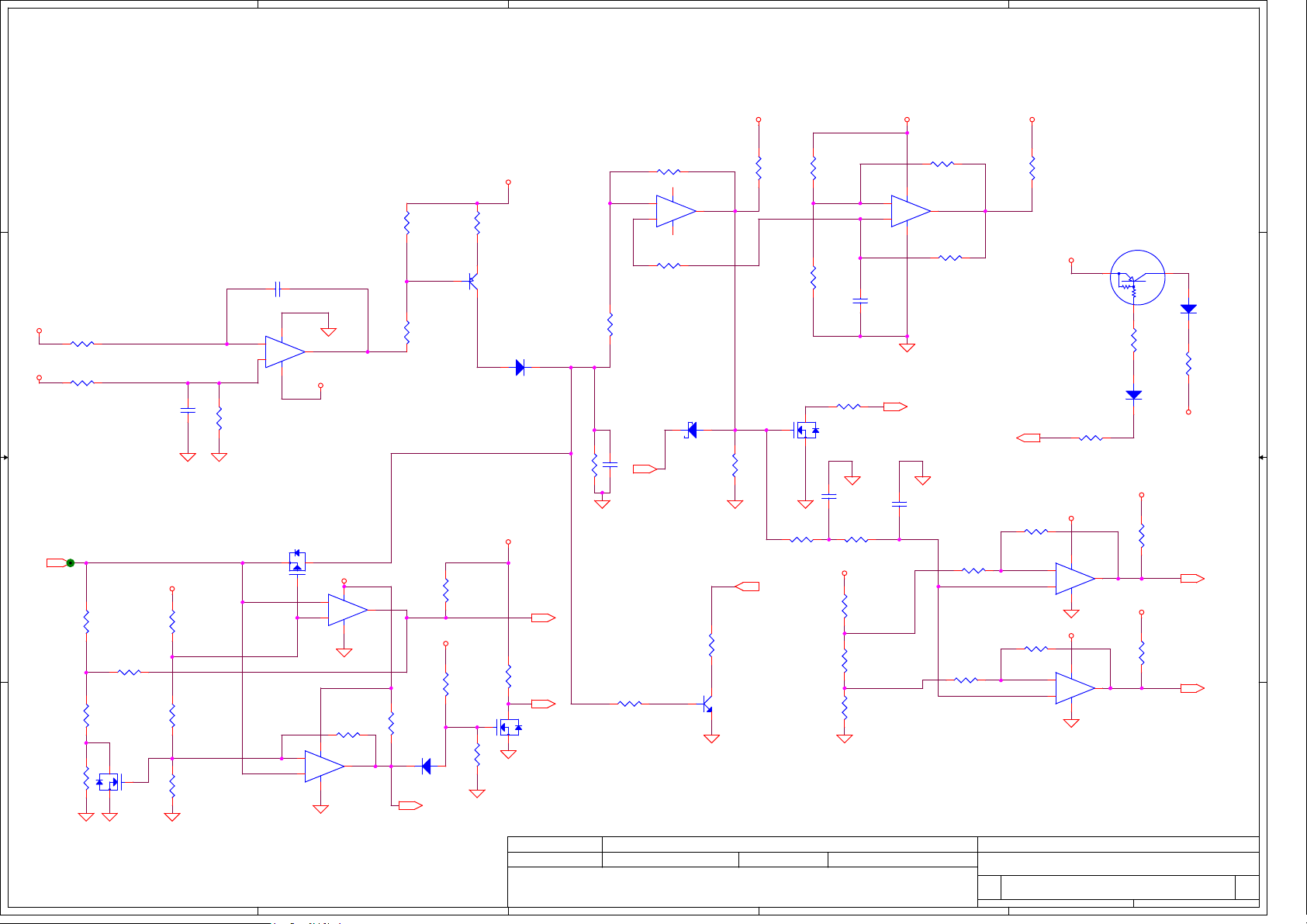

Page 3

A

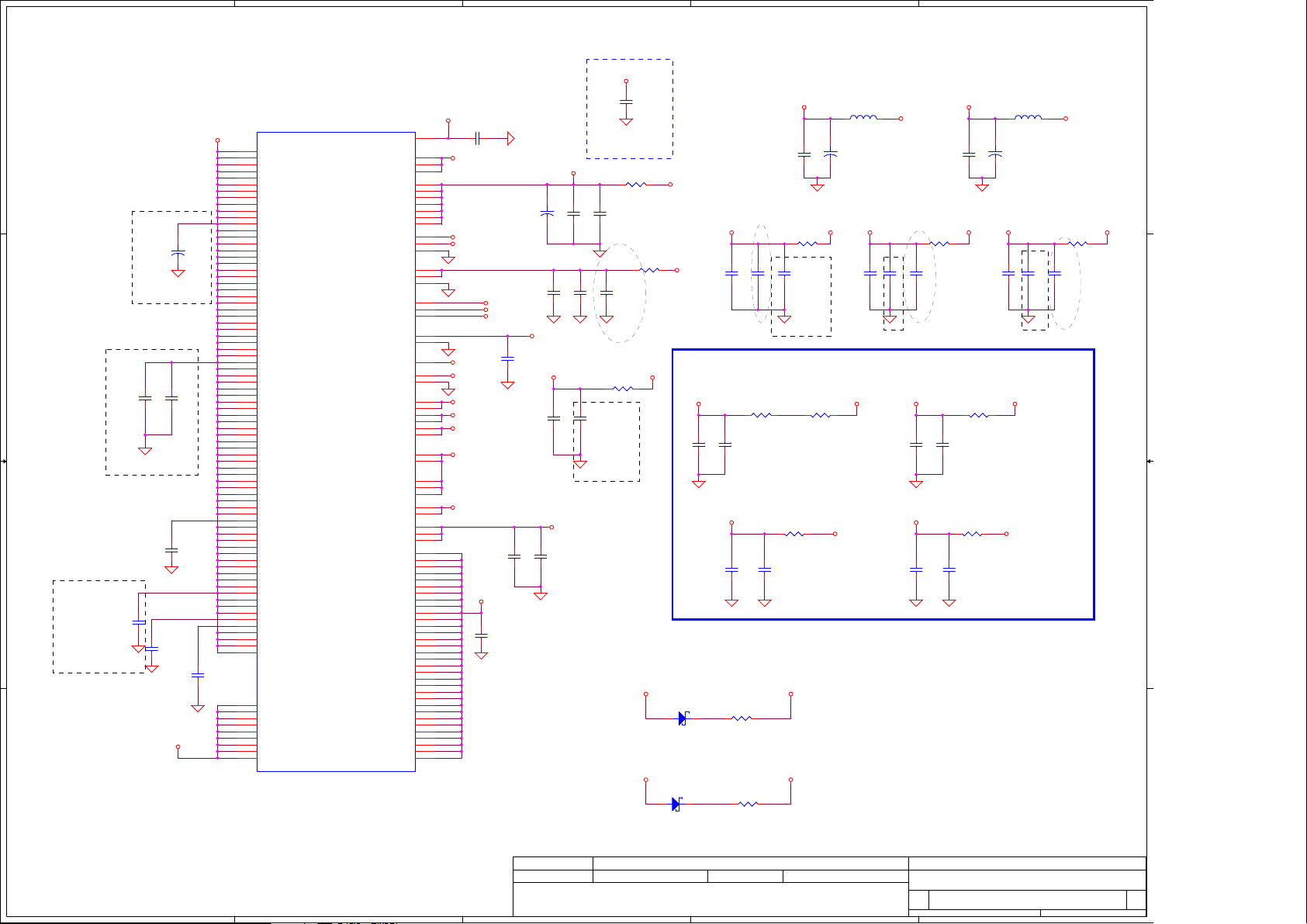

Voltage Rails Symbol note:

Power Plane

VIN

B+

+CPU_CORE

+VCCP

+0.9VS

+1.5VS

+1.8V

+2.5VS

+3VALW

+3V

+5VALW

+5V

+5VS

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Description

Adapter power supply (19V)

AC or battery power rail for power circuit

Core voltage for CPU

1.05V power rail for Processor I/O and MCH core power

0.9V switched power rail for DDRII Vtt

1.5V switched power rail for PCI-E interface

1.8V power rail for DDRII

3.3V always on power rail

3V power rail

3.3V switched power rail+3VS

5V always on power rail

5V power rail

5V switched power rail

RTC power

S0-S1

N/A

ON OFF

ON

ON

ON

ON

ON

ON

ON OFF

ON

ON

ON

ON

S3

N/A

N/A

OFF

OFF

OFF

ON

ON2.5V always on power rail+2.5VALW ON*ON

OFF

ON

ON

OFF

ON

ON

OFF

ON

S5

N/A

N/AN/A

OFF

OFF

OFF

OFF

OFF

OFF2.5V switched power rail for MCH video PLL

ON*

OFF

ON*

OFF

OFF

ONON

:means digital ground.

:means analog ground.

:means reserved.@

@ : means just reserve , no build

SPI@ : means just build when SPI I/F BIOS function enable.

FWH@ : means just build when FWH I/F BIOS function enable.

NOXDP@ : means just build when XDP function disable.

XDP@ : means just build when XDP function enable. When this time, docking PCI express will not work.

TPM@ : means just build when TPM1.2 function enable.

250@ : means just build when SMsC LPC47N250 chip selected.

1021@ : means just build when SMsC KBC1021 chip selected.

45@ : means need be mounted when 45 level assy or rework stage.

ACCEL@ : means just build when Accelerometer chip LIS3LV02DQ selected.

DVI_7307@ : means just build when DVI chip CH7307 selected.

DVI_1362@ : means just build when DVI chip SIL1362 selected.

1 1

Internal PCI Devices

DE VICE

L AN

Az ali a D27

USB1 .1/2 .0

PCI to PC I (D MI to PCI)

AC9 7 MO DEM

AC9 7 Au di o

PA TA /S ATA

LPC I/F

SM BU S

PCI Devi ce ID

D8

D28PCI- E

D29

D30

D30

D30

D31

D31

D31

IDS EL #

AD2 4

AD1 1

AD1 2

AD1 3

AD1 4

AD1 4

AD1 4

AD1 5

AD1 5

AD1 5

(D is ab le d by BI OS )

(D is ab le d by BI OS )

(P AT A is D is abled b y B IOS)

External PCI Devices

DE VICE

CA RD BU S

PCI Devi ce ID

D6

I2C / SMBUS ADDRESSING

DE VICE

DDR S O-DIMM 0

DDR S O-DIMM 1

CL OC K G EN ER ATOR (E XT.)

HEX

A0

A4

D2

IDS EL #

AD2 2

AD DRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 1 0 0

1 1 0 1 0 0 1 0

REQ /G NT #

2

PIR Q

C D E G

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

Title

Size Docume nt Number Re v

Date : Sheet o f

Compal Electronics, Inc.

Notes List

LA-3031P

3 49Tuesd ay, Febru ary 28, 2006

0.5

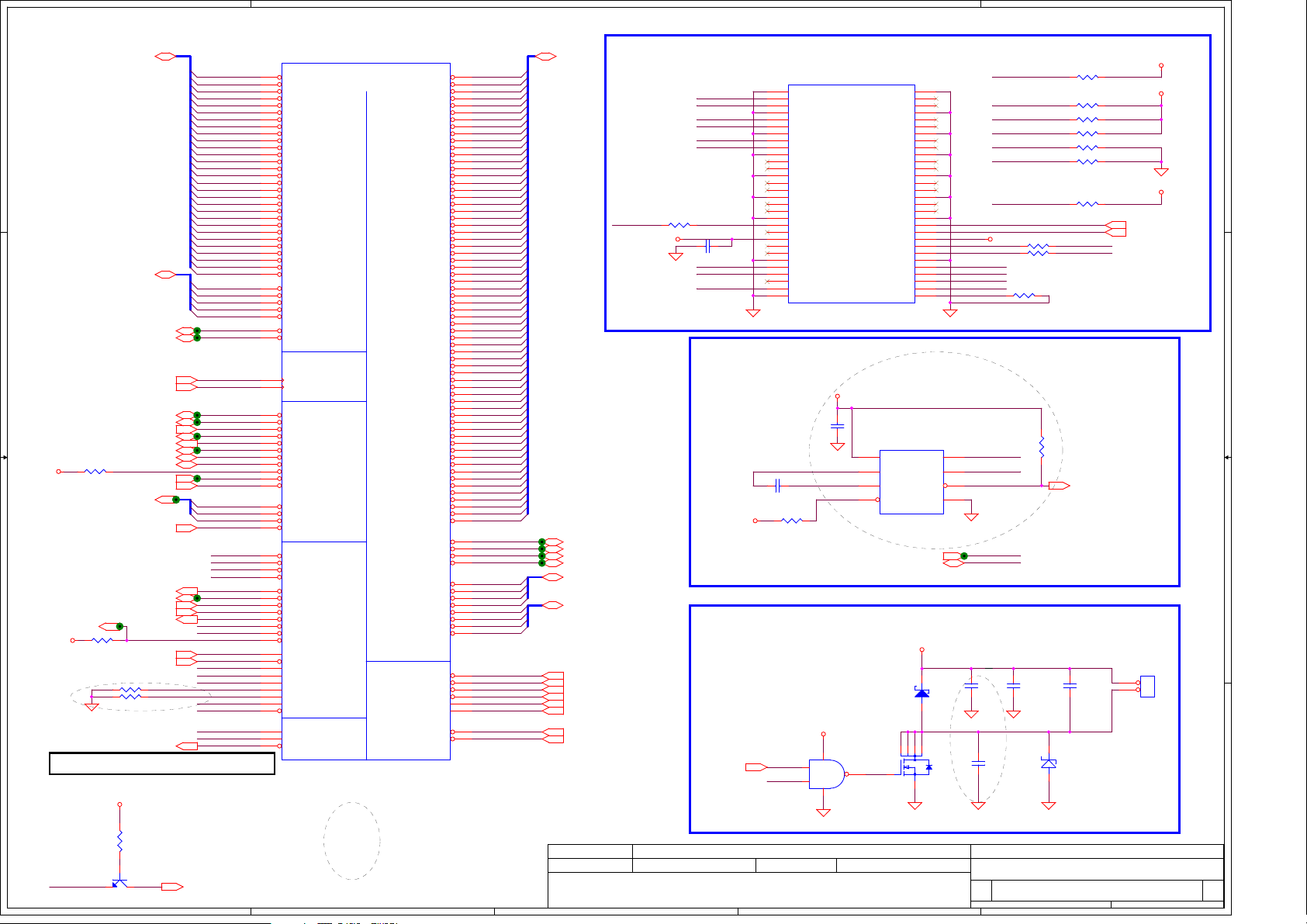

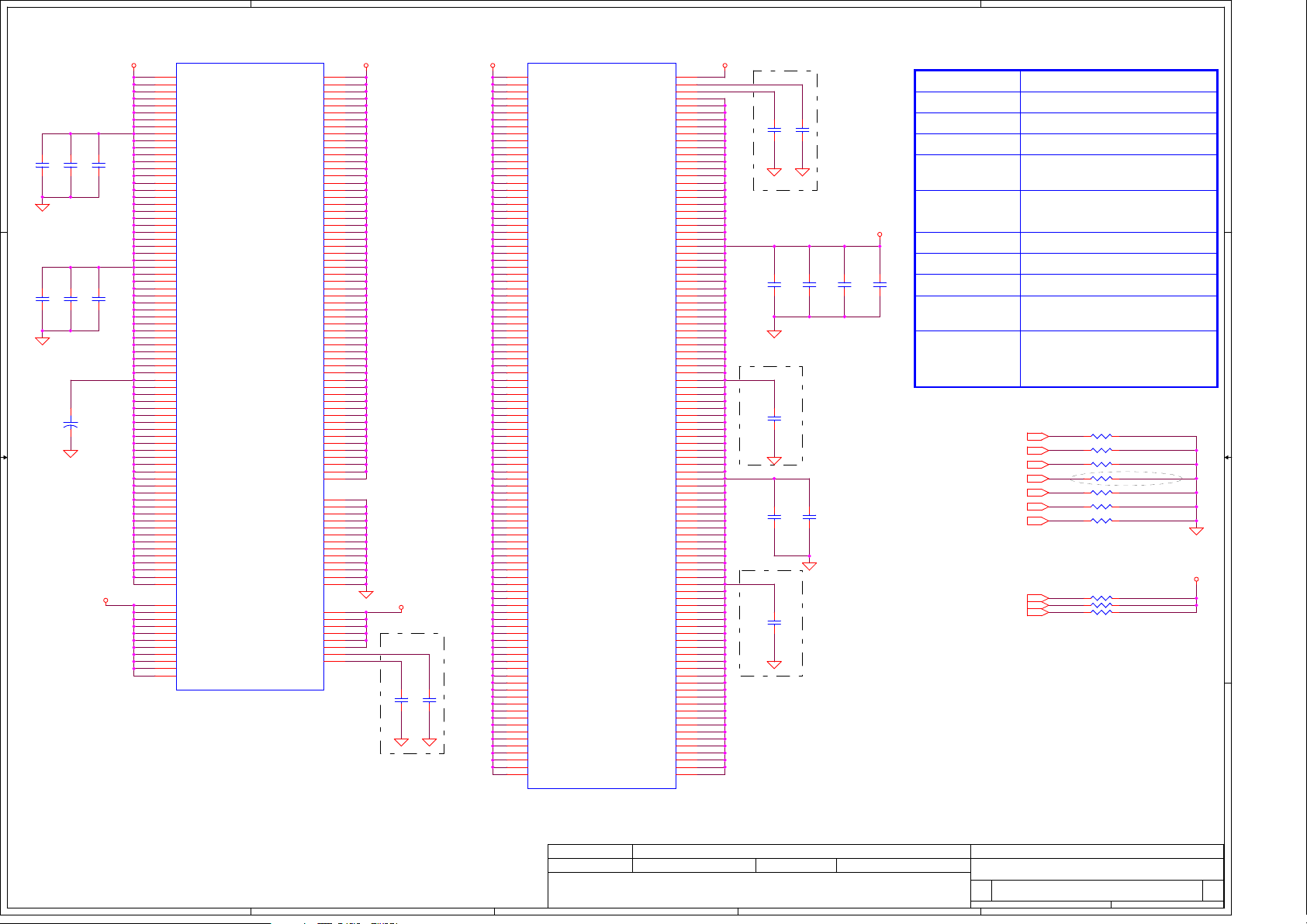

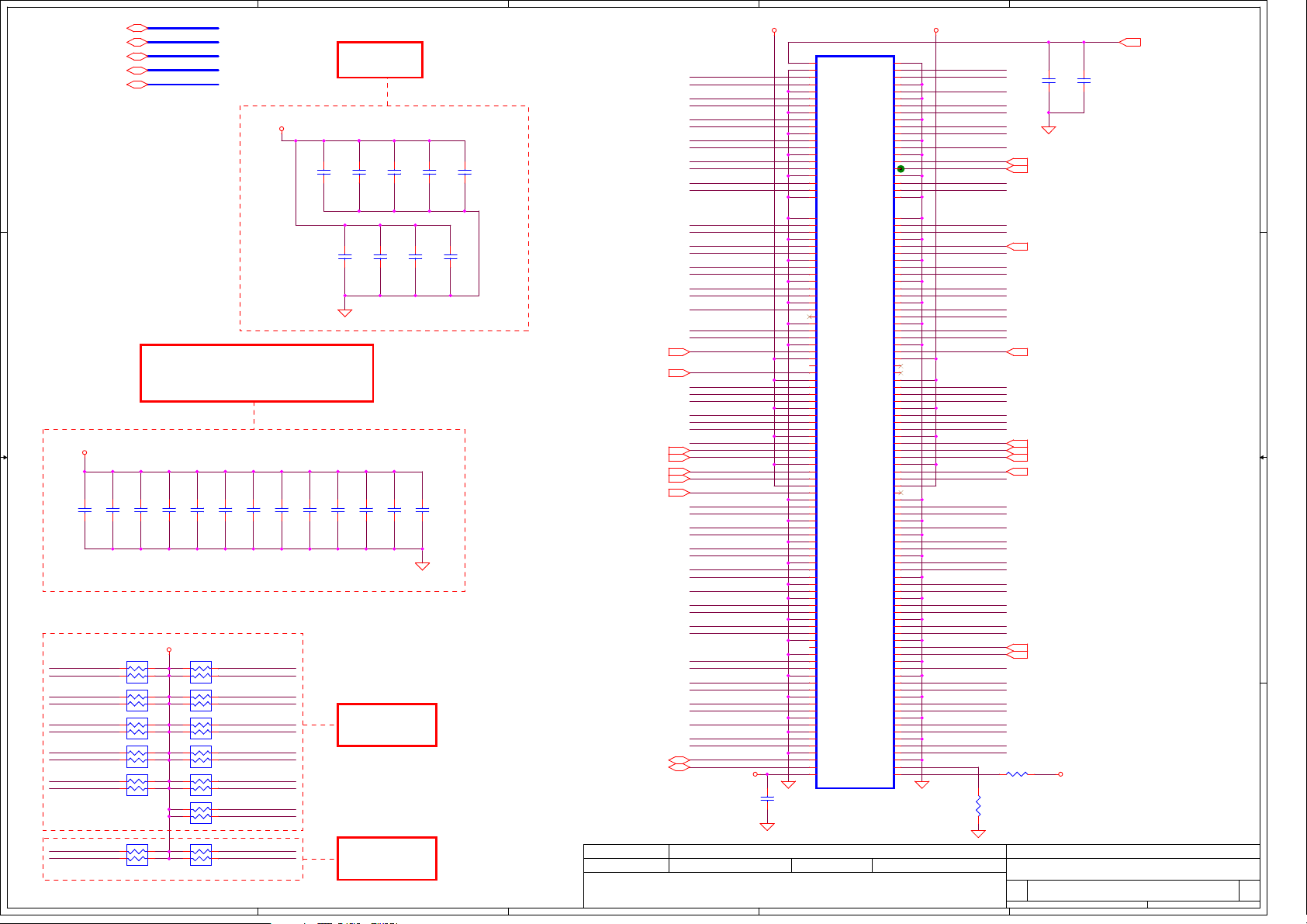

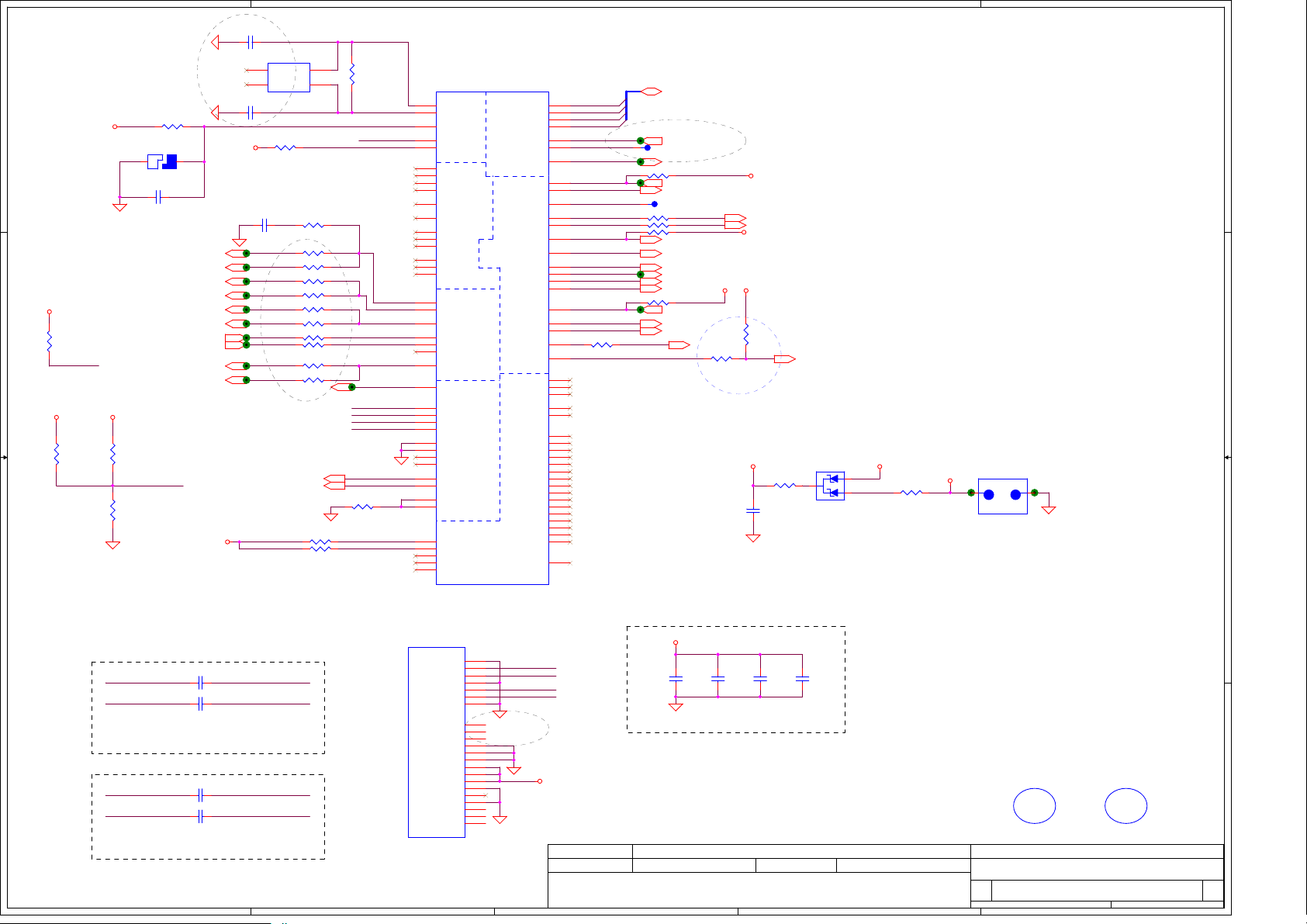

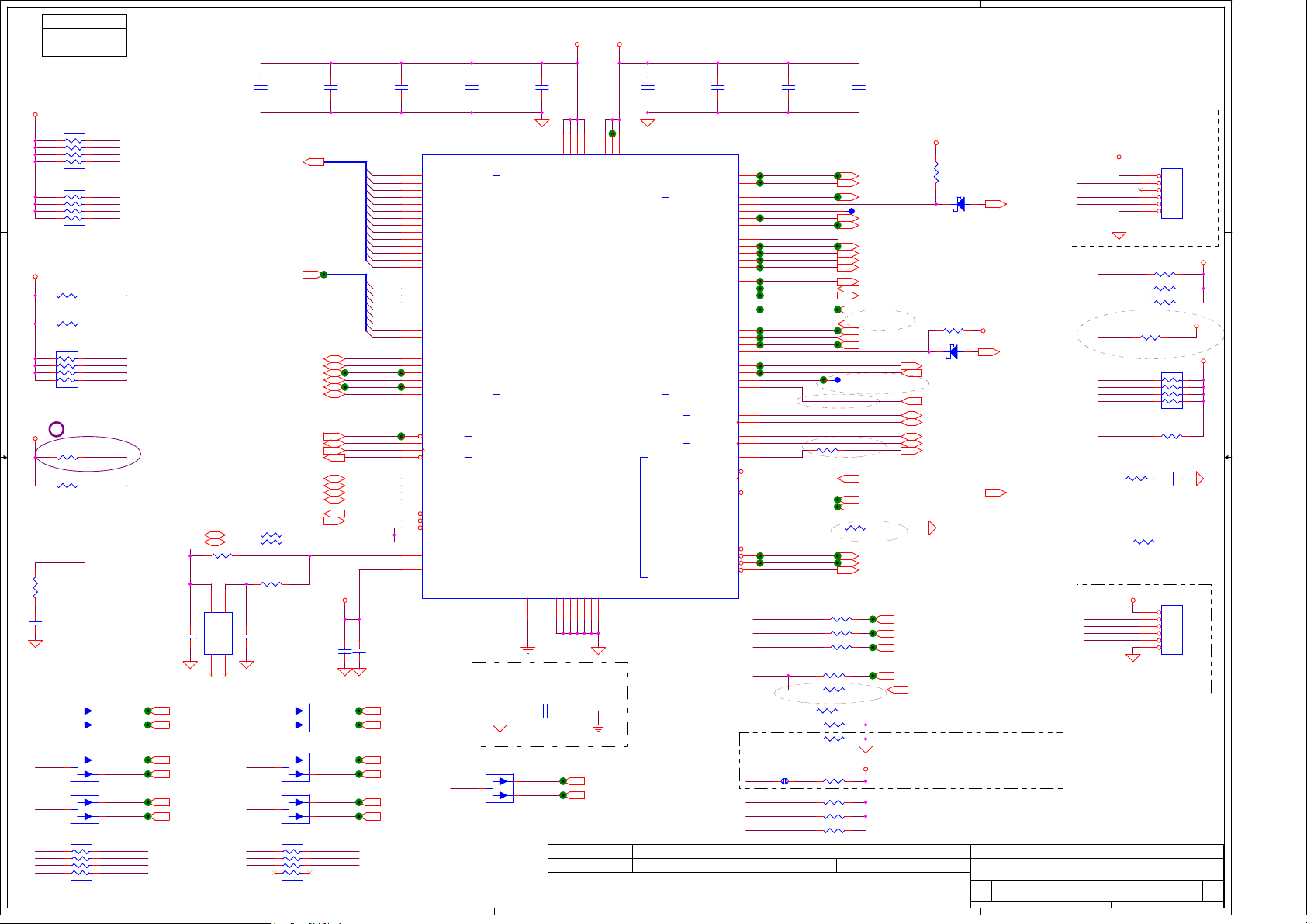

Page 4

5

4

3

2

1

H_A#[3 ..31]7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ# [0..4]7

H_ADSTB#07

C C

R560

56_0402_5%

1 2

+VCCP

B B

H_PROCHOT #43

1 2

+VCCP

68_0402_5%

H_ADSTB#17

CLK_CPU _BCLK15

CLK_CPU_ BCLK#15

H_BPRI#7

H_DEF ER#7

H_D RDY#7

H_HITM#7

H_LOCK#7

H_RESET#7

H_RS# [0..2]7

H_TR DY#7

XDP_DBRESET#20

H_DB SY#7

H_DPSLP#19

H_DPRSTP#19,43

H_DPW R#7

R561

H_PWR GOOD19

H_CPUSLP #7

R562 1K_0402_5%@

1 2

R563 51_0402_5%

1 2

H_ADS#7

H_BNR #7

H_BR0#7

H_HIT#7

7/14

H_THERMDA, H _THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

H_PROCHOT # OCP#

H_THERMTRIP#7,19

+VCCP

12

R564

B

2

E

3 1

Q73

MMBT3904_SOT23

@

56_0402_5%@

C

5

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CP U_BCLK

CLK_CPU _BCLK#

H_ADS#

H_BN R#

H_BPRI #

H_BR0#

H_DEF ER#

H_D RDY#

H_HIT#

H_HITM#

H_I ERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_T RDY#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_DBRESET#

H_DB SY#

H_DPSLP#

H_DPRSTP#

H_DPW R#

XDP_BPM#4

XDP_BPM#5

H_PROCHOT #

H_PW RGOOD

H_CPUSL P#

XDP_TCK

XDP_TDI

XDP_TDO

TEST1

TEST2

XDP_TMS

XDP_TRST#

H_THERMDA

H_THERM DC

H_THERMTRIP#

OCP# 20,44

JP12A

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

ADDR G ROUP

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

AD4

AD3

AD1

AC4

C20

E1

B5

E5

D24

AC2

AC1

D21

D6

D7

AC5

AA6

AB3

C26

D25

AB5

AB6

A24

A25

C7

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMAL

THERMDA

DIODE

THERMDC

THERMTRIP#

FOX_PZ4790 3-2741-42_YONAH

YONAH

DATA GROUP

MISC

LEGACY CPU

7/19

4

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

H_D#0

E22

D0#

H_D#1

F24

D1#

H_D#2

E26

D2#

H_D#3

H22

D3#

H_D#4

F23

D4#

H_D#5

G25

D5#

H_D#6

E25

D6#

H_D#7

E23

D7#

H_D#8

K24

D8#

H_D#9

G24

D9#

H_D#10

J24

H_D#11

J23

H_D#12

H26

H_D#13

F26

H_D#14

K22

H_D#15

H25

H_D#16

N22

H_D#17

K25

H_D#18

P26

H_D#19

R23

H_D#20

L25

H_D#21

L22

H_D#22

L23

H_D#23

M23

H_D#24

P25

H_D#25

P22

H_D#26

P23

H_D#27

T24

H_D#28

R24

H_D#29

L26

H_D#30

T25

H_D#31

N24

H_D#32

AA23

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

W25

H_D#37

U23

H_D#38

U25

H_D#39

U22

H_D#40

AB25

H_D#41

W22

H_D#42

Y23

H_D#43

AA26

H_D#44

Y26

H_D#45

Y22

H_D#46

AC26

H_D#47

AA24

H_D#48

AC22

H_D#49

AC23

H_D#50

AB22

H_D#51

AA21

H_D#52

AB21

H_D#53

AC25

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AE21

H_D#59

AD21

H_D#60

AE25

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

H_DI NV#0

J26

H_DI NV#1

M26

H_DI NV#2

V23

H_DI NV#3

AC20

H_DSTBN#0

H23

H_DSTBN#1

M24

H_DSTBN#2

W24

H_DSTBN#3

AD23

H_DSTBP#0

G22

H_DSTBP#1

N25

H_DSTBP#2

Y25

H_DSTBP#3

AE24

H_A20M#

A6

H_F ERR#

A5

H_IG NNE#

C4

H_INIT #

B3

H_INT R

C6

H_NMI

B4

H_STPCLK#

D5

H_SMI#

A3

H_D#[ 0..63] 7

R556

1K_0402_5%

+VCCP +VCCP

H_DIN V#0 7

H_DIN V#1 7

H_DIN V#2 7

H_DIN V#3 7

H_DST BN#[0..3] 7

H_DST BP#[0..3] 7

H_A20M# 19

H_FE RR# 19

H_IGN NE# 19

H_INIT# 19

H_INT R 19

H_NMI 19

H_STPCLK# 19

H_SMI# 19

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/27 2007/02/27

ITP-XDP Connector

JP19

1

XDP_BPM#5

XDP_BPM#4

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

H_PW RGOOD_RH_PWRGOOD CLK_CPU_XDP

12

12

C590 0.1U_0402_16 V4Z

ICH_SMBDATA

ICH_SMBC LK

XDP_TCK

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

SAMTE_BSH-030-01-L-D-A

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

GND15

TRST#

TMS

GND17

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

CLK_CPU_XDP#

42

44

46

48

50

XDP_TDO

52

TD0

TDI

XDP_TRST#

54

XDP_TDI

56

XDP_TMS

58

XDP_PRE

60

Thermal Sensor ADM1032

+3VS

2

C273

0.1U_0402_ 16V4Z

C264

1 2

2200P_0402_50V7K

1 2

+3VS

PWM Fan Control circuit

FAN_PWM32

THERM#

Compal Secret Data

Deciphered Date

1

U16

1

VDD

H_THERMDA

H_THERM DC THERM_SCI#

R228

10K_0402_5%

+3VS

5

1

INB

2

INA

3

2

3

THERM#

Address:1001 _101

CH751H-40 _SC76

U24

P

4

O

G

TC7SH00FUF _SSOP5

2

SCLK

D+

SDATA

ALERT#

D-

THERM#4GND

ADM1032ARMZ-2REEL MSOP8

ICH_SMBCL K13,14,15,2 0,24,26

ICH_SMBDATA13,14,15,2 0,24,26

+5VS

2 1

6

2

1

G

3

S

4 5

AO6402_TSOP6

ICH_SMBC LK

8

ICH_SMBDATA

7

6

5

ICH_SMBC LK

ICH_SMBDATA

1

D11

2

1000P_0402_50V7K

Q33

D

Title

Size Docume nt Number Re v

Date : Sheet of

XDP_DBRESET#_R

XDP_TDI

XDP_TMS

XDP_BPM#5

XDP_TRST#

XDP_TCK

This shall place near JP19

XDP_TDO

1K_0402_1%

R557

1 2

R558

200_0402_1%

1 2

R549

1 2

This shall place near CPU

R550 56_0402_5%

1 2

R551 56_0402_1%

1 2

R553 56_0402_5%

1 2

R554 56_0402_5%

1 2

R555 56_0402_5%

1 2

R552 56_0402_5%

1 2

H_RESET#H_RESET#_R

XDP_DBRESET#XDP_DBRESET#_R

12

R559

0_0402_5%

9/2

12

R227

10K_0402_5%

THERM_SCI# 20

1

C932

2

7/28

1

C933

2

1000P_0402_50V7K

C122

4.7U_0805_ 10V4Z

12

ZD1

RLZ5.1B_LL 34@

1

C125

2

0.1U_0402_16 V4Z

FAN

Compal Electronics, Inc.

Yonah CPU in mFCPGA479

LA-3031P

1K_0402_5%@

CLK_CPU_XDP 15

CLK_CPU_XDP# 15

ACES_85205-0200

1

JP8

1

2

4 49Tuesd ay, Febru ary 28, 2006

+3VS

+VCCP

+VCCP

0.5

Page 5

5

4

3

2

1

+VCCP

D D

V_CPU_GTLR EF

Close to CPU pin AD26

within 500mils.

C C

B B

12

R567

1K_0402_1%

12

R570

2K_0402_1%

+VCC_C ORE

R568

100_0402_1%

1 2

R569

100_0402_1%

1 2

VCCSENS E

VSSSENSE

Close to CPU pin

within 500mils.

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

12

R571

27.4_0402_1%

0 0

0

12

R573

R572

54.9_0402_1%

Length match within 25 mils

The trace width 18 mils space

7 mils

+1.5VS

1

C592

C591

2

.01U_0402_16V7K

10U_0805_10V4Z

CPU_BSEL0

1

1

12

12

R574

54.9_0402_1%

27.4_0402_1%

1

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any

other toggling signal.

1

2

CPU_V ID043

CPU_V ID143

CPU_V ID243

CPU_V ID343

CPU_V ID443

CPU_V ID543

CPU_V ID643

V_CPU_GTLR EF

CPU_BSEL015

CPU_BSEL115

CPU_BSEL215

VCCSENS E43

VSSSENSE43

H_PSI#43

+VCCP

+VCC_C ORE

VCCSENS E

VSSSENSE

H_PSI#

CPU_ VID0

CPU_ VID1

CPU_ VID2

CPU_ VID3

CPU_ VID4

CPU_ VID5

CPU_ VID6

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

COMP0

COMP1

COMP2

COMP3

JP12B

AF7

VCCSENSE

AE7

VSSSENSE

B26

VCCA

K6

VCCP

J6

VCCP

M6

VCCP

N6

VCCP

YONAH

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

GTLREF

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

FOX_PZ4790 3-2741-42_YONAH

W21

AD26

AB20

AA20

AF20

AE20

AB18

AB17

AA18

AA17

AD18

AD17

AC18

AC17

AF18

AF17

T6

R6

K21

J21

M21

N21

T21

R21

V21

V6

G21

AE6

AD6

AF5

AE5

AF4

AE3

AF2

AE2

B22

B23

C21

R26

U26

U1

V1

E7

D2

F6

D3

C1

AF1

D22

C23

C24

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

T22

B25

+VCC_C ORE

AB26

VSS

AA25

VSS

AD25

VSS

AE26

VSS

AB23

VSS

AC24

VSS

AF24

VSS

AE23

VSS

AA22

VSS

AD22

VSS

AC21

VSS

AF21

VSS

AB19

VSS

AA19

VSS

AD19

VSS

AC19

VSS

AF19

VSS

AE19

VSS

AB16

VSS

AA16

VSS

AD16

VSS

AC16

VSS

AF16

VSS

AE16

VSS

AB13

VSS

AA14

VSS

AD13

VSS

AC14

VSS

AF13

VSS

AE14

VSS

AB11

VSS

AA11

VSS

AD11

VSS

AC11

VSS

AF11

VSS

AE11

VSS

AB8

VSS

AA8

VSS

AD8

VSS

AC8

VSS

AF8

VSS

AE8

VSS

AA5

VSS

AD5

VSS

AC6

VSS

AF6

VSS

AB4

VSS

AC3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

POWER, GROU NG, RE SERVED S IGNALS AND NC

JP12C

AE18

VCC

AE17

VCC

AB15

VCC

AA15

VCC

AD15

VCC

AC15

VCC

AF15

VCC

AE15

VCC

AB14

VCC

AA13

VCC

AD14

VCC

AC13

VCC

AF14

VCC

AE13

VCC

AB12

VCC

AA12

VCC

AD12

AC12

AF12

AE12

AB10

AB9

AA10

AA9

AD10

AD9

AC10

AC9

AF10

AF9

AE10

AE9

AB7

AA7

AD7

AC7

B20

A20

F20

E20

B18

B17

A18

A17

D18

D17

C18

C17

F18

F17

E18

E17

B15

A15

D15

C15

F15

E15

B14

A13

D14

C13

F14

E13

B12

A12

D12

C12

F12

E12

B10

A10

D10

C10

F10

E10

B9

A9

D9

C9

F9

E9

B7

A7

F7

YONAH

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOX_PZ4790 3-2741-42_YONAH

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

Title

Size Docume nt Number Re v

2

Date : Sheet

Compal Electronics, Inc.

Yonah CPU in mFCPGA479

LA-3031P

1

o f

5 49Tuesd ay, Febru ary 28, 2006

0.5

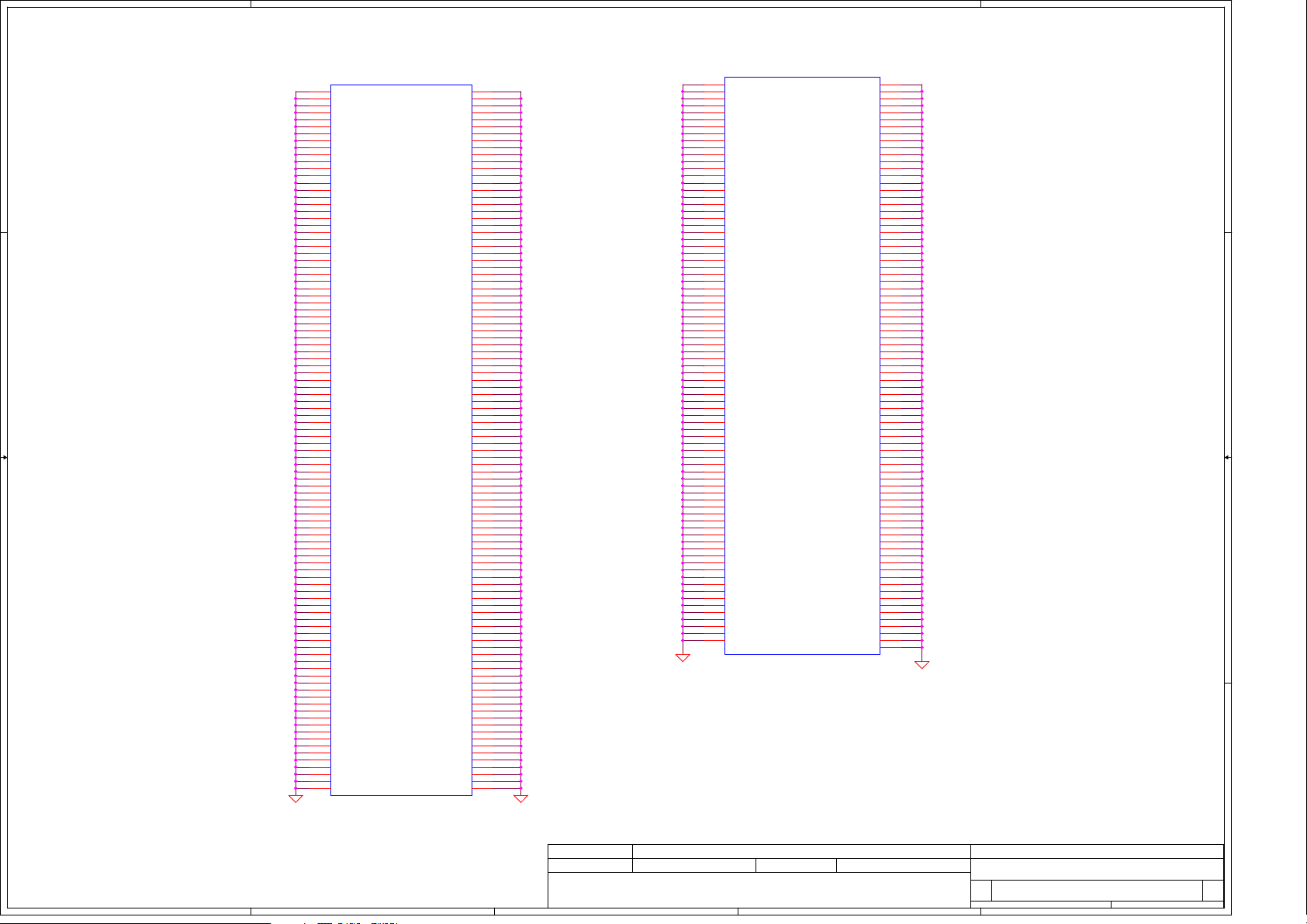

Page 6

5

4

3

2

1

D D

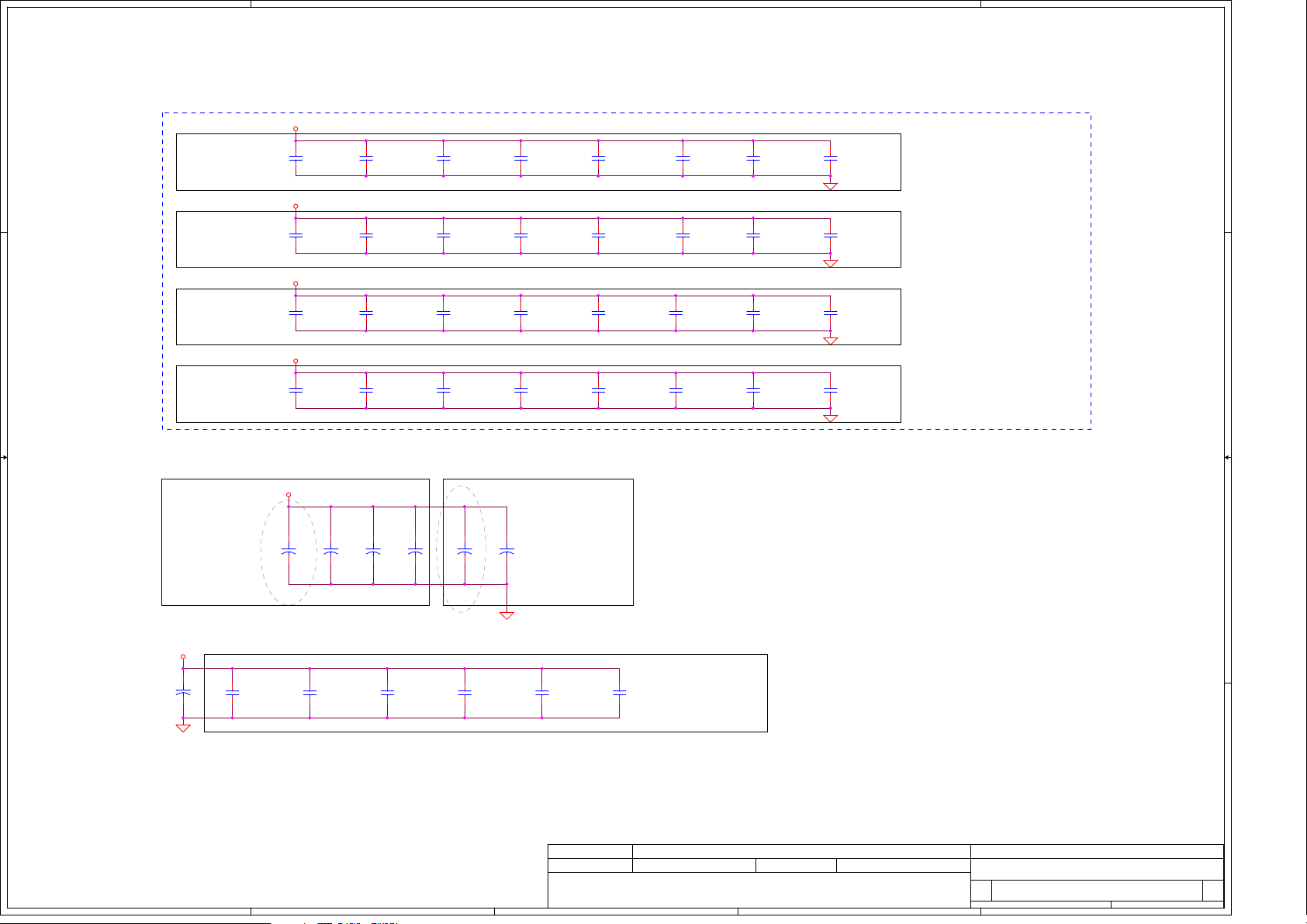

Place these capacitors on L8

(North side ,Secondary Layer)

Place these capacitors on L8

(North side ,Secondary Layer)

Place these capacitors on L8

(Sorth side ,Secondary Layer)

C C

Place these capacitors on L8

(Sorth side ,Secondary Layer)

South Side S econdary

B B

330U_D2E_2. 5VM_R9@

+VCC_C ORE

1

C593

10U_0805_6.3V6M

2

+VCC_C ORE

1

C601

10U_0805_6.3V6M

2

+VCC_C ORE

1

C609

10U_0805_6.3V6M

2

+VCC_C ORE

1

C617

10U_0805_6.3V6M

2

+VCC_C ORE

1

+

C626

C625

2

330U_D2E_2. 5VM_R9

1/4 1/4

330U_D2E_2. 5VM_R9

1

+

C627

2

1

C594

10U_0805_6.3V6M

2

1

C602

10U_0805_6.3V6M

2

1

C610

10U_0805_6.3V6M

2

1

C618

10U_0805_6.3V6M

2

1

+

C628

2

330U_D2E_2. 5VM_R9

@

1

+

2

1

2

1

2

1

2

1

2

330U_D2E_2. 5VM_R9

C629

C595

10U_0805_6.3V6M

C603

10U_0805_6.3V6M

C611

10U_0805_6.3V6M

C619

10U_0805_6.3V6M

1

+

C630

2

1

C596

10U_0805_6.3V6M

2

1

C604

10U_0805_6.3V6M

2

1

C612

10U_0805_6.3V6M

2

1

C620

10U_0805_6.3V6M

2

North Side S econdary

1

+

2

330U_D2E_2. 5VM_R9

1

C597

10U_0805_6.3V6M

2

1

C605

10U_0805_6.3V6M

2

1

C613

10U_0805_6.3V6M

2

1

C621

10U_0805_6.3V6M

2

1

C598

10U_0805_6.3V6M

2

1

C606

10U_0805_6.3V6M

2

1

C614

10U_0805_6.3V6M

2

1

C622

10U_0805_6.3V6M

2

1

C599

10U_0805_6.3V6M

2

1

C607

10U_0805_6.3V6M

2

1

C615

10U_0805_6.3V6M

2

1

C623

10U_0805_6.3V6M

2

ESR = 1.5m ohm

Capacitor = 1980uF

1

C600

10U_0805_6.3V6M

2

1

C608

10U_0805_6.3V6M

2

1

C616

10U_0805_6.3V6M

2

1

C624

10U_0805_6.3V6M

2

Mid Frequence Decoupling

+VCCP

220U_D2_2VK_R9

1

+

C634

2

A A

1

C635

0.1U_0402_16 V4Z

2

1

C636

0.1U_0402_ 16V4Z

2

1

C637

0.1U_0402_16 V4Z

2

1

C638

0.1U_0402_16 V4Z

2

1

C639

0.1U_0402_16 V4Z

2

1

C640

0.1U_0402_16 V4Z

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Place these inside

socket cavi ty on L8

(North side

Secondary)

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

2

Title

Size Docume nt Number Re v

Date : Sheet of

Compal Electronics, Inc.

CPU Bypass capacitors

LA-3031P

6 49Tuesd ay, Febru ary 28, 2006

1

0.5

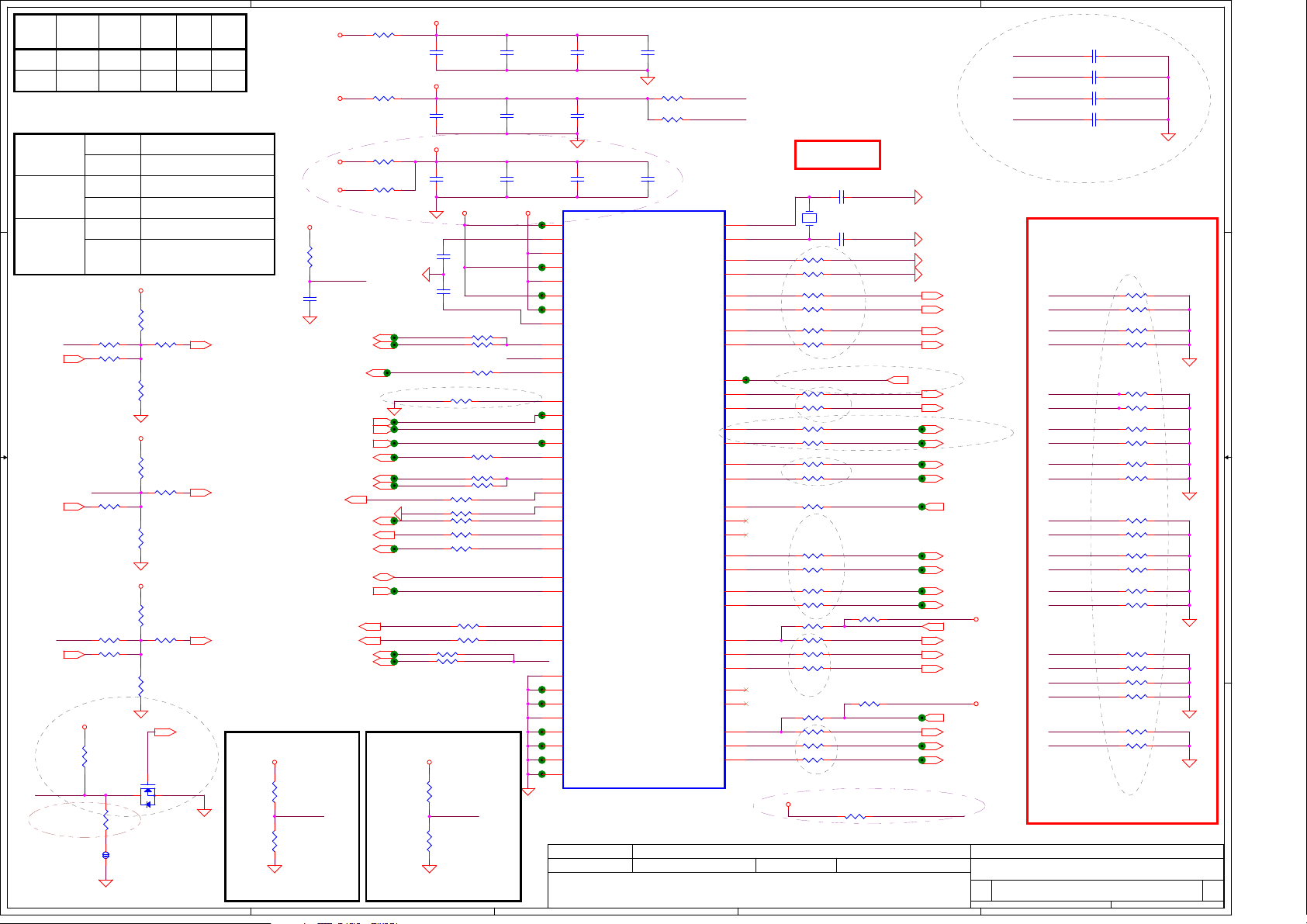

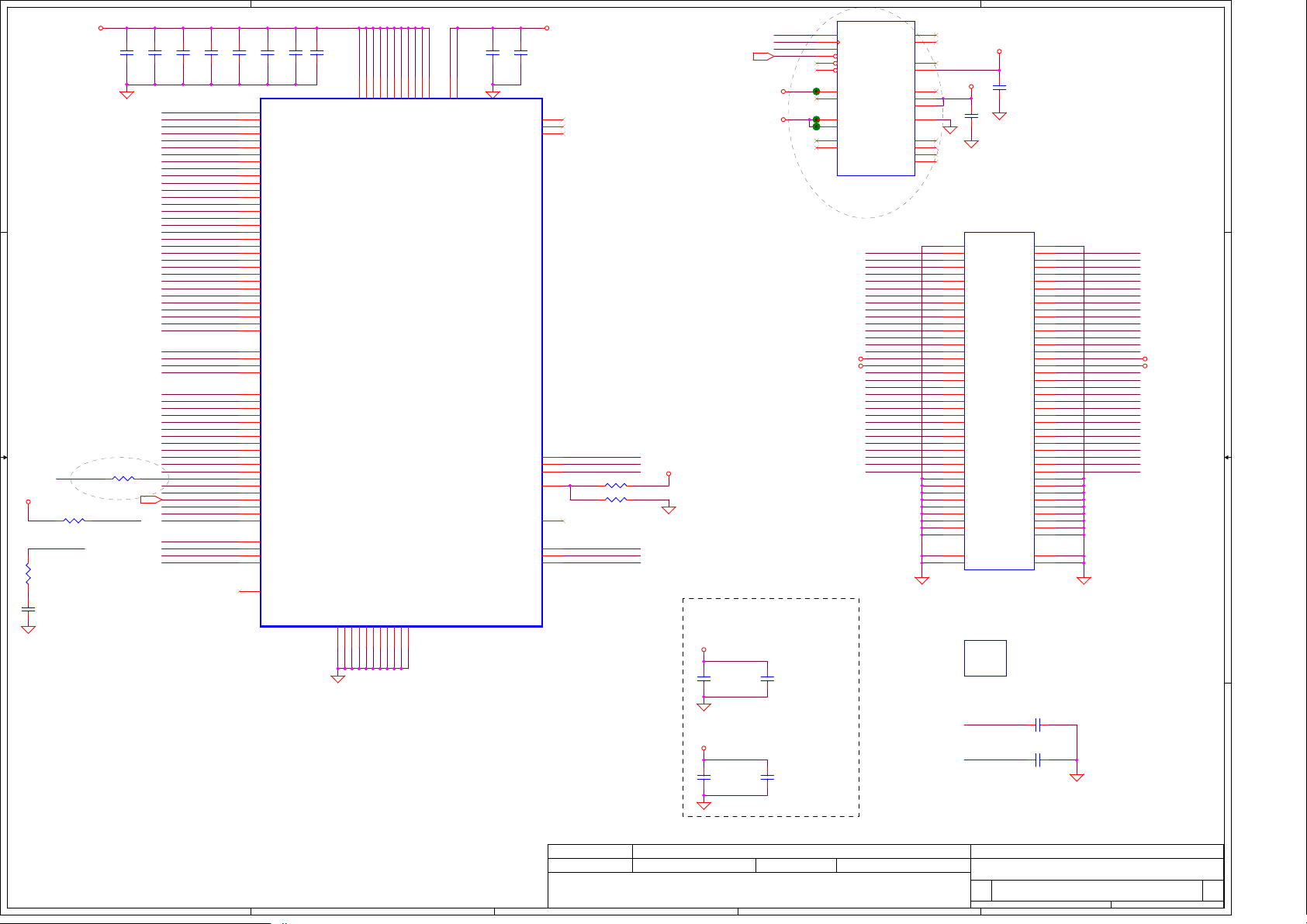

Page 7

5

4

3

2

1

H_D# [0..63]4

D D

C C

+VCCP

12

12

R577

R578

54.9_0402_1%

L

H_XS COMP /H_Y SCOM P tr ace

width a nd spacin g is 5/20.

B B

A A

54.9_0402_1%

12

R583

24.9_0402_1%

+VCCP

12

R597

100_0402_1%

12

R601

200_0402_1%

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VR EF

H_XRCOMP

H_XSCOMP

H_YR COMP

H_YSCO MP

H_SWN G0

H_SWN G1

12

R584

24.9_0402_1%

Layout Note:

H_XRCOMP / H _YRCOMP / H_VREF / H_SWNG0 /

H_SWNG1 trac e width and spacing is 18/20.

H_VR EF

1

C644

2

0.1U_0402_16 V4Z

5

U15A

F1

HD0#

J1

HD1#

H1

HD2#

J6

HD3#

H3

HD4#

K2

HD5#

G1

HD6#

G2

HD7#

K9

HD8#

K1

HD9#

K7

HD10#

J8

HD11#

H4

HD12#

J3

HD13#

K11

HD14#

G4

HD15#

T10

HD16#

W11

HD17#

T3

HD18#

U7

HD19#

U9

HD20#

U11

HD21#

T11

HD22#

W9

HD23#

T1

HD24#

T8

HD25#

T4

HD26#

W7

HD27#

U5

HD28#

T9

HD29#

W6

HD30#

T5

HD31#

AB7

HD32#

AA9

HD33#

W4

HD34#

W3

HD35#

Y3

HD36#

Y7

HD37#

W5

HD38#

Y10

HD39#

AB8

HD40#

W2

HD41#

AA4

HD42#

AA7

HD43#

AA2

HD44#

AA6

HD45#

AA10

HD46#

Y8

HD47#

AA1

HD48#

AB4

HD49#

AC9

HD50#

AB11

HD51#

AC11

HD52#

AB3

HD53#

AC2

HD54#

AD1

HD55#

AD9

HD56#

AC1

HD57#

AD7

HD58#

AC6

HD59#

AB5

HD60#

AD10

HD61#

AD4

HD62#

AC8

HD63#

J13

HVREF0

K13

HVREF1

E1

HXRCOMP

E2

HXSCOMP

Y1

HYRCOMP

U1

HYSCOMP

E4

HXSWING

W1

HYSWING

QG82945GM QK56 A3 FCBGA 1466

HOST

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

12

R595

12

R599

221_0603_1%

100_0402_1%

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

D8

G8

B8

F8

A8

B9

C13

AG1

AG2

K4

T7

Y5

AC4

K3

T6

AA5

AC5

J7

W8

U3

AB10

B7

E8

E7

J9

H8

C3

D4

D3

B3

C7

C6

F6

A7

E3

B4

E6

D6

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCL K#

CLK_MCH_B CLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DI NV#0

H_DI NV#1

H_DI NV#2

H_DI NV#3

H_RESET#

H_ADS#

H_T RDY#

H_DPW R#

H_D RDY#

H_DEF ER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BN R#

H_BPRI #

H_DB SY#

H_CPUSL P#

H_RS#0

H_RS#1

H_RS#2

H_SWN G0

1

C642

2

0.1U_0402_16 V4Z

4

+VCCP+VCCP

12

R596

12

R600

H_A#[3 ..31] 4

H_REQ# [0..4] 4

H_ADSTB#0 4

H_ADSTB#1 4

CLK_MCH_BCL K# 15

CLK_MCH_BCL K 15

H_DST BN#[0..3] 4

H_DSTBP #[0..3] 4

H_DIN V#0 4

H_DIN V#1 4

H_DIN V#2 4

H_DIN V#3 4

H_RESET# 4

H_ADS# 4

H_TR DY# 4

H_DPW R# 4

H_D RDY# 4

H_DEF ER# 4

H_HITM# 4

H_HIT# 4

H_LOCK# 4

H_BR0# 4

H_BNR # 4

H_BPRI # 4

H_DB SY# 4

H_CPUSLP # 4

H_RS# [0..2] 4

221_0603_1%

H_SWN G1

1

2

100_0402_1%

0.1U_0402_16 V4Z

U15B

AE35

DMIRXN0

AF39

DMIRXN1

AG35

DMIRXN2

AH39

DMIRXN3

AC35

DMIRXP0

AE39

DMIRXP1

AF35

DMIRXP2

AG39

DMIRXP3

AE37

DMITXN0

AF41

DMITXN1

AG37

DMITXN2

AH41

DMITXN3

AC37

DMITXP0

AE41

DMITXP1

AF37

DMITXP2

AG41

DMITXP3

AY35

SM_CK0

AR1

SM_CK1

AW7

SM_CK2

AW40

SM_CK3

AW35

SM_CK0#

AT1

SM_CK1#

AY7

SM_CK2#

AY40

SM_CK3#

AU20

SM_CKE0

AT20

SM_CKE1

BA29

SM_CKE2

AY29

SM_CKE3

AW13

SM_CS0#

AW12

SM_CS1#

AY21

SM_CS2#

AW21

SM_CS3#

AL20

SM_OCDCOMP0

AF10

SM_OCDCOMP1

BA13

SM_ODT0

BA12

SM_ODT1

AY20

SM_ODT2

AU21

SM_ODT3

AV9

SM_RCOMPN

AT9

SM_RCOMPP

AK1

SM_VREF0

AK41

SM_VREF1

G28

PM_BMBUSY#

F25

PM_EXTTS0#

H26

PM_EXTTS1#

G6

PM_THERMTRIP#

AH33

PWROK

AH34

RSTIN#

K28

ICH_SYNC#

QG82945GM QK56 A3 FCBGA 1466

Layout Note :

Route as sh ort

as possible

12

12

R591

R590

40.2_0402_1%@

40.2_0402_1%@

DMI

DDR MUXING

M_OCDOCMP0

M_OCDOCMP1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG

CFG17

CFG18

CFG19

CFG20

G_CLKP

G_CLKN

D_REF_CLKN

D_REF_CLKP

CLKNC

D_REF_SSCLKN

D_REF_SSCLKP

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

RESERVED1

RESERVED2

RESERVED

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

PM_EXTTS#0

PM_EXTTS#1

PM

V_DDR_ MCH_REF13,14

DDR_THERM #13,14

DPRSLPV R20, 43

9/29

+1.8V

12

12

R587

100_0402_1%

12

R592

100_0402_1%

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_CLK_DD R0

M_CLK_DD R1

M_CLK_DD R2

M_CLK_DD R3

M_CLK_DDR #0

M_CLK_DDR #1

M_CLK_DDR #2

M_CLK_DDR #3

DDR_CKE0 _DIMMA

DDR_CKE1 _DIMMA

DDR_CKE2 _DIMMB

DDR_CKE3 _DIMMB

DDR_CS0_D IMMA#

DDR_CS1_D IMMA#

DDR_CS2_D IMMB#

DDR_CS3_D IMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1

H_THERMTRIP#

PWROK

PLTRST_R#

PWROK

DMI_TXN020

DMI_TXN120

DMI_TXN220

DMI_TXN320

DMI_TXP020

DMI_TXP120

DMI_TXP220

DMI_TXP320

DMI_RXN020

DMI_RXN120

DMI_RXN220

DMI_RXN320

DMI_RXP020

DMI_RXP120

DMI_RXP220

DMI_RXP320

M_CLK_DDR 013

M_CLK_DDR 113

M_CLK_DDR 214

M_CLK_DDR 314

M_CLK_DDR# 013

M_CLK_DDR# 113

M_CLK_DDR# 214

M_CLK_DDR# 314

DDR_CKE0_ DIMMA13

DDR_CKE1_ DIMMA13

DDR_CKE2_ DIMMB14

DDR_CKE3_ DIMMB14

DDR_CS0_DI MMA#13

DDR_CS1_DI MMA#13

DDR_CS2_DI MMB#14

DDR_CS3_DI MMB#14

+1.8V

R575 80.6_0402_1%

R576 80.6_0402_1%

10/6

R579

0_0402_5%

PLT_RST#17,18,20, 22,24,26,30,31,3 2

VGATE15,20, 43

PM_POK20,32

R581 0_0402_5%@

M_ODT013

M_ODT113

M_ODT214

M_ODT314

1 2

1 2

V_DDR_ MCH_REF

PM_BMBUSY#20

1 2

R1027 0_0402_5%

1 2

H_THERMTRIP#4,19

R580 100_0402_1%

MCH_ ICH_SYNC #18

1 2

1 2

R582 0_0402_5%

Layout Note :

V_DDR_MCH_R EF

trace width and

spacing is 20/20.

8/29

V_DDR_ MCH_REF

1

C641

2

0.1U_0402_16 V4Z

Stuff R590 & R591 for A1 Calistoga

C643

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

2

Title

Size Docume nt Number Re v

Date : Sheet of

Description at page11.

MCH_CLKSEL0

K16

MCH_CLKSEL1

K18

MCH_CLKSEL2

J18

CFG3

F18

CFG4

E15

CFG5

F15

CFG6

E18

CFG7

D19

CFG8

D16

CFG9

G16

CFG10

E16

CFG11

D15

CFG12

G15

CFG13

K15

CFG14

C15

CFG15

H16

CFG16

G18

CFG17

H15

CFG18

J25

CFG19

K27

CFG20

J26

CLK_MCH_3GPLL

AG33

CLK_MCH_3GPLL#

AF33

CLK_MC H_DREFCLK#

A27

CLK_MC H_DREFCLK

A26

MCH_SS CDREFCLK#

C40

MCH_SS CDREFCLK

D41

CLKREQ C#

H32

A3

A39

A4

A40

AW1

AW41

AY1

BA1

BA2

BA3

BA39

BA40

BA41

C1

AY41

B2

B41

C41

D1

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A34

D28

D27

A35

R585 10K_0402_5%

R586

10K_0402_5%@

12

12

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

+3VS

MCH_CLKSEL0 15

MCH_CLKSEL1 15

MCH_CLKSEL2 15

T1

T2

CFG5 11

T3

CFG7 11

T4

CFG9 11

T5

CFG11 11

CFG12 11

CFG13 11

T6

T7

CFG16 11

T8

CFG18 11

CFG19 11

CFG20 11

CLK_MCH_3GPLL 15

CLK_MCH_3GPLL# 15

CLK_MC H_DREFCLK# 15

CLK_MC H_DREFCLK 15

MCH_SS CDREFCLK# 15

MCH_SS CDREFCLK 15

CLKREQC # 15

7/25

Compal Electronics, Inc.

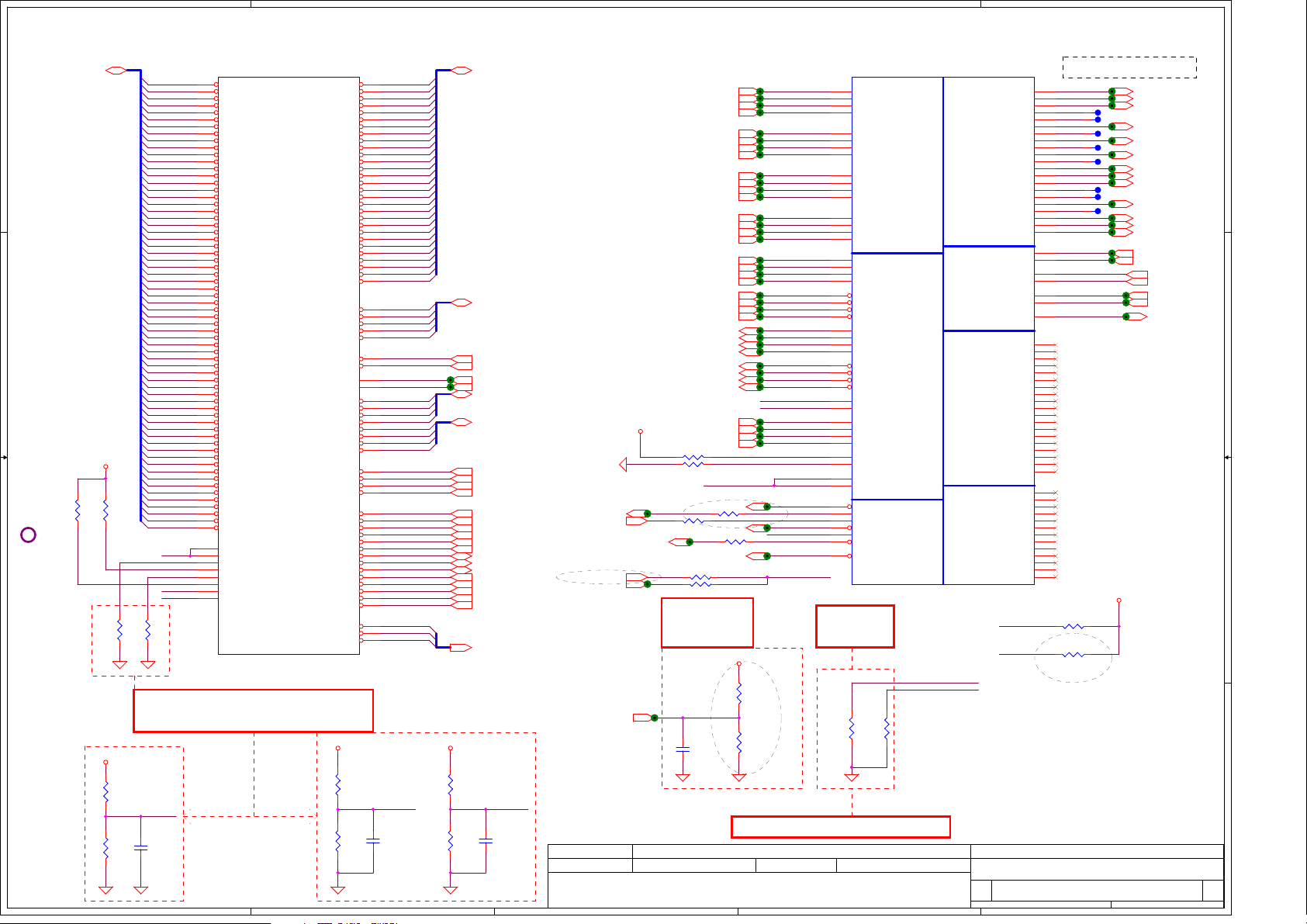

Calistoga (1/6)

LA-3031P

7 49Tuesd ay, Febru ary 28, 2006

1

0.5

Page 8

5

D D

4

3

2

1

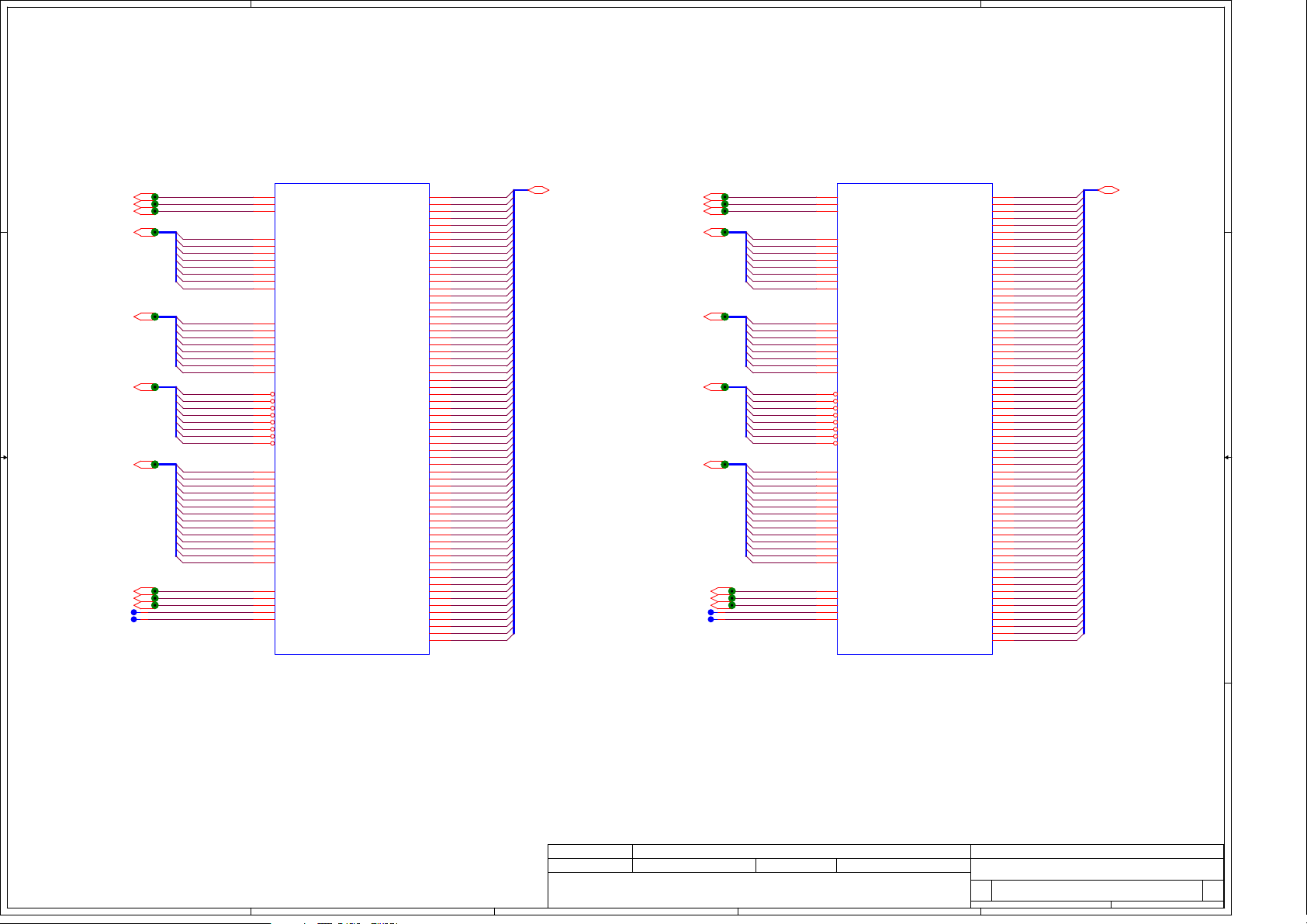

DDR_A_BS# 013

DDR_A_BS# 113

DDR_A_BS# 213

DDR_A_ DM[0..7]13

DDR_A _DQS[0..7 ]13

C C

DDR_A_ DQS#[0..7 ]13

DDR_A_ MA[0..13]13

B B

DDR_A_ CAS#13

DDR_A_ RAS#13

DDR_A_W E#13

T9 P AD

T11 P AD

DDR_A_BS #0

DDR_A_BS #1

DDR_A_BS #2

DDR_A_DM 0

DDR_A_DM 1

DDR_A_DM 2

DDR_A_DM 3

DDR_A_DM 4

DDR_A_DM 5

DDR_A_DM 6

DDR_A_DM 7

DDR_A_ DQS0

DDR_A_ DQS1

DDR_A_ DQS2

DDR_A_ DQS3

DDR_A_ DQS4

DDR_A_ DQS5

DDR_A_ DQS6

DDR_A_ DQS7

DDR_A_ DQS#0

DDR_A_ DQS#1

DDR_A_ DQS#2

DDR_A_ DQS#3

DDR_A_ DQS#4

DDR_A_ DQS#5

DDR_A_ DQS#6

DDR_A_ DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11 DDR_B_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_ CAS#

DDR_A_ RAS#

DDR_A_W E#

SA_RCVE NIN#

SA_RCVENOUT #

U15D

AU12

SA_BS0

AV14

SA_BS1

BA20

SA_BS2

AJ33

SA_DM0

AM35

SA_DM1

AL26

SA_DM2

AN22

SA_DM3

AM14

SA_DM4

AL9

SA_DM5

AR3

SA_DM6

AH4

SA_DM7

AK33

SA_DQS0

AT33

SA_DQS1

AN28

SA_DQS2

AM22

SA_DQS3

AN12

SA_DQS4

AN8

SA_DQS5

AP3

SA_DQS6

AG5

SA_DQS7

AK32

SA_DQS0#

AU33

SA_DQS1#

AN27

SA_DQS2#

AM21

SA_DQS3#

AM12

SA_DQS4#

AL8

SA_DQS5#

AN3

SA_DQS6#

AH5

SA_DQS7#

AY16

SA_MA0

AU14

SA_MA1

AW16

SA_MA2

BA16

SA_MA3

BA17

SA_MA4

AU16

SA_MA5

AV17

SA_MA6

AU17

SA_MA7

AW17

SA_MA8

AT16

SA_MA9

AU13

SA_MA10

AT17

SA_MA11

AV20

SA_MA12

AV12

SA_MA13

AY13

SA_CAS#

AW14

SA_RAS#

AY14

SA_WE#

AK23

SA_RCVENIN#

AK24

SA_RCVENOUT#

QG82945GM QK56 A3 FCBGA 1466

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

DDR SYS MEMORY A

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A_ D10

DDR_A_ D11

DDR_A_ D12

DDR_A_ D13

DDR_A_ D14

DDR_A_ D15

DDR_A_ D16

DDR_A_ D17

DDR_A_ D18

DDR_A_ D19

DDR_A_ D20

DDR_A_ D21

DDR_A_ D22

DDR_A_ D23

DDR_A_ D24

DDR_A_ D25

DDR_A_ D26

DDR_A_ D27

DDR_A_ D28

DDR_A_ D29

DDR_A_ D30

DDR_A_ D31

DDR_A_ D32

DDR_A_ D33

DDR_A_ D34

DDR_A_ D35

DDR_A_ D36

DDR_A_ D37

DDR_A_ D38

DDR_A_ D39

DDR_A_ D40

DDR_A_ D41

DDR_A_ D42

DDR_A_ D43

DDR_A_ D44

DDR_A_ D45

DDR_A_ D46

DDR_A_ D47

DDR_A_ D48

DDR_A_ D49

DDR_A_ D50

DDR_A_ D51

DDR_A_ D52

DDR_A_ D53

DDR_A_ D54

DDR_A_ D55

DDR_A_ D56

DDR_A_ D57

DDR_A_ D58

DDR_A_ D59

DDR_A_ D60

DDR_A_ D61

DDR_A_ D62

DDR_A_ D63

DDR_ A_D[0..63 ] 13 DDR_ B_D[0..63 ] 14

DDR_B_BS# 014

DDR_B_BS# 114

DDR_B_BS# 214

DDR_B_ DM[0..7]14

DDR_B _DQS[0..7 ]14

DDR_B _DQS#[0.. 7]14

DDR_B_ MA[0..13]14

DDR_B_ CAS#14

DDR_B_ RAS#14

DDR_B_W E#14

T10 PAD

T12 PAD

DDR_B_BS# 0

DDR_B_BS #1

DDR_B_BS #2

DDR_B_DM 0

DDR_B_DM 1

DDR_B_DM 2

DDR_B_DM 3

DDR_B_DM 4

DDR_B_DM 5

DDR_B_DM 6

DDR_B_DM 7

DDR_B_ DQS0

DDR_B_ DQS1

DDR_B_ DQS2

DDR_B_ DQS3

DDR_B_ DQS4

DDR_B_ DQS5

DDR_B_ DQS6

DDR_B_ DQS7

DDR_B_ DQS#0

DDR_B_ DQS#1

DDR_B_ DQS#2

DDR_B_ DQS#3

DDR_B_ DQS#4

DDR_B_ DQS#5

DDR_B_ DQS#6

DDR_B_ DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6DDR_A_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA12

DDR_B_MA13

DDR_B_ CAS#

DDR_B_ RAS#

DDR_B_W E#

SB_RCVE NIN#

SB_RCVENOUT #

U15E

AT24

SB_BS0

AV23

SB_BS1

AY28

SB_BS2

AK36

SB_DM0

AR38

SB_DM1

AT36

SB_DM2

BA31

SB_DM3

AL17

SB_DM4

AH8

SB_DM5

BA5

SB_DM6

AN4

SB_DM7

AM39

SB_DQS0

AT39

SB_DQS1

AU35

SB_DQS2

AR29

SB_DQS3

AR16

SB_DQS4

AR10

SB_DQS5

AR7

SB_DQS6

AN5

SB_DQS7

AM40

SB_DQS0#

AU39

SB_DQS1#

AT35

SB_DQS2#

AP29

SB_DQS3#

AP16

SB_DQS4#

AT10

SB_DQS5#

AT7

SB_DQS6#

AP5

SB_DQS7#

AY23

SB_MA0

AW24

SB_MA1

AY24

SB_MA2

AR28

SB_MA3

AT27

SB_MA4

AT28

SB_MA5

AU27

SB_MA6

AV28

SB_MA7

AV27

SB_MA8

AW27

SB_MA9

AV24

SB_MA10

BA27

SB_MA11

AY27

SB_MA12

AR23

SB_MA13

AR24

SB_CAS#

AU23

SB_RAS#

AR27

SB_WE#

AK16

SB_RCVENIN#

AK18

SB_RCVENOUT#

QG82945GM QK56 A3 FCBGA 1466

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

DDR SYS MEMORY B

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B_ D10

DDR_B_ D11

DDR_B_ D12

DDR_B_ D13

DDR_B_ D14

DDR_B_ D15

DDR_B_ D16

DDR_B_ D17

DDR_B_ D18

DDR_B_ D19

DDR_B_ D20

DDR_B_ D21

DDR_B_ D22

DDR_B_ D23

DDR_B_ D24

DDR_B_ D25

DDR_B_ D26

DDR_B_ D27

DDR_B_ D28

DDR_B_ D29

DDR_B_ D30

DDR_B_ D31

DDR_B_ D32

DDR_B_ D33

DDR_B_ D34

DDR_B_ D35

DDR_B_ D36

DDR_B_ D37

DDR_B_ D38

DDR_B_ D39

DDR_B_ D40

DDR_B_ D41

DDR_B_ D42

DDR_B_ D43

DDR_B_ D44

DDR_B_ D45

DDR_B_ D46

DDR_B_ D47

DDR_B_ D48

DDR_B_ D49

DDR_B_ D50

DDR_B_ D51

DDR_B_ D52

DDR_B_ D53

DDR_B_ D54

DDR_B_ D55

DDR_B_ D56

DDR_B_ D57

DDR_B_ D58

DDR_B_ D59

DDR_B_ D60

DDR_B_ D61

DDR_B_ D62

DDR_B_ D63

DDR_B _D0

AK39

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

2

Title

Size Docume nt Number Re v

Date : Sheet of

Compal Electronics, Inc.

Calistoga (2/6)

LA-3031P

8 49Tuesd ay, Febru ary 28, 2006

1

0.5

Page 9

5

4

3

2

1

D D

U15C

LIBG

12

12

255_0402_1%

L64

L66

L68

H27

SDVOCTRL_DATA

H28

SDVOCTRL_CLK

B37

LA_DATA0

B34

LA_DATA1

A36

LA_DATA2

C37

LA_DATA#0

B35

LA_DATA#1

A37

LA_DATA#2

F30

LB_DATA0

D29

LB_DATA1

F28

LB_DATA2

G30

LB_DATA#0

D30

LB_DATA#1

F29

LB_DATA#2

A32

LA_CLK

A33

LA_CLK#

E26

LB_CLK

E27

LB_CLK#

D32

LBKLT_CTL

J30

LBKLT_EN

H30

LCTLA_CLK

H29

LCTLB_DATA

G26

LDDC_CLK

G25

LDDC_DATA

F32

LVDD_EN

B38

LIBG

C35

LVBG

C33

LVREFH

C32

LVREFL

A16

TVDAC_A

C18

TVDAC_B

A19

TVDAC_C

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

J29

TV_DCONSEL1

K30

TV_DCONSEL0

C26

DDCCLK

C25

DDCDATA

H23

VSYNC

G23

HSYNC

E23

BLUE

D23

BLUE#

C22

GREEN

B22

GREEN#

A21

RED

B21

RED#

J22

CRT_IREF

QG82945GM QK56 A3 FCBGA 1466

TV CRT

D_RE D 16,34

D_GREE N 16,34

D_BLUE 16,34

LVDS

PCI-EXPRESS GRAPHICS

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SDVO_SDAT17

SDVO_SCLK17

TXA0+17

TXA1+17

TXA2+17

TXA0-17

TXA1-17

TXA2-17

TXB0+17

TXB1+17

TXB2+17

+3VS

12

12

R603

C C

LCD_CL K17

LCD_DAT17

TV-Out Termination

COMPS

LUMA

CRMA

B B

10K_0402_5%

LCD_CL K

LCD_DAT

Place close t o U15

R608

12

R609

75_0402_1%

12

75_0402_1%

CRT Termination/EMI Filter

C_RE D

C_BLU

R611

12

75_0402_1%

5

A A

12

75_0402_1%

R612

HLC0603CSCC 39NJT_0603

HLC0603CSCC 39NJT_0603

HLC0603CSCC 39NJT_0603

12

R613

75_0402_1%

12

R610

75_0402_1%

L63

1 2

L65

1 2

L67

1 2

R604

10K_0402_5%

1

2

18P_0402_50V8J

C655

TXB0-17

TXB1-17

TXB2-17

TXACLK+17

TXACLK-17

TXBCLK+17

TXBCLK-17

ENAVD D17

DDCC LK16

DDCDAT A16

VSYNC16

HSYNC16

Place close t o U15

C_RED_ L

C_GRN _LC_G RN

C_BLU_L

1

C656

2

18P_0402_50V8J

TXB0+

TXB1+

TXB2+

TXB0TXB1TXB2-

TXBCLK+

TXBCLK-

BKLT_CTL

ENABLT

ENAV DD

R605 1.5K_0402_1%

COMPS

LUMA

CRMA

12

R606

4.99K_0603_1%

C_BLU

C_G RN

C_RE D

R607

1 2

HLC0603CSCC R11JT_0603

1 2

HLC0603CSCC R11JT_0603

1 2

HLC0603CSCC R11JT_0603

1

C657

18P_0402_50V8J

2

4

PEG COM P t race wid th

and s paci ng i s 18/ 25 mi ls.

D40

EXP_COMPI

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

3

EXP_COMPO

+1.5VS_PCIE

PEGCOMP

1 2

R602 24.9_0402_1%

SDVOB_INT- 17

7/14

SDVOB_INT+ 17

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

C647 0.1U_0402_16 V4Z

1 2

C648 0.1U_0402_16 V4Z

1 2

C649 0.1U_0402_16 V4Z

C650 0.1U_0402_16 V4Z

C651 0.1U_0402_16 V4Z

C652 0.1U_0402_16 V4Z

C653 0.1U_0402_16 V4Z

C654 0.1U_0402_16 V4Z

2006/02/27 2007/02/27

1 2

1 2

1 2

1 2

1 2

1 2

C14

82P_0402_50V8J

Compal Secret Data

Deciphered Date

LUMA

CRMA

COMPS

1

2

82P_0402_50V8J

1

C30

2

SDVOB_R- 17

SDVOB_G- 17

SDVOB_B- 1 7

SDVOB_CLK- 17

SDVOB_R+ 17

SDVOB_G+ 17

SDVOB_B+ 17

SDVOB_CLK+ 17

LID_SW #20,33

L3

1 2

FCM1608C-121T_0603

L5

1 2

FCM1608C-121T_0603

L4

1 2

FCM1608C-121T_0603

1

C6

82P_0402_50V8J

2

Please close to U15

2

+5VS+3VS

12

G

2

BKLT_CTL

R509

2.2K_0402_5%

LID_SW #

ENABLT

100K_0402_5%

82P_0402_50V8J

S

12

BSS138_SOT23

+3VS

5

U35

1

P

IN1

2

IN2

G

R501

3

1 2

SN74AHC 1G08DCKR_SC70-5

1

C318

C317

2

82P_0402_50V8J

Title

Size Docume nt Number Re v

Date : Sheet of

R510

Q56

2.2K_0402_5%

13

D

Q53

DTA114YKA_S C59

+5VS

47K

10K

2

13

4

O

R360

1

2

2

G

100K_0402_5%

1 2

LUMA_CL

CRMA_CL

COMPS_CL

1

C316

82P_0402_50V8J

2

D

S

Compal Electronics, Inc.

Calistoga (3/6)

LA-3031P

1

BKLT_CTL_C 17

13

Q36

BSS138_SOT23

LUMA_CL 16,34

CRMA_CL 16,34

COMPS_CL 1 6,34

9 49Tuesd ay, Febru ary 28, 2006

+5VS_INV

0.5

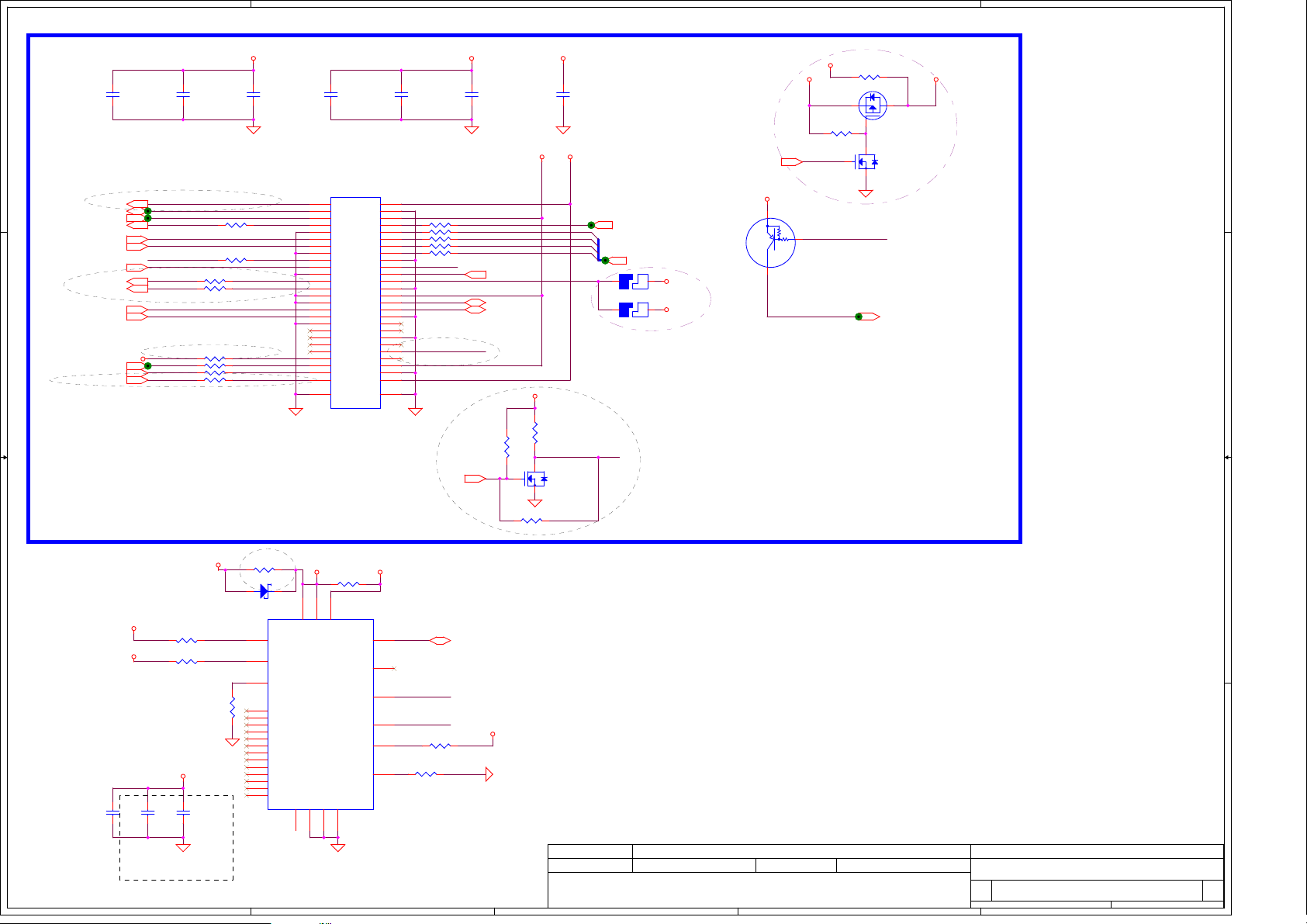

Page 10

5

D D

C669

Place o n edge

C C

1

C679

2

C678 4. 7U_0805_10V4Z

+VCCP

1

+

2

220U_D2_2VK_ R9

1

2

2.2U_0805_16V 4Z

Place i n cavity.

MCH_A6

1

C686

2

B B

1

C693

2

0.22U_0603_10V7K

Place o n edge

A A

0.47U_0603_10V7K

MCH_D2

1

C695

MCH_AB1

2

1

0.22U_0603_10V7K

C696

2

0.47U_0603_10V7K

+1.5VS

U15H

AC14

VTT0

AB14

VTT1

W14

VTT2

V14

VTT3

T14

VTT4

R14

VTT5

P14

VTT6

N14

VTT7

M14

VTT8

L14

VTT9

AD13

VTT10

AC13

VTT11

AB13

VTT12

AA13

VTT13

Y13

VTT14

W13

VTT15

V13

VTT16

U13

VTT17

T13

VTT18

R13

VTT19

N13

VTT20

M13

VTT21

L13

VTT22

AB12

VTT23

AA12

VTT24

Y12

VTT25

W12

VTT26

V12

VTT27

U12

VTT28

T12

VTT29

R12

VTT30

P12

VTT31

N12

VTT32

P O W E R

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

VTT52

VTT53

VTT54

VTT55

VTT56

VTT57

VTT58

VTT59

VTT60

VTT61

VTT62

VTT63

VTT64

VTT65

VTT66

VTT67

VTT68

VTT69

VTT70

VTT71

VTT72

VTT73

VTT74

VTT75

VTT76

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

QG82945GM QK5 6 A3 FCBGA 1466

AG14

AF14

AE14

AF13

AE13

AF12

AE12

AD12

M12

L12

R11

P11

N11

M11

R10

P10

N10

M10

P9

N9

M9

R8

P8

N8

M8

P7

N7

M7

R6

P6

M6

A6

R5

P5

N5

M5

P4

N4

M4

R3

P3

N3

M3

R2

P2

M2

D2

AB1

R1

P1

N1

M1

Y14

4

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC2

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCDQ_TVDAC

VCC_SYNC

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCCHV0

VCCHV1

VCCHV2

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

H22

B30

C30

A30

AB41

AJ41

L41

N41

R41

V41

Y41

AC33

G41

H41

E21

F21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

H19

A23

B23

B25

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

P19

P16

AH15

P15

AH14

+2.5VS

1 2

C659

0.1U_0402_16 V4Z

+2.5VS

W=40 mils

+1.5VS_3GPLL

+2.5VS

MCH_ CRTDAC

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+1.5VS_MPLL

+3VS_TVBG

+3VS_TVDACA

+3VS_TVDACB

+3VS_TVDACC

+1.5VS

+1.5VS_TVDAC

+1.5VS

1

C694

2

3

+2.5VS

1

C658

2

0.1U_0402_16V 4Z

close pin G41

+1.5VS_PCIE

1

C664

220U_D2_2V K_R9

1

C912

2

0.1U_0402_16V 4Z

1

2

C687

0.1U_0402_16V 4Z

0.1U_0402_16V 4Z

+

2

10U_0805_6.3V6M

1

2

+2.5VS

1

2

+3VS

1

C688

10U_0805_6.3V6M

2

1

2

C676

2200P_0402_50V7K

C899

2200P_0402_50V7K

0_0805_5%

C666

C667

1

10U_0805_6.3V6M

2

1

1

C677

C927

2

2

0.1U_0402_16V 4Z

R940

0_0805_5%

1

C900

2

0.1U_0402_16V 4Z

Close to U15.H20

R614

12

+1.5VS

1 2

7/19

47U_1210_6.3V 4Z

@

12

R960

+3VS+3VS_TVBG

0_0603_5%

+2.5VS

C680

1

2

0.1U_0402_16V 4Z

10U_0805_6.3V6M

1

2

1

C681

2

+1.5VS_MPLL

1

C670

2

2200P_0402_50V7K

7/19

R618

1 2

0.5_0805_1%

45mA Max. 45mA Max.

1

C689

2

0.1U_0402_16V 4Z

+VCCP

D57

2 1

CH751H-4 0_SC76

+1.5VS +3VS

D58

2 1

CH751H-4 0_SC76

R961

10_0402_5%

R962

10_0402_5%

12

2

+1.5VS_DPLLA +1.5VS_DPLLB

1

C662

2

0.1U_0402_16 V4Z

R615

0_0805_5%

1

C926

C671

2

0.1U_0402_16V 4Z

47U_1210_6.3 V4Z

@

Close to U15.E20

CHB1608U301_0 603

1

+

C910

2

330U_D2E_2.5VM

12

L69

12

1

2

0.1U_0402_16 V4Z

R616

12

0_0805_5%

1

1

1

2

2

2

47U_1210_6.3V 4Z@

0.1U_0402_16V 4Z

C673

C672

2200P_0402_50V7K

C1033

9/27

Close to U15.C20 Close to U15.E19

PCI-E/MEM/PSB PLL decoupling

R621

0_0805_5%

1

C690

10U_0805_6.3V6M

2

+2.5VS

12

R619

0_0805_5%

12

+1.5VS+1.5VS_3GPLL

12

+1.5VS_TVDAC +1.5VS

2200P_0402_50V7K

1

C683

2

+1.5VS_HPLL

1

C691

2

0.1U_0402_16 V4Z

0.1U_0402_16V 4Z

0_0805_5%

1

C684

2

R622

0_0805_5%

1

C692

10U_0805_6.3V6M

2

R620

CHB1608U301_0 603

1

+

C663

2

C911

1

2

12

12

+1.5VS+1.5VS

1

L70

12

+1.5VS+1.5VS

330U_D2E_2.5VM

+3VS+3VS_TVDACA+3VS+3VS_TVDACB+3VS+3VS_TVDACC

R617

12

0_0805_5%

1

2

C1034

9/27

47U_1210_6.3V 4Z@

1

2

2200P_0402_50V7K

0.1U_0402_16V 4Z

C675

C674

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/27 2007/02/27

Compal Secret Data

Deciphered Date

Title

Size Document Number Re v

2

Date: Sheet of

Compal Electronics, Inc.

Calistoga (4/6)

LA-3031P

10 49Tuesday , February 28, 2006

1

0.5

Page 11

5

4

3

2

1

Strap Pin Table

CFG[3:17] h ave internal pull up

+VCCP

D D

1

1

C699

2

0.22U_0603_10V7K

10U_0805_6.3V6M

1

C707

C706

2

10U_0805_6.3V6M

C C

B B

C700

C709

2

0.22U_0603_10V7K

1

2

1

+

2

220U_D2_2VK _R9

1

C701

2

0.22U_0603_10V7K

1

C708

2

1U_0603_10V4Z

+VCCP

U15F

AD27

VCC_NCTF0

AC27

VCC_NCTF1

AB27

VCC_NCTF2

AA27

VCC_NCTF3

Y27

VCC_NCTF4

W27

VCC_NCTF5

V27

VCC_NCTF6

U27

VCC_NCTF7

T27

VCC_NCTF8

R27

VCC_NCTF9

AD26

VCC_NCTF10

AC26

VCC_NCTF11

AB26

VCC_NCTF12

AA26

VCC_NCTF13

Y26

VCC_NCTF14

W26

VCC_NCTF15

V26

VCC_NCTF16

U26

VCC_NCTF17

T26

VCC_NCTF18

R26

VCC_NCTF19

AD25

VCC_NCTF20

AC25

VCC_NCTF21

AB25

VCC_NCTF22

AA25

VCC_NCTF23

Y25

VCC_NCTF24

W25

VCC_NCTF25

V25

VCC_NCTF26

U25

VCC_NCTF27

T25

VCC_NCTF28

R25

VCC_NCTF29

AD24

VCC_NCTF30

AC24

VCC_NCTF31

AB24

VCC_NCTF32

AA24

VCC_NCTF33

Y24

VCC_NCTF34

W24

VCC_NCTF35

V24

VCC_NCTF36

U24

VCC_NCTF37

T24

VCC_NCTF38

R24

VCC_NCTF39

AD23

VCC_NCTF40

V23

VCC_NCTF41

U23

VCC_NCTF42

T23

VCC_NCTF43

R23

VCC_NCTF44

AD22

VCC_NCTF45

V22

VCC_NCTF46

U22

VCC_NCTF47

T22

VCC_NCTF48

R22

VCC_NCTF49

AD21

VCC_NCTF50

V21

VCC_NCTF51

U21

VCC_NCTF52

T21

VCC_NCTF53

R21

VCC_NCTF54

AD20

VCC_NCTF55

V20

VCC_NCTF56

U20

VCC_NCTF57

T20

VCC_NCTF58

R20

VCC_NCTF59

AD19

VCC_NCTF60

V19

VCC_NCTF61

U19

VCC_NCTF62

T19

VCC_NCTF63

AD18

VCC_NCTF64

AC18

VCC_NCTF65

AB18

VCC_NCTF66

AA18

VCC_NCTF67

Y18

VCC_NCTF68

W18

VCC_NCTF69

V18

VCC_NCTF70

U18

VCC_NCTF71

T18

VCC_NCTF72

M19

VCC100

L19

VCC101

N18

VCC102

M18

VCC103

L18

VCC104

P17