Page 1

A

1 1

2 2

B

C

D

E

Compal Confidential

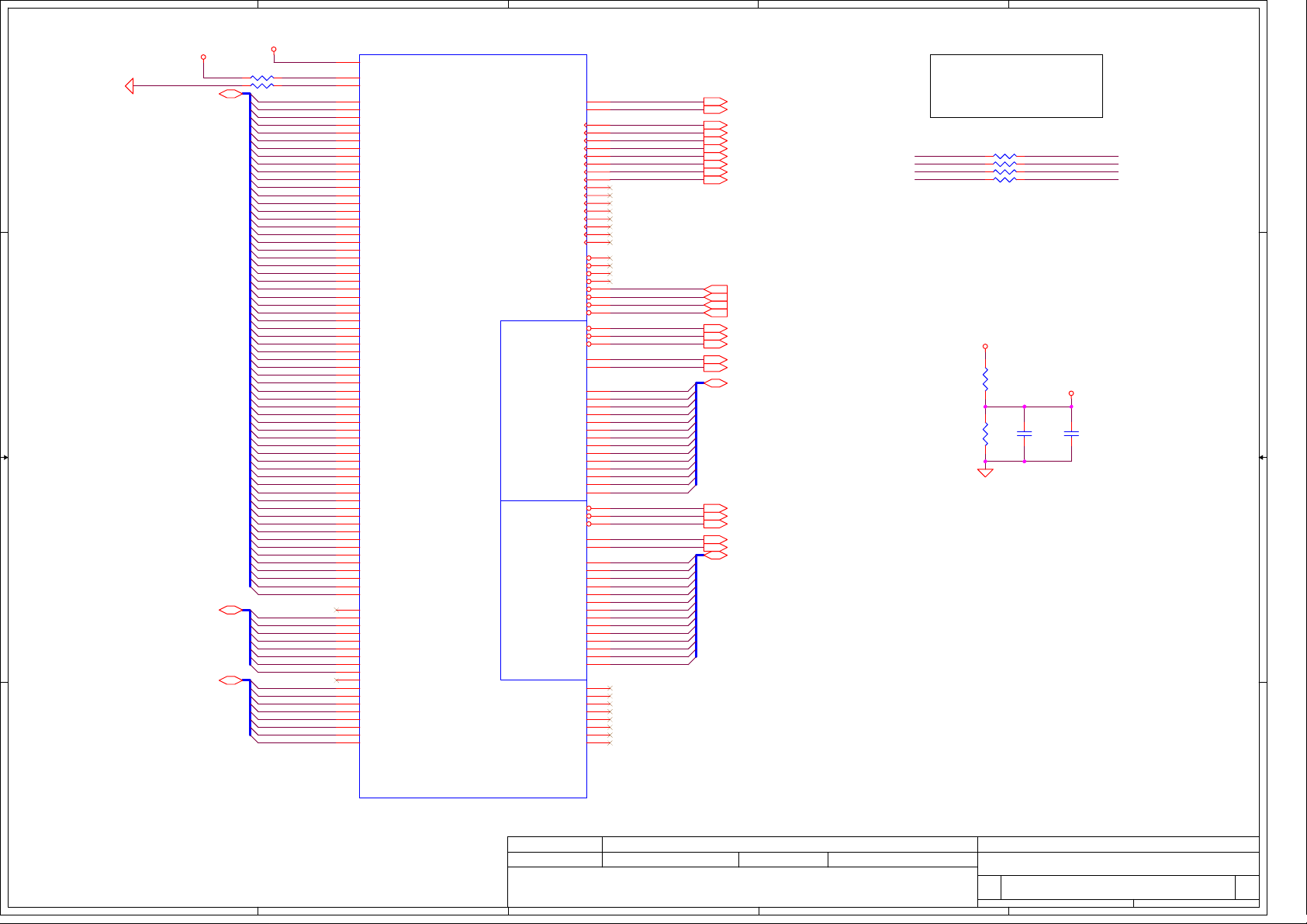

HGW51 Schematics Document

AMD/Sempron/ATI RS482M/SB450

3 3

4 4

A

2005 / 08 / 18 For C test

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev:0.3

2005/05/09 2006/03/08

C

Compal Secret Data

Deciphered Date

D

Title

Cover Sheet

Size Document Number Rev

Custom

LA-2931

Date: Sheet

148Thursday, August 18, 2005

E

of

0.3

Page 2

A

Compal confidential

B

C

D

E

Project Code: HGW51

File Name : LA-2931

1 1

Thermal Se nsor

ADM1032ARM

page 4 page 15

CRT & TV-OUT

page 16

Clock Generator

ICS951412

AMD Turion/Sempron CPU

page 4,5,6,7

H_A#(3..31)

ATI-RS482M

705 BGA

page 11,12,13,14

H_D#(0..63)

HT 16x16 800MHZ

DDR-1

One Channel DDR-1

DDRI-SO-DIMM X2

BANK 0, 1, 2, 3

page 8,9,10

A-Link Express

LCD CONN

2 x PCIE

page 17

2 2

ATI-SB450

PCI BUS

Mini PCI

Socket

page 31

3 3

Realtek

RTL8100CL

page 26

RJ45 CONN

page 26

ENE Controller

CB714

page 24

Slot 0

page 25

6in1 CardReader

Slot

page 25

1394 Controller

VT6311S

page 27

1394

Conn.

page 27

LPC BUS

564 BGA

page 18,19,20,21

USB 2.0

USB 2.0

AC-LINK

SATA

PATA

USB conn x 3

BT Conn

page 35

page 30

Audio CKT

AD1888

page 28

MDC Conn.

page 30

SATA HDD Conn.

page 23

HDD Conn.

CDROM Conn.

page 23

AMP & Audio Jack

page 29

RJ11 CONN

page 26

Power On/Off CKT.

page 36

DC/DC Interface CKT.

page 37

RTC CKT.

page 18

SMsC LPC47N207

page 32

ENE KB910L

page 33

Power Circuit DC/DC

4 4

Button

page 36

page 39~48

LED

A

Power OK CKT.

page 36

B

FIR module

page 32

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Touch Pad

CONN.

2005/05/09 2006/03/08

C

page 30

Compal Secret Data

Deciphered Date

Int. KBD

page 30

BIOS

page 34

Title

Block Diagrams

Size Document Number Rev

Custom

LA-2931

D

Date: Sheet

248Thursday, August 18, 2005

E

0.3

of

Page 3

A

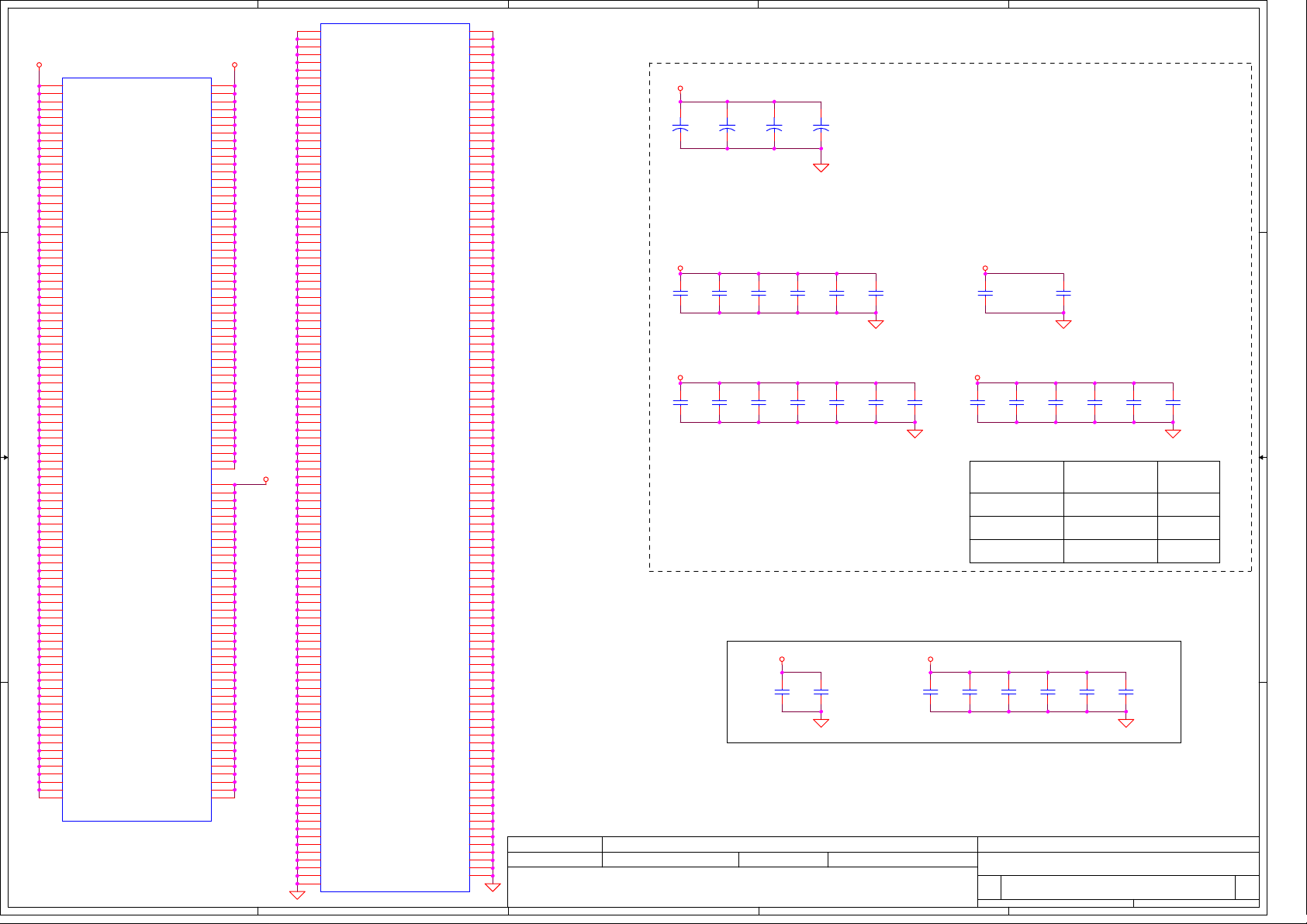

Voltage Rails

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+1.05VS

+DDRVTT 0.9V switched power rail for DDR terminator

+1.5VALW 1.5V always on power rail

+1.5VS

+1.8VS 1.8V switched power rail

+DDRVCC

+2.5VS

+3VALW

+3V

+3VS

+5VALW

+5VS

+5VMO D 5 V sw i tc he d po we r rail for Module Bay

+12VALW 12V always on power rail

+RTC V C C RTC power

Adapter power supply (19V)

AC or batte ry power rail for power circuit.

Core voltage for CPU

1.05V switched power rail

1.5V switched power rail

1.8V power rail for DDR

2.5V switched power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

B

S1 S3 S4/ S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF OF F

ON

ON OFF OF F

ON OFF OF F

ON

ON

ON

ON

ON

ON

ON ONON

N/AN/AN/A

OFF

OFF

ON*ON

OFF

ON

OFF

OFF

ON ON*

OFF

ON

OFF

OFF

ON

ON*

OFF

OFFON

OFF OFFON

ONON ON*

C

STATE

Full ON

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra / Rc

Rb / Rd V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

D

SLP_S4# SLP_S5# +VA LW +V +VS Clock

ON

LOW

LOW

LOW

HIGH

LOW LOW LOW LOW

AD_BID

0 V

HIGHHIGHHIGH

HIGH

HIGH

LOWLOWLOW

ON

ON

ON

ON

Vtyp

AD_BID

0 V 0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

ON

ON

ON

OFF

OFF

V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

E

ON ON

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

max

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device IDSEL # REQ # / GNT # Interrupts

CardBus

1394

SD

Mini-PCI

LAN

3 3

AD20

AD16 0

AD20

AD18

AD22 3

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

1010 000X b

1011 000Xb

2

2

1

PIRQE/PIRQH

PIRQE

PIRQE/PIRQH

PIRQF

PIRQG

EC SM Bus2 address

Device

ADM1032

1001 110X b0001 011X b

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

BTO Item BOM Structure

BTO Option Table

SB450 SM Bus address

Device

4 4

Clock Generator

(ICS 951412AGT)

DDRII DIMM0

DDRII DIMM2

A

Address

1101 001Xb

1001 000Xb

1001 010Xb

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/08 2006/03/08

C

Compal Secret Data

Deciphered Date

Title

Notes

Size Document Number Rev

Custom

EFL50 LA-2761

D

Date: Sheet

348Thursday, August 18, 2005

E

0.3

of

Page 4

A

B

C

D

E

H_CADIP15

H_CADIN15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIN9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP1

H_CTLIN1

H_CTLIP0

H_CTLIN0

R646

44.2_0603_1%

H_CADIP[0..15]

H_CADIN[0..15]

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

AF27

AE26

LVREF0

12

U50A

Claw Hammer-DTR

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_REF1

L0_REF0

FOX_PZ75403-2941-42

CONN@

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

HTT Interface

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

LDTSTOP_L

H_CADIP[0..15]<11>

4 4

3 3

+1.2V_HT

R642 49.9_0402_1%

1 2

R643 49.9_0402_1%

1 2

+1.2V_HT

2 2

H_CLKIP1<11>

H_CLKIN1<11>

H_CLKIP0<11>

H_CLKIN0<11>

H_CTLIP0<11>

H_CTLIN0<11>

R645 44.2_0603_1%

12

LVREF1

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP15

N26

H_CADON15

N27

H_CADOP14

L25

H_CADON14

M25

H_CADOP13

L26

H_CADON13

L27

H_CADOP12

J25

H_CADON12

K25

H_CADOP11

G25

H_CADON11

H25

H_CADOP10

G26

H_CADON10

G27

H_CADOP9

E25

H_CADON9

F25

H_CADOP8

E26

H_CADON8

E27

H_CADOP7

N29

H_CADON7

P29

H_CADOP6

M28

H_CADON6

M27

H_CADOP5

L29

H_CADON5

M29

H_CADOP4

K28

H_CADON4

K27

H_CADOP3

H28

H_CADON3

H27

H_CADOP2

G29

H_CADON2

H29

H_CADOP1

F28

H_CADON1

F27

H_CADOP0

E29

H_CADON0

F29

H_CLKOP1

J26

H_CLKON1

J27

H_CLKOP0

J29

H_CLKON0

K29

N25

P25

H_CTLOP0

P28

H_CTLON0

P27

LDTSTOP#

AJ27

H_CADOP[0..15] <11>

H_CADON[0..15] <11>H_CADIN[0..15]<11>

H_CTLOP0 <11>

H_CTLON0 <11>

1 2

R644 680_0402_5%

LDTSTOP# <13,18>

H_CLKOP1 <11>

H_CLKON1 <11>

H_CLKOP0 <11>

H_CLKON0 <11>

+2.5VS

EN_DFAN1<33>

0.1U_0402_16V4Z

C698

1U_0603_10V4Z

C696

EN_DFAN1

1

2

R641

1

2

3

+IN

2

-IN

100K_0402_5%

1 2

12

150K_0402_5%

FAN Conn

+VSB

8

U3A

P

FAN1

1

OUT

G

LM358A_SO8

4

C697

2200P_0402_50V7K

1 2

R640

D25

RB751V_SOD323

+VSB

+5VS

6

2

1

D

Q47

G

3

S

SI3456DV-T1_TSOP6

4 5

FANVOUT1

2

1

C700

C1

2 1

22U_1206_10V4Z

1

2

0.001U_0402_50V7M

+3VS

12

1

@

2

JP43

ACES_85205-0300

CONN@

R639

10K_0402_5%

C699

0.01U_0402_16V7K

1

2

3

5

+IN

OUT

6

-IN

FAN_SPEED1 <33>

U3B

7

LM358A_SO8

+3VS

1

2

THERMDA_CPU

THERMDC_CPU

THERMDA_CPU

THERMDC_CPU

EC_SMB_CK2

EC_SMB_DA2

from EFL50

U53

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

1

C702

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

1

6

THERM#

4

5

THERMDA_CPU<6>

THERMDC_CPU<6>

C703

2200P_0402_50V7K

EC_SMB_CK2<33>

1 1

EC_SMB_DA2<33>

Thermal Sensor

ADM1032

12

R647

10K_0402_5%@

SMBus Address: 1001110X (b)

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/05/09 2006/03/11

C

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet of

Claw Harmmer CPU (Host Bus)

LA-2931

448Thursday, August 18, 2005

E

0.3

Page 5

A

B

C

D

E

+2.5V

DDR_SDQ[0..63]<8>

1 1

2 2

3 3

DDR_SDM[0..7]<8>

DDR_SDQS[0..7]<8>

+1.25VREF_CPU

50 mil width

R64834.8_0603_1%

12

R64934.8_0603_1%

12

DDR_SDQ63

DDR_SDQ62

DDR_SDQ61

DDR_SDQ60

DDR_SDQ59

DDR_SDQ58

DDR_SDQ57

DDR_SDQ56

DDR_SDQ55

DDR_SDQ54

DDR_SDQ53

DDR_SDQ52

DDR_SDQ51

DDR_SDQ50

DDR_SDQ49

DDR_SDQ48

DDR_SDQ47

DDR_SDQ46

DDR_SDQ45

DDR_SDQ44

DDR_SDQ43

DDR_SDQ42

DDR_SDQ41

DDR_SDQ40

DDR_SDQ39

DDR_SDQ38

DDR_SDQ37

DDR_SDQ36

DDR_SDQ35

DDR_SDQ34

DDR_SDQ33

DDR_SDQ32

DDR_SDQ31

DDR_SDQ30

DDR_SDQ29

DDR_SDQ28

DDR_SDQ27

DDR_SDQ26

DDR_SDQ25

DDR_SDQ24

DDR_SDQ23

DDR_SDQ22

DDR_SDQ21

DDR_SDQ20

DDR_SDQ19

DDR_SDQ18

DDR_SDQ17

DDR_SDQ16

DDR_SDQ15

DDR_SDQ14

DDR_SDQ13

DDR_SDQ12

DDR_SDQ11

DDR_SDQ10

DDR_SDQ9

DDR_SDQ8

DDR_SDQ7

DDR_SDQ6

DDR_SDQ5

DDR_SDQ4

DDR_SDQ3

DDR_SDQ2

DDR_SDQ1

DDR_SDQ0

DDR_SDM7

DDR_SDM6

DDR_SDM5

DDR_SDM4

DDR_SDM3

DDR_SDM2

DDR_SDM1

DDR_SDM0

DDR_SDQS7

DDR_SDQS6

DDR_SDQS5

DDR_SDQS4

DDR_SDQS3

DDR_SDQS2

DDR_SDQS1

DDR_SDQS0

MEMZN

MEMZP

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

U50B

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

Claw Hammer-DTR

DDR Memory

A CHANGEL ADDRESSB CHANGEL ADDRESS

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

DDR_CKE0

DDR_CKE1

DDR_CLK7

DDR_CLK7#

DDR_CLK6

DDR_CLK6#

DDR_CLK5

DDR_CLK5#

DDR_CLK4

DDR_CLK4#

DDR_SCS#3

DDR_SCS#2

DDR_SCS#1

DDR_SCS#0

DDR_SMAA13

DDR_SMAA12

DDR_SMAA11

DDR_SMAA10

DDR_SMAA9

DDR_SMAA8

DDR_SMAA7

DDR_SMAA6

DDR_SMAA5

DDR_SMAA4

DDR_SMAA3

DDR_SMAA2

DDR_SMAA1

DDR_SMAA0

DDR_SMAB13

DDR_SMAB12

DDR_SMAB11

DDR_SMAB10

DDR_SMAB9

DDR_SMAB8

DDR_SMAB7

DDR_SMAB6

DDR_SMAB5

DDR_SMAB4

DDR_SMAB3

DDR_SMAB2

DDR_SMAB1

DDR_SMAB0

DDR_CKE0 <8>

DDR_CKE1 <9>

DDR_CLK7 <8>

DDR_CLK7# <8>

DDR_CLK6 <9>

DDR_CLK6# <9>

DDR_CLK5 <8>

DDR_CLK5# <8>

DDR_CLK4 <9>

DDR_CLK4# <9>

DDR_SCS#3 <9>

DDR_SCS#2 <9>

DDR_SCS#1 <8>

DDR_SCS#0 <8>

DDR_SRASA# <8>

DDR_SCASA# <8>

DDR_SWEA# <8>

DDR_SBSA1 <8>

DDR_SBSA0 <8>

DDR_SMAA[0..13] <8>

DDR_SRASB# <9>

DDR_SCASB# <9>

DDR_SWEB# <9>

DDR_SBSB1 <9>

DDR_SBSB0 <9>

DDR_SMAB[0..13] <9>

DDR_CLK5/5# & DDR_CLK7/7#

route to nearest DIMM

DDR_CLK4/4# & DDR_CLK6/6#

route to farthest DIMM

R650 120_0402_5%

DDR_CLK6

DDR_CLK5

DDR_CLK4

1 2

R651 120_0402_5%

1 2

R652 120_0402_5%

1 2

R653 120_0402_5%

1 2

within 1.00"

+2.5V

12

R654

1K_0402_1%

12

1

C704

R655

1K_0402_1%

2

0.1U_0402_16V4Z

DDR_CLK7#DDR_CLK7

DDR_CLK6#

DDR_CLK5#

DDR_CLK4#

+1.25VREF_CPU

1

C705

1000P_0402_50V7K

2

4 4

A

FOX_PZ75403-2941-42

CONN@

B

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/11

C

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet

Claw Harmmer (Memory Bus)

LA-2931

E

548Thursday, August 18, 2005

of

0.3

Page 6

A

H_RST_CPU#

R656

H_RST#<18>

1 1

CPUCLK0_H<15>

CPUCLK0_L<15>

Place 169 Ohm within 0.5" from CPU

Route as DIF 5/5/5/20

+2.5VDDA

2 2

+2.5VS

R660 680_0402_5%

1 2

1 2

0_0402_5%

C709

3900P_0402_50V7K

169_0402_1%

C719 3900P_0402_50V7K

L47

LQG21F4R7N00_0805

1 2

1

+

C730

100U_D2_10VM

2

4.7U_0805_6.3V6K

H_PWRGD

1

C720

470P_0402_50V7K@

1

C706

0.001U_0402_50V7M@

2

12

12

Route as DIFF pair 10/5/10

1

C731

2

H_PWRGD<18>

12

R657

CPU_COREFB<46>

CPU_COREFB#<46>

3300P_0402_50V7K

1

C732

2

0.22U_0603_10V7K

R658 80.6_0402_1%

Place within 0.5" from CPU

Route as 80 Ohm DIFF impedence 8/5/20

+VDDA_CPU

1

C733

2

T4PAD

T6PAD

T8PAD

H_THERMTRIP_S#

H_RST_CPU#

R100

1 2

0_0402_5%

12

CPU_COREFB

CPU_COREFB#

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

50 mils width

VID4<46>

VID3<46>

VID2<46>

VID1<46>

VID0<46>

H_PWRGD_R

CLKIN

CLKIN#

FBCLKOUT

FBCLKOUT#

VID4

VID3

VID2

VID1

VID0

2

THERMDA_CPU<4>

THERMDC_CPU<4>

+1.2V_HT

JOPEN@

1 2

H_RST#

R663

100_0402_5%

@

J3

use plane

as heavy as possible

1

3 3

+2.5VS

1 2

R157 680_0402_5%

0.22U_0603_10V7K

H_RST#

D

S

C737

2

13

SUSP

2

G

Q55

2N7002_SOT23@

1

0.22U_0603_10V7K

2

T17PAD

T18PAD

SUSP <37>

8/9 modify close to U50

4 4

1

C738

C739

4.7U_0805_6.3V6K

2

+1.25V +1.25V

TP_K8_A28

TP_K8_AJ28

B

U50C

A20

THERMTRIP_L

AF20

RESET_L

AE18

PWROK

AJ21

CLKIN_H

AH21

CLKIN_L

AH19

FBCLKOUT_H

AJ19

FBCLKOUT_L

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AH25

VDDA1

AJ25

VDDA2

AG13

VID4

AF14

VID3

AG14

VID2

AF15

VID1

AE15

VID0

AH17

DBRDY

AE19

DBREQ_L

A26

THERMDA

A27

THERMDC

A22

TDO

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

D29

VLDT0_A

D27

VLDT0_A

D25

VLDT0_A

C28

VLDT0_A

C26

VLDT0_A

B29

VLDT0_A

B27

VLDT0_A

D17

VTT_A

A18

VTT_A

B17

VTT_A

C17

VTT_A

C16

VTT_A

A28

KEY1

AJ28

KEY0

FOX_PZ75403-2941-42

CONN@

Claw Hammer-DTR

Miscellaneous

Clock

Debug

JTAG

H_THERMTRIP_S# H_THERMTRIP#

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_SENSE

+2.5VS

AG10

NC

E14

NC

D12

NC

E13

NC

C12

NC

D22

NC

C22

NC

B13

NC

B7

NC

C3

NC

K1

NC

R2

NC

AA3

NC

F3

NC

C23

NC

AG7

NC

AE22

NC

C24

NC

A25

NC

C9

NC

AE23

NC

AF23

NC

AF22

NC

AF21

NC

C1

NC

J3

NC

R3

NC

AA2

NC

D3

NC

AG2

NC

B18

NC

AH1

NC

AE21

NC

C20

NC

AG4

NC

C6

NC

AG6

NC

AE9

NC

AG9

NC

AF18

NC

AJ23

NC

AH23

NC

AE24

NC

AF24

NC

C15

NC

AG18

NC

AH18

NC

AG17

NC

AJ18

NC

C18

NC

A19

NC

D20

NC

C21

NC

D18

NC

C19

NC

B19

NC

AH29

AH27

AG28

AG26

AF29

AE28

AF25

AG15

AF16

AG16

AH16

AJ17

AE13

12

R678

680_0402_5%

TP_M_RESET#

TP_K8_D22

TP_K8_C22

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

BPSCLK

BPSCLK#

TP_K8_AE24

TP_K8_AF24

TP_K8_C15

TP_CPU_BP3

TP_CPU_BP2

BP1

BP0

SINCHN

BRN#

SCANCLK1

SCANCLK2

SCANEN

SCANSHENB

SCANSHENA

+1.2V_HT

VTT_SENSE

+2.5VS

12

R669

1K_0402_5%

2

Q48

3 1

MMBT3904_SOT23

C

T20 PAD

T2 PAD

T3 PAD

T5 PAD

T7 PAD

T9 PAD

T10 PAD

+2.5V

R661 820_0402_5%

1 2

R662 820_0402_5%

1 2

T11 PAD

T12 PAD

T13 PAD

T14 PAD

T15 PAD

R664 680_0402_5%

1 2

R665 680_0402_5%

1 2

R666 680_0402_5%

1 2

R667 680_0402_5%

1 2

R668 680_0402_5%

1 2

T16 PAD

+3VALW

12

R679

10K_0402_5%

+2.5V

+3VALW

12

R670

1K_0402_5%@

2

Q49

MMBT3904_SOT23@

3 1

H_THERMTRIP# <19>

+2.5VS

220U_D2_4VM

D

+1.25V

1

+

C707

2

+1.25V

4.7U_0805_6.3V6K

1

C710

2

4.7U_0805_6.3V6K

+1.25V

0.22U_0603_10V7K

1

C721

2

0.22U_0603_10V7K

+3VS +2.5VDDA

1U_0603_10V4Z@

+1.2V_HT

MAINPWON <39,40,42>

Near Power Supply

1

+

C708

220U_D2_4VM

2

4.7U_0805_6.3V6K

1

C712

2

0.22U_0603_10V7K

1

C723

2

1 2

RP25

4 5

3 6

2 7

1 8

680_0804_8P4R_5%

1

C741

2

0.22U_0603_10V7K

1

2

1

2

R101

0_0402_5%@

C713

C724

1

2

1

C711

2

4.7U_0805_6.3V6K

1

C722

2

0.22U_0603_10V7K

2

C734

1

SCANCLK2

SCANCLK1

SCANEN

SCANSHENB

0.22U_0603_10V7K

250 mil

1

+

C740

2

100U_D2_10VM

1

C714

2

4.7U_0805_6.3V6K

1

C725

2

0.22U_0603_10V7K

U54

1

IN

2

GND

SHDN3BYP

0.22U_0603_10V7K

1

C742

C743

2

4.7U_0805_6.3V6K

1

C715

2

4.7U_0805_6.3V6K

0.22U_0603_10V7K

1

C726

2

0.22U_0603_10V7K

+2.5VS

1 2

5

OUT

4

G914E_SOT23-5@

0.01U_0402_16V7K@

0.22U_0603_10V7K

1

C744

2

0.22U_0603_10V7K

E

4.7U_0805_6.3V6K

1

C716

2

0.22U_0603_10V7K

1

C727

2

R659

0_0805_5%

1

C736

2

1

C745

2

0.22U_0603_10V7K

1

C717

2

4.7U_0805_6.3V6K

1

C728

2

0.22U_0603_10V7K

2

C735

1U_0603_10V4Z

1

1

C746

2

1

C718

2

1

C729

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/11

C

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Claw Harmmer (MISC)

LA-2931

648Thursday, August 18, 2005

E

0.3

of

Page 7

A

U50E

B2

VSS

AH20

VSS

AB21

VSS

W22

+CPU_CORE +2.5V

U50D

L7

VDD

AC15

VDD

H18

VDD

B20

VDD

E21

VDD

H22

1 1

2 2

3 3

4 4

VDD

J23

VDD

H24

VDD

F26

VDD

N7

VDD

L9

VDD

V10

VDD

G13

VDD

K14

VDD

Y14

VDD

AB14

VDD

G15

VDD

J15

VDD

AA15

VDD

H16

VDD

K16

VDD

Y16

VDD

AB16

VDD

G17

VDD

J17

VDD

AA17

VDD

AC17

VDD

AE17

VDD

F18

VDD

K18

VDD

Y18

VDD

AB18

VDD

AD18

VDD

AG19

VDD

E19

VDD

G19

VDD

AC19

VDD

AA19

VDD

J19

VDD

F20

VDD

H20

VDD

K20

VDD

M20

VDD

P20

VDD

T20

VDD

V20

VDD

Y20

VDD

AB20

VDD

AD20

VDD

G21

VDD

J21

VDD

L21

VDD

N21

VDD

R21

VDD

U21

VDD

W21

VDD

AA21

VDD

AC21

VDD

F22

VDD

K22

VDD

M22

VDD

P22

VDD

T22

VDD

V22

VDD

Y22

VDD

AB22

VDD

AD22

VDD

E23

VDD

G23

VDD

L23

VDD

N23

VDD

R23

VDD

U23

VDD

W23

VDD

AA23

VDD

AC23

VDD

B24

VDD

D24

VDD

F24

VDD

K24

VDD

M24

VDD

P24

VDD

T24

VDD

V24

VDD

Y24

VDD

AB24

VDD

AD24

VDD

AH24

VDD

AE25

VDD

K26

VDD

P26

VDD

V26

VDD

FOX_PZ75403-2941-42

CONN@

POWER

A

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

+CPU_CORE

VSS

M23

VSS

L24

VSS

AG25

VSS

AG27

VSS

D2

VSS

AF2

VSS

W6

VSS

Y7

VSS

AA8

VSS

AB9

VSS

AA10

VSS

J12

VSS

B14

VSS

Y15

VSS

AE16

VSS

J18

VSS

G20

VSS

R20

VSS

U20

VSS

W20

VSS

AA20

VSS

AC20

VSS

AE20

VSS

AG20

VSS

AJ20

VSS

D21

VSS

F21

VSS

H21

VSS

K21

VSS

M21

VSS

P21

VSS

T21

VSS

V21

VSS

Y21

VSS

AD21

VSS

AG21

VSS

B22

VSS

E22

VSS

G22

VSS

J22

VSS

L22

VSS

N22

VSS

R22

VSS

U22

VSS

AG29

VSS

AA22

VSS

AC22

VSS

AG22

VSS

AH22

VSS

AJ22

VSS

D23

VSS

F23

VSS

H23

VSS

K23

VSS

P23

VSS

T23

VSS

V23

VSS

Y23

VSS

AB23

VSS

AD23

VSS

AG23

VSS

E24

VSS

G24

VSS

J24

VSS

N24

VSS

R24

VSS

U24

VSS

W24

VSS

AA24

VSS

AC24

VSS

AG24

VSS

AJ24

VSS

B25

VSS

C25

VSS

B26

VSS

D26

VSS

H26

VSS

M26

VSS

T26

VSS

Y26

VSS

AD26

VSS

AF26

VSS

AH26

VSS

C27

VSS

B28

VSS

D28

VSS

G28

VSS

F15

VSS

H15

VSS

AB17

VSS

AD17

VSS

B16

VSS

G18

VSS

AA18

VSS

AC18

VSS

D19

VSS

F19

VSS

H19

VSS

K19

VSS

Y19

VSS

AB19

VSS

AD19

VSS

AF19

VSS

J20

VSS

L20

VSS

N20

VSS

FOX_PZ75403-2941-42

CONN@

B

POWER

B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

Security Classification

F17

H17

K17

Y17

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+CPU_CORE

820U_E9_2_5V_M_R7

+

C747

10U_0805_10V4Z

C751

4.7U_0805_6.3V6K

C759

1

+

C748

2

1

C752

2

10U_0805_10V4Z

1

C760

2

4.7U_0805_6.3V6K

330U_D_2VM_R15

1

2

820U_E9_2_5V_M_R7

+CPU_CORE

1

2

10U_0805_10V4Z

4 in Socket Cavity,

2 on backside under Socket

+CPU_CORE

1

2

4.7U_0805_6.3V6K

1

+

2

10U_0805_10V4Z

1

C753

2

4.7U_0805_6.3V6K

1

C761

2

330U_D_2VM_R15

1

+

C749

2

1

C754

2

10U_0805_10V4Z

1

C762

2

4.7U_0805_6.3V6K

CPU Decouping Capacitor

4.7U_0805_6.3V6K

1

1

C773

C772

2

2

4.7U_0805_6.3V6K

2005/03/01 2006/03/11

C

Compal Secret Data

Deciphered Date

C750

10U_0805_10V4Z

1

C755

2

4.7U_0805_6.3V6K

1

C763

2

D

1

C756

2

1

C764

2

4.7U_0805_6.3V6K

D

+CPU_CORE

+CPU_CORE

1

C765

2

0.22U_0603_10V7K

Near Socket

+2.5V+2.5V

1

C774

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

2

E

1

C757

1000P_0402_50V7K

2

0.22U_0603_10V7K

1

1

C766

2

2

In Socket CavityClose to Socket

Loop Bandwidth

KHz

20

50

* 300 3300

1

C776

C775

2

0.22U_0603_10V7K

Title

Size Document Number Rev

Custom

Date: Sheet

1

C758

0.1U_0402_16V4Z

2

1

C767

C768

2

0.22U_0603_10V7K

Bulk Cappacitance

uF

0.22U_0603_10V7K

1

C769

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

C770

2

23000

9000

0.22U_0603_10V7K

1

C777

2

0.22U_0603_10V7K

Claw Harmmer (Power & Ground)

1

2

LA-2931

0.22U_0603_10V7K

1

C778

2

C779

E

1

C771

2

Total

ESR

2.5m ohm

(AMD)

0.9m ohm

1.5m ohm

748Thursday, August 18, 2005

of

0.3

Page 8

A

+1.25VREF_MEM

+2.5V

DDR_DQ0

DDR_DQ5

DDR_DQS0

A

DDR_DQ3

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ28

DDR_DQ24

DDR_DQS3

DDR_DQ26

DDR_DQ27

KBD_DATA

KBD_CLK

DDR_CKE0

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0

DDR_SWEA#

DDR_SCS#0

DDR_SMAA13

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ55

DDR_DQ56

DDR_DQ61

DDR_DQS7

DDR_DQ58

DDR_DQ59

+3VS

1 1

DDR_CLK5<5>

DDR_CLK5#<5>

2 2

KBD_DATA<9,33>

KBD_CLK<9,33>

DDR_CKE0<5>

DDR_SBSA0<5>

DDR_SWEA#<5>

DDR_SCS#0<5>

3 3

4 4

SMB_CK_DAT1<9,15,19>

SMB_CK_CLK1<9,15,19>

JP45

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

QTC_C106A-040SP11

CONN@

B

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

RAS#

CAS#

S1#

DU

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

B

C

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

40mil

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ11

DDR_DQ16

DDR_DQ21

DDR_DM2

DDR_DQ22

DDR_DQ23

DDR_DQ25

DDR_DQ29

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_CKE0

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

DDR_SCASA#

DDR_SCS#1

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ35

DDR_DQ39

DDR_DQ41

DDR_DQ45

DDR_DM5

DDR_DQ42

DDR_DQ43

DDR_DQ53

DDR_DQ52

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ63

STANDARD

SO-DIMM0

C

1

C780

0.1U_0402_16V4Z

2

DDR_SBSA1 <5>

DDR_SRASA# <5>

DDR_SCASA# <5>

DDR_SCS#1 <5>

DDR_CLK7# <5>

DDR_CLK7 <5>

D

DDR_SDQS[0..7]<5>

DDR_SDQ[0..63]<5>

+1.25VREF_MEM

DDR_SDQ0 DDR_DQ0

DDR_SDQ4

DDR_SDQ5

DDR_SDQ1

DDR_SDM0

DDR_SDQS0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ7

DDR_SDQ9

DDR_SDQ6

DDR_SDQ8

DDR_SDQ12

DDR_SDQS1

DDR_SDM1 DDR_DM1

DDR_SDQ14

DDR_SDQ11

DDR_SDQ16 DDR_DQ16

DDR_SDQ21 DDR_DQ21

DDR_SDQ17

DDR_SDM2 DDR_DM2

DDR_SDQ18

DDR_SDQ28

DDR_SDQ25

DDR_SDQ24

DDR_SDQ29

DDR_SDQS3

DDR_SDM3

DDR_SDQ26

DDR_SDQ27

DDR_SDQ30

DDR_SDQ31

DDR_SDM[0..7]<5>

DDR_SMAA[0..13]<5>

RP27

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP30

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP33

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP36

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP39

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP40

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP42

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP44

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP46

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP48

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

2005/03/01 2006/03/11

E

DDR_SDQS[0..7]

DDR_SDQ[0..63]

DDR_SDM[0..7]

DDR_SMAA[0..13]

DDR_DQ4

DDR_DQ5

DDR_DQ1

DDR_DM0

DDR_DQS0

DDR_DQ2

DDR_DQ3

DDR_DQ7

DDR_DQ9

DDR_DQ6

DDR_DQ8

DDR_DQ12

DDR_DQS1

DDR_DQ13DDR_SDQ13

DDR_DQ14

DDR_DQ15DDR_SDQ15

DDR_DQ10DDR_SDQ10

DDR_DQ11

DDR_DQ20DDR_SDQ20

DDR_DQ17

DDR_DQS2DDR_SDQS2

DDR_DQ18

DDR_DQ22DDR_SDQ22

DDR_DQ19DDR_SDQ19

DDR_DQ23DDR_SDQ23

DDR_DQ28

DDR_DQ25

DDR_DQ24

DDR_DQ29

DDR_DQS3

DDR_DM3

DDR_DQ26

DDR_DQ27

DDR_DQ30

DDR_DQ31

Compal Secret Data

Deciphered Date

E

F

RP26

DDR_SDQ32 DDR_DQ32

DDR_SDQ33

DDR_SDQ36 DDR_DQ36

DDR_SDQ37

DDR_SDQS4

DDR_SDQ34

DDR_SDM4 DDR_DM4

DDR_SDQ39

DDR_SDQ38

DDR_SDQ35

DDR_SDQ45

DDR_SDQ44

DDR_SDQS5

DDR_SDM5

DDR_SDQ42

DDR_SDQ43

DDR_SDQ47

DDR_SDQ46

DDR_SDQ48

DDR_SDQ53

DDR_SDQ49

DDR_SDQ52

DDR_SDQ54

DDR_SDQ50

DDR_SDQ51

DDR_SDQ55

DDR_SDQ57

DDR_SDQ61

DDR_SDM7

DDR_SDQS7 DDR_DQS7

DDR_SDQ62

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQ59

F

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP29

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP32

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP35

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP38

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP41

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP43

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP45

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP47

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP49

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_DQ33

DDR_DQ37

DDR_DQS4

DDR_DQ34

DDR_DQ39

DDR_DQ38

DDR_DQ35

DDR_DQ40DDR_SDQ40

DDR_DQ45

DDR_DQ44

DDR_DQ41DDR_SDQ41

DDR_DQS5

DDR_DM5

DDR_DQ42

DDR_DQ43

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ53

DDR_DQ49

DDR_DQ52

DDR_DM6DDR_SDM6

DDR_DQS6DDR_SDQS6

DDR_DQ54

DDR_DQ50

DDR_DQ51

DDR_DQ55

DDR_DQ60DDR_SDQ60

DDR_DQ56DDR_SDQ56

DDR_DQ57

DDR_DQ61

DDR_DM7

DDR_DQ62

DDR_DQ58

DDR_DQ59

G

DDR_DQ[0..63] <9>

DDR_DQS[0..7] <9>

DDR_DM[0..7] <9>

DDR_SMAA13

DDR_SWEA#

DDR_SCASA#

DDR_SCS#0

DDR_SCS#1

DDR_CKE0

Note:

DDR_SMAA13 Recommend for AMD

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

1 2

1 2

1 2

H

RP28

47_0804_8P4R_5%

RP31

47_0804_8P4R_5%

RP34

47_0804_8P4R_5%

RP37

47_0804_8P4R_5%

R6 47_0402_5%

R1 47_0402_5%

R5 47_0402_5%

R8 47_0402_5%

1 2

R10 47_0402_5%

1 2

R9 47_0402_5%

1 2

+1.25V

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

+2.5V

12

R686

1K_0402_1%

12

R687

1K_0402_1%

Title

Size Document Number Rev

Custom

Date: Sheet

G

DDR-SODIMM SLOT0

LA-2931

+1.25VREF_MEM

1

C781

0.1U_0402_16V4Z

2

1

C782

1000P_0402_50V7K

2

848Thursday, August 18, 2005

of

H

0.3

Page 9

A

+2.5V

JP46

1

VREF

3

DDR_DQ0

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ7

1 1

DDR_CLK4<5>

DDR_CLK4#<5>

2 2

3 3

4 4

KBD_DATA<8,33>

KBD_CLK<8,33>

DDR_CKE1<5>

DDR_SBSB0<5>

DDR_SWEB#<5>

DDR_SCS#2<5>

SMB_CK_DAT1<8,15,19>

SMB_CK_CLK1<8,15,19>

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ28

DDR_DQ24

DDR_DQS3

DDR_DQ26

DDR_DQ27

KBD_DATA

KBD_CLK

DDR_CKE1 DDR_CKE1

DDR_SMAB12

DDR_SMAB9

DDR_SMAB7

DDR_SMAB5

DDR_SMAB3

DDR_SMAB1

DDR_SMAB10

DDR_SBSB0

DDR_SWEB#

DDR_SCS#2 DDR_SCS#3

DDR_SMAB13

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ55

DDR_DQ56

DDR_DQ61

DDR_DQS7

DDR_DQ58

DDR_DQ59

+3VS

A

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

QTC_C106A-040SP11

CONN@

DU/RESET#

DIMM1

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

BA1

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

A11

S1#

B

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

20 mil width

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ11

DDR_DQ16

DDR_DQ21

DDR_DM2

DDR_DQ22

DDR_DQ23

DDR_DQ25

DDR_DQ29

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_SMAB11

DDR_SMAB8

DDR_SMAB6

DDR_SMAB4

DDR_SMAB2

DDR_SMAB0

DDR_SBSB1

DDR_SRASB#

DDR_SCASB#

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ35

DDR_DQ39

DDR_DQ41

DDR_DQ45

DDR_DM5

DDR_DQ42

DDR_DQ43

DDR_DQ53

DDR_DQ52

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ63

+3VS

+1.25VREF_MEM

1

C783

0.1U_0402_16V4Z

2

DDR_SBSB1 <5>

DDR_SRASB# <5>

DDR_SCASB# <5>

DDR_SCS#3 <5>

DDR_CLK6# <5>

DDR_CLK6 <5>

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/03/01 2006/03/11

C

Compal Secret Data

Note:

DDR_SMAB13 Recommend

for AMD.

DDR_DQ63

1 8

DDR_DQ62

2 7

DDR_DM7

3 6

DDR_DQ57

4 5

68_0804_8P4R_5%

DDR_DQ60

1 8

DDR_DQ51

2 7

DDR_DQ54

3 6

DDR_DM6

4 5

68_0804_8P4R_5%

DDR_DQ52

1 8

DDR_DQ53

2 7

DDR_DQ43

3 6

DDR_DQ42

4 5

68_0804_8P4R_5%

DDR_DM5

1 8

DDR_DQ45

2 7

DDR_DQ41

3 6

DDR_DQ39

4 5

68_0804_8P4R_5%

DDR_DQ35

1 8

DDR_DM4

2 7

DDR_DQ33

3 6

DDR_DQ37

4 5

68_0804_8P4R_5%

DDR_DQ31

1 8

DDR_DQ30

2 7

DDR_DM3

3 6

DDR_DQ29

4 5

68_0804_8P4R_5%

DDR_DQ25

1 8

DDR_DQ23

2 7

DDR_DQ22

3 6

DDR_DM2

4 5

68_0804_8P4R_5%

RP68

DDR_DQ21

1 8

DDR_DQ16

2 7

DDR_DQ11

3 6

DDR_DQ10

4 5

68_0804_8P4R_5%

RP70

DDR_DM1

1 8

DDR_DQ13

2 7

DDR_DQ8

3 6

DDR_DQ6

4 5

68_0804_8P4R_5%

RP72

DDR_DQ2

1 8

DDR_DM0

2 7

DDR_DQ1

3 6

DDR_DQ4

4 5

68_0804_8P4R_5%

DDR_DQS[0..7]<8>

DDR_DQ[0..63]<8>

DDR_DM[0..7]<8>

DDR_SMAB[0..13]<5>

Deciphered Date

RP52

RP55

RP58

RP61

RP63

RP65

RP66

DDR_DQS[0..7]

DDR_DQ[0..63]

DDR_DM[0..7]

DDR_SMAB[0..13]

D

+1.25V

D

E

+1.25V

DDR_DQ59

DDR_DQ58

DDR_DQS7

DDR_DQ61

DDR_DQ56

DDR_DQ55

DDR_DQ50

DDR_DQS6

68_0804_8P4R_5%

DDR_DQ49

DDR_DQ48

DDR_DQ46

DDR_DQ47

DDR_DQS5

DDR_DQ44

DDR_DQ40

DDR_DQ38

DDR_DQ34

DDR_DQS4

DDR_DQ36

DDR_DQ32

68_0804_8P4R_5%

DDR_DQ27

DDR_DQ26

DDR_DQS3

DDR_DQ24

DDR_DQ28

DDR_DQ19

DDR_DQ18

DDR_DQS2

DDR_DQ17

DDR_DQ20

DDR_DQ15

DDR_DQ14

DDR_DQS1

DDR_DQ12

DDR_DQ9

DDR_DQ7

DDR_DQ3

DDR_DQS0

DDR_DQ5

DDR_DQ0

RP51

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP54

1 8

2 7

3 6

4 5

RP57

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP60

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP62

1 8

2 7

3 6

4 5

RP64

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP67

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP69

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP71

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP73

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

DDR_SBSB0

DDR_SMAB10

DDR_SMAB1

DDR_SMAB3

DDR_SMAB5

DDR_SMAB7

DDR_SMAB9

DDR_SMAB12

DDR_SMAB8

DDR_SMAB11

DDR_CKE1

DDR_SMAB0

DDR_SMAB2

DDR_SMAB4

DDR_SMAB6

DDR_SMAB13

DDR_SWEB#

DDR_SCASB#

DDR_SBSB1

DDR_SRASB#

DDR_SCS#2

DDR_SCS#3

RP50

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP53

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP56

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP59

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

RP3

47_0804_8P4R_5%

RP4

47_0804_8P4R_5%

Layout note

Place these resistor

closely DIMM1,

all trace

length<=800mil

Title

Size Document Number Rev

Custom

Date: Sheet

DDR-SODIMM SLOT1

LA-2931

E

+1.25V

18

27

36

45

18

27

36

45

0.3

948Thursday, August 18, 2005

of

Page 10

A

B

C

D

E

07/07/'05

+2.5V

1

C784

2

1 1

1

+

+

C785

2

330U_D_4VM

330U_D_4VM

4.7U_0805_6.3V6K

1

C786

2

4.7U_0805_6.3V6K

1

C787

2

Near DIMMs

Layout note :

Place one cap close to every 2 pull up resistors termination to

+1.25V

+1.25V

+2.5V

C1657

100P_0402_25V8K@

100P_0402_25V8K@

C1658

Please Close to DDR_CLK4/5 via hole

1

C788

2

0.1U_0402_16V4Z

+1.25V

2 2

1

C800

2

0.1U_0402_16V4Z

+1.25V

1

C812

2

0.1U_0402_16V4Z

+1.25V

1

C824

3 3

2

0.1U_0402_16V4Z

+1.25V

1

C836

2

0.1U_0402_16V4Z

+1.25V

1

C789

2

0.1U_0402_16V4Z

1

C801

2

0.1U_0402_16V4Z

1

C813

2

0.1U_0402_16V4Z

1

C825

2

0.1U_0402_16V4Z

1

C837

2

0.1U_0402_16V4Z

1

C790

2

0.1U_0402_16V4Z

1

C802

2

0.1U_0402_16V4Z

1

C814

2

0.1U_0402_16V4Z

1

C826

2

0.1U_0402_16V4Z

1

C838

2

0.1U_0402_16V4Z

1

C791

2

0.1U_0402_16V4Z

1

C803

2

0.1U_0402_16V4Z

1

C815

2

0.1U_0402_16V4Z

1

C827

2

0.1U_0402_16V4Z

1

C839

2

0.1U_0402_16V4Z

1

C792

2

0.1U_0402_16V4Z

1

C804

2

0.1U_0402_16V4Z

1

C816

2

0.1U_0402_16V4Z

1

C828

2

0.1U_0402_16V4Z

1

C840

2

0.1U_0402_16V4Z

1

C793

2

0.1U_0402_16V4Z

1

C805

2

0.1U_0402_16V4Z

1

C817

2

0.1U_0402_16V4Z

1

C829

2

0.1U_0402_16V4Z

1

C841

2

0.1U_0402_16V4Z

1

C794

2

0.1U_0402_16V4Z

1

C806

2

0.1U_0402_16V4Z

1

C818

2

0.1U_0402_16V4Z

1

C830

2

0.1U_0402_16V4Z

1

C842

2

0.1U_0402_16V4Z

1

C795

2

0.1U_0402_16V4Z

1

C807

2

0.1U_0402_16V4Z

1

C819

2

0.1U_0402_16V4Z

1

C831

2

0.1U_0402_16V4Z

1

C843

2

0.1U_0402_16V4Z

1

C796

2

0.1U_0402_16V4Z

1

C808

2

0.1U_0402_16V4Z

1

C820

2

0.1U_0402_16V4Z

1

C832

2

0.1U_0402_16V4Z

1

C844

2

0.1U_0402_16V4Z

1

C797

2

0.1U_0402_16V4Z

1

C809

2

0.1U_0402_16V4Z

1

C821

2

0.1U_0402_16V4Z

1

C833

2

0.1U_0402_16V4Z

1

C845

2

0.1U_0402_16V4Z

1

C798

2

0.1U_0402_16V4Z

1

C810

2

0.1U_0402_16V4Z

1

C834

2

0.1U_0402_16V4Z

1

C846

2

0.1U_0402_16V4Z

1

C799

2

0.1U_0402_16V4Z

1

C811

2

0.1U_0402_16V4Z

1

C835

2

0.1U_0402_16V4Z

+2.5V

1

C847

2

0.1U_0402_16V4Z

+2.5V

10U_0805_10V4Z

+1.25V

1

2

C822

1

C823

10U_0805_10V4Z

2

1

C848

2

0.1U_0402_16V4Z

4 4

1

2

0.1U_0402_16V4Z

A

C849

1

C850

2

0.1U_0402_16V4Z

1

C851

2

0.1U_0402_16V4Z

1

C852

2

0.1U_0402_16V4Z

B

1

C853

2

0.1U_0402_16V4Z

1

C854

2

0.1U_0402_16V4Z

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C855

2

0.1U_0402_16V4Z

1

C856

2

0.1U_0402_16V4Z

2005/03/01 2006/03/11

C

1

C857

2

0.1U_0402_16V4Z

+2.5V

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet of

DDR SODIMM Decoupling

LA-2931

E

0.3

10 48Thursday, August 18, 2005

Page 11

5

4

3

2

1

H_CADIP[0..15]<4>

H_CADIN[0..15]<4>

H_CADOP[0..15]<4>

D D

H_CADOP15

H_CADON15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

1 2

1 2

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

C C

H_CLKOP1<4>

H_CLKON1<4>

H_CLKOP0<4>

H_CLKON0<4>

H_CTLOP0<4>

H_CTLON0<4>

+1.2V_HT

B B

R1157 49.9_0402_1%

R1159 49.9_0402_1%

H_CADON[0..15]<4>

U55A

T26

HT_RXCAD15P

R26

HT_RXCAD15N

U25

HT_RXCAD14P

U24

HT_RXCAD14N

V26

HT_RXCAD13P

U26

HT_RXCAD13N

W25

HT_RXCAD12P

W24

HT_RXCAD12N

AA25

HT_RXCAD11P

AA24

HT_RXCAD11N

AB26

HT_RXCAD10P

AA26

HT_RXCAD10N

AC25

HT_RXCAD9P

AC24

HT_RXCAD9N

AD26

HT_RXCAD8P

AC26

HT_RXCAD8N

R29

HT_RXCAD7P

R28

HT_RXCAD7N

T30

HT_RXCAD6P

R30

HT_RXCAD6N

T28

HT_RXCAD5P

T29

HT_RXCAD5N

V29

HT_RXCAD4P

U29

HT_RXCAD4N

Y30

HT_RXCAD3P

W30

HT_RXCAD3N

Y28

HT_RXCAD2P

Y29

HT_RXCAD2N

AB29

HT_RXCAD1P

AA29

HT_RXCAD1N

AC29

HT_RXCAD0P

AC28

HT_RXCAD0N

Y26

HT_RXCLK1P

W26

HT_RXCLK1N

W29

HT_RXCLK0P

W28

HT_RXCLK0N

P29

HT_RXCTLP

N29

HT_RXCTLN

D27

HT_RXCALN

E27

HT_RXCALP

216RS480M_BGA706

H_CADIP[0..15]

H_CADIN[0..15]

H_CADOP[0..15]

H_CADON[0..15]

HYPER TRANSPORT CPU

I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

H_CADIP15

R24

H_CADIN15

R25

H_CADIP14

N26

H_CADIN14

P26

H_CADIP13

N24

H_CADIN13

N25

H_CADIP12

L26

H_CADIN12

M26

H_CADIP11

J26

H_CADIN11

K26

H_CADIP10

J24

H_CADIN10

J25

H_CADIP9

G26

H_CADIN9

H26

H_CADIP8

G24

H_CADIN8

G25

H_CADIP7

L30

H_CADIN7

M30

H_CADIP6

L28

H_CADIN6

L29

H_CADIP5

J29

H_CADIN5

K29

H_CADIP4

H30

H_CADIN4

H29

H_CADIP3

E29

H_CADIN3

E28

H_CADIP2

D30

H_CADIN2

E30

H_CADIP1

D28

H_CADIN1

D29

H_CADIP0

B29

H_CADIN0

C29

H_CLKIP1

L24

H_CLKIN1

L25

H_CLKIP0

F29

H_CLKIN0

G29

H_CTLIP0

M29

H_CTLIN0

M28

R1158 100_0402_1%

B28

1 2

A28

H_CLKIP1 <4>

H_CLKIN1 <4>

H_CLKIP0 <4>

H_CLKIN0 <4>

H_CTLIP0 <4>

H_CTLIN0 <4>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C1637

C1638

+2.5VS

U55B

AF17

MEM_A0

AK17

MEM_A1

AH16

MEM_A2

AF16

MEM_A3

AJ22

MEM_A4

AJ21

MEM_A5

AH20

MEM_A6

AH21

MEM_A7

AK19

MEM_A8

AH19

MEM_A9

AJ17

MEM_A10

AG16

MEM_A11

AG17

MEM_A12

AH17

MEM_A13

AJ18

MEM_A14

AG26

MEM_DM0

AJ29

MEM_DM1

AE21

MEM_DM2

AH24

MEM_DM3

AH12

MEM_DM4

AG13

MEM_DM5

AH8

MEM_DM6

AE8

MEM_DM7

AF25

MEM_DQS0P

AH30

MEM_DQS1P

AG20