Page 1

5

4

3

2

1

REV : A01

ZRS

D D

@ : Nopop Component

1@ : ZUMA Used Only

2@ : Riker Used Only

3@ : ZRS with discrete Used Only

4@ : ZUMA & Zanzibar Used Only

C C

with BCM4401E w/o Docking and Smart card

5@ : Rikers & Suva Used Only

with BCM5752/Docking/Smart Card

6@ : Suva Used Only

7@ : Rikers/Zanzibar/ZUMA Used Only

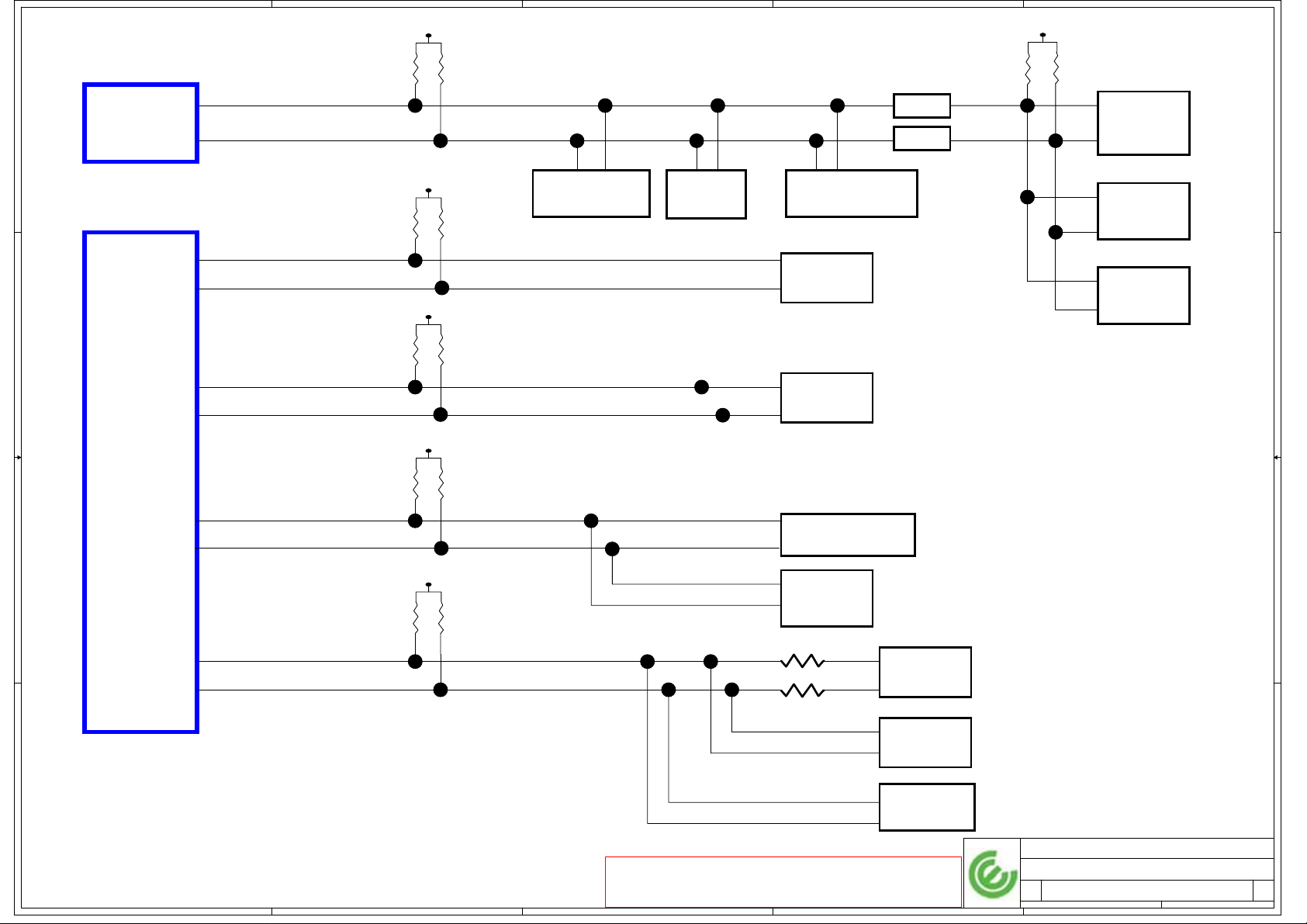

Config. TABLE

Project Config.

B B

ZUMA 1@ + 4@ +7@

Zanzibar 3@ + 4@ + 7@

Suva 3@ + 5@ + 6@

Rikers 2@ + 3@ + 5@ + 7@

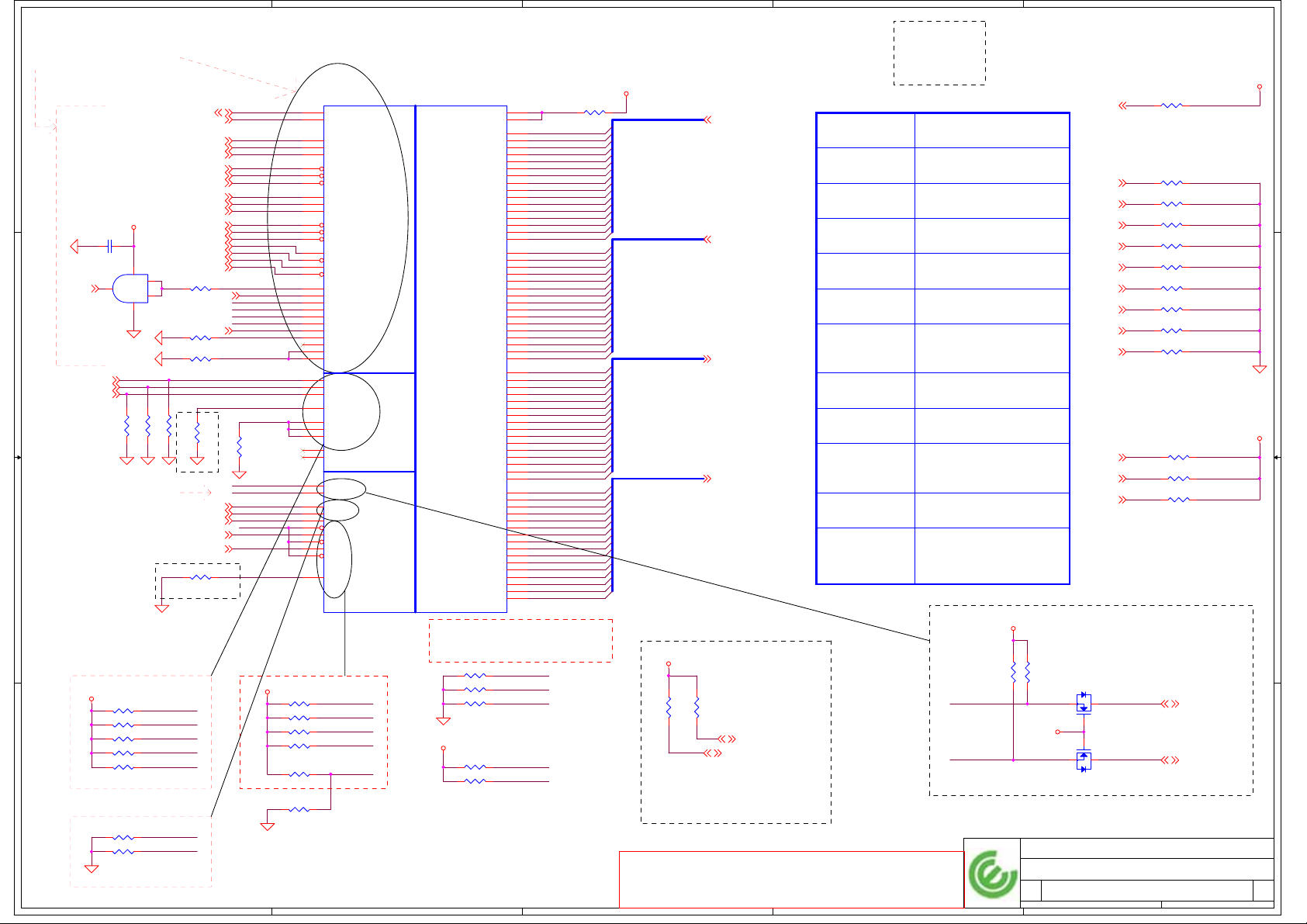

Yonah Schematics with Capture CIS and Function Field

A A

uFCPGA Yonah

12/13/2005

REV : 2.0

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-2881P

162Tuesday, December 13, 2005

1

of

2.0

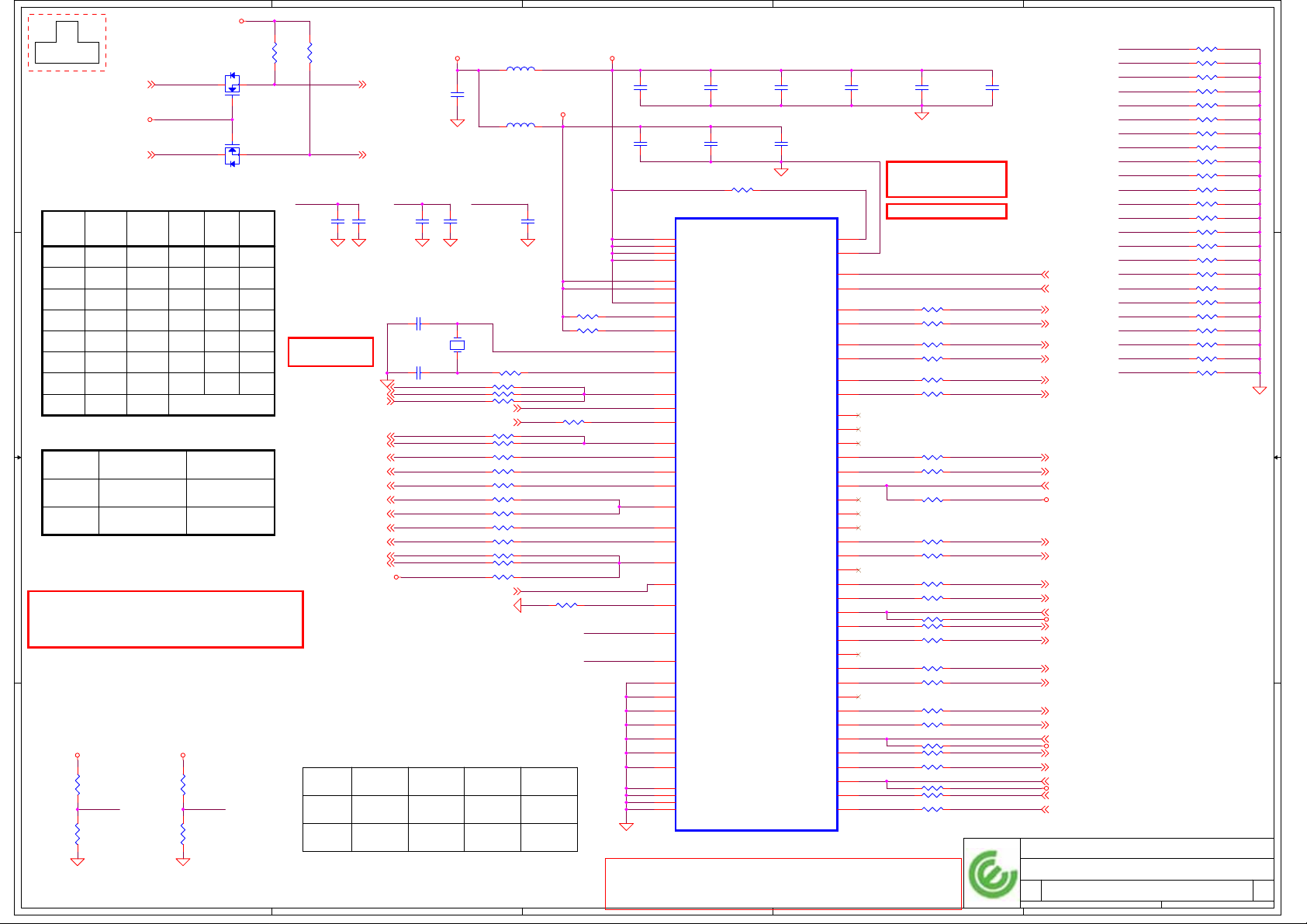

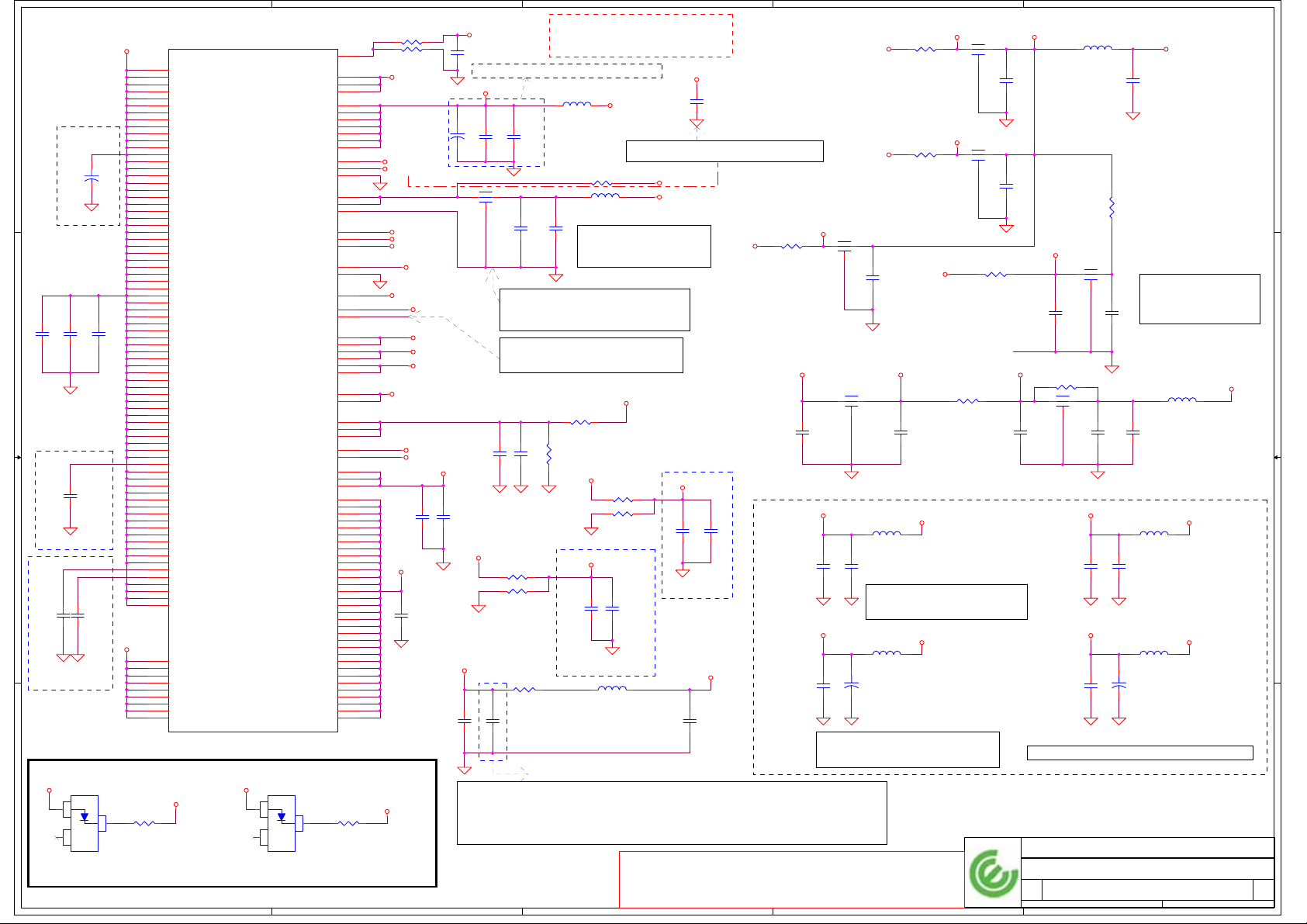

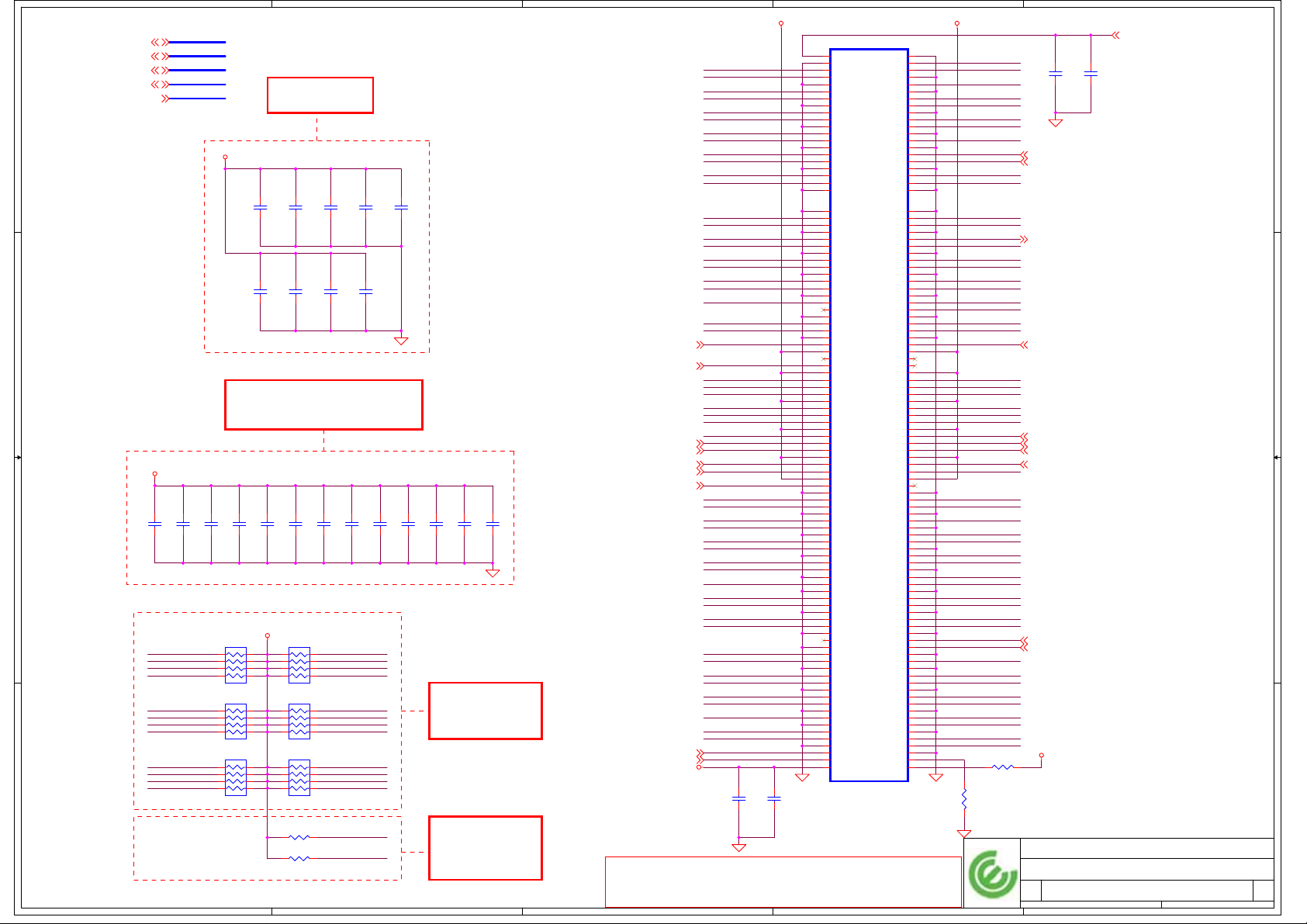

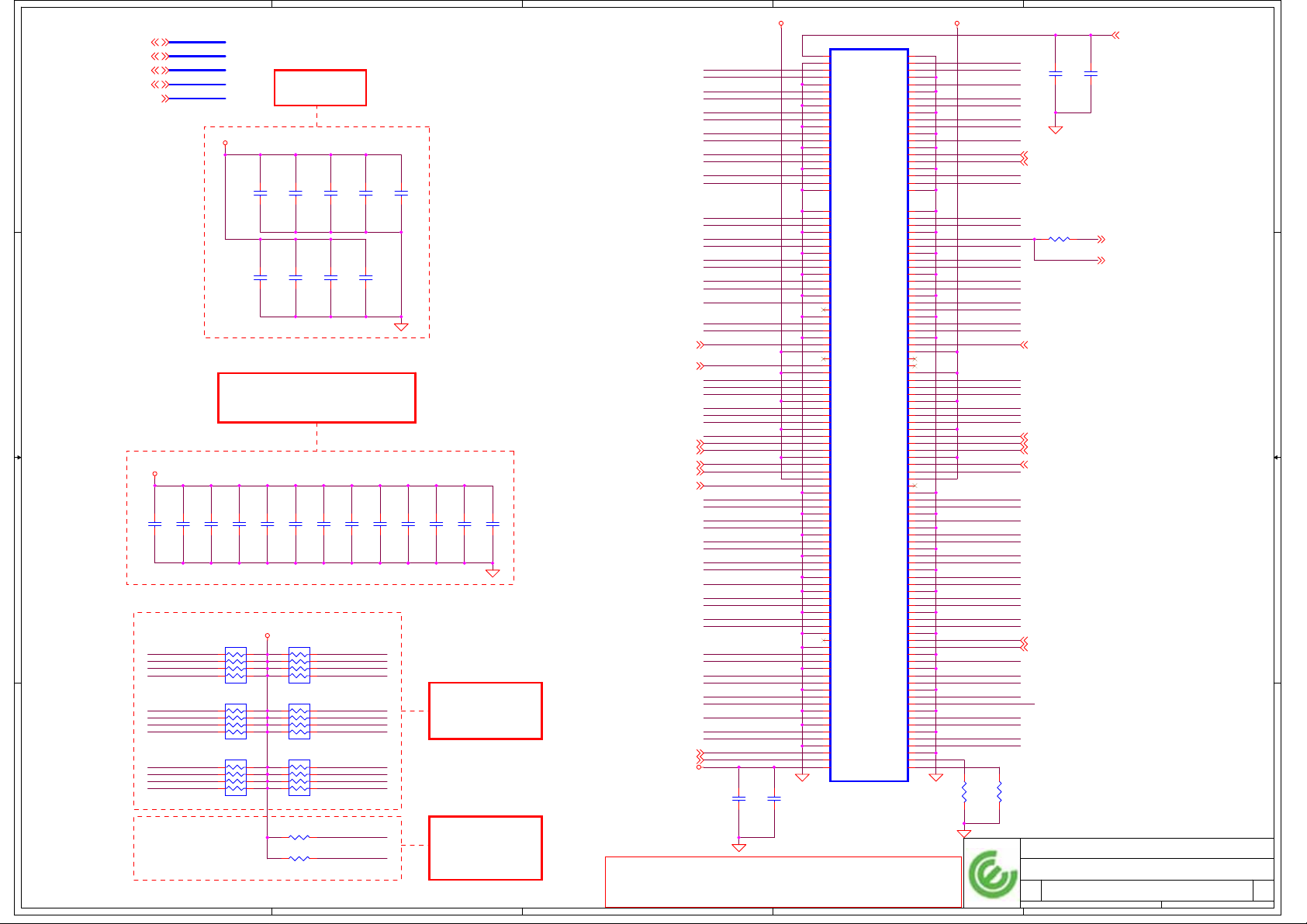

Page 2

5

4

3

2

1

Compal confidential

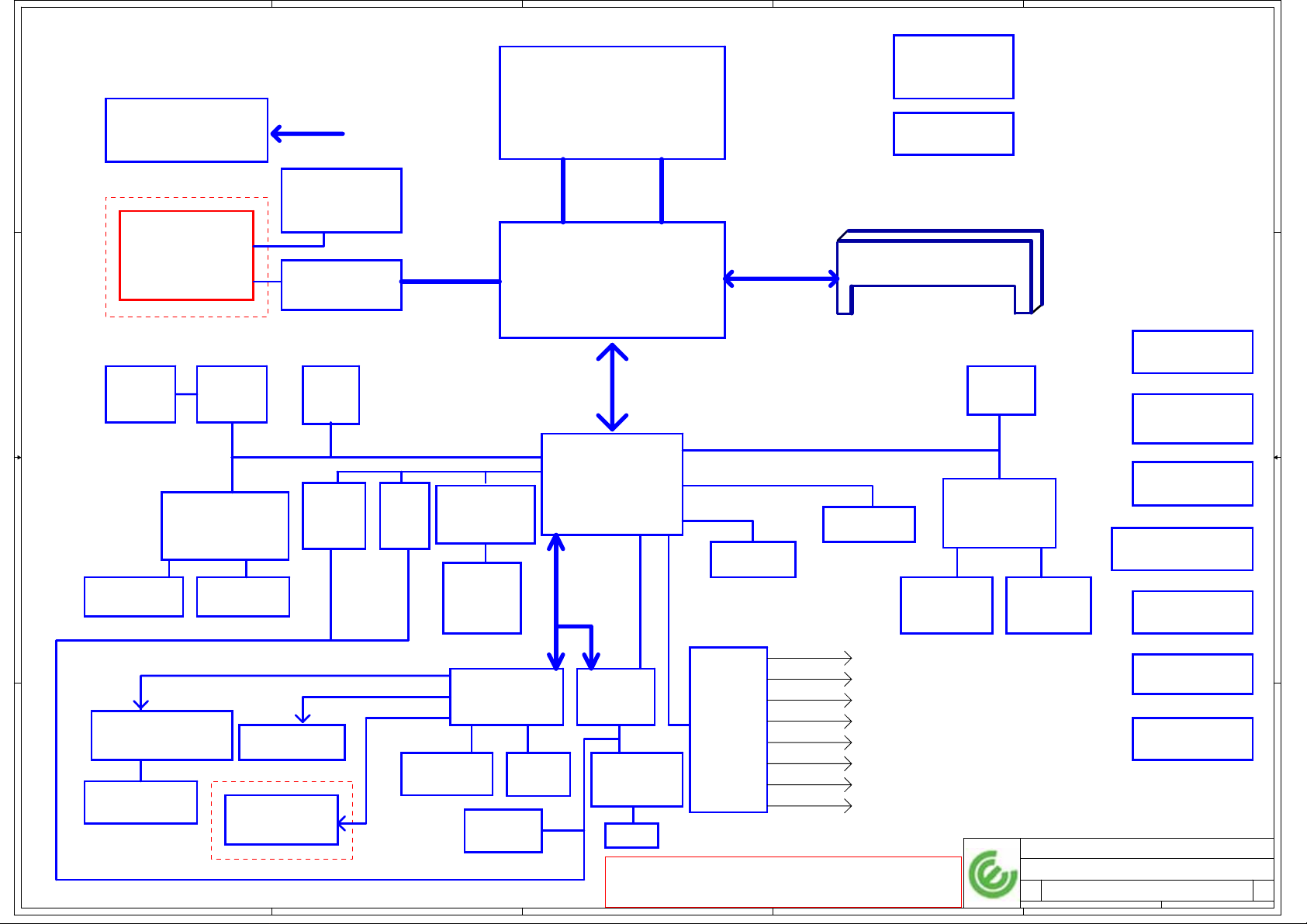

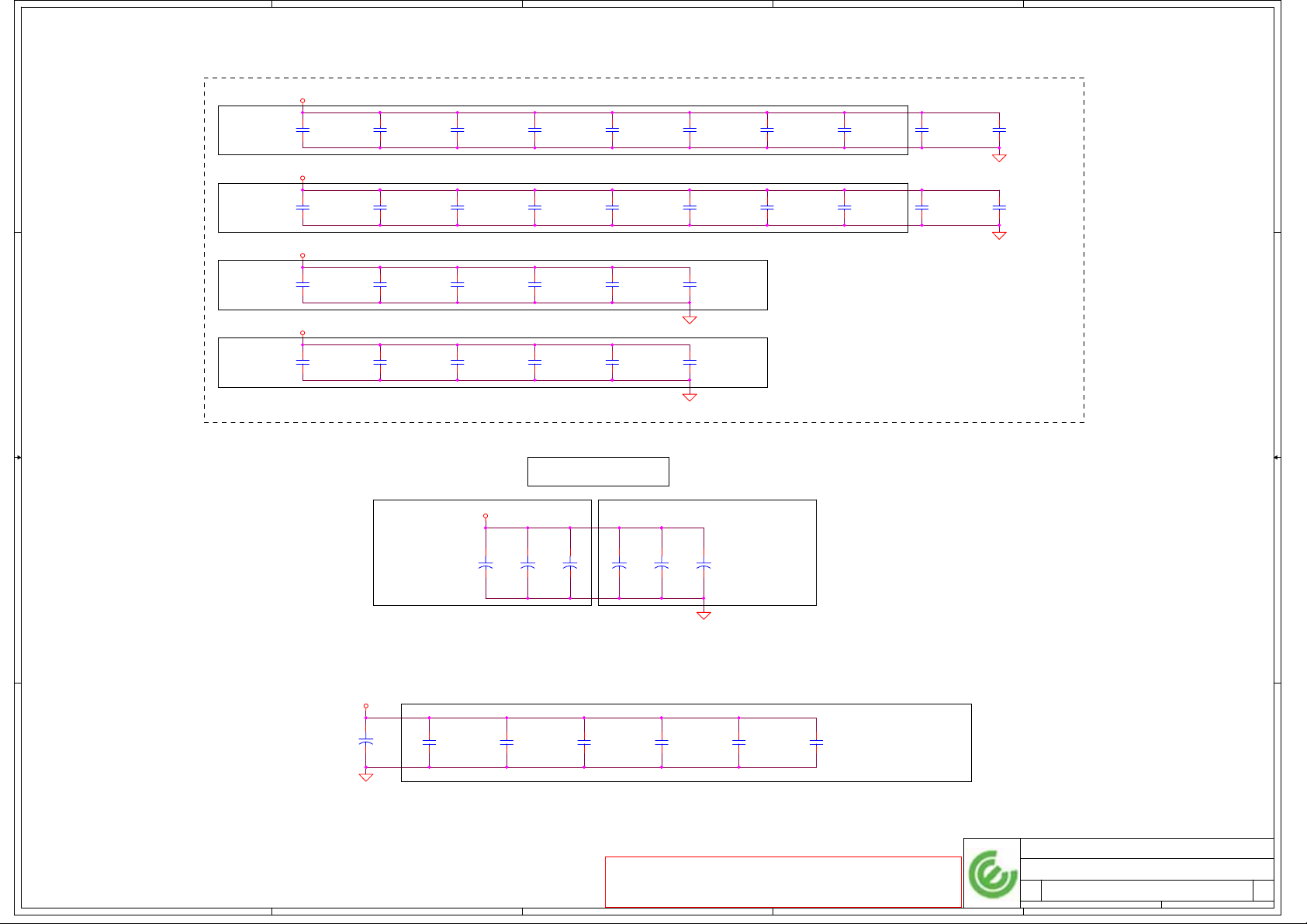

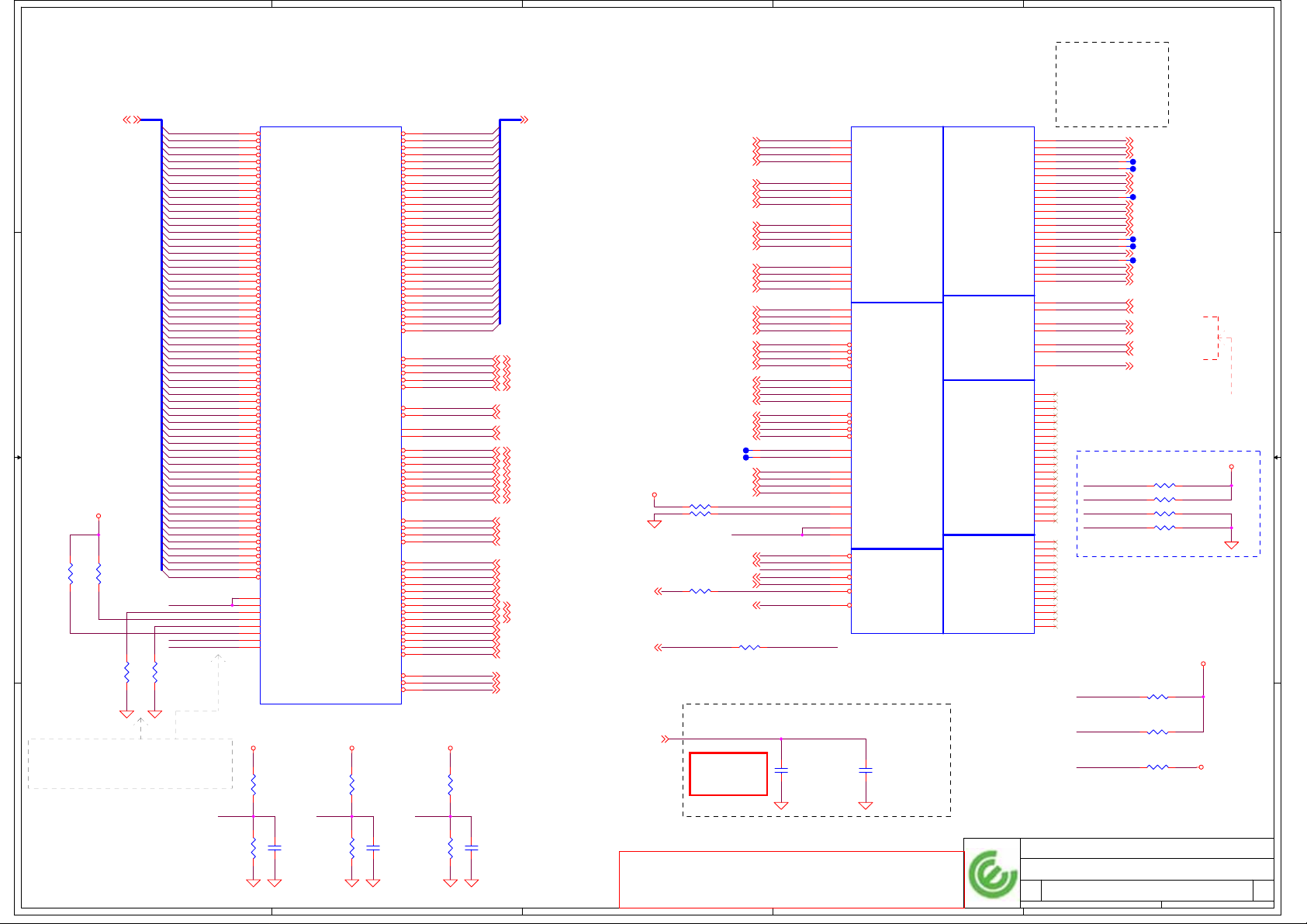

Clock Generator

Block Diagram

CK410M+

Yonah

D D

C C

B B

5 in 1 CONN.

Media/Touch Pad

CONN.

A A

Multi-media

Thermal

GUARDIAN II

EMC4000

+3.3V_SUS

VGA

Board

Docking

Port

page 36

IDSEL:AD17

(PIRQA/B#,GNT#2,REQ#2)

Docking

Buffer

Memory Card &

1394 Controller

RICOH R5C832

1394 CONN.

page33

page39

Board

5

SMBus

page 16

CRT CONN.

& TV-OUT

VGA CONN.

page 35

3.3V 33MHz

Express

Card

page 33

page33

ST M25P80

+3.3V_ALW

page 37

LED Controller

PAC9532

Rikers Used Only

page 41

LOM

4401E

page 31

page 34

USB3

page 20

page 19

PCI-E 16X

MINI

Card

page 34

USB1

GPIO

SPI

SMBus

Touch Pad

USB

4

PCI BUS

PCIe BUS

LOM

BCM5752

page 31

RJ45 with

Giga

Magnetic

page 32

MEC5004

LPC to X-BUS

PS2

page 39

Bluetooth

page 28

uFCPGA CPU

HA#(3..31)

System Bus

533 / 667 MHz

Calistoga

GMCH-M

1466 FC-BGA

Intel 945PM/945GM

DMI

1.5V

100MHz

ICH7-M

652 BGA

Intel 82801GBM

page 22,23,24,25

LPC BUS

3.3V 33MHz

ECE5018

Super I/O

page 38

Int.KBD

page 39

USB4

Smart Card

Fan Control

page 7,8,9

HD#(0..63)

Memory

BUS(DDRII)

1.8V 533 / 667 MHz

page 10,11,12,13,14,15

DDRII-SODIMM X2

BANK 0, 1, 2, 3

Azalia

3.3V or 5V SATA

SATA

ATA100

HDD

USB5

CDROM

page 26

page 26

Phone Jack

48MHz / 480Mb

USB0

page 37

USB2

OZ77C6

page 34

USB2.0

IO PORT

page 30

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

USBPORT 6

USBPORT 7

Ext. USB

Ext. USB

Ext. USB

Ext. USB

Ext. USB

SIO ECE5018

Ext. USB

Dock

Slot

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

AMP &

page 6

page 16

page 17,18

MDC

page 29

Azalia CODEC

STAC9200

page 27

Subwoofer

page 28

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

1.5V/1.05V(+VCCP)

page 29

Compal Electronics, Inc.

Block Diagram

LA-2881P

DC IN

page 43

BATT IN/+2.5V

page 44

3.3V/5V/15V

page 45

page 46

1.8V / 0.9V

page 47

IMVP6 VCORE

3 Phase

page 48

CHARGER

page 49

262Tuesday, December 13, 2005

1

of

2.0

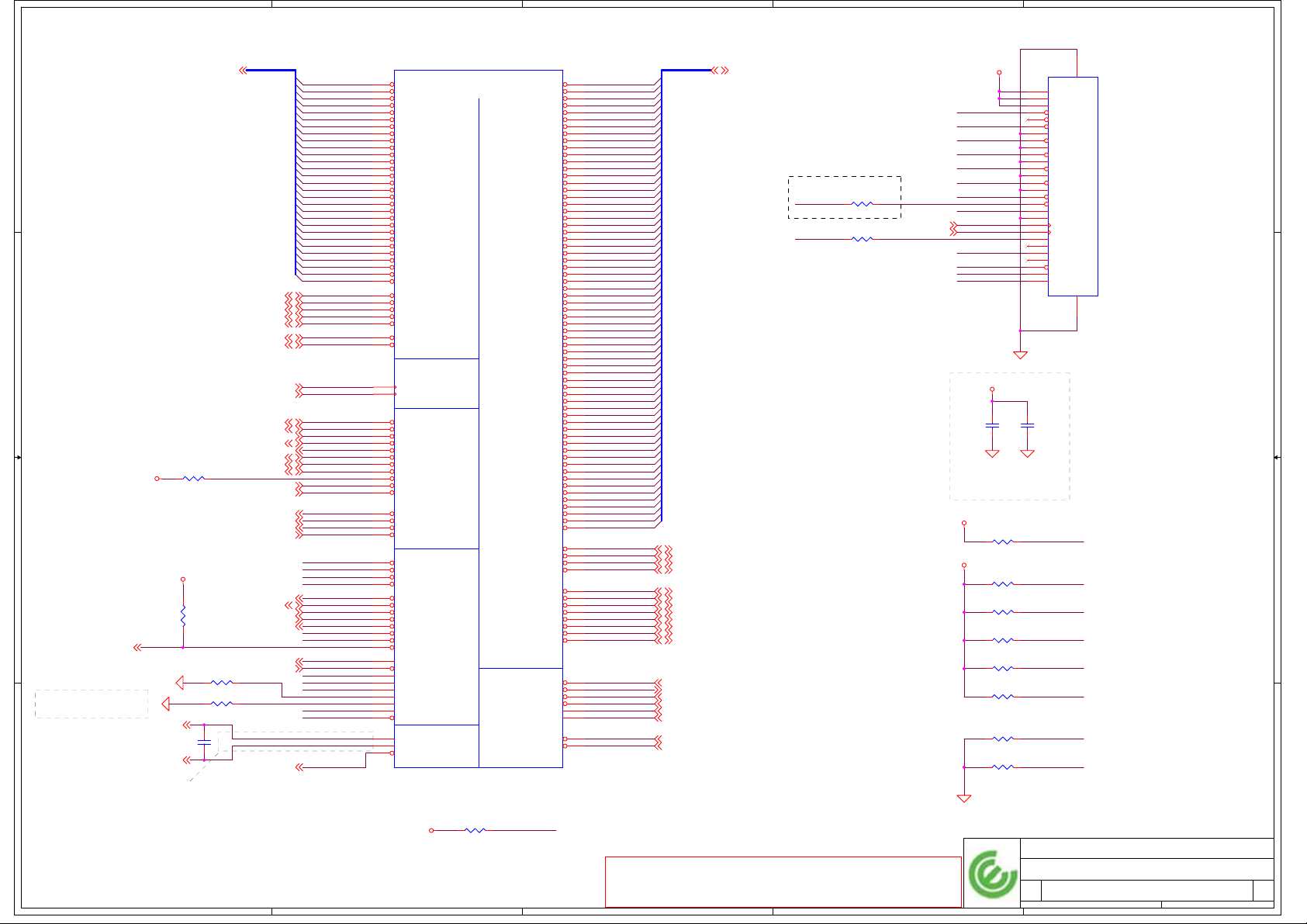

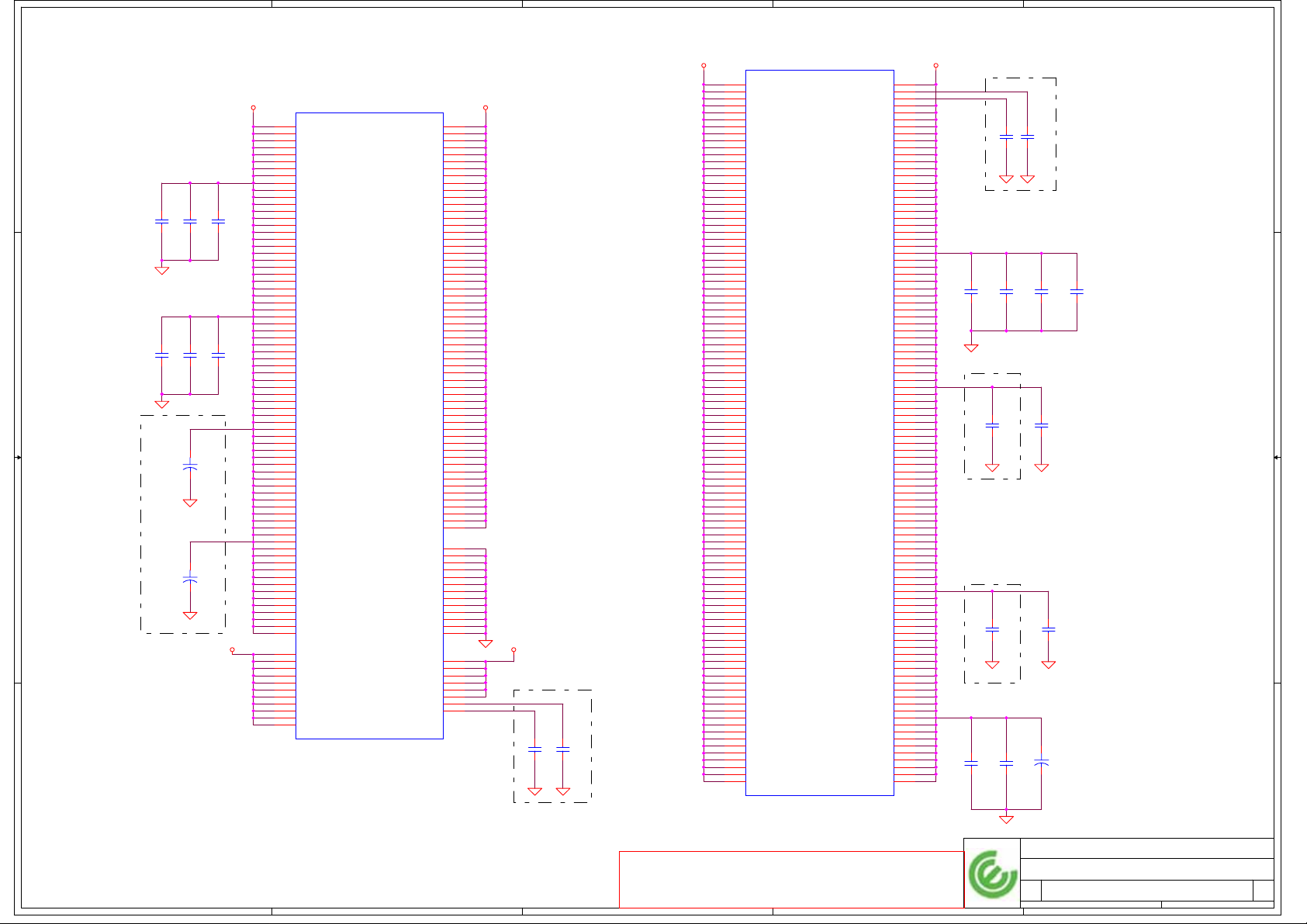

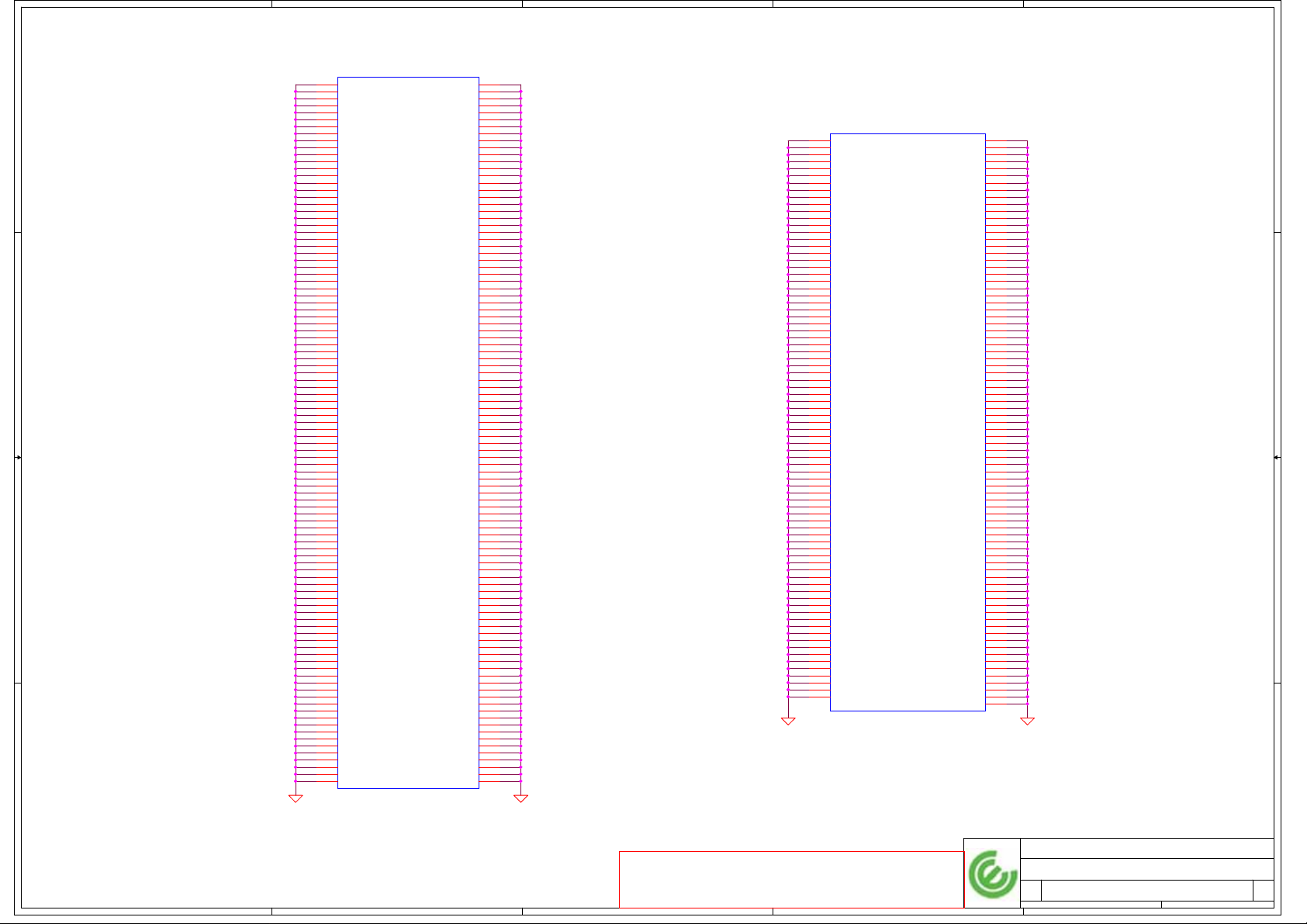

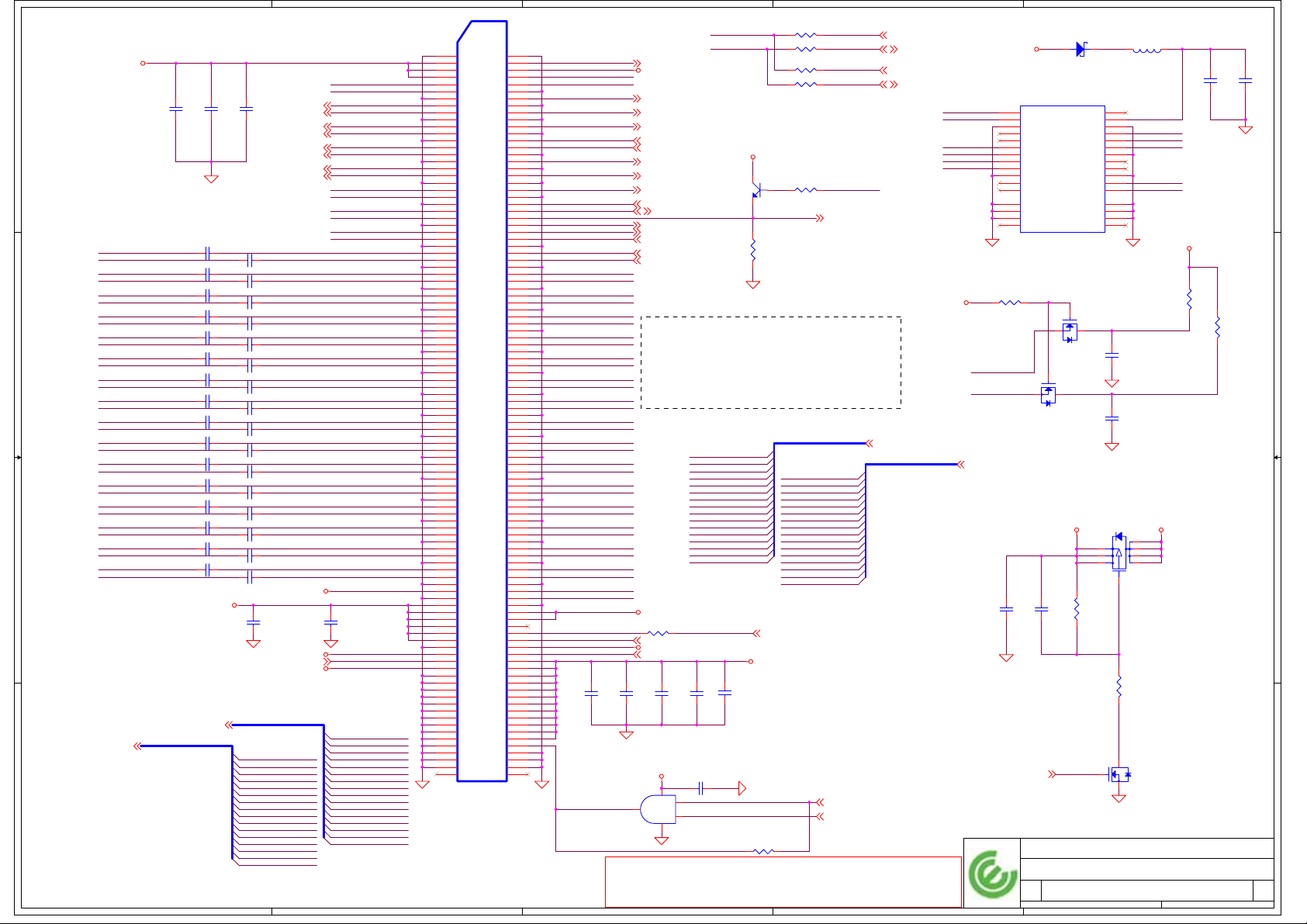

Page 3

5

4

3

2

1

D D

C C

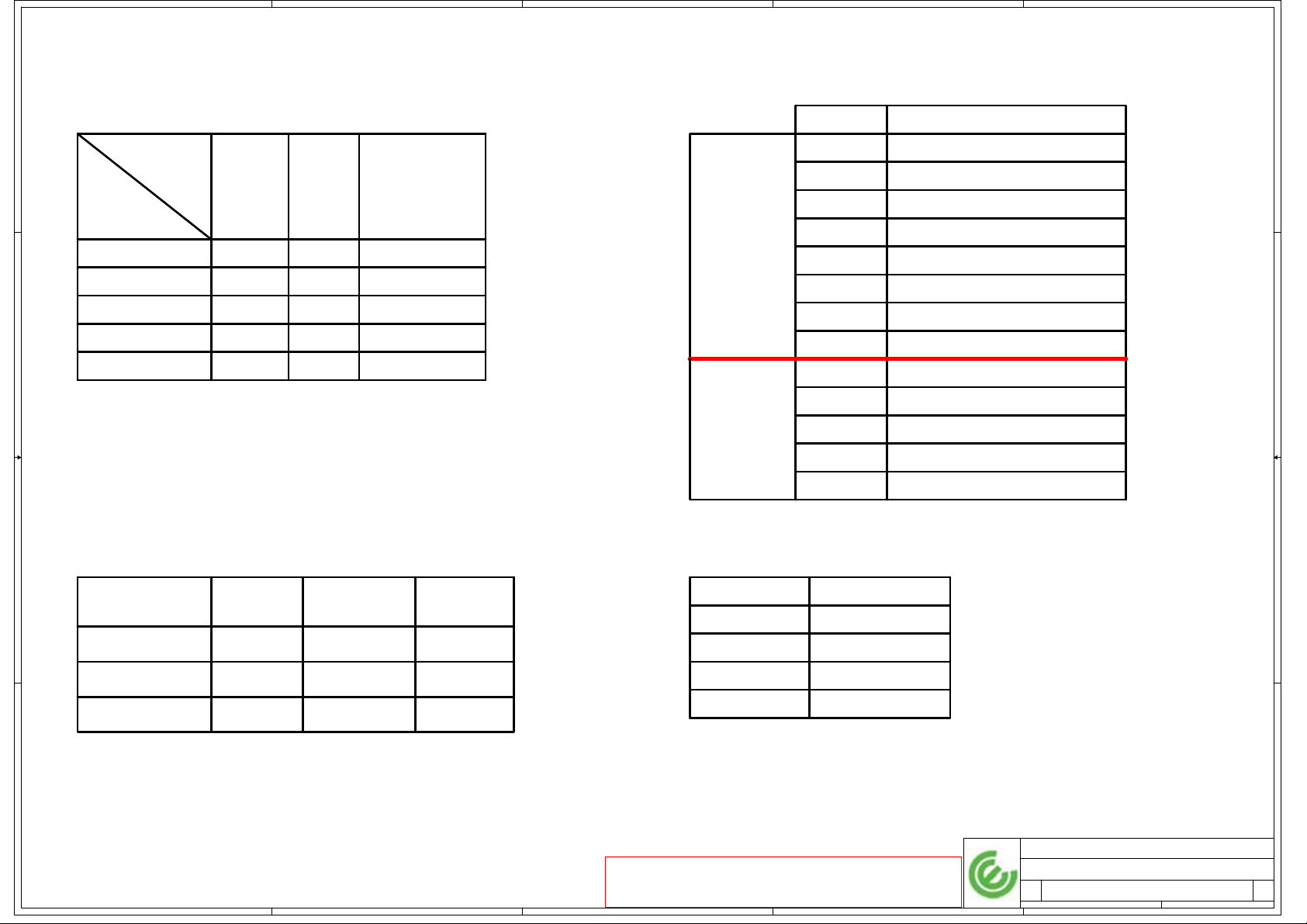

PM TABLE

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

power

plane

+5V_ALW

+3.3V_ALW

+3.3V_SRC

ON

ON

ON

ON

+5V_RUN

+15V_SUS

+5V_SUS

+3.3V_SUS

+1.8V_SUS

ON ON

ON

ON

OFF

OFFOFF

+3.3V_RUN

+2.5V_RUN

+1.8V_RUN

+0.9V_DDR_VTT

+VCC_CORE

+1.05V_VCCP

ON

OFF

OFF

OFF

ICH7-M

SIO

ECE5018

USB PORT#0Description

SUPER I/O ECE5018

1

2

3

4

5

6

JUSB_R (Ext Back Right Bottom)

JUSB_S (Ext Side Bottom)

JUSB_R (Ext Back Right Top)

JUSB_L (Ext Back Left Top)

JUSB_S (Ext Side Top)

JUSB_L (Ext Back Left Bottom)

7 DOCKING

0

1

2

3

4

ICH7-M

MINI CARD WLAN

SMART CARD

EXPRESS CARD

BLUE TOOTH

B B

A A

PCI TABLE

PCI DEVICE IDSEL

LAN

Dock

AD24 REQ#0/GNT#0 IRQA

REQ#/GNT#

REQ#3/GNT#3AD16 IRQB

PIRQ

R5C832 AD17 REQ#2/GNT#2 IRQC,D

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

DESTINATION

No

MINI CARD WLAN

GIGA LAN

EXPRESS CARD

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Index and Config.

LA-2881P

362Tuesday, December 13, 2005

1

2.0

of

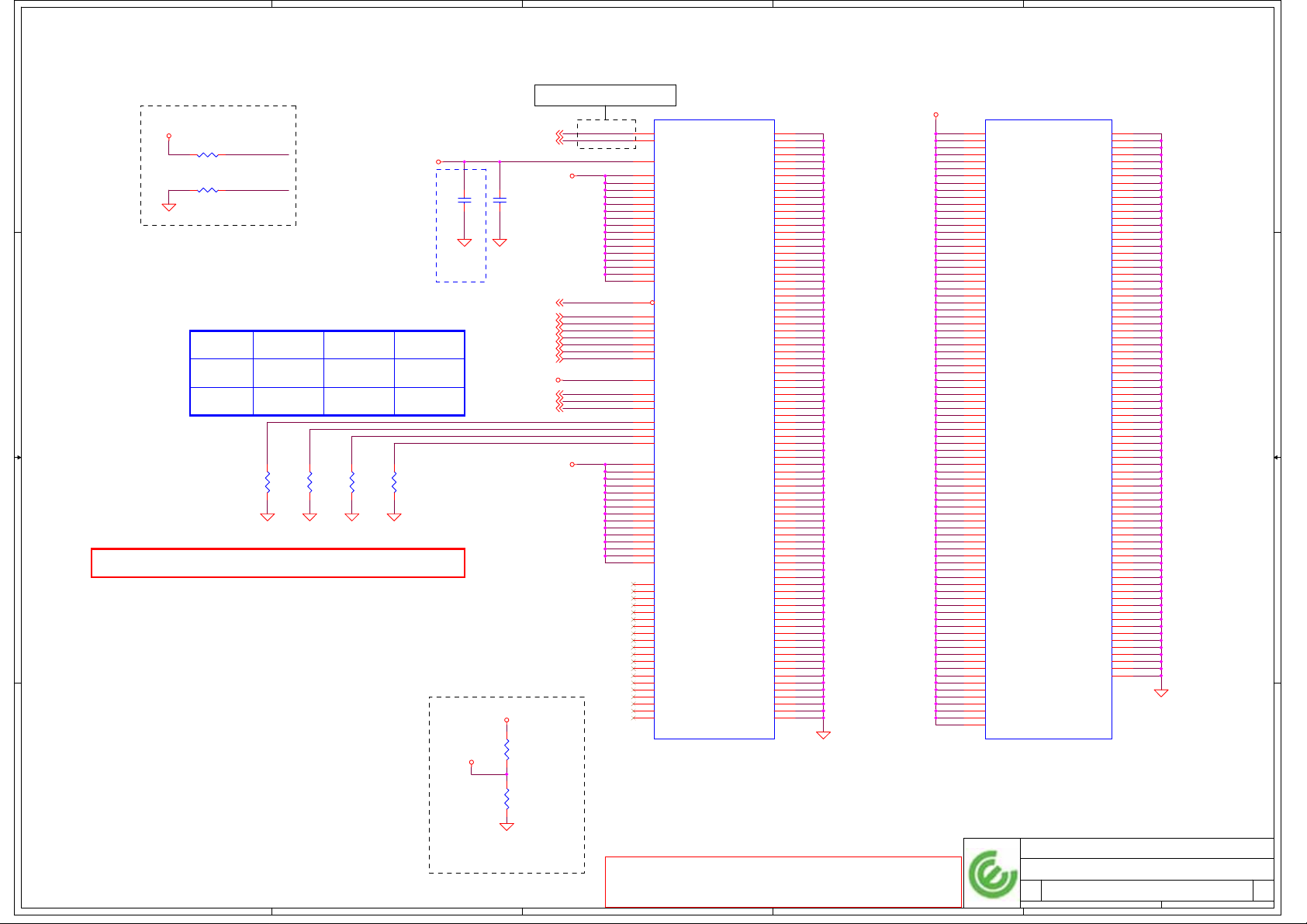

Page 4

5

4

3

2

1

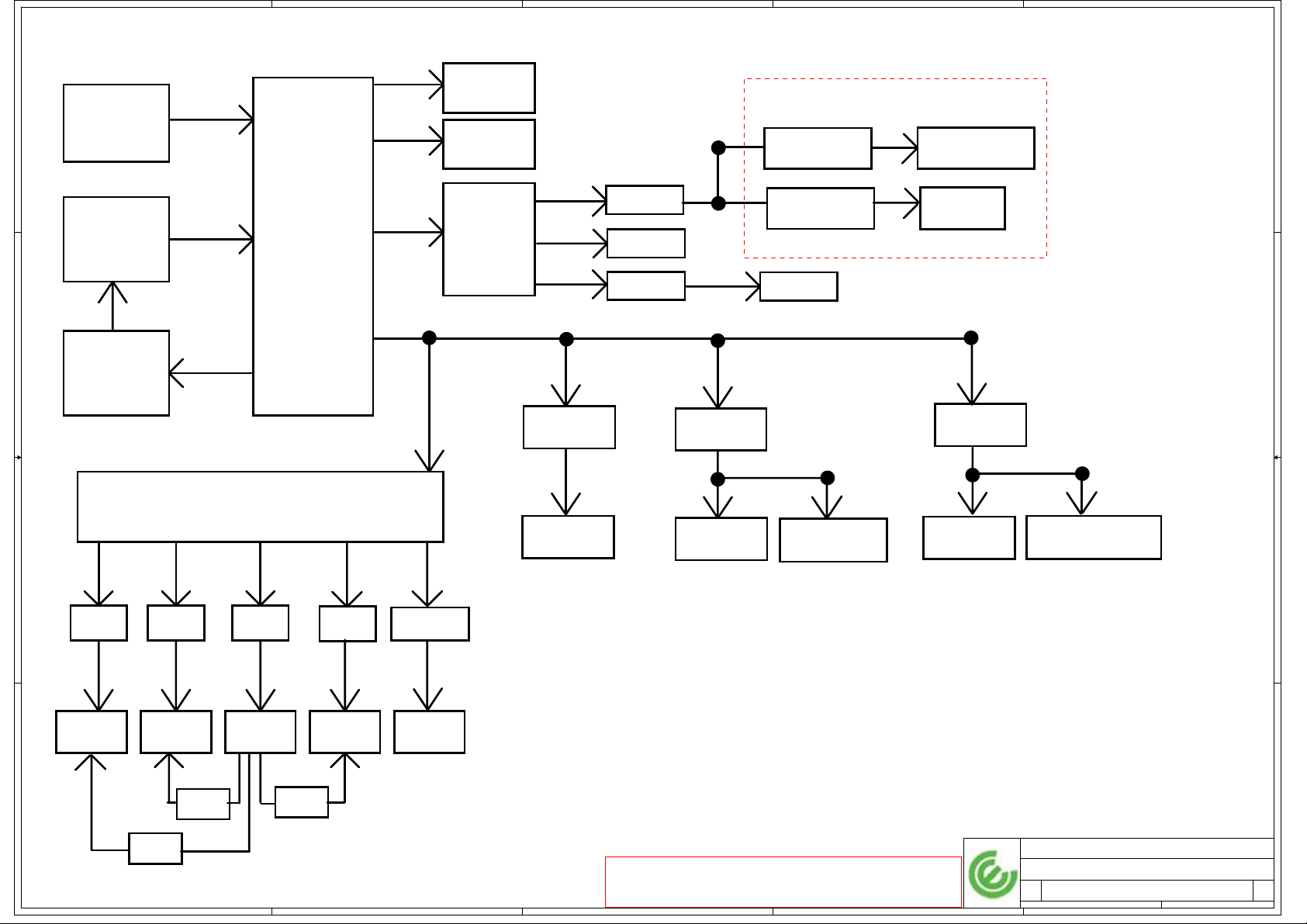

ALWON

D D

ADAPTER

ALWON

+PWR_SRC

BATTERY

+3.3V_ALW

C C

+5V_ALW

+3.3V_ALW

+3.3V_SRC

ENAB_3VLAN

SUS_ON

RUN_ON

+3.3V_LAN

+3.3V_SUS

+3.3V_RUN

Guardian II

5752 Only

REGCTL_PNP12

MMJT9435T1G

( Q102 )

REGCTL_PNP25

BCP69

( Q103 )

+2.5V_RUN

+1.2V_1.8V_LAN

+2.5V_LAN

Charger

MAX8632

(PU6)

SUSPWROK_5V

+1.8V_SUS

RUN_ON

+0.9V_DDR_VTT

+5V_SUS

SUS_ON

ISL6220

(PU8)

RUN_ON

+VCC_CORE

ISL6227

(PU5)

RUNPWROK

+1.5V_RUN

RUN_ON

+1.05V_VCCP

B B

SI3456

(Q22)

HDDC_EN#

+5V_HDD +5V_MOD +5V_RUN +VDDA

A A

SI3456

(Q24)

MODC_EN#

PJP19

( Option )

5

PJP20

( Option )

SI4810

(Q61)

RUN_ON

AUDIO_AVDD_ON

L31

(Option)

793475

(U12)

PL8 & PD8

+15V_SUS

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Power Rail

LA-2881P

462Tuesday, December 13, 2005

1

of

2.0

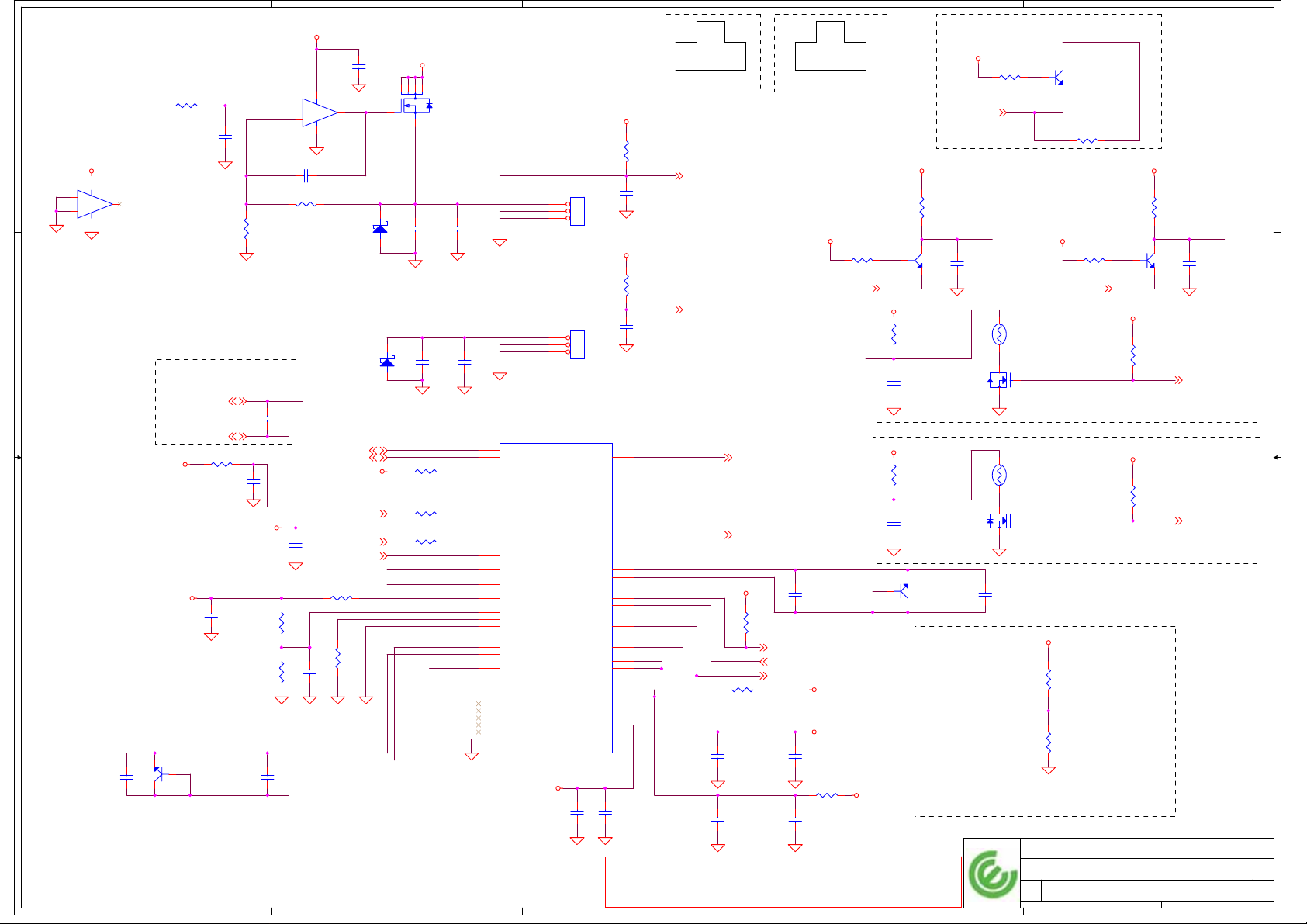

Page 5

5

ICH_SMBCLK

C22

D D

ICH7-M

ICH_SMBDATA

B22

CLK_SMB

10

DAT_SMB

9

4

+3.3V_SUS

2.2K 2.2K 2.2K 2.2K

+3.3V_SUS

+3.3V_ALW

87

Express Card

2.2K 2.2K

SMBUS Address [TBD]

+3.3V_ALW

+5V_ALW

3

5752M

LOM

SMBUS Address [C8]

2

+3.3V_RUN

2N7002

2N7002

C8C7

3032

CLK_SCLK

CLK_SDATA

MINI WLAN Card

SMBUS Address [TBD]

8

GUARDIAN

7

SMBUS Address [5E]

16

17

197

195

197

195

1

CLK GEN.

SMBUS Address [D2]

DIMMA

SMBUS Address [A0]

DIMMB

C C

DOCK_SMB_CLK

6

DOCK_SMB_DAT

SIO

Macallan IV

B B

5

112

111

8

7

SBAT_SMBCLK

SBAT_SMBDAT

PBAT_SMBCLK

PBAT_SMBDAT +3V_ALW

10K 10K

+3.3V_ALW

2.2K 2.2K

+3.3V_ALW

2.2K 2.2K

+5V_ALW

+3.3V_ALW

39

DOCK

40

6

LVDS connector

5

10

Discrete

8

Graphic

100

100

SMBUS Address [C4, 72, 70, 48]

Inverter

SMBUS Address [58]

SMBUS Address [98]

3

BATTERY

4

CONN

9

CHARGER

10

SMBUS Address [16]

SMBUS Address [12]

SMBUS Address [A4]

A A

23

22

LED PWM

SMBUS Address [C0]

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-2881P

562Tuesday, December 13, 2005

1

2.0

of

Page 6

5

D

1

G S

2

D D

FSC FSB FSA CPU

CLKSEL2 CLKSEL0CLKSEL1

2N7002

3

ICH_SMBDATA<23,30,34> CLK_SDATA <17,18>

+3.3V_RUN

ICH_SMBCLK<23,30,34>

000

00

*

0

0

C C

1

1

1

11

1

0

1

11

00

1

0

1

0

1

+3.3V_RUN

ICH_SMBDATA

ICH_SMBCLK

MHz

266

133

200

166

333

100

400

Reserve

Table : ICS954305AK

CPU_BSEL CPU_BSEL2(FSC) CPU_BSEL1(FSB)

133

166

B B

0

0

D

1 3

1 3

D

SRC

MHz

100

100

100

100

100

100

100

G

2

2

G

0

1

2.2K_0402_5%~D

12

R232

S

Q51

2N7002_SOT23~D

S

Q52

2N7002_SOT23~D

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

33.3

2.2K_0402_5%~D

12

R233

CLK_SDATA

CLK_SCLK

+CK_VDD_A

C508

4.7U_0805_10V4Z~D

1

2

Place crystal within

500 mils of CK410M

CLK_ICH_48M<23>

CLK_SMCARD_48M<34>

CPU_MCH_BSEL0<8,10,12>

CLK_PCI_5004<38>

CLK_PCI_5018<37>

CLK_PCI_LAN_LPC<30>

CLK_PCI_PCCARD<33>

CLK_PCI_DOCK<36>

CLK_ICH_14M<23>

CLK_SIO_14M<37>

MCH_DREFCLK<10>

MCH_DREFCLK#<10>

CLK_PCI_ICH<21>

CLK_PCI_LAN<31>

Layout Notes:

Trace length between R255.2, R222.2 and R579.2 =< 50 mils

Trace length between R176.2, R175.2 =< 50 mils

Trace length between R191.2, R190.2 =< 50 mils

+3.3V_RUN

R578

A A

10K_0402_5%~D

1 2

FSA

12

R575

10K_0402_5%~D@

5

+3.3V_RUN

R204

1 2

PCI_SIO

12

R203

FCTSEL1

10K_0402_5%~D3@

(PIN34)

0

10K_0402_5%~D1@

1

4

0.1U_0402_16V4Z~D

CLK_SCLK <17,18>

C511

0.047U_0402_10V7K~D

1

2

27P_0402_50V8J~D

27P_0402_50V8J~D

+3.3V_RUN

PIN43

+3.3V_RUN

1

C509

2

+CK_VDD_48

C532

4.7U_0805_10V4Z~D

C232

1 2

C236

1 2

CLK_ICH_48M

CLK_SMCARD_48M

CPU_MCH_BSEL0

CLK_PCI_5004

CLK_PCI_5018

CLK_PCI_LAN_LPC

CLK_PCI_PCCARD

CLK_ICH_14M

CLK_SIO_14M

MCH_DREFCLK

CLK_PCI_ICH PCI_ICH

CLK_PCI_LAN

C525

0.047U_0402_10V7K~D

1

1

2

2

12

R213 15_0402_5%~D

R222 15_0402_5%~D

R579 8.2K_0402_5%~D

CPU_MCH_BSEL1<8,10>

CPU_MCH_BSEL2<8,10>

R176 15_0402_5%~D

R175 15_0402_5%~D

R202 33_0402_5%~D

R201 33_0402_5%~D

R200 33_0402_5%~D

R191 15_0402_5%~D

R190 15_0402_5%~D

R228 33_0402_5%~D1@

R236 33_0402_5%~D1@

R205 15_0402_5%~D

R206 15_0402_5%~D4@

R180 10K_0402_5%~D

CLK_ENABLE#<48>

PIN44

L48

1 2

BLM21PG600SN1D_0805~D

+CK_VDD_MAIN2

L51

1 2

BLM21PG600SN1D_0805~D

+CK_VDD_REF

Y1

14.31818MHz_20P_1BX14318CC1A~D

R199 220_0402_5%~D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

0.047U_0402_10V7K~D

1

2

12

12

12

12

R563 475_0603_1%~D

PIN47 PIN48

DOT96T DOT96C 96/100M_T 96/100M_C

27M_out

4

27M SSout

SRCT0

SRCC0

C528

R582

1_0603_5%~D

1 2

1 2

R585

2.2_0603_5%~D

CLK_XTAL_IN

CLK_XTAL_OUT

R588 8.2K_0402_5%~D

1 2

3

+CK_VDD_MAIN

1

C504

0.1U_0402_16V4Z~D

2

1

C530

0.1U_0402_16V4Z~D

2

2.2_0603_5%~D

1 2

U16

1

VDDSRC

VDDSRC

VDDSRC

VDDSRC

VDDPCI

VDDPCI

VDDCPU

VDDREF

VDD48

XIN

XOUT

USB_48MHz/FSLA

FSLB/TEST_MODE

REF0/FSLC/TEST_SEL

PCICLK4/FCTSEL1

PCICLK3

PCICLK2

PCICLK1

REF1

DOTT_96MHz/27MHz

DOTC_96MHz/27MHz

ITP_EN/PCICLK_F0

Vtt_PwrGd#/PD

9

IREF

SMBCLK

SMBDAT

4

GNDSRC

GNDCPU

GNDREF

GNDPCI

GNDPCI

GND48

GNDSRC

THRM_PAD

THRM_PAD

THRM_PAD

THRM_PAD

ICS954305EKLFT_MLF72~D

R556

1

C506

0.1U_0402_16V4Z~D

2

1

C531

0.1U_0402_16V4Z~D

2

+CK_VDD_A

VDDA

GNDA

PCI_STOP#

CPU_STOP#

CPUT1

CPUC1

CPUT0

CPUC0

CPUT_ITP/SRCT10

CPUC_ITP/SRCC10

SRCT9

SRCC9

CLKREQ9#

SRCT8

SRCC8

CLKREQ8#

SRCT7

SRCC7

CLKREQ7#

SRCT6

SRCC6

CLKREQ6#

SRCT5

SRCC5

CLKREQ5#

SRCT4

SRCC4

CLKREQ4#

SRCT3

SRCC3

CLKREQ3#

SRCT2

SRCC2

CLKREQ2#

SRCT1

SRCC1

CLKREQ1#

LCD100/96/SRC0_T

LCD100/96/SRC0_C

1

C512

0.1U_0402_16V4Z~D

2

7

8

H_STP_PCI#

25

H_STP_CPU#

24

11

10

CPU_BCLK

14

13

CPU_ITP

6

CPU_ITP#

5

3

2

72

70

PCIE_SATA#

69

SATA_CLKREQ#

71

66

67

38

PCIE_ICH

63

PCIE_ICH#

64

62

MCH_3GPLL

60

MCH_3GPLL#

61

CLK_3GPLLREQ#

29

PCIE_LOM

58

PCIE_LOM#

59

57

PCIE_VGA CLK_PCIE_VGA

55

56

28

PCIE_EXPCARD CLK_PCIE_EXPCARD

52

PCIE_EXPCARD# CLK_PCIE_EXPCARD#

53

CARD_CLK_REQ#

26

PCIE_MINI

50

PCIE_MINI#

51

MINICLK_REQ#

46

DOT96_SSC

47

DOT96_SSC#

48

+CK_VDD_REF

+CK_VDD_48

FSA

CPU_MCH_BSEL1

FSC

12

PCI_SIO

PCI_LOM

PCI_PCCARD

PCI_DOCKCLK_PCI_DOCK

CLKREF

DOT96

DOT96#MCH_DREFCLK#

CLK_ENABLE#

CLKIREF

CLK_SCLK

CLK_SDATA

1

C499

10U_0805_10V4Z~D

2

C534

10U_0805_10V4Z~D

49

54

65

30

36

12

18

40

20

19

41

45

23

34

33

32

27

22

43

44

37

39

16

17

15

21

31

35

42

68

73

74

75

76

Solder Thermal Pad to GND. Add Min. 4 vias.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

1

C520

0.1U_0402_16V4Z~D

2

1

2

Place near each pin

W>40 mil

Place near CK410+

CLK_MCH_BCLKMCH_BCLK

CLK_MCH_BCLK#MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#CPU_BCLK#

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_PCIE_SATAPCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_PCIE_VGA#PCIE_VGA#

CLK_PCIE_MINI

CLK_PCIE_MINI#

DREF_SSCLK

DREF_SSCLK#

1 2

R239 33_0402_5%~D

1 2

R248 33_0402_5%~D

1 2

R224 33_0402_5%~D

1 2

R231 33_0402_5%~D

1 2

R255 33_0402_5%~D

1 2

R260 33_0402_5%~D

1 2

R276 33_0402_5%~D

1 2

R277 33_0402_5%~D

1 2

R547 10K_0402_5%~D

1 2

R279 33_0402_5%~D

1 2

R278 33_0402_5%~D

1 2

R281 33_0402_5%~D

1 2

R280 33_0402_5%~D

R590 10K_0402_5%~D

1 2

1 2

R283 33_0402_5%~D5@

1 2

R282 33_0402_5%~D5@

1 2

R285 33_0402_5%~D3@

1 2

R284 33_0402_5%~D3@

1 2

R270 33_0402_5%~D

1 2

R272 33_0402_5%~D

R589 10K_0402_5%~D

1 2

1 2

R257 33_0402_5%~D

1 2

R264 33_0402_5%~D

R566 10K_0402_5%~D

1 2

1 2

R241 33_0402_5%~D1@

1 2

R252 33_0402_5%~D1@

2

1

C699

0.1U_0402_16V4Z~D

H_STP_PCI# <23>

H_STP_CPU# <23>

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CLK_CPU_BCLK <7>

CLK_CPU_BCLK# <7>

CLK_CPU_ITP <7>

CLK_CPU_ITP# <7>

CLK_PCIE_SATA <22>

CLK_PCIE_SATA# <22>

SATA_CLKREQ# <23>

+3.3V_RUN

CLK_PCIE_ICH <23>

CLK_PCIE_ICH# <23>

CLK_MCH_3GPLL <10>

CLK_MCH_3GPLL# <10>

CLK_3GPLLREQ# <10>

+3.3V_RUN

CLK_PCIE_LOM <30>

CLK_PCIE_LOM# <30>

CLK_PCIE_VGA <19>

CLK_PCIE_VGA# <19>

CLK_PCIE_EXPCARD <34>

CLK_PCIE_EXPCARD# <34>

CARD_CLK_REQ# <34>

+3.3V_RUN

CLK_PCIE_MINI# <34>

MINICLK_REQ# <34>

+3.3V_RUN

DREF_SSCLK <10>

DREF_SSCLK# <10>

CLK_PCIE_MINI <34>

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_MINI

CLK_PCIE_MINI#

CLK_PCIE_EXPCARD

CLK_PCIE_EXPCARD#

MCH_DREFCLK

MCH_DREFCLK#

DREF_SSCLK

DREF_SSCLK#

R254 49.9_0402_1%~D

R259 49.9_0402_1%~D

R238 49.9_0402_1%~D

R247 49.9_0402_1%~D

R223 49.9_0402_1%~D

R230 49.9_0402_1%~D

R292 49.9_0402_1%~D

R291 49.9_0402_1%~D

R287 49.9_0402_1%~D

R288 49.9_0402_1%~D

R290 49.9_0402_1%~D

R289 49.9_0402_1%~D

R294 49.9_0402_1%~D5@

R293 49.9_0402_1%~D5@

R296 49.9_0402_1%~D3@

R295 49.9_0402_1%~D3@

R258 49.9_0402_1%~D

R265 49.9_0402_1%~D

R271 49.9_0402_1%~D

R273 49.9_0402_1%~D

R229 49.9_0402_1%~D1@

R237 49.9_0402_1%~D1@

R242 49.9_0402_1%~D1@

R253 49.9_0402_1%~D1@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

12

12

12

12

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Clock Generator

LA-2881P

662Tuesday, December 13, 2005

1

of

2.0

Page 7

5

4

3

2

1

H_A#[3..31]<10>

D D

H_REQ#0<10>

H_REQ#1<10>

H_REQ#2<10>

H_REQ#3<10>

H_REQ#4<10>

H_ADSTB#0<10>

CPU_PROCHOT#

R714

1 2

1K_0402_5%~D@

1 2

1

2

H_ADSTB#1<10>

CLK_CPU_BCLK<6>

CLK_CPU_BCLK#<6>

H_ADS#<10>

H_BNR#<10>

H_BPRI#<10>

H_BR0#<10>

H_DEFER#<10>

H_DRDY#<10>

H_HIT#<10>

H_HITM#<10>

H_LOCK#<10>

H_RESET#<10>

H_RS#0<10>

H_RS#1<10>

H_RS#2<10>

H_TRDY#<10>

ITP_DBRESET#<23,38>

H_DBSY#<10>

H_DPSLP#<22>

H_DPRSTP#<22,48>

H_DPWR#<10>

H_PWRGOOD<22>

H_CPUSLP#<10,22>

H_THERMTRIP#<16>

C C

R715

2200P_0402_50V7K~D@

H_THERMDA<16>

H_THERMDC<16>

5

1 2

56_0402_5%~D

+1.05V_VCCP

75_0402_5%~D

12

R576

R718 51_0402_5%~D

C20

+1.05V_VCCP

B B

CPU_PROCHOT#<37>

Populate R718 for

Yonah B0 and forward.

A A

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI H_A20M#

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

JCPUA

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

ADDR GROUP

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

AD4

AD3

AD1

AC4

C20

E1

B5

E5

D24

AC2

AC1

D21

D6

D7

AC5

AA6

AB3

C26

D25

AB5

AB6

A24

A25

C7

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMAL

THERMDA

DIODE

THERMDC

THERMTRIP#

TYCO_1-1674770-2_Yonah~D

+1.05V_VCCP

4

YONAH

MISC

R721

56_0402_5%~D

1 2

DATA GROUP

LEGACY CPU

H_THERMTRIP#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

H_NMI <22>

H_D#[0..63] <10>

Notes: Can be nopop on X00 board.

R725

22.6_0402_1%~D

H_RESET#

1 2

ITP_TDO

1 2

22.6_0402_1%~D

R726

CLK_CPU_ITP<6>

CLK_CPU_ITP#<6>

2

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

H_D#1

F24

H_D#2

E26

H_D#3

H22

H_D#4

F23

H_D#5

G25

H_D#6

E25

H_D#7

E23

H_D#8

K24

H_D#9

G24

H_D#10

J24

H_D#11

J23

H_D#12

H26

H_D#13

F26

H_D#14

K22

H_D#15

H25

H_D#16

N22

H_D#17

K25

H_D#18

P26

H_D#19

R23

H_D#20

L25

H_D#21

L22

H_D#22

L23

H_D#23

M23

H_D#24

P25

H_D#25

P22

H_D#26

P23

H_D#27

T24

H_D#28

R24

H_D#29

L26

H_D#30

T25

H_D#31

N24

H_D#32

AA23

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

W25

H_D#37

U23

H_D#38

U25

H_D#39

U22

H_D#40

AB25

H_D#41

W22

H_D#42

Y23

H_D#43

AA26

H_D#44

Y26

H_D#45

Y22

H_D#46

AC26

H_D#47

AA24

H_D#48

AC22

H_D#49

AC23

H_D#50

AB22

H_D#51

AA21

H_D#52

AB21

H_D#53

AC25

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AE21

H_D#59

AD21

H_D#60

AE25

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

H_DINV#0

J26

H_DINV#1

M26

H_DINV#2

V23

H_DINV#3

AC20

H_DSTBN#0

H23

H_DSTBN#1

M24

H_DSTBN#2

W24

H_DSTBN#3

AD23

H_DSTBP#0

G22

H_DSTBP#1

N25

H_DSTBP#2

Y25

H_DSTBP#3

AE24

A6

H_FERR#

A5

H_IGNNE#

C4

H_INIT#

B3

H_INTR

C6

H_NMI

B4

H_STPCLK#

D5

H_SMI#

A3

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

H_DINV#0 <10>

H_DINV#1 <10>

H_DINV#2 <10>

H_DINV#3 <10>

H_DSTBN#0 <10>

H_DSTBN#1 <10>

H_DSTBN#2 <10>

H_DSTBN#3 <10>

H_DSTBP#0 <10>

H_DSTBP#1 <10>

H_DSTBP#2 <10>

H_DSTBP#3 <10>

H_A20M# <22>

H_FERR# <22>

H_IGNNE# <22>

H_INIT# <22>

H_INTR <22>

H_STPCLK# <22>

H_SMI# <22>

H_D#0

E22

+1.05V_VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CLK_CPU_ITP

CLK_CPU_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

+1.05V_VCCP

+3.3V_SUS

+1.05V_VCCP

29

JITP

28

VTT1

27

GND6

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D@

30

@

@

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

1

C695

C697

2

2

Place near JITP

R729

150_0402_5%~D

1 2

51_0402_5%~D

51_0402_5%~D

39_0402_5%~D

@

54.9_0402_1%~D

150_0402_5%~D

680_0402_5%~D

27_0402_5%~D

ITP_DBRESET#

R730

ITP_TDO

R723

H_RESET#

R733

ITP_TMS

R735

ITP_BPM#5

R734

ITP_TDI

This shall place near CPU

R732

ITP_TRST#

R731

ITP_TCK

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Yonah Processor(1/2)

LA-2881P

1

762Tuesday, December 13, 2005

2.0

of

Page 8

5

4

3

2

1

Place R719 and R722 near CPU

D D

C C

+VCC_CORE

Route VCCSENSE and VSSSENSE trace at

27.4 ohms, 50 mils spacing a nd 1 inch (max)

R719

1 2

100_0402_1%~D

R722

1 2

100_0402_1%~D

VCCSENSE

VSSSENSE

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

00

01

27.4_0402_1%~D

54.9_0402_1%~D

12

12

R15

R16

+1.5V_RUN

0.01U_0402_16V7K~D

C19

1

2

Close to

pin B26

CPU_BSEL0

1

1

27.4_0402_1%~D

54.9_0402_1%~D

12

R727

Resistor pl aced within

12

0.5" of CPU pin.Trace

R728

should be at least 25

mils away from any

other toggling signal.

CPU_MCH_BSEL0<6,10,12>

CPU_MCH_BSEL1<6,10>

CPU_MCH_BSEL2<6,10>

Layout Note:

COMP0,2 connect with Z0=27.4 ohm, make trace length shorter than 0.5".

B B

A A

COMP1,3 connect with Z0=55.5 ohm, make trace length shorter than 0.5".

+1.05V_VCCP

V_CPU_GTLREF

Length match within 25 mils

VCCSENSE<48>

VSSSENSE<48>

10U_0805_10V4Z~D

+1.05V_VCCP

C21

1

2

H_PSI#<48>

VID0<48>

VID1<48>

VID2<48>

VID3<48>

VID4<48>

VID5<48>

VID6<48>

V_CPU_GTLREF

+VCC_CORE

12

R716

1K_0402_1%~D

12

R717

2K_0402_1%~D

VCCSENSE

VSSSENSE

H_PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

COMP0

COMP1

COMP2

COMP3

W21

AD26

AB20

AA20

AF20

AE20

AB18

AB17

AA18

AA17

AD18

AD17

AC18

AC17

AF18

AF17

AF7

AE7

B26

K21

J21

M21

N21

T21

R21

V21

G21

AE6

AD6

AF5

AE5

AF4

AE3

AF2

AE2

B22

B23

C21

R26

U26

AF1

D22

C23

C24

AA1

AA4

AB2

AA3

T22

B25

K6

J6

M6

N6

T6

R6

V6

U1

V1

E7

D2

F6

D3

C1

M4

N5

T2

V3

B2

C3

JCPUB

VCCSENSE

VSSSENSE

VCCA

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

GTLREF

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

YONAH

TYCO_1-1674770-2_Yonah~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB26

AA25

AD25

AE26

AB23

AC24

AF24

AE23

AA22

AD22

AC21

AF21

AB19

AA19

AD19

AC19

AF19

AE19

AB16

AA16

AD16

AC16

AF16

AE16

AB13

AA14

AD13

AC14

AF13

AE14

AB11

AA11

AD11

AC11

AF11

AE11

AB8

AA8

AD8

AC8

AF8

AE8

AA5

AD5

AC6

AF6

AB4

AC3

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

+VCC_CORE

AE18

AE17

AB15

AA15

AD15

AC15

AF15

AE15

AB14

AA13

AD14

AC13

AF14

AE13

AB12

AA12

AD12

AC12

AF12

AE12

AB10

AA10

AD10

AC10

AF10

AE10

JCPUC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB9

VCC

VCC

AA9

VCC

VCC

AD9

VCC

VCC

AC9

VCC

VCC

AF9

VCC

VCC

AE9

VCC

AB7

VCC

AA7

VCC

AD7

VCC

AC7

VCC

B20

VCC

A20

VCC

F20

VCC

E20

VCC

B18

VCC

B17

VCC

A18

VCC

A17

VCC

D18

VCC

D17

VCC

C18

VCC

C17

VCC

F18

VCC

F17

VCC

E18

VCC

E17

VCC

B15

VCC

A15

VCC

D15

VCC

C15

VCC

F15

VCC

E15

VCC

B14

VCC

A13

VCC

D14

VCC

C13

VCC

F14

VCC

E13

VCC

B12

VCC

A12

VCC

D12

VCC

C12

VCC

F12

VCC

E12

VCC

B10

VCC

B9

VCC

A10

VCC

A9

VCC

D10

VCC

D9

VCC

C10

VCC

C9

VCC

F10

VCC

F9

VCC

E10

VCC

E9

VCC

B7

VCC

A7

VCC

F7

VCC

YONAH

POWER, GROUND

TYCO_1-1674770-2_Yonah~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

Layout close CPU PIN AD26

0.5 inch (max)

5

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Yonah Processor(2/2)

LA-2881P

862Tuesday, December 13, 2005

1

of

2.0

Page 9

5

+VCC_CORE

D D

C C

Place these inside

socket cavity on L8

(North side

Secondary)

Place these inside

socket cavity on L8

(North side

Secondary)

Place these inside

socket cavity on L8

(North side

Secondary)

Place these inside

socket cavity on L8

(North side

Secondary)

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C5

10U_0805_4VAM~D

C7

10U_0805_4VAM~D

C688

10U_0805_4VAM~D

C669

10U_0805_4VAM~D

4

1

C8

10U_0805_4VAM~D

2

1

C4

10U_0805_4VAM~D

2

1

C682

10U_0805_4VAM~D

2

1

C663

10U_0805_4VAM~D

2

1

C11

10U_0805_4VAM~D

2

1

C687

10U_0805_4VAM~D

2

1

C678

10U_0805_4VAM~D

2

1

C664

10U_0805_4VAM~D

2

1

C13

10U_0805_4VAM~D

2

1

C681

10U_0805_4VAM~D

2

1

C675

10U_0805_4VAM~D

2

1

C689

10U_0805_4VAM~D

2

3

1

C16

10U_0805_4VAM~D

2

1

C677

10U_0805_4VAM~D

2

1

C673

10U_0805_4VAM~D

2

1

C686

10U_0805_4VAM~D

2

1

C18

10U_0805_4VAM~D

2

1

C674

10U_0805_4VAM~D

2

1

C671

10U_0805_4VAM~D

2

1

C658

10U_0805_4VAM~D

2

1

C17

10U_0805_4VAM~D

2

1

C672

10U_0805_4VAM~D

2

10uF 0805 X6S

1

C15

10U_0805_4VAM~D

2

1

C670

10U_0805_4VAM~D

2

2

1

C12

10U_0805_4VAM~D

2

1

C668

10U_0805_4VAM~D

2

1

C10

10U_0805_4VAM~D

2

1

C662

10U_0805_4VAM~D

2

1

High Frequence Decoupling

Near VCORE regulator

+VCC_CORE

330U_D_2VM_R6~D

1

South Side Secondary

B B

+1.05V_VCCP

1

+

330U_D2E_2.5VM~D@

A A

C657

2

CRB was 270uF

1

C659

0.1U_0402_10V7K~D

2

+

2

6mOhm

PS CAP

C685

6mOhm

PS CAP

1

C660

0.1U_0402_10V7K~D

2

@

330U_D_2VM_R6~D

330U_D_2VM_R6~D

1

C667

+

2

6mOhm

PS CAP

1

C666

+

2

1

C661

2

330U_D_2VM_R6~D

1

C665

+

2

6mOhm

6mOhm

PS CAP

PS CAP

0.1U_0402_10V7K~D

@

330U_D_2VM_R6~D

1

C676

+

2

1

C690

0.1U_0402_10V7K~D

2

330U_D_2VM_R6~D

1

C683

North Side Secondary

+

2

6mOhm

PS CAP

1

C691

0.1U_0402_10V7K~D

2

ESR <= 1.5m ohm

1

C692

0.1U_0402_10V7K~D

2

Place these inside

socket cavity on L8

(North side

Secondary)

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Bypass

LA-2881P

962Tuesday, December 13, 2005

1

2.0

of

Page 10

5

4

3

2

1

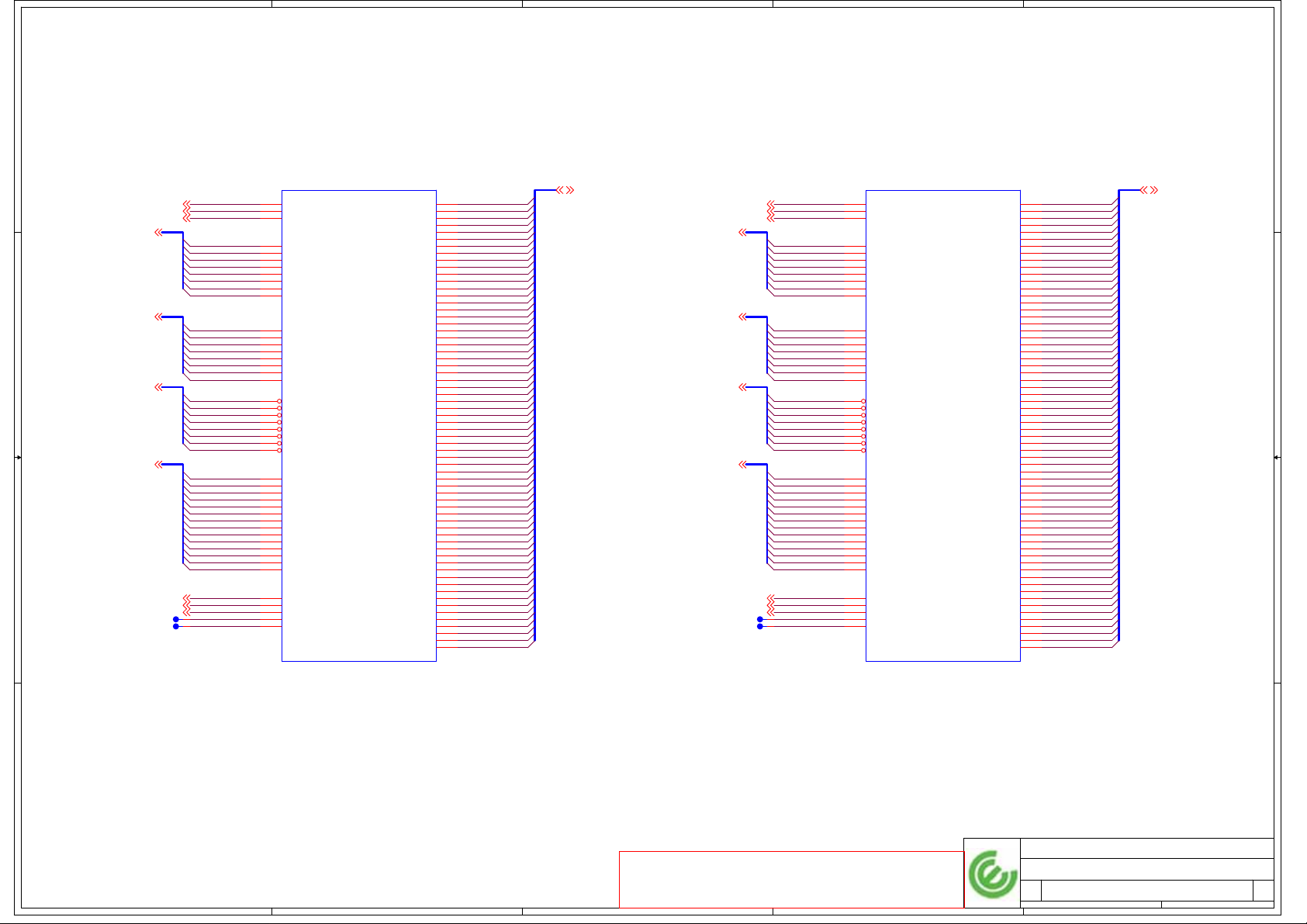

ZUMA use 945GM ( P/N: SA0000059GL )

ZRS use 945PM ( P/N: SA00000KDBL)

54.9_0402_1%~D

H_D#[0..63]<7>

+1.05V_VCCP

12

R60

24.9_0402_1%~D

12

R56

54.9_0402_1%~D

12

R61

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_SWNG0

H_SWNG1

12

R59

24.9_0402_1%~D

200_0402_1%~D

5

U6A

F1

HD0#

J1

HD1#

H1

HD2#

J6

HD3#

H3

HD4#

K2

HD5#

G1

HD6#

G2

HD7#

K9

HD8#

K1

HD9#

K7

HD10#

J8

HD11#

H4

HD12#

J3

HD13#

K11

HD14#

G4

HD15#

T10

HD16#

W11

HD17#

T3

HD18#

U7

HD19#

U9

HD20#

U11

HD21#

T11

HD22#

W9

HD23#

T1

HD24#

T8

HD25#

T4

HD26#

W7

HD27#

U5

HD28#

T9

HD29#

W6

HD30#

T5

HD31#

AB7

HD32#

AA9

HD33#

W4

HD34#

W3

HD35#

Y3

HD36#

Y7

HD37#

W5

HD38#

Y10

HD39#

AB8

HD40#

W2

HD41#

AA4

HD42#

AA7

HD43#

AA2

HD44#

AA6

HD45#

AA10

HD46#

Y8

HD47#

AA1

HD48#

AB4

HD49#

AC9

HD50#

AB11

HD51#

AC11

HD52#

AB3

HD53#

AC2

HD54#

AD1

HD55#

AD9

HD56#

AC1

HD57#

AD7

HD58#

AC6

HD59#

AB5

HD60#

AD10

HD61#

AD4

HD62#

AC8

HD63#

J13

HVREF0

K13

HVREF1

E1

HXRCOMP

E2

HXSCOMP

Y1

HYRCOMP

U1

HYSCOMP

E4

HXSWING

W1

HYSWING

CALISTOGA A3 _ FCBGA1466~D

12

R684

100_0402_1%~D

H_VREF H_SWNG0 H_SWNG1

R689

0.1U_0402_16V4Z~D

12

1

C623

2

HOST

12

R700

221_0402_1%~D

100_0402_1%~D

12

R695

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

0.1U_0402_16V4Z~D

1

2

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

D8

G8

B8

F8

A8

B9

C13

AG1

AG2

K4

T7

Y5

AC4

K3

T6

AA5

AC5

J7

W8

U3

AB10

B7

E8

E7

J9

H8

C3

D4

D3

B3

C7

C6

F6

A7

E3

B4

E6

D6

+1.05V_VCCP+1.05V_VCCP+1.05V_VCCP

100_0402_1%~D

C634

4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_RESET#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

12

R55

221_0402_1%~D

12

R58

1

2

0.1U_0402_16V4Z~D

D D

C C

B B

Layout Note:

H_XRCOMP & H_YRCOMP / H_SWNG0 &

H_SWNG1 trace width and spacing is 10/20

A A

H_REQ#0 <7>

H_REQ#1 <7>

H_REQ#2 <7>

H_REQ#3 <7>

H_REQ#4 <7>

H_ADSTB#0 <7>

H_ADSTB#1 <7>

CLK_MCH_BCLK# <6>

CLK_MCH_BCLK <6>

H_DSTBN#0 <7>

H_DSTBN#1 <7>

H_DSTBN#2 <7>

H_DSTBN#3 <7>

H_DSTBP#0 <7>

H_DSTBP#1 <7>

H_DSTBP#2 <7>

H_DSTBP#3 <7>

H_DINV#0 <7>

H_DINV#1 <7>

H_DINV#2 <7>

H_DINV#3 <7>

H_RESET# <7>

H_ADS# <7>

H_TRDY# <7>

H_DPWR# <7>

H_DRDY# <7>

H_DEFER# <7>

H_HITM# <7>

H_HIT# <7>

H_LOCK# <7>

H_BR0# <7>

H_BNR# <7>

H_BPRI# <7>

H_DBSY# <7>

H_CPUSLP# <7,22>

H_RS#0 <7>

H_RS#1 <7>

H_RS#2 <7>

C58

H_A#[3..31] <7>

U6B

AE35

DMIRXN0

AF39

DMIRXN1

AG35

DMIRXN2

AH39

DMIRXN3

AC35

DMIRXP0

AE39

DMIRXP1

AF35

DMIRXP2

AG39

DMIRXP3

AE37

DMITXN0

AF41

DMITXN1

AG37

DMITXN2

AH41

DMITXN3

AC37

DMITXP0

AE41

DMITXP1

AF37

DMITXP2

AG41

DMITXP3

AY35

SM_CK0

AR1

SM_CK1

AW7

SM_CK2

AW40

SM_CK3

AW35

SM_CK0#

AT1

SM_CK1#

AY7

SM_CK2#

AY40

SM_CK3#

AU20

SM_CKE0

AT20

SM_CKE1

BA29

SM_CKE2

AY29

SM_CKE3

AW13

SM_CS0#

AW12

SM_CS1#

AY21

SM_CS2#

AW21

SM_CS3#

AL20

SM_OCDCOMP0

AF10

SM_OCDCOMP1

BA13

SM_ODT0

BA12

SM_ODT1

AY20

SM_ODT2

AU21

SM_ODT3

AV9

SM_RCOMPN

AT9

SM_RCOMPP

AK1

SM_VREF0

AK41

SM_VREF1

G28

PM_BMBUSY#

F25

PM_EXTTS0#

H26

PM_EXTTS1#

G6

PM_THERMTRIP#

AH33

PWROK

AH34

RSTIN#

K28

ICH_SYNC#

CALISTOGA A3 _ FCBGA1466~D

1

C702

0.1U_0402_16V4Z~D

2

T24

T25

M_ODT0<18>

M_ODT1<18>

M_ODT2<17>

M_ODT3<17>

+0.9V_DDR_REF

R683

0_0402_5%~D

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1_R

THERMTRIP_MCH#

ICH_PWRGD

PLTRST1_R#

MCH_ICH_SYNC#

+0.9V_DDR_REF

1

C146

0.1U_0402_16V4Z~D

2

DMI_MRX_ITX_N0<23>

DMI_MRX_ITX_N1<23>

DMI_MRX_ITX_N2<23>

DMI_MRX_ITX_N3<23>

DMI_MRX_ITX_P0<23>

DMI_MRX_ITX_P1<23>

DMI_MRX_ITX_P2<23>

DMI_MRX_ITX_P3<23>

DMI_MTX_IRX_N0<23>

DMI_MTX_IRX_N1<23>

DMI_MTX_IRX_N2<23>

DMI_MTX_IRX_N3<23>

DMI_MTX_IRX_P0<23>

DMI_MTX_IRX_P1<23>

DMI_MTX_IRX_P2<23>

DMI_MTX_IRX_P3<23>

M_CLK_DDR0<18>

M_CLK_DDR1<18>

M_CLK_DDR2<17>

M_CLK_DDR3<17>

M_CLK_DDR#0<18>

M_CLK_DDR#1<18>

M_CLK_DDR#2<17>

M_CLK_DDR#3<17>

DDR_CKE0_DIMMA<18>

DDR_CKE1_DIMMA<18>

DDR_CKE2_DIMMB<17>

DDR_CKE3_DIMMB<17>

DDR_CS0_DIMMA#<18>

DDR_CS1_DIMMA#<18>

DDR_CS2_DIMMB#<17>

DDR_CS3_DIMMB#<17>

+1.8V_SUS

R681 80.6_0402_1%~D

1 2

1 2

R687 80.6_0402_1%~D

PM_BMBUSY#<23>

PM_EXTTS#0<18>

THERMTRIP_MCH#<16>

ICH_PWRGD<23,40>

PLTRST1#<21,23,30>

DPRSLPVR<23,48>

+0.9V_DDR_REF<17,18,47>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

12

R625 100_0402_1%~D

MCH_ICH_SYNC#<21>

DPRSLPVR PM_EXTTS#1_R

Place Close To

AK1 and AK41

DMI

2

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG

CFG18

CFG19

CFG20

G_CLKP

G_CLKN

D_REF_CLKN

D_REF_CLKP

CLKNC

D_REF_SSCLKN

D_REF_SSCLKP

DDR MUXING

PM

CLK_REQ#

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

Description at page12

Note :

CFG3:17 has

internal pullup,

CFG18:19 has

internal pulldown

CPU_MCH_BSEL0

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

K16

CPU_MCH_BSEL1

K18

CPU_MCH_BSEL2

J18

CFG3

F18

CFG4

E15

CFG5

F15

CFG6

E18

CFG7

D19

CFG8

D16

CFG9

G16

CFG10

E16

CFG11

D15

CFG12

G15

CFG13

K15

CFG14

C15

CFG15

H16

CFG16

G18

CFG17

H15

CFG18

J25

CFG19

K27

CFG20

J26

CLK_MCH_3GPLL

AG33

CLK_MCH_3GPLL#

AF33

MCH_DREFCLK#

A27

MCH_DREFCLK

A26

DREF_SSCLK#

C40

DREF_SSCLK

D41

CLK_3GPLLREQ#

H32

A3

A39

A4

A40

AW1

AW41

AY1

BA1

Pop R92/R96/R114/R115 for discrete only

BA2

BA3

BA39

BA40

BA41

MCH_DREFCLK

C1

AY41

DREF_SSCLK

B2

B41

MCH_DREFCLK#

C41

D1

DREF_SSCLK#

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A34

D28

D27

A35

PM_EXTTS#0

PM_EXTTS#1_R

THERMTRIP_MCH#

CPU_MCH_BSEL0 <6,8,12>

CPU_MCH_BSEL1 <6,8>

CPU_MCH_BSEL2 <6,8>

T17

T22

CFG5 <12>

CFG6 <12>

CFG7 <12>

T20

CFG9 <12>

CFG10 <12>

CFG11 <12>

CFG12 <12>

CFG13 <12>

T21

T16

CFG16 <12>

T19

CFG18 <12>

CFG19 <12>

CFG20 <12>

CLK_MCH_3GPLL <6>

CLK_MCH_3GPLL# <6>

MCH_DREFCLK# <6>

MCH_DREFCLK <6>

DREF_SSCLK# <6>

DREF_SSCLK <6>

CLK_3GPLLREQ# <6>

These connection for UMA only

+1.5V_RUN

1 2

R92 0_0402_5%~D3@

1 2

R115 0_0402_5%~D3@

1 2

R96 0_0402_5%~D3@

1 2

R114 0_0402_5%~D3@

+3.3V_RUN

R643

12

10K_0402_5%~D

R623

12

10K_0402_5%~D@

R690

1 2

75_0402_5%~D

+1.05V_VCCP

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(1 of 6)

LA-2881P

10 62Tuesday, December 13, 2005

1

of

2.0

Page 11

5

D D

4

3

2

1

DDR_A_BS0<18>

DDR_A_BS1<18>

DDR_A_BS2<18>

DDR_A_DM[0..7]<18>

DDR_A_DQS[0..7]<18>

C C

DDR_A_DQS#[0..7]<18>

DDR_A_MA[0..13]<18>

B B

DDR_A_CAS#<18>

DDR_A_RAS#<18>

DDR_A_WE#<18>

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

SA_RCVENIN#

T13

SA_RCVENOUT#

T14

U6D

AU12

SA_BS0

AV14

SA_BS1

BA20

SA_BS2

AJ33

SA_DM0

AM35

SA_DM1

AL26

SA_DM2

AN22

SA_DM3

AM14

SA_DM4

AL9

SA_DM5

AR3

SA_DM6

AH4

SA_DM7

AK33

SA_DQS0

AT33

SA_DQS1

AN28

SA_DQS2

AM22

SA_DQS3

AN12

SA_DQS4

AN8

SA_DQS5

AP3

SA_DQS6

AG5

SA_DQS7

AK32

SA_DQS0#

AU33

SA_DQS1#

AN27

SA_DQS2#

AM21

SA_DQS3#

AM12

SA_DQS4#

AL8

SA_DQS5#

AN3

SA_DQS6#

AH5

SA_DQS7#

AY16

SA_MA0

AU14

SA_MA1

AW16

SA_MA2

BA16

SA_MA3

BA17

SA_MA4

AU16

SA_MA5

AV17

SA_MA6

AU17

SA_MA7

AW17

SA_MA8

AT16

SA_MA9

AU13

SA_MA10

AT17

SA_MA11

AV20

SA_MA12

AV12

SA_MA13

AY13

SA_CAS#

AW14

SA_RAS#

AY14

SA_WE#

AK23

SA_RCVENIN#

AK24

SA_RCVENOUT#

CALISTOGA A3 _ FCBGA1466~D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

DDR SYS MEMORY A

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_BS0<17>

DDR_B_BS1<17>

DDR_B_BS2<17>

DDR_B_DM[0..7]<17>

DDR_B_DQS[0..7]<17>

DDR_B_DQS#[0..7]<17>

DDR_B_MA[0..13]<17>

DDR_B_CAS#<17>

DDR_B_RAS#<17>

DDR_B_WE#<17>

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

SB_RCVENIN#

SB_RCVENOUT#

T18

T15

Add a VIAAdd a VIA

U6E

AT24

SB_BS0

AV23

SB_BS1

AY28

SB_BS2

AK36

SB_DM0

AR38

SB_DM1

AT36

SB_DM2

BA31

SB_DM3

AL17

SB_DM4

AH8

SB_DM5

BA5

SB_DM6

AN4

SB_DM7

AM39

SB_DQS0

AT39

SB_DQS1

AU35

SB_DQS2

AR29

SB_DQS3

AR16

SB_DQS4

AR10

SB_DQS5

AR7

SB_DQS6

AN5

SB_DQS7

AM40

SB_DQS0#

AU39

SB_DQS1#

AT35

SB_DQS2#

AP29

SB_DQS3#

AP16

SB_DQS4#

AT10

SB_DQS5#

AT7

SB_DQS6#

AP5

SB_DQS7#

AY23

SB_MA0

AW24

SB_MA1

AY24

SB_MA2

AR28

SB_MA3

AT27

SB_MA4

AT28

SB_MA5

AU27

SB_MA6

AV28

SB_MA7

AV27

SB_MA8

AW27

SB_MA9

AV24

SB_MA10

BA27

SB_MA11

AY27

SB_MA12

AR23

SB_MA13

AR24

SB_CAS#

AU23

SB_RAS#

AR27

SB_WE#

AK16

SB_RCVENIN#

AK18

SB_RCVENOUT#

CALISTOGA A3 _ FCBGA1466~D

AK39

SB_DQ0

AJ37

SB_DQ1

AP39

SB_DQ2

AR41

SB_DQ3

AJ38

SB_DQ4

AK38

SB_DQ5

AN41

SB_DQ6

AP41

SB_DQ7

AT40

SB_DQ8

AV41

SB_DQ9

AU38

SB_DQ10

AV38

SB_DQ11

AP38

SB_DQ12

AR40

SB_DQ13

AW38

SB_DQ14

AY38

SB_DQ15

BA38

SB_DQ16

AV36

SB_DQ17

AR36

SB_DQ18

AP36

SB_DQ19

BA36

SB_DQ20

AU36

SB_DQ21

AP35

SB_DQ22

AP34

SB_DQ23

AY33

SB_DQ24

BA33

SB_DQ25

AT31

SB_DQ26

AU29

SB_DQ27

AU31

SB_DQ28

AW31

SB_DQ29

AV29

SB_DQ30

AW29

SB_DQ31

AM19

SB_DQ32

AL19

SB_DQ33

AP14

SB_DQ34

AN14

SB_DQ35

AN17

SB_DQ36

AM16

SB_DQ37

AP15

SB_DQ38

AL15

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

DDR SYS MEMORY B

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] <17>DDR_A_D[0..63] <18>

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistogo(2 of 6)

LA-2881P

11 62Tuesday, December 13, 2005

1

2.0

of

Page 12

5

No connection for discrete

SDVO_CTRLDATA<19>

D D

+3.3V_RUN

C705

0.1U_0402_16V4Z~D1@

BIA_PWM<19,20,38>

C C

12

4

O

TV_CVBS_NB<20>

TV_Y_NB<20>

TV_C_NB<20>

150_0402_1%~D1@

SDVO_CTRLCLK<19>

LCD_A0+<20>

LCD_A1+<20>

LCD_A2+<20>

LCD_A0-<20>

LCD_A1-<20>

LCD_A2-<20>

LCD_B0+<20>

LCD_B1+<20>

LCD_B2+<20>

LCD_B0-<20>

LCD_B1-<20>

LCD_B2-<20>

LCD_ACLK+<20>

LCD_ACLK-<20>

LCD_BCLK+<20>

LCD_BCLK-<20>

5

R112 0_0402_5%~D1@

1

P

IN1

2

IN2

G

3

R86

12

150_0402_1%~D1@

PANEL_BKEN<20>

U49

1@

74AHC1G08GW_SOT353-5~D

R629 1.5K_0402_1%~D1@

R635 0_0402_5%~D1@

R85

R80

12

12

4.99K_0402_1%~D1@

150_0402_1%~D1@

Close to U6.J20

No connection for discrete

VSYNC_NB<20>

HSYNC_NB<20>

BLU_NB<20>

GRN_NB<20>

RED_NB<20>

B B

Close to U6.J22

R647

255_0402_1%~D1@

Trace CRT_IREF should be at

least 20 miles away from any

other toggling signal.

Connect to +1.5V_RUN for discrete

+1.5V_RUN

R77 0_0402_5%~D3@

R82 0_0402_5%~D3@

R83 0_0402_5%~D3@

R649 0_0402_5%~D3@

R669 0_0402_5%~D3@

A A

Connect to GND for discrete

R644 0_0402_5%~D3@

R650 0_0402_5%~D3@

12

12

12

12

12

12

12

5

TV_CVBS_NB

TV_Y_NB

TV_C_NB

TVIREF

TV_IRTN

VSYNC_NB

HSYNC_NB

SDVO_CTRLDATA

SDVO_CTRLCLK

LCD_A0+

LCD_A1+

LCD_A2+

LCD_A0LCD_A1LCD_A2-

LCD_B0+

LCD_B1+

LCD_B2+

LCD_B0LCD_B1LCD_B2LCD_ACLK+

LCD_ACLKLCD_BCLK+

LCD_BCLK-

BIA_PWM_MCH

12

PANEL_BKEN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

ENVDD<20>

12

ENVDD

L_IBG

12

LVREF

12

TV_CVBS_NB

TV_Y_NB

TV_C_NB

TVIREF

TV_IRTN

R648

12

0_0402_5%~D1@

R674

G_CLK_DDC2

G_DAT_DDC2

VSYNC_NB

HSYNC_NB

BLU_NB

CRT_RGB#

GRN_NB

RED_NB

CRT_IREF

12

Connect to +1.05V for discrete

+1.05V_VCCP

R645 0_0402_5%~D3@

R651 0_0402_5%~D3@

R656 0_0402_5%~D3@

R654 0_0402_5%~D3@

R661 0_0402_5%~D3@

R662 0_0402_5%~D1@

U6C

H27

SDVOCTRL_DATA

H28

SDVOCTRL_CLK

B37

LA_DATA0

B34

LA_DATA1

A36

LA_DATA2

C37

LA_DATA#0

B35

LA_DATA#1

A37

LA_DATA#2

F30

LB_DATA0

D29

LB_DATA1

F28

LB_DATA2

G30

LB_DATA#0

D30

LB_DATA#1

F29

LB_DATA#2

A32

LA_CLK

A33

LA_CLK#

E26

LB_CLK

E27

LB_CLK#

D32

LBKLT_CTL

J30

LBKLT_EN

H30

LCTLA_CLK

H29

LCTLB_DATA

G26

LDDC_CLK

G25

LDDC_DATA

F32

LVDD_EN

B38

LIBG

C35

LVBG

C33

LVREFH

C32

LVREFL

A16

TVDAC_A

C18

TVDAC_B

A19

TVDAC_C

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

J29

TV_DCONSEL1

K30

TV_DCONSEL0

C26

DDCCLK

C25

DDCDATA

H23

VSYNC

G23

HSYNC

E23

BLUE

D23

BLUE#

C22

GREEN

B22

GREEN#

A21

RED

B21

RED#

J22

CRT_IREF

CALISTOGA A3 _ FCBGA1466~D

BLU_NB

12

GRN_NB

12

RED_NB

12

CRT_IREF

12

CRT_RGB#

12

12

4

R113

24.9_0402_1%~D

PEGCOMP

D40

EXP_COMPI

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

RED_NB

GRN_NB

BLU_NB

LCTLA_CLK

LCTLB_DATA

EXP_COMPO

LVDS

TV CRT

PCI-EXPRESS GRAPHICS

1@ is for UMA Implemetation.

3@ is for Discrete Implementation.

1 2

R657 150_0402_1%~D1@

1 2

R652 150_0402_1%~D1@

1 2

R646 150_0402_1%~D1@

+3.3V_RUN

1 2

R637 10K_0402_5%~D1@

1 2

R639 10K_0402_5%~D1@

1 2

PEG_MRX_GTX_N0

PEG_MRX_GTX_N1

PEG_MRX_GTX_N2

PEG_MRX_GTX_N3

PEG_MRX_GTX_N4

PEG_MRX_GTX_N5

PEG_MRX_GTX_N6

PEG_MRX_GTX_N7

PEG_MRX_GTX_N8

PEG_MRX_GTX_N9

PEG_MRX_GTX_N10

PEG_MRX_GTX_N11

PEG_MRX_GTX_N12

PEG_MRX_GTX_N13

PEG_MRX_GTX_N14

PEG_MRX_GTX_N15

PEG_MRX_GTX_P0

PEG_MRX_GTX_P1

PEG_MRX_GTX_P2

PEG_MRX_GTX_P3

PEG_MRX_GTX_P4

PEG_MRX_GTX_P5

PEG_MRX_GTX_P6

PEG_MRX_GTX_P7

PEG_MRX_GTX_P8