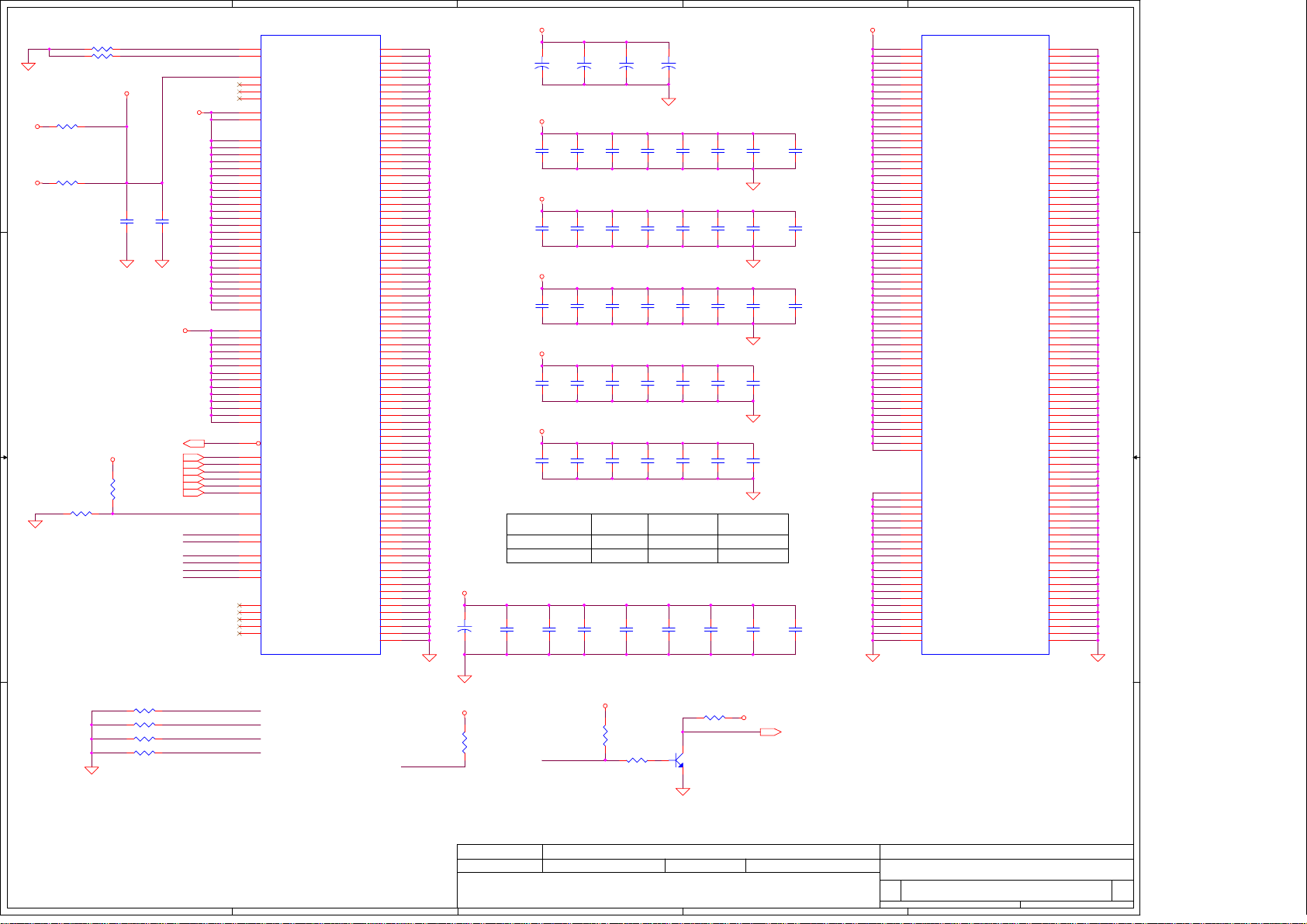

Compal LA-2811 HBT10 Sakhir 10E, Satellite A80, Satellite A85 Schematic

5

4

COMPAL CONFIDENTIAL

3

2

1

D D

MODEL NAME :

COMPAL P/N :

PCB NO :

Revision :

LA-2811

1.0

HBT10

DA600001K10

Sakhir 10E

C C

LA-2811 Rev1.0 Schematic

HBT10 Schematics Document

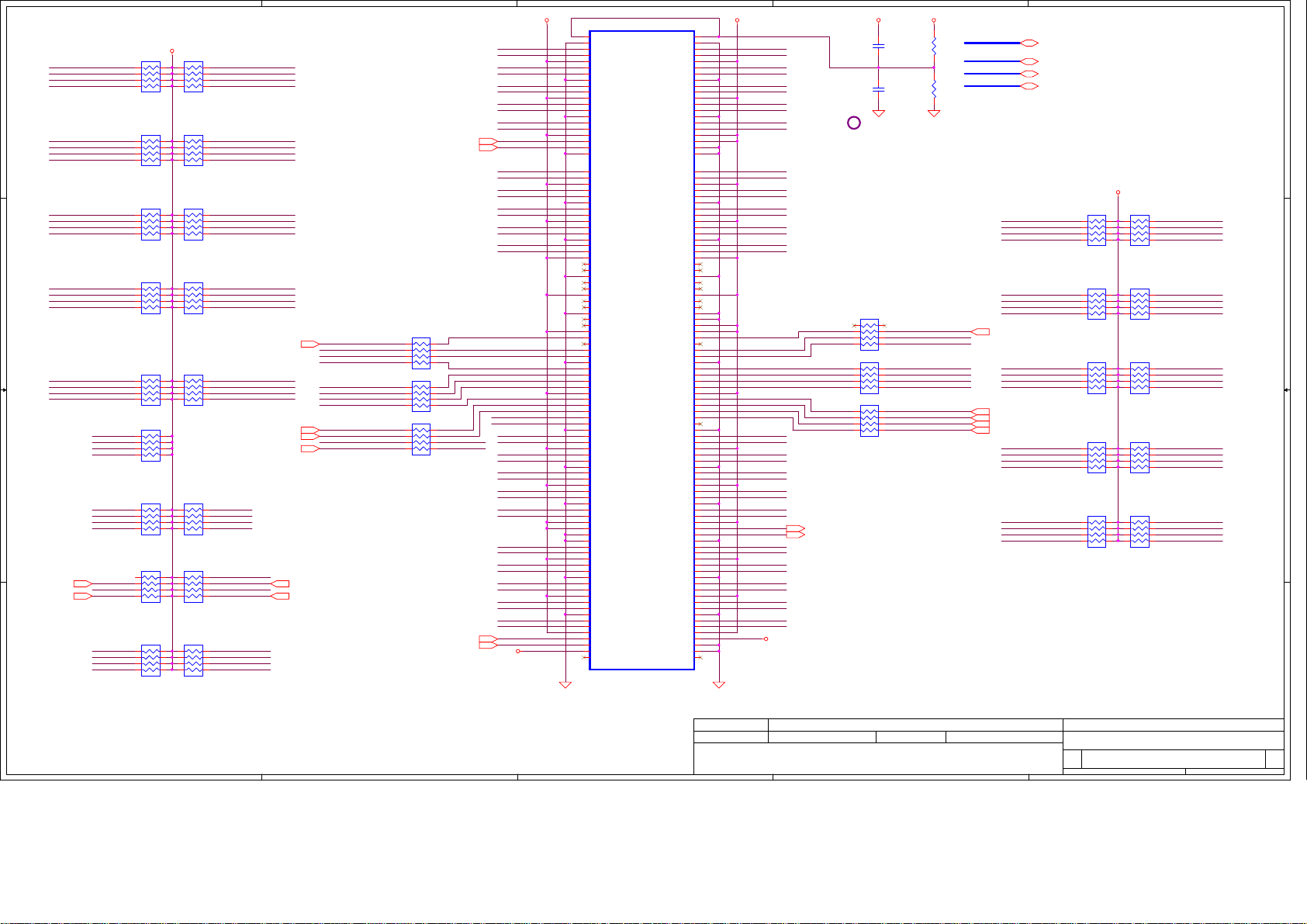

uFCBGA/uFCPGA Mobile Dothan

B B

ATI RL300MB + SB200(IXP150)

2005-05-04<A>

Function/B

LS-2811

LAN/B

LS-2812

M/B LA-2811

USB/B

LS-2813

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRO NICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED F RO M T HE CUSTO DY OF THE COM PETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/03/01 2006/03/01

Compal Secret Data

Deciphered Date

2

TP/B

LS-2814

Title

Cover Sheet

Size Docu ment Number Re v

Sakhir 10E<HBT10> 1.0

Custom

Date: Sheet

星期三 五月

04, 2005

1

of

144,

A

B

C

D

E

Compal confidential

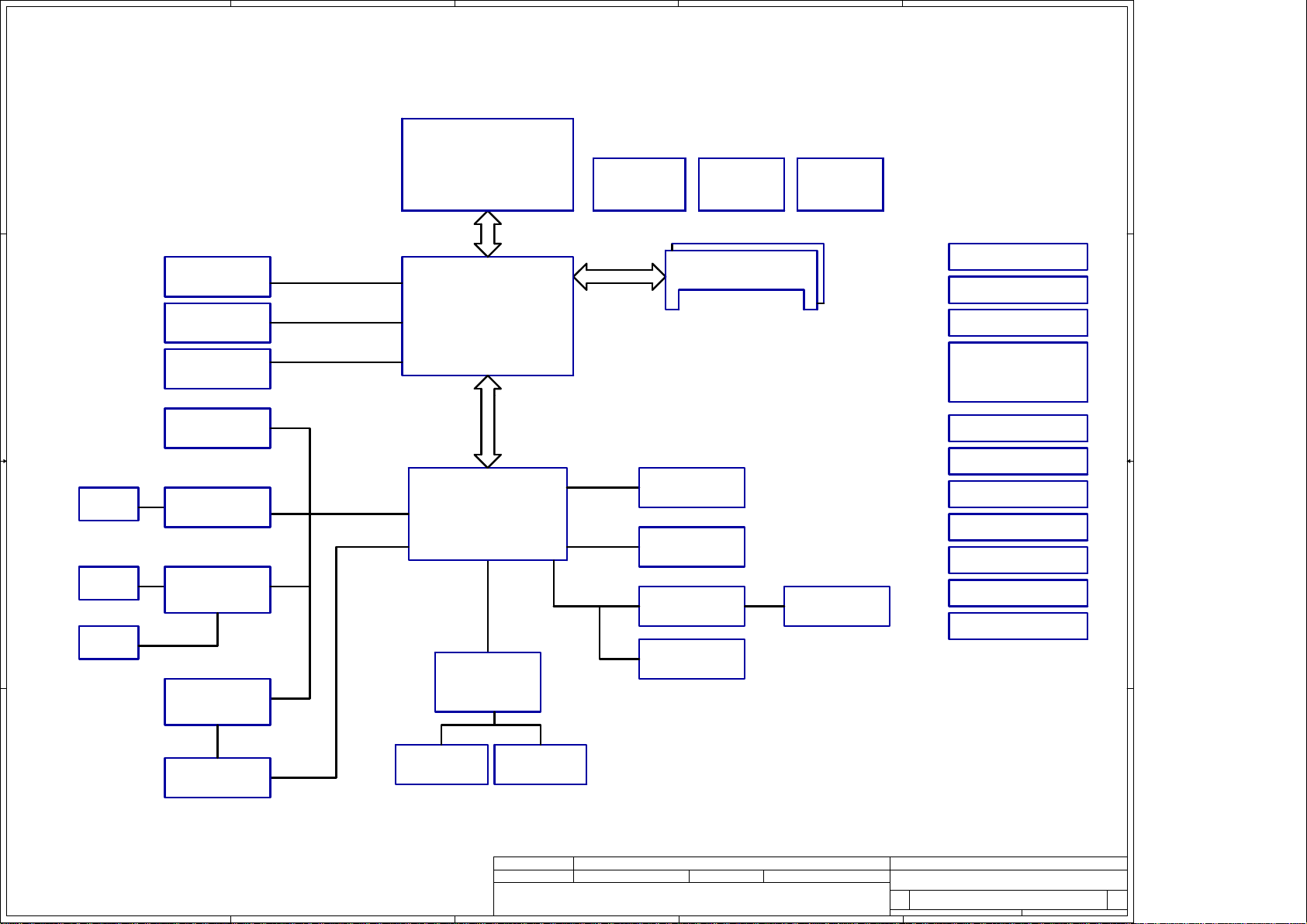

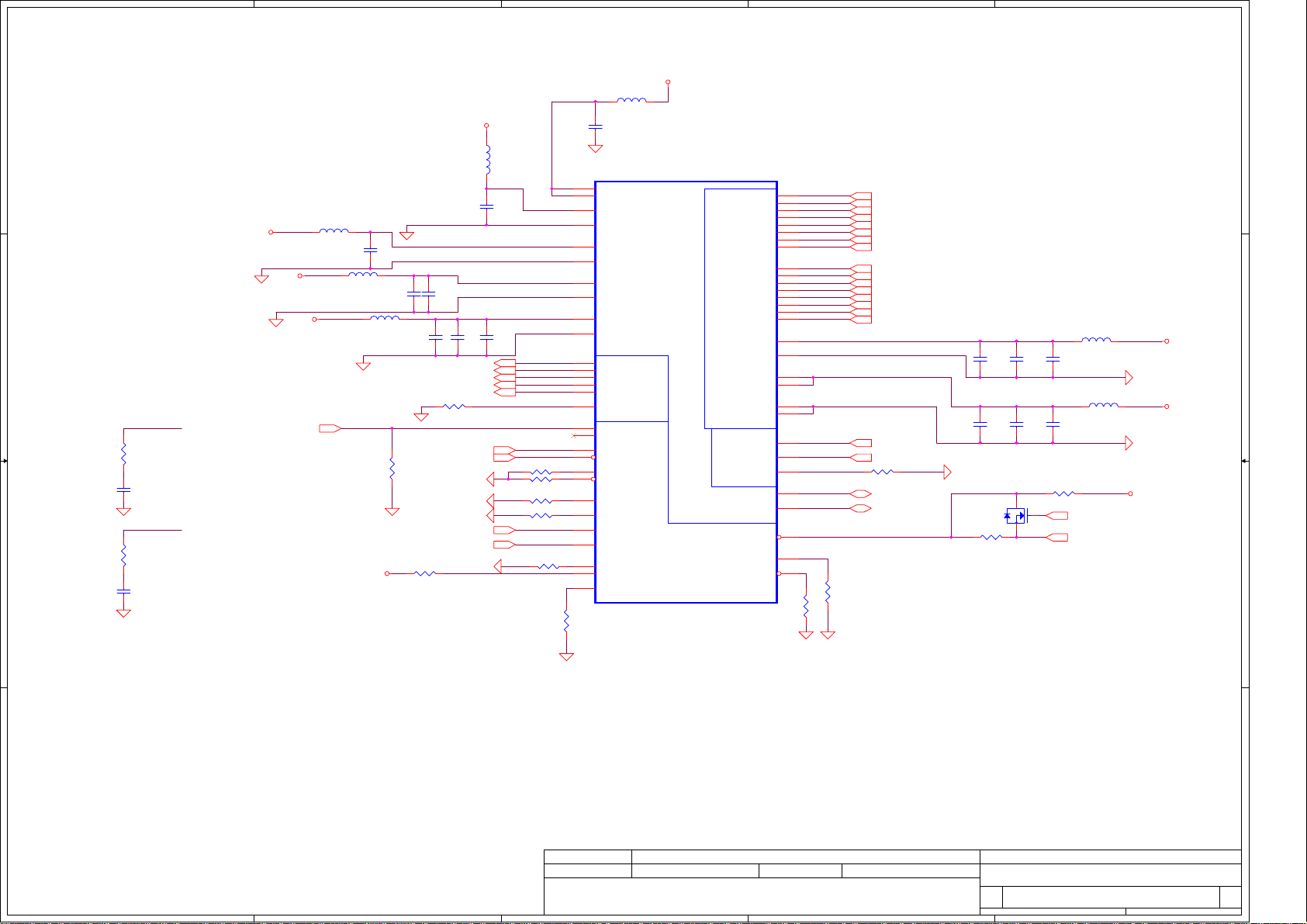

BLOCK DIAGRAM

Model Name : HBT10

File Na m e : L A-2811 Rev: 0.1

4 4

Dothan

(uFCPGA-478)

PAGE 4,5

Thermal Sensor

ADM1032

PAGE 4

Clock G enerator

ICS951402AGT

PAGE 16

CPU VID

PAGE 40

FSB

400/533MHz

266/333MHz

LVDS

PAGE 15

(2.5V)

Memory Bus

SO-DI M M x 2 ( DDR)

BANK 0,1,2,3

PAGE 1 2 , 1 3,14

ATI-RL300MB

TV-OUT

3 3

RJ-45

PAGE 29

2 2

Slot 0

PAGE 27

CB PWR SW

TPS2211AIDBR

PAGE 27

PAGE 15

CRT

PAGE 15

Mini PCI

PAGE 25

LAN

RTL8100CL

CARDBUS

TI-1410

PAGE 24

PAGE 26

PCI BUS

33MHz (3.3V)

NEC USB

Controller

PAGE 41

VGA M9 Embeded

868 pin u-BGA

66MHz(3.3V)

ATI-IXP150

BGA 457 pin

LPC BUS 33MHz (3.3V)

Embedded

Controller

ENE KB910

PAGE 6-->11

A-Link

PAGE 17-->20

PAGE 28

Primary

ATA-100 (5V)

Secondary

ATA-100 (5V)

AC-LINK

24.576MHz(3.3V)

IDE HDD

IDE ODD

AC97 CODEC

ALC 250D

MDC

Connector

PAGE 21

PAGE 21

PAGE 22

PAGE 32

Audio Amplifier

APA2121

PAGE 23

FAN Conn

RTC Battery

DC/DC Interface

LID/ Kill Sw itch

Power Buttom&

LED & Hibernation

DCIN&DETECTOR

BATT CONN/OTP

CHARGER

3V/5V/12V

DDR_1.5V/2.5V

1.8V/1.05V/1.25V

CPU_CORE

PAGE 30

PAGE 17

PAGE 33

PAGE 3 0,32

PAGE 34

PAGE 35

PAGE 36

PAGE 37

PAGE 38

PAGE 39

PAGE 40

USB 2.0 Port *3

0, 2, 4

1 1

A

480MHz(5V)

PAGE 29

B

Scan KB

PAGE 29

BIOS(512K)

& I/O PORT

PAGE 31

Security Classification

Issued Date

THIS SH EE T OF E NG INE E RIN G DRA WI NG IS T H E PR OPR IE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRA DE S EC RE T IN FO RM AT IO N. T H IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELEC TRONICS , INC. NEITHER THIS SHEET NOR THE INFORMATIO N IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTE N CONSEN T OF COMPA L ELECTRONICS, I NC.

2005/03/01 2006/03/01

C

Compa l S e c r et Data

Deciphered Date

D

Title

Notes

Size Document Num ber Re v

Sakhir 10E<HBT10> 1.0

Custom

Dat e: Sheet

星期三 五月

4, 2005

E

of

244, 0

A

B

C

D

E

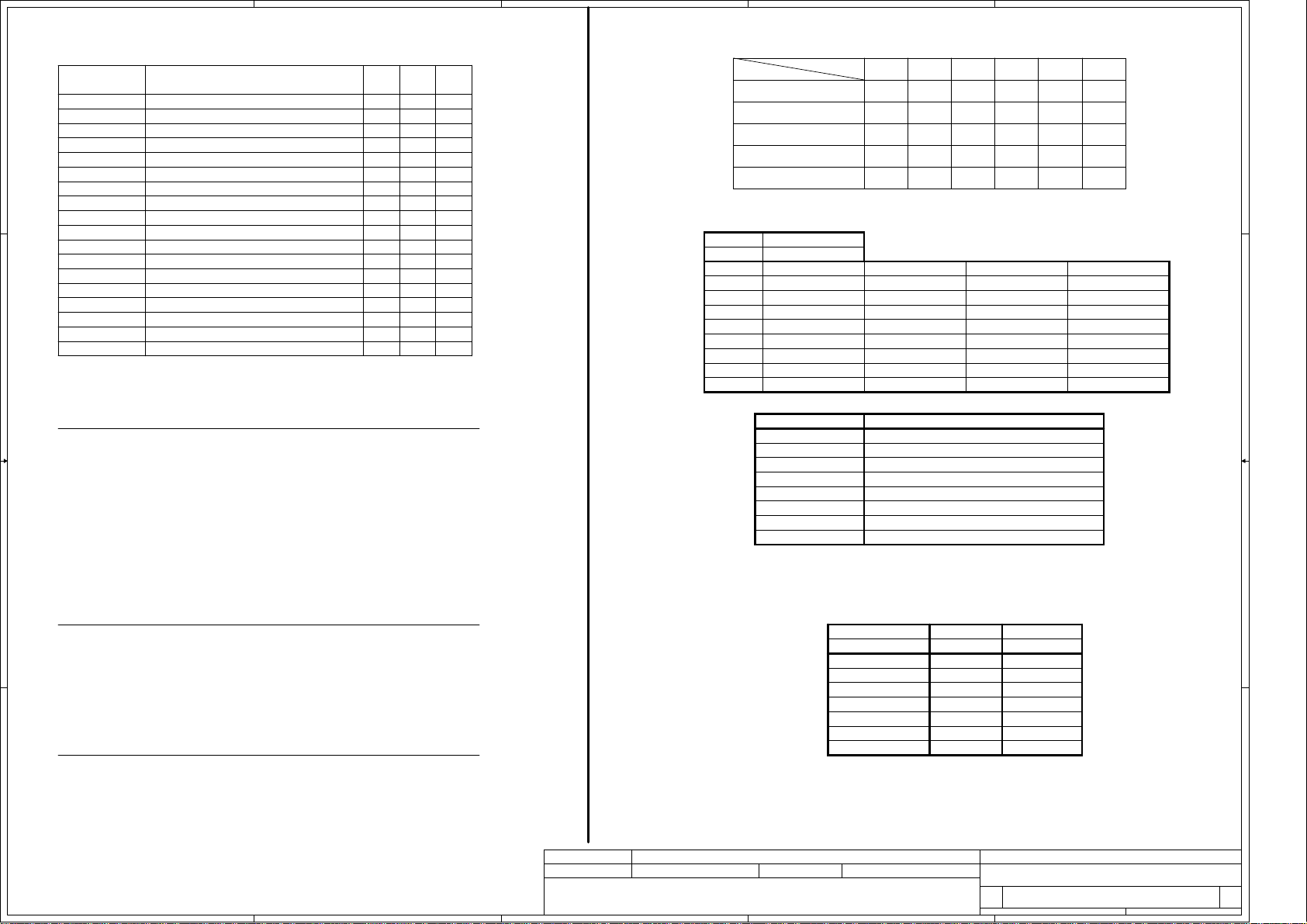

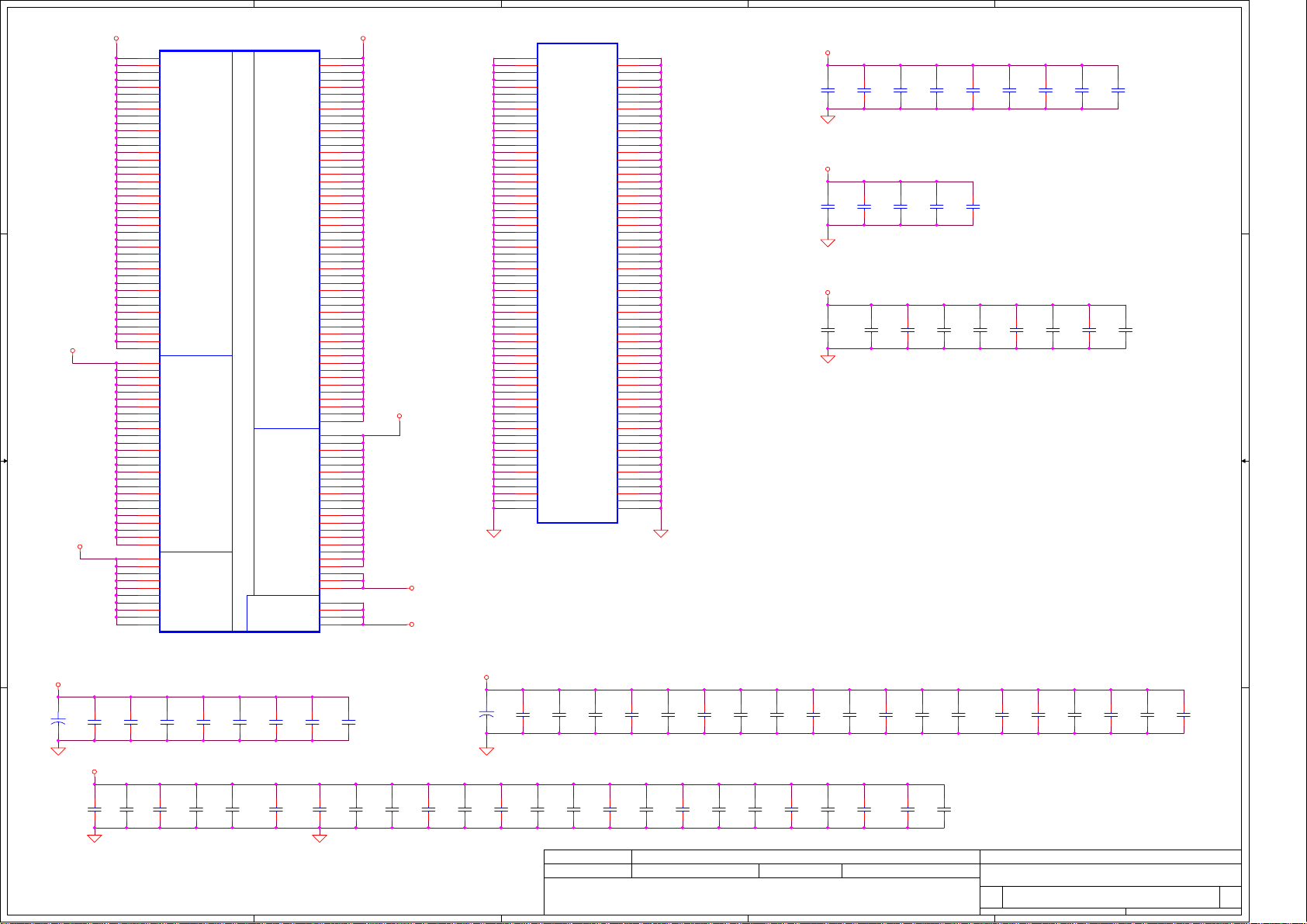

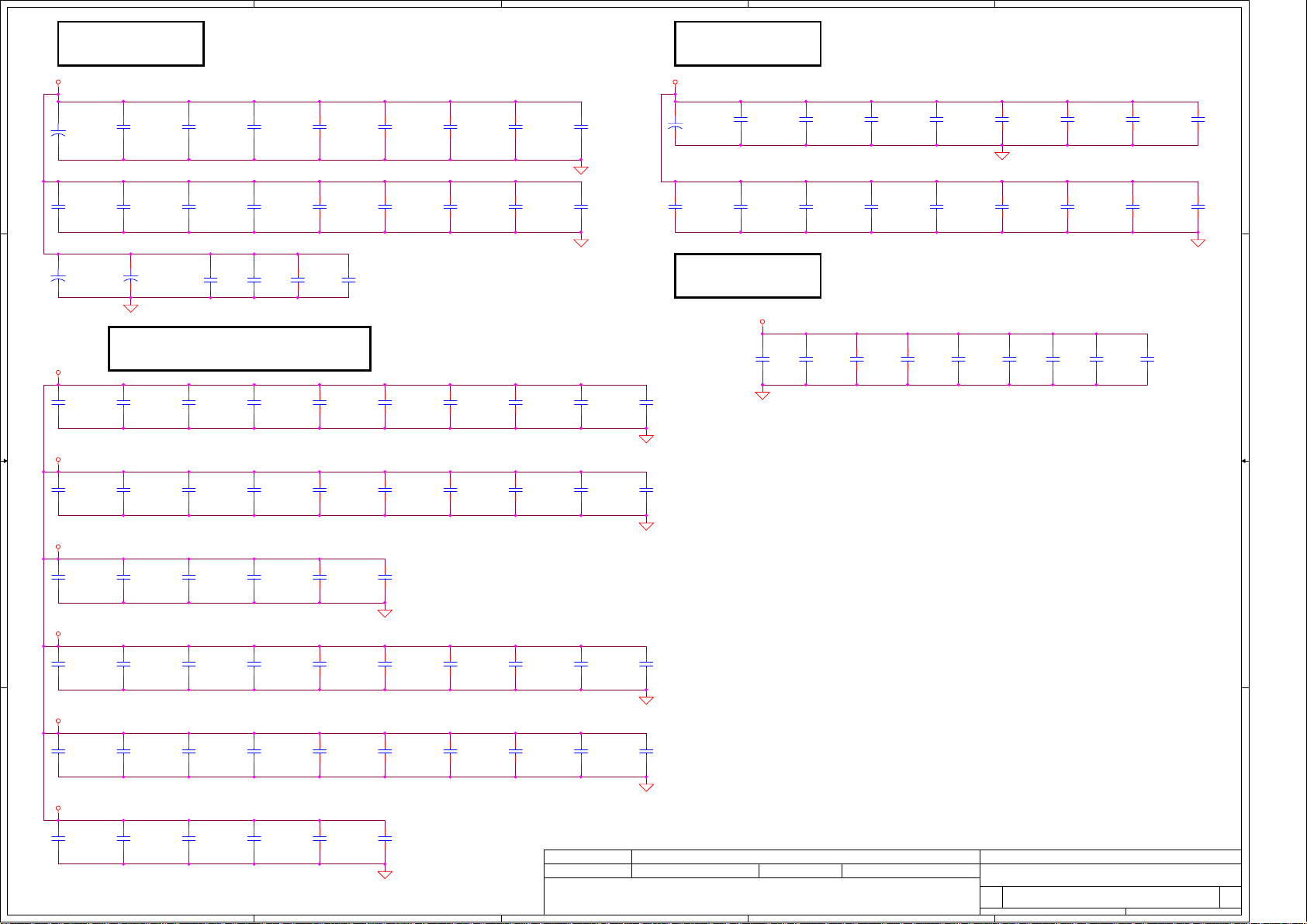

Voltage Rails

Power Plane Description

VIN

1 1

2 2

B+

+CPU_CORE

+CPUVID

+VGA_CORE ON OF F O F F1.0V/1 . 2V sw i t c h ed p o w e r r ai l f o r VGA chip

+1.25VS 1.25V switched power rail

+1.5VS

+1.8VS 1.8VS switched power rail OFFOFFON

+2.5VALW 2.5V always on power rail ON*ONON

+2.5V

+3VALW

+3V

+3VS

+5VS

+12VALW

+RTCVCC

Adapter power supply (19V)

AC or bat t er y p o w e r ra i l fo r p o w er circuit.

Core v o ltage for CPU

1.2V swi tch ed p ower rai l f or CPU AG TL Bus

AGP 4X/8X

2.5V po wer rail

2.5V switched power rail+2.5VS

3.3V always on power rail

3.3V po wer rail

3.3V switched power rail

5V always on power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

ON

ON ONONON

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON ON

ON

ON

ON

ON

ON+5VALW

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

OFF

OFF

OFF

OFF

ON*ON

OFF

OFF

ON*

OFF

ON*

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM) ON

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table f or AD channel

Vcc

Ra

Board ID

0

1

2

3

4

5

6

3.3V +/- 5%

100K +/- 5%

Rb

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC7

SIGNAL

Note : O N * mean s that thi s po wer p lan e is ON o nl y wi th AC p ow er avail abl e, o therw ise i t is O FF .

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

CardBus

LAN

Mini-PCI1

AD20

AD19

AD18

2

3PIRQD

1(for W i r eless Lan)

PIRQA

PIRQC/P IRQD

Board ID

0

1

2

3

4

5

6

7

HIGH

LOW

LOW

AD_BID

0.436 V

0.712 V

1.036 V

1.935 V

2.500 V

SLP_S5#STATE

HIGHHIGH

HIGH

HIGH

HIGH

LOWLOW

minV

0 V

PCB Revision

+VALW

ON

ON

ON

ON

ON

0.1

+V

ON

ON

OFF

OFF

AD_BID

0.503 V

0.819 V

1.650 V1.453 V

2.200 V

3.300 V

typV

0 V

+VSSL P_S3#

ON

OFF

OFF

OFF

Clock

ONON

LOW

OFF

OFF

OFF

V

AD_BID

0.289 V0.250 V0.216 V

0.538 V

0.875 V

1.264 V1.185 V

1.759 V

2.341 V

3.300 V

max

0 V

3 3

SKU ID

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

1001 110X b0001 011X b

Table

10E

SKU_ID

1-Button

7-Buttons-W

7-Buttons-J

1-Butt on-J -HDD

Board ID Scan Code

7

5

4

3

2

10

311

IXP150 SM Bus address

Device

Clock Generator

4 4

(ICS951402AGT)

DDR DIMM0

DDR DIMM2

A

Address

1101 001Xb

1010 000Xb

1010 001Xb

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

C

Compal S e cr e t Data

Deciphered Date

Title

Notes

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10>

Custom

星期三 五月

D

Date: Sheet

005

E

1.0

of

344, 04, 2

5

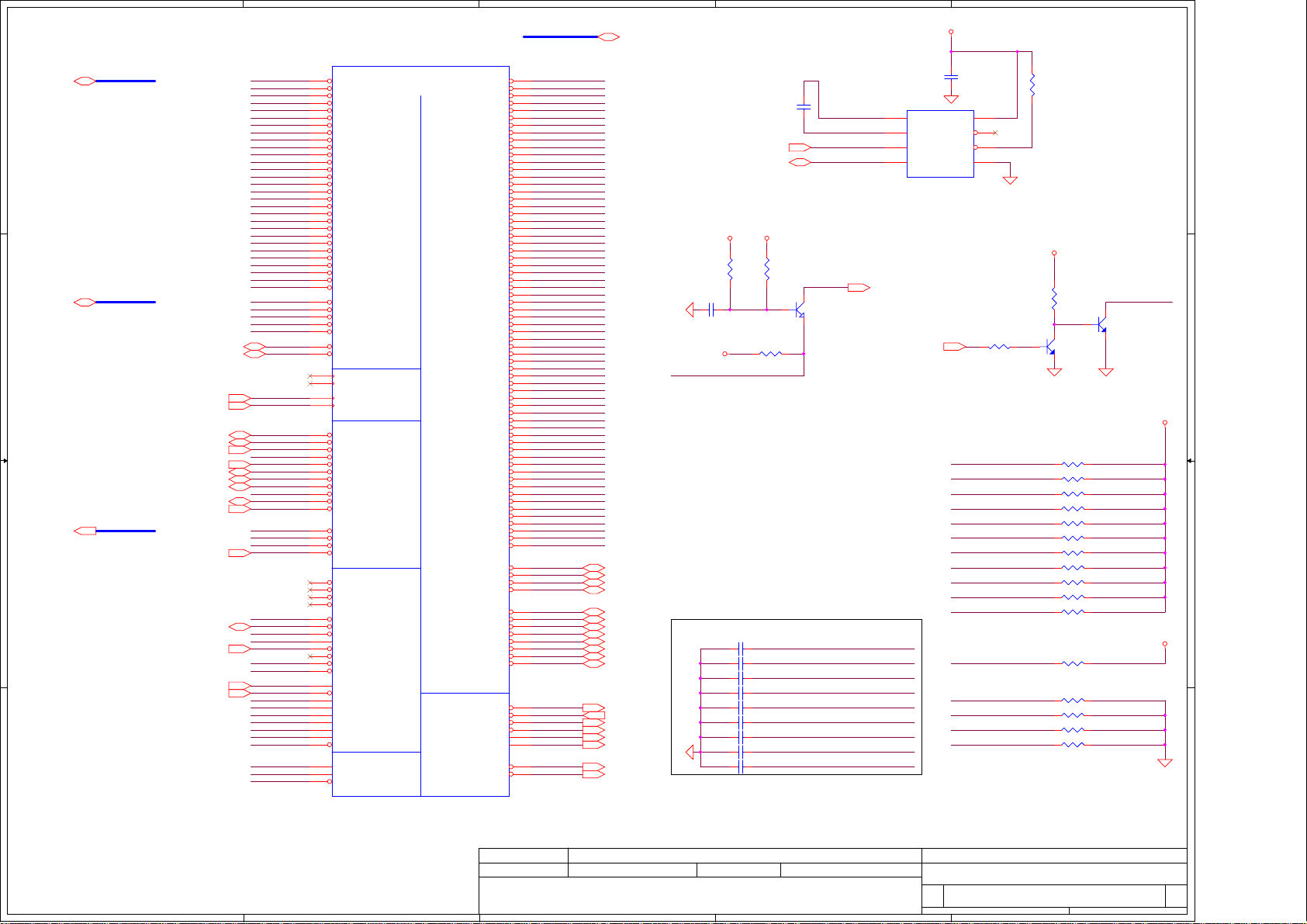

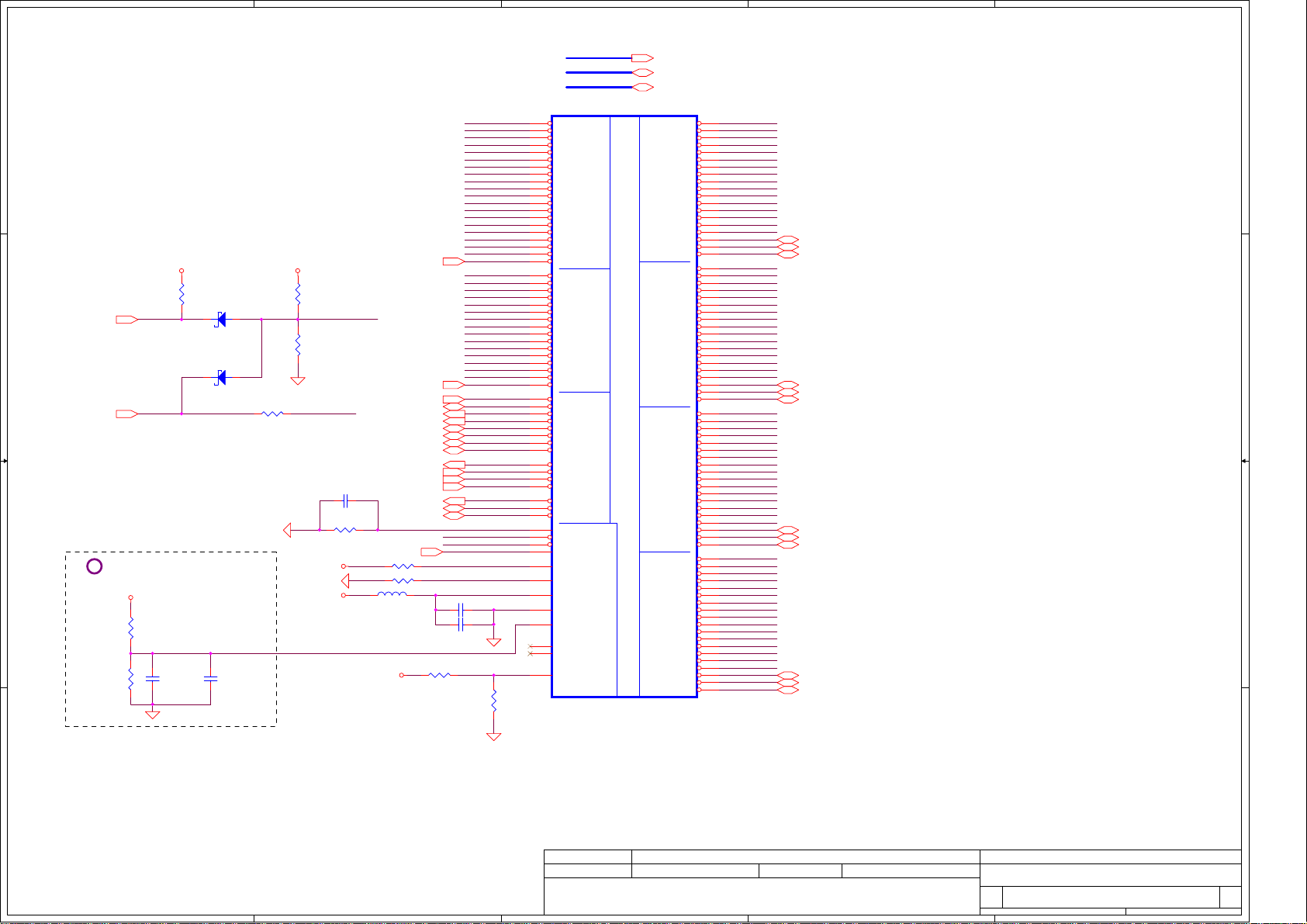

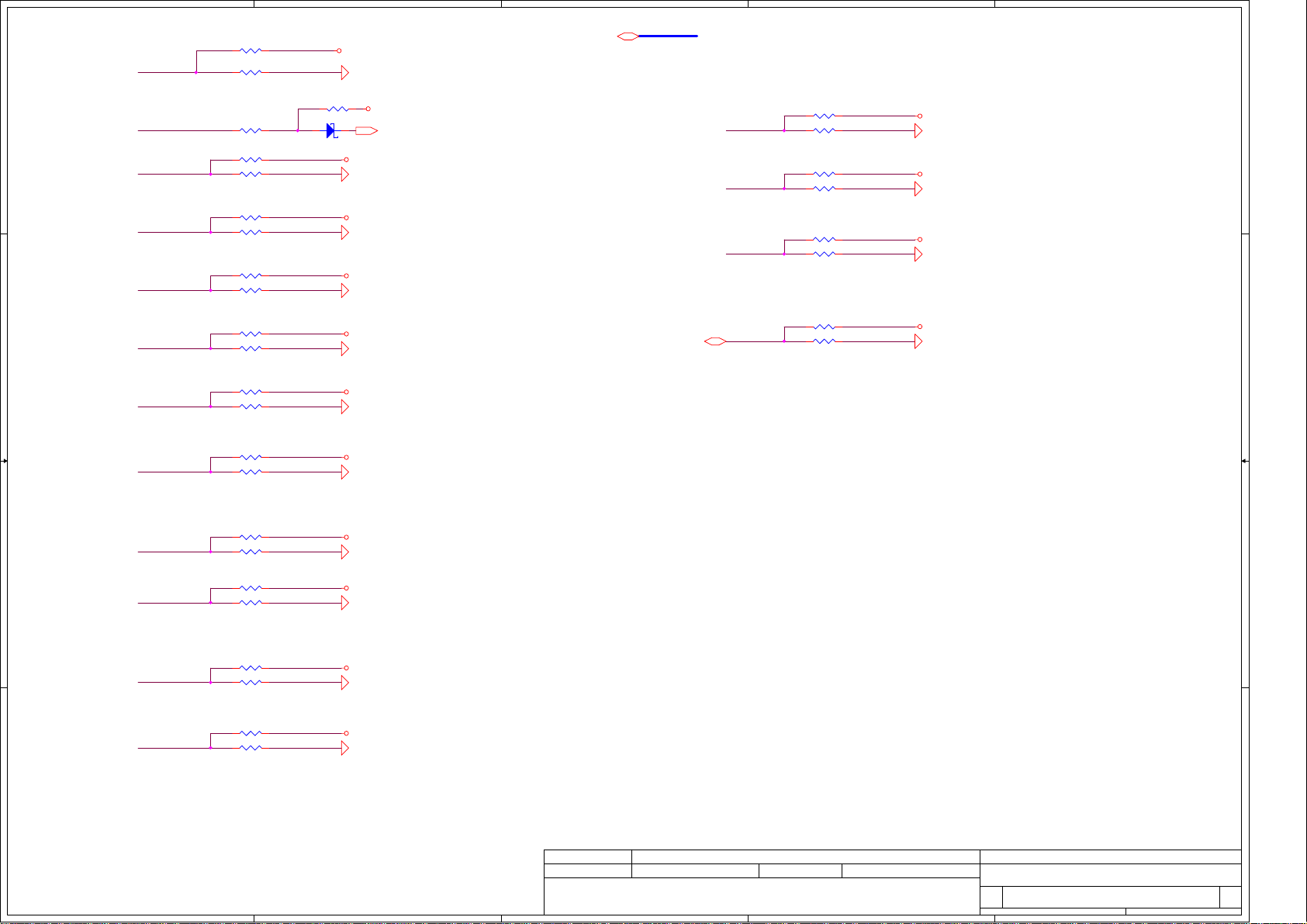

H_A#[ 3. .31]6

D D

H_REQ#[0..4]6

C C

H_RS#[0..2]6

B B

A A

H_A#[3..31]

H_REQ#[0..4]

H_RS#[0..2]

H_ADSTB#06

H_ADSTB#16

CLK_BCLK16

CLK_BCLK#16

H_ADS#6

H_BNR#6

H_BPRI#6

H_DEFER#6

H_DRDY#6

H_HIT#6

H_HITM#6

H_LOCK#6

H_RESET#6

H_TRDY#6

H_DBSY#6

H_DPWR#6

H_PW RGOOD17

H_SLP#17

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_BR0#

H_IERR#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

ITP_DBRRESET#

H_DPSLP#

H_DPRSLP#

PREQ#

H_PROCHOT#

H_PW RGOOD

H_SLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

THERMDA

THERMDC

H_THERMTRIP#

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A16

A15

B15

B14

B11

C19

A10

B10

B17

A13

C12

A12

F23

C11

B13

B18

A18

C17

4

JP5A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

A14#

Y3

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

ADDR GROUP

A25#

A26#

A27#

A28#

A29#

A30#

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

ADSTB1#

ITP_CLK0

ITP_CLK1

BCLK0

HOST CLK

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

A4

J2

H1

K1

L2

M3

C8

B8

A9

C9

A7

M2

B7

G1

E4

A6

C5

CONTROL GROUP

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMDA

THERMDC

THERMTRIP#

TYCO_ 1612365- 1_Dothan

Dothan

MISC

THERMAL

DIODE

DATA GROUP

LEGACY CPU

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#[0..63]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

3

H_D#[0..63] 6

H_DINV#0 6

H_DINV#1 6

H_DINV#2 6

H_DINV#3 6

H_DSTBN#0 6

H_DSTBN#1 6

H_DSTBN#2 6

H_DSTBN#3 6

H_DSTBP#0 6

H_DSTBP#1 6

H_DSTBP#2 6

H_DSTBP#3 6

H_A20M# 17

H_FERR# 17

H_IGNNE# 17

H_INIT# 17

H_INTR 17

H_NMI 17

H_STPCLK# 17

H_SMI# 17

2

1

EC_SMB_CK228

EC_SMB_DA228

1 2

R34

56_0402_5%

C32

12

R7

47K_0402_5%

2

B

2

1

C

Q5

E

2SC2411K_SC59

3

THERMDA

THERMDC

H_INIT#

H_A20M#

H_SLP#

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_IGNNE#

H_PW RGOOD

2200P_0402_50V7K

+1.05VS +CPU_CORE

12

R6

@

47K_0402_5%

1 2

C13

0.1U_0603_25V7K@

+1.05VS

H_THERMTRIP#

Place Caps Close to CPU Socket

C31 180P_0402_50V8J

1 2

C33 180P_0402_50V8J

1 2

C30 180P_0402_50V8J

1 2

C35 180P_0402_50V8J

1 2

C21 180P_0402_50V8J

1 2

C28 180P_0402_50V8J

1 2

C29 180P_0402_50V8J

1 2

C34 180P_0402_50V8J

1 2

C20 180P_0402_50V8J

1 2

U4

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

MAINPWON 34,35,37

PM_STPCPU#9,16,17,40

+3VS

1

C36

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

PREQ#

H_DPSLP#

H_BR0#

H_DPRSLP#

ITP_TDI

ITP_TDO

H_RESET#

ITP_TMS

H_PROCHOT#

H_IERR#

H_PW RGOOD

ITP_DBRRESET#

ITP_TRST#

ITP_TCK

TEST1

TEST2

1

6

4

5

R14

470_0402_5%

1

12

R27

10K_0402_5%@

+1.05VS

R11

470_0402_5%

1 2

Q1

2

12

2

Q7

MMBT3904_SOT23

3 1

3 1

MMBT3904_SOT23

R19 56_0402_5%@

R46 200_0402_5%

R22 200_0402_5%

R36 56_0402_5%@

R21 150_0402_5%

R38 54.9_0402_1%@

R37 54.9_0402_1%@

R43 40.2_0402_1%

R41 56_0402_5%

R35 56_0402_5%

R15 200_0402_5%

R45 150_0402_5%

R39 680_0402_5%

R40 27.4_0402_1%

R10 1K_0402_5%@

R55 1K_0402_5%@

12

1 2

1 2

12

12

12

12

12

12

12

12

12

12

12

12

12

H_DPSLP#

+1.05VS

+3VS

THERMDA & THERMDC Trace / Space = 10 / 10 mil

5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FRO M TH E CU ST OD Y O F T HE COMPETENT DIVISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE I NFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHO UT PRIOR W RITTEN CONSENT O F COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

3

Compal Secret Data

Deciphered Date

Title

Dothan(1/2)

Size Document Number R e v

Sakhir 1 0 E <H B T10> 1.0

Custom

Date: Sheet

星

T, 04, 2005

2

薑五月

444

1

of

5

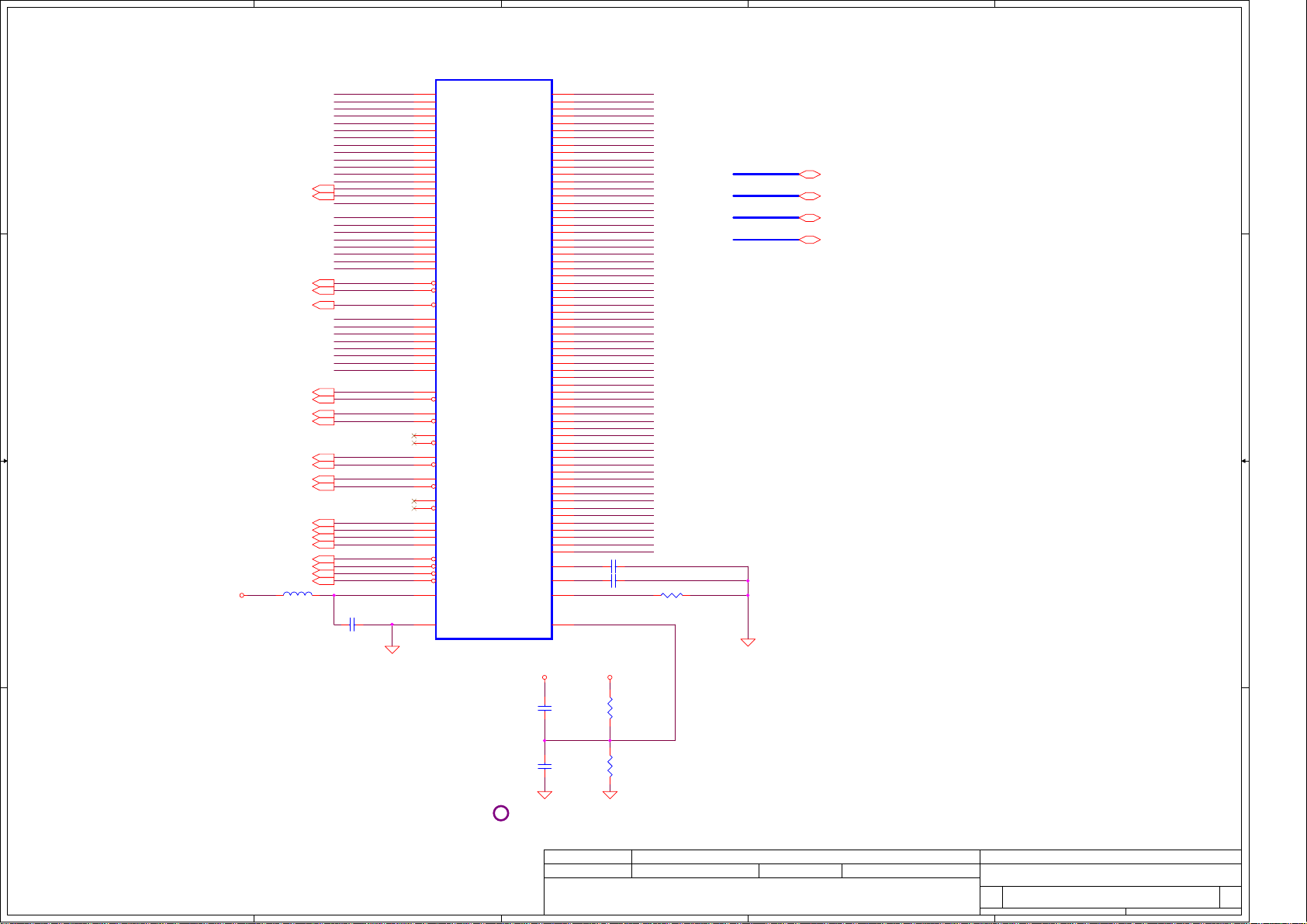

JP5B

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

B2

RSVD

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

TYCO_1612365-1_Dothan

1

2

+1.05VS

C49

VCCSENSE

VSSSENSE

GTL_REF0

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

R79 54.9_0402_1%@

1 2

R78 54.9_0402_1%@

1 2

+VCCA

1.8V FOR DOTHAN-A

D D

1 2

+1.8VS

R51 0_1206_5%@

1.5V FOR DOTHAN-B

1 2

+1.5VS

R54 0_1206_5%

C C

R58

1K_0402_1%

1 2

R59 2K_0402_1%

B B

20mils

1

C48

2

0.01U_0402_16V7K

10U_0805_6.3V6M

+CPU_CORE

+1.05VS

12

PSI#40

CPU_VID040

CPU_VID140

CPU_VID240

CPU_VID340

CPU_VID440

CPU_VID540

4

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

Dothan

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

POWER, GROUNG, RESERVED SIGNALS AND NC

+1.05VS

1

+

2

150U_D2_6.3VM

330U_D_2VM

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

Vcc-core

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

0.1U_0402_16V4Z

1

C411

C403

2

+CPU_CORE

1

+

C99

2

+CPU_CORE

10U_0805_6.3V6M

1

C50

2

+CPU_CORE

10U_0805_6.3V6M

1

C401

2

+CPU_CORE

10U_0805_6.3V6M

1

C105

2

+CPU_CORE

10U_0805_6.3V6M

1

C56

2

+CPU_CORE

10U_0805_6.3V6M

1

C53

2

0.1U_0402_16V4Z

1

2

3

330U_D_2VM

1

2

1

C68

2

1

C106

2

1

C61

2

1

C54

2

1

+

C100

2

C58

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

330U_D_2VM

1

C417

2

1

C414

2

1

C104

2

1

C426

2

1

C418

2

330U_D_2VM@

1

+

C402

2

10U_0805_6.3V6M

1

C69

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C65

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C423

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C107

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C102

2

10U_0805_6.3V6M

1

+

C421

4 x 270uF(12mOhm/4)

2

1

C422

2

1

C67

2

1

C425

2

1

C57

2

1

C60

2

C,uF ESR, mohm ESL,nH

2X330uF 7m ohm/2 3.5nH/2

35X10uF 5m ohm/35 0.6nH/35

0.1U_0402_16V4Z

1

1

C396

C397

2

0.1U_0402_16V4Z

C406

2

0.1U_0402_16V4Z

1

C409

2

10U_0805_6.3V6M

1

C404

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C66

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C424

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C51

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C405

2

10U_0805_6.3V6M

0.1U_0402_16V4Z

1

C420

2

0.1U_0402_16V4Z

C413

C103

C52

C415

C101

1

2

1

2

1

2

1

2

1

2

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C408

0.1U_0402_16V4Z

2

+CPU_CORE

1

C395

2

1

C398

2

1

C400

2

1

C410

2

JP5C

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA19

VCC

AA21

VCC

AB6

VCC

AB8

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

TYCO_1612365-1_Dothan

Dothan

POWER, GROUND

1

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

R57 27.4_0402_1%

1 2

R56 54.9_0402_1%

1 2

R80 27.4_0402_1%

1 2

R77 54.9_0402_1%

1 2

TRACE CLOSELY CPU < 0.5'

COMP0, COMP2 layout : Width 18mils and Space 25mils

A A

COMP1, COMP3 layout : Space 25mils

COMP0

COMP1

COMP2

COMP3

CPU_BSEL1

+1.05VS

R20

56_0402_5%

1 2

CPU_BSEL0

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PRO PERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED F RO M T HE CUSTO DY OF THE COM PETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.05VS

R42

56_0402_5%

1 2

R18

2

12

470_0402_5%

2005/03/01 2006/03/01

3

Compal Secret Data

1 2

Q2

MMBT3904_SOT23

3 1

Deciphered Date

R171K_0402_1%

+3VS

BSEL0 11,16

Title

Dothan(2/2)

Size Document Nu mber Re v

Sakhir 10E<HBT10> 1.0

Custom

Date: Sheet

星期三 五月

2

04, 2005

1

of

544,

5

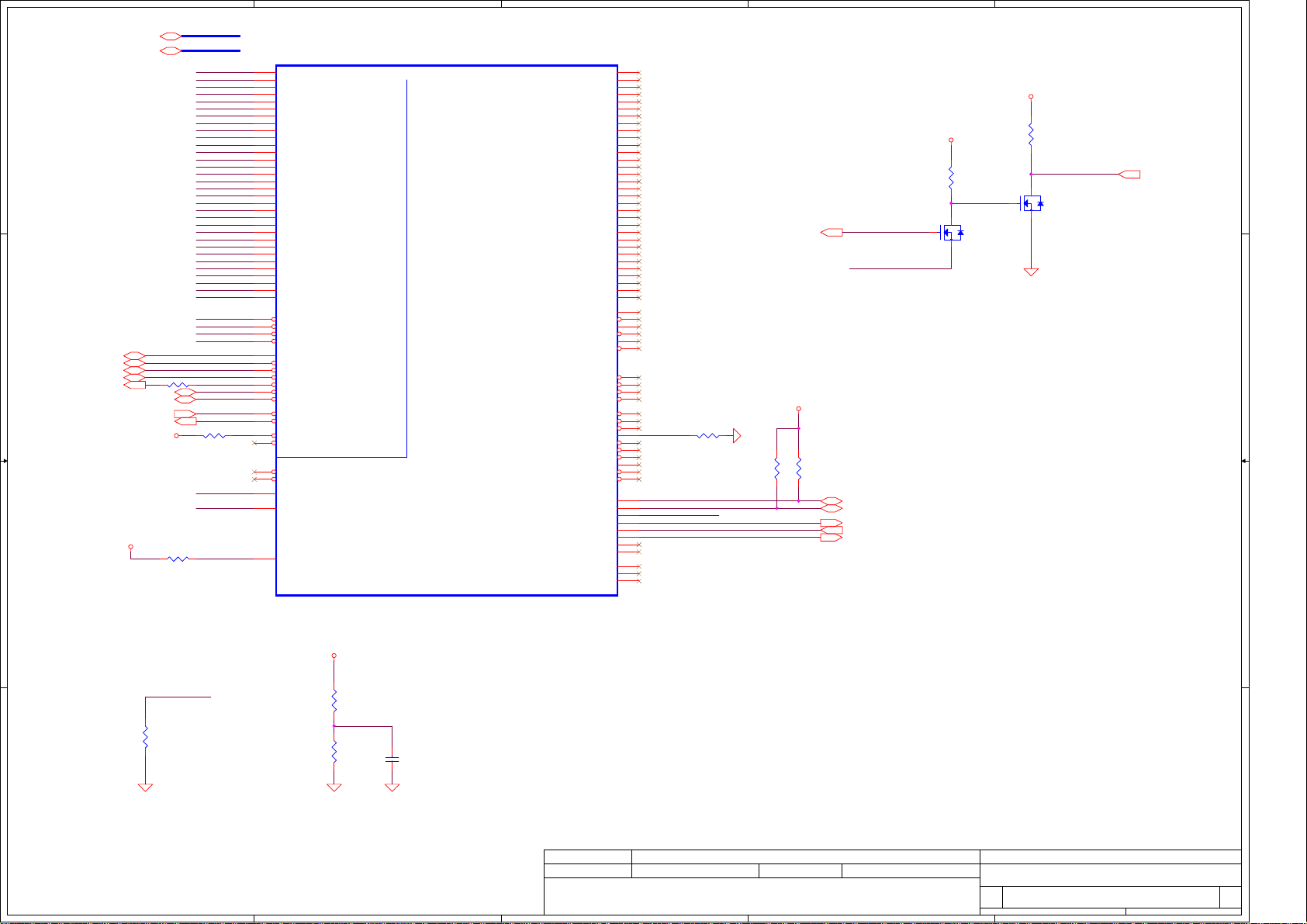

4

3

2

1

H_A#[3..31]

H_REQ#[0..4]

H_D#[0..63]

U6A

M28

CPU_A3#

P25

CPU_A4#

M25

CPU_A5#

N29

CPU_A6#

N30

CPU_A7#

M26

CPU_A8#

N28

CPU_A9#

P29

CPU_A10#

P26

CPU_A11#

R29

CPU_A12#

P30

CPU_A13#

P28

CPU_A14#

N26

CPU_A15#

N27

CPU_A16#

M29

CPU_REQ0#

N25

CPU_REQ1#

R26

CPU_REQ2#

L28

CPU_REQ3#

L29

CPU_REQ4#

R27

CPU_ADSTB0#

U30

CPU_A17#

T30

CPU_A18#

R28

CPU_A19#

R25

CPU_A20#

U25

CPU_A21#

T28

CPU_A22#

V29

CPU_A23#

T26

CPU_A24#

U29

CPU_A25#

U26

CPU_A26#

V26

CPU_A27#

T25

CPU_A28#

V25

CPU_A29#

U27

CPU_A30#

U28

CPU_A31#

T29

CPU_ADSTB1#

L27

CPU_ADS#

K25

CPU_BNR#

H26

CPU_BPRI#

J27

CPU_DEFER#

L26

CPU_DRDY#

G27

CPU_DBSY#

F25

CPU_BR0#

K26

CPU_LOCK#

A17

CPU_CPURSET#

G25

CPU_RS2#

G26

CPU_RS1#

J25

CPU_RS0#

F26

CPU_TRDY#

J26

CPU_HIT#

H25

CPU_HITM#

A9

CPU_RSET

AH5

SUS_STAT#

AG5

SYSRESET#

C7

POWERGOOD

V28

CPU_COMP_N

W29

CPU_COMP_P

H23

CPVDD

J23

CPVSS

W28

CPU_VREF

Y29

THERMALDIODE_N

Y28

THERMALDIODE_P

B17

TESTMODE

CHS-216IGP9050A21_BGA718

R60

0_0402_5%@

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_DPWR#

H_LOCK#

H_RESET#

H_RS#2

H_RS#1

H_RS#0

H_TRDY#

H_HIT#

H_HITM#

NB_SUS_STAT_A#

NB_RST_A#

COMP_N

COMP_P

CPVDD

C442

CPVSS

1 2

1 2

C45510U_0805_10V4Z

12

R61

10_0402_5%

D D

H_ADSTB#04

H_ADSTB#14

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#4

H_DBSY#4

H_DPWR#4

H_LOCK#4

H_RESET#4

H_RS#24

H_RS#14

H_RS#04

H_TRDY#4

H_HIT#4

H_HITM#4

NB_PWRGD8,15,20

R65 24.9_0402_1%

1 2

R67 49.9_0402_1%

1 2

L32

1 2

1U_0603_10V4Z@

NB_GTLREF

+1.05VS

1 2

R108

1 2

270K_0402_5%

+1.8VS+2.5V

12

12

+1.05VS

R104

27K_0402_5%

NB_SUS_STAT_A#

R103

330K_0402_5%

NB_RST_A#

0.1U_0402_10V6K

C89

R72

1 2

330_0402_5%

+1.8VS

12

HB-1M2012-121JT03_0805

**

12

R109

27K_0402_5%

D15

NB_SUS_STAT#18

C C

NB_RST#9,17

Note: P LACE CLOSE TO RC300M,

B B

L

USE 10/10 WIDTH/SPACE

+1.05VS

12

R64

49.9_0402_1%

R66

100_0402_1%

1 2

1

C84

1U_0603_10V4Z

2

21

RB751V_SOD323

D14

21

RB751V_SOD323

1

C88

220P_0402_50V7K

2

H_A#[3..31] 4

H_REQ#[0..4] 4

H_D#[0..63] 4

H_D#0

L30

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

PART 1 OF 6

CPU_D9#

CPU_D10#

CPU_D11#

DATA GROUP 0DAT A GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTBN0#

CPU_DSTBP0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

MISC.

CPU_DSTBN1#

CPU_DSTBP1#

AGTL+ I/F

PENTIUM

IV

CPU_DSTBN2#

CPU_DSTBP2#

CPU_DSTBN3#

CPU_DSTBP3#

CPU_DBI1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

ADDR. GROUP 1 ADDR. GROUP 0CONTROL

H_D#1

K29

H_D#2

J29

H_D#3

H28

H_D#4

K28

H_D#5

K30

H_D#6

H29

H_D#7

J28

H_D#8

F28

H_D#9

H30

H_D#10

E30

H_D#11

D29

H_D#12

G28

H_D#13

E29

H_D#14

D30

H_D#15

F29

H_DINV#0

E28

H_DSTBN#0

G30

H_DSTBP#0

G29

H_D#16

B26

H_D#17

C30

H_D#18

A27

H_D#19

B29

H_D#20

C28

H_D#21

C29

H_D#22

B28

H_D#23

D28

H_D#24

D26

H_D#25

B27

H_D#26

C26

H_D#27

E25

H_D#28

E26

H_D#29

A26

H_D#30

B25

H_D#31

C25

H_DINV#1

A28

H_DSTBN#1

D27

H_DSTBP#1

E27

H_D#32

F24

H_D#33

D24

H_D#34

E23

H_D#35

E24

H_D#36

F23

H_D#37

C24

H_D#38

B24

H_D#39

A24

H_D#40

F21

H_D#41

A23

H_D#42

B23

H_D#43

C22

H_D#44

B22

H_D#45

C21

H_D#46

E21

H_D#47

D22

H_DINV#2

D23

H_DSTBN#2

E22

H_DSTBP#2

F22

H_D#48

B21

H_D#49

F20

H_D#50

A21

H_D#51

C20

H_D#52

E20

H_D#53

D20

H_D#54

A20

H_D#55

D19

H_D#56

C18

H_D#57

B20

H_D#58

E18

H_D#59

B19

H_D#60

D18

H_D#61

B18

H_D#62

C17

H_D#63

A18

H_DINV#3

F19

H_DSTBN#3

E19

H_DSTBP#3

F18

H_DINV#0 4

H_DSTBN#0 4

H_DSTBP#0 4

H_DINV#1 4

H_DSTBN#1 4

H_DSTBP#1 4

H_DINV#2 4

H_DSTBN#2 4

H_DSTBP#2 4

H_DINV#3 4

H_DSTBN#3 4

H_DSTBP#3 4

A A

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

3

Compal S e cr e t Data

Deciphered Date

Title

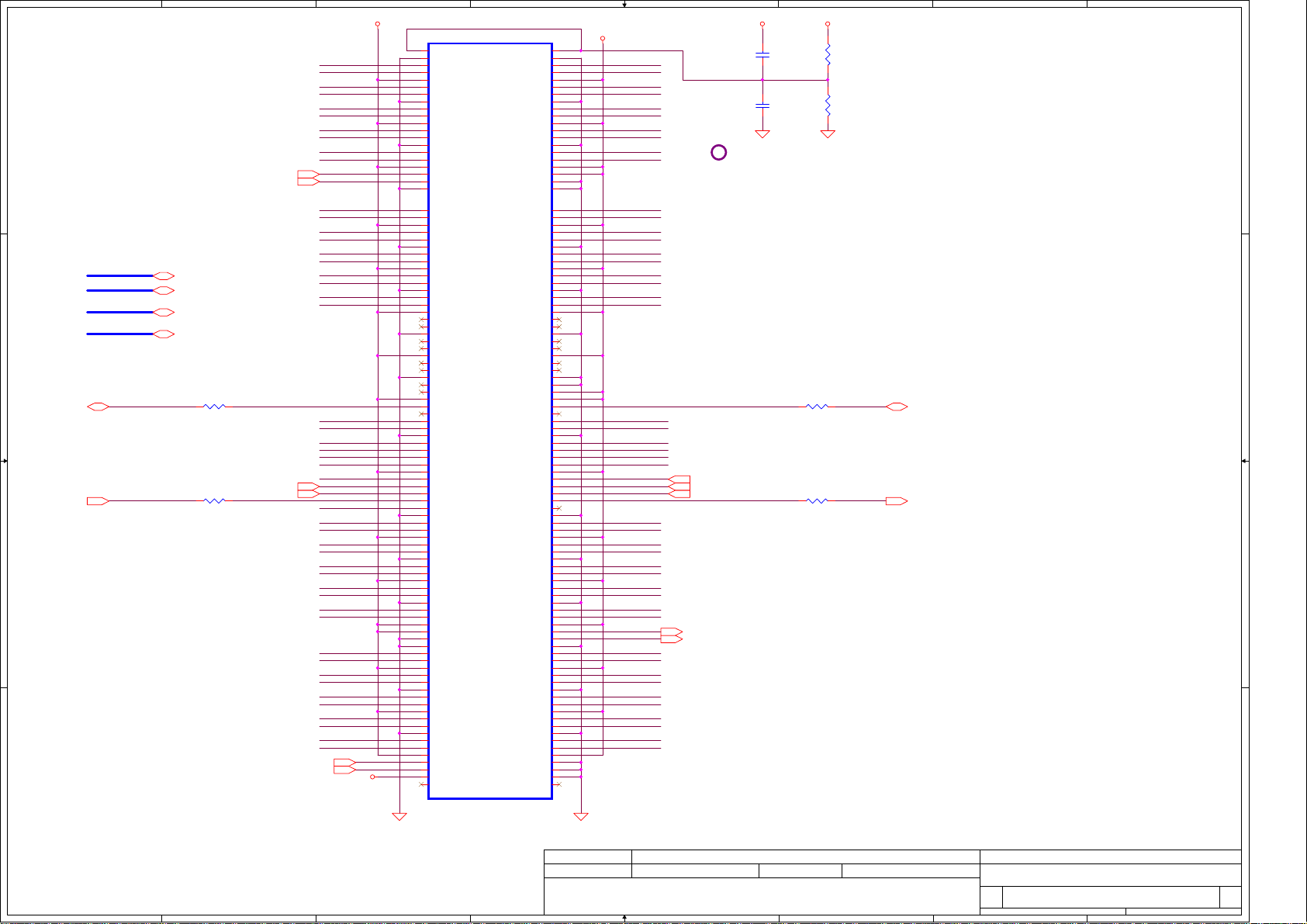

ATI RL300MB-AGTL+

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10> 1 .0

Custom

星期三 五月

2

Date: Sheet

005

1

of

644, 04, 2

5

D D

DDR_SBS012,13

DDR_SBS112,13

DDR_SRAS#12,13

DDR_SCAS#12,13

DDR_SWE#12,13

C C

DDR_CLK012

DDR_CLK0#12

DDR_CLK112

DDR_CLK1#12

DDR_CLK313

DDR_CLK3#13

DDR_CLK413

DDR_CLK4#13

DDR_SCKE012,13

DDR_SCKE112,13

DDR_SCKE213

DDR_SCKE313

DDR_SCS#012,13

DDR_SCS#112,13

B B

+1.8VS

DDR_SCS#213

DDR_SCS#313

L12

1 2

HB-1M2012-121JT03_0805

2.2U_0805_16V4Z

4

U6B

DDR_SMA0

DDR_SMA1

DDR_SMA2 DDR_DQ2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA13

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM7

DDR_SRAS#

DDR_SCAS#

DDR_SWE#

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CLK0

DDR_CLK0#

DDR_CLK1

DDR_CLK1#

DDR_CLK3

DDR_CLK3#

DDR_CLK4

DDR_CLK4#

DDR_SCKE0

DDR_SCKE1

DDR_SCKE2

DDR_SCKE3

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

MPVDD

C115

MPVSS

1 2

AH19

AJ17

AK17

AH16

AK16

AF17

AE18

AF16

AE17

AE16

AJ20

AG15

AF15

AE23

AH20

AE25

AF10

AJ14

AF21

AH23

AK28

AD29

AB26

AF24

AF25

AE24

AH13

AE21

AJ23

AJ27

AC28

AA25

AK10

AH10

AH18

AJ19

AG30

AG29

AK11

AJ11

AH17

AJ18

AF28

AG28

AF13

AE13

AG14

AF14

AH26

AH27

AF26

AG27

AC18

AD18

AH7

AJ8

AF9

PART 2 OF 6

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_DQS0

MEM_DQS1

MEM_DQS2

MEM_DQS3

MEM_DQS4

MEM_DQS5

MEM_DQS6

MEM_DQS7

MEM_CK0

MEM_CK0#

MEM_CK1

MEM_CK1#

MEM_CK2

MEM_CK2#

MEM_CK3

MEM_CK3#

MEM_CK4

MEM_CK4#

MEM_CK5

MEM_CK5#

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS#0

MEM_CS#1

MEM_CS#2

MEM_CS#3

MPVDD

MPVSS

CHS-216IGP9050A21_BGA718

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM I/F

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP1

MEM_CAP2

MEM_COMP

MEM_DDRVREF

AG6

AJ7

AJ9

AJ10

AJ6

AH6

AH8

AH9

AE7

AE8

AE12

AF12

AF7

AF8

AE11

AF11

AJ12

AH12

AH14

AH15

AH11

AJ13

AJ15

AJ16

AF18

AG20

AG21

AF22

AF19

AF20

AE22

AF23

AJ21

AJ22

AJ24

AK25

AH21

AH22

AH24

AJ25

AK26

AK27

AJ28

AH29

AH25

AJ26

AJ29

AH30

AF29

AE29

AB28

AA28

AE28

AD28

AC29

AB29

AC26

AB25

Y26

W26

AE26

AD26

AA26

Y27

C118 0.47U_0603_10V7K

AF6

C90 0.47U_0603_10V7K

AA29

AK19

AK20

3

DDR_DQ0

DDR_DQ1

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23DDR_DM6

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

1 2

1 2

MEN_COMP

R93 49.9_0402_1%

1 2

DDR_DM[0..7]

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_SMA[0..13]

2

DDR_DM[0..7] 12,13

DDR_DQ[0..63] 12,13

DDR_DQS[0..7] 12,13

DDR_SMA[0.. 13] 12,13

1

+2.5V+2.5V

Issued Date

12

R87

1K_0402_1%

12

R88

1K_0402_1%

3

2005/03/01 2006/03/01

Compal S e cr e t Data

Deciphered Date

2

Title

ATI RL 30 0MB-DDR I/F

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10> 1 .0

Custom

星期三 五月

Date: Sheet

005

1

of

744, 04, 2

2

C110

0.1U_0402_10V6K

0.1U_0402_10V6K

A A

L

1

DDR_VREF

2

C112

1

DDR_VREF trace width of

20mils and space

20mils(min)

Security Classification

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2

1

A_AD[0..31]11,17

A_CBE#[0..3]17

D D

C C

?

B B

A_PAR11,17

A_STROBE#17

A_ACAT#17

A_END#17

PCI_PIRQA#17,26,41

+1.5VS

A_DEVSEL#17

A_SBREQ#17

A_SBGNT#17

R102

A_AD[0..31]

A_CBE#[0..3]

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

A_PAR

A_STROBE#

A_ACAT#

1 2

1 2

169_0402_1%@

A_END#

A_DEVSEL#

A_OFF#

A_SBREQ#

A_SBGNT#

R381

4.7K_0402_5%

AGP8X_DET#

AGPREF_8X

AGP_COMP

R99 0_0402_5%

A_OFF#17

+3VS

AK5

AJ5

AJ4

AH4

AJ3

AJ2

AH2

AH1

AG2

AG1

AG3

AF3

AF1

AF2

AF4

AE3

AE4

AE5

AE6

AC2

AC4

AB3

AB2

AB5

AB6

AA2

AA4

AA5

AA6

Y3

Y5

Y6

AG4

AE2

AC3

AA3

AD5

AC6

AC5

AD2

W4

AD3

AD6

W5

W6

12

V5

V6

K5

K6

M5

J6

J5

U6C

ALINK_AD0

ALINK_AD1

ALINK_AD2

ALINK_AD3

ALINK_AD4

ALINK_AD5

ALINK_AD6

ALINK_AD7

ALINK_AD8

ALINK_AD9

ALINK_AD10

ALINK_AD11

ALINK_AD12

ALINK_AD13

ALINK_AD14

ALINK_AD15

ALINK_AD16

ALINK_AD17

ALINK_AD18

ALINK_AD19

ALINK_AD20

ALINK_AD21

ALINK_AD22

ALINK_AD23

ALINK_AD24

ALINK_AD25

ALINK_AD26

ALINK_AD27

ALINK_AD28

ALINK_AD29

ALINK_AD30

ALINK_AD31

ALINK_CBE#0

ALINK_CBE#1

ALINK_CBE#2

ALINK_CBE#3

PCI_PAR/ALINK_NC

PCI_FRAME#/ALINK_STROBE#

PCI_IRDY#/ALINK_ACAT#

PCI_TRDY#/ALINK_END#

INTA#

ALINK_DEVSEL#

PCI_STOP#/ALINK_OFF#

ALINK_SBREQ#

ALINK_SBGNT#

PCI_REQ#0/ALINK_NC

PCI_GNT#0/ALINK_NC

AGP2_GNT#/AGP3_GNT

AGP2_REQ#/AGP3_REQ

AGP8X_DET#

AGP_VREF/TMDS_VREF

AGP_COMP

CHS-216IGP9050A21_BGA718

PART 3 OF 6

PCI Bus 0 / A-Link I/F

AGP_AD0/TMD2_HSYNC

AGP_AD1/TMD2_VSYNC

AGP_AD11/TMD2_D11

AGP_AD12/TMD2_D10

AGP_AD16/TMD1_VSYNC

AGP_AD17/TMD1_HSYNC

AGP_AD18/TMD1_DE

AGP_AD28/TMD1_D11

AGP_AD29/TMD1_D10

AGP_AD30/TMDS_HPD

AGP2_SBSTB/AGP3_SBSTBF/NC/LVDS_BLON

AGP2_SBSTB#/AGP3_SBSTBS/NC/ENA_BL

AGP2_ADSTB0/AGP3_ADSTBF0/TMD2_CLK#

AGP2_ADSTB0#/AGP3_ADSTBS0/TMD2_CLK

AGP2_ADSTB1/AGP3_ADSTBF1/TMD1_CLK#

AGP2_ADSTB1#/AGP3_ADSTBS1/TMD1_CLK

AGP2_CBE#0/AGP3_CBE0/TMD2_D7

AGP2_CBE#1/AGP3_CBE1/TMD2_DE

AGP2_CBE#2/AGP3_CBE2

AGP2_CBE#3/AGP3_CBE3/TMD1_D5

AGP2_IRDY#/AGP3_IRDY/GPIO8/I2C_CLK

AGP2_TRDY#/AGP3_TRDY/TMDS_DVI_CLK

AGP2_STOP#/AGP3_STOP/GPIO10/DDC_DATA

AGP2_FRAME#/AGP3_FRAME/TMDS_DVI_DATA

AGP2_DEVSEL#/AGP3_DEVSEL/GPIO9/I2C_DATA

PCI BUS 1 / AGP Bus (GPIO , TMDS , ZVPort)

AGP2_SBA0/AGP3_SBA#0/GPIO0/VDDC_CNTL0

AGP2_SBA1/AGP3_SBA#1/GPIO1/VDDC_CNTL1

AGP2_SBA2/AGP3_SBA#2/GPIO2/LVDS_BLON#

AGP2_SBA3/AGP3_SBA#3/GPIO3/LVDS_DIGON

AGP2_SBA4/AGP3_SBA#4/GPIO4/STP_AGP#

AGP2_SBA5/AGP3_SBA#5/GPIO5/AGP_BUSY#

AGP2_SBA6/AGP3_SBA#6/GPIO6/LVDS_SSOUT

AGP2_SBA7/AGP3_SBA#7/GPIO7/LVDS_SSIN

AGP2_PIPE#/AGP3_DBI_HI

AGP2_NC/AGP3_DBI_LO

AGP2_RBF#/AGP3_RBF

AGP2_WBF#/AGP3_WBF

AGP_AD2/TMD2_D1

AGP_AD3/TMD2_D0

AGP_AD4/TMD2_D3

AGP_AD5/TMD2_D2

AGP_AD6/TMD2_D5

AGP_AD7/TMD2_D4

AGP_AD8/TMD2_D6

AGP_AD9/TMD2_D9

AGP_AD10/TMD2_D8

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD19/TMD1_D0

AGP_AD20/TMD1_D1

AGP_AD21/TMD1_D2

AGP_AD22/TMD1_D3

AGP_AD23/TMD1_D4

AGP_AD24/TMD1_D7

AGP_AD25/TMD1_D6

AGP_AD26/TMD1_D9

AGP_AD27/TMD1_D8

AGP_AD31

AGP_PAR

AGP_ST0

AGP_ST1

AGP_ST2

Y2

W3

W2

V3

V2

V1

U1

U3

T2

R2

P3

P2

N3

N2

M3

M2

L1

L2

K3

K2

J3

J2

J1

H3

F3

G2

F2

F1

E2

E1

D2

D1

E5

E6

T3

U2

G3

H2

R3

M1

L3

H1

P5

R6

T6

T5

P6

R5

C1

D3

N6

N5

C3

C2

D4

E4

F6

F5

G6

G5

L6

M6

L5

AGP_PAR

NB_EDID_CLK

NB_EDID_DAT

ENBKL#

R380

10K_0402_5%@

12

R89

2.2K_0402_5%

NB_PWRGD6,15,20

1 2

+3VS

2.2K_0402_5%

1 2

R91

2N7002_SOT23

ENBKL#

NB_EDID_CLK 15

NB_EDID_DAT 15

ENVDD 15

AGP_STP# 18

AGP_BUSY# 18

R374

10K_0402_5%

Q42

2

G

+3VALW

+3VS

R373

10K_0402_5%

1 2

13

1 2

13

D

S

2

G

D

S

Q43

2N7002_SOT23

ENBKL 28

+1.5VS

AGP8X_DET#

12

R101

0_0402_5%@

A A

5

12

R379

1K_0402_1%

AGPREF_8X

12

R377

1K_0402_1%

2

1

4

C513

0.1U_0402_10V6K

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

3

Compal S e cr e t Data

Deciphered Date

2

Title

ATI RL300MB-AGP, ALINK BUS

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10> 1 .0

Custom

星期三 五月

Date: Sheet

005

1

of

844, 04, 2

5

4

3

2

1

FBM-11-160808-700T_0603

+3VS_VDDR3

D D

KC FBM-L11-201209-221LMAT_0805

KC FBM-L11-201209-221LMAT_0805

L31

+1.8VS

C C

CLK_AGP_66M

12

R86

10_0402_5%@

1

C98

15P_0402_50V8J@

2

CLK_MEM

12

R85

B B

10_0402_5%@

1

C97

15P_0402_50V8J@

2

1 2

0.1U_0402_10V6K

L9

+1.8VS

+1.8VS

REFCLK1_NB16

1 2

KC FBM-L11-201209-221LMAT_0805

L33

KC FBM-L11-201209-221LMAT_0805

1

C433

2

0.1U_0402_10V6K

1 2

10U_0805_10V4Z

+3VS

1

1

C74

2

2

C482

0.1U_0402_10V6K

R63 715_0402_1%

R84

56_0402_5%

1 2

R76

10K_0402_5%

+2.5VS

L30

C76

0.1U_0402_10V6K

1

1

C497

2

2

NB_CRT_R15

NB_CRT_G15

NB_CRT_B15

CRT_HSYNC15

CRT_VSYNC15

1 2

CLK_NB_BCLK16

CLK_NB_BCLK#16

CLK_AGP_66M16

CLK_MEM16

12

12

1

C431

0.1U_0402_10V6K

2

+1.8VS_AVDDDI

+1.8VS_AVDDQ

PLLVDD_18

1

PLLVSS_18

C479

0.1U_0402_10V6K

2

CRT_HSYNC

CRT_VSYNC

CLK_NB_BCLK

CLK_NB_BCLK#

10K_0402_5%@

1 2

1 2

10K_0402_5%@

1 2

1 2

CLK_AGP_66M

CLK_MEM

+2.5VS_AVDD

1 2

R81

R83

R37110K_0402_5%@

R37510K_0402_5%@

R37210K_0402_5%@

1 2

1

C476

0.1U_0402_10V6K

2

U6D

G9

VDDR3

H9

VDDR3

A14

AVDD_25

B13

AVSSN

B14

AVDDDI_18

C13

AVSSDI

A15

AVDDQ

B15

AVSSQ

H11

PLLVDD_18

G11

PLLVSS

F14

RED

F15

GREEN

E14

BLUE

C8

DACHSYNC

D9

DACVSYNC

C14

RSET

A4

XTALIN

B4

XTALOUT

A5

HCLKIN

B5

HCLKIN#

B6

SYS_FBCLKOUT

A6

SYS_FBCLKOUT#

D8

ALINK_CLK

B2

AGPCLKOUT

B3

AGPCLKIN

A3

EXT_MEM_CLK

D7

USBCLK

B7

REF27

C5

OSC

CHS-216IGP9050A21_BGA718

R82

10K_0402_5%@

1 2

+3VS

L34

PART 4 OF 6

CRT

CLK. GEN.

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

LVDS

TXCLK_UN

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXCLK_LN

TXCLK_LP

LPVDD_18

LPVSS

LVDDR_18

LVDDR_18

LVSSR

LVSSR

C_R

Y_G

COMP_B

SVID

DACSCL

DACSDA

CPUSTOP#

SYSCLK

SYSCLK#

10K_0402_5%@

D12

E12

F11

F12

D13

D14

E13

F13

E10

D10

B9

C9

D11

E11

B10

C10

A12

A11

B12

C12

B11

C11

TV_CRMA

E15

TV_LUMA

C15

TV_COMPS

D15

3VDDCCL

D6

3VDDCDA

C6

D5

A8

B8

R74

1 2

+1.8VS_LPVDD

+1.8VS_LVDDR

R370 75_0402_1%

R73

@

10K_0402_5%

1 2

TXB0-_NB 15

TXB0+_NB 15

TXB1-_NB 15

TXB1+_NB 15

TXB2-_NB 15

TXB2+_NB 15

TXBCLK-_NB 15

TXBCLK+_NB 15

TXA0-_NB 15

TXA0+_NB 15

TXA1-_NB 15

TXA1+_NB 15

TXA2-_NB 15

TXA2+_NB 15

TXACLK-_NB 15

TXACLK+_NB 15

TV_CRMA 15

TV_LUMA 15

1 2

3VDDCCL 15

3VDDCDA 15

0.1U_0402_10V6K

1

C85

C82

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C79

C80

2

0.1U_0402_10V6K

Q12

@

2N7002_SOT23

1 2

R8 0_0402_5%@

KC FBM-L11-201209-221LMAT_0805

1 2

1

1

C81

2

2

10U_0805_10V4Z

KC FBM-L11-201209-221LMAT_0805

1

1

C75

2

2

10U_0805_10V4Z

1 2

R92 1K_0402_5%

13

D

2

NB_RST# 6,17

G

S

PM_STPCPU# 4,16,17,40

L10

1 2

L8

+1.8VS

+1.8VS

+3VS

A A

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

3

Compal S e cr e t Data

Deciphered Date

Title

ATI RL300MB-AGP, ALINK BUS

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10> 1 .0

Custom

星期三 五月

2

Date: Sheet

005

1

of

944, 04, 2

5

4

3

2

1

+1.5VS +2.5V

U6E

F10

VDD_CORE

F9

VDD_CORE

G12

VDD_CORE

H12

VDD_CORE

H13

VDD_CORE

M12

VDD_CORE

M13

VDD_CORE

M14

VDD_CORE

M17

VDD_CORE

D D

C C

B B

+1.05VS

+3VS

M18

VDD_CORE

M19

VDD_CORE

N12

VDD_CORE

N13

VDD_CORE

N14

VDD_CORE

N17

VDD_CORE

N18

VDD_CORE

N19

VDD_CORE

P12

VDD_CORE

P13

VDD_CORE

P14

VDD_CORE

P17

VDD_CORE

P18

VDD_CORE

P19

VDD_CORE

U12

VDD_CORE

U13

VDD_CORE

U14

VDD_CORE

U17

VDD_CORE

U18

VDD_CORE

U19

VDD_CORE

V12

VDD_CORE

V13

VDD_CORE

V14

VDD_CORE

V17

VDD_CORE

V18

VDD_CORE

V19

VDD_CORE

W12

VDD_CORE

W13

VDD_CORE

W14

VDD_CORE

W17

VDD_CORE

W18

VDD_CORE

W19

VDD_CORE

C16

VDDR2_CPU

D16

VDDR2_CPU

D17

VDDR2_CPU

E16

VDDR2_CPU

E17

VDDR2_CPU

F16

VDDR2_CPU

F17

VDDR2_CPU

G17

VDDR2_CPU

G21

VDDR2_CPU

G23

VDDR2_CPU

G24

VDDR2_CPU

H16

VDDR2_CPU

H17

VDDR2_CPU

H19

VDDR2_CPU

H21

VDDR2_CPU

H24

VDDR2_CPU

K23

VDDR2_CPU

K24

VDDR2_CPU

M23

VDDR2_CPU

P23

VDDR2_CPU

P24

VDDR2_CPU

T23

VDDR2_CPU

T24

VDDR2_CPU

U23

VDDR2_CPU

U24

VDDR2_CPU

W30

VDDR2_CPU

AA1

VDDL_ALINK

AA7

VDDL_ALINK

AA8

VDDL_ALINK

AC7

VDDL_ALINK

AC8

VDDL_ALINK

AD1

VDDL_ALINK

AD7

VDDL_ALINK

AD8

VDDL_ALINK

AK3

VDDL_ALINK

W8

VDDL_ALINK

CHS-216IGP9050A21_BGA718

CORE PWR

CPU I/F PWRALINK PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

PART 5 OF 6

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

MEM I/F PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

POWER

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

AGP PWR

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDD_18

VDD_18

VDD_18

VDD_18

AA23

AA27

AB30

AC10

AC12

AC13

AC15

AC17

AC19

AC21

AC23

AC24

AC25

AC27

AD10

AD12

AD13

AD15

AD17

AD19

AD21

AD23

AD24

AD25

AD27

AE10

AE14

AE15

AE19

AE20

AE30

AE9

AF27

AG11

AG12

AG17

AG18

AG23

AG24

AG26

AG8

AG9

AJ30

AK14

AK23

AK8

V23

W23

W24

W25

Y25

A2

G4

H5

H6

H7

J4

K8

L4

M7

M8

N4

P1

P7

P8

R4

T8

U4

U5

U6

E7

F7

G8

AC22

AC9

H10

H22

+1.5VS

+3VS

+1.8VS

U6F

PART 6 OF 6

A29

VSS

AB23

VSS

AB24

VSS

AB27

VSS

AB4

VSS

AB8

VSS

AC1

VSS

AC11

VSS

AC14

VSS

AC16

VSS

AC20

VSS

AC30

VSS

AD11

VSS

AD14

VSS

AD16

VSS

AD20

VSS

AD4

VSS

AE27

VSS

AF30

VSS

AF5

VSS

AG10

VSS

AG13

VSS

AG16

VSS

AG19

VSS

AG22

VSS

AG25

VSS

AG7

VSS

AH28

VSS

AH3

VSS

GND

AJ1

VSS

AK13

VSS

AK2

VSS

AK22

VSS

AK29

VSS

AK4

VSS

AK7

VSS

B1

VSS

B16

VSS

B30

VSS

C19

VSS

C23

VSS

C27

VSS

C4

VSS

D21

VSS

D25

VSS

E3

VSS

E8

VSS

E9

VSS

F27

VSS

F4

VSS

F8

VSS

G14

VSS

G15

VSS

G18

VSS

G20

VSS

H14

VSS

H15

VSS

H18

VSS

H20

VSS

H27

VSS

H4

VSS

H8

VSS

J7

VSS

CHS-216IGP9050A21_BGA718

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R23

R7

R8

T12

T13

T14

T15

T16

T17

T18

T19

T27

T4

U15

U16

U7

U8

V15

V16

V27

V4

V7

V8

W15

W16

W27

Y1

Y23

Y24

Y30

Y4

Y7

Y8

R19

R18

R17

R16

R15

R14

R13

R12

R1

P4

P27

P16

P15

N8

N24

N23

N16

N15

M4

M27

M16

M15

L8

L7

L25

L24

L23

K4

K27

J8

C59

22U_1206_10V4Z

C63

10U_0805_10V4Z

C123

10U_0805_10V4Z

+1.05VS

1

2

+1.8VS

1

2

0.1U_0402_10V6K

+3VS

1

2

0.1U_0402_10V6K

1

C447

C454

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C481

C491

2

1

C557

2

0.1U_0402_10V6K

1

C448

2

0.1U_0402_10V6K

1

C534

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C545

C552

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C451

2

1

2

0.1U_0402_10V6K

1

C532

2

1

1

C437

2

2

0.1U_0402_10V6K

1

C440

0.1U_0402_10V6K

2

1

C541

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C444

C456

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C525

2

2

1

2

0.1U_0402_10V6K

1

C489

2

0.1U_0402_10V6K

1

C445

0.1U_0402_10V6K

2

1

C487

2

+1.5VS

0.1U_0402_10V6K

1

1

C500

2

2

0.1U_0402_10V6K

1

1

C474

C527

2

2

1

C519

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C503

2

0.1U_0402_10V6K

C508

4

1

C515

2

0.1U_0402_10V6K

150U_D2_6.3VM

1

2

1

1

C509

2

2

0.1U_0402_10V6K

1

C464

2

0.1U_0402_10V6K

5

0.1U_0402_10V6K

1

C549

C501

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C494

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C485

2

1

C502

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

+

C505

C116

220U_D2_4VM

2

A A

C514

2

0.1U_0402_10V6K

+1.5VS

0.1U_0402_10V6K

1

C522

C517

2

0.1U_0402_10V6K

1

2

+2.5V

C124

0.1U_0402_10V6K

1

C477

C496

2

0.1U_0402_10V6K

1

1

+

C492

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C484

2

1

C555

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C526

2

0.1U_0402_10V6K

1

1

C547

C523

2

2

0.1U_0402_10V6K

1

1

C495

C467

2

2

0.1U_0402_10V6K

Compal S e cr e t Data

Deciphered Date

0.1U_0402_10V6K

1

1

C486

2

2

0.1U_0402_10V6K

0.01U_0402_25V4Z

1

2

0.01U_0402_25V4Z

C521

1

2

C493

2

0.1U_0402_10V6K

C465

1

C498

2

0.1U_0402_10V6K

1

1

C466

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C510

2

0.1U_0402_10V6K

C504

1

C470

2

0.1U_0402_10V6K

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

0.1U_0402_10V6K

1

1

C530

C524

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C506

C478

2

2

0.1U_0402_10V6K

2005/03/01 2006/03/01

0.1U_0402_10V6K

1

1

C472

2

2

1

C536

2

4.7U_0805_10V4Z

0.1U_0402_10V6K

1

C459

C537

2

0.1U_0402_10V6K

1

C540

2

4.7U_0805_10V4Z

Title

Size D ocu m ent N um b er R e v

Custom

Date: Sheet

1

1

C551

2

2

0.1U_0402_10V6K

ATI RL300MB-POWER

Sakhir 1 0 E<HBT10> 1 .0

星期三 五月

0.1U_0402_10V6K

1

C480

2

0.1U_0402_10V6K

005

C516

0.1U_0402_10V6K

1

C528

2

1

1

1

C462

2

2

0.1U_0402_10V6K

of

10 44, 04, 2

5

4

3

2

1

1 2

A_AD31

D D

C C

A_AD30

A_AD29

A_AD28

A_AD27

A_AD26

A_AD25

A_AD24

R388 4.7K_0402_5%@

1 2

R385 4.7K_0402_5%

R384

1 2

4.7K_0402_5%

1 2

R402 4.7K_0402_5%

1 2

R396 4.7K_0402_5%@

1 2

R390 4.7K_0402_5% @

1 2

R387 4.7K_0402_5%

1 2

R410 4.7K_0402_5%

1 2

R406 4.7K_0402_5%@

1 2

R405 4.7K_0402_5%

1 2

R399 4.7K_0402_5%@

1 2

R392 4.7K_0402_5%@

1 2

R389 4.7K_0402_5%

1 2

R408 4.7K_0402_5%@

1 2

R403 4.7K_0402_5%

+3VS

1 2

D45

2 1

CH751H-40_SC76

R38610K_0402_5%

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

BSEL0 5,16

A_AD[ 3 1 . . 3 0 ] : F SB CLK SPEED

DEFAULT: 01

00: 100 MHZ

01: 133 MHZ

10: 200MHZ

11:166 MHZ

A_AD2 9 : ST RAP CONFIGURATION

DEFAULT:1

0: REDU C EDE SET

1: FULL SET

A_AD28: SPREAD SPECTRUM ENABLE

DEFAULT:0

0: DISABLE

1: ENABLE

A_AD27: FrcShortReset#

DEFAULT: 1

0: TEST MODE

1: NORMAL MODE

A_AD26 : ENABLE IOQ

DEFAULT: 1

0: IOQ=1

1: IOQ=12

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 10

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

AD25=1 DESTOP CPU

AD25=0 MOBILE CPU

AD17--DON'T CARE

A_AD2 4 : M O B I L E C P U SELECT

DEFAULT: 1

0: BANIAS CPU

1: OTHER CPU

A_AD[0..31]8, 17

A_AD[0..31]

R415 4.7K_0402_5%

A_AD19

A_AD18

A_AD17

A_PAR8,17

A_PAR

1 2

1 2

R413 4.7K_0402_5%@

R397 4.7K_0402_5%@

1 2

1 2

R393 4.7K_0402_5%

R404 4.7K_0402_5%@

1 2

1 2

R398 4.7K_0402_5%

R407 4.7K_0402_5%

1 2

1 2

R401 4.7K_0402_5%@

+3VS

+3VS

+3VS

+3VS

A_AD19 : MEMORY IO VOLTAGE

DEFAULT: 1

0: 1.8V

1: 2.5V

A_AD1 8 : ENABLE PHASE CALIBRATION

DEFAULT: 0

0: DISABLE

1:ENABLE

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 0

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

PAR: EXTENDED DEBUG MODE

DEFAULT : 1

0: DEBUG MODE

1: NORMAL

1 2

A_AD23

B B

A_AD22

A_AD21

A_AD20

A A

5

R394 4.7K_0402_5%

1 2

R391 4.7K_0402_5%@

1 2

R414 4.7K_0402_5%

1 2

R411 4.7K_0402_5%@

1 2

R412 4.7K_0402_5%

1 2

R409 4.7K_0402_5%@

1 2

R400 4.7K_0402_5%@

1 2

R395 4.7K_0402_5%

+3VS

+3VS

+3VS

+3VS

4

A_AD2 3 : C L O CK BYPASS DISABLE

DEFAULT: 1

0: TEST MODE

1: NORMAL

A_AD22 : OSC PAD OUTPUT PCICLK

DEFAULT : 1

0: PCICLK OUT

1: OSC CLK OUT

A_AD2 1 : A UTO_CAL ENABLE

DEFAULT : 1

0: DISABLE

1: ENABLE

A_AD20 : INTERNAL CLK GEN ENABLE

DEFAULT : 0

0: DISABLE

1: ENABLE

Security Classification

Issued Date

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/01

3

Compal S e cr e t Data

Deciphered Date

Title

ATI RL3 00MB-SYSTEM STRAP

Size D ocu m ent N um b er R e v

Sakhir 1 0 E<HBT10> 1 .0

Custom

星期三 五月

2

Date: Sheet

005

1

of

11 44, 04, 2

A

1 1

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_SMA[0..13]

2 2

DDR_SCKE17,13

DDR_SCS#07,13

3 3

4 4

DDR_DQ[0..63] 7,13

DDR_DQS[0..7] 7,13

DDR_DM[0..7] 7,13

DDR_SMA[0..13] 7,13

10_0402_5%

10_0402_5%

R383

1 2

R378

1 2

B

DDR_DQ1

DDR_DQ4

DDR_DQS0

DDR_DQ3

DDR_DQ2

DDR_DQ13

DDR_DQ15

DDR_DQS1

DDR_DQ14

DDR_DQ10

DDR_CLK07

DDR_CLK0#7

DDR_DQ17

DDR_DQ21

DDR_DQS2

DDR_DQ23

DDR_DQ18

DDR_DQ29

DDR_DQ25

DDR_DQS3

DDR_DQ30

DDR_DQ31

DDR_CKE1DDR_SCKE1

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS07,13

DDR_SWE#7,13

DDR_SBS0

DDR_SWE#

DDR_CS#0DDR_SCS#0

DDR_SMA13

DDR_DQ33

DDR_DQ37

DDR_DQS4 DDR_DM4

DDR_DQ39

DDR_DQ35

DDR_DQ45

DDR_DQ41

DDR_DQS5

DDR_DQ43

DDR_DQ47

DDR_DQ49

DDR_DQ53

DDR_DQ55

DDR_DQ51

DDR_DQ56

DDR_DQ63

DDR_DQS7

DDR_DQ62

DDR_DQ58

SMDATA13,16,18

SMCLK13,16,18

C

+2.5V +2.5V +2.5V

JP9

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

+3VS

197

VDD_SPD

199

VDD_ID

AMP_1565917-1

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

VSS

DM8

VDD

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39