Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

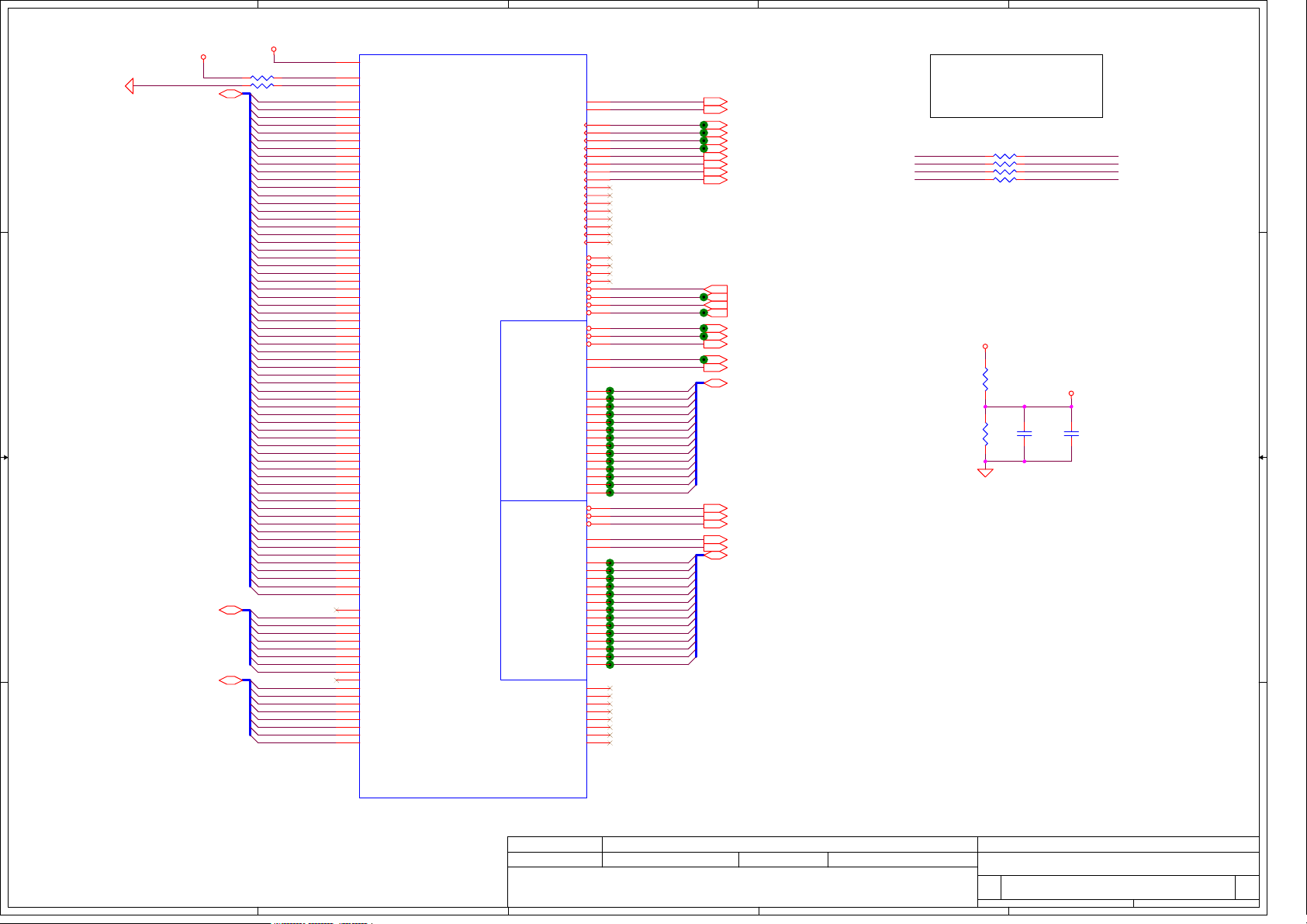

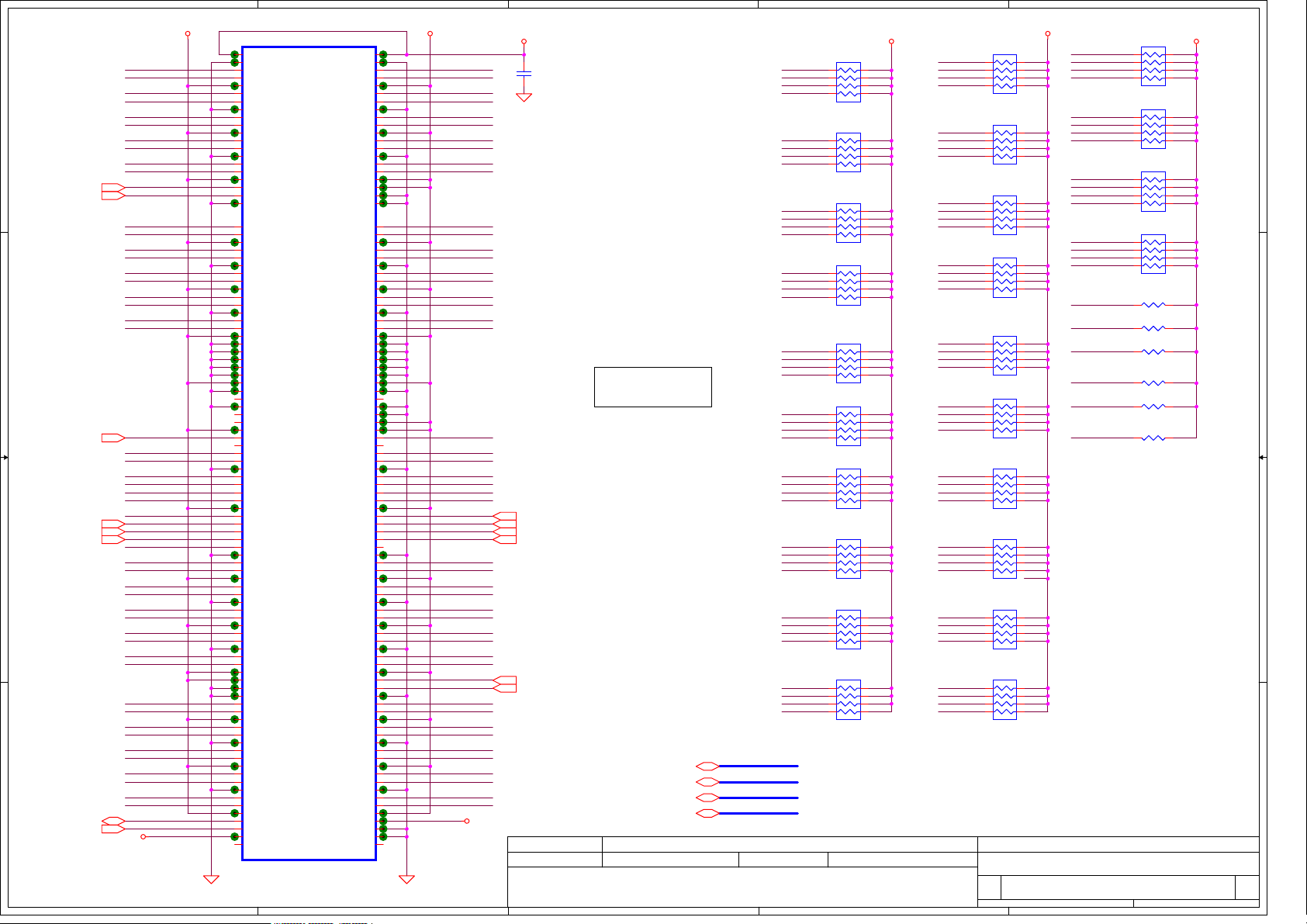

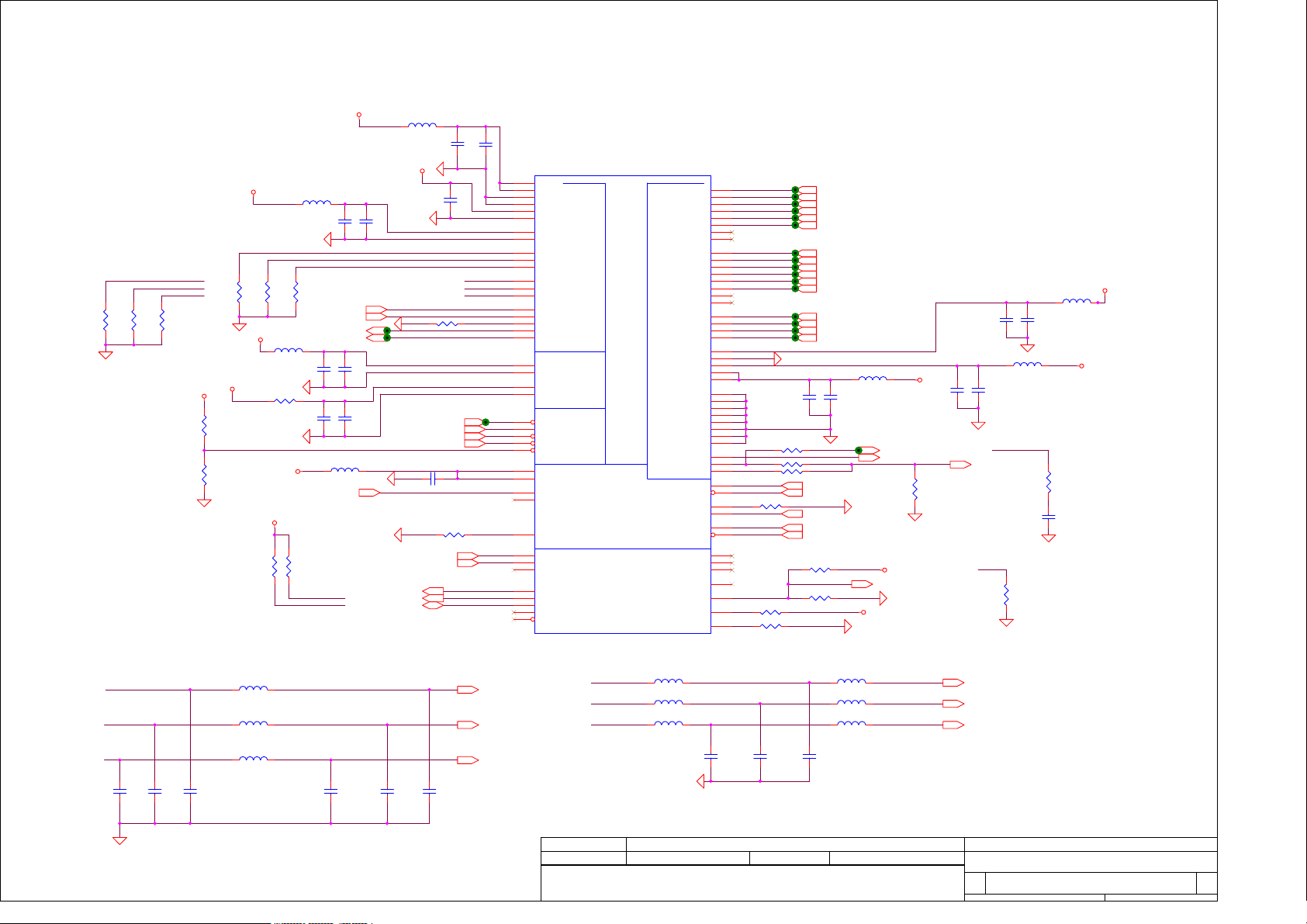

EPW00 Schematics Document

Mobile AMD Athlon 64 with

3 3

4 4

A

ATI RS480M+ATI SB400

2005-04-15

REV:0.5

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/03/11 2006/03/11

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet

Cover Sheet

LA-2541

E

of

158Friday, April 15, 2005

0.4

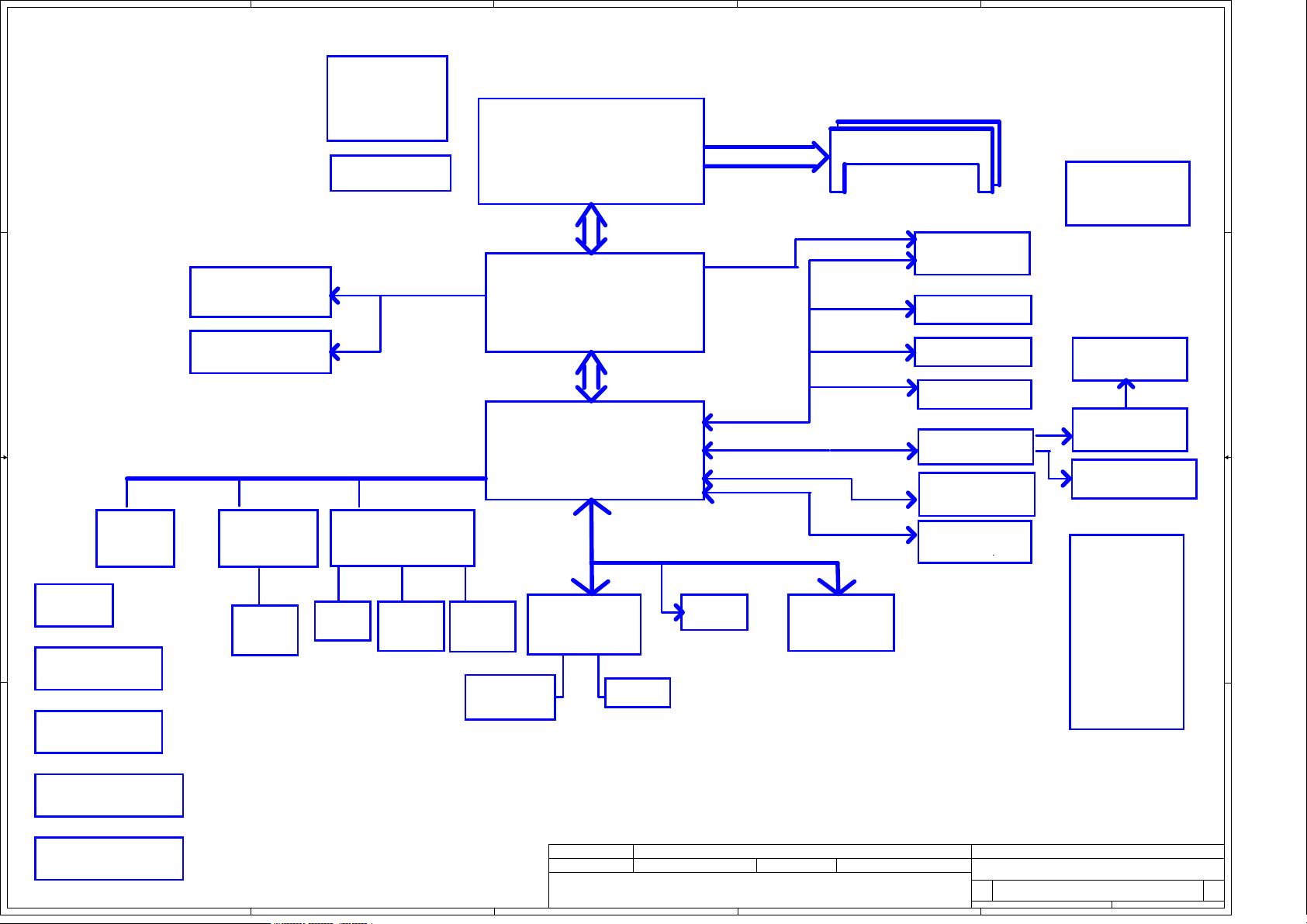

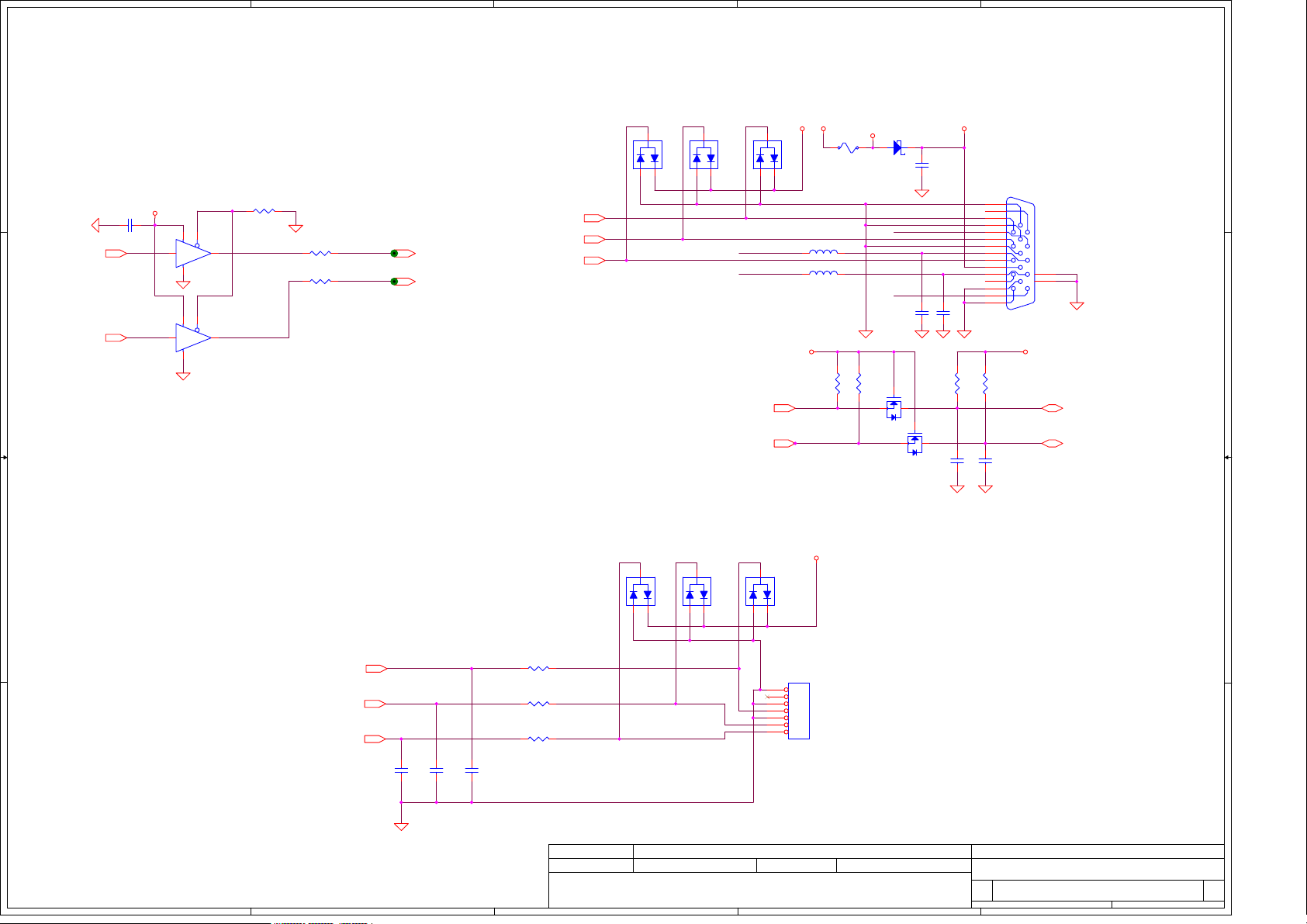

Page 2

A

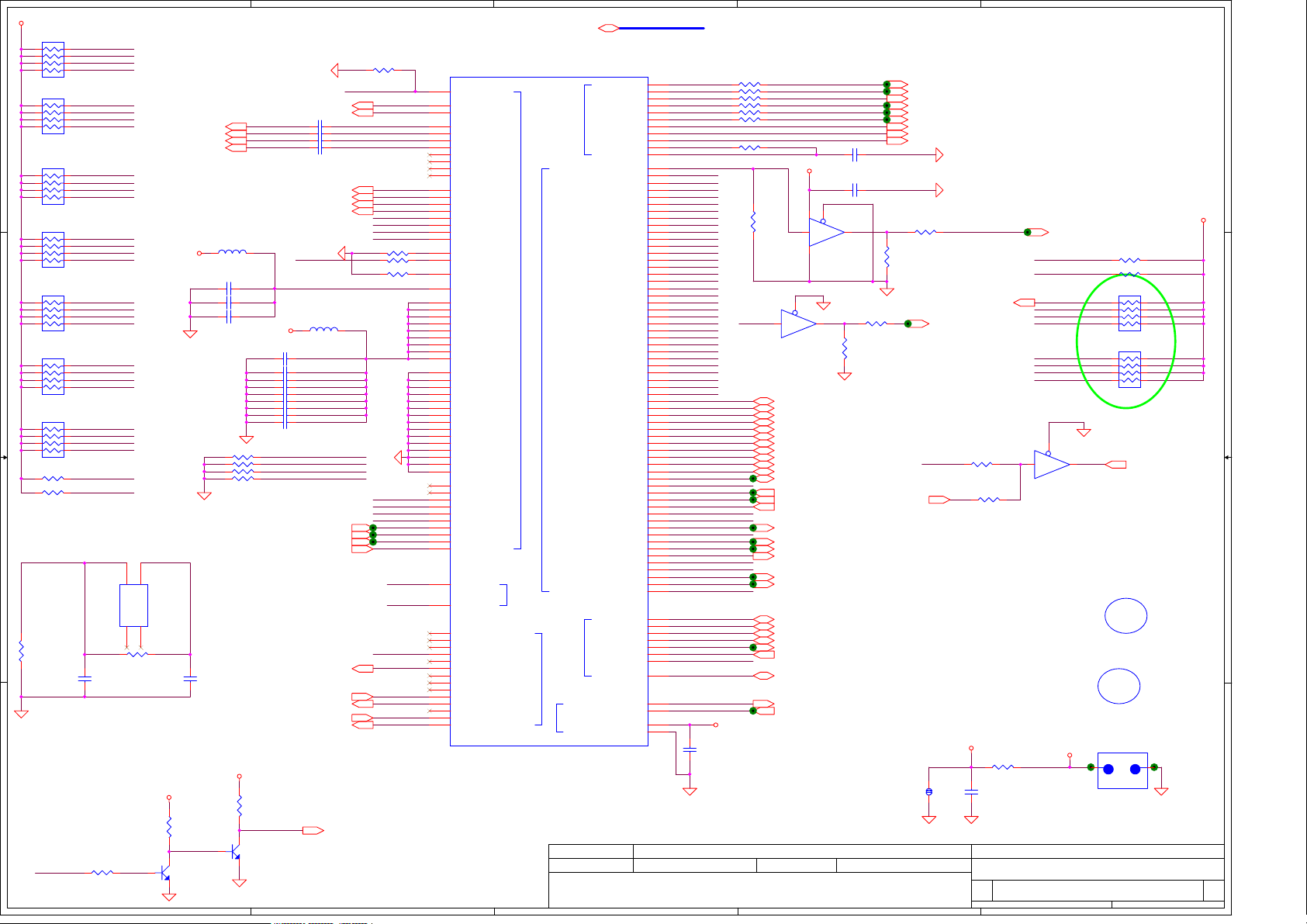

Compal confidential

File Name : LA-2541

B

C

D

E

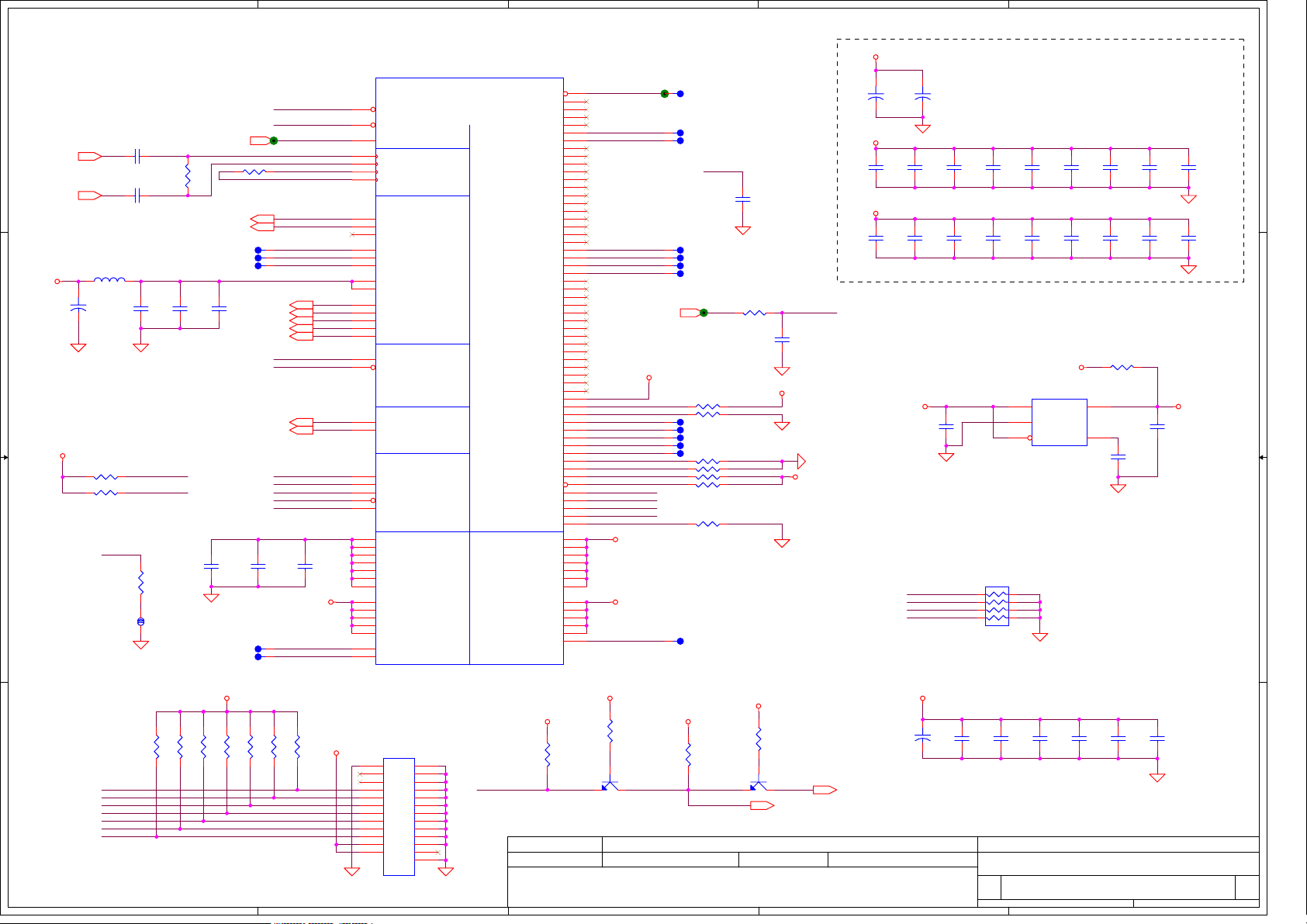

Thermal Sensor

1 1

ADM1032

page 4

Mobile

AMD Athlon 64

Fan Control

page 4

LVDS Panel

Interface

2 2

IDSEL:AD18

(PIRQH#,GNT#1,REQ#1)

CRT & TV OUT

Mini PCI

socket

3 3

page 28

BCM5788M

page 16

page 17

3.3V 33 MHz

IDSEL:AD17

(PIRQG#,GNT#3,REQ#3)

LAN

page 26

PCI BUS

IDSEL:AD20

(PIRQE#/F#,GNT#2,REQ#2)

CardBus & 1394

Controller

TI 7611

page 23,24

RTC CKT.

page 18

RJ45

CONN

page 27

Slot 0

page 24

Card

reader

page 23

1394

CONN

page 23

Power OK CKT.

page 40

Touch Pad

CONN

page 33

Power On/Off CKT.

page 38

754-pin

page 4, 5, 6, 7

HT 16x16 1000MHZ

ATI-RS480M

705 BGA

page 11, 12, 13, 14

A-Link Express

2 x PCIE

ATI-SB400

564 BGA

LPC BUS

EC SMSC

LPC47N250

page 37

Int.KBD

page 38

Memory BUS(DDR)

Single Channel

1 x PCIE

USB2.0

AC-LINK

BIOS

page 38

ATA-100

ATA-100

Primary IDE

Secondary IDE

DDR-SO-DIMM X2DDR1 -333

BANK 0, 1, 2, 3

SUPER I/O

LPC47N217

page 36

page 8,9,10

New Card

Connector

USB conn X3

Finger print

BT Conn

Audio CKT

HDD

Connector

CDROM

Connector

page 25

page 33

page 33

page 33

page 29

page 34

page 34

Clock Generator

ICS 951418

page 15

RJ11 CONN

page 30,39

MODEM

page 30

AMP & Audio Jack

page 31page 18,19,20,21

SPR Conn.

*RJ11 Conn

*RJ45 Conn

*Line IN Jack

*Line OUT Jack

*PS/2x2

*Parallel Port

*Serial Port

*CRT

*TV-OUT

*PCI Express

*USB x2

page 39

DC/DC Int erface CKT.

4 4

Power Circuit DC/DC

page 41

page 40~47

A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/03/01 2006/03/11

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Block Diagram

LA-2541

E

0.4

of

258Friday, April 15, 2005

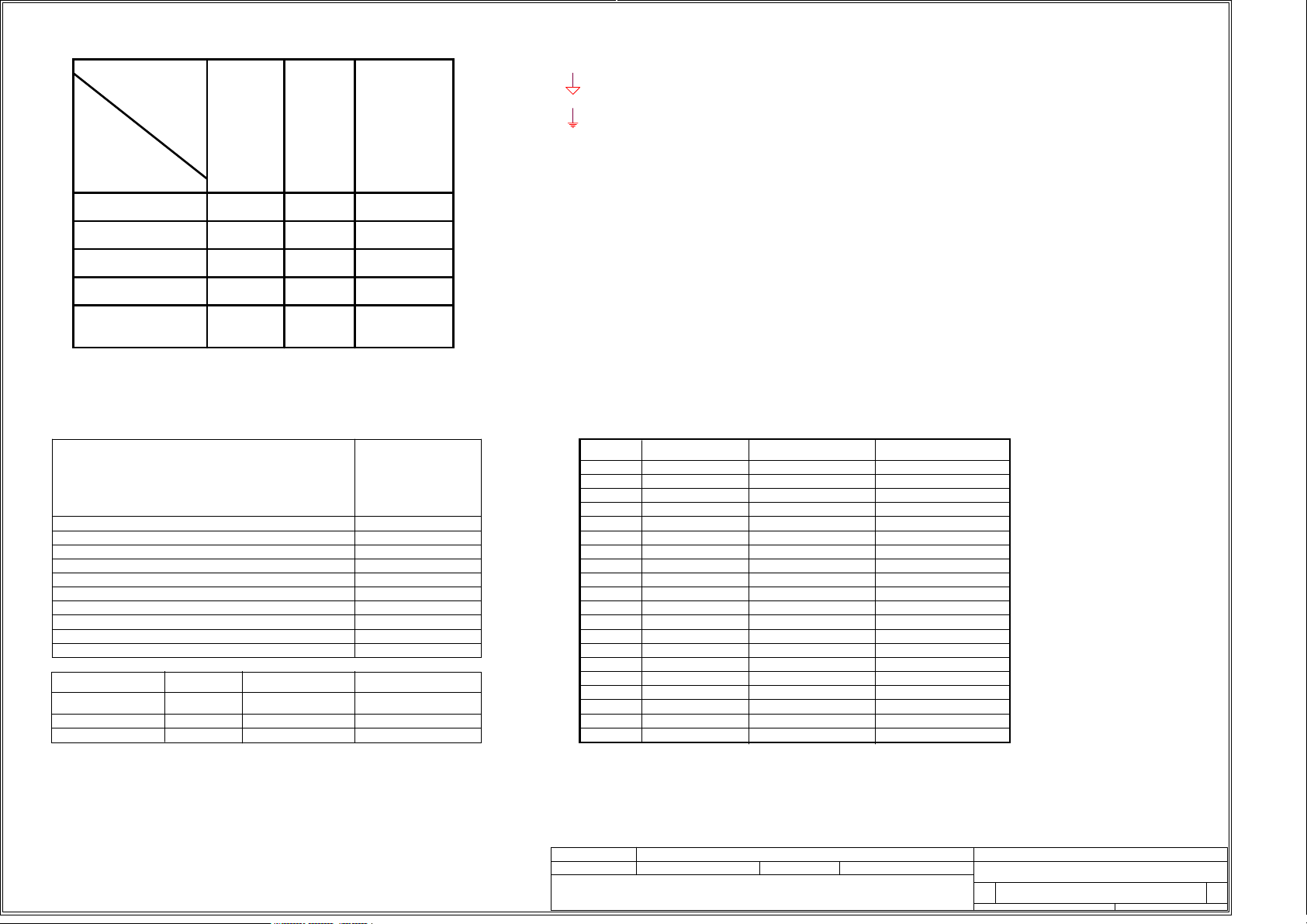

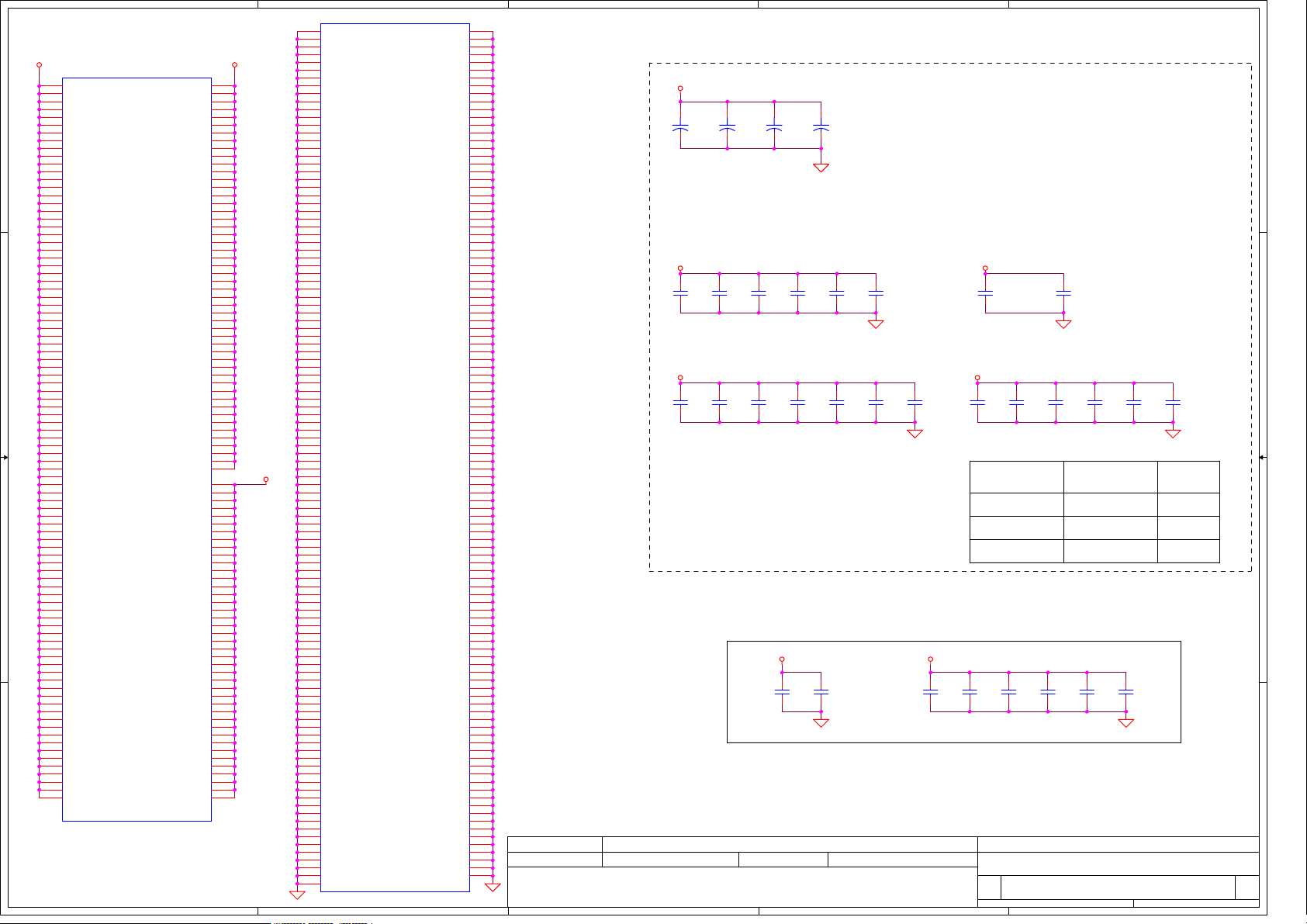

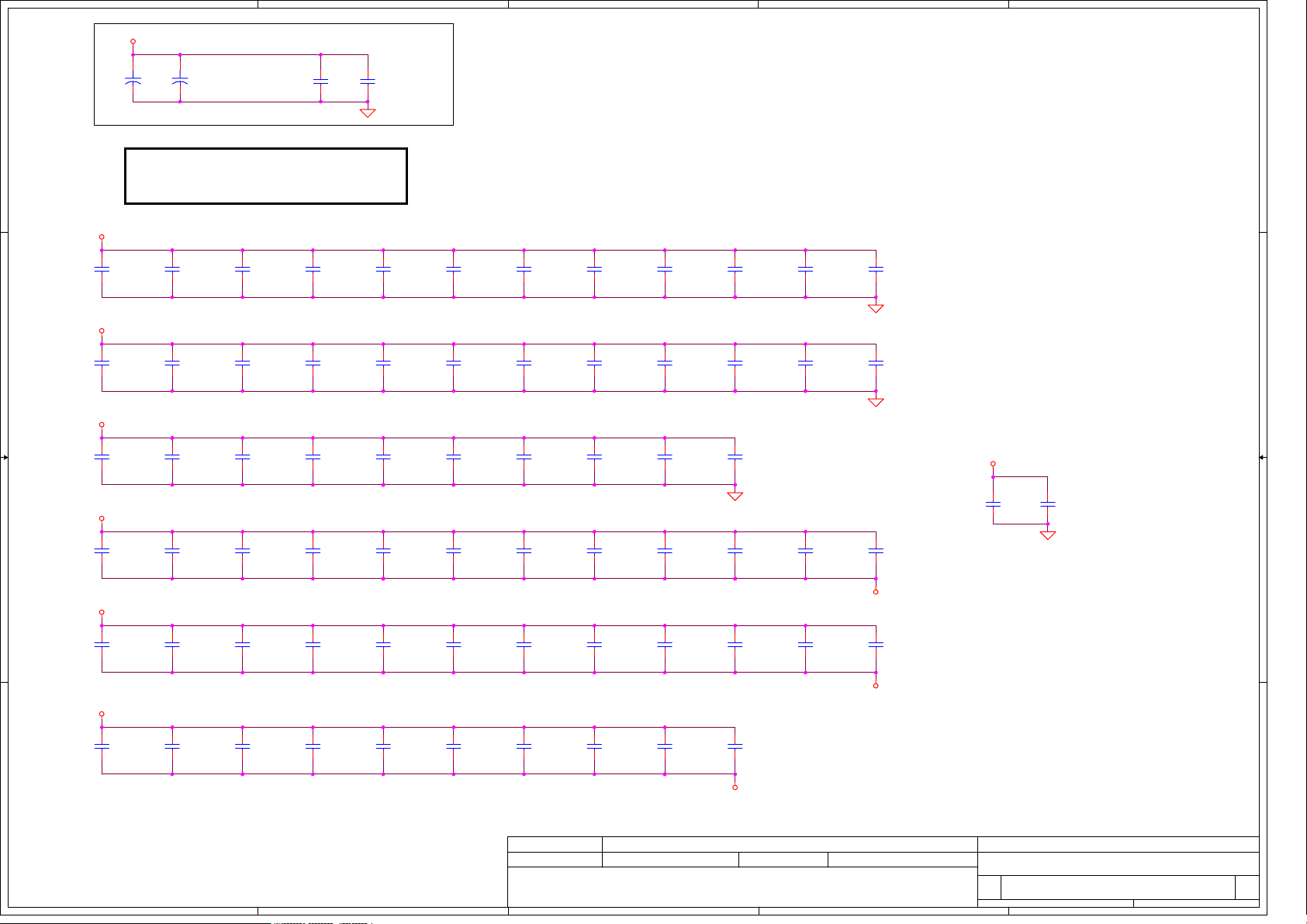

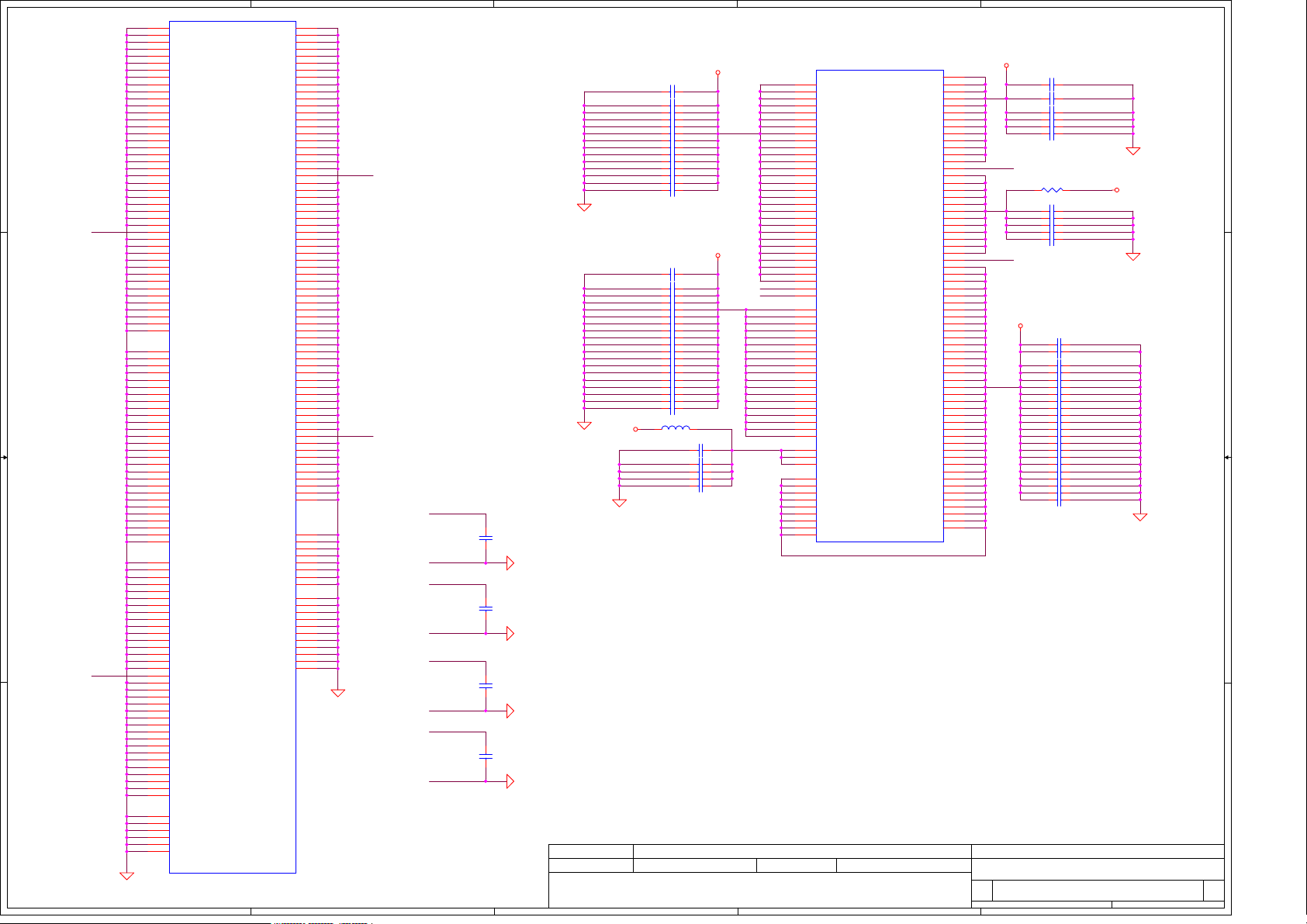

Page 3

A

Voltage Rails

power

plane

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

O MEANS ON

X MEANS OFF

+5VALW

+3VALW

+1.8VALW

O

O

O

O

Only +3VL ON

+5VS

+3VS

+5V

+2.5V

+1.25V

+2.5VS

+1.8VS

+1.5VS

+2.5VDDA

+CPU_CORE

+1.2V_HT

+RS480_Core

OO

OO

O

X

XX

XX

Symbol note:

:means digital ground.

:means analog ground.

:means reserved(un-mount).@

4401@

5788@

7611@

4510@

:means populate for BCM4401 only.

:means populate for BCM5788M only.

:means populate for PCI7611 only.

:means populate for PCI4510 only.

PCI Devices

1 1

INTERNAL

PIRQ

A

B

B

D

D

D

A

A

E, F

H

GAD18

EXTERNAL

CARD BUS & 1394

LAN

Mini-PCI

DEVICE

SMBUS

IDE

LPC I/F

PCI to PCI

AC97 AUDIO

AC97 MODEM

OHCI#1 USB

OHCI#1 USB

EHCI USB

SATA#1

SATA#2

IDSEL #

AD20

AD17

REQ/GNT #

2

3

1

Jump

PJ1

PJ3

PJ4

PJ5

PJ6

PJ7

PJ8

PJ9

PJ11

PJ12

PJ14

Normal operation KBC Internal ROM flash

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

J1

J2

J3

J4

Short Pad

Short Pad

No Short Pad

No Short Pad No Short Pad

J5

J6

J7

J8

J9

No Short Pad Short Pad

No Short Pad Short Pad

Short Pad No Short Pad

No Short Pad Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

Short Pad

No Short Pad

No Short Pad

No Short Pad

Short PadNo Short Pad

Comment

+3VL

+3VALW

+1.8VALW

+5VALW

+1.5VS

+2.5V

+1.25V

+1.2V_HT

+RS480_Core

For ATE

For ATE

Clear CMOS

For ATE

For ATE

For ATE

For ATE

For ATE

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2005/03/01 2006/03/11

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

Date: Sheet

Notes List

LA-2541

of

358Friday, Ap ril 15, 2005

0.4

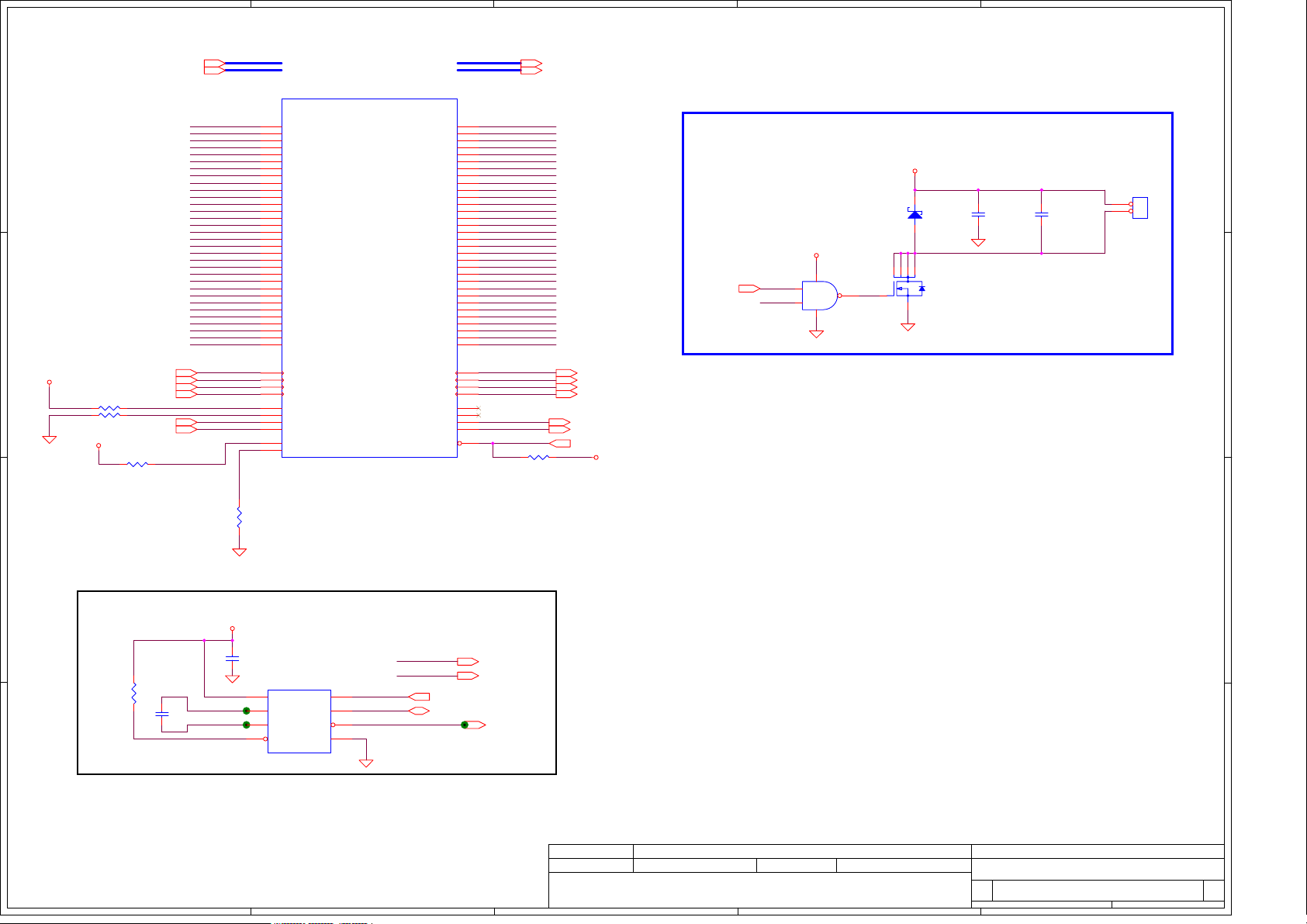

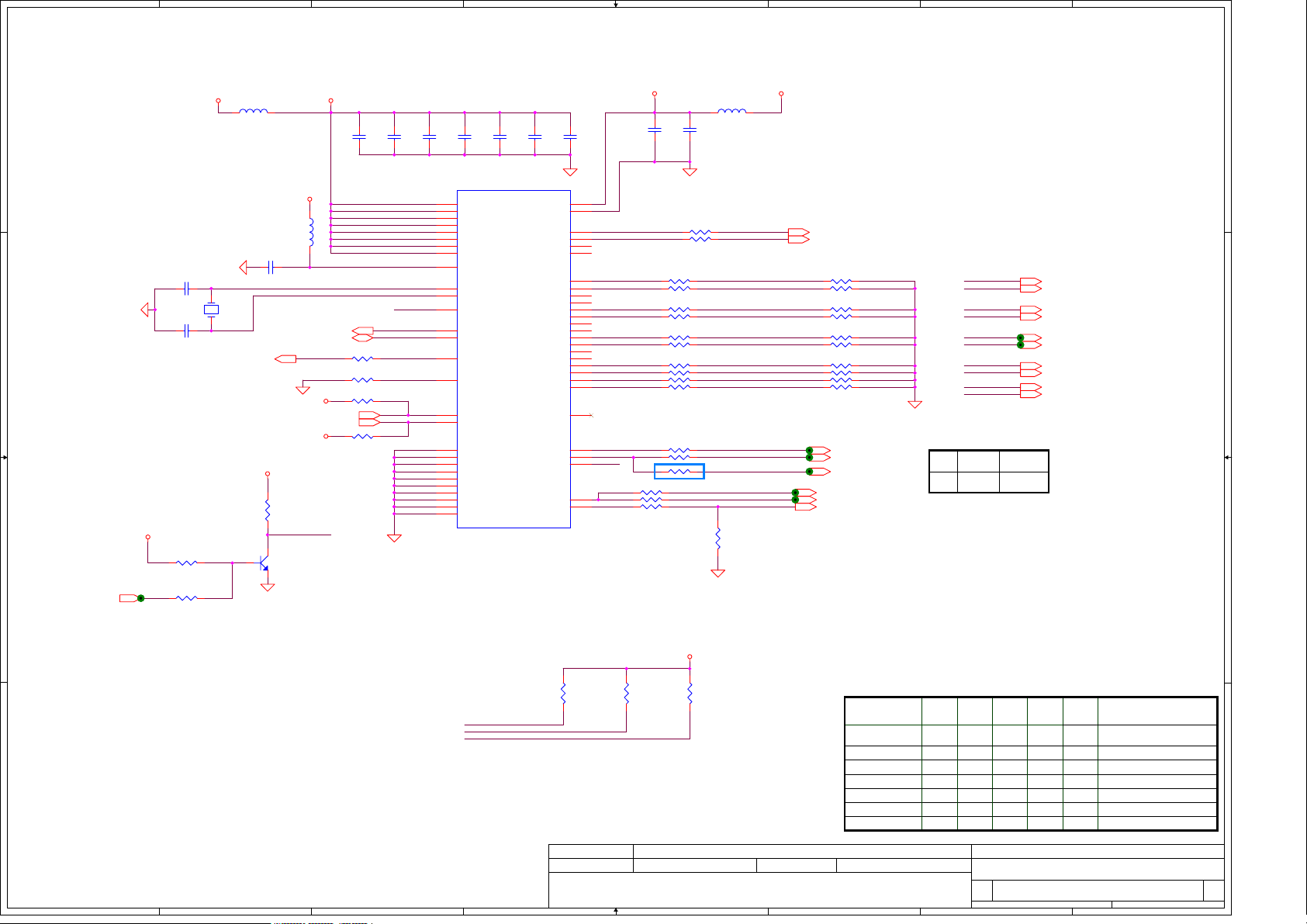

Page 4

A

B

C

D

E

H_CADIP15

H_CADIN15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIN9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP1

H_CTLIN1

H_CTLIP0

H_CTLIN0

LVREF1

44.2_0603_1%

H_CADIP[0..15]

H_CADIN[0..15]

LVREF0

12

R350

U10A

T25

L0_CADIN_H15

R25

L0_CADIN_L15

U27

L0_CADIN_H14

U26

L0_CADIN_L14

V25

L0_CADIN_H13

U25

L0_CADIN_L13

W27

L0_CADIN_H12

W26

L0_CADIN_L12

AA27

L0_CADIN_H11

AA26

L0_CADIN_L11

AB25

L0_CADIN_H10

AA25

L0_CADIN_L10

AC27

L0_CADIN_H9

AC26

L0_CADIN_L9

AD25

L0_CADIN_H8

AC25

L0_CADIN_L8

T27

L0_CADIN_H7

T28

L0_CADIN_L7

V29

L0_CADIN_H6

U29

L0_CADIN_L6

V27

L0_CADIN_H5

V28

L0_CADIN_L5

Y29

L0_CADIN_H4

W29

L0_CADIN_L4

AB29

L0_CADIN_H3

AA29

L0_CADIN_L3

AB27

L0_CADIN_H2

AB28

L0_CADIN_L2

AD29

L0_CADIN_H1

AC29

L0_CADIN_L1

AD27

L0_CADIN_H0

AD28

L0_CADIN_L0

Y25

L0_CLKIN_H1

W25

L0_CLKIN_L1

Y27

L0_CLKIN_H0

Y28

L0_CLKIN_L0

R27

L0_CTLIN_H1

R26

L0_CTLIN_L1

T29

L0_CTLIN_H0

R29

L0_CTLIN_L0

AF27

L0_REF1

AE26

L0_REF0

FOX_PZ75403-2941-42

Claw Hammer-DTR

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

HTT Interface

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

LDTSTOP_L

H_CADIP[0..15]<11>

4 4

3 3

+1.2V_HT

R353 49.9_0402_1%

R354 49.9_0402_1%

+1.2V_HT

1 2

1 2

H_CLKIP1<11>

H_CLKIN1<11>

H_CLKIP0<11>

H_CLKIN0<11>

H_CTLIP0<11>

H_CTLIN0<11>

R347 44.2_0603_1%

12

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP15

N26

H_CADON15

N27

H_CADOP14

L25

H_CADON14

M25

H_CADOP13

L26

H_CADON13

L27

H_CADOP12

J25

H_CADON12

K25

H_CADOP11

G25

H_CADON11

H25

H_CADOP10

G26

H_CADON10

G27

H_CADOP9

E25

H_CADON9

F25

H_CADOP8

E26

H_CADON8

E27

H_CADOP7

N29

H_CADON7

P29

H_CADOP6

M28

H_CADON6

M27

H_CADOP5

L29

H_CADON5

M29

H_CADOP4

K28

H_CADON4

K27

H_CADOP3

H28

H_CADON3

H27

H_CADOP2

G29

H_CADON2

H29

H_CADOP1

F28

H_CADON1

F27

H_CADOP0

E29

H_CADON0

F29

H_CLKOP1

J26

H_CLKON1

J27

H_CLKOP0

J29

H_CLKON0

K29

N25

P25

H_CTLOP0

P28

H_CTLON0

P27

LDTSTOP#

AJ27

H_CADOP[0..15] <11>

H_CADON[0..15] <11>H_CADIN[0..15]<11>

H_CLKOP1 <11>

H_CLKON1 <11>

H_CLKOP0 <11>

H_CLKON0 <11>

H_CTLOP0 <11>

H_CTLON0 <11>

1 2

R336 1.2K_0402_5%

LDTSTOP# <13,18>

+2.5VS

PWM Fan Control circuit

+3VS

5

U28

1

FAN_PWM<38>

THERM#

INB

2

INA

P

4

O

G

TC7SH00FU_SSOP5

3

+5VS

JP7

1

2

ACES_85205-0200

FAN

1

C400

0.1U_0402_16V4Z

2

1

D21

RB751V_SOD323

2 1

6

2

1

D

Q28

G

3

SI3456DV-T1_TSOP6

S

4 5

C399

4.7U_0805_10V4Z

2

2 2

W=15mil

12

R124

10K_0402_5%

1 1

C202

2200P_0402_50V7K

A

+3VS

2

1

THERMDA_CPU

THERMDC_CPU

THERM#

C199

0.1U_0402_16V4Z

U11

1

VDD

2

D+

3

DTHERM#4GND

ADM1032AR_SOP8

SCLK

SDATA

ALERT#

8

7

6

5

Thermal Sensor

ADM1032

THERMDA_CPU

THERMDC_CPU

SB_SCLK <8,9,15,19>

THERM_SCI#

B

SB_SDAT <8,9,15,19>

THERMDA_CPU <6>

THERMDC_CPU <6>

THERM_SCI# <19>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/03/01 2006/03/11

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet

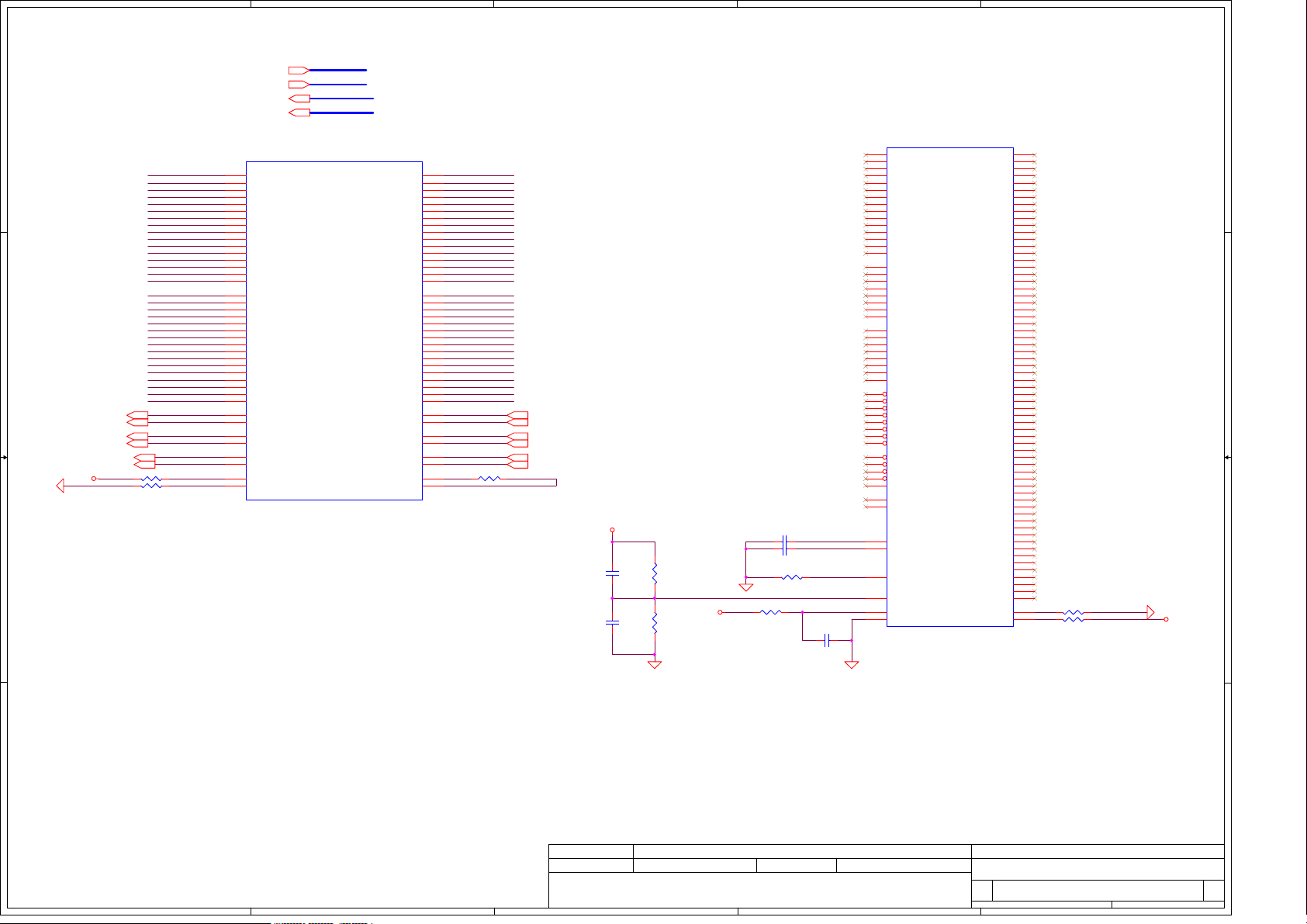

Claw Harmmer CPU (Host Bus)

LA-2541

458Friday, April 15, 2005

E

of

0.4

Page 5

A

B

C

D

E

+2.5V

DDR_SDQ[0..63]<8>

1 1

2 2

3 3

DDR_SDM[0..7]<8>

DDR_SDQS[0..7]<8>

+1.25VREF_CPU

50 mil width

R37034.8_0603_1%

12

R36934.8_0603_1%

12

DDR_SDQ63

DDR_SDQ62

DDR_SDQ61

DDR_SDQ60

DDR_SDQ59

DDR_SDQ58

DDR_SDQ57

DDR_SDQ56

DDR_SDQ55

DDR_SDQ54

DDR_SDQ53

DDR_SDQ52

DDR_SDQ51

DDR_SDQ50

DDR_SDQ49

DDR_SDQ48

DDR_SDQ47

DDR_SDQ46

DDR_SDQ45

DDR_SDQ44

DDR_SDQ43

DDR_SDQ42

DDR_SDQ41

DDR_SDQ40

DDR_SDQ39

DDR_SDQ38

DDR_SDQ37

DDR_SDQ36

DDR_SDQ35

DDR_SDQ34

DDR_SDQ33

DDR_SDQ32

DDR_SDQ31

DDR_SDQ30

DDR_SDQ29

DDR_SDQ28

DDR_SDQ27

DDR_SDQ26

DDR_SDQ25

DDR_SDQ24

DDR_SDQ23

DDR_SDQ22

DDR_SDQ21

DDR_SDQ20

DDR_SDQ19

DDR_SDQ18

DDR_SDQ17

DDR_SDQ16

DDR_SDQ15

DDR_SDQ14

DDR_SDQ13

DDR_SDQ12

DDR_SDQ11

DDR_SDQ10

DDR_SDQ9

DDR_SDQ8

DDR_SDQ7

DDR_SDQ6

DDR_SDQ5

DDR_SDQ4

DDR_SDQ3

DDR_SDQ2

DDR_SDQ1

DDR_SDQ0

DDR_SDM7

DDR_SDM6

DDR_SDM5

DDR_SDM4

DDR_SDM3

DDR_SDM2

DDR_SDM1

DDR_SDM0

DDR_SDQS7

DDR_SDQS6

DDR_SDQS5

DDR_SDQS4

DDR_SDQS3

DDR_SDQS2

DDR_SDQS1

DDR_SDQS0

MEMZN

MEMZP

AG12

D14

C14

C13

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AE2

AF1

AH3

AH9

AG5

AH5

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AA1

AG1

AH7

AH13

AB1

AJ13

A16

B15

A12

B11

A17

A15

A11

A10

AJ4

AJ3

AJ5

AJ6

AJ7

AJ9

A13

A14

AJ2

AJ8

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

U10B

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

Claw Hammer-DTR

DDR Memory

A CHANGEL ADDRESSB CHANGEL ADDRESS

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

DDR_CKE0

DDR_CKE1

DDR_CLK7

DDR_CLK7#

DDR_CLK6

DDR_CLK6#

DDR_CLK5

DDR_CLK5#

DDR_CLK4

DDR_CLK4#

DDR_SCS#3

DDR_SCS#2

DDR_SCS#1

DDR_SCS#0

DDR_SMAA13

DDR_SMAA12

DDR_SMAA11

DDR_SMAA10

DDR_SMAA9

DDR_SMAA8

DDR_SMAA7

DDR_SMAA6

DDR_SMAA5

DDR_SMAA4

DDR_SMAA3

DDR_SMAA2

DDR_SMAA1

DDR_SMAA0

DDR_SMAB13

DDR_SMAB12

DDR_SMAB11

DDR_SMAB10

DDR_SMAB9

DDR_SMAB8

DDR_SMAB7

DDR_SMAB6

DDR_SMAB5

DDR_SMAB4

DDR_SMAB3

DDR_SMAB2

DDR_SMAB1

DDR_SMAB0

DDR_CKE0 <8>

DDR_CKE1 <9>

DDR_CLK7 <8>

DDR_CLK7# <8>

DDR_CLK6 <9>

DDR_CLK6# <9>

DDR_CLK5 <8>

DDR_CLK5# <8>

DDR_CLK4 <9>

DDR_CLK4# <9>

DDR_SCS#3 <9>

DDR_SCS#2 <9>

DDR_SCS#1 <8>

DDR_SCS#0 <8>

DDR_SRASA# <8>

DDR_SCASA# <8>

DDR_SWEA# <8>

DDR_SBSA1 <8>

DDR_SBSA0 <8>

DDR_SMAA[0..13] <8>

DDR_SRASB# <9>

DDR_SCASB# <9>

DDR_SWEB# <9>

DDR_SBSB1 <9>

DDR_SBSB0 <9>

DDR_SMAB[0..13] <9>

DDR_CLK5/5# & DDR_CLK7/7#

route to nearest DIMM

DDR_CLK4/4# & DDR_CLK6/6#

route to farthest DIMM

R130 120_0402_5%

DDR_CLK6

DDR_CLK5

DDR_CLK4

1 2

R129 120_0402_5%

1 2

R92 120_0402_5%

1 2

R83 120_0402_5%

1 2

within 1.00"

+2.5V

12

R320

1K_0402_1%

12

1

C418

R326

1K_0402_1%

2

0.1U_0402_16V4Z

DDR_CLK7#DDR_CLK7

DDR_CLK6#

DDR_CLK5#

DDR_CLK4#

+1.25VREF_CPU

1

C413

1000P_0402_50V7K

2

4 4

A

FOX_PZ75403-2941-42

B

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/11

C

Compal Secret Data

Deciphered Date

D

Title

Size Document Number Rev

Custom

Date: Sheet

Claw Harmmer (Memory Bus)

LA-2541

E

558Friday, April 15 , 2005

of

0.4

Page 6

A

H_THERMTRIP_S#

1 1

CPUCLK0_H<15>

CPUCLK0_L<15>

Place 169 Ohm within 0.5" from CPU

Route as DIF 5/5/5/20

+2.5VDDA

2 2

+2.5VS

3 3

@

4 4

C414

3900P_0402_50V7K

169_0402_1%

C415 3900P_0402_50V7K

L8

LQG21F4R7N00_0805

1 2

1

+

C84

100U_D2_10VM

2

4.7U_0805_6.3V6K

H_RST#

R319

JOPEN

DBREQ#

DBRDY

TCK

TMS

TDI

TRST#

TDO

H_RST#

H_PWRGD

J3

R445

560_0402_5%

A

1 2

R157 680_0402_5%

1 2

R324 680_0402_5%

100_0402_5%

12

R335

1

C92

2

0.22U_0603_10V7K

0.22U_0603_10V7K

H_PWRGD<18>

R334 80.6_0402_1%

Place within 0.5" from CPU

Route as 80 Ohm DIFF impedence 8/5/20

CPU_COREFB<49>

CPU_COREFB#<49>

+VDDA

1

C88

2

THERMDA_CPU<4>

THERMDC_CPU<4>

1

C535

12

12

Route as DIFF p air 10/5/10

3300P_0402_50V7K

1

C90

2

2

1 2

+2.5VS

560_0402_5%

R444

12

12

12

12

R441

@

R443

560_0402_5%

560_0402_5%

@

@

T4PAD

T5PAD

T3PAD

0.22U_0603_10V7K

T18PAD

T1PAD

560_0402_5%

R438

@

H_RST_CPU#

H_PWRGD

CLKIN

CLKIN#

FBCLKOUT

12

FBCLKOUT#

CPU_COREFB

CPU_COREFB#

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

50 mils width

VID4<49>

VID3<49>

VID2<49>

VID1<49>

VID0<49>

1

C534

2

12

@

R436

560_0402_5%

12

VID4

VID3

VID2

VID1

VID0

DBRDY

DBREQ#

TDO

TMS

TCK

TRST# SCANCLK2

TDI

4.7U_0805_6.3V6K

1

C532

2

+1.25V +1.25V

TP_K8_A28

TP_K8_AJ28

R435

12

560_0402_5%

+2.5VS

@

@

B

U10C

A20

THERMTRIP_L

AF20

RESET_L

AE18

PWROK

AJ21

CLKIN_H

AH21

CLKIN_L

AH19

FBCLKOUT_H

AJ19

FBCLKOUT_L

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AH25

VDDA1

AJ25

VDDA2

AG13

VID4

AF14

VID3

AG14

VID2

AF15

VID1

AE15

VID0

AH17

DBRDY

AE19

DBREQ_L

A26

THERMDA

A27

THERMDC

A22

TDO

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

D29

VLDT0_A

D27

VLDT0_A

D25

VLDT0_A

C28

VLDT0_A

C26

VLDT0_A

B29

VLDT0_A

B27

VLDT0_A

D17

VTT_A

A18

VTT_A

B17

VTT_A

C17

VTT_A

C16

VTT_A

A28

KEY1

AJ28

KEY0

FOX_PZ75403-2941-42

JP29

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

@

B

Claw Hammer-DTR

Miscellaneous

Clock

Debug

JTAG

H_THERMTRIP_S# H_THERMTRIP#

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_SENSE

+2.5VS

Issued Date

AG10

NC

E14

NC

D12

NC

E13

NC

C12

NC

D22

NC

C22

NC

B13

NC

B7

NC

C3

NC

K1

NC

R2

NC

AA3

NC

F3

NC

C23

NC

AG7

NC

AE22

NC

C24

NC

A25

NC

C9

NC

AE23

NC

AF23

NC

AF22

NC

AF21

NC

C1

NC

J3

NC

R3

NC

AA2

NC

D3

NC

AG2

NC

B18

NC

AH1

NC

AE21

NC

C20

NC

AG4

NC

C6

NC

AG6

NC

AE9

NC

AG9

NC

AF18

NC

AJ23

NC

AH23

NC

AE24

NC

AF24

NC

C15

NC

AG18

NC

AH18

NC

AG17

NC

AJ18

NC

C18

NC

A19

NC

D20

NC

C21

NC

D18

NC

C19

NC

B19

NC

AH29

AH27

AG28

AG26

AF29

AE28

AF25

AG15

AF16

AG16

AH16

AJ17

AE13

12

R131

680_0402_5%

TP_M_RESET#

TP_K8_D22

TP_K8_C22

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

BPSCLK

BPSCLK#

TP_K8_AE24

TP_K8_AF24

TP_K8_C15

TP_CPU_BP3

TP_CPU_BP2

BP1

BP0

SINCHN

BRN#

SCANCLK1

SCANEN

SCANSHENB

SCANSHENA

+1.2V_HT

VTT_SENSE

+2.5VS

12

R132

1K_0402_5%

2

Q9

3 1

MMBT3904_SOT23

C

+1.25V

T2 PAD

220U_D2_2.5VM

T17 PAD

T16 PAD

H_PWRGD

1

C416

470P_0402_50V7K@

T13 PAD

T11 PAD

T10 PAD

T9 PAD

H_RST#<18>

+2.5V

R323 820_0402_5%

1 2

R322 820_0402_5%

1 2

T12 PAD

T14 PAD

T15 PAD

T8 PAD

T7 PAD

R328 680_0402_5%

1 2

R333 680_0402_5%

1 2

R128 680_0402_5%

1 2

R127 680_0402_5%

1 2

R368 680_0402_5%

1 2

T6 PAD

+3VALW

12

2005/03/01 2006/03/11

C

2

R325

1 2

0_0402_5%

+3VALW

12

R126

10K_0402_5%

2

3 1

Compal Secret Data

Deciphered Date

H_RST_CPU#

1

C417

0.001U_0402_50V7M@

2

+2.5V

+2.5VS

R125

1K_0402_5%@

Q8

MMBT3904_SOT23@

H_THERMTRIP# <19>

+1.25V

4.7U_0805_6.3V6K

+1.25V

0.22U_0603_10V7K

MAINPWON <44,45,50>

D

E

Near Power Supply

1

1

2

1

2

1

2

+

+

C222

C201

C207

1U_0603_10V4Z@

D

C85

220U_D2_2.5VM

2

4.7U_0805_6.3V6K

1

C226

2

0.22U_0603_10V7K

1

C223

2

+3VS +2.5VDDA

C407

4.7U_0805_6.3V6K

1

C230

2

4.7U_0805_6.3V6K

0.22U_0603_10V7K

1

C224

2

0.22U_0603_10V7K

2

1

C231

2

1

C232

2

1

SCANCLK2

SCANCLK1

SCANEN

SCANSHENB

+1.2V_HT

1

+

2

100U_D2_10VM

C436

RP52

4 5

3 6

2 7

1 8

680_1206_8P4R_5%

0.22U_0603_10V7K

250 mil

1

1

C434

C433

2

2

0.22U_0603_10V7K

Title

Size Document Number Rev

Custom

Date: Sheet of

4.7U_0805_6.3V6K

1

C55

2

4.7U_0805_6.3V6K

0.22U_0603_10V7K

1

C51

2

0.22U_0603_10V7K

+2.5VS

U29

1

IN

OUT

2

GND

SHDN3BYP

G914E_SOT23-5@

0.22U_0603_10V7K

1

C425

2

0.22U_0603_10V7K

1

C53

2

1

C50

2

1

2

Claw Harmmer (MISC)

LA-2541

4.7U_0805_6.3V6K

1

C58

2

4.7U_0805_6.3V6K

1

C52

2

0.22U_0603_10V7K

R318

1 2

0_0805_5%

5

4

1

C406

0.01U_0402_16V7K@

2

0.22U_0603_10V7K

1

C423

C426

2

1

2

0.22U_0603_10V7K

1

2

0.22U_0603_10V7K

E

1

C225

2

4.7U_0805_6.3V6K

1

C229

2

0.22U_0603_10V7K

2

C408

1U_0603_10V4Z

1

1

C424

2

658Friday, April 15 , 2005

C91

C89

0.4

Page 7

A

U10E

B2

VSS

AH20

VSS

AB21

VSS

W22

+CPU_CORE +2.5V

U10D

L7

VDD

AC15

VDD

H18

VDD

B20

VDD

E21

VDD

H22

1 1

2 2

3 3

4 4

VDD

J23

VDD

H24

VDD

F26

VDD

N7

VDD

L9

VDD

V10

VDD

G13

VDD

K14

VDD

Y14

VDD

AB14

VDD

G15

VDD

J15

VDD

AA15

VDD

H16

VDD

K16

VDD

Y16

VDD

AB16

VDD

G17

VDD

J17

VDD

AA17

VDD

AC17

VDD

AE17

VDD

F18

VDD

K18

VDD

Y18

VDD

AB18

VDD

AD18

VDD

AG19

VDD

E19

VDD

G19

VDD

AC19

VDD

AA19

VDD

J19

VDD

F20

VDD

H20

VDD

K20

VDD

M20

VDD

P20

VDD

T20

VDD

V20

VDD

Y20

VDD

AB20

VDD

AD20

VDD

G21

VDD

J21

VDD

L21

VDD

N21

VDD

R21

VDD

U21

VDD

W21

VDD

AA21

VDD

AC21

VDD

F22

VDD

K22

VDD

M22

VDD

P22

VDD

T22

VDD

V22

VDD

Y22

VDD

AB22

VDD

AD22

VDD

E23

VDD

G23

VDD

L23

VDD

N23

VDD

R23

VDD

U23

VDD

W23

VDD

AA23

VDD

AC23

VDD

B24

VDD

D24

VDD

F24

VDD

K24

VDD

M24

VDD

P24

VDD

T24

VDD

V24

VDD

Y24

VDD

AB24

VDD

AD24

VDD

AH24

VDD

AE25

VDD

K26

VDD

P26

VDD

V26

VDD

FOX_PZ75403-2941-42

POWER

A

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

+CPU_CORE

VSS

M23

VSS

L24

VSS

AG25

VSS

AG27

VSS

D2

VSS

AF2

VSS

W6

VSS

Y7

VSS

AA8

VSS

AB9

VSS

AA10

VSS

J12

VSS

B14

VSS

Y15

VSS

AE16

VSS

J18

VSS

G20

VSS

R20

VSS

U20

VSS

W20

VSS

AA20

VSS

AC20

VSS

AE20

VSS

AG20

VSS

AJ20

VSS

D21

VSS

F21

VSS

H21

VSS

K21

VSS

M21

VSS

P21

VSS

T21

VSS

V21

VSS

Y21

VSS

AD21

VSS

AG21

VSS

B22

VSS

E22

VSS

G22

VSS

J22

VSS

L22

VSS

N22

VSS

R22

VSS

U22

VSS

AG29

VSS

AA22

VSS

AC22

VSS

AG22

VSS

AH22

VSS

AJ22

VSS

D23

VSS

F23

VSS

H23

VSS

K23

VSS

P23

VSS

T23

VSS

V23

VSS

Y23

VSS

AB23

VSS

AD23

VSS

AG23

VSS

E24

VSS

G24

VSS

J24

VSS

N24

VSS

R24

VSS

U24

VSS

W24

VSS

AA24

VSS

AC24

VSS

AG24

VSS

AJ24

VSS

B25

VSS

C25

VSS

B26

VSS

D26

VSS

H26

VSS

M26

VSS

T26

VSS

Y26

VSS

AD26

VSS

AF26

VSS

AH26

VSS

C27

VSS

B28

VSS

D28

VSS

G28

VSS

F15

VSS

H15

VSS

AB17

VSS

AD17

VSS

B16

VSS

G18

VSS

AA18

VSS

AC18

VSS

D19

VSS

F19

VSS

H19

VSS

K19

VSS

Y19

VSS

AB19

VSS

AD19

VSS

AF19

VSS

J20

VSS

L20

VSS

N20

VSS

FOX_PZ75403-2941-42

B

POWER

B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

Security Classification

F17

H17

K17

Y17

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+CPU_CORE

820U_E9_2_5V_M_R7

+

C76

10U_0805_10V4Z

C126

4.7U_0805_6.3V6K

C511

1

+

C217

2

1

C137

2

10U_0805_10V4Z

1

C452

2

4.7U_0805_6.3V6K

330U_D_2VM_R15

1

2

820U_E9_2_5V_M_R7

+CPU_CORE

1

2

10U_0805_10V4Z

4 in Socket Cavity,

2 on backside under Socket

+CPU_CORE

1

2

4.7U_0805_6.3V6K

1

+

2

10U_0805_10V4Z

1

C154

2

4.7U_0805_6.3V6K

1

C544

2

330U_D_2VM_R15

1

+

C227

2

1

C127

2

10U_0805_10V4Z

1

C517

2

4.7U_0805_6.3V6K

CPU Decouping Capacitor

4.7U_0805_6.3V6K

1

1

2

4.7U_0805_6.3V6K

2005/03/01 2006/03/11

C

Compal Secret Data

Deciphered Date

C121

C203

2

C228

10U_0805_10V4Z

1

C138

2

4.7U_0805_6.3V6K

1

C545

2

D

1

C155

2

1

C460

2

4.7U_0805_6.3V6K

D

+CPU_CORE

+CPU_CORE

1

C521

2

0.22U_0603_10V7K

Near Socket

+2.5V+2.5V

1

C194

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

2

E

1

C477

1000P_0402_50V7K

2

0.22U_0603_10V7K

1

C486

2

In Socket CavityClose to Socket

Loop Bandwidth

KHz

20

50

* 300 3300

1

C200

2

0.22U_0603_10V7K

Title

Size Document Number Rev

Custom

Date: Sheet

1

C476

0.1U_0402_16V4Z

2

1

C498

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

C478

2

Bulk Cappacitance

uF

1

C499

2

0.22U_0603_10V7K

1

C487

2

23000

9000

0.22U_0603_10V7K

1

C136

C164

2

0.22U_0603_10V7K

Claw Harmmer (Power & Ground)

1

2

LA-2541

0.22U_0603_10V7K

1

C124

2

C148

E

0.22U_0603_10V7K

1

C479

2

Total

ESR

2.5m ohm

(AMD)

0.9m ohm

1.5m ohm

758Friday, April 15 , 2005

of

0.4

Page 8

A

+1.25VREF_MEM

+2.5V

DDR_DQ0

DDR_DQ5

DDR_DQS0

SB_SCLK<4,9,15,19>

SB_SDAT<4,9,15,19>

A

DDR_DQ3

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ28

DDR_DQ24

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_CKE0

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0

DDR_SWEA#

DDR_SCS#0

DDR_SMAA13

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ55

DDR_DQ56

DDR_DQ61

DDR_DQS7

DDR_DQ58

DDR_DQ59

+3VS

1 1

DDR_CLK5<5>

DDR_CLK5#<5>

2 2

DDR_CKE0<5>

DDR_SBSA0<5>

DDR_SWEA#<5>

DDR_SCS#0<5>

3 3

4 4

JP27

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

QTC_C106A-040SP11

B

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

RAS#

CAS#

S1#

DU

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

B

C

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

40mil

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ11

DDR_DQ16

DDR_DQ21

DDR_DM2

DDR_DQ22

DDR_DQ23

DDR_DQ25

DDR_DQ29

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_CKE0

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

DDR_SCASA#

DDR_SCS#1

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ35

DDR_DQ39

DDR_DQ41

DDR_DQ45

DDR_DM5

DDR_DQ42

DDR_DQ43

DDR_DQ53

DDR_DQ52

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ63

STANDARD

SO-DIMM0

C

1

C63

0.1U_0402_16V4Z

2

DDR_SBSA1 <5>

DDR_SRASA# <5>

DDR_SCASA# <5>

DDR_SCS#1 <5>

DDR_CLK7# <5>

DDR_CLK7 <5>

D

DDR_SDQS[0..7]<5>

DDR_SDQ[0..63]<5>

+1.25VREF_MEM

DDR_SDQ0 DDR_DQ0

DDR_SDQ4

DDR_SDQ5

DDR_SDQ1

DDR_SDM0

DDR_SDQS0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ12

DDR_SDQS1

DDR_SDM1 DDR_DM1

DDR_SDQ14

DDR_SDQ11

DDR_SDQ16 DDR_DQ16

DDR_SDQ17

DDR_SDQ21 DDR_DQ21

DDR_SDM2 DDR_DM2

DDR_SDQ18

DDR_SDQ28

DDR_SDQ25

DDR_SDQ24

DDR_SDQ29

DDR_SDQS3

DDR_SDM3

DDR_SDQ26

DDR_SDQ30

DDR_SDQ27

DDR_SDQ31

DDR_SDM[0..7]<5>

DDR_SMAA[0..13]<5>

RP8

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP11

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP14

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP15

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP16

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP17

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP20

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP23

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP24

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP27

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

2005/03/01 2006/03/11

E

DDR_SDQS[0..7]

DDR_SDQ[0..63]

DDR_SDM[0..7]

DDR_SMAA[0..13]

DDR_DQ4

DDR_DQ5

DDR_DQ1

DDR_DM0

DDR_DQS0

DDR_DQ2

DDR_DQ3

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ12

DDR_DQ13DDR_SDQ13

DDR_DQS1

DDR_DQ14

DDR_DQ10DDR_SDQ10

DDR_DQ15DDR_SDQ15

DDR_DQ11

DDR_DQ20DDR_SDQ20

DDR_DQ17

DDR_DQS2DDR_SDQS2

DDR_DQ18

DDR_DQ22DDR_SDQ22

DDR_DQ19DDR_SDQ19

DDR_DQ23DDR_SDQ23

DDR_DQ28

DDR_DQ25

DDR_DQ24

DDR_DQ29

DDR_DQS3

DDR_DM3

DDR_DQ26

DDR_DQ30

DDR_DQ27

DDR_DQ31

Compal Secret Data

Deciphered Date

E

F

RP36

DDR_SDQ32 DDR_DQ32

DDR_SDQ37

DDR_SDQ36 DDR_DQ36

DDR_SDQ33

DDR_SDQS4

DDR_SDM4 DDR_DM4

DDR_SDQ34

DDR_SDQ35

DDR_SDQ38

DDR_SDQ39

DDR_SDQ44

DDR_SDQ45

DDR_SDQS5

DDR_SDM5

DDR_SDQ47

DDR_SDQ42

DDR_SDQ46

DDR_SDQ43

DDR_SDQ48

DDR_SDQ53

DDR_SDQ49

DDR_SDQ52

DDR_SDQ54

DDR_SDQ50

DDR_SDQ51

DDR_SDQ55

DDR_SDQ57

DDR_SDQ61

DDR_SDM7

DDR_SDQS7 DDR_DQS7

DDR_SDQ62

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQ59

F

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP37

10_0804_8P4R_5%

RP40

10_0804_8P4R_5%

RP43

10_0804_8P4R_5%

RP44

10_0804_8P4R_5%

RP47

10_0804_8P4R_5%

RP48

10_0804_8P4R_5%

RP51

10_0804_8P4R_5%

RP53

10_0804_8P4R_5%

RP56

10_0804_8P4R_5%

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_DQ37

DDR_DQ33

DDR_DQS4

DDR_DQ34

DDR_DQ35

DDR_DQ38

DDR_DQ39

DDR_DQ40DDR_SDQ40

DDR_DQ41DDR_SDQ41

DDR_DQ44

DDR_DQ45

DDR_DQS5

DDR_DM5

DDR_DQ47

DDR_DQ42

DDR_DQ46

DDR_DQ43

DDR_DQ48

DDR_DQ53

DDR_DQ49

DDR_DQ52

DDR_DM6DDR_SDM6

DDR_DQS6DDR_SDQS6

DDR_DQ54

DDR_DQ50

DDR_DQ51

DDR_DQ55

DDR_DQ60DDR_SDQ60

DDR_DQ56DDR_SDQ56

DDR_DQ57

DDR_DQ61

DDR_DM7

DDR_DQ62

DDR_DQ58

DDR_DQ59

G

DDR_DQ[0..63] <9>

DDR_DQS[0..7] <9>

DDR_DM[0..7] <9>

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0

DDR_SMAA11

DDR_SMAA8

12

R51

1K_0402_1%

12

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

DDR_SMAA13

DDR_SWEA#

DDR_SCASA#

DDR_SCS#0

DDR_SCS#1

DDR_CKE0

1

C64

0.1U_0402_16V4Z

2

BOM change

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

Note:

DDR_SMAA13 Recommend for AMD

+2.5V

R60

1K_0402_1%

Title

Size Document Number Rev

Custom

Date: Sheet

G

DDR-SODIMM SLOT0

LA-2541

H

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

1 2

R116 47_0402_5%

1 2

R110 47_0402_5%

1 2

R109 47_0402_5%

R113 68_0402_5%

1 2

1 2

R108 68_0402_5%

1 2

R101 68_0402_5%

+1.25VREF_MEM

1

C62

2

858Friday, April 15 , 2005

H

+1.25V

RP29

18

27

36

45

RP33

18

27

36

45

RP28

18

27

36

45

RP32

18

27

36

45

1000P_0402_50V7K

of

0.4

Page 9

A

+2.5V

JP28

1

VREF

3

DDR_DQ0

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ7

1 1

DDR_CLK4<5>

DDR_CLK4#<5>

2 2

DDR_CKE1<5>

DDR_SBSB0<5>

DDR_SWEB#<5>

DDR_SCS#2<5>

3 3

4 4

SB_SDAT<4,8,15,19>

SB_SCLK<4,8,15,19>

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ28

DDR_DQ24

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_CKE1 DDR_CKE1

DDR_SMAB12

DDR_SMAB9

DDR_SMAB7

DDR_SMAB5

DDR_SMAB3

DDR_SMAB1

DDR_SMAB10

DDR_SBSB0

DDR_SWEB#

DDR_SCS#2 DDR_SCS#3

DDR_SMAB13

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ55

DDR_DQ56

DDR_DQ61

DDR_DQS7

DDR_DQ58

DDR_DQ59

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU/A13

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

TYCO_1612560-1

DU/RESET#

DIMM1

REVERSE

A

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

CKE0

VSS

VDD

BA1

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

A11

S1#

B

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

DU

100

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

20 mil width

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ11

DDR_DQ16

DDR_DQ21

DDR_DM2

DDR_DQ22

DDR_DQ23

DDR_DQ25

DDR_DQ29

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_SMAB11

DDR_SMAB8

DDR_SMAB6

DDR_SMAB4

DDR_SMAB2

DDR_SMAB0

DDR_SBSB1

DDR_SRASB#

DDR_SCASB#

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ35

DDR_DQ39

DDR_DQ41

DDR_DQ45

DDR_DM5

DDR_DQ42

DDR_DQ43

DDR_DQ53

DDR_DQ52

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ63

+3VS

+1.25VREF_MEM

1

C65

0.1U_0402_16V4Z

2

DDR_SBSB1 <5>

DDR_SRASB# <5>

DDR_SCASB# <5>

DDR_SCS#3 <5>

DDR_CLK6# <5>

DDR_CLK6 <5>

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ2

68_0804_8P4R_5%

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DM1

68_0804_8P4R_5%

DDR_DQ10

DDR_DQ11

DDR_DQ16

DDR_DQ21

68_0804_8P4R_5%

DDR_DM2

DDR_DQ22

DDR_DQ23

DDR_DQ25

68_0804_8P4R_5%

DDR_DQ29

DDR_DM3

DDR_DQ30

Note:

DDR_SMAB13 Recommend

for AMD.

Layout note

Place these resistor

close by DIMM1,

all trace length

Max=0.8"

DDR_DQS[0..7]<8>

DDR_DQ[0..63]<8>

DDR_DM[0..7]<8>

DDR_SMAB[0..13]<5>

2005/03/01 2006/03/11

C

DDR_DQS[0..7]

DDR_DQ[0..63]

DDR_DM[0..7]

DDR_SMAB[0..13]

Compal Secret Data

DDR_DQ31

68_0804_8P4R_5%

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ35

68_0804_8P4R_5%

DDR_DQ39

DDR_DQ41

DDR_DQ45

DDR_DM5

68_0804_8P4R_5%

DDR_DQ42

DDR_DQ43

DDR_DQ53

DDR_DQ52

68_0804_8P4R_5%

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ60

68_0804_8P4R_5%

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ63

68_0804_8P4R_5%

Deciphered Date

RP10

1 8

2 7

3 6

4 5

RP13

1 8

2 7

3 6

4 5

RP18

1 8

2 7

3 6

4 5

RP22

1 8

2 7

3 6

4 5

RP26

1 8

2 7

3 6

4 5

RP38

1 8

2 7

3 6

4 5

RP42

1 8

2 7

3 6

4 5

RP45

1 8

2 7

3 6

4 5

RP49

1 8

2 7

3 6

4 5

RP54

1 8

2 7

3 6

4 5

D

+1.25V

DDR_DQ0

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

68_0804_8P4R_5%

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ28

DDR_DQ24

DDR_DQS3

DDR_DQ26

DDR_DQ27

68_0804_8P4R_5%

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ55

DDR_DQ56

DDR_DQ61

DDR_DQS7

DDR_DQ58

DDR_DQ59

Layout note

Place these resistor

closely DIMM1,

all trace

length<=800mil

D

E

+1.25V

RP9

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP12

1 8

2 7

3 6

4 5

RP19

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP21

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP25

1 8

2 7

3 6

4 5

RP39

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP41

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP46

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP50

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP55

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

Title

Size Document Number Rev

Custom

Date: Sheet

DDR_SMAB12

DDR_SMAB9

DDR_SMAB7

DDR_SMAB5

DDR_SMAB3

DDR_SMAB1

DDR_SMAB10

DDR_SBSB0

DDR_SMAB11

DDR_SMAB8

DDR_SMAB6

DDR_SMAB4

DDR_SMAB2

DDR_SMAB0

DDR_SBSB1

DDR_SRASB#

DDR_SMAB13

DDR_SWEB#

DDR_SCASB#

DDR_SCS#2

DDR_CKE1

DDR_SCS#3

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

1 2

R117 47_0402_5%

1 2

R111 47_0402_5%

1 2

R112 47_0402_5%

1 2

R114 68_0402_5%

1 2

R102 68_0402_5%

1 2

R115 68_0402_5%

DDR-SODIMM SLOT1

LA-2541

E

RP30

RP34

RP31

RP35

958Friday, April 15 , 2005

+1.25V

of

0.4

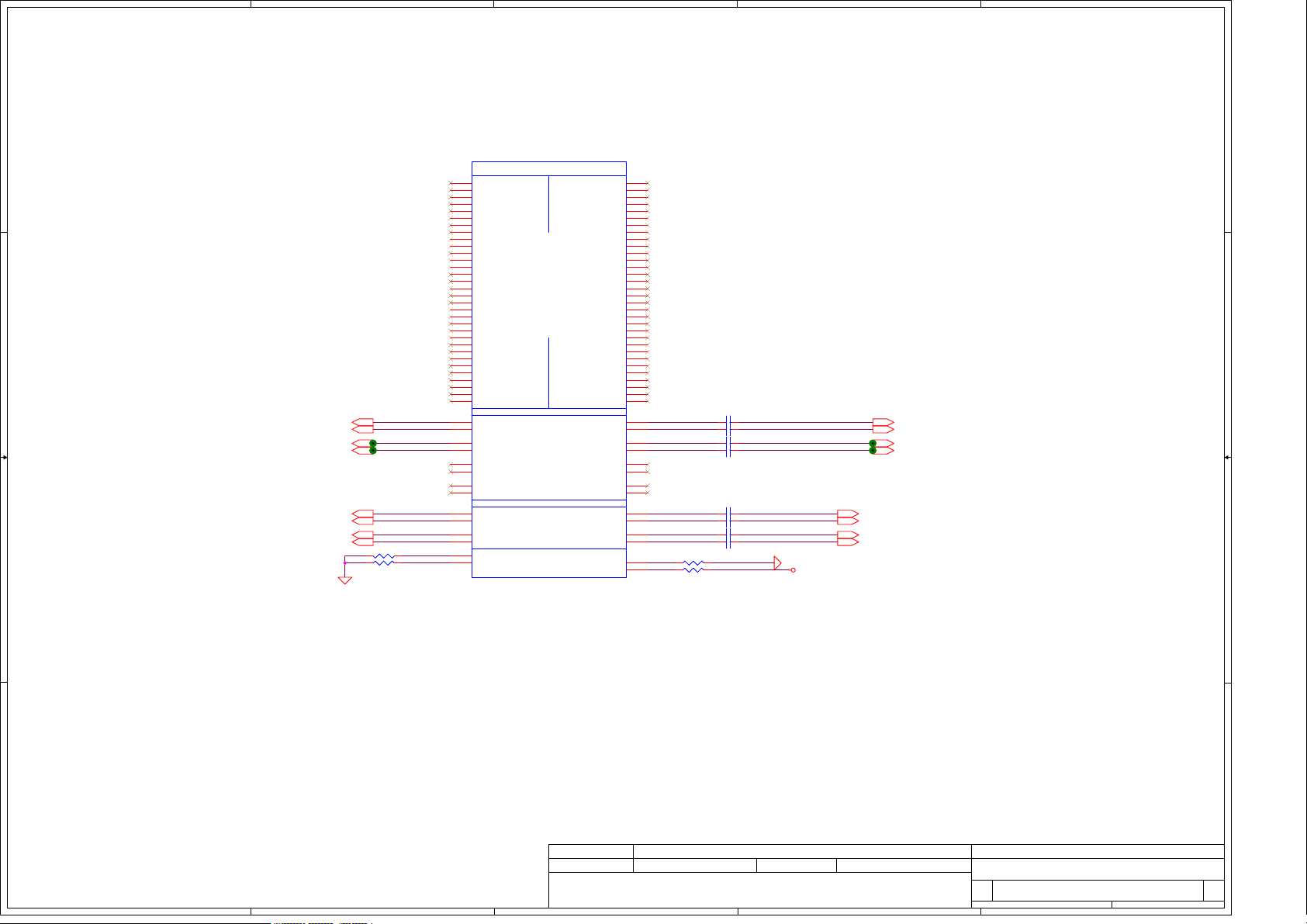

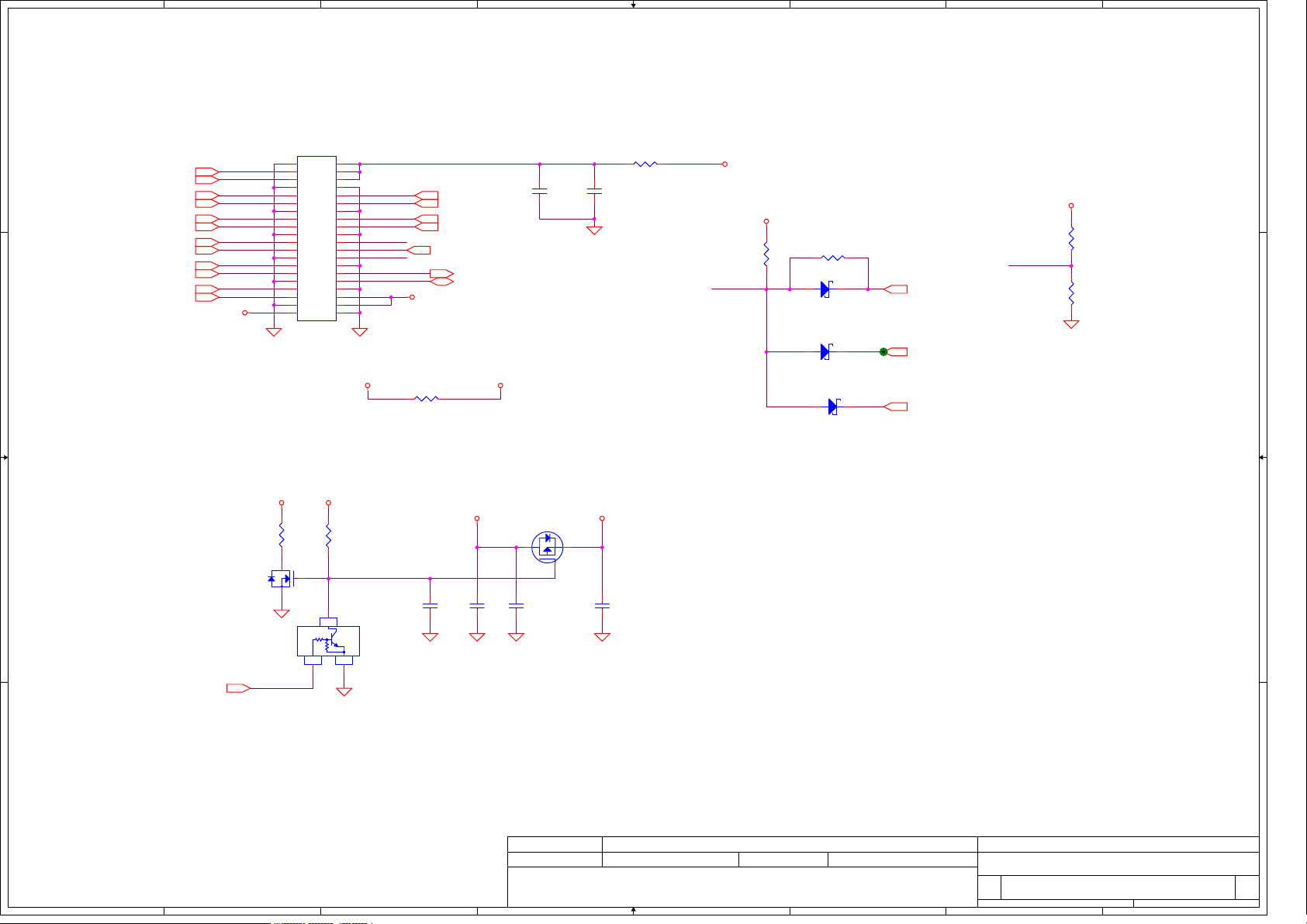

Page 10

A

+2.5V

1

1

+

2

330U_6.3V_M

1 1

C180

+

C213

330U_6.3V_M

2

1

C95

2

4.7U_0805_6.3V6K

B

4.7U_0805_6.3V6K

1

C125

2

Near DIMMs

C

D

E

Layout note :

Place one cap close to every 2 pull up resistors termination to

+1.25V

+1.25V

1

C66

2

0.1U_0402_16V4Z

+1.25V

2 2

1

C215

2

0.1U_0402_16V4Z

+1.25V

1

C139

2

0.1U_0402_16V4Z

+1.25V

1

C73

3 3

2

0.1U_0402_16V4Z

+1.25V

1

C221

2

0.1U_0402_16V4Z

+1.25V

1

C77

2

0.1U_0402_16V4Z

1

C204

2

0.1U_0402_16V4Z

1

C130

2

0.1U_0402_16V4Z

1

C80

2

0.1U_0402_16V4Z

1

C210

2

0.1U_0402_16V4Z

1

C128

2

0.1U_0402_16V4Z

1

C186

2

0.1U_0402_16V4Z

1

C141

2

0.1U_0402_16V4Z

1

C131

2

0.1U_0402_16V4Z

1

C192

2

0.1U_0402_16V4Z

1

C111

2

0.1U_0402_16V4Z

1

C182

2

0.1U_0402_16V4Z

1

C151

2

0.1U_0402_16V4Z

1

C107

2

0.1U_0402_16V4Z

1

C184

2

0.1U_0402_16V4Z

1

C113

2

0.1U_0402_16V4Z

1

C175

2

0.1U_0402_16V4Z

1

C165

2

0.1U_0402_16V4Z

1

C115

2

0.1U_0402_16V4Z

1

C179

2

0.1U_0402_16V4Z

1

C119

2

0.1U_0402_16V4Z

1

C120

2

0.1U_0402_16V4Z

1

C152

2

0.1U_0402_16V4Z

1

C122

2

0.1U_0402_16V4Z

1

C123

2

0.1U_0402_16V4Z

1

C174

2

0.1U_0402_16V4Z

1

C114

2

0.1U_0402_16V4Z

1

C166

2

0.1U_0402_16V4Z

1

C178

2

0.1U_0402_16V4Z

1

C116

2

0.1U_0402_16V4Z

1

C181

2

0.1U_0402_16V4Z

1

C106

2

0.1U_0402_16V4Z

1

C168

2

0.1U_0402_16V4Z

1

C183

2

0.1U_0402_16V4Z

1

C110

2

0.1U_0402_16V4Z

1

C189

2

0.1U_0402_16V4Z

1

C150

2

0.1U_0402_16V4Z

1

C153

2

0.1U_0402_16V4Z

1

C193

2

0.1U_0402_16V4Z

1

C158

2

0.1U_0402_16V4Z

1

C205

2

0.1U_0402_16V4Z

1

C78

2

0.1U_0402_16V4Z

1

C135

2

0.1U_0402_16V4Z

1

C211

2

0.1U_0402_16V4Z

1

C81

2

0.1U_0402_16V4Z

1

C214

2

0.1U_0402_16V4Z

1

C129

2

0.1U_0402_16V4Z

1

C220

2

0.1U_0402_16V4Z

1

C132

2

0.1U_0402_16V4Z

1

C67

2

0.1U_0402_16V4Z

1

C140

2

0.1U_0402_16V4Z

1

C75

2

0.1U_0402_16V4Z

+2.5V

1

C146

2

0.1U_0402_16V4Z

+2.5V

10U_0805_10V4Z

+1.25V

1

2

C209

1

C218

10U_0805_10V4Z

2

1

C145

2

0.1U_0402_16V4Z

4 4

1

2

0.1U_0402_16V4Z

A

C133

1

C147

2

0.1U_0402_16V4Z

1

C159

2

0.1U_0402_16V4Z

1

C169

2

0.1U_0402_16V4Z

B

1

C160

2

0.1U_0402_16V4Z

1

C170

2

0.1U_0402_16V4Z

1

C172

2

0.1U_0402_16V4Z

1

C161

2

0.1U_0402_16V4Z

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/01 2006/03/11

C

1

C144

2

0.1U_0402_16V4Z

+2.5V

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet of

DDR SODIMM Decoupling

LA-2541

E

0.4

10 58Friday, April 15 , 2005

Page 11

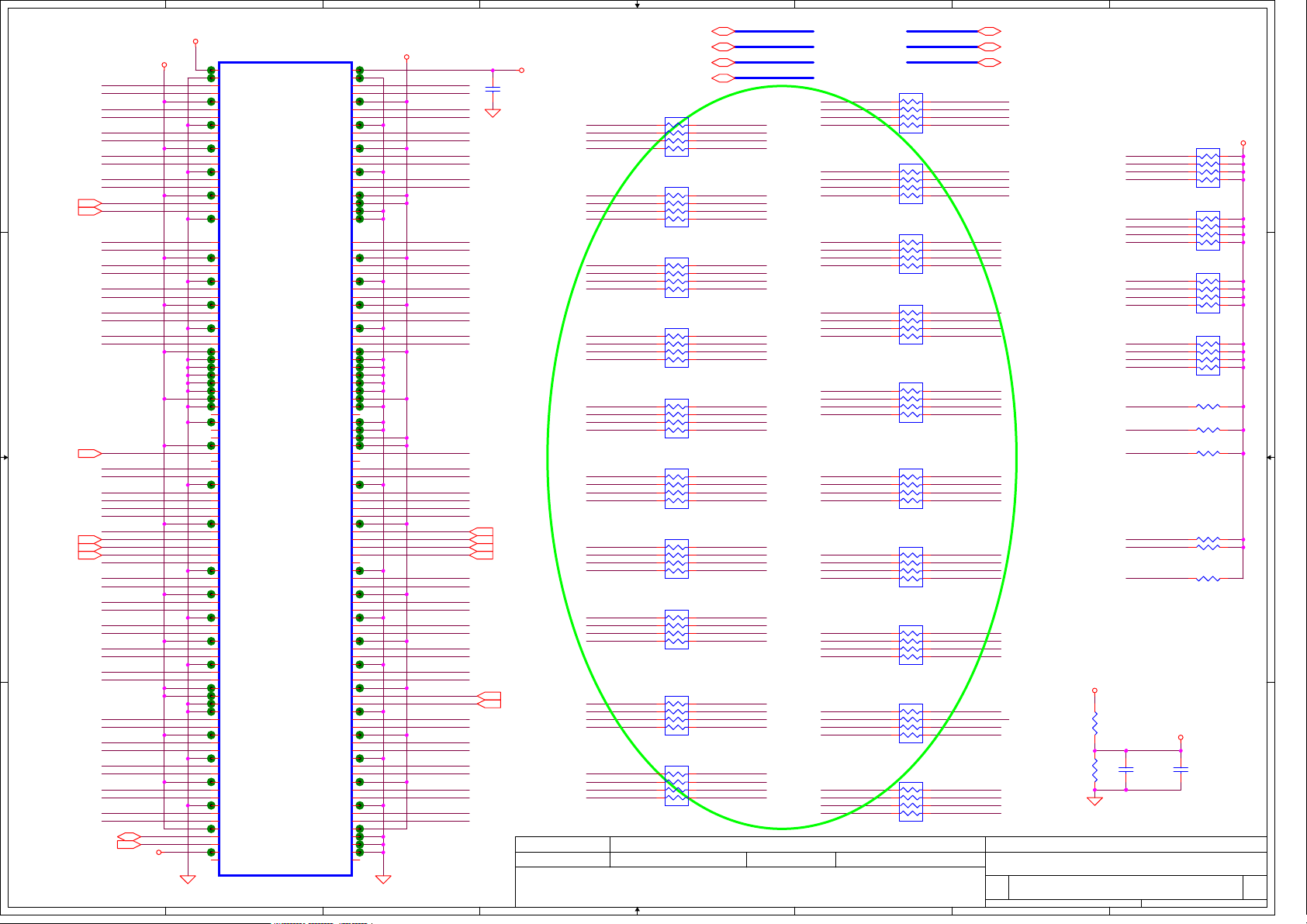

5

4

3

2

1

H_CADIP[0..15]<4>

H_CADIN[0..15]<4>

H_CADOP[0..15]<4>

D D

H_CADOP15

H_CADON15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

1 2

1 2

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

C C

H_CLKOP1<4>

H_CLKON1<4>

H_CLKOP0<4>

H_CLKON0<4>

H_CTLOP0<4>

H_CTLON0<4>

+1.2V_HT

B B

R346 49.9_0402_1%

R348 49.9_0402_1%

H_CADON[0..15]<4>

U9A

T26

HT_RXCAD15P

R26

HT_RXCAD15N

U25

HT_RXCAD14P

U24

HT_RXCAD14N

V26

HT_RXCAD13P

U26

HT_RXCAD13N

W25

HT_RXCAD12P

W24

HT_RXCAD12N

AA25

HT_RXCAD11P

AA24

HT_RXCAD11N

AB26

HT_RXCAD10P

AA26

HT_RXCAD10N

AC25

HT_RXCAD9P

AC24

HT_RXCAD9N

AD26

HT_RXCAD8P

AC26

HT_RXCAD8N

R29

HT_RXCAD7P

R28

HT_RXCAD7N

T30

HT_RXCAD6P

R30

HT_RXCAD6N

T28

HT_RXCAD5P

T29

HT_RXCAD5N

V29

HT_RXCAD4P

U29

HT_RXCAD4N

Y30

HT_RXCAD3P

W30

HT_RXCAD3N

Y28

HT_RXCAD2P

Y29

HT_RXCAD2N

AB29

HT_RXCAD1P

AA29

HT_RXCAD1N

AC29

HT_RXCAD0P

AC28

HT_RXCAD0N

Y26

HT_RXCLK1P

W26

HT_RXCLK1N

W29

HT_RXCLK0P

W28

HT_RXCLK0N

P29

HT_RXCTLP

N29

HT_RXCTLN

D27

HT_RXCALN

E27

HT_RXCALP

216MPA4AKA22HK RS480M BGA 706P

H_CADIP[0..15]

H_CADIN[0..15]

H_CADOP[0..15]

H_CADON[0..15]

HYPER TRANSPORT CPU

I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

H_CADIP15

R24

H_CADIN15

R25

H_CADIP14

N26

H_CADIN14

P26

H_CADIP13

N24

H_CADIN13

N25

H_CADIP12

L26

H_CADIN12

M26

H_CADIP11

J26

H_CADIN11

K26

H_CADIP10

J24

H_CADIN10

J25

H_CADIP9

G26

H_CADIN9

H26

H_CADIP8

G24

H_CADIN8

G25

H_CADIP7

L30

H_CADIN7

M30

H_CADIP6

L28

H_CADIN6

L29

H_CADIP5

J29

H_CADIN5

K29

H_CADIP4

H30

H_CADIN4

H29

H_CADIP3

E29

H_CADIN3

E28

H_CADIP2

D30

H_CADIN2

E30

H_CADIP1

D28

H_CADIN1

D29

H_CADIP0

B29

H_CADIN0

C29

H_CLKIP1

L24

H_CLKIN1

L25

H_CLKIP0

F29

H_CLKIN0

G29

H_CTLIP0

M29

H_CTLIN0

M28

R345 100_0402_5%

B28

1 2

A28

H_CLKIP1 <4>

H_CLKIN1 <4>

H_CLKIP0 <4>

H_CLKIN0 <4>

H_CTLIP0 <4>

H_CTLIN0 <4>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C529

C524

+2.5VS

U9B

AF17

MEM_A0

AK17

MEM_A1

AH16

MEM_A2

AF16

MEM_A3

AJ22

MEM_A4

AJ21

MEM_A5

AH20

MEM_A6

AH21

MEM_A7

AK19

MEM_A8

AH19

MEM_A9

AJ17

MEM_A10

AG16

MEM_A11

AG17

MEM_A12

AH17

MEM_A13

AJ18

MEM_A14

AG26

MEM_DM0

AJ29

MEM_DM1

AE21

MEM_DM2

AH24

MEM_DM3

AH12

MEM_DM4

AG13

MEM_DM5

AH8

MEM_DM6

AE8

MEM_DM7

AF25

MEM_DQS0P

AH30

MEM_DQS1P

AG20

MEM_DQS2P

AJ25

MEM_DQS3P

AH13

MEM_DQS4P

AF14

MEM_DQS5P

AJ7

MEM_DQS6P

AG8

MEM_DQS7P

AG25

MEM_DQS0N

AH29

MEM_DQS1N

AF21

MEM_DQS2N

AK25

MEM_DQS3N

AJ12

MEM_DQS4N

AF13

MEM_DQS5N

AK7

MEM_DQS6N

AF9

MEM_DQS7N

AE17

MEM_RAS#

AH18

MEM_CAS#

AE18

MEM_WE#

AJ19

MEM_CS#

AF18

MEM_CKE

AK16

MEM_CKP

AJ16

MEM_CKN

C520 0.47U_0603_16V7K

1 2

C188 0.47U_0603_16V7K

12

1

2

1

2

R358

1K_0402_1%

12

R359

1K_0402_1%

MEM_VREF

+1.8VS

1 2

R357

1 2

R123

1 2

0_0805_5%

0_0402_5%

1U_0603_10V4Z

C191

1 2

AE28

MEM_CAP1

AJ4

MEM_CAP2

AJ20