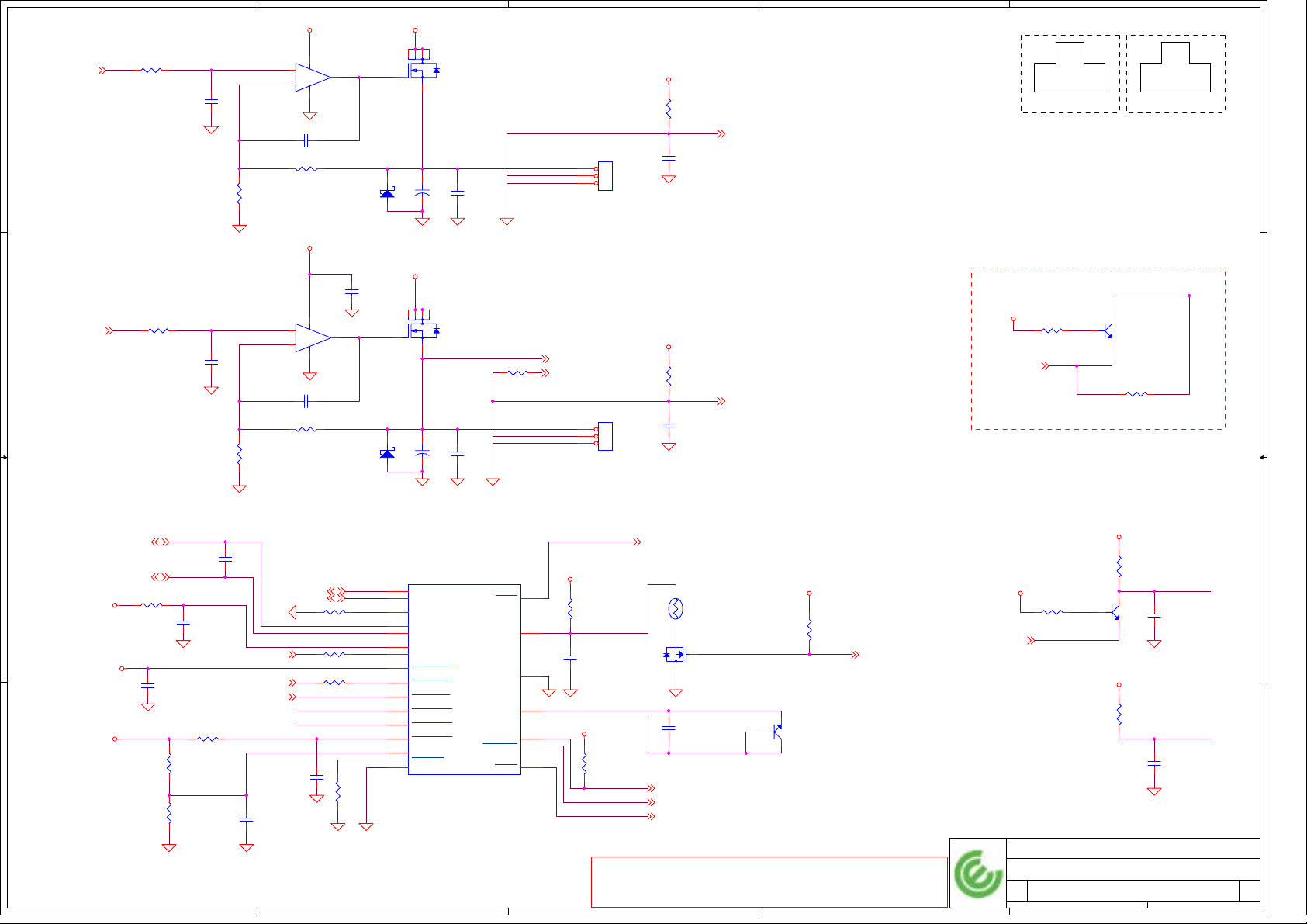

COMPAL LA-2501 Schematics

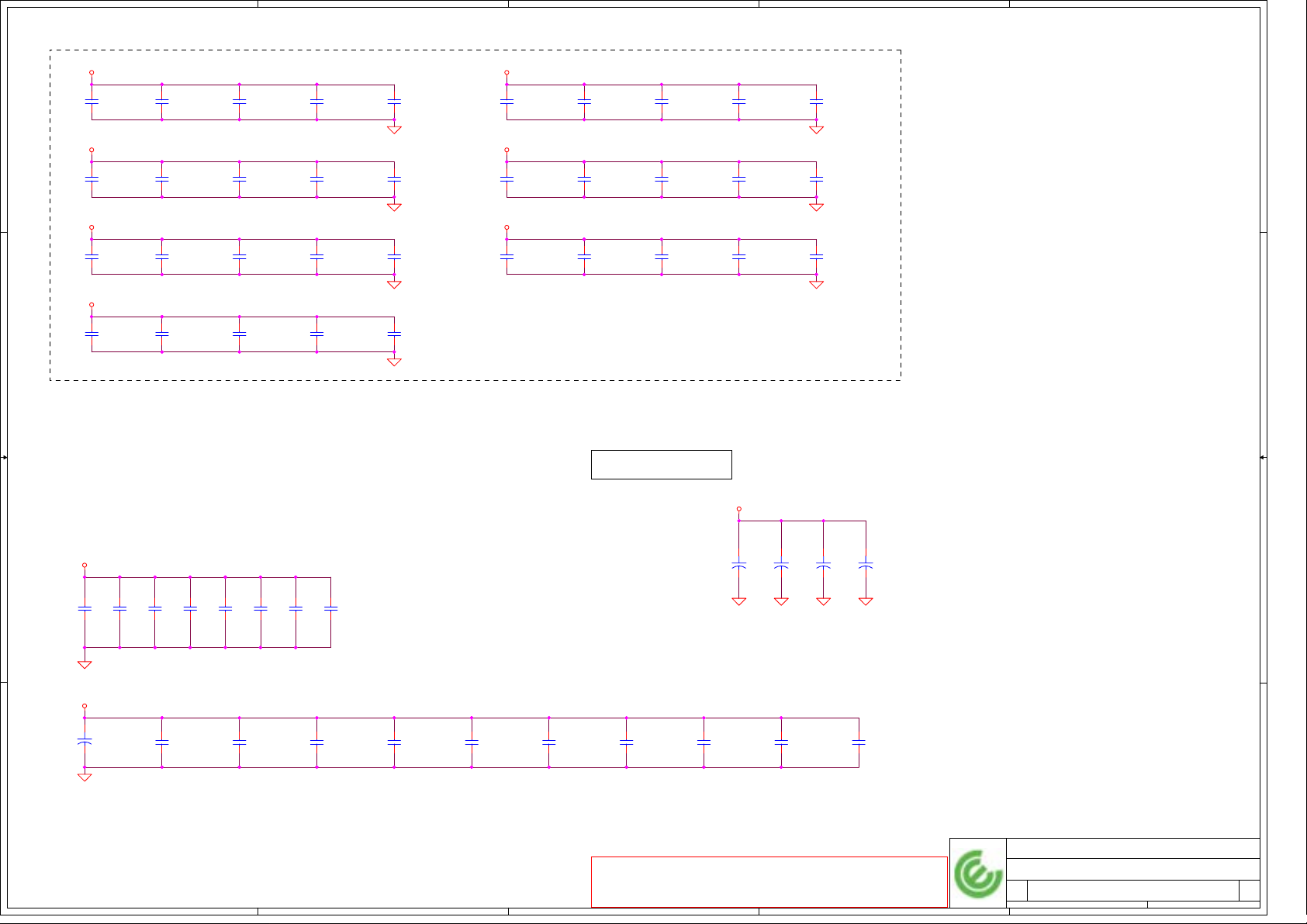

5

4

3

2

1

D D

Gilbert

REV : A00

@ : Nopop Component

C C

B B

Dothan Schematic with Capture CIS and Function field

uFCPGA Dothan

10-04-2004

A A

REV: 1.0

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-2501

148Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

Compal confidential

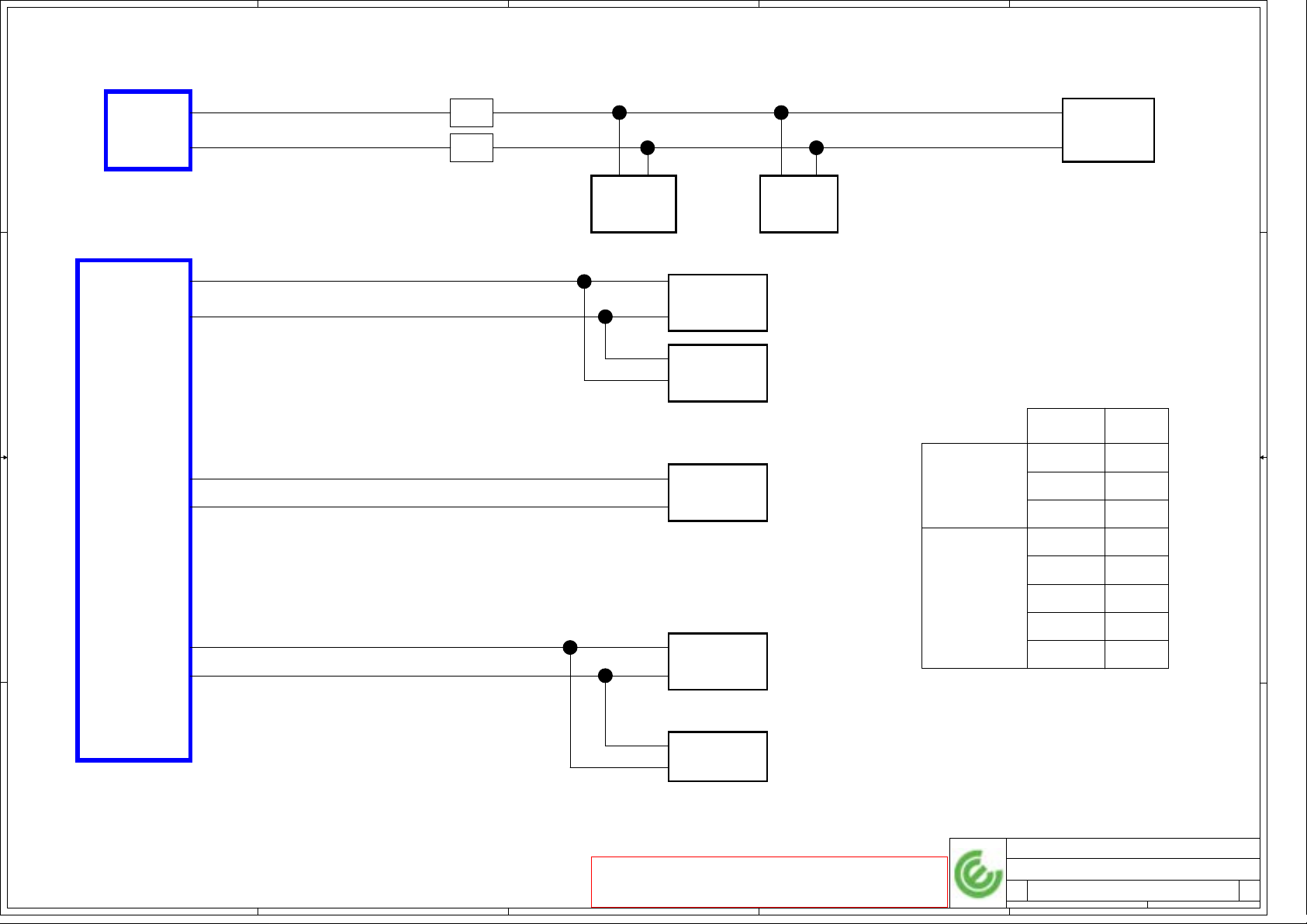

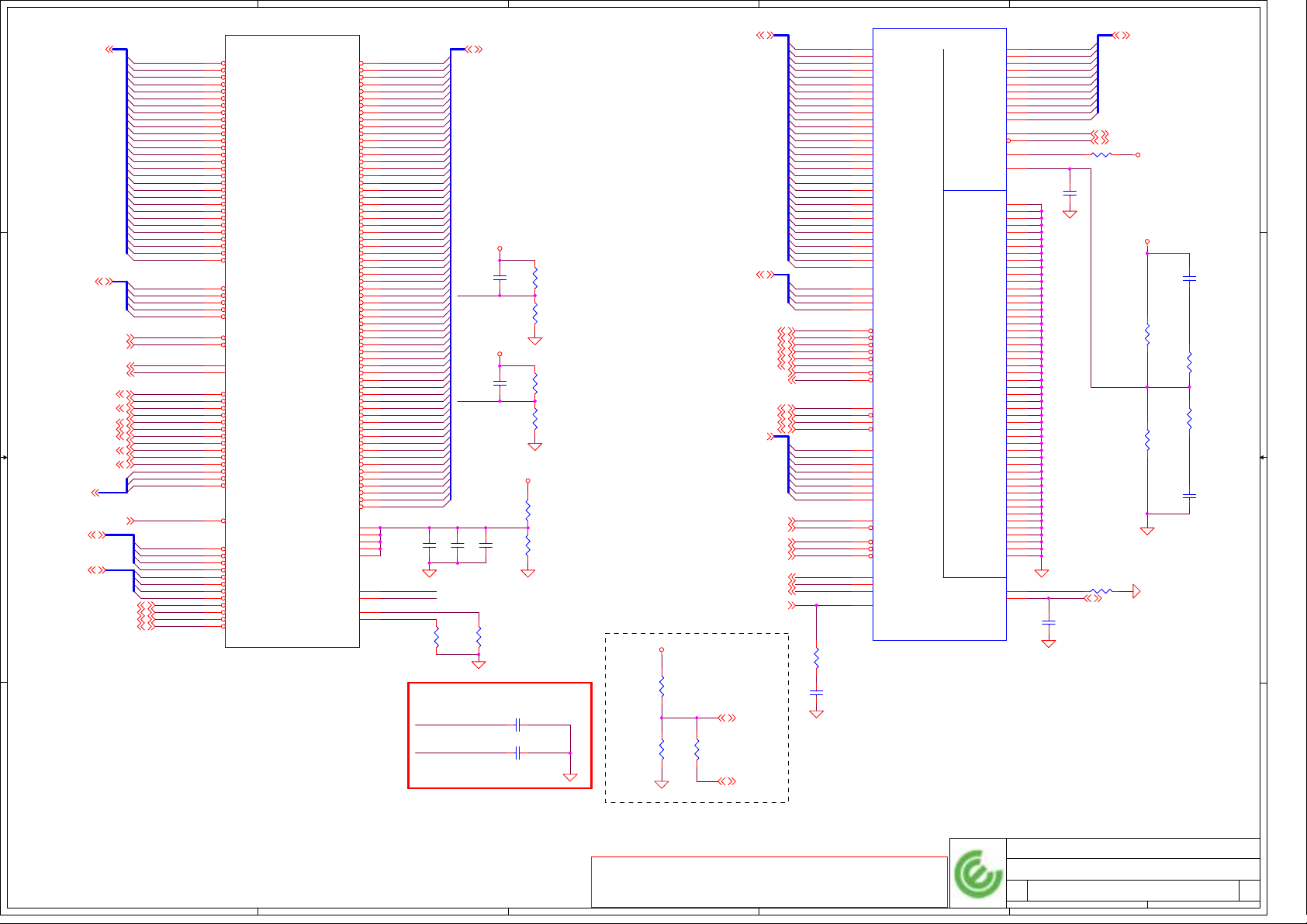

HA#(3..31)

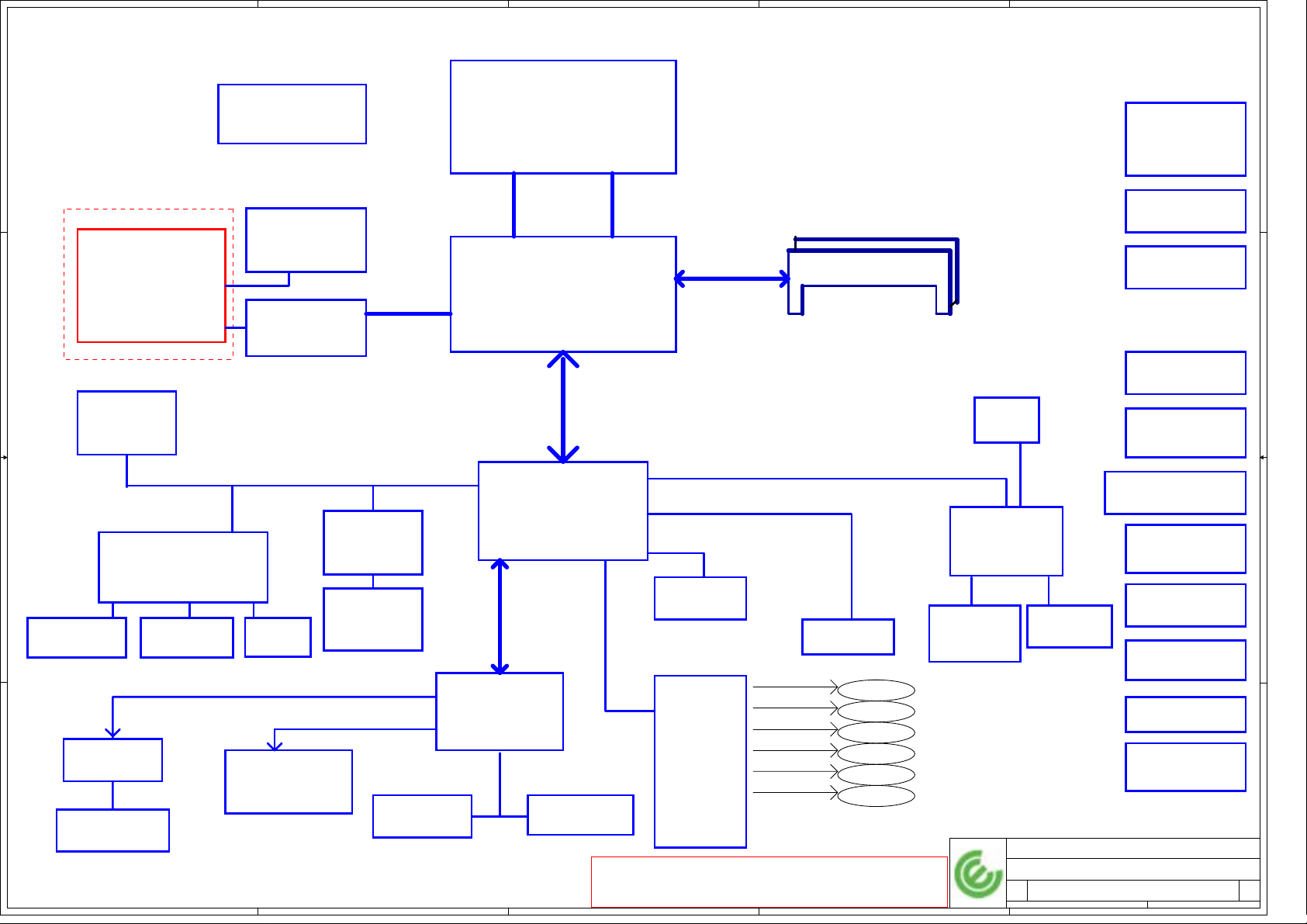

Dothan/Banias

uFCPGA CPU

System Bus

400MHz

Odem-B

MCH-M

593 FC-BGA

page 10,11,12

page 7,8,9

HD#(0..63)

Memory

BUS(DDRI)

2.5V 333MHz

SO-DIMM X2

BANK 0, 1, 2, 3

page 14,15

GUARDIAN

D D

EMC6N300

page 13

CRT CONN.

& TV-OUT

VGA

page 17

Board

AGP4X

VGA CONN.

C C

page 16

Block Diagram

Clock Generator

CK408M

page 6

Fan Control

page 13

LED/B

page 35

DC IN

page 37

MINI PCI

page 30

PCI BUS

IDSEL:AD17

(PIRQA/B#,GNT#2,REQ#2)

3.3V 33MHz

LAN

BCM4401

CardBus Controller

B B

RICHO R5C841

page 28,29

page 26

Transformer

SDIO CONN.

page 29

1394 CONN.

page 28

Slot 0

page 29

& RJ45

page 27

LPC BUS

3.3V 33MHz

GPIO

X BUS

LCM CONN.

page33

A A

Multi-media

SST39VF080

page 33

Touch Pad

page 33

Hub Link

ICH4M

421 BGA

Macallan III

LPC to X-BUS

& Super I/O

page 31,32

page 18,19,20,21

48MHz / 480Mbps

Int.KBD

page 33

3.3V 14.318MHz

ATA100

CDROM

USB2.0

page 25

page 25

ATA100

HDD

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

page 19

JUSB3 U

JUSB3 D

Blue Tooth

NEW CARD

JUSB2 U

JUSB2 D

Board

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

MDC

page 24

AC-LINK

AC97 CODEC

STAC9750

AMP &

Phone Jack

page 23

BATT IN/+2.5V

page 38

1.5V/1.05V(+VCCP)

page 39

5V/3.3V/15V

page 22

page 40

2.5V / 1.25V

Subwoofer

page 24

VCORE

page 41

page 42

CHARGER

page 43

1.2V/1.8V

page 44

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Block Diagram

LA-2501

248Tuesday, October 05, 2004

1

of

1.0

5

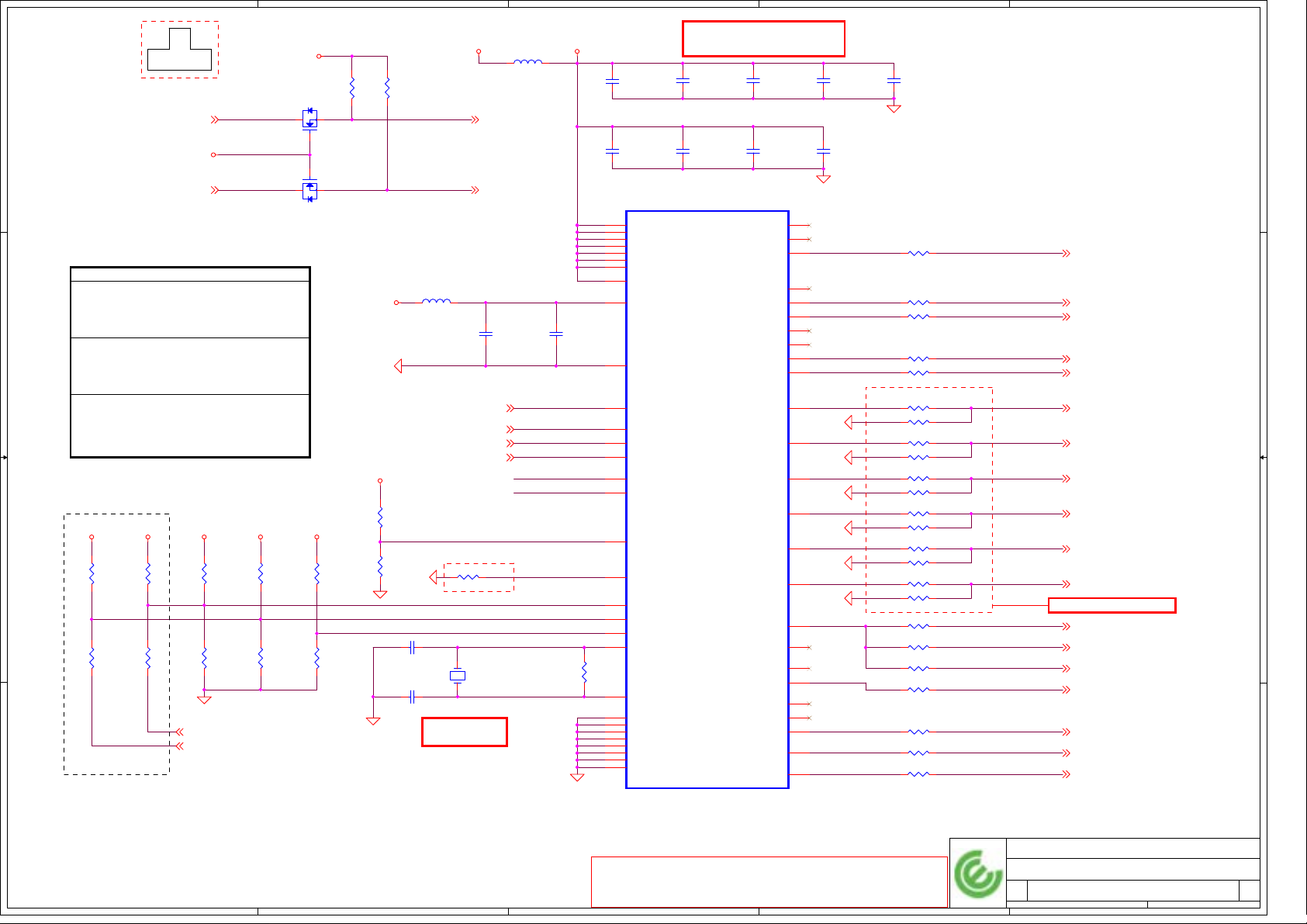

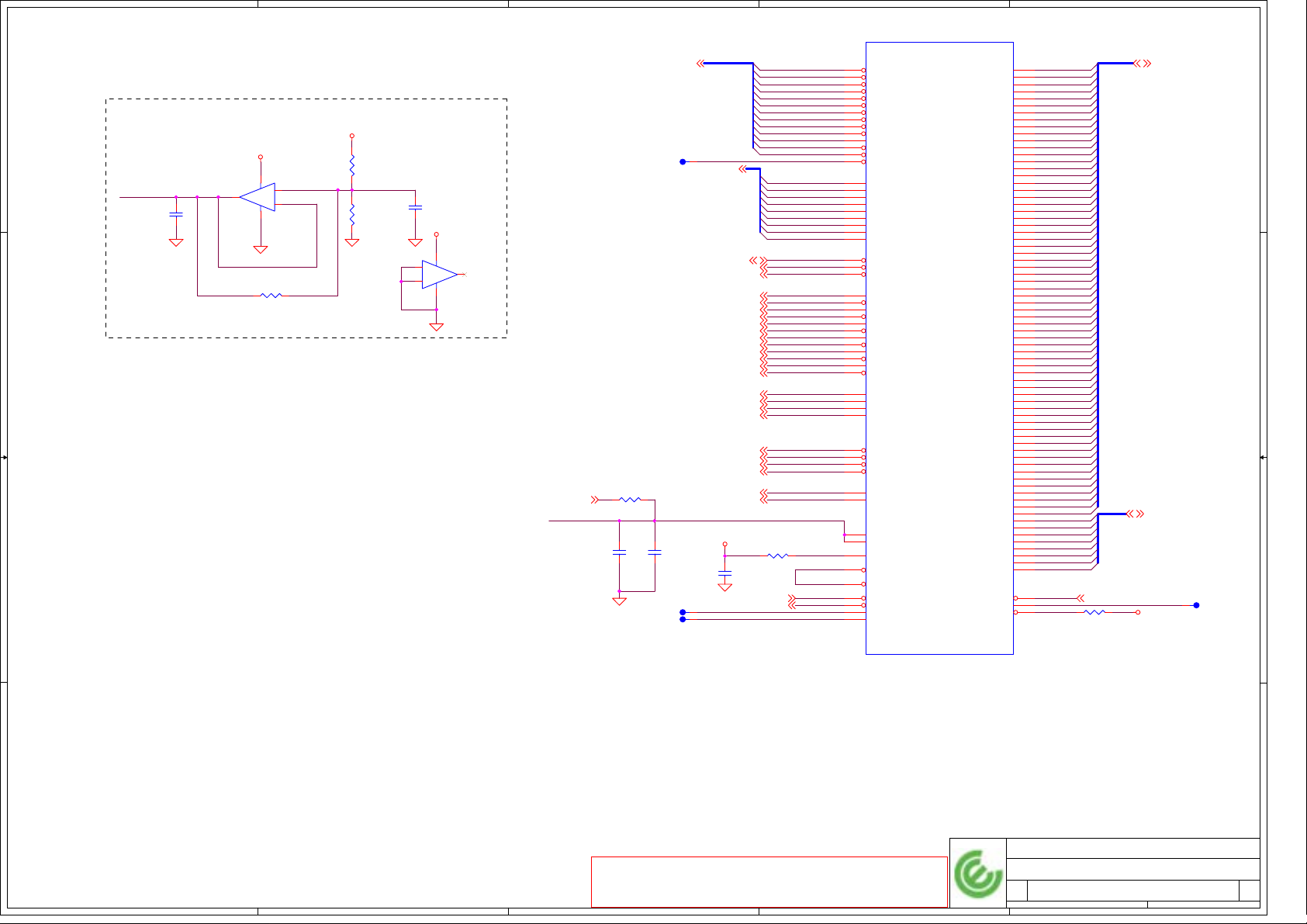

D D

4

3

2

1

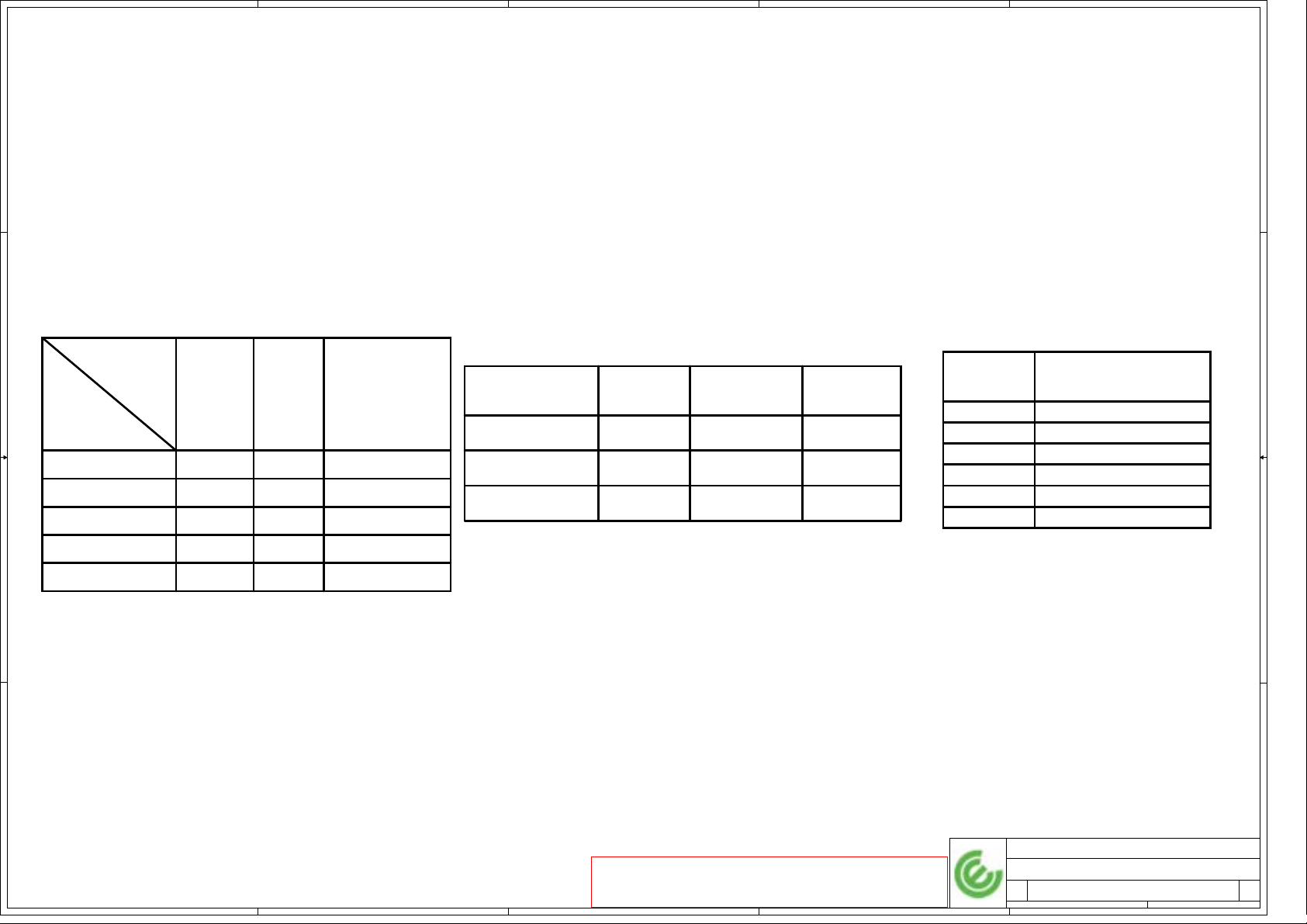

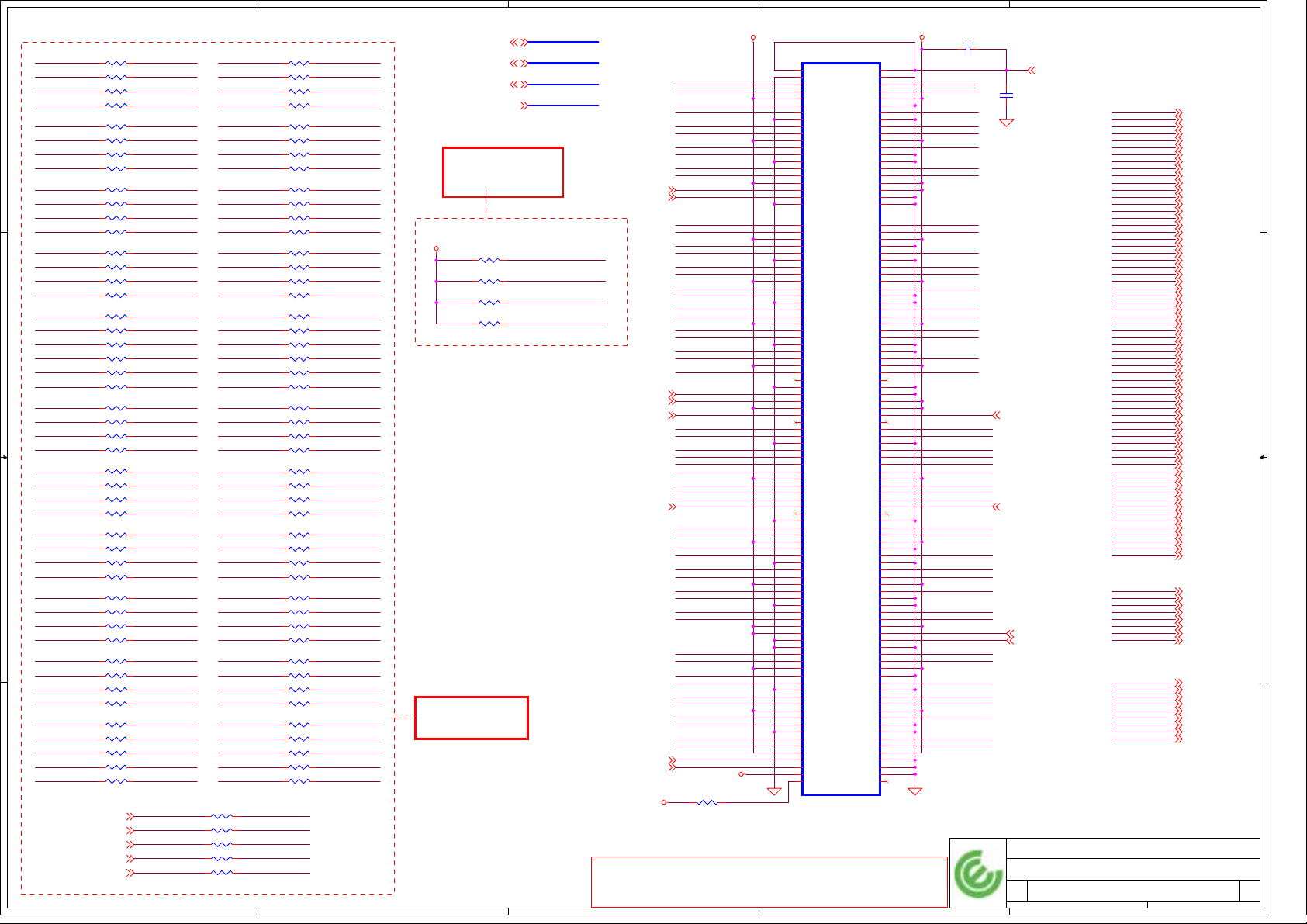

PM TABLE

C C

power

plane

State

S0

S1

S3

S5 S4/AC

B B

S5 S4/AC don't exist

+3VALW

+5VALW

ON

ON

ON

ON

+3VSUS

+5VSUS

+2.5V_MEM

+1.5VSUS

+15V

ON ON

ON

ON

OFF

OFFOFF

+5VRUN

+3VRUN

+1.8VRUN

+1.5VRUN

+1.2VRUN

+VCC_CORE

+VCCP

V_1P25V_DDR_VTT

ON

OFF

OFF

OFF

PCI TABLE

PCI DEVICE

CARD BUS

MINI PCI

IDSEL

AD17

AD19

REQ#/GNT#

1

3

LAN AD16 4 C

PIRQ

B,C,D

D,B

USB TABLE

USB PORT#0DESTINATION

JUSB3 (Top)

1

2

3

4

JUSB3 (Bottom)

Blue Tooth

NEW CARD

JUSB2 (Top)

5 JUSB2 (Bottom)

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Index and Config.

LA-2501

348Tuesday, October 05, 2004

1

1.0

of

5

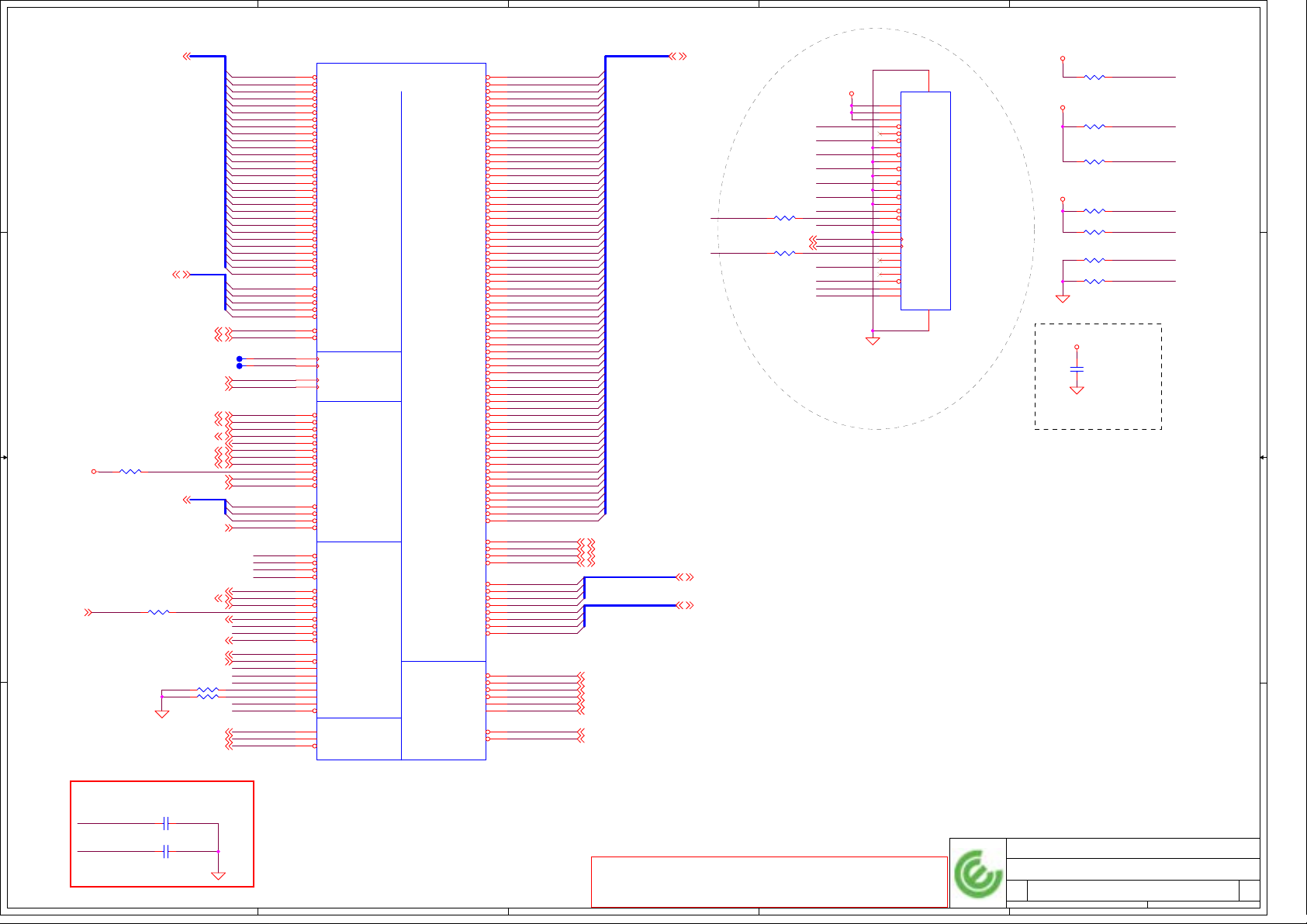

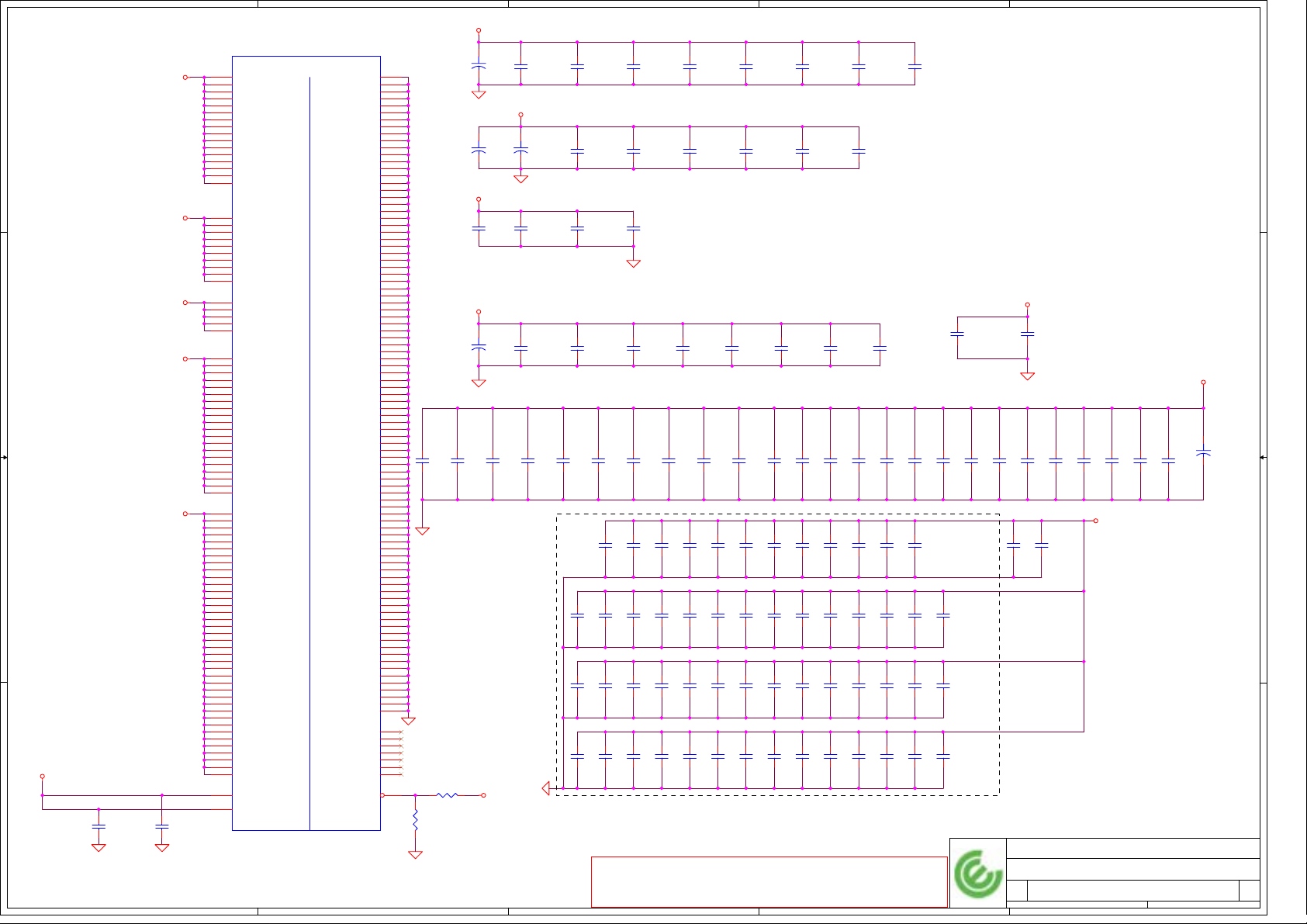

D D

4

3

2

1

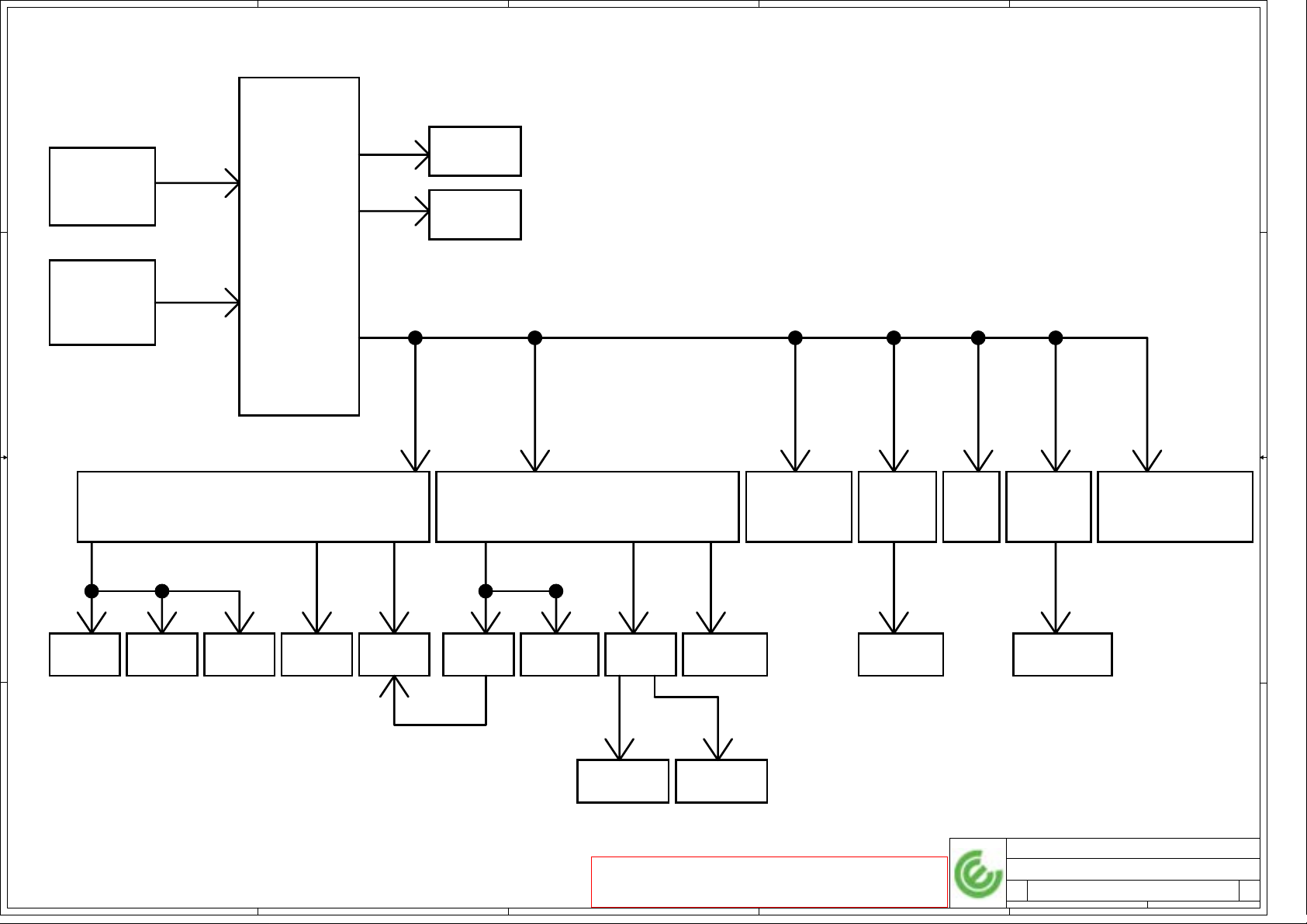

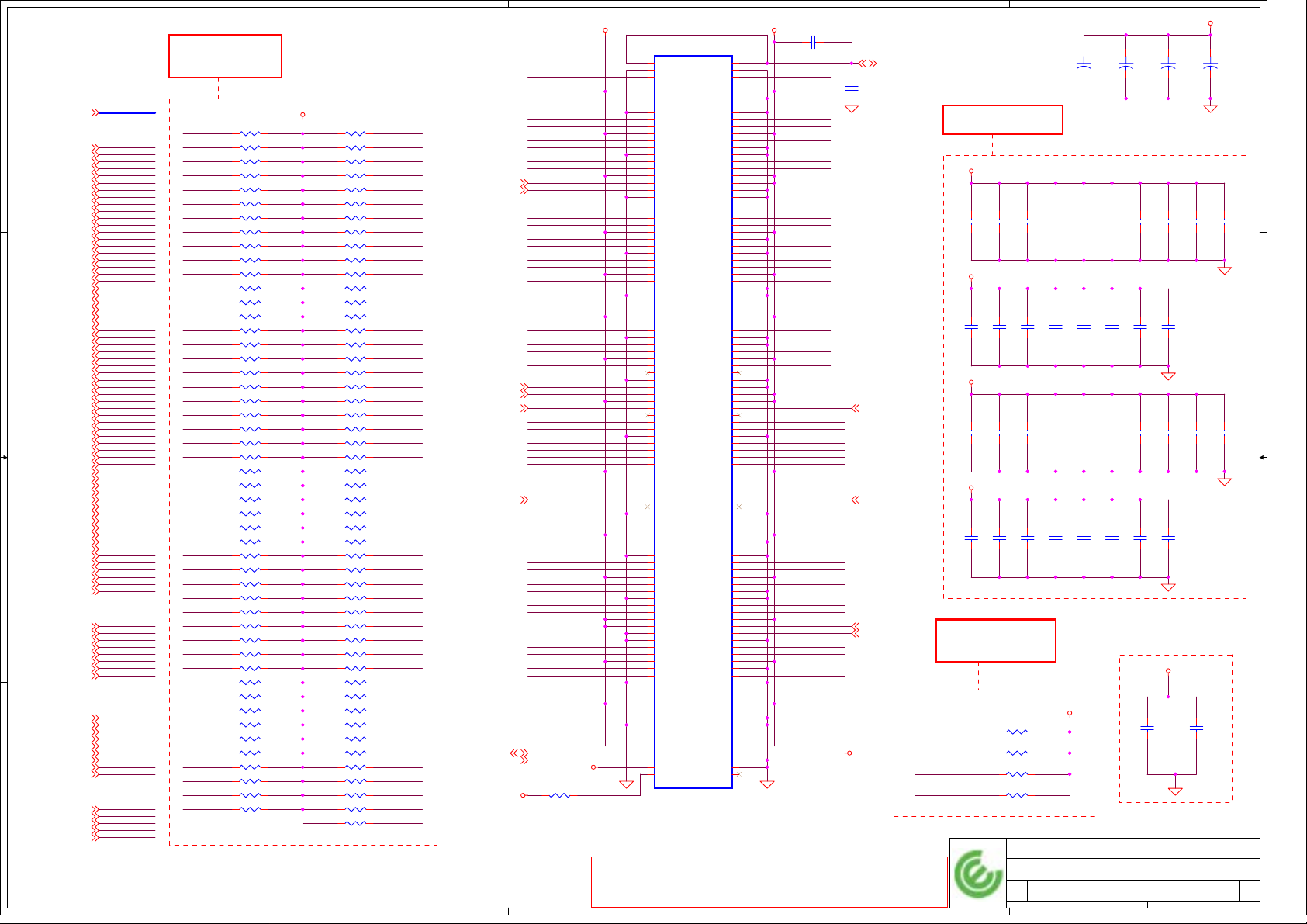

+5VALW

ADAPTER

PWR_SRC

+3VALW

BATTERY

C C

SUS_ON

+5VSUS

B B

+5VHDD +5VMOD +5VRUN VDDA

A A

RUN_ON

PL11, PD15

+15V +2.5VRUN

(Option)

AUDIO_AVDD_ON

+3VRUN

L25

SUS_ON

+3VSRC

RUN_ON

V3P3LAN

SUSPWROK_5V

+3VSUS

RUN_ON_D

+1.8VRUN

+VCC_CORE

RUN_ON_D

RUN_ON

+1.2VRUN

RUNPWROK

+1.5VSUS

RUN_ON SUSPWROK_1.5V

+1.5VRUN

RUNPWROK

+VCCP

SUSPWROK_5V

SUSPWROK_5V

+2.5VSUSP V_1P25V_DDR_VTT

PJP11,PJP12

+2.5V_MEM

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Power Rail

LA-2501

448Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

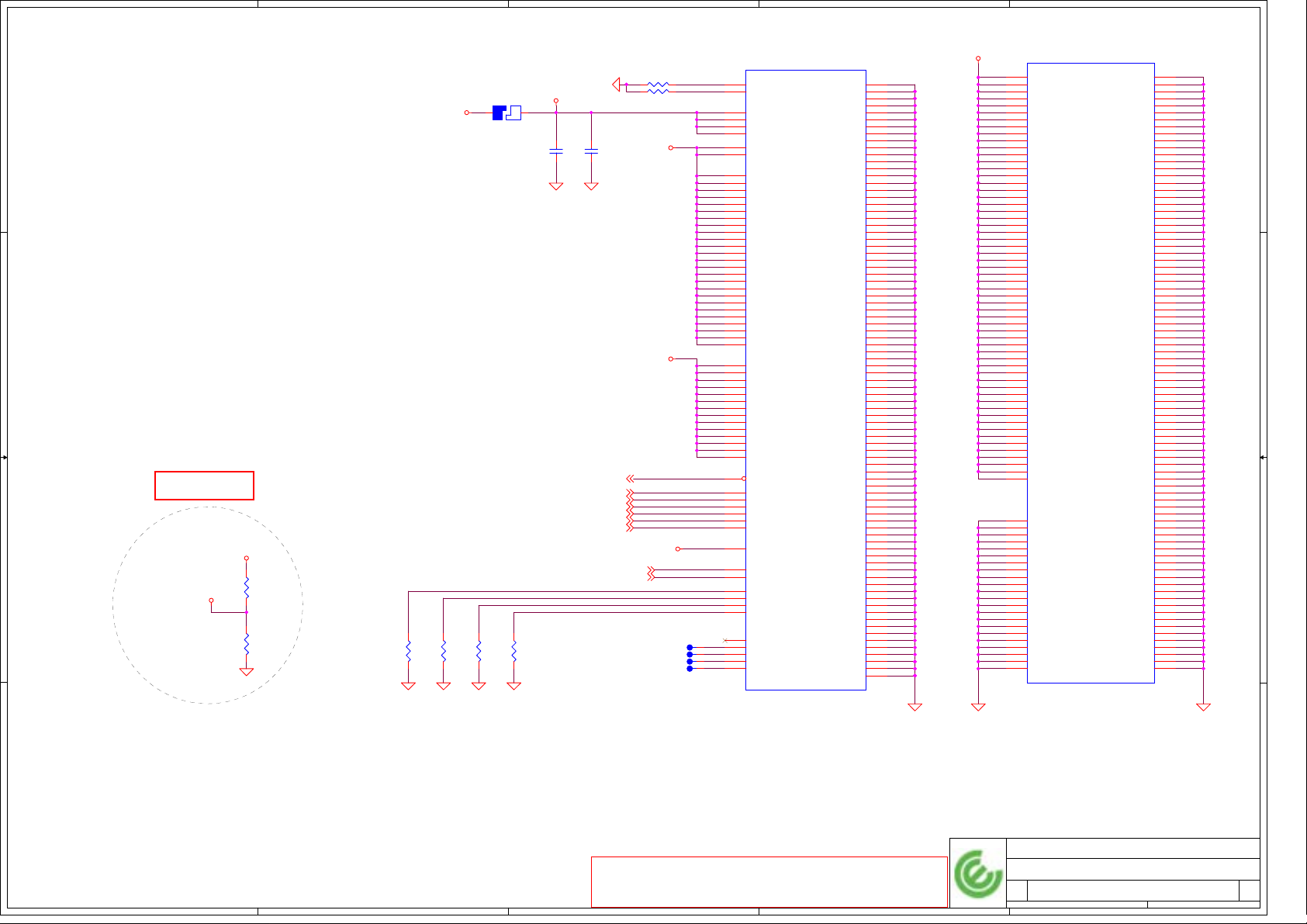

ICH_SMBCLK

D D

ICH4M

ICH_SMBDATA

+3VSUS

7002

+3VRUN

7002

CK_SCLK

CK_SDATA

CLK GEN.

DIMM1DIMM0

CLK_SMB

DAT_SMB

C C

+3VALW

GUARDIAN

24C04

Device Address

SIO

LPC47N354

Macallan III

SMBCLK_VGA

SMBDAT_VGA +5VALW VGA

ICH4M-SMBus

DIM0

DIM1

CLK GEN.

GUARDIAN

A0h

A2h

D2h

5Eh

B B

EC-SMBus

PBAT_SMBCLK

PBAT_SMBDAT +5VALW BATTERY

24C04

VGA

Battery

Charger

A2h

58h

16h

12h

CHARGER

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-2501

548Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

D

1

3

G

S

2

2N7002

D D

ICH_SMBDATA<19>

ICH_SMBCLK<19>

ICH_SMBDATA

+3VRUN

ICH_SMBCLK

+3VRUN

D

1 3

1 3

D

S

G

2

2

G

S

12

R118

R117

Q9

2.2K_0402_5%~D

2N7002_SOT23~D

Q10

2N7002_SOT23~D

12

2.2K_0402_5%~D

CK_SDATA

CK_SCLK

S2 S1 S0 CPU 3V66[0..4] 3V66_5/66IN

1 0 0 66 66IN 66 Input

1 0 1 100 66IN 66 Input

+3VRUN

BLM11A601S_0603~D

1 2

1 1 0 200 66IN 66 Input

1 1 1 133 66IN 66 Input

C C

0 0 0 66 66 66 Input

0 0 1 100 66 66 Input

*

0 1 0 200 66 66 Input

+3VRUN

1 2

BLM21PG600SN1D_0805~D

CK_SDATA <14,15>

CK_SCLK <14,15>

W=20 mils

L21

1

C401

10U_0805_10V4M~D

2

L20

CLK_VDD_CORE

1

2

CK_VDD_MAIN

C57

0.1U_0402_16V4Z~D

CK_VDD_MAIN

2

C42

10U_0805_10V4M~D

1

1

C78

0.1U_0402_10V6K~D

2

U7

1

VDD_REF

8

VDD_PCI

14

VDD_PCI

19

VDD_3V66

32

VDD_3V66

46

VDD_CPU

50

VDD_CPU

37

VDD_48MHZ

26

VDD_CORE

27

GND_CORE

0 1 1 133 66 66 Input

Mid

0

0

Mid

Mid

1

Mid

12

B B

R398

1K_0402_5%~D@

12

R395

0_0402_5%~D@

0

0

1

+VCCP+VCCP

Hi-z

TCLK/21

Reserve1

Reserve

12

R394

1K_0402_5%~D@

12

R400

0_0402_5%~D@

Hi-z

TCLK/2

Reserve

Reserve

+3VRUN

R571

1K_0402_5%~D

1 2

R574

1K_0402_5%~D

@

1 2

CPU_BSEL0 <8>

CPU_BSEL1 <8>

TCLK/2

Reserve

Reserve

+3VRUN

1 2

1 2

Hi-z

R572

1K_0402_5%~D

@

R575

1K_0402_5%~D

+3VRUN

1 2

1 2

R573

1K_0402_5%~D

@

R576

1K_0402_5%~D

CK_VDD_MAIN

12

R569

10K_0402_5%~D

R570

1K_0402_5%~D

@

1 2

C83

18P_0402_50V8J~D

C77

18P_0402_50V8J~D

H_STP_CPU#<20,42>

H_STP_PCI#<20>

CLK_ENABLE#<42>

ICH_SLP_S1#<20>

Please closely pin42

R385

1 2

475_0603_1%~D

12

12

Y1 14.31818MHz_20P_1BX14318CC1A~D

12

Place crystal within

500 mils of CK408

H_STP_CPU#

H_STP_PCI#

CLK_ENABLE#

ICH_SLP_S1#

CK_SCLK

CK_SDATA

MULT0

CLKIREF

CLKSEL0

CLKSEL1

CLKSEL2

CK_XTAL_OUT

CK_XTAL_IN

Dothan B only

A A

12

R577

2M_0603_5%~D

53

CPU_STOP#

34

PCI_STOP#

28

VTT_PWRGD#

25

PWR_DWN#

30

SCLK

29

SDATA

43

MULT0

42

IREF

54

SEL0

55

SEL1

40

SEL2

3

XTAL_OUT

@

2

XTAL_IN

4

GND_REF

9

GND_PCI

15

GND_PCI

20

GND_3V66

31

GND_3V66

36

GND_48MHZ

41

GND_IREF

47

GND_CPU

CY28346ZCT_TSSOP56~D

Place near each pin

W>40 mil

1

C49

0.1U_0402_10V6K~D

2

1

C89

0.1U_0402_10V6K~D

2

CK408

Rev 1.1

1

C62

0.1U_0402_10V6K~D

2

1

C69

0.1U_0402_10V6K~D

2

PCICLK_F0

PCICLK_F1

PCICLK_F2

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2

CPUCLKC2

3V66_0/DRCG

48MHZ_DOT

48MHZ_USB

3V66_1/VCH_CLK

66MHZ_IN/3V66_5

66MHZ_OUT0/3V66_2

66MHZ_OUT1/3V66_3

66MHZ_OUT2/3V66_4

REF

5

6

7

10

11

12

13

16

17

18

52

51

49

48

45

44

56

33

38

39

35

24

21

22

23

1

C44

0.1U_0402_10V6K~D

2

1

C72

0.1U_0402_10V6K~D

2

PCICLK_F2

PCICLK1 CK_33M_SIOPCI

PCICLK2

PCICLK5

PCICLK6 CK_33M_MINIPCI

CK_CPU0

CK_CPU0#

CK_CPU1

CK_CPU1#

CK_CPU2

CK_CPU2#

CLKREF

CLK48M_OUT0

CLK66M_OUT0

CLK66M_OUT2

CLK66M_OUT3

1

C53

0.1U_0402_10V6K~D

2

R83

1 2

33_0402_5%~D

R95

1 2

33_0402_5%~D

R123

1 2

33_0402_5%~D

R93

1 2

33_0402_5%~D

R106

1 2

33_0402_5%~D

R81

1 2

33_0402_5%~D

R80

1 2

49.9_0402_1%~D

R76

1 2

33_0402_5%~D

R75

1 2

R59

1 2

33_0402_5%~D

R58

1 2

R54

1 2

33_0402_5%~D

R53

1 2

R71

1 2

33_0402_5%~D

R70

1 2

R66

1 2

33_0402_5%~D

R65

1 2

49.9_0402_1%~D

R116

1 2

33_0402_5%~D

R112

1 2

10_0402_5%~D

R122

1 2

10_0402_5%~D

R84

1 2

33_0402_5%~D

R578

1 2

33_0402_5%~D

R579

1 2

33_0402_5%~D

R580

1 2

33_0402_5%~D

CK_33M_ICHPCI

CK_33M_LANPCI

CK_33M_CBPCI

CK_BCLK

CK_BCLK#

49.9_0402_1%~D

CK_ITP

49.9_0402_1%~D

CK_ITP#

49.9_0402_1%~D

CK_MCH_BCLK

49.9_0402_1%~D

CK_MCH_BCLK#

CK_14M_ICH

CK_14M_SIO

CK_14M_CODEC

CK_48M_ICH

CK_66M_ICH

CK_66M_MCH

CK_66M_AGP

CK_33M_ICHPCI <18>

CK_33M_SIOPCI <31>

CK_33M_LANPCI <26>

CK_33M_CBPCI <28>

CK_33M_MINIPCI <30>

CK_BCLK <7>

CK_BCLK# <7>

CK_ITP <7>

CK_ITP# <7>

CK_MCH_BCLK <10>

CK_MCH_BCLK# <10>

Place near CK408

CK_14M_ICH <19>

CK_14M_SIO <31>

CK_14M_CODEC <22>

CK_48M_ICH <19>

CK_66M_ICH <19>

CK_66M_MCH <10>

CK_66M_AGP <16>

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Clock Generator

LA-2501

648Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

H_A#[3..31]<10>

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]<10>

H_ADSTB#0<10>

H_RS#[0..2]<10>

1 2

R9

H_ADSTB#1<10>

CK_BCLK<6>

CK_BCLK#<6>

H_ADS#<10>

H_BNR#<10>

H_BPRI#<10>

H_BR0#<10>

H_DEFER#<10>

H_DRDY#<10>

H_HIT#<10>

H_HITM#<10>

H_LOCK#<10>

H_RESET#<10>

ITP_DBRESET#<35>

H_DBSY#<10>

H_DPSLP#<11,18>

H_PROCHOT#<32>

H_PWRGOOD<18>

H_CPUSLP#<18>

1K_0402_5%~D@

1 2

1 2

@

1K_0402_5%~D

H_THERMDA<13>

H_THERMDC<13>

H_THERMTRIP#<13,20>

T29 PAD~D

T30 PAD~D

H_TRDY#<10>

H_DPWR#<11>

R99

R717

C C

R92

56_0402_5%~D

1 2

+VCCP

B B

DPRSLPVR<20,42>

0_0402_5%~D@

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_CK_ITP

CPU_CK_ITP#

CK_BCLK

CK_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSLPVRDPRSLPVR

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

JCPUA

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

AMP_1473129-1~D

Dothan

ADDR GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

DATA GROUP

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <10>

H_DINV#1 <10>

H_DINV#2 <10>

H_DINV#3 <10>

H_A20M# <18>

H_FERR# <18>

H_IGNNE# <18>

H_INIT# <18>

H_INTR <18>

H_NMI <18>

H_STPCLK# <18>

H_SMI# <18>

H_D#0H_A#3

A19

H_D#[0..63] <10>

H_RESET#

ITP_TDO

H_DSTBN#[0..3] <10>

H_DSTBP#[0..3] <10>

R20

22.6_0603_1%~D

1 2

CK_ITP<6>

CK_ITP#<6>

1 2

R31

22.6_0603_1%~D

Check ITP connector.

+VCCP

ITP_DBRESET# ITP_TDO

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CK_ITP

CK_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

29

JITP

28

VTT1

27

GND6

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D@

30

+3VSUS

R11

150_0402_5%~D

1 2

+VCCP

R36

54.9_0603_1%~D

1 2

R19

54.9_0603_1%~D

1 2

+VCCP

R61

39.2_0603_1%~D

1 2

R62

150_0402_5%~D

1 2

R45

680_0402_5%~D

1 2

R44

27.4_0603_1%~D

1 2

+VCCP

1

C20

0.1U_0402_10V7K~D

2

Place near JITP

ITP_DBRESET#

H_RESET#

ITP_TMS

ITP_TDI

This shall place near CPU

ITP_TRST#

ITP_TCK

A A

Placed near CPU

CK_BCLK

CK_BCLK#

C936

12

2.2P_0402_50V8C~D@

C937

12

2.2P_0402_50V8C~D@

5

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Dothan Processor(1/2)

LA-2501

748Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

R208

54.9_0603_1%~D@

+VCCA_PROC

+1.5VRUN

D D

C C

PJP3

2 1

PAD-OPEN 2x2m~D

SHORT

C117

0.01U_0402_16V7K~D

C122

1

2

Layout Note:

500 mil max length

+VCCP

B B

Layout close CPU

V_CPU_GTLREF

R_A

12

R201

1K_0603_1%~D

R_B

12

R203

2K_0603_1%~D

12

12

12

R416

R417

27.4_0603_1%~D

R426

54.9_0603_1%~D

12

Resistor placed within

0.5" of CPU pin.Trace

R427

27.4_0603_1%~D

54.9_0603_1%~D

should be at least 25

miles away from any

other toggling signal.

10U_0805_4VAM~D

1

2

H_PSI#<42>

VID0<42>

VID1<42>

VID2<42>

VID3<42>

VID4<42>

VID5<42>

54.9_0603_1%~D@

+VCC_CORE

V_CPU_GTLREF

CPU_BSEL0<6>

CPU_BSEL1<6>

1 2

1 2

R207

+VCCP

H_PSI#

VID0

VID1

VID2

VID3

VID4

VID5

T42 PAD~D

T43 PAD~D

T44 PAD~D

T45 PAD~D

VCCSENSE

VSSSENSE

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

JCPUB

AE7

AF6

F26

B1

N1

AC26

P23

W4

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L5

L21

M6

M22

N5

N21

P6

P22

R5

R21

T6

T22

U21

D6

D8

D18

D20

D22

E5

E7

E9

E17

E19

E21

F6

F8

F18

E1

E2

F2

F3

G3

G4

H4

AD26

C16

C14

P25

P26

AB2

AB1

B2

C3

E26

AF7

AC1

AMP_1473129-1~D

VCCSENSE

VSSSENSE

VCCA0

VCCA1

VCCA2

VCCA3

VCCQ0

VCCQ1

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

GTLREF

BSEL0

BSEL1

COMP0

COMP1

COMP2

COMP3

RSVD

RSVD

RSVD

RSVD

RSVD

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

Dothan

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

POWER, GROUNG, RESERVED SIGNALS AND NC

+VCC_CORE

JCPUC

F20

F22

G5

G21

H6

H22

J5

J21

K22

U5

V6

V22

W5

W21

Y6

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

AMP_1473129-1~D

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Dothan

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Dothan Processor(2/2)

LA-2501

848Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

+VCC_CORE

1

C213

10U_0805_4VAM~D

D D

C C

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C463

10U_0805_4VAM~D

C165

10U_0805_4VAM~D

C214

10U_0805_4VAM~D

1

C138

10U_0805_4VAM~D

2

1

C464

10U_0805_4VAM~D

2

1

C127

10U_0805_4VAM~D

2

1

C465

10U_0805_4VAM~D

2

1

C128

10U_0805_4VAM~D

2

1

C208

10U_0805_4VAM~D

2

1

C166

10U_0805_4VAM~D

2

1

C209

10U_0805_4VAM~D

2

1

C139

10U_0805_4VAM~D

2

1

C163

10U_0805_4VAM~D

2

1

C215

10U_0805_4VAM~D

@

2

1

C466

10U_0805_4VAM~D

2

1

C212

10U_0805_4VAM~D

2

1

C168

10U_0805_4VAM~D

2

1

C211

10U_0805_4VAM~D

2

1

C210

10U_0805_4VAM~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C167

10U_0805_4VAM~D

C443

10U_0805_4VAM~D

C144

10U_0805_4VAM~D

1

C526

10U_0805_4VAM~D

2

1

C532

10U_0805_4VAM~D

@

2

1

C441

10U_0805_4VAM~D

2

10uF 0805 X6S -> (-55 ~ 105C, +/-22%) degree

1

C528

10U_0805_4VAM~D

2

1

C527

10U_0805_4VAM~D

2

1

C531

10U_0805_4VAM~D

2

1

C530

10U_0805_4VAM~D

2

1

C440

10U_0805_4VAM~D

2

1

C525

10U_0805_4VAM~D

@

2

1

C529

10U_0805_4VAM~D

2

1

C207

10U_0805_4VAM~D

@

2

1

C444

10U_0805_4VAM~D

2

X6S

High Frequence Decoupling

Near VCORE regulator.

+VCC_CORE

@

@

330U_D2E_2.5VM_R9~D

C85

1

+

2

330U_D2E_2.5VM_R9~D

C665

ESR <= 3m ohm

Capacitor > 880 uF

330U_D2E_2.5VM_R9~D

330U_D2E_2.5VM_R9~D

1

1

C415

B B

+VCCA_PROC

C938

1

2

0.1U_0402_16V4Z~D

C939

0.1U_0402_16V4Z~D

C940

1

1

2

2

C941

C942

C943

1

1

2

2

10U_0805_4VAM~D

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

10U_0805_4VAM~D

10U_0805_4VAM~D

C944

1

2

10U_0805_4VAM~D

C945

1

1

2

2

+

2

1

C416

+

+

2

2

+VCCP

1

+

C160

150U_D2_6.3VM~D

2

A A

1

C446

0.1U_0402_10V7K~D

2

1

C447

0.1U_0402_10V7K~D

2

1

C448

0.1U_0402_10V7K~D

2

1

C457

0.1U_0402_10V7K~D

2

1

C452

0.1U_0402_10V7K~D

2

1

C437

0.1U_0402_10V7K~D

2

1

C436

0.1U_0402_10V7K~D

2

1

C432

0.1U_0402_10V7K~D

2

1

C435

0.1U_0402_10V7K~D

2

1

C445

0.1U_0402_10V7K~D

2

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Dothan Bypass

LA-2501

948Tuesday, October 05, 2004

1

1.0

of

5

U15A

H_A#[3..31]<7>

D D

H_REQ#[0..4]<7>

H_ADSTB#0<7>

C C

B B

A A

H_ADSTB#1<7>

CK_MCH_BCLK#<6>

CK_MCH_BCLK<6>

H_ADS#<7>

H_TRDY#<7>

H_DRDY#<7>

H_DEFER#<7>

H_HITM#<7>

H_HIT#<7>

H_LOCK#<7>

H_BR0#<7>

H_BNR#<7>

H_BPRI#<7>

H_DBSY#<7>

H_RS#[0..2]<7>

H_DSTBN#[0..3]<7>

H_DSTBP#[0..3]<7>

H_RESET#<7>

H_DINV#0<7>

H_DINV#1<7>

H_DINV#2<7>

H_DINV#3<7>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CK_MCH_BCLK#

CK_MCH_BCLK

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

H_RESET#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

U6

T5

R2

U3

R3

P7

T3

P4

P3

P5

R6

N2

N5

N3

J3

M3

M4

M5

L5

K3

J2

N6

L6

L2

K5

L3

L7

K4

J5

U2

T7

R7

U5

T4

R5

N7

K8

J8

U7

V4

W2

Y4

Y3

Y5

W3

V7

V3

Y7

V5

W7

W5

W6

AE17

AD4

AF6

AD11

AC15

AD3

AG6

AE11

AC16

AD5

AG5

AH9

AD15

RG82855PM_UFCBGA593

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

BCLK#

BCLK

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BR0#

BNR#

BPRI#

DBSY#

RS#0

RS#1

RS#2

CPURST#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DBI#0

DBI#1

DBI#2

DBI#3

Odem

HOST

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

HSWNG1

HSWNG0

HRCOMP1

HRCOMP0

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

4

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AE5

AF3

AC6

AC3

AF4

AE2

AG4

AG2

AE7

AE8

AH2

AC7

AG3

AD7

AH7

AE6

AC8

AG8

AG7

AH3

AF8

AH5

AC11

AC12

AE9

AC10

AE10

AD9

AG9

AC9

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

M7

P8

AA9

AB12

220P_0603_50V8J~D

AB16

H_SWNG1

AD13

H_SWNG0

AA7

H_RCOMP1

AC13

H_RCOMP0

AC2

27.4_0603_1%~D

C671

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

1

2

220P_0603_50V8J~D

R593

1 2

C667

0.01U_0402_16V7K~D

H_SWNG1

C669

0.01U_0402_16V7K~D

H_SWNG0

MCH_GTLREF

1

2

C672

Placed near MCH

CK_MCH_BCLK

CK_MCH_BCLK#

H_D#[0..63] <7>

+VCCP

1

2

+VCCP

1

2

+VCCP

1

C673

1U_0805_10V6K~D

2

R594

27.4_0603_1%~D

1 2

C676

2.2P_0402_50V8C~D@

C677

2.2P_0402_50V8C~D@

12

12

12

12

12

R590

49.9_0603_1%~D

12

R591

100_0603_1%~D

12

12

R582

301_0402_1%~D

R583

150_0402_1%~D

R586

301_0402_1%~D

R587

150_0402_1%~D

3

R596

1K_0603_1%~D

R597

1K_0603_1%~D

+1.5VRUN

12

R_M

R_N

1 2

2

G_AD[0..31]<16>

G_C/BE#[0..3]<16>

G_FRAME#<16>

G_DEVSEL#<16>

G_IRDY#<16>

G_TRDY#<16>

G_STOP#<16>

G_PAR<16>

G_REQ#<16>

G_GNT#<16>

G_AD_STB0<16>

G_AD_STB0#<16>

G_AD_STB1<16>

G_AD_STB1#<16>

G_SBA[0..7]<16>

G_SB_STB<16>

G_SB_STB#<16>

G_RBF#<16>

G_WBF#<16>

G_PIPE#<16>

G_ST0<16>

G_ST1<16>

G_ST2<16>

CK_66M_MCH<6>

VREFCG <16>

12

R598

0_0402_5%~D@

VREFGC <16>

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

G_FRAME#

G_DEVSEL#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

G_AD_STB0

G_AD_STB0#

G_AD_STB1

G_AD_STB1#

G_SBA0

G_SBA1

G_SBA2

G_SBA3

G_SBA4

G_SBA5

G_SBA6

G_SBA7

G_SB_STB

G_SB_STB#

G_RBF#

G_WBF#

G_PIPE#

G_ST0

G_ST1

G_ST2

CK_66M_MCH

12

1

@

2

U15B

R27

GAD0

R28

GAD1

T25

GAD2

R25

GAD3

T26

GAD4

T27

GAD5

U27

GAD6

U28

GAD7

V26

GAD8

V27

GAD9

T23

GAD10

U23

GAD11

T24

GAD12

U24

GAD13

U25

GAD14

V24

GAD15

Y27

GAD16

Y26

GAD17

AA28

GAD18

AB25

GAD19

AB27

GAD20

AA27

GAD21

AB26

GAD22

Y23

GAD23

AB23

GAD24

AA24

GAD25

AA25

GAD26

AB24

GAD27

AC25

GAD28

AC24

GAD29

AC22

GAD30

AD24

GAD31

V25

GCBE#0

V23

GCBE#1

Y25

GCBE#2

AA23

GCBE#3

Y24

GFRAME#

W28

GDEVSEL#

W27

GIRDY#

W24

GTRDY#

W23

GSTOP#

W25

GPAR

AG24

GREQ#

AH25

GGNT#

R24

AD_STB0

R23

AD_STB#0

AC27

AD_STB1

AC28

AD_STB#1

AH28

SBA0

AH27

SBA1

AG28

SBA2

AG27

SBA3

AE28

SBA4

AE27

SBA5

AE24

SBA6

AE25

SBA7

AF27

SB_STB

AF26

SB_STB#

AE22

RBF#

AE23

WBF#

AF22

PIPE#

AG25

ST0

AF24

ST1

AG26

ST2

P22

66IN

RG82855PM_UFCBGA593

R595

22_0402_5%~D@

C675

10P_0402_50V8J~D

Odem

AGP

HUB

GND

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

GRCOMP

AGPREF

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

AB9

AD10

AF9

AJ9

A7

F8

J7

L8

N8

R8

U8

W8

AA8

AD8

AF7

AJ7

D5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

AF5

AJ5

A3

J4

L4

N4

R4

U4

W4

AA4

AC4

AE4

AJ3

E1

J1

L1

N1

R1

U1

W1

AA1

AC1

AE1

AG1

AD25

AA21

HUB_HL0

HUB_HL1

HUB_HL2

HUB_HL3

HUB_HL4

HUB_HL5

HUB_HL6

HUB_HL7

HUB_HL8

HUB_HL9

HUB_HL10

HUB_HLSTRB

HUB_HLSTRB#

HUB_RCOMP

HL_REF

C666

0.01U_0402_16V7K~D

AGP_RCOMP

1

C674

0.1U_0603_16V7K~D

2

1 2

1

2

36.5_0603_1%~D

1 2

HUB_HLSTRB <18>

HUB_HLSTRB# <18>

R581

36.5_0603_1%~D

150_0402_1%~D

R_C

150_0402_1%~D

R_D

R592

VREFGC <16>

1

HUB_HL[0..10] <18>

+1.8VRUN

+1.8VRUN

12

R584

HL_REF

12

R589

2

C668

1

HLREF_TERMHHLREF_TERML

R585

56.2_0402_1%~D@

1 2

R588

0_0402_5%~D

1 2

1

C670

2

470P_0402_50V7K~D@

0.01U_0402_16V7K~D

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Odem(1/3)

LA-2501

10 48Tuesday, October 05, 2004

1

1.0

of

5

NEED CHECK THIS POWER

1

+15V

O

1 2

8

IN+

4

R601

0_0402_5%~D@

PLANE

U39A

LM358M_SO8~D@

3

P

2

IN-

G

D D

NEED CHECK THIS POWER

PLANE

DDR_VREF_MCH

10U_0805_10V4M~D@

C C

B B

C679

1

2

+2.5V_MEM

12

12

R600

R599

10K_0603_1%~D@

10K_0603_1%~D@

4

1

C678

0.1U_0603_16V7K~D@

2

+15V

8

U39B

LM358M_SO8~D@

5

P

IN+

7

O

6

IN-

G

4

V_DDR_MCH_REF<14,15,41>

DDR_VREF_MCH

R602

0_0603_5%~D

1 2

1

C680

2

0.1U_0603_16V7K~D

3

C681

DDR_MA[0..12]<14,15>

1

2

0.1U_0603_16V7K~D

T46

PAD

DDR_DS[0..8]<14>

DDR_WE#<14,15>

CK_DDR_CK0#<14>

CK_DDR_CK1#<14>

CK_DDR_CK2#<14>

CK_DDR_CK3#<15>

CK_DDR_CK4#<15>

CK_DDR_CK5#<15>

DDR_CKE0_DIMM0<14>

DDR_CKE1_DIMM0<14>

DDR_CKE2_DIMM1<15>

DDR_CKE3_DIMM1<15>

DDR_CS0_DIMM0#<14>

DDR_CS1_DIMM0#<14>

DDR_CS2_DIMM1#<15>

DDR_CS3_DIMM1#<15>

V_1P25V_DDR_VTT

T48

PAD

T49

PAD

DDR_RAS#<14,15>

DDR_CAS#<14,15>

CK_DDR_CK0<14>

CK_DDR_CK1<14>

CK_DDR_CK2<14>

CK_DDR_CK3<15>

CK_DDR_CK4<15>

CK_DDR_CK5<15>

DDR_BS0<14,15>

DDR_BS1<14,15>

1

C682

0.1U_0603_16V7K~D

2

H_DPSLP#<7,18>

H_DPWR#<7>

DDR_CKE0_DIMM0

DDR_CKE1_DIMM0

DDR_CKE2_DIMM1

DDR_CKE3_DIMM1

DDR_CS0_DIMM0#

DDR_CS1_DIMM0#

DDR_CS2_DIMM1#

DDR_CS3_DIMM1#

R603

30.1_0603_1%~D

1 2

DDR_MA0

DDR_MA1

DDR_MA2

DDR_MA3

DDR_MA4

DDR_MA5

DDR_MA6

DDR_MA7

DDR_MA8

DDR_MA9

DDR_MA10

DDR_MA11

DDR_MA12

DDR_DS0

DDR_DS1

DDR_DS2

DDR_DS3

DDR_DS4

DDR_DS5

DDR_DS6

DDR_DS7

DDR_DS8

DDR_WE#

DDR_RAS#

DDR_CAS#

CK_DDR_CK0

CK_DDR_CK0#

CK_DDR_CK1

CK_DDR_CK1#

CK_DDR_CK2

CK_DDR_CK2#

CK_DDR_CK3

CK_DDR_CK3#

CK_DDR_CK4

CK_DDR_CK4#

CK_DDR_CK5

CK_DDR_CK5#

DDR_BS0

DDR_BS1

DDR_RCOMP

100mils

M_RCV#

AD26

AD27

E12

F17

E16

G17

G18

E18

F19

G20

G19

F21

F13

E20

G21

G22

F26

C26

C23

B19

D12

C8

C5

E3

E15

G11

F11

G8

J25

K25

G5

F5

G24

E24

G25

J24

G6

G7

K23

J23

G23

E22

H23

F23

E9

F7

F9

E7

G12

G13

J9

J21

J28

G15

G14

V8

Y8

2

U15C

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

RSVD2

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SWE#

SRAS#

SCAS#

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCKE0

SCKE1

SCKE2

SCKE3

SCS#0

SCS#1

SCS#2

SCS#3

SBS0

SBS1

SMVREF0

SMVREF1

SMRCOMP

RCVENIN#

RCVENOUT#

DPSLP#

DPWR#

NC0

NC1

Odem

MEMORY

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

RSTIN#

RSVD1

TESTIN#

G28

F27

C28

E28

H25

G27

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

C9

D8

E8

E11

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E4

C3

D3

F4

F3

B2

C2

E2

G4

C16

D16

B15

C14

B17

C17

C15

D14

J27

H27

H26

DDR_D0

DDR_D5

DDR_D3

DDR_D6

DDR_D1

DDR_D4

DDR_D2

DDR_D7

DDR_D8

DDR_D9

DDR_D15

DDR_D11

DDR_D13

DDR_D12

DDR_D10

DDR_D14

DDR_D16

DDR_D17

DDR_D18

DDR_D22

DDR_D20

DDR_D23

DDR_D21

DDR_D19

DDR_D24

DDR_D25

DDR_D29

DDR_D27

DDR_D28

DDR_D26

DDR_D30

DDR_D31

DDR_D32

DDR_D37

DDR_D38

DDR_D39

DDR_D33

DDR_D36

DDR_D34

DDR_D35

DDR_D44

DDR_D45

DDR_D46

DDR_D42

DDR_D40

DDR_D41

DDR_D43

DDR_D47

DDR_D48

DDR_D52

DDR_D51

DDR_D55

DDR_D49

DDR_D53

DDR_D54

DDR_D50

DDR_D56

DDR_D60

DDR_D62

DDR_D59

DDR_D57

DDR_D61

DDR_D58

DDR_D63

DDR_CB2

DDR_CB0

DDR_CB7

DDR_CB3

DDR_CB1

DDR_CB4

DDR_CB5

DDR_CB6

MCH_TEST#

PCIRST_MCH# <18>

1 2

R604

4.7K_0603_5%~D@

1

DDR_CB[0..7] <14>

+1.5VRUN

DDR_D[0..63] <14>

T47

PAD

RG82855PM_UFCBGA593

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Odem(2/3)

LA-2501

11 48Tuesday, October 05, 2004

1

1.0

of

5

U15D

+1.5VRUN

D D

+1.2VRUN

+1.8VRUN

C C

B B

+1.8VRUN

A A

one .01uf and 10

uf each two pins

1

C797

10U_0805_10V4M~D

2

+VCCP

+2.5V_MEM

1

C798

0.01U_0402_16V7K~D

2

5

R29

VCCAGP0

W29

VCCAGP1

AC29

VCCAGP2

AG29

VCCAGP3

U26

VCCAGP4

AA26

VCCAGP5

AE26

VCCAGP6

AJ25

VCCAGP7

AD23

VCCAGP8

AF23

VCCAGP9

R22

VCCAGP10

U22

VCCAGP11

W22

VCCAGP12

AA22

VCCAGP13

AB21

VCCAGP14

AD21

VCCAGP15

P17

VCC0

N16

VCC1

P15

VCC2

R16

VCC3

T15

VCC4

U16

VCC5

N14

VCC6

P13

VCC7

R14

VCC8

U14

VCC9

L29

VCCHL0

L25

VCCHL1

N26

VCCHL2

N23

VCCHL3

M22

VCCHL4

AG23

VCCP0

AJ23

VCCP1

AE21

VCCP2

AG21

VCCP3

AJ21

VCCP4

AB20

VCCP5

AC19

VCCP6

AD20

VCCP7

AE19

VCCP8

AF20

VCCP9

AG19

VCCP10

AJ19

VCCP11

AB18

VCCP12

AD18

VCCP13

AF18

VCCP14

AB14

VCCP15

AB10

VCCP16

M8

VCCP17

T8

VCCP18

AB8

VCCP19

C29

VCCSM0

G29

VCCSM1

A25

VCCSM2

D25

VCCSM3

K26

VCCSM4

D23

VCCSM5

H24

VCCSM6

K24

VCCSM7

L23

VCCSM8

A21

VCCSM9

F22

VCCSM10

H22

VCCSM11

K22

VCCSM12

D19

VCCSM13

H20

VCCSM14

A17

VCCSM15

F18

VCCSM16

H18

VCCSM17

D15

VCCSM18

F16

VCCSM19

H16

VCCSM20

A13

VCCSM21

F14

VCCSM22

H14

VCCSM23

D11

VCCSM24

H12

VCCSM25

A9

VCCSM26

F10

VCCSM27

H10

VCCSM28

D7

VCCSM29

H8

VCCSM30

K7

VCCSM31

A5

VCCSM32

E5

VCCSM33

H5

VCCSM34

J6

VCCSM35

C1

VCCSM36

G1

VCCSM37

T17

VCCGA

T13

VCCHA

RG82855PM_UFCBGA593

Odem

POWER GND

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

ETS#

4

E29

J29

N29

U29

AA29

AE29

A27

K27

AJ27

E26

G26

J26

L26

R26

W26

AC26

AF25

A23

F24

L24

M23

AC23

AH23

D21

H21

J22

L22

N22

T22

V22

Y22

AB22

AC21

AD22

AF21

AG22

AH21

A19

F20

H19

AB19

AC20

AD19

AE20

AF19

AG20

AH19

D17

H17

N17

R17

U17

AB17

AC18

1

AE18

AF17

AG18

2

AJ17

A15

F15

H15

N15

P16

R15

T16

U15

AB15

AD16

AF15

AJ15

D13

E14

H13

N13

P14

R13

T14

U13

AB13

AD14

AF13

AJ13

A11

F12

H11

AB11

AD12

AF11

AJ11

D9

H9

G16

G10

G9

H7

G2

G3

internal pull up

H3

H4

12

R606

4

C716

0.047U_0402_16V4Z~D

R605

10K_0402_5%~D@

1 2

1K_0402_5%~D@

1

2

+1.5VRUN

C683

150U_D2_4VK~D

C692

150U_D2_4VK~D

+1.8VRUN

C700

10U_0805_10V4M~D

+VCCP

C706

150U_D2_4VK~D

C717

1

+

2

1

+

2

1

2

1

+

2

0.047U_0402_16V4Z~D

+2.5V_MEM

3

C722

C742

C757

C771

C785

0.047U_0402_16V4Z~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

C687

2

0.01U_0402_16V7K~D

1

C696

2

0.015U_0402_16V7K~D

1

C710

2

0.1U_0402_16V4Z~D

1

2

C723

0.047U_0402_16V4Z~D

1

1

2

2

C743

0.1U_0402_10V6K~D

1

1

2

2

C758

0.1U_0402_10V6K~D

1

1

2

2

C772

0.1U_0402_10V6K~D

1

1

2

2

C786

0.1U_0402_10V6K~D

1

2

C744

C759

C773

C787

1

C688

2

0.01U_0402_16V7K~D

1

C697

2

0.01U_0402_16V7K~D

1

C711

2

0.1U_0402_16V4Z~D

1

2

C724

C725

0.047U_0402_16V4Z~D

1

1

2

2

C745

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

2

C760

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

2

C774

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

2

C788

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.047U_0402_16V4Z~D

C746

C761

C775

C789

C712

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_16V4Z~D

1

2

1

2

1

2

1

2

1

2

1

C689

2

0.01U_0402_16V7K~D

1

C698

2

0.022U_0402_16V7K~D

C726

C747

C762

C776

C790

0.047U_0402_16V4Z~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

C713

2

0.1U_0402_16V4Z~D

1

1

2

2

C727

0.047U_0402_16V4Z~D

1

1

2

2

C748

0.1U_0402_10V6K~D

1

1

2

2

C763

0.1U_0402_10V6K~D

1

1

2

2

C777

0.1U_0402_10V6K~D

1

1

2

2

C791

0.1U_0402_10V6K~D

1

2

C719

0.047U_0402_16V4Z~D

1

C685

2

10U_0805_10V4M~D

1

C694

2

2.2U_0805_16VFZ~D

1

C702

2

0.1U_0402_16V4Z~D

1

C708

2

0.1U_0402_16V4Z~D

1

2

C720

0.047U_0402_16V4Z~D

1

2

1

2

1

2

1

C684

2

10U_0805_10V4M~D

+1.2VRUN

1

+

C693

150U_D2_4VK~D

2

1

C701

2

0.1U_0402_16V4Z~D

1

C707

2

0.1U_0402_16V4Z~D

1

1

2

2

C718

0.047U_0402_16V4Z~D

C755

C769

C783

1

C686

2

0.01U_0402_16V7K~D

1

C695

2

0.22U_0603_10V7K~D

1

C703

2

0.1U_0402_16V4Z~D

1

C709

2

0.1U_0402_16V4Z~D

1

1

2

2

C721

0.047U_0402_16V4Z~D

1

1

2

2

C741

0.1U_0402_10V6K~D

1

1

2

2

C756

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

2

C770

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

2

C784

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

C690

C699

C728

C749

C764

C778

C792

0.01U_0402_16V7K~D

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

1

2

C714

0.1U_0402_16V4Z~D

1

2

C729

1

2

C750

1

2

C765

1

2

C779

1

2

C793

2

C691

0.01U_0402_16V7K~D

1

22U_1206_10V4Z~D

2

1

2

C730

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

1

2

C751

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

C766

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

C780

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

C794

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

2

+2.5V_MEM

C733

0.047U_0402_16V4Z~D

1

C705

2

1

1

2

2

C734

0.047U_0402_16V4Z~D

V_1P25V_DDR_VTT

10U_0805_10V4M~D

C753

1

C754

2

C735

1

2

0.047U_0402_16V4Z~D

1

2

10U_0805_10V4M~D

C736

1

2

0.047U_0402_16V4Z~D

1

1

2

2

C737

C738

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

V_1P25V_DDR_VTT

C739

0.047U_0402_16V4Z~D

1

2

+2.5V_MEM

C740

0.047U_0402_16V4Z~D

1

+

C715

2

150U_D2_4VK~D

1

C704

22U_1206_10V4Z~D

2

C731

C752

C767

C781

C795

0.047U_0402_16V4Z~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

2

1

2

1

2

1

2

1

2

C732

0.047U_0402_16V4Z~D

0402

C768

0.1U_0402_10V6K~D

C782

0.1U_0402_10V6K~D

C796

0.1U_0402_10V6K~D

1

2

1

2

1

2

1

2

1

2

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Odem(3/3)

LA-2501

12 48Tuesday, October 05, 2004

1

1.0

of

5

+15V

R104

100K_0402_5%~D

FAN1_PWM<32>

D D

FAN2_PWM<32>

C C

1 2

R111

100K_0402_5%~D

1 2

FAN1VREF

FAN1_VFB

1

C75

2

1U_0603_10V4Z~D

R483

1 2

150K_0402_5%~D

FAN2VREF

FAN2_VFB

1

C84

2

1U_0603_10V4Z~D

R96

1 2

150K_0402_5%~D

8

3

P

IN+

O

2

IN-

G

4

C583

2200P_0402_50V7K~D@

1 2

R481

100K_0402_5%~D

12

RB751V_SOD323~D

+15V

8

5

P

IN+

O

6

IN-

G

4

C74

2200P_0402_50V7K~D@

1 2

R82

100K_0402_5%~D

12

RB751V_SOD323~D

U4A

LM358M_SO8~D

U4B

LM358M_SO8~D

1

7

FAN1_ON

D18

1

C51

2

FAN2_ON

D5

4

+5VRUN

6

2

1

D

Q47

G

3

S

SI3456DV-T1_TSOP6~D

4 5

1000P_0402_50V7K~D

1000P_0402_50V7K~D

FAN1_VOUT

1 2

R716

0_0402_5%~D

FAN2_5V

FAN2_5V <16>

FAN2_TACH_FB <16>

1

1

+

C257

C560

2

2

2 1

47U_D_16VM_R70~D

@

+5VRUN

6

2

1

0.1U_0603_25V7K~D

2 1

D

Q7

G

3

S

SI3456DV-T1_TSOP6~D

4 5

1

1

+

C65

2

47U_D_16VM_R70~D

C64

@

2

3

JFAN1

1

1

2

2

3

3

MOLEX_53398-0390~D

CPU

FAN1

JFAN2

1

1

2

2

3

3

MOLEX_53398-0390~D

VGA

FAN2

+3VRUN

12

R476

10K_0402_5%~D

1

C559

1000P_0402_50V7K~D

@

2

+3VRUN

12

R57

10K_0402_5%~D

1

C54

1000P_0402_50V7K~D

@

2

2

FAN1 Control and Tachometer

FAN1_TACH <32>

FAN2 Control and Tachometer

FAN2_TACH <32>

1

C

B

E3

2

2222 SYMBOL(SOT23-NEW)

Note: +3VRUN leakage issue from ATI M22

THERMATRIP_VGA#

+3VRUN

OTEMP<16>

R37

1 2

2.2K_0402_5%~D

C

2

B

E

3 1

Q12

MMBT3904_SOT23~D

R47

1 2

0_0402_5%~D@

1

H_THERMDA<7>

B B

A A

H_THERMDC<7>

+3VSUS

+RTC_CELL

+3VSUS

2200P_0402_50V7K~D

R428

49.9_0603_1%~D

1 2

C496

0.1U_0402_16V4Z~D

1

2

5

C508

0.1U_0402_16V4Z~D

12

R421

51.1K_0603_1%~D

12

R418

12.1K_0603_1%~D

C505

1

2

R430

8.2K_0402_5%~D

1 2

1

2

SUSPWROK<20,35>

ICH_PWRGD#<35>

POWER_SW#<32,35>

DAT_SMB<32,33>

CLK_SMB<32,33>

C483

0.1U_0402_16V4Z~D

1

C478

2200P_0402_50V7K~D

2

1 2

R453 1K_0402_5%~D

+3VSUS_R

1 2

R444 1K_0402_5%~D

1 2

R433 1K_0402_5%~D

THERMATRIP2#

THERMATRIP_VGA#

1

2

R452

1 2

U25

1

THDAT_SMB

2

THCLK_SMB

13

SMBADDRSEL

18

REM_DIODE2_P

17

REM_DIODE2_N

4

+3VSUS

11

VSUS_PWRGD

10

+RTC_PWR3V

5

+3V_PWROK

21

POWER_SW

6

THERMTRIP1

7

THERMTRIP2

8

THERMTRIP3

22

VSET

14

HW_LOCK

3

VSS

EMC6N300_SSOP24~D

1K_0402_5%~D

4

ATF_INT

RESSERVED

REM_DIODE1_N

REM_DIODE1_P

THERMTRIP_SIO

THERM_STP

INTRUDER

VCP

+5VSUS

12

9

23

16

19

20

15

24

12

R424

2.21K_0603_1%~D

1

C489

2

2200P_0402_50V7K~D

+3VALW

12

ATF_INT# <31>

E

B

2

+5VSUS

12

R450

10K_0402_5%~D

3

Q40

C

MMBT3904_SOT23~D

1

5V_CAL_SIO# <31>

2

12

R475

10KB_0603_1%_TSM1A103F34D3R~D

13

D

Q46

2N7002_SOT23~D

REN_DIODE_NTHERMATRIP1#

REN_DIODE_P

R451

100K_0402_5%~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

G

S

1

C503

2

2200P_0402_50V7K~D

THERMTRIP_SIO <32>

THERM_STP# <40>

INTRUDER# <19>

Trace width = 10mil

+VCCP

R120

2.2K_0402_5%~D

1 2

MMBT3904_SOT23~D

H_THERMTRIP#<7,20>

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

LA-2501

Date: Sheet

+3VSUS

12

R124

8.2K_0402_5%~D

THERMATRIP1#

1

C

E

3

12

1

C95

0.1U_0402_16V4Z~D

2

R386

8.2K_0402_5%~D

THERMATRIP2#

1

C406

0.1U_0402_16V4Z~D

2

2

B

Q8

+3VSUS

Compal Electronics, Inc.

Thermal sensor and Fan

13 48Tuesday, October 05, 2004

1

1.0

of

5

4

3

2

1

DDR_D[0..63]<11>

DDR_D5

R850

R851

R852

R853

R756

R758

R760

R761

R858

R860

R862

R864

R762

R764

R766

R768

R721

R724

R770

R771

R772

R774

R870

R871

R872

R873

R778

R779

R780

R782

R878

R879

R880

R882

R786

R787

R788

R789

R888

R890

R892

R894

R896

R898

R900

R901

R902

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D

10_0402_5%~D