Page 1

A

B

C

D

E

http://hobi-elektronika.net

MODEL NAME : EDX20

PCB NO : LA-2481

1 1

PVT

COMPAL CONFIDENTIAL

2 2

EDX20 Schematics Document

2005-02-22

REV: 0.5

3 3

4 4

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

PROPRIETARY NOTE

A

B

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

COVER SHEET

Size Document Number Rev

EDX20 LA-2481

Date: Sheet

E

of

148Tuesday, F e b ru a r y 22, 2005

0.5

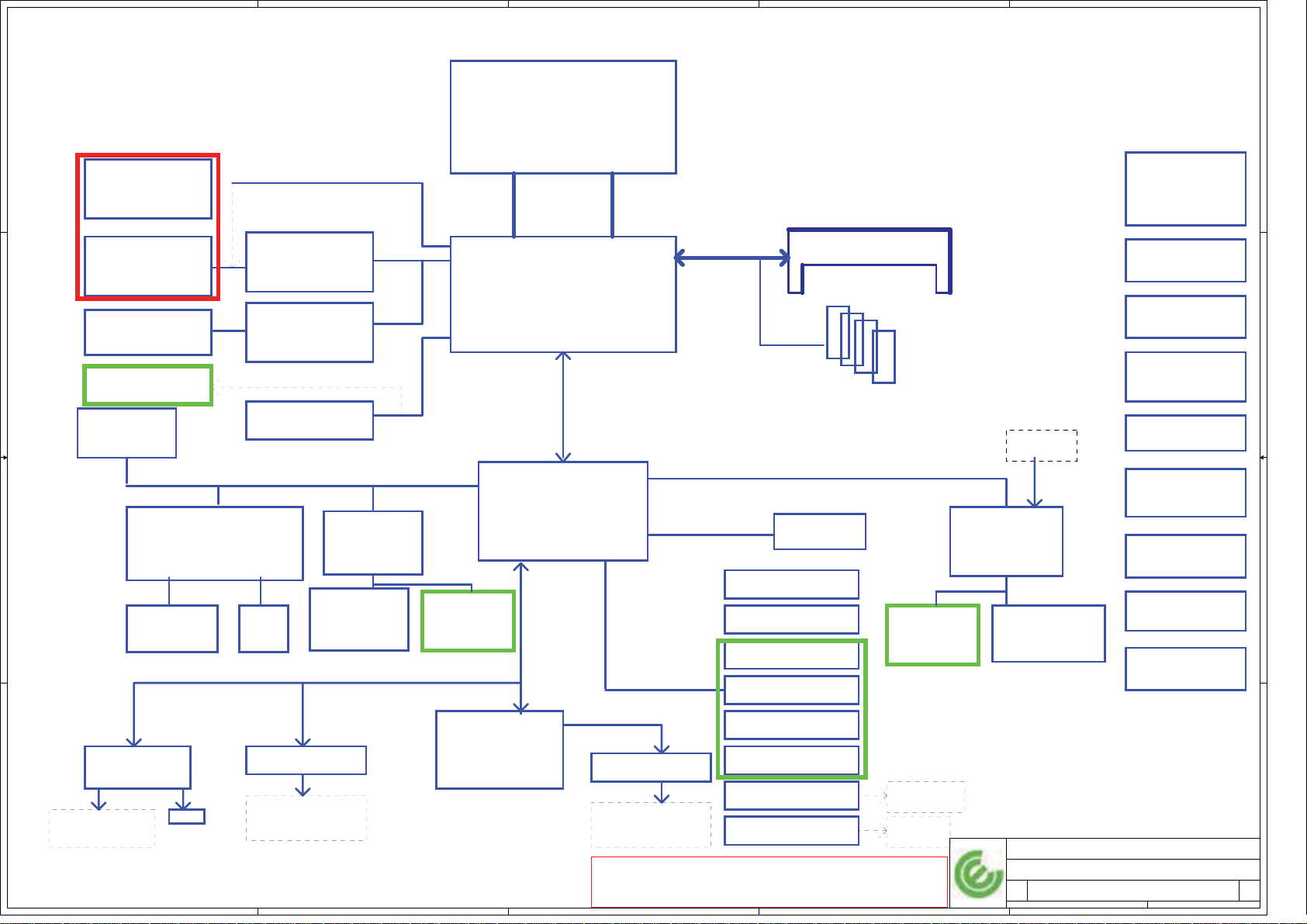

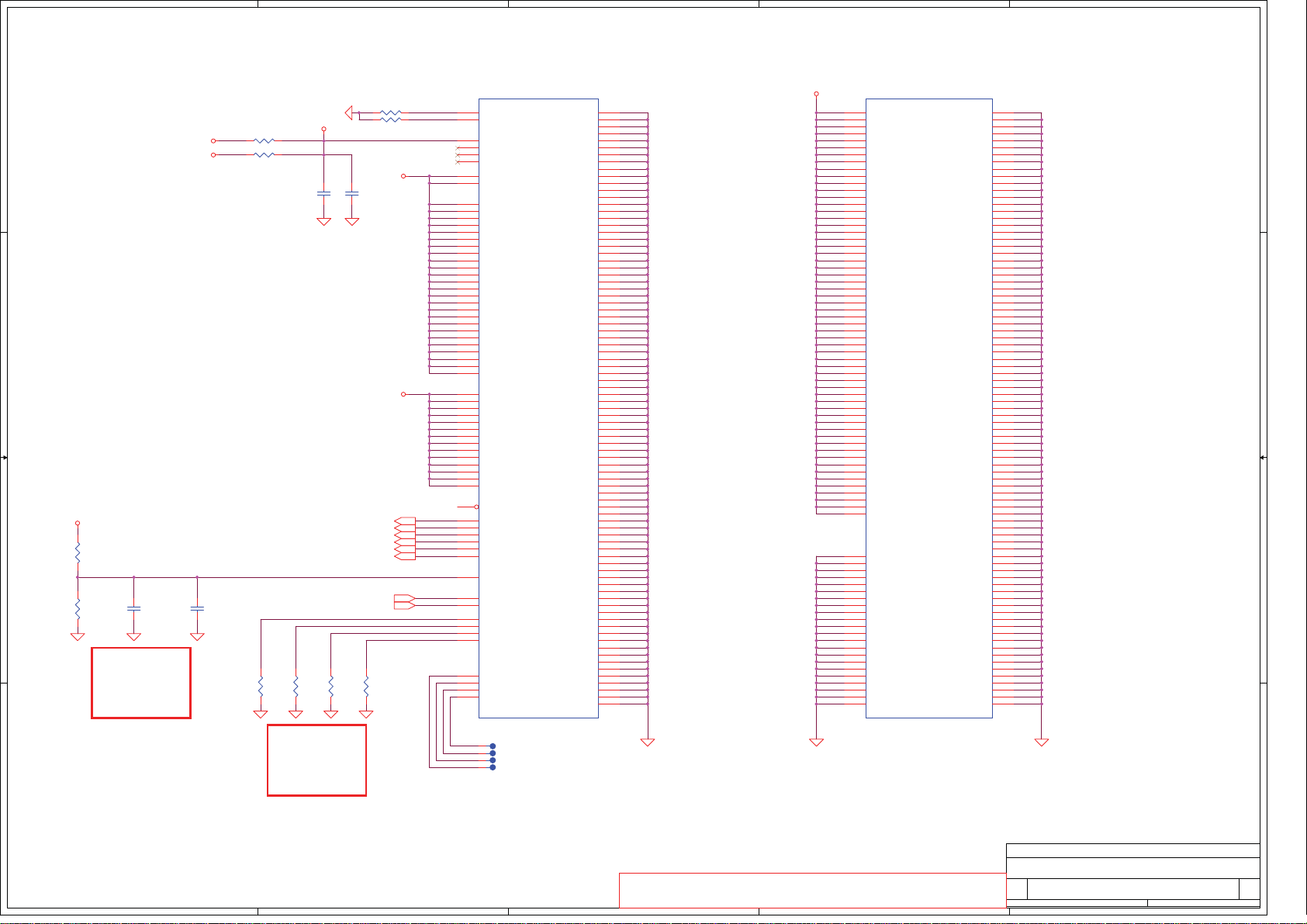

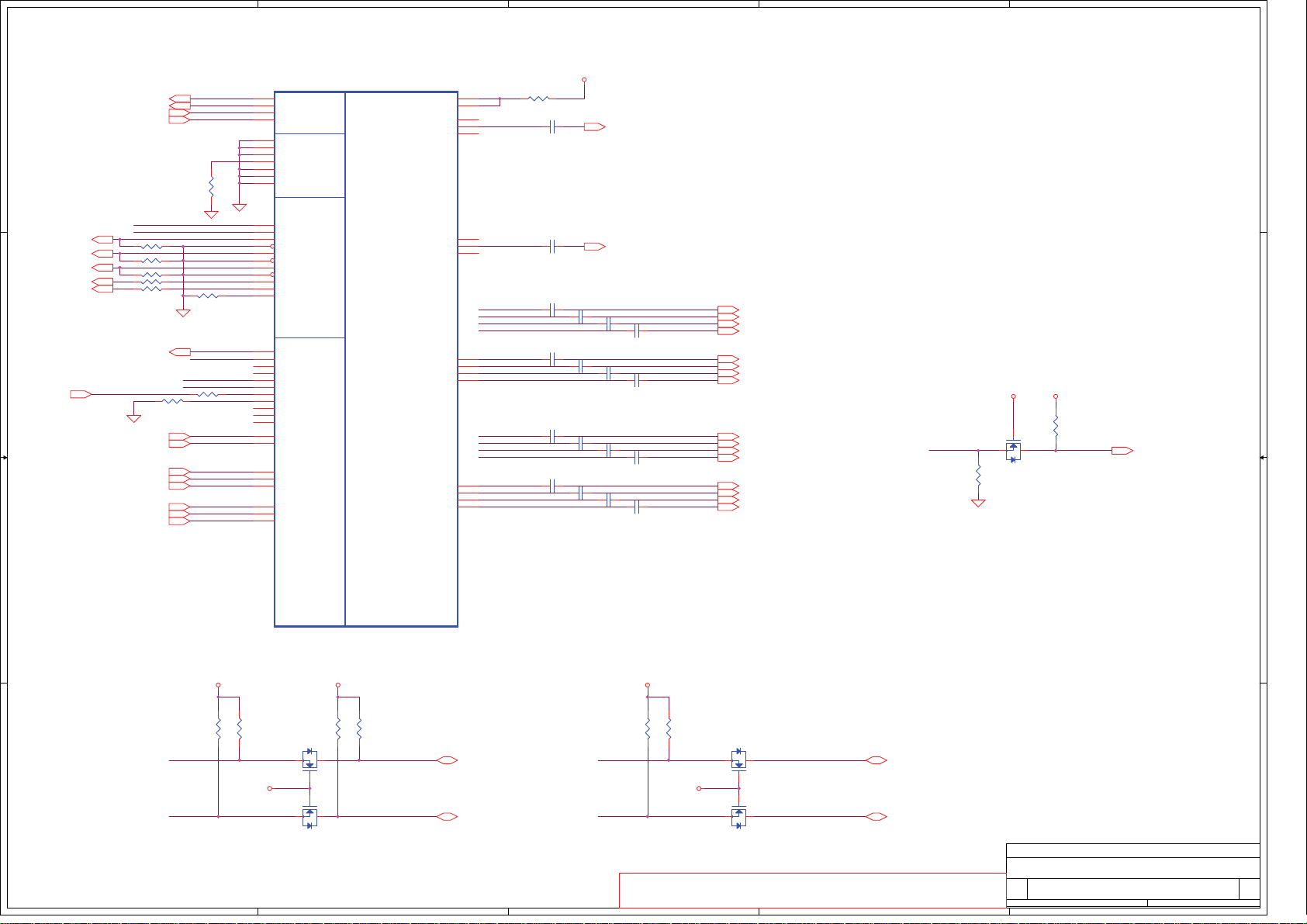

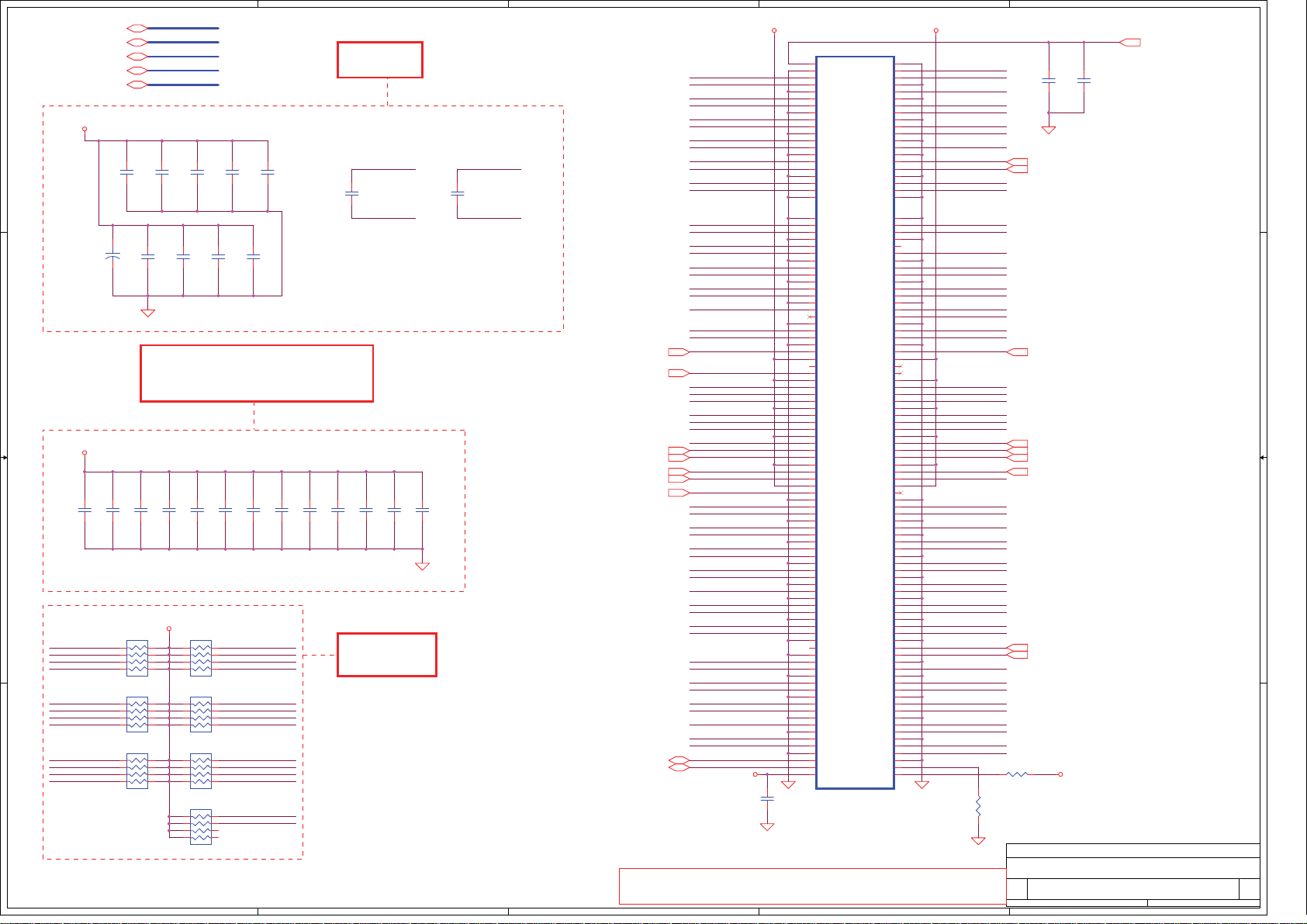

Page 2

5

4

3

2

1

Compal confidential

D D

Hydias/Toshiba

LCD 12.1" XGA

page 17

LCD 12.1" SXGA

page 17 page 17

LVDS Transmitter

CH7308

LVDS

SDVO

DVI Controller

C C

HDMI CONN.

page 16

SiL1362/CH7307

page 16

Docking/CRT

MINI PCI

CRT CONN.

page 26

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

CardBus Controller

B B

CardReader

SIO

ENE CB712

page 24

Slot 0

page 25 page 25 page 28

page 35 page 35

TPM CONN.

page 18

3.3V 33MHz

IDSEL:AD17

(PIRQF#,GNT#3,REQ#3)

Gigabit Lan

RTL8110SBL

page 27

Transformer

& RJ4 5

3.3V 33MHz

PCI BUS

Docking

RJ45

LPC BUS

Keyboard Controller

ENE KB910

LPC47N217D

A A

Digitizer

FIR

5

TPM

SLD9630TT

4

Dothan-LV

uFCBGA CPU

page 5,6

HA#(3..31)

System Bus

400MHz

HD#(0..63)

Intel 915 GMS (Alviso)

GMCH-M

FC-BGA840

DMI

page 8,9,10,11

1.5V

100MHz

AC-LINK

ICH6-M

609 BGA

page 19,20,21,22

page 32,33

XBUS

BIOS CONN.

1MB ROM BIOS

SST39VF080

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

ATA100

USB 2.0

48MHz / 480Mb

3

Memory BUS

(DDR2)

Channel A

1.8V 400MHz

page 34

SO-DIMM X 1

On Board 512 MB (8-Cell)

3.3V 24.576MHz

HDD 1.8"

page 23

Pecos USB port0

Pecos USB port1

LLANO USB port2

LLANO USB port3

LLANO USB port4

Travel Dock USB port5

Bluetooth USB port6

Finger Printer USB port7

page 31

page 31

page 36

page 36

page 36

page 36

page 36

page 36

BANK 0

page 14

page 12,13

AC97 CODEC

Docking

Phone/Mic

BT Module

FPR brd

2

Block Diagram

Clock Generator

IDT CV140

Fan Control X1

SW LED BD

BATT IN/+2.5V

Mic 1/2/3

STAC9758

page 29

AMP & Phone

MIC

Title

Size Document Number Rev

Date: Sheet

page 30

Compal Electronics, Inc.

1.05V(+VCCP)

5V/3.3V/15V

1.8V / 0.9V

VCORE

CHARGER

Block Diagram

EDX20 LA-2481

1

page 15

page 5

page 42

page 44

page 41

page 42,43

page 45

page 39

248Tuesday, Fe b r u a r y 22, 2005

of

0.5

http://hobi-elektronika.net

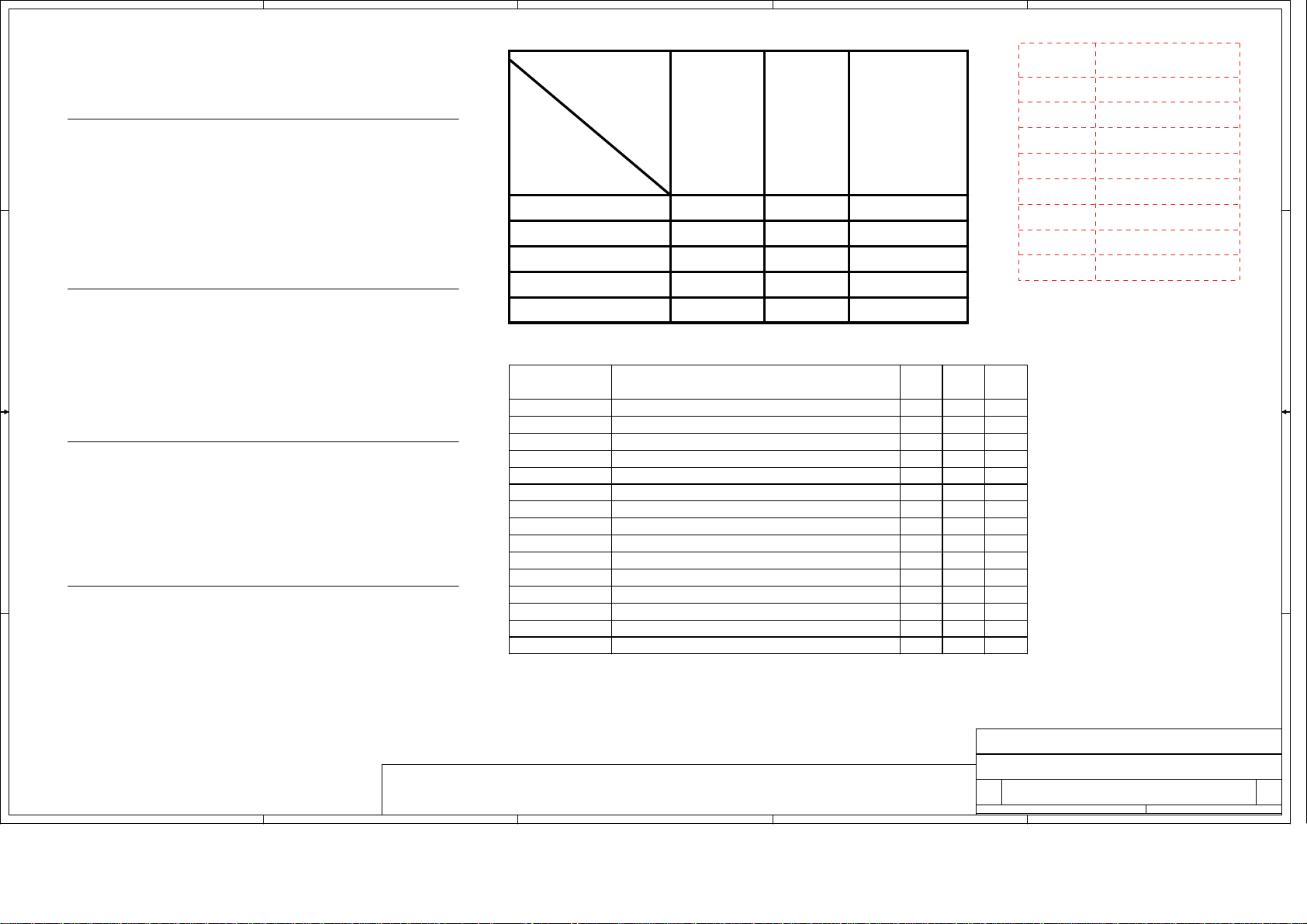

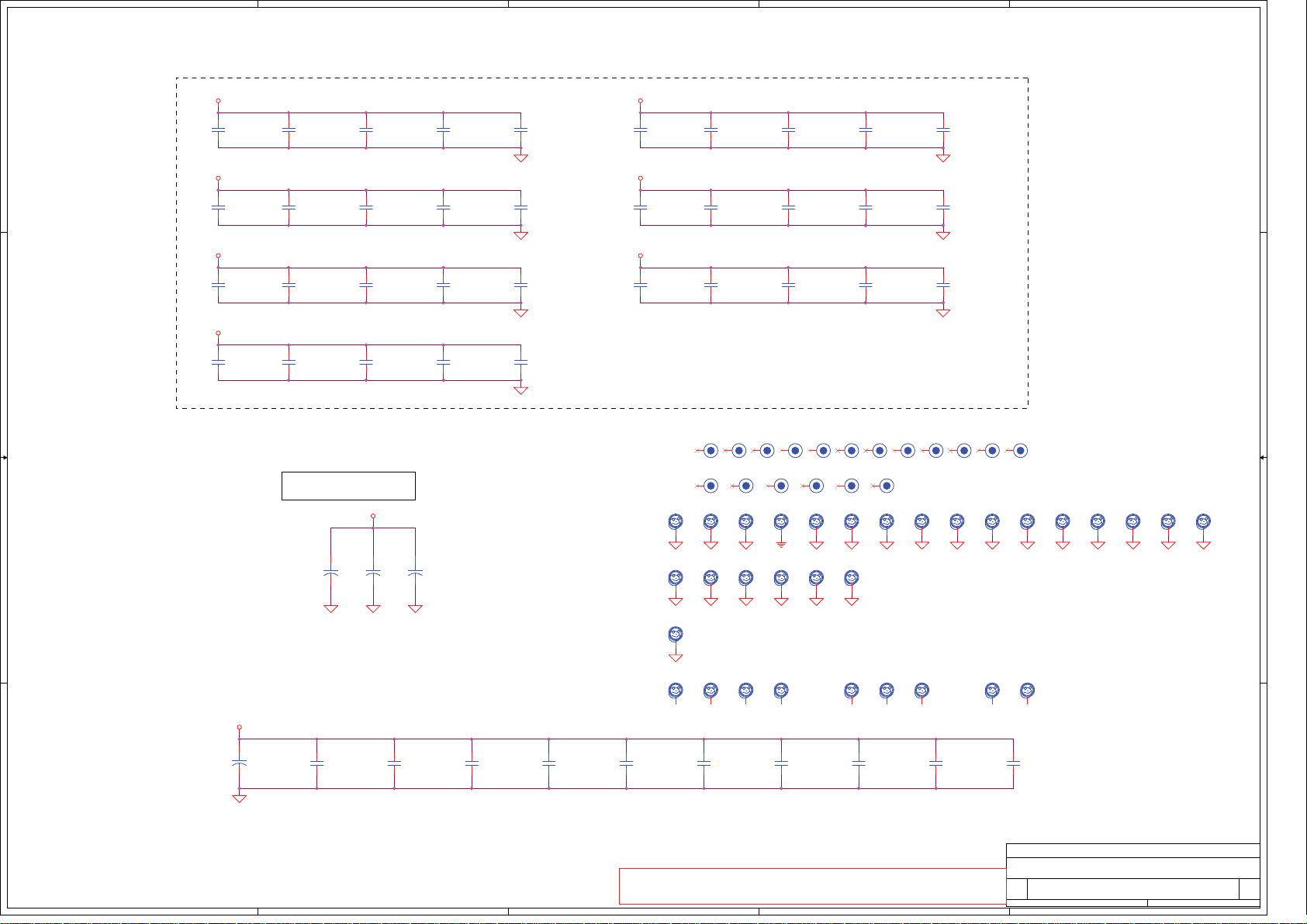

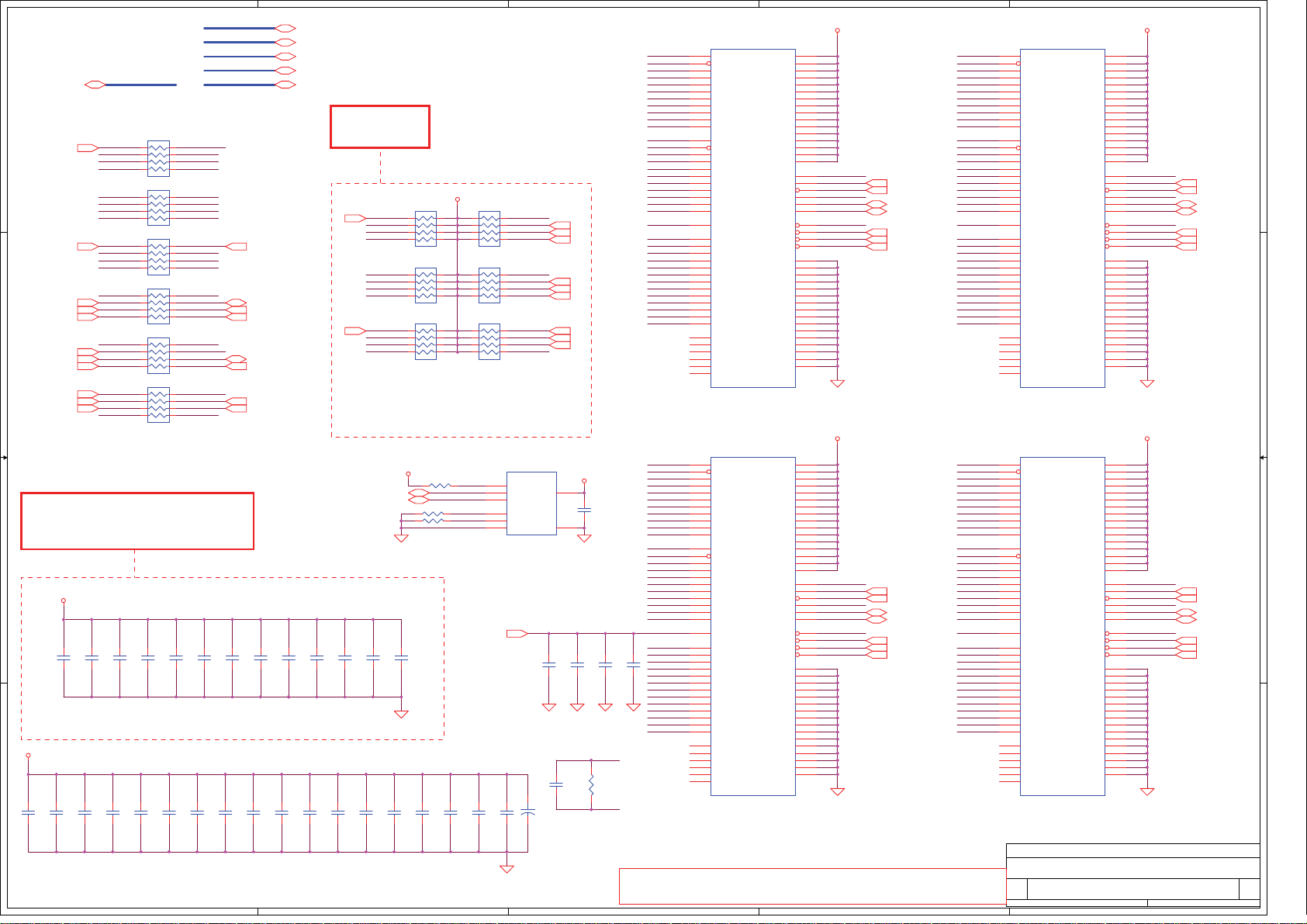

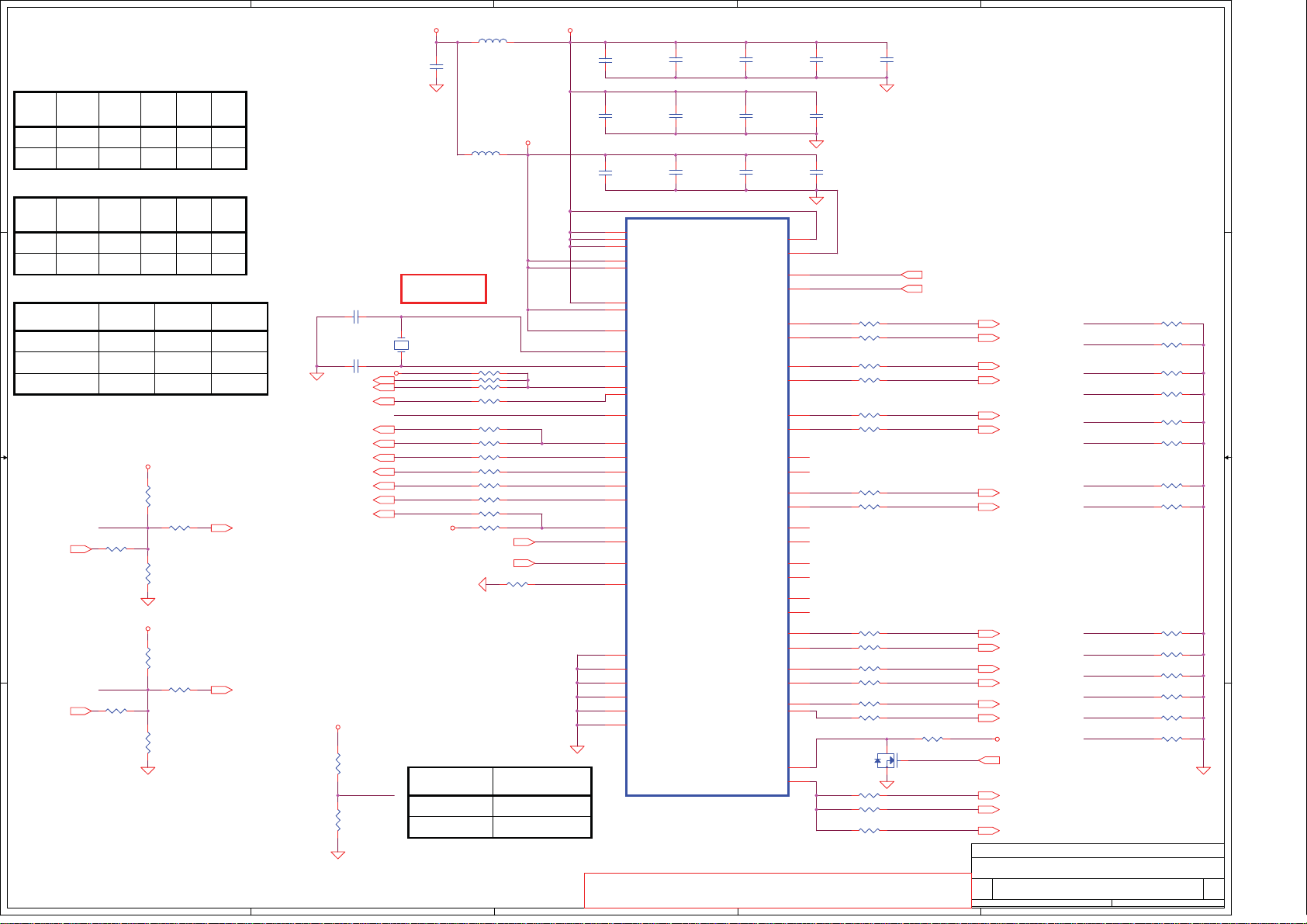

Page 3

5

4

3

2

1

http://hobi-elektronika.net

Power Management table

+12VALW

External PCI Devices

D D

DEVICE

Mini-PCI

LAN AD17 3 F

IDSEL #

AD18

AD20

REQ/GNT #

1

2A BCARD BUS

PIRQ

G,H

State

Signal +1.8VS

+5VALW

+3VALW

+1.8V

+5VS

+3VS

+2.5VS

+1.5VS

+0.9VS

+VCCP

+CPU_CORE

ON

S1

ICH6M SM Bus Address

DEVICE

C C

Clock Generator

DDR2 On Board

DDR2 DIMM1

TPM

Address

1101 001Xb

1010 000Xb

1010 001Xb

EC SM Bus1 Address

AddressDEVICE

Smart Battery 1

AT24C16AN-10SI-2.7(U24) 1011 XXX R/W#b

B B

0001 011Xb

EC SM Bus2 Address

DEVICE

Smart Battery 2

ALS TSL2550T

ADM1032

TC74A1-5.0VCT(U34) 1001 001Xb

TC74A2-5.0VCT(U43) 1001 010Xb

Address

0001 011Xb

1001 100Xb

S3

S5 S4/AC

S5 S4/AC don't exist

Voltage Rails

Power Plane

VIN

B+

+CPU_CORE

+VCCP

+0.9VS

+1.5VS

+1.8V

+2.5VS

+3VALW

+3VS 3.3V switched power rail

+5VALW

+5VS

+12VALW

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Description

Adapter power supply (19V)

AC or battery power rail for power circuit

Core voltage for CPU

1.05V power rail for Processor I/O and MCH core power

0.9V switched power rail for DDRII Vtt

1.5V switched power rail for PCI-E interface

1.8V power rail for DDRII

1.8V switched power rail+1.8VS ON

2.5V switched power rail for MCH video PLL

3.3V always on power rail

5V always on power rail

5V switched power rail

12V always on power rail

ON ON

ON ON

ON

OFF

ON

OFF

ONONS0

OFF

OFFOFF

OFF

S0-S1

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ONRTC power

S3

N/A

N/A

OFF

OFF

OFF

ON

OFF OFF

OFF

ON ON*

OFF

ON

OFF

ON ON*

ON

USB PORT TABLE

PORT FUNCTION

PORT 0

PORT 1

PORT 2

PORT 3

PORT 4

PORT 5

PORT 6

PORT 7

S5

N/A

N/A

OFF

OFFOFF

OFF

OFF

OFF

OFF

OFF

ON*

OFF

ON

PECOS PORT 0

PECOS PORT 1

LLANO PORT 2

LLANO PORT 0

LLANO PORT 1

TRAVEL DOCKING

BLUETOOTH

FINGER PRINTER

A A

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

PROPRIETARY NOTE

5

4

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

NOTE&Revision

Size Document Number Rev

EDX20 LA-2481

Date: Sheet

1

of

348Tuesday, February 22, 2005

0.5

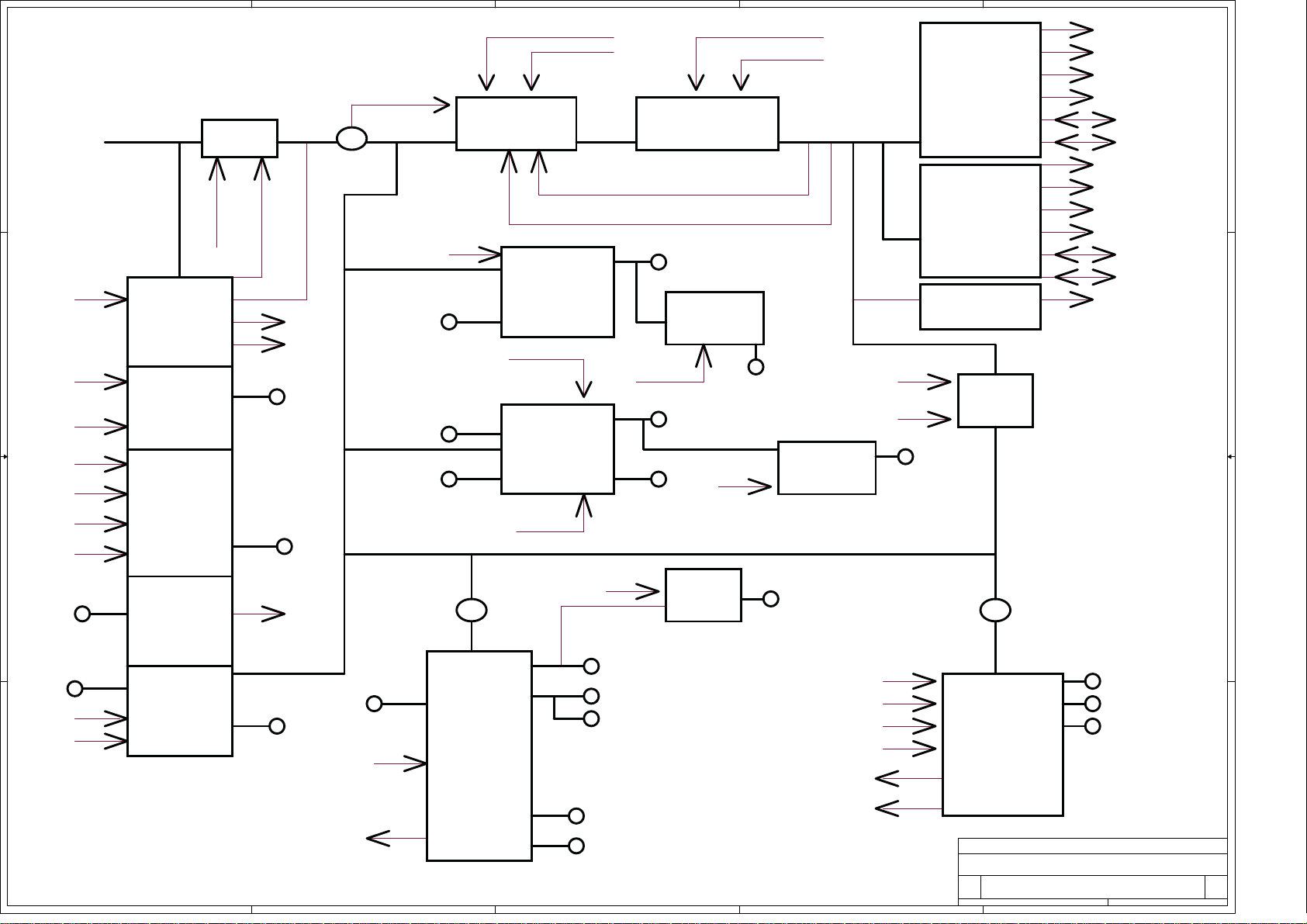

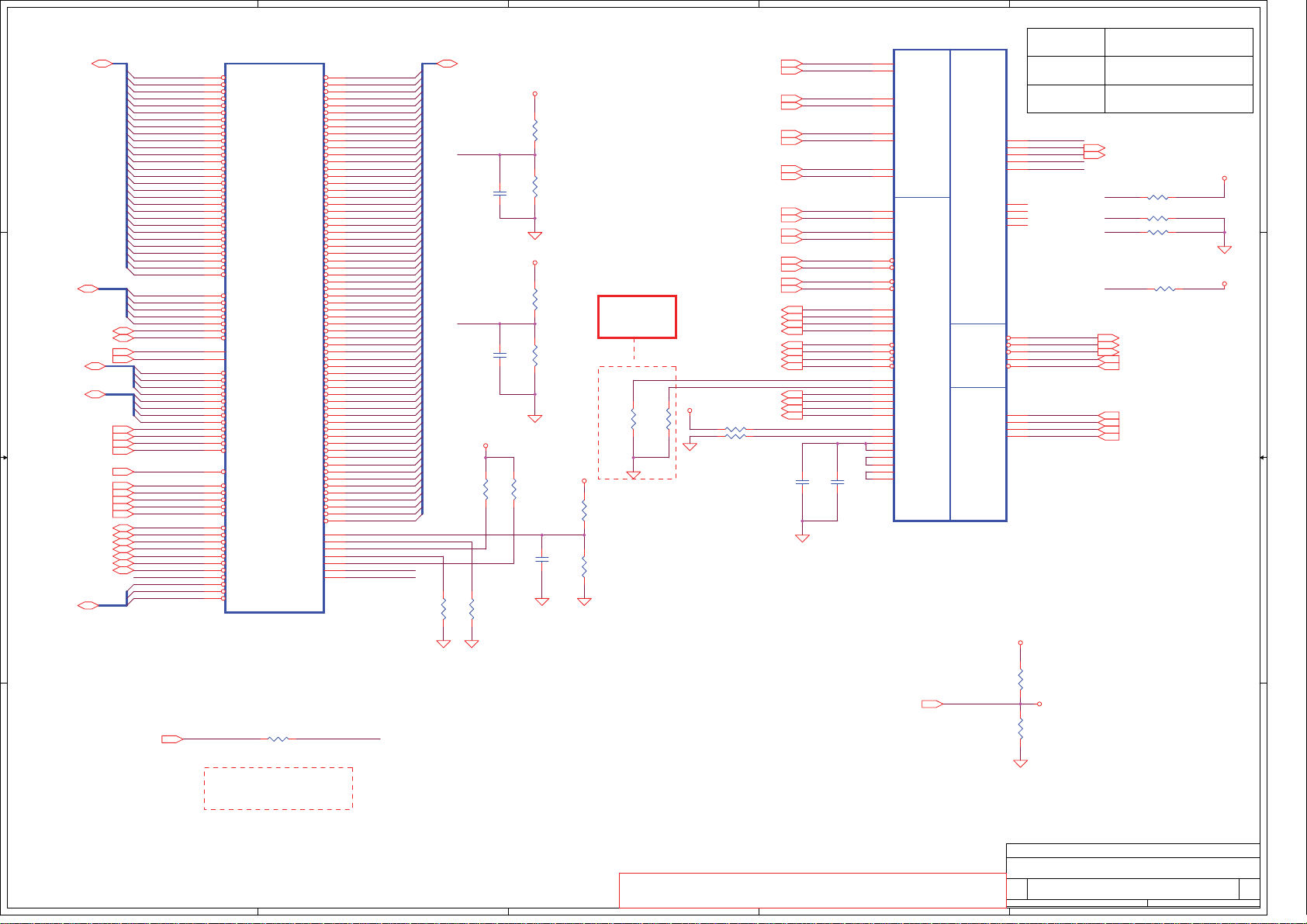

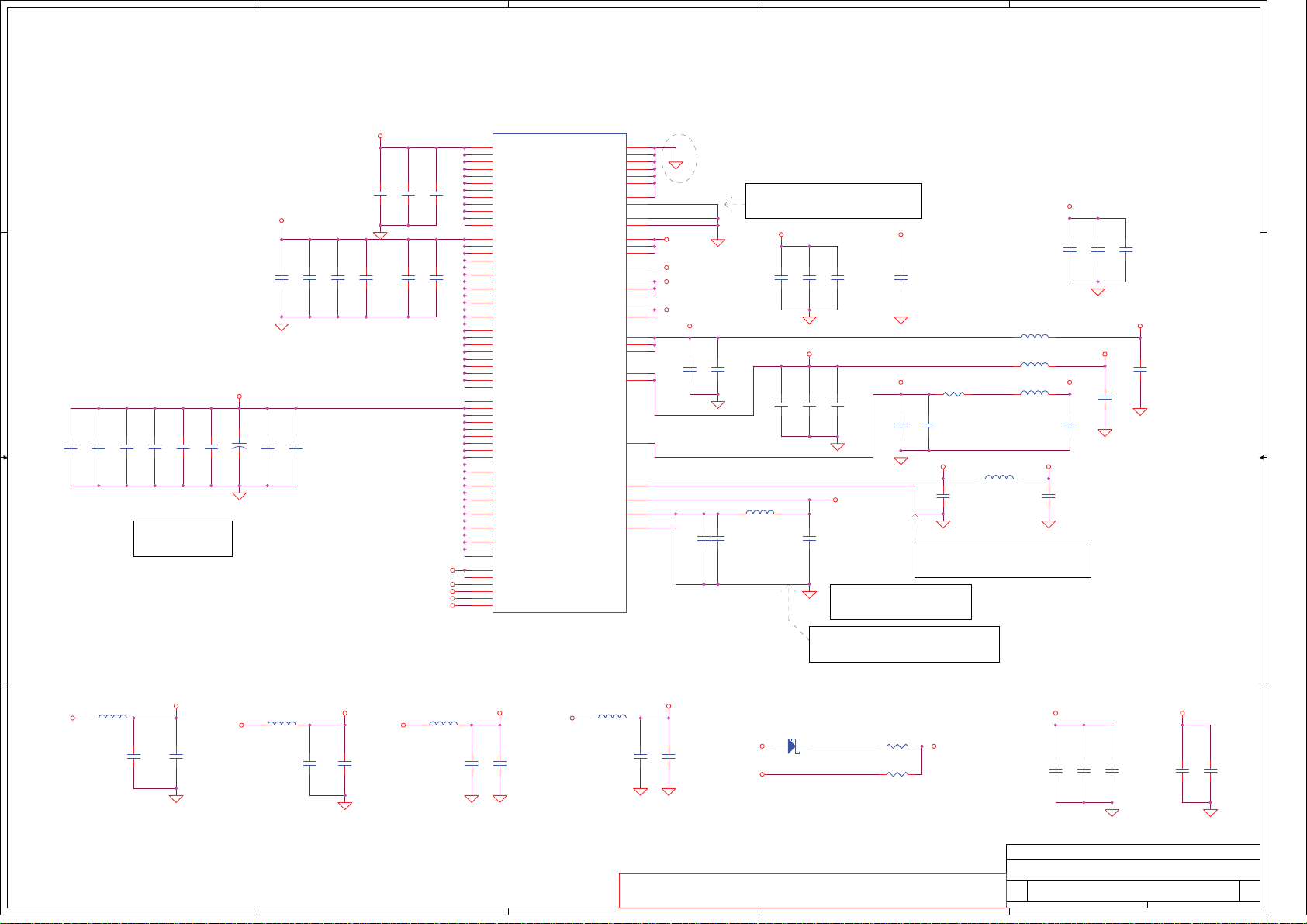

Page 4

5

Input Current Sense

D D

C C

PACIN

VIN

VIN

Vin

Detector

+VS

EC_ON#

VIN

VSB

BATT_A

BATT_B

B B

RTC

Charger

OVER

VL

TEMP.

P2

SWITCH

ACOFF#

RTCVREF

MAINPWRON

P3

PACIN

PACIN

ACIN

VS

PROTECT

+12VALW

Bridge

SPOK

SUSP#

A A

battery

5

VSB

MAINPWRON

SPOK

4

IREF

B+

CHG_B+

B+

+3VALW

+5VALW

+1.8VPGD

+VCCP_PWRGD

VS

DC-DC

MAX1902

4

3

http://hobi-elektronika.net

FSTCHG

MAX1908

Charger

Output Current Sense

VMB Feedback

Batt selector

BATSELB_A#

FSTCHG

MAX1538

+1.5VALWP

DC-DC

FAN5234

LM358

SYSON SYSON#

+1.2VP

+1.8VP

DC-DC

ISL6227

SUSP

+VCCPP

SUSP#

SUSP#

B+++

LDO

G965

+3VALWP

+5VALWP

+12VPALWP

VL

2.5VREF

3

BATT+

LDO

+2.5VSP

VR_ON

PM_DPRSLPVR

H_DPSLP#

SYSPOK

VGATE

CLKEN#

2

A or B

VIN

ACOFF

+0.9VSPAPL5331

2

1

BATT_A+ PIN1

ID PIN2

A Battery

B Battery

OVP

B/I PIN3

TS PIN4

SMD PIN5

SMC PIN6

BATT_A+ PIN1

ID PIN2

B/I PIN3

TS PIN4

SMD PIN5

SMC PIN6

BATT-OVP

Protector

SWITCH

CPU_B+

+CPU_CORE

DC-DC

MAX1907

Title

POWER Tree

Size Do cu ment Number Rev

EDX20 LA-2481

Date: Sheet

REF

+5VALWP

448Tuesday, February 22, 2005

1

0.5

of

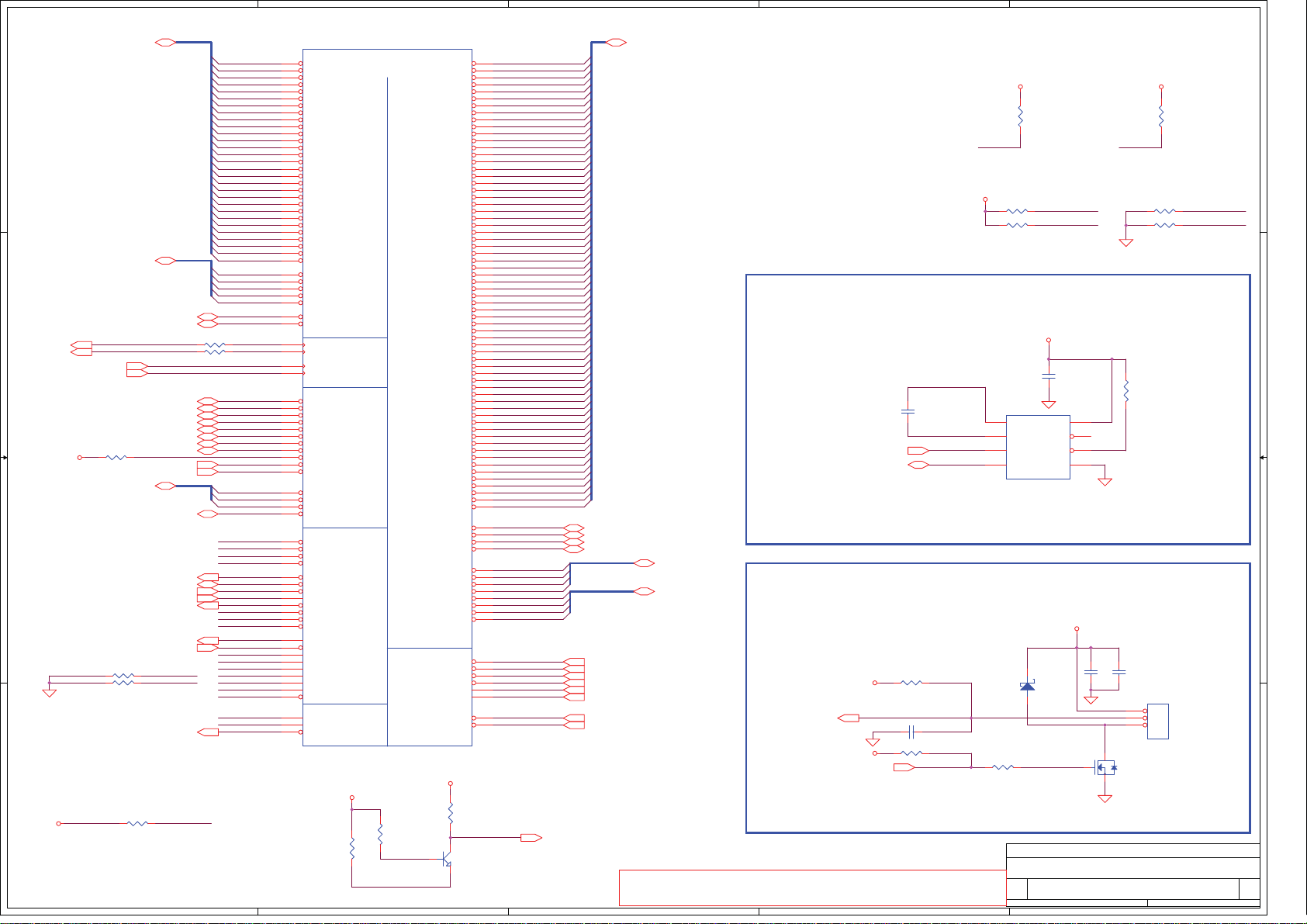

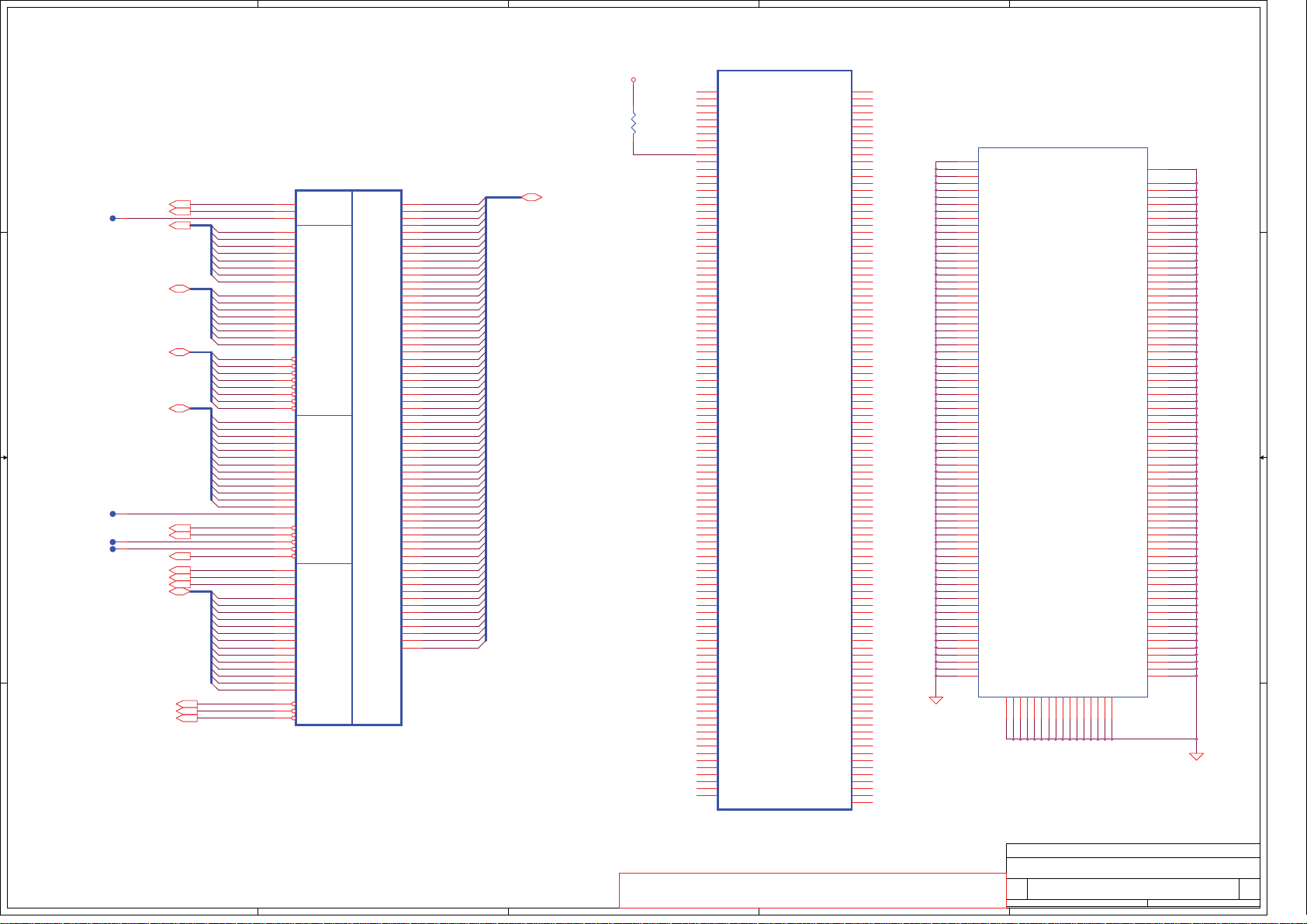

Page 5

5

4

3

2

1

H_A#[3..31]<8>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

R399 0_0402_5%@

1 2

1 2

R398 0_0402_5%@

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_CK_ITP

CPU_CK_ITP#CK_ITP#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

D D

H_REQ#[0..4]<8>

H_ADSTB#0<8>

H_ADSTB#1<8>

H_RS#[0..2]<8>

12

12

1 2

5

CK_ITP

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#<8>

H_BNR#<8>

H_BPRI#<8>

H_BR0#<8>

H_DEFER#<8>

H_DRDY#<8>

H_HIT#<8>

H_HITM#<8>

H_LOCK#<8>

H_RESET#<8>

H_TRDY#<8>

ITP_DBRESET#<21>

H_DBSY#<8>

H_DPSLP#<20,45>

H_DPRSTP#<20>

H_DPWR#<8>

H_PWRGOOD<20>

H_CPUSLP#<8,20>

TEST1

R1571K_0402_5%@

TEST2

R1871K_0402_5%@

H_THERMTRIP#<8,20>

H_PWRGOOD

CK_ITP<15>

C C

CK_ITP#<15>

CLK_CPU_BCLK<15>

CLK_CPU_BCLK#<15>

R153

1 2

+VCCP

56_0402_5%

B B

A A

+VCCP

R154 200_0402_1%

U1A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

FOX_PZ47803-2749-01

56_0402_5%

Dothan

ADDR GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

+VCCP

12

R400

H_PROCHOT#

DATA GROUP

LEGACY CPU

12

R397

56_0402_5%

4

2

B

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

IGNNE#

STPCLK#

+3VS

C

E

http://hobi-elektronika.net

H_D#0

A19

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

A20M#

FERR#

INIT#

LINT0

LINT1

SMI#

12

R396

1K_0402_5%

1

Q37

2SC2411K_SC59

3

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

PROCHOT#

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

PROCHOT# <32>

H_D#[0..63] <8>

Thermal Sensor

1

SMB_EC_CK2<32,34,36,38>

SMB_EC_DA2<32,34,36,38>

+5VS

R93 10K_0402_5%@

C86 1000P_0402_50V7K

+3VS

R73 8.2K_0402_5%

EC_PWM4<32>

2

C452

2

1 2

1 2

1 2

2200P_0402_50V7K

H_DINV#0 <8>

H_DINV#1 <8>

H_DINV#2 <8>

H_DINV#3 <8>

H_A20M# <20>

H_FERR# <20>

H_IGNNE# <20>

H_INIT# <20>

H_INTR <20>

H_NMI <20>

H_STPCLK# <20>

H_SMI# <20>

H_DSTBN#[0..3] <8>

H_DSTBP#[0..3] <8>

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

PWM Fan Control circuit

FAN_SPEED1<32>

+VCCP +VCCP

R26

54.9_0402_1%

1 2

H_RESET# ITP_TDO

+VCCP

1 2

R21 39.2_0603_1%

1 2

R22 150_0402_5%

+3VS

1

H_THERMDA

H_THERMDC

SMB_EC_CK2

SMB_EC_DA2

U36

2

3

8

7

G781_SOP8

1 2

R106

100_0402_1%

Title

Size Document Number Rev

Custom

Date: Sheet

C451

0.1U_0402_16V4Z

2

VDD1

D+

ALERT#

D-

THERM#

SCLK

GND

SDATA

D2

CH355_SC76

2 1

Dothan Processor in mFCPGA479

EDX20 LA-2481

R27

54.9_0402_1%

1 2

ITP_TMS

ITP_TDI

+5VS

1

6

THERM#

4

5

1

C83

2

2

G

1 2

R24 680_0402_5%

1 2

R23 27.4_0402_1%

12

R394

10K_0402_5%@

1

C92

0.1U_0402_16V4Z

2

10U_0805_10V4Z

JP5

1

1

2

2

3

3

MOLEX_53780-0310

13

D

Q9

FDN359AN_SOT23

S

Compal Electronics, Inc.

1

548Tuesday, F e br u a r y 22, 2005

ITP_TRST#

ITP_TCK

0.5

of

Page 6

5

4

3

2

1

http://hobi-elektronika.net

R278

54.9_0402_1%@

D D

R193 0_0805_5%@

+1.8VS

R188 0_0805_5%

+1.5VS

1 2

1 2

+1.8VS FOR NON-LV/ULV PROCESSOR

+1.5VS FOR LV/ULV PROCESSOR

C C

+VCCP

12

R247

B B

A A

1K_0402_1%

12

R249

2K_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

miles away from any

other toggling signal.

1

C242

1U_0603_10V4Z

@

2

1

C248

220P_0402_50V7K

@

2

27.4_0402_1%

R220

+CPU_VCCA

C153

0.01U_0402_16V7K

12

12

54.9_0402_1%

27.4_0402_1%

R224

R274

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

miles away from any

other toggling signal.

54.9_0402_1%@

1

1

C151

2

2

10U_1206_6.3V6M

+VCC_CORE

CPU_VID0<45>

CPU_VID1<45>

CPU_VID2<45>

CPU_VID3<45>

CPU_VID4<45>

CPU_VID5<45>

CPU_BSEL0<15>

CPU_BSEL1<15>

12

12

54.9_0402_1%

R267

1 2

1 2

R279

+VCCP

+CPU_GTLREF

VCCSENSE

VSSSENSE

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

U1B

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

FOX_PZ47803-2749-01

Dothan

POWER, GROUNG, RESERVED SIGNALS AND NC

T17 PAD

T18 PAD

T8 PAD

T5 PAD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

+VCC_CORE

U1C

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA19

VCC

AA21

VCC

AB6

VCC

AB8

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

FOX_PZ47803-2749-01

Dothan

POWER, GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Dothan Processor in mFCPGA479

EDX20 LA-2481

1

of

648Tuesday, F e br u a r y 22, 2005

0.5

Page 7

5

4

3

2

1

http://hobi-elektronika.net

+VCC_CORE

D D

C C

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C155

10U_1206_6.3V6M

C246

10U_1206_6.3V6M

C161

10U_1206_6.3V6M

C277

10U_1206_6.3V6M

@

1

C169

10U_1206_6.3V6M

2

1

C247

10U_1206_6.3V6M

2

1

C160

10U_1206_6.3V6M

2

1

C278

10U_1206_6.3V6M

2

@

1

C178

10U_1206_6.3V6M

2

1

C237

10U_1206_6.3V6M

2

1

C183

10U_1206_6.3V6M

2

1

C279

10U_1206_6.3V6M

2

@

1

C195

10U_1206_6.3V6M

2

1

C232

10U_1206_6.3V6M

2

1

C184

10U_1206_6.3V6M

2

1

C280

10U_1206_6.3V6M

2

@

1

C211

10U_1206_6.3V6M

2

1

C212

10U_1206_6.3V6M

2

1

C210

10U_1206_6.3V6M

2

1

C281

10U_1206_6.3V6M

2

@

Near VCORE regulator.

+VCC_CORE

1

+

2

1

+

C238

2

330U_D2E_2.5VM_R9

9mOhm

7343

PS CAP

1

C215

0.1U_0402_16V4Z

2

1

C202

0.1U_0402_16V4Z

2

1

C148

0.1U_0402_16V4Z

2

1

B B

9mOhm

7343

PS CAP

+VCCP

1

+

C187

150U_D2_4VM

2

A A

+

C260

2

330U_D2E_2.5VM_R9

9mOhm

7343

PS CAP

1

C234

0.1U_0402_16V4Z

2

@

C252

330U_D2E_2.5VM_R9

9mOhm

7343

PS CAP

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

1

C149

0.1U_0402_16V4Z

2

C231

10U_1206_6.3V6M

C196

10U_1206_6.3V6M

C227

10U_1206_6.3V6M

1

1

H2

HOLEA

1

H7

HOLEB

1

H25

HOLEC

1

H3

HOLED

1

1

C236

10U_1206_6.3V6M

2

1

C179

10U_1206_6.3V6M

2

1

C273

10U_1206_6.3V6M

2

@

CF12

1

FD1

1

H4

HOLEA

1

H11

HOLEB

1

H22

HOLED

1

1

C150

0.1U_0402_16V4Z

2

CF10

FD2

H5

HOLEA

1

H15

HOLEB

1

H10

HOLED

1

CF4

1

1

CF5

FD5

H27

HOLEA

1

H24

HOLEB

1

H1

HOLEE

1

1

C244

10U_1206_6.3V6M

2

1

C156

10U_1206_6.3V6M

2

1

C275

10U_1206_6.3V6M

2

@

CF2

1

FD4

1

H26

HOLEA

1

H29

HOLEE

1

1

C188

0.1U_0402_16V4Z

2

1

C245

10U_1206_6.3V6M

2

1

C162

10U_1206_6.3V6M

2

1

C276

10U_1206_6.3V6M

2

@

CF1

CF11

1

1

H20

H21

HOLEA

HOLEA

1

CL3

HOLED

C225

0.1U_0402_16V4Z

CF3

1

1

1

H28

HOLEA

CL2

HOLED

1

2

H16

HOLEA

1

1

1

C139

0.1U_0402_16V4Z

H12

HOLEA

1

H14

HOLEA

1

H8

HOLEA

1

H6

HOLEA

1

CF7

CF6

1

1

H17

HOLEA

1

H50

HOLEE

1

1

2

1

C243

10U_1206_6.3V6M

2

1

C170

10U_1206_6.3V6M

2

1

C274

10U_1206_6.3V6M

2

@

CF8

CF9

1

H9

HOLEA

H13

HOLEB

H19

HOLED

1

FD3

1

1

1

1

1

C175

0.1U_0402_16V4Z

2

1

H18

HOLEA

H23

HOLEB

FD6

1

1

1

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

CPU Bypass

EDX20 LA-2481

1

0.5

of

748Tuesday, F e br u a r y 22, 2005

Page 8

5

4

3

2

1

http://hobi-elektronika.net

AE31

AJ29

AF31

AJ28

AC23

AC25

AH21

AJ21

AD11

AG13

AL14

AH12

AB27

AF12

AG12

AK13

AJ12

AA25

AC10

AD10

W29

U24

W31

U26

AF5

AH5

AE5

AE9

AD7

AE7

AE1

V24

V29

V26

V31

AJ5

Y30

Y24

U31B

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

SM_CK0

SM_CK1

SM_CK3

SM_CK4

SM_CK0#

SM_CK1#

SM_CK3#

SM_CK4#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SMOCDCOMP0

SMOCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO_BGA840

CFG0

CFG1

CFG2

CFG5

CFG6

DMIDDR MUXING

RSVD23

RSVD24

RSVD25

RSVD1

CFG/RSVD

BM_BUSY#

EXT_TS0#

THRMTRIP#

PWROK

PM

RSTIN#

DREF_CLKN

CLK

DREF_CLKP

DREF_SSCLKP

DREF_SSCLKN

C56

0.1U_0402_16V4Z

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

DDR_CLK0

DDR_CLK1

DDR_CLK3

DDR_CLK4

DDR_CLK0#

DDR_CLK1#

DDR_CLK3#

DDR_CLK4#

DDR_CKE0

DDR_CKE1

DDR_CKE2

DDR_CKE3

DDR_CS0#

DDR_CS1#

DDR_CS2#

DDR_CS3#

M_OCDOCMP0

M_OCDOCMP1

DDR_ODT0

DDR_ODT1

DDR_ODT2

DDR_ODT3

SMRCOMPN

SMRCOMPP

DDR_VREF

1

C52

2

1

2

0.1U_0402_16V4Z

G11

E12

C11

B11

A11

D12

F13

E11

A13

C12

G12

G14

G13

H14

B13

A14

C13

H12

E13

C14

F14

E14

D13

B14

F11

H15

AA3

AA4

AA5

J14

J15

J12

G5

G4

W5

G9

G1

C6

B8

C9

A8

B7

A9

A7

Y3

K8

U1

L9

U2

J6

L7

R7

F7

E9

A4

E5

C3

B2

C4

F9

E8

B3

F8

C5

A5

B5

C7

U31A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

HCLKN

HCLKP

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

Alviso

HOST

ALVISO_BGA840

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

F5

F2

E2

J5

F3

G3

F4

E3

J9

F6

J7

J8

J1

F1

K9

G7

K3

K4

P1

R2

K5

J3

J2

L5

U8

K7

U9

V9

R1

K6

U3

R9

V3

V4

R6

P5

P3

R8

P7

P9

W3

R4

R3

R5

U6

U5

V5

V6

W7

W8

W1

V2

W4

Y2

Y5

AA9

AA8

AA1

V7

AA6

Y6

Y8

W9

Y7

J11

K1

E6

L1

K2

J13

L3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_SWNG0

H_SWNG1

12

R74

24.9_0402_1%

H_SWNG1

H_SWNG0

C59

+VCCP

R45

54.9_0402_1%

12

R58

24.9_0402_1%

C71

0.1U_0402_16V4Z

0.1U_0402_16V4Z

12

R78

1

R75

2

R35

1

R39

2

12

R57

54.9_0402_1%

+VCCP

12

221_0603_1%

12

100_0402_1%

+VCCP

12

221_0603_1%

12

100_0402_1%

1

C62

2

220P_0402_50V7K

+VCCP

12

R50

100_0402_1%

12

R48

200_0402_1%

Layout Note:

Route as short

as possible

12

R44

40.2_0402_1%

@

12

+1.8VS

R94

R96 80.6_0402_1%

R92 80.6_0402_1%

40.2_0402_1%

@

DMI_TXN0<21>

DMI_TXN1<21>

DMI_TXP0<21>

DMI_TXP1<21>

DMI_RXN0<21>

DMI_RXN1<21>

DMI_RXP0<21>

DMI_RXP1<21>

DDR_CLK0<12,13>

DDR_CLK1<12,13>

DDR_CLK3<14>

DDR_CLK4<14>

DDR_CLK0#<12,13>

DDR_CLK1#<12,13>

DDR_CLK3#<14>

DDR_CLK4#<14>

DDR_CKE0<13>

DDR_CKE1<13>

DDR_CKE2<14>

DDR_CKE3<14>

DDR_CS0#<13>

DDR_CS1#<13>

DDR_CS2#<14>

DDR_CS3#<14>

DDR_ODT0<13>

DDR_ODT1<13>

DDR_ODT2<14>

DDR_ODT3<14>

1 2

1 2

H_A#[3..31]<5> H_D#[0..63] <5>

D D

H_REQ#[0..4]<5>

H_ADSTB#0<5>

C C

B B

H_ADSTB#1<5>

CLK_MCH_BCLK#<15>

CLK_MCH_BCLK<15>

H_DSTBN#[0..3]<5>

H_DSTBP#[0..3]<5>

H_DINV#0<5>

H_DINV#1<5>

H_DINV#2<5>

H_DINV#3<5>

H_RESET#<5>

H_ADS#<5>

H_TRDY#<5>

H_DPWR#<5>

H_DRDY#<5>

H_DEFER#<5>

H_HITM#<5>

H_HIT#<5>

H_LOCK#<5>

H_BR0#<5>

H_BNR#<5>

H_BPRI#<5>

H_DBSY#<5>

H_RS#[0..2]<5>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_R_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

D15

E17

F15

G17

H17

H19

F29

E27

W2

J26

J27

J18

W27

W25

A22

A21

J31

H31

+1.8V

CFG[2:0]

CFG5

CFG6

CFG0

MCH_CLKSEL1

MCH_CLKSEL0

CFG5

CFG6

PM_BMBUSY#

EC_EXTTS#0

H_THERMTRIP#

VGATE

PLT_RST#

DREFCLK#

DREFCLK

DREF_SSCLK

DREF_SSCLK#

Refer to page15 for FS B

frequency select

Low = DMI x 2

High = DMI x 4

Low = DDR-II

High = DDR-I

MCH_CLKSEL1 <15>

MCH_CLKSEL0 <15>

CFG0

CFG5

CFG6

EC_EXTTS#0

PM_BMBUSY# <21>

EC_EXTTS#0 <32>

H_THERMTRIP# <5,20>

VGATE <15,21,32,45>

PLT_RST# <16,17,19,21,23,35>

DREFCLK# <15>

DREFCLK <15>

DREF_SSCLK <15>

DREF_SSCLK# <15>

12

R31 10K_0402_5%

1 2

R38 2.2K_0402_5%

1 2

R41 2.2K_0402_5%

R12 10K_0402_5%

*

*

+VCCP

+2.5VS

12

12

R34

DDR_VREF<12,13,14>

R47

H_CPUSLP#<5,20>

H_CPUSLP# H_R_CPUSLP#

0_0402_5%

1 2

DDR_VREF

1K_0402_1%

12

R37

1K_0402_1%

DDR_VREF

MCH-R

Note:

Not install MCH-R for Dothan-A,

A A

5

Install MCH-R for Dothan-B"

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Alviso(1 of 4)

EDX20 LA-2481

1

0.5

of

848Tuesday, F e br u a r y 22, 2005

Page 9

5

4

3

2

1

http://hobi-elektronika.net

Sonoma_Platform_MOW_04WW25

+2.5VS

M13

NC

M14

NC

AB18

M15

M16

M17

M18

M19

M20

M21

M22

N10

N11

N12

N13

N14

N15

N16

N17

N18

N19

N20

N21

N22

R10

R11

R12

R13

R14

R18

R19

R20

R21

R22

U10

U11

U12

U13

U14

U18

U19

U20

U21

U22

W10

W11

W12

W13

W14

W15

W16

W17

W18

W19

W20

W21

W22

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

T11

T12

T13

T14

T18

T19

T20

T21

V10

V11

V12

V13

V14

V15

V16

V17

V18

V19

V20

V21

V22

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y17

Y18

Y19

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

ALVISO_BGA840

12

D D

DDR2_

ADDR_A

DDR2_DATA

DDR2_ADDR_B DDR2_ADDR_A DDR2_DQS

ALVISO_BGA840

U31C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Y27

Y28

AC29

AE29

AA28

AA29

AB31

AC30

AG29

AG28

AJ26

AL26

AG30

AG31

AL27

AK27

AF29

AE28

AE25

AE24

AE27

AF27

AE23

AC26

AL25

AJ25

AG27

AG26

AK25

AL24

AG23

AG24

AK11

AL11

AJ7

AL9

AL12

AJ11

AH9

AJ9

AG10

AF10

AH7

AF6

AH11

AG11

AG6

AE6

AL7

AK7

AK2

AJ2

AK6

AJ6

AK3

AH2

AH1

AG1

AC6

AC7

AF3

AE3

AD3

AC2

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_ABA0<13>

DDR_ABA1<13>

T2 PAD

DDR_DM[0..7]<12,14>

DDR_DQS[0..7]<12,14>

C C

B B

A A

T4 PAD

T3 PAD

T1 PAD

DDR_DQS#[0..7]<12,14>

DDR_AA[0..12]<13>

DDR_ACAS#<13>

DDR_ARAS#<13>

DDR_AWE#<13>

DDR_BBA0<14>

DDR_BBA1<14>

DDR_BBA2<14>

DDR_BA[0..13]<14>

DDR_BCAS#<14>

DDR_BRAS#<14>

DDR_BWE#<14>

DDR_ABA0

DDR_ABA1

DDR_ABA2

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_DQS#0

DDR_DQS#1

DDR_DQS#2

DDR_DQS#3

DDR_DQS#4

DDR_DQS#5

DDR_DQS#6

DDR_DQS#7

DDR_AA0

DDR_AA1

DDR_AA2

DDR_AA3

DDR_AA4

DDR_AA5

DDR_AA6

DDR_AA7

DDR_AA8

DDR_AA9

DDR_AA10

DDR_AA11

DDR_AA12

DDR_AA13

DDR_ACAS#

DDR_ARAS#

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

DDR_AWE#

DDR_BBA0

DDR_BBA1

DDR_BBA2

DDR_BA0

DDR_BA1

DDR_BA2

DDR_BA3

DDR_BA4

DDR_BA5

DDR_BA6

DDR_BA7

DDR_BA8

DDR_BA9

DDR_BA10

DDR_BA11

DDR_BA12

DDR_BA13

DDR_BCAS#

DDR_BRAS#

DDR_BWE#

AE15

AD13

AB25

AA31

AJ30

AF24

AK24

AJ10

AG7

AD6

AB29

AL28

AF25

AJ23

AK10

AG9

AH3

AE2

AA30

AK28

AF26

AJ24

AL10

AF9

AG5

AF2

AC21

AC20

AC19

AD20

AE19

AE20

AF20

AF21

AE21

AA24

AC11

AB23

AB24

AF13

AE12

AG15

AC27

AB26

AJ15

AJ14

AG14

AL21

AC12

AE14

AC15

AD14

AG19

AJ19

AJ20

AK20

AL19

AH20

AF14

AL20

AG20

AL13

AJ13

AH14

AK14

AL5

SA_BS0

SA_BS1

SA_BS2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SB_BS0

SB_BS1

SB_BS2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_WE#

DDR_DQ[0..63] <12,14>

R16

10K_0402_5%

U31F

A10

NC

A2

NC

A29

NC

A3

NC

A30

NC

A31

NC

AA10

NC

AA11

NC

AA12

NC

AA13

NC

AA14

NC

AA15

NC

AA16

NC

AA17

NC

AA18

NC

AA19

NC

AA20

NC

AA21

NC

AA22

NC

AB1

NC

AB10

NC

AB11

NC

AB12

NC

AB13

NC

AB14

NC

AB15

NC

AB17

NC

AB19

NC

AB2

NC

AB20

NC

AB21

NC

AB22

NC

AB3

NC

AB5

NC

AB6

NC

AB7

NC

AB9

NC

AC22

NC

AE22

NC

AF22

NC

AG22

NC

AJ1

NC

AJ22

NC

AJ31

NC

AK1

NC

AK22

NC

AK31

NC

AL1

NC

AL2

NC

AL22

NC

AL29

NC

AL3

NC

AL30

NC

AL31

NC

B1

NC

B10

NC

B31

NC

C1

NC

C10

NC

C31

NC

E10

NC

F10

NC

G10

NC

J10

NC

K10

NC

K11

NC

K12

NC

K13

NC

K14

NC

K15

NC

K17

NC

K18

NC

K19

NC

K20

NC

K21

NC

K22

NC

K23

NC

K25

NC

K26

NC

K27

NC

K29

NC

K30

NC

K31

NC

L10

NC

L11

NC

L12

NC

L13

NC

L14

NC

L15

NC

L16

NC

L17

NC

L18

NC

L19

NC

L20

NC

L21

NC

L22

NC

M10

NC

M11

NC

M12

NC

Y20

NC

Y21

NC

Y22

NC

AA23

AA26

AA27

AB28

AB30

AC24

AC28

AD12

AD15

AD19

AD21

AE10

AE11

AE13

AE26

AE30

AF11

AF15

AF19

AF23

AF28

AF30

AG21

AG25

AH10

AH13

AH15

AH19

AJ27

AK12

AK15

AK19

AK21

AK23

AK26

AK29

A15

A18

A20

A25

A27

AA2

AA7

AC9

AD2

AD5

AD9

AF7

AG2

AG3

AH6

AJ3

AK5

AK9

B12

B15

B22

B27

C15

C17

C19

C25

C30

D11

D14

U23

U25

U27

V28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B9

VSS

VSS

VSS

VSS

C2

VSS

VSS

VSS

C8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U29

VSS

VSS

VSS

VSS

VSS

VSS

U4

W24

W26

W28

W30

U31G

VSSW6VSS

Y23

B30

VSSALVDS

D18

VSS

D19

VSS

D25

VSS

E15

VSS

E21

VSS

E23

VSS

E26

VSS

E29

VSS

E30

VSS

E4

VSS

E7

VSS

F12

VSS

F17

VSS

F23

VSS

F27

VSS

G15

VSS

G2

VSS

G21

VSS

G22

VSS

G25

VSS

G29

VSS

G31

VSS

G6

VSS

G8

VSS

H11

VSS

H13

VSS

H18

VSS

H20

VSS

H23

VSS

H26

VSS

H30

VSS

J17

VSS

J20

VSS

J22

VSS

J4

VSS

L2

VSS

L25

VSS

L27

VSS

L29

VSS

L4

VSS

L6

VSS

L8

VSS

M23

VSS

M25

VSS

M27

VSS

M29

VSS

N25

VSS

N27

VSS

N29

VSS

N31

VSS

P2

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

P4

VSS

P6

VSS

P8

VSS

R16

VSS

R24

VSS

R25

VSS

R26

VSS

R27

VSS

R29

VSS

U15

VSS

U17

VSS

U7

VSS

V1

VSS

V25

VSS

V30

VSS

V8

VSS

VSS

VSS

VSS

VSS

VSS

VSSY4VSSY9VSS

Y25

Y26

ALVISO_BGA840

Y29

Y31

V27

U31

Title

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Alviso(2 of 4)

EDX20 LA-2481

1

0.5

of

948Tuesday, F e br u a r y 22, 2005

Page 10

5

4

3

2

1

http://hobi-elektronika.net

+1.5VS_PCIE

U31E

MISCTVVGALVDS

PCI - EXPRESS GRAPHICS

EXP_COMPI

EXP_ICOMPO

SDVO_TVCLKIN#

SDVO_INT#

SDVO_FLDSTALL#

SDVO_TVCLKIN

SDVO_INT

SDVO_FLDSTALL

SDVOB_RED#

SDVOB_GREEN#

SDVOB_BLUE#

SDVOB_BLKN

SDVOB_RED

SDVOB_GREEN

SDVOB_BLUE

SDVOB_BLKP

P26

L26

M28

P28

U28

L28

N28

R28

M30

N26

P30

U30

L30

M26

N30

R30

12

220_0402_1%

12

W23

H27

G27

V23

A17

C18

A19

J19

B17

B18

B19

J23

J25

D23

C23

E22

D22

F21

F22

G23

H22

J21

G26

F26

D26

C26

E25

F25

H25

F30

G30

J29

H29

D27

C27

F31

D31

D29

E31

D30

C29

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

SDVO_SDAT<16>

SDVO_SCLK<16>

CLK_MCH_3GPLL#<15>

D D

CRT_VSYNC<18>

CRT_HSYNC<18>

C C

ENVDD<17>

CLK_MCH_3GPLL<15>

12

R388

CRT_DDCCL

CRT_B<18>

CRT_G<18>

CRT_R<18>

CRT_DDCDA

150_0402_5%

150_0402_5%

150_0402_5%

39_0402_5%

39_0402_5%

GM_PWM_L<17>

ENVDD

1 2

R8 1.5K_0402_1%

TXACLK-<17>

TXACLK+<17>

TXA0-<17>

TXA1-<17>

TXA2-<17>

TXA0+<17>

TXA1+<17>

TXA2+<17>

4.99K_0603_1%

R25

12

R28

12

R33

12

R1152

12

R1153

12

R36

GM_PWM_L

ENABLT_R

LDDC_CLK

LDDC_DATA

LIBG

R30 0_0402_5%

TXACLKTXACLK+

TXA0TXA1TXA2-

TXA0+

TXA1+

TXA2+

R32

24.9_0402_1%

1 2

SDVO_INT-

SDVO_INT+

SDVO_RSDVO_GSDVO_BSDVO_CLK-

SDVO_RSDVO_GSDVO_BSDVO_CLK-

SDVO_R+

SDVO_G+

SDVO_B+

SDVO_CLK+

SDVO_R+

SDVO_G+

SDVO_B+

SDVO_CLK+

C43

0.1U_0402_16V4Z

C40

0.1U_0402_16V4Z

C402 0.1U_0402_16V4Z@2CH

C400 0.1U_0402_16V4Z@2CH

C31 0.1U_0402_16V4Z

C16 0.1U_0402_16V4Z

C401 0.1U_0402_16V4Z@2CH

C399 0.1U_0402_16V4Z@2CH

C21 0.1U_0402_16V4Z

C12 0.1U_0402_16V4Z

SDVOB_INT- <16>

SDVOB_INT+ <16>

C406 0.1U_0402_16V4Z@2CH

C405 0.1U_0402_16V4Z

C37 0.1U_0402_16V4Z

C49 0.1U_0402_16V4Z

C404 0.1U_0402_16V4Z

C403 0.1U_0402_16V4Z

@2CH

C34 0.1U_0402_16V4Z

C46 0.1U_0402_16V4Z

@2CH

@2CH

2CH_SDVOB_R- <17>

2CH_SDVOB_G- <17>

2CH_SDVOB_B- <17>

2CH_SDVOB_CLK- <17>

SDVOB_R- <16>

SDVOB_G- <16>

SDVOB_B- <16>

SDVOB_CLK- <16>

2CH_SDVOB_R+ <17>

2CH_SDVOB_G+ <17>

2CH_SDVOB_B+ <17>

2CH_SDVOB_CLK+ <17>

SDVOB_R+ <16>

SDVOB_G+ <16>

SDVOB_B+ <16>

SDVOB_CLK+ <16>

ENABLT_R

R5

100K_0402_5%

+2.5VS +5VS

S

BSS138_SOT23

1 2

12

G

2

R4

Q1

2.2K_0402_5%

13

D

ENABKL <17,32>

B B

ALVISO_BGA840

+2.5VS

12

12

2.2K_0402_5%

<BOM Structure>

+2.5VS

2N7002_SOT23

R1

2.2K_0402_5%

Q2

2N7002_SOT23

Q3

R2

LDDC_CLK

A A

LDDC_DATA LCD_DDCDATA

5

+3VS +2.5VS

12

12

2.2K_0402_5%

<BOM Structure>

R19

2.2K_0402_5%

4

LCD_DDCCLK

LCD_DDCCLK <17>

LCD_DDCDATA <17>

R20

D

S

13

G

2

G

2

13

D

S

12

12

R1154

CRT_DDCCL

CRT_DDCDA 3VDDCDA

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2.2K_0402_5%

<BOM Structure>

+2.5VS

2N7002_SOT23

R1155

2.2K_0402_5%

Q54

2N7002_SOT23

Q55

D

S

13

G

2

G

2

13

D

S

3VDDCCL

3VDDCCL <18,36>

3VDDCDA <18,36>

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Alviso(3 of 4)

EDX20 LA-2481

1

of

10 48Tuesday, Fe b r u a r y 22, 2005

0.5

Page 11

5

4

3

2

1

http://hobi-elektronika.net

D D

+VCCP

1

1

C57

C87

2

2

0.47U_0603_10V7K

C C

+1.8V

1

1

C79

2

2

0.47U_0402_6.3V4Z

B B

1

1

C76

C73

2

2

0.47U_0402_6.3V4Z

0.47U_0402_6.3V4Z

Note : All VCCSM pin

shorted internally.

1

C69

2

0.47U_0402_6.3V4Z

1

1

C75

2

0.47U_0402_6.3V4Z

1

+

C78

2

@

0.1U_0402_16V4Z

1

C423

220U_D2_4VM

C432

2

C433

2

10U_1206_6.3V6M

10U_1206_6.3V6M

+VCCP

L23

VCC

L24

VCC

M24

VCC

N23

VCC

N24

VCC

P24

1

1

1

C85

C80

C81

2

10U_1206_6.3V6M

1

1

C64

C51

2

2

0.47U_0603_10V7K

0.22U_0603_10V7K

0.22U_0603_10V7K

2

10U_1206_6.3V6M

1

C47

2

4.7U_0805_10V4Z

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+1.5VS_MPLL

@

C68

2

10U_1206_6.3V6M

1

2

2.2U_0805_16V4Z

+1.5VS

AD18

AE17

AE18

AF17

AF18

AH17

AH18

AJ17

AJ18

AK17

AK18

AK30

AL17

AL18

AL23

AG17

AG18

AC17

AC18

AC31

AD17

AC3

AC5

AD1

AC1

R15

R17

T15

T16

T17

U16

A6

A12

E1

M1

M2

M3

M4

M5

M6

M7

M8

M9

N1

N2

N3

N4

N5

N6

N7

N8

N9

Y1

AF1

AL6

B21

J30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCD_HMPLL1

VCCD_HMPLL2

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

ALVISO_BGA840

U31D

POWER

VCCA_TVDACA

VCCA_TVDACA

VCCA_TVDACB

VCCA_TVDACB

VCCA_TVDACC

VCCA_TVDACC

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS

VCCD_LVDS

VCCD_LVDS

VCCA_LVDS

VCCHV

VCCHV

VCCHV

VCCTX_LVDS

VCCTX_LVDS

VCCA_SM

VCCA_SM

VCCA_SM

VCC3G

VCC3G

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCC_SYNC

VCCA_CRTDAC

VCCA_CRTDAC

VSSA_CRTDAC

F18

G18

F19

G19

F20

G20

E19

E20

E18

D17

A23

B23

B25

B29

B20

C21

C22

A26

B26

AC13

AC14

AL15

P31

R31

R23

M31

L31

H21

C20

D21

D20

+1.5VS

+2.5VS

+2.5VS_CRTDAC

+2.5VS

+1.5VS_DDRDLL

1

C77

2

0.1U_0402_16V4Z

22U_1206_16V4Z_V1

+2.5VS_CRT

C41

0.022U_0402_16V7K

1

C88

2

L2 BLM18PG600SN1_0603

1 2

1

1

C42

2

2

0.1U_0402_16V4Z

Route VSSATVBG gnd from GMCH to

decoupling cap ground lead and

then connect to the gnd plane.

C18

C407

+2.5VS

1

2

0.022U_0402_16V7K

1

2

47U_1210_10V3M

+1.5VS_PCIE

1

1

C20

C10

2

2

0.1U_0402_16V4Z

0.022U_0402_16V7K

1

1

C44

C45

2

2

0.22U_0603_10V7K

10U_1206_6.3V6M

+2.5VS_CRTDAC

1

C15

2

0.1U_0402_16V4Z

CRTDAC: Route caps within

250mil of Alviso. Route FB

within 3" of Alviso.

Route VSSACRTDAC gnd from GMCH to

decoupling cap ground lead and then

connect to the gnd plane.

+1.5VS

1

C50

2

0.1U_0402_16V4Z

+1.5VS_3GPLL

1

C58

2

0.1U_0402_16V4Z

C27

L6

BLM18PG600SN1_0603

BLM18PG600SN1_0603

BLM18PG600SN1_0603

3GRLL_R

1 2

R51 0.5_0805_1%

1

C72

@

2

10U_1206_6.3V6M

1

2

Route VSSA3GBG gnd from GMCH to

decoupling cap ground lead and

then connect to the gnd plane.

L33

BLM18PG600SN1_0603

C38

0.1U_0402_16V4Z

12

L34

12

L4

12

C65

+2.5VS+2.5VS_3GBG

12

1

2

+1.5VS

1

1

C26

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.5VS

+1.5VS

C82

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

C8

0.1U_0402_16V4Z

1

C33

2

0.1U_0402_16V4Z

+1.5VS

1

C104

2

1

0.1U_0402_16V4Z

2

+1.5VS_DPLLA

L3

BLM18PG600SN1_0603

1 2

+1.5VS

1

1

C35

C36

2

2

0.1U_0402_16V4Z

A A

22U_1206_16V4Z_V1

5

BLM18PG600SN1_0603

1 2

+1.5VS +1.5VS

+1.5VS_DPLLB

L1

1

1

2

22U_1206_16V4Z_V1

C32

C19

2

0.1U_0402_16V4Z

4

BLM18PG600SN1_0603

1 2

+1.5VS_HPLL

L7

1

1

C95

C101

2

2

0.1U_0402_16V4Z

22U_1206_16V4Z_V1

+1.5VS

BLM18PG600SN1_0603

1 2

+1.5VS_MPLL

L5

D14

+VCCP_CRTDAC_D

1

1

C93

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

C90

2

2

0.1U_0402_16V4Z

22U_1206_16V4Z_V1

+VCCP

+2.5VS

2 1

RB751V_SOD323

R384

1K_0805_1%

1 2

R383

0_0805_5%

1 2

2

+2.5VS_CRTDAC

+2.5VS

1

1

C2

C6

10U_1206_6.3V6M

Title

Size Document Number Rev

Custom

EDX20 LA-2481

Date: Sheet

C3

2

2

0.01U_0402_16V7K

0.1U_0402_16V4Z

Compal Electronics, Inc.

Alviso(4 of 4)

+2.5VS_CRTDAC

1

1

2

1

1

C13

C48

2

2

0.1U_0402_16V4Z

10U_1206_6.3V6M

of

11 48Tuesday, Fe b r u a r y 22, 2005

0.5

Page 12

5

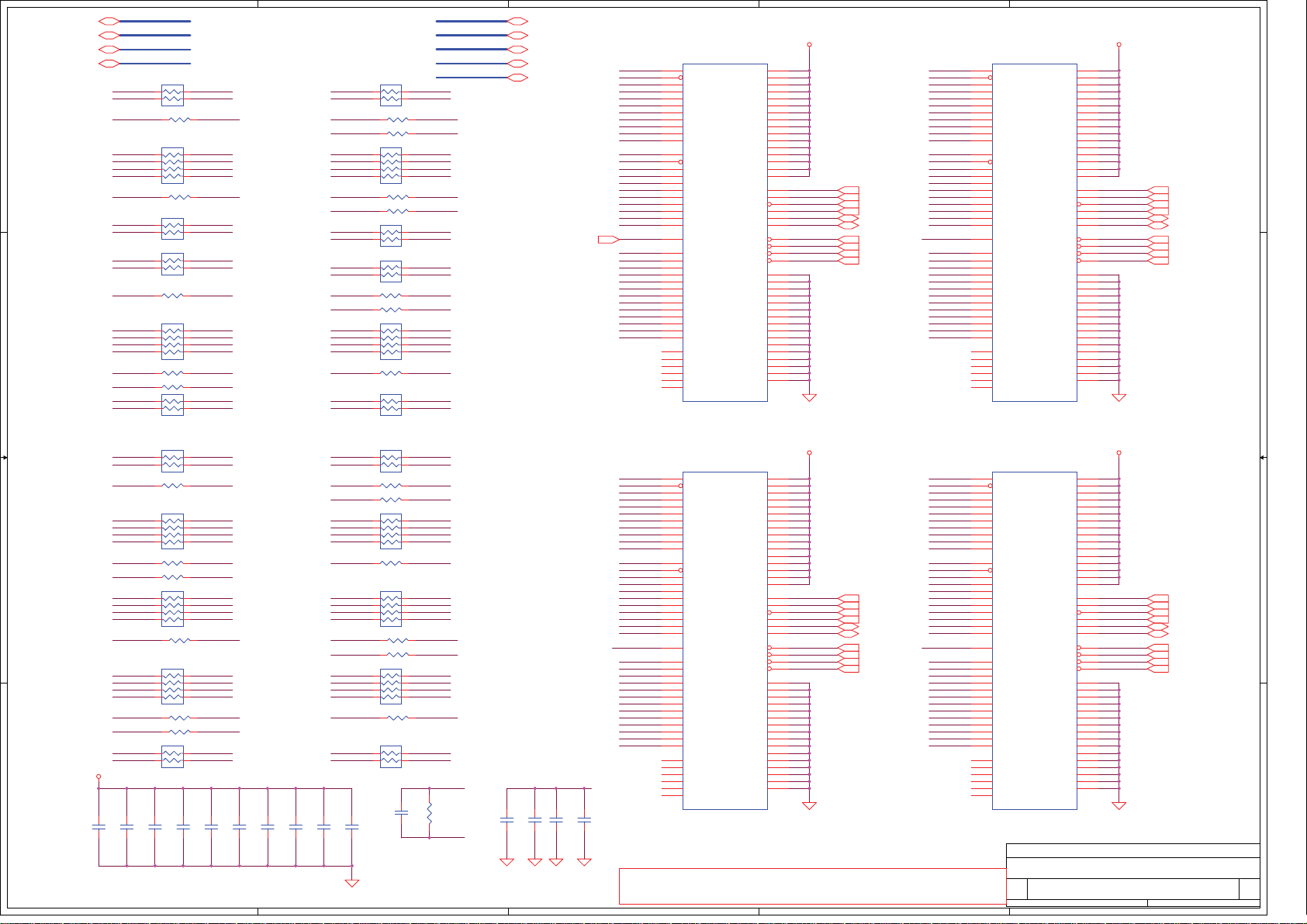

DDR_DM[0..7]<9,14>

DDR_DQS[0..7]<9,14>

DDR_DQS#[0..7]<9,14>

DDR_DQ[0..63]<9,14>

DDR_DQ0

DDR_DQ6

D D

DDR_DQ2

DDR_DQ3

DDR_DQ15

DDR_DQ11

DDR_DQ21

DDR_DM2

DDR_DQ18

C C

B B

A A

DDR_DQ28

DDR_DQS3

DDR_DQS#3

DDR_DQ31

DDR_DQ29 DDR_DQ30

DDR_DQ36 DDR_DQ37

DDR_DQ35

DDR_DQ34

DDR_DQ45

DDR_DQ44

DDR_DQS5 DDR_DM5

DDR_DQS#5

DDR_DQ54

DDR_DQ55

DDR_DQ61

DDR_DQ57

DDR_DQS7 DDR_DM7

DDR_DQS#7

DDR_DQ62

DDR_DQ59

+1.8V

2.2U_0805_16V4Z

2.2U_0805_16V4Z

1

2

C287

RP28

1 4

2 3

22_0404_4P2R_5%

1 2

R257 10_0402_5%

RP30

4 5

3 6

2 7

1 8

22_0804_8P4R_5%

1 2

R261 10_0402_5%

RP31

2 3

1 4

22_0404_4P2R_5%

RP29

2 3

1 4

22_0404_4P2R_5%

1 2

R268 10_0402_5%

RP32

4 5

3 6

2 7

1 8

22_0804_8P4R_5%

1 2

R263 10_0402_5%

1 2

R262 10_0402_5%

RP33

1 4

2 3

22_0404_4P2R_5%

RP34

1 4

2 3

22_0404_4P2R_5%

1 2

R264 10_0402_5%

RP35

4 5

3 6

2 7

1 8

22_0804_8P4R_5%

1 2

R266 10_0402_5%

1 2

R265 10_0402_5%

RP36

4 5

3 6

2 7

1 8

22_0804_8P4R_5%

1 2

R258 10_0402_5%

RP37

4 5

3 6

2 7

1 8

22_0804_8P4R_5%

1 2

R260 10_0402_5%

1 2

R259 10_0402_5%

RP27

1 4

2 3

22_0404_4P2R_5%

0.1U_0402_16V4Z

1

1

2

2

C294

C290

5

DDR_SDQ0

DDR_SDQ6

DDR_SDM0 DDR_SDQS0

DDR_SDQ2

DDR_SDQ3

DDR_SDM1

DDR_SDQ15

DDR_SDQ21

DDR_SDQ20DDR_DQ20

DDR_SDM2

DDR_SDQ18

DDR_SDQ22DDR_DQ22

DDR_SDQ28

DDR_SDQS3

DDR_SDQS#3

DDR_SDQ31

DDR_SDQ29 DDR_SDQ30

DDR_SDQ36 DDR_SDQ37

DDR_SDM4

DDR_SDQ35

DDR_SDQ34

DDR_SDQ45

DDR_SDQ44

DDR_SDQS5

DDR_SDQS#5

DDR_SDQ49 DDR_DQ48DDR_DQ49

DDR_SDM6

DDR_SDQ54

DDR_SDQ55

DDR_SDQ61

DDR_SDQ57

DDR_SDQS7

DDR_SDQS#7

DDR_SDQ62

DDR_SDQ59

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

2

2

C296

C283

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

2

2

C288

C291

DDR_DQ1 DDR_SDQ1

DDR_DQ5

DDR_DQS0DDR_DM0

DDR_DQS#0

DDR_DQ4

DDR_DQ12DDR_DQ13

DDR_DQ8DDR_DQ9

DDR_DQS1DDR_DM1

DDR_DQS#1

DDR_DQ10

DDR_DQ14

DDR_DQ16

DDR_DQ17

DDR_DQS2

DDR_DQS#2

DDR_DQ23

DDR_DQ19

DDR_DQ26DDR_DQ27

DDR_DQ25

DDR_DM3

DDR_DQ24

DDR_DQ32DDR_DQ33

DDR_DQS4DDR_DM4

DDR_DQS#4

DDR_DQ39

DDR_DQ38

DDR_DQ41

DDR_DQ40

DDR_DQ42DDR_DQ43

DDR_DQ46DDR_DQ47

DDR_DQ52DDR_DQ53

DDR_DQS6DDR_DM6

DDR_DQS#6

DDR_DQ50

DDR_DQ51

DDR_DQ60 DDR_SDQ60

DDR_DQ56

DDR_DQ63

DDR_DQ58

0.1U_0402_16V4Z

1

1

2

2

C295

C284

1 4

2 3

R236 10_0402_5%

R235 10_0402_5%

4 5

3 6

2 7

1 8

R238 10_0402_5%

R237 10_0402_5%

2 3

1 4

2 3

1 4

1 2

R226 10_0402_5%

1 2

R225 10_0402_5%

4 5

3 6

2 7

1 8

1 2

R227 10_0402_5%

1 4

2 3

1 4

2 3

1 2

R229 10_0402_5%

1 2

R228 10_0402_5%

4 5

3 6

2 7

1 8

1 2

R230 10_0402_5%

4 5

3 6

2 7

1 8

R232 10_0402_5%

R231 10_0402_5%

4 5

3 6

2 7

1 8

R233 10_0402_5%

1 4

2 3

0.1U_0402_16V4Z

1

2

C289

4

RP6

DDR_SDQ5

22_0404_4P2R_5%

1 2

DDR_SDQS#0

1 2

RP7

DDR_SDQ4

DDR_SDQ7DDR_DQ7

DDR_SDQ12DDR_SDQ13

DDR_SDQ8DDR_SDQ9

22_0804_8P4R_5%

DDR_SDQS1

1 2

DDR_SDQS#1

1 2

RP16

DDR_SDQ10DDR_SDQ11

DDR_SDQ14

22_0404_4P2R_5%

RP8

DDR_SDQ16

DDR_SDQ17

22_0404_4P2R_5%

DDR_SDQS2

DDR_SDQS#2

RP9

DDR_SDQ23

DDR_SDQ19

DDR_SDQ26DDR_SDQ27

DDR_SDQ25

22_0804_8P4R_5%

DDR_SDM3

RP10

DDR_SDQ24

22_0404_4P2R_5%

RP13

DDR_SDQ32DDR_SDQ33

22_0404_4P2R_5%

DDR_SDQS4

DDR_SDQS#4

RP15

DDR_SDQ39

DDR_SDQ38

DDR_SDQ41

DDR_SDQ40

22_0804_8P4R_5%

DDR_SDM5

RP11

DDR_SDQ42DDR_SDQ43

DDR_SDQ46DDR_SDQ47

DDR_SDQ48

DDR_SDQ52DDR_SDQ53

22_0804_8P4R_5%

DDR_SDQS6

1 2

DDR_SDQS#6

1 2

RP12

DDR_SDQ50

DDR_SDQ51

DDR_SDQ56

22_0804_8P4R_5%

DDR_SDM7

1 2

RP14

DDR_SDQ63

DDR_SDQ58

22_0404_4P2R_5%

3.3P_0402_50V8C

1

C524

@

2

4

DDR_CLK0

12

R283

100_0402_5%

DDR_CLK0#

3

DDR_SDM[0..7] <13>

http://hobi-elektronika.net

DDR_SDQS[0..7] <13>

2.2U_0805_16V4Z

1

2

C302