Page 1

A

1 1

B

C

D

E

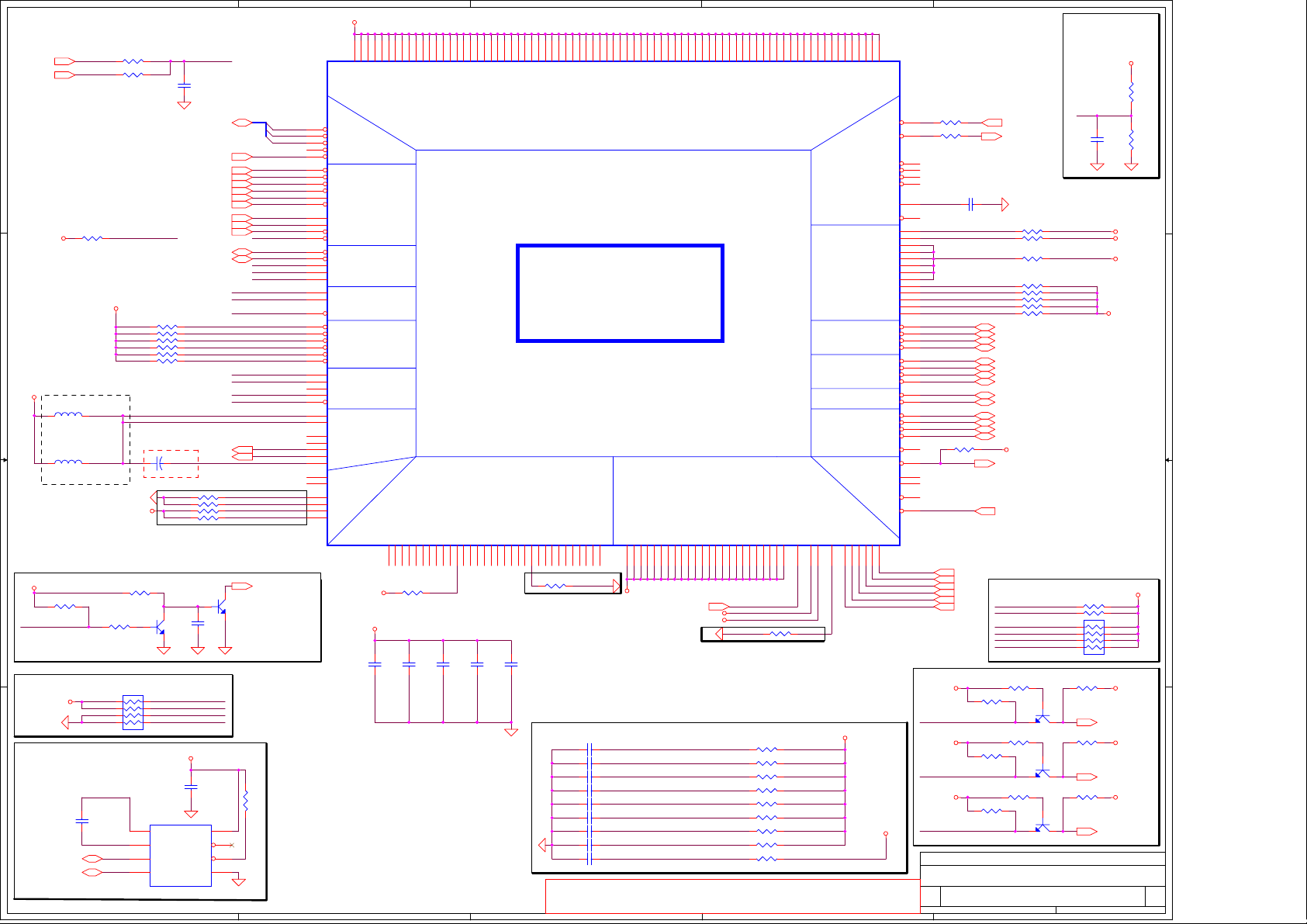

LongBeach 100

2 2

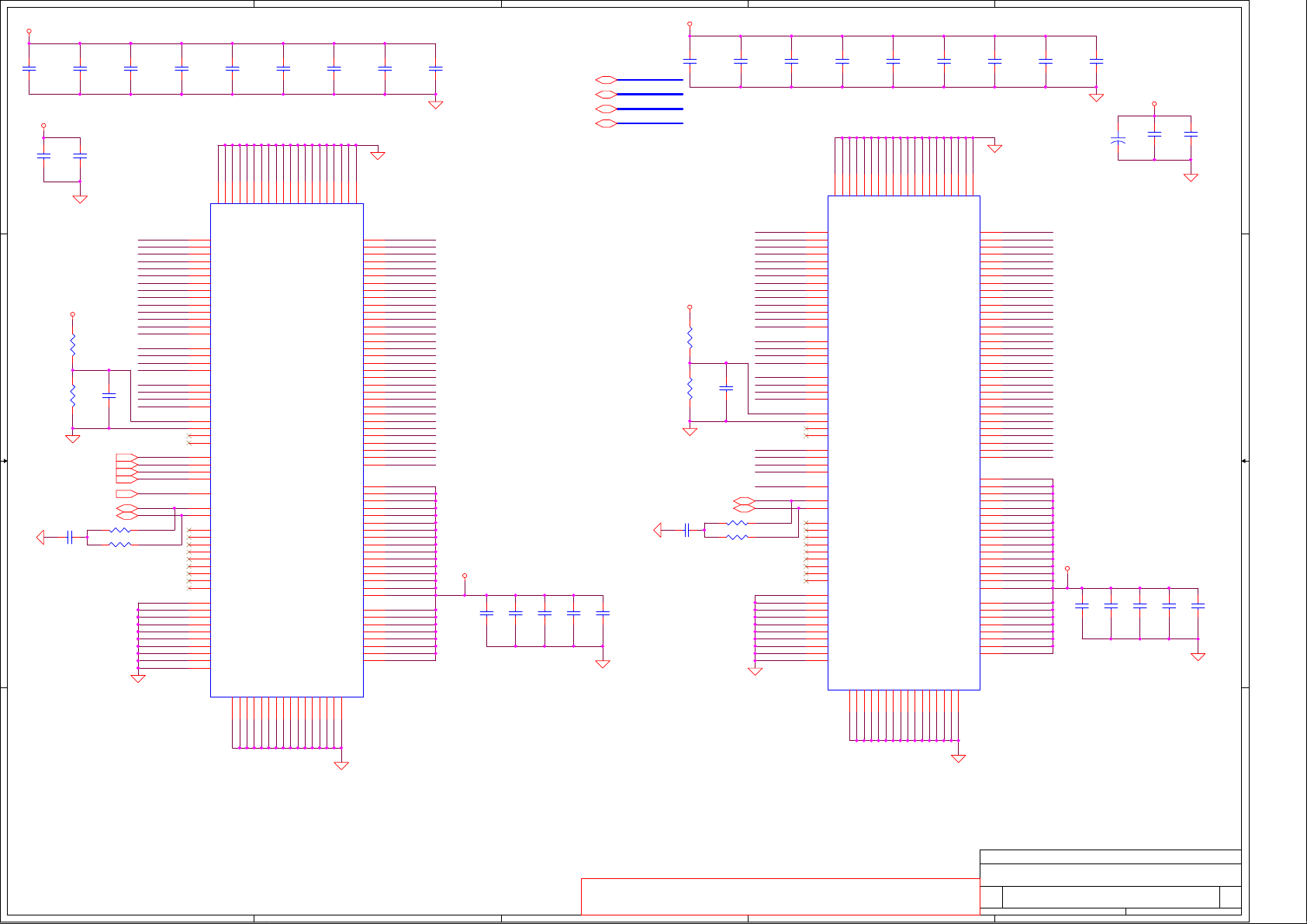

LA-2451 REV 0.4 Schematic

Desktop LGA-775 Package

3 3

RXC400M(RU400M)+SB400+ATI M22P/M24P(64/128MB VRAM)

2004-11-08<A>

4 4

Compal El ectronics, I nc.

Title

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Cover Page

Size Doc u m ent Nu m b er R e v

Custom

星期一 十一月

Date: Sheet

2004

E

of

153, 08,

0.1

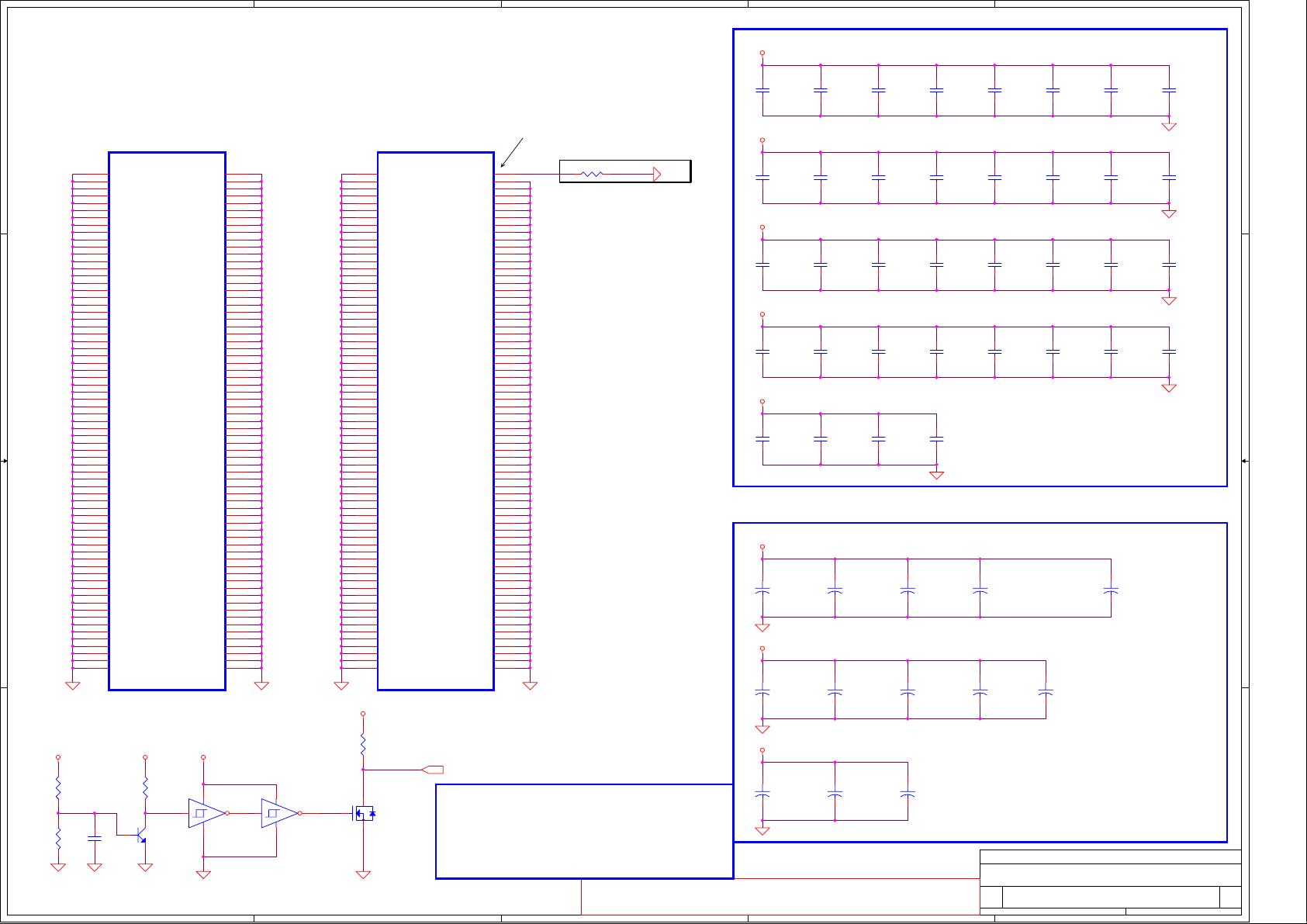

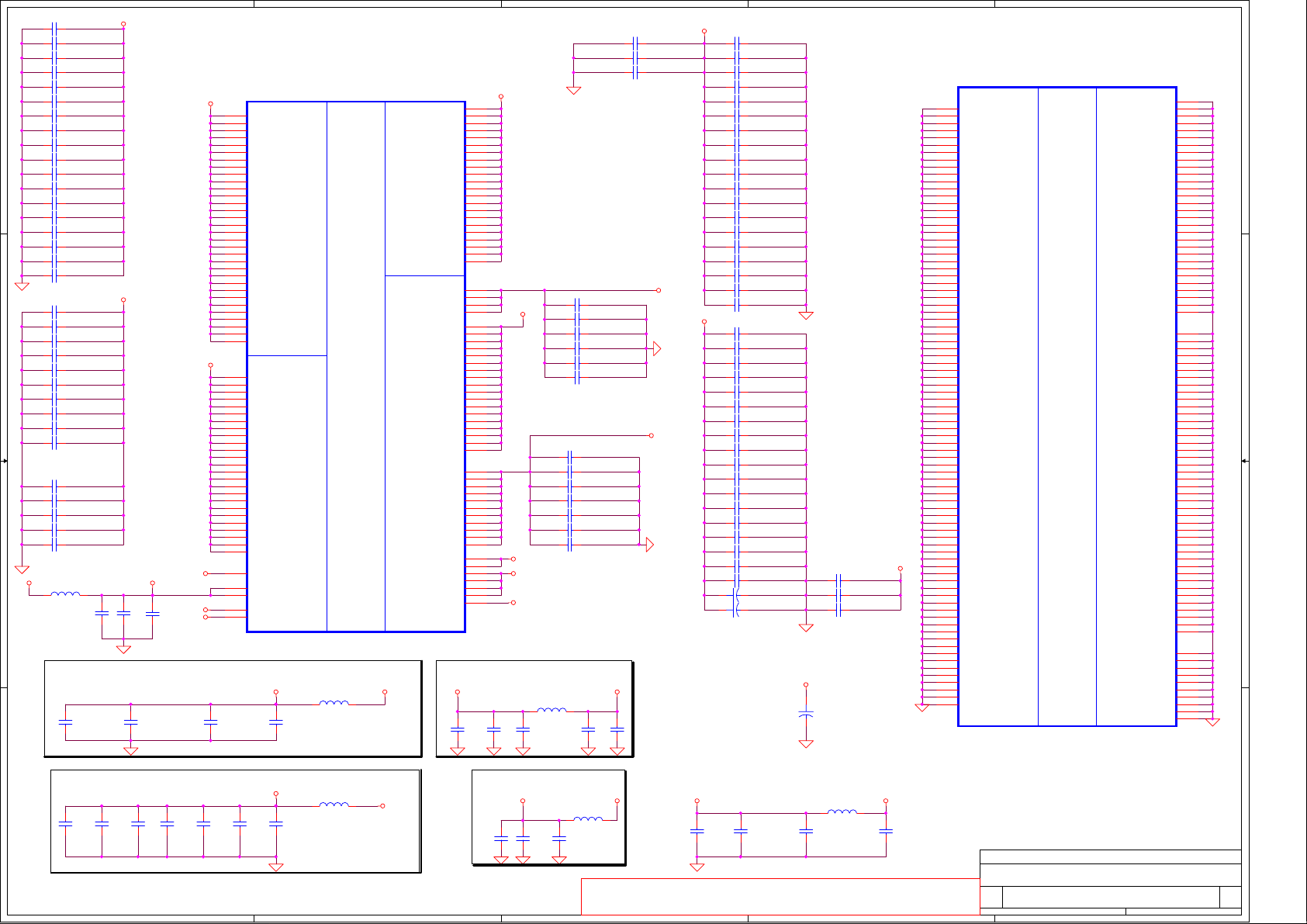

Page 2

A

B

C

D

E

EAQ11 LA-2451

4 4

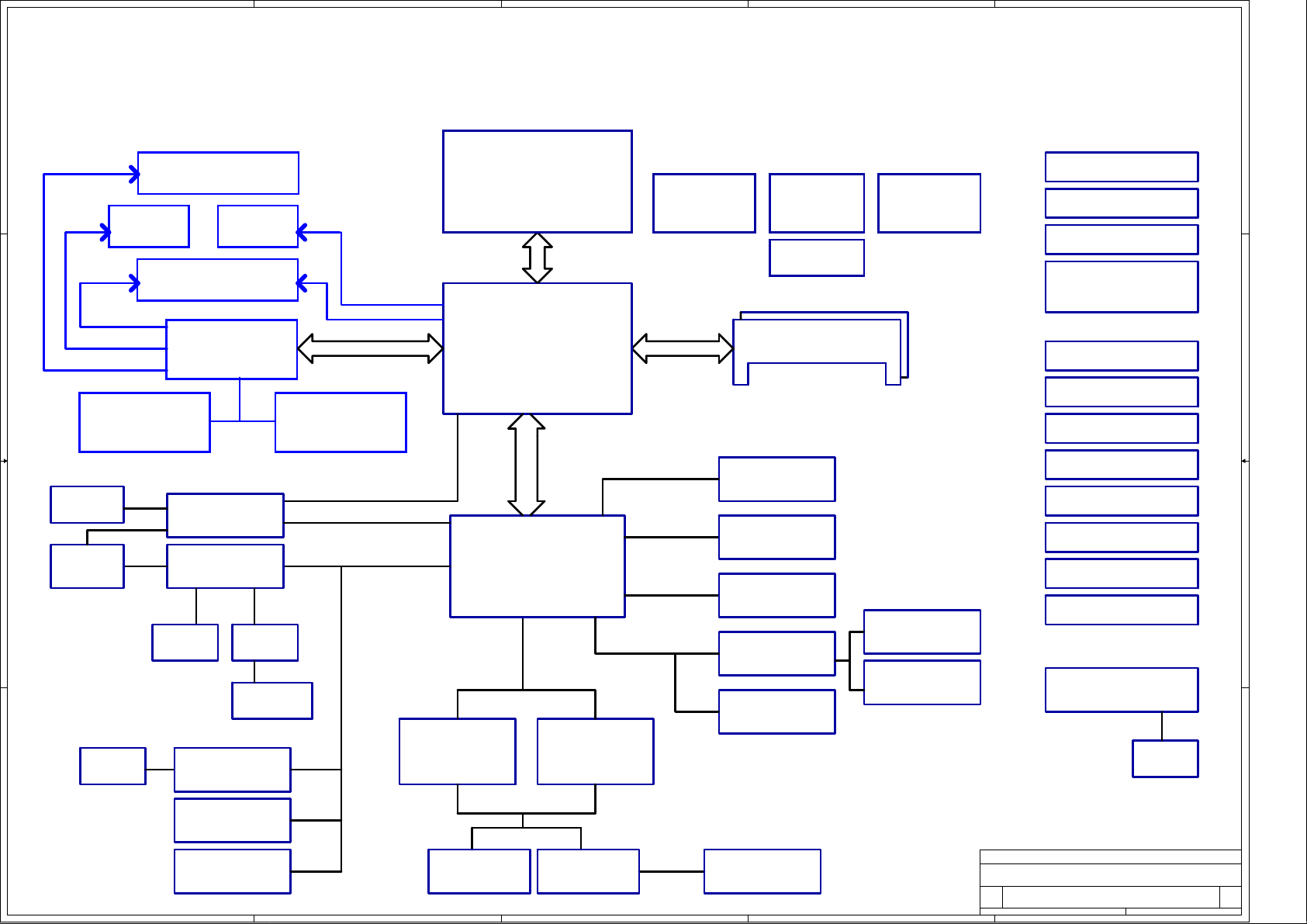

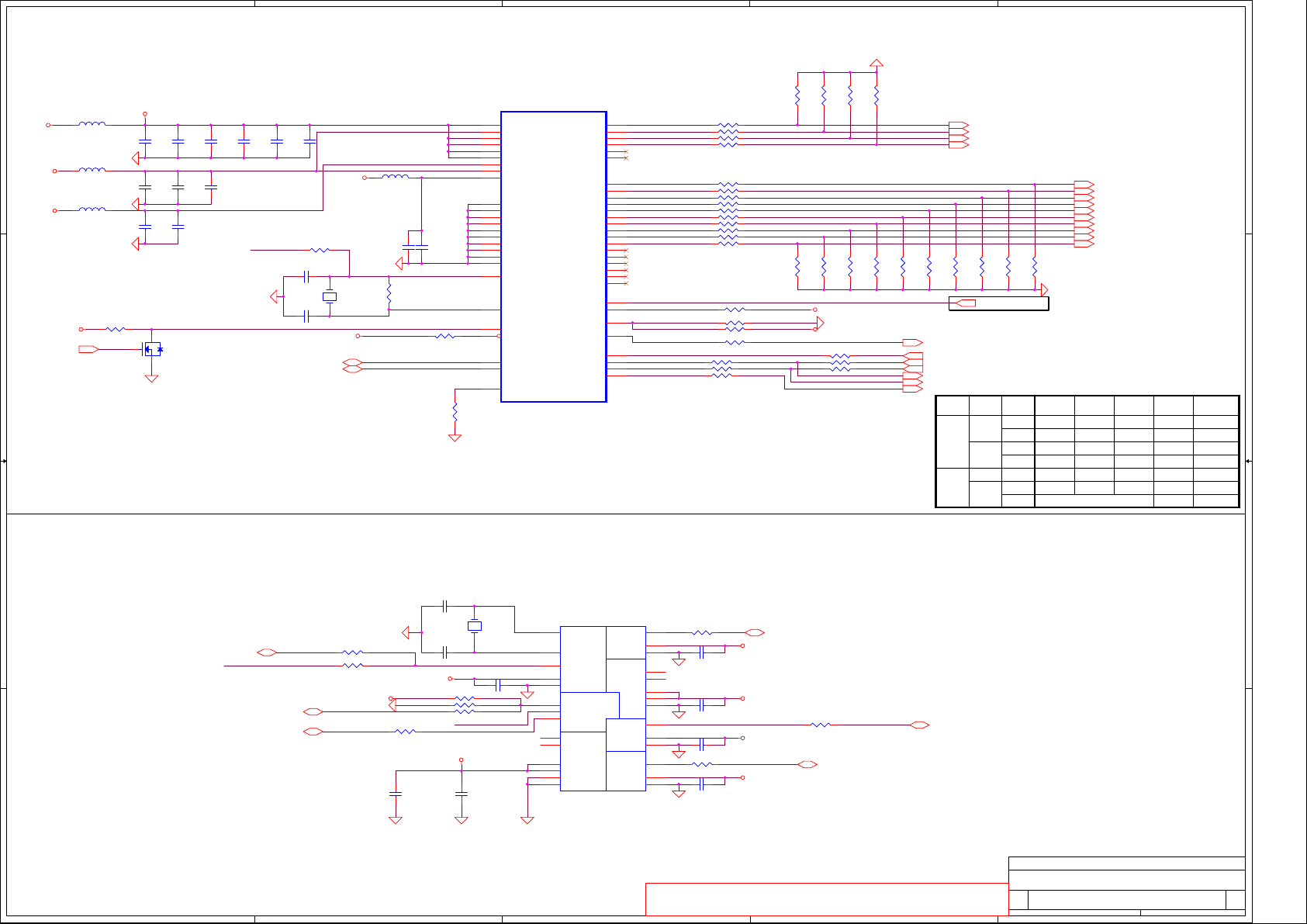

FUNCTION BLOCK DIAGRAM

Desktop Prescott

CRT Conn.

page 20

LCD Conn 1

page 19

LVDS & TV-O UT Conn.

W/EXT VGA CHIP

3 3

VGA DDR CHA

4M32/8M32-1.8V

x 2

NC PWR SW

TPS2231PWPR

PAGE 30

CB PWR SW

2 2

1 1

TPS2220ADBR

PAGE 30

RJ-45

PAGE 26

page 16 page 17

1394-Port

A

LCD Conn 2

page 19

page 19

ATI-M22P/M24P

page 14,15,18

New Card

Cardbus

Connecter

CARDBUS

TI-PCI 7411

PAGE 28

Mini PCI

FOR WLAN

Mini PCI

Int. TV Tuner

PAGE 30

PAGE 27,28

5in1 Socket

TAITW

5 in 1 PWR SW

G528

LAN

RTL8100CL

PAGE 29

PAGE 30

PAGE 26

PAGE 31

PAGE 32

W/INT VGA

PCI-Express x 16

2.5GHz(1.2V)

Bandwidth 4GB

VGA DDR CHB

4M32/8M32-1.8V

x 2

PCI-E Port 2

USB Port 5-480MHz(5V)

PCI BUS

33MHz (3.3V)

B

LGA-775

775 pin

FSB

(ATI-RU400M)

ATI-RC400M

VGA M10P Embeded

703 pin BGA

A-Link E x p r ess x 4

2.5GHz(1.2V)

Bandwidth 500MB

ATI-SB400

564 pin BGA

PAGE 21,22,23,24,25

LPC B US 33MHz (3.3V)

Embedded

Cont r olle r

ENE KB910

PAGE 37

BIOS(1M)

& I/O PORT

PAGE 38 PAGE 37

PAGE 4, 5,6

400/533/800MHz

PAGE 7, 8,9

Embedded

Cont r olle r

ENE KB910L

Scan KB

PAGE 53

Thermal Sensor

ADM1032ARM

266/333/400MHz

(2.5V)

Memory Bus

480MHz(5V)

Primary

ATA-100 (5V)

Secondary

ATA-100 (5V)

AC-LINK

24.576MHz(3.3V)

C

Clock Generator

ICS951411AGT

PAGE 5

PCLK

ICS960011

SO-DIM M x 2(DDR)

BANK 0,1,2,3

USB 2.0 Port *3

0,2,4

IDE HDD

IDE ODD

AC97 CODEC

ALC 250

MDC

Connector

CIR

Contr oller

PAGE 39

PAGE 36

PAGE 35

PAGE 35

PAGE 33

PAGE 41

PAGE 13

PAGE 13

PAGE 10,11,12

CPU VID

Audio Amplifier

APA2121

Audio Amplifier

APA2121

D

PAGE 5

PAGE 34

PAGE 34

Compal El ectronics, I nc.

Title

Block Digram

Size Doc u m ent Nu m b er R e v

Custom

星期六 十一月

Date: Sheet

FANContr oller

RTC Battery

DC/DC Interface

PAGE 41

PAGE 21

PAGE 42

LID/Kill Switch

Power Buttom

PAGE 39

DCIN&DETECTOR

BATT CONN/OTP

CHARGER

3V/5V/12V

DDR_2.5V/1.25VEP

1.8V/VGA_CORE/1.25V

1.5V/PROCHOT

CPU_CORE

PAGE 43

PAGE 44

PAGE 45

PAGE 46

PAGE 47

PAGE 48

PAGE 49

PAGE 50,51,52

TP Board ( LS -2371)

Connector

PAGE 39

CIR

2004

253, 06,

E

0.1

of

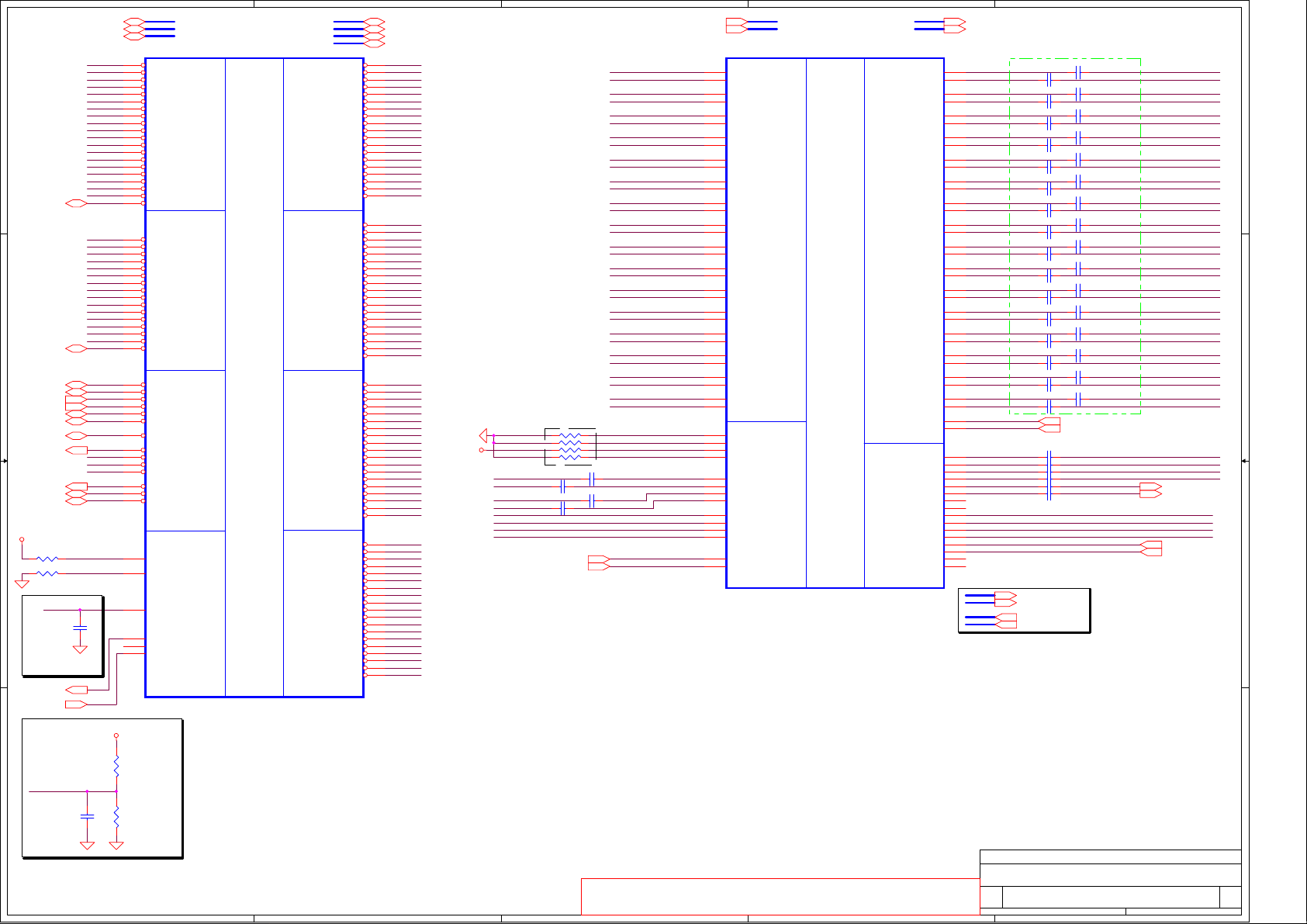

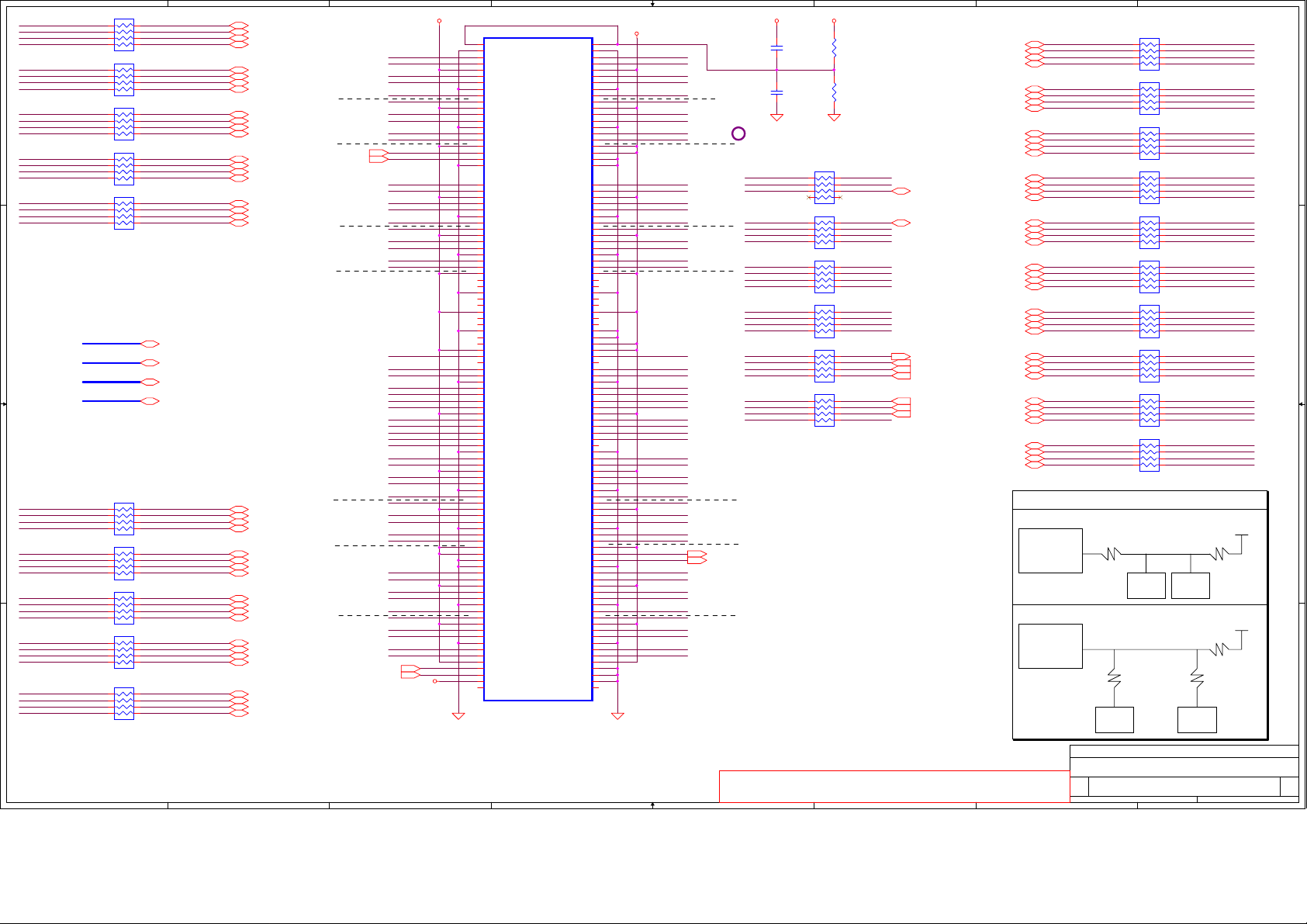

Page 3

A

B

C

D

E

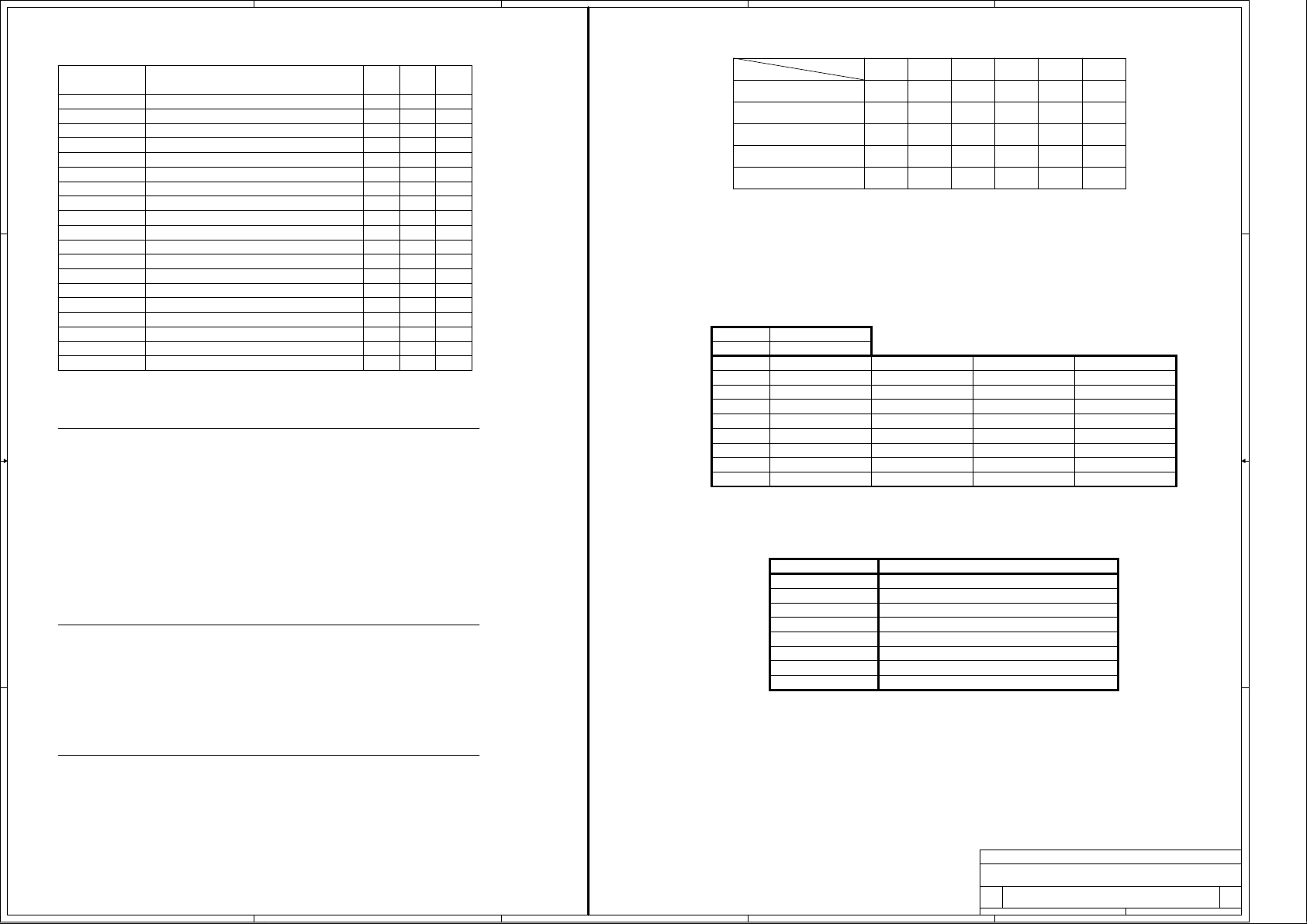

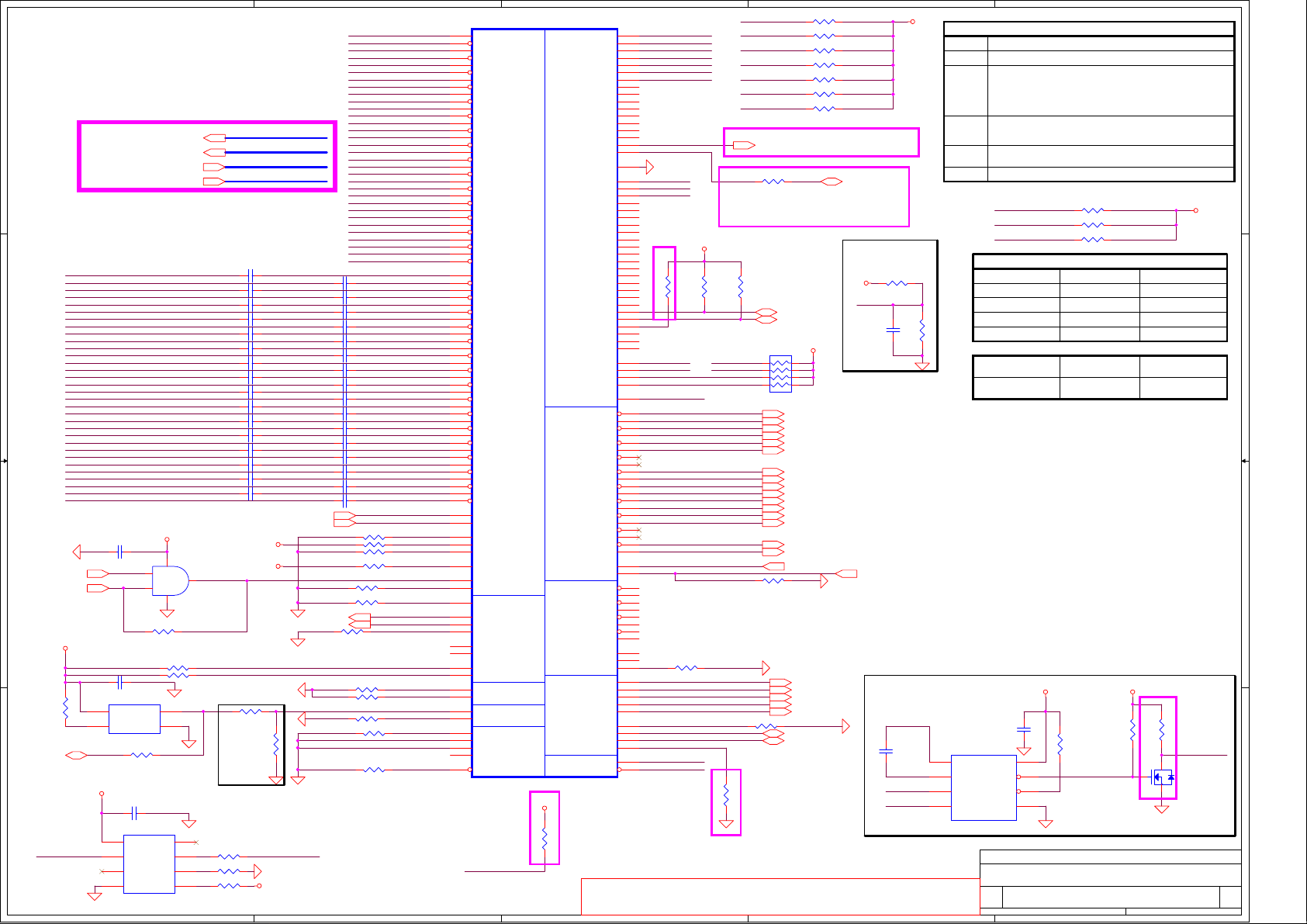

Voltage Rails

Power Plane Description

VIN

1 1

2 2

B+

+CPU_CORE

+CPUVID

+VGA_CORE ON OF F O F F1.0V/1 . 2V sw i t c h ed p o w e r r ai l f o r VGA chip

+1.2VS 1.2VS for PCI-Express O FFON OFF

+1.25VS 1.25V switched power rail

+1.5VS

+1.8VS 1.8VS switched power rail OFFOFFON

+1.8VALW 1.8V always on power rail ON*ONON

+2.5V

+3VALW

+3VS

+5VS

+12VALW

+RTCVCC

Note : O N * mean s that thi s po wer p lan e is ON o nl y wi th AC p ow er avail abl e, o therw ise i t is O FF .

Adapter power supply (19V)

AC or bat t er y p o w e r ra i l fo r p o w er circuit.

Core v o ltage for CPU

1.2V swi tch ed p ower rai l f or CPU AG TL Bus

AGP 8X

2.5V po wer rail

2.5V switched power rail+2.5VS

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

CardBus(PCI7411)

LAN

Mini-PCI(WLAN)

Mini- P C I (T V -T uner)

AD20

AD22

AD18

AD23

2

1 PIRQG/ PIR QC

3

4

S1 S3 S5

ON

ON ONONON

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON ON

ON

ON

ON

ON+5VALW

ON

ON

ON

PIRQE/PIRQF/PIRQG/PIRQH

PIRQF:PIRQG/PIRQC:PIRQD

PIRQH:PIRQE/PIRQD:PIRQA

OFF

OFF

ON

OFF

ON

ON

ON

OFF

OFF

OFF

OFF

ON*ON

OFF

ON*

OFF

ON*12V always on power rail

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM) ON

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table f or AD channel

Vcc

Ra

Board ID

0

1

2

3

4

5

6

3.3V +/- 5%

100K +/- 5%

Rb

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC7

SIGNAL

HIGH

LOW

LOW

SLP_S5#STATE

HIGHHIGH

HIGH

HIGH

HIGH

LOWLOW

minV

AD_BID

0 V

0.436 V

0.712 V

1.036 V

1.935 V

2.500 V

+VALW

ON

ON

ON

ON

ON

+V

ON

ON

OFF

OFF

AD_BID

0.503 V

0.819 V

1.650 V1.453 V

2.200 V

3.300 V

typV

0 V

+VSSL P_S3#

ON

OFF

OFF

OFF

Clock

ONON

LOW

OFF

OFF

OFF

V

AD_BID

0.289 V0.250 V0.216 V

0.538 V

0.875 V

1.264 V1.185 V

1.759 V

2.341 V

3.300 V

max

0 V

3 3

Board ID

0

PCB Revision

0.1

1

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

ICS960011

1001 110X b0001 011X b

1101 110X b

2

3

4

5

6

7

SB400 SM Bus address

Device

Clock Generator

4 4

(ICS951411BGLFT)

DDR DIMM0

DDR DIMM2

A

Address

1101 001Xb

1010 000Xb

1010 001Xb

Compal Electronics, Inc.

Title

Size Doc u m ent Nu m b er R e v

Custom

B

C

D

Date: Sheet

Notes

Longbeach 100 <LA-2451>

星期六 十一月

2004

0.1

of

353, 06,

E

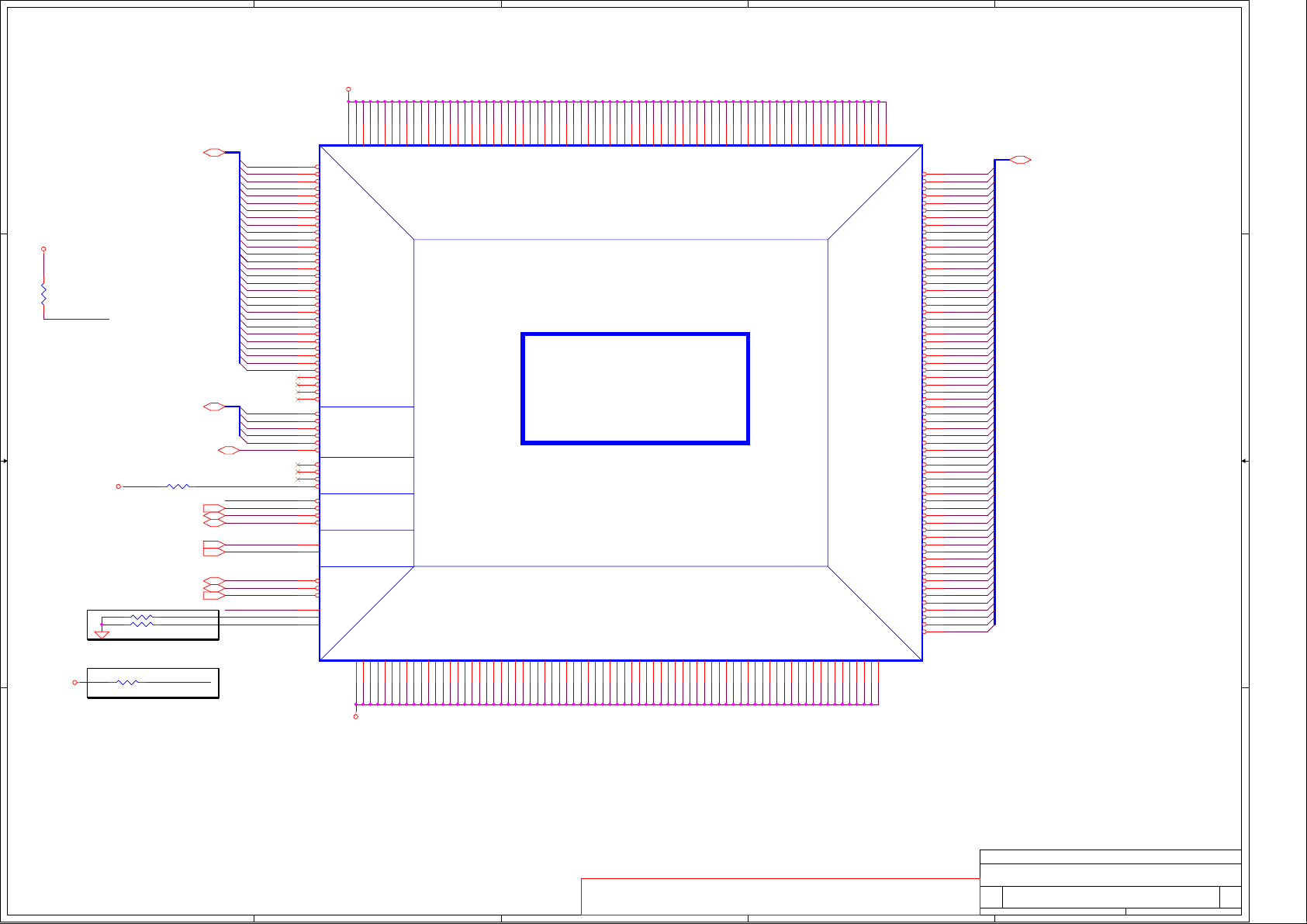

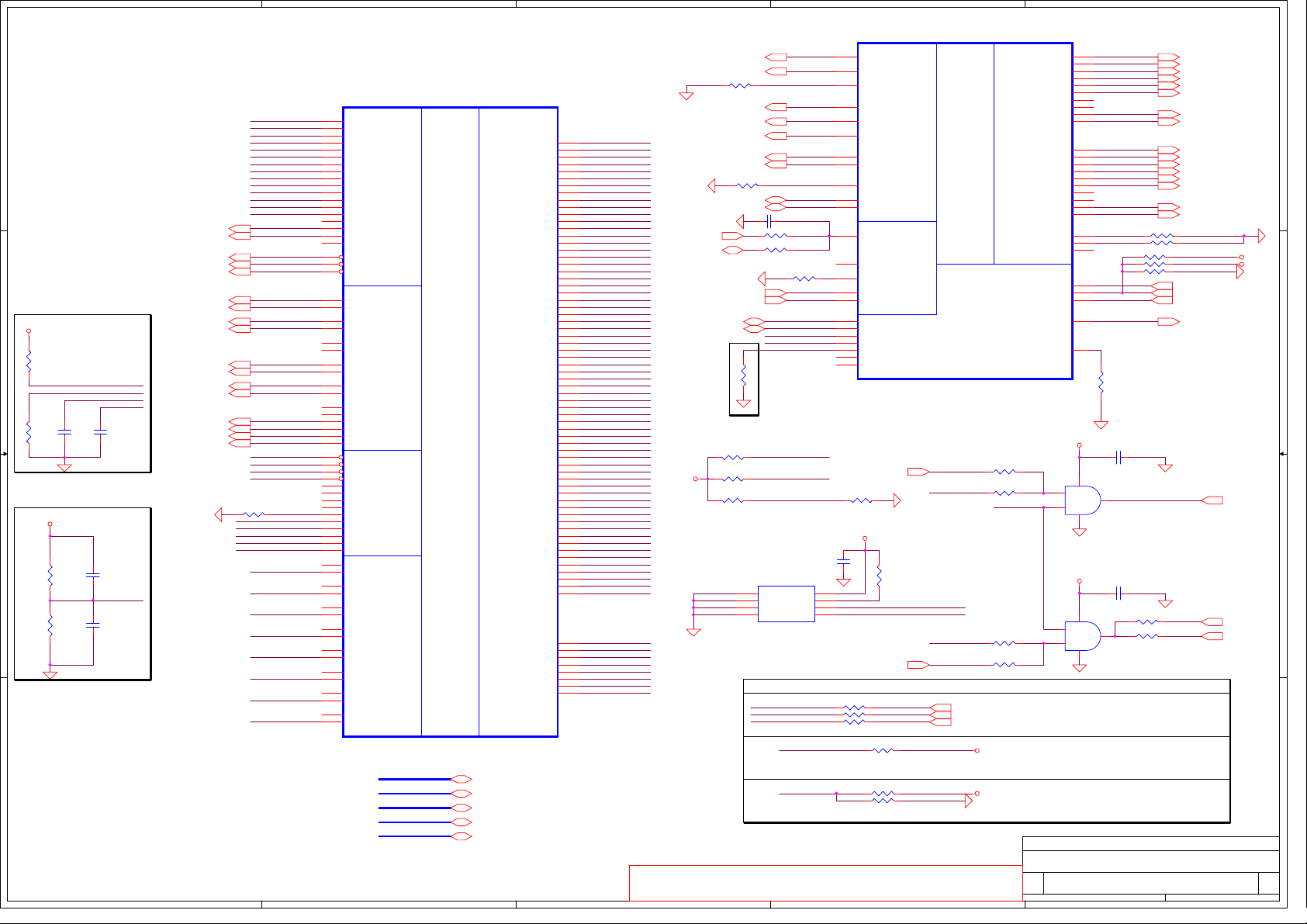

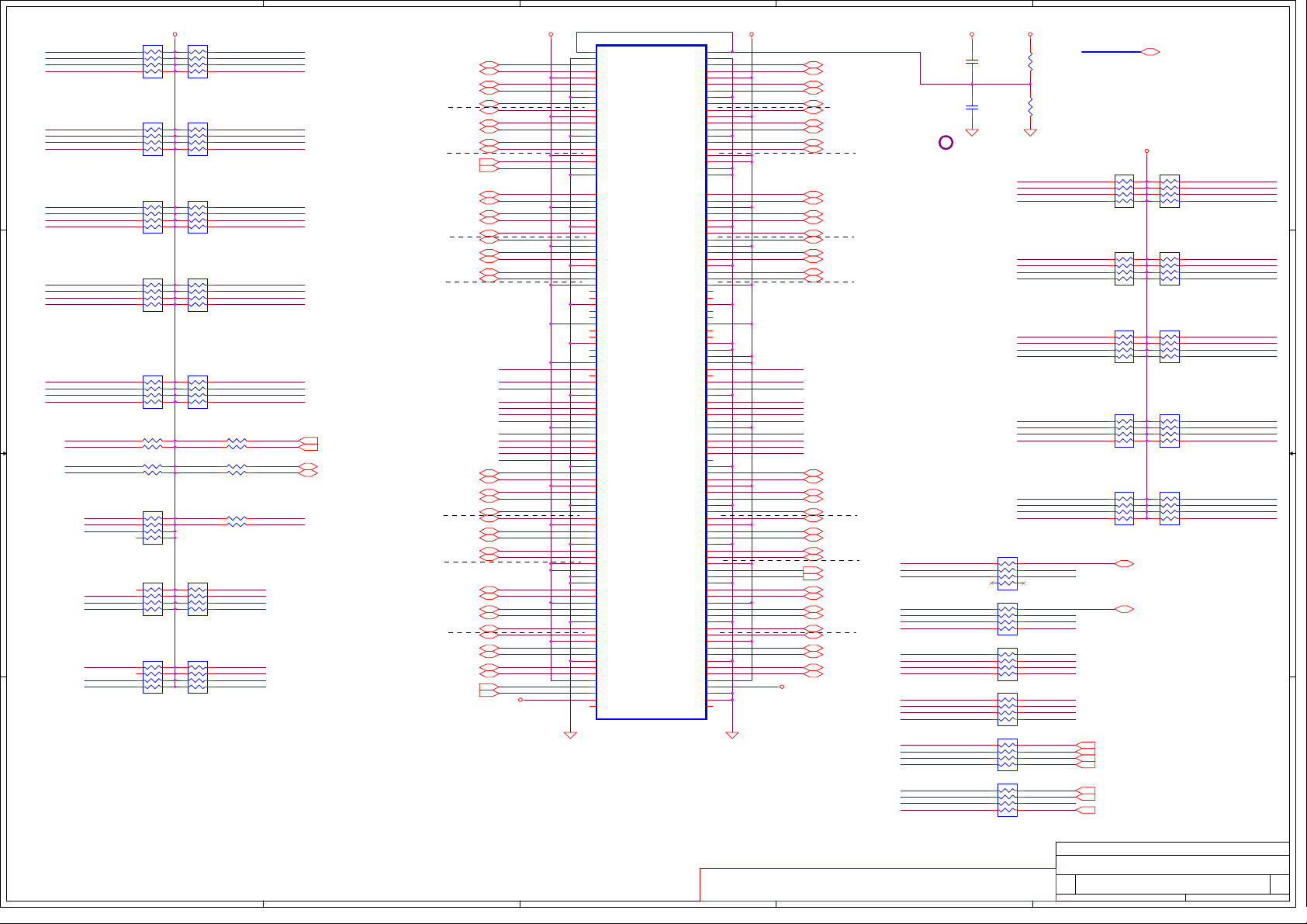

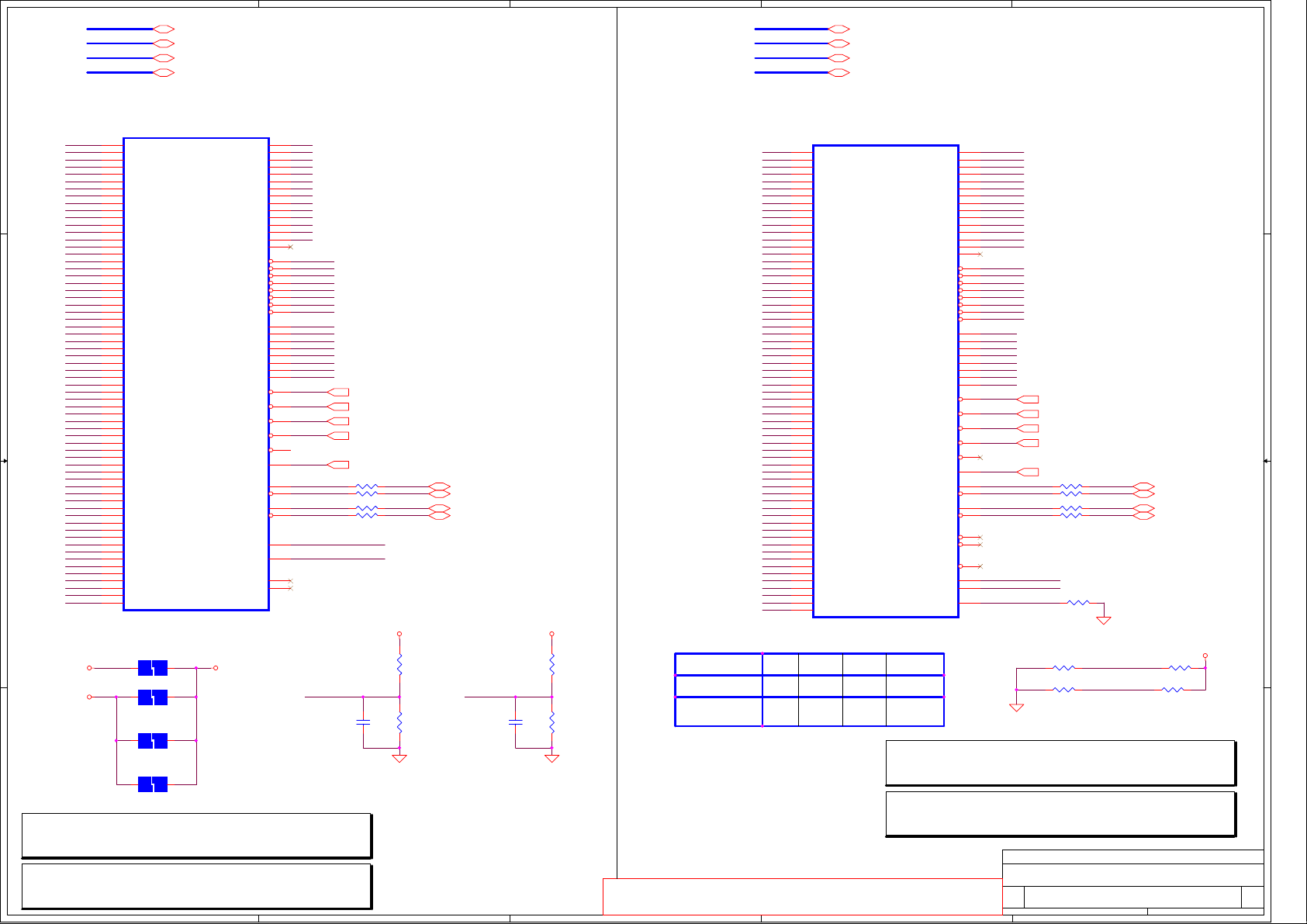

Page 4

A

+CPU_CORE

B

C

D

E

1 1

H_A#[3..31]7

+VTT_OUT_LEFT

12

62_0402_5%

R179

H_BR0#

2 2

H_REQ#[0..4]7

H_ADS#7

R598 62_0402_5%

1 2

1 2

1 2

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_BCLK13

CLK_BCLK#13

H_HIT#7

H_HITM#7

H_DEFER#7

+V_FSB_VTT

3 3

R596 @1K_0402_5%

R597 @1K_0402_5%

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_IERR#

H_BR0#

H_BOOTSELECT

LL_ID0

LL_ID1

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AD3

AB2

G28

AA2

Reserve for Testability

+VTT_OUT_RIGHT

1 2

H_BOOTSELECT

R587 @1K_0402_5%

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

W6

Y6

Y4

AJ5

AJ6

K4

J5

M6

K6

J6

D2

U2

U3

F3

G8

C2

C3

F28

D4

E4

G7

Y1

V2

JP21A

A03#

A04#

A05#

A06#

A07#

A08#

A09#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

AP0#

AP1#

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

BOOTSELECT

LL_ID0

LL_ID1

AG22

VCCP1

K29

AM26

VCCP2

VCCP76

U25

VCCP3

VCCP77Y8VCCP78

AL8

VCCP4

AJ12

AE12

AE11

VCCP5

VCCP79

U23

AD27

W23

W24

VCCP6

VCCP7

VCCP80

VCCP81

M23

AG29

T25

W25

VCCP8

VCCP9

VCCP82

VCCP83

N27

AM22

Y28

AL18

VCCP10

VCCP11

VCCP84

VCCP85

K28

U28

AC25

W30

VCCP12

VCCP13

VCCP86

VCCP87U8VCCP88

AK18

Y30

AN14

VCCP14

VCCP15

VCCP89

K24

AD8

AD28

Y26

VCCP16

VCCP17

VCCP90

VCCP91

AH28

AH21

AC29

M29

VCCP18

VCCP19

VCCP92

VCCP93

AK12

AH22

U24

J23

VCCP20

VCCP21

VCCP94

VCCP95

T29

AM14

AC27

AM18

VCCP22

VCCP23

VCCP96

VCCP97

AE9

AM25

AM19

AB8

VCCP24

VCCP25

VCCP98

VCCP99

Y29

AK25

AC26

VCCP26

VCCP27

VCCP28J8VCCP29

VCCP100

VCCP101

VCCP102

AK19

AG15

J28

T30

AM9

AF15

AC8

AE14

N23

W29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

LGA-775

(1/4)

VCCP103

VCCP104

VCCP105

VCCP106

VCCP107

VCCP108

VCCP109

VCCP110

J22

J25

T24

U30

AL21

AG21

AG25

AM21

U29

AC24

VCCP37

VCCP38

VCCP111

VCCP112

J19

AJ18

AC23

Y23

VCCP39

VCCP40

VCCP113

VCCP114

J15

AH30

AN26

AN25

VCCP41

VCCP42

VCCP115

VCCP116

AJ22

AG12

AN11

AN18

VCCP43

VCCP44

VCCP117

VCCP118

J20

AH18

Y27

Y25

VCCP45

VCCP46

VCCP119

VCCP120

W27

AH26

AD24

AE23

VCCP47

VCCP48

VCCP121

VCCP122

AN8

AL25

AE22

AN19

VCCP49

VCCP50

VCCP123

VCCP124

U27

AH14

AE21

AM30

VCCP51V8VCCP52K8VCCP53

VCCP125

VCCP126R8VCCP127

T23

AK22

AN29

AE19

AC30

VCCP54

VCCP55

VCCP56

VCCP128

VCCP129

VCCP130

AK26

AG11

AE15

M30

VCCP57

VCCP58

VCCP131

VCCP132

J10

AJ15

K27

M24

VCCP59

VCCP60

VCCP133

VCCP134

AN9

AG26

AN21

VCCP61

VCCP62T8VCCP63

VCCP135

VCCP136

AF18

AH15

AC28

N25

VCCP64

VCCP137

VCCP138

J26

AL15

AE18

W26

VCCP65

VCCP66

VCCP139

VCCP140

J18

J21

AD25

VCCP67

VCCP68M8VCCP69

VCCP141

VCCP142

AK15

AG27

N30

AD26

VCCP70

VCCP143

VCCP144

AF11

AD23

AJ26

AM29

VCCP71

VCCP72

VCCP145

VCCP146

AF8

AM15

M25

M26

VCCP73

VCCP74

VCCP147

VCCP148

AK21

AG30

L8

VCCP75

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G16

D32#

E15

D33#

E16

D34#

G18

D35#

G17

D36#

F17

D37#

F18

D38#

E18

D39#

E19

D40#

F20

D41#

E21

D42#

F21

D43#

G21

D44#

E22

D45#

D22

D46#

G22

D47#

D20

D48#

D17

D49#

A14

D50#

C15

D51#

C14

D52#

B15

D53#

C18

D54#

B16

D55#

A17

D56#

B18

D57#

C21

D58#

B21

D59#

B19

D60#

A19

D61#

A22

D62#

B22

D63#

FOX_PE077507-0741-01

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25H_A#29

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_D#[0..63] 7

Reserve for Stability.

+CPU_CORE

In Intel CPU datasheet:

LL_ID[1:0], VTT_SEL, GTLREF_SEL and VID_SELECT are signals that

are implement on the processor package.

That is they are either connected directly to Vss or open lands.

4 4

Compal Electronics, Inc.

Title

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

LGA-775(1/3)

Size Doc u m ent Nu m b er R e v

Custom

Longbeach 100 <LA-2451>

星期六 十一月

Date: Sheet

2004

E

of

453, 06,

0.1

Page 5

A

LDT_RST#21

H_RESET#7

1 1

+VTT_OUT_LEFT

2 2

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

+V_FSB_VTT

12 mils(min)

L48 LQG21 F4R7N00_0805

1 2

1 2

L49 LQG21 F4R7N00_0805

1.Place cap within 600 mils of

the V CCA a nd VSSA pins.

Note: Please change to 10uH, DC current

of 120mA parts and close to cap

DC Voltage drop from VTT to VCCA should

be < 70mV

3 3

+V_FSB_VTT

R584

62_0402_5%

H_THERMTRIP#

Un-used JTAG Pins,

Place Close to the CPU

+VTT_OUT_RIGHT

1 2

R604 0_0402_5%

1 2

R582 @0_0402_5%

R595

1 2

62_0402_5%

+VTT_OUT_RIGHT

+V_FSB_VTT

1 2

100K_0805_5%

12

1 2

R583 300_0402_5%

4 5

3 6

2 7

1 8

RP26 1K_1206_8P4R_5%

CPU_RESET#

R602 62_0402_5%

R603 62_0402_5%

R599 62_0402_5%

R601 62_0402_5%

R600 62_0402_5%

R178 62_0402_5%

Thermal Sensor

4 4

2200P_0402_50V7K

H_THERMDA

1

C788

2

H_THERMDC

EC_SMB_CK233,37,53

EC_SMB_DA233,37,53

A

CPU_RESET#

2

1

1 2

1 2

1 2

1 2

1 2

1 2

H_VCCSENSE

H_VSSSENSE

+

1 2

C680

33U_D2_8M_R35

R525 60.4_0402_1%

R586 60.4_0402_1%

R592 100_0402_1%

R585 100_0402_1%

R608

Q47

2

3 1

0.1U_0402_16V4Z

MMBT3904_SOT23

ITP_TMS

ITP_TDI

ITP_TCK

ITP_TRST#

+3VS

1

2

0.1U_0402_16V4Z

U37

2

3

8

7

VDD1

D+

ALERT#

D-

THERM#

SCLK

SDATA

ADM1032ARM_RM8

C989

@1000P_0402_50V7K

H_RS#[0..2]7

H_TRDY#7

H_A20M#21

H_FERR#21

H_IGNNE#21

H_SMI#21

H_PWRGD21

H_STPCLK#21

H_INTR21

H_NMI21

H_INIT#21

H_DBSY#7

H_DRDY#7

15mil

12

12

12

12

Q46

2

1

3 1

C793

2

MMBT3904_SOT23

C789

1

6

4

5

GND

H_RS#0

H_RS#1

H_RS#2

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_INTR

H_NMI

H_INIT#

CPU_RESET#

H_CP U_ CL KSEL 0

H_CP U_ CL KSEL 1

H_CP U_ CL KSEL 2

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

H_VCCA

H_VSSA

COMP0

COMP1

COMP2

COMP3

MAINPWON 43,44,46

12

R589

@10K_0402_5%

+CPU_CORE

JP21B

B3

RS0#

F5

RS1#

A3

RS2#

H4

RSP#

E3

TRDY#

K3

A20M#

R3

FERR#/PBE#

N2

IGNNE#

P2

SMI#

N1

PWRGOOD

M3

STPCLK#

K1

LINT0

L1

LINT1

P3

INIT#

G23

RESET#

B2

DBSY#

C1

DRDY#

G29

BSEL0

H30

BSEL1

G30

BSEL2

AL1

THERMDA

AK1

THERMDC

M2

THERMTRIP#

AJ2

BPM0#

AJ1

BPM1#

AD2

BPM2#

AG2

BPM3#

AF2

BPM4#

AG3

BPM5#

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST#

C23

VCCIOPLL

A23

VCCA

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AN3

VCCSENSE

AN4

VSSSENSE

B23

VSSA

AK3

ITP_CLK0

AJ3

ITP_OUT1

A13

COMP0

T1

COMP1

G2

COMP2

R1

COMP3

+VTT_OUT_LEFT

B

AJ21

AM11

AL11

AJ11

VCCP149

VCCP150

VCCP151

VCCP152

+V_FSB_VTT

1

2

B

K30

AL14

AN30

VCCP153

VCCP154

RSVD1N4RSVD2P5RSVD3

1 2

@62_0402_5%

C609

10U_0805_10V4Z

C

AH25

AL12

AJ9

AK11

AG14

N29

AL30

AJ25

AH9

J29

J11

K25

K23

AL19

AM8

T26

N28

AH12

AL22

AN15

AJ8

U26

AJ19

T27

AK8

AN12

AG9

N26

AF9

AF22

AH11

AJ14

AH19

AH29

AH27

AG28

AL26

AM12

J24

J13

T28

W28

J12

J27

AG19

AL9

AD30

AF21

Y24

AK14

M27

AF14

J30

VCCP155

VCCP156

VCCP157

VCCP158

VCCP159

VCCP160

VCCP161

VCCP162

VCCP163

VCCP164

VCCP165

VCCP166

VCCP167

VCCP168P8VCCP169

VCCP170

VCCP171

VCCP172

VCCP173

VCCP174

VCCP175

VCCP176

VCCP177

VCCP178

VCCP179

VCCP180

VCCP181

VCCP182

VCCP183

VCCP184

VCCP185

VCCP186

VCCP187

VCCP188

VCCP189

VCCP190

VCCP191

VCCP192

VCCP193

VCCP194

VCCP195

VCCP196

VCCP197

VCCP198

VCCP199

VCCP200

VCCP201

VCCP202

VCCP203

VCCP204

VCCP205

VCCP206

VCCP207J9VCCP208

VCCP209

LGA-775

(2/4)

RSVD4

RSVD5

RSVD6

RSVD9

RSVD10

RSVD11G6RSVD12

RSVD13N5RSVD14

RSVD15C9RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22H2RSVD23J2RSVD24

RSVD26F6RSVD27T2RSVD28Y3RSVD29

RSVD31E7RSVD32

RSVD25

RSVD7D1RSVD8

E5

F29

D23

AE4

AK6

R188

AE6

AH2

C638

1

1

2

2

10U_0805_10V4Z

AC4

AM5

C622

1

2

10U_0805_10V4Z

F23

A20

E23

E24

D16

G10

1 2

R593 @1K_0402_5%

Reserve for Testability

C650

C658

1

2

10U_0805_10V4Z

10U_0805_10V4Z

RSVD30

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

J3

E6

B13

A29

B25

B29

B30

A26

B27

A25

A28

A27

D14

AE3

C29

+V_FSB_VTT

C28

C30

VID_PWRGD6,50

+VTT_OUT_RIGHT

+VTT_OUT_LEFT

A30

C25

Reserve for Testability

C296 180P_0402_50V8J

1 2

C294 180P_0402_50V8J

1 2

C293 180P_0402_50V8J

1 2

C292 180P_0402_50V8J

1 2

C290 680P_0402_50V7K

1 2

C295 180P_0402_50V8J

1 2

C297 180P_0402_50V8J

1 2

C289 180P_0402_50V8J

1 2

C355 180P_0402_50V8J

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC .

C

H_INIT#

H_A20M#

H_CPUSLP#

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_IGNNE#

H_PWRGD

VTT21

B26

C26

B28

C27

D27

D28

D25

D26

VID_PWRGD

+VTT_OUT_RIGHT

+VTT_OUT_LEFT

R149 200_0402_5%

1 2

R153 200_0402_5%

1 2

R147 200_0402_5%

1 2

R152 200_0402_5%

1 2

R154 200_0402_5%

1 2

R148 200_0402_5%

1 2

R151 200_0402_5%

1 2

R150 200_0402_5%

1 2

R184 100_0402_1%

1 2

AG18

VCCP210

VTT22

D29

AA8

VCCP211

VTT23

D30

AG8

VCCP212

VCCP213

VTT24

D

AL29

AD29

AH8

N24

AN22

J14

K26

AF19

AF12

M28

AK9

VCCP214

VCCP215

VCCP216W8VCCP217

VCCP218

VCCP219

VCCP220

VCCP221

VCCP222

VTTPWRGD

VTT_OUT1

VTT_OUT2J1VTT_SEL

VID4

VID5

F27

AL6

AL4

AA1

AM6

12

R58@1K_0402_5%

AK4

+V_FSB_VTT

+VTT_OUT_LEFT

D

EDRDY#,H_PCREQ# is not a

VCCP223N8VCCP224

VCCP225

VCCP226

feature of the Pentium 4 processor

in the 775-land package.

F2

EDRDY#

PCREQ#

GTLREF

SKTOCC#

TESTHI00

TESTHI01

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

TESTHI08

TESTHI09

TESTHI10

TESTHI11

TESTHI12

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

ADSTB0#

ADSTB1#

PROCHOT#

MCERR#

VID2

VID3

AL5

AM3

R591 0_0402_5%

G5

R186 0_0402_5%

J16

DP0#

H15

DP1#

H16

DP2#

J17

DP3#

H1

AE8

F26

W3

F25

G25

G27

G26

G24

F24

G3

G4

H5

P1

W2

C8

G12

G20

A16

B9

E12

G19

C17

R6

AD5

A8

DBI0#

G11

DBI1#

D19

DBI2#

C20

DBI3#

AC2

DBR#

AL2

W1

MS_ID0

V1

MS_ID1

AB3

L2

SLP#

VID0

VID1

FOX_PE077507-0741-01

AM2

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

Title

Size Docu m ent Nu m ber Re v

Date: Sheet

1 2

1 2

180P_0402_50V8J

+GTLREF

1 2

C340

H_TESTHI0

H_TESTHI1

H_TESTHI2_7

H_TESTHI8

H_TESTHI9

H_TESTHI10

H_TESTHI11

H_TESTHI12

1 2

@62_0402_5%

H_CPUSLP#

H_CP U_ CL KSEL 0

H_CP U_ CL KSEL 1

H_CP U_ CL KSEL 2

R60 62_0402_5%

R175 62_0402_5%

R59 62_0402_5%

R192 62_0402_5%

R185 62_0402_5%

R191 62_0402_5%

R177 62_0402_5%

R176 62_0402_5%

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_ADSTB#0 7

H_ADSTB#1 7

R590

H_PROCHOT# 49

MS_ID[0:1] are provided to indicate the Market

Segment for the processor and may be used

for fut ure p r o c e ssor compatibility.

H_CPUSLP# 21

H_VID0 50

H_VID1 50

H_VID2 50

H_VID3 50

H_VID4 50

H_VID0

H_VID5 50

H_VID1

H_VID3

H_VID4

H_VID5

H_VID2

1 2

1K_0402_5%

R52

1 2

560_0402_5%

1 2

1K_0402_5%

R56

1 2

560_0402_5%

1 2

1K_0402_5%

R45

1 2

560_0402_5%

Compal Electronics, Inc.

LGA-775(2/3)

Custom

Longbeach 100 <LA-2451>

星期六 十一月

H_EDRDY# 7

H_PCREQ# 7

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

+V_FSB_VTT

R51

Q6

3 1

MMBT3904_SOT23

R55

Q7

3 1

MMBT3904_SOT23

R44

Q4

3 1

MMBT3904_SOT23

2004

E

2

2

2

E

GTLR E F Voltage

should be

0.63*VTT=0.75V

+VTT_OUT_RIGHT

**

Width : Space

10 :15(mil)

+GTLREF

1

C794

2

1U_0603_10V4Z

+VTT_OUT_LEFT

+VTT_OUT_RIGHT

1 2

1 2

45

36

27

18

RP27680_1206_8P4R_5%

R40

1 2

1K_0402_5%

CPU_CLKSEL0 8,13

R47

1 2

1K_0402_5%

CPU_CLKSEL1 8,13

R39

1 2

1K_0402_5%

CPU_CLKSEL2 8,13

553, 06,

of

12

R606

100_0402_1%

R605

12

169_0402_1%

+V_FSB_VTT

+VTT_OUT_LEFT

+V_FSB_VTT

R588680_0402_5%

R174680_0402_5%

+3VS+V_FSB_VTT

+3VS+V_FSB_VTT

+3VS+V_FSB_VTT

0.1

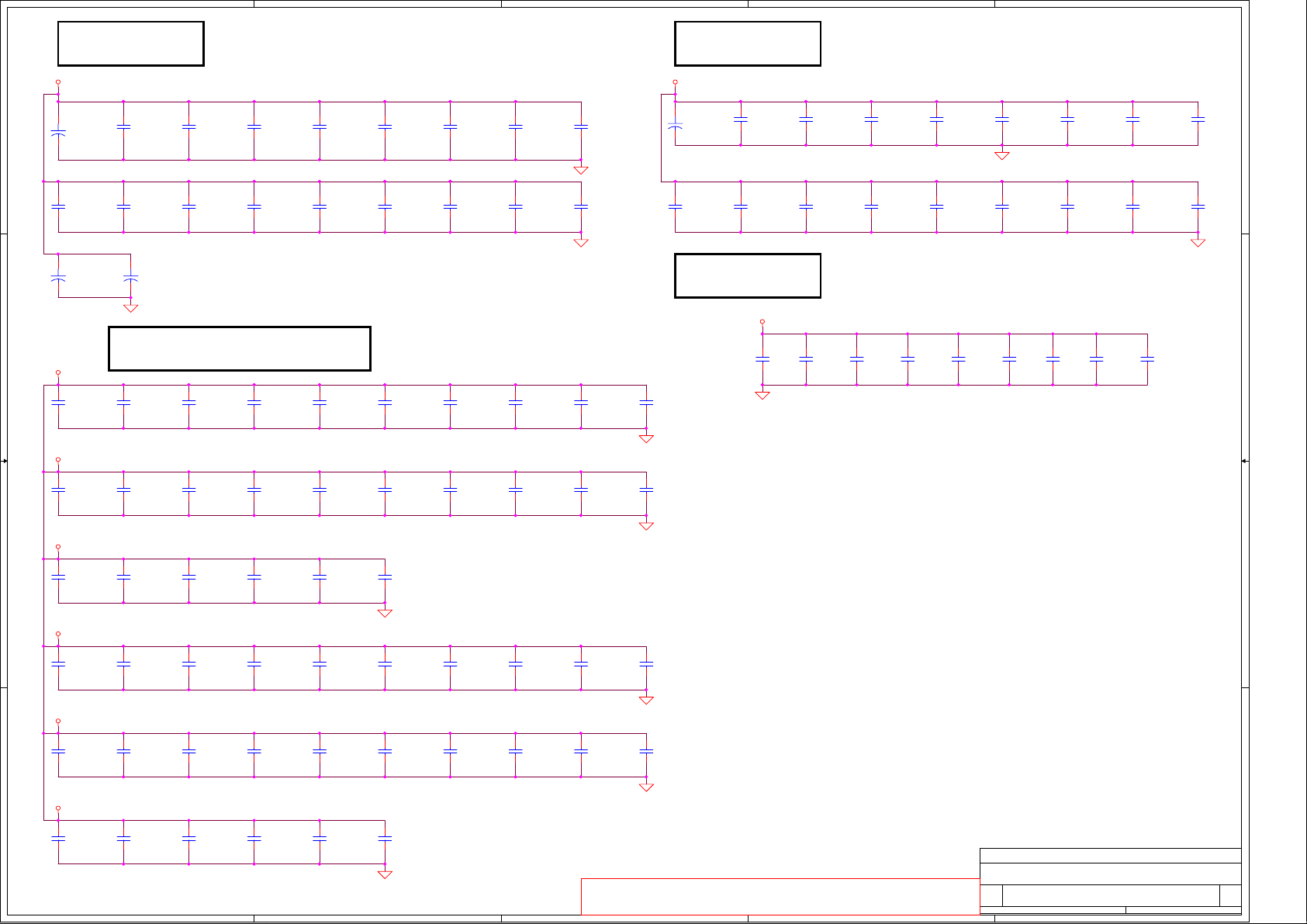

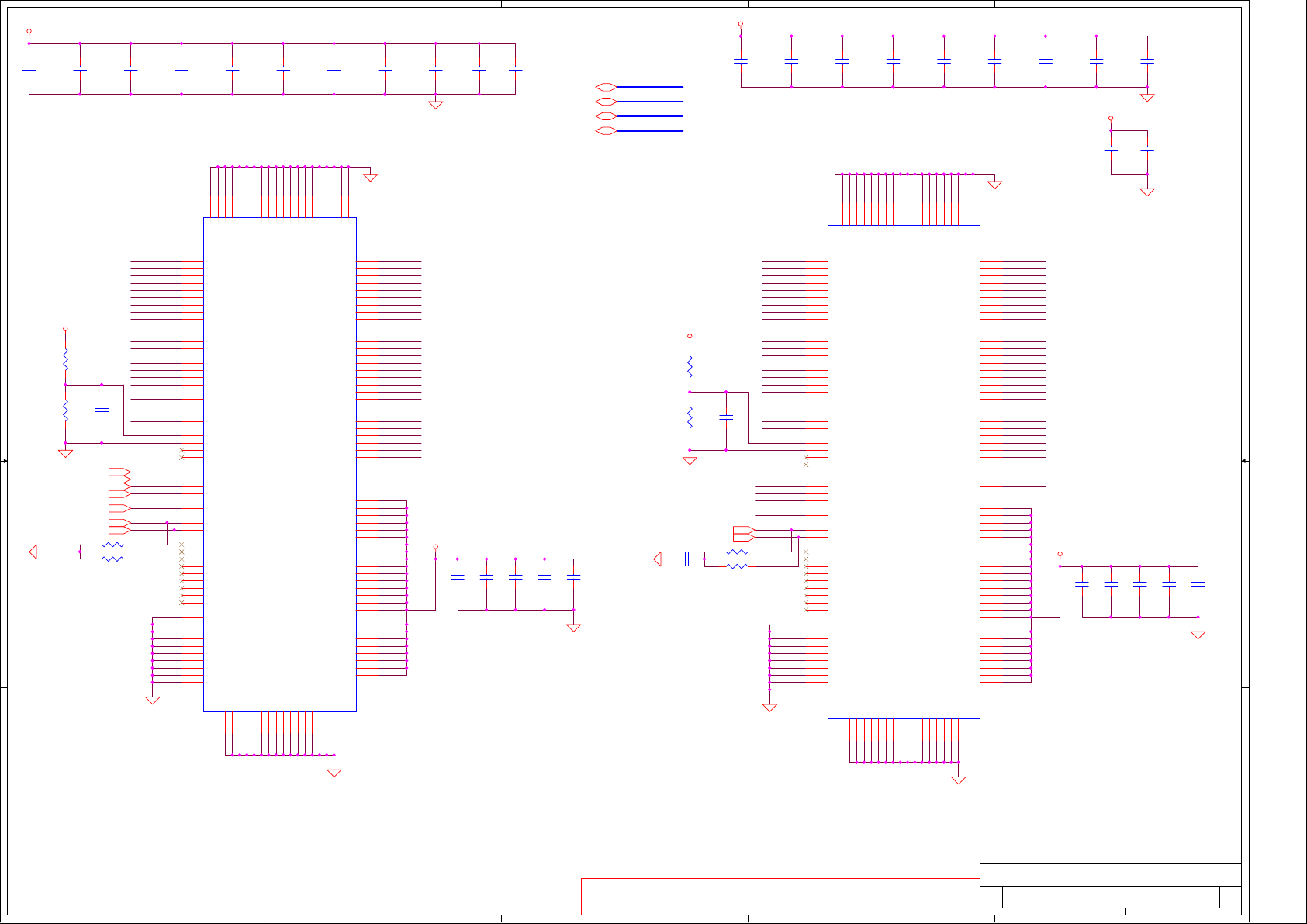

Page 6

A

B

C

Place all 10U_0805_6.3V6M of 8 pcs inside CPU socket cavity

Place all 10U_0805_6.3V6M of 8 pcs on another sideof CPU socket cavity

+CPU_CORE

D

E

1

C274

10U_0805_10V4Z

2

1

C740

10U_0805_10V4Z

2

1

C276

10U_0805_10V4Z

2

1

C227

10U_0805_10V4Z

2

1

C245

10U_0805_10V4Z

2

1

C282

10U_0805_10V4Z

2

1

C745

10U_0805_10V4Z

2

1

C285

10U_0805_10V4Z

2

1

C283

10U_0805_10V4Z

2

1

C246

10U_0805_10V4Z

2

820U_E9_2.5V_M_R7 (P/N:CB8200WM000)

820U_E9_2_5V_M_R7

1

+

C726

2

1

+

C675

2

220U_C6_6.3V_M_R15

1

+

C594

2

220U_C6_6.3V_M_R15

1

+

C753

2

220U_C6_6.3V_M_R15

1

+

C598

2

220U_C6_6.3V_M_R15

1

+

C595

2

D

820U_E9_2_5V_M_R7

220U_C6_6.3V_M_R15

1

C259

10U_0805_10V4Z

2

1

C720

10U_0805_10V4Z

2

1

C747

10U_0805_10V4Z

2

1

C284

10U_0805_10V4Z

2

1

+

C599

2

1

+

C597

2

Compal Electronics, Inc.

Title

Size Doc u m ent Nu m b er R e v

Custom

Date: Sheet

1

C267

10U_0805_10V4Z

2

1

C729

10U_0805_10V4Z

2

1

C252

10U_0805_10V4Z

2

1

C226

10U_0805_10V4Z

2

1

C232

10U_0805_10V4Z

2

820U_E9_2_5V_M_R7

1

C260

10U_0805_10V4Z

H29This pin in CPU is GTLREF_SEL, but not VSS.

1 1

JP21C

LGA-775

A12

VSS1

A15

VSS2

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

R723

R721

2.4K_0402_5%

1 2

12

C992

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

1

2

MMBT3904_SOT23

2 2

3 3

4 4

20K_0402_1%

(3/4)

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

FOX_PE077507-0741-01

+3VALW +3VALW+V_FSB_VTT

12

R722

10K_0402_5%

Q68

2

3 1

1U_0603_10V6K

A

11

SN74LVC14APWLE_TSSOP14

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

14

P

G

7

U39E

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AL7

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AM7

AN1

AN10

AN13

AN16

O10I

14

U39F

P

13

O12I

G

7

SN74LVC14APWLE_TSSOP14

JP21D

AN17

AN2

AN20

AN23

AN24

AN27

AN28

AN7

B1

B11

B14

B17

B20

B24

B5

B8

C10

C13

C16

C19

C22

C24

C4

C7

D12

D15

D18

D21

D24

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

E29

E8

F10

F13

F16

F19

F22

F4

F7

G1

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

FOX_PE077507-0741-01

+VTT_OUT_LEFT

12

R195

680_0402_5%

VID_PWRGD

13

D

Q15

2

G

S

2N7002_SOT23

B

LGA-775

VSS139

VSS140

(4/4)

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VID_PWRGD 5,50

Decoupling Reference Document:

Grantsdale Chipset Platform Design guide Rev1.2

(15434)Page263

Decoupling Reference Requirement:

560uF Polymer, ESR:6m ohm(each) * 10

22uF X5R * 8

10uF X5R * 10

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

H29

H3

H6

H7

H8

H9

J4

J7

K2

K5

K7

L23

L24

L25

L26

L27

L28

L29

L3

L30

L6

L7

M1

M7

N3

N6

N7

P23

P24

P25

P26

P27

P28

P29

P30

P4

P7

R2

R23

R24

R25

R26

R27

R28

R29

R30

R5

R7

T3

T6

T7

U1

U7

V23

V24

V25

V26

V27

V28

V29

V3

V30

V6

V7

W4

W7

Y2

Y5

Y7

1 2

R57 @1K_0402_5%

Reserve for Testability

P4 Processor output GTLREF_SEL = 0

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2

+CPU_CORE

1

C719

10U_0805_10V4Z

2

+CPU_CORE

1

C238

10U_0805_10V4Z

2

+CPU_CORE

1

C702

10U_0805_10V4Z

2

+CPU_CORE

1

C231

10U_0805_10V4Z

2

SANYO OS-CON 820uF _ERS7m ohm* 6

SANYO OS-CON 220uF _ERS13m ohm* 8

+CPU_CORE

820U_E9_2_5V_M_R7

1

+

C688

2

+CPU_CORE

220U_C6_6.3V_M_R15

1

+

C762

2

+CPU_CORE

220U_C6_6.3V_M_R15

1

+

C593

2

1

C266

10U_0805_10V4Z

2

1

C730

10U_0805_10V4Z

2

1

C710

10U_0805_10V4Z

2

1

C701

10U_0805_10V4Z

2

820U_E9_2_5V_M_R7

1

+

C596

2

220U_C6_6.3V_M_R15

LGA-775(3/3)

Longbeach 100 <LA-2451>

星期六 十一月

2004

1

C273

10U_0805_10V4Z

2

1

C741

10U_0805_10V4Z

2

1

C703

10U_0805_10V4Z

2

1

C700

10U_0805_10V4Z

2

1

+

C585

2

E

1

C281

10U_0805_10V4Z

2

1

C746

10U_0805_10V4Z

2

1

C709

10U_0805_10V4Z

2

1

C748

10U_0805_10V4Z

2

of

653, 06,

0.1

Page 7

A

H_A#[3..31]4

H_REQ#[0..4]4

H_RS#[0..2]5

U33A

H_A#3

G28

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

***

R94

12

R484

12

CPU_VREF

C170

C179

1

2

1

2

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

HSCOMP

HRCOMP

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_RS#2

H_RS#1

H_RS#0

+V_FSB_VTT

1U_0603_10V4Z

1 1

H_ADSTB#05

H_ADSTB#15

2 2

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#5

H_DBSY#5

H_LOCK#4

H_RESET#5

H_TRDY#5

H_HIT#4

H_HITM#4

+V_FSB_VTT

27.4_0402_1%

3 3

47_0402_1%

180P_0402_50V8J

Place C close

to Ball H22

H_PCREQ#5

H_EDRDY#5

CPU_ VR EF

Trace=12Mil

Space=15Mil

CPU_VREF

4 4

CPU_A3#

H26

CPU_A4#

G27

CPU_A5#

G30

CPU_A6#

G29

CPU_A7#

G26

CPU_A8#

H28

CPU_A9#

J28

CPU_A10#

H25

CPU_A11#

K28

CPU_A12#

H29

CPU_A13#

J29

CPU_A14#

K24

CPU_A15#

K25

CPU_A16#

F29

CPU_REQ0#

G25

CPU_REQ1#

F26

CPU_REQ2#

F28

CPU_REQ3#

E29

CPU_REQ4#

H27

CPU_ADSTB0#

M28

CPU_A17#

K29

CPU_A18#

K30

CPU_A19#

J26

CPU_A20#

L28

CPU_A21#

L29

CPU_A22#

M30

CPU_A23#

K27

CPU_A24#

M29

CPU_A25#

K26

CPU_A26#

N28

CPU_A27#

L26

CPU_A28#

N25

CPU_A29#

L25

CPU_A30#

N24

CPU_A31#

L27

CPU_ADSTB1#

F25

CPU_ADS#

F24

CPU_BNR#

E23

CPU_BPRI#

E25

CPU_DEFER#

G24

CPU_DRDY#

F23

CPU_DBSY#

E27

CPU_LOCK#

C11

CPU_CPURSET#

D23

CPU_RS2#

G23

CPU_RS1#

E26

CPU_RS0#

F22

CPU_TRDY#

D26

CPU_HIT#

E24

CPU_HITM#

D11

CPU_COMP_N

B11

CPU_COMP_P

H22

CPU_VREF

D25

RESERVED0

E11

RESERVED1

G22

RESERVED2

216CPP4AKA21HK_BGA707

12

R100

49.9_0402_1%

***

12

R102

100_0402_1%

A

PART 1 OF 6

ADDR. GROUP 1 A DDR. GROUP 0CONTROLMISC.

CPU I/F

RC400M

DATA GROUP 0

CPU_DSTBN0#

CPU_DSTBP0#

DATA GROUP 1

CPU_DSTBN1#

CPU_DSTBP1#

DATA GROUP 2DATA GROUP 3

CPU_DSTBN2#

CPU_DSTBP2#

CPU_DSTBN3#

CPU_DSTBP3#

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

B

H_D#[0..63] 4

H_DINV#[0..3] 5

H_DSTBN#[0..3] 5

H_DSTBP#[0..3] 5

H_D#0

E28

H_D#1

D28

H_D#2

D29

H_D#3

C29

H_D#4

D30

H_D#5

C30

H_D#6

B29

H_D#7

C28

H_D#8

C26

H_D#9

B25

H_D#10

B27

H_D#11

C25

H_D#12

A27

H_D#13

C24

H_D#14

A24

H_D#15

B26

H_DINV#0

C27

H_DSTBN#0

A28

H_DSTBP#0

B28

H_D#16

C19

H_D#17

C23

H_D#18

C20

H_D#19

C22

H_D#20

B22

H_D#21

B23

H_D#22

C21

H_D#23

B24

H_D#24

E21

H_D#25

B21

H_D#26

B20

H_D#27

G19

H_D#28

F21

H_D#29

B19

H_D#30

E20

H_D#31

D21

H_DINV#1

A21

H_DSTBN#1

D22

H_DSTBP#1

E22

H_D#32

C18

H_D#33

F19

H_D#34

E19

H_D#35

A18

H_D#36

D19

H_D#37

B18

H_D#38

C17

H_D#39

B17

H_D#40

E17

H_D#41

B16

H_D#42

C15

H_D#43

A15

H_D#44

B15

H_D#45

F16

H_D#46

G18

H_D#47

F18

H_DINV#2

C16

H_DSTBN#2

D18

H_DSTBP#2

E18

H_D#48

E16

H_D#49

D16

H_D#50

C14

H_D#51

B14

H_D#52

E15

H_D#53

D15

H_D#54

C13

H_D#55

E14

H_D#56

F13

H_D#57

B13

H_D#58

A12

H_D#59

C12

H_D#60

E12

H_D#61

D13

H_D#62

D12

H_D#63

B12

H_DINV#3

E13

H_DSTBN#3

F15

H_DSTBP#3

G15

B

Place R

Close to Ball

+1.2VS

SB_A_RXN0 NB_A_TXN0

C718

C714 0.1U_0402_10V6K

SB_A_RXN1

C711

SB_A_RXP1

NB_A_RXN0

C708 0.1U_0402_10V6K

NB_A_RXP0

NB_A_RXN1

NB_A_RXP1

CLK_PCIE_MCH-ICH#13

CLK_PCIE_MCH- ICH13

R51910K_0402_1%

12

R52010K_0402_1%

12

R115100_0402_1%

12

R124150_0402_1%

12

1 2

0.1U_0402_10V6K

1 2

1 2

0.1U_0402_10V6K

1 2

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

NBGFX_RXN0

NBGFX_RXP0

NBGFX_RXN1

NBGFX_RXP1

NBGFX_RXN2

NBGFX_RXP2

NBGFX_RXN3

NBGFX_RXP3

NBGFX_RXN4

NBGFX_RXP4

NBGFX_RXN5

NBGFX_RXP5

NBGFX_RXN6

NBGFX_RXP6

NBGFX_RXN7

NBGFX_RXP7

NBGFX_RXN8

NBGFX_RXP8

NBGFX_RXN9

NBGFX_RXP9

NBGFX_RXN10

NBGFX_RXP10

NBGFX_RXN11

NBGFX_RXP11

NBGFX_RXN12

NBGFX_RXP12

NBGFX_RXN13

NBGFX_RXP13

NBGFX_RXN14

NBGFX_RXP14

NBGFX_RXN15

NBGFX_RXP15

PCE_RXISET

PCE_TXISET

PCE_NCAL

PCE_PCAL

C

NBGFX_RXN[0..15]14

NBGFX_RXP[0..15]14

10 mils

10 mils

10 mils

10 mils

NB_A_TXP0SB_A_RXP0

NB_A_TXN1

NB_A_TXP1

U33C

J4

GFX_RX0N

J5

GFX_RX0P

L4

GFX_RX1N

K4

GFX_RX1P

L5

GFX_RX2N

L6

GFX_RX2P

M4

GFX_RX3N

M5

GFX_RX3P

P4

GFX_RX4N

N4

GFX_RX4P

P5

GFX_RX5N

P6

GFX_RX5P

R4

GFX_RX6N

R5

GFX_RX6P

T3

GFX_RX7N

T4

GFX_RX7P

U5

GFX_RX8N

U6

GFX_RX8P

V4

GFX_RX9N

V5

GFX_RX9P

W3

GFX_RX10N

W4

GFX_RX10P

Y5

GFX_RX11N

Y6

GFX_RX11P

AA4

GFX_RX12N

AA5

GFX_RX12P

AB3

GFX_RX13N

AB4

GFX_RX13P

AC5

GFX_RX14N

AC6

GFX_RX14P

AD4

GFX_RX15N

AD5

GFX_RX15P

AJ12

PCE_ISET

AK13

PCE_TXISET

AG12

PCE_NCAL

AH12

PCE_PCAL

AJ11

SB_TX0N

AJ10

SB_TX0P

AK10

SB_TX1N

AK9

SB_TX1P

AG10

SB_RX0N

AG9

SB_RX0P

AF10

SB_RX1N

AE9

SB_RX1P

L2

SB_CLKN

K2

SB_CLKP

216CPP4AKA21HK_BGA707

A-LINK EXPRESS I/F

D

GFX_TX0N

GFX_TX0P

GFX_TX1N

GFX_TX1P

GFX_TX2N

GFX_TX2P

PART 3 OF 6

PCI EXPRESS I/F

RC400M

GFX_TX3N

GFX_TX3P

GFX_TX4N

GFX_TX4P

GFX_TX5N

GFX_TX5P

GFX_TX6N

GFX_TX6P

GFX_TX7N

GFX_TX7P

GFX_TX8N

GFX_TX8P

GFX_TX9N

PCI EXPRESS I/F

GFX_TX9P

GFX_TX10N

GFX_TX10P

GFX_TX11N

GFX_TX11P

GFX_TX12N

GFX_TX12P

GFX_TX13N

GFX_TX13P

GFX_TX14N

GFX_TX14P

GFX_TX15N

GFX_TX15P

GFX_CLKN

GFX_CLKP

GPP_TX0N/SB_TX2N

GPP_TX0P/SB_TX2P

GPP_TX1N/SB_TX3N

GPP_TX1P/SB_TX3P

GPP_TX2N

GPP_TX2P

GPP_TX3N

GPP_TX3P

GPP_RX0N/SB_RX2N

GPP_RX0P/SB_RX2P

GPP_RX1N/SB_RX3N

GPP_RX1P/SB_RX3P

GPP_RX2N

GPP_RX2P

GPP_RX3N

GPP_RX3P

D

E

VGA_PCIE_RXN[0..15] 14

VGA_PCIE_RXP[0..15] 14

Place AC capacitors close to transmiter

In t h i s case, th ese cap s should place clo se to NB ASIC

N2

N1

R2

P2

T1

R1

U2

T2

V1

V2

W2

W1

AA2

Y2

AB1

AA1

AC2

AB2

AD1

AD2

NBGFX_TXN10

AE2

NBGFX_TXP10

AE1

NBGFX_TXN11

AG2

NBGFX_TXP11

AF2

NBGFX_TXN12

AH1

NBGFX_TXP12

AG1

NBGFX_TXN13

AJ2

NBGFX_TXP13

AH2

NBGFX_TXN14

AJ4

NBGFX_TXP14

AJ3

NBGFX_TXN15

AJ5

NBGFX_TXP15

AK4

M1

M2

AJ9

AJ8

AF6

AE6

NB_PCIEC_TXN0

AK6

NB_PCIEC_TXP0

AJ6

AF4

AE4

AG8

AF8

AG7

AG6

AJ7

AK7

AH4

AG4

NBGFX_TXN0

NBGFX_TXP0

NBGFX_TXN1

NBGFX_TXP1

NBGFX_TXN2

NBGFX_TXP2

NBGFX_TXN3

NBGFX_TXP3

NBGFX_TXN4

NBGFX_TXP4

NBGFX_TXN5

NBGFX_TXP5

NBGFX_TXN6

NBGFX_TXP6

NBGFX_TXN7

NBGFX_TXP7

NBGFX_TXN8

NBGFX_TXP8

NBGFX_TXN9

NBGFX_TXP9

C607 0.1U_0402_10V6K

C620 0.1U_0402_10V6K

C704 0.1U_0402_10V6K

C697 0.1U_0402_10V6K

C216 0.1U_0402_10V6K

C209 0.1U_0402_10V6K

C690 0.1U_0402_10V6K

C687 0.1U_0402_10V6K

SB_A_RXN[0..3] 21

SB_A_RXP[0..3] 21

NB_A_RXN[0..3] 21

NB_A_RXP[0..3] 21

1 2

C604 0.1U_0402_10V6K

1 2

1 2

C626 0.1U_0402_10V6K

1 2

1 2

C621 0.1U_0402_10V6K

1 2

C617 0.1U_0402_10V6K

1 2

C640 0.1U_0402_10V6K

1 2

C635 0.1U_0402_10V6K

1 2

C634 0.1U_0402_10V6K

1 2

C637 0.1U_0402_10V6K

1 2

C653 0.1U_0402_10V6K

1 2

C648 0.1U_0402_10V6K

1 2

C651 0.1U_0402_10V6K

1 2

C644 0.1U_0402_10V6K

1 2

C662 0.1U_0402_10V6K

1 2

C660 0.1U_0402_10V6K

1 2

C661 0.1U_0402_10V6K

1 2

C656 0.1U_0402_10V6K

1 2

C665 0.1U_0402_10V6K

1 2

C667 0.1U_0402_10V6K

1 2

C666 0.1U_0402_10V6K

1 2

C664 0.1U_0402_10V6K

1 2

C672 0.1U_0402_10V6K

1 2

C670 0.1U_0402_10V6K

1 2

C671 0.1U_0402_10V6K

1 2

C669 0.1U_0402_10V6K

1 2

C679 0.1U_0402_10V6K

1 2

C677 0.1U_0402_10V6K

1 2

C678 0.1U_0402_10V6K

1 2

C676 0.1U_0402_10V6K

1 2

C684 0.1U_0402_10V6K

1 2

C683 0.1U_0402_10V6K

CLK_PCIE_MCH-VGA# 13

CLK_PCIE_MCH-VGA 13

1 2

1 2

1 2

1 2

1 2

1 2

VGA_PCIE_RXN0

VGA_PCIE_RXP0

VGA_PCIE_RXN1

VGA_PCIE_RXP1

VGA_PCIE_RXN2

VGA_PCIE_RXP2

VGA_PCIE_RXN3

VGA_PCIE_RXP3

VGA_PCIE_RXN4

VGA_PCIE_RXP4

VGA_PCIE_RXN5

VGA_PCIE_RXP5

VGA_PCIE_RXN6

VGA_PCIE_RXP6

VGA_PCIE_RXN7

VGA_PCIE_RXP7

VGA_PCIE_RXN8

VGA_PCIE_RXP8

VGA_PCIE_RXN9

VGA_PCIE_RXP9

VGA_PCIE_RXN10

VGA_PCIE_RXP10

VGA_PCIE_RXN11

VGA_PCIE_RXP11

VGA_PCIE_RXN12

VGA_PCIE_RXP12

VGA_PCIE_RXN13

VGA_PCIE_RXP13

VGA_PCIE_RXN14

VGA_PCIE_RXP14

VGA_PCIE_RXN15

VGA_PCIE_RXP15

To SB A-PCIE Link

Compal Electronics, Inc.

Title

RC400M-FSB,PC I E,A-PCIE(1/3)

Size Doc u m ent Nu m b er R e v

Custom

Longbeach 100 <LA-2451>

星期六 十一月

Date: Sheet

2004

E

SB_A_RXN2NB_A_TXN2

SB_A_RXP2NB_A_TXP2

SB_A_RXN3NB_A_TXN3

SB_A_RXP3NB_A_TXP3

PCIEC_RXN0 30

PCIEC_RXP0 30

NB_A_RXN2

NB_A_RXP2

NB_A_RXN3

NB_A_RXP3

NB_PCIEC_RXN0 30

NB_PCIEC_RXP0 30

of

753, 06,

0.1

Page 8

A

B

C

D

E

U33D

RSET

15mil

R459

R462

C995

8

7

WP

6

5

R467 4.7K_0402_5%

R468 4.7K_0402_5%

R460 4.7K_0402_5%

F9

Y

D9

C

E9

COMP

F10

RED

E10

GREEN

D10

BLUE

C3

DACHSYNC

B3

DACVSYNC

B10

RSET

B2

DACSCL

C2

DACSDA

G1

OSCIN

F1

OSCOUT

G2

TVCLKIN

J1

CPU_CLKP

K1

CPU_CLKN

D2

I2C_CLK

C1

I2C_DATA

H3

DDC_DATA

D1

STRP_DATA

C4

TESTMODE

AH13

THERMALDIODE_P

AJ13

THERMALDIODE_N

216CPP4AKA21HK_BGA707

ENBKLS14

R476

1 2

4.7K_0402_5%

+3VS

2

12

R727

1

@1K_0402_5%

NB_EDID_CLK

STRP_DATA

ENVDDS14

1 2

1 2

1 2

R463 10K_0402_5%

1 2

R457 4.7K_0402_5%

1 2

R455 @4.7K_0402_5%

1 2

D

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXCLK_UN

PART 4 OF 6

CRT & TV I/F

RC400M

CLK. GEN.

1 2

R772

LVDS_ENBKL

LVDS_ENVDD

NB STRAPING PINS

1 2

R773

1 2

R776

1 2

R777

CPU_CLKSEL2 5,13

CPU_CLKSEL1 5,13

CPU_CLKSEL0 5,13

+3VS

+3VS

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

LVDS

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

LVDS_BLON

LVDS_DIGON

LVDS_BLEN

SYSRESET#

SUS_STAT#

POWERGOOD

BMREQ#

TMDS_HPD

0_0402_5%

@0_0402_5%

NB_PWRGD

@0_0402_5%

0_0402_5%

BM_RE Q #/HSYNC / V SYNC: FSB CLK SPEED

DEFAULT: 010 (200MHZ)

OTHERS COMBINATION ARE SHOWED AT CLK PAGE

NB_DDC_CLK: CPU VCC SEL

DEFAULT: 1

1: DESKTOP CPU

0: MOBILE CPU

STRP_DA TA: DEBUG STRAP

DEFAULT: 1

0: MEMORY CHANNEL STRAPING

1: E2PROM STRAPING

Compa l Electr oni cs, I nc.

Title

Size Document Number Rev

Custom

Date: S heet

NB_LUMA19

NB_CRMA19

1 2

1 1

DDR_SBS010,11

DDR_SBS110,11

DDR_SRAS#10,11

DDR_SCAS#10,11

DDR_SWE#10,11

DDR_CLK0#10

DDR_CLK010

+2.5V

R539

12

2 2

***

61.9_0603_1%

R526

12

C731

61.9_0603_1%

Place these R and C

close to relative Ball.

+2.5V

3 3

4 4

12

1K_0603_1%

12

1K_0603_1%

R114

R119

MEM_COMPN

MEM_COMPP

MEM_CAP1

MEM_CAP2

1

1

C243

2

2

0.47U_0603_10V7K

0.47U_0603_10V7K

1

C235

2

0.1U_0402_10V6K

+DDR_VREF

1

C236

2

0.1U_0402_10V6K

A

DDR_CLK1#10

DDR_CLK110

DDR_CLK3#11

DDR_CLK311

DDR_CLK4#11

DDR_CLK411

DDR_SCKE010,11

DDR_SCKE110,11

DDR_SCKE211

DDR_SCKE311

R535 1K_0402_5%

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA13

***

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

MEM_VMODE: 0V:DDR

1 2

MEM_CAP1

MEM_CAP2

MEM_COMPP

MEM_COMPN

+DDR_VREF

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

10mil

10mil

10mil

10mil

20mil

U33B

AK27

MEM_A0

AJ27

MEM_A1

AH26

MEM_A2

AJ26

MEM_A3

AH25

MEM_A4

AJ25

MEM_A5

AH24

MEM_A6

AH23

MEM_A7

AJ24

MEM_A8

AJ23

MEM_A9

AH27

MEM_A10

AH22

MEM_A11

AJ22

MEM_A12

AF28

MEM_A13

AJ21

MEM_A14

AG27

MEM_A15

AJ28

MEM_A16

AH21

MEM_A17

AJ29

MEM_RAS#

AG28

MEM_CAS#

AH30

MEM_WE#

AC26

MEM_CK0N

AC25

MEM_CK0P

AF16

MEM_CK1N

AE16

MEM_CK1P

V29

MEM_CK2N

V30

MEM_CK2P

AC24

MEM_CK3N

AC23

MEM_CK3P

AG17

MEM_CK4N

AF17

MEM_CK4P

W29

MEM_CK5N

W28

MEM_CK5P

AH20

MEM_CKE0

AJ20

MEM_CKE1

AE24

MEM_CKE2

AE21

MEM_CKE3

AH29

MEM_CS#0

AG29

MEM_CS#1

AH28

MEM_CS#2

AF29

MEM_CS#3

AG30

MEM_ODT0

AE28

MEM_ODT1

AC30

MEM_ODT2/RSV2

Y30

MEM_ODT3/RSV3

AD28

MEM_VMODE

AJ14

MEM_CAP1

N30

MEM_CAP2

AJ15

MEM_COMPP

AE29

MEM_COMPN

AB27

MEM_VREF

AH17

MEM_DQS0N

AJ18

MEM_DQS0P

AF15

MEM_DQS1N

AE14

MEM_DQS1P

AE22

MEM_DQS2N

AF22

MEM_DQS2P

AF26

MEM_DQS3N

AE25

MEM_DQS3P

W26

MEM_DQS4N

W27

MEM_DQS4P

AB30

MEM_DQS5N

AB29

MEM_DQS5P

R25

MEM_DQS6N

P25

MEM_DQS6P

R30

MEM_DQS7N

R29

MEM_DQS7P

216CPP4AKA21HK_BGA707

ADDRESS

DATA CLKMISC

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_SCS#[0..3]

DDR_SMA[0..13]

B

PART 2 OF 6

MEMORY I/F

DATA

RC400M

DDR_DQ[0..63] 10

DDR_DQS[0..7] 10

DDR_DM[0..7] 10

DDR_SCS#[0..3] 10,11

DDR_SMA[0..13] 10,11

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

AJ16

AH16

AJ19

AH19

AH15

AK16

AH18

AK19

AF13

AF14

AE19

AF19

AE13

AG13

AF18

AE17

AF20

AF21

AG23

AF24

AG19

AG20

AG22

AF23

AD25

AG25

AE27

AD27

AE23

AD24

AE26

AD26

AA25

Y26

W24

U25

AA26

Y25

V26

W25

AC28

AC29

AA29

Y29

AD30

AD29

AA30

Y28

U27

T27

N26

M27

U26

T26

P27

P26

U29

T29

P29

N29

U28

T28

P28

N27

AJ17

AG15

AE20

AF25

Y27

AB28

R26

R28

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

THIS S HE ET O F E NG I NE ERI NG DRA WI N G IS T HE PR OP RI ET A RY PROPERTY OF CO MPAL ELECTRO NICS, I NC. AND CONTAI NS CONFIDENTIAL

AND TRAD E SEC RET INF ORM ATI O N. T HIS SHE ET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

R95 75_0402_5%

NB_CRT_R20

NB_CRT_G20

NB_CRT_B20

NB_CRT_HSYNC20

NB_CRT_VSYNC20

1 2

R480 715_0402_1%

NB_DDC_CLK20

NB_DDC_DATA20

***

CLK_NB_14M13

NB_PCLK13

CLK_NB_BCLK13

CLK_NB_BCLK#13

NB_EDID_CLK19

NB_EDID_DATA19

R469

1 2

Low: Normal Mode(Fixed)

High: Test Mode

R450

1 2

4.7K_0402_5%

R456

1 2

+3VS

4.7K_0402_5%

R470

1 2

@4.7K_0402_5%

NB_COMPS

C125

12

@15P_0402_50V8D

12

10_0402_5%

12

@10_0402_5%

1 2

R466 10K_0402_5%

NB_EDID_CLK

NB_EDID_DATA

NB_DVI_DDCDATA

STRP_DATA

TESTMODE

4.7K_0402_5%

NB_EDID_CLK

NB_EDID_DATA

NB_DVI_DDCDATA

@0.1U_0402_10V6K

U49

1

NC

2

3

4

VCC

A1

A2

SCL

VSS

SDA

@AT24C04N-10SI-2.7_SO8~D

**

BM_REQ#

NB_CRT_HSYNC

NB_CRT_VSYNC

NB_DDC_CLK

STRP_DATA

NB_TZOUT0-

B4

NB_TZOUT0+

A4

NB_TZOUT1-

B5

NB_TZOUT1+

C6

NB_TZOUT2-

B6

NB_TZOUT2+

A6

B7

A7

NB_TZCLK-

F7

NB_TZCLK+

F8

NB_TXOUT0-

E5

NB_TXOUT0+

F5

NB_TXOUT1-

D5

NB_TXOUT1+

C5

NB_TXOUT2-

E6

NB_TXOUT2+

D6

E7

E8

NB_TXCLK-

G6

NB_TXCLK+

F6

LVDS_ENBKL

G3

LVDS_ENVDD

E2

F2

***

A3

AH14

E3

H2

J2

+3VS

C997 0.1U_0402_16V4Z

5

U50

1

P

B

Y

2

A

G

TC7SH08FU_SSOP5

3

+3VS

C998 0.1U_0402_16V4Z

5

U51

1

P

B

Y

2

A

G

TC7SH08FU_SSOP5

3

R125 @4.7K_0402_5%

R123 2.2K_0402_5%

R786 5.6K_0402_5%

NB_PWRGD

BM_REQ#

12

R471

10K_0402_5%

4

***

1 2

R774

1 2

4

R775

NB_TZOUT0- 19

NB_TZOUT0+ 19

NB_TZOUT1- 19

NB_TZOUT1+ 19

NB_TZOUT2- 19

NB_TZOUT2+ 19

NB_TZCLK- 19

NB_TZCLK+ 19

NB_TXOUT0- 19

NB_TXOUT0+ 19

NB_TXOUT1- 19

NB_TXOUT1+ 19

NB_TXOUT2- 19

NB_TXOUT2+ 19

NB_TXCLK- 19

NB_TXCLK+ 19

**

R743 @4.7K_0402_5%

1 2

@4.7K_0402_5%

1 2

R744

1 2

1 2

1 2

NB_RST# 14,21,30

NB_SUS_STAT# 22

NB_PWRGD 23

BM_REQ# 21

0_0402_5%

@0_0402_5%

RC400M-DDR,DISP,MISC(2/3)

Longbeach 100 <LA-2451>

星期六 十一月

2004

E

853, 06,

+1.8VS

+2.5V

ENBKL 37,53

ENVDD 19

NB_ENVDD 19

of

0.1

Page 9

A

C624

C149

0.1U_0402_16V4Z

+V_FSB_VTT

1

2

0.1U_0402_16V4Z

1

C133

2

+1.2VS

1

2

0.1U_0402_16V4Z

###

+AVDDQ

2

C1131

C608

1

1U_0603_10V4Z

1U_0603_10V4Z

1

C629

0.1U_0402_16V4Z

2

###

C1133

C1134

1

1

2

2

0.1U_0402_16V4Z

A

+V_FSB_VTT

5A

+AVDD

+CPVDD

+MPVDD

0.1U_0402_16V4Z

+1.2VS

5A

1

1U_0603_10V4Z

2

C654

1

2

U33E

M13

VDD_CORE

M15

VDD_CORE

M17

VDD_CORE

M19

VDD_CORE

N12

VDD_CORE

N14

VDD_CORE

N16

VDD_CORE

N18

VDD_CORE

P13

VDD_CORE

P15

VDD_CORE

P17

VDD_CORE

P19

VDD_CORE

R12

VDD_CORE

R14

VDD_CORE

R16

VDD_CORE

R18

VDD_CORE

T13

VDD_CORE

T15

VDD_CORE

T17

VDD_CORE

T19

VDD_CORE

U12

VDD_CORE

U14

VDD_CORE

U16

VDD_CORE

U18

VDD_CORE

V13

VDD_CORE

V15

VDD_CORE

V17

VDD_CORE

V19

VDD_CORE

W12

VDD_CORE

W14

VDD_CORE

W16

VDD_CORE

W18

VDD_CORE

A10

VDD_CPU

F11

VDD_CPU

F12

VDD_CPU

F17

VDD_CPU

G11

VDD_CPU

G12

VDD_CPU

G13

VDD_CPU

G14

VDD_CPU

G16

VDD_CPU

G17

VDD_CPU

G20

VDD_CPU

H11

VDD_CPU

H12

VDD_CPU

H13

VDD_CPU

H14

VDD_CPU

H16

VDD_CPU

H17

VDD_CPU

H19

VDD_CPU

H23

VDD_CPU

H24

VDD_CPU

L23

VDD_CPU

L24

VDD_CPU

N23

VDD_CPU

P23

VDD_CPU

P24

VDD_CPU

C9

AVDD

B8

AVDDQ

D8

AVDDDI

H21

CPVDD

AB26

MPVDD

216CPP4AKA21HK_BGA707

C583

1

C603

2

10U_0805_10V4Z

0.1U_0402_16V4Z

+AVDD

1

C127

0.1U_0402_16V4Z

2

+LPVDD

1

C643

1U_0603_10V4Z

2

CORE PWR

L39

1 2

CHB2012U170_0805

L44

1 2

CHB2012U170_0805

1 2

C175 10U_0805_10V4Z

1 2

C190 10U_0805_10V4Z

1 2

C160 0.1U_0402_16V4Z

1 2

C165 0.1U_0402_16V4Z

1 2

C166 0.1U_0402_16V4Z

1 2

C171 0.1U_0402_16V4Z

1 2

C172 0.1U_0402_16V4Z

1 1

1 2

C181 0.1U_0402_16V4Z

1 2

C182 0.1U_0402_16V4Z

1 2

C194 0.1U_0402_16V4Z

1 2

C198 0.1U_0402_16V4Z

1 2

C206 0.1U_0402_16V4Z

1 2

C197 0.1U_0402_16V4Z

1 2

C193 0.1U_0402_16V4Z

1 2

C203 0.1U_0402_16V4Z

1 2

C207 0.1U_0402_16V4Z

1 2

C211 0.1U_0402_16V4Z

1 2

C210 0.1U_0402_16V4Z

1 2

C153 10U_0805_10V4Z

1 2

C164 10U_0805_10V4Z

1 2

C222 0.1U_0402_16V4Z

2 2

1 2

C228 0.1U_0402_16V4Z

1 2

C200 0.1U_0402_16V4Z

1 2

C192 0.1U_0402_16V4Z

1 2

C191 0.1U_0402_16V4Z

1 2

C213 0.1U_0402_16V4Z

1 2

C205 0.1U_0402_16V4Z

1 2

C212 0.1U_0402_16V4Z

1 2

C137 0.1U_0402_16V4Z

1 2

C147 0.1U_0402_16V4Z

1 2

C151 0.1U_0402_16V4Z

1 2

C145 0.1U_0402_16V4Z

1 2

C146 0.1U_0402_16V4Z

Place C between

Ball D8,C8

+1.8VS

3 3

4 4

L9

1 2

CHB1608U301_0603

***

1

10U_0805_10V4Z

2

1

C128

2

B

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

PART 5 OF 6

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

MEM I/F PWRCPU I/F PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

POWER

RC400M

+3VS

+1.8VS

B

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

LVDDR18D

LVDDR18A

LVDDR18A

+2.5V

2A

AB23

AB24

AC13

AC16

AC19

AC21

AC22

AD13

AD16

AD19

AD21

AD22

AD23

AK21

AK24

AK28

T23

T24

V23

V24

Y23

Y24

0.1A

AB22

VDD_18

AB9

VDD_18

J22

VDD_18

VDD_18

VDDR3

VDDR3

LPVDD

PLLVDD

C1129

1

2

+1.2VS

J9

2.25A

AB7

AC7

AC8

AD9

H4

H5

J6

K6

L7

L8

M7

M8

P7

P8

T7

T8

W7

W8

0.75A

AB8

AC10

AC9

AD10

AE11

AF11

AG11

U7

U8

Y7

Y8

0.1A

G4

+AVDD

G5

J8

+LPVDD

C7

H7

H8

H10

+PLLVDD

Place L close to Ball H21

Place C between Ball H21,H20

L46

1 2

CHB1608U301_0603

1

1

C659

10U_0805_10V4Z

Place L close to Ball AB26

Place C between Ball AB26,AA27

C749

C1128

0.1U_0402_16V4Z

2

2

1U_0603_10V4Z

+MPVDD +1.8VS

1

1

C744

2

2

10U_0805_10V4Z

C

**

1 2

C1055 0.1U_0402_16V4Z

1 2

C1056 0.1U_0402_16V4Z

1 2

C1057 0.1U_0402_16V4Z

***

1 2

C139 0.1U_0402_16V4Z

1 2

C180 0.1U_0402_16V4Z

1 2

C187 0.1U_0402_16V4Z

1 2

C256 0.1U_0402_16V4Z

1 2

C1064 10U_0805_10V4Z

1 2

C1065 10U_0805_10V4Z

***

***

1 2

C619 0.1U_0402_16V4Z

1 2

C728 1U_0603_10V4Z

1 2

C156 0.1U_0402_16V4Z

1 2

C161 0.1U_0402_16V4Z

1 2

C162 0.1U_0402_16V4Z

1 2

C155 0.1U_0402_16V4Z

1 2

C734 10U_0805_10V4Z

###

***

1U_0603_10V4Z

+1.8VS+CPVDD

1

1

C655

C1127

2

2

10U_0805_10V4Z

1U_0603_10V4Z

L46

1 2

CHB1608U301_0603

1

C1130

0.1U_0402_16V4Z

2

THIS S HE ET O F ENG I NEERI NG DRAWING IS THE PROP RIETARY PROPERTY O F COMPAL EL ECTRONICS, INC. AND CO NTAINS CONFI DENTIAL

AND TR ADE SECRET INFORM ATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY O F THE COMPETENT DI VISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

0.1U_0402_16V4Z

C

+2.5V

1 2

C752 10U_0805_10V4Z

1 2

C739 10U_0805_10V4Z

1 2

C742 10U_0805_10V4Z

1 2

C750 10U_0805_10V4Z

1 2

C239 0.1U_0402_16V4Z

1 2

C240 0.1U_0402_16V4Z

1 2

C229 0.1U_0402_16V4Z

1 2

C230 0.1U_0402_16V4Z

1 2

C208 0.1U_0402_16V4Z

1 2

C257 0.1U_0402_16V4Z

1 2

C255 0.1U_0402_16V4Z

1 2

C215 0.1U_0402_16V4Z

1 2

C201 0.1U_0402_16V4Z

1 2

C234 0.1U_0402_16V4Z

1 2

C254 0.1U_0402_16V4Z

1 2

C244 0.1U_0402_16V4Z

1 2

C248 0.1U_0402_16V4Z

+1.8VS

+1.8VS

Place C between H10,H9

Place L after C

C642

1 2

C249 0.1U_0402_16V4Z

1 2

C241 0.1U_0402_16V4Z

+1.2VS

1 2

C578 10U_0805_10V4Z

1 2

C576 10U_0805_10V4Z

1 2

C582 10U_0805_10V4Z

1 2

C581 10U_0805_10V4Z

1 2

C587 10U_0805_10V4Z

1 2

C586 10U_0805_10V4Z

1 2

C577 10U_0805_10V4Z

1 2

C186 1U_0603_10V4Z

1 2

C185 1U_0603_10V4Z

1 2

C143 1U_0603_10V4Z

1 2

C134 0.1U_0402_16V4Z

1 2

C135 0.1U_0402_16V4Z

1 2

C142 0.1U_0402_16V4Z

1 2

C148 0.1U_0402_16V4Z

1 2

C152 0.1U_0402_16V4Z

1 2

C174 0.1U_0402_16V4Z

1 2

C178 0.1U_0402_16V4Z

1 2

C176 0.1U_0402_16V4Z

+

1 2

470U_D2_2.5VM

C1030

+

1 2

470U_D2_2.5VM

C1031

###

+PLLVDD +1.8VS

1

1

2

C636

1U_0603_10V4Z

2

**

***

+1.8VS

1

+

2

1

10U_0805_10V4Z