Page 1

5

D D

4

3

2

1

C C

Compal Confidential

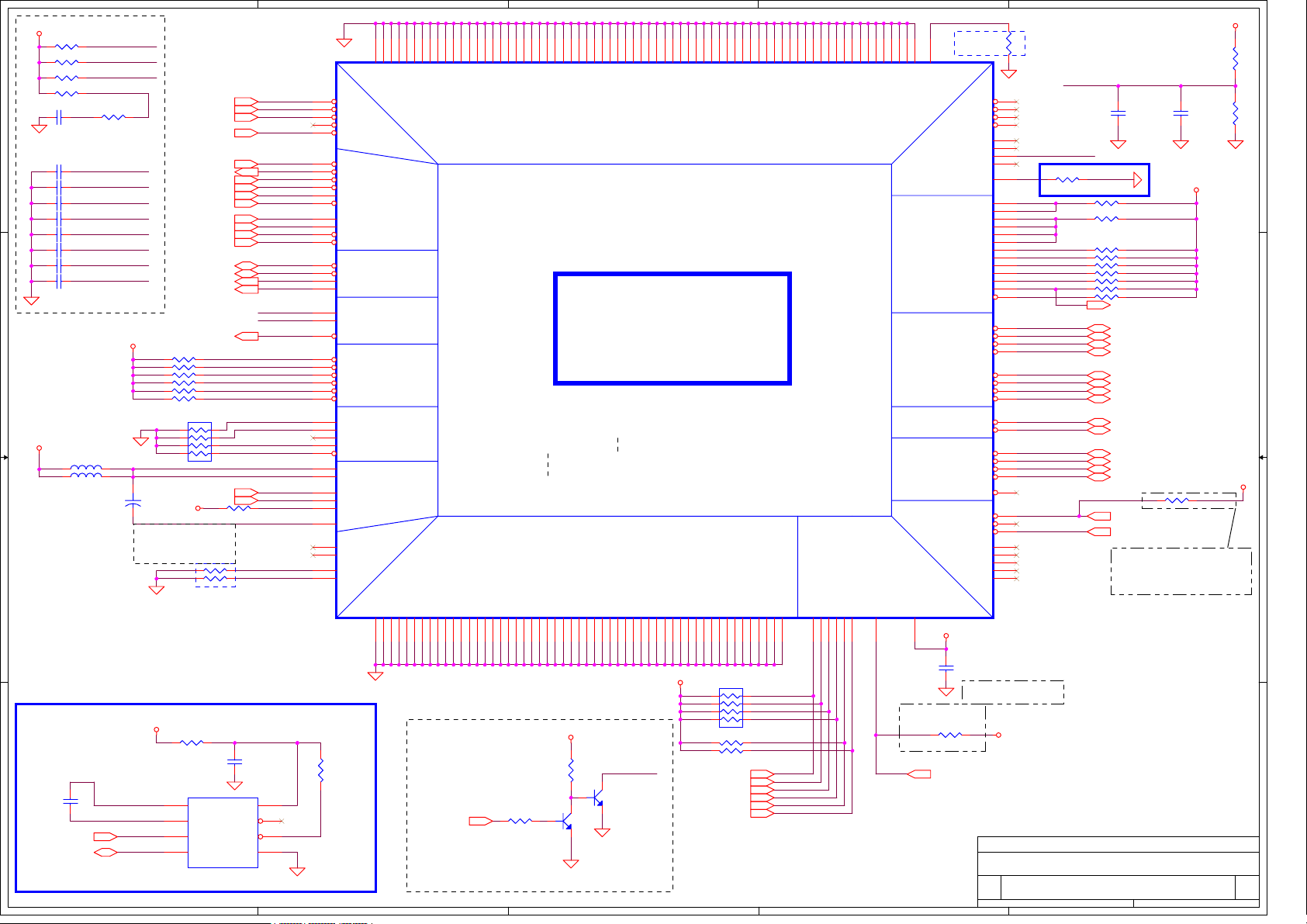

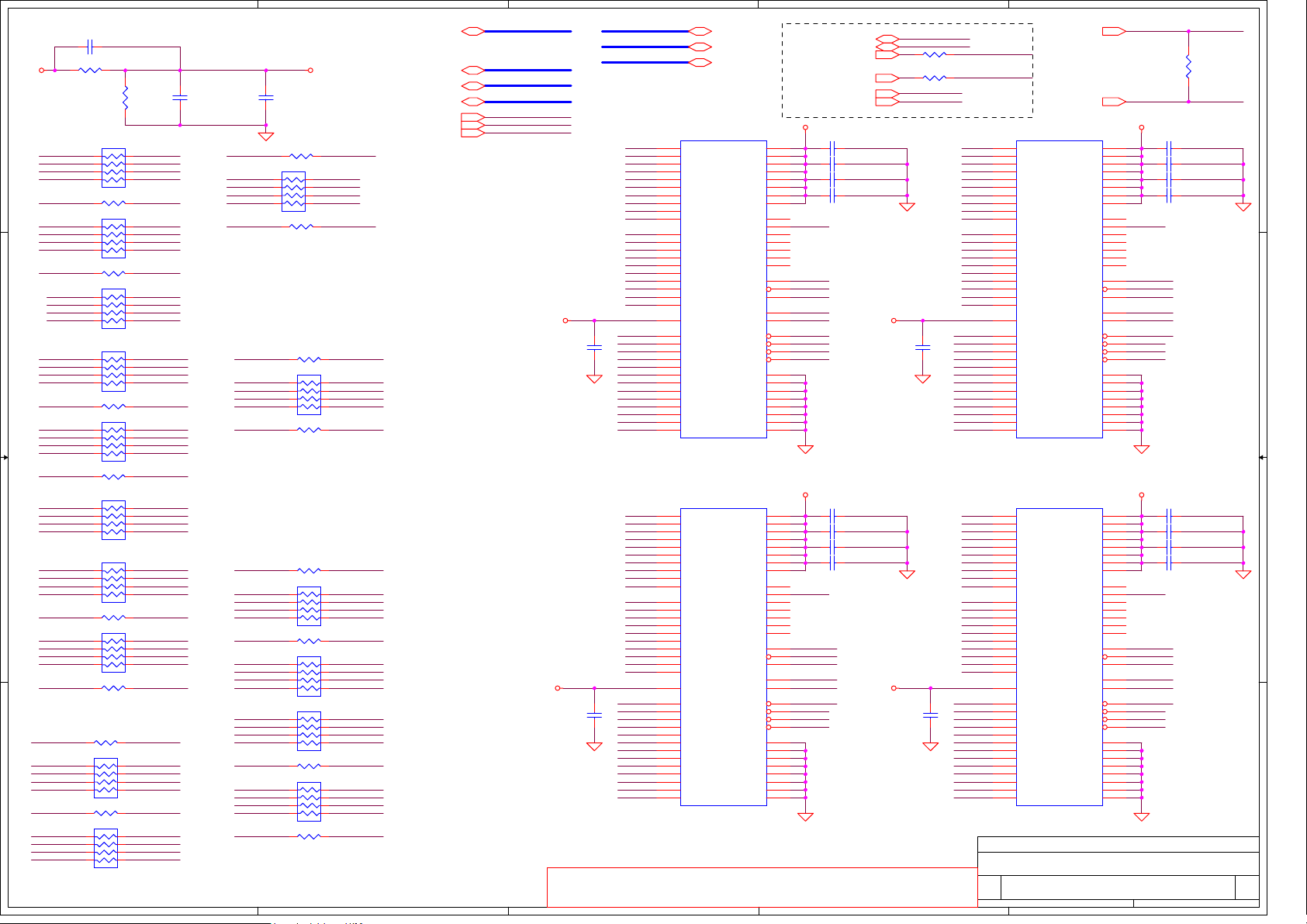

Fortworth20 EDW10 Schematic Document

Intel Protability Processor with ATi RC300ML + IXP150

2004-05-26

B B

REV: 1.0

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-2301

148Tuesday, May 18, 2004

1

1.0

of

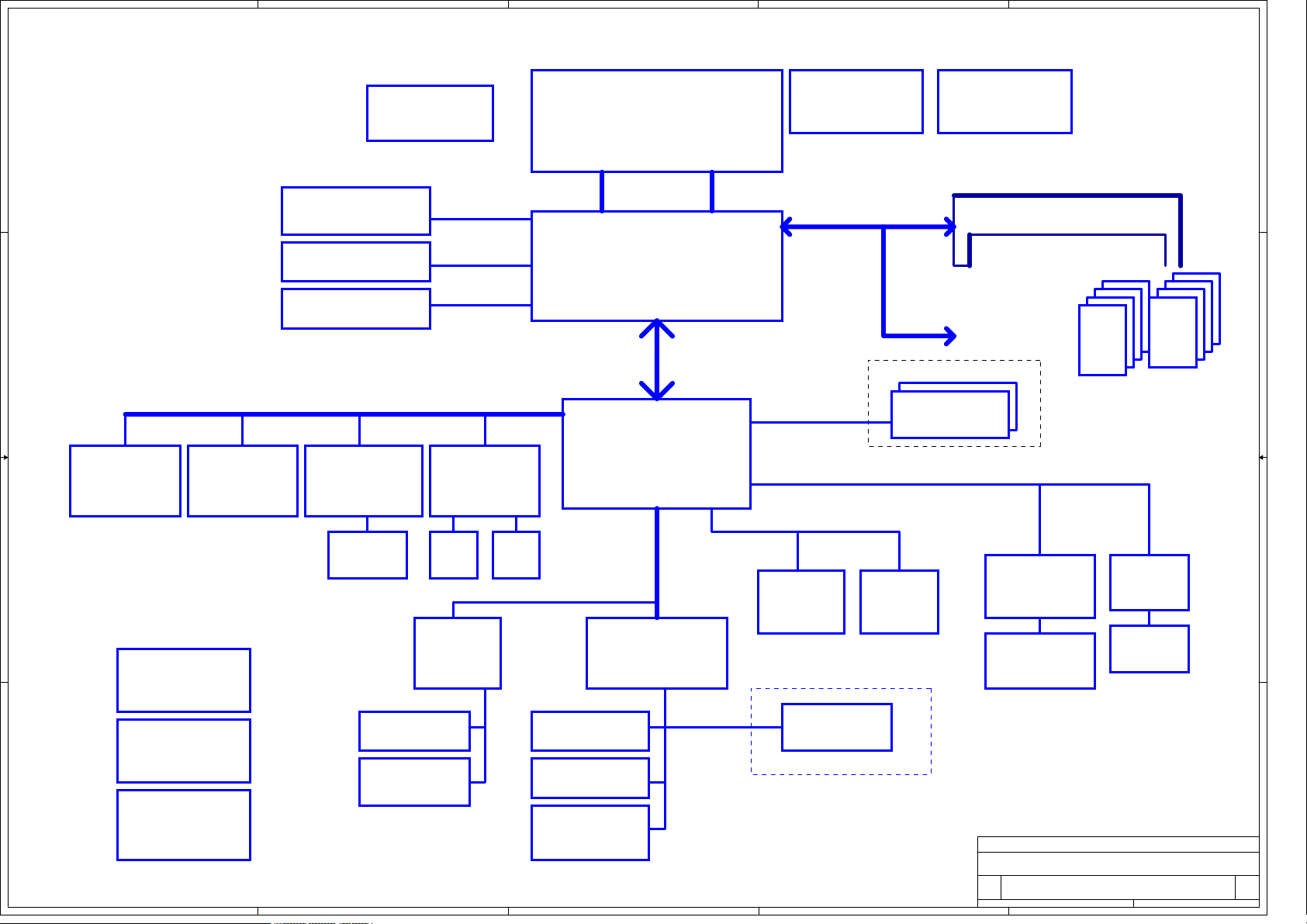

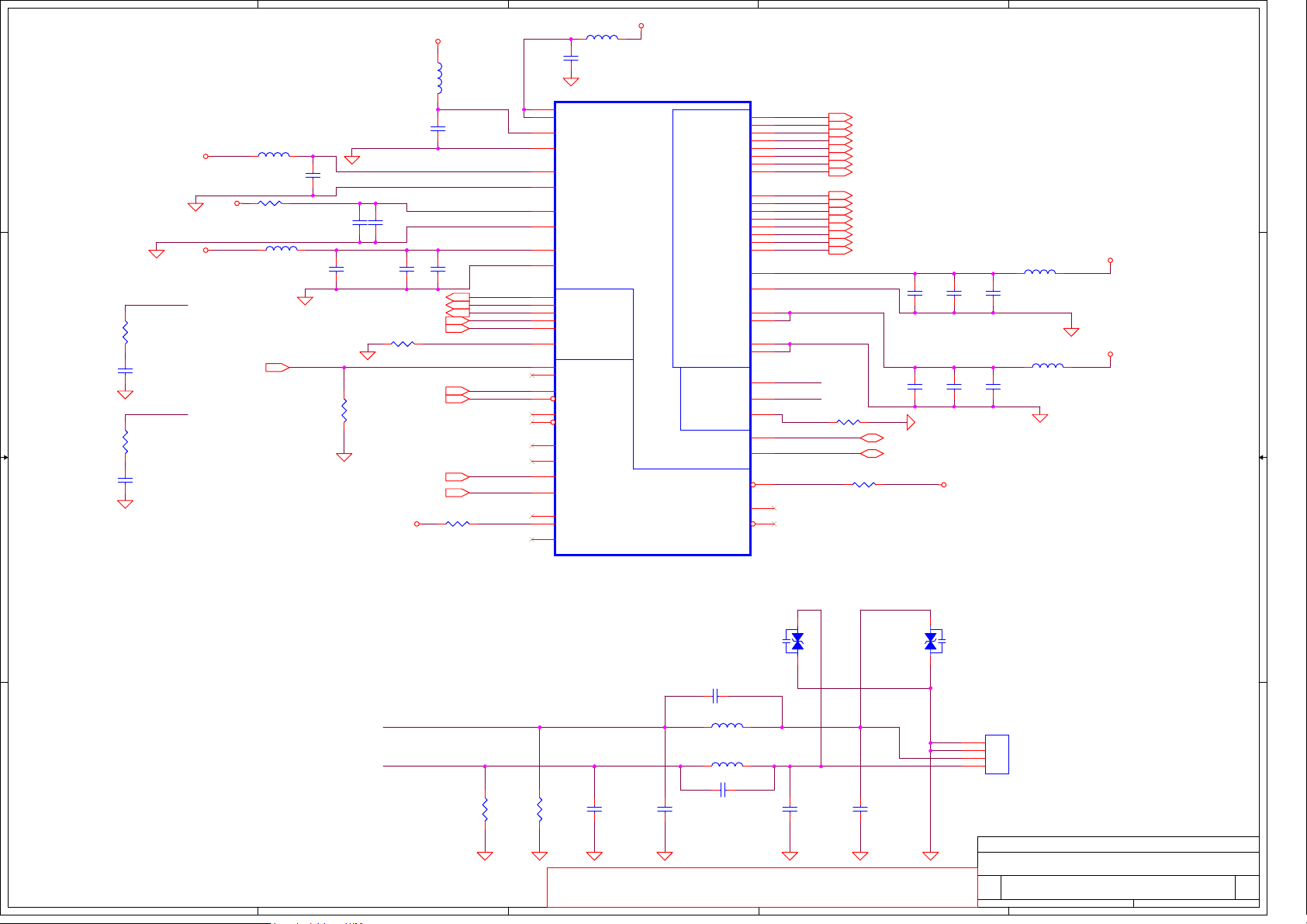

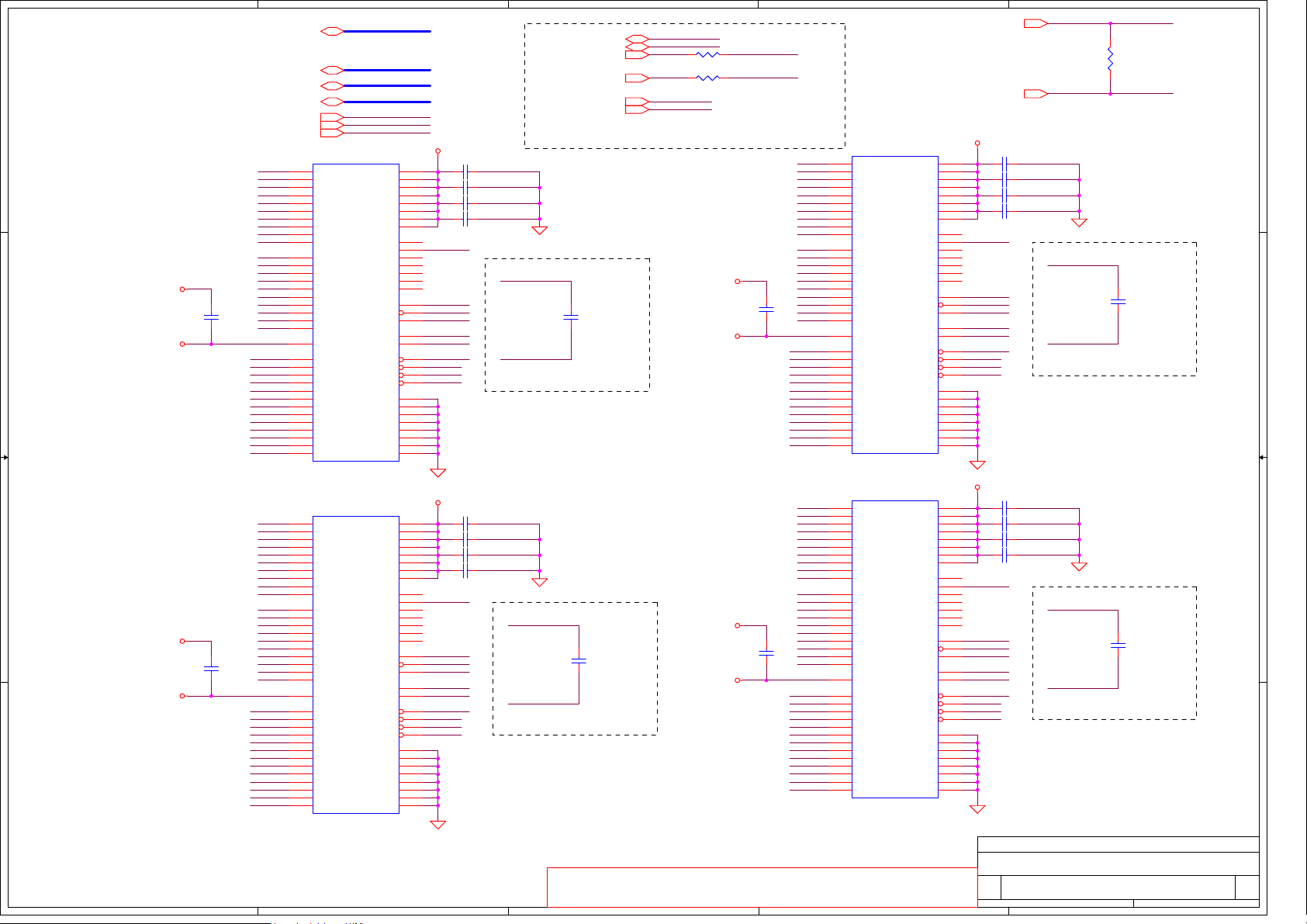

Page 2

5

Compal confidential

4

3

2

1

Block Diagram

Model Name : Fortworth 20

D D

File Name : LA-2301 Rev: 0.1

Fan Control

page 37

CRT Connector

page 18

LVDS Connector

TV Connector

C C

Mini-PCI

page 28

B B

IEEE 1394

TI TSB43AB21A

page 27

Realtek RTL8100CL

LAN

RJ45

page 26

page 18

page 10

PCI BUS

page 26

3.3V 33MHz

CardBus / SD / SM /

MMC / MS Pro / XD

ENE CB714

Slot 0

page 25

page 24

5 in 1

Conn.

page 25

Super I/O

SMsC

Power On/Off

Reset & RTC

page 35

LPC47N217

page 32

NorthWood-MT -- 533

Presscot-MT--533

uFCPGA 478 Pin

FSB

400/533 MHz

ATi RC300ML

BGA-718 Pin

page 7,8,9,10,11,12

A-Link

66MHz 4X 266MB/s

ATi SB200C

IXP 150

BGA-457Pin

page 19,20,21,22

LPC BUS

3.3V 33MHz

K/B Controller

ENE KB910

page 4,5,6

HD#(0..63)HA#(3..31)

3.3V 48MHz USB2.0

page 33

Thermal Sensor

ADM1032

Memory BUS(DDR)

2.5V 200MHz DDR266/333

3.3V 24.576MHz

3.3V ATA100

HDD

page 23

page 5

USB port 0, 1, 2, 3

USB conn

AC-Link

CDROM

page 23

Clock Generator

ICS951402

page 17

200pin DDR-SODIMM X1

BANK 0, 1, 2, 3

page 15,16

page 13,14

On Board RAM

x 8 cells

USBx3

page 29

AC97 Codec

ALC250

page 30

AMP& Phone

Jack

page 31

MDC

page 30

RJ11

page 30

DC/DC Interface

Suspend

A A

page 37

Parallel Port

FIR Module

page 32

TFDU6102-TR3

page 32

Int.KBD

page 33

EC I/O Buffer

page 34

Touch Pad

T/P Switch Board

Power Circuit

DC/DC

page 38,39,40,41

42,43,44,45,46

5

4

Flash ROM

SST39VF040-90-4C-NH

page 34

Title

Size Document Number Re v

B

3

2

Date: Sheet

Compal Electronics, Inc.

Block Diagram

LA-2301

248Tuesday, May 18, 2004

1

1.0

of

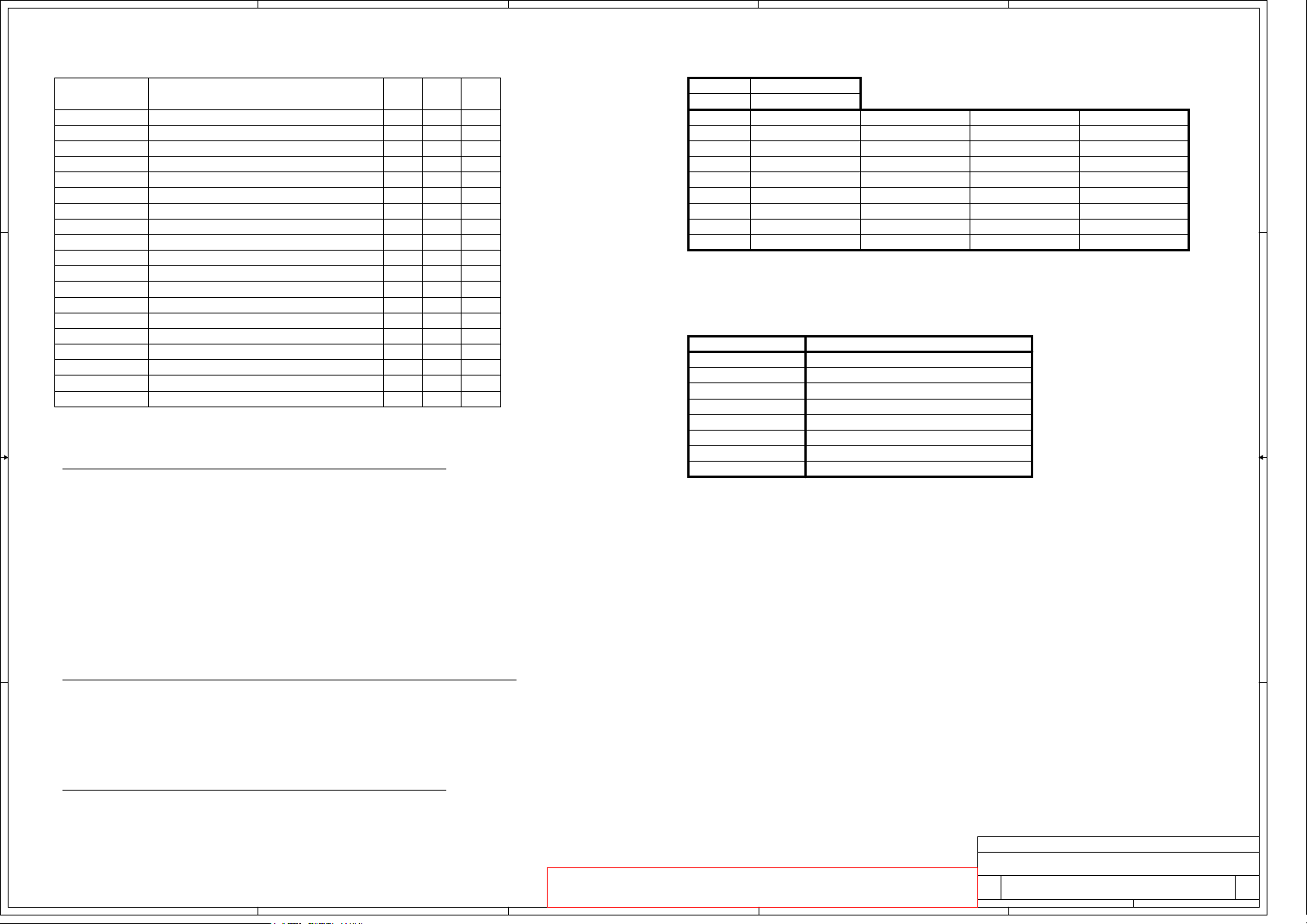

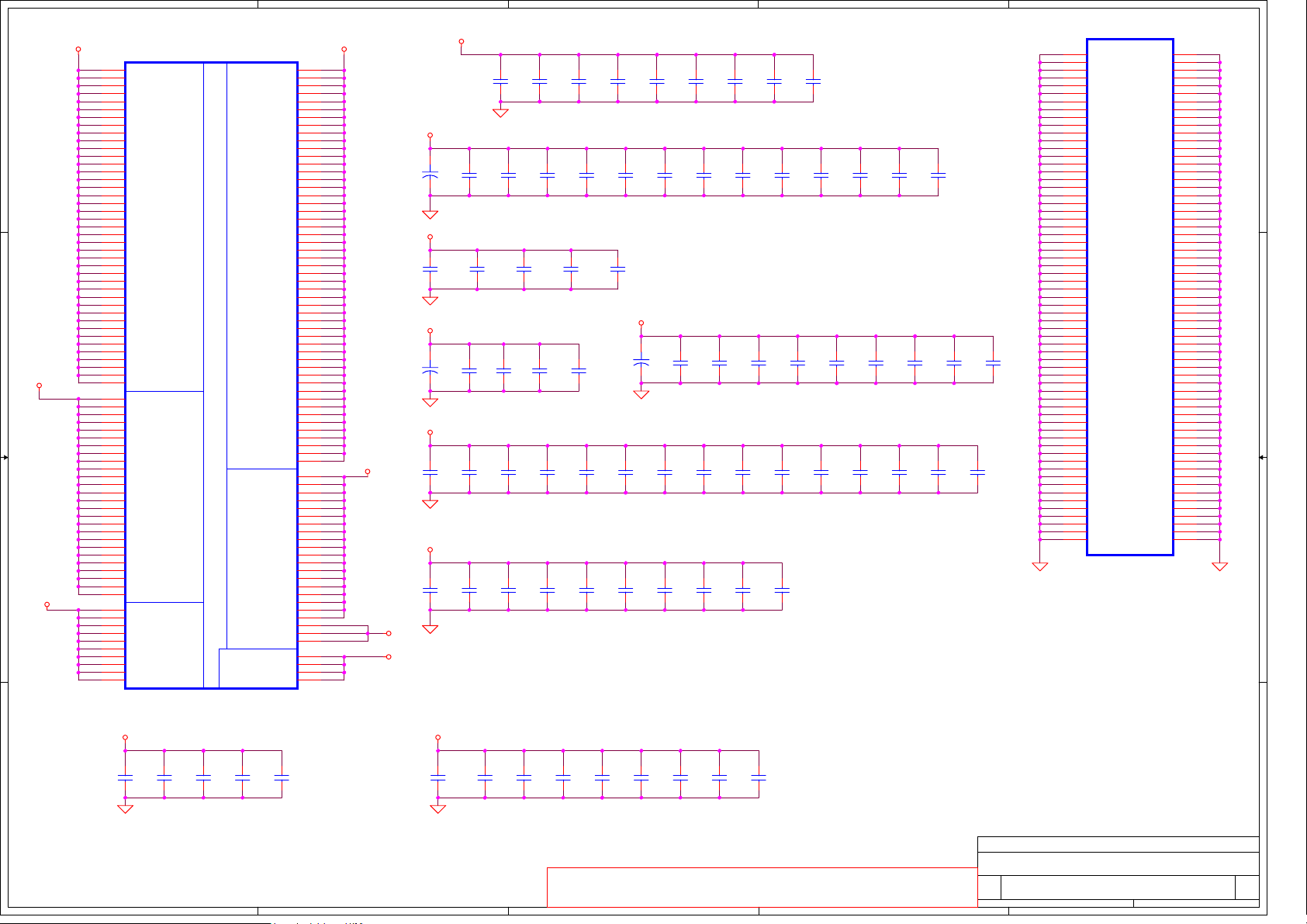

Page 3

5

4

3

2

1

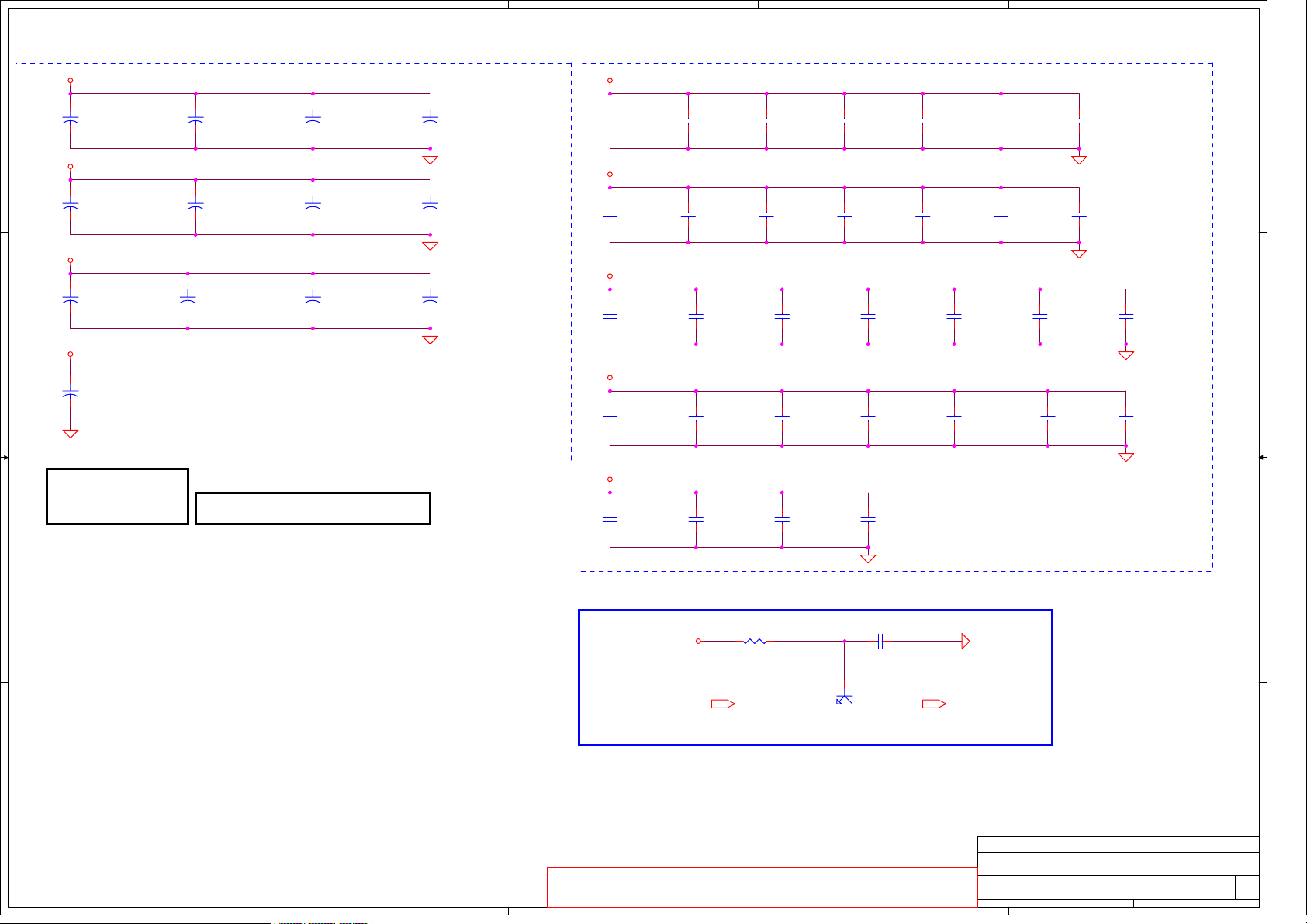

Voltage Rails

Power Plane Description

D D

C C

VIN

B+

+CPU_CORE

+CPU_VID ON OFF OFF1.2V rail for Processor VID

+1.25VS 1.25V switched power rail

+1.8VS

+2.5VALW ON*ON*

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW

+5V 5V power rail OFFONON

+5VS

+12VALW

RTCVCC

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.8V switched power rail

2.5V always on power rail

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

12V always on power rail

RTC power

S0-S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF

OFF OFF

ON

ON

ON

ON

OFF

ON

ON ON *

ON

ON

ON

OFF

ON

ON

ON

OFF

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF

OFF

OFF

ON*

OFF

ON*

ON

Board ID Table for AD channel

Vcc 3.3V +/- 5%

0

1

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BI D

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

0.1

Board ID

0

1

2

3

4

5

6

7 NC

Board ID PCB Revision

Vtyp

AD_BI D

V

AD_BI D

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

2

3

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

4

5

6

7

IDSEL # PIRQREQ/GNT #DEVICE

NB Internal VGA

LAN

CARD BUS

B B

5 in 1 AD20 2 B

Mini-PCI AD18 3

N/A

AD19

AD20 2

N/A

1

A

A1394 0AD16

D

A

C/D

EC SM Bus1 address

Device Address Address

Smart Battery

EEPROM(24C16)

1010 000X b

EC SM Bus2 address

Device

ADM1032

ALC250

1001 100X b0001 011X b

0000 000X b

I2C / SMBUS ADDRESSING

A A

DEVICE HEX ADDRESS

DDR SO-DIMM 0

CLOCK GENERATOR (EXT.)

5

A0

D2

1 0 1 0 0 0 1 X

1 1 0 1 0 0 1 X

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

Notes

LA-2301

348Tuesday, May 18, 2004

1

1.0

of

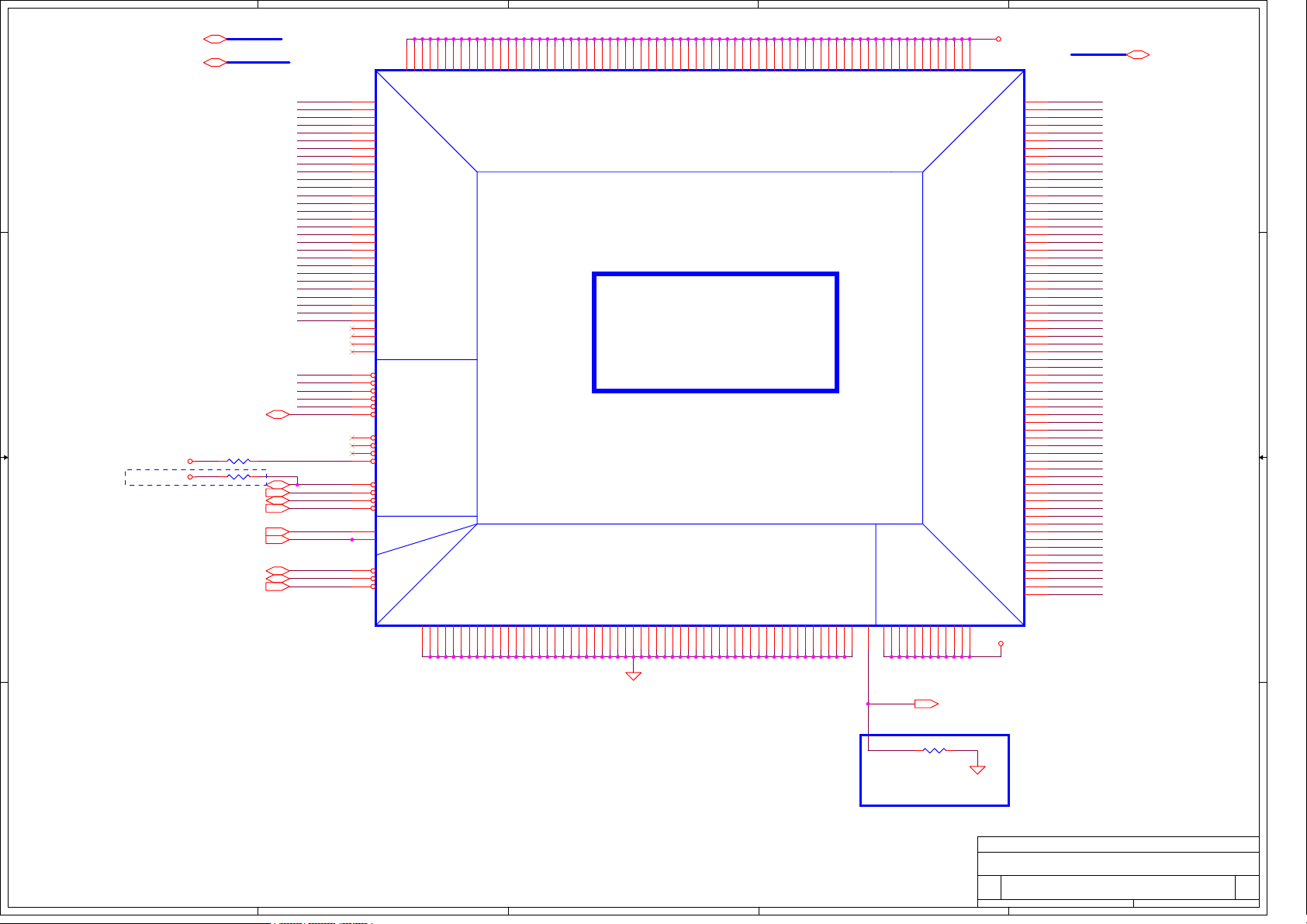

Page 4

5

4

3

2

1

HA#[3..31]7

H_REQ#[0..4]7

D D

C C

H_BR0# PU R :

Intel 220 Ohm

ATi RC300 51 Ohm

ATi RS250 56 Ohm

B B

+CPU_CORE

+CPU_CORE

HA#[3..31]

H_REQ#[0..4]

H_ADS#7

R1 56_0402_5%

1 2

R2 51_0402_5%

1 2

H_BREQ0#7

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_EXT_CPU17

CLK_EXT_CPU#17

H_HIT#7

H_HITM#7

H_DEFER#7

CLK_EXT_CPU

CLK_EXT_CPU#

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADS#

H_IERR#

H_BREQ0#

AB1

AC1

AA3

AC3

AF22

AF23

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

J1

K5

J4

J3

H3

G1

V5

H6

D2

G2

G4

F3

E3

E2

A10

A12

JP1A

VCC_0

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

HOST

A#21

A#22

ADDR

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

CONTROL

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

CLK

BCLK0

BCLK1

CON

HIT#

TROL

HITM#

DEFER#

AMP_1473129-1

A14

VCC_1

A16

VCC_2

VSS_0H1VSS_1H4VSS_2

A18

VCC_3

H23

A20

VCC_4

H26

VCC_5

VSS_3

A11

AA10

AA12

VCC_6A8VCC_7

VSS_4

VSS_5

A13

A15

AA14

VCC_8

VSS_6

A17

AA16

VCC_9

VSS_7

A19

AA18

VCC_10

VCC_11

VSS_8

VSS_9

A21

AA8

VCC_12

VSS_10

A24

AB11

VCC_13

VSS_11

A26

AB13

VCC_14

VSS_12A3VSS_13A9VSS_14

AB15

VCC_15

AB17

VCC_16

AA1

AB19

VCC_17

VSS_15

AA11

AB7

VCC_18

VSS_16

AA13

AB9

VCC_19

VSS_17

AA15

AC10

VCC_20

VSS_18

AA17

AC12

VCC_21

VSS_19

AA19

AC14

VCC_22

VSS_20

AA23

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

POWER

Northwood-MT

Prescott-MT

GND

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

AA4

AA7

AA9

AA26

AB10

AB12

AB14

AB3

AB6

AB16

AB18

AB8

AB20

AB21

AB24

AC11

AC13

AE8

VCC_40

VSS_38

AC15

AF11

VCC_41

VSS_39

AC17

AF13

VCC_42

VSS_40

AC19

AF15

VCC_43

VSS_41

AC2

AF17

VCC_44

VSS_42

AC22

AF19

VCC_45

VSS_43

AC25

AF2

VCC_46

VSS_44

AC5

AF21

VCC_47

VSS_45

AC7

AF5

VCC_48

VSS_46

AC9

AF7

VCC_49

VSS_47

AD10

AF9

VCC_50

VSS_48

AD12

B11

VCC_51

VSS_49

AD14

B13

VCC_52

VSS_50

AD16

B15

VCC_53

VSS_51

AD18

B17

VCC_54

VSS_52

AD21

B19

VCC_55

VCC_56B7VCC_57B9VCC_58

VSS_53

VSS_54

AD4

AD23

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65C8VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

HOST

ADDR

POWER

VCC_77

VCC_78

VCC_82

F15

VCC_83

F17

VCC_84

F19

VCC_85

F9

VCC_79E8VCC_80

F11

E16

E18

E20

BOOTSELECT

VSS_55

VCC_81

F13

AD1

AD8

D9

E10

VCC_71D7VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

E12

E14

+CPU_CORE

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

+CPU_CORE

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#[0..63]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63] 7

H_BOOTSELECT 44

1 2

R5

R_C

@0_0402_5%

@

Pop: Northwood

2

Depop: Prescott

Title

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

CPU(1/2)

LA-2301

448Tuesday, May 18, 2004

1

of

1.0

A A

5

4

3

Page 5

5

+CPU_CORE

1 2

R11 56_0402_1%

1 2

R13 300_0402_1%

1 2

R14 56_0402_1%

1 2

R15 51_0402_5%

D D

12

C1

@10P_0402_50V8J

12

C4 180P_0402_50V8J

12

C5 180P_0402_50V8J

12

C6 180P_0402_50V8J

12

C7 180P_0402_50V8J

12

C8 180P_0402_50V8J

12

C9 180P_0402_50V8J

12

C10 180P_0402_50V8J

12

C11 180P_0402_50V8J

Place within 1.5" from CPU

C C

+CPU_CORE

LQG21F4R7N00_0805

L1

1 2

L2

1 2

LQG21F4R7N00_0805

33U_D2_8M_R35

B B

H_FERR#

H_PWRGD

H_THERMTRIP#

H_RESET#

1 2

R17

@22_0402_5%

H_INTR

H_NMI

H_CPUSLP#

H_SMI#

H_STPCLK#

H_IGNNE#

H_A20M#

H_INIT#

+CPU_CORE

C12

H_RS#07

H_RS#17

H_RS#27

H_TRDY#7

H_A20M#19

H_FERR#19

H_IGNNE#19

H_SMI#19

H_PWRGD19

H_STPCLK#19

H_INTR19

H_NMI19

H_INIT#19

H_RESET#7

H_DBSY#7

H_DRDY#7

BSEL012,17

BSEL112,17

H_THERMTRIP#6

R28 51_0402_5%

1 2

R29 51_0402_5%

1 2

R30 51_0402_5%

1 2

R31 51_0402_5%

1 2

R32 51_0402_5%

1 2

R33 51_0402_5%

1 2

RP1

1 8

2 7

3 6

4 5

1K_1206_8P4R_5%

1

+

2

R25 ->

Pop: Prescott

Depop: Northwood

VCCSENSE44

VSSSENSE44

+CPU_VID

R36 61.9_0603_1%

1 2

R37 61.9_0603_1%

1 2

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

+VCCIOPLL

+VCCA

VCCSENSE

VSSSENSE

1 2

R35 0_0603_5%

+VCCVIDLB

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

VSSA

25mil

COMP0

COMP1

AB2

AB23

AB25

AD6

AD5

AC6

AB5

AC4

AA5

AB4

AD20

AE23

AF3

AD22

AC26

AD26

JP1B

F1

G5

F4

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

Y6

D4

C1

D5

F7

E6

A5

A4

L24

P1

GND

RS#0

RS#1

RS#2

RSP#

TRDY#

CON

TROL

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LEGACY

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

4

AE11

AE13

AE15

VSS_57

VSS_58

MISC

THER

MAL

MISC

MISC

ITP

CLK

AE17

AE19

VSS_59

VSS_60

ITP

3

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

E26

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

C19

C22

C25

D10

D12

VSS_61

VSS_62

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

GROUND

Northwood-MT

Prescott-MT

GROUND MISC

2

H_SKTOCC#

R10

0_0402_5%

F10

F12

F14

F16

F18

VSS_121

VSS_122

VSS_123

F22

F25

F5

VSS_124

VSS_125F2VSS_126

VSS_127

VSS_128

REF

OPTIMIZED/COMPAT#

ITP

DATA

ADDR

DATA

MISC

AF26

SKTOCC#

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

NC1

NC2

NC3

NC4

NC5

GTL Reference Voltage

12

1. < 1.5" from the CPU Ball.

2. 220P cap. has to be closed

to the ball as possible.

3. Intel: 0.63VCC.

ATi: 0.66VCC.

+GTLVREF1

J26

K25

K26

L25

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

A22

A7

AF25

AF24

AE21

220P_0402_50V7K

+GTLVREF1

R_G

1 2

R18 @0_0402_5%

R21 56_0402_5%

R22 56_0402_5%

R23 56_0402_5%

R24 56_0402_5%

R25 56_0402_5%

CPU_GHI#

R26 300_0402_5%

H_DPSLPR#

R27 56_0402_5%

NC: W/O ITP

H_PROCHOT#

H_CPUSLP#

R19 56_0402_5%

R20 56_0402_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1

51.1_0603_1%

1

C2

1U_0603_10V6K

2

CPU_GHI# 20

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_ADSTB#0 7

H_ADSTB#1 7

H_DBI#0 7

H_DBI#1 7

H_DBI#2 7

H_DBI#3 7

H_PROCHOT# 43

H_CPUSLP# 19

Intel 852GME RDDP 56Ohm.

ATi RC300 51Ohm

ATi RS250 56 Ohm

1

C3

86.6_0603_1%

2

Pop: Northwood Imp: 50 Ohm

Depop: Prescott Imp:60 Ohm

+CPU_CORE

for mobile CPU

1 2

R34 51_0402_5%

+CPU_CORE

12

R12

15mil

12

R16

+CPU_CORE

width= 10mil

51.1 Ohm for Northwood,

61.9 Ohm for Prescott

AMP_1473129-1

CPU Temperature Sensor

+3VS

R39

1 2

200_0402_5%

A A

1

C15

@2200P_0603_50V7K

2

EC_SMC230,33

EC_SMD230,33

H_THERMDA

H_THERMDC

10mil

10mil

5

U1

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

+3VS_THMSEN

1

C14

0.1U_0402_10V6K

2

VDD1

ALERT#

THERM#

GND

12

R42

10K_0402_5%

1

6

4

5

VSS_129F8VSS_130

G21

4

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

G24

VSS_136

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

J22

J25

PM_STPCPU#17,19,44

L23

K21

L26

K24

M22

M25

4.7K_0402_5%

R93

1 2

4.7K_0402_5%

MMBT3904_SOT23

N21

R86

2

N24

P22

P25

+3VS

12

2

3 1

Q3

T21

T24

R23

R26

H_DPSLPR#

Q4

MMBT3904_SOT23

3 1

3

V23

V26

U22

U25

+3VS

W21

W24

RP2

1 8

2 7

3 6

4 5

10K_1206_8P4R_5%

R40 10K_0402_5%

1 2

R41 10K_0402_5%

1 2

CPU_VID044

CPU_VID144

CPU_VID244

CPU_VID344

CPU_VID444

CPU_VID544

Y22

Y25

VSS_180

Y5

VSS_181

VID0

VID1

VID2

VID3

VID4

VID5

AE5

AE4

AE3

AE2

AE1

AD3

CPU_VID3

CPU_VID4

CPU_VID1

CPU_VID0

CPU_VID2

CPU_VID5

VCCVID

VIDPWRGD

+CPU_VID

AF4

AD2

25mil

1

C13

0.1U_0402_10V6K

2

Pop: Prescott

Depop: Northwood

R38

680_0402_5%

12

+CPU_VID

H_VID_PWRGD 35

Title

Size Document Number Re v

B

2

Date: Sheet

Compal Electronics, Inc.

CPU(2/2)

LA-2301

548Tuesday, May 18, 2004

1

1.0

of

Page 6

5

4

3

2

1

+CPU_CORE

1

+

D D

C C

C16

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C28

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C649

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C651

@220U_6SVPC220MV_6.3VM_R15

2

1

+

C18

220U_6SVPC220MV_6.3VM_R15

2

1

+

C30

220U_6SVPC220MV_6.3VM_R15

2

1

+

C17

220U_6SVPC220MV_6.3VM_R15

2

1

+

C19

220U_6SVPC220MV_6.3VM_R15

2

1

+

C31

220U_6SVPC220MV_6.3VM_R15

2

1

+

C29

@220U_6SVPC220MV_6.3VM_R15

2

1

+

C20

220U_6SVPC220MV_6.3VM_R15

2

1

+

C32

220U_6SVPC220MV_6.3VM_R15

2

1

+

C650

220U_6SVPC220MV_6.3VM_R15

2

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

Sanyo : SGA27221300 (220uF, 13m Ohm)

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

C21

22U_1206_10V4Z

C33

22U_1206_10V4Z

C40

@22U_1206_10V4Z

C47

@22U_1206_10V4Z

C55

@22U_1206_10V4Z

1

C22

@22U_1206_10V4Z

2

1

C34

@22U_1206_10V4Z

2

1

C41

@22U_1206_10V4Z

2

1

C48

@22U_1206_10V4Z

2

1

C56

@22U_1206_10V4Z

2

1

C23

22U_1206_10V4Z

2

1

C35

22U_1206_10V4Z

2

1

C42

@22U_1206_10V4Z

2

1

C49

@22U_1206_10V4Z

2

1

C57

@22U_1206_10V4Z

2

1

C24

22U_1206_10V4Z

2

1

C36

22U_1206_10V4Z

2

1

C43

@22U_1206_10V4Z

2

1

C50

@22U_1206_10V4Z

2

1

C54

@22U_1206_10V4Z

2

1

C25

22U_1206_10V4Z

2

1

C37

22U_1206_10V4Z

2

1

2

1

2

1

C26

22U_1206_10V4Z

2

1

C38

22U_1206_10V4Z

2

C44

@22U_1206_10V4Z

C51

@22U_1206_10V4Z

1

2

1

2

1

C45

@22U_1206_10V4Z

2

1

C52

22U_1206_10V4Z

2

C27

22U_1206_10V4Z

C39

22U_1206_10V4Z

1

2

1

2

C46

@22U_1206_10V4Z

C53

22U_1206_10V4Z

B B

+CPU_CORE

H_THERMTRIP#5 MAINPWON 38,39,41

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

12

R43 300_0402_5%

H_THERMTRIP#

3

2SC2411K_SC59

12

C58 @1U_ 0603_10V6K

2

Q1

CBE

1

2

Title

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

CPU Decoupling

LA-2301

648Tuesday, May 18, 2004

1

of

1.0

Page 7

5

4

3

2

1

D D

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

10U_0805_10V4Z

1 2

C656

H_ADSTB#0

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_ADSTB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BREQ0#

H_LOCK#

H_RESET#

H_RS#2

H_RS#1

H_RS#0

H_TRDY#

H_HIT#

H_HITM#

SUS_STAT#_R

NB_RST#_R

COMP_N

COMP_P

CPVDD

CPVSS

+NB_GTLREF

H_ADSTB#05

H_ADSTB#15

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#5

H_DBSY#5

H_BREQ0#4

H_LOCK#4

H_RESET#5

H_RS#25

H_RS#15

H_RS#05

H_TRDY#5

H_HIT#4

H_HITM#4

NB_PWRGD22

R710 24.9_0603_1%

1 2

R711 49.9_0402_1%

1 2

L40

1 2

R801

1 2

270K_0402_5%

1

C658

220P_0402_50V8K

2

+1.8VS+2.5V

12

R800

27K_0402_5%

SUS_STAT#_R

12

R803

330K_0402_5%

NB_RST#_R

+CPU_CORE

0.1U_0402_10V6K

1 2

330_0402_5%

+1.8VS

C655

12

R709

HB-1M2012-121JT03_0805

C C

SUS_STAT#20

NB_RST#19,23,32,33

B B

L

R716

51.1_0603_1%

R712

86.6_0603_1%

A A

12

R802

27K_0402_5%

D70

21

RB751V_SOD323

D71

21

RB751V_SOD323

Note: PLACE CLOSE TO RC300M,

USE 10/10 WIDTH/SPACE

+CPU_CORE

PLACE CLOSE TO U27 Ball

W28, USE 20/20

WIDTH/SPACE

1 2

12

1

C657

1U_0603_10V6K

2

12

R713

4.7K_0402_5%

M28

P25

M25

N29

N30

M26

N28

P29

P26

R29

P30

P28

N26

N27

M29

N25

R26

R27

U30

T30

R28

R25

U25

T28

V29

T26

U29

U26

V26

T25

V25

U27

U28

T29

H26

G27

F25

K26

A17

G25

G26

F26

H25

AH5

AG5

V28

W29

H23

W28

Y29

Y28

B17

L28

L29

L27

K25

J27

L26

J25

J26

J23

A9

C7

HA#[3..31]

H_REQ#[0..4]

HD#[0..63]

U51A

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_BR0#

CPU_LOCK#

CPU_CPURSET#

CPU_RS2#

CPU_RS1#

CPU_RS0#

CPU_TRDY#

CPU_HIT#

CPU_HITM#

CPU_RSET

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_N

CPU_COMP_P

CPVDD

CPVSS

CPU_VREF

THERMALDIODE_N

THERMALDIODE_P

TESTMODE

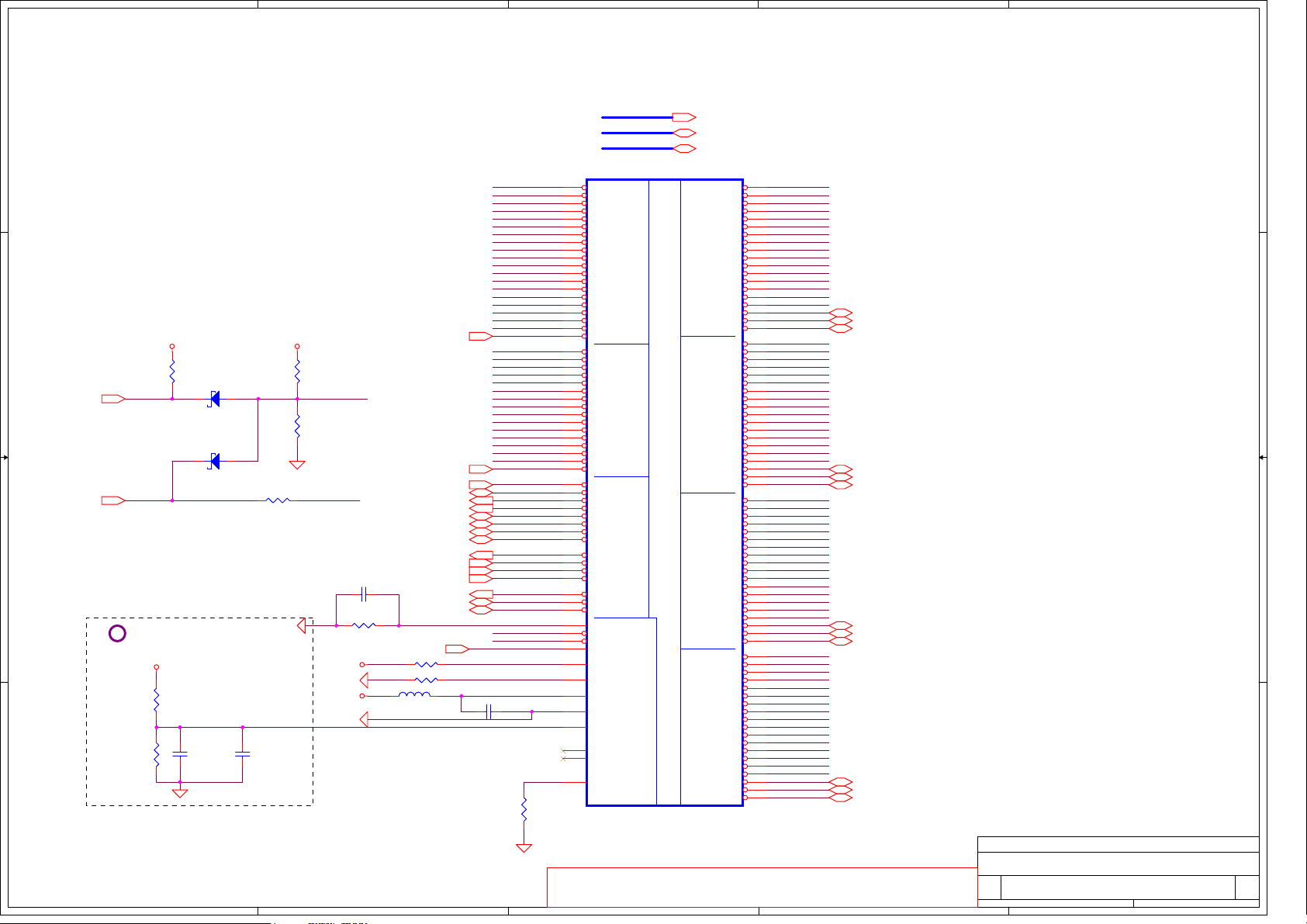

CHS-216IGP9050A21_BGA718

ADDR. GROUP 1 ADDR. GROUP 0CONTROL

PART 1 OF 6

AGTL+ I/F

PENTIUM

MISC.

HA#[3..31] 4

H_REQ#[0..4] 4

HD#[0..63] 4

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTBN0#

CPU_DSTBP0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTBN1#

CPU_DSTBP1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

IV

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_DSTBN2#

CPU_DSTBP2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

CPU_DSTBN3#

CPU_DSTBP3#

L30

K29

J29

H28

K28

K30

H29

J28

F28

H30

E30

D29

G28

E29

D30

F29

E28

G30

G29

B26

C30

A27

B29

C28

C29

B28

D28

D26

B27

C26

E25

E26

A26

B25

C25

A28

D27

E27

F24

D24

E23

E24

F23

C24

B24

A24

F21

A23

B23

C22

B22

C21

E21

D22

D23

E22

F22

B21

F20

A21

C20

E20

D20

A20

D19

C18

B20

E18

B19

D18

B18

C17

A18

F19

E19

F18

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

H_DBI#0

H_DSTBN#0

H_DSTBP#0

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

H_DBI#1

H_DSTBN#1

H_DSTBP#1

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

H_DBI#2

H_DSTBN#2

H_DSTBP#2

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_DBI#3

H_DSTBN#3

H_DSTBP#3

H_DBI#0 5

H_DSTBN#0 5

H_DSTBP#0 5

H_DBI#1 5

H_DSTBN#1 5

H_DSTBP#1 5

H_DBI#2 5

H_DSTBN#2 5

H_DSTBP#2 5

H_DBI#3 5

H_DSTBN#3 5

H_DSTBP#3 5

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

ATi RC300ML-HOST(1/5)

LA-2301

1

1.0

748Friday, May 28, 2004

of

Page 8

5

4

3

2

1

12

R661

1K_0603_1%

AGPREF_4X

12

R662

1K_0603_1%

A_AD[0..31]

A_CBE#[0..3]

A_STROBE#19

PCI_PIRQA#19,24,27

A_DEVSEL#19

+1.5VS+ 1.5VS

A_PAR12,19

A_ACAT#19

A_END#19

A_OFF#19

A_SBREQ#19

A_SBGNT#19

+3VS

AGPREF_4X

R660

1 2

@52.3_0603_1%

Ra

AGP8X_DET#

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

A_PAR

A_STROBE#

A_ACAT#

A_END#

A_DEVSEL#

A_OFF#

A_SBREQ#

A_SBGNT#

1 2

8.2K_0402_5%

AGP8X_DET#

C663

1 2

0.1U_0402_10V6K

AGP_COMP

+3VS

R663

@47K_0402

1 2

U51C

AK5

ALINK_AD0

AJ5

ALINK_AD1

AJ4

ALINK_AD2

AH4

ALINK_AD3

AJ3

ALINK_AD4

AJ2

ALINK_AD5

AH2

ALINK_AD6

AH1

ALINK_AD7

AG2

ALINK_AD8

AG1

ALINK_AD9

AG3

ALINK_AD10

AF3

ALINK_AD11

AF1

ALINK_AD12

AF2

ALINK_AD13

AF4

ALINK_AD14

AE3

ALINK_AD15

AE4

ALINK_AD16

AE5

ALINK_AD17

AE6

ALINK_AD18

AC2

ALINK_AD19

AC4

ALINK_AD20

AB3

ALINK_AD21

AB2

ALINK_AD22

AB5

ALINK_AD23

AB6

ALINK_AD24

AA2

ALINK_AD25

AA4

ALINK_AD26

AA5

ALINK_AD27

AA6

ALINK_AD28

Y3

ALINK_AD29

Y5

ALINK_AD30

Y6

ALINK_AD31

AG4

ALINK_CBE#0

AE2

ALINK_CBE#1

AC3

ALINK_CBE#2

AA3

ALINK_CBE#3

AD5

PCI_PAR/ALINK_NC

AC6

PCI_FRAME#/ALINK_STROBE#

AC5

PCI_IRDY#/ALINK_ACAT#

AD2

PCI_TRDY#/ALINK_END#

W4

INTA#

AD3

ALINK_DEVSEL#

AD6

PCI_STOP#/ALINK_OFF#

W5

ALINK_SBREQ#

W6

ALINK_SBGNT#

R659

V5

PCI_REQ#0/ALINK_NC

V6

PCI_GNT#0/ALINK_NC

K5

AGP2_GNT#/AGP3_GNT

K6

AGP2_REQ#/AGP3_REQ

M5

AGP8X_DET#

J6

AGP_VREF/TMDS_VREF

J5

AGP_COMP

CHS-216IGP9050A21_BGA718

PART 3 OF 6

AGP2_SBSTB/AGP3_SBSTBF/NC/LVDS_BLON

AGP2_SBSTB#/AGP3_SBSTBS/NC/ENA_BL

AGP2_ADSTB0/AGP3_ADSTBF0/TMD2_CLK#

AGP2_ADSTB0#/AGP3_ADSTBS0/TMD2_CLK

AGP2_ADSTB1/AGP3_ADSTBF1/TMD1_CLK#

AGP2_ADSTB1#/AGP3_ADSTBS1/TMD1_CLK

PCI Bus 0 / A-Link I/F

AGP2_IRDY#/AGP3_IRDY/GPIO8/I2C_CLK

AGP2_TRDY#/AGP3_TRDY/TMDS_DVI_CLK

AGP2_STOP#/AGP3_STOP/GPIO10/DDC_DATA

AGP2_FRAME#/AGP3_FRAME/TMDS_DVI_DATA

AGP2_DEVSEL#/AGP3_DEVSEL/GPIO9/I2C_DATA

PCI BUS 1 / AGP Bus (GPIO , TMDS , ZVPort)

AGP2_SBA0/AGP3_SBA#0/GPIO0/VDDC_CNTL0

AGP2_SBA1/AGP3_SBA#1/GPIO1/VDDC_CNTL1

AGP2_SBA2/AGP3_SBA#2/GPIO2/LVDS_BLON#

AGP2_SBA3/AGP3_SBA#3/GPIO3/LVDS_DIGON

AGP2_SBA4/AGP3_SBA#4/GPIO4/STP_AGP#

AGP2_SBA5/AGP3_SBA#5/GPIO5/AGP_BUSY#

AGP2_SBA6/AGP3_SBA#6/GPIO6/LVDS_SSOUT

AGP2_SBA7/AGP3_SBA#7/GPIO7/LVDS_SSIN

AGP_AD0/TMD2_HSYNC

AGP_AD1/TMD2_VSYNC

AGP_AD2/TMD2_D1

AGP_AD3/TMD2_D0

AGP_AD4/TMD2_D3

AGP_AD5/TMD2_D2

AGP_AD6/TMD2_D5

AGP_AD7/TMD2_D4

AGP_AD8/TMD2_D6

AGP_AD9/TMD2_D9

AGP_AD10/TMD2_D8

AGP_AD11/TMD2_D11

AGP_AD12/TMD2_D10

AGP_AD13

AGP_AD14

AGP_AD16/TMD1_VSYNC

AGP_AD17/TMD1_HSYNC

AGP2_CBE#0/AGP3_CBE0/TMD2_D7

AGP2_CBE#1/AGP3_CBE1/TMD2_DE

AGP2_CBE#2/AGP3_CBE2

AGP2_CBE#3/AGP3_CBE3/TMD1_D5

AGP2_PIPE#/AGP3_DBI_HI

AGP2_NC/AGP3_DBI_LO

AGP2_WBF#/AGP3_WBF

AGP_AD15

AGP_AD18/TMD1_DE

AGP_AD19/TMD1_D0

AGP_AD20/TMD1_D1

AGP_AD21/TMD1_D2

AGP_AD22/TMD1_D3

AGP_AD23/TMD1_D4

AGP_AD24/TMD1_D7

AGP_AD25/TMD1_D6

AGP_AD26/TMD1_D9

AGP_AD27/TMD1_D8

AGP_AD28/TMD1_D11

AGP_AD29/TMD1_D10

AGP_AD30/TMDS_HPD

AGP_AD31

AGP_PAR

AGP2_RBF#/AGP3_RBF

AGP_ST0

AGP_ST1

AGP_ST2

Y2

W3

W2

V3

V2

V1

U1

U3

T2

R2

P3

P2

N3

N2

M3

M2

L1

L2

K3

K2

J3

J2

J1

H3

F3

G2

F2

F1

E2

E1

D2

D1

E5

E6

T3

U2

G3

H2

R3

M1

L3

H1

P5

R6

T6

T5

P6

R5

C1

D3

N6

N5

C3

C2

D4

E4

F6

F5

G6

G5

L6

M6

L5

C659

@10U_0805_6.3V6M

AGP_SBA6

AGP_SBA7

@0.1U_0402_10V6K

1

1

C660

12

2

@0_0402_5%

@0_0402_5%

12

2

R652

R655

Note: PLACE CLOSE TO U2 (NB RC300M)

L

R653

@0_0402_5%

12

12

@SM561BS_SO8

R656

@0_0402_5%

EDID_CLK 18

EDID_DAT 18

ENBK# 33

ENVDD 18

AGP_STP# 20

AGP_BUSY# 20

U52

1

Xin/CLK

S0

7

S0

6

S1

S1

LVDS SPREAD SPECTRUM

+3VS_SSVDD

@0_0402_5%

R715

2

VDD

SSCLK

Xout

SSCC

VSS

3

R657

@0_0402_5%

12

4

8

5

12

L41

1 2

@BLM21P300S_0805

12

R651

@0_0402_5%

1

C662

@10P_0402_25V8K

12

2

R658

@0_0402_5%

LVDS_SSOUT

1

C661

@10P_0402_25V8K

2

LVDS_SSIN

+3VS

@0_0402_5%

@0_0402_5%

R714

R654

AGP_SBA6

12

AGP_SBA7

12

D D

C C

B B

A A

A_AD[0..31]12,19

A_CBE#[0..3]19

Close to Pin J6

5

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

ATi RC300ML-A-LINK/AGP(2/5)

LA-2301

848Tuesday, May 18, 2004

1

1.0

of

Page 9

5

D D

C C

B B

+1.8VS

A A

4

DDR_SBA013,14,15,16

DDR_SBA113,14,15,16

DDR_SRAS#13,14,15,16

DDR_SCAS#13,14,15,16

DDR_SWE#13,14,15,16

DDR_CLK014,15

DDR_CLK0#14,15

DDR_CLK114,15

DDR_CLK1#14,15

DDR_CLK313

DDR_CLK3#13

DDR_CLK413

DDR_CLK4#13

DDR_SCKE014,16

DDR_SCKE115,16

DDR_SCKE213,16

DDR_SCKE313,16

DDR_SCS#014,16

DDR_SCS#115,16

DDR_SCS#213,16

DDR_SCS#313,16

L42

1 2

HB-1M2012-121JT03_0805

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA13

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_SRAS#

DDR_SCAS#

DDR_SWE#

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CLK0

DDR_CLK0#

DDR_CLK1

DDR_CLK1#

DDR_CLK3

DDR_CLK3#

DDR_CLK4

DDR_CLK4#

DDR_SCKE0

DDR_SCKE1

DDR_SCKE2

DDR_SCKE3

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

MPVDD

C666

MPVSS

1 2

10U_0805_10V4Z

U51B

AH19

AJ17

AK17

AH16

AK16

AF17

AE18

AF16

AE17

AE16

AJ20

AG15

AF15

AE23

AH20

AE25

AH7

AF10

AJ14

AF21

AH23

AK28

AD29

AB26

AF24

AF25

AE24

AF9

AH13

AE21

AJ23

AJ27

AC28

AA25

AK10

AH10

AH18

AJ19

AG30

AG29

AK11

AJ11

AH17

AJ18

AF28

AG28

AF13

AE13

AG14

AF14

AH26

AH27

AF26

AG27

AC18

AD18

AJ8

PART 2 OF 6

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_DQS0

MEM_DQS1

MEM_DQS2

MEM_DQS3

MEM_DQS4

MEM_DQS5

MEM_DQS6

MEM_DQS7

MEM_CK0

MEM_CK0#

MEM_CK1

MEM_CK1#

MEM_CK2

MEM_CK2#

MEM_CK3

MEM_CK3#

MEM_CK4

MEM_CK4#

MEM_CK5

MEM_CK5#

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS#0

MEM_CS#1

MEM_CS#2

MEM_CS#3

MPVDD

MPVSS

CHS-216IGP9050A21_BGA718

3

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM I/F

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP1

MEM_CAP2

MEM_COMP

MEM_DDRVREF

DDR_DQ0

AG6

DDR_DQ1

AJ7

DDR_DQ2

AJ9

DDR_DQ3

AJ10

DDR_DQ4

AJ6

DDR_DQ5

AH6

DDR_DQ6

AH8

DDR_DQ7

AH9

DDR_DQ8

AE7

DDR_DQ9

AE8

DDR_DQ10

AE12

DDR_DQ11

AF12

DDR_DQ12

AF7

DDR_DQ13

AF8

DDR_DQ14

AE11

DDR_DQ15

AF11

DDR_DQ16

AJ12

DDR_DQ17

AH12

DDR_DQ18

AH14

DDR_DQ19

AH15

DDR_DQ20

AH11

DDR_DQ21

AJ13

DDR_DQ22

AJ15

DDR_DQ23

AJ16

DDR_DQ24

AF18

DDR_DQ25

AG20

DDR_DQ26

AG21

DDR_DQ27

AF22

DDR_DQ28

AF19

DDR_DQ29

AF20

DDR_DQ30

AE22

DDR_DQ31

AF23

DDR_DQ32

AJ21

DDR_DQ33

AJ22

DDR_DQ34

AJ24

DDR_DQ35

AK25

DDR_DQ36

AH21

DDR_DQ37

AH22

DDR_DQ38

AH24

DDR_DQ39

AJ25

DDR_DQ40

AK26

DDR_DQ41

AK27

DDR_DQ42

AJ28

DDR_DQ43

AH29

DDR_DQ44

AH25

DDR_DQ45

AJ26

DDR_DQ46

AJ29

DDR_DQ47

AH30

DDR_DQ48

AF29

DDR_DQ49

AE29

DDR_DQ50

AB28

DDR_DQ51

AA28

DDR_DQ52

AE28

DDR_DQ53

AD28

DDR_DQ54

AC29

DDR_DQ55

AB29

DDR_DQ56

AC26

DDR_DQ57

AB25

DDR_DQ58

Y26

DDR_DQ59

W26

DDR_DQ60

AE26

DDR_DQ61

AD26

DDR_DQ62

AA26

DDR_DQ63

Y27

C664 0.47U_0603_16V7K

AF6

AA29

AK19

1 2

C665 0.47U_0603_16V7K

1 2

MEN_COMP

R664 49.9_0402_1%

AK20

1 2

+DDR_VREF

+2.5V

1

2

1

2

2

DDR_DM[0..7]

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_SMA[0..13]

C668

0.1U_0402_10V6K

C669

0.1U_0402_10V6K

DDR_DM[ 0..7] 13,14,16

DDR_DQ[0..63] 13,14,16

DDR_DQS[0..7] 13,14,16

DDR_SMA[0..13] 13,14,15,16

R665

1K_0603_1%

R666

1K_0603_1%

1

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

ATi RC300ML-DDR(3/5)

LA-2301

1

1.0

948Friday, May 28, 2004

of

Page 10

5

KC FBM-L11-201209-221LMAT_0805

D D

KC FBM-L11-201209-221LMAT_0805

L45

+1.8VS

+1.8VS

CLK_EXT_AGP66

12

R667

C C

B B

@10_0402_5%

1

C681

@15P_0402_50V8J

2

CLK_EXT_MEM66

12

R671

@10_0402_5%

1

C685

@15P_0402_50V8J

2

1 2

0.1U_0402_10V6K

1 2

+1.8VS

L47

1 2

KC FBM-L11-201209-221LMAT_0805

10U_0805_10V4Z

REFCLK1_NB17

1

C672

2

L46 10_0603_5%

0.1U_0402_10V6K

C675

56_0402_5%

C673

1

2

R669

4

+2.5VS

L44

+1.8VS_AVDDDI

+1.8VS_AVDDQ

1

1

C674

0.1U_0402_10V6K

2

2

1

C676

0.1U_0402_10V6K

R668 715 _0402_1%

12

CRT_R18

CRT_G18

CRT_B18

CRT_HSYNC18

CRT_VSYNC18

1 2

CLK_EXT_NB17

CLK_EXT_NB#17

CLK_EXT_AGP6617

CLK_EXT_MEM6617

+3VS

2

12

+2.5VS_AVDD

1

C671

0.1U_0402_10V6K

2

1

C677

0.1U_0402_10V6K

2

R673

1 2

10K_0402_5%

+PLLVDD_18

NB_RSET

CLK_EXT_NB

CLK_EXT_NB#

CLK_EXT_AGP66

CLK_EXT_MEM66

+3VS_VDDR

1 2

1

C670

0.1U_0402_10V6K

2

U51D

G9

VDDR3

H9

VDDR3

A14

AVDD_25

B13

AVSSN

B14

AVDDDI_18

C13

AVSSDI

A15

AVDDQ

B15

AVSSQ

H11

PLLVDD_18

G11

PLLVSS

F14

RED

F15

GREEN

E14

BLUE

C8

DACHSYNC

D9

DACVSYNC

C14

RSET

A4

XTALIN

B4

XTALOUT

A5

HCLKIN

B5

HCLKIN#

B6

SYS_FBCLKOUT

A6

SYS_FBCLKOUT#

D8

ALINK_CLK

B2

AGPCLKOUT

B3

AGPCLKIN

A3

EXT_MEM_CLK

D7

USBCLK

B7

REF27

C5

OSC

CHS-216IGP9050A21_BGA718

3

+3VS

L43

FBM-11-160808-121-T_0603

PART 4 OF 6

CRT

CLK. GEN.

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXCLK_UN

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXCLK_LN

TXCLK_LP

LPVDD_18

LVDS

LVDDR_18

LVDDR_18

COMP_B

SVID

DACSCL

DACSDA

CPUSTOP#

SYSCLK

SYSCLK#

LPVSS

LVSSR

LVSSR

C_R

Y_G

D12

E12

F11

F12

D13

D14

E13

F13

E10

D10

B9

C9

D11

E11

B10

C10

A12

A11

B12

C12

B11

C11

E15

C15

D15

D6

C6

D5

A8

B8

+1.8VS_LPVDD

LPVSS

+1.8VS_LVDDR

LVSSR

TV_CRMA

TV_LUMA

TV_COMPS

1 2

R670 @75_0402_1%

1 2

R672 1K_0402_5%

2

TZOUT0- 18

TZOUT0+ 18

TZOUT1- 18

TZOUT1+ 18

TZOUT2- 18

TZOUT2+ 18

TZCLK- 18

TZCLK+ 18

TXOUT0- 18

TXOUT0+ 18

TXOUT1- 18

TXOUT1+ 18

TXOUT2- 18

TXOUT2+ 18

TXCLK- 18

TXCLK+ 18

0.1U_0402_10V6K

NB_DDC_CLK 18

NB_DDC_DATA 18

0.1U_0402_10V6K

1

C679

C678

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C683

C682

2

KC FBM-L11-201209-221LMAT_0805

1

2

1

2

+3VS

1 2

1

C680

2

10U_0805_10V4Z

KC FBM-L11-201209-221LMAT_0805

1 2

1

C684

2

10U_0805_10V4Z

1

+1.8VS

L48

+1.8VS

L49

V-PORT-0603-220 M-V05_0603

TV-OUT CONN.

TV_LUMA

TV_CRMA

A A

5

4

12

R101

75_0402_1%

12

R102

75_0402_1%

1

C109

100P_0402_25V8K

2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

C103 @33P_0402_50V8J

1 2

L4 CHB2012U121_0805

1 2

L5 CHB2012U121_0805

1 2

1 2

C104 @33P_0402_50V8J

1

C110

100P_0402_25V8K

2

D1

2 1

1

C111

100P_0402_25V8K

2

LUMA_1

CRMA_1

1

C112

100P_0402_25V8K

2

2

D2

V-PORT-0603-220 M-V05_0603

2 1

JP2

1

1

2

2

3

3

4

4

SUYIN_030008FR004T100ZL

Title

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

ATi RC300ML-VEDIO(4/5)

LA-2301

1

1.0

10 48Tuesday, May 18, 2004

of

Page 11

5

4

3

2

1

22U_1206_10V4Z

+2.5V

1

+

C695

2

0.1U_0402_10V6K

+2.5V

1

C709

2

+1.5VS

1

+

C715

2

0.1U_0402_10V6K

+1.5VS

1

C730

C729

2

+1.5VS

@0.01U_0402_16V7Z

1

C744

2

+CPU_CORE

1

C686

2

0.1U_0402_10V6K

1

C696

C697

2

0.1U_0402_10V6K

1

C710

0.1U_0402_10V6K

C725

0.1U_0402_10V6K

C711

2

0.1U_0402_10V6K

1

C726

2

0.1U_0402_10V6K

1

C731

2

ATI request

1

C746

C745

2

@0.01U_0402_16V7Z

0.1U_0402_10V6K

1

C687

2

0.1U_0402_10V6K

1

1

C698

2

2

0.1U_0402_10V6K

1

C712

2

0.1U_0402_10V6K

1

1

C727

2

2

0.1U_0402_10V6K

1

1

C732

2

2

0.1U_0402_10V6K

@0.01U_0402_16V7Z

1

1

C747

2

2

1

C688

C689

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C700

C699

2

0.1U_0402_10V6K

1

2

0.1U_0402_10V6K

1

C728

47U_B_6.3VM

2

0.1U_0402_10V6K

1

C734

C733

2

0.1U_0402_10V6K

@0.01U_0402_16V7Z

1

C749

C748

2

@0.01U_0402_16V7Z

0.1U_0402_10V6K

1

1

C690

2

2

0.1U_0402_10V6K

1

C701

2

1

C713

0.1U_0402_10V6K

2

+1.5VS

1

+

C714

C716

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C735

2

1

C750

2

@0.01U_0402_16V7Z

0.1U_0402_10V6K

1

C692

C691

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C702

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C717

2

1

1

C736

2

2

0.1U_0402_10V6K

@0.01U_0402_16V7Z

1

1

C751

2

2

@0.01U_0402_16V7Z

1

C693

2

0.1U_0402_10V6K

1

C703

C704

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C718

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C737

C738

2

0.1U_0402_10V6K

@0.01U_0402_16V7Z

1

C752

2

1

2

0.1U_0402_10V6K

1

C705

2

1

C719

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C739

2

1

C753

2

1

C694

0.1U_0402_10V6K

2

1

C706

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C720

C721

2

1

C740

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C707

2

2

1

C722

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C741

2

2

1

C708

0.1U_0402_10V6K

2

0.1U_0402_10V6K

1

1

C723

2

2

0.1U_0402_10V6K

1

C742

C743

2

0.1U_0402_10V6K

1

C724

2

0.1U_0402_10V6K

1

2

+1.5VS +2.5V

U51E

F10

VDD_CORE

F9

VDD_CORE

G12

VDD_CORE

H12

VDD_CORE

H13

VDD_CORE

M12

VDD_CORE

M13

VDD_CORE

D D

C C

+CPU_CORE

B B

+3VS

M14

VDD_CORE

M17

VDD_CORE

M18

VDD_CORE

M19

VDD_CORE

N12

VDD_CORE

N13

VDD_CORE

N14

VDD_CORE

N17

VDD_CORE

N18

VDD_CORE

N19

VDD_CORE

P12

VDD_CORE

P13

VDD_CORE

P14

VDD_CORE

P17

VDD_CORE

P18

VDD_CORE

P19

VDD_CORE

U12

VDD_CORE

U13

VDD_CORE

U14

VDD_CORE

U17

VDD_CORE

U18

VDD_CORE

U19

VDD_CORE

V12

VDD_CORE

V13

VDD_CORE

V14

VDD_CORE

V17

VDD_CORE

V18

VDD_CORE

V19

VDD_CORE

W12

VDD_CORE

W13

VDD_CORE

W14

VDD_CORE

W17

VDD_CORE

W18

VDD_CORE

W19

VDD_CORE

C16

VDDR2_CPU

D16

VDDR2_CPU

D17

VDDR2_CPU

E16

VDDR2_CPU

E17

VDDR2_CPU

F16

VDDR2_CPU

F17

VDDR2_CPU

G17

VDDR2_CPU

G21

VDDR2_CPU

G23

VDDR2_CPU

G24

VDDR2_CPU

H16

VDDR2_CPU

H17

VDDR2_CPU

H19

VDDR2_CPU

H21

VDDR2_CPU

H24

VDDR2_CPU

K23

VDDR2_CPU

K24

VDDR2_CPU

M23

VDDR2_CPU

P23

VDDR2_CPU

P24

VDDR2_CPU

T23

VDDR2_CPU

T24

VDDR2_CPU

U23

VDDR2_CPU

U24

VDDR2_CPU

W30

VDDR2_CPU

AA1

VDDL_ALINK

AA7

VDDL_ALINK

AA8

VDDL_ALINK

AC7

VDDL_ALINK

AC8

VDDL_ALINK

AD1

VDDL_ALINK

AD7

VDDL_ALINK

AD8

VDDL_ALINK

AK3

VDDL_ALINK

W8

VDDL_ALINK

CHS-216IGP9050A21_BGA718

CORE PWR

CPU I/F PWRALINK PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

PART 5 OF 6

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

MEM I/F PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

POWER

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

AGP PWR

VDDP_AGP

VDDP_AGP

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

VDD_18

VDD_18

VDD_18

VDD_18

AA23

AA27

AB30

AC10

AC12

AC13

AC15

AC17

AC19

AC21

AC23

AC24

AC25

AC27

AD10

AD12

AD13

AD15

AD17

AD19

AD21

AD23

AD24

AD25

AD27

AE10

AE14

AE15

AE19

AE20

AE30

AE9

AF27

AG11

AG12

AG17

AG18

AG23

AG24

AG26

AG8

AG9

AJ30

AK14

AK23

AK8

V23

W23

W24

W25

Y25

A2

G4

H5

H6

H7

J4

K8

L4

M7

M8

N4

P1

P7

P8

R4

T8

U4

U5

U6

E7

F7

G8

AC22

AC9

H10

H22

100U_D2_10VM

0.1U_0402_10V6K

47U_B_6.3VM

+1.5VS

0.1U_0402_10V6K

@0.01U_0402_16V7Z

+3VS

+1.8VS

U51F

PART 6 OF 6

A29

VSS

AB23

VSS

AB24

VSS

AB27

VSS

AB4

VSS

AB8

VSS

AC1

VSS

AC11

VSS

AC14

VSS

AC16

VSS

AC20

VSS

AC30

VSS

AD11

VSS

AD14

VSS

AD16

VSS

AD20

VSS

AD4

VSS

AE27

VSS

AF30

VSS

AF5

VSS

AG10

VSS

AG13

VSS

AG16

VSS

AG19

VSS

AG22

VSS

AG25

VSS

AG7

VSS

AH28

VSS

AH3

VSS

GND

AJ1

VSS

AK13

VSS

AK2

VSS

AK22

VSS

AK29

VSS

AK4

VSS

AK7

VSS

B1

VSS

B16

VSS

B30

VSS

C19

VSS

C23

VSS

C27

VSS

C4

VSS

D21

VSS

D25

VSS

E3

VSS

E8

VSS

E9

VSS

F27

VSS

F4

VSS

F8

VSS

G14

VSS

G15

VSS

G18

VSS

G20

VSS

H14

VSS

H15

VSS

H18

VSS

H20

VSS

H27

VSS

H4

VSS

H8

VSS

J7

VSS

CHS-216IGP9050A21_BGA718

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R23

R7

R8

T12

T13

T14

T15

T16

T17

T18

T19

T27

T4

U15

U16

U7

U8

V15

V16

V27

V4

V7

V8

W15

W16

W27

Y1

Y23

Y24

Y30

Y4

Y7

Y8

R19

R18

R17

R16

R15

R14

R13

R12

R1

P4

P27

P16

P15

N8

N24

N23

N16

N15

M4

M27

M16

M15

L8

L7

L25

L24

L23

K4

K27

J8

4

+3VS

10U_0805_10V4Z

1

C759

2

0.1U_0402_10V6K

1

C761

C760

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C762

2

0.1U_0402_10V6K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C763

2

2

0.1U_0402_10V6K

1

C764

C765

2

0.1U_0402_10V6K

3

1

2

0.1U_0402_10V6K

1

C766

2

0.1U_0402_10V6K

1

C767

2

2

Title

Size Document Number Re v

B

Date: Sheet

Compal Electronics, Inc.

ATi RC300ML-Power(5/5)

LA-2301

1

11 48Tuesday, May 18, 2004

of

1.0

+1.8VS

0.1U_0402_10V6K

1

1

C755

C754

A A

10U_0805_10V4Z

2

0.1U_0402_10V6K

5

1

C756

C757

2

2

0.1U_0402_10V6K

1

1

2

C758

0.1U_0402_10V6K

2

Page 12

5

4

3

2

1

A_CBE#[0..3]

A_AD[0..31]8,19

D D

R674 10K_0402_5%

A_AD31

A_AD30

A_AD29

R676 4.7K_0402_5%

1 2

R679 4.7K_0402_5%

1 2

R681 10K_0402_5%

1 2

R683 @4.7K_0402_5%

1 2

1 2

R678 10K_0402_5%

1 2

2 1

D51

RB751V_SOD323

2 1

D52

RB751V_SOD323

+3VS

+3VS

BSEL1 5, 17

+3VS

BSEL0 5, 17

A_AD29: STRAP CONFIGURATION

DEFAULT:1

0: REDUCEDE SET

A_AD[31.. 30] : FSB CL K SPEED

DEFAULT: 01

00: 100 MHZ

01: 133 MHZ

10: 200MHZ

11:166 MHZ

1: FULL SET(internal Pull high)

R684 @10K_0402_5%

A_AD28

C C

A_AD27

A_AD26

A_AD24

1 2

R686 4.7K_0402_5%

1 2

R688 10K_0402_5%

1 2

R689 @4.7K_0402_5%

1 2

R692 10K_0402_5%

1 2

R693 @4.7K_0402_5%

1 2

R694 10K_0402_5%

1 2

+3VS

+3VS

+3VS

+3VS

A_AD28: SP READ SPECTRUM ENABLE

DEFAULT:0

0: DISABLE

1: ENABLE

A_AD27: FrcShortReset#

DEFAULT: 1

0: TEST MODE

1: NORMAL

MOD E

A_AD26 : ENABLE IOQ

DEFAULT: 1

0: IOQ=1

1:

IOQ=12

A_AD24 : MOBILE CPU SELECT

DEFAULT: 1

0: BANIAS CPU

1: OTHER CPU

A_AD[0..31]

R675 @4.7K_0402_5%

A_AD18

A_AD17

A_AD25

A_PAR8,19

A_PAR

1 2

R677 4.7K_0402_5%

1 2

R680 @4.7K_0402_5%

1 2

R682 4.7K_0402_5%

1 2

R685 10K_0402_5%

1 2

R687 @4.7K_0402_5%

1 2

R690 @4.7K_0402_5%

1 2

R691 4.7K_0402_5%

1 2

+3VS

+3VS

+3VS

+3VS

A_AD18 : ENABLE PHASE CALIBRATION

DEFAULT: 0

0: DISABLE

1:ENABLE

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 0

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 10

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

AD25=1 DESTOP CPU

AD25=0 MOBILE CPU

AD17--DON'T CARE

PAR: EXTENDED DEBUG MODE

DEFAULT : 1

0: DEBUG MODE

1: NORMAL

A_CBE#[0..3] 8,19

R695 10K_0402_5%

B B

A A

A_AD23

A_AD22

A_AD21

A_AD20

1 2

R696 @4.7K_0402_5%

1 2

R697 @4.7K_0402_5%

1 2

R698 10K_0402_5%

1 2

R699 @4.7K_0402_5%

1 2

R700 @4.7K_0402_5%

1 2

R701 4.7K_0402_5%

1 2

5

+3VS

+3VS

+3VS

A_AD23 : CL OCK BYPASS DISABLE

DEFAULT: 1

0: TEST MODE

1: NORMAL(internal Pull high)

A_AD22 : OSC PAD OUTPUT PCICLK

DEFAULT : 1

0:PCICLK OUT

1: OSC CLK OUT

A_AD21 : AUTO_CAL ENABLE

DEFAULT : 1

0: DISABLE

1: ENABLE

A_AD20 : INTERNAL CLK GEN ENABLE

DEFAULT : 0

0: DISABLE

1: ENABLE

4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Title

Size Document Number Re v

B

Date: Sheet of

Compal Electronics, Inc.

ATi RC300ML-SYS. CONFIG.

LA-2301

1

12 48Tuesday, May 18, 2004

1.0

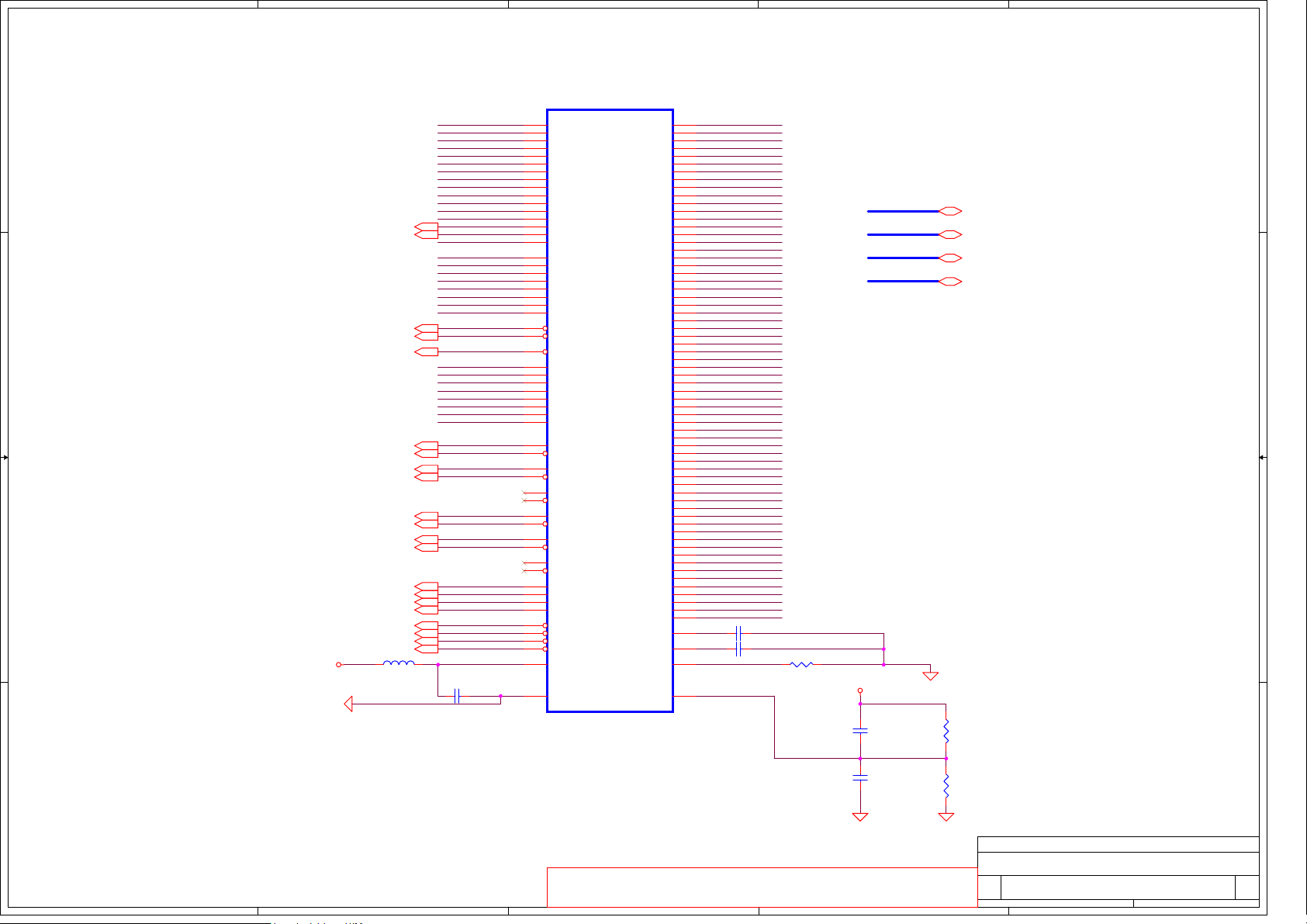

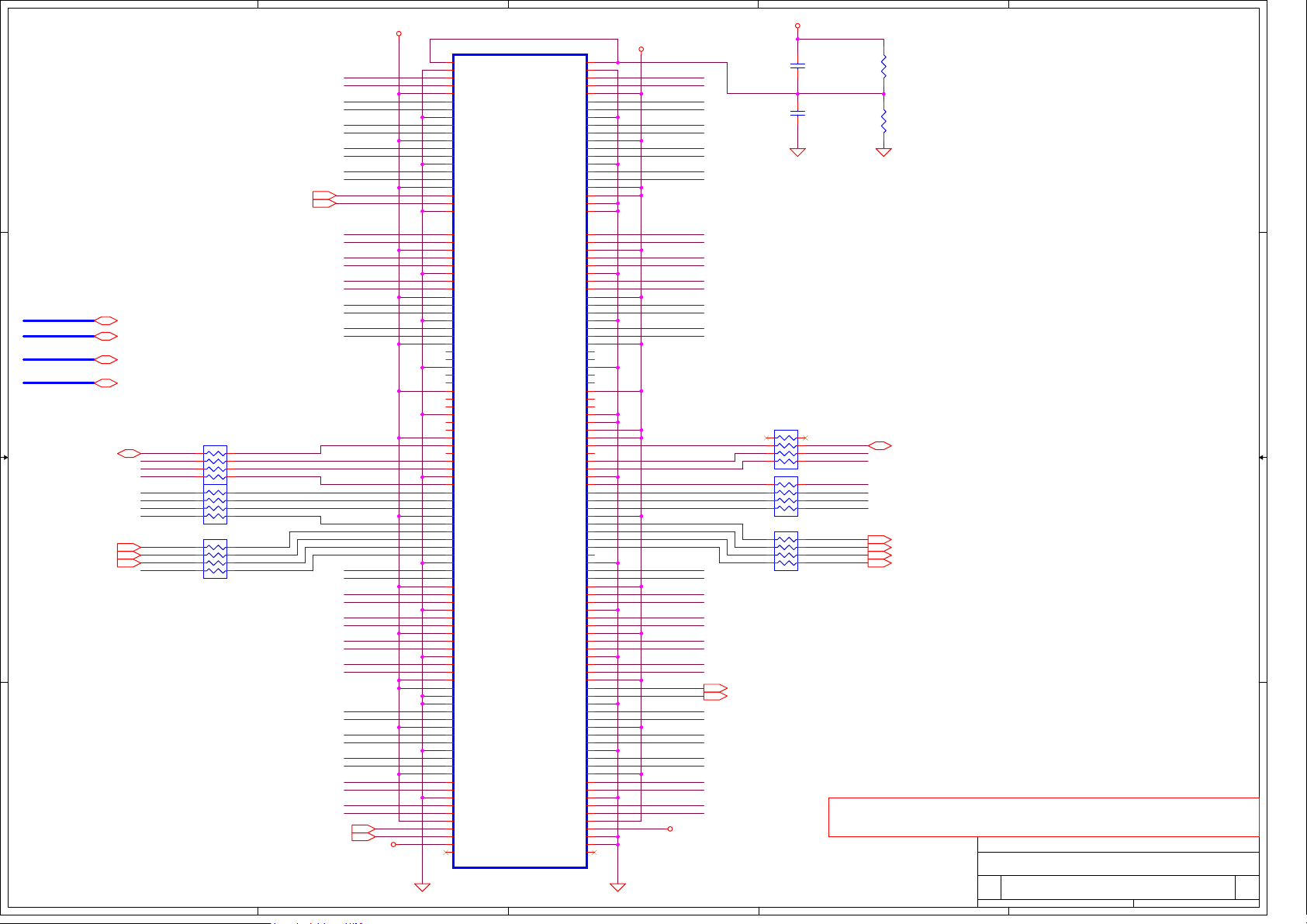

Page 13

5

D D

DDR_CLK39

DDR_CLK3#9

DDR_DQ[0..63]

DDR_DQS[0..7]

C C

DDR_DM[0..7]

DDR_SMA[0..13]

DDR_SCKE39,16

DDR_SBA09,14,15,16

B B

A A

DDR_SCS#29,16 DDR_SCS#3 9,16

DDR_DQ[0..63] 9,14,16

DDR_DQS[0..7] 9,14,16

DDR_DM[0..7] 9,14,16

DDR_SMA[0..13] 9,14,15,16

RP112

10_0804_8P4R_5%

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

RP113

10_0804_8P4R_5%

DDR_SMA13

RP115

10_0804_8P4R_5%

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

5

DDR_CKE3

45

DDR_SMAA12

36

DDR_SMAA9

27

DDR_SMAA7

18

DDR_SMAA5

45

36

DDR_SMAA1

27

DDR_SMAA10

18

45

36

27

18

SM_DATA_SB17,20

SM_CLK_SB17,20

DDR_DQ1

DDR_DQS0

DDR_DQ6

DDR_DQ2

DDR_DQ8

DDR_DQ12

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ18

DDR_DQ22

DDR_DQ24

DDR_DQ29

DDR_DQS3

DDR_DQ26

DDR_DQ30

DDR_BA0

DDR_WE#

DDR_CS#2

DDR_SMAA13

DDR_DQ33

DDR_DQ36

DDR_DQS4

DDR_DQ38

DDR_DQ39

DDR_DQ45

DDR_DQ40

DDR_DQS5

DDR_DQ46

DDR_DQ43

DDR_DQ52

DDR_DQ49

DDR_DQS6

DDR_DQ50

DDR_DQ51

DDR_DQ60

DDR_DQ61

DDR_DQS7

DDR_DQ62

DDR_DQ58

+3VS

4

+2.5V

JP3

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

A13

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

TYCO_1-1612781-1

4

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

VSS

VDD

BA1

RAS#

CAS#

S1#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

NC.TEST

A8

A6

A4

A2

A0

DU

3

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46