Page 1

A

B

COMPAL CONFIDENTIAL

C

D

E

1 1

COMPAL P/N :

MODEL NAME :

PCB NO :

Revision :

2 2

LA2151

1.0 (DELL: A00)

TOBAGO

45128331001/45128331002

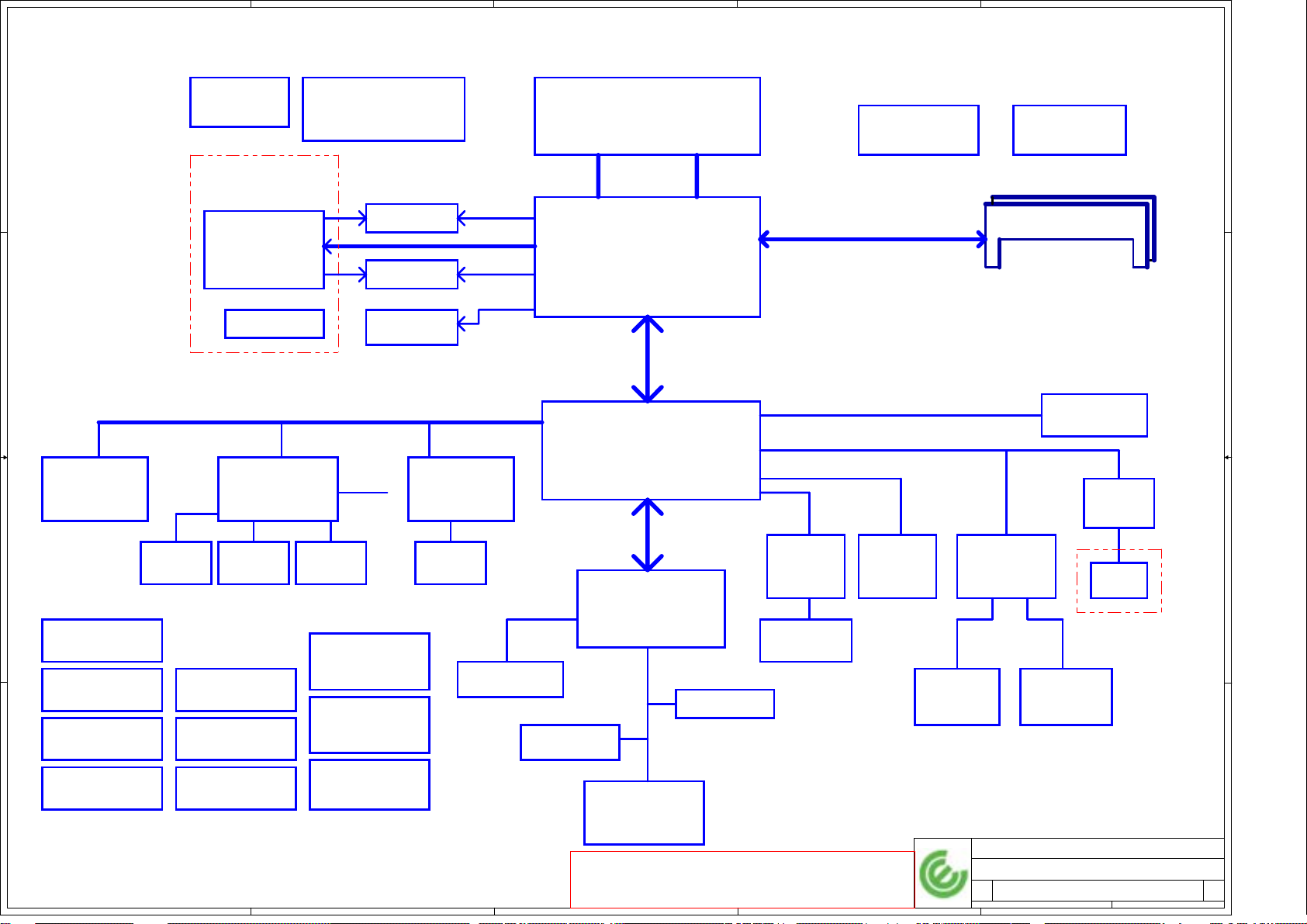

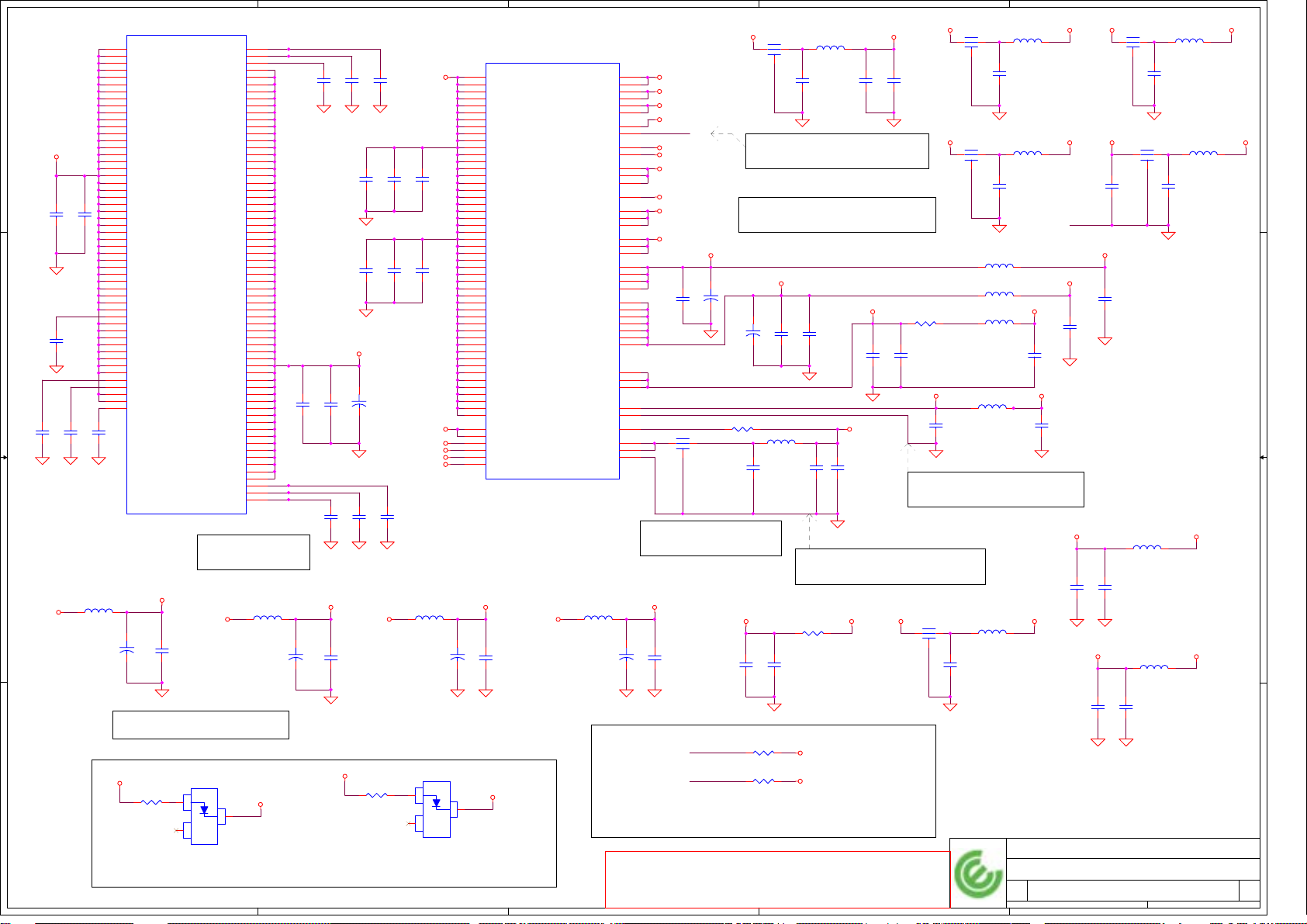

TOBAGO Schematics Document

uFCBGA/uFCPGA Mobile Dothan

Intel Alviso + ICH6M

2004-11-03

REV : 1.0 (DELL: A00)

3 3

4 4

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

A

B

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

TOBAGO-LA2151

151Wednesday, November 03, 2004

E

0.6

of

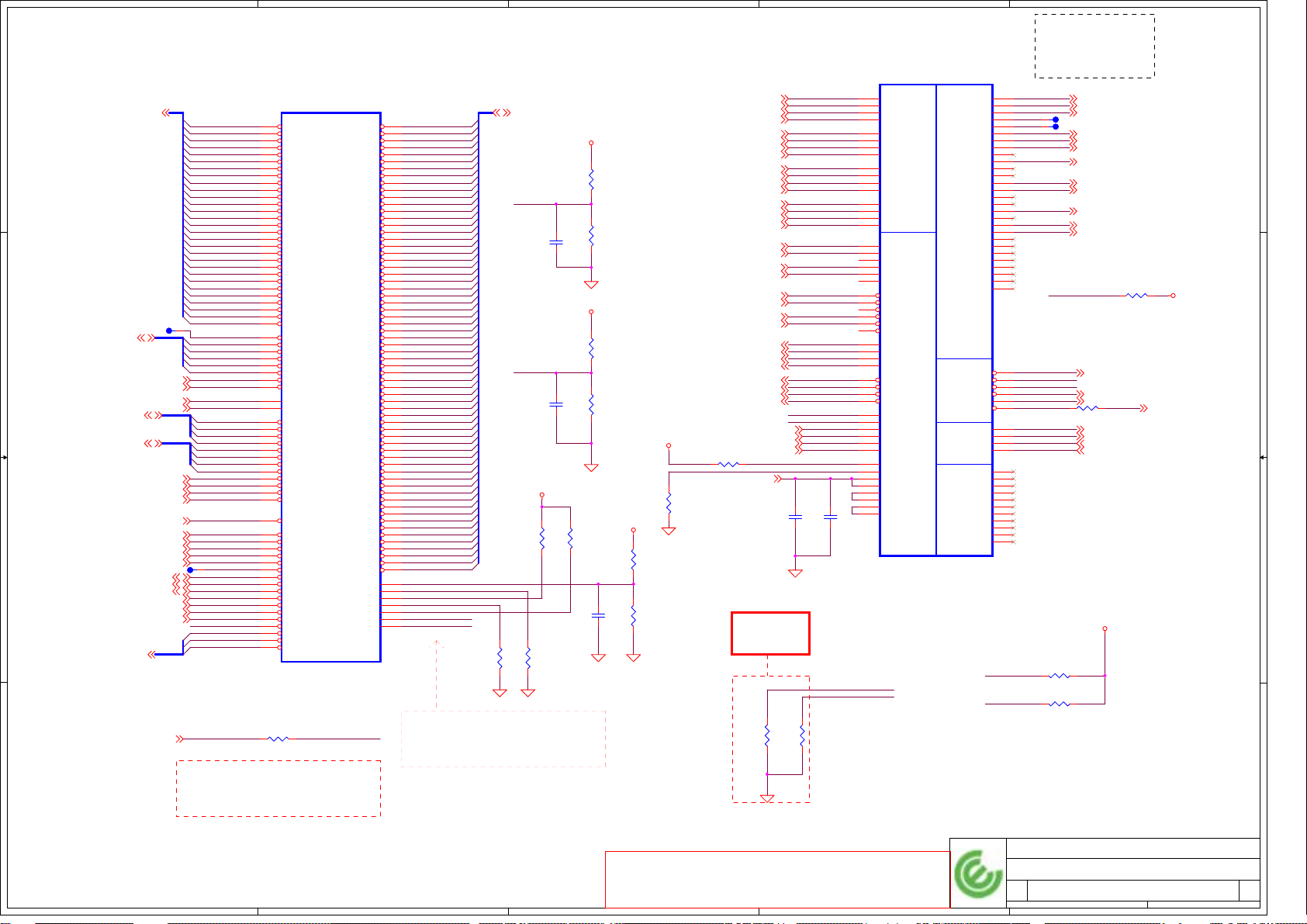

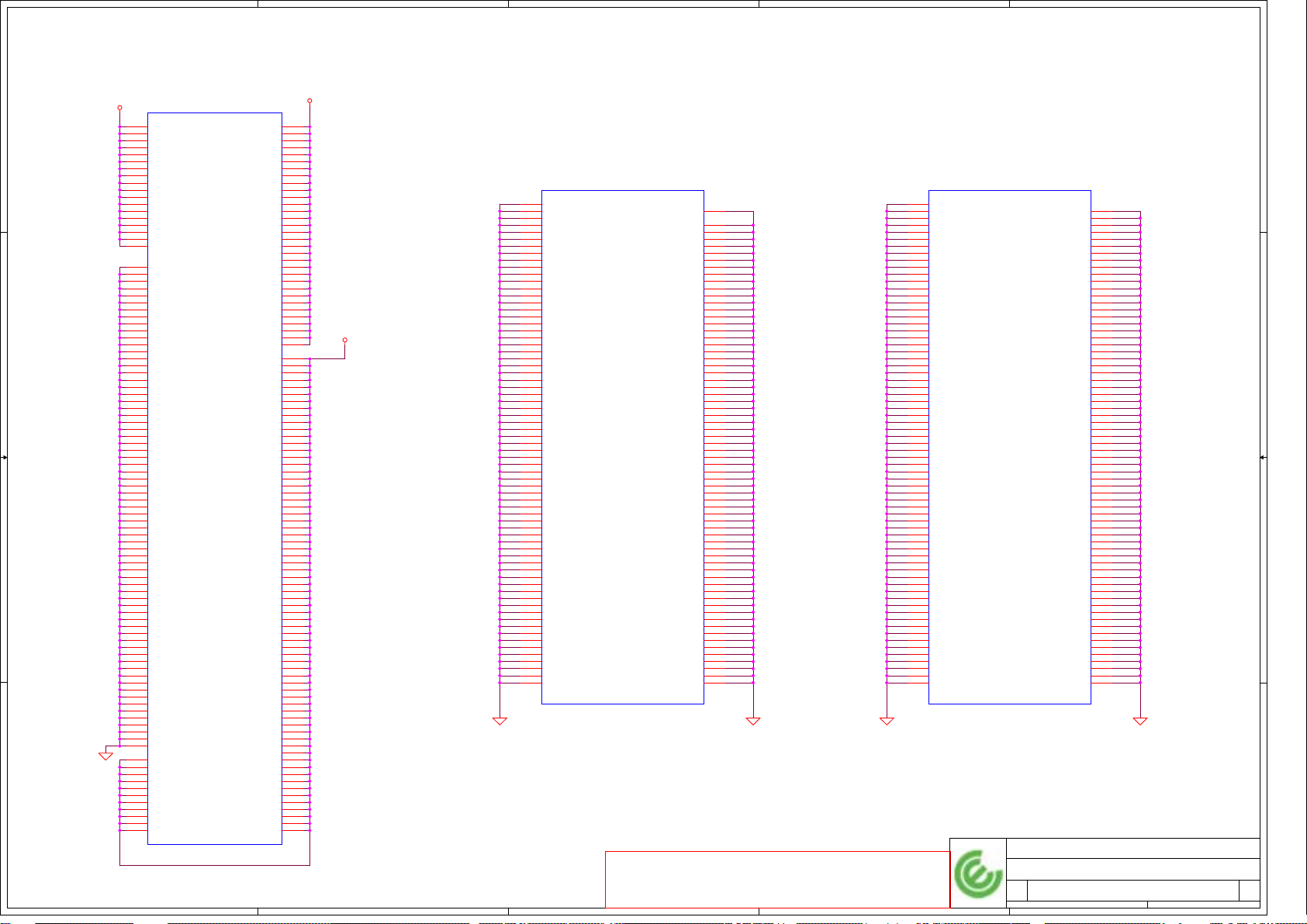

Page 2

A

Compal confidential

Model : Tobago

B

C

D

E

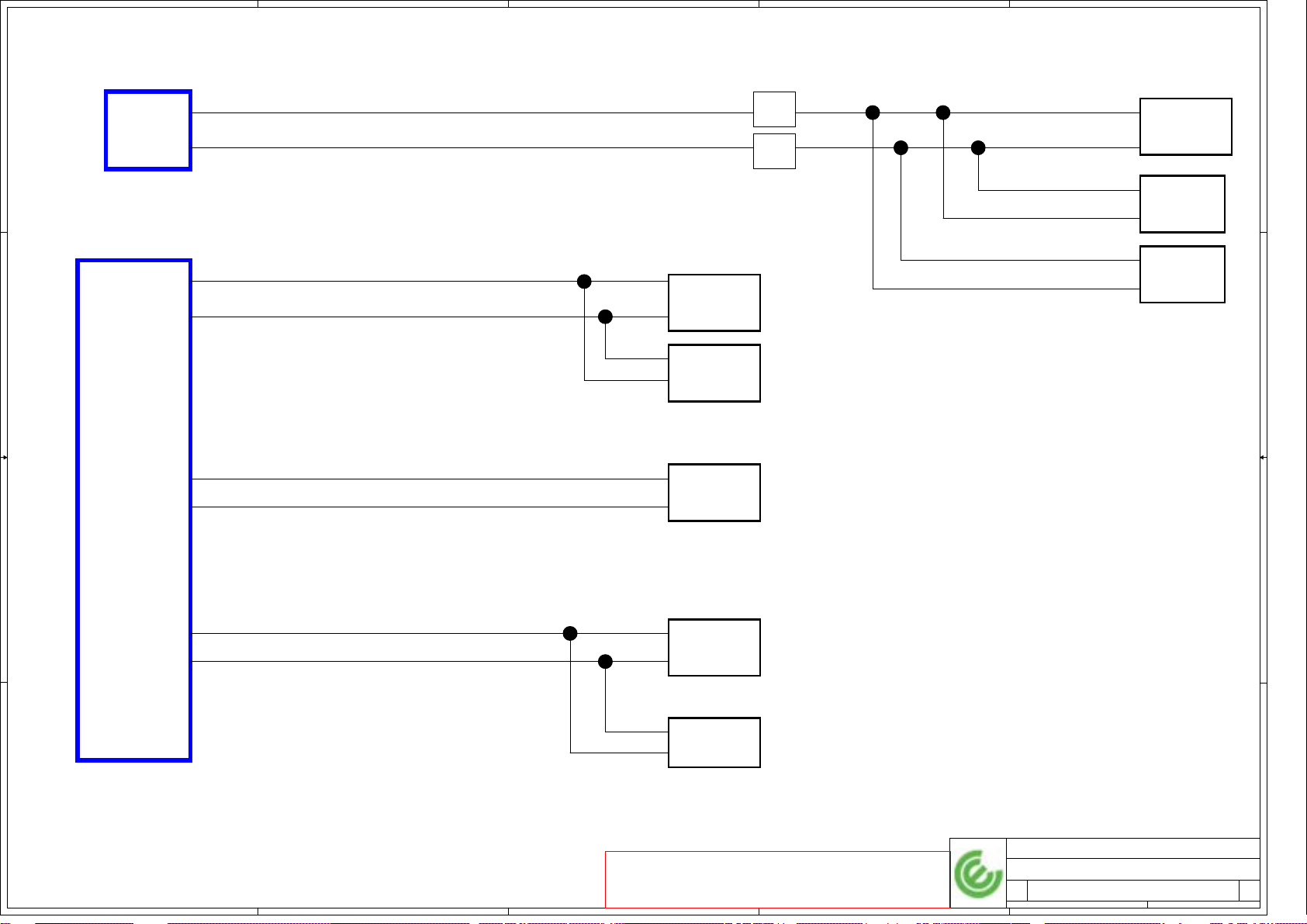

Block Diagram

FAN

1 1

+5VRUN

page 15

VGA Board

VGA CONN

page 18

LVDS CONN

on VGA Board

2 2

IDSEL:AD19

(PIRQB,D#,GNT#3,REQ#3)

Minipci CONN

WIRELESS

+3VRUN

+3VSUS

+5VRUN

page 33

SD card

3 3

SLOT

page 32

CardBus

& 1394

R5C841

+3VSUS

page 31,32

Card Bus

SLOT CONN

page 32

1.5V/1.05V

page 43

1.8V/0.9V

VCORE

page 44

page 45

DC IN

page 40

BATT IN/2.5V

page 41

Thermal

GUARDIAN

EMC6N300

+3VSUS

TV OUT

CRT CONN

LVDS CONN

on M/B Board

+3VRUN 33MHz

IDSEL:AD17

(PIRQC,D#,GNT#1,REQ#1)

48MHz

USB[3]

1394

page 31

Power Sequence

& RTC BATT

Power On/Off

SW & LED

page 15

page 20

page 20

page 19

PCI BUS

IDSEL:AD16

(PIRQC#,GNT#4,REQ#4)

BCM4401KQL

+3VLAN

RJ45

page 38

page 39

PCI-E 16X

CRT Signal

Internal LVDS

page 30

page 30

SST39VF080

+3VALW

+VCCP (1.05V)

+VCC_CORE

+1.5VRUN

+1.8VSUS

+VCCP

+3VRUN

+2.5VRUN

+3VRUN

+3VSUS

+1.5VRUN

+1.5VSUS

+2.5VRUN

X BUS

EC DEBUG

+3VALW

Pentium-M

Dothan

uFCPGA CPU

+VCCP 400/533 MHz

1257BGA

DMI

+1.5VRUN

100MHz

LPC BUS

LPC47N354

MACALLAN III

+3VRUN

+3VALW

page 36

478pin

System Bus

INTEL

Alviso

page 10,11,12,13,14

INTEL

ICH6-M

609 BGA

page 21,22,23,24

+3VRUN

33MHz

page 34,35

page 7,8

H_D#(0..63)H_A#(3..31)

Int.KBD

page 36

Memory BUS

(DDR2)

48MHz

24.576MHz

SATA

88SA8040

+1.8VRUN

+3VRUN

page 25

Parallel ATA

+5VHDD

page 25

CPU ITP Port

+VCCP

USB[4,5,6,7]

ATA100

CD-ROM

+5VMOD

page 7

+1.8VSUS 400MHz

AC-LINK

IDE

+3VRUN

page 25

+VDDA

AMP & INT.

Speaker

+5VRUN +5VRUN

page 27

Clock Generator

CY28411ZCT

+3VRUN

DDRII-DIMM X2

BANK 0, 1, 2, 3

+0.9V_DDR_VTT

+1.8VSUS

AC97 Codec

STAC9751

page 26

HeadPhone &

MIC Jack

page 6

page 16,17

USB Ports X4

+5VSUS

page 28

MDC

+3VSUS

page 29

RJ11

page 27

Cable

4 4

CHARGER

page 46

A

3V/5V/15V

page 42

DC/DC Interface

page 37

B

LCM SW & Touch

Pad & LID SW

+5VRUN

+3VALW

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

page 29

C

D

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Block Diagram

TOBAGO-LA2151

251Monday, October 18, 2004

E

of

0.6

Page 3

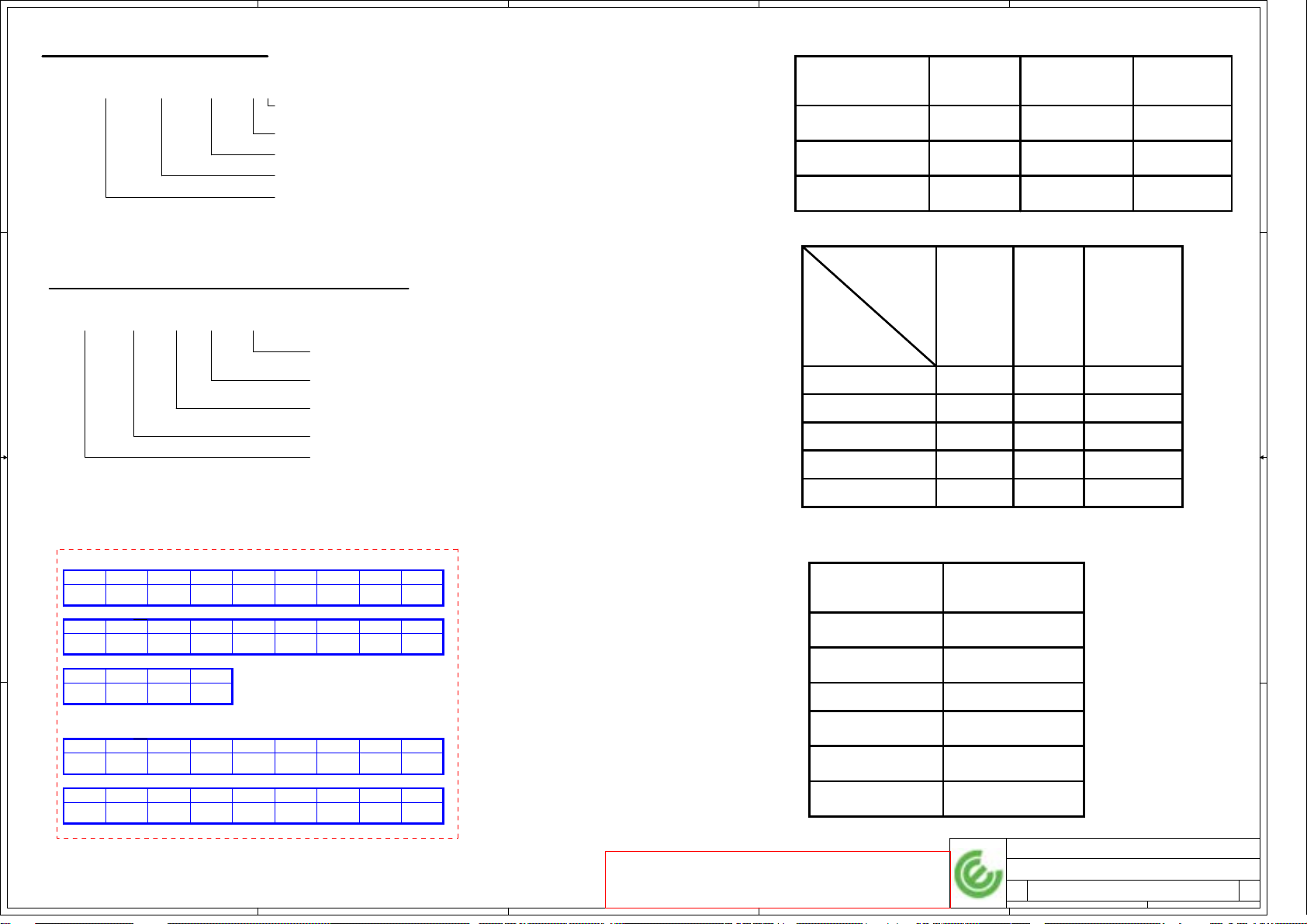

5

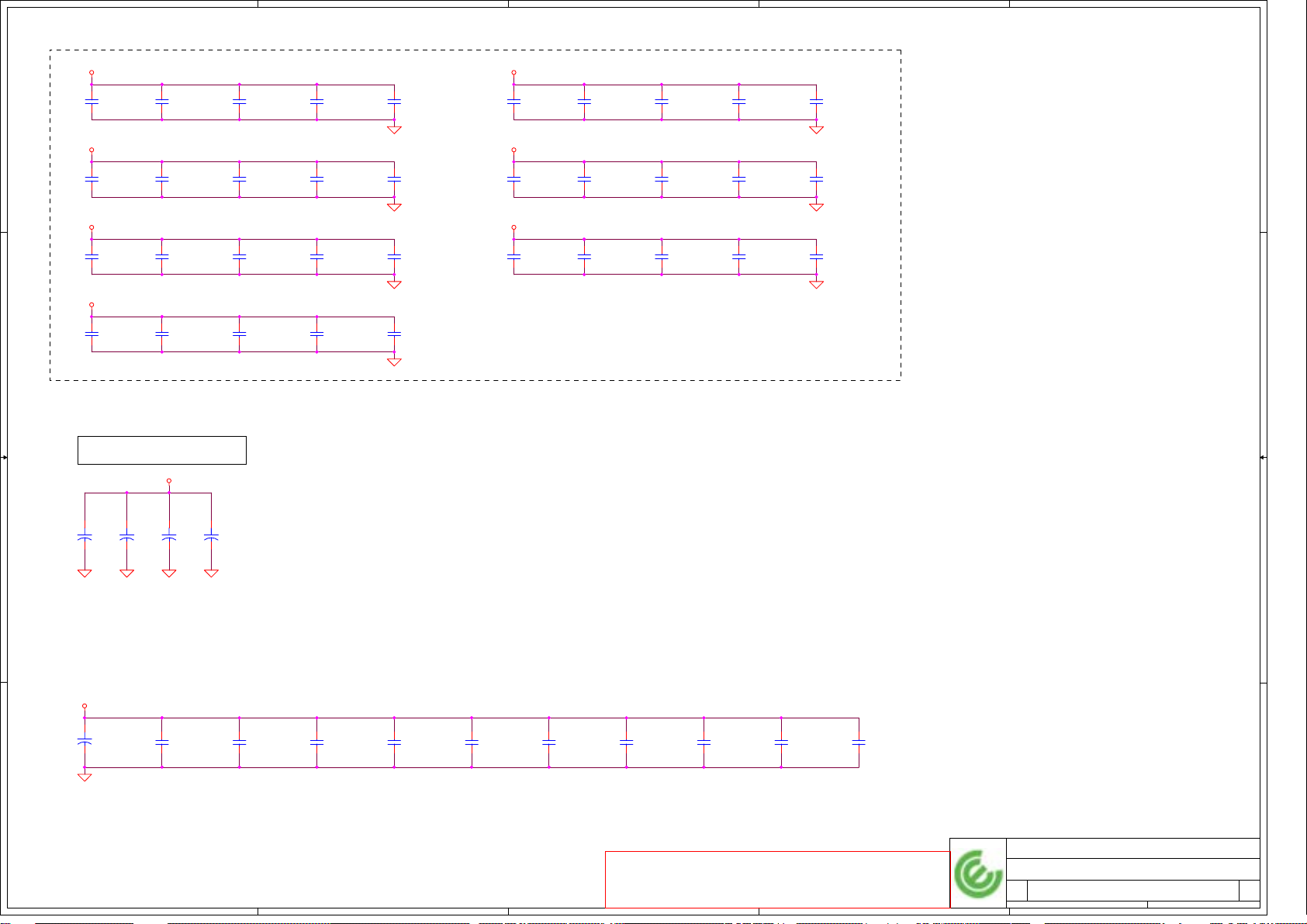

Ceramic Capacitors :

4

3

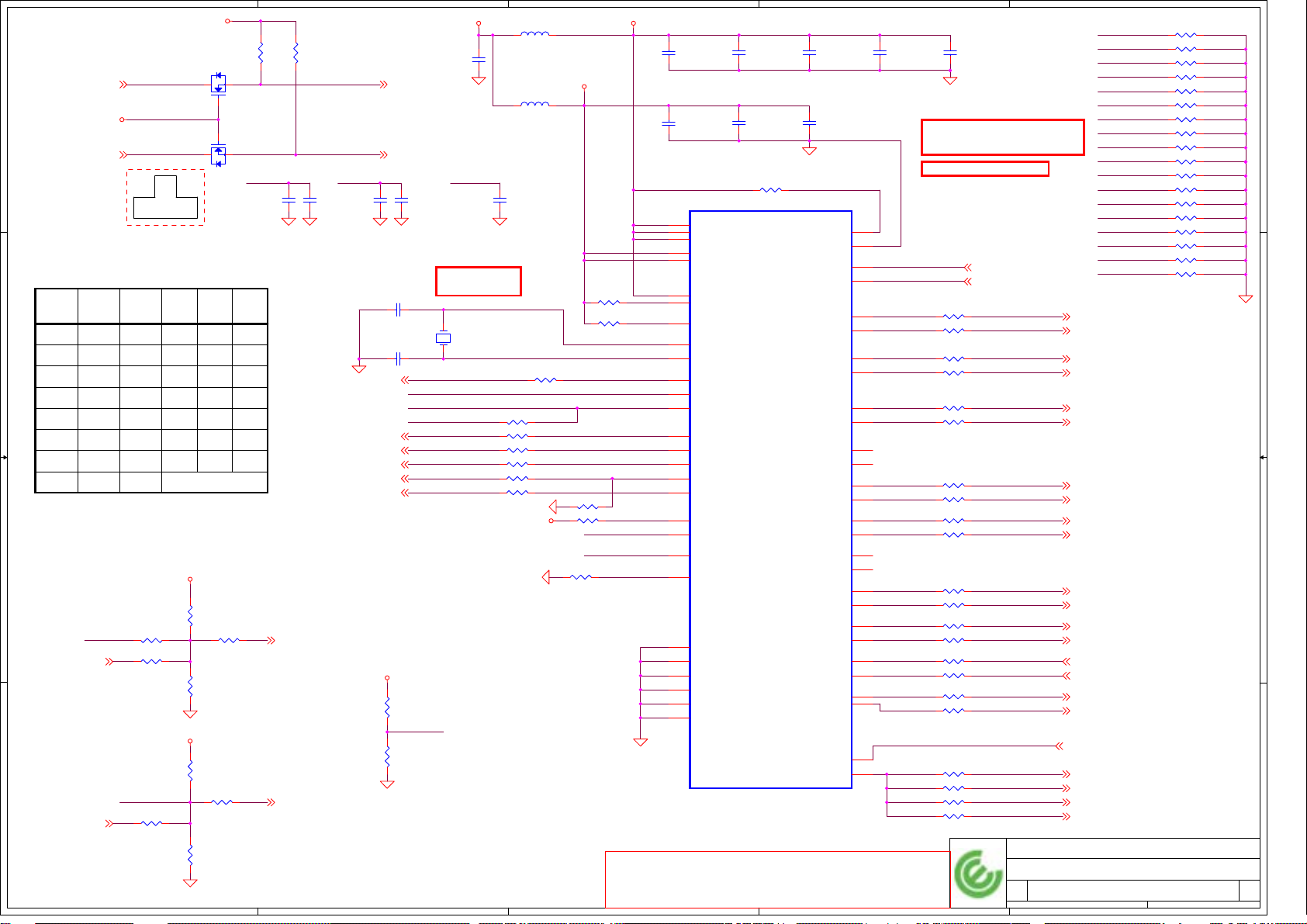

TABLE

PCI

2

1

0.1U_0402_6.3VXX

D D

Tolerance

Temperatur e Characteristics

Rated Voltage

PCI DEVICE

CARD BUS

LAN

IDSEL

AD17

AD16

REQ#/GNT#

1

4

PIRQ

D,C

C

Package Size

Value

MINI PCI

AD19

3

PM TABLE

+5VRUN

Tantalum or Polymer Capacitors :

power

plane

10U_D2_10VX_R45

C C

Low ESR Mark : 45 m ohm

Tolerance

Rated Voltage

Package Size

Value

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

+3VALW

+5VALW

+3VSUS

+5VSUS

+1.8VSUS

+1.5VSUS

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

+3VRUN

+1.8VRUN

+0.9V_DDR_VTT

+1.5VRUN

+VCC_CORE

+VCCP

+15V

D,B

ON

ON

OFF

OFF

OFFOFF

Capacitor Spec Guide:

Temperature Characteristics:

B B

A A

Symbol

CODE

Tolerance:

Symbol

CODE

Z5U

8

9

COG SJ

HI J

UK

UJ

A

+-0.05PF

+-0.1PF

M

K

+-20%

+-10%

+-30%

Z5V

X6SNPO

SL

N

A

1

B

2

Z5P

B

BJ

K

X5S

C

+-0.25PF

P

+100,-0%

4

5

G

X

6

X5R

SH

H

+-3%

Z

+80,-20%

30

Y5V

Y5U X7R

C

CH

D

+-0.5PF +-1PF

Q

+20,-10%

+30,-10%

Y5P

DEFG

CJ

CK

F

+-2%

V

+40,-20%

7

J

+-5%

NOTE1:

@XX : Depop component

1@XX : Pop for Integrated Graphic

2@XX : Pop for External Graphic

USB

TABLE

USB PORT#

0

1

2

3

4,5

6,7

DESTINATION

NC

NC

Blue tooth

PCMCIA

REAR

SIDE

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Index and Config.

TOBAGO-LA2151

351Monday, October 18, 2004

1

0.6

of

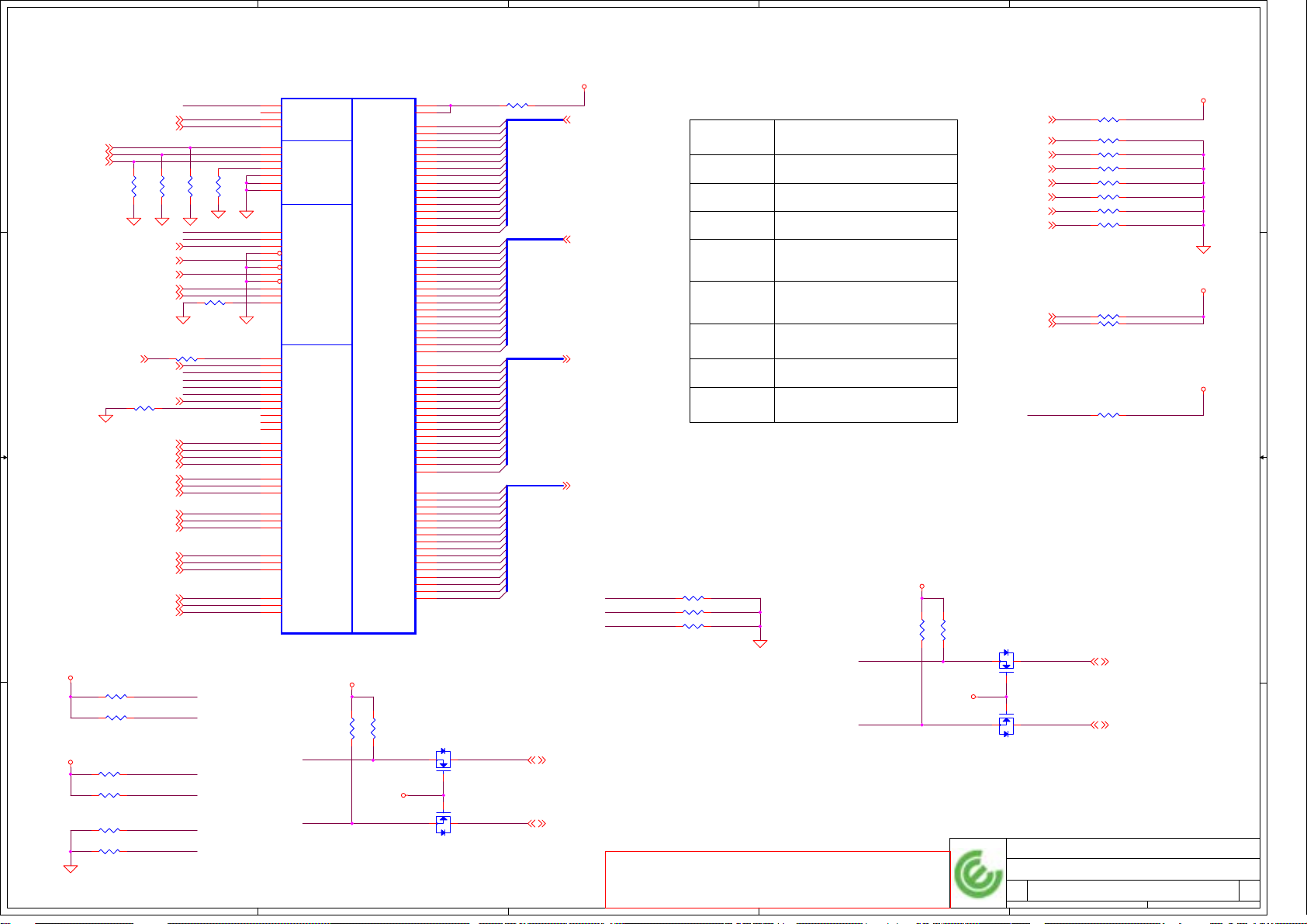

Page 4

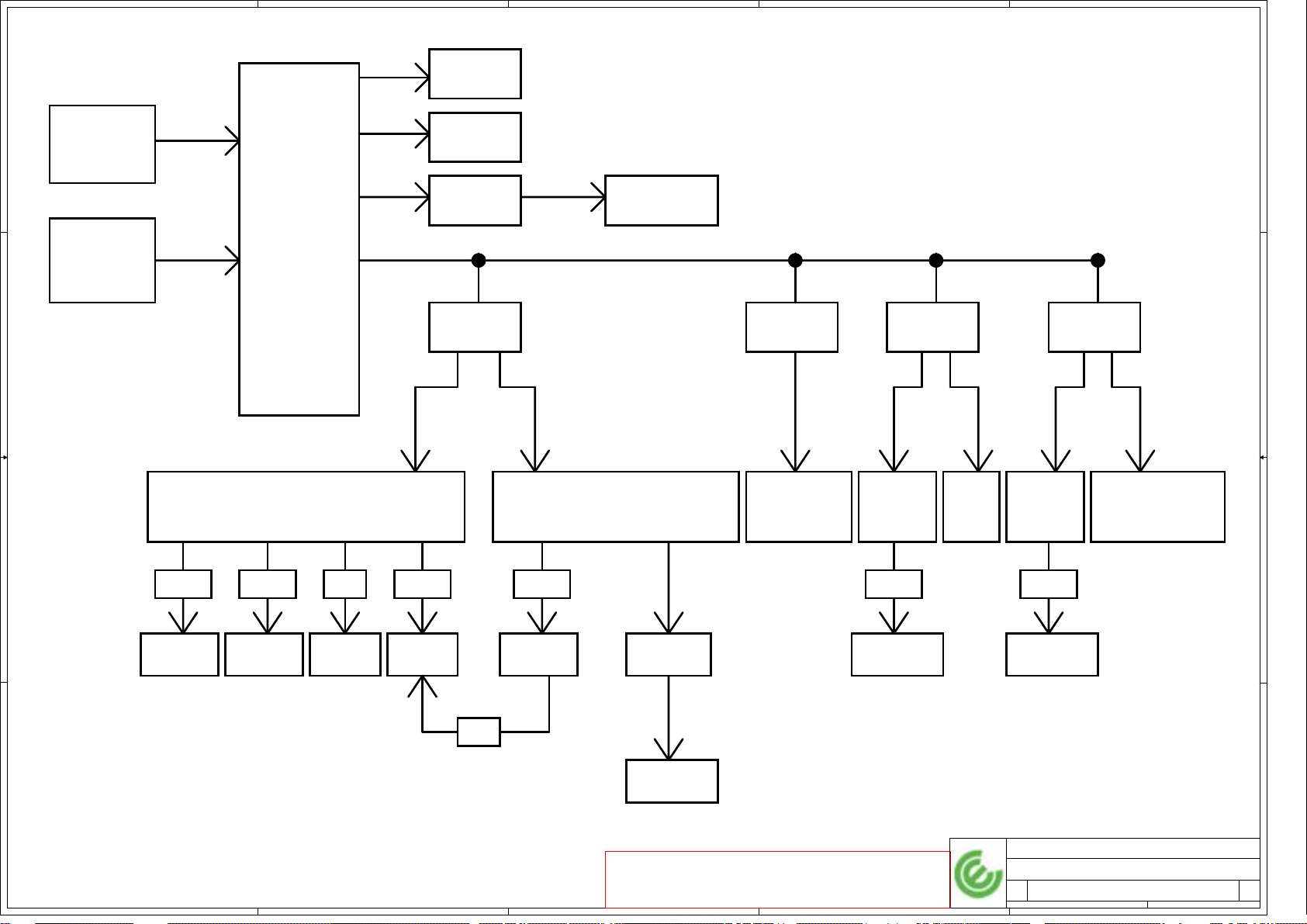

5

4

3

2

1

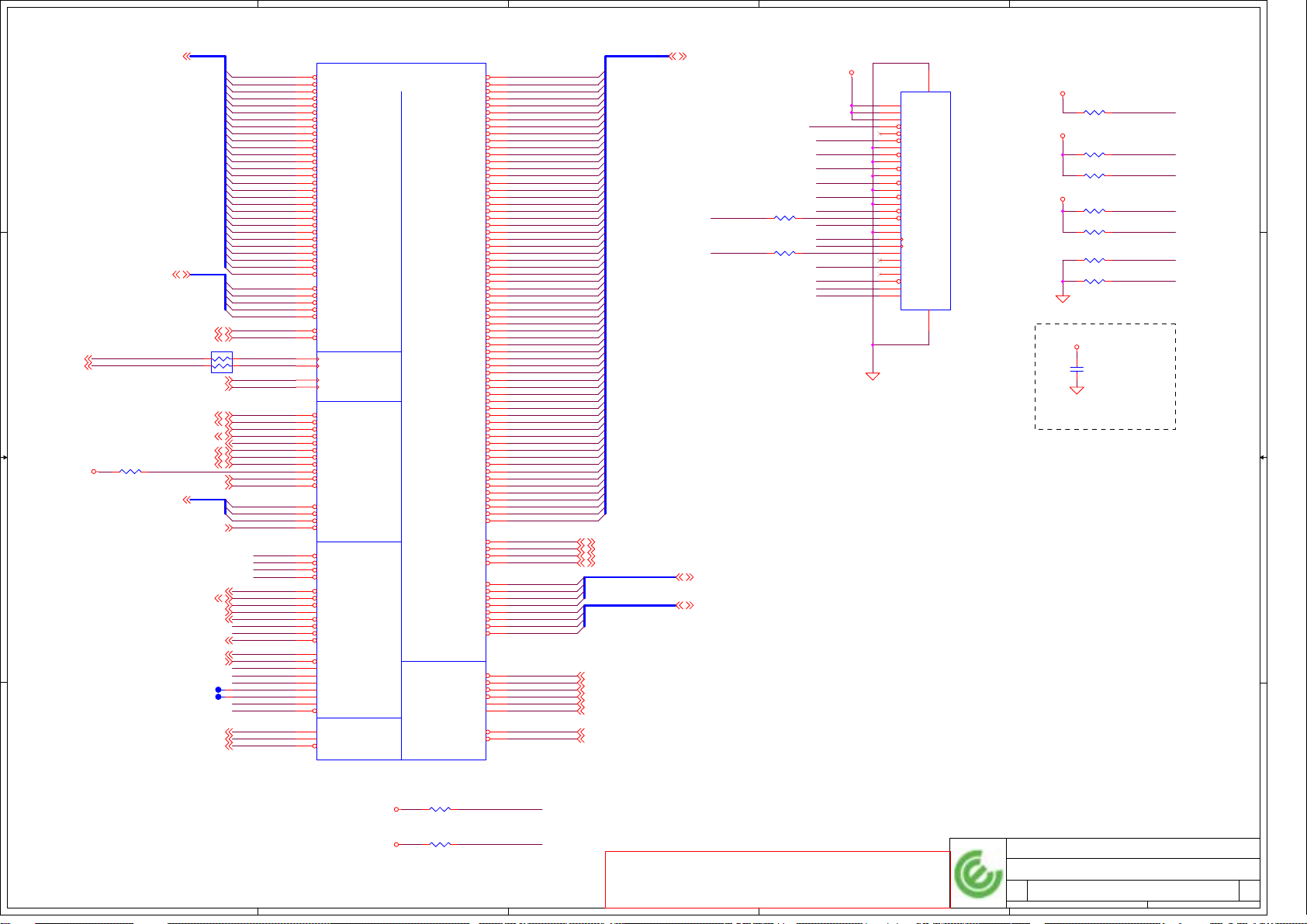

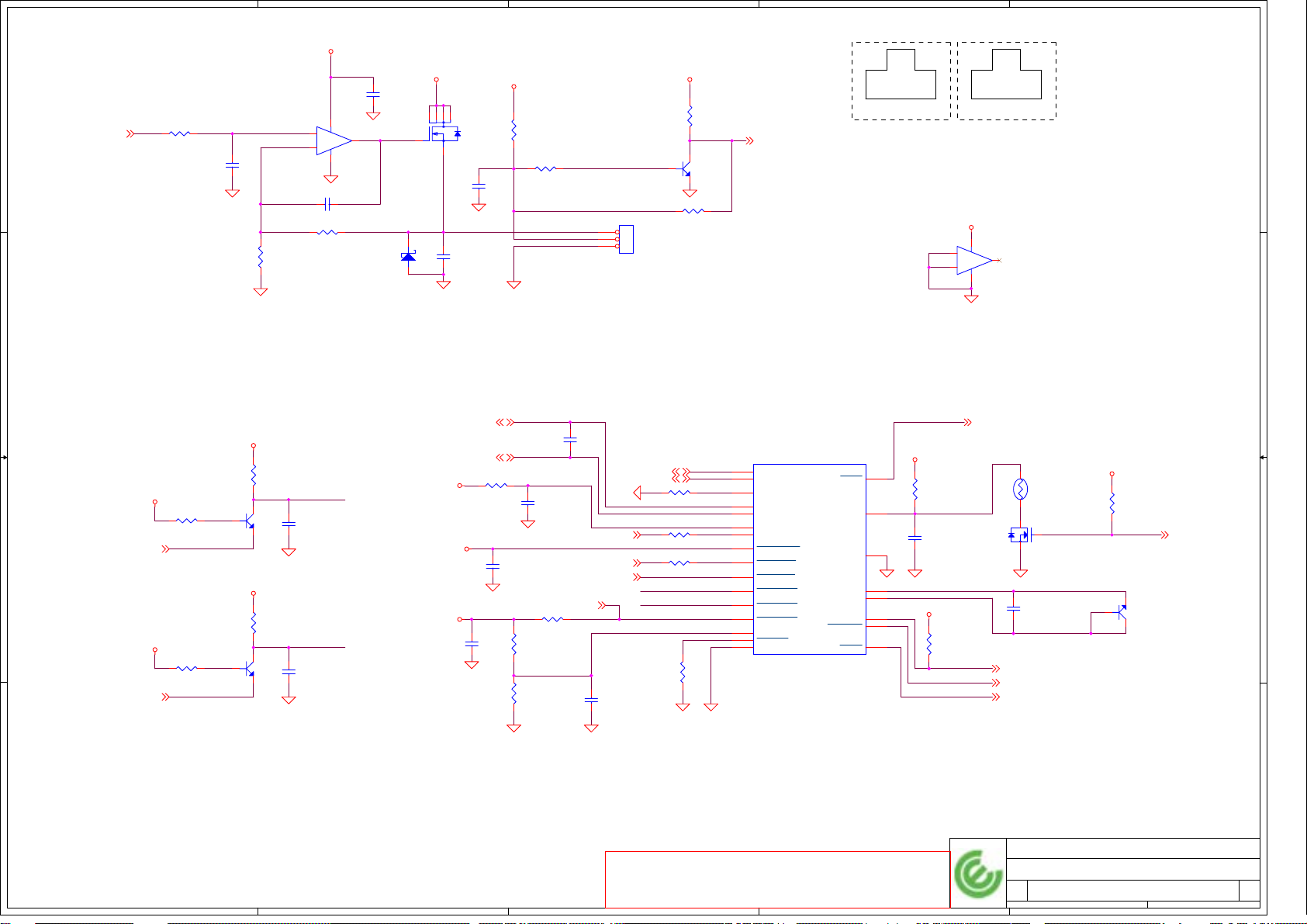

+5VALW

D D

ADAPTER

+3VALW

PWR_SRC

FDS4435 G_PWR_SRC

+5VRUN

BATTERY

MAX1999 MAX1987 MAX1845 MAX8550

C C

SUS_ON

+5VSUS

B B

HDDC_EN#

RUN_ON

PL8

793333

AUDIO_AVDD_ON

(Option)

SUS_ON

SI4810

RUN_ON

+3VSUS

RUNPWROK

+VCC_CORE

RUN_ON

MAX1845_VCC

+1.5VSUS

SI4810

RUN_ON

(Integrated)

+VCCP

RUN_ON_D

(Discreted)

RUNPWROK

SUSPWROK_5V

+1.8SUS +0.9V_DDR_VTT

SI4810SI3456SI3456

RUN_ON

SUSPWROK_5V

L47

+3VRUN

MAX1806 +1.8VRUN

RUN_ON

+1.5VRUN

+2.5VRUN

+5VHDD +5VRUN VDDA

A A

+15V

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Power Rail

TOBAGO-LA2151

451Monday, October 18, 2004

1

0.6

of

Page 5

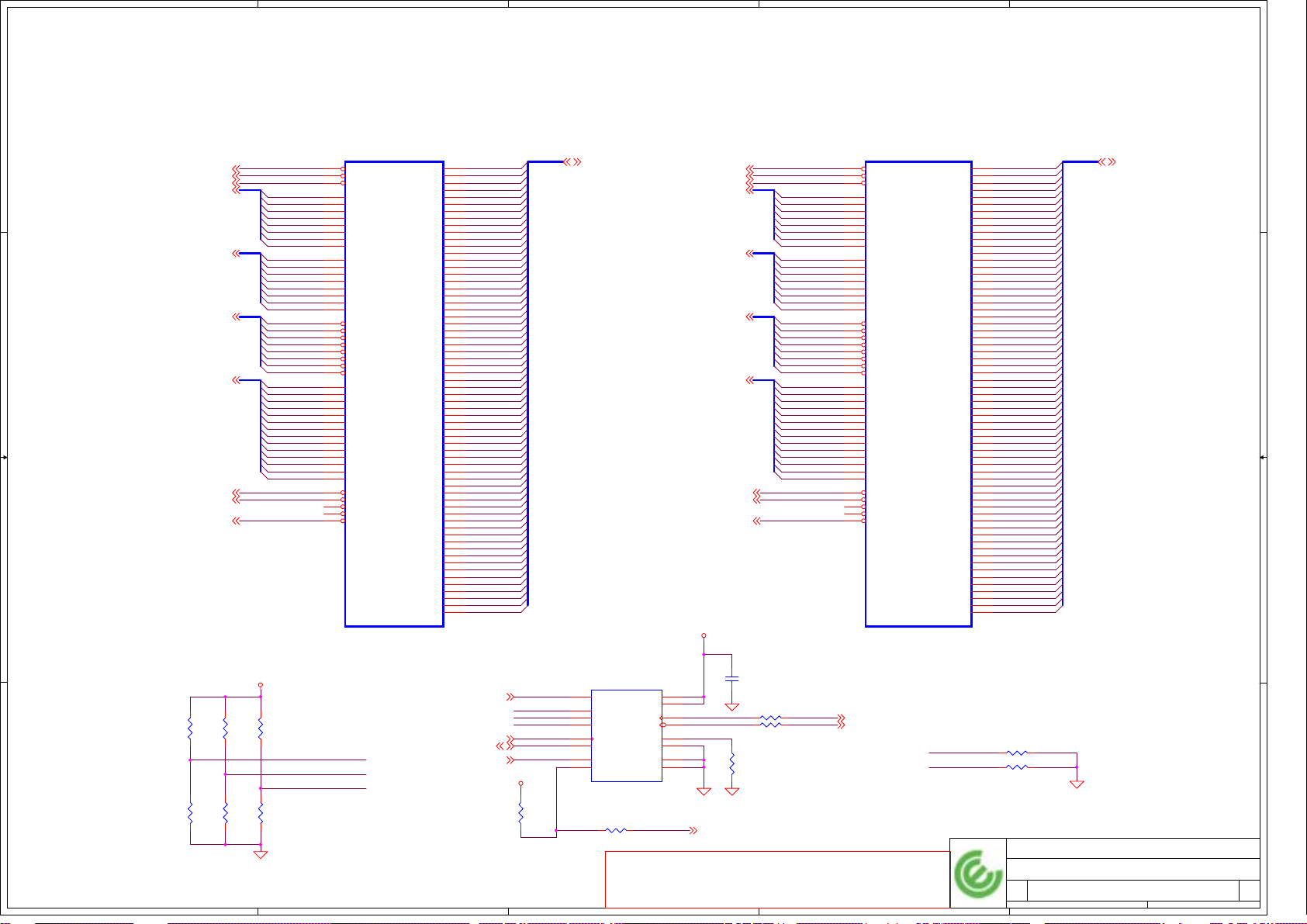

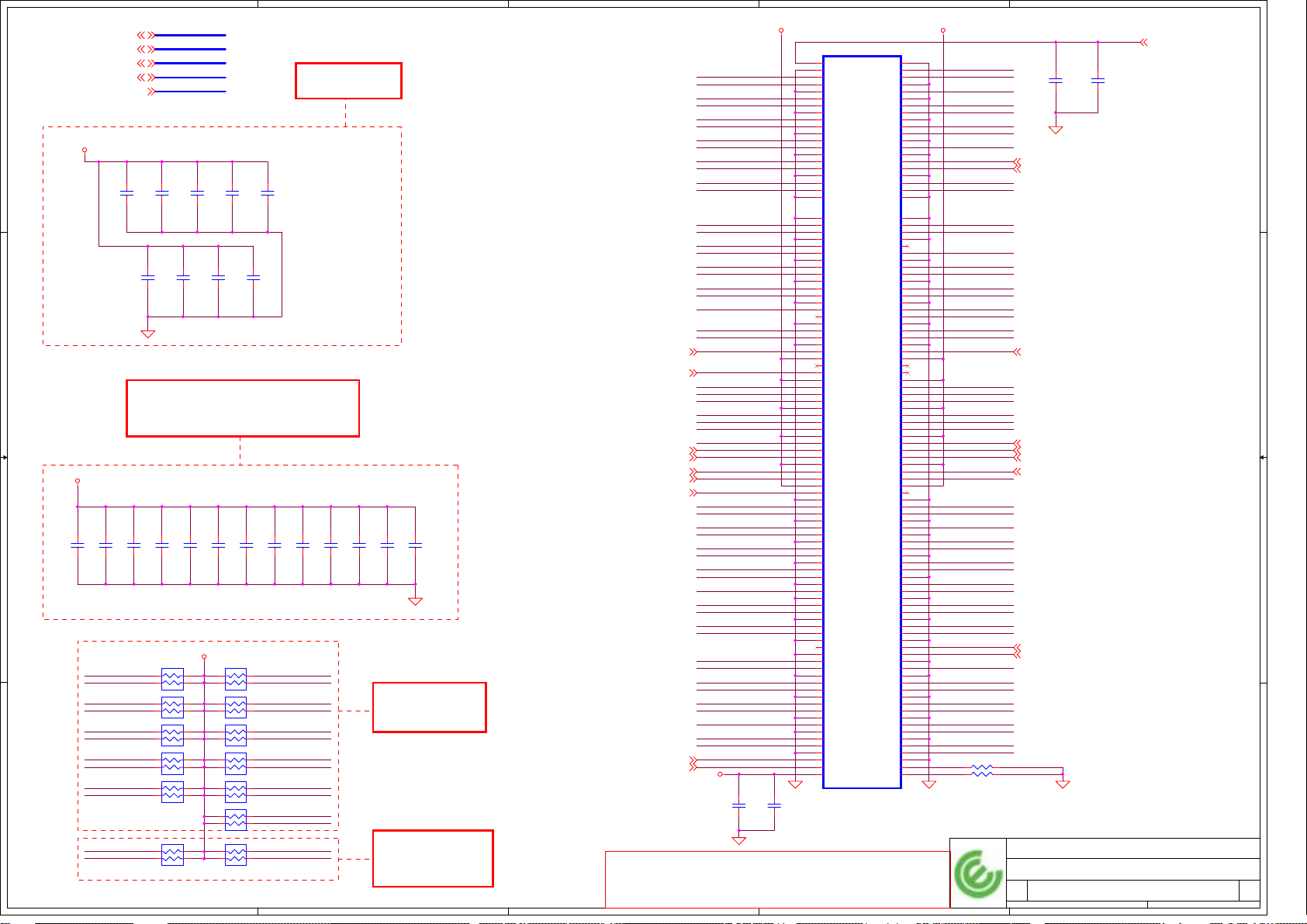

5

4

3

2

1

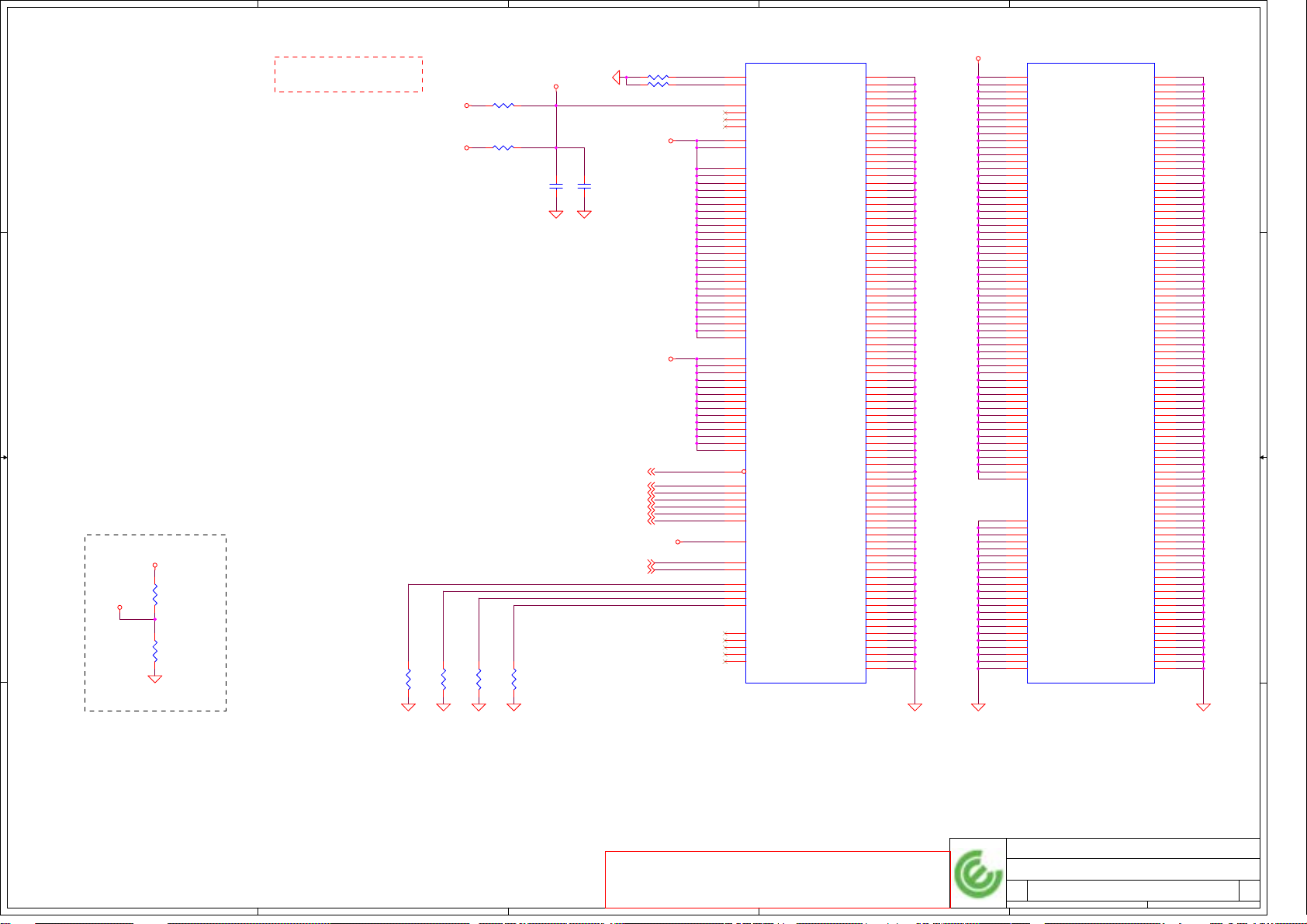

+3VRUN

ICH_SMBCLK

D D

ICH6-M

ICH_SMBDATA

+3VSUS

7002

7002

CLK_SCLK

CLK GEN.

CLK_SDATA

DIMM0

CLK_SMB

DAT_SMB

C C

+3VALW

GUARDIAN

DIMM1

24C04

SIO

Macallan III

B B

SBAT_SMBCLK

SBAT_SMBDAT

+5VALW

PBAT_SMBCLK

PBAT_SMBDAT +5VALW

INVERTER

BATTERY

CHARGER

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SMBUS TOPOLOGY

TOBAGO-LA2151

551Monday, October 18, 2004

1

0.6

of

Page 6

5

+3VRUN

R270

D

ICH_SMBDATA<23>

D D

ICH_SMBCLK<23>

ICH_SMBDATA

+3VRUN

ICH_SMBCLK

1 3

2

2

1 3

D

S

Q36

2N7002_SOT23~D

G

G

Q38

2N7002_SOT23~D

S

D

1

3

G

S

2

2N7002

FSC FSB FSA CPU

CLKSEL0 CLKSEL2CLKSEL1

C C

000

0

0

00

1

11

*

1

1

0

1

1

1

0

00

1

0

111

MHz

266

133

200

166

333

100

400

SRC

MHz

100

100

100

100

100

100

100

RESERVED

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

33.3

12

12

R275

2.2K_0402_5%~D

2.2K_0402_5%~D

C68

CLK_SDATA

CLK_SCLK

1

1

2

2

C61

4.7U_0805_10V4Z~D

0.047U_0402_16V4Z~D

Table : ICS954201BG

R531

1 2

1 2

0_0402_5%~D

5

12

+VCCP

+VCCP

@

R342

1K_0402_5%~D

1 2

@

R305

0_0402_5%~D

1 2

@

R353

1K_0402_5%~D

1 2

1 2

R354

0_0402_5%~D

@

R364

0_0402_5%~D

1 2

1 2

R330

0_0402_5%~D

MCH_CLKSEL0 <10>

MCH_CLKSEL1 <10>

B B

8.2K_0402_5%~D

CLKSEL0

CPU_BSEL0<8>

A A

CPU_BSEL1<8>

R329

0_0402_5%~D

R343

4

1

C326

0.1U_0402_16V4Z~D

CLK_SDATA <11,16,17>

CLK_SCLK <11,16,17>

CK_VDD_48CK_VDD_A CK_VDD_REF

1

1

2

2

C50

CLK_ICH_48M<23>

CLK_PCI_PCM<31>

CLK_PCI_SIO<34>

CLK_PCI_MINI<33>

CLK_PCI_LOM<30>

CLK_PCI_ICH<21>

C51

4.7U_0805_10V4Z~D

27P_0402_50V8J~D

27P_0402_50V8J~D

+3VRUN

0.047U_0402_16V4Z~D

C329

12

C333

12

CLK_ICH_48M CLKSEL2

CLKSEL1

CLKSEL0

CLK_CODEC_14M

CLK_PCI_PCM PCI_PCM

CLK_PCI_LOM PCI_LOM

CLK_PCI_ICH P CI_ICH

R271

10K_0402_5%~D

1 2

CLKSEL2

R278

10K_0402_5%~D

@

1 2

4

2

Place crystal within

500 mils of CK410

X2

12

14.31818MHz_20P_1BX14318CC1A~D

1 2

L40

BLM21PG600SN1D_0805~D

BLM21PG600SN1D_0805~D

1

2

CLK_XTAL_IN

CLK_XTAL_OUT

R532 12.1_0402_1%~D

R302 33_0402_5%~D

R294 33_0402_5%~D

R293 33_0402_5%~D

R277 33_0402_5%~D

R331

33_0402_5%~D

CK_VDD_MAIN2

1 2

L32

C52

0.047U_0402_16V4Z~D

R298 33_0402_5%~D

@

12

12

12

12

12

12

+3VRUN

10K_0402_5%~D

CK_VDD_MAIN+3VRUN

1 2

R274

1_0603_5%~D

1 2

R273

2.2_0603_5%~D

12

PCI_SIOCLK_PCI_SIO

PCI_MINICLK_PCI_MINI

R538

@

12

100K_0402_5%~D

1 2

R316

1 2

R362 475_0603_1%~D

PCICLKF0

CLK_SCLK

CLK_SDATA

CLKIREF

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

CK_VDD_REF

CK_VDD_48

3

CK_VDD_MAIN

2

C402

10U_0805_10V4M~D

1

2

C308

10U_0805_10V4M~D

1

U16

21

VDD_SRC0

28

VDD_SRC1

34

VDD_SRC2

1

VDD_PCI0

7

VDD_PCI1

42

VDD_CPU

48

VDD_REF

11

VDD_48

50

XTAL_IN

49

XTAL_OUT

12

FSA/USB_48

16

FSB/TEST_MODE

53

FSC/TEST_SEL

5

PCI5

4

PCI4

3

PCI3

56

PCI2/REQ_SEL

9

PCIF1/SELPCIEX_LCDCLK#

8

PCIF0/ITP_EN

46

SCLOCK

47

SDATA

39

IREF

13

VSS_48

29

VSS_SRC

2

VSS_PCI0

45

VSS_CPU

51

VSS_REF

6

VSS_PCI1

ICS954226AG_TSSOP56~D

1

C384

0.1U_0402_16V4Z~D

2

1

C344

0.1U_0402_16V4Z~D

2

R401

2.2_0603_5%~D

1 2

1

C58

0.1U_0402_16V4Z~D

2

1

C330

0.1U_0402_16V4Z~D

2

CK_VDD_A

VDD_A

VSS_A

PCI_STOP#

CPU_STOP#

CPU1

CPU1#

CPU0

CPU0#

CPU_2_ITP/SRC_7

CPU_2_ITP/SRC7#

SRC6

SRC6#

SRC5

SRC5#

SRC4

SRC4#

SRC3

SRC3#

SRC2

SRC2#

SRC1

SRC1#

SRC0/LCDCLK_SS

SRC0#/LCDCLK_SS

DOT96

DOT96#

VTT_PWRGD#/PD

REF

2

1

C64

0.1U_0402_16V4Z~D

2

1

C389

0.1U_0402_16V4Z~D

2

Place near each pin

W>40 mil

Place near CK410

37

38

H_STP_PCI#

55

H_STP_CPU#

54

MCH_BCLK

41

MCH_BCLK#

40

CPU_BCLK

44

CPU_BCLK#

43

36

CPU_ITP# CLK_CPU_ITP#

35

33

32

MCH_3GPLL

31

MCH_3GPLL# CLK_MCH_3GPLL#

30

PCIE_SATA CLK_PCIE_SATA

26

PCIE_SATA#

27

24

25

PCIE_VGA

22

PCIE_VGA#

23

PCIE_ICH CLK_PCIE_ICH

19

PCIE_ICH#

20

DOT96_SSC

17

DOT96_SSC#

18

DOT96 DREFCLK

14

15

CLK_ENABLE#

10

CLKREF

52

H_STP_PCI# <23>

H_STP_CPU# <23,45>

1 2

R348 33_0402_5%~D

1 2

R359 33_0402_5%~D

1 2

R321 33_0402_5%~D

1 2

R337 33_0402_5%~D

1 2

R368 33_0402_5%~D

1 2

R376 33_0402_5%~D

1 2

R397 33_0402_5%~D

1 2

R402 33_0402_5%~D

1 2

R394 33_0402_5%~D

1 2

R400 33_0402_5%~D

1 2

R382 33_0402_5%~D

1 2

R386 33_0402_5%~D

1 2

R366 33_0402_5%~D

1 2

R375 33_0402_5%~D

1 2

R524 33_0402_5%~D1@

1 2

R525 33_0402_5%~D1@

1 2

R345 33_0402_5%~D

1 2

R356 33_0402_5%~D

1 2

R266 12.1_0402_1%~D

1 2

R259 12.1_0402_1%~D

1 2

R250 12.1_0402_1%~D

1 2

R301 12.1_0402_1%~D@

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_CPU_ITPCPU_ITP

CLK_MCH_3GPLL

CLK_PCIE_SATA#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_ICH#

DREFCLK#DOT96#

CLK_ICH_14M

CLK_CODEC_14M

CLK_SIO_14MCLKSEL1

CLK_SSC_IN

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_VGA

CLK_PCIE_VGA#

DREFCLK

DREFCLK#

DREF_SSCLK

DREF_SSCLK#

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CLK_CPU_BCLK <7>

CLK_CPU_BCLK# <7>

CLK_CPU_ITP <7>

CLK_CPU_ITP# <7>

CLK_MCH_3GPLL <12>

CLK_MCH_3GPLL# <12>

CLK_PCIE_SATA <22>

CLK_PCIE_SATA# <22>

CLK_PCIE_VGA <18>

CLK_PCIE_VGA# <18>

CLK_PCIE_ICH <23>

CLK_PCIE_ICH# <23>

DREF_SSCLK <10,11>

DREF_SSCLK# <10,11>

DREFCLK <10>

DREFCLK# <10>

CLK_ENABLE# <11,45>

CLK_ICH_14M <23>

CLK_CODEC_14M <26>

CLK_SIO_14M <34>

CLK_SSC_IN <11>

Compal Electronics, Inc.

Clock Generator

TOBAGO-LA2151

1

R369 49.9_0402_1%~D

R377 49.9_0402_1%~D

R349 49.9_0402_1%~D

R360 49.9_0402_1%~D

R322 49.9_0402_1%~D

R338 49.9_0402_1%~D

1 2

R392 49.9_0402_1%~D

1 2

R403 49.9_0402_1%~D

1 2

R381 49.9_0402_1%~D

1 2

R385 49.9_0402_1%~D

1 2

R365 49.9_0402_1%~D

1 2

R374 49.9_0402_1%~D

1 2

R393 49.9_0402_1%~D

1 2

R399 49.9_0402_1%~D

1 2

R344 49.9_0402_1%~D

1 2

R355 49.9_0402_1%~D

1 2

R522 49.9_0402_1%~D1@

1 2

R523 49.9_0402_1%~D1@

651Monday, October 18, 2004

1

12

12

12

12

12

12

0.6

of

Page 7

5

4

3

2

1

H_A#[3..31]<10>

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

RN28

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_ITTP

CPU_ITTP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

ITP_BPM#4

ITP_BPM#5

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

D D

H_REQ#[0..4]<10>

H_ADSTB#0<10>

C C

CLK_CPU_ITP<6>

CLK_CPU_ITP#<6>

R422

56_0402_5%~D

1 2

+VCCP

B B

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

H_ADSTB#1<10>

@

2 3

1 4

0_0404_4P2R_5%~D

CLK_CPU_BCLK<6>

CLK_CPU_BCLK#<6>

H_ADS#<10>

H_BNR#<10>

H_BPRI#<10>

H_BR0#<10>

H_DEFER#<10>

H_DRDY#<10>

H_HIT#<10>

H_HITM#<10>

H_LOCK#<10>

H_RESET#<10>

H_RS#[0..2]<10>

H_TRDY#<10>

ITP_DBRESET#<38>

H_DBSY#<10>

H_DPSLP#<22>

H_DPRSTP#<22>

H_DPWR#<10>

H_PROCHOT#<35>

H_PWRGOOD<22>

H_CPUSLP#<10,22>

@

T37 PAD~D

T38 PAD~D

@

H_THERMDA<15>

H_THERMDC<15>

H_THERMTRIP#<15>

5

JCPUA

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

TYCO_1612364-1~D

Dothan

ADDR GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

+VCCP

+VCCP

4

DATA GROUP

LEGACY CPU

R398

56_0402_5%~D

1 2

R423

200_0402_5%~D

1 2

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

H_THERMTRIP#

H_PWRGOOD

H_D#0H_A#3

A19

H_D#1

A25

H_D#2

A22

H_D#3

B21

H_D#4

A24

H_D#5

B26

H_D#6

A21

H_D#7

B20

H_D#8

C20

H_D#9

B24

H_D#10

D24

H_D#11

E24

H_D#12

C26

H_D#13

B23

H_D#14

E23

H_D#15

C25

H_D#16

H23

H_D#17

G25

H_D#18

L23

H_D#19

M26

H_D#20H_A#23

H24

H_D#21

F25

H_D#22

G24

H_D#23

J23

H_D#24

M23

H_D#25

J25

H_D#26

L26

H_D#27

N24

H_D#28

M25

H_D#29

H26

H_D#30

N25

H_D#31

K25

H_D#32

Y26

H_D#33

AA24

H_D#34

T25

H_D#35

U23

H_D#36

V23

H_D#37

R24

H_D#38

R26

H_D#39

R23

H_D#40

AA23

H_D#41

U26

H_D#42

V24

H_D#43

U25

H_D#44

V26

H_D#45

Y23

H_D#46

AA26

H_D#47

Y25

H_D#48

AB25

H_D#49

AC23

H_D#50

AB24

H_D#51

AC20

H_D#52

AC22

H_D#53

AC25

H_D#54

AD23

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AF20

H_D#59

AE21

H_D#60

AD21

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <10>

H_DINV#1 <10>

H_DINV#2 <10>

H_DINV#3 <10>

H_A20M# <22>

H_FERR# <22>

H_IGNNE# <22>

H_INIT# <22>

H_INTR <22>

H_NMI <22>

H_STPCLK# <22>

H_SMI# <22>

Add pullups for PWRGOOD and THERMTRIP per INTEL

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

H_D#[0..63] <10>

H_RESET#

ITP_TDO

H_DSTBN#[0..3] <10>

H_DSTBP#[0..3] <10>

+VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

R424

22.6_0603_1%~D

1 2

R434

22.6_0603_1%~D

1 2

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CLK_CPU_ITP

CLK_CPU_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

Check ITP connector.

29

JITP

28

VTT1

27

GND6

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D

30

@

+3VSUS

+VCCP

+VCCP

+VCCP

R367

150_0603_1%~D

1 2

R415

54.9_0603_1%~D

1 2

R416

54.9_0603_1%~D

1 2

R387

39.2_0603_1%~D

1 2

R417

150_0603_1%~D

1 2

This shall place near CPU

R391

680_0402_5%~D

1 2

R436

27.4_0603_1%~D

1 2

1

C381

0.1U_0402_16V4Z~D

2

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

Place near JITP

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

Dothan Processor in mFCPGA479

TOBAGO-LA2151

751Monday, October 18, 2004

1

0.6

of

Page 8

5

4

3

2

1

JCPUB

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

B2

RSVD

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

TYCO_1612364-1~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Dothan

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

+VCC_CORE

H_PSI#<45>

VID0<45>

VID1<45>

VID2<45>

VID3<45>

VID4<45>

VID5<45>

V_CPU_GTLREF

CPU_BSEL0<6>

CPU_BSEL1<6>

R159

54.9_0603_1%~D@

1 2

1 2

R158

54.9_0603_1%~D@

+VCCP

VCCSENSE

VSSSENSE

H_PSI#

VID0

VID1

VID2

VID3

VID4

VID5

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

Note:

Pop R97 for Dothan-A,

Pop R92 for Dothan-B

+1.8VRUN

D D

+1.5VRUN

C C

B B

+VCCP

R_A

12

V_CPU_GTLREF

R140

1K_0603_1%~D

R_B

12

R147

2K_0603_1%~D

Layout close CPU

12

R129

R124

27.4_0603_1%~D

@

0_0805_5%~D

1 2

0_0805_5%~D

1 2

12

12

R465

27.4_0603_1%~D

54.9_0603_1%~D

+VCCA_PROC

R97

R92

1

1

C88

C87

2

2

10U_0805_10V4M~D

0.01U_0402_16V7K~D

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

12

miles away from any

other toggling signal.

R457

54.9_0603_1%~D

+VCC_CORE

JCPUC

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA19

VCC

AA21

VCC

AB6

VCC

AB8

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

TYCO_1612364-1~D

Dothan

POWER, GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Dothan Processor in mFCPGA479

TOBAGO-LA2151

851Monday, October 18, 2004

1

0.6

of

Page 9

5

4

3

2

1

+VCC_CORE

1

C100

10U_0805_4VAM~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

@

C428

10U_0805_4VAM~D

C468

10U_0805_4VAM~D

@

C448

10U_0805_4VAM~D

D D

C C

1

C429

10U_0805_4VAM~D

2

1

C138

10U_0805_4VAM~D

2

1

C140

10U_0805_4VAM~D

2

1

C432

10U_0805_4VAM~D

2

1

C98

10U_0805_4VAM~D

2

1

C447

10U_0805_4VAM~D

2

1

C139

10U_0805_4VAM~D

2

1

C426

10U_0805_4VAM~D

2

1

C430

10U_0805_4VAM~D

2

1

C470

10U_0805_4VAM~D

2

1

@

C446

10U_0805_4VAM~D

2

1

C427

10U_0805_4VAM~D

2

1

C99

10U_0805_4VAM~D

2

1

C469

10U_0805_4VAM~D

2

1

C466

10U_0805_4VAM~D

2

1

@

C431

10U_0805_4VAM~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C472

10U_0805_4VAM~D

C467

10U_0805_4VAM~D

C137

10U_0805_4VAM~D

1

2

1

2

1

2

10uF 0805 X6S -> 105 degree C

1

C473

10U_0805_4VAM~D

C471

10U_0805_4VAM~D

C120

10U_0805_4VAM~D

@

C119

10U_0805_4VAM~D

2

1

C97

10U_0805_4VAM~D

2

1

@

C118

10U_0805_4VAM~D

2

High Frequence Decoupling

1

C142

10U_0805_4VAM~D

2

1

C102

10U_0805_4VAM~D

2

1

C117

10U_0805_4VAM~D

2

1

C141

10U_0805_4VAM~D

2

1

C433

10U_0805_4VAM~D

2

1

C101

10U_0805_4VAM~D

2

Near VCORE regulator.

+VCC_CORE

1

1

+

+

C496

330U_D_2VM~D

2

9mOhm

7343

PS CAP

C354

330U_D_2VM~D

9mOhm

7343

PS CAP

C352

330U_D_2VM~D

2

@

B B

9mOhm

7343

PS CAP

1

1

+

+

C497

330U_D_2VM~D

2

2

@

9mOhm

7343

PS CAP

ESR <= 3m ohm

Capacitor > 880uF

+VCCP

1

+

C455

150U_D2_4VK~D

2

A A

1

C415

0.1U_0402_10V7K~D

2

1

C439

0.1U_0402_10V7K~D

2

1

C451

0.1U_0402_10V7K~D

2

1

C416

0.1U_0402_10V7K~D

2

1

C462

0.1U_0402_10V7K~D

2

1

C414

0.1U_0402_10V7K~D

2

1

C438

0.1U_0402_10V7K~D

2

1

C445

0.1U_0402_10V7K~D

2

1

C457

0.1U_0402_10V7K~D

2

1

C474

0.1U_0402_10V7K~D

2

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Bypass

TOBAGO-LA2151

951Monday, October 18, 2004

1

0.6

of

Page 10

5

D D

C C

Layout Guide

will show these

signals routed

differentially.

B B

A A

H_A#[3..31]<7>

T32 PAD~D

CLK_MCH_BCLK#<6>

CLK_MCH_BCLK<6>

H_CPUSLP#<7,22>

@

H_ADSTB#0<7>

H_ADSTB#1<7>

H_DINV#0<7>

H_DINV#1<7>

H_DINV#2<7>

H_DINV#3<7>

H_RESET#<7>

H_ADS#<7>

H_TRDY#<7>

H_DPWR#<7>

H_DRDY#<7>

H_DEFER#<7>

T33 PAD~D

H_HITM#<7>

H_HIT#<7>

H_LOCK#<7>

H_BR0#<7>

H_BNR#<7>

H_BPRI#<7>

H_DBSY#<7>

H_REQ#[0..4]<7>

H_DSTBN#[0..3]<7>

H_DSTBP#[0..3]<7>

H_RS#[0..2]<7>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

TP_H_EDRDY#

@

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_R_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP# H_R_CPUSLP#

Note:

"Do not install R88 for Dothan-A,

Install R88 for Dothan-B"

U4A

G9

HA3#

C9

HA4#

E9

HA5#

B7

HA6#

A10

HA7#

F9

HA8#

D8

HA9#

B10

HA10#

E10

HA11#

G10

HA12#

D9

HA13#

E11

HA14#

F10

HA15#

G11

HA16#

G13

HA17#

C10

HA18#

C11

HA19#

D11

HA20#

C12

HA21#

B13

HA22#

A12

HA23#

F12

HA24#

G12

HA25#

E12

HA26#

C13

HA27#

B11

HA28#

D13

HA29#

A13

HA30#

F13

HA31#

A11

HPCREQ#

A7

HREQ#0

D7

HREQ#1

B8

HREQ#2

C7

HREQ#3

A8

HREQ#4

B9

HADSTB#0

E13

HADSTB#1

AB1

HCLKN

AB2

HCLKP

G4

HDSTBN#0

K1

HDSTBN#1

R3

HDSTBN#2

V3

HDSTBN#3

G5

HDSTBP#0

K2

HDSTBP#1

R2

HDSTBP#2

W4

HDSTBP#3

H8

HDINV#0

K3

HDINV#1

T7

HDINV#2

U5

HDINV#3

H10

HCPURST#

F8

HADS#

B5

HTRDY#

G6

HDPWR#

F7

HDRDY#

E6

HDEFER#

F6

HEDRDY#

D6

HHITM#

D4

HHIT#

B3

HLOCK#

E7

HBREQ0#

A5

HBNR#

D5

HBPRI#

C6

HDBSY#

G8

HCPUSLP#

A4

HRS0#

C5

HRS1#

B4

HRS2#

ALVISO-915PM-B0_BGA1257~D

R88

0_0402_5%~D

1 2

Alviso

HOST

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

4

H_D#0

E4

H_D#1

E1

H_D#2

F4

H_D#3

H7

H_D#4

E2

H_D#5

F1

H_D#6

E3

H_D#7

D3

H_D#8

K7

H_D#9

F2

H_D#10

J7

H_D#11

J8

H_D#12

H6

H_D#13

F3

H_D#14

K8

H_D#15

H5

H_D#16

H1

H_D#17

H2

H_D#18

K5

H_D#19

K6

H_D#20

J4

H_D#21

G3

H_D#22

H3

H_D#23

J1

H_D#24

L5

H_D#25

K4

H_D#26

J5

H_D#27

P7

H_D#28

L7

H_D#29

J3

H_D#30

P5

H_D#31

L3

H_D#32

U7

H_D#33

V6

H_D#34

R6

H_D#35

R5

H_D#36

P3

H_D#37

T8

H_D#38

R7

H_D#39

R8

H_D#40

U8

H_D#41

R4

H_D#42

T4

H_D#43

T5

H_D#44

R1

H_D#45

T3

H_D#46

V8

H_D#47

U6

H_D#48

W6

H_D#49

U3

H_D#50

V5

H_D#51

W8

H_D#52

W7

H_D#53

U2

H_D#54

U1

H_D#55

Y5

H_D#56

Y2

H_D#57

V4

H_D#58

Y7

H_D#59

W1

H_D#60

W3

H_D#61

Y3

H_D#62

Y6

H_D#63

W2

H_VREF

J11

H_XRCOMP

C1

H_XSCOMP

C2

H_YRCOMP

T1

H_YSCOMP

L1

H_SWNG0

D1

H_SWNG1

P1

12

R90

24.9_0603_1%~D

Layout Note:

H_XRCOMP & H_YRCOMP trace width

and spacing is 10/20

H_D#[0..63] <7>

H_SWNG1

C65

0.1U_0402_16V4Z~D

H_SWNG0

C48

0.1U_0402_16V4Z~D

+VCCP

12

R52

54.9_0603_1%~D

12

R57

24.9_0603_1%~D

3

DMI_TXN0<23>

DMI_TXN1<23>

DMI_TXN2<23>

DMI_TXN3<23>

M_CLK_DDR0<16>

M_CLK_DDR1<16>

M_CLK_DDR3<17>

M_CLK_DDR4<17>

M_CLK_DDR#0<16>

M_CLK_DDR#1<16>

M_CLK_DDR#3<17>

M_CLK_DDR#4<17>

DDR_CKE0_DIMMA<16>

DDR_CKE1_DIMMA<16>

DDR_CKE2_DIMMB<17>

DDR_CKE3_DIMMB<17>

DDR_CS0_DIMMA#<16>

DDR_CS1_DIMMA#<16>

DDR_CS2_DIMMB#<17>

DDR_CS3_DIMMB#<17>

R142

1 2

V_DDR_MCH_REF<16,17,44>

DMI_TXP0<23>

DMI_TXP1<23>

DMI_TXP2<23>

DMI_TXP3<23>

DMI_RXN0<23>

DMI_RXN1<23>

DMI_RXN2<23>

DMI_RXN3<23>

DMI_RXP0<23>

DMI_RXP1<23>

DMI_RXP2<23>

DMI_RXP3<23>

80.6_0603_1%~D

Layout Note:

Rote as short

as possible

@

+VCCP

12

R85

221_0603_1%~D

12

1

R86

2

100_0603_1%~D

+VCCP

12

R64

221_0603_1%~D

12

1

R65

2

R80

100_0603_1%~D

12

54.9_0603_1%~D

1

C363

2

0.1U_0402_16V4Z~D

+1.8VSUS

12

R141

80.6_0603_1%~D

+VCCP

R326

100_0603_1%~D

R325

200_0603_1%~D

12

12

DMI_TXN0

DMI_TXN1 MCH_CLKSEL1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT0<16>

M_ODT1

M_ODT1<16>

M_ODT2

M_ODT2<17>

M_ODT3

M_ODT3<17>

SMRCOMPN

R435

40.2_0402_1%~D

SMRCOMPP

1

1

C435

C425

2

2

0.1U_0402_16V4Z~D

2.2U_0805_6.3V6K~D

M_OCDOCMP0

M_OCDOCMP1

12

12

R437

@

40.2_0402_1%~D

2

Note :

CFG3:17 has

internal pullup,

CFG18:19 has

internal pulldown

CFG0

MCH_CLKSEL0

@

@

CFG5

CFG6

CFG7

CFG9

CFG12

CFG13

CFG16

CFG18

CFG19

THERMTRIP_MCH#

PM_EXTTS#0

PM_EXTTS#1

IMVP_PWRGD

PLTRST_R#

1 2

R441 100_0603_1%~D

R336

10K_0402_5%~D

R253

10K_0402_5%~D

12

12

CFG0 <12>

MCH_CLKSEL1 <6>

MCH_CLKSEL0 <6>

CFG5 <12>

CFG6 <12>

CFG7 <12>

CFG9 <12>

CFG12 <12>

CFG13 <12>

CFG16 <12>

CFG18 <12>

CFG19 <12>

DREFCLK# <6>

DREFCLK <6>

DREF_SSCLK <6,11>

DREF_SSCLK# <6,11>

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

AE10

AJ33

AF5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

DMIDDR MUXING

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO-915PM-B0_BGA1257~D

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

CFG/RSVD

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

PM

DREF_CLKN

DREF_CLKP

DREF_SSCLKP

DREF_SSCLKN

CLK

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC

NC10

NC11

U4B

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

D37

C37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

PM_EXTTS#0

PM_EXTTS#1

1

T34PAD~D

T35PAD~D

R335

56_0402_5%~D

1 2

PM_BMBUSY# <23>

THERMTRIP_MCH# <15>

IMVP_PWRGD <23,38,45>

+2.5VRUN

PLTRST# <21,23,25,34>

+VCCP

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Alviso(1 of 5)

TOBAGO-LA2151

10 51Wednesday, November 03, 2004

1

0.6

of

Page 11

5

D D

4

3

2

1

DDR_A_BS#0<16>

DDR_A_BS#1<16>

DDR_A_BS#2<16>

DDR_A_DM[0..7]<16>

DDR_A_DQS[0..7]<16>

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

C C

B B

DDR_A_DQS#[0..7]<16>

DDR_A_MA[0..13]<16>

DDR_A_CAS#<16>

DDR_A_RAS#<16>

DDR_A_WE#<16>

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AK36

AP33

AN29

AP23

AK35

AP34

AN30

AN23

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

AM8

AM4

AN8

AM5

AH1

AP9

AP4

AJ2

AD3

AJ1

AE5

AE4

U4C

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

ALVISO-915PM-B0_BGA1257~D

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

DDR MEMORY SYSTEM A

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

DDR_B_DQS#[0..7]<17>

DDR_B_BS#0<17>

DDR_B_BS#1<17>

DDR_B_BS#2<17>

DDR_B_DM[0..7]<17>

DDR_B_DQS[0..7]<17>

DDR_B_MA[0..13]<17>

+3VRUN

DDR_B_BS#0

DDR_B_BS#1 DDR_B_D1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#<17>

DDR_B_RAS#<17>

DDR_B_WE#<17>

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

U4D

AJ15

SB_BS0#

AG17

SB_BS1#

AG21

SB_BS2#

AF32

SB_DM0

AK34

SB_DM1

AK27

SB_DM2

AK24

SB_DM3

AJ10

SB_DM4

AK5

SB_DM5

AE7

SB_DM6

AB7

SB_DM7

AF34

SB_DQS0

AK32

SB_DQS1

AJ28

SB_DQS2

AK23

SB_DQS3

AM10

SB_DQS4

AH6

SB_DQS5

AF8

SB_DQS6

AB4

SB_DQS7

AF35

SB_DQS0#

AK33

SB_DQS1#

AK28

SB_DQS2#

AJ23

SB_DQS3#

AL10

SB_DQS4#

AH7

SB_DQS5#

AF7

SB_DQS6#

AB5

SB_DQS7#

AH17

SB_MA0

AK17

SB_MA1

AH18

SB_MA2

AJ18

SB_MA3

AK18

SB_MA4

AJ19

SB_MA5

AK19

SB_MA6

AH19

SB_MA7

AJ20

SB_MA8

AH20

SB_MA9

AJ16

SB_MA10

AG18

SB_MA11

AG20

SB_MA12

AG15

SB_MA13

AH14

SB_CAS#

AK14

SB_RAS#

AF15

SB_RCVENIN#

AF14

SB_RCVENOUT#

AH16

SB_WE#

ALVISO-915PM-B0_BGA1257~D

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

DDR SYSTEM MEMORY B

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D0

AE31

SBDQ0

AE32

DDR_B_D[0..63] <17>DDR_A_D[0..63] <16>

+3VRUN

+3VRUN

CLK_SSC_IN

SSC_S3

SSC_S2

SSC_S1

CLK_SCLK

CLK_SDATA

CLK_ENABLE#

R310

@

10K_0402_5%~D

1 2

CLK_SSC_IN<6>

R291

R292

@

1 2

1 2

10K_0402_5%~D

12

A A

5

12

R313

@

10K_0402_5%~D

R311

@

@

1 2

10K_0402_5%~D

12

R312

@

@

10K_0402_5%~D

R290

SSC_S3

10K_0402_5%~D

SSC_S2

SSC_S1

10K_0402_5%~D

4

CLK_SCLK<6,16,17>

CLK_SDATA<6,16,17>

CLK_ENABLE#<6,45>

U18

1

CLKIN

2

SSC_S3

3

SSC_S2

4

SSC_S1

7

SCLOCK

8

SDATA

5

PWRDWN

6

REFOUT/SEL

R289

1 2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

VDDA

VDD

CLKOUT

CLKOUT#

IREF

VSSIREF

VSS

VSSA

@CY25823

33_0402_5%~D

@

3

16

9

12

11

14

13

10

15

DREFSSCLK

DREFSSCLK#

1

C385

0.1U_0402_16V4Z~D

2

@

R390 33_0402_5%~D

1 2

R389 33_0402_5%~D

1 2

12

R395

475_0603_1%~D

@

REFOUT_14M

@

@

DREF_SSCLK <6,10>

DREF_SSCLK# <6,10>

DREF_SSCLK

DREF_SSCLK#

@

R388

49.9_0402_1%~D

1 2

1 2

@

R384

49.9_0402_1%~D

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

Alviso(2 of 5)

TOBAGO-LA2151

11 51Monday, October 18, 2004

1

0.6

of

Page 12

5

4

3

2

1

SDVO_CTRLDATA

D D

C C

B B

+2.5VRUN

+3VRUN

A A

CLK_MCH_3GPLL#<6>

CLK_MCH_3GPLL<6>

COMP/B<18>

Y/G<18>

C/R<18>

BIA_PWM<18,35>

R283 2.2K_0402_5%~D

R279 2.2K_0402_5%~D

R247 2.2K_0402_5%~D

R37 2.2K_0402_5%~D

R285 100K_0402_5%~D

R300 100K_0402_5%~D

INTCRT_B<18>

INTCRT_G<18>

INTCRT_R<18>

1@

1 2

1@

1 2

1@

1 2

1@

1 2

@

1 2

@

1 2

12

R25

150_0603_1%~D

INT_VSYNC<18>

INT_HSYNC<18>

PANEL_BKEN<19>

ENVDD<19>

R251

1.5K_0603_1%~D

1@

LCD_ACLK-<19>

LCD_ACLK+<19>

LCD_BCLK-<19>

LCD_BCLK+<19>

LCD_A0-<19>

LCD_A1-<19>

LCD_A2-<19>

LCD_A0+<19>

LCD_A1+<19>

LCD_A2+<19>

LCD_B0-<19>

LCD_B1-<19>

LCD_B2-<19>

LCD_B0+<19>

LCD_B1+<19>

LCD_B2+<19>

5

12

R23

R24

150_0603_1%~D

R533

1@

0_0402_5%~D

12

LCTLA_CLK

LCTLB_DATA

LCD_DDCCLK

LCD_DDCDATA

BIA_PWM_MCH

PANEL_BKEN

12

12

R314

150_0603_1%~D

G_CLK_DDC2

G_DAT_DDC2

1@

R284

255_0603_1%~D

BIA_PWM_MCH

12

PANEL_BKEN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

L_IBG

TVIREF

4.99K_0603_1%~D

12

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO-915PM-B0_BGA1257~D

1@

LDDC_CLK

LDDC_DATA

MISC

TVVGALVDS

+2.5VRUN

R34

2.2K_0402_5%~D

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

PCI - EXPRESS GRAPHICS

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

12

12

R242

1@

+2.5VRUN

4

U4G

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

1@

S

2.2K_0402_5%~D

G

2

G

2

S

PEGCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

D

LCD_DDCCLK

13

Q33

BSS138_SOT23~D

LCD_DDCDATA

13

D

Q7

BSS138_SOT23~D1@

24.9_0603_1%~D

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

PEG_TXN[0..15]

PEG_TXP[0..15]

R287

+1.5VRUN_PCIE

PEG_RXN[0..15] <18>

PEG_RXP[0..15] <18>

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

PEG_TXN[0..15] <18>

PEG_TXP[0..15] <18>

INTCRT_R

INTCRT_G

INTCRT_B

LCD_DDCCLK <19>

LCD_DDCDATA <19>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

1 2

R261 150_0603_1%~D

1 2

R260 150_0603_1%~D

1 2

R295 150_0603_1%~D

3

Strap Table

CFG5

CFG6

CFG7

CFG9

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

CFG18

(VCC Select)

CFG19

(VTT Select)

SDVO_CTRLDATA

Low = DMI x 2

High = DMI x 4

Low = DDR-II

High = DDR-I

*

*

Low = DT/Transportable CPU

High = Mobile CPU

Low = Reverse Lane

High = Normal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

(Default)

*

*

*

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

Low = 1.05V (Default)

High = 1.2V

Low = No SDVO Device Present

(Default)

High = SDVO Device Present

*

*

G_CLK_DDC2

G_DAT_DDC2

2

1@

*

*

+2.5VRUN

R229

2.2K_0402_5%~D

12

1@

+2.5VRUN

+VCCP

R333 10K_0402_5%~D

CFG0<10>

R307 2.2K_0402_5%~D@

CFG5<10>

R299 2.2K_0402_5%~D

CFG6<10>

R281 2.2K_0402_5%~D @

CFG7<10>

R282 2.2K_0402_5%~D @

CFG9<10>

R288 2.2K_0402_5%~D @

CFG12<10>

R323 2.2K_0402_5%~D @

CFG13<10>

R346 2.2K_0402_5%~D @

CFG16<10>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

CFG[3:17] have internal pullup

+2.5VRUN

1 2

1 2

@

R308 1K_0402_5%~D

CFG18<10>

CFG19<10>

R306 1K_0402_5%~D@

CFG[18:19] have internal pulldown

+2.5VRUN

SDVO_CTRLDATA

1 2

R334 1K_0402_5%~D@

Have internal pulldown

12

R232

2.2K_0402_5%~D

S

G

2

G

2

S

1@

D

INT_CLK_DDC2

13

Q31

BSS138_SOT23~D

INT_DAT_DDC2

13

D

Q27

BSS138_SOT23~D1@

INT_CLK_DDC2 <18>

INT_DAT_DDC2 <18>

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Alviso(3 of 5)

TOBAGO-LA2151

12 51Monday, October 18, 2004

1

0.6

of

Page 13

5

U4F

10U_MLZ2012E100PTAIN_60mA_25%_0805~D

1 2

+2.5VRUN

1

D14

MMBD4148_SOT23~D1@

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

L33

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

1

C160

2

10U_0805_4VAM~D

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

+1.5VRUN_DPLLB

1

+

C335

2

1@

220U_D2_4VM_R45~D

C158

C331

1

2

1

2

10U_0805_4VAM~D

1

2

1